User's Guide

HP 10314D Intel 80386DX Preprocessor Interface

0

## HP 10314D Intel 80386DX Preprocessor Interface User's Guide

for the HP 1650A, HP 1650B, HP 1652B, HP 16510A, HP 16510B, HP 16511B, HP 16540/16541A, D and HP 16550A Logic Analyzers

©Copyright Hewlett-Packard Company 1992

Manual Part Number 10314-90915 Microfiche Part Number 10314-90815 Printed in U.S.A. February 1992

New editions are complete revisions of the manual. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The dates on the title page change only when a new edition is published.

A software code may be printed before the date; this indicates the version of the software product at the time the manual or update was issued. Many product updates and fixes do not require manual changes and, conversely, manual corrections may be done without accompanying product changes. Therefore, do not expect a one to one correspondence between product updates and manual updates.

Edition 1

February 1992

10314-90915

#### **List of Effective Pages**

The List of Effective Pages gives the date of the current edition and of any pages changed in updates to that edition. Within the manual, any page changed since the last edition is indicated by printing the date the changes were made on the bottom of the page. If an update is incorporated when a new edition of the manual is printed, the change dates are removed from the bottom of the pages and the new edition date is listed in the Printing History and on the title page.

Pages

Effective Date

| Product<br>Warranty | This Hewlett-Packard product has a warranty against defects in<br>material and workmanship for a period of 1 year from date of<br>shipment. During warranty period, Hewlett-Packard Company will, at<br>its option, either repair or replace products that prove to be defective.                                                                                                                                                                                                                                                                                                             |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | For warranty service or repair, this product must be returned to a<br>service facility designated by Hewlett-Packard. However, warranty<br>service for products installed by Hewlett-Packard and certain other<br>products designated by Hewlett-Packard will be performed at Buyer's<br>facility at no charge within the Hewlett-Packard service travel area.<br>Outside Hewlett-Packard service travel areas, warranty service will be<br>performed at Buyer's facility only upon Hewlett-Packard's prior<br>agreement and Buyer shall pay Hewlett-Packard's round trip travel<br>expenses. |

|                     | For products returned to Hewlett-Packard for warranty service, the<br>Buyer shall prepay shipping charges to Hewlett-Packard and<br>Hewlett-Packard shall pay shipping charges to return the product to<br>the Buyer. However, the Buyer shall pay all shipping charges, duties,<br>and taxes for products returned to Hewlett-Packard from another<br>country.                                                                                                                                                                                                                               |

|                     | Hewlett-Packard warrants that its software and firmware designated by<br>Hewlett-Packard for use with an instrument will execute its<br>programming instructions when properly installed on that instrument.                                                                                                                                                                                                                                                                                                                                                                                  |

|                     | Hewlett-Packard does not warrant that the operation of the instrument, software, or firmware will be uninterrupted or error-free.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

**Limitation of** Warranty The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by the Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environmental specifications for the product, or improper site preparation or maintenance.

> NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HEWLETT-PACKARD SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

**Exclusive** THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HEWLETT-PACKARD SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

**Assistance** Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For assistance, contact your nearest Hewlett-Packard Sales and Service Office.

- **Certification** Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility, and to the calibration facilities of other International Standards Organization members.

- **Safety** This product has been designed and tested according to International Safety Requirements. To ensure safe operation and to keep the product safe, the information, cautions, and warnings in this user's guide must be heeded.

## Contents

|            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|            | Logic Analyzers Supported<br>How to Use This Manual                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Chapter 1: | Setting Up the HP 10314D<br>Introduction<br>Duplicating the Master Disk<br>Equipment Supplied<br>Equipment Required<br>Installation Overview<br>Jumpers<br>The State/Timing Switch<br>Installing the HP 10314D in the HP 10269C<br>Connecting to the Target System<br>Connecting to the HP 10269C<br>Setting Up the Analyzer from the Disk                                                                    |  |  |

| Chapter 2: | Analyzing the Intel 80386DX         Introduction         Format Specification         Symbols         Listing Menu         The 80386DX Inverse Assemblers         Interpreting Data         Error Messages         Coprocessor Support         Instruction Decoding         Additional Information on Instruction Decoding         Timing Analysis         Timing Format Specification         Waveforms Menu |  |  |

| Chapter 3: | General Information<br>Preprocessor Interface Characteristics<br>Preprocessor Interface Description<br>Servicing                                                                                                                                                                                                                                                                                              |  |  |

**Contents-1**

| Appendix A: | Troubleshooting                                       |     |

|-------------|-------------------------------------------------------|-----|

| •••         | Target Board Will Not Bootup                          | A-1 |

|             | "Slow or Missing Clock"                               |     |

|             | Slow Clock                                            |     |

|             | "No Configuration File Loaded"                        |     |

|             | "Selected File is Incompatible"                       |     |

|             | " Inverse Assembler Not Found"                        |     |

|             | No Inverse Assembly                                   |     |

|             | Incorrect Inverse Assembly                            |     |

|             | No Activity on Activity Indicators                    |     |

|             | Capacitive Loading                                    |     |

|             | "State Clock Violates Overdrive Specification"        |     |

|             | Unwanted Triggers                                     |     |

|             | "Waiting for Trigger"                                 |     |

|             | Intermittent Data Errors                              |     |

|             | Bent Pins                                             |     |

|             | "Time from Arm Greater Than 41.93 ms."                | A-6 |

|             | No Setup/Hold Field on Format Screen                  |     |

|             | "Default Calibration Factors Loaded" (16540/16541A,D) |     |

### Introduction

The HP 10314D Preprocessor Interface, when installed in the HP 10269C General Purpose Probe Interface, provides a complete interface between any 80386DX target system and the following logic analyzers: HP 1650A, HP 1650B, HP 16510A, HP 16510B, HP 16511B, HP 1652B, HP 16540/16541A,D, or HP 16550A.

The 80386DX configuration software on the flexible disk sets up the format specification menu of the logic analyzer for compatibility with the 80386DX microprocessor. It also loads the inverse assembler for obtaining displays of 80386DX data in 80386DX assembly language mnemonics.

#### Logic The following logic analyzers are supported by the HP 10314D **Preprocessor Interface:** Analyzers Supported HP 1650A, HP 1650B, HP 16510A, HP 16510B, and HP 1652B These logic analyzers provide 1 k of memory depth with either 80 channels of 35 MHz state analysis (25 MHz state analysis for the HP 1650A or HP 16510A) or 80 channels of 100 MHz timing analysis. HP 16511B This logic analyzer combination provides 1 k of memory depth with either 160 channels of 35 MHz state analysis or 80 channels of 35 MHz state analysis and 80 channels of 100 MHz timing analysis. HP 16540A,D with two HP 16541A,D Expansion Cards This logic analyzer combination provides 4 k of memory depth

This logic analyzer combination provides 4 k of memory depth (16 k with the D version) with 112 channels of 100 MHz state or timing analysis.

#### HP 16550A

This logic analyzer provides 4 k of memory depth with 102 channels per card of 100 MHz state analysis or 250 MHz of timing analysis. The logic analyzer will also support various combinations of mixed state/timing analysis.

| How to Use<br>This Manual | This manual is organized into three chapters and one appendix:                                                                                                                                                  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | • Chapter 1 explains how to install and configure the HP 10314D<br>Preprocessor Interface for state and timing analysis with the<br>supported logic analyzers.                                                  |

|                           | • Chapter 2 provides reference information on the format<br>specification and symbols configured by the HP 10314D software.<br>It also provides information about the inverse assembler and<br>status encoding. |

|                           | • Chapter 3 contains additional reference information including<br>the characteristics and signal mapping for the HP 10314D<br>Preprocessor Interface. It also contains information on servicing.               |

|                           | • Appendix A contains information on troubleshooting problems or difficulties which may occur with the preprocessor interface.                                                                                  |

| Introduction                   | The HP 10314D Preprocessor Interface, when installed in the<br>HP 10269C General Purpose Probe Interface, provides a complete<br>interface between an 80386DX target system and the following<br>HP logic analyzers: HP 1650A, HP 1650B, HP 1652B, HP 16510A,<br>HP 16510B, HP 16511B, HP 16550A, and an HP 16540A,D with two<br>HP 16541A,D expansion cards. The preprocessor interface connects<br>the signals from the 80386DX target microprocessor to the logic<br>analyzer inputs and generates all status and clock signals required by<br>the software for inverse assembly of the 80386DX instruction set. |  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                | The 80386DX Preprocessor Interface operates in the bus mode. In the bus mode all bus cycles, including prefetches, are sent to the logic analyzer as they occur. All coprocessor cycles on the local bus are also captured.                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                | The 80386DX configuration software on the flexible disk sets up the<br>format specification of the logic analyzer for compatibility with the<br>80386DX microprocessor. It also loads the inverse assembler routine<br>for obtaining displays of 80386DX data in assembly language<br>mnemonics.                                                                                                                                                                                                                                                                                                                    |  |

|                                | The preprocessor interface can be used for timing analysis as well as<br>state analysis. The State/Timing switch on the preprocessor interface<br>board determines which type analysis is obtained. In the Timing<br>position, a minimal amount of skew is added between the signals.                                                                                                                                                                                                                                                                                                                               |  |

| Duplicating the<br>Master Disk | Before you use the HP 10314D software, use the Duplicate Disk<br>operation in the disk menu of your logic analyzer to make a duplicate<br>copy of the HP 10314D master disk. Store the master disk and use the<br>back-up copy to configure your logic analyzer. This will help prevent<br>the possibility of losing or destroying the original files in the event the<br>disk wears out, is damaged, or a file is accidentally deleted.                                                                                                                                                                            |  |

| Equipment<br>Supplied | <ul> <li>The HP 10314D Preprocessor Interface consists of the following equipment:</li> <li>The preprocessor interface hardware, which includes the preprocessor interface circuit card and cable assembly.</li> <li>The inverse assembly software on a 3.5-inch disk.</li> <li>This user's guide.</li> </ul>                                                                                                                                                                      |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note                  | The preprocessor interface socket assembly pins are covered at the<br>time of shipment with either a conductive foam wafer or a conductive<br>plastic pin protector. This is done to protect the delicate gold-plated<br>pins of the assembly from damage due to impact. When you're not<br>using the preprocessor interface, protect the socket assembly pins from<br>damage by covering them with the foam or plastic pin protector.                                             |

| Equipment<br>Required | <ul> <li>The minimum hardware required for analysis of an 80386DX target system consists of the following equipment:</li> <li>An HP 1650A, HP 1650B, HP 1652B, HP 16510A, HP 16510B, HP 16511B, HP 16550A, or HP 16540A,D with two HP 16541A,D expansion cards.</li> <li>The HP 10269C General Purpose Probe Interface, which connects the preprocessor interface to the logic analyzer.</li> <li>The 80386DX Preprocessor Interface and Inverse Assembler (HP 10314D).</li> </ul> |

| Installation<br>Overview | The following procedure describes the major steps required to perform<br>measurements with the HP 10314D Preprocessor Interface. The page<br>numbers listed in the various steps refer you to sections in the manual<br>that offer more detailed information. |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Caution 🍟                | To prevent equipment damage, remove the power from both the logic<br>analyzer and the target system whenever the preprocessor interface or<br>microprocessor is being connected or disconnected.                                                              |

|                          | <ol> <li>If required, move jumpers J5 through J8 to select between signals<br/>for analysis. Then update the Format menu to match your<br/>current selections (see "Jumpers" page 1-4).</li> </ol>                                                            |

| Note                     | To disable the HLDA line from stopping the logic analyzer clocks,<br>move jumper J9 to the ON position (see page 2-12).                                                                                                                                       |

|                          | 2. Move the State/Timing switch to the appropriate position for state or timing analysis (see page 1-4).                                                                                                                                                      |

|                          | 3. Install the 80386DX preprocessor interface (HP 10314D) into the HP 10269C Probe Interface (see page 1-6).                                                                                                                                                  |

|                          | 4. Connect the 80386DX microprocessor connector to the target system (see page 1-8).                                                                                                                                                                          |

|                          | 5. Plug the logic analyzer probes into the probe interface as listed in table 1-1 on page 1-10. Note that the logic analyzers are grouped into three categories. These same groupings apply to the configuration files.                                       |

|                          | 6. Load the logic analyzer configuration and inverse assembler for<br>the specified logic analyzer (see page 1-12). Table 1-2 lists the<br>configuration files and the inverse assemblers (see page 1-10).                                                    |

7. For timing analysis, select the configuration menu of the logic analyzer and select Timing as the analyzer "Type" (see page 2-15).

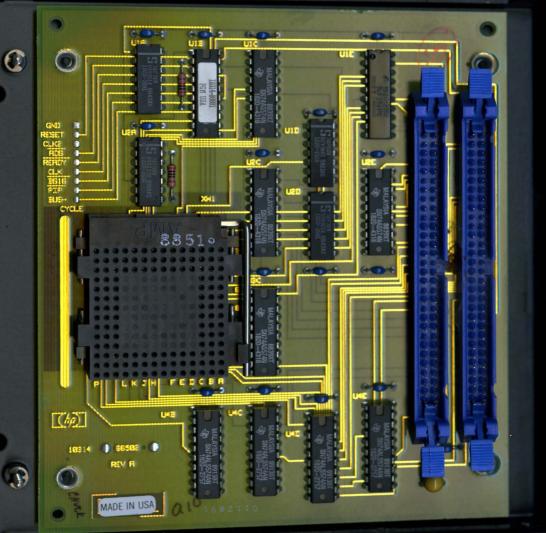

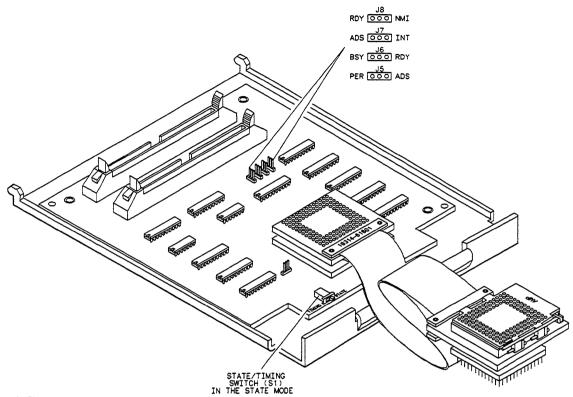

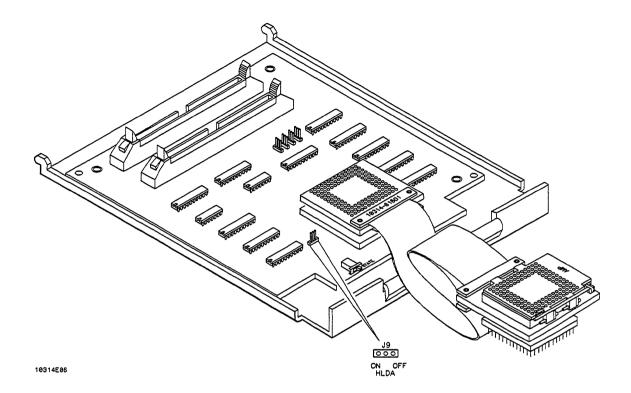

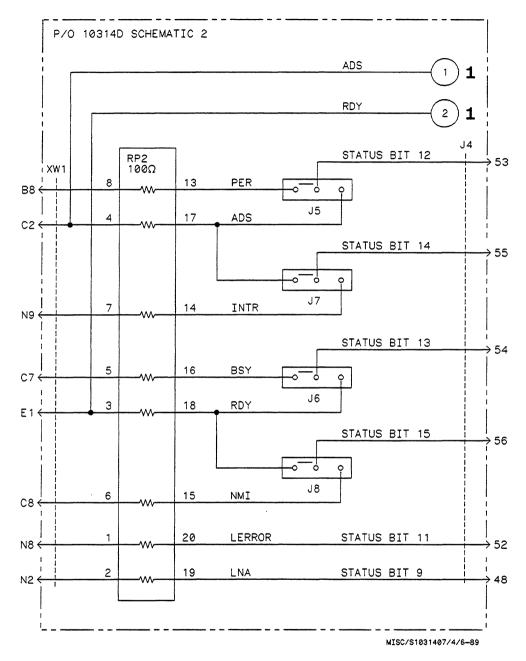

| Jumpers                       | The jumpers on the preprocessor interface board allow you to select<br>different signals for analysis. These jumpers are set at the factory to<br>view the READY, ADS, BUSY, and PEREQ signals on status bits 12<br>through 15. Figure 1-1 shows the location of the jumpers.                                                                             |  |  |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                               | <ul> <li>J8 (pod 5, bit 15) allows you to select between READY and NMI.</li> <li>J7 (pod 5, bit 14) allows you to select between ADS and INTR.</li> <li>J6 (pod 5, bit 13) allows you to select between BUSY and READY.</li> <li>J5 (pod 5, bit 12) allows you to select between PER and ADS.</li> </ul>                                                  |  |  |  |  |

|                               | If you move the jumpers, you must update the Format menu to reflect<br>your changes. To update the Format menu:                                                                                                                                                                                                                                           |  |  |  |  |

|                               | 1. If you move the jumper on J8 to the NMI position, change the READY label to read NMI.                                                                                                                                                                                                                                                                  |  |  |  |  |

|                               | <ol> <li>If you move the jumper on J7 to the INTR position, modify the ADS label to read INTR.</li> <li>If you move the jumper on J6 to the READY position, assign pod 5 of the READY label to bit 13 instead of bit 15.</li> <li>If you move the jumper on J5 to the ADS position, assign pod 5 of the ADS label to bit 12 instead of bit 14.</li> </ol> |  |  |  |  |

|                               |                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                               |                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                               | 5. Turn off any unused labels.                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

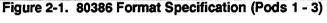

|                               | Figure 2-2 (page 2-2) shows the Format menu when the jumpers are set<br>to select the NMI, INTR, READY, and ADS signals.                                                                                                                                                                                                                                  |  |  |  |  |

| The<br>State/Timing<br>Switch | The State/Timing switch allows you to configure the HP 10314D preprocessor interface for either state or timing analysis. For state analysis, this switch must be set to the far-right position as shown on the preprocessor interface board (see figure 1-1).                                                                                            |  |  |  |  |

|                               | For timing analysis, this switch is set to the far-left position. In this position the signals are buffered straight through the preprocessor interface, adding only minimal skew to signals.                                                                                                                                                             |  |  |  |  |

| Setting Up the HP 10314       | D HP 10314D<br>80386DX Preprocessor Interface                                                                                                                                                                                                                                                                                                             |  |  |  |  |

10314E04

## Note

The State/Timing switch can be accessed through the slot in the metal cover for the target system ribbon cable without removing the preprocessor interface from the HP 10269C.

HP 10314D 80386DX Preprocessor Interface

#### Installing the HP 10314D in the HP 10269C

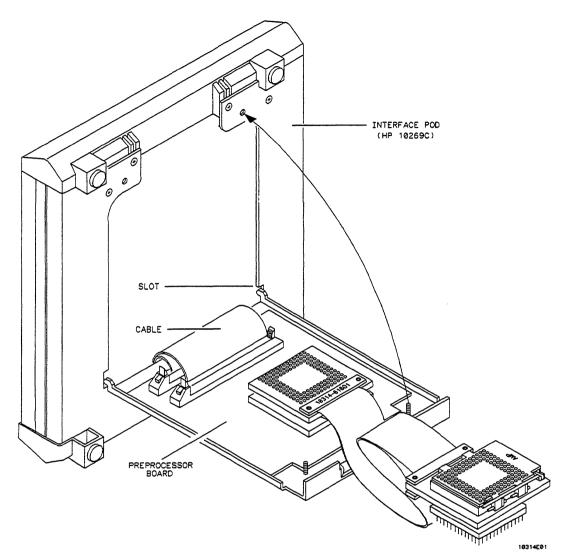

The HP 10269C General Purpose Probe Interface routes the signals from the HP 10314D Preprocessor Interface and provides the correct mechanical connections for the logic analyzer probes. To install the HP 10314D in the HP 10269C:

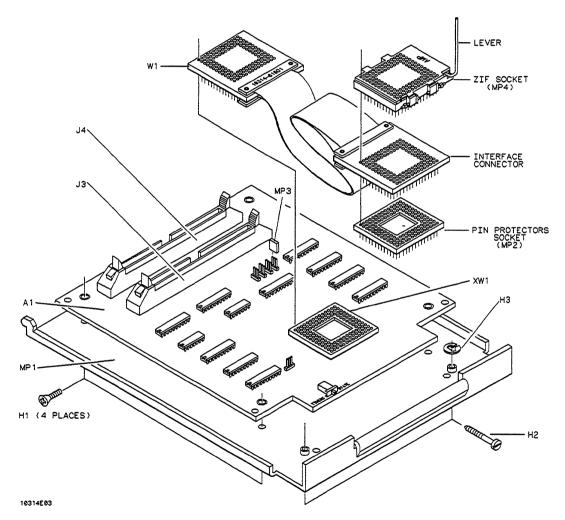

1. Install the HP 10314D Preprocessor Interface on the underside of the HP 10269C General Purpose Probe Interface Pod (see figure 1-2).

Care must be used when handling the preprocessor interface to avoid damaging the preprocessor interface cable. Avoid bending, twisting, making contact with sharp edges, and other mechanical stress which may damage the cable.

- 2. Insert the metal tabs of the preprocessor interface card in the slots of the pod.

- 3. Connect the two internal pod cables to the preprocessor interface card.

- 4. Gently fold the preprocessor interface card into the pod and fasten the cable end of the preprocessor interface card to the pod with the two captive screws on the preprocessor interface card.

To prevent equipment damage, remove the power from both the logic analyzer and the target system whenever the preprocessor interface or microprocessor is being connected or disconnected.

Figure 1-2. Installing the HP 10314D in the HP 10269C

# Connecting to the Target System

#### PROTECT AGAINST STATIC DISCHARGE

The preprocessor interface contains devices that are susceptible to damage by Electrostatic Discharge (ESD). Therefore, precautionary measures should be taken before handling the microprocessor connector attached to the end of the preprocessor interface cable in order to avoid damaging the internal components of the preprocessor interface with static electricity.

Do not install the microprocessor connector of the preprocessor interface in the target microprocessor socket while power is applied to the target system. The preprocessor interface may be damaged if power is not removed from the target system prior to installation.

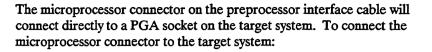

- 1. Remove the 80386DX microprocessor from the target system microprocessor socket.

- 2. Store the microprocessor in a protected environment.

- 3. Place the microprocessor connector, attached to the end of the cable from the preprocessor interface, in the target system microprocessor socket (see figure 1-3).

Serious damage to the target system and/or preprocessor interface can result from incorrect connection. Take care to note the position of pin A1 on both the connector and socket prior to inserting the connector in the socket. Also, take care to align the microprocessor connector with the target system socket so that all microprocessor pins are making contact.

4. If the ZIF socket is not already installed on the target system side of the HP 10314D cable, install it on top of the microprocessor connector (see figure 1-3).

Setting Up the HP 10314D 1-8

HP 10314D 80386DX Preprocessor Interface 5. Place the microprocessor in the ZIF socket on top of the microprocessor connector.

The ZIF socket on the top of the microprocessor connector allows you to easily load and unload the microprocessor without damaging the device or the microprocessor connector. However, this socket does increase the capacitive load on the target system.

Heavily loaded systems may not operate properly with this additional capacitance. If this is the case, remove the ZIF socket from the microprocessor connector and carefully install the 80386DX directly on the microprocessor connector.

Figure 1-3. Installing the Cable in the PGA Socket

HP 10314D 80386DX Preprocessor Interface

#### **Connecting to** the HP 10269C

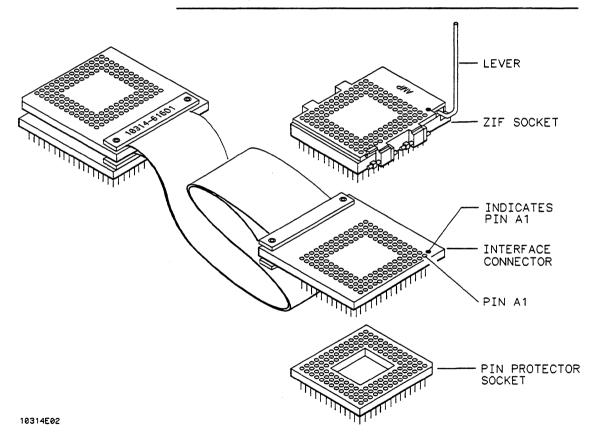

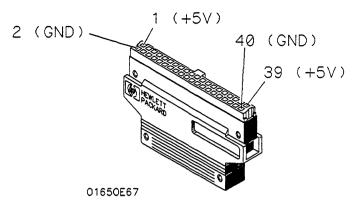

Connect the logic analyzer pods to the HP 10269C General Purpose Probe Interface as listed in table 1-1. Note that the logic analyzers are grouped into three categories. These same groupings apply to the configuration files.

| HP 16540/<br>16541A,D | HP 16511B<br>Logic Analyzer | All Other<br>Logic Analyzers | (Into) | HP 10269C |

|-----------------------|-----------------------------|------------------------------|--------|-----------|

| Logic Analyzer<br>Pod | Pod                         | Pod                          |        | Connector |

| Master Card, Pod 1    | Expander Card, Pod 1        | 1                            |        | 1         |

| *Exp. Card 2, Pod 1   | Expander Card, Pod 2        | 2                            |        | 2         |

| *Exp. Card 1, Pod 1   | Expander Card, Pod 3        | 3                            |        | 3         |

| *Exp. Card 1, Pod 2   | Expander Card, Pod 4        | 4                            |        | 4         |

| *Exp. Card 1, Pod 3   | Expander Card, Pod 5        | 5                            |        | 5         |

| Table | 1-1. | Connections |

|-------|------|-------------|

|-------|------|-------------|

refers to the next physically highest HP 16541A,D card (see figure 1-4).

#### Table 1-2. Configuration and Inverse Assembler Files

| Logic<br>Analyzer | Configuration<br>Filename | Inverse<br>Assembler<br>Filename | Capability                                                              |

|-------------------|---------------------------|----------------------------------|-------------------------------------------------------------------------|

| HP 16540/16541A,D | E80386D_I                 | I80386D_I                        | Works with all coprocessors. Does not attempt to decode the             |

| HP 16511B         | D80386D_I                 | I80386D_I                        | coprocessor instructions when an ESC instruction is encountered.        |

| all others        | C80386D_I                 | I80386D_I                        |                                                                         |

| HP 16540/16541A,D | E80386D_87                | I80386D_87                       | Works with systems that use only 80287/80387 coprocessors. When         |

| HP 16511B         | D80386D_87                | I80386D_87                       | an ESC instruction is encountered,<br>the inverse assembler decodes the |

| all others        | C80386D_87                | I80386D_87                       | math coprocessor operation.                                             |

Figure 1-4. Logic Analyzer Card Locations (relative locations, actual slots used may vary)

| Setting Up the<br>Analyzer from<br>the Disk | The logic analyzer can be configured for 80386DX analysis by loading<br>the appropriate configuration file. Loading this file will also load the<br>inverse assembler file. The configuration file depends on which logic<br>analyzer you use and which coprocessor your target system is using.<br>Three configuration files can be used with 80386DX systems that use<br>any coprocessor. The other three configuration files should only be<br>used in systems that have an 80287 or 80387 math coprocessor. |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                             | To load the configuration file and inverse assembler:                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                             | 1. Install the flexible disk in the front disk drive of the logic analyzer.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                             | 2. Select one of the following menus:                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                             | <ul> <li>For the HP 1650 series logic analyzers, select the I/O Disk<br/>Operations menu;</li> <li>For the HP 16500 series logic analyzers, select the System<br/>Front Disk menu.</li> </ul>                                                                                                                                                                                                                                                                                                                   |

|                                             | 3. Configure the menu to "Load" the analyzer with the appropriate configuration file (see table 1-2, page 1-10).                                                                                                                                                                                                                                                                                                                                                                                                |

|                                             | 4. For HP 16500 series logic analyzers, select the configuration file with the knob, then touch "All" and select the correct module.                                                                                                                                                                                                                                                                                                                                                                            |

|                                             | 5. Execute the load operation to load the file into the logic analyzer.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## Analyzing the Intel 80386DX

| Introduction            | This chapter provides reference information on the format<br>specification and symbols configured by the HP 10314D software. It<br>also contains information about the inverse assemblers, status encoding<br>and timing analysis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

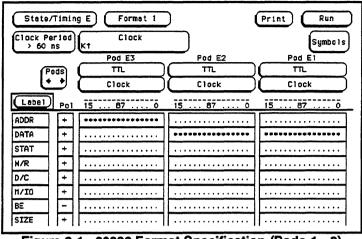

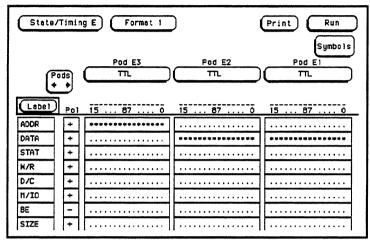

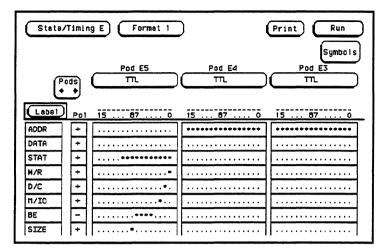

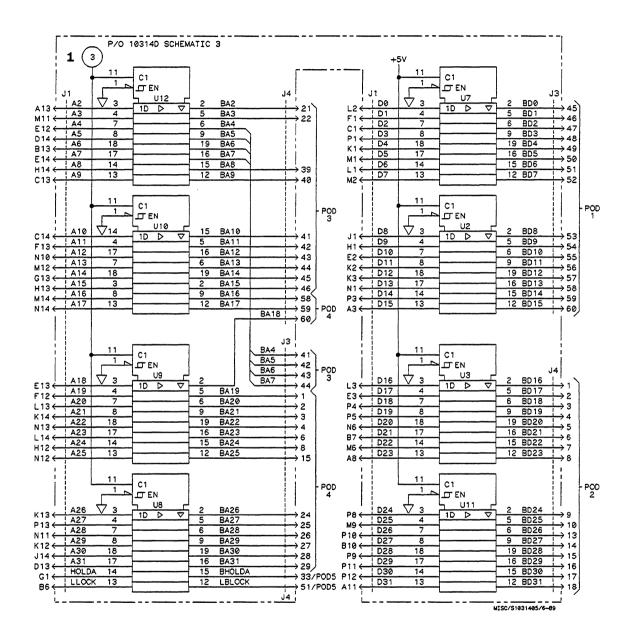

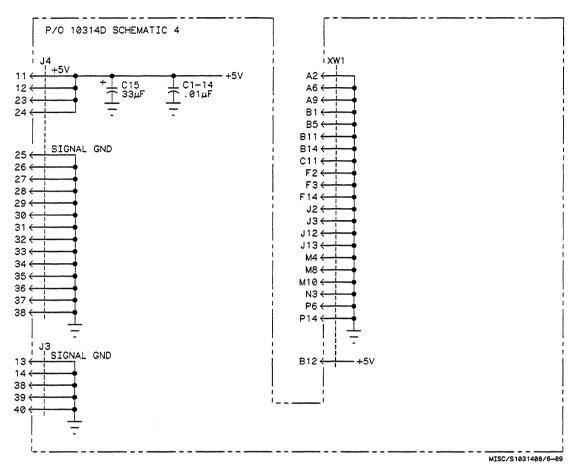

| Format<br>Specification | The 80386DX configuration files contain predefined format<br>specifications. These format specifications include all labels for<br>monitoring the 80386DX microprocessor and any coprocessors<br>connected directly to the microprocessor (see figures 2-1 and 2-2).<br>There are some slight differences in the displays, according to which<br>logic analyzer you are using. For example, some logic analyzers do not<br>have a Clock Period field. Refer to your logic analyzer manual to see<br>which fields and displays are available.<br>Table 3-1 in chapter 3 lists the 80386DX signals for the HP 10314D<br>Preprocessor Interface and their corresponding lines to the logic<br>analyzers. |  |

| Note                    | For those logic analyzers which have a Clock Period field (HP 1650A, HP 1650B, HP 1652B, HP 16510A, HP 16510B, and HP 16511B), the Clock Period field in figures 2-1 and 2-2 should remain in the current selection (> 60 ns) for proper HP 10314D operation. For more information on the Clock Period field, refer to the reference manual for your logic analyzer.                                                                                                                                                                                                                                                                                                                                  |  |

Ten additional labels are listed off the screen. To view these signals, select the Label field and rotate the knob on the front panel clockwise. Figure 2-2 shows some of the lower labels, with the NMI, INTR, READY, and ADS signals selected by jumper (see page 1-4).

#### **Symbols**

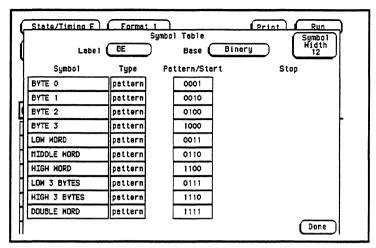

The HP 10314D configuration software sets up symbol tables on the logic analyzers. The tables contain alphanumeric symbols which identify data patterns or ranges. Additional labels have been defined in the format specification menu to make triggering on specific 80386DX cycles easier. Four of the defined labels are:

- The "STAT" label, which displays 15 status lines.

- The "BE" label, which monitors lines LBE0 to LBE3. These lines indicate valid bytes of the 32-bit data bus during specific transfers.

- The "SIZE" label, which indicates the size of the transfer on the data bus (16-bit or 32-bit transfer).

- The "HALT" label, which differentiates between a HALT cycle caused by executing the HALT instruction and a shutdown caused by protection fault while attempting to process a double fault.

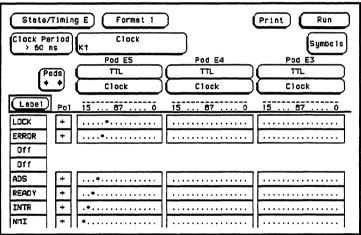

Figures 2-3 and 2-4 show the symbol tables for the STAT and BE labels. Table 2-1 lists the bits assigned to the STAT label. Table 2-2 lists the Status Label encoding for all types of 80386DX microprocessor cycles.

| Ģ | State/Timing E | Format 1 | Imbol Teble      | Print Run                 |

|---|----------------|----------|------------------|---------------------------|

| ( | Label          |          | Base Bin         | ary Symbol<br>Hidth<br>13 |

|   | Symbol         | Туре     | Pattern/Start    | Stop                      |

|   | INTERRUPT ACK  | pattern  | XXXXXXXXX000     |                           |

|   | I/O READ       | pattern  | XXXXXXXXXXX 10   |                           |

|   | I/O WRITE      | pettern  | XXXXXXXXXX011    |                           |

| ٦ | OPCODE FETCH   | pattern  | XXXXXXXXXX 100   | E E                       |

| H | HALT/SHUTDOWN  | pettern  | XXXXXXXXXXXX 101 |                           |

| H | MEMORY READ    | pattern  | XXXXXXXXXXXX110  |                           |

| Ħ | MEMORY WRITE   | pettern  | XXXXXXXXXXXXX111 |                           |

| H |                |          | <u></u>          |                           |

| Ī |                |          |                  |                           |

| Ħ |                |          |                  |                           |

| Ħ |                |          |                  | Done                      |

Figure 2-3. Symbol Table for the STAT Label

Figure 2-4. Symbol Table for the BE Label

Table 2-1. Description of the Status Bits

| Bit | Status<br>Signals | Description                                                                   |

|-----|-------------------|-------------------------------------------------------------------------------|

| 0   | D/LC              | Signal is high for a data cycle and low for a control cycle.                  |

| 1   | M/LIO             | Signal is high for memory and low for I/O.                                    |

| 2   | W/LR              | Signal is high for a write cycle and low for a read.                          |

| 3   | HLDA              | Signal goes high when the microprocessor has relinquished control of the bus. |

| Bit   | Status<br>Signals | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 - 7 | LBE0 - LBE3       | Byte Enables with BE0 the least significant byte and BE3 the<br>most significant byte. For opcode fetches, the microprocessor<br>will fetch four bytes unless LBS16 is asserted. When LBS16 is<br>asserted, the microprocessor fetches two bytes.                                                                                                                                                                            |

| 8     | LBS16             | If this signal is low for a 16-bit bus cycle, the microprocessor<br>will perform an additional bus cycle if required. For instance,<br>if LBS16 was low during a memory write with all byte enable<br>(LBE) lines low, the microprocessor would perform a second<br>bus cycle using the data from the upper two bytes of the data<br>bus of the first cycle, on the lower two bytes of the data bus for<br>the second cycle. |

| 9     | LNA*              | When this signal is low it indicates that the system is requesting the next address from the microprocessor.                                                                                                                                                                                                                                                                                                                 |

| 10    | LLOCK             | When this signal is low it indicates that the microprocessor has<br>the bus locked to prevent interruption by other bus devices.                                                                                                                                                                                                                                                                                             |

| 11    | LERROR*           | When this signal is low it indicates that the previous coprocessor instruction generated a coprocessor error.                                                                                                                                                                                                                                                                                                                |

| 12    | PEREQ*            | When this signal is high it requests that the microprocessor perform a data operand transfer for a coprocessor extension.                                                                                                                                                                                                                                                                                                    |

| 13    | LBUSY*            | When this signal is low it indicates the coprocessor is still executing an instruction.                                                                                                                                                                                                                                                                                                                                      |

| 14    | LADS*             | When this signal is low it indicates a valid bus cycle and address is available on the microprocessor pins.                                                                                                                                                                                                                                                                                                                  |

| 15    | LREADY*           | When this signal is low it terminates the bus cycle. This signal is ignored during bus hold acknowledge.                                                                                                                                                                                                                                                                                                                     |

#### Table 2-1. Description of the Status Bits (Continued)

\* This signal is used for timing analysis purposes when the HP 10314D is operating in the timing mode.

| 80386                                               | Status Bit<br>10 9 8 7 6 5 4 3 2 1 0 |

|-----------------------------------------------------|--------------------------------------|

| Cycle Type                                          |                                      |

| Interrupt Acknowledge                               | x x x x x x x x 0 0 0                |

| I/O Read                                            | * * * * * * * * 0 1 0                |

| I/O Write                                           | x x x x x x x x 0 1 1                |

| Opcode Fetch                                        | x x x x x x x x 1 0 0                |

| Halt/Shutdown                                       | * * * * * * * * 1 0 1                |

| Memory Read                                         | x x x x x x x x 1 1 0                |

| Memory Write                                        | x x x x x x x x 1 1 1                |

| Valid Bytes in Transfer<br>(from LBE0 through LBE3) |                                      |

| Double Word (all bytes valid)                       | x x x 0 0 0 0 x x x x                |

| Higher 3 Bytes                                      | x x x 0 0 0 1 x x x x                |

| High Word                                           | x x x 0 0 1 1 x x x x                |

| Byte 3                                              | x x x 0 1 1 1 x x x x                |

| Lower 3 Bytes                                       | x x x 1 0 0 0 x x x x                |

| Middle Word                                         | x x x 1 0 0 1 x x x x                |

| Byte 2                                              | x x x 1 0 1 1 x x x x                |

| Low Word                                            | x x x 1 1 0 0 x x x x                |

| Byte 1                                              | x x x 1 1 0 1 x x x x                |

| Byte 0                                              | x x x 1 1 1 0 x x x x                |

| Size of Transfer                                    |                                      |

| 16-bit Transfer                                     | x x 0 x x x x x x x x x              |

| 32-bit Transfer                                     | x x 1 x x x x x x x x x              |

Table 2-2. Status Field Encoding

Note: X = don't care. The actual status field is a 15 bit field; however, bits 11 through 14 are not shown since they are "don't cares."

Analyzing the Intel 80386DX 2-6

#### **Listing Menu**

Captured data is displayed in the Listing menu as shown in figure 2-5. The inverse assembler is constructed so the mnemonic output closely resembles the actual assembly source code.

| State/Ti<br>Markers<br>Off | ming E                           | Listing 1 Invesm (Print)                      | Run                     |

|----------------------------|----------------------------------|-----------------------------------------------|-------------------------|

| Label>                     | ADDR                             | 80386 Mnemonic                                |                         |

| Base>                      | Hex                              | hex                                           |                         |

| 1 2                        | 0000DBD8<br>0000DBDC             | MOV BX, WO120H<br>XOR DX, DX                  | OPCOD<br>OPCOD          |

| 3                          | OOOODBEO                         | MOV DI,WOO1OH<br>MOV AX,CS<br>DIV DI          | OPCOD                   |

| 4<br>5<br>6                | 0000DBE4<br>0000DBE8<br>0000DBEC | DR DX, W0030H<br>CHP DL, W3AH<br>JL 0000DBF1H | OPCOD<br>OPCOD<br>OPCOD |

| 7                          | OOOODBFO                         | ADD DL,#07H<br>DEC BX                         | OPCOD                   |

| 8                          | 0000DBF4                         | MOV (BX),DL<br>XOR DX,DX<br>OR AX,AX          | OPCOD                   |

| 9                          | 0000DBF8                         | JNZ OCOODBE3H                                 | OPCOD                   |

Figure 2-5. Listing Menu for the 80386

If your state trace doesn't appear to be correct (capturing the same RAM address twice, for example), make sure the state/timing switch is in the state position. If it is not in the proper position, place it in the state position and run the trace again.

An incorrect state trace may also result from system noise causing the internal clock of the preprocessor interface to become out of phase with the internal clock of the 80386DX. To get the HP 10314D back in synchronization with the 80386DX, reset the target system and run the trace again.

| The 80386DX<br>Inverse<br>Assemblers | The 80386DX inverse assemblers have been designed to support the 80386DX microprocessor with or without coprocessors. The following paragraphs explain the operation of the inverse assemblers and the results you can expect in certain conditions.                                                                                                                                              |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | The 80386DX microprocessor can fetch instructions up to 4 bytes (32 bits) wide in a single bus cycle. However, the microprocessor does not indicate externally which of the bytes fetched is the first byte of a code fetch. You must "point" to the first byte of an instruction fetch. Once synchronized, the inverse assembler will disassemble from this state through the end of the screen. |

|                                      | In addition, the 80386DX microprocessor can execute two types of object code. The 80386DX can execute the 80386DX instruction set (32-bit), and it can also execute object code from Intel's 16-bit microprocessor family, including software designed for the Intel 8086 and the Intel 80286. The user must tell the logic analyzer what "size" of code is being executed by the microprocessor. |

| Note 🗳                               | Size, as used here, has no relationship to the physical size of the microprocessor's data bus. In this reference, size is used to indicate whether the code being executed was originally designed to run on Intel's 16-bit or 32-bit microprocessors.                                                                                                                                            |

.

To point to the first byte of a code fetch and to indicate the size of the opcode, do the following:

- 1. Identify a line on the display that you know contains the first byte of an instruction fetch.

- 2. Roll this line to the top of the listing.

Note

The cursor location is not the top of the listing. In figure 2-5, line 1 is the top of the listing.

- 3. Select the "Invasm" field at the top of the display. A pop-up will appear with the following choices:

- Size 16 Byte 0 Size 16 Byte 1 Size 16 Byte 2 Size 16 Byte 3 Size 32 Byte 0 Size 32 Byte 1 Size 32 Byte 2 Size 32 Byte 3

- 4. Select the field in this pop-up that describes which byte of the captured state contains the first byte of the code fetch and what kind of object code is being executed by the microprocessor (Size 16 or 32 for Intel's 16- or 32-bit microprocessor families).

The listing will inverse assemble from the top line down. Any data before this screen is left unchanged. Rolling the screen up will inverse assemble the lines as they appear on the bottom of the screen. If you jump to another area of the screen by entering a new line number, you must re-synchronize the inverse assembler by repeating the above steps.

Each time you inverse assemble a block of memory, the analyzer will keep that block in the inverse assembled condition. You can inverse assemble several different blocks in the analyzer memory, but the activity between those blocks will not be inverse assembled.

## **Interpreting Data** Unless followed by a lower-case letter, all numeric output from the inverse assembler is in hexadecimal format. Decimal values are indicated by a lower-case "d" (as in the INT instruction).

Up to four instructions may be displayed for a single analyzer state because the 80386DX can fetch a double word with four instruction bytes from program memory. If the least significant byte of this double word contains a single-byte instruction, the next sequential instruction begins in the next higher byte. This process continues from the least significant byte to the most significant byte until all of the bytes of the fetched double word are used. When a single state contains more than one instruction, each instruction will be displayed on a separate line. For example:

| +0015 | = NEG ECX                     | OPCODE FETCH |

|-------|-------------------------------|--------------|

|       | = MOV BYTE PTR [EBP][-1BH].CL |              |

| +0016 | =XXXXXXDAH READ MEM           | MEMORY READ  |

Line number +0015 displays two instructions from a double-word.

Since instructions may begin in any byte position, the last bytes of a multiple-byte instruction may extend into the lower bytes of the next double word fetched. In this instance, the next sequential instruction begins in the next higher byte of the next double-word after the previous instruction and operands. When interpreting a given state, the inverse assembler will ignore bytes used by a previous instruction and will only display the instructions that begin in that state. For example:

| Byte Position |    | n  |    |                                                                                                                                     |

|---------------|----|----|----|-------------------------------------------------------------------------------------------------------------------------------------|

| 3             | 2  | 1  | 0  |                                                                                                                                     |

| 01            | 20 | BB | 24 | Single byte instruction MOV BX (BB) starts in byte 1.                                                                               |

| 10            | BF | D2 | 31 | Double byte instruction XOR DX,DX (31D2) begins in byte 0 and continues into byte 1. Next instruction MOV DI (BF) begins in byte 2. |

| <b>F</b> 7    | 8  | 8C | 00 | Double byte instruction DIVDI (F7F7) starts in byte 3 and continues into byte 0 of next double word fetched.                        |

| 30            | CA | 81 | F7 | Next instruction ORDX (81CA) begins in byte 2 immediately after last instruction.                                                   |

Asterisks (\*) in the inverse assembler output indicate that a portion (or portions) of an instruction was not captured by the analyzer. Missing opcodes occur frequently and are primarily due to microprocessor

Analyzing the Intel 80386DX 2-10

HP 10314D 80386DX Preprocessor Interface prefetch activity. Storage qualification, or the use of storage windows, can also lead to such occurrences.

The 80386DX has two possible default operand/address sizes, 16 or 32 bits. This attribute is set when a code segment descriptor is loaded, and is impossible for the inverse assembler to detect. Therefore, it must be declared manually by selecting the correct field under the "Invasm" pop-up. Any instruction with an operand size of 32 bits (either by default, or by using the operand override prefix) will be marked with an "=" symbol in the first column of the 80386DX mnemonic field to help you distinguish 32-bit operands from 16-bit operands.

If the inverse assembler seems to be disassembling incorrectly, and the problem is neither prefetch activity nor storage qualification, it is likely that the size attribute is set incorrectly.

The 80386DX microprocessor can perform byte, word, and three-byte transfers, as well as double-word transfers between microprocessor registers and memory. Byte transfers can occur in any byte on the 32-bit data bus. Word and three-byte transfers can occur across any contiguous set of bytes that will hold the transfer. The bytes that are valid in a transfer are indicated by the microprocessor LBE0 through LBE3 lines. The inverse assembler will display "xx" (don't care) for the bytes of a transfer that are ignored by the microprocessor. In this way it is possible to determine exactly which bytes were used by the microprocessor. For example:

| xxxxxDBH  | read memory | (Byte transfer on byte 0)              |

|-----------|-------------|----------------------------------------|

| xxxx28xxH | read memory | (Byte transfer on byte 1)              |

| xxB3xxxxH | read memory | (Byte transfer on byte 2)              |

| ECxxxxxH  | read memory | (Byte transfer on byte 3)              |

| xxx28DBH  | read memory | (Word transfer on lower word)          |

| xxB328xxH | read memory | (Word transfer on middle word)         |

| ECB3xxxH  | read memory | (Word transfer on upper word)          |

| xxB328DBH | read memory | (3-byte transfer on lower three bytes) |

| ECB328xxH | read memory | (3-byte transfer on upper three bytes) |

| ECB328DBH | read memory | (Double-word transfer)                 |

Physical, rather than logical addresses, are used to perform symbolic address mapping. Most instructions, however, specify a 32-bit intrasegment offset and may indicate a segment different from the default segment for that particular instruction. Since the physical address cannot be determined from this information alone, the inverse assembler must attempt to locate the resulting bus cycle so that the physical address may be obtained. If a bus cycle of the type indicated by the initiating instruction is not found, the physical address cannot be determined and an unmapped logical address (segment override, if any, and the 32-bit intrasegment offset) is displayed instead of a mapped physical address.

#### **Error Messages**

Any of the following list of error messages may appear during analysis of your target software. Included with each message is a brief explanation.

| Illegal Task Request | Displayed if the inverse assembler is used with an instrument other than the supported logic analyzers.                                                    |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fatal Data Error     | Displayed if the trace memory could not be read properly on entry into the inverse assembler.                                                              |

| Invalid Status       | Displayed if the status field for the current state is not valid.                                                                                          |

| Illegal Opcode       | Displayed if the inverse assembler encounters an illegal 80386DX instruction.                                                                              |

| Reserved Opcode      | Displayed if the I80386_87 inverse assembler encounters a reserved coprocessor instruction.                                                                |

| No Operand           | Displayed if the inverse assembler cannot find a complete operand field for an instruction. Prefetch activity or storage qualification is often the cause. |

#### Coprocessor Support

The HP 10314D Preprocessor Interface fully supports the 80287 and 80387 math coprocessors. Using the configuration files which end in "\_87," the math coprocessor instructions are inverse assembled and all operand transfers are decoded as I/O reads and writes. When using the configuration files which end in "\_I," the inverse assembler will not attempt to inverse assemble coprocessor instructions. Instead, it will display an ESC and the hexadecimal data that followed it.

Analyzing the Intel 80386DX 2-12

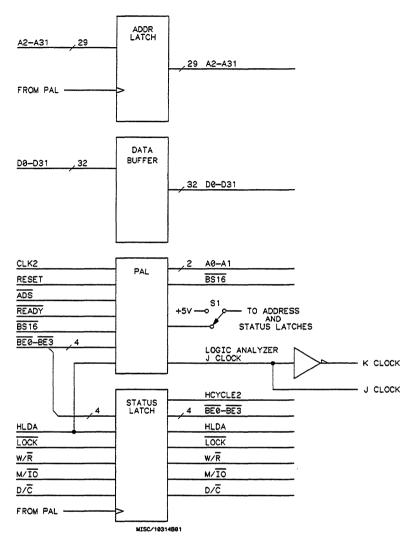

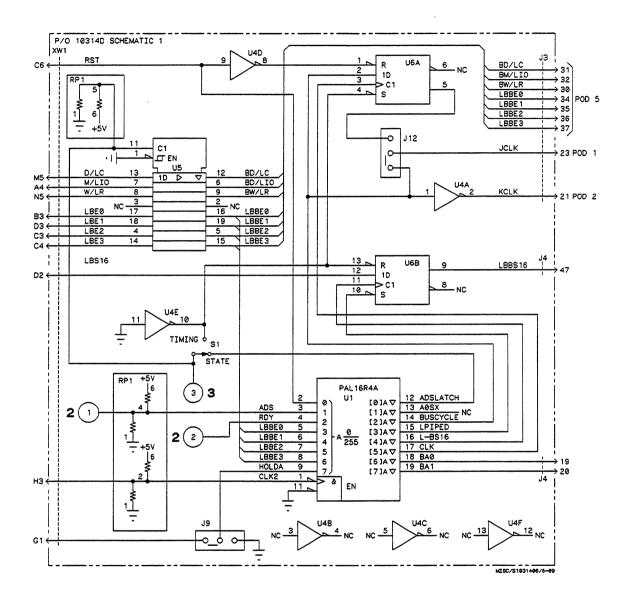

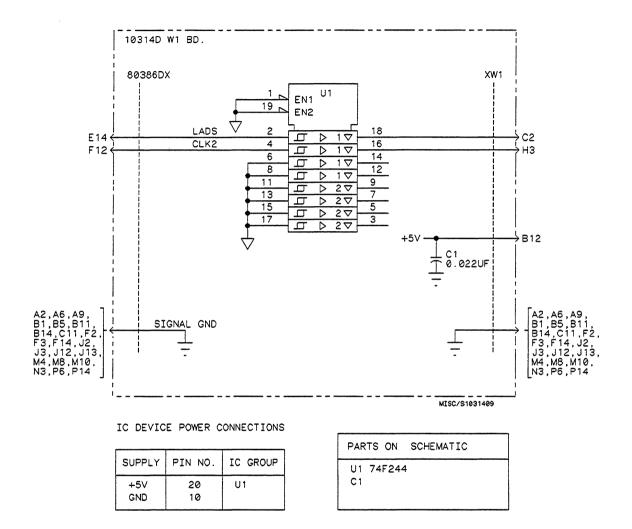

| Instruction<br>Decoding                                 | The HP 10314D Preprocessor Interface will send all of the bus<br>transactions by both the microprocessor and coprocessor to the logic<br>analyzer. The time count will accurately reflect when the end of the<br>bus cycle occurred. No distinction is made between instructions that<br>are executed and those that are only prefetched by the microprocessor.<br>Typically, several states separate the memory (or I/O) transfer from the<br>instruction that caused the transfer.            |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                         | The logic analyzer is clocked once each bus cycle. The preprocessor<br>interface hardware ensures that the logic analyzer will reliably capture<br>the address, data, and status information during both pipelined and<br>non-pipelined cycles by latching this information during the current bus<br>cycle and sending it to the logic analyzer during the succeeding bus<br>cycle. See the "Preprocessor Interface Description" section in chapter<br>3 for complete details of this process. |

| Additional<br>Information on<br>Instruction<br>Decoding | A 32-bit memory cycle on a 16-bit bus is sent to the logic analyzer as<br>two bus transactions.<br>The preprocessor interface stops generating logic analyzer clocks when<br>the 80386DX asserts HLDA. Bus cycles that assert HLDA, such as<br>DMA cycles, will not be captured by the logic analyzer.                                                                                                                                                                                          |

|                                                         | To disable the HLDA line from stopping the logic analyzer clocks,<br>move the jumper on J9 to the ON position (see figure 2-6). This will<br>bypass the HLDA control on the preprocessor interface leaving the<br>preprocessor interface active (ON) for all bus cycles.                                                                                                                                                                                                                        |

| Note                                                    | The ADS and READY lines must be operating in normal 80386DX<br>bus cycles when the HLDA line is disabled. If these lines are not<br>present during the HLDA (hold acknowledge) period, the<br>preprocessor interface will not remain in step with following bus cycles.<br>This will result in incorrect capturing of data.                                                                                                                                                                     |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Figure 2-6. HLDA Jumper J9

HP 10314D 80386DX Preprocessor Interface

Analyzing the Intel 80386DX 2-14

# Timing Analysis The same format specification loa

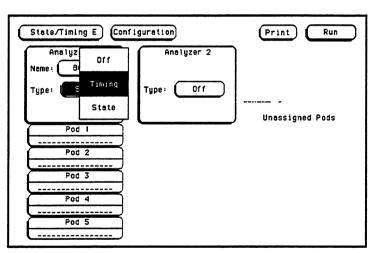

The same format specification loaded for state analysis is also used for timing analysis. To configure the logic analyzer for timing analysis:

- 1. Move the State/Timing switch (S1) on the preprocessor interface board to the timing position (see figure 1-1, page 1-5).

- 2. Select the Configuration menu of the logic analyzer.

- 3. Select the Type field for the 80386DX analyzer and select Timing (see figure 2-7).

BS16 and RESET are not available for timing analysis.

BS16 appears on the format specification, but is not accurate for timing analysis because it is delayed by an edge-triggered latch on the preprocessor interface board.

Figure 2-7. Setting Machine 1 to Timing

### Timing Format Specification

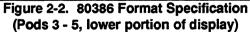

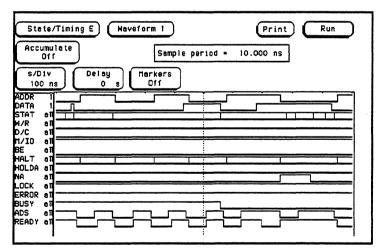

When the preprocessor interface is used for timing analysis, the format specification will be set up as shown in figures 2-8 and 2-9.

Figure 2-8. Timing Format Specification (Pods 1-3)

The timing format specification has ten additional labels which are listed offscreen. To view these signals, select the Label field and rotate the knob on the front panel clockwise.

Figure 2-9. Timing Format Specification (Pods 3-5)

**Waveforms** Menu

Captured data is displayed in the Waveforms menu as shown below.

Figure 2-10. Waveforms Display

Analyzing the Intel 80386DX 2-17

# **General Information**

| Preprocessor<br>Interface<br>Characteristics | The following operating characteristics are not specifications, but are<br>typical operating characteristics for the HP 10314D Preprocessor<br>Interface. These characteristics are included as additional information<br>for the user. |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microprocessor<br>Compatibility:             | Intel 80386DX and all microprocessors made by other manufacturers that comply with Intel 80386DX specifications.                                                                                                                        |

| CPU Package Supported:                       | 132-pin PGA                                                                                                                                                                                                                             |

| Accessories Required:                        | HP 10269C                                                                                                                                                                                                                               |

| Maximum Clock Speed:                         | 33 MHz clock output (CLK); 66 MHz clock input (CLK2)                                                                                                                                                                                    |

| Note                                         | For the following logic analyzers, the data must be valid for 10 ns<br>before READY is sampled with the rising edge of CLK2: HP 1650A,<br>HP 1650B, HP 1652B, HP 16510A, HP 16510B, and HP 16511B.                                      |

| State Speed:                                 | Four CLK2 cycles per bus cycle.                                                                                                                                                                                                         |

| Maximum Analyzer<br>Clock Speed:             | 16.5 MHz state speed with CLK2 at 66 MHz.                                                                                                                                                                                               |

| Signal Line Loading:                         | 1 "F" TTL load plus approximately 45 pF on the following lines:                                                                                                                                                                         |

|                                              | D0-D31                                                                                                                                                                                                                                  |

|                                              | 1 "F" TTL load plus approximately 50 pF on the following lines:                                                                                                                                                                         |

|                                              | A2-A31, LBS16, LREADY, LLOCK, D/LC, M/LIO, W/LR,<br>LBE0-LBE3                                                                                                                                                                           |

|                                              | 2 "F" TTL loads plus approximately 60 pF on the following line:                                                                                                                                                                         |

|                                              | HLDA                                                                                                                                                                                                                                    |

2 "F" TTL loads plus approximately 70 pF on the following line:

LRESET

1 "F" TTL loads plus approximately 20 pF on the following lines:

CLK2, LADS

Because of capacitive loading, the HP 10314D may not be compatible with target systems that extensively use CMOS devices.

| Microprocessor               |                                                                                                   |

|------------------------------|---------------------------------------------------------------------------------------------------|

| <b>Operations Displayed:</b> | Memory Read/Write                                                                                 |

|                              | I/O Read/Write<br>Opcode Fetch                                                                    |

|                              | Interrupt Acknowledge Type 0-255                                                                  |

|                              | Halt                                                                                              |

|                              | Shutdown                                                                                          |

|                              | 80287 or 80387 Coprocessor Operations                                                             |

| <b>Timing Analysis:</b>      | All signals are buffered except the following signals:                                            |