## TurbosPort 386 Portable Computer

#### Technical Reference Manual

|       |      |      |      |   | <br> |

|-------|------|------|------|---|------|

|       |      |      |      |   | <br> |

|       | <br> |      |      |   |      |

| <br>  | <br> | <br> | <br> |   | <br> |

|       |      |      |      |   | <br> |

|       | <br> | <br> |      |   | <br> |

| <br>  | <br> | <br> | <br> |   | <br> |

| <br>  | <br> | <br> | <br> |   | <br> |

|       | <br> | <br> | <br> |   |      |

|       |      |      |      |   | <br> |

| <br>  | <br> | <br> | <br> |   | <br> |

|       |      |      |      |   |      |

| <br>  |      | <br> | <br> |   |      |

|       |      |      |      |   |      |

| <br>- | <br> | <br> |      |   | <br> |

|       |      |      |      |   |      |

| <br>  | <br> | <br> | <br> |   | <br> |

|       |      |      |      |   |      |

| <br>_ | <br> | <br> | <br> |   |      |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

| <br>  | <br> | <br> | <br> |   |      |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

| <br>  |      | <br> | <br> |   |      |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

|       |      | <br> | <br> |   |      |

|       |      | <br> |      |   |      |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

| <br>  | <br> | <br> | <br> |   | <br> |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

| <br>  | <br> |      | <br> |   | <br> |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

| <br>  |      | <br> |      |   | <br> |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

| <br>  | <br> | <br> | <br> |   | <br> |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

| <br>  |      |      | <br> |   | <br> |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

| <br>  | <br> | <br> | <br> |   | <br> |

|       |      |      |      | - |      |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

| <br>  | <br> | <br> | <br> |   | <br> |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

|       |      |      |      |   |      |

Printed in U.S.A

### FEDERAL COMMUNICATIONS COMMISSION RADIO FREQUENCY INTEREFERENCE STATEMENT

WARNING: As sold by the manufacturer, the equipment described in this manual has been certified to comply with the limits for a Class B computing device, pursuant to Subpart J of Part 15 of FCC rules. Only peripherals (computer input/output devices, terminals, printers, etc.) certified to comply with the Class B limits may be attached to this computer. Operation with non-certified peripherals is likely to result in interference with radio and TV reception.

NOTE: In order to meet Class B emission limits, the I/O cables that interconnect between the computer and any peripheral (such as a printer, external modem, etc.) must be shielded.

#### **USER MODIFICATIONS**

The user is responsible for any interference with radio or TV reception caused by a user-modified computer. The manufacturer supplied this manual for the sole purpose of providing technical information concerning its product(s). The user is responsible for any user-modifications made to the software, firmware, or hardware that are the result of information supplied in this manual.

The manufacturer reserves the right to make changes at any time to the design of the product(s) without obligation to update existing product(s), including the information in this manual

#### **Limited Rights Legend**

Contractor is Zenith Data Systems of St. Joseph, Michigan 49085. The entire document is subject to Limited Rights data provisions.

Copyright 1988 by Zenith Data Systems Corporation.

Printed in the United States of America

Zenith Data Systems Corporation St. Joseph, Michigan 49085

| Chapter 1 — Introduction and General Information 1-1 |

|------------------------------------------------------|

| Manual Description1-2                                |

| Related Publications1-2                              |

| Recommended Environment                              |

| Memory Expansion1-5                                  |

| Coprocessors                                         |

| Video Options1-5                                     |

| Mass Storage                                         |

| Specifications                                       |

|                                                      |

| Chapter 2 — Installation                             |

| Operating Environment                                |

| Unpacking and Setting Up2-1                          |

| Connecting Peripherals2-2                            |

| Opening the Computer                                 |

| Keyboard                                             |

| Controls and Indicators2-10                          |

| Up and Running                                       |

| Power-Up Procedure                                   |

| Entering the Monitor Program                         |

| Setting the Clock and Calendar                       |

|                                                      |

| Loading a Disk                                       |

| Resetting Your Computer2-19                          |

| Booting Manually and Autobooting2-20                 |

| Transporting the Computer2-21                        |

|                                                      |

| Chapter 3 — Disassembly3-1                           |

| Battery Pack                                         |

| Observant Oscillaria                                 |

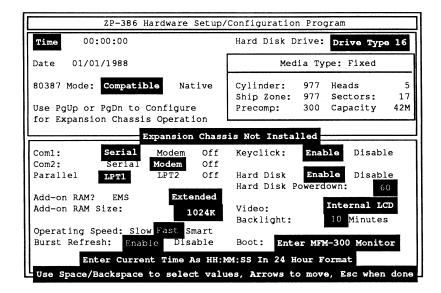

| Chapter 4 — Configuration                            |

| Setup/Configuration Program                          |

| Error Messages                                       |

| Time and Date                                        |

| 80387 Mode                                           |

| Hard Disk Drive4-4                                   |

| COM1 and COM24-4                                     |

| Parallel                                             |

| Add-On RAM                                           |

#### Page **iv**

|                                                                                                                                                                                                                                                                                                                                                     | 4                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Operating Speed                                                                                                                                                                                                                                                                                                                                     | 5                               |

| Burst Refresh                                                                                                                                                                                                                                                                                                                                       | 5                               |

| Keyclick4-                                                                                                                                                                                                                                                                                                                                          |                                 |

| Hard Disk                                                                                                                                                                                                                                                                                                                                           |                                 |

| Hard Disk Powerdown                                                                                                                                                                                                                                                                                                                                 |                                 |

| Video                                                                                                                                                                                                                                                                                                                                               |                                 |

| Backlight                                                                                                                                                                                                                                                                                                                                           |                                 |

| Boot                                                                                                                                                                                                                                                                                                                                                |                                 |

| Doot                                                                                                                                                                                                                                                                                                                                                | •                               |

| <b>Chapter 5 — Operation</b>                                                                                                                                                                                                                                                                                                                        | 4                               |

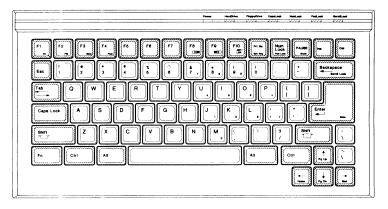

| Keyboard5-                                                                                                                                                                                                                                                                                                                                          |                                 |

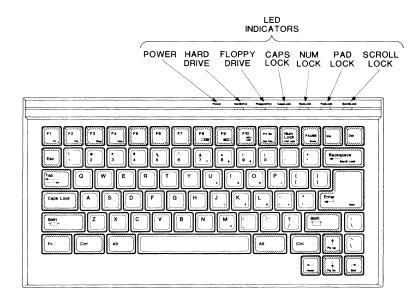

| Keyboard Indicator LEDs                                                                                                                                                                                                                                                                                                                             |                                 |

|                                                                                                                                                                                                                                                                                                                                                     |                                 |

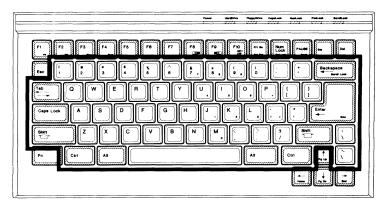

| Alphanumeric Keys5-                                                                                                                                                                                                                                                                                                                                 |                                 |

| Control and Special Purpose Keys                                                                                                                                                                                                                                                                                                                    |                                 |

| Cursor Control Keys                                                                                                                                                                                                                                                                                                                                 |                                 |

| Numeric Keypad                                                                                                                                                                                                                                                                                                                                      |                                 |

| Keyboard-Selectable Modes5-12                                                                                                                                                                                                                                                                                                                       |                                 |

| Key Combinations5-1                                                                                                                                                                                                                                                                                                                                 |                                 |

| Battery Operation                                                                                                                                                                                                                                                                                                                                   | 5                               |

|                                                                                                                                                                                                                                                                                                                                                     |                                 |

| Chapter 6 — Software Interface                                                                                                                                                                                                                                                                                                                      |                                 |

| The Monitor Program                                                                                                                                                                                                                                                                                                                                 | 1                               |

| ZBIOS6-6                                                                                                                                                                                                                                                                                                                                            | 2                               |

| User Commands6-9                                                                                                                                                                                                                                                                                                                                    | 9                               |

|                                                                                                                                                                                                                                                                                                                                                     |                                 |

| Machine Language Debugger6-14                                                                                                                                                                                                                                                                                                                       |                                 |

| Machine Language Debugger6-14 Interrupts6-29                                                                                                                                                                                                                                                                                                        | 5                               |

| Interrupts                                                                                                                                                                                                                                                                                                                                          |                                 |

| Interrupts                                                                                                                                                                                                                                                                                                                                          | 8                               |

| Hardware Interrupt Requests                                                                                                                                                                                                                                                                                                                         | 8<br>9                          |

| Interrupts                                                                                                                                                                                                                                                                                                                                          | 8<br>9<br>9                     |

| Interrupts                                                                                                                                                                                                                                                                                                                                          | 8<br>9<br>9                     |

| Interrupts                                                                                                                                                                                                                                                                                                                                          | 8<br>9<br>9                     |

| Interrupts 6-29 Hardware Interrupt Requests 6-29 Masking Hardware Interrupt Requests 6-29 Internal CPU Interrupts 6-29 Program Interrupts 6-30 Programming Interrupt Service Routines 6-30                                                                                                                                                          | 8<br>9<br>0<br>0                |

| Interrupts                                                                                                                                                                                                                                                                                                                                          | 8<br>9<br>0<br>0                |

| Interrupts 6-28 Hardware Interrupt Requests 6-28 Masking Hardware Interrupt Requests 6-29 Internal CPU Interrupts 6-29 Program Interrupts 6-30 Programming Interrupt Service Routines 6-30  Chapter 7 — CPU Interrupts 7- Divide by Zero (INT 00H) 7-                                                                                               | 8<br>9<br>9<br>0<br>1<br>1      |

| Interrupts                                                                                                                                                                                                                                                                                                                                          | 8<br>9<br>9<br>0<br>1<br>1<br>2 |

| Interrupts 6-29 Hardware Interrupt Requests 6-29 Masking Hardware Interrupt Requests 6-29 Internal CPU Interrupts 6-29 Program Interrupts 6-30 Programming Interrupt Service Routines 6-30  Chapter 7 — CPU Interrupts 7- Divide by Zero (INT 00H) 7-3 Single Step (INT 01H) 7-3 Non-Maskable Interrupt (INT 02H) 7-3                               | 89900 1122                      |

| Interrupts 6-29 Hardware Interrupt Requests 6-29 Masking Hardware Interrupt Requests 6-29 Internal CPU Interrupts 6-29 Program Interrupts 6-30 Programming Interrupt Service Routines 6-30  Chapter 7 — CPU Interrupts 7- Divide by Zero (INT 00H) 7- Single Step (INT 01H) 7- Non-Maskable Interrupt (INT 02H) 7- Software Breakpoint (INT 03H) 7- | 89900 11222                     |

| Interrupts 6-29 Hardware Interrupt Requests 6-29 Masking Hardware Interrupt Requests 6-29 Internal CPU Interrupts 6-29 Program Interrupts 6-30 Programming Interrupt Service Routines 6-30  Chapter 7 — CPU Interrupts 7- Divide by Zero (INT 00H) 7-3 Single Step (INT 01H) 7-3 Non-Maskable Interrupt (INT 02H) 7-3                               | 89900 112222                    |

| Equipment Configuration (INT 11H)                          |

|------------------------------------------------------------|

| Device Control Interrupt (INT 15H)                         |

| Set/Read Time-of-Day (INT 1AH)7-13                         |

| User Alarm (INT 4AH)7-16                                   |

| Tick Timer (INT 1CH)                                       |

| Real-Time Clock Alarm Interrupt (INT 70H)                  |

|                                                            |

| Programming Sound7-17                                      |

| Chapter 8 — Keyboard Interrupts                            |

| Programming Keyboard Interrupts                            |

| Key Pressed (INT 09H)8-1                                   |

| Keyboard Input/Output (INT 16H)8-3                         |

| Keyboard Break (INT 1BH)8-9                                |

| Keyboard Codes8-10                                         |

| System Scan Codes                                          |

| Alphabetic Keys                                            |

| Numeric/Punctuation Keys                                   |

| Function and Control Keys                                  |

| Make/Break Key Codes                                       |

| Make/Dieak Rey Codes0-27                                   |

| Chapter 9 I/O Interrupts                                   |

| Print Screen (INT 05H)                                     |

| Custom Communications (INT 0BH, INT 0CH,                   |

| INT 0DH, and INT 0FH)9-2                                   |

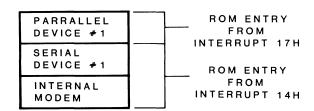

| Serial Input/Output (INT 14H)9-2                           |

| Printer Input/Output (INT 17H)                             |

| Parallel/Serial Configuration (INT 18H)                    |

| Parallel Format                                            |

| Serial Format9-9                                           |

|                                                            |

| Chapter 10 — Disk Drive Interrupts                         |

| Floppy and Hard Disk Drive Hardware Interrupt Return       |

| (INT 0EH and INT 76H)10-1                                  |

| Disk Input/Output (INT 13H and INT 40H)                    |

| Drive Selection                                            |

| Error Status Codes                                         |

| Function Call Codes                                        |

| Booting an Operating System (INT 19H)10-16                 |

| Floppy Disk Parameters (INT 1EH)                           |

| Hard Disk Parameters (INT 41H, INT 46H, and INT 4BH) 10-23 |

#### Page **vi**

| Chapter 11 — Video Interrupts      |

|------------------------------------|

| Video Input/Output (INT 10H)11-1   |

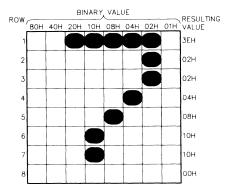

| Defining Characters (INT 1FH)11-13 |

| EGA Video Considerations11-14      |

| Monochrome Video Modes11-14        |

| Normal Color Video Modes11-15      |

| Enhanced Color Video Modes         |

| Basic Modes of Operation           |

| Text (Alphanumeric) Modes          |

| Graphics Modes                     |

| Medium-Resolution Color            |

| High-Resolution Color11-21         |

| Mode F                             |

| Mode 10                            |

|                                    |

| Chapter 12 — The CPU               |

| Introduction                       |

| 80386 Base Architecture            |

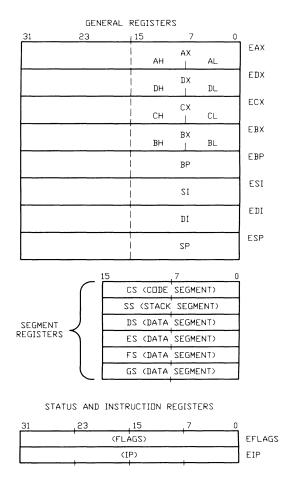

| Register Resources                 |

| General Purpose Registers12-9      |

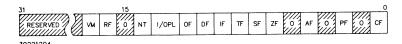

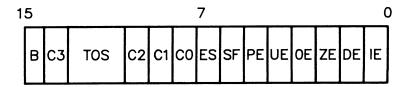

| Instruction Pointer and Flags12-9  |

| Segment Registers                  |

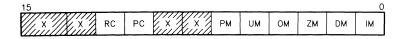

| Control Registers                  |

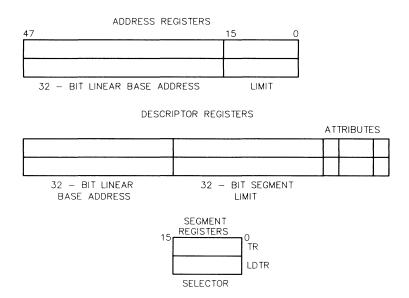

| Address Registers12-14             |

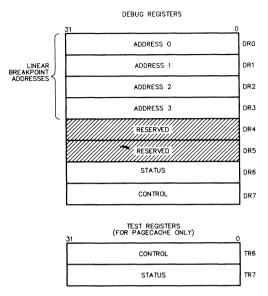

| Debug and Test Registers           |

| Processor Addressing               |

| Memory12-18                        |

| Input/Output                       |

| Interrupts                         |

| Debug Registers                    |

| Test Registers12-26                |

| Real Mode                          |

| Protected Architecture             |

| General Protection Concepts        |

| Descriptors                        |

| Segment Access12-32                |

| Privilege                          |

| Privilege Types                    |

| Inter-Segment Privilege Transfers | 12-34 |

|-----------------------------------|-------|

| Call Gates                        | 12-35 |

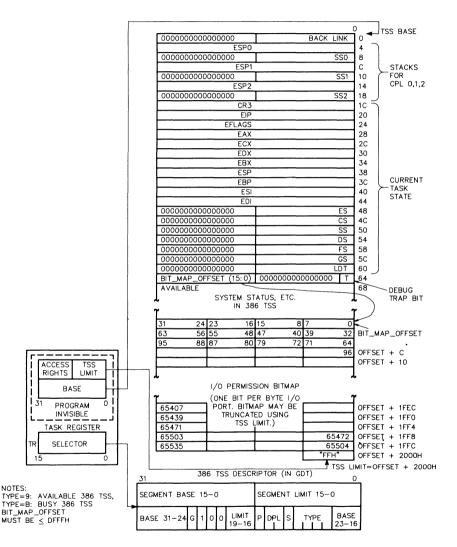

| Task Switching                    |       |

| Paging                            |       |

| Translation Lookaside Buffer      | 12-41 |

| Descriptor Attributes             |       |

| Code and Data Descriptors         |       |

| System Segment Descriptors        |       |

| Memory Addressing                 |       |

| Protected Mode Initialization     |       |

| Virtual 8086 Mode                 |       |

| Virtual Mode Addressing           |       |

| Paging                            |       |

| Protection and I/O Permission     | 12-55 |

| Interrupts                        |       |

| Virtual Mode Transitions          |       |

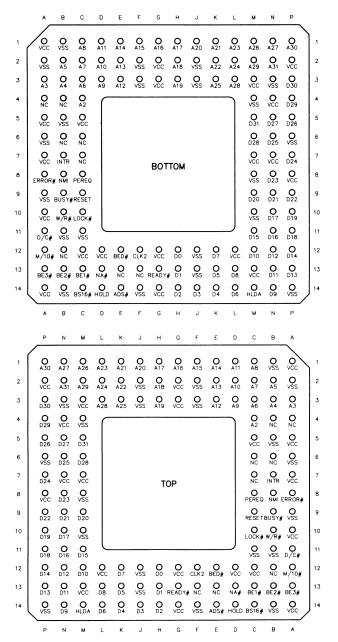

| 80386 Pinouts.                    |       |

| Signal Descriptions               |       |

| •                                 |       |

| Bus Signals                       |       |

| Bus Arbitration                   |       |

| Bus Cycle Definition              |       |

| Bus Control                       |       |

| Coprocessor Interface             |       |

| Interrupt Signals                 |       |

| Miscellaneous                     | 12-68 |

| Ohantar 40 Oanvaaaaa              | 40.4  |

| Chapter 13 — Coprocessors         |       |

| 80387                             |       |

| Architecture                      |       |

| Bus Control Logic Unit            |       |

| Data Interface/Control Unit       |       |

| Floating Point Unit               |       |

| Register Resources                |       |

| Operation                         |       |

| Programming                       |       |

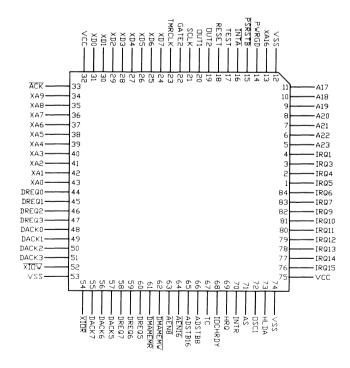

| Device Pinout                     |       |

| 80387 Pin Descriptions            |       |

| Control Signals                   |       |

| Handshake Signals                 |       |

| Bus Interface Signals             |       |

| Chip Select Signals               |       |

| Power Signals                     | 13-17 |

#### Page **viii**

| Chapter 14 — Support Circuits                | <br>. 14-1 |

|----------------------------------------------|------------|

| The 82C206 Integrated Peripherals Controller | <br>. 14-1 |

| The Interrupt Controllers                    | <br>. 14-2 |

| Interrupt Controller Operation               | <br>. 14-2 |

| Interrupt Sequence                           | <br>. 14-4 |

| End of Interrupt                             | <br>. 14-5 |

| Priority Assignment                          | <br>. 14-6 |

| Fixed Priority Mode                          | <br>. 14-8 |

| Automatic Rotation Mode                      | <br>. 14-8 |

| Specific Rotation Mode                       | <br>. 14-8 |

| Programming The Interrupt Controllers        | <br>14-11  |

| Initialization Commands                      | <br>14-11  |

| Operational Command Words                    | <br>14-14  |

| The Programmable Counter/Timer               | <br>14-17  |

| Operation                                    | <br>14-17  |

| The Timer Control Word                       | <br>14-18  |

| Mode Definitions                             | <br>14-20  |

| Programming Considerations                   | <br>14-22  |

| The DMA Controllers                          | <br>14-23  |

| Operation                                    | <br>14-24  |

| Internal Registers                           |            |

| Operating Modes                              |            |

| Transfer Modes                               |            |

| Self-Initialization                          | <br>14-37  |

| Priority Management                          | <br>14-38  |

| Compressed Timing                            | <br>14-38  |

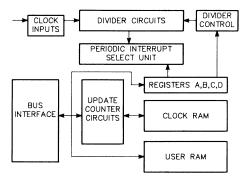

| The Real-Time Clock                          | <br>14-39  |

| Real Time Clock Operation                    | <br>14-39  |

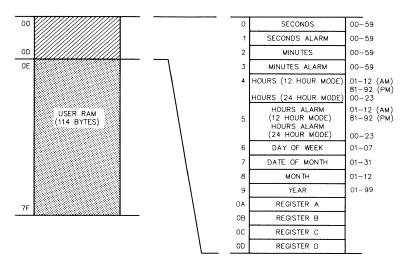

| Internal Registers                           |            |

| Register A (0AH)                             | <br>14-41  |

| Register B (0BH)                             |            |

| Register C (0CH)                             |            |

| Register D (0DH)                             |            |

| Time, Calendar, and Alarm Registers          |            |

| Programming                                  |            |

| Initialization                               |            |

| Interrupts                                   |            |

| Update Cycle                                 |            |

| Memory                                       |            |

| System Control Processor                     |            |

| SCP Commands                                 |            |

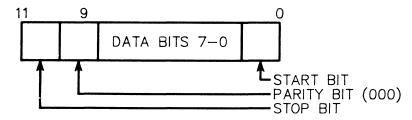

| Keyboard Control                             | 14-62      |

| Receiving Keyboard Data                    | . 14-62 |

|--------------------------------------------|---------|

| Sending Keyboard Data                      | . 14-63 |

| Slushware                                  |         |

| CPU Protected Mode                         | . 14-64 |

| SCP Pinout                                 | . 14-64 |

| Special Programming Features               | . 14-68 |

| Scratchpad RAM Enable                      | . 14-69 |

| NMI Enable                                 | . 14-69 |

| Chapter 15 — Memory                        |         |

| User Memory                                |         |

| Address Format                             |         |

| Address Decoding                           |         |

| Memory Data Bus                            | 15-5    |

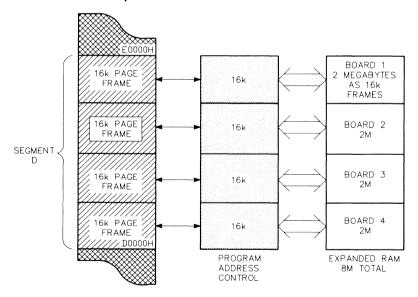

| EMS Memory                                 | 15-6    |

| Slushware Memory                           | . 15-10 |

| Chapter 16 — Mass Storage                  |         |

| Supported Drives                           |         |

| Error Detection and Invalid Commands       |         |

| Floppy Disk Control                        |         |

| DMA and Non-DMA Modes                      |         |

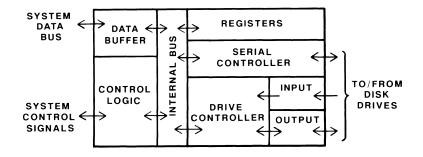

| Master Control Logic                       |         |

| Serial Controller                          | 16-3    |

| Drive Controller                           | 16-4    |

| FDC Control Registers                      |         |

| Main Status Register (Port 3F4H)           | 16-7    |

| Floppy Control Register (Port 3F7H)        | 16-8    |

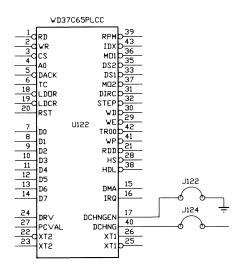

| FDC Pinout                                 | . 16-12 |

| Programming Floppy Disk Operations         | . 16-17 |

| Floppy Disk Controller Commands            | . 16-19 |

| Hard Disk Control                          |         |

| Hard Disk Drive Control Registers          |         |

| Data Register (Port 1F0H)                  |         |

| Error Register (Port 1F1H)                 |         |

| Write-Precompensation Register (Port 1F1H) |         |

| Sector Count Register (Port 1F2H)          | . 16-42 |

| Sector Number Register (Port 1F3H) 16               | -42                                    |

|-----------------------------------------------------|----------------------------------------|

| Cylinder Low and Cylinder High Registers            |                                        |

| (Ports 1F4H and 1F5H)16                             |                                        |

| Drive and Head Register (Port 1F6H) 16              | -42                                    |

| Status Register (Port 1F7H)                         | -43                                    |

| Command Register (Port 1F7H) 16                     | -45                                    |

| Fixed Disk Register (Port 3F6H) 16                  | -47                                    |

| Digital Input Register (Port 3F7H) 16               | -48                                    |

| Programming Hard Disk Operations16                  | -49                                    |

| Hard Disk Controller Commands16                     |                                        |

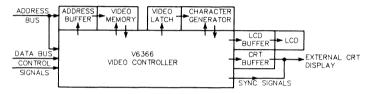

| Chapter 17 — Video Circuits                         | 7-1                                    |

| The V6366 Video Controller                          | 7-2                                    |

| Input/Output Ports                                  | 7-3                                    |

| 6845 Pointer Address and Data Ports                 |                                        |

| Video Mode Register                                 | 7-8                                    |

| Color Palette Register1                             |                                        |

| Status Register/Extended Port                       |                                        |

| Light Pen Registers                                 |                                        |

| Register Bank Pointer Address and Data Ports        |                                        |

| Control/ID Register (Register F, 3DFH)              |                                        |

| Operating Modes17                                   |                                        |

|                                                     |                                        |

| Chapter 18 — Serial and Parallel Communications 1   |                                        |

| Serial Port1                                        |                                        |

| Handshaking1                                        |                                        |

| Serial Port Programming                             |                                        |

| Receiver Buffer and Transmitter Holding Registers 1 |                                        |

| Divisor Latch Registers                             |                                        |

| Interrupt Registers                                 |                                        |

| Line Control Register                               |                                        |

| Modem Control Register                              |                                        |

| Line Status Register                                |                                        |

| Modem Status Register                               | 40                                     |

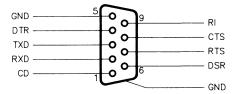

| Serial Port Connector                               |                                        |

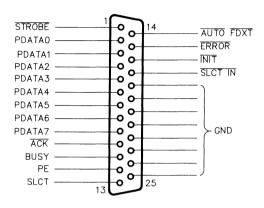

| Parallel Port                                       | -13                                    |

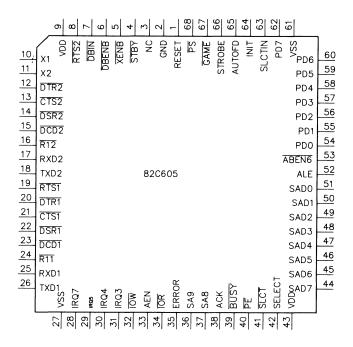

| The 82C605 Multifunction Controller                 | -13<br>-14                             |

| 82C605 Pinout                                       | -13<br>-14<br>-16                      |

|                                                     | -13<br>-14<br>-16<br>-17               |

| Clock and Control Signals18                         | -13<br>-14<br>-16<br>-17<br>-20        |

| PC Bus Interface Signals                            | -13<br>-14<br>-16<br>-17<br>-20        |

|                                                     | -13<br>-14<br>-16<br>-17<br>-20<br>-20 |

|                                              | Game Port Signal                                                                                                                                                                                      | 8-24                                                         |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Self-Selec                                   | Tests                                                                                                                                                                                                 | 19-1<br>19-2<br>19-3<br>19-3<br>19-4<br>19-4<br>19-5<br>19-5 |

| Disk-  Appe 8038                             | Error Messages Related to The Setup/Configuration Program General Error Messages Error Summary Lines Based Diagnostics Islandix A — 80386 Instruction Instruction Set Data Transfer Instructions      | 19-8<br>19-9<br>9-11<br>9-12<br>. A-1<br>. A-2               |

| ;<br>!<br>!                                  | Arithmetic Instructions.  String Instructions.  Logical Instructions  Bit Manipulation Instructions.  Program Control Instructions  High Level Language Instructions.  Processor Control Instructions | . A-4<br>. A-4<br>. A-5<br>. A-6<br>. A-7                    |

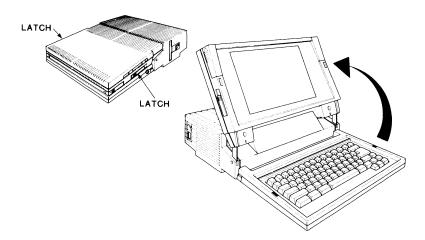

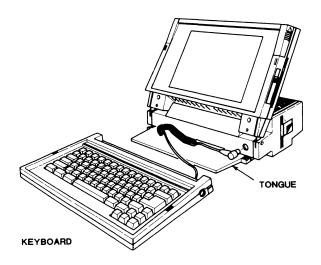

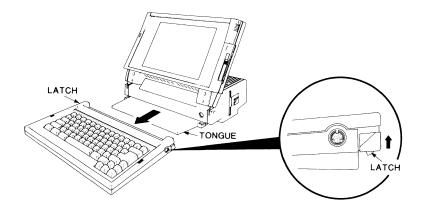

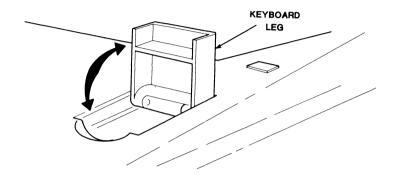

| 1-1.                                         | TurbosPort 386 Portable Computer                                                                                                                                                                      | . 1-1                                                        |

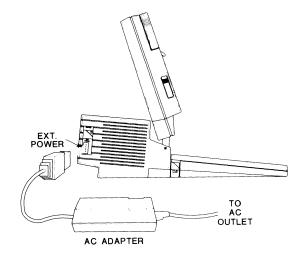

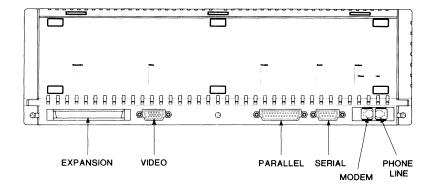

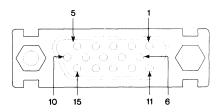

| 2-1.<br>2-2.<br>2-3.<br>2-4.<br>2-5.<br>2-6. | AC Adapter Connection The Back Panel Opening the Computer Attaching the Keyboard Removing the Keyboard Keyboard Tilt Adjustment                                                                       | 2-3<br>2-6<br>2-7<br>2-8                                     |

#### Page **xii**

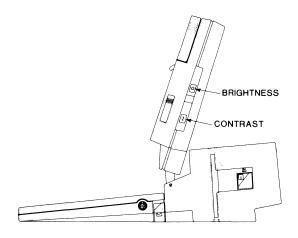

| 2-7.  | Brightness and Contrast Controls 2-10 |

|-------|---------------------------------------|

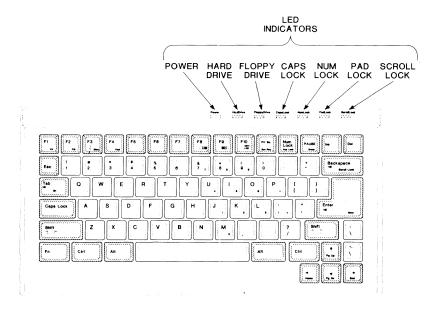

| 2-8.  | LED Indicators                        |

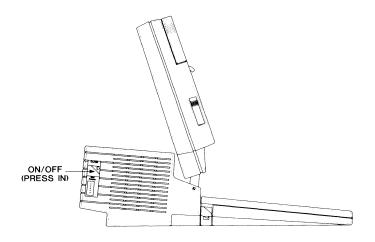

| 2-9.  | Turning On the Power                  |

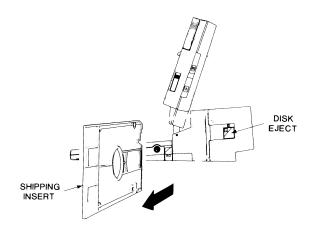

| 2-10. | Removing the Shipping Insert          |

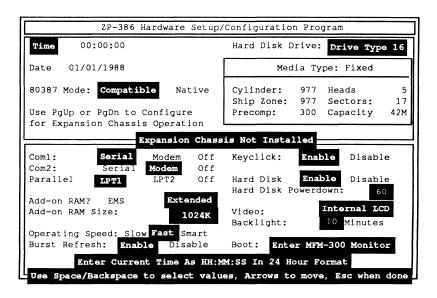

| 2-11. | Setup/Configuration Menu              |

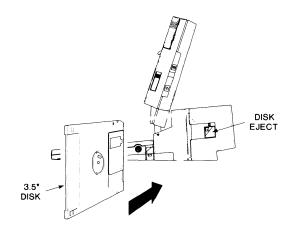

| 2-12. | Inserting a Disk2-18                  |

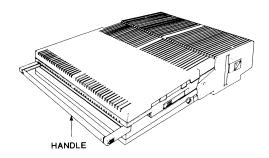

| 2-13. | Built-In Handle                       |

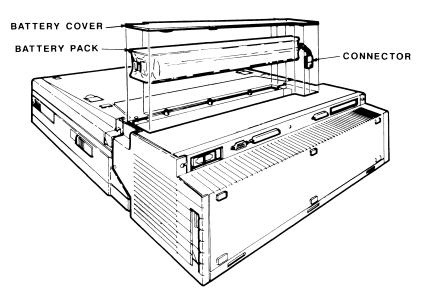

| 3-1.  | Battery Pack Installation             |

| 4-1.  | Setup/Configuration Menu              |

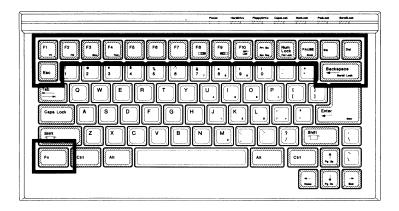

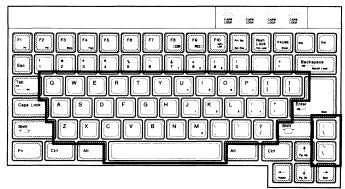

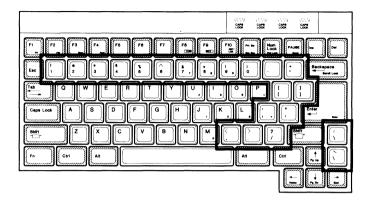

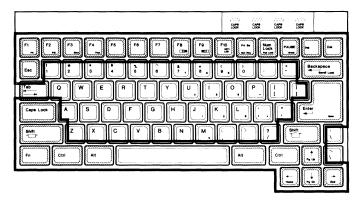

| 5-1.  | Keyboard Arrangement                  |

| 5-2.  | Keyboard Indicator LEDs               |

| 5-3.  | Alphanumeric Keys                     |

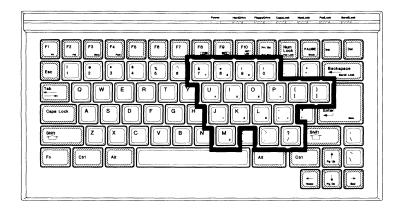

| 5-4.  | Control and Special Purpose Keys 5-6  |

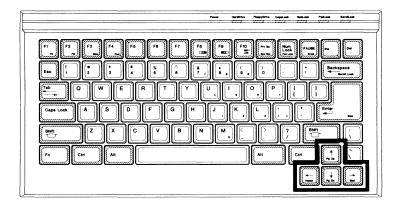

| 5-5.  | Cursor Control Keypad5-8              |

| 5-6.  | Numeric Keypad5-10                    |

| 6-1.  | Monitor Command Summary Menu 6-9      |

| 8-1.  | Keyboard                              |

| 8-2.  | Alphabetic Keys                       |

| 8-3.  | Numeric/Punctuation Keys 8-21         |

| 8-4.  | Function and Control Keys 8-22        |

| 9-1.  | Serial and Parallel Device Layout     |

| 11-1. | Character Design Matrix11-14          |

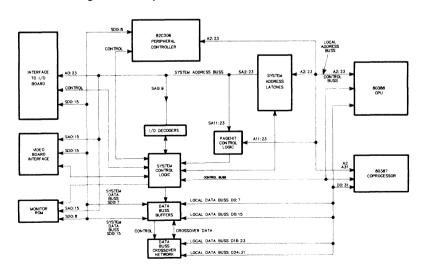

| 12-1. | CPU Block Diagram                     |

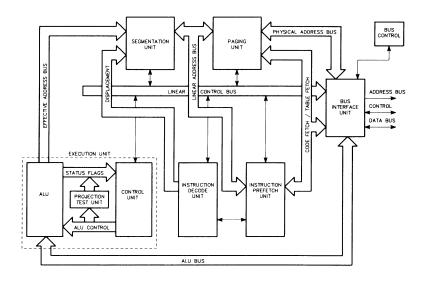

| 12-2. | 80386 Processor Architecture          |

| 12-3. | 80386 Internal Register Structure     |

| 12-4. | 80386 Flags Register                  |

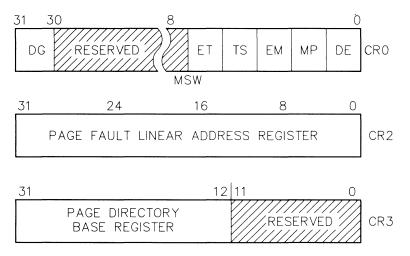

| 12-5. | 80386 Control Registers               |

| 12-6. | 80386 System Segment Registers        |

| 12-7. | 80386 Debug and Test Registers12-16   |

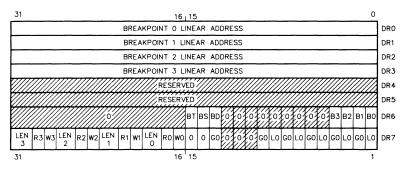

| 12-8. | 80386 Debug Registers                 |

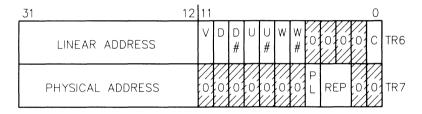

| 12-9. | 80386 Test Registers                  |

| 12-10 |                                       |

| 12-11 | <b>5</b>                              |

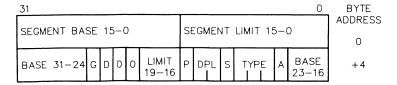

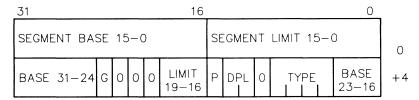

| 12-12 | . Segment Descriptor Format           |

| 12-13.                      |                                                                         |      |

|-----------------------------|-------------------------------------------------------------------------|------|

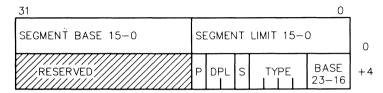

| 12-14.                      | System Segment Descriptor Format                                        | 2-48 |

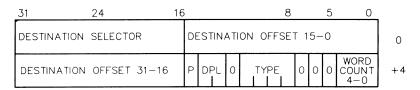

| 12-15.                      | Gate Descriptor Format                                                  | 2-49 |

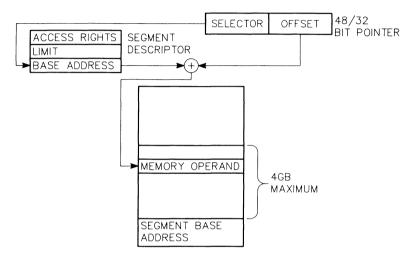

| 12-16.                      | Protected Mode Addressing                                               | 2-51 |

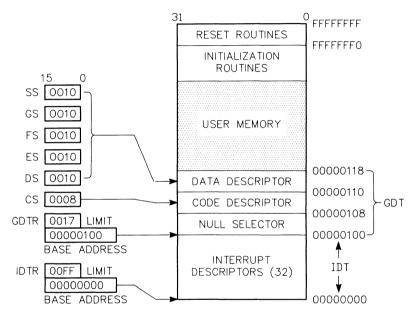

| 12-17.                      | Protected System Model                                                  | 2-52 |

| 12-18.                      |                                                                         |      |

| 12-19.                      |                                                                         |      |

| 12-20.                      | •                                                                       |      |

| 12-21.                      |                                                                         |      |

| 13-1.                       | 80387 Block Diagram                                                     | 13-2 |

| 13-1.<br>13-2.              | 80387 Status Word Format                                                |      |

| 13-2.                       | 80287 Control Word Format                                               |      |

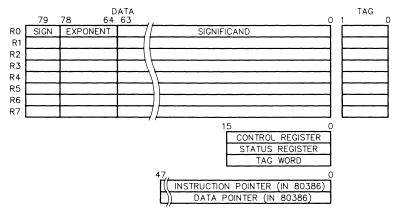

| 13-3.<br>13-4.              | 80387 Registers                                                         |      |

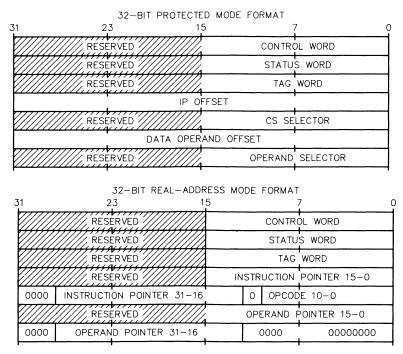

| 13-5.                       | 32-Bit Format Register Differences                                      |      |

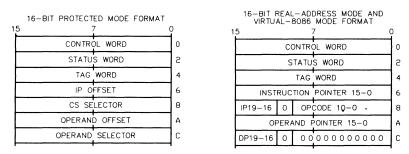

| 13-6.                       | 16-Bit Format Register Differences                                      |      |

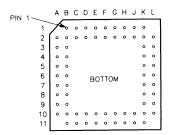

| 13-0.<br>13-7.              | 80387 Device Pinout                                                     |      |

| 10 7.                       | Occor Bevice i modt                                                     | 0 10 |

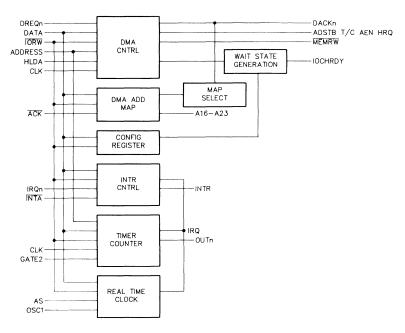

| 14-1.                       | 82C206 Integrated Peripherals Controller                                |      |

| 440                         | Block Diagram                                                           |      |

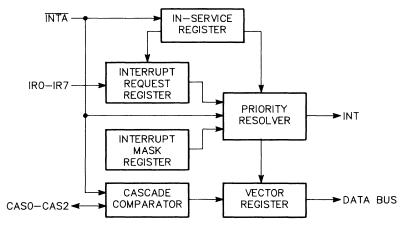

| 14-2.<br>14-3.              | Interrupt Controller Block Diagram                                      |      |

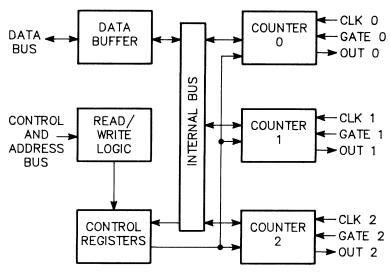

| 14-3.<br>14-4.              | Programmable Counter/Timer Block Diagram 1 DMA Controller Block Diagram |      |

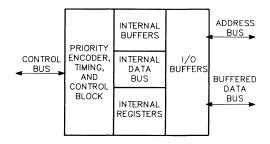

| 14-4.<br>14-5.              | Real-Time Clock Block Diagram                                           |      |

| 14-5.<br>14-6.              | Internal Address Map                                                    |      |

| 14-0.<br>14-7.              | Real Time Clock Status Registers                                        |      |

| 1 <del>4</del> -7.<br>14-8. | 82C206 Integrated Peripheral Controller Pinout 1                        |      |

| 14-0.<br>14-9.              | Keyboard Data Format                                                    |      |

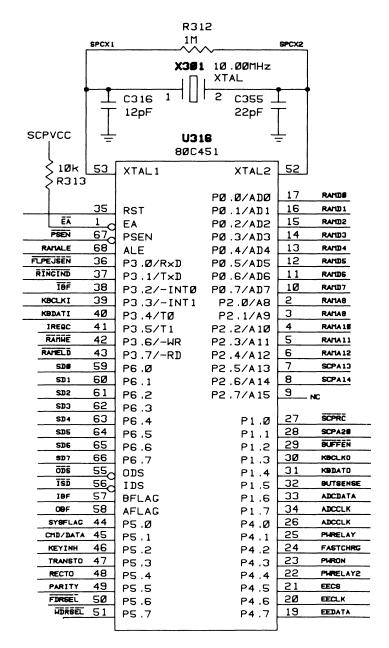

| 14-3.<br>14-10.             | SCP Pinout1                                                             |      |

| 14-10.                      | Ool Finout.                                                             | 7 00 |

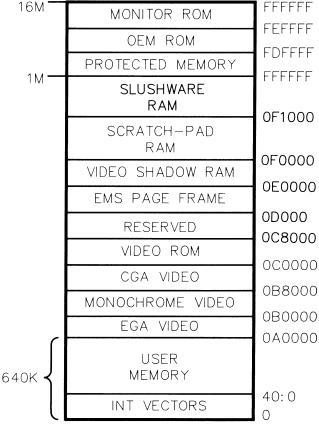

| 15-1.                       | Memory Map                                                              | 15-1 |

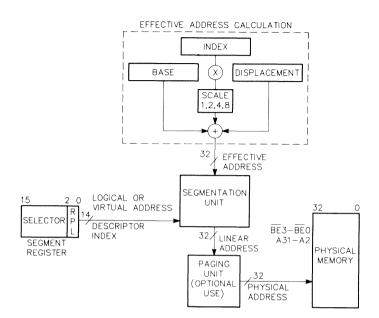

| 15-2.                       | 80386 Address Translation Process                                       | 15-4 |

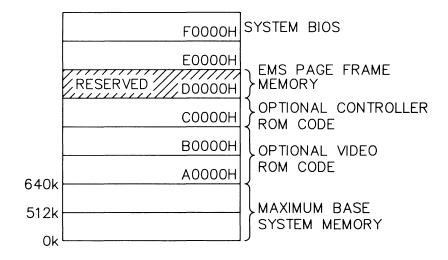

| 15-3.                       | Conventional Memory                                                     |      |

| 15-4.                       | Expanded Memory                                                         |      |

| 16-1.                       | 765 Disk Controller Block Diagram                                       | 16-3 |

| 16-2.                       | 3765 FDC Pinout                                                         |      |

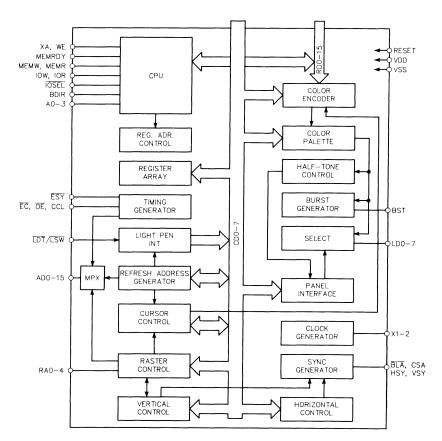

| 17-1.                       | Video Block Diagram                                                     | 17-1 |

| 17-2.                       | V6366 Controller Block Diagram                                          |      |

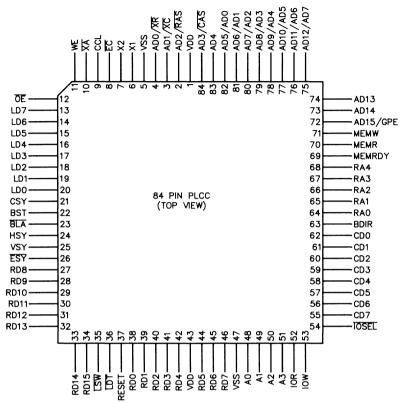

| 17-3.                       | V6366 Pinout                                                            | 7-32 |

#### Page **xiv**

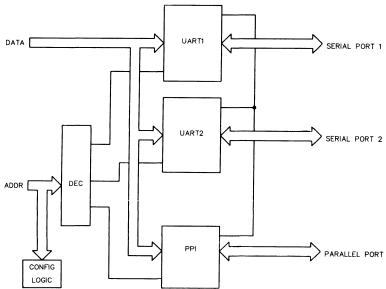

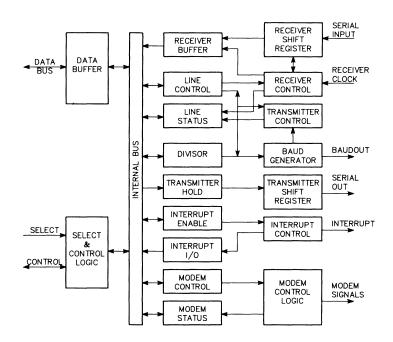

| 18-1.<br>18-2.<br>18-3.<br>18-4.<br>18-5.                                              | General Design of the 82C60518-1UART Block Diagram18-3Serial Connector Pin Locations18-13Parallel Connector Pin Locations18-1582C605 Pin Locations18-17 |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19-1.                                                                                  | Test Menu19-2                                                                                                                                           |

| Table                                                                                  | s                                                                                                                                                       |

| 2-1.<br>2-2.<br>2-3.<br>2-4.<br>2-5.                                                   | Video Connector Pinout2-3Serial Connector Pinout2-4Parallel Connector Pinout2-4Expansion Connector Pinout2-5Power LED Indications2-11                   |

| 5-1.<br>5-2.<br>5-3.                                                                   | Keypad Results5-11Keyboard-Selectable Modes5-13Key Combinations5-14                                                                                     |

| 6-1.<br>6-2.<br>6-3.<br>6-4.<br>6-5.<br>6-6.<br>6-7.<br>6-8.<br>6-9.<br>6-11.<br>6-12. | ZBIOS Functions                                                                                                                                         |

| 7-1.<br>7-2.                                                                           | CPU Interrupts                                                                                                                                          |

| 7-3.<br>7-4.<br>7-5.<br>7-6.<br>7-7.<br>7-8.                                           | Interrupt 15H Functions                                                                                                                                 |

| 7-9.           | INT 15 Extended Functions                   |

|----------------|---------------------------------------------|

| 7-10.          | INT 1AH Functions                           |

| 8-1.           | Keyboard Interrupts                         |

| 8-2.           | INT 16H Functions                           |

| 8-3.           | Keyboard Status Report                      |

| 8-4.           | Keyboard Status (0040:0018) 8-6             |

| 8-5.           | Repetition Rates8-6                         |

| 8-6.           | Keyboard Status Report (Register AL)8-8     |

| 8-7.           | Keyboard Status Report (Register AH)8-9     |

| 8-8.           | Alphabetic Keycode Sets 8-10                |

| 8-9.           | Numeric and Punctuation Keycode Sets 8-11   |

| 8-10.          | Function and Control Key Keycode Sets 8-12  |

| 8-11.          | 101-Key Keyboard-Compatible Screen Control  |

|                | Keycode Sets                                |

| 8-12.          | Numeric Key Keycode Sets 8-16               |

| 8-13.          | Alphabetic Key Scan Codes (AT Mode) 8-19    |

| 8-14.          | Numeric/Punctuation Key Scan Codes 8-21     |

| 8-15.          | Function and Control Keys8-22               |

| 8-16.          | Function and Control Key Scan Codes8-26     |

| 8-17.          | Make/Break Key Codes                        |

| 0.4            | UO latamenta                                |

| 9-1.           | I/O Interrupts                              |

| 9-2.           | Serial Device Function Codes                |

| 9-3.           | Mode-Select Byte Breakdown                  |

| 9-4.           | Word Length Selection                       |

| 9-5.           | Parity Selection                            |

| 9-6.           | Baud Rate Selection                         |

| 9-7.           | Line Control Status (Register AH)           |

| 9-8.           | Modern Control Status (Register AL)         |

| 9-9.           | Parallel Device Function Codes              |

| 9-10.          | Parallel Map Format                         |

| 9-11.          | Serial Map Format                           |

| 9-12.<br>9-13. | Serial Byte #1 Breakdown9-9                 |

| 9-13.<br>9-14. | Serial Byte #2 Breakdown                    |

| 9-14.          | Serial Byte #7 Breakdown                    |

| 10-1.          | Disk Drive Interrupts10-1                   |

| 10-2.          | Disk Drive Function Codes                   |

| 10-3.          | Drive Identification Codes                  |

| 10-4.          | INT 13H and INT 40H Error Status Codes 10-6 |

#### Page **xvi**

| 10-5.  | CPU Register Initialization — Function Codes          |

|--------|-------------------------------------------------------|

|        | 02H - 04H and 0AH - 0BH                               |

| 10-6.  | CPU Register Initialization — Function Code 05H 10-10 |

| 10-7.  | CPU Register Results — Function Code 08H 10-11        |

| 10-8.  | CPU Register Initialization — Function Code 0CH 10-13 |

| 10-9.  | CPU Register Results — Function Code 10H 10-14        |

| 10-10. | CPU Register Initialization — Function Code 11H 10-15 |

| 10-11. | ROM Disk Parameters                                   |

| 10-12. | Drive Parameters — INT 1EH 10-20                      |

| 10-13. | Floppy Disk Parameters                                |

| 10-14. | Hard Disk Parameters                                  |

| 11-1.  | Video Interrupts                                      |

| 11-2.  | Video Input/Output Function Codes                     |

| 11-3.  | Video Modes                                           |

| 11-4.  | Palette and Pixel Colors                              |

| 11-5.  | Row Specifier Options                                 |

| 11-6.  | Register Values to Return Information                 |

|        | for Function Code 11H11-10                            |

| 11-7.  | EGA Information Returned by Function Code 12H11-10    |

| 11-8.  | Register, String, and Cursor Data                     |

|        | for Function Code 13H11-11                            |

| 11-9.  | Video Initialization Default Values                   |

| 11-10. | Monochrome Video Modes                                |

| 11-11. | Normal Color Video Modes                              |

| 11-12. | Enhanced Color Video Modes                            |

| 11-13. | Monochrome Attribute Byte Characteristics 11-19       |

| 11-14. | Color Attribute Byte Characteristics                  |

| 11-15. | Color Selection                                       |

| 11-16. | Palette Colors                                        |

| 11-17. | Mode F Attributes                                     |

| 11-18. | Mode 10 Memory Plane Assignments 11-23                |

| 11-19. | Mode 10 Base Colors                                   |

| 11-20. | Palette Register Color Attributes                     |

| 12-1.  | 80386 Register Usage                                  |

| 12-2.  | 80386 Internal Registers                              |

| 12-3.  | 80386 Flag Definitions                                |

| 12-4.  | Register CR0 Bit Definitions12-13                     |

| 12-5.  | Interrupt Priorities                                  |

| 12-6.  | 80386 Interrupt Vector Assignments 12-21              |

| 12-7.  | DR6 Register Definitions 12-23                        |

| 12-8.  | Register DR7 Bit Definitions               | 12-24 |

|--------|--------------------------------------------|-------|

| 12-9.  | Test Bit Definitions                       | 12-27 |

| 12-10. | Page Directory/Page Table Entries          | 12-40 |

| 12-11. | Page Fault Error Code Bits                 | 12-43 |

| 12-12. |                                            | 12-46 |

| 12-13. | System Segment Type                        | 12-48 |

| 12-14. | Device Pinout Grouped by Function          | 12-61 |

| 12-15. | Device Pinout Grouped by Connection        | 12-62 |

| 12-16. | A0, A1 Address Line Generation             | 12-63 |

| 12-17. | Data Duplication as a Function of the Byte |       |

|        | Enable Lines                               | 12-64 |

| 12-18. | Bus Cycle Definition                       | 12-65 |

| 13-1.  | 80387 Status Word Bit Definitions          | 13-4  |

| 13-2.  | 80387 Condition Codes                      | 13-6  |

| 13-3.  | 80387 Quotient Results                     | 13-7  |

| 13-4.  | 80287 Control Word Bit Definitions         | 13-8  |

| 13-5.  | 80387 Pinout by Function                   | 13-13 |

|        |                                            |       |

| 14-1.  | Interrupt Line Assignments                 |       |

| 14-2.  | Initialization Command Word 1 (020H, 0A0H) |       |

| 14-3.  | Initialization Command Word 2 (021H, 0A1H) |       |

| 14-4.  | Initialization Command Word 3 (021H, 0A1H) |       |

| 14-5.  | Initialization Command Word 4 (021H, 0A1H) | 14-14 |

| 14-6.  | Operation Command Word 2 (020H, 0A0H)      |       |

| 14-7.  | Operational Function Definition Bits 5-7   |       |

| 14-8.  | Operation Command Word 3 (020H, 0A0H)      | 14-16 |

| 14-9.  | Control Word Bit Definitions (043H)        | 14-18 |

| 14-10. |                                            |       |

| 14-11. |                                            |       |

| 14-12. | Timer Read and Write Operations            | 14-23 |

| 14-13. | DMA Controller Registers                   | 14-26 |

| 14-14. | <b>5</b> ****                              |       |

| 14-15. | <b>5</b>                                   |       |

| 14-16. |                                            | 14-32 |

|        | Mask Register                              |       |

| 14-18. |                                            |       |

| 14-19. |                                            |       |

| 14-20. |                                            |       |

|        | Periodic Interrupt Time Interval Options   |       |

| 14-22. |                                            |       |

| 14-23. |                                            |       |

| 14-24. | Time, Calendar, and Alarm Data Modes       | 14-45 |

|        |                                            |       |

#### Page **xviii**

| . 14-55                                            | Pin Descriptions                                |                                                          |

|----------------------------------------------------|-------------------------------------------------|----------------------------------------------------------|

|                                                    |                                                 |                                                          |

| 14-56                                              | SCP Status Register Bit Definitions             |                                                          |

|                                                    | SCP Command Codes                               |                                                          |

|                                                    | SCP Command Byte Description                    |                                                          |

| . 14-59                                            | Zenith Extended Commands                        | 14-29.                                                   |

| . 14-66                                            | 80C451 SCP Pinout                               | 14-30.                                                   |

| 15-9                                               | EMS I/O Addresses                               | 15-1.                                                    |

|                                                    | <b>5</b> . <b>5</b> . <b>6 15 5</b>             |                                                          |

|                                                    | Floppy Drive Control Register Port Addresses    | 16-1.                                                    |

|                                                    | Digital Output Register                         | 16-2.                                                    |

|                                                    | Drive Select                                    | 16-3.                                                    |

|                                                    | Main Status Register                            | 16-4.                                                    |

|                                                    | Floppy Control Register                         | 16-5.                                                    |

|                                                    | Floppy Data Registers ST0-ST3                   | 16-6.                                                    |

|                                                    | 3765 FDC Signal Descriptions                    | 16-7.                                                    |

|                                                    | Floppy Disk Controller Commands                 | 16-8.                                                    |

|                                                    | Controller Command Bits                         | 16-9.                                                    |

| . 16-22                                            | Read Data Command                               | 16-10.                                                   |

| . 16-24                                            | Read Deleted Data Command                       | 16-11.                                                   |

| . 16-25                                            | Write Data Command                              | 16-12.                                                   |

| . 16-26                                            | Write Deleted Data Command                      | 16-13.                                                   |

| . 16-28                                            | Read a Track Command                            | 16-14.                                                   |

|                                                    |                                                 | 16-15.                                                   |

|                                                    |                                                 | 16-16.                                                   |

|                                                    |                                                 | 16-17.                                                   |

|                                                    | · · · · · · · · · · · · · · · · · · ·           | 16-18.                                                   |

|                                                    |                                                 | 16-19.                                                   |

| . 16-35                                            | Recalibrate Command                             | 16-20.                                                   |

| . 16-36                                            | Sense Interrupt Status Command                  | 16-21.                                                   |

| . 16-36                                            | Specify Command                                 | 16-22.                                                   |

| . 16-37                                            | Drive Status Command                            | 16-23.                                                   |

| . 16-37                                            | Seek Command                                    | 16-24.                                                   |

| . 16-38                                            | Hard Disk Drive Control Register Port Addresses | 16-25.                                                   |

|                                                    |                                                 | 16-26.                                                   |

|                                                    |                                                 | 16-27.                                                   |

|                                                    | ·                                               | 16-28.                                                   |

|                                                    |                                                 | 16-29.                                                   |

|                                                    | Command Register Coding                         | 16-30.                                                   |

|                                                    | Seek and Restore Step Rate Codes                |                                                          |

| . 16-47                                            | Fixed Disk Register Codes                       |                                                          |

| . 16-48                                            |                                                 | 16-33.                                                   |

| . 16-<br>. 16-<br>. 16-<br>. 16-<br>. 16-<br>. 16- | Seek Command                                    | 16-24.<br>16-25.<br>16-26.<br>16-27.<br>16-28.<br>16-29. |

|        | Format Track Command Track Layout16-52                |

|--------|-------------------------------------------------------|

| 16-35. | 2 to 1 Sector Interleave                              |

| 17-1.  | Video Output/Input Port Addresses                     |

| 17-2.  | 6845-Compatible Registers                             |

| 17-3.  | Cursor Display Modes                                  |

| 17-4.  | Video Mode Register Bit Descriptions 17-8             |

| 17-5.  | Color Palette Register Bit Descriptions               |

| 17-6.  | Status Register/Extended Port Bit Descriptions 17-10  |

| 17-7.  | Additional V6366 Registers                            |

| 17-8.  | Color Palette Control                                 |

| 17-9.  | Display Mode Register Bit Descriptions 17-15          |

| 17-10. | Register A Bit Functions17-16                         |

| 17-11. | Register B Bit Descriptions17-18                      |

| 17-12. | Register C Bit Descriptions17-19                      |

| 17-13. | Register D Bit Descriptions17-20                      |

| 17-14. | Register E Bit Descriptions17-22                      |

| 17-15. | Register F Bit Descriptions                           |

| 17-16. |                                                       |

|        | Bit Descriptions17-25                                 |

| 17-17. | Underline/Double-Scan Register Bit Descriptions 17-26 |

| 17-18. | Control/ID Register Bit Descriptions 17-27            |

| 17-19. | V6366 Video Controller Pin Functions                  |

| 18-1.  | Serial Channel Register Ports                         |

| 18-2.  | Baud Rate and Divisor Latch Values 18-6               |

| 18-3.  | Serial Port Interrupts                                |

| 18-4.  | Line Control Register                                 |

| 18-5.  | Modem Control Register                                |

| 18-6.  | Line Status Register Report                           |

| 18-7.  | Modem Status Register Report                          |

| 18-8.  | Serial Connector Signals                              |

| 18-9.  | Parallel Connector Signals                            |

| 18-10. | 82C605 Signal Names by Pin Number18-18                |

| 18-11. | 82C605 Pins by Signal Name                            |

#### Page **xx**

# Part I Introduction

# Chapter 1 Introduction and General Information

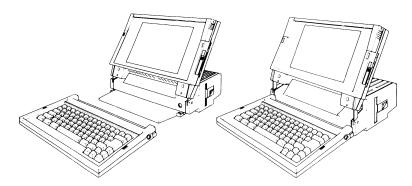

The High-Performance TurbosPort 386, illustrated in Figure 1-1, offers increased computing power while maintaining compatibility with earlier PC's. Some of the features of this computer are:

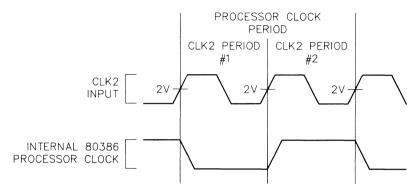

- An Intel 80386 microprocessor operating at 12 or 6 Mhz

- Optional support for the 80387 coprocessor

- A 79-key keyboard with an integrated numeric keypad that can emulate a 101-key advanced keyboard

- 2M of system memory

- Optional memory expansion up to 3M

- Internal hardware support for EMS memory

- CGA video support

- High-density 3.5-inch floppy disk drive and 40M hard disk drive

- 640 x 400 pixel black-on-white flat panel liquid crystal display

- · Fluorescent backlighting.

Figure 1-1. TurbosPort 386 Portable Computer

#### **Manual Description**

This manual contains information on computer operation and programming methods. It is a companion manual for the *MS-DOS Programmer's Utility Pack* (CB-3163-30). Refer to the Owner's Manual for this computer for explanations of commonly used acronyms and terms.

This technical manual contains the following parts, plus an appendix, and an index:

- Part I contains an introduction to the computer, including information on installation, system configuration, operation, and disassembly.

- Part II describes system programming. This includes the Monitor program and the software-based interrupts common to PCcompatible computers.

- Part III provides information on the base configuration and the hardware used to implement that configuration. This includes a discussion of each major programmable integrated circuit in the computer. Part III also includes a chapter on common problems and how to resolve them.

- The Appendix contains the instruction sets for the CPU and coprocessor.

#### **Related Publications**

Several available publications contain information related to the topics discussed in this manual. This material may be helpful in increasing your knowledge and understanding of this computer.

TurbosPort 386 Portable Computer Owner's Manual (595-4063)

— This manual describes the installation and operation of the computer from a user's point of view. It also includes a brief discussion of the hardware, configuration, and maintenance.

Intel Introduction to the 80386 — This manual, published by the Intel Corporation, provides an overview and introduction to the 80386 microprocessor. The Intel order number for this publication is 231252.

Intel Microsystems Component Handbook, Vol. 1 & 2 — These manuals, published by Intel Corporation, provide information on the architecture and programming of the 80287 and 80387 coprocessors. They also contain information relating to system support circuitry and microprocessors. The Intel order number for this set is 230843-004.

Intel 80386 Programmer's Reference Manual — This manual, published by Intel Corporation, contains detailed information on the architecture, instruction set, and programming procedures required for the 80386 microprocessor. The Intel order number for this manual is 230985-001.

Intel 80386 Hardware Reference Manual — This manual, published by the Intel Corporation, contains detailed descriptions of the architecture and operation of the 80386 microprocessor. Device timing diagrams and pinouts are also included in this manual. The Intel order number for this publication is 231732-001.

Lotus/Intel Expanded Memory Device Interface Specification—This publication is available directly from Intel Corporation. This specification details the software and hardware interface for EMS memory systems. Intel Technical Support provides a toll free number, 1-800-538-3373, that you may call to obtain this specification.

Intel publications may be obtained by writing to the following address:

Intel Literature Sales P.O. Box 58130 Santa Clara, CA 95052-8130

Intel also provides a toll-free number (1-800-548-4725) for literature requests.

**MS-DOS Programmer's Utility Pack (CB-3163-30)** — This software package, produced by Microsoft and Zenith Data Systems, contains information and software for writing and assembling MS-DOS and native 8086, 8088, 80286, and 80386 assembly language programs.

#### **Recommended Environment**

Most computers will operate over a wide range of environmental conditions; temperature and humidity most affect the way a computer operates. In general, always be aware of the published specifications for the equipment you are trying to use. Unusual applications may require you to contact the manufacturer for information. The TurbosPort 386 is designed to meet working conditions in the average business office, at home, or "on the road." Use these guidelines to maintain a proper operating environment for your computer:

- Keep the computer away from sources of heat, including direct sunlight.

- Keep the computer away from moisture sources that might cause liquid to come into contact with the computer. Do not allow drinks or other liquids in the work area.

- Place the computer in an area that allows free air flow around the computer. Restricted ventilation around the computer can result in overheating problems.

- Computers are extremely sensitive to dust and dirt particles.

Consider using protective covers whenever the computer is not in operation.

- Computers and floppy disks are also sensitive to electromagnetic radiation. The work area should be free of potential sources of high electromagnetic emissions. Keep floppy disks at least two feet from telephones and associated wiring.

Computers can be sensitive to mechanical shock and external vibrations. Place the computer on a secure work surface that is free from vibration. Always place dot-matrix and daisy wheel printers on separate printer stands. These devices are vibration sources and it is best to isolate them from the computer.

#### **Memory Expansion**

The basic computer comes with 2M of installed memory. The maximum internal memory for the computer is 3M. Additional expansion memory can be added by installing optional EMS memory cards in an external expansion chassis.

#### Coprocessors

Coprocessors are integrated circuits that increase performance in a specific area. An optional math coprocessor is available for this computer: the 80387. Intel refers to this device as a "numeric processor extension." This term, and the term "coprocessor" refer to the same type of device in this manual. This device provides increased performance on computation-intensive operations.

#### **Video Options**

The basic computer provides direct support for CGA video operation. This enhanced level video system provides screen resolution of 640 x 400 pixels double scan (640 x 200) with up to eight gray scales selectable from eight palettes. By attaching an external RGBI color monitor to the video connector, 16 colors from a palette of 64 are available. Other video options are available by installing optional video cards in the external expansion chassis.

#### **Mass Storage**

The term "mass storage" refers to any means of storing large amounts of data. The basic computer provides one 3.5-inch microfloppy disk drive with a formatted capacity of 1.4M on high-density disks or 720K on double-density disks and one 3.5-inch hard disk drive with a formatted capacity of 40M.

#### **Specifications**

CPU

Processor: 80386, CMOS technology. Type: 32-bit internal/external.

Clock speed: 12 MHz or 6 MHz, keyboard and

program selectable.

Memory: 2M dynamic RAM, expandable to 3M.

Hardware support for EMS memory.

Display: Fluorescent backlit, black-on-white,

liquid crystal display. Text mode: 80 x 25 characters; 640 x 400 pixels. Graphics mode: double scan 640 x 200 pixels. PC-compatible in normal

text and graphics modes.

Sound: Miniature transducer.

Input/output

Serial port: Asynchronous serial RS-232C port

(AT- style DB-9 connector). One start bit; 7- or 8-bit word length; one or two stop bits; selectable baud rates of 110, 150, 300, 600, 1200, 2400, 4800, or 9600 baud; RD, CTS, DSR, CD signals recognized; TD, RTS, DTR control signals generated; half- or

full-duplex operation.

#### Introduction and General Information

Parallel port: Centronics-type parallel output port

(DB-25 connector).

Video: RGB (color) video with intensity

signals from a single 15-pin connector.

Disk drives: 3.5-inch double-sided, high-density

microfloppy disk drive, 1.4M formatted capacity per drive, 135 tpi, nine sectors per track. Write-protection

recognized.

3.5-inch hard disk drive, 40M capacity.

Keyboard: 79 keys. 101-key keyboard com-

patibility maintained by using multiple keys to duplicate keypad and special function key operation. Duplicate CTRL, ALT, and SHIFT keys, 4-key cursor

control pad. CAPS LOCK, SCROLL LOCK, PAD LOCK, and NUM LOCK keys use

status LEDs.

Power requirements

AC adapter/charger: Input: 95 to 132 VAC, 48 to 64 Hz.

Output: 25 to 29 VDC, 30 watts continuous, 500 mVpp maximum

ripple.

Battery power: 24 V (2.2 AHr) removable battery pack

with overcharge and short circuit protection. Battery life is 1000 charge/

discharge cycles.

#### Introduction and General Information

**Environment**

Operating: 60° - 85° F (16° - 30° C) at 20% - 80%

relative humidity (non-condensing).