Microdata

# Microprogramming Handbook

# Microprogramming Handbook

APRIL 1972 2nd Edition

Microdata

second Edition

# MICROPROGRAMMING HANDBOOK

## **Second Edition**

**Microdata**

TM

Microdata Corporation 644 East Young Street Santa Ana, California Copyright 1971 by Microdata Corporation 644 E. Young St. Santa Ana, California

Reissued 14 April 1972

PRINTED IN U.S.A.

### PART I

### MICROPROGRAMMED COMPUTER PRIMER

### **PART II**

# APPLICATION OF THE MICROPROGRAMMED COMPUTERS

PART III

MICRO 800 USERS MANUAL

**PART IV**

MICRO 1600 REFERENCE MANUAL

PART V

SYSTEM DESIGN PROCEDURES USING MICROPROGRAMMING

PART VI

PRODUCT CATALOG

### **FOREWORD**

This is the second edition of a handbook written and published by Microdata Corporation, which introduces the computer user to microprogramming and its advantages in computing and control applications. The book provides detailed instructions to the system designer for the most economical and efficient use of microprogramming technology.

Microprogrammable architecture permits development and production of a single system of compatible hardware which can be program-tailored to a wide range of requirements.

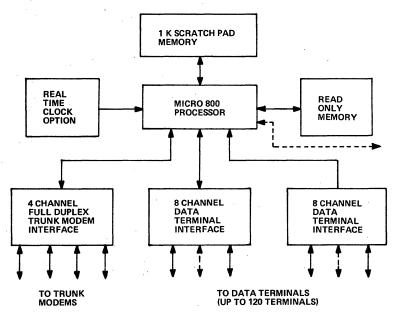

Microdata recognized and put to use the microprogramming concept at an early date. The company's MICRO 800 series of computers was introduced early in 1969, and the MICRO 1600 family more recently. The MICRO 1600 family builds on MICRO 800 technology, offering significant performance improvements at a lower cost.

This publication is offered as an aid to users and potential users of computers who intend to avail themselves of microprogramming. Comments and additions by readers who wish to help expand the growing body of knowledge in this field are encouraged and solicited by Microdata.

### **TABLE OF CONTENTS**

|         | Introduction                                                                               | 1                |

|---------|--------------------------------------------------------------------------------------------|------------------|

| PART I  | MICROPROGRAMMED COMPUTER PRIMER                                                            | 3                |

|         | Introduction                                                                               | 4                |

|         | Organization of the Microprogrammed Computer                                               | 4                |

|         | The Fixed Instruction Computer                                                             | 4                |

| ·.      | Arithmetic Unit                                                                            | 4<br>5<br>5      |

|         | The Microprogrammed Computer                                                               | 6                |

|         | Input/Output                                                                               | 6<br>7<br>7<br>7 |

|         | Cost and Performance Advantages of the Microprogrammed Computer                            | 8                |

|         | Comparison of a Microprogrammable Computer to a General Purpose Fixed Instruction Computer | 9                |

|         | Instruction Repertoire                                                                     | 9                |

|         | Instruction Speeds                                                                         | 0                |

|         | Glossary                                                                                   | 3                |

| PART II | APPLICATION OF THE MICROPROGRAMMED                                                         |                  |

| . ,     | COMPUTER                                                                                   | 7                |

|         | Introduction                                                                               | 8                |

|         | Classes of Application                                                                     | 8                |

|         | General Purpose Computers                                                                  | 1<br>7           |

|         |                                                                                            |                  |

|          | Application Examples                                                                                                | 59             |

|----------|---------------------------------------------------------------------------------------------------------------------|----------------|

|          | Automatic Test System Floating Point Processor (Special Purpose) Fast Fourier Transform Processor (Special Purpose) | 59<br>60<br>60 |

|          | Multilane Parking Facility Computer                                                                                 | 61             |

|          | Numerical Control of Vertical Machining Center                                                                      | 63             |

|          | Vibration Analyzer (Special Purpose)                                                                                | 64             |

|          | Interface for Campus Central Processor, Satellite Computers                                                         | 64             |

| PART III | MICRO 800 USERS MANUAL                                                                                              | 67             |

|          | Chapter 1. System Design Features                                                                                   | 69             |

|          | General Characteristics                                                                                             | 70             |

|          | System Organization                                                                                                 | 70             |

| tre.     | Registers and File                                                                                                  | 71             |

|          | Core Memory                                                                                                         | 73             |

|          | Control Memory                                                                                                      | 73             |

| -        | Arithmetic Functions                                                                                                | 74             |

|          | Status and Condition Flags                                                                                          | 78<br>79       |

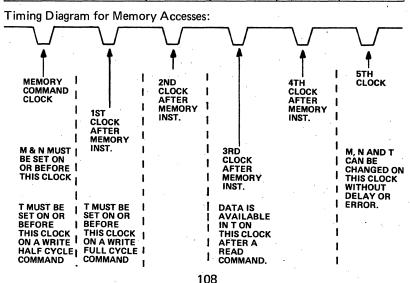

| •        | Command Timing                                                                                                      | ./9            |

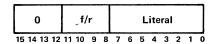

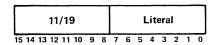

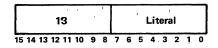

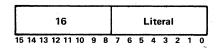

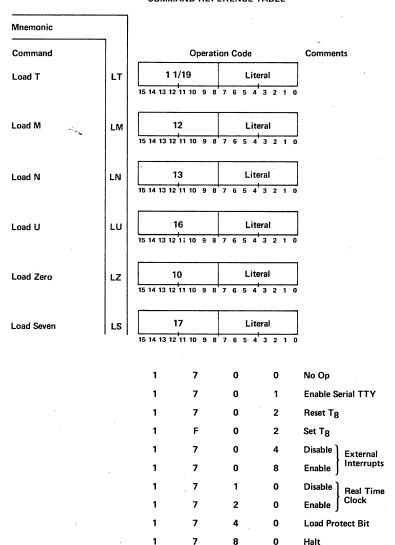

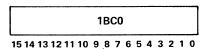

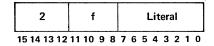

|          | Chapter 2. Microcommand Repertoire                                                                                  | 80             |

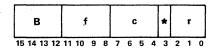

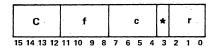

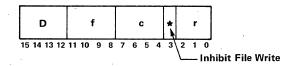

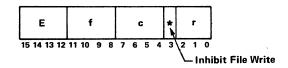

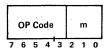

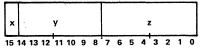

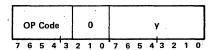

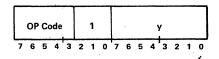

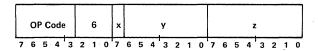

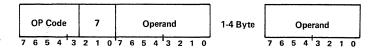

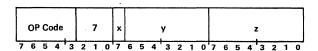

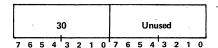

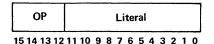

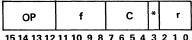

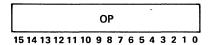

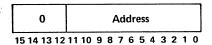

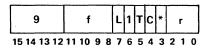

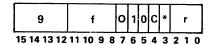

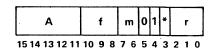

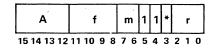

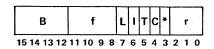

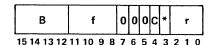

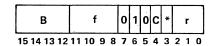

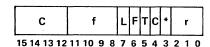

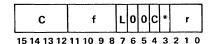

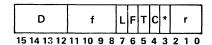

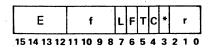

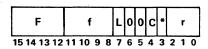

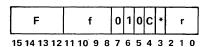

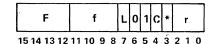

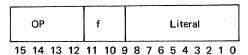

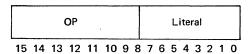

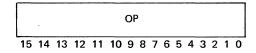

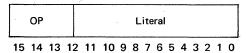

|          | Command Formats                                                                                                     | 80             |

| •        | Terms and Symbols Used in the Command                                                                               |                |

|          | Descriptions                                                                                                        | 82             |

|          | Microcommands—Formats, Descriptions and                                                                             | -00            |

|          | Examples                                                                                                            | 82             |

|          | Load T <sup>-</sup>                                                                                                 | 83             |

|          | Load M                                                                                                              | 83             |

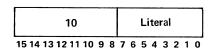

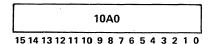

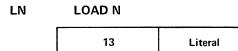

| •        | Load N                                                                                                              | 84             |

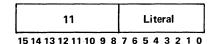

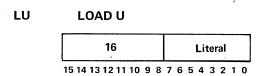

| •        | Load U                                                                                                              | 84             |

|          | Load Zero Control                                                                                                   | 85             |

| , .      | Load Seven Control                                                                                                  | 86             |

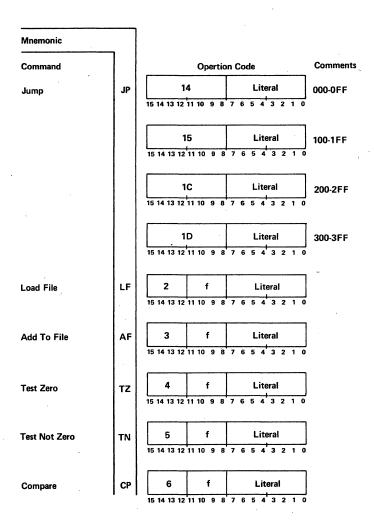

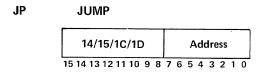

|          | Jump                                                                                                                | 87             |

|          | Load File                                                                                                           | 89             |

|          | Add to File                                                                                                         | 90             |

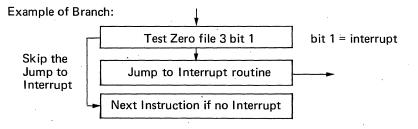

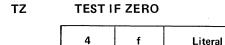

| -        | Test If Zero                                                                                                        | 91             |

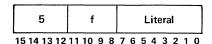

|          | Test If Not Zero                                                                                                    | 92             |

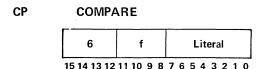

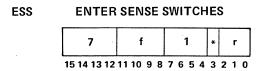

|          | Compare                                                                                                             | 94             |

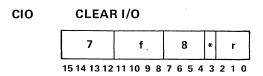

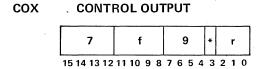

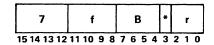

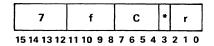

|          | Control                                                                                                             | 94             |

|          | Add                                                                                                                 | 101            |

|          | Subtract                                                                                                            | 104            |

|          | Read Memory, Write Memory                                                                                           | 106            |

|          | Copy                                                                                                                | 110            |

|          | OR                                                                                                                  | 112            |

|          | Exclusive OR                                                                                                        | 114            |

|          | AND                                                                                                                 | 116            |

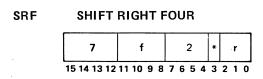

|          | Shift                                                                                                               | 118            |

|          | Execute                                                                                                             |                |

|     | CPU Microcommand Repertoire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C   | Chapter 3. Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

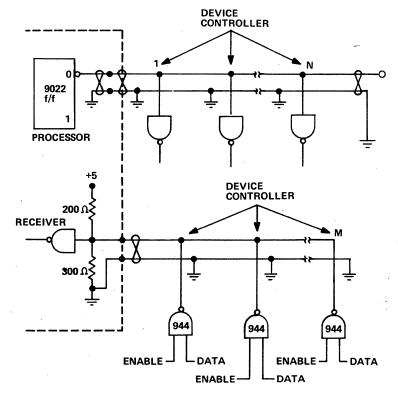

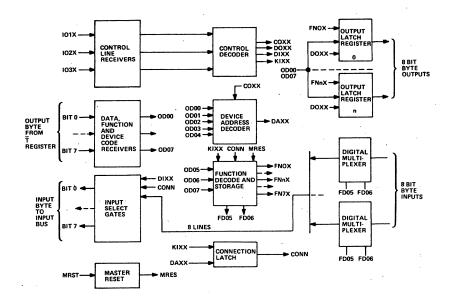

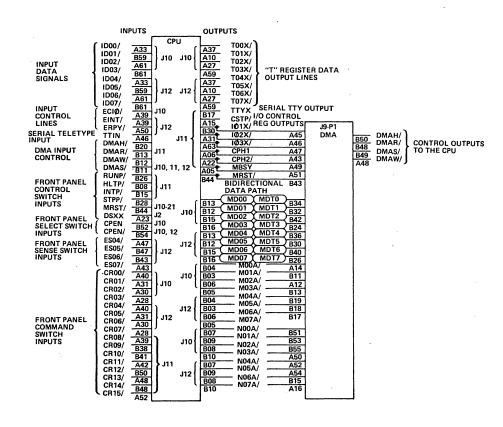

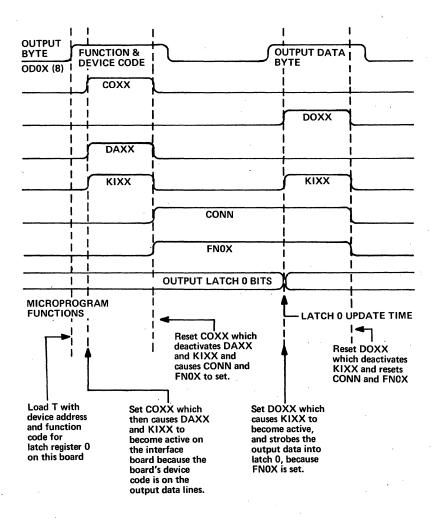

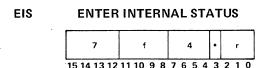

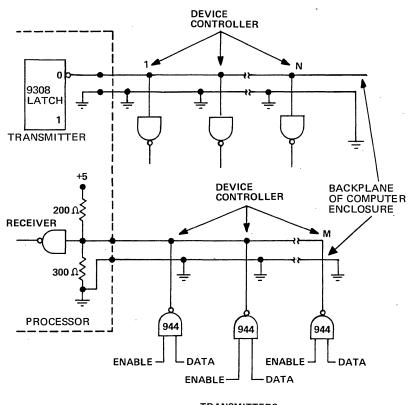

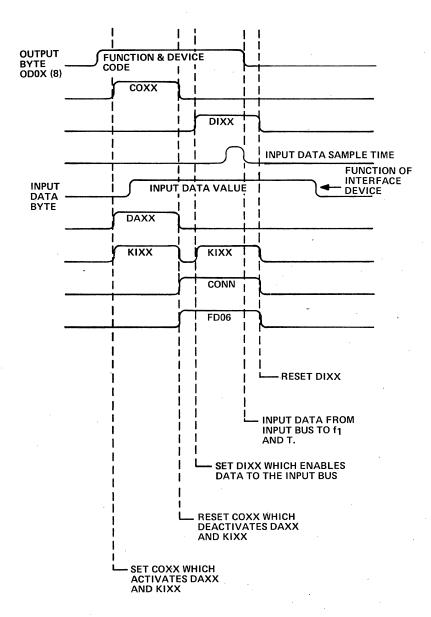

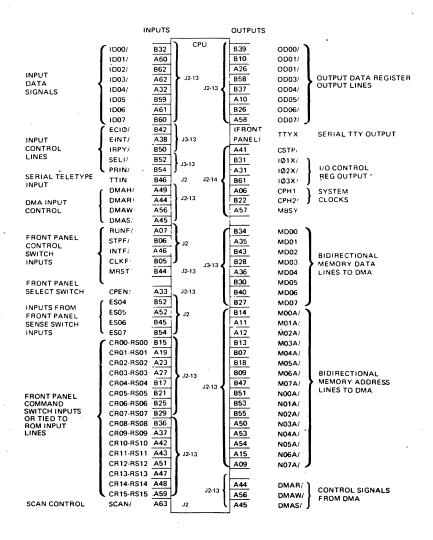

|     | Internal Status Interrupt       133         Bus Lines       133         Input Lines       133         Output Lines       135         Serial Interface       137         Direct Memory Access       137         Typical Byte I/O Interface       137                                                                                                                                                                                                                                                                                                                                                                                                        |

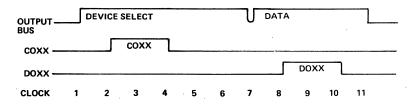

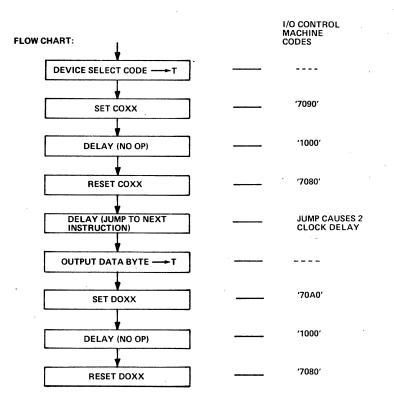

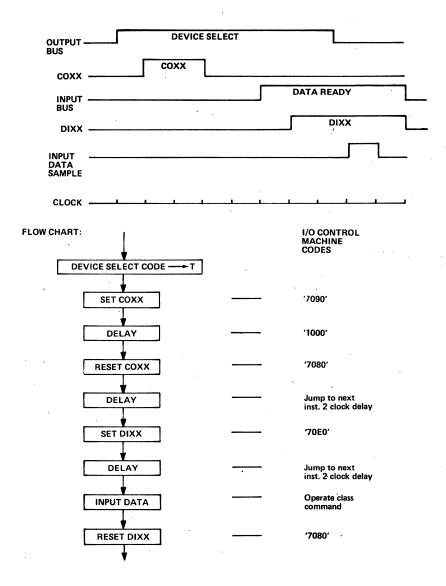

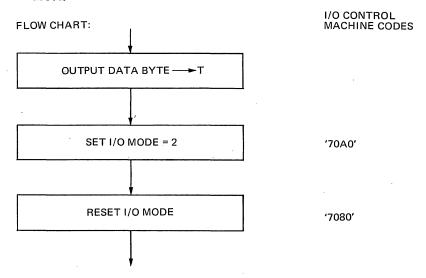

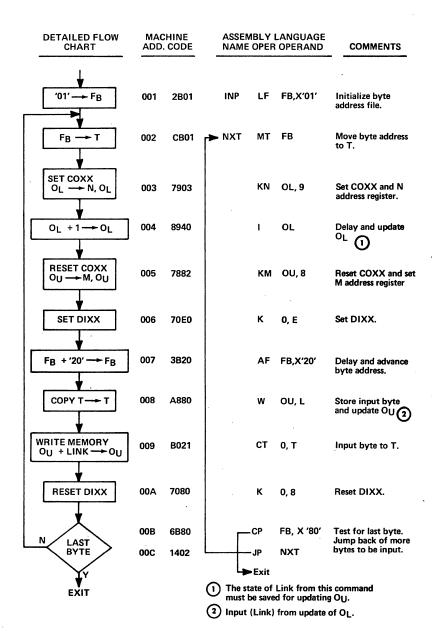

|     | Examples of I/O Microprogramming 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| C   | Chapter 4. Central Processor Options 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | Real-Time Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

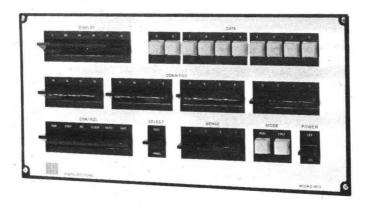

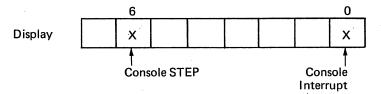

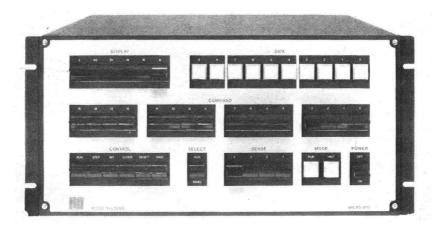

| C   | Chapter 5. Operator Controls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | Consoles       144         Displays       145         Switches       145         Operating Procedures — System Console       146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

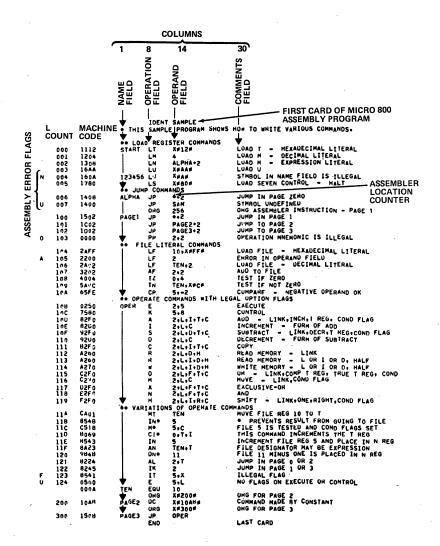

| · C | Chapter 6. Programming Systems for MICRO 800 Firmware Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

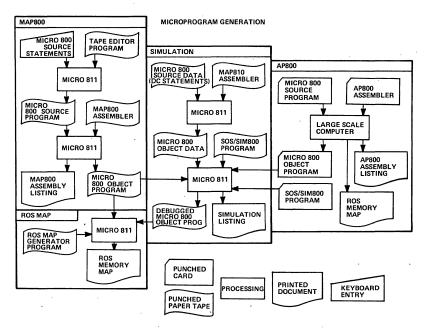

|     | AP800 Cross Assembler       153         MAP800 Cross Assembler       153         Symbolic Language       153         Machine Commands       155         Operand Field Expressions       155         Microcommands       156         Alphabetic List of Commands       157         Assembler Instructions       157         Assembly Listing and Diode Map       158         Format for AP800       158         Error Flags       159         Diode Map for AP800       159         Sample Listing       159         Operation Program Card Deck From AP800       163         Simulator Operating System (SOS) and       163         Introduction       163 |

|     | Instruction for Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | Alterable Read-Only Memory Operating System (AROS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | <b>,</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Progr<br>Sumr  | ators                                                                              | 176<br>177 |

|----------------|------------------------------------------------------------------------------------|------------|

| -              | Techniques and Examples                                                            | 188        |

| Techniq        | ues for Efficient Microprogramming                                                 | 188        |

| 1.             | Generation of delays for memory accesses, U Register Applications and input/output | 189        |

| 2.             | Double Functions on a Single Command                                               | 190        |

| 3.             | Uses, Setting and Testing Link                                                     |            |

| 4.             | Uses of the U Register                                                             | 190        |

| 5.             | Setting and Using Condition flags                                                  | 191        |

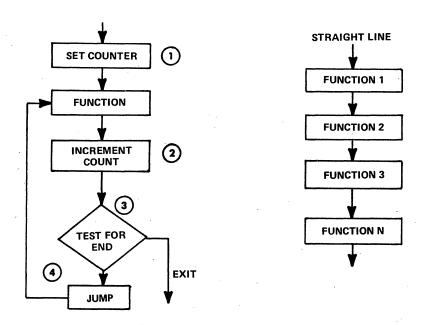

| 6.             | Use of Loops vs Straight Line Programming                                          | 192        |

| 7.             | Small General Purpose Subroutines                                                  | 193        |

| 8.             | Use of shift Right 4 Command                                                       | 193        |

| 9.             | Use of File Register for Flags, Counters, and                                      |            |

|                | Reference Data                                                                     | 193        |

| 10.            | Organization of Op Codes, File Register numbers, and Core Memory Addresses to      |            |

|                | minimize Commands                                                                  | 102        |

| 11.            | Saving of Diodes by Selection of Files and                                         | 193        |

| • • •          | Instructions                                                                       | 103        |

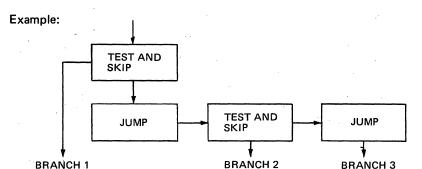

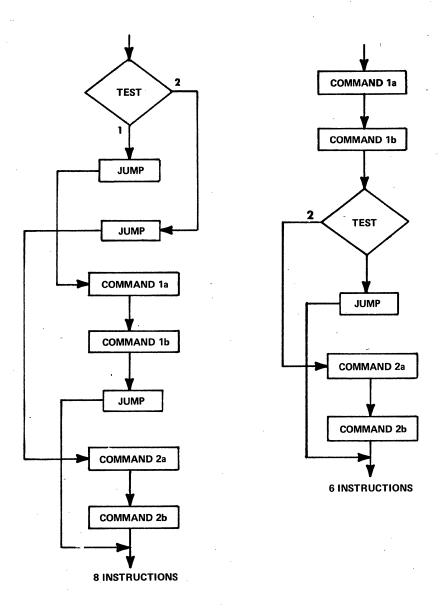

| 12.            | Saving Jump Instructions when Branching                                            | 10/        |

| 13.            | Reducing two Branches to one by Multi-                                             | 134        |

| 10.            | Function Commands                                                                  | 105        |

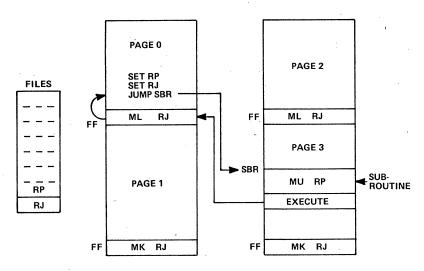

| 14.            | Interlacing vs. Cascading of Subroutines                                           | 196        |

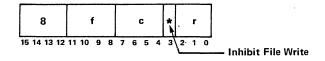

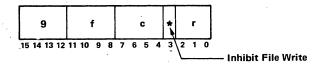

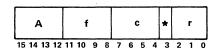

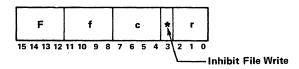

| 15.            | Use of Inhibit File Write                                                          | 196        |

| 16.            | Moving Data from a File to a Register                                              | 196        |

|                | ogramming Examples                                                                 |            |

|                |                                                                                    |            |

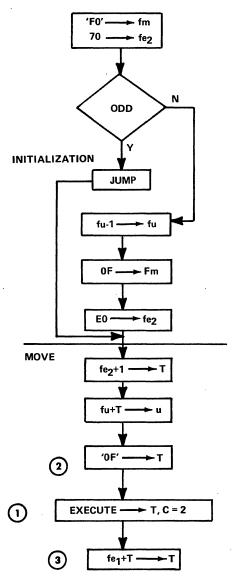

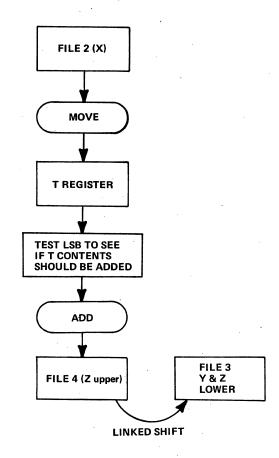

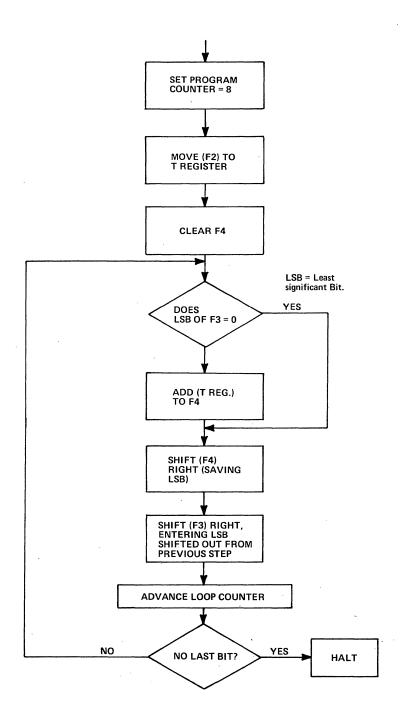

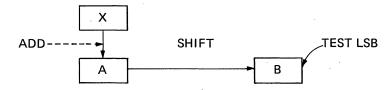

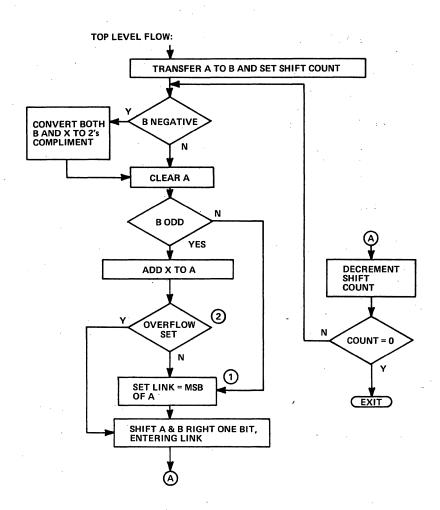

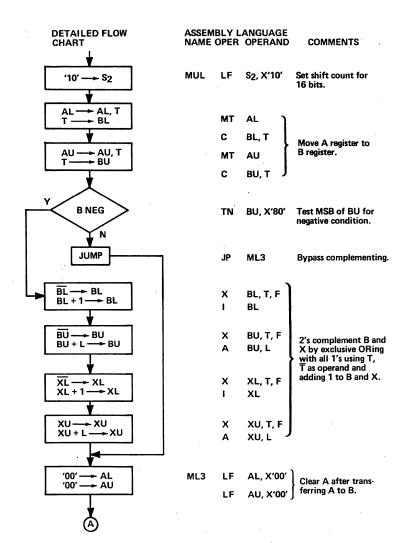

| 1.             | Multiply Two Positive Numbers                                                      | 198        |

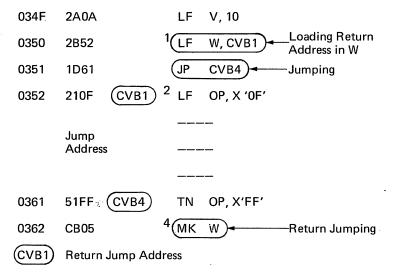

| 2.             | Subroutine Jumps                                                                   | 201        |

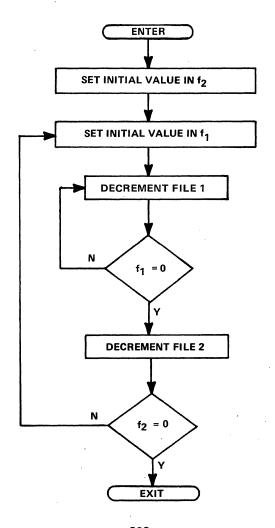

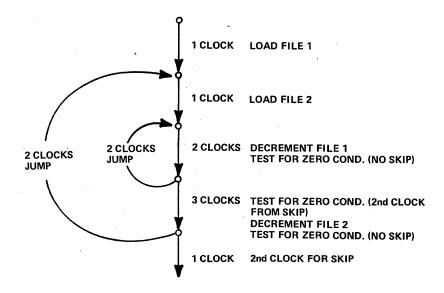

| 3.             | Time Delay Routine                                                                 |            |

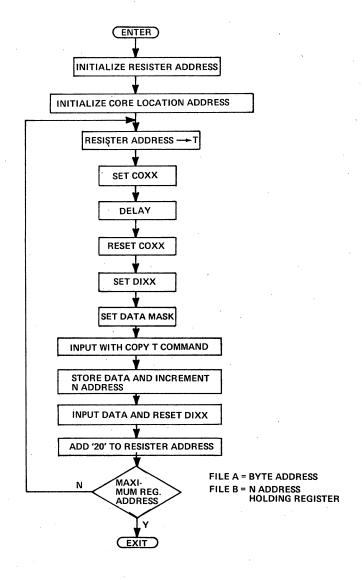

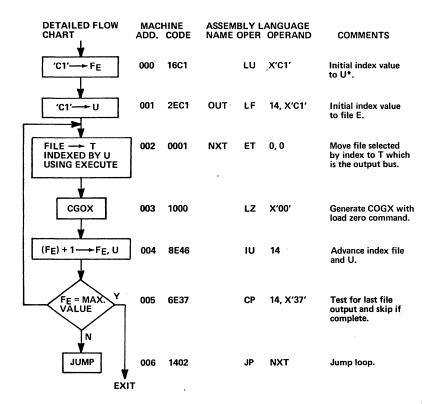

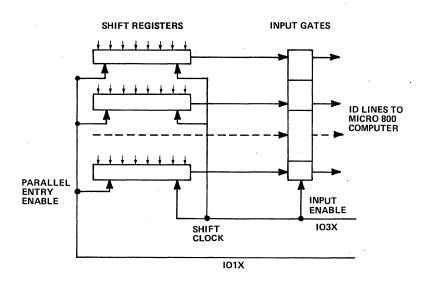

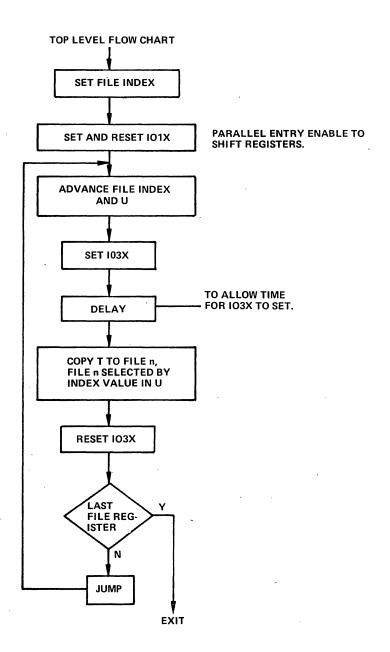

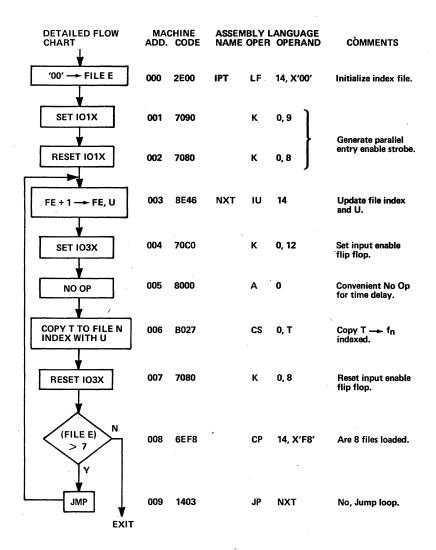

| 4.             | Data Input from 4 External Registers                                               | 206        |

| 5.             | Load 8 successive File Registers from 8                                            | 200        |

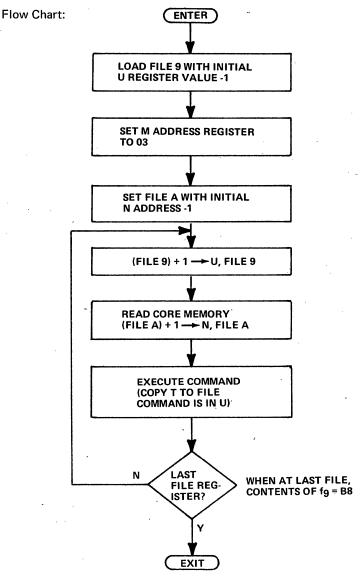

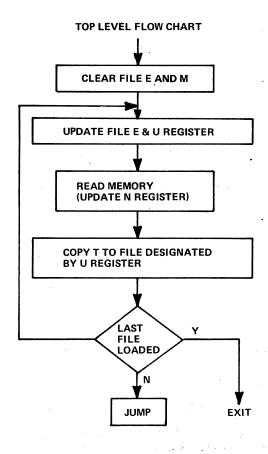

| ·              | successive core locations                                                          | 208        |

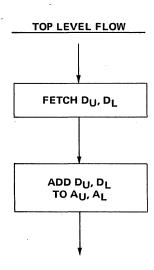

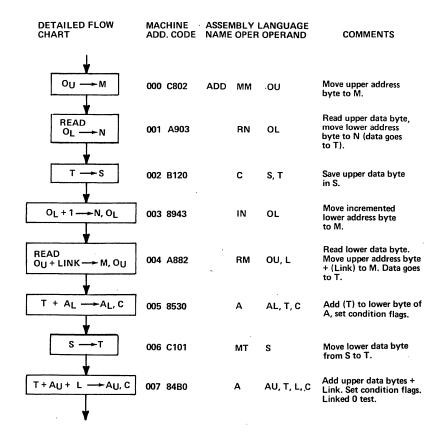

| 6.<br>7        | 16 Bit Add (Core to File)                                                          | 210        |

| 7.             |                                                                                    | 011        |

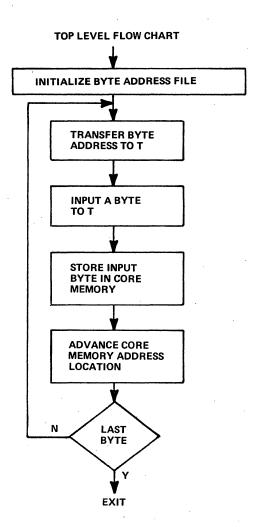

| 8.             | to Core Memory                                                                     | 211        |

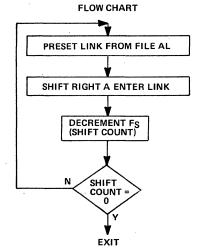

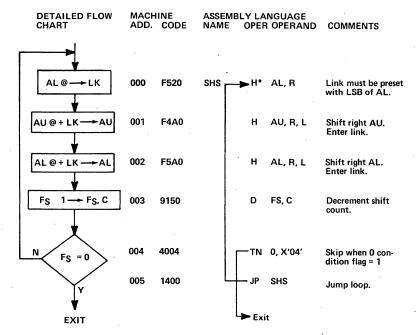

| <b>o.</b>      | 16 Bit Right Shift with End Around Carry with the Shift Count in File Register S   | 04.4       |

|                | A ORed with P to A                                                                 | 214        |

| 9.<br>10.      | A ORed with B to A                                                                 | 215        |

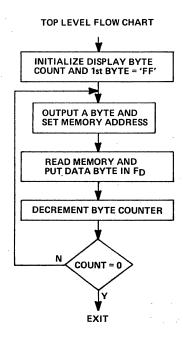

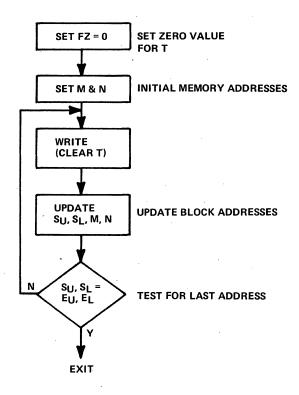

| 10.<br>11.     | Update 10 BCD Digit Display from Core                                              | 210        |

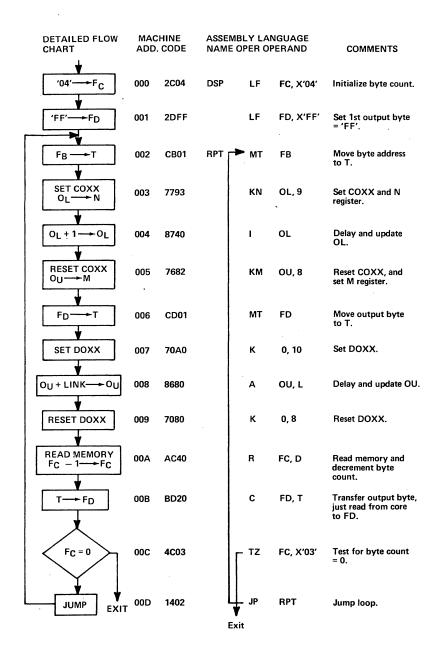

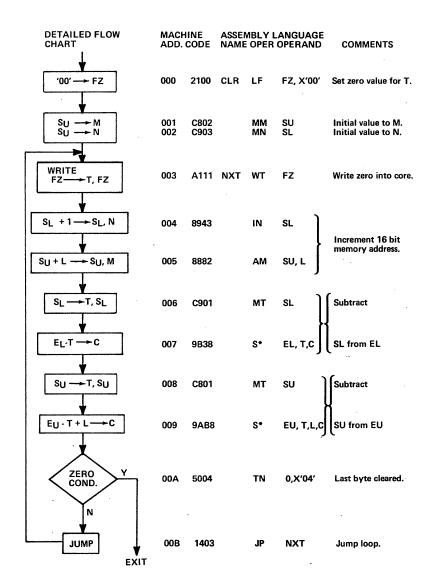

| 11.<br>12a.    | Clear a Block of Core Memory                                                       | 210        |

| ı∠d.           | Read 8 consecutive Core locations into 8                                           | 220        |

| 12b.           | consecutive File Registers                                                         | 220        |

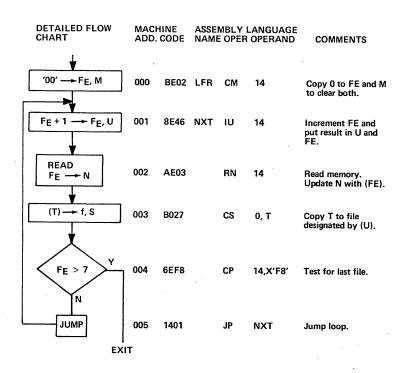

| 120.           | Write 8 consecutive Files into 8 consecutive                                       | 221        |

| . 13a.         | Core locations                                                                     | 221        |

| . 13a.<br>13b. | File to Register; with Hardware Rotation                                           | 223        |

| 130.           | of Bit Pattern                                                                     | 226        |

|                | O: D::: attolii                                                                    | ~~~        |

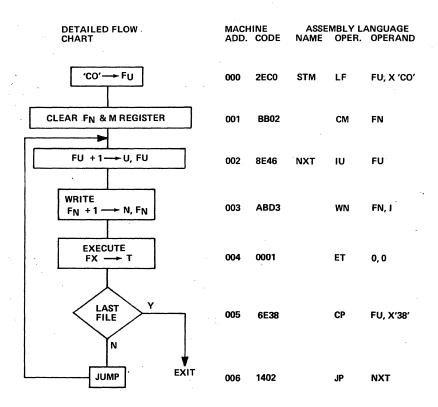

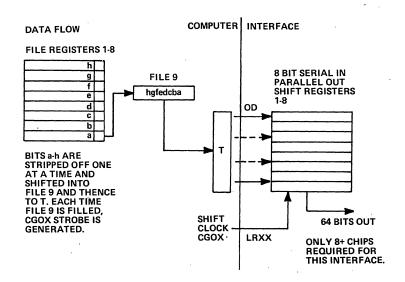

|         | 14.<br>15.                    | Input from 8 Shift Registers to 8 Files in MICRO 800 | . 228                                  |

|---------|-------------------------------|------------------------------------------------------|----------------------------------------|

|         | 16.                           | Converter                                            | . 231                                  |

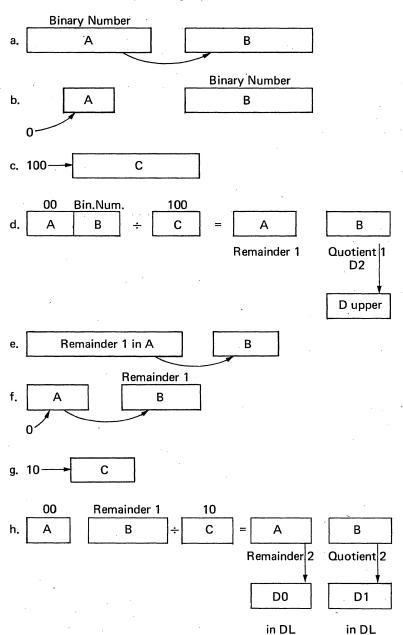

|         | 17.                           | Binary to BCD Conversion                             | 235                                    |

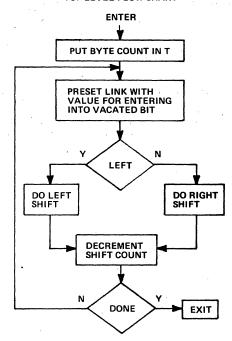

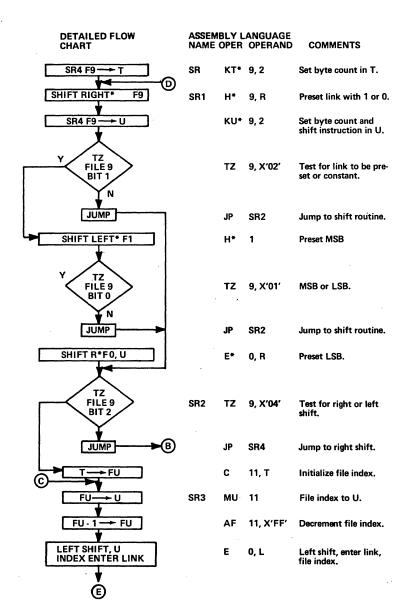

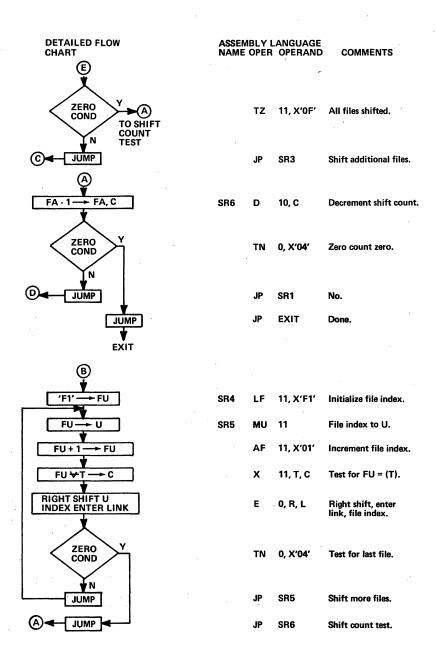

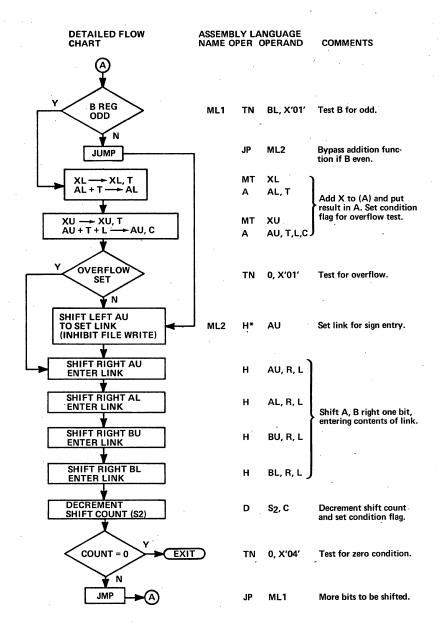

|         | 18.                           | General Purpose Multiple File Shift Routine          |                                        |

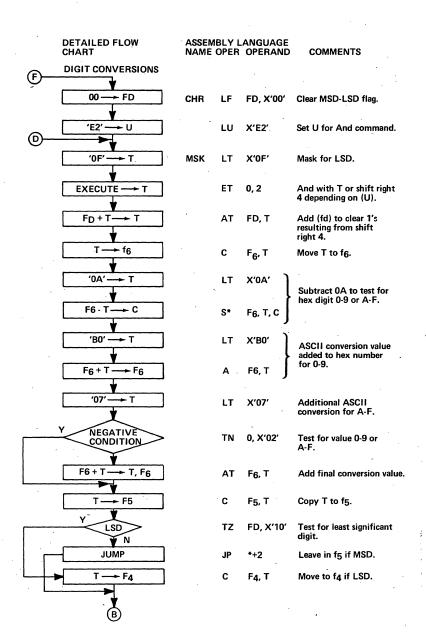

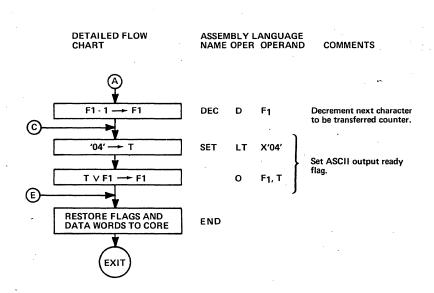

|         | 19.                           | Hexadecimal to ASCII Conversion Routine.             |                                        |

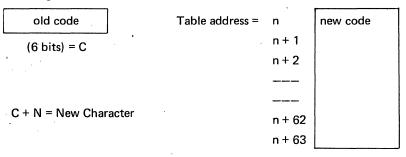

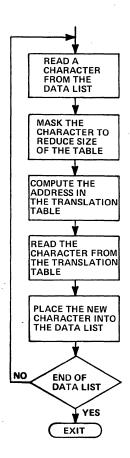

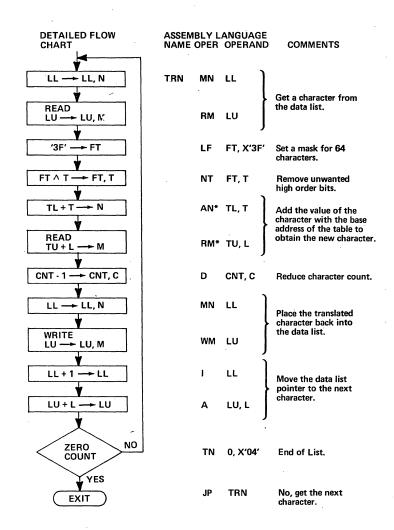

| •       | 20.                           | General Purpose Code Conversion by Table             |                                        |

| ٠       | 21.                           | Translation                                          | . 255                                  |

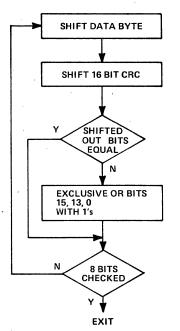

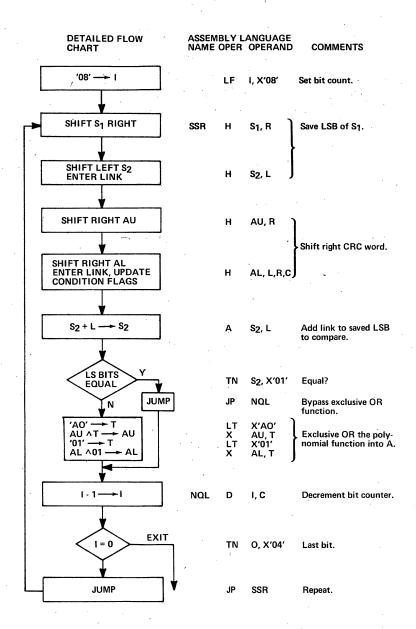

|         | 22.                           | Generate Cyclic Code for One 8 Bit Data<br>Byte      |                                        |

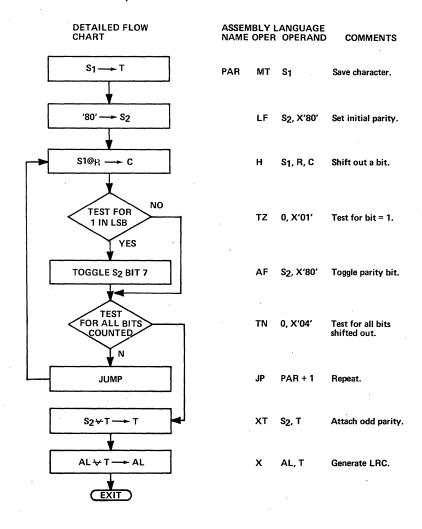

|         | 23.                           | Generate ASCII Parity                                | . 261                                  |

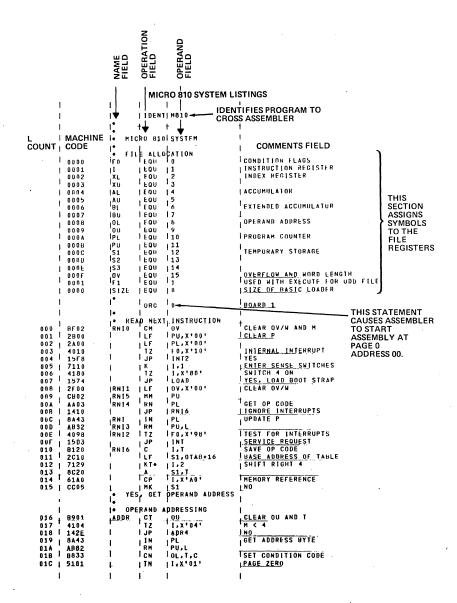

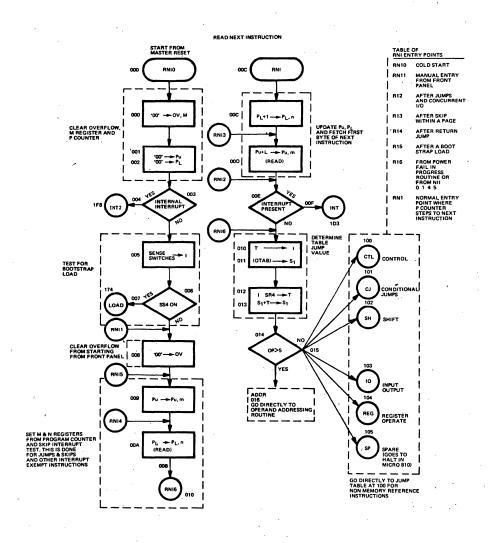

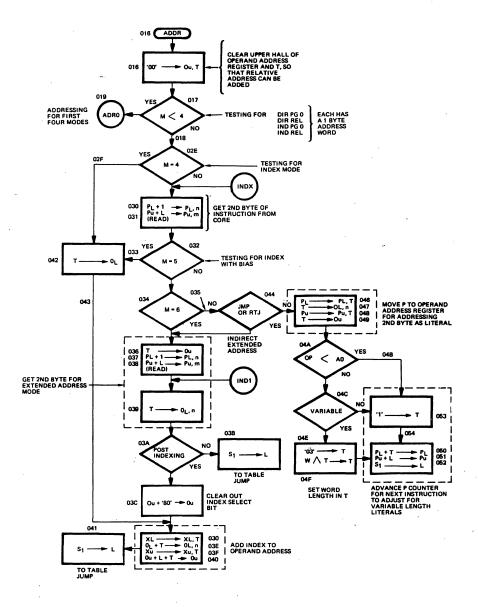

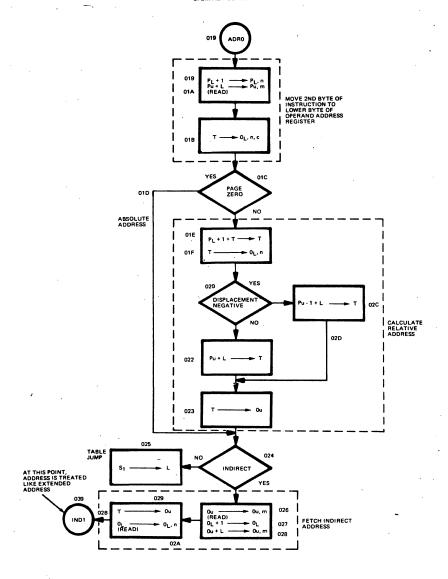

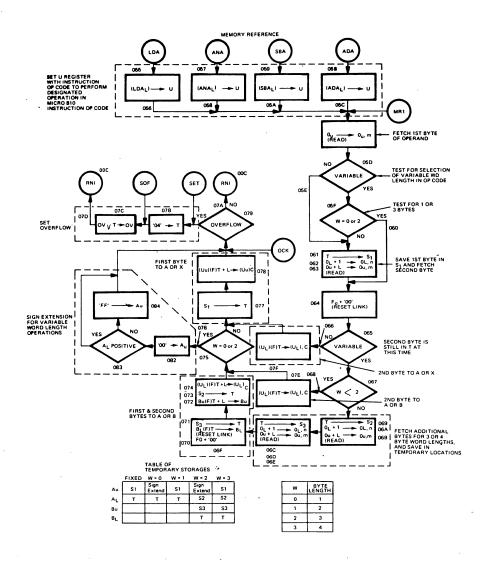

|         | Chapter 8.                    | MICRO 810 Firmware Manual                            | 262                                    |

|         |                               | 810 Functions                                        |                                        |

|         | File Reg                      | gister Assignments                                   | 264                                    |

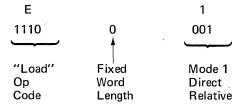

|         |                               | ition Formats                                        | 266                                    |

|         |                               | d Addressing Modes                                   | 267<br>271                             |

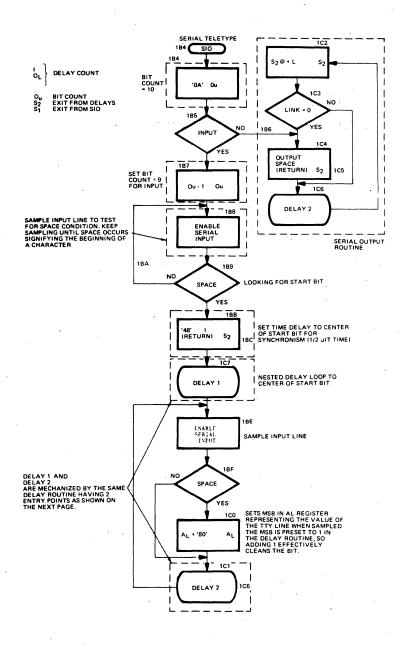

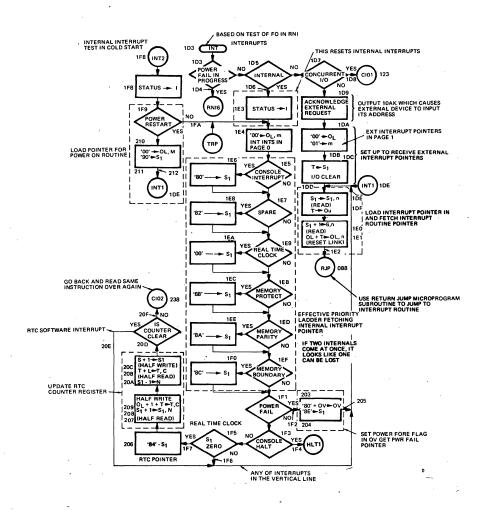

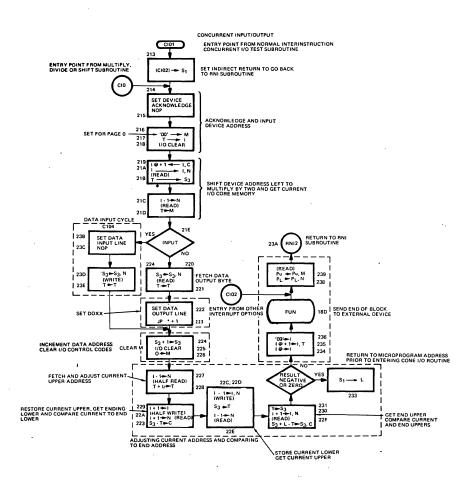

|         | Conc<br>Seria<br>Byte         | rupts                                                | 273<br>273<br>273<br>274<br>275        |

|         | MICRO                         | 810 Assembly Listings                                | 300                                    |

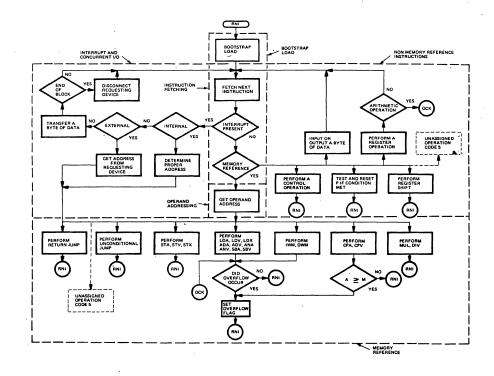

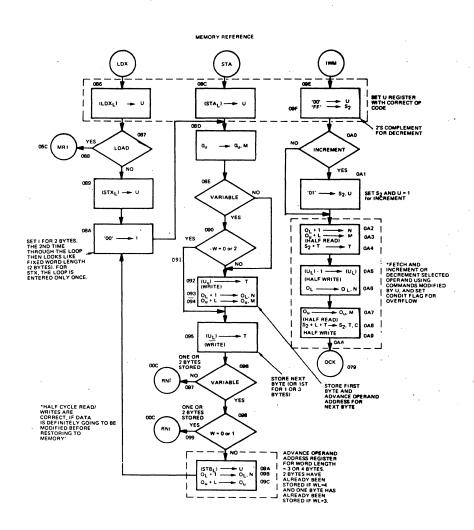

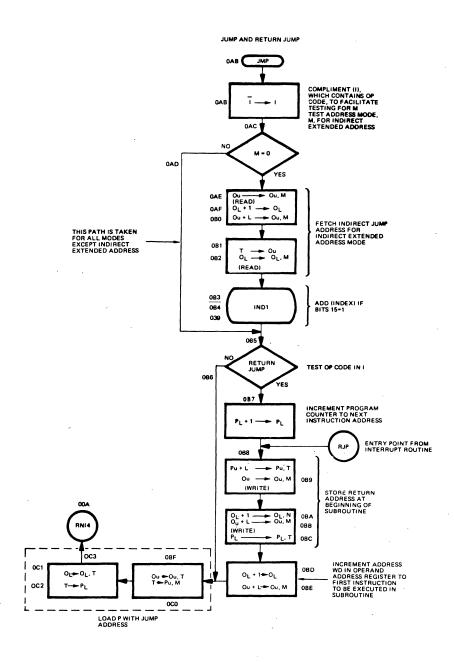

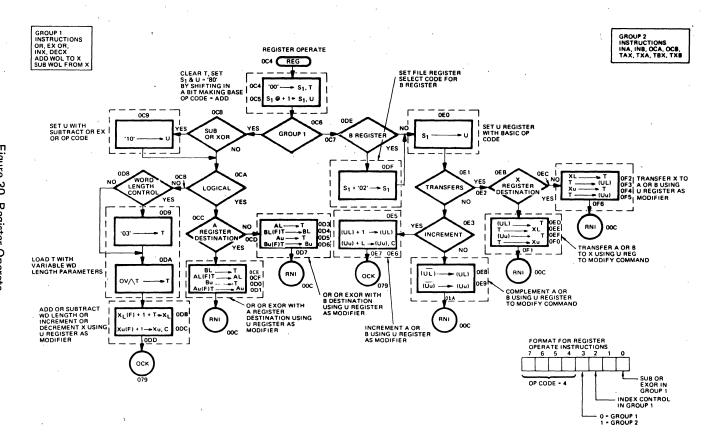

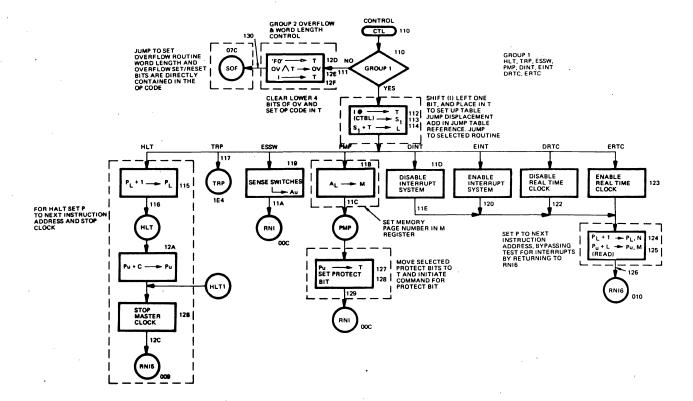

|         |                               | tion Flow Examples of a MICRO 810                    | 300                                    |

| PART IV |                               | 00 REFERENCE MANUAL                                  | 309                                    |

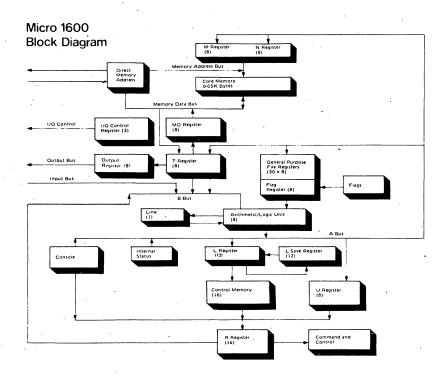

|         | Chapter 1.                    | MICRO 1600 Design Features                           | 310                                    |

|         | General                       | Characteristics                                      | 311                                    |

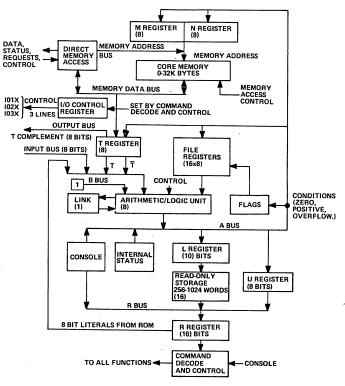

|         | Chapter 2.                    | System Description                                   | 312                                    |

|         | Register<br>Control<br>Memory | O Flags and Internal Status                          | 312<br>315<br>316<br>317<br>318<br>319 |

|         | Chapter 3.                    | Microcommand Repertoire                              |                                        |

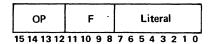

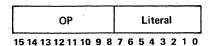

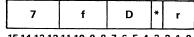

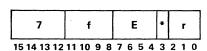

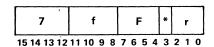

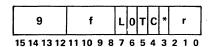

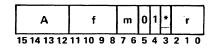

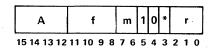

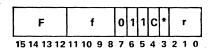

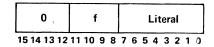

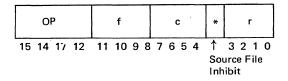

| •       | Comma                         | nd Formats                                           | 321                                    |

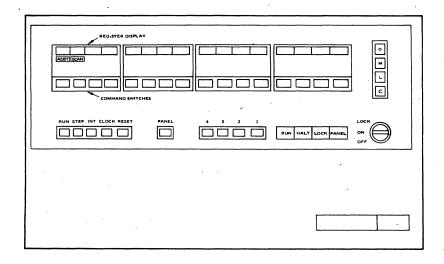

|        | Chapter 4. Control Panel Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 352                                                                                     |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|        | Displays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 352<br>353<br>353<br>355                                                                |

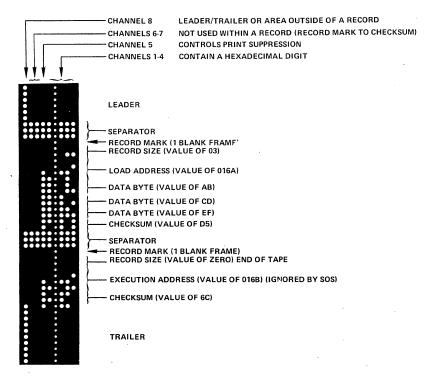

|        | Chapter 5. Micro Assembler Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 357                                                                                     |

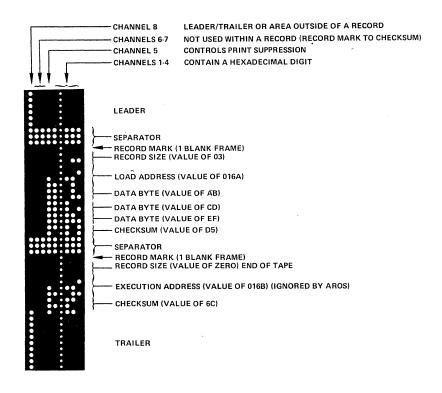

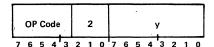

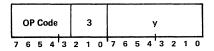

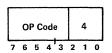

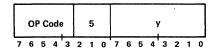

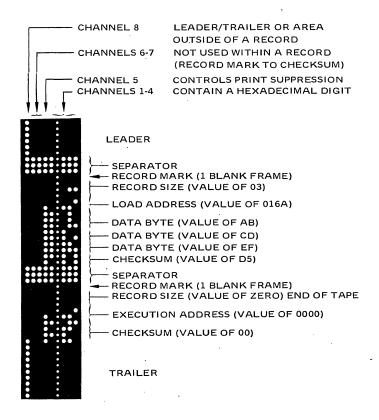

|        | Statement Format Operand Field Expressions Machine Commands Class One Class Two Class Three Class Four Class Five Assembler Instructions Assembly Listing Error Flags Program Tape Format Sample Listing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 357<br>358<br>359<br>360<br>361<br>361<br>361<br>362<br>362<br>363<br>364<br>365<br>368 |

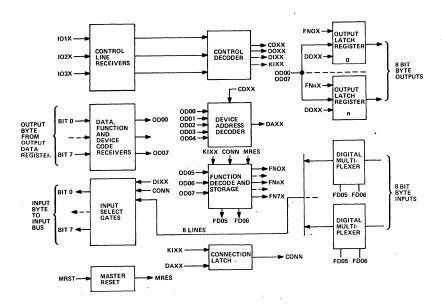

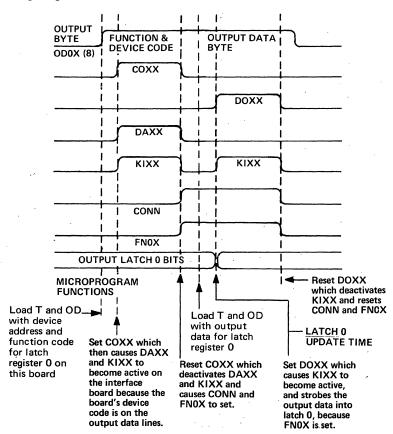

|        | Chapter 6. Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 371                                                                                     |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 361<br>371<br>377                                                                       |

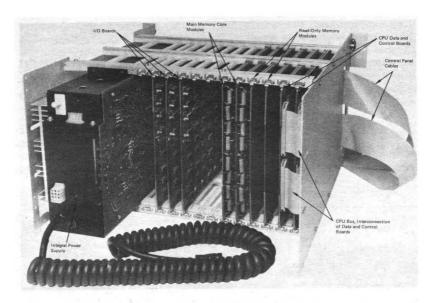

|        | Chapter 7. Physical Characteristics and System Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 384                                                                                     |

|        | The state of the s | 384<br>384                                                                              |

|        | Appendix A. Microcommand Reference Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 392                                                                                     |

| PART V |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 395                                                                                     |

|        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 397                                                                                     |

|        | Outline of System Definition Procedures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 397                                                                                     |

|        | <ol> <li>System Configuration Definition</li> <li>Detailed System Performance Specifications</li> <li>Interface Performance Specifications</li> <li>Program Specifications</li> <li>Tradeoffs</li> <li>Hardware Specs</li> <li>Software or Firmware Program Specifications</li> <li>Detailed Program Functions Analysis</li> <li>Definitions and Programming</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

|        | Microprogramming Aids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 405                                                                                     |

| PART VI | PRODUCT CATALOG 40                                    | )7         |

|---------|-------------------------------------------------------|------------|

|         | MICRO 400 Computer                                    | 96         |

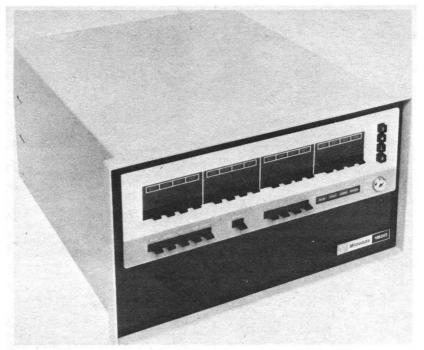

|         | MICRO 800 Computer                                    | 12         |

|         | MICRO 810 Computer                                    | 13         |

|         | MICRO 820 Computer                                    | 14         |

|         | MICRO 800 Series Computer System Elements and Options | 15         |

|         | MICRO 1600 Computer                                   | 19         |

|         | MICRO 1600/21 Computer                                | 21         |

|         | MICRO 1600 Computer Series System Elements            |            |

|         | and Options                                           | 23         |

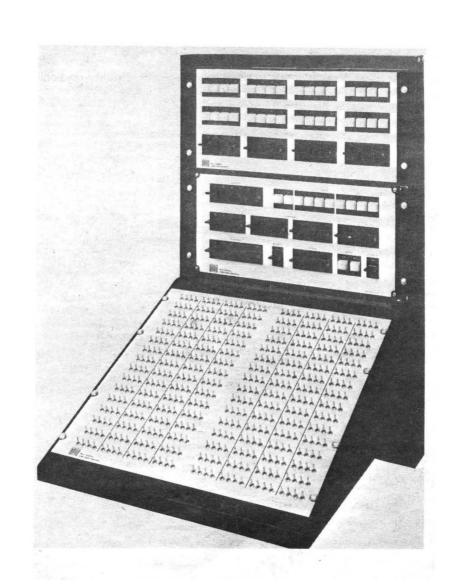

|         | Firmware Training System                              | 28         |

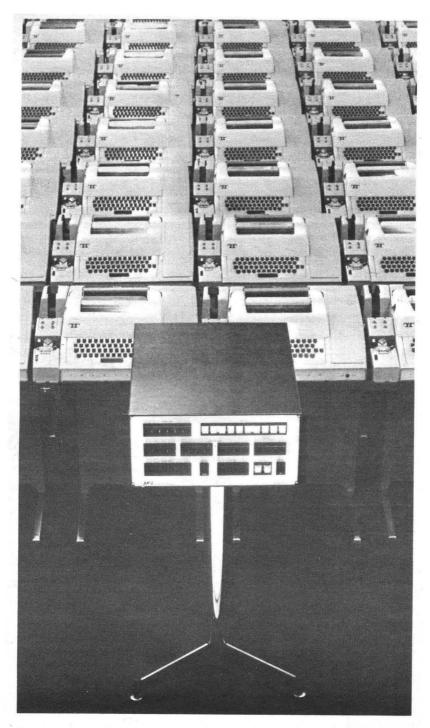

|         | Microprogramming System 43                            | <b>)</b> 1 |

### INTRODUCTION

Microprogramming techniques are the secret of the demonstrable advantages of Microdata's advanced microprogrammable computers over fixed-instruction minicomputers.

The major difference between Microdata's products and conventional minicomputers is the incorporation of microprogrammed control memories as a major adjunct to the usual basic elements of any computer—control unit, main memory, arithmetic/logic unit and input/output.

Microprogrammed control memories provide ease of programming using a wide choice of languages.

Microprogramming also means higher speed and more efficient use of the main memory of the computer.

In many cases, the usable storage of the main memory is increased because the programs used in conventional minicomputers to perform certain operational instructions are stored in the control memory, thus freeing storage capacity in the main memory for the purpose it was intended—problem-solving.

Inherently, microprogramming gives the user the flexibility to tailor the computer to his specific needs, no matter how complex or simple, and he can change the system at will, swiftly and economically. In addition to telling the computer what to do, microprogramming makes it possible to tell the computer how to do it.

The result is high performance at minimum cost, high memory efficiency and the availability of a wide variety of languages from which to choose. In short, Microdata has reached a pinnacle in the only meaningful measurement of computer performance—the ability to solve specific problems accurately and efficiently in terms of time and therefore cost to the user.

Microprogrammed computers also have ripped away many barriers to broader application of minicomputers. The way is clear for use of Microdata's products in business and scientific applications because of the ease and flexibility of programming techniques.

A number of factors have contributed to these advances by Microdata Corporation, including modern facilities geared to volume production, exploitation of the most advanced techniques and concepts available, and the field-proven reliability of more than 1000 microdata computers.

All of these elements are available to and benefit the user of Microdata's products.

# PART I MICROPROGRAMMED COMPUTER PRIMER

### INTRODUCTION

December 1945, ENIAC, the first electronic high-speed stored program general purpose computer was completed. Six years later Professor M.V. Wilkes of Cambridge University coined the word microprogramming to describe computer instructions that carry out numerous information transfers in a single execution cycle. Cost-performance improvements as a result of 25 years of advancement in computer technologies have been almost overwhelming. In 1965 it became practical and possible to build computers with control units driven by microprograms. The concept was not exploited on a widespread basis until recently. In large and medium scale computers microprogramming provides the capability to emulate other computers, and to maintain upward/downward compatibility over a wide range of models within a computer series.

The small or so called minicomputer incorporating microprogramming now exploits the advances in semiconductor and memory technologies with microprogramming far beyond the larger model computers. Full advantage of new low cost memories are realized only by users of small microprogrammed computers. The spectrum of applications between the special purpose computer, where the entire program is implemented in a microprogram, to the general purpose computer implemented by microprogram can be selected by the user to achieve a meaningful price/performance ratio for the application.

### ORGANIZATION OF THE MICROPROGRAMMED COMPUTER

The organization of the microprogrammed computer can best be described after we first review the organization of its predecessor, the fixed instruction stored program general purpose computer.

### The Fixed Instruction Computer

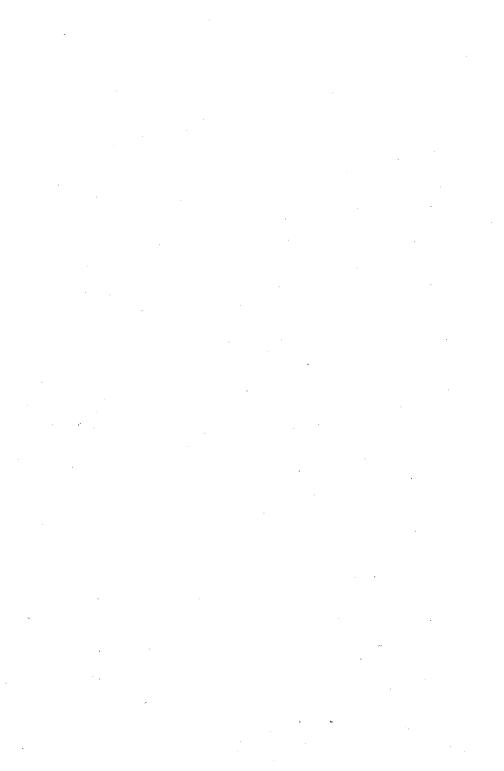

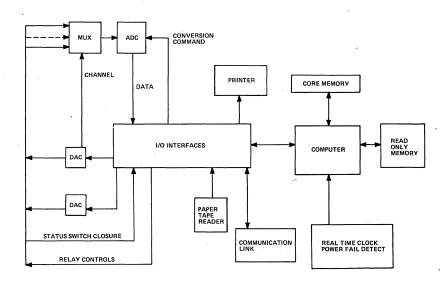

In simple terms the fixed instruction stored program computer is built around a storage and retrieval scheme, typically a magnetic core memory. The structure and information paths of a computer are represented in the simplified block diagram (Figure 1).

As defined in most textbooks, the five elements comprising a digital computer are: memory, arithmetic unit, input, output and control unit.

Memory: Modern computer memories are implemented using high speed semiconductors or magnetic core memory systems. These memories are high-speed random access devices of which information, usually in a binary form, is written or read from any addressed section of the memory.

**Arithmetic Unit:** In many instances is referred to as the arithmetic and logic unit (ALU). As the name implies it performs the arithmetic operations on data transferred within the computer, the memory, the input and the output.

**Input/Output:** Communication with a wide variety of devices in the language of the operator are made possible by transfer channels referred to as the input and output sections of a computer. Devices connected to the input/output of a computer referred to as computer peripherals include elementary switches and indicator lamps, typewriters, magnetic or paper tape units, line printers, analog converters, cathode ray tube displays (TV type devices), card readers and punches, communication lines, etc.

Figure 1. Simplified Block Diagram

Fixed Instruction Stored Program General Purpose Computer

In addition to man communication type devices the input/output of a computer may be connected to intermediate storage devices for mass memory requirements. Such mass memory devices include but are not limited to magnetic disc storage systems, magnetic drums, and a larger scale computer memory.

Control Unit: The control unit may be referred to as the "brain" portion of any computer because it coordinates all units of the computer in timed logical sequence. The control unit of a small fixed instruction computer receives sequences of instructions from memory. These sequences, called programs, reside in the memory and are referred to as "software." The control unit is closely synchronized to the memory cycle speed and execution time of each fixed instruction is usually a multiple of the memory speed.

### The Microprogrammed Computer

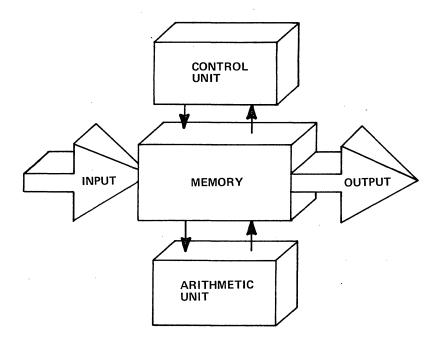

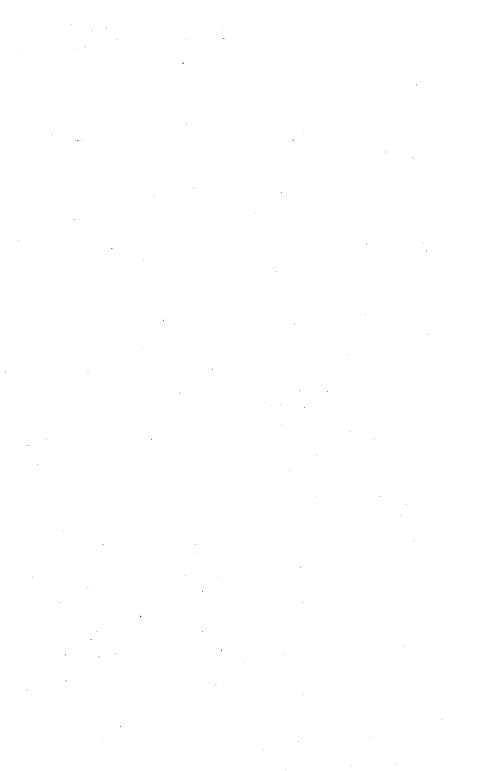

Four of the elements of the microprogrammed computer are nearly identical to the fixed instruction computer. The significant difference is in the control unit ("Brain"). The basic control sequences of a microprogrammed computer originate in a separate "control memory," usually a read-only memory (ROM) which operates at speeds many times faster than the main memory section of the computer. Thus the simplified block diagram (Figure 2) of the microprogrammed computer has one more element than the fixed instruction computer.

Figure 2. Simplified Block Diagram Microprogrammed Computer

Memory: The random access main memory of the microprogrammed computer differs little from the fixed instruction computer. It is implemented with magnetic core or semiconductor systems in similar sizes and speeds to the fixed instruction computer. The basic difference is the timing and control of the memory system. The control unit of the microprogrammed computer is clocked to a significantly higher speed separate memory system. Hence, the main memory speed is essentially independent of the processor speed and is operated in a manner similar to an input/output device.

Arithmetic Unit: The arithmetic and logic unit in a microprogrammed computer operates on fixed data lengths, typically 8 bits. The speed of the unit is 10 to 50 times faster than fixed instruction computer arithmetic units operating on smaller portions of arithmetic problems at each step. Microcommands are much more intimately related to the computer architecture and to bit patterns. This allows high versatility in problem solution and minimizes the restrictions usually encountered at the software level.

Input/Output: Microprogrammed computers provide extremely fast elementary I/O capabilities. Data paths are fixed length, typically 8 bits, and the I/O control functions are simple elements sequenced by high speed control memory firmware. This permits special I/O systems to be designed for the users' requirements. The microprogrammed computer offers all of the I/O capabilities found in fixed instruction computers coupled with the unique advantage of providing only the capabilities needed, and the versatility to be changed when required.

Control Unit: The control unit of the microprogrammed computer is simple and straightforward. It operates and controls all elements of the computer system including two levels of memory. Because it is more basic than the control units in fixed instruction computers it provides capability to solve problems in an added dimension. The control unit is programmable, not fixed. Programs operating upon the control unit are called microprograms, and are referred to as firmware. These programs are as easy to write and implement as is software in the fixed instruction computer.

If we refer to the control unit of any computer as the "Brain," then the microprogrammed computer control unit could be referred to as a brain ingredient, which we can readily adjust to suit our needs.

Control Memory: The control memory is the element that most dramatically distinguishes the microprogrammed computer. The control memory contains the stored sequence of control functions that dictate end user architecture of the microprogrammed computer. These stored sequences are called "microprograms" or "firmware" corresponding to fixed instruction computer sequences called "programs" or "software."

The control memory has been called many other names including, readonly store (ROS), read-only memory (ROM) and control store. Terminology relating to the control memory of microprogrammed computers is most complex because of many misnomers coined by computer and semiconductor manufacturers. Present terminology that relates to the mechanization of control memory are:

**ROM:** Read-Only Memory: Any memory system in which the bit patterns of each word are fixed, and unalterable.

In application, few ROM's can be modified after manufacture. Those ROM's that can, may be called modifiable. To make any change requires a hardware modification such as adding or deleting diodes in a diode matrix ROM or rerouting of wires in a core ROM.

**BROM:** Bipolar Read Only Memory: Large scale integration (LSI) bipolar devices are used for volume manufacture. Original setup masking is expensive. Cost for manufactured elements is low.

PROM: Programmable Read Only Memory: A semiconductor diode array is programmed by fusing or burning out diode junctions. Cost for setup is minimal. Manufacturing cost is moderate to high. The PROM is usually used for final shake down of a system prior to investing in the BROM setup.

AROM: Alterable Read Only Memory: A true misnomer. The AROM is actually a read-write memory that is used for initial checkout of firmware. The firmware is typically loaded into the AROM via a paper tape input device. Once loaded the AROM operates the control unit as does any ROM control memory. The advantage of the AROM is programming within a few minutes rather than a manufacturing process. Cost is high; however, the devices are used indefinitely for checkout and analysis of numerous firmware implementations.

### COST AND PERFORMANCE ADVANTAGES OF THE MICROPRO-GRAMMED COMPUTER

Fixed instruction minicomputers are basically application sensitive. Even with numerous models to choose from only a few offer good price performance for any specific application. Even more important to note is the fact that if a specific fixed instruction computer offers the best price performance for a given application at one level of complexity it may offer less relative value as the complexity changes.

Typically, to increase the performance of the fixed instruction computer the main memory (usually core memory) is increased in size.

In the final analysis, the performance of any computer is measured by its ability to solve a specific problem within a given period of time.

For most project managers the selection of a minicomputer is a traumatic experience. They are exposed to numerous technical concepts, specifications and a variety of salesmen and skilled technicians from companies with one goal—to sell him their solution to his technical problem. If a thorough up-to-date evaluation were performed with all minicomputer manufacturers the evaluation could cost him more than the project implementation. The prime criteria for selection of the appropriate minicomputer is time and cost of implementation over the entire project life. In this light, the microprogrammed minicomputer offers an answer to this enigma. The user selects the cost/performance lines between three elements; hardware, firmware, and software for his specific application.

One of the primary purposes of this "Microprogramming Handbook", is to educate and illustrate for the user the capabilities of specific product lines and to assist in these cost/performance trade-off selections.

The following comparison chart illustrates five capability levels comparing one of the more popular fixed instruction minicomputers, referred to as brand X, and a microprogrammable minicomputer, the MICRO 1600. Each level represents computer problem solving capability with corresponding notation on price, memory use and relative speed (micro vs. fixed). Within

any capability level numerous trade-offs between control memory size and core memory size can be established for the MICRO 1600.

For example, level number 4 shown in the comparison chart represents a computer capability for a time-sharing system employing high-level interpretive language and executive programs. Implementation of floating point arithmetic and executive subroutines in firmware thus expands the ROM from 768 words to 8,192 words. As a result, the MICRO 1600 cost is reduced approximately 15 percent and execution time is improved by a factor of approximately 20.

This comparison clearly illustrates that as the size of the control memory increases advantages result in price and relative speed. In addition, programming costs and implementation time can be significantly reduced once the users' needs are established in firmware. Now, with the availability of supporting systems from Microdata, firmware development is in the same dimension in price and turn-around time normally associated with fixed instruction computers. The result: computer users can benefit from microprogramming along with the computer manufacturer.

|           | Microprogrammed Computer (MICRO 1600) |                           |                      |                   |                 | nstruction<br>er (Brand X) |

|-----------|---------------------------------------|---------------------------|----------------------|-------------------|-----------------|----------------------------|

| Level     | Core<br>Memory<br>Size                | Control<br>Memory<br>Size | System<br>Price      | Relative<br>Speed | System<br>Price | Core<br>Memory<br>Size     |

| 1.        | 8K X 8<br>4K X 8                      | 512 X 16<br>1024 X 16     | \$5,910<br>\$5,420   | 1:2<br>2:1        | \$6,250         | 4K X 16                    |

| 2.        | 16K X 8<br>12K X 8                    | 512 X 16<br>2048 X 16     | \$8,610<br>\$7,690   | 1:2<br>5:1        | \$8,950         | 8K X 16                    |

| . 3.      | 32K X 8<br>24K X 8                    | 512 X 16<br>1024 X 16     | \$14,010<br>\$11,470 | 1:2<br>10:1       | \$14,350        | 16K X 16                   |

| <b>4.</b> | 48K X 8<br>24K X 8                    | 768 X 16<br>8192 X 16     | \$19,770<br>\$16,750 | 2:3<br>15:1       | \$19,750        | 24K X 16                   |

| 5.        | 65K X 8<br>32K X 8                    | 1024 X 16<br>12K X 16     | \$25,170<br>\$22,250 | 1:1<br>20:1       | \$27,000        | 32K X 16                   |

# COMPARISON OF A MICROPROGRAMMABLE COMPUTER TO A GENERAL PURPOSE FIXED INSTRUCTION COMPUTER

In the general purpose fixed instruction computer, the instructions are stored in core memory along with data. Both instructions and data can be altered by the program. In a microprogrammable computer, the instructions are stored in a read only memory along with permanent (or constant) data. Only variable data, pointer, and flags are stored in core memory.

### Instruction Repertoire

In the general purpose fixed instruction computer there is usually a limited instruction repertoire with variations of instruction, and memory reference instructions having limited addressing modes.