MIME-I

TECHNICAL MANUAL

Copyright Micro-Term, Inc., 1978

# TABLE OF CONTENTS

| SEC | TION                                   |                                                                                                                                                                                                                                                                                 | PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.  | Gene                                   | ral Description of the MIME-I                                                                                                                                                                                                                                                   | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | 1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7 | Power Supply<br>Keyboard<br>Input/Output Interfaces<br>Microprocessor Control Unit<br>Synchronization Generator<br>Refresh Display Memory<br>Video Generator<br>Operating Examples<br>1.8.1 Receiving/Displaying Characters<br>1.8.2 Keying/Sending Characters                  | $1-1 \\ 1-1 \\ 1-3 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-5 \\ 1-5 \\ 1-6 \\ 1-6 \\ 1-6 \\ 1-6 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 \\ 1-1 $ |

| 2.  | 2.1                                    | r Supply<br>Minus Voltage Supplies<br>Plus Voltage Supplies                                                                                                                                                                                                                     | 2-1<br>2-1<br>2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.  | Keyb                                   | oard                                                                                                                                                                                                                                                                            | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | 3.2<br>3.3                             | Encoding Regular Keys<br>Repeat Function<br>Cursor Control Keys<br>Insertion of Cable Into Jl                                                                                                                                                                                   | 3-2<br>3-2<br>3-3<br>3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.  | Inpu                                   | t/Output Circuits                                                                                                                                                                                                                                                               | 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | 4.2<br>4.3<br>4.4<br>4.5               | I/O UART<br>Character Transmission from the Keyboard in LINE Mode<br>4.2.1 Half Duplex Operation<br>4.2.2 Full Duplex Operation<br>RS232C Interface<br>Block Mode Transmission in LOCAL MODE<br>UART Clock Generation<br>Bell Circuit<br>Printer Port<br>Current Loop Interface | 4-1<br>4-2<br>4-6<br>4-6<br>4-6<br>4-7<br>4-8<br>4-8<br>4-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.  | CPU                                    | - Processor Circuits                                                                                                                                                                                                                                                            | 5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | 5.1<br>5.2                             | Data Bus Control<br>CPU I/O Port Assignments<br>5.2.1 I/O Port Ø                                                                                                                                                                                                                | 5-1<br>5-6<br>5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# TABLE OF CONTENTS (continued)

| SEC | TION       |                                                                                                                                                                                                            | PAGE                                          |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 6.  | Sync       | hronization Generation Circuits                                                                                                                                                                            | 6-1                                           |

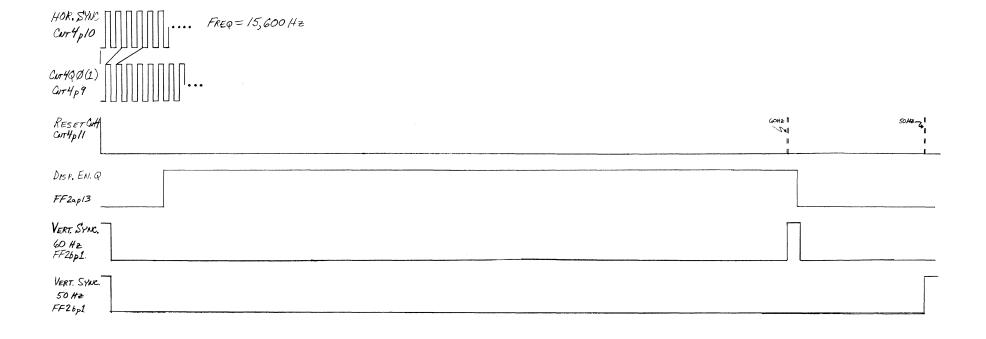

|     |            | Dot Oscillator and Counter<br>Horizontal Position Character Counter (CNT2, CNT#)                                                                                                                           | 6-1                                           |

|     | 6.4<br>6.5 | Display Column Counters<br>Dot Oscillator Enable Flip-Flop<br>Horizontal Sync. Generation<br>Vertical Sync. and Display Enable Generation<br>Row Offset Pointer - CNT6                                     | 6-1<br>6-4<br>6-5<br>6-7                      |

| 7.  | Refr       | esh Arm                                                                                                                                                                                                    | 7-1                                           |

|     |            | Addressing<br>Data Bus Interfacing                                                                                                                                                                         | 7-1<br>7-3                                    |

| 8.  | Vide       | o Generator Circuit                                                                                                                                                                                        | 8-1                                           |

|     | 8.2        | Character Font<br>Display Sequencing<br>Video Signal Composition                                                                                                                                           | 8-1<br>8-2<br>8-4                             |

| 9.  | Trou       | bleshooting                                                                                                                                                                                                | 9-1                                           |

|     | 9.1        | Troubleshooting Hints<br>9.1.1 Keyboard Fault Diagnosis<br>9.1.2 I/O Fault Diagnosis<br>9.1.3 Sync. Generation<br>9.1.4 Refresh RAM Diagnosis<br>9.1.5 Testing the Video Generator Circuits<br>Disassembly | 9-1<br>9-2<br>9-2<br>9-2<br>9-2<br>9-3<br>9-3 |

|     | J•L        | 9.2.1 Board Removal                                                                                                                                                                                        | 9-3                                           |

# APPENDIX I

# PAGE

| 10-1 | MAIN LOGIC BOARD, Parts List |

|------|------------------------------|

|      | Intergrated Circuits         |

| 10-2 | Capacitors                   |

|      | Resistors                    |

|      | Voltage Regulator            |

|      | Circuit Board                |

|      | Transistors                  |

| 10-3 | Diodes                       |

|      | Switches                     |

|      | Sockets/Connectors           |

|      | Crystals                     |

|      |                              |

## APPENDIX 2

# Technical Drawings

| 11-1  | Mime Character Generator         |

|-------|----------------------------------|

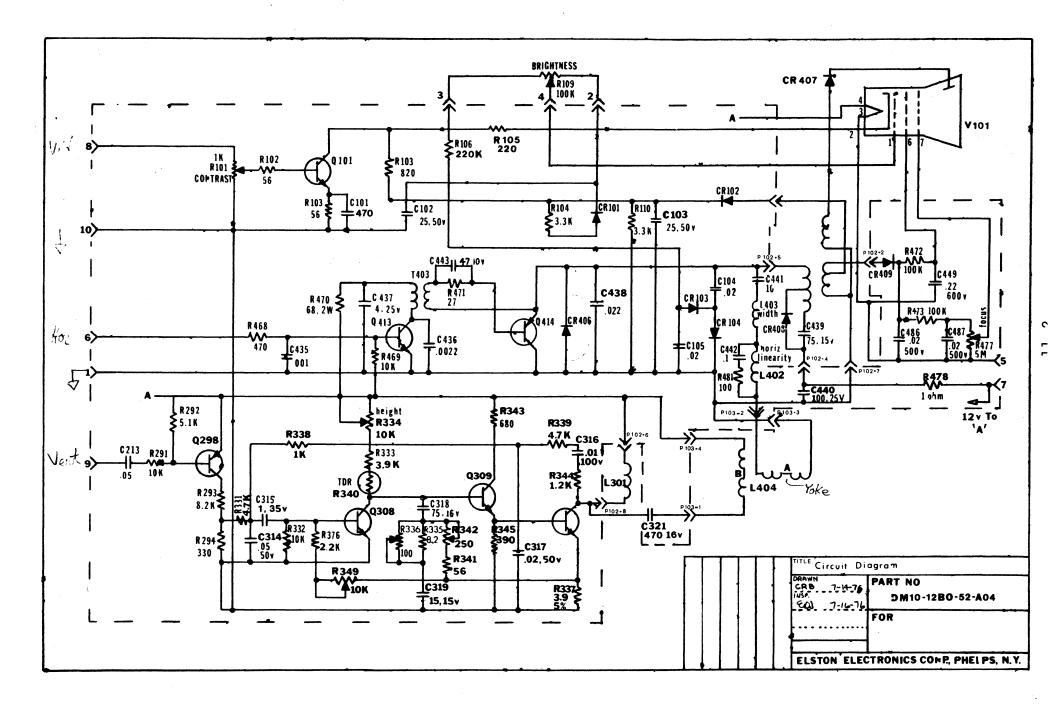

| 11-2  | Elston Monitor Schematic         |

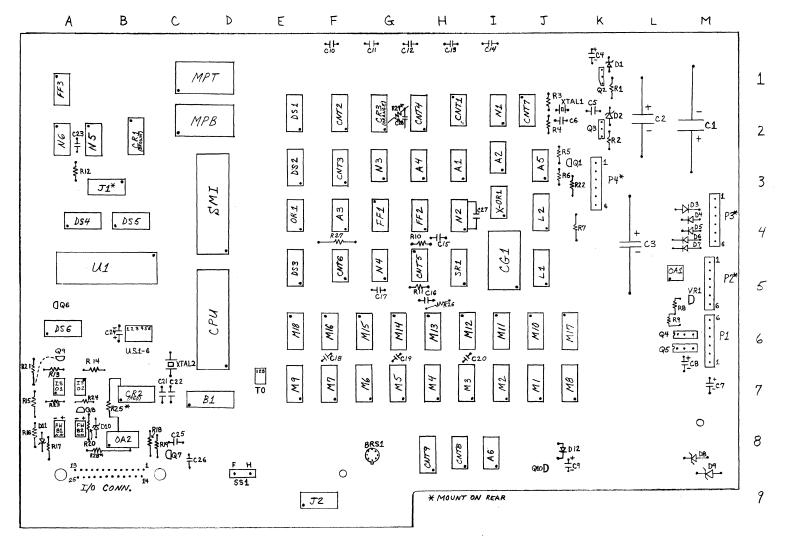

| 11-3  | Main Logic Board, Parts Location |

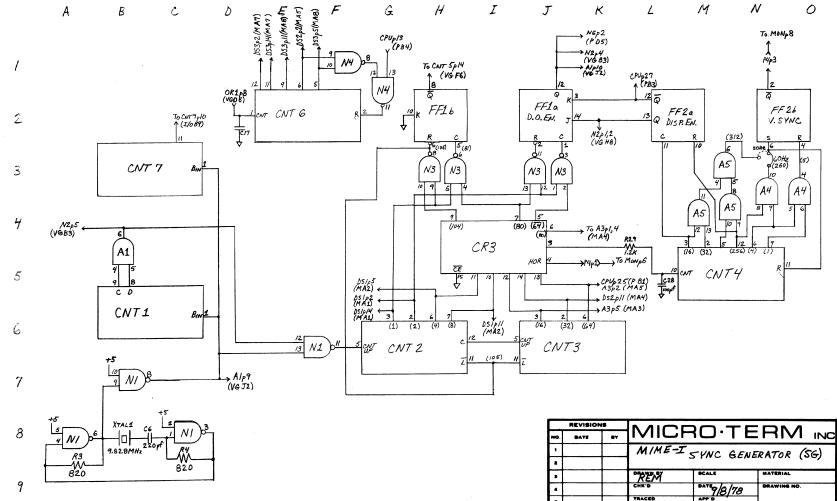

| 11-4  | Sync Generator (SG) Schematic    |

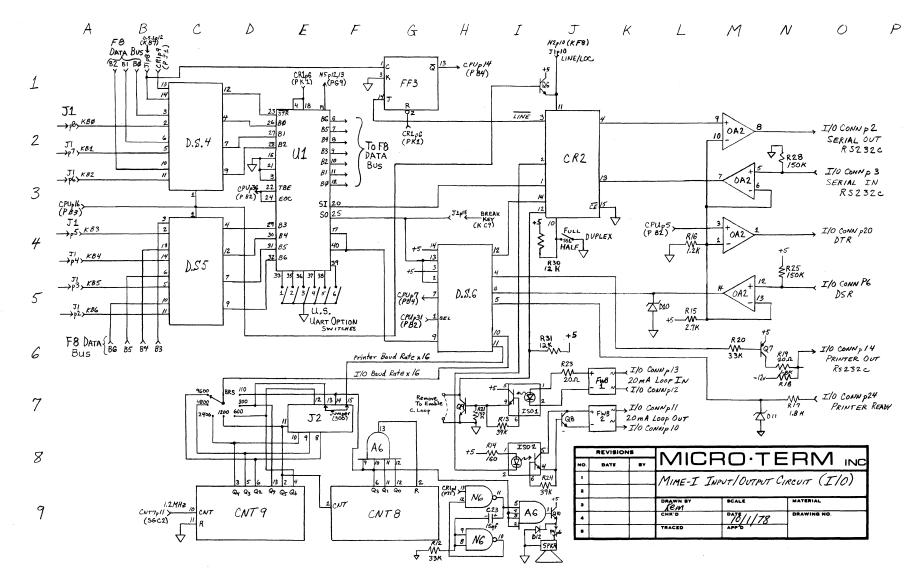

| 11-5  | Input/Output (I/O) Schematic     |

| 11-6  | Processor (P) Schematic          |

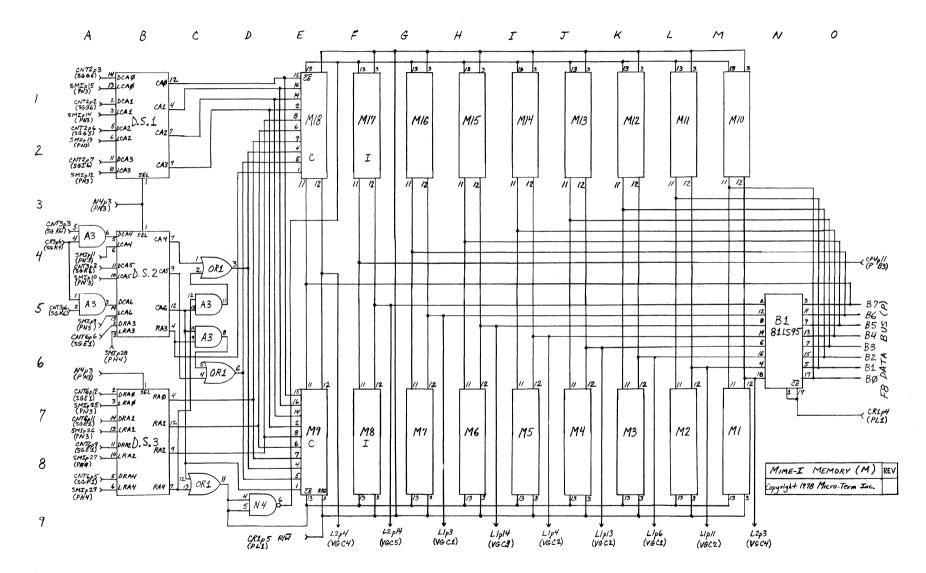

| 11-7  | Memory (M) Schematic             |

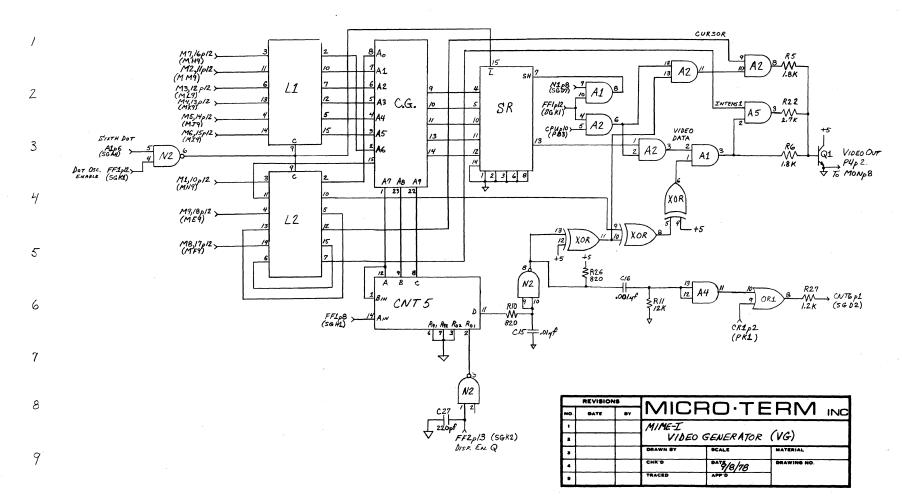

| 11-8  | Video Generator (VG) Schematic   |

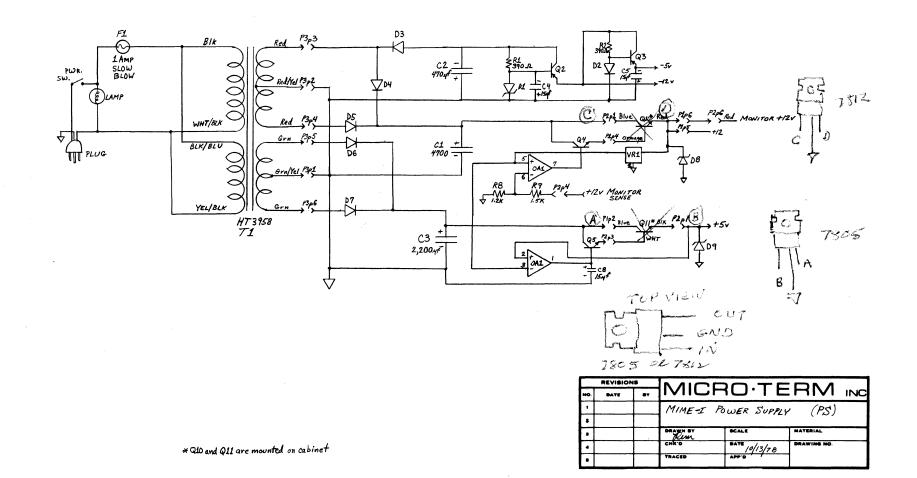

| 11-9  | Power Supply (PS) Schematic      |

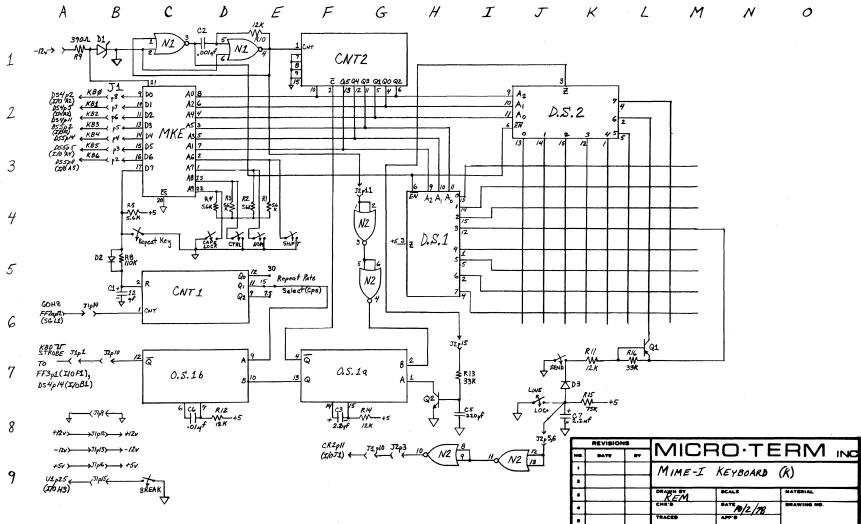

| 11-10 | Keyboard (K) Schematic           |

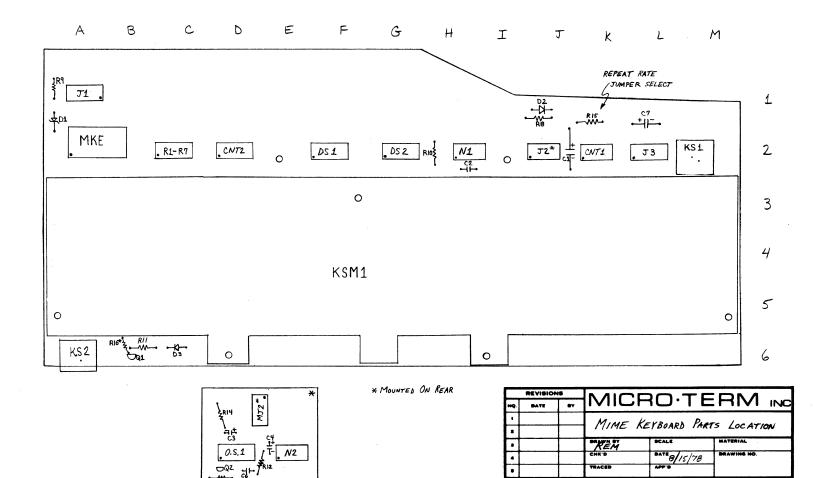

| 11-11 | Keyboard Parts Location          |

#### 1. GENERAL DESCRIPTION OF THE MIME-I

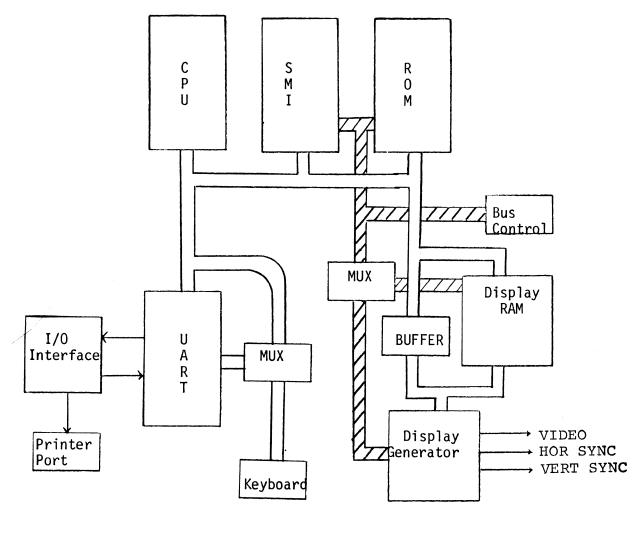

The MIME-I computer terminal provides a communication channel between humans and computers. It is equipped with many features that facilitate the man-machine interface. Figure 1.1 presents the MIME-I block diagram. There are seven major circuits in the MIME-I. These are:

- 1) Power Supply

- 2) Keyboard

- 3) Input/Output Interfaces

- 4) Microprocessor Control Unit

- 5) Synchronization Generator

- 6) Refresh Display Memory

- 7) Video Generator

Each of these circuits is described in detail in the later sections of this manual. In this section the operation of the MIME-I will be discussed at the block-diagram level. Circuit diagrams and other technical data can be found in the Appendices.

First, each of the seven circuits will be briefly described. Then the interactions between the circuits will be demonstrated through descriptions of the two basic terminal functions; i.e. receiving/displaying characters and keying/ sending characters.

1.1 Power Supply

The MIME-I power supply produces +5 volts at 1.5 amps, +12 volts at 200ma and -12 volts at 250ma. Minus five volts is derived from minus twelve in the video generator circuit.

### 1.2 Keyboard

The MIME-I keyboard uses a scanning encoding technique to generate the ASCII character set. Several keys on the keyboard are auto-repeating. When they are held dows for more than one second the keyboard circuit generates a series of strobe pulses at the rate of 15 characters per second.

\_\_\_\_\_ = Data Bus

ZTTTT = Address Bus

Figure 1.1: MIME-I Block Diagram

Auto repeat keys are Space,  $\rightleftharpoons$ ,  $\uparrow \downarrow$  and period. Any key may be made to repeat by first depressing it and then holding the repeat key down. The CAPS LOCK key forces the keyboard to generate only upper case alphabetic codes when alphabetic keys are struck. When the CAPS LOCK key is disengaged the entire 128 character ASCII set can be generated. All data generated by the keyboard is sent to the Input/Output section regardless of whether the terminal is in the LOCAL or LINE mode.

Depressing the NUM key modifies the outputs of the J, K, L, V, I and O keys only. It causes these six keys to produce numeric codes rather than alphabetic codes.

#### 1.3 Input/Output Interfaces

The MIME-I communicates with external devices through its I/O interface circuit. This circuit converts internal TTL parallel data into either serial RS232C or 20ma current loop data for transmission to the computer. Likewise it converts serial RS232C or 20ma current loop data received from the computer into parallel TTL data for internal processing. The I/O circuit can operate in several modes: LINE, LOCAL, Full or Half Duplex.

In LINE mode each character is transmitted to the computer as it is struck on the keyboard. If in LINE/Half Duplex the character is "echoed" back to the Input circuit as it is transmitted by the output circuit.

In LOCAL mode characters generated by the keyboard are echoed to the receiver circuit but are not transmitted to the computer until either the SEND key or the SHIFT SEND keys are depressed. This permits use of the MIME-I editing features. While in the LOCAL mode characters sent by the computer are displayed on the MIME-I screen.

A Printer Port output facilitates local hard copy output by providing a serial RS232C output port to a printer.

Data rates and UART options are conveniently switch selectable to modify various communications parameters.

### 1.4 Microprocessor Control Unit

The heart of the MIME-I is the F8 microprocessor which completely controls and characterizes the operation of the MIME-I. Its principal function is to decode received characters and perform the operations required to obtain the desired result. These operations include reading data from and writing data to the UART and display memory. Two 1024 by 8 ROMs hold the program that causes the F8 to act like a computer terminal. These ROMs can be altered to change the operation of the MIME-I.

#### 1.5 Synchronization Generator

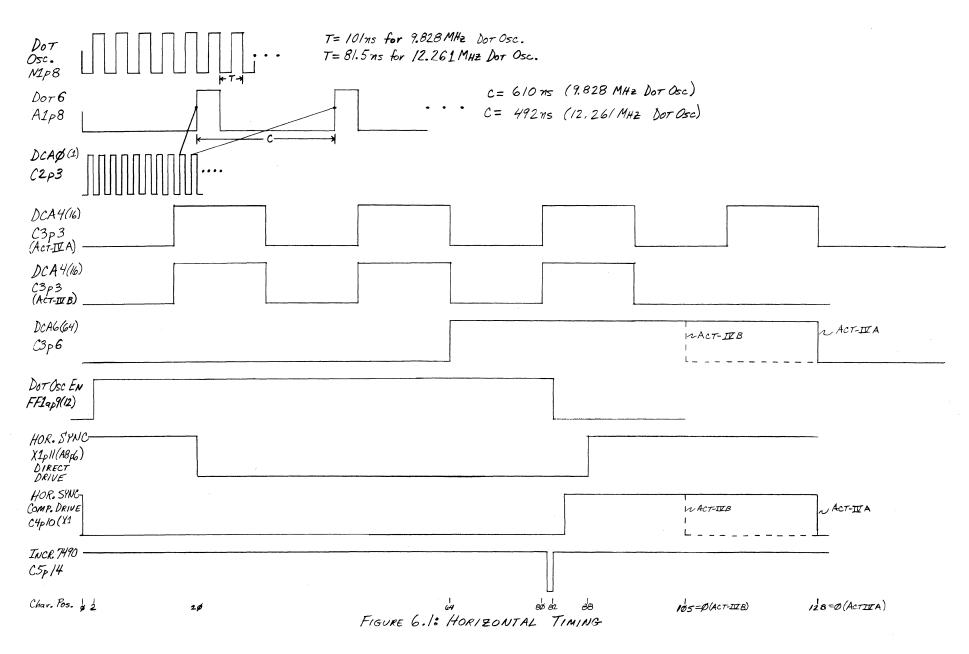

All timing signals required to synchronize both internal circuits and internal or external video monitors (CRTs) are generated by this circuit. All signals except the 2 MHz CPU clock are derived from a crystal controlled 9.828 MHz oscillator. The F8 2 MHz clock is generated by its internal clock circuit and an external 2 MHz crystal.

### 1.6 Refresh Display Memory

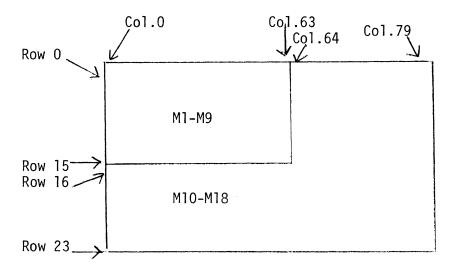

The ASCII codes for characters displayed in the 1920 (80x24) positions on the MIME-I screen are stored in a 2048 by 9 bit random access memory (RAM). Nine bits are required to store the seven bit ASCII code plus a cursor bit and a full/ half intensity (Un/Protected) bit. This refresh RAM is shared by the F8 and the video generator circuit. The F8 both reads and writes from and to the RAM while the video generator only reads from the RAM.

### 1.7 Video Generator

The video generator circuit reads ASCII data from the refresh RAM and generates a dot pattern for display on the monitor. This circuit generates a video signal for

### direct drive (or data display) monitors.

Further details concerning the operation of the above circuits can be found in the following sections of this manual.

**1.8** Operating Examples

The operating examples discussed in this section indicate the manner in which the various blocks in the MIME-I block diagram of Figure 1.1 interact to perform the required operation.

### 1.8.1 Receiving/Displaying Characters

When the UART assembles a complete ASCII character it raises its data available flag and interrupts the F8. The F8 reads the character from the UART into its accumulator and resets the UART flag.

The character is then tested to determine if it is a displayable or a control character. If it is displayable the F8 waits until the next horizontal retrace period, takes control of the multiplexed address lines to the display RAM and writes the character into the RAM with the cursor bit low. During the next horizontal sync pulse the F8 takes control of the RAM address lines and reads the character code stored in the position where the cursor is to be moved. The cursor bit is set and the character is replaced during still another horizontal retrace pulse. The maximum time required to perform these operations is 192usec (64x3).

If the received character causes a scroll operation (i.e. it is either the 80th character to be loaded on the bottom line or a line feed code) the execution time is increased to approximately 700 usec. After loading the character in the display memory the F8 waits to be interrupted by the UART flag when the next character is received.

When the MIME-I receives control characters from either its keyboard (in the Local mode) or from the external computer it responds as programmed in the 2708

### Master Control ROMs (MPB, PT).

### 1.8.2 Keying/Sending Characters

When in the on LINE mode of operation the MIME-I keyboard has control of the transmitter half of the I/O UART at all times except for a few moments when the F8 takes control to report the cursor position after receiving such a request. Each character is transmitted as soon as the key is struck. If the half duplex mode has been selected the characters will be presented simultaneously to the external computer and the MIME-I I/O UART for immediate display (local echo).

In the Local mode characters typed on the MIME-I keyboard are locally echoed but are not sent to the external computer until the SEND key or the SHIFT SEND keys are depressed. When the F8 receives this locally echoes send command it commences passing the required amount of data to the UART for transmission to the external computer. During this time characters typed on the keyboard are not transmitted or echoed locally.

#### 2. POWER SUPPLY

The MIME-I power supply generates the following D.C. voltages: +12v, +5v, -5v, and -12v. The power supply is fed by a transformer with dual primaries (to allow for either 110 or 220 volt operation) and dual center-tapped secondaries. The secondaries are both rated at 12.6 volts, 2.5 amps. The first secondary (Red, Red/Yel, Red) provides AC power to the -12 and -5volt supplies for the main board and also provides current to the +12 volt monitor and main board supplies. The other secondary provides AC power to the +5 volt supply for the logic on the main board.

### 2.1 Minus Voltage Supplies

Both the -12 and -5 volt supplies are lightly loaded and consequently are implemented with zener diodes and pass transistors. They are not short circuit protected.

### 2.2 Plus Voltage Supplies

The +12 and +5 volt power supplies are also of the pass transistor type; however, each of these employs an operational amplifier to provide feedback for regulation rather than rely on zener diode regulation. The positive supplies are not short circuit protected; however, high power zener diodes (D8 and D9) are placed across their outputs to protect the logic circuits from overvoltage conditions. The pass transistors Q10 and Q11 are mounted to the MIME-I chassis (with insulating hardware) allowing the cabinet to act as a heat sink.

### 3. KEYBOARD

The MIME-I keyboard is capable of generating the complete set of ASCII codes (0-7F Hex). The assignment of ASCII codes to keyswitches is listed below. Key-switches are either auto repeating or regular.

|   |     |     |         |   |        |   |        |         |   |        |            |     |        |        | Lay    | /01    | ut     |   |        |   |        |        |       |                                      |          | NE<br>DC• |

|---|-----|-----|---------|---|--------|---|--------|---------|---|--------|------------|-----|--------|--------|--------|--------|--------|---|--------|---|--------|--------|-------|--------------------------------------|----------|-----------|

|   | ESC |     | !<br>1  |   | "<br>2 |   | #<br>3 | \$<br>4 |   | %<br>5 | &<br>6     |     | /<br>7 |        | (<br>8 | )<br>9 |        | 0 | -      |   | $\sim$ |        | <br>/ | RUI<br>—                             | BR BR    | EAK       |

|   | ТА  | В   | 6       | ç | v      | N | E      | F       | 2 | т      | Τ          | Y   | 4<br>U |        | 5<br>1 | Τ      | 6<br>0 | Р | Τ      | @ |        | }      | REPE  |                                      | NE<br>ED |           |

| С | TRL | CAF | рs<br>ж | A | Τ      | S | 5      | D       | F |        | ELL<br>G   | н   | Τ      | 1<br>J |        | 2<br>K | l      | 3 | +<br>; | : |        | {<br>[ | F     | RET                                  | JRN      |           |

| s | END | Sł  | łIFT    | T | z      |   | х      | c       |   | v      | E          | 3   | N      |        | М      |        | <<br>, | > |        | ? | SH     | IIFT   |       | $\stackrel{\rightarrow}{\leftarrow}$ | ↑↓       |           |

|   | UM  |     |         |   |        |   |        |         |   | s      | <b>SPA</b> | CEE | BAR    |        |        |        |        |   |        |   |        |        |       |                                      |          |           |

Main Keyboard

|   |                      |        |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |                                 |                      |                      | 0                    | ut                   | pt                   | ıt                   |                      |                     |                     |                     |                     |                     |                     |                     |                      | LINE                |

|---|----------------------|--------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|----------------------|---------------------|

|   | 1B<br>1B<br>1B<br>1B |        | 31<br>21<br>00<br>* |                     | 32<br>22<br>00<br>* |                     | 33<br>23<br>00<br>* |                     | 34<br>24<br>00<br>* |                     | 35<br>25<br>00<br>* | 36<br>26<br>00<br>* |                                 | 37<br>27<br>00<br>37 |                      | 38<br>28<br>00<br>38 |                      | 39<br>29<br>00<br>39 |                      | 30<br>00<br>00<br>30 |                     | 20<br>30<br>00<br>* |                     | 5E<br>7E<br>1E<br>* |                     | 5C<br>7C<br>1C<br>* |                     | 5F<br>7F<br>1F<br>*  | BREAK               |

|   | 0<br>0<br>0<br>0     | 9<br>9 | 7<br>5<br>1<br>*    | 1                   | 1                   | 77<br>57<br>17<br>* |                     | 65<br>45<br>05<br>* |                     | 72<br>52<br>12<br>* | 74<br>54<br>14<br>* |                     | 79<br>59<br>19<br>*             |                      | 75<br>55<br>15<br>34 |                      | 69<br>49<br>09<br>35 |                      | 6F<br>4F<br>0F<br>36 |                      | 70<br>50<br>10<br>* |                     | 40<br>60<br>00<br>* | 5 <br>7 <br>1 <br>* | D<br>D<br>D<br>*    | REP                 | ЕАТ                 | 0A<br>0A<br>0A<br>0A |                     |

| c | TRL                  | CAP    |                     | 61<br>41<br>01<br>* |                     | 73<br>53<br>13<br>* |                     | 64<br>44<br>04<br>* |                     | 66<br>46<br>06<br>* |                     | 67<br>47<br>07<br>* | 61<br>41<br>01<br>*             | B<br>B               | 6/<br>4/<br>0/<br>3  | A                    | 6B<br>4B<br>0B<br>32 | - [                  | 4                    | 8000<br>8            | 3E<br>2E<br>0(<br>* | B                   | 3A<br>2A<br>00<br>* |                     | 5B<br>7B<br>1B<br>* |                     |                     | 0D<br>0D<br>0D<br>0D |                     |

| • | END†                 | Sł     | liFT                |                     | 7/<br>5/<br>1/      |                     | 71<br>51<br>11<br>* |                     | 63<br>43<br>03<br>* |                     | 76<br>56<br>16<br>* | ] ;                 | 62<br>42<br>02                  | 4                    | E<br>E<br>E          | 6<br>4<br>0          | B                    | 2C<br>3C<br>00<br>*  | ì                    | 3                    | E<br>E<br>10        | 2F<br>3F<br>00<br>* | :                   | SH                  | lift                |                     | 08<br>18<br>00<br>* |                      | 0B<br>1A<br>00<br>* |

| Ŀ | IUM                  |        |                     |                     |                     |                     |                     |                     |                     |                     |                     | 20<br>20            | Unshi<br>Shifte<br>CTRL<br>Nume | d                    |                      |                      |                      |                      |                      |                      |                     |                     |                     |                     |                     |                     |                     |                      |                     |

Main Keyboard

### 3.1 Encoding Regular Keys

The MIME-I uses a grid scanning routine to encode the keyboard. CNT2 provides address information to D.S.1 and D.S.2. When a key is depressed one of the output lines from D.S.1 will be shorted to one of the input pins of D.S.2 and D.S.2 pin 3 will go high for the duration the key is held down. This rising signal is delayed by C5 and applied to the base of Q2 which drives the A input of 0.S.1. 0.S.1 is a retriggerable one-shot with a period of 8ms (determined by R14 and C3). This period is long enough to prevent keybounce from generating multiple strobes. When 0.S.1a fires and its  $\overline{Q}$  output drops low CNT2 is halted with a count value that corresponds to the depressed key. This value provides six of the ten address lines to a 1k by 8 ROM (MKE). The other four address lines are provided by the CAPS LOCK, NUM, CTRL and SHIFT keyswitches. MKE performs a table look-up to produce the required ASCII code at its parallel outputs (D0 through D6). The output at D7 indicates whether the key is auto-repeating or not (see Section 3.2 below). When 0.S.1a fires it triggers 0.S.1b which generates a 300usec strobe pulse.

### 3.2 Repeat Function

0.S.lb can be forced to generate multiple strobe pulses by sending a pulse train into its A trigger input from the selected output of CNT 1. The standard repetition rate of 15 characters per second is implemented by dividing the 60Hz display enable signal by four at CNT1pl1. CNT1 is normally held to the zero state by virtue of pin 2 (reset) being pullsed up to +5 through R5 and D2. When an auto-repeating key is held down MKEp17 (D7) goes low and discharges C1 through R8. After about one second the voltage at CNT1p2 is sufficiently low to enable the counter and produce multiple strobes. Regular keys may be made to repeat by depressing the REPEAT key. This also discharges C1 and enables CNT1.

### 3.3 Cursor Control Keys

Since the ASCII code - keyswitch assignment of the MIME-I keyboard is set by MKE it is not possible to have the cursor control keys to generate codes required by all of the four terminals that the MIME-I is capable of mimicing. The output codes for the  $\bigoplus$  and  $\bigwedge$  keys are those specified by the ACT-IV cursor control feature. The keyboard code assignments may be altered by modifying the contents of the MKE (MIME Keyboard Encoder) ROM.

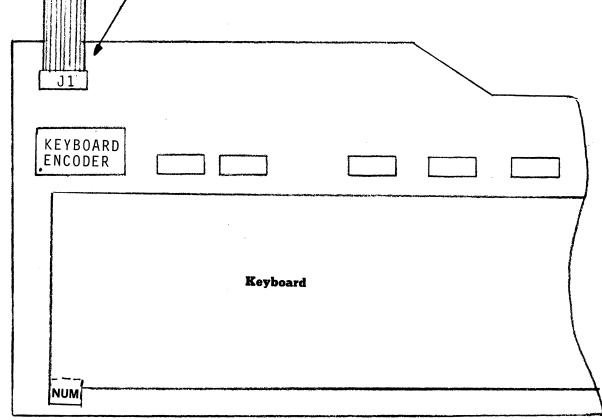

### 3.4 Insertion of Cable Into Jl

The proper orientation of the ribbon connector in socket Jl is illustrated below:

### 4. INPUT/OUTPUT CIRCUITS

The input/output (I/O) circuits of the MIME-I establish all necessary communications links between the terminal and remote devices such as computers or modems. The serial to parallel and parallel to serial conversions that are required to permit communication between the parallel-bus oriented MIME-I and serial ASCII oriented computer interfaces are performed in the I/O circuits.

### 4.1 I/O UART

All serial communications to and from the I/O and printer ports on the MIME-I are processed by the I/O UART (U1). Relevant UART pin assignments and functions are listed below.

| Pin Number | Name (Symbol)                 | Function                                                                                                                                                   |

|------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4          | Received Data Enable(RDE)     | A logic O places the received<br>data onto the F-8 data bus.                                                                                               |

| 5-12       | Received Data Bits(RD8-RD1)   | Tri-state data out lines. LSB of<br>ASCII code appears at RD1 (pin 12).                                                                                    |

| 17         | Receiver clock                | Clock of 16 times the desired data rate.                                                                                                                   |

| 18         | Reset Data Available(RDAV)    | A low pulse on this line will reset<br>the data available flag (pin 19).                                                                                   |

| 19         | Data Available(DAV)           | This line goes to a logical l when<br>an entire character has been re-<br>ceived and transferred to the tri-<br>tate receiver holding register.            |

| 20         | Serial Data Input(SI)         | This line accepts the serial input<br>data. A marking (logical l) to<br>spacing (logical 0) transition is<br>required for initiation of data<br>reception. |

| 22         | Transmitter Buffer empty(TBE) | This tri-state line goes high when<br>the transmitter is ready to accept<br>another character.                                                             |

| 23         | Data Strobe(DS)               | A strobe on this line loads a char-<br>acter into the transmitter buffer.<br>Transmission is <u>i</u> nitiated by the                                      |

rising edge of  $\overline{\text{DS}}$ .

| Pin Number | Name (Symbol)                | Function                                                                                                                                                     |

|------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24         | End of Character(EOC)        | This line goes to a logic l each<br>time a full character is trans-<br>mitted. It remains there until<br>the start of transmission of the<br>next character. |

| 25         | Serial Output(SO)            | This line will serially provide the<br>entire transmitted character. When<br>not transmitting this line stays<br>at a logical l.                             |

| 26-33      | Data Bit Inputs(DB1-DB8)     | There are up to 8 data bit input<br>lines available.                                                                                                         |

| 35         | No parity(NP)                | A logic l on this line inhibits<br>transmission of the parity bit.                                                                                           |

| 36         | Number of Stop Bits          | A logic l selects 2 stop bits,<br>a logic O selects l stop bit.                                                                                              |

| 37,38      | Number of Bits/Char(NB2,NB1) | These leads determine the number of<br>data bits to be transmitted per<br>character, as follows:                                                             |

|            |                              | NB2 NB1  # of Bits/Character                                                                                                                                 |

|            |                              | 0 0 5<br>0 1 6<br>1 0 7<br>1 1 8                                                                                                                             |

| 39         | Odd/Even Parity Select(EPS)  | A logic l selects even parity,<br>a logic O selects odd parity.                                                                                              |

| 40         | Transmitter Clock(TCP)       | This line is driven by a clock rate<br>of l6 times the desired data rate.                                                                                    |

Proper selection of the UART option switches attached to pins 35-39 can be achieved by referring to Section 4.7 of the MIME-I Operation Manual.

4.2 Character Transmission from the Keyboard in LINE Mode

When the MIME-I is operating in the LINE mode characters are transmitted when the keys are struck. Either half or full duplex transmission can be selected.

4.2.1 Half Duplex Operation

In half duplex the keyboard strobe (J1p8, STR) sets FF3 and forces the data

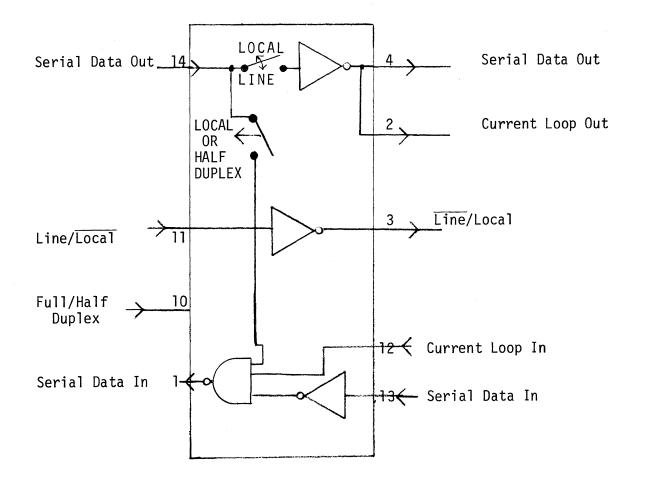

strobe input of the UART (Ulp23) low through data switch D.S.4pl2 since the keyboard has been selected to provide the inputs to the transmitter section of the UART. This selection is made by the F8. The keyboard is normally chosen unless the F8 needs to send characters out in the block transmit mode. The keyboard strobe pulse sets FF3 to indicate the character originated from the keyboard. When Ulp23 ( $\overline{DS}$ ) returns high the character data present at Ulp26-32 is transmitted serially out Ulp25. The serial data out at Ulp25 is normally marking (logical 1 = +5v). It drives two inputs on DS6 (pins 2 and 13). Depending on whether the CPU has selected the I/O or the printer as the destination port (via CPUp31 to D.S.6pl) the serial data will emerge at either DS6pl2 or DS6p4. Printer port serial data at DS6p4 drives a TTL to RS232C level converter consisting of R18, 19, 20 and Q7. The RS232C output of this circuit drives an external printer via pin 14 of the 25 pin EIA connector (I/O Conn p 14). The operation of the printer port is described further in Section 4.7 below. Serial data emerging at DS6p12 provides one of the five inputs to CR2 (control ROM). Table 4.1 lists the other inputs and outputs of CR2. Figure 4.1 illustrates the operation of CR2. In the on line, half duplex mode serial data at CR2p14 is passed on to both CR2p4 (for transmission out of the MIME-I via OA2p8 and I/O Conn p 2 for RS232C or via ISO2, FWB2 and I/O Conn p 10, 11 for loop out and CR2p1 for internal echo. Note that if the current loop interface has been enabled and no current is flowing in the loop in of the MIME-I CR2p12 will be low and will prevent the internal echo of data in either the half duplex or local modes due to the manner in which these signals are gated internally in CR2.

| INPUTS TO CR2                | PIN # |

|------------------------------|-------|

| I/O Serial Data Out (H=Mark) | 14    |

| I/O Serial Data In (L=Mark)  | 13    |

| Current Loop In (L=Mark)     | 12    |

| Line/Local (H=Line)          | 11    |

| Full/Half Duplex (H=Full)    | 10    |

| OUTPUTS OF CR2               |       |

| Serial Data In (To UART)     | 1     |

| Current Loop Out (L=Mark)    | 2     |

| Line/Local (L=Line)          | 3     |

| Serial Data Out (L=Mark)     | 4     |

Table 4.1: Inputs and Outputs of CR2

Figure 4.1: CR2 Functional Diagram

#### 4.2.2 Full Duplex Operation

In the full duplex mode serial data at CR2p14 is routed only to CR2 pins 2 and 4. There is no internal echo unless the LINE/LOC $\cdot$  switch is in the LOC(al) position.

### 4.3 RS232C Interface

Two of the four operational amplifiers in OA2 are used to provide an RS232C line driver and receiver. Serial data at Ulp25 is routed to CR2p4 as described in the previous paragraphs. When Ulp25 is in the mark (logical 1) state CR2p4 and OA2p9 are low (zero volts). OA2p10, 6, 2 and 13 are all held at approximately 1.5 volts by the voltage divider circuit of R15 and R16. This voltage provides a threshold reference for all four amplifiers in OA2. The combination of a low level at OA2p9 and a higher level at OA2p10 forces OA2p8 to -12 volts (an RS232C mark). When Ulp25 is in the space state OA2p8 is high (+5 volts). The BREAK key holds the serial output in the space state when it is depressed.

RS232C serial data into the MIME-I at I/O Conn p 3 is fed to OA2p5 where it is compared to the 1.5 volt reference. When no connection is made to I/O Conn p 3 R28 holds that line in mark state.

### 4.4 Block Mode Transmission in LOCAL Mode

When operating in the LOCAL mode CR2 echoes data back to the receiver half of the UART for immediate display and no data is sent out the MIME-I serial out lines (RS232C or Current Loop) until the SEND key is depressed either alone or in conjunction with the SHIFT key. Depressing the SEND key forces the MIME-I into the LOCAL mode and also sends the code IC hex to the UART receiver.

The F8 recognized this and sends all of the full intensity characters on the line containing the cursor. This is accomplished by pulling the select line of DS4 and DS5 and CR2pll high. This allows the F8 data bus to drive the UART transmitter buffer inputs and also forces the I/O circuit into the line mode regardless

of the position of the LINE/LOC<sup>•</sup> switch.

Before sending each character in the block mode the F8 samples the Data Set Ready (DSR) line at pin 6 of the I/O Connector and will not transmit until this line assumes the high state. If the external device (modem or computer) does not use this line to indicate readiness R25 will hold the line high to permit transmission. If for some reason I/O Conn p 6 is grounded and a SEND or SHIFT SEND operation is initiated the MIME-I will enter an "infinite loop" waiting for this line to rise. When transmission is completed the MIME-I sounds its beeper.

4.5 UART Clock Generation

The clock rates of 16 times (16x) the desired serial bit (baud) rate are generated by a digital divide-down chain which is driven by the dot-oscillator of the MIME-I. This dot oscillator's frequency is 9.828 MHz.

A 7493 divide-by-eight counter, CNT7, provides a 1.2 MHz square wave into CNT9. CNT9 is a binary counter that divides the 1.2 MHz signal from CNT7 by successive factors of two and yields the 16x clock rates for 9600 B/S to 300 B/S at the following pins:

| Data Rate (Bits/sec) | 16x Clock Frequency (KHz) | Origin  |

|----------------------|---------------------------|---------|

| 9,600                | 153.6                     | CNT9p6  |

| 4,800                | 76.8                      | CNT9p5  |

| 2,400                | 38.4                      | CNT9p3  |

| 1,200                | 19.2                      | CNT9p2  |

| 600                  | 9.6                       | CNT9p4  |

| 300                  | 4.8                       | CNT9p13 |

| 110                  | 1.76                      | CNT8p6  |

Note that the 16x clock for the 110 baud rate is obtained by dividing the 1200 baud 16x rate by 11 with CNT8 and A6. A common problem that arises with the MIME-I I/O circuits is for the user to position the baud select switch in the null position. Be sure to refer to your operating manual to assist in selecting the data rate.

### 4.6 Bell Circuit

When the MIME-I receives a bell code (07 hex), completes a SEND or SHIFT SEND operation or removes the cursor from the screen in the hold screen mode it sounds an audible tone. The F8 causes a negative going pulse to appear at CR1p1 and N6p13. This pulse triggers the one-shot whose output at N6p11 gates the 16x 110 baud UART clock of 1760 Hz through A6p1 to Q10 which drives the speaker. The tone lasts for about one half of a second.

### 4.7 Printer Port

The unidirectional printer port of the MIME-I provides a serial RS232C output signal at pin 14 of the 25 pin I/O connector. Serial data out of the UART at Ulp25 is routed through DS6p4 to R20 which is tied to the base of Q7. A high level (mark) at Ulp25 and DS6p4 cuts off Q7 and I/O Conn p 14 is then pulled to -12 volts by R18. A low level at Ulp25 and DS6p4 turns Q7 on and pulls I/O Conn p 14 high. When the F8 routes the serial data through DS6 to the printer output interface it also routes the printer baud rate clock from J2p15 to Ulp17 and 40. Printer readiness is reported at I/O Conn p 24. Before transmitting each character during a PRINT operation the F8 samples this printer ready line and suspends transmission if it is low. If no connection is made to this pin the F8 will assume the printer is ready.

### 4.8 Current Loop Interface

The current loop interface consists of two full wave bridges and two optical isolators. When the MIME-I serial output at Ulp25 is marking (High) CR2p2 is low, the LED in the optical isolator is on and causes the isolator transistor to conduct. This transistor combines with Q8 to form a Darlington pair which drives the full wave bridge such that current will flow in either direction through the AC inputs to the bridge. When the serial output is spacing (low) the LED in the optical isolator is cut off and no current will flow in either direction through the AC inputs of the bridge.

### 5. CPU - PROCESSOR CIRCUITS

The following integrated circuits are considered to be integral components of the microprocessor which controls and defines the MIME-I: CPU(F8 3850 microprocessor), SMI (3853 Static Memory Interface), MPB,MPT (Master Control Roms -2708), CR1 (Control Rom 1), and the gates in N5 and N6.

Familiarity with microprocessor concepts and practices in general and those of the F8 in particular are helpful -- if not mandatory -- in understanding the discussion that follows. The interested reader should refer to the F8 Users Guide (published by Fairchild Semiconductor, a division of Fairchild Camera and Instrument Corporation, 464 Ellis Street, Mountain View, California 94042) for detailed descriptions of the F8 operation not included in this manual.

5.1 Data Bus Control

In order for the F8 to completely control the functioning of the MIME-I it is interconnected to the other circuits in a number of ways. These interconnections permit the F8 to perform the functions described in the following sections.

The principal channel of communication between the F8 and the other circuits in the MIME-I is the 8-bit bi-directional data bus. Devices connected to this bus are categorized as either drivers (sources) or receivers (sinks). Some devices possess both source and sink capabilities. Devices connected to the data bus and their capabilities are:

| DRIVER | RECEIVER    |

|--------|-------------|

| Х      | х           |

| X      | Х           |

| Х      | Х           |

| Х      | Х           |

| Х      |             |

|        | X<br>X<br>X |

Selection of the data bus driver/receiver pair at any given time is controlled by the three most significant SMI address lines (Al3, 14 and 15), CPU Read (SMIp34) and RAM Write (SMIp6). All of these signals provide inputs (addresses) to CR1. CR1 decodes these input signals and produces outputs under the circumstances given in Figure 5.1 and Table 5.1.

The next few paragraphs contain explanations of the actions caused by the eight outputs of CR].

### <u>PIN 1:</u>

A negative going pulse out of this pin triggers the one-shot whose output at N6pll enables the 110 baud UART clock (1760 Hz) to drive the speaker and produce an audible beep when the MIME-I receives the Bell code or when block transmission to either the host computer or the local printer terminates.

PIN 2: Incr Row Offset Pointer (C6)

When the MIME-I scrolls all data in the RAM memory locations corresponding to the top row of the display is changed to an ASCII SPACE (code 20 Hex) and the Row Offset Pointer (ROP) is incremented. Incrementing the ROP causes the old second line to be displayed at the top of the screen while the old top line "moves" to the bottom of the display. Increment pulses from the F8 are OR-ed with those from the display circuit at OR1p8 and C6p1. Increment pulses from the F8 occur during the Horizontal retrace period and therefore do not collide with increment pulses from the display circuit.

PIN 3: Read Master Control ROMs (MPB, MPT)

The 2048 word Master Control ROMs of the MIME-I reside in the first 2k of the 65k address space of the F8. Any reference to these locations (0-7FF) by the F8 results in CR1p3 producing a negative going pulse that allows the MCR to drive the data bus. All is used in conjunction with CR1p3 to select either MPB (0-3FF) or MPT (400-7FF).

### PIN 4: Read Display RAM

This line goes low to enable the Display RAM to drive the F8 data bus. This takes place each time a displayable character is received by the I/O UART and read into the F8. First the location pointed to by the cursor is loaded with the received character and a low (off) cursor bit. Then the next position to be pointed to by the cursor is read in and written back with a high (on) cursor bit. The display RAM is also read during SEND and PRINT operations.

### PIN 5: Write to RAM

A negative going pulse on this line causes the data placed on the F8 data bus during the execution of an F8 STORE instruction to be loaded into the display RAM in the location specified by the F8 Data Counter. F8 access to the display RAM is restricted to Horizontal and Vertical Sync periods. Hence the display RAM appears to have a 64 usec access time to the F8.

### PIN 6: Read I/O UART

A negative going pulse here causes the I/O UART to drive the F8 data bus with the contents of its receiver holding register. This operation is performed each time the I/O UART receives a character and the F8 reads it.

### PIN 7:

This line, in conjunction with the "blank the display line" at CPUplO and the dot oscillator enable line (FFlapl2), controls the address multiplexer to the display RAM (DSl,2,3). This line is asserted whenever the F8 reads or writes data from or to the RAM.

### PIN 9: Write to UART

This line in conjunction with Bit 0 of I/O port 1 controls transmission of parallel data to the UART. The write pulse emanating from CR1p9 drives the multiplexer on the Data Strobe ( $\overline{\text{DS}}$ ) line of the transmitter in the I/O UART. The LSB of I/O Port Ø in the F8 (CPUp16) is tied to the select lines of the

Figure 5.1: CR1 Connections

|                | SMI | INPUT<br>SMI | SMI   | RAM   | 2 OUTPUTS OF CR1 | WRITE TO UART | ACCESS RAM | READ UART | WRITE TO RAM | <u>READ</u> RAM | READ MP (Bor T) | INCR CNT 6 | RING BELL |

|----------------|-----|--------------|-------|-------|------------------|---------------|------------|-----------|--------------|-----------------|-----------------|------------|-----------|

| OPERATION      | A13 | <u>A14</u>   | A15   | WRITE | READ             | _             |            |           |              |                 |                 |            |           |

| Read MP(Bor T) | 0   | 0            | 0     | ]     | 1                | 1             | 0          | 1         | 1            | I               | ] ]             | 0          | ר         |

| Ring Bell      | 1   | 1            | 1     | 0     | 0                | 1             | 0          | 1         | 1            | 1               | 0               | 0          | 0         |

| Read RAM       | 0   | 1            | 0     | 1     | 1                | 1             | 1          | 1         | 1            | 0               | 0               | 0          | 1         |

| Write to RAM   | 0   | 1            | 0     | 0     | 0                | 1             | 1          | 1         | 0            | 1               | 0               | 0          | ]         |

| Read UART      | 0   | 0            | 1     | 1     | 1                | 1             | 0          | 0         | 1            | 1               | 0               | 0          | 1         |

| Write to UART  | 0   | 0            | 1     | 0     | 0                | 0             | 0          | 1         | 1            | 1               | 0               | 0          | ר         |

| Incr CNT 6     | 1   | 0            | 0     | 0     | 0                | 1             | 0          | 1         | 1            | ר               | 0               | 1          | ר         |

| NONE           |     | AL           | L OTH | ERS   |                  | 1             | 0          | 1         | 1            | 1               | 0               | 0          | 1         |

Table 5.1: Inputs and Outputs of CR1

multiplexers feeding data and strobe signals to the I/O UART's transmitter. When the F8 raises this line high write pulses to the UART will load the data on the F8 data bus into the UART for transmission to either the host computer via pin 2 of the EIA I/O connector or to the printer via pin 14 of the EIA I/O connector. This line is normally low when the MIME-I is in the (on) LINE mode. Hence the keyboard drives the UART transmitter unless the MIME-I receives a request for cursor position. Receipt of this code causes the F8 to take control of the I/O transmitter by raising CPUp16 while transmitting the values of the row and column counters. In the LOCAL mode the select line from CPUp16 remains low until the SEND key is depressed on the keyboard. The F8 then takes control of the I/O transmitter while sending data out the RS232C interface to pin 2 of the EIA connector. During this period the MIME-I's Data Terminal Ready (DTR) line at pin 20 of the I/O connector is held low to indicate that it is busy transmitting data and is ignoring characters received at the UART until the transmission is complete.

#### 5.2 CPU I/O Port Assignments

The F8 uses its two 8-bit bi-directional I/O ports to observe and control the state of the MIME-I. A description of the electrical characteristics of the F8 I/O ports can be found in the F8 Users Guide published by Fairchild. The I/O port assignments and a description of their uses are as follows:

### 5.2.1 I/O Port Ø

<u>Bit Ø (CPUp16)</u>: UART Transmitter select. This line controls whether the keyboard or the F8 drives the UART transmitter buffer. A high level selects the F8 and a low level selects the keyboard.

<u>Bit 1 (CPUp11</u>): Intensity Bit to RAM. This line provides the intensity information to the display RAM when characters are written to it. A high level indicates full intensity (unprotected data) and a low level indicates half intensity (protected field). Intensity information is read back from the display RAM to the F8 on the MSB of the data bus.

<u>Bit 2 (CPUp10)</u>: Display Blanking. When this line goes low the video output to the CRT is blanked. This is done when the F8 performs operations that require display RAM access at times other than during horizontal retrace (add or delete a line are two examples).

<u>Bit 3 (CPUp5</u>): DTR. This line drives pin 20 (Data Terminal Ready) of the 25 pin I/O connector through an Operational Amplifier (OA2) to indicate readiness on the part of the MIME-I to accept data. This line goes low during a SEND or PRINT operation and remains high otherwise.

<u>Bit 4 (CPUp36</u>): Transmitter Buffer Empty/End of Character (TBE/EOC). This line is pulled low by the UART when it is busy transmitting a character. The F8 senses this and suspends transmission of characters to the UART until it returns high.

<u>Bit 5 (CPUp31</u>): UART Select. This line controls the multiplexer (DS6) that routes either the I/O baud rate clock (from B.R.S.1) or the printer baud rate clock (from J2p15) to the UART clock pins (40 and 17). It also routes the UART serial output (from U1p25) to either the printer output at I/O connector pin 14 (via R20 and Q7) or to pin 14 of the I/O control rom (CR2). If the MIME-I is in the LINE mode the serial data emerges at CR2p4 and drives I/O connector pin 2 (RS232 data out) through Op. Amp 2. The UART select line also chooses either the Data Set or printer ready lines to pass on to CPUp7 -- see description below.

<u>Bit 6 (CPUp30</u>): Terminal Option Switch 3. This line reports the status of T.O. Sw. 3 to the F8. When low (T.O Sw. 3 = 0) the selected terminal is not enhanced. When high the terminal selected is enhanced.

<u>Bit 7 (CPUp25</u>): Display Column Address 7. This input line is sampled by the F8 to detect the advent of the horizontal sync pulse.

5.2.2 I/O Port 1

Bit  $\emptyset$  (CPUp27): Character Origin. This input line is driven by FF3pl3 to indicate whether the most recently received character was from the MIME-I or from the remote computer.

<u>Bit 1 (CPUp13)</u>: Reset Row Offset Pointer. During the power on sequence this line is pulsed low when the F8 senses the display has entered the displayoff period prior to the start of the next vertical scan. This pulse is inverted at N4pll and applied to the reset line of Cnt 6 (p2). Resetting the Row Offset Pointer in this manner establishes an agreement as to the row address of the first line of characters between the display and loading circuits.

<u>Bit 2 (CPUp8</u>): Terminal Option Switch 2. This line reports the position of T.O. Sw. 2 to the F8 to allow it to determine the type of terminal desired.

<u>Bit 3 (CPUp7</u>): Computer/Printer Ready. This line is driven by DS6p7 which is the translated ready signal. A high level at CPUp7 indicates readiness on the part of the computer or printer to accept data.

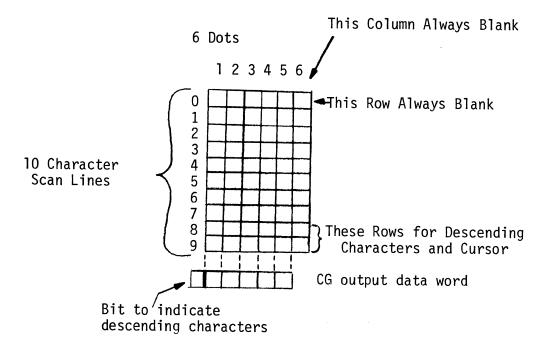

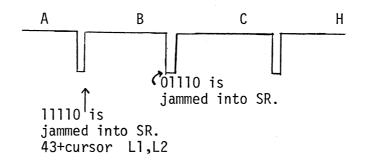

Bit 4 (CPUp<sub>34</sub> Not Used.