# MEMOREX

3672 Storage Control Unit Theory of Operations Manual Publication Number 3672.21-00 and Publication Bulletin Number 3672.21-0001

Part Number

304065

November 1975 edition

The information in this publication is subject to periodic revisions and to updates by Publications Bulletins. A bulletin is identified as Publication Number 3672.21-00XX, where "XX" equals "01" for the first bulletin released.

To request copies of this publication or any bulletin, send a Supplies Requisition (form number 7020) using the publication number to: Memorex Corporation, Marketing Distribution Center, San Tomas at Central Expressway, Santa Clara, California 95052.

A readers' comments form is provided at the back of this publication. If the form has been removed, please send comments to Memorex Corporation, Department 6940, M/S 14-07, San Tomas at Central Expressway, Santa Clara, California 95052.

©1974, 1975, MEMOREX CORPORATION

## **PREFACE**

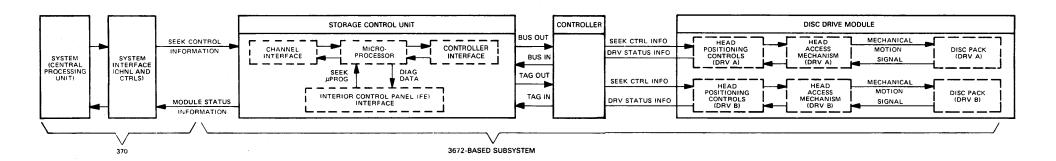

This manual provides the Memorex Field Engineer (FE) with detailed operating theory about the 3672 Storage Control Unit, used in 3672-based disc storage subsystems with the 3673 Disc Drive Controller and 3670/3675 Disc Drive Modules. It is intended for use by the FE during training as essential course material, and during servicing as an aid in identifying equipment difficulties. The manual consists of six sections:

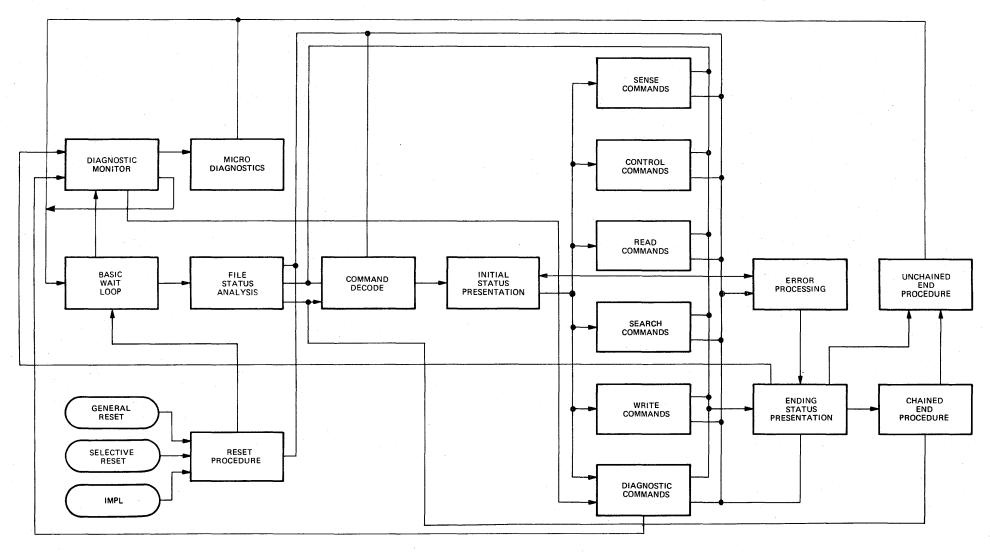

- Section 1 Describes briefly the overall functions performed by the 3672 Storage Control Unit and the 3672-based subsystem.

- Section 2 Describes commands executed by the 3672. Includes command format and summary information, and a detailed flow diagram of each command.

- Section 3 Presents details about the 3672/channel interface.

- Section 4 Contains a description of the microinstructions and microprograms used to execute commands.

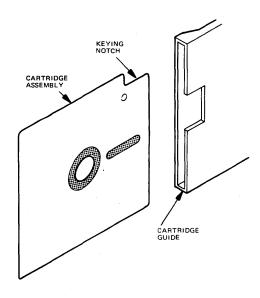

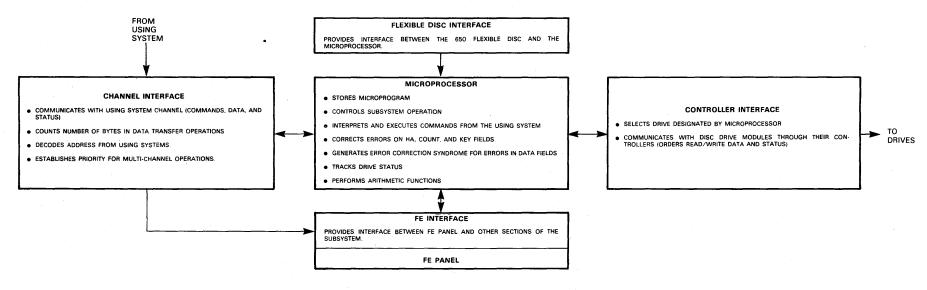

- Section 5 Describes operation of the 650 Flexible Disc File, used to store operating and diagnostic microprograms executed by the 3672.

- Section 6 Describes the detailed operation of the 3672 logic.

Maximum benefit of this manual is achieved when used with the 3672 Storage Control Unit Logic Diagram Manual, P/N 308312. The alphanumeric numbers which appear in each functional block of the block diagrams in Section 6 refer to corresponding pages of logic in the Logic Diagram

Other manuals that support the 3672 Storage Control Unit which may be of use to the FE are listed below:

3672.22-00 — 3672 Storage Control Unit Installation Manual

3672.20-00 - 3672 Storage Control Unit Maintenance Manual

3672.50-01 — 3672 Storage Control Unit Microdiagnostics Reference Manual (two volumes)

# **TABLE OF CONTENTS**

| Section |         |                                           | Page | Section |                                     | Page         |

|---------|---------|-------------------------------------------|------|---------|-------------------------------------|--------------|

| 1       | GENERA  | AL DESCRIPTION                            | 1-1  |         | SEEK CYLINDER                       | 2-8          |

|         | 1.1     | SCOPE                                     | 1-1  |         | SEEK HEAD<br>SPACE COUNT            | 2-8<br>2-9   |

|         | 1.1     | SUBSYSTEM CHARACTERISTICS                 | 1-1  |         | RECALIBRATE                         | 2-9<br>2-10  |

|         | 1.3     | STANDARD FEATURES                         | 1-1  |         | RESTORE                             | 2-10         |

|         | 1.4     | OPTIONAL FEATURES                         | 1-1  |         | SET FILE MASK                       | 2-12         |

|         | 1.5     | COMPATIBILTY                              | 1-3  |         | DIAGNOSTIC LOAD                     | 2-14         |

|         | 1.6     | SPECIFICATIONS SUMMARY                    | 1-3  |         | DIAGNOSTIC WRITE                    | 2-15         |

|         | 1.7     | UNIT CHARACTERISTICS                      | 1-3  |         | -                                   |              |

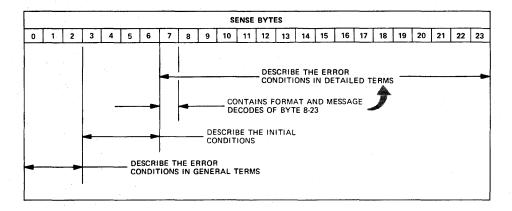

|         | 1.7.1   | 3672 Storage Control Unit                 | 1-3  | 2.5     | SENSE COMMANDS                      | 2-16         |

|         | 1.7.2   | 3673 Disc Drive Controller                | 1-4  | 2.5.1   | Sense Byte Information              | 2-16         |

|         | 1.7.3   | 3670 (3675) Disc Drive Module             | 1-4  | 2.5.2   | Sense Control Block                 | 2-16         |

|         | 1.8     | DATA INTERFACE REQUIREMENTS               | 1-6  | 2.5.3   | Sense Byte Bit Definitions          | 2-16         |

|         |         | D/11/1 1111 2111 / 102 112 2011 2111 2111 | . •  | 2.5.4   | Assembling Sense Bytes 8 through 23 | 2-16         |

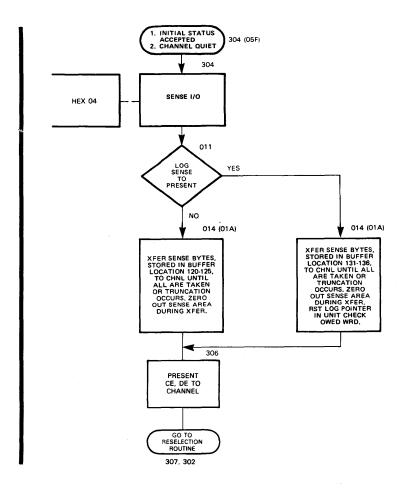

|         |         |                                           |      | 2.5.5   | Command Descriptions SENSE I/O      | 2-16         |

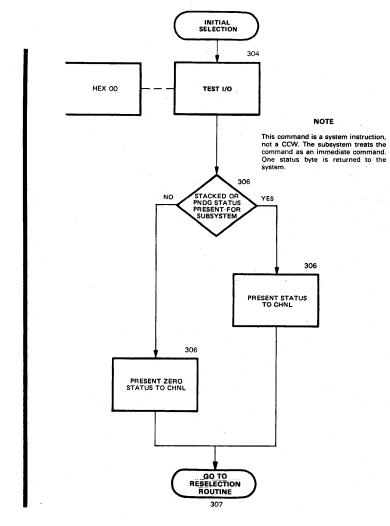

| 2       | COMMA   | NDC                                       | 2-1  |         | TEST I/O                            | 2-21<br>2-22 |

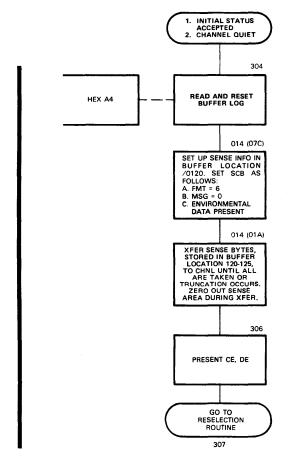

| 2       | COMINIA | NDS                                       | 2-1  |         | READ AND RESET BUFFERED LOG         | 2-22         |

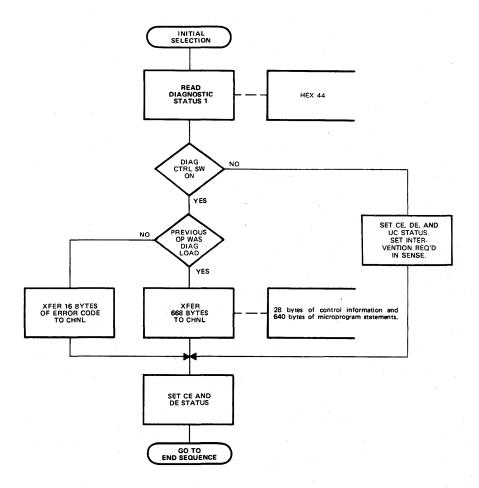

|         | 2.1     | GENERAL                                   | 2-1  |         | READ DIAGNOSTIC STATUS 1            | 2-23         |

|         | 2.2     | COMMAND SUMMARY                           | 2-1  |         | DEVICE RESERVE                      | 2-25         |

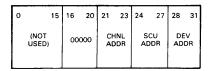

|         | 2.3     | INSTRUCTION AND WORD FORMAT               | 2-1  |         | DEVICE RELEASE                      | 2-25         |

|         | 2.3.1   | Introduction                              | 2-1  | 2.5.6   | Transfer In-Line Diagnostics to SCU | 2-26         |

|         | 2.3.2   | I/O Instructions                          | 2-1  | 2.5.6.1 | Introduction                        | 2-26         |

|         | 2.5.2   | START I/O                                 | 2-1  | 2.5.6.2 | System                              | 2-26         |

|         |         | START I/O FAST RELEASE                    | 2-1  | 2.5.6.3 | Channel                             | 2-26         |

|         |         | TEST I/O                                  | 2-1  | 2.5.6.4 | Channel Interface                   | 2-26         |

|         |         | HALT I/O                                  | 2-1  | 2.5.6.5 | Storage Control Unit (SCU)          | 2-26         |

|         |         | HALT DEVICE                               | 2-1  | 2.5.6.6 | Control Storage                     | 2-26         |

|         | 2.3.3   | Channel Address Word                      | 2-1  | 2.6     | READ COMMANDS                       | 2-27         |

|         | 2.3.4   | Channel Command Word                      | 2-3  | 2.6.1   | Operation Block Diagram             | 2-27         |

|         | 2.3.5   | Channel Status Word                       | 2-3  | 2.6.1.1 | System                              | 2-27         |

|         | 2.3.5.1 | Status Presentation                       | 2-4  | 2.6.1.2 | Channel                             | 2-27         |

|         | 2.3.5.2 | Initial Status                            | 2-4  | 2.6.1.3 | Channel Interface                   | 2-27         |

|         | 2.3.5.3 | Ending Status                             | 2-4  | 2.6.1.4 | Microprocessor                      | 2-27         |

|         | 2.3.5.4 | Pending Status                            | 2-4  | 2.6.1.5 | Controller                          | 2-27         |

| _       | 2.3.5.5 | Contingent Connection                     | 2-4  | 2.6.1.6 | Read Circuit                        | 2-27         |

|         | 2.3.6   | Program Status Word                       | 2-4  | 2.6.1.7 | Read/Write Head                     | 2-27         |

| 1       | 2.4     | CONTROL COMMANDS                          | 2-5  | 2.6.1.8 | Pack                                | 2-27         |

| 1       | 2.4.1   | Operational Block Diagram                 | 2-5  | 2.6.2   | Command Descriptions                | 2-27         |

|         | 2.4.1.1 | System                                    | 2-5  |         | READ DATA                           | 2-28         |

| _       | 2.4.1.2 | System Interface                          | 2-5  |         | READ KEY AND DATA                   | 2-28         |

|         | 2.4.1.3 | Storage Control Unit                      | 2-5  |         | READ COUNT, KEY, AND DATA           | 2-29         |

|         | 2.4.1.4 | Drive Controller                          | 2-5  |         | READ RECORD ZERO                    | 2-32         |

|         | 2.4.1.5 | Disc Drive Module                         | 2-5  |         | READ COUNT                          | 2-32         |

|         | 2.4.2   | Command Descriptions                      | 2-5  |         | READ HOME ADDRESS                   | 2-33         |

|         |         | NO-OP                                     | 2-7  |         | READ IPL                            | 2-36         |

|         |         | SEEK                                      | 2-7  |         | READ SECTOR                         | 2-36         |

| Section |          |                                       | Page         | Section | on      |                                          | Pa  | ge         |

|---------|----------|---------------------------------------|--------------|---------|---------|------------------------------------------|-----|------------|

|         | 2.6.2    | Read Data Transfer                    | 2-38         |         | 2.11.7  | Index Detected in Data Field             | 2-6 | 84         |

|         | 2.6.4    | Read Diagnostic to System             | 2-38         |         | 2.11.8  | Command Retry Flowcharts                 | 2-6 |            |

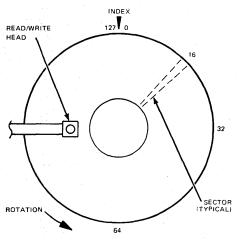

|         | 2.6.4.1  | Introduction                          | 2-38         |         | 2.12    | ROTATIONAL POSITION SENSING              | 2-3 | -          |

|         | 2.6.4.2  | System                                | 2-38         |         | 2.12.1  | Introduction                             | 2-  |            |

|         | 2.6.4.3  | Channel                               | 2-38         |         | 2.12.2  | Read Sector                              | 2-  |            |

|         | 2.6.4.4  | Channel Controls                      | 2-38         |         | 2.12.3  | Set Sector                               | 2-  |            |

|         | 2.6.4.5  | 650 Drive                             | 2-38         |         | 2.12.4  | Disc and Track Layout                    | 2-  |            |

|         | 2.6.4.6  | 650 Interface                         | 2-38         |         | 2.13    | MULTITRACK OPERATION                     | 2-  |            |

|         | 2.6.4.7  | Control Storage                       | 2-38         |         | 2.14    | OVERFLOW RECORD                          | 2-8 |            |

|         | 2.6.4.7  | Control Unit                          | 2-38         |         | 2.14.1  | Introduction                             | 2-8 |            |

|         | 2.0.4.6  | WRITE COMMANDS                        | 2-42         |         | 2.14.2  | Formatting                               | 2-8 |            |

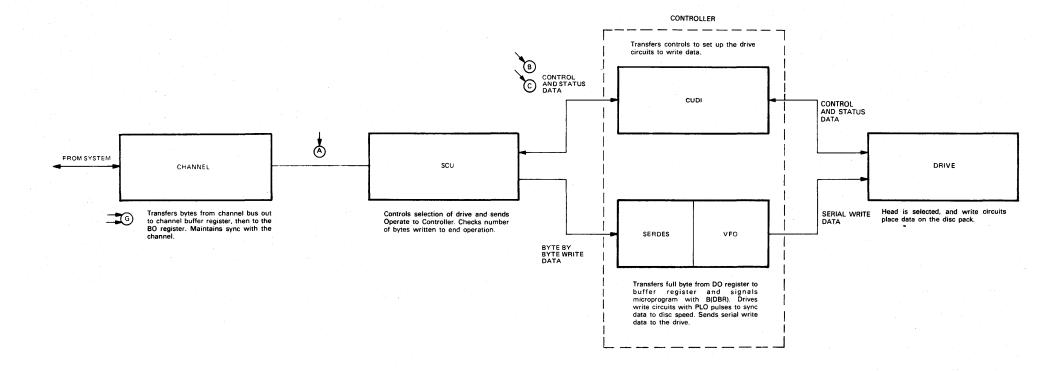

|         | 2.7.1    | Operation Block Diagram               | 2-42         |         | 2.14.3  | Processing                               | 2-8 | -          |

|         | 2.7.1    | · · · · · · · · · · · · · · · · · · · | 2-42         |         | 2.15    | MULTICHANNEL OPERATION                   | 2-8 |            |

|         |          | System<br>Channel                     | 2-42         |         | 2.10    | WOLTICHANNEL OFERATION                   | 2-0 | 21         |

|         | 2.7.1.2  | =                                     | 2-42         |         |         |                                          |     |            |

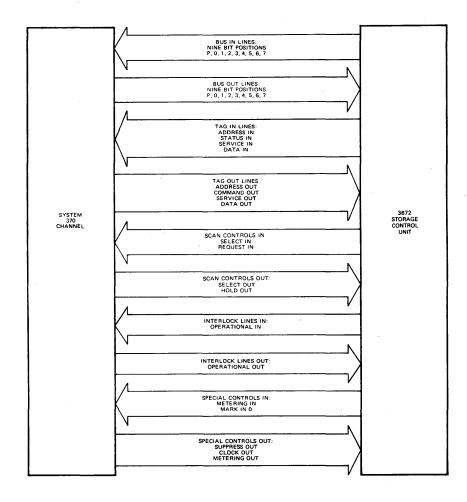

|         | 2.7.1.3  | Channel Interface                     | 2-42         | 3       | CHANNE  | LINTERFACE DESCRIPTION                   | 2   | 3-1        |

|         | 2.7.1.4  | Microprocessor                        | 2-42         | 3       | CHANNE  | LINIENPACE DESCRIPTION                   |     | )= I       |

|         | 2.7.1.5  | Controller                            | 2-43         |         | 3.1     | GENERAL                                  | ,   | 3-1        |

|         | 2.7.1.6  | Write Circuits                        |              |         |         | <del></del>                              | -   |            |

|         | 2.7.1.7  | Read/Write Head                       | 2-42<br>2-42 |         | 3.2     | CHANNEL INTERFACE LINES DESCRIPTION      |     | 3-2<br>3-2 |

|         | 2.7.1.8  | Pack                                  |              |         | 3.2.1   | Inbound Lines                            | -   | _          |

|         | 2.7.2    | Command Descriptions                  | 2-44         |         | 3.2.2   | Outbound Lines                           |     | 3-2        |

|         |          | WRITE DATA                            | 2-43         |         | 3.3     | INTERFACE SEQUENCES                      |     | 3-4        |

|         |          | WRITE KEY AND DATA                    | 2-43         |         | 3.3.1   | Overall Descriptions                     |     | 3-4        |

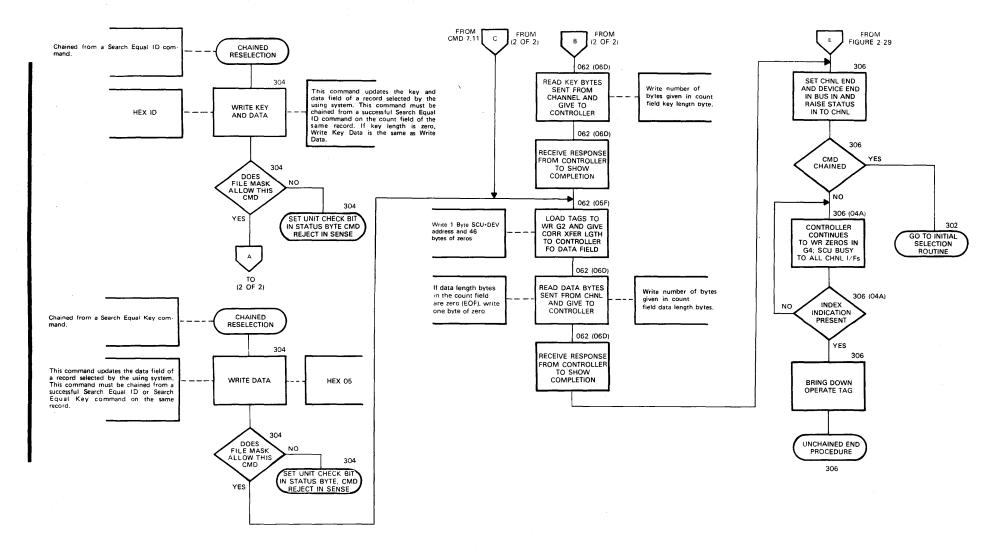

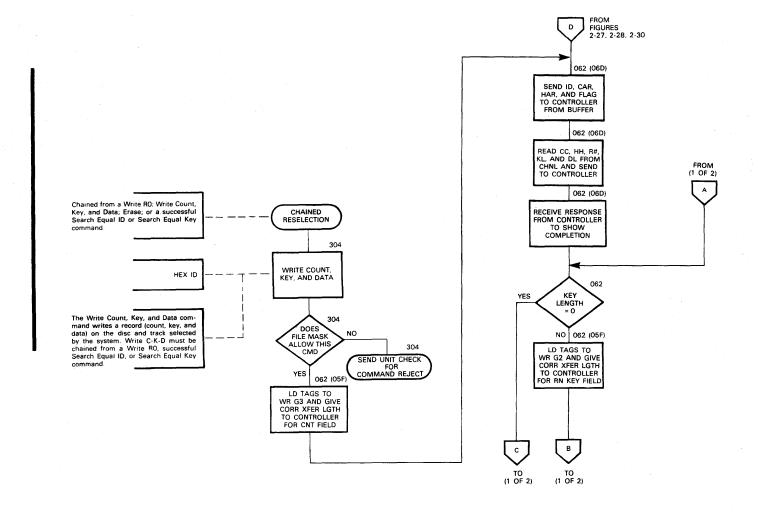

|         |          | WRITE COUNT, KEY, AND DATA            | 2-46         |         | 3.3.1.1 | Initial Selection Sequence               |     | 3-4        |

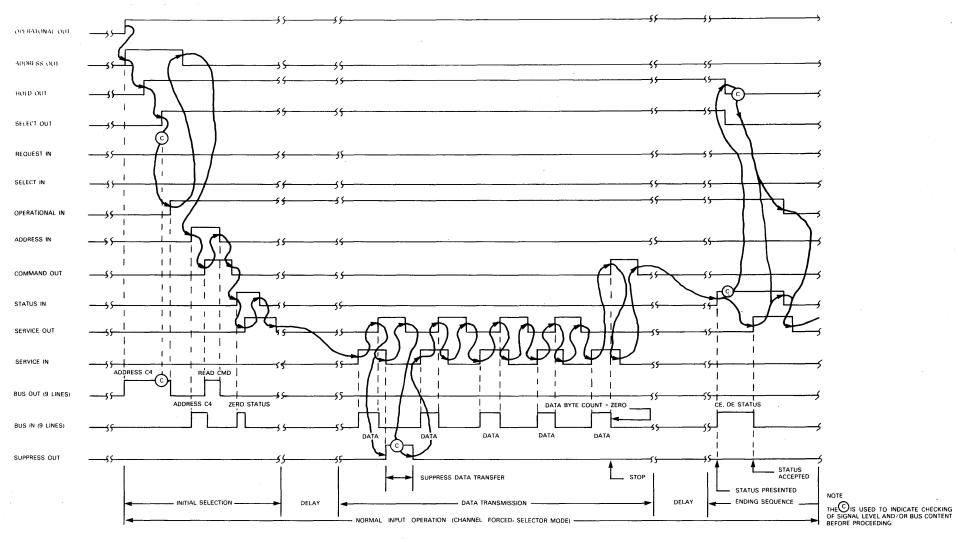

|         |          | WRITE SPECIAL COUNT, KEY, AND DATA    | 2-47         |         | 3.3.1.2 | Data Transmission Sequence               |     | 3-4        |

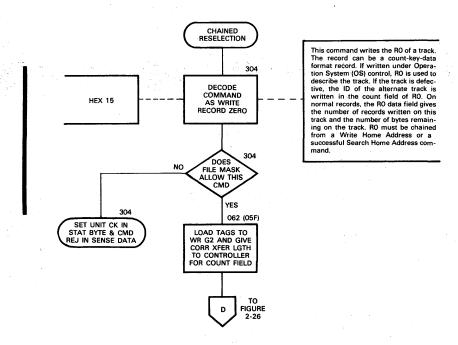

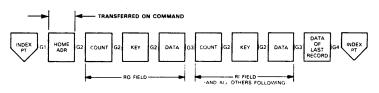

|         |          | WRITE RECORD ZERO                     | 2-48         |         | 3.3.1.3 | Ending Sequence                          |     | 3-4        |

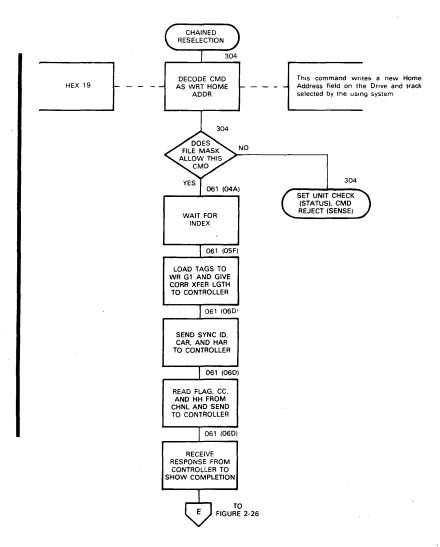

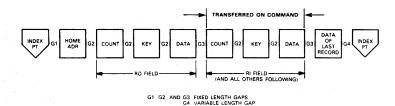

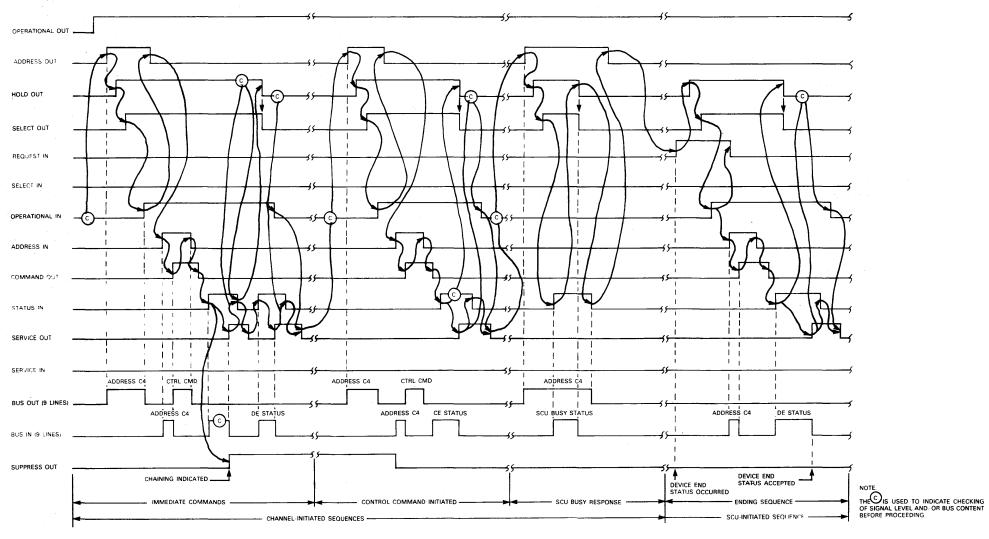

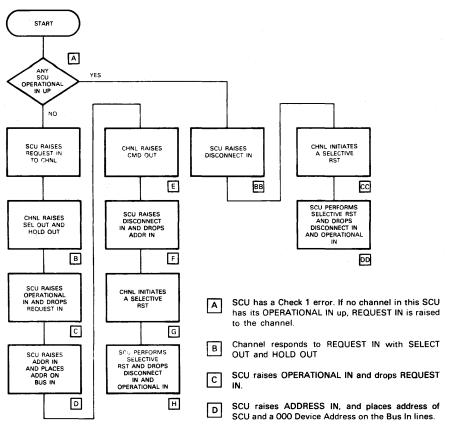

|         |          | WRITE HOME ADDRESS                    | 2-49         |         | 3.3.1.4 | SCU Busy Response                        |     | 3-4        |

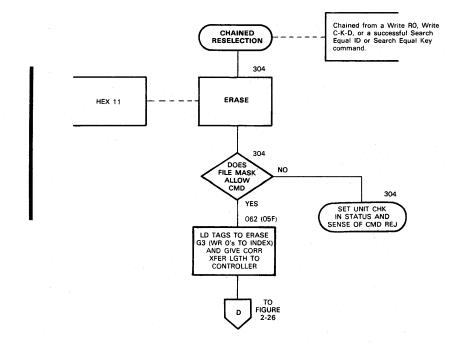

|         |          | ERASE                                 | 2-50         |         | 3.3.1.5 | SCU-Initiated Sequence                   | -   | 3-4        |

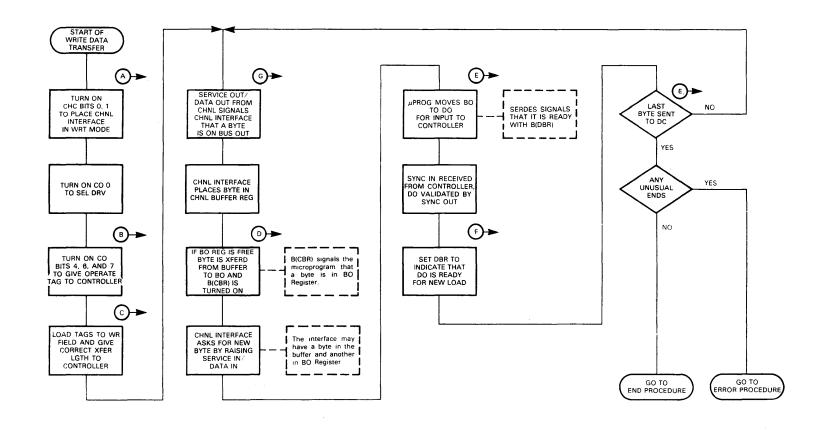

|         | 2.7.3    | Write Data Transfer                   | 2-51         |         | 3.3.1.6 | Immediate Command Sequence               |     | 3-4        |

|         | 2.8      | SEARCH COMMANDS                       | 2-54         |         | 3.3.2   | Initial Selection Sequence               |     | 3-4        |

|         |          | SEARCH HOME ADDRESS EQUAL             | 2-54         |         | 3.3.2.1 | Simplified Sequence                      |     | 3-4        |

|         |          | SEARCH ID EQUAL                       | 2-56         |         | 3.3.2.2 | Detailed Sequence                        |     | 3-6        |

|         |          | SEARCH ID HIGH                        | 2-56         |         | 3.3.3   | Ending Sequence                          |     | 3-6        |

|         |          | SEARCH ID EQUAL OR HIGH               | 2-57         |         | 3.3.3.1 | Simplified Sequence                      |     | 3-6        |

|         |          | SEARCH KEY EQUAL                      | 2-59         |         | 3.3.3.2 | Detailed Sequence                        |     | 3-7        |

|         |          | SEARCH KEY HIGH                       | 2-59         |         | 3.3.4   | Polling Sequence and Status Presentation |     | 3-7        |

|         |          | SEARCH KEY EQUAL OR HIGH              | 2-60         |         | 3.3.4.1 | Simplified Sequence                      |     | 3-7        |

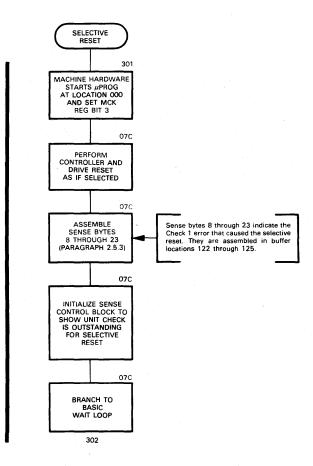

|         | 2.9      | SELECTIVE RESET                       | 2-62         |         | 3.3.4.2 | Detailed Sequence                        |     | 3-7        |

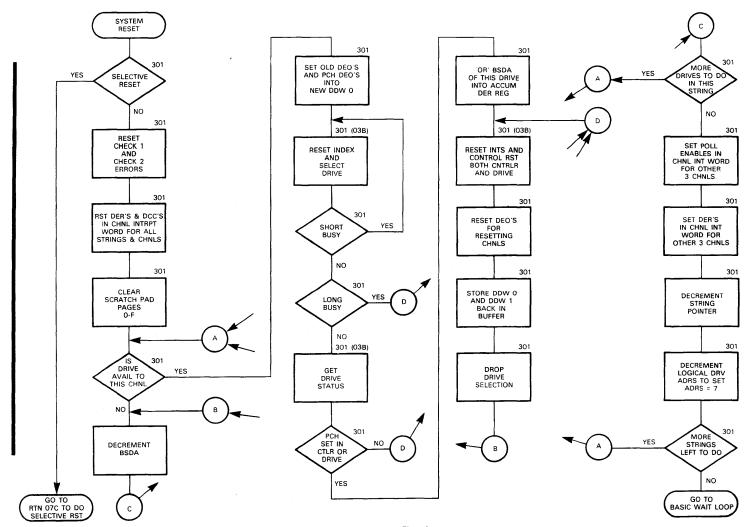

|         | 2.10     | SYSTEM RESET                          | 2-63         |         | 3.4     | CHANNEL OPERATION                        |     | 3-8        |

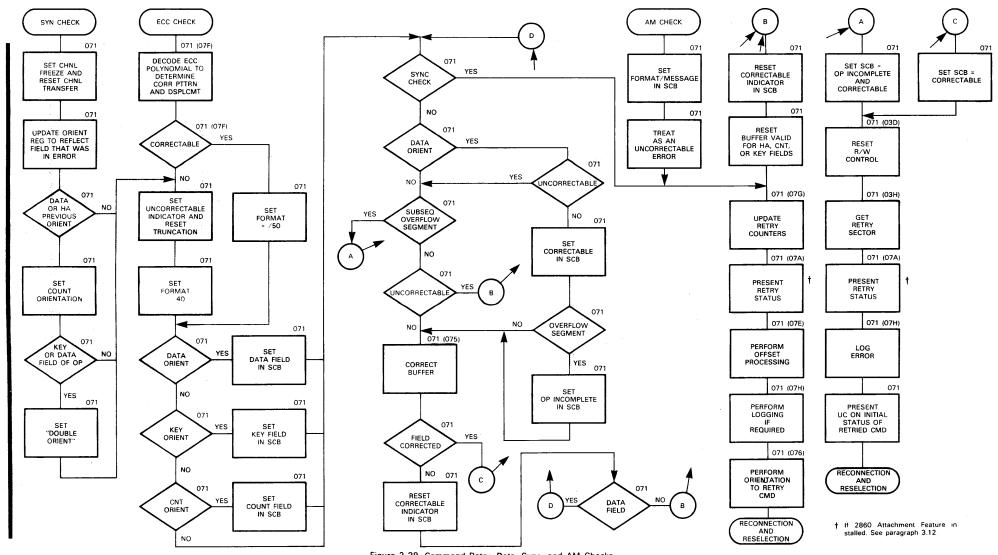

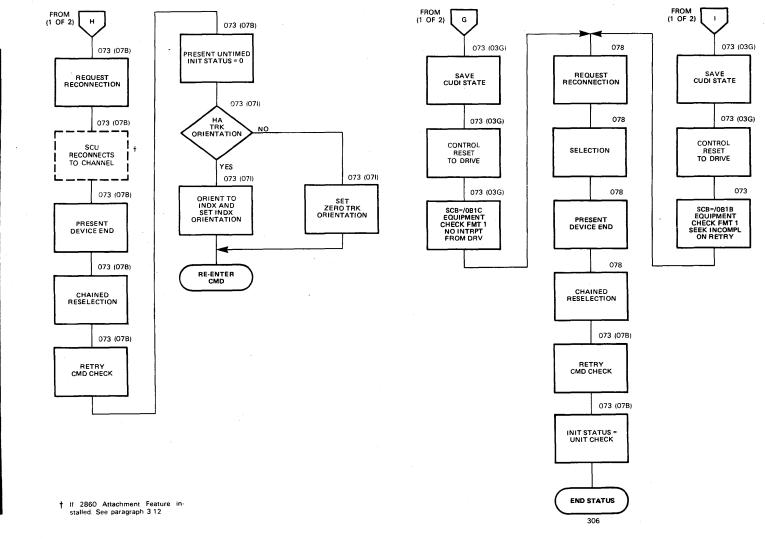

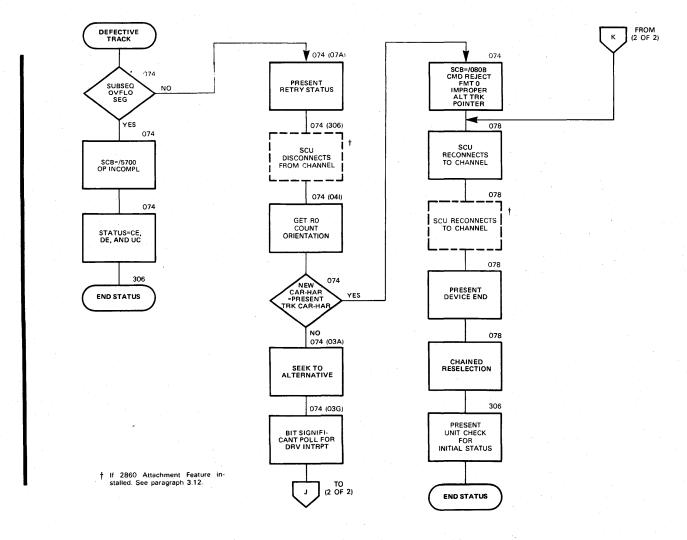

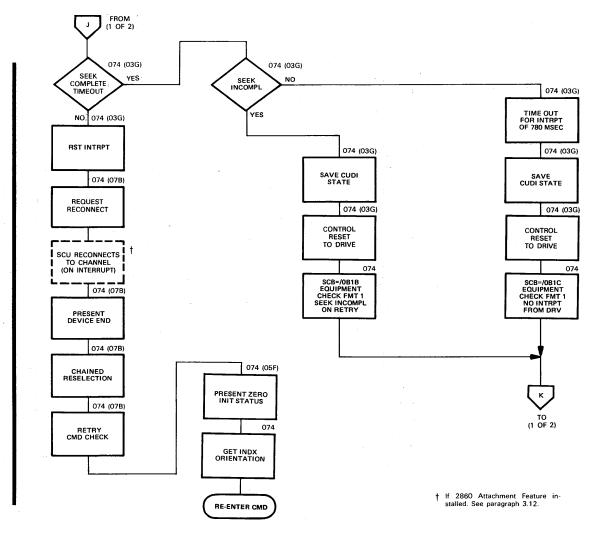

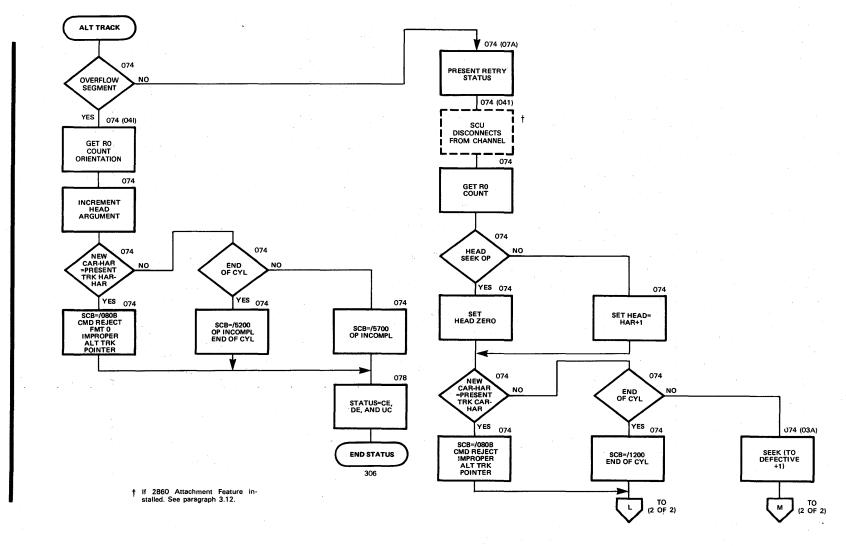

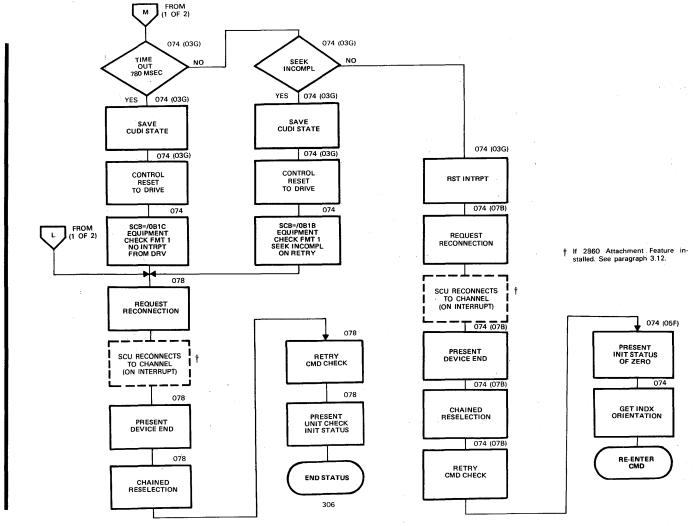

|         | 2.11     | COMMAND RETRY                         | 2-64         |         | 3.4.1   | Selector Channel Operation               |     | 8-8        |

|         | 2.11.1   | Check and Error-Initiated Retry       | 2-74         |         | 3.4.2   | Block Multiplexer Operation              |     | 8-8        |

|         | 2.11.1.1 | Data Checks                           | 2-64         |         | 3.4.2.1 | Introduction                             |     | 8-8        |

|         | 2.11.1.2 | Sync Check                            | 2-64         |         | 3.4.2.2 | Rotational Position Sensing              |     | 8-8        |

|         | 2.11.1.3 | AM Check                              | 2-64         |         | 3.4.2.3 | Disconnected Command Chaining            | -   | 8-8        |

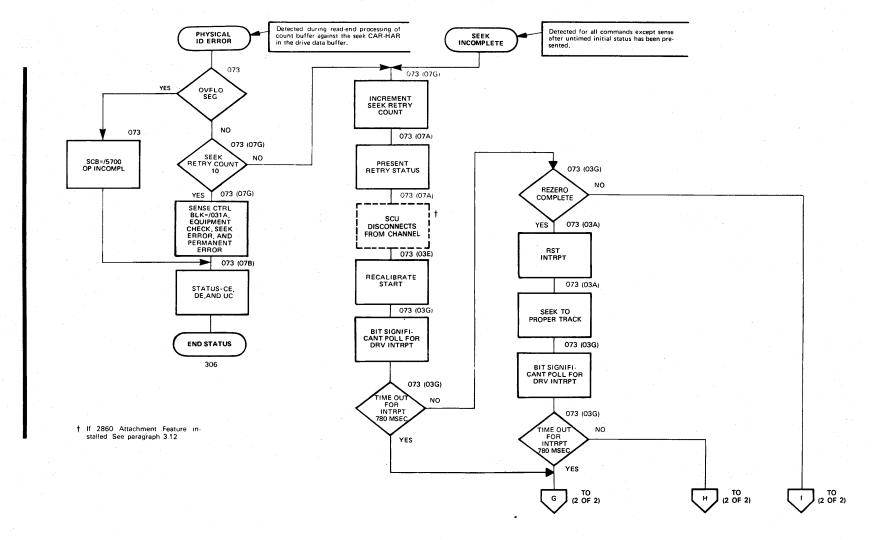

|         | 2.11.1.4 | Physical ID Error                     | 2-66         |         | 3.4.2.4 | Multiplexer Channel Operation            |     | 8-8        |

|         | 2.11.1.5 | Seek Incomplete Error                 | 2-64         |         | 3.5     | SEQUENCE CONTROLS                        |     | 13         |

|         | 2.11.2   | Defective or Alternate Track          | 2-64         |         | 3.5.1   | Command Chaining                         |     | 13         |

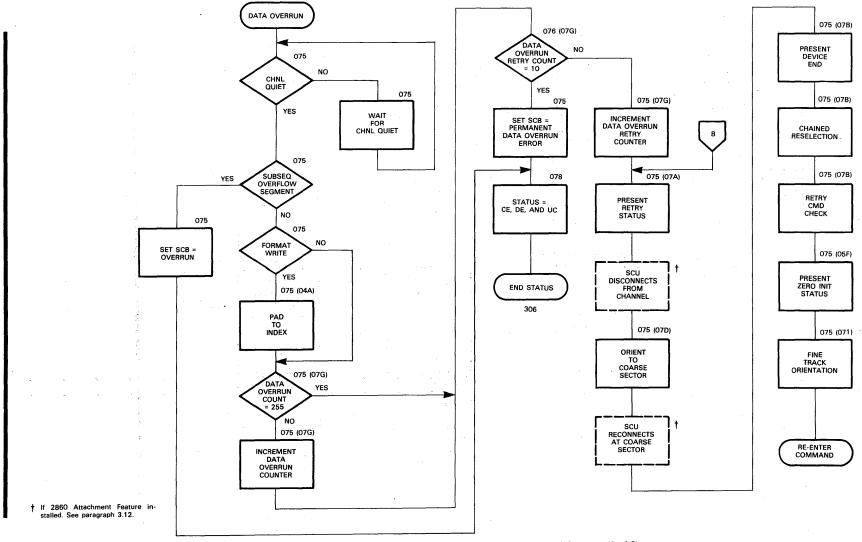

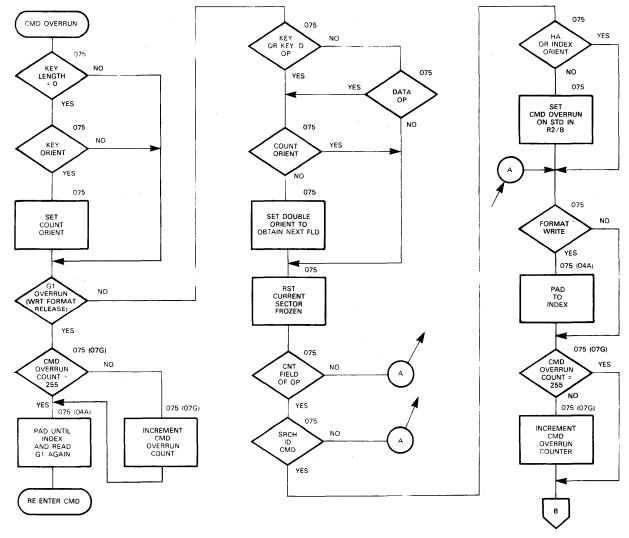

|         | 2.11.3   | Command and Data Overrun              | 2-64         |         | 3.5.2   | Data Chaining                            | 3-  | 13         |

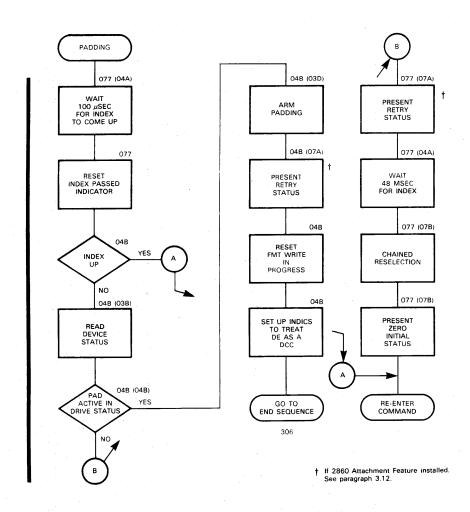

|         | 2.11.4   | Padding                               | 2-64         |         | 3.5.3   | Branching in Channel Programs            |     | 13         |

|         | 2.11.5   | Write Offset                          | 2-64         |         | 3.5.4   | Unit Selection and Device Addressing     | 3-  |            |

|         | 2.11.6   | Invalid Count Field Sync Detected     | 2-64         |         | 3.5.5   | Stack Status                             | 3-  | 13         |

|         |          |                                       |              |         |         |                                          |     |            |

| Section |          |                                                          | Page | Section       |                                          | Page |

|---------|----------|----------------------------------------------------------|------|---------------|------------------------------------------|------|

|         | 3.5.6    | Suppress Status                                          | 3-13 | ■ 3.12.3.2    | Status Condition Exceptions              | 3-35 |

|         | 3.5.7    | Disconnect In                                            | 3-13 | 3.12.3.3      | I/O Interrupts                           | 3-35 |

|         | 3.5.8    | Interface Disconnect                                     | 3-13 | _             | ·                                        |      |

|         | 3.5.9    | Selective Reset                                          | 3-13 | 4 MICRO       | DDOCDAM                                  | 4-1  |

|         | 3.5.10   | Command Retry                                            | 3-14 | 4 MICRO       | PROGRAM                                  | 4-1  |

|         | 3.5.11   | Proceed                                                  | 3-14 | 4.1           | MICROINSTRUCTION                         | 4-1  |

|         | 3.5.12   | Stop (or Truncation)                                     | 3-14 | 4.1<br>4.1,1  | General                                  | 4-1  |

|         | 3.5.13   | Suppress Data                                            | 3-14 | 4.1.2         | Microinstruction Word Description        | 4-1  |

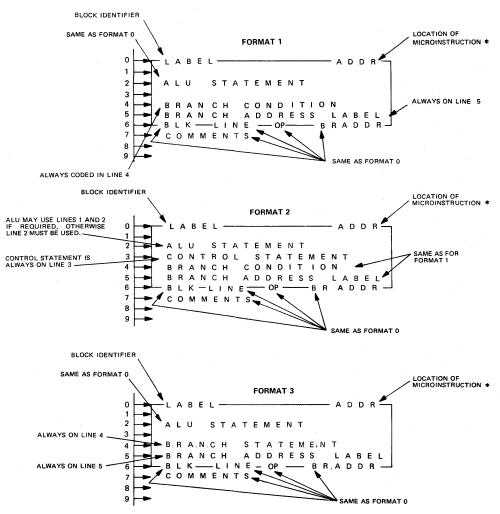

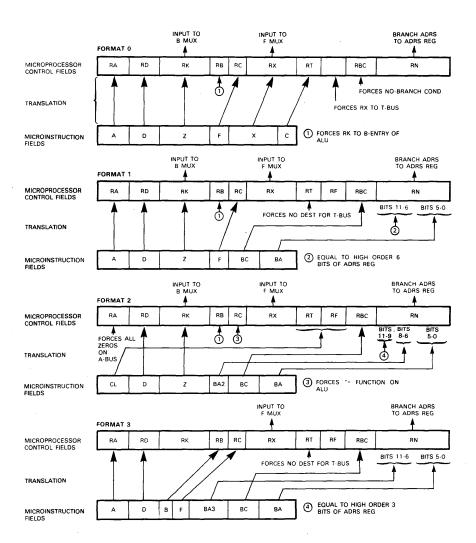

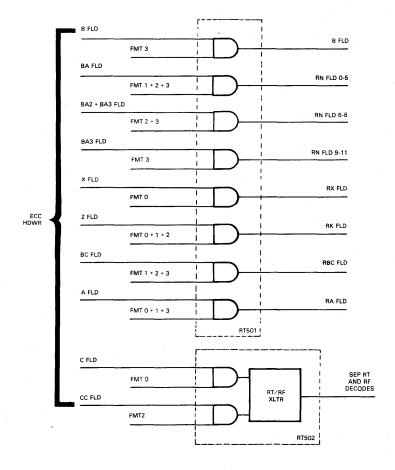

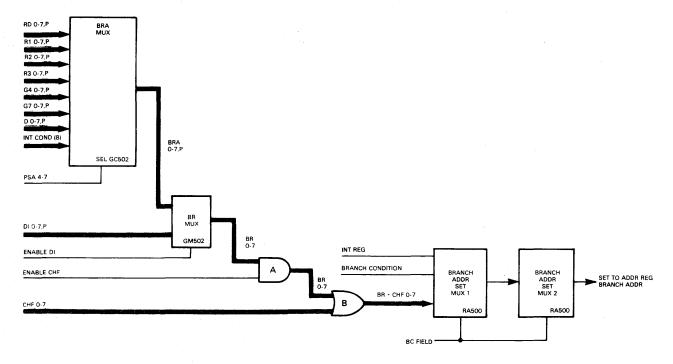

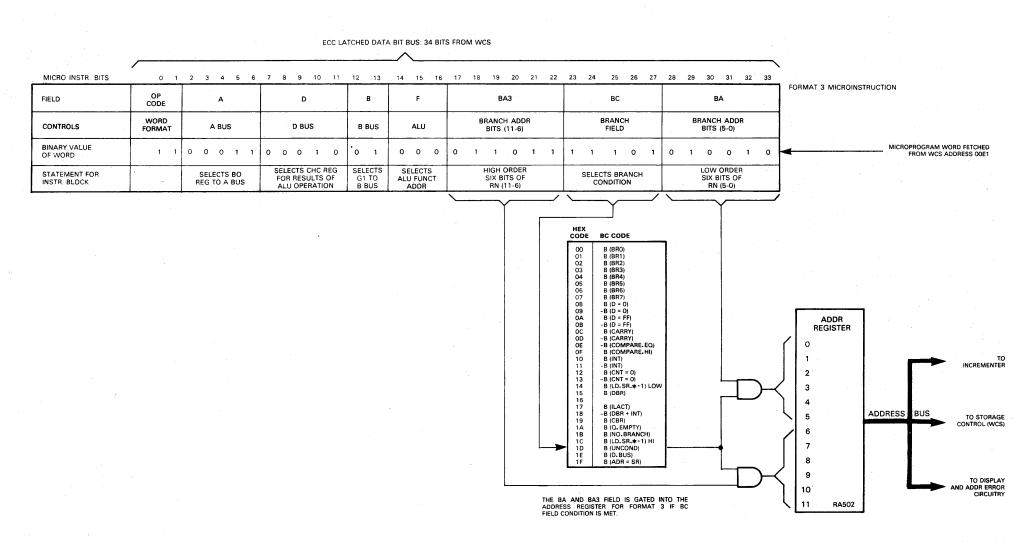

|         | 3.5.14   | Data Acceptance                                          | 3-14 | 4.1.3         | Microinstruction Format                  | 4-1  |

|         | 3.5.15   | Data Ready                                               | 3-14 | 4.1.3.1       | Format 0 Microinstructions               | 4-1  |

|         | 3.5.16   | Status Acceptance                                        | 3-14 | 4.1.3.2       | Format 1 Microinstructions               | 4-1  |

|         | 3.5.17   | System Reset                                             | 3-14 | 4.1.3.3       | Format 2 Microinstructions               | 4-1  |

|         | 3.6      | STATUS CONDITIONS                                        | 3-15 | 4.1.3.4       | Format 3 Microinstructions               | 4-1  |

|         | 3.6.1    | Overview                                                 | 3-15 | 4.1.4         | Microinstruction Field Definitions       | 4-1  |

|         | 3.6.2    | Description of Status Conditions                         | 3-15 | 4.1.5         | Field Translation                        | 4-1  |

|         | 3.6.2.1  | Status Modifier                                          | 3-15 | 4.2           | MICROPROGRAM                             | 4-5  |

|         | 3.6.2.2  | Control Unit End                                         | 3-15 | 4.2.1         | Microprogram Block Format                | 4-5  |

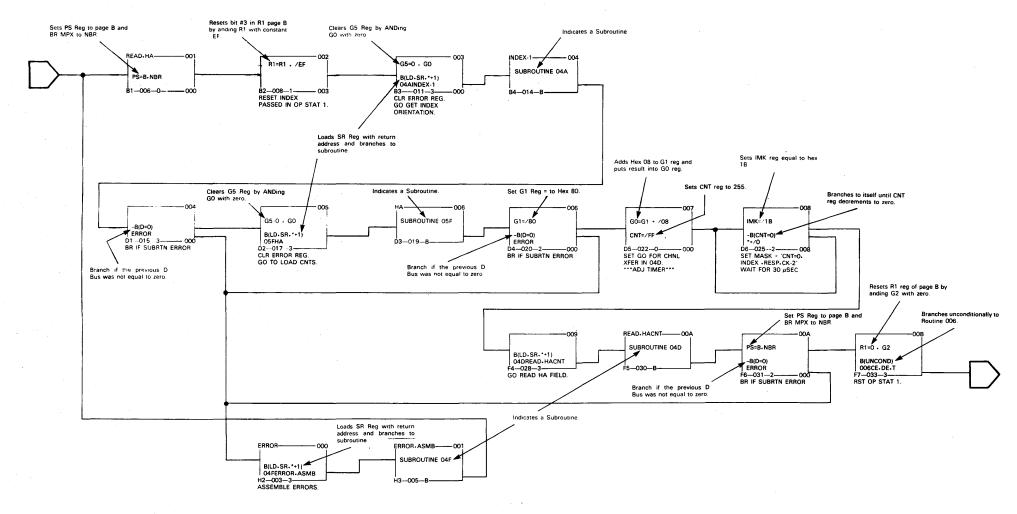

|         | 3.6.2.3  | Busy                                                     | 3-15 | 4.2.2         | Example Microprogram                     | 4-5  |

|         | 3.6.2.4  | Channel End                                              | 3-15 | 4.2.3         | Microprogram Routine Organization        | 4-5  |

|         | 3.6.2.5  | Device End                                               | 3-15 | 4.2.3         | Wilcroprogram Noatine Organization       |      |

|         | 3.6.2.6  | Unit Check                                               | 3-16 |               |                                          |      |

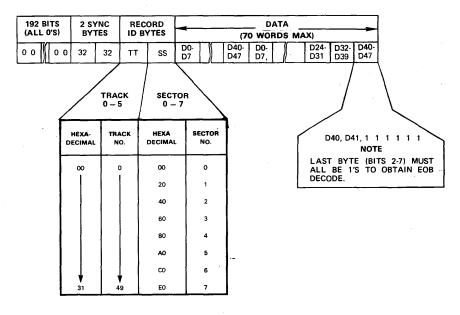

|         | 3.6.2.7  | Unit Exception                                           | 3-16 | 5 FLEXIB      | LE DISC FILE                             | 5-1  |

|         | 3.7      | SENSE CONDITIONS                                         | 3-17 |               |                                          |      |

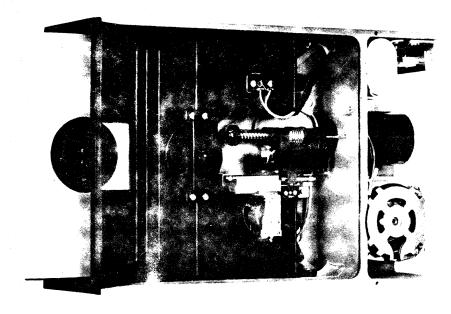

|         | 3.7.1    | Overview                                                 | 3-17 | 5.1           | GENERAL DESCRIPTION                      | 5-1  |

|         | 3.7.2    | Conditions Indicated by Bits of Sense Byte 0             | 3-17 | 5.2           | SPECIFICATIONS                           | 5-2  |

|         | 3.7.3    | Conditions Indicated by Bits of Sense Bytes 1 through 23 | 3-17 | 5.2.1         | Machine Characteristics                  | 5-2  |

|         | 3.8      | READ DATA                                                | 3-18 | 5.2.2         | Operating Capabilities                   | 5-2  |

|         | 3.8.1    | Description                                              | 3-18 | 5.2.3         | Power Requirements                       | 5-2  |

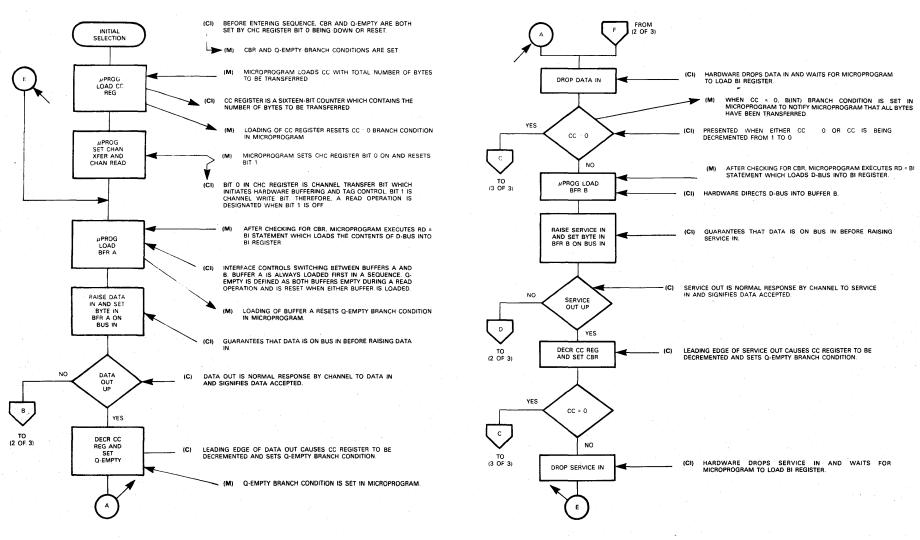

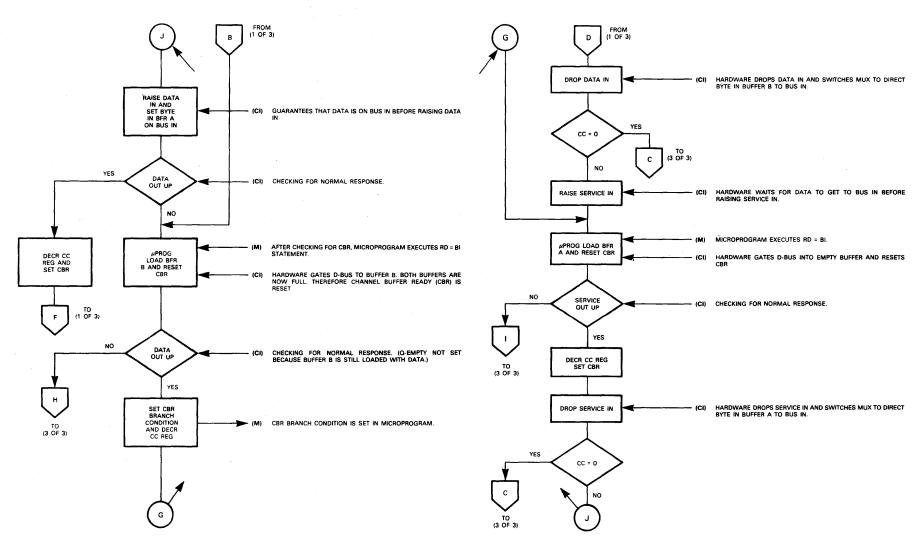

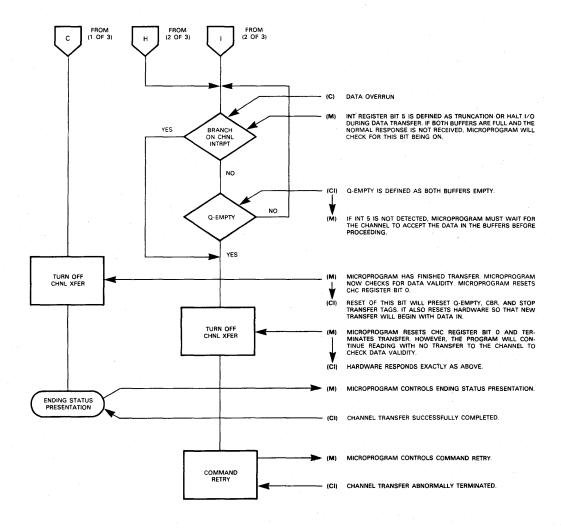

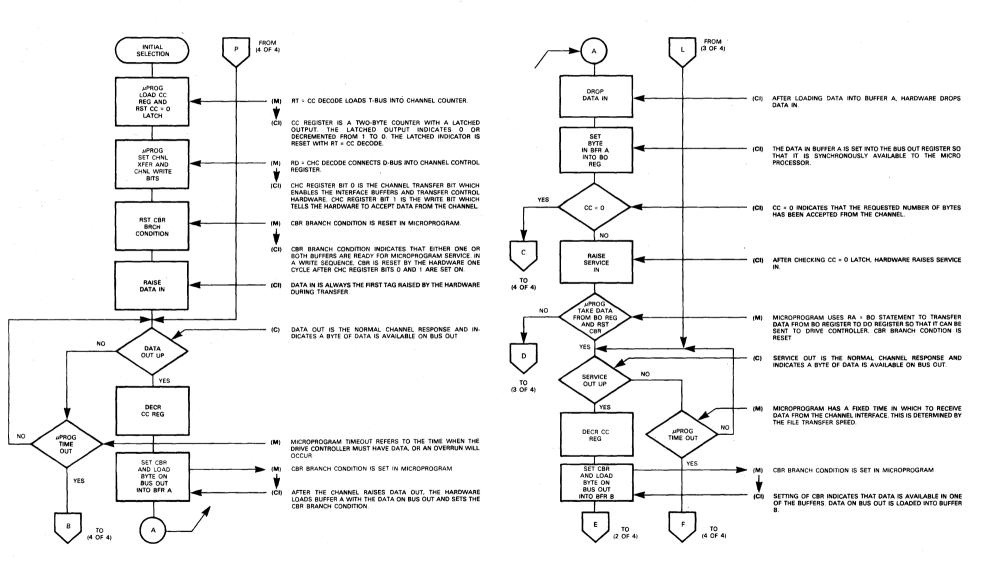

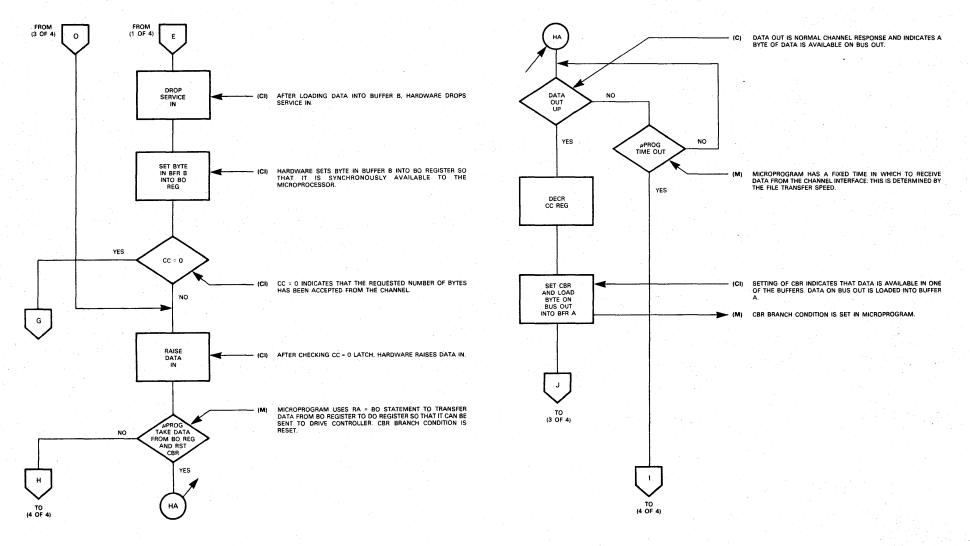

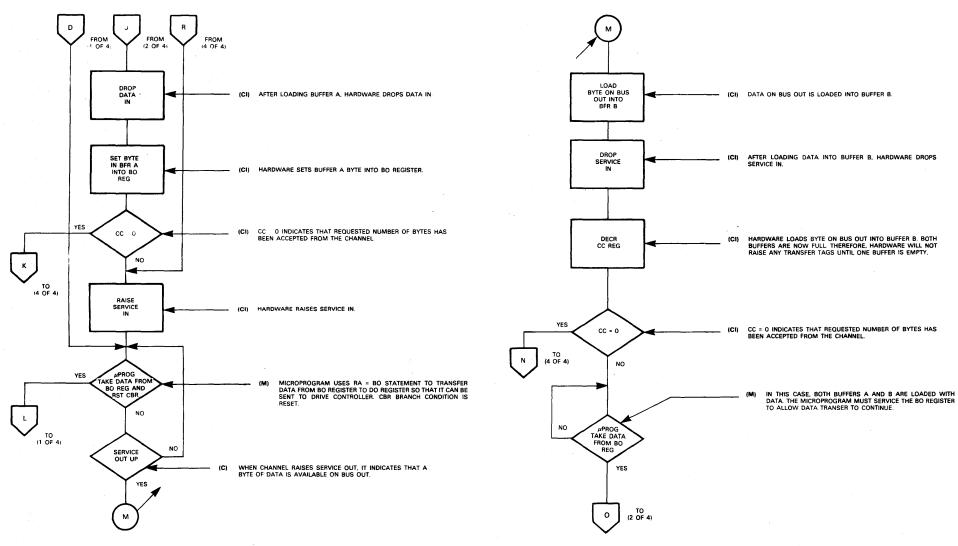

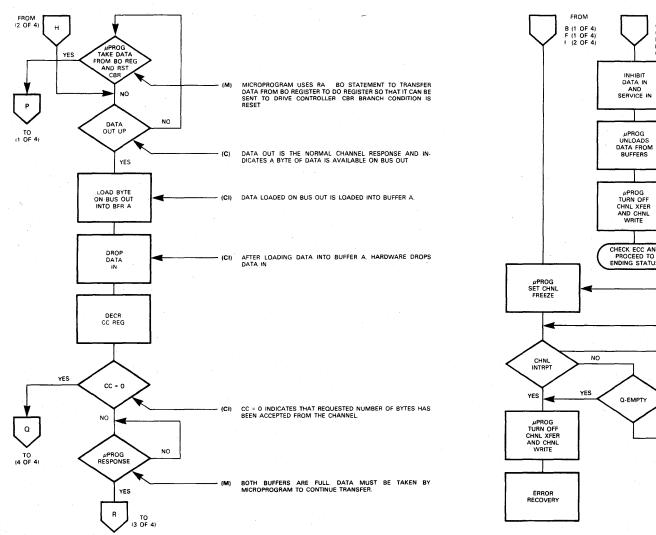

|         | 3.8.2    | Flow Diagram                                             | 3-19 | 5. <b>3</b>   | SPECIAL PRECAUTIONS                      | 5-3  |

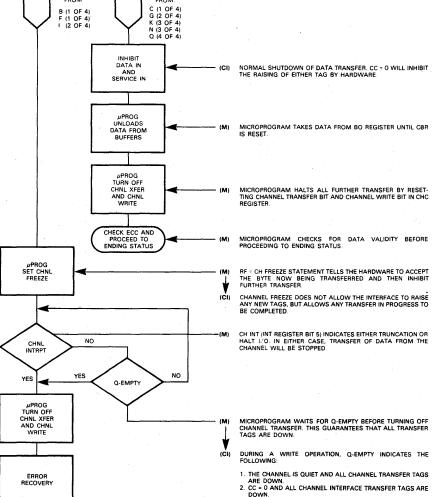

|         | 3.9      | WRITE DATA TRANSFER                                      | 3-23 | 5.3.1         | Cartridge Loading                        | 5-3  |

|         | 3.9.1    | Description                                              | 3-23 | 5.3.2         | Disc Interchangeability                  | 5-3  |

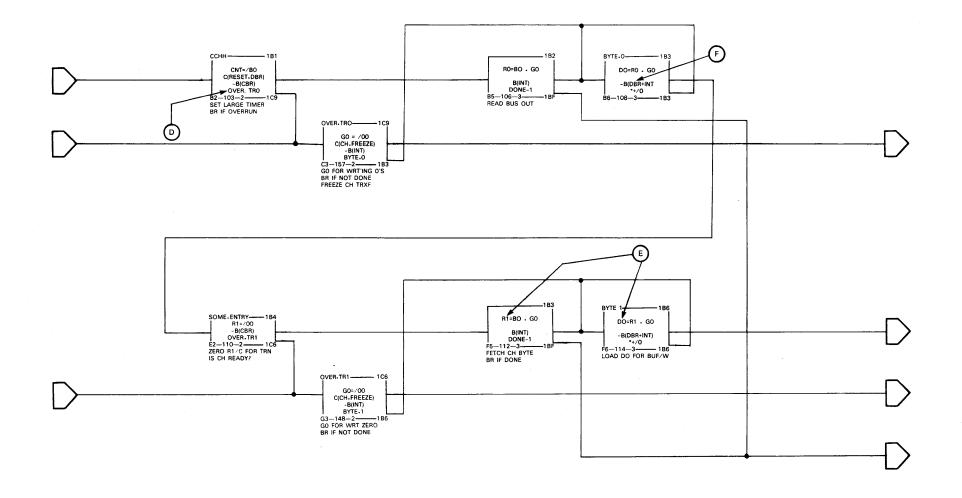

|         | 392      | Flow Diagram                                             | 3-24 | 5.3.3         | Physical Damage                          | 5-3  |

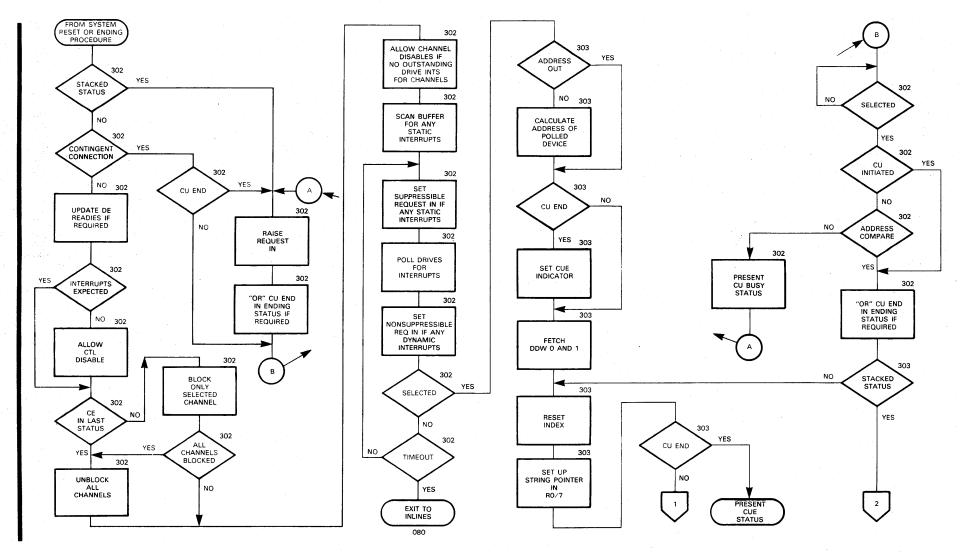

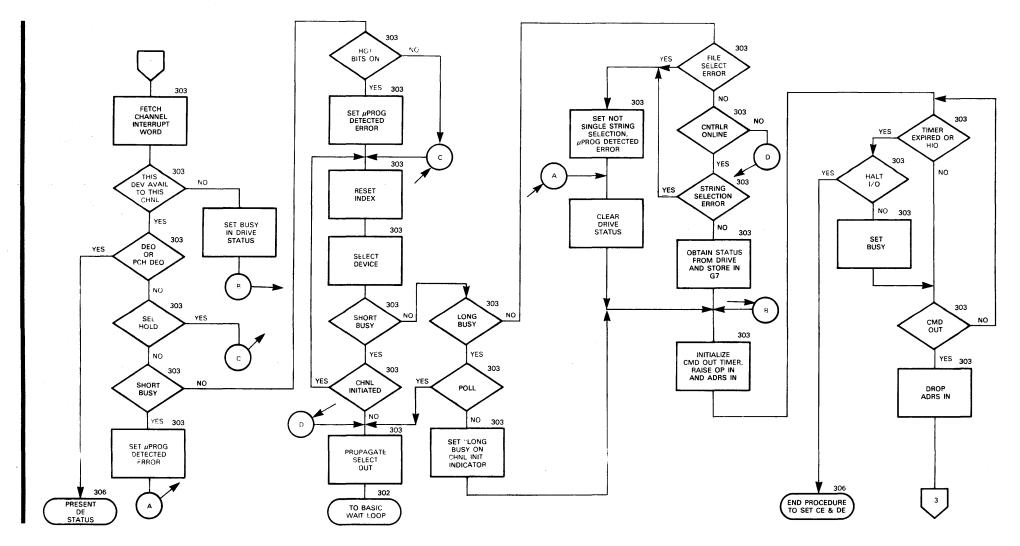

|         | (3.10)   | SCU-INITIATED CHECK 1 ERROR CONTROL                      |      | 5.3.4         | Safety                                   | 5-3  |

|         |          | SEQUENCE (POLLING), SIMPLIFIED                           | 3-29 | 5.4           | PRINCIPLES OF OPERATION                  | 5-4  |

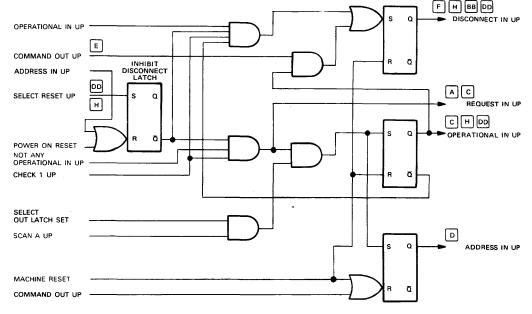

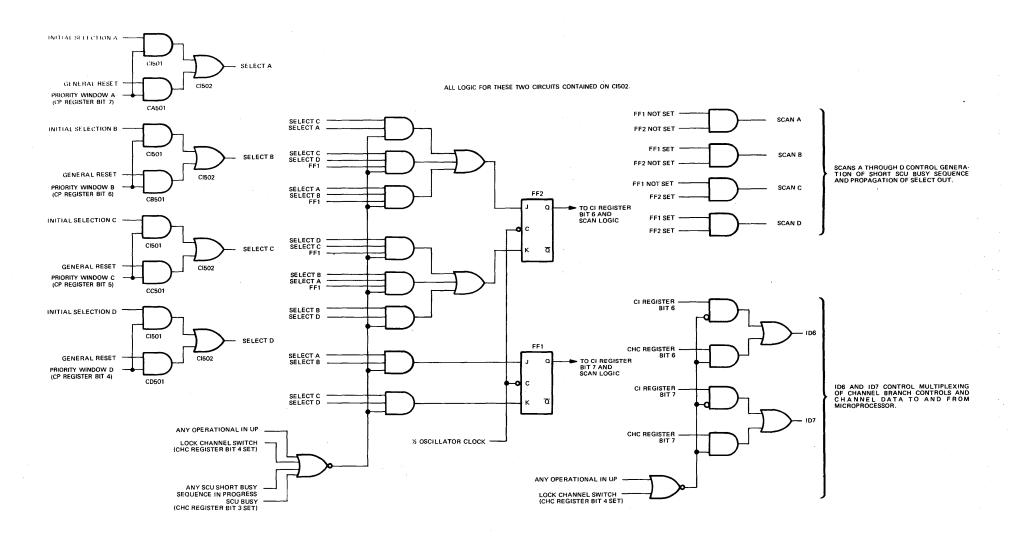

|         | 3.11     | MULTICHANNEL SWITCH OPERATION                            | 3-30 | 5.4.1         | General Operation                        | 5-4  |

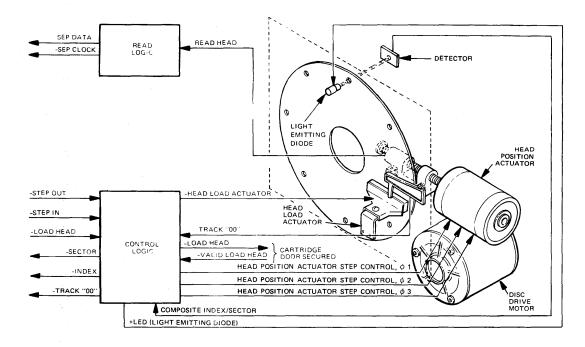

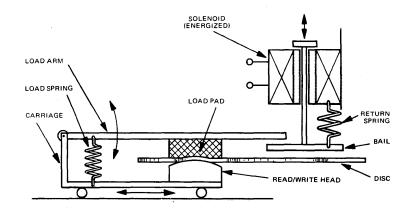

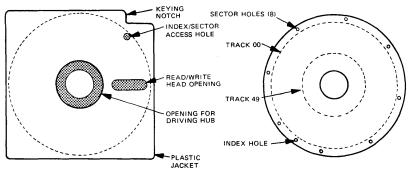

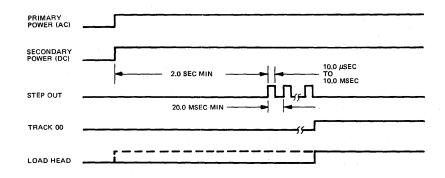

|         | 3.11.1   | Channel Selection Switch                                 | 3-30 | 5.4.2         | Functional Assemblies                    | 5-5  |

|         | 3.11.2   | Instantaneous Connection                                 | 3-30 | 5.4. <b>3</b> | Logic and Analog Functional Descriptions | 5-6  |

|         | 3.11.3   | Long Connection                                          | 3-30 | 5.4.3.2       | Control and Status Logic                 | 5-6  |

|         | 3.11.4   | Device Status                                            | 3-30 | 5.4.3.2       | Read Logic                               | 5-6  |

|         | 3.11.5   | Addressing                                               | 3-30 | 5.4.4         | Functional Operation                     | 5-6  |

|         | 3.11.6   | Resets                                                   | 3-30 | 5.4.4.1       | Initialization Phase                     | 5-6  |

| ı       | 3.12     | 2860 SELECTOR CHANNEL ATTACHMENT FEATURE                 | 3-32 | 5.4.4.2       | Track Access Phase                       | 5-6  |

|         | 3.12.1   | Description                                              | 3-32 | 5.4.4.3       | Read Phase                               | 5-7  |

|         | 3.12.2   | Functional Characteristics                               | 3-32 | 5.4.5         | Interface Signal Description             | 5-7  |

|         | 3.12.2.1 | General                                                  | 3-32 | 5.4.5.1       | Control                                  | 5-8  |

|         | 3.12.2.2 | Channel Commands                                         | 3-33 | 5.4.5.2       | Data                                     | 5-9  |

|         | 3.12.2.3 | Disconnected Command Chaining                            | 3-34 | 5.4.5.3       | Power                                    | 5-9  |

| 1       | 3.12.2.4 | Error Recovery                                           | 3-34 | 5.5           | CONTROL CIRCUITRY DESCRIPTION            | 5-10 |

| 1       | 3.12.2.5 | Non-RPS Mode Operation                                   | 3-35 | 5.5.1         | Functional Description                   | 5-10 |

| 1       | 3.12.3   | I/O Programming                                          | 3-35 | 5.5.2         | Printed Circuit Board                    | 5-10 |

|         | 3.12.3.1 | Channel Programs                                         | 3-35 | 5.5. <b>3</b> | Harness Assembly                         | 5-10 |

|                                            | Page       | Section                     |                                   | Page                      |

|--------------------------------------------|------------|-----------------------------|-----------------------------------|---------------------------|

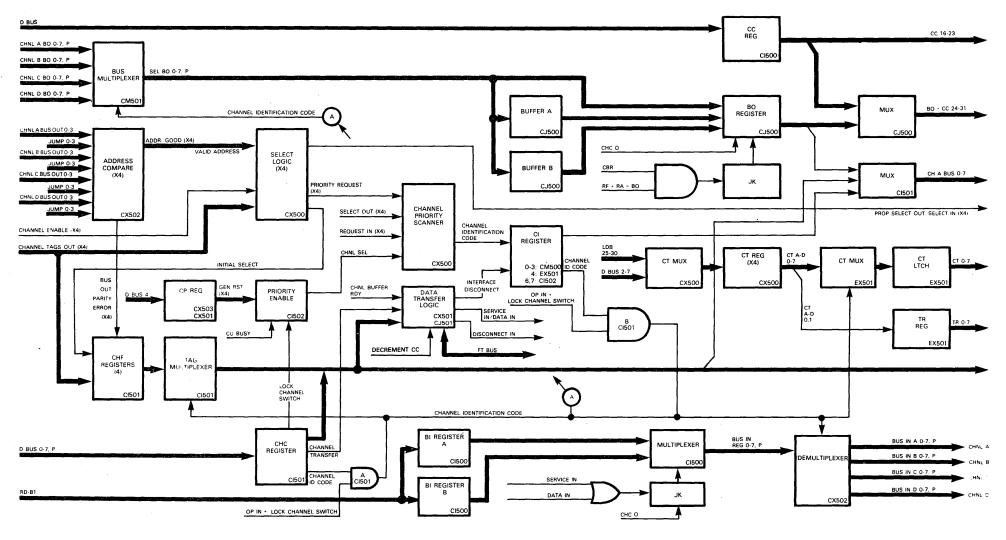

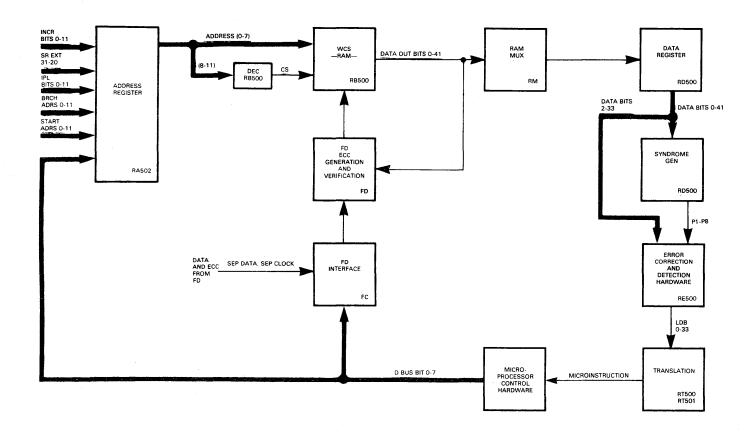

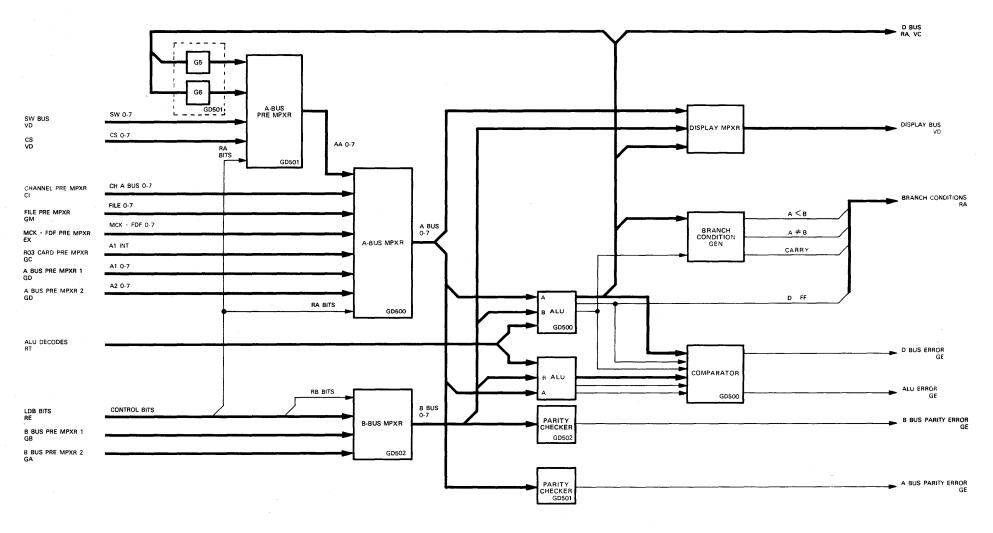

| L UNIT OPERATIONS                          | 6-1        | 6.3.4.1                     | Buses                             | 6-12                      |

|                                            |            | 6.3.4.2                     | Registers                         | 6-14                      |

| DESCRIPTION                                | 6-2        | 6.3.4.3                     | Arithmetic Logic Unit             | 6-16                      |

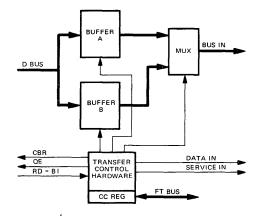

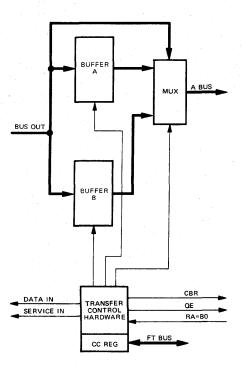

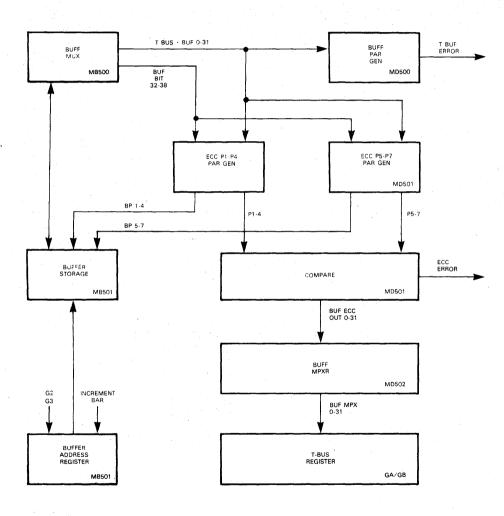

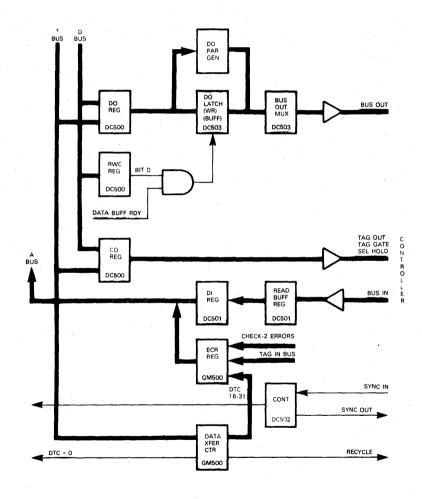

| . INTERFACE DESCRIPTION                    | 6-2        | 6.3.5                       | Buffer Storage                    | 6-16                      |

| İ                                          | 6-2        | 6.3.5.1                     | General                           | 6-16                      |

| escription                                 | 6-2        | 6.3.5.2                     | Description                       | 6-16                      |

| ss Compare Logic                           | 6-2        | 6.3.5.3                     | Buffer Control Commands           | 6-18                      |

| Logic                                      | 6-2        | 6.3.5.4                     | Error Correction Code             | 6-18                      |

| y Logic                                    | 6-2        | 6.3.5.5                     | Buffer Storage Allocation         | 6-19                      |

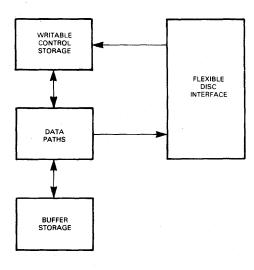

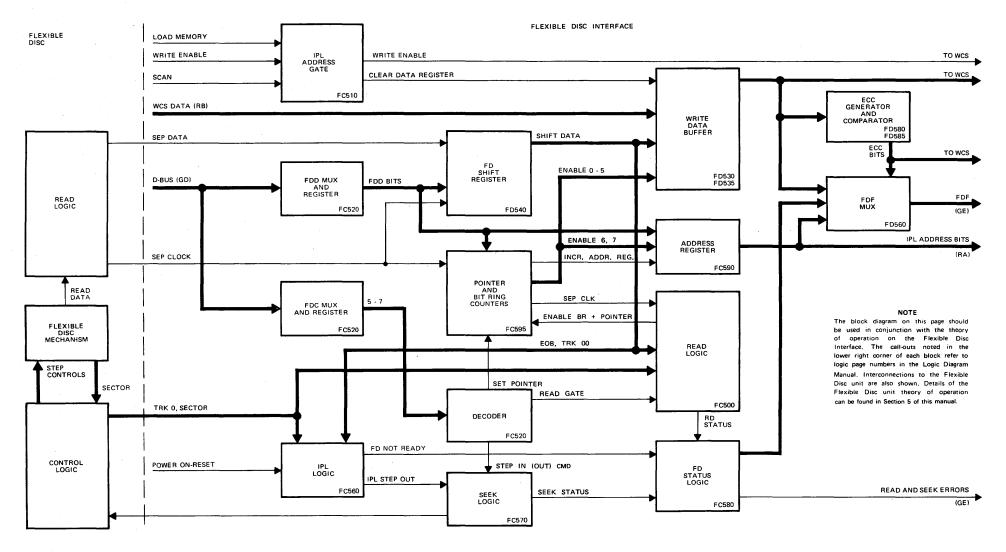

| lexer/Demultiplexer Circuits               | 6-2        | 6.3.6                       | Flexible Disc Interface           | 6-19                      |

| ers                                        | 6-2        | 6.3.6.1                     | General                           | 6-19                      |

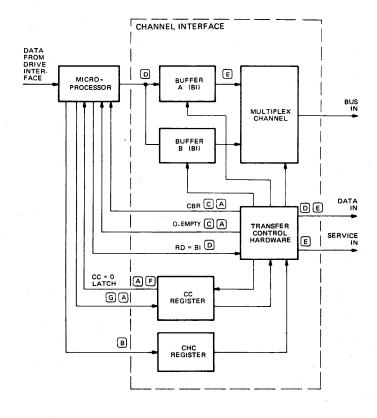

| ansfer Organization                        | 6-5        | 6.3.6.2                     | Functional Description            | 6-19                      |

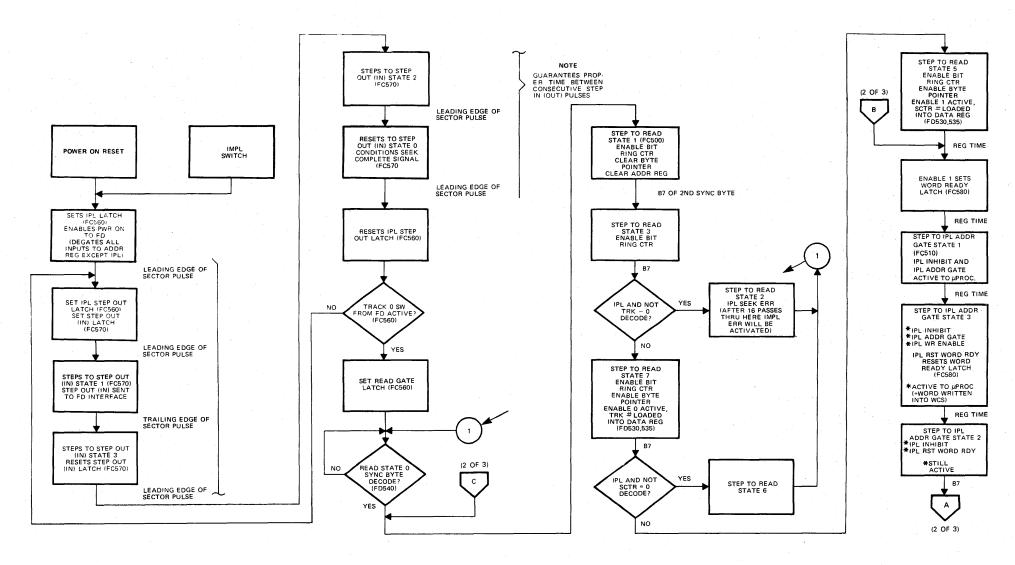

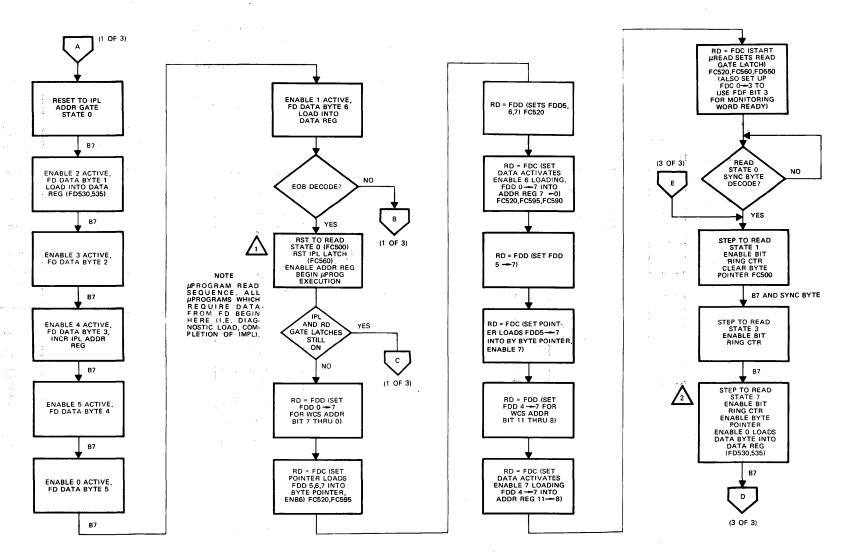

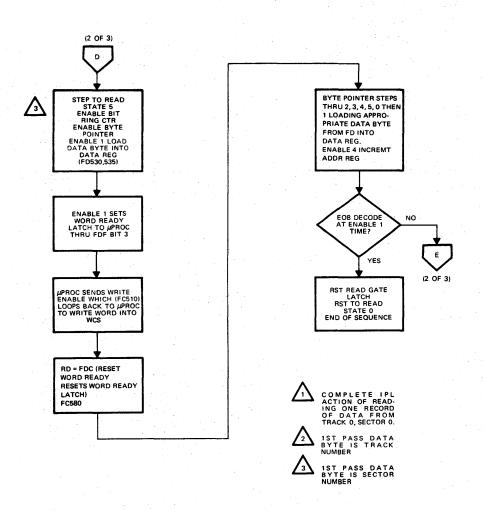

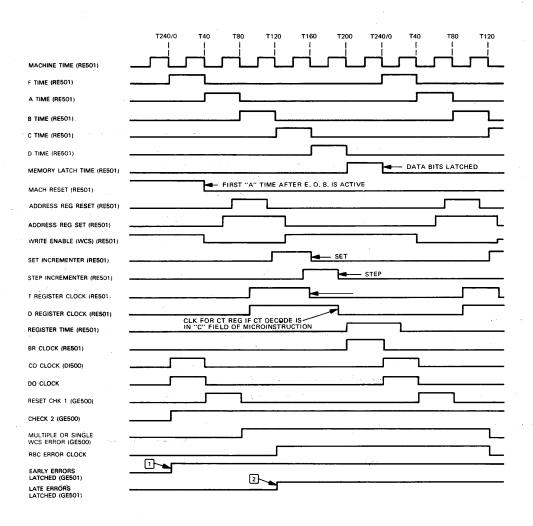

| al                                         | 6-5        | 6.3.6.3                     | IPL Flow Chart                    | 6-23                      |

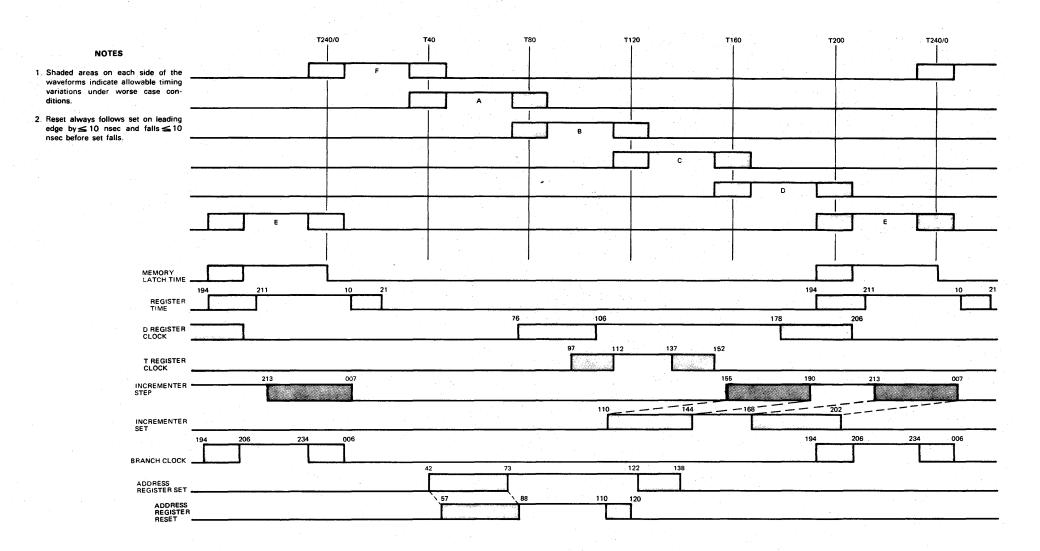

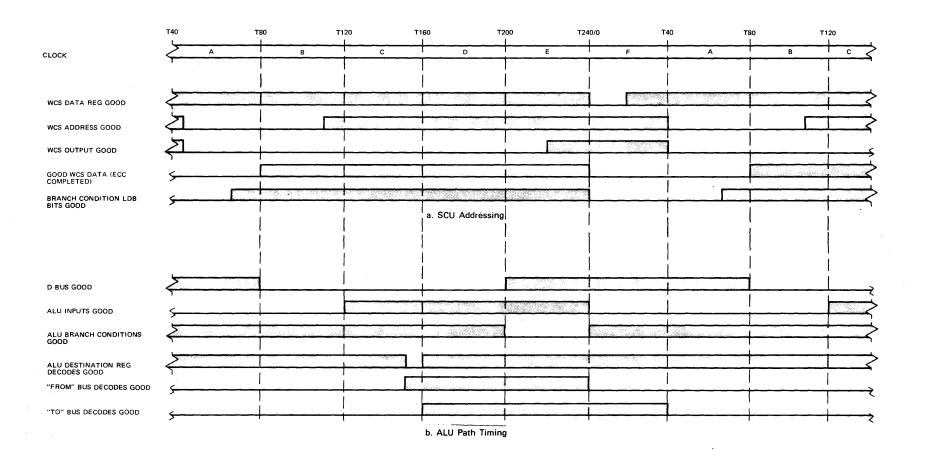

| Operations                                 | 6-5        | 6.3.7                       | Microprocessor Timing             | 6-23                      |

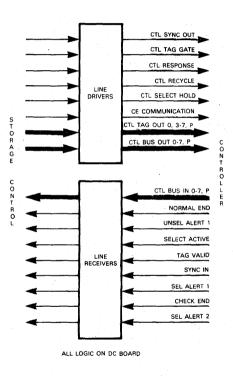

| Operations                                 | 6-5        | 6.4                         | CONTROLLER INTERFACE              | 6-30                      |

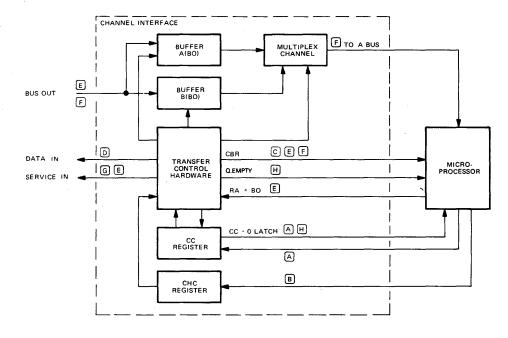

| Interface Branch Conditions                | 6-6        | 6.4.1                       | General                           | 6-30                      |

| el Buffer Ready (CBR)                      | 6-6        | 6.4.2                       | Interface Signals                 | 6-30                      |

| Empty                                      | 6-6        | 6.4.2.1                     | SCU to Controller Signals         | 6-31                      |

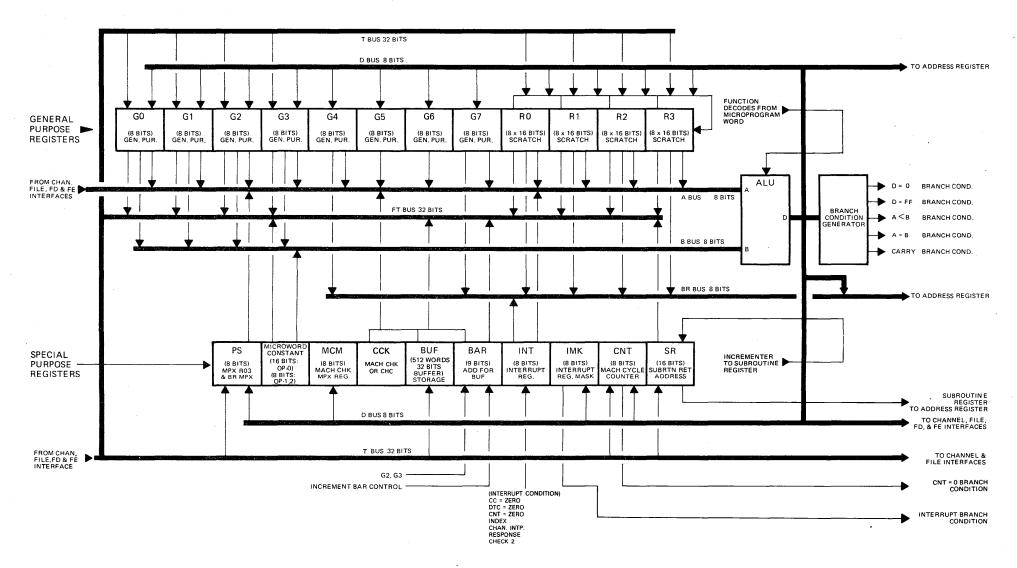

| OCESSOR DESCRIPTION                        | 6-7        | 6.4.2.2                     | Controller to SCU Signals         | 6-31                      |

| ocessor General Description                | 6-7        | 6.4.3                       | Register Definitions              | 6-31                      |

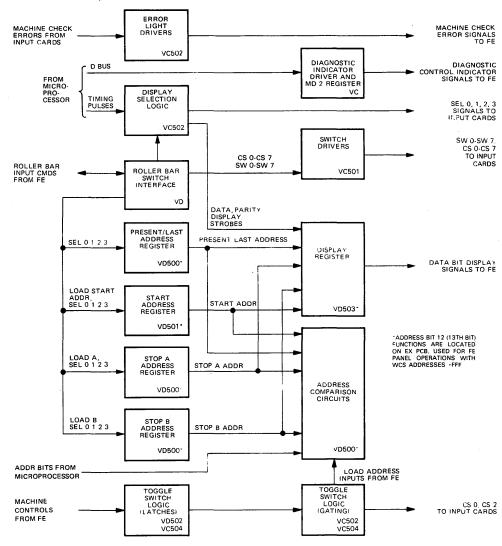

| structions                                 | 6-7        | 6.5                         | FE INTERFACE                      | 6-33                      |

| ptions and Formats                         | 6-7        | 6.5.1                       | General                           | 6-33                      |

| nstruction Field Translation and Branching | 6-7        | 6.5.2                       | Functional Description            | 6-33                      |

| nstruction Execution Example               | 6-8        | 6.6                         | CHECK-1 ERRORS                    | 6-34                      |

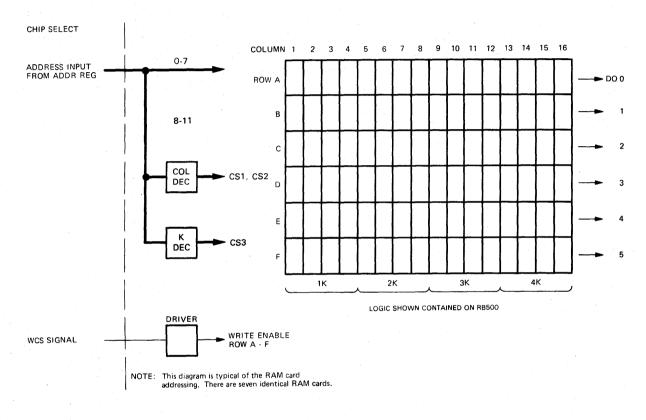

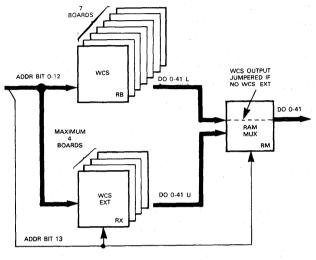

| Control Storage                            | 6-8        | 6.6.1                       | Error Detection and Sequences     | 6-34                      |

| al                                         | 6-8        | 6.6.2                       | Machine Check (MCK) Register      | 6-34                      |

| g From WCS                                 | 6-8        | 6.6.3                       | Check-1 Error Display             | 6-34                      |

| Into WCS                                   | 6-9        | 6.6.4                       | Reset of Check-1 Error Conditions | 6-34                      |

| Correction Code                            | 6-9        |                             |                                   |                           |

| xpansion                                   | 6-12       |                             |                                   |                           |

| ths                                        | 6-12       | GLOSSA                      | ARY OF TERMS                      | G-1                       |

| orre<br>xpar                               | ction Code | ction Code 6-9<br>sion 6-12 | ction Code 6-9 sion 6-12          | ction Code 6-9 asion 6-12 |

# LIST OF ILLUSTRATIONS

| 1   3672-Based Disc. Storage Subsystem Components   1,2   2,41   Command Rarry, Alternate Track   2,72   2,81   2,42   Command Rarry, Patenate Track   2,73   2,43   Command Rarry, Patenate Track   2,74   2,14   Initial Selection Flow Diagram   2,5   2,44   Command Rarry, Patenate Track   2,74   2,14   Initial Selection Flow Diagram   2,7   2,44   Command Rarry, Patenate Selection Flow Diagram   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,7   2,   |   | Figure |                                                  | Page |     | Figure |                                                        | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------|--------------------------------------------------|------|-----|--------|--------------------------------------------------------|------|

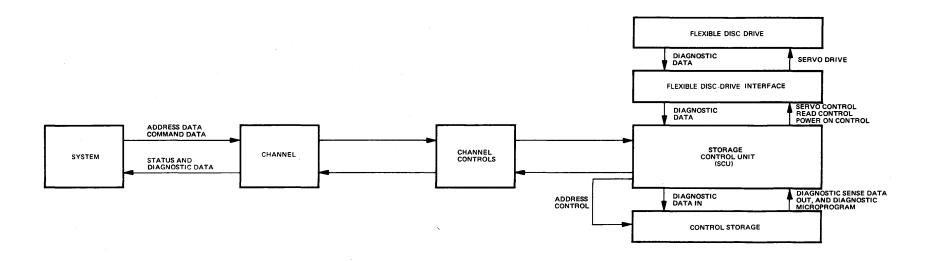

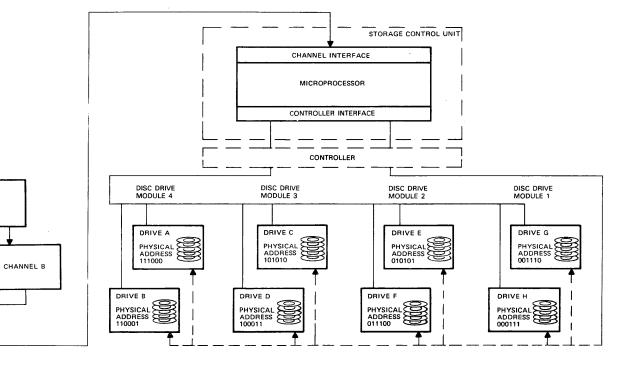

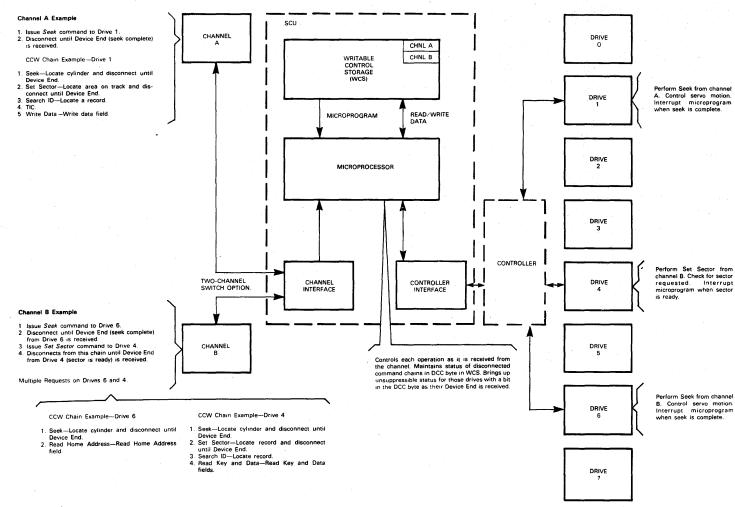

| 1-2   3672-Rased Dies Storage Subsystem Configurations   1-3   2-42   Command Retry, Data and Command Overruns   2-72   2-73   Seek Operation Block Diagram   2-5   2-44   Command Retry, Write Offset   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-74   2-   |   | 1-1    | 3672-Based Disc Storage Subsystem Components     | 1-2  |     | 2-41   | Command Retry, Alternate Track                         | 2-70 |

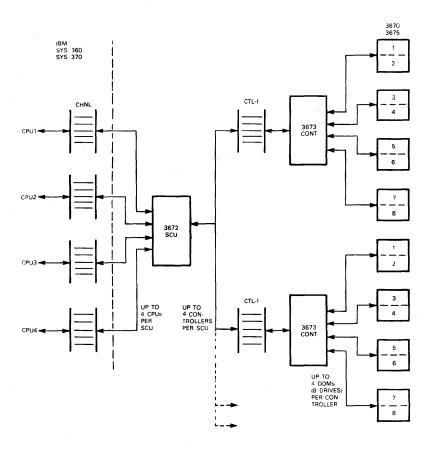

| 1-3   Disc Storage Subsystem Operational Block Diagram   1-5   2-43   Command Retry, Padding   2-74   2-14   Initial Selection Flow Diagram   2-5   2-46   Command Retry, Invalid Count Flield Sync Detected and Index Detected in Data Field   2-75   2-86   Pievo Diagram   2-76   2-86   Pievo Diagram   2-77   Track Sentor Index Detected The Pievo Diagram   2-10   2-86   Pievo Diagram   2-11   2-89   Pievo Diagram   2-12   2-89   Pievo Diagram   2-13   2-86   Pievo Diagram   2-14   2-89   Pievo Diagram   2-15   Pievo Diagram   2-16   Pievo Diagram   2-16   Pievo Diagram   2-17   Pievo Diagram   2-18   Pievo Diagram   2-19   Pievo Diagram   2-10   Pievo Piev   |   | 1-2    | 3672-Based Disc Storage Subsystem Configurations | 1-3  | l l | 2-42   | • •                                                    |      |

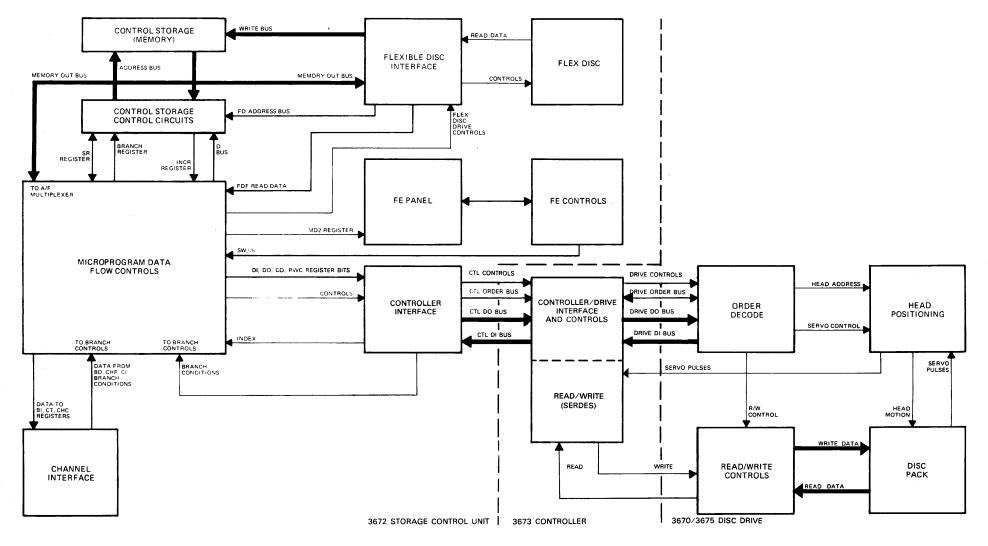

| 2-15   Seek Operation Block Diagram   2-5   2-44   Command Retry, Invalid Count Field Sync Detected and India Selection Flow Diagram   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2-7   2   |   | 1-3    |                                                  | 1-5  |     |        |                                                        |      |

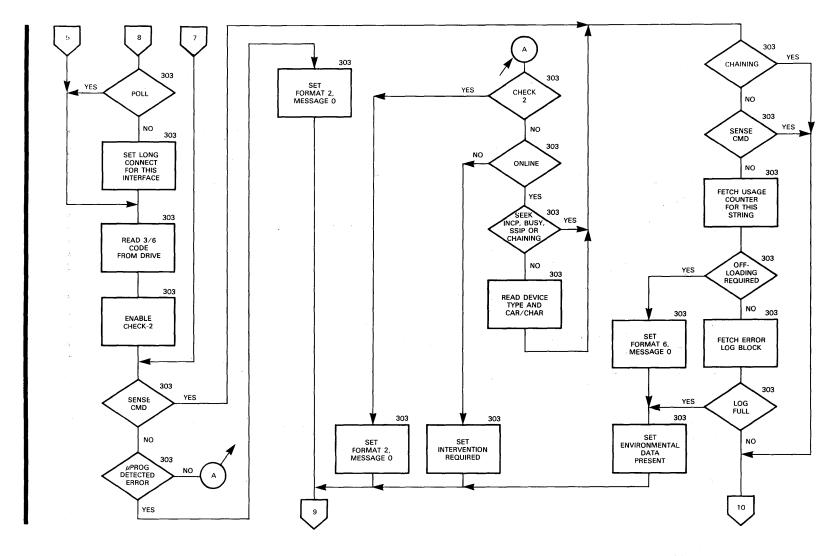

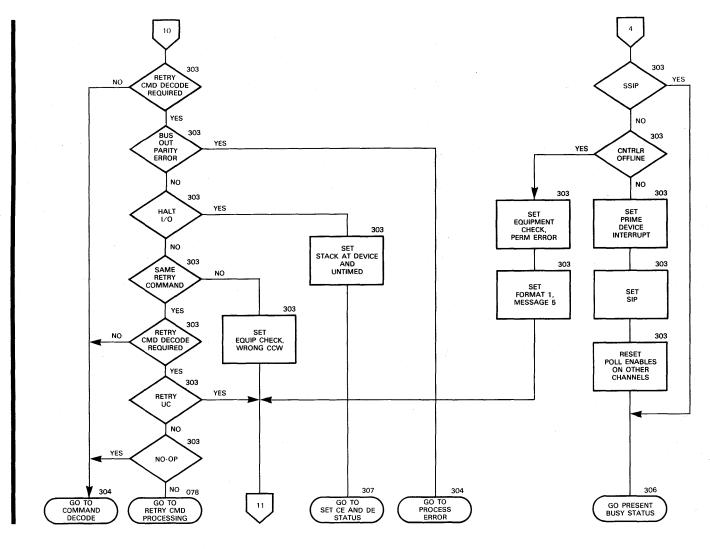

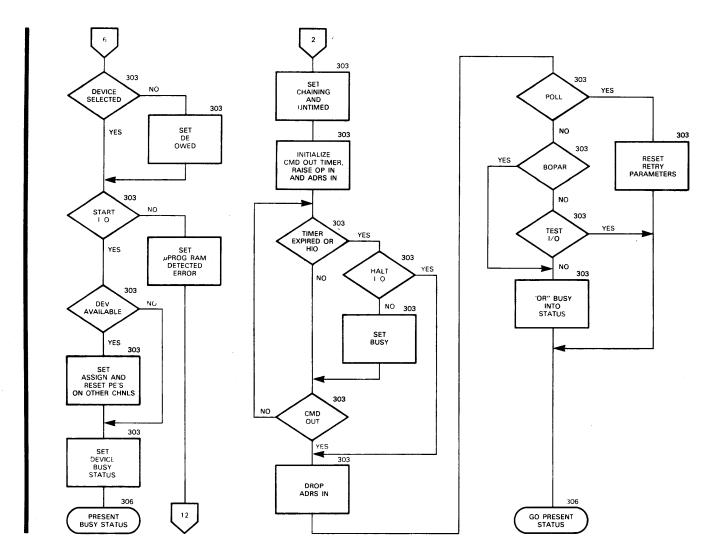

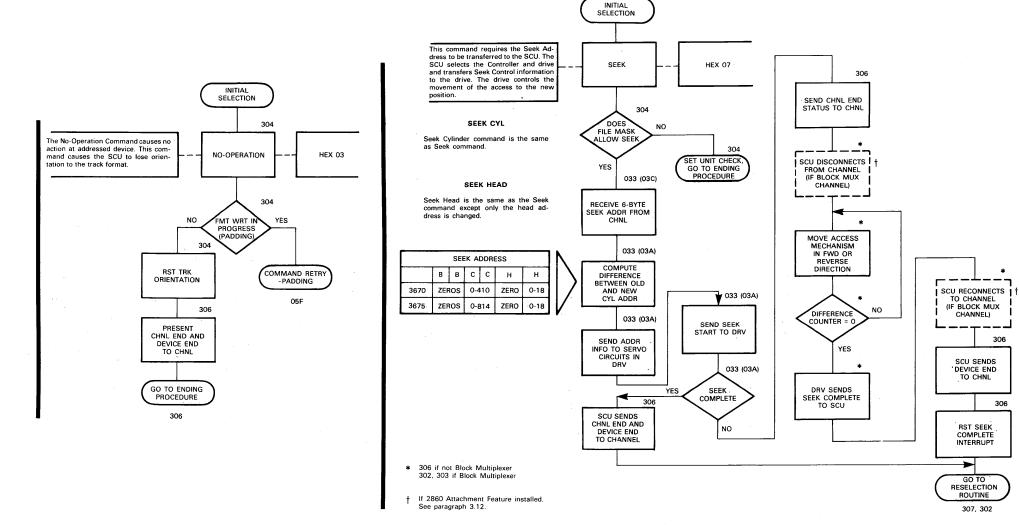

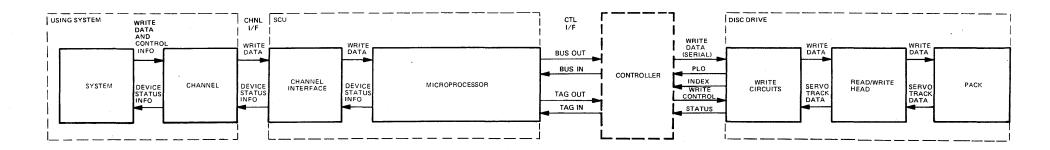

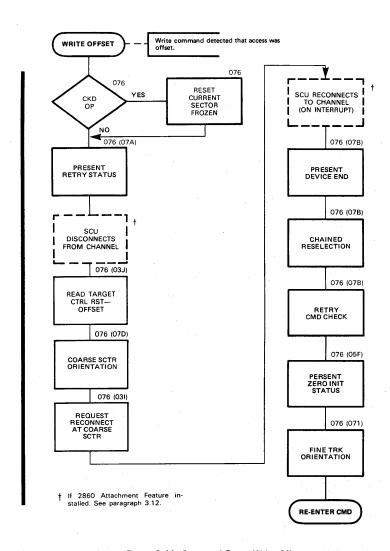

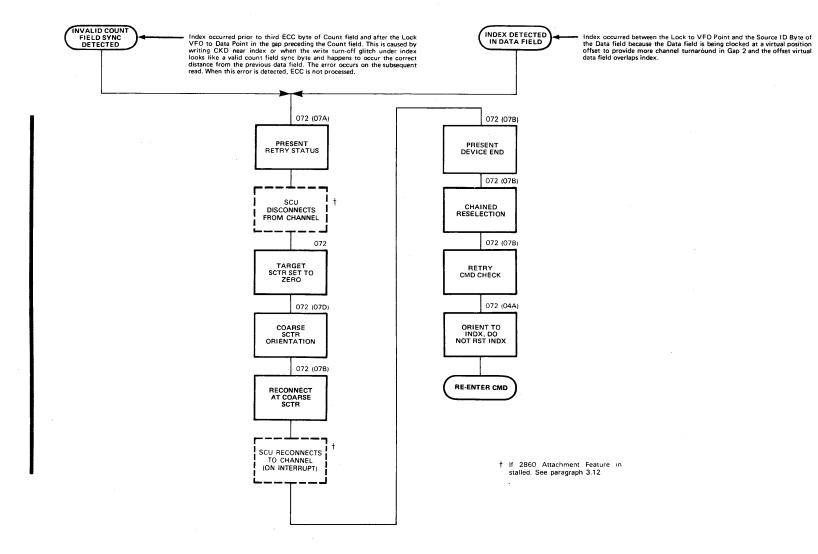

| 2-14   Initial Selection Flow Diagram   2-7   2-8   2-9   Command Retry, Invalid Count Field Sync Detected and Index Detected in Data Field   2-75   2-3   Seek Flow Diagram   2-7   2-46   Read/Set Sector Operation   2-77   2-46   Read/Set Sector Operation   2-78   2-78   2-79   2-46   Read/Set Sector Operation   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2   |   | 2-1    | Seek Operation Block Diagram                     | 2-5  |     | 2-44   |                                                        | 2-74 |

| 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 | 2-1A   |                                                  |      | 1   | 2-45   |                                                        |      |

| 2-7   2-6   Read/Set Sector Operation   2-77   2-6   Read/Set Sector Operation   2-77   2-74   7-7ack Sector Layout   2-78   2-78   Recalibrate Flow Diagram   2-10   2-48   Typical Track Flidid Layout   2-78   2-78   2-78   Recalibrate Flow Diagram   2-11   2-49   Multirock Operation   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79   2-79      |   | 2-2    | •                                                |      |     | -      |                                                        | 2-75 |

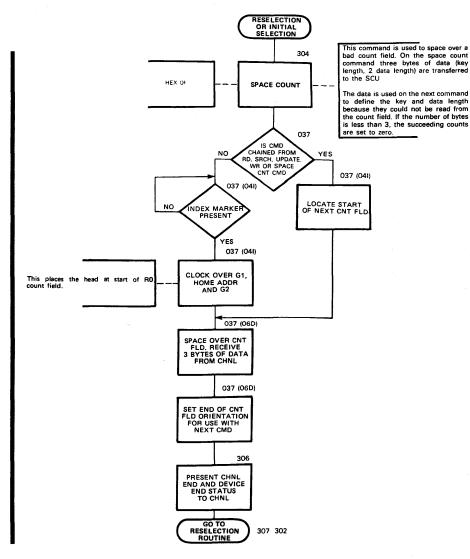

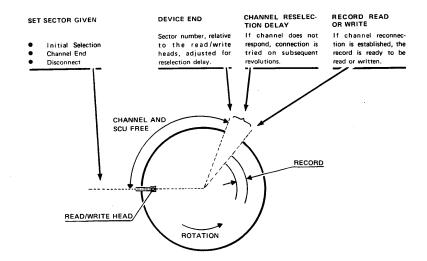

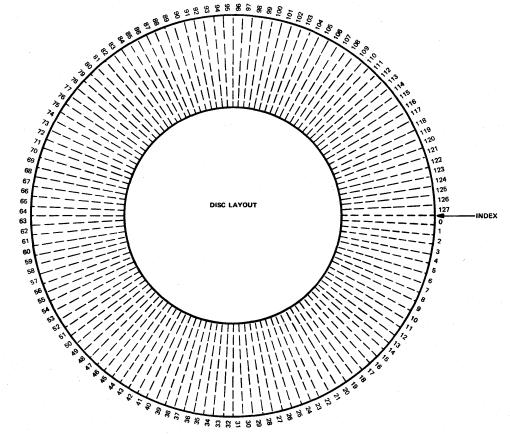

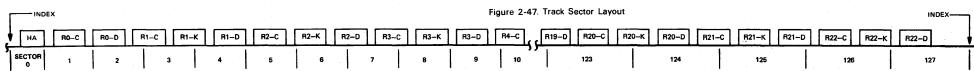

| 2-48 Space Court Flow Diagram 2-10 2-98 2-47 Track Sector Layout 2-78 8-65 Reaction Flow Diagram 2-10 2-79 8-75 Reaction Flow Diagram 2-11 2-49 Multitrack Operation 2-79 8-75 Reaction Flow Diagram 2-11 2-49 Multitrack Operation 2-79 8-75 Reaction Flow Diagram 2-12 2-15 Overlow Record Operation Block Diagram 2-89 Diagnostic Load Flow Diagram 2-14 3-15 Serie Connection of SELECT IN/SELECT OUT 3-3-3 1-15 Serie Connection of SELECT IN/SELECT OUT 3-3-3 1-15 Serie Connection of SELECT IN/SELECT OUT 3-3-3 Selector Channel Operation, Data Transfer Sequences 3-5 1-15 Sense I/O Flow Diagram 2-15 3-15 Series Byte Definitions 2-16 3-3 Selector Channel Operation, Data Transfer Sequences 3-5 Sense I/O Flow Diagram 2-15 3-15 Sense I/O Flow Diagram 3-10 Sense I/O  |   | 2-3    |                                                  |      |     | 2-46   | Read/Set Sector Operation                              | 2-77 |

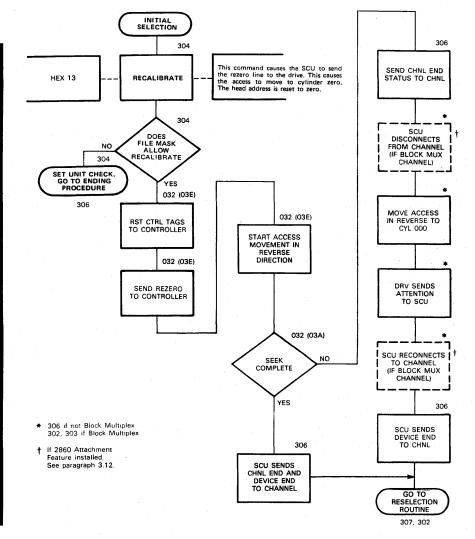

| 2-5         Recalibrate Flow Diagram         2-10         2-48         Typical Track, Fleid Layout         2-78           2-6         Restore Flow Diagram         2-11         2-49         Multitrack Operation         2-79           2-7         Set File Mask Flow Diagram         2-12         2-50         Overflow Record Operation         2-80           2-8         Set Sector Flow Diagram         2-13         3-25         Selector Channel Operation, Both Chapter         3-3           2-10         Diagnostic Write Flow Diagram         2-16         3-3         Selector Channel Operation, Data Transfer Sequences         3-5           2-11         Series Bwte Definitions         2-16         3-3         Selector Channel Operation, Data Transfer Sequences         3-5           2-17         Series Bwte Definitions         2-16         3-3         Selector Channel Operation, Data Transfer Sequences         3-5           2-18         Series Bwte Definitions         2-16         3-3         Selector Channel Operation, Data Transfer Sequences         3-8           2-18         Read and Reset Buffer Log Flow Diagram         2-23         3-6         Biock Multiplexer Channel Operation (1 of 2)         3-11           2-16         Read Diagnostic to Stutus 1- Flow Diagram         2-25         3-8         Beloc Multiplexer Channel Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 2-4    | •                                                |      |     |        | •                                                      |      |

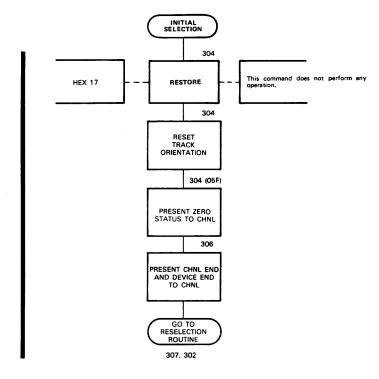

| 2-6 Restore Flow Diagram 2-11 2-49 Multitrack Operation 2-79 2-79 Set File Mask Flow Diagram 2-12 2-50 Overflow Record Operation 2-79 1-79 Set File Mask Flow Diagram 2-14 3-13 2-51 Multichannel Operation Set Diagram 2-14 3-13 2-51 Multichannel Operation Of SELECT IN/SELECT OUT 3-3-3 2-51 Operation Set Diagram 2-14 3-1 Serial Connection of SELECT IN/SELECT OUT 3-3-3 2-51 Set Diagram 3-10 Operation Mission Operation, Data Transfer Sequences 3-5 Set Diagram 3-10 Operation Mission Operation, Data Transfer Sequences 3-5 Set Diagram 3-10 Operation Mission Operation, Data Transfer Sequences 3-5 Operation Operation (Detail Operation, Data Transfer Sequences 3-5 Operation Operation Operation, Data Transfer Sequences 3-5 Operation Operation (Detail Operation Operation, Data Transfer Sequences 3-5 Operation Operation Operation, Data Transfer Sequences 3-5 Operation Operati  |   | 2-5    |                                                  |      |     | 2-48   |                                                        | 2-78 |

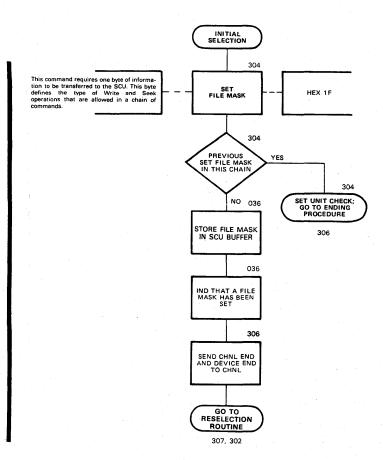

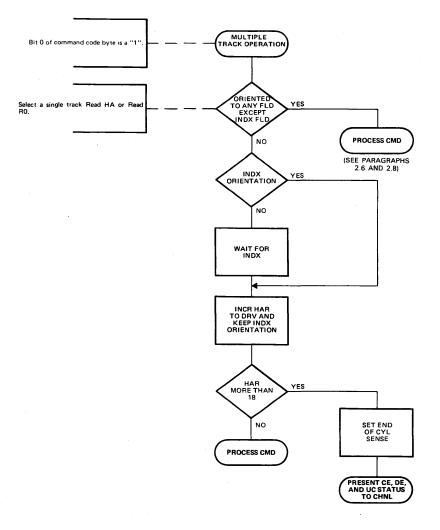

| 2-8         Set Sector Flow Diagram         2-13         2-51         Multichannel Operation Block Diagram         2-19           2-9         Diagnostic Load Flow Diagram         2-14         3-1         Serial Connection of SELECT IN/SELECT OUT         3-3           2-10         Diagnostic Write Flow Diagram         2-16         3-2         Selector Channel Operation, Data Transfer Sequences         3-5           2-12         Sense I/O Flow Diagram         2-21         3-4         Disc Track Sector Format         3-10           2-13         Test I/O Flow Diagram         2-22         3-5         Disconnect Command Chaining Block Diagram and Examples         3-10           2-15         Read and Reset Buffer Log Flow Diagram         2-23         3-6         Block Multiplexer Channel Operation (1 of 2)         3-11           2-16         Device Reserve and Device Release Flow Diagrams         2-26         3-9         Write Data Transfer Flow Diagram (1 of 3)         3-20           2-17         Transfer In-Line Diagnositics to SCU Block Diagram         2-26         3-9         Write Data Transfer Flow Diagram (1 of 4)         3-22           2-18         Read Data Transfer In-Line Diagnositic to SCU Block Diagram         2-27         3-10         Write Data Transfer Flow Diagram (1 of 4)         3-22           2-19         Read Pactorio Taro, Read Count, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 2-6    | Restore Flow Diagram                             | 2-11 |     | 2-49   |                                                        | 2-79 |

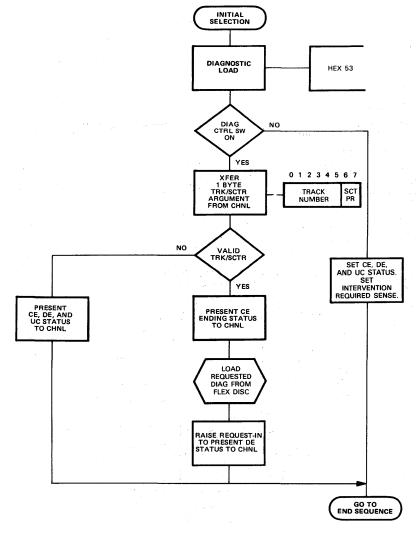

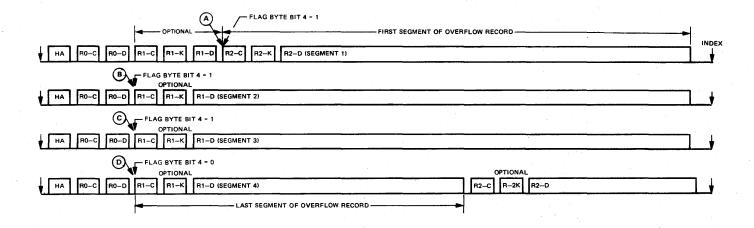

| 2-9 Diagnostic Load Flow Diagram 2-10 Diagnostic Wire Flow Diagram 2-11 Sense Byte Definitions 2-16 3-2 Selector Channel Operation. Data Transfer Sequences 3-5 2-11 Sense Byte Definitions 2-12 Sense Byte Definitions 3-10 Diagnostic Wire Flow Diagram 2-12 Sense Byte Definitions 3-10 Diagnostic Wire Flow Diagram 3-10 Diagnostic Wire Special Court, Rey, and Data Flow Diagram 2-22 3-5 Diagnostic Status 1 Flow Diagram 3-10 Diagnostic Status 1 Flow Diagram 3-10 Diagnostic Status 1 Flow Diagram 3-10 Diagnostic Status 1 Flow Diagram 3-11 Read Diagnostic Status 1 Flow Diagram 3-12 Read Diagnostic Status 1 Flow Diagram 3-13 Read Diagnostic Status 1 Flow Diagram 3-14 Read Diagnostic Status 1 Flow Diagram 3-15 Device Reserve and Device Releases Flow Diagrams 3-16 Device Reserve and Device Releases Flow Diagrams 3-17 Read Diagnostic Status 1 Flow Diagrams 3-18 Read Diagnostic Status 1 Flow Diagrams 3-20 Read Operation Biotock Diagram 3-21 Read Operation Biotock Diagram 3-22 Read Operation Biotock Diagram 3-23 Nitre Data Transfer Flow Diagram (1 of 3) 3-20 Read Operation Biotock Diagram (1 of 3) 3-20 Read Operation Biotock Diagram (1 of 4) 3-25 Read Post Reserve Canada Read Count, Key, and Data Flow Diagrams 3-26 Read Record Zero, Read Count, and Read Home Address Flow Diagram 3-27 Read Data Transfer Flow and Block Diagram 3-28 Read Data Transfer Flow and Block Diagram 3-29 Write Data Transfer Flow and Block Diagram 3-20 Read Diagnostic Status 1 Flow Diagram 3-21 Mirro Control Diagnostic Status 1 Flow Diagram 3-22 Read Diagnostic Status 1 Flow Diagram 3-23 Status 1 Read Read Record Zero, Read Count, Rey, and Data Flow Diagram 3-24 Read Diagnostic Status 1 Read Read Count, Rey, and Data Flow Diagram 3-25 Search Home Address Equal Provision Diagram   |   | 2-7    | Set File Mask Flow Diagram                       | 2-12 |     | 2-50   | Overflow Record Operation                              | 2-80 |

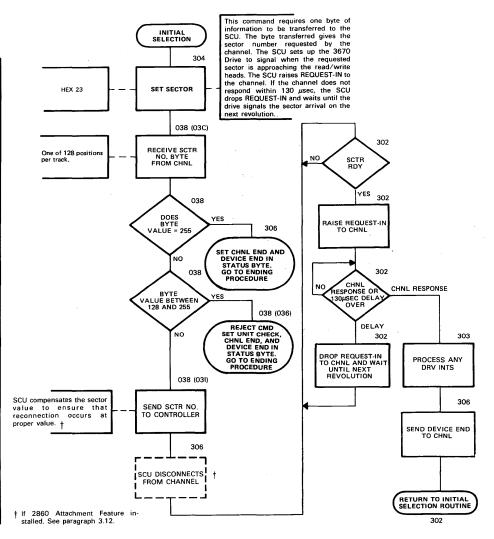

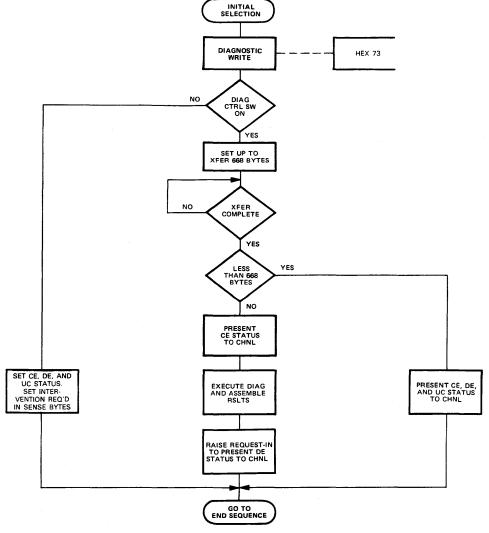

| 2-10   Diagnostic Write Flow Diagram   2-15   3-2   Selector Channel Operation, Data Transfer Sequences   3-5   2-11   Sense BYDe Definitions   2-16   3-3   Selector Channel Operation, Miscellaneous Sequences   3-9   2-12   Sense I/O Flow Diagram   2-21   3-4   Disconnect Command Chaining Block Diagram and Examples   3-10   2-13   Test I/O Flow Diagram   2-22   3-5   Disconnect Command Chaining Block Diagram and Examples   3-10   2-14   Read and Reset Buffer Log Flow Diagram   2-23   3-6   Block Multiplexer Channel Operation (1 of 2)   3-11   2-15   Read Diagnostic Status 1 Flow Diagram   2-24   3-7   Read Data Transfer Block Diagram   3-18   2-16   Device Reserve and Device Release Flow Diagrams   2-25   3-8   Read Data Transfer Flow Diagram (1 of 3)   3-20   2-17   Transfer In-Line Diagnostic Is to SCU Block Diagram   2-27   3-10   Write Data Transfer Flow Diagram (1 of 4)   3-25   2-18   Read Operation Block Diagram   2-27   3-10   Write Data Transfer Flow Diagram (1 of 4)   3-25   2-19   Read Board Sex Read Count, and Read Home Address Flow Diagram   2-30   3-11   Check I: Error Controlling Sequence Flowchart and Logic Diagram   3-29   2-20   Read Record Zero, Read Count, and Read Home Address Flow Diagram   2-30   3-11   Check I: Error Controlling Sequence Flowchart and Logic Diagram   3-33   2-22   Read Data Transfer Flow and Block Diagram   2-30   3-11   Multi-Channel Switching Logic   3-31   2-23   Read Data Transfer Flow and Block Diagram   2-30   4-1   Microinstruction Formats   4-2   2-24   Read Logo Microgram Subroutine   2-40   4-2   Microinstruction Formats   4-2   2-25   Write Operation Clock Diagram   2-40   4-2   Microinstruction Formats   4-5   2-26   Write Operation Clock Diagram   2-40   4-2   Microinstruction Formats   4-5   2-27   Write Special Count, Key, and Data; Write Data Flow Diagram   2-40   Microprogram Format Example   4-7   2-26   Write Operation Clock Diagram   2-40   Microprogram Format Example   4-7   2-27   Write Data Transfer Flow Diagram   2-40   Microprogram Format Examp   |   | 2-8    | Set Sector Flow Diagram                          | 2-13 |     | 2-51   | Multichannel Operation Block Diagram                   | 2-81 |

| 2-10   Diagnostic Write Flow Diagram   2-15   3-2   Selector Channel Operation, Data Transfer Sequences   3-5   2-12   Sense IV De Flomithitions   2-16   3-3   Selector Channel Operation, Miscellaneous Sequences   3-9   2-13   Test IV De Flow Diagram   2-21   3-4   Disconnect Command Chaining Block Diagram and Examples   3-10   2-14   Read and Reset Buffer Log Flow Diagram   2-22   3-5   Disconnect Command Chaining Block Diagram and Examples   3-10   2-15   Read Diagnostic Status 1 Flow Diagram   2-23   3-6   Block Multiplexer Channel Operation (1 of 2)   3-11   2-16   Device Reserve and Device Release Flow Diagram   2-25   3-8   Read Data Transfer Flow Diagram (1 of 3)   3-20   2-17   Transfer In-Line Diagnostic to St CUB lock Diagram   2-27   3-10   Write Data Transfer Flow Diagram (1 of 3)   3-20   2-18   Read Operation Block Diagram   2-27   3-10   Write Data Transfer Flow Diagram (1 of 4)   3-25   2-19   Read Data Read Easter Flow Diagram   2-30   3-11   Cheek-I Error Controlling Sequence Flowchart and Logic Diagram   3-29   2-20   Read Record Zero, Read Count, and Read Home Address Flow Diagram   2-34   3-12   Multi-Channel Switching Logic   3-31   2-21   Read Data Transfer Flow and Block Diagram   2-39   3-13   3-14   Microinstruction Formats   4-2   2-24   Read Logo Microprogram Subroutine   2-40   4-2   Microinstruction Formats   4-2   2-25   Write Count, Key, and Data; Write Data Flow Diagram   2-44   4-3   Microprogram Subroutine   4-8   2-26   Write Operation Clock Diagram   2-44   4-5   Microprogram Format Example   4-7   2-26   Write Devantion Clock Diagram   2-40   4-2   Microinstruction Formats   4-2   2-27   Write Data Transfer Flow Diagram   2-40   4-2   Microinstruction Formats   4-2   2-28   Write Data Transfer Flow Diagram   2-40   4-2   Microprogram Format Example   4-7   2-29   Write Data Transfer Flow Diagram   2-40   4-2   Microprogram Format Example   4-7   2-20   Write Data Transfer Flow Diagram   2-40   4-2   Microprogram Format Example   4-7   2-21   Write Data Transfer Flow Diagr   |   | 2-9    | Diagnostic Load Flow Diagram                     | 2-14 |     | 3-1    | Serial Connection of SELECT IN/SELECT OUT              | 3-3  |

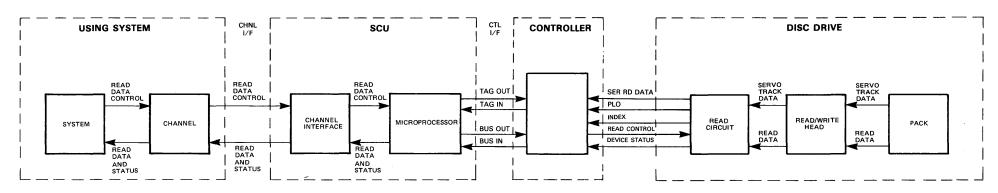

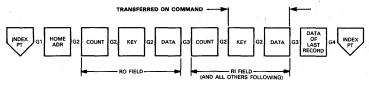

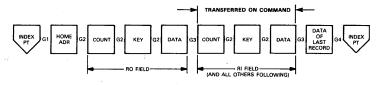

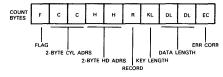

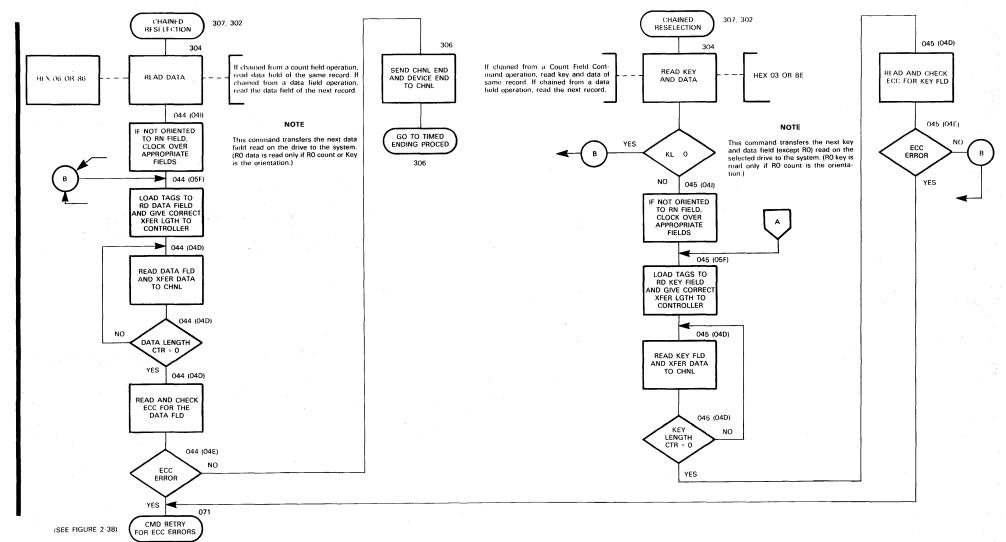

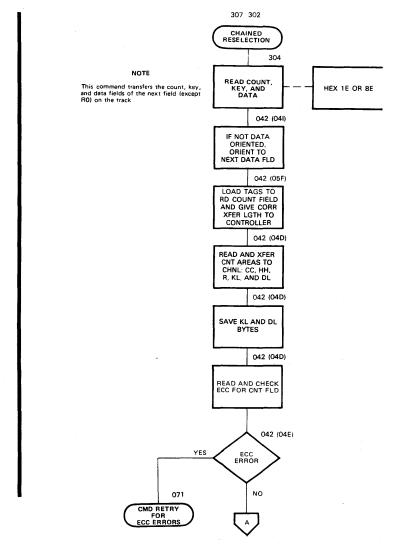

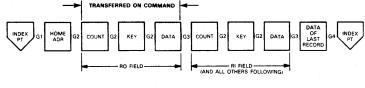

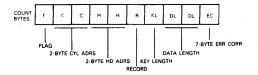

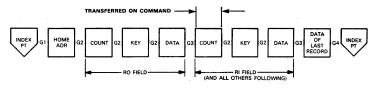

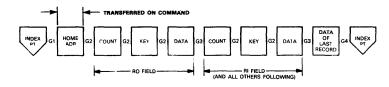

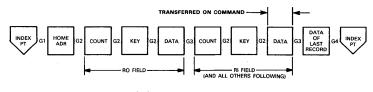

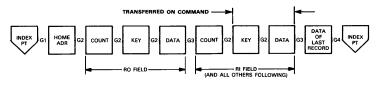

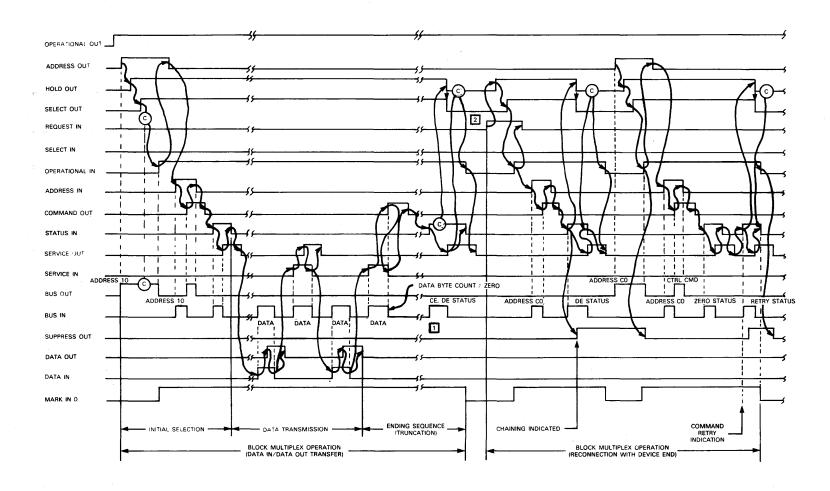

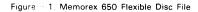

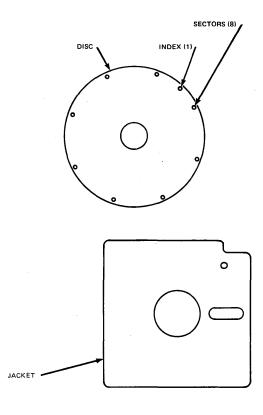

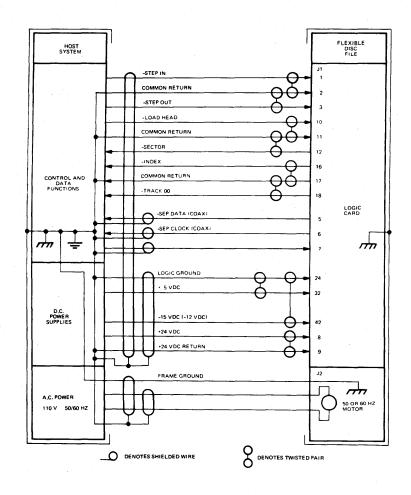

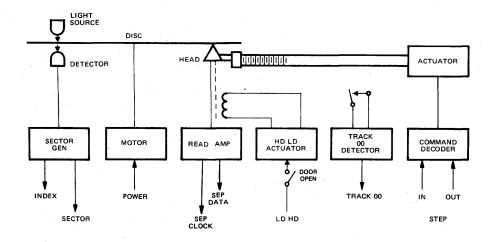

| 2-12 Sense I V F I Flow Diagram 2-21 3-4 Disc Track Sector Format 3-10 2-14 Read and Reset Buffer Log Flow Diagram 2-22 3-5 Disconnect Command Chaining Block Diagram and Examples 3-10 2-14 Read and Reset Buffer Log Flow Diagram 2-23 3-6 Block Multiplexer Channel Operation (1 of 2) 3-11 2-15 Read Diagnostic Status 1 Flow Diagram 2-24 3-7 Read Data Transfer Block Diagram (1 of 3) 3-10 2-16 Device Reserve and Device Release Flow Diagram 2-25 3-8 Read Data Transfer Block Diagram (1 of 3) 3-20 2-17 Transfer I i Line Diagnostics to SCU Block Diagram 2-26 3-8 Write Data Transfer Flow Diagram (1 of 3) 3-20 2-18 Read Operation Block Diagram 2-27 3-10 Write Data Transfer Flow Diagram (1 of 4) 3-25 2-19 Read Data, Read Key and Data, and Read Count, Key, and Data Flow Diagrams 2-30 3-11 Check-1 Error Controlling Sequence Flowchart and Logic Diagram 3-29 2-20 Read Record Zero, Read Count, and Read Home Address Flow Diagram 2-34 3-12 2-21 Read IPL and Read Sector Flow Diagram 2-39 4-1 Microinstruction Formats 4-2 2-23 Read Logo Microprogram Subroutine 2-40 4-2 Microprogram Subroutine 8-240 Microprogram Subroutine 4-4 2-24 Read Diagnostic to System Operation 4-4 2-25 Write Count, Key, and Data; Write Data Flow Diagram 2-44 4-5 Microprogram Block Formats 4-6 2-26 Write Count, Key, and Data; Write Data Flow Diagram 2-47 5-1 Memorex 650 Flexible Disc File Punctional Block Diagram 3-49 2-30 Erase Flow Diagram 2-49 5-3 Cantridge Loading 5-3 2-31 Write Data Transfer Devail Diagram 2-49 5-3 Cantridge Loading 5-3 2-32 Search Home Address Equal Flow Diagram 2-55 5-1 Flexible Disc File Functional Block Diagram 3-10 Microprogram Block Diagram 3-10 Microprogram Sequence 3-7 2-33 Search Home Address Equal Flow Diagram 2-56 5-1 Flexible Disc File Functional Block Diagram 3-57 2-58 Search Key Equal, Search ID High, and Search ID Equal or 5-7 2-59 Search Key Equal, Search Key High, and Search Rey Equal or High Flow 5-7 2-59 Search Key Equal, Search Key High, and Search Rey Equal or High Flow 5-7 2-59 Search Key Equal, Search Key High, and S  |   | 2-10   | Diagnostic Write Flow Diagram                    | 2-15 |     | 3-2    |                                                        | 3-5  |

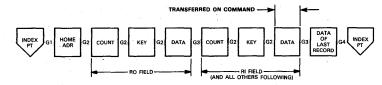

| 2-12 Sense I/O Flow Diagram 2-13 Test I/O Flow Diagram 2-14 Read and Reset Buffer Log Flow Diagram 2-15 Read and Reset Buffer Log Flow Diagram 2-16 Read and Reset Buffer Log Flow Diagram 2-17 Pransfer In-Line Diagnostic Status 1 Flow Diagram 2-18 Peace and Device Release Flow Diagram 2-19 Per Read Diagnostic Status 1 Flow Diagram 2-10 Pevice Reserve and Device Release Flow Diagram 2-10 Pevice Reserve and Device Release Flow Diagram 2-11 Pransfer In-Line Diagnostics to SCU Block Diagram 2-12 Transfer In-Line Diagnostics to SCU Block Diagram 2-13 Read Operation Block Diagram 2-14 Read Operation Block Diagram 2-15 Read Operation Block Diagram 2-16 Read Operation Block Diagram 2-17 Read Device Read Count, Key, and Data Flow Diagram 2-18 Read Device Read Reserve And Data, and Read Count, Key, and Data Flow Diagram 2-19 Read Plan Read Sector Flow Diagram Pransfer Flow And Block Diagram 2-20 Read India Read Sector Flow Diagram Pransfer Flow And Block Diagram Pransfer Flow Pransfer   |   | 2-11   | Sense Byte Definitions                           | 2-16 |     | 3-3    | Selector Channel Operation, Miscellaneous Sequences    | 3-9  |

| 2-14 Read and Reset Buffer Log Flow Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 2-12   | Sense I/O Flow Diagram                           | 2-21 |     | 3-4    |                                                        | 3-10 |

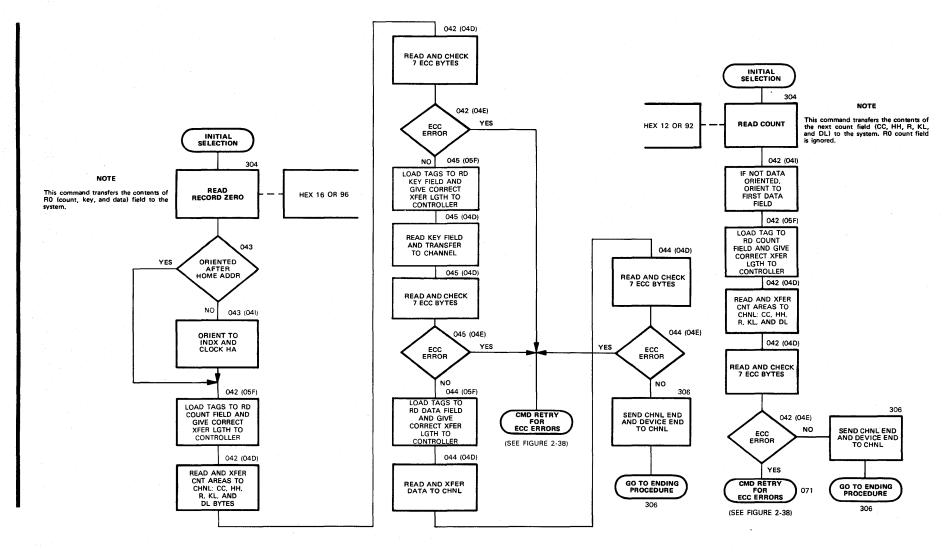

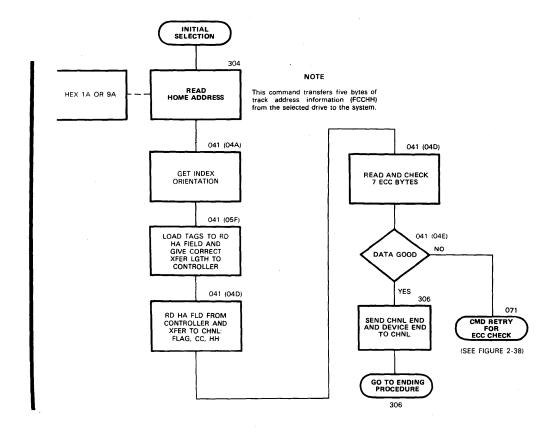

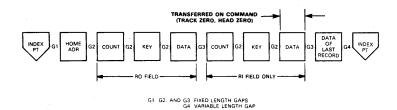

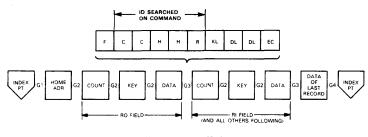

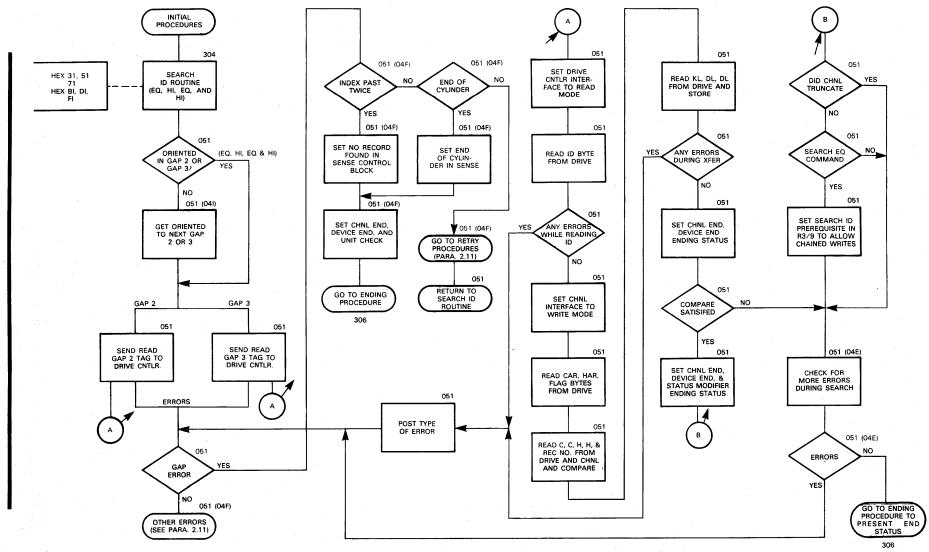

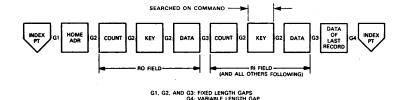

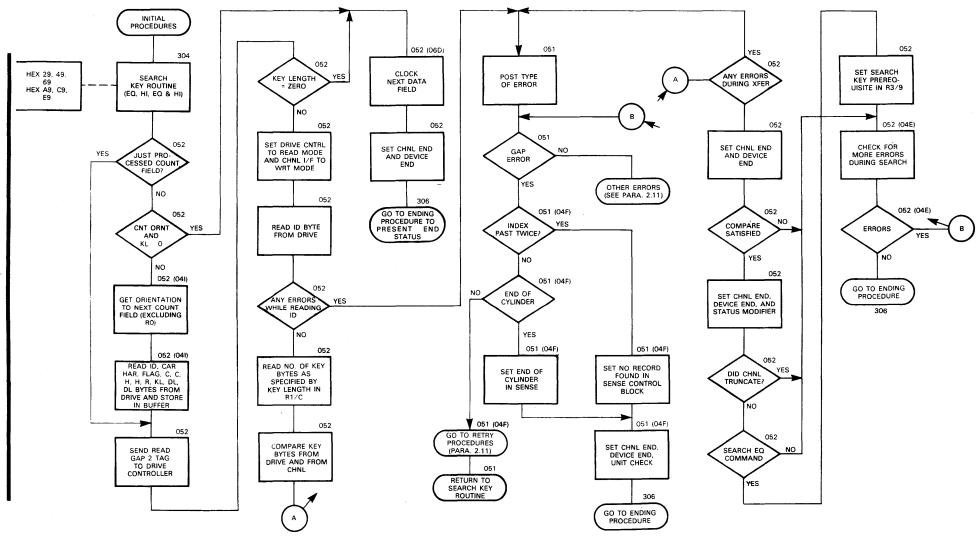

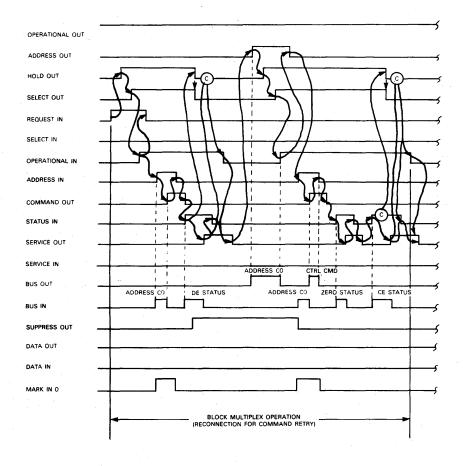

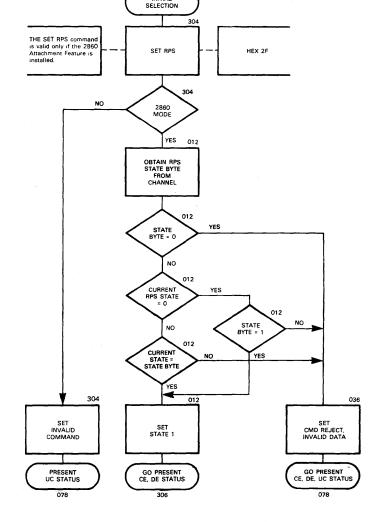

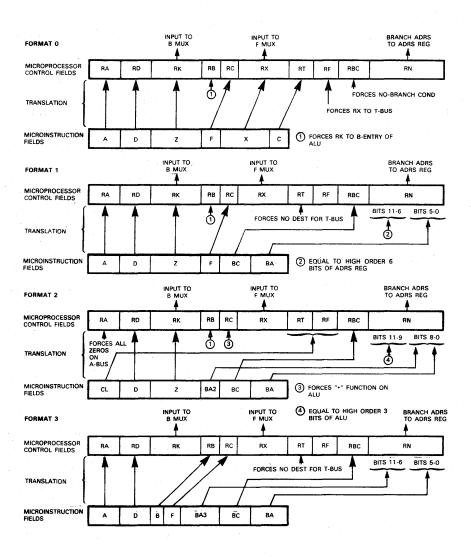

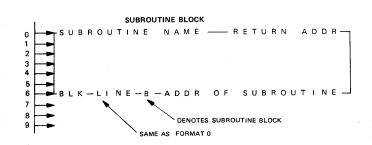

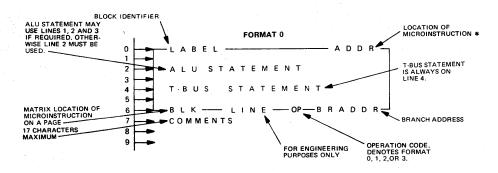

| 2-14 Read and Reset Buffer Log Flow Diagram 2-15 Read Diagnostic Status 1 Flow Diagram 2-16 Device Reserve and Device Release Flow Diagram 2-26 3-8 Read Data Transfer Block Diagram (1 of 2) 3-10 2-17 Transfer In-Line Diagnostics to SCU Block Diagram 2-27 3-10 Write Data Transfer Block Diagram (1 of 3) 3-20 2-18 Read Operation Block Diagram 2-28 Read Departson Block Diagram 2-29 Read Departson Block Diagram 2-29 Read Record Zero, Read Count, and Read Home Address Flow Diagrams 2-30 3-11 Check-1 Error Controlling Sequence Flowchart and Logic Diagram 3-29 Read Record Zero, Read Count, and Read Home Address Flow Diagram 2-31 Write Data Transfer Flow Diagram (1 of 4) 3-25 2-20 Read Record Zero, Read Count, and Read Home Address Flow Diagram 2-34 3-11 Multi-Channel Switching Logic 3-31 2-21 Read IPL and Read Sector Flow Diagrams 2-37 3-13 Set RPS Flow Diagram 3-33 2-22 Read Data Transfer Flow and Block Diagram 2-39 4-11 Microinstruction Formats 4-2 2-23 Read Logo Microprogram Subroutine 2-40 4-2 Microinstruction Expansion 4-4 2-24 Read Diagnostic to System Operation 2-41 4-3 Microprogram Block Formats 4-6 2-25 Write Operation Clock Diagram 2-42 4-4 Microprogram Format Example 4-7 2-26 Write Count, Key, and Data; Write Data Flow Diagram 2-47 5-1 Memorex 650 Flexible Disc Flie 5-1 2-29 Write Home Address Flow Diagram 2-49 5-3 Cartridge Loading 5-1 2-29 Write Home Address Flow Diagram 2-49 5-3 Cartridge Loading 5-3 2-30 Erase Flow Diagram 2-50 5-5 5-7 Disc Cartridge and Disc Configuration 5-5 2-31 Search ID Equal, Search Key Equal or High Flow Diagram 2-60 5-14 Flexible Disc Flie Functional Block Diagram 5-18 2-35 Search Home Address Equal Flow Diagram 2-60 5-14 Flexible Disc Flie Functional Block Diagram 5-18 2-36 Selective Reset Flow Diagram 2-60 5-10 Flexible Disc Flie Functional Block Diagram 5-18 2-37 System Reseaf Equal Flow Diagram 2-60 5-11 Flexible Disc Flie Interface Diagram 5-10 2-38 Command Retry, Data, Sync, and AM Checks 2-66 6-12 Command Retry, Data, Sync, and AM Checks 6-12 Command Retry, Data, Sync, an  |   | 2-13   | Test I/O Flow Diagram                            | 2-22 |     | 3-5    | Disconnect Command Chaining Block Diagram and Examples | 3-10 |

| 2-15         Read Diagnostic Status I Flow Diagram         2-24         3-7         Read Data Transfer Block Diagram         3-18           2-16         Device Reserve and Device Release Flow Diagrams         2-25         3-8         Read Data Transfer Flow Diagram         3-20           2-17         Transfer In-Line Diagnostics to SCU Block Diagram         2-26         3-9         Write Data Transfer Flow Diagram         3-23           2-18         Read Operation Block Diagram         2-27         3-10         Write Data Transfer Flow Diagram         3-23           2-19         Read Read Kae Key and Data, and Read Count, Key, and Data Flow Diagrams         2-30         3-11         Check-I Error Controlling Sequence Flowchart and Logic Diagram         3-29           2-20         Read Record Zero, Read Count, and Read Home Address Flow Diagram         2-34         3-11         Multi-Channel Switching Logic         3-31           2-21         Read IPL and Read Sector Flow Diagrams         2-39         4-1         Multi-Channel Switching Logic         3-31           2-22         Read Lop Microprogram Subroutine         2-40         4-2         Microprogram Block Formats         4-2           2-24         Read Diagnostic to System Operation         2-41         4-3         Microprogram Block Formats         4-6           2-25         Write Count, Key, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 2-14   | Read and Reset Buffer Log Flow Diagram           | 2-23 |     | 3-6    |                                                        | 3-11 |

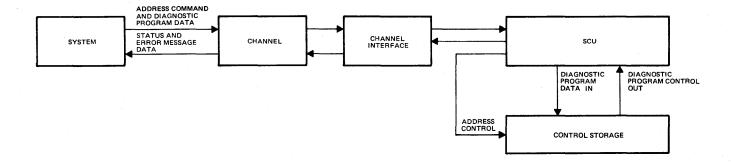

| 2-17   Transfer In-Line Diagnostics to SCU Block Diagram   2-26   3-9   Write Data Transfer Block Diagram   3-23   3-25   3-10   Write Data Transfer Flow Diagram   10-4)   3-25   3-25   3-20   3-21   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-227   3-22   |   | 2-15   | Read Diagnostic Status 1 Flow Diagram            | 2-24 |     | 3-7    |                                                        | 3-18 |

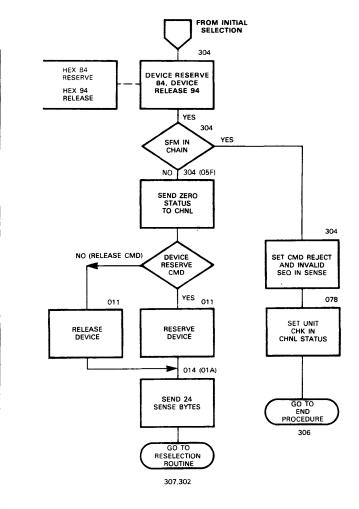

| 2-17   Transfer In-Line Diagnostics to SCU Block Diagram   2-26   3-9   Write Data Transfer Block Diagram   3-23   3-12   3-15   Write Data Transfer Flow Diagram   10-4)   3-25   3-15   2-19   Read Data, Read Key and Data, and Read Count, Key, and Data Flow Diagram   2-30   3-11   Check-1 Error Controlling Sequence Flowchart and Logic Diagram   3-29   2-20   Read Record Zero, Read Count, and Read Home Address Flow Diagram   2-34   3-12   Multi-Channel Switching Logic   3-31   3-12   Read IPL and Read Sector Flow Diagram   3-33   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   |   | 2-16   | Device Reserve and Device Release Flow Diagrams  | 2-25 |     | 3-8    | Read Data Transfer Flow Diagram (1 of 3)               | 3-20 |

| 2-18   Read Operation Block Diagram   2-27   3-10   Write Data Transfer Flow Diagram (1 of 4)   3-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 2-17   |                                                  | 2-26 |     | 3-9    |                                                        | 3-23 |