# **THE K-1 ARCHITECTURE MANUAL**

# THE K-1 ARCHITECTURE MANUAL

Version 3.0

June 5, 1989

## CONFIDENTIAL

CONFIDENTIAL

This document contains information proprietary to Amdahl Key Computer Laboratories (KCL). Use or disclosure without the written permission of an officer of KCL is expressly forbidden. Copyright © KCL 1987, 1988, 1989.

Report number KC-101

# Contents 1019 Income a ABIPAHO

| List o | of Figu | ıres                                                                                                            | vii  |

|--------|---------|-----------------------------------------------------------------------------------------------------------------|------|

| LISU   | n rabi  |                                                                                                                 |      |

| CHA    | PTER    | ferral de la vectar el se se se se submendant de fanada de la deserva de la serva de la serva de la serva de la |      |

| CHA    | PTER    | 2. K-1 ARCHITECTURE OVERVIEW                                                                                    | 2-1  |

|        | 2.1     | Introduction                                                                                                    |      |

|        | 2.2     | Conventions                                                                                                     |      |

|        | 2.3     | Data Types                                                                                                      | 2-3  |

|        |         | 2.3.1 Integers                                                                                                  |      |

|        |         | 2.3.2 Floating-Point Numbers                                                                                    | 2-4  |

|        | 2.4     | Instruction Formats                                                                                             | 2-6  |

|        | 2.5     | General Registers                                                                                               |      |

|        | 2.6     | Flags and Conditional Branching                                                                                 | 2-7  |

|        | 2.7     | ELF Flags                                                                                                       |      |

|        | 2.8     | Memory                                                                                                          | 2-7  |

|        |         | 2.8.1 Precision and Alignment                                                                                   |      |

|        |         | 2.8.2 Addressing Modes                                                                                          | 2-8  |

|        | 2.9     | Processor States                                                                                                |      |

|        | 2.10    | Virtual Memory                                                                                                  | 2-9  |

|        |         | 2.10.1 Address Mapping                                                                                          |      |

|        |         | 2.10.1.1 Instruction Mapping                                                                                    |      |

|        |         | 2.10.1.2 Data Mapping                                                                                           |      |

|        | 2.11    | Cache Effects                                                                                                   |      |

|        |         | 2.11.1 Cache Organization and Addressing                                                                        |      |

|        |         | 2.11.2 Instruction Stache                                                                                       |      |

|        |         | 2.11.3 Cache Coherence                                                                                          | 2-15 |

|        |         | 2.11.4 Interprocessor Synchronization                                                                           |      |

|        | 2.12    | Program Execution                                                                                               |      |

|        |         | 2.12.1 Delayed Branching                                                                                        | 2-17 |

|        |         | 2.12.2 Conditional Execution                                                                                    | 2-18 |

|        | 2.13    | Early Load                                                                                                      | 2-18 |

|        | 2.14    | Processor Status                                                                                                | 2-19 |

|        | 2.15    | Input/Output                                                                                                    | 2-23 |

|        |         | 2.15.1 I/O Interrupts                                                                                           | 2-23 |

|        | 2.16    | Timers                                                                                                          | 2-23 |

|        | 2.17    | Traps, Interrupts, and Machine Checks                                                                           |      |

|        |         | 2.17.1 The Trap Sequence                                                                                        | 2-26 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.18     | Reset    | Operation                                        | 2-29 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|--------------------------------------------------|------|

| CHA                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PTER     | 3.       | K-1 Instructions                                 | 3-1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.1      | Instruc  | ction Formats                                    | 3-1  |

| CHA                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PTER     | 4.       | Floating-Point Instructions                      | 4-1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.1      | Floatin  | _                                                |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.2      |          |                                                  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.3      | Floatin  | ng-Point Computation Instructions                | 4-13 |

| CHA                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PTER     | 5.       | Load and Store Instructions                      | 5-1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.1      |          |                                                  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.2      |          |                                                  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |          |                                                  |      |

| CHAPTER 3.       K-1 Instructions       3-1         3.1       Instruction Formats       3-1         CHAPTER 4.       Floating-Point Instructions       4-1         4.1       Floating-Point Compare Instructions       4-1         4.2       Floating-Point Conversion Instructions       4-5         4.3       Floating-Point Computation Instructions       4-13         CHAPTER 5.       Load and Store Instructions       5-1         5.1       Referencing Memory       5-1 |          |          |                                                  |      |

| 5.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |          |                                                  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | ELF F    | lag Instructions                                 |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.7      | Data v   |                                                  |      |

| CHA                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PTER     | 6.       |                                                  | 6-1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6.1      | Intege   | r Arithmetic Instructions                        | 6-1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |          |                                                  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |          | •                                                |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |          |                                                  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |          |                                                  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |          |                                                  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | -        |                                                  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.8      | Cneck    | Instructions                                     | 0-01 |

| CHA                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PTER     | 7.       | Transfer of Control Instructions                 | 7-1  |

| СНА                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PTER     | 8.       | Processor Status Register and Timer Instructions | 8-1  |

| СНА                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PTER     | 9        | Virtual Memory and Cache Instructions            | 9-1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |          |                                                  |      |

| СНА                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PTER     | 10.      |                                                  |      |

| CHA                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PTER     | 11.      | I/O Instructions                                 | 11-1 |

| СНА                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PTER     | 12.      | Miscellaneous Instructions                       | 12-1 |

| СНА                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PTER     | 13.      | Undefined Opcodes                                |      |

| 101 N                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2014 B.S |          |                                                  |      |

| Appe                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ndix A   | <b>.</b> | Instruction Index (Alphabetic)                   | A-1  |

| Appe                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ndix B   | 3.       | Instruction Index (Numeric)                      | B-1  |

| 8: S                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |          |                                                  |      |

| Appendix | C.      | Instruction Timing Considerations              | C-1       |

|----------|---------|------------------------------------------------|-----------|

| C.1      | Clock   | Cycles                                         | C-1       |

| C.2      | Instruc | ction Issue                                    | C-1       |

| C.3      | Pipelin | ing                                            |           |

| C.4      | *       | onal Unit Latency and Interlocks               |           |

| C.5      | K-1 In  | terlocks                                       | C-3       |

| 0.5      | C.5.1   | Register Interlocks                            |           |

|          | C.5.2   | Flag Interlocks                                |           |

|          | C.5.3   | I1/I0 Interlocks                               |           |

|          | 0.3.5   | C.5.3.1 I0 Interlocked                         |           |

|          |         |                                                |           |

|          |         | C.5.3.2 Serial Instructions                    |           |

|          |         | C.5.3.3 I1/I0 Read Port Conflicts              |           |

|          | 0.5.4   | C.5.3.4 I1/I0 Register and Flag Conflicts      |           |

|          | C.5.4   | Floating-Point Divide/Square Root Unit         |           |

|          | C.5.5   | Load/Store Unit                                |           |

| C.6      |         | ning                                           |           |

|          | C.6.1   | Branching to a PC-Relative or Absolute Address |           |

| 11.7     | C.6.2   | Branching to an Address in a Register          |           |

| C.7      |         | 1 Instructions                                 |           |

|          | C.7.1   | nop                                            |           |

|          | C.7.2   | rps, wps, spl, and srm                         |           |

|          | C.7.3   | Trap Instructions and Instructions Which Trap  |           |

|          | C.7.4   | exts                                           |           |

|          | C.7.5   | ickill                                         |           |

|          | C.7.6   | iskill                                         | C-10      |

| C.8      | Load/S  | Store Timing                                   | C-11      |

|          | C.8.1   | load instructions                              | C-11      |

|          | C.8.2   | store instructions                             | C-11      |

|          | C.8.3   | ldpage                                         | C-11      |

|          | C.8.4   | pcl and zcl                                    |           |

|          | C.8.5   | dflush                                         | C-12      |

|          | C.8.6   | rfec and wfec                                  | C-12      |

|          | C.8.7   | rios and wios                                  |           |

| 1.A.     |         |                                                |           |

| Appendix | D.      | Trap Handling                                  | D-1       |

| D.1      | Trap D  | Data and Trap Recovery                         | D-1       |

|          | D.1.1   | Primary Trap Data                              | D-1       |

|          |         | D.1.1.1 Trap Summary                           | D-1       |

|          |         | D.1.1.2 Trap Locators                          |           |

|          |         | D.1.1.2.1 IMA Trap Locators                    |           |

|          |         | D.1.1.2.2 L/S Trap Locators                    |           |

|          |         | D.1.1.2.3 Divide Trap Locators                 |           |

|          | D.1.2   | Reading Primary Trap Data                      |           |

|          | D.1.3   | Load/Store Trap Data                           |           |

|          | D.1.4   | Storing Load/Store Trap Data                   |           |

| D.2      |         | exts Instructions                              |           |

|          | 00001   |                                                | $D^{-1}J$ |

| D.3      | Example Trap Handler                             |     |

|----------|--------------------------------------------------|-----|

| Appendix | E. Memory System Specifics                       | E-1 |

| E.1      | Introduction                                     | E-1 |

| E.2      | Data Order                                       | E-1 |

| E.3      | Error-Correcting Code                            | E-3 |

| E.4      | CPU Features for Diagnosing the Memory System    |     |

| E.5      | Console Interactions and Error Logging           |     |

| E.6      | Cache Coherency                                  |     |

| E.7      | Memory System Timing                             |     |

| Appendix | F. I/O System Specifics                          | F-1 |

| F.1      | Introduction                                     |     |

| F.2      | Instruction Descriptions                         |     |

|          | F.2.1 wios                                       |     |

|          | F.2.2 rios                                       |     |

| F.3      | Control and Status Register Formats              |     |

|          | F.3.1 Channel Control Register Format            |     |

|          | F.3.2 Channel Status Register Format             |     |

|          | F.3.3 IOCA Status Register Format                |     |

| Appendix | G. Console Specifics                             | G-1 |

| G.1      | Introduction                                     | G-1 |

| G.2      | Interrupts                                       | G-1 |

| G.3      | TTY Interface                                    |     |

| G.4      | Performance Counters                             | G-2 |

| G.5      | Clock Control                                    | G-2 |

| G.6      | Scan Control and Hidden State                    | G-2 |

| G.7      | Bootstrap Procedure                              | G-2 |

| Appendix | H. Implementation Dependencies                   | H-1 |

| H.1      | The Version 1 Implementation                     | H-1 |

| Appendix | I. Floating-Point Operation Details              |     |

| I.1      | Abbreviations                                    | I-1 |

| I.2      | Use of NaN                                       | I-1 |

| I.3      | Floating-Point Overflow and Underflow            |     |

| I.4      | Floating-Point Operation Tables                  |     |

|          | I.4.1 Floating-Point Addition                    |     |

| I.5      | Floating-Point Negation                          | I-5 |

| I.6      | Floating-Point Subtraction                       | I-5 |

| I.7      | Floating-Point Multiplication                    | I-6 |

| I.8      | Floating-Point Division                          |     |

| I.9      | Floating-Point Square Root                       |     |

| I.10     | Floating-Point Conversions                       |     |

| 1.1 - Fl | I.10.1 Conversion Between Floating-Point Formats |     |

#### Contents v

|       | I.10.2 | Conversion Between Floating-Point and Integer FormatsI-11 |

|-------|--------|-----------------------------------------------------------|

| INDEX |        | Index-1                                                   |

CONFIDENTIAL

aki ww

# List of Figures

| Figure 2-1.  | The K-1 Processor and Its Interconnections      | 2-2  |

|--------------|-------------------------------------------------|------|

| Figure 2-2.  | Signed 64-Bit Integer Data Type                 | 2-4  |

| Figure 2-3.  | IEEE 32-Bit Precision Floating-Point Format     | 2-5  |

| Figure 2-4.  | IEEE 64-Bit Precision Floating-Point Format     |      |

| Figure 2-5.  | Address Calculation for Load/Store Instructions | 2-8  |

| Figure 2-6.  | Virtual Address Format                          | 2-10 |

| Figure 2-7.  | Instruction Page Table Format                   | 2-11 |

| Figure 2-8.  | Virtual Page Number                             | 2-13 |

| Figure 2-9.  | Data Page Table Format                          | 2-13 |

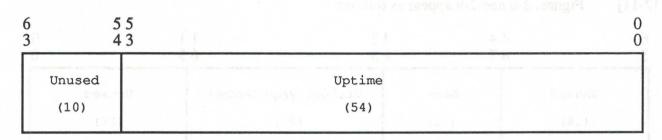

| Figure 2-10. | Uptime Counter                                  | 2-24 |

| Figure 2-11. | Interval Timer Register                         | 2-24 |

| Figure 2-12. | Restart PC                                      | 2-26 |

| Figure 3-1.  | Register Instruction Format                     | 3-2  |

| Figure 3-2.  | Unconditional Short Constant Instruction Format | 3-3  |

| Figure 3-3.  | Conditional Short Constant Instruction Format   | 3-3  |

| Figure 3-4.  | Long Constant Instruction Format                | 3-4  |

| Figure 3-5.  | PC-Relative Branch Instruction Format           | 3-4  |

| Figure 3-6.  | Absolute Branch Instruction Format              | 3-5  |

| Figure 3-7.  | Register Branch Instruction Format              | 3-6  |

| Figure 3-8.  | exts Instruction Format                         | 3-6  |

| Figure 4-1.  | Floating-Point Conversion srcb Argument         | 4-5  |

| Figure 5-1.  | Data Watchpoint Table Entry Format              | 5-53 |

| Figure 6-1.  | boof srca Argument                              | 6-59 |

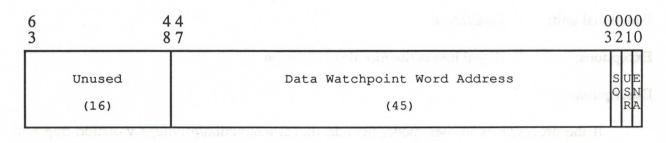

| Figure D-1.  | Trap Summary                                    | D-2  |

| Figure D-2.  | Divide Trap Locator                             | D-5  |

| Figure D-3.  | Load/Store Trap Locator                         | D-5  |

| Figure D-4.  | IMA Trap Locator                                | D-5  |

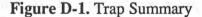

| Figure D-5.  | IMA Trap Byte                                   | D-6  |

| Figure D-6.  | IMA Trap Word                                   | D-6  |

| Figure D-7.  | Load/Store Trap Data                            | D-12 |

| Figure D-8.  | addr Data Field Format                          |      |

| Figure D-9.  | Combined srca/srcb Data Field Format            | D-13 |

| Figure D-10. | ldpage Data Field Format                        | D-13 |

| Figure D-11. | slstrpd srcb Operand Format                               | D-14 |

|--------------|-----------------------------------------------------------|------|

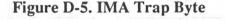

| Figure E-1.  | ECC Groupings Within a Sub-Line                           | E-2  |

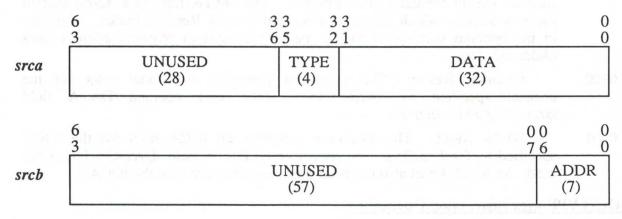

| Figure F-1.  | srca and srcb Operand Format                              | F-3  |

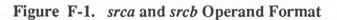

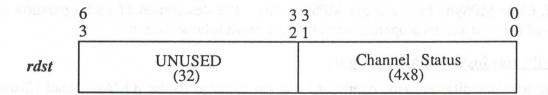

| Figure F-2.  | CRP and NCRP Pointer Structure                            | F-5  |

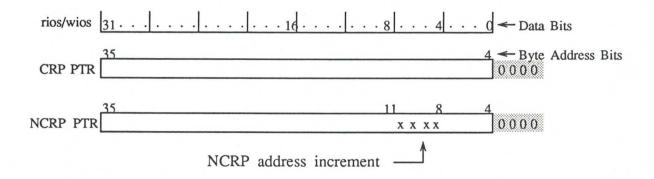

| Figure F-3.  | Type 0001 rdst Register Format                            | F-8  |

| Figure F-4.  | Type 0010 rdst Register Format                            |      |

| Figure F-5.  | Type 0011 rdst Register Format                            | F-9  |

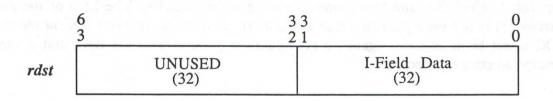

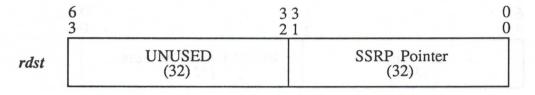

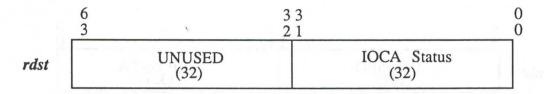

| Figure F-6.  | Type 0100 rdst Register Format                            | F-9  |

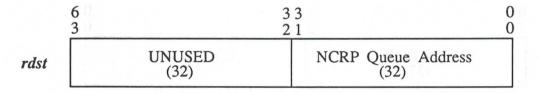

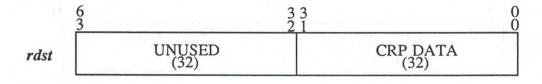

| Figure F-7.  | Type 100x rdst Register Format CRP Queue Pointers         | F-10 |

| Figure F-8.  | Type 100x rdst Register Format NCRP Queue Pointers        | F-10 |

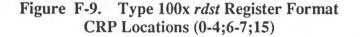

| Figure F-9.  | Type 100x rdst Register Format CRP Locations (0-4;6-7;15) | F-10 |

## **List of Tables**

| Table 2-1.  | IEEE 32-Bit Precision Floating-Point Values                       | 2-5             |

|-------------|-------------------------------------------------------------------|-----------------|

| Table 2-2.  | IEEE 64-Bit Precision Floating-Point Values                       | 2-6             |

| Table 2-3.  | Instruction Page Table Size Specifier2-                           |                 |

| Table 2-4.  | Memory Reference Modes                                            | 12              |

| Table 2-5.  | Processor Status Register                                         | 20              |

| Table 2-6.  | Arithmetic Trap Enables and Exception Flags                       | 20              |

| Table 2-7.  | Rounding Modes                                                    | -21             |

| Table 2-8.  | Low-to-High Byte Addressing2-                                     | -22             |

| Table 2-9.  | External Interrupt Priority Levels                                | 27              |

| Table 2-10. | Trap Vectoring                                                    | -27             |

| Table 2-11. | D0 and D1 Decoding for 32-bit Instructions2-                      | 28              |

| Table 2-12. | D0 and D1 Decoding for a 64-bit Instruction2-                     | 28              |

| Table 3-1.  | Source Operand Control                                            | 3-2             |

| Table 3-2.  | Delayed Execution Control Decoding                                | 3-5             |

| Table 4-1.  | Floating-Point Comparisons                                        | 1-2             |

| Table 5-1.  | Memory Referencing Instruction Traps                              | 5-3             |

| Table 6-1.  | boof Code (BC) Decoding                                           | -59             |

| Table 9-1.  | dflush srcb Control Functions                                     | <del>)</del> -7 |

| Table C-1.  | Functional Unit Latencies C                                       | 2-3             |

| Table D-1.  | Trap Encodings D                                                  | )-3             |

| Table D-2.  | Machine Check Encoding                                            | )-4             |

| Table D-3.  | Trap Bit Field Encodings                                          | )-7             |

| Table D-4.  | I0 and I1 Decoding for 32-bit Instructions D                      | )-7             |

| Table D-5.  | I0 and I1 Decoding for a 64-bit Instruction                       | )-8             |

| Table D-6.  | rtrpd srca encodingD-                                             | 11              |

| Table D-7.  | TY EncodingD-                                                     | 14              |

| Table I-1.  | Addition Results                                                  | I-4             |

| Table I-2.  | Multiplication Results                                            | I-6             |

| Table I-3.  | Division Results                                                  | I-7             |

| Table I-4.  | Square Root Results                                               | I-8             |

| Table I-5.  | Double to Single Conversion Results                               |                 |

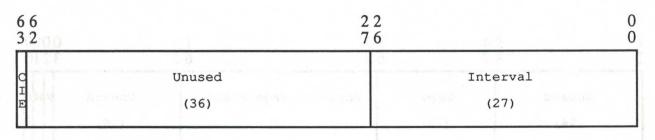

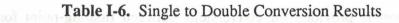

| Table I-6.  | Single to Double Conversion ResultsI-                             | 10              |

| Table I-7.  | Signed or Unsigned Integer to Floating-Point Conversion ResultsI- |                 |

| Table I-8.  | Floating-Point to Signed Integer Conversion ResultsI-             | 11              |

### **CHAPTER 1. INTRODUCTION**

The Amdahl Key Computer Laboratories K-1 family of supercomputers is designed to meet the needs of the modern large computer user. Equipped with an extremely large address space, very high I/O and memory bandwidths, and pipelined functional units, the K-1 is ideally suited to tackling today's highly compute intensive problems. At the same time, a simple, straightforward, yet powerful instruction set makes the K-1 architecture one of the best possible targets for optimizing compilers. A complete set of virtual memory features rounds out the architecture and makes it possible to run modern operating systems smoothly and efficiently.

This manual describes the architecture of the central processing unit of the K-1 family. Different members of this family may contain different numbers of central processing units or have different physical memory sizes or attached I/O processors, but the central processing units all function identically. The main body of this manual contains all the information necessary for programming the K-1, with the exception of instruction timing information which is provided in Appendix C.

The following sections describe the main features of the K-1 architecture and are followed by individual instruction descriptions. Instruction indexes are provided in Appendices A and B for quick reference. Appendix C gives detailed instruction timing information and Appendix D gives trap handling details along with an example of a trap handler. Appendices E, F and G give memory system, I/O system, and Front-End system specifics, respectively. Implementation dependent aspects of the K-1 architecture are noted in the text with square brackets ([]) and are references to Appendix H, which explains features particular to this implementation.

The examples used in this manual to describe K-1 machine instructions conform to the K-1 assembly language syntax, which is described in a separate manual, *The K-1* Assembly Language Reference Manual.

Other documents of interest are:

KC-126: K-1/IOP Software Interface Specification KC-109: The K-1 Assembly Language Reference Manual ANSI/IEEE Std 754-1985: IEEE Standard for Binary Floating-Point Arithmetic

## CHAPTER 2. K-1 ARCHITECTURE OVERVIEW

#### 2.1 Introduction

The K-1 architecture is designed for general purpose/scientific computing. It has been optimized to allow extremely high performance implementations such as the Amdahl Key Computer Laboratories K-1 system. It provides an extensive set of high-precision, IEEE-compatible, floating-point instructions, as well as a full complement of integer, logical and addressing operations. In addition, there are instructions to manipulate the virtual memory system, to control the caching of main memory data, and to control input/output.

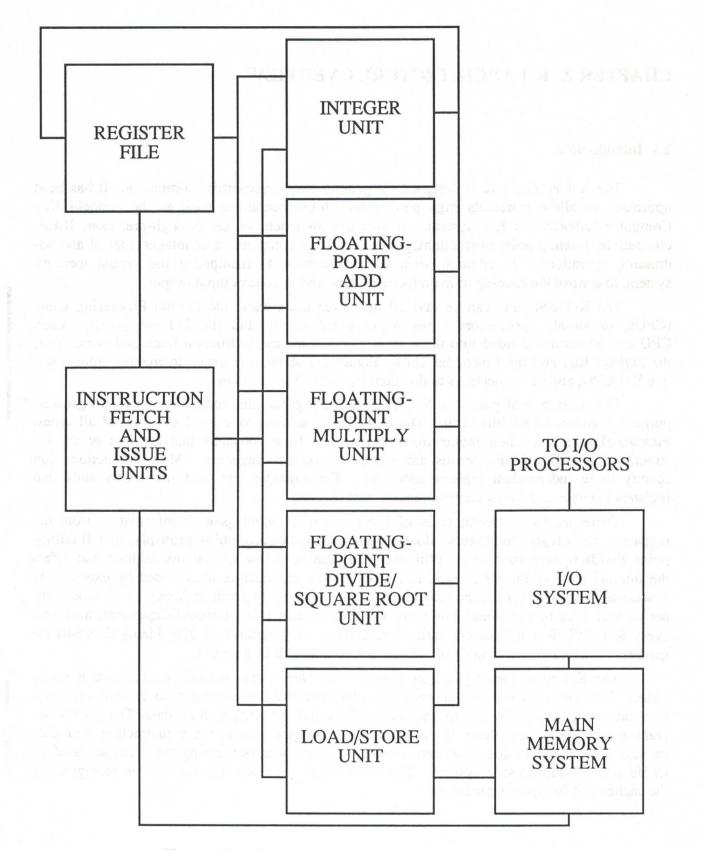

The K-1 computer can be divided into three main parts: the Central Processing Units (CPUs, or simply "processors"), the memory subsystem, and the I/O subsystem. Each CPU can be further divided into three main subsections: the instruction fetch and issue units, the register file, and the functional units. Figure 2-1 shows the major interconnections within a K-1 CPU, and its connections to the memory and I/O subsystems.

The most central part of a K-1 CPU is the register file, containing up to 64 generalpurpose registers of 64 bits each. The register file is used to store data items of all types. Functional units take their inputs from registers, or from constants that are part of the instruction. Functional unit results are always stored into registers. Most instructions can specify three independent register addresses. For example, the **add** instruction adds two registers together and stores the result into a third register.

There are five different types of functional units which process information from the registers: the integer, load/store, floating-point add, floating-point multiply, and floating-point divide/square root units. With the exception of a few special instructions that affect the internal state of the CPU, each instruction in the architecture is executed by exactly one functional unit. Timings for the individual functional units are given in Appendix C. The number of each type of functional unit present in a given K-1 CPU is model-dependent; however, every K-1 CPU has at least one unit of each type. A program will give identical results regardless of the number of units; only the execution time will be affected.

The K-1 main memory system consists of a very large, uniformly addressed memory space. Two large caches insulate each K-1 processor from the access time of main memory. One cache is used exclusively to hold instructions and the other to hold data. The caches operate transparently, but there is no hardware coherence between the instruction and data caches. The hardware does, however, maintain cache coherence among the data caches of all CPUs in a multiprocessor system. The architecture provides instructions for manipulating the caches and for updating memory.

Introduction

Figure 2-1. The K-1 Processor and Its Interconnections

K-1 Architecture Manual

CONFIDENTIAL

Amdahl Key Computer Labs

#### Conventions

I/O in the K-1 architecture is performed through attached I/O processors that interface via a number of very high speed I/O busses. These busses are operated by I/O controllers within the K-1, which transfer data directly to and from main memory. Instructions are provided to send control information to, and receive status from, the I/O subsystem.

#### 2.2 Conventions

Every numeric data type in this manual is assumed to have its most significant bit on the left and its least significant bit on the right. Bits are numbered in ascending order from least significant to most significant, right-to-left, starting with zero. Bytes are numbered in the reverse order from most significant to least significant, left-to-right. This numbering scheme is commonly referred to as "big endian". The only exception to this is related to the **Byte Order Low-to-High** feature which allows the ordering of bytes in memory to be in ascending order from least significant to most significant, right-to-left (commonly referred to as "little endian"). However, even in this case, the bit numbering remains right-to-left.

A data type can be *zero-extended* from its natural size to a larger size by appending sufficient high-order zero bits to make up the difference. For example, a byte can be zero-extended to 64 bits by appending 56 high-order zero bits. Similarly, a signed quantity can be *sign-extended* by appending sufficient high-order copies of the sign bit. For example, a 32-bit data type can be sign-extended to 64 bits by appending 32 high-order copies of bit 31.

The letters K and M indicate 1,024 and 1,048,576 units of something, usually bytes.

The notation m..n indicates a contiguous range of bits within a word or field. Bit number m is the most significant end of the range, and bit number n is the least significant end. If the name of the field is NAME, then such a range is indicated by NAME< m..n >.

#### 2.3 Data Types

The K-1 architecture supports a number of data types and precisions. When a data item is in a register, it may be a signed or unsigned integer of length 8, 16, 32, or 64 bits, or a 32-bit or 64-bit IEEE floating-point number. When in memory, only the precision of the data item (8, 16, 32, or 64 bits) is important. Quantities smaller than 64 bits are always right-adjusted within a register.

#### 2.3.1 Integers

Integers are 8-, 16-, 32-, 33-, 53-, or 64-bit quantities and may be either signed or unsigned. Signed integers are two's complement values whose most significant bit is the sign bit, S. Figure 2-2 shows the format of a signed 64-bit integer. The 53-bit integer format is used only for the integer multiply instructions; the 33-bit integer format is used only for the integer.

CONFIDENTIAL

K-1 Architecture Manual

| 66 |              | en e sedande e nav 0 os   |

|----|--------------|---------------------------|

| s  | Integer Data | California bars a labrica |

|    | (63)         | LI Cohrendines            |

Figure 2-2. Signed 64-Bit Integer Data Type

#### 2.3.2 Floating-Point Numbers

Two precisions of floating-point numbers are supported: 32-bit (single) and 64-bit (double). Separate instructions are provided for each floating-point operation for each precision. The formats conform to the ANSI/IEEE Standard 754-1985 floating-point single and double formats.

Both floating-point precisions contain a sign bit, an exponent field, and a fraction field. The value represented is always a sign-magnitude mantissa times a power of two determined by the exponent. The mantissa consists of a "hidden" bit followed by the fraction. The floating-point format also provides certain special values, such as NaN (Not-a-Number), infinity, negative zero and denormalized numbers (allowing for gradual underflow).

The IEEE standard specifies two types of NaNs: signaling and quiet. Both types of NaNs must have a maximum exponent and a non-zero fraction. The K-1 recognizes a NaN as quiet if the most significant fraction bit is a one, and as signaling if it is zero. When given a NaN as input, all non-trapping floating-point operations (except compares and negate) will generate a quiet NaN. When given as operands to floating-point instructions, signaling NaNs cause an invalid operation trap if enabled. Whenever a NaN is output by a floating-point operation (except negate), it will be a quiet NaN in the form shown in Tables 2-1 and 2-2 with the sign bit set to zero. The floating-point negate function is considered to be a data moving operation, and thus never changes its input (except for the sign bit), and never causes a trap.

Most floating-point numbers are normalized, meaning that their most significant mantissa bit (called the hidden bit) is a one. This bit, therefore, does not need to be present in the representation and is omitted. When computing the value represented by a floatingpoint number, the hidden bit must be reinserted. However, in order to extend the negative exponent range and allow for gradual underflow, the floating-point format provides a class of numbers called denormalized numbers. These numbers, which are very close to zero in value, have a hidden bit of zero (and are therefore not normalized).

32-bit (single) precision floating-point format numbers have a sign bit S, an 8-bit exponent **EXP**, and a 23-bit fraction F (Figure 2-3). The value, V, represented by this format is computed as in Table 2-1. Note that Figure 2-3 shows this format as it would be stored in a 64-bit register; 32-bit precision floating-point numbers can be stored in 32 bits in memory.

1

| 6<br>3 | ente Values | 333<br>210 | 32 | Paris 2-2 | 0 |

|--------|-------------|------------|----|-----------|---|

|        | Unused      | SE         | XP | F         |   |

|        | (32)        |            | 8) | (23)      |   |

Figure 2-3. IEEE 32-Bit Precision Floating-Point Format

| <b>Table 2-1.</b> | IEEE 32-Bit | Precision | Floating-Point | Values |

|-------------------|-------------|-----------|----------------|--------|

|                   |             |           |                |        |

| S | EXP           | F                | V                                            |

|---|---------------|------------------|----------------------------------------------|

| x | 255           | 0xx <sup>†</sup> | NaN (signaling)                              |

| x | 255           | 1yy <sup>‡</sup> | NaN (quiet)                                  |

| s | 255           | 0                | (-1) <sup>S</sup> INFINITY                   |

| s | 0 < EXP < 255 | F                | (-1) <sup>S</sup> 2 <sup>EXP-127</sup> (1.F) |

| s | 0             | ≠0               | (-1) <sup>S</sup> 2 <sup>-126</sup> (0.F)    |

| S | 0             | 0                | (-1) <sup>S</sup> 0                          |

64-bit (double) precision floating-point format numbers have a sign bit S, an 11-bit exponent **EXP**, and a 52-bit fraction F (Figure 2-4). The value, V, represented by this format is computed as in Table 2-2.

| 66    | 55        |                                                         |      |                         | 0      |

|-------|-----------|---------------------------------------------------------|------|-------------------------|--------|

| S EXP |           | <mark>nin an an</mark> | F    | n and on the control of | 0      |

| (11)  | 3002 5000 |                                                         | (52) |                         | di saf |

## Figure 2-4. IEEE 64-Bit Precision Floating-Point Format

CONFIDENTIAL

<sup>&</sup>lt;sup>†</sup> x..x is any non-zero bit pattern on input. Signaling NaNs are never generated by the K-1.

<sup>&</sup>lt;sup>‡</sup> y..y is any bit pattern on input, and is all ones if generated by the K-1.

| s | EXP            | F                | V                                             |

|---|----------------|------------------|-----------------------------------------------|

| x | 2047           | 0xx <sup>†</sup> | NaN (signaling)                               |

| x | 2047           | 1yy <sup>‡</sup> | NaN (quiet)                                   |

| S | 2047           | 0                | (-1) <sup>S</sup> INFINITY                    |

| S | 0 < EXP < 2047 | F                | (-1) <sup>S</sup> 2 <sup>EXP-1023</sup> (1.F) |

| s | 0              | ≠0               | (-1) <sup>S</sup> 2 <sup>-1022</sup> (0.F)    |

| S | 0              | 0                | (-1) <sup>S</sup> 0                           |

Table 2-2. IEEE 64-Bit Precision Floating-Point Values

Note that due to the sign-magnitude nature of the floating-point formats, there are distinct representations for both positive and negative zero.

Refer to Appendix I for details on floating-point computations and exceptions in the K-1.

#### **2.4 Instruction Formats**

The K-1 uses a three-address instruction format: most instructions require three register addresses, two of which specify source operands and the third of which specifies the destination for the result. The way in which the K-1 specifies the use of immediate constants as operands, however, is quite different from other machines.

Whereas most machines use different opcodes to distinguish instructions which allow an immediate constant operand from instructions which only have register operands, the K-1 distinguishes these types of instructions with a **format code**. The format code is a separate field in the instruction from the opcode; it regularizes the instruction set by separating the *function* of an instruction (e.g., addition, loading from memory, etc.), from the *sources* of its operands (constants or registers). For example, the **add** opcode with one format code will add two registers; with another format code it will add a register and an immediate 9-bit constant; and with another format code it will add a register and an immediate 36-bit constant.

For instruction formats with immediate constants, the format code also controls the order of the constant operand and the register operand. That is, one format code will perform constant *op* register, and another will perform register *op* constant. This provides more flexibility and allows the K-1 to have fewer opcodes than would otherwise be needed. (Only one form of asymmetric instructions such as subtract and magnitude comparison is required).

<sup>&</sup>lt;sup>†</sup> x..x is any non-zero bit pattern on input. Signaling NaNs are never generated by the K-1.

$<sup>\</sup>ddagger$  y...y is any bit pattern on input, and is all ones if generated by the K-1.

Instruction formats are fully explained in Chapter 3.

#### 2.5 General Registers

The register file comprises up to 64 registers containing 64 bits each, and are referred to as **r0** to **r63**. Implementations of the K-1 architecture may support less than 64 registers [2-1]. All of the registers are general purpose and may be used to hold the operands or the results of any operation. The architecture treats all registers identically.

#### 2.6 Flags and Conditional Branching

The Processor Status register contains seven flags, named f0 through f6, that can each store a binary value; an additional flag, f7, always contains the value one. These flags control conditional branching, and allow conditional execution of instructions in most formats. (See Chapter 3 for a description of instruction formats). A number of different instructions, such as the compare instructions, may set or clear a flag; a field in the instruction determines which flag is affected. In addition, boolean operations may be performed on flags and the result may be written to a flag or to a register. During a conditional branch instruction, any flag may determine if the branch should be taken. The flag to be used and its polarity are specified by fields in the branch instruction. There are actually no unconditional branch instructions in the K-1 architecture. "Unconditional" branches are accomplished by specifying flag f7 as the branch condition. Similarly, in most instruction formats, unconditional execution can only be achieved by conditional execution with respect to f7. As will be seen in Chapter 3, conditional branching and conditional execution of instructions are specified in exactly the same fashion.

#### 2.7 ELF Flags

Associated with each general register is an Early Load Fault (ELF) flag [2-2]. These flags are set and cleared by load and eload instructions, and may be interrogated by an echk instruction. The ELF flags are used to indicate that an eload instruction encountered an illegal condition. (See the section on Early Load below for a description of the eload instruction and its differences from normal load instructions). The relf and welf instructions can be used to save and restore the ELF flags.

#### 2.8 Memory

Though most operations in a K-1 program will be of the register-to-register type, there must still be some way to move data in registers into and out of memory. The K-1 load/store instructions serve this purpose. These instructions operate on a number of different sizes of data in memory, and are blind to the data types being moved. For example, a 64-bit integer and a 64-bit floating-point number are treated identically by the load/store instructions.

Main memory can be thought of as a very large array of 8-bit bytes which are numbered starting from zero. The architectural limit to the size of memory is the number of bytes that can be addressed in 48 bits, approximately 281 trillion bytes. Implementations of the K-1 architecture may support smaller address spaces [2-3].

#### 2.8.1 Precision and Alignment

When a load/store instruction references memory, it specifies the precision in which the operation is to be done: either 1, 2, 4, or 8 bytes. The address given must be aligned according to the precision. This means that the address for a 2-byte operation must be evenly divisible by 2; for a 4-byte operation, it must be evenly divisible by 4; and for an 8-byte operation, it must be evenly divisible by 8. A load/store instruction with an address that is not properly aligned will cause a trap (except for eload instructions, as explained in the section on Early Load, below).

The address given in a load/store instruction normally specifies the most significant byte of the data item. However, there is a bit in the **Processor Status** register called **Byte Order Low-to-High**, which, if set, causes the address to refer to the least significant byte of the data item. In either case, the address of a data item of any precision always refers to byte 0 of the data item. (**Byte Order Low-to-High** is described in more detail in the section on the **Processor Status** register.)

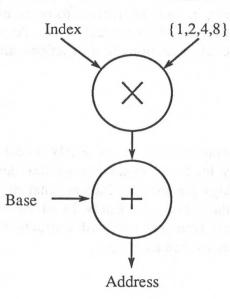

Figure 2-5. Address Calculation for Load/Store Instructions

#### 2.8.2 Addressing Modes

Addresses in load/store instructions are computed in one of two ways. The address may come directly from a single register or constant operand, or it may be calculated as the

#### **Processor States**

sum of two terms: the **base** and the **index**. The index is multiplied by an additional factor, the **memory precision** (Figure 2-5).

The memory precision is either 1, 2, 4, or 8, and is implicitly specified in the opcode of the load/store instruction; it cannot come from a register. The base and index can come from registers or constants depending upon the instruction formats and opcodes used.

#### 2.9 Processor States

The processor can be in one of three modes of operation (states) depending on the settings of some bits in the **Processor Status** register and whether a trap has just occurred. These states are called **user** mode, **supervisor** mode, and **Trap State**. **User** mode has the least privileges; all applications will normally run in **user** mode. **Supervisor** mode is intended for use by the operating system; it provides more capabilities than **user** mode, such as the ability to set more bits in the **Processor Status** register, the ability to write data that is read-only in **user** mode, and the ability to execute privileged instructions.

Whenever a trap is taken, the processor enters **Trap State**, which provides all the privileges of **supervisor** mode, plus the ability to read and modify special internal state information which aids in trap diagnosis and recovery.

Trap State, user mode, and supervisor mode are described more fully in the sections on Processor Status and Traps, Interrupts, and Machine Checks.

#### 2.10 Virtual Memory

Data addresses (produced by the address calculations of load/store instructions) and instruction addresses are called **virtual addresses**, and are the only type of address that an application programmer ever uses. The virtual memory system allows multiple users to coexist in a common physical memory by providing hardware support for sharing between users, protection from other users, and efficient execution of modern operating systems such as

the UNIX<sup>®</sup> operating system.<sup>†</sup>

In order to facilitate porting application programs from an all-32-bit environment, a **Small Address Compatibility** mode is provided. In this mode, all user program and data addresses are assumed to be 32-bit addresses: the high-order bits of any address are set to zero and the low-order 32 bits are retained. This mode is controlled by the **Small Address Compatibility Mode** bit in the **Processor Status** register.

The term *reference* is used throughout this manual to mean a memory operation (generally a load or a store) at a given address. Memory references can be made in either **supervisor** mode or **user** mode. The **mode** of the reference controls the mapping of the virtual addresses used in the processor to the physical addresses used in the memory system. **Supervisor** mode references, used by the operating system, employ a different mapping scheme than **user** mode references.

<sup>&</sup>lt;sup>†</sup> UNIX is a registered trademark of AT&T.

#### Address Mapping

#### 2.10.1 Address Mapping

The address of an instruction or of a data operand in a load/store instruction is translated to a physical address before being sent to the memory system. This process is known as virtual-to-physical address mapping.

The mapping of a contiguous block of memory, called a page, is specified by a single entry in a table, called a page table or page map. Specifically, a page is a 64K-byte block of addresses starting at an address that is evenly divisible by 64K. This is equivalent to saying that the address of the first byte of a page has 16 low-order zeros in binary. There are separate page tables for instructions and for data.

When a memory data reference is a supervisor mode reference (see the section on **Data Mapping**, below), the mapping from virtual to physical addresses is the identity function. In other words, there is no distinction between virtual and physical addresses for supervisor mode data references.

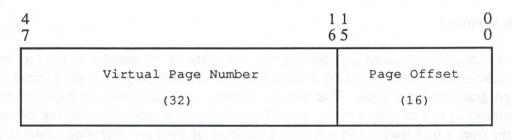

As part of the mapping process, a 48-bit virtual address is divided into two pieces. The high-order 32 bits are called the virtual page number and the low-order 16 bits are called the page offset (Figure 2-6) [2-4]. The virtual page number is mapped into a physical page number while the page offset remains the same. The physical page number and the page offset are concatenated to produce the physical address.

Figure 2-6. Virtual Address Format

#### 2.10.1.1 Instruction Mapping

The instruction page table consists of eight entries, individually loadable with the privileged instruction lipage, that specify the mapping of eight different virtual regions for user mode instruction references. In supervisor mode, instruction mapping is done in an implementation-dependent fashion [2-5]. In user mode, instruction mapping is done using the instruction page table. Figure 2-7 shows the format of an instruction page table entry (the operand to a lipage instruction) [2-6].

The N field, sometimes called the Instruction Page ID, specifies which of the eight instruction page table entries is to be affected. If the valid bit, V, is a zero, then page table entry N is invalid and the rest of the fields are ignored. If the valid bit is a one, then page table entry N maps a virtual page range into a physical page range. The virtual and physical page ranges begin with the pages specified by the Virtual Page Number and Physical Page Number fields, respectively [2-7]. These page ranges must always be aligned on a bound-

#### 2.10.1.2

#### Data Mapping

ary which is a multiple of their size. Note that an instruction virtual page number is architecturally limited to 25 bits, and therefore instruction addresses are architecturally limited to 41 bits.

| 666<br>320 |     | 5                   | 33 and $5$ and $5$ and $5$ and $5$ and $6$ $0$ and $0$ and $0$ and $0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|-----|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V N        | ss  | Virtual Page Number | Physical Page Number 1000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| (3)        | (3) | (25)                | and and a store same state (32) and a store so in a store state (32) and the state of the state |

Figure 2-7. Instruction Page Table Format

The extent of the page ranges is determined by the size specifier, SS, field. It indicates how many contiguous pages are referenced by this instruction map entry. The interpretation of this field is implementation-dependent (Table 2-3) [2-8].

Note that it does not matter which page table entry (which value of N) is used for a particular mapping entry, but mapping a given virtual address with more than one page table entry will produce unpredictable results. Therefore, the virtual page ranges specified by the valid page table entries must be non-overlapping.

| Table 2-3. | Instruction | Page | Table | Size | Specifier |

|------------|-------------|------|-------|------|-----------|

|------------|-------------|------|-------|------|-----------|

| SS  | # of Pages Mapped                              |

|-----|------------------------------------------------|

| 0-7 | See Implementation<br>Dependencies, Appendix H |

#### 2.10.1.2 Data Mapping

It is intended that the operating system and applications program(s) occupy separate address spaces. Whether a reference is treated as a supervisor mode reference or a user mode reference is a function of the User Mode Load, User Mode Store, and User Protection bits of the Processor Status register, as well as the type of reference (Table 2-4). When the processor is in user mode, it can only make user mode references to memory. But when the processor is in supervisor mode (and not in Trap State), it can make *either* user mode references *or* supervisor mode references depending on the settings of the User Mode Load and User Mode Store bits and the type of reference. This allows the operating system to perform memory references with the user's address mapping. For example, if the operating system wanted to copy data into the user's area at a virtual address provided by the user (such as in response to an I/O request), it could set the User Mode Store bit; load

Amdahl Key Computer Labs

CONFIDENTIAL

K-1 Architecture Manual

Data Mapping

instructions would then use the operating system's address mapping, but store instructions would use the user's address mapping and protection. Using the user's protection prevents malicious users from providing invalid addresses.

In Table 2-4, all load, eload, ldecc, ldnecc, loadcpu, and pcl instructions are considered to make "load" (i.e., memory read) references, and all store, storecpu, dflush, and zcl instructions are considered to make "store" (i.e., memory write) references. The swat instruction, which does both a memory read and a memory write, is considered to be both a load and a store. swat instructions require the User Mode Load and User Mode Store bits to have the *same* value or the results will be unpredictable.

|   | User<br>Mode<br>Load | User<br>Mode<br>Store | Load<br>Reference<br>Mode | Store<br>Reference<br>Mode |

|---|----------------------|-----------------------|---------------------------|----------------------------|

|   | Off                  | Off                   | Supervisor                | Supervisor                 |

|   | Off                  | On                    | Supervisor                | User                       |

| 1 | On                   | Off                   | User                      | Supervisor                 |

|   | On                   | On                    | User                      | User                       |

Table 2-4.

Memory Reference Modes

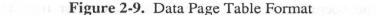

User mode references always use the data page table to perform the mapping from virtual to physical addresses and to determine the legal access modes (read or write) and sharability of that page. Supervisor mode references do not use the data page table; both read and write supervisor mode references are always permitted. Supervisor mode references are always shared. Only shared pages participate in the multiprocessor cache-coherence scheme. Thus, all supervisor mode references and any user mode references which are designated as shared in the data page table are cache-coherent.

The page control bits of a data page table entry (described below) control the types of access (read and write) that are allowed for user mode references to that page. In addition, they control whether the page can be shared among processes. For user mode references when the User Protection bit in the Processor Status register is *off*, the page control bits are ignored: *both* read and write references are permitted if *either* type of reference is permitted. This allows the supervisor to modify user data without the user's access restrictions.

Data page table information is stored differently from instruction page table entries. The data page table is a cache, while the instruction page table is a fully-associative memory [2-9].