USER'S MANUAL Revision D September 1990

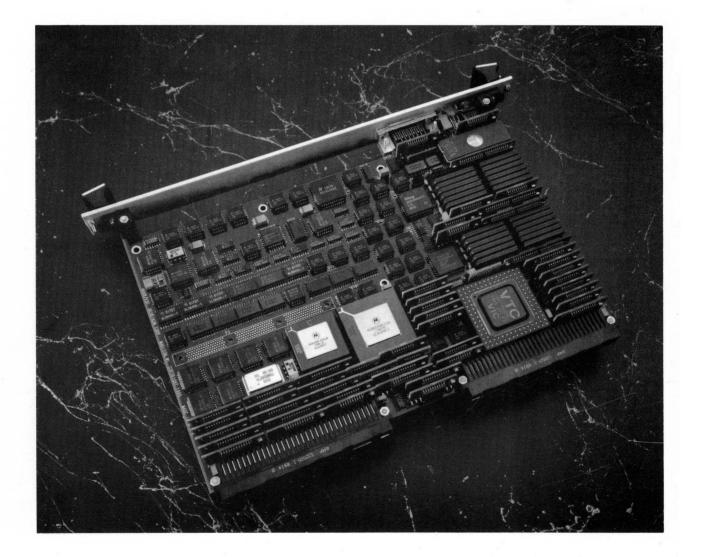

# HK68/V3F

### Heurikon Corebus™68030-based Computer

# HK68/V3F

# Heurikon Corebus<sup>™</sup> 68030-based Computer

USER'S MANUAL Revision D September 1990

The information in this manual has been checked and is believed to be accurate and reliable. HOWEVER, NO RESPONSIBILITY IS ASSUMED BY HEURIKON FOR ITS USE OR FOR ANY INACCURACIES. Specifications are subject to change without notice. HEURIKON DOES NOT ASSUME ANY LIABILITY ARISING OUT OF USE OR OTHER APPLICATION OF ANY PRODUCT, CIRCUIT OR PROGRAM DESCRIBED HEREIN. This document does not convey any license under Heurikon's patents or the rights of others.

Heurikon, HK68/V, Hbug, and Corebus are trademarks of Heurikon Corporation.

#### **REVISION HISTORY**

| Revision Level  | Principal Changes                     | Date of Publication |

|-----------------|---------------------------------------|---------------------|

| A (Preliminary) |                                       | April 1990          |

| B (Preliminary) |                                       | May 1990            |

| C (Preliminary) | · · · · · · · · · · · · · · · · · · · | August 1990         |

| D               | Release version, board revision P     | September 1990      |

Copyright 1990 Heurikon Corporation. All rights reserved. Portions of the chapter entitled "Timer Clock Peripheral" are copyrighted by National Semiconductor Corporation and have been reprinted with permission.

# Contents

| 1 — Overv | /iew                                                     |       |  |

|-----------|----------------------------------------------------------|-------|--|

| 1.1       | Introduction                                             | 1-1   |  |

| 1.2       | HK68/V3F Feature Summary                                 | 1-1   |  |

| 1.3       | <ol> <li>Block Diagram</li> <li>Component Map</li> </ol> |       |  |

| 1.4       |                                                          |       |  |

| 1.5       | Bus Summary                                              | 1-4   |  |

| 1.6       | Connectors, Jumpers, and Switches                        | 1-5   |  |

|           | 1.6.1 Connectors                                         | 1-5   |  |

|           | 1.6.2 Jumpers                                            | 1-5   |  |

|           | 1.6.3 Reset Switch                                       | 1-5   |  |

| 1.7       | Overview of the Manual                                   | 1-6   |  |

|           | 1.7.1 Terminology and Notation                           | 1-6   |  |

|           | 1.7.2 Additional Technical Information                   | 1-6   |  |

| 2 — Set-u | p and Installation                                       |       |  |

| 2.1       | Equipment                                                | 2-1   |  |

| 2.2       | Preliminary Considerations                               | 2-1   |  |

|           | 2.2.1 Electrical                                         | 2-1   |  |

|           | 2.2.2 Physical                                           | 2-2   |  |

|           | 2.2.3 Environmental                                      | 2-2   |  |

| 2.3       | Installation and Power-up                                | 2-2   |  |

| 2.4       | Troubleshooting and Service Information                  | 2-3   |  |

| 2.5       | Monitor Summary                                          | 2-5   |  |

| 3 — Main  | Processor Unit                                           | ····· |  |

| 3.1       | Introduction                                             | 3-1   |  |

| 3.2       | MPU Interrupts                                           | 3-1   |  |

| 3.3       | MPU Exception Vectors                                    | 3-2   |  |

| 3.4       | Status LEDs                                              | 3-4   |  |

| 3.5       | MPU Cache Control                                        | 3-4   |  |

|           | 3.5.1 Instruction Cache                                  | 3-4   |  |

|           | 3.5.2 Data Cache                                         | 3-5   |  |

| 3.6       | Coprocessor                                              | 3-5   |  |

| 3.7       | Watchdog Timer                                           | 3-5   |  |

### 4 — Floating Point Coprocessor (FPP)

7.10 Watchdog and Bus Timer

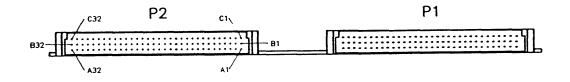

7.12 VMEbus Pin Assignments (P1)

7.13 VMEbus/VSB Pin Assignments (P2)

7.11 VMEbus Interface

| 4.1 | Introduction        | 4-1 |

|-----|---------------------|-----|

| 4.2 | FPP Feature Summary | 4-1 |

| 4.3 | FPP Bypass          | 4-2 |

### 5 — System Error Handling

| 6 — On-ca | ard Memory Configuration                    |       |

|-----------|---------------------------------------------|-------|

| 6.1       | Introduction                                | 6-1   |

| 6.2       | ROM                                         | 6-1   |

| 6.3       | On-card RAM                                 | 6-3   |

|           | 6.3.1 On-card Memory Sizing                 | 6-4   |

| 6.4       | Bus Memory                                  | 6-4   |

| 6.5       | Physical Memory Map                         | 6-4   |

| 6.6       | Memory Timing                               | 6-5   |

| 6.7       | EEPROM                                      | 6-6   |

| 7 VMEL    | ous Control                                 |       |

| 7.1       | Introduction                                | 7-1   |

| 7.2       | Bus Control Signals, VMEbus P1 Descriptions | . 7-2 |

| 7.3       | VIC Register Map                            | 7-4   |

| 7.4       | VMEbus Interrupts                           | 7-7   |

|           | 7.4.1 Interrupter Operation                 | 7-8   |

|           | 7.4.2 Interrupt Handler Operation           | 7-9   |

|           | 7.4.2.1 VIC Interrupt Requests              | 7-9   |

|           | 7.4.2.2 VIC Interrupt Acknowledges          | 7-9   |

| 7.5       | Mailbox Interface                           | 7-12  |

| 7.6       | VMEbus System Controller                    | 7-13  |

| 7.7       | VMEbus Master Interface                     | 7-14  |

| 7.8       | VMEbus Slave Interface                      | 7-15  |

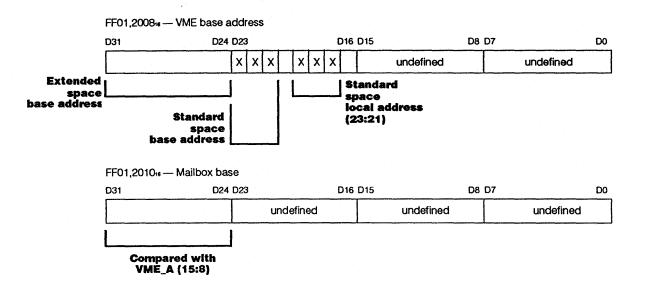

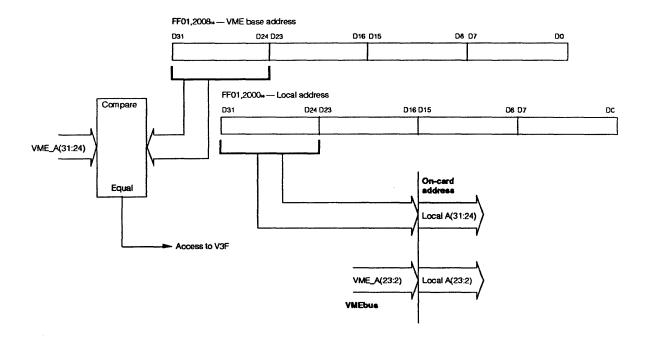

|           | 7.8.1 Extended Space                        | 7-16  |

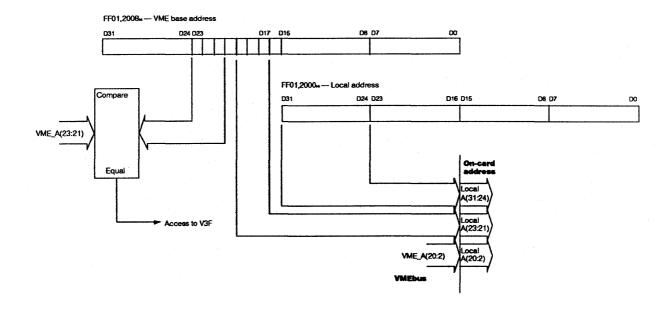

|           | 7.8.2 Standard Space                        | 7-17  |

|           | 7.8.3 Short Space                           | 7-20  |

| 7.9       | SYSFAIL Control                             | 7-20  |

7-20

7-21

7-21

7-22

### 8 — VME Subsystem Bus (VSB) Control

| 8.1 | Introdu | ction       | 8-1                     |     |

|-----|---------|-------------|-------------------------|-----|

| 8.2 | Bus Cor | ntrol Signa | ls, VSB P2 Descriptions | 8-1 |

| 8.3 | VSB Int | erface      |                         | 8-3 |

|     | 8.3.1   | VSB Op      | peration                | 8-3 |

|     |         | 8.3.1.1     | Release Modes           | 8-3 |

|     |         | 8.3.1.2     | Arbiter Enable          | 8-4 |

|     |         | 8.3.1.3     | Slave Enable            | 8-4 |

|     |         | 8.3.1.4     | Block Transfers         | 8-6 |

|     |         |             |                         |     |

### 9 — Front Panel Interface

10

| <br>Seria | I I/O                              | • • • |  |

|-----------|------------------------------------|-------|--|

| 10.1      | Introduction                       | 10-1  |  |

| 10.2      | RS-232 Pin Assignments (P4)        | 10-1  |  |

| 10.3      | Signal Naming Conventions (RS-232) | 10-3  |  |

| 10.4      | Connector Conventions              | 10-4  |  |

| 10.5      | SCC Initialization Sequence        | 10-5  |  |

| 10.6      | Port Address Summary               | 10-6  |  |

| 10.7      | Baud Rate Constants                | 10-6  |  |

| 10.8      | RS-422 Operation                   | 10-7  |  |

| 10.9      | Relevant Jumpers (Serial I/O)      | 10-7  |  |

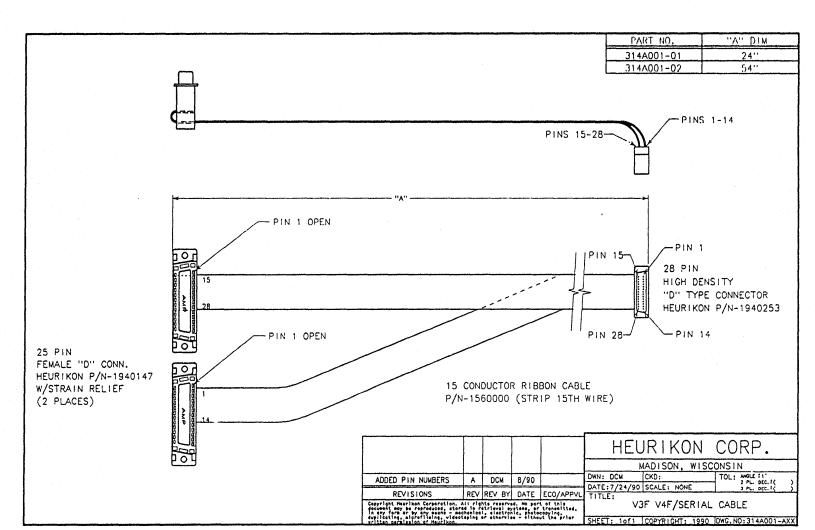

| 10.10     | Serial I/O Cable Drawing           | 10-8  |  |

|           |                                    |       |  |

### 11 — Timer Clock Peripheral (TCP)

| 11.1 | Introduction                                       |       |

|------|----------------------------------------------------|-------|

| 11.2 | Real-Time Clock                                    | 11-5  |

|      | 11.2.1 Reading the Clock                           | 11-6  |

|      | 11.2.2 Initializing and Setting the Calendar-Clock | 11-7  |

| 11.3 | Counter/Timers                                     | 11-7  |

|      | 11.3.1 Timer Initialization                        | 11-7  |

|      | 11.3.2 Reading the Timers                          | 11-10 |

| 11.4 | Programmable Prescaler/Oscillator                  | 11-10 |

| 11.5 | TCP Implementation                                 | 11-10 |

|      | 11.5.1 Interrupts                                  | 11-11 |

| 11.6 | Battery Life                                       | 11-12 |

| 12 — | Core | bus Interface                          |       |

|------|------|----------------------------------------|-------|

|      | 12.1 | Introduction                           | 12-1  |

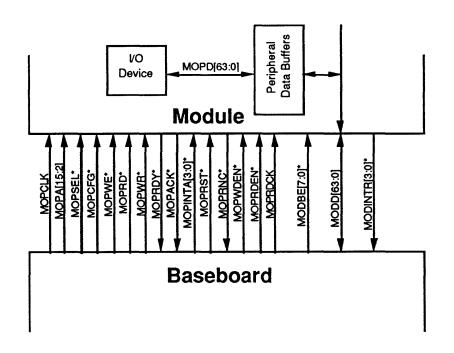

|      | 12.2 | Corebus Module Synchronous Bus         | 12-2  |

|      | 12.3 | Corebus Module Peripheral Bus          | 12-2  |

|      | 12.4 | Corebus Signals                        | 12-4  |

|      |      | 12.4.1 Module Synchronous Bus          | 12-4  |

|      |      | 12.4.1.1 Arbitration Signals           | 12-4  |

|      |      | 12.4.1.2 Slave Control Signals         | 12-4  |

|      |      | 12.4.1.3 Address Bus Signals           | 12-5  |

|      |      | 12.4.1.4 Data Bus Signals              | 12-5  |

|      |      | 12.4.1.5 Cycle Control Signals         | 12-6  |

|      |      | 12.4.1.6 Central Control Signals       | 12-7  |

|      |      | 12.4.2 Module Peripheral Bus           | 12-8  |

|      |      | 12.4.2.1 Cycle Control Signals         | 12-8  |

|      |      | 12.4.2.2 Interrupt Signals             | 12-9  |

|      |      | 12.4.2.3 Configuration Signals         | 12-9  |

|      |      | 12.4.2.4 Central Control Signals       | 12-9  |

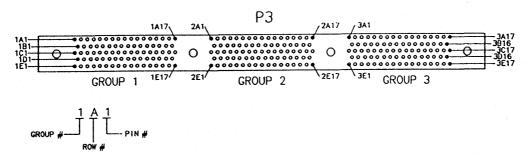

|      | 12.5 | Corebus Interface Pin Assignments (P3) | 12-10 |

| 13 — | Sum  | mary Information                       |       |

|      | 13.1 | Software Initialization Summary        | 13-1  |

|      | 13.2 | On-card I/O Addresses                  | 13-2  |

|      | 13.3 | Hardware Configuration Jumpers         | 13-4  |

|      | 13.4 | Power Requirements                     | 13-6  |

|      | 13.5 | Environmental Requirements             | 13-6  |

|      | 13.6 | Mechanical Specifications              | 13-6  |

### Index

| Figur | es          |                                                                                                                                                                                                                                    |       |

|-------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|       | Figure 1-1  | HK68/V3F Block Diagram                                                                                                                                                                                                             | 1-3   |

|       | Figure 1-2  | HK68/V3F Component Map                                                                                                                                                                                                             | 1-4   |

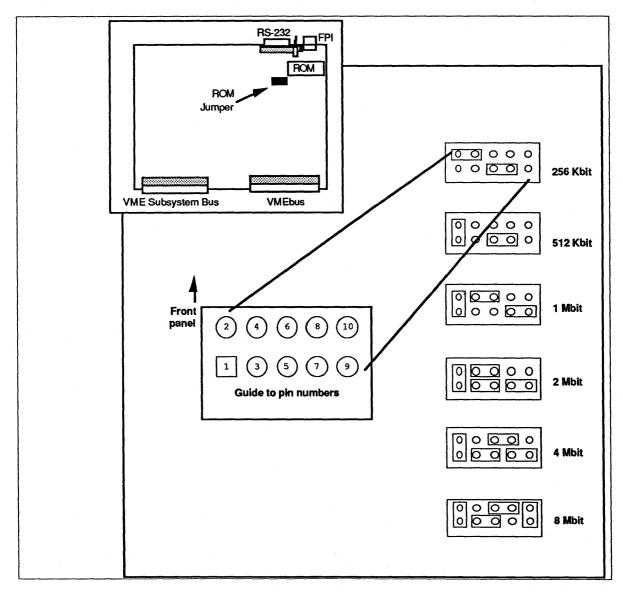

|       | Figure 6-1  | Jumper Settings for ROM Options                                                                                                                                                                                                    | 6-2   |

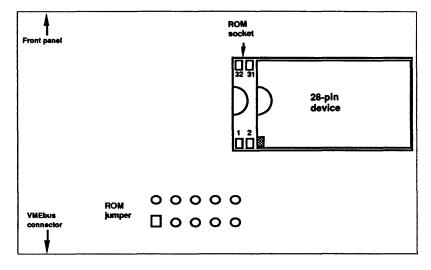

|       | Figure 6-2  | Placement for a 28-pin ROM                                                                                                                                                                                                         | 6-3   |

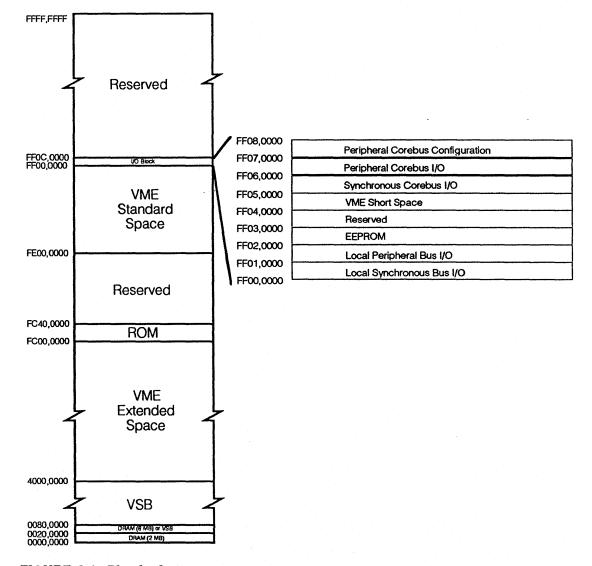

|       | Figure 6-3  | Physical Memory Map                                                                                                                                                                                                                | 6-4   |

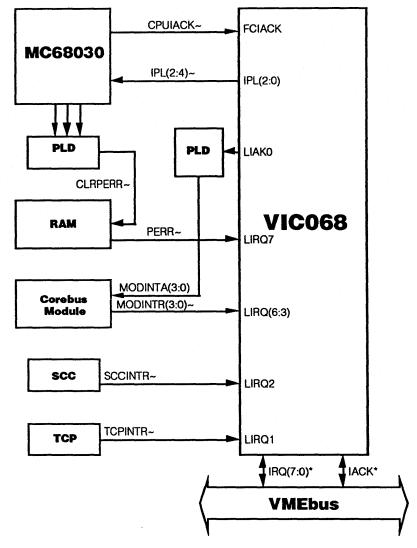

|       | Figure 7-1  | HK68/V3F Interrupt Architecture                                                                                                                                                                                                    | 7-8   |

|       | Figure 7-2  | VMEbus Mailbox Structure                                                                                                                                                                                                           | 7-13  |

|       | Figure 7-3  | VME Control Space During Slave Cycles                                                                                                                                                                                              | 7-16  |

|       | Figure 7-4  | Extended Space Slave Access                                                                                                                                                                                                        | 7-17  |

|       | Figure 7-5  | Standard Space Slave Access                                                                                                                                                                                                        | 7-18  |

|       | Figure 7-6  | VMEbus and VME Subsystem Bus Connectors                                                                                                                                                                                            |       |

|       |             | P1 and P2                                                                                                                                                                                                                          | 7-21  |

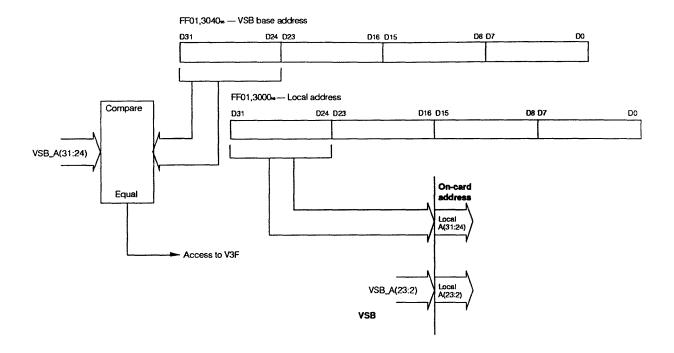

|       | Figure 8-1  | Extended Space Slave Access                                                                                                                                                                                                        | 8-5   |

|       | Figure 8-2  | VSB System Address Space Base                                                                                                                                                                                                      | 8-5   |

|       | Figure 8-3  | Local Address for Slave Cycles                                                                                                                                                                                                     | 8-6   |

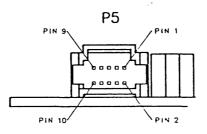

|       | Figure 9-1  | Front Panel Interface Connector, P5                                                                                                                                                                                                | 9-1   |

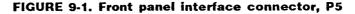

|       | Figure 10-1 | RS-232-C Connector, P4                                                                                                                                                                                                             | 10-1  |

|       | Figure 10-2 | Serial I/O Cable                                                                                                                                                                                                                   | 10-8  |

|       | Figure 11-1 | TCP Memory Map                                                                                                                                                                                                                     | 11-3  |

|       | Figure 12-1 | Typical Corebus Application                                                                                                                                                                                                        | 12-1  |

|       | Figure 12-2 | The Corebus Module Peripheral Bus                                                                                                                                                                                                  | 12-3  |

|       | Figure 12-3 | Corebus Connector, P3                                                                                                                                                                                                              | 12-10 |

|       | Figure 13-1 | HK68/V3F Jumper Configurations                                                                                                                                                                                                     | 13-5  |

| Table | )S          | ан на такжа на кака на такжа на кака на кака на такжа на такжа на такжа на такжа на такжа на кака на кака на т<br>Кака на такжа на кака на такжа на кака на такжа н |       |

|       | Table 1-1   | Technical References                                                                                                                                                                                                               | 1-7   |

|       | Table 2-1   | Power Requirements                                                                                                                                                                                                                 | 2-2   |

|       | Table 2-2   | Standard Jumper Settings                                                                                                                                                                                                           | 2-4   |

|       | Table 3-1   | MPU Exception Vectors                                                                                                                                                                                                              | 3-3   |

|       | Table 3-2   | Status LEDs                                                                                                                                                                                                                        | 3-4   |

.

\_

| Table 6-1                 | ROM Address Summary                        | 6-1   |

|---------------------------|--------------------------------------------|-------|

| Table 6-2                 | ROM Capacity and J4 Jumper Positions       | 6-2   |

| Table 6-3                 | Access Time Required for No Wait States    | 6-5   |

| Table 6-4                 | RAM Access Time Required for the HK68/V3F  | 6-6   |

| Table 6-5                 | EEPROM Addresses                           | 6-7   |

| Table 6-6                 | EEPROM Contents (partial)                  | 6-7   |

|                           |                                            |       |

| Table 7-1                 | VIC Register Map                           | 7-5   |

| Table 7-2                 | Interrupt Priorities                       | 7-11  |

| Table 7-3                 | Bus Control Jumpers                        | 7-14  |

| Table 7-4                 | Relationship of Physical Address to VMEbus |       |

|                           | and VSB Memory Region                      | 7-14  |

| Table 7-5                 | Registers Used for Slave Accesses          | 7-15  |

| Table 7-6                 | HK68/V3F "Standard" Space Slave Mapping    |       |

|                           | on VMEbus, 2-Mbyte HK68/V3F                | 7-18  |

| Table 7-7                 | HK68/V3F "Standard" Space Slave Mapping    |       |

|                           | on VMEbus, 8-Mbyte HK68/V3F                | 7-19  |

| Table 7-8                 | VMEbus Connector Pin Assignments (P1)      | 7-21  |

| Table 7-9                 | VMEbus/VSB Pin Assignments (P2)            | 7-23  |

| Table 8-1                 | VSB Release Modes                          | 8-4   |

| Table 8-2                 | VSB Arbiter Enable                         | 8-4   |

| Table 8-3                 | VSB Slave Enable                           | 8-6   |

| Table 8-4                 | VSB Block Transfer                         | 8-6   |

| Table 9-1                 | Front Panel Interface Connector            |       |

| 10010 / 1                 | Pin Assignments, P5                        | 9-1   |

| Table 9-2                 | Addresses of User-programmable Outputs     | 9-2   |

| Table 10-12               | Serial Port Pin Assignments (P4) — Port A  | 10-2  |

|                           | Serial Port Pin Assignments (P4) — Port B  | 10-2  |

| Table 10-10<br>Table 10-2 | -                                          | 10-2  |

| Table 10-2<br>Table 10-3  | RS-232 Reversal Cable                      | 10-5  |

| Table 10-9<br>Table 10-4  | SCC Initialization Sequence                | 10-4  |

| Table 10-4<br>Table 10-5  | SCC Register Addresses                     | 10-5  |

| Table 10-5                | Baud Rate Constants                        | 10-0  |

| Table 10-0<br>Table 10-7  | Relevant Jumpers — Serial I/O              | 10-0  |

| 1able 10-7                | Relevant Junipers — Senar 1/O              | 10-7  |

| Table 11-1                | TCP Register Addresses                     | 11-1  |

| Table 11-2                | Register/Counter/RAM Addressing            | 11-4  |

| Table 11-3                | Timer Registers                            | 11-8  |

| Table 11-4                | TCP Register Summary                       | 11-8  |

| Table 11-5                | Cascading TCP Counters                     | 11-11 |

| Table 12-1 | Summary of MODBE7*            |       |

|------------|-------------------------------|-------|

|            | Through MODBE0* Functions     | 12-5  |

| Table 12-2 | Summary of MOSTA[1:0]* States | 12-6  |

| Table 12-3 | Summary of MODBE7*            |       |

|            | Through MODBE0* Functions     | 12-8  |

| Table 12-4 | Corebus Pin Assignments       | 12-10 |

|            |                               |       |

| Table 13-1 | Address Summary               | 13-3  |

| Table 13-2 | Jumper Summary                | 13-4  |

| Table 13-3 | Power Requirements            | 13-6  |

| Table 13-4 | Mechanical Specifications     | 13-6  |

# Overview

#### **1.1 INTRODUCTION**

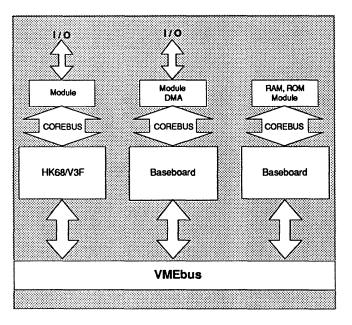

The HK68/V3F is a 32-bit single-board computer designed as a high-performance base for modular additions that interface to the board via Corebus<sup>TM</sup>, a Heurikon-designed interface. The HK68/V3F uses the Motorola 68030 microprocessor and has two RS-232 serial ports, mailbox interrupt support, a built-in real-time clock, and full VMEbus compatibility.

#### 1.2 HK68/V3F FEATURE SUMMARY

- **MPU** The MPU is a Motorola 68030 32-bit microprocessor chip running at 25 or 33 MHz, depending on the option ordered. It has 32-bit internal architecture; 32-bit address and data paths; 4-Gbyte addressing range; a 256-byte instruction cache; and a 256-byte data cache. Section 3 contains details on the MPU.

- **FPP option** The optional floating point coprocessor is a 32-bit Motorola 68882 for executing transcendental, trigonometric, and basic arithmetic functions. The FPP implements the IEEE standard for binary floating point arithmetic (ANSI/IEEE Std. 754-1985). FPP features are described in section 4.

- **RAM** The RAM has 2- or 8-Mbyte capacity and optional parity (one bit per byte). It uses 256K x 4 or 1M x 4 static-column DRAMs. Hardware logic controls refresh. Section 6.3 contains details on RAM.

- **EPROM** There is one 32-pin ROM socket with 1 Mbyte total capacity and an 8-bit data path. Section 6.2 contains details on the EPROM.

- **EEPROM** An internal EEPROM provides 8 Kbytes of nonvolatile storage for user-definable and system parameters. The EEPROM has 100-year retention and 10,000 write-cycle lifetime. (Refer to section 6.7 for details.)

| VMEbus | The VMEbus interface is provided by a VTC VIC068 intelligent        |

|--------|---------------------------------------------------------------------|

|        | VMEbus controller/arbiter with a 32-bit address bus; 24- or 32-bit  |

|        | address modes (4-Gbyte range); a 32-bit data bus with 8-, 16-, or   |

|        | 32-bit board compatibility; and seven bus interrupts. Section 7 has |

|        | details on the VMEbus interface.                                    |

**VSB** This high-speed local memory expansion subsystem supports secondary bus masters. See section 8 for details.

Mailbox The mailbox allows remote control of the HK68/V3F via specified VMEbus addresses. (Refer to section 7.5 for details.)

Serial I/O The HK68/V3F has two serial I/O ports controlled by a single Zilog Z85C30 serial communication controller (SCC). There are separate baud rate generators for each port, and asynchronous and synchronous modes. RS-232C interface is standard; RS-422 is optional. Section 10 contains details on the serial I/O.

**TCP** The timer clock peripheral provides a built-in real-time clock module. The TCP has a full-function real-time clock/calendar, power fail features, and 44 bytes of CMOS RAM. The TCP has two 16-bit timers, each with its own prescaler and selectable clock input with eight choices. Details on the TCP are in section 11.

LEDs There are three MPU/BUS status LEDs. Section 9 contains details.

**Front Panel Interface** The front panel interface connector has RESET input and HALT output. There are four user-programmable outputs. Details are in section 9.

**Corebus Plugover Modules**

Corebus is a 32-bit interface that allows the addition of plugover modules such as Ethernet or SCSI for custom configurations. Corebus is described in section 12.

1-2

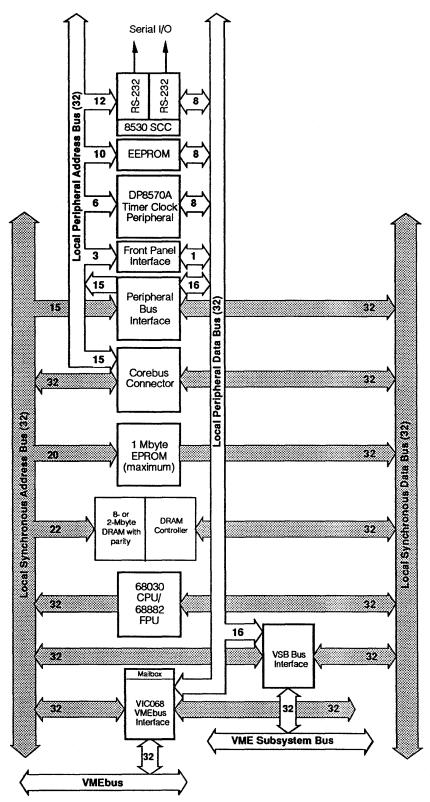

#### 1.3 BLOCK DIAGRAM

FIGURE 1-1. HK68/V3F block diagram

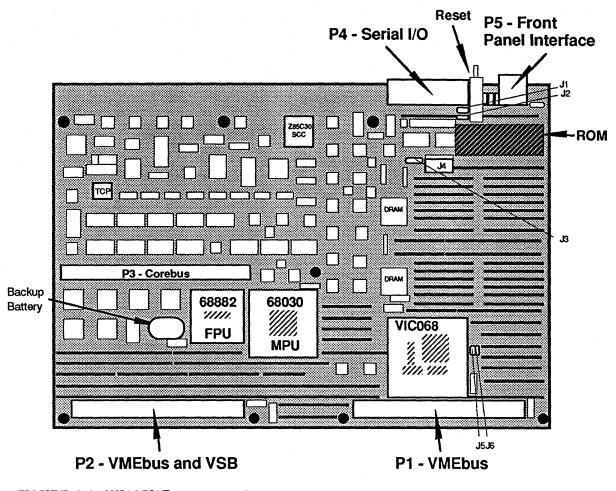

#### 1.4 COMPONENT MAP

#### 1.5 BUS SUMMARY

The HK68/V3F uses the Corebus Module Synchronous Bus and Module Peripheral Bus interfaces to provide a high level of performance along with the flexibility to expand on-card resources with plugover modules. The Corebus interface is described in section 12.

The VMEbus provides high throughput for data transfers between board or subsystems on the VMEbus, and is the main conduit for transferring system level information between processor subsystems. The VMEbus interface is described in section 7 and the VSB interface is described in section 8.

#### 1.6 CONNECTORS, JUMPERS, AND SWITCHES

#### 1.6.1 Connectors

The HK68/V3F has five connectors:

- **P1 and P2** P1 and P2 provide a standard interface for the VMEbus.

- P3 Corebus connector for the two Corebus interfaces Module Synchronous Bus and Module Peripheral Bus. The Corebus interface provides external connections for modules that contain Corebus-compatible extensions. The Corebus master interface allows modules to arbitrate for and gain control of the local bus. The arbitration supports the bus clear feature so that the module may retain ownership of the local bus until the bus is needed by a master. The Corebus master interface supports burst transfers, locked cycles, and other features. The Corebus master interface has highest priority as a requestor for the local bus. The VMEbus slave and VSB slave interfaces arbitrate at a lower priority.

Details and pin assignments are in section 12.

- P4 The RS-232-C connector is a high-density 28-pin connector that holds two serial cables. Details and pin assignments are in section 10.

- **P5** The front panel interface uses a 10-pin connector. Pin assignments and details are in section 9.

#### 1.6.2 Jumpers

There are five jumpers for custom configurations. Default settings and factory settings are summarized in Tables 2-1 and 13-2.

- J1 +5V power control for port A of P4.

- J2 +5V power control for port B or P4.

- J3 RS-232 handshaking

- J4 ROM size

- J5 System controller

#### 1.6.3 Reset Switch

This switch resets the HK68/V3F and also resets the VMEbus if the HK68/V3F is the VME system controller.

#### **1.7 OVERVIEW OF THE MANUAL**

The manual has four main parts:

- Chapters 1 and 2 contain set-up information.

- Chapters 3 through 11 contain information for programming board components.

- Chapter 12 describes the Corebus interfaces.

- Chapter 13 contains summary information, including on-card I/O addresses and a jumper diagram.

#### **1.7.1 Terminology and Notation**

We have used *byte* for 8-bit quantities; *word* for 16-bit quantities; *long word* for 32-bit quantities; and *quad word* for 4-word quantities (that is, 64-bit quantities) throughout the manual. Hexadecimal numbers are shown with a subscript 16 and binary numbers with a subscript 2.

#### **1.7.2** Additional Technical Information

This manual describes Heurikon's implementation of the intelligent components of this board. Further information on basic operation and programming can be found in the following documents:

| Technical references |                                                                                                                                                                                                                |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MPU                  | <i>MC68030 User's Manual</i> , 2nd ed. (Englewood Cliffs, NJ: Prentice-Hall, 1989).                                                                                                                            |  |  |

| FPU                  | MC68881/MC68882 Floating Point Coprocessor<br>User's Manual, 1st ed. (Englewood Cliffs, NJ:<br>Prentice-Hall, 1985).                                                                                           |  |  |

| Corebus              | <i>Corebus Technical Specification</i> (Madison, WI:<br>Heurikon Corp., 1989).                                                                                                                                 |  |  |

| VMEbus               | VIC068 VMEbus Interface Controller Specification<br>(Bloomington, MN: VTC Incorporated, 1989) and<br>The VMEbus Specification C.1 (Motorola, 1985).                                                            |  |  |

| VME Subsystem Bus    | <i>The Parallel Sub-System Bus of the IEC 821 Bus,</i><br><i>Revision C</i> (International Electromechanical<br>Commission, 1986).                                                                             |  |  |

| Serial Interface     | ElA Standard RS-232-C (Washington, DC:<br>Electronic Industries Association, 1969) and Z8030<br>Z-BUS SCC/Z8530 SCC Serial Communications<br>Controller Technical Manual (Campbell, CA: Zilog,<br>Inc., 1989). |  |  |

| Real-Time Clock      | Advanced Peripherals: Real Time Clock Handbook<br>(Santa Clara, CA: National Semiconductor<br>Corporation, 1989).                                                                                              |  |  |

TABLE 1-1 Technical references

Feel free to contact our Customer Support Department at 1-800-327-1251 if you have questions. We are prepared to answer general questions and provide help with specific applications.

.

## Set-up and Installation

#### 2.1 EQUIPMENT

Here is what you need to get the Heurikon HK68/V3F "on-the-air":

- Heurikon HK68/V3F microcomputer board

- VME card cage and power supply

- Serial interface cable (RS-232)

- CRT terminal

- Heurikon EPROM, which includes both monitor and bootstrap

- CAUTION: All semiconductors should be handled with care. Static discharges can easily damage the components on the HK68/V3F. Keep the board in an antistatic bag whenever it is out of the system chassis and *do not handle the board* unless absolutely necessary. Ground your body before touching the HK68/V3F board.

- CAUTION: Do not install the board in a rack or remove the board from a rack while power is applied, at risk of damage to the board.

#### 2.2 PRELIMINARY CONSIDERATIONS

#### 2.2.1 Electrical

If you are adding the HK68/V3F to an enclosure, the power supply must be sufficient for the additional board.

**RS-232** interface

| TABLE 2-1<br>Power requi |         |                  |  |

|--------------------------|---------|------------------|--|

| Voltage                  | Current | Usage            |  |

| +5                       | 9 A     | All logic        |  |

| +12                      | .5 A    | RS-232 interface |  |

.5 A

\_\_\_\_

-12

Note: All of the "+5" and "Gnd" pins on P1 and P2 must be connected to ensure proper operation.

#### 2.2.2 Physical

The board is a single-height VMEbus board (9.187" W x 6.299" H x 0.6" D) that occupies one slot in a VMEbus card cage.

#### 2.2.3 Environmental

CAUTION: High operating temperatures will cause unpredictable operation. Because of the high chip density, fan cooling is required for all configurations, even when cards are placed on extenders.

> As with any printed circuit board, be sure that air flow to the board is adequate. Recommended air flow rate is about 2-3 cubic feet per minute, depending on card cage constraints and other factors. Operating temperature is specified at 0° to 55° C ambient, as measured at the board.

#### 2.3 INSTALLATION AND POWER-UP

All products are fully tested before they are shipped from the factory (please contact us if you would like to have current information on mean time between failures). When you receive your HK68/V3F, follow these steps to assure yourself that the system is operational:

1. Visually inspect the board(s) for components that could have loosened during shipment. Visually inspect the chassis and all cables. Be sure the ROM is in place and the board is jumpered correctly (see the jumper diagram in section 13.3). Be sure all boards are seated properly in the VME card cage. Be sure all cables are securely in place.

- 2. Connect a CRT terminal to serial port B (port A for the VxWorks operating system), via connector P4. If you are making your own cable, refer to section 10.10. Set the terminal as follows:

- 9600 baud, full duplex

- Eight data bits (no parity)

- Two stop bits for transmit data

- One stop bit for receive data

- If your terminal does not have separate controls for transmit and receive stop bits, select one stop bit for both transmit and receive.

- 3. Turn the system on.

- 4. Push the system RESET button. A sign-on message and prompt from the monitor should appear on the screen. If not, check your power supply voltages and CRT cabling.

- 5. Read the monitor manual and the operating system literature. Short course: type **bf** (for "boot floppy") to boot the operating system or **bw** to boot from Winchester.

- 6. Reconfigure the jumpers, etc., as necessary for your application. See section 13 for a summary of I/O device addresses and configuration jumpers.

#### 2.4 TROUBLESHOOTING AND SERVICE INFORMATION

•

In case of difficulty, use this checklist:

- 1. Be sure the system is not overheating.

- 2. Inspect the power cables and connectors.

- 3. If the monitor program is executing, run the diagnostics by using the monitor command **uc** or **um**.

- 4. Check your power supply for proper DC voltages. If possible, use an oscilloscope to look for excessive power supply ripple or noise. Note that the use of P2 is required to meet the power specifications.

- 5. Check the chips to be sure they are firmly in place. Look for chips with bent or broken pins. In particular, check the EPROM.

- 6. Check your terminal switches and cables. Be sure the P4 connector is secure. If you have made your own cables, pay particular attention to the cable drawing in section 10.

- 7. Check the jumpers to be sure your board is configured properly. All jumpers should be in the "standard configu-

ration" positions shown in Table 2-2. Check the EPROM jumpers, especially.

| Standar | d jumper settings    |                      | · · · · · · · · · · · · · · · · · · · |

|---------|----------------------|----------------------|---------------------------------------|

| Jumper  | Function             | Reference<br>Section | Standard<br>Configuration             |

| 1       | +5V power for Port A | 10                   | Not installed.                        |

| 2       | +5V power for Port B | 10                   | Not installed.                        |

| 3       | RS-232 handshaking   | 10                   | J3-A True                             |

|         | A: +12V              |                      | J3-B False                            |

|         | B:-12V               |                      |                                       |

| 4       | ROM size             | 6                    | Front panel 1                         |

|         |                      |                      | 0 0 0 0 0<br>0 0 0 0<br>512 Kbit      |

| 5       | System controller    | 3                    | Not installed.                        |

| TABLE 2-2  | 2      |          |

|------------|--------|----------|

| Standard j | jumper | settings |

- 8. Since the HK68/V3F monitor uses its on-card EEPROM to configure and set the baud rates for its console port, the lack of a prompt might be caused by incorrect terminal settings, an incorrect configuration of the EEPROM, or a malfunctioning EEPROM. Try pressing the H character a few times after a reset. If the prompt comes up, the EEPROM was most likely configured incorrectly. For more information about the way that the EEPROM configures the console port baud rates, refer to the *Heurikon Hbug User's Manual*.

- 9. After you have checked all of the above items, call our Customer Service Department for help. Please have the following information handy:

- The monitor program revision level (part of sign-on message)

- The serial number of the operating system.

- The HK68/V3F p.c.b. serial number (inscribed along the card edge).

- Whether your board has been customized for options such as processor speed or configuration for networking and peripherals.

If you plan to return the board to Heurikon for service, contact our Customer Service Department at 1-800-327-1251 to obtain a **Return Merchandise Authorization** (RMA) number. We will ask you to list which items you are returning and the board serial number, plus your purchase order number and billing information if your HK68/V3F is out of warranty. If you return

the board, be sure to enclose it in an antistatic bag, such as the one in which it was originally shipped. Send it prepaid to:

Heurikon Corporation Factory Service Department 8310 Excelsior Drive Madison, WI 53717

Please put the RMA number on the outside of the package so we can handle your problem efficiently. Our service department cannot accept material received without an RMA number.

#### 2.5 MONITOR SUMMARY

An optional EPROM-based debug-monitor/bootstrap for the HK68/V3F is available. General features and functions include the ability to:

- Manually download data or MC68030 program code.

- Check the processor, memory, VME, VSB, and I/O devices.

- Execute a bootstrap (for example, boot an operating system).

The monitor uses the area between  $0000,000_{16}$  and  $0000,1000_{16}$  for stack and uninitialized-data space. Any *writes* to that area can cause unpredictable operation of the monitor. The monitor initializes this area (that is, writes to it) to prevent parity errors, but it is the programmer's responsibility to initialize any other memory areas that are accessed.

A full description of monitor commands is in the Heurikon Hbug Monitor User's Manual.

### Main Processor Unit

#### 3.1 INTRODUCTION

This section details some of the important features of the 68030 MPU and the specifics of its implementation on the Heurikon HK68/V3F.

Refer to the MC68030 User's Manual for more information on the features described in this section.

#### 3.2 MPU INTERRUPTS

The MPU can internally set an interrupt priority level in such a way that interrupts of a lower priority will not be honored.

The MPU has seven interrupt levels. The VIC chip acts as interrupt controller for 19 possible interrupt sources. All interrupt priorities are handled by the VIC. These interrupts have a fixed priority within the VIC, but the encoding on the MPU IPL lines is programmable. The source of the interrupt vector — VIC or device — is programmable. A summary of the VIC interrupt levels is shown in section 7.4.2.

When the MPU recognizes an interrupt, it completes the current instruction and initiates an interrupt acknowledge sequence to acquire an interrupt vector from the interrupting device. The vector number is used to select one of 256 exception vectors located in reserved memory locations (see section 3.3 for a listing). The exception vector specifies the address of the interrupt service routine.

In case there are two interrupts pending at the same level, the oncard device is serviced before the bus interrupt.

Section 7.4.2 has more information on the HK68/V3F interrupt logic. The VMEbus interrupts are vectored; the vector is automatically read from the interrupting device.

#### 3.3 MPU EXCEPTION VECTORS

Exception vectors are memory locations from which the MPU fetches the address of a routine to handle an exception (interrupt). All exception vectors are two words (four bytes) long, except for the reset vector, which is four words long. The listing below shows the vector space as it appears to the HK68/V3F MPU. It is more specific than the 68030 MPU manual listing because of particular implementations on the HK68/V3F board. Refer to the MPU documentation for more details. The vector table normally occupies the first 1024 bytes of RAM, but may be moved to other locations under software control. Unused vector positions may be used for other purposes (such as code or data) or point to an error routine.

| MPU exc | MPU exception vectors |                                               |  |  |

|---------|-----------------------|-----------------------------------------------|--|--|

| Vector  | Address<br>Offset     | Assignment                                    |  |  |

| 0       | 000                   | Reset: Initial SSP (Supervisor Stack Pointer) |  |  |

| 1       | 004                   | Reset: Initial PC (Supr Program Counter)      |  |  |

| 2       | 008                   | Bus Error (Watchdog Timer)                    |  |  |

| 3       | 00C                   | Address Error                                 |  |  |

| 4       | 010                   | Illegal Instruction                           |  |  |

| 5       | 014                   | Divide by Zero                                |  |  |

| 6       | 018                   | CHK Instruction (register bounds)             |  |  |

| 7       | 01C                   | TRAPV Instruction (overflow)                  |  |  |

| 8       | 020                   | Privilege Violation (STOP, RESET, RTE, etc.)  |  |  |

| 9       | 024                   | Trace (for program development)               |  |  |

| 10      | 028                   | Instruction Group 1010 Emulator               |  |  |

| 11      | 02C                   | FPP coprocessor not present                   |  |  |

| 12      | 030                   | (reserved)                                    |  |  |

| 13      | 034                   | FPP Coprocessor Protocol Violation            |  |  |

| 14      | 038                   | Format Error                                  |  |  |

| 15      | 03C                   | Uninitialized Interrupt                       |  |  |

| 16-23   | 040-05F               | (reserved — 8)                                |  |  |

| 24      | 060                   | Spurious Interrupt.                           |  |  |

| 25      | 064                   | Level 1 autovector                            |  |  |

| 26      | 068                   | Level 2 autovector                            |  |  |

| 27      | 06C                   | Level 3 autovector                            |  |  |

| 28      | 070                   | Level 4 autovector                            |  |  |

| 29      | 074                   | Level 5 autovector                            |  |  |

| 30      | 078                   | Level 6 autovector                            |  |  |

| 31      | 07C                   | Level 7 autovector                            |  |  |

| 32-47   | 080-0BF               | TRAP Instruction Vectors — 16                 |  |  |

| 48-54   | 0C0-0DB               | FPP Exceptions — 8                            |  |  |

| 55      | ODC                   | (reserved)                                    |  |  |

| 56      | 0E0                   | MMU Configuration Error                       |  |  |

| 57-63   | 0E4-0FF               | (reserved — 6)                                |  |  |

| 64-255  | 100-3FF               | User Interrupt Vectors — 192                  |  |  |

|         |                       |                                               |  |  |

| TABL | .E 3-1   |  |

|------|----------|--|

| MOH  | overtion |  |

#### 3.4 STATUS LEDs

Three status LEDs continuously show the state of the board as follows:

#### TABLE 3-2

| Status LEDs  |         |                                                                                                                                  |  |

|--------------|---------|----------------------------------------------------------------------------------------------------------------------------------|--|

| LED<br>Label | Name    | Meaning                                                                                                                          |  |

| HLT          | HALT    | The MPU has halted. (Double bus fault, odd<br>stack address or the system reset line or<br>mailbox halt line is active.)         |  |

| ALT          | ALT     | A device other than the MPU owns the local<br>bus. This device could be the VME bus, the<br>VSB, or the Corebus plugover module. |  |

| SYF          | SYSFAIL | The SYSFAIL line is being driven active by this board.                                                                           |  |

#### 3.5 MPU CACHE CONTROL

The MPU cache is always enabled externally; however, it can be disabled by means of the cache control register (CACR). When D0 = 0, cache is enabled (default). When D0 = 1, cache is disabled.

The cache control register in the 68030 must be set properly to enable the MPU cache and cache burst accesses. See section 6.1 of the Motorola *MC68030 User's Manual*.

If caching is enabled, data and instructions from on-card ROM and DRAM will be cached. Data and instructions from the VMEbus will also be cached. VMEbus is cached for the standard or extended space when the CIOUT signal of the MPU is not asserted. The CIOUT pin follows a bit in the MMU page table entries. The bit allows caching on a page-by-page basis. See section 7.4.3 for further information on VMEbus caching.

#### 3.5.1 Instruction Cache

The MC68030 contains a 256-byte direct-mapped instruction cache organized as 16 lines. Each line is composed of four longword blocks. Each long word constitutes a separate cache entry. The instruction cache is controlled by five bits, 4-0, in the cache control register.

A tag for each line contains the 24 most significant logical address bits, the function code bit used to distinguish between user and supervisor accesses, and four valid bits corresponding to each long word. A comparator compares the address and function code bits in the selected tag with bits from the internal prefetch request to determine if the requested word is in the cache. The result of the comparison determines whether a word is supplied to the instruction pipe or a normal instruction prefetch occurs.

The instruction cache enhances the MC68030's performance by storing instruction prefetches (instruction words and extension words).

The instruction cache may be enabled or disabled via the **movec** instruction. See the MC68030 user's manual for details.

#### 3.5.2 Data Cache

The MC68030 also contains a 256-byte direct-mapped data cache organized as 16 lines. Like the instruction cache, each line is composed of four long-word blocks. Each long word constitutes a separate cache entry. The data cache is controlled by six bits, bits 8-13 of the cache, in the cache control register.

Operation of the data cache is similar to the instruction cache. A tag for each line contains the 24 most significant logical address bits, the function code bit used to distinguish between user and supervisor accesses, and four valid bits corresponding to each long word. The tag is used to determine the cacheability of the data.

The data cache stores data references to any address space except CPU space. The data cache may be enabled or disabled via the **movec** instruction. See the MC68030 user's manual for details.

#### 3.6 COPROCESSORS

The HK68/V3F supports a floating point coprocessor, which is described in section 4.

#### 3.7 WATCHDOG TIMER

The HK68/V3F watchdog timer is controlled by the VIC chip. The timeout period is programmable from 4 to 512 microseconds and can be disabled. See section 7.11 for more details on the watch-dog timer.

4

# Floating Point Coprocessor

#### 4.1 INTRODUCTION

The HK68/V3F allows the use of an optional MC68882 floating point processor chip. It runs as a coprocessor with the MPU.

#### 4.2 FPP FEATURE SUMMARY

- Allows fully concurrent instruction execution with the main processor.

- Eight general-purpose floating-point data registers, each supporting a full 80-bit extended-precision real data format (a 64-bit mantissa plus a sign bit, and a 15-bit biased exponent).

- A 67-bit ALU to allow very fast calculations, with intermediate precision greater than the extended-precision format.

- A 67-bit barrel shifter for high-speed shifting operations (for normalizing, etc.)

- 46 instruction types, including 35 arithmetic operations.

- Fully conforms to the IEEE P754 standard, including all requirements and suggestions. Also supports functions not defined by the IEEE standard, including a full set of trigonometric and logarithmic functions.

- Supports seven data types: byte, word, and long integers; single, double, and extended-precision real numbers; and packed binary coded decimal string real numbers.

- Efficient mechanisms for procedure calls, context switches, and interrupt handling.

FPP programming details are available in the MC68881/MC68882 User's Manual.

#### 4.3 FPP BYPASS

The HK68/V3F will operate without the FPP chip. Simply unplug the FPP if it is not required. No wires or jumpers are needed.

If the watchdog timer is enabled (via the VIC068), the software can determine if the FPP chip is installed. An attempt to access a nonexistent FPP causes a watchdog timeout and a bus error, forcing a Line 1111 MPU exception, vector number 11.

# System Error Handling

Error conditions can result from many sources. The following error conditions might occur during MPU cycles:

| CONDITION        | MEANING                                                                                                                                                                                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAM Parity       | Incorrect parity was detected during a read cycle from on-card<br>RAM memory. This may be due to a true parity error (RAM data<br>changed) or because the memory location was not initialized<br>prior to the read and it contained garbage.                                                                                            |

|                  | Parity errors generate a level 7 autovector interrupt.                                                                                                                                                                                                                                                                                  |

|                  | A pointer to the parity error handling routine should be loaded at Vector Base Register offset $00007C_{16}$ .                                                                                                                                                                                                                          |

| Watchdog Timeout | During an on-card access or VMEbus slave access, no acknowl-<br>edge was received within a fixed time interval defined by a regis-<br>ter in the VIC068. The usual cause is that no bus device was<br>assigned to the specified address. A timeout could also occur if an<br>access from the bus is not terminated by the bus master.   |

|                  | For an on-card bus cycle, the memory cycle is terminated, the BERR ( <i>Bus Error</i> ) exception is taken by the MPU and execution resumes at the location specified by the exception vector.                                                                                                                                          |

|                  | If an access <i>from</i> the bus was in progress, no BERR exception occurs.                                                                                                                                                                                                                                                             |

| Double Bus Fault | Another bus error occurred during the processing of a previous<br>bus error, address error, or reset exception. This error is the result<br>of a major software bug or a hardware malfunction. A typical soft-<br>ware bug that could cause this error is an improperly initialized<br>stack pointer that points to an invalid address. |

|                  | A double bus fault forces the MPU to enter the <i>HALT</i> state.<br>Processing stops. The HALT status LED will come on. The only<br>way out of this condition is a hardware reset from the reset switch,<br>SYSRESET* on the VMEbus, or another VMEbus master writing to<br>ICR7 bit 6.                                                |

| Divide by Zero      | The value of the divisor for a divide instruction is zero. The instruction is aborted and <i>vector 5</i> is used to transfer to an error routine.                               |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Privilege Violation | A program executing in the user state attempted to execute a privileged instruction. The instruction is not executed. Exception <i>vector</i> $8$ is used to transfer control.   |

| Address Error       | An odd address has been specified for an instruction. The bus cycle is aborted and <i>vector 3</i> is used to transfer control.                                                  |

| Illegal Instruction | The bit pattern for the fetched instruction is not legal or is unimplemented. The instruction is not executed. Exception vector 4, $10$ , or $11$ is used to transfer control.   |

| Format Error        | The format of the stack frame is not correct for an RTE instruc-<br>tion. The instruction is aborted and exception <i>vector 14</i> is used to<br>transfer control.              |

| Line 1111 Emulator  | The FPP coprocessor is not present and a coprocessor instruction was fetched. The instruction is not executed. Exception vector 11 will be taken.                                |

| FPP Exceptions      | The FPP coprocessor has detected a data processing error, such as an overflow or a divide by zero. The FPP causes the MPU to take one of eight exceptions in the range 48 to 54. |

### **On-card Memory Configuration**

#### 6.1 INTRODUCTION

The Heurikon HK68/V3F microcomputer will accommodate several RAM and ROM configurations. There is one 32-pin ROM socket for PROM or page-addressable ROM or EEPROM; 24 ZIP RAM positions; and an electrically erasable PROM (EEPROM). Off-card memory may be accessed via the VMEbus, the VSB, or Corebus.

#### 6.2 ROM

The ROM occupies a fixed 1-Mbyte physical address space. At power-up or after a system reset, ROM is mirrored throughout the entire MPU address space. The MPU fetches the reset vector from location 0, which specifies the initial program counter and stack pointer values. Then RAM is turned on and the standard memory map is activated on the first access to the range FC00,0000<sub>16</sub> – FC40,0000<sub>16</sub> where EPROM usually resides. Thus, the reset vector may point directly to ROM (at base address FC00,0000<sub>16</sub>).

The ROM contains consecutive (both even and odd) addresses.

#### TABLE 6-1

| <b>ROM address sum</b>  | mary |

|-------------------------|------|

| <b>Base Address</b>     | ROM  |

| FC00,0000 <sub>16</sub> | 0    |

Associated with the ROM socket is a set of jumpers that must be set according to the type of ROM being used. The HK68/V3F supports EPROM from 256 Kbits to 8 Mbits (27256 – 27080), as shown in Table 6-2. The ROM size and associated configuration are shown in Figure 6-1:

| PROM Type | ROM<br>Capacity | Jumper Positions            |

|-----------|-----------------|-----------------------------|

| 27256     | 256 Kbits       | J4: 2-4 and 5-7             |

| 27512     | 512 Kbits       | J4: 1-2 and 5-7             |

| 27010     | 1 Mbits         | J4: 1-2, 4-6, and 7-9       |

| 27020     | 2 Mbits         | J4: 1-2, 3-5, 4-6, and 7-9  |

| 27040     | 4 Mbits         | J4: 1-2, 3-5, 6-8, and 7-9  |

| 27080     | 8 Mbits         | J4: 1-2, 3-5, 6-8, and 9-10 |

### FIGURE 6-1. Jumper settings for ROM options

Revision D / September 1990

The ROM socket has 32 pins. If you use a 28-pin device, justify it so that socket pins 1, 2, 31, and 32 are empty. Twenty-four-pin devices are not supported. The ROM access time must be  $\leq$ 250 nanoseconds.

FIGURE 6-2. Placement for a 28-pin ROM

You may also use electrically erasable or paged PROMs. An EEPROM allows specific addresses to be changed by writing to the ROM. When writing to the EEPROM, a delay must be provided by *the software* between write operations. For the 2864, this delay is 10 milliseconds.

Paged ROMs allow future growth of ROM capacity without adding address pins. A single device can contain multiple 16-Kbyte pages. A specific page is selected by *writing* the page value to the ROM. For example, to select page three of a 27513, write  $03_{16}$  to address FC00,0000<sub>16</sub>.

#### 6.3 ON-CARD RAM

The HK68/V3F uses 16 ZIP RAM packages, each four bits wide, for data storage. There is optional parity of one bit per byte; 8 ZIPs are used for parity. Standard memory configurations are 2 or 8 Mbytes. On-card RAM occupies physical addresses starting at 0000,0000<sub>16</sub>. The base address of the HK68/V3F RAM on the VMEbus is controlled by a set of base address bits in the VMEbus slave control register. The HK68/V3F is able to match 24-bit or 32-bit addresses and therefore resides in either the VMEbus standard or extended space. The address of the space is set by bits in the VMEbus control latch. The VSB base address is controlled by the VSB slave control register.

#### 6.3.1 On-card Memory Sizing

The size of on-card memory is fixed at 2 Mbytes or 8 Mbytes with VSB following, so memory sizing is not possible.

### 6.4 **BUS MEMORY**

The bus interface is described in section 7.

## 6.5 PHYSICAL MEMORY MAP

See section 13.2 for an I/O device address summary.

FIGURE 6-3. Physical memory map

## 6.6 MEMORY TIMING

The HK68/V3F memory logic has been carefully tuned for optimum memory cycle times under a variety of conditions.

The base cycle time for a MC68030 is two clock cycles for a RAM read or write and one clock cycle for subsequent burst cycles. The following chart shows total access times required to get these base cycle times out of a RAM interface. It should be noted that this is the time from address valid to data input setup of the MC68030, including clock skew and various other factors.

## TABLE 6-3

Access time required for no wait states

| CPU Speed | (read cycle) | (write cycle) | (burst cycle) |  |

|-----------|--------------|---------------|---------------|--|

| 25 MHz 👢  | - 18 ns      | 38 ns         | 38 ns         |  |

| 33 MHz    | 15 ns        | 30 ns         | 30 ns         |  |

The HK68/V3F utilizes several features to provide the memory bandwidth the processor requires.

Reads The HK68/V3F provides a bank interleave memory structure that allows the concurrent access of adjacent long words in memory. The bank interleaving of read cycles allows the processor to achieve no wait state on the second, third, and fourth accesses of a burst read cycle at 33 MHz.

WritesThe HK68/V3F also performs write posting of memory write<br/>cycles. This allows the processor to terminate the write cycle<br/>early, permitting the memory to complete the write cycle.<br/>With the combination of bank interleaving and write posting,<br/>the HK68/V3F can achieve no-wait-state cycles for writes and<br/>burst writes.

The use of bank interleaving and write posting provides the HK68/V3F with nearly no-wait-state performance. The only wait state occurs on read cycles and the first cycle of a read burst cycle.

Table 6-4 describes the expected wait states for the HK68/V3F:

| Cycle        | Total Clocks | Wait States |

|--------------|--------------|-------------|

| Reads        | 4            | 2           |

| Writes       | 2            | 0           |

| Burst Read   | 7            | 2-0-0-0     |

| (4 accesses) |              |             |

| Burst Write  | 5            | 0-0-0       |

| (4 accesses) |              |             |

TABLE 6-4

The HK68/V3F will provide either 2 or 8 Mbytes of memory using 70-nanosecond DRAMs.

There are two other sources of wait states that DRAM architectures can exhibit.

The first is caused when a refresh must be performed and the DRAM controller is unable to perform the refresh during non-RAM cycles. This happens so infrequently that any performance degradation is usually unnoticeable.

The second occurs when the processor is required to perform back-to-back memory cycles with no delays. This also rarely occurs because of the instruction cache and data cache. In the event of a back-to-back memory cycle, an additional two-clockcycle wait is inserted between accesses.

While the above information is important in comparing the relative performance of DRAM designs, the performance of individual DRAM designs has much less impact on overall system performance than one might expect. The reason for this is that the internal instruction and data caches built into the 68030 chip help to decouple the processor from slower speed memories such as DRAMs.

To summarize, the higher the cache hit rates, the less impact external memory has on system performance.

#### 6.7 EEPROM

The HK68/V3F has an EEPROM for storing and recovering data or system configurations across power cycles.

The HK68/V3F has 8 Kbytes of EEPROM, which is configured for byte-wide (8-bit) access. There are 8 bytes between each byte, so EEPROM occupies 64 Kbytes of address space. The EEPROM is accessible as shown below.

| Address<br>(hex)        | Mode | Function                                                                                                                                                            |

|-------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FF02,0000 <sub>16</sub> | R/W  | Read/Write EEPROM contents.<br>Writes must be enabled through<br>access to a separate location.                                                                     |

| FF01,0C00 <sub>16</sub> | RMW  | Temporarily enables writes to<br>EEPROM. EEPROM write must be<br>next peripheral operation. The<br>68030 <b>tas</b> instruction must be used<br>for this operation. |

| TABLE 6- | 5         |

|----------|-----------|

| EEPROM   | addresses |

Write operations take a maximum of 10 milliseconds to complete. Upon writing, reads from the location written will return complimented data until the write completes, at which point the data written will be read.

There is no limit on read operations, but operation is only guaranteed up to 10,000 write cycles to any single location. The use of a **tas** instruction to enable writes was implemented to prevent unintentional writes by an errant program or power failure.

The EEPROM is mapped from  $FF02,0000_{16}$  to  $FF03,0000_{16}$ ; however, the upper quarter from  $FF02,C000_{16}$  to  $FF03,0000_{16}$  is hardware protected and can only be modified when the EEPROM protect jumper is installed.

The HK68/V3F monitor (Hbug) and certain system programs use the EEPROM. The exact amount reserved for Heurikon usage depends on the system. A major portion of the device, however, is available for customer use. Heurikon usage is summarized in Table 6-6 below (details are available separately):

## TABLE 6-6 EEPROM contents (partial)

| Function                                     |

|----------------------------------------------|

| Magic Number                                 |

| Checksum                                     |

| Accumulated number of writes                 |

| Board type, serial number and revision level |

| Hardware configuration information           |

| Software configuration information           |

| System configuration information             |

7

# **VMEbus** Control

## 7.1 INTRODUCTION

The HK68/V3F has a VMEbus interface that conforms to the specifications set forth in the following section. The VMEbus interface consists of the VIC068 VMEbus Interface Controller (VIC) and required support circuitry to perform all VMEbus functions. The control logic for the VMEbus allows numerous bus masters to share the resources on the bus. Up to 21 boards may be used on the VMEbus.

Please refer to the VIC068 VMEbus Interface Controller Specification from VTC for detailed descriptions of the registers.

The HK68/V3F VME interface has the following features:

- Address The VMEbus interface uses 32 address lines for a total of 4 Gbytes of VMEbus address space. Supported are the "short," "standard," and "extended" address modes, which use 16, 24, and 32 address lines, respectively.

- Data The VMEbus interface uses 32 data lines to support 8-, 16-, 24-, or 32-bit data transfers.

- Interrupts The VIC handles the seven VMEbus interrupts and multiple local interrupts.

- MailboxThe mailbox consists of a collection of 8-bit<br/>registers that can be used for interprocessor<br/>communications over the VMEbus.

- System Controller The HK68/V3F may be configured as the VMEbus system controller to perform the necessary system controller functions of SYSCLK, BCLR, SYSRESET, bus watchdog, and bus arbiter.

#### 7.2 BUS CONTROL SIGNALS, VMEbus P1 DESCRIPTIONS

VME pins are defined on P1 and part of P2. VSB is defined on the rest of P2. Refer to the Motorola VMEbus specification, revision C.1, for detailed usage of these signals. All signals are bidirectional unless otherwise stated. Refer to sections 7.12 and 7.13 for a complete listing of the pins.

The bus request level is set in the arbiter and requestor configuration register (B3).

The following signals on connectors P1 and P2 are used for the VMEbus interface.

- A01-A15 ADDRESS bus (bits 1-15). Three-state address lines that are used for short, standard, and extended addresses.

- A16-A23 ADDRESS bus (bits 16-23). Three-state address lines that are used for standard and extended addresses.

- A24-A31 ADDRESS bus (bits 24-31). Three-state address lines that are used for extended addresses only.

- ACFAIL\* AC FAILURE. This signal is an input to the HK68/V3F and may be used to generate an interrupt to the MC68030 by programming the VIC accordingly.

- AM0-AM5 ADDRESS MODIFIER (bits 0-5). Three-state lines that are used to broadcast information such as address size and cycle type.

- AS\* ADDRESS STROBE. A three-state signal that indicates when a valid address has been placed on the address bus.

- **BBSY\*** BUS BUSY. An open-collector signal driven low by the current MASTER to indicate that it is using the bus. When the MASTER releases this line, the resultant rising edge causes the ARBITER to sample the bus request lines and grant the bus to the highest priority requester. Early release mode is supported.

- **BCLR\*** BUS CLEAR. A totem-pole signal generated by the ARBITER to indicate when there is a higher priority request for the bus. This signal requests the current MASTER to release the bus.

| BERR* | BUS ERROR. An open-collector signal generated by a SLAVE   |

|-------|------------------------------------------------------------|

|       | or BUS TIMER. This signal indicates to the MASTER that the |

|       | data transfer was not completed.                           |

- **BG0IN\*-BG3IN\*** BUS GRANT (0-3) IN. Totem-pole signals generated by the ARBITER and REQUESTERS. Bus-grant-in and bus-grant-out signals form bus grant daisy chains. An input to the HK68/V3F, the bus-grant-in signal indicates that it may use the bus if it wants.

- **BG0OUT\*-BG3OUT\*** BUS GRANT (0-3) OUT. Totem-pole signals generated by REQUESTERS. An output from the HK68/V3F, the bus-grantout signal indicates to the next board in the daisy-chain that it may use the bus.

- **BR0\*-BR3\*** BUS REQUEST (0-3). Open-collector signals generated by REQUESTERS. Assertion of one of these lines indicates that some MASTER needs to use the bus.

- **D00-D31** DATA BUS. Three-state bidirectional data lines used to transfer data between MASTERS and SLAVES.

- **DS0\*, DS1\*** DATA STROBE ZERO, ONE. A three-state signal used in conjunction with LWORD\* and A01 to indicate how many data bytes are being transferred (1, 2, 3, or 4). During a write cycle, the falling edge of the first data strobe indicates that valid data are available on the data bus.

- **DTACK\*** DATA TRANSFER ACKNOWLEDGE. An open-collector signal generated by a SLAVE. The falling edge of this signal indicates that valid data are available on the data bus during a read cycle, or that data have been accepted from the data bus during a write cycle. The rising edge indicates when the SLAVE has released the data bus at the end of a READ CYCLE.

- IACK\* INTERRUPT ACKNOWLEDGE. An open-collector or threestate signal used by an INTERRUPT HANDLER acknowledging an interrupt request. It is routed, via a backplane signal trace, to the IACKIN\* pin of slot one, where it forms the beginning of the IACKIN\*-IACKOUT\* daisy-chain.

- IACKIN\* INTERRUPT ACKNOWLEDGE IN. A totem-pole signal and an input to the HK68/V3F. The IACKIN\* indicates that the board may respond to the INTERRUPT ACKNOWLEDGE CYCLE that is in progress.

- IACKOUT\* INTERRUPT ACKNOWLEDGE OUT. A totem-pole signal and an output from the HK68/V3F. The IACKIN\* and IACKOUT\* signals form a daisy-chain. The IACKOUT\* signal indicates to the next board in the daisy-chain that it may respond to the INTERRUPT ACKNOWLEDGE CYCLE in progress.

| IRQ1*-IRQ7* | INTERRUPT REQUEST (1-7). Open-collector signals, generated<br>by an INTERRUPTER, which carry interrupt requests. When<br>several lines are monitored by a single INTERRUPT<br>HANDLER, the highest numbered line is given the highest<br>priority.                                                                                                                                                                                                              |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LWORD*      | LONG WORD. A three-state signal used in conjunction with DS0*, DS1*, and A01 to select which byte location(s) within the 4-byte group are accessed during the data transfer.                                                                                                                                                                                                                                                                                    |

| RESERVED    | RESERVED. A signal line reserved for future VMEbus<br>enhancements. This line must not be used.                                                                                                                                                                                                                                                                                                                                                                 |

| SERCLK      | SERIAL CLOCK. A totem-pole signal that is used to synchro-<br>nize the data transmission on the VMEbus. This signal is not<br>implemented on the HK68/V3F.                                                                                                                                                                                                                                                                                                      |

| SERDAT*     | SERIAL DATA. An open-collector signal that is used for VMEbus data transmission. This signal is not implemented on the HK68/V3F.                                                                                                                                                                                                                                                                                                                                |

| SYSCLK      | SYSTEM CLOCK. A totem-pole signal that provides a constant 16-MHz clock signal that is independent of any other bus tim-<br>ing. This signal is driven if the HK68/V3F is a system controller.                                                                                                                                                                                                                                                                  |

| SYSFAIL*    | SYSTEM FAIL. An open-collector signal that indicates a failure<br>has occurred in the system. Also used at power-on to indicate<br>that at least one VMEbus board is still in its power-on initial-<br>ization phase. This signal may be generated by any board on<br>the VMEbus. The VIC drives this signal low at power-up and<br>may be programmed to generate an interrupt if asserted by<br>another board in the system. Details are given in section 7.9. |

| SYSRESET*   | SYSTEM RESET. An open-collector signal that, when asserted, causes the system to be reset.                                                                                                                                                                                                                                                                                                                                                                      |