# **AFIPS** CONFERENCE PROCEEDINGS **VOLUME 27** PART 1 1965 FALL JOINT COMPUTER CONFERENCE

The ideas and opinions expressed herein are solely those of the authors and are not necessarily representative of or endorsed by the 1965 Fall Joint Computer Conference Committee or the American Federation of Information Processing Societies.

> Library of Congress Catalog Card Number 55–44701 Spartan Books, Div. of Books, Inc. 1250 Connecticut Avenue, N. W. Washington, D. C.

© 1965 by the American Federation of Information Processing Societies, 211 E. 43rd St., New York, N. Y. 10017. All rights reserved. This book, or parts thereof, may not be reproduced in any form without permission of the publishers.

> Sold distributors in Great Britain, the British Commonwealth, and the Continent of Europe:

> > Macmillan and Co., Ltd. 4 Little Essex Street London W. C. 2

# PREFACE

This volume records in part the technical material presented at the 1965 Fall Joint Computer Conference. Contained in this publication are the formal papers selected from a record number of contributions submitted to the Technical Program Committee. No attempt has been made to incorporate the material presented at panels and tutorial sessions of the Conference, nor have the invited papers presented on the final day of the Conference been included. The Conference Committee hopes that a subsequent volume will emerge to catch the living spirit of such deliberations.

Still, the size of this volume is large, just as the scope of the Conference is broad. This is, in part, deliberate, since the Conference attempted to provide the opportunity for professional communication on every level. Recognizing the increasing degree of specialization in the hardware and software fields, the Technical Program Committee added a third information channel to the Conference to focus attention on management and applications. These sessions dealt with questions of marketing and economics as well as applications in the scientific and humanistic fields. Thus to the *orientation* in hardware and software was added the *direction* of applications and management in the disciplines that are concerned with information processing.

The most distinctive feature of this Conference, however, must be the five "discuss-only" sessions for which preprints were available before the Conference. Hopefully, new dimensions were added to the papers through a searching examination of the material on the floor of the Conference. We regret that we cannot record the results and evaluate the technique.

The real and permanent contribution of the 1965 Fall Joint Computer Conference is still the technical material presented in this volume. The credit goes to the authors with greatful appreciation of the role of the Technical Program Committee and Session Chairmen who engineered the structure. Behind them are the contributions of many others who, as members of the various committees, made the Conference possible.

> ROBERT W. RECTOR, General Chairman 1965 Fall Joint Computer Conference

# CONTENTS

| Preface                                                                             |                                             | Page<br>iii |

|-------------------------------------------------------------------------------------|---------------------------------------------|-------------|

| Fielace                                                                             |                                             | 111         |

| SESSION 1: PROGRAMMING                                                              | LANGUAGES                                   |             |

| Universal Programming Languages and Processors:<br>A Brief Summary and New Concepts | Walter H. Burkhardt                         | 1           |

| Digital Simulation Languages: A Critique and A Guide                                | John J. Clancy<br>Mark S. Fineberg          | 23          |

| Automatic Simplification of Mathematical Expressions —<br>The Formac Algorithm      | R. G. Tobey<br>R. J. Bobrow<br>S. N. Zilles | 37          |

| The New Block Diagram Compiler for Simulation of<br>Sampled-Data Systems            | B. J. KARAFIN                               | 53          |

| Two-Dimensional Programming                                                         | Melvin Klerer<br>Jack May                   | 63          |

| SESSION 2: ADVANCES IN COMPUT                                                       | TER ORGANIZATION                            |             |

| Microprogramming for Data Acquisition and Control                                   | W. C. McGee<br>H. E. Petersen               | 77          |

| Picoprogramming: A New Approach to Internal<br>Computer Control                     | R. E. Briley                                | 93          |

| A Precession Pattern in a Delay Line Memory                                         | S. P. Frankel<br>J. Hernandez               | 99          |

| An Associative Parallel Processor with Application<br>to Picture Processing         | R. M. Bird<br>R. H. Fuller                  | 105         |

| Computer Organization for Array Processing                                          | D. N. Senzig<br>R. V. Smith                 | 117         |

| SESSION 3: EFFICIENCY AND M<br>COMPUTER INSTALLA                                    |                                             |             |

| Management Problems of Aerospace Computer Centers                                   | G. A. GARRETT                               | 129         |

| The Multi-Discipline Approach: A Marketing Application                              | B. G. Mendelson<br>R. V. Monaghan           | 139         |

| Organizational Philosophy and the Computer Center                                   | M. H. Gotterer<br>A. W. Stalnaker           | 145         |

|                                                                              |                                                  | Page |

|------------------------------------------------------------------------------|--------------------------------------------------|------|

| Planning for Generalized Business Systems                                    | R. V. HEAD                                       | 153  |

| Computer Systems Design and Analysis Through Simulation                      | G. K. Hutchinson<br>J. N. Maguire                | 161  |

| Basic Concepts for Planning an Electronic Data<br>Processing System          | A. F. Moravec                                    | 169  |

|                                                                              |                                                  |      |

| SESSION 6: A NEW REMOTE ACCESSED N                                           | IAN-MACHINE SYSTEM                               | [    |

| Introduction and Overview of the Multics System                              | F. J. Corbato<br>V. A. Vyssotsky                 | 185  |

| System Design of a Computer for<br>Time-Sharing Applications                 | E. L. Glaser                                     | 197  |

|                                                                              | G. A. OLIVER                                     |      |

| Structure of the Multics Supervisor                                          | V. A. Vyssotsky<br>F. J. Corbató<br>R. M. Graham | 203  |

| A General-Purpose File System for Secondary Storage                          | R. C. Daley<br>P. G. Neumann                     | 213  |

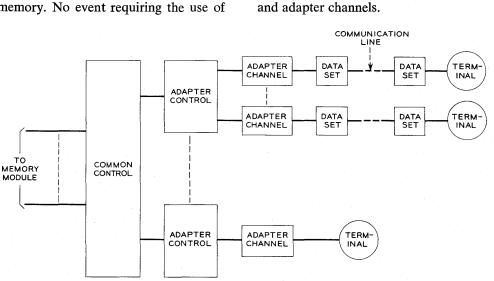

| Communications and Input-Output Switching in a<br>Multiplex Computing System | J. F. Ossanna<br>L. Mikus<br>S. D. Dunten        | 231  |

| Some Thoughts About the Social Implications of Accessible Computing          | E. E. David, Jr.<br>R. M. Fano                   | 243  |

| SESSION 7: APPLICATIONS OF SIMULA                                            | ATION                                            |      |

| Structure and Dynamics of Military Simulations                               | E. Levine                                        | 249  |

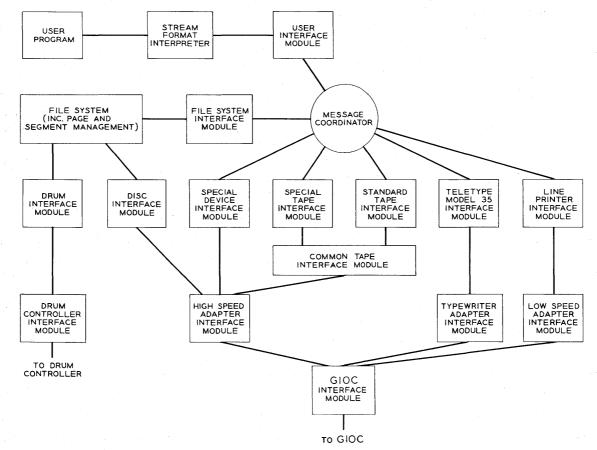

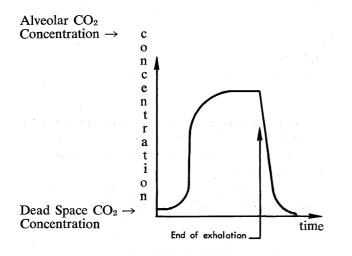

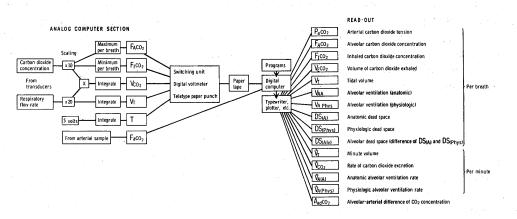

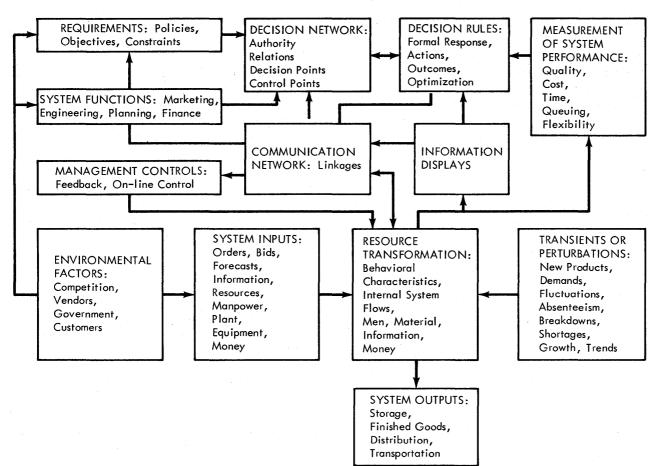

| Analogue-Digital Data Processing of Respiratory Parameters                   | T. W. MURPHY                                     | 253  |

| Computer Simulation: A Solution Technique for<br>Management Problems         | A. J. Rowe                                       | 259  |

| The Role of the Computer in Humanistic Scholarship                           | E. A. Bowles                                     | 269  |

| The Structure and Character of Useful Information-<br>Processing Simulations | L. Fein                                          | 277  |

| SESSION 8: NATURAL LANGUAG                                                   | E PROCESSING                                     |      |

| Catalogs: A Flexible Data Structure for Magnetic Tape                        | Martin Kay<br>Theodore Ziehe                     | 283  |

vi

|                                                                         |                                                                           | Page |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------|------|

| Information Search Optimization and Iterative<br>Retrieval Techniques   | J. J. ROCCHIO<br>G. SALTON                                                | 293  |

| An Economical Program for Limited Parsing of English                    | D. C. Clarke<br>R. E. Wall                                                | 307  |

| The Mitre Syntactic Analysis Procedure for<br>Transformational Grammars | Arnold M. Zwicky<br>Joyce Friedman<br>Barbara C. Hall<br>Donald E. Walker | 317  |

### SESSION 9: CELLULAR TECHNIQUES FOR LOGIC, MEMORY AND SYSTEMS

| Cobweb Cellular Arrays          | R. C. MINNICK  | 327 |

|---------------------------------|----------------|-----|

| Two-Dimensional Iterative Logic | R. H. CANADAY  | 343 |

| Two-Rail Cellular Cascades      | R. H. SHORT    | 355 |

| Associative Memory Structure    | B. T. MCKEEVER | 371 |

# SESSION 11: THE REVOLUTION IN WRITTEN COMMUNICATION

| Computer Editing, Typesetting and Image Generation                                              | on M. V. Mathews 389<br>Joan E. Miller |

|-------------------------------------------------------------------------------------------------|----------------------------------------|

| The Left Hand of Scholarship: Computer Experimen<br>with Recorded Text as a Communication Mediu |                                        |

|                                                                                                 |                                        |

# SESSION 12: ON-LINE INTERACTIVE SOFTWARE SYSTEMS

| MATHLAB: A Program for On-Line Machine Assistance<br>in Symbolic Computations                           | C. Engelman                           | 413 |

|---------------------------------------------------------------------------------------------------------|---------------------------------------|-----|

| An Integrated Computer System for Engineering Problem Solving                                           | D. Roos                               | 423 |

| AESOP: A Prototype for On-Line User Control of<br>Organizational Data Storage, Retrieval and Processing | E. Bennett<br>E. Haines<br>J. Summers | 435 |

| Structuring Programs for Multi-Program Time-Sharing<br>On-Line Applications                             | К. Lock                               | 457 |

| Interactive Machine Language Programming                                                                | B. W. LAMPSON                         | 473 |

vii

|                                             | Page                                                                       |

|---------------------------------------------|----------------------------------------------------------------------------|

| CHARLES W. ADAMS                            | 483                                                                        |

| HC CIRCUITS                                 |                                                                            |

| LEONARD W. COTTON                           | 489                                                                        |

| W. H. Howe                                  | 505                                                                        |

| A. Feller<br>H. R. Kaupp<br>J. J. Digiacomo | 511                                                                        |

|                                             | HC CIRCUITS<br>Leonard W. Cotton<br>W. H. Howe<br>A. Feller<br>H. R. Kaupp |

# SESSION 14: COMPUTERS IN THE BIOLOGICAL AND SOCIAL SCIENCES

| Integrating Computers into Behavioral Science Research   | Harold Borko                        | 527 |

|----------------------------------------------------------|-------------------------------------|-----|

| Data Analysis in the Social Sciences                     | Geoffrey H. Ball                    | 533 |

| Nonlinear Regression Models in Biology                   | Joseph A. Steinborn                 | 561 |

| Computer Correlation of Intracellular Neuronal Responses | Frederick F. Hiltz                  | 567 |

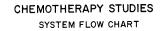

| Information Processing of Cancer Chemotherapy Data       | Alice R. Holmes<br>Robert K. Ausman | 583 |

# SESSION 18: TIME-SHARED COMPUTER SYSTEMS: SOFTWARE/HARDWARE CONSIDERATIONS

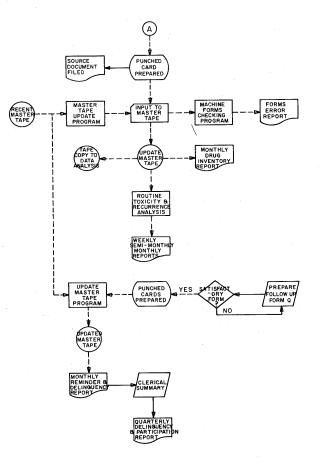

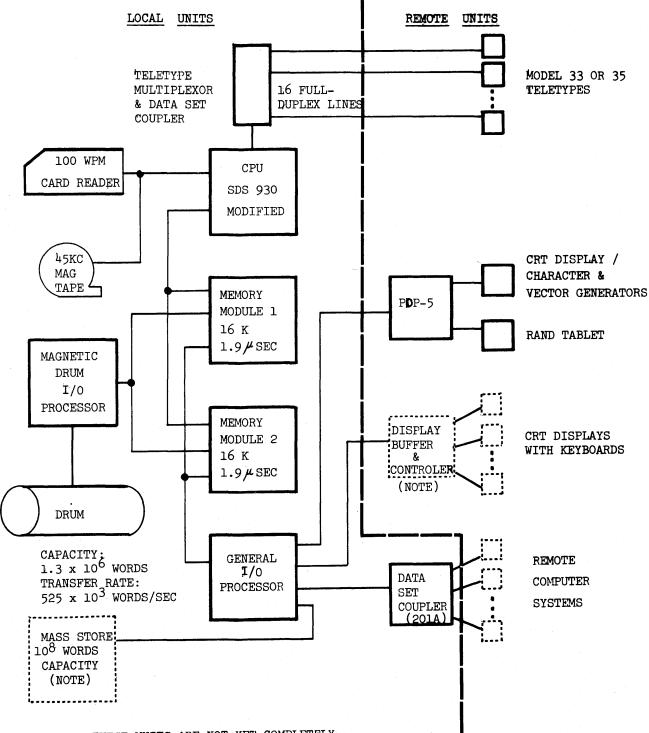

| A Facility for Experimentation in Man-Machine<br>Interaction                            | R. Wayne Lichtenberger<br>Melvin W. Pirtle                      | 589 |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----|

| A Time- and Memory-Sharing Executive Program<br>for Quick-Response On-Line Applications | JAMES W. FORGIE                                                 | 599 |

| Design for a Multiple User Multiprocessing System                                       | James D. McCullough<br>Kermith H. Speierman<br>Frank W. Zurcher | 611 |

| A Computing System Design for User Service                                              | WEBB T. COMFORT                                                 | 619 |

# SESSION 19: SCRATCHPAD MEMORIES

| Design Considerations for a 25-Nsec Tunnel Diode Memory | D. J. CRAWFORD<br>R. L. MOORE<br>J. A. PARISI<br>J. K. PICCIANO<br>W. D. PRICER | 627 |

|---------------------------------------------------------|---------------------------------------------------------------------------------|-----|

| SMID: A New Memory Element                              | W. D. PRICER<br>R. P. SHIVELY                                                   | 637 |

|                                                                                                        |                                            | ix   |

|--------------------------------------------------------------------------------------------------------|--------------------------------------------|------|

|                                                                                                        |                                            | Page |

| An Experimental Sixty-Five Nanosecond Thin Film<br>Scratchpad Memory System                            | G. J. Ammon<br>C. Neitzert                 | 649  |

| Impact of Scratchpads in Design; Multi-Functional<br>Scratchpad Memories in the Burroughs B8500        | S. E. GLUCK                                | 661  |

| Scratchpad Oriented Designs in the RCA Spectra 70                                                      | A. T. Ling                                 | 667  |

| Scratchpad Memories at Honeywell: Past, Present<br>and Future                                          | N. NISENOFF                                | 679  |

| SESSION 20: ARITHMETIC TECHNIQU                                                                        | ES AND SYSTEMS                             |      |

| A Bounded Carry Inspection Adder for Fast<br>Parallel Arithmetic                                       | Emanuel Katell                             | 689  |

| A Fast Conditional Sum Adder Using Carry Bypass Logic                                                  | Joseph F. Kruy                             | 695  |

| A Checking Arithmetic Unit                                                                             | RICHARD A. DAVIS                           | 705  |

| Serial Arithmetic Techniques                                                                           | M. Lehman<br>D. Senzig<br>J. Lee           | 715  |

| SESSION 23: SIMULATION OF HUM                                                                          | AN BEHAVIOR                                |      |

| Simulation Models for Psychometric Theories                                                            | C. E. Helm                                 | 727  |

| Human Decision Making Under Uncertainty and Risk:<br>Computer-Based Experiments and a Heuristic        |                                            |      |

| Simulation Program                                                                                     | N. V. FINDLER                              | 737  |

| Computer Experiments in Motor Learning                                                                 | G. R. BUSSEY                               | 753  |

| SESSION 24: HIGH SPEED READ ON                                                                         | LY MEMORIES                                |      |

| A Survey of Read Only Memories                                                                         | Morton H. Lewin                            | 775  |

| A High-Speed, Woven Read-Only Memory                                                                   | M. Takashima<br>H. Meada<br>A. J. Kolk Jr. | 789  |

| A Thin Magnetic Film Computer Memory Using a Resonant<br>Absorption Non-Destructive Read-Out Technique | M. May<br>J. L. Armstrong<br>W. W. Powel   | 801  |

| Development of an E-Core Read-Only Memory                                                              | P. S. Sidhu<br>B. Bussell                  | 809  |

SESSION 25: INPUT/OUTPUT EQUIPMENT FOR CLOSER MAN-MACHINE INTERFACE Page

| MAGIC: A Machine for Automatic Graphics<br>Interface to a Computer                            | D. E. Rippy<br>D. E. Humphries<br>J. A. Cunningham | 819 |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------|-----|

| A Magnetic Device for Computer Graphic Input                                                  | M. H. LEWIN                                        | 831 |

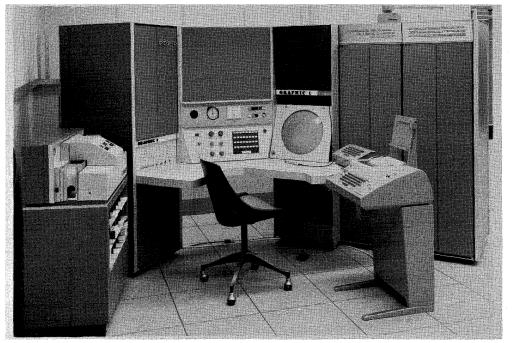

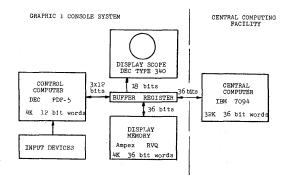

| Graphic I — A Remote Graphical Display Console System                                         | m W. H. NINKE                                      | 839 |

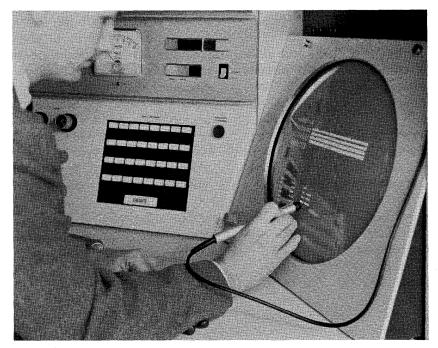

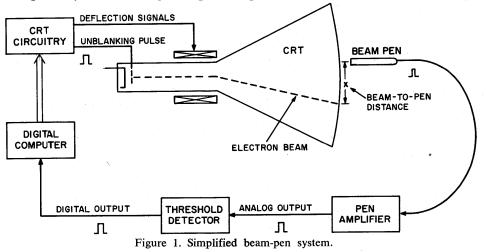

| The Beam Pen: A Novel High Speed, Input/Output<br>Device for Cathode-Ray-Tube Display Systems | D. R. Haring                                       | 847 |

| Voice Output from IBM System/360                                                              | A. B. URQUHART                                     | 857 |

| SESSION 26: INDUSTRIAL A                                                                      | APPLICATIONS                                       |     |

| Corrugator Plant Operating System                                                             | Walter J. Koch                                     | 867 |

| Real Time Programming and Athena Support at<br>White Sands Missile Range                      | WILLIAM G. DAVIDSON                                | 871 |

| Quality Evaluation of Test Operation via<br>Electronic Data Processing                        | A. A. Daush                                        | 879 |

| The Introduction of Man-Computer Graphics into the Aerospace Industry                         | S. H. Chasen                                       | 883 |

| SESSION 27: HYBRID COMPUTERS F                                                                | OR FUTURE SYSTEMS                                  |     |

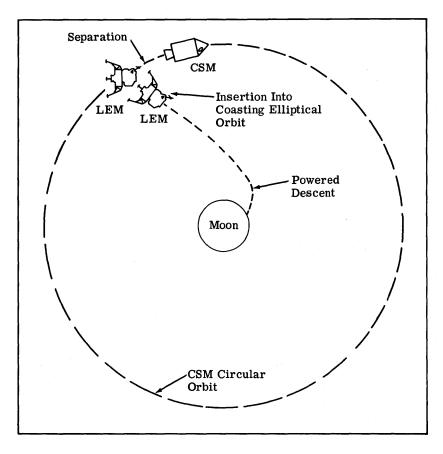

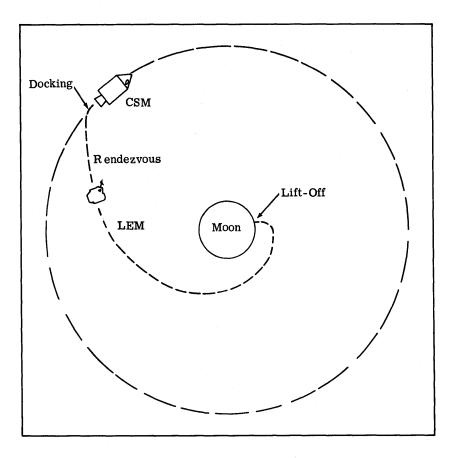

| Hybrid Computation for Lunar Excursion Module Studies                                         | Arthur Burns                                       | 893 |

| Optimum Design and Error Analysis of Digital<br>Integrators for Discrete System Simulation    | Roger W. Burt<br>Andrew P. Sage                    | 903 |

| Sequential Analog-Digital Computer (SADC)                                                     | Herman Schmid                                      | 915 |

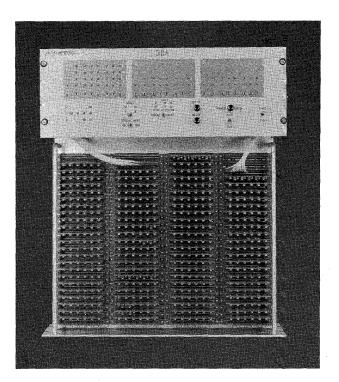

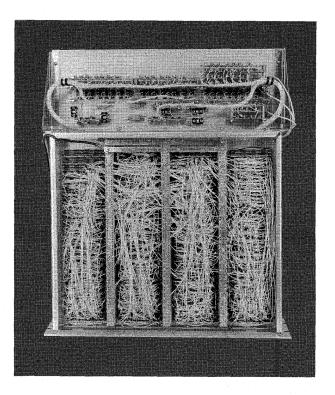

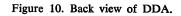

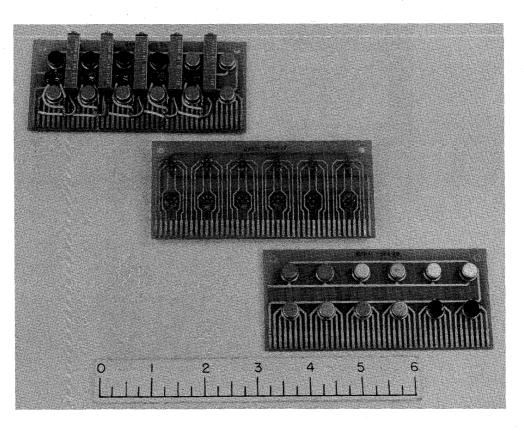

| Design of a High Speed DDA                                                                    | M. W. GOLDMAN                                      | 929 |

| SESSION 28: COMPUTER DIMENS                                                                   | IONS IN LEARNING                                   |     |

| Engineering Mathematics via Computers                                                         | John Staudhammer                                   | 951 |

| The Computer: Tutor and Research Assistant                                                    | Robert J. Meyer                                    | 959 |

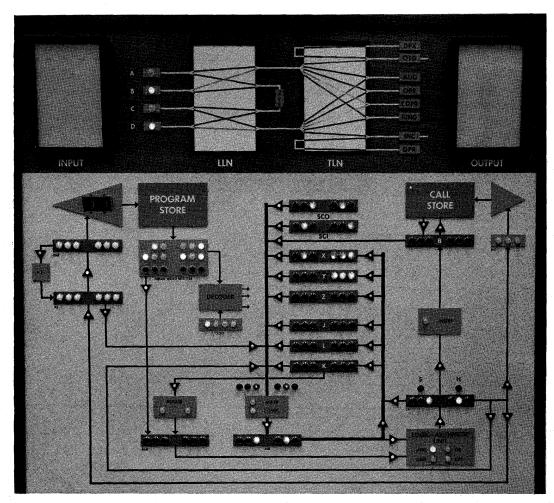

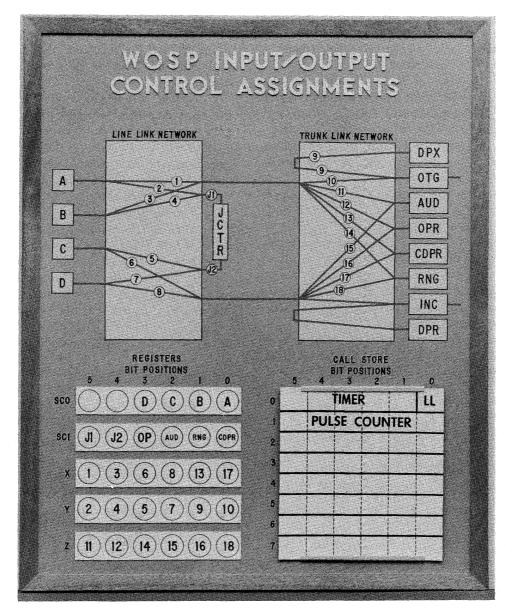

| WOSP: A Word-Organized Stored-Program Training Aid                                            | M. RASPANTI                                        | 965 |

| CASE: A Program for Simulation of Concept Learning                                            | FRANK B. BAKER                                     | 979 |

|                                                                                               |                                                    |     |

х

|                                                                             |                                                   | Page |

|-----------------------------------------------------------------------------|---------------------------------------------------|------|

| SESSION 29: MEMORIES FOR FUTUR                                              | RE COMPUTERS                                      |      |

| A 375 Nanosecond Main Memory System Utilizing 7 Mil Core                    | es G. E. Werner<br>R. M. Whalen                   | 985  |

| Monolithic Ferrite Memories                                                 | I. Abeyta<br>M. Kaufman<br>P. Lawrence            | 995  |

| High Speed Ferrite 2-1/2D Memory System                                     | T. J. GILLIGAN                                    | 1011 |

| Design and Fibrication of a Magnetic Thin Film<br>Integrated Circuit Memory | T. J. MATCOVICH<br>W. Flannery                    | 1023 |

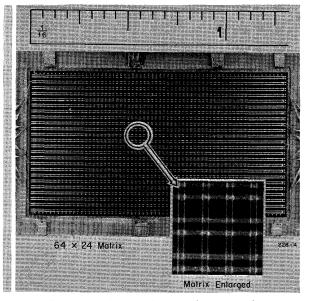

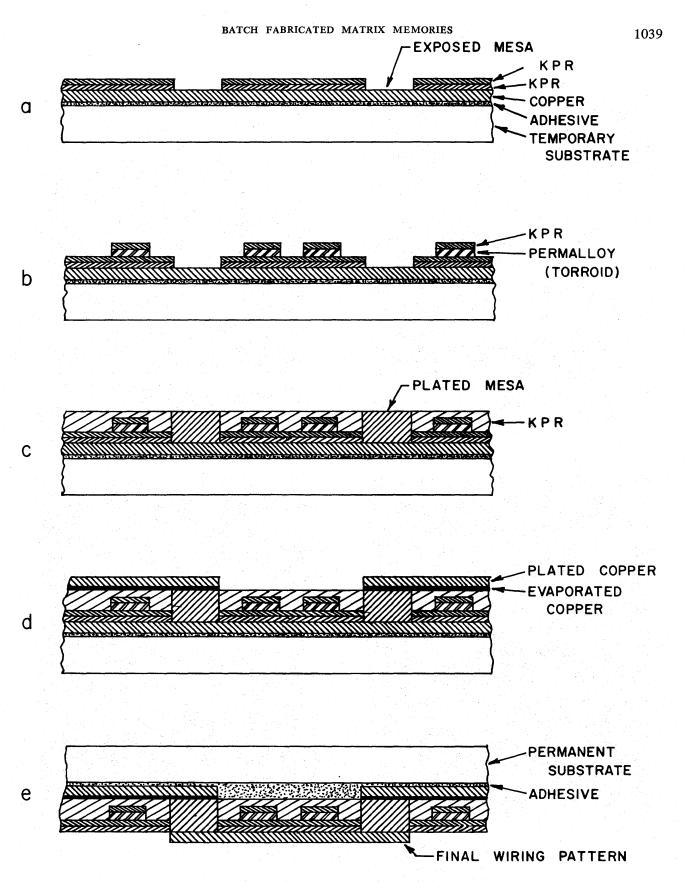

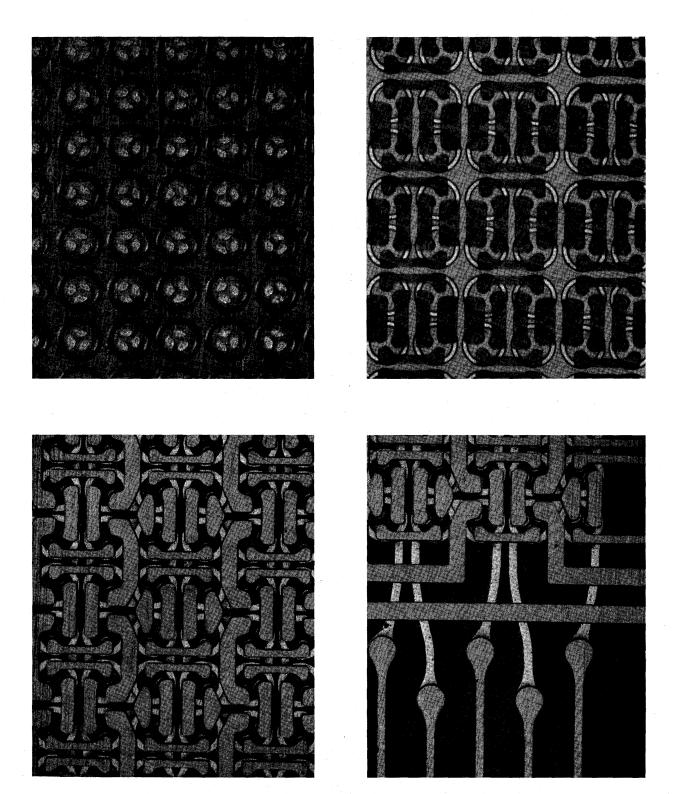

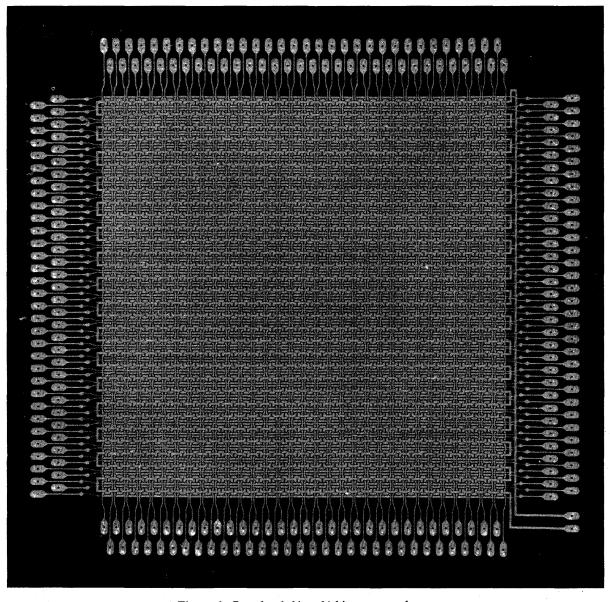

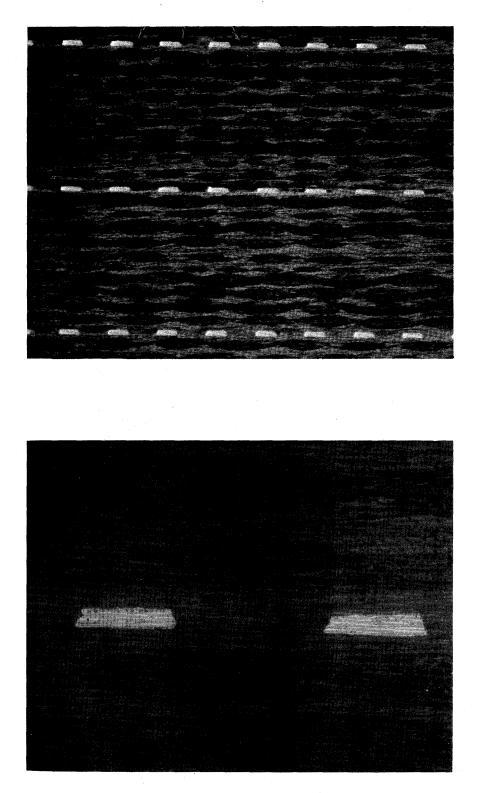

| Batch Fabricated Matrix Memories                                            | T. L. McCormack<br>C. R. Brittard<br>H. W. Fuller | 1035 |

| Integrated Semi-Conductor Memory System                                     | Harley A. Perkins<br>Jack D. Schmidt              | 1053 |

| SESSION 30: COMPUTER-AIDED DESIGN                                           | N & MAINTENANCE                                   | х.   |

| Strobes-Shared Time Repair of Big Electronic Systems | J. T. QUATSE                     | 1065 |

|------------------------------------------------------|----------------------------------|------|

| A Self-Diagnosable Computer                          | R. E. Forbes<br>D. H. Rutherford | 1073 |

|                                                      | C. B. STIEGLITZ<br>L. H. TUNG    |      |

| An Automated Interconnect Design System              | W. E. PICKRELL                   | 1087 |

| Systematic Design of Automata                        | J. Р. <b>К</b> отн               | 1093 |

# UNIVERSAL PROGRAMMING LANGUAGES AND PROCESSORS: A BRIEF SURVEY AND NEW CONCEPTS

Walter H. Burkhardt Computer Control Company, Inc. Framingham, Massachusetts

#### INTRODUCTION

Progress in any field depends on the materialization of new ideas. But before this is possible, these ideas have to be found, investigated, developed and adapted to the changing world.

In computing, i.e., the use of computers for the solution of problems, new ideas are available everywhere, although the implications behind them and the influence on the state-of-the-art are generally not very well understood. Therefore it is often difficult to separate the wheat from the chaff.

But even valuable ideas are not always useful and welcome. That is especially the case when the basis for them is not adquately prepared. To know which ideas are useful at present, it is necessary to evaluate the state-of-the-art to determine how developments in the field will proceed. There are other reasons. One might be to give the nonspecialist a fast orientation; another is to readjust the basis in a fast growing and changing field.

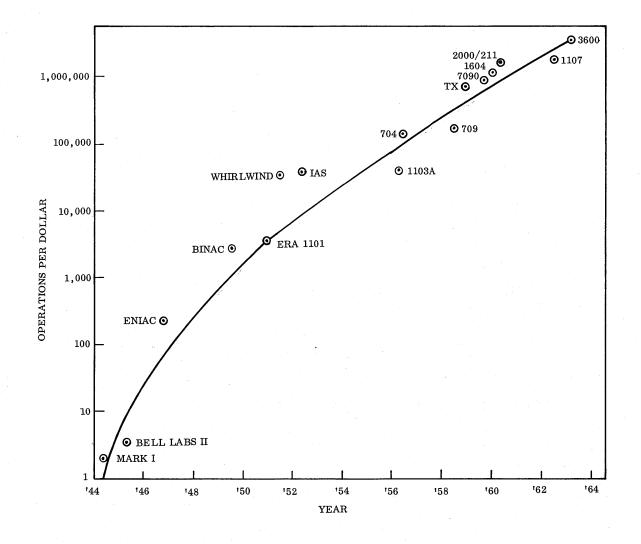

The last decade brought a tremendous gain in overall computer power and for a unit outlay as well. Therefore, it is not too surprising if many old values have to be changed and new ones appear.

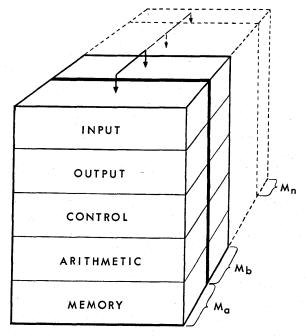

The advent of computers gave a very useful tool for the solution of many tasks for which the statment of the problem was given in a fixed mathematical form. This is due to the special nature of computers, with the memories, the circuit logic, and electronic switching elements having easy adaptation to mathematical problems and to a tremendous bulk of knowledge in the form of mathematical formalism.

There are now on the one side machines with more or less special features for the solution of particular problems, and on the other the problems, given sometimes in a self-contained formulation, sometimes in only a vague and inexact form, and ranging over the whole spectrum of life, science, and society. The medium to combine both is known as programming. This function consists of mapping a solution given to the problems on the machine, but now better defined as dividing the problems into elementary task-components and translating them into terms of the machine.

In this paper, the interface between the problems and the machines will be discussed with emphasis on the tools for the solutions—the programming languages and processors.

#### Statement of Problem

The application of computers for solving problems in technical, scientific, and commercial fields has been very successful. But progress is hampered by the fact that the machines accept primarily only their own special language, on digital computers composed of number sequences. These sequences are mostly long chains of zeros and ones—which is rather unintelligible to humans and quite different from the languages in which the tasks are and can be easily described.

#### **Possible Solutions**

There are two possibilities for solving the difficulties made by the gap between the languages of machines and the languages of problems. One solution would be to adapt the languages of the machines by developing machine languages more general and closer to the problems encountered, the high-level language computers, the other one would be to adapt the problems to the machines. This is done presently with intermediate languages, between machines and problems, which are easier for people to use than contemporary absolute machine languages.

High-Level Language Computers. This would mean to develop a machine which could communicate in a higher language. Suggested rather early, and attempted to implement to some extent (for example, in the SEAC machine,<sup>1</sup> this idea could give an elegant solution to the problem. Therefore perhaps it is revived in newer designs,<sup>2,3</sup> and it is even suggested to use a language of the ALGOL-type<sup>4</sup> as machine language.\* In addition to the drawbacks due to the insufficiencies of contemporary programming languages (and these are the only candidates at present for high-level machine languages) there are several factors opposed to such a development.

The arguments of high cost for circuitry and restrictions to the applications area are mainly based on the economic feasibility of such designs. But with an advent of very cheap components and assembly methods, these restrictions could change in the future.

The arguments of altering bases must be taken more seriously. The development is neither fixed on the problem side nor on the machine side.

Development on the Problem Side. To illustrate this point a simple example might be taken. In applications to commercial problems a basic function is certainly sorting, which is used over and over again. So it would seem natural to include a machine operation for sorting in the repertoire of such high-level commercial machines. But what technique of sorting<sup>5</sup> should be implemented? The best technique to be selected depends on the data formats and on the machine configurations so that selecting only one technique is not very feasible. But inclusion of several different techniques is highly unlikely. This example will show the difficulties for only one task function. The overall requirements complicate the situation so much that no reasonable solution is in sight.

Development on Machine Side. Many opinions state the view that the development on the machine side is now fixed.<sup>6</sup> But this belief seems prejudiced and premature. For example, in the near future memory hierarchies (let's say a memory of 128word diode storage with 50 nanoseconds and 2048 words thin film or thin wire with 200 nanoseconds and back-up storage of 32,768 words at 600 nanosecond cycle time. Behind these might be bulk core storage, drums, disks and tapes) could give a user more computer power (according to the principle of limited resources) than the more conventional recent design; or mastery of parallel execution features, etc. Although this argument affects mainly the internal design of a possible high-level language machine, it complicates the picture and eliminates many suggestions for solutions. The potentialities for a standard machine (or assembly) language are impeded too by this aspect.

Solutions by Intermediate Languages. The solution by intermediate steps between problem and machine languages via programming was at least in the past the most successful one. It can easily be seen that the closer to the problem the steps are taken, the more powerful and quickened the solution will be. So the region between problems and machines contains software levels of differing machine and problem independence.

Efficiency of Machine Use. Whenever a programming language is different from actual low-level machine language, questions concerning the efficient use of the hardware are apt to arise. These seem to be of greatest importance on slow and expensive machines. Linearly extrapolated, the emphasis on these questions is decreased to 2 percent when relating a machine with 0.5-miscrosecond cy-

<sup>\*</sup>A similar step in this direction is sometimes attempted in microprogrammed machines with some higher-level language implemented in memory in a semifixed manner.

cle time in 1965 to one with 25-miscrosecond cycle time in 1951 at the same price. Interestingly, the highest requirements for run-time optimization with compilers are imposed on hardware which is inadquate for the intended problem solutions (e.g., optimization in FORTRAN II on the 704 and in ALPHA on the M20<sup>8</sup> for the solution of difficult partial differential equations). With the need for faster computers<sup>9</sup> and a decline in prices for hardware, as in the past decade, these efficiency questions are bound to diminish and perhaps to disappear altogether.

*Hierarchy of Programming Languages*. Different hierarchies of programming languages are already proposed,<sup>10</sup> where the criterion is the machine configuration concerned. Of course, many other characteristics could be chosen for classification of programming languages, but the one here presented in respect to machine independence seems to be most interesting. A good measure for the level is the degee of declarative freedom for the user. Therefore on the lowest level would be the absolute machine languages and with more declarative possibilities gradually increasing up to the problem level of declarative languages as follows:

| Absolute | machine    | lan-   | No | declarative | freedom |  |

|----------|------------|--------|----|-------------|---------|--|

| guages   | (machine ] | level) |    |             |         |  |

| Assembly languages                                      | No specification of names<br>and locations necessary                    |

|---------------------------------------------------------|-------------------------------------------------------------------------|

| Procedural languages                                    | No detailed machine commands necessary                                  |

| Problem oriented<br>languages                           | Language elements from<br>problem but command<br>structure procedural   |

| Specification languages,<br>augmented by seman-<br>tics | Description of relations<br>in the problem, freedom<br>of procedure     |

| Declarative languages<br>(problem level)                | Description of the prob-<br>lem, freedom of proce-<br>dure and solution |

The levels from absolute machine language to procedural languages are very well known from the literature of recent years. (Sometimes in the past, procedural languages like FORTRAN, ALGOL and JOVIAL were incorrectly denoted as problemoriented languages.) Examples for problem-oriented languages are found in APT, COGO, Simscript, etc.<sup>11</sup> The block-notation languages<sup>12</sup> for analog-hybrid simulation on digital computers are examples of augmented specification languages. Semantic content is there defined by the fixed meaning of the block names (in MIDAS<sup>13</sup> they are the operations and the operands by means of the successor specification). Recently an example for another use of a specification language in an applications program was published<sup>14</sup> where Backus-Naur-Form specification was adopted. As can be expected, the experience reported stresses the improved facilities (compared with conventional programming languages) in programming, check-out, and incorporating changes into the program over conventional programming languages. Perhaps the first example in declarative languages, although not on the level designed by the term today, was the dynamic analysis language DYANA.<sup>15</sup> Some other approaches are described in a recent paper.<sup>16</sup>

Translation among Programming Languages. All programming languages above the actual machine language impose the necessity for translation to that language. This task is done by a translator, compiler or assembler, hereafter called a processor.

Two different aspects have to be distinguished concerning the translation of programs:

- 1. Translations horizontally on one level

- 2. Translations vertically to other levels

Obviously, all translations can be regarded as composed of these two possibilities to various degrees. The requirements for the practicability of translation are:

- The rules for the connections of elements in the languages (the grammars or syntaxes).

- The elements of the languages (the dictionaries).

- Their respective relations in both languages as well.

1. Translations Horizontally. Horizontal translations of programs among different programming languages of the same level are in general not possible. The reason is, that the results of one operation (in extended sense) in a program in source language (the language of the input) may determine the kind of operation to be used next in the program, and that often the target equivalent of a source language item is not available. The criterion for translatability is that all operations in the source language can be translated separately into the target language (the language of the output) in respect to power and extend. Translatability from one source language A to a target language B gives, however, no indications for translatability from B to A. Whenever some operations are not translatable, they may be simulated, e.g., interpreted at run time. Because of the huge number of redundant operation parts involved, interpreted programs run normally orders of magnitudes slower than comparable translated ones on the same machine.

2. Translation Vertically. Vertical translation of programs is divided in (a) upward and (b) downward translation.

(a) Upward translations impose generally the same requirements as those detailed for horizontal translations. A special case governs the upward translation or previously downward translated programs. Contrary to some opinion,<sup>17</sup> no relevant information for the execution of a program is lost in the translation process, only the redundant. Therefore, if the translation algorithm is given, all necessary information can be retrieved from programs, that had been translated before, to build a fully equivalent program on the former level.

(b) Downward translations are normally not difficult, because the languages on the higher levels are so designed as to give a specific and determined target equivalent on the lower level for each source language element.

Now, by the mechanical transformation of the program (a description of a problem or its solution) into representations of other levels with or without intermediate levels (e.g., DYANA  $\rightarrow$  FORTRAN II, FORTRAN II  $\rightarrow$  SAP704, SAP704  $\rightarrow$  704) not more solutions of a problem are obtained, but only different representations of the program. Therefore, with regard to problem considerations, all different representations of one program (e.g., diagrams augmented by text, DYANA, FORTRAN II, SAP and 704), and all programs giving the same results for the same sets of data, are said to be equivalent. A similar relation is given among specification languages or notations.<sup>18</sup> Continuing this thought, most efficiency questions, grammar and syntax peculiarities and details, though interesting and necessary for the development of the transformation processors, are definitely unimportant and sometimes even undesirable for the solution of a task in applications programming.

Experience with High-Level Programming Languages. The aspects of the historical development of high-level programming languages (with regard to machine independence) are described in detail elsewhere.<sup>11</sup> It might be stressed that FORTRAN was not the first high-level language of algebraic type but had forerunners in Rutishauser's algebraic language on the Ermeth in Zurich and in Lanig and Zirler's language on Whirlwind in MIT. Even MATH-MATIC for the Univac I, a commercially available machine, was earlier. But the small UI (a decimal and alphanumeric machine with only 45 instructions) did not really necessitate and justify a high-level algebraic language; this was later required with the more complex machines of von Neumann-type, like the 704.

The advantages of high-level programming languages are more apparent the more the considered languages are independent from the machines. These advantages are:

- 1. Easier learning and use than lower-level languages, because they are less complicated,

- 2. Time savings in programming of solutions for problems,

- 3. Time savings in debugging and correcting possibilities for slightly different problems,

- 5. Higher machine independence for transition to other computers, and otherwise for compatibility with hardware,

- 6. Better documentation (compatibility among programs and different programmers,

- 7. More powerful structuring in terms of problem.

Points (1), (2), and (3) were stressed in the past and found most important.<sup>19</sup> Nowadays (4) and (5) receive more attention and in the future (5), (6), and (7) may become the dominant ones.

It is interesting to note that points (1) through (4) have been similarly known to engineers for decades for the solution of problems in formal instead of numerical notation.

Most astonishing is the large number of programs still written in a low-level language.<sup>20</sup> This can only be explained by a steep information gradient between the knowledge in the field and the application programmers, or better, their managers.

# Development of New High-Level Programming Languages

*Introduction.* The development of new high-level programming languages, at least in the past, has been more evolutionary than revolutionary. So the

step from FORTRAN to ALGOL brought with it these advantages in order of their estimated importance:

- Chained logical decision sequences

- Block structure of program parts

- Free notation format

- Lifting of various machine restrictions (i.e., number of subscripts in variables, modes of expressions, etc.)

Unfortunately, due perhaps to the ambiguities embedded in ALGOL and its definition, the gain from switching over to ALGOL programming from FORTRAN is considered marginal. Despite all the efforts in the past, less than 10 percent of all programs for scientific and engineering applications are coded in ALGOL<sup>20</sup> — which is not a striking triumph for a successor to FORTRAN.<sup>21</sup> Similarly, less than 5 percent of the programs in the same area are coded in FORTRAN IV --- what can be cautiously described as failure of the new facilities incorporated in FORTRAN IV over FORTRAN II. The use of a programming language by applications programmers has to be the measure for its success. If one is not sufficiently used, a programming language is certainly as dead and obsolete as Mayan or Babylonian and perhaps of just academic interest.

Requirements for a New High-Level Programming Language. Several important design criteria — often violated even in recent designs — have to be stressed:

Close Relationship to the Problems in the Desired Area. This allows the user a concise and powerful description of the processes and concepts.

Uniqueness. Each item in a correct program has to have one unique and defined meaning. This is required by all compatibility reasons.

Simplicity and Clearness of Notation. The language has to be developed and designed with a programming notation for ease of learning, use and handling of the language in the intended problem area. (Of course, that does not exclude a formal and rigid definition of the language. But such a definition should hardly ever be imposed upon a user.) Requirements for readability and intelligibility are included here. This point of convenience has to be the main criterion for the standardization of programming languages. Admittedly, generally one proposed standard is better than another, if it is more convenient for the user.

Completeness. A good programming language should be able to handle all occurring tasks within its designed scope, without need for using means from outside. Good counter-examples are the missing string-handling facilities in FORTRAN and the input/output part in ALGOL 60.

Segmentation. For the practical application of programming languages to large problems, efficient segmentation features are desirable so that parts of problems can be handled independently.

Compatibility with Existing Programming Languages. In addition to compatibility in other respects, one is important in regard to the already accumulated knowledge of problem solutions (the program libraries). These libraries consist of two parts—one created by the present user working with the language and the other developed elsewhere or earlier with other languages. The first part requires elements in the language to build up and use older programs and program parts in new connotations; the second demands some means for translation or interpretation of old libraries.

Development Possibilities. There are three ways of developing a new programming language:

- Cleaning up and refining existing languages;

- Elaboration and combination of known useful features;

- Development from the basic requirements of a problem area.

All three methods were used in the past either separately or combined.

*Proliferation and Solutions.* The application of computers with high-level languages to different problem areas causes a proliferation of programming languages according to the vernaculars in the application fields. There are two different possibilities:

- 1. If single programming languages are to be developed close to the vernaculars, then some incompatibility will exist between these.

- 2. On the other hand, if an intermediate language somewhere in the middle between problems and machines will be accepted as the programming standard, then much

more effort has to be spent on defining the problems to the computers.

The historical development of progress in the computer field favors the first alternative, while computer manufacturers and operations managers of computer installations try to hold to the second one. Possible solutions to the dilemma might be found in:

- (a) Inclusion of language elements of neighboring problem areas into programming languages presently in use or being developed, or opening the borders to that area; for an intermediate language with the scope of an UNCOL<sup>22</sup> but on a higher level or as a subset of a universal programming language.

- (b) Development of universal programming languages.

- (c) Development of universal processors.

Universality in this respect is meant to comprise at least the elements of two really different problem areas (not vertical combinations or notations).<sup>22</sup>

Several proposals for the first of these solutions (inclusion of language elements) are already reported. Of these, BEEF<sup>24</sup> and ALGOL-Genius<sup>25</sup> are both designed to combine a programming language for algorithmic with one for commercial procedures. More ambitious in this respect is the NPL-SHARE<sup>26,27</sup> language to combine in addition the elements of real-time and command languages.

It is most noticeable that software systems (languages and processors) developed upwards from the machines by combinatinn of existing elements do not tend to please many users. Despite the desirability of larger extended systems, there are always users who do not need the new scope and are unwilling to pay for the clumsiness and complication due to inadequate design.

Other development possibilities going from a fixed base are found in the features of open-ended systems. To some extent at present, the combining of languages of two areas results in at least a partial universal programming language.

#### UNIVERSAL PROGRAMMING LANGUAGES

#### Definition

A universal programming language can be defined as a complete set of elements to describe the problems and solutions in all problem areas. If such a language can be developed, the design requirements will be the same as for a single high-level programming language (see the requirements listed above), but much more valid.

#### Mathematical Definition and Development.

It is easy to define mathematically the design and development of a universal programming language in general.

The complete set  $S_i$  of all equivalent programs\*  $p_{ik1}$  for the solution of problem k in one area is given by

$$S_i = U_i p_{ik1}$$

Then the operation  $\delta$  selects from this set a program, maximal in respect to power of problem description

$$D_k = \delta U_i p_{ik1}$$

Now all maximal programs of one problem area form a new complete set  $S_k$ :

$$S_k = U_k \,\delta \, U_i p_{ik1}$$

From this new set, operation  $\gamma$  extracts the language elements and operations for the given area to form the language for the problem area  $G_j$ :

$$G_j = \gamma \ U_k \ \delta \ U_i p_{ik1}$$

For the generalized and universal programming language  $\Lambda_u$ , the complete set  $S_1$ , generated by  $U_1$ , of all languages  $G_1$  has to be considered, combined and integrated by the operation  $\lambda$  to give

#### $\Lambda_u = \lambda \ U_1 \ \gamma \ U_k \ \delta \ U_i p_{ik1}$

As may be recognized, the operations,  $\delta$ ,  $\gamma$ , and  $\lambda$  are very complex and difficult, but the most serious drawback seems to be the large extent of the various sets required. But this is the only way for development, be it by methods of evolution via open-ended languages or by revolution via problem analysis and then language determination (as given by an example in reference 28.

#### Old Proposals

The problem of proliferation of programming languages was recognized rather early especially in respect to the effects on processor production.<sup>22,29</sup> So UNCOL, a universal computer-oriented language was proposed as an interface between high-level programming languages and computers. Due to the open-endedness on both sides of problems and machines, such a scheme cannot easily be designed on the basis of a fixed language. On the other hand, 30 examples for this scheme are known as notations,

```

*See "Translation among Programming Languages" above.

```

e.g., the prefix notation.<sup>30</sup> But this design level seems to be inadequate for a satisfactory solution to the problem.

A similar restriction is imposed on the wellknown flow-chart notation to be used as a universal programming language, or even as a programming language. (Recent rumors suggest flow charts to be used on oscilloscope terminals for on-line programming.)

#### **Design** Possibilities

As mentioned in the section on Solutions, there are two possibilities for the design of universal languages. One is a conventional approach with openended languages and processors so that the users will develop gradually the required high-level programming languages in the interesting problem areas. Then from time to time the now achieved status of a system should be re-evaluated and reshaped to avoid and eliminate inefficiencies and obsolescence. So gradually the best language for a problem area will mature. As soon as there are enough languages developed for different problem areas, then the design of a universal one can be envisaged.

The more direct method suggested by the mathematical definition is to investigate the nature of the problems, depict the elements for description and solution, and combine these into a high-level programming language. This method was used to develop the new programming language BEST for commercial applications.<sup>28</sup> The reported five years of labor seem relatively high, but the rewards justify the effort to eliminate all the inadequacies and inconsistencies which arrive at the fire-line with programming languages, designed by mutual conconsent at conference tables.

#### UNIVERSAL PROCESSORS

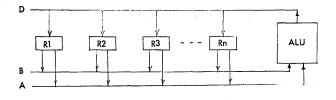

#### General Requirements and Notation

Definition and Feasibility. A universal processor can be defined as a program for transformation of all programs from all required problem areas into all required target languages. The extent of such a processor is dependent on the definition of the requirements of the problems and of the machines.

Processors which accept programs in a number of different programming languages are well known.<sup>31</sup> But no successful experience (aside from the projects outlined below could be found for easy com-

bining of different target languages. This is certainly no accident, as will be stressed later. The target language area poses heavier and more stringent requirements on processors than the source language area where it is possible to easily combine several compilers for different languages (but for the same machine) into one system and to invoke the one momentarily required by control cards (e.g., in IBSYS.<sup>31</sup> The difficulties for the target language arise mainly because of a third language parameter in a processor, its own language, i.e., the one in which the processor is written or the language of the machine on which the processor has to run.

Design and Implementation. At the source language side of a processor, besides the simple IBSYS concept, a higher degree of integration could be obtained by (1) accepting mixtures of statements of different languages, perhaps with indicators as to which languages they belong; and (2) accepting the elements of different languages intermixed. This requires that incompatibilities among the languages are removed. (For example, the definitions of identifiers in FORTRAN and COBOL are incompatible, with blanks having no meaning in FORTRAN, but used as separators in COBOL.) So it is proven that a fairly universal programming language cannot be developed by simply combining useful features from different other languages.

If only a restricted universal processor can be developed, then by feeding a copy of it to itself a desired less-restricted one could be produced automatically.

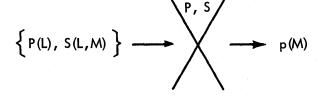

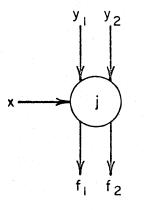

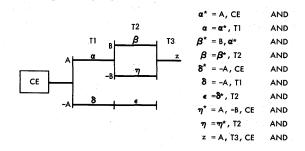

General Notation. A processor can be defined as a function (f) for transformation of a program given in one language into that of another. The parameters of this function f are then:

- $\alpha$ ) Source language of programs to the processor;

- $\beta$ ) Target language of programs from the processor;

- $\gamma$ ) Own language of the processor;

- $\delta$ ) Variables for measuring the efficiencies;

- $\epsilon$ ) A variable for the method used in the processor; etc.

So the processor can be designated by  $f(\alpha,\beta,\gamma,\delta,\epsilon,\ldots)$ .

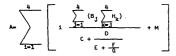

Transformation of Programs by Processors. A source program is, for example, a given set  $V_{1i}$  of (i) statements  $(s_i)$  in source language A for the solution of problem 1 and similarly a target program can be defined:

$P_1 = V_{1i}s_i(A)$  as source program  $P'_1 = V_{1k}s_k(B)$  as target program in language B

The application of the transformation function gives the relations:

| $V_{1k}S_k(B) = fV_{1i}S_i(A)$ | for languages separate<br>translatable only on<br>the program level                                            |

|--------------------------------|----------------------------------------------------------------------------------------------------------------|

| $= V_{1i}gs_i(A)$              | requires a different<br>transformation al-<br>gorithm                                                          |

| $= V_{1j} f V_{jm} S_m(A)$     | for languages separate<br>translatable on<br>block level; (a block<br>is defined as the set<br>$V_{m}s_{m}(A)$ |

| $= V_{1i}fs_i(A)$              | for languages separate<br>translatable on the<br>statement level                                               |

| $= V_{1i}s_i(fA)$              | for languages separate<br>translatable on the<br>language level                                                |

Simplified Notation. The most interesting and important questions with processors are concerned with the function of changing the language representation of programs, (especially by translating them to actual machine language). Therefore, if no regard is given to other than the language parameters, the function is reduced to

f = f(A,B,C).

Of course, the other parameters cannot be completely ignored, but they depend on other variables. (Measured efficiency of a processor depends on the methods used, while efficiency requirements are functions of hardware speeds and costs again, etc., so other parameters are omitted here.)

Now a new symbol for a processor is introduced:

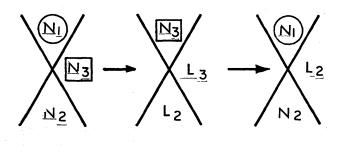

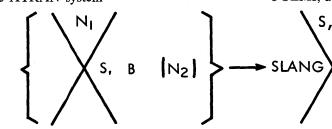

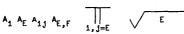

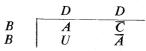

It designates a processor translating from source Language A into target language B and is itself written in (its own) language C. Sometimes a label as a name for a processor will be used and inserted into the empty space at the left side of the symbol. Where one language parameter in the following is

not specified or pertinent, the space for it is left empty.

#### Examples of the New Symbol

is a FORTRAN compiler written in SAP, translating from FORTRAN to SAP

is a SAP assembler given in 704 machine language and translating from SAP to 704 machine language

is a NELIAC compiler translating from NELIAC to 1401 SPS and running on the 709

is a precompiler translating into the source language (e.g., for error checking in programs) and running on machine with language L3.

*Mode of Processor Use.* Basically two different modes of processor use can be distinguished: translative and interpretive.

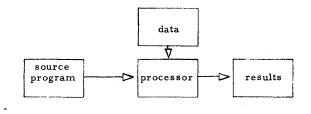

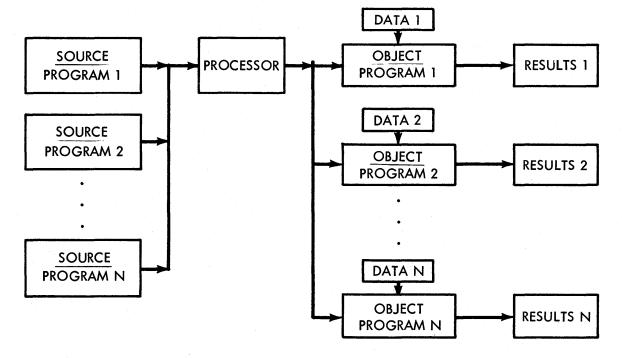

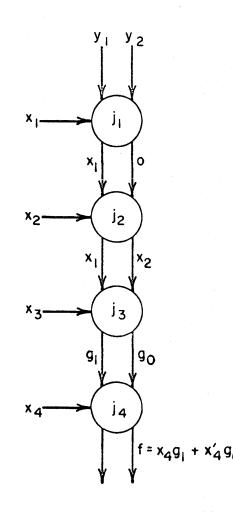

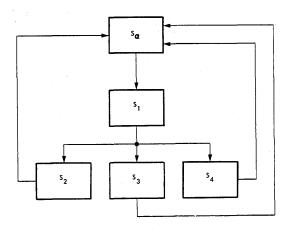

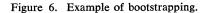

1. Interpretive Mode. The interpretive mode of processor use is characterized by the handling of data and source statements at the same time, according to the diagram:

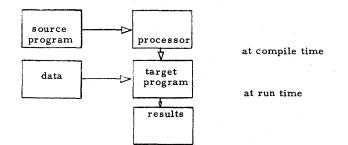

2. Translative Mode. The translative mode is characterized by the processing of source program and data at different times, at compile time and at run time, respectively:

It must be understood that the execution of the target program at run time is itself considered again as interpretation.

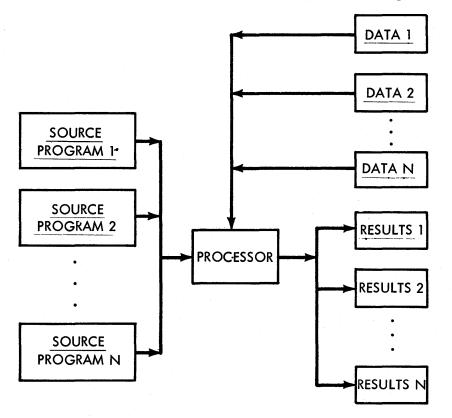

In real-time concurrent processing, the schemes would look like

3. For Real-Time Interpretive:

4. For Real-Time Translative:

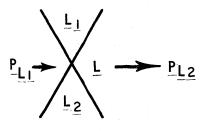

General Use of Processors. The general use of processors is given by feeding (designated by the simple arrow  $\rightarrow$ ) a program into the processor to receive (designated by the double arrow  $\blacktriangleright$ ) the program in another representation:

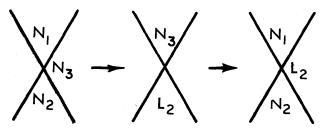

is the translation process of a program from source language  $L_1$  to target language  $L_2$  by a processor running on a machine with language  $L_3$ .

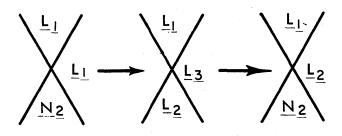

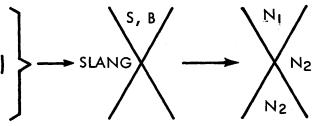

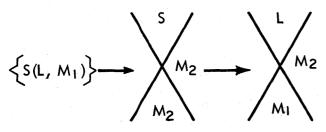

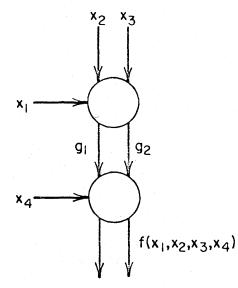

A more interesting case is that the program fed to the processor can itself be a processor. When it is written in its own-source language it is according to:

Here it is explained that a processor written in its source language can be translated to any other language for which a processor exists. From this prospect was derived the old requirement that each processor should be written in its source language. On the same process is based nowadays the production of assemblers for new machines. Details on that method will be explained later.

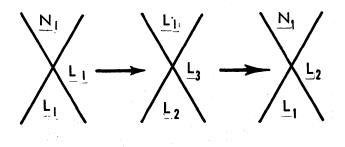

When the processor is written in its own-target language, this gives:

This is the ancient method of processor construction by writing it in its target language. So it is possible to build up on already available processors. An example of this is the old FORTRAN compiler written in SAP and translating to SAP, which is then translated by the SAP assembler into 704 machine language, but it needed the SAP assembler in the translating process from FORTRAN to 704 code.

Restrictions on the Parameters. The variables in the transformation function f(A,B,C) of a processor are certainly not independent even among themselves. The following functional relations among the language parameters are interesting. Previous mention has been made of the relation between the target and the own language of a processor. Another, but not a very stringent one, governs the relation between source language elements and their target language equivalents.

It will now be assumed that the relations can be defined and the variables separated. Several cases are then distinguished:

- The source language parameter A is independent of the other ones, so that no functional relation is given there: A ≠ h<sub>1</sub>(B); A ≠ h<sub>2</sub>(C).

- 2. The target language variable B depends not on the source or on the own language:

$B \neq h_3(A); \qquad B \neq h_4(C).$

- Both source and target language are not related to the own language (but might depend on each other):

A ≠ h<sub>2</sub>(C); B ≠ h<sub>4</sub>(C).

- 4. All language parameters are independent among themselves.

The design of universal processors will now be investigated according to these restrictions.

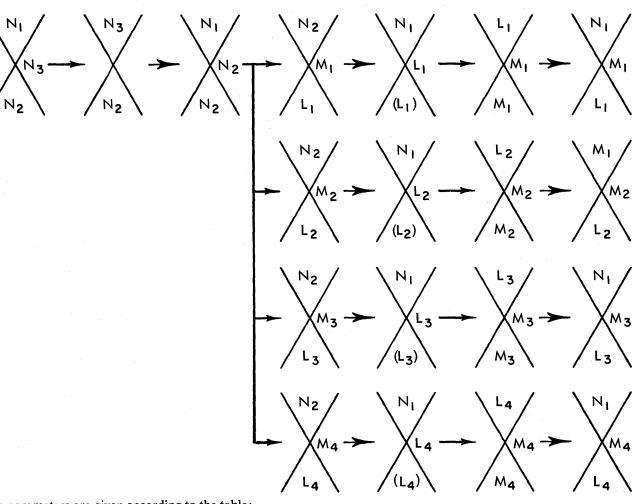

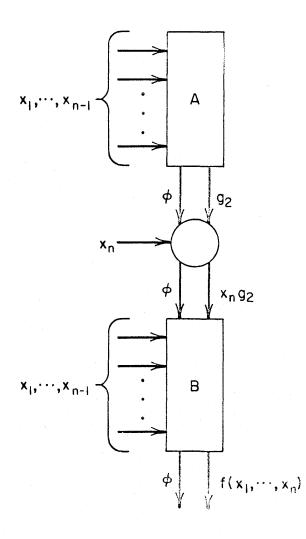

Universal Processors. Universal Processors can be designed under the restrictions of the previous paragraph and will be treated in the same order.

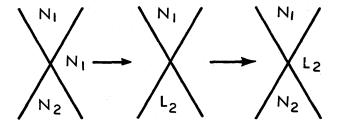

1. A scheme for a universal processor limited by restriction (1) could be derived as follows. If the processor is not dependent with the source language either on target or on the own language, then the source language part could be made exchangeable. As soon as one processor with this characteristic would be available, processors for all different source languages could be constructed running and translating for the same machines. By transforming another processor with the same characteristic according to:

processors could be written in all languages for which exchangeable definitions exist, and then translated to the designated machines. The task of writing  $2m \times n$  processors for *n* languages and *m* machines (there are only  $m \times n$  processors if the possibility of translation of programs on one machine for running on another machine is excluded) is now reduced to the writing of 2m processors or *m*, respectively) for the *m* machines and of *n* language descriptions for the *n* source languages.

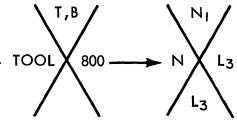

2. The case where the target language is considered independent of source and own language is even more interesting. Then target language descriptions for the machine could be developed and inserted into the processor to give a scheme for processors to translate for all machines.

Applying the same principle to the translation of processors could give a universal processor with any desired target and own language requirements:

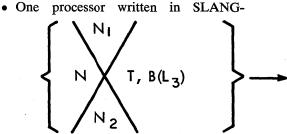

The requirements for a universal processor system would now be to write n processors for n source languages and m target language definitions for mmachines. These n processors would be written preferably in a high-level language ( $N_3$ ) for which a processor with the same characteristics for exchangeable target equivalents has been given already.

3. The case that source and target language are independent from the own processor language (al-

though they may depend on each other, case 1) would give a very powerful and general system. By the application of the scheme to itself, any desired own language and so a rather general universal processor scheme could be obtained:

The implementation requirements would now be to develop: one processor with removable source and target language equivalent parts in two copies, and the definitions for each pair of source-target languages, giving  $m \ge n$  definitions if they are dependent on each other (case 1) or m + n definitions if they are independent (case 2).

4. When all language parameters are independent, then we have the most general universal processor scheme. Of course, this brings not more solutions than could already be obtained in case 2. The requirements here would be to have one processor with the desired characteristics and m + n descriptions of source, target, and own languages.

Discussion. The schemes for universal processors described in the preceding section are outlined on the assumption that the language parameters of processors are independent of other variables and among themselves, at least to a certain degree. Some relationships among source, target and own language are known. But up to now it was never proved or disproved that perhaps they could be separated, and if so, under what conditions. It can be seen, for example, that between source and target language only a simple connective relationship exists, but the requirements then imposed on the own language were not yet evaluated.

The area of source languages is now fairly well understood, although the techniques are still not in the best conceivable state; much work is left to be done; some is going on and progressing satisfactorily. But knowledge of the others is very insufficient and incomplete.

Many investigations in the past were dedicated to the theory of automata. However, most results from these investigations are too general or of too low a level to be of great value to present-day computers with their variety of special hardware features. Only in the recent past some work was performed on models of more contemporary machines.<sup>29</sup>

As long as actual computers are not well understood there will not be much hope for very successful development of useful universal processors.

The following section describes the various reported projects for automated processor production and compares these to the described scheme of universal processors.

#### Projects for Universal Processors

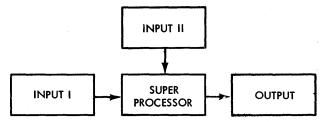

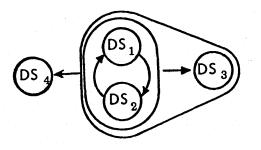

General Scheme and Survey. All literature uncovered in recent years regarding projects for proposals on universal processors fit into the same general scheme. There is always input I, consisting of a processor or its description, or the description of the source language. Input II is sometimes missing (in some cases of a processor description for I), or consists of specifications of the target language, and of a source program in interpretive cases in addition to that.

The different elements for input and the obtained output are summarized in Table 1.

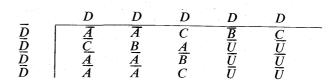

| Project                                   | Input I                                                                      | Input II                                                        | Resulting Processor                                   | Special Features                                                                          |

|-------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------|

| High-level and spe-<br>cial language use. | Processor written in high-<br>level or special processor<br>writing language |                                                                 | Processor in low-<br>level language                   | High-level languages ap-<br>plied to processor con-<br>struction                          |

| UNCOL                                     | Processor in UNCOL to translate to UNCOL                                     |                                                                 | Processor for UN-<br>COL on designed machine          | Reduction in number of processors required                                                |

| CLIP-JOVIAL                               | Processor in high-level<br>language                                          |                                                                 | Processor in low-<br>level for original<br>language   | "Boot-strapping"                                                                          |

| NELIAC                                    | Processor in high-level language                                             | —                                                               | Same as above                                         | Same as above                                                                             |

| XTRAN                                     | Processor in high-level<br>language (with connec-<br>tors?)                  | Target machine<br>macros                                        | Processor in low-<br>level for designated<br>language | Exchangeability of target language equivalent                                             |

| SLANG                                     | Processor in SLANG —<br>POLMI                                                | Target language de-<br>scription to generate<br>the equivalents | Same as above                                         | Generation of target<br>equivalents from a de-<br>scription                               |

| TOOL                                      | Processor in TOOL                                                            | Library of macros                                               | Same as above                                         | Translation for new ma-<br>chines                                                         |

| Syntax method                             | Language specification in terms of $M$                                       | Source program in L                                             | Target program in<br>M                                | Interpretive processor accepting language L specification                                 |

| TGS                                       | 1. Language specification<br>L                                               | 1. Macros for M                                                 | Same as above                                         | Interpretive processor<br>with extensive descrip-<br>tions and specifications             |

|                                           | 2. Generation statement tables for selection                                 | 2. Source program                                               | Processor in M                                        |                                                                                           |

| Meta A                                    | Description of language $L$ in terms of $M$                                  |                                                                 |                                                       | System written in specifi-<br>cation languages                                            |

| Meta B                                    | Description of language $L$ with connectors                                  | List of target equiv-<br>alents (macros)                        | Same as above                                         | System in specification<br>language separable for<br>given source and target<br>languages |

| Applicative<br>Expressions                | Description of $L$ in Applicative Expressions                                | Machine definition<br>in Applicative Ex-<br>pressions           | Same as above                                         | Same as above with Ap-<br>plicative Expressions as<br>specification language              |

Table 1.

Two different approaches can be distinguished, one starting with a processor or the description of a translation process and the other starting with definitions for the source language. The processorbased projects are generally the older ones, thus reflecting the progress in the field.

#### Processor Based Projects

1. High-Level or Special High-Level Language Use. To gain the advantages of programming using high-level languages (see Introduction "Experience with High-Level Programming Languages") in the construction of processors, projects based on this were tried rather early and often abandoned immediately. The main reasons were the inadequacies of high-level languages of those days (mainly FOR-

TRAN and ALGOL) for processor descriptions, and unfamiliarity with the new technique. To alleviate the difficulties special high-level languages were developed.<sup>33,34</sup> The scheme here is working like:

However, the gains by these projects for the construction of universal processors can be considered marginal, because the original number of processors required is not reduced and, in addition to that, one processor for the high-level description language is required for each machine. This scheme is reported only for the sake of completeness and because it is used heavily in other projects.

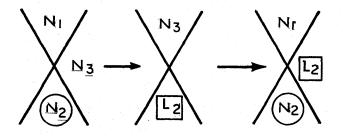

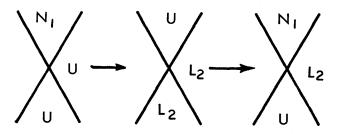

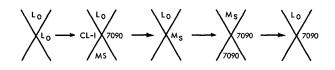

2. UNCOL. In this project the first suggestion for a system of some sort of a universal processor was given.<sup>22,29</sup> It calls for an intermediate language (see "Old Proposals" above) together with the appropriate processors. The requirements are here reduced to m + n processors for n languages and m machines, instead of  $m \times n$  (without translation of programs to run on other machines). For each source language a processor has to be written in UNCOL translating into UNCOL and then for each machine one translating into machine language. In the production process the processor (written in UNCOL) for the source language is translated by a processor from UNCOL to machine language:

All programs then written in source language  $N_1$  are translated by this new processor, running on machine with language  $L_2$ , into programs in UNCOL. These programs are then finally translated to machine language  $L_2$  by the translator from UNCOL to machine language  $L_2$  (already required above):

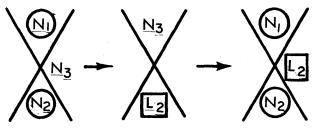

3. *CLIP-JOVIAL*. Very similar to both the UN-COL and high-level language project is basically the CLIP-JOVIAL approach. Several different versions are reported, one without intermediate language and another, more advanced, with it.<sup>35</sup> The diagram for the simpler version looks like:

Practically, the high-level language scheme where the source language is used for description with:

- $N_1$  the CLIP language (a dialect of AL-GOL 58 with additional features for table packing, string handling, storage overlapping, and local and global declarations)

- $N_2$  assembly language

- $L_2$  709 machine language

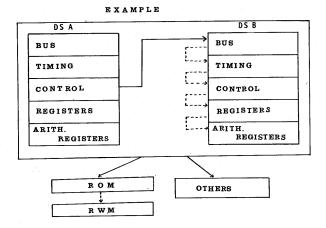

The more advanced version uses an interesting "bootstrapping" method for adapting the processors to different machines:

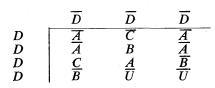

The parameters are given according to the table:

| NI     | N <sub>2</sub> | N3   | Lį    | L2     | L <sub>3</sub> | Lą         | MI  | M2   |

|--------|----------------|------|-------|--------|----------------|------------|-----|------|

| JOVIAL | INTERMEDIATE   | CLIP | 709-A | 2000-A | ANFSQ-A        | MILITARY-A | 709 | 2000 |

| M3    | Mg       |

|-------|----------|

| ANFSQ | MILITARY |

with the indication of -A after a computer name standing for assembly language for that machine, and the computer name alone standing for its machine language. The parameters  $(L_i)$  enclosed in parentheses indicate the insertion of the appropriate target language equivalents for the intermediate language  $N_2$  and the patching up for it. A processor is written in CLIP to translate from source to intermediate language and is itself translated by the CLIP processor into intermediate language. For each machine, a processor is now written for translation from intermediate to assembly language of that machine. With these processors, the former processor is translated into assembly language, and the target equivalent in intermediate language is exchanged for the one in assembly language. At last, the resulting processors are translated by the assemblers to the appropriate machines.

A universal processor scheme requires:

- One processor for each source language written in CLIP and translating to the intermediate language;

- One processor for each machine to translate from intermediate language to assembly language, the target equivalents for the intermediate language for patching up in the insertion;

- One CLIP processor for the intermediate language (and the assemblers for the different machines).

The main difficulty here is to design an intermediate language in a fixed form for many source languages (e.g., the UNCOL concept, see Section IIC).

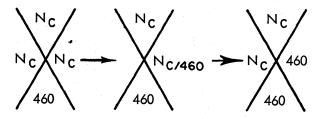

4. NELIAC. In NELIAC likewise the high-level language is used for the programming of the processors.<sup>36</sup> The most interesting feature here is the bootstrapping scheme to obtain the processors for different machines.<sup>37</sup> In the original version on the U460 (Countess), about 20 percent of the processor was handwritten and in machine language inserted into the processor (indicated by  $N_{C/460}$ ), after completion of writing the processor in its source language.

In the notation, symbols for the original names are retained as follows:

$\frac{N_C}{N_{709}}$ NELIAC for the Countess NELIAC for the 709

The NELIAC-Countess processor was produced with the patched-up processor:

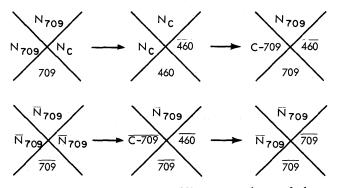

This version was used in the production of the processors for the B200, the CDC 1604, IBM 704 and the 709 machines according to the diagram for the 709:

For each machine, two different versions of the processors have to be written, one in the NELIAC language for the Countess and the other in the NELIAC language for the desired machine.

The procedure is to write a processor for a source language to a target language in a high-level language for which there is a compiler running on a machine. This processor is first translated to run on that machine. Then the processor is written in its source language and translated to its proper machine by the one already obtained. This process is the direct equivalent of the old assembler production method, which has been writing the assembler for a new machine first in an assembly language of a running machine and then translating it to run on this machine. The assembler was then again written, but in its source language and translated by the already obtained assembler to run on and translate for its proper machine.

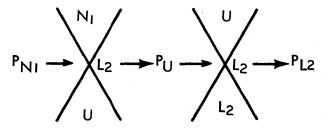

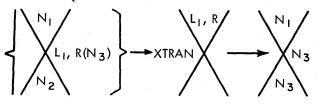

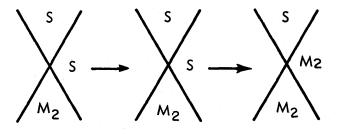

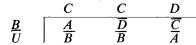

5. XTRAN. To adapt the processors for different source languages, the XTRAN system<sup>21</sup> accepts those written in a simplified version of ALGOL '58 with string handling facilities (XTRAN language) and the set of the macros for the particular machine. Two different sets of macros are used, one is machine-independent of the three-address type (as an intermediate language) and the other consists of the macros of an actual machine in assembly or machine language. The XTRAN system translates the processor for a source language into the machineindependent macros, accepts the definition of these macros in terms of the machine-dependent ones, and then replaces the former with the latter:

The requirements for a scheme of universal processors are:

- One processor for each source language written in XTRAN (L<sub>1</sub>)

- One set of machine-dependent macros for each machine

- The XTRAN system

Of course, the building up of the target equivalents from a machine description is usually a very difficult task, if in general possible at all. And the POL-MI language might not be definable in a fixed set. Therefore, it is not surprising that no further experience with this system is yet reported in the literature.

The requirements for a universal processor scheme using this system are:

In this case, the universal processor scheme would require: