# MICROVERTER SERIES

USER GUIDE

3629 W. MacArthur Blvd Suite 210 Santa Ana, CA. 92704 Phone: (714) 979-7893

#### MICROVERTER SERIES

USER GUIDE NUMBER: 10353X07

April 1985

ABLE Computer

3080 Airway Avenue

Costa Mesa, California 92626

(714) 979-7030

TWX 910-595-1729

#### (C) Copyright 1984 ABLE Computer

The material in this manual is for informational purposes and is subject to change without notice.

DEC, PDP, UNIBUS, RSX, and RSTS are trademarks of Digital Equipment Corporation.

# CONTENTS

| CHA P                                         | rer                     | 1                              | H                               | OW                       | TO                             | US                | ε                            | ТН               | IS              | MZ                    | MU   | JA I     | •       |     |            |   |                                 |

|-----------------------------------------------|-------------------------|--------------------------------|---------------------------------|--------------------------|--------------------------------|-------------------|------------------------------|------------------|-----------------|-----------------------|------|----------|---------|-----|------------|---|---------------------------------|

| CHAP                                          | rer                     | 2                              | T                               | HE                       | MIC                            | RC                | VE                           | RT               | ER              | SE                    | ER I | ŒS       | i       |     |            |   |                                 |

| 2.1                                           | GE                      | NER                            | AL                              | DE                       | SCF                            | RIP               | TI                           | ON               | •               | •                     | •    |          | •       | •   | •          | • | 2-1                             |

|                                               | 2.<br>2.<br>2.          | 1.1<br>1.2<br>1.3              | , ,<br>, ,                      | 4 IC<br>4 IC<br>4 IC     | ROV<br>ROV                     | /ER<br>/ER<br>/ER | TE<br>TE                     | R<br>R<br>R      | 73<br>PL:<br>BD | us<br>•               | •    | •        | •       | •   | •          | • | 2-2<br>2-5<br>2-7               |

| 2.2                                           | F E                     | a tu<br>Ec i                   | RES<br>FIC                      | S<br>Cat                 | 101                            | is                | •                            | •                | •               | •                     | •    | •        | •       | • . | •          | • | 2-9<br>2-11                     |

|                                               | 2.                      | 3. 2<br>3. 3                   | 1                               | Sen<br>Phy               | era<br>sic                     | l<br>al           | Sp<br>S                      | ec<br>Pe         | ifi<br>ci       | lca<br>Elc            | t i  | on<br>io | s<br>ns | •   | •          | • | 2-11<br>2-11<br>2-12<br>2-12    |

| 2.4                                           | F UT<br>H O             | NCT<br>V T                     | 101°                            | ia l<br>Js e             | DE<br>M I                      | SC<br>CR          | RI<br>OVI                    | PT<br>ER'        | IO:<br>Tef      | N.<br>R.              | •    | •        | •       | •   | •          | • | 2-1 3<br>2-1 4                  |

| CHA PI                                        | ER                      | 3                              | MI                              | CR                       | OVE                            | RT                | ER                           | 7                | 3 1             | CNS                   | TA   | LL       | ΑT      | 'IO | <b>k</b> . |   |                                 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | EQU<br>SOI<br>LS:<br>1- | JIP<br>TW<br>[-1<br>1EG<br>EIN | MEN<br>ARE<br>1/7<br>ABY<br>STA | IT<br>R<br>3<br>TE<br>LL | NEE<br>EQU<br>PRC<br>Q-<br>ATI | IR<br>CE<br>BU    | D.<br>Emi<br>SS(<br>SI<br>P! | ENT<br>OR<br>MEN | rs<br>10F       | ·<br>·<br>·<br>·<br>· | E    | •        | •       | •   | •          | • | 3-2<br>3-4<br>3-4<br>3-5<br>3-5 |

| 3.8                                           |                         |                                |                                 |                          |                                |                   |                              |                  |                 |                       |      |          |         |     |            |   |                                 |

| CHAPT                                                                       | ER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                             | MIC                                                     | CRO                                                 | VER                                           | TER                                    | PI                             | .US        | I   | NS | TA | ננ | TI  | :01 | 1 |                            |                                           |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------|----------------------------------------|--------------------------------|------------|-----|----|----|----|-----|-----|---|----------------------------|-------------------------------------------|

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11 | EQUISOR SOR INSTANTAL STATE OF THE PROPERTY OF | IP<br>TW<br>EINS<br>TA<br>I-1<br>RIF<br>I-1   | ARE<br>5 TA  <br>1 / 2  <br>1 / 2  <br>1 / 2  <br>1 / 7 | r Ni<br>REI<br>LLA'<br>FIOI<br>3 PI<br>FIOI<br>3 PI | CEDUI<br>TIO<br>N P<br>ROC<br>N.<br>PRO<br>N. | ED.<br>REM<br>N P<br>ROC<br>ESS<br>CES | ENT<br>ROC<br>EDI<br>OR<br>SOF | SEI<br>JRE | UR  | E  | •  | •  |     |     | • | 4                          | 4<br>2<br>3<br>4<br>4<br>1<br>1<br>2<br>7 |

| CHAP                                                                        | rer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                                             | MI                                                      | cro                                                 | VER                                           | TER                                    | В                              | <b>D</b> 1 | [NS | TA | LL | AΤ | IOI | 4   |   |                            | ,                                         |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11 | PRI<br>LS:<br>VEI<br>LS<br>VEI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ein<br>Sta<br>I-l<br>Rif<br>I-l<br>Rif<br>I-l | ICA<br>1/2<br>ICA<br>1/7                                | TIO<br>3 P<br>TIO<br>3+<br>TIO<br>3 P               | N E<br>ROC<br>N .<br>PRO<br>N .               | ESS                                    | ED<br>SOR<br>SOR               | URI        | E   |    | •  | •  | •   | •   | • | 5-<br>5-<br>5-<br>5-<br>5- | ·3<br>·4<br>·8<br>·11<br>·15              |

| CHAP                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |                                                         |                                                     |                                               |                                        |                                |            |     |    |    |    |     |     |   |                            |                                           |

| 6.1<br>6.2<br>5.3<br>6.4                                                    | GE<br>I/<br>MA<br>SO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NER<br>O M<br>PPI<br>FTW                      | AL<br>AP<br>NG<br>ARE                                   | REG<br>MA                                           | IS:                                           | ENA!                                   | S LE                           | EG         | :   | ·  | •  | •  | •   | •   | • | 6-<br>6-<br>6-             | -1<br>-5<br>-5                            |

| CHAPTER    | 7 SERVICING AND SUPPORT           |

|------------|-----------------------------------|

| 7.2 FOR    | RVICE                             |

| 7.3 FOR    | SERVICE OUTSIDE THE UNITED        |

| APPENDI    | X A BACKPLANE MODIFICATION        |

| A PPE NDI: | X B PATCHING RSTS/E V7.0 AND V7.1 |

| A PPENDI   | X C UNIBUS MEMORY                 |

| APPENDI    | X D INSTALLATION TROUBLESHOOTING  |

# LIST OF FIGURES

| Figure | 2-1  | MICROVERTER 73               | . 2-4        |

|--------|------|------------------------------|--------------|

| Figure | 2-1  | MICROVERTER PLUS             | . 2-5        |

| Figure |      | MICROVERTER Board            | . 2-8        |

| Figure |      | Barras Basulatas/Cansala     |              |

| •      |      | Interface Board              | . 2-1 Ø      |

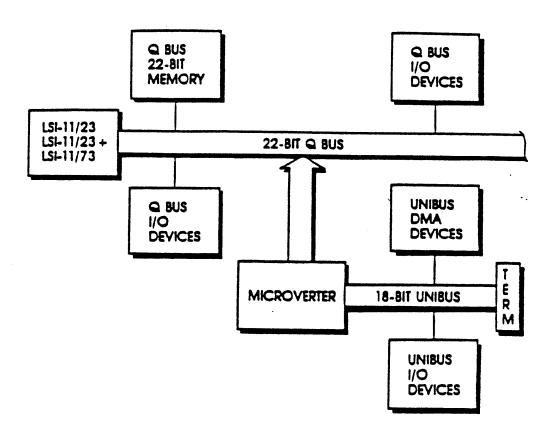

| Figure | 2-5  | System Block Diagram         | .2-l7        |

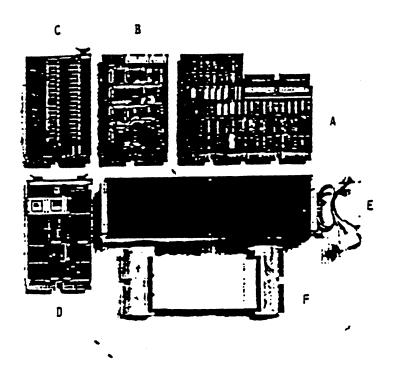

| Figure |      | MICROVERTER 73 Components    | . 3-3        |

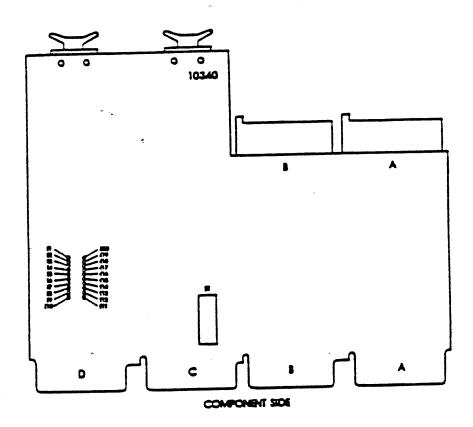

| Figure |      | MICROVERTER Board Layout     | 3-8          |

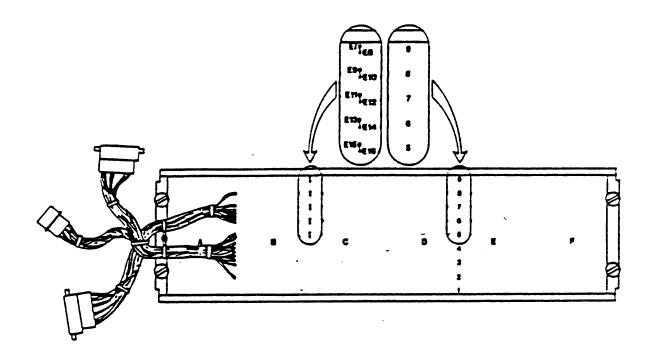

| Figure |      | NPG Jumpers                  |              |

| Figure |      | Installation of MICROVERTER  |              |

| •      |      | Backplane                    | 3-13         |

| Figure | 3-5  | UNIBUS and Front Panel       | •            |

|        |      | Interface Cables             | 3-15         |

| Figure | 3-6  | MICROVERTER 73 Configuration | 3-21         |

| Figure |      | MICROVERTER Backplane Layout | 3-22         |

| Figure |      | MICROVERTER Board Layout     | 4-6          |

| Figure |      | NPG Jumpers                  | 4-9          |

| Figure |      | Installation of MICROVERTER  |              |

| , , ,  |      | Backplane                    | 4-11         |

| Figure | 4 -4 | UNIBUS and Front Panel       |              |

| ,      |      | Interface Cables             | 4-13         |

| Figure | 4 -5 | MICROVERTER PLUS             |              |

|        |      | Configuration                | 4-16         |

| Figure | 4 -6 | MICROVERTER Backplane Layout |              |

| Figure |      | Modification to LSI-11/23+   |              |

| . ,    |      |                              | 4-20         |

| Figure | 4 -8 | Modification to LSI-11/73    |              |

| ,      |      |                              | 4-31         |

| Figure | 4-9  | LSI-11/73 Processor Board    |              |

| 3      | -    |                              | 4-32         |

| Figure | 5-1  |                              | 5-5          |

| Figure |      |                              | 5-10         |

| Figure | 5-3  | Modification to LSI-11/23+   | <del>-</del> |

| - ,    |      | Processor                    | 5-13         |

| 4          |                                       |

|------------|---------------------------------------|

| Figure 5-4 | LSI-11/73 Processor Board             |

|            | Temporary Modification 5-20           |

| Figure 5-5 | LSI-11/73 Processor Board             |

|            | Permanent Modification 5-21           |

| Figure 6-1 |                                       |

| Figure 6-2 | · · · · · · · · · · · · · · · · · · · |

| Figure 6-3 | •                                     |

| ,          | Status Register 6-6                   |

| Figure D-1 |                                       |

| ,          |                                       |

|            |                                       |

|            |                                       |

|            | LIST OF TABLES                        |

|            | LIST OF TABLES                        |

|            | •                                     |

| m-1-63     | T/O Man Bandahan lilinasaina ( A      |

| Table 6-1  | I/O Map Register Addressing6-4        |

| Table C-1  | I/O Map Lower Limit Jumpers . C-3     |

| Table C-2  | I/O Map Upper Limit Jumpers . C-4     |

|            | Ty Table 19 Page 1 and 1 and 1        |

#### CHAPTER 1

#### How To Use This Manual

Congratulations on your purchase of a MICROVERTER SERIES product from ABLE Computer. We are sure that it will provide you with years of satisfactory service. We have prepared this manual to help you maximize the effectiveness of this product in your system.

This manual is provided to assist you with the installation, use and care of your MICROVERTER product. Repair information is not provided; if repair is ever needed, the work should be performed at the ABLE factory.

This manual is organized into the following chapters:

- \* Chapter 2 provides a general description, a functional description and a list of the primary features of MICROVERTER products. It also includes electrical, physical, and environmental specifications and a description of the use of the device.

- \* Chapter 3 contains the installation procedure for MICROVERTER 73.

- \* Chapter 4 .contains the installation procedure for MICROVERTER PLUS.

- \* Chapter 5 contains the installation procedure for MICROVERTER BD.

- \* Chapter 6 contains programming information, which includes information on the I/O map registers, the clock status register, and the software Map Enable.

- \* Chapter 7 contains information on servicing and support.

- \* Appendix A contains directions for modifying a backplane for 22-bit Q-Bus addressing.

- \* Appendix B contains patching information to allow RSTS/E V7.0 and V7.1 to operate with 22-bit parity memory.

- \* Appendix C contains directions for addressing UNIBUS memory for use with MICROVERTER.

- \* Appendix D contains installation troubleshooting information.

The following publications are delivered with MICROVERTER 73:

- \* DEC LSI-11/73 User Guide

- \* User guide for 1-Megabyte Q-Bus Memory

To understand the contents of this manual, you should be familiar with the PDP-11 UNIBUS

and LSI-11 Q-Bus architectures. For information on these architectures, refer to the following DEC documents:

- \* Microcomputers and Memories Handbook

- \* PDP-11 Bus Handbook

- \* PDP-11 Terminals and Communications

Handbook

These manuals are available from DEC either by placing an order by telephone, or by mail. The following information has been supplied by DEC for your convenience:

#### BY TELEPHONE:

| FROM                               | CALL             |

|------------------------------------|------------------|

| New Hampshire,<br>Alaska or Hawaii | . (603) 884-6660 |

| Continental U.S.A. or Puerto Rico  | . (800) 258-1710 |

| Canada (Ottawa-Hull)               | . (613) 234-7726 |

| Canada (British Columbia)          | . (800) 267-6146 |

| Canada (All other)                 | . (800) 267-6146 |

#### BY DIRECT MAIL:

# FROM U.S.A OR PUERTO RICO:

DIGITAL EQUIPMENT CORPORATION

Attn: Accessories and Supplies Center

P.O. Box CS2008

Nashua, NH 03061

#### FROM CANADA:

DIGITAL EQUIPMENT OF CANADA, LTD.

940 Belfast Road Ottawa, Ontario KlG 4C2 Attn: ASG Business Manager

# FROM ANY OTHER AREA:

DIGITAL EQUIPMENT CORPORATION

Accessories and Supplies Center

ASG Business Manager

c/o Digital's local subsidiary or

approved distributor

#### CHAPTER 2

#### THE MICROVERTER SERIES

#### 2.1 GENERAL DESCRIPTION

There are three products in the ABLE MICROVERTER SERIES:

- \* MICROVERTER 73, a complete product for upgrading a PDP-11/34 (or similar system) to LSI-11/73 performance. MICROVERTER 73 includes an LSI-11/73 processor and Q-Bus memory, has its own backplane, and is installable in a PDP-11/34 system chassis.

- \* MICROVERTER PLUS, similar in function to MICROVERTER 73 but supplied without an LSI-11 processor and Q-Bus memory. These are supplied by the user. MICROVERTER PLUS is compatible with LSI-11/23, -11/23+, and -11/73 processors.

- \* MICROVERTER BD, a single-board product which allows UNIBUS peripheral device controllers to be coupled to the Q-Bus of an LSI-ll system. MICROVERTER BD is installable in an

LSI-11 system backplane, and is compatible with the LSI-11/23, -11/23+, and -11/73 processors.

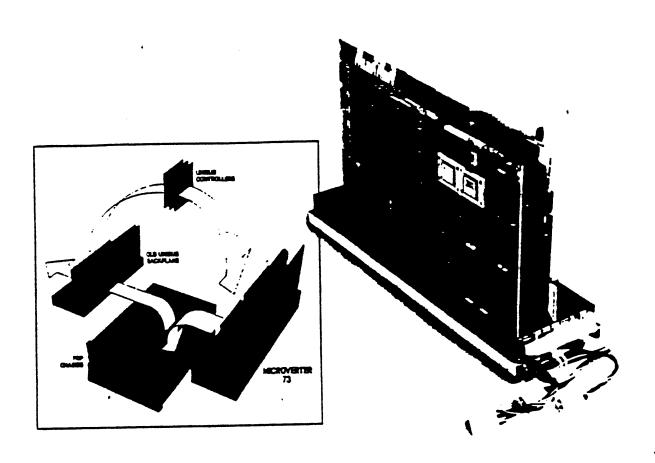

#### 2.1.1 MICROVERTER 73

MICROVERTER 73 is a Q-Bus to UNIBUS converter which upgrades a PDP-11/34 computer system to LSI-11/73 performance. The PDP-11 processor and UNIBUS memory are replaced with an LSI-11/73 processor and 1 megabyte of Q-Bus memory. MICROVERTER 73 is shown in Figure 2-1.

MICROVERTER 73 consists of the following:

- \* ABLE MICROVERTER board

- \* ABLE power regulator/console interface board

- \* DEC 1-megabyte Q-Bus memory board

- \* DEC LSI-11/73 processor board (modified)

- \* ABLE hybrid (Q-Bus and UNIBUS) backplane

- \* UNIBUS cable

- \* Optional front panel interface cable (for use with KY11-LA front panel).

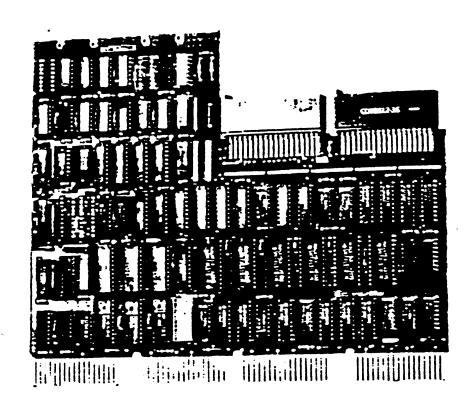

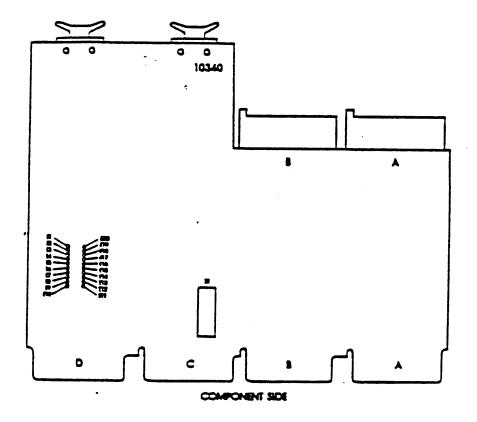

The MICROVERTER board is a quad-width board (shown in the photograph of Figure 2-3) which performs the following principal functions:

- \* Serves as a Q-Bus to UNIBUS converter.

- \* Increases the addressing capability of

UNIBUS DMA controllers from 256K bytes up to 4 megabytes on the Q-Bus.

\* Provides a KW11-L compatible line time clock.

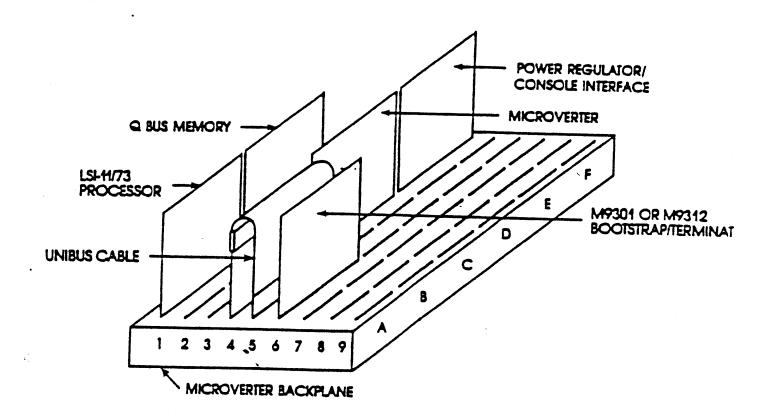

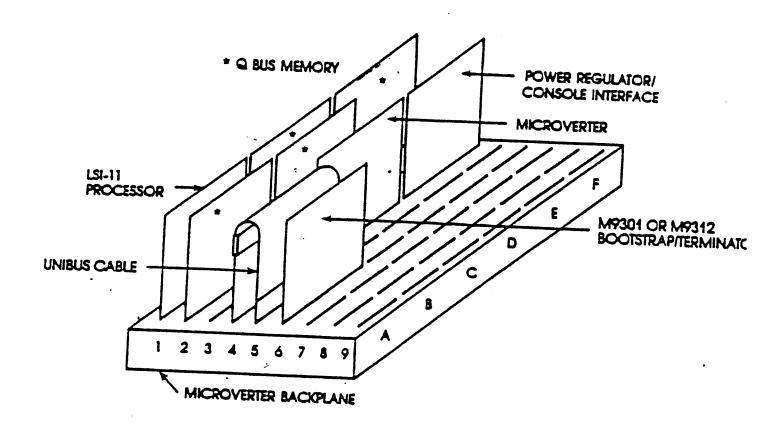

The MICROVERTER backplane is a 9-slot backplane with four slots (1 through 4) configured as Q-Bus slots and five slots (5 through 9) configured as UNIBUS slots. The MICROVERTER board must be installed in slot 4, sockets A through D, of this backplane.

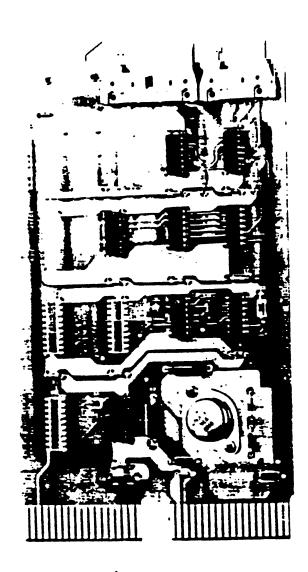

The power regulator/console interface is a dual-width board which provides PDP-11/34 front panel bootstrap and control functions, receives the line time clock signal, and receives +15 volts from the UNIBUS and regulates it to +12 volts for the Q-Bus. The power regulator/console interface board must be installed in slot 4, sockets E and F, of the special backplane. This board is shown in Figure 2-4.

Figure 2-1: MICROVERTER 73

#### 2.1.2 MICROVERTER PLUS

MICROVERTER PLUS consists of MICROVERTER 73 without the LSI-11/73 processor and the Q-Bus memory. Like MICROVERTER 73, MICROVERTER PLUS is installable in a PDP-11/34 computer system. However, with MICROVERTER PLUS, the supplies the LSI-11 processor and Q-Bus memory. MICROVERTER PLUS is compatible with the LSI-11/23+, and LSI-11/73 LSI-11/23, The LSI-11/23+ processor board processors. requires a simple modification for use with MICROVERTER PLUS. The LSI-11/73 processor requires modification using a cable supplied with the product by ABLE Computer.

MICROVERTER PLUS is shown in Figure 2-2. The MICROVERTER board is shown in Figure 2-3.

Figure 2-2: MICROVERTER PLUS

#### 2.1.3 MICROVERTER BD

MICROVERTER BD consists of the MICROVERTER board only, and is installable in a Q-Bus backplane. This allows UNIBUS peripheral devices to be coupled to the Q-Bus and use Q-Bus memory.

MICROVERTER BD is compatible with the LSI-11/23, LSI-11/23+, and LSI-11/73 processors. The LSI-11/23+ processor requires a simple modification for use with MICROVERTER BD, and the LSI-11/73 processor requires modification using a cable supplied with the product by ABLE Computer.

With MICROVERTER, the LSI-11 processor, Q-Bus memories, and Q-Bus interrupt devices reside on the Q-Bus. 18-bit UNIBUS DMA device controllers and UNIBUS interrupt devices reside on the UNIBUS. The 18-bit addresses of NPR devices are mapped through the MICROVERTER onto the 22-bit Q-Bus.

MICROVERTER is installable in a quad slot of an LSI-11 backplane and interfaces to the Q-Bus via the A and B connectors on the board. Two UNIBUS connectors on the MICROVERTER provide connection to a UNIBUS cable (supplied with MICROVERTER 73 and MICROVERTER PLUS). MICROVERTER provides one end of UNIBUS termination.

Figure 2-3: MICROVERTER Board

#### 2.2 FEATURES

MICROVERTER SERIES products provide the following significant features:

- \* LSI-11/23, LSI-11/23+, and LSI-11/73 systems are supplied with the I/O mapping capability of PDP-11/44 or PAX-enhanced PDP-11/24 computers with up to 4 megabytes of main memory fully available for optimization of CPU, Q-Bus and/or UNIBUS operations.

- \* A line time clock (LTC) function to maintain software compatibility with existing operating systems.

- \* I/O map (IOM) functions providing software-compatible 4-megabyte addressing for 18-bit UNIBUS DMA devices.

- \* Supports the addition of up to 19 UNIBUS loads to any existing LSI-11/23 system.

- \* Front-end UNIBUS termination.

- \* Special memory implementations, such as UNIBUS bus window and UNIBUS dual port memory, are allowed.

- \* Software compatible with current versions of RSTS/E and RSX-11M (with no Q-Bus DMA devices present).

Figure 2-4: Power Regulator/Console Interface Board

# 2.3 SPECIFICATIONS

### 2.3.1 Electrical Specifications

# MICROVERTER 73

# Q-Bus Loading

| MICROVERTER | 1 DC | bs al |

|-------------|------|-------|

| LSI-11/73   | 1 DC | Lo ad |

| 1 MB memory | 1 DC | Lo ad |

Drive Capability 19 UNIBUS loads

# Power Requirement

| MICROVERTER       | 5.1 amps @ +5V                                |

|-------------------|-----------------------------------------------|

| 1 MB memory       | 2 amps @ +5V                                  |

| LSI-11/73         | 4.5 amps @ +5V                                |

| Power regulator/  |                                               |

| console interface | 4 amps @ +12V<br>(power supplied<br>to Q-Bus) |

#### 2.3.2 General Specifications

Priority Level LTC has fixed interrupt level of 6.

Vector Setting LTC has fixed vector setting of 100 (octal).

#### 2.3.3 Physical Specifications

MICROVERTER board Std. quad-width board, measuring 10.45" x 8.40" (26.54 x 21.33 cm)

Power regulator/ Std. dual-width board, console interface measuring 5.2" x 8.4" (13.2 x 21.3 cm)

Backplane 9-slot hex-width backplane: 4 Q-Bus slots 5 UNIBUS slots

LSI-11/73 Std. dual-width board, measuring 5.2" x 8.4" (13.2 x 21.3 cm)

1 MB memory Std. dual-width board, measuring 5.2" x 8.4" (13.2 x 21.3 cm)

#### 2.3.4 Environmental Specifications

Operating 5 C to 40 C Temperature (41 F to 104 F).

Derate max. temperature by one degree Calsius for each 1,000 feet above 8,000.

Storage -40 C to 65 C Temperature (-40 F to 149 F)

Rel. Humidity 10 to 90% noncondensing

Altitude To 15,000 feet

# 2.4 FUNCTIONAL DESCRIPTION

MICROVERTER converts accesses on the Q-Bus into UNIBUS accesses. Q-Bus lines BDAL18 through BDAL21 and BBS7 are monitored for addresses in the range 3840K to 4096K bytes. Master sync (MSYNC) is asserted onto the UNIBUS only for accesses in that range.

Interrupt cycles on the UNIBUS are converted into interrupt cycles on the Q-Bus at the same level. For example, BR4 is converted to BIRQ4. MICROVERTER adheres to the position-independent priority rules of the Q bus. There are four interrupt request levels implemented on the For position independent operation, Q-Bus. each device must monitor bus interrupt requests so that when an interrupt acknowledge is received the device checks for interrupt levels higher than itself. If a higher interrupt request is received, the device does not accept the interrupt acknowledge, but passes it on to the next device.

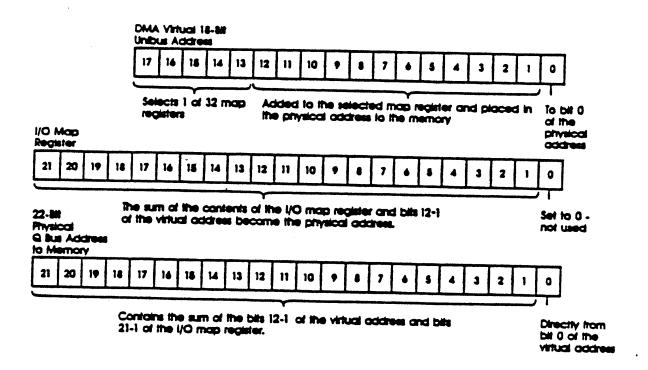

DMA cycles on the UNIBUS are converted to DMA cycles on the Q-Bus. This includes mapping from 18-bit UNIBUS addresses to 22-bit Q-Bus addresses. BSYNC is asserted on the Q-Bus only for UNIBUS addresses in the range Ø to 256K bytes. When memory must be placed on the UNIBUS, a window within this range can be excluded in 8K-byte increments between Ø and 256K bytes via upper and lower limit jumpers on the MICROVERTER board. When a DMA cycle addresses I/O address space 124K to 128K words, the I/O map function is disabled and the UNIBUS address is asserted onto the Q-Bus, with BBS7 also asserted.

Mapping of UNIBUS DMA devices is enabled by

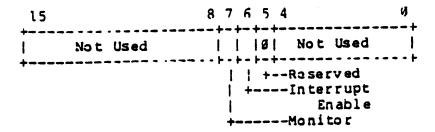

setting bit 5 of Status Register 3 in the Memory Management Unit of the LSI-11/23, LSI-11/23+, or LSI-11/73 processor.

A programmable line time clock (LTC) is provided on the MICROVERTER board. When interrupts are enabled in its CSR, an interrupt to 100 (octal) is generated at BR6 for every clock tick. The clock signal is received from the BEVNT line of the Q-Bus. This line is generally sourced by the power supply, but may also be generated by a bootstrap board. The frequency is generally 50 or 60 Hz. The LTC can be disabled by opening a switch on the MICROVERTER board. If the LTC is used, the BEVNT interrupt of the LSI-11/23 processor must be disabled. If an LSI-11/23+ or an LSI-11/73 processor is used, the LTC must be disabled.

The power regulator/console interface has a jumper which determines whether the 60 Hz timing signal for LTC operation is to be supplied by the UNIBUS or by the bootstrap board.

# 2.5 HOW TO USE MICROVERTER

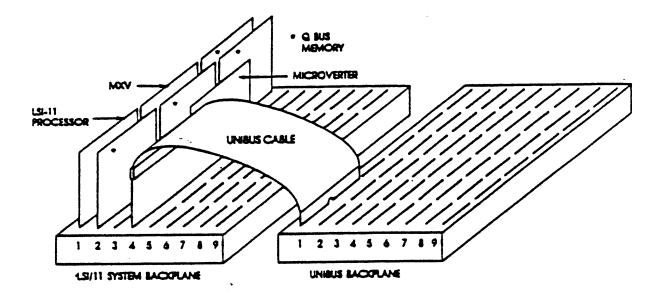

MICROVERTER SERIES products allow the wide range of PDP-11 UNIBUS peripherals to address up to four megabytes of Q-Bus memory. In the MICROVERTER 73 and MICROVERTER PLUS configurations, the MICROVERTER board must be installed in slot 4 (connectors A, B, C, and D) of the hybrid MICROVERTER backplane. In the MICROVERTER BD configuration (MICROVERTER board only), the MICROVERTER board can be installed in any quad slot of an LSI-11/23, LSI-11/23+, or LSI-11/73 system backplane. LSI-11

interfaces can be located either ahead of or behind the MICROVERTER. Devices located behind MICROVERTER have a lower priority than UNIBUS devices of the same level attached to the MICROVERTER. A typical MICROVERTER system block diagram is shown in Figure 2-5.

UNIBUS peripheral controller boards installed in a UNIBUS backplane, which must be supplied with the appropriate power. With MICROVERTER 73 and MICROVERTER PLUS, five UNIBUS slots are provided in the hybrid backplane, and the MICROVERTER board is connected via a UNIBUS cable to the first INIBUS slot of the backplane. With MICROVERTER BD, the UNIBUS backplane is connected to the MICROVERTER board with a standard UNIBUS extender cable connected between the first UNIBUS connectors in the UNIBUS backplane and the connectors at the top of the MICROVERTER board. In all MICROVERTER configurations, a UNIBUS terminator must be installed in connectors A and B of the last slot of the last UNIBUS backplane.

MICROVERTER provides the LSI-11 system with a second bus structure, UNIBUS. The LSI-11 processor controls the arbitration of both buses.

All 18-bit DMA devices must be installed on the UNIBUS. This permits 18-bit DMA addresses to be mapped through the MICROVERTER to form 22-bit addresses. MICROVERTER's "window" feature allows memory to be placed on the UNIBUS. This feature is used when an area of UNIBUS is used for special memory, such as multi-port memory or a bus window.

· • • •

#### NOTE

Due to software limitations, ABLE does not recommend installation of Q-Bus 22-bit DMA devices with MICROVERTER, which would require the application of customer-supplied patches to the operating system.

Figure 2-5: System Block Diagram

#### CHAPTER 3

#### MICROVERTER 73 INSTALLATION

#### 3.1 GENERAL

This chapter contains procedures for installing the ABLE MICROVERTER 73 in a PDP-11/34 computer system. MICROVERTER 73 is compatible with a number of other PDP-11 systems; however, the detailed procedures given here apply to the PDP-11/34 (and /34A). If you are installing MICROVERTER 73 in any other PDP-11 system, some details may be different. In such cases, change the procedure as required to suit the particular system.

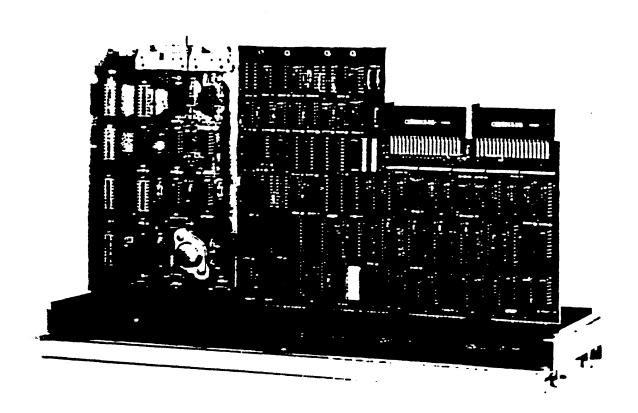

MICROVERTER 73 consists of the following components (the letter following each component indicates its label in Figure 3-1):

- \* ABLE MICROVERTER board (A)

- \* ABLE power regulator/console interface board (B)

- \* 1-Megabyte Q-Bus memory board (C)

- \* DEC LSI-11/73 processor board, modified for use with MICROVERTER (D)

- \* ABLE special MICROVERTER backplane (E)

- \* UNIBUS cable (F)

- \* Optional front panel interface cable.

MICROVERTER 73 is delivered with the following documentation:

- \* MICROVERTER Series User Guide, ABLE Number 18353X87

- \* LSI-11/73 Processor user guide

- \* Q-Bus Memory user guide.

#### 3.2 EQUIPMENT NEEDED

Other than the PDP-11/34 system, no additional equipment is required to install and operate MICROVERTER 73. (However, additional Q-Bus memory modules can be added optionally, to a maximum of four megabytes.)

Figure 3-1: MICROVERTER 73 Components

# 3.3 SOFTWARE REQUIREMENTS

MICROVERTER 73 adds UNIBUS Mapping Registers (UMRs) to the Q-Bus system to give 18-bit UNIBUS devices access to 22-bit Q-Bus address space. The operating system must include software to handle UMRs. For example, RSX can be conditioned by being configured for operation on a PDP-11/44 computer. Other operating systems may need to be conditioned appropriately.

DEC operating systems RSTS/E V7.0 and V7.1 require patching to make them operate correctly with 22-bit parity memory. INIT 7.0 does not initialize the entire memory when run on a 22-bit system, and this can cause problems for RSTS/E after a power-up, due to random data and parity left in memory. See Appendix B for patches which allow INIT to correct all parity bits.

#### 3.4 LSI-11/73 PROCESSOR

Configuration procedures for the LSI-11/73 processor board are given in the DEC LSI-11/73 user guide. When using either the DEC M9301 or M9312 bootstrap/terminator, set the processor to the micro-ODT power-up mode. Then enter the desired starting address and the micro-ODT command "G" for execution. Starting addresses (octal) are:

M9301 17773000

M9312 with diagnostics 17765020

M9312 without diagnostics 17765144

# 3.5 1-MEGABYTE Q-BUS MEMORY

Configuration procedures for the 1-megabyte memory board are given in the memory user guide delivered with MICROVERTER 73.

#### 3.6 PREINSTALLATION PROCEDURE

Before beginning installation, all components should be unpacked and inspected, as follows:

### STEP 1. Unpack Components

Verify that the correct equipment has been received by checking product numbers. Product numbers are:

| MICROVERTER board                    | 10340000    |

|--------------------------------------|-------------|

| MICROVERTER backplane                | 10341000    |

| Power regulator/console interface    | 10342000    |

| UNIBUS cable                         | 538-000-001 |

| DSI-11/73 processor assembly         | 10377000    |

| 1-MB Q-Bus memory                    | 920-810-888 |

| Optional front panel interface cable | 90000666    |

| MICROVERTER Series<br>User Guide     | 10353X07    |

| LSI-11/73 User Guide                 | xxxxxxx     |

1-Megabyte memory user guide

xxxxxxx

If your shipment is not complete and correct, notify the ABLE factory immediately.

#### STEP 2. Inspect Components.

- a. Inspect components for damage: if damage is detected, notify the carrier.

- b. Save the protective containers used to ship MICROVERTER 73 for possible future use.

# , 3.7 INSTALLATION PROCEDURE

The detailed procedures given in this chapter are correct for the PDP-11/34 and PDP-11/34A computer systems. MICROVERTER 73 is compatible with and can be installed in many other PDP-11 systems. However, variations in the construction of some systems may require differences in the detailed procedures for installing MICROVERTER 73. In such cases, the intent of the procedure should be followed rather than the exact procedure itself. For special problems, call the ABLE Support Services department (see Chapter 7).

# STEP 1. Set MICROVERTER Switches

Set switches S1-1 through S1-10 on the MICROVERTER board as shown here.

Switch Sl is shown in Figure 3-2.

"C" = CLOSED (ON), "-" = OPEN (OFF)

# STEP 2. Configure MICROVERTER for memory resident on UNIBUS (optional).

If the application requires the use of memory resident on the UNIBUS, configure the MICROVERTER board appropriately, using the procedure given in Appendix C.

# STEP 3a. Remove NPG jumpers from backplane for DMA operation.

a. Determine the slots in the backplane which are to be used for DMA controllers.

b. Remove the NPG jumper from each of these slots. In the MICROVERTER backplane, these jumpers are located at E points adjacent to connector C, as shown in Figure 3-3.

| Slot number | Jum per |    |     |  |  |  |  |

|-------------|---------|----|-----|--|--|--|--|

| 5           | E15     | to | E16 |  |  |  |  |

| 6           | E13     | to | E14 |  |  |  |  |

| 7           | E11     | to | E12 |  |  |  |  |

| 8           | E9      | to | Elø |  |  |  |  |

| ā           | F7      | to | FR  |  |  |  |  |

Figure 3-2: MICROVERTER Board Layout

If a DMA controller is to reside in a UNIBUS backplane other than the MICROVERTER backplane, NPG jumpers CAl to CB1 must be removed from the appropriate slot. Consult the backplane manufacturer's documentation for the procedure.

## STEP 3b. Remove IAK and DMG jumpers from backplane for Q-Bus I/O operation.

This step is required only if a Q-Bus I/O controller is to be installed in the MICROVERTER backplane.

IAK (Interrupt Acknowledge) and `DMG (DMA Grant) jumpers are installed in the MICROVERTER backplane as follows:

| Slot Number | Connectors |

|-------------|------------|

| 1           | C, E       |

| 2           | A, C, E    |

| 3           | A, C, E    |

In each of these connectors, the IAK jumper is across pins M2 and N2, and the DMG jumper is across pins R2 and S2.

If a Q-Bus I/O controller is to reside in any of these slots, remove these jumpers from the associated connectors. (The jumpers are soldered to the pins.)

## STEP 4. Select source of 60 Hz timing signal for LTC operation.

If the 60 Hz signal for the LTC is to be supplied by the UNIBUS via the power

regulator/console interface board, install a jumper across El and E2 on the power regulator/console interface board. See Figure 2-4 for location of E1-E2.

If the 68 Hz signal for the LTC is to be supplied by a Q-Bus board, verify that E1-E2 on the power regulator/console interface board is left open (i.e., no jumper).

### STEP 5. Remove boards from PDP-11 backplane.

- a. Turn off power to the PDP-11 system.

- b. Pull out the drawer containing the system.

- c. Locate the backplane containing the PDP-11/34 processor.

- d. Locate the cable connecting front panel with the interface board. Determine whether the cable is connected to the top of the interface board (PDP-11/34A, with keypad on front panel), or to the backplane (PDP-11/34, with no keypad on front panel). If the cable is the top of connected to interface board, disconnect the cable from the interface board but leave it connected to the front panel. If the cable is connected to the backplane, remove the cable from the interface board and from the front panel.

Figure 3-3: NPG Jumpers

- e. Remove all boards from the processor backplane.

- f. If the processor backplane is connected to the next backplane, disconnect the UNIBUS connecting cable from the processor backplane.

Leave the cable connected to the next backplane.

### STEP 6. Remove PDP-11 backplane from system.

- a. Actuate the drawer release and swing the drawer up to expose the wirewrap side of the backplane.

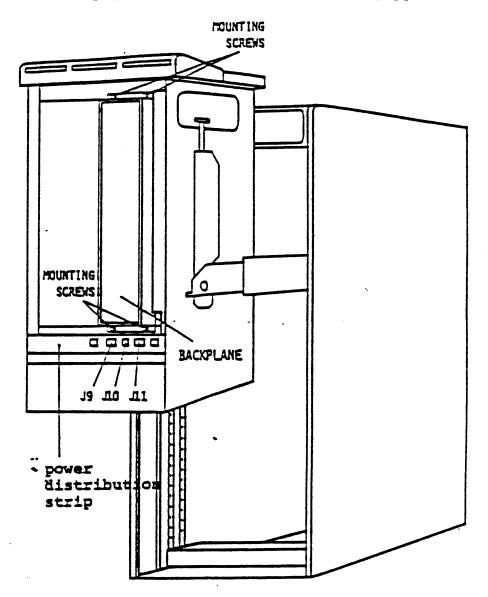

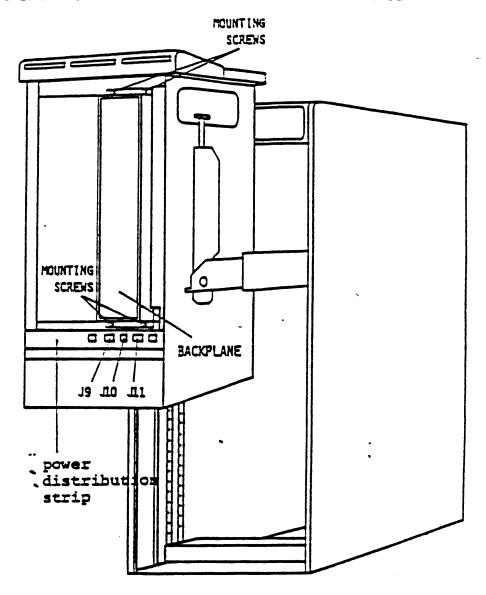

- b. Figure 3-4 is a view of the wirewrap side of the backplane showing the mounting screws and cable connectors. The cables are not shown.

- c. Disconnect the backplane from the power distribution strip.

- d. Unscrew the four mounting screws holding the backplane to the enclosure.

- e. Remove the PDP-11 backplane from the system.

Figure 3-4: Installation of MICROVERTER Backplane

### STEP 7. Install the MICROVERTER Backplane.

- a. Place the MICROVERTER backplane in the space left by the PDP-11 backplane.

- b. Secure the backplane in place with the four captive mounting screws.

- c. Connect the backplane to the power distribution strip.

- d. Swing the drawer back to its horizontal position.

### STEP 8. Insert MICROVERTER Board

Insert the MICROVERTER board into slot 4 of the backplane, using sockets A through D. Insert the board so that the component side faces slot 1 of the backplane (to the right).

### STEP 9. Connect UNIBUS Cable.

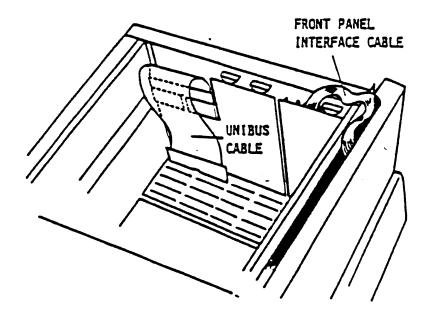

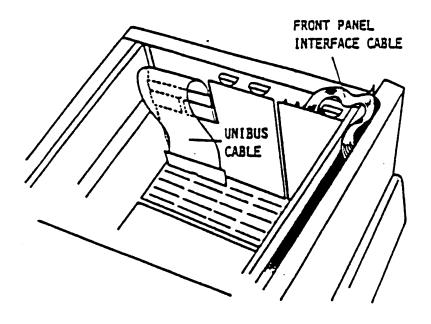

- a. Attach one end of the UNIBUS cable (the one supplied with MICROVERTER 73) to connectors A and B at the top of the MICROVERTER board. (See Figure 3-5).

- b. Insert the other end of the UNIBUS cable into slot 5 of the backplane, using sockets A and B.

Figure 3-5: UNIBUS and Front Panel Interface Cables

## STEP 18. Insert Power Regulator/Console Interface Board

Insert the power regulator/console interface board into slot 4 of the backplane, using sockets E and F. Insert the board so that the component side faces slot 1 of the backplane.

(The power regulator/console interface board and the MICROVERTER board should now be side by side in slot 4 of the backplane.)

### STEP 11. Insert LSI-11/73 Processor Board

Insert the LSI-11/73 processor board into slot 1 of the backplane, using sockets A and B. Insert the board so that the component side faces the near edge of the backplane. There is a cable attached to the processor board; it passes through a strain-relief tie at the top of the board and terminates in a 4-pin connector. Plug this connector into the 4-pin socket at the top of the MICROVERTER board.

### STEP 12. Insert Memory Board

Insert the 1-megabyte memory board into slot 1 of the backplane. For a dual-width board, use sockets C and D; for a quad-width board, use sockets C, D, E, and F. Insert the board so that the component side faces the near edge of the backplane. (Processor and memory are now side by side in slot 1 of the backplane.)

## STEP 13. Insert Additional Memory Boards (If Any)

If additional Q-Bus memory boards are to be installed in the system, insert them into slot 2 of the backplane. Insert the boards so that the component side of each board faces slot 1 of the backplane.

# STEP 14. Connect Front Panel to Power Regulator/Console Interface Board (See Figure 3-5.)

- a. Determine the front panel type. If the front panel has two toggle switches, it is a (KY11/LA). If it has a group of pushbuttons, it is a KY11/LB.

- b. If you have the KY11/LA front panel:

locate the optional front panel

interface cable supplied with

MICROVERTER 73 (part number

90000666) and use this cable to

connect J1 of the front panel to J2

of the power regulator/console

interface board. Make this

connection pin 1 to pin 1.

- c. If you have the KY11/LB front panel: using the existing front panel interface cable, connect one end of the cable to the front panel, and plug the other end into connector J1 of the power regulator/console interface board. Make this connection pin 1 to pin 20.

(In Figure 3-5, the cable is shown

connected to J1 of the power regulator/console interface board, as it would be for a KY11-LB front panel.)

## STEP 15. Install PDP-11 Boards in MICROVERTER Backplane.

- a. If the PDP-11 backplane (removed earlier) was connected to the next backplane, insert the connecting UNIBUS cable into slot 9 of the MICROVERTER backplane, using sockets A and B.

- b. Retrieve the circuit boards removed from the PDP-11 backplane.

- c. Set aside the PDP-11 processor boards, the front panel interface board, and memory boards; they will not be used. (They are replaced by the LSI-11/73 processor board, the MICROVERTER power regulator/ console interface board, and the Q-Bus memory board.)

- d. Insert the remaining boards into the MICROVERTER backplane, using slots 5 through 9. (Note: you should have removed the NPG jumpers from slots to be used for DMA devices.)

- e. Insert the existing DEC M9301 or M9312 bootstrap/terminator in slot 6, connectors A and B, for the front-end termination of the UNIBUS. NOTE: Do not connect the bootstrap cable to the M9301 or M9312, because booting is provided through the

LSI-11/73 processor.

Check your configuration against Figure 3-6, which shows the MICROVERTER backplane with boards installed (UNIBUS controllers and bus grant cards not shown).

Check your configuration against Figure 3-7, which shows the layout of the MICROVERTER backplane.

- f. Close the drawer containing the system.

- g. Turn on power to the system.

- h. Press the BOOT button (if necessary) to boot the system.

#### 3.8 VERIFICATION

The system is now ready to be exercised under DEC X/11, using the "E" monitor. The KWA module can be used to exercise the Line Time Clock.

Use appropriate diagnostics to verify correct installation.

If the system does not operate correctly, go back to Step 1 of the installation procedure and verify that the entire procedure was completed correctly.

If the system still does not operate correctly, consult Appendix D, which contains installation troubleshooting

procedures.

If these measures fail to result in correct system operation, call the ABLE Support Service department (see Chapter 7 for details).

Figure 3-6: MICROVERTER 73 Configuration

| •                     |   | A                        | 8                 | С       | D                | E                                     | · F |  |

|-----------------------|---|--------------------------|-------------------|---------|------------------|---------------------------------------|-----|--|

|                       | 1 | LSI-11/73 CPU            |                   | 1 M8 M  | IEMORY           | (1 M8 MEMORY)                         |     |  |

|                       | 2 | (1 MB MEMORY)            |                   | (1 M8 M | IEMORY)          | PVO                                   |     |  |

| SLOTS                 | 3 | PI/C                     | ) ``~             | PI      | 10               | P                                     | 10  |  |

| -                     | 4 |                          | MICRO             | VERTER  |                  | POWER REGULATOR/<br>CONSOLE INTERFACE |     |  |

|                       | 5 | UNIBUS                   | N                 | SPC     |                  |                                       |     |  |

|                       | 6 | M9301 OR<br>BOOTSTRAP/TE | M9312<br>RMINATOR |         | s <sub>P</sub> C |                                       |     |  |

| UNIBUS<br>SLOIS       | 7 | HEX-SIZE CONTROLLER      |                   |         |                  |                                       |     |  |

| 8 HEX-SIZE CONTROLLER |   |                          |                   |         |                  |                                       |     |  |

|                       | , | UNIBUS                   | DUT TUC           |         | 3                | c                                     |     |  |

MICROVERTER BACKPLANE

Figure 3-7: MICROVERTER Backplane Layout

#### CHAPTER 4

#### MICROVERTER PLUS INSTALLATION

#### 4.1 GENERAL

This chapter contains procedures for installing the ABLE MICROVERTER PLUS in a PDP-11/34 computer system. MICROVERTER PLUS is compatible with a number of PDP-11 systems. However, the procedures given here apply in detail to the PDP-11/34. If you are installing MICROVERTER PLUS in another PDP-11 system, some details may be different. In such cases, change the procedure as required for the particular system.

MICROVERTER PLUS consists of the following components:

- \* ABLE MICROVERTER board

- \* ABLE Power regulator/console interface board

- \* ABLE hybrid MICROVERTER backplane

- \* 'UNIBUS cable

- \* Processor cable (required for LSI-11/73 only)

- \* Optional front panel interface cable

- \* MICROVERTER Series User Guide.

### 4.2 EQUIPMENT NEEDED

The following equipment, supplied by the user, is required to install and operate MICROVERTER PLUS:

- \* An LSI-11/23, LSI-11/23+, or LSI-11/73 processor

- \* Q-Bus memory modules (maximum of four megabytes)

- \* A DEC M9301 or M9312 bootstrap/terminator board

- \* A BAll-Kx expansion box

- \* UNIBUS controllers.

### 4.3 SOFTWARE REQUIREMENTS

MICROVERTER PLUS adds UNIBUS mapping registers (UMRs) to the Q-Bus system to give 18-bit UNIBUS devices access to 22-bit Q-Bus address space. The operating system must

include software to handle UMRs. For example, RSX can be conditioned by being configured for operation on a PDP-11/44 computer. Other operating systems may need to be conditioned differently.

DEC operating systems RSTS/E V7.0 and V7.1 require patching to make them operate correctly with 22-bit parity memory. INIT 7.0 does not initialize the entire memory when run on a 22-bit system, and this can cause problems for RSTS/E after a power-up, due to random data and parity left in memory. See Appendix B for patches which allow INIT to correct all parity bits.

### 4.4 PREINSTALLATION PROCEDURE-

Before beginning installation, all components should be unpacked and inspected.

## STEP 1. Verify Contents of Shipment

Verify that the correct equipment has been received by checking product numbers of the components. Product numbers are as follows:

90000655

| MICROVERTER board                 | 10340000    |

|-----------------------------------|-------------|

| MICROVERTER backplane             | 10341000    |

| Power regulator/console interface | 10342000    |

| UNIBUS cable                      | 538-000-001 |

Processor cable

Optional front panel interface cable

90000666

If your shipment is not complete and correct, notify the ABLE factory immediately.

### STEP 2. Inspect Components

- a. Inspect components for damage. If damage is detected, notify the carrier immediately.

- b Save the protective shipping containers for possible future use.

## 4.5 INSTALLATION PROCEDURE

The detailed procedures given in this chapter are correct for the installation of and PDP-11/34 MICROVERTER PLUS in a PDP-11/34A computer system. MICROVERTER PLUS is compatible with other PDP-11 systems. systems with differences in However. construction may require different detailed procedures for installing MICROVERTER PLUS. In such cases, follow the intent of the procedure rather than the exact procedure itself. For special problems, call the ABLE Support Services Department (see Chapter 7).

## 4.6 LSI-11/23 Processor

## STEP 1. Set MICROVERTER Switches

This procedure applies to the installation of MICROVERTER PLUS in a system containing an

LSI-11/23 processor.

Set switches S1-1 through S1-10 on the MICROVERTER board as shown here. Switch S1 is shown in Figure 4-1. If the MICROVERTER LTC is not to be used, disable it by setting S1-10 open.

|             | +<br> |     |   | SW I | TCH      | SI |     |    |   |    | ۰+<br>ا |

|-------------|-------|-----|---|------|----------|----|-----|----|---|----|---------|

| MAP ENABLE  | 1 1   | 2   | 3 | 4    | 5        | 6  | 7   | 8  | 9 | 10 |         |

| AH1         | C     | -   | - | -    | -        | _  | С   | c  | С | С  | .       |

| Software    | i -   | _   | С | -    | <b>-</b> | C  | С   | C  | - | С  | i       |

| "C" = CLOSE | D (O  | N), |   | • =  | OP       | EN | (OF | F) |   |    | •       |

## STEP 2. Configure MICROVERTER for memory resident UNIBUS (optional).

If the application requires the use of memory resident on the UNIBUS, consult Appendix C for the procedure.

## STEP 3a. Remove NPG jumpers from backplane for DMA operation.

- a. Determine the slots in the backplane which are to be used for DMA controllers.

- b. Remove the NPG jumper from each of these slots. The jumpers are located on the MICROVERTER backplane at E points adjacent to connector C:

Figure 4-1: MICROVERTER Board Layout

| Slot | Number | Jumper |    |     |  |  |  |

|------|--------|--------|----|-----|--|--|--|

| 5    |        | E15    | to | E16 |  |  |  |

| 6    |        | E13    | to | E14 |  |  |  |

| 7    |        | E11    | to | E12 |  |  |  |

| 8    |        | E9     | to | Elø |  |  |  |

| ٥    |        | F7     | to | FR  |  |  |  |

See Figure 4-2 for the locations of these jumpers. If DMA controllers are to reside in other UNIBUS backplanes, NGP jumpers must be removed from the slots involved. Consult the backplane manufacturer's documentation for the procedure.

## STEP 3b. Remove IAK and IMG jumpers from backplane for Q-Bus I/O operation.

This step is required only if a Q-Bus I/O controller is to be installed in the MICROVERTER backplane.

IAK (Interrupt Acknowledge) and DMG (DMA Grant) jumpers are installed in the MICROVERTER backplane as follows:

| • | Slot Number | Connectors |

|---|-------------|------------|

| • | 1           | C, E       |

|   | 2           | A, C, E    |

|   | 3           | A, C, E    |

In each of these connectors, the IAK jumper is across pins M2 and N2, and the DMG jumper is across pins R2 and S2.

If a Q-Bus I/O controller is to reside in any of these slots, remove these jumpers from the

associated connectors.

### STEP 4. Disable BEVNT if required.

If the LTC on the MICROVERTER is to be used, disable BEVNT on the LSI-11/23 processor by installing jumper W4 on the processor board. Refer to the DEC Microcomputers and Memories Handbook for the location of jumper W4. If the MICROVERTER LTC is not to be used, disable it by opening switch S1-10 on the MICROVERTER.

### STEP 5. Remove boards from PDP-11 backplane.

- a. Turn off power to the PDP-11 system.

- b. Pull out the drawer containing the system.

- c. Locate the backplane containing the PDP-11/34 processor.

- d. Remove the front panel interface cable.

- e. Remove all boards from the processor backplane.

- f. If the processor backplane is connected to the next backplane, disconnect the UNIBUS connecting cable from the processor backplane. Leave the cable connected to the next backplane.

### STEP 6. Remove PDP-11 backplane from system.

- a. Actuate the drawer release and swing the drawer up to expose the wirewrap side of the backplane.

- b. Figure 4-3 is a view of the wirewrap side of the backplane showing the mounting screws and cable connectors. The cables are not shown.

- c. Disconnect the backplane from the power distribution strip.

- d. Unscrew the four mounting screws holding the backplane to the enclosure.

- e. Remove the PDP-11 backplane from the system.

### STEP 7. Install the MICROVERTER Backplane.

- a. Place the special MICROVERTER backplane in the space left by the PDP-11 backplane.

- b. Secure the backplane in place with the four captive mounting screws.

- c. Connect the backplane to the power distribution strip.

- d. Swing the drawer back to its horizontal position.

Figure 4-3: Installation of MICROVERTER Backplane

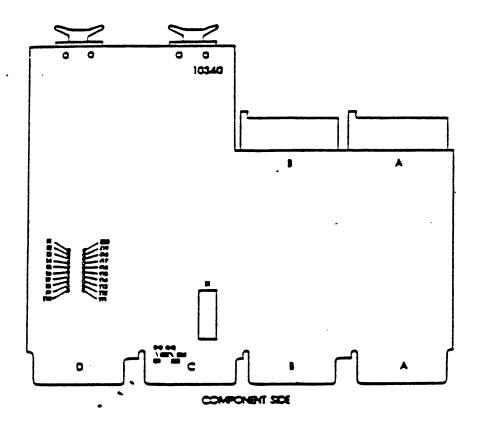

### STEP 8. Insert MICROVERTER Board

Insert the MICROVERTER board into slot 4 of the backplane, using sockets Athrough D. Insert the board so that the component side faces slot 1 of the backplane.

### STEP 9. Connect UNIBUS Cable.

- a. Attach one end of the UNIBUS (supplied with MICROVERTER PLUS) to connectors A and B at the top of the MICROVERTER board. (See Figure 4-4).

- b. Insert the other end of the UNIBUS cable into slot 5 of the backplane, using sockets A and B.

#### Insert Power Regulator/Console STEP 10. Interface Board.

Insert the power regulator/console interface board into slot 4 of the backplane, using sockets E and F. Insert the board so that the component side faces slot 1 of the backplane.

(The power regulator/console interface board and the MICROVERTER board should now be side by side in slot 4 of the backplane.)

## STEP 11. Insert LSI-11/23 Processor Board

Insert the LSI-11/23 processor board into slot 1 of the backplane, using sockets A and B. Insert the board so that the component side faces the near edge of the backplane.

Figure 4-4: UNIBUS and Front Panel Interface Cables

### STEP 12. Insert Memory Boards

Insert Q-Bus memory boards into slots 1 and 2 of the backplane. Insert each board so that the component side faces the near edge of the backplane.

## STEP 13. Install PDP-11 Boards in MICROVERTER Backplane.

- a. If the PDP-11 backplane (removed in Step 6) was connected to the next backplane, insert the connecting UNIBUS cable into slot 9 of the MICROVERTER backplane, using sockets A and B.

- b. Retrieve the circuit boards removed from the PDP-11 backplane in step 5.

- c. Set aside the two PDP-11 processor boards, the front panel interface board, and the UNIBUS memory boards: they will not be used in this system. (They are replaced by the LSI-11/23 processor board, the MICROVERTER power regulator/console interface board, and Q-Bus memory boards.)

- d. Insert the remaining boards into the MICROVERTER backplane, using slots 5 through 9.

- e. Insert the existing DEC M9301 or M9312 bootstrap/terminator in slot 6, connectors A and B, for the front-end termination of the UNIBUS.

- f. Check your configuration against Figure 4-5, which shows the MICROVERTER backplane

with boards installed (UNIBUS controllers and bus grant cards not shown).

- g. Check your configuration against Figure 4-6, which shows the MICROVERTER backplane layout.

- h. Close the drawer containing the system.

- i. Turn on power to the system.

- j. Press the BOOT button (if necessary) to boot the system.

#### 4.7 VERIFICATION

The system is now ready to be exercised under DEC X/11, using the "E" monitor. The KWA module can be used to exercise the Line Time Clock.

Use appropriate diagnostics to verify correct installation.

If the system does not operate correctly, go back to Step 1 of the installation procedure and verify that the entire procedure was completed correctly.

If the system still does not operate correctly, consult Appendix D, which contains installation troubleshooting procedures.

If these measures fail to result in correct system operation, call the ABLE Support Service department (see Chapter 7 for details).

figure 4-5: MICROVERTER PLUS Configuration

|                              |                       | A B                                    | С             | D   | E             | F                     |  |

|------------------------------|-----------------------|----------------------------------------|---------------|-----|---------------|-----------------------|--|

| •                            | 1 LSI-H CPU           |                                        | 1 MB MEM      | ORY | (1 MB MEMORY) |                       |  |

| Q BUS                        | 2                     | (1 M8 MEMORY)                          | (1 M8 MEMORY) |     | P             | 10                    |  |

| SLOIS                        | 3                     | PI/O                                   | PI/O          |     | PI            | 10                    |  |

| -                            | 4                     | MICRO                                  | VERTER        |     | POWER RE      | GULATOR/<br>INTERFACE |  |

|                              | 5                     | Unibus in                              | •             | SP  | С             |                       |  |

|                              | 6                     | M9301 OR M9312<br>BOOTSTRAPITERMINATOR | SP            | C   |               |                       |  |

| UNIBUS 7 HEX-SIZE CONTROLLER |                       |                                        |               |     |               |                       |  |

|                              | 8 HEX-SIZE CONTROLLER |                                        |               |     |               |                       |  |

|                              | 9                     | nvisns on                              | •             | SPC | •             |                       |  |

MICROVERTER BACKPLANE

Figure 4-6: MICROVERTER Backplane Layout

#### 4.8 LSI-11/23+ Processor

This procedure applies to the installation of MICROVERTER PLUS in a system containing an LSI-11/23+ processor.

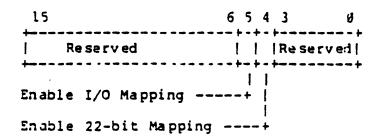

The Map Enable signal on pin AHI, set switch S1-1 closed. Switch S1-6 can optionally be set closed to enable the software-settable Map Enable function. If the software-settable Map Enable Map Enable function is desired, hardware Map Enable switch positions S1-1 and S1-2 must be set open, as shown in the table below. Switch S1-18 must be set open, to disable the LTC.

| -          | +<br> |   |   | SW I | TCH | 51 | · |   |   |    | + |

|------------|-------|---|---|------|-----|----|---|---|---|----|---|

| MAP ENABLE | 1 1   | 2 | 3 | 4    | 5   | 6  | 7 | 8 | 9 | 18 | - |

| AH1**      | C     | - | _ | _    | _   | -  | С | c | _ | -  |   |

| Software   | -     | - | c | -    | -   | C  | C | С | • | -  | İ |

"C" = CLOSED (ON), "-" = OPEN (OFF)

"\*\*" Requires change to processor board

## STEP 2. Configure MICROVERTER for memory resident on the UNIBUS (optional).

If the application requires the use of memory resident on the UNIBUS, consult Appendix C for the procedure.

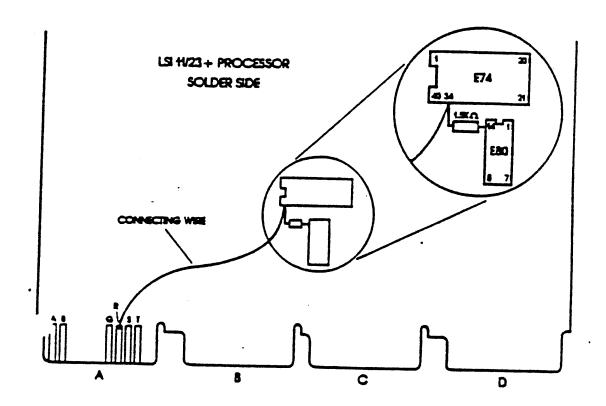

### STEP 3. Modify processor board.

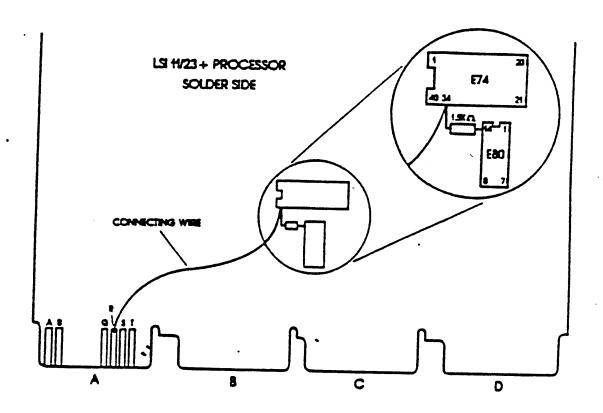

The LSI-11/23+ processor does not provide the UBMAPL signal required by the MICROVERTER board. However, the signal is present on the processor board, and it can be brought out to the MICROVERTER board by making the following modifications (see Figure 4-7):

- 1. Add a 1.5K-Ohm resistor from E74 pin 34 to E80 pin 14.

- 2. Add a 30-gauge wire from E74 pin 34 to backplane connector A, finger R2.

#### NOTE

Please contact Digital Equipment Corporation to determine whether this modification affects the warranty.

Figure 4-7: Modification to LSI-11/23+ Processor Board

## STEP 4a. Remove NPG jumpers from backplane for DMA operation.

- a. Determine the slots in the backplane which are to be used for DMA controllers.

- b. Remove the NPG jumper from each of these slots. The jumpers are located on the MICROVERTER backplane at E points adjacent to connector C:

| For | slot | 5, | r emov e | jumper | from | E15 | to | E16 |

|-----|------|----|----------|--------|------|-----|----|-----|

|     |      | 6  |          | •      |      | E13 | to | E14 |

|     |      | 7  |          |        |      | E11 | to | E12 |

|     |      | 8  |          |        |      | E9  | to | ElØ |

|     |      | 9  |          |        |      | E7  | to | E8  |

See Figure 4-2 for the locations of these jumpers. If DMA controllers are to reside in other UNIBUS backplanes, NPG jumpers must be removed from the slots involved. Consult the backplane manufacturer's documentation for the procedure.

# STEP 4b. Remove IAK and DMG jumpers from backplane for Q-Bus I/O operation.

This step is required only if a Q-Bus I/O controller is to be installed in the MICROVERTER backplane.

IAK (Interrupt Acknowledge) and DMG (DMA Grant) jumpers are installed in the MICROVERTER backplane as follows:

| Slot Number | Connectors |

|-------------|------------|

| 1           | C, E       |

| 2           | A, C, E    |

|             | A, C, E    |

In each of these connectors, the IAK jumper is across pins M2 and N2, and the DMG jumper is across pins R2 and S2.

If a Q-Bus I/O controller is to reside in any of these slots, remove these jumpers from the associated connectors.

### STEP 5. Remove boards from PDP-11 backplane.

- a. Turn off power to the PDP-11 system.

- b. Pull out the drawer containing the system.

- c. Locate the backplane containing the PDP-11/34 processor.

- d. Remove the cable connecting the front panel with the interface board.

- e. Remove all circuit boards from the PDP-11 backplane.

- f. If the processor backplane is connected to the next backplane, disconnect the UNIBUS connecting cable from the processor backplane, but leave the cable connected to the next backplane.

### STEP 6. Remove PDP-11 backplane from system.

- a. Actuate the drawer release and swing the drawer up to expose the wirewrap side of the backplane. (See Figure 4-3.)

- b. Disconnect the backplane from the power distribution strip.

- c. Remove the PDP-11 backplane from the system.

### STEP 7. Install the MICROVERTER backplane.

- a. Place the MICROVERTER backplane in the space left by the PDP-11 backplane.

- b. Secure the backplane in place with the four captive mounting screws.

- c. Connect the backplane to the power distribution strip.

- d. Swing the drawer back to its horizontal position.

### STEP 8. Insert the MICROVERTER board.

Insert the MICROVERTER board into slot 4 (A, B, C, and D) of the MICROVERTER backplane. Insert the board so that the component side faces slot 1 of the backplane.

#### NOTE

Slots 1 through 4 of the MICROVERTER backplane are wired for the Q-Bus. If UNIBUS boards are placed in these slots, damage can occur, resulting in repair costs not covered by warranty!

### STEP 9. Connect UNIBUS cable.

- a. Connect the UNIBUS cable (supplied with MICROVERTER PLUS) to connectors A and B at the top of the MICROVERTER board. (See Figure 4-4.)

- b. Insert the other end of the UNIBUS cable

- c. Set aside the PDP-11 processor boards, the front panel interface board, and the UNIBUS memory: they will not be used in this system. (They are replaced by the LSI-11/23+ processor board, the power regulator/console interface board, and the Q-Bus memory.)

- d. Insert the remaining boards into the MICROVERTER backplane, using slots 5 through 9.

NOTE: If a slot is used for a DMA controller, the associated NPG jumper must be removed from the backplane (see Step 6).

- e. Insert the existing DEC M9301 or M9312 bootstrap/terminator in slot 6, connectors A and B, for the front-end termination of the UNIBUS.

- f. Check your configuration against Figure 4-5, which shows the MICROVERTER backplane with boards installed (UNIBUS controllers and bus grant cards not shown).

- g. Check your configuration against Figure 4-6, which shows the MICROVERTER backplane layout.

- h. Close the drawer containing the system.

- i. Turn on power to the system.

- j. Press the BOOT button (if necessary) to boot the system.

### 4.9 VERIFICATION

The system is now ready to be exercised under DEC X/11, using the "E" monitor. The KWA module can be used to exercise the Line Time Clock.

the appropriate diagnostics to verify correct installation.

If the system does not operate correctly, go back to Step 1 of the installation procedure and verify that the entire procedure was completed correctly.

If the system still does not operate correctly, consult Appendix D, which contains installation troubleshooting procedures.

If these measures fail to result in correct system operation, call the ABLE Support Service department (see Chapter 7 for details).

### 4.9.1 LSI-11/73 Processor

This procedure applies to the installation of MICROVERTER PLUS in a system containing an LSI-11/73 processor.

### STEP 1. Set MICROVERTER switches.

Set switch S1 on the MICROVERTER board as shown below. (Set switches S1-3, S1-8, and S1-9 closed). Switch S1-6 can optionally be set closed to enable the Map Enable signal to be set by software. Switch S1-10 must be set open, to disable the LTC.

| <del> </del> | +<br> |   |   | SW I | TC H |   |   |   |   |    |

|--------------|-------|---|---|------|------|---|---|---|---|----|

| MAP ENABLE   | j 1   |   |   | 4    |      | 6 | 7 | 8 | 9 | 10 |

| Hardware*    |       |   |   |      |      | - | - | С | C | -  |

| Software     | i -   | - | С | -    | -    | C | C | С | _ | -  |

"C" = CLOSED (ON), "-" = OPEN (OFF)

# STEP 2. Configure MICROVERTER for memory resident on the UNIBUS (optional).

If the application requires the use of memory resident on the UNIBUS, consult Appendix C for the procedure.

## STEP 3. Select source of 60 Hz timing signal for LTC operation.

If the 60 Hz signal for the LTC is to be supplied by the UNIBUS via the power regulator/console interface board, install a jumper across El and E2 on the power

regulator/console interface board. (See Figure 2-4 for location of El-E2.)

If the 60 Hz signal for the LTC is to be supplied by a Q-Bus board, verify that E1-E2 on the power regulator/console interface board is left open (i.e., no jumper).

## STEP 4. Modify processor board

The Map Enable signal and the Address Latch Enable (ALE) Timing Strobe signal have their sources on the LSI-11/73 processor board, but are not available to the MICROVERTER board.

The processor cable is supplied with MICROVERTER PLUS for the purpose of bringing these signals to the MICROVERTER board. Two procedures are given here. The first procedure, using the cable as supplied, with two leads attached, is suitable for initial installation and product verification. The second procedure, in which the leads are cut off and the wires are soldered to the board, is recommended for permanent installation.

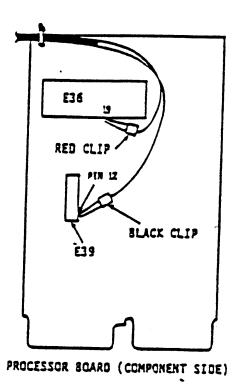

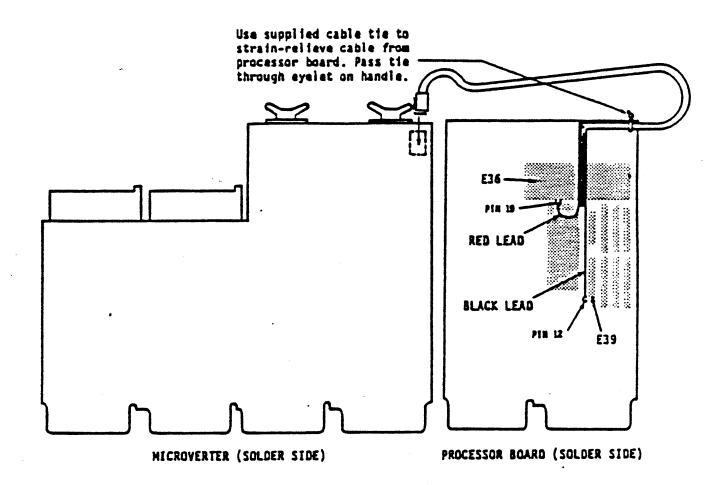

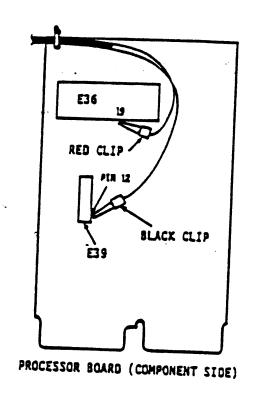

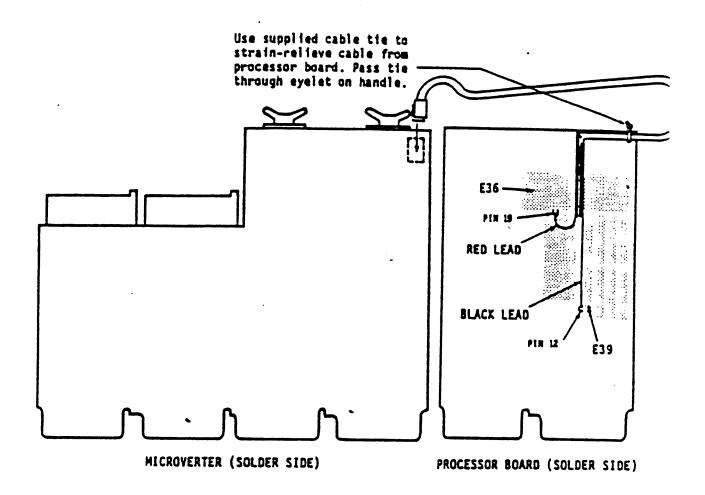

### Interim Procedure

The processor cable has two color-coded leads, one red and one black.