### GaAs DAC Synthesizes 100-MHz WAVEFORMS

A PENTON PUBLICATION U.S. \$10.00

40 YEARS OF EDITORIAL EXCELLENCE

DESIGN IT RIGHT THE FIRST TIME WITH EDA TOOLS

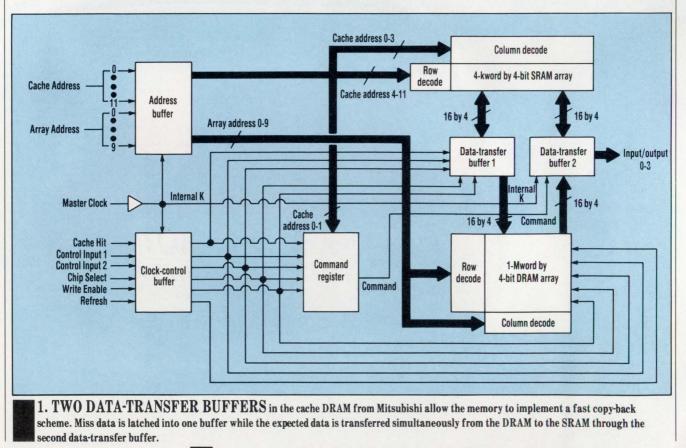

CACHED DRAM TRIMS ACCESS TO 10 ns

**PC DESIGN SECTION**

### Still the Leader

in DOS based Electronic Design

Introducing Schematic Design Tools version 4.10

#### The leader in PC based EDA tools.

Why? Because we never stop improving our products. One example is our world famous *Schematic Design Tools* package with the *ESP framework*.

OrCAD has just released version 4.10 with these new features.

- dramatic increase in capacity

- utilities like netlist output have increased speed

- introducing new "hotkeys" in the ESP framework

#### The ESP Framework

The *ESP framework* is the first PC based framework that allows seamless integration between OrCAD tools and those of third party vendors. ESP framework is a part of Schematic Design Tools; no need to pay extra.

Call (503)690-9881 or write today for your FREE demo disk!

#### The OrCAD Difference

*Schematic Design Tools* still comes with the features you'd expect to pay more for:

- A library of over <u>20,000</u> unique parts you can browse through in a breeze.

- Utilities to generate Bill-of-Materials, electrical rules check, create custom library parts.

- Support for over 30 netlist formats.

- Over a hundred supported display adapters, 50 printer drivers, a dozen plotter drivers.

- User definable "smart" macros

As ever, all OrCAD products come with one year of product updates, telephone technical support and 24 hour BBS, and a subscription to The Pointer newsletter.

If you would like information about this or any OrCAD product, contact your local OrCAD Value Added Reseller.

| WA, OR, MT,<br>ID, AK, WY | ND, SD, MN,<br>MI, WI, IL, IN, |

|---------------------------|--------------------------------|

| Avcom/EDA                 | OH, KY, WV.                    |

| (206)828-2726             | W. PA, NE, KS,                 |

| . ,                       | IA, MO                         |

| N. CA, HI, Reno           | MacKellar                      |

| NV                        | Associates, Inc.               |

| Elcor Associates<br>Inc.  | (313) 335-4440                 |

| (408) 980-8868            | VA, TN, NC,<br>SC              |

| So. CA                    | Tingen Technical               |

| Advanced Digital          | Sales                          |

| Group                     | (919) 870-6670                 |

| (714) 897-0319            |                                |

|                           | E. PA, NJ, NY,                 |

| Las Vegas NV,             | DE, MD, DC                     |

| UT, AZ, NM,               | Beta Lambda,                   |

| CO                        | Inc.                           |

| <b>Tusar</b> Corporation  | (800) 282-5632                 |

| (602) 998-3688            |                                |

|                           | CT, RI, MA,                    |

| TX, OK, AR, LA            | VT, NH, ME                     |

| Abcor, Inc.               | Tri-Logic                      |

Abcor, Inc. Tri-Logic (713) 486-9251 (508) 658-3800

> CANADA Pegasus Circuits (416)567-6840

CIRCLE 148 FOR U.S. RESPONSE CIRCLE 149 FOR RESPONSE OUTSIDE THE U.S.

### Finally, engineering software that clears the way to problem solving without programming.

void service int eid: { int stat, b /\*serial poll. byte=hpib\_spol if ( (byte<0) printf("SRQ Problem return; } stat=my\_read(eid, DVM if (stat>0) {  $buffy[stat] = ' \setminus 0';$ printf("Data from instrument: else printf("I/O read error\n") return; ) main() int busid, stat, MTA, MLA; char command [MAXCHARS];

busid=open("/dev/hpib7", O\_RDWR); /\* open raw HP-IB for MTA=hpib\_bus\_status(busid, CURRENT\_BUS\_ADDRESS) + 64; MLA=hpib\_bus\_status(busid, CURRENT\_BUS\_ADDRESS) + 32; stat = BUTTON\_BIT ; sprintf(command, "KM%02o", stat); /\* 2 octal digits; no

#### With HP VEE, you simply link the icons.

Computers are great for problem solving, if only programming didn't get in the way and slow you down. And now, it doesn't have to. Because the HP visual engineering environment (HP VEE) lets you solve problems without programming.

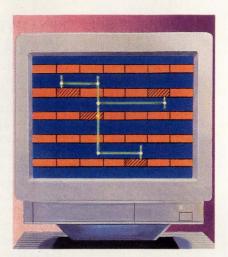

With HP VEE, you explore solutions visually by arranging and linking icons on the CRT. Each icon represents and executes a specific function for data collection, analysis —from simple mathematics to complex algorithms—and presentation. You don't have to write a single line of code.

There are two HP VEE software packages for prototyping, experimentation, and problem modeling. HP VEE-Engine, at \$995\*, is a general-purpose tool for analysis and presentation of existing data. HP VEE-Test includes HP VEE-Engine and adds extensive I/O capability, including soft panels and device I/O objects for \$5,000\*.

write

So, if programming is keeping you from solutions, call **1-800-452-4844**.\*\*\* Ask for **Ext. 2382**, and we'll send you a brochure on clearing the way with HP VEE.

There is a better way.

\*\* In Canada call 1-800-387-3867, Dept. 430.

©1991 Hewlett-Packard Co. TMMSO108C/ED

**CIRCLE 106 FOR U.S. RESPONSE**

# The Official Flag Of The

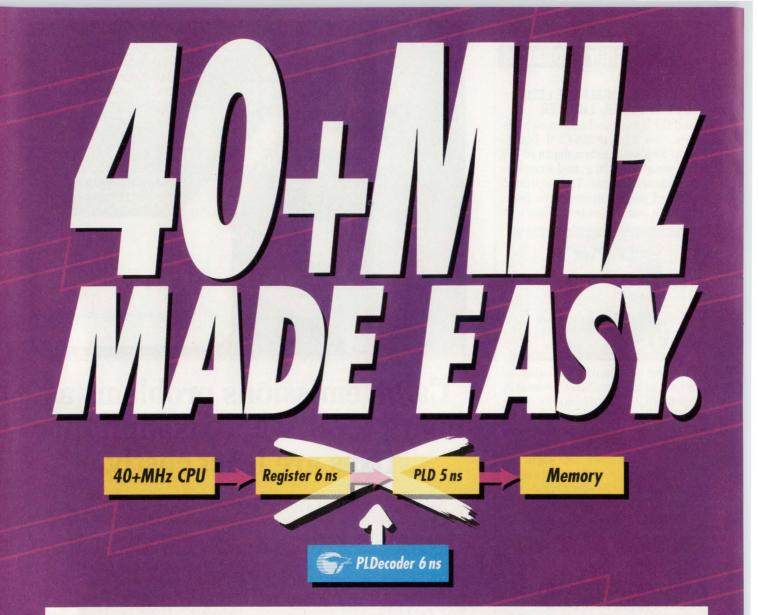

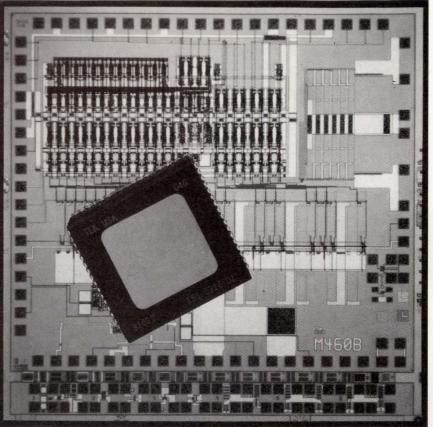

#### AMD Delivers The World's Fastest 386s.

The great 386 race is over. And the clear winner is the Am386 microprocessor family.

111111111

The fact is, no other 386 microprocessors available today can rival the sheer speed and performance of the Am386 microprocessors. The Am386DXL-40 CPU brings 40MHz,

The 40MHz DXL-40 and the 33MHz SXL-33 are available in low-cost PQFP packaging.

full 32-bit 386 performance to the desktop. The Am386SXL-33 CPU makes 33MHz the stan-

dard for 386SX machines both at the desktop and for battery powered applications.

In either case, they're over 20% faster than those run-of-the-mill 386's.

901 Thompson Place, P.O. Box 3453. Sunnyvale, CA 94088 © 1991 Advanced Micro Devices. Inc. "We're Not Your Competition" is a service mark and Am 386

# Am386 Microprocessors.

And of course, they're proven-compatible with the IBM\*standard.

Best of all, they're available now, available in quantity, and available at surprisingly low prices. So don't just keep up with the competition with ordinary 386 systems. Blow them away with the world's fastest 386 systems—built around the Am386 microprocessors from Advanced Micro Devices. Call **1-800-222-9323** for more information.

is a trademark of Advanced Micro Devices. Inc. All brand or product names mentioned are trademarks or registered trademarks of their respective holders

# FEBRUARY 20, 1992 VOL. 40, NO. 4

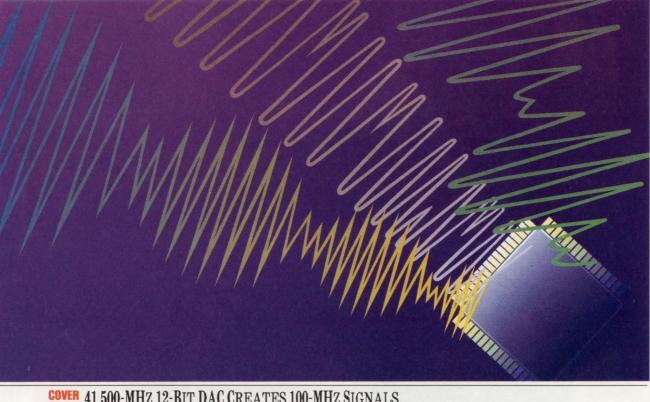

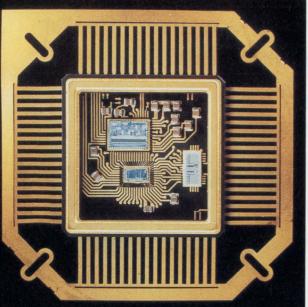

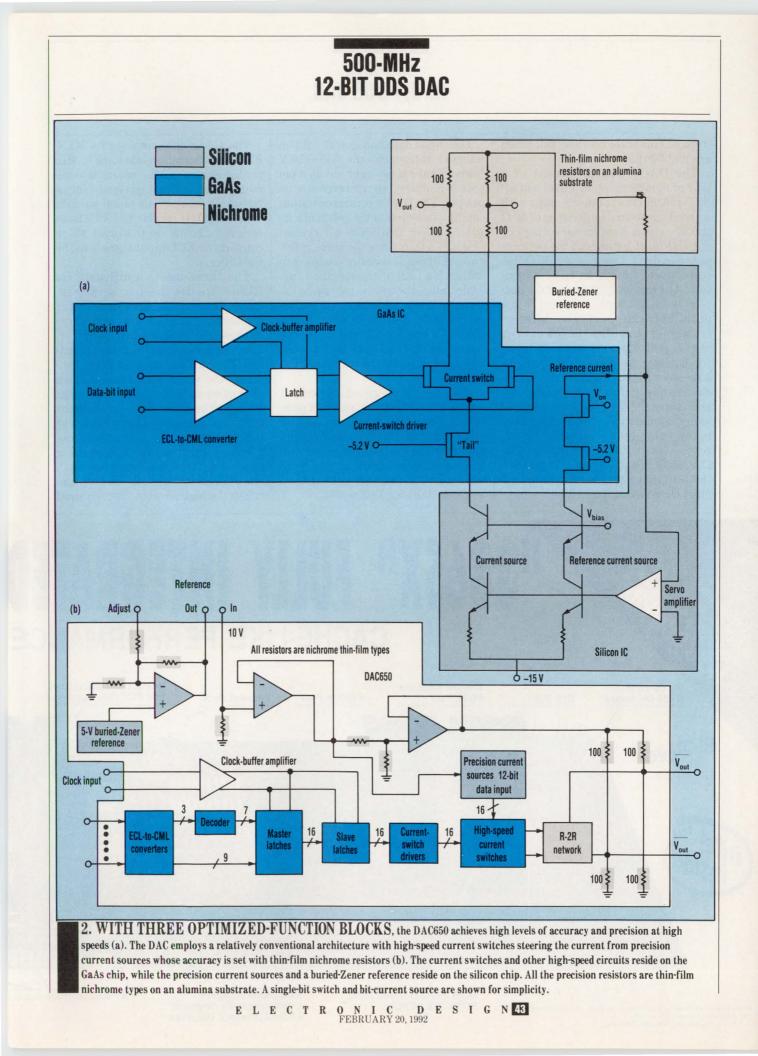

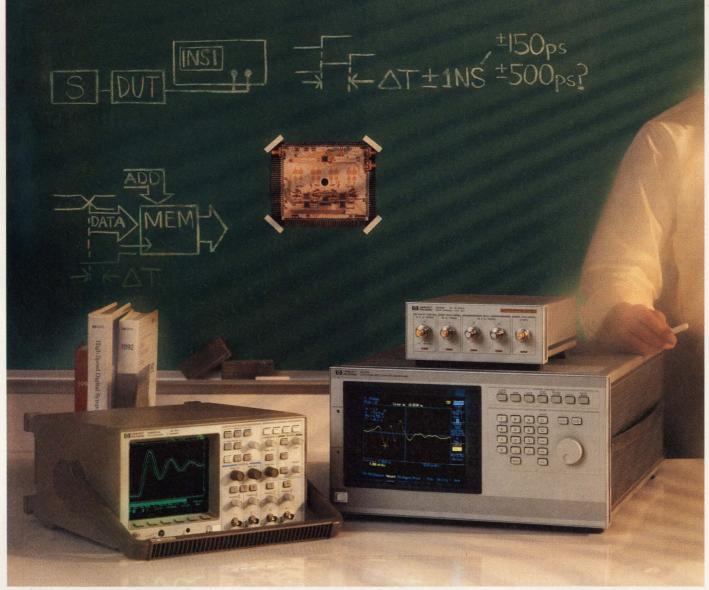

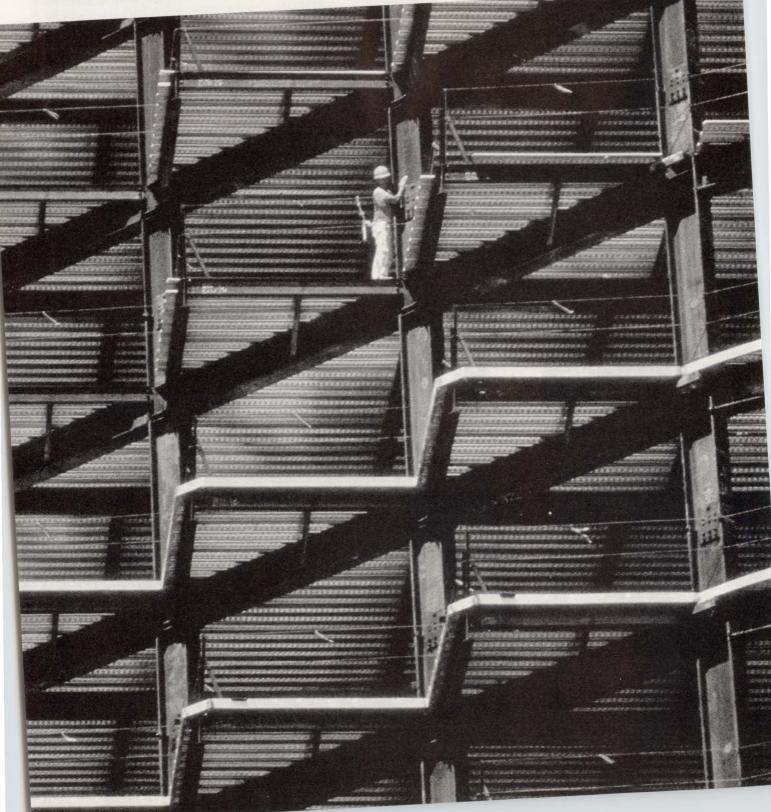

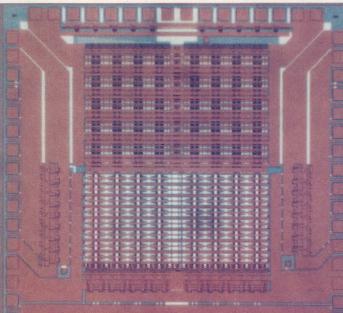

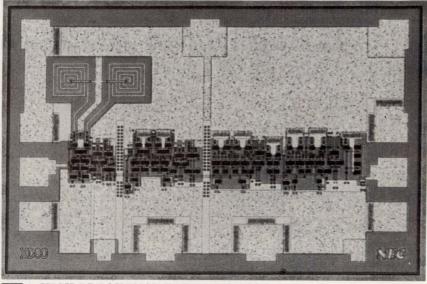

#### COVER 41 500-MHZ 12-BIT DAC CREATES 100-MHZ SIGNALS

FEATURE GaAs switches, silicon current sources, and nichrome resistors combine for direct digital synthesis at high speeds.

#### **ELECTRONIC 47 ISSCC REVIEW INTRODUCTION DESIGN REPORT**

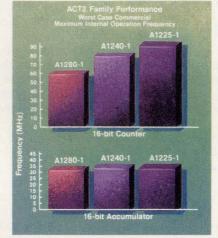

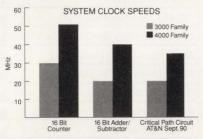

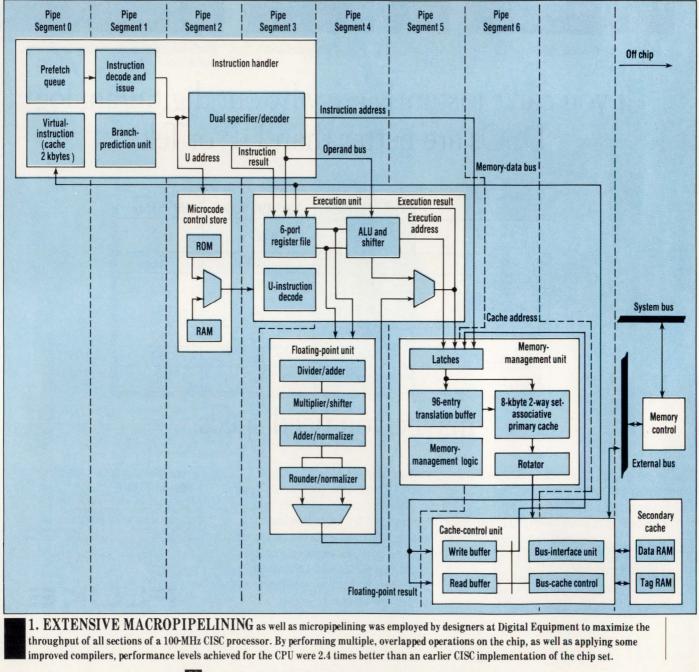

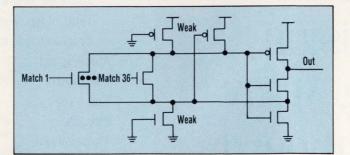

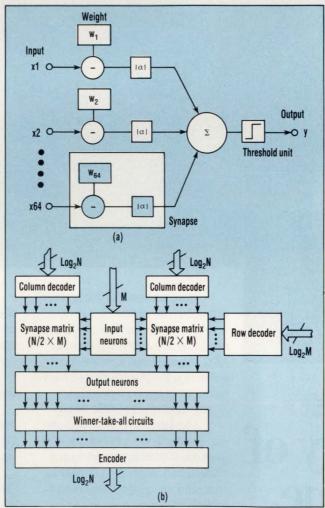

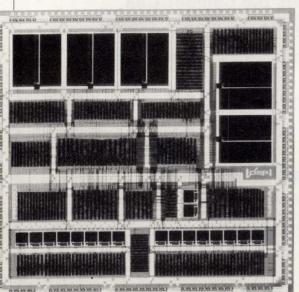

#### **48 ISSCC REVIEW: DIGITAL TECHNOLOGY**

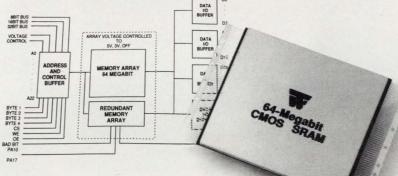

Major advances are reported in CISC and RISC processors, memories, and neural-net chips.

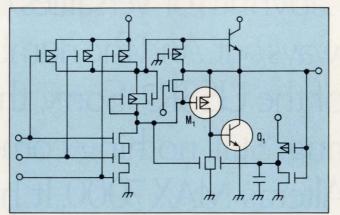

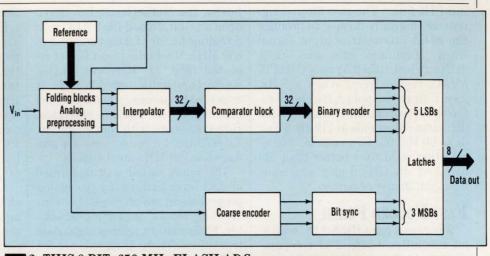

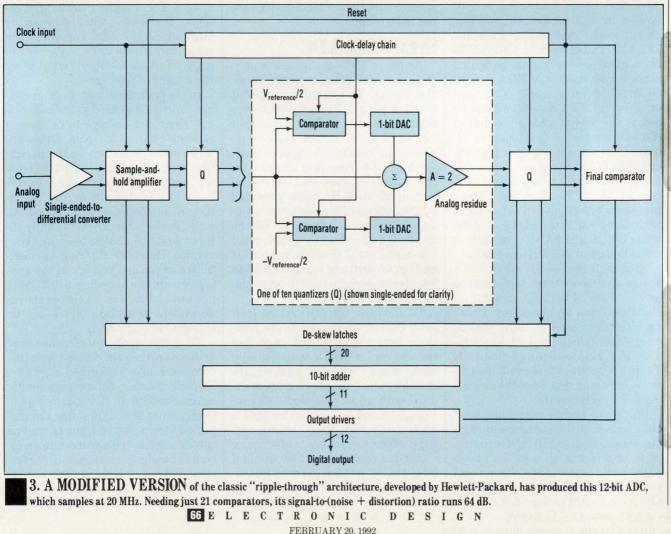

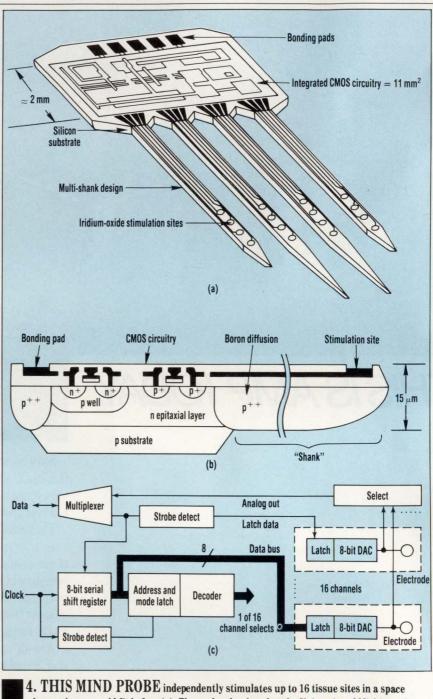

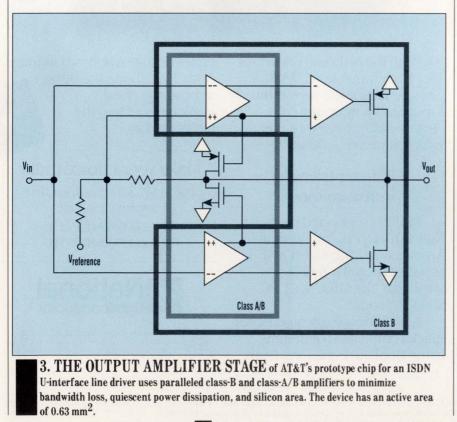

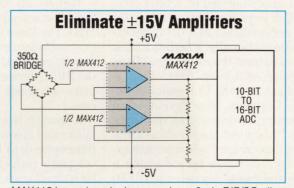

#### 64 ISSCC REVIEW: ANALOG TECHNOLOGY

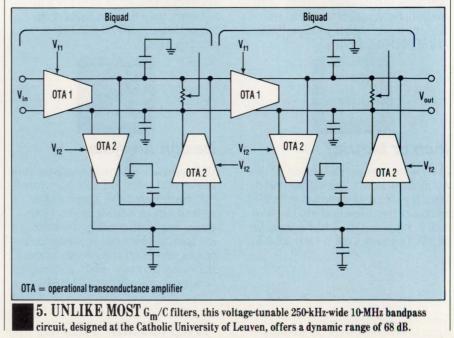

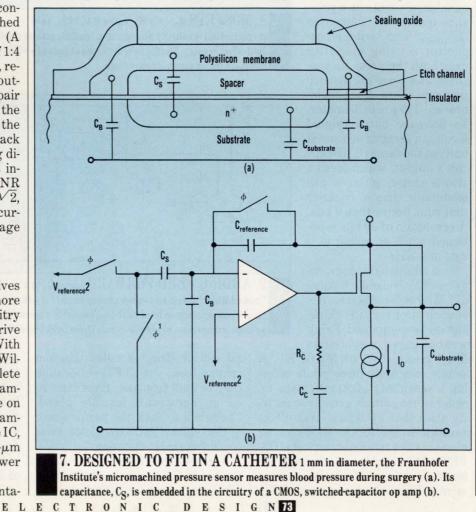

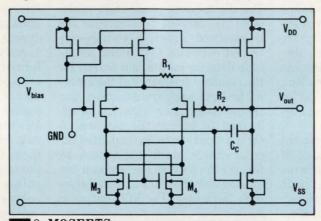

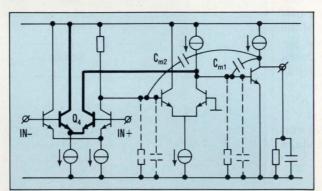

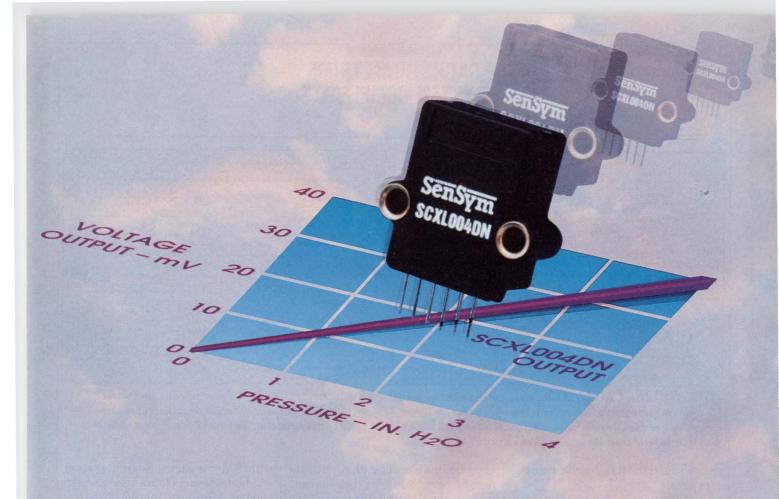

Data converters, sensors, filters, disk-drive controllers, and display drivers lead the way in analog developments.

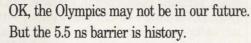

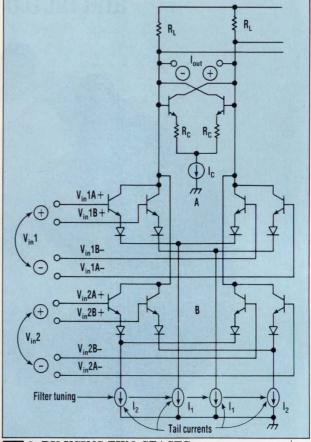

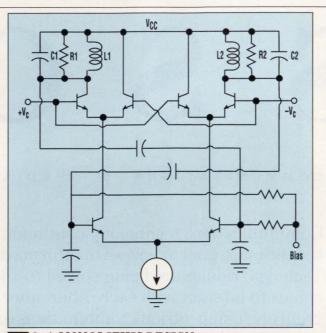

#### **79 ISSCC REVIEW: COMMUNICATIONS TECHNOLOGY**

A host of device enhancements for telecommunication and data-communication networks are on tap.

**APPLICATIONS**

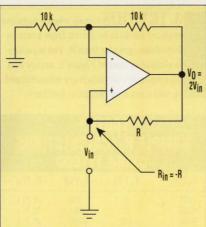

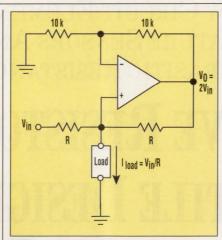

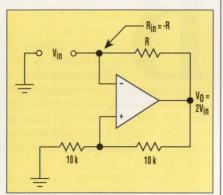

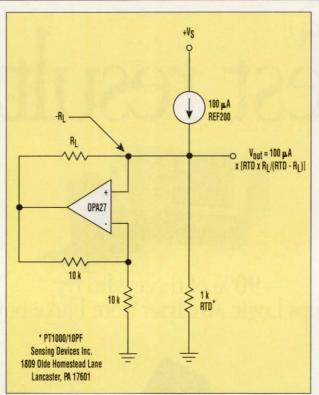

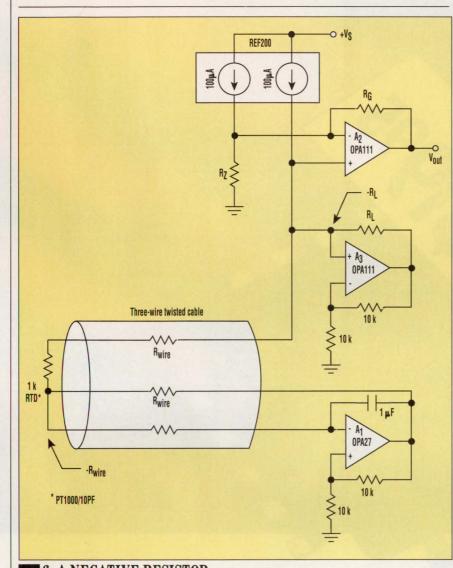

#### DESIGN 93 NEGATIVE RESISTORS ARE VERSATILE DESIGN AIDS

Use these handy circuit elements to linearize RTD temperature sensors and eliminate parasitic resistance.

**OVATIONS**

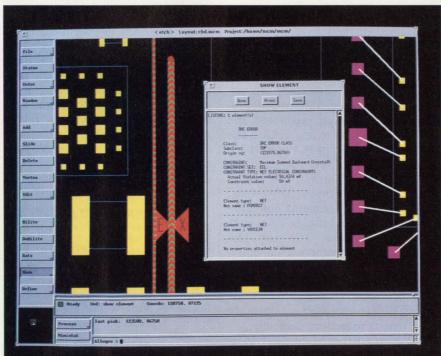

#### PRODUCT 139 CONSTRAINT-DRIVEN TOOLS LAY OUT HIGH-END DESIGNS

A correct-by-design EDA system helps engineers build high-speed boards, MCMs, and hybrids without errors.

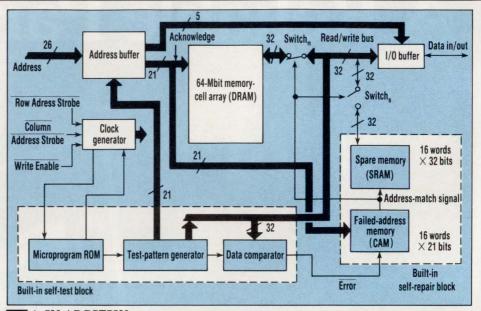

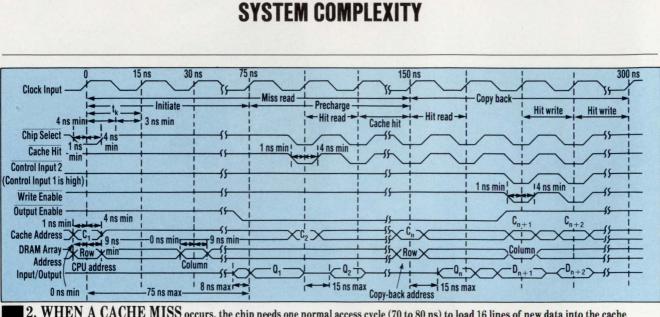

#### 142 INTEGRATED CACHED DRAM LETS DATA FLOW AT 100 MHZ Build more efficient systems with highly integrated memories that merge the cache and DRAM into one IC.

4 E L E C T R O N I C FEBRUARY 20, 1992 DESIGN

#### **14 EDITORIAL**

#### **18 TECHNOLOGY BRIEFING**

Disk arrays and beyond

#### **23 TECHNOLOGY NEWSLETTER**

• Fiducial-mark standard smoothes SMD placement

• First alternative to 486 coming from AMD

• Modulation analysis is possible at over 5 GHz

• IC FM receivers target low-power systems

• Silicon process yields 30-GHz MOSFETs

• New CPU, graphics ICs upgrade workstations

#### **30 TECHNOLOGY ADVANCES**

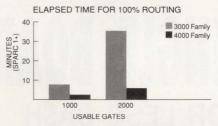

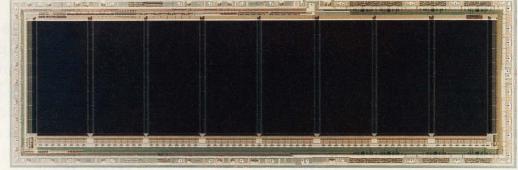

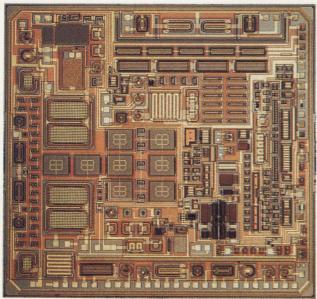

• Interleaved gates on basic cells in gate arrays boost routability

• Planar process yields commercial high-temperature SQUIDs

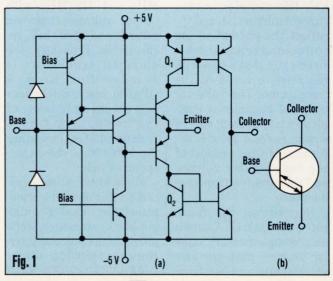

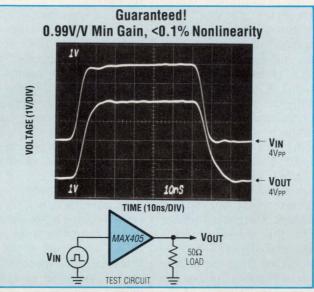

• Transconductance IC amp has bandwidth of over 300 MHz

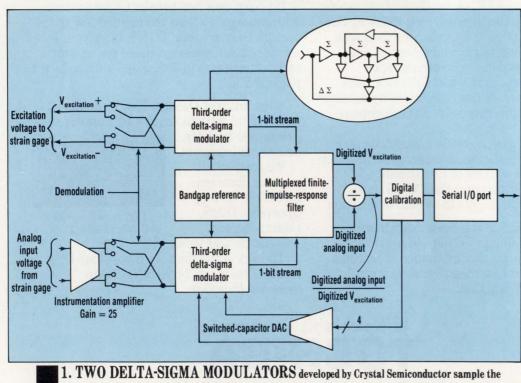

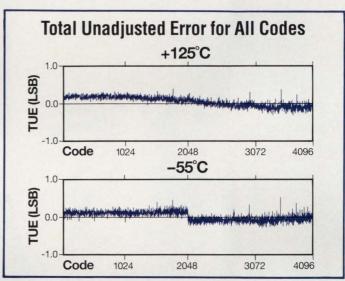

• Geophysicists get 24-bit, 0.1-W ADC to sense seismic signals

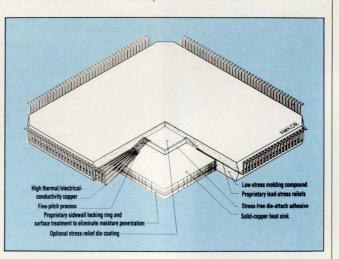

• Plastic packages dissipate high heat of ICs

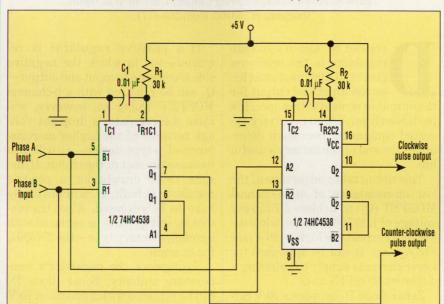

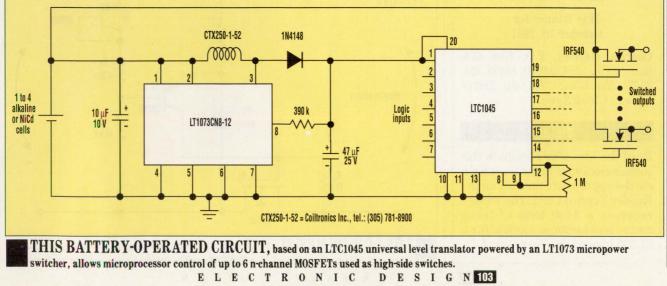

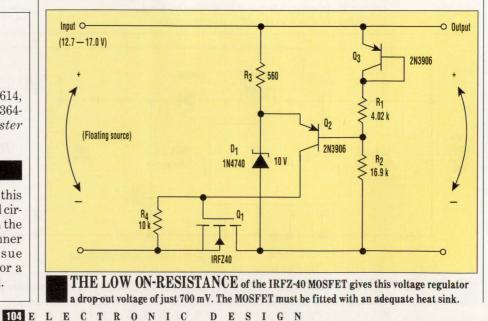

#### **103 IDEAS FOR DESIGN**

• Detect quadrature waveforms

• Level translator switches MOSFETs

• 20-A regulator has low drop-out

Jesse H. Neal Editorial Achievement Awards: 1967 First Place Award 1968 First Place Award 1972 Certificate of Merit 1975 Two Certificates of Merit 1976 Certificate of Merit 1980 Certificate of Merit 1986 First Place Award 1989 Certificate of Merit

Cover Illustration: Tony Vitolo

#### **109 QUICK LOOK**

- Small companies can win government contracts

- EMI/RFI shielding market is growing

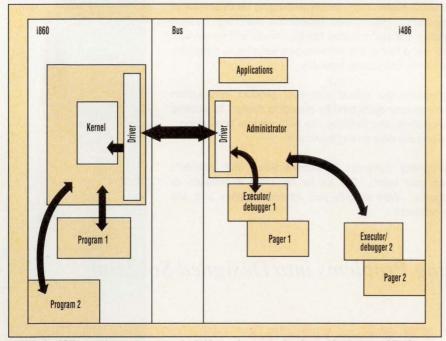

- Free offers you can't refuse

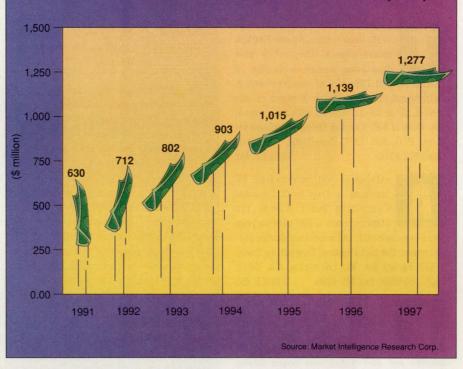

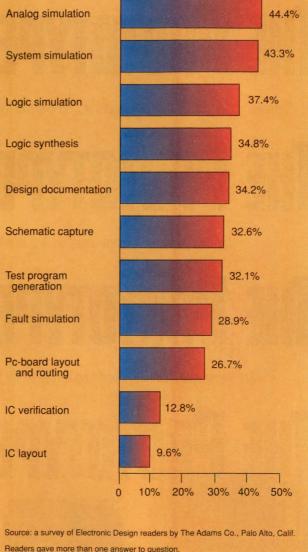

• CAD/CAE survey: With improved tools, which functions would you use more often?

#### **113 PEASE PORRIDGE**

Bob's Mailbox

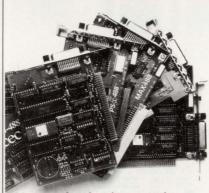

#### PC DESIGN SPECIAL SECTION

119 PC Design Newsletter

120 PC Graphics Watch

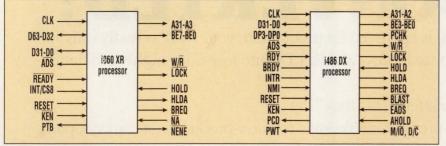

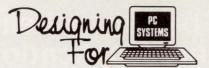

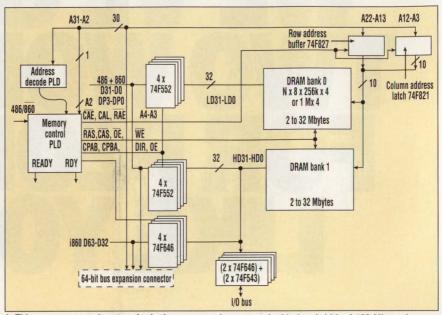

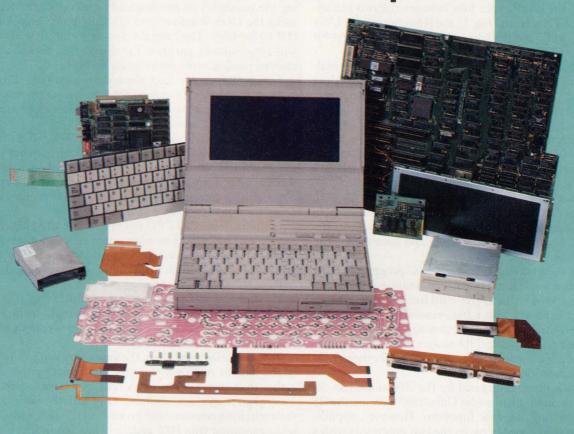

122 Dual processors boost computer power

134 PC Design Products

#### **NEW PRODUCTS**

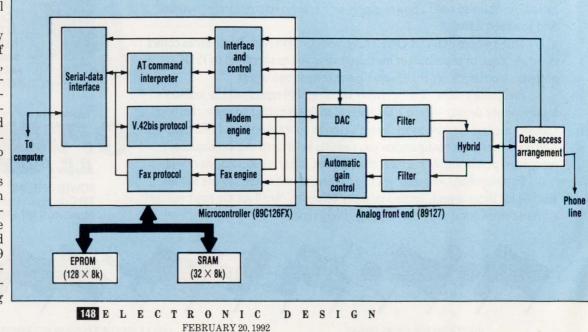

148 Communications Two-chip modem sends and receives data and fax signals

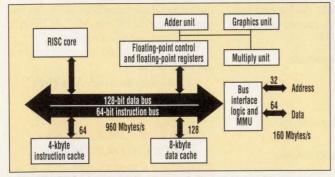

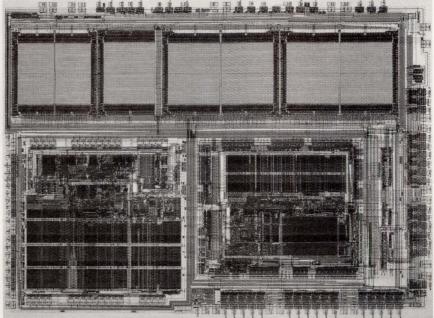

150 Digital ICs High-integration RISC processor targets ACE platform designs

151 Computers & Peripherals

152 Analog 100-MHz DAC creates 10-MHz sine waves with an SFDR of 55 dB

153 Instruments 154 Computer-Aided Engineering 156 Components

#### **160 INDEX OF ADVERTISERS**

#### **161 READER SERVICE CARD**

#### **COMING NEXT ISSUE**

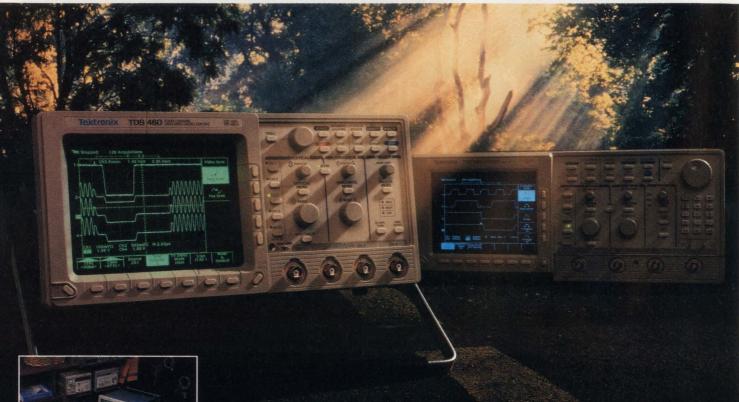

• DSP: Converting an analog prototype to a digital filter

- Special Section: Test & Measurement Update

- Digital technology simplifies spectrum analyzer operation

- Accelerate RF mixer measurements

- First details on a new data/pulse generator

- A new modem chip set for laptop PCs

- Cutting the size of switching regulators

- PLUS: Ideas for Design

Pease Porridge Technology Advances QuickLook

ELECTRONIC DESIGN (USPS 172-080; ISSN 0013-4872) is published semi monthly by Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543. Paid rates for a one year subscription are as follows: \$95 U.S., \$175 Canada, \$255 International. Second-class postage paid at Cleveland, OH, and additional mailing offices. Editorial and advertising addresses: ELECTRONC DESIGN, 611 Route #46 West, Hasbrouck Heights, NJ 07604. Telephone (201) 393-6060. Facsimile (201) 393-0204.

Printed in U.S.A. Title registered in U.S. Patent Office. Copyright © 1992 by Penton Publishing Inc. All rights reserved. The contents of this publication may not be reproduced in whole or in part without the consent of the copyright owner.

Permission is granted to users registered with the Copyright Clearance Center Inc. (CCC) to photocopy any article, with the exception of those for which separate copyright ownership is indicated on the first page of the article plus \$.50 per page is paid directly to the CCC, 27 Congress St., Salem, MA 01970 (Code No. 0013-4872/92 \$1.00 + .50). (Can. GST # R126431964) Copying done for other than personal or internal reference use without the express permission of Penton Publishing, Inc. is prohibited. Requests for special permission or bulk orders should be addressed to the editor. For subscriber change of address and subscrip-

For subscriber change of address and subscription inquiries, call (216) 696-7000.

POSTMASTER: Please send change of address to ELECTRONIC DESIGN, Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543.

E L E C T R O N I C D E S I G N 5 FEBRUARY 20, 1992

## Now you can afford to

Presenting a very small development in Ethernet.\*

Chipsets that are matched to your system and your budget. In fact, they cost you as little as 5 square inches. Which, by the way, is less total real estate than any competitive solution. But sizable reductions don't stop with board space, because we're also reducing the price up to 30 percent. Needless to say, true plug-and-play simplicity requires an intelligent network interface. So our new high-integration 82503 Dual Serial Transceiver goes beyond IEEE 802.3 to include automatic port selection, polarity switching and a jumperless interface to AUI or TPE.

For unmatched desktop performance, we offer

© 1992 Intel Corporation. Intel386 and Intel486 are trademarks of Intel Corporation. \*Ethernet is a registered trademark of Xerox and Diamond is a registered trademark of Diamond Brands, Inc.

## put Ethernet in any box.

a complete family of 82596 LAN coprocessors, each optimized to a specific Intel486<sup>™</sup> CPU for maximum throughput. And our 82593 is the perfect LAN controller for Intel386<sup>™</sup> SL notebooks.

Best of all, these true two-chip solutions give you the flexibility to simplify your design and deliver your product to market in the smallest of timeframes. So look into today's hottest Ethernet chipsets. Call (800) 548-4725 and ask for Lit. Packet #YA23. And learn why we have the perfect match for your

next box.

#### SPECIAL RF Coils & Chokes in 2 Weeks

Sample RF coils and RF chokes designed to meet your special requirements are shipped within 10 days to 2 weeks. Production quantity shipments start within 3 to 4 weeks after approval of samples. Intensive specialization in coil design and manufacture assures a high degree of optimum performance.

Most popular standard inductors available from stock for immediate shipment. Full line catalog on

request.

#### J.W. Miller Division BELL INDUSTRIES

306 E. Alondra Blvd., Gardena, CA 90248 Phone: 310-515-1720 FAX: 310-515-1962 Since 1924, leading manufacturer of standard and custom inductors.

Editor-in-Chief: Stephen E. Scrupski

**Executive Editor:** Roger Allan

Managing Editor: Bob Milne

Senior Editors: Frank Goodenough, Milt Leonard, John Novellino

Technology Editors: Analog & Power: Frank Goodenough Communications & Industrial: Milt Leonard (San Jose) Components & Packaging: David Maliniak Computer-Aided Engineering: Lisa Maliniak Computer Systems: Richard Nass Semiconductors: Dave Bursky (San Jose) Software: Sherrie Van Tyle Test & Measurement: John Novellino

#### Field Bureaus:

West Coast Executive Editor: Dave Bursky (San Jose) Communications & Industrial: Milt Leonard (San Jose) Dallas: Jon Campbell Frankfurt: John Gosch London: Peter Fletcher

Chief Copy Editor: Roger Engelke, Jr.

Contributing Editors: Ron Kmetovicz, Robert A. Pease

Editorial Production Manager: Lisa Iarkowski

Production Coordinator: Pat A. Boselli

Associate Art Director: Tony Vitolo

Staff Artist/Designer: Tom Pennella

**Editorial Support Supervisor:** Mary James

Editorial Assistant: Ann Kunzweiler

Editorial Secretary: Bradie Guerrero

Editorial Offices: (201) 393-6262

Advertising Production: (201) 393-6093 or FAX (201) 393-0410

Production Manager: Michael McCabe Production Assistants: Donna Marie Bright, Lucrezia Hlavaty, Eileen Slavinsky

Circulation Manager: Robert Clark

Promotion Manager: Clifford Meth

Reprints: Helen Ryan 1-800-835-7746

Group Art Director: Peter K. Jeziorski

Published by Penton Publishing Vice President-Editorial: Perry Pascarella

Publisher: Paul C. Mazzacano

CIRCLE 88 FOR U.S. RESPONSE CIRCLE 89 FOR RESPONSE OUTSIDE THE U.S. B E L E C T R O N I C

**FEBRUARY 20, 1992**

DESIGN

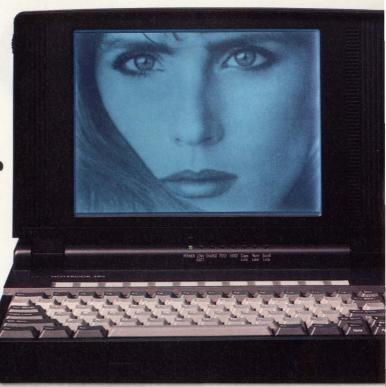

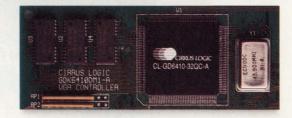

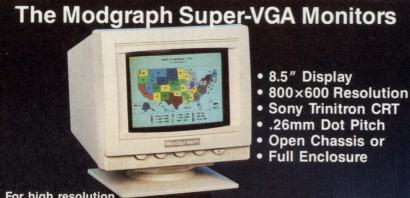

# For a Spectacular VGA Display...

### It's the Least You Can Do.

#### Introducing the LCD VGA that rivals CRT displays

Your next LCD display will look great with the CL-GD6410. Proprietary color mapping techniques offer 64 shades of gray on monochrome LCD panels or a palette of 24,000 colors on 512-color active-matrix LCD panels, with virtually no flickering. Linear gray scales give you display images unmatched by any other LCD VGA controller.

For a palette of up to 256,000 brilliant colors, simply add our CL-GD6340 Color LCD Interface Controller.

#### SimulSCAN: Exclusive! Drive notebook and external displays simultaneously

This hot new feature is ideal for portables used in audience presentations. Get it now for the first time in a single-chip LCD controller without extra external circuitry. Any notebook computer without it will be unpresentable.

#### One-chip LCD VGA control for smaller, lighter notebooks

Integrated features give you the smallest form factor available. Simply add DRAMs and a clock synthesizer and you have a complete solution in 5 ICs, requiring less than 4 square inches of board space. Making it the ideal solution for your next notebook design.

#### Lowest power requirements for longer battery life

Our frame accelerator architecture allows you to run the LCD with clock frequencies half those of other solutions and with half the power consumption. Operating down to 4.5 V extends battery life as much as 10%. Three on-chip power-down modes and a variety of system design options provide flexibility in power management.

The least you can do to get a most impressive image is to look into the CL-GD6410.

©1991 Cirus Logic, Inc., 3100 West Warren Avenue, Fremont, CA 94538 (510)623-8300; Japan: (813-5389-5300, Singapore: (85)8532122, Taiwan: (886)2-718-4533, Germany: (49)8152-2030, United Kingdom: (44)0727-872424 Cirus Logic, Inc. All other trademarks of Cirus Logic, Inc. All other trademarks are registered to their respective companies.

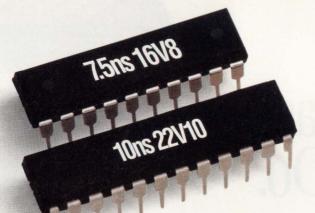

# Low Delays.

#### High-Speed 7.5ns CMOS PAL<sup>®</sup> Devices.

There's nothing we hate more than delays. That's why we developed high speed CMOS PAL devices that no one can beat—our CMOS 7.5ns 16V8H-7 and 10ns 22V10H-10 PAL devices.

In fact, nobody even comes close to our in-system performance, with the fastest set-up

and clock-to-out times available. Both come in PLCC and DIP varieties. All on state-of-the-art submicron EE CMOS.

#### High-Volume, High-Speed Delivery.

Again, there's nothing we hate more than delays. You can get huge volumes of our new CMOS PAL devices now.

And they're on the shelf at your local dis-

# No Delays.

tributor, too. So you can get the quantity and speed you need, whenever you need them.

What more can you expect from the company that sells more programmable logic than all of its competitors combined?

So pick up the phone and place your order today, or call **1-800-222-9323** for more information.

Because at AMD, we don't believe in long delays either.

901 Thompson Place, P.O. Box 3453, Sunnyvale, CA 94088 © 1991 Advanced Micro Devices, Inc. PAL is a registered trademark of Advanced Micro Devices. All brand or product names mentioned are trademarks or registered trademarks of their respective holders.

### If you think DSPs are priced Our TMS320 family starts at

### out of reach, think again. just <sup>\$</sup>3.

Ost is no longer a barrier to using DSPs. At Texas Instruments, our TMS320 family is well within your reach, thanks in large part to a decade of DSP leadership.

#### 16-bit DSPs as low as \$3

Our 16-bit, fixed-point solutions begin at \$3. At that, they are on a price par with microcontrollers and are as easy to use, yet give you 10X the performance. These DSPs are extremely

DSP

MS320C51

well suited to highvolume applica-

tions, providing you with opportunities to optimize price/performance

ratios. In fact, our 16-bit DSPs are replacing microcontrollers in mainstream applications such as answering machines and disk drives.

#### 32-bit DSPs starting at \$25

You can get floating-point performance at a fixed-point price. Starting as low as \$25, our 32-bit floating-point DSPs are finding widespread use in embedded, cost-sensitive applications. Performance is superior to RISC processors because of highly paralleled architectures.

In addition to a low unit price, several features contribute to overall cost-effectiveness. These devices are inherently easy to use and are optimized for use with high-level-language compilers, which helps you get to market faster. When you require a custom approach, we have the unique capability to adapt our 16- and 32-bit DSPs to your needs.

The entire TMS320 family is supported by an extensive array of development tools, readily accessible applications help and full documentation to help enhance your productivity and cut development time.

TM5320C

#### Passing savings on to you

In the 10 years since TI introduced its first single-chip DSP, we have shipped tens of millions of these devices worldwide. And we have applied the principles of manufacturing excellence learned from our commitment to DRAM manufacturing. This has resulted in the economies of scale that enable us to provide you with true value and dependable prices.

#### To put TI's DSPs within reach, call 1-800-336-5236, ext. 3536

We'll send you information on our TMS320 family, world-class support and customizable capability (cDSP). You'll also get our interactive disk, "Designing with DSPs is Easy" – a look at TMS320 support and the TMS320 Programmer's Interface.

08-12081

### Million Steps and back!

Is your motor earthbound by sluggish controllers that

can't give you the performance you need? Look at

what you get with the new CY545 single chip stepper motor controller:

- 40-pin, CMOS, + 5v chip

- Speeds up to 27K Steps/sec

- 16 Million steps per motion

- Programmable start rate, accel/decel, slew rate

- Pulse and Direction Output

- Separate Limit Switches

- Jog operation

- Home seek command

- ASCII or binary commands

- Parallel or Serial interface

- 8 General Purpose I/O lines

- External memory control

- LCD & LED Display interface

- Thumbwheel Switch interface

Break the single chip speed barrier and the high performance price barrier. You can't afford to pass up this latest innovation from the company that, ten years ago, brought you the first stepper motor controller on a

single chip! Order by Fax or phone or call today for free info.

**Cybernetic Micro Systems** PO Box 3000 • San Gregorio CA 94074 Ph: (415) 726-3000 • Fax: (415) 726-3003

#### EDITORIAL

#### THE MIND TENDS TO DRIFT

andom thoughts while stuck in morning traffic on I-80 in Saddle Brook, N.J., and the only sports news is about player contracts and a few basketball scores....I hope the Pentagon realizes that its plan to put prototypes on the shelf until they're needed, and then put them into production, is chancy at best. Although there's been great strides made in smoothing the transition from design to manufacturing with concurrent-engineering schemes, experience shows that you're still never really sure about a product until you can do final testing on production models....Despite the deep cuts planned in defense procurement for airplanes, submarines, and other weapons platforms, shouldn't there still be a strong market for upgraded military electronics subsystems? Even if we don't build more airframes, tank bodies, and rocket enclosures, we still must continue to improve communications, guidance, countermeasures, and other subsystems. Electronics technology is advancing at a dizzying pace, and, if the systems were designed properly in the first place, it shouldn't be difficult to retrofit them with the latest technology....Speaking of today's technology, isn't it amazing to look back and realize that, in 1969, we landed men on the moon and brought them back using 1960'svintage guidance and communications systems?....Japanese politicians aren't doing any good for Japanese business by characterizing America as Japan's subcontractor, or calling American workers lazy. The next thing you know, they'll claim that U.S. semiconductors and computers, like American cars, are designed only for driving on the right side of the road – that would make as much sense as their earlier statements....On the other hand, we must acknowledge the need to revitalize the American educational system. Conversations with U.S. manufacturers reveal that many companies must put employees through the three-R courses to bring them to a productive working level....Has anyone else ever noted the fundamental difference in baseball and football philosophies and wondered if there are any links between those philosophies and business management philosophy? In baseball, you play just about every day in a season comprising 162 games. You know games will be lost, so you take a long-range approach and make a series of individual, day-by-day decisions to produce an overall optimum result. In football, you play once a week in a 16-game season, so you take a short-range, must-win attitude for every game. Given the growth of interest in pro football in American business over the past two decades, is this football philosophy reflected in the short-range, quarter-by-quarter planning that prevailed in business throughout the 1970s and 1980s? Maybe

some sports-minded MBA student should investigate this for a master's thesis.

tepten Erupski

Editor-in-Chief

14 E L E C T R O N I C DESIGN **FEBRUARY 20, 1992**

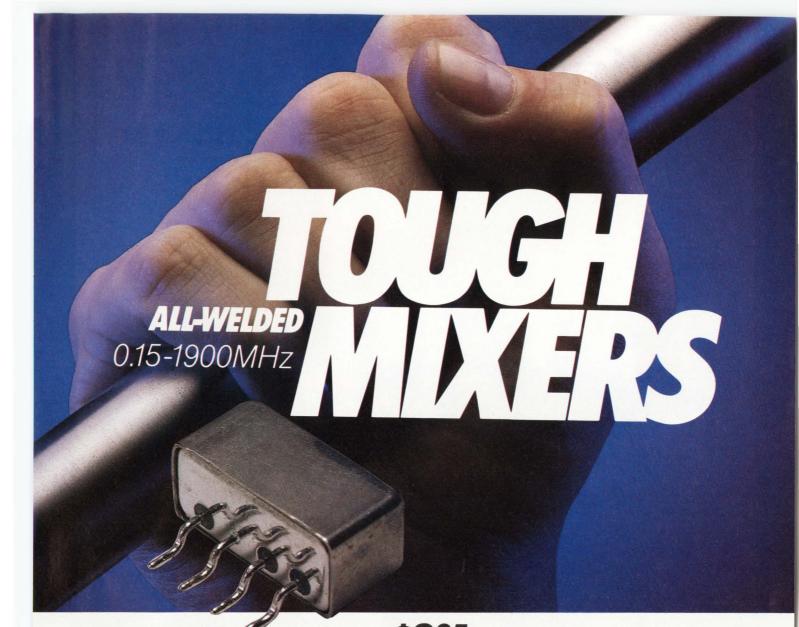

#### SURFACE-MOUNT or PLUG-IN FROM

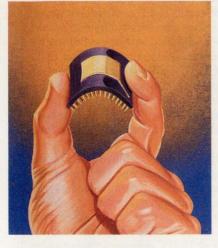

Let Mini-Circuits' new TUF-mixers stew in a sizzling 250°C environment for five minutes and then compare specs against room temperature performance...no trace of degradation. That's a tough mixer!

TUF-mixer components can take the extreme shock and vibration stresses of MIL-STD-28837 as well as more than 200 cycles of thermal shock ranging from -55° to +100°C; the Ultra-Rel diodes used can withstand 168 hours at 300°C.

Performance features include very low conversion loss (flat over the entire band), high isolation (LO-RF, LO-IF), and well-matched VSWR at all ports. A fully-detailed database on all performance characteristics is available, along with an experienced application staff to guide users upon request.

All-welded internal and external construction is used to assemble and package the TUF-unit in a tiny 0.5 by 0.2 by 0.25 inch metal case. The non-hermetic, miniature mixers are available for surface mounting (-SM) or plug-in applications. Only four leads extend from the mixer, simplifying lead placement.

Also guaranteed on these Ultra-Rel<sup>TM</sup> mixers is unprecedented 4.5 sigma unitto-unit repeatability, meaning units ordered today or next year will provide performance identical to those delivered last year. Major distribution centers as well as local distributors enable shipments of volume quantities from stock.

Tough, tiny, and with tight repeatability...Mini-Circuits' Ultra-Rel<sup>™</sup> TUFmixers, with a 5-yr. guarantee, priced from \$3.95...only from Mini-Circuits.

| SPECIFICA    | TIONS    |

|--------------|----------|

| A d = st = 1 | <b>F</b> |

| Μ | odel                                                                                                           | Freq.<br>L-R | (d   | *    | lsol.<br>L-R | Price, \$<br>each |  |

|---|----------------------------------------------------------------------------------------------------------------|--------------|------|------|--------------|-------------------|--|

|   | A CONTRACTOR OF THE OWNER OF THE | (MHz)        | X    | δ    | (dB)         | (10 qty)          |  |

|   | JF-3<br>JF-3SM                                                                                                 | 0.15-400     | 4.98 | 0.34 | 46           | 5.95              |  |

|   | JF-1<br>JF-1SM                                                                                                 | 2-600        | 5.82 | 0.19 | 42           | 3.95              |  |

|   | JF-2<br>JF-2SM                                                                                                 | 50-1000      | 5.73 | 0.30 | 47           | 4.95              |  |

|   | JF-5<br>JF-5SM                                                                                                 | 20-1500      | 6.58 | 0.40 | 42           | 8.95              |  |

|   | JF-860<br>JF-860SM                                                                                             | 860-1050     | 6.2  | 0.37 | 35           | 8.95              |  |

|   | JF-11A<br>JF-11ASM                                                                                             | 1400-1900    | 6.83 | 0.30 | 33           | 14.95             |  |

**X** = average conversion loss at upper end of midband ( $f_U/2$ )  $\delta$  = sigma or standard deviation

with extra long life due to unique HP monolithic diode construction, 300°C high temp. storage, 1000 cycles thermal shock, vibration, acceleration, and mechanical shock exceeding MIL requirements.

setting higher standards actual size Miniper Circuits P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661

finding new ways.

Distribution Centers/NORTH AMERICA 800-654-7949 • 417-335-5935 Fax 417-335-5945 EUROPE 44-252-835094 Fax 44-252-837010

For detailed specs and computer-automated performance data (CAPD), refer to Thomas Register Vol. 23, MicroWaves Product Directory, EEM, or Mini-Circuits' 718-pg Handbook

**CIRCLE 139 FOR RESPONSE OUTSIDE THE U.S.**

### Putting you 3.3V ahead of

### the portable market.

These days, a dream design for a portable system can become a nightmare overnight. By the time you launch, you may be late to market.

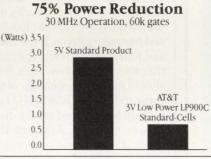

"Customerizing" means helping you differentiate your product. By providing a 3.3 volt, reduced-heat route to a smaller, lighter, longer-operating notebook, disc drive or cellular system. And by giving you all the latitude you need to add product enhancements of your own. CMOS ASIC library that includes over 400 3.3V standard cells, optimized from our existing, industry-standard 5V library.

Our 3.3V performance also extends to industry standard PC macrocells including RAM, ROM, a DMA controller, UART and 80C51-compatible microcontroller.

More 3.3V ASICs design tools Our libraries are ported to CAD tools like AT&T, Mentor Graphics, Synopsys, Verilog and Viewlogic, providing the symbols, simulation models

3 times longer battery life

packages. And achieve tighter IC

3.3 volt CMOS ASIC library

LP900C 3.3V library. A 0.9 micron,

Speed and simplify your 3.3

design-in with AT&T's exclusive

Our 3.3V ASIC solution enables you to slash system power requirements. Lets you pack more circuit gates within inexpensive plastic

packaging densities.

P900C ells mum 3.3V circuit operation. So if 3.3 sounds like a "portable" number you'd

and ERC tools

you need to

ensure opti-

like to try, ask for our 3.3 Volt ASIC Information Package, including Data Book and Product Brief. Just call AT&T Microelectronics at 1800 372-2447, ext. 633.

© 1991 AT&T

CIRCLE 200 FOR U.S. RESPONSE

CIRCLE 192 FOR U.S. RESPONSE CIRCLE 193 FOR RESPONSE OUTSIDE THE U.S.

#### TECHNOLOGY BRIEFING

#### **DISK ARRAYS AND BEYOND**

ith computers weaving their way into all areas of business, the amount of data that requires storage has grown exponentially. In nearly every business, it's essential that archival data be preserved so that it's always accessible and can't be lost. More and more, system designers faced with this problem turn to a disk array – a group of disk drives, which supplyhundreds of gigabytes of capacity, that are tied together specifically to recover all data if the disk fails. Disk arrays offer still another benefit: They help increase the disk transfer rates. That's because if two disks in a disk array can be accessed simultaneously, then the access time is theoretically cut in half.

RICHARD NASS COMPUTER SYSTEMS

Disk arrays aren't a new technology. Most fault-tolerant systems have employed some type of disk array to prevent any data loss under any circumstance. And, before disk arrays, parallel-transfer drives (PTDs), striping, and mirroring were some of the methods used to reduce the I/O bottleneck between the processor and the disk drive.

PTDs increase the transfer rate by reading and writing from multiple heads simultaneously on one large drive. The transfer rate may increase with this method, but it doesn't address the reliability problem (if the drive fails, it's difficult to recover the data). Striping divides the data into many pieces, than transfers the pieces to multiple drives in parallel. This action may occur in the host software or in the drive controller. Mirroring simply duplicates the data on a second drive. If one drive fails, the same data is on the second drive in its original form. This is expensive because it doubles the hardware requirements.

One recent disk-array architecture was developed by NCR Corp., Fort Collins, Colo., which developed a concept called Redundant Array of Inexpensive Disks, or RAID. By using RAID, data lost due to drive failure can be reconstructed when the faulty drive is replaced. The data-reconstruction principle is a fairly simple one: In a five-drive system, there would be four data drives and one parity drive. If the four data drives contained numbers one, two, three, and four, respectively, the parity drive would contain number ten, the sum of the other four drives. Then, if drive two fails and is replaced, the recovered data should equal the contents of the parity drive minus the contents of the other three drives. NCR'S RAID Level Five, currently being implemented, doesn't contain a dedicated parity disk. Instead, the parity information is spread out onto every drive. Although this method is slightly slower than the dedicated drive, it lowers cost by eliminating one drive.

That methodology has been taken to the next level by the Iceberg disk-array storage subsystem for mainframe, midrange, and network-attached systems. Iceberg, from StorageTek Corp., Louisville, Colo., is based on the company's Extended Storage Architecture (XSA). Ryal Poppa, StorageTek's president and CEO claims, "This technology puts us at least two years ahead of the competition, probably three years." The heart of XSA is a mapping capability that presents an IBM 3990 interface to the host, user, and system programmer. Tables of pointers in the Iceberg controller supply dynamic mapping between the functional configuration that the host system sees and the physical devices that make up the Iceberg subsystem.

Built-in hardware buffers minimize the losses caused by the creation of redundancy data. Because XSA rewrites all updates to a new disk location, redundancy information isn't rewritten, as is the case with conventional diskarray designs. Consequently, XSA eliminates the write-performance penalty associated with updates to conventional disk arrays. Moreover, the parallelism built into XSA helps ensure a real-time response for functional track recovery by allowing virtually all drives in the array to seek, read, or transfer data simultaneously.

**18** E L E C T R O N I C D E S I G N FEBRUARY 20, 1992

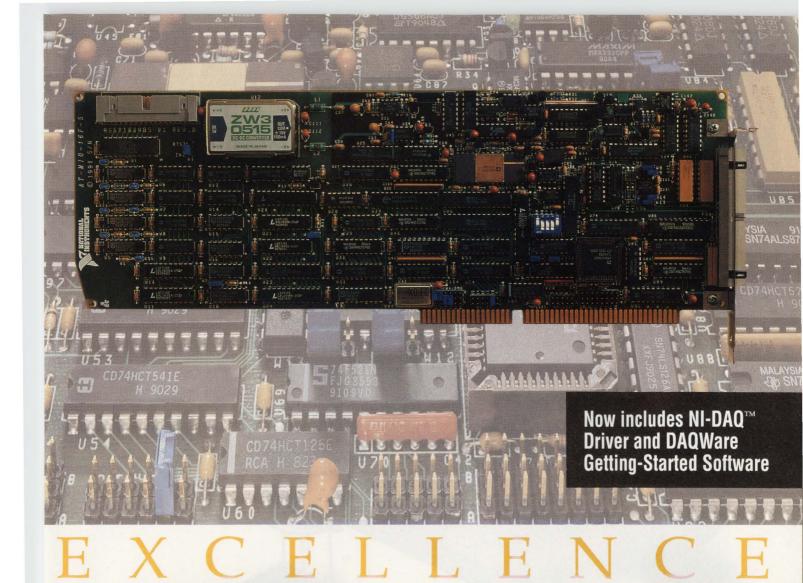

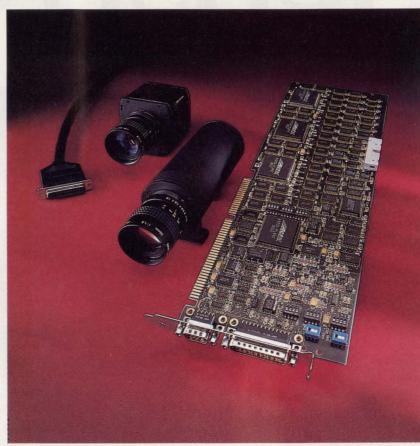

### Setting the New Standard in PC Data Acquisition

It takes a serious commitment to quality to deliver data acquisition boards that reliably meet the most demanding specifications. The National Instruments AT-MIO-16F-5 board creates a new standard in excellence with features not found on typical data acquisition boards.

Software for programming the AT-MIO-16F-5 ranges from drivers for Microsoft Windows and DOS to LabWindows<sup>®</sup> application software. The quality, innovation, and performance of the AT-MIO-16F-5 sets the new standard in PC data acquisition. For more information on the AT-MIO-16F-5,

| These features include:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               |                | -             | - /        |       | ,                           |                                  | -   | -       |            |                                          | 100   | 1/00   | 2/           | -       | -   | ,           | our complete line of data                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------|---------------|------------|-------|-----------------------------|----------------------------------|-----|---------|------------|------------------------------------------|-------|--------|--------------|---------|-----|-------------|-------------------------------------------------------------|

| 200 ksamples/sec samples/sec samples/se | ling rate                     | /              | Board         | //         | 1     | Rate                        | ANALOG INF                       | 907 | -       | /          | 10                                       | 5/    | annel  | 2/           | 1       | /   | 7           | acquisition boards, signal conditioning products, or        |

| <ul> <li>Software-configurable an<br/>input and gain</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ling rate<br>halog<br>Data h  | auisitio       | Computer      | hanels hat | ampli | Resolution Dits             | W Bains                          | /   | channel | Aesolution | an a | Count | er Tim | of the state | ADY DOS | Win | Sure Vision | software, call us.<br>(512) 794-0100 or                     |

| Optimum noise control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | EISA-A2000                    | EISA           | 4.05          | 1,000,00   | 1     | ſ                           | 1                                | -   | -       | -          | -                                        | 1     |        |              | 1       | 1   | 1           | (800) 433-3488<br>(U.S. and Canada)                         |

| True self-calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (                             | 4              | 16 SE         |            | 4     |                             | 0512510                          | 4   | -       | 4          | 4                                        | 4     | Ż      | 2            | 7       | 7   | 7           |                                                             |

| Dither generator for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | AT-MIO-16F-5                  | AT             | 16 SE<br>8 DI | 200,000    | 12    | ±5, 0 to 10                 | 0.5, 1, 2, 5, 10,<br>20, 50, 100 | 2   | 12      | 8          | 3                                        | 1     | 1      | 1            |         |     | 1           |                                                             |

| extended resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | AT-MIO-16H-9<br>AT-MIO-16H-25 | AT             | 16 SE<br>8 DI | 100,000    | 12    | ±10, ±5,<br>0 to 10         | 1, 2, 4, 8                       | 2   | 12      | 8          | 3                                        | 1     | 1      |              | 11      |     | 1           | Contract of the relation realist                            |

| RTSI <sup>®</sup> bus for multi-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | AT-MIO-16L-9<br>AT-MIO-16L-25 | AT             | 16 SE<br>8 DI | 100,000    | 12    | ±10, ±5,<br>0 to 10         | 1, 10, 100,<br>500               | 2   | 12      | 8          | 3                                        | 1     | 1      |              | 11      | :   | 1           |                                                             |

| board synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Lab-PC                        | XT             | 8 SE          | 62,500     | 12    | ±5, 0 to 10                 | 1, 2, 5, 10, 20,<br>50, 100      | 2   | 12      | 24         | 3                                        | 1     |        |              | / /     |     | 1           | INSTRUMENTS                                                 |

| <ul> <li>Custom instrumentation<br/>amplifier</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PC-LPM-16                     | ХТ             | 16 SE         | 50,000     | 12    | ±5, 0 to 10<br>±2.5, 0 to 5 | 1                                | -   | -       | 16†        | 3                                        | 1     |        |              | 1       |     |             | The Software is the Instrument<br>6504 Bridge Point Parkway |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | AT-DIO-32F<br>PC-DIO-96       | AT<br>XT<br>XT | -             | -          | -     | -                           | -                                | -   | -       | 32<br>96   | -                                        | 1     | 1      |              | (       |     | -           | Austin, TX 78730-5039                                       |

| Microsoft Windows and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PC-DI0-96<br>PC-DI0-24        | XT             | -             | -          | -     | -                           | =                                | -   | -       | 24         | -                                        | 12    | 1      |              | 1       |     | 1           |                                                             |

| DOS driver software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PC-TIO-10                     | ХТ             | -             | -          | -     | -                           |                                  | -   | -       | 16         | 10                                       | 1     | 1      |              | /       |     |             | CIRCLE 146 FOR U.S. RESPONSE                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | + CE Cinale                   | -Ende          | d DI          | Different  | ial i | ce Cimulton                 | aque Campling                    |     |         |            | - 0                                      | Cha   | nnal   | 0.10         | 0.0     | han | nolo (      | CIPCLE 147 FOR RESPONSE OUTSIDE THE US                      |

AUSTRALIA (03) 879 9422 - BELGIUM (02) 757 00 20 - CANADA (519) 622 9310 - DENMARK (45) 76 73 22 - FRANCE (1) 48 65 33 70 - GERMANY (089) 714 5093 - ITALY (02) 4830 1892 JAPAN (03) 3788 1921 - NETHERLANDS (01720) 45761 - NORWAY (03) 846 866 - SPAIN (908) 604 304 - SWEDEN (08) 984 970 - SWITZERLAND (056) 45 58 80 - U.K. (0635) 523 545

Product names listed are trademarks of their respective manufacturers. Company names listed are trademarks or trade names of their respective companies. ©Copyright 1991 National Instruments Corporation. All rights reserved.

# Over 50 off-the-shelf models...

Having difficulty locating RF or pulse transformers with low droop, fast risetime or a particular impedance ratio over a specific frequency range?...Mini-Circuits offers a solution.

Choose impedance ratios from 1:1 to 36:1, connector or pin versions (plastic or metal case built to meet MIL-T-21038 and MIL-T-55831 requirements\*). Ultra-wideband response achieves low droop and fast risetime for pulse applications. Ratings up to 1000M ohms insulation resistance and up to 1000V dielectric voltage. For wide dynamic range applications involving up to 100 mA DC primary current, use the T-H series. Coaxial connector models are offered with 50 and 75 ohm impedance; BNC standard; request other types. Available for immediate delivery with one-year guarantee.

. Pro

Call or write for 68-page catalog or see our catalog in EEM, or Microwaves Product Data Directory. \*units are not QPL listed

T, TH, TT

ТО

тмо

T, TH, TT

T, TH, TT bent lead version style KK81

bent lead version style X 65

#### case styles T, TH, case W 38, X 65 bent lead version, KK81 bent lead version TMO, case A 11, † case B 13 FT, FTB, case H 16 NEW TC SURFACE MOUNT MODELS from 1MHz to 1500 MHz

| NSN GUI   | DE<br>NSN        | MCL NO.   | NSN     |

|-----------|------------------|-----------|---------|

| FTB1-1-75 | 5950-01-132-8034 | TMO2-1    | 5950-01 |

| FTB1-6    | 5950-01-225-8773 | TMO2.5-6  | 5950-01 |

| T1-1      | 5950-10-128-3745 | TMO2.5-6T | 5950-01 |

| T1-1T     | 5950-01-153-0668 | TMO3-1T   | 5950-01 |

| T2-1      | 5950-01-106-1218 | TMO4-1    | 5950-01 |

| T3-1T     | 5950-01-153-0298 | TMO4-2    | 5950-01 |

| T4-1      | 5950-01-024-7626 | TMO4-6    | 5950-01 |

| T9-1      | 5950-01-105-8153 | TMO5-1T   | 5950-01 |

| T16-1     | 5950-01-094-7439 | TMO9-1    | 5950-01 |

| TMO1-1    | 5950-01-178-2612 | TMO16-1   | 5950-01 |

|           |                  |           |         |

| NO.   | NSN            |

|-------|----------------|

| -1    | 5950-01-183-64 |

| .5-6  | 5950-01-215-40 |

| .5-6T | 5950-01-215-86 |

| -1T   | 5950-01-168-75 |

| -1    | 5950-01-067-10 |

| -2    | 5950-01-091-38 |

| -6    | 5950-01-132-81 |

| -1T   | 5950-01-183-07 |

| -1    | 5950-01-141-01 |

| 6-1   | 5950-01-138-45 |

|       |                |

# FORMERS 3KHz-800MHz from \$325

|    |                                     |                      |                                                                                                                                                                                                                         | Ω<br>RATIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | FREQUENCY<br>MHz                                                                                                                                                                                                              | 11                                                                                                                                                                                                                                                                  | SERTION LO                                                                                                                                                                                              | OSS                                                                                                                                                                                                                                                                                                              | PRICE \$                                                                                                                                     |

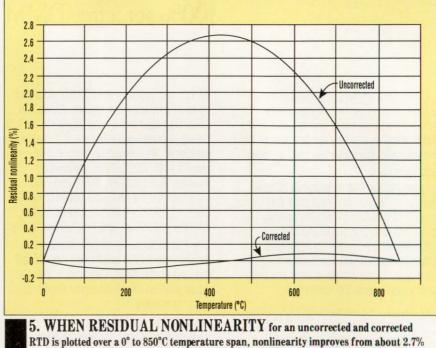

|----|-------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|