# NOW SHIPPING

Once again, Lattice leads the market with the world's fastest CMOS 22V10. The 10ns, **GAL22V10B-10**. Thanks to our E<sup>2</sup>CMOS<sup>®</sup> technology, this GAL<sup>®</sup> device runs at a cool 90mA typical lcc. And it's 100% tested. When it comes to high performance and high quality, no one can match the Lattice family of leading-edge, E<sup>2</sup>CMOS GAL devices. To have a free sample and a GAL Data Book shipped to you, just call **1-800-FASTGAL**. Ask for

Department 304.

Leader in E<sup>2</sup>CMOS PLDs."

Copyright © 1991, Lattice Semiconductor Corporation. GAL and E<sup>2</sup>CMOS are registered trademarks of Lattice Semiconductor Corporation.

CIRCLE 157 FOR LITERATURE

## Once again, HP has its name in lights.

Leave it to HP to premiere the very first SMT LED offering the brightness, clarity, and color choices of through-hole LEDs.

As one of the world's most experienced LED suppliers, HP wrote the book on high-performance LEDs. Now you can see the same star performance on tape, because our new LED is compatible with tape-fed automatic pick & place equipment and SMT solder processes.

Its small footprint means you can pack more imprints per board. Yet it conforms to the EIA-535 BAAC standard specification for case size 3528 tantalum capacitors.

But we haven't let the bright lights go to our head. Our new SMT LED is competitively priced and multi-sourced.

A class production all the way, these new LEDs are designed to meet most quality and reliability standards, eliminating the need for incoming inspection.

Once again, HP sets the stage for quality, reliability, and innovation. To get the star treatment from HP, call **1-800-752-0900, ext. 2367,** and ask for our FREE red & green SMT LED sample kit. And see what the biggest name in lights can do for you.

There is a better way.

# Outside, all disc drives look t It's really what's inside that co

Zone Bit Recording, ZBR, Seagate and the Seagate logo are registered trademarks of Seagate Technology. Inc.

# he same. unts.

Apart from our nameplate, a Seagate disc drive looks much like any other when viewed from the outside. But it's the tangible and intangible elements we put inside that make a Seagate drive really shine.

If you could see inside you'd find the best components available. Many of them—such

as discs, motors, semiconductors and thinfilm heads — we design and build ourselves, allowing us to control their quality, cost and availability. Most of what we don't manufacture is obtained from a select group of vendors who must meet our strict Supplier Certification Program criteria. This guarantees consistently high quality and continual conformance to our customers' requirements.

Technology is another key Seagate ingredient. As the holder of over 200 disc drive patents, we constantly develop state-of-the-art technologies to enhance the value of our products to our customers. For example, Zone Bit Recording<sup>™</sup> increases the amount of information that can be stored on a disc. But besides increasing the drive's capacity and throughput. ZBR<sup>™</sup> technology can reduce the required number of heads and discs, thereby reducing costs, increasing performance and making the drive significantly more reliable.

The third major factor that sets Seagate drives apart is our commitment. You see it in the inspired dedication of our employees: like our engineers, who apply the latest technology advances to our current models. In our assemblers and technicians, who are committed to producing defect-free products. And in our sales, customer service and technical support groups, who continually go the extra mile to ensure complete customer satisfaction.

But most of all, Seagate drives are built upon experience: the market insight and tech-

nical knowhow that can only come from selling more than 25 million drives since the industry's inception. It's the kind of experience you won't find at any other disc drive company.

To be sure you're getting Seagate quality and technology inside where it counts, make sure there's a Seagate nameplate on the outside. For more information, contact Seagate at 800-468-DISC, or 408-438-6550.

**Seagate**

The first name in disc drives

#### **14 EDITORIAL**

#### **18 TECHNOLOGY BRIEFING**

EDA vendors validate CFI efforts

#### **23 TECHNOLOGY NEWSLETTER**

- Low-power CW laser writes circuit lines

- SSI gets Signetics' 13-GHz QUBiC process

- $\bullet$  X-ray stepper crafts features under 0.35  $\mu m$

- Power, packages shrink for LCD drivers

- SGS readies class-0.1 fab in Grenoble

- JEDEC task force eyes package standards

- Software simplifies system diagnostics

- Multichip-module pact promises lower costs

- USAF contracts MCC for module coatings

#### **31 TECHNOLOGY ADVANCES**

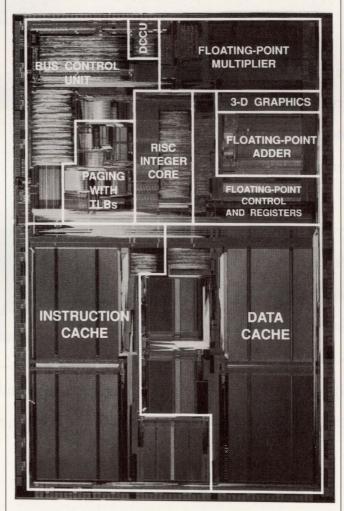

• Multimillion-transistor budget delivers supercomputer-like chip

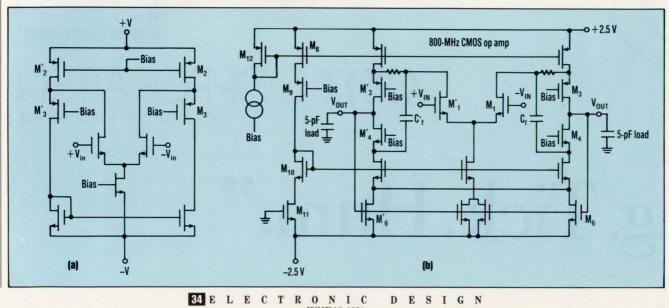

- Digital 1.2-µm process yields CMOS op amp with gain bandwidth of 800 MHz

- Hardwired FPGAs trim system costs once patterns are firmed up

- Automatic on-line inspection and repair boosts LCD production yield

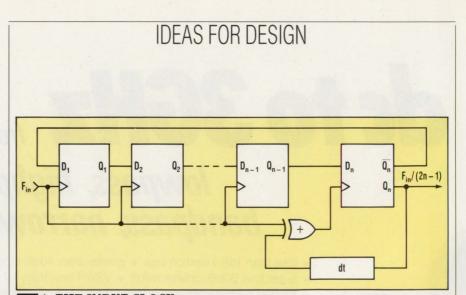

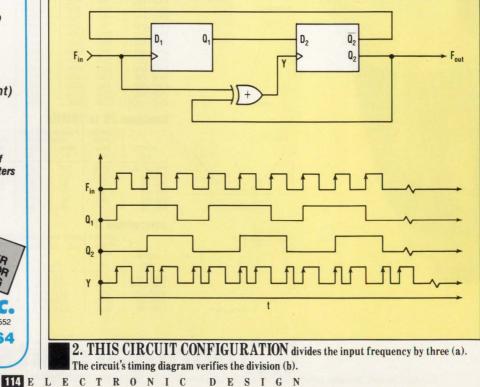

#### **109 IDEAS FOR DESIGN**

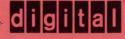

- 15-V supply is isolated to 2500 V

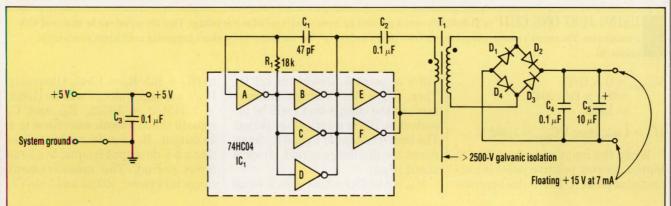

- Circuit converts period to voltage

- Divide input clock frequency

#### **117 CAREER SURVEY**

Bringing a reliable product to market on time—there's the rub, engineers say

#### **123 QUICK LOOK**

• Perspectives on Time-to-Market: Executing a project plan

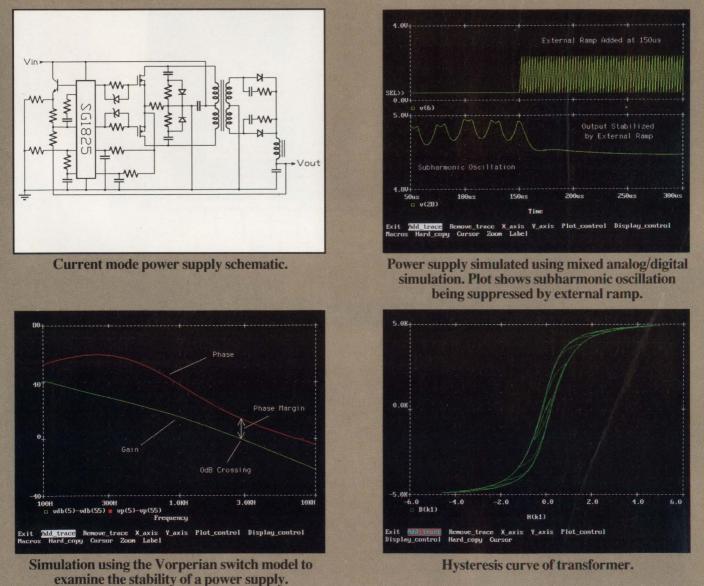

- Down-to-earth forecast for multichip modules

- IEEE standards go onto CD ROM disks

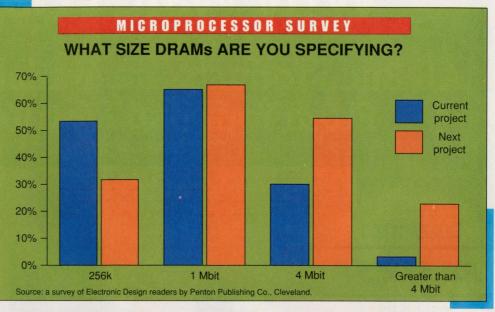

• Survey: How designers are specifying DRAMs

#### **129 PEASE PORRIDGE**

What's all this cottage-cheese stuff, anyhow?

#### **NEW PRODUCTS**

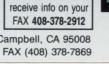

139 Digital ICs Microcontrollers deliver high-end features with 8-bit prices

142 Software

143 Computer Boards 68040 VME SBC bolsters performance using ASICs

145 Computers & Peripherals

146 Computer-Aided Engineering

**147 Instruments**

#### **152 INDEX OF ADVERTISERS**

#### **153 READER SERVICE CARD**

#### **COMING NEXT ISSUE**

- Design team issues: Using boundary scan in design for testability

- Attaining testability with hierarchical design

- $\bullet$  Sort out RISC and CISC processors for embedded systems

- Using new, powerful mid-range digital storage oscilloscopes

- Innovative energy-management chips for PC battery systems

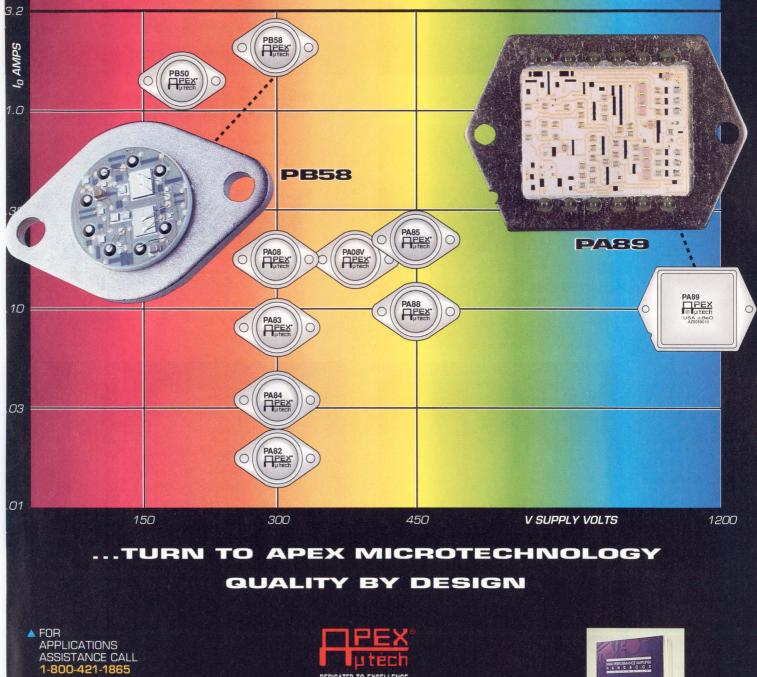

- First details on new high-voltage op amps

- Flexible programming for FPGAs keeps delays short

- PLUS: Pease Porridge QuickLook Ideas for Design Technology Advances

ELECTRONIC DESIGN (USPS 172-080; ISSN 0013-4872) is published semi monthly by Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543. Paid rates for a one year subscription are as follows: 885 U.S., \$160 Canada, \$230 International. Second-class postage paid at Cleveland, OH, and additional mailing offices. Editorial and advertising addresses: ELECTRONIC DESIGN, 611 Route #46 West, Hasbrouck Heights, NJ 07604. Telephone (201) 393-6060. Facsimile (201) 393-0204.

Printed in U.S.A. Title registered in U.S. Patent Office. Copyright©1991 by Penton Publishing Inc. All rights reserved. The contents of this publication may not be reproduced in whole or in part without the consent of the copyright owner.

Permission is granted to users registered with the Copyright Clearance Center Inc. (CCC) to photocopy any article, with the exception of those for which separate copyright ownership is indicated on the first page of the article, provided that a base fee of \$1 per copy of the article plus \$.50 per page is paid directly to the CCC, 27 Congress St., Salem, MA 01970 (Code No. 0013-4872/91 \$1.00 + .50). (Can. GST # R126431964) Copying done for other than personal or internal reference use without the express permission of Penton Publishing, Inc. is prohibited. Requests for special permission or bulk orders should be addressed to the editor. For subscriber change of address and subscrip-

For subscriber change of address and subscription inquiries, call (216) 696-7000. POSTMASTER: Please send change of address

POSTMASTER: Please send change of address to ELECTRONIC DESIGN, Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543.

Hased Hadel

Certificate of Merit Winner, 1988 Jesse H. Neal Editorial Achievement Awards

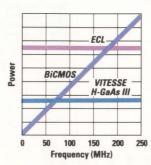

#### **ONE MILLION TRANSISTORS AND**

We're talking better than the best ECL performance at a fraction of the power. And for high frequency designs, Vitesse GaAs chips are lower power than BiCMOS.

Our prices won't guzzle your budget either – our GaAs chips can give you better performance for your dollar than BiCMOS.

#### THE BLINDING SPEED OF GaAs.

For more information on our ASIC and standard products with integration levels up to 350K gates, call Vitesse at (805) 388-7455. And leave the competition in the dust.

| FX Arrays | <b>Raw Gates</b> | Usable Gates  | Availability |  |  |

|-----------|------------------|---------------|--------------|--|--|

| FX100K    | 102,000          | Up To 70,000  | Now          |  |  |

| FX200K    | 195,000          | Up To 137,000 | Now          |  |  |

| FX350K    | 353,000          | Up To 177,000 | Summer 1991  |  |  |

**CIRCLE 130**

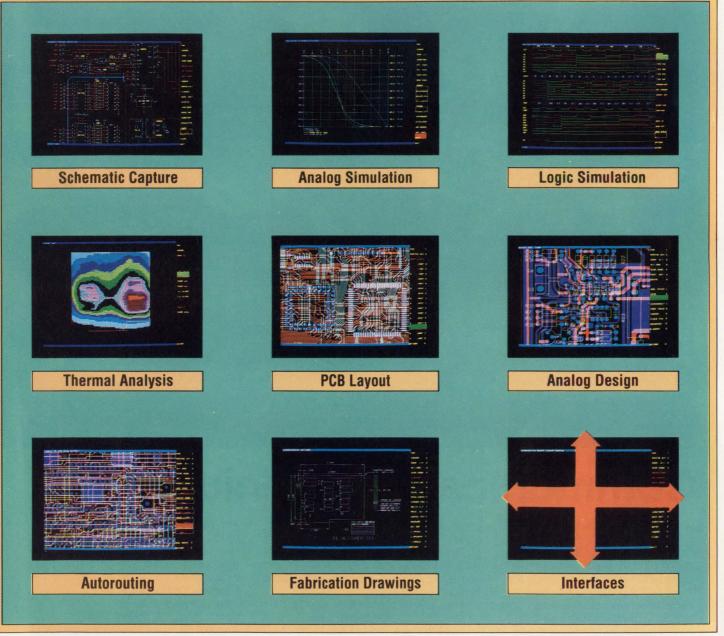

## SIEMENS NIXDORF CALAY Present

SIGRAPH-ELECTRONIC

A New EDA Solution from a World Leader in Technology Including:

#### **SIFRAME Framework**

#### **DESIGN ENTRY**

Schematic Capture

VHDL

• EDIF Netlist

#### **DESIGN VERIFICATION**

• Analog, Digital & Mixed-mode Simulation

- Hardware Modeling

- Soft Macro LibraryTiming Analysis

- LOGIC SYNTHESIS

#### TEST ENGINEERING

- Thermoanalysis

- Reliability Analysis

- Auto Test Pattern Generation

#### PCB LAYOUT ASIC LAYOUT CAM

- Panelization

- Optimization

- Auto Insertion

- Test Preparation

Previewing at the 28th Design Automation Conference June 17-21, 1991, San Francisco Booth 539

#### Siemens Nixdorf Information Systems

Calay Systems 16842 Von Karman, Irvine, CA 92714 (800) 477-7005 FAX (714) 863-0310

## ELECTRONIC DESIGN

Editor-in-Chief: Stephen E. Scrupski

Executive Editor: Roger Allan

Managing Editor: Bob Milne

Senior Editors: Frank Goodenough, Milt Leonard, John Novellino

Technology Editors: Analog & Power: Frank Goodenough Communications & Industrial: Milt Leonard (San Jose) Components & Packaging: David Maliniak Computer-Aided Engineering: Lisa Maliniak Computer Systems: Richard Nass Semiconductors: Dave Bursky (San Jose) Test & Measurement: John Novellino

News Editor: Sherrie Van Tyle

Field Bureaus: West Coast Executive Editor: Dave Bursky (San Jose) Boston: Lawrence Curran Dallas: Jon Campbell Frankfurt: John Gosch London: Peter Fletcher

Chief Copy Editor: Roger Engelke, Jr.

Contributing Editors: Ron Kmetovicz, Robert A. Pease

Editorial Production Manager: Lisa Iarkowski

**Editorial Support Supervisor: Mary James**

Editorial Assistant: Ann Kunzweiler

Editorial Secretary: Bradie Guerrero

Editorial Offices: (201) 393-6262

Advertising Production: (201) 393-6093 or FAX (201) 393-0410

Production Manager: Michael McCabe Production Assistants: Donna Marie Bright, Lucrezia Hlavaty, Eileen Slavinsky

Circulation Manager: Robert Clark

Promotion Manager: Clifford Meth

Reprints: Helen Ryan 1-800-835-7746

Group Art Director: Peter K. Jeziorski

**Computer Systems Administrator:** Anne Gilio Turtoro

Published by Penton Publishing Vice President-Editorial: Perry Pascarella Group Editorial Director: Leland Teschler

Publisher: Paul C. Mazzacano

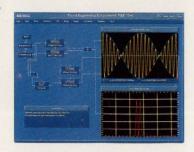

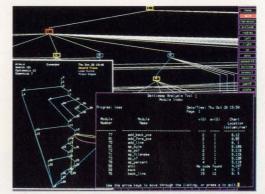

## Finally, engineering software that clears the way to problem solving without programming.

void service int eid; { int stat, by /\*serial poll∢ byte=hpib spoll if ( (byte<0) | !! printf("SRQ Prob return; } stat=my\_read(eid, DVM if (stat>0) {  $buffy[stat] = ' \setminus 0'$ printf("Data from inst write else printf("I/O read error return; } main() { int busid, stat, MTA, MLA; char command[MAXCHARS]; busid=open("/dev/hpib7", O\_RDWR); /\* open raw HP-IB for MTA=hpib\_bus\_status(busid, CURRENT\_BUS\_ADDRESS) + 64;

MLA=hpib\_bus\_status(busid, CURRENT\_BUS\_ADDRESS) + 32; stat = BUTTON\_BIT; sprintf(command, "KM%02o", stat); /\* 2 octal digits \*/

#### With HP VEE, you simply link the icons.

Computers are great for problem solving, if only programming didn't get in the way and slow you down. And now, it doesn't have to. Because the HP visual engineering environment (HP VEE) lets you solve problems without programming.

With HP VEE, you explore solutions visually by arranging and linking icons on the CRT. Each icon represents and executes a specific function for data collection, analysis —from simple mathematics to complex algorithms—and presentation. You don't have to write a single line of code.

There are two HP VEE software packages for prototyping, experimentation, and problem modeling. HP VEE-Engine, at \$995\*, is a general-purpose tool for analysis and presentation of existing data. HP VEE-Test includes HP VEE-Engine and adds extensive I/O capability, including soft panels and device I/O objects for \$5,000\*.

So, if programming is keeping you from finding solutions, call **1-800-752-0900.** Ask for **Ext. 2382**, and find out how HP VEE clears the way. \* U.S. list prices.

There is a better way.

# Because Speed We'll Stop

## MACH

Fastest High Density CMOS PLDs At 15ns

PALCE16V8H-10

Fast Universal CMOS PLD Family At 10ns

PAL16L8-5

Fast Bipolar PLD Family At 5ns

# Is Everything, At Nothing.

---- 15NS

20N5

10<sub>NS</sub>

PALIELB-4 Fastest TTL Bipolar PLD At 4.5ns

## Whatever kind of PLD you need, the fastest comes from AMD.

We'd love it if all our work amounted to "zero." As in zero delay. And we're not far off.

Not surprising—because AMD invented the PAL<sup>®</sup> device. That's why we know programmables better. And offer you the most choices of the best devices.

Say you want speed, but can't sacrifice density. Don't. Use our new MACH™ products (Macro Array CMOS High-density) that give you up to 3600 gates and 15ns performance. They're two to three times faster than the competition and cost 40% less.

For more speed, along with low power consumption, try our new 10- and 15-nanosecond CMOS PLDs. Use our 16V8-10s and 20V8-10s anywhere you'd use a GAL® device. Or choose the everpopular AMD-invented 22V10, at 15ns.

Faster still are our seventh generation bipolar PAL devices. Complete families of 16L8-5s, 20L8-5s, and the 22V10-10s. And for real speed freaks, we're now shipping a 4.5ns bipolar PAL device—the world's fastest TTL programmable logic.

Along with all this speed, we're providing equally fast delivery. In quantity. In fact, we deliver more programmable logic devices than all our competitors combined.

For details, call AMD now at **1-800-222-9323**. And let nothing stand between you and your need for speed.

901 Thompson Place. PO. Box 3453. Sunnyvale. CA 94088 © 1991 Advanced Micro Devices. Inc. MACH is a trademark and PAL is a registered trademark of Advanced Micro Devices. GAL is a registered trademark of Lattice Semiconductor.

## The IBM RISC System/ The power you've been seeking

It's a never-ending quest for power seekers. You're always looking for ways to run your favorite applications faster. Well, search no more. The RISC System/6000<sup>™</sup> family of POWERstations and POWERservers gives you power that soars as high as 23 MFLOPS.

|                     | MFLOPS | MIPS | SPECmark™ |

|---------------------|--------|------|-----------|

| POWERstation 320    | 8.5    | 29.5 | 24.6      |

| DECstation 5000-200 | 3.7    | 24.2 | 18.5      |

When it comes to porting, your ship has come in. Of course, all the speed in the world wouldn't mean much without the applications you need. So the RISC System/6000 family already has more than 2,500 of the most popular technical and commercial applications up, running and running fast. And if you think you know a good thing when you see it, so do software vendors. That's why you'll also be seeing more and more applications coming on board the RISC System/6000 platform all the time. And if you like to build your own solutions, there's a full arsenal of enablers and relational data bases from leading vendors, as well as CASE tools and a host of popular programming languages.

A smorgasbord of solutions. Applications already announced include the IBM engineering design packages CADAM, CAEDS, CBDS,

MFLOPS are the results of the double-precision, all FORTRAN Linpack test 100x100 array suite. The Dhrystone Version 1.1 test results are used to compute RISC System/6000 Integer MIPS value where 1,757 Dhrystones/second is 1 MIPS (Vax 11/780). SPECmark is a geometric mean of ten benchmark tests. All performance data are based on published benchmark information.

IBM is a registered trademark, and RISC System/6000 and CAEDS are trademarks of International Business Machines Corporation. SPECmark is a trademark of Standard Performance Evaluation Corporation. UNIX is a registered trademark of UNIX System Laboratories, Inc. CADAM is a trademark of CADAM INC. CATIA is a trademark of Destauration Corporation. LONIX System CADO and CAEDS are trademark of Digital Equipment Corporation. Add THE NORRIBLE Character(s) © 1990 King Features Syndicate, Inc. © IBM Corp. 1991, all rights reserved.

## 6000 family. for all your applications.

CATIA<sup>™</sup> and AES. Also available are a broad spectrum of solutions from vendors like Valid Logic, MacNeal Schwendler, Swanson Analysis, SAS Institute, SPSS, Wavefront, Alias, Polygen, Cadence, Fluid Dynamics International, Western Atlas, ECL Petro and creare.X. Scientific and technical applications are available in areas like physics, structural analysis, chemistry, securities trading, mathematics, earth resources, operations research, visualization, graphics, technical publishing and more. There's also accounting software like FourGen and support for leading UNIX<sup>®</sup>-based office automation packages. And there are key industry applications for businesses in medical groups, retail stores, newspapers, pharmacies and many more.

#### Command enormous processing clout.

The RISC System/6000 family is built to boost the performance of the software power seekers use most. It's got the best floating point processor in the business for numerically intensive applications, plus a new superscalar processor and incredible 3D

graphics capabilities. To find out more, call your IBM marketing representative or IBM Business Partner. For literature, call 1 800 IBM-6676, ext. 990.

For the Power Seeker.

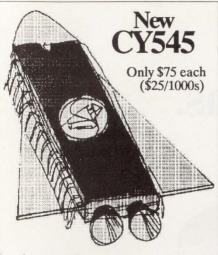

# Accelerate your Stepper Motor to 27,000 Steps/second! Travel 16 Million Steps and back!

Is your motor earthbound by sluggish

controllers that can't give you the performance you need? Look at

what you get with the new CY545 single chip stepper motor controller:

- 40-pin, CMOS, + 5v chip

Speeds up to 27K Steps/sec

- 16 Million steps per motion

- Programmable start rate, . accel/decel, slew rate

- Pulse and Direction Output

- Separate Limit Switches

- Jog operation

- Home seek command .

- ASCII or binary commands

- Parallel or Serial interface

- 8 General Purpose I/O lines .

- External memory control .

- LCD & LED Display interface .

- Thumbwheel Switch interface

Break the single chip speed barrier and the high performance price barrier. You can't afford to pass up this latest innovation from the company that, ten years ago, brought you the first stepper motor controller on a

single chip! Order by Fax or phone or call today for free info.

**Cybernetic Micro Systems** PO Box 3000 • San Gregorio CA 94074 Ph: (415) 726-3000 • Fax: (415) 726-3003

**CIRCLE 126**

## **TECHNOLOGY-TRANSPARENT DESIGN**

**EDITORIAL**

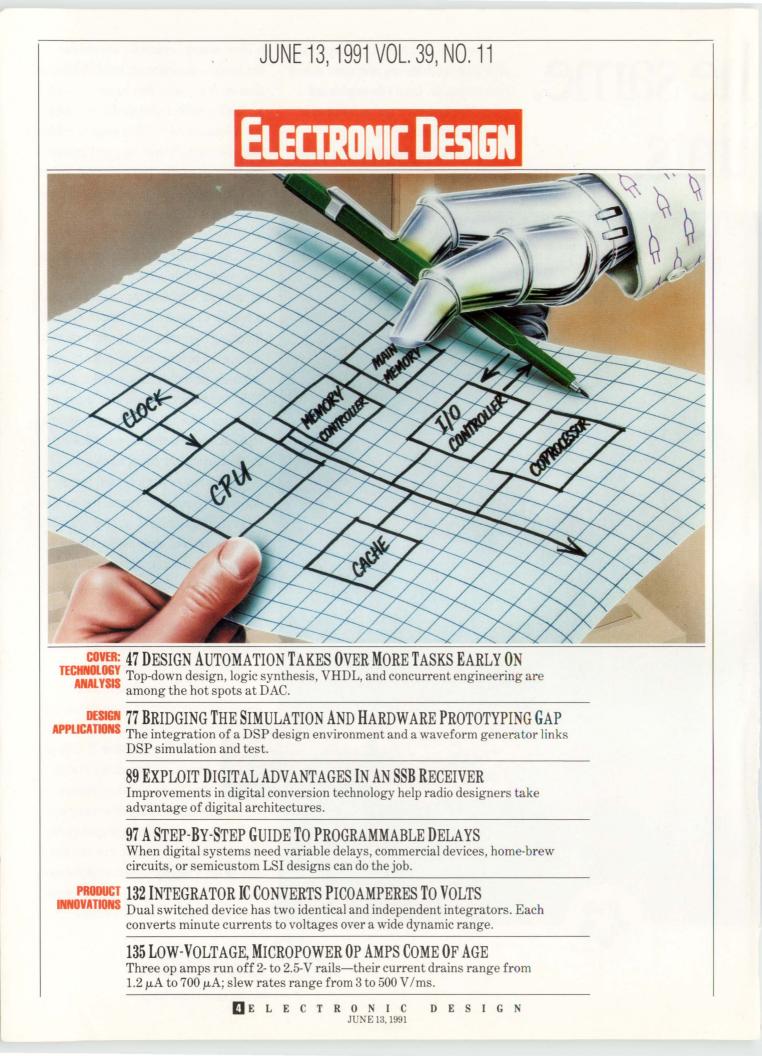

n recent years, the month of June has come to represent the annual convening of the top computer-aided-engineering companies at the Design Automation Conference. This conference, with its focus on better, faster methods of handling complex designs, continuously grows in importance to us at ELEC-TRONIC DESIGN because it lies at the very heart of our editorial charter. This year, the conference is set for the Moscone Convention Center in San Francisco from June 16-20 (stop by booth 418 and say hello to ELECTRONIC DESIGN's editors, who will be there in force). Our preview of this year's conference, which begins on page 47 of this issue, is once again written by CAE Editor Lisa Maliniak, who gives an incisive analysis of the major trends at DAC '91. It primarily covers the many new developments in techniques for easing top-down system design.

Much of the top-down design's success, however, depends on the ease with which designers can convert their designs to hardware-in particular, gate arrays. Here, designers are clearly telling the manufacturers that they want totally open systems, where they need not commit to a particular device until they complete the design. In other words, they want "technology-transparent design" capability. Technology transparency is a term coined by Alberto Sangiovanni-Vincentelli, a professor in the EE and Computer Science departments at the University of California at Berkeley, to describe a designer's ability to design a system without getting locked in to a particular manufacturer's device. Designers want the easiest possible way to implement gate arrays without translating their files, or redesigning logic because their system timing, say, is incompatible with the hardware implementation. Basically, says Sangiovanni-Vincentelli, the designer should be able to go effortlessly from one design to the next.

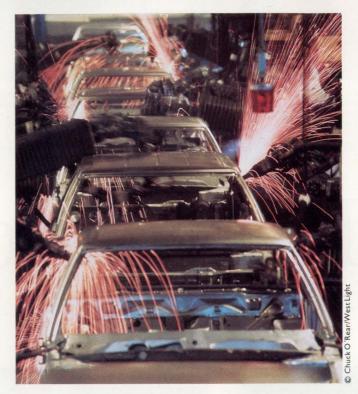

This viewpoint is being echoed by almost everyone in the industry. For example, John East, president and CEO of Actel Inc., says that it's not just a few customers that have expressed this conviction, but a full 100% of them. However, as a maker of field-programmable gate arrays, he acknowledges that companies like his must swallow hard to support this concept. After all, they are loosening their hold on customers by allowing them to change devices at any time during design or production with ease. However, if they don't do it, their competitors will, as has been replayed over and over in recent years. East cites, as an example, the early signals given by automobile buyers, as evidenced in the increased sales of Volkswagens, indicating the public's desire for affordable, gas-efficient automobiles. U.S. auto manufacturers ignored such early warning signals, and have been trying to catch up ever since.

Right now, the electronics industry is also facing early warning signals from its

customers. Let's go for total customer satisfaction now with totally transparent technology, and not wait until it's too late.

# SPDT&SP4 SVJTCHES WITH BUILT-IN DRIVERS

## 10 to 3000MHz from \$3995

MCL OSW 42

Now, high-speed, high-isolation switches with with built-in drivers, tough enough to pass stringent MIL-STD-202 tests. There's no longer any need to hassle with the complexities of designing a TTL driver interface and then adding yet another component to your subsystem...it's already included in a rugged, low-cost, compact assembly. Available in the popular hermetically-sealed TO-8 package or a small EMI-shielded metal connectorized case, these tiny PIN-diode reflective switches, complete with driver, can operate over a 10 to 3000MHz span with a fast 2µsec switching speed. Despite their small size, these units offer

isolation as high as 40dB(typ), insertion loss of only 1.1dB(typ), and a 1dB compression point of +27dBm over most of the frequency range. All models are TTL-compatible and operate from a dc supply voltage of 4.5 to 5.5 V with 1.8mA quiescent current. Switch to Mini-Circuits for highest quality innovative products... and leave the driving to us.

> finding new ways ... setting higher standards Miniper Standards A Division of Scientific Components Corporation P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661 Domestic and International Telexes; 6852844 or 620156

|                | TOSW-230<br>ZFSW-230DR |

|----------------|------------------------|

| eq. Range(MHz) | 10-3000                |

SPECIFICATIONS

| Freq. Range(MHz)          | 10-300  | 00        | 10-250      | 00   |  |

|---------------------------|---------|-----------|-------------|------|--|

| nsert. Loss (dB)          | typ.    | max.      | typ.        | max  |  |

| 10-100MHz                 | 1.3     | 1.9       | 1.3         | 1.7  |  |

| 100-1500MHz               | 1.1     | 1.9       | 1.1         | 1.7  |  |

| 1500-3000MHz              | 1.8     | 2.7       | 1.8         | 2.5  |  |

| solation(dB)              | typ.    | min.      | typ.        | min. |  |

| 10-100MHz                 | 60      | 40        | 60          | 40   |  |

| 100-1500MHz               | 40      | <b>28</b> | 40          | 30   |  |

| 1500-3000MHz              | 35      | 22        | 35          | 22   |  |

| 1dB Compression(dBm)      | typ.    | min.      | typ.        | min. |  |

| 10-100MHz                 | 17      | 6         | 17          | 6    |  |

| 100-1500MHz               | 27      | 19        | 27          | 19   |  |

| 1500-3000MHz              | 30      | 28        | 30          | 28   |  |

| VSWR(ON)                  | typ.    | max.      | typ.        | max  |  |

|                           | 1.3     | 1.6       | 1.3         | 1.6  |  |

| Switching Time (µsec)     | typ.    | max.      | typ.        | max  |  |

| (from 50% TTL to 90% RF)  | 2.0     | 4.0       | 2.0         | 4.0  |  |

| oer. Temp.(°C) -55 to +10 |         | +100      | -55 to +100 |      |  |

| Stor. Temp.(°C) -55 to -  |         | +100      | -55 to +100 |      |  |

| Price (10-24)             | \$39.95 |           | \$59.95     |      |  |

| (1-9)                     | \$89.95 |           | \$109.95    |      |  |

TOSW-425

ZFSW-425DR

WE ACCEPT AMERICAN EXPRESS

# Whether you fax it, fire it, send it, measure it, wire it, compute it, The Analog family of

#### Precision

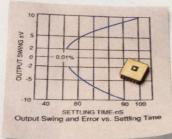

With the AD840, AD841 and AD842, there's no need to trade speed for accuracy. All three settle to 0.01% within 100 ns (840/842) and 110 ns (841) – critical in data acquisition and instrumentation applications – and offer low offset voltages and drifts, and fast slew rates.

#### **FET Input**

For op amps requiring low input current, the OP-42, OP-44, AD845 and AD843 are all remarkably fast – slew rates are 58, 120, 100 and 250 V/ $\mu$ s, respectively. In addition, they offer offset voltages of less than 1 mV and extremely low current noise.

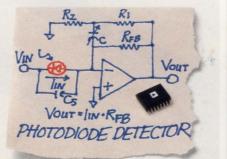

**Transimpedance Amplifiers**

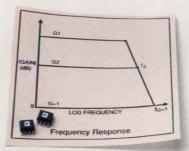

The OP-160, OP-260, AD844, AD846, AD9617 and AD9618 all utilize a current feedback architecture to achieve slew rates from 450 to 2000 V/ $\mu$ s without compromising stability – even in hostile environments. Other benefits include low power dissipation and high unity-gain bandwidth.

If whatever it is you're trying to do involves high-speed op amps, Analog Devices is the company to call. With our current products and new introductions, we have the broadest line of high-speed op amps available. A line that gives you the right combination of speed, precision, noise and price. So chances are, we've got exactly what you need for

Authorized North American Distributors: Alliance Electronics 505-292-3360 Allied Electronics 817-595-3500 Anthem Electronics 408-453-1200 Bell Industries 213-826-6778

# shoot it, launch it, land it, test it, display it or air it, we've got it. high-speed op amps.

#### **Buffers**

If you're looking for extremely low distortion buffers, look at the specs of the AD9620 and AD9630 – distortion at 20 MHz: - 73 dBc and - 66 dBc, respectively; fast settling time: less than 8ns to 0.02%; and extremely low noise: 2.2 nV/ \/ Hz.

#### **General Purpose**

With the right combination of speed, precision, power dissipation and high output drive capability, the AD827, AD829, AD847, AD848, AD849 and OP-64 are ideal general purpose solutions. And they're ideally priced solutions – most singles are under \$3, and duals are under \$5.

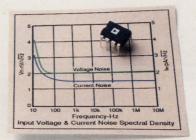

#### Low Noise

It used to be you had to choose between speed or low noise. But with the AD829, you get both. It features voltage noise of 2 nV/ $\sqrt{Hz}$  and current noise of 1.5 pA/ $\sqrt{Hz}$  with a 50 MHz unity-gain bandwidth. Those specs, combined with the low price of \$2.95/100s, make it ideal for both audio and video applications.

whatever application you're working in. Call us at 1-800-262-5643, or write to Analog Devices, P.O. Box 9106, Norwood, MA 02062-9106, for a complete high-speed op amp selection guide and a *free copy of our SPICE model library*.

Analog Devices, One Technology Way, Norwood, MA 02062-9106. Distribution, offices and applications support available worldwide.

Future Electronics (Canada) 514-694-7710 · Hall-Mark Electronics 214-343-5000 · Newark Electronics 708-784-5100 · Pioneer Technologies Group 216-587-3600

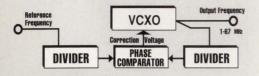

## VCXO's and PHASE-LOCKED-LOOP-VCXO

#### VCXO's Series M2000 1MHz to 67 Mhz

These VCXO's are used to improve a phase distorted or noisy signal by replacing it with the extremely low jitter of the crystal. Typical uses are in T1 (12.352 MHz), DS3 (44.736 MHz) and Sonet. VCXO's are now available with ECL output.

With MF VCXO's, since the specification is computer-tested over the full operating temperatures, you can be assured that the specified frequency- deviation is what you get for capture range.

|        | Control Voltage | Deviation    |  |  |

|--------|-----------------|--------------|--|--|

| M 2001 | 0.3 to 10V      | ±175 ppm     |  |  |

| M 2002 | 0.2 to 4V       | ± 75 ppm     |  |  |

| M 2003 | 0.3 to 10V      | ±300 ppm     |  |  |

| M 2004 | 0.3 to 10V      | ±125 ppm     |  |  |

| M 2005 | 1.0 to 4V       | ± 75-300 ppm |  |  |

| M 2006 | 0 to 5V         | ±150 ppm     |  |  |

| M 2007 | 0.5 to 4.5V     | ±250 ppm     |  |  |

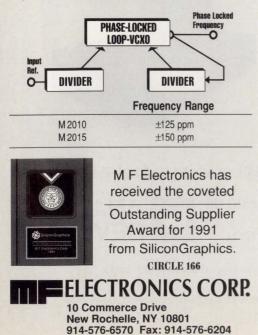

#### PHASE-LOCKED LOOP-VCXO'S Series M2010, M2015

This is the complete loop, including the phase-comparator and the VCXO, in just one package. Add the dividers to match the frequencies. Oscillators from 10 to 30MHz.

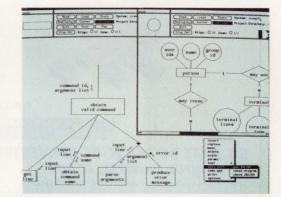

#### TECHNOLOGY BRIEFING

#### **EDA VENDORS VALIDATE CFI EFFORTS**

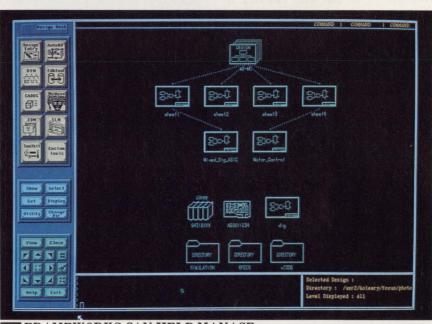

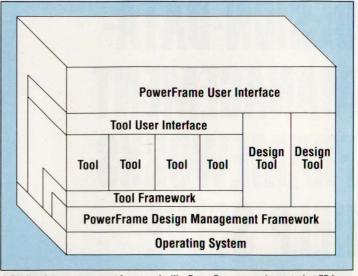

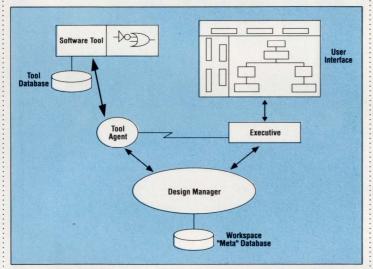

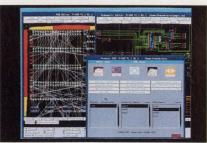

few years ago, serious doubts were raised on whether EDA vendors would rally around industry standards. Despite that sentiment, the CAD Framework Initiative (CFI) has spent the past year working on a set of three specifications that allow EDA tools to be integrated easily and effectively into a CAD framework. The specifications will be demonstrated at CFI's 1991 integration project next week during the Design Automation Conference (DAC) in San Francisco. In addition, several vendors will show prototypes of their CFI-compliant products. The project's success lies not only in the electronic-designautomation industry's ability to create framework standards, but also if it can support them.

LISA MALINIAK COMPUTER-AIDED ENGINEERING

CFI's theme for its 1990 integration project was "cooperation in action." It was a first attempt at large-scale standardization in the EDA industry, and was viewed as a trial implementation with lots of disposable code. This year's project focuses on a "real standards for real products" theme. The 1991 project has frameworks and tools from multiple companies exchanging data using the new specifications. Andy Graham, CFI's president, explains that the undertaking introduces entirely new capabilities for tool abstraction, design representation, and intertool communications. "Broad participation in the project enabled validation of many of the concepts in the specifications and accelerated the implementation of CFI specifications in commercial products." And the success of a standard, Graham points out, is market acceptance.

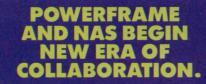

Tools from multiple vendors often can't work together effectively in the current, non-standardized situation. In fact, an end user typically spends more time making tools work together than they do with each individual tool. The three biggest problem areas involve access and modification of design information, adding tools to the design environment, and tool interaction in real time. CFI addresses these problems with a common data model, and tool-encapsulation and intertool-communication standards.

More than 22 organizations were enlisted to modify their tools for the newly developed specifications. According to project coordinator Paul Painter, a researcher at Microelectronics and Computer Technology's (MCC) CAD Framework Laboratory, Austin, Texas, the CFI specifications allow for true "plugand-play" capability among the various participants. CAD vendors and users from North America, Europe, and Asia worked together to integrate 34 different software products using the same set of CFI-developed interfaces. Integration labs were established at MCC in North America, CADLab in Europe, and at Cadence and Mentor Graphics facilities in Japan to complete the project. Final integration of the tools took place over the past few weeks at MCC CAD Framework Laboratory.

The 1991 integration project consists of three parts. Part one focuses on uniform methods for integrating tools into a framework. The second part emphasizes a single way of representing design data, and the third part allows tools to communicate with each other in an open, non-proprietary fashion. Project participants supplied either a framework cockpit to control the tools, a design-representation server to store design information, or an application tool that produces or consumes net-list information.

Eight project participants will show CFI-compliant product prototypes at DAC. They are: Cadence Design Systems, Computervision, Mentor Graphics, Objectivity, Siemens Nixdorf, Sun Microsystems, Valid Logic Systems, and Viewlogic. Mentor's Mitch Weaver, the chairman of the Electronic Design Automation Companies (EDAC) standards committee, proclaims that "adoption of standards is the key enabler for growing the industry." Apparently, a good portion of the industry is starting to think that way.

**18** E L E C T R O N I C D E S I G N JUNE 13, 1991 Looking for a function generator with all the bells and whistles, like direct digital synthesis, arbitrary waveforms, and modulation, that doesn't cost an arm and a leg?

Take a look at the DS345 from SRS.

## At \$1895, it's the only function generator you need.

It's a general purpose signal generator with standard waveforms, frequency sweeps, and synthesized accuracy. It's a 40 Msample/sec arbitrary waveform generator with 16k points of non-volatile memory. It's a complex signal source with amplitude, frequency, and phase modulation, complete with synthesized modulation waveforms. It's a remarkably agile source capable of making phase continuous frequency jumps in only 25 ns. And it's all available at the touch of a button.

What other generator has everything you want, and more? For more information about the DS345, call SRS at (408) 744-9040.

- · 30 MHz direct digitally synthesized source

- 1 µHz resolution

- 12 bit arbitrary waveforms

- Fast phase continuous frequency switching

- Low phase noise and distortion

- Sine, square, ramp, and triangle waveforms

- Linear and log sweep with markers

- · Frequency, amplitude, and phase modulation

- Arbitrary and burst modulation

- Optional GPIB/RS232 interfaces with Arbitrary Waveform Composer Software

#### STANFORD RESEARCH SYSTEMS

1290 D Reamwood Avenue, Sunnyvale, CA 94089 TEL (408)744-9040 FAX 4087449049 TLX 706891 SRS UD

# Over 50 off-the-shelf models...

Having difficulty locating RF or pulse transformers with low droop, fast risetime or a particular impedance ratio over a specific frequency range?...Mini-Circuits offers a solution.

Choose impedance ratios from 1:1 to 36:1, connector or pin versions (plastic or metal case built to meet MIL-T-21038 and MIL-T-55831 reguirements\*). Ultra-wideband response achieves low droop and fast risetime for pulse applications. Ratings up to 1000M ohms insulation resistance and up to 1000V dielectric voltage. For wide dynamic range applications involving up to 100 mA DC primary current, use the T-H series. Coaxial connector models are offered with 50 and 75 ohm impedance; BNC standard; request other types. Available for immediate delivery with one-year guarantee.

JNBAL TB

Call or write for 68-page catalog or see our catalog in EEM, or Microwaves Product Data Directory. \*units are not QPL listed

#### case styles

T, TH, case W 38, X 65 bent lead version, KK81 bent lead version TMO, case A 11, † case B 13 FT, FTB, case H 16 NEW TC SURFACE MOUNT MODELS from 1 MHz to 1500 MHz

тмо

| DE               |                                                                                                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NSN              | MCL NO                                                                                                                                                             |

| 5950-01-132-8034 | TMO2-1                                                                                                                                                             |

| 5950-01-225-8773 | TM02.5-6                                                                                                                                                           |

| 5950-10-128-3745 | TM02.5-6                                                                                                                                                           |

| 5950-01-153-0668 | TMO3-1T                                                                                                                                                            |

| 5950-01-106-1218 | TMO4-1                                                                                                                                                             |

| 5950-01-153-0298 | TMO4-2                                                                                                                                                             |

| 5950-01-024-7626 | TMO4-6                                                                                                                                                             |

| 5950-01-105-8153 | TMO5-1T                                                                                                                                                            |

| 5950-01-094-7439 | TMO9-1                                                                                                                                                             |

| 5950-01-178-2612 | TMO16-1                                                                                                                                                            |

|                  | NSN<br>5950-01-132-8034<br>5950-01-225-8773<br>5950-01-128-3745<br>5950-01-153-0668<br>5950-01-106-1218<br>5950-01-06-1218<br>5950-01-024-7626<br>5950-01-094-7439 |

T, TH, TT

T, TH, TT bent lead version style X 65

TO

MCL NO. NSN 5950-01-183-6414 TMO2.5-6 TMO2.5-6T 5950-01-215-4038 5950-01-215-8697 5950-01-168-7512 5950-01-067-1012 TMO3-1T 5950-01-091-3553 5950-01-132-8102 TMO5-1T 5950-01-183-0779

T, TH, TT bent lead version style KK81

## FOR EKS 3KHz-800MHz from \$325

|    |                                        |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                          | FREQUENCY<br>MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CY INSERTION LOSS                                                                                                                                                                                                                                                              |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PRICE \$                                                                                                                                                                             |

|----|----------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | case style number<br>see opposite page |                      | MODEL<br>NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | i vino                                                                                                                                                                                                                                                                                   | 1411.12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3dB<br>MHz                                                                                                                                                                                                                                                                     | 2dB<br>MHz                                                                                                                                                                                               | 1dB<br>MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Qty.<br>(1-9)                                                                                                                                                                        |

| A* | PR SEC                                 | T<br>TH<br>TMO       | T1-1T<br>T1-6T<br>T2-1T<br>T2.5-6T<br>T3-1T<br>T4-1<br>T5-1T<br>T5-1T<br>T8-1T<br>T13-1T<br>T16-6T<br>T4-1H<br>TMO1-1T<br>TMO2-1T<br>TMO2-5-6T<br>TMO3-1T<br>TMO13-1T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1<br>1<br>2<br>25<br>3<br>4<br>4<br>5<br>8<br>3<br>16<br>4<br>1<br>2<br>2.5<br>3<br>4<br>5<br>3<br>4<br>5<br>3<br>4<br>5<br>3<br>4<br>5<br>3<br>4<br>5<br>3<br>4<br>5<br>3<br>4<br>5<br>3<br>4<br>5<br>3<br>4<br>5<br>5<br>3<br>4<br>4<br>5<br>5<br>5<br>3<br>4<br>4<br>5<br>5<br>5<br>5 | 05-200<br>003-300<br>07-200<br>01-100<br>05-250<br>2-350<br>02-250<br>3-300<br>03-140<br>.3-120<br>.03-75<br>10-350<br>05-200<br>07-200<br>01-100<br>.05-250<br>2-350<br>3-300<br>3-120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .05-200<br>003-300<br>07-200<br>01-100<br>05-200<br>2-350<br>02-250<br>03-140<br>03-140<br>03-75<br>10-350<br>05-200<br>0.7-200<br>0.7-200<br>0.7-200<br>0.7-200<br>0.7-200<br>0.7-200<br>0.7-200<br>0.7-200<br>0.7-200<br>0.7-200<br>0.7-200<br>0.7-200<br>0.7-200<br>0.3-120 | .08-150<br>.01-150<br>.02-50<br>.1-200<br>.35-300<br>.05-150<br>.6-200<br>.0-90<br>.7-80<br>.06-30<br>.15-300<br>.08-150<br>.1-100<br>.02-50<br>.1-100<br>.02-50<br>.1-200<br>.35-300<br>.6-200<br>.7-80 | .2-80<br>.02-50<br>.5-50<br>.50-20<br>.5-70<br>.2-100<br>0.1-100<br>1-60<br>5-20<br>.1-20<br>25-200<br>.2-80<br>.5-50<br>.05-20<br>.5-70<br>2-100<br>5-100<br>5-100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.45<br>6.95<br>4.95<br>4.95<br>4.95<br>3.25<br>4.45<br>4.95<br>5.95<br>5.65<br>5.95<br>7.95<br>8.45<br>8.45<br>8.45<br>8.45                                                         |

| B* |                                        | тт<br>ттмо           | TT1-6<br>TT1.5-1<br>TT2.5-6<br>TT4-1<br>TT4-1A<br>TT25-1<br>TTMO25-1<br>TTMO1-1<br>TTMO1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1<br>1.5<br>2.5<br>3<br>4<br>25<br>25<br>1<br>4                                                                                                                                                                                                                                          | .004-500<br>.075-500<br>.01-50<br>.05-200<br>.02-30<br>.02-30<br>.005-100<br>0.1-300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .004-500<br>.075-500<br>.01-50<br>.2-50<br>0.1-300<br>.02-30<br>.005-100<br>0.1-300                                                                                                                                                                                            | .02-200<br>.2-100<br>.025-25<br>.2-50<br>0.2-250<br>.05-20<br>.05-20<br>.01-75<br>0.2-250                                                                                                                | .1-50<br>1-50<br>.05-10<br>1-30<br>0.3-180<br>.1-10<br>.1-10<br>.05-40<br>0.3-180                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6.95<br>5.95<br>6.45<br>5.95<br>6.95<br>9.95<br>11.95<br>11.45<br>13.95                                                                                                              |

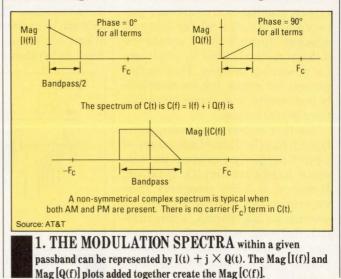

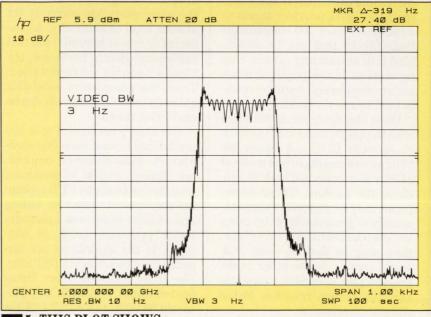

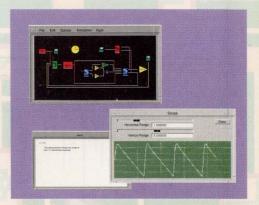

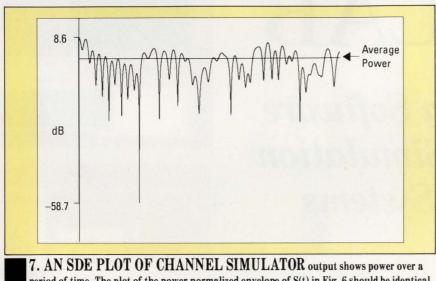

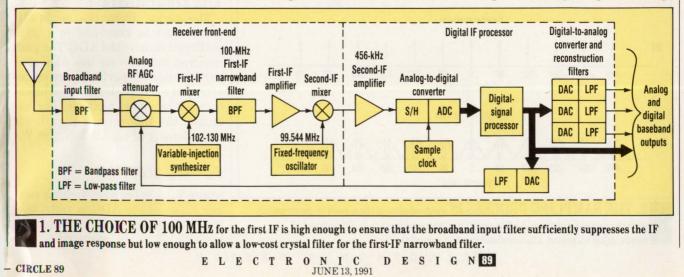

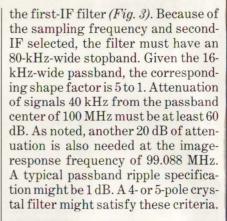

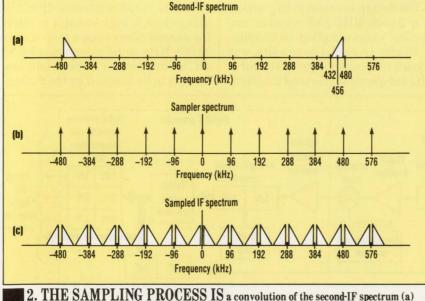

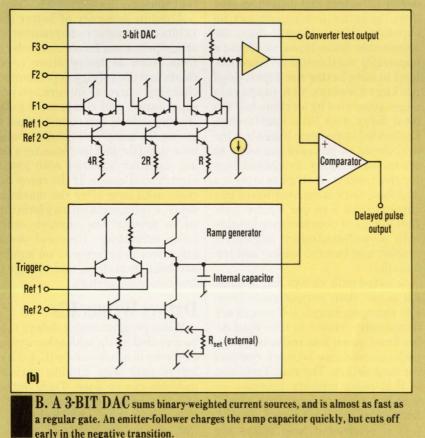

| C  | PR SEC                                 | T<br>TO<br>TH<br>TMO | $\begin{array}{c} T1-1\\T1.18-3\\T1-6\\T1.5-1\\T1.5-6\\T2.5-6\\T4-6\\T9-1\\T16-1\\T36-1\\T0-75\\T1-1H\\T0-75\\T1-1H\\T16-H\\T16-H\\TM01-02\\TM01-1\\TM01-5-1\\TM02.5-6\\TM06-1\\TM06-1\\TM09-1\\TM001-1\\TM001-1\\TM001-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM00-1\\TM$ | 1<br>1.18<br>1.5<br>1.5<br>2.5<br>4<br>9<br>16<br>36<br>1<br>1<br>9<br>16<br>1<br>1<br>1.5<br>2.5<br>4<br>6<br>9<br>16                                                                                                                                                                   | 15-400<br>0.01-250<br>.01-150<br>.1-300<br>.02-100<br>.01-100<br>.02-200<br>.15-200<br>.3-120<br>.03-20<br>10-500<br>8-300<br>2-90<br>.15-400<br>.15-400<br>.15-400<br>.15-400<br>.15-400<br>.15-200<br>.3-200<br>.3-200<br>.3-200<br>.3-200<br>.3-200<br>.3-200<br>.3-200<br>.3-200<br>.3-200<br>.3-200<br>.3-200<br>.3-200<br>.3-200<br>.3-200<br>.3-200<br>.3-200<br>.3-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200<br>.5-200 | 15-400<br>0.01-250<br>0.1-250<br>0.1-300<br>0.2-100<br>0.01-100<br>0.2-200<br>0.3-120<br>0.3-20<br>                                                                                                                                                                            | 35-200<br>0.2-200<br>0.2-100<br>2-150<br>0.2-50<br>0.2-50<br>0.5-150<br>3-150<br>7-80<br>10-500<br>10-200<br>3-75<br>10-65<br>2-500<br>3-5-150<br>2-150<br>0.2-150<br>5-150<br>5-150<br>3-150            | $\begin{array}{c} 2-50\\ 0.03-50\\5-80\\5-80\\5-80\\5-20\\1-25\\05-20\\1-100\\5-20\\1-5\\40\\5-20\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8\\5-8$ | 3.25<br>5.65<br>5.65<br>4.45<br>5.65<br>4.45<br>3.95<br>4.45<br>6.95<br>6.95<br>6.95<br>6.95<br>6.95<br>6.45<br>6.45<br>6.45<br>6.25<br>8.45<br>6.25<br>8.45<br>7.95<br>7.95<br>7.95 |