# Out-of-this-world performance at a down-to-earth price.

The new 2900 Programming System brings the cost of high-performance programming down to earth. Buy only the device libraries you need today and expand capability when you need it with simple software updates.

The 2900 supports virtually every programmable logic and memory

device on the market even surfacemount packages. Its innovative technology makes programming faster, easier, and more affordable than ever before. And with Data I/O®'s industry-standard design and testing software, you can create a complete PLD development solution. For more than 15 years, Data I/O has set the standard in device programming. Call today to learn how

the 2900 is setting a new standard for both price and performance.

Call today for a FREE tutorial.

2900 Storennin

### 1-800-247-5700

Data I/O Corporation 10525 Willows Road N.E., P.O. Box 97046, Redmond, WA 98073-9746, I.S.A. (206) 881-64447-800-247-5700 Data I/O Canada 6725 Airport Road, Suite 302, Mississuga, Ontario L4V 102 (416) 678-0761 Data I/O Europe World Trade Center, Strawinskylaan 633, 1077 XX Amstendam, The Netherlands + 31 (0)20-6622866 Data I/O Instrumatic Electronic Systems Vertrieba GmbH Lochhamer Schlag 5A, 8032 Graefelfing, W. Germany, + 49 (0)89-858580 Data I/O Japan Sumitomoseimei Higashishinbashi Bidg, 8F, 2-1-7, Higashi-Shinbashi, Minato-Ku, Tokyo 105, Japan Data I/O Japan Sumitomoseimei Higashishinbashi Bidg, 8F, 2-1-7, Higashi-Shinbashi, Minato-Ku, Tokyo 105, Japan 0 (2) 1991 Data I/O Corporation DATA I/O Corporation

While HP's high-performance plastic optocouplers may all look alike, the similarity is only skin deep.

Because with five complete lines of plastic devices, there's clearly more to our optocouplers than meets the eye.

Like a wide variety of single- and dual-channel devices that provide you with an equally wide range of performance options.

Such as an innovative dual-channel design that combines a photon-emitting diode with a high-speed photon detector to produce data rates up to 40 MBd. You also get high-output gain from low-input current or high-speed logic gates. Wide Vcc from 4.5 to 20 volts. And a unique AC/DC interface.

Plus they're compatible with TTL, STTL, LSTTL and, in many cases, CMOS logic families.

All of which makes HP's optocouplers the ideal solution for problems caused by ground loops and induced common mode noise.

Best of all, they're from HP. So you're assured of our commitment to excellence in service, support and reliability. Which, come to think of it, is the one thing that makes all our optocouplers exactly alike.

To find out more about HP's optocouplers, call **1-800-752-0900**, ext. **644G.** And see why looks aren't everything.

There is a better way.

CG08907

# Recently, our customers have a few choice words for us.

Seagate and the Seagate logo are registered trademarks of Seagate Technology, Inc. ICL, Olivetti and AT&T are registered trademarks of their respective companie © 1990 Seagate Technology, Inc.

### had

For years Seagate has been best-known as the volume producer of disc storage products. But our reputation as solely a manufacturing

powerhouse is beginning to change.

In the past several months Seagate has received three Disc Drive Supplier of the Year awards from some of our valued OEM customers. In every case, the commendations have been earned not just for supplying quality products, but for providing superior customer service.

ICL, Britain's leading information technology company, honored us with their Vendor Award Citation for being responsive to their flexibility of delivery and cost of ownership requirements. In addition, our Wren drives exceeded their stringent reliability and "plug-and-play" criteria.

Olivetti, the Italian computer company, awarded us their Quality Award for Customer

> Satisfaction for the same reasons. By meeting Just-in-Time delivery schedules, listening to the customer, exchanging data from the field and providing training and support, we

have helped Olivetti provide superior products and service to their customers.

Most recently, AT&T's Oklahoma City Works presented Seagate with its 1990 "Partner in Excellence" award during their Quality Month observance. Once again, Seagate was selected for its ability to meet AT&T's high standards of quality, delivery, service, cost and technical support.

So while Seagate is still the first name in disc drives, we're making quite a name for ourselves in quality and customer service, as well. To learn more about the benefits of a partnership with Seagate, call us at 800-468-DISC, or 408-438-6550.

And to our customers, we offer a couple of choice words of our own: Thank you.

The first name in disc drives CIRCLE 119

### FEBRUARY 14, 1991 VOL. 39, NO. 3

### ELECTRONIC DESIGN

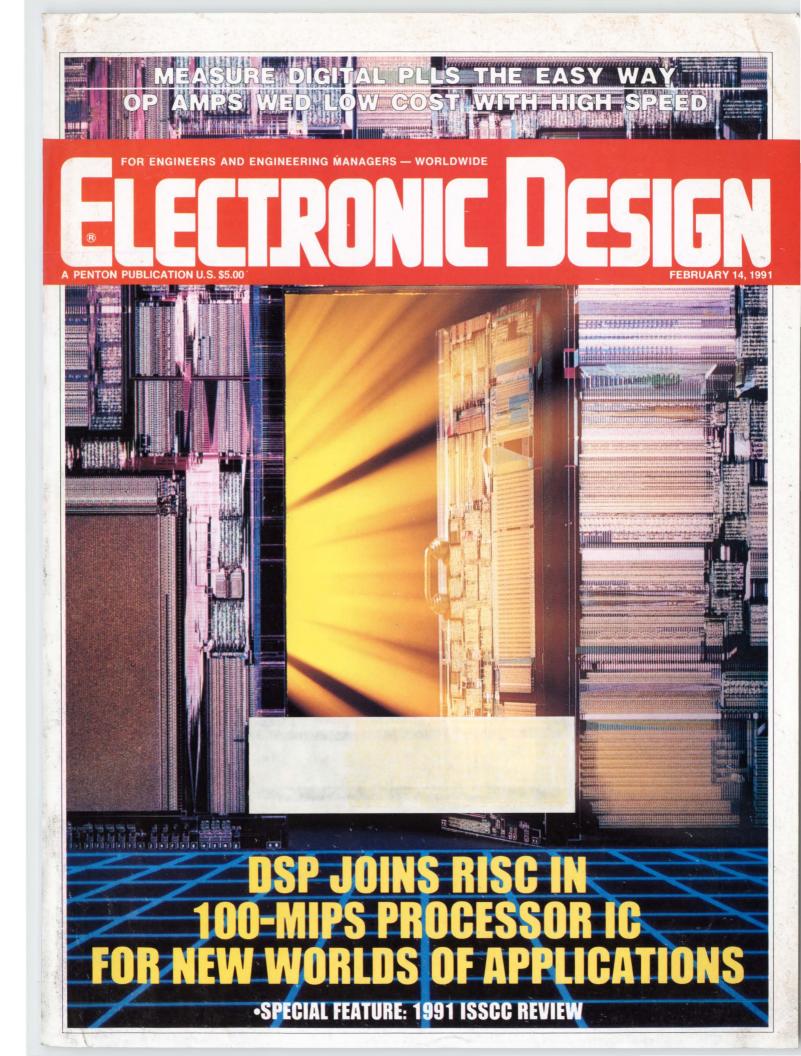

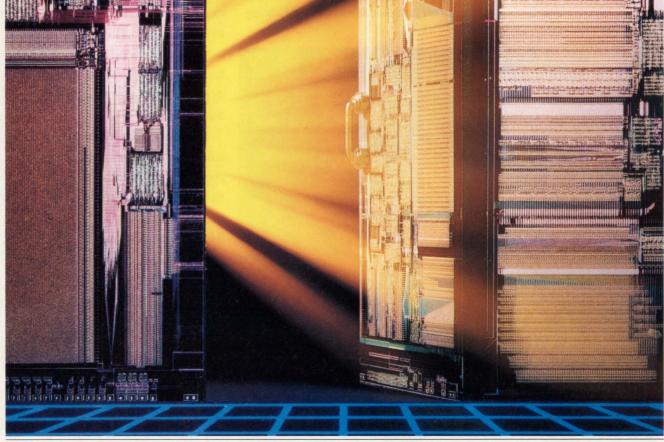

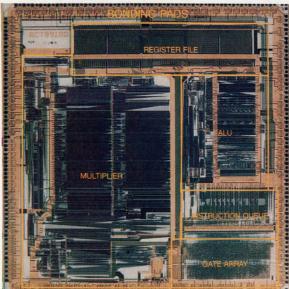

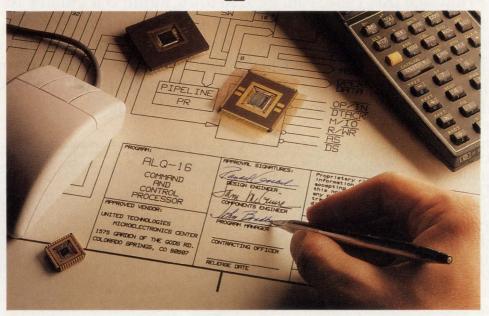

### COVER 41 COMBO CPU AND DSP CHIP PERFORMS A SEA OF TASKS

**FEATURE** With a peak throughput of 100 MIPS, a 64-bit embedded controller packs DSP enhancements to also handle image and signal processing.

ELECTRONIC 51 ISSCC REVIEW INTRODUCTION

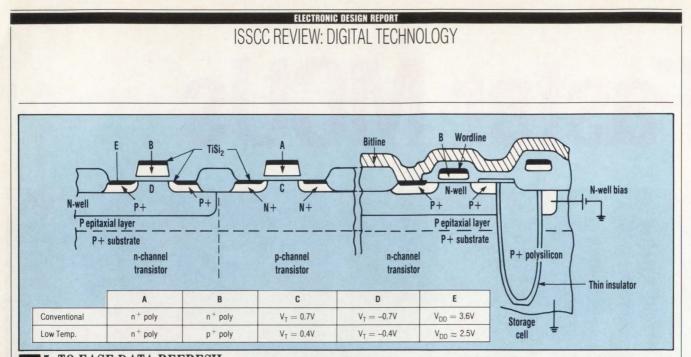

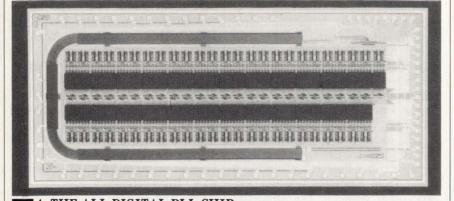

### 53 ISSCC REVIEW: DIGITAL TECHNOLOGY

With more on-chip parallelism and closely coupled on-chip memory, CPUs are hitting supercomputer-level performance numbers.

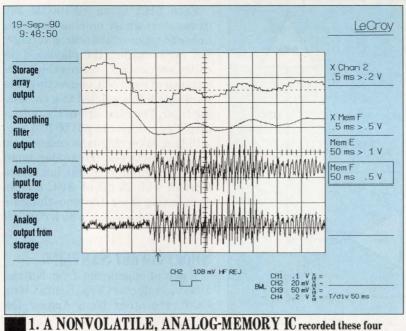

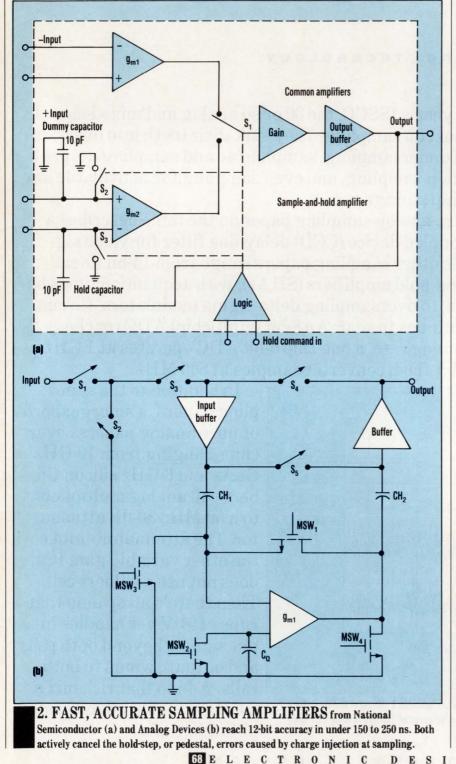

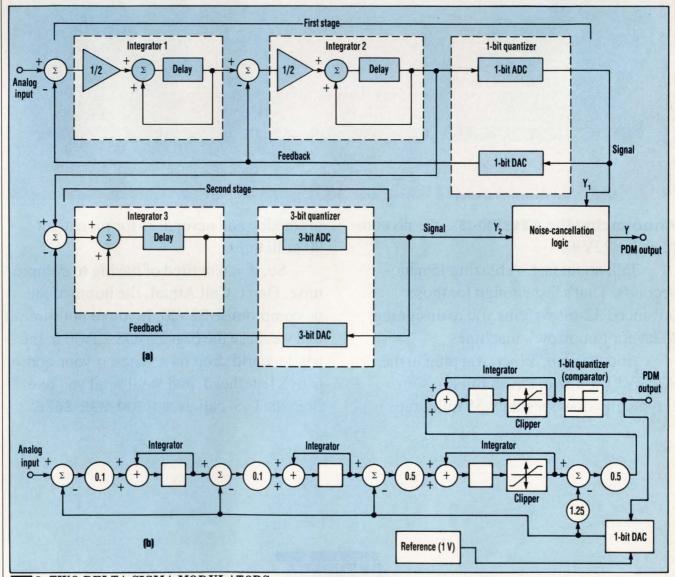

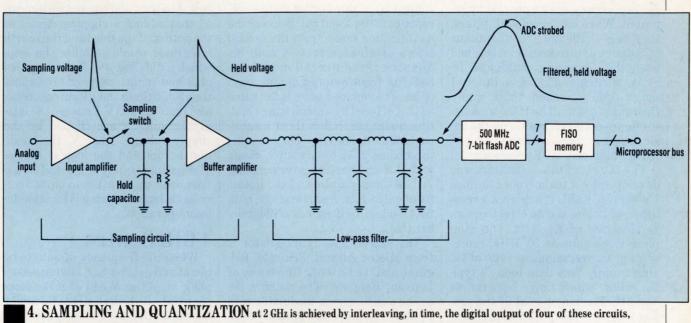

### 67 ISSCC REVIEW: ANALOG TECHNOLOGY

A vast range of sampling techniques dominate the conference's analog and mixed-signal papers.

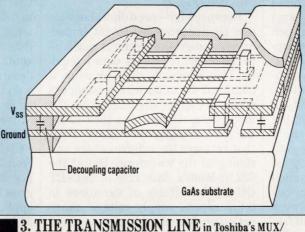

### **79 ISSCC REVIEW: COMMUNICATIONS**

Across-the-board improvements in communication-system building blocks bring about smaller, less-costly, and more user-friendly products.

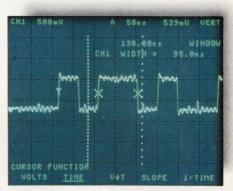

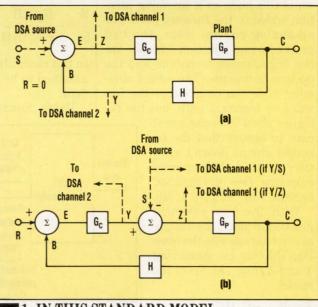

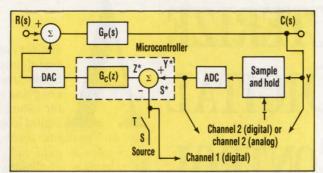

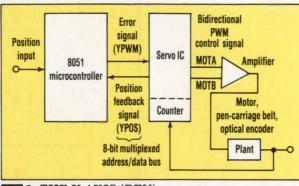

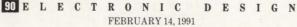

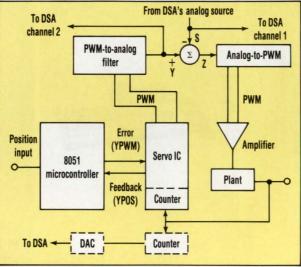

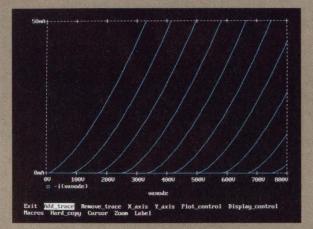

### DESIGN 89 CHARACTERIZE DIGITAL CONTROL LOOPS

A software summing junction and a dynamic signal analyzer make easy work of open-loop measurements.

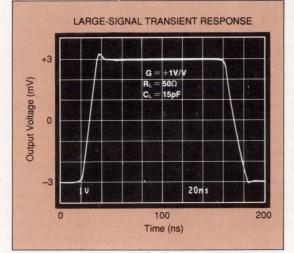

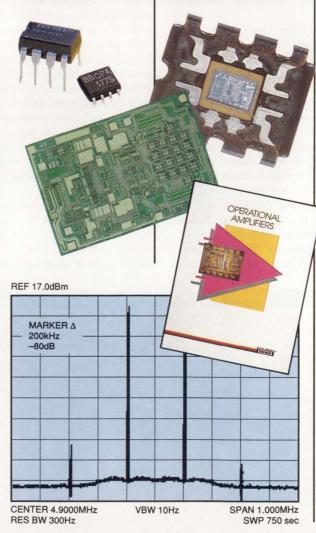

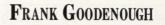

### PRODUCT 119 PROCESS AND DESIGN BRING FAST, LOW-COST OP AMPS

INNOVATION Op amps from an 18-V, standard bipolar process challenge the speed/bandwidth of complementary-process devices.

### **14 EDITORIAL**

### **18 TECHNOLOGY BRIEFING**

Spotlight on Soviet technology

### **25 TECHNOLOGY NEWSLETTER**

• Enhanced sputtering source improves yield

• Turnkey board service helps shrink systems

• ASIC offers laser-printer alternative

• Solid light cubes glow without power

• PLD tool incorporates schematic support

• Test detects IC defects from quiescent current

• Fusion program boosts software availability

• Company merger forms largest GaAs IC maker

• New specification lets Unix access AppleTalk

### **33 TECHNOLOGY ADVANCES**

• Next-generation RISC CPU gets 50 to 100 MIPS from 64-bit internal architecture

• Automotive gas sensor works in 10 ms at a temperature up to 1000°C

• Apple Macintosh clones now possible with three-chip set and software

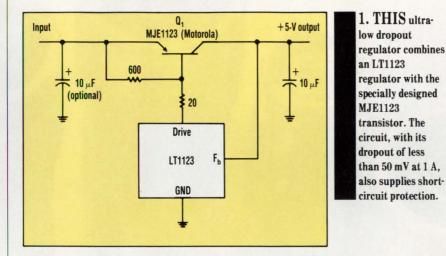

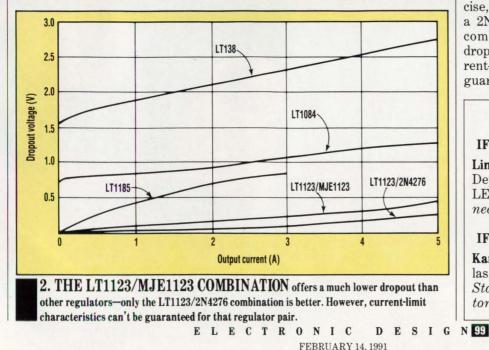

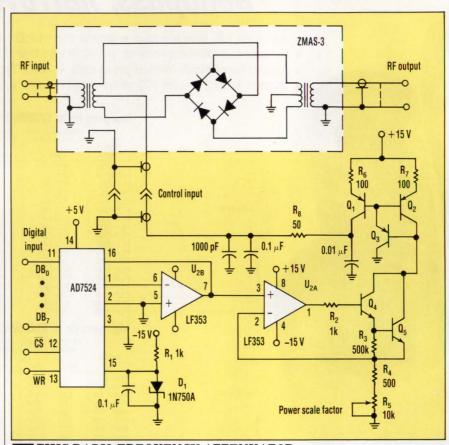

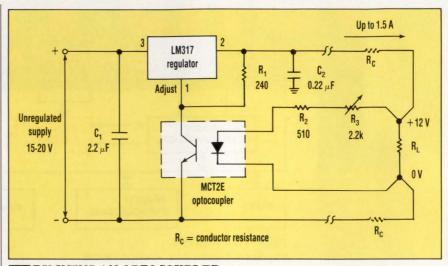

- Build ultra-low dropout regulator

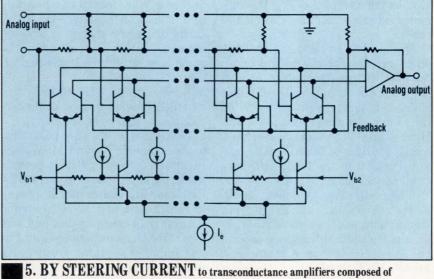

- Control RF signals digitally

- Add sensing to LM317 regulator

### **109 OUICK LOOK**

- Too much planning slows time to market

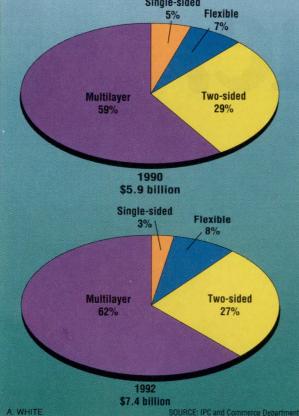

- Pc boards show steady growth

• What are the best-selling technical books in Silicon Valley?

• Engineering investors: When you roll over CDs

### **115 PEASE PORRIDGE**

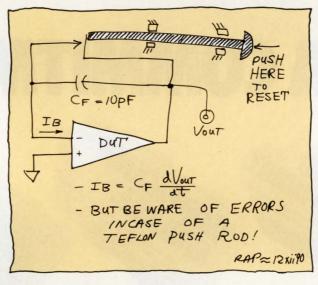

What's all this Teflon stuff, anyhow?

### **NEW PRODUCTS**

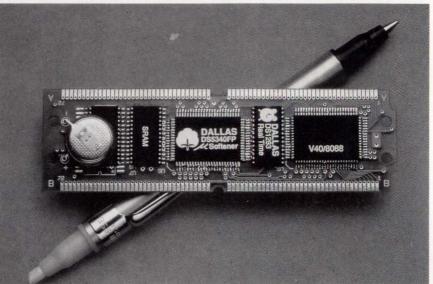

**122 Digital ICs** Embedded controller board offers in-system reconfigurability

**124 Computer-Aided Engineering** 125 Power Dual PWM-controller IC fixes ac power factor, regulates dc out **126 Instruments 127** Components

130 Analog

### **136 INDEX OF ADVERTISERS**

### **137 READER SERVICE CARD**

Certificate of Merit Winner, 1988 Jesse H. Neal Editorial Achievement Awards

### **COMING NEXT ISSUE**

• Special Report: Designing multichip-module packaging systems with CAE tools

• New Feature: Test & Measurement Update

• The trends in VXIbus instrumentation

Configuring your first VXIbus test setup

• First details on a broadband analog multiplier

• Designing cache memory systems for the 68030

• A new multiprotocol controller for telecom and datacom

• Synthesis tools complete front-toback EDA system

• PLUS: Pease Porridge QuickLook Ideas for Design **Technology** Advances

ELECTRONIC DESIGN (USPS 172-080; ISSN 0013-4872) is published semi monthly by Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543. Paid rates for a one year subscription are as follows: \$75 U.S., \$140 Canada, \$230 International. Second-class postage paid at Cleveland, OH, and additional mailing offices. Editorial and advertising addresses: ELECTRONIC DESIGN, 611 Route #46 West, Hasbrouck Heights, NJ 07604. Telephone (201) 393-6060. Facsimile (201) 393-0204.

Printed in U.S.A. Title registered in U.S. Patent Office. Copyright©1991 by Penton Publishing Inc. All rights reserved. The contents of this publica-tion may not be reproduced in whole or in part without the consent of the copyright owner.

Permission is granted to users registered with the Copyright Clearance Center Inc. (CCC) to pho-tocopy any article, with the exception of those for which separate copyright ownership is indicated on the first page of the article, provided that a base fee of \$1 per copy of the article plus \$.50 per page is paid directly to the CCC, 27 Congress St., Salem, MA 01970 (Code No. 0013-4872/91 \$1.00 + .50). Copying done for other than personal or internal software use without the article plus for the software of the reference use without the express permission of Penton Publishing, Inc. is prohibited. Requests for special permission or bulk orders should be addressed to the editor.

To subscriber change of address and subscrip-tion inquiries, call (216) 696-7000. POSTMASTER: Please send change of address to ELECTRONIC DESIGN, Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543.

**Cover: Joe Drivas**

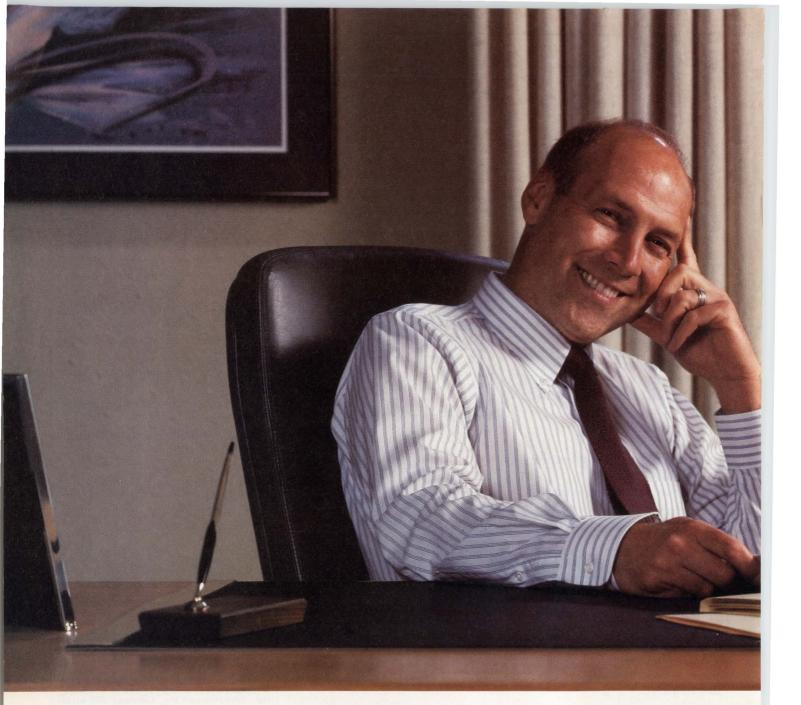

### THIS MAN MANAG MULTIPLE DESIGN DISCIPLIN DEADLINES THAT COULD KIL

The dilemma rears its ugly head time and time again. Do the impossible. By tomorrow. Worse yet, do it with an intimidating hodge-podge of design automation tools and data formats. And while you're at it, make sure all these tools and data play together freely and efficiently. No problem. Right? To avoid this kind of chaos, you need to consider a fundamental change in your engineering strategy. Which is why we now offer you our Concurrent Design Environment.™

Simply put, the Concurrent Design Environment allows tools from virtually any source to work together. Within it, our new Falcon Framework™ lets you assemble precisely the design automation environment your situation requires — without sacrificing the considerable benefits of integration. And our OpenDoor™ program ensures that your choice of tools includes the best the entire industry has to offer.

### ES 125 ENGINEERS, ES, DISPARATE TOOLS AND L. SO WHY IS HE SMILING?

The Concurrent Design Environment also includes engineering management tools of unprecedented scope and power. Like our Decision Support System, which automatically monitors any aspect of the design process you care to specify. So you spot and correct little problems long before they grow into big ones. No matter how tight your deadlines, no matter how large your engineering teams, our Concurrent Design Environment will keep you ahead of the game. Which, after all, is a very nice place to be. For a free videotape, call **1-800-547-7390.**

### For The Health Of Your Monitoring Systems, Burr-Brown Prescribes PWR13XX.

### The DIP DC/DC Converter For Ultra High Isolation: 4000V.

Medical grade isolation is yours with a dose of 1.5 watts of unregulated output power from the PWR13XX. Its dual-in-line package uses only 1 inch<sup>2</sup> of PC Board space and comes in low prices that are easy to swallow.

Úse as needed for applications where system integrity and reliability are critical. No external parts required.

Contact your salesperson for quick delivery.

CALL 1-800-548-6132 ext. 532 Fax 1-602-741-3895 Write P.O. Box 11400 - Tucson, Arizona 85734

CIRCLE 158

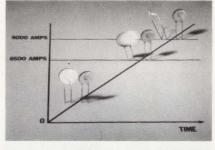

### HOW TO CONTROL COMPLEX DRIVE SYSTEMS SIMPLY

Simpler is better. Which is why the M-Track Digital Synchronization Control makes set-up and programming simple, easy and fast. M-Track's self-learning capabilities mean far less operator intervention, too. It detects trends, such as variations in spacing, automatically maintaining correct synchronization. M-Track handles quadrature encoders, so it knows if the line is moving forward or backward. Manual adjustments and restarts are trouble-free. Call 1 800 FIC-4411. Or write: Fenner, 8900 Zachary Lane North, P.O. Box 9000, Maple Grove, MN 55369. Fax: 612 424 8734.

ELECTRONIC DESIGN

Editor-in-Chief: Stephen E. Scrupski

Executive Editor: Roger Allan

Managing Editor: Bob Milne

Senior Editors: Frank Goodenough, Milt Leonard, John Novellino

Technology Editors: Analog & Power: Frank Goodenough Communications & Industrial: Milt Leonard (San Jose) Components & Packaging: David Maliniak Computer-Aided Engineering: Lisa Maliniak Computer Systems: Richard Nass Semiconductors: Dave Bursky (San Jose) Test & Measurement: John Novellino

News Editor: Sherrie Van Tyle

New Products Editor: Susan Nordyk

Field Bureaus: West Coast Executive Editor: Dave Bursky (San Jose) Boston: Lawrence Curran Dallas: Jon Campbell Frankfurt: John Gosch London: Peter Fletcher

Chief Copy Editor: Roger Engelke, Jr.

Editorial Production Manager: Lisa Iarkowski

Administrative Assistant: Janis Kunkel

**Editorial Support Supervisor: Mary James**

Editorial Assistant: Ann Kunzweiler

Editorial Secretary: Bradie Guerrero

Editorial Offices: (201) 393-6272

Advertising Production: (201) 393-6093 or FAX (201) 393-0410

**Production Manager:** Michael McCabe *Production Assistants:* Donna Marie Bright, Doris Carter, Eileen Slavinsky

Circulation Manager: Robert Clark

Promotion Manager: Clifford Meth

Reprints: Helen Ryan (201) 423-3600

Group Art Director: Peter K. Jeziorski

**Computer Systems Administrator:** Anne Gilio Turtoro

Published by Penton Publishing Vice President-Editorial: Perry Pascarella Group Editorial Director: Leland Teschler

Publisher: Paul C. Mazzacano

CIRCLE 2 **8** E L E C T R O N I C D E S I G N FEBRUARY 14, 1991

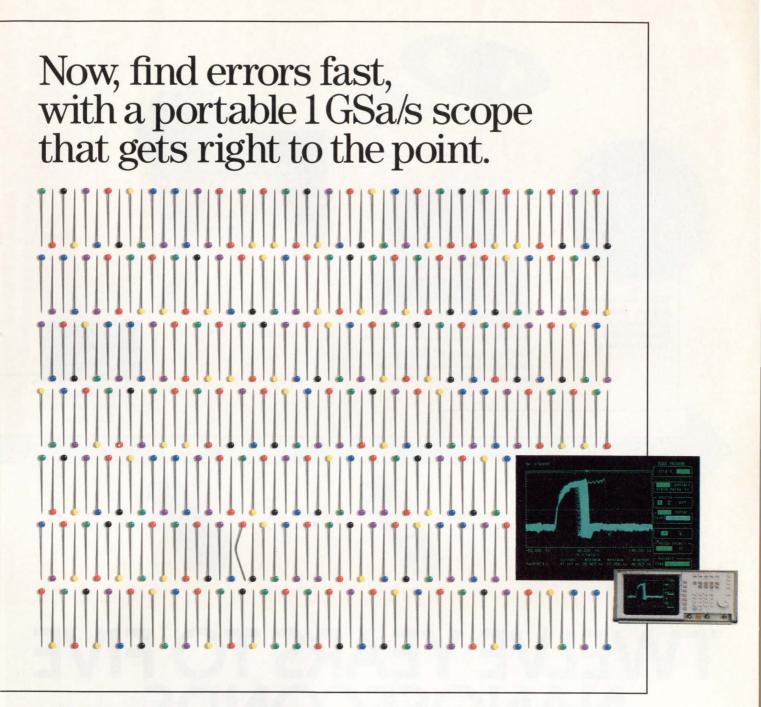

### At \$10,950\*, you won't find a better value in a digitizing scope.

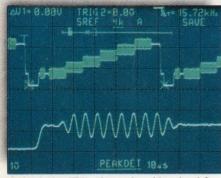

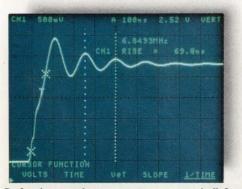

When you need to troubleshoot and debug digital designs fast, you can't afford to miss a thing. And now, you don't have to. The HP 54510A looks at a billion samples a second with a timequalified pattern triggering and an infinite persistence display to pinpoint rare events and elusive glitches the instant they happen. You don't have to stick around to watch, either. The HP 54510A has 8k of memory per channel to capture and store single events. So, you can go back and get all the details you need—with razor-sharp, 8-bit resolution and track the problem to its source. And to point you to the right solution, the HP 54510A gives you 17 pulse-parameter measurements, with better horizontal and vertical accuracy than the Tek DSA 602, at onethird of the cost. So, if you're looking for a solution to high-speed troubleshooting, call **1-800-752-0900**\*\*. Ask for **Ext. 2111**, and we'll send you an application note on the HP 54510A that shows you how to find faults fast.

\*U.S. price only. \*\*In Canada call 1-800-387-3867, Dept. 423.

There is a better way.

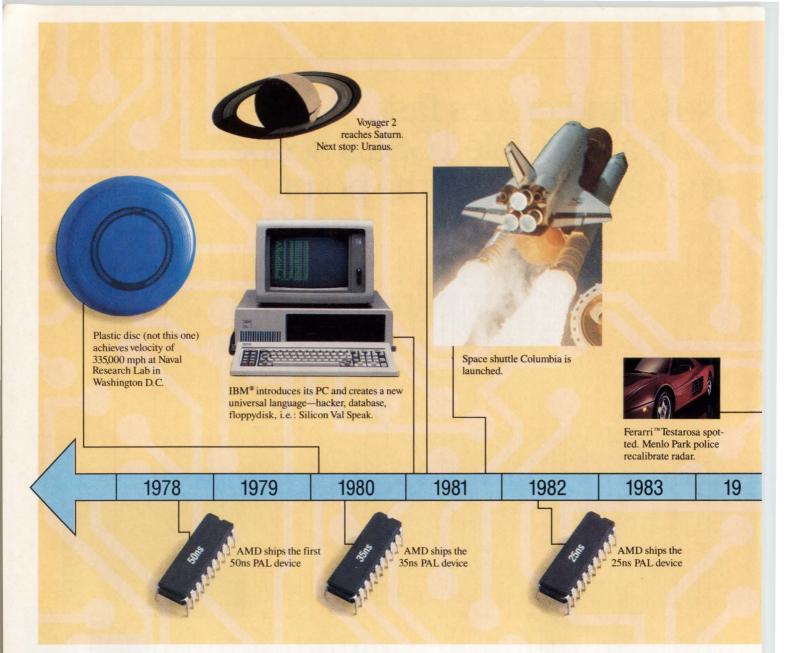

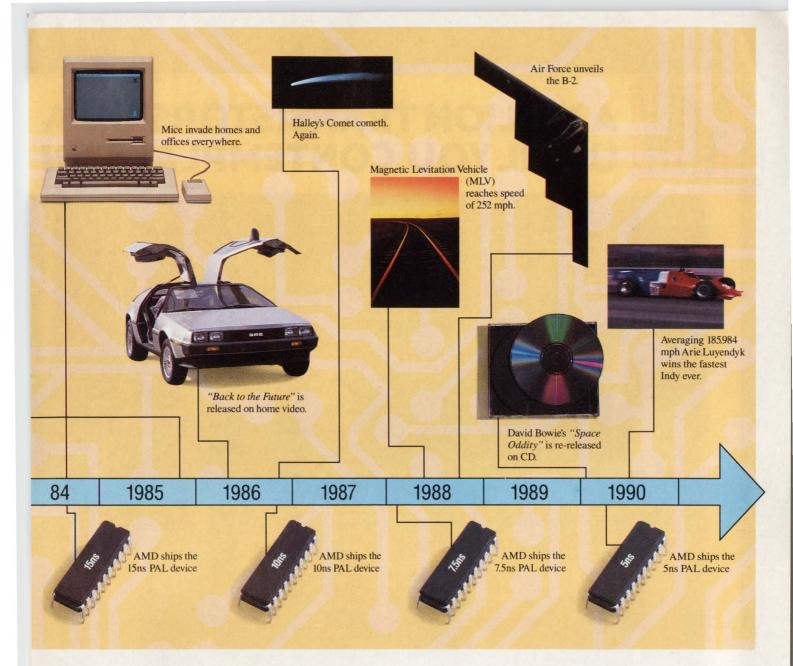

### TWELVE YEARS TO FIVE NANOSECONDS.

Here's a quick message from the people who invented the first PAL<sup>®</sup> device a dozen years ago:

"Five nanoseconds." The fastest TTL logic in the world.

16R8-5 and 20R8-5 families on the shelf

now, in 20 and 24 pin configurations.

At 117MHz, these puppies run rings around

40 to 60MHz CISC and RISC processors.

For you critical pathfinders, we have a

16R8-4 family that moves at a crisp 4.5 nanoseconds. And for the fastest version of the standard in field programmable logic, ask for our 10ns 22V 10.

<u>Big Cache Savings.</u> This kind of super fast logic is the smart, cost-effective solution for increased performance and lower cost cache memory.

Big Comfort Zone. AMD® has the best

programming and design software support in the industry. And a veritable army of careercrazed FAE's. No wonder we sell more PAL devices than all our competitors combined. Do something nice for your whole system. Write Advanced Micro Devices today.

### Advanced Micro Devices 21

901 Thompson Place, P.O. Box 3453, Sunnyvale, CA 94088. For more information call (800) 222-9823.

### **MW A MILLION TRANSISTORS ON A UNTIL YOU CONTEMPLATE AN**

### MICROPROCESSOR IS IMPRESSIVE, SRAM WITH SIX TIMES AS MANY.

The recently introduced Samsung 1-meg SRAMs have a transistor count of 6.6 million.

In a day and age when makers of advanced microprocessors take understandable pride in the 1 million transistors on their chips, we think it's forgivable for us to be proud of the vastly greater number on these SRAMs.

They're among the most difficult of all semiconductors to produce, and only a few manufacturers can make them.

We offer the 1-meg slow SRAM in several speeds, several power ratings, and several package types. We're currently developing the part in the revolutionary TSOP packaging.

All those things—plus forthcoming high-density fast and ultra-fast SRAMs, plus additional slow parts for main store and buffer applications—give you an idea of Samsung's commitment to this demanding technology.

Besides the 1-meg slow SRAM, in the main-store and buffer areas we'll sample next year a 1-meg fast static RAM family, and go into production with a 1-meg pseudo-SRAM.

### THE SAMSUNG I-MEG SRAM

Speeds: 70°, 85, 100, 120 ns. Package types: TSOP°, DIP, SOIC. Power ratings: Low-low°, low, standard. Organization: 128K x 8.

For information on the 1-meg SRAM or our 1-meg pseudo-static, write today to SRAM Marketing, Samsung Semiconductor, 3725 No. First St., San Jose, CA 95134. Or call 1-800-669-5400, or 408-954-7229.

After all, the best way to contemplate the 6.6 million transistors on the part, is to get your hands on one.

### LCD Proto Kit

Everything you need to start your LCD application .... create complex screens in just a few hours!

240 x 64 Kit provides pixel Supertwist LCD serial inter-face to IBM PC for quick mounts prototyping. Board also directly onto CYB003 supports displays up to 240 x 128 proto-typing board. pixels. Interface to 6 soft keys or x 4 key matrix. Dial 0-25k ohms for LCD contrast The CY325 LCD Windows Controller Wire area for custom parallel or circuitry or back light. serial high-level control of Instrument size LCDs. Up to 256 built-in ndows support window-relative text, bargraphs, waveforms, and plots. Text and graphics are main tained in separate planes, facilitating special effects. RJ 11 Complete User serial jack for RxD, TxD, CTS, and nual included Add your own 8051 CPU for stand 5 Pin Iternate GND, plus Powe Power DIN Connector alone operation 2 spa Kit also includes:

### Power supply provides +5v and Gnd for board, -12v for LCD, and + 12v spare. Sam Sample routines in 8051 Assembler and QuickBasic LCD Paint™ for graphics images 4-wire RJ11 style cable with DB25F connector for your IBM PC. \$495 - Kit Demo routines preprogrammed into 8751 for Popular LCD Starter Kit. immediate gratification (MC) VISA AMEX (\$595 pre-assembled & tested) \*The CY325 40-pin CMOS LCD Controller IC is available from stock @ \$75/singles, \$20/1000s (Surface mount also avail in qty.) CyberneticMicroSystems Box 3000 • San Gregorio CA 94074 Tel: 415-726-3000 • Fax: 415-726-3003 **CIRCLE 142**

# <image>

**FDITORIAL**

### THE ISSCC IN A YEAR OF UNCERTAINTY

remors of uncertainty are shaking today's world: Clouds of recession have loomed over global business and industry, while in the Middle East, much more ominous clouds darken the skies as military forces rise to an armed challenge. With so many problems coming over the horizon, it's impossible to predict how the overall picture will develop in the coming months. However, one effect of this uncertainty is abundantly clear—electronics technology has become critical in military operations.

Nevertheless, it seems a relief to focus on a subject where the difficulties do not involve human lives, international politics, or financial management. Once again, the International Solid State Circuits Conference is underway, carrying reports of man's advances in the struggle against the laws of physics involving semiconductor devices. Electronic Design's annual report on the ISSCC (a total of about 20 pages beginning on page 51) describes a broad swath of innovative designs in 64-Mbit DRAMs, high-speed analog-to-digital converters, radio-frequency receivers on a chip, and the like.

But even the ISSCC, with its elaborate array of advanced VLSI devices, carries a certain degree of uncertainty. Yet this is the type of uncertainty that we have all become accustomed to dealing with: some of the devices described there will not end up as commercial products. Of those, most will probably "fail" because of their complexity and attendant yield problems, causing them to miss their market window. But that fact hardly negates the importance of the basic developmental achievements described in each of the ISSCC paper presentations.

Undoubtedly, some of the devices described in past conferences are now deployed in war zones; let's hope that their use contributes to a lasting peace. And let's also hope that this year's devices, described in their infancy in San Francisco this week, will grow to serve their part in man's most pressing needs: life, liberty, and the pursuit of happiness. There's no uncertainty about those needs.

lepten Ser

Stephen E. Scrupski Editor-in-Chief

14 E L E C T R O N I C D E S I G N FEBRUARY 14, 1991

### SPECIFICATIONS

| MODEL | FREQ.<br>MHz | 100<br>MHz | AIN, d<br>1000<br>MHz | 2000 | Min.<br>(note) | • MAX.<br>PWR.<br>dBm | NF<br>dB | PRICE<br>Ea. | \$<br>Qty. |  |

|-------|--------------|------------|-----------------------|------|----------------|-----------------------|----------|--------------|------------|--|

| MAR-1 | DC-1000      | 18.5       | 15.5                  | _    | 13.0           | 0                     | 5.0      | 0.99         | (100)      |  |

| MAR-2 | DC-2000      | 13         | 12.5                  | 11   | 8.5            | +3                    | 6.5      | 1.50         | (25)       |  |

| MAR-3 | DC-2000      | 13         | 12.5                  | 10.5 | 8.0            | +8□                   | 6.0      | 1.70         | (25)       |  |

| MAR-4 | DC-1000      | 8.2        | 8.0                   | _    | 7.0            | +11                   | 7.0      | 1.90         | (25)       |  |

| MAR-6 | DC-2000      | 20         | 16                    | 11   | 9              | 0                     | 2.8      | 1.29         | (25)       |  |

| MAR-7 | DC-2000      | 13.5       | 12.5                  | 10.5 | 8.5            | +3                    | 5.0      | 1.90         | (25)       |  |

| MAR-8 | DC-1000      | 33         | 23                    | -    | 19             | +10                   | 3.5      | 2.20         | (25)       |  |

NOTE: Minimum gain at highest frequency point and over full temperature range. 1dB Gain Compression

+4dBm1 to 2 GHz

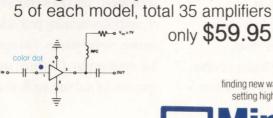

designers amplifier kit, DAK-2

### dc to 2000 MHz amplifier series

Unbelievable, until now...tiny monolithic wideband amplifiers for as low as 99 cents. These rugged 0.085 in.diam.,plastic-packaged units are 50ohm\* input/output impedance, unconditionally stable regardless of load\*, and easily cascadable. Models in the MAR-series offer up to 33 dB gain, 0 to +11dBm output, noise figure as low as 2.8dB, and up to DC-2000MHz bandwidth.

MAR-8, Input/Output Impedance is not 50ohms, see data sheet Stable for source/load impedance VSWR less than 3:1

Also, for your design convenience, Mini-Circuits offers chip coupling capacitors at 12 cents each.†

| Size            | Tolerance       | Temperature    |

|-----------------|-----------------|----------------|

| (mils)          |                 | Characteristic |

| 80 × 50         | 5%              | NPO            |

| $80 \times 50$  | 10%             | X7R            |

| $120 \times 60$ | 10%             | X7R            |

| Minimum         | Order EO per Va | due.           |

Value

10, 22, 47, 68, 100, 220, 470, 680, 1000 pf 2200, 4700, 6800, 10,000 pf .022, .047. .068, .1µf

+ Minimum Order 50 per Value Designers kit, KCAP-1, 50 pieces of each capacitor value, only \$99.95

finding new ways.

P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661 Domestic and International Telexes: 6852844 or 620156

CIRCLE 186

# What's

Analyzing TV and complex video signals?

Testing telecommunications signals?

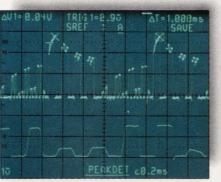

Uncovering elusive glitches?

Finding aberrations buried within a signal?

### You can't depend on banner specs alone to solve problems like these.

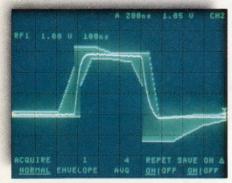

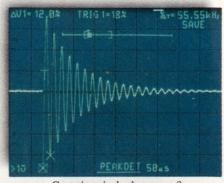

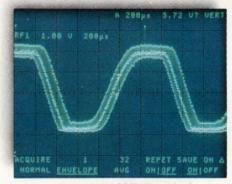

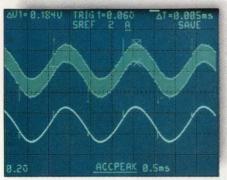

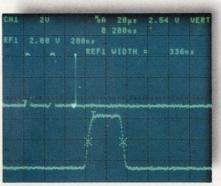

Whether you're trying to measure waveform parameters or analyze long data streams, identify infrequent events or track down glitches as narrow as 2 ns — there's all the difference between the depth of Tek troubleshooting and the trade-offs in other DSOs that compromise your results.

Spec for spec, feature for feature, no other company offers the credentials Tek does to

Capturing single-shot events?

Automatic PASS/FAIL testing?

effectively match DSO performance to your application needs. Whatever your criteria, you'll find a perfect solution in our line of problem-solving portable DSOs, from 10 to 500 MS/s.

Select the features to support your application. Tek DSOs offer a diverse set of capabilities including peak detect to uncover elusive glitches. Fast update rate for live signal display. Combined analog/digital operation for real-time verification of your

# r problem?

Characterizing signal noise?

Capturing and analyzing long data streams?

Performing complex measurements automatically?

Expanding glitches for close analysis?

Measuring timing relationship between signals?

Windowing in on signal details?

One company measures up.

signal. Or Save on Delta to automatically verify that all parts of your signal fall within prescribed limits. Best of all, Tek's line of 100 MS/s digitizing scopes start at just \$3995.

To find out which Tek scope is right for you, contact your Tek representative, return the card or call Tek direct. We can answer your questions and show you a scope that doesn't just look good on paper. It makes your toughest troubleshooting challenges routine.

CIRCLE 112

VISA

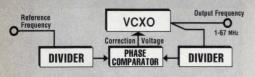

### ELECTRONICS CORP. VCXO's and PHASE-LOCKED-LOOP-VCXO

### VCXO's Series M2000 1MHz to 67 Mhz

These VCXO's are used to replace a distorted incoming reference signal (e.g. 1.544 MHz, T1), with a stable crystal-controlled signal of the same or any multiple frequency, from 1 to 67 MHz.

With MF VCXO's, since the specification is computer-tested over the full operating temperatures, you can be assured that the specified frequency- deviation is what you get for capture range.

|        | Control Voltage | Deviation    |  |  |  |  |

|--------|-----------------|--------------|--|--|--|--|

| M 2001 | 0.3 to 10V      | ±175 ppm     |  |  |  |  |

| M 2002 | 0.3 to 4V       | ± 75 ppm     |  |  |  |  |

| M 2003 | 0.3 to 10V      | ±175-300 ppm |  |  |  |  |

| M 2004 | 0.3 to 4V       | ±125 ppm     |  |  |  |  |

| M 2005 | 1.0 to 4V       | ± 75-300 ppm |  |  |  |  |

| M 2006 | 0 to 5V         | ±150 ppm     |  |  |  |  |

| M 2007 | 0.5 to 4.5V     | ±125-250 ppm |  |  |  |  |

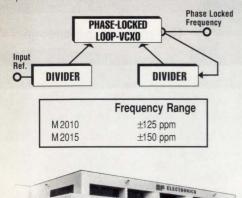

### PHASE-LOCKED LOOP-VCXO'S Series M2010, M2015

This is the complete loop, includ-

ing the phase-comparator and the VCXO, in just one package. Add the dividers to match the frequencies. Oscillators from 10 to 30MHz.

Headquarters and manufacturing plant: 36,000 sq. feet

### **TECHNOLOGY BRIEFING**

### SPOTLIGHT ON SOVIET TECHNOLOGY

his year's International Solid State Circuits Conference presents a special session on semiconductor technology in the Soviet Union, offering some rare insights into that country's manufacturing and R&D capabilities. An overview of Microelectronics in the U.S.S.R., by Prof. Richard Jaeger of Auburn University, Auburn, Ala., summarizes the impressions garnered from a multi-facility tour taken by a U.S. scientific delegation in late 1990. The delegation found that Soviet researchers are active in both silicon as well as compound semiconductors, with much of the research activity being state of the art. However, product manufacturing appears to lag western industry by 3 to 5 years.

DAVE BURSKY SEMICONDUCTORS

According to Jaeger, the most advanced manufacturing line is just ramping up—a 0.9- $\mu$ m facility that will mass-manufacture 1-Mbit dynamic RAMs. Most of the other silicon-fabrication systems are still at 1.5- to 2- $\mu$ m minimum-feature size. But some facilities handling compound materials claim they can achieve submicron features.

Due to import limitations, Russian technologists are forced to create almost all of their own manufacturing hardware, including the most critical item—the step-and-repeat lithography system. Their stepper, which has a 1- $\mu$ m feature size, 0.1- $\mu$ m precision, and a measurement accuracy that's within 0.02  $\mu$ m, does offer some cost/performance advantages over other commercially available systems.

The need for quick-turnaround manufacturing for small quantities of custom chips appears to be just as important in the U.S.S.R. as it is in the rest of the world. At the Nauchny Center in Moscow, a completely automated mini fabrication center was created for this purpose. The highly modularized chipfabrication line occupies about 200 square meters, consumes about 100 kVA of electrical power, and requires 10 people to run. The line produces silicon as well as GaAs and other compound semiconductor-based products that range from simple MOS circuits to biCMOS, to integrated sensors with on-chip microprocessors.

Each of the nearly 30 manufacturing modules, hermetically sealed to maintain a class-1 environment, performs a number of related processes in a miniature reactor. Laser-based and electron-beam inspection of incoming wafers is done to ensure uniformity, while super-cleaning and drying of each wafer reduces particulates. Wafers are moved on a conveyor-type line with individual wafer processing in miniature reactors. The single-wafer-at-a-time processing reduces the amount of reagents and gases employed during fabrication. However, the wafers typically contain just one VLSI chip, eliminating the need for scribing and breaking. Wafers with diameters of up to 200 mm can be handled, with a maximum chip area of 200 mm<sup>2</sup> on each wafer. Between 5 and 10 chips per hour can be pushed through the mini-fab facility, with a total input-to-output time (from CAD data base to finished silicon) of from 10 to over 90 hours.

When transported from module to module, the wafers are kept in hermetically sealed chambers to avoid contamination from the class-1000 working environment. Using sealed containers diminishes the high cost that would be associated with keeping the general work area at a class-1 rating. Control of the environment in each module achieves a wafer-to-wafer repeatability of the process in each module to within 0.2%.

An X-ray lithography module is currently being developed by Soviet scientists. All aspects of the X-ray lithography system are automated—from the CAD process for circuit design to wafer processing to device sealing. However, control levels can range from local autonomy within a particular module to central-processor program control.

### EXTRACTING A LARGE PGA DEVICE CAN BE HAZARDOUS WORK...

If you thought inserting a high pin count PGA device was a strain, just try removing it. As the number of pins pile up, so do the insertion and extraction forces. Delicate chip packages can be easily damaged.

But now there's a breakthrough: the new ultra low force PGA socket from Preci-Dip.® It's a modification of

aged. socket b ew ultra low wide .02 dification of accept b specially

OR CHILD'S PLAY. the low force PGA socket we introduced in 1986. Our earlier socket became popular with its

wide .028" diameter target and greater compliancy to accept bent or misaligned pins. Inside each socket is a specially coined 6-finger inner contact that drastically reduces forces. It's still the preferred choice for most

PGA applications.

But chips are getting more complex. So we anticipated the need for an inner contact designed exclusively for large PGA devices with 150 pins or more. Our ultra low force option will cut insertion and extraction forces by two-thirds. It's available in standard molded polyester up to 21x21 grid, or we can turn unusual custom footprints into child's play using machined epoxy insulators.

Insertion/Extraction Forces Cut by 2/3

Remember, damaged chips are nothing to kid around with. So call us at (516) 922-6000 and start prying into ways to solve your PGA socket problems, large and small.

| NAME                                    |       | STATE OF THE OWNER |         |         |

|-----------------------------------------|-------|--------------------|---------|---------|

| COMPANY                                 |       |                    |         |         |

| ADDRESS                                 |       |                    |         |         |

| ADDRESS                                 |       | -                  | NNEOTO  | RS FROM |

| CITY                                    | STATE |                    | INNECTO | HS FROM |

| ZIP PHONE                               |       |                    |         |         |

| Mail to: Mill-Max,<br>Oyster Bay, NY 11 |       | Rd.,               |         |         |

In developing our new ultra-low force PGA socket, we did our homework. Call or write for our data sheet summarizing force comparison tests that we conducted using actual PGA devices.

CIRCLE 149

### THE WORLD'S LARGEST SELECTION OF **POWER SPLITTERS/ COMBINERS**

m Min

### 2 KHz to 8 GHz from \$1045

With over 300 models, from 2-way to 48-way, 0,° 90° and 180,° a variety of pin and connector packages, 50 and 75 ohm, covering 2KHz to 8000MHz, Mini-Circuits offers the world's largest selection of off-theshelf power splitter/combiners. So why compromise your systems design when you can select the power splitter/combiner that closely matches your specific package and frequency band requirements at lowest cost and with immediate delivery.

And we will handle your "special" needs, such as wider bandwidth, higher isolation, intermixed connectors, etc. courteously with rapid turnaround time.

Of course, all units come with our one-year guarantee. For detailed specs and performance data, refer to the MicroWaves Product Directory, EEM or Mini-Circuits RF/IF Signal Processing Handbook, Vol. II. Or contact us for our free 68-page RF/IF Signal Processing Guide.

> finding new ways ... setting higher standards

P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661 Domestic and International Telexes: 6852844 or 620156 WE ACCEPT AMERICAN EXPRESS

**CIRCLE 185**

# When you're looking for a sure they provide these

Your supplier should offer applications support around the world. Analog Devices has offices in 34 countries, as well as worldwide manufacturing and stocking facilities.

Does your supplier have 25 years of signal processing expertise? Analog Devices does, and you can tap into it by simply picking up the phone. And with our recent acquisition of PMI – a leader in precision op amps and Class S mil/aerospace applications – you have even more experience to call upon. record. We're the leading worldwide supplier of data converters, and the top analog supplier to the military/aerospace and instrumentation markets. Plus we're a growing force in the high-volume arena, providing three of the top five Japanese consumer electronics firms, and seven of the top 10 hard disk drive manufacturers with high-performance components.

1856

Few suppliers can match our

With Analog Devices, you get direct access to the most knowledgeable applications engineers in real-world

signal processing.

You get the design tools – macromodels, evaluation boards, on-line support, technical seminars and application notes, among other things – necessary to get your products up and running quickly.

And you get 25 years of design expertise – expertise evidenced by the most complete line of high-performance linear, DSP and mixed-signal components. ICs made possible by one of the broadest manufacturing process portfolios,

### mixed-signal supplier, make high-performance parts.

A good supplier also helps you do your job better. That's why we publish more newsletters, technical books, application notes and seminar handbooks filled with the latest information on linear, DSP and mixed-signal technology.

A good supplier works to save you time and money. One way we do it is by providing state-of-the-art macromodel design tools that let you quickly and easily simulate the performance of many of our op amps. We also offer you evaluation boards for our data converters, and complete design kits for our DSP processors.

Do you get the service of a small company backed by the resources of a large one? If your supplier is Analog Devices, you do. Analog and digital experts work together to solve your problems. And top management takes a hands-on approach to customer support.

which includes leading edge BiCMOS, Flash, Complementary Bipolar and many others.

As a \$540 million operation, we have the resources that help you achieve top performance from our ICs.

Performance that translates into higher levels of system integration, greater reliability and a better end product.

Whatever high-performance part you're looking for, we are the one company that can deliver it.

Call us at 1-800-262-5643 for a free copy of our recent booklet on

Mixed-Signal Technology.

Analog Devices, Inc., One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106. Headquarters: (617) 329-4700. Offices and applications support available worldwide.

CIRCLE 178

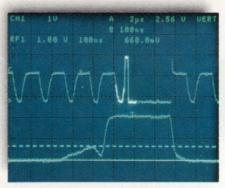

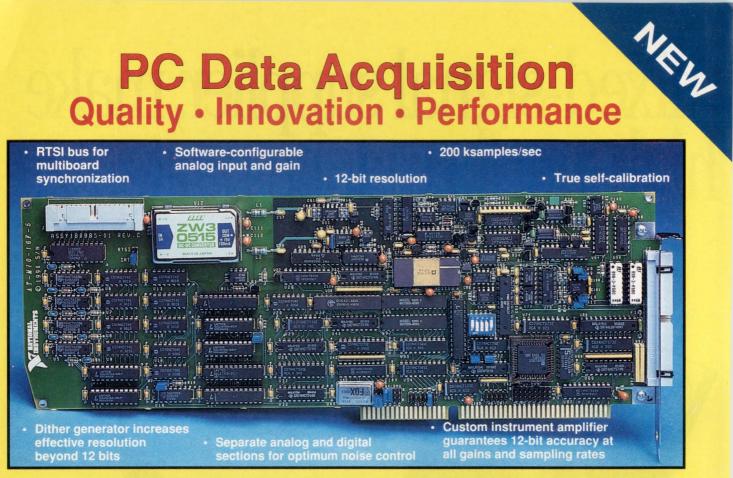

### The National Instruments AT-MIO-16F-5 Sets the New Standard

It takes a serious commitment to quality to deliver data acquisition boards that reliably meet the most demanding specifications. Our new AT-MIO-16F-5 creates a new standard in excellence with several firsts, including a proprietary ultra high-performance instrumentation amplifier, a dither generator for extended resolution, and self-calibration that eliminates the need for external signals required by other "self-calibrating" boards. The quality, innovation, and

performance of our AT-MIO-16F-5 sets the new standard in PC data acquisition. As the table below shows, the rest of our extensive PC product line surpasses industry standards. Each board undergoes a 48-hour burn-in, and passes a thorough system test to guarantee linearity, fast analog input settling, high common-mode rejection, and low noise. At National Instruments, we're serious about data acquisition.

|                                                | /              | 6             | 1            | /          | 11.11                       | Analog Input                     |       |           | /              | Ou       | nalog<br>tput | /            | 7         | 7           |          | Software            |

|------------------------------------------------|----------------|---------------|--------------|------------|-----------------------------|----------------------------------|-------|-----------|----------------|----------|---------------|--------------|-----------|-------------|----------|---------------------|

| Date Acc                                       | uistion P      | mpuer Bus     | amels hat se | mpinges pr | ase panon bis panon         | Sall Cains                       | 15    | annels Pr | 250 Ution      | dital 10 | Channer       | abwindow of  | a laborit | er clanonve | essue Vi | son score must rent |

| AT-MIO-16F-5                                   | АТ             | 16 SE<br>8 DI | 200,000      | 12         | ±5, 0 to 10                 | 0.5, 1, 2, 5, 10,<br>20, 50, 100 | 2     | 12        | 8              | 3        | V             | V            |           |             |          | Featu<br>Produ      |

| AT-MIO-16H-9<br>AT-MIO-16H-15<br>AT-MIO-16H-25 | AT             | 16 SE<br>8 DI | 100,000      | 12         | ±10, ±5,<br>0 to 10         | 1, 2, 4, 8                       | 2     | 12        | 8              | 3        | ~ ~ ~         | ~~~          |           | ~ ~ ~       |          | 222                 |

| AT-MIO-16L-9<br>AT-MIO-16L-15<br>AT-MIO-16L-25 | АТ             | 16 SE<br>8 DI | 100,000      | 12         | ±10, ±5,<br>0 to 10         | 1, 10, 100,<br>500               | 2     | 12        | 8              | 3        | ~ ~ ~         | ~~~          |           | ~~~         |          | ~ ~ ~               |

| Lab-PC                                         | ХТ             | 8 SE          | 62,500       | 12         | ±5, 0 to 10                 | 1, 2, 5, 10, 20, 50,<br>100      | 2     | 12        | 24             | 3        | V             | $\checkmark$ | V         | 1           |          | V                   |

| PC-LPM-16                                      | хт             | 16 SE         | 50,000       | 12         | ±5, 0 to 10<br>±2.5, 0 to 5 | 1                                | -     | -         | 16†            | 3        | V             | $\checkmark$ | V         |             |          |                     |

| AT-DIO-32F<br>PC-DIO-96<br>PC-DIO-24           | AT<br>XT<br>XT | 1 1 1         |              | 111        | Ē                           |                                  | 1 1 1 |           | 32<br>96<br>24 | 1 1 1    | ~ ~ ~         | ~~~          | * *       |             |          | V<br>V              |

| PC-TIO-10                                      | ХТ             | -             | -            | -          | -                           |                                  | -     | -         | 16             | 10       | $\checkmark$  | . 1          | V         |             |          |                     |

| EISA-A2000                                     | EISA           | 4 SE<br>SS    | 1,000,000    | 12         | ±5                          | 1                                | -     | -         | -              | -        | V             | 1            |           |             | ~        |                     |

MANTIONAL **CIRCLE 122** NSTRUMENTS The Software is the Instrument ® 6504 Bridge Point Parkway Austin, TX 78730-5039

Nihon National Instruments K.K. (Japan) 03 3788 1921 • National Instruments France 1 4865 3370 National Instruments Italy 02 4830 1892 • National Instruments Switzerland 056 45 58 80 National Instruments United Kingdom 0635 523 545 · National Instruments Germany 089 436 1447

Call for FREE Catalog

(512) 794-0100 or (800) 433-3488 (U.S. and Canada)

### TECHNOLOGY NEWSLETTER

**ENHANCED SPUTTERING** A new planar magnetron sputtering source, which operates at pressures a full decade lower than established sources, lets physical vapor deposition SOURCE IMPROVES YIELD (PVD) handle submicron device metallization. The Quantum Source from Varian Associates Inc., Palo Alto, Calif., offers better step coverage, more consistent via filling, fewer particles, and lasts 50% longer than previous sources. Operating at lower pressure levels reduces gas scattering and low-angle vapor that typically occurs with other PVD processes. Those improvements translate into better lateral control of the metal-film growth. They also result in a substantial increase in bottom and sidewall coverage in high-aspect-ratio submicron contacts and vias across a 200-mm wafer. For deposited films less than 0.1-µm thick, step coverage as high as 35% can be obtained in contact holes that are 1-µm deep and 0.45-µm wide. In addition, the low pressure allows high-speed cryogenic baffles to be used to quadruple the pump-down speed during production. Lower background levels of residual gas are also present during film deposition, which results in more uniformly grained and bettercontrolled film purity. Sources are available for aluminum alloys as well as for refractory metals and their reactively formed compounds. Contact Varian at (415) 424-5532. DB

TURNKEY BOARD SERVICE As computer-system geometries shrink, OEMs may find contract manufac-turing preferable to the capital-intensive acquisition of new production HELPS SHRINK SYSTEMS equipment. To that end, S-MOS Systems, San Jose, Calif., is now offering board-level design and packaging, and overall subsystem manufacturing, test, and assembly capabilities. The company's Raleigh, N.C.-based business unit offers OEMs access to highly advanced board-assembly technologies, including TAB and chip-on-glass. Boards are built with up to eight layers and can carry 0.5-mm-pitch quad flat-pack devices with up to 256 pins. In addition, boards can have any combination of TAB, chip-on-board, through-hole, and surface-mounted devices. S-MOS expects its board-assembly technology to progress in time. TAB pin counts are expected to rise from their current level of 200 to 500, with inner- and outer-lead bond pitches to reach 80 and 140 µm, respectively. Call Dave Perry at (919) 878-1120. DM

ASIC OFFERS LASER- Laser-printer makers can now compete directly with Hewlett-Packard's LaserJet III printer by using a custom ASIC chip set printer controller. Destiny PRINTER ALTERNATIVE Technology Corp., Milpitas, Calif., developed the Edge Enhancement Technology (EET) D9001 chip set that improves the appearance of 300-dot/in. laser-printer output to 400 dots/in., thanks to smoothing and reducing jagged edges. While EET is technically different from HP's Resolution Enhancement Technique (RET), its effectiveness is equivalent to, or in some cases surpasses, the RET in improving the output images. Destiny's EET examines one line of pixels for line-segment changes, and determines how to readjust the laser spot to smooth the segment transitions. The D9001 looks for edges, which minimizes the character distortion. HP's RET, on the other hand, examines a window area around each pixel. The D9001 is programmable for different resolution and printer-engine characteristics. It works independently from printer-controller microprocessors and controller emulation software. The chip set is available now for under \$20 in quantities of 1000. RN

SOLID LIGHT CUBES Researchers at Sandia National Laboratories, Albuquerque, N.M., have de-veloped a glowing piece of plastic—an aerogel—that requires no electrical GLOW WITHOUT POWER power, can be made in various sizes and shapes, and produces almost any desired color. In the inorganic version, a phosphor, such as zinc sulfide, is dispersed in a porous silica matrix that effectively is a low-density glass sponge. Tritium gas, a source of radiation, is chemically bonded to the aerogel silica matrix. Radiation emitted by the decaying tritium excites the phosphor particles, causing them to emit light. Because the aerogel is transparent, a large part of the light escapes. Beta radiation is attenuated inside the matrix. Inorganic light cubes or sticks can be ten times brighter than commercial radioluminescent lights and can operate over 20 years. Organic versions use a styrene matrix into which organic dyes can be dissolved for colored light, but discoloration with time limits useful life. Application possibilities range from emergency lighting to photovoltaic power supplies. ML

# How to ge customs with

### Custom IC Solutions

Need a custom IC? You'll bypass the usual red tape by working with an experienced custom IC partner like Silicon Systems.

Our 20 years of experience developing ICs for mass storage, communications and automotive applications means we can move quickly from your inspiration to a working custom prototype in no time.

And speed your custom IC into volume production. In our MSICs <sup>™</sup> (Mixed-Signal Integrated Circuits) world we combine high-performance analog and digital circuitry on a single chip and allow you to take full advantage of our state-of-the-art design systems. From there we will optimize the performance and integration of your design in CMOS, Bipolar or BiCMOS

# et through ut any delays.

### process technologies.

Enough said? Move to the front of the line and discuss your custom design requirements with a Silicon Systems representative. Or call us for lit package CUST-1.

Circle 124 for Product Info Circle 125 for Career Info Silicon Systems, Inc.,

14351 Myford Road, Tustin, CA 92680 Ph 1-800-624-8999, ext.151 Fax (714) 669-8814 European Hdq. U.K. Ph (44) 79-881-2331 Fax (44) 79-881-2117

### TECHNOLOGY NEWSLETTER

PLD TOOL INCORPORATES Engineers can now create a programmable logic device (PLD) with familiar TTL levels and then generate a standard Jedec file, thanks to new additions SCHEMATIC SUPPORT to Version 1.20 of Tango-PLD from Accel Technologies Inc., San Diego, Calif. The enhancements include a schematic-to-PLD translator and an 84-part schematic component library. They translate and then compile the logic into the Tango Design Language format, resulting in the Jedec file. The new component library consists of 42 TTL components, 35 generic gates, and 7 miscellaneous parts that include ports, power, and ground symbols. Also new with Version 1.20 is support for power-up reset, an option to disable logic minimization, and 13 new devices. Tango-PLD Version 1.20 costs \$495. Designers may obtain a free evaluation package by calling (800) 433-7801. LM

TEST DETECTS IC DEFECTS A long series of test vectors is used as an input, and the circuit's output is FROM QUIESCENT CURRENT monitored for proper responses. But these tests get very cumbersome with large ICs, and they can't find defects that could cause the circuit to fail. To locate hidden defects in the CMOS ICs it fabricates, Sandia National Laboratories, Albuquerque, N.M., developed a test based on the IC's quiescent current. The quiescent current is the amperage through a chip in its resting state when no switching voltage is applied. In a good CMOS chip, the quiescent current is low in all logic states. But a defective chip will have a greatly increased current in at least one logic state. Sandia says a chip with a high quiescent current should be considered defective because the current can cause premature battery failure or a malfunction in a customer's system. In addition to being more comprehensive, the new test requires fewer vectors and simpler software than the logic-response technique. For further information, contact Roy A. Hamil, (505) 844-7143. JN

FUSION PROGRAM BOOSTS Whenever new hardware emerges, the software needed to support new de-velopment efforts often seems to trickle out slowly. In an effort to correct SOFTWARE AVAILABILITY that for its new Mach family of PLDs as well as for other forthcoming PLDs, Advanced Micro Devices Inc., Sunnyvale, Calif., created a Fusion program. It's a value-added support arrangement with third-party software, design tool, and programming-aid developers to accelerate the development of support products. To speed the process, AMD created silicon-specific software modules that are transferred to the tool developers and incorporated into the final product, hastening its release. The end products are then certified by AMD and released by the third-party tool suppliers. As a result, the support products can be released simultaneously with the release of the PLDs from AMD. Contact Andy Robin at (408) 732-2400. DB

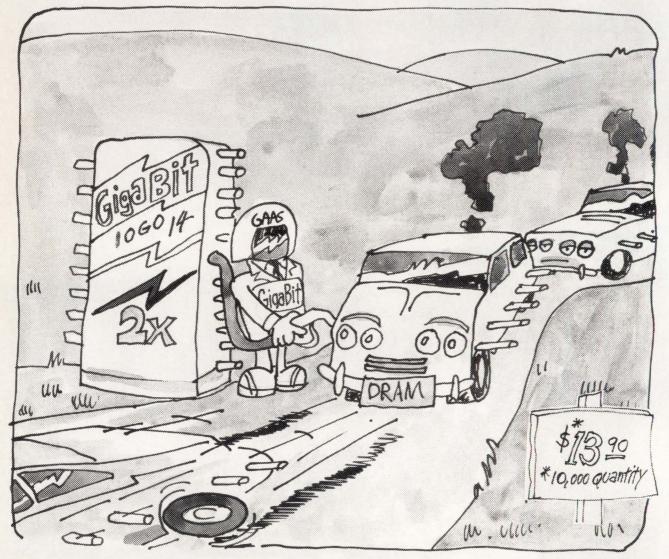

COMPANY MERGER FORMS The proposed merger of two of the leading gallium arsenide chip manufac-turers—Gigabit Logic Inc., Newberry Park, Calif., and TriQuint Semicon-LARGEST GAAS IC MAKER ductor Inc., Beaverton, Ore.-promises to yield the world's largest merchant GaAs chip manufacturer. Such a merger should improve the efficiency of research and development activities because there will be less duplication of research projects and R&D funding will stretch further. The new company will be jointly owned by the existing investors and retain the TriQuint name. Digital logic products will be marketed under the well-established Gigabit Logic name, while monolithic microwave ICs (MMICs) and analog circuits will be sold under the TriQuint name. DB

NEW SPECIFICATION LETS A specification developed jointly by Apple Computer Inc., Cupertino, Calif., and AT&T Computer Systems, Berkeley Heights, N.J., will offer a standard UNIX ACCESS APPLETALK framework for programmers accessing the AppleTalk networking protocols from AT&T's Unix operating system (System V, release 4). With the specification, software developers can create Unix-based AppleTalk networking application programs that perform file sharing or handle electronic mail or client-server applications. The specification also enables the AppleTalk application software to be ported quickly from one vendor's Unix system to another's system. AppleTalk application programming interfaces, as described in the specification, are already implemented by AT&T. They're installed on the company's StarGroup server for Apple Macintosh clients. Apple plans to implement the interfaces on its next release of the portable AppleTalk source code that it licenses to developers. Contact Randy Battat at (408) 996-1010. DB

> 28 E L E C T R O N I C D E S I G N **FEBRUARY 14, 1991**

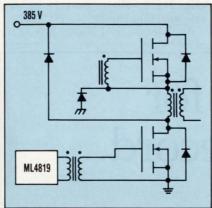

# A NEW CONCEPT DC-DC CONVERTER

**CIRCLE 126**

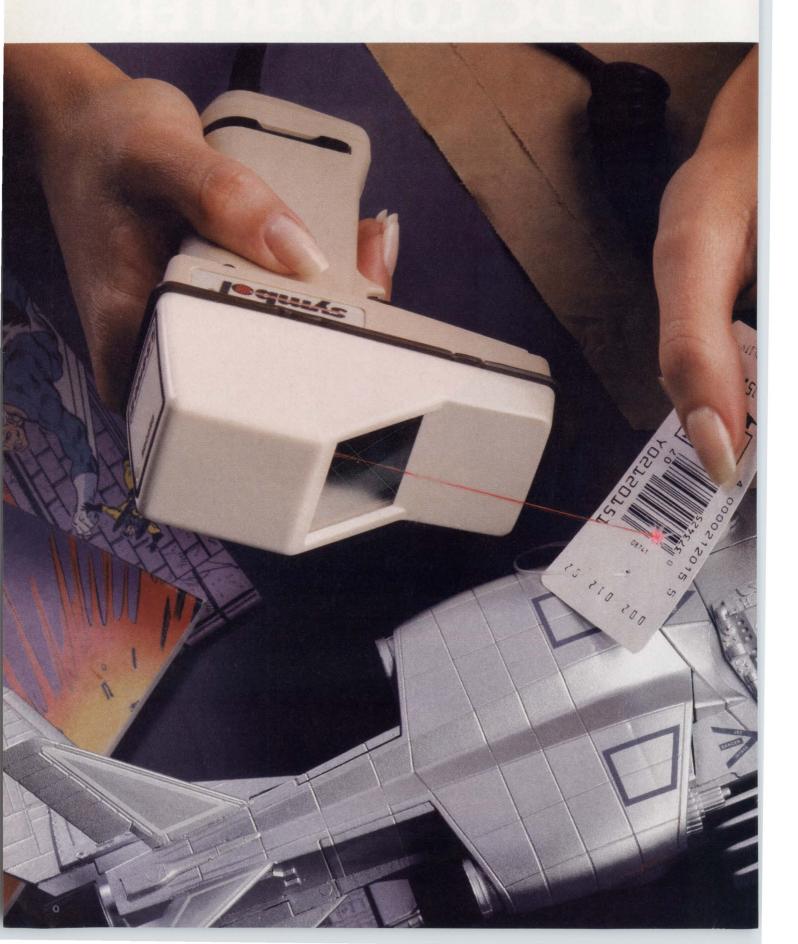

### From Star Wars

### to Price Wars

Our High Rel/Aerospace linear array experience is paying off for companies with high-volume, low-cost applications.

*Symbol Technologies* is a good example. A tiny Raytheon instrumentation amplifier helped them combine both bar code scanner and decoder in a single, lightweight, handheld unit—that's tough enough to take a five foot drop onto concrete,

Symbol also took advantage of our *Win-Win* program. It let them get to market quickly with a semicustom array, then shift to full custom as sales volumes increased.

*Win-Win* is fast, flexible, and makes good business sense because it eliminates the risk of getting into a full custom array before you're really ready.

Raytheon is committed to analog technology. From our design kits and engineering support to our fab and plastic assembly facility. We have the experience it takes to help you develop creative, cost effective solutions.

Find out how. Call **1-800 722-7074** for our new analog brochure.

Raytheon Company, Semiconductor Division. 350 Ellis St., Mountain View, CA 94039.

CIRCLE 95

Where quality starts with fundamentals

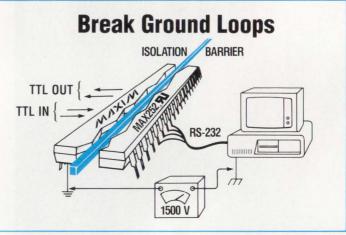

# **ISOLATED RS-232 INONE PACKAGE!**

### **New UL Approved MAX252 Delivers Up To 1500V Protection**

Maxim's new MAX252 delivers voltage isolation up to UL requirement levels (1500V for 1sec) – providing a *complete* isolation solution in one +5V-powered package. Whether you need to break ground-loops or protect your equipment from destructive transients, Maxim's new MAX252 solves your interface isolation problems.

### **Reduce Complexity**

- No External Components

- 50μW Low Power Shutdown

- Single +5V Supply

- 2 Transmitters & 2 Receivers

- Isolated Data Interface

1500Vrms (1 second) MAX252A

### **Isolated RS-232 Options For Your Specific Application**

Need more than 20kbits/sec or more than 1500V voltage isolation? The MAX250/251 chip set – with external components – lets you design your own system if size is not important.

| PARTS   | PACKAGES           | FEATURES                                                             | PRICE<br>(1000-up) |  |

|---------|--------------------|----------------------------------------------------------------------|--------------------|--|

| MAX252A | 40 Pin Plastic DIP | All-in-one package isolated RS-232<br>(1500V isolation, UL Approval) | \$50.00            |  |

| MAX252B | 40 Pin Plastic DIP | All-in-one package isolated RS-232<br>(Economical 500V isolation)    | \$29.50            |  |

| MAX250  | 14 Pin DIP, SO     | Two chip isolated RS-232 (4 External                                 | \$3.20             |  |

| MAX251  | and 20 Pin LCC     | opto-isolators and isolation transformer)                            | \$3.20             |  |

Call your Maxim representative or distributor today for applications information, datasheets and samples. Or, write Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086, (408) 737-7600, FAX (408)737-7194.

Distributed by Arrow, Bell/Graham, Hall-Mark, Nu Horizons, Pioneer, and Wyle. Authorized Maxim Representatives: Alabama, (205) 830-0498; Arizona, (602) 730-8093; California, (408) 248-5300, (619) 278-8021, (714) 261-2123; (818) 704-1655; Colorado, (303) 799-3435; Connecticut, (203) 384-1112; Delaware, (609) 778-5353; Florida, (305) 426-4601, (407) 682-4800; Georgia, (404) 447-6124; Idaho, (503) 292-8840; Illinois, (708) 358-6622; Indiana, (317) 844-8462; Iowa, (319) 393-2232; Kansas, (816) 436-6445; Louisiana, (214) 238-7500; Maryland, (301) 644-5700; Massachusetta, (617) 329-3454; Michigan, (313) 583-1500; Minnesota, (612) 944-8545; Mississippi, (205) 830-0498; Missouri, (314) 839-0033, (816) 436-6445; Montata, (503) 292-8840; Nebraska, (816) 436-6445; Novata, (408) 248-5300; New Hampshire, (617) 329-3454; New Jersey, (201) 428-0600, (609) 778-5353; New Mexico, (602) 730-8093; New York, (201) 428-0600, (607) 754-2171; N. Carolina, (919) 851-0010; Ohio, (216) 659-9224, (513) 278-0714, (614) 895-1447; Oklahoma, (214) 238-7500; Oregon, (503) 292-8840; E. Pennsylvania, (609) 778-5353; W. Pennsylvania, (614) 895-1447; S. Carolina, (919) 851-0010; Tennessee, (404) 447-6124; Texas, (214) 238-7500, (512) 835-5822, (713) 789-2426; Utah, (801) 561-5099; Virginia, (301)644-5700; Washington, (206) 823-9535; W. Virginia, (513) 278-0714; Wisconsin, (414) 792-0920; Canada, (416) 238-0366, (613) 225-5161, (604) 276-8735, (514) 337-7540.

Maxim is a registered trademark of Maxim Integrated Products. © 1991 Maxim Integrated Products

CIRCLE 153

### TECHNOLOGY ADVANCES

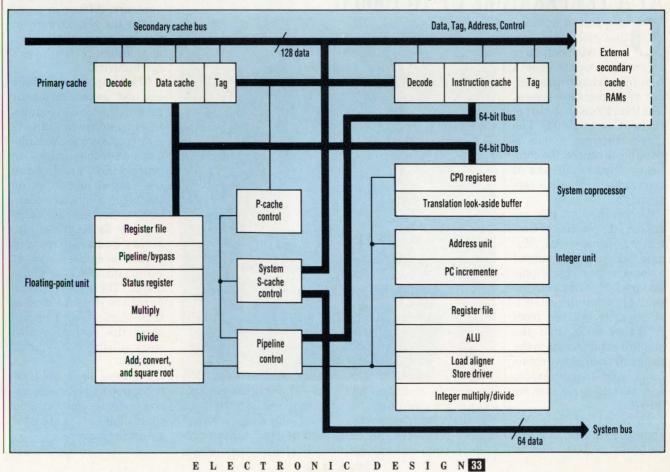

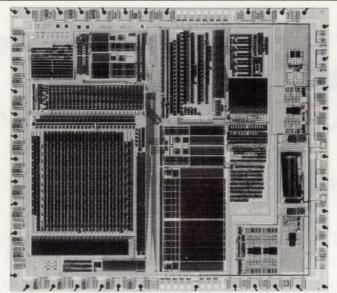

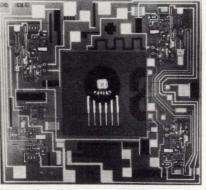

### NEXT-GENERATION RISC CPU GETS 50 TO 100 MIPS FROM 64-BIT INTERNAL ARCHITECTURE

ttracting customers has been relatively easy for CPU manufacturers-just make the CPUs faster and larger to achieve major improvements in throughput and system integration. However, most companies have already reached the practical limits of scaling. Consequently, attention must be paid to architectural changes so that the advantages of fine-line CMOS or bipolar processes are maximized.

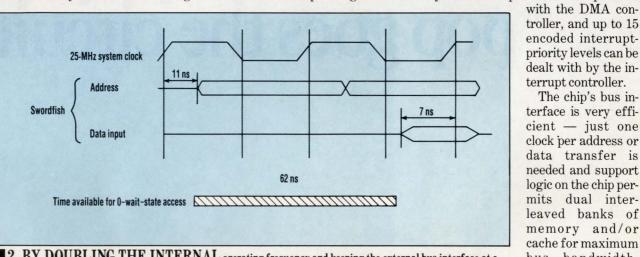

The RISC architecture of the R2000 and R3000 family processors from Mips Computer Systems Inc., Sunnyvale, Calif., was innovative when first released. Since then, however, many tricks have been learned, both in silicon architecture implementation and in compiler design. Mips puts many of those improvements to work in its next-generation family, the R4000 series, to achieve throughputs of 50 to over 100 MIPS from a CMOS CPU.

The first change from the previous families is a move to a two-instructionissue superpipeline. It increases the integer and floating-point performance beyond that expected for the clock speed. The approach employed by Mips also extracts instruction-level parallelism with no issue restrictions for load/load, load/store, store/store, and ALU/ ALU operations. A deeper instruction pipeline than the 5-stage pipeline employed on the R3000 enables the two instructions to be issued during each clock period so that more can be done every cycle.

Integration also plays a part in the forthcoming processor. Mips designers moved the processor to a full 64-bit architecture to give programmers access to a flat, unsegmented address space many times that of a 32-bit CPU. This type of address space will be needed by applications such as large data bases, display-list based graphics, and others.

To call the processor a

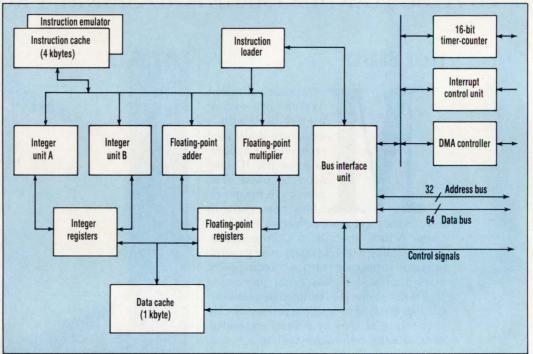

true 64-bit machine, designers at Mips feel the chip must handle a 64-bit virtual address, have a 64bit integer ALU, contain 64-bit integer registers, offer 64-bit compatibility with 32-bit products, maintain 64-bit data paths to cache and main memory, and pack a 64-bit IEEE-754 compliant floating-point ALU. Making all of that possible on one chip required a considerable amount of integration to keep the pin-count reasonable. As a result, designers have combined a full 64-bit floating-point unit, instruction and data caches of 8 kbytes each with a 128bit-wide interface to external memory, and a 64-bit integer processor with a 64bit interface to external systems (see the figure).

The embedded cache

FEBRUARY 14, 1991

### **TECHNOLOGY ADVANCES**

controllers ensure data integrity by providing parity protection on the primary caches, and error checking and correction on the secondary, off-chip cache of 128 kbytes to 4 Mbytes. That secondary cache can be set as either a split instruction/data cache, or as a joint secondary cache. An on-chip translation lookaside buffer holds up to 96 entries, all lockable, and permits a cache coherency policy to be set on a perpage basis. Both the cache depth and line size are configurable. Furthermore, to ease multiprocessing applications, physical tags supply flags to programs.

As part of the multipro-

cessing features, the cache controller responds to requests for secondary cache snoops, cache invalidates, and updates, all independent of the CPU. Synchronization primitives are designed around cache coherency mechanisms; synchronization doesn't depend on long bus locks. The controllers support snoopy, directory-based, and other interconnection schemes. As a result, they give designers the ability to fine-tune the memory subsystem for optimal performance in a particular application.

To ease system software development and hardware debugging, Mips also

included some debug features on the chip—a watch breakpoint register for software debugging, a fine-grained process timer. and exception-state and diagnostic registers. Also included is a JTAG-compatible external boundaryscan test port, and a tightly coupled master/checker interface if redundant CPUs are needed to ensure maximum system software integrity. Many other system interface features have been added so that hardware designers can optimize the interfaces for memory timing, signal slew rates, and data ordering.

DAVE BURSKY

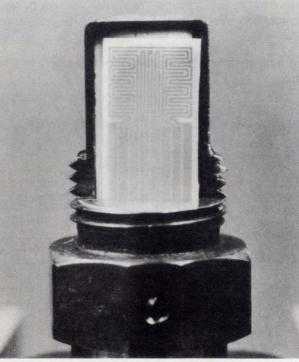

### **AUTOMOTIVE GAS SENSOR WORKS IN 10 MS** AT A TEMPERATURE UP TO 1000°C

esigners of automotive electronic systems will soon have a new component to use: a thin-film exhaust-gas sensor with a response time of less than 10 ms that can operate at up to 1000°C. The quick response makes it possible to control the combustion process in each of the engine's cylinders separately.

Developed at the research laboratories of Germany's Siemens AG, Munich, the sensor is made of a semiconducting ceramic material. It permits engine control so that the catalyzer is partly relieved from its usual tasks, and the amount of pollutants in the exhaust, such as hydrocarbons, carbon monoxide, and nitrous oxide, are reduced.

In today's catalyzerequipped vehicles, a lambda probe made of zirconi-

**FEBRUARY 14, 1991**

um dioxide measures the exhaust's composition. However, because of the probe's relatively long response time-about 100

ms-the engine-control system reacts, with some delay, only to the average lambda combustion-process value of all cylinders. 34 E L E C T R O N I C DESIGN

It then adjusts the composition of the fuel-air mixture accordingly. The control system can't optimize the combustion process in individual cylinders.

The new Siemens exhaust gas sensor overcomes this problem to help provide a cleaner exhaust. Its short, 10-ms response time results from the thin sensor laver it uses. In fabricating the sensor, a 1-µm film consisting of a semiconducting metal-oxide material is deposited by reactive-cathode sputtering on a ceramic substrate of aluminum oxide. The sensor is about 3000 times thinner than conventional lambda probes.

The materials' sensing effect derives from the oxygen ions that, in accordance with the environment's partial oxygen pressure, diffuse into and out of the sensitive layer. Consequently, the oxygen ions influence the layer's conductivity.

The temperature of the exhaust gases varies by several hundred degrees Celsius, depending on engine rotation and the lambda value of the combustion process. So, in addition to the contact electrodes on the layer, there are platinum conductors that, functioning as heating elements and temperature probes, keep the sensor at a constant 1000°C, or thereabout. The sensor's temperature dependence is thus eliminated. This enables the device to also work during cold-engine starts.

Siemens sees applications not only in automotive vehicles but also in controllable household and industrial furnaces.

**IOHN GOSCH**

## **Count On IDT**

### The R3001 RISController™: The Embedded Processing Solution

The R3001 is the first derivative of the R3000 processor designed specifically for embedded control applications. Compared to the Intel 960 and AMD 29K processors, the R3001 is the most cost-effective solution for these applications—we have the data to prove it! Call and ask for **KIT CODE 0091A** to get an **R3001 Performance** *Comparison Report*.

### BiCEMOS<sup>™</sup> ECL SRAMs: Technology for the '90s

Design the fastest systems with IDT's BiCEMOS ECL family. At 7ns, the IDT10494 is the fastest BiCMOS 64K ECL SRAM in production. 256K and synchronous self-timed SRAMs are also available in 10K/100K/101K configurations. Call and ask for KIT CODE 0091B to get a copy of the BiCEMOS ECL Product Information booklet.

### FCT-T Logic: Fastest Speed/ Lowest Ground Bounce

DT's FCT-T Logic Family is the fastest logic family available and has the lowest ground bounce—up to 40% less than previous FCT devices! The FCT-T family provides direct TTL logic compatibility and is available in FCT, FCT-AT, and FCT-CT speeds. Call today for **KIT CODE 0091C** and get a copy of the **High-Speed CMOS** Logic Design Guide.

### The SyncFIFO<sup>™</sup> Family: Double Your FIFO Performance

SyncFIFOs offer leading-edge performance that is 50% faster than other FIFOs. The synchronous architecture is easy to implement and reduces chip count 9-to-1. SyncFIFOs have 18-bit buses and are ideal for 32bit systems. Ask for KIT CODE 0091D to get AN-60: Designing with the IDT SyncFIFO<sup>™</sup>.

### IDT Subsystem Modules: Building Blocks for the '90s

DT offers a complete line of board-level subsystem products, including cache memory, shared-port memory, writable control store, RISC CPU, high integration modules, and custom designs for specific applications. Call today for **KIT CODE 0091E** and receive technical data and *a* **free IDT puzzle**!

### 12ns Cache Tag SRAMs: Wait No Longer

**I**DT's cache tag SRAMs have the features you want to design in: single-pin block reset, totem-pole match output, 4K and 8K depths, industry standard pinouts, and an on-board comparator to simplify design. Call and ask for **KIT CODE 0091F** to get *free samples* of the IDT6178 cache tag.

RISController, BiCEMOS, and SyncFIFO are trademarks of Integrated Device Technology. In The 1DT logo is a registered trademark of Integrated Device Technology, Inc.

Contact us today to receive data sheets and other design information on IDT's products.

(800) 345-7015 FAX: 408-492-8454

3236 Scott Boulevard, P.O. Box 58015, Santa Clara, CA 95052-8015

When cost-effective performance counts

Integrated Device Technology, Inc.

### TECHNOLOGY ADVANCES

### APPLE MACINTOSH CLONES NOW POSSIBLE WITH THREE-CHIP SET AND SOFTWARE

soon-to-appear landmark chip set will let designers create a fully compatible system that runs Apple Macintosh software without tapping into an original ROM set. Start-up Nutek Computers Inc., Cupertino, Calif., the set's developer, states that it has worked in a "total clean-room environment" for the last two years. The company has been crafting the motherboard chip set and system software to duplicate all of the functions of the Macintosh, making it possible for companies to build low-cost NuBusbased compatibles.

Currently, the market for Macintosh-compatible computers is very small since most require that another Macintosh be cannibalized or that a ROMbased operating system be obtained from Apple. However, if a legal, compatible operating system, user interface, and underlying hardware such as Nutek's can be established, analysts predict a market with a high growth potential.

Nutek is hoping to create an Apple-compatible marketplace similar to the IBM PC-compatible market that chip-set makers in the last decade created. It has designed the three key elements needed by a computer system manufacturer-the logic chip set, the internal operating system, and a graphical user interface. The chip set will consist of three rather complex custom chips that replicate the principle logic functions of a Macintosh system board. Designers only need to add the SCSI controller, CPU, up to 64 Mbytes of RAM, and some glue logic.

A Macintosh-compatible operating system will be supplied on a disk and boot ROM combination. The combination is similar to that used by the IBM PCs, allowing simple software updates of the operating system. It will enable companies to design full-function personal computers that run all Macintosh published specifications. The combination will also work with nearly all standard add-in boards and peripherals that come from both Apple and third-party developers.

Of the three chips, two incorporate a NuBus interface that can tie into standard Motorola 680X0 microprocessors and supply all of the memory management. The third chip handles all of the I/O functions. Included on it are the serial ports, sound input and output channels, flop-

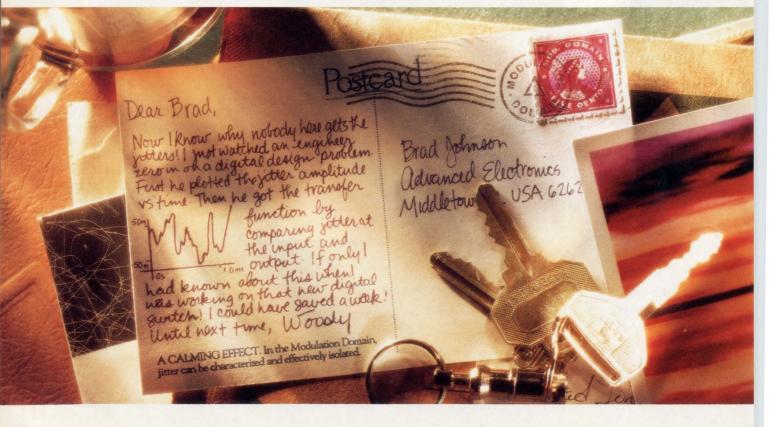

### Visit the Modulation Domain and get

### TECHNOLOGY ADVANCES

py-disk controller, and keyboard and mouse interfaces.

The chips have been implemented in prototype form and are undergoing simulation and validation testing at the company's laboratories. They're designed to support burstmode memory transfers, DMA, sound generation, and as part of the floppy disk controller, to give the user the same capability as the Macintosh Superdrive, reading and writing Macintosh and DOS-compatible 3.5-in disks.

With the chips, systems operating at clocks up to 33 MHz can be implemented. Although that clock speed is lower than the 40 MHz used by Apple's top-of-theline 68030-based IIfx, designers can actually leapfrog the IIfx's performance by basing system designs on the more powerful 68040. The 68040 operates at 25 MHz, and will probably have a 33-MHz upgrade option in the next year.

One minor difference in Nutek's system implementation is that there will be no equivalent to the Apple Desktop Bus that's typically used to connect the keyboard and mouse to the CPU. Instead, system designers will have to employ direct-connect keyboard and mouse ports, much like the IBM PC and compatibles world.

Written from the ground up without reference to the internal code of the Macintosh, the operating-system software will replicate the more than 760 specific functions performed by Apple's operating system. The company will base its user interface on a nativelanguage version of the Motif graphical user interface from the Open Software Foundation, and will incorporate the functionality of Apple's version 6 of the Macintosh operating system. Although the software incorporates the same windowing functionality as the Macintosh user interface, the Motif images have a more three-dimensional appearance. Furthermore, in the Nutek approach, the menu bar appears at the upper edge of

the top-most window instead of always just appearing at the top of the screen, as in a Macintosh display.

The Motif-based interface will also be offered as a standalone package for existing Macintosh users. Samples of the chips and final software will be ready in the fourth quarter. However, unlike chip-set suppliers in the PC industry who offer products to all purchasers, Nutek would like to establish partnerships with a limited number of system manufacturers. Licensing fees, chip prices, and royalty arrangements haven't yet been established. Contact Benjamin Chou at (408) 973-8857.

DAVE BURSKY

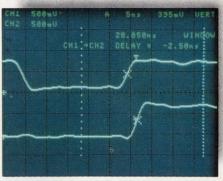

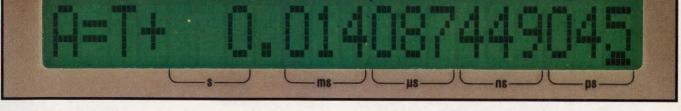

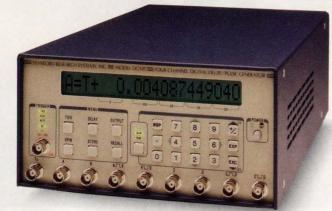

### a fix on jitter.

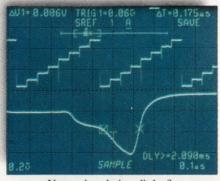

Until now, when you looked at jitter on an oscilloscope, all you could see was fuzz. And the only way to find the source was by trial and error. In the Modulation Domain, you can actually display jitter as a function of time. That way, you know exactly how much there is and when it occurs, so it's easier to tell where it comes from. You can even examine the jitter spectrum and quantify the jitter gain (transfer function). All in a matter of minutes.

Jitter analysis is just one way the Modulation Domain can help make you a better designer. To see more, call Hewlett-Packard at **1-800-752-0900\*** Ask for **Ext. 1831**, and we'll send you the *Visitor's Guide to the Modulation Domain* on floppy disk with complete descriptions of major landmarks and points of interest.

There is a better way. CIRCLE 80

\*In Canada, call 1-800-387-3867, Dept. 417. Any similarity to existing persons or companies is purely coincidental. © 1990, Hewlett-Packard Co. TMSCD055A/ED

PACKARD

### Because you're thinking fast...

### With Comlinear's new fast op amps...

#### 14-bit, 25ns settling keeps up with fast converters.

Here are two new op amps that give you big design margins on fast, highresolution A/D and D/A converters. The new 175MHz CLC402 and 150MHz CLC502 have extremely fast settling to 0.0025% accuracy. Plus a low 1.6mV max. offset. And, the CLC502 gives you output voltage clamping to protect downstream circuits from damaging or saturating signals. That's a lot of good news for your high-speed, high-accuracy converter designs. CIRCLE 143

**350MHz BW** with low distortion drives

flash A/Ds.

At last, there's a wide-bandwidth op amp with extremely low distortion for your flash A/D converters. The new 350MHz CLC409 is spec'd at a low -65/-72dBc, 2nd/3rd harmonic distortion (20MHz, 100 ohms, 2V<sub>p-p</sub>). And it does it without burning much power. Dissipation is a low 142mW at  $\pm 5V$ . Add to that its low input

noise and you have an ideal driver for today's fast 6- to 10-bit flash A/D converters. CIRCLE 144

### Comlinear

Solutions with speed

©1990 Comlinear Corporation

4800 Wheaton Drive Fort Collins, CO 80525 (303) 226-0500 1-800-776-0500 (USA)

### Now, highspeed AGC is easier than ABC

Take the new CLC520, add  $\pm 5V$  and two resistors, and you have a total high-speed AGC solution for fast converter applications. 160MHz small-signal and 100MHz gain-control bandwidth-with a 40dB range from max. gain-give you a very flexible solution in a single 14-pin DIP. CIRCLE 145

### High performance at low gains.

Optimized for a gain of +2, the

200MHz CLC400 has 10ns settling to 0.1%, making it an

ideal data converter driver. Its excellent gain flatness makes it great for video applications too. And it's priced at just \$5.95\* (1000s). **CIRCLE 146**

### Fast op amp cuts cost and power.

For only \$4.25\* ea. (1000s) the CLC406 provides 160MHz smallsignal bandwidth  $(2V_{p-p})$  at only 50mW power dissipation  $(\pm 5V)$ . It's your lowcost answer for remote-site applications, video systems, or driving/buffering fast data converters. \*U.S. price only

CIRCLE 147

### SIEMENS

### International Exchange.

Siemens integrated circuits help bring the world closer together with telecommunications.

Siemens is continuing to provide innovative solutions in communications which are making a sound impact, throughout the industry. And the world.

We offer the most comprehensive communication IC family in the world, facilitating the incorporation of data, speech, and picture sources, to meet your applicationspecific needs.

With the development of our PEB2091 ISDN Echo High-integration echo cancellation Cancellation Circuit (IEC-Q), transceiver for ISDN. we introduced the industry's first single-chip CMOS solution for the standardized U-interface. It can double the traffic-handling capability of existing

© 1991 Siemens Components, Inc. M12A 010

telephone lines. And it's ideal for transmission systems such as digital added main line and other pair gain systems and intelligent channel banks.

For applications such as cellular or full-featured telephones or line cards. which require lower power consumption. we offer CMOS 8-bit microcontrollers based CMOS 8-bit Microcontrollers on the 8051 architecture. Like the SAB80C537, which features 16-bit hardware multiply/divide, and 8 data pointers.

Siemens CMOS ASIC technology features both Sea-of-Gates and standard-cell families. Our 1.5, 1.0 and sub-micron technologies are compatible with Toshiba even at the GDS2 database level, for true alternate sourcing

worldwide. And they come with the European content and U.S. design support you need, as well as the best service in the industry.

**ASIC** solutions in both Sea-of-Gates and standard-cell.

For the most advanced telecommunications ICs, hook up with the leader.

For details, call (800) 456-9229, or write:

Siemens Components, Inc. 2191 Laurelwood Road Santa Clara, CA 95054-1514. Ask for literature package M12A 010.

Siemens World Wise, Market Smart.

### COVER FEATURE

### COMBO CPU AND DSP CHIP PERFORMS A SEA OF TASKS With A Peak Throughput Of 100 MIPS, A 64-Bit Embedded Controller Packs DSP Enhancements To Also Handle Image And Signal Processing.

### **DAVE BURSKY**