## Knock-your-socks-off PLD software on a shoestring budget.

tate Dias tate Live

late Sta

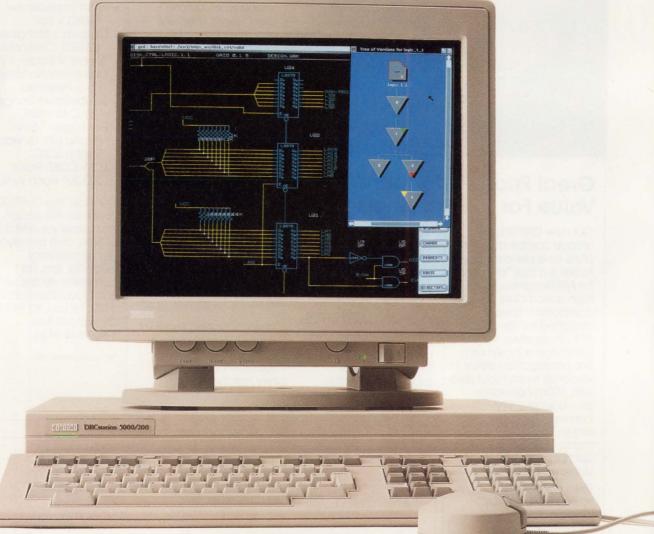

Who says you can't afford the world's best PLD development tools? Data I/O®'s industry-standard design software and programming solutions are more powerful-and more affordable-than ever before. So now the best tools on the market are also the best value.

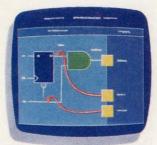

**NEW** ABEL<sup>™</sup>-4 marks a major milestone in PLD software. The leader in device support, ABEL-4 automatically identifies which PLDs match your design needs with new SmartPart<sup>™</sup> intelligent device selection. New optional device fitters automatically assign pins and

configure macrocells for complex device architectures. And an all-new user interface speeds the entire PLD design process.

A major new version of the leading schematic capture software, NEW FutureNet®-5, redefines "ease-of-use" with pop-up menus, extensive dialog boxes and a fast symbol browsing feature.

To make designing for testability practical, choose NEW PLDgrade.™ This inexpensive fault grading software helps you optimize your design for testability before production.

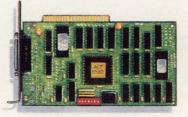

And the affordable NEW 2900 **Programming System** brings the cost of high-performance programming down to earth. Its innovative technology makes programming any PLD-even surface-mount devices. fast and easy.

**CALL TODAY for your FREE tutorial on** designing with PLDs a \$12.95 value.

1-800-247-5700

Data I/O Corporation 10525 Willows Road N.E., P.O. Box 97046, Redmond, WA 98073-9746, U.S.A. (206) 881-6444/1-800-247-5700 Data I/O Canada 6725 Airport Road, Suite 302, Mississauga, Ontario LAV 1V2 (416) 678-0761 Data I/O Lorope World Trade Center, Strawinskylaan 633, 1077 XX Amsterdam, The Netherlands + 31 (0)20-6622866/Telex 16616 DATIO NL Data I/O Linstrumatic Electronic Systems Vertriebs GmbH Lochhamer Schlag 5A, 8032 Graefelfing, W. Germany, + 49 (0)89-858580 Data I/O Japan Sumitomoseimei Higashishinbashi Bldg, 8F, 2-1-7, Higashi-Shinbashi, Minato-Ku, Tokyo 105, Japan (3)3 432-6991/Telex 2522685 DATAIO J

© 1990 Data I/O Corporation

The Personal Silicon Experts

#### Finally, FDDI worthy of the name.

It's one thing to set the standard for an entire industry, as HP helped to do with FDDI. But it's quite another to follow it up with products that set the standard for performance and quality. Of course, that's just the HP way.

Case in point, our new integrated FDDI transceiver with integral MIC receptacle makes the most of its HP heritage. Engineered to meet and beat FDDI standards, this single-piece solution provides consistent performance over a wide range of operating temperatures and voltages. The bottom line is a 14.5dB power budget that exceeds the 11dB FDDI PMD standard, resulting in a comfortable 3.5dB design margin.

Attributes that stem directly from HP's role as a vertically integrated supplier. Which means we have direct control over all the active elements of our FDDI designs, ensuring you a consistently high quality product – and a constant high volume supply.

What's more, our new FDDI transceiver is just one part of a growing family of 1300nm products. Like our individual transmitter/receiver pair – for FDDI and general-purpose applications – that offer data speeds up to 200MBd. With more new and innovative products on the way.

So, if you're in the process of building a name in fiber optic networks, remember this – there's only one supplier of FDDI products worthy of the HP name. For more information, call HP today at **1-800-752-0900**, **ext. 1960**. We'll make it worthy of your time.

There is a better way.

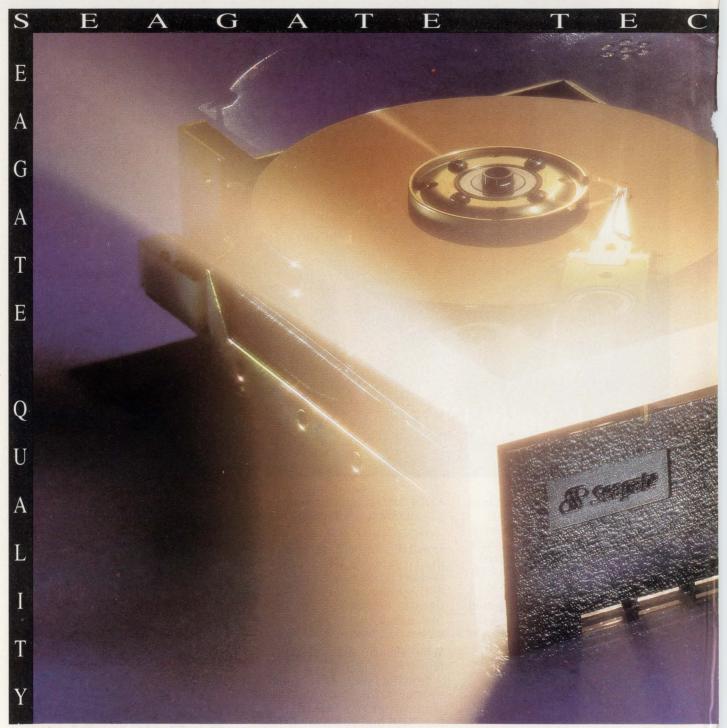

## Outside, all disc drives look t It's really what's inside that co

Zone Bit Recording, ZBR, Seagate and the Seagate logo are registered trademarks of Seagate Technology, Inc.

## he same. unts.

Apart from our nameplate, a Seagate disc drive looks much like any other when viewed from the outside. But it's the tangible and intangible elements we put inside that make a Seagate drive really shine.

If you could see inside you'd find the best components available. Many of them—such

as discs, motors, semiconductors and thinfilm heads — we design and build ourselves, allowing us to control their quality, cost and availability. Most of what we don't manufacture is obtained from a select group of vendors who must meet our strict Supplier Certification Program criteria. This guarantees consistently high quality and continual conformance to our customers' requirements.

Technology is another key Seagate ingredient. As the holder of over 200 disc drive patents, we constantly develop state-of-the-art technologies to enhance the value of our products to our customers. For example, Zone Bit Recording<sup>™</sup> increases the amount of information that can be stored on a disc. But besides increasing the drive's capacity and throughput, ZBR<sup>™</sup> technology can reduce the required number of heads and discs, thereby reducing costs, increasing performance and making the drive significantly more reliable.

The third major factor that sets Seagate drives apart is our commitment. You see it in the inspired dedication of our employees: like our engineers, who apply the latest technology advances to our current models. In our assemblers and technicians, who are committed to producing defect-free products. And in our sales, customer service and technical support groups, who continually go the extra mile to ensure complete customer satisfaction.

But most of all, Seagate drives are built upon experience: the market insight and tech-

nical knowhow that can only come from selling more than 25 million drives since the industry's inception. It's the kind of experience you won't find at any other disc drive company.

To be sure you're getting Seagate quality and technology inside where it counts, make sure there's a Seagate nameplate on the outside. For more information, contact Seagate at 800-468-DISC, or 408-438-6550.

The first name in disc drives

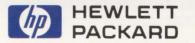

#### JANUARY 10, 1991 VOL. 39, NO. 1

ECTRONIC DES

SALEH DESIGN • TIME TO MARKET • MANUARE

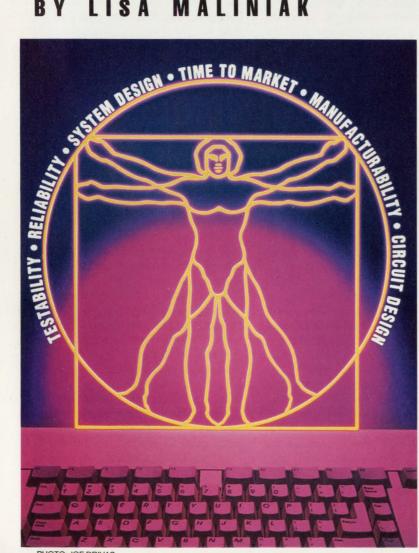

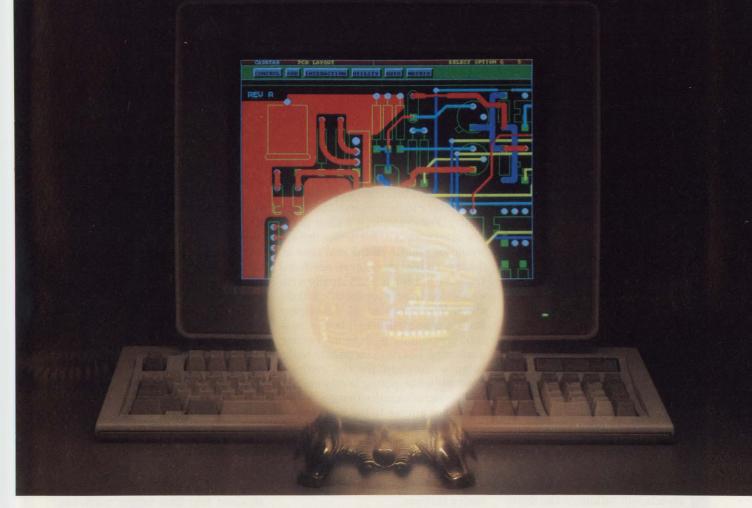

**1991 TECHNOLOGY 41 TEAMWORK IS THE KEY TO CONCURRENT DESIGN FORECAST** Future design teams will need all disciplines to work in parallel.

V . REI

56 DESIGN TEAMS EVOLVE TO FACE TESTABILITY More teamwork and new tools will help offset the complex-system challenge.

**79 CONCURRENT ENGINEERING MEETS DESIGN AUTOMATION** Design tools merging under frameworks pave the way for true automation.

**95 WILL COMPUTER-AIDED SOFTWARE ENGINEERING COME OF AGE?** CASE tools lag about five to seven years behind their CAE counterparts.

**111 OUTRUNNING THE PACK IN FASTER PRODUCT DEVELOPMENT** Overcome 15 common barriers to trimming product-development cycles.

121 DESIGN FOR RELIABILITY RESHAPES DESIGNING Rising customer expectations are driving design for reliability.

**135 INTERVIEW SECTION**

Industry experts look at the coming decade.

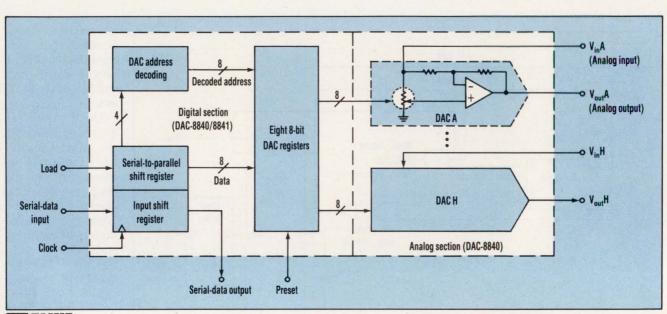

**PRODUCT 178 1-MHZ MDACS REPLACE GAIN-SETTING TRIMMERS** Eight, 8-bit DACs on an IC control dc levels, gain, phase, and modulation.

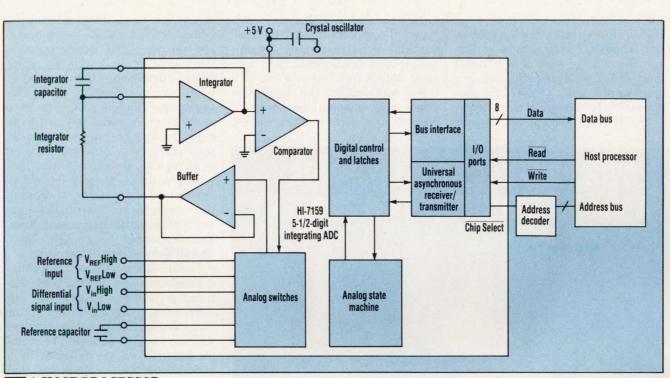

> **181 5-1/2-DIGIT INTEGRATING ADC RUNS 15 CONVERSIONS/S** At 4-1/2 digit resolution, the chip zips along at 60 conversions/s.

**184 LINEAR ISOLATOR STANDS OFF 7500 V FOR 1 SECOND** Optocoupler with two diodes sports linear isolation approaching 0.01%.

> 4 E L E C T R O N I C D E S I G N JANUARY 10, 1991

#### **14 EDITORIAL**

#### **18 TECHNOLOGY BRIEFING**

Europe banks on JESSI

#### **25 TECHNOLOGY NEWSLETTER**

• Indium tin oxide to improve image sensors

Software consortium publishes guidelines

• CAD conferencing aids in concurrent design

Electrons accelerated to 150.000 eV

• 1/4-in. cartridge tape drives improving

• EDAC re-elects management team

- Font generator speeds printing 100 times

- Database selected for framework research

• Military VME chip set gets second sourcing

#### **33 TECHNOLOGY ADVANCES**

• Glasnost comes to ISSCC as advanced ICs are unveiled

• GaAs switch turns on 8.5 MW in nanoseconds

Certificate of Merit Winner, 1988 Jesse H. Neal Editorial Achievement Awards

#### **149 OUICK LOOK**

- Good planning is crucial in improving time to market

- A \$99 version of the Unix operating system

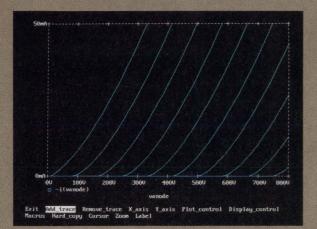

- Flat-panel display market keeps growing

- How engineers can save for their children's college expenses

#### PC DESIGN SPECIAL EDITORIAL SECTION

**155 PC Design Newsletter** 157 PC Design Editorial Feature Boost PC's floating-point speed with an add-on DSP coprocessor board **170 PC Design Products**

#### **172A PEASE PORRIDGE**

What's all this testing stuff, anyhow?

#### **173 IDEAS FOR DESIGN**

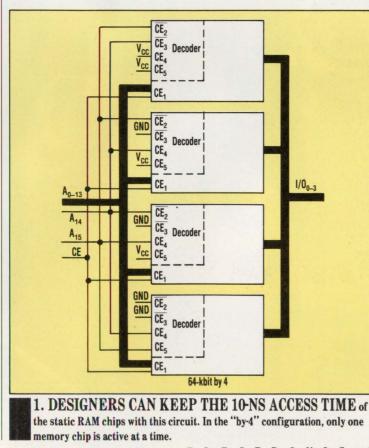

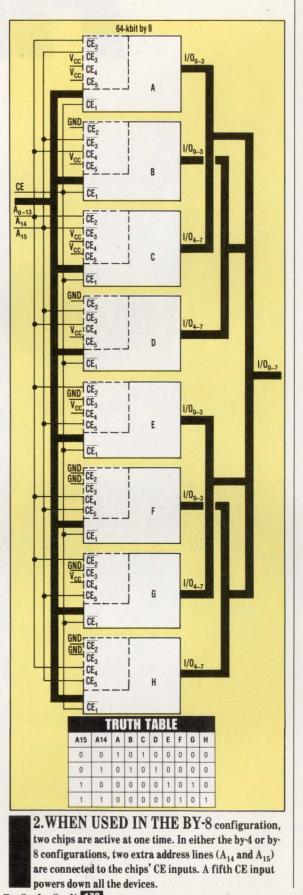

- Decoder retains access time

- Monitor logic-line state

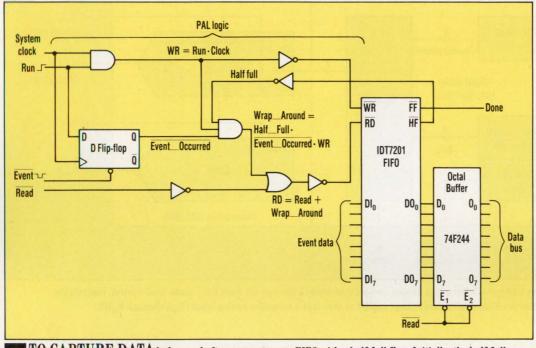

• Capture data before and after an event

#### **NEW PRODUCTS**

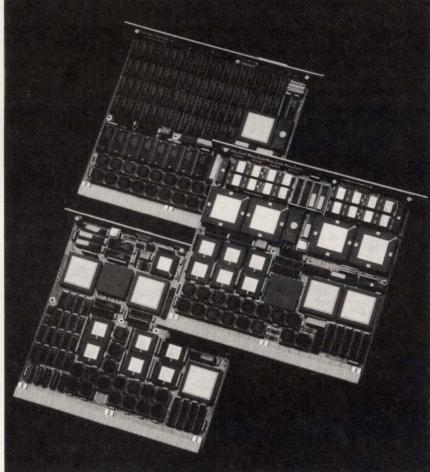

**186 Computer Boards** DSP-based array processors take on tough compute tasks **187 Instruments**

**189 Computer-Aided Engineering** 190 Power **191** Communications **192 Analog**

#### **196 INDEX OF ADVERTISERS**

#### **197 READER SERVICE CARD**

#### **COMING NEXT ISSUE**

• First details on a new method of analog-signal storage

• PIPS—A special section on power, interconnections, passive components, and switches and relays; includes a design article, manufacturer listings, and latest products

• A user's guide to power-conversion modules

• What's new in computer boards at **Buscon West**

• Protecting expensive hybrid power op amps

• New filtering scheme cuts switcher's noise to linear supply levels

• Plus regular features: Pease Porridge Ideas for Design Technology Advances

ELECTRONIC DESIGN (USPS 172-080; ISSN 0013-4872) is published semi monthly by Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543. Paid rates for a one year subscription are as follows: \$75 U.S., \$140 Canada, \$230 International. Second-class postage paid at Cleveland, OH, and additional mailing offices. Editorial and advertis-ing addresses Electropoly Consult Porte # 46 ing addresses: ELECTRONIC DESIGN, 611 Route #46 West, Hasbrouck Heights, NJ 07604. Telephone (201) 393-6060. Facsimile (201) 393-0204.

Printed in U.S.A. Title registered in U.S. Patent Office. Copyright® 1990 by Penton Publishing Inc. All rights reserved. The contents of this publica-tion may not be reproduced in whole or in part without the consent of the copyright owner.

Permission is granted to users registered with the Copyright Clearance Center Inc. (CCC) to photocopy any article, with the exception of those for which separate copyright ownership is indicated on the first page of the article, provided that a base fee of \$1 per copy of the article plus \$.50 per page is paid directly to the CCC, 27 Congress St., Salem, MA 01970 (Code No. 0013-4872/91 \$1.00 + .50). Copying done for other than personal or internal reference use without the express permission of Penton Publishing, Inc. is prohibited. Requests for special permission or bulk orders should be ad-dressed to the editor.

For subscriber change of address and subscrip-

tion inquiries, call (216) 696-7000. POSTMASTER: Please send change of address to ELECTRONIC DESIGN, Penton Publishing Inc., 1100 Superior Ave., Cleveland, OH 44114-2543.

**Cover: Joe Drivas**

## IN 1990, WE'RE FINA JOE, BOB, BEN AND FRAN

Nowadays it's called "Concurrent Engineering". Back then it was simply the way the job got done. A small group of people in constant communication. From flowchart changes to thermal problems. From concept to manufacturing.

Did it work? You bet. It gave us things we now use every day. Like

television. Radio. And computers.

But time passed, the technology got more complex, and the people became departments. "Over the wall" engineering carried the day. Unfortunately, a lot was lost in the process. Projects began to control people, instead of people controlling projects. Now there's a way to regain the human dimension that makes concurrent engineering such a powerful competitive weapon. It's called the Concurrent Design Environment.™

No matter how many engineers, no matter how complex the technology, no matter how many design disciplines involved, the Concurrent

## LLY BACK TO WHAT K WERE DOING IN 1963.

Design Environment binds your engineering force into a highly interactive team. Its Falcon Framework™ combines state of the art design tools with unprecedented engineering management capacity. For virtually all electronics technologies and engineering disciplines. With tools from any source, including third party and in-house.

So let us show you how to turn back the clock by moving your engineering forward. For a free videotape about the Concurrent Design Environment, call **1-800-547-7390.**

ANCOT'S SCSI instruments are powerful, easier to use, and cost less. Proven in use worldwide, Ancot's portable equipment travels from bench to field and back again without ever slowing down. They are time and labor saving instruments, for design, manufacturing, repairing, and inspection applications.

Call today for product data sheets, demo disc, or to make arrangements for a free evaluation unit in your facility.

**CIRCLE 86**

Editor-in-Chief: Stephen E. Scrupski

**Executive Editor:** Roger Allan

Managing Editor: Bob Milne

Senior Editors: Frank Goodenough, Milt Leonard, John Novellino

Technology Editors: Analog & Power: Frank Goodenough Communications & Industrial: Milt Leonard (San Jose) Components & Packaging: David Maliniak Computer-Aided Engineering: Lisa Maliniak Computer Systems: Richard Nass Semiconductors: Dave Bursky (San Jose) Test & Measurement: John Novellino

News Editor: Sherrie Van Tyle

New Products Editor: Susan Nordyk

Field Bureaus: West Coast Executive Editor: Dave Bursky (San Jose) Boston: Lawrence Curran Dallas: Jon Campbell Frankfurt: John Gosch London: Peter Fletcher

Chief Copy Editor: Roger Engelke, Jr.

Editorial Production Manager: Lisa Iarkowski

Administrative Assistant: Janis Kunkel

**Editorial Support Supervisor: Mary James**

Editorial Assistant: Ann Kunzweiler

Editorial Secretary: Bradie Guerrero

Editorial Offices: (201) 393-6272

Advertising Production: (201) 393-6093 or FAX (201) 393-0410

**Production Manager:** Michael McCabe *Production Assistants:* Donna Marie Bright, Doris Carter, Eileen Slavinsky

Circulation Manager: Robert Clark

**Promotion Manager:** Clifford Meth

Reprints: Helen Ryan (201) 423-3600

Group Art Director: Peter K. Jeziorski

Computer Systems Administrator: Anne Gilio Turtoro

Published by Penton Publishing Vice President-Editorial: Perry Pascarella Group Editorial Director: Leland Teschler

Publisher: Paul C. Mazzacano

BELECTRONIC DESIGN JANUARY 10, 1991

fax: (415) 322-0455

115 Constitution Drive Menlo Park, CA 94025

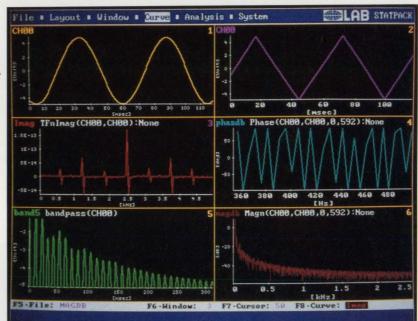

Our HP 4195A 500 MHz Network/Spectrum analyzer video shows you how to get the measurement capability you need along with the convenience and flexibility that you want. All in one instrument, for \$25,000.\* You'll see how the HP 4195A handles a wide range of applications with balanced specs. Like spectrum analysis performance of -135 dBm sensitivity, 3 Hz to 300 kHz RBW. And > 100 dB vector network analysis dynamic range with  $\pm 0.05$  dB/ $\pm 0.3$  degree accuracy.

So get the picture. Call 1-800-752-0900. Ask for Ext. 1148 and receive your There is a better way.

Welcome to Warp Speed: The Am27H010 from AMD. At 45ns, it's faster than any other megabit CMOS EPROM. Fast enough to eliminate those irritating short term memory lapses.

AMD's 1 micron CMOS technology delivers zero wait state performance with no cost or density penalty. So now you can replace those high-ticket, low-density

We have commodity EPROM solutions beat, too. Their program code must get routed to fast RAMs to achieve high speed. With the Am27H010 rocket chip you PROMs you've been putting up with. execute directly from the EPROM.

And no one can give you the range of densities—and the fastest part at every density—like AMD can.

Fact is, we make and sell more megabit EPROMs than anyone.

The Am27H010 is ready in volume and priced right. So call 800-222-9323 and get the parts worth not waiting for. Advanced Micro Devices 7 901 Thompson Place, P.O. Box 3453, Sunnyvale, CA 94088

CIRCLE 81

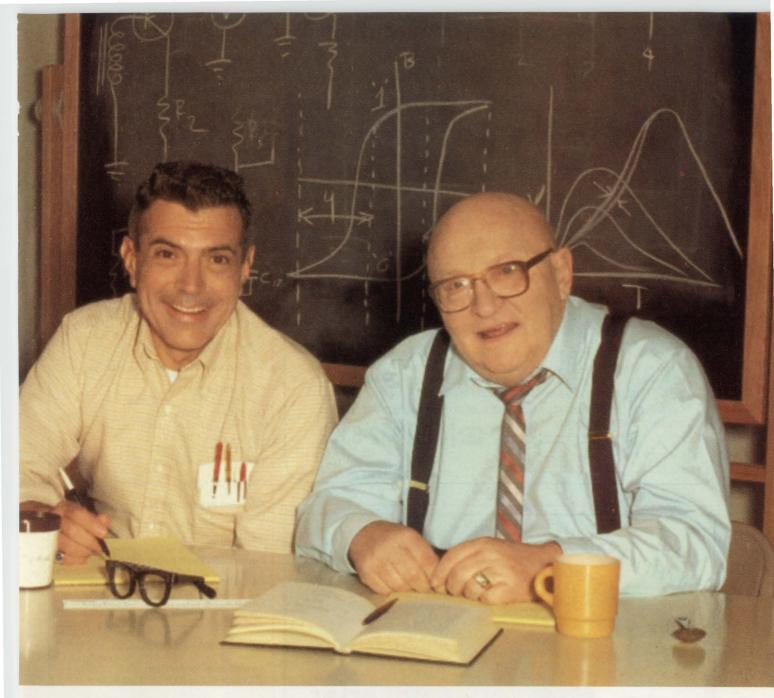

## Here's one reason that over half of all SCSI devices sold are NCR.

#### We created the market... and we still lead the way.

Meet NCR's SCSI development team. In 1983, they gave the computer industry its first SCSI device. By providing easy connectability and significantly reducing time to market, a new product era was born.

Since then needs have changed. By combining our system skills, highperformance standard cell methodology, and in-house manufacturing, NCR has maintained its leadership role with innovative new ideas like the 53C700 product family. And the joint

development of LADDR — a new architecture aimed at cutting the development time of OS/2 device drivers by 90%.

> Today SCSI is becoming the leading I/O standard — adopted by industry giants like Apple, IBM, HP, and DEC. And no one is selling more SCSI chip level products than NCR. In fact, no one even comes close.

Part of the NCR SCSI Development Team: (left to right) Jerry Armstrong, Sr.Software Engineer; Harry Mason, Strategic Marketing Manager; John Lohmeyer, NCR Sr. Consulting Engineer and Chairman of the ANSI X3T9.2 Committee and Dave Skinner, SCSI ProductManager.

North American Sales Headquarters 1731 Technology Drive, Suite 600 San Jose, CA 95110 (408) 453-0303

## Here's another.

#### The NCR 53C700 SCSI I/O Processor... So good, *Electronic Design* named it the product of the year.

"You can't tell a good SCSI chip just by looking at it..." and according to Electronic Design, NCR's 53C700 is the best there is.

The only third generation SCSI device on the market today, it concentrates all the functions of an intelligent SCSI adapter board on a single, smart and extremely fast, chip... for about 15% of the cost.

As the first SCSI I/O processor on a chip, the 53C700 allows your CPU to work at maximum speed while initiating I/O operations up to thousands of times faster than any non-intelligent host adapter. DMA controllers can burst data at speeds of up to 50 Mbytes/s. This new chip cuts down system time hookup to a fraction of what it has been.

Those are just a few of the reasons Electronic Design's "Best of the Digital IC's" award went to NCR's 53C700 last year.

#### And now the NCR 53C710!

For the complete story on the NCR SCSI product line featuring the new 53C710, as well as the upcoming SCSI seminars with the NCR SCSI Development Team, please call:

1-800-334-5454

European Sales Headquarters Gustav-Heinemann-Ring 133 8000 Munchen 83 West Germany 49 89 632202

Creating value

**CIRCLE 179**

Asia/Pacific Sales Headquarters 2501, Vicwood Plaza 199 Des Voeux Road Central Hong Kong 825 859 6044

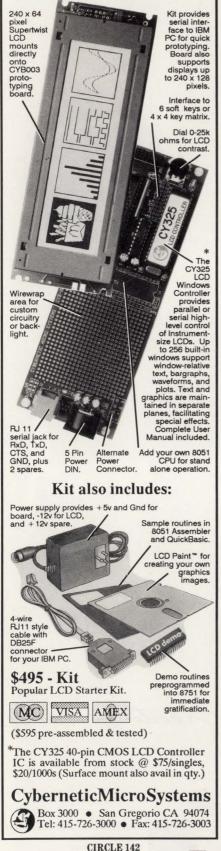

#### LCD Proto Kit

Everything you need to start your LCD application .... create complex screens in just a few hours!

#### FORECASTING TECHNOLOGY TRENDS

or the past several years, Electronic Design has published its forecast of technology developments in the year's first issue. For 1990, we focused on how computer-aided engineering and application-specific integrated circuits will impact the way designers go about their jobs. In our 1991 Technology Forecast (p. 41), we focus on the emerging "renaissance" design team—a multidisciplinary team with a broad mix of expertise. Such teams will be anchored by concurrent-engineering techniques, and include specialists in designing for testability, for manufacturability, for reliability, and so on.

Many unstoppable forces are shaping today's electronics marketplace the need for quality, the growing complexity of devices, and the intensified time-to-market pressures, to name a few. When these forces combine with improvements in the raw computing power of workstations, local-network bandwidth and connectability, and more powerful arrays of CAE design tools, concurrent engineering emerges as the accepted method for future product design and development.

The 1991 Technology Forecast is a multi-part package. It begins with two staff-written articles that discuss the need for and growth of concurrent engineering and design for testability. Four contributed technical articles follow: design environments needed to support concurrent engineering; the potential of computer-aided software engineering; coming to grips with time-to-market pressures; and designing for reliability. The report package concludes with a series of seven one-page pieces on future developments in: programmable logic devices, semiconductor test equipment, real-time software, high-density interconnects, packages for complex semiconductor devices, passive components, and power sources.

Finally, the editors of Electronic Design wish all our readers a healthy and prosperous New Year.

lepten Sering

Stephen E. Scrupski Editor-in-Chief

#### EDITORIAL

14 E L E C T R O N I C D E S I G N JANUARY 10, 1991

## **PRECISION TTL-CONTROLLED ATTENUATORS**

Now...precision TTL-controlled attenuators accurate over 10 to 1000MHz and -55 to +100°C. Four models are available in the new TOAT-series, each with 3 discrete attenuators switchable to provide 7 discrete and accurate attenuation levels (see chart). Cascade all four models for up to 64.5dB control in 0.5dB steps. Custom values available on request. The 50-ohm TOAT-series performs with 6µsec switching speed

and can handle power levels up to 0dBm. Units are housed in a rugged hermetically-sealed TO-8 package to withstand the shock, vibration, and temperature stresses of MIL-STD-883. Connector versions are available. Take advantage of the \$59.95 (1-9 qty) price breakthrough to stimulate new applications as you implement present designs and plan future systems.

up to 35dB 10 to 1000MHz \$5995

> finding new ways ... setting higher standards

| TOAT-R512<br>Accuracy<br>(dB) (+/dB) |      | TOAT-124<br>Accuracy<br>(dB) (+/-dB) |     | TOAT-3610<br>Accuracy<br>(dB) (+/-dB) |     | TOAT-51020<br>Accuracy<br>(dB) (+/-dB) |     |

|--------------------------------------|------|--------------------------------------|-----|---------------------------------------|-----|----------------------------------------|-----|

| 0.5                                  | 0.12 | 1.0                                  | 0.2 | 3.0                                   | 0.3 | 5.0                                    | 0.3 |

| 1.0                                  | 0.2  | 2.0                                  | 0.2 | 6.0                                   | 0.3 | 10.0                                   | 0.3 |

| 1.5                                  | 0.32 | 3.0                                  | 0.4 | 9.0                                   | 0.6 | 15.0                                   | 0.6 |

| 2.0                                  | 0.2  | 4.0                                  | 0.3 | 10.0                                  | 0.3 | 20.0                                   | 0.4 |

| 2.5                                  | 0.32 | 5.0                                  | 0.5 | 13.0                                  | 0.6 | 25.0                                   | 0.7 |

| 3.0                                  | 0.4  | 6.0                                  | 0.5 | 16.0                                  | 0.6 | 30.0                                   | 0.7 |

| 3.5                                  | 0.52 | 7.0                                  | 0.7 | 19.0                                  | 0.9 | 35.0                                   | 1.0 |

bold faced values are individual elements in the units

CIRCLE 210

WE ACCEPT AMERICAN EXPRESS

P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661 Domestic and International Telexes: 6852844 or 620156

rcui

# What's you

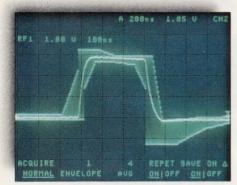

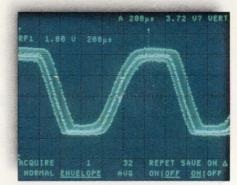

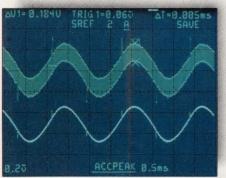

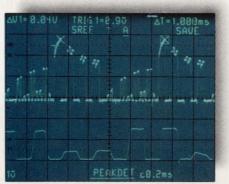

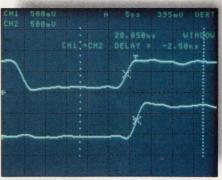

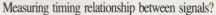

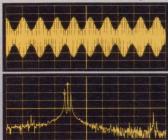

Analyzing TV and complex video signals?

Testing telecommunications signals?

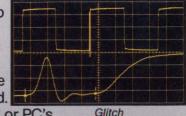

Uncovering elusive glitches?

Finding aberrations buried within a signal?

You can't depend on banner specs alone to solve problems like these.

Whether you're trying to measure waveform parameters or analyze long data streams, identify infrequent events or track down glitches as narrow as 2 ns — there's all the difference between the depth of Tek troubleshooting and the trade-offs in other DSOs that compromise your results.

Spec for spec, feature for feature, no other company offers the credentials Tek does to

Capturing single-shot events?

Automatic PASS/FAIL testing?

effectively match DSO performance to your application needs. Whatever your criteria, you'll find a perfect solution in our line of problem-solving portable DSOs, from 10 to 500 MS/s.

Select the features to support your application. Tek DSOs offer a diverse set of capabilities including peak detect to uncover elusive glitches. Fast update rate for live signal display. Combined analog/digital operation for real-time verification of your

# r problem?

Characterizing signal noise?

Capturing and analyzing long data streams?

Performing complex measurements automatically?

Expanding glitches for close analysis?

Windowing in on signal details?

One company measures up.

signal. Or Save on Delta to automatically verify that all parts of your signal fall within prescribed limits. Best of all, Tek's line of 100 MS/s digitizing scopes start at just \$3995.

To find out which Tek scope is right for you, contact your Tek representative, return the card or call Tek direct. We can answer your questions and show you a scope that doesn't just look good on paper. It makes your toughest troubleshooting challenges routine.

VISA

#### TIMING DIAGRAMS

- I Hard to Draw

- **<u><u><u>Tough</u>** to Modify</u></u>

- Painful to Analyze

- Required for

- Reliable Designs

#### The Timing Diagram Drawing and Analysis Software that ...

- Lets you create and modify timing diagrams in minutes instead of hours.

- Automatically performs worst case timing analysis.

- Instantly highlights timing violations.

- Generates standardized timing documentation.

#### TimingDesigner™ will belp you develop better designs more quickly!

Pick up the phone now and call for more information.

#### TECHNOLOGY BRIEFING

#### **EUROPE BANKS ON JESSI**

f there were a Richter scale recording the world's most significant cross-border cooperative efforts in electronics, JESSI, the Joint European Submicron Silicon Initiative, would register a hefty 7 or 8 on that scale. The numbers for this endeavor, which was launched in 1989 to help Europe catch up with Japan and the U.S. in microelectronics, speak for themselves: JESSI is an eight-year project comprising more than 100 companies from six countries. It calls for some 21,400 engineering man-hours and an outlay of more than \$5 billion for R&D until 1996.

In today's European semiconductor industry, JESSI is widely regarded as Europe's last-ditch effort to stand on its own in microelectronics. They want to become less dependent on Japan's memory technology and America's know-how in advanced devices.

"Nothing less than Europe's economic well-being is at stake," says Klaus Knapp, spokesman for the project in Munich, Germany, where JESSI's board of management is based. Knapp points out that Europe's vital—and exportintensive—industries, such as automobiles, machine tools, processing equipment, and precision optics and mechanics increasingly depend on a strong native microelectronics capability. The fear exists that if other regions dominate the microelectronics field, they could manipulate the flow of crucial components to favor their own industries at the expense of Europe's.

Half of JESSI's \$5 billion comes from industry and one-quarter each from national governments and the European Commission, the executive branch of the 12-nation European Community. Despite governmental delays in funding, JESSI is on schedule, Knapp says. Adds Raimondo Paletto, chairman of JESSI's management board, "The organization and its programs are in place and the first 50 projects have been started. What JESSI needs now is the full commitment of Europe's national governments to fund and participate in the effort with quick decisions and a minimum of bureaucracy."

Aimed at acquiring know-how and technology, JESSI is to take device development only to the prototype stage (unlike Mega, Europe's \$2-billion product-oriented high-density memory effort; the Mega project ended in 1988 with Germany's Siemens AG and Philips NV of the Netherlands developing 4-Mbit DRAMs and 1-Mbit SRAMs, respectively).

JESSI is often equated to the U.S.'s Sematech program, yet it's much broader in scope. It not only emphasizes production technology and equipment (as does Sematech), but other aspects of microelectronics as well. The project is based on four subprograms: basic research, technology, applications, and equipment and materials. Milestones pinpointed by JESSI for the next half decade include: engineering samples of 0.5- $\mu$ m devices by mid-1991 and their pilot production by the end of that year, as well as first silicon of 0.3micron parts by mid-1993 and engineering samples by mid-1994. Such 0.3-micron parts are to be ready for pilot production by the end of 1995.

Mirroring this multiprogram structure is the nature of the cooperating firms. In addition to Europe's semiconductor makers, the more than 100 members include chemical producers, production equipment manufacturers,-and, as device users, communications houses, auto makers, and computer and office equipment companies. Moreover, JESSI participation isn't limited to European firms. If a foreign company has R&D, manufacturing, and marketing activities in Europe, if it proposes a worthwhile project, and if there's reciprocal participation in similar foreign R&D programs, it qualifies as a JESSI member. Because IBM Europe meets all of these conditions, it became a participant in late November. The company cooperated with European firms in work that involved deep ultraviolet lithography and the preparation of gate dielectrics by rapid thermal processing.

JOHN GOSCH Field Editor

**18** E L E C T R O N I C D E S I G N JANUARY 10, 1991

## Two state-of-the-art FIFOs from Sharp to solve your toughest data flow challenges.

They're both synchronous, which greatly simplifies your board circuit and design requirements. Their proprietary look-ahead access architecture delivers speedier access and cycle times while reducing power consumption.

#### Introducing: The LH5492 4K x 9 Clocked FIFO.

Sharp's new LH5492 is a dual-port clocked FIFO, with a 4K x 9 configuration. The clocked interface is a significant enhancement in FIFO design over previous asynchronous parts. The clocked enables on the LH5492 eliminate the requirement to shape waveforms, resulting in simpler design tasks, and lower parts count.

Its high-speed clocked interface can be used directly with the typical 40%/60% duty cycle system clock. And a separate OE control signal provides independent control over output buffers.

The second enable pin on each part can be directly tied to the flags to simplify external logic requirements.

The LH5492 4K x 9 clocked FIFO comes in a 32-pin PLCC. It is available with access times of 20 ns, 25 ns and 35 ns, and cycle times of 25 ns, 35 ns and 50 ns, respectively.

#### Introducing: The LH5420 256 x 36 x 2 Bidirectional FIFO.

Sharp's new LH5420 is actually two 256 x 36-bit FIFOs in one. Operating in parallel but opposite directions to provide bidirectional data buffering that would normally require multiple independent devices.

Its 36-bit word width is an industry first. And ideal for interfacing with new generation higher-speed 32/36-bit and 64/72-bit microprocessors and buses. Moreover, a choice of 9, 18, or 36-bit word widths on Port B means efficient word width matching.

Programmable Almost Empty and Almost Full status flags on each port—in addition to Full, Half Full and Empty flags—allow you to either leave the flags set at their initialized setting of 8, or program them over the entire FIFO depth.

The LH5420 comes in a 132-pin plastic QFP package. It is available with access times of 15 ns, 20 ns and 25 ns, and cycle times of 25 ns, 30 ns and 35 ns, respectively.

SHARP. By Design.

Sharp Electronics Corporation For more information call: 1-201-529-8757 FAX: 1-201-512-2020.

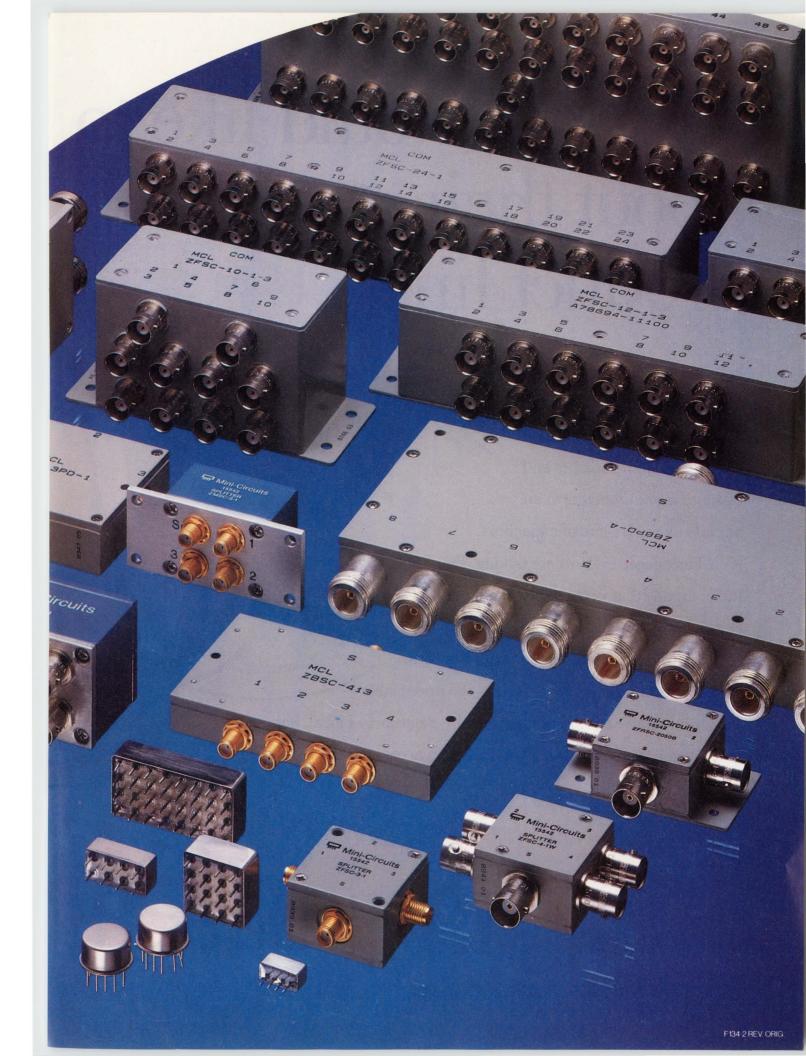

## THE WORLD'S LARGEST SELECTION OF **POWER SPLITTERS/ COMBINERS**

m Mir

#### 2 KHz to 8 GHz from \$1045

With over 300 models, from 2-way to 48-way, 0,° 90° and 180,° a variety of pin and connector packages, 50 and 75 ohm, covering 2KHz to 8000MHz, Mini-Circuits offers the world's largest selection of off-the-shelf power splitter/combiners. So why compromise your systems design when you can select the power splitter/combiner that closely matches your specific package and frequency band requirements at lowest cost and with immediate delivery.

And we will handle your "special" needs, such as wider bandwidth, higher isolation, intermixed connectors, etc. courteously with rapid turnaround time.

Of course, all units come with our one-year guarantee. For detailed specs and performance data, refer to the MicroWaves Product Directory, EEM or Mini-Circuits RF/IF Signal Processing Handbook, Vol. II. Or contact us for our free 68-page RF/IF Signal Processing Guide.

## AVX would like to about their expanded product line.

Feedback has been tremendous. Since we added clock oscillators, piezo devices, resonators and trimmer potentiometers to an already extensive line of capacitors, AVX has people everywhere talking. Because the company that wrote the book on passive components has added another chapter.

Through our association with Kyocera, AVX has firmly established itself as the undeniable leader in passive components. And with a network of local, national and international distributors, we give you access to any part you need. Anytime. Anywhere.

## "Beep. Buzz. Ri

## make a little noise

Ours is an industry where thinking globally is not just the key to victory, but to survival. That's why we've created distribution capabilities that offer solutions. No matter where you are. Or what you need. Plus the firm commitment to world-class quality, service, technology and manufacturing you've always come to expect. From the company that always makes sound decisions. AVX.

For more information about the AVX/Kyocera product line, contact AVX Corporation today by calling (803) 448-9411, or fax us at (803) 448-1943. Write to:

AVX Corporation, 17th Avenue South,

P.O. Box 867, Myrtle Beach, SC 29577.

AVAX CORPORATION A KYOCERA GROUP COMPANY

CIRCLE 205

## ng. Tick. Hum."

#### TECHNOLOGY NEWSLETTER

INDIUM TIN OXIDE TO IMPROVE IMAGE SENSORS Indium tin oxide (ITO) promises to be an alternative to polycrystalline silicon in solid-state image sensors, according to Christ Weytens, a scientist at the Philips Research Laboratories in Eindhoven, the Netherlands. Conventional image sensors use polycrystalline silicon gates to convert light into an electric signal. But their poor transparency to visible light is a major limitation on their use in future high-performance imagers. ITO, however, one of the rare materials that's not electrically conductive, is transparent to visible light. To gain insights into applying ITO to ICs, Weytens gives special attention to the material's compatibility with standard silicon processing. ITO films are deposited by reactive dc-magnetron sputtering from an indium-tin target in an argon-oxygen environment. Smooth ITO layers are deposited in a well-controlled, reproducible manner if theoxygen concentration is higher than 25%. A typical deposition rate is 1.7 nm/min., with an applied power of 730 mW and an environment with 41% oxygen. After deposition, heat treatment is necessary to meet resistivity and etch-characteristics requirements. So far, Weytens finds rapid thermal annealing at 950°C to be the best heat treatment. JG

**SOFTWARE CONSORTIUM PUBLISHES GUIDELINES** The Object Management Architecture (OMA) Guide is a framework and set of implementation guidelines for object-oriented computing environments available from the Object Management Group (OMG), Framingham, Mass. OMG is an international consortium of information-systems vendors, software developers, and users that promote the theory and practice of object-oriented technology in software development. The OMA Guide uses a reference model to explain the major components of an object-oriented environment, including the interfaces needed to facilitate interoperability and homogeneous extensibility. In addition, the guide contains applications, a glossary of terms commonly used in object-oriented programming, and the technical objectives of the OMG. Copies of the OMA Guide are available directly from OMG for \$30. Contact Liz Berry at (508) 820-4300. *LM*

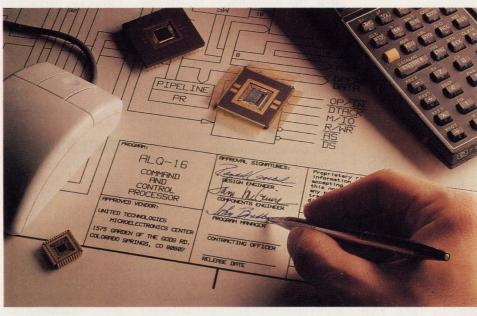

**CAD CONFERENCING AIDS IN CONCURRENT DESIGN** Huntsville, Ala. The product enables a computer graphics image to be viewed simultaneously on workstations at as many as eight sites. With an accompanying voice connection, conferees can discuss the on-screen image. Consequently, engineering and management teams around the globe can work on projects together in real time without leaving their offices. During CAD conferencing, participants can redline drawings and engineering-change orders interactively. Moreover, they can sign-off on a project by putting their signature on the displayed image. The product includes conferencing software that manages interactive communication between workstations, a telecommunications interface card for each workstation, and an electronic tablet and stylus for communications and signatures. To input information, the system uses both an on-screen graphical user interface and a graphics tablet. For more information, call (800) 826-3515. LM

**ELECTRONS ACCELERATED TO 150,000 EV** Researchers at Jerusalem's Racah Institute of Physics claim to have developed a new technique to accelerate electromagnetic waves and electrons to energy levels of 150,000 electron volts. Their ultimate target is 500,000 eV. Such a high-energy beam would be suitable to use in free-electron lasers. The system they built uses a 10,000-eV electron gun and a radar transmitter. Electrons are fired along a tube "immersed" in a magnetic field, the intensity of which is varied along the length of the tube. As the beam passes through the tube, it's forced to follow a helical path, with the speed of rotation depending on the field's strength. Circular-polarized electromagnetic pulses from the radar transmitter are aimed along the axis of the electron beam, with a pulse repetition rate similar to the electron rotational frequency. That way, they say, energy is transferred to the electron beam. For more information, contact the Britain/Israeli Public Affairs Center, 21-22 Great Sutton St., London, ECIV 0DN. Telephone +44(0)714905373. PF

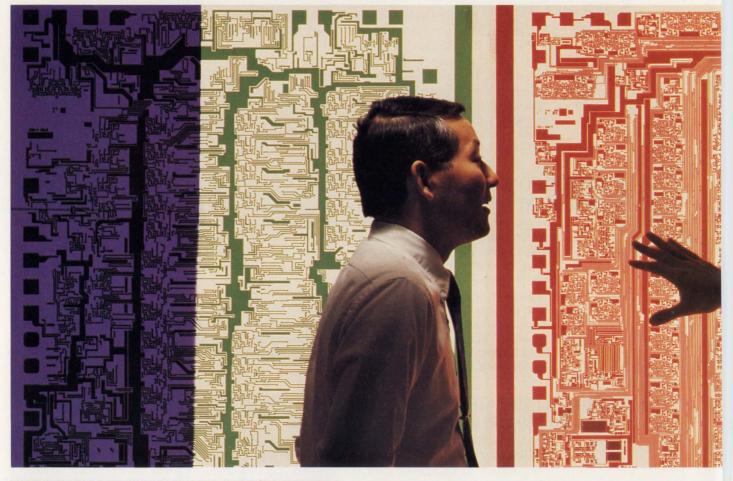

# How to ge customs with

#### Custom IC Solutions

Need a custom IC? You'll bypass the usual red tape by working with an experienced custom IC partner like Silicon Systems.

Our 20 years of experience developing ICs for mass storage, communications and automotive applications means we can move quickly from your inspiration to a working custom prototype in no time.

And speed your custom IC into volume production. In our MSICs <sup>™</sup> (Mixed-Signal Integrated Circuits) world we combine high-performance analog and digital circuitry on a single chip and allow you to take full advantage of our state-of-the-art design systems. From there we will optimize the performance and integration of your design in CMOS, Bipolar or BiCMOS

## et through out any delays.

process technologies.

Enough said? Move to the front of the line and discuss your custom design requirements with a Silicon Systems representative. Or call us for lit package CUST-1.

Circle 124 for Product Info Circle 125 for Career Info Silicon Systems, Inc., 14351 Myford Road, Tustin, CA 92680 Ph 1-800-624-8999, ext.151 Fax (714) 669-8814 European Hdq. U.K. Ph (44) 79-881-2331 Fax (44) 79-881-2117

#### TECHNOLOGY NEWSLETTER

1/4-IN. CARTRIDGE TAPE DRIVES IMPROVING TAPE DRIVES IMPROVING ed a migration path to assure that the performance and capacity goals of the DC2000- and DC6000-class drives are reached. The path outlines performance goals through 1995. The QIC group also made a commitment to ensure that all future drives will be backwardly readcompatible with existing drives, protecting users' investments. The path for the 3-1/2-in. drives surpasses 8 Gbytes with a transfer rate better than 1.5 Mbytes/s by 1995. In the same time frame, the 5-1/4-in. drives should hold 24 Gbytes of data with a 2.4-Mbyte/s transfer rate. These numbers are for drives using data-compression techniques. *RN*

**EDAC RE-ELECTS** MANAGEMENT TEAM At its annual election, the Association of Electronic Design Automation Companies (EDAC) re-elected all existing committee members for a second term. EDAC's organization consists of an executive committee and four operating committees: communications, standards, steering, and trade show. The chairman of the executive committee is Jim Hammock, president of the Silicon Design Div. of Mentor Graphics Corp., Beaverton, Ore. Co-chairmen are Joe Costello, president and CEO of Cadence Design Systems Inc., San Jose, Calif.; and Alain Hanover, president of Viewlogic Systems Inc., Marlboro, Mass. EDAC has 46 members that represent almost 90% of commercial EDA revenues worldwide. For more information on becoming an EDAC member, call (408) 988-3322. LM

**FONT GENERATOR SPEEDS PRINTING 100 TIMES** An outline font generator from Yamaha LSI, San Jose, Calif., is 100 times faster than software now available for high-quality laser-printer output. According to the company, the GC1001, one of the few font generators available as an off-the-shelf chip, can generate 1000 characters/s for a 64-by-64-dot character using static RAM to store the generated character data. Operations include character enlargement, reduction, rotation, tilt, and a parallel move. All operations are facilitated by built-in coordinate-change functions. Curved-line-generation algorithms add support for almost all outline fonts. A large-size font can be generated by subdividing the character to be displayed. In addition to laser-printer controllers, the GC1001 can be used for desktop publishing systems, PCs and workstations, and large typesetting and cut-text machines. Prices start at \$65 in quantities of 500. Samples are available now; production will start in February. *RNCIRCLE 331*

DATABASE SELECTED<br/>FOR FRAMEWORK RESEARCHThe Microelectronics and Computer Technology Corp. (MCC), Austin, Texas,<br/>has chosen the Objectivity/DB database as a prototyping vehicle for CAD<br/>framework research. Objectivity/DB is an object-oriented database manage-<br/>ment system from Objectivity Inc., Menlo Park, Calif. MCC believes that object-oriented<br/>technology plays a significant role in engineering frameworks. The company chose Objectivi-<br/>ty's database because of its commitment to the engineering community and CAD Framework<br/>Initiative (CFI) standards. Objectivity also announced relationships with Chips and Technolo-<br/>gies Inc., Cimplex Corp., Digital Equipment Corp., Matra Datavision, Pie Design Systems<br/>Inc., Sony Corp., and Valid Logic Systems Inc. LM

MILITARY VME CHIP SET GETS SECOND SOURCING CAVICS) currently supplied by Newbridge Microsystems, Kanata, Ontario, Canada. The AVICS solution consists of two CMOS VLSI devices: the CA91C014 advanced-system architecture-control circuit (ACC) and the CA91C015 data/address register file (DARF). The ACC, which can be used in standalone medium-performance applications, is packaged in a 144-pin PGA, while the DARF is housed in a 224-pin PGA. The arrangement between the two companies also calls for the second sourcing of the 64-bit AVICS-64 now under development. With the AVICS 64-bit-block burst capability, which is defined in the IEEE-1014 Rev. D standard, transfers of 60 Mbytes/s are possible. Current 32-bit DARF chips can be upgraded to 64 bits using the pin-compatible solution. *RN*

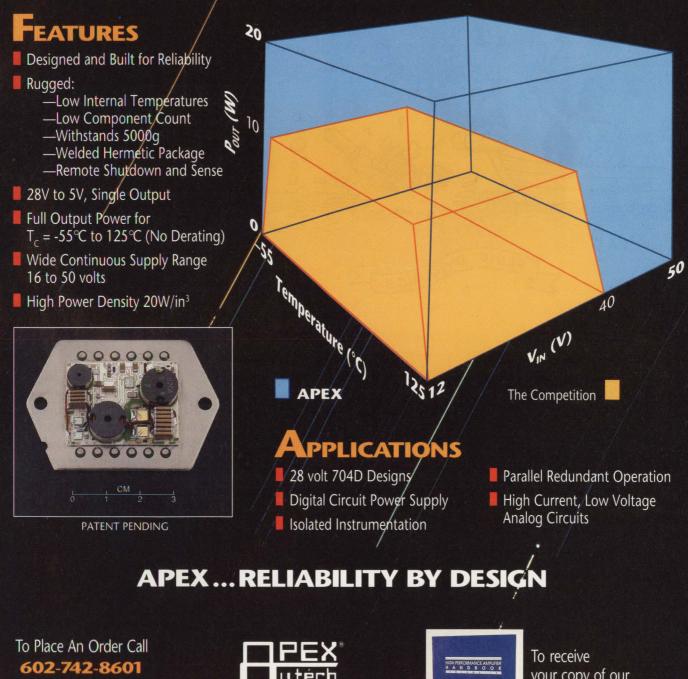

## A NEW CONCEPT DC-DC CONVERTER MILIVARY GRADE

For Applications Assistance Call 1-800-421-1865

APEX MICROTECHNOLOGY CORPORATION

To receive your copy of our High Performance Amplifier Handbook please call toll free **1-800-448-1025**

## The IBM RISC System/ The power you've been seeking

It's a never-ending quest for power seekers. You're always looking for ways to run your favorite applications faster. Well, search no more. The RISC System/6000<sup>™</sup> family of POWERstations and POWERservers gives you power that soars as high as 23 MFLOPS and 56 MIPS.

|                     | MFLOPS | MIPS | SPECmark™ |

|---------------------|--------|------|-----------|

| POWERstation 320    | 7.4    | 29.5 | 22.4      |

| DECstation 5000-200 | 3.7    | 24.2 | 18.5      |

When it comes to porting, your ship has come in. Of course, all the speed in the world wouldn't mean much without the applications you need. So the RISC System/6000 family already has more than 2,000 of the most popular technical and commercial applications up, running and running fast. And if you think you know a good thing when you see it, so do software vendors. That's why you'll also be seeing more and more applications coming on board the RISC System/6000 platform all the time. And if you like to build your own solutions, there's a full arsenal of enablers and relational data bases from leading vendors, as well as CASE tools and a host of popular programming languages.

A smorgasbord of solutions. Applications already announced include the IBM engineering design packages CADAM, CAEDS, CBDS,

MFLOPS are the results of the double-precision, all FORTRAN Linpack test 100x100 array suite. The Dhrystone Version 1.1 test results are used to compute RISC System/6000 Integer MIPS value where 1,757 Dhrystones/second is 1 MIPS (Vax 11/780). SPECmark is a geometric mean of ten benchmark tests. All performance data are based on published benchmark information.

IBM is a registered trademark, and RISC System/6000 and CAEDS are trademarks of International Business Machines Corporation. SPECmark is a trademark of Standard Performance Evaluation Corporation. UNIX is a registered trademark of UNIX System Laboratories, Inc. CADAM is a trademark of CADAM INC. CATIA is a trademark of Dassault Systemes. CBDS is a trademark of Bell Northern Research Corporation. DECstation is a trademark of Digital Equipment Corporation. HAGAR THE HORRIBLE Character(s) © 1990 King Features Syndicate, Inc. © IBM Corp. 1991, all rights reserved.

## 6000 family. for all your applications.

CATIA<sup>\*\*</sup> and AES. Also available are a broad spectrum of solutions from vendors like Valid Logic, MacNeal Schwendler, Swanson Analysis, SAS Institute, SPSS, Wavefront, Alias, Polygen, Cadence, Fluid Dynamics International, Western Atlas, ECL Petro and creare.X. Scientific and technical applications are available in areas like physics, structural analysis, chemistry, securities trading, mathematics, earth resources, operations research, visualization, graphics, technical publishing and more. There's also accounting software like FourGen and support for leading UNIX<sup>®</sup>-based office automation packages. And there are key industry applications for businesses in medical groups, retail stores, newspapers, pharmacies and many more.

#### Command enormous processing clout.

The RISC System/6000 family is built to boost the performance of the software power seekers use most. It's got the best floating point processor in the business for numerically intensive applications, plus a new superscalar processor

and incredible 3D graphics capabilities. To find out more, call your IBM marketing representative or IBM Business Partner. For literature, call 1 800 IBM-6676, ext. 990.

#### For the Power Seeker.

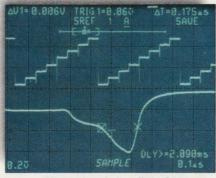

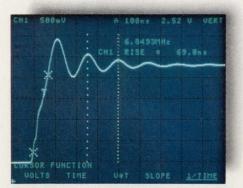

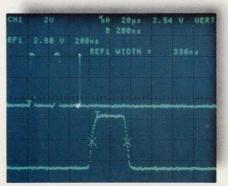

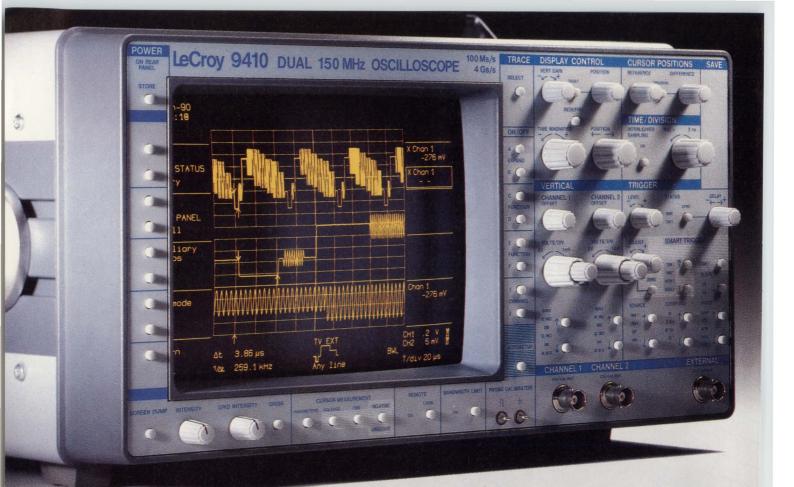

## At last, a LeCroy you won't have to beg for.

Now you can get LeCroy Digital Oscilloscope performance for the price of an ordinary oscilloscope. At just **\$6,990**, the new Model 9410 offers you unrivaled measurement capabilities. Waveforms are digitized with high signal fidelity into 10K acquisition memories and presented on the sharpest display of any oscilloscope (the above picture speaks for

itself). One can zoom in on fine details, expand signals, and use the 9410's digital cursors to get the ultimate in precision.

The Model 9410 doesn't stop there. It also includes LeCroy's SMART trigger that detects buried glitches, timing violations, and logic states (you'll be prepared for the most elusive signals). Internal signal processing calculates time, voltage and frequency parameters in fractions of a second.

Trigger

Spectrum Analysis Option

And all the data can be transferred directly to printers, plotters or PC's using the 9410's high-speed GPIB or RS-232.

Price being equal, wouldn't you rather have a LeCroy?

LeCroy Corporate Headquarters 700 Chestnut Ridge Road - Chestnut Ridge, NY 10977-6499 Tel.: 1-800-5 LeCroy - (914) 425 2000 / TWX: (710) 577-2832 Fax: (914) 425-8967

Innovators in Instrumentation

#### TECHNOLOGY ADVANCES

#### GLASNOST COMES TO ISSCC AS Advanced ICs Are Unveiled

This year's forthcoming rendition of the International Solid State Circuits Conference will break with history, hosting a special session on technology in the USSR. A paper from an Easternbloc country is more than a rarity at the ISSCC, even though half of the papers to be presented are from European or Asian-based companies. There will be four presentations by Soviet researchers, as well as a technology overview of the state of microelectronics in the USSR by a U.S. delegation that visited the Soviet Union in the fall of 1990.

ISSCC, which will run from February 13-15 in San Francisco, Calif., will also host dozens of papers that show the latest research advances in a number of device areas. These include 4-Mbit static RAMs, 64-Mbit dynamic RAMs, Josephson-junction supercooled circuitry, 32- and 64bit microprocessors, digital signal processors, math chips, logic arrays, novel communications chips, analog circuits, and analogto-digital converters. A trio of invited addresses will open the conference with discussions on microelectronics for planetary spacecraft (presented by the Jet Propulsion Laboratory, Pasadena, Calif.), the future of notebook computers (presented by Toshiba Corp., Tokyo, Japan), and the need for design for testability (presented by the Center for Reliable Computing, Stanford University, Calif.)

The special session on technology in the USSR

will include papers on a 4kbit NMOS nonvolatile RAM with an extended 16kbit nonvolatile memory, n-channel 256-kbit and 1-Mbit flash EEPROMs, and an automated mini-fab for low-volume and fast-turnaround chip manufacturing. A fourth paper describes the use of spacecharge waves in two-valley gallium arsenide thin films to process microwave signals-gain, filtering, correlation and other signalprocessing functions are possible at microwave frequencies. All four papers will be presented by engineers from the Perceptive Institute. Research Nauchny Center, Moscow.

#### CRYOGENIC SYSTEMS

In a session on low-temperature circuits, researchers from the T.J. Watson Research Center of IBM Corp., Yorktown Heights, N.Y., describe how they brought the operating temperature of a 4-Mbit DRAM down to 85K. and achieved a three-fold improvement in access time and a charge storage time of over 50 minutes. Such a large storage time could drastically reduce the number of refresh cycles needed to restore the charge, severely cutting the standby power consumed by the memory chip.

Cryogenic systems are also the focal point of a pair of papers from Fujitsu Laboratories Ltd., Atsugi, Japan. The first paper shows a sub-ns-clocking system for Josephson computers. The system connects a packaged 4-bit Josephson microprocessor that's kept at 4.4K to a circuit kept at 300K. The communication occurs over a 60-line cable that enables the system to operate at 1.1 GHz. The second paper shows off an all-niobium 24-bit Josephson carry-select adder that achieves a 360-ps addition speed and a 300-ps carry propagation delay—the shortest times achieved for such a function.

Continuing their push for high speed with GaAs high-electron-mobility transistors, Fujitsu designers upped the integration level for a GaAs memory chip to 64 kbits while keeping the access time to just 1.2 ns. The chip employs ECL I/O levels and consumes close to 6 W-a consequence of the highspeed circuitry. ECL I/O levels for biCMOS memories also yield high-speed chips, but with 64 times the density.

A 4-Mbit static RAM developed by Fujitsu with a 0.6-µm biCMOS process will be described—it accesses in just 7 ns and consumes only about 600 mW in its 4-Mword-by-1-bit organization. Details on a 4-Mbit TTL-I/O biCMOS SRAM with a 10-ns access time, also from Fujitsu, will also be presented.

Able to access in about 4 ns, a 512-kbit CMOS chip with ECL interfaces will be described by IBM designers. The synchronous memory has a 2-ns cycle time and employs a pipelined architecture with self-resetting circuit blocks.

DRAMs are also getting faster, especially if implemented in biCMOS as Hitachi Ltd., Tokyo, Japan, will describe. An experimental 4-Mbit chip built with 0.8µm features achieves a 17ns access time and a 40-ns cycle time-in comparison, the fastest commercial CMOS DRAMs available have access times about three times longer than Hitachi's chip. By using a nonmultiplexed address input approach, researchers from the microelectronics laboratory of Toshiba Corp., Kawasaki, Japan, will show off an all-CMOS 17-ns DRAM.

Even the highest-density DRAMs are getting faster-in the session on high-density DRAMs, five of the six papers will detail experimental 64-Mbit chips with access times of 50 ns or less (see the tuble). The fastest and the smallest of the group comes from Toshiba. The DRAM accesses in 33 ns, measures 9.22-by-19.13 mm, and operates from a 3.3-V supply. The most novel structures come from Hitachi and Matsushita Electric Industrial Co. Ltd., Osaka, Japan.

The Hitachi chip has a

#### WANT TO GO?

he International Solid State Circuits Conference will be held at the San Francisco Hilton Hotel, Feb. 13-15. To register for the conference, contact Diane Suiters,

Courtesy Associates, (202) 639-4355 (phone) or (202) 347-6109 (fax). Advance registration discounts end January 31. For hotel reservations, call the San Francisco Hilton, (415) 771-1400.

ELECTRONICDESIGNES JANUARY 10, 1991

#### TECHNOLOGY ADVANCES

novel series-connected cell that reduces cell area considerably over its previous design by eliminating many of the data-line contacts. As many as 64 times the number of cells can be connected to a sense amplifier for an 8-fold reduction in bit-line capacitance, improving access time. With a 4-Mword-by-16-bit architecture, the 64-Mbit Matsushita chip employs a meshed power-line network over the surface of the chip. The network reduces power-line drops that can potentially occur during I/O operations in which all lines are active.

Nonvolatile memories are also improving in density and speed, as papers from Intel Corp., Folsom, Calif., Toshiba, and Mitsubishi will illustrate. A 29-ns 8-Mbit EPROM will be Intel's focal point. The chip employs a novel dual-reference column-address-transition-detection scheme to achieve the short access time. A 16-Mbit EPROM from Toshiba achieves a 62-ns access time by using sense-line equalization and data-out latches that are enabled by the addresstransition-detection circuits on the chip. With a comparable 60-ns access time, a 16-Mbit flash EE-PROM developed by Mitsubishi was designed for more flexibility-the storage array is divided into 64 subblocks, each of which can be independently erased and rewritten.

The need for such highdensity and high-speed memories is driven by the increasingly more complex microprocessors operating at ever-higher clock rates. A 100-MHz CMOS microprocessor with an 80486 architecture will be described by Intel Corp., Aloha, Ore. The CPU chip, implemented with three levels of metal interconnections to keep wire lengths as short as possible, crams 1.2 million transistors onto a 6.8-by-11.8mm chip thanks to a submicron process.

A 100-MIPS superscalar 64-bit RISC processor that packs two integer units as well as a floating-point processor, instruction and data caches, and enhancements for DSP operations, will be unveiled by National Semiconductor Corp. The devices were developed at National Semiconductor's design center in Herzlia, Israel.

Tackling control tasks, a

University, Japan. The chip achieves a 32-bit throughput of 50 MFLOPS in vector-processing applications, and employs selftimed circuits and a shared memory that facilitates the processor's use in multiprocessor configurations. Running at 65 MHz, a floating-point coprocessor developed by Texas Instruments Inc., Dallas, and Hewlett-Packard Co., Ft. Collins, Colo., delivers a throughput of 33.2 MFLOPS. Designed as a coprocessor for a RISC CPU, the chip employs 64bit-wide internal buses and dissipates about 2.3 W when running at top speed.

Able to do a 54-bit mantissa division in just 160 ns,

One chip includes 64 processors that execute the same instruction on different pieces of data. A selflearning chip with the equivalent of 336 neurons and 28k synapses will also be unveiled by Mitsubishi. In addition, AT&T Bell Labs, Holmdel, N.J., will present details on an analog neural-net processor that can implement a wide range of network topologies. The chip contains 4096 synapses and achieves a sustained throughput of  $5 \times 10^9$  connection updates/s.

Dealing with real-world signals, papers in the analog sessions at ISSCC will also show many impressive gains. One of the most

| COMPARING 64-MBIT CHIPS |             |                   |                   |                        |  |  |  |  |

|-------------------------|-------------|-------------------|-------------------|------------------------|--|--|--|--|

| Manufacturer            | Access time | Chip size         | Cell size         | Storage-cell capacitor |  |  |  |  |

| Toshiba                 | 33 ns       | 9.22 by 19.13 mm  | 0.9 by 1.7 μm     | Asymmetrical stacked   |  |  |  |  |

| Fujitsu                 | 40 ns       | 11.27 by 19.94 mm | 1.0 by 1.8 µm     | N.A.                   |  |  |  |  |

| Mitsubishi              | 45 ns       | 12.50 by 18.70 mm | 1.0 by 1.7 µm     | N.A.                   |  |  |  |  |

| Matsushita              | 50 ns       | 10.85 by 21.60 mm | 2 µm <sup>2</sup> | Tunnel stacked         |  |  |  |  |

| Hitachi                 | N.A.        | N.A.              | N.A.              | Crown-shaped stacked   |  |  |  |  |

single-chip microcontroller with a field-programmable 20-MOPS intelligent subprocessor will be unveiled by Hitachi. The subprocessor can schedule up to 12 tasks with 50-ns resolution in real-time applications. With a 64-bitwide instruction, up to five internal operations can take place every cycle. An on-chip multitask scheduler enables the chip to handle multiple tasks without it having to perform a context switch. Dual EPROM blocks provide the configurability.

A data-driven processor that employs superpipelining was designed jointly by Mitsubishi Electric Corp., Itami, Japan, and Osaka 34 E L E C T R O N I C JANUARY 10, 1991

a CMOS divider circuit, jointly designed by Silicon Engines Inc., Stanford, Calif., and Stanford Univ., employs self-timing schemes to reduce delays so that results appear in 45 to 160 ns, depending on the data operands.

#### **NEURAL DEVICES**

Designers at Adaptive Solutions Inc., Beaverton, Ore., and Inova Microelectronics Inc., Santa Clara, Calif., created an 11-million-transistor neural processor by modeling thought processes with a digital neural-network execution engine. The chip performs 1.6 billion connections/s using a multifield imaging approach.

DESIGN

novel analog circuits, described in the Emerging Technologies session, is actually based on EEPROM technology—an analog memory that doesn't have to convert data into digital form for storage. The memory achieves a storage density about eight times that of digital memories, and can connect directly to a microphone or loudspeaker to implement a single-chip voice recorder.

Three papers will highlight advances in ADCs. One paper describes a 500,000-sample/s 14-bit delta-sigma converter from the Catholic University, Leuven, Belgium. Another from the Center for

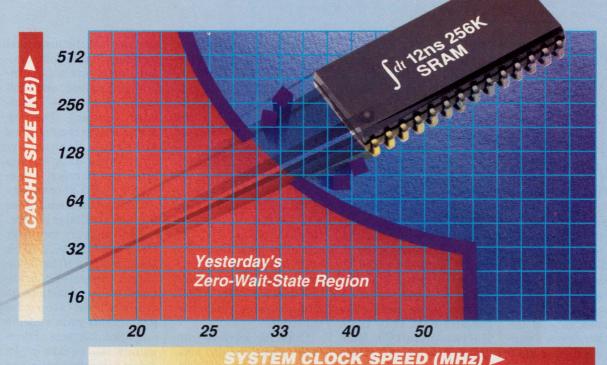

### **Smash the Cache Barrier**

#### **6K TTL SRAMs 12ns BiCEM**

#### Speed and Density

Now you can get cost-effective 12ns speed and 256K density. IDT's 256K BiCEMOS TTL Static RAMs are the ideal solution for high-density cache systems for applications like workstations, file servers, and graphics systems. These new-generation SRAMs provide the highest system speed without sacrificing system chip count or increasing power consumption.

#### Fastest 256K SRAMs

IDT's 12ns and 15ns 256K BiCEMOS Static RAMs are the fastest available 256Ks today and are the perfect match for optimizing the high performance needs of RISC and CISC processors. These SRAMs smash the barrier to efficient cache operation at the highest clock speeds.

**BiCEMOS** process technology achieves performance levels equivalent to "next-generation" CEMOS technology and is the path to achieve zero-waitstate processing beyond 33MHz.

#### **Technology for the '90s**

IDT's BiCEMOS technology offers the best of both worlds: the low power consumption of CMOS with the high speed of bipolar technology. And

BiCEMOS technology makes IDT's SRAMs the pace setters with ever-faster system designs. BiCEMOS is the technology for the '90s!

#### **300mil Packaging**

All of IDT's BiCEMOS SRAMs are available in 300mil PDIP and SOJ packages for easy design and layout. The 71B258 64K x 4 SRAM is available in

Phor

Ser

24-pin DIP and SOJ packages, and the 71B256 32K x 8 and 61B298 64K x 4 SRAMs are available in 28-pin packages.

#### **Free Samples Now!**

Get your free samples of IDT's BiCEMOS TTL SRAMs today. Just fill out the coupon and send it in by FAX or mail, or call our Marketing Hotline at (800) 544-SRAM.

PLEASE COMPLETE AND FAX, OR MAIL IN AN ENVELOPE WITH YOUR BUSINESS CARD

| Name                                                                                                     |

|----------------------------------------------------------------------------------------------------------|

| Company Address Zip Zip                                                                                  |

| Address Zip Zip                                                                                          |

| City/State Zip                                                                                           |

|                                                                                                          |

| Phone () FAX ()                                                                                          |

|                                                                                                          |

| Send to:                                                                                                 |

| FAX: 408-758-4056<br>IDT SRAM Marketing<br>1566 Moffett Street<br>Salinas, CA 93905<br>Salinas, CA 93905 |

**CIRCLE 117**

#### TECHNOLOGY ADVANCES

Integrated Systems at Stanford Univ. discusses a 12-bit oversampling ADC with a 1.5-MHz conversion rate. The third paper concerns an 18-bit, 20-kHz dual delta-sigma unit jointly developed by Analog Devices Inc., Wilmington, Mass., and Ensoniq Corp., Malvern, Pa.

A pair of DACs from Philips, Eindhoven, the Netherlands, will also be described in the converter session. The first is an 18bit-bitstream dual-channel DAC with a total harmonic distortion of 120 dB and a signal-to-noise ratio of 108 dB. The other chip is a multibit DAC for digital audio with a dynamic range of 115 dB. This current-mode 5-bit sign-magnitude DAC operates at 128 times the oversampling rate. A complete codec, operating at 25 kHz, will be the highlight of a paper from NEC Corp., Kawasaki, Japan. The codec includes a 24-bit DSP filter, a 16-bit ADC, and an 18-bit DAC. It has signalto-noise ratios of 96 and 108 dB, in ADC and DAC operations, respectively.

High-speed data-acquisition circuits, such as 14bit sample-and-hold amplifiers, will be described by Analog Devices and National Semiconductor. A 20-MHz video-speed sample-and-hold chip from Hughes Aircraft Co., Manhattan Beach, Calif., is also on tap. Both Sony Corp., Atsugi, Japan, and Matsushita will unveil details of 500-MHz ADCs. The Sony ADC delivers 8 bits at 500 MHz with dc linearity within  $\pm 0.4$  LSB. The Matsushita chip actually has two 500-MHz ADCs on one chip. The two converters are interleaved to obtain a conversion rate of 1 Gsample/s, and a resolution of 6 bits. A complete 2-GHz 8bit data-acquisition system will be highlighted by Hewlett-Packard Co., Colorado Springs, Colo. The system consists of a fourphase sampler chip and two dual 500-MHz ADCs. all combined on a thick-film substrate.

Chips for wireless communications are also making an appearance—a single-chip VHF and UHF receiver for radio-paging systems will be described by Philips Radio Communications Systems, Cambridge, England, and Philips Components, Hamburg, Germany. The 500-MHz receiver can extract a 1200-baud frequencyshift-keyed data stream from the carrier. From AT&T Bell Laboratories will come a baseband codec for digital cellular phones. On one chip are two 8-bit DACs, a 9-bit DAC, a 10-bit DAC, and two 10-bit deltasigma converters. Additional on-chip functions include a 2-dB/step programmable-gain receive amplifier, two sets of decimators, an equalizer, dcoffset correction logic, and control and timing circuits. DAVE BURSKY

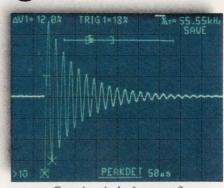

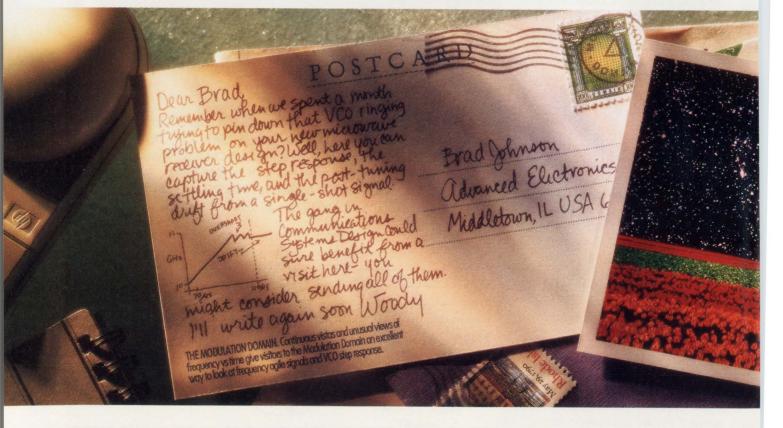

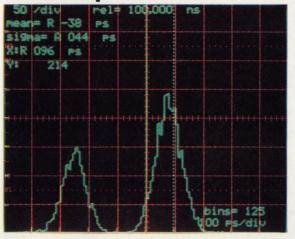

#### Venture into the Modulation Domain and

#### TECHNOLOGY ADVANCES

#### GAAS SWITCH TURNS ON 8.5 MW IN NANOSECONDS

mploying gallium arsenide, scientists at Sandia National Laboratories, Albuquerque, N.M., have developed a photoconductive semiconductor switch (PCSS) that turns on large amounts of power rapidly. In a recent experiment, the PCSS was able to switch 8.5 MW of power using light from an 850-W laser-diode array. Until now, the highest power switched with such a device using the same laser-diode array was 0.25 MW.

The PCSS held off 55 kV until it was activated, and delivered 470 A into a  $38\text{-}\Omega$

load. Pulse current peaked in just 3.5 ns, even though the optical pulse that triggered the switch had a rise time of 21 ns. Subsequent experiments have illustrated that rise times as short as 0.5 ns could be accommodated.

According to the Sandia researchers involved with the PCSS development, such results provide the foundation for a switch technology that can produce tens-of-kilovolt pulses with subnanosecond rise times at high repetition rates in a compact package.

The PCSS was operated

in a high-gain switching mode developed at Sandia. With the "lock-on" mode, the switch is able to trigger rapidly with minimal laser energy.

The switch consists of a small disk of undoped and bulk semi-insulating GaAs about 1 in. in diameter. Such material has insulating properties in the dark. However, when light shines upon on it, the material becomes conductive.

The device has many possible applications. One such application could be a small, fast-rise-time, repetitive switch for ultra-wideband impulse radar. This type of radar is currently being studied at several research laboratories. Other applications include optically activated firesets to trigger explosives, pulsepower systems to drive compact high-power accelerators, and fast-rise-time switches for electromagnetic-pulse testing.

The experiments done on PCSS were carried out by Sandia scientists Fred J. Zutavern, Guillermo M. Loubriel, Daniel L. McLaughlin, Martin M. O'Malley, and Wesley D. Helgeson, in Sandia's Repetitive Pulsed Power Research Division. Assisting the scientists were electrical engineers Paul Stabile and Arve Rosen of the David Sarnoff Research Center, Princeton, N.J., where the laser-diode array was developed.

ROGER ALLAN

#### improve your powers of observation.

When characterizing VCO responses and frequency agile signals, most designers depend on their powers of deductive reasoning. The Modulation Domain offers a more direct approach. It brings changes in frequency vs. time clearly into view. So you can see the transient response and post-tuning drift of a single-shot VCO step, or the chirp linearity and staggered PRI of a frequency agile signal. On a single display. In seconds.

Find out how looking at frequency vs. time in the Modulation Domain can make you a better designer, call Hewlett-Packard at **1-800-752-0900**\* Ask for **Ext. 1828**, and we'll send you a *Visitor's Guide to the Modulation Domain* on floppy disk, complete with a list of sights and excursions you won't want to miss.

There is a better way.

\*In Canada, call 1-800-387-3867, Dept. 419. Any similarity to existing persons or companies is purely coincidental. ©1990, Hewlett-Packard Co. TMSCD054A/ED

### From Outer Space to Your Place,

### We're Your Best Defense.

**B**y putting our military experience to work in high-volume, low-cost applications, we're giving

new meaning to the term *National Defense*. Our Power Supply Supervisory Chips are a good example.

These Raytheon Linear Arrays (*RLAs*) act as a computer's early warning system. They monitor internal voltage levels to 0.3% accuracy—and signal a shut down before power surges can fry the system.

It's "Defense Technology" with a peaceful purpose. And it's helping take computers into places they've never been.

Our RLAs have business benefits, too. If you can't decide between a custom or semicustom device, don't. Our *Win-Win* program lets you get to market quickly with a semicustom array, then shift to full custom as sales increase.

*Win-Win* is fast, flexible, and makes good business sense because it eliminates the risk of getting into a full custom array before you're really ready.

Raytheon is committed to analog technology. From our design kits and engineering support to our fab and plastic assembly facility. We have the experience it takes to help you develop creative, cost effective solutions.

Find out how. Call **1-800-722-7074** for our new analog brochure.

Raytheon Company, Semiconductor Division. 350 Ellis St. Mountain View, CA 94039.

CIRCLE 180

Where quality starts with fundamentals

### **Gain Without Pain.**

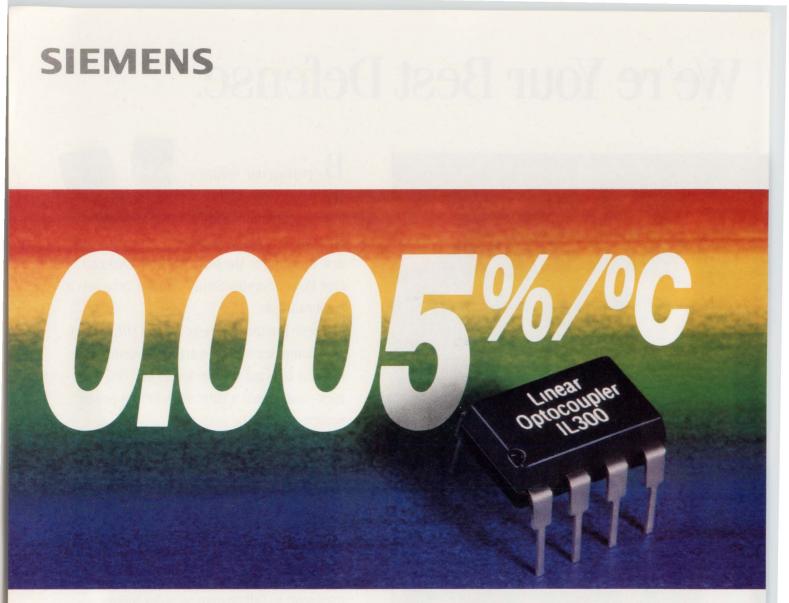

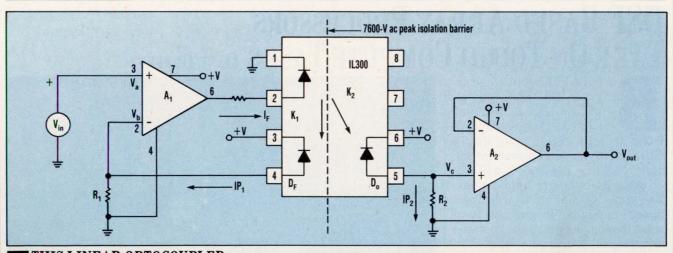

#### New linear optocoupler – Rx for stability.

The phrase "linear optocoupler" has always been a contradiction in terms.

#### Until now.

Siemens new IL300 optocoupler uses a unique, optical feedback loop to neutralize gain and offset

drift caused by temperature and LED degradation. The results will change the way you

think about optocouplers: DC gain stability of  $\pm 0.005\%$ /°C,  $\pm 0.01\%$  servo linearity, a wide (>200KHz) bandwidth, power consumption

lo1

under 15mw, and 7500 VAC Withstand Test Voltage.

The IL300's stable operational characteristics are achieved by controlling the AlGaAs IRLED output flux with an optical feedback circuit. The servo PIN photodiode captures a percentage of the flux and generates a signal that can be used to control the LED drive

current. This compensates for the LED's inherent nonlinear, time, and temperature characteristics.

The IL300's stability and excellent isolation characteristics make it ideal for power supply regulation, medical sensor isolation, audio signal interfacing, digital telephone isolation, and many other applications.

It gives engineers a flexible, cost and power efficient component for applications in which optocouplers were never practical before.

For complete information on our new linear optocoupler, including application tips, call 408-725-3543.

Siemens Components, Inc. Optoelectronics Division 19000 Homestead Road Cupertino, CA 95014-1799

The IL300 linear optocoupler. Gain without pain.

Distributors: Advent Electronics, Inc., Hall-Mark, Insight Electronics, Marshall, Summit, Western Microtechnology.

Siemens Practical Solutions By Design.

© 1991 Siemens Components, Inc.

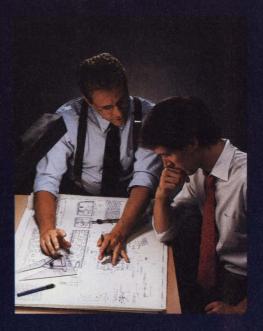

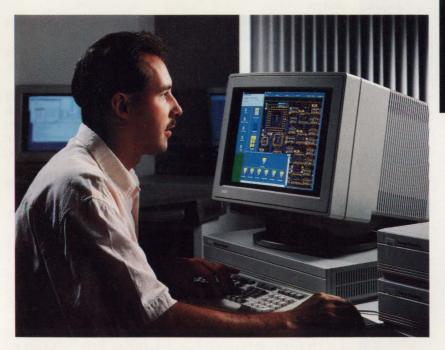

### **TEAMWORK IS THE KEY TO CONCURRENT** DESIGN

FUTURE DESIGN TEAMS WILL NEED ALL DISCIPLINES TO WORK IN PARALLEL.

#### MALINIAK RY LISA

ncreasing design complexity, intense competition, and tighter time-to-market deadlines will soon render the traditional "over-the-wall" operation of a design team obsolete. No longer can the engineering group complete its portion of the design before turning it over to the test group, and the test group finish its segment before the design reaches the manufacturing group, and so on. This serial approach has problems because the designers in the cycle's later stages don't have any input into the design until it's almost finished. In other words, each group hands off not only its portion of the design, but also a slew of problems.

Dataguest estimates that in a traditional serial design environment, the cost of making a change increases by an order of magnitude for each phase of the design cycle. For example, in a large manufacturing operation, a change that costs \$1000 during design would cost \$10,000 during testing.

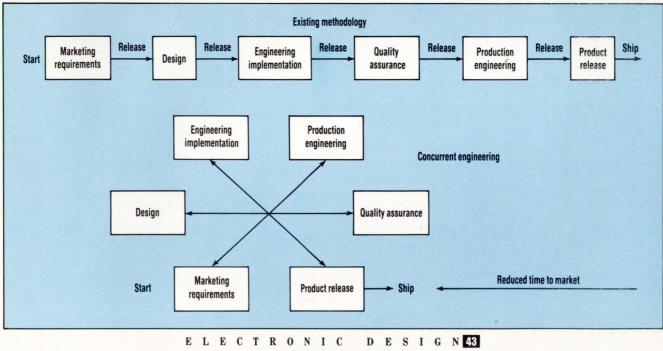

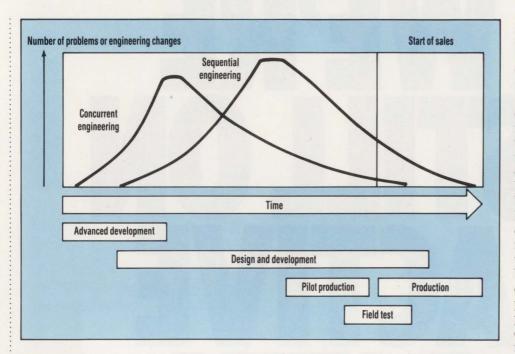

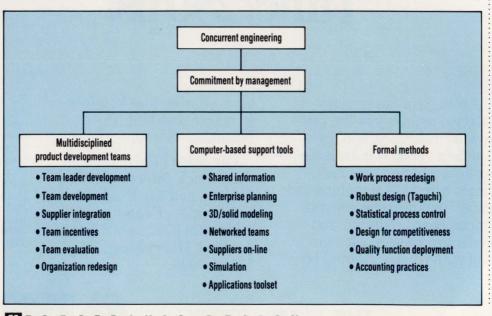

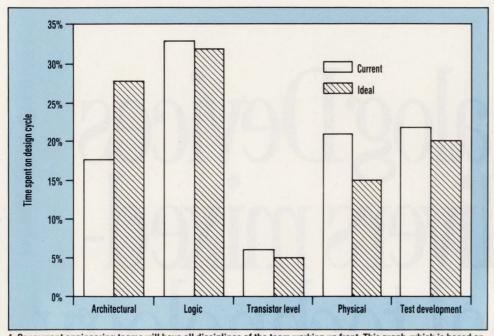

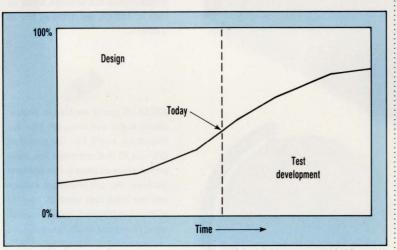

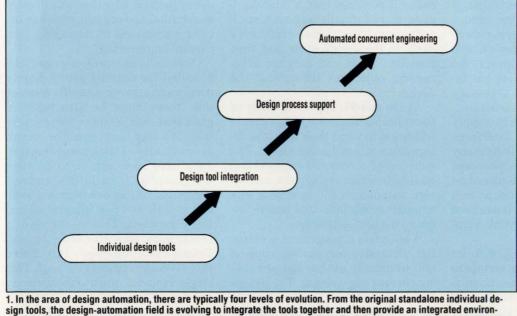

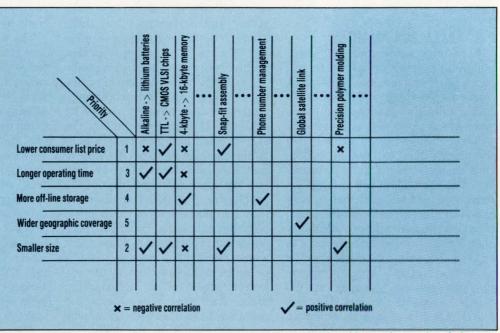

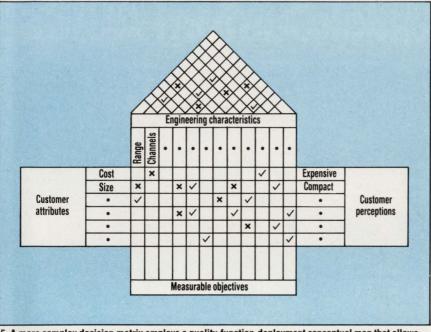

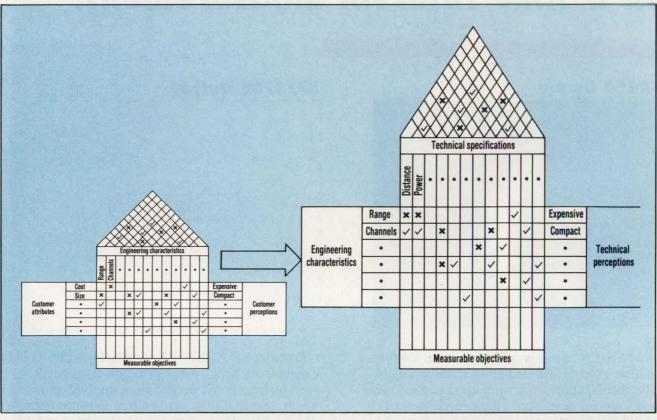

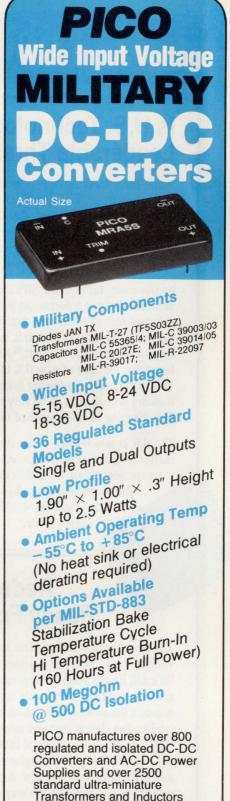

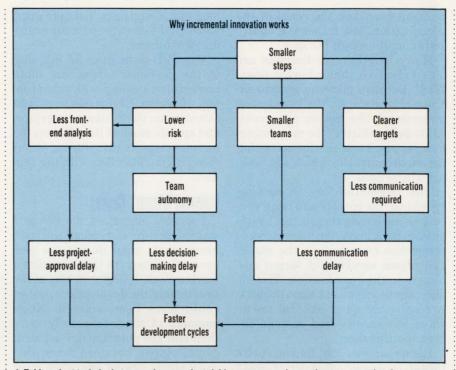

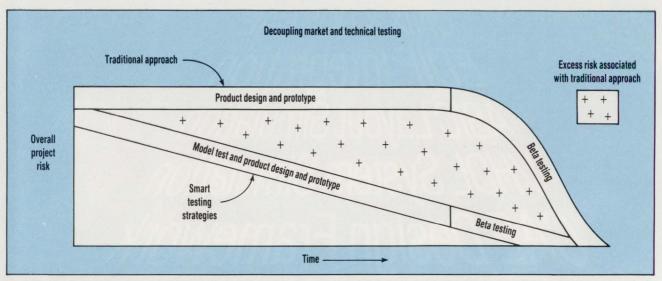

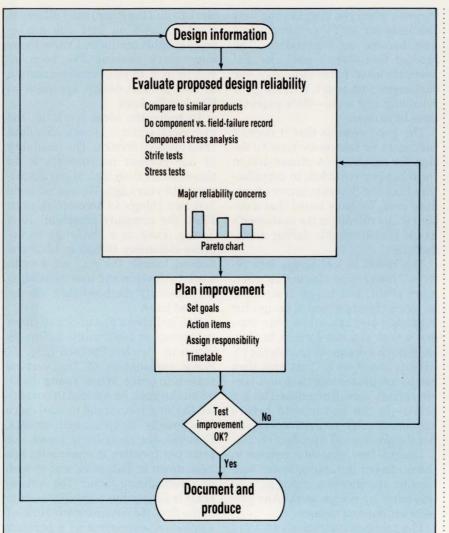

To offset these headaches, the design teams of the 1990s and beyond will turn to a multidisciplinary, concurrent approach. In other words, all types of disciplines from every phase of product development will work together up front (concurrently) to define the product specifications (Fig. 1). These disciplines include hardware design, software development, test, manufacturing, packaging, documentation, marketing, and even the customers themselves. The team will work together to make the right trade-offs right from the beginning, when mistakes are less costly and easy to fix (Fig. 2).

This new team will require a change in the design environment, and adjustments in team management and the way engineers interact with each other. Some companies have already begun implementing the changes. In fact, there are successful concurrent, multidiscipline design teams in operation today (see "A success story," p. 42). According to data from the National Institute of Standards and Technology, Thomas Group Inc., and the Institute for Defense Analyses, concurrentengineering methodologies can reduce development time by 30 to 70%, result in 65 to 90% fewer engineering changes, reduce time to market by up to 90%, and result in quality improvement of 200 to 600%.

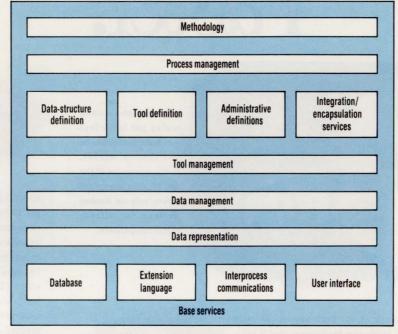

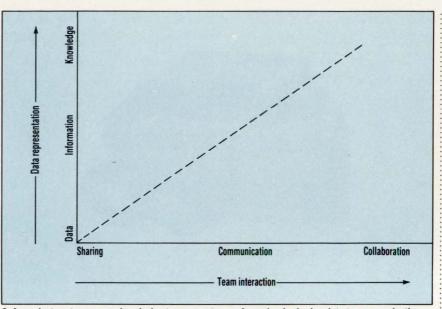

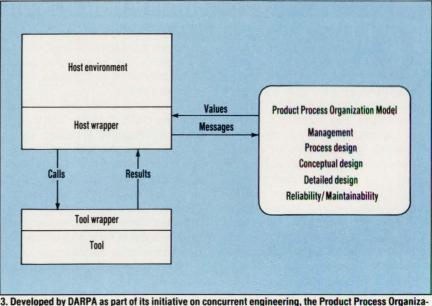

Engineers at Digital Equipment Corp., Marlboro, Mass., claim that three resources are needed to implement a multidiscipline, concurrent-engineering environment: human, computer, and methodology (Fig. 3). Human resources are mainly the members of the project teams, but may also include other people inside and outside the enterprise who

PHOTO: JOE DRIVAS

DESIGN41 E LECTR ONIC **JANUARY 10, 1991**

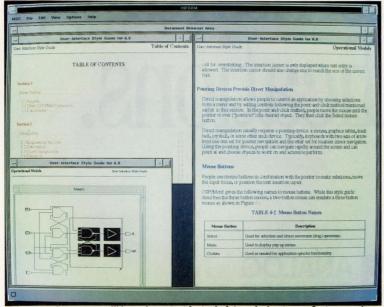

will be consulted in the project development. Computer resources consist of the basic hardware, software, and systems that support the project team. Methodology resources are the formal techniques used in decision-making for product and process development. Although they may be supported by special software, methodologies mainly involve engineering philosophies and procedures.

The key to a successful design team is to emphasize *team*. "The biggest problem with design teams is that none of us were taught at home or in school to solve problems in a group environment," points out Dick Jensen, vice president of new business development at Applied Microsystems Corp., Redmond, Wash. "We don't have the mental tools to do group problem solving very well. It's foreign to most people." The most important challenge facing project managers in the future is

wo years ago, the Department of Defense commissioned the Institute for Defense Analyses to report on claims of improved product quality at lower costs and shortened product development time through concurrent-engineering practices. The study's results, summarized in IDA report R-338, included many detailed cases of successful concurrent engineering.

One company that successfully implemented the change is IBM Corp., Poughkeepsie, N.Y. The Poughkeepsie mechanical-packaging group designs portions of the company's 3090 mainframes. Before the change, product development took place at the laboratory, and manufacturing operations were done at the plant.

The move to concurrent engineering was initiated by the product's design group. They were concerned about the high level of product-engineering support needed for design changes after the product was released to manufacturing. Many engineering modifications were occurring despite early manufacturing involvement in product development. The design process was serial, and communication between the laboratory and manufacturing group wasn't as effective as it

#### A SUCCESS STORY

could be.

The laboratory, working with the manufacturing plant, established a Total Concept Facility (TCF). A team of specialists from different disciplines concerned with designing, producing, and supporting a product could work together at the facility throughout all product design phases. The team consisted of about 70 people, mostly from development and manufacturing. Marketing, quality assurance, and field engineering were also represented.