WD42C22C

Winchester Disk Subsystem

Controller Device

### **TABLE OF CONTENTS**

| Section | Title                                                       |                                                               |                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page                                                                                                       |

|---------|-------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 1.0     | INTR<br>1.1<br>1.2                                          | FEATUR                                                        | RES IPTION ENHANC ADVANC ADAPTAI FLEXIBIL TYPICAL                                                                       | EED HOST INTERFACE ED BUFFER MANAGEMENT BLE DISK CONTROLLER LITY OF APPLICATION APPLICATION CRIPTIONS                                                                                                                                                                                                                                                                                                                                     | 33-1<br>33-2<br>33-2<br>33-3<br>33-3<br>33-3                                                               |

| 2.0     | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9 | POWER DRIVE I DRIVE ( PROGR MAGNIT CRC/EC MFM/RL ADDRE: CONTR | RE R-QUALIFII NTERFAC CONTROL AMMABLE FUDE COM CC GENEF LL ENCOD SS MARK OLLER TO                                       | ED RESET  EE LOGIC  LER ORGANIZATION  E LOGIC ARRAY (PLA) CONTROLLER  MPARATOR  RATOR AND CHECKER  DING AND MFM/RLL DECODING  DETECTOR  D DATA SEPARATOR INTERFACE                                                                                                                                                                                                                                                                        | . 33-10<br>. 33-10<br>. 33-10<br>. 33-10<br>. 33-11<br>. 33-11<br>. 33-13<br>. 33-13                       |

| 3.0     | INTE<br>3.1<br>3.2                                          | HOST I                                                        | NTERFACE T INTERF READ DA WRITE D HARDWA 3.2.3.1 3.2.3.2 3.2.3.3 3.2.3.4 3.2.3.5 3.2.3.6 CONTRO DRIVE C (HA1 THI CONTRO | ID TASK FILES E ORGANIZATION FACE  ATA PORT (HA1 THRU HA0 = 0, READ)  ATA PORT (HA1 THRU HA0 = 0, WRITE)  ARE STATUS (HA1 THRU HA0 = 1, READ)  BIT 5 INTERRUPT REQUEST  BIT 4 DMA REQUEST  BIT 3 XT BUSY  BIT 2 COMMAND / DATA  BIT 1 INPUT / OUTPUT  BIT 0 REQUEST  OLLER RESET (HA1 THRU HA0 = 1, WRITE)  ONFIGURATION INFORMATION  RU HA0 = 2, READ)  OLLER SELECT (HA1 THRU HA0 = 2, WRITE)  ONTERRUPT MASK (HA1 THRU HA0 = 3, WRITE) | . 33-16<br>. 33-16<br>. 33-16<br>. 33-16<br>. 33-17<br>. 33-17<br>. 33-17<br>. 33-17<br>. 33-17<br>. 33-17 |

|         | 3.3                                                         |                                                               | T INTERF                                                                                                                | ACE  REGISTER (HA9, HA2 THRU HA0 = 01, READ)  BIT 7 BAD BLOCK  BIT 6 CRC/ECC DATA FIELD ERROR                                                                                                                                                                                                                                                                                                                                             | . 33-17<br>. 33-18<br>33-18                                                                                |

| Section | Title |        |                   |                                                                                                                                 | Page  |

|---------|-------|--------|-------------------|---------------------------------------------------------------------------------------------------------------------------------|-------|

|         |       |        | 3.3.1.3           | BIT 5 RESERVED                                                                                                                  | 33-18 |

|         |       |        | 3.3.1.4           | BIT 4 ID NOT FOUND                                                                                                              | 33-18 |

|         |       |        | 3.3.1.5           | BIT 3 RESERVED                                                                                                                  | 33-19 |

|         |       |        | 3.3.1.6           | BIT 2 ABORTED COMMAND                                                                                                           | 33-19 |

|         |       |        | 3.3.1.7           | BIT 1 TRACK 0 ERROR                                                                                                             | 33-19 |

|         |       |        | 3.3.1.8           | BIT 0 DATA ADDRESS MARK NOT FOUND                                                                                               | 33-19 |

|         |       | 3.3.2  | WRITE P           | RECOMP CYLINDER REGISTER (HA9, HA2 THRU                                                                                         |       |

|         |       |        |                   | , WRITE)                                                                                                                        |       |

|         |       | 3.3.3  | SECTOR            | COUNT (HA9, HA2 THRU HA0 = 02, READ/WRITE)                                                                                      | 33-19 |

|         |       | 3.3.4  | SECTOR            | NUMBER (HA9, HA2 THRU HA0 = 03, READ/WRITE)                                                                                     | 33-19 |

|         |       | 3.3.5  | (CYLIND<br>READ/W | R NUMBER LOW AND HIGH REGISTERS ER NUMBER LOW: HA9, HA2 THRU HA0 = 04, RITE. CYLINDER NUMBER HIGH: HA9, HA2 THRU F, READ/WRITE) | 33-19 |

|         |       | 3.3.6  |                   | GISTER (HA9, HA2 THRU HA0 = 06, READ/WRITE)                                                                                     |       |

|         |       |        | 3.3.6.1           | BIT 7 ECC/CRC SELECT                                                                                                            |       |

|         |       |        | 3.3.6.2           | BIT 5 SECTOR SIZE                                                                                                               |       |

|         |       |        | 3.3.6.3           | BIT 4 DRIVE SELECT                                                                                                              | 33-20 |

|         |       |        | 3.3.6.4           | BITS 3 THROUGH 0 HEAD NUMBER                                                                                                    | 33-20 |

|         |       | 3.3.7  | HOST ST           | TATUS REGISTER (HA9, HA2 THRU HA0 = 7, READ)                                                                                    | 33-20 |

|         |       |        | 3.3.7.1           | BIT 7 AT BUSY                                                                                                                   | 33-20 |

|         |       |        | 3.3.7.2           | BIT 6 DRIVE READY                                                                                                               | 33-20 |

|         |       |        | 3.3.7.3           | BIT 5 WRITE FAULT                                                                                                               | 33-20 |

|         |       |        | 3.3.7.4           | BIT 4 SEEK COMPLETE                                                                                                             | 33-20 |

|         |       |        | 3.3.7.5           | BIT 3 DATA REQUEST                                                                                                              | 33-20 |

|         |       |        | 3.3.7.6           | BIT 2 DATA WAS CORRECTED                                                                                                        | 33-20 |

|         |       |        | 3.3.7.7           | BIT 1 INDEX                                                                                                                     | 33-20 |

|         |       |        | 3.3.7.8           | BIT 0 ERROR                                                                                                                     | 33-20 |

|         |       | 3.3.8  |                   | DMMAND REGISTER (HA9, HA2 THRU HA0 = 7,                                                                                         |       |

|         |       |        | •                 |                                                                                                                                 | 33-20 |

|         |       | 3.3.9  |                   | ATE STATUS REGISTER                                                                                                             |       |

|         |       |        | •                 | 2 THRU HA0 = E, READ)                                                                                                           | 33-20 |

|         |       | 3.3.10 |                   | SK REGISTER                                                                                                                     | 00.00 |

|         |       |        |                   | 2 THRU HA0 = E, WRITE)                                                                                                          |       |

|         |       |        |                   | BIT 3 HEAD SELECT 3 ENABLE                                                                                                      |       |

|         |       |        | 3.3.10.2          | BIT 2 RESET                                                                                                                     |       |

|         |       | 2 2 11 |                   | INPUT REGISTER                                                                                                                  | 33-21 |

|         |       | 3.3.11 |                   | 11                                                                                                                              | 33-21 |

|         |       |        | 3.3.11.1          | BIT 6 WRITE GATE ON                                                                                                             |       |

|         |       |        | 3.3.11.2          | BIT 5 HEAD SELECT 3/                                                                                                            | JJ-21 |

|         |       |        | 0.0.11.2          | REDUCE WRITE CURRENT                                                                                                            | 33-21 |

|         |       |        | 3.3.11.3          | BIT 4, BIT 3, AND BIT 2 HEAD SELECTS                                                                                            |       |

|         |       |        |                   |                                                                                                                                 |       |

| Title |         |          |                                                                                          | Page   |

|-------|---------|----------|------------------------------------------------------------------------------------------|--------|

|       |         | 3.3.11.4 | BIT 1 AND BIT 0 DRIVE SELECTS                                                            | .33-21 |

| 3.4   |         |          | ERFACE                                                                                   |        |

| 3.5   |         |          | NTROLLER INTERFACE ORGANIZATION                                                          |        |

| 3.6   | DISK CO |          | ER TASK FILE (AD7 THRU AD0 = 20 THRU 27)                                                 |        |

|       | 3.6.1   |          | REGISTER (AD7 THRU AD0 = 21, READ)                                                       |        |

|       |         | 3.6.1.1  | BIT 7 BAD BLOCK                                                                          |        |

|       |         | 3.6.1.2  | BIT 6 CRC/ECC DATA FIELD ERROR                                                           |        |

|       |         | 3.6.1.3  | BIT 5 RELOCATION ID FOUND                                                                |        |

|       |         | 3.6.1.4  | BIT 4 ID NOT FOUND                                                                       |        |

|       |         | 3.6.1.5  | BIT 3 RESERVED                                                                           |        |

|       |         | 3.6.1.6  | BIT 2 ABORTED COMMAND                                                                    |        |

|       |         | 3.6.1.7  | BIT 1 RESERVED                                                                           |        |

|       |         | 3.6.1.8  | BIT 0 DATA ADDRESS MARK NOT FOUND                                                        |        |

|       | 3.6.2   |          | GTH REGISTER (AD7 THRU AD0 = 21, WRITE)                                                  |        |

|       | 3.6.3   |          | COUNT (AD7 THRU AD0 = 22, READ/WRITE)                                                    |        |

|       | 3.6.4   |          | NUMBER (AD7 THRU AD0 = 23, READ/WRITE)                                                   | 33-25  |

|       | 3.6.5   |          | R NUMBER REGISTERS (CYLINDER NUMBER LOW:<br>U AD0 = 24, READ WRITE CYLINDER NUMBER HIGH: |        |

|       |         |          | U AD0 = 25, READ/WRITE)                                                                  | 33-25  |

|       | 3.6.6   |          | R NUMBER REGISTERS (CYLINDER NUMBER LOW:                                                 | 00 20  |

|       | 0.0.0   |          | U AD0 = 24, READ/WRITE CYLINDER NUMBER HIGH:                                             |        |

|       |         |          | U AD0 = 25, READ/WRITE)                                                                  | 33-26  |

|       | 3.6.7   | SDH REC  | GISTER (AD7 THRU AD0 = 26, READ/WRITE)                                                   | 33-26  |

|       |         | 3.6.7.1  | SDH REGISTER, THREE-BIT HEAD NUMBER                                                      | .33-26 |

|       |         | 3.6.7.2  | SDH REGISTER, FOUR-BIT HEAD NUMBER                                                       | .33-26 |

|       |         | 3.6.7.3  | BIT 7 ECC/CRC SELECT                                                                     | .33-26 |

|       |         | 3.6.7.4  | BIT 6 AND BIT 5 SECTOR SIZE                                                              | .33-26 |

|       |         | 3.6.7.5  | BIT 4 AND BIT 3 RESERVED                                                                 |        |

|       |         |          | BIT 4 DRIVE NUMBER RESERVED                                                              | .33-26 |

|       |         | 3.6.7.6  | BIT 2, BIT 1, AND BIT 0 THREE BIT HEAD NUMBER                                            | 00.00  |

|       |         |          | COLUDERIS DE CORMAT DATE                                                                 | .33-26 |

|       |         | 3.6.7.7  | SDH ID FIELD FORMAT BYTE (THREE BIT HEAD MODE)                                           | 33-27  |

|       |         | 3.6.7.8  | SDH ID FIELD FORMAT BYTE                                                                 | .00-21 |

|       |         | 0.0.7.0  | (FOUR BIT HEAD MODE)                                                                     | .33-27 |

|       | 3.6.8   | STATUS   | REGISTER (AD7 THRU AD0 = 27, READ)                                                       |        |

|       |         | 3.6.8.1  | BIT 7 ALWAYS 0                                                                           |        |

|       |         | 3.6.8.2  | BIT 6 DRIVE READY                                                                        |        |

|       |         | 3.6.8.3  | BIT 5 WRITE FAULT                                                                        | .33-27 |

|       |         | 3.6.8.4  | BIT 4 ALWAYS 1                                                                           |        |

|       |         | 3.6.8.5  | BIT 3 ALWAYS 0                                                                           | .33-27 |

|       |         | 3.6.8.6  | BIT 2 NOT USED                                                                           | .33-27 |

|       |         | 3.6.8.7  | BIT 1 ALWAYS 0                                                                           | .33-27 |

Section

| Section | Title |        |          |                                                 | Page    |

|---------|-------|--------|----------|-------------------------------------------------|---------|

|         |       |        | 3.6.8.8  | BIT 0 ERROR                                     | . 33-27 |

|         |       | 3.6.9  | COMMA    | ND REGISTER (AD7 THRU AD0 = 27, WRITE)          | . 33-27 |

|         | 3.7   | XT INT | ERFACE F | PORTS                                           | . 33-27 |

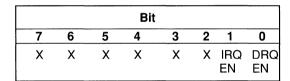

|         |       | 3.7.1  | XT HOS   | T HARDWARE STATUS                               |         |

|         |       |        | (AD7 TH  | RU AD0 = 2D, READ/WRITE)                        | . 33-27 |

|         |       |        | 3.7.1.1  | BITS 6 AND 7 UNDEFINED                          | . 33-28 |

|         |       |        | 3.7.1.2  | BIT 5 INTERRUPT REQUEST                         | . 33-28 |

|         |       |        | 3.7.1.3  | BIT 4 DMA REQUEST                               | . 33-28 |

|         |       |        | 3.7.1.4  | BIT 3 XT BUSY                                   | . 33-28 |

|         |       |        | 3.7.1.5  | BIT 2 COMMAND / DATA                            | . 33-28 |

|         |       |        | 3.7.1.6  | BIT 1 INPUT / OUTPUT                            | . 33-28 |

|         |       |        | 3.7.1.7  | BIT 0 REQUEST                                   | . 33-28 |

|         |       | 3.7.2  | HOST D   | RIVE CONFIGURATION (AD7 THRU AD0 = 2E, WRITE)   | . 33-28 |

|         |       | 3.7.3  |          | R MANAGER REGISTERS (AD7 THRU AD0 = 30 THRU 37) |         |

|         |       |        |          | UFFER POINTER LOW (AD7 THRU AD0 = 30, READ/WRIT | E)      |

|         |       |        |          | UFFER POINTER HIGH                              | 00.00   |

|         |       | 0.7.4  | ,        | RU ADO = 31, READ/WRITE)                        | . 33-28 |

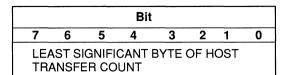

|         |       | 3.7.4  |          | RANSFER COUNT LOW<br>IRU AD0 = 32, READ/WRITE   |         |

|         |       |        |          | RANSFER COUNT HIGH                              |         |

|         |       |        |          | IRU AD0 = 33, READ/WRITE)                       | . 33-28 |

|         |       | 3.7.5  | *        | IFFER POINTER LOW                               |         |

|         |       |        |          | RU AD0 = 34, READ/WRITE)                        |         |

|         |       |        |          | JFFER POINTER HIGH                              |         |

|         |       |        |          | IRU AD0 = 35, READ/WRITE)                       |         |

|         |       | 3.7.6  |          | CONTROLLER RAM ACCESS PORT (AD7 THRU AD0 = 36,  |         |

|         |       | 077    |          | /RITE)                                          |         |

|         |       | 3.7.7  |          | R CONTROL REGISTER (AD7 THRU AD0 = 37, WRITE)   |         |

|         |       |        | 3.7.7.1  | BIT 7 AT / XT INTERFACE CONTROL                 |         |

|         |       |        | 3.7.7.2  | BIT 6 READ CONFIGURATION                        |         |

|         |       |        | 3.7.7.3  | BIT 5 RESET TRANSFER COUNTER                    |         |

|         |       |        | 3.7.7.4  | BIT 4 ARM HOST BUFFER POINTER                   |         |

|         |       |        | 3.7.7.5  | BIT 3 HOST READ / WRITE                         |         |

|         |       |        | 3.7.7.6  | BIT 2 DISK READ / WRITE                         |         |

|         |       |        | 3.7.7.7  | BIT 1 BURST DMA ENABLE                          |         |

|         |       |        | 3.7.7.8  | BIT 0 ARM DISK BUFFER POINTER                   | . 33-30 |

|         |       | 3.7.8  |          | R STATUS REGISTER<br>IRU AD0 = 37, READ)        | . 33-30 |

|         |       |        | 3.7.8.1  | BIT 7 AT / XT INTERFACE MODE                    | . 33-30 |

|         |       |        | 3.7.8.2  | BIT 6 READ CONFIGURATION                        | . 33-30 |

|         |       |        | 3.7.8.3  | BIT 5 RESET TRANSFER COUNTER                    | . 33-30 |

|         |       |        | 3.7.8.4  | BIT 4 HOST BUFFER POINTER ARMED                 | . 33-30 |

|         |       |        | 3.7.8.5  | BIT 3 HOST READ / WRITE                         | . 33-30 |

| Section | Title |        |          |                                                   | Page   |

|---------|-------|--------|----------|---------------------------------------------------|--------|

|         |       |        | 3.7.8.6  | BIT 2 DISK READ / WRITE                           | .33-30 |

|         |       |        | 3.7.8.7  | BIT 1 BURST DMA ENABLE                            | .33-30 |

|         |       |        | 3.7.8.8  | BIT 0 DISK BUFFER POINTER ARMED                   | .33-30 |

|         |       | 3.7.9  |          | RY BUFFER CONTROL REGISTER (AD7 THRU AD0 = $2F$ , |        |

|         |       |        | WRITE) . |                                                   | 33-31  |

|         |       |        | 3.7.9.1  | BIT 7 HOST DMA                                    |        |

|         |       |        | 3.7.9.2  | BIT 6 HOST SLAVE / MASTER                         | .33-31 |

|         |       |        | 3.7.9.3  | BIT 5 BURST CONTINUOUS                            |        |

|         |       |        | 3.7.9.4  | BIT 4 INTELLIGENT DRIVE DECODE                    |        |

|         |       |        | 3.7.9.5  | BIT 3 DRIVE SELECT                                |        |

|         |       |        | 3.7.9.6  | BIT 1 HOST 16 / 8 BIT                             | .33-31 |

|         |       |        | 3.7.9.7  | BIT 0 SYNCHRONOUS CLOCK SWITCH                    | .33-31 |

|         |       | 3.7.10 |          | RY BUFFER STATUS REGISTER (AD7 THRU AD0 = 2F,     |        |

|         |       |        |          |                                                   |        |

|         |       |        |          | BIT 7 HOST DMA                                    |        |

|         |       |        |          | BIT 6 HOST SLAVE / MASTER                         |        |

|         |       |        | 3.7.10.3 | BIT 5 BURST CONTINUOUS                            |        |

|         |       |        | 3.7.10.4 | BIT 4 INTELLIGENT DRIVE DECODE                    |        |

|         |       |        | 3.7.10.5 | BIT 3 DRIVE SELECT                                |        |

|         |       |        | 3.7.10.6 |                                                   |        |

|         |       |        |          | BIT 1 HOST 16 / 8                                 |        |

|         |       |        | 3.7.10.8 | BIT 0 SYNCHRONOUS CLOCK SWITCH                    | .33-32 |

|         |       | 3.7.11 |          | CE STATUS REGISTER                                |        |

|         |       |        |          | RU AD0 = 38, READ)                                | 33-32  |

|         |       |        | 3.7.11.1 |                                                   |        |

|         |       |        |          | JPT                                               |        |

|         |       |        | 3.7.11.2 |                                                   |        |

|         |       |        | 3.7.11.3 |                                                   |        |

|         |       |        |          | BIT 4 FIFO ERROR INTERRUPT                        | .33-32 |

|         |       |        | 3.7.11.5 |                                                   | 00.00  |

|         |       |        |          | JPT                                               | .33-32 |

|         |       |        |          | BIT 2 HOST POINTER READY<br>JPT                   | 22.22  |

|         |       |        |          | BIT 1 DISK BDRQ INTERRUPT                         |        |

|         |       |        |          | BIT 0 COMMAND WRITE / SELECT / SLAVE              |        |

|         |       |        | 3.7.11.0 | INTERRUPT                                         |        |

|         |       | 3.7.12 | INTERFA  | CE CONTROL REGISTER                               | .00 00 |

|         |       | 0.7.12 |          | RU AD0 = 38, WRITE)                               | 33-33  |

|         |       |        | 3.7.12.1 | BIT 7 SET INTERRUPT                               |        |

|         |       |        | 3.7.12.2 |                                                   |        |

|         |       |        | 3.7.12.3 |                                                   |        |

|         |       |        |          | BIT 4 RESET FIFO ERROR INTERRUPT                  |        |

|         |       |        |          | BIT 3 RESET BUSY                                  |        |

|         |       |        | 5.7.12.5 | 5., 6., LOE   500                                 | .00 00 |

| Section | Title |          |          |                                                   | Page  |

|---------|-------|----------|----------|---------------------------------------------------|-------|

|         |       |          | 3.7.12.6 | BIT 2 RESET HOST POINTER READY INTERRUPT          | 33-33 |

|         |       |          | 3.7.12.7 | BIT 1 RESET DISK BDRQ INTERRUPT                   | 33-33 |

|         |       |          | 3.7.12.8 |                                                   |       |

|         |       |          |          | INTERRUPT                                         | 33-33 |

|         |       | 3.7.13   |          | JRATION STATUS REGISTERS                          |       |

|         |       |          |          | 7 THRU AD0 = 39, READ<br>7 THRU AD0 = 3A, READ)   | 33-33 |

|         |       | 3.7.14   |          | ITERFACE STATUS                                   | 00 00 |

|         |       | •        |          | RU AD0 = 3B, READ)                                | 33-34 |

|         |       |          | 3.7.14.1 | BIT 7 RESET DRIVE CONTROLLER                      | 33-34 |

|         |       |          | 3.7.14.2 | BIT 6 DRIVE READY                                 | 33-34 |

|         |       |          | 3.7.14.3 | BIT 5 WRITE FAULT                                 | 33-34 |

|         |       |          | 3.7.14.4 | BIT 4 HOST DRIVE SELECT                           | 33-34 |

|         |       |          | 3.7.14.5 | BIT 3 MICROCONTROLLER ACCESS CONTROL              | 33-34 |

|         |       |          | 3.7.14.6 | BIT 2 DISABLE RESET OUTPUT                        | 33-34 |

|         |       |          | 3.7.14.7 | BIT 1 INPUT POLARITY                              | 33-34 |

|         |       |          | 3.7.14.8 | BIT 0 DISABLE SECTOR NUMBER                       | 33-34 |

|         |       | 3.7.15   |          | ITERFACE CONTROL                                  |       |

|         |       |          |          | RU AD0 = 3B, WRITE)                               |       |

|         |       |          | 3.7.15.1 | BIT 7 RESET DRIVE CONTROLLER                      |       |

|         |       |          | 3.7.15.2 | BIT 3 MICROCONTROLLER ACCESS CONTROL              |       |

|         |       |          | 3.7.15.3 | BIT 2 DISABLE RESET OUTPUT                        |       |

|         |       |          | 3.7.15.4 | BIT 1 INPUT POLARITY                              |       |

|         |       |          | 3.7.15.5 | BIT 0 DISABLE SECTOR NUMBER                       | 33-35 |

|         |       |          | 3.7.16   | ALTERNATE SECTOR NUMBER (AD7 THRU AD0 = 3C, READ) | 22.25 |

|         | 3.8   | AT INITI | EDEACE D | ORTS                                              |       |

|         | 3.0   | 3.8.1    |          | ROL REGISTER                                      | აა-აა |

|         |       | 3.0.1    |          | RU AD0 = 2A, READ/WRITE)                          | 33-35 |

|         |       |          | 3.8.1.1  | BITS 7 THROUGH 2 RESERVED                         |       |

|         |       |          | 3.8.1.2  | BIT 1 AUTO-DRQ 7 BYTE ECC                         |       |

|         |       |          | 3.8.1.3  | BIT 0 AUTO-DRQ ENABLE                             |       |

|         |       |          | 3.8.2    | DRIVE ZERO STATUS                                 |       |

|         |       |          |          | (AD7 THRU AD0 = 3D, READ/WRITE)                   | 33-35 |

|         |       | 3.8.3    | DRIVE O  | NE STATUS                                         |       |

|         |       |          | `        | RU AD0 = 3E, READ/WRITE)                          | 33-36 |

|         |       | 3.8.4    |          | ISK REGISTER<br>RU AD0 = 3F, READ)                | 33.36 |

|         |       | 3.8.5    | •        | INPUT REGISTER                                    | 55-50 |

|         |       | 5.6.5    |          | RU AD0 = 3F, WRITE)                               | 33-36 |

|         |       |          | 3.8.5.1  | BIT 7 ECC MODE                                    |       |

|         |       |          | 3.8.5.2  | BIT 6 ECC 7 BYTES/ DISABLE BDRQ                   |       |

|         |       |          | 3.8.5.3  | BIT 5 REDUCE WRITE CURRENT                        |       |

|         |       |          |          |                                                   |       |

| Section | Title |         |                                                                   | Page  |

|---------|-------|---------|-------------------------------------------------------------------|-------|

|         |       |         | 3.8.5.4 BIT 1 DRIVE SELECT 1                                      |       |

|         |       | 3.8.6   | 3.8.5.5 BIT 0 DRIVE SELECT 0                                      |       |

|         |       | 5.6.6   | (AD7 THRU AD0 = 40 THRU 47, READ/WRITE)                           | 33-36 |

| 4.0     | BUFF  | ER MAN  | AGER ORGANIZATION                                                 |       |

|         | 4.1   |         | ING BUFFER RAM FROM THE MICRO-CONTROLLER                          |       |

|         | 4.2   |         | IG HOST TRANSFERS TO/FROM BUFFER RAM                              |       |

|         | 4.3   |         | DLLER COMMANDS                                                    |       |

|         | 4.4   | СОММА   | ND DESCRIPTIONS                                                   | 33-40 |

|         |       | 4.4.1   | READ SECTOR                                                       | 33-40 |

|         |       | 4.4.2   | READ NEXT DATA                                                    | 33-42 |

|         |       | 4.4.3   | WRITE SECTOR                                                      | 33-42 |

|         |       | 4.4.4   | WRITE ID                                                          | 33-44 |

|         |       | 4.4.5   | SCAN ID                                                           | 33-45 |

|         |       | 4.4.6   | FORMAT TRACK                                                      | 33-45 |

|         |       | 4.4.7   | FORMAT SINGLE SECTOR                                              | 33-47 |

|         |       | 4.4.8   | COMPUTE CORRECTION                                                | 33-48 |

|         |       | 4.4.9   | SET PARAMETER                                                     | 33-49 |

|         |       | 4.4.10  | LOAD PARAMETER BLOCK                                              | 33-50 |

|         |       | 4.4.11  | SLEEP                                                             | 33-51 |

|         |       | 4.4.12  | DUMP                                                              | 33-51 |

| 5.0     | ELEC  | TRICAL  | AND TIMING SPECIFICATIONS                                         | 33-53 |

|         | 5.1   | MAXIMU  | M RATINGS                                                         | 33-53 |

|         | 5.2   | DC OPE  | RATING CHARACTERISTICS                                            |       |

|         | 5.3   | AC TIMI | NG CHARACTERISTICS                                                | 33-56 |

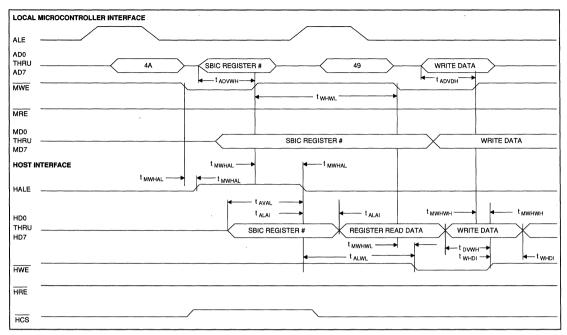

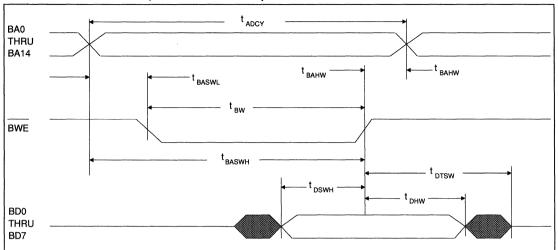

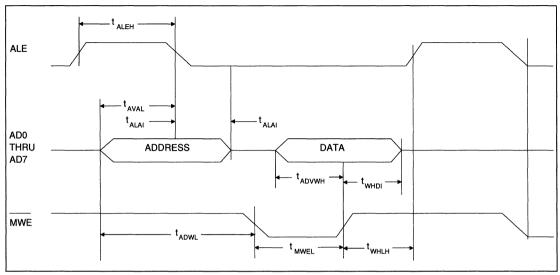

|         |       | 5.3.1   | AT/XT HOST PROGRAMMED I/O WRITE TIMING                            |       |

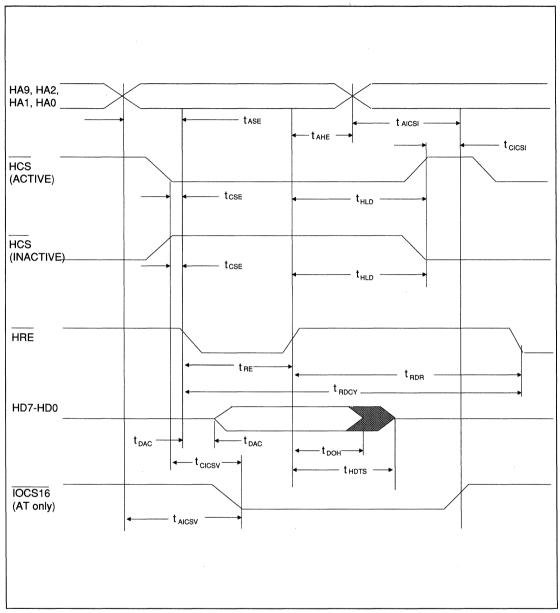

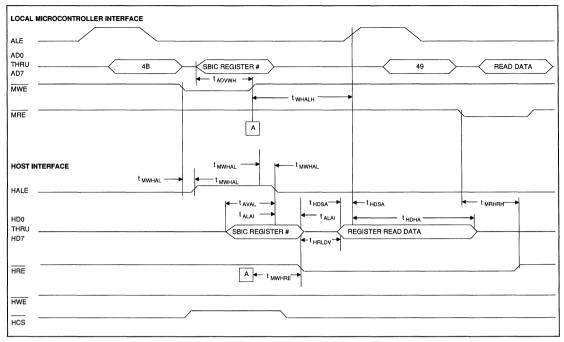

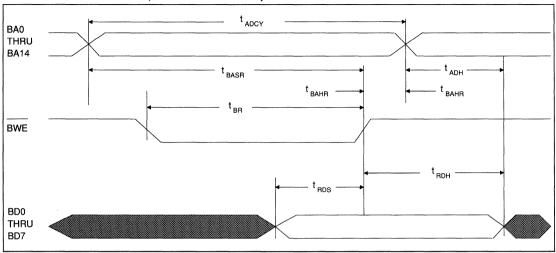

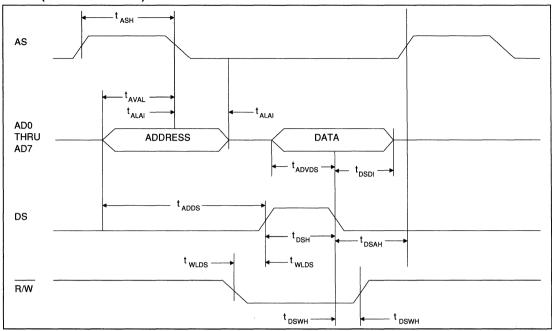

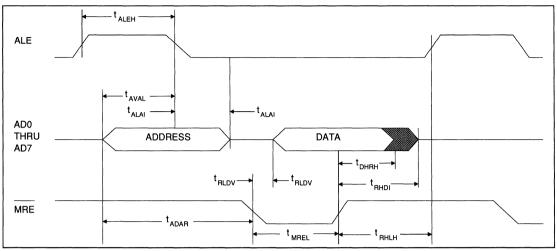

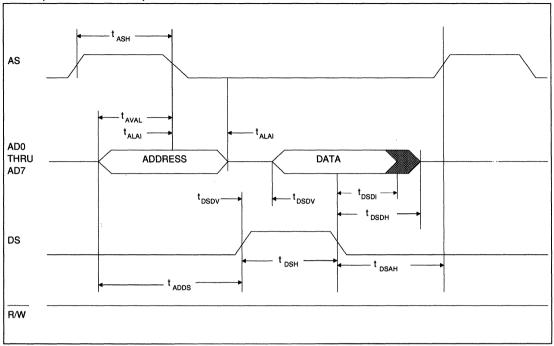

|         |       | 5.3.2   | AT/XT HOST PROGRAMMED I/O READ TIMING                             | 33-59 |

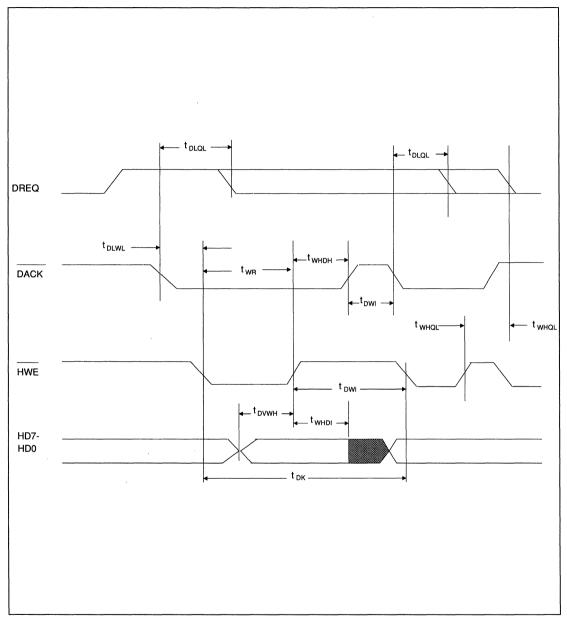

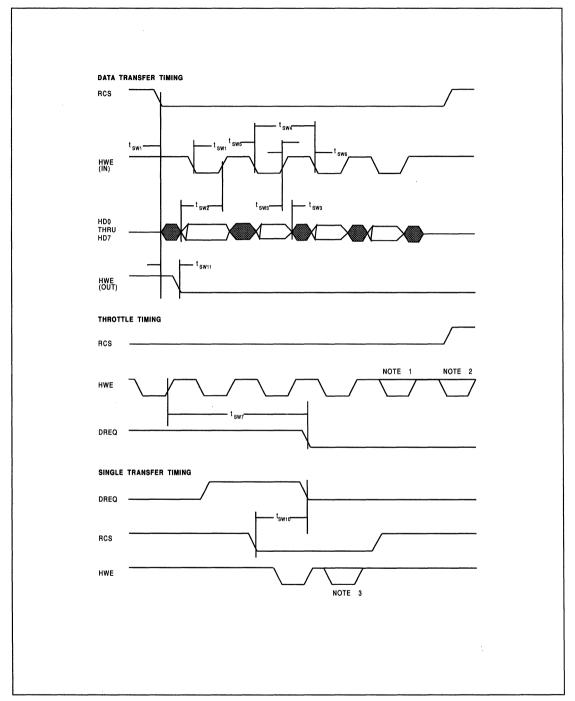

|         |       | 5.3.3   | AT/XT HOST DMA WRITE TIMING                                       | 33-60 |

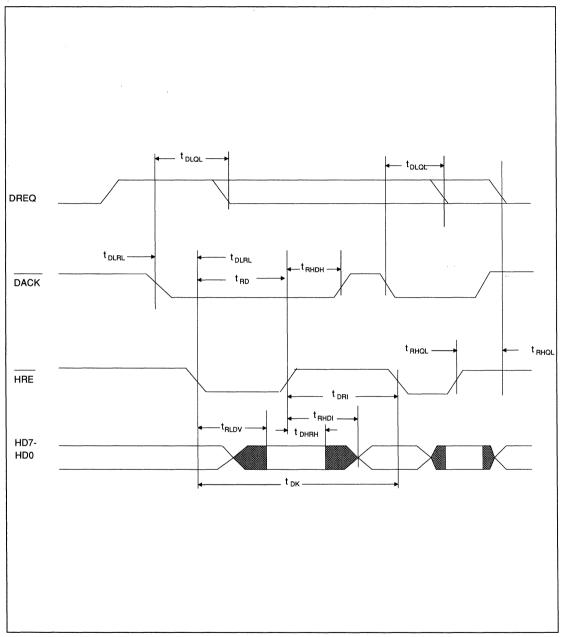

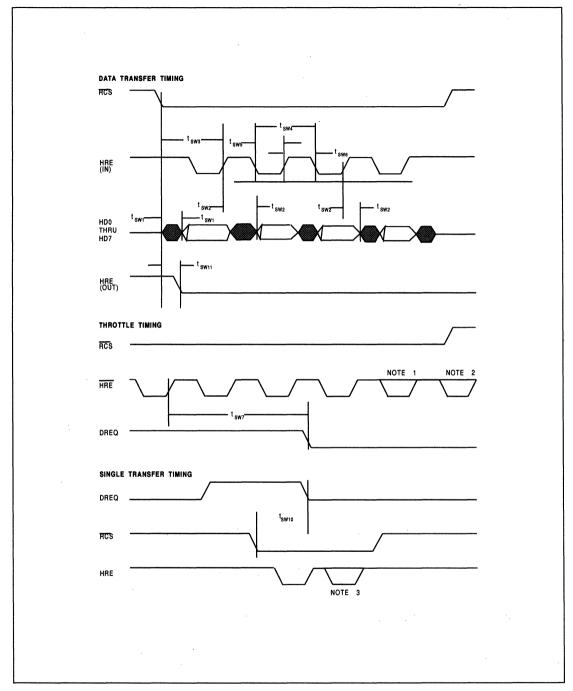

|         |       | 5.3.4   | AT/XT HOST DMA READ TIMING                                        | 33-62 |

|         |       | 5.3.5   | SLAVE HOST WRITE TIMINGS                                          | 33-64 |

|         |       | 5.3.6   | SLAVE HOST READ TIMINGS                                           |       |

|         |       | 5.3.7   | SLAVE HOST DMA WRITE TIMING                                       | 33-67 |

|         |       | 5.3.8   | SLAVE HOST DMA READ TIMING                                        | 33-69 |

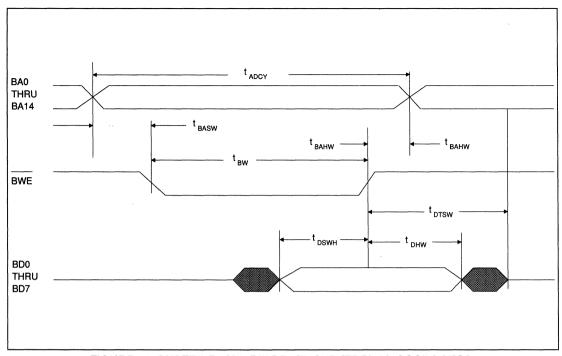

|         |       | 5.3.9   | BUFFER RAM WRITE TIMING (INTERNAL OSCILLATO XTAL = 8 - 25 MHZ)    |       |

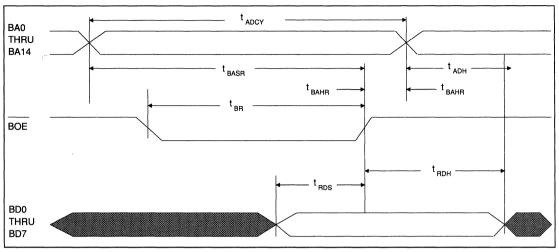

|         |       | 5.3.10  | BUFFER RAM READ TIMING (INTERNAL OSCILLATO) XTAL = 8 - 25 MHZ)    |       |

|         |       | 5.3.11  | BUFFER RAM WRITE TIMING (EXTERNAL OSCILLATO<br>XTAL = 8 - 25 MHZ) | OR;   |

|         |       | 5.3.12  | BUFFER RAM READ TIMING (EXTERNAL OSCILLATO XTAL = 8 - 20 MHZ)     | R;    |

|         |       | 5.3.13  | MICROPROCESSOR WRITE TIMING (INTEL BUS)                           |       |

| Section | Title |        |                                                    | Page    |

|---------|-------|--------|----------------------------------------------------|---------|

|         |       | 5.3.14 | MICROPROCESSOR WRITE TIMING (MOTOROLA BUS)         | . 33-76 |

|         |       | 5.3.15 | MICROPROCESSOR READ TIMING (INTEL BUS)             | . 33-77 |

|         |       | 5.3.16 | MICROPROCESSOR READ TIMING (MOTOROLA BUS)          | . 33-78 |

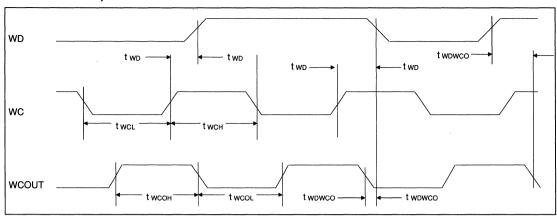

|         |       | 5.3.17 | WRITE DATA TIMING (MFM/RLL MODE; WC 5 to 15 MHz)   | . 33-79 |

|         |       | 5.3.18 | WRITE DATA TIMING (NRZ MODE; WC 5 to 15 MHz)       | . 33-80 |

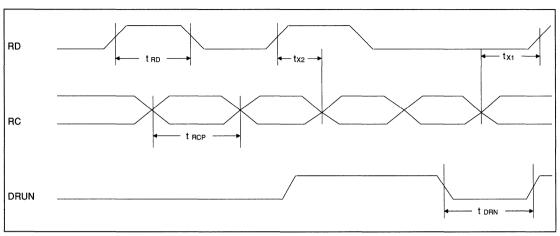

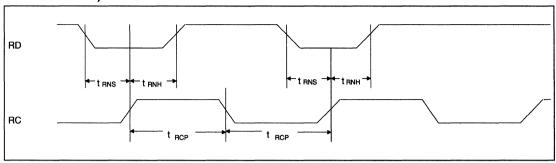

|         |       | 5.3.19 | READ DATA TIMING (MFM/RLL MODE; RC/WC 5 to 15 MHz) | . 33-81 |

|         |       | 5.3.20 | READ DATA TIMING (NRZ MODE; WC 5 to 20 MHz)        | . 33-82 |

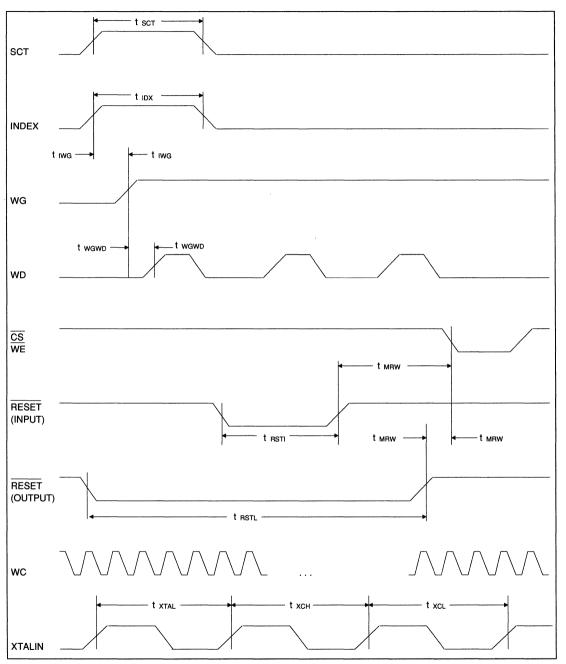

|         |       | 5.3.21 | MISCELLANEOUS TIMING                               | . 33-83 |

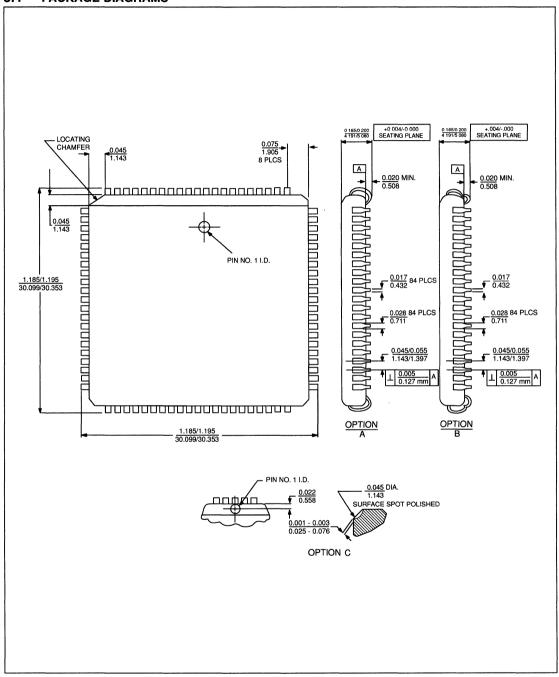

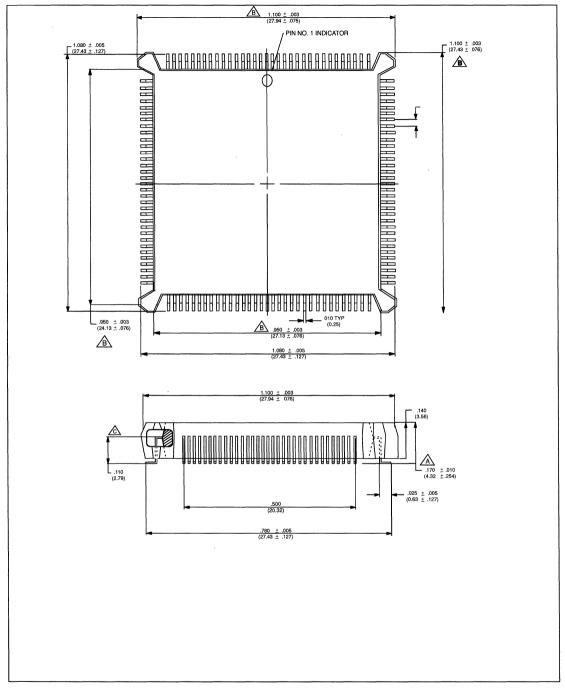

|         | 5.4   | PACKA  | GE DIAGRAMS                                        | . 33-91 |

### LIST OF ILLUSTRATIONS

| Figure | Title                                                  | Page  |

|--------|--------------------------------------------------------|-------|

| 1      | PIN DESIGNATION                                        | 33-1  |

| 2      | WD42C22C BLOCK DIAGRAM                                 | 33-2  |

| 3      | DRIVE CONTROLLER BLOCK DIAGRAM                         | 33-11 |

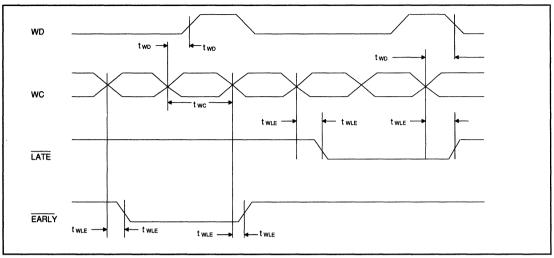

| 4      | PLL CONTROL (ID FIELD)                                 | 33-14 |

| 5      | PLL CONTROL (DATA FIELD)                               | 33-15 |

| 6      | POWER QUALIFIED RESET VOLTAGE THRESHOLD                | 33-55 |

| 7      | AT/XT HOST PROGRAMMED I/O WRITE TIMING                 | 33-56 |

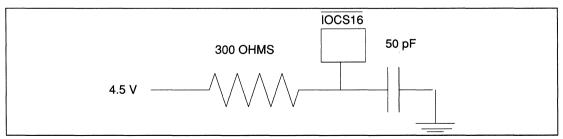

| 8      | TEST CIRCUIT 1                                         | 33-57 |

| 9      | AT/XT HOST PROGRAMMED I/O READ TIMING                  | 33-58 |

| 10     | AT/XT HOST DMA WRITE TIMING                            | 33-60 |

| 11     | AT/XT HOST DMA READ TIMING                             | 33-62 |

| 12     | SLAVE HOST WRITE TIMING                                | 33-64 |

| 13     | SLAVE HOST READ TIMING                                 | 33-65 |

| 14     | SLAVE HOST DMA WRITE TIMING                            | 33-66 |

| 15     | SLAVE HOST DMA READ TIMING                             | 33-68 |

| 16     | BUFFER RAM WRITE TIMING (INTERNAL OSCILLATOR)          | 33-70 |

| 17     | BUFFER READ TIMING (INTERNAL OSCILLATOR)               | 33-71 |

| 18     | BUFFER RAM WRITE TIMING (EXTERNAL OSCILLATOR)          | 33-72 |

| 19     | BUFFER RAM READ TIMING (EXTERNAL OSCILLATOR)           | 33-74 |

| 20     | MICROPROCESSOR WRITE TIMING (INTEL BUS)                | 33-75 |

| 21     | MICROPROCESSOR WRITE TIMING (MOTOROLA BUS)             | 33-76 |

| 22     | MICROPROCESSOR READ TIMING (INTEL BUS)                 | 33-77 |

| 23     | MICROPROCESSOR READ TIMING (MOTOROLA BUS)              | 33-78 |

| 24     | WRITE DATA TIMING (MFM/RLL MODE)                       | 33-79 |

| 25     | WRITE DATA TIMING (NRZ MODE)                           | 33-80 |

| 26     | READ DATA TIMING (MFM/RLL)                             | 33-81 |

| 27     | READ DATA TIMING (NRZ MODE)                            | 33-82 |

| 28     | MISCELLANEOUS TIMING                                   | 33-83 |

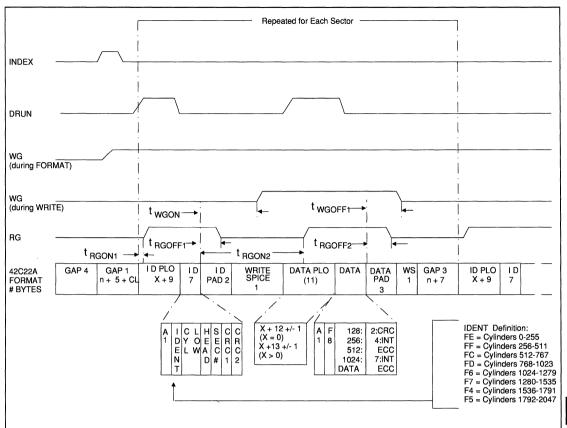

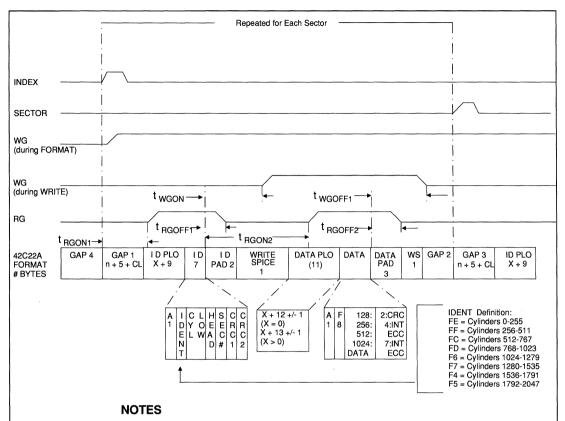

| 29     | SOFT SECTOR MFM/RLL TRACK FORMAT                       | 33-85 |

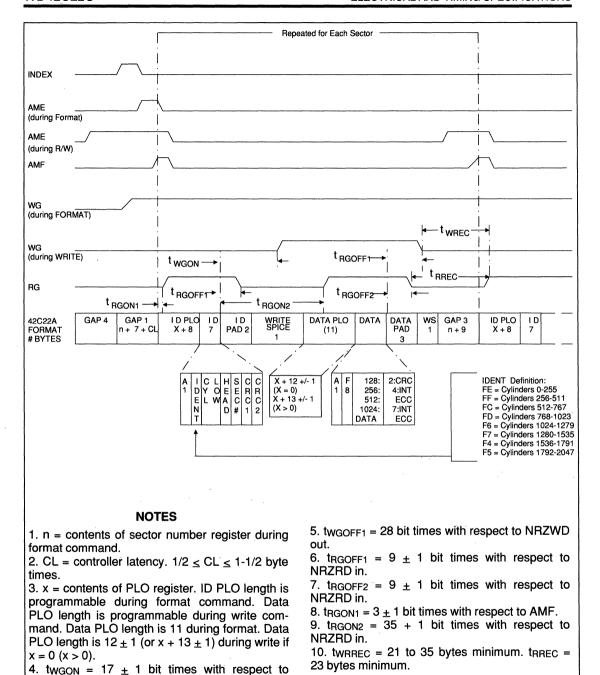

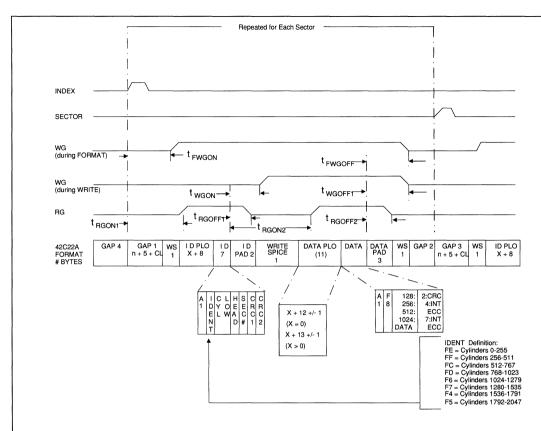

| 30     | SOFT SECTOR NRZ TRACK FORMAT                           | 33-86 |

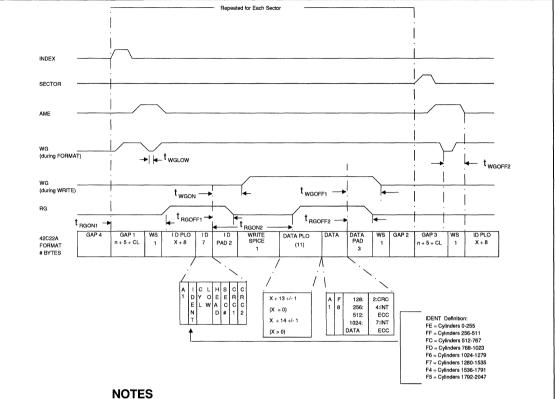

| 31     | HARD SECTOR RLL/MRM TRACK FORMAT                       |       |

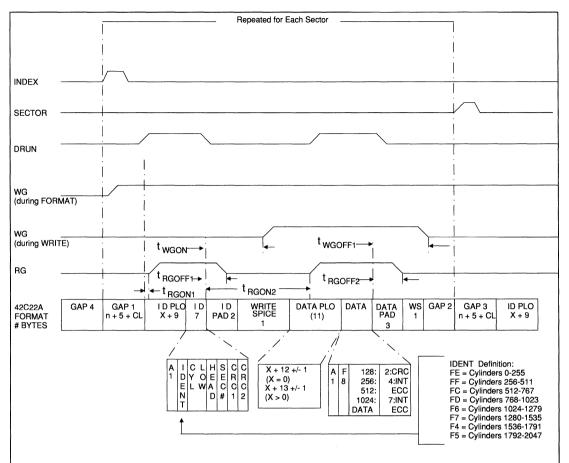

|        | (WITH SOFT SECTOR READ/WRITE)                          | 33-87 |

| 32     | HARD SECTOR RLL/MFM TRACK FORMAT                       |       |

|        | (WITH HARD SECTOR READ/WRITE AND CONTINUOUS WG OPTION) | 33-88 |

| 33     | HARD SECTOR RLL/MRM TRACK FORMAT                       | 00.00 |

| 24     | (WITH HARD SECTOR READ/WRITE AND WG PULSE OPTION)      |       |

| 34     |                                                        |       |

| 35     | 84-LEAD PLCC PACKAGE DIAGRAM                           |       |

| 36     | 84-LEAD PQFP PACKAGE DIAGARAM                          | 33-92 |

### LIST OF TABLES

| Table | Title                                            | Page  |

|-------|--------------------------------------------------|-------|

| 1     | HOST INTERFACE PIN DESCRIPTION                   | 33-5  |

| 2     | LOCAL MICROCONTROLLER INTERFACE PIN DESCRIPTION  | 33-7  |

| 3     | BUFFER INTERFACAE PIN DESCRIPTION                | 33-8  |

| 4     | DRIVE INTERFACE PIN DESCRIPTION                  | 33-9  |

| 5     | RLL CODING RULES                                 | 33-13 |

| 6     | EARLY AND LATE DELAYS                            |       |

| 7     | EARLY AND LATE GENERATION (RLL MODE)             | 33-15 |

| 8     | EARLY AND LATE GENERATION (MFM - NRZ)            | 33-16 |

| 9     | XT PORT DESCRIPTION                              | 33-16 |

| 10    | AT MODE PORT DESCRIPTIONS                        | 33-18 |

| 11    | LOCAL MICROCONTROLLER REGISTER MAP               | 33-22 |

| 12    | COMMAND AND COMMAND CODES                        | 33-39 |

| 13    | OPTION SUMMARY TABLE                             |       |

| 14    | DC OPERATING CHARACTERISTICS                     |       |

| 15    | AT/XT HOST PROGRAMMED I/O WRITE TIMING           | 33-57 |

| 16    | AT/XT HOST PROGRAMMED I/O READ TIMING            | 33-59 |

| 17    | AT/XT DMA WRITE TIMING                           | 33-61 |

| 18    | AT/XT DMA READ TIMING                            | 33-63 |

| 19    | SLAVE HOST WRITE TIMING                          | 33-64 |

| 20    | SLAVE HOST READ TIMING                           | 33-65 |

| 21    | SLAVE HOST DMA WRITE TIMING                      | 33-67 |

| 22    | SLAVE HOST DMA READ TIMING                       | 33-69 |

| 23    | BUFFER RAM WRITE TIMING (INTERNAL OSCILLATOR)    | 33-70 |

| 24    | BUFFER RAM READ TIMING                           | 33-71 |

| 25    | BUFFER RAM WRITE TIMING (XTAL = 8 TO 20 MHZ)     | 33-73 |

| 26    | BUFFER RAM READ TIMING (EXTERNAL OSCILLATOR)     | 33-74 |

| 27    | MICROPROCESSOR WRITE TIMING (INTEL BUS)          |       |

| 28    | MICROPROCESSOR WRITE TIMING (MOTOROLA BUS)       | 33-76 |

| 29    | MICROPROCESSOR READ TIMING (INTEL BUS)           | 33-77 |

| 30    | MICROPROCESSOR READ TIMING (MOTOROLA BUS)        | 33-78 |

| 31    | WRITE DATA TIMING (MFM/RLL MODE; WC 5 TO 15 MHZ) | 33-79 |

| 32    | WRITE DATA TIMING (NRZ MODE; RW/WC 5 TO 15 MHZ)  | 33-80 |

| 33    | READ DATA TIMING (MFM/RLL; RW/WC TO 15 MHZ)      | 33-81 |

| 34    | READ DATA TIMING (NRZ MODE; RW/WC 5 TO 15 MHZ)   | 33-82 |

| 35    | MISCELL ANEOLIS TIMING                           | 33-84 |

### 1.0 INTRODUCTION

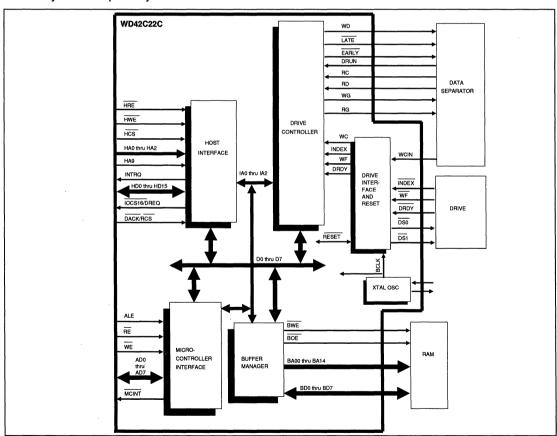

Western Digital's WD42C22C integrates a high performance, low cost Winchester formatter/controller, host interface, a buffer manager, and CRC/ECC generator/checker in a single 84-pin LSI device. Operating from a single +5V power supply, the WD42C22C is implemented in a low power CMOS design and is available in an 84-pin PLCC or PQFP (Figure 1). Figure 2 is a block diagram of the WD42C22C.

### 1.1 FEATURES

- Enhanced host interface

- IBM Personal Computer AT and XT port compatible

- Supports AT speeds up to 16 MHz, 1 wait state I/O and 0 wait state memory using 120 ns static RAM (SRAM)

- Supports AT speeds up to 16 MHz, 1 wait state I/O and 0 wait state memory using 100 ns SRAM

- Selectable DMA or programmed I/O data transfers in all host interface modes

- Host port slave mode compatible with ALE based peripherals such as the WD33C93 SBIC

- Host transfer rates up to 4 Mwords/sec for AT, 4 MB/sec for XT, 10 MB/sec for SCSI

- Internal 12 mA high current drivers for direct connection to the XT or AT system bus

- Advanced buffer manager

- Supports 1:1 interleave without resorting to wait states

- Direct interface for up to 32 KB of static RAM

- Sustained RAM bandwidth up to 10 MB/sec

- Pipelined host and disk address counters

- Operates as either ring or scatter-gather buffer

- Allows full track buffering and facilitates look ahead cacheing algorithms

- Adaptable disk controller

- Software selectable MFM, RLL 2,7, or NRZ disk interface

- Software selectable 56 bit ECC, 32 bit ECC, or 16 bit CRC

- Software selectable 5, 11, or 22 bit error correction span

**FIGURE 1. PIN DESIGNATION**

- Software selectable default sector lengths of 128, 256, 512, and 1024 bytes

- User programmable sector size up to 2048 bytes

- Software selectable 3 bit or 4 bit head number field

- Reads and writes at 1:1 Interleave regardless of the formatted interleave

- . 15 Mbs data transfer rate for MFM and RLL

- 24 Mbs data transfer rate for NRZ

- Supports hard or soft sectored formats

- Supports "zero latency" read operations

- Internal defect management of sector and track level alternates

- . Able to read ESDI defect list format

- Supports sector servo schemes by disabling WRITE GATE over servo when formatting

- Internal 48 mA drivers and Schmitt trigger input receivers for direct connection to the drive control cable

- Integrated support features

- Programmable master/slave mode allows two Integrated Drive Electronics (IDE) disks on one connector

- Supports both Intel-type(80xx) and Motorola-type(68xx) microcontrollers

Internal power-qualified reset to detect low VDD

- · Low power sleep mode

- · Available in 84-pin PLCC or 84-pin PQFP

### 1.2 DESCRIPTION

### 1.2.1 ENHANCED HOST INTERFACE

The WD42C22C host interface port directly connects to the host system bus via internal 12 mA drivers. When operating in either AT or XT mode, all host control, data, and task file address lines directly connect to the WD42C22C. Mapping the device to the desired host system I/O addresses requires external address decode logic. Integrated I/O port compatible AT and XT task file registers assure system compatibility.

To satisfy requirements for faster system bus rates and data transfers, the WD42C22C can operate in 12 MHz or 16 MHz, 1 wait state I/O channels (0 wait state memory) of 286 or 386 microprocessors. DMA or PIO data operations transfer at a rate of 4 Mwords/sec (AT mode) or 4 MB/sec (XT mode). In addition to traditional single mode DMA, burst mode DMA transfers are also available.

An alternative host mode, slave mode, allows communication between the microcontroller and a peripheral device through the host interface. The slave device transfers data to the buffer RAM by using a slave DMA scheme such as the WD-BUS mode in the WD33C93 SCSI bus interface controller (SBIC).

FIGURE 2. WD42C22C BLOCK DIAGRAM

### 1.2.2 ADVANCED BUFFER MANAGEMENT

The WD42C22C contains an advanced buffer manager satisfying the interface requirements between a byte or word wide host interface bus and a high speed serial disk interface. Optimized for the block oriented data structures of a disk controller, the WD42C22C can manage multiple sector buffers up to 32 KB. Each sector buffer can be any size to 2055 bytes. Pipelined host and disk address counters enable sustained, simultaneous transfers on each port. Sufficient RAM buffer bandwidth is available to support 1:1 interleaved 20 Mb/sec disk transfers while simultaneously performing 16-bit host transfers at a rate in excess of 3 Mwords/sec. Achieving maximum RAM bandwidth requires using 70 nsec static RAM.

The pipelined structure of the buffer manager controls the buffer RAM in either a simple ring structure or a more advanced scatter-gather structure.

### 1.2.3 ADAPTABLE DISK CONTROLLER

The WD42C22C's versatile design makes the device adaptable for a wide variety of disk interface operations. A designer can select from three data formats, MFM, RLL 2,7, or NRZ. Disk data rates range up to 15 Mbits/sec with MFM and RLL 2,7 encoding, while NRZ data rates range up to 24 Mbits/sec. To support varied data format requirements, the WD42C22C operates in hard or soft sectored mode with programmable sector sizes to 2048 bytes and programmable ID PLO, data PLO, and GAP lengths.

Software selectable retry algorithms and 32 or 56-bit ECC polynomials enhance data integrity. Data integrity can further be ensured through the use of the device's built-in advanced defect management. The WD42C22C can be programmed to automatically detect the presence of a previously assigned defective sector and identify the location of the alternate sector. This allows access to alternate sectors without the typical additional rotational latency associated with defect handling.

With the pipelined architecture of the buffer manager, the designer can program the disk controller to execute "zero-latency" multiple sector read operations. In this mode of operation, the WD42C22C immediately commences data trans-

fer to the RAM buffer upon encountering the first sector on the desired track. All subsequent sectors transfer to the buffer within a single rotational period. Host transfers begin upon location of the first requested sector within the buffer. Simultaneous host and disk transfers continue until all sectors are read from the drive. Zero-latency operation makes available an entire track of data to the host within one rotational period from the time the host requested the data. This differs from traditional implementations which read the entire track within one rotational period AFTER the first requested sector has been located. Zero latency read operations eliminate the typical one-half rotational period average latency required to locate the first sector in full track data transfers

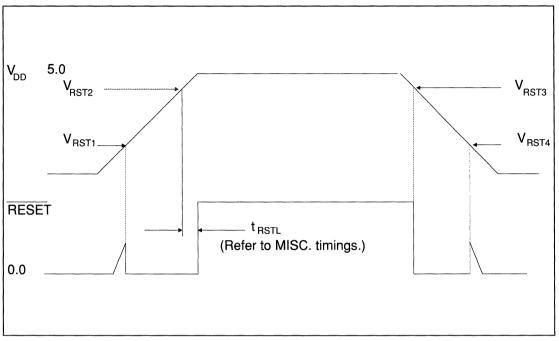

The WD42C22C includes an internal power qualified reset circuit for power up and power down conditions. This circuit eliminates the need for costly external circuitry that traditionally performed this function.

The WD42C22C features a multiplexed address/data bus on the microcontroller interface port and supports both Intel (80XX) and Motorola (68XX) type microcontrollers. An internal circuit automatically determines the connected microcontroller and configures the ports for direct interfacing.

Internal 48 mA drivers and Schmitt triggers input receivers provide direct connection to the drive control cable. Programmable input polarities assist in integrated drive electronics (IDE) designs.

### 1.2.4 FLEXIBILITY OF APPLICATION

As a result of its level of integration, a designer can create a wide variety of products. In addition to traditional stand alone Winchester controller boards, the WD42C22C is ideal for multi-function boards, direct system motherboards, and IDE applications. Special design considerations within the WD42C22C facilitate these applications.

### 1.2.5 TYPICAL APPLICATION

With an external microcontroller, buffer RAM, and a data separator such as the WD10C22B, the WD42C22C forms the basis of a Winchester disk controller product. For AT and XT applications, direct interfacing is available to the system bus. In

these applications, the WD42C22C requires external address decoding to select the primary and secondary I/O address range of the WD42C22C. Other bus interfaces are supported via auxiliary bus controllers such as the WD33C93A SCSI Bus Interface Controller.

For ST506 (MFM) and ST412HP (RLL) applications, the WD42C22C directly connects to the WD10C22 data separator. (Like the WD42C22C, the WD10C22B supports both MFM and RLL encoding methods.) An external microcontroller implements interface specific control lines, e.g. the ST506's STEP and DIRECTION signals. For

ESDI applications, the WD42C22C operates in NRZ mode.

### 1.2.6 PIN DESCRIPTIONS

This section lists the pin number, signal name, and function for all the WD42C22C's pins. The pin descriptions are arranged by functions. Table 1 describes the pin designations for the host interface. Table 2 describes the pin designations for the local microcontroller interface. Table 3 describes the pin designations for the buffer interface. Table 4 describes the pin designations for the drive interface.

| PIN<br>NUMBER    | MNEMONIC                          | SIGNAL NAME                                                                       | I/O               | FUNCTION                                                                                                                                                                                                                                                                                                                                           |

|------------------|-----------------------------------|-----------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4 | HA0<br>HA1<br>HA2<br>HA9/<br>HALE | HOST ADDRESS 0<br>HOST ADDRESS 1<br>HOST ADDRESS 2<br>HOST ADDRESS 9/<br>HOST ALE | <br> <br> <br> /O | Schmitt-triggered input. These four inputs are used to address the internal registers. Internal decoding of these address signals is a function of the AT/XT and HSMB mode bits. Port compatibility is maintained for both the AT and XT. In slave host mode HALE is used by the peripheral device to latch the address from HD0 through HD7.      |

| 5                | HRE                               | HOST READ<br>ENABLE                                                               | I/O               | Schmitt-triggered input. HRE is asserted by the AT or XT with HCS to read an internal register or the FIFO. In slave mode, HRE is asserted when MRE is asserted. It can also be asserted by the slave peripheral in DMA mode.                                                                                                                      |

| 6                | HWE                               | HOST WRITE<br>ENABLE                                                              | I/O               | Schmitt-triggered input. HWE is asserted by the AT or XT with HCS to write an internal register or the FIFO. In slave mode, HRE is asserted when MRE is asserted. It is also asserted by the slave peripheral in DMA mode.                                                                                                                         |

| 7                | HCS                               | HOST CHIP<br>SELECT                                                               | I/O               | Schmitt-triggered input. HCS should be decoded from the AT or XT address bus and is used to qualify HRE and HWE for host accesses. In slave mode, HCS is asserted when the local microcontroller is accessing the slave device address space.                                                                                                      |

| 8                | IOCS16/<br>DREQ                   | <u>I/O</u> CHIP SELECT<br>16/<br>DMA REQUEST                                      | 0                 | This output is <u>program</u> mable to function as the AT bus signal IOCS16 when the PIO mode is selected or as a DMA Request signal (DREQ) in the DMA mode. This output is tri-stated at power-up and remains tri-stated until the interface mode is set by the local microcontroller. IOCS16 is an open-drain ouput. DREQ is a tri-state output. |

| 9                | DACK/<br>RCS                      | DMA ACKNOW-<br>LEDGE/<br>RAM CHIP SELECT                                          | l                 | Schmitt-triggered input. DACK is asserted by the host in response to the DREQ signal assertion in order to complete the DMA handshake. RCS is used in slave mode to qualify host data transfers to/from the FIFO.                                                                                                                                  |

**TABLE 1. HOST INTERFACE PIN DESCRIPTION**

| PIN<br>NUMBER                                              | MNEMONIC            | SIGNAL NAME                      | I/O | FUNCTION                                                                                                                                                                                                                           |

|------------------------------------------------------------|---------------------|----------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23                                                         | RESET               | RESET                            | I/O | Open-drain output and Schmitt input, can be wire-ORed with an external reset. The WD42C22C resets all logic except the Task File when this input is asserted. On power-up, or when requested by the host, this output is asserted. |

| 75<br>thru<br>82,<br>40,<br>41,<br>42,<br>44<br>thru<br>48 | HD0<br>thru<br>HD15 | HOST DATA 0 thru<br>HOST DATA 15 | I/O | Schmitt-triggered inputs. These 16 pins are used during host 16-bit data transfers, and the lower eight bits (HD0-HD7) are used for bytewide host data transfers as well as all command and status information transfers.          |

| 74                                                         | INTRQ               | INTERRUPT<br>REQUEST             | I/O | INTRQ indicates to the AT or XT that a data blocktransfer is requested or a command has been completed. In slave host mode INTRQ is asserted by the slave peripheral device.                                                       |

| 83                                                         | $V_{SS}$            | GROUND                           |     | Ground.                                                                                                                                                                                                                            |

| 84                                                         | V <sub>DD</sub>     | +5V                              |     | +5V                                                                                                                                                                                                                                |

TABLE 1. HOST INTERFACE PIN DESCRIPTION (CONT'D)

| PIN<br>NUMBER    | MNEMONIC             | SIGNAL NAME                                   | I/O | FUNCTION                                                                                                                                                                                                          |

|------------------|----------------------|-----------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22               | Vss                  | GROUND                                        |     | Ground.                                                                                                                                                                                                           |

| 24               | MCINT                | <u>μCONTROLE</u> R<br>INTERRUPT               | 0   | This output is used as an interrupt signal in order to alert the local microcontroller it is necessary to check command parameters or status. For the XT mode, MCINT is asserted when the controller is selected. |

| 25               | ALE/AS               | ADDRESS LATCH<br>ENABLE/<br>ADDRESS STROBE    | I   | Schmitt-triggered input. ALE is used to latch the lower eight address bits from the multiplexed address/data lines (AD7-AD0). AS is used for this function when tied to a Motorola type microcontroller.          |

| 26               | MRE/DS               | μCONTROLLER<br>READ ENABLE<br>/DATA STROBE    | I   | Schmitt-triggered input. MRE is asserted by the local microcontroller to read an internal register or the buffer. DS is used in Motorola type microcontrollers to enable the data transfer.                       |

| 27               | MW <u>E/</u><br>MR/W | μCONTROLLER<br>WRITE ENABLE/<br>uC READ/WRITE | I   | Schmitt-triggered input. MWE is asserted by the local microcontroller to write an internal register or the buffer. MR/W is used by Motorola type microcontrollers to set the direction of data transfers.         |

| 28<br>thru<br>35 | AD0<br>thru<br>AD7   | ADDRESS/DATA 0<br>thru<br>ADDRESS/DATA 7      | I/O | Schmitt-triggered inputs. These multiplexed address/data lines are used to load the register/buffer address on the falling edge of ALE, and are used for data transfers to/from the local microcontroller.        |

| 43               | V <sub>SS</sub>      | GROUND                                        |     | Ground.                                                                                                                                                                                                           |

TABLE 2. LOCAL MICROCONTROLLER INTERFACE PIN DESCRIPTION

| PIN<br>NUMBER    | MNEMONIC            | SIGNAL NAME                             | I/O | FUNCTION                                                                                                                                                                                                 |

|------------------|---------------------|-----------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38               | XTALIN              | CRYSTAL<br>INPUT                        | i   | Crystal oscillator input. The crystal frequency is twice the buffer data rate.                                                                                                                           |

| 39               | XTALOUT             | CRYSTAL<br>OUTPUT                       | 0   | Crystal oscillator output.                                                                                                                                                                               |

| 49               | BOE                 | BUFFER OUTPUT<br>ENABLE                 | 0   | BOE is asserted by the chip to read data from the external SRAM buffer.                                                                                                                                  |

| 50               | BWE                 | BUFFER WRITE ENABLE                     | 0   | BWE is asserted by the chip to write data into the external SRAM buffer.                                                                                                                                 |

| 51<br>thru<br>58 | BD0<br>thru<br>BD7  | BUFFER DATA 0<br>thru<br>BUFFER DATA 7  | I/O | Schmitt-triggered. Buffer data bus, which connects directly to a static RAM.                                                                                                                             |

| 59<br>thru<br>73 | BA0<br>thru<br>BA14 | BUFFER ADDR 0<br>thru<br>BUFFER ADDR 14 | I/O | Buffer address bus, for direct connection to 32 KB of SRAM. In XT mode, also used to read jumper configuration data in Read Configuration Mode. In input mode, there is a low current internal pulldown. |

**TABLE 3. BUFFER INTERFACE PIN DESCRIPTION**

| PIN<br>NUMBER | MNEMONIC       | SIGNAL NAME                           | I/O | FUNCTION                                                                                                                                                                                                                                                                          |

|---------------|----------------|---------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10            | WD             | WRITE DATA                            | 0   | WD is the MFM/NRZ write data written to the disk. It is shifted out at a rate determined by write clock. MFM write data should be synchronized by a D flip flop clocked at 10 MHz (for 5 Mbs operation).                                                                          |

| 11            | LATE/<br>WCOUT | LATE/<br>WCOUT                        | 0   | LATE is used along with EARLY in the Write Precompensation circuitry to control the delay of WD.                                                                                                                                                                                  |

|               |                |                                       |     | In NRZ mode WCOUT is write clock out which can be used to qualify WD in an ESDI application.                                                                                                                                                                                      |

| 12            | AME/<br>EARLY  | ADDRES <u>S MAR</u> K<br>ENABLE/EARLY | Ο   | In NRZ mode, this output is the Address Mark Enable signal for an ESDI drive. In MFM or RLL mode, this output is EARLY. EARLY and LATE are used in the Write Precompensation circuitry to control the delay of WD.                                                                |

| 13            | WG             | WRITE GATE                            | 0   | WG is asserted when valid data is to be written to the disk. It enables write current to the head and is immediately de-asserted if a WRITE FAULT (WF) is detected.                                                                                                               |

| 14            | WC             | WRITE CLOCK                           | I   | A clock used internally to control WD. (Up to 10 MHz for ST412, up to 15 MHz for ESDI).                                                                                                                                                                                           |

| 15            | INDEX          | INDEX                                 | 1   | Schmitt-triggered INDEX input for direct connection to the drive control cable.                                                                                                                                                                                                   |

| 16            | SCT/<br>DRUN   | SECTOR/<br>DATA RUN                   | l   | Schmitt-triggered input. In hard sector mode, SCT is used to indicate the start of a sector. In soft sector NRZ mode, SCT indicates Address Mark Found. In soft sector MFM or RLL mode, DRUN indicates a sequence of MFM or RLL '0's or a sequence of MFM '1's has been detected. |

| 17            | RD             | READ DATA                             | l   | RD is MFM or NRZ read data from the drive. Data and clocks are separated internally for MFM data.                                                                                                                                                                                 |

| 18            | RG             | READ GATE                             | 0   | RG is asserted to initiate a search for an address mark. It remains asserted until the end of the ID or data field.                                                                                                                                                               |

**TABLE 4. DRIVE INTERFACE PIN DESCRIPTION**

| PIN<br>NUMBER | MNEMONIC   | SIGNAL NAME                      | I/O | FUNCTION                                                                                       |

|---------------|------------|----------------------------------|-----|------------------------------------------------------------------------------------------------|

| 19            | RC         | READ CLOCK                       | I   | RC is typically generated from an oscillator phase-locked to the read data.                    |

| 20            | WF         | WRITE FAULT                      | 1   | Schmitt-triggered. WRITE FAULT input for direct connection to the drive control cable.         |

| 21            | DRDY       | DRIVE READY                      | I   | Schmitt-triggered. DRIVE READY input for direct connection to the drive control cable.         |

| 36<br>37      | DS0<br>DS1 | DRIVE SELECT 0<br>DRIVE SELECT 1 | 0   | High-current open-drain DRIVE SELECT outputs for direct connection to the drive control cable. |

TABLE 4. DRIVE INTERFACE PIN DESCRIPTION (CONT'D)

### 2.0 ARCHITECTURE

### 2.1 POWER-QUALIFIED RESET

This integrated function is used to reliably initialize flip-flops to a predictable state during the application of  $V_{DD}$ . It causes the RESET output signal to be asserted until VDD reaches a given threshold. It also forces a reset if the  $V_{DD}$  falls below a specified threshold.

### 2.2 DRIVE INTERFACE LOGIC

The drive interface contains high-current 48 mA drivers for direct connection of the drive select outputs to the drive control cable. Schmitt trigger input receivers connect the drive interface logic directly to the control cable inputs.

### 2.3 DRIVE CONTROLLER ORGANIZATION

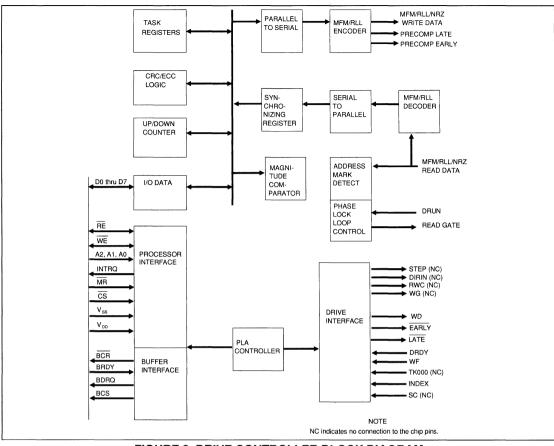

The controller is composed of the following major sections:

- PLA Control

- CRC/ECC Logic

- MFM/RLL Decoding

- · Address Mark Detector

- · Buffer and DMA Control

- · Task Register File

The controller is designed to operate with 2 clock inputs, READ CLOCK (RC) and WRITE CLOCK (WC). The PLA controller, processor interface, and buffer control sections use the write clock input. The clock inputs are used for MFM, RLL, or NRZ decoding. The clock frequency is 10 MHz for a 10 Mbs data rate.

The controller reads or writes disk data to a 15 Mbs rate for MFM and RLL and 24 Mbs for NRZ. The RLL implementation is a (2,7,2,4,3) code based on the IBM 3370 code. The only difference lies in the assignments of the code words to the 7 different data streams possible. Error propagation for a single bit error is limited to 4 bits.

When programmed in the NRZ mode, the WD42C22C qualifies NRZ disk data using the Sector / Address Mark Detect signal, and also modifies the RG and WG signals to meet ESDI specifications.

In all modes, the length of the PLO sync and gap fields are software programmable. The ID PLO sync field length, the Gap1/Gap3 length, the Gap1/Gap3 data bytes and the ID CRC pad bytes are programmable during the format command. The data PLO sync field length and the data CRC/ECC pad bytes are programmable during the Write command.

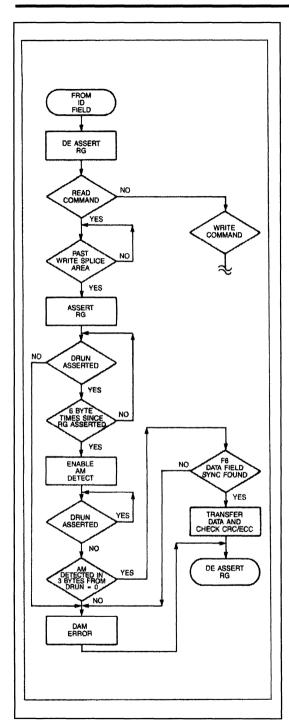

Figure 3 is a block diagram of the drive controller section of the WD42C22C.

## 2.4 PROGRAMMABLE LOGIC ARRAY (PLA) CONTROLLER

The Programmabla Logic Array (PLA) controller interprets commands, e.g. write, read format, etc. This circuitry's operation is synchronized with the WC input. The PLA controller is started when a command is written into the command register. It generates control signals and operates in a hand-

FIGURE 3. DRIVE CONTROLLER BLOCK DIAGRAM

shake mode when communicating with the MFM/RLL decoding block. The MFM/RLL decoding block uses the RC input which may be asynchronous to WC.

### 2.5 MAGNITUDE COMPARATOR

An 11-bit magnitude comparator calculated drive step direction and number of step pulses between present cylinder position and desired position in earlier Winchester controller versions. This comparator is **not** used in the WD42C22C. A separate high speed equivalence comparator is used to compare ID field bytes when searching for a sector ID field.

### 2.6 CRC/ECC GENERATOR AND CHECKER

The CRC/ECC generator computes and checks the cyclic redundancy check characters appended to the ID and data fields written on the disk. The CRC mode of operation, defined by the SDH register (bit 7 set to 0) provides a means of verifying the accuracy of the data read from the disk but does not attempt to correct it. (Bit 7 of the SDH register will not implement CRC mode for data fields when RLL mode is selected.) The CRC polynomial used is:

$$X^{16} + X^{12} + X^5 + 1$$

The CRC register is preset to all ones before computation starts.

WD42C22C ARCHITECTURE

If the CRC character being generated while reading the data does not equal the one previously written, an error exists. If there is a CRC failure in the ID field, an ID not found is indicated by setting bit 4 of the error register. If the failure is in the data field, bit 6 of the error register is set.

A 32 bit or 56 bit ECC polynomial may be selected instead of the CRC polynomial for the data field. The CRC/ECC selection is controller by bit 7 of the SDH register when the controller is in MFM or NRZ modes. CRC is selected when bit 7 of the SDH register is 0 in MFM or NRZ modes. ECC is selected when bit 7 of the SDH register is 1 in MFM or NRZ modes. Bit 2 in the set parameter command selects either the 32 bit or 56 bit polynomial. RLL mode defaults to the 56 bit polynomial. The CRC or 32 bit ECC options are **not** usable in RLL mode.

The ECC mode of operation (SDH bit 7 = 1) is only applicable to the data field. This feature built into the WD42C22C provides the user with the ability to detect and correct errors in the data field automatically.

The following is a summary of the parameters considered when ECC is used:

- 1. SDH register bit 7.

- 2. Read and write command bit 1 (L).

- 3. Compute correction command.

- 4. Set parameter command.

- 5. Error occurred, bit 0 of the status register.

- 6. On any ECC error the controller stops regardless of the T bit. (Refer to the read command description.)

The SDH register bit 7 must be equal to one to change from the CRC mode to the ECC mode, for MFM and NRZ only.

When an ECC error is detected, no attempt is made to correct it and bit 0 of the status register and bit 6 of the error register are set. The user now has two choices:

- 1. Ignore the error and make no attempt to correct it.

- 2. Use the compute correction command to determine the pattern and location of the error, and correct it within the user's program.

When implementing the compute correction command, use it before executing commands that alter the content of the ECC register. The read, write, scan, and format commands can alter the syndrome and make correction impossible. If the compution correction command determines that the error is uncorrectable, then the error bits in the status register and error register are set.

Although ECC generation starts with the first bit of the F8 byte in the data ID field, the actual ECC bytes produced for the sector are the same as if the A1 byte was included.

The 32-bit ECC polynomial is:

$$X^{32} + X^{28} + X^{26} + X^{19} + X^{17} + X^{10} + X^{6} + X^{2} + 1$$

and is the same one used in the WD1002, WD1003, and WD1006 controller boards. The 32-bit ECC polynomial has an 11 bit maximum single burst correction span. The reverse 32-bit ECC polynomial is:

$$X^{32} + X^{30} + X^{26} + X^{22} + X^{15} + X^{13} + X^{6} + X^{4} + 1$$

The non-detection probability for the 32-bit ECC polynomial is:

2.3 (E-10),

$$r^{\dagger} = 516 \times 8$$

,  $b^{\dagger} = 5$

and the miscorrection probability is:

1.57 (E-5),

$$r^{\dagger}$$

= 516 x 8,  $b^{\dagger}$  = 5

The 56-bit ECC polynomial is:

$$X^{56} + X^{52} + X^{50} + X^{43} + X^{41} + X^{34} + X^{30} + X^{26} + X^{24} + X^{8} + 1$$

The 56-bit ECC polynomial has a 22 bit maximum single burst correction span.

The reverse 56-bit ECC polynomial is:

$$X^{56} + X^{48} + X^{32} + X^{30} + X^{26} + X^{22} + X^{15} + X^{13} + X^{6} + X^{4} + 1$$

The non-detection probability for the 56-bit ECC polynomial is:

1.39 (E-17),

$$r^{\dagger} = 519 \times 8$$

,  $b^{\dagger} = 11$

and the miscorrection probability is:

5.84 (E-11),

$$r^{\dagger}$$

= 519 x 8,  $b^{\dagger}$  = 11

The set parameter command selects the number of bits in the correction span, through the use of bit 0.

Read and write commands, with the L bit (bit 1) set to one, are referred to as read long and write long commands. With these commands, no ECC or CRC characters are generated or checked by the WD42C22C. In effect, the four or seven bytes are handled as an additional four or seven bytes of data which pass through the data buffer. With proper use of the write, read long, write long, and read commands, a diagnostic routine may be developed to test the accuracy of the error correction process.