WD9500 (PWGA) Enhanced 8514/A Compatible Chip Set

## TABLE OF CONTENTS

| Section                         | Title |                                                                                                              | Page             |  |  |  |

|---------------------------------|-------|--------------------------------------------------------------------------------------------------------------|------------------|--|--|--|

| 1.0                             | INTR  |                                                                                                              |                  |  |  |  |

|                                 | 1.1   | FEATURES                                                                                                     |                  |  |  |  |

|                                 | 1.2   | DESCRIPTION                                                                                                  |                  |  |  |  |

| 2.0                             | ARCI  |                                                                                                              |                  |  |  |  |

|                                 | 2.1   | FUNCTIONAL ORGANIZATION                                                                                      |                  |  |  |  |

|                                 | 2.2   | BOARD OPERATION OVERVIEW                                                                                     |                  |  |  |  |

| 1.0<br>2.0<br>3.0<br>4.0<br>5.0 | WD9   | 00 INTERFACES                                                                                                |                  |  |  |  |

|                                 | 3.1   | CPU INTERFACE                                                                                                |                  |  |  |  |

|                                 | 3.2   | VRAM DESIGN AND INTERFACE                                                                                    |                  |  |  |  |

|                                 |       | 3.2.1 INTEGRATED BACK-END VRAM DESIGN                                                                        |                  |  |  |  |

|                                 |       | 3.2.2 EXTERNAL BACK-END VRAM DESIGN                                                                          |                  |  |  |  |

|                                 | 3.3   | VIDEO DAC AND INTERFACE SUBSYSTEM                                                                            |                  |  |  |  |

|                                 | 3.4   | OTHER BOARD DESIGN ELEMENTS                                                                                  |                  |  |  |  |

|                                 |       | 3.4.1 EPROM                                                                                                  |                  |  |  |  |

|                                 |       | 3.4.2 PAM-PDM INTERFACE                                                                                      |                  |  |  |  |

|                                 |       | 3.4.3 CONFIGURATION STRAPPING                                                                                |                  |  |  |  |

|                                 |       | 3.4.4 CLOCK CONSIDERATIONS                                                                                   |                  |  |  |  |

| 4.0                             | ABSC  | 3.4.4       CLOCK CONSIDERATIONS       25-14         LUTE MAXIMUM RATINGS AND DC CHARACTERISTICS       25-17 |                  |  |  |  |

| 5.0                             | AC T  | ING CHARACTERISTICS                                                                                          |                  |  |  |  |

| 6.0                             | WD9   | 00 REGISTERS                                                                                                 |                  |  |  |  |

|                                 | 6.1   | DAC INTERFACE REGISTERS                                                                                      |                  |  |  |  |

|                                 | 6.2   | ADVANCED FUNCTION CONTROL REGISTER (WRITE ONL                                                                | Y - 4AE8H) 25-22 |  |  |  |

|                                 | 6.3   | VIDEO TIMING SETUP REGISTERS                                                                                 |                  |  |  |  |

|                                 |       | 6.3.1 HORIZONTAL TOTAL REGISTER (WRITE ONLY -                                                                |                  |  |  |  |

|                                 |       | ADDRESS 02E8H)                                                                                               |                  |  |  |  |

|                                 |       | 6.3.2 HORIZONTAL DISPLAYED (WRITE ONLY -                                                                     |                  |  |  |  |

|                                 |       | ADDRESS 06E8H)                                                                                               |                  |  |  |  |

|                                 |       | 6.3.3 HORIZONTAL SYNC START REGISTER (WRITE OF                                                               |                  |  |  |  |

|                                 |       | ADDRESS 0AE8H)                                                                                               |                  |  |  |  |

|                                 |       | 6.3.4 HORIZONTAL SYNC WIDTH REGISTER (WRITE OF ADDRESS 0EE8H)                                                |                  |  |  |  |

|                                 |       | 6.3.5 VERTICAL TOTAL REGISTER (WRITE ONLY - ADD                                                              |                  |  |  |  |

|                                 |       | 6.3.6 VERTICAL DISPLAYED REGISTER (WRITE ONLY - ADD                                                          | ,                |  |  |  |

|                                 |       | ADDRESS 16E8H)                                                                                               |                  |  |  |  |

|                                 |       | 6.3.7 VERTICAL SYNC START REGISTER (WRITE ONLY                                                               |                  |  |  |  |

|                                 |       | ADDRESS 1AE8H)                                                                                               |                  |  |  |  |

|                                 |       | 6.3.8 VERTICAL SYNC WIDTH POLARITY REGISTER (W                                                               |                  |  |  |  |

|                                 |       | ADDRESS 1EE8H)                                                                                               |                  |  |  |  |

|                                 |       | 6.3.9 DISPLAY CONTROL REGISTER (WRITE ONLY - AD                                                              |                  |  |  |  |

|                                 | 6.4   | ROM PAGE SELECT REGISTER (WRITE ONLY -                                                                       | ,                |  |  |  |

|                                 |       | ADDRESS 46E8 MC/36E8 AT)                                                                                     |                  |  |  |  |

|                                 | 6.5   | SUBSYSTEM CONTROL REGISTER (WRITE ONLY - ADDRI                                                               | ESS 42E8H) 25-26 |  |  |  |

| Section | Title |        |                                                                                                             | Page    |

|---------|-------|--------|-------------------------------------------------------------------------------------------------------------|---------|

|         | 6.6   | DRAWI  | NG CONTROL REGISTERS                                                                                        | 25-27   |

|         |       | 6.6.1  | CURRENT Y POSITION REGISTER (READ/WRITE -                                                                   |         |

|         |       |        | ADDRESS 82E8H)                                                                                              |         |

|         |       | 6.6.2  | CURRENT X REGISTER (READ/WRITE - ADDRESS 86E8H)                                                             | 25-27   |

|         |       | 6.6.3  | DESTINATION Y POSITION/AXIAL STEP CONSTANT REGISTER<br>(WRITE ONLY - ADDRESS 8AE8H)                         |         |

|         |       | 6.6.4  | DESTINATION X POSITION/DIAGONAL STEP CONSTANT REGISTI<br>(WRITE ONLY - ADDRESS 8EE8H)                       |         |

|         |       | 6.6.5  | ERROR TERM REGISTER (READ/WRITE - 92E8H)                                                                    |         |

|         |       | 6.6.6  | MAJOR AXIS PIXEL COUNT REGISTER (WRITE ONLY -<br>ADDRESS 96E8H)                                             | 25-28   |

|         |       | 6.6.7  | COMMAND REGISTER (WRITE ONLY - ADDRESS 9AE8H)                                                               |         |

|         |       | 6.6.8  | COMMAND REGISTER (WRITE ONLY - ADDRESS 9AE8H)                                                               | 25-28   |

|         |       | 6.6.9  | SHORT STROKE VECTOR TRANSFER REGISTER (WRITE ONLY - ADDRESS 9EE8H)                                          |         |

|         |       | 6.6.10 | BACKGROUND COLOR REGISTER (WRITE ONLY -                                                                     |         |

|         |       |        | ADDRESS A2E8H)                                                                                              | 25-30   |

|         |       | 6.6.11 | FOREGROUND COLOR REGISTER (WRITE ONLY -<br>ADDRESS A6E8H)                                                   |         |

|         |       | 6.6.12 | WRITE MASK REGISTER (WRITE ONLY - ADDRESS AAE8H)                                                            | 25-30   |

|         |       | 6.6.13 | READ MASK REGISTER (WRITE ONLY - ADDRESS AEE8H)                                                             | 25-30   |

|         |       | 6.6.14 | COLOR COMPARE REGISTER (WRITE ONLY -<br>ADDRESS B2E8H)                                                      | 25-30   |

|         |       | 6.6.15 | BACKGROUND MIX REGISTER (WRITE ONLY -<br>ADDRESS B6E8H)                                                     | 25-30   |

|         |       | 6.6.16 | FOREGROUND MIX REGISTER (WRITE ONLY -<br>ADDRESS BAE8H)                                                     | 25-30   |

|         |       | 6.6.17 | MULTIFUNCTION CONTROL REGISTER (WRITE ONLY -<br>ADDRESS BEE8-0,1,2,3,4)                                     |         |

|         |       | 6.6.18 | MEMORY CONTROL INDEX REGISTER (WRITE ONLY -<br>ADDRESS BEE8-5)                                              |         |

|         |       | 6.6.19 | FIXED PATTERN LOW INDEX REGISTER FIXED PATTERN HIGH<br>INDEX REGISTER (WRITE ONLY - ADDRESS BEE8-8, BEE8-9) |         |

|         |       | 6.6.20 | PIXEL CONTROL INDEX REGISTER (WRITE ONLY -                                                                  |         |

|         |       | 6.6.21 | ADDRESS BEE8-A) PIXEL DATA TRANSFER REGISTER (READ/WRITE -                                                  |         |

|         | 07    | OTATU  |                                                                                                             |         |

|         | 6.7   | 6.7.1  | S REGISTERS                                                                                                 | 25-33   |

|         |       |        | ADDRESS 42E8H)                                                                                              | 25-33   |

|         |       | 6.7.2  | GRAPHICS PROCESSOR STATUS REGISTER (READ ONLY -<br>ADDRESS 9AE8H)                                           | 25-35   |

|         |       | 6.7.3  | DISPLAY STATUS REGISTER (READ ONLY -<br>ADDRESS 02E8H)                                                      | . 25-35 |

|      | 6.8.1 | WESTERN DIGITAL ESCAPE REGISTER (READ ONLY -                        |

|------|-------|---------------------------------------------------------------------|

|      | 6.8.2 | ADDRESS 28E9)                                                       |

|      | 6.8.3 | WESTERN DIGITAL CONTROL REGISTER (WRITE ONLY -<br>ADDRESS 96E8)     |

|      | 6.8.4 | TEXTURE PATTERN START/END REGISTER (WRITE ONLY -<br>ADDRESS 96E8-3) |

| 6.9  | ENHA  | NCED SOLID LINE DRAWING 25-4                                        |

| 6.10 | TEXTU | JRED-LINE DRAWING 25-4                                              |

| 6 11 | FLICK | ER-FREE PALETTE LOADING 25-4                                        |

## Figure Title

Section

Title

| 1 - | Architecture                                    | 25-3  |

|-----|-------------------------------------------------|-------|

| 2   | Functional Organization                         | 25-4  |

| 3   | CPU Interface Logic - AT Bus                    |       |

| 4   | Bit Plane Read Mask Register                    |       |

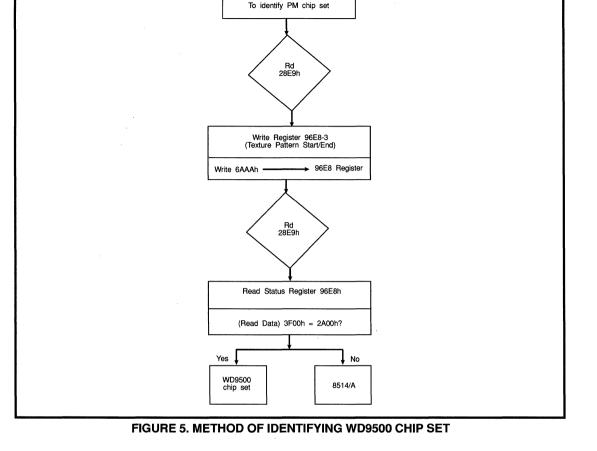

| 5   | Method of Identifying WD9500 Chip Set           | 25-36 |

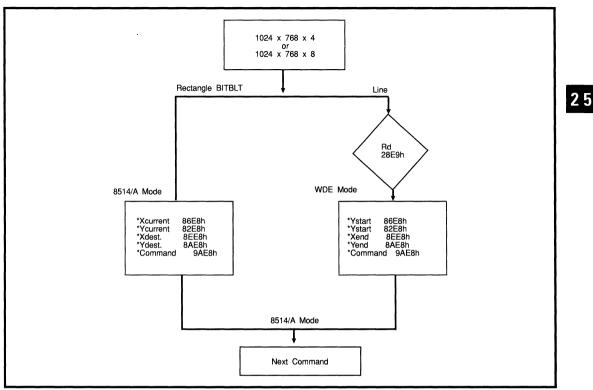

| 6   | WD Enhanced Mode Usage in 1024 x 768 Resolution | 25-37 |

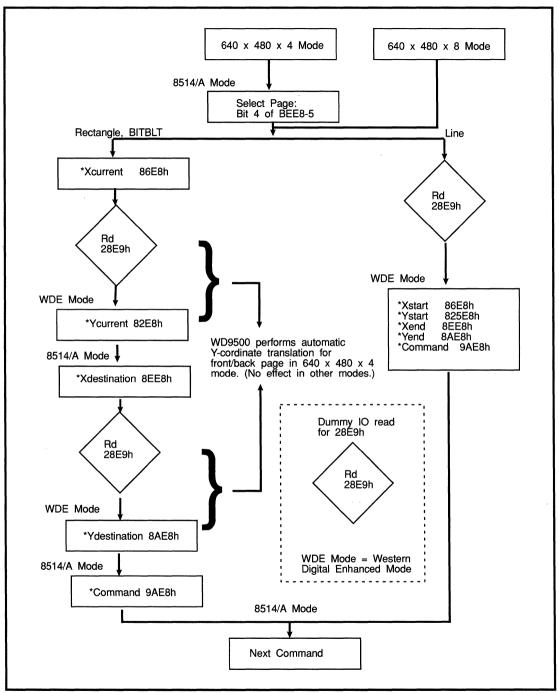

| 7   | WD Enhanced Mode Usage in 640 x 480 Resolution  | 25-38 |

## LIST OF TABLES

| Table | Title                                      | Page   |

|-------|--------------------------------------------|--------|

| 1     | CPU Interface Pins (PAM) for Micro Channel | . 25-6 |

| 2     | CPU Interface Pins (PAM) for AT Bus        |        |

| 3     | VRAM Parameters                            |        |

| 4     | PAM Pin Interface to VRAM                  | 25-10  |

| 5     | PDM Pin Interface to VRAM                  | 25-11  |

| 6     | PDM Pin Interface to Video Subsystem       | 25-12  |

| 7     | EPROM Interface Pins                       | 25-13  |

| 8     | BIOS EPROM Address Mapping                 | 25-13  |

| 9     | Interchip Interface Pins                   | 25-14  |

| 10    | Configuration Strapping Pins               | 25-15  |

| 11    | Chip Count Strapping                       | 25-15  |

| 12    | Monitor Selection                          | 25-15  |

| 13    | Monitor ID Interpretation                  | 25-16  |

| 14    | Pixel Clock Frequency Derivation           | 25-16  |

25

## WD9500

#### Table Title Page 15 16 17 18 19 20 POS Register Interface (Micro Channel Only) ..... 25-21 21 22 23 CRT Control Register Parameters and Timing ..... 25-25 24 25 IBM 8514/A Compatible Registers ...... 25-43 26

## 1.0 INTRODUCTION

The Western Digital Imaging WD9500-SET1 is a set of two proprietary VLSI chips (Pixel Address Manager and Pixel Data Manager). These chips are designed to serve as the primary components of intelligent high-resolution graphics add-in boards and motherboards for PC/AT, PS/2 Micro Channel and E.I.S.A. computer systems and compatibles. When the remaining board-level components and software are properly selected and integrated, the WD9500-SET1 will provide full compatibility with the IBM 8514/A Display Adapter with superior performance plus functional enhancements (Western Digital Extensions). In order to take full advantage of all features, including the unique extensions. Western Digital supplies key software drivers, with specific performance improvements including 8514/A Adapter compatible interface, Microsoft Windows 286 and 386 drivers, and Display List drivers for AutoCAD.

## 1.1 FEATURES

Full functional compatibility with the IBM 8514/A Display Adapter, including hardware compatibility with the registers that any application would access.

- Integrated bus interface: PC/AT, PS/2 Micro Channel and E.I.S.A.

- Transparently runs software written for 8514/A interlaced monitors on non-interlaced monitors.

- Performance averages 30% to 100% faster than 8514/A on graphics operations.

- BITBLT performance 4.5 times that of IBM 8514/A in Turbo 4-bit mode. Turbo 4-bit BITBLT is two times faster than regular 4-bit or 8-bit BITBLT.

- Enhanced resolution: one page of 1280x1024 pixels 256 colors; two pages of 1024x768 pixels 256 colors; two pages of 640x480 pixels 256 colors.

- Enhanced graphics commands for high-speed hardware generation of textured lines and enhanced solid lines.

- Flicker-free video DAC programming.

- 60MHz Graphics Processor Clock Rate.

- All features, including most extensions, are supported by Western Digital Imaging Adapter Interface (A.I.) driver software.

- Performance enhanced software drivers for key software packages including Windows 286/386 and AutoCAD.

- Supports 256Kx4 VRAM in different speed grades (120ns or faster) with programmable VRAM timing to minimize wait states.

- · Independent Video and Data Clocks.

- Supports both INMOS and Brooktree video DACs and compatibles, with back-end integration to minimize external glue logic.

- Supports both interlaced and non-interlaced monitors up to 70Hz vertical refresh rate.

Software written for 8514/A interlaced monitors needs no modification for non-interlaced monitors.

- 132-Pin JEDEC Plastic Quad Fine Pitch Flat Pack.

- 1.25 Micron CMOS Technology.

## 1.2 DESCRIPTION

In addition to full compatibility with the IBM 8514/A, which provides intelligent graphics functions such as polyline drawing, pattern fill for rectangles, "areas" (polygons), and "scissoring" (clipping), the WD9500-SET1 provides several functional enhancements and options as well as superior performance.

A major enhancement is the support of higher screen resolution, 1280x1024 pixels with 256 simultaneously displayable colors, as opposed to the 1024x768 maximum for the IBM 8514/A. Alternatively, the WD9500-SET1 can support a second screen page at the highest 8514/A resolution.

The WD9500-SET1 will give end user dramatic speed improvement in almost all graphics operation. In regular 4-bit mode, the WD9500-SET1 performs Bit Block Transfers (BITBLTs) twice as fast as the IBM 8514/A. In Turbo 4-bit mode, it is 4.5 times as fast. In particular, enhanced performance will be obvious when moving large images on the screen (e.g. scrolling). Under turbo mode all horizontal data movement will be twice as fast. This includes BITBLT, rectangle fill, horizontal line, and polygon search and fill.

Users will also notice considerable performance improvement with the WD9500-SET1 in all new line-drawing operations, because it directly performs several functions that the IBM 8514/A must perform in much slower CPU software. One such improvement is the direct generation of textured line; another is the automatic, high-speed calculation of line parameters by the WD9500-SET1, replacing the tedious CPU software procedures with simple specifications of only the beginning and ending points of any line.

Whereas the IBM Display Adapter 8514/A is designed only for use in the PS/2 computer models that use the Micro Channel bus, the WD9500-SET1 provides an alternate interface to allow full 8514/A functionality (with extensions) for the Micro Channel, and more importantly, for all PC/AT computers and compatibles. The interface selection is made with a single device pin that is "strapped" at board design time.

Many graphics applications result in noticeable screen flickering when the software steals refresh cycles to modify the color palette in the video DAC. A unique low-cost board design option will provide flicker-free display operation by allowing the WD9500-SET1 to buffer the new palette values and apply them during the monitor's horizontal retrace (flyback).

WD9500-SET1 based boards can accommodate both interlaced display monitors, such as the IBM 8514, and non-interlaced monitors; the WD9500-SET1 will drive either, automatically configuring itself at reset time based on the signals in the monitor interface cable (for IBM-compatible interlaced monitors) or on user selection through onboard switches or on user selection through a software utility. End users can thus exploit cost/performance tradeoffs that are not available with the IBM 8514/A board.

Software written directly to 8514/A registers programs the video registers to IBM 8514/A display interlaced timing for 1024x768 resolution. To achieve maximum flexibility for driving different monitors, two sets of video registers are provided; one for 1024x768 resolution and one for 640x480 resolution. These registers can be programmed by the BIOS EPROM at power up and their values locked in so that direct access by software later will not affect the preset video timing.

For the board designer, the WD9500-SET1 provides several further cost/function/performance trade-off opportunities, and also saves design time, board space, and component costs by integrating much of the peripheral logic into its design. The designer can choose among several

video memory (VRAM) architectures, using 256Kx4 VRAM chips, with back-end logic integrated into the WD9500-SET1 for 8514/A emulation and extension to two pages of 1024x768x8 (1280x1024 extended resolution requires off-chip logic support). The designer may also exploit the use of different clock rates for the drawing process and the screen refresh process; and bypass design of video data multiplexing and serializing, as these functions are integrated into the WD9500-SET1 chips.

## 2.0 ARCHITECTURE

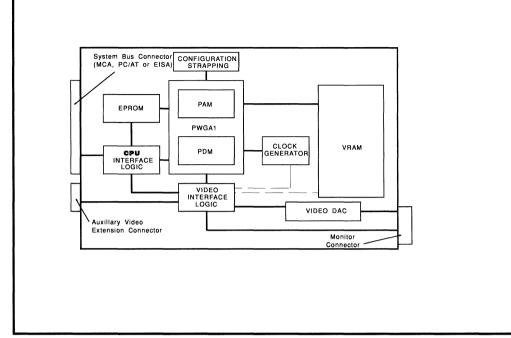

Figure 1 illustrates the logical architecture of a WD9500-SET1 based board in block diagram style. Each of its major elements, which for now are presented as functional "black boxes", is discussed below.

The WD9500-SET1 consists of two 132-pin chips: the PAM (Pixel Address Manager) and the PDM (Pixel Data Manager).

The VRAM block in Figure 1 represents the video memory subsystem, used to store screen images generated in the WD9500-SET1 (as a result of CPU drawing instructions) or sent from the CPU (typically for the purpose of restoring previously drawn images that had been stored elsewhere in the system). The WD9500-SET1 then accesses these images for automatic display-screen refresh. Drawing operations take place within a pixel coordinate space of 2K by 2K; similar to the 8514/A, remaining VRAM storage is available to the WD9500-SET1 and the CPU for "off-screen" use, including storage of fill patters and scratchpad data. Section 3.2 describes VRAM operation and defines the detailed interface of the VRAM subsystem to the WD9500-SET1 chip set.

In the standard board configuration, the WD9500-SET1 is responsible for serializing and multiplexing data extracted form VRAM for screen refresh, and then forwarding the data to the DAC via the video interface logic block. In VRAM architectures using external back-end support, which is necessary to achieve 1280x1024 pixel resolution, serializing and multiplexing is done within the VRAM block, and the resultant screen refresh data bypasses the WD9500-SET1, as shown in Figure 1.

${\prime \prime}$

FIGURE 1. ARCHITECTURE

The video DAC (Digital-to-Analog Converter) has the primary function of generating analog intensity signals for the red, green, and blue guns of the display monitor, carrying these values in synchronization with pixel coordinates as the guns sweep across the screen. The source of these values is the "pixel data" that the WD9500-SET1 reads out of VRAM in its screen refresh operation. With external back-end support, extra intelligence is required in the DAC to assist in the data formatting begun in the serializing and multiplexing logic within the VRAM block. The DAC contains the color palette, a small memory that maps a given pixel data valued into a specific combination of RGB intensities according to the contents of each of the cells in palette memory. For example, in a 256-color arrangement, an eight- bit pixel data value select one of 256 palette memory cells. Each of the latter have been loaded with an 18-bit datum partitioned into three 6-bit fields whose values are in turn converted into red. green, and blue signal intensities when that cell is

selected. Palette values may be loaded directly from the CPU, or with the Western Digital flickerfree option, indirectly through the WD9500-SET1.

The video DAC and its interfaces, the auxiliary video extension (used to drive the monitor from an off-board source, normally the system VGA), the monitor interface, and other related logic and interfaces together comprise the "video DAC and interface subsystem", described in detail in Chapter. Note that the small block in Figure 1 labeled "Video Interface Logic" represents only a modest amount of logic and, in fact, consists largely of pass-through routing of signals; the block is drawn chiefly for convenience in explanation.

The CPU Interface Logic block contains the bus transceivers and TTL glue logic necessary to interface the WD9500-SET1 chips to the system bus (either the IBM PS/2 Micro Channel of the IBM PC/AT bus, or compatible busses). This block also provides a data path to the DAC used by the CPU to directly access palette values, and to the

**FIGURE 2. FUNCTIONAL ORGANIZATION**

EPROM. The CPU interface logic is described in detail in Section 3.1.

The remaining board elements are the EPROM (containing Western Digital-supplied BIOS extension firmware), the clock generators, and a group of minor components (pull-up/down logic and DIP switches) used by the WD9500-SET1 to sense its environmental configuration; whether Micro Channel or AT bus, VRAM organization, etc. These elements are described in Section 3.0, together with the inter-chip (PAM-PDM) connections.

Finally, the WD9500-SET1 contains a set of useraccessible internal register that are compatible with those on the IBM 8514/A board, plus certain extra registers to support Western Digital extensions. From the user's point of view, these registers exist chiefly as destinations for software commands ("orders" in IBM terminology) and their parameters.

## 2.1 FUNCTIONAL ORGANIZATION

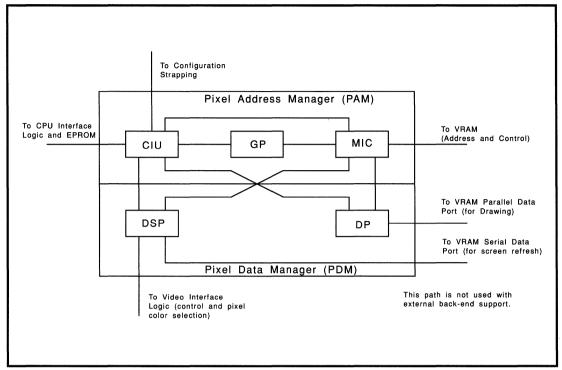

Figure 2 introduces the internal functional blocks of the PAM and PDM chips. Communication between the two chips is mediated by two Internal Bus Interface Units (IBIUs); they are transparent to user operations, and are not shown in the diagram.

In addition to the internal registers and the IBIUs, the functional modules within the WD9500-SET1 are as follows:

Within the **PAM**:

- CIU: CPU Interface Unit

- GP: Graphics Processor

- MIC: Memory Interface Controller

Within the PDM:

- **DP:** Data Processor

- DSP: Display Processor

The **CIU** controls communication with the system bus (via the CPU interface logic block external to the chip set), and passes data to and from all the other units on the chip set. It also performs certain miscellaneous functions, such as forwarding addresses from the system bus to the EPROM.

The **GP** performs the actual drawing computations; it supports all 8514/A graphics modes, plus Western Digital extensions. The modes include line drawing, area fill area outline drawing (arbitrary polygons), rectangle drawing, image transfer from the CPU, BITBLT copying (Bit Block Transfer within VRAM), and scissoring. The GP receives its drawing instructions form the CIU and sends the resulting pixel coordinates to the MIC.

The **MIC** controls VRAM addressing and access. In a typical drawing operation, it will convert the DP supplied pixel coordinates into VRAM addresses, cause the VRAM to send the addressed data (pixel color values) to the DP for modification, and then rewrite back into VRAM. When not involved in a drawing or special-purpose access, the MIC manages the VRAM addressing portion of the constantly on-going screen refresh process. The MIC gives screen refresh the highest priority for VRAM access; next is timer-based VRAM chip refresh, with DP-requested drawing access given the lowest priority.

The **DP** is responsible for updating VRAM in support of drawing and data transfer operations and altering pixel data (color values) according to masks and parameters, including "mix" specifications supplied in shared internal registers by the DP and GP. The DP receives pixel data on a bidirectional bus from the VRAM, modifies it, and then writes it back to the VRAM on the same bus.

The **DSP** manages the DAC and monitor, coordinating its role in the screen refresh process with the MIC. With an integrated back-end VRAM design, the DSP serializes and multiplexes pixel data, "pumped" out of VRAM by the MIC, to the DAC, in synchronization with the timing of the monitor's sweep across the display screen. (With external back-end support, this DSP function is assumed by external logic within the VRAM block and the DAC).

## 2.2 BOARD OPERATION OVERVIEW

The functions of any WD9500-SET1 based board, as well as those of the IBM 8514/A, can be summarized as follows:

**A. Screen refresh:** A key function is driving the display monitor. The board reads data form its VRAM stored representation of the screen image, and then converts the data, pixel by pixel, into RGB signal for the display monitor, in synchronization with the sweeping of the monitor's RGB guns across its screen.

**B. Drawing:** The other major board function , less time-critical then screen refresh, is the generation of new lines and areas within VRAM in response to commands from the system CPU. In this context, "drawing" includes filling polygon shapes with patters, establishing boundaries for "scissoring" (clipping), and similar operations. Drawing operations can involve complex algorithms, and they require correspondingly sophisticated processing by the WD9500-SET1.

**C. Image transfer:** In most graphics work, it is common to save board-drawn images (e.g. popup menus) elsewhere in main system memory and/or on disk for later restoration to on-board video memory and thence to the display screen.

**D. VGA input:** The host CPU may request that the monitor be driven by the VGA (Video Graphics Array), a similar but less sophisticated graphics facility located elsewhere in the system; in this case the WD9500-SET1 based board (or the 8514/A) essentially becomes a passive pass-through channel, taking video data and sync signals from the "auxiliary video extension" bus connector. Note that another monitor can be attached directly to the VGA; if the WD9500-SET1 based board (or 8514/A) is not in pass-through mode, then the two monitors can simultaneously display different images.

**E. Palette loading:** Pixel color interpretation is mediated by a small "palette" memory in the video DAC on the board. The CPU can very rapidly effect changes on the screen by changing the contents of this memory, as distinct from issuing drawing commands.

| PIN NUMBER     | PIN SYMBOL | TYPE                                                                                                                                                            | DESCRIPTION                                               |  |

|----------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|

| 62-69, 71-82   | A0-A19     | 1                                                                                                                                                               | CPU addaress bits 0 through 19                            |  |

| 85             | AUP        | I Decoding of upper CPU address bits 23-20, p<br>MADE24; all these should be 0 if the lower 20<br>address are to be considered valid for the WE<br>based board. |                                                           |  |

| 57             | M/ĪO       |                                                                                                                                                                 | Distinguishes memory access from I/O access               |  |

| 59             | S0         | 1                                                                                                                                                               | Status Bit 0                                              |  |

| 58             | S1         | 1                                                                                                                                                               | Status Bit 1                                              |  |

| 61             | ADL        | 1                                                                                                                                                               | Address Latch                                             |  |

| 60             | CMD        | I                                                                                                                                                               | Command                                                   |  |

| 56             | SBHE       | 1                                                                                                                                                               | System Byte High Enable                                   |  |

| 52             | RESET      | 1                                                                                                                                                               | Channel Reset                                             |  |

| 86             | CDSETUP    | 1                                                                                                                                                               | Card Setup                                                |  |

| 90             | CD CHRDY   | 0                                                                                                                                                               | Channel Ready                                             |  |

| 88             | IRQ        | 0                                                                                                                                                               | Interrupt Request; tied to Micro Channel IRQ 9            |  |

| 89             | CD SFFBK   | 0                                                                                                                                                               | Card Selected Feedback                                    |  |

| 55             | CD DS16    | 0                                                                                                                                                               | Card Data Size 16                                         |  |

| 91             | DBEN       | 0                                                                                                                                                               | Data Bus Enable                                           |  |

| 94-98, 100-110 | D0-D15     | I/O                                                                                                                                                             | CPU Data Bus Bits 0 through 16                            |  |

| 92             | DBDIR      | 0                                                                                                                                                               | Data Bus Direction (high for CPU read, low for CPU write) |  |

## TABLE 1. CPU INTERFACE PINS (PAM) FOR MICRO CHANNEL

**F. EPROM access:** The board includes a small EPROM containing a BIOS extension available to the CPU. The EPROM is mainly for initialization an diagnostic testing during power up. (Note that a portion of EPROM contains certain board configuration information read by the WD9500-SET1 upon power up.)

**G.** *Other:* Finally, the board design must provide for customary CPU handshaking, interrupts, and miscellaneous bus interface signals.

## 3.0 WD9500 INTERFACES

## 3.1 CPU INTERFACE

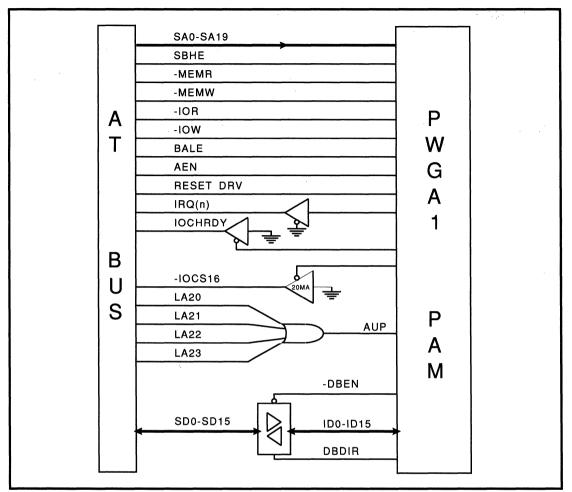

The PAM provides interface pins to connect to either the IBM PS/2 Micro Channel of the AT bus via a small amount of external logic, illustrated in Figures 1 and 2. The CIO configures itself for one of the two different interfaces according to the value of a configuration strapping pin, described later in this chapter (Table 12).

Because of the two possible external environments, most of these CPU interface pins have two alternate interpretations, as shown in the following tables. In both cases, however, the names and uses of most of these pins correspond precisely to the IBM specifications for theMicro Channel or AT bus, and so do not need special explanation.

| PIN NUMBER     | PIN SYMBOL | TYPE                                                                                                                                                            | DESCRIPTION                                               |

|----------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 62-69, 71-82   | SA0-SA19   | 1                                                                                                                                                               | CPU addaress bits 0 through 19                            |

| 85             | AUP        | I Decoding of upper CPU address bits 23-20, p<br>MADE24; all these should be 0 if the lower 20<br>address are to be considered valid for the WE<br>based board. |                                                           |

| 56             | SBHE       | <u> </u>                                                                                                                                                        | System Byte High Enable                                   |

| 57             | MEMR       |                                                                                                                                                                 | Memory Read                                               |

| 59             | MEMW       | 1                                                                                                                                                               | Memory Write                                              |

| 58             | IOR        | 1                                                                                                                                                               | I/O Read                                                  |

| 60             | IOW        | 1                                                                                                                                                               | I/O Write                                                 |

| 61             | BALE       | 1                                                                                                                                                               | Buffered Address Latch Enable                             |

| 86             | AEN        | 1                                                                                                                                                               | Address Enable                                            |

| 52             | RESET      | 1                                                                                                                                                               | System Reset                                              |

| 88             | IRQ        | 0                                                                                                                                                               | Interrupt Request; tied to any AT bus interrupt           |

| 55             | CD CS16    | 0                                                                                                                                                               | I/O 16-bit Chip Select                                    |

| 91             | DBEN       | 0                                                                                                                                                               | Data Bus Enable                                           |

| 94-98, 100-110 | SD0-SD15   | I/O                                                                                                                                                             | CPU Data Bus Bits 0 through 16                            |

| 92             | DBDIR      | 0                                                                                                                                                               | Data Bus Direction (high for CPU read, low for CPU write) |

| 84             | ATCLK      |                                                                                                                                                                 | AT Bus Clock                                              |

## TABLE 2. CPU INTERFACE PINS (PAM) FOR AT BUS

FIGURE 3. CPU INTERFACE LOGIC - AT BUS

| I/E* | NUMBER OF<br>CHIPS | PIXEL<br>RESOLUTION | PIXEL DEPTH | NUMBER OF<br>SCREEN<br>PAGES | S/W** |

|------|--------------------|---------------------|-------------|------------------------------|-------|

| 1    | 4                  | 1024x768            | 4           | 1                            | S     |

|      |                    | 640x480             | 4           | 2                            | S     |

|      | 8                  | 1024x768            | 8           | 1                            | S     |

|      |                    | 1024x768            | 4           | 2                            | W     |

|      |                    | 640x480             | 8           | 1                            | S     |

|      | 16                 | 1024x768            | 8           | 2                            | W     |

|      |                    | 1024x768            | 4           | 2                            | W     |

|      |                    | 640x480             | 8           | 2                            | W     |

| Е    | 8                  | 1280X1024           | 4           | 1                            | W     |

|      |                    | 1024x768            | 8           | 1                            | S     |

|      |                    | 1024x768            | 4           | 2                            | W     |

|      |                    | 640x480             | 8           | 1                            | S     |

|      | 16                 | 1280x1024           | 8           | 1                            | W     |

|      |                    | 1024x768            | 8           | 2                            | W     |

|      |                    | 1024x768            | 4           | 2                            | W     |

|      |                    | 640x480             | 8           | 2                            | W     |

\*I = Integrated Back-end Support

E = External Back-end Support

\*\*S = Standard capability within 8514/A emulation

W = Western Digital extension to 8514/A capability

## TABLE 3. VRAM PARAMETERS

## 3.2 VRAM DESIGN AND INTERFACE

The WD9500-SET1 supports two VRAM designs. Each of these in turn can be implemented with two or three levels of chip population, for a total of five implementations. The design choice depends on the desired combination of the following criteria (with only certain combinations possible):

- pixel resolution: 640x480, 1024x768, 1280x1024

- pixel depth: 4 or 8 bits per pixel

- number of screen pages: one or two

- number of VRAM chips (and hence board size)

- field upgradeability

- type of design: with back-end (serializing and multiplexing of pixel data for screen refresh) integrated within the WD9500-SET1, or with external back-end support

External back-end support: includes the use of a more sophisticated DAC - is required to achieve 1280x1024 resolution.

## 3.2.1 INTEGRATED BACK-END VRAM DESIGN

The capabilities of the various VRAM designs, with their several levels of chip population, are shown in Table 3. Note: Although not shown, each level of chip loading for a given design includes the capabilities of the smaller chip population(s).

If maximum IBM 8514/A resolution is desired, this design should be implemented to at least the 8-chip level; implementation at the 16-chip level provides for the extended capability of doubling the number of screen pages supported by the 8-

| PIN NUMBER | PIN SYMBOL | DESCRIPTION                                                                                                                                                                          |

|------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19, 16-10  | MA7-MA0    | Low order address lines, into all quads.                                                                                                                                             |

| 34         | LA13       | Used as high-order address bit (MA8) for quads Q1, Q3, and their counterparts, in all designs.                                                                                       |

| 35         | LA24       | Used as high-order address bit (MA8) for quads Q2, Q4, and their counterparts, in all designs.                                                                                       |

| 22         | RAS0       | Row Address Strobe 0 (Quads 1 & 2)                                                                                                                                                   |

| 23         | RAS1       | Row Address Strobe 1 (Quads 3 & 4)                                                                                                                                                   |

| 20         | CAS12      | Column Address Strobe 1 (Quads 1 & 2)                                                                                                                                                |

| 21         | CAS34      | Column Address Strobe (Quads 3 & 4)                                                                                                                                                  |

| 31-24      | WE7-WE0    | Pixel data Write Enable lines to enable writing<br>into VRAM on the PD bus (bidirectional Parallel<br>Data bus, between VRAM and DP; A given quad<br>receives either WE0-3 or WE4-7. |

| 32         | DT/OE      | Transfer cycle control and serial data output<br>enable, used by all quads.                                                                                                          |

## TABLE 4. PAM PIN INTERFACE TO VRAM

chip version. See Appendix A for an illustration of the 16-chip version with indications of which chips should be left unpopulated if field upgradeable 4chip and/or 16-chip versions are to be produced. The same diagram can also serve as the basis for an 8-chip design, with half of those chips omitted for future field upgrade if desired.

See Appendix A for a detailed connection drawing for VRAM to PAM and PDM.

Tables 4 and 5 show the PAM and PDM pins used to form the VRAM interface. See Appendix A for VRAM design diagrams.

All the Pins in Table 4 drive control signals generated by the MIC.

The PD Pixel Data bus is managed by the Data Processor module (DP); all other pins in Table 5 are managed by the Display Processor (DSP).

WE0-3 are for pixel positions 0-3, respectively. In turbo mode, WE4-7 are for positions 4-7. For x8 mode, WE4-7 are the same as WE0-3.

In the VRAM design diagrams (see Appendix A), the PD lines connect to the parallel data ports of the VRAM chips, while the SD lines connect to their serial data ports. The different resolution modes require different memory addressing schemes to configure the display memory properly for screen pixel position.

#### 3.2.2 EXTERNAL BACK-END VRAM DESIGN

See Appendix A for an illustration of the 16-chip version with external back-end support. A Brooktree 8-bit video DAC BT458 is used.

## 3.3 VIDEO DAC AND INTERFACE SUB-SYSTEM

This section includes the following information for the board designer:

Routing of VRAM pixel data to the DAC. This involves two alternative designs, depending on weather back-end support is performed by the WD9500-SET1 or by external components.

Routing of control information from the WD9500-SET1 to the DAC and the monitor.

Signal routing in support of "VGA modes", in which the monitor is driven by control and data signals originating off-board, in the system VGA, and passed through to the monitor from the auxiliary extension connector.

| PIN NUMBER                        | PIN SYMBOL                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 90-93, 95-98, 100-114,<br>117-125 | PD31-PD0                      | Parallel Data bus connecting the DP module to<br>the VRAM block; data is bidirectional. (This is the<br>path through which the DP first reads, then<br>rewrites pixels in support of drawing operations).                                                                                                                                                                                                                                                                                                                                                                                                             |

| 46-49, 52-67, 71-82               | SD31-SD0                      | Serial Data bus, in VRAM designs with integrated<br>back-end support, this is the path by which<br>screen refresh data is extracted (by a transfer<br>cycle) from the serial ports of the VRAM chips<br>and then moved to the DSP module for serializing<br>and multiplexing before being sent to the DAC. In<br>VRAM designs with external back-end support,<br>the serial data bus to the DSP is not used; in-<br>stead, the DSP reconfigures itself to use some of<br>these pins (SD0, SD1, SD4, SD5, SD6) as output<br>drivers for additional control signals to the VRAM<br>(see External Back-End VRAM Design). |

| 87,85,86,84                       | SE12A, SE34A,<br>SE12B, SE34B | Serial Data Output Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 88                                | SC13                          | Serial Data Clock 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 89                                | SC24                          | Serial Data Clock 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| The following pins are ch         | nanged for external back-e    | nd support:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 82                                | SC3 (SD0)                     | Serial Data Clock 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 81                                | SC2(SD1)                      | Serial Data Clock 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 78                                | SEL0(SD4)                     | Mux Select 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 77                                | SEL1(SD5)                     | Mux Select 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 76                                | LDCLK (SD6)                   | LDCLK signal to the DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

## TABLE 5. PDM PIN INTERFACE TO VRAM

Palette access, with the board design option of implementing "flicker-free mode", a Western Digital extension.

Note that a related topic, WD9500-SET1 recognition of monitor type, is grouped with other configuration strapping issues, and is discussed later in this chapter.

The PDM pins associated with the video interface subsystem are all outputs from the DSP, and are shown in Table 6.

Appendix B describes board implementation of the video DAC and interface subsystem with integrated and external back-end support. The flicker-free option applies to both and is discussed later. The WD9500-SET1 chip set supports INMOS IMS G171/176/178, Brooktree BT471/478 and compatible video DACs for 8514/A modes. It also supports Brooktree BT451/458 and compatible DACs for Western Digital enhanced 1280x1024 mode. The Brooktree BT471 DACs include a 256x18 palette, loaded with 6-bit R, G, and B color intensity values; the high two bits of the 8-bit data lines supplying these values are ignored. The BT478 substitute a 256x24 palette, with all eight bits used for finer control of color. The DAC8 pin from the PAM can be used to select 6-bit or 8-bit palette fields. Note that the palette overlay capabilities are not used; the DAC's RS2 and OL0-OL3 pins should be tied down. Without the flicker-free option, CPU software writes data into the DAC's color palette on the low eight bits of the system CPU data bus.

| PIN NUMBER   | PIN SYMBOL | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30-27, 24-21 | VDATA0-7   | 0    | With integrated back-end support, these<br>pins output the video data for the DAC. With<br>external back-end support, they are not<br>used for this purpose, since the DAC<br>receives its data from the external logic<br>within the VRAM block. In both cases, how-<br>ever, these same pins are the source of<br>palette-loading data in flicker-free mode. (tri-<br>state output) |

| 132          | SELVD      | 0    | With the flicker-free design option, this pin<br>selects the source of palette-loading data to<br>be either the low eight bits of the PC data<br>bus (normal mode) or VDATA0-7 (flicker-free<br>mode). SELVD is also the tri-state control<br>signal for DACRD and DACWR from the<br>PAM. When high, PAM DACRD and<br>DACWR signals are disabled.                                     |

| 25           | VCLK       | 0    | Video clock for the DAC (tri-state output)                                                                                                                                                                                                                                                                                                                                            |

| 20           | BLANK      | 0    | Video blank signal for the DAC (tri-state out-<br>put)                                                                                                                                                                                                                                                                                                                                |

| 31           | DACRD      | 0    | DAC palette read. Note that data read from<br>the palette is always routed to the PC data<br>bus in the CPU interface logic.                                                                                                                                                                                                                                                          |

| 32           | DACWR      | 0    | DAC palette write (see SELVD above)                                                                                                                                                                                                                                                                                                                                                   |

| 33           | HSYNC      | 0    | Horizontal sync to the monitor (tri-state out-<br>put).                                                                                                                                                                                                                                                                                                                               |

| 34           | VSYNC      | 0    | Vertical sync to the monitor (tri-state output)                                                                                                                                                                                                                                                                                                                                       |

| 42           | ENVGA      | 0    | Enables VGA pass-through mode. This sig-<br>nal selects the source of video data to the<br>DAC (either VDATA0-7 from the PDM or P0-<br>7 from the auxiliary vedeo extension). It also<br>selects the control sitgnals to the DAC<br>(either VCLK and BLANK from the PDM, or<br>HSYNC and VSYNC from the PDM, or<br>HSYNC and VSYNC from the auxiliary video<br>extension).            |

| 76           | LDCLK      | 0    | For external back-end support. This output<br>signal drives the LD (load) input of the<br>BT458/451 DAC, where it synchronizes the<br>serialization of the 32 bits of pixel data from<br>the VRAM into four 8-bit pixel color selec-<br>tions. With integrated back-end support this<br>pin is SD6 of the serial data bus from VRAM.                                                  |

## TABLE 6. PDM PIN INTERFACE TO VIDEO SUBSYSTEM

25

| PIN NUMBER    | PIN SYMBOL | I/O | DESCRIPTION              |

|---------------|------------|-----|--------------------------|

| 54, 53, 49-37 | BSA0-BSA14 | 0   | EPROM BIOS address lines |

| 36            | BSOE       | 0   | EPROM BIOS output enable |

## TABLE 7. EPROM INTERFACE PINS

|                      | MICRO CHANNEL | AT BUS      |             |

|----------------------|---------------|-------------|-------------|

|                      |               | IAD5 = 0*   | IAD5 = 1*   |

| 2K (Fixed)           | C6800-C6FFF   | C8800-C8FFF | D8800-D8FFF |

| 4K (Bank Selectable) | C7000-C7FFF   | C9000-C9FFF | D9000-D9FFF |

| 2K (Fixed)           | CA000-CA7FFF  | N/A         | N/A         |

## TABLE 8. BIOS EPROM ADDRESS MAPPING

The WD9500-SET1 intercepts CPU addressing and controls DAC access using the low two bits of its EPROM address bus, BIOSA1 and BIOSA0. When the flicker-free option is incorporated into the board design, as shown in Appendix B, the CPU software can invoke flicker-free mode. In this mode, palette data is buffered by the WD9500-SET1 and released to the DAC over the VDATA0-7 lines, with the SELD control signal activated to select the VDATA lines in preference to the system data bus. Routing of the latter lines to the DAC via the SELD multiplexer is still required, both to allow for non-flicker- free mode (8514/A emulation) and for palette reads.

Appendix B shows the implementation of 1280x1024 resolution with external back-end support and two DACs. The fast DAC BT451/458 is used for 1280x1024 and 1024x768 resolutions. The slow DAC BT471/478 is used for VGA pass-through. The flicker-free capabilities do not apply to that DAC.

#### 3.4 OTHER BOARD DESIGN ELEMENTS 3.4.1 EPROM

A 27256 32K UV EPROM is used on the Micro Channel board to store the Western Digital BIOS extension plus two configuration parameters that the WD9500-SET1 loads into internal registers upon board reset: the POS ID (for PS/2 Micro Channel system integration), chosen by the customer, and a VRAM wait-state control parameter (dependant upon characteristics of the VRAM chips chosen for the board, and automatically selected from among four choices depending on how two configuration parameter pins are strapped); see Appendix C.

The EPROM is remapped for the AT bus board because of VGA conflict and widespread use of Shadow RAM in 80386 machines. BIOS EPROM Address mapping for WD9500-SET1 chip set is as stated in Table 7.

For PC/AT and compatibles, 2 sets of addresses that minimize memory conflict with other products have been selected, i.e. C8800-C9FFF or D8800-D9FFF. Either address can be selected by a jumper in a board design.

The EPROM is accessed through the CIU on the PAM, which generates addressing for the EPROM and activated an output enable line. Data from EPROM ties to both the CIU and the system data bus through an 8-bit connection to the internal data bus. (See Figures 1 and 2). The PAM pins involved are shown in Table 8.

## 3.4.2 PAM-PDM INTERFACE

The PAM and PDM are connected to each other through a 22-pin interface. Both chips include an internal bus interface unit (IBIU) which controls inter-chip communication; one of its functions is to buffer data transfers larger than eight bits, since the general purpose inter-chip bus is eight-bits wide due to pin count constraints. Inter-chip communication is transparent to the user. See Table 9.

| PAM PIN NUMBER | SIGNAL DIRECTION  | PDM PIN NUMBER | PIN SYMBOL |

|----------------|-------------------|----------------|------------|

| PAM 125-132    | $\leftrightarrow$ | PDM 9-2        | IAD0-7     |

| . PAM 124      | $\rightarrow$     | PDM 10         | IADSTAT    |

| PAM 8          | $\rightarrow$     | PDM 126        | RWCAS      |

| PAM 123        | $\rightarrow$     | PDM 11         | RD/WR      |

| PAM 122        | $\rightarrow$     | PDM 12         | AS         |

| PAM 121        | $\rightarrow$     | PDM 13         | DS         |

| PAM 114        | ←                 | PDM 19         | RMWE       |

| PAM 2          | ←                 | PDM 132        | SELVD      |

| PAM 119        | ←                 | PDM 15         | SLC        |

| PAM 118        | <i>←</i>          | PDM 16         | SLD        |

| PAM 6          | $\rightarrow$     | PDM 128        | WROE       |

| PAM 3          | $\rightarrow$     | PDM 131        | MDT0       |

| PAM 4          | $\rightarrow$     | PDM 130        | MDT1       |

## TABLE 9. INTERCHIP INTERFACE PINS

## 3.4.3 CONFIGURATION STRAPPING

The WD9500-SET1 configures itself to its board design environment by latching the values of certain strapped input pins on the rising edge of the CPU's RESET signal. (It also reads two parameters from the EPROM, as mentioned earlier). One of these pins, which distinguishes between the Micro Channel and PC/AT bus CPU interfaces, is dedicated to this purpose. Three other dedicated pins receive monitor type information. The remaining pins, which all deal with VRAM configuration information, are actually part of the inter-chip communication interface; the strapped values are driven to the inter-chip lines through tri-state buffers. See Tables 10 - 13.

Note: If a field-upgradeable VRAM design is selected (with the VRAM chips partially populated), the appropriate strappings should be implemented with jumpers, switches or some other method that allows the use to change the strapped values in the course of field upgrade.

## 3.4.4 CLOCK CONSIDERATIONS

A major design element of the WD9500-SET1 is the provision for two separate and independent clock rates; one for drawing operations, the other for screen refresh. In particular, faster monitors can be used without changing the clock rate of the drawing facilities within the WD9500-SET1, and conversely, use of slower monitors will not degrade drawing speed.

The system clock signal, provided by an external 60MHz oscillator, drives the drawing process within the WD9500-SET1, and is used to generated VRAM timing. The pixel clock, used to drive the screen refresh process, is selected from among eight oscillator outputs to accommodate different types of monitors. Three PDM output signals, CLKSEL2, CLKSEL1, and CLKSEL0, are provided to make the selection.

In the United States, non-interlaced video monitors use a vertical refresh frequency of 60Hz; in Europe, the standard is 70Hz. Including the interlaced IBM 8514 monitor (vertical frequency 43.48Hz) produces Table 14, in which the "Pixel Frequency" is the frequency of the oscillator selected by CLKSEL2, CLKSEL1, and CLKSEL0 as input to the PDM's PCLK pin.

The typical WD9500-SET1 board will therefore be configured with oscillators at 25.28, 44.90 and 64.37MHz for use with U.S. standard monitors, or with oscillators at 31.40, 44.90, and 74.16MHz for use with European standard monitors. A more am-

25

| PAM PIN<br>NUMBER | PDM PIN<br>NUMBER | PIN SYMBOL | DESCRIPTION                                                                                                                                                                                            |

|-------------------|-------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 120               |                   | MC/AT      | High if Micro Channel; low if PC/AT bus                                                                                                                                                                |

|                   | 36-38             | MID2-MID0  | Monitor ID Bits 2-0                                                                                                                                                                                    |

| 130               | 3                 | IAD5       | EPROM location for AT bus design (not used in<br>Micro Channel); low for EPROM memory ad-<br>dress at C8800H-C9FFFH, high for address at<br>D8800H-D9FFFH.                                             |

| 131               | 3                 | IAD6       | Test Mode. Low for test mode; high for normal operation.                                                                                                                                               |

| 132               | 2                 | IAD7       | DAC Type.Low foar 6-bit DAC; high for 8-bit DAC.                                                                                                                                                       |

| 129               | 5                 | IAD4       | VRAM Chip Speed. Low for -8 spec; high for -10 spec.                                                                                                                                                   |

| 128               | 6                 | IAD3       | External Back-End. This pin specifies the maxi-<br>mum resolution allowed by VRAM design: low for<br>1280 x 1024 resolution (external back-end re-<br>quired), high for 1024 x 768 (internal back-end) |

| 125               | 9                 | IAD0       | VRAM Chip Type. Must be tied high.                                                                                                                                                                     |

| 126               | 8                 | IAD1       | Chip Count 0. Low order bit of 2-bit VRAM chip<br>count field (see below)                                                                                                                              |

| 127               | 7                 | IAD2       | Chip Count 1. High order bit of 2-bit VRAM chip count field (see below.                                                                                                                                |

| 122               | 12                | ĀS         | Monitor Type 0 (see below)                                                                                                                                                                             |

| 123               | 11                | RD/WR      | Monitor Type 1 (see below)                                                                                                                                                                             |

TABLE 10. CONFIGURATION STRAPPING PINS

|          | Chip Count 1 | Chip Count 0 |

|----------|--------------|--------------|

| 4 Chips  | 0            | 0            |

| 8 Chips  | 0            | 1            |

| 16 Chips | 1            | 0            |

| Reserved | 1            | 1            |

## TABLE 11. CHIP COUNT STRAPPING

| Type of<br>Monitor | Monitor Type 0 | Monitor Type 1 |

|--------------------|----------------|----------------|

| 8514 Display       | 0              | 0              |

| 60 Hz monitor      | 0              | 1              |

| Reserved           | 1              | 0              |

| 70 Hz monitor      | 1              | 1              |

## TABLE 12. MONITOR SELECTION

bitious design might include all seven clock frequencies, with the MID2-MID0 inputs (as per "Configuration Strapping" earlier in this chapter) aiding in the selection.

The WD9500-SET1 pins involved in clock signal generation and use are summarized in Table 14.

| MID2 | MID1 | MID0          | MONITOR TYPE                                          |  |

|------|------|---------------|-------------------------------------------------------|--|

| 0    | 0    | 0 Not Defined |                                                       |  |

| 0    | 0    | 1             | Not Defined                                           |  |

| 0    | 1    | 0             | IBM 8514 (color monitor, 1024 x 768 interlaced)       |  |

| 0    | 1    | 1             | Not defined                                           |  |

| 1    | 0    | 0             | Not defined                                           |  |

| 1    | 0    | 1             | IBM 8503 (monochrome, 640 x 480, non-inter-<br>laced) |  |

| 1    | 1    | 0             | IBM 8513 (color, 640 x 480, non-interlaced & 8514     |  |

| 1    | 1    | 1             | Other display*                                        |  |

Note: MID2-0 have internal pull-up resistors. During reset, MID2-0 can also be used to test PDM internal counters. For in-circuit board test, MID2-0 should be high when REST is asserted.

## TABLE 13. MONITOR ID INTERPRETATION

|   | CLKSEL |   | <b>RESOLUTION*</b> | VERTICAL FRE- | HORIZONTAL | PIXEL        |  |

|---|--------|---|--------------------|---------------|------------|--------------|--|

| 2 | 1      | 0 |                    | QUENCY        | FREQUENCY  | FREQUENCY    |  |

| 0 | 0      | 0 | 640 X 480N         | 60 Hz         | 31.47 KHz  | 25.18 MHz    |  |