WD90C00 (PVGA1B) VGA Controller

# **TABLE OF CONTENTS**

| Section     | Title                                 | Page    |  |  |  |  |

|-------------|---------------------------------------|---------|--|--|--|--|

| 1.0         | Introduction                          |         |  |  |  |  |

|             | 1.1 Features                          |         |  |  |  |  |

|             | 1.2 Description                       |         |  |  |  |  |

| 2.0         | Architecture                          |         |  |  |  |  |

| 3.0         | WD90C00 Interfaces                    |         |  |  |  |  |

|             | 3.1 CPU and BIOS ROM Interface        |         |  |  |  |  |

|             | 3.2 DRAM Display Buffer Interface     |         |  |  |  |  |

|             | 3.3 Video and RAMDAC Interface        |         |  |  |  |  |

|             | 3.4 Clock Interface                   |         |  |  |  |  |

| 4.0         | 3.5 WD90C00 Power-Up Configuration    |         |  |  |  |  |

| 4.0         | Pin Description                       |         |  |  |  |  |

| 5.0         | Absolute Maximum Ratings              |         |  |  |  |  |

| 6.0         | Standard Test Conditions              |         |  |  |  |  |

| 7.0         | DC Characteristics                    | . 20-18 |  |  |  |  |

| 8.0         | AC Timing Characteristics             | . 20-19 |  |  |  |  |

| 9.0         | WD90C00 Registers                     | . 20-31 |  |  |  |  |

|             | 9.1 VGA Registers Summary             |         |  |  |  |  |

|             | 9.2 PR Registers Summary              |         |  |  |  |  |

|             | 9.3 Compatibility Registers Summary   |         |  |  |  |  |

|             | 9.4 VGA Registers                     |         |  |  |  |  |

|             | 9.5 General Registers                 |         |  |  |  |  |

|             | 9.6 Sequencer Registers               |         |  |  |  |  |

|             | 9.7 CRT Controller Registers          |         |  |  |  |  |

|             | 9.8 Graphics Controller Registers     |         |  |  |  |  |

|             | 9.9 Attribute Controller Registers    |         |  |  |  |  |

|             | 9.10 Compatibility Registers          | . 20-59 |  |  |  |  |

|             | 9.11 WD90C00 PR Registers             |         |  |  |  |  |

|             | 9.12 Internal I/O Ports               | . 20-79 |  |  |  |  |

|             | 9.13 Video RAMDAC Ports               | . 20-81 |  |  |  |  |

|             | 9.14 External I/O Port Considerations | . 20-83 |  |  |  |  |

|             |                                       |         |  |  |  |  |

|             | APPENDICES                            |         |  |  |  |  |

| Section     | Title                                 | Page    |  |  |  |  |

| A.1         | EGA Mode                              | . 20-84 |  |  |  |  |

| A.2         | General Registers                     |         |  |  |  |  |

| A.3         | Sequencer Registers                   |         |  |  |  |  |

| A.4         | CRT Controller Registers              |         |  |  |  |  |

| A.5         |                                       |         |  |  |  |  |

|             | Graphics Controller Registers         |         |  |  |  |  |

| A.6         | Attribute Controller Registers        |         |  |  |  |  |

| A.7         | Applications                          |         |  |  |  |  |

| A.8         | WD90C00 Power-Up Configuration        |         |  |  |  |  |

| <b>A</b> .9 | References                            | 20-106  |  |  |  |  |

|             |                                       |         |  |  |  |  |

20-ii

# LIST OF ILLUSTRATIONS

|        | EIGT OF TEEGOTTIATIONS                         |          |

|--------|------------------------------------------------|----------|

| Figure | Title                                          | Page     |

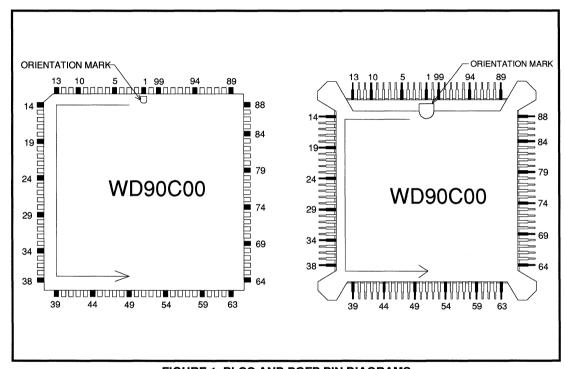

| 1      | PLCC and PQFP Pin Diagrams                     | 20-2     |

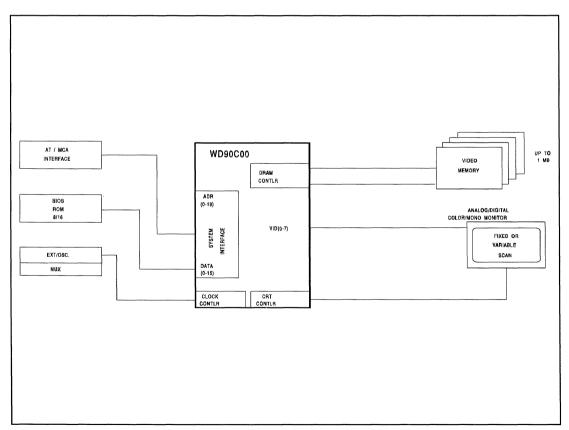

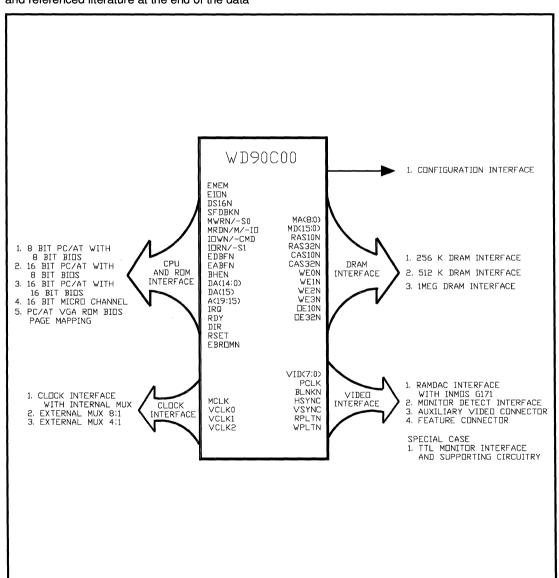

| 2      | System Block Diagram                           | 20-4     |

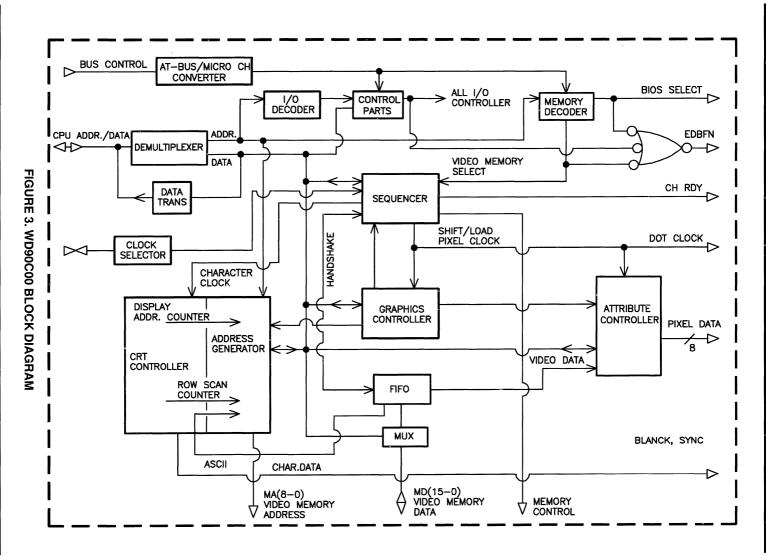

| 3      | WD90C00 Block Diagram                          | 20-5     |

| 4      | Reset Timing                                   | 20-25    |

| 5      | Clock and Video Timing                         | 20-25    |

| 6      | AT Mode I/O and Memory Read/Write Timing       | 20-26    |

| 7      | Micro Channel I/O and Memory Read/Write Timing | 20-27    |

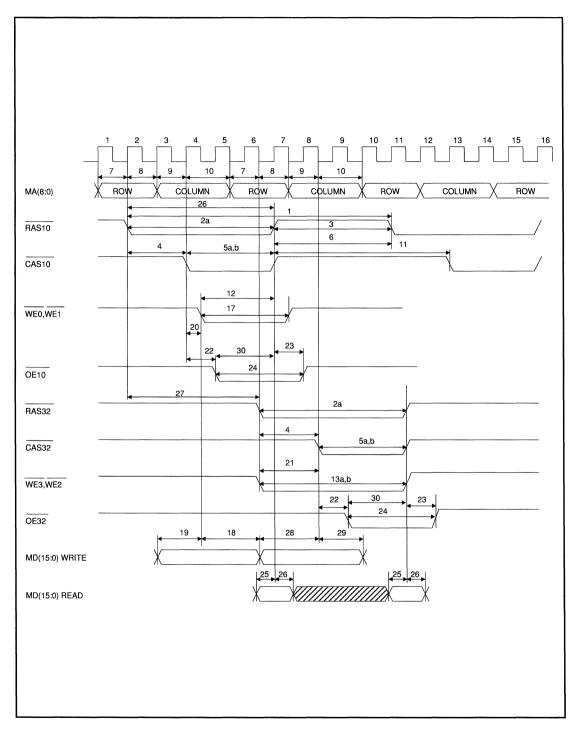

| 8      | CPU Read/Write DRAM Timing                     | 20-28    |

| 9      | DRAM Page Mode Read Timing                     | 20-29    |

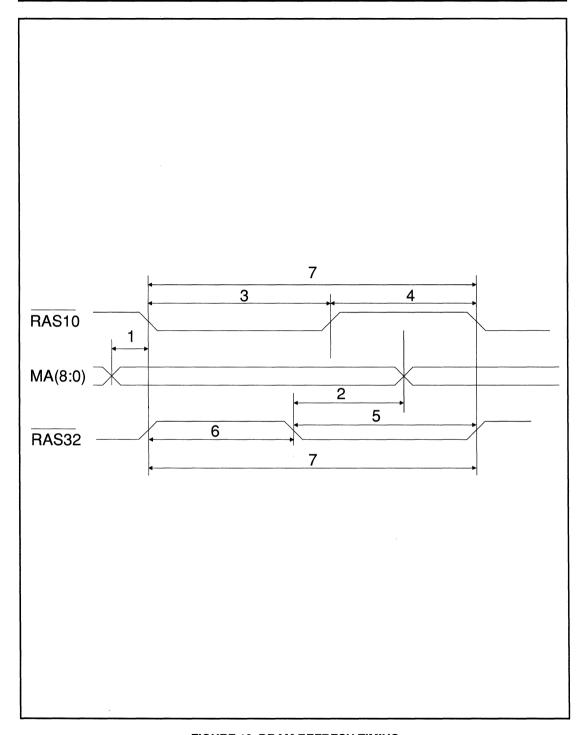

| 10     | DRAM Refresh Timing                            | 20-30    |

| 11     | WD90C00 Processor, Memory, and I/O Interfaces  | 20-92    |

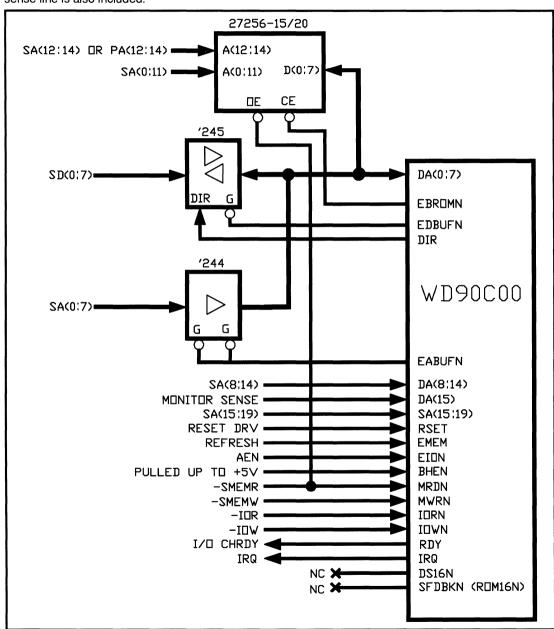

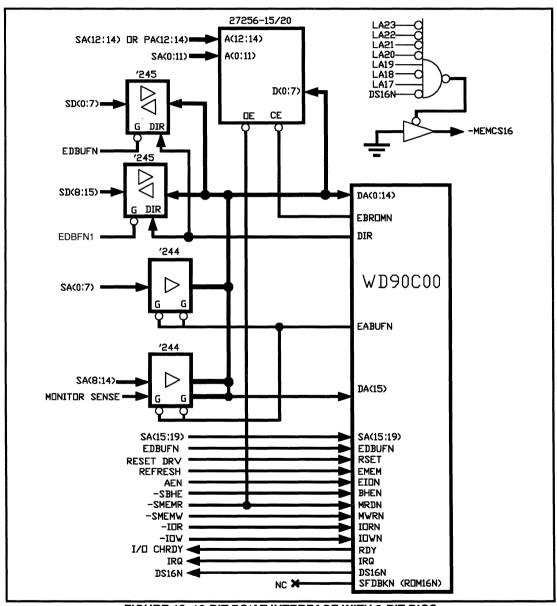

| 12     | 8-Bit PC/AT Interface with 8-Bit BIOS          | 20-93    |

| 13     | 16-Bit PC/AT Interface with 8-Bit BIOS         | 20-94    |

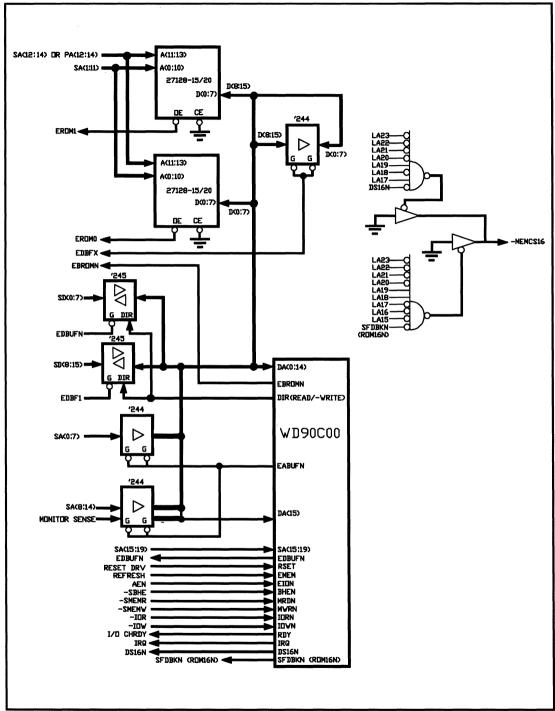

| 14     | 16-Bit PC/AT Interface with 16-Bit BIOS        | 20-96    |

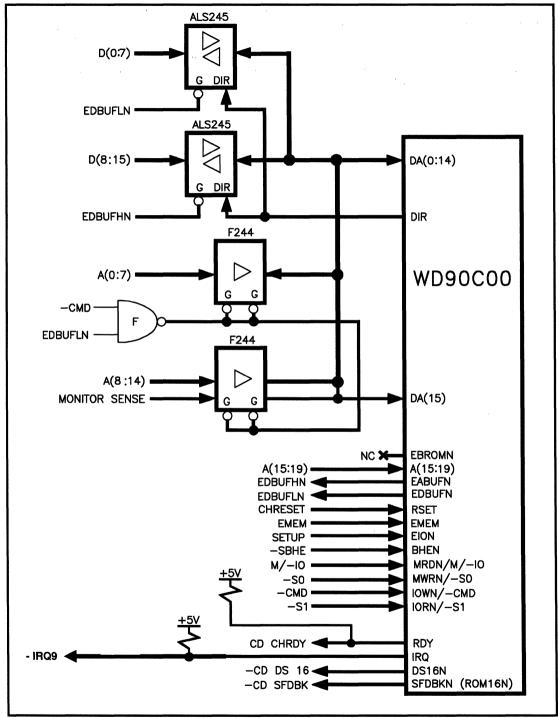

| 15     | 16-Bit Micro Channel Interface                 | 20-98    |

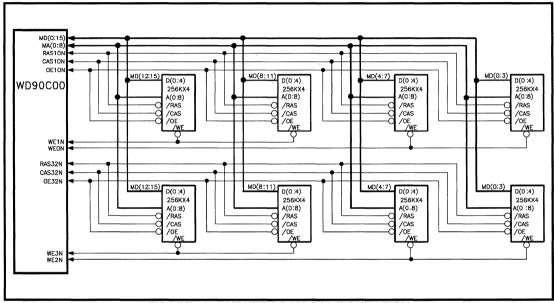

| 16     | 1 Mbyte DRAM Configuration                     | 20-99    |

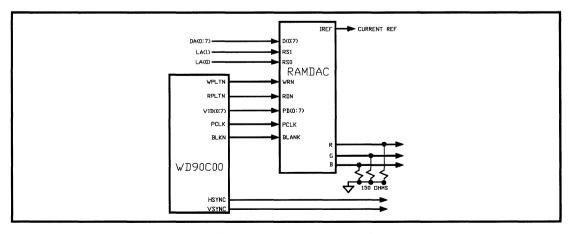

| 17     | RAMDAC Interface                               | 20-99    |

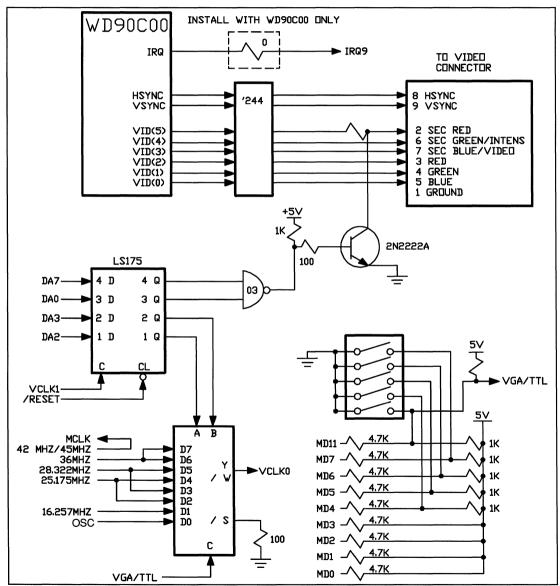

| 18     | WD90C00 TTL Monitor Connections                | . 20-100 |

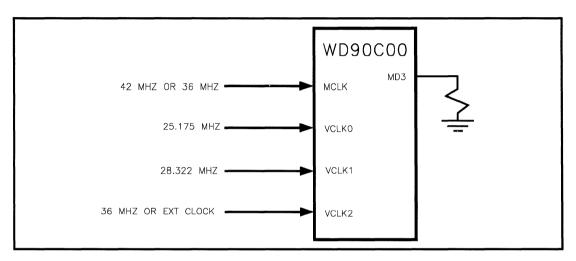

| 1.9    | Clock Interface                                | . 20-101 |

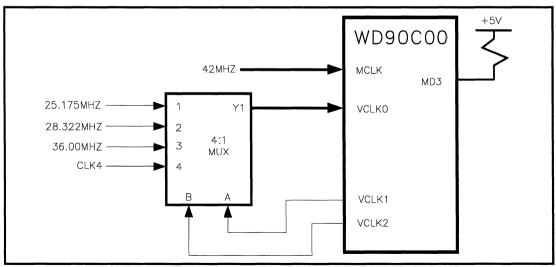

| 20     | External Multiplexing of the Video Clocks      | . 20-101 |

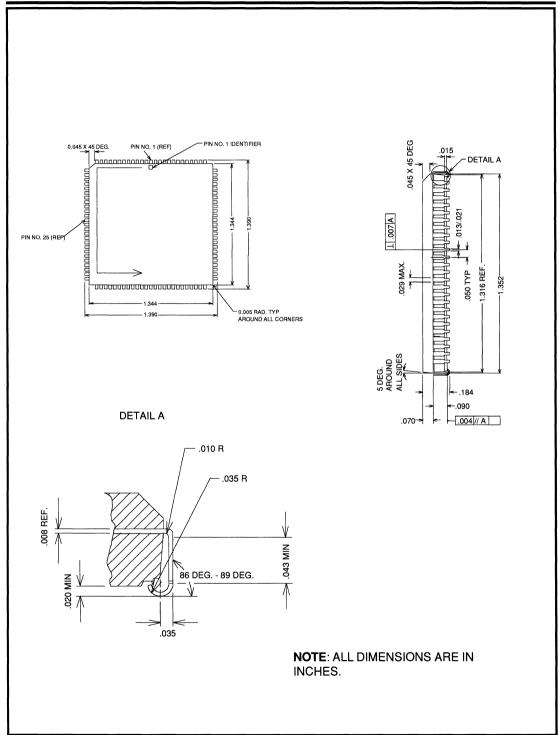

| 21     | 100-Pin PLCC Package Dimensions                | . 20-103 |

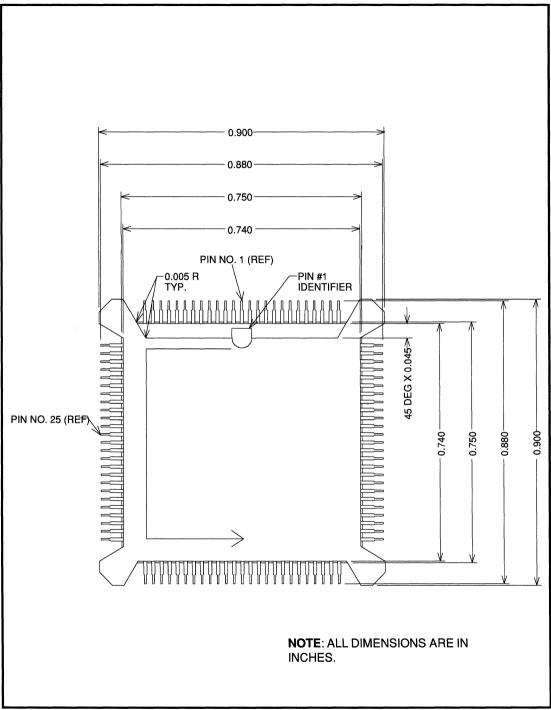

| 22     | 100-Pin JEDEC Plastic Quad Flat Package (PQFP) | . 20-104 |

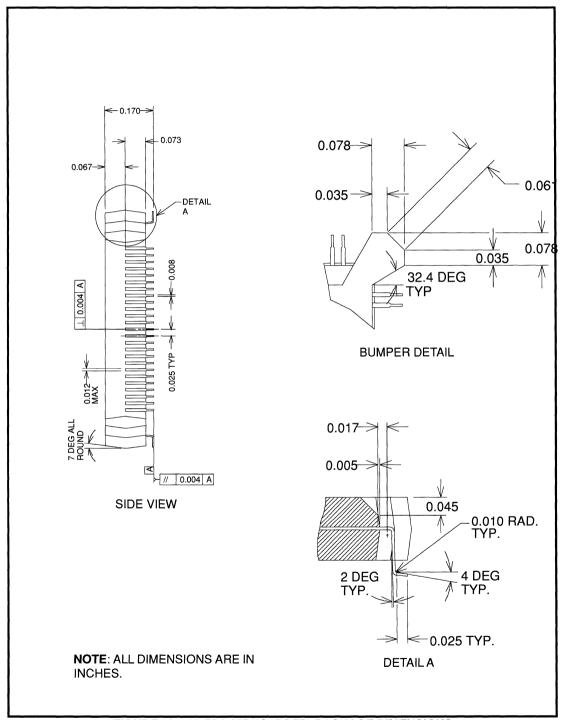

| 23     | 100-Pin JEDEC (PQFP) Packaging Dimensions      | . 20-105 |

|        | LIST OF TABLES                                 |          |

| Table  | Title                                          | Page     |

| 1      | Pin Assignments                                | 20-3     |

| 2      | DC Characteristics                             | 20-18    |

| 3      | AC Timing Characteristics                      | 20-19    |

| 4      | VGA Registers Summary                          | 20-31    |

| 5      | PR Registers Summary                           | 20-32    |

| 6      | Compatibility Registers Summary                | 20-32    |

| 7      | CRT Controller Registers                       | 20-39    |

10-25-90

#### 1.0 INTRODUCTION

Many applications require greater graphics capability than is available through the IBM Monochrome Display Adapter (MDA), Color Graphics Adapter (CGA), Enhanced Graphics Adapter (EGA), Multi Color Graphics Array (MCGA), and the Video Graphics Array (VGA). The WDI WD90C00 is a 1.25 micron, 15,000 gate CMOS VLSI device that fulfills this need and allows for the design of very high performance VGA graphics subsystems that are able to interface with the PC/AT Bus, as well as the IBM Micro Channel Bus, while maintaining backwards compatibility with previous video standards.

A major advantage of using the WD90C00 is that designs implementing this graphics controller will be able to run applications requiring MDA, CGA, EGA, Hercules graphics, AT&T (640 by 400 graphics mode), VGA hardware and BIOS level compatibility on analog and TTL monitors. In addition, it includes full support for running extended high resolution 1024 by 768 by 16 colors interlaced graphics mode on 8514 Color Displays. A Noninterlaced 1024 by 768 by 16 colors graphics mode requires external circuitry along with a 56 MHz MCLK and 80 ns DRAMs.

#### 1.1 FEATURES

- Provides single chip Video Graphics Solution for IBM PC/XT/AT and Personal System/2 compatible systems

- 100% hardware compatible with IBM's VGA card in all modes

- 100% EGA, CGA, MDA, Hercules Graphics, AT&T Model 6300 compatible

- Integrated bus interface for PC/XT/AT, and Micro Channel

- 800 by 600 x 16 colors, 640 by 400 x 256 colors

- 640 by 480 x 256 colors (512 Kbytes DRAM)

- 800 by 600 x 256 colors (512 Kbytes DRAM)

- 1024 by 768 x 16 colors interlaced graphics mode support - 8514 monitor compatible

- 1024 by 768 x 16 colors noninterlaced with external logic

- 132 column text modes, with 25, 43, or 50 rows

- Up to four simultaneous displayable fonts

- Special register locking for flat panel applications

- Lockable palette, RAMDAC, and overscan registers

- Display memory offset registers to control 4 Kbyte windows or 64 Kbyte windows

- Provides adapter video BIOS ROM decoding

- True 7, 8, 9, 10, and 16 pixel wide fonts

- Supports up to 1 Mbyte display memory addressing

- · Load up to 16 fonts

- Special underlining in color text mode

- Two additional bits for a total of 18 address bits for cursor location and start address

- · Special double scanning

- Special display enable or blanking output signal

- · Special border disable

- Page mode addressing for CRTC refresh cycles

- High performance FIFO memory architecture

- Includes 8- or 16-bit wide CPU data bus

- Support for external color lookup table (Palette Chip) with 256K available colors

- Pin for pin compatible with the PVGA1A (AT bus mode)

- · Enhanced virtual VGA support

- Up to 45 MHz maximum video clock rate

- Up to 56 MHz maximum memory clock rate

- 1.25 micron CMOS VLSI technology

- 100-pin Plastic Leadless Chip Carrier (PLCC) or Plastic Quad Flat Pack (PQFP)

JEDEC package

- Minimizes circuit board space requirements and lowers system cost

Western Digital is a registered trademark of Western Digital Corporation. All other marks mentioned herein belong to their respective companies.

# 1.2 DESCRIPTION

The Western Digital Imaging (WDI) WD90C00 is a 1.25 micron, 15,000 gate CMOS VLSI device designed to implement the IBM Personal System/2 Standard video modes along with all of the popular modes used in the IBM PC/AT family. The WD90C00 is designed to offer more improvements for a wider range of applications. These

enhancements include additional extended PR registers for EGA register level compatibility for analog and TTL monitors, high resolution interlaced graphics support, improved bus interface design, and an improved memory and video interface for higher performance.

FIGURE 1. PLCC AND PQFP PIN DIAGRAMS

| PIN | SIGNAL | PIN | SIGNAL | PIN | SIGNAL | PIN | SIGNAL |

|-----|--------|-----|--------|-----|--------|-----|--------|

| 1   | GND    | 26  | GND    | 51  | GND    | 76  | MCLK   |

| 2   | MD4    | 27  | A18    | 52  | VCC    | 77  | GND    |

| 3   | MD3    | 28  | A19    | 53  | VID4   | 78  | VCC    |

| 4   | MD2    | 29  | IOR    | 54  | VID3   | 79  | RAS10  |

| 5   | MD1    | 30  | IOW    | 55  | VID2   | 80  | CAS10  |

| 6   | MD0    | 31  | MRD    | 56  | VID1   | 81  | OE10   |

| 7   | EBROM  | 32  | MWR    | 57  | VID0   | 82  | RAS32  |

| 8   | DS16   | 33  | EIO    | 58  | WPLT   | 83  | CAS32  |

| 9   | BHE    | 34  | RDY    | 59  | PCLK   | 84  | OE32   |

| 10  | SFDBK  | 35  | IRQ    | 60  | HSYNC  | 85  | WE0    |

| 11  | EABUF  | 36  | RSET   | 61  | VSYNC  | 86  | WE1    |

| 12  | DA8    | 37  | DIR    | 62  | BLNK   | 87  | WE2    |

| 13  | DA9    | 38  | EDBUF  | 63  | MA8    | 88  | WE3    |

| 14  | DA10   | 39  | DA0    | 64  | GND    | 89  | MD15   |

| 15  | GND    | 40  | DA1    | 65  | MA7    | 90  | MD14   |

| 16  | DA11   | 41  | DA2    | 66  | MA6    | 91  | MD13   |

| 17  | DA12   | 42  | DA3    | 67  | MA5    | 92  | MD12   |

| 18  | DA13   | 43  | DA4    | 68  | MA4    | 93  | MD11   |

| 19  | DA14   | 44  | DA5    | 69  | MA3    | 94  | MD10   |

| 20  | DA15   | 45  | DA6    | 70  | MA2    | 95  | MD9    |

| 21  | EMEM   | 46  | DA7    | 71  | MA1    | 96  | MD8    |

| 22  | A15    | 47  | RPLT   | 72  | MA0    | 97  | MD7    |

| 23  | A16    | 48  | VID7   | 73  | VCLK2  | 98  | MD6    |

| 24  | A17    | 49  | VID6   | 74  | VCLK1  | 99  | MD5    |

| 25  | VCC    | 50  | VID5   | 75  | VCLK0  | 100 | VCC    |

**TABLE 1. PIN ASSIGNMENTS**

10-25-90

20-3

# 2.0 ARCHITECTURE

The WD90C00 is a highly integrated device that internally contains four major modules. These are the CRT Controller, the Sequencer, the Graphics controller and the Attribute Controller.

# CRT Controller

The CRT Controller maintains screen refresh functions for the various display modes defined by the programming of its registers either by the BIOS ROM resident firmware or from the application program. These screen refresh functions include display page control, cursor control, sync generation and resolution.

# Sequencer

The Sequencer functions as a timing generator for the AT bus or Micro Channel interface, in I/O or memory cycles. It also provides the character

clock and the dot clock for the CRT, Graphics and Attribute controllers.

### · Graphics Controller

The Graphics Controller manages data flow between video memory and the Attribute Controller during active display (non-blanked) periods. It also controls system microprocessor reads from and writes to the video memory, using the time slots defined by the Sequencer.

# Attribute Controller

The Attribute Controller modifies the CRT display data stream in graphics and character modes. It controls display attributes such as blinking, underlining, cursor, pixel panning, reverse video, overscan color and background or foreground color.

**FIGURE 2. SYSTEM BLOCK DIAGRAM**

*\\\*

### 3.0 WD90C00 INTERFACES

The WD90C00 has four major interfaces: the CPU and BIOS ROM interface, the DRAM Display Buffer interface, the Video and RAMDAC interface, and the Clock interface.

#### 3.1 CPU AND BIOS ROM INTERFACE

The WD90C00 is designed to operate in two different bus architecture configurations. These are the PC/AT Bus and the PS/2 Micro Channel Bus. The selection of the mode is dependant on the pin strapping upon power up that sets Configuration Register CNF(2).

When configured for AT or Micro Channel operation, the WD90C00 operates functionally in a manner that is conducive to PC/AT or Micro Channel interfacing respectively. The signal pins, memory maps, and I/O ports all operate to optimize this interface with minimal external circuitry.

The WD90C00 provides all the signals and decodes all the necessary memory and I/O addresses for either an 8 or 16 bit data bus. It also provides the necessary decoding of the Adapter Video BIOS ROM and has additional signals and registers to help with BIOS ROM page mapping as done on the IBM PS/2 Display adapter. Using the provided signals, the customer can implement designs which multiplex the address/data signals to the WD90C00 in 8 or 16 bit mode, control an 8 or 16 bit BIOS ROM, and generate the desired control and handshake signals such as -MEMCS16.

The I/O data path is eight bit. The memory display buffer data path can be eight or sixteen bits wide. EGA Planar modes have a mandatory eight bit data path with the CPU. Text modes, odd/even, and 256 color modes can support a sixteen bit data path if the video subsystem supports a 16 bit bus implementation. The WD90C00 will provide the necessary wait states for CPU accesses to the video memory. Wait states for I/O accesses and BIOS ROM accesses are not generated. Special I/O ports such as 46E8H (AT mode) and 102H for VGA Enable have been implemented internally in the

WD90C00. VGA Subsystem Enable port 3C3h (MCA mode) needs to be implemented externally.

# 3.2 DRAM DISPLAY BUFFER INTER-FACE

The WD90C00 has an optimized interface to the video memory display buffer. The video memory DRAMS can be considered as being organized as four planes. Three configurations of DRAMs exist for the WD90C00 where each plane can be configured as 64 Kbytes (256 Kbytes total), 128 Kbytes (512 Kbytes total), or 256 Kbytes (1 Mbyte total).

The Video memory address range can be up to 1 Mbyte depending on the configuration. Its range is usually from A000:0H to BFFF:FH. External circuitry can be used to map the video memory in different (up to) 1 Mbyte windows.

Eight 64K by 4 page mode DRAM chips are supported for the default IBM memory size. Sixteen 64K by 4 DRAMs and a multiplexer are needed to have a total of 512 KB DRAM. This configuration is needed to support extended video modes such as 640 by 480 x 256 colors and 1024 by 768 x 16 colors. Eight 256 KB by 4 DRAMs are needed to support 1 Mbyte total memory. The WD90C00 provides the support to access all of the available memory. As the WD90C00 has a separate memory clock, 36 MHz to 40 MHz clocks are needed to drive 120 ns DRAMs. With 100 ns DRAMs, up to a 44.9 MHz clock can be used. The WD90C00 can support up to a 56 MHz MCLK which allows it to support much higher extended resolutions such as an 800 by 600 x 256 color mode.

The combination of video clock and memory clock and DRAM speed will determine the video modes available. Usually, a 44.9 MHz MCLK and 44.9 MHz VCLK will support the 1024 by 768 resolution modes. A 42 MHz MCLK will be needed to support the extended 256 color modes but the 44.9 MHz is recommended. A 36 MHz MCLK and VCLK will support the 800 by 600 x 16 color mode.

//

# 3.2.1 DRAM Cycle Types

The WD90C00 will do standard RAS/CAS single cycle accesses to the DRAM during CPU writes and reads in graphics modes and alphanumeric modes. For CRTC display refresh cycles, the WD90C00 will do page mode access reads for all cycles in graphics modes. It will also do page mode reads to the DRAM when selected to do so to increase performance in alphanumeric modes. The default mode of DRAM access in alphanumeric mode is the standard single RAS/CAS cycle. The WD90C00 provides the necessary control signals and address/data lines to access the video memory as two 16 bit data interleaved banks. The WD90C00 will also refresh the DRAMs with 3 or 5 refresh cycles after every horizontal scan line.

#### 3.3 VIDEO AND RAMDAC INTERFACE

#### 3.3.1 RAMDAC

The WD90C00 is designed to connect to an analog CRT monitor through an external RAM-DAC, but it may also be used to drive other types of displays such as TTL monitors along with the correct register programming and clocks. All the necessary signals to interface to the video RAM-DAC are provided.

The video interface for a CRT is very dependent on the CRT requirements and the resolution and depth (bits/pixels) of the image desired. New monitors, such as multifrequency monitors, are less stringent because of the many sync frequencies available. The WD90C00 can be programmed to directly generate all the CRT signals for up to 8 bits/pixel (256 color). In addition,

external hardware can be added to allow higher display resolutions by trading off the number of bits/pixel such as a 1024 by 768 noninterlaced mode.

The Micro Channel Auxiliary Video Connector and the AT Feature Connector can be connected to the WD90C00. The WD90C00 also provides an input for a monitor type detection interface as done on the IBM VGA using comparators.

#### 3.4 CLOCK INTERFACE

The WD90C00 has four clock input signal pins. These are: separate memory clock, MCLK, which drives the DRAM timing in graphics and alpha modes; and the three video clocks, VCLK0, VCLK1, and VCLK2, which drive the video timing. WD90C00 also provides the option to externally control a multiplexer that supplies the video clock. The MCLK can also be selected as the video dot clock.

# 3.5 WD90C00 POWER-UP CONFIGURA-TION

The WD90C00 uses the memory data pins that are "strapped" to ground or Vcc through resistors to configure an internal configuration register upon powerup/reset. CNF(2) will determine whether the WD90C00 will operate in AT or Micro Channel Architecture (MCA) implementation. Other CNF bits configured by WD90C00 at power-up/reset are used as status bits, or for clock source control. For more information on WD90C00 power-up configuration, refer to the PR Register section of this data sheet.

# 4.0 PIN DESCRIPTION

The following tables provide WD90C00 pin definitions for the 100-Pin Plastic Leadless Chip Carrier (PLCC) and Plastic Flat Pack (PQFP) package.

The WD90C00 mnemonics are used. For more design details in AT or Micro Channel modes refer to the application notes and reference section of this document.

| PIN NO | PIN SYMBOL | TYPE    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|--------|------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|        | POWER ON   |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 36     | RSET       | I       | RESET: This signal input will reset the WD90C00 in order for the WD90C00 to initialize during Reset. PR registers PR1, PR11, and CNF are initialized at power-up reset based on the logic level on the MD(7:0), MD(15:11) bus as determined by pull-up/pull-down resistors. Outputs EABUF and EDBUF are tri-stated during reset. The active high reset pulse width should be at least ten MCLK clock periods.                                                                                           |  |  |  |

|        | C          | LOCK SE | LECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 76     | MCLK       | 1       | MEMORY CLOCK: This clock signal determines the VGA graphics and alpha mode video DRAM read/write access timing as well as system microprocessor I/O and memory timing. MCLK should be equal to or greater than VCLK. It is 36 to 40 MHz for 120 ns DRAMs, and recommended to be 44.9 MHz for 100 ns DRAMs.                                                                                                                                                                                              |  |  |  |

| 74     | VCLK1      | I/O     | VIDEO CLOCK 1: This pin can be either the second video display clock input or an output selection signal to the external clock selection module. Pin direction is determined on Reset by a pull-up/down register on pin MD3. A VCLK1 input frequency of 28.322 MHz is used to display 720 pixels per horizontal line. When it is an output, VCLK1 can be an active low pulse during I/O writes to port 3C2H or the state of 3C2H bit 2 as per PR15(5). Refer to the Configuration Register description. |  |  |  |

| 73     | VCLK2      | 1/0     | VIDEO CLOCK 2: This pin can be a third video display clock input or an output to external clock selection module. Pin direction is programmed simultaneously with that of VCLK1. It acts as either a user defined external clock input, or as an output reflecting the content of bit PR2(1) or the state of 3C2H bit 3 as per PR15(5) if CNF(3) is set to 1. Refer to the Configuration Register description.                                                                                          |  |  |  |

| PIN NO.                                                                          | PIN SYMBOL                                                           | TYPE                                                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                  | CLOCK SELECTION (CONT)                                               |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 75                                                                               | VCLK0                                                                | 1                                                                 | VIDEO CLOCK 0: This input is the video display clock for alphanumeric and graphics display modes. Typically, VCLK0 is 25.175 MHz to display 640 pixels per horizontal display line. The Miscellaneous Output Register (3C2H) bits 3 and 2 when both are set to 0 will select this clock.                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                                                                                  |                                                                      | CPU                                                               | ADDRESS BUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 28<br>27<br>24<br>23<br>22                                                       | A19<br>A18<br>A17<br>A16<br>A15                                      |                                                                   | ADDRESS ONLY BUS A(19:15): These active high inputs form the high-order five bits of video memory address. These addresses (19:16) are not decoded during I/O accesses in AT or MCA implementation. These inputs are directly connected to the system bus.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                                                                                  |                                                                      | CP                                                                | U DATA BUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 20<br>19<br>18<br>17<br>16<br>14<br>13<br>12<br>46<br>45<br>44<br>43<br>42<br>41 | DAI5(*) DA14 DA13 DA12 DA11 DA10 DA9 DA8 DA7 DA6 DA5 DA4 DA3 DA2 DA1 | /O<br> /O<br> /O<br> /O<br> /O<br> /O<br> /O<br> /O<br> /O<br> /O | DATA/ADDRESS BUS DA(15:0): These signals comprise an active high multiplexed data/address bus for I/O and memory accesses. Only the low eight bits are used for data during I/O read and write cycles. During every I/O read and write, the voltage level on DA15 is used to help determine the monitor type, and can be read at port 3C2H bit 4. A logic 0 or logic 1 on DA15 places a logic 0 or a logic 1 into bit 4 of the Input Status Register 0, respectively. Refer to the general register description for more information.  NOTE: "*" DA15 signal is multiplexed with data bit 15 and CRT monitor sense input for auto monitor detection. |  |  |  |

| 39                                                                               | DA0                                                                  | I/O<br>CBU                                                        | CONTROL PLIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 21                                                                               | ЕМЕМ                                                                 | I                                                                 | ENABLE DISPLAY MEMORY: This signal is active high in both Micro Channel and AT modes. In AT Mode, EMEM enables video memory accesses. BIOS ROM accesses are not controlled by EMEM. If the video memory is within the lowest 1MB of the processor address space, EMEM signal must be active during video memory access. Otherwise, EMEM should be generated by external logic when the WD90C00 video memory is accessed. During AT Bus refresh time, EMEM can be connected to REFRESH to disable the WD90C00. In Micro Channel mode this signal enables I/O and video memory access. External logic is required to implement the function EMEM.      |  |  |  |

| PIN NO. | PIN SYMBOL     | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10      | ROM16<br>SFDBK | 0    | 16 BIT WIDE BIOS ROM: In AT mode this active low status signal is the inverted value of register PR1(1), which determines BIOS ROM data path width selection. It may be used to control data buffers for a 16 bit data path BIOS ROM and to generate the signal -MEMCS16 in AT mode. In Micro Channel mode, SFDBK is the unlatched address decode (active low) when a memory, I/O, or BIOS ROM access is done from the system bus and may be considered as adapter or VGA feedback.                                                                                                                    |

| 34      | RDY            | 0    | READY: An active high output which signals to the system processor that a memory access is completed and is only used to add wait states to the CPU bus cycles during video memory accesses. It is pulled inactive by WD90C00 to allow additional time to complete a bus operation. This signal is not generated on I/O cycles and accesses to the BIOS ROM. This is a tristate signal.                                                                                                                                                                                                                |

| 35      | IRQ            | 0    | INTERRUPT REQUEST: It is enabled via bit 5 in the Vertical Retrace End register. It is active high in AT mode and active low in Micro Channel mode. When the end of a Vertical Display occurs, this signal will transition active at the start of vertical retrace, causing the interrupt. It will stay latched until CRTC11 bit 4 clears it. In a AT mode, IRQ is tri-state upon power up reset and may be enabled by PR14(7). In Micro Channel mode, PR14(7) will power up IRQ enabled. This is a tri-state signal.                                                                                  |

| 8       | DS16           | 0    | DATA SIZE 16: Active low enable for 16 bit video memory word transfers. It is a mode dependent signal. In AT mode, DS16 is a status signal as programmed in bit PR1(2) (and other registers) and is used to control the high and low byte 16 bit external data buffers. See the PR Register (PR1) description for further details. This status signal is also used to generate -MEMCS16 using external logic for AT mode designs. In Micro Channel mode, the signal is active only during BIOS ROM accesses (if enabled) by PR(1) and/or during memory 16 bit data path access (if enabled by PR1(2)). |

| PIN NO. | PIN SYMBOL      | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|-----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33      | EIO<br>VGASETUP | 1    | ENABLE I/O: In AT mode, this active low signal enables I/O accesses to the WD90C00. In Micro Channel mode, this signal is the VGASETUP input pin and is connected to the latched card setup or the VGA setup. The externally designed system I/O port signals (96H for Adapter card or 94H bit 5 for system board design) is connected to the EIO pin. When this signal is high, the WD90C00 is enabled or in the operating state. An active low signal on this pin puts the WD90C00 into set up mode. During the set up mode, write logic 1H to WD90C00 internal port 102H to awaken the WD90C00 after power on. |

| 9       | BHE             | I    | BUS HIGH ENABLE: In both AT and MCA mode, this active low signal enables and indicates a 16 bit transfer of data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 31      | MRD<br>M/-I/O   |      | MEMORY READ: In AT mode, this is an active low memory read strobe. It is asserted in 8/16 bit memory read cycles. In Micro Channel mode, the signal is called M/-IO. It distinguishes between memory and I/O cycles. When (M/-I/O) is high, a memory cycle is in process. A low on (M/-IO) shows that an I/O cycle is in process.                                                                                                                                                                                                                                                                                 |

| 32      | MWR<br>-S0      | 1    | MEMORY WRITE: The Active low memory write strobe in AT mode for 8/16 bit data transfers. In Micro Channel mode, it becomes -S0 and is the channel status signal which indicates the start and type of a channel cycle. Along with -S1, M/-IO, and -CMD signals, it is decoded to interpret I/O and memory commands.                                                                                                                                                                                                                                                                                               |

| 29      | IOR<br>-S1      | I    | I/O READ: Active low I/O read strobe in AT mode. It is asserted in I/O read bus cyclesS1 is the alternate mnemonic used in Micro Channel mode to indicate the start and type of a channel cycle.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 30      | IOW<br>-CMD     | 1    | I/O WRITE: Active low strobe. In AT mode, the strobe signals an I/O write cycle. In Micro Channel mode it is synonymous with -CMD; address bus validity is signaled by -CMD going low while the rising edge of -CMD indicates the end of a Micro Channel bus cycle.                                                                                                                                                                                                                                                                                                                                               |

| PIN NO.                                                                                 | PIN SYMBOL                                                            | TYPE     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                         | VID                                                                   | DRY DATA |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 89<br>90<br>91<br>92<br>93<br>94<br>95<br>96<br>97<br>98<br>99<br>2<br>3<br>4<br>5<br>6 | MD15 MD14 MD13 MD12 MD11 MD10 MD9 MD8 MD7 MD6 MD5 MD4 MD3 MD2 MD1 MD0 | I/O      | DISPLAY MEMORY DATA MD(15:0): These lines are the data bus to the video display DRAMS. Data lines MD(7:0) are pulled up or down with resistors to provide set up information on power-up (reset) as follows:  Power-Up Register MD Function (Bit)  15 EGA SW4 PR11(7)+  14 EGA SW3 PR11(6)+  13 EGA SW2 PR11(5)+  12 EGA SW1 PR11(4)+  11 ANALOG/TTL Display CNF(8) *  7 General Purpose CNF(7) *  6 General Purpose CNF(6) *  5 General Purpose CNF(6) *  4 General Purpose CNF(5) *  NOTE:  "*" Pulldown resistor sets these bits to logic 1.  "+" Pullup resistor sets these bits to logic 1.  For more details refer to PR Registers. |

|                                                                                         | VIDE                                                                  | O MEMOR  | Y ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 63<br>65<br>66<br>67<br>68<br>69<br>70<br>71                                            | MA8+<br>MA7+<br>MA6+<br>MA5+<br>MA4+<br>MA3+<br>MA2+<br>MA1+<br>MA0+  | 0        | MEMORY ADDRESS MA(8:0): Display memory DRAM address.  NOTE: "+" For testing purposes, these pins can be tri-stated by setting PR Register PR4(4) = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                         | VIDEO ME                                                              | MORY CO  | NTROL SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 80<br>83                                                                                | CAS10+<br>CAS32+                                                      | 0        | COLUMN ADDRESS STROBE: Active low<br>Memory Maps 1 & 0 CAS output signal.<br>COLUMN ADDRESS STROBE: Active low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 79                                                                                      | RAS10+                                                                | 0        | memory maps 3 & 2 CAS output signal. ROW ADDRESS STROBE: Active low Memory Maps 1 & 0 RAS output signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PIN SYMBOL                       | TYPE      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIDEO M                          | EMORY CO  | NTROL SIGNALS                                                                                                                                                                                                                                                                                                                                    |

| RAS32+                           | 0         | ROW ADDRESS STROBE: Active low Memory Maps 3 & 2 RAS output signal.                                                                                                                                                                                                                                                                              |

| OE10+                            | 0         | OUTPUT ENABLE: Active low Memory Maps                                                                                                                                                                                                                                                                                                            |

| ŌE32+                            | 0         | 1 & 0 DRAM output enable. OUTPUT ENABLE: Active low Memory Maps 3 & 2 DRAM output enable.                                                                                                                                                                                                                                                        |

| WE0+                             | 0         | WRITE ENABLE: Active low Write Enable to DRAM bank 0, upper byte (Memory map 0).                                                                                                                                                                                                                                                                 |

| WE1+                             | 0         | WRITE ENABLE: Active low Write Enable for DRAM bank 0, upper byte (Memory map 1)                                                                                                                                                                                                                                                                 |

| WE2+                             | 0         | WRITE ENABLE: Active low Write Enable for DRAM bank 1, lower byte (Memory map 2).                                                                                                                                                                                                                                                                |

| WE3+                             | 0         | WRITE ENABLE: Active low Write Enable for DRAM bank 1, upper byte (Memory map 3).                                                                                                                                                                                                                                                                |

|                                  |           | NOTE: 1. "+" For testing purposes, these pins can be tri-stated by setting PR Register PR4(4) = 1.                                                                                                                                                                                                                                               |

| F                                | RAMDAC IN |                                                                                                                                                                                                                                                                                                                                                  |

| VID7*<br>VID6*<br>VID5*<br>VID4* | 0         | VIDEO VID(7:0): Pixel video data output to DAC.  NOTE:                                                                                                                                                                                                                                                                                           |

| VID3*<br>VID2*<br>VID1*<br>VID0* |           | "*" For testing purposes, these pins can be tri-<br>stated by setting PR Register PR4 (5) = 1.                                                                                                                                                                                                                                                   |

| RPLT                             | 0         | READ PALETTE: Video DAC register and color palette read signal. Active low during I/O read to addresses at 3C6H, 3C8H, and 3C9H.                                                                                                                                                                                                                 |

| WPLT                             | 0         | WRITE PALETTE: Video DAC register and color palette write signal. Active low during I/O write to addresses at 3C6H-3C9H.                                                                                                                                                                                                                         |

| PCLK                             | 0         | PIXEL CLOCK: Video pixel clock output used by the RAMDAC to latch video signals VID(7:0). Its source is one of the video clock inputs: VCLK0, VCLK1, or VCLK2 as determined by the Miscellaneous Output register. Note that VCLK0, 1, or 2 is divided by two in 320/360 pixel display mode to derive PCLK. MCLK can be the source of this clock. |

| BLNK *                           | 0         | BLANK: Active low RAMDAC blank pulse.  NOTE:  "*" For testing purposes, this pin can be tri-                                                                                                                                                                                                                                                     |

| BLNK                             | *         | * O                                                                                                                                                                                                                                                                                                                                              |

20-13

| PIN NO.     | PIN SYMBOL | TYPE     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-------------|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CRT CONTROL |            |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 60          | HSYNC+     | 0        | HORIZONTAL SYNC: Display monitor horizontal synchronization pulse. Active high or low depending on the Miscellaneous register programming. SEE NOTE BELOW.                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 61          | VSYNC+     | 0        | VERTICAL SYNC: Active high display monitor vertical synchronization pulse. It is active high or low, depending on the Miscellaneous Output Register.  NOTES:  1. "+" For testing purposes, these pins can be tri-stated by setting PR Register PR4(5)=1.                                                                                                                                                                                                                                                                                        |  |

|             | Bi         | OS ROM ( |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 7           | EBROM      | 0        | ENABLE BIOS ROM ACCESS: In both AT and Micro Channel modes this signal is active (low) during memory reads in the address range (C000:0H-C7FF:FH) if enabled by bit PR1(0). It is not active for accesses to addresses in the range C600:0H-C67F:FH. However, the C600:0H-C67F:FH address range can be mapped in to increase BIOS space by setting PR17(0) = 0. In AT mode only, a write to the WD90C00 internal I/0 port address 46E8H causes this signal to be used as a write strobe for an external register used in BIOS ROM page mapping. |  |

|             | В          | ONTROL   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 11          | EDBUFH     | 0        | ENABLE ADDRESS BUFFER: This active low signal permits control of an external address buffer for multiplexing aqyddress and data to WD90C00. It is tri-stated while Reset is active. When in MCA implementation, this output becomes the high byte data bus enable signal during the 16 bit data transfers and is referred as EDBUFH.                                                                                                                                                                                                            |  |

| 38          | EDBUF      | 0        | ENABLE DATA BUFFER: Allows control of an external data buffer for multiplexing address and data to WD90C00. It is tri-stated while Reset is active.                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 37          | DIR        | 0        | DIRECTION CONTROL: Active high Direction Control for reads of the DA(15:0) data bus in AT and MCA implementation. The default state is low until a read cycle occurs, and the WD90C00 will drive DIR high to change the direction of the data buffers.                                                                                                                                                                                                                                                                                          |  |

| PIN NO. | PIN SYMBOL       | TYPE | DESCRIPTION |  |  |  |

|---------|------------------|------|-------------|--|--|--|

|         | POWER AND GROUND |      |             |  |  |  |

| 25      | VCC              |      | +5VDC       |  |  |  |

| 52      | VCC              |      | +5VDC       |  |  |  |

| 78      | VCC              |      | +5VDC       |  |  |  |

| 100     | VCC              | _    | +5VDC       |  |  |  |

| 1       | GND              | _    | Ground      |  |  |  |

| 15      | GND              |      | Ground      |  |  |  |

| 26      | GND              |      | Ground      |  |  |  |

| 51      | GND              |      | Ground      |  |  |  |

| 64      | GND              |      | Ground      |  |  |  |

| 77      | GND              |      | Ground      |  |  |  |

20-15

# 5.0 ABSOLUTE MAXIMUM RATINGS

| Ambient temperature under bias | 0 °C to 70 °C     |

|--------------------------------|-------------------|

| Storage temperature            | - 40 °C to 125 °C |

| Voltage on all inputs          |                   |

| and outputs to Vss             | - 0.3 to 7 Volts  |

| Power dissipation              | 1.0 Watt          |

# NOTE

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

# 6.0 STANDARD TEST CONDITIONS

The characteristics below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to Vss (0V Ground). Positive current flows into the reference pin.

| Operating tempera-   |                    |

|----------------------|--------------------|

| ture range           | 0° C to 7 °C       |

| Power supply voltage | 4.75 to 5.25 Volts |

# 7.0 D.C CHARACTERISTICS

| SYMBOL | PARAMETER                                         | MIN.  | MAX  | UNITS | CONDITIONS                      |

|--------|---------------------------------------------------|-------|------|-------|---------------------------------|

| V(IL)  | Input Low Voltage                                 |       | 0.8  | V     | VCC=5V±5%                       |

| V(IH)  | Input High Voltage                                | 2.0   |      | V     | VCC=5V±5%                       |

| I(IL)  | Input Low Current                                 |       | ±10  | uA    | VIN=0.0V                        |

| I(IH)  | Input High Current                                |       | ±10  | uA    | VIN=VCC                         |

| V(OL)  | Output Low Voltage                                |       | 0.4  | V     | IOL +4.0mA <sup>1</sup>         |

| V(OH)  | Output High Voltage                               | 2.4   |      | V     | IOH=4.0mA <sup>1</sup>          |

| I(OZ)  | High Impedance<br>Leakage Current                 | -10.0 | 10.0 | uA    | ov                              |

| I(CC)  | Stand By Current<br>(All Inputs at TTL<br>Levels) |       | 22   | mA    | VCC=5.25 VDC<br>TA=0 °C, Static |

| I(DD)  | Operating current                                 |       | 130  | mA    | VCC=5.25V,<br>MCLK=VCLK=45 MHz  |

| C(IN)  | Input Capacitance                                 |       | 10   | pF    | FC=1 MHz                        |

| C(OUT) | Output Capacitance                                |       | 10   | pF    | FC=1 MHz                        |

**TABLE 2. DC CHARACTERISTICS**

# **NOTES**

- 1. WD90C00 outputs have 4.0 mA maximum source and sink capability except for pin RDY = 24.0 mA sink and 4.0 mA source and pin IRQ = 24.0 mA sink and 4.0 mA source.

- 2. Pullups on MD(0:15), DA(0:15),  $\overline{\text{EDBUF}}$ ,  $\overline{\text{EABUF}}$  = 100 K ohms. Pullup on  $\overline{\text{BHE}}$  = 50 K ohms.

# 8.0 AC TIMING CHARACTERISTICS

$C_L$  = load capacitance = 70 pf unless specified otherwise.

t=1/MCLK in all modes Units are in nanoseconds (ns).

| NUMBER       | PARAMETER                                                                         | MIN    | MAX  | NOTES |  |  |

|--------------|-----------------------------------------------------------------------------------|--------|------|-------|--|--|

| RESET TIMING |                                                                                   |        |      |       |  |  |

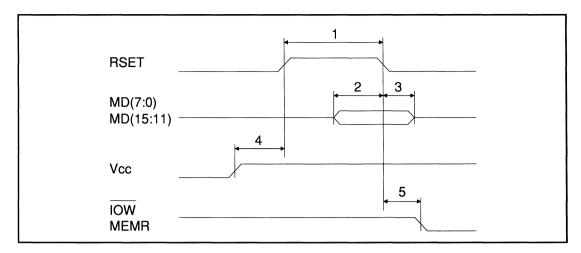

| 1            | Reset Pulse Width                                                                 | 10t    |      | 1     |  |  |

| 2            | MD Setup to RSET low                                                              | 2t     |      |       |  |  |

| 3            | MD Hold from RSET low                                                             | 2t     |      |       |  |  |

| 4            | Vcc high to RSET high setup                                                       | 100    |      |       |  |  |

| 5            | RSET low to first MRD/ IOW                                                        | 10t    |      |       |  |  |

|              | CLOCK TIMING                                                                      |        |      |       |  |  |

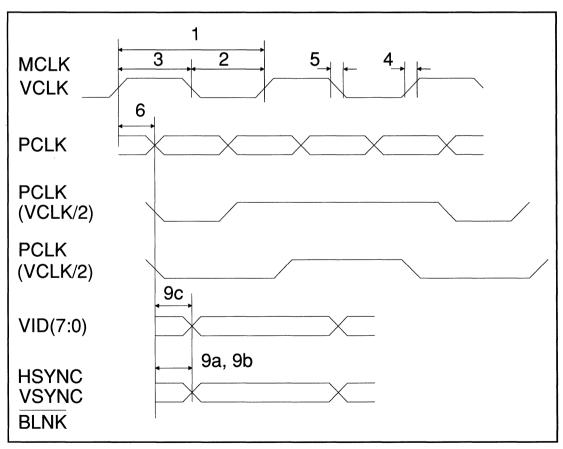

| 1            | Input Clock (MCLK or VCLK) Period                                                 | t      | t    |       |  |  |

| 2            | Clock low                                                                         | 40%t   |      | 2     |  |  |

| 3            | Clock high                                                                        |        | 60%t | 2     |  |  |

| 4            | Clock Rise Time                                                                   |        | 3    | 3     |  |  |

| 5            | Clock Fall Time                                                                   |        | 3    | 3     |  |  |

| 6            | Input VCLK to PCLK Delay                                                          |        | 13   |       |  |  |

| 9a           | PCLK to Hsync and Vsync Delay                                                     |        | 6.5  |       |  |  |

| 9b           | PCLK to BLNK Delay                                                                |        | 6.5  |       |  |  |

| 9c           | PCLK to VID(7:0) Delay                                                            |        | 3    |       |  |  |

|              | AT MODE I/O & MEMORY READ/WRITE                                                   | TIMING |      |       |  |  |

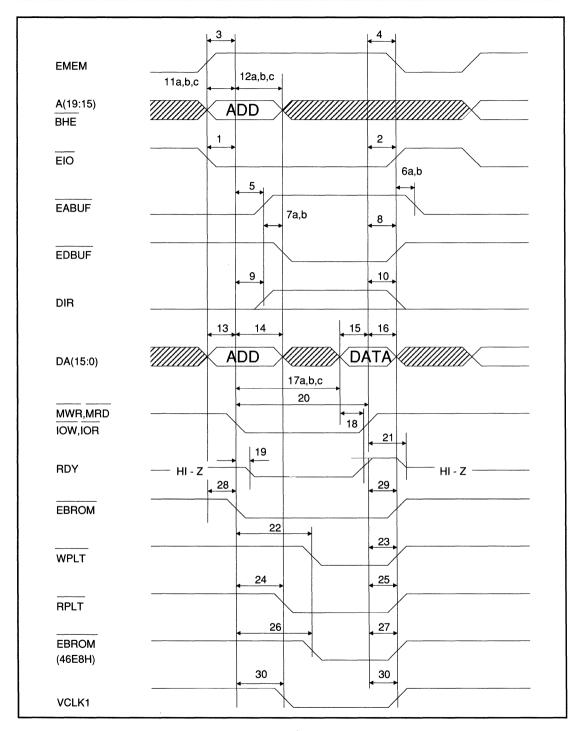

| 1            | EIO setup to IOR and IOW active                                                   | 8      |      |       |  |  |

| 2            | EIO hold from IOR and IOW inactive                                                | 5      |      |       |  |  |

| 3            | EMEM setup to $\overline{MR}$ and $\overline{MW}$ active                          | 4      |      |       |  |  |

| 4            | EMEM hold from $\overline{MR}$ and $\overline{MW}$ inac-                          |        |      |       |  |  |

|              | tive                                                                              | 4      |      |       |  |  |

| 5            | $\overline{EABUF}$ inactive from $\overline{IOR}/\overline{W}$ , $\overline{MR}/$ |        |      |       |  |  |

|              | W active                                                                          |        | 30   |       |  |  |

| 6a           | EABUF active from EDBUF inactive                                                  |        |      |       |  |  |

|              | (I/O R&W)                                                                         |        | 21   |       |  |  |

| 6b           | EABUF active from EDBUF inactive                                                  |        |      |       |  |  |

|              | (M R&W)                                                                           |        | 15   |       |  |  |

| 7a           | EDBUF active from EABUF inactive                                                  |        |      |       |  |  |

| •            | (I/O R&W)                                                                         |        | 13   |       |  |  |

| 7b           | EDBUF active from EABUF inactive                                                  |        |      |       |  |  |

|              | (M R&W)                                                                           |        | 35   |       |  |  |

**TABLE 3. AC TIMING CHARACTERISTICS**

- 1. The MCLK should be running with the reset applied.

- 2. Measured at 1.4V.

- 3. Measured between 0.8V and 2.0V.

| NUMBER | PARAMETER                                                                         | MIN     | MAX     | NOTES |

|--------|-----------------------------------------------------------------------------------|---------|---------|-------|

| AT     | MODE I/O & MEMORY READ/WRITE TIMING                                               | (CONTIN | UED)    |       |

| 8      | EDBUF inactive from IOR/ W, MR/                                                   |         |         |       |

|        | W inactive                                                                        |         | 21      |       |

| 9      | DIR active from IOR and MR active                                                 |         | 24      |       |

| 10     | DIR inactive from IOR and MR inac-                                                |         |         |       |

|        | tive                                                                              |         | 21      |       |

| 11a    | $\overline{BHE}$ setup to $\overline{MR}$ and $\overline{MW}$ active              | 4       |         |       |

| 11b    | Address setup to IOR and IOW ac-                                                  |         |         |       |

|        | tive                                                                              | 8       |         |       |

| 11c    | Address setup to MR and MW ac-                                                    |         |         |       |

|        | tive                                                                              | 4       |         |       |

| 12a    | BHE hold to MR and MW active                                                      | 6       |         |       |

| 12b    | Address hold to IOR and IOW active                                                | 4       |         |       |

| 12c    | Address hold to $\overline{MR}$ and $\overline{MW}$ active                        | 6       |         |       |

| 13     | DA(15:0) valid address setup to                                                   |         |         |       |

|        | $\overline{IOR}/\overline{W}, \overline{MR}/\overline{W}$                         | 13      |         |       |

| 14     | DA(15:0) valid address hold from                                                  |         |         |       |

|        | $\overline{IOR}/\overline{W}, \overline{MR}/\overline{W}$                         | 4       |         |       |

| 15     | Data setup to IOW inactive                                                        | 10      |         |       |

| 16     | Data hold from $\overline{IOR}/\overline{W}$ , $\overline{MR}/\overline{W}$ inac- |         |         |       |

|        | tive                                                                              | 8       |         |       |

| 17a    | Data valid from IOR active                                                        |         | 2t + 42 |       |

| 17b    | Data valid (CAS32 inactive) from                                                  |         |         |       |

|        | MR active                                                                         | 11.5t   |         |       |

| 17c    | Write data valid from $\overline{MW}$ active                                      | 4.5t-50 |         | 4     |

| 18     | Read data setup to RDY high                                                       | 3.5t-40 |         | 5     |

| 19     | RDY inactive from MR and MW ac-                                                   |         |         |       |

|        | tive                                                                              |         | 13      |       |

| 20     | RDY active from $\overline{MW}$ , $\overline{MR}$ active                          | 15t     |         |       |

| 21     | RDY tri-state from MW, MR inactive                                                |         | 10      |       |

| 22     | WPLT active from IOW active                                                       |         | 2t+35   |       |

| 23     | WPLT inactive from IOW inactive                                                   |         | 22      |       |

| 24     | RPLT active from IOR active                                                       |         | 31      |       |

| 25     | RPLT inactive from IOR inactive                                                   |         | 21      |       |

| 26     | EBROM active from IOW active                                                      |         | 01.00   |       |

| 07     | (46E8)                                                                            |         | 2t+29   |       |

| 27     | EBROM inactive from IOW inactive                                                  |         | 20      |       |

| 28     | EBROM active from valid address                                                   |         | 20      |       |

| 29     | EBROM inactive from MRD inactive                                                  |         | 23      |       |

| 30     | VCLK1 (as output) delay from IOW                                                  |         | 2t+33   |       |

**TABLE 3. AC TIMING CHARACTERISTICS (CONT)**

- 4. This spec includes 50 ns worst case delay from DA to MD bus.5. This spec includes 40 ns worst case delay from MD to DA bus.

| NUMBER | PARAMETER                                                                         | MIN       | MAX  | NOTES |

|--------|-----------------------------------------------------------------------------------|-----------|------|-------|

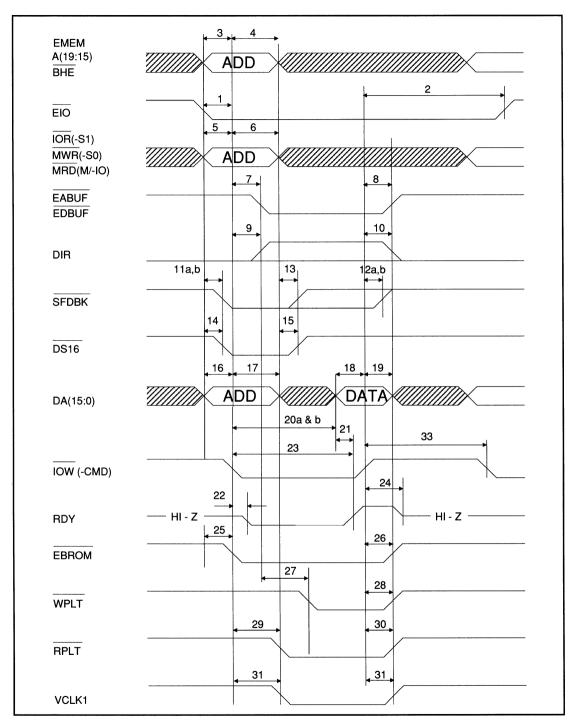

| N      | MICRO CHANNEL I/O & MEMORY READ AND \                                             | WRITE TIM | IING |       |

| 1      | CDSETUP setup to CMD active                                                       | 0         |      |       |

| 2      | CDSETUP hold from CMD inative                                                     | 4         |      |       |