PVGA1A Video Graphics Array Device

## TABLE OF CONTENTS

| Section | Title                                                    | Page   |

|---------|----------------------------------------------------------|--------|

| 1.0     |                                                          | 19-1   |

|         | 1.1 Description                                          | 19-1   |

|         | 1.2 Features                                             | 19-1   |

| 2.0     | SCOPE                                                    | 19-4   |

|         | 2.1 PVGA1A Description                                   | 19-4   |

|         | 2.2 PVGA1A Modules                                       | 19-4   |

| 3.0     | PVGA1A INTERFACES                                        | 19-5   |

|         | 3.1 CPU And BIOS ROM Interfaces                          | 19-5   |

|         | 3.2 DRAM Interface                                       | 19-5   |

|         | 3.3 Video Interface                                      | 19-5   |

|         | 3.4 Clock Interface                                      | 19-6   |

|         | 3.5 PVGA1A Power-Up Configuration                        | 19-6   |

| 4.0     | PIN DESCRIPTION                                          | 19-7   |

| 5.0     | RATINGS/DC PARAMETERS                                    | 19-15  |

|         | 5.1 DC Characteristics                                   | 19-15  |

|         | 5.2 AC Characteristics                                   | 19-16  |

| 6.0     | TIMING DIAGRAMS.                                         | 19-18  |

|         | 6.1 AT Mode                                              | 19-18  |

|         | 6.2 Microchannel Mode.                                   | 19-24  |

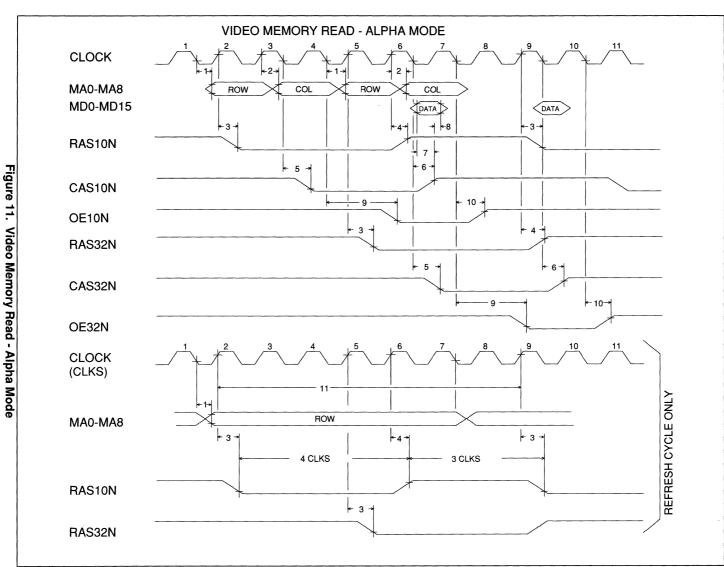

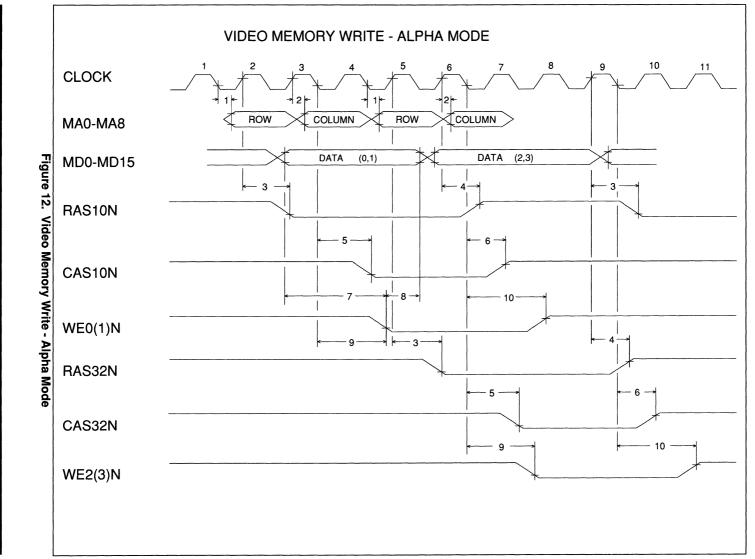

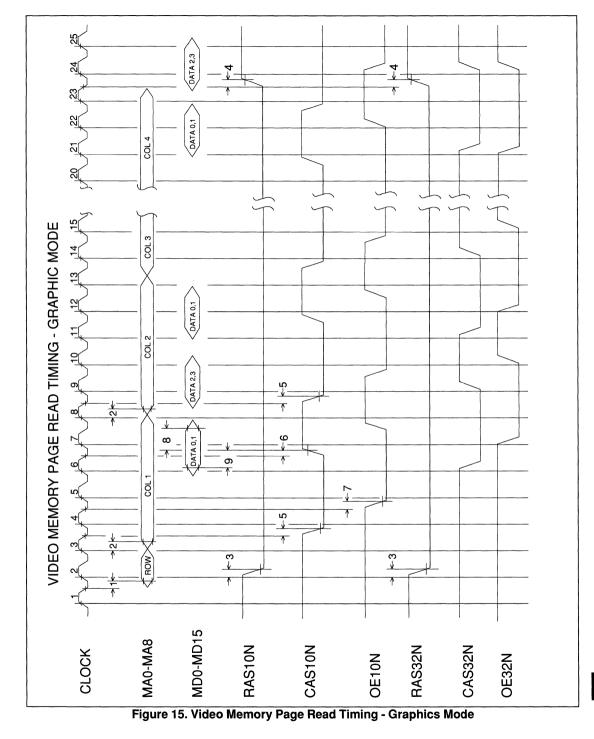

|         | 6.3 Video Memory                                         | 19-32  |

|         | 6.4 CRT Timing                                           | 19-42  |

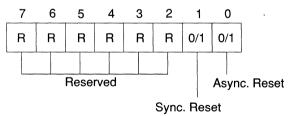

| 7.0     | VGA REGISTERS                                            | 19-44  |

|         | 7.1 General Registers                                    | 19-46  |

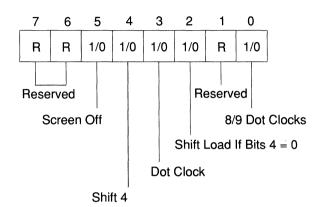

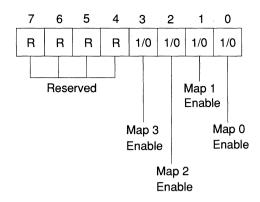

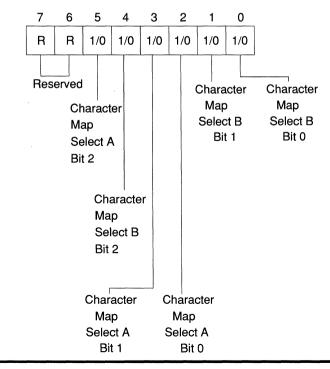

|         | 7.2 Sequencer Registers.                                 | 19-50  |

|         | 7.3 CRT Controller Registers                             | 19-55  |

|         | 7.4 Graphics Controller Registers                        | 19-64  |

|         | 7.5 Attribute Controller Registers                       | 19-72  |

|         | 7.6 Compatibility Registers                              | 19-77  |

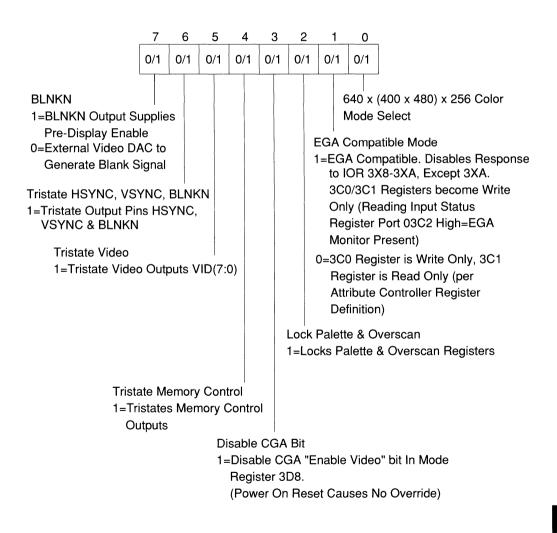

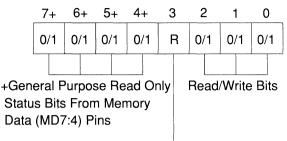

| 8.0     | PARADISE REGISTERS                                       | 19-84  |

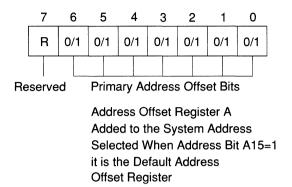

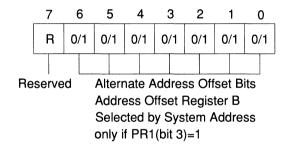

|         | 8.1 PR0A, PR0B - Address Offset Registers                | 19-84  |

|         | 8.2 PR1 - Memory Size Register                           |        |

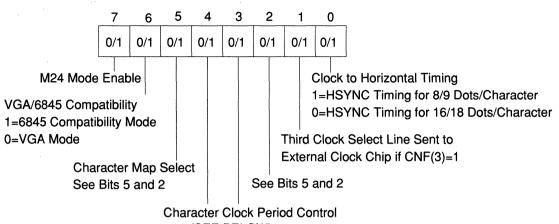

|         | 8.3 PR2 - Video Monitor Timing Register                  | 19-90  |

|         | 8.4 PR3 - CRT Control And Group Lock Register            | 19-91  |

|         | 8.5 PR4 - Video Monitor Output Control Register          | 19-93  |

|         | 8.6 PR5 - Status/Paradise Registers Lock/Unlock Register | 19-95  |

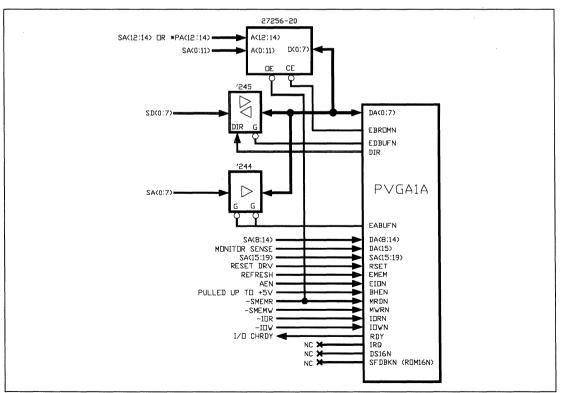

| 9.0     | APPLICATIONS.                                            | 19-98  |

|         | 9.1 I/O Port 3C3H Video Subsystem Enable Register        |        |

| REFEREN | NCES                                                     | 19-111 |

## LIST OF ILLUSTRATIONS

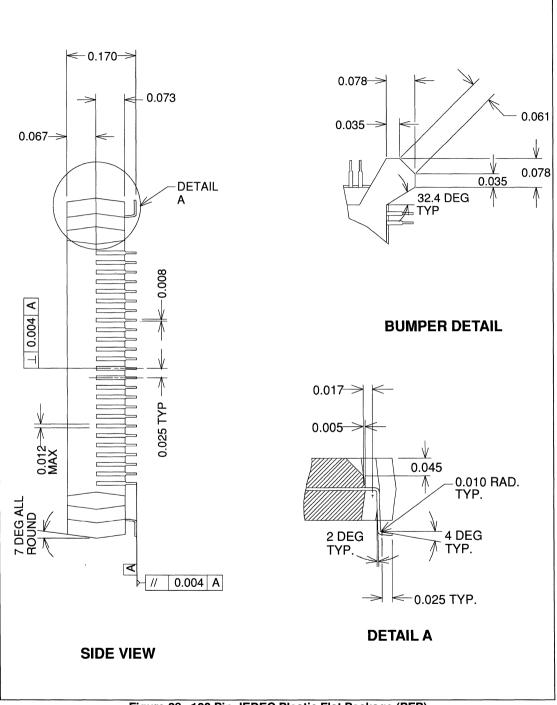

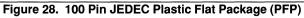

#### Figure Title Page 16-Bit PC/AT Interface with 8-Bit BIOS .....19-99 100 Pin JEDEC Plastic Flat Package (PFP) .....19-109 100 Pin JEDEC Plastic Flat Package (PFP) .....19-110

## **1.0 INTRODUCTION**

### 1.1 DESCRIPTION

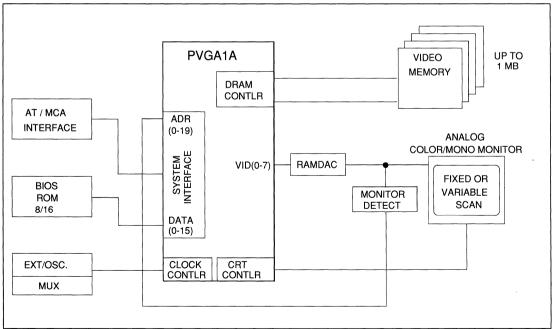

The Paradise Video Graphics Array (PVGA1A) is designed to enhance the VGA subsystem in IBM PC AT Bus or Personal System 2 (PS/2) Micro Channel compatible applications. The AT or Micro Channel Bus interface switch is set through the Configuration Register after power up.

Other improvements, such as an 8/16 bit wide CPU data path, a DRAM controller for up to 1 MB of video memory space, support for an 8/16 bit wide BIOS ROM data path, auto monitor detect input, and a CRT controller for fixed or variable scan analog monitors, are offered as standard features.

## 1.2 FEATURES

- Provides single Chip Video Graphics Solution for IBM PC / XT / AT and Personal System/2 compatible systems

- 100% hardware compatible with IBM's VGA card in all modes

- 100% IBM VGA and EGA BIOS compatible

- 100% CGA, MDA, Hercules Graphics, AT&T Model 6300 compatible

- Integrated bus interface for PC / XT / AT, Micro Channel

- High performance FIFO memory architecture

- Includes 8- or 16-bit wide CPU data bus

- 800 by 600 by 16 colors, 640 x 400 x 256 colors

- 640 by 480 by 256 colors (512K DRAM)

- 132 column text modes, with 25, 43, or 50 rows

- Support for external Color Lookup Table (Palette Chip) with 256 Kbyte available colors

- Up to 40 MHz maximum video clock rate

- 1.25 Micron CMOS VLSI technology

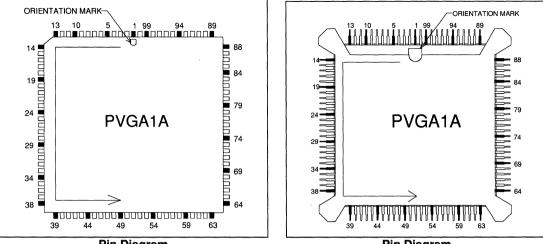

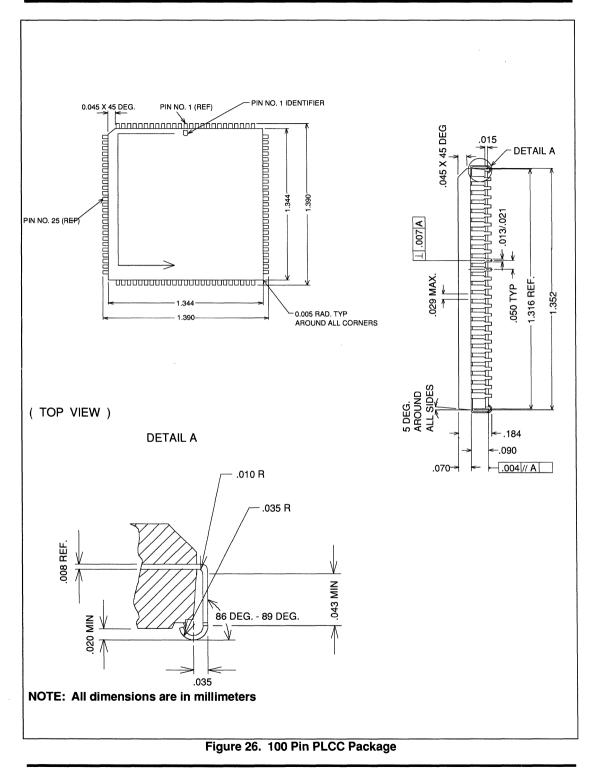

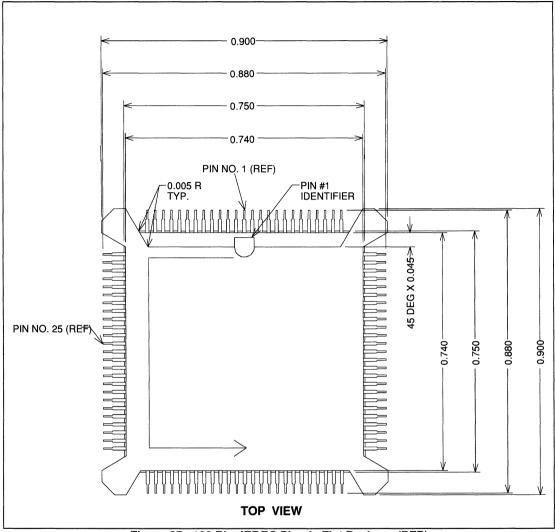

- 100 pin Plastic Leadless Chip Carrier (PLCC), or 100 pin Plastic Flat Pack (PFP) JEDEC package

- Minimizes circuit board space requirements.

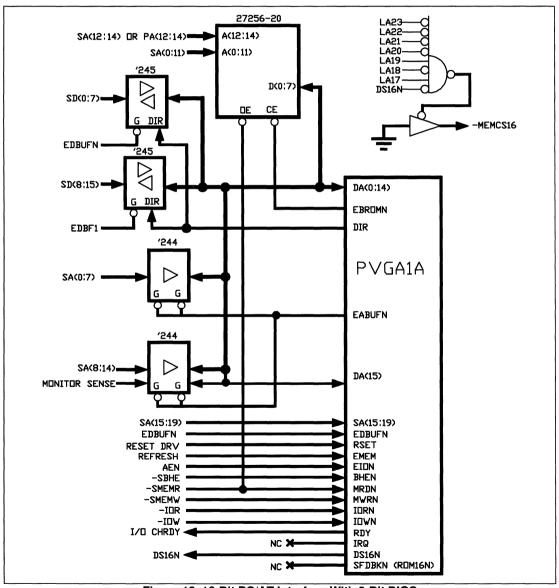

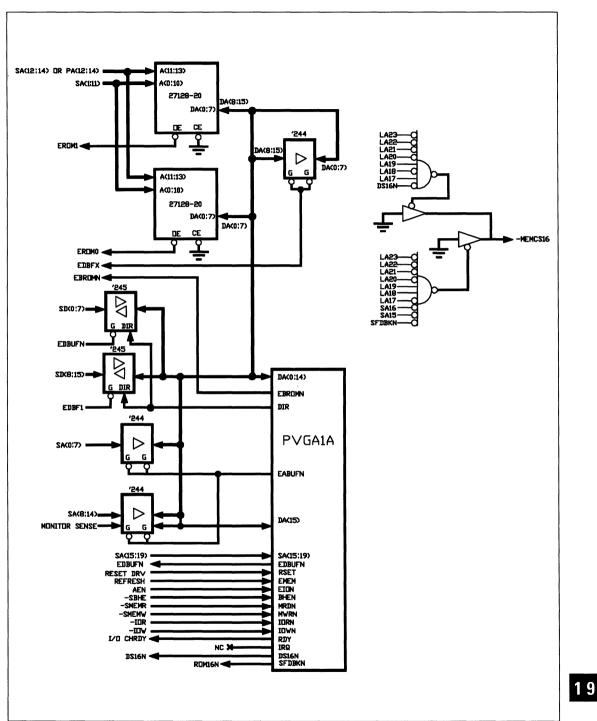

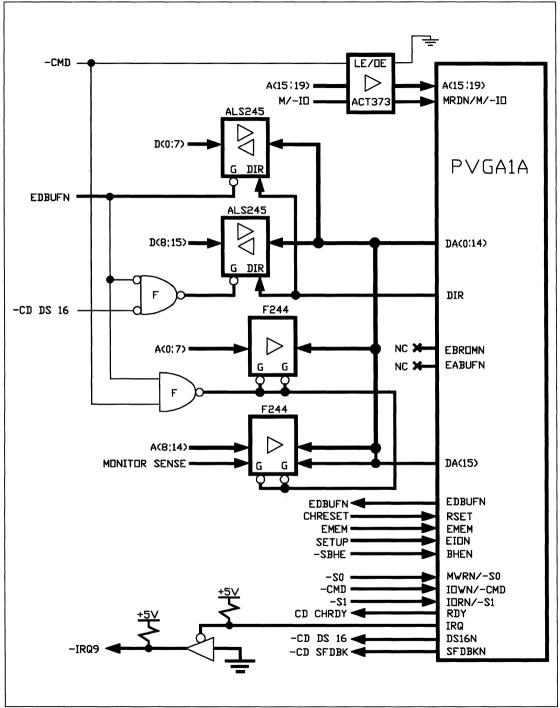

Figure 1. System Diagram

Pin Diagram

**Pin Diagram**

| PIN | SYMBOL | PIN | SYMBOL | PIN | SYMBOL  | PIN | SYMBOL |

|-----|--------|-----|--------|-----|---------|-----|--------|

|     |        |     |        | 54  |         | 70  | MOLK   |

| 1   | GND    | 26  | GND    | 51  | GND     | 76  | MCLK   |

| 2   | MD4    | 27  | A18    | 52  | VCC     | 77  | GND    |

| 3   | MD3    | 28  | A19    | 53  | VID4    | 78  | VCC    |

| 4   | MD2    | 29  | IORN   | 54  | VID3    | 79  | RAS10N |

| 5   | MD1    | 30  | IOWN   | 55  | VID2    | 80  | CAS10N |

| 6   | MD0    | 31  | MRDN   | 56  | VID1    | 81  | OE10N  |

| 7   | EBROMN | 32  | MWRN   | 57  | VID0    | 82  | RAS32N |

| 8   | DS16N  | 33  | EION   | 58  | WPLTN   | 83  | CAS32N |

| 9   | BHEN   | 34  | RDY    | 59  | PCLK    | 84  | OE32N  |

| 10  | SFDBKN | 35  | IRQ    | 60  | HSYNC   | 85  | WE0N   |

| 11  | EABUFN | 36  | RSET   | 61  | VSYNC   | 86  | WE1N   |

| 12  | DA8    | 37  | DIR    | 62  | BLNKN   | 87  | WE2N   |

| 13  | DA9    | 38  | EDBUFN | 63  | MA8     | 88  | WE3N   |

| 14  | DA10   | 39  | DA0    | 64  | GND     | 89  | MD15   |

| 15  | GND    | 40  | DA1    | 65  | MA7     | 90  | MD14   |

| 16  | DA11   | 41  | DA2    | 66  | MA6     | 91  | MD13   |

| 17  | DA12   | 42  | DA3    | 67  | MA5     | 92  | MD12   |

| 18  | DA13   | 43  | DA4    | 68  | MA4     | 93  | MD11   |

| 19  | DA14   | 44  | DA5    | 69  | MA3     | 94  | MD10   |

| 20  | DA15   | 45  | DA6    | 70  | MA2     | 95  | MD9    |

| 21  | EMEM   | 46  | DA7    | 71  | MA1     | 96  | MD8    |

| 22  | A15    | 47  | RPLTN  | 72  | MA0     | 97  | MD7    |

| 23  | A16    | 48  | VID7   | 73  | VCLK2   | 98  | MD6    |

| 24  | A17    | 49  | VID6   | 74  | VCLK1   | 99  | MD5    |

| 25  | VCC    | 50  | VID5   | 75  | VCLK0 1 | 00  | vcc    |

**PVGA1A Pin Descriptions**

19-3

6

INTRODUCTION

**PVGA1A**

## 2.0 SCOPE

Many applications require greater graphics capability than is available through the IBM Monochrome Display Adapter (MDA), Color Graphics Adapter (CGA), Enhanced Graphics Adapter (EGA), Multicolor Graphics Arrav (MCGA), and the Video Graphics Array (VGA), The Paradise PVGA1A is a 1.25 micron. 12.000 gate CMOS VLSI device that allows the design of a very high performance VGA graphics subsystem able to interface with the PC/XT/AT Bus, as well as the IBM Micro Channel Bus, while maintaining backwards compatibility with previous video standards. A major advantage of the PVGA1A is that designs implementing this graphics controller will be able to run applications requiring MDA, CGA, Hercules, AT&T 6300, and VGA hardware and BIOS compatibility, and also EGA BIOS compatibility, on analog or multifrequency monitors.

This data sheet supplies sales order information, a functional overview, signal pin details, a block diagram, internal register descriptions, AC/DC characteristics, timing diagrams, VLSI package mechanical information, and a list of associated references.

#### 2.1 PVGA1A DESCRIPTION

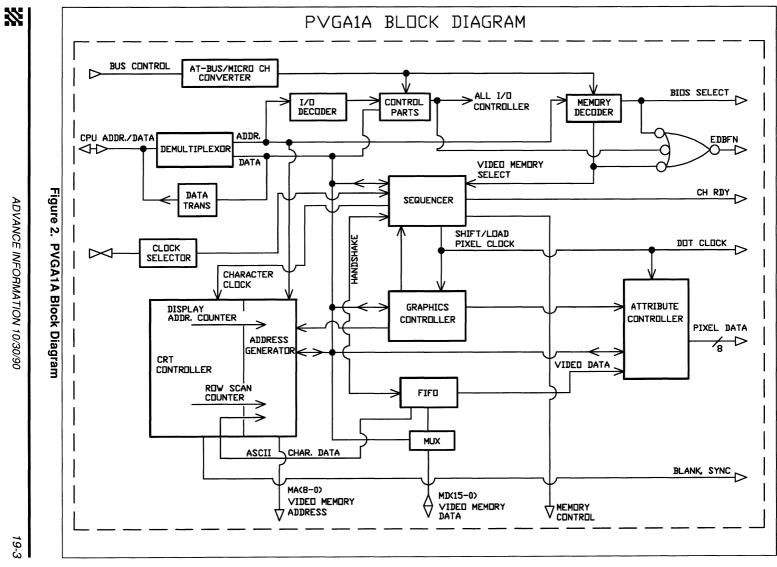

The PVGA1A internally contains four major modules. These are the CRT Controller, the Sequencer, the Graphics Controller and the Attribute Controller. The PVGA1A has 4 major interfaces: the CPU and BIOS ROM interface, the Clock interface, the DRAM Display Buffer interface, and the Video and RAMDAC interface.

The PVGA1A internally contains four major modules. These are the CRT Controller, the Sequencer, the Graphics Controller and the Attribute Controller. The PVGA1A has 4 major interfaces: the CPU and BIOS ROM interface, the Clock interface, the DRAM Display Buffer interface, and the Video and RAMDAC interface. The PVGA1A controls the interfacing between the system microprocessor and video memory. Because PVGA1A controls arbitration for video memory between the system microprocessor and the CRT Controller function contained within the PVGA1A, all data passes through PVGA1A when the system microprocessor writes to or reads from video memory.

A FIFO is used internally to achieve the video display bandwidth necessary between CPU accesses and display refresh cycles, using standard DRAMs.

#### 2.2 PVGA1A MODULES

The CRT Controller section within the PVGA1A maintains screen refresh functions for the various display modes defined by the BIOS ROM resident firmware. The PVGA1A CRT Controller also generates horizontal sync (HSYNC), vertical sync (HSYNC), and blank pulses for the display monitor.

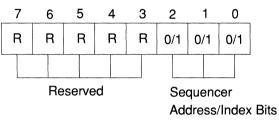

The Sequencer functions as a timing generator for the AT bus or Micro Channel interface, in I/O or memory cycles. It also provides the character clock in the alphanumeric mode, and the dot clock in the graphics mode, for the CRT, Graphics, and Attribute Controllers.

The Graphics Controller manages data flow between video memory and the Attribute Controller during active display (non-blanked) periods. It also controls system microprocessor reads from and writes to the video memory, using the time slots defined by the Sequencer.

The Attribute Controller modifies the CRT display data stream in graphics and character modes. It controls display attributes such as blinking, underlining, cursor, scrolling, reverse video, and background or foreground video, in VGA and enhanced VGA BIOS modes.

## 3.0 PVGA1A INTERFACES

#### 3.1 CPU AND BIOS ROM INTERFACE

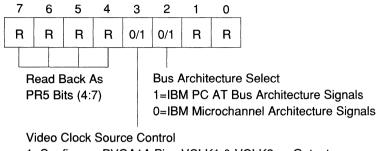

The PVGA1A is designed to operate in two different bus architecture configurations. These are the PC/XT/AT Bus and the PS/2 Micro Channel Bus. The selection of the mode is dependant on the setting of a configuration register bit CNF(2), which is determined upon power-up/reset, and is described in the PVGA1A Paradise Register section of this data sheet.

The I/O data path is eight bit. The DRAM display buffer data path can be 8- or 16-bit. EGA Planar modes have an eight bit data path with the CPU. Text modes and 256 color extended modes (packed pixel modes) can have a 16-bit data path if the video subsystem supports a 16-bit bus.

The PVGA1A will provide the necessary waitstates for CPU accesses to the video memory. Wait states for I/O accesses and BIOS ROM accesses are not generated.

Special I/O ports, such as 46E8H(AT) for setup, and 102H for VGA enable, have been implemented internally in the PVGA1A.

When configured for AT or Micro Channel operation, the PVGA1A operates functionally in a manner that is conducive to PC/XT/AT or Micro Channel interfacing respectively. The signal pins, memory maps and I/O ports all operate to optimize this interface with minimal external circuitry.

The PVGA1A provides all the signals, and decodes all the necessary memory and I/O addresses to interface with the AT bus or the Micro Channel bus, in 8- or 16-bit data path modes. PVGA1A also provides the necessary decoding of the adapter video BIOS ROM, and has additional signals and registers to help with BIOS ROM page mapping as done on the IBM PS/2 display adapter. Using the provided signals, the user can implement designs able to multiplex the address/data signals to the PVGA1A in 8- or 16-bit mode, control an 8- or 16-bit BIOS ROM, and generate the desired control/handshake signals (such as -MEMCS16 in AT mode).

#### 3.2 DRAM INTERFACE

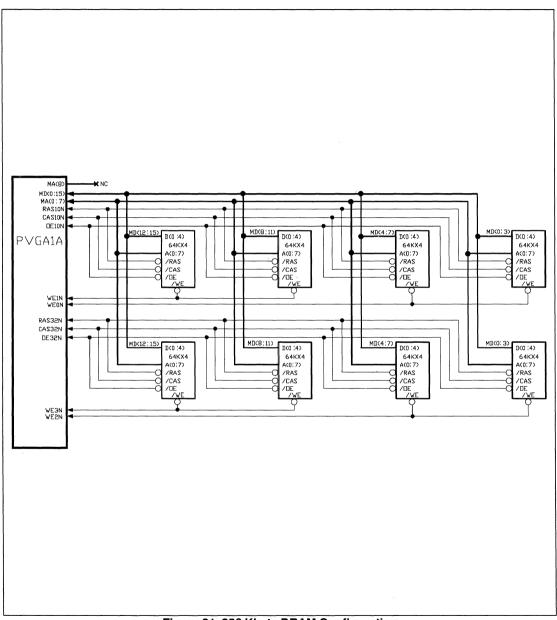

The PVGA1A optimizes its interface to the video memory display buffer. The video memory DRAMs are organized as 4 planes and the PVGA1A is designed for 3 configurations of DRAMs. Each plane can be configured as 64 Kbytes (256 Kbyte total), 128 Kbytes (512 Kbyte total), or 256 Kbytes (1 Mbyte total). cycles. PVGA1A will also refresh the DRAMs with 3 or 5 refresh cycles (page mode in graphics or RAS refresh in alpha) after every horizontal scan line.

The PVGA1A supports 256 Kbytes of DRAM by using eight 64 Kbyte by 4 page mode DRAM chips; 512 Kbytes of DRAM by using sixteen 64 Kbyte by 4 page mode DRAM chips; or 1 Mbyte of DRAM using eight 256 Kbyte by 4 page mode DRAM chips. Usually a 36 MHz MCLK and 120ns DRAMs are used. A 640 by 400 by 256 color mode is supported when 100 ns DRAMs and a 42 MHz MCLK is used. 640 by 480 by 256 color mode is supported when the 512 Kbyte DRAM configuration along with 100ns DRAMs and a 42 MHz MCLK are used. The PVGA1A Paradise registers provide support for accesses of up to 1 Mbyte of video memory.

The PVGA1A provides the necessary control signals and address/data lines to access the video memory as two 16-bit data interleaved banks. For display refresh cycles, the PVGA1A will perform page mode Read operations on the video memory in graphics modes, and in alpha modes it will generate standard RAS/CAS.

#### 3.3 VIDEO INTERFACE

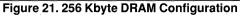

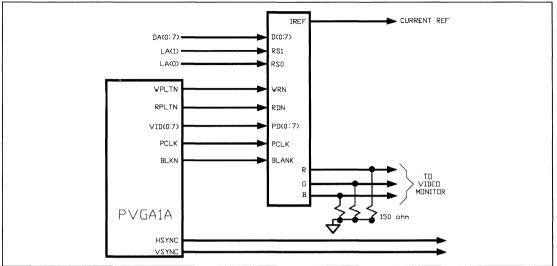

The PVGA1A is optimized to connect to an analog CRT monitor through a RAMDAC, but it may also be used to drive other types of displays, such as TTL monitors. In interfacing to an analog monitor through an external RAMDAC, the PVGA1A provides all the necessary signals to interface to the video RAMDAC.

The video interface for a CRT is very dependent on the CRT requirements and the resolution and depth (bits/pixels) of the image desired. New monitors, such as multifrequency monitors, are less stringent because of the many sync frequencies available. The PVGA1A can be programmed to directly generate all the CRT signals for up to 8 bits/pixel (256 color) displays. In addition, external hardware can be added to allow higher display resolutions by trading off the number of bits/pixel.

The Micro Channel Auxiliary Video Connector and the AT Feature Connector can be connected to PVGA1A. PVGA1A also provides an input for a monitor type detection interface as done on the IBM VGA using comparators.

#### 3.4 CLOCK INTERFACE

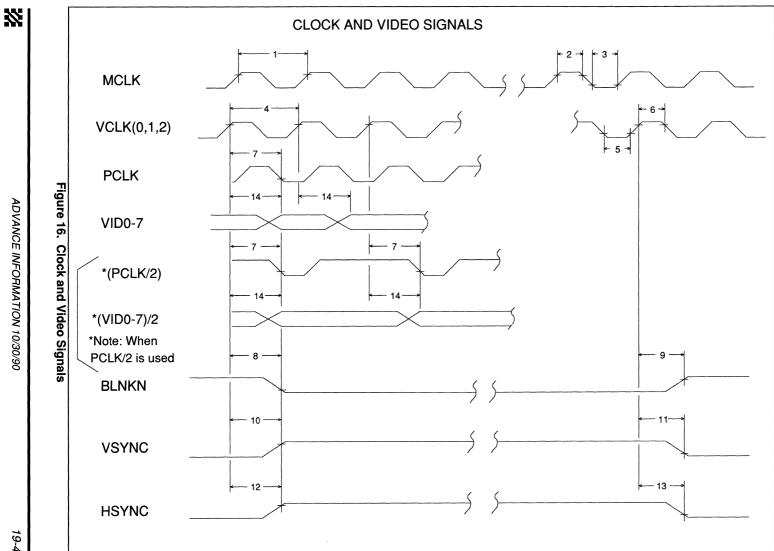

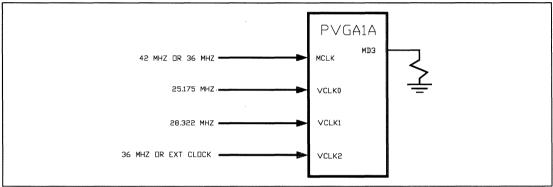

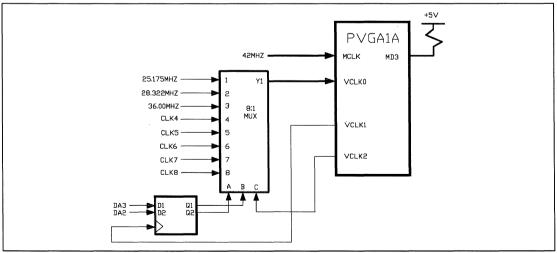

The PVGA1A has four clock input signal pins. These are: the separate memory clock, MCLK, which drives the DRAM timing in graphics modes; and the three video clocks, VCLK0, VCLK1, and VCLK2, which drive the video timing and DRAM timing in alphanumeric modes. PVGA1A also provides the option to externally control a multiplexer that supplies the video clock.

#### 3.5 PVGA1A POWER-UP CONFIGURATION

The PVGA1A uses the memory data pins to configure an internal configuration register upon power-up/reset. CNF(2) will determine whether the PVGA1A will operate in AT or Micro Channel bus mode.

Other CNF bits configured by PVGA1A at powerup/reset are used as status bits, or for clock source control. For more information on PVGA1A power-up configuration, refer to the Paradise Register section of this data sheet.

## 4.0 PIN DESCRIPTION

The table below provides PVGA1A pin definitions for the 100 Pin Plastic Leadless Chip Carrier (PLCC)and Plastic Flat Pack (PFP) package. The PVGA1A mnemonics are used. For more design details in AT or Micro Channel modes refer to the application notes and reference section of this document.

| PIN NO.  | PIN<br>SYMBOL   | PIN<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|----------|-----------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| POWER ON |                 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 36       | RSET            | I           | RESET: This signal input will reset the PVGA1A. MCLK<br>and VCLK0 should be connected to PVGA1A in order for the<br>PVGA1A to initialize during Reset. Paradise registers PR1,<br>and CNF are initialized at power-up reset based on the logic<br>level on the MD7-0 bus as determined by pull-up/ pull-down<br>resistors. Outputs EABUFN and EDBUFN are 3-stated during<br>reset. The reset pulse width should be at least <b>ten</b> MCLK<br>clock periods.                                      |  |  |  |  |  |  |

|          | CLOCK SELECTION |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 76       | MCLK            | I           | MEMORY CLOCK: This clock signal determines the VGA graphics mode video DRAM read/write access timing as well as system microprocessor I/O and memory timing. MCLK should be approximately 36 MHz for 120 ns DRAMS, and 42.0 MHz for 100 ns DRAMS.                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

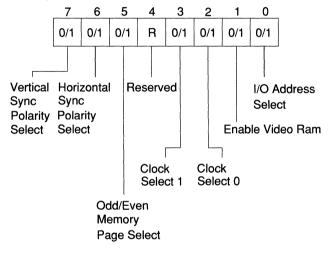

| 75       | VCLK0           | I           | VIDEO CLOCK 0: This input is the video display clock for<br>alphanumeric and graphics display modes. Typically, VCLK0<br>is 25.175 MHz to display 640 pixels per horizontal display<br>line. MCLK should be greater than or equal to VCLK0. The<br>Miscellaneous Output Register bits 2 and 3, both set to 0, will<br>select this clock if VCLK1 and VCLK2 are used as inputs.                                                                                                                     |  |  |  |  |  |  |

| 74       | VCLK1           | I/O         | VIDEO CLOCK 1: This pin can be a second video display<br>clock input or an output to external clock selection module.<br>Pin direction is determined on Reset by a pull-up/down<br>resistor on pin MD3. A VCLK1 input frequency of<br>28.322 MHz is used to display 720 pixels per horizontal line.<br>When it is an output, VCLK1 is an active low pulse during<br>I/O writes to port 3C2H. Refer to the Configuration Register<br>description. MCLK should be greater than or equal to<br>VCLK1. |  |  |  |  |  |  |

| PIN NO.                                                                                                 | PIN<br>SYMBOL                                                                                                                       | PIN<br>TYPE                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 73                                                                                                      | VCLK2                                                                                                                               | I/O                                                | VIDEO CLOCK 2: This pin can be a third video display clock input<br>or an output to external clock selection module. Pin direction is<br>programmed simultaneously with that of VCLK1. It acts as either a<br>user-defined external clock input, or as an output reflecting the content<br>of bit PR2(1) if CNF (3) is set to 1. Refer to the Configuration Register<br>description. MCLK should be greater than or equal to VCLK2.                                                                                                                                                                                                                                         |

|                                                                                                         |                                                                                                                                     |                                                    | CPU ADDRESS AND DATA BUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 28<br>27<br>24<br>23<br>22                                                                              | A19<br>A18<br>A17<br>A16<br>A15                                                                                                     | <br> <br> <br>                                     | ADDRESS-ONLY BUS (A15-A19): These active high inputs form<br>the high-order five bits of video memory address. These addresses<br>are not decoded during I/O accesses in AT or Micro Channel modes.<br>These inputs are directly connected to the system bus.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 20<br>19<br>18<br>17<br>16<br>14<br>13<br>2<br>46<br>45<br>44<br>45<br>44<br>43<br>42<br>41<br>40<br>39 | DA15(*)<br>DA14<br>DA13<br>DA12<br>DA11<br>DA10<br>DA9<br>DA8<br>DA7<br>DA6<br>DA5<br>DA4<br>DA5<br>DA4<br>DA3<br>DA2<br>DA1<br>DA0 | <pre>//O //O //O //O //O //O //O //O //O //O</pre> | DATA/ADDRESS BUS (DA0-DA15): These signals comprise an<br>active high multiplexed data/address bus for I/O and memory<br>accesses. Only the low eight bits are used for data during I/O read<br>and write cycles. During every I/O read and write, the voltage level<br>on DA15 is used to help determine the monitor type, and can be read<br>at port 3C2H bit 4. A logic 0 or logic 1 on DA15 places a logic 0 or a<br>logic 1 into bit 4 of the Input Status Register 0, respectively. Refer<br>to the general register description for more information.                                                                                                                |

|                                                                                                         |                                                                                                                                     |                                                    | CPU CONTROL BUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 21                                                                                                      | ЕМЕМ                                                                                                                                | I                                                  | ENABLE DISPLAY MEMORY: This signal is active high in both<br>Micro Channel and AT modes. In AT Mode, EMEM enables video<br>memory accesses. BIOS ROM accesses are not controlled by<br>EMEM. If the video memory is within the lowest 1MB of the<br>processor address space, EMEM signal must be active during<br>video memory access. Otherwise, EMEM should be generated<br>by external logic when the PVGA1A video memory is accessed.<br>During AT Bus refresh time, EMEM can be connected to REFRESH<br>to disable the PVGA1A. In Micro Channel mode this signal enables<br>I/O and video memory access. External logic is required to<br>implement the function EMEM. |

| PIN NO. | PIN<br>SYMBOL | PIN<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|---------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10      | SFDBKN        | 0           | 16-BIT WIDE BIOS ROM: In AT mode this active low<br>signal is the inverted value of register PR1(1), which<br>determines BIOS ROM data path width selection. It may be<br>used to control data buffers for a 16 bit data path BIOS ROM<br>and to generate the BIOS ROM chip enable signal MEMCS16<br>in AT mode. In Micro Channel mode, its mnemonic is<br>-CD SFDBKCD SFDBK is the unlatched decode (active<br>low) when a memory, I/O, or BIOS ROM access is done from<br>the system bus and may be considered as adapter or VGA<br>feedback. For further details, refer to the reference literature.                                                                              |

| 34      | RDY           | 0           | READY: An active high output which signals to the system<br>processor that a memory access is completed and is only used<br>to add wait states to the MCA or CPU bus cycles during<br>video memory accesses. It is pulled inactive by PVGA1A<br>to allow additional time to complete a bus operation. This<br>signal is not generated on I/O cycles and accesses to the<br>BIOS ROM. For further details, refer to the reference<br>literature.                                                                                                                                                                                                                                      |

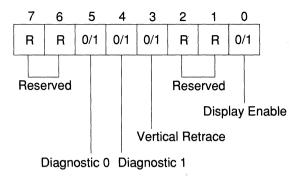

| 35      | IRQ           | 0           | INTERRUPT REQUEST: Programmable processor interrupt<br>request. It is enabled via bit 5 in the Vertical Retrace End<br>register. It is active high in AT mode and active low in<br>Micro Channel mode. When the end of Vertical Display<br>occurs, this signal will transition active, causing the interrupt.<br>It will stay latched until CRTC11 bit 4 clears it. In an AT<br>system IRQ is not connected, but may be connected if desired.<br>-IRQ9 is used to generate interrupt in the Micro Channel<br>mode. For further details, refer to the reference literature and<br>the CPU section in the introduction.                                                                |

| 8       | DS16N         | 0           | DATA SIZE 16: Active low enable for 16-bit video memory<br>word transfers. It is a mode dependent signal. In AT mode,<br>the signal level is as programmed in bit PR1(2) and may be<br>used to control 16 bit external data buffers. See the Paradise<br>Register (PR1) description for further details. This signal is<br>used to generate -MEMCS16 using external logic for AT<br>mode designs. In Micro Channel mode, the signal is active<br>only during BIOS ROM accesses (if enabled) by PR1(1))<br>and/or during memory 16-bit data path access (if enabled by<br>PR1(2)). See the section on Paradise Registers or consult the<br>reference literature for more information. |

| PIN NO. | PIN<br>Symbol | PIN<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|---------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33      | EION          | I           | ENABLE I/O: In AT mode, this active low signal enables I/O<br>accesses to the PVGA1A. In Micro Channel mode, this signal<br>is the set up input pin and is connected to the card set up<br>or the VGA setup. The externally designed system I/O<br>(96H for Adapter card or 94H bit 5 for system board design)<br>is connected to the EION pin. When this signal is high, the<br>PVGA1A is enabled or in the operating state. An active low<br>signal on this pin puts the PVGA1A into set up mode. |

|         |               |             | During the set up mode, write logic 1 to PVGA1A internal<br>port 102H to awaken the PVGA1A after power on. Refer<br>to application note for more information. When in set up<br>mode, the PVGA1A will only respond to the internal I/O<br>register located at 102H. Accesses to port 3C3H (external)<br>and BIOS ROM addresses are not affected by setup mode, so<br>they can be accessed.                                                                                                          |

| 9       | BHEN          | I           | BUS HIGH ENABLE: In both AT and MCA mode, this active<br>low signal enables and indicates transfer of data on the high<br>byte of the data bus (DA8-D15) when PVGA1A is in 16-bit<br>mode. With address A0, it distinguishes between high byte<br>(DA15-8) and low byte (DA0-7) data transfers. It is not used<br>for I/O transfers in either AT mode or Micro Channel mode.                                                                                                                        |

| 31      | MRDN          | I           | MEMORY READ: In AT mode, this signal is called<br>-SMEMR and is an active low memory read strobe. It is<br>asserted in 8/16 bit memory read cycles. In Micro Channel<br>mode, the signal is called M/-IO. It distinguishes between<br>memory and I/O cycles. When (M/-IO) is high, a memory<br>cycle is in process. A low on (M/-IO) shows that an I/O<br>cycle is in process. For further details, refer to the reference<br>literature.                                                           |

| 32      | MWRN          | 1           | MEMORY WRITE: The Active low memory write strobe in<br>AT mode for 8/16 bit data transfers. In Micro Channel mode,<br>it becomes -S0 and is the channel status signal which indicates<br>the start and type of a channel cycle. Along with -S1, M/-IO,<br>and -CMD signals, it is decoded to interpret I/O and memory<br>commands. For further details, refer to the reference literature.                                                                                                          |

| 29      | IORN          | I           | I/O READ: Active low I/O read strobe in AT mode. It is<br>asserted in 8/16 bit I/O read bus cyclesS1 is the alternate<br>mnemonic used in Micro Channel mode to indicate the start<br>and type of a channel cycle. For further details, refer to the<br>reference literature.                                                                                                                                                                                                                       |

| PIN NO.                                            | PIN<br>SYMBOL                                                                 | PIN<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                            |                      |  |  |  |

|----------------------------------------------------|-------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| 30                                                 | IOWN                                                                          | I           | I/O WRITE: Active low strobe. In AT mode, the strobe<br>signals an I/O write for 8/16 bit I/O write cycles. In Micro<br>Channel mode it is synonymous with -CMD; address bus<br>validity is signaled by -CMD going low while the rising edge<br>of -CMD indicates the end of a Micro Channel bus cycle.<br>For further details, refer to the reference literature. |                                                                                                                                                                                                            |                      |  |  |  |

|                                                    |                                                                               |             | ٧                                                                                                                                                                                                                                                                                                                                                                  | IDEO MEMORY DATA                                                                                                                                                                                           |                      |  |  |  |

| 89<br>90<br>91<br>92<br>93<br>94<br>95             | MD15<br>MD14<br>MD13<br>MD12<br>MD11<br>MD10<br>MD9                           | I/O         | data bus<br>pulled up                                                                                                                                                                                                                                                                                                                                              | DISPLAY MEMORY DATA (D0-D15): These lines are the data bus to the video display DRAMS. Data lines MD0-7 are pulled up or down with resistors to provide set up information on power-up (reset) as follows: |                      |  |  |  |

| 96                                                 | MD8                                                                           |             | MD                                                                                                                                                                                                                                                                                                                                                                 | Power-Up                                                                                                                                                                                                   | Affected             |  |  |  |

| 97                                                 | MD7                                                                           |             |                                                                                                                                                                                                                                                                                                                                                                    | Function                                                                                                                                                                                                   | Register (bit)       |  |  |  |

| 98                                                 | MD6                                                                           |             |                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                            |                      |  |  |  |

| 99                                                 | MD5                                                                           |             | 7                                                                                                                                                                                                                                                                                                                                                                  | General Purpose                                                                                                                                                                                            | CNF(7) *             |  |  |  |

| 2                                                  | MD4                                                                           |             | 6                                                                                                                                                                                                                                                                                                                                                                  | General Purpose                                                                                                                                                                                            | CNF(6) *             |  |  |  |

| 3                                                  | MD3                                                                           |             | 5                                                                                                                                                                                                                                                                                                                                                                  | General Purpose                                                                                                                                                                                            | CNF(5) *             |  |  |  |

| 4                                                  | MD2<br>MD1                                                                    |             | 4                                                                                                                                                                                                                                                                                                                                                                  | General Purpose<br>VCLK1,2 Input/Output                                                                                                                                                                    | CNF(4) *             |  |  |  |

| 5<br>6                                             | MD1<br>MD0                                                                    |             | 3<br>2                                                                                                                                                                                                                                                                                                                                                             | AT/Micro Channel Mode                                                                                                                                                                                      | CNF(3) +<br>CNF(2) + |  |  |  |

| 0                                                  | MDU                                                                           |             | 2                                                                                                                                                                                                                                                                                                                                                                  | BIOS ROM Data Path                                                                                                                                                                                         | PR1(1) *             |  |  |  |

|                                                    |                                                                               |             | 0                                                                                                                                                                                                                                                                                                                                                                  | BIOS ROM Mapping                                                                                                                                                                                           | PR1(0) *             |  |  |  |

|                                                    |                                                                               |             |                                                                                                                                                                                                                                                                                                                                                                    | NOTE : " * " Pulldown resistor sets these bits to logic 1.<br>" + " Pullup resistor sets these bits to logic 1.<br>For more details refer to the section on Paradise Registe                               |                      |  |  |  |

|                                                    |                                                                               |             | VID                                                                                                                                                                                                                                                                                                                                                                | EO MEMORY ADDRESS                                                                                                                                                                                          |                      |  |  |  |

| 63<br>65<br>66<br>67<br>68<br>69<br>70<br>71<br>72 | MA8 †<br>MA7 †<br>MA6 †<br>MA5 †<br>MA4 †<br>MA3 †<br>MA2 †<br>MA1 †<br>MA0 † |             | O MEMORY ADDRESS (MA0-MA8): Display memory<br>DRAM address.                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                            |                      |  |  |  |

Note: "†" For testing purposes, these pins can be tri-stated by setting Paradise Register PR4(4)=1.

| PIN NO. | PIN<br>SYMBOL  | PIN<br>TYPE | DESCRIPTION                                                                       |

|---------|----------------|-------------|-----------------------------------------------------------------------------------|

|         |                |             | VIDEO MEMORY CONTROL SIGNALS                                                      |

| 80      | CAS10N †       | 0           | COLUMN ADDRESS STROBE: Active low Memory Maps<br>1 & 0 CAS output signal.         |

| 83      | CAS32N †       | 0           | COLUMN ADDRESS STROBE: Active low Memory Maps<br>3 & 2 CAS output signal.         |

| 79      | RAS10N †       | 0           | ROW ADDRESS STROBE: Active low Memory Maps 1 & 0<br>RAS output signal.            |

| 82      | RAS32N †       | 0           | ROW ADDRESS STROBE: Active low Memory Maps 3 & 2<br>RAS output signal.            |

| 81      | OE10N <b>†</b> | 0           | OUTPUT ENABLE: Active low Memory Maps 1 & 0<br>DRAM output enable.                |

| 84      | OE32N †        | 0           | OUTPUT ENABLE: Active low Memory Maps 3 & 2<br>DRAM output enable.                |

| 85      | WEON †         | 0           | WRITE ENABLE: Active low Write Enable to DRAM bank 0, lower byte (Memory map 0).  |

| 86      | WE1N †         | 0           | WRITE ENABLE: Active low Write Enable for DRAM bank 0, upper byte (Memory map 1). |

| 87      | WE2N <b>†</b>  | 0           | WRITE ENABLE: Active low Write Enable for DRAM bank 1, lower byte (Memory map 2). |

| 88      | WE3N †         | 0           | WRITE ENABLE: Active low Write Enable for DRAM bank 1, upper byte (Memory map 3). |

| PIN<br>SYMBOL                                                                | PIN<br>TYPE                                                                                                                            | DESCRIPTION                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| RAMDAC INTERFACE                                                             |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

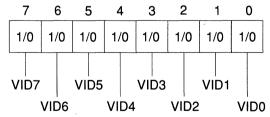

| VID7 §<br>VID6 §<br>VID5 §<br>VID4 §<br>VID3 §<br>VID2 §<br>VID1 §<br>VID0 § | 0                                                                                                                                      | VIDEO (VD0-VD7): Pixel video output to DAC and color palette.                                                                                                                                                                                                                                                    |  |  |  |  |  |

| RPLTN                                                                        | 0                                                                                                                                      | READ PALETTE: Video DAC register and color palette read signal. Active low during I/O read to addresses 3C6H, 3C8H, and 3C9H.                                                                                                                                                                                    |  |  |  |  |  |

| WPLTN                                                                        | 0                                                                                                                                      | WRITE PALETTE: Video DAC register and color palette<br>write signal. Active low during I/O write to addresses<br>3C6H-3C9H.                                                                                                                                                                                      |  |  |  |  |  |

| PCLK                                                                         | 0                                                                                                                                      | PIXEL CLOCK: Video pixel clock output used by the DAC<br>to latch video signals VID0-7. Its source is one of the video<br>clock inputs: VCLK0, VCLK1, or VCLK2 as determined by<br>the Miscellaneous Output register. Note that VCLK0, 1 or 2<br>is divided by two in 320/360 pixel display mode to derive PCLK. |  |  |  |  |  |

| BLNKN ‡                                                                      | 0                                                                                                                                      | BLANK: Active low display monitor blank pulse.                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| ·····                                                                        |                                                                                                                                        | CRT CONTROL                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| HSYNC <b>‡</b>                                                               | 0                                                                                                                                      | HORIZONTAL SYNC: Display monitor horizontal synchronization pulse. Active high or low depending on the Miscellaneous register programming.                                                                                                                                                                       |  |  |  |  |  |

| VSYNC ‡                                                                      | 0                                                                                                                                      | VERTICAL SYNC: Active high display monitor vertical<br>synchronization pulse. It is active high or low, depending on<br>the Miscellaneous Output Register.                                                                                                                                                       |  |  |  |  |  |

|                                                                              | SYMBOL<br>VID7 §<br>VID6 §<br>VID5 §<br>VID4 §<br>VID3 §<br>VID2 §<br>VID1 §<br>VID0 §<br>RPLTN<br>WPLTN<br>PCLK<br>BLNKN ‡<br>HSYNC ‡ | SYMBOLTYPEVID7 §<br>VID6 §<br>VID5 §<br>VID4 §<br>VID3 §<br>VID2 §<br>VID0 §ORPLTNOWPLTNO                                                                                                                                                                                                                        |  |  |  |  |  |

Notes: "§" For testing purposes, these pins can be tri-stated by setting Paradise Register PR4(5)=1. "‡" For testing purposes, these pins can be tri-stated by setting Paradise Register PR4(6)=1.

| PIN NO.                         | PIN<br>SYMBOL                          | PIN<br>TYPE                           | E DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|---------------------------------|----------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| BIOS ROM CONTROL                |                                        |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 7                               | EBROMN                                 | 0                                     | ENABLE BIOS ROM ACCESS: In both AT and Micro<br>Channel modes this signal is active (low) during memory<br>reads in the address range (C0000H-C7FFFH) if enabled by<br>bit PR1(0). It is not active for accesses to addresses in the<br>range C6000H-C67FFH. In AT mode only, a write to the<br>PVGA1A internal I/O port address 46E8H causes this signal<br>to be used as a write strobe for an external register used in<br>BIOS ROM page mapping. |  |  |  |  |  |

|                                 |                                        |                                       | BUFFER CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 11                              | EABUFN                                 | 0                                     | ENABLE ADDRESS BUFFER: This active low signal permits control of an external address buffer for multiplexing address and data to PVGA1A. It is 3-stated while Reset is active.                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 38                              | EDBUFN                                 | 0                                     | ENABLE DATA BUFFER: Allows control of an external data buffer for multiplexing address and data to PVGA1A. It is 3-stated while Reset is active.                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

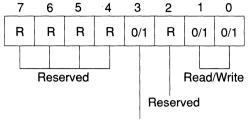

| 37                              | DIR                                    | 0                                     | DIRECTION CONTROL: Active high Direction Control for<br>reads of the MD0-15 data bus in AT and Micro Channel<br>modes. The default state is low until a read/write cycle occurs.<br>Then the PVGA1A will drive DIR high to change the<br>direction of the data buffers.                                                                                                                                                                              |  |  |  |  |  |

|                                 |                                        | · · · · · · · · · · · · · · · · · · · | POWER AND GROUND                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 25<br>52<br>78<br>100           | VCC<br>VCC<br>VCC<br>VCC               |                                       | +5VDC<br>+5VDC<br>+5VDC<br>+5VDC                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 1<br>15<br>26<br>51<br>64<br>77 | GND<br>GND<br>GND<br>GND<br>GND<br>GND |                                       | Ground<br>Ground<br>Ground<br>Ground<br>Ground<br>Ground                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

## 5.0 ABSOLUTE MAXIMUM RATINGS

Ambient temperature under bias Storage temperature Voltage on all inputs and outputs with respect to  $V_{\rm SS}$  Power dissipation

NOTE: Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of the specification is not implied. Exposure to absolute maximum rating con-

| Operating temperature range | 0 <sup>o</sup> to 70 <sup>o</sup> C |

|-----------------------------|-------------------------------------|

| Power supply voltage        | 4.75 to 5.25 Volts                  |

#### NOTE :

#### 5.1 D.C. CHARACTERISTICS

0°C to 70°C -40°C to 125°C -0.3 to 7 Volts 1.0 Watt

ditions for extended periods may affect product reliability.

#### STANDARD TEST CONDITIONS

The characteristics below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to  $V_{SS}$  (0V Ground). Positive current flows into the referenced pin.

| SYMBOL | PARAMETER                  | MIN.  | MAX     | UNITS | CONDITIONS                                | NOTE |

|--------|----------------------------|-------|---------|-------|-------------------------------------------|------|

| VIL    | Input Low Voltage          | -0.3  | 0.8     | v     | VCC = 5V +/-5%                            |      |

| VIH    | Input High Voltage         | 2.0   | VCC+0.3 | V     | VCC = 5V +/-5%                            |      |

| IIL    | Input Low Current          |       | +/-10   | uA    | VIN = 0.0V                                |      |

| IIH    | Input High Current         |       | +/-10   | uA    | VIN = VCC                                 |      |

| VOL    | Output Low Voltage         |       | 0.4     | V     | IOL +4.0 mA                               | 1    |

| VOH    | Output High Voltage        | 2.4   |         | V     | IOH = 4.0 mA                              | 1    |

| IOZ    | High Impedance             |       |         |       |                                           |      |

|        | Leakage Current            | -10.0 | 10.0    | uA    | OV <vout<vcc< td=""><td></td></vout<vcc<> |      |

| ICC    | Stand By Current           |       | 22      | mA    | VCC = 5.25 VDC                            |      |

|        | (All Inputs at TTL Levels) |       |         |       | $TA = 0^{\circ}C$ , Static                |      |

| CIN    | Input Capacitance          |       | 10      | pF    | FC = 1MHZ                                 |      |

| COUT   | Output Capacitance         |       | 10      | pF    | FC = 1MHZ                                 |      |

1. PVGA1A outputs have 4.0 mA maximum source and sink capability except as follows: RDY = 12.0 mA sink and 4.0 mA source.

### 5.2 AC CHARACTERISTICS

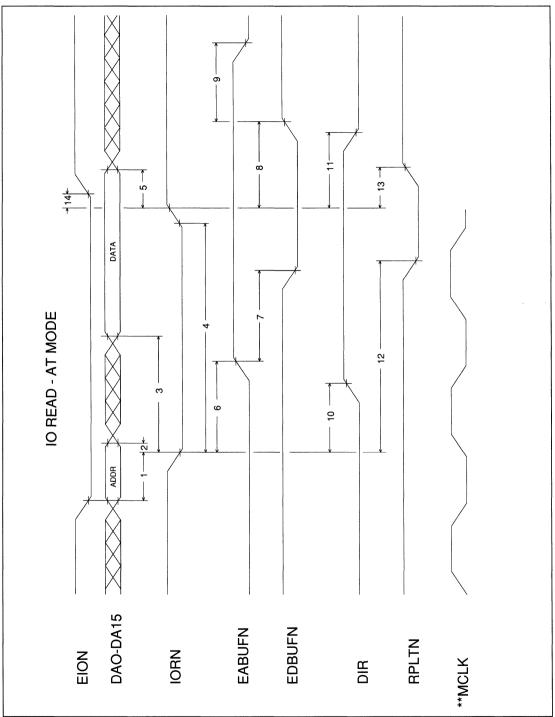

#### I/O READ - AT MODE TIMING DIAGRAM

#### (See Figure 4)

| SYMBOL | PARAMETER                          | MIN    | MAX NOTES <sup>*+</sup> |

|--------|------------------------------------|--------|-------------------------|

|        |                                    |        |                         |

| 1      | Address, EION Setup to IORN        | 13     | '                       |

| 2      | Address Hold from IORN Active      | 4      |                         |

| 3      | Read Data Valid from IORN Active   |        | 2Tp+20 1                |

| 4      | IORN Pulse Width                   | 2Tp+50 | 1                       |

| 5      | Read Data Hold from IORN Inactive  | 16     |                         |

| 6      | EABUFN Inactive from IORN Active   |        | 29                      |

| 7      | EDBUFN Active from EABUFN Inactive |        | 31                      |

| 8      | EDBUFN Inactive from IORN Inactive |        | 30                      |

| 9      | EABUFN Active from EDBUFN Inactive |        | 31                      |

| 10     | DIR Active to IORN Active          |        | 25                      |

| 11     | DIR Inactive from IORN Inactive    |        | 26                      |

| 12     | RPLTN Active from IORN Active      |        | 2Tp+34 1,2              |

| 13     | RPLTN Inactive from IORN Inactive  | 13     | 2                       |

| 14     | EION Hold from IORN Inactive       | 5      |                         |

#### NOTES:

19-16

- \* Units are in nanoseconds (ns)

- + Tested with C<sub>L</sub> = 70 pf unless specified otherwise.

- 1. Tp = 1/MCLK in all modes.

- 2. RPLTN signal active only with I/O addresses 03C6H-03C9H, except 03C7H.

- 3. For the signals that change between AT and Micro Channel modes, based upon CNF(2), the PVGA1A pnemonics ( Refer to equivalence table in the pin description section) are used in the AT mode timing diagrams.

- \*\* For reference only. RPLTN is in synchronization with MCLK.

.....

### 6.0 TIMING DIAGRAMS

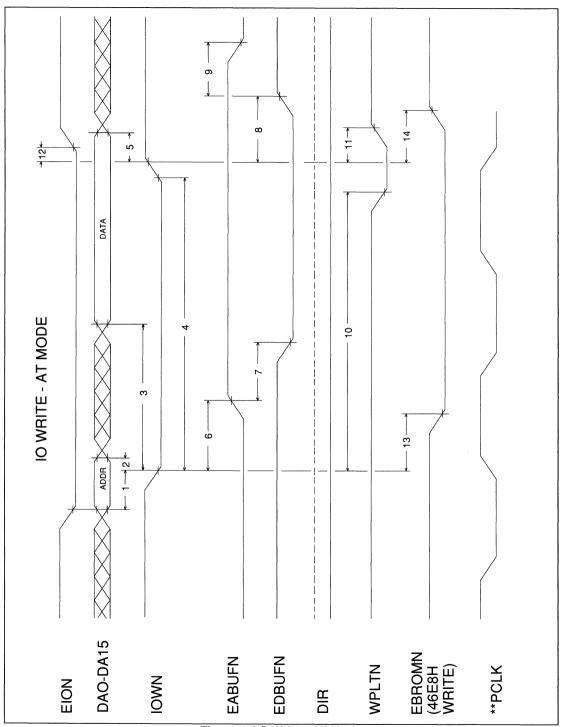

#### 6.1 I/O WRITE - AT MODE TIMING DIAGRAM (See Figure 5)

| SYMBOL | PARAMETER                          | MIN    | MAX     | NOTES <sup>*+</sup> |

|--------|------------------------------------|--------|---------|---------------------|

|        |                                    |        |         |                     |

| 1      | Address, EION Setup to IOWN        | 13     |         |                     |

| 2      | Address Hold From IOWN Active      | 4      |         |                     |

| 3      | Write Data Valid from IOWN Active  |        | 3Tp-8   | 1                   |

| 4      | IOWN Pulse Width                   | 3Tp+50 |         | 1                   |

| 5      | Write Data Hold from IOWN Inactive | 16     |         |                     |

| 6      | EABUFN Inactive from IOWN Active   |        | 29      |                     |

| 7      | EDBUFN Active from EABUFN Inactive |        | 31      |                     |

| 8      | EDBUFN Inactive from IOWN Inactive |        | 30      |                     |

| 9      | EABUFN Active from EDBUFN Inactive |        | 31      |                     |

| 10     | WPLTN Active from IOWN Active      |        | 3Tp+Tv+ | 15 1,2              |

| 11     | WPLTN Inactive from IOWN Inactive  | 16     |         | 2                   |

| 12     | EION Hold from IOWN Inactive       | 5      |         |                     |

| 13     | EBROMN Active from IOWN Active     |        | 29      | 3                   |

| 14     | EBROMN Inactive from IOWN Inactive |        | 27      | 3                   |

#### NOTES:

- \* Units are in nanoseconds (ns)

- + Tested with  $C_L = 70$  pf unless specified otherwise.

- 1. Tp = 1/MCLK in all modes. Tv = 2/VCLK0 or 2/VCLK1 or 2/VCLK2 depending on selected video clock.

- 2. WPLTN signal active only with I/O addresses 03C6H-03C9H.

- 3. EBROMN signal is active only during I/O port 46E8H write operation.

- 4. For the signals that change between AT and Micro Channel modes, based upon CNF(2), the PVGA1A pnemonics (Refer to equivalence table in the pin description section) are used in the AT mode timing diagrams.

- \*\* For reference only. WPLTN is in synchronization with PCLK.

Figure 4. I/O Write - AT Mode

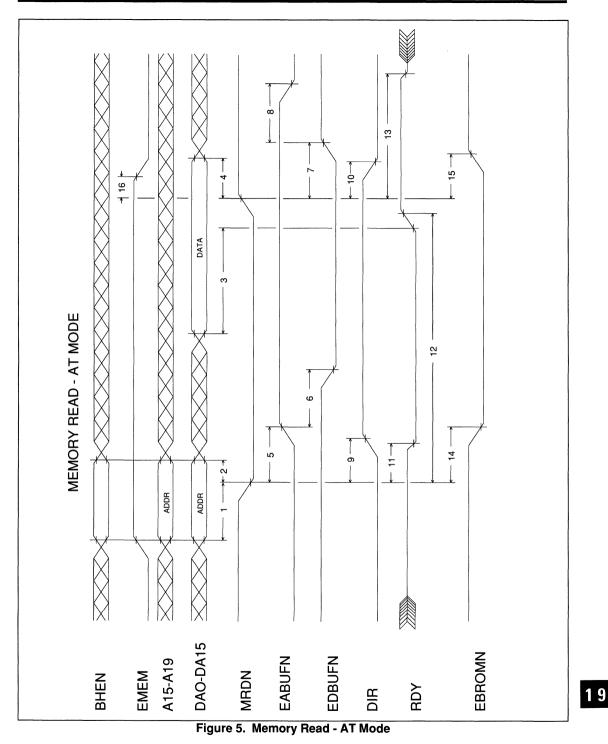

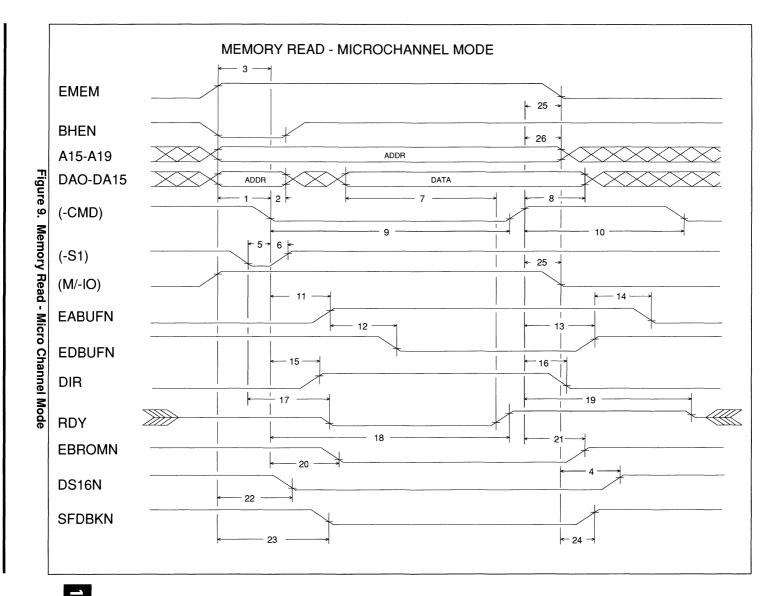

| MEMORY READ - AT MODE TIMING DIAGRAM |                                      | ( See Figure | 96)  |                     |

|--------------------------------------|--------------------------------------|--------------|------|---------------------|

| SYMBOL                               | PARAMETER                            | MIN          | MAX  | NOTES <sup>*+</sup> |

|                                      |                                      |              |      |                     |

| 1                                    | Address, BHEN, EMEM Setup to MRDN    | 13           |      |                     |

| 2                                    | Address, BHEN Hold from MRDN Active  | 4            |      |                     |

| 3                                    | Data Valid Setup to RDY              | Tp+25        |      | 5                   |

| 4                                    | Data Hold from MRDN Inactive         | 10           |      |                     |

| 5                                    | EABUFN Inactive from MRDN Active     |              | 29   |                     |

| 6                                    | EDBUFN Active from EABUFN Inactive   |              | 31   |                     |

| 7                                    | EDBUFN Inactive from MRDN Inactive   |              | 30   |                     |

| 8                                    | EABUFN Active from EDBUFN Inactive   |              | 31   |                     |

| 9                                    | DIR Active to MRDN Active            |              | 25   |                     |

| 10                                   | DIR Inactive from MRDN Inactive      |              | 26   |                     |

| 11                                   | RDY Inactive from MRDN Active        |              | 18   |                     |

| 12                                   | RDY Active High from MRDN Active     |              | 2000 |                     |

| 13                                   | RDY Inactive (Tri-state) from        |              | 180  | 4                   |

|                                      | MRDN Inactive                        |              |      |                     |

| 14                                   | EBROMN Active from MRDN Active       |              | 29   | 2                   |

| 15                                   | EBROMN Inactive from MRDN Inactive - | -            | 27   | 2                   |

| 16                                   | EMEM Hold from MRDN Inactive         | 4            |      |                     |

#### NOTES:

- \* Units are in nanoseconds (ns)

- + Tested with C<sub>L</sub> = 70 pf unless specified otherwise.

- 1. Duration of RDY signal inactive is dependent on video memory access contention and phase of clock.

The Clock is MCLK, VCLK0, VCLK1, or VCLK2 depending on clock selection.

- 2. EBROMN signal active for addresses C0000-C7FFFH excluding addresses C6000-C67FFH.

- For the signals that change between AT and Micro Channel modes, based upon CNF(2), the PVGA1A pnemonics (Refer to equivalence table in the pin description section) are used in the AT mode timing diagrams.

- 4. On AT bus, this signal is tri-state and pulled up to +5V externally.

- 5. Tp = 1 / MCLK

- \*\* For reference only. WPLTN is in synchronization with PCLK

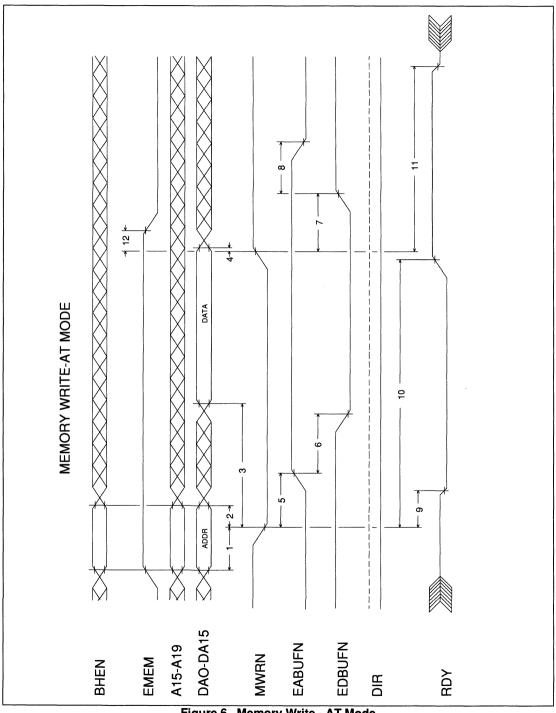

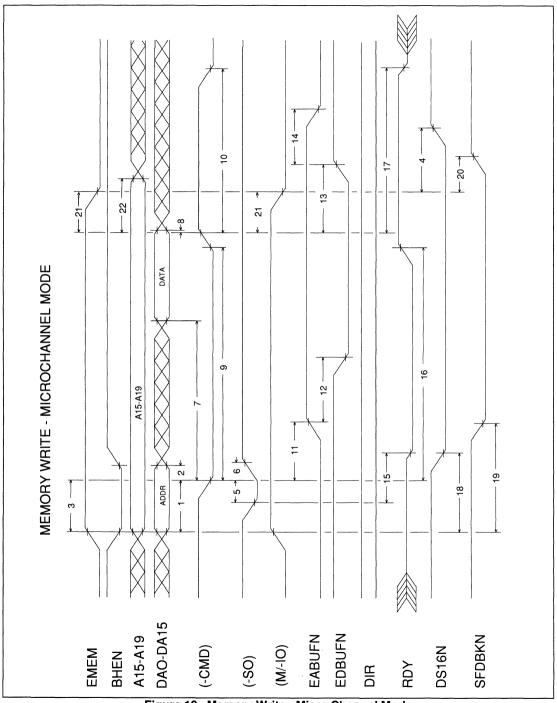

#### **MEMORY WRITE- AT MODE TIMING DIAGRAM**

#### (See Figure 7)

| SYMBOL | PARAMETER                                      | MIN | MAX NOTES <sup>*+</sup> |

|--------|------------------------------------------------|-----|-------------------------|

|        | · · · · · · · · · · · · · · · · · · ·          |     |                         |

| 1      | Address, BHEN, EMEM Setup to MWRN              | 13  |                         |

| 2      | Address, BHEN Hold from MWRN Active            | 4   |                         |

| 3      | Data Valid from MWRN Active                    |     | 3.5Tp-23 1              |

| 4      | Data Hold from MWRN Inactive                   | 0   |                         |

| 5      | EABUFN Inactive from MWRN Active               |     | 29                      |

| 6      | EDBUFN Active from EABUFN Inactive             |     | 31                      |

| 7      | EDBUFN Inactive from MWRN Inactive             |     | 30                      |

| 8      | EABUFN Active from EDBUFN Inactive             |     | 31                      |

| 9      | RDY Inactive from MWRN Active                  |     | 18                      |

| 10     | RDY Active High from MWRN Active               |     | 2000 2                  |

| 11     | RDY Inactive (Tri-state) from<br>MWRN Inactive |     | 180 4                   |

| 12     | EMEM Hold from MWRN Inactive                   | 4   |                         |

#### NOTES:

- \* Units are in nanoseconds (ns)

- + Tested with C<sub>L</sub> = 70 pf unless specified otherwise.

- 1. Tp = 1/MCLK in all modes.

- 2. Duration of RDY signal inactive is dependent on video memory access contention and phase of clock.

The Clock is MCLK, VCLK0, VCLK1, or VCLK2 depending on clock selection.

- 3. For the signals that change between AT and Micro Channel modes, based upon CNF(2), the PVGA1A pnemonics ( Refer to equivalence table in the pin description section) are used in the AT mode timing diagrams.

- 4. On AT bus, this signal is tri-state and pulled up to +5V externally.

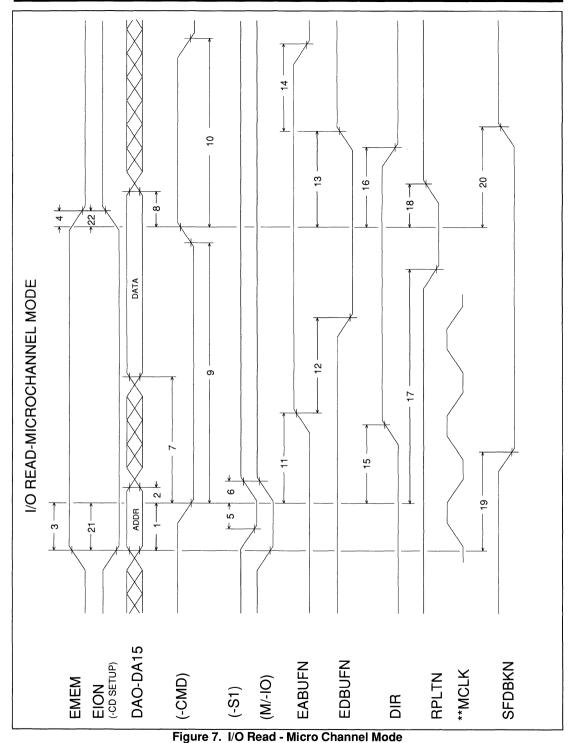

| SYMBOL | PARAMETER                              | MIN    | MAX    | NOTES <sup>*+</sup> |

|--------|----------------------------------------|--------|--------|---------------------|

| 1      | Address, M/IO Setup to -CMD            | 13     |        |                     |

| 2      | Address Hold from -CMD                 | 4      |        |                     |

| 3      | EMEM Active to -CMD Active             | 13     |        |                     |

| 4      | EMEM Hold from -CMD Active             | 4      |        |                     |

| 5      | -S1 Active to -CMD Active              | 3      |        |                     |

| 6      | -S1 and M/IO Inactive from -CMD Active | 5      |        |                     |

| 7      | Read Data Valid from -CMD Active       |        | 2Tp+22 | 1                   |

| 8      | Read Data Hold from -CMD Inactive      | 18     | `      |                     |

| 9      | -CMD Pulsewidth                        | 2Tp+50 |        | 1,5                 |

| 10     | -CMD Inactive to next -CMD Active      | 80     |        |                     |

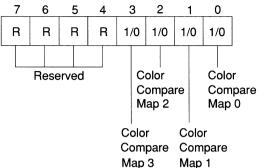

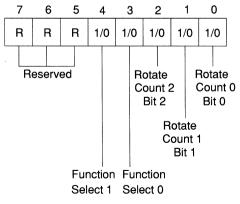

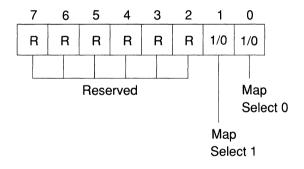

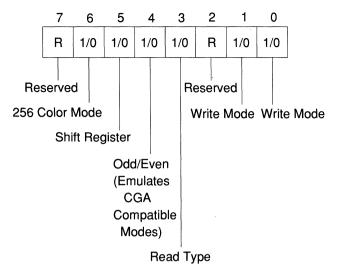

| 11     | EABUFN lactive from -CMD Active        |        | 30     |                     |