WD6030 Cache/DRAM and Channel Control Device

# TABLE OF CONTENTS

| 1.0 | INTRODUCTION                                                    | 15-1    |

|-----|-----------------------------------------------------------------|---------|

|     | 1.1 DESCRIPTION                                                 | 15-1    |

|     | 1.2 FEATURES                                                    | 15-1    |

| 2.0 | PIN DESCRIPTION                                                 |         |

|     | 2.1 LOCAL BUS INTERFACE                                         | 15-3    |

|     | 2.2 CACHE CONTROLLER                                            |         |

|     | 2.3 DRAM CONTROLLER                                             |         |

|     | 2.4 CHANNEL CONTROLLER                                          |         |

|     | 2.5 CHANNEL BUFFER CONTROLLER                                   | 15-3    |

|     | 2.6 MISCELLANEOUS                                               |         |

| 3.0 | DRAM CONTROLLER                                                 | . 15-21 |

|     | 3.1 MEMORY ORGANIZATION                                         | 15-21   |

|     | 3.1.1 Memory Maps                                               | 15-23   |

|     | 3.1.2 Memory Configuration                                      | 15-27   |

|     | 3.1.2.1 Memory Control Register 0103H (W/O)                     |         |

|     | 3.1.2.2 Memory Card Definition Register 0103H (R/O)             | 15-27   |

|     | 3.1.2.3 Memory Encoding Register 1 00E1H And Shadow RAM (R/W)   | 15-28   |

|     | 3.1.2.4 Memory Encoding Register 2 00E0H                        | 15-29   |

|     | 3.1.2.5 Split Address Extension Register ESF:0183H              | 15-29   |

|     | 3.1.2.6 Bank Enable And Version Number Register ESF:0182H (R/W) |         |

|     | 3.1.2.7 Memory Size Register ESF:0181H (R/W)                    |         |

|     | 3.1.2.8 Memory Window Bank 0 Register ESF:0184 (R/W)            | 15-31   |

|     | 3.1.2.9 Memory Window Bank 1 Register ESF:0185 (R/W)            | 15-31   |

|     | 3.1.2.10 Memory Window Bank 2 Register ESF:0186H (R/W)          | 15-31   |

|     | 3.1.2.12 Memory Configuration Register ESF:0180H                | 15 22   |

|     | 3.1.2.12 Memory Configuration Register ESF:0180H                | 15-32   |

|     | 3.1.2.14 RAS Precharge Delay Register ESF:0189H (R/W)           | 15-33   |

|     | 3.1.2.15 RAS Pulse Width Register ESF:018AH (R/W)               |         |

|     | 3.1.2.16 RAS Access Time Register ESF:018BH (R/W)               | 15-34   |

|     | 3.1.2.17 System Configuration Register                          | 15-35   |

|     | 3.1.3 Operating Modes                                           |         |

|     | 3.2 MEMORY INITIALIZATION                                       |         |

|     | 3.3 TIMING CONFIGURATION                                        |         |

| 4.0 | CACHE CONTROLLER                                                |         |

|     | 4.1 CACHE ORGANIZATION                                          | 15-38   |

|     | 4.2 CACHE POLICY                                                | 15-38   |

|     | 4.3 CACHE INITIALIZATION AND DIAGNOSTICS                        | 15-39   |

|     | 4.4 CACHE TIMING                                                | 15-40   |

|     | CHANNEL CONTROLLER                                              |         |

| 6.0 | EXTENDED SETUP FACILITY (ESF)                                   | 15-42   |

|     | 6.1 ESF ADDRESS MAP                                             | 15-42   |

|     | 6.2 ESF ACCESS                                                  | 15-45   |

| 7.0 | PERFORMANCE                                                     |         |

|     | 7.1 MEMORY PERFORMANCE                                          | 15-46   |

|     | 7.2 TYPICAL CHANNEL ACCESS PERFORMANCE                          | 15-46   |

|     | 7.3 PERFORMANCE FOR OTHER BUS CYCLES                            |         |

| 8.0  | TECHNICAL SPECIFICATIONS                                 | 8         |

|------|----------------------------------------------------------|-----------|

|      | 3.1 ABSOLUTE MAXIMUM RATINGS                             | 8         |

|      | 3.2 NORMAL OPERATING CONDITIONS                          | 8         |

|      | 3.3 DC CHARACTERISTICS UNDER NORMAL OPERATING CONDITIONS | 8         |

|      | 8.4 AC LOAD SPECIFICATIONS                               | 9         |

| 9.0  | ГIMING                                                   | 9         |

| 10.0 | PACKAGE DIMENSIONS                                       | <b>;4</b> |

# LIST OF ILLUSTRATIONS

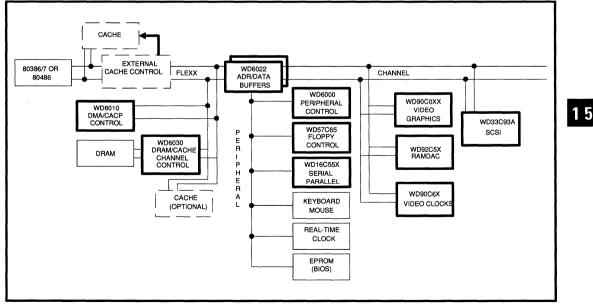

| Figure 1  | System Block Diagram                            |

|-----------|-------------------------------------------------|

| Figure 2  | WD6030 Block Diagram                            |

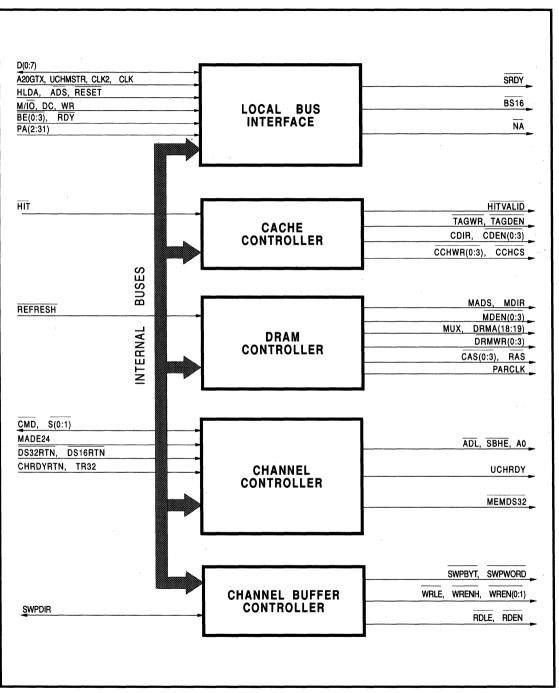

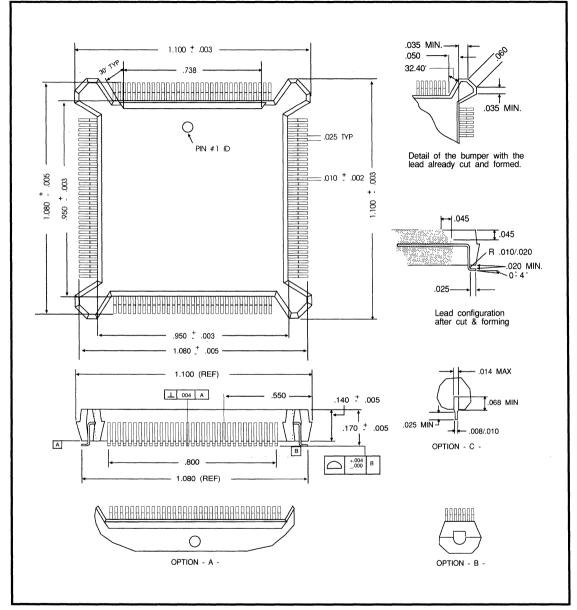

| Figure 3  | 132-Pin Plastic Quad Flat Pack                  |

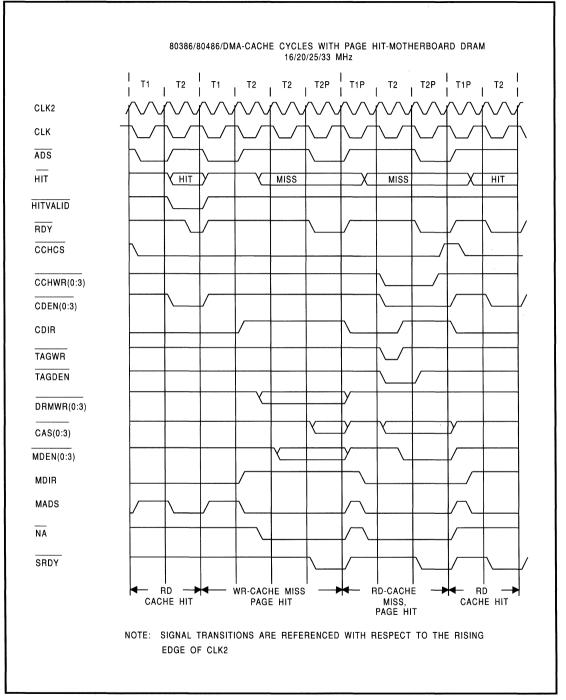

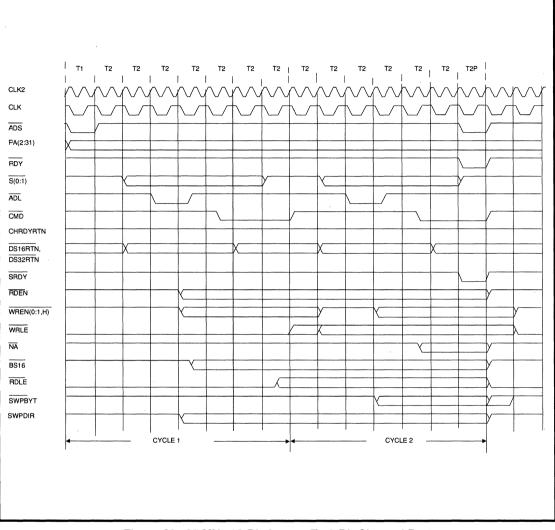

| Figure 4  | Cache Cycle with Page Hits                      |

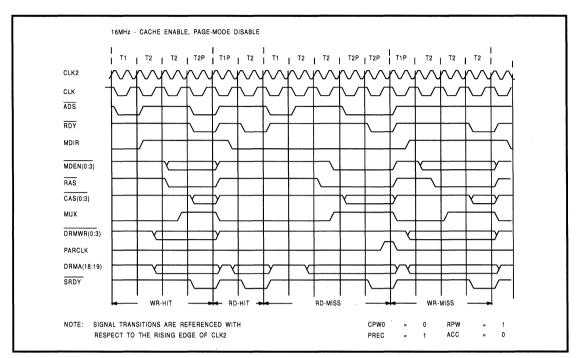

| Figure 5  | 80386/80486/DMA 16 MHz DRAM Access              |

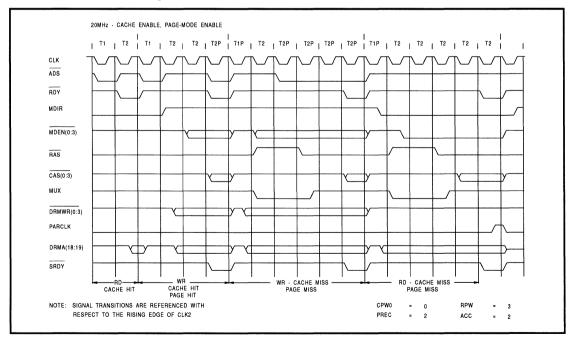

| Figure 6  | 80386/80486/DMA 20 MHz DRAM Access              |

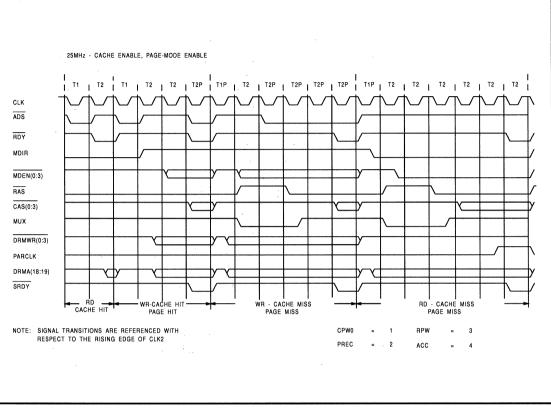

| Figure 7  | 80386/80486/DMA 25 MHz DRAM Access              |

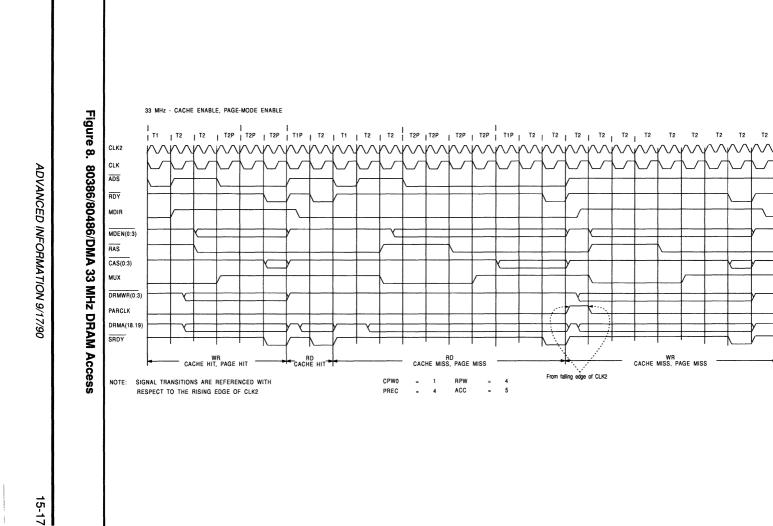

| Figure 8  | 80386/80486/DMA 33 MHz DRAM Access              |

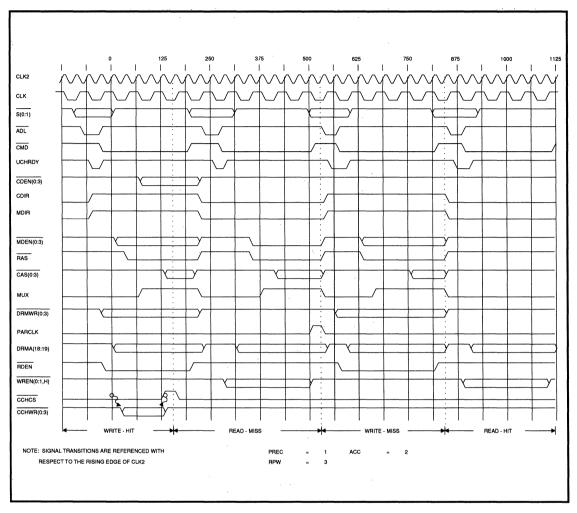

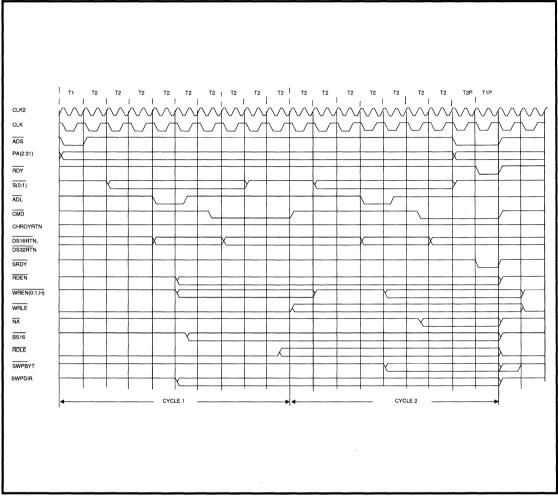

| Figure 9  | 16 MHz Synchronous Extended Master Cycle        |

| Figure 10 | 20 MHz Synchronous Extended Master Cycle        |

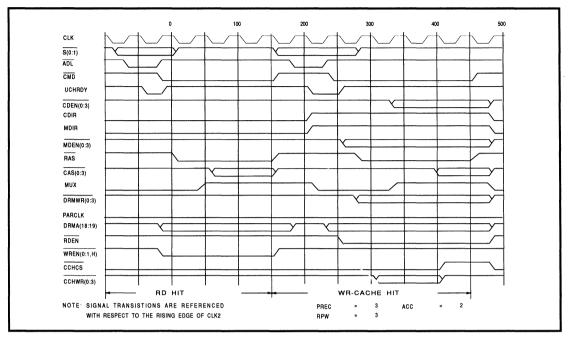

| Figure 11 | 25 MHz Synchronous Extended Master Cycle        |

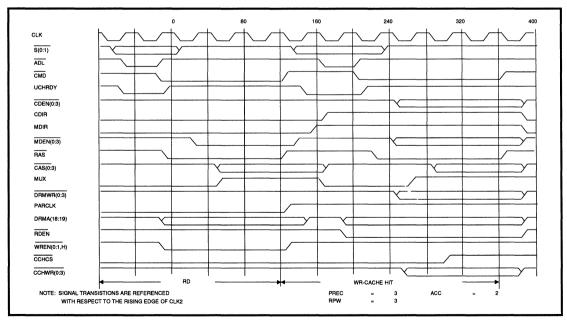

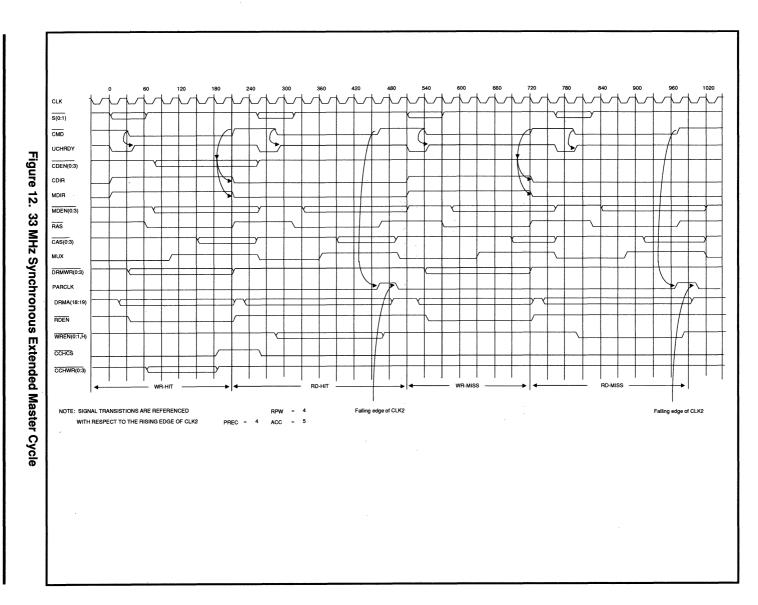

| Figure 12 | 33 MHz Synchronous Extended Master Cycle        |

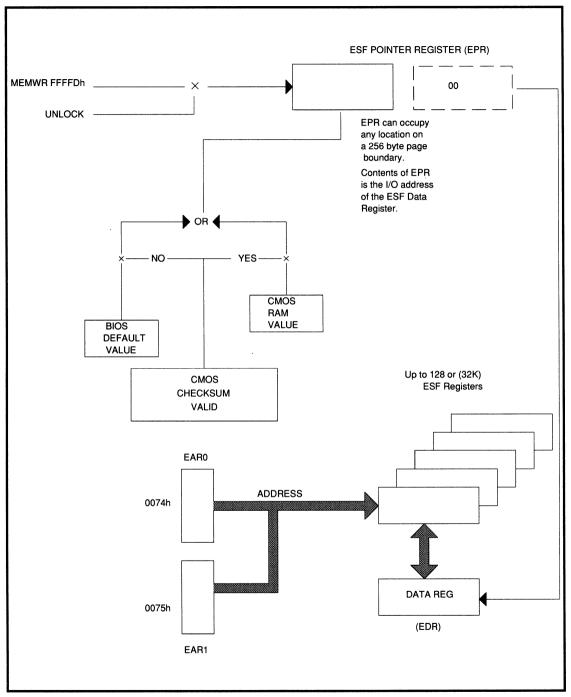

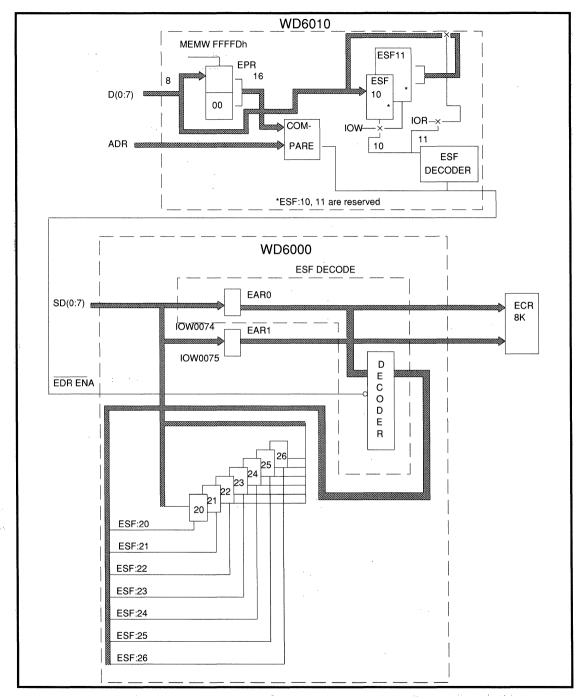

| Figure 13 | ECR And ESF Block Diagram                       |

| Figure 14 | Extended Set-Up Facility Overview               |

| Figure 15 | 80386/80486 Bus Interface Input Setup And Hold  |

| Figure 16 | 80386/80486 Bus Interface Output Valid Delay    |

| Figure 17 | WD6030 Cache Interface Timing                   |

| Figure 18 | Data Cache SRAM Timing                          |

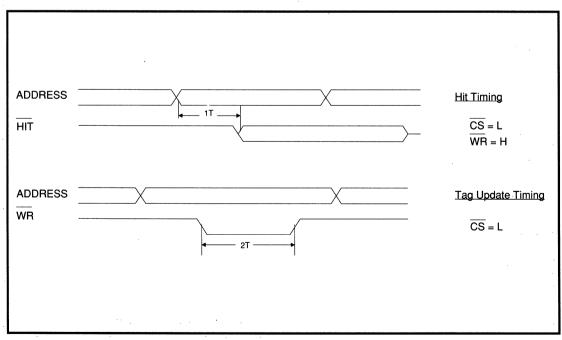

| Figure 19 | WD6030 TagRAM Timing                            |

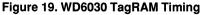

| Figure 20 | DRAM Interface Output Valid Delay Timing        |

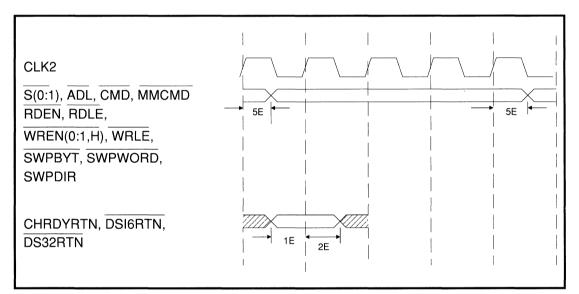

| Figure 21 | Channel Controller Timing                       |

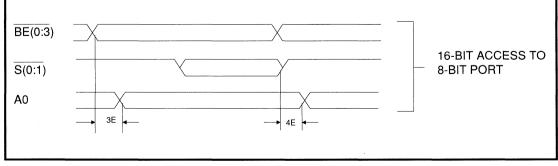

| Figure 22 | Channel Controller: 16-Bit Access to 8-Bit Port |

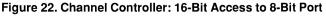

| Figure 23 | Channel Master Accesses to System Board DRAM    |

| Figure 24 | Central Translator Function                     |

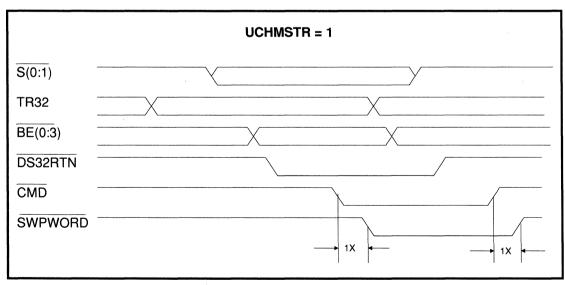

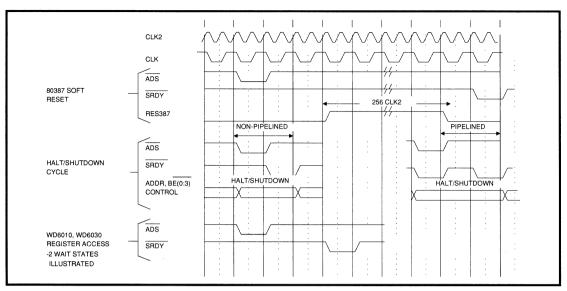

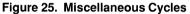

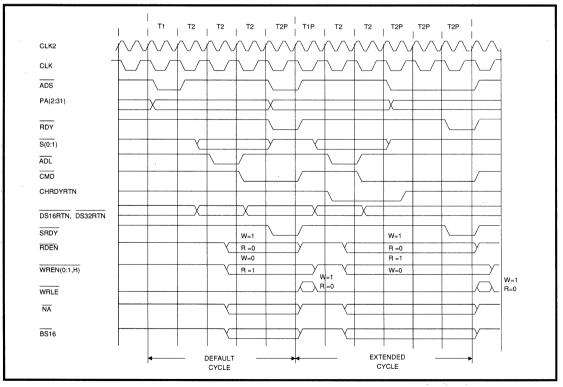

| Figure 25 | Miscellaneous Cycles                            |

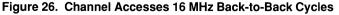

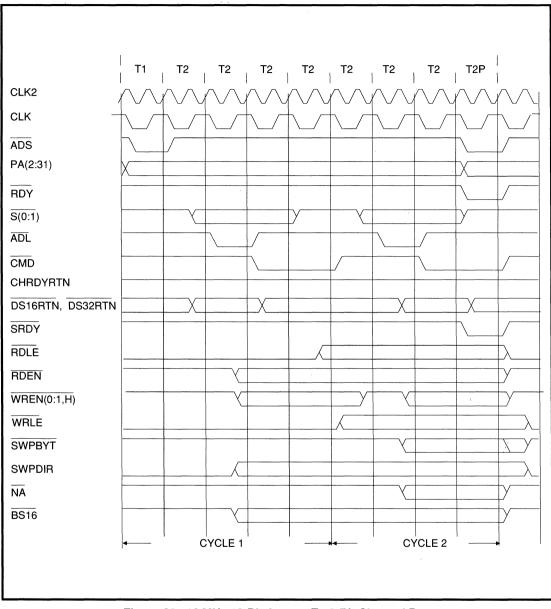

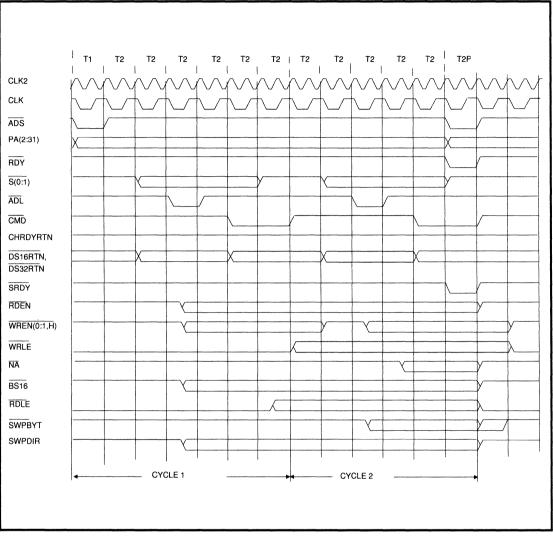

| Figure 26 | Channel Accesses 16 MHz Back-to-Back Cycles     |

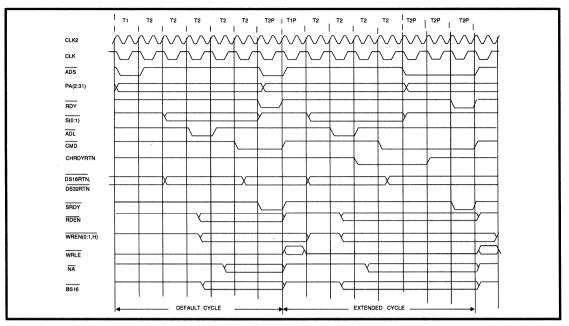

| Figure 27 | Channel Accesses 20 MHz Back-to-Back Cycles     |

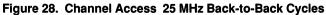

| Figure 28 | Channel Accesses 25 MHz Back-to-Back Cycles     |

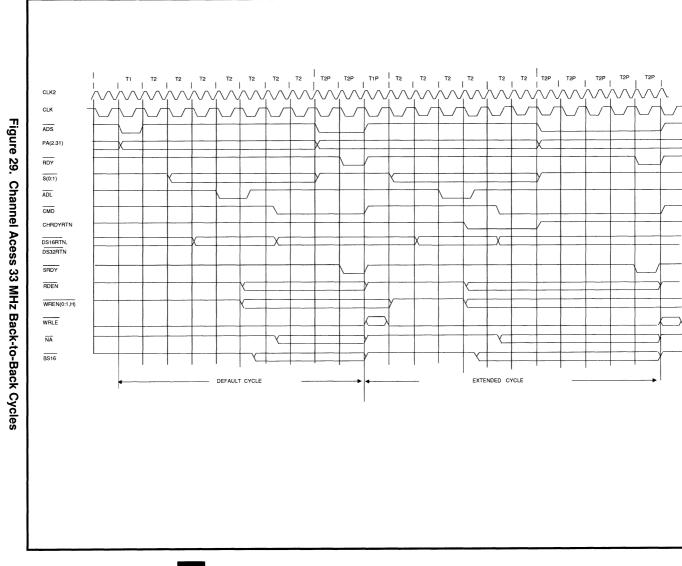

| Figure 29 | Channel Accesses 33 MHz Back-to-Back Cycles     |

| Figure 30 | 16 MHz 16-Bit Access to 8-Bit Channel Port      |

| Figure 31 | 20 MHz 16-Bit Access to 8-Bit Channel Port      |

| Figure 32 | 25 MHz 16-Bit Access to 8-Bit Channel Port      |

| Figure 33 | 33 MHz 16-Bit Access to 8-Bit Channel Port      |

| Figure 34 | 132-Pin JEDEC Flat Pack Packaging Diagram       |

# LIST OF TABLES

| Table 1  | Pin Description                                 | . 15-5 |

|----------|-------------------------------------------------|--------|

| Table 2  | Pin State After Reset                           | 15-13  |

| Table 3  | Memory Size Options                             | 15-21  |

| Table 4  | Page Mode DRAM Address Assignments              | 15-22  |

| Table 5  | Addresses for Different Sized DRAMs             | 15-22  |

| Table 6  | Memory Map 1                                    |        |

| Table 7  | Memory Map 2                                    |        |

| Table 8  | Memory Map 3                                    | 15-24  |

| Table 9  | Memory Map 4                                    | 15-24  |

| Table 10 | Memory Map 5                                    | 15-25  |

| Table 11 | Memory Map 6                                    | 15-25  |

| Table 12 | Memory Map 7                                    |        |

| Table 14 | Memory Control Register                         | 15-26  |

| Table 15 | Memory Card Definition Register                 | 15-27  |

| Table 16 | Model 80 Compatibility Mode                     | 15-27  |

| Table 17 | Memory Encoding Register 1                      | 15-27  |

| Table 18 | ENSPLIT, SIX40, and ROMEN Memory Configurations | 15-28  |

| Table 19 | Memory Encoding Register 2                      | 15-28  |

| Table 20 | DRAM Encodings                                  | 15-29  |

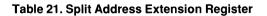

| Table 21 | Split Address Extension Register                | 15-29  |

| Table 22 | Bank Enable Register                            | 15-29  |

| Table 23 | Memory Size Register                            |        |

| Table 24 | Memory Window Bank 0 Register                   | 15-29  |

| Table 25 | Memory Window Bank 1 Register                   | 15-31  |

| Table 26 | Memory Window Bank 2 Register                   |        |

| Table 27 | Memory Window Bank 3 Register                   |        |

| Table 28 | Memory Configuration Register                   | 15-32  |

| Table 29 | CAS Pulse Width Register                        | 15-32  |

| Table 30 | RAS Precharge Delay Register                    | 15-34  |

| Table 31 | RAS Pulse Width Register                        |        |

| Table 32 | RAS Access Time Register                        |        |

| Table 33 | System Configuration Register                   |        |

| Table 34 | Typical RAM Program Parameters                  | 15-37  |

| Table 35 | Typical Cache Values                            | 15-38  |

| Table 36 | Cache Operation in Different Bus Cycles         | 15-39  |

| Table 37 | Cache Timing                                    | 15-40  |

| Table 38 | Frequency Table                                 | 15-41  |

| Table 39 | ESF Address Map In A WD6500 System Environment  | 15-42  |

| Table 40 | Typical Performance on a Memory Subsystem       | 15-46  |

| Table 41 | Channel Bus Cycle                               | 15-46  |

| Table 42 | Typical Performance for Accesses to Local I/O   | 15-47  |

# **ADDITIONAL REFERENCES**

IBM PS/2 Model 70 Technical Reference Manual IBM PS/2 Model 80 Technical Reference Manual Intel Microprocessor and Peripheral Handbook

# **1.0 INTRODUCTION**

# 1.1 DESCRIPTION

The WD6030 integrated circuit forms part of Western Digital's innovative WD6500 chip set. It facilitates the design and implementation of system boards compatible with IBM's Micro Channel architecture, decreases design complexity, saves space by combining the functions of many discrete arrays and components, and reduces system cost and increases system reliability.

The Extended Setup Facility, or ESF, is a Western Digital enhancement designed to allow more functionality such as a Winchester Controller, LAN Adapter, or additional Serial Port to be added onto the system board. It provides product differentiation at the system level and helps reduce costs. The block diagram in Figure 1 illustrates a typical system utilizing the WD6500 chip set. Devices with bold outlines are available from Western Digital Corporation.

# **1.2 FEATURES**

- Hardware (register level) and software compatible to the IBM Personal System/2 Micro Channel implementations

- Direct-Mapped Cache Controller

- Direct-mapped, write-through implementation

- □ Line size equals four bytes

- Page mode hits on cache misses

- DRAM Controller

- Memory Configuration Registers

- Complete 256 KB, 1 MB, and 4 MB DRAM support

- Ability to mix DRAM sizes in different banks

- Support for up to four banks (up to 64 M-Bytes) of memory

- Channel Controller

- Channel Buffer Controls

- Programmable Wait States

- □ Shadow RAM for fast BIOS execution

- □ Extended Setup Facility (ESF)

- Low Power 0.9 Micron CMOS Technology

- 132-Lead JEDEC Plastic Quad Flat Pack

Figure 1. System Block Diagram

# Figure 2. WD6030 Block Diagram

# 2.0 PIN DESCRIPTION

The signals assigned to different pins are grouped according to their function and discussed individually in Table 1.

# 2.1 LOCAL BUS INTERFACE

The WD6030 sits directly on the CPU bus, controlling the CPU/DMA accesses to local memory, I/O, and the Channel. The WD6030 also controls Micro Channel master accesses to the local memory.

# 2.2 CACHE CONTROLLER

The Cache Controller in the WD6030 implements a direct-mapped cache for the 80386, which improves performance significantly by allowing the majority of memory cycles to be run at zero wait states. These signals form part of the interface between the cache controller and the external cache and TagRAMs. See Section 3.0 for a detailed description of the cache controller.

# 2.3 DRAM CONTROLLER

The DRAM Controller supports Page Mode and allows DRAMs of different sizes to be used together. Pipelined operation, which allows fast accesses to the DRAMs, is also supported.

## 2.4 CHANNEL CONTROLLER

The Channel controller implements the interface to the system board. The WD6030 generates the Channel interface signals whenever the CPU or the DMA controller accesses any resource on the Channel.

### 2.5 CHANNEL BUFFER CONTROLLER

The Channel Buffer signals control the data buffers between the local processor data bus and the Channel data bus. The data buffers are integrated in the WD6022 device providing the interface to that device. Note that the WD6022 must be strapped in the Data Buffer Mode.

### 2.6 MISCELLANEOUS

This set of signals includes the  $V_{SS}$  and  $V_{DD}$  signal pins, as well as the reserved pins, which should not be connected but left open in the system.

1

# Figure 3. 132-PIN PLASTIC QUAD FLAT PACK

| PIN | _ | NAME            | PIN |   | NAME     | PIN | - | NAME    | PIN | - | NAME            |

|-----|---|-----------------|-----|---|----------|-----|---|---------|-----|---|-----------------|

| 1   | - | PA2             | 34  |   | N.C.     | 67  | _ | WREN1   | 100 | - | CDEN2           |

| 2   | - | PA3             | 35  | - | TR32     | 68  | - | WRENH   | 101 | _ | CDEN1           |

| 3   | - | PA4             | 36  | - | CHRDYRTN | 69  | - | WRLE    | 102 |   | CDEN0           |

| 4   | - | PA5             | 37  | _ | DS16RTN  | 70  | - | SWPWORD | 103 | - | CDIR            |

| 5   | - | PA6             | 38  | - | DS32RTN  | 71  | - | Vss     | 104 | - | TAGWR           |

| 6   | - | PA7             | 39  |   | VDD      | 72  | - | SWPBYT  | 105 | - | TAGDEN          |

| 7   | - | PA8             | 40  | - | MEMDS32  | 73  |   | SWPDIR  | 106 | - | Vss             |

| 8   | - | PA9             | 41  | - | UCHRDY   | 74  | - | RAS     | 107 | - | HITVALID        |

| 9   | - | PA10            | 42  | - | SO       | 75  | - | CAS0    | 108 | - | SRDY            |

| 10  | - | PA11            | 43  | - | S1       | 76  | - | CAS1    | 109 | - | MADS            |

| 11  | - | PA12            | 44  | - | Vss      | 77  | - | CAS2    | 110 | - | RDY             |

| 12  | - | PA13            | 45  | - | CMD      | 78  | - | CAS3    | 111 | - | HIT             |

| 13  | - | PA14            | 46  | - | A0       | 79  |   | DRMWR0  | 112 | - | MADE24          |

| 14  | - | PA15            | 47  | - | SBHE     | 80  |   | DRMWR1  | 113 | - | BE0             |

| 15  | - | PA16            | 48  | - | ADL      | 81  | - | DRMWR2  | 114 | - | BE1             |

| 16  |   | PA17            | 49  | - | N.C.     | 82  | - | DRMWR3  | 115 | - | BE2             |

| 17  | - | Vss             | 50  | - | Vss      | 83  | - | Vss     | 116 | - | Vss             |

| 18  | - | PA18            | 51  | - | PARCLK   | 84  | - | DRMA19  | 117 | - | BE3             |

| 19  | - | PA19            | 52  | - | NA       | 85  | - | DRMA18  | 118 | - | W/R             |

| 20  | - | PA20            | 53  | - | BS16     | 86  | - | MUX     | 119 | - | D/C             |

| 21  | - | PA21            | 54  | - | D0       | 87  | - | MDEN3   | 120 | - | M/IO            |

| 22  | - | PA22            | 55  | - | D1       | 88  | - | MDEN2   | 121 | - | ADS             |

| 23  |   | PA23            | 56  | - | D2       | 89  | - | MDEN1   | 122 | - | V <sub>DD</sub> |

| 24  |   | V <sub>DD</sub> | 57  | - | D3       | 90  | - | MDEN0   | 123 | - | REFRESH         |

| 25  | — | PA24            | 58  | - | Vss      | 91  | - | MDIR    | 124 | - | RESET           |

| 26  | - | PA25            | 59  | - | D4       | 92  | - | VDD     | 125 | - | HLDA            |

| 27  | — | PA26            | 60  |   | D5       | 93  |   | CCHCS   | 126 | - | UCHMSTR         |

| 28  | - | Vss             | 61  | - | D6       | 94  | - | CCHWR3  | 127 | - | A20GTX          |

| 29  |   | PA27            | 62  | - | D7       | 95  | - | Vss     | 128 | — | N.C.            |

| 30  | - | PA28            | 63  | - | RDEN     | 96  | - | CCHWR2  | 129 |   | TEST            |

| 31  | - | PA29            | 64  | - | RDLE     | 97  | - | CCHWR1  | 130 | - | CLK             |

| 32  | - | PA30            | 65  | - | WREN0    | 98  | - | CCHWR0  | 131 | - | CLK2            |

| 33  | - | PA31            | 66  | - | VDD      | 99  | - | CDEN3   | 132 | - | Vss             |

|     |   |                 |     |   |          |     |   |         |     |   |                 |

| PIN NO.            | NAME                | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|--------------------|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                    | LOCAL BUS INTERFACE |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 127                | A20GTX              | 1    | GATE<br>At power-up, the state of A20GTX is latched at the trailing edge of RESET<br>and, in conjunction with UCHMSTR, determines the frequency at which the<br>WD6030 operates. The following table lists the clock frequencies available.                                                                                                                                                                                                                              |  |  |  |  |  |  |

|                    |                     |      | FREQUENCY         UCHMSTR         A20GTX           16 MHz         0         0           20 MHz         0         1           25 MHz         1         1           33 MHz         1         0                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                    |                     |      | After power-up, A20GTX is used to wrap around addresses in the Real and Virtual 8086 modes of the processor. The signal is generated by the WD6010 and is a combination of the A20GATE generated by the 8742 and the Alternate Gate A20 signal from Port 0092H, bit 1. The WD6030 uses this signal internally to generate the address for memory accesses. Depending on the frequency configuration required, this signal should be pulled up/down with a 470K resistor. |  |  |  |  |  |  |

| 126                | UCHMSTR             | 1    | CHANNEL MASTER<br>At power-up, the state of UCHMSTR is latched at the trailing edge of $\overline{\text{RESET}}$ ,<br>and in conjunction with A20GTX, determines the frequency at which the<br>WD6030 operates.                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                    |                     |      | After power-up, UCHMSTR functions as a signal from the Central Arbitration<br>Control Point (CACP) in the WD6010. When active, it indicates that a<br>Channel master has the bus. A 2.7K resistor is used to pull up/down this<br>signal.                                                                                                                                                                                                                                |  |  |  |  |  |  |

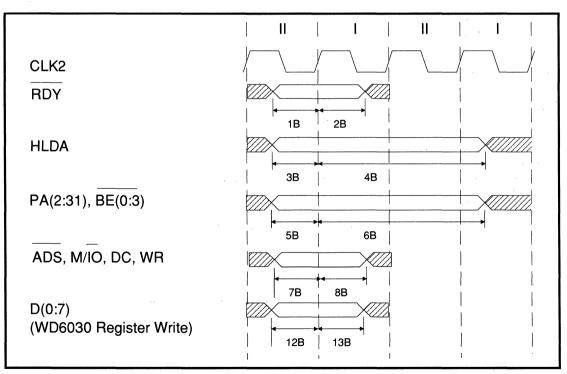

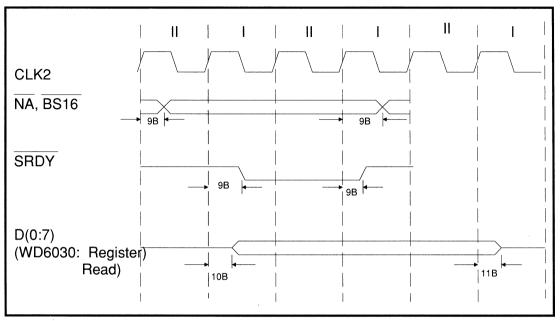

| 54 - 57<br>59 - 62 | D0 - D7             | I/O  | CHANNEL DATA BUS<br>The WD6030 internal registers are programmed via the Channel Data Bus.<br>These registers can only be accessed by <u>8-bit operations</u> . When the<br>registers are accessed, a Channel cycle (S0, S1, CMD, etc.) is initiated, and<br>the controls for the Channel buffers are activated to complete the cycle.                                                                                                                                   |  |  |  |  |  |  |

| 131<br>130         | CLK2<br>CLK         | 1    | CLOCKS<br>Both CLK and CLK2 are CMOS level signals. CLK is of the same frequency<br>as the processor clock, while CLK2 is twice the frequency of the processor<br>clock. The WD6030 shares CLK2 with the CPU.                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 125                | HLDA                | 1    | HOLD ACKNOWLEDGE<br>HLDA indicates that the CPU has given control of the system local bus to a<br>different master (Channel Bus Master or DMA Controller). HLDA prevents<br>non-system CPU accesses to locations 0000-00FFH in the WD6000 during<br>master cycles.                                                                                                                                                                                                       |  |  |  |  |  |  |

# Table 1. Pin Description

1

| PIN NO.                                 | NAME                                                    | TYPE |                                                                                                                                                                                                                                                                                                                                                                | <u> </u>                                                                                  | FUNCT                                                             | ION                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------|---------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 124                                     | RESET                                                   | I    |                                                                                                                                                                                                                                                                                                                                                                | -                                                                                         |                                                                   | ) and is asserted at power-on. It initializes gisters to the power-up default values.                                                                                                                                                                                                                                                 |

| 121                                     | ADS                                                     | I    | ADDRESS S<br>The WD6030<br>data, and sta                                                                                                                                                                                                                                                                                                                       | uses AD                                                                                   | •                                                                 | track of bus cycles on the CPU address,                                                                                                                                                                                                                                                                                               |

| 120<br>119<br>118                       | M/ĪO<br>D/Ċ<br>W/R                                      | I    | MEMORY I/O, DATA/CONTROL, WRITE/READ<br>The M/IO, D/C, and W/R signals define the type of bus cycle being executed on<br>the CPU local bus. When the CPU is in control of the CPU local bus, M/IO, D/C,<br>and W/R are input from the CPU. When the WD6010 DMA Controller is in control<br>of the CPU local bus, M/IO, D/C, and W/R are input from the WD6010. |                                                                                           |                                                                   |                                                                                                                                                                                                                                                                                                                                       |

|                                         |                                                         |      | M/IO                                                                                                                                                                                                                                                                                                                                                           | D/C                                                                                       | W/R                                                               | WD6030 OPERATION                                                                                                                                                                                                                                                                                                                      |

|                                         |                                                         |      | 0                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                         | 0                                                                 | Reserved                                                                                                                                                                                                                                                                                                                              |

|                                         |                                                         |      | 0                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                         | 1                                                                 | Reserved                                                                                                                                                                                                                                                                                                                              |

| s                                       |                                                         |      | 0                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                         | 0                                                                 | I/O Read                                                                                                                                                                                                                                                                                                                              |

|                                         |                                                         |      | 0                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                         | 1                                                                 | I/O Write                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                         |      | 1                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                         | 0                                                                 | Memory Code Read                                                                                                                                                                                                                                                                                                                      |

|                                         |                                                         |      | 1                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                         | 1                                                                 | Reserved                                                                                                                                                                                                                                                                                                                              |

|                                         |                                                         |      | 1                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                         | 0                                                                 | Memory Read                                                                                                                                                                                                                                                                                                                           |

|                                         |                                                         |      | 1                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                         | . 1                                                               | Memory Write                                                                                                                                                                                                                                                                                                                          |

| 117<br>115<br>114<br>113                | BE3<br>BE2<br>BE1<br>BE0                                | I    | BYTE ENAB<br>These Byte-<br>controller, or                                                                                                                                                                                                                                                                                                                     | Enable s                                                                                  |                                                                   | driven by the CPU, the WD6010 DMA                                                                                                                                                                                                                                                                                                     |

| 110                                     | RDY                                                     | I    |                                                                                                                                                                                                                                                                                                                                                                | als from t                                                                                | he chip se                                                        | ck bus cycles on the CPU local bus. The<br>t are combined externally to generate one                                                                                                                                                                                                                                                  |

| 1 - 16<br>18 - 23<br>25 - 27<br>29 - 33 | PA2 - PA17<br>PA18 - PA23<br>PA24 - PA26<br>PA27 - PA31 | 1    | and interface                                                                                                                                                                                                                                                                                                                                                  | PA31 is<br>s directly                                                                     | the local p<br>with the 80                                        | rocessor address bus on the motherboard<br>0386/80486 address bus. This address bus<br>roller, or a Channel Master.                                                                                                                                                                                                                   |

| 108                                     | SRDY                                                    | 0    | bus, including<br>80386, 80486<br>to the nume<br>resulting in a<br>the other sou                                                                                                                                                                                                                                                                               | ) generate<br>g the loca<br>5, or DMA<br>ric coproc<br>cache hit<br>urces of F<br>e READY | I DRAM. 1<br>Controller<br>æssor (803<br>. This sign<br>EADY to g | Y signal for system resources not on the local<br>The SRDY signal is generated whenever the<br>performs a bus cycle that is neither an access<br>887 or Weitek 3167) nor a memory access<br>al is logically ORed on the system board with<br>generate READY to the CPU. Note that the<br>ne 80386, 80486, or DMA Controller is a "not |

| PIN NO. | NAME     | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53      | BS16     | 0    | BUS SIZE 16<br>BS16 is used to indicate whether the CPU or WD6030 is accessing a 32-bit,<br>16-bit, or 8-bit port. When a 32-bit port is accessed, BS16 is de-asserted and<br>all byte enables should be active. When a 16-bit or 8-bit port is ac-<br>cessed, BS16 is asserted and the byte enables are sampled to determine<br>whether the access is to a 16-bit or 8-bit port.               |

| 52      | NA       | 0    | NEXT ADDRESS<br>The Next Address signal is asserted when a pipelined cycle can be supported<br>by the system. The WD6030 requests a pipeline cycle whenever a cycle<br>other than a Cache-Read-Hit occurs.                                                                                                                                                                                      |

| 1       |          |      | CACHE CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                |

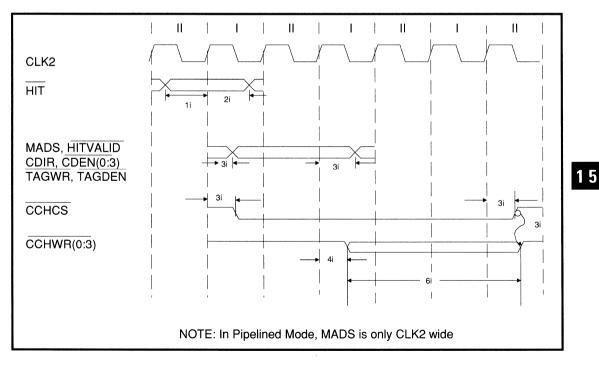

| 111     | HIT      | I    | CACHE HIT<br>The external tag subsystem sends this signal to the WD6030 to indicate that<br>the current cycle resulted in a match of the Tag. Depending on whether or<br>not the DRAM cycle can be cached, this signal is internally qualified to<br>generate a cache hit indication. If a cache hit occurs on a memory read cycle,<br>a zero wait state operation is accomplished.             |

| 107     | HITVALID | 0    | CACHE HIT QUALIFIER<br>The WD6030 asserts the HITVALID signal to indicate that the HIT signal from<br>the tag subsystem is valid and can be sampled by the external logic. HIT<br>and HITVALID are logically ANDed externally to assert the READY signal to<br>the 80386, 80486, or DMA Controller, resulting in a zero wait state cycle on<br>a Cache-Read-Hit.                                |

|         |          |      | For a cycle requiring a cache update, $\overline{\text{HIT}}$ may be inactive in the early part of the cycle and active in the latter part when the Tag is updated. $\overline{\text{HITVALID}}$ is de-asserted in the latter part of the cycle to prevent generating a spurious READY signal to the CPU.                                                                                       |

| 105     | TAGDEN   | 0    | TAG DATA ENABLE<br>TAGDEN opens a "Tag Buffer", such as a 74F244, during a Tag update cycle.<br>Tag updates occur on a Cache-Miss cycle on cachable memory areas.                                                                                                                                                                                                                               |

| 104     | TAGWR    | 0    | TAG WRITE<br>TAGWR updates the Tag in the TagRAM for a Cache-Update cycle. A<br>pipelined cycle is requested and TAGWR updates the Tag value when a<br>Cache-Miss occurs.                                                                                                                                                                                                                       |

| 103     | CDIR     | Ο    | CACHE BUFFER DIRECTION<br>CDIR determines the direction of the data flow between the Processor Data<br>Bus (PD) and Cache Data Bus (CD) for the 74F245 buffers. The 74F245<br>buffers minimize the loading on the CPU local bus and permit more relaxed<br>timings on the Cache Data SRAMs. The 74F245 buffers also permit the use<br>of SRAMs which do not require the Output Enable function. |

|         |          |      | CDIR         Direction           0         CD(0:31) to PD(0:31)           1         PD(0:31) to CD(0:31)                                                                                                                                                                                                                                                                                        |

1/

| PIN NO.                 | NAME                                 | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------|--------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

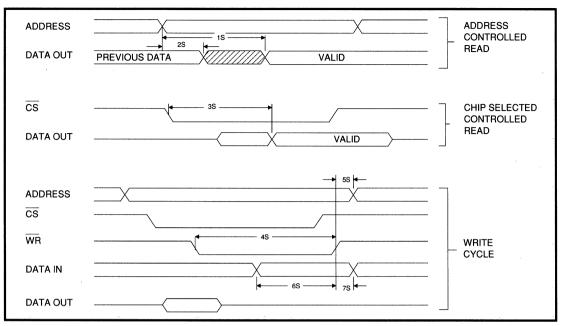

| 102<br>101<br>100<br>99 | CDEN0<br>CDEN1<br>CDEN2<br>CDEN3     | 0    | CACHE BUFFER ENABLES<br>CDEN(0:3) provides the enable signals for the 74F245 buffers between the<br>Processor Data Bus (PD) and the Cache Data Bus (CD). Each data byte<br>has a separate enable which is qualified internally by the byte enable from<br>the 80386, 80486, or DMA Controller. Figure 4 illustrates a typical cache<br>cycle with page hits.                                                        |

| 98<br>97<br>96<br>94    | CCHWR0<br>CCHWR1<br>CCHWR2<br>CCHWR3 | 0    | DATA CACHE WRITE<br>CCHWR(0:3) individually enables each of the four bytes of the cache data.<br>The WD6030 asserts the write signal corresponding to the byte enable<br>asserted during the cycle.                                                                                                                                                                                                                 |

| 93                      | CCHCS                                | Ο    | DATA CACHE CHIP SELECT<br>CCHCS is the Chip Select signal to the Cache Data SRAMs. CCHCS is<br>always asserted at the beginning of a cycle, permitting the slowest possible<br>SRAMs to be used. CCHCS is only de-asserted for a cache update<br>operation.                                                                                                                                                         |

|                         |                                      |      | DRAM CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                     |

| 123                     | REFRESH                              | 1    | REFRESH<br>REFRESH from the WD6010 indicates that a Refresh cycle is in progress<br>and a Memory Read cycle is taking place run on the local bus. When<br>REFRESH is asserted, the DRAM controller initiates a RAS-only cycle, with<br>the address supplied by the WD6010. Simultaneously, a Memory Read<br>cycle is initiated on the Channel. A READY signal is generated when both<br>cycles have been completed. |

| 109                     | MADS                                 | 0    | MEMORY ADDRESS STROBE<br>The MADS signal from the WD6030 latches all addresses for the external<br>cache data and DRAM to the external address latches 74AS373. Figures 5<br>through 8 illustrate a typical cycle to the DRAM.                                                                                                                                                                                      |

| 91                      | MDIR                                 | ο    | DRAM BUFFER DIRECTIONMDIR determines the direction of the data flow for the 74F657 bidirectional<br>transceivers between the Processor Data Bus (PD), and the DRAM Data<br>Bus (MD).MDIRDirection0MD(0:31) to PD(0:31)                                                                                                                                                                                              |

|                         |                                      |      | 1 PD(0:31) to MD(0:31)                                                                                                                                                                                                                                                                                                                                                                                              |

| 90<br>89<br>88<br>87    | MDEN0<br>MDEN1<br>MDEN2<br>MDEN3     | ο    | DRAM BUFFER ENABLES<br>MDEN(0:3) are the enable signals for the 74F657 transceivers between the<br>Processor Data Bus (PD) and DRAM Data Bus (MD). Each data byte has<br>its own enable which is qualified internally by the byte enables from the<br>80386, 80486, or DMA Controller.                                                                                                                              |

| PIN NO.              | NAME                                 | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------|--------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 86                   | MUX                                  | 0    | ADDRESS MULTIPLEXER<br>MUX interfaces with the external address multiplexers and controls the<br>generation of the row and column addresses to the DRAM.                                                                                                                                                                                                                                                                                                                            |

|                      |                                      |      | MUX     Function       0     Row Address                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 85<br>84             | DRMA18<br>DRMA19                     | ο    | 1 Column Address<br>DRAM SPLIT MEMORY ADDRESS<br>DRMA(18:19) provide Address Bits 18 and 19 for DRAM accesses, which are<br>sent to the external DRAM address multiplexers. These signals implement<br>the split addressing memory feature.                                                                                                                                                                                                                                         |

| 82<br>81<br>80<br>79 | DRMWR3<br>DRMWR2<br>DRMWR1<br>DRMWR0 | 0    | DRAM WRITE<br>DRMWR(3:0) are the enable signals to the system DRAM. Each data byte<br>has a separate enable which is internally qualified by the byte enables from<br>the 80386, 80486, or DMA Controller. The four write enable signals to the<br>DRAM should be buffered by a 74AS1832.                                                                                                                                                                                           |

| 78<br>77<br>76<br>75 | CAS3<br>CAS2<br>CAS1<br>CAS0         | ο    | DRAM CAS<br>Each of the four banks has its own CAS signal. The bank being accessed<br>has its CAS signal asserted during a cycle. At the end of the cycle, all CAS<br>signals are de-asserted. These signals should be buffered by a 74AS1832.<br>Page Mode DRAMs can be employed because the WD6030 de-asserts this<br>signal at the end of each cycle. Static Column DRAMs may also be used,<br>however, they will operate in Page Mode.                                          |

| 74                   | RAS                                  | 0    | DRAM RAS<br>RAS connects to the RAS inputs of all the DRAMs and should be buffered by<br>a 74AS1832.<br>This signal is active in Page Mode as long as the accesses remain within the<br>same row. RAS remains active even if the accesses are made to addresses<br>in different memory banks which share the same row address, because the<br>row addresses are shared by the different memory banks. In normal<br>RAS/CAS Mode, a RAS precharge takes place for every DRAM access. |

| 51                   | PARCLK                               | 0    | PARITY ERROR CLOCK<br>PARCLK is used as a clock to latch in parity error information during DRAM<br>read cycles. At the rising edge of this signal, the parity error information is<br>latched in. The Parity Error Latch function is implemented on the system<br>board.                                                                                                                                                                                                           |

|                      |                                      |      | CHANNEL CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 45                   | CMD                                  | I/O  | COMMAND<br>CMD defines when data to or from the Channel is valid. CMD is an input<br>during Channel Master Cycles and an output during all other cycles.                                                                                                                                                                                                                                                                                                                            |

| 43<br>42             | S1<br>S0                             | I/O  | CHANNEL STATUS<br>S1 and S0, along with M/IO, identify the type of cycle taking place on the<br>channel. S1 and S0 are input signals during a Channel Master Cycle and an<br>output during all other cycles.                                                                                                                                                                                                                                                                        |

| PIN NO.  | NAME       | TYPE       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|----------|------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 112      | MADE24     | I          | MEMORY ADDRESS ENABLE 24<br>MADE24 is asserted by the channel when an address greater than 16<br>Mbytes is placed on the Processor Address Bus (PA). The WD6022 Address<br>Buffer Device de-asserts MADE24 whenever the CPU or DMA Controller<br>performs a Channel Memory access above the 16 Mbyte boundary.                                                                                                                                                |  |  |  |

| 38       | DS32RTN    | <b>I</b> . | DATA SIZE 32 RETURN<br>DS32RTN corresponds to, and directly interfaces with, the DS32RTN signal<br>on the Channel and is generated by ORing all the CDDS32N signals on the<br>Channel. Asserting DS32RTN during a Channel cycle indicates that the<br>slave being addressed is capable of transferring 32 bits of data.                                                                                                                                       |  |  |  |

| 37       | DS16RTN    | <b>I</b> . | DATA SIZE 16 RETURN<br>DS16RTN corresponds to, and directly interfaces with, the DS16RTN signal<br>on the Channel and is generated by ORing all the CDDS16N signals on the<br>Channel. Asserting DS16RTN during a Channel cycle indicates that the<br>slave being addressed is capable of transferring 16 bits of data.                                                                                                                                       |  |  |  |

| 36       | CHRDYRTN   | 1          | CHANNEL READY RETURN<br>CHRDYRTN is an AND of all CDCHRDY signals present on the Channel,<br>i.e., the individual Channel slots, video subsystem, WD6000 (IORDY) and<br>the system board DRAM (UCHRDY). A Channel slave uses CHRDYRTN<br>to extend the Channel cycle.                                                                                                                                                                                         |  |  |  |

| 35       | TR32       | I          | TRANSLATE 32<br>TR32 facilitates communication between a 16-bit master and a 32-bit slave.<br>TR32 generates the necessary control signals used in data swapping.<br>When asserted, it indicates that a 16-bit master has the Channel and that<br>the Central Translator function should be turned on. The CPU and DMA<br>Controller are 32-bit masters, therefore, the WD6022 de-assertes TR32<br>when the Channel is accessed by the CPU or DMA Controller. |  |  |  |

| 48       | ADL        | ο          | ADDRESS DECODE LATCH<br>ADL provides the slave with an appropriate method to latch valid addresses<br>and status signals.                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 47<br>46 | SBHE<br>A0 | <b>O</b>   | SYSTEM BYTE HIGH ENABLE<br>ADDRESS BIT 0<br>SBHE and A0 are used by 16-bit slaves to determine the byte that con-<br>tains data during the current transfer of data.<br>A0 SBHE DATA AVAILABLE                                                                                                                                                                                                                                                                |  |  |  |

|          |            |            | 0         0         D(0:15)           0         1         D(0:7)           1         0         D(8:15)           1         1         Reserved           Note that this signal is not used by 8-bit or 32-bit slaves. The latter uses           BE(0:3) signals to perform the same function.                                                                                                                                                                  |  |  |  |

|          |            |            | BE(0:3) signals to perform the same function.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| PIN NO. | NAME    | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                   |

|---------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 41      | UCHRDY  | 0    | LOCAL DRAM CHANNEL READY<br>UCHRDY is used to extend cycles when a Channel Master accesses the<br>system board DRAM. UCHRDY is also used in the external logic to generate<br>CHRDYRTN. Figures 9 through 12 indicate typical Channel Master cycles<br>to the system board DRAM.                                                                                           |

| 40      | MEMDS32 | 0    | LOCAL DRAM MEMORY SIZE 32<br>MEMDS32 is used in external logic on the system board to generate the<br>DS16RTN and DS32RTN signals. MEMDS32 is driven by the WD6030<br>when a Channel Master accesses the system board DRAM and indicates<br>that the memory accessed is 32 bits wide.                                                                                      |

|         |         |      | CHANNEL BUFFER CONTROLLER                                                                                                                                                                                                                                                                                                                                                  |

| 73      | SWPDIR  | I/O  | SWAP DIRECTION<br>At power-up, the state of SWPDIR is latched by the trailing edge of RESET<br>to determine the presence or absence of the numeric processor.                                                                                                                                                                                                              |

|         |         |      | SWPDIR RESET STATE FUNCTION                                                                                                                                                                                                                                                                                                                                                |

|         |         |      | 0 Numeric coprocessor present                                                                                                                                                                                                                                                                                                                                              |

|         |         |      | 1 Numeric coprocessor absent                                                                                                                                                                                                                                                                                                                                               |

|         |         |      | After power-up, SWPDIR indicates the direction of the byte and word swap buffers.                                                                                                                                                                                                                                                                                          |

|         | į       |      | SWPDIR de-asseted indicates a read operation, byte swap D(0:7) to D(8:15) or a Channel Master write operation, word swap D(0:15) to D(16:31).                                                                                                                                                                                                                              |

|         |         |      | SWPDIR asserted indicates a write operation, byte swap D(8:15) to D(0:7) or a Channel Master read operation, word swap D(16:31) to D(0:15).                                                                                                                                                                                                                                |

| 72      | SWPBYT  | 0    | BYTE SWAP<br>When the CPU or DMA accesses an 8-bit port, the cycle is split into two.<br>This signal is used to swap data to the correct bytes.<br>D(0:7) is swapped to D(8:15) for a read and normal operation<br>D(8:15) is swapped to D(0:7) for a write operation                                                                                                      |

| 70      | SWPWORD | 0    | WORD SWAP<br>SWPWORD swaps words when a 16-bit Channel Master communicates with<br>a 32-bit slave. The cycle is split into two and SWPWORD is used to swap<br>data to the correct word. D(16:31) is swapped to D(0:15) for a Channel<br>Master read operation, D(0:15) is swapped to D(16:31) for a Channel Master<br>write operation. This function is known as steering. |

| 69      | WRLE    | 0    | WRITE LATCH ENABLE<br>WRLE latches the write data during a CPU or DMA write operation to the<br>Channel. It provides the write-data-hold time required by the Channel during<br>these operations. WRLE also latches data when the CPU or DMA writes to<br>an 8-bit port and the cycle must be split in two.                                                                |

|         |         |      |                                                                                                                                                                                                                                                                                                                                                                            |

1/2

| PIN NO.                                                      | NAME                    | TYPE         | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------|-------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 68<br>67<br>65                                               | WRENH<br>WREN1<br>WREN0 | 0            | WRITE ENABLE (HIGH, 0:1)<br>These signals enable the buffer during data flow from the Processor Data<br>Bus (PD) to the Channel Data Bus (D). These signals control byte 0 (0:7)<br>(WREN0), byte 1 (8:15) (WREN1), and the upper word (16:31) (WRENH).<br>These signals are valid when the CPU or DMA controller performs a write<br>operation to the Channel or when a Channel Master performs a read<br>operation from the system board DRAM. |

| 64                                                           | RDLE                    | 0            | READ LATCH ENABLE<br>RDLE is the latch enable signal for byte 0 (0:7). When the CPU or DMA<br>controller performs a cycle to an 8-bit device on the Channel, the cycle is<br>split in two. This signal latches the first 8 bits (0:7) during the first cycle,<br>reads the next 8 bits (8:15) during the second cycle, and then presents the<br>16 bits to the CPU.                                                                              |

| 63                                                           | RDEN                    | 0            | READ ENABLE<br>RDEN enables the buffer for the Processor Data Bus (PD) when the data<br>flows from the Channel Data Bus (D) to the Processor Data Bus (PD).<br>RDEN is asserted when the CPU or DMA controller performs a read from<br>the Channel or when a Channel Master writes to the system board DRAM.                                                                                                                                     |

|                                                              |                         |              | MISCELLANEOUS                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 24, 39,<br>66, 92,<br>122                                    | V <sub>DD</sub>         | 1            | +5 V Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 17, 28,<br>44, 50,<br>58, 71,<br>83, 95,<br>106,<br>116, 132 | Vss                     | <b>I</b><br> | 0 V Ground                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 34, 49,<br>128                                               | N.C.                    |              | Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 129                                                          | TEST                    |              | TEST PIN<br>This is an active low signal that facilitates board-level testing. When low,<br>this signal tri-states all outputs and bidirectional signal lines, allowing an<br>ATE tester to drive these signals. When high, the outputs and bidirectional<br>lines are enabled by the WD6030.                                                                                                                                                    |

Table 2 details the state of the pins on the WD6030 after a reset.

| SIGNAL                                                                                                                                                                                                                                                                                                                         | BUS STATE<br>AFTER RESET                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| D (0:7)<br>NA, BS16<br>S (0:1), ADL, CMD<br>SBHE, A0<br>MEMDS32<br>UCHRDY, SRDY<br>MADS<br>HITVALID<br>CCHCS<br>CDIR, MDIR<br>CCHWR (0:3), CDEN (0:3)<br>TAGWR, TAGDEN<br>RAS, CAS (0:3)<br>MUX, PARCLK<br>DRMWR (0:3)<br>DRMA (18:19)<br>MDEN (0:3)<br>RDEN<br>RDLE<br>WREN (0:1), WRENH<br>WREN<br>SWPBYT, SWPWORD<br>SWPDIB | Z*<br>High<br>High<br>High<br>High<br>High<br>High<br>High<br>Low<br>High<br>High<br>High<br>High<br>High<br>High<br>High<br>High |

| * Z = High Impedance                                                                                                                                                                                                                                                                                                           |                                                                                                                                   |

Table 2. Pin State After Reset

Figure 4. Cache Cycle with Page Hits

Figure 7. 80386/80486/DMA 25 MHz DRAM Access

$\sim$

WR CACHE MISS, PAGE MISS

From falling edge of CLK2

RPW

ACC

= 4

= 5

Figure 9. 16 MHz Synchronous Extended Master Cycle

1/2

Figure 10. 20 MHz Sysnchronous Extended Master Cycle

ADVANCED INFORMATION 9/17/90

15-20

$\gg$

WD6030

# 3.0 DRAM CONTROLLER

# 3.1 MEMORY ORGANIZATION

The WD6030 supports up to four banks of DRAMs, each consisting of 36 bits, with each byte having an associated parity bit. The total memory capacity on the system board is dependent on the type of memory used and the number of banks populated, and could range from 1 MB to 64 MB. Table 3 lists the memory size options that are available.

| DRAM TYPE | MEMORY CAPACITY           |

|-----------|---------------------------|

| 256K x 1  | 1 MB x (Number of Banks)  |

| 1M x 1    | 4 MB x (Number of Banks)  |

| 4M x 1    | 16 MB x (Number of Banks) |

#### **Table 3. Memory Size Options**

The Model 80-071 provides two banks, each with 1 MB of memory. The Model 80-111 has two banks of 2 MB each. The WD6030 default setting at power-up is compatible with the Model 80-071 and Model 80-111: two 1 MB memory banks. The Extended Setup Facility feature can be used to enable more memory on the board.

Each of the banks can be enabled or disabled by programming the Memory Configuration Register. In addition, banks can be swapped, in order to map around defective memory banks.

The WD6030 permits DRAMs of different sizes to be used in the four banks. However, all the DRAMs within a bank should be of the same size. For example, if Bank 0 were composed of 1M x 1 DRAMs, Bank 1 of 256K x 1 DRAMs, and Banks 2 and 3 were unpopulated, this would be a valid use of differentsized DRAMs. Certain restrictions that apply to mixing DRAM sizes should be noted carefully:

The WD6030 does not support Page Mode operation when DRAMs of different sizes are used in different banks; therefore, in such cases, the DRAMs must be set in Forced Row Misses Mode through the Memory Configuration register. This will result in degraded performance when compared to Page Mode operation for the DRAMs.