FE3001A

AT Clock Generation and

Cycle Control Device

# **TABLE OF CONTENTS**

| Section | Title |             | Pa                                   | ge  |

|---------|-------|-------------|--------------------------------------|-----|

| 1.0     | INTR  | ODUCTIO     | N                                    |     |

|         | 1.1   | Descriptio  | n                                    | 2-1 |

|         | 1.2   | Features    |                                      | 2-1 |

| 2.0     | FUNC  | CTIONAL D   | DESCRIPTION 2                        | 2-8 |

|         | 2.1   | Functiona   | l Overview 2                         | 2-8 |

|         | 2.2   | Cllock Ge   | nerator                              | 2-8 |

|         |       | 2.2.1       | PROCLK                               | 2-8 |

|         |       | 2.2.2       | DMACLK 2                             | 2-8 |

|         |       | 2.2.3       | CLK287 2                             | 2-9 |

|         |       | 2.2.4       | SYSCLK 2                             | 2-9 |

|         |       | 2.2.5       | PCLK/EADRO, PCLK and TMRCLK          | 2-9 |

|         |       | 2.2.6       | Stopping the Clocks (Sleep Mode)     | 2-9 |

|         | 2.3   | Command     | d Control                            |     |

|         |       | 2.3.1       | On-board Cycles 2-                   | 10  |

|         |       | 2.3.2       | AT Bus Cycles 2-                     | 10  |

|         |       | 2.3.3       | Other Cycles                         |     |

|         | 2.4   | Bus Contr   | rol2-                                | -11 |

|         | 2.5   | A0/BHE      | Generator                            | -11 |

|         |       | 2.5.1       | ADRO2-                               | -11 |

|         |       | 2.5.2       | ABHE2-                               | -11 |

|         |       | 2.5.3       | EBHE2-                               | -11 |

|         |       | 2.5.4       | EADRO2-                              | -11 |

|         | 2.6   | Priority Co | ontrol                               | 12  |

|         |       | 2.6.1       | Refresh Cycles                       |     |

|         |       | 2.6.2       | DMA Cycles & Request Arbitration 2-  |     |

|         | 2.7   | DMA Con     | trol2-                               |     |

|         | 2.8   |             | trol 2-                              |     |

|         | 2.9   | Coproces    | sor Interface 2-                     | 13  |

|         | 2.10  | •           | ntrol                                |     |

|         | 2.11  | General N   | lotes                                | 14  |

| 3.0     | FE30  |             | STERS 2-                             |     |

|         | 3.1   |             | trol Register (061H), Read/Write 2-  |     |

|         | 3.2   |             | elect (063H), Write                  |     |

|         | 3.3   | -           | ole (070H), Write 2-                 |     |

|         | 3.4   |             | d Control Registers                  |     |

|         | 3.5   |             | d Register Pointer 2-                |     |

|         | 3.6   |             | ning                                 |     |

|         | 3.7   |             | nory & 8/16-bit I/O Command Delay 2- |     |

|         | 3.8   |             | ory & I/O Wait States                |     |

# FE3001A

| Section  | Title  |                                        | Page |

|----------|--------|----------------------------------------|------|

|          | 3.9    | 16-bit I/O Wait States                 | 2-20 |

|          | 3.10   | 16-bit AT Bus Memory Timing            | 2-20 |

|          | 3.11   |                                        | •    |

|          | 3.12   | On-board Memory Timing                 |      |

|          |        | On-board I/O Timing                    |      |

|          |        | Enhanced Features Enable (R13)         |      |

|          |        | Clear 80287 Busy (0F0H), Write         |      |

|          |        | Reset 80287 (0F1H), Write              |      |

| 4.0      | PACK   | KAGE                                   | 2-22 |

| 5.0      | ABSO   | OLUTE MAXIMUM RATINGS                  | 2-22 |

| 6.0      | DC C   | CHARACTERISTICS                        | 2-22 |

| 7.0      | FE30   | 001A TIMING PARAMETERS                 | 2-23 |

| Appendix | A FE30 | 001A Recommended Bus Cycle Programming | 2-58 |

|          | A.1    | 6.25 MHz System Clock Speed            |      |

|          | A.2    | 8 MHz System Clock Speed               |      |

|          | A.3    | 12.5 and 16 MHz System Clock Speed     |      |

|          | Λ 1    |                                        |      |

# **LIST OF ILLUSTRATIONS**

| Figure | Title F                                                                                  | Page  |

|--------|------------------------------------------------------------------------------------------|-------|

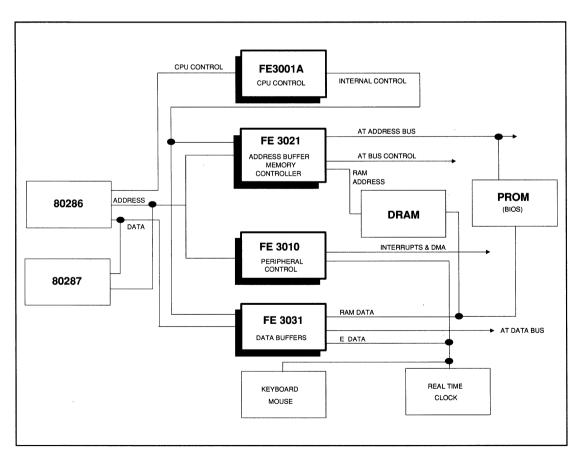

| 1-1    | FE3600B/C Chip Set Functional Block Diagram                                              | 2-1   |

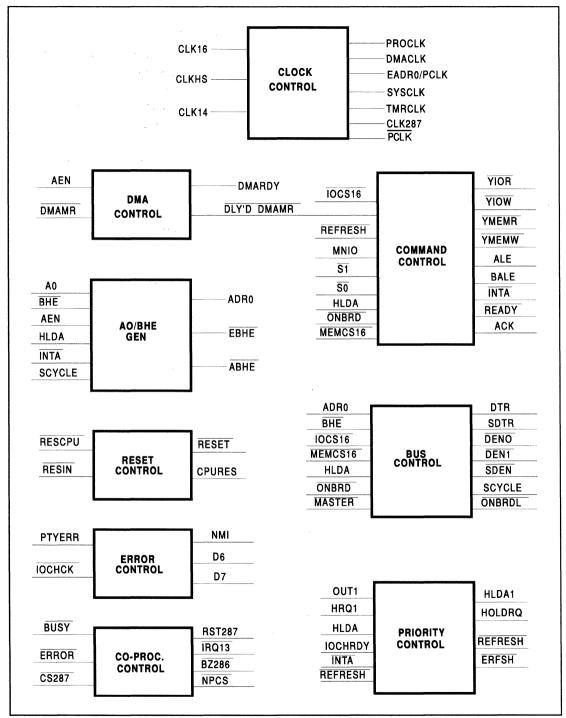

| 1-2    | FE3001A Block Diagram                                                                    | . 2-2 |

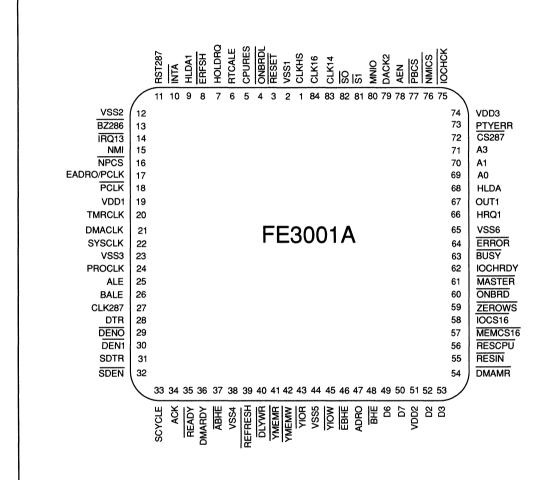

| 1-3    | FE3001A Pin Assignments                                                                  | . 2-3 |

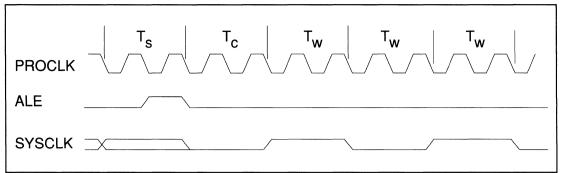

| 2-1    | SYSCLK Timing During High Speed Operation                                                | . 2-9 |

| 3-1    | Error Control Register, Read/Write                                                       | 2-15  |

| 3-2    | Speed Select, Write                                                                      | 2-16  |

| 3-3    | NMI Enable, Write                                                                        | 2-17  |

| 3-4    | Programmable Command Timing                                                              | 2-18  |

| 3-5    | Command Register Pointer                                                                 | 2-19  |

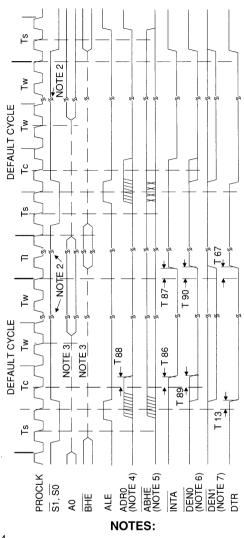

| 7-1    | CPU Cycle Timing for ALE, Byte Select, ONBRD and READY                                   | 2-31  |

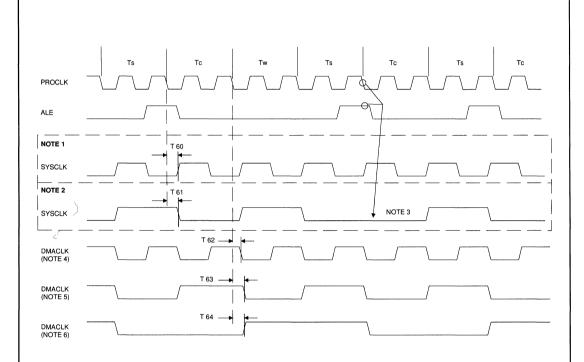

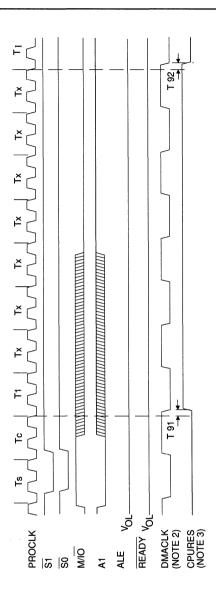

| 7-2    | Clock Timing (1 of 2)                                                                    | 2-32  |

| 7-3    | Clock Timing (2 of 2)                                                                    | 2-33  |

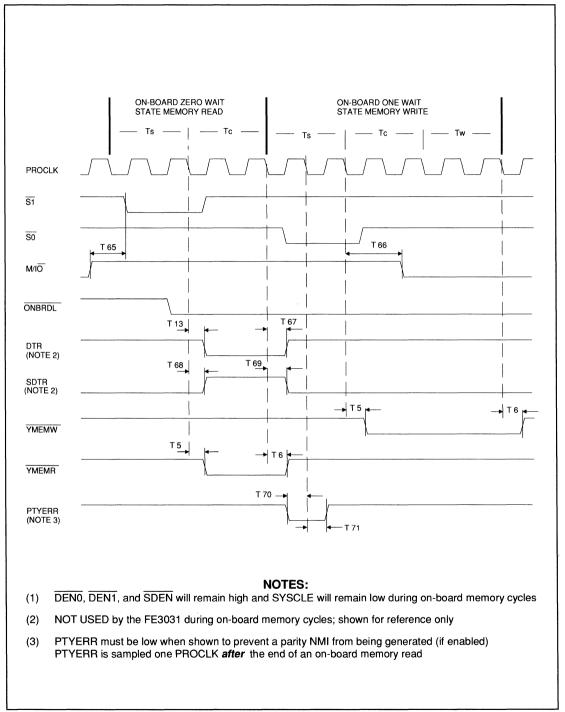

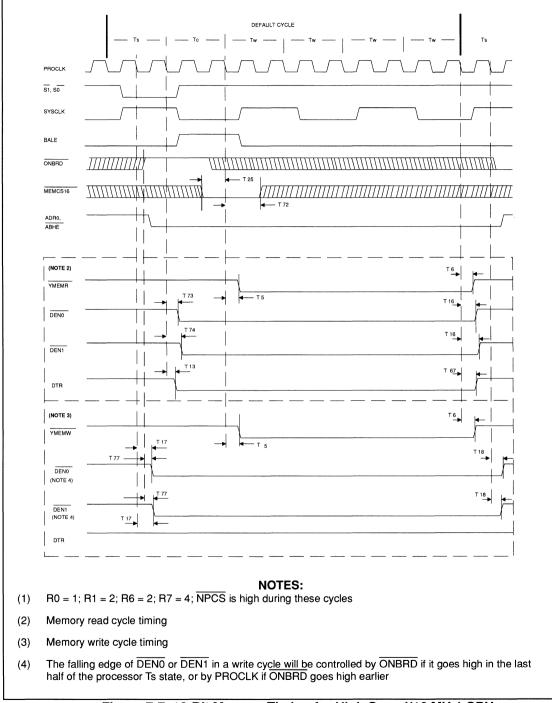

| 7-4    | On-board Memory Cycle Timing                                                             | 2-34  |

| 7-5    | 16-bit Memory Read Timing for Low Speed CPU Clock                                        | 2-35  |

| 7-6    | 16-bit Memory Write timing for Low Speed CPU Clock                                       | 2-36  |

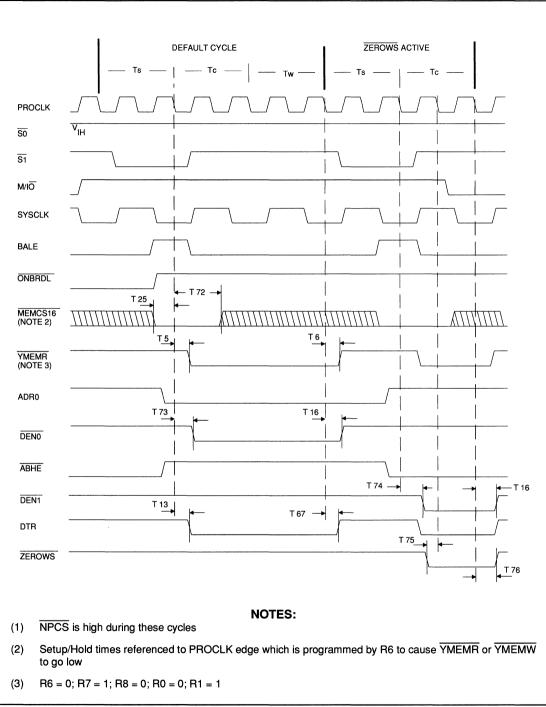

| 7-7    | 16-bit Memory Timing for High Speed (16 MHz) CPU                                         | 2-37  |

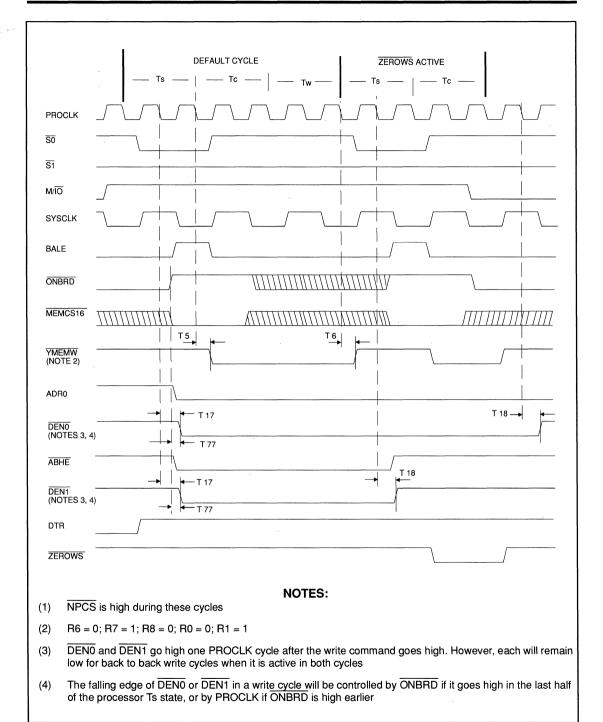

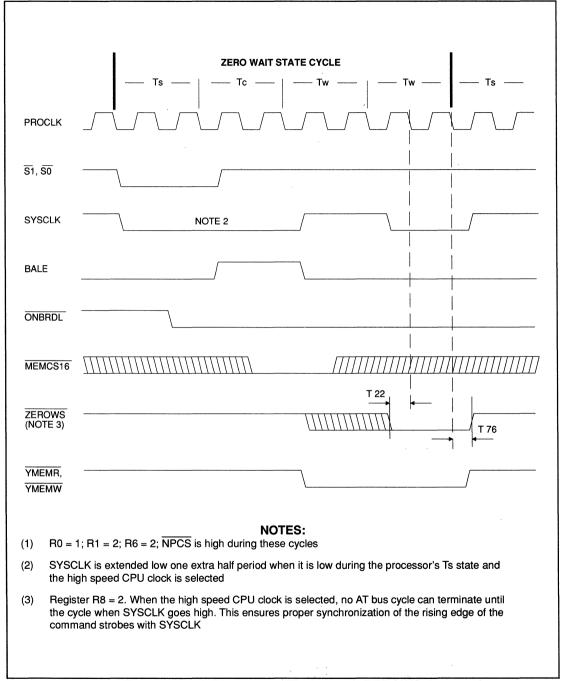

| 7-8    | 16-bit Memory Timing with ZEROWS Asserted and High Speed (16 MHz) CPU                    | 2-38  |

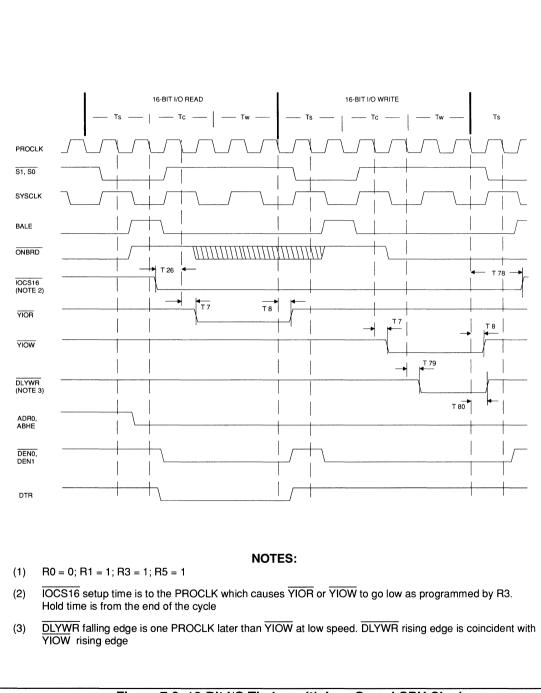

| 7-9    | 16-bit I/O Timing with Low Speed CPU Clock                                               | 2-39  |

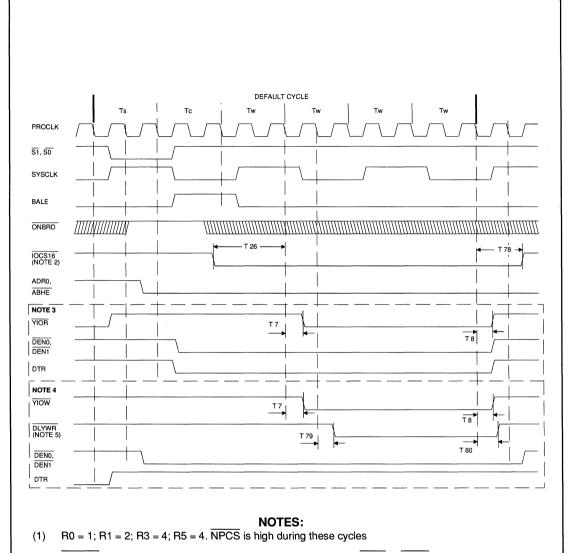

| 7-10   | 16-bit I/O Timing with High Speed (16 MHz) CPU Clock                                     | 2-40  |

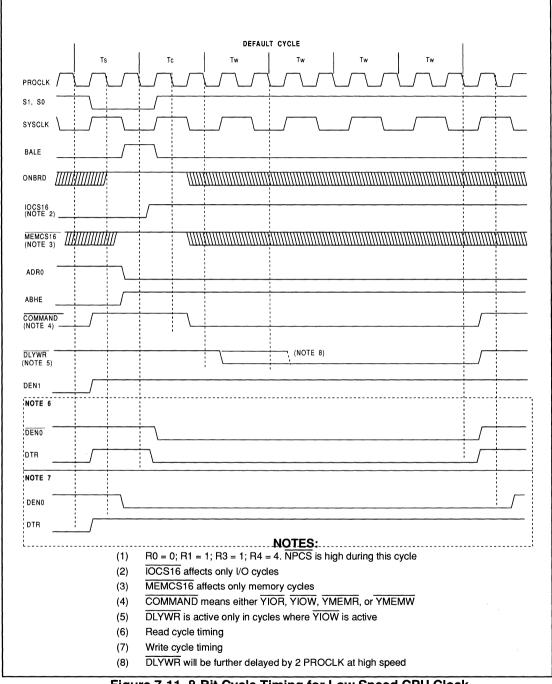

| 7-11   | 8-bit Cycle Timing for Low Speed CPU Clock — Even Byte Access                            | 2-41  |

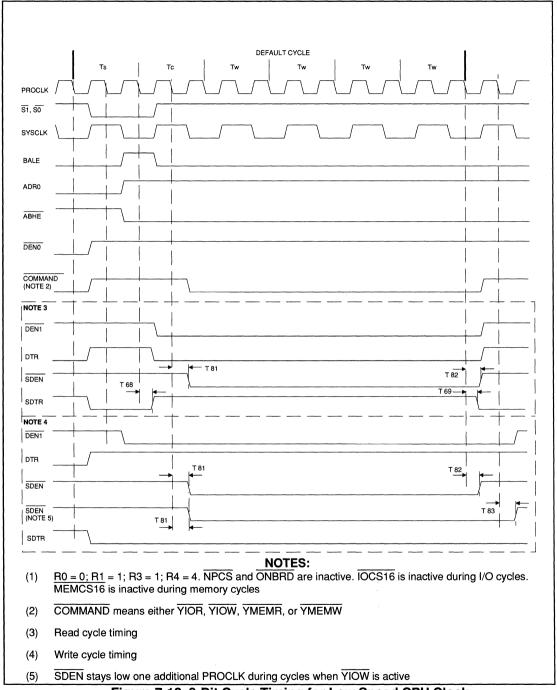

| 7-12   | 8-bit Cycle Timing for Low Speed CPU Clock — Odd Byte Access                             | 2-42  |

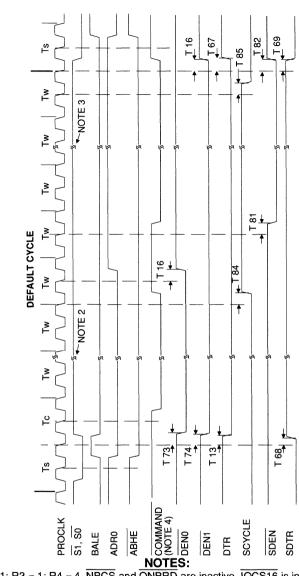

| 7-13   | 8-bit Cycle Timing for Low Speed Clock— Word Read from Even Address                      | 2-43  |

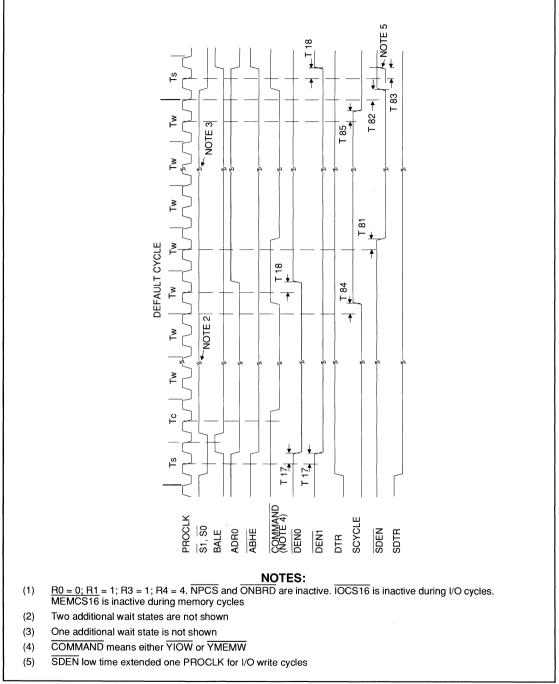

| 7-14   | 8-bit Cycle Timing for Low Speed CPU Clock — Word Write to Even Address                  | 2-44  |

| 7-15   | Interrupt Acknowledge Cycle for Low Speed CPU Clock                                      | 2-45  |

| 7-16   | Shutdown Cycle Timing                                                                    | 2-46  |

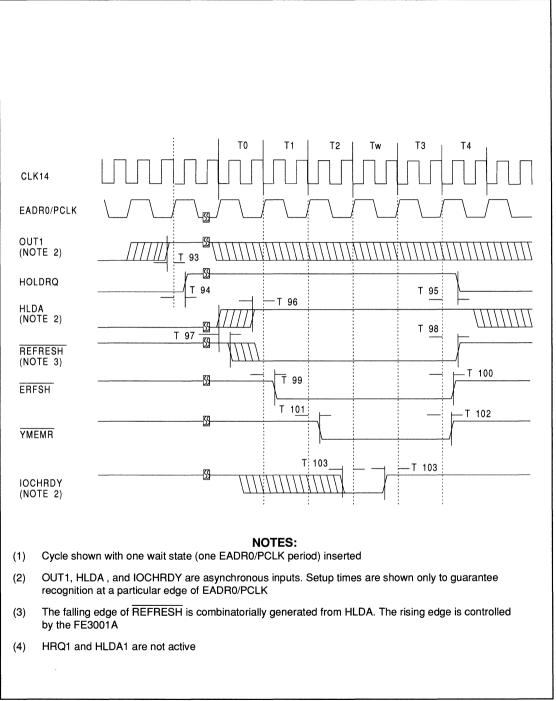

| 7-17   | Refresh Cycle Timing                                                                     | 2-47  |

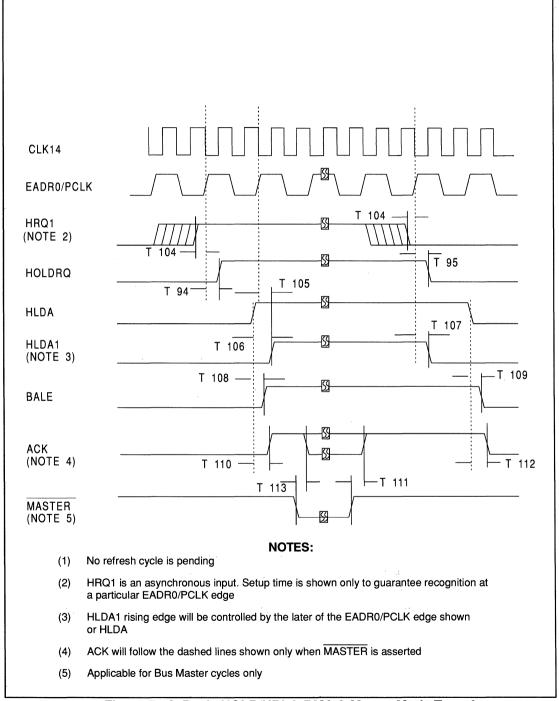

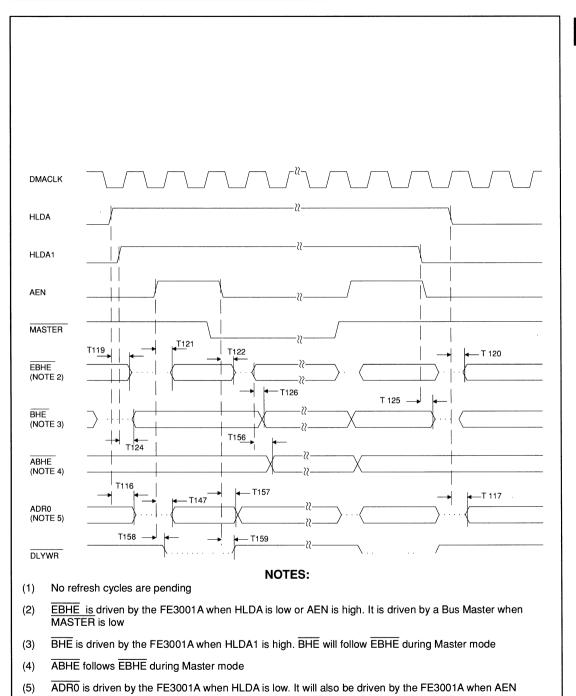

| 7-18   | Basic HOLD/HLDA Timing for DMA and Master Mode Transfers                                 | 2-48  |

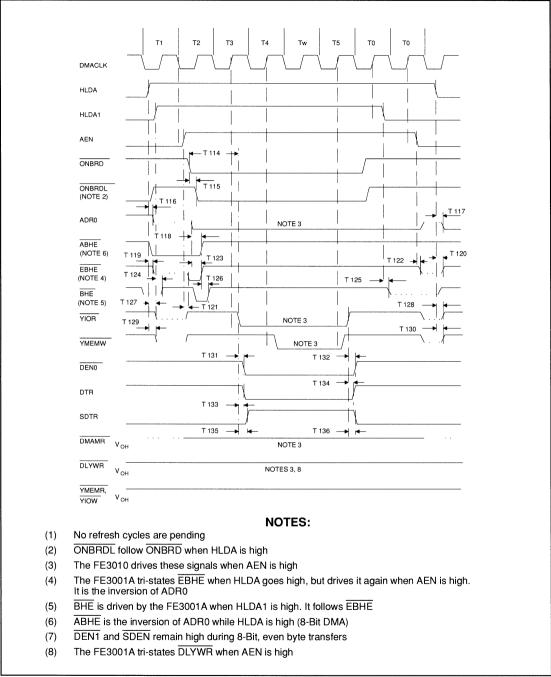

| 7-19   | DMA Transfer Timing: 8-bit, I/O to On-board Memory, Even Byte, with No Added Wait States | 2-49  |

| 7-20   | DMA Transfer Timing: 8-bit, On-board Memory to I/O, Odd Byte, with No Added Wait States  | 2-50  |

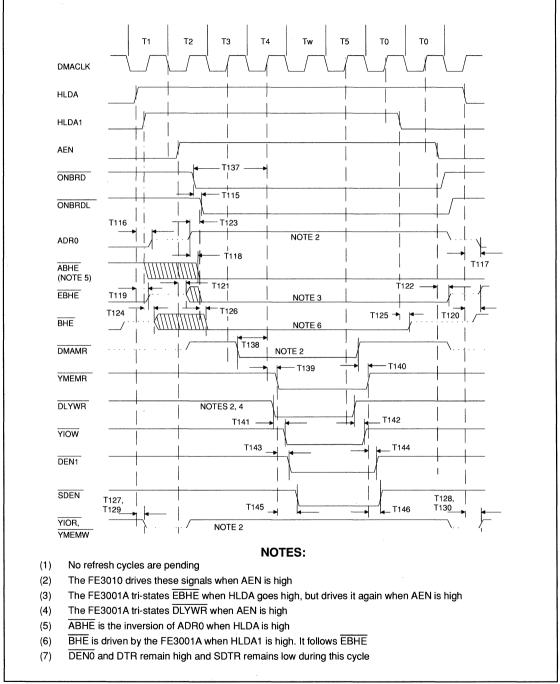

| 7-21   | DMA Transfer Timing: 16-bit, I/O to On-board Memory, Wait State Added                    | 2-51  |

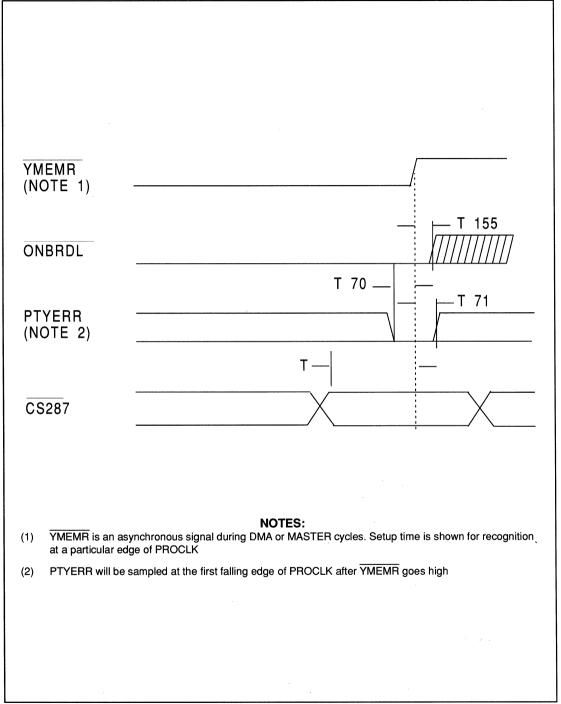

| 7-22   | Parity Error Timing for DMA or Master Mode Transfer                                      | 2-52  |

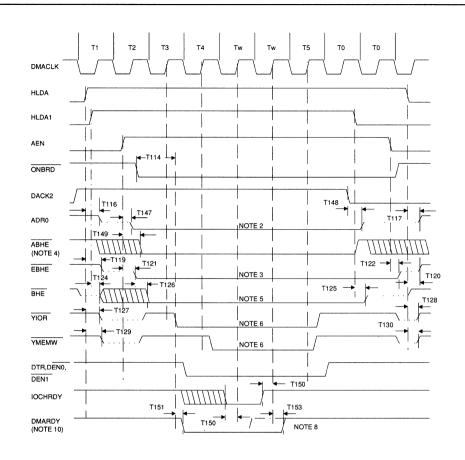

| 7-23   | Basic Master Mode Transfer Timing                                                        | 2-53  |

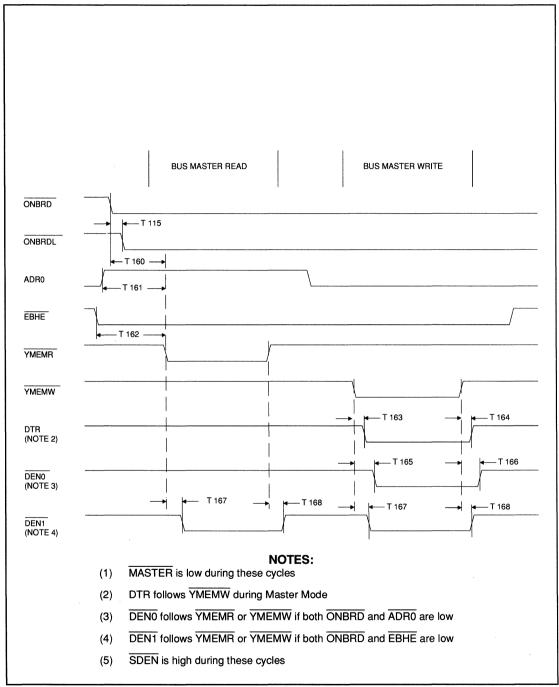

| 7-24   | Master Mode Transfer Timing: On-board Memory Read/Write                                  |       |

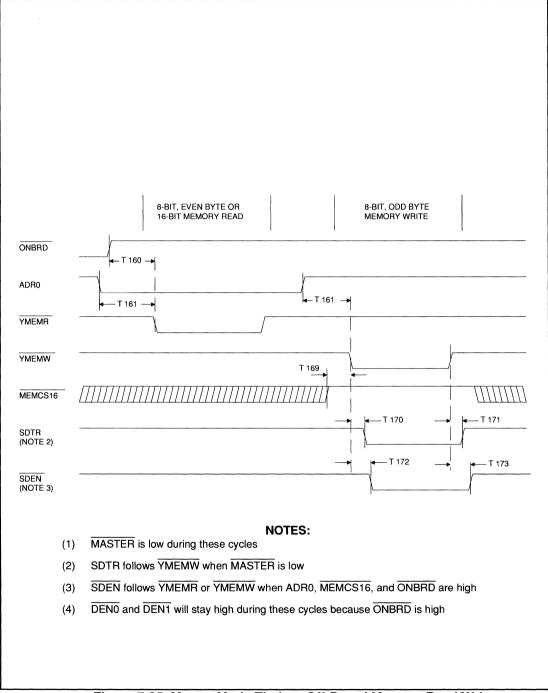

| 7-25   | Master Mode Timing: Off-board Memory Read/Write                                          |       |

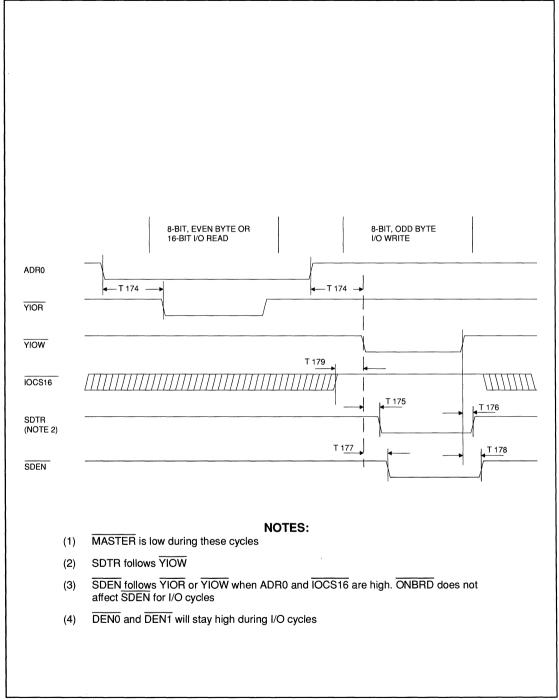

| 7-26   | Master Mode Timing: Off-board I/O Read/Write                                             | 2-56  |

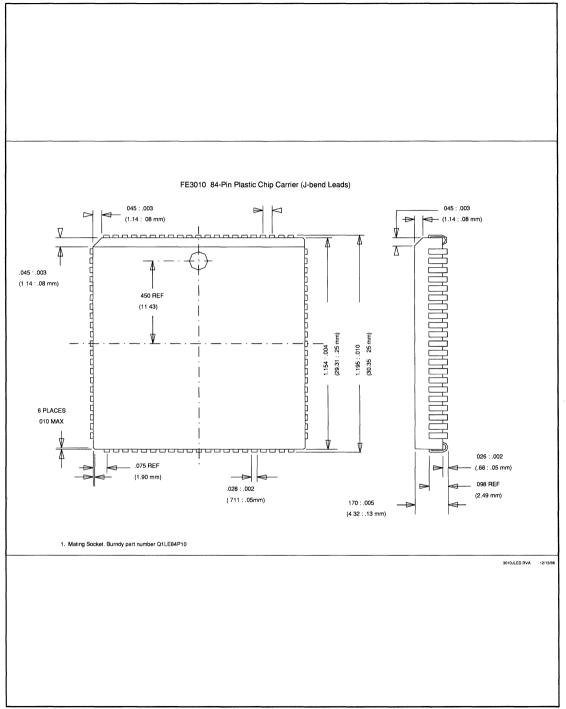

| 7-27   | 84-pin PLCC Packaging Diagram                                                            | 2-57  |

# **LIST OF TABLES**

| Table | Title                               | Page |

|-------|-------------------------------------|------|

| 1-1   | Signal Descriptions                 | 2-4  |

| 2-1   | Bus Cycles                          | 2-13 |

| 3-1   | Summary of Command Timing Registers | 2-18 |

| 6-1   | DC Characteristics                  | 2-22 |

| 7-1   | FE3001A Timing Parameters           | 2-23 |

# **ADDITIONAL REFERENCES**

IBM AT Technical Reference Manual

Intel Microprocessor and Peripheral Handbook

#### 1.0 INTRODUCTION

#### 1.1 DESCRIPTION

The FE3001A contains all of the clock generation and cycle control logic necessary to implement an IBM AT compatible computer. It is part of the FE3600B/C chip set intended to simplify the design of 80286/80386SX based AT computers.

Its features include programmable CPU and DMA clock generation, system clock generation, programmable bus timing, programmable wait state generator, refresh and DMA controls, bus arbitration logic, NMI generator and parity error logic, reset/shutdown control, sleep mode, 80286 interface logic and is packaged in an 84-pin PLCC.

#### 1.2 FEATURES

- Programmable CPU and DMA clock generator

- System clock generator

- Programmable bus timing

- Programmable wait state generator

- Refresh and DMA controls

- Bus arbitration logic

- NMI generator and parity error logic

- Reset/shutdown control

- Sleep mode

- 80286 interface logic

- 1.25 micron HCMOS technology

- 84-pin PLCC

FIGURE 1-1, FE3600B/C CHIP SET FUNCTIONAL BLOCK DIAGRAM

FIGURE 1-2. FE3001A BLOCK DIAGRAM

FIGURE 1-3. FE3001A PIN ASSIGNMENTS

| PIN# | SIGNAL           | TYPE | DESCRIPTION                                                                                                                                                              |  |

|------|------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | CLKHS            | 1    | High speed clock input. This provides the high speed clock when selected. When CLK16 (pin 84 is pulled high, this input (divided by two) is used as the low speed clock. |  |

| 2    | V <sub>SS1</sub> |      | Ground.                                                                                                                                                                  |  |

| 3    | RESET            | 0    | Reset to the system.                                                                                                                                                     |  |

| 4    | ONBRDL           | 0    | ONBRD input latched by ALE internally. Follows ONBRD when HLDA high.                                                                                                     |  |

| 5    | CPURES           | 0    | Reset to 80286.                                                                                                                                                          |  |

| 6    | RTCALE           | 0    | Real Time Clock Address Latch Enable (I/O address 70H).                                                                                                                  |  |

| 7    | HOLDRQ           | 0    | Hold request to 80286 for DMA or Refresh.                                                                                                                                |  |

| 8    | ERFSH            | 0    | Enable refresh address signal to 3010. Puts refresh address on address bus.                                                                                              |  |

| 9    | HLDA1            | 0    | DMA hold acknowledge signal to FE3010. Not active during refresh.                                                                                                        |  |

| 10   | ĪNTA             | 0    | Interrupt acknowledge to FE3010.                                                                                                                                         |  |

| 11   | RST287           | 0    | Reset to 80287 (Write to I/O address F1H or system reset).                                                                                                               |  |

| 12   | V <sub>SS2</sub> |      | Ground.                                                                                                                                                                  |  |

| 13   | BZ286            | 0    | 80287 busy signal to 80286. Latched low by 80287 ERROR signal.                                                                                                           |  |

| 14   | IRQ13            | 0    | Interrupt request 13 for 80287 error to FE3010.                                                                                                                          |  |

| 15   | NMI              | 0    | Non-Maskable Interrupt to 80286. Generated in response to a parity error or bus IOCHCK.                                                                                  |  |

| 16   | NPCS             | 0    | 80287 Co-processor chip select. (I/O Addresses F8H, FAH and FCH).                                                                                                        |  |

| 17   | EADR0/<br>PCLK   | 0    | 7.16 MHz clock for keyboard controller/ EADRO for AT bus.                                                                                                                |  |

| 18   | PCLK             | 0    | Inverted PCLK for keyboard controller.                                                                                                                                   |  |

| 19   | V <sub>DD1</sub> |      | +5 V V <sub>DD</sub> .                                                                                                                                                   |  |

| 20   | TMRCLK           | 0    | 1.19 MHz timer clock to FE3010.                                                                                                                                          |  |

| 21   | DMACLK           | 0    | Software selectable clock for DMA to FE3010.                                                                                                                             |  |

**TABLE 1-1. SIGNAL DESCRIPTIONS**

| PIN# | SIGNAL           | TYPE | DESCRIPTION                                                                                                |  |  |

|------|------------------|------|------------------------------------------------------------------------------------------------------------|--|--|

| 22   | SYSCLK           | 0    | System clock needed for bus timing. See description in synchronization section.                            |  |  |

| 23   | V <sub>SS3</sub> |      | Ground.                                                                                                    |  |  |

| 24   | PROCLK           | 0    | Software selectable 80286 /80386SX clock.                                                                  |  |  |

| 25   | ALE              | 0    | Local Address Latch Enable.                                                                                |  |  |

| 26   | BALE             | 0    | Bus Address Latch Enable. (Programmable)                                                                   |  |  |

| 27   | CLK287           | 0    | Clock for 80287. See clock section for details.                                                            |  |  |

| 28   | DTR              | 0    | Data direction to FE3031 data buffer.                                                                      |  |  |

| 29   | DEN0             | 0    | Low byte PC/AT Bus data enable to FE3031 data buffer.                                                      |  |  |

| 30   | DEN1             | 0    | High byte PC/AT Bus data enable to FE3031 data buffer.                                                     |  |  |

| 31   | SDTR             | 0    | PC/AT Bus byte swap direction to FE3031 data buffer.                                                       |  |  |

| 32   | SDEN             | 0    | PC/AT Bus byte swap enable to FE3031 data buffer.                                                          |  |  |

| 33   | SCYCLE           | 0    | Latch low byte during byte swap read.                                                                      |  |  |

| 34   | ACK              | 0    | DMA or Refresh Acknowledge signal to the PC/AT bus.                                                        |  |  |

| 35   | READY            | 0    | Ready to 80286.                                                                                            |  |  |

| 36   | DMARDY           | 0    | When high allows FE3010 to complete a DMA cycle.                                                           |  |  |

| 37   | ABHE             | 0    | High byte enable for devices on local bus.                                                                 |  |  |

| 38   | V <sub>SS4</sub> |      | Ground.                                                                                                    |  |  |

| 39   | REFRESH          | I/O  | Refresh cycle. Generated from FE3010 timer signal OUT1 or externally from the bus.                         |  |  |

| 40   | DLYWR            | I/O  | YIOW delayed to the FE3010, active edge delayed one PROCLK. Input from FE3010 during DMA to generate YIOW. |  |  |

| 41   | YMEMR            | I/O  | Memory read. Input during Master cycle.                                                                    |  |  |

| 42   | YMEMW            | I/O  | Memory write. Input during HLDA cycle.                                                                     |  |  |

| 43   | YIOR             | I/O  | I/O read. Input during HLDA cycle.                                                                         |  |  |

TABLE 1-1. SIGNAL DESCRIPTIONS (Continued)

| PIN# | SIGNAL           | TYPE       | DESCRIPTION                                                                                                                     |  |

|------|------------------|------------|---------------------------------------------------------------------------------------------------------------------------------|--|

| 44   | V <sub>SS5</sub> |            | Ground.                                                                                                                         |  |

| 45   | YIOW             | I/O        | I/O write. Input during Master cycle.                                                                                           |  |

| 46   | EBHE             | I/O        | High byte enable to expansion bus. Input during Master cycle.                                                                   |  |

| 47   | ADR0             | I/O        | Low byte enable. Latched with ALE during a CPU cycle, driven low during 16-Bit DMA cycles.                                      |  |

| 48   | BHE              | I/O        | High byte enable from the 80286. Output during Master and DMA cycles for use by the FE3021.                                     |  |

| 49   | D6               | 1/0        | Peripheral data bus bit 6.                                                                                                      |  |

| 50   | D7 ·             | 1/0        | Peripheral data bus bit 7.                                                                                                      |  |

| 51   | V <sub>DD2</sub> |            | +5 V V <sub>DD</sub> .                                                                                                          |  |

| 52   | D2               | ı          | Peripheral data bus bit 2.                                                                                                      |  |

| 53   | D3               | ı          | Peripheral data bus bit 3.                                                                                                      |  |

| 54   | DMAMR            | ı          | DMA memory read from DMA controller.                                                                                            |  |

| 55   | RESIN            | ı          | System reset input.                                                                                                             |  |

| 56   | RESCPU           | I          | CPU reset input from keyboard controller.                                                                                       |  |

| 57   | MEMCS16          | <b>I</b> . | Signals 16-bit memory transfer capability on the PC/AT bus.                                                                     |  |

| 58   | ĪOCS16           | 1          | Signals 16-bit I/O transfer capability on PC/AT bus.                                                                            |  |

| 59   | ZEROWS           | I          | Zero wait state bus cycle request. See description for more details.                                                            |  |

| 60   | ONBRD            | I          | 16-bit on-board DRAM memory, BIOS, or I/O device. Implies local memory on memory cycles and fast I/O bus timing for I/O cycles. |  |

| 61   | MASTER           | I          | Master on PC/AT bus has control of the bus when asserted.                                                                       |  |

| 62   | IOCHRDY          | I          | Current bus cycle may complete when high. May be used to extend CPU, DMA, or refresh cycles.                                    |  |

| 63   | BUSY             | ı          | 80287/80387SX co-processor busy.                                                                                                |  |

| 64   | ERROR            | 1          | Error from 80287/80387SX.                                                                                                       |  |

| 65   | V <sub>SS6</sub> |            | Ground.                                                                                                                         |  |

TABLE 1-1. SIGNAL DESCRIPTIONS (Continued)

| PIN | SIGNAL           | TYPE | DESCRIPTION                                                                                                                                            |  |

|-----|------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 66  | HRQ1             | ı    | Hold request from DMA controller in FE3010.                                                                                                            |  |

| 67  | OUT1             | l    | Refresh timer input from FE3010.                                                                                                                       |  |

| 68  | HLDA             | 1    | Hold acknowledge from 80286.                                                                                                                           |  |

| 69  | A0               | I    | Local 80286 address bus 0.                                                                                                                             |  |

| 70  | A1               | l    | Local 80286 address bus 1.                                                                                                                             |  |

| 69  | A0               | l l  | Local 80286 address bus 0.                                                                                                                             |  |

| 70  | → <b>A1</b>      | 1    | Local 80286 address bus 1.                                                                                                                             |  |

| 71  | A3               | l    | Local 80286 address bus 3.                                                                                                                             |  |

| 72  | CS287            | 1    | 80287 select decode from FE3021 (0E0H - 0FFH) during I/O cycle. ROM chip select decode during memory cycle                                             |  |

| 73  | PTYERR           | I    | On-board RAM parity error. Sampled on the first falling edge of PROCLK after YMEMR goes high.                                                          |  |

| 74  | V <sub>DD3</sub> |      | +5 V V <sub>DD.</sub>                                                                                                                                  |  |

| 75  | IOCHCK           | I    | Error from PC/AT bus.                                                                                                                                  |  |

| 76  | NMICS            | ı    | NMI port enable decode (07XH). Also used for programming bus control registers.                                                                        |  |

| 77  | PBCS             | ı    | Port B chip select decode (061H - 06FH, 0DD). See register description for decode definitions.                                                         |  |

| 78  | AEN              | ı    | DMA cycle enable from FE3010.                                                                                                                          |  |

| 79  | DACK2            | 1    | 16-bit DMA acknowledge from FE3010.                                                                                                                    |  |

| 80  | M/TO             | I    | 80286 memory/IO select. High indicates memory halt, or shutdown cycles. Low indicates I/O or interrupt acknowledge cycles.                             |  |

| 81  | S1               | 1    | 80286 Status 1.                                                                                                                                        |  |

| 82  | <del>S0</del>    | 1    | 80286 Status 0.                                                                                                                                        |  |

| 83  | CLK14            | 1    | 14.318 MHz clock input used to derive TMRCLK, EADR0/PCLK, and PCLK.                                                                                    |  |

| 84  | CLK16            | 1    | 16 MHz clock input. This provides the low speed CPU clock for 8 MHz operation. When this pin is pulled high, CLKHS ÷ 2 is used as the low speed clock. |  |

**TABLE 1-1. SIGNAL DESCRIPTIONS (Continued)**

#### 2.0 FUNCTIONAL DESCRIPTION

# 2.1 FUNCTIONAL OVERVIEW

The FE3001A is designed to run with the FE3010 peripheral controller, and the FE3021 and FE3031 buffers/memory controls to create a 16 MHz or 20 MHz PC/AT compatible system. The basic architecture of an AT compatible system using the FE3600B/C chip set involves putting the system DRAM on the local data and command bus, allowing high speed access. The BIOS ROM can be put on the local bus or expansion bus; the FE3021 has special provisions to use the ROM on the higher speed bus. During accesses to local memory, the data buffer controls in the FE3001A prevent data collisions between the local and expansion buses. The FE3021 and FE3031 also inhibit memory read and write signals to the expansion bus for local memory accesses.

The FE3001A generates all of the clocks needed in the system. The CPU clock to the 80286/80386SX processor (PROCLK) is programmable, as is the DMA clock for the DMA controller in the FE3010 (DMACLK). The expansion bus clock (SYSCLK) and coprocessor clock for the 80287 (CLK287) automatically adjust to the current operating configuration. The clock for the timers in the FE3010 (TMRCLK) is fixed at 1.19 MHz, and the clocks for the keyboard controller (PCLK and PCLK) are fixed at 7.16 MHz.

The FE3001A has registers to delay the five commands (memory read and write, I/O read and write, interrupt acknowledge) during a CPU cycle and control the length of the commands based on various input signals (16-bit memory, 16-bit I/O, on-board memory, fast 16-bit I/O device, and zero wait state device). On power-up, these registers are loaded with values to run the system with a 16 MHz PROCLK (8 MHz system) with full AT compatibility and no register programming necessary. Before switching to high speed operation, it is necessary to program the registers for proper bus emulation. These registers eliminate the need to either slow down the processor for expansion bus operations or run the bus asynchronously. Note that a 16 MHz system can be made to exactly match the bus timing of an 8 MHz system.

## 2.2 CLOCK GENERATOR

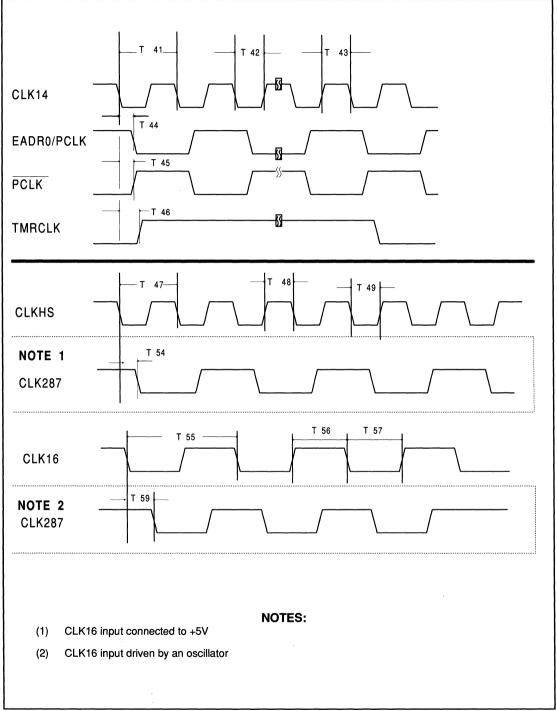

This module generates clocks for the CPU, DMA, 8042 keyboard controller, timer and 80287 numeric processor. The CPU clock is software selectable for low speed or high speed CPU operation. The DMA clock is also software selectable between standard and high speed. The 80287 clock is fixed at the low speed CPU clock.

#### 2.2.1 PROCLK

The CLK16 and CLKHS input clocks to the FE3001A are used to create the low speed and high speed clocks to the CPU. The CLKHS input is used when the high speed CPU clock is selected. If the CLK16 input is connected to an oscillator, it will be used when the low speed CPU clock is selected (typically from 6 to 8 MHz CPU speed). Alternatively, if CLK16 is tied high through a pullup resistor, then CLKHS+2 will be used as the low speed clock, saving an oscillator.

The CPU clock circuitry ensures a glitchless speed switch. PROCLK will be held high at no more than 1 1/2 clock periods of the clock being selected in order to achieve synchronization. Since SYSCLK and DMACLK are based on PROCLK, they will also switch speeds without glitches.

#### 2.2.2 DMACLK

DMACLK can be software selected between standard speed and a special high speed mode. Standard speed provides a 4 MHz DMA clock to the DMA controller on a 16 MHz system, the same as an 8 MHz IBM PC/AT. This will be the most common selection of DMA speed. Selecting high speed DMA runs the DMA controller at twice standard speed. This would likely be confined to special dedicated systems where only well defined DMA peripherals that can run that fast are used.

DMACLK is PROCLK ÷ 4 when the low speed CPU clock is selected. DMACLK is PROCLK ÷ 8 when the high speed CPU clock is selected. When R13 bit 7 is set, DMACLK is PROCLK +12 at high speed. DMACLK will always change on CPU "t" state boundaries, but no other synchronization is attempted. The previous discussion applies to standard speed DMA. If high speed DMA is selected, it runs twice as fast in all cases.

FIGURE 2-1. SYSCLK TIMING DURING HIGH SPEED OPERATION

#### 2.2.3 CLK287

CLK287 is always the same as the low speed CPU clock. It is not affected by speed switching. It follows CLK16 if that input is toggling or is CLKHS ÷ 2 if CLK16 is pulled high.

#### 2.2.4 SYSCLK

When the low speed clock is selected, SYSCLK is PROCLK ÷ 2. During high speed operation, SYSCLK is PROCLK ÷ 4. When R13 bit 7 is set, SYSCLK is PROCLK ÷ 6. In the high speed case, SYSCLK is brought into synchronization with the PC/AT bus at the end of ALE. See Figure 4 for SYSCLK functional timing.

# 2.2.5 PCLK/EADRO, PCLK, and TMRCLK

The CLK14 <u>input</u> is used to generate EADR0/PCLK, <u>PCLK</u>, and TMRCLK. It must be 14.31818 MHz in order for TMRCLK to be 1.1932 MHz, as required for the timers in the FE3010 to be AT compatible. TMRCLK is CLK14  $\pm$  12. EADR0/PCLK is CLK14  $\pm$  2 (7.16 MHz). PCLK is the <u>complement</u> of EADR0/PCLK. EADR0/PCLK and PCLK can be used to drive the 8042 keyboard controller.

During power up, PCLK/EADRO will behave like PCLK. When RESIN goes high while RESET is low, the DMAMEMR input will be sampled. If sampled high, this pin will behave as PCLK until the next rising edge of RESIN. If sampled low, this pin will behave as EADRO. See Section 2.5.4 for details.

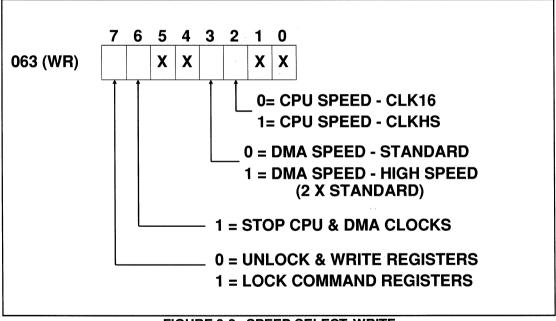

## 2.2.6 Stopping the Clocks (Sleep Mode)

Software may put the FE3001A in sleep mode by setting port 063H bit 6. In sleep mode, PROCLK and DMACLK will be stopped at a high level. SYSCLK will also be stopped, but at an indeterminate logic level. DMACLK and PROCLK will each stop on their rising edge of phase 2 after HLDA is seen active by the FE3001. Typically, this would be the first refresh cycle after the sleep bit is written. SYSCLK will stop with PROCLK.

By stopping these clocks, power can be conserved in battery operated systems. Note that a static CMOS 80286 must be used in order to stop the CPU clock. EADRO/PCLK, PCLK, TMRCLK, and CLK287 will continue to run in sleep mode, allowing the keyboard controller, timers, and coprocessor to operate. Either a keyboard interrupt or a system clock interrupt is a likely choice to wake the CPU up.

To restart the clocks (wake up the CPU), the RESCPU input must be pulsed low. The rising edge of RESCPU will kick off internal synchronization that will restart the clocks roughly 2 EADRO/PCLK periods later. No glitches will occur on the clocks as a result of a restart. Also note that the pulse on RESCPU will not reset the CPU if the FE3001A is in sleep mode. Refer to Application Notes for information on external logic needed to implement sleep mode.

#### 2.3 COMMAND CONTROL

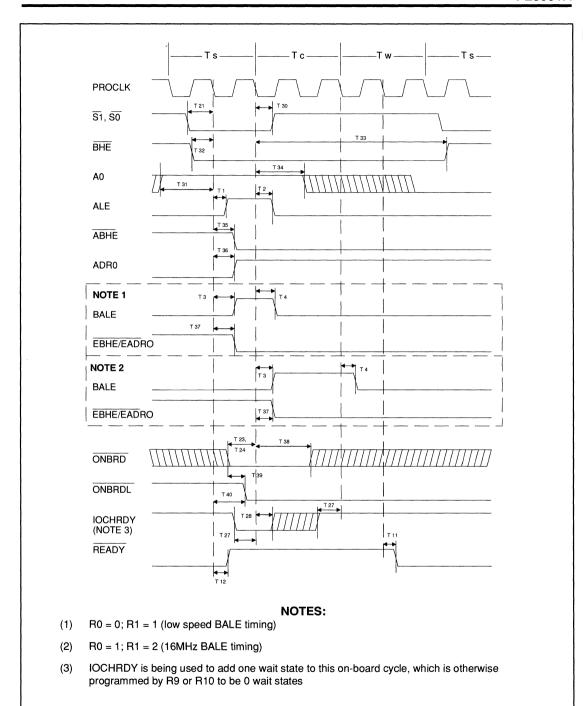

This module generates the I/O read and write commands, memory read and write comm<u>ands</u>, interrupt acknowledge, ALE and BALE from S1, S0, and MNIO. It also controls the number of wait states used during each CPU cycle. See the register descriptions for programming information. For recommended program values, refer to Appendix A.

# 2.3.1 On-Board Cycles

When the ONBRD signal is active, then this cycle is directed toward 16-bit, high speed local DRAM, BIOS, or I/O. The timing for this cycle is defined by registers R9, R10, and R12. The AT bus timing signals MEMCS16 and IOCS16 have no effect. IOCHRDY can be used to lengthen the cycle, and indeed is used by the FE3021 to add wait states for a DRAM page miss or EMS cycles.

The wait states for on-board reads and writes are individually programmable by registers R9 and R10 in order to optimize DRAM access speed. Both memory and I/O cycles use these values. The command delay for on-board I/O cycles is set by register R12. The command delay for on-board memory cycles is always zero.

## 2.3.2 AT Bus Cycles

All I/O and memory cycles where ONBRD is inactive will be directed to the AT bus. The command delay and wait states are programmable for each type of AT bus cycle.

Memory cycles use 16-bit timing when MEMCS16 is driven low before either the memory command (YMEMR or YMEMW) is programmed to go active or BALE falls, whichever is earlier. I/O cycles use 16-bit timing when IOCS16 is driven low before the I/O command (YIOR or YIOW) is programmed to go active. Otherwise, all cycles use 8-bit timing.

ZEROWS can be driven low for either 8-bit or 16-bit cycles to terminate the cycle early. As on the AT, it should not be driven until a command is active. It will cause the cycle to end after the prescribed minimum number of wait states in register R8 is met. Note that the FE3001A contains circuitry to ensure that an AT bus cycle will end (command goes high) on a rising edge of SYSCLK and will add a wait state if needed to enforce this. This synchronization circuitry will override register programming and the IOCHRDY and ZEROWS inputs.

# 2.3.3 Other Cycles

Interrupt acknowledge cycles follow the same command timing as an 8-bit AT bus cycle. HALT cycles do not generate ALE, BALE or cause the READY output to go high. Effectively, the FE3001A does not respond to a HALT cycle. A SHUTDOWN cycle is handled like a HALT, except that it causes the CPURES line to be pulsed, resetting the CPU only.

#### 2.4 BUS CONTROL

This module generates the data <u>buffer</u> controls for CPU, DMA, and refresh cycles. DENO and DEN1 are used to enable the lower and upper bytes of the FE3031 AT bus data buffers, respectively. DTR sets the direction of these buffers. SDEN and SDTR control the enable and direction of a buffer which transfers data between the upper and lower bytes of the AT data bus. The rising edge of SCYCLE latches data on the lower byte of the AT bus into the FE3031, needed for 16-bit to 8-bit bus conversion cycles. ONBRDL is ONBRD latched by ALE to keep it valid throughout the cycle.

The ONBRD signal is used to indicate on-board DRAM and I/O operations. On-board memory and fast on-board I/O devices are assumed to be 16-bit devices. During CPU cycles which access on-board memory, the AT data buffers will be disabled. For Bus Master and DMA cycles, ONBRD must be decoded only for on-board memory.

#### 2.5 A0/BHE GENERATOR

This module generates the system ADRO, ABHE, EBHE, and EADRO using A0 and BHE from the 80286 CPU and AEN and DACK2 from the DMA controller in the FE3010.

## 2.5.1 ADR0

During CPU cycles, A0 from the 80286 is latched with ALE to produce ADR0. For 16-bit DMA transfers and interrupt acknowledge cycles, ADR0 is forced low so that the low byte of the data bus is activated. For all other CPU hold conditions ADR0 is tri-stated. The FE3001A performs two cycles when the CPU attempts a 16-bit operation to an 8-bit device on an even address boundary. ADR0 is automatically forced to one at the start of the second cycle to select the second byte.

# 2.5.2 ABHE

ABHE is the local upper byte select used by the FE3031. During CPU cycles, ABHE is BHE latched with ALE. It is forced low during 16-bit DMA (DACK2 and AEN inputs high) so that the upper byte is always selected. For 8-bit DMA, it is the inversion of ADR0 so that only one byte is selected at a time. During master mode, ABHE follows the EBHE input.

# 2.5.3 EBHE

EBHE is the upper byte select of the AT bus. During CPU cycles, EBHE is ABHE latched with BALE to provide proper AT bus timing. During DMA, EBHE follows ABHE. During refresh the EBHE output is disabled. It is an input during master mode transfers.

#### 2.5.4 EADRO

EADRO is the lower byte select of the AT bus. During CPU cycles, EADRO is ADRO latched with BALE to provide proper AT bus timing. During DMA and refresh, EADRO follows ADRO. This pin will disable during master mode transfer.

#### 2.6 PRIORITY CONTROL

The priority control module generates the hold request signal to the CPU in response to a request from the DMA controller or refresh timer.

## 2.6.1 Refresh Cycles

The FE3001A generates a hold request in response to a rising edge on the OUT1 input, signalling that a refresh cycle is needed. Arefresh cycle is initiated when HLDA comes back from the CPU. The FE3001A refresh state machine drives REFRESH low to signal a refresh cycle to the AT bus, and sets ERFSH low to the FE3010 to enable the refresh address onto the CPU address bus. YMEMR will also be strobed low during a refresh cycle. Refer to the timing diagrams for more detail. Note that REFRESH is a bidirectional open-collector signal, and a refresh cycle can be started by an expansion card.

# 2.6.2 DMA Cycles and Request Arbitration

Requests for control by the DMA controller are made by taking the HRQ1 input high. The FE3001A grants control to the DMA controller by setting HLDA1 high.

When the FE3001A receives a HLDA, it grants control either to the refresh state machine (REFRESH goes low) or to the DMA controller (HLDA1 goes high). Priority is given to the refresh state machine in the event of simultaneous requests. Note that if simultaneous requests do exist, then HOLDRQ will not be dropped after the first request is satisfied. Instead, the FE3001A will grant control sequentially to both requestors with the same HLDA.

## 2.7 DMA CONTROL

This module generates the DMARDY signal for the FE3010 peripheral controller. This signal indicates that the DMA may complete its cycle. The module also generates YMEMR during DMA by delaying the leading (falling) edge of the FE3010 DMAMR signal by one DMA clock.

#### 2.8 ERROR CONTROL

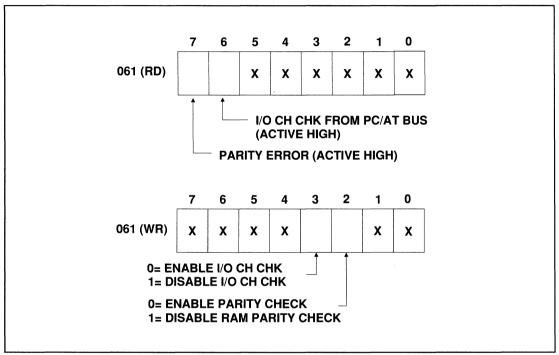

This module generates a non-maskable interrupt (NMI) to the 80286 when a parity error or system bus error is encountered. Parity error, system bus error or NMI can be enabled or disabled from software. They are all disabled on system reset.

The PTYERR input is examined each time YMEMR goes high and it is an on-board cycle (ONBRDL low). The state of the PTYERR input is actually latched on the first falling edge of PROCLK after YMEMR goes high for all on-board CPU reads. When HLDA is active, the PTYERR input is sampled on the riding edge of YMEMR. If PTYERR was high, it signals a parity failure and will generate an NMI to the CPU if enabled. However, when R13 bit 6 is set, FE3001A will disqualify the PTYERR with the CS287 signal. So, NMI will not be generated for ROM cycles. This can eliminate the external glue I ogic. The PTYERR from FE3031 can be connected to PTYERR input of the FE3001A directly. The parity error latch can be cleared by disabling and then enabling parity errors.

The IOCHCK input is driven low by a device on the AT bus to signal a catastrophic error, such as a parity error on a plug-in RAM card. A low on the IOCHCK input will generate an NMI to the CPU if enabled. The error condition can be cleared by disabling and then enabling IOCHCK. However, the IOCHCK input must also be reset high or it will generate another NMI.

When the CPU receives an NMI, it can interrogate I/O register 061H (PORT B) to determine whether a parity error or an IOCHCK is the source of the interrupt. Note that this is the only time the FE3001A will drive the data bus. All other I/O locations are write only. Also, only bits 6 and 7 will be driven during the read. The FE3010 will supply the 6 lower order bits.

#### 2.9 COPROCESSOR INTERFACE

The coprocessor interface module provides the system interface to the 80287 numeric processor extension. The reset and chip select to the 80287 are generated in this module in addition to the busy signal to the CPU and interrupt request 13 to the interrupt controller.

In a FE3600B/C system, as in any PC/AT compatible system, ERROR from the 80287 coprocessor is not connected to the  $\overline{ERROR}$  input on the 80286/80386SX. Instead, the  $\overline{ERROR}$  input on the 80286/80386SX is tied high, while BUSY and interrupt request 13 are used to flag errors. The  $\overline{FE300}1A$  has a  $\overline{BZ286}$  output which connects to the  $\overline{BUSY}$  input of the 80286/80386SX. It also has  $\overline{ERROR}$  and  $\overline{BUSY}$  inputs which hook to those outputs from the 80287/80387SX.

Normally, BZ286 just follows the BUSY input. However, when ERROR goes low while BUSY is low, IRQ13 will go active to signal the CPU that a coprocessor error has occurred. IRQ13 will stay active until ERROR goes back high. Also, BZ286 will be latched low to prevent another coprocessor instruction from being loaded. BZ286 will stay low until either the 80287/80387SX is reset or there is a write to I/O address 0F0H. When either of these occurs, then BZ286 will return to following the BUSY input.

The FE3001A RST287 output connects to the 80287 RESET input. This allows the coprocessor to be reset through software by an I/O write to

address 0F1H. It will also be reset when the system RESET output is active.

The FE3001A expects the CS287 input to be active for addresses 0E0H-0FFH. This is used to provide the NPCS chip select decode output for the 80287. It will be active for addresses 0E8H-0EFH and 0F8H-0FFH when INTA is high and M/ IO from the CPU was low for this cycle.

#### 2.10 RESET ONTROL

This module generates the CPURES signal which is used to reset only the 80286/80386SX and the RESET signal which resets the rest of the system (including the FE3001A). The RESIN input causes a full system reset when driven low. Both CPURES and RESET will go active for as long as RESIN is low and for at least 30 PROCLK cycles after RESIN goes high.

The RESCPU input, when driven low, causes only the CPURES output to go high. RESCPU would normally be connected to both the 8042 keyboard controller and the FE3021 (to provide "hot" reset). The CPURES output will stay high for at least 16 CPUCLK periods, longer if RESCPU remains low. CPURES will also go high for 16 CPUCLK periods if the 80286 executes a shutdown cycle.

| M/ IO | S1 | <del>S</del> 0 | TYPE OF BUS CYCLE                       |

|-------|----|----------------|-----------------------------------------|

| 0     | 0  | 0              | Interrupt Acknowledge                   |

| 0     | 0  | 1              | I/O Read                                |

| 0     | 1  | 0              | I/O Write                               |

| 0     | 1  | 1              | None, not a status cycle                |

| 1     | 0  | 0              | Halt (if A1 =1) or Shutdown (if A1 = 0) |

| 1     | 0  | 1              | Memory Read                             |

| 1     | 1  | 0              | Memory Write                            |

|       |    |                |                                         |

**TABLE 2-1. BUS CYCLES**

## 2.11 GENERAL NOTES

ONBRD must not be active during interrupt acknowledge cycles.

For memory cycles with ONBRD asserted, the system will use the MDATA bus of the FE3031 for data transfers. For I/O cycles with ONBRD asserted, the system will use the expansion bus (DATA) of the FE3031 for data transfers.

On-board I/O devices must drive  $\overline{IOCS16}$  in order for a Bus Master to access them as 16-bit devices. Otherwise,  $\overline{SDEN}$  will go low for Bus Master I/O cycles where ADR0 is high.

$\frac{\text{Inputs CLK16,}}{\text{YMEMR, YMEMW, YIOR, YIOW, ADRO, BHE and CS287 have internal 100k }\Omega\text{ (approx.) pullup resistors.}$

# 3.0 FE3001A REGISTERS

# 3.1 ERROR CONTROL REGISTER (061H), READ/WRITE

The error control register contains masks for the on-board RAM parity check and I/O channel check signals. It also provides a read port to check the status of these signals.

FIGURE 3-1. ERROR CONTROL REGISTER, READ/WRITE

## 3.2 SPEED SELECT (063H), WRITE

The speed select register controls the speed of the CPU and DMA clocks. This register is also used to stop the CPU (sleep mode) and unlock the command control and speed select registers for access. The lock bit must be reset and D7 must be low to change speed or stop clocks.

The stop clock bit stops all the clocks except for the timer clock, coprocessor clock, and keyboard controller clocks. This allows refresh to continue. Bits 2, 3, and 6 in the register are cleared and bit 7 is set by system reset.

FIGURE 3-2. SPEED SELECT, WRITE

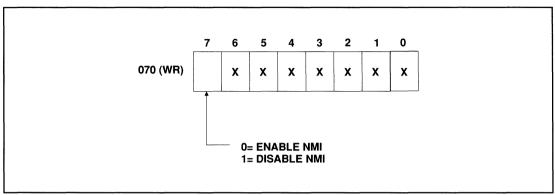

# 3.3 NMI ENABLE (070H), WRITE

The NMI enable register contains the mask for NMI to the 80286. Bit 7 is set on power-up.

FIGURE 3-3. NMI ENABLED, WRITE

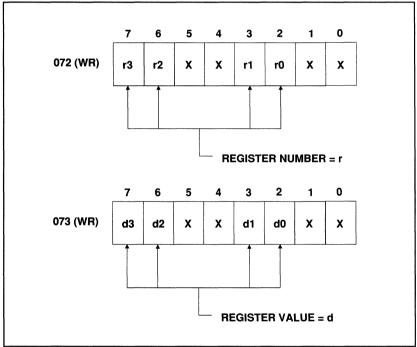

# 3.4 COMMAND CONTROL REGISTERS (072H,073H), WRITE

The timing of the command controls on the expansion bus is programmable via the command control registers. These registers control the timing of BALE, YMEMR, YMEMW, YIOR, YIOW, INTA and the number of wait states in a CPU cycle. This section describes the programming of these

registers. Recommended program values for CPU clock speeds of 16, 25, 32 and 40 MHz are provided in Appendix A.

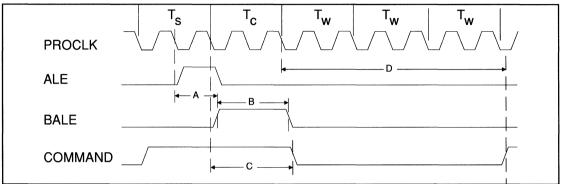

The programmable bus signals are shown in Figure 3-4. A summary of the timing registers is shown in Table 3-1.

FIGURE 3-4. PROGRAMMABLE COMMAND TIMING

| REG             | BITS | FUNCTION W                                                          | AVEFORM | DEFAULT | RANGE  |

|-----------------|------|---------------------------------------------------------------------|---------|---------|--------|

| R <sub>0</sub>  | 2    | BALE delay from ALE leading edge                                    | Α       | 0       | 0 - 3  |

| R1              | 4    | BALE width                                                          | В       | 1       | 1 - 3  |

| R <sub>2</sub>  |      | Not used                                                            |         |         |        |

| R <sub>3</sub>  | 4    | 8-bit mem., 8/16 bit I/O-command de                                 | lay C   | 1       | 0 - 15 |

| R <sub>4</sub>  | 4    | 8-bit operation - wait states                                       | D       | 4       | 0 - 15 |

| R <sub>5</sub>  | 4    | 16-bit I/O operation - wait states                                  | D       | 1       | 0 - 15 |

| R <sub>6</sub>  | 4    | 16-bit mem command delay                                            | С       | 0       | 0 - 15 |

| R <sub>7</sub>  | 4    | 16-bit memory operation - wait states                               | s D     | 1       | 0 - 15 |

| R <sub>8</sub>  | 4    | Minimum number of wait states when ZEROWS is asserted - wait states | n D     | 0       | 0 - 15 |

| R <sub>9</sub>  | 4    | On-board 16-bit read cycle - wait star                              | tes D   | 1       | 0 - 15 |

| R <sub>10</sub> | 4    | On-board 16-bit write cycle - wait sta                              | tes D   | 1       | 0 - 15 |

| R <sub>11</sub> |      | Not used                                                            |         |         |        |

| R <sub>12</sub> | 4    | On-board I/O op command delay                                       | С       | 1       | 0 - 15 |

| R <sub>13</sub> | 4    | Enhanced Features Enable                                            | N/A     | OFF     | N/A    |

TABLE 3-1. SUMMARY OF COMMAND TIMING REGISTERS

- Command delay is number of PROCLKs from end of T<sub>s</sub>

- Each wait state is two PROCLKs.

- One wait state may be added in high speed mode for synchronization.

# 3.5 COMMAND REGISTER POINTER (072H)

The command register pointer points to one of 11 registers at location 073H. Each register contains a command timing parameter based on the selected CPU clock. Whichever register number is loaded in bits 7, 6, 3, and 2 in location 072H is the register which is loaded with the next write to address 073H. Refer to Table 3-5 for details.

FIGURE 3-5. COMMAND REGISTER POINTER

# 3.6 BALE TIMING $(R_0,R_1)$

The leading edge and width of BALE are controlled by these two registers. BALE delay is defined as the number of PROCLK cycles from the leading edge of ALE. BALE width is the width in PROCLK cycles.

Default values: Dela

Delay (R<sub>0</sub>) - 0

Width  $(R_1)$  - 1

## 3.7 8-BIT MEMORY AND 8/16 BIT (R<sub>3</sub>)

This register controls the command delay for 8 bit memory and 8/16 bit I/O operations. Command delay is defined as the number of PROCLK cycles from the trailing edge of ALE to the start of the command.

Default value:

Command Delay (R<sub>3</sub>) - 1

# 3.8 8-BIT MEMORY AND I/O WAIT STATES (R<sub>4</sub>)

This register controls the number of wait states for 8 bit operations. The number of wait states is the number of CPU wait states required for these operations.

Default value:

Wait States (R<sub>4</sub>) - 4

#### 3.9 16-BIT I/O WAIT STATES (R<sub>5</sub>)

This register controls the number of wait states for 16-bit I/O cycles. These cycles are indicated by the assertion of IOCS16. The number of wait states is the number of CPU wait states required for this operation.

Default values:

Wait States (R<sub>5</sub>) - 1

## 3.10 16-BIT AT BUS MEMORY TIMING (R<sub>6</sub>,R<sub>7</sub>)

These registers control the command delay and number of wait states for 16-bit memory operations. These cycles are indicated by the assertion of MEMCS16. Command delay is defined as the number of PROCLK cycles from the trailing edge of ALE. The number of wait states is the number of CPU wait states required for this operation.

Default values:

Command Delay (R<sub>6</sub>) - 0 Wait States (R<sub>7</sub>) - 1

# 3.11 ZEROWS BUS CYCLE WAIT STATES

This register sets the minimum number of wait states which must occur before the assertion of the ZEROWS signal can terminate a cycle.

Default values:

Wait States, ZWS (R8) - 0

# 3.12 ON-BOARD MEMORY TIMING (R<sub>9</sub>,R<sub>10</sub>)

These two registers control the number of wait states for on-board operations. These cycles are indicated by the assertion of ONBRD during CPU cycles. Command delay is zero for all on-board memory operations. The number of wait states is the number of CPU wait states required for this operation. There are separate registers to program the number of wait states for read and write operations to give the system designer added flexibility and potential for greater speed.

Default values:

Wait States, Read (R<sub>9</sub>) - 1

Wait States.Write (R<sub>10</sub>) - 1

## 3.13 ON-BOARD I/O TIMING (R<sub>12</sub>)

This register controls the command delay for 16-bit on-board I/O operations. These cycles are indicated by the assertion of ONBRD during CPU I/O cycles. Command delay is defined as the number of PROCLK cycles from the trailing edge of ALE. The number of wait states for on-board I/O is defined by the on-board memory registers described above. Additional wait states can be added by using the IOCHRDY signal.

Default values: Command Delay (R<sub>12</sub>) - 1

## 3.14 ENHANCED FEATURES ENABLE (R13)

Bit 2 provides one extra CPU cycle (2 CPUCLKs) data hold time for AT bus cycles at high speed. Bit 3 must be programmed to '0'. When Bit 6 is set, CS287 will be treated as ROMCS for all memory cycles. Bit 7 enables SYSCLK = PROCLK ÷ 6 and DMACLK = PROCLK ÷ 12 option at high speed.

## 3.15 CLEAR 80287 BUSY (0F0H), WRITE

When an error signal is received from the 80287, the BZ286 signal is latched low. The latch is cleared by an OUT instruction to this port. The output data is don't care.

# 3.16 RESET 80287 (0F1H), WRITE

An OUT instruction to this port generates a reset to the 80287.

## 4.0 PACKAGE

The FE3001 is packaged in a 84-pin PLCC.

# 5.0 ABSOLUTE MAXIMUMRATINGS

Ambient

Temperature (operating): . . . . . . 0° to + 70° C

Storage Temperature: .....-40° to +125° C

Voltage on any pin to ground: . . . - .5 V to +7 V

Power Dissipation: ..... 400 mW

#### 6.0 DC CHARACTERISTICS

Refer to Table 6-1 below.

| SYMBOL          | PARAMETER                             | MIN  | MAX  | UNIT | TEST CONDITION          |

|-----------------|---------------------------------------|------|------|------|-------------------------|

| VıL             | Input LOW Voltage                     |      | 0.8  | ٧    |                         |

| ViH             | Input HIGH Voltage                    | 2.0  |      | ٧    | ·                       |

| loL             | LOW V Output Current <sup>1,4</sup>   | 4    |      | mA   | V <sub>OL</sub> = 0.4 V |

| Юн              | HIGH V Output Current <sup>1</sup>    | -4   |      | mA   | V <sub>OH</sub> = 2.4 V |

| loL             | LOW V Output Current <sup>3</sup>     | 20   |      | mA   | V <sub>OL</sub> = 0.4 V |

| Юн              | HIGH V Output Current <sup>2</sup>    | -8   |      | mA   | V <sub>OH</sub> = 2.4 V |

| Vонс            | PROCLK Out HIGH Volt                  | 3.8  |      | ٧    | I <sub>OH</sub> = -2 mA |

| V <sub>DD</sub> | Supply Voltage (Any V <sub>DD</sub> ) | 4.75 | 5.25 | ٧    |                         |

| IDD             | Supply Current (Total)                |      |      | mA   |                         |

| loL             | Low V Output Current <sup>2</sup>     | 8    |      | mA   | V <sub>OL</sub> =0.4V   |

**TABLE 6-1. DC CHARACTERISTICS**

- 1. Output currents are for DMACLK, TMRCLK, PCLK, PCLK, CLK287, CPURES, ALE, RTCALE, DTR, SDTR, DENO, DENO, SDEN, SCYCLE, READY, DMARDY, NPCS, RST287, BZ286, IRQ13, NMI, HOLDRQ, ERFSH, HLDA1, INTA, DLYWR, ABHE, BHE, ONBRDL.

- 2. Output currents are for RESET, YMEMR, YMEMW, YIOR, YIOW, D6, D7, ADR0, SYSCLK, BALE, EBHE, ACK.

- 3. Output current for REFRESH should be 20 mA at 0.4V. This is an I/O pin which is only driven low in output mode. It is in a tri-state condition otherwise. A 300 ohm pullup resistor is needed to bring the output high.

- 4. Output low current for PROCLK.

# 7.0 FE3001A TIMING PARAMETERS

$(T_a=0^{\circ} \text{ to } 70^{\circ}C, V_{DD}=4.5 \text{ to } 5.5V, C_L=50pf)$

| SYMBOL | PARAMETER                                | 16 MHz<br>MIN MAX (NS) | 20 MHz<br>MIN MAX |

|--------|------------------------------------------|------------------------|-------------------|

| T1     | ALE rising edge delay from PROCLK        | 18                     | 18                |

| T2     | ALE falling edge delay from PROCLK       | 18                     | 15                |

| Т3     | BALE rising edge delay from PROCLK       | 21                     | 21                |

| T4     | BALE falling edge delay from PROCLK      | 20                     | 20                |

| T5     | YMEMR, YMEMW fall delay from PROCLK      | 16                     | 13                |

| T6     | YMEMR, YMEMW rise delay from PROCLK      | 19                     | 19                |

| T7     | YIOR, YIOW falling delay from PROCLK     | 20                     | 20                |

| T8     | YIOR, YIOW rising delay from PROCLK      | 20                     | 20                |

| T11    | READY falling edge delay from PROCLK     | 12                     | 9                 |

| T12    | READY rising edge delay from PROCLK      | 12                     | 9                 |

| T13    | DTR fall delay from PROCLK; read cycle   | 20                     | 20                |

| T16    | DEN0, DEN1 rise delay from PROCLK; read  | 16                     | 12                |

| T17    | DEN0, DEN1 low delay from PROCLK; write  | 28                     | 28                |

| T18    | DEN0, DEN1 rise delay from PROCLK; write | 29                     | 29                |

| T21    | S1, S0 setup time to PROCLK              | 11                     | 8                 |

| T23    | ONBRD setup time to PROCLK; memory cycle | 22                     | 16                |

| T24    | ONBRD setup time to PROCLK; I/O cycle    | 32                     | 24                |

| T25    | MEMCS16 setup time to PROCLK             | 32                     | 32                |

| T26    | IOCS16 setup time to PROCLK              | 35                     | 35                |

| T27    | IOCHRDY setup time to PROCLK             | 11                     | 7                 |

| T28    | IOCHRDY hold time from PROCLK            | 0                      | 0                 |

| T30    | S1, S0 hold time from PROCLK             | 1                      | 1                 |

| T31    | A0 setup time to PROCLK                  | 30                     | 30                |

| T32    | BHE setup time to PROCLK                 | 15                     | 15                |

| T33    | BHE hold time from PROCLK                | 15                     | 15                |

**Table 7-1. FE3001A TIMING PARAMETERS**

| SYMBOL | PARAMETER                                                             | 16<br>MIN | MHz<br>MAX (NS) | 20<br>MIN | MHz<br>MAX |

|--------|-----------------------------------------------------------------------|-----------|-----------------|-----------|------------|

| T34    | A0 hold time from PROCLK                                              | 15        |                 | 15        | 111/3/1    |

| T35    | ABHE delay from PROCLK                                                |           | 28              |           | 26         |

| T36    | ADR0 delay from PROCLK                                                |           | 29              |           | 26         |

| T37    | EBHE/EADRO delay from PROCLK                                          |           | 30              |           | 30         |

| T38    | ONBRD hold time from PROCLK                                           | 10        |                 | 10        |            |

| T39    | ONBRDL delay from ONBRD                                               |           | 30              |           | 23         |

| T40    | ONBRDL delay from PROCLK                                              |           | 24              |           | 24         |

| T41    | CLK14 period                                                          | 69        |                 | 69        |            |

| T42    | CLK14 low time                                                        | 27        |                 | 27        |            |

| T43    | CLK14 high time                                                       | 27        |                 | 27        |            |

| T44    | EADR0 /PCLK rise/fall delay from CLK14 falling                        |           | 29              |           | 29         |

| T45    | PCLK rise/fall delay from CLK14 falling                               |           | 33              |           | 33         |

| T46    | TMRCLK rise/fall delay from CLK14 falling                             |           | 35              | -         | 35         |

| T47    | CLKHS period                                                          | 31        |                 | 31        |            |

| T48    | CLKHS high time                                                       | 14        |                 | 14        |            |

| T49    | CLKHS low time                                                        | 14        |                 | 14        |            |

| T54    | CLK287 rise/fall delay from CLKHS falling;<br>CLK16 input tied to +5V |           | 27              |           | 27         |

| T55    | CLK16 period                                                          | 62        |                 | 62        |            |

| T56    | CLK16 high time                                                       | 28        |                 | 28        | ta anngena |

| T57    | CLK16 low time                                                        | 28        |                 | 28        |            |

| T59    | CLK287 rise/fall delay from CLK16 ;<br>CLK16 toggling                 |           | 27              |           | 27         |

| T60    | SYSCLK rise/fall delay from PROCLK;<br>Low speed PROCLK selected      |           | 17              |           | 17         |

| T61    | SYSCLK rise/fall delay from PROCLK;<br>High speed PROCLK selected     |           | 17              |           | 17         |

| T62    | DMACLK rise/fall delay from PROCLK;<br>Divide by 2                    | ,         | 37              |           | 37         |

Table 7-1. FE3001A TIMING PARAMETERS (Continued)

|        |                                                                     | 1   | 16 MHz  |     | 20 MHz |  |

|--------|---------------------------------------------------------------------|-----|---------|-----|--------|--|

| SYMBOL | PARAMETER                                                           | MIN | MAX(NS) | MIN | MAX    |  |

| T63    | DMACLK rise/fall delay from PROCLK;<br>DIvide by 4                  |     | 37      |     | 37     |  |

| T64    | DMACLK rise/fall delay from PROCLK;<br>Divide by 8                  |     | 37      |     | 37     |  |

| T65    | M/IO setup time to S0, S1 falling edge                              | 4   |         | 4   |        |  |

| T66    | M/IO hold time from PROCLK (end of Ts)                              | 15  |         | 15  |        |  |

| T67    | DTR rise delay from PROCLK; read cycle                              |     | 30      |     | 30     |  |

| T68    | SDTR rise delay from PROCLK                                         |     | 28      |     | 28     |  |

| T69    | SDTR fall delay from PROCLK                                         |     | 35      |     | 35     |  |

| T70    | PTYERR setup time to PROCLK                                         | 11  |         | 11  |        |  |

| T71    | PTYERR hold time from PROCLK                                        | 4   |         | 4   |        |  |

| T72    | MEMCS16 hold time from PROCLK                                       | 17  |         | 17  |        |  |

| T73    | DEN0 low delay from PROCLK; read cycle                              |     | 33      |     | 33     |  |

| T74    | DEN1 low delay from PROCLK; read cycle                              |     | 33      |     | 33     |  |

| T75    | ZEROWS setup time to PROCLK                                         | 24  |         | 24  |        |  |

| T76    | ZEROWS hold time from PROCLK                                        | 0   |         | 0   |        |  |

| T77    | DEN0, DEN1 low delay from ONBRD high; write cycle                   |     | 28      |     | 28     |  |

| T78    | IOCS16 hold time from PROCLK                                        | 15  |         | 15  |        |  |

| T79    | DLYWR falling edge delay from PROCLK                                |     | 13      | 13  |        |  |

| T80    | DLYWR rising edge delay from PROCLK                                 |     | 25      | 25  |        |  |

| T81    | SDEN falling edge delay from PROCLK                                 |     | 42      | 42  |        |  |

| T82    | SDEN rising edge delay from PROCLK;<br>YMEMR, YMEMW, or YIOR active |     | 47      | 47  |        |  |

| T83    | SDEN rising edge delay from PROCLK; YIOW active                     |     | 47      | 47  |        |  |

| T84    | SCYCLE rising edge delay from PROCLK                                |     | 17      | 17  |        |  |

| T85    | SCYCLE falling edge delay from PROCLK                               |     | 22      | 22  |        |  |

| T86    | INTA falling edge delay from PROCLK                                 |     | 25      | 25  |        |  |

Table 7-1. FE3001A TIMING PARAMETERS (Continued)

| SYMBOL | PARAMETER                                                | 16<br>MIN | MHz<br>MAX (NS) | 20<br>MIN | MHz<br>MAX |

|--------|----------------------------------------------------------|-----------|-----------------|-----------|------------|

| T87    | INTA rising edge delay from PROCLK                       |           | 25              | 25        |            |

| T88    | ADR0 low delay from PROCLK; interrupt acknowledge cycle  |           | 21              | 21        |            |

| T89    | DENO low delay from PROCLK; interrupt acknowledge cycle  |           | 33              | 33        | ,          |

| T90    | DEN0 rise delay from PROCLK; interrupt acknowledge cycle |           | 16              | 12        |            |

| T91    | CPURES rising edge delay from PROCLK; shutdown cycle     | 5         | 17              | 5         | 14         |

| T92    | CPURES falling edge delay from PROCLK; shutdown cycle    | 5         | 17              | 5         | 14         |

| T93    | OUT1 to CLK14; asynchronous input                        | 15        |                 | 15        |            |

| T94    | HOLDRQ rising edge delay from CLK14                      |           | 46              | 46        |            |

| T95    | HOLDRQ falling edge delay from CLK14                     |           | 46              | 46        |            |

| T96    | HLDA to CLK14; asynchronous input                        | 26        |                 | 26        | ,          |

| T97    | REFRESH low delay from HLDA high                         |           | 31              | 31        |            |

| T98    | REFRESH output tri-state delay from CLK14                |           | 9               | 9         |            |

| T99    | ERFSH falling edge delay from CLK14                      |           | 43              | 43        |            |

| T100   | ERFSH rising edge delay from CLK14                       |           | 43              | 43        |            |

| T101   | YMEMR falling edge delay from CLK14; refresh cycle       |           | 40              | 40        |            |

| T102   | YMEMR rising edge delay from CLK14; refresh cycle        |           | 40              |           | 40         |

| T103   | IOCHRDY setup time to CLK14                              | 19        |                 |           |            |

| T104   | HRQ1 to CLK14; asynchronous input                        | 18        |                 |           |            |

| T105   | HLDA1 rising edge delay from CLK14                       |           | 43              |           | 43         |

| T106   | HLDA1 high delay from HLDA high                          |           | 30              |           | 30         |

| T107   | HLDA1 falling edge delay from CLK14                      |           | 43              |           | 43         |

| T108   | BALE high delay from HLDA high                           |           | 20              |           | 20         |

| T109   | BALE low delay from HLDA low                             |           | 20              |           | 20         |

Table 7-1. FE3001A TIMING PARAMETERS (Continued)

| SYMBOL | PARAMETER                        | 16 MHz<br>MIN MAX (NS) | 20 MHz<br>MIN MAX |

|--------|----------------------------------|------------------------|-------------------|

| T110   | ACK high delay from HLDA high    | 21                     | 21                |

| T111   | ACK high delay from MASTER high  | 19                     | 19                |

| T112   | ACK low delay from HLDA low      | 21                     | 21                |

| T113   | ACK low delay from MASTER low    | 19                     | 19                |

| T114   | ONBRD setup before YIOR falls    | 9                      |                   |

| T115   | ONBRD to ONBRDL delay; HLDA high | 30                     | 30                |

| T116   | HLDA high to ADR0 float delay    | 20                     | 20                |

| T117   | HLDA low to ADR0 enable delay    | 20                     | 20                |

| T118   | ADR0 input to ABHE output delay  | 19                     | 19                |

| T119   | HLDA high to EBHE float delay    | 23                     | 23                |

| T120   | HLDA low to EBHE enable delay    | 23                     | 23                |

| T121   | AEN high to EBHE enable delay    | 23                     | 23                |

| T122   | AEN low to EBHE float delay      | 22                     | 22                |

| T123   | ADR0 input to EBHE output delay  | 28                     | 28                |

| T124   | HLDA1 high to BHE enable delay   | 10                     | 10                |

| T125   | HLDA1 low to BHE float delay     | 11                     | 11                |

| T126   | EBHE to BHE delay                | 11                     | 11                |

| T127   | HLDA high to YIOR float delay    | 21                     | 21                |

| T128   | HLDA low to YIOR enable delay    | 23                     | 23                |

| T129   | HLDA high to YMEMW float delay   | 21                     | 21                |

| T130   | HLDA low to YMEMW enable delay   | 23                     | 23                |

| T131   | YIOR low to DEN0 low delay       | 25                     | 25                |

| T132   | YIOR high to DEN0 high delay     | 25                     | 25                |

| T 133  | YIOR low to DTR low delay        | 23                     | 23                |

| T134   | YIOR high to DTR high delay      | 23                     | 23                |

| T135   | YIOR low to SDTR high delay      | 31                     | 31                |

| T136   | YIOR high to SDTR low delay      | 31                     | 31                |

Table 7-1. FE3001A TIMING PARAMETERS (Continued)

| SYMBOL | PARAMETER                                                 | 16<br>MIN | MHz<br>MAX (NS) | 20<br>MIN | MHz<br>MAX |

|--------|-----------------------------------------------------------|-----------|-----------------|-----------|------------|

| T137   | ONBRD setup before DMACLK which causes YMEMR to go low    | 22        |                 | 22        |            |

| T138   | DMAMR setup time to DMACLK                                | 16        |                 | 16        |            |

| T139   | YMEMR falling edge delay from DMACLK                      |           | 15              |           | 15         |

| T140   | DMAMR high to YMEMR high delay                            |           | 19              |           | 19         |

| T141   | DLYWR input low to YIOW output low                        |           | 19              |           | 19         |

| T142   | DLYWR input high to YIOW output high                      |           | 19              |           | 19         |

| T143   | YMEMR low to DEN1 low delay                               |           | 25              |           | 25         |

| T144   | YMEMR high to DEN1 high delay                             |           | 25              |           | 25         |

| T145   | YMEMR low to SDEN low delay                               |           | 30              |           | 30         |

| T146   | YMEMR high to SDEN high delay                             |           | 30              |           | 30         |

| T147   | AEN high to ADR0 enable delay; DACK2 high                 |           | 25              |           | 25         |

| T148   | DACK2 low to ADR0 float delay                             |           | 20              |           | 20         |

| T149   | AEN high to ABHE low delay; DACK2 high                    |           | 27              |           | 27         |

| T150   | IOCHRDY setup time before DMACLK                          | 15        |                 | 15        |            |

| T151   | YIOR low to DMARDY low delay                              |           | 27              |           | 27         |

| T152   | DMAMR low to DMARDY low delay                             |           | 27              |           | 27         |

| T153   | DMARDY rising edge delay from DMACLK                      |           | 25              |           | 25         |

| T156   | EBHE to ABHE delay; master mode                           |           | 22              |           | 22         |

| T157   | AEN low to ADR0 float delay; master mode                  |           | 23              |           | 23         |

| T158   | AEN high to DLYWR float delay                             |           | 20              |           | 20         |

| T159   | AEN low to DLYWR enable delay                             |           | 21              |           | 21         |

| T160   | ONBRD setup time before memory command falls; master mode | 18        |                 | 18        |            |

| T161   | ADR0 setup time before memory command falls; master mode  | 6         |                 | 6         |            |

| T162   | EBHE setup time before memory command falls; master mode  | 6         |                 | 6         | ·          |

Table 7-1. FE3001A TIMING PARAMETERS (Continued)

| SYMBOL | PARAMETER                                                              | 16 MHz<br>MIN MAX (NS) | 20 MHz<br>MIN MAX |

|--------|------------------------------------------------------------------------|------------------------|-------------------|

| T163   | DTR low delay from memory command low; master mode                     | 23                     | 23                |

| T164   | DTR high delay from memory command high; master mode                   | 23                     | 23                |

| T165   | DENO low delay from memory command low; master mode                    | 25                     | 25                |

| T166   | DENO high delay from memory command high; master mode                  | 25                     | 25                |

| 167    | DEN1 low delay from memory command low; master mode                    | 25                     | 25                |