# INTEGRATED CIRCUITS FOR

# STORAGE PRODUCTS

1992 Data Book

# The Company

Silicon Systems' Santa Cruz facility, site of new six-inch wafer fabrication line.

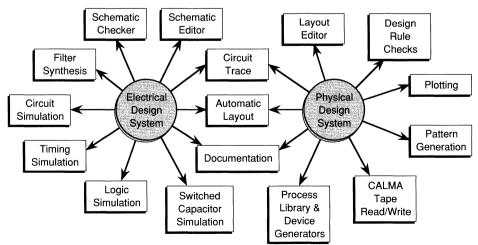

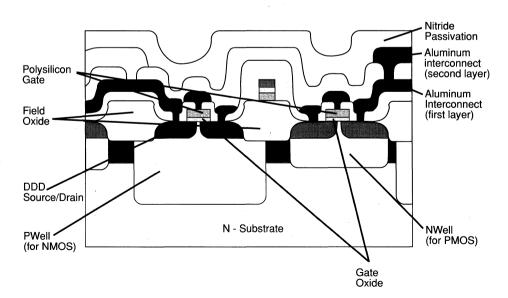

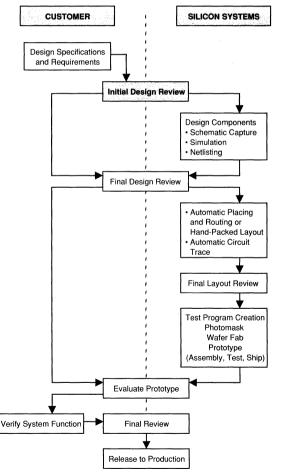

Silicon Systems specializes in the design and manufacture of application-specific, mixed-signal integrated circuits (MSICs<sup>TM</sup>). If offers a sophisticated line of custom and standard ICs aimed primarily at the storage, communications and automotive products marketplace.

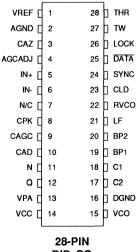

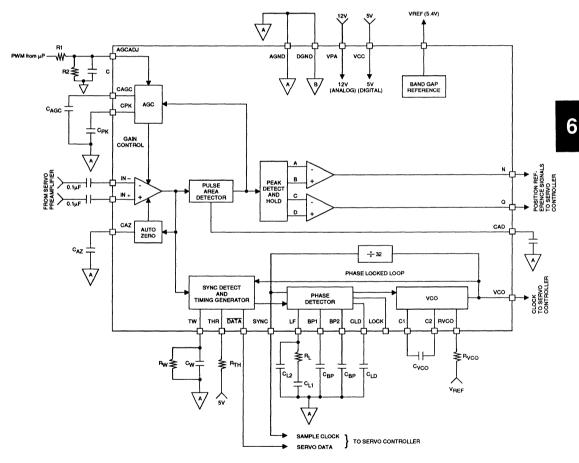

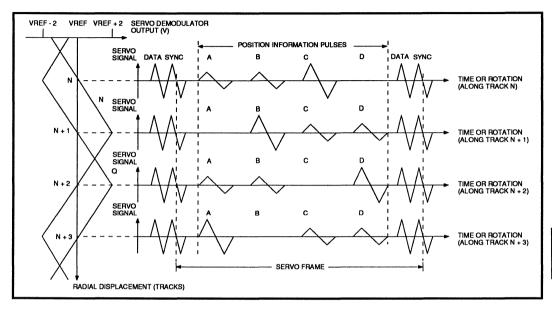

The company, which is headquartered in California, 30 miles south of Los Angeles, was founded in 1972 as a design center. It soon entered into manufacturing and today has three fabrication facilities in California and 2,000 employees worldwide. Additional operations include assembly and test facilities in California and Singapore and design engineering centers in California as well as in Tokyo and Singapore.

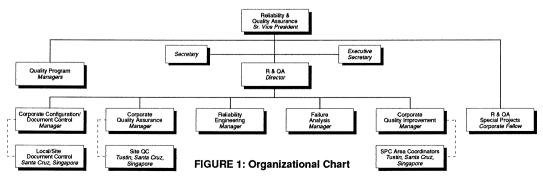

Silicon Systems is a leader in the development of high performance, mixed-signal ICs for custom or standard applications, in addition to providing pure analog or digital ICs. Reliability and quality are built into Silicon Systems' products through the use of statistical problem solving techniques, analytical controls, and other quantitative methods.

Silicon Systems is committed to the goal of customer satisfaction through the on-time delivery of defect-free products that meet or exceed the customer's expectations and requirements. This statement reflects the corporate quality mission and contains key elements instrumental in attaining true customer satisfaction. Listed in the back of this publication is a worldwide network of sales representatives and distributors ready to serve you.

# **Table of Contents**

**Advanced and Preliminary Information** In this data book the following conventions are used in designating a data sheet "Advanced" or "Preliminary:"

#### Advance Information-

Indicates a product still in the design cycle, and any specifications are based on design goals only. Do not use for final design.

#### Preliminary Data-

Indicates a product not completely released to production. The specifications are based on preliminary evaluations and are not guaranteed. Small quantities are available, and Silicon Systems should be consulted for current information.

|                                     | DEX  |    |

|-------------------------------------|------|----|

| Section HDD READ/W 1 AMPLIF         |      | 1  |

| Section HDD PU<br>2 DETECT          |      | 2  |

| Section PROGRAMMA 3 ELECTRONIC FILT |      | 3  |

| Section HDD D RECOV                 |      | 4  |

| Section READ CHAN 5 COMBINATION DEV |      | 5  |

| Section HDD H 6 POSITIO             |      | 6  |

| Section HDD SPIN 7 MOTOR CONT       |      | 7  |

| Section HDD CONTROL INTERE          |      | 8  |

| Section FLOPPY DRIVE CIRC           |      | 9  |

| Section CUSTOM SOLUT                | IONS | 10 |

| Section RELIABIL QUALITY ASSURA     |      | 11 |

| Section PACKAGING/ORDE INFORMA      |      | 12 |

| Section SALES OFF DISTRIBUT         |      | 13 |

#### **DISCLAIMER**

All products listed herein and subsequently sold by Silicon Systems, Inc. are covered by the warranty, limitation of liability and patent indemnification provisions reflected in the Silicon Systems Order Acknowledgement Form only. Silicon Systems, Inc. makes no warranty, express or implied, statutory or by description regarding the information set forth herein and/or freedom from patent infringement. Silicon Systems, Inc. reserves the right to discontinue production, change specifications and prices at any time and without notice.

Applications requiring mechanical and electrical parameters outside of the published specifications are not recommended without additional review and acceptance by Silicon Systems, Inc. Silicon Systems, Inc. further assumes no responsibility for the use of any integrated circuit technology other than integrated circuit technology embodied in a Silicon Systems, Inc. product. These products are not authorized for use as components in life support devices or systems. No patents or licenses regarding the integrated circuit technology herein are implied unless otherwise stated.

# Index

|               |                  |                                                    | rage # |

|---------------|------------------|----------------------------------------------------|--------|

| Customer Re   | · •              |                                                    |        |

| Table of Cor  | ntents           |                                                    |        |

| Disclaimer    |                  |                                                    |        |

| Index         |                  |                                                    |        |

| Discontinued  | d Parts List     |                                                    | V      |

|               |                  |                                                    |        |

|               |                  |                                                    |        |

| r loudet Sele | cioi Guide       |                                                    | V II   |

| Section 1.    | HDD READ/WRIT    | TE AMPLIFIERS                                      |        |

|               | 32R104C          | 4-Channel Read/Write Device                        |        |

|               | 32R117/117R      | 2-, 4-, 6-Channel Read/Write Device                |        |

|               | 32R501/501R      | 4-, 6-, 8-Channel Read/Write Device                |        |

|               | 32R510A/510AR    | 2-, 4-, 6-Channel Read/Write Device                |        |

|               | 32R511/511R      | 4-, 6-, 8-Channel, Ferrite Read/Write Device       |        |

|               | 32R512/512R      | 8-, 9-Channel, Thin Film Read/Write Device         |        |

|               | 32R5121/5121R    | 14-Channel, Thin Film Read/Write Device            |        |

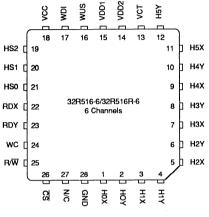

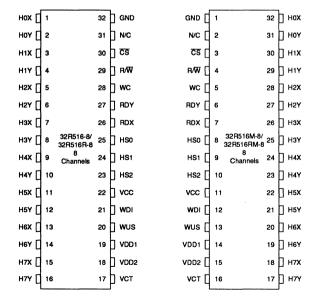

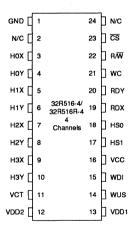

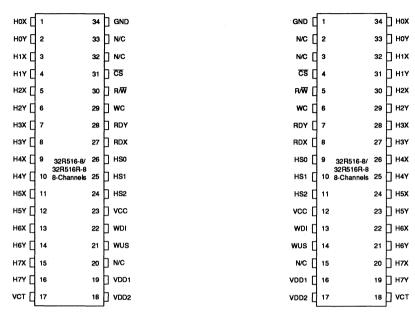

|               | 32R516/516R      | 4-, 6-, 8-Channel, Ferrite Read/Write Device       |        |

|               | 32R5161R         | 10-Channel, Ferrite/ MIG Read/Write Device         |        |

|               | 32R520/520R      | 4-Channel, Thin Film Read/Write Device             | *      |

|               | 32R521/521R/5211 | 6-Channel, Thin Film Read/Write Device             | *      |

|               | 32R522/522R      | 4-, 6-Channel, Thin Film Read/Write Device         | *      |

|               | 32R524R          | 8-Channel, Thin Film Read/Write Device             |        |

|               | 32R525R          | 4-Channel, Thin Film Read/Write Device             |        |

|               | 32R527R          | 8-, 9-Channel, Thin Film Read/Write Device         |        |

|               | 32R528R          | 8-, 9-Channel, Thin Film Read/Write Device         |        |

| NEW           | 32R5281R         | 14-Channel, 2-Terminal Read/Write Device           |        |

|               | 32R1200/1201     | +5V, 4-Channel, Ferrite/MIG, Read/Write Device     |        |

| NEW           |                  | +5V, 2-,4-Channel, Ferrite MIG R/W Device          |        |

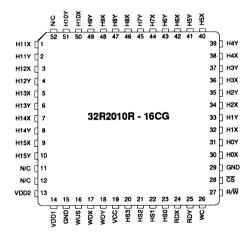

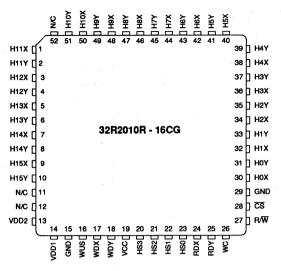

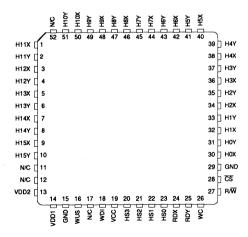

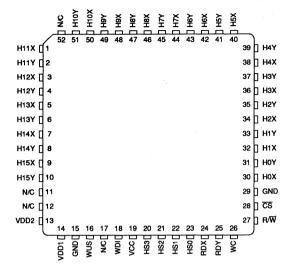

|               | 32R2010R         | 10-, 16-Channel, Thin Film Read/Write Device       |        |

| NEW           | 32R2015R         | 10-, 16-Channel, Thin Film Read/Write Device       |        |

| NEW           | 32R2020R/2021R   | +5V, 2-, 4-Channel Read/Write Device               |        |

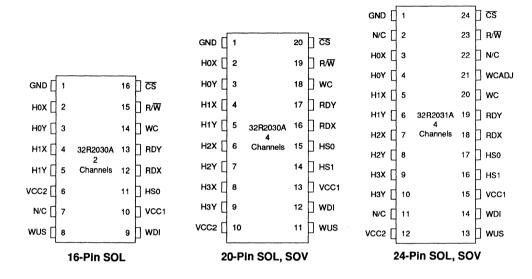

| NEW           | 32R2030A/2031A   | +5V, 2-, 4-Channel, 2-Terminal Read/Write Device   |        |

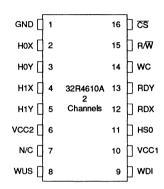

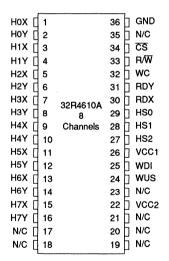

|               | 32R4610A/4611A   | 2-, 4-, 8-Channel, Thin Film Read/Write Device     | 1-129  |

| Section 2.    | HDD PULSE DET    | ECTION                                             |        |

|               | 32P540 Series    | Read Data Processor                                | *      |

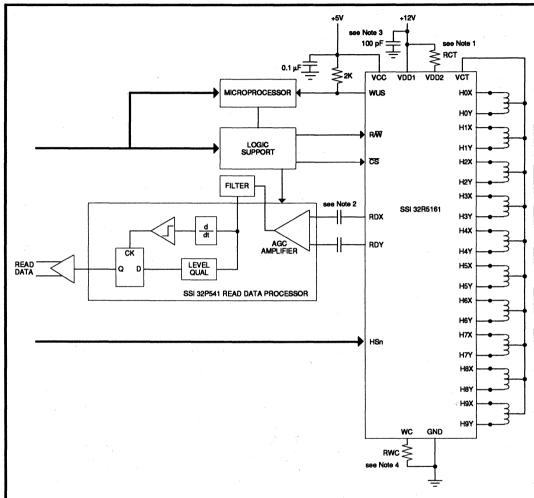

|               | 32P541           | Read Data Processor                                |        |

|               | 32P541B          | Read Data Processor                                | 2-11   |

| NEW           | 32P5411B         | Read Data Processor                                | 2-25   |

|               | 32P544           | Read Data Processor and Servo Demodulator          |        |

|               | 32P546           | Read Data Processor with Pulse Slimming            |        |

|               | 32P547           | High Performance Pulse Detector                    |        |

|               | 32P549           | Pulse Detector                                     |        |

| new           | 32P5491          | Pulse Detector                                     |        |

| 0.000.00      | 32P3000          | Pulse Detector with Internal Filter                |        |

| NEW           | 32P3010          | Pulse Detector with Internal Filter, Servo Capture |        |

| NEW           | 32P3030          | Pulse Detector and Servo Demodulator               |        |

| NEW           | 32P3040          | Pulse Detector with Programmable Filter            | 2-143  |

| Section 3.    | PROGRAMMABL      | E ELECTRONIC FILTERS                               |        |

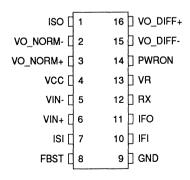

| NEW           | 32F8000          | Programmable Electronic Filter                     | 3-1    |

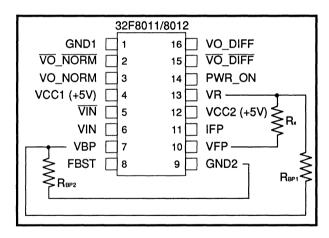

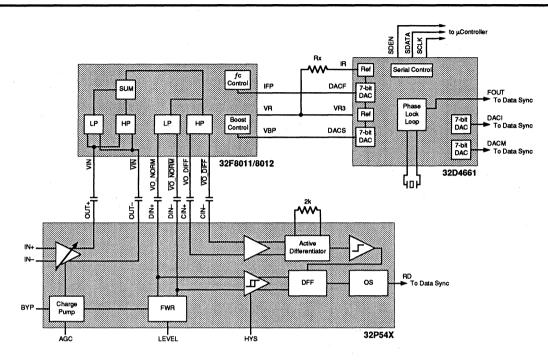

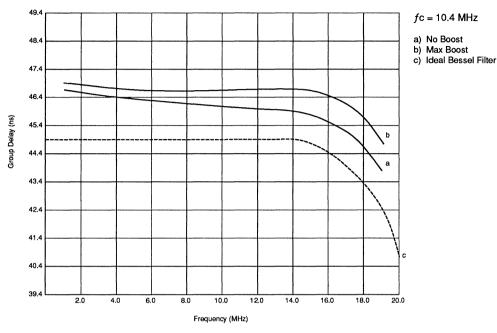

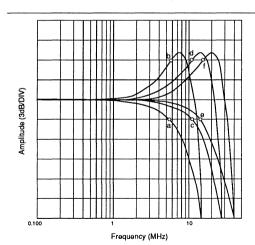

|               | 32F8011/8012     | Programmable Electronic Filter                     |        |

| NEW           | 32F8020/8022     | Programmable Electronic Filter                     |        |

| NEW           | 32F8021/8023     | Programmable Electronic Filter                     |        |

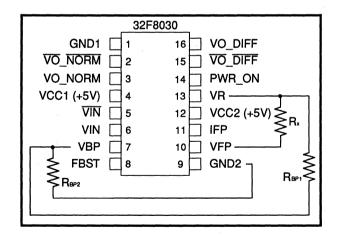

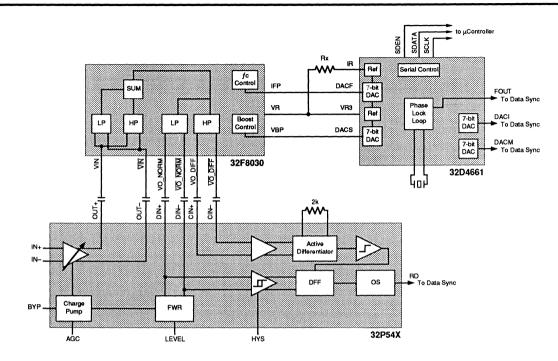

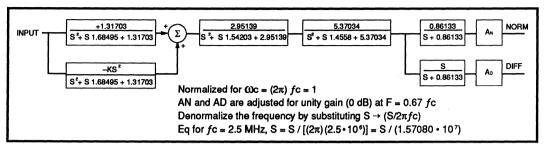

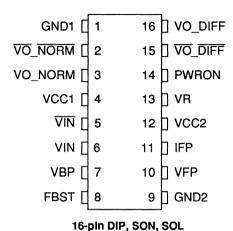

| NEW           | 32F8030          | Programmable Electronic Filter                     |        |

|               | 32F8120          | Low Power Programmable Electronic Filter           |        |

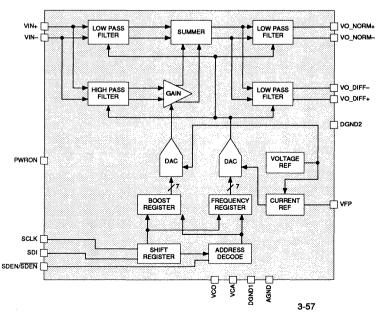

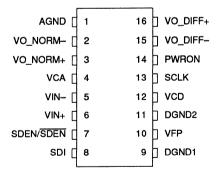

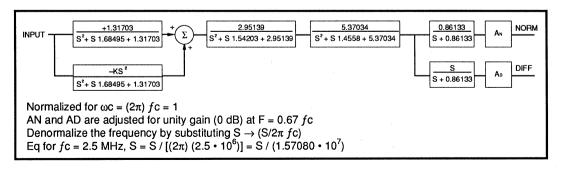

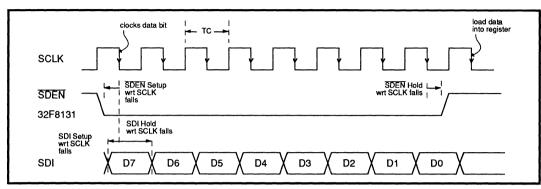

|               | 32F8130/8131     | Low Power Programmable Electronic Filter           | 3-57   |

# Index (Continued)

|            |                      |                                                            | Page # |

|------------|----------------------|------------------------------------------------------------|--------|

| Section 4. | HDD DATA REC         | OVERY                                                      | _      |

|            | 32D5321              | Data Synchronizer/2, 7 RLL ENDEC                           | 4.4    |

|            | 32D5321              | Data Synchronizer, 2, 7 RLL ENDEC                          |        |

|            | 32D534A              | Data Synchronizer/MFM ENDEC                                |        |

|            | 32D535               | Data Synchronizer, 2, 7 RLL ENDEC/Write Precompensation    |        |

|            | 32D5351A             | Data Synchronizer, 2, 7 RLL ENDEC/Write Precompensation    |        |

|            | 32D5362A             | Data Synchronizer, 1, 7 RLL ENDEC/Write Precompensation    |        |

| NEW        | 32D5371/72/73/74     | Data Synchronizer, 1, 7 RLL ENDEC Write Precompensation    |        |

| 10 G 90    | 32D539               | Data Synchronizer, 1, 7 RLL ENDEC 74/16 Precompensation    |        |

| new        | 32D5391              | Data Synchronizer, 1, 7 FIELE ERDEG, Serial NRZ            |        |

| NEW        | 32D5392              | Data Synchronizer, 1, 7 ENDEC, Dual-Bit NRZ                |        |

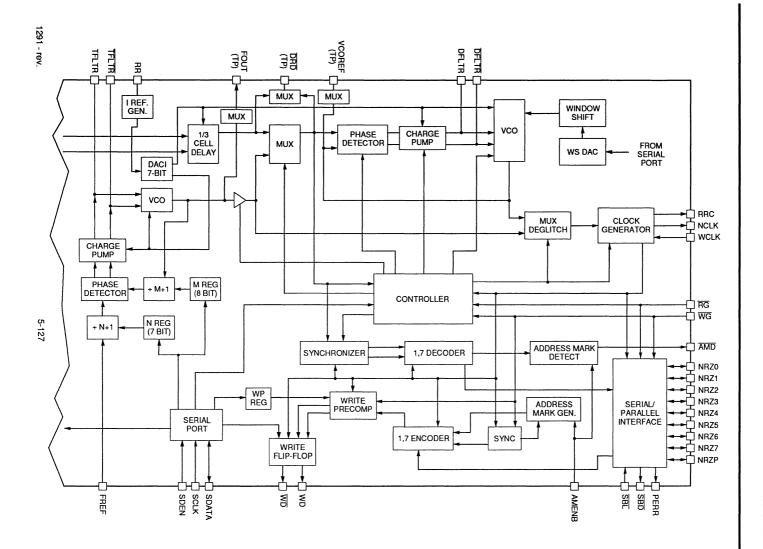

| NEW        | 32D4010              | Data Synchronizer, 1, 7 ENDEC, Window Shift, Power Down    |        |

| NEW        | 32D4420              | Programmable Filter and Frequency Reference                |        |

|            | 32D4660              | Time Base Generator                                        |        |

| NEW        | 32D4661/4662         | Time Base Generator                                        |        |

| new        | 32D4665              | Time Base Generator                                        |        |

| 50250      |                      | Family Applications Note                                   |        |

| Section 5. |                      |                                                            |        |

| Section 5. |                      | L COMBINATION DEVICES                                      |        |

| o.acetnor  | 32P548               | Pulse Detector and Data Synchronizer Combination Device    |        |

| new        | 32P5481/5482         | Low Power Pulse Detector and Data Synchronizer             |        |

| 0.4570.04  | 32P4622              | Pulse Detector and Data Separator Combination Device       |        |

| NEW        | 32P4720/4721         | Pulse Detector and Data Separator Combination Device       |        |

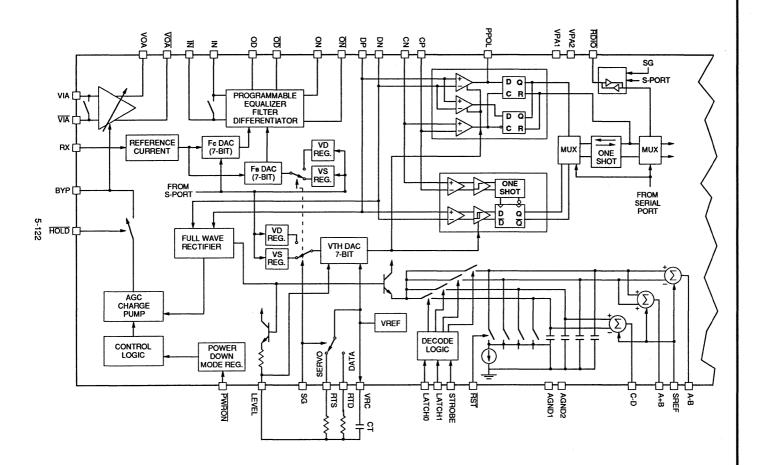

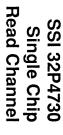

| NEW        | 32P4730              | Single Chip Read Channel, 1, 7 RLL 12-24 Mbit/s            |        |

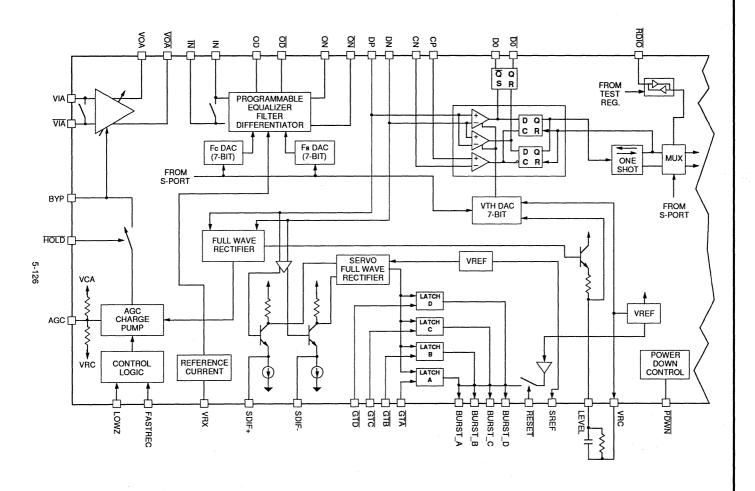

| new        | 32P4740              | Single Chip Read Channel, 1, 7 RLL 24-48 Mbit/s            | 5-125  |

| Section 6. | HDD HEAD POS         | SITIONING                                                  |        |

|            | 32H101               | Differential Amplifier                                     | *      |

|            | 32H116A              | Differential Amplifier                                     |        |

|            | 32H523AR             | Servo Read/Write, Thin Film                                |        |

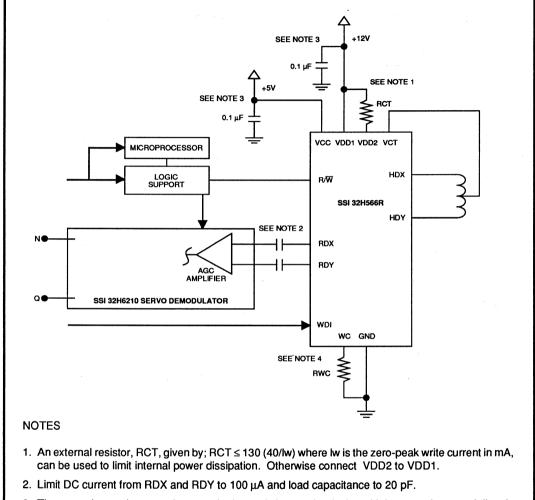

|            | 32H566R              | Servo Read/Write, Ferrite                                  | 6-13   |

|            | 32H569               | Servo Motor Driver                                         |        |

|            | 32H4631/4632         | Hybrid Servo & Spindle Motor Controller                    |        |

|            | 32H6110              | Differential Amplifier                                     |        |

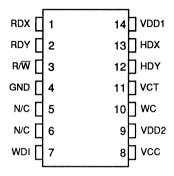

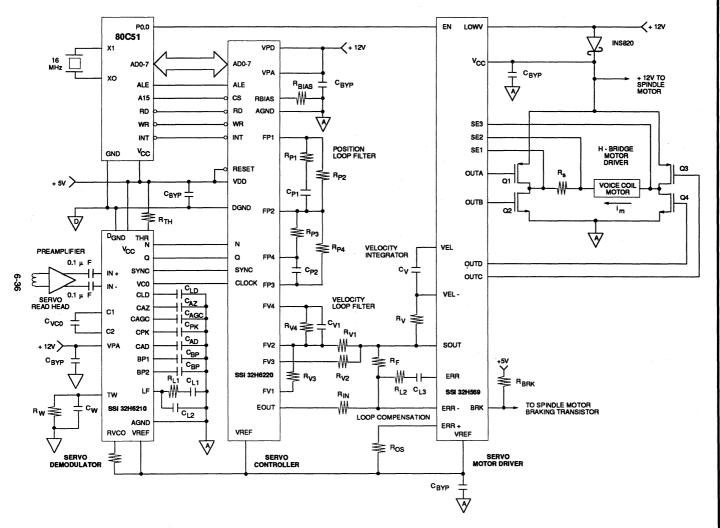

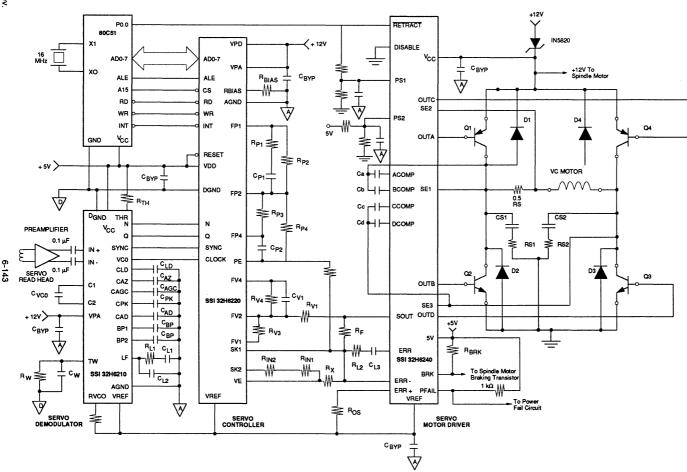

|            | 32H6210              | Servo Demodulator                                          |        |

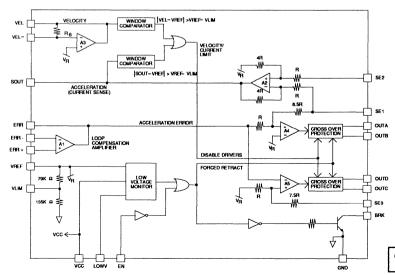

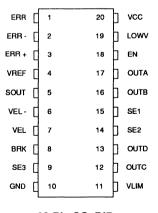

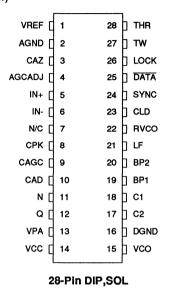

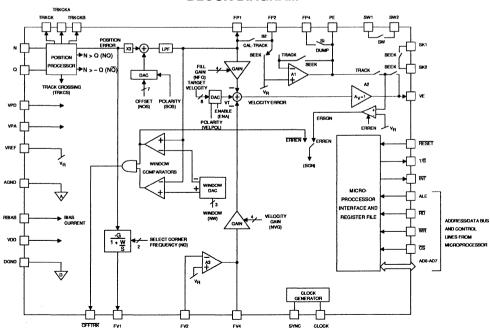

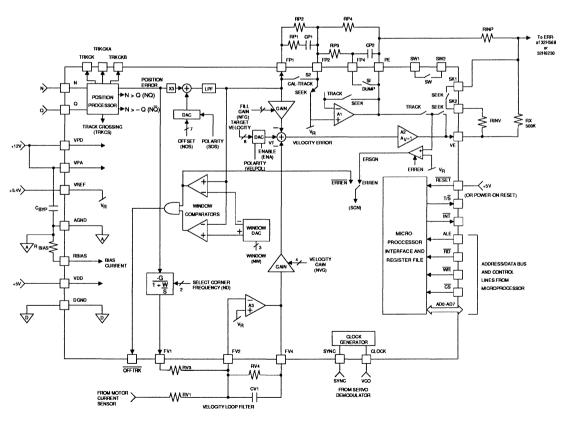

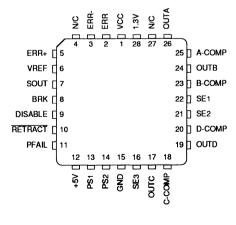

|            | 32H6220              | Servo Controller                                           |        |

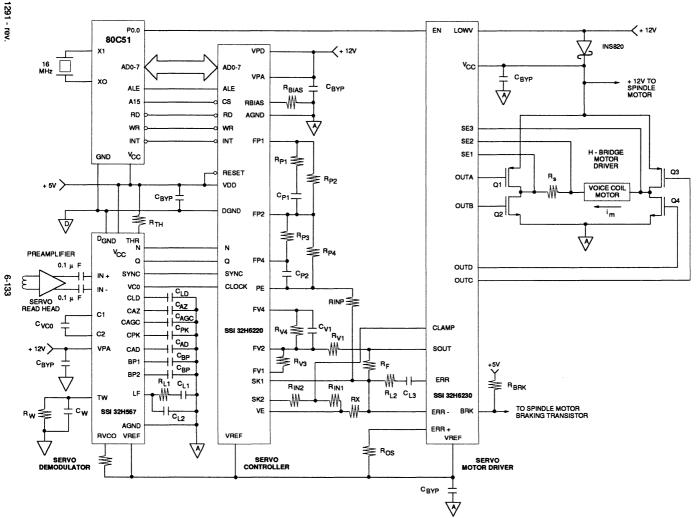

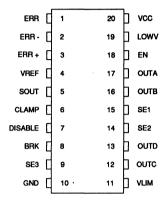

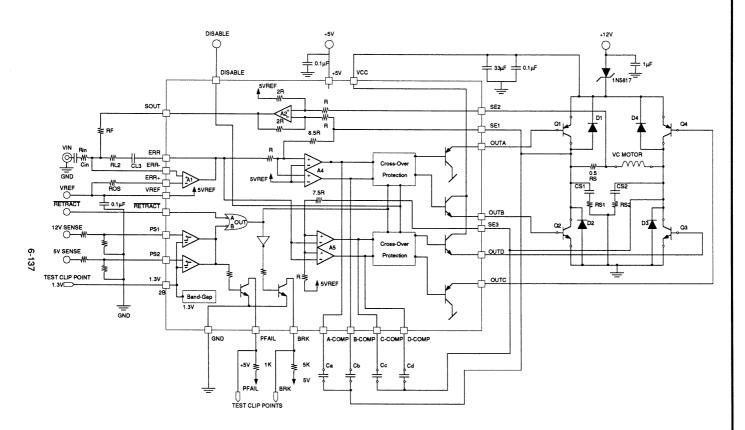

|            | 32H6230              | Servo Motor Driver                                         | 6-121  |

|            | 32H6240              | Servo Motor Driver                                         |        |

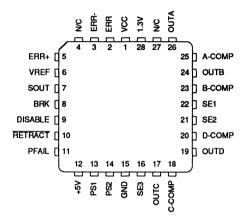

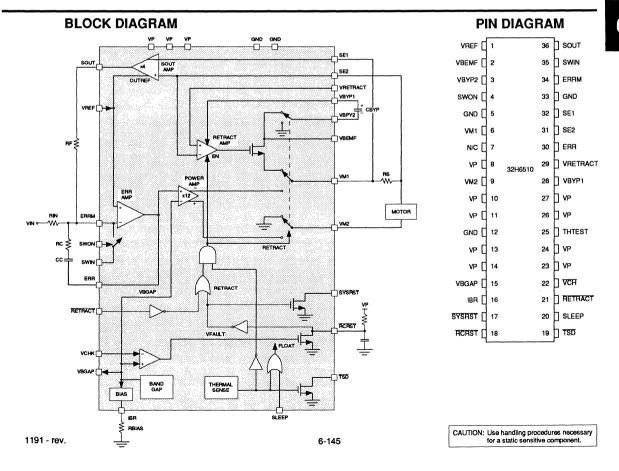

| NEW        | 32H6510              | 5V Servo Motor Driver                                      |        |

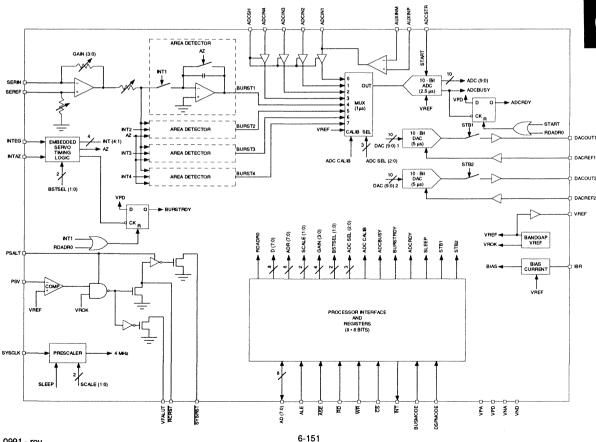

| NEW        | 32H6520              | Embedded Servo Controller                                  |        |

| NEW        | 32H6810              | 5V Servo & Motor Speed Drivers                             |        |

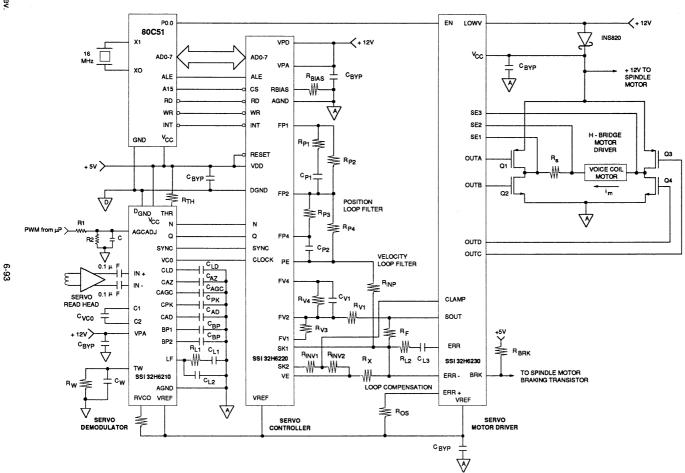

|            | Servo Applications I | Note                                                       |        |

| Section 7. | HDD SPINDLE N        | MOTOR CONTROL                                              |        |

|            | 32M593A              | Three-Phase Delta 5-1/4" Winchester Motor Speed Controller | 7-1    |

|            | 32M594               | Three-Phase Delta Motor Speed Controller                   | 7-13   |

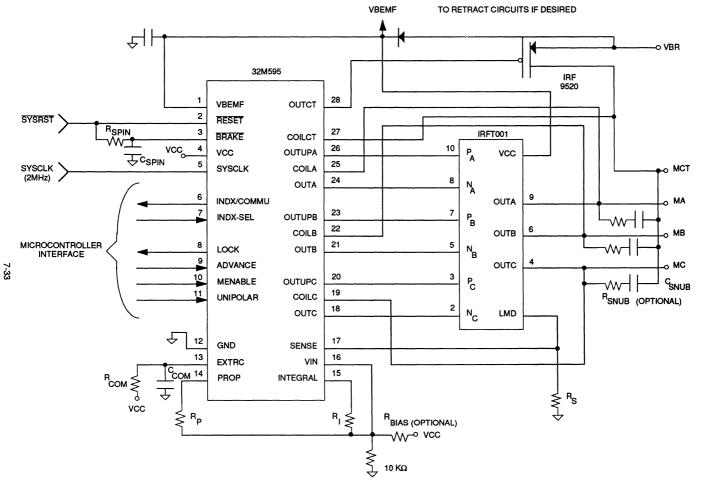

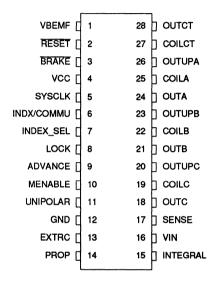

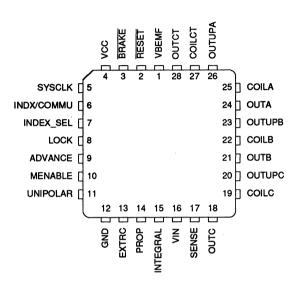

|            | 32M595               | Hall Sensor-Less Motor Speed Controller                    |        |

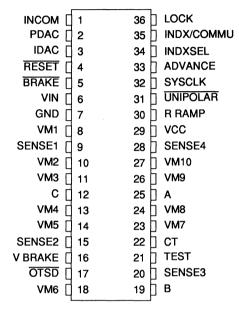

| NEW        | 32M7010              | Hall Sensor-Less Motor Speed Driver/Controller             |        |

| new        | 32M7011              | Hall Sensor-Less Motor Speed Driver/Controller             |        |

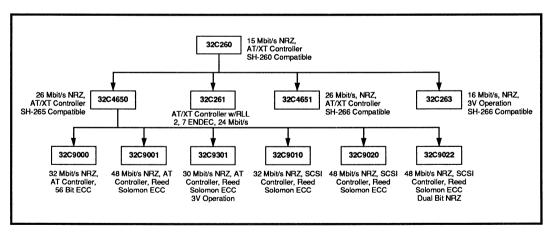

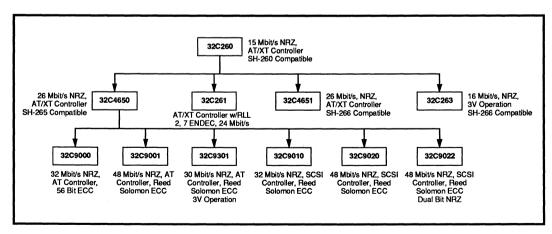

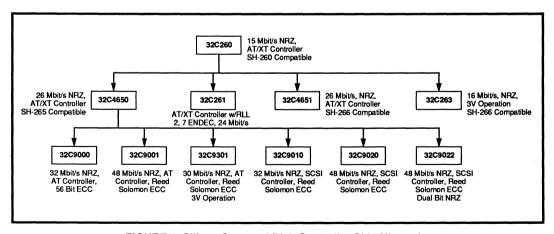

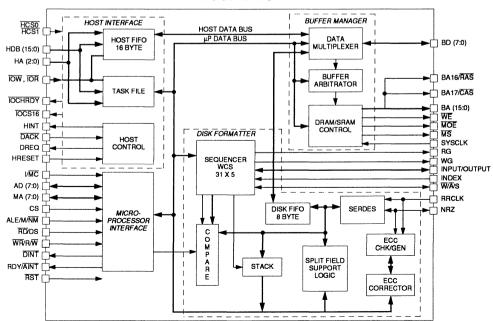

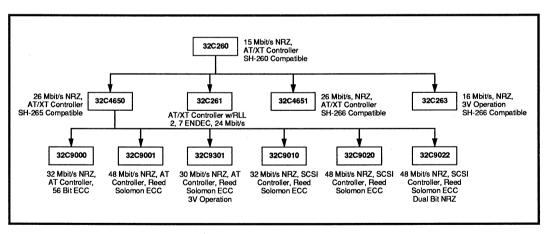

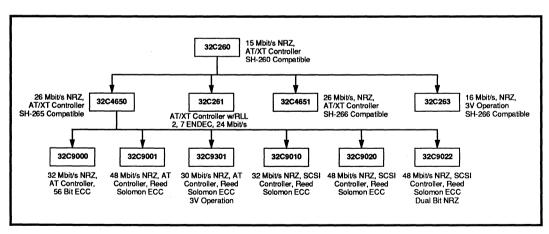

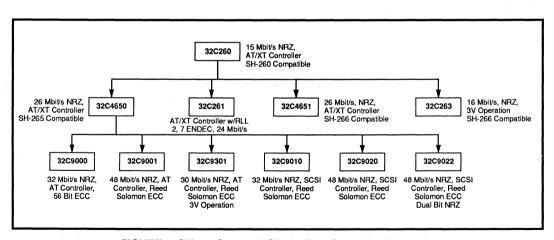

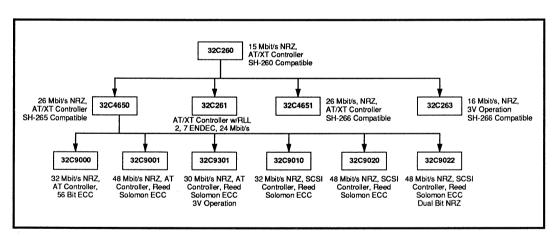

| Section 8. | HDD CONTROL          | LER/INTERFACE                                              |        |

|            | 32C260               | PC AT/XT Combo Controller – 15 Mbit/s                      | 8-1    |

| NEW        | 32C261               | PC AT/XT Combo Controller with RLL (2, 7) ENDEC, 24 Mbit/s |        |

| New        | 32C263               | PC AT/XT Combo Controller with 3V operation, 16 Mbit/s     |        |

| new        | 32C4650              | PC XT/AT Combo Controller, 26 Mbit/s                       |        |

| New        | 32C4651              | PC AT/XT Combo Controller, 26 Mbit/s                       |        |

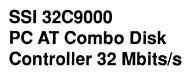

| NEW        | 32C9000              | PC AT Combo Controller, 32 Mbit/s                          |        |

<sup>\*</sup> Data Sheet available upon request.

| NEW         | 32C9001     | Combo AT Controller, 48 Mbit/s                                 | 8-83  |

|-------------|-------------|----------------------------------------------------------------|-------|

| NEW         | 32C9010     | SCSI Combo Controller, 32 Mbit/s                               |       |

| NEW         | 32C9020     | Combo SCSI Controller, 48 Mbit/s                               |       |

| new         | 32C9022     | Combo SCSI Controller, Dual-Bit NRZ, 48 Mbit/s                 |       |

| NEW         | 32C9301     | High Performance AT Combo Controller, 3V operation, 30 Mbit/s  | 8-109 |

| Section 9.  | FLOPPY DISH | K DRIVE CIRCUITS                                               |       |

|             | 34D441      | Data Synchronizer & Write Precompensation Device               | *     |

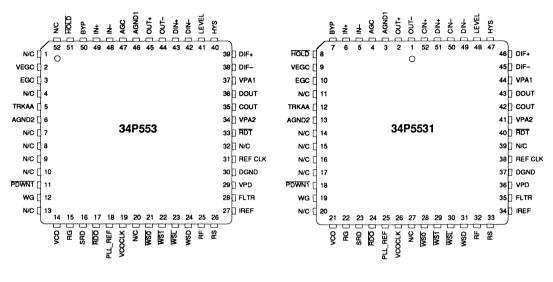

| NEW         | 34P553/5531 | Pulse Detector and Synchronizer                                | 9-1   |

|             | 34R575      | 2, 4-Channel Floppy Disk Read/Write Device                     |       |

|             | 34B580      | Port Expander Floppy Disk Drive                                |       |

| Section 10. | CUSTOM SOI  | LUTIONS                                                        | 10-1  |

| Section 11. | QUALITY AS  | SURANCE AND RELIABILITY                                        | 11-1  |

|             | QUALITY AC  | OUTAINOL AIRO FILLIADILIT I                                    |       |

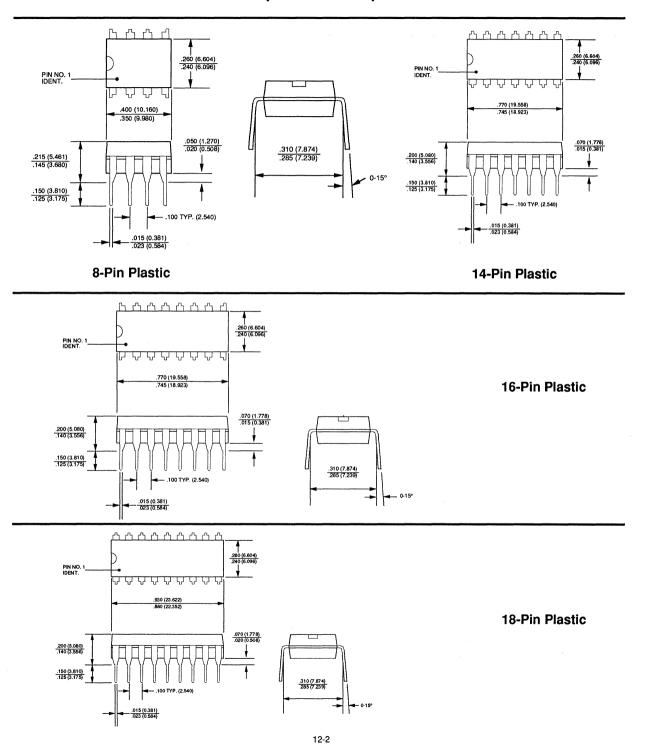

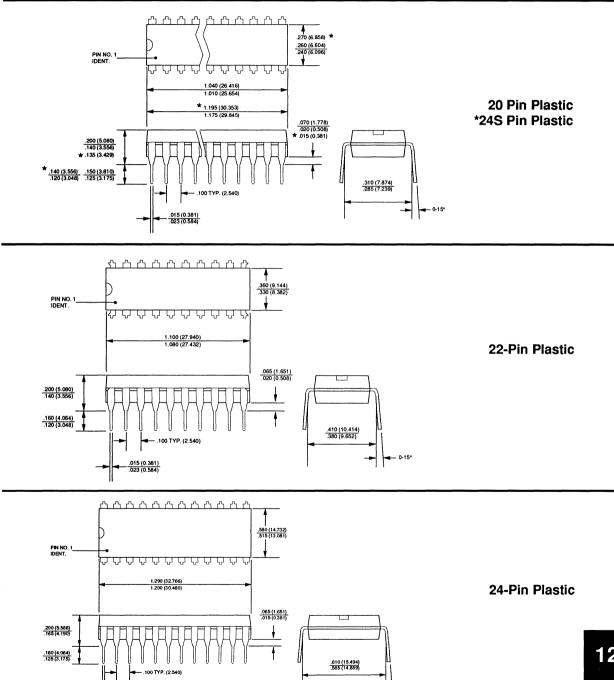

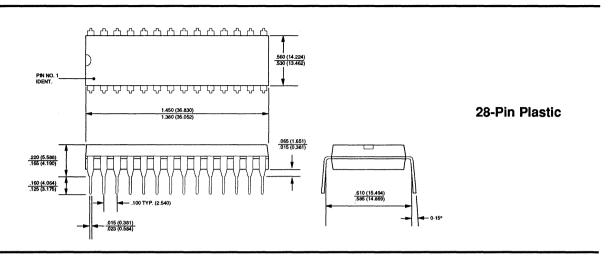

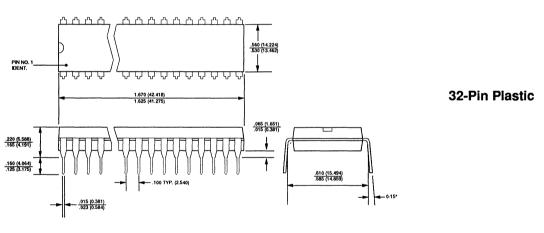

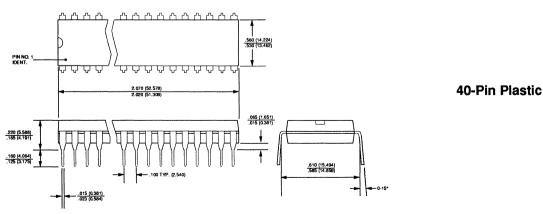

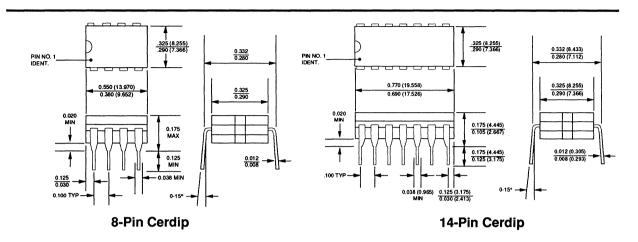

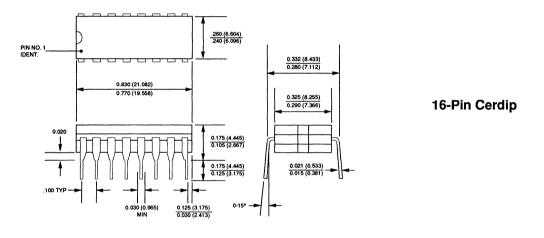

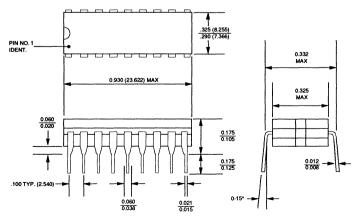

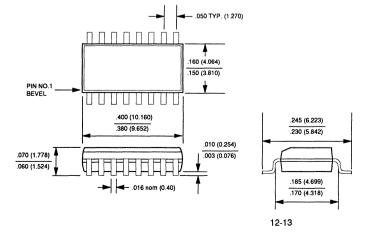

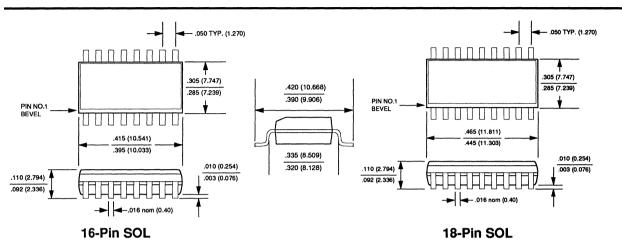

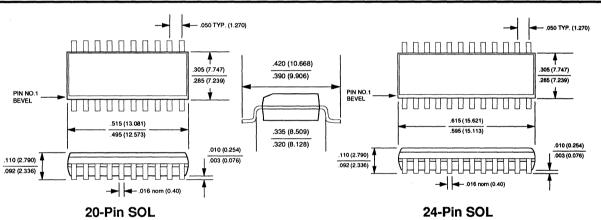

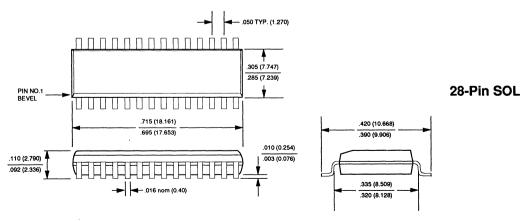

| Section 12. | PACKAGING   | ORDERING INFORMATION                                           |       |

|             |             |                                                                |       |

|             |             | ation                                                          |       |

|             |             | l, 16 and 18 Pins                                              |       |

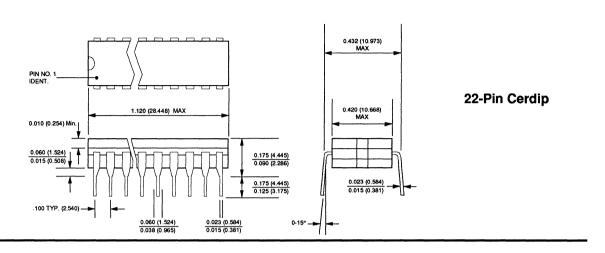

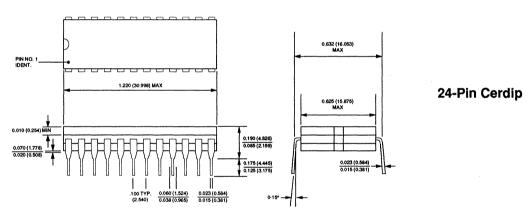

|             |             | 22, 24 and 24S Pins                                            |       |

|             |             | 32 and 40 Pins                                                 |       |

|             |             | and 18 Pins                                                    |       |

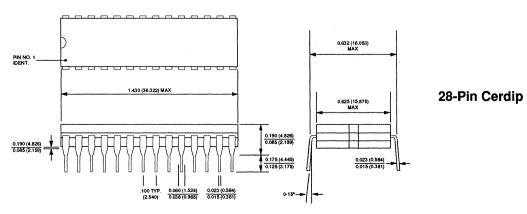

|             |             | nd 28 Pins                                                     |       |

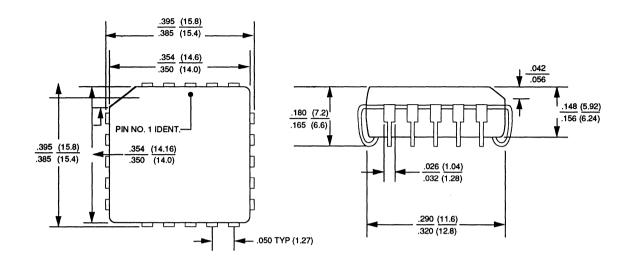

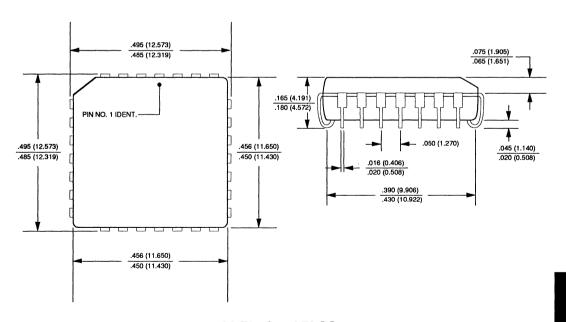

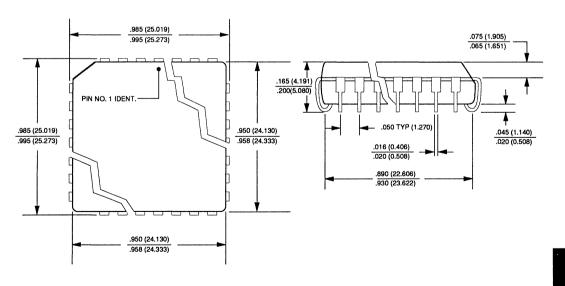

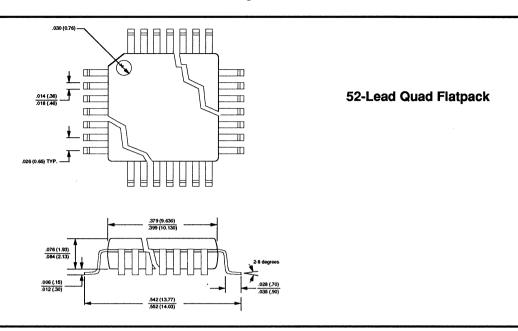

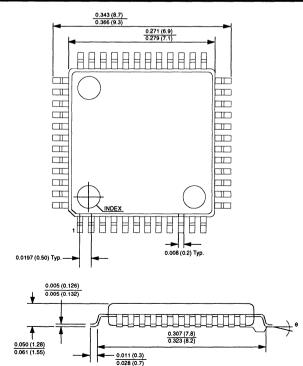

|             |             | Device (PLCC) 20 and 28 Leads<br>Device (PLCC) 32 and 44 Leads |       |

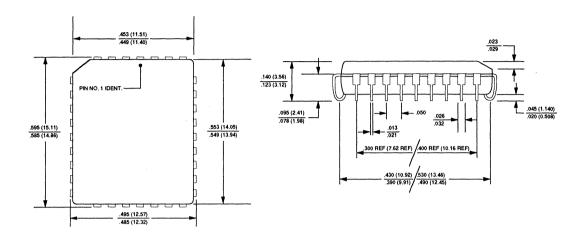

|             |             | Device (PLCC) 52 and 68 Leads                                  |       |

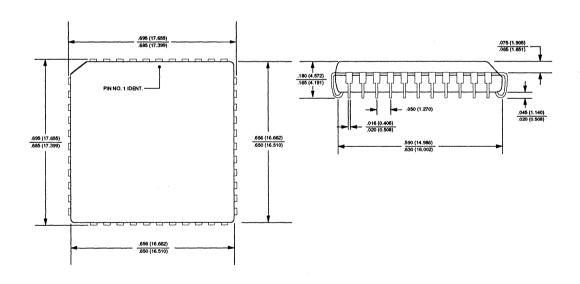

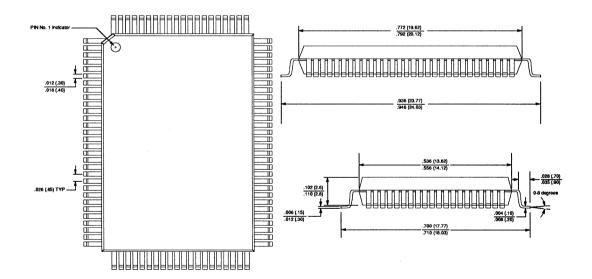

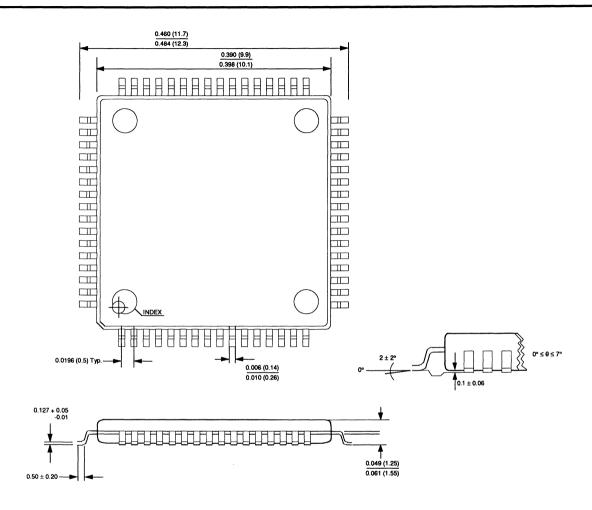

|             |             | ads                                                            |       |

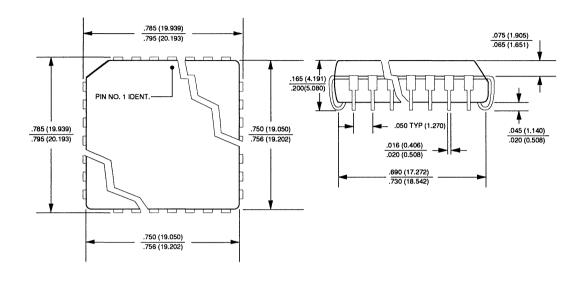

|             |             | ads                                                            |       |

|             |             | aus                                                            |       |

|             |             | 6 Leads                                                        |       |

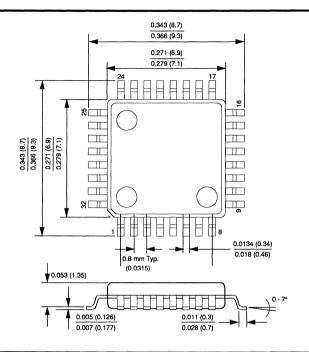

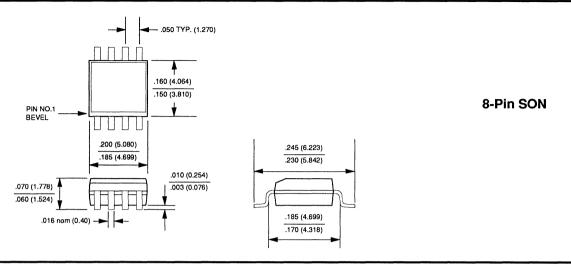

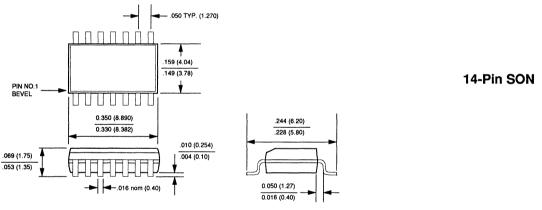

|             |             | 24 and 28 Leads                                                |       |

|             |             |                                                                |       |

|             |             |                                                                |       |

|             |             |                                                                |       |

|             |             |                                                                |       |

|             |             | ads                                                            |       |

| Section 13. | SALES OFFIC | CES/DISTRIBUTORS                                               |       |

|             |             |                                                                |       |

### **Discontinued Parts List**

The following parts are no longer supplied or supported by Silicon Systems. Please note alternate sources.

| Part #      | Alternate Source | Part #              | Alternate Source |

|-------------|------------------|---------------------|------------------|

| SSI 32B450A | SSI 32B451       | SSI 32P541A         | SSI 32P541B      |

| SSI 32B451  | None             | SSI 32P542          | None             |

| SSI 32B453  | None             | SSI 32R108M, 32R122 | None             |

| SSI 32B545  | None             | SSI 32R114          | SSI 32R525R      |

| SSI 32C452A | None             | SSI 32R115          | None             |

| SSI 32D531  | None             | SSI 32R188          | None             |

| SSI 32D536  | SSI 32D5362A     | SSI 32R502          | None             |

| SSI 32D537  | SSI 32D5371/5372 | SSI 32R514          | None             |

| SSI 32D5381 | Signetics        | SSI 32R515          | None             |

| SSI 32H567  | SSI 32H6210      | SSI 32R526R         | None             |

| SSI 32H568  | SSI 32H6220      | SSI 32R529          | None             |

| SSI 32H4630 | None             | SSI 32R5111         | None             |

| SSI 32M590  | None             | SSI 34P550          | None             |

| SSI 32M591  | None             | SSI 34P570          | None             |

# **Numerical Index**

| SSI Device Numbers     | Page # | SSI Device Numbers | Page # |

|------------------------|--------|--------------------|--------|

| 32C260                 | 8-1    | 32M7010            | 7-35   |

| 32C261                 | 8-17   | 32M7011            | 7-43   |

| 32C263                 | 8-37   | 32P540             | *      |

| 32C4650                | 8-43   | 32P541             | 2-1    |

| 32C4651                | 8-59   | 32P541B            | 2-11   |

| 32C9000                | 8-75   | 32P5411B           | 2-25   |

| 32C9001                | 8-83   | 32P544             | 2-39   |

| 32C9010                | 8-91   | 32P546             | *      |

| 32C9020                | 8-97   | 32P547             | 2-61   |

| 32C9022                | 8-103  | 32P548             | 5-1    |

| 32C9301                | 8-109  | 32P5481/5482       | 5-29   |

| 32D5321                | 4-1    | 32P549             | 2-79   |

| 32D5322                | 4-19   | 32P5491            | 2-91   |

| 32D534A                | *      | 32P3000            | 2-103  |

| 32D535                 | 4-37   | 32P3010            | 2-115  |

| 32D5351A               | 4-57   | 32P3030            | 2-127  |

| 32D5362A               | 4-77   | 32P3040            | 2-143  |

| 32D5371/5372/5373/5374 |        | 32P4622            | 5-55   |

| 32D539                 | 4-113  | 32P4720/4721       |        |

| 32D5391                |        | 32P4730            |        |

| 32D5392                |        | 32P4740            |        |

| 32D4010                |        | 32R104C            |        |

| 32D4420                |        | 32R117/117R        |        |

| 32D4660                |        | 32R501/501R        |        |

| 32D4661/4622           |        | 32R510A/510AR      |        |

| 32D4665                |        | 32R511/511R        |        |

| 32F8000                |        | 32R512/512R        |        |

| 32F8011/8012           |        | 32R5121/5121R      |        |

| 32F8020/8022           |        | 32R516/516R        |        |

| 32F8021/8023           |        | 32R5161R           |        |

| 32F8030                |        | 32R520/520R        |        |

| 32F8120                |        | 32R521/521R/5211   |        |

| 32F8130/8131           |        | 32R522/522R        |        |

| 32H101                 |        | 32R524R            |        |

| 32H116A                |        | 32R525R            |        |

| 32H523AR               |        | 32R525R            |        |

| 32H566R                |        | 32R528/528R        |        |

| 32H569                 |        | 32R5281R           |        |

| 32H4631/4632           |        | 32R1200/1201       |        |

| 32H6110                |        | 32R1220/1221/1222  |        |

| 32H6210                |        | 32R1220/1221/1222  |        |

| 32H6220                |        | 32R2016R           |        |

|                        |        |                    |        |

| 32H6230                |        | 32R2020R/2021R     |        |

| 32H6240                |        | 32R2030A/2031A     |        |

| 32H6510                |        | 32R4610A/4611A     |        |

| 32H6520                |        | 34B580             |        |

| 32H6810                |        | 34D441             |        |

| 32M593A                |        | 34P553/5531        |        |

| 32M594                 |        | 34R575             | 9-25   |

| 32M595                 | 7-25   |                    |        |

# STORAGE PRODUCTS REFERENCE

| Device Number       | Head Type                                                                                             | Number of<br>Channels                | Max Input<br>Noise<br>(nV/√Hz)    | Max Input<br>Capacitance<br>(pF)                         | Read<br>Gain<br>(typ)    | Write Current<br>Range<br>(mA) | Power<br>Supplies<br>(V) | Write<br>Data Ports         | Min. Head<br>Swing                 |

|---------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------|----------------------------------------------------------|--------------------------|--------------------------------|--------------------------|-----------------------------|------------------------------------|

| HDD READ/WRITE AMI  | PLIFIERS                                                                                              | <u> konstruentationen automatika</u> | T. 158 S. 11 (813) 1813 1813 1813 | 54 K. (1) 1002   1408 (143) (150)                        | Indicate (2072) Granting | k                              | <b>3</b>                 |                             | Lutin manufacturi de disconsidente |

| SSI 32R117/117R     | 3 Terminal                                                                                            | 2, 4, 6                              | 2.1                               | 20                                                       | 100                      | 10 to 50                       | +5, +12                  | ΠL                          | 8.0 (0-pk)                         |

| SSI 32R501/501R     | 3 Terminal                                                                                            | 4, 6, 8                              | 1.5                               | 23                                                       | 100                      | 10 to 50                       | +5, +12                  | Пι                          | 7.5 (0-pk)                         |

| SSI 32R510A/510AR   | 3 Terminal                                                                                            | 2, 4, 6                              | 1.5                               | 20                                                       | 100                      | 10 to 40                       | +5, +12                  | ΠL                          | 7.0 (0-pk)                         |

| SSI 32R511/511R     | 3 Terminal                                                                                            | 4, 6, 8                              | 1.5                               | 20                                                       | 100                      | 10 to 40                       | +5, +12                  | ΠL                          | 7.0 (0-pk)                         |

| SSI 32R516          | 3 Terminal                                                                                            | 4, 6, 8                              | 1.3                               | 18                                                       | 120                      | 10 to 60                       | +5, +12                  | ΠL                          | 7.0 (0-pk)                         |

| SSI 32R5161R        | 3 Terminal                                                                                            | 10                                   | 1.3                               | 18                                                       | 150                      | 10 to 60                       | +5, +12                  | ΠL                          | 7.0 (0-pk)                         |

| SSI 32R1200/1201    | 3 Terminal                                                                                            | 2, 4                                 | 1.2                               | 17                                                       | 200                      | 15 to 50                       | +5                       | ΠL                          | 6.0 (0-pk)                         |

| SSI 32R1220/21/22   | 3 Terminal                                                                                            | 2, 4                                 | 0.8                               | 17                                                       | 250                      | 15 to 40                       | +5                       | ΠL                          | 6.0 (0-pk)                         |

| SSI 32R512/512R     | 2 Terminal                                                                                            | 8, 9                                 | 0.85                              | 35                                                       | 150                      | 10 to 40                       | +5, +12                  | ΠL                          | 7.0 (pk-pk)                        |

| SSI 32R5121/5121R   | 2 Terminal                                                                                            | 14                                   | 0.85                              | 35                                                       | 250                      | 10 to 40                       | +5, +12                  | ΠL                          | 7.0 (pk-pk)                        |

| SSI 32R521/521R     | 2 Terminal                                                                                            | 6                                    | 0.9                               | 65                                                       | 150                      | 20 to 70                       | +5, +12                  | ΠL                          | 3.4 (pk-pk)                        |

| SSI 32R5211         | 2 Terminal                                                                                            | 6                                    | 0.9                               | 65                                                       | 250                      | 20 to 70                       | +5, +12                  | ΠL                          | 3.4 (pk-pk)                        |

| SSI 32R522/522R     | 2 Terminal                                                                                            | 4, 6                                 | 1.0                               | 32                                                       | 100                      | 6 to 35                        | +5, +12                  | ΠL                          | 3.4 (pk-pk)                        |

| SSI 32R524R         | 2 Terminal                                                                                            | 8                                    | 0.75                              | 60                                                       | 100                      | 20 to 60                       | +5, +12                  | ΠL                          | 7.0 (pk-pk)                        |

| SSI 32R525R         | 2 Terminal                                                                                            | 4                                    | 0.8                               | 35                                                       | 150                      | 25 to 40                       | +5, −5                   | Differential / Differential | 3.8 (pk-pk)                        |

| SSI 32R528R         | 2 Terminal                                                                                            | 8, 9                                 | 0.85                              | 35                                                       | 150                      | 10 to 40                       | +5, +12                  | Differential                | 7.0 (pk-pk)                        |

| SSI 32R5281R        | 2 Terminal                                                                                            | 14                                   | 0.85                              | 35                                                       | 250                      | 10 to 40                       | +5, +12                  | Differential                | 7.0 (pk-pk)                        |

| SSI 32R2010R/2011   | 2 Terminal                                                                                            | 10, 16                               | 0.84                              | 26                                                       | 150                      | 10 to 25                       | +5, +12                  | Differential                | 7.0 (pk-pk)                        |

| SSI 32R2015R        | 2 Terminal                                                                                            | 10, 16                               | 0.84                              | 26                                                       | 150                      | 10 to 25                       | +5, +12                  | ΠL                          | 7.0 (pk-pk)                        |

| SSI 32R2020R/2021R  | 2 Terminal                                                                                            | 2, 4, 10                             | 0.8                               | 20                                                       | 300                      | 5 to 35                        | +5                       | ΠL                          | 3.4 (pk-pk)                        |

| SSI 32R2030A/2031A  | 2 Terminal                                                                                            | 2, 4                                 | 0.85                              | 35                                                       | 250                      | 10 to 35                       | +5                       | ΠL                          | 3.4 (pk-pk)                        |

| SSI 32R4610A/4611A  | 2 Terminal                                                                                            | 2, 4, 8                              | 0.85                              | 35                                                       | 200                      | 10 to 35                       | +5                       | ΠL                          | 3.4 (pk-pk)                        |

| Device Number       | Circuit Function                                                                                      | on .                                 |                                   | Features                                                 |                          |                                |                          |                             |                                    |

| HDD PULSE DETECTION |                                                                                                       |                                      |                                   | CT STOTELLE STOTE AND A THE SERVE                        |                          |                                | <del>-</del>             |                             | And Annual Maria                   |

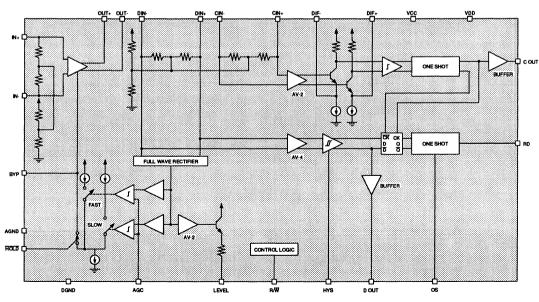

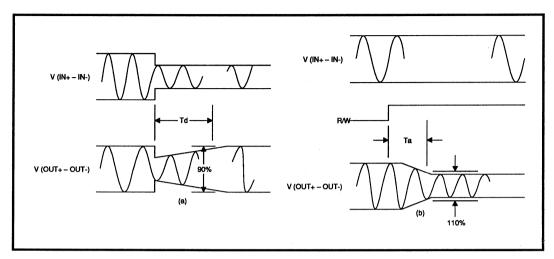

| SSI 32P541          | Read Data Proce                                                                                       | essor                                |                                   | AGC, Amplitude & Tin                                     | ne Pulse Quali           | fication, RLL Compatible       | 9                        |                             |                                    |

| SSI 32P541B         | Read Data Proce                                                                                       | essor                                | ·                                 | 32P541 pin compatibl                                     | e, 32P541A v             | v/ Increased Data Rate         | to 24 Mbit/s             |                             |                                    |

| SSI 32P544          | Pulse Detector                                                                                        |                                      |                                   | 32P541-type Pulse De                                     | tector w/ Emb            | edded Servo Electronic         | s                        |                             |                                    |

| SSI 32P547          | Pulse Detector                                                                                        |                                      |                                   | 32P544-type Pulse De                                     | tector w/ Filte          | r Multiplexer, Pulse Slim      | ming Support             |                             |                                    |

| SSI 32P549          | Read Data Processor                                                                                   |                                      |                                   | 32P541 pin compatibl                                     | e, Low Power,            | +5V only, Enhanced V           | Vrite to Read Reco       | overy                       |                                    |

| SSI 32P5491         | Read Data Processor                                                                                   |                                      |                                   | 32P549 pin compatible, 5 mW Idle Mode power, Pd = 170 mW |                          |                                |                          |                             |                                    |

| SSI 32P3000         | Pulse Detector / Programmable Filter                                                                  |                                      |                                   | 48 Mb/s Pulse Detecto                                    | or w/9-27 MH             | z Bessel filter, +5V only      | ,                        |                             |                                    |

| SSI 32P3010         | Pulse Detector / Programmable Filter                                                                  |                                      |                                   |                                                          |                          |                                |                          |                             |                                    |

| SSI 32P3030         | Pulse Detector /                                                                                      | Servo Demodulator                    |                                   | Pulse Detector w/2-bu                                    |                          |                                |                          |                             |                                    |

| SSI 32P3040         | Pulse Detector / Programmable Filter 24-32 Mbit/s Pulse Detector w/2.5-13 MHz Bessel Filter, +5V only |                                      |                                   |                                                          |                          |                                |                          |                             |                                    |

# STORAGE PRODUCTS REFERENCE

| HDD READ CHANNEL   | COMBINATION DEVICES                       |                                                                                                          |

|--------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------|

| SSI 32D4420        | Programmable Filter / Time Base Generator | 7-pole Equiripple Filter, Control DACs, 72 MHz Frequency Synthesizer                                     |

| SSI 32P548         | Pulse Detector / Data Synchronizer        | 32P544-type w/ 2, 7 Synchronizer, Low Power, +5V only, <700 mW                                           |

| SSI 32P5481        | Pulse Detector / Data Synchronizer        | Low power 32P548-type device (375 mW)                                                                    |

| SSI 32P5482        | Pulse Detector / Data Synchronizer        | Low power 32P548-type device (350 mW), no Write Precompensation                                          |

| SSI 32P4620        | Pulse Detector / Data Separator           | 32P541-type + 32D537-type Data Separator w/Pulse Slimming & Constant Density Recording Support           |

| SSI 32P4622        | Pulse Detector / Data Separator           | 32P541-type + 32D537-type, no Filter Section, 52-pin QFP, 900 mW                                         |

| SSI 32P4720        | Pulse Detector / Data Separator           | 32P548-type + 1, 7 ENDEC, Window Shift, Power-down, 52-pin QFP, 650 mW                                   |

| SSI 32P4721        | Pulse Detector / Data Separator           | 32P4720 @12 to 24 Mbit/s, <700 mW                                                                        |

| HDD ACTIVE FILTERS |                                           |                                                                                                          |

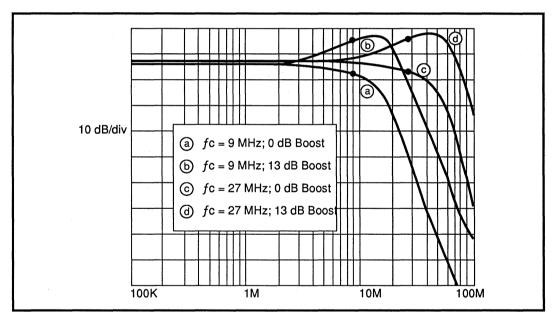

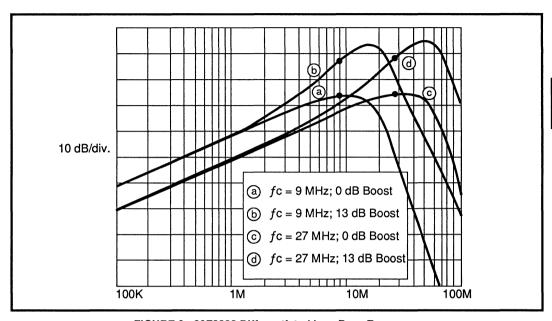

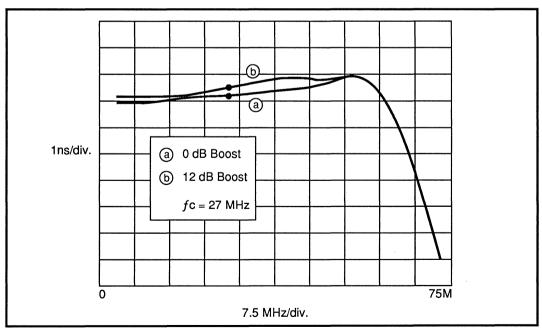

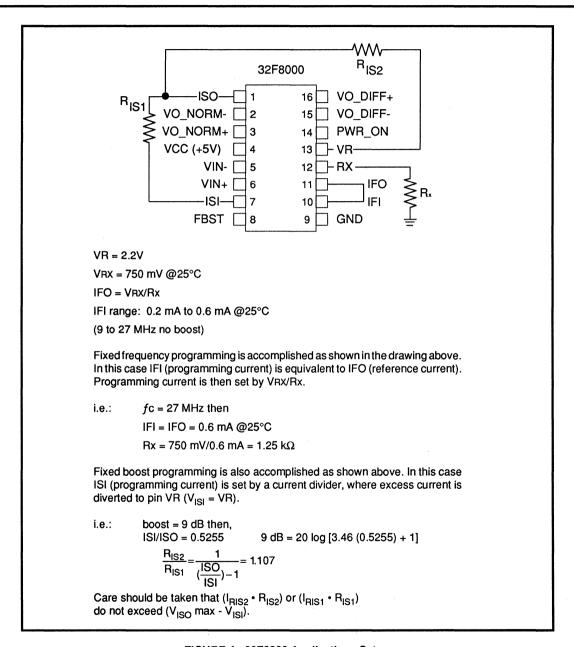

| SSI 32F8000        | Programmable Channel Filter               | 7-Pole Equiripple Active Filter, Programmable Cutoff Frequency / Pulse Slimming, 9 - 27 MHz              |

| SSI 32F8011        | Programmable Channel Filter               | 7-Pole Bessel Active Filter, Programmable Cutoff Frequency / Pulse Slimming, 5 - 13 MHz                  |

| SSI 32F8020        | Programmable Channel Filter               | 7-Pole Equiripple Active Filter, Programmable Cutoff Frequency / Pulse Slimming, 1.5 - 8 MHz             |

| SSI 32F8030        | Programmable Channel Filter               | 7-Pole Equiripple Active Filter, Programmable Cutoff Frequency / Pulse Slimming, 250 kHz - 2.5 MHz       |

| SSI 32F8120        | Digitally Programmable Filter             | 32F8020 with serial port and DACs                                                                        |

| SSI 32F8130/31     | Digitally Programmable Filter             | 32F8030 with serial port and DACs / 32F8131 = 150 kHz < Fc < 1.5 MHz                                     |

| HDD DATA RECOVERY  |                                           |                                                                                                          |

| SSI 32D4010        | Data Separator                            | Data Synchronizer / 1, 7 RLL ENDEC 12 to 24 Mbit/s / Write Precompensation / Window Shift / Low Power    |

| SSI 32D5321        | Data Separator                            | Data Synchronizer / 2, 7 RLL ENDEC 7.5 to 10 Mbit/s                                                      |

| SSI 32D5322A       | Data Separator                            | Data Synchronizer / 2, 7 RLL ENDEC 7.5 to 13 Mbit/s                                                      |

| SSI 32D534A        | Data Separator                            | Data Synchronizer / MFM ENDEC / Write Precompensation                                                    |

| SSI 32D5351A       | Data Separator                            | Data Synchronizer / 2, 7 RLL ENDEC / Write Precompensation 8 to 18 Mbit/s                                |

| SSI 32D5362A       | Data Separator                            | Data Synchronizer / 1, 7 RLL ENDEC / Write Precompensation 10 to 20 Mbit/s                               |

| SSI 32D5371/2      | Data Separator                            | Data Synchronizer / 1, 7 RLL ENDEC / Write Precompensation 12 to 24 Mbit/s                               |

| SSI 32D5373/4      | Data Separator                            | Data Synchronizer / 1, 7 RLL ENDEC / Write Precompensation 15 to 32 Mbit/s                               |

| SSI 32D539         | Data Separator                            | Data Synchronizer / 1.7 RLL ENDEC / 8-bit parallel NRZ 24 to 48 Mbit/s                                   |

| SSI 32D5391        | Data Separator                            | Data Synchronizer / 1, 7 RLL ENDEC / Serial NRZ 24 to 40 Mbit/s                                          |

| SSI 32D5392        | Data Separator                            | Data Synchronizer / 1, 7 RLL ENDEC / Dual-bit NRZ 24 to 48 Mbit/s                                        |

| SSI 32D4660/1/2    | Time Base Generator                       | Up to 100 MHz Reference Frequency PLC for Constant Density Recording                                     |

| HDD HEAD POSITION  | ING                                       |                                                                                                          |

| SSI 32H101         | Preamplifier -Ferrite head                | $AV = 93$ , $BW = 10$ MHz, $e_n = 7.0$ nV/ $\sqrt{Hz}$                                                   |

| SSI 32H116A        | Preamplifier -Thin Film head              | $AV = 250$ , $BW = 20$ MHz, $e_n = 0.94$ nV/ $\sqrt{Hz}$                                                 |

| SSI 32H523R        | Servo Read/Write                          | Single-channel Thin Film Read/Write Device                                                               |

| SSI 32H566R        | Servo Read/Write                          | Single-channel Ferrite Read/Write Device                                                                 |

| SSI 32H569         | Servo Motor Driver                        | Head Parking, Spindle Motor Braking                                                                      |

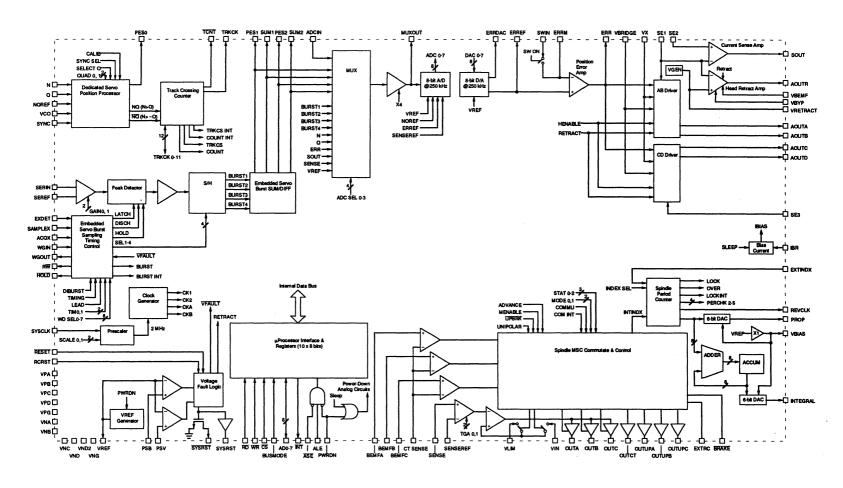

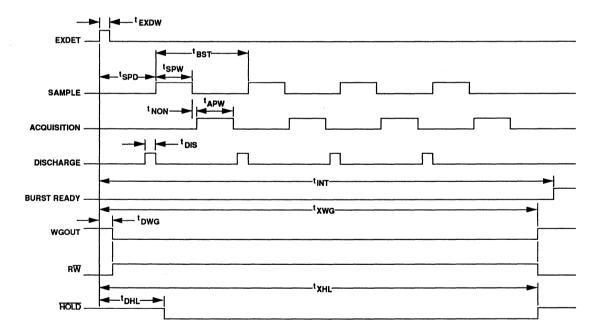

| SSI 32H4631/32     | Combo Servo & Motor Speed Control         | Embedded & Hybrid Servo, Hall Sensor-less Motor Speed Control, +5V only, 3600 RPM (4631) 5400 RPM (4632) |

| SSI 32H6110        | Preamplifier -Thin Film head              | $AV = 250 \text{ or } 300, BW = 20 \text{ MHz}, e_n = 0.85 \text{ nV}/\sqrt{\text{Hz}}$                  |

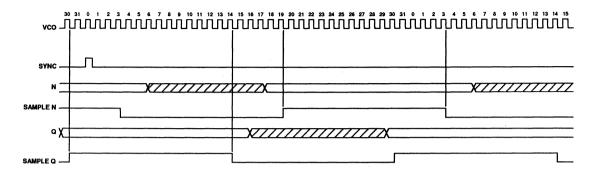

| SSI 32H6210        | Servo Demodulator                         | Di-bit Quadrature Servo Pattern; PLL Synchronization AGC Adjustment                                      |

| SSI 32H6220        | Servo Controller                          | Track & Seek Mode Operation; Microprocessor Interface                                                    |

| Device Number      | Circuit Function                   | Features                                                                            |

|--------------------|------------------------------------|-------------------------------------------------------------------------------------|

| HDD HEAD POSITION  | NING (Continued)                   |                                                                                     |

| SSI 32H6230        | Servo Motor Driver                 | Head Parking, Spindle Motor Braking, Voltage Clamp                                  |

| SSI 32H6240        | Servo Motor Driver                 | Predriver for Bipolar H-bridge                                                      |

| SSI 32H6510        | Servo 5V Driver                    | Low Voltage Retract, $1\Omega$ drivers                                              |

| SSI 32H6520        | Servo Acquisition and D/A          | 10-bit A/D D/A circuits, DSP interface                                              |

| HDD SPINDLE MOTO   | R CONTROL                          |                                                                                     |

| SSI 32M593A        | 3-Phase Motor Speed Control        | ±0.037% Speed Accuracy; Bipolar Operation, 5 1/4" Drives                            |

| SSI 32M594         | 3-Phase Motor Speed Control        | ±0.037% Speed Accuracy; Bipolar Operation, 3 1/2" & 5 1/4" Drives                   |

| SSI 32M595         | 3-Phase Sensor-less MSC            | Hall Sensor-less; Motor Speed Control                                               |

| SSI 32M7010        | Motor Speed Control 5V Driver      | Hall Sensor-less; Commutator Digital Speed Control, 5V $1\Omega$ Driver             |

| SSI 32M7011        | Motor Speed Control 5V Commutator  | Hall Sensor-less; Commutator, 5V $1\Omega$ Driver                                   |

| HDD CONTROLLER/II  | NTERFACE                           |                                                                                     |

| SSI 32C260         | PC AT/XT Combo Controller          | 15 Mbit/s Combo Buffer Manager/Disk Controller/AT/XT                                |

| SSI 32C261         | PC AT/XT Combo Controller          | (RLL 2, 7 ENDEC: SH-260 Compatible) / AT/XT Interface                               |

| SSI 32C4650        | PC AT/XT Combo Controller          | 26 Mbit/s Disk Controller/AT/XT; SH-265 compatible                                  |

| SSI 32C4651        | PC AT/XT Combo Controller          | 26 Mbit/s Disk Controller/AT/XT; SH-266 compatible; EISA Type-B Demand Mode Support |

| SSI 32C9000        | High Perf. PC AT Combo Controller  | 32 Mbit/s; High Performance AT Disk Controller                                      |

| SSI 32C9001        | PC AT Combo Controller             | 48 Mbit/s                                                                           |

| SSI 32C9010        | High Perf. SCSI Combo Controller   | 32 Mbit/s; SCSI-2 compatible; Fast SCSI; single ended                               |

| SSI 32C9020        | High Perf. SCSI Combo Controller   | 48 Mbit/s; SCSI-2 compatible; Fast SCSI; single ended                               |

| SSI 32C9022        | Combo SCSI Controller              | Dual-Bit NRZ, 48 Mbit/s                                                             |

| SSI 32C9301        | High Perf. AT Combo Controller     | 3V operation, 30 Mbit/s                                                             |

| FLOPPY DISK DRIVES | <b>)</b>                           |                                                                                     |

| SSI 34D441         | Data Separator                     | High Performance Analog Data Separator, NEC 765 Compatible                          |

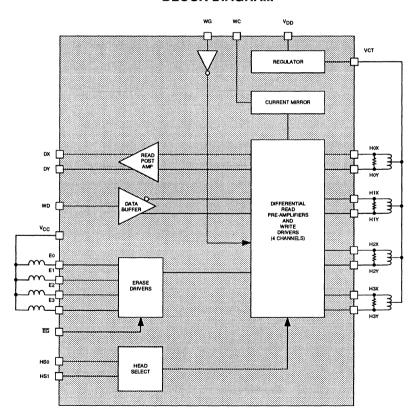

| SSI34P553          | Pulse Detector / Data Synchronizer | 0.6 - 1.6 Mbit/s data rate, MFM or 2, 7 RLL code                                    |

| SSI 34R575         | Read/Write                         | 2, 4 Channel Read/Write Circuit                                                     |

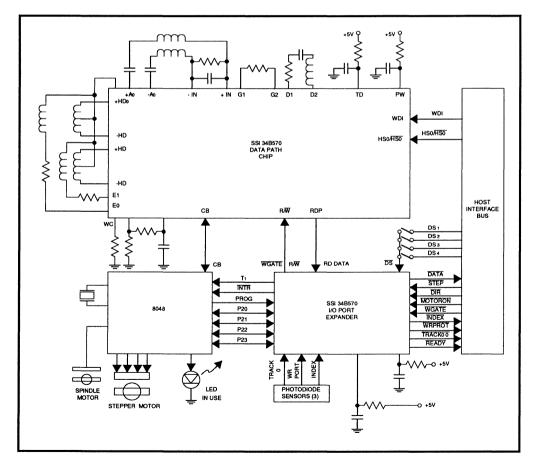

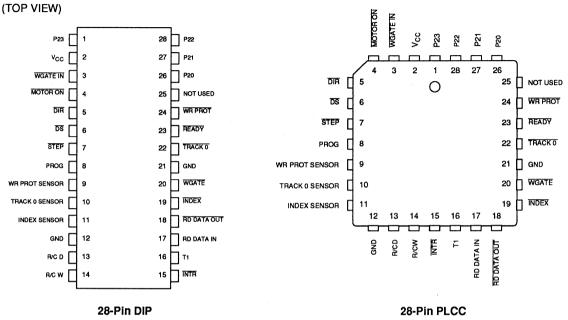

| SSI 34B580         | Support Logic                      | Port Expander, Includes SA400 Interface Drivers/Receivers                           |

Section

# HDD READ/WRITE AMPLIFIERS

November 1991

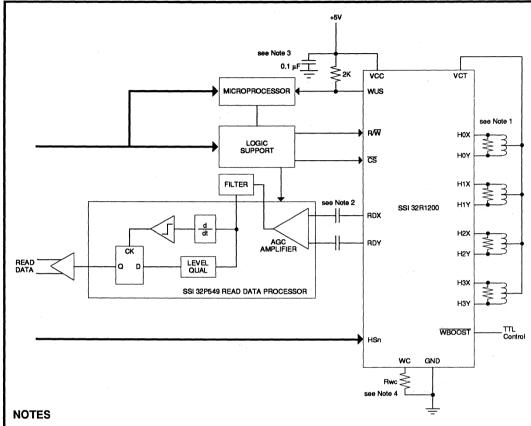

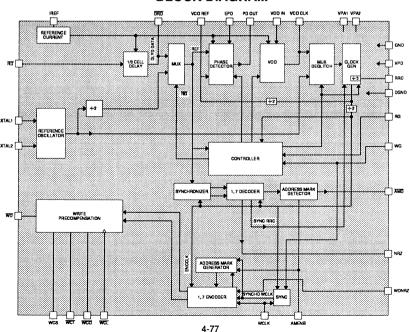

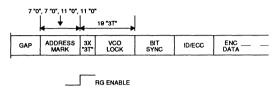

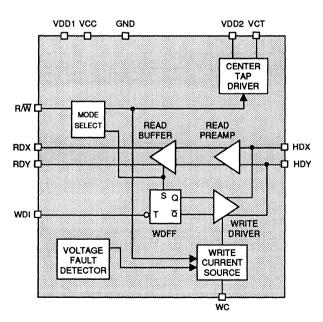

#### DESCRIPTION

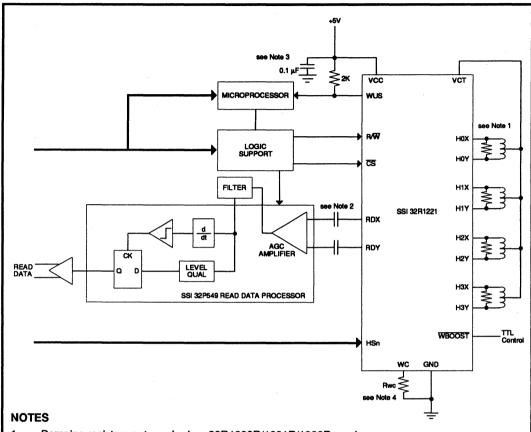

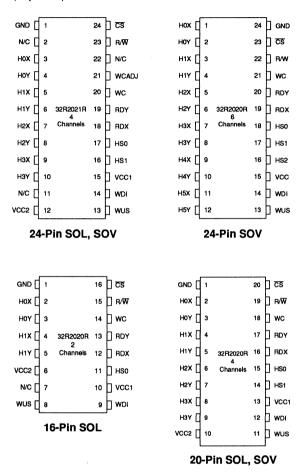

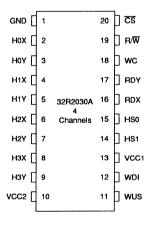

The SSI 32R510A/510AR Read/Write devices are bipolar monolithic integrated circuits designed for use with center-tapped ferrite recording heads. They provide a low noise read amplifier, write current control and data protection circuitry for as many as six channels. The R option provides internal 750 $\Omega$  damping resistors. Power supply fault protection is provided by disabling the write current generator during power sequencing. System write to read recovery time is significantly improved by controlling the read channel common mode output voltage shift in the write mode. They are available in a variety of package and channel configurations.

#### **FEATURES**

- High performance:

- Read mode gain = 100 V/V (32R510A)

- Input noise = 1.5 nV/ $\sqrt{\text{Hz}}$  max.

- Input capacitance = 20 pF max.

- Write current range = 10 mA to 40 mA

- Enhanced system write to read recovery time

- Power supply fault protection

- Plug compatible to the SSI 32R117

- Designed for center-tapped ferrite heads

- Programmable write current source

- Write unsafe detection

- TTL compatible control signals

- +5V, +12V power supplies

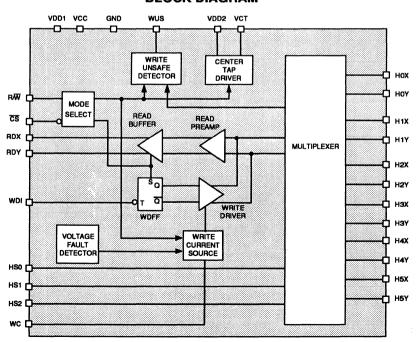

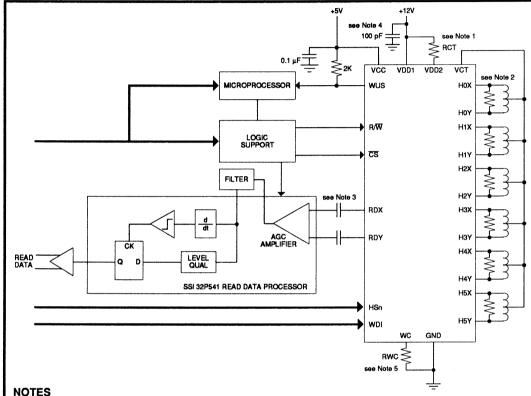

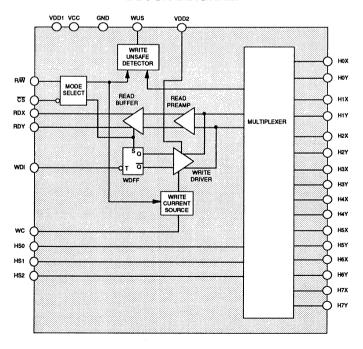

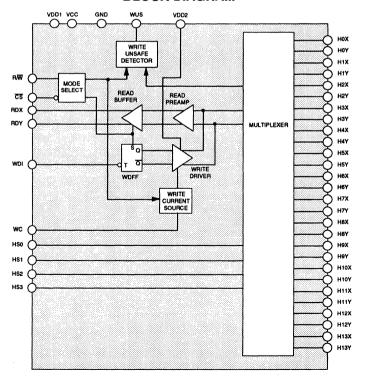

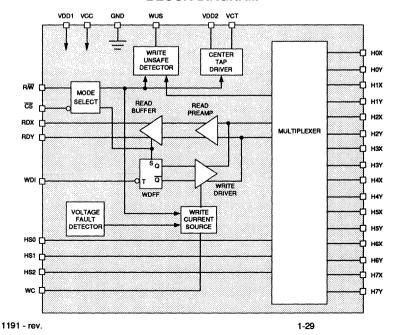

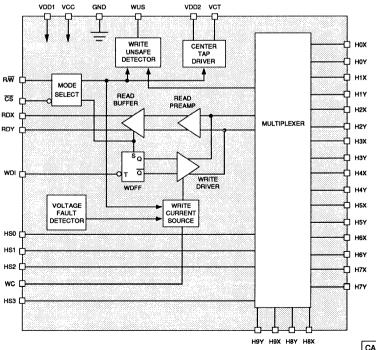

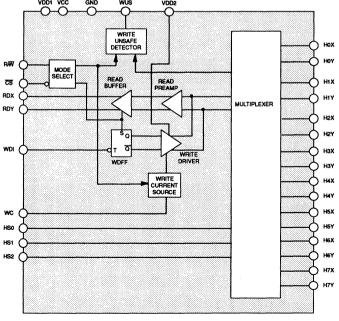

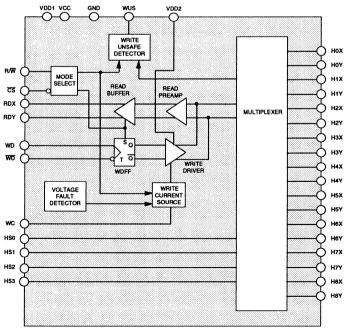

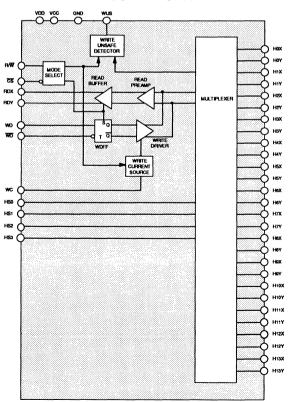

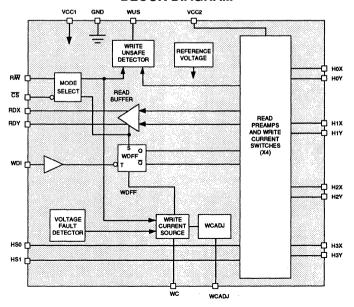

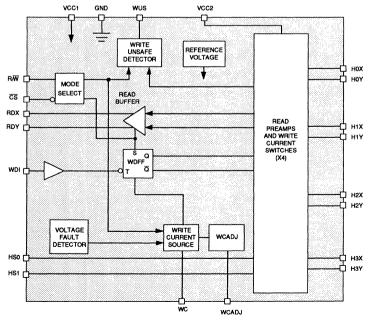

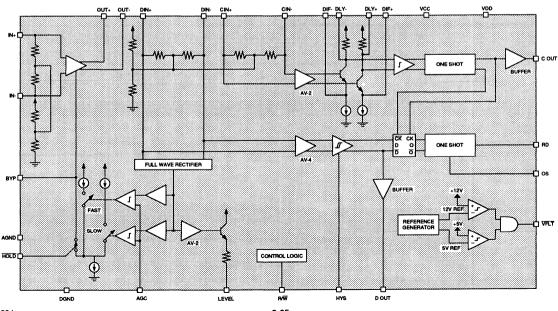

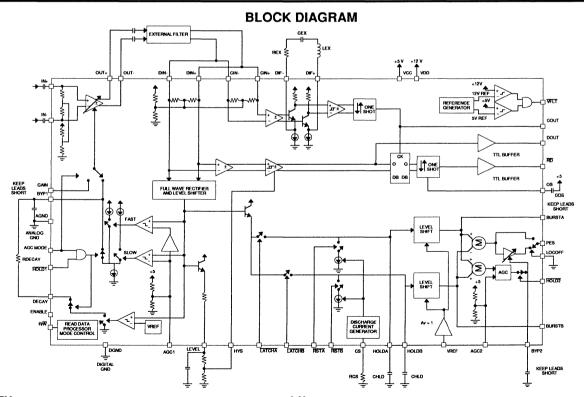

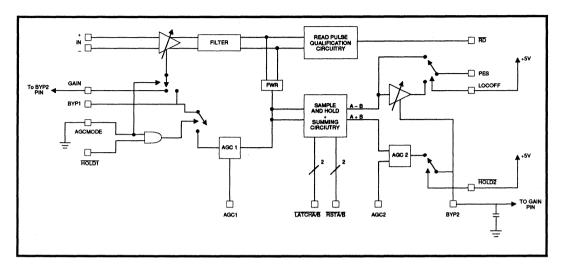

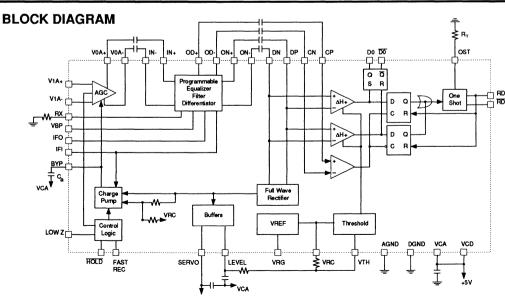

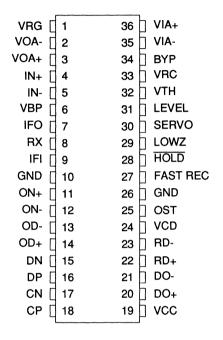

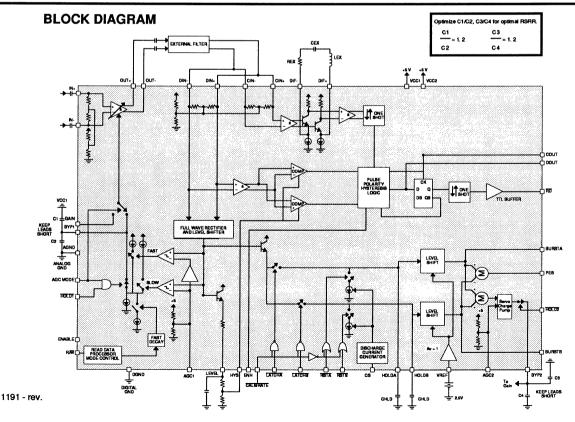

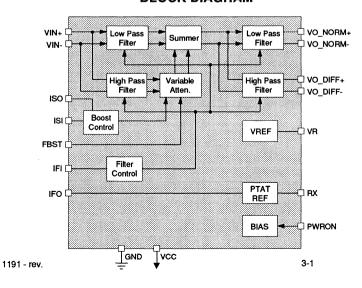

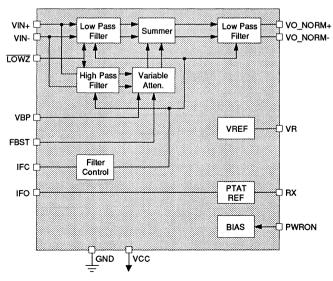

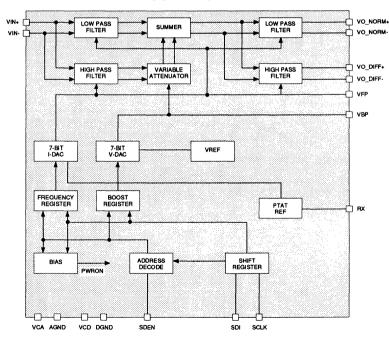

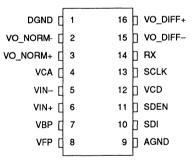

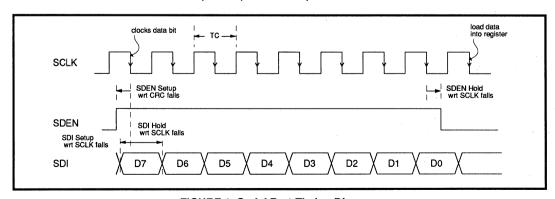

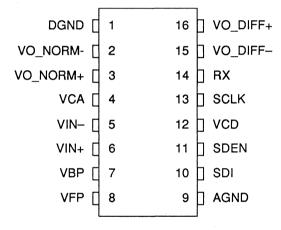

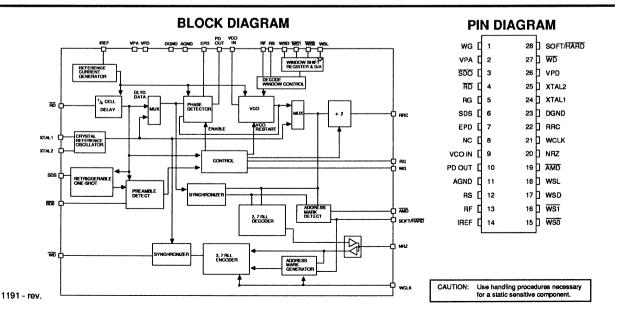

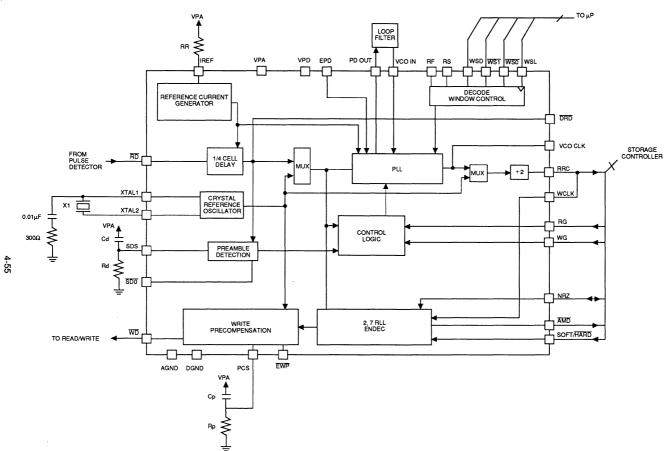

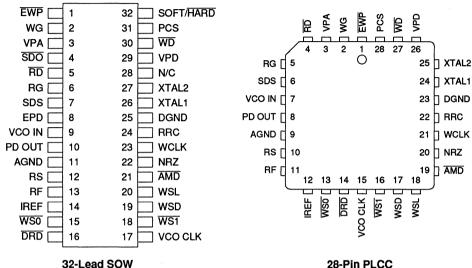

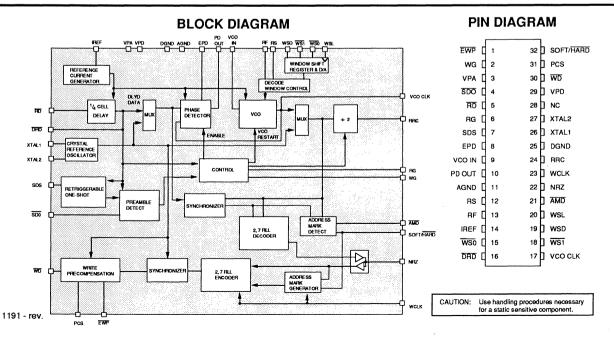

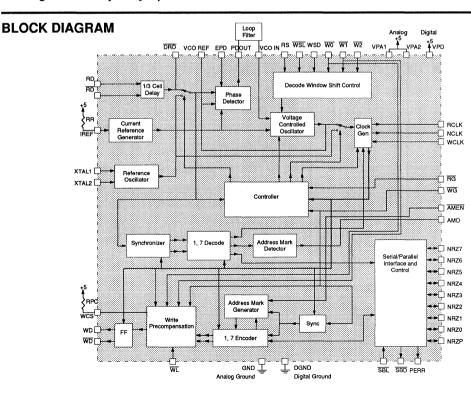

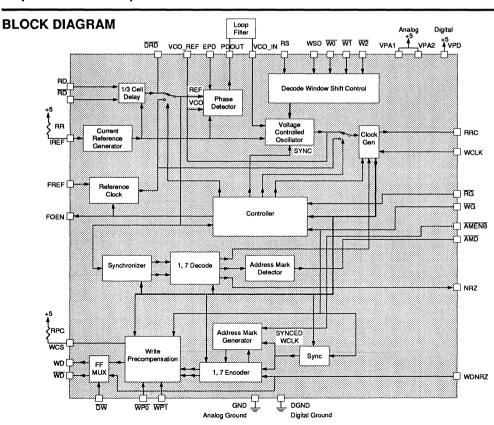

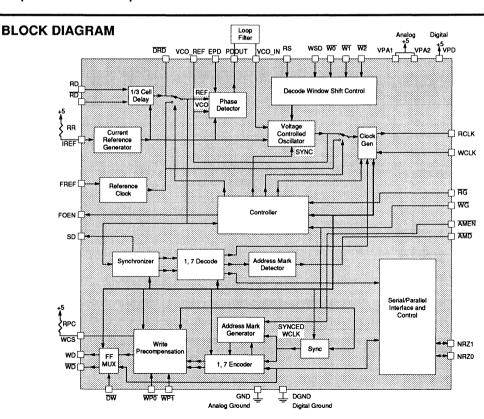

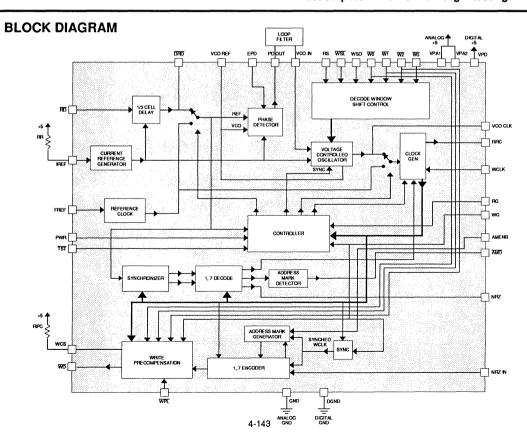

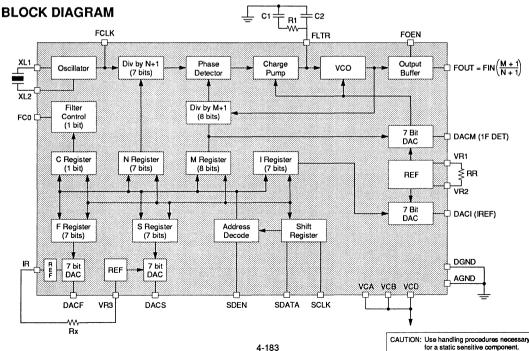

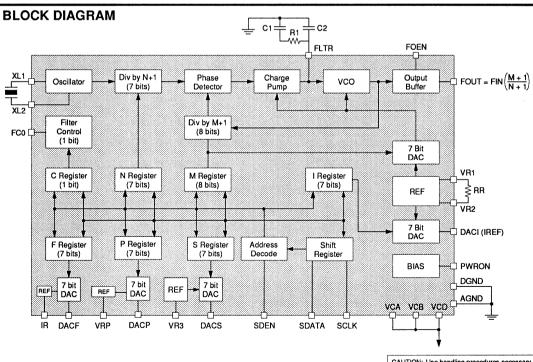

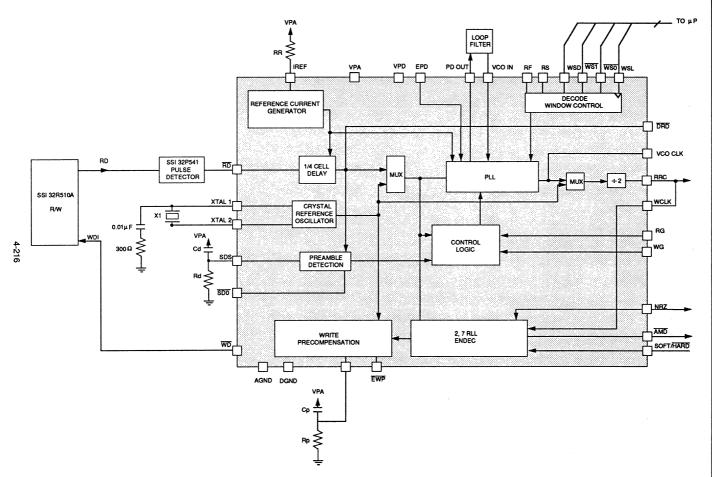

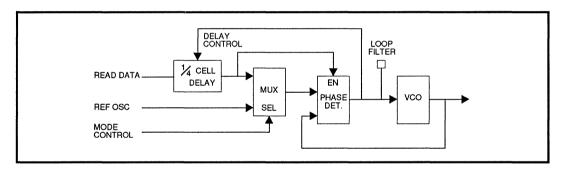

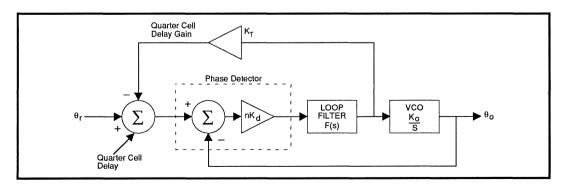

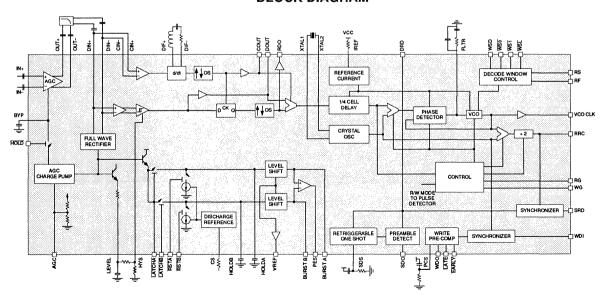

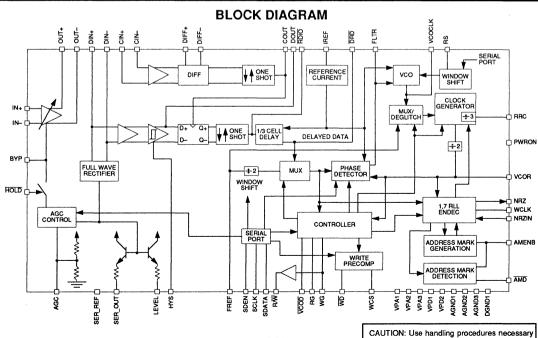

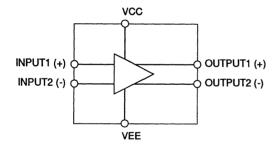

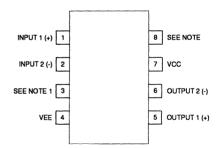

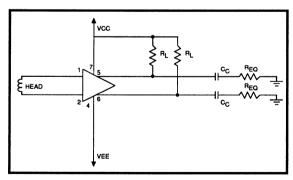

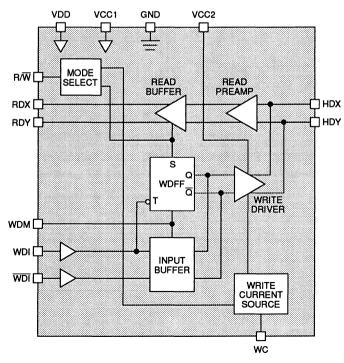

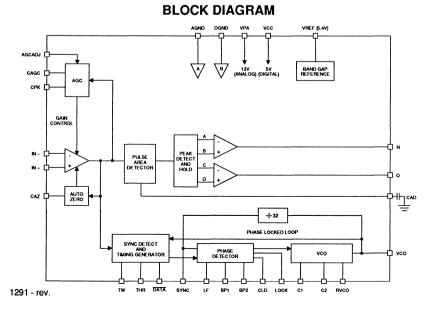

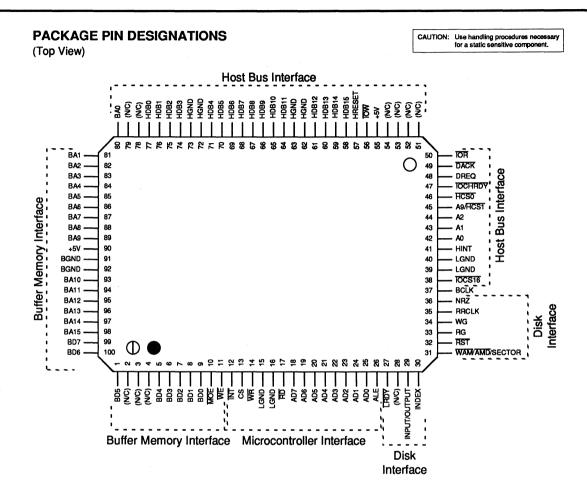

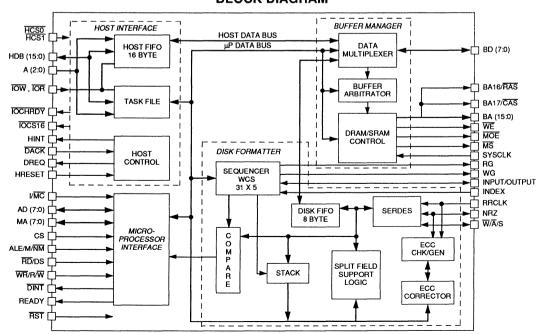

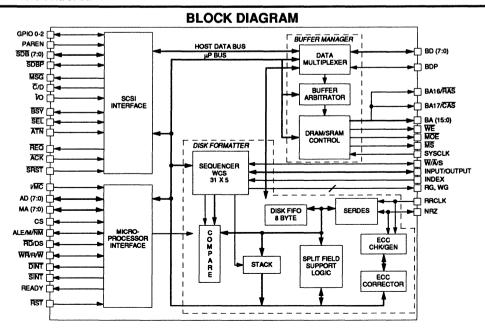

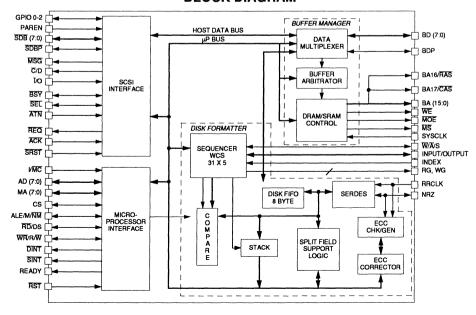

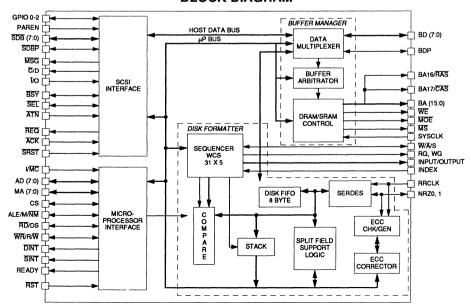

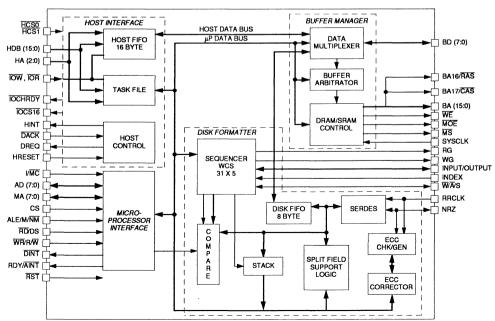

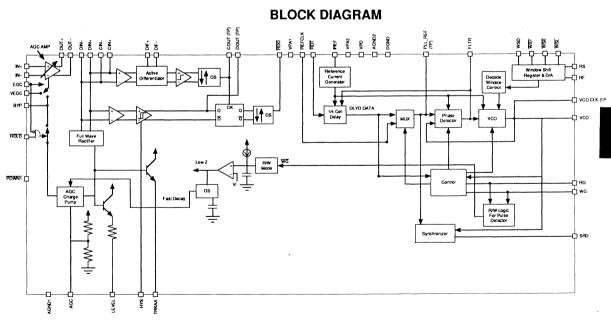

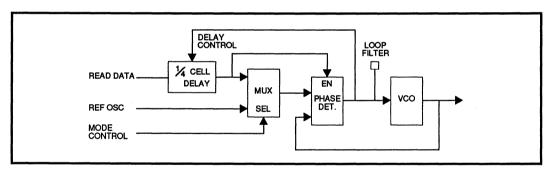

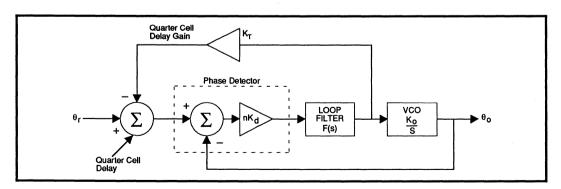

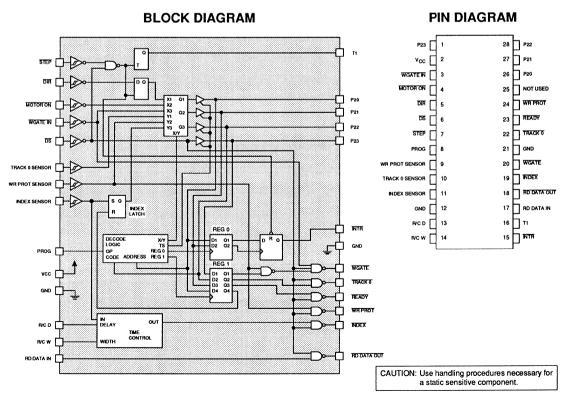

#### **BLOCK DIAGRAM**

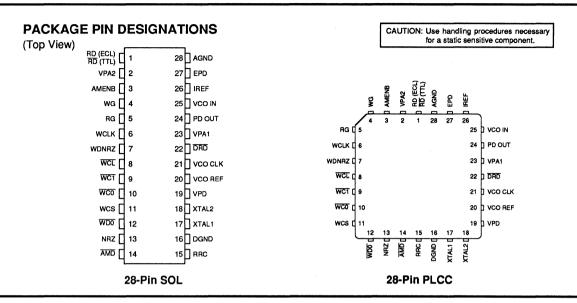

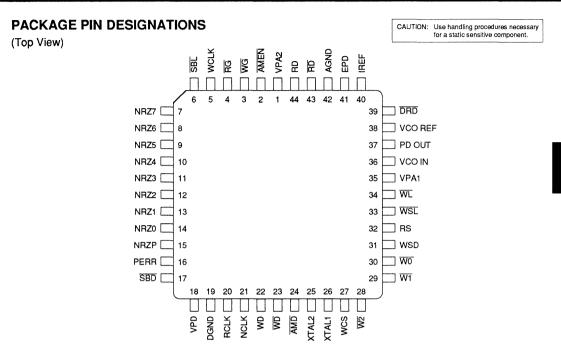

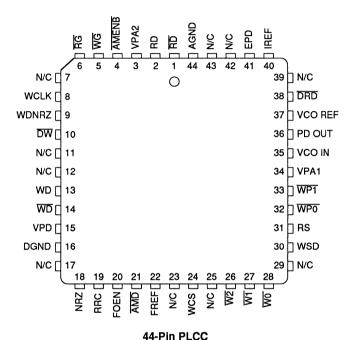

CAUTION: Use handling procedures necessary for a static sensitive component.

#### **CIRCUIT OPERATION**

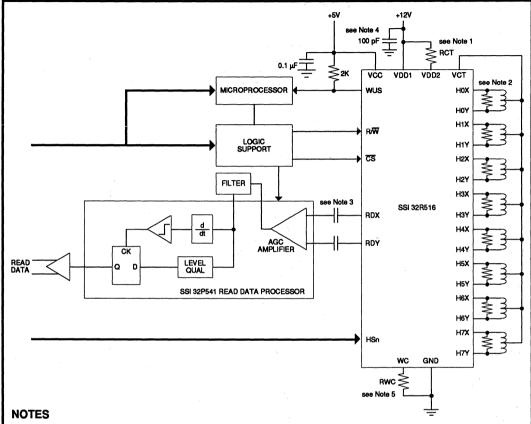

These devices address up to six center-tapped ferrite heads providing write drive or read amplification. Head selection and mode control is accomplished with pins HSn,  $\overline{CS}$ , and  $R/\overline{W}$ , as shown in Tables 1 & 2. Internal resistor pullups, provided on pins  $\overline{CS}$  and  $R/\overline{W}$ , will force the device into a non-writing condition if either control line is opened accidentally.

**TABLE 1: Mode Select**

| <u>cs</u> | R/W | MODE  |

|-----------|-----|-------|

| 0         | 0   | Write |

| 0 .       | 1   | Read  |

| 1         | Х   | Idle  |

**TABLE 2: Head Select**

| HS2 | HS1 | HS0 | HEAD |

|-----|-----|-----|------|

| 0   | 0   | 0   | 0    |

| 0   | 0   | 1   | 1    |

| 0   | 1   | 0   | 2    |

| 0   | 1   | 1   | 3    |

| 1   | 0   | 0   | 4    |

| 1   | 0   | 1   | 5    |

| 1   | 1   | Х   | None |

0 = Low level 1 = High level X=Don't care

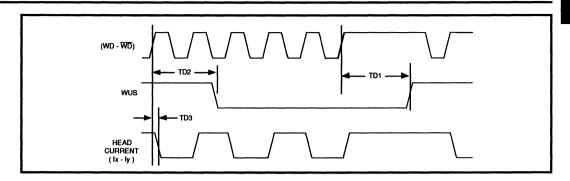

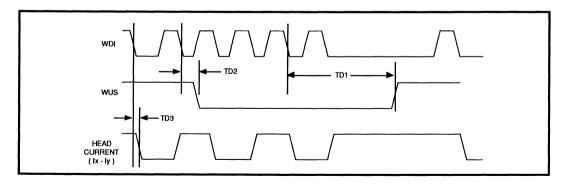

#### **WRITE MODE**

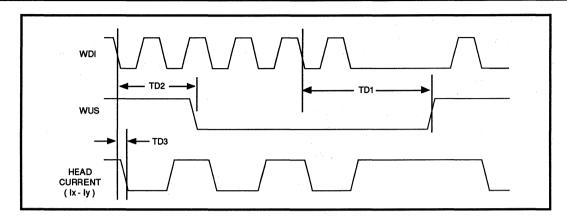

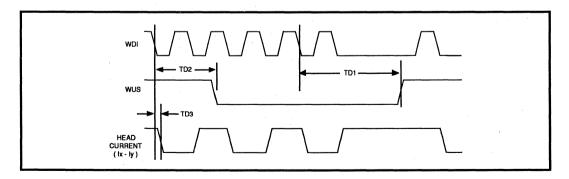

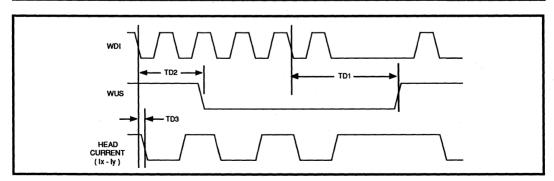

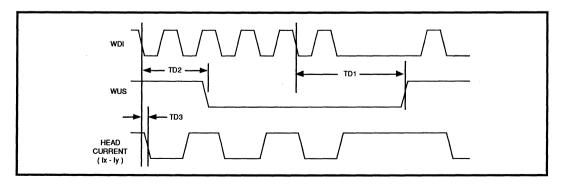

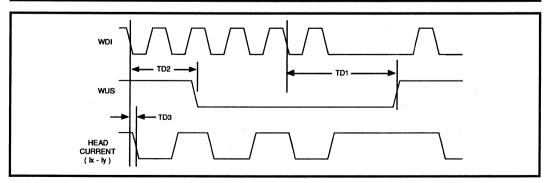

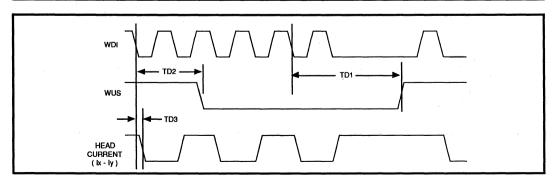

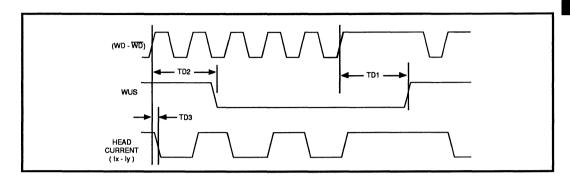

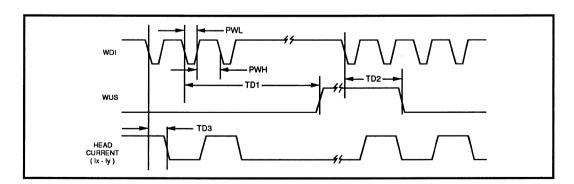

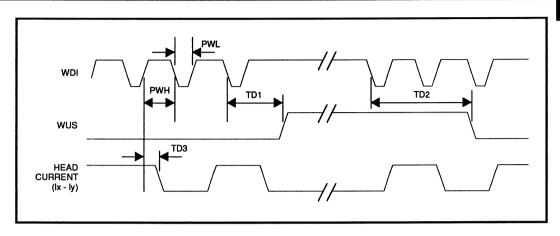

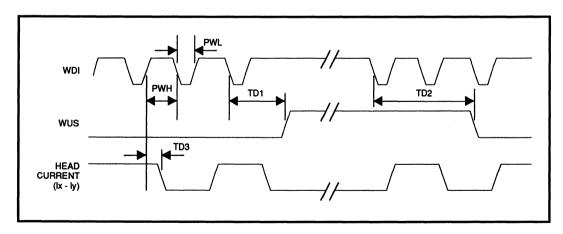

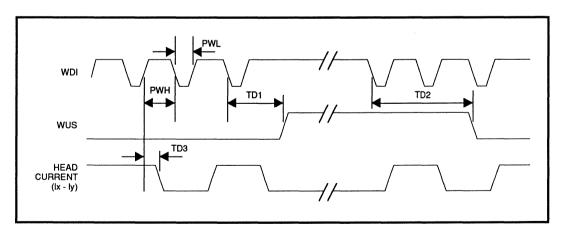

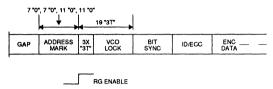

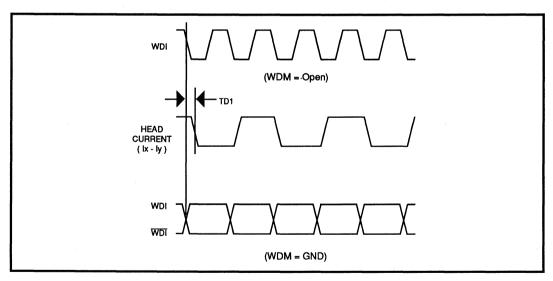

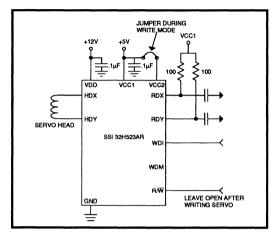

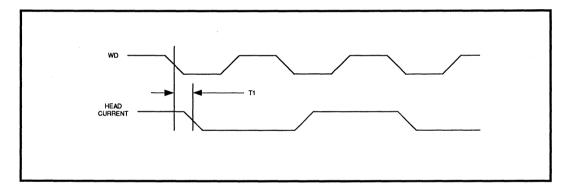

The write mode configures the device as a current switch and activates the Write Unsafe (WUS) detection circuitry. Write current is toggled between the X and Y side of the selected head on each high to low transition of the Write Data Input (WDI).

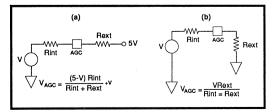

The magnitude of the write current (0-pk) is programmed by an external resistor RWC, connected from pin WC to ground and is given by:

where K is the Write Current Constant. In multiple device applications, a single RWC resistor may be made common to all devices.

Power supply fault protection improves data security by disabling the write current generator during a voltage fault or power supply sequencing. Additionally, the write unsafe detection circuitry monitors voltage transitions at the selected head connections and flags any of the conditions listed below as a high level on the open collector output pin, WUS. Two negative transitions on pin WDI, after the fault is corrected, are required to clear the WUS flag.

· Head open

Head center tap open

WDI frequency too low

Device in read mode

Device not selected

· No write current

To reduce internal power dissipation, an optional external resistor, RCT, given by RCT  $\leq$  130 $\Omega$  x 40/lw (lw in mA), is connected between pins VDD1 and VDD2. Otherwise connect pin VDD1 to VDD2.

To initialize the Write Data Flip Flop (WDFF) to pass current through the X-side of the head, pin WDI must be low when the previous read mode was commanded.

#### **READ MODE**

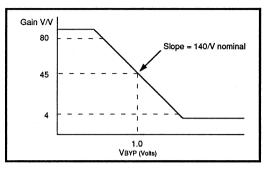

The read mode configures the device as a low noise differential amplifier and deactivates the write current generator and write unsafe circuitry. The RDX and RDY outputs are emitter followers and are in phase with the "X" and "Y" head ports. These outputs should be AC coupled to the load. The RDX, RDY common mode voltage is maintained in the write mode, minimizing the transient between write mode and read mode, substantially reducing the write to read recovery time in the subsequent pulse detection circuitry.

#### **IDLE MODE**

The idle mode deactivates the internal write current generator, the write unsafe detector, and switches the RDX, RDY outputs into a high impedance state. This facilitates multiple device applications by enabling the read outputs to be wire OR'ed and the write current programming resistor to be common to all devices.

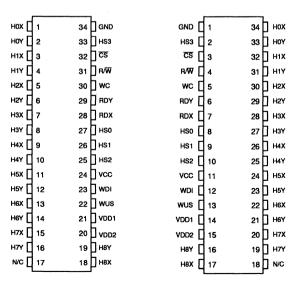

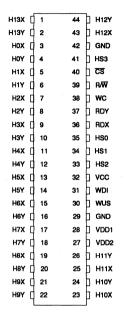

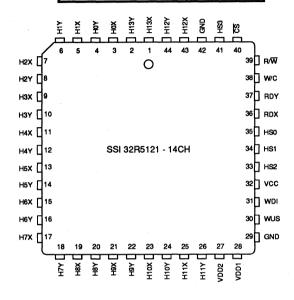

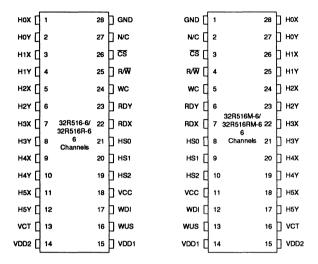

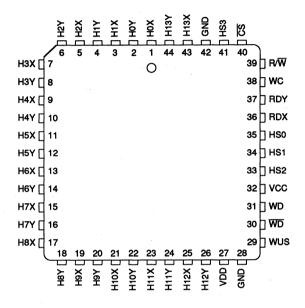

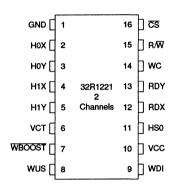

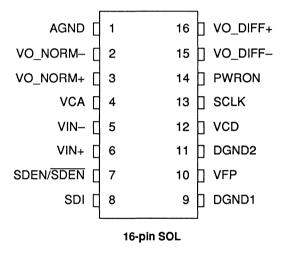

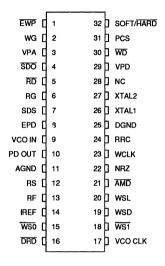

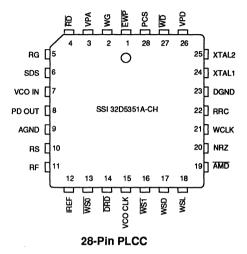

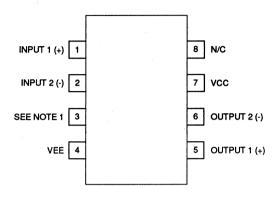

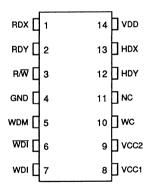

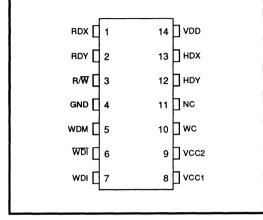

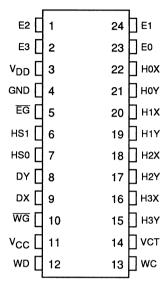

#### PIN DESCRIPTION

| NAME               | I/O | DESCRIPTION                                                          |

|--------------------|-----|----------------------------------------------------------------------|

| HS0-HS2            | ı   | Head Select                                                          |

| <del>CS</del>      | 1   | Chip Select: a low level enables device                              |

| R/W                | 1   | Read/Write: a high level selects Read mode                           |

| WUS                | O*  | Write Unsafe: a high level indicates an unsafe writing condition     |

| WDI                | 1   | Write Data In: negative transition toggles direction of head current |

| H0X-H5X<br>H0Y-H5Y | 1/0 | X,Y head connections                                                 |

| RDX, RDY           | O*  | X, Y Read Data: differential read signal output                      |

| wc                 | *   | Write Current: used to set the magnitude of the write current        |

| VCT                | -   | Voltage Center Tap: voltage source for head center tap               |

| vcc                | -   | +5V                                                                  |

| VDD1               | -   | +12V                                                                 |

| VDD2               | -   | Positive power supply for the center-tap voltage source              |

| GND                | -   | Ground                                                               |

<sup>\*</sup>When more than one R/W device is used, these signals can be wire OR'ed.

#### **ELECTRICAL SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

(All voltages referenced to GND. Currents into device are positive.)

| PARAMETER                                       |      | VALUE              | UNITS |

|-------------------------------------------------|------|--------------------|-------|

| DC Supply Voltage                               | VDD1 | -0.3 to +14        | VDC   |

| DC Supply Voltage                               | VDD2 | -0.3 to +14        | VDC   |

| DC Supply Voltage                               | VCC  | -0.3 to +6         | VDC   |

| Digital Input Voltage Range                     | VIN  | -0.3 to VCC + 0.3  | VDC   |

| Head Port Voltage Range                         | VH   | -0.3 to VDD1 + 0.3 | VDC   |

| WUS Pin Voltage Range                           | Vwus | -0.3 to +14        | VDC   |

| Write Current (0-pk)                            | lw   | 60                 | mA    |

| RDX, RDY Output Current                         | lo   | -10                | mA    |

| VCT Output Current                              | Ivct | -60                | mA    |

| WUS Output Current                              | lwus | +12                | mA    |

| Storage Temperature Range                       | Tstg | -65 to 150         | °C    |

| Lead Temperature PDIP,<br>(10 sec Soldering)    |      | 260                | °C    |

| Package Temperature PLCC,<br>SO (20 sec Reflow) |      | 215                | °C    |

1191 - rev. 1-3

#### RECOMMENDED OPERATING CONDITIONS

| PARA | METER                      | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MIN  | МОМ  | MAX  | UNITS |

|------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| VDD1 | DC Supply Voltage          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10.8 | 12.0 | 13.2 | VDC   |

| vcc  | DC Supply Voltage          | W Control of the Cont | 4.5  | 5.0  | 5.5  | VDC   |

| Lh   | Head Inductance            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5    |      | 15   | μН    |

| RD   | Damping Resistor           | 32R510A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 500  |      | 2000 | Ω     |

| RCT* | RCT Resistor               | lw = 40 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 123  | 130  | 137  | Ω     |

| lw   | Write Current (0-pk)       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10   |      | 40   | mA    |

| Tj   | Junction Temperature Range |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | +25  |      | +135 | °C    |

<sup>\*</sup>For lw = 40 mA. At other lw levels refer to Applications Information that follows this specification.

#### **DC CHARACTERISTICS**

(Recommended operating conditions apply unless otherwise specified.)

#### **POWER SUPPLY**

| PARAMETER                       | CONDITIONS                                           | MIN | NOM | MAX     | UNITS |

|---------------------------------|------------------------------------------------------|-----|-----|---------|-------|

| VCC Supply Current              | Read/Idle Mode                                       |     |     | 35      | mA    |

|                                 | Write Mode                                           |     |     | 30      | mA    |

| VDD Supply Current              | Idle Mode                                            |     |     | 20      | mA    |

| (sum of VDD1 and VDD2)          | Read Mode                                            |     |     | 35      | mA    |

|                                 | Write Mode                                           |     |     | 20 + lw | mA    |

| Power Dissipation (Tj = +135°C) | Idle Mode                                            |     |     | 400     | . mW  |

|                                 | Read Mode                                            |     |     | 600     | mW    |