# TELECOMS IC Handbook

RUNKA (CHANDR

**PLESSEV**

**Plessey Semiconductors**

# TELECOMS IC Handbook

# Foreword

Plessey Semiconductors is committed to the development of exciting and innovative products for telecommunications systems. Working in conjunction with major equipment manufacturers and PTTs has resulted in a wide range of IC products for all aspects of telecommunications equipment from central office to subscriber.

Two new devices typifying this philosophy are the **MV3000** and **SL376M**. Together these offer a highly integrated line card solution with great flexibility. The **MV3000** SLAC (Subscriber Line Audio Circuit) is DSP in action, a highly complex audio/digital processing circuit implemented in low power CMOS technology, whilst the **SL376M** SLIC (Subscriber Line Interface Circuit) is a Bipolar high voltage interface and control circuit. Both combine to offer the ultimate in performance and cost effectiveness.

In addition to innovative new products, Plessey offer a wide range of industry standard devices including DTMF circuits, LD dialers, Codecs and PCM building blocks.

This Handbook gives details of all current and soon-to-be-introduced products; Plessey are continually assessing the needs of equipment manufacturers and will be expanding the range in the future.

## Contents

|                                        | Page |

|----------------------------------------|------|

| Foreword                               | 2    |

| Product index                          | 4    |

| Product list - alpha numeric           | 6    |

| Technical data                         | 7    |

| Application notes                      |      |

| A single channel codec                 | 257  |

| An HDB3-coded PCM link                 | 271  |

| PABX/line card control circuit         | 276  |

| MV3000 evaluation board and controller | 282  |

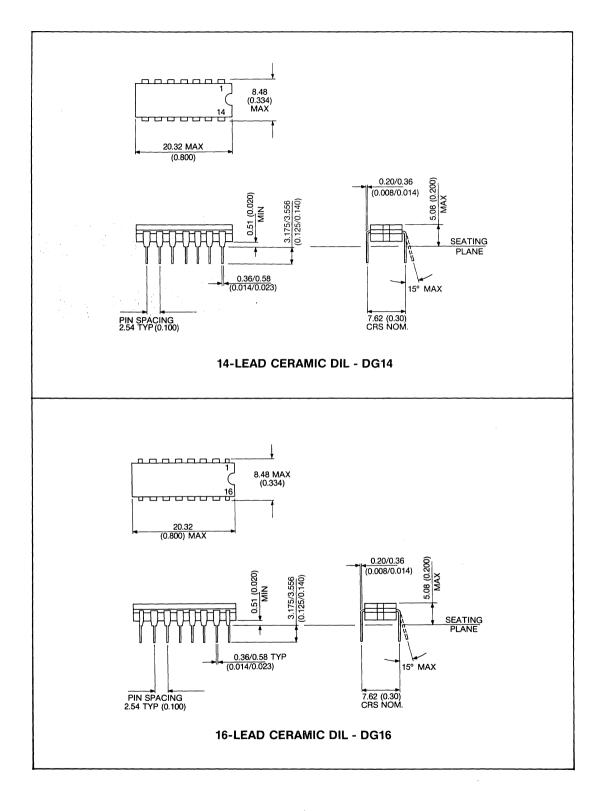

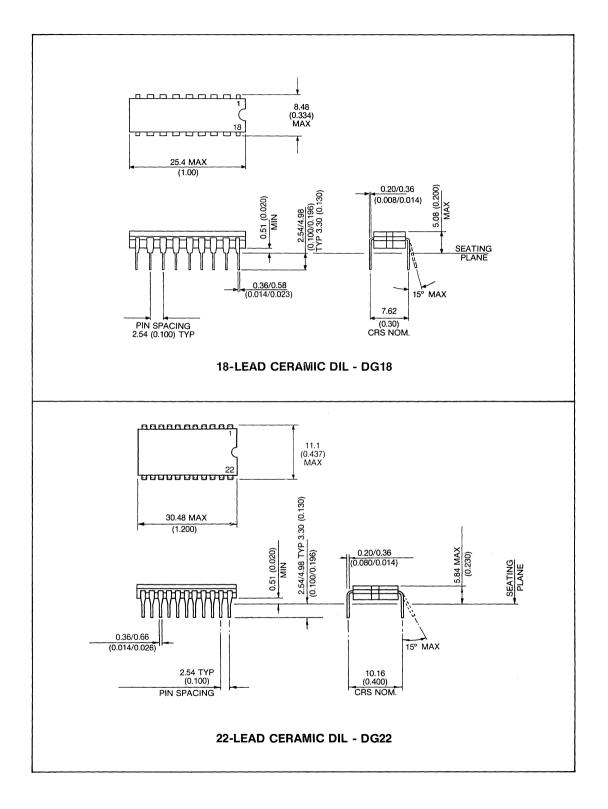

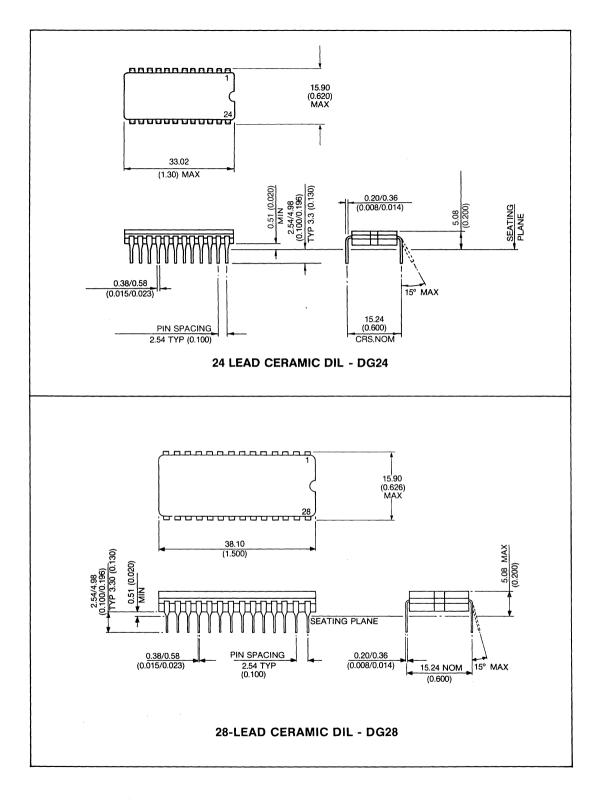

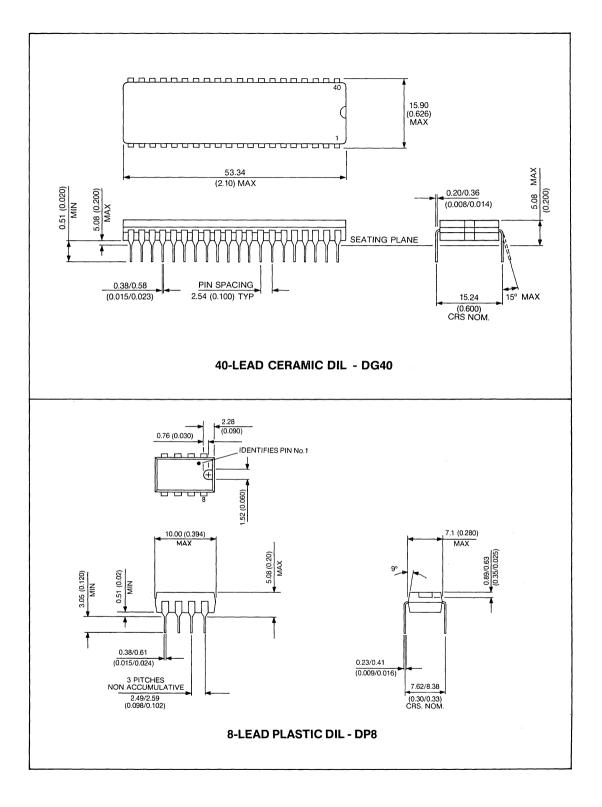

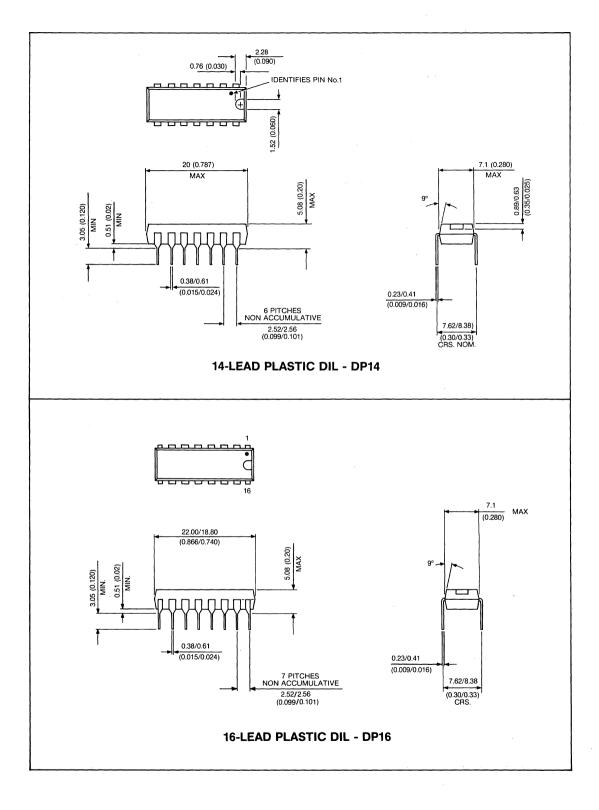

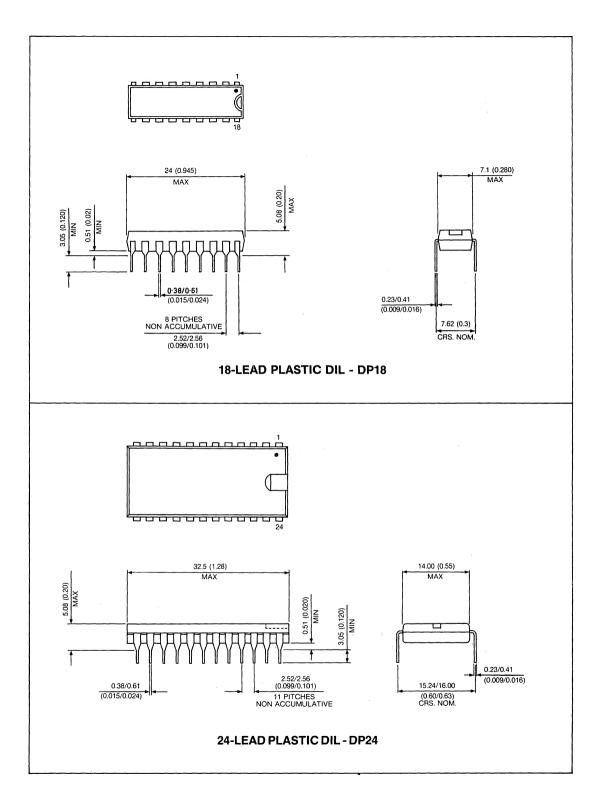

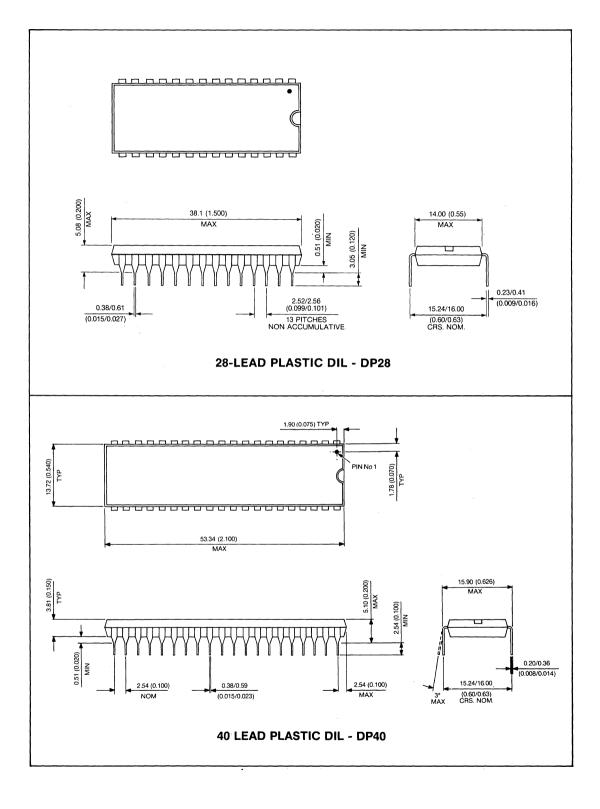

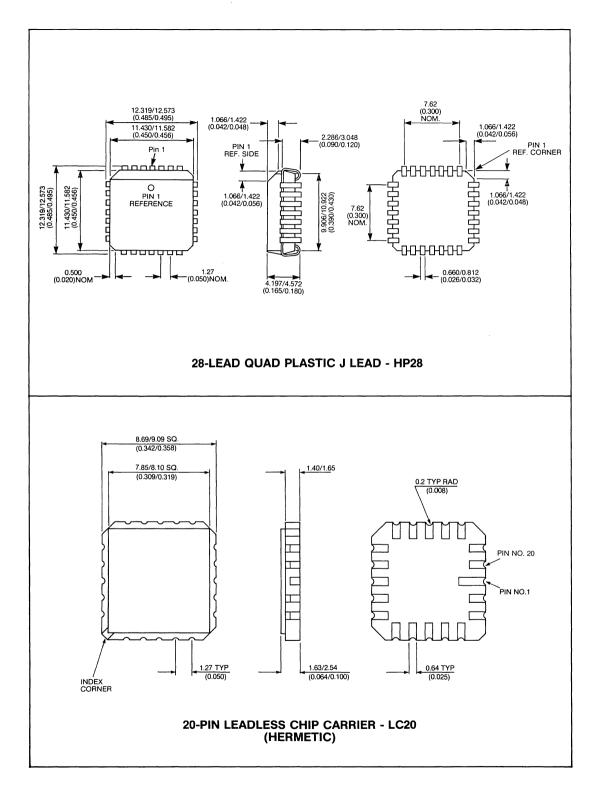

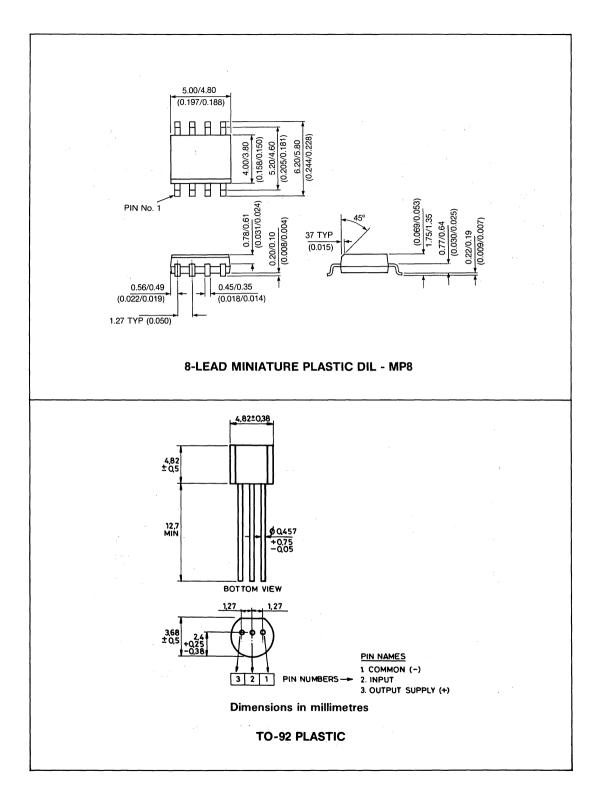

| Package outlines                       | 289  |

| Plessev Semiconductors locations       | 299  |

## **Product Index**

## Subscriber and line card circuits

| Туре         | Function                                                                                                                                                                                                                       | Page |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| MV3000       | Subscriber line audio circuit, automatic 2 to 4 wire balance; A to D; D to A;<br>Time Slot Alignment; fully programmable                                                                                                       | 61   |

| MV4320       | Keypad pulse dialler with selectable pulse mark/space ratio 2:1 or 3:1;<br>selectable outpulsing rate of 10,16, 20 or 932Hz; M1 masking output;<br>+2.5V to +5.5V supply and low power: $375\mu$ W at +13V; last number redial | 97   |

| MV5087       | DTMF generator for 2 of 8 (Form A) keypad, single contact                                                                                                                                                                      | 101  |

| MV5089       | DTMF generator for 2 of 8 active keypad, or electronic input                                                                                                                                                                   | 106  |

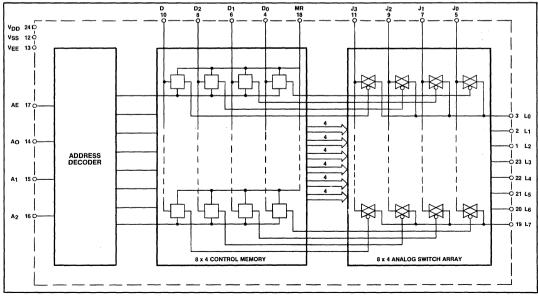

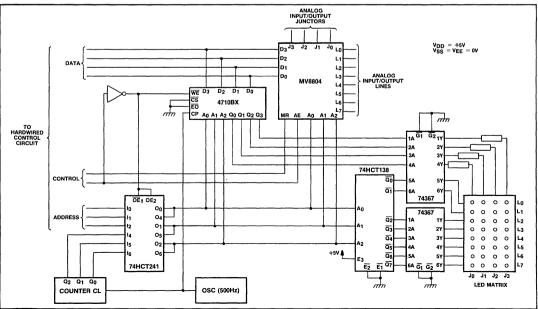

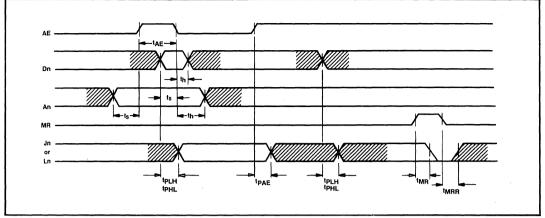

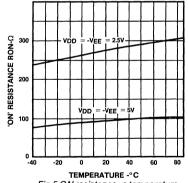

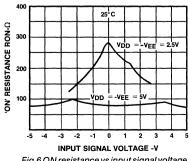

| MV8804       | 8 x 4 analog switch array (32 crosspoint switch for PABX and key systems),<br>5V to 13V operation, bandwidth up to 40MHz                                                                                                       | 121  |

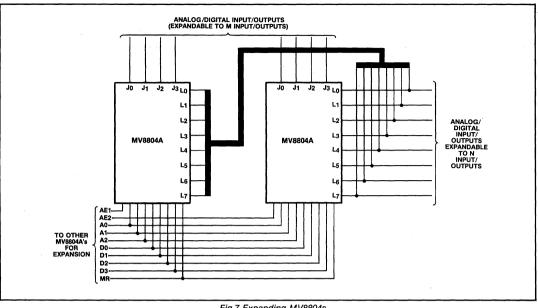

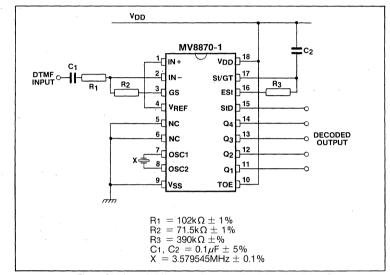

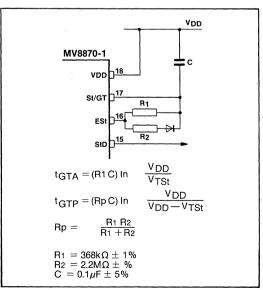

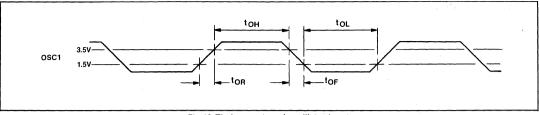

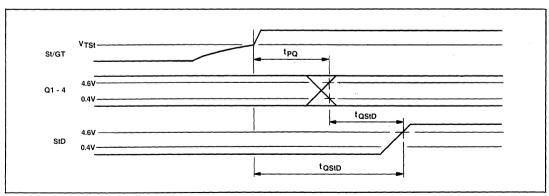

| MV8870       | Combined DTMF tone separation filter and decoder with 4-bit binary output code and low/high group outputs                                                                                                                      | 127  |

| MV8870-1     | Combined DTMF tone separation filter and decoder with 4-bit binary output code                                                                                                                                                 | 135  |

| SL376M       | Subscriber line interface circuit, line power feed; hybrid function; signalling; handles meter pulses                                                                                                                          | 145  |

| ZN470 series | Microphone amplifiers                                                                                                                                                                                                          | 198  |

| ZN482/483    | Buffer amplifiers for electret microphones                                                                                                                                                                                     | 237  |

| ZN480E       | Ring detector, TTL logic output                                                                                                                                                                                                | 224  |

| ZN488E       | Tone ringer, single ended or balanced output                                                                                                                                                                                   | 231  |

## PCM circuits

| Туре    | Function                                                                                                                                                                       | Page |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| MJ1410  | 8-bit format converter, 2MBit/s; 5V; 40mA                                                                                                                                      | 9    |

| MJ1440  | HDB3 coder/decoder, 2MBit/s; 5V; 20mA                                                                                                                                          | 14   |

| MJ1444  | Time slot zero transmitter, 2MBit/s; 5V; 20mA                                                                                                                                  | 19   |

| MJ1445  | Time slot zero receiver, 2MBit/s; 5V; 20mA                                                                                                                                     | 22   |

| MJ1446  | Time slot access, 2MBit/s; 5V; 20mA                                                                                                                                            | 25   |

| MS2002  | 256 x 256 serial digital switch, 32-channel PCM, 2MBit/s, 5V, 40mA                                                                                                             | 37   |

| MV1441  | HDB3 with clock regeneration, 2MBit/s; 5V                                                                                                                                      | 49   |

| MV1448  | HDB3 coder/decoder, 8MBit/s; 5V                                                                                                                                                | 55   |

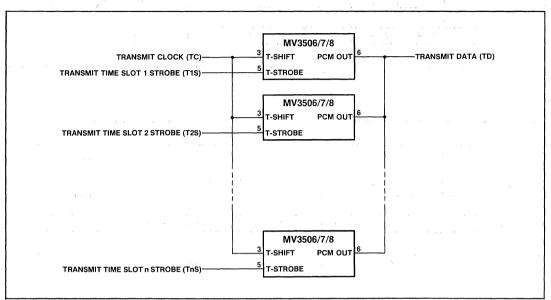

| MV3506  | Single channel PCM A-law codec with filter: featuring low power<br>(60mW operating, 5mW standby), stable on-chip voltage reference and<br>idle channel noise reduction circuit | 86   |

| MV3507  | Single channel PCM $\mu$ -law codec with filter: other features as for <b>MV3506</b>                                                                                           | 86   |

| MV3507A | Single channel PCM $\mu$ -law codec with filter and A/B signalling capability: other features as for <b>MV3506</b>                                                             | 86   |

| MV3508  | Single channel PCM A-law filter/codec with optional squelch                                                                                                                    | 86   |

| MV3508A | Single channel PCM µ-law filter/codec with optional squelch                                                                                                                    | 86   |

## PCM circuits (cont.)

| Туре       | Function                                                                                        | Page |

|------------|-------------------------------------------------------------------------------------------------|------|

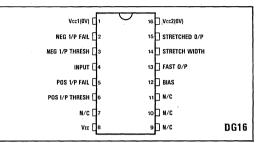

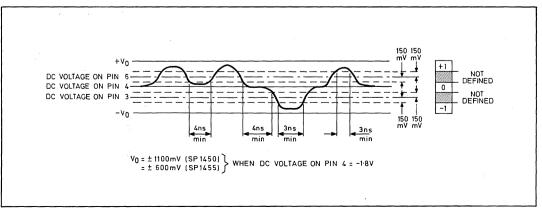

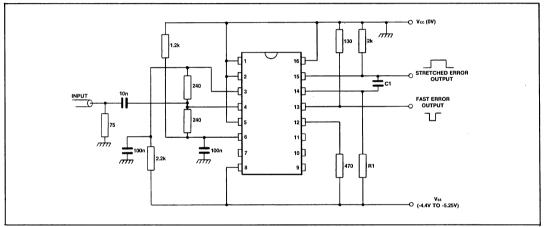

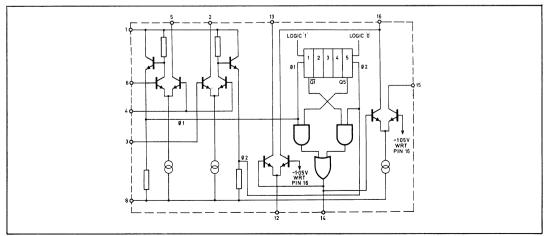

| SP1450B(B) | 34MBit/s PCM signal monitor 5V/2.5mA supply                                                     | 159  |

| SP1455B(B) | 40MBit/s PCM signal monitor 5V/2.5mA supply                                                     | 159  |

| ZNPCM1     | Single channel PCM A-law codec                                                                  | 177  |

| ZNPCM2     | Delta sigma modulator/demodulator                                                               | 191  |

| ZN1003     | 8 channel time slot assigner for use with codecs without on-chip timeslot assignment facilities | 244  |

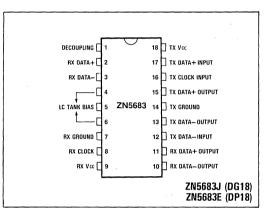

| ZN5683E/J  | PCM line interface, 8MBit/s; 5V                                                                 | 251  |

## Other telecoms products

| Туре     | Function                                                      | and the second |

|----------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| D3702    | 5 relay drivers, -65V output, to BT approved spec.            | 158                                                                                                              |

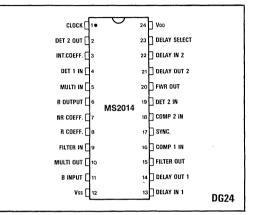

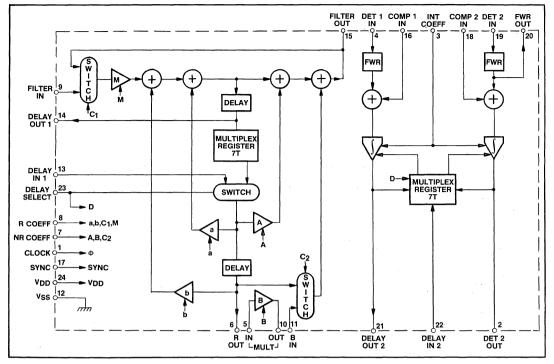

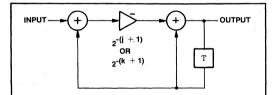

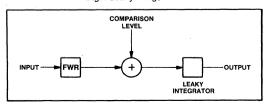

| MS2014   | Digital 16-bit filter and detector - signalling tone detector | 29                                                                                                               |

| MV6001   | Fast HDLC/DMA controller (e.g. for ISDN)                      | 111                                                                                                              |

| SL9009   | Adaptive line equaliser                                       | 147                                                                                                              |

| SP1404BW | 5 relay drivers, -65V output                                  | 158                                                                                                              |

## Fibre optic links/LANs

| Туре   | Function                  | Page |

|--------|---------------------------|------|

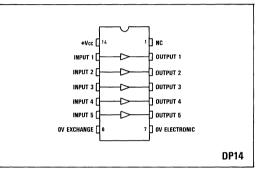

| SL9901 | Trans-impedance amplifier | 155  |

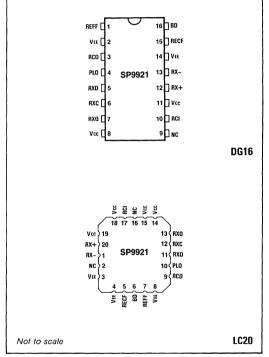

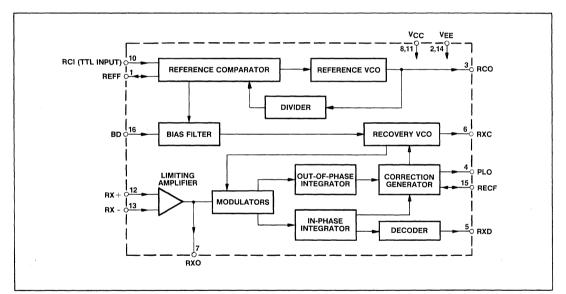

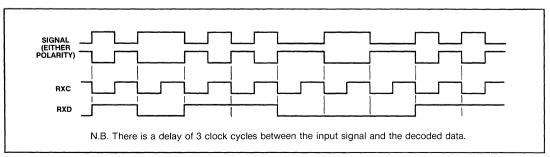

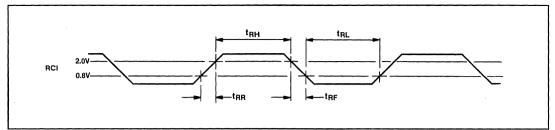

| SP9921 | Manchester decoder        | 163  |

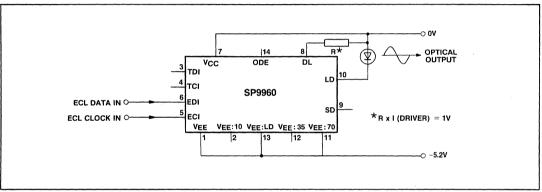

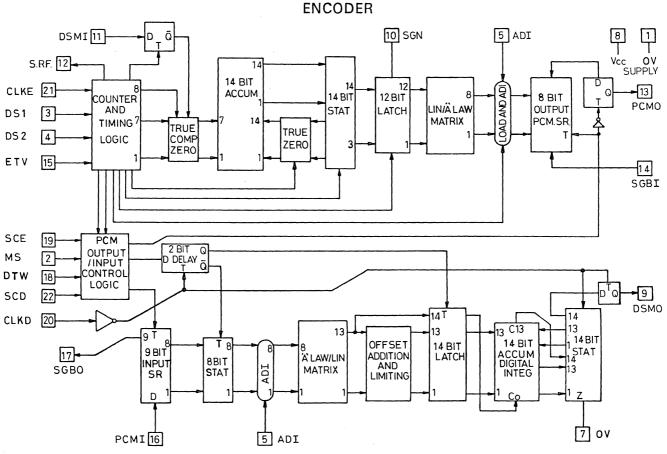

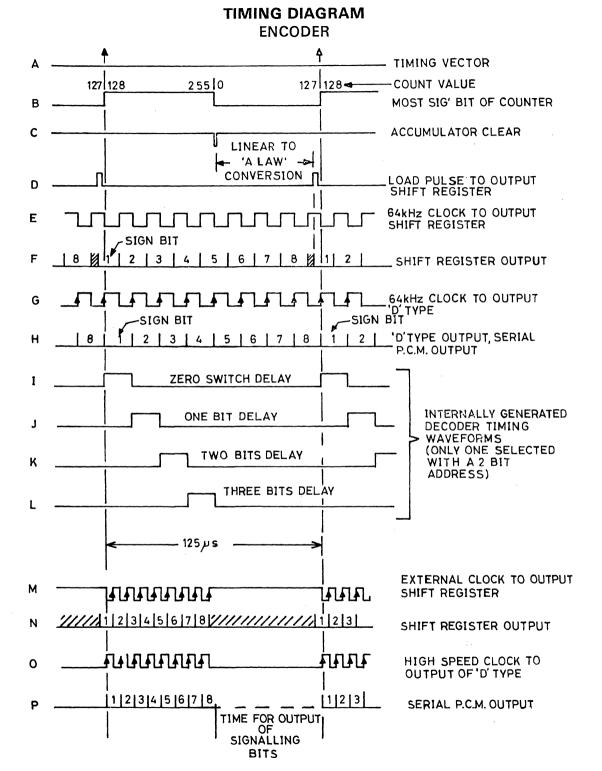

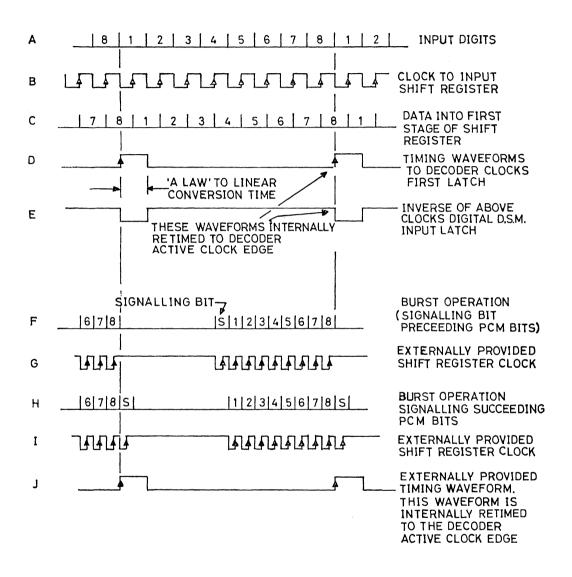

| SP9960 | Encoder/LED driver        | 171  |

## Product List - alpha numeric

TYPE No. DESCRIPTION PAGE D3702 High voltage interface circuit 158 MJ1410 8-Bit format converter 9 MJ1440 HDB3 encoder/decoder 14 MJ1444 PCM synchronising word generator 19 MJ1445 PCM synchronising receiver 22 MJ1446 Time slot 16 receiver and transmitter 25 MS2014 Digital filter and detector (FAD) 29 MS2002 Digital switch module (DSM) 37 MV1441 HDB3 encoder/decoder/clock regenerator 49 MV1448 HDB3 encoder/decoder 55 MV3000A/B Subscriber line audio circuit (SLAC) 61 MV3506 A-Law filter/codec 86 MV3507 u-Law filter/codec 86 MV3507A u-Law filter/codec with A/B signalling 86 MV3508 A-Law filter/codec with optional squelch 86 MV3509  $\mu$ -Law filter/codec with optional squelch 86 MV4320 Keypad pulse dialler 97 MV5087 **DTMF** generator 101 MV5089 DTMF generator modulus 106 MV6001 HDLC/DMA controller 111 MV8804 8 x 4 Bidirectional analog switch array 121 MV8870 DTMF receiver with high and low group filter outputs 127 MV8870-1 DTMF receiver 135 **SL376M** Metering subscriber line interface circuit (SLIC) 145 SL9009 Adaptive balance circuit 147 SL9901 50MHz transimpedance amplifier 155 **SP1404BW** High voltage interface circuit 158 SP1450B(B) PCM signal monitor circuits 159 SP1455B(B) PCM signal monitor circuits 159 SP9921 50MBit Manchester Biphase - mark decoder 163 SP9960 50MBit Manchester Biphase - mark encoder and LED driver 171 ZNPCM1 Single channel codec 177 Delta sigma modulator/demodulator ZNPCM2 191 **ZN470AE** Microphone amplifier for telephone circuits 198 **ZN472E** Microphone amplifier for telephone circuits 198 ZN475E Microphone amplifier for telephone circuits 203 **ZN476E** Microphone amplifier for telephone circuits 208 **ZN477E** Microphone amplifier for telephone circuits 214 **ZN478E** Microphone amplifier for telephone circuits 219 ZN480E **Ring detector** 224 **ZN488E** Tone ringer 231 ZN482Z Buffer amplifier for electret microphones 237 ZN483Z Buffer amplifier for electret microphones 237 ZN1003 Eight channel time-slot assigner 244 ZN5683E/J PCM line interface circuit 251

# Technical Data

•• · · ·

8

## **MJ1410** 8 BIT FORMAT CONVERTER

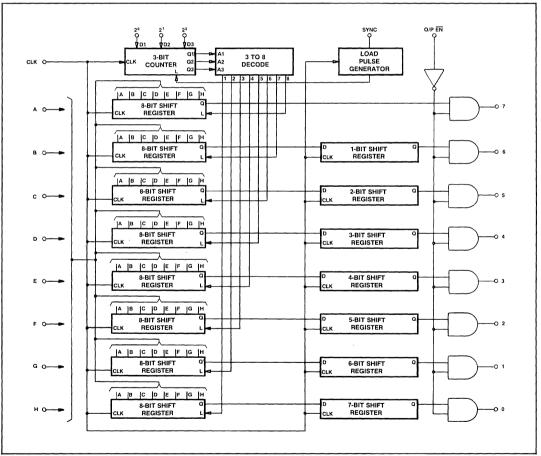

The MJ1410 is realised in N-channel MOS technology and operates from a single 5V supply. The circuit can be clocked from d.c. up to 2.5MHz and has 3-state output buffers capable of driving two LSTTL loads. All inputs are TTL compatible.

The MJ1410 performs the complementary functions of serial-to-parallel and parallel-to-serial data conversion on 8 bits of data. Both these conversions are achieved using the same time-position matrix, which has eight inputs and eight outputs.

An 8-bit parallel word clocked into the eight inputs appears as a serial 8-bit data stream on one of the eight outputs. Successive parallel words at the inputs appear as serial data streams on each of the eight outputs in turn.

Conversely, a serial 8-bit data stream on one of the eight inputs appears as an 8-bit parallel word on the eight outputs. Successive parallel words appearing at the eight outputs correspond to the serial data on each of the eight inputs in rotation.

The conversion can be 'programmed' to start in any register by setting the appropriate binary value on the counter pre-load inputs and applying a pulse to the Sync input. If the loading sequence produced by the counter is not required it can be disabled by connecting 'clock' to 'sync'. At each positive clock edge the register loaded will depend on the data on the counter inputs on the previous positive clock edge.

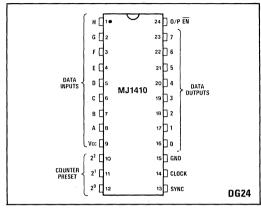

Fig.1 Pin connections

#### FEATURES

Single 5V supply.

Three-state outputs.

All inputs TTL compatible.

| Pin No.                              | Title                           | Function                                                                                                                                                                                       |

|--------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | H<br>G<br>F<br>D<br>C<br>B<br>A | Data i/p H<br>Data i/p G<br>Data i/p F<br>Data i/p E<br>Data i/p D<br>Data i/p B<br>Data i/p A<br>See Figs. 3 and 4                                                                            |

| 9<br>10                              | Vcc<br>2 <sup>2</sup>           | Positive supply, $5V \pm 5\%$                                                                                                                                                                  |

| 11                                   | 21                              | Counter preset i/p bit 2 The counter is preset to the data on these i/ps<br>Counter preset i/p bit 1 on the 3rd positive clock edge following a                                                |

| 12                                   | 20                              | Counter preset i/p bit 1 on the ord positive clock edge following a negative edge on the 'sync' input.                                                                                         |

| 13                                   | SYNC                            | A negative edge on this i/p initiates the counter preset sequence which causes the conversion cycle to start in the register which corresponds to the binary value of the counter preset i/ps. |

| 14                                   | CLOCK                           | System clock                                                                                                                                                                                   |

| 15                                   | GND                             | Zero volts                                                                                                                                                                                     |

| 16                                   | 0)                              | Three state data o/p '0'                                                                                                                                                                       |

| 17                                   | 1                               | Three state data o/p '1'                                                                                                                                                                       |

| 18                                   | 2                               | Three state data o/p '2'                                                                                                                                                                       |

| 19                                   | 3 Data                          | Three state data o/p '3' See Figs. 3 and 4                                                                                                                                                     |

| 20                                   | 4 outputs                       |                                                                                                                                                                                                |

| 21                                   | 5                               | Three state data o/p '5'                                                                                                                                                                       |

| 22                                   | 6                               | Three state data o/p '6'                                                                                                                                                                       |

| 23                                   | 7 <u>)</u>                      | Three state data o/p '7'                                                                                                                                                                       |

| 24                                   | O/P EN                          | A logic '1' on this i/p forces all the data outputs to a high impedance state.                                                                                                                 |

#### FUNCTIONAL DESCRIPTION

#### MJ1410

ELECTRICAL CHARACTERISTICS Test conditions (unless otherwise stated): Vcc = 5V, Tamb = 22 °C ± 2 °C, Test circuit: Fig.6. Supply voltage Vcc = 5V ± 10%, Ambient operating temperature Tamb = 10 °C to +70 °C

#### STATIC CHARACTERISTICS

| Characteristic                                     | 0h.al  | Direct                                        |      | Value | 1 Incides | Oradikiana |                 |

|----------------------------------------------------|--------|-----------------------------------------------|------|-------|-----------|------------|-----------------|

| Characteristic                                     | Symbol | Pins                                          | Min. | Тур.  | Max.      | Units      | Conditions      |

| Low level I/P<br>voltage                           | Vil    | 1,2,3,4,<br>5,6,7,8,<br>10,11,12,<br>13,14,24 | -0.3 |       | 0.8       | Volts      |                 |

| High level I/P<br>voltage                          | Vн     | 1,2,3,4,<br>5,6,7,8,<br>10,11,12,<br>13,14,24 | 2.5  |       | Vcc       | Volts      |                 |

| Low level I/P<br>current/high level<br>I/P current | hn .   | 1,2,3,4,<br>5,6,7,8,<br>10,11,12,<br>13,14,24 |      | · 1   | 50        | ЩA         |                 |

| Low level O/P<br>voltage                           | Vol    | 16,17,18,<br>19,20,21,<br>22,23               |      |       | 0.5       | Volts      | Isync = 1.6mA   |

| High level O/P<br>voltage                          | Vон    | 16,17,18,<br>19,20,21,<br>22,23               | 2.5  |       |           | Volts      | ISOURCE = 100uA |

| Low level O/P<br>current sink capa-<br>bility      | lo∟    | 16,17,18,<br>19,20,21,<br>22,23               | -1.6 |       |           | mA         |                 |

| High level O/P<br>current source<br>capability     | Іон    | 16,17,18,<br>19,20,21,<br>22,23               | 100  |       | т.<br>Т   | μA         |                 |

| OFF state O/P<br>current                           | IOFF L | 16,17,18,<br>19,20,21,<br>22,23               |      |       | 40        | μA         | Vout = GND      |

|                                                    | Іогг н | 16,17,18,<br>19,20,21,<br>22,23               |      |       | -40       | μA         | Vout = Vcc      |

| Power dissipation                                  | Poiss  |                                               | 90   |       | 500       | mW         | Vcc = 5.5V      |

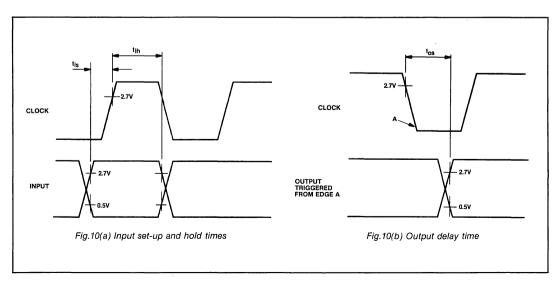

#### **DYNAMIC CHARACTERISTICS**

| Chave stavistic                                          | Complexit | Value     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |            |  |

|----------------------------------------------------------|-----------|-----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|--|

| Characteristic                                           | Symbol    | Min. Typ. |          | Max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Units | Conditions |  |

| Max.clock frequency                                      | Fmax.     | 2.4       |          | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | MHz   |            |  |

| Min. clock frequency                                     | Fmin.     | 0         |          | i e e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MHz   |            |  |

| Sync. pulse width<br>(positive)                          | tspp      | 60        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ns    | Fig. 6     |  |

| Sync. pulse width (negative)                             | tspn      | 100       |          | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ns    | Fig. 6     |  |

| Lead of sync. clocking<br>edge on positive clock<br>edge | ts∟       | 130       |          | 1<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ns    | Fig. 6     |  |

| Set up time of counter inputs (2º,21,22)                 | tsc       | 70        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ns    | Fig. 6     |  |

| Hold time of counter<br>inputs                           | thc       | 60        |          | a a construction de la construcción de la construcc | ns    | Fig. 6     |  |

| Set up time of data inputs (A-H)                         | tsp       | 80        | et a sur |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ns    | Fig. 6     |  |

#### **DYNAMIC CHARACTERISTICS**

| Characteristic                                                     | Symbol | Value |      |      |       | Conditions |

|--------------------------------------------------------------------|--------|-------|------|------|-------|------------|

| Characteristic                                                     | Symbol | Min.  | Тур. | Max. | Units | Conditions |

| Hold time of data inputs                                           | tнo    | 85    |      |      | ns    | Fig. 6     |

| Propagation delay, data<br>out valid from output<br>ENABLE low     | tpde - |       |      | 100  | ns    | Fig. 6     |

| Propagation delay, data<br>out disabled from output<br>ENABLE high | tpop   |       |      | 100  | ns    | Fig. 6     |

| Propagation delay, clock to data out valid                         | tpcp   |       |      | 200  | ns    | Fig. 6     |

Fig.2 Block diagram

#### **ABSOLUTE MAXIMUM RATINGS**

Voltage on any pin w.r.t. ground = 7V max. Storage temperature = -55°C to +125°C

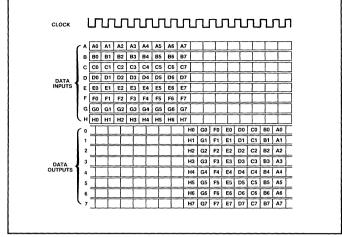

Fig.3 Data conversion

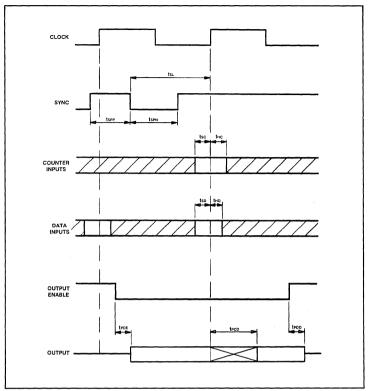

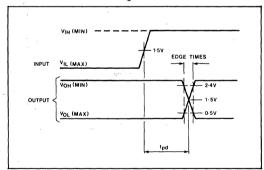

Fig.4 Input and output waveforms

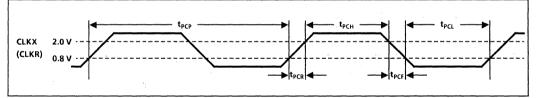

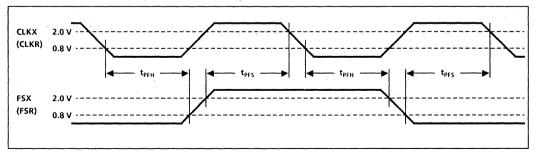

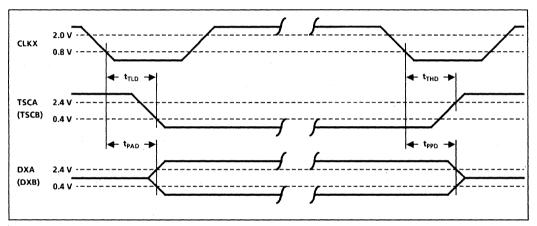

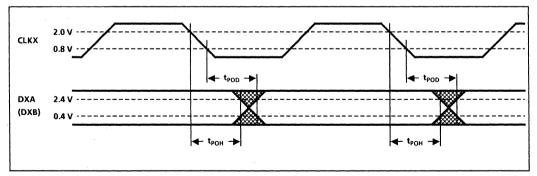

Fig.5 Timing details

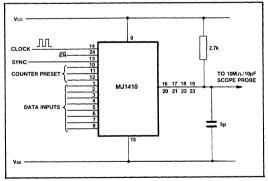

Fig.6 Test conditions

## 2 MBIT PCM SIGNALLING CIRCUIT **MJ 1440** HDB3 ENCODER/DECODER

The 2.048 MBit PCM Signalling Circuits comprise a group of circuits which will perform the common signalling and error detection functions for a 2.048 MBit PCM transmission link operating to the appropriate CCITT recommendations. The circuits are fabricated in N-channel metal gate MOS and operate from a single 5 volt supply, relevant inputs and outputs are TTL compatible.

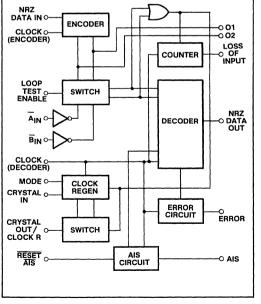

The MJ1440 is an encoder/decoder for the pseudoternary transmission code, HDB3 (CCITT Orange Book Vol III.2 Annex to Rec. G703). The device encodes and decodes simultaneously and asynchronously. Error monitoring functions are provided to detect violations of HDB3 coding, all ones detection and loss of input (all zeroes detection). In addition a loop back function is provided for terminal testing.

- 5v ± 5% Supply 50mA Max

- HDB3 Encoding and Decoding to CCITT rec. G703.

- Asynchronous Operation.

- Simultaneous Encoding and Decoding.

- Clock Recovery Signal Generated from Incoming HDB3 Data.

- Loop Back Control.

- HDB3 Error Monitor

- All Ones' Error Monitor

- Loss of Input Alarm (All Zeros Detector).

- Decode Data in NRZ Form.

#### **ABSOLUTE MAXIMUM RATINGS**

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded.

#### Electrical Ratings

| +Vcc    | 7V                    |

|---------|-----------------------|

| Inputs  | Vcc + 0.5V Gnd - 0.3V |

| Outputs | Vcc, Gnd –0.3V        |

#### **Thermal Ratings**

| Max Junction Temperature 175°C   |              |

|----------------------------------|--------------|

| Thermal Resistance: Chip to Case | Chip to Amb. |

| 40°C/Watt                        | 120°C/Watt   |

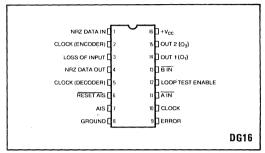

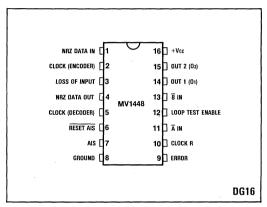

Fig. 1 Pin connections

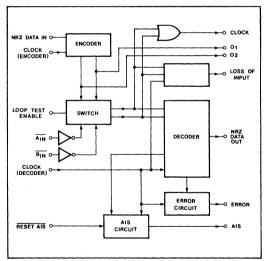

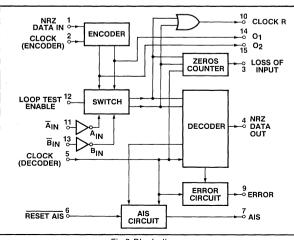

Fig. 2 Block diagram

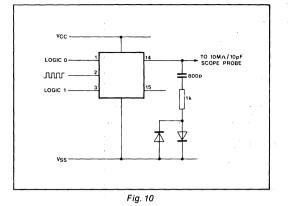

#### **ELECTRICAL CHARACTERISTICS**

### Test conditions (unless otherwise stated): Supply voltage, $V_{CC} = 5V \pm 0.25V$ Ambient temperature, $T_{amb} = 0^{\circ}C$ to +70°C

#### Static characteristics

| Characteristic                                       | Symbol                             | Pins                     | Value             |     |                       | Units        | Conditions                                            |

|------------------------------------------------------|------------------------------------|--------------------------|-------------------|-----|-----------------------|--------------|-------------------------------------------------------|

| Characteristic                                       | Symbol                             | FIIIS                    | Min               | Тур | Max                   | Units        | Conditions                                            |

| Low level input voltage                              | · V <sub>IL</sub>                  |                          | -0.3              |     | 0.8                   | v            |                                                       |

| Low level input current<br>High level input voltage  | l <sub>IL</sub><br>V <sub>IH</sub> | 1,2,5,6<br>10,11,12,13   | 2.5               |     | 50<br>V <sub>cc</sub> | μA<br>V      | V <sub>IL</sub> = 0V                                  |

| High level input current<br>Low level output voltage | I <sub>IH</sub><br>V <sub>OL</sub> | /<br>10,14,15<br>3.4.7.9 |                   |     | 50<br>0.5<br>0.4      | Ац<br>V<br>V | V <sub>IH</sub> = 5V<br>Isink = 80µA<br>Isink = 1.6mA |

| High level output voltage                            | V <sub>он</sub>                    | 3,4,7,9<br>14,15<br>10   | 2.7<br>2.8<br>2.8 |     |                       | v<br>v<br>v  | Isource = 60µA<br>Isource = 2mA<br>Isource = 1mA      |

| Supply current                                       | I <sub>cc</sub>                    |                          |                   | 20  | 50                    | mA           | All inputs to 0V<br>All outputs open circuit          |

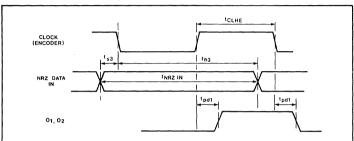

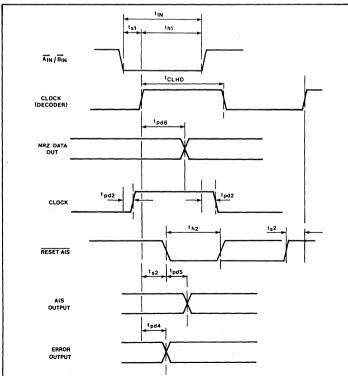

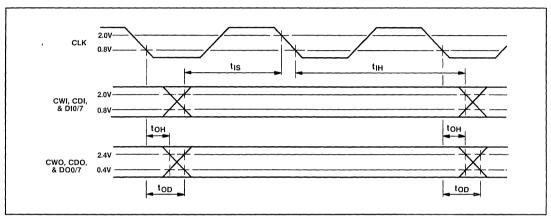

#### **Dynamic Characteristics**

| Characteristic                                                     | Symbol              |      | Valu        |      | Units | Conditions                            |

|--------------------------------------------------------------------|---------------------|------|-------------|------|-------|---------------------------------------|

|                                                                    |                     | Min. | тур.        | Max. |       |                                       |

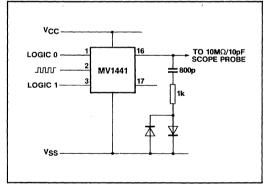

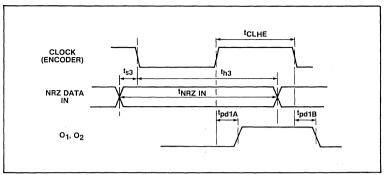

| Max. Clock (Encoder) frequency                                     | fmax <sub>enc</sub> | 4.0  |             |      | MHz   | Figs.10, 15                           |

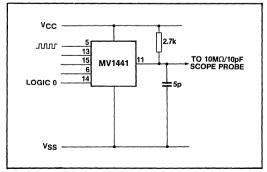

| Max. Clock (Decoder) frequency                                     | fmax <sub>dec</sub> | 2.2  |             |      | MHz   | Figs.11, 15                           |

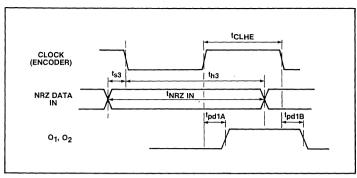

| Propagation delay Clock (Encoder) to $O_1, O_2$                    | tpd1A/B             |      |             | 100  | ns    | Figs.10, 15. See Note 1               |

| Rise and Fall times $O_1, O_2$                                     |                     |      |             | 20   | ns    | Figs.10, 15                           |

| tpd1A-tpd1B                                                        |                     |      |             | 20   | ns    | Figs.10, 15                           |

| Propagation delay Clock (Encoder) to Clock                         | tpd3                |      |             | 150  | ns    | Loop test enable = Figs.13, 15        |

| Setup time of NRZ data in to Clock (Encoder)                       | ts3                 | 30   |             |      | ns    | Figs.8, 10, 15                        |

| Hold time of NRZ data in                                           | th3                 | 55   |             |      | ns    | Figs.10, 15                           |

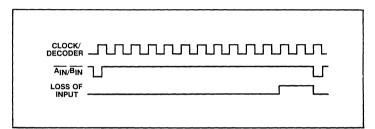

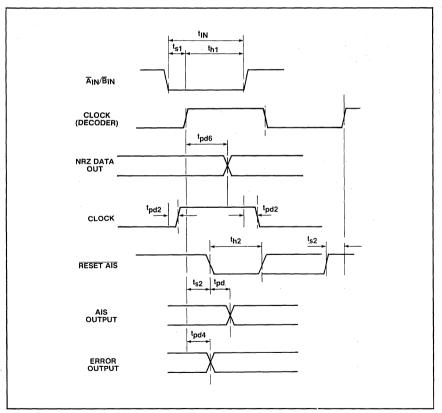

| Propagation delay A <sub>in</sub> , B <sub>in</sub> to Clock       | tpd2                |      |             | 150  | ns    | Loop test enable = '0' Figs.9, 13, 15 |

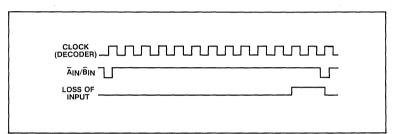

| Propagation delay Clock (Decoder) to loss of input                 |                     |      |             | 150  | ns    |                                       |

| Propagation delay Clock (Decoder) to error                         | tpd4                |      |             | 200  | ns    | Figs.12, 15                           |

| Propagation delay Reset AIS to AIS                                 | tpd5                |      |             | 200  | ns    | Loop test enable = '0' Figs.14, 15    |

| Propagation delay Clock (Decoder) to NRZ data out                  | tpd6                |      |             | 150  | ns    | Figs.9, 11, 15. See Note 2            |

| Setup time of A <sub>in</sub> , B <sub>in</sub> to Clock (Decoder) | ts1                 | 75   |             |      | ns    | Figs.9, 11, 15                        |

| Hold time of A <sub>in</sub> , B <sub>in</sub> to Clock (Decoder)  | th1                 | 5    |             |      | ns    | Figs.9, 11, 15                        |

| Hold time of $\overline{\text{Reset AIS}} = '0'$                   | th2                 | 100  | а.<br>      |      | ns    | Figs.9, 14, 15                        |

| Setup time Clock (Decoder) to Reset AIS                            | ts2                 | 200  | - 10<br>- 5 | -    | ns    | Figs.9, 14, 15                        |

| Setup time $\overline{\text{Reset AIS}} = 1$ to Clock (Decoder)    | ts2′                | 0    |             |      | ns    | Figs.14, 15                           |

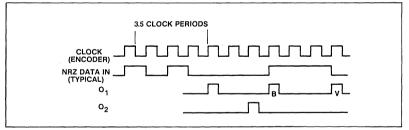

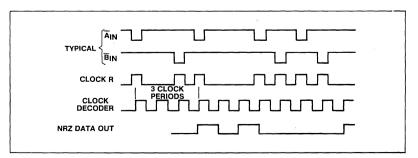

NOTES

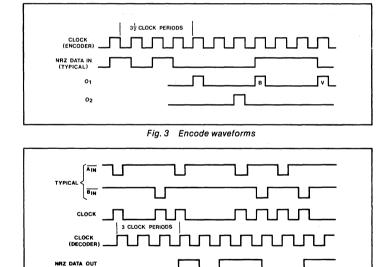

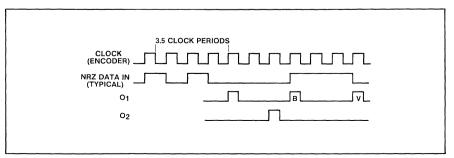

Encoded HDB3 outputs (O<sub>1</sub>, O<sub>2</sub>) are delayed by 3<sup>1/2</sup> clock periods from NRZ data in (Fig.3).

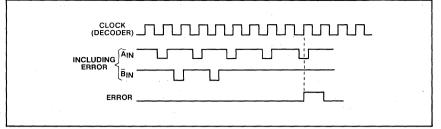

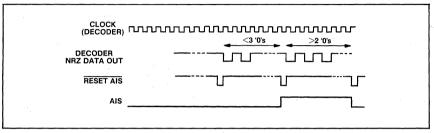

The decoded NRZ output is delayed by 3 clock periods from the HDB3 inputs (A<sub>IN</sub>, B<sub>IN</sub>) (Fig.4).

#### FUNCTIONAL DESCRIPTION

#### **Functions Listed by Pin Number**

#### 1. NRZ data in

Input data for encoding into ternary HDB3 form. The NRZ data is clocked by the negative edge of the Clock (Encoder).

#### 2. Clock (Encoder)

Clock for encoding data on pin 1.

#### 3. Loss of input alarm

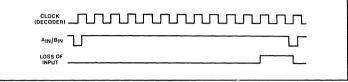

This output goes to logic '1' if eleven consecutive zeroes are detected in the incoming HDB3 data. The output is set to logic '0' on receipt of a '1'.

#### 4. NRZ data out

Decoded data in NRZ form from ternary HDB3 input data (Ain, Bin), data is clocked out by positive going edge of clock (Decoder).

#### Clock (Decoder) 5.

Clock for decoding ternary data Ain, Bin.

#### Reset AIS, AIS 6

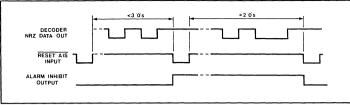

Logic '0' on Reset AIS resets a decoded zero counter and either resets AIS outputs to zero provided 3 or more zeroes have been decoded in the preceding  $\overline{\text{Reset AIS}} = 1$  period or sets AIS to '1' if less than 3 zeroes have been decoded in the preceding two Reset AIS = 1 periods.

Logic '1' on Reset AIS enables the internal decoded zero counter.

#### Ground 8.

Zero volts.

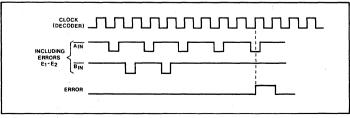

#### 9. Error

A logic '1' indicates that a violation of the HDB3 coding has been received i.e. 3 '1's of the same polarity.

#### 10. Clock

'OR' function of  $\overline{A}_{in}$ ,  $\overline{B}_{in}$  for clock regeneration when pin 12 = '0', 'OR' function of O<sub>1</sub>, O<sub>2</sub> when pin 12 = '1'. 11,13. A<sub>in</sub>, B<sub>in</sub>

Inputs representing the received ternary HDB3 PCM signal.  $\overline{A}_{in} = '0'$  represents a positive going '1',  $\overline{B}_{in} = '0'$  represents a negative going '1',  $\overline{A}_{in}$  and  $\overline{B}_{in}$  are sampled by the positive going edge of the Clock (Decoder).  $\overline{A}_{in}$  and  $\overline{B}_{in}$  may be interchanged.

#### 12. Loop test enable

Input to select normal or loop back operation. Pin  $12 = 0^{\circ}$ selects normal operation, encode and decode are independent and asynchronous. When pin 12 = '1'  $O_1$  is connected internally to A<sub>in</sub>. O<sub>2</sub> is connected to B<sub>in</sub>. Clock becomes the OR function  $O_1 + O_2$ . The delay from NRZ in to NRZ out is 6% clock periods in the loop back condition. 14,15. O., O,

Outputs representing the ternary encoded data for line transmission  $O_1 = '1'$  representing a positive going '1',  $O_2 = '1'$  represents a negative going '1'.  $O_1$  and  $O_2$  may be interchanged.

16.  $V_{cc}$ Positive supply, 5V  $\pm$  5%.

Fig. 4 Decode waveforms

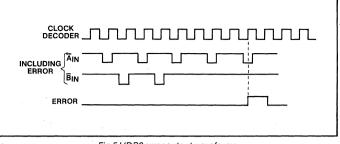

Fig. 5 HDB3 error output waveforms

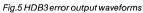

Fig. 6 AIS error and reset waveforms

Fig. 7 Loss of input waveforms

Fig. 8 Encoder timing relationship

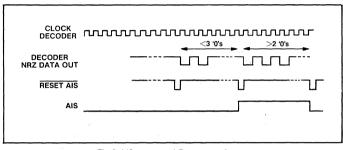

Fig. 9 Decoder timing relationship

17

#### MJ1440

٧cc

Fig. 12

#### **DEFINITION OF THE HDB3 CODE**

Coding of a binary signal into an HDB3 signal is done according to the following rules:

**1.** The HDB3 signal is psuedo-ternary; the three states are denoted  $B_{+}$ ,  $B_{-}$  and  $O_{-}$

2. Spaces in the binary signal are coded as spaces in the HDB3 signal. For strings of four spaces however, special rules apply (see 4. below).

3. Marks in the binary signal are coded alternately as B<sub>+</sub> and B<sub>-</sub> in the HDB3 signal (alternate mark inversion). Violations of the rule of alternate mark inversion are introduced when coding strings of four spaces (see 4. below).

4. Strings of four spaces in the binary signal are coded according to the following rules:

a The first space of a string is coded as a space if the

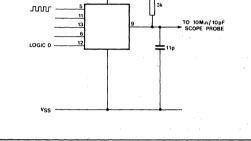

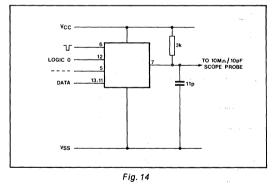

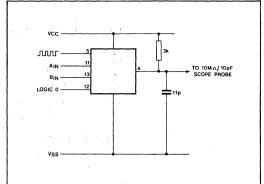

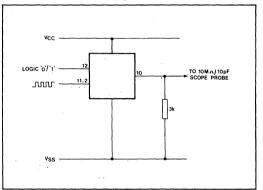

Fig. 11

Fig. 15 Test timing definitions

preceding mark of the HDB3 signal has a polarity opposite to the polarity of the preceding violation and is not a violation by itself; it is coded as a mark, i.e. not a violation (i.e.  $B_+$ ,  $B_-$ ), if the preceding mark of the HDB3 signal has the same polarity as that of the preceding violation or is by itself a violation.

This rule ensures that successive violations are of alternative polarity so that no DC component is introduced

**b** The second and third spaces of a string are always coded as spaces.

c The last space of a string of four is always coded as a mark, the polarity of which is such that it/violates the rule of alternate mark inversion. Such violations are denoted  $V_{\perp}$  or  $V_{-}$  according to their polarity.

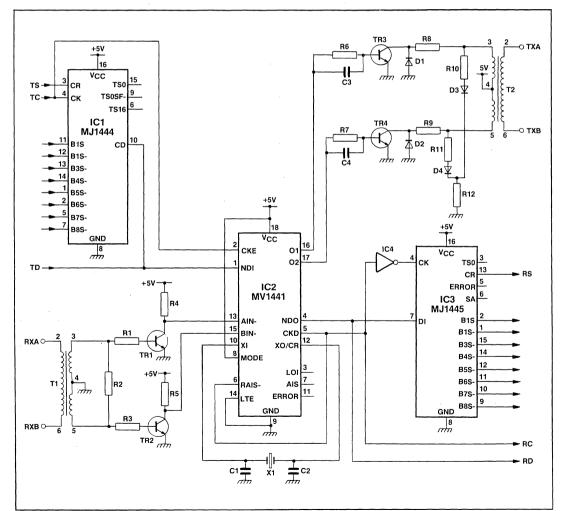

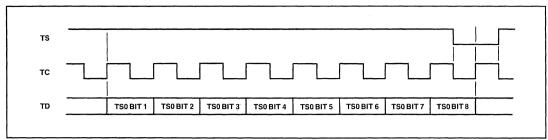

### 2 MBIT PCM SIGNALLING CIRCUIT MJ 1444 PCM SYNCHRONISING WORD GENERATOR

The 2.048 Mbit PCM signalling circuits comprise a group of circuits which will perform the common signalling and error detection functions for a 2.048 Mbit 30 channel PCM transmission link operating to the appropriate CCITT recommendations. The circuits are fabricated in N-channel metal gate MOS and operate from a single 5 volt supply. Relevant inputs and outputs are TTL compatible.

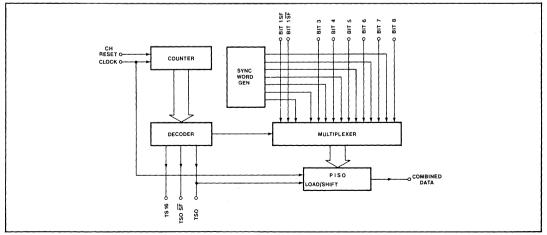

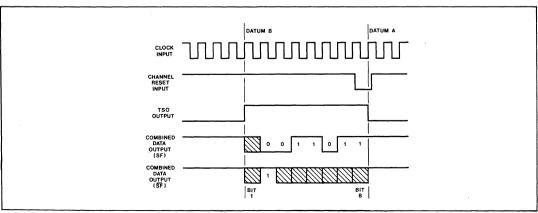

The MJ1444 generates the synchronising word in accordance with CCITT recommendations G732. The MJ1445 has been designed to detect this synchronising word when received at the remote end of the transmission system.

The synchronising word is injected onto the PCM data highway during time slot 0 in alternate frames. The spare time slot 0 data bits, bit 1 in every frame and bits 3 to 8 inclusive in alternate frames (i.e. those not containing the synchronising word) are available as parallel inputs and are output onto the PCM data highway.

The data output of the MJ1444 is 'open collector' and can be wire OR'd directly onto the highway.

The device also provides a time slot 0 channel pulse 'TS0', time slot 0 non-sync. frame 'TS0 SF', and time slot 16 'TS16' outputs.

#### FEATURES

- 5V ±5% Supply - 20 mA Typical

- Fully Conforms to CCITT Recommendation G732

- er i Outputs Directly Onto PCM Data Highway

- Provides Both Time Slot 0 and Time Slot 16 14 **Channel Pulses**

- 置 All Inputs and Outputs are TTL Compatible

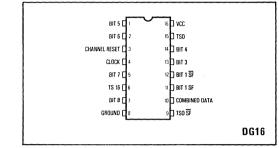

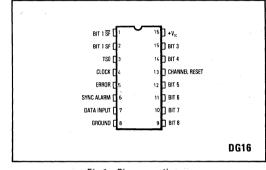

Fig.1 Pin connections

#### ABSOLUTE MAXIMUM RATINGS

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded.

#### Electrical Ratings

| +Vcc    | 7V                    |

|---------|-----------------------|

| Inputs  | Vcc + 0.5V Gnd - 0.3V |

| Outputs | Vcc, Gnd –0.3V        |

#### **Thermal Ratings**

| Max Junction Temperature 175°C   |              |

|----------------------------------|--------------|

| Thermal Resistance: Chip to Case | Chip to Amb. |

| 35°C/Watt                        | 120°C/Watt   |

Fig.2 MJ1444 block diagram

#### MJ1444

#### **ELECTRICAL CHARACTERISTICS**

### Test conditions (unless otherwise stated): Supply voltage, $V_{CC} = 5V \pm 0.25V$ Ambient operating temperature – 10°C to + 70°C

#### Static Characteristics

| Characteristic                                          | Symbol Pins     |                                         |      | Value |            | Units      | Conditions                                       |  |

|---------------------------------------------------------|-----------------|-----------------------------------------|------|-------|------------|------------|--------------------------------------------------|--|

| Characteristic                                          | Symbol          | PIIIS                                   | Min. | Тур.  | Max.       | Units      | Conumons                                         |  |

| Low level input voltage                                 | V <sub>IL</sub> | 1, 2, 3, 4, 5,<br>7, 11, 12, 13,<br>14. | -0.3 |       | 0.8        | <b>v</b> , |                                                  |  |

| Low level input current )<br>High level input current } | I <sub>IN</sub> | 11                                      |      | 1     | 50         | μA         |                                                  |  |

| High level input voltage                                | VIH             | 11                                      | 2.4  |       | $V_{cc}$   | ,<br>,     |                                                  |  |

| Low level output voltage                                | V <sub>oL</sub> | 6, 9, 15<br>10                          |      |       | 0.5<br>0.7 | V<br>V     | I <sub>sink</sub> =2mA<br>I <sub>sink</sub> =5mA |  |

| High level output voltage                               | V <sub>он</sub> | 6, 9, 15                                | 2.8  |       |            | v          | I <sub>source</sub> = 200μA                      |  |

| High level output leakage current                       | I <sub>он</sub> | 10                                      |      |       | 20         | μA         | $V_{OUT} = V_{CC}$                               |  |

| Supply current                                          | I <sub>cc</sub> |                                         |      | 20    | 40         | mA         | V <sub>CC</sub> = 5.25V                          |  |

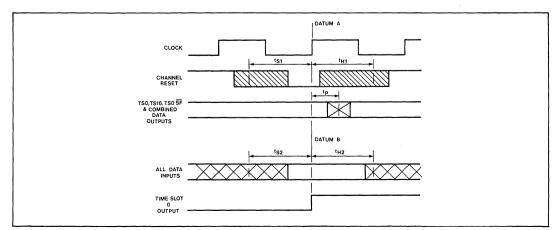

#### **Dynamic Characteristics**

| Characteristic                                                           |                  |      | Value |      | Units | Conditions                     |

|--------------------------------------------------------------------------|------------------|------|-------|------|-------|--------------------------------|

|                                                                          | Symbol           | Min. | Тур.  | Max. | Units | Conditions                     |

| Max clock frequency                                                      | F <sub>max</sub> | 3    |       |      | MHz   |                                |

| Propagation delay, clock to TS0, TS0 SF, TS16 and combined data outputs. | t <sub>P</sub>   | 80   |       | 200  | ns    | See Figs.5 and 6               |

| Set up time channel reset to clock                                       | T <sub>S1</sub>  | 100  |       | 450  | ns    | f <sub>clock</sub> = 2.048 MHz |

| Hold time of channel reset input                                         | t <sub>H1</sub>  | 20   |       | 400  | ns    |                                |

| Set up time of bit 1 (SF) to datum B                                     | t <sub>s2</sub>  | 100  |       |      | ns    |                                |

| Hold time of bit 1 (SF) wrt datum B                                      | t <sub>H2</sub>  | 300  |       |      | ns    |                                |

| Set up time of bit 1 ( $\overline{SF}$ ) and data bits 3 – 8 to datum B  | t <sub>S2</sub>  | 100  |       | ]    | ns    |                                |

| Hold time of bit 1 ( $\overline{SF}$ ) and data bits 3 — 8 wrt datum B   | t <sub>H2</sub>  | 300  |       |      | ns    |                                |

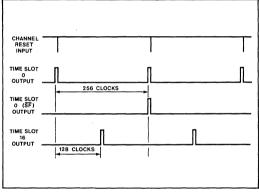

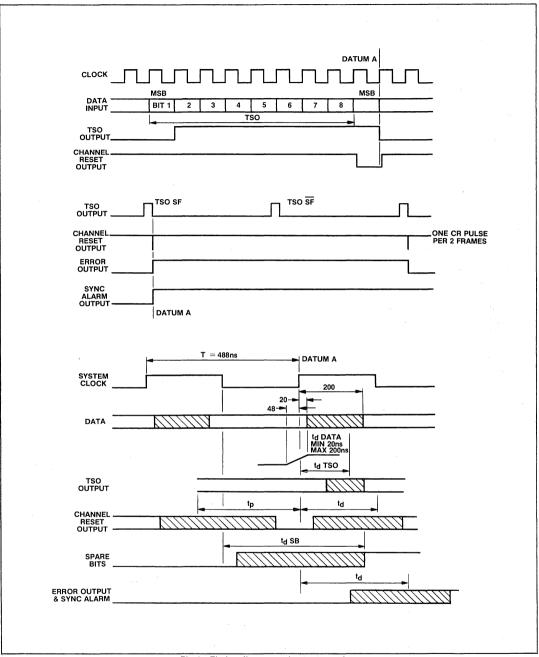

Fig.3 Data timing

#### **FUNCTIONAL DESCRIPTION**

#### Functions Listed by pin number

#### 1, 2, 5, 7, 13, 14. Bits 3 to 8

Parallel data on these inputs is asynchronously loaded into bits 3 to 8 of the PISO shift register for transmission during Time slot 0 of non-sync. frames.

#### 3. Channel Reset

A low going pulse at this input synchronises the MJ1444 with the other devices at the transmit end of the PCM link. It may be applied as a start pulse or repeated at the same instant in successive frames.

#### 4. Clock

System clock input (2.048 MHz for a 2 Mbit PCM system).

#### 6. TS16

This output provides a positive pulse equivalent to 8 clock periods during time slot 16 of every 30 + 2 channel PCM frame.

#### 8. GND

Zero volts.

#### 9. TSO SF

This output provides a positive pulse equivalent to 8 clock periods during time slot 0 of non-sync. frames.

#### 10. Combined data

This 'open collector' output injects the contents of the PISO shift register onto the PCM data highway during time slot 0 in successive frames. The contents of the PISO shift register are defined as follows:

|                 | Bit 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|-----------------|-------|---|---|---|---|---|---|---|

| Sync. Frame     | X     | 0 | 0 | 1 | 1 | 0 | 1 | 1 |

| Non-sync. frame | х     | 1 | Х | Х | X | X | Х | Х |

X—indicates that these bits may be set according to the parallel data inputs.

#### 11. Bit 1 SF

Data on this input is asynchronously loaded into bit 1 of the PISO shift register for transmission during time slot 0 of sync. frames.

#### 12. Bit 1 SF

Data on this input is asynchronously loaded into bit 1 of the PISO shift register for transmission during time slot 0 of non-sync. frames.

#### 15. TS0

This output provides a positive pulse equivalent to 8 clock period during time slot 0 of every 30 channel PCM frame.

#### 16. V<sub>cc</sub>

Positive supply, 5V ±5%.

Fig.4 Sync. timing

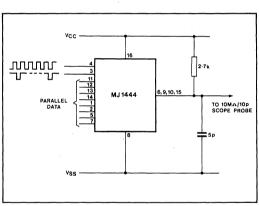

Fig.5 Test conditions (all outputs)

Fig.6 Timing definitions

#### **2 MBIT PCM SIGNALLING CIRCUIT**

## **MJ1**445

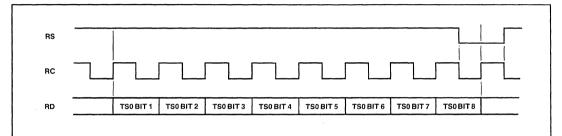

#### PCM SYNCHRONISING WORD RECEIVER

The 2.048 Mbit PCM signalling circuits comprise a group of circuits which will perform the common signalling and error detection functions for a 2.048 MBit 30 channel PCM transmission link operating to the appropriate CCITT recommendations. The circuits are fabricated in N-channel metal gate MOS and operate from a single 5volt supply. Relevant inputs and outputs are TTL compatible.

The MJ1445 establishes synchronisation by detecting the synchronising word when it is received at the remote end of the transmission system. The MJ1444 has been designed to generate this synchronisation word at the sending end of the system in accordance with CCITT recommendation G732.

Corruption of individual synchronisation words is signified by an 'Error' output, loss of synchronisation is indicated by a 'Sync Alarm' output and follows CCITT G732 in that loss of synchronism is assumed when 3 consecutive synchronisation words have been received with errors.

The 'Channel Reset' output goes low for the first period of the clock after time slot 0 in sync frames whenever the MJ1445 has established that the receiver terminal is in synchronisation in order that the rest of the receiver terminal may be reset.

The 'TSO' output is high for a period of 8 bits starting from the end of the first bit of the synchronising word. The spare data bits from the synchronising word are provided as parallel outputs.

#### ABSOLUTE MAXIMUM RATINGS

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded.

#### Electrical Ratings

#### **Thermal Ratings**

Max Junction Temperature 175°C Thermal Resistance: Chip to Case 35°C/Watt

Chip to Amb. 120°C/Watt

Fig.1 Pin connections

#### FEATURES

- $5V \pm 5\%$  Supply 20 mA Typical.

- Conforms to CCITT Recommendation G732

- Synchronising Word Error Monitor

- Out of Sync. Alarm

- All Inputs and Outputs are TTL Compatible

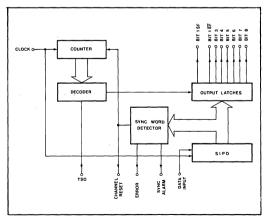

Fig.2 Block diagram MJ1445

#### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated): Supply voltage,  $V_{CC} = 5V \pm 0.25V$ Ambient temperature,  $T_{amb} = -10^{\circ}C$  to  $+70^{\circ}C$

#### Static Characteristics

| Characteristic                              | Symbol                             | Pins                                         |      | Value |                 |       | Conditions                                              |  |

|---------------------------------------------|------------------------------------|----------------------------------------------|------|-------|-----------------|-------|---------------------------------------------------------|--|

|                                             | Symbol                             | PINS                                         | Min. | Тур.  | Max.            | Units | Conditions                                              |  |

| Low level input voltage                     | V <sub>IL</sub>                    | 4, 7                                         | -0.3 |       | 0.8             | v     |                                                         |  |

| Low level input current                     | J <sub>IN</sub>                    | 4, 7                                         |      | 1     | 50              | μΑ    |                                                         |  |

| High level input voltage                    | VIH                                | 4, 7                                         | 2.4  |       | v <sub>cc</sub> | v     |                                                         |  |

| Low level output voltage                    | V <sub>oL</sub>                    | 1, 2, 3, 5, 6<br>9, 10, 11, 12<br>13, 14, 15 |      |       | 0.5             | V     | I <sub>sink</sub> =2mA                                  |  |

| High level output voltage<br>Supply current | V <sub>он</sub><br>I <sub>сс</sub> |                                              | 2.8  | 20    | 40              | mA    | I <sub>source</sub> = 200μA<br>V <sub>CC</sub> = 5.25 V |  |

#### **Dynamic Characteristics**

| Characteristic                                                                | Symbol  |      | Value |      | Units | Conditions              |

|-------------------------------------------------------------------------------|---------|------|-------|------|-------|-------------------------|

|                                                                               | Symbol  | Min. | Тур.  | Max. | Units | Conditions              |

| Max. clock frequency                                                          | fmax    | 2.2  |       |      | MHz   |                         |

| Input delay of data input                                                     | td data | 20   |       | 200  | ns    | $f_{clock} = 2.048 MHz$ |

| Propagation delay, clock to TS0 output                                        | td TSO  | 40   |       | 200  | ns    | Fig.3                   |

| Propagation delay clock to error output, sync alarm and CH. Reset output high | ta      | 50   |       | 400  | ns    | Fig.3                   |

| Propagation delay, clock to CH.<br>Reset output low $(T - t_P)$               | tp      | 100  |       | 450  | ns    | Fig.3                   |

| Propagation delay clock to spare bits                                         | td SB   | 50   |       | 300  | ns    | Fig.3                   |

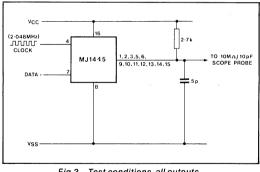

Fig.3 Test conditions, all outputs

#### **FUNCTIONAL DESCRIPTION**

#### Functions listed by pin number

#### 1. Bit 1 SF

This output is set to the level of data bit 1 during time slot 0 of non sync frames. The data becomes true on the first falling edge of the clock during TS1.

#### 2. Bit 1 SF

This output is set to the level of data bit 1 during time slot 0 of sync frames. The data becomes true on the first falling edge of the clock during TS1.

#### 3. TS0

This output provides a positive pulse of 8 clock periods in every frame starting from the end of the first bit of the synchronising word of the received data.

#### 4. Clock

System clock input (2.048 MHz for a 2MBit PCM system).

#### 5.Error

This output goes high at the end of time slot 0 in the 2nd sync frame following the frame with sync word errors. If consecutive sync words occur with errors this output will remain high. If a sync alarm is generated this output will remain high until sync is regained.

#### 6. Sync Alarm

This output goes high at the end of time slot 0 output in the 3rd consecutive sync frame containing sync word errors. It returns low at the end of TS0 output in the 3rd consecutive frame received correctly (sync and non sync).

#### 7. Data input

Serial data (2MBit/s) at this input is clocked through the SIPO shift register and examined by the sync word detector.

#### 8. GND

Zero volts

#### 9, 10, 11, 12, 14, 15. Bits 3 to 8

These parallel outputs are set to the level of the spare data bits (3 to 8) of time slot 0 of non sync frames. The data becomes true on the first falling edge of the clock during TS1.

#### 13. Channel reset

This output goes low for the first period of the clock after time slot 0 of the received data as long as synchronisation has been established. This pulse can be used to reset the rest of the receiver terminal.

#### 16. V<sub>cc</sub>

Positive supply 5V ±5%.

Fig.4 Timing diagram and output waveforms

## 2 MBIT PCM SIGNALLING CIRCUIT MJ1446

TIME SLOT 16 RECEIVER AND TRANSMITTER

The 2.048 Mbit PCM signalling circuits comprise a group of circuits which will perform the common signalling and error detection functions for a 2.048 Mbit 30 channel PCM transmission link operating to the appropriate CCITT recommendations. The circuits are fabricated in N-channel metal gate MOS and operate from a single 5volt supply. Relevant inputs and outputs are TTL compatible.

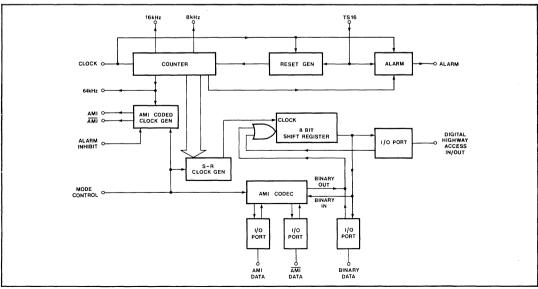

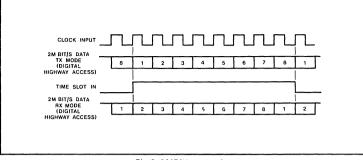

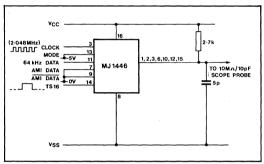

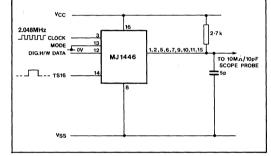

The MJ1446 has two modes of operation dependent on the state of the mode control input. With the mode control high the device is in the transmit mode and with the mode control low the device is in the receive mode.

In the transmit mode the device accepts 64kbits/sec signalling information in either binary or AMI format and outputs it at 2Mbits/sec on to the digital highway during time slot 16.

In the receive mode the device accepts 2Mbit/sec information from the digital highway, during time slot 16 and output is at 64kbits/sec in both binary and AMI format.

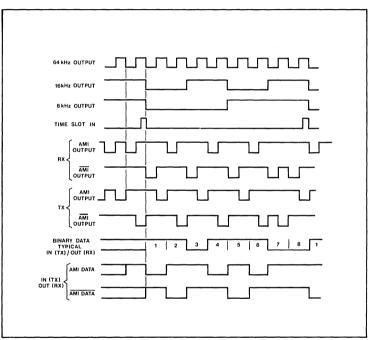

In both receive and transmit mode there is an AMI coded clock output, AMI output and  $\overline{AMI}$  output which conforms to CCITT recommendation no G372 for a 64k bits/sec contradirectional interface. The alarm inhibit input causes the 8kHz timing signal to be removed from the AMI clock output.

The device is reset in both modes by a time slot 16 channel pulse and the alarm output provides an indication that the internal counter is operating correctly.

Also provided are 64 kHz, 16 kHz and 8 kHz clock outputs.

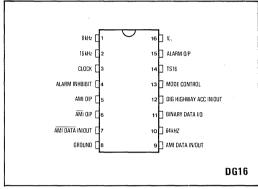

Fig.1 Pin connections

#### FEATURES

- 5V ±5% Supply 20 mA Typical

- Conforms to CCITT Recommendations

- Provides Both AMI and Binary Format Data Outputs

- Single Chip Receivelor Transmit

- All Inputs and Outputs are TTL Compatible.

Fig.2 Block diagram

#### MJ1446

#### ELECTRICAL CHARACTERISTICS

Test conditions (unless otherwise stated):

Supply voltage Vcc = 5V  $\pm$  0.25V, Ambient temperature T<sub>amb</sub> = -10 °C to +70 °C, Static Characteristics

#### Value Characteristic Symbol Pins Units Conditions Min. Тур. Max. 3, 4, 7, 9, 11, v Low level input voltage V<sub>II</sub> -0.3 0.8 12, 13, 14 Low level input current 1 50 11 μA $I_{IN}$ High level input current High level input voltage V<sub>ін</sub> 11 2.4 Vcc ۷ 1, 2, 5, 6, 7, 0.5 v Low level output Vol $I_{sink} = 2mA$ 9, 10, 11, 15 12 0.5 ٧ $I_{sink} = 5mA$ 1, 2, 10, 5, 6, 2.8 $I_{source} = 200 \mu A$ V<sub>OH</sub> v High level output voltage 15 High level output leakage current 7, 9, 11, 12 20 μA $V_{OUT} = V_{CC}$ I<sub>CH</sub> Supply current 20 $V_{\rm CC} = 5.25 V$ mΑ lcc

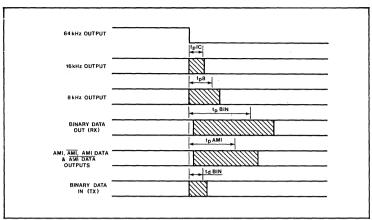

#### Dynamic Characteristics ( $f_{clock} = 2.048 \text{ MHz}$ )

| Characteristic                                             | Sumbol              |      | Value |      | Units | Conditions |  |

|------------------------------------------------------------|---------------------|------|-------|------|-------|------------|--|

|                                                            | Symbol              | Min. | Тур.  | Max. | Units | Conditions |  |

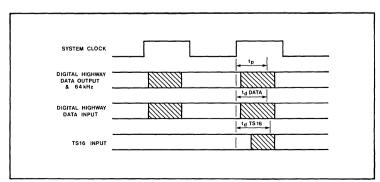

| Propogation delay clock to data out to digital highway     | tp                  | 20   |       | 200  | ns    | Fig.7      |  |

| Propogation delay clock to 64 kHz out                      | t                   | 20   |       | 200  | ns    | Fig.7      |  |

| Input delay, clock to digital highway access               | t <sub>d DATA</sub> | 20   |       | 200  | ns    |            |  |

| Input delay, clock to time slot 16                         | t <sub>d TS16</sub> | 80   |       | 200  | ns    |            |  |

| Output delay 64 kHz to 16 kHz output                       | t <sub>p 16</sub>   |      |       | 70   | • ins | Fig.7      |  |

| Output delay, 64 kHz to 8 kHz output                       | t <sub>p 8</sub>    |      |       | 170  | ns    | Fig.7      |  |

| Output delay, 64kHz to binary data output (64kHz)          | t <sub>p BIN</sub>  | 20   |       | 450  | ns    | Fig.8      |  |

| Output delay 64 kHz to AMI, AMI, AMI data & AMI data o/p's | t <sub>p AMI</sub>  | 20   |       | 400  | ns    | Fig.8      |  |

| Input delay, 64 kHz to binary data in (64 kHz)             | t <sub>d BIN</sub>  |      |       | 100  | ns    |            |  |

#### FUNCTIONAL DESCRIPTION Functions listed by pin number

#### 1.8 kHz

8kHz square wave output.

#### 2.16 kHz

16 kHz square wave output.

#### 3. Clock

System clock input (2.048 MHz for a 2Mbit PCM system)

#### 4. Alarm inhibit

A high level on this input inhibits the 8kHz timing signal on the AMI clock outputs.

#### 5. AMI output

Alternative Mark Inversion coded 64 kHz.

#### 6. AMI output

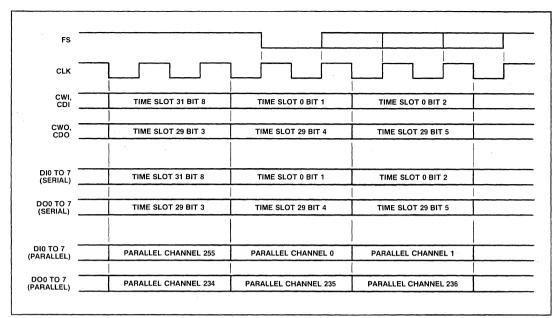

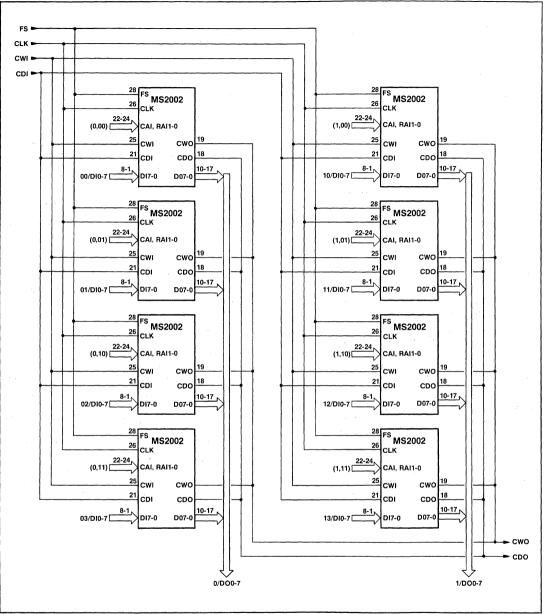

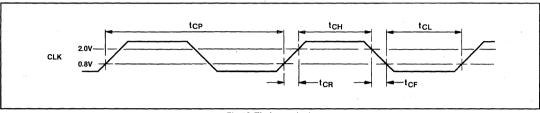

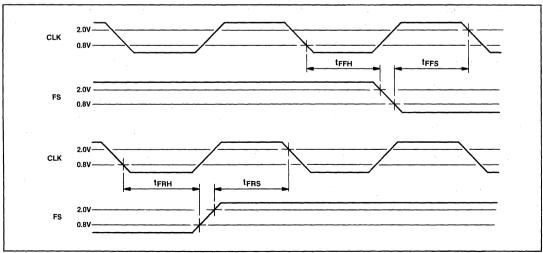

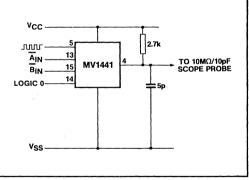

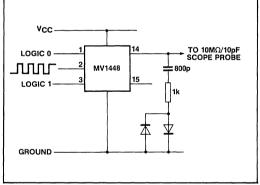

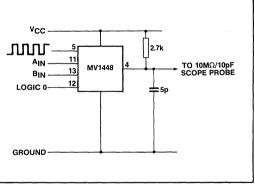

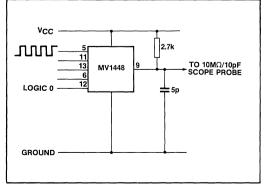

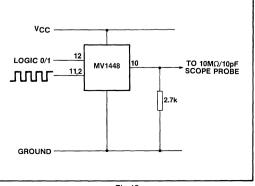

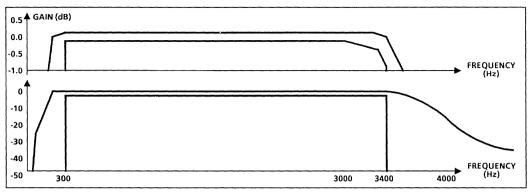

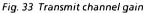

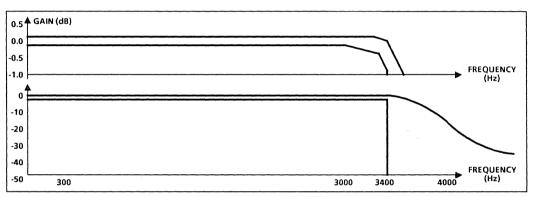

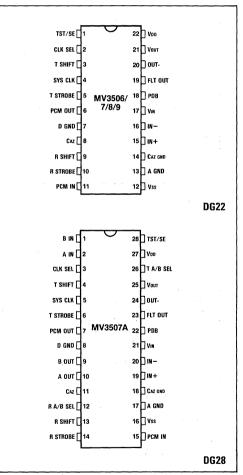

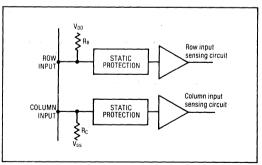

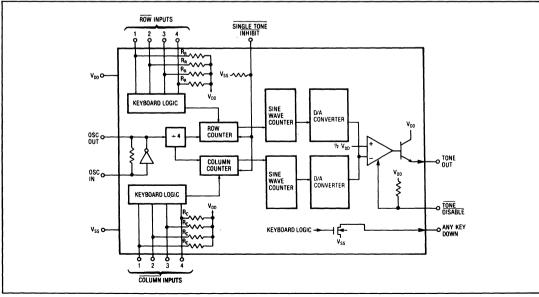

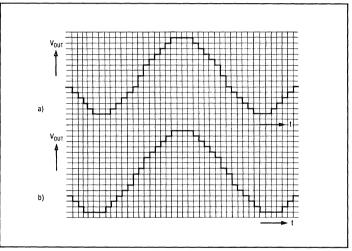

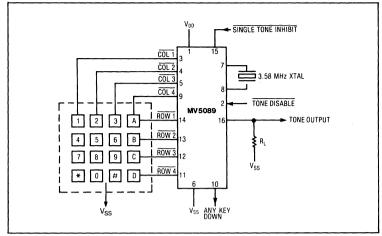

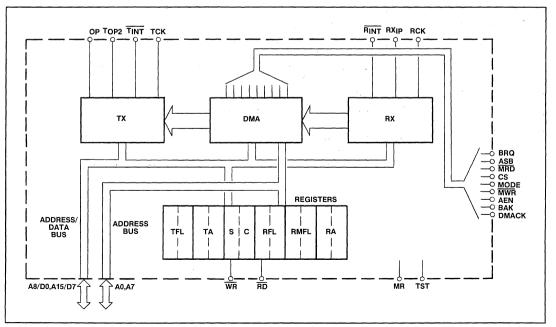

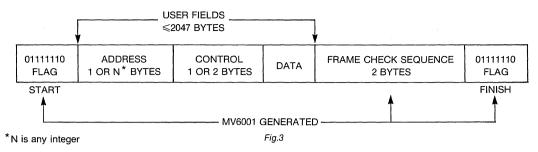

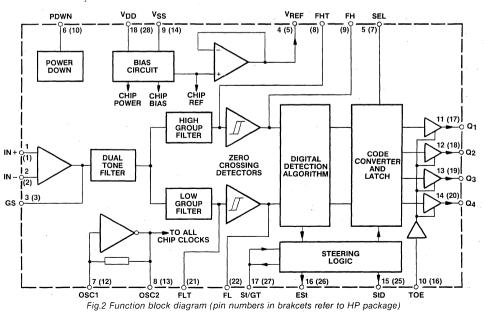

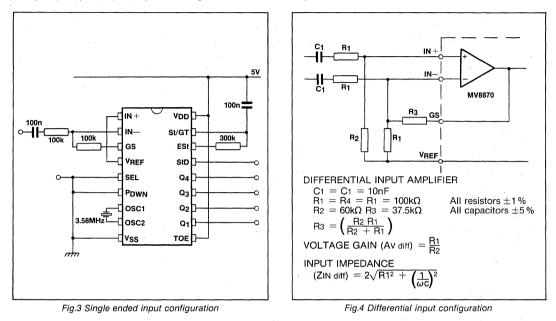

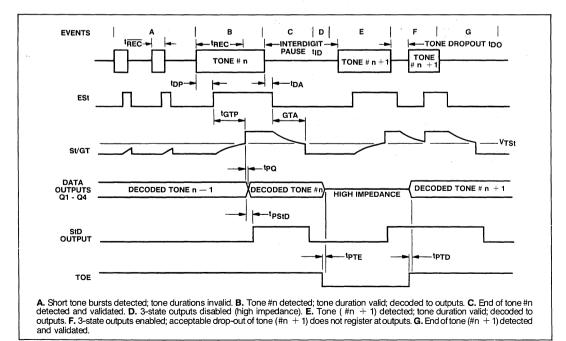

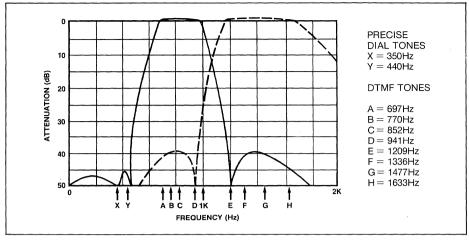

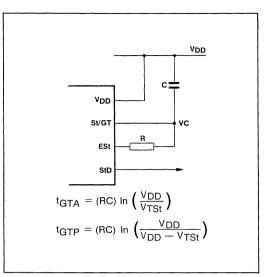

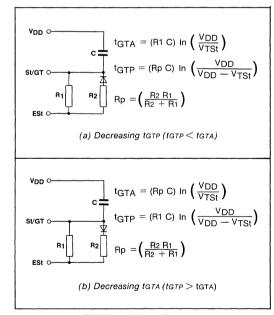

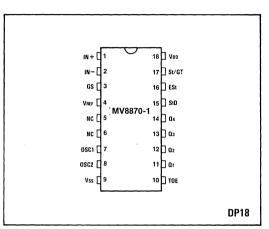

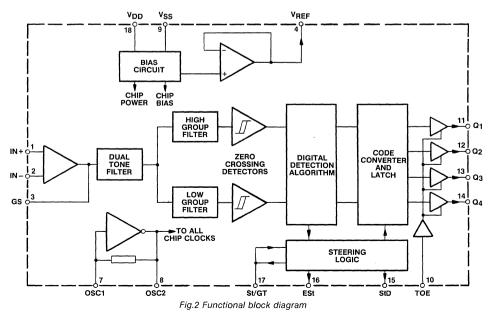

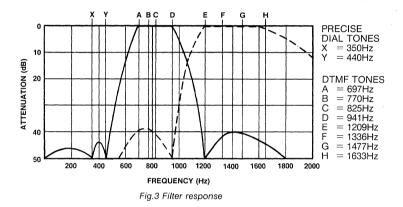

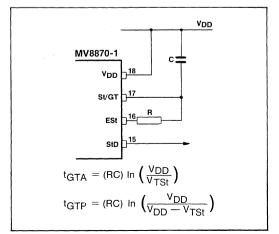

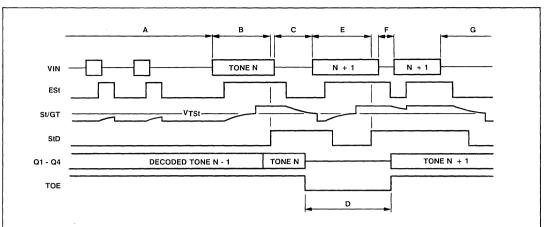

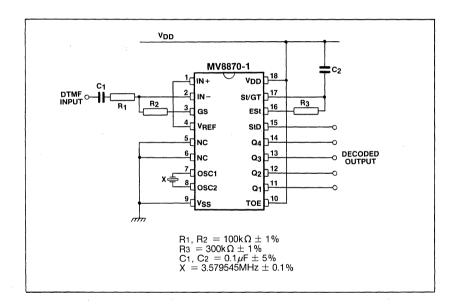

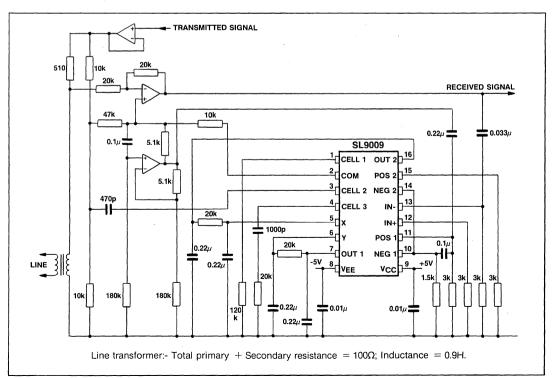

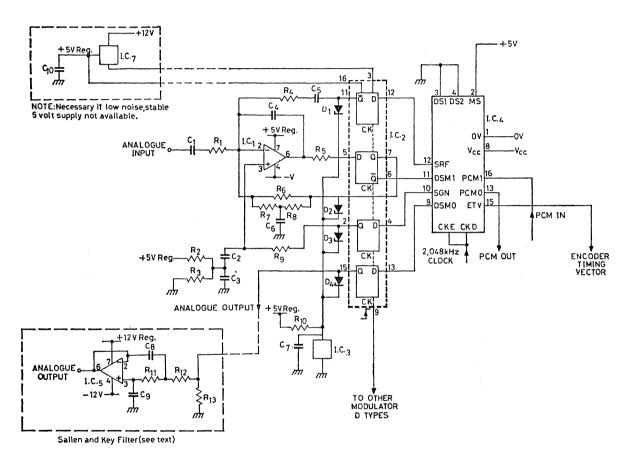

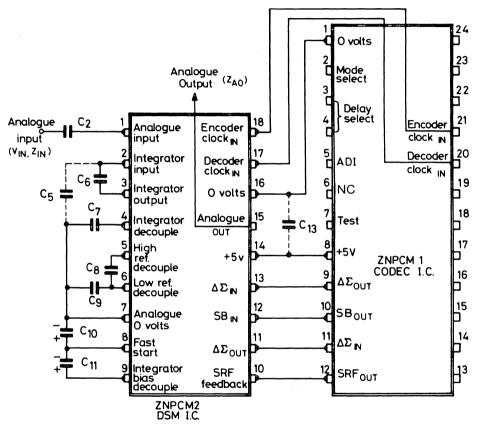

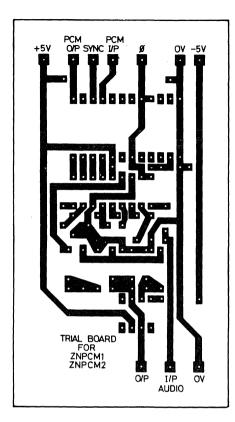

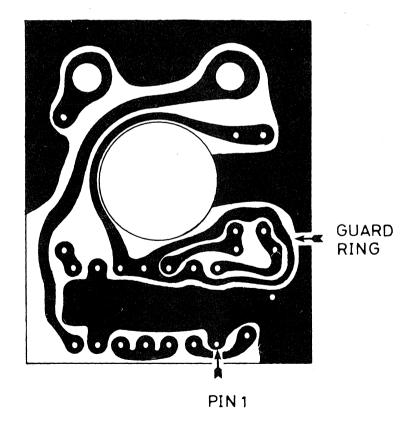

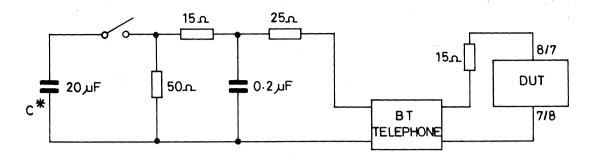

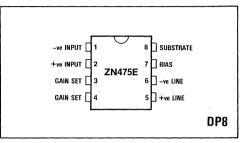

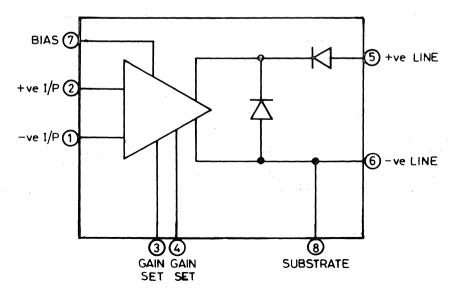

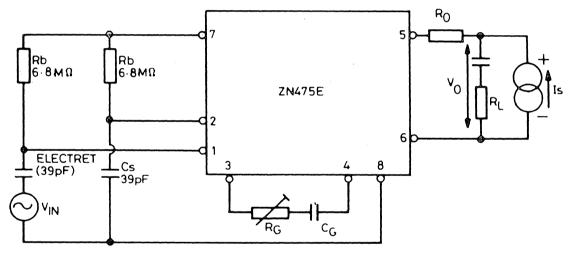

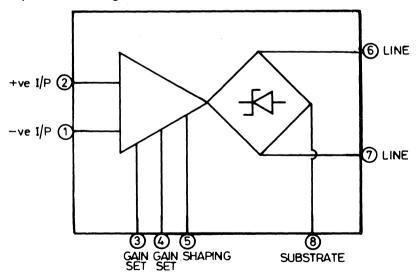

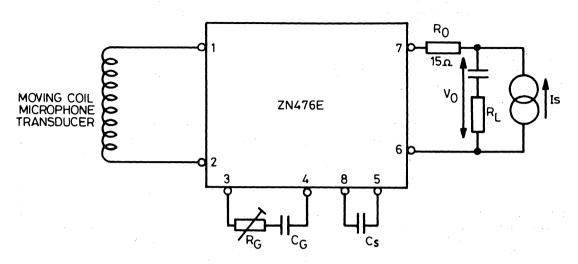

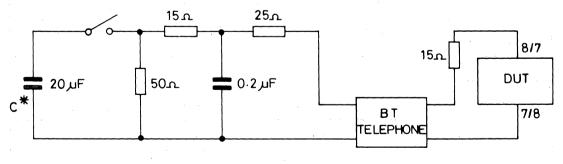

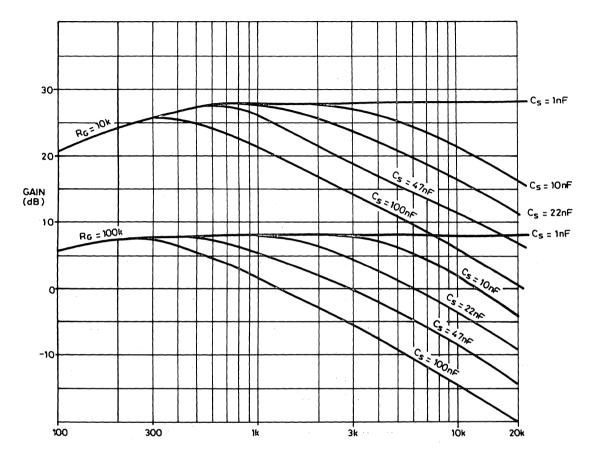

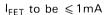

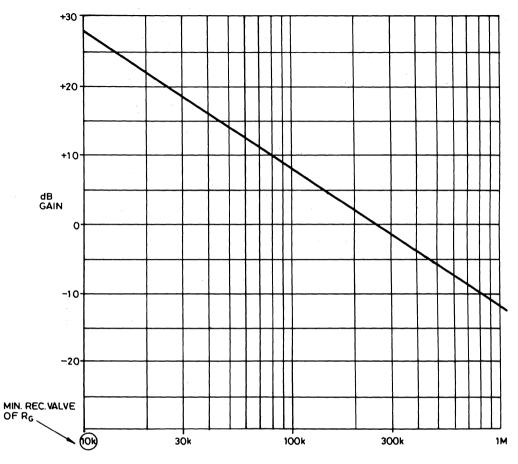

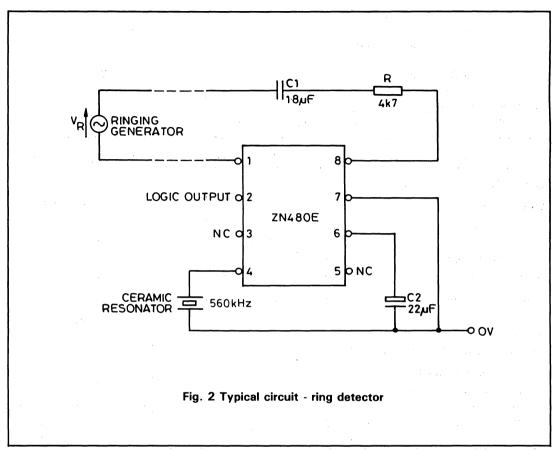

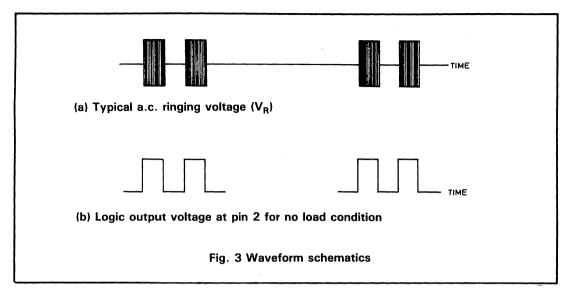

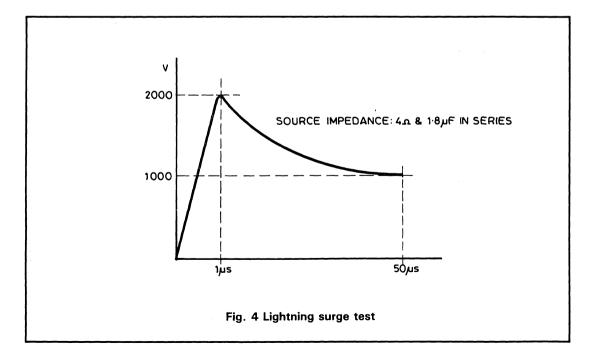

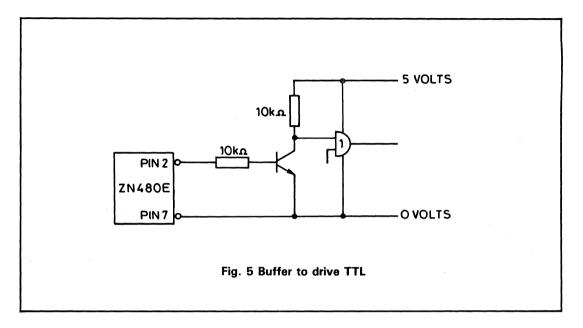

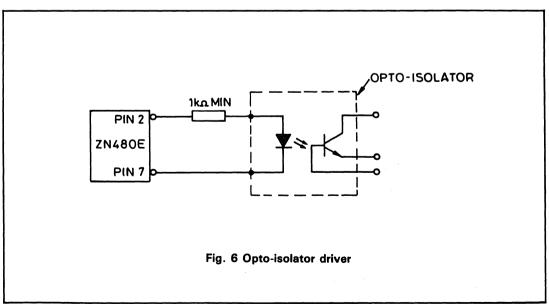

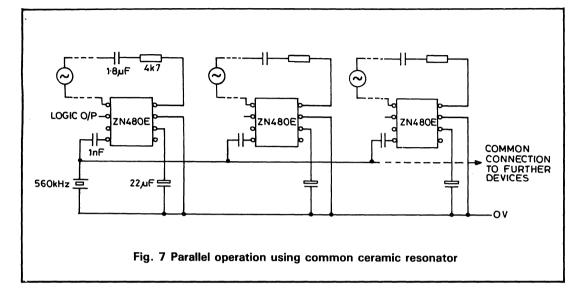

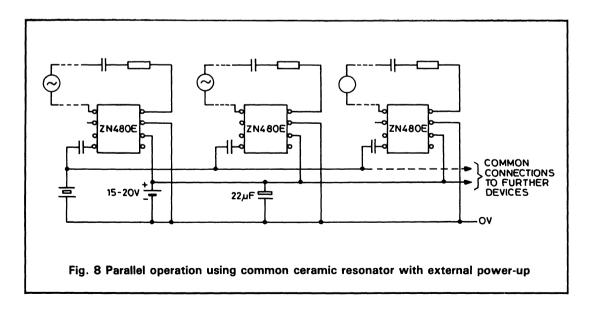

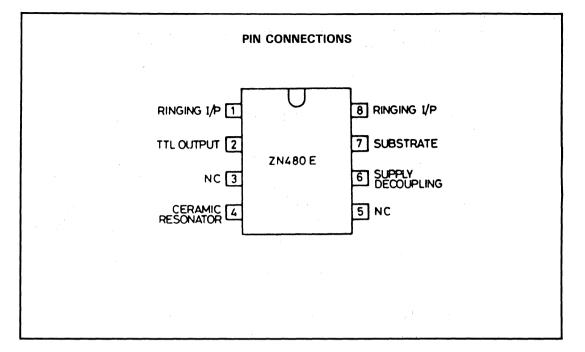

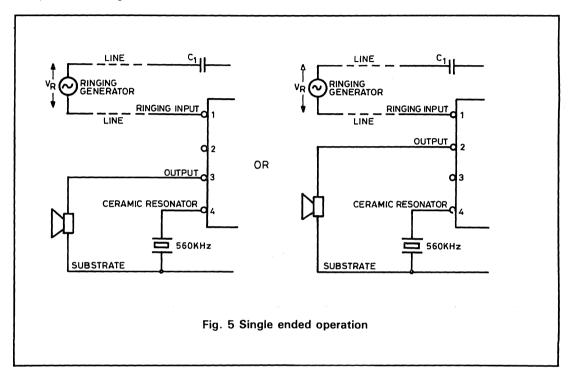

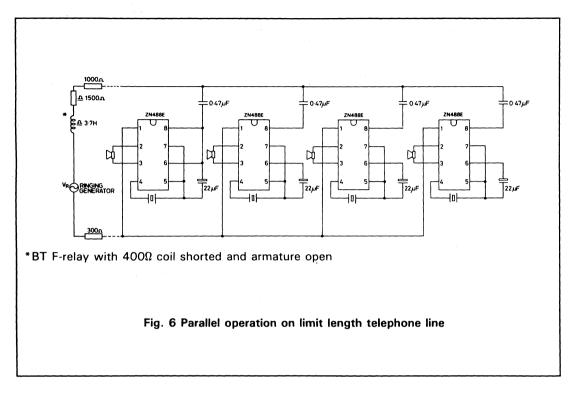

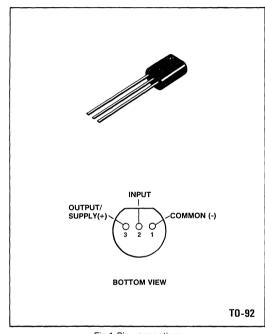

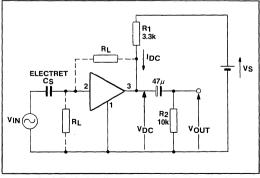

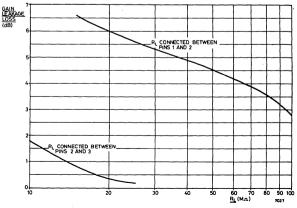

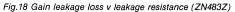

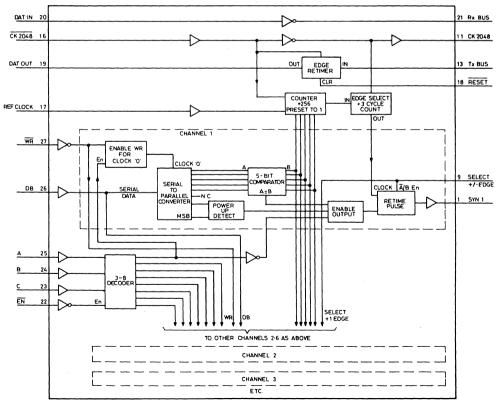

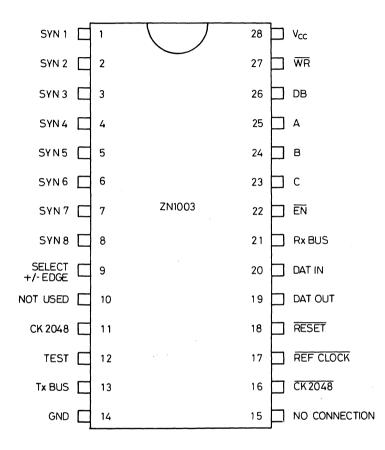

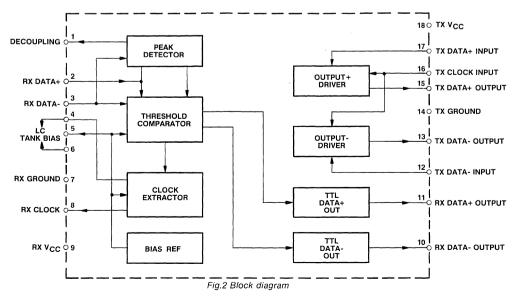

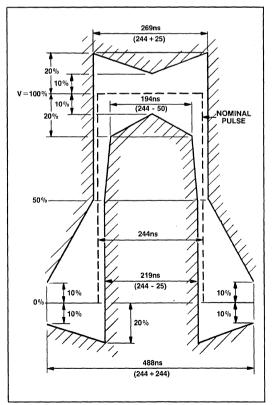

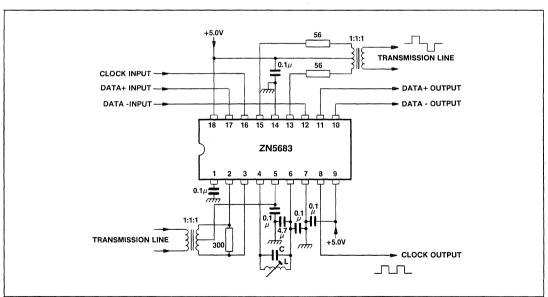

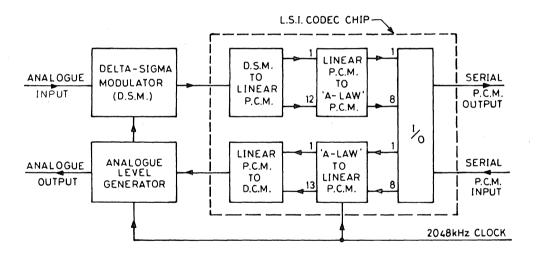

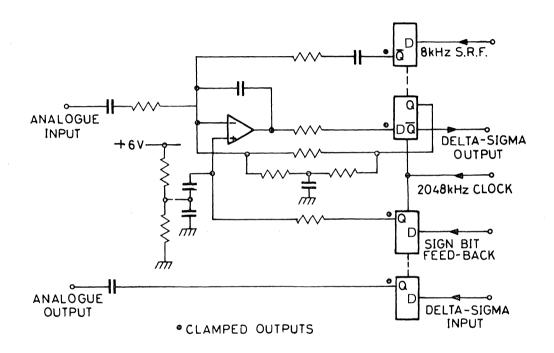

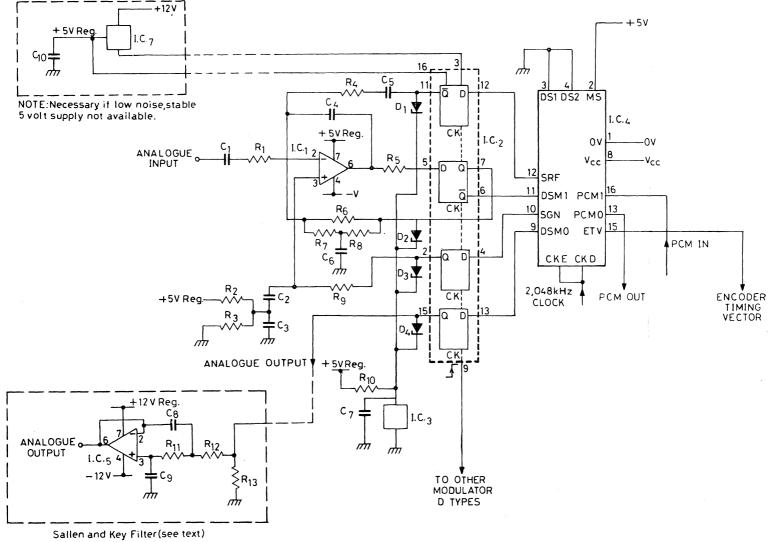

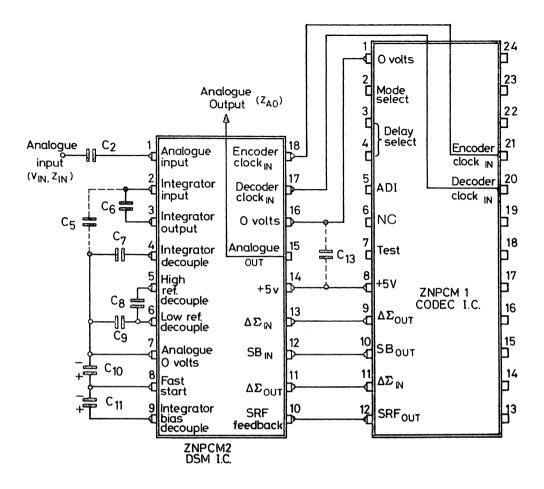

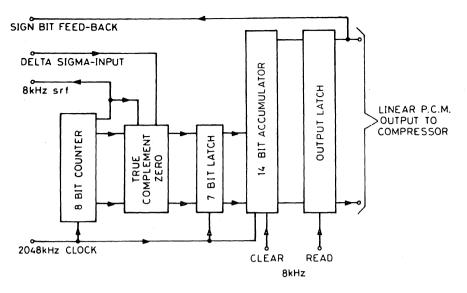

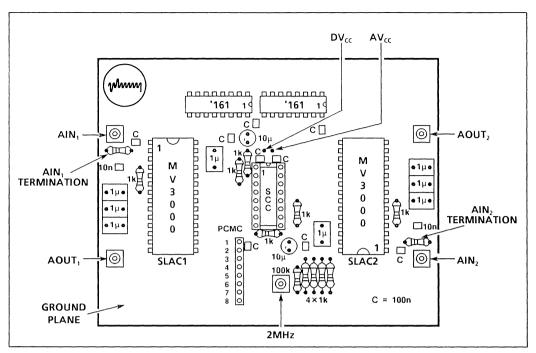

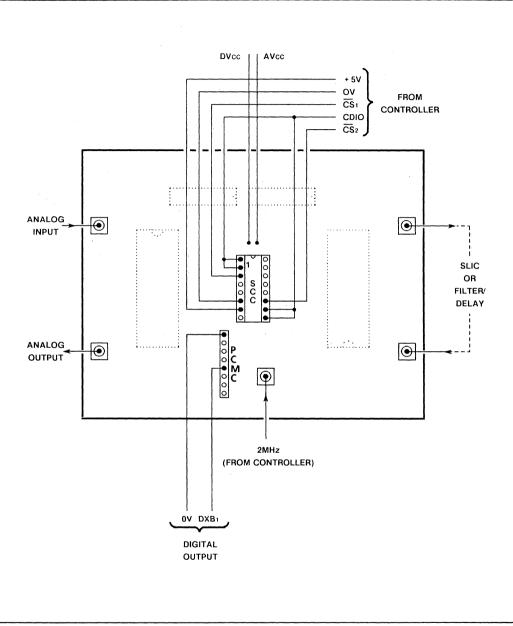

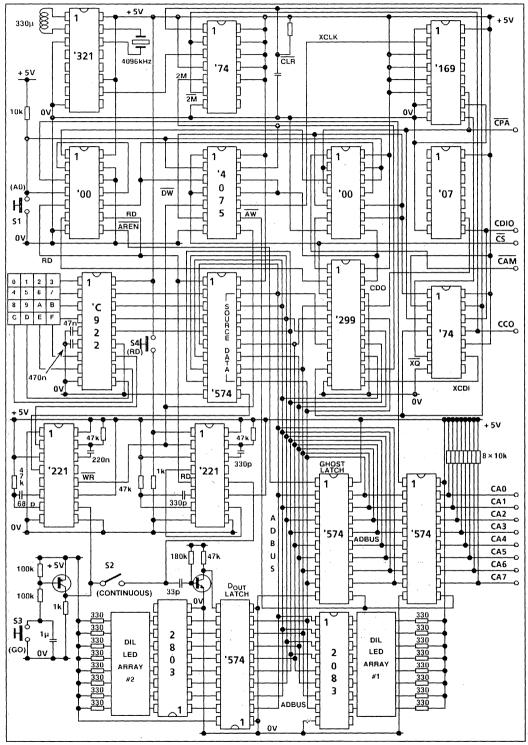

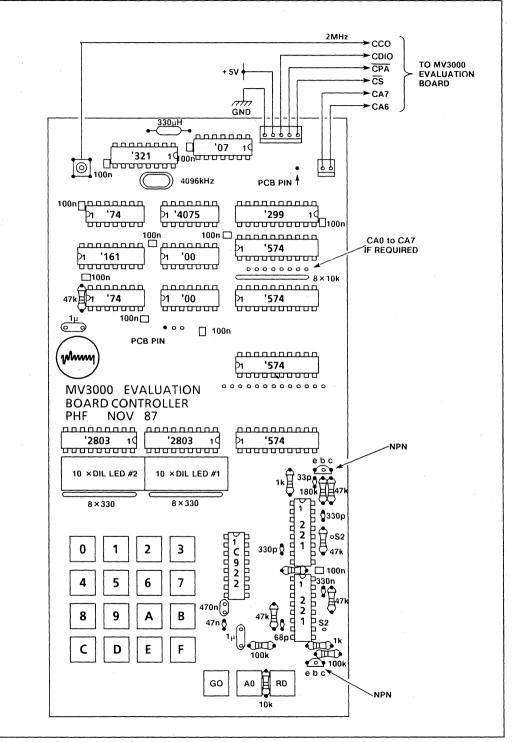

#### 7. AMI Data in/out