TELECOMMS INTEGRATED CIRCUIT HANDBOOK

ductors

KAR

### TELECOMS INTEGRATED CIRCUIT HANDBOOK

© The Plessey Company plc 1985 Publication No. P.S. 1913 December 1985

This publication is issued to provide outline information only and (unless specifically agreed to the contrary by the Company in writing) is not to be reproduced or to form part of any order or contract or to be regarded as a representation relating to the products or services concerned. Any applications of products shown in this publication are for illustration purposes only and do not give or imply any licences or rights to use the information for any purposes whatsoever. It is the responsibility of any person who wishes to use the application information to obtain any necessary licence for such use. We reserve the right to alter without notice the specification, design, price or

conditions of supply of any product or service. PLESSEY and the Plessey symbol, Plessey Megacell, Plessey Microcell, Plessey Paracell and Plessey Supracell are registered trademarks of The Plessey Company plc.

# Contents

|                                   | Page |

|-----------------------------------|------|

| Product index                     | 5    |

| Selection guide                   | 6    |

| The quality concept               | 7    |

| Screening to BS9400               | 8    |

| Plessey Hi-Rel screening          | 9    |

| Semi-custom design                | 10   |

| Plessey Megacell                  | 11   |

| Thermal design                    | 12   |

| Technical data                    | 15   |

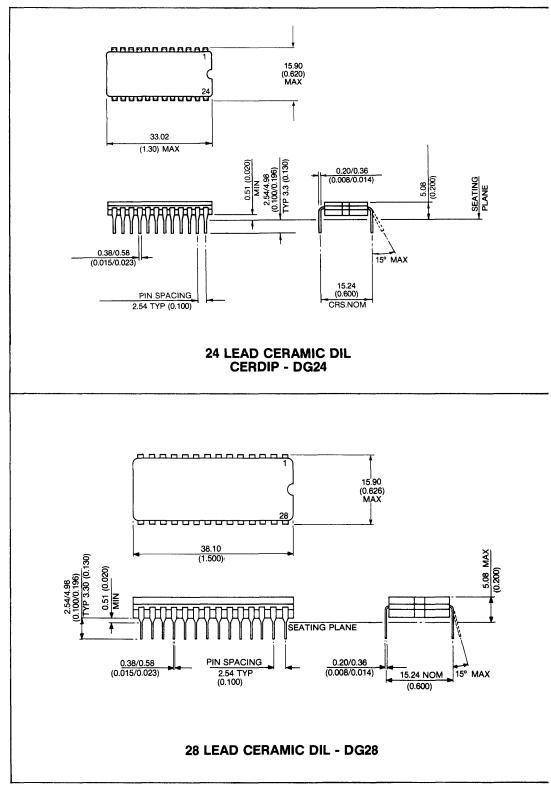

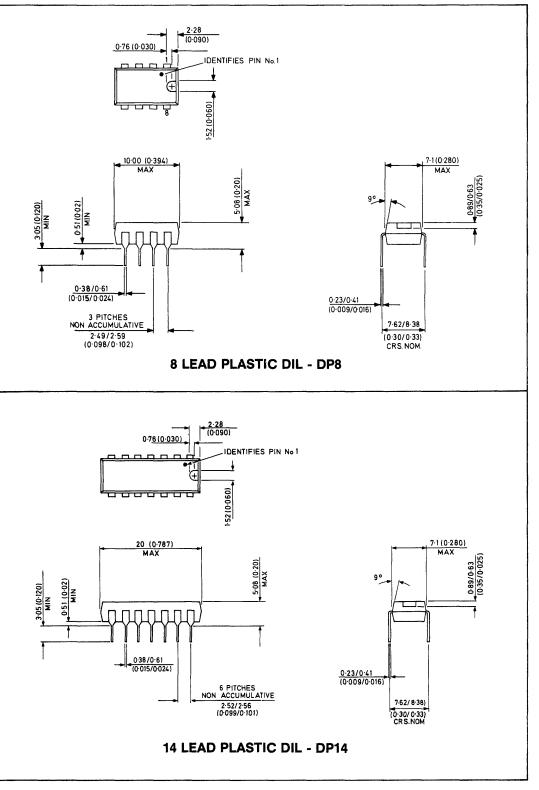

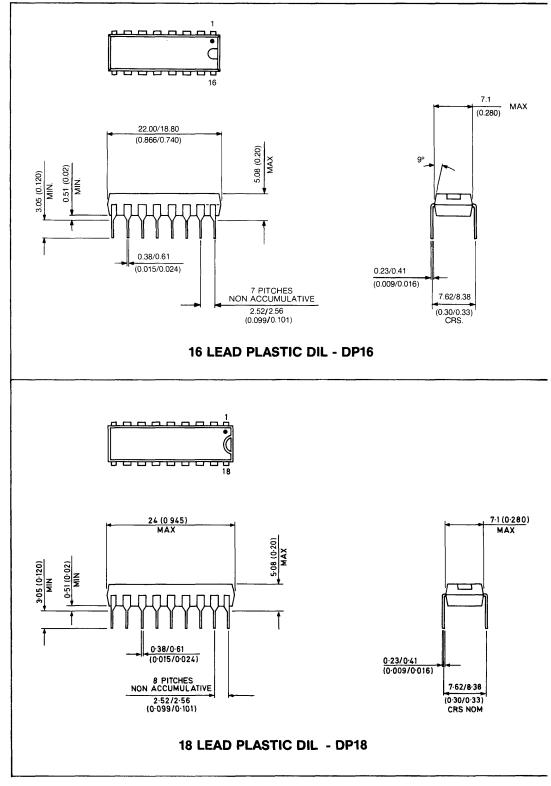

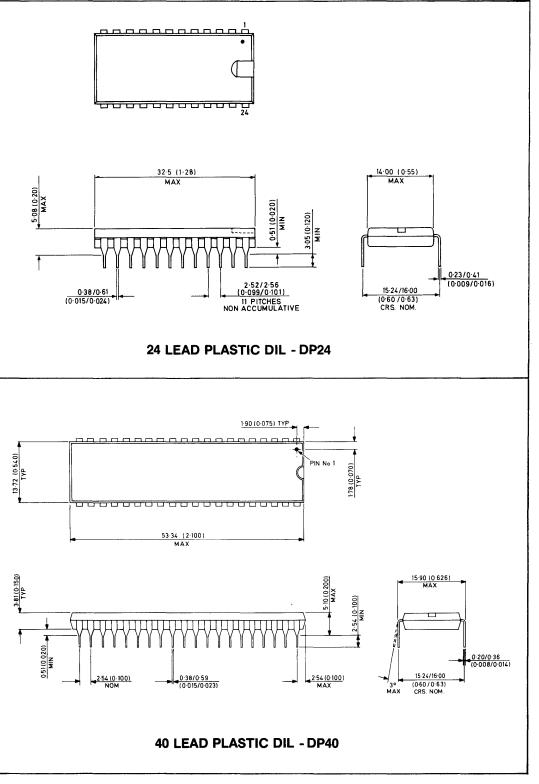

| Package outlines                  | 181  |

| Ordering information              | 188  |

| Plessey Semiconductors World-Wide | 189  |

## **Product** index

| TYPE NO.              | DESCRIPTION                                                                                  | PAGE       |

|-----------------------|----------------------------------------------------------------------------------------------|------------|

| N-channel             | MOS                                                                                          |            |

| MJ1410                | 8-bit format converter                                                                       | 17         |

| MJ1440                | HDB3 encoder/decoder                                                                         | 23         |

| MJ1444                | Time slot zero transmitter                                                                   | 29         |

| MJ1445                | Time slot zero receiver                                                                      | 33         |

| MJ1446<br>MJ1471      | Time slot access<br>AM1/HDB3 encoder/decoder                                                 | 37<br>41   |

| MJ1472                | PCM receiving circuit                                                                        | 47         |

| MJ1473                | PCM transmitter circuit                                                                      | 51         |

| MJ1474                | PCM elastic store                                                                            | 55         |

| N-channel             | silicon gate                                                                                 |            |

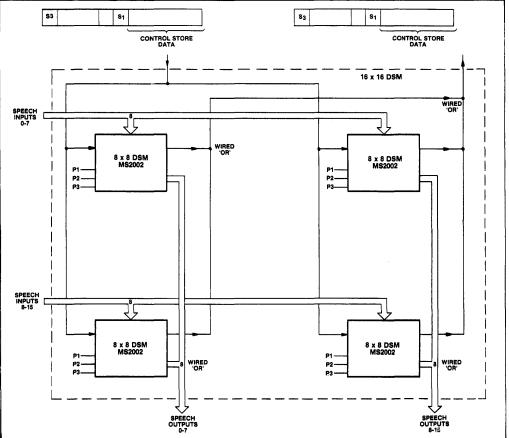

| MS2002EXP             | Digital switch module (DSM) for CCITT 32-channel PCM                                         | 59         |

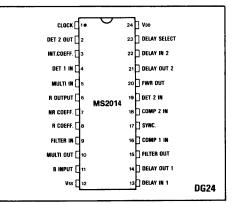

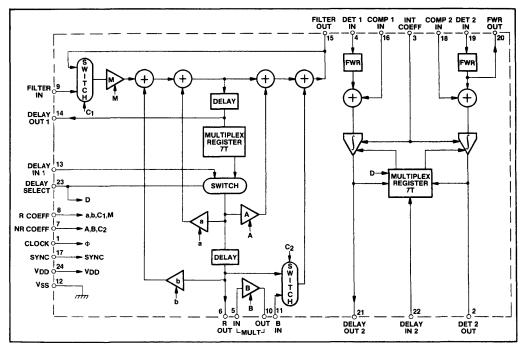

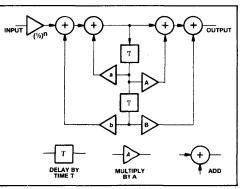

| MS2014                | Digital filter and detector (FAD)                                                            | 67         |

| CMOS                  |                                                                                              |            |

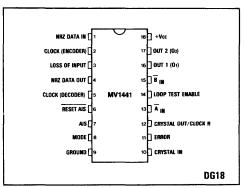

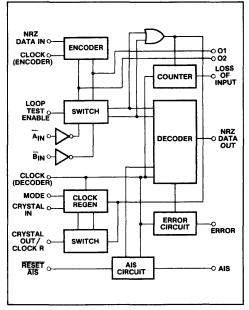

| MV1441                | HDB3 encoder/decoder/clock regenerator                                                       | 75         |

| MV1448                | HDB3 encoder/decoder                                                                         | 81         |

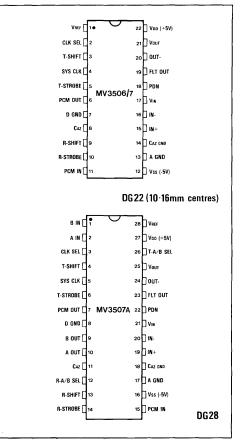

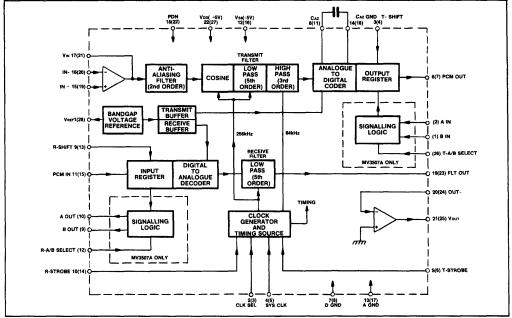

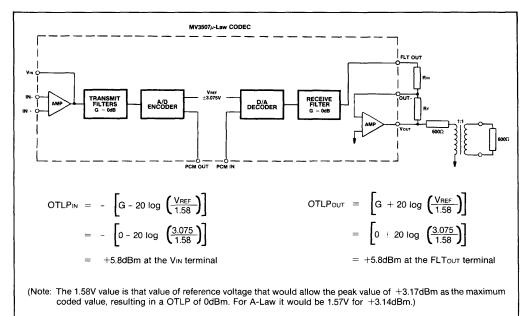

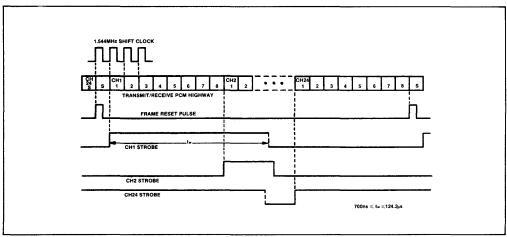

| MV3506                | A-law codec with filter                                                                      | 87         |

| MV3507                | $\mu$ -law codec with filter and $\Lambda/\mathbb{R}$ signalling                             | 87         |

| MV3507A<br>MV4320     | $\mu$ -law codec with filter and A/B signalling<br>Keypad pulse dialler with M1 masking      | 87<br>99   |

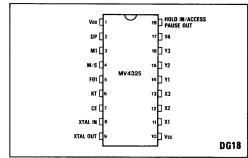

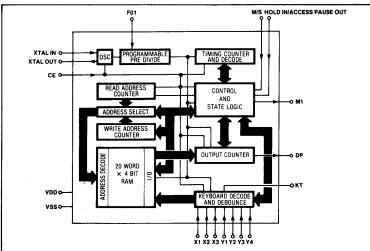

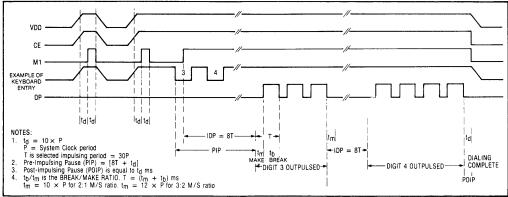

| MV4325                | Programmable keypad pulse dialler with M1 masking                                            | 103        |

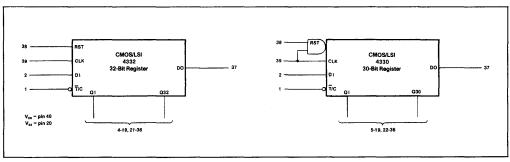

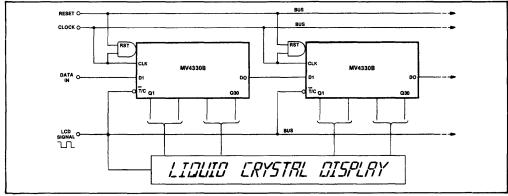

| MV4330                | 30-bit static shift register/LCD driver                                                      | 109        |

| MV4332                | 32-bit static shift register/LCD driver                                                      | 109        |

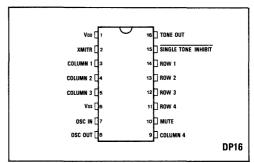

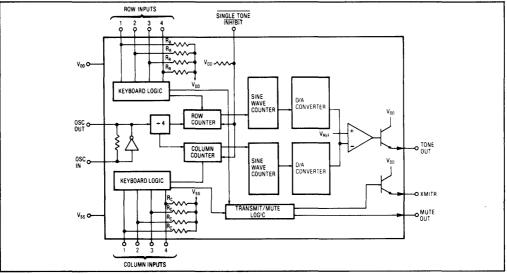

| MV5087                | DTMF generator                                                                               | 113        |

| MV5089                | DTMF generator                                                                               | 119        |

| MV8804                | 8 x 4 analog switch array                                                                    | 125        |

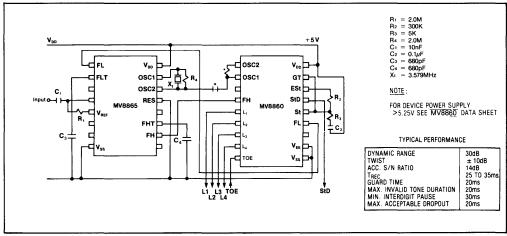

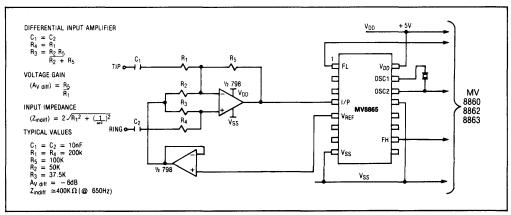

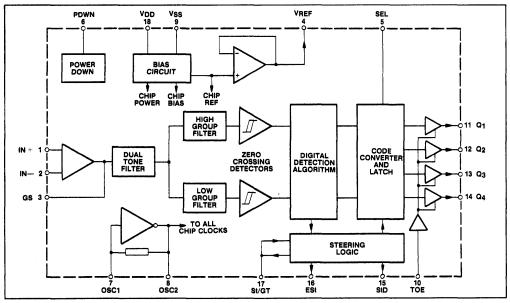

| MV8860                | DTMF decoder with 4-bit binary output                                                        | 131        |

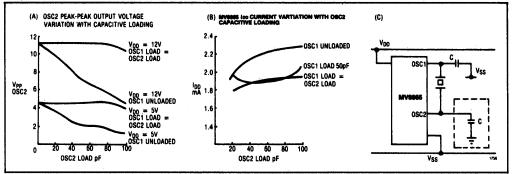

| MV8865<br>MV8870EXP   | DTMF filter<br>DTMF receiver                                                                 | 139<br>145 |

| MV9009EXP             | V21 modem TX/RX                                                                              | 145        |

| Bipolar               |                                                                                              | 100        |

| SL650B,C              | Modulator/phase lock loop circuits for modems                                                | 159        |

| SL651B,C              | Modulator/phase lock loop circuits for modems                                                | 159        |

| SL652C                | Modulator/phase lock loop                                                                    | 163        |

| SL8204                | Telephone tone ringer                                                                        | 167        |

| SL9009EXP             | Adaptive cancellation filter                                                                 | 171        |

| SP1404BW              | High voltage interface circuit                                                               | 175        |

| D3702                 | High voltage interface circuit to BT Spec.                                                   | 175        |

| SP1450B               | 34Mbit/s PCM signal monitor                                                                  | 177        |

| SP1450B(B)<br>SP1455B | As SP1450B but screened to MIL-STD-883, Method 5004, Class B                                 | 177<br>177 |

| SP1455B(B)            | 140Mbit/s PCM signal monitor<br>As SP1455B but screened to MIL-STD-883, Method 5004, Class B | 177        |

| . ,                   |                                                                                              |            |

EXP products are new designs designated 'Experimental' but which are, nevertheless, serious development projects. Details given may, therefore, change without notice and no undertaking is given or implied as to future availability. Please consult your local Plessey sales office for details of the current status

# Selection guide

| JEICI                 | uon guiae                                                                                   |            |

|-----------------------|---------------------------------------------------------------------------------------------|------------|

| TYPE NO.              | DESCRIPTION                                                                                 | PAGE       |

| NMOS PCN              | I circuits                                                                                  |            |

| MJ1410                | 8-bit format converter                                                                      | 17         |

| MJ1440                | HDB3 encoder/decoder                                                                        | 23         |

| MJ1444<br>MJ1445      | Time slot zero transmitter<br>Time slot zero receiver                                       | 29<br>33   |

| MJ1446                | Time slot access                                                                            | 33         |

| MJ1471                | AM1/HDB3 encoder/decoder                                                                    | 41         |

| MJ1472                | PCM receiving circuit                                                                       | 47         |

| MJ1473                | PCM transmitter circuit                                                                     | 51         |

| MJ1474                | PCM elastic store                                                                           | 55         |

| CMOS PCN              | 1 circuits                                                                                  |            |

| MV1441                | HDB3 encoder/decoder/clock regenerator                                                      | 75         |

| MV1448                | HDB3 encoder/decoder                                                                        | 81         |

| MV3506                | A-law codec with filter                                                                     | 87         |

| MV3507<br>MV3507A     | $\mu$ -law codec with filter<br>$\mu$ -law codec with filter and A/B signalling             | 87<br>87   |

|                       |                                                                                             | 07         |

|                       | communications circuits                                                                     |            |

| SL8204                | Tone ringer                                                                                 | 167        |

| SP1450B               | 34Mbit/s PCM signal monitor<br>As SP1450B but screened to MIL-STD-883, Method 5004, Class B | 177<br>177 |

| SP1450B(B)<br>SP1455B | 140Mbit/s PCM signal monitor                                                                | 177        |

| SP1455B(B)            | As SP1455B but screened to MIL-STD-883, Method 5004, Class B                                | 177        |

| Interface ci          | rcuite                                                                                      |            |

| SP1404BW              | High voltage interface                                                                      | 175        |

| D3702                 | High voltage interface (BT Spec.)                                                           | 175        |

|                       |                                                                                             |            |

|                       | phone dialling circuits - loop disconnect                                                   | 00         |

| MV4320<br>MV4325      | Keypad pulse dialler with M1 masking<br>Programmable keypad pulse dialler with M1 masking   | 99<br>103  |

|                       |                                                                                             | 100        |

|                       | phone dialling circuits - DTMF/MF4                                                          |            |

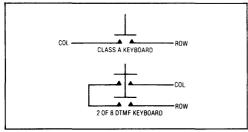

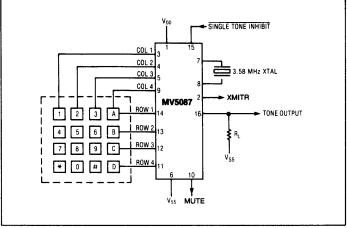

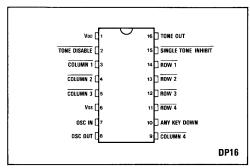

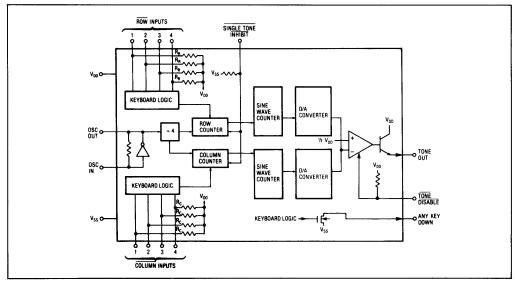

| MV5087                | DTMF generator (Form A keypad)                                                              | 113        |

| MV5089<br>MV8860      | DTMF generator (active keypad)<br>DTMF decoder with 4-bit binary output                     | 119<br>131 |

| MV8865                | DTMF filter                                                                                 | 139        |

| MV8870EXP             | DTMF receiver (combined filter and decoder)                                                 | 145        |

| Signal proc           | essing and switching                                                                        |            |

| MS2002EXP             | 256 x 256 digital switch module for CCITT 32-channel PCM                                    | 59         |

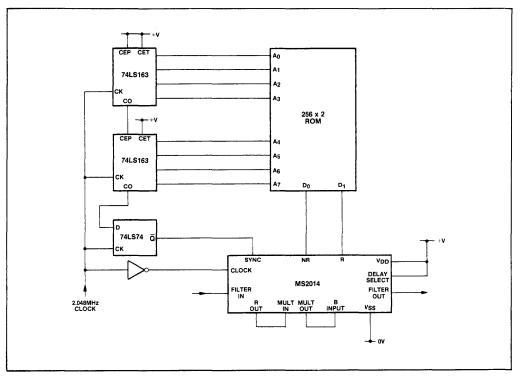

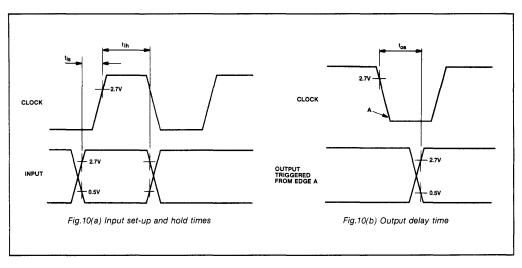

| MS2002LXF             | Digital filter and detector (FAD)                                                           | 67         |

| MV8804                | Bi-directional 8 x 4 analog switch array                                                    | 124        |

| Data trans            | nission modems                                                                              |            |

| MV9009EXP             | V21 modem RX/TX                                                                             | 153        |

| SL9009EXP             | Adaptive cancellation filter                                                                | 171        |

| SL650B,C              | Modulator/PLL                                                                               | 159        |

| SL651B,C              | Modulator/PLL                                                                               | 159        |

| SL652C                | Modulator/PLL                                                                               | 163        |

| CMOS inte             | rface circuits                                                                              |            |

| MV4330                | 30-bit static shift register/LCD driver                                                     | 109        |

| MV4332                | 32-bit static shift register/LCD driver                                                     | 109        |

| 6                     |                                                                                             |            |

# The quality concept

In common with most semiconductor manufacturers, Plessey Semiconductors perform incoming piece parts check, in-line inspections and final electrical tests. However, quality cannot be inspected into a product; it is only by careful design and evaluation of materials, parts and processes - followed by strict control and ongoing assessment to ensure that design requirements are still being met - that quality products will be produced.

In line with this philosophy, all designs conform to standard layout rules (evolved with performance and reliability in mind), all processes are thoroughly evaluated before introduction and all new piece part designs and suppliers are investigated before authorisation for production use.

The same basic system of evaluation, appraisals and checks is used on all products up to and including device packing for shipment. It is only at this stage that extra operations are performed for certain customers in terms of lot qualification or release procedure.

By working to common procedures for materials and processes for all types of customers advantages accrue to all users - the high reliability user gains the advantage of scale hence improving the confidence factor in the quality achieved whilst the large scale user gains the benefits associated with basic high reliability design concepts.

Plessey Semiconductors have the following factory approvals. **BS9300** and **BS9400** (BSI Approval No. 1053/M).

DEF-STAN 05-21 (Reg. No. 23H POD).

In addition a number of U.S., European and British customers manufacturing electronics for space have approved our facilities.

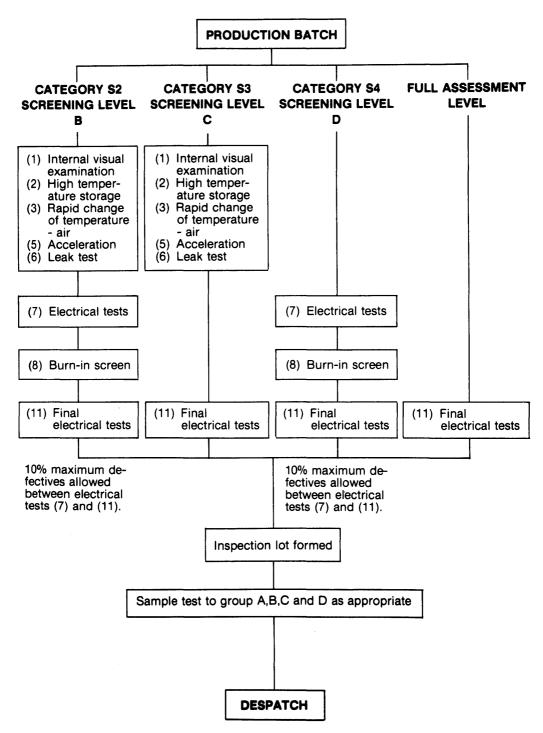

## Screening to BS9400

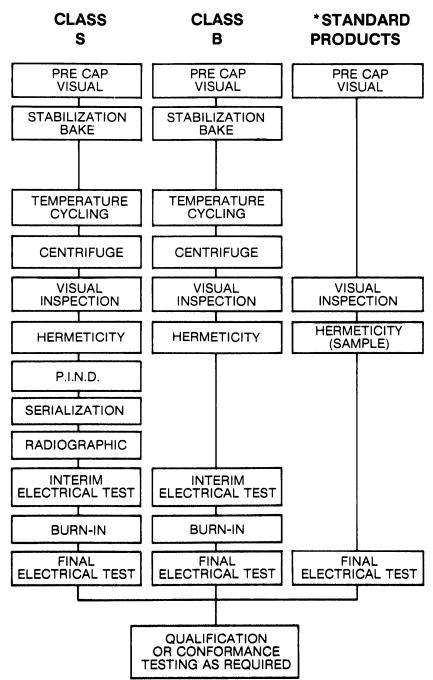

# Plessey Hi-Rel screening

The following Screening Procedures are available from Plessey Semiconductors.

\* Plessey Semiconductors reserve the right to change the Screening Procedure for Standard Products.

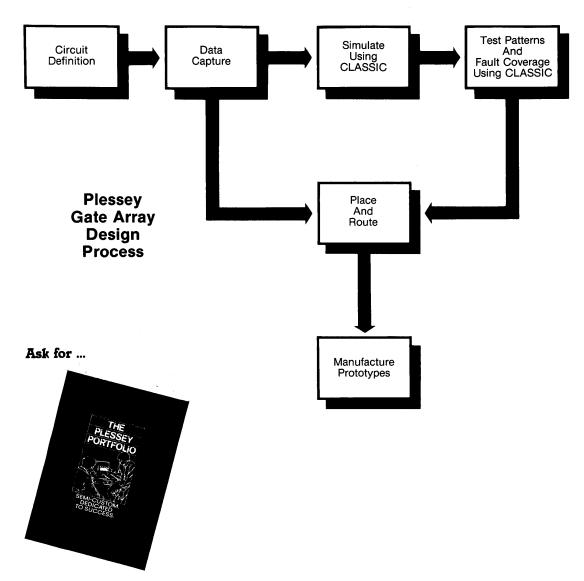

# Semi-custom design

Plessey Semiconductors' advanced work in the Semi-Custom field enables us to offer our customers the opportunity to develop their own high performance circuits using our CLASSIC software. Among the many advantages are:

• CLASSIC is cost effective and user friendly • Prototypes in 6 weeks • Close coordination with customer throughout design and production process • State-of-the-art high performance produces • Up to 10044 gates available

### Microgate-C (Si-Gate CMOS)

#### **CLA 2000 SERIES**

- Double layer metallisation

- 5 micron channel length

- Product family: CLA 21XX 840 Gates CLA 23XX 1400 Gates CLA 25XX 2400 Gates

- 7ns max. prop delay (2 input NAND fanout of 2 with 2mm track 0-70°C 4.5-5.5V)

- 14MHz system clock rate

- 30MHz toggle rate

- Fully auto-routed

#### **CLA 3000 SERIES**

- Double layer metallisation

- 4 micron channel length

- Product family: CLA 31XX 840 Gates CLA 33XX 1440 Gates CLA35XX 2400 Gates CLA 37XX 4200 Gates CLA 39XX 6000 Gates

- 5ns max. prop delay

- 20MHz system clock rate

- 50MHz toggle rate

- · Fully auto-routed

#### **CLA 5000 SERIES**

- Double layer metallisation

- 2 micron channel length

- Product family: CLA 51XX 640 Gates CLA 52XX 1232 Gates CLA 53XX 2016 Gates CLA 54XX 3060 Gates CLA 55XX 4408 Gates CLA 56XX 5984 Gates CLA 58XX 8064 Gates CLA 59XX 10044 Gates

- 2.5ns max. prop delay

- 40MHz system clock rate

- 100MHz toggle rate

- Fully auto-routed

## Plessey Megacell™

Now there's a VLSI design system available that's perfect for solving your Application Specific Integrated Circuit (ASIC) problems. It's **PLESSEY MEGACELL** - a complete set of advanced computer-aided engineering and design tools coupled with an advanced CMOS process for implementing VLSI integrated circuits in the system design environment.

**PLESSEY MEGACELL** redefines semicustom integrated circuit design. It allows system engineers to design complex circuits with a high level of confidence of first time success in silicon - thanks to one of the best simulation facilities available in the world. This greatly reduces time to market, eliminating the many prototyping iterations that are all too common now in VLSI design.

**PLESSEY MEGACELL** is just about as close as you can get to achieving hand-crafted results short of full custom itself. System engineers can directly create their designs using the advanced layout and routing tools provided - without the aid of integrated circuit designers. So none of the system designers' application expertise is ever lost in transition, while chips of the smallest size and lowest production cost are regularly achieved.

Supporting the **PLESSEY MEGACELL** design capability is one of the most advanced CMOS processes available. It uses a 2-micron geometry capable of providing performance comparable with advanced Schottky TTL, with clock speeds to 40MHz and toggle rates of 100MHz achievable. And Plessey has established a 200,000 square foot dedicated processing facility to guarantee the manufacturing capacity required by even the most aggressive volume considerations.

**PLESSEY MEGACELL** is truly the gateway to the future - custom VLSI performance, with confidence of first time success and fast time to market. And it's going to stay that way - with Plessey's commitment to add future capabilities for high-speed ECL processes, 1 micron and submicron CMOS processes, and advanced analog capabilities.

# Thermal design

The temperature of any semiconductor device has an important effect upon its long term reliability. For this reason, it is important to minimise the chip temperature; and in any case, the maximum junction temperature should not be exceeded.

Electrical power dissipated in any device is a source of heat. How quickly this heat can be dissipated is directly related to the rise in chip temperature: if the heat can only escape slowly, then the chip temperature will rise further than if the heat can escape quickly. To use an electrical analogy: energy from a constant voltage source can be drawn much faster by using a low resistance load than by using a high resistance load.

The thermal resistance to the flow of heat from the semiconductor junction to the ambient temperature air surrounding the package is made up of several elements. These are the thermal resistance of the junction-to-case, case-to-heatsink and heatsink-to-ambient interfaces. Of course, where no heatsink is used, the case-to-ambient thermal resistance is used.

These thermal resistances may be represented as

$\begin{array}{l} \theta_{ja} = \theta_{jc} + \theta_{ch} + \theta_{ha} \\ \text{where } \theta_{ja} \text{ is thermal resistance junction-to-ambient }^\circ\text{C/W} \\ \theta_{jc} \text{ is thermal resistance junction-to-case }^\circ\text{C/W} \\ \theta_{ch} \text{ is thermal resistance case-to-heatsink }^\circ\text{C/W} \\ \theta_{ha} \text{ is thermal resistance heatsink-to-ambient }^\circ\text{C/W} \end{array}$

The temperature of the junction is also dependent upon the amount of power dissipated in the device — so the greater the power, the greater the temperature.

Just as Ohm's Law is applied in an electrical circuit, a similar relationship is applicable to heatsinks.

$T_j = T_{amb} + P_D(\theta_{ja})$

T<sub>j</sub> = junction temperature

$T_{amb} = ambient temperature$

P<sub>D</sub> = dissipated power

From this equation, junction temperature may be calculated, as in the following examples.

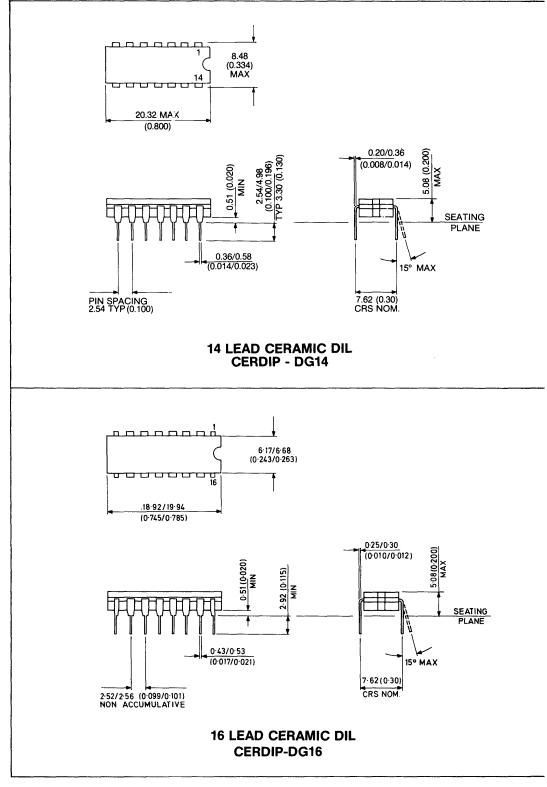

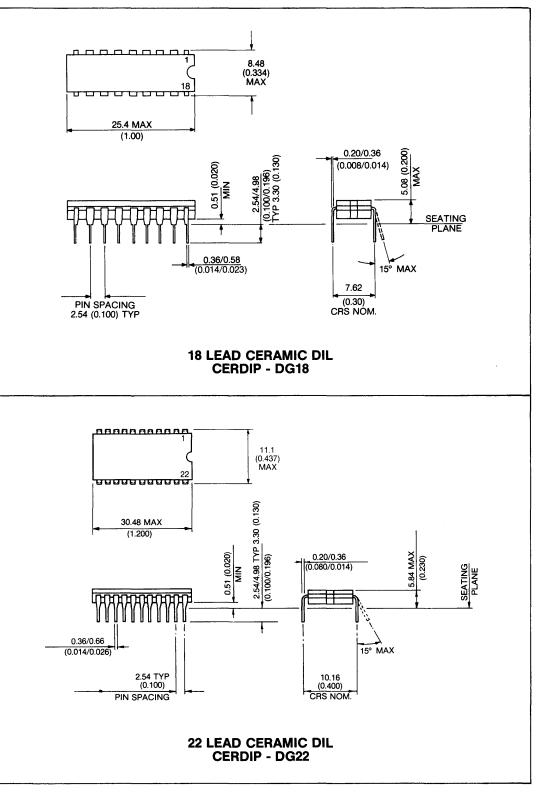

#### Example 1

A device is to be used at an ambient temperature of  $+50^{\circ}$  C.  $\theta_{ja}$  for the DG14 package with a chip of approximately 1mm sq is 107° C/W. Assuming the datasheet for the device gives P<sub>D</sub> = 330mW and T<sub>j</sub> max = 175° C.

$T_{j} = T_{amb} + P_{D} \theta_{ja}$ = 50 + (0.33 x 107) = 85.31°C (typ.)

Where operation in a higher ambient temperature is necessary, the maximum junction temperature can easily be exceeded unless suitable measures are taken:

### Thermal design (cont'd)

#### Example 2

A device with  $T_{amb}$  max. = +175° C is to be used at an ambient temperature of +150° C. Again,  $\theta_{ja} = 107^{\circ}$  C/W, P<sub>D</sub> = 330mW and T<sub>j</sub> max. = +175° C.

$T_j = 150 + (0.33 \times 107)$ = +185.3°C (typ.)

This clearly exceeds the maximum permissible junction temperature and therefore some means of decreasing the junction-to-ambient thermal resistance is required.

As stated earlier,  $\theta_{ia}$  is the sum of the individual thermal resistances; of these,  $\theta_{ic}$  is fixed by the design of device and package and so only the case-to-ambient thermal resistance,  $\theta_{ca}$ , can be reduced.

If  $\theta_{ca}$ , and therefore  $\theta_{ja}$ , is reduced by the use of a suitable heatsink, then the maximum  $T_{amb}$  can be increased:

#### Example 3

Assume that an IERC LIC14A2U dissipator and DC000080B retainer are used. This device is rated as providing a  $\theta_{ja}$  of 55° C/W for the DG14 package. Using this heatsink with the device operated as in Example 2 would result in a junction temperature given by:

$T_j = 150 + (0.33 \times 55)$ = 168° C

Nevertheless, it should be noted that these calculations are not necessarily exact. This is because factors such as  $\theta_{jc}$  may vary from device type to device type, and the efficacy of the heatsink may vary according to the air movement in the equipment.

In addition, the assumption has been made that chip temperature and junction temperature are the same thing. This is not strictly so, as not only can hot spots occur on the chip, but the thermal conductivity of silicon is a variable with temperature, and thus the  $\theta_{jc}$  is in fact a function of chip temperature. Nevertheless, the method outlined above is a practical method which will give adequate answers for the design of equipment.

It is possible to improve the dissipating capability of the package by the use of heat dissipating bars under the package, and various proprietary items exist for this purpose.

Under certain circumstances, forced air cooling can become necessary, and although the simple approach outlined above is useful, more factors must be taken into account.

# Technial data

#### **8 BIT FORMAT CONVERTER**

The MJ1410 is realised in N-channel MOS technology and operates from a single 5V supply. The circuit can be clocked from d.c. up to 2.5MHz and has 3-state output buffers capable of driving two LSTTL loads. All inputs are TTL compatible.

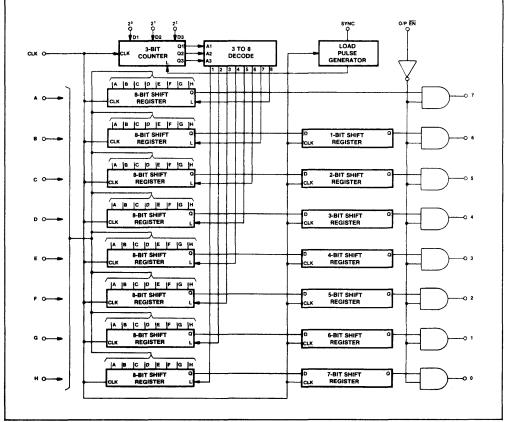

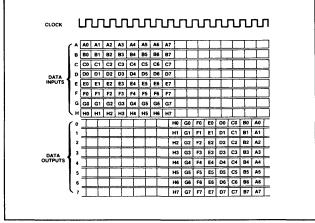

The MJ1410 performs the complementary functions of serial-to-parallel and parallel-to-serial data conversion on 8 bits of data. Both these conversions are achieved using the same time-position matrix, which has eight inputs and eight outputs.

An 8-bit parallel word clocked into the eight inputs appears as a serial 8-bit data stream on one of the eight outputs. Successive parallel words at the inputs appear as serial data streams on each of the eight outputs in turn.

Conversely, a serial 8-bit data stream on one of the eight inputs appears as an 8-bit parallel word on the eight outputs. Successive parallel words appearing at the eight outputs correspond to the serial data on each of the eight inputs in rotation.

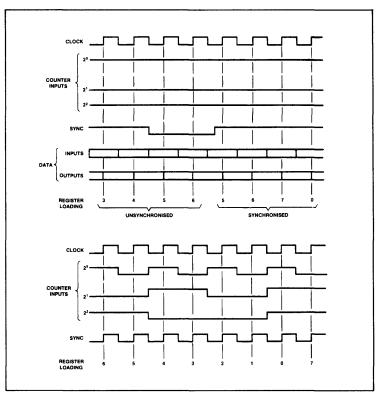

The conversion can be 'programmed' to start in any register by setting the appropriate binary value on the counter pre-load inputs and applying a pulse to the Sync input. If the loading sequence produced by the counter is not required it can be disabled by connecting 'clock' to 'sync'. At each positive clock edge the register loaded will depend on the data on the counter inputs on the previous positive clock edge.

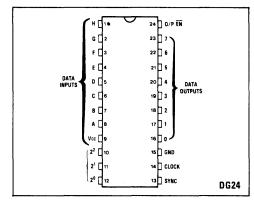

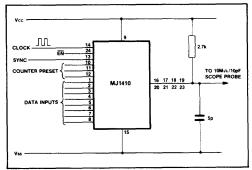

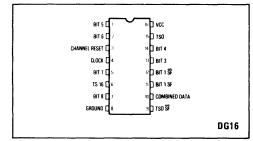

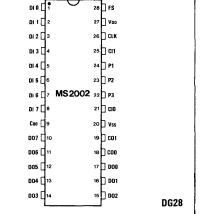

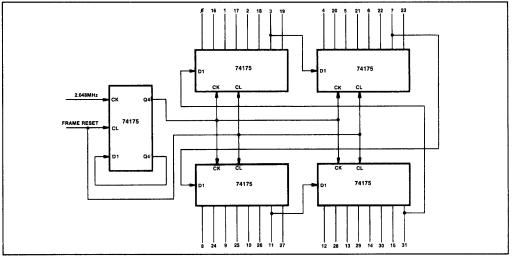

Fig.1 Pin connections

#### FEATURES

- Single 5V supply.

- Three-state outputs.

- All inputs TTL compatible.

| Pin No.                                                        | Title                                                                           | Function                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11          | H<br>G<br>F<br>E<br>D<br>C<br>B<br>A<br>Vcc<br>2 <sup>2</sup><br>2 <sup>1</sup> | Data i/p H<br>Data i/p G<br>Data i/p F<br>Data i/p D<br>Data i/p D<br>Data i/p C<br>Data i/p B<br>Data i/p A<br>Positive supply, 5V ± 5%<br>Counter preset i/p bit 2<br>Counter preset i/p bit 2<br>Counter preset i/p bit 2<br>Counter preset i/p bit 1<br>Counter preset i/p bit 1                                                                                                                                |

| 12<br>13                                                       | 20<br>SYNC                                                                      | Counter preset i/p bit 0 / negative edge on the 'sync' input.<br>A negative edge on this i/p initiates the counter preset sequence which                                                                                                                                                                                                                                                                            |

| 14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>22<br>23 | CLOCK<br>GND<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7                            | causes the conversion cycle to start in the register which corresponds to the<br>binary value of the counter preset i/ps.<br>System clock<br>Zero volts<br>Three state data o/p '0'<br>Three state data o/p '1'<br>Three state data o/p '2'<br>Three state data o/p '3'<br>Three state data o/p '3'<br>Three state data o/p '5'<br>Three state data o/p '6'<br>Three state data o/p '6'<br>Three state data o/p '7' |

| 24                                                             | O/P EN                                                                          | A logic '1' on this i/p forces all the data outputs to a high impedance state.                                                                                                                                                                                                                                                                                                                                      |

#### FUNCTIONAL DESCRIPTION

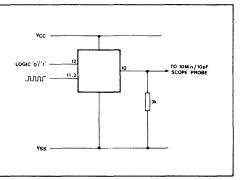

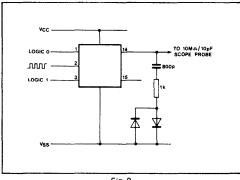

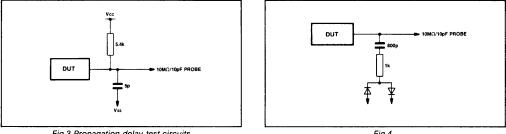

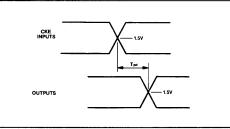

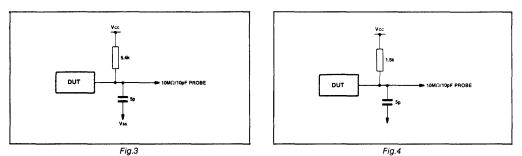

#### ELECTRICAL CHARACTERISTICS

Test conditions (unless otherwise stated): Vcc = 5V, T<sub>amb</sub> = 22°C ± 2°C, Test circuit: Fig. 6. Supply voltage Vcc 5V ± 10% Ambient operating temperature T<sub>amb</sub> -10°C to +70°C

#### STATIC CHARACTERISTICS

| Characteristic                                     | Symbol | Pins                                          |      | Value |      | Units | Conditions      |

|----------------------------------------------------|--------|-----------------------------------------------|------|-------|------|-------|-----------------|

| Characteristic                                     | Symbol | F103                                          | Min. | Тур.  | Max. | Units | Conditions      |

| Low level I/P<br>voltage                           | VıL    | 1,2,3,4,<br>5,6,7,8,<br>10,11,12,<br>13,14,24 | -0.3 |       | 0.8  | Volts |                 |

| High level I/P<br>voltage                          | Viн    | 1,2,3,4,<br>5,6,7,8,<br>10,11,12,<br>13,14,24 | 2.5  |       | Vcc  | Volts |                 |

| Low level I/P<br>current/high level<br>I/P current | lin    | 1,2,3,4,<br>5,6,7,8,<br>10,11,12,<br>13,14,24 |      | . 1   | 50   | ЦЦ    |                 |

| Low level O/P<br>voltage                           | Vol    | 16,17,18,<br>19,20,21,<br>22,23               |      |       | 0.5  | Volts | ISYNC = 1.6mA   |

| High level O/P<br>voltage                          | Vон    | 16,17,18,<br>19,20,21,<br>22,23               | 2.5  |       |      | Volts | Isource = 100uA |

| Low level O/P<br>current sink capa-<br>bility      | łοι    | 16,17,18,<br>19,20,21,<br>22,23               | -1.6 |       |      | mA    |                 |

| High level O/P<br>current source<br>capability     | ЮН     | 16,17,18,<br>19,20,21,<br>22,23               | 100  |       |      | μA    |                 |

| OFF state O/P<br>current                           | IOFF L | 16,17,18,<br>19,20,21,<br>22,23               |      |       | 40   | ДЦ    | Vout = GND      |

|                                                    | IOFF H | 16,17,18,<br>19,20,21,<br>22,23               |      |       | -40  | μA    | Vout = Vcc      |

| Power dissipation                                  | Poiss  |                                               | 90   |       | 500  | mW    | Vcc = 5.5V      |

#### DYNAMIC CHARACTERISTICS

| Ohana stanistia Durah                                    |        |      | Value |      |       | -          |

|----------------------------------------------------------|--------|------|-------|------|-------|------------|

| Characteristic                                           | Symbol | Min. | Тур.  | Max. | Units | Conditions |

| Max.clock frequency                                      | Fmax.  | 2.4  |       | 10   | MHz   |            |

| Min. clock frequency                                     | Fmin.  | 0    |       |      | MHz   |            |

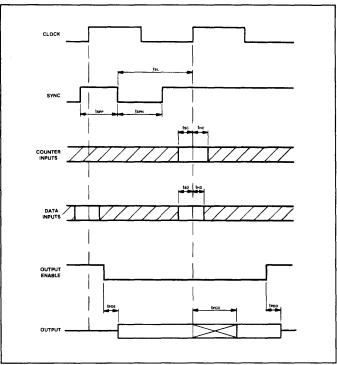

| Sync. pulse width<br>(positive)                          | tspp   | 60   |       |      | ns    | Fig. 6     |

| Sync. pulse width<br>(negative)                          | tspn   | 100  |       |      | ns    | Fig. 6     |

| Lead of sync. clocking<br>edge on positive clock<br>edge | tsı    | 130  |       |      | ns    | Fig. 6     |

| Set up time of counter inputs (20,21,22)                 | tsc    | 70   |       |      | ns    | Fig. 6     |

| Hold time of counter inputs                              | tнc    | 60   |       |      | ns    | Fig. 6     |

| Set up time of data inputs (A-H)                         | tsp    | 80   |       |      | ns    | Fig. 6     |

#### **DYNAMIC CHARACTERISTICS**

| Characteriatio                                                     | Chal          |      | Value |      | 11-14- | Conditions |  |

|--------------------------------------------------------------------|---------------|------|-------|------|--------|------------|--|

| Characteristic                                                     | Symbol        | Min. | Тур.  | Max. | Units  |            |  |

| Hold time of data inputs                                           | tнo           | 85   |       |      | ns     | Fig. 6     |  |

| Propagation delay, data<br>out valid from output<br>ENABLE low     | tpoe .        |      |       | 100  | ns     | Fig. 6     |  |

| Propagation delay, data<br>out disabled from output<br>ENABLE high | tрор          |      |       | 100  | ns     | Fig. 6     |  |

| Propagation delay, clock to data out valid                         | t <b>p</b> cb |      |       | 200  | ns     | Fig. 6     |  |

Fig.2 Block diagram

#### **ABSOLUTE MAXIMUM RATINGS**

Voltage on any pin w.r.t. ground = 7V max. Storage temperature = -55°C to +125°C

Fig.3 Data conversion

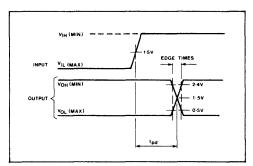

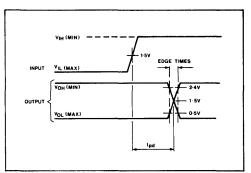

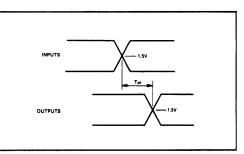

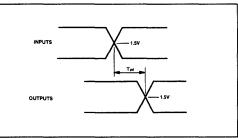

Fig.4 Input and output waveforms

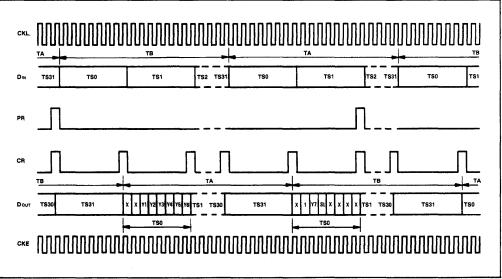

Fig.5 Timing details

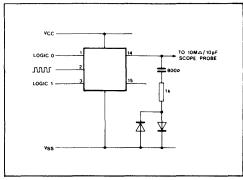

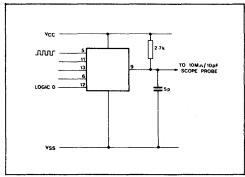

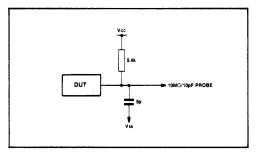

Fig.6 Test conditions

### 2 MBIT PCM SIGNALLING CIRCUIT MJ 1440 HDB3 ENCODER/DECODER

The 2.048 MBit PCM Signalling Circuits comprise a group of circuits which will perform the common signalling and error detection functions for a 2.048 MBit PCM transmission link operating to the appropriate CCITT recommendations. The circuits are fabricated in N-channel metal gate MOS and operate from a single 5 volt supply, relevant inputs and outputs are TTL compatible.

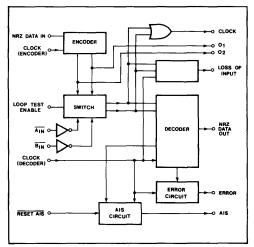

The MJ1440 is an encoder/decoder for the pseudoternary transmission code, HDB3 (CCITT Orange Book Vol III.2 Annex to Rec. G703). The device encodes and decodes simultaneously and asynchronously. Error monitoring functions are provided to detect violations of HDB3 coding, all ones detection and loss of input (all zeroes detection). In addition a loop back function is provided for terminal testing.

#### FEATURES

- 5v ± 5% Supply 50mA Max

- HDB3 Encoding and Decoding to CCITT rec. G703.

- Asynchronous Operation.

- Simultaneous Encoding and Decoding.

- Clock Recovery Signal Generated from Incoming HDB3 Data.

- Loop Back Control.

- HDB3 Error Monitor

- 'All Ones' Error Monitor

- Loss of Input Alarm (All Zeros Detector).

- Decode Data in NRZ Form.

#### **ABSOLUTE MAXIMUM RATINGS**

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded.

#### **Electrical Ratings**

| +Vcc    | 7V                    |

|---------|-----------------------|

| Inputs  | Vcc + 0.5V Gnd - 0.3V |

| Outputs | Vcc, Gnd –0.3V        |

#### **Thermal Ratings**

| Max Junction Temperature 175°C   |              |

|----------------------------------|--------------|

| Thermal Resistance: Chip to Case | Chip to Amb. |

| 40°C/Watt                        | 120°C/Watt   |

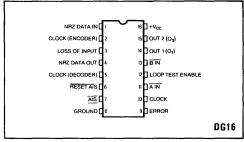

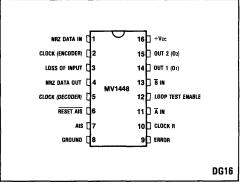

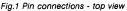

Fig. 2 Block diagram

#### **ELECTRICAL CHARACTERISTICS**

### Test conditions (unless otherwise stated): Supply voltage, $V_{CC} = 5V \pm 0.25V$ Ambient temperature, $T_{amb} = 0^{\circ}C$ to $+70^{\circ}C$

#### Static characteristics

| Characteristic                                                                                                                           | Symbol                                                                          | Pins                                                                    |                          | Value |                                           | Units                             | Conditions                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------|-------|-------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                          | Symbol                                                                          | F1115                                                                   | Min                      | Тур   | Max                                       | Units                             | Conditions                                                                                                                    |

| Low level input voltage                                                                                                                  | V <sub>IL</sub>                                                                 |                                                                         | -0.3                     |       | 0.8                                       | v                                 |                                                                                                                               |

| Low level input current<br>High level input voltage<br>High level input current<br>Low level output voltage<br>High level output voltage | I <sub>IL</sub><br>VIH<br>I <sub>IH</sub><br>V <sub>OL</sub><br>V <sub>OH</sub> | 1,2,5,6<br>10,11,12,13<br>10,14,15<br>3,4,7,9<br>3,4,7,9<br>14,15<br>10 | 2.5<br>2.7<br>2.8<br>2.8 |       | 50<br>V <sub>cc</sub><br>50<br>0.5<br>0.4 | μΑ<br>ν<br>μΑ<br>ν<br>ν<br>ν<br>ν | $V_{IL} = 0V$<br>$V_{IH} = 5V$<br>$Isink = 80\mu A$<br>Isink = 1.6mA<br>$Isource = 60\mu A$<br>Isource = 2mA<br>Isource = 1mA |

| Supply current                                                                                                                           | I <sub>cc</sub>                                                                 |                                                                         |                          | 20    | 50                                        | mA                                | All inputs to 0V<br>All outputs open circuit                                                                                  |

#### **Dynamic Characteristics**

| Characteristic                                                     | Symbol              |      | Valu |      | Units | Conditions                            |  |

|--------------------------------------------------------------------|---------------------|------|------|------|-------|---------------------------------------|--|

|                                                                    | Symbol              | Mín. | Тур. | Max. | Units | Conditions                            |  |

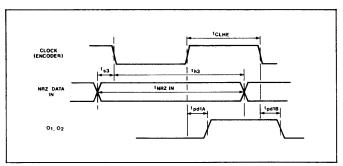

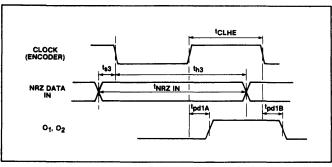

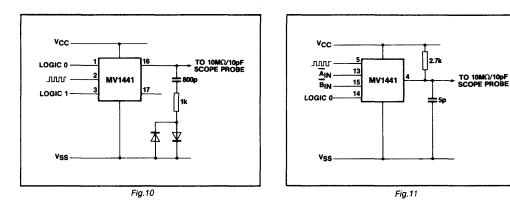

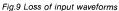

| Max. Clock (Encoder) frequency                                     | fmax <sub>enc</sub> | 4.0  |      |      | MHz   | Figs.10, 15                           |  |

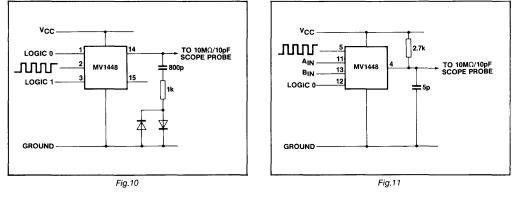

| Max. Clock (Decoder) frequency                                     | fmax <sub>dec</sub> | 2.2  |      |      | MHz   | Figs.11, 15                           |  |

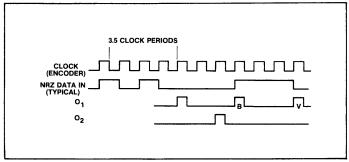

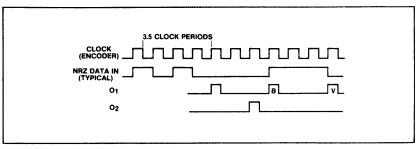

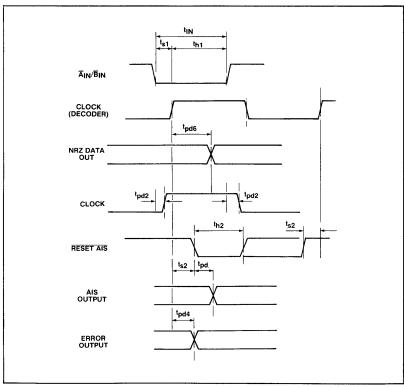

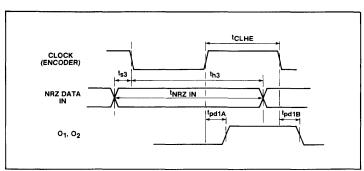

| Propagation delay Clock (Encoder) to $O_1, O_2$                    | tpd1A/B             |      |      | 100  | ns    | Figs.10, 15. See Note 1               |  |

| Rise and Fall times $O_1, O_2$                                     |                     |      |      | 20   | ns    | Figs.10, 15                           |  |

| tpd1A-tpd1B                                                        |                     |      |      | 20   | ns    | Figs.10, 15                           |  |

| Propagation delay Clock (Encoder) to Clock                         | tpd3                |      |      | 150  | ns    | Loop test enable = Figs.13, 15        |  |

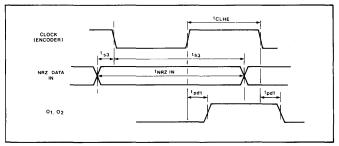

| Setup time of NRZ data in to Clock (Encoder)                       | ts3                 | 30   |      |      | ns    | Figs.8, 10, 15                        |  |

| Hold time of NRZ data in                                           | th3                 | 55   |      |      | ns    | Figs.10, 15                           |  |

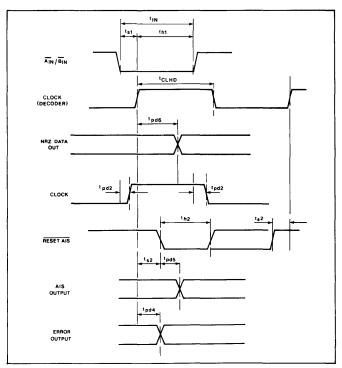

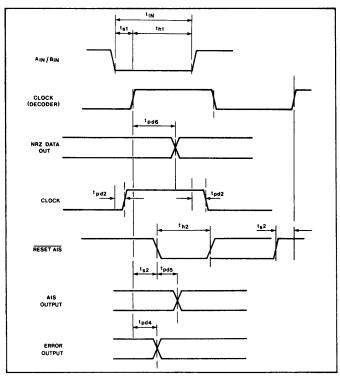

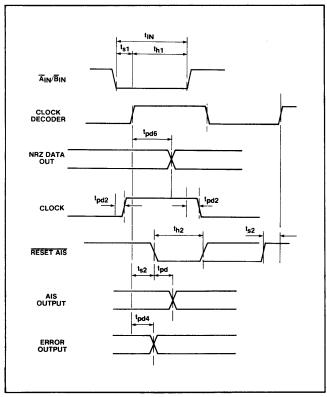

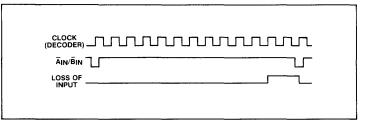

| Propagation delay A <sub>in</sub> , B <sub>in</sub> to Clock       | tpd2                |      |      | 150  | ns    | Loop test enable = '0' Figs.9, 13, 15 |  |

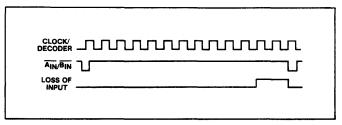

| Propagation delay Clock (Decoder) to loss of input                 |                     |      |      | 150  | ns    |                                       |  |

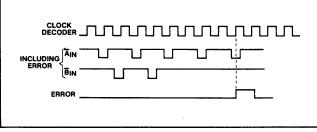

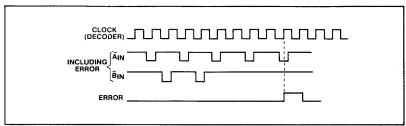

| Propagation delay Clock (Decoder) to error                         | tpd4                |      |      | 200  | ns    | Figs.12, 15                           |  |

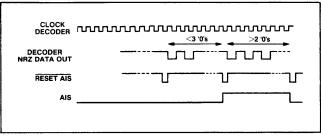

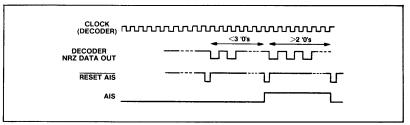

| Propagation delay Reset AIS to AIS                                 | tpd5                |      |      | 200  | ns    | Loop test enable = '0' Figs.14, 15    |  |

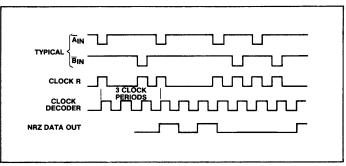

| Propagation delay Clock (Decoder) to NRZ data out                  | tpd6                |      |      | 150  | ns    | Figs.9, 11, 15. See Note 2            |  |

| Setup time of A <sub>in</sub> , B <sub>in</sub> to Clock (Decoder) | ts1                 | 75   |      |      | ns    | Figs.9, 11, 15                        |  |

| Hold time of A <sub>in</sub> , B <sub>in</sub> to Clock (Decoder)  | th1                 | 5    |      |      | ns    | Figs.9, 11, 15                        |  |

| Hold time of Reset AIS = '0'                                       | th2                 | 100  |      |      | ns    | Figs.9, 14, 15                        |  |

| Setup time Clock (Decoder) to Reset AIS                            | ts2                 | 200  |      |      | ns    | Figs.9, 14, 15                        |  |

| Setup time Reset AIS = 1 to Clock (Decoder)                        | ts2                 | 0    |      |      | ns    | Figs.14, 15                           |  |

NOTES

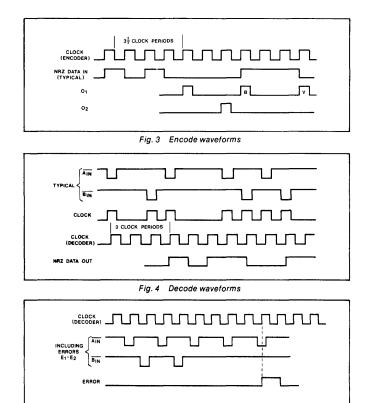

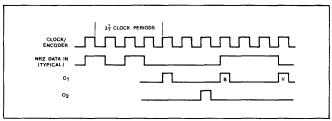

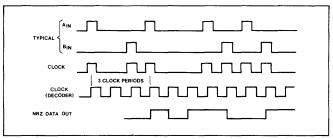

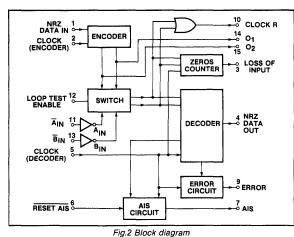

Encoded HDB3 outputs (O<sub>1</sub>, O<sub>2</sub>) are delayed by 3½ clock periods from NRZ data in (Fig.3).

The decoded NRZ output is delayed by 3 clock periods from the HDB3 inputs (A<sub>IN</sub>, B<sub>IN</sub>) (Fig.4).

#### FUNCTIONAL DESCRIPTION

#### Functions Listed by pin number

#### 1. NRZ Data in

Input data for encoding into ternary HDB3 form. The NRZ data is clocked by the negative edge of the Clock (Encoder).

#### 2. Clock (Encoder)

Clock for encoding data on pin 1

#### 3. Loss of input alarm

This output goes to logic '1' if eleven consecutive zeroes are detected in the incoming HDB3 data. The output is set to logic '0' on receipt of a '1'.

#### 4. NRZ data out

Decoded data in NRZ form from ternary HDB3 input data  $(A_{in}, B_{in})$ , data is clocked out by positive going edge of clock (Decoder).

#### 5. Clock (Decoder)

Clock for decoding ternary data Ain, Bin.

#### 6, 7. Reset AIS, AIS

Logic '0' on Reset AIS resets a decoded zero counter and either resets AIS outputs to zero provided 3 or more zeroes have been decoded in the preceding Reset AIS = 1 period or sets AIS to '1' if less than 3 zeroes have been decoded in the preceding two Reset AIS = 1 periods.

Logic '1' on Reset AIS enables the internal decoded zero counter.

#### 8. Ground

Zero volts

#### 9. Error

A logic '1' indicates that a violation of the HDB3 coding has been received i.e. 3 '1's of the same polarity. **10. Clock**

'OR' function of  $\overline{A_{in}}, \overline{B_{in}}$  for clock regeneration when pin 12 = '0', 'OR' function of  $O_1, O_2$  when pin 12 = '1'. 11,13.  $\overline{A_{in}}, \overline{B_{in}}$

Inputs representing the received ternary HDB3 PCM signal.  $\overline{A_{in}} = '0'$  represents a positive going '1',  $\overline{B_{in}} = '0'$  represents a negative going '1',  $\overline{A_{in}}$  and  $\overline{B_{in}}$  are sampled by the positive going edge of the Clock (Decoder).  $\overline{A_{in}}$  and  $\overline{B_{in}}$  may be interchanged.

#### 12. Loop test enable

Input to select normal or loop back operation. Pin 12 = '0' selects normal operation, encode and decode are independent and asynchronous. When pin 12 = '1' O<sub>1</sub> is connected internally to A<sub>in</sub>. O<sub>2</sub> is connected internally to B<sub>in</sub>. Clock becomes the OR function O<sub>1</sub> + O<sub>2</sub>. The delay from NRZ in to NRZ out is 6% clock periods in the loop back condition.

#### 14, 15. O1, O2

Outputs representing the ternary encoded data for line transmission  $O_1 = 11$  representing a positive going 11,  $O_2 = 11$  represents a negative going 11,  $O_1$  and  $O_2$  may be interchanged.

**16.**  $V_{\infty}$ Positive supply, 5V ± 5%

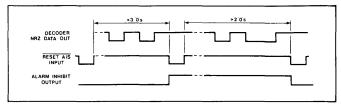

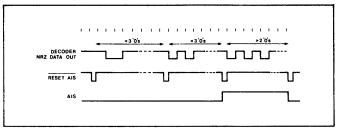

Fig. 5 HDB3 error output waveforms

Fig. 6 AIS error and reset waveforms

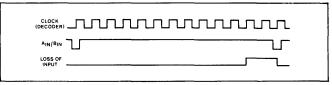

Fig. 7 Loss of input waveforms

Fig. 8 Encoder timing relationship

Fig. 9 Decoder timing relationship

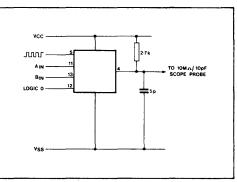

Fig. 10

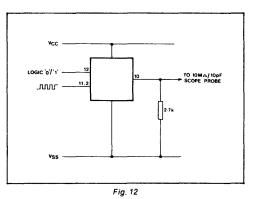

Fig. 12

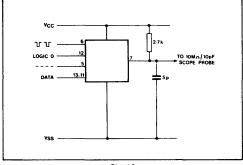

Fig. 14

#### **DEFINITION OF THE HDB3 CODE**

Coding of a binary signal into an HDB3 signal is done according to the following rules:

1. The HDB3 signal is psuedo-ternary; the three states are denoted  $B_{+}$ ,  $B_{-}$  and  $O_{-}$

2. Spaces in the binary signal are coded as spaces in the HDB3 signal. For strings of four spaces however, special rules apply (see 4. below).

3. Marks in the binary signal are coded alternately as B<sub>+</sub> and B<sub>-</sub> in the HDB3 signal (alternate mark inversion). Violations of the rule of alternate mark inversion are introduced when coding strings of four spaces (see 4. below).

4. Strings of four spaces in the binary signal are coded according to the following rules:

a The first space of a string is coded as a space if the

Fig. 13

Fig. 15 Test timing definitions

preceding mark of the HDB3 signal has a polarity opposite to the polarity of the preceding violation and is not a violation by itself; it is coded as a mark, i.e. not a violation (i.e.  $B_+$ ,  $B_-$ ), if the preceding mark of the HDB3 signal has the same polarity as that of the preceding violation or is by itself a violation.

This rule ensures that successive violations are of alternative polarity so that no DC component is introduced

**b** The second and third spaces of a string are always coded as spaces.

c The last space of a string of four is always coded as a mark, the polarity of which is such that it violates the rule of alternate mark inversion. Such violations are denoted  $V_{2}$  or  $V_{2}$  according to their polarity.

### 2 MBIT PCM SIGNALLING CIRCUIT MJ 1444

PCM SYNCHRONISING WORD GENERATOR

The 2.048 Mbit PCM signalling circuits comprise a group of circuits which will perform the common signalling and error detection functions for a 2.048 Mbit 30 channel PCM transmission link operating to the appropriate CCITT recommendations. The circuits are fabricated in N-channel metal gate MOS and operate from a single 5 volt supply. Relevant inputs and outputs are TTL compatible.

The MJ1444 generates the synchronising word in accordance with CCITT recommendations G732. The MJ1445 has been designed to detect this synchronising word when received at the remote end of the transmission system.

The synchronising word is injected onto the PCM data highway during time slot 0 in alternate frames. The spare time slot 0 data bits, bit 1 in every frame and bits 3 to 8 inclusive in alternate frames (i.e. those not containing the synchronising word) are available as parallel inputs and are output onto the PCM data highway.

The data output of the MJ1444 is 'open collector' and can be wire-OR'd directly onto the highway.

The device also provides a time slot 0 channel pulse 'TS0', time slot 0 non-sync. frame 'TS0 SF', and time slot 16 'TS16' outputs.

#### FEATURES

- 5V ± 5% Supply --- 20 mA Typical

- Fully Conforms to CCITT Recommendation G732

- Outputs Directly Onto PCM Data Highway

- Provides Both Time Slot 0 and Time Slot 16 Channel Pulses

- All Inputs and Outputs are TTL Compatible

Fig.1 Pin connections

#### **ABSOLUTE MAXIMUM RATINGS**

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded.

#### **Electrical Ratings**

| +Vcc    | 7V                    |

|---------|-----------------------|

| Inputs  | Vcc + 0.5V Gnd - 0.3V |

| Outputs | Vcc, Gnd -0.3V        |

#### Thermal Ratings

| Max Junction Temperature 175°C   |              |

|----------------------------------|--------------|

| Thermal Resistance: Chip to Case | Chip to Amb. |

| 35°C/Watt                        | 120°C/Watt   |

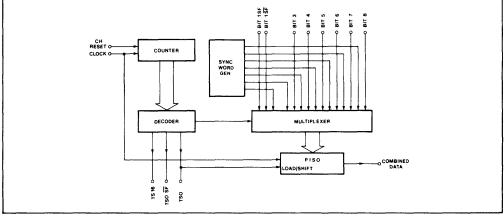

Fig.2 MJ1444 block diagram

#### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated): Supply voltage,  $V_{CC}=5\,V\pm0.25\,V$  Ambient operating temperature – 10°C to + 70°C

#### **Static Characteristics**

| Characteristic                                          | Sumbal          | Pins                                    | Value |      |                 | Units | Conditions                                         |

|---------------------------------------------------------|-----------------|-----------------------------------------|-------|------|-----------------|-------|----------------------------------------------------|

|                                                         | Symbol          | Pins                                    | Min.  | Typ. | Max.            | Units | Conditions                                         |

| Low level input voltage                                 | V <sub>IL</sub> | 1, 2, 3, 4, 5,<br>7, 11, 12, 13,<br>14. | -0.3  |      | 0.8             | v     |                                                    |

| Low level input current }<br>High level input current } | I <sub>IN</sub> | 11                                      |       | 1    | 50              | μA    |                                                    |

| High level input voltage                                | VIH             | 11                                      | 2.4   |      | V <sub>cc</sub> |       |                                                    |

| Low level output voltage                                | V <sub>o∟</sub> | 6, 9, 15<br>10                          |       |      | 0.5<br>0.7      | v     | l <sub>sink</sub> = 2mA<br>I <sub>sink</sub> = 5mA |

| High level output voltage                               | V <sub>OH</sub> | 6, 9, 15                                | 2.8   |      |                 | v     | I <sub>source</sub> = 200μA                        |

| High level output leakage current                       | I <sub>он</sub> | 10                                      |       |      | 20              | μA    | V <sub>OUT</sub> = V <sub>CC</sub>                 |

| Supply current                                          | I <sub>CC</sub> |                                         |       | 20   | 40              | mA    | $V_{CC} = 5.25 V$                                  |

#### **Dynamic Characteristics**

| Characteristic                                                           | Symbol Value     |      |      |      | Units | Conditions                     |  |

|--------------------------------------------------------------------------|------------------|------|------|------|-------|--------------------------------|--|

| Characteristic                                                           | Symbol           | Min. | Тур. | Max. | Units | Conditions                     |  |

| Max clock frequency                                                      | F <sub>max</sub> | 3    |      |      | MHz   |                                |  |

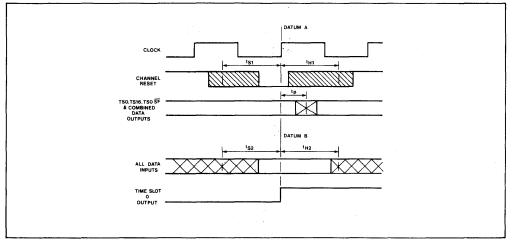

| Propagation delay, clock to TS0, TS0 SF, TS16 and combined data outputs. | tp               | 80   |      | 200  | ns    | See Figs.5 and 6               |  |

| Set up time channel reset to clock                                       | T <sub>S1</sub>  | 100  |      | 450  | ns    | f <sub>clock</sub> = 2.048 MHz |  |

| Hold time of channel reset input                                         | t <sub>H1</sub>  | 20   |      | 400  | ns    |                                |  |

| Set up time of bit 1 (SF) to datum B                                     | t <sub>s2</sub>  | 100  |      | 1    | ns    |                                |  |

| Hold time of bit 1 (SF) wrt datum B                                      | t <sub>H2</sub>  | 300  |      |      | ns    |                                |  |

| Set up time of bit 1 (SF) and data bits 3-8 to datum B                   | t <sub>s2</sub>  | 100  |      |      | ns    |                                |  |

| Hold time of bit 1 ( $\overline{SF}$ ) and data bits 3 – 8 wrt datum B   | t <sub>H2</sub>  | 300  |      |      | ns    |                                |  |

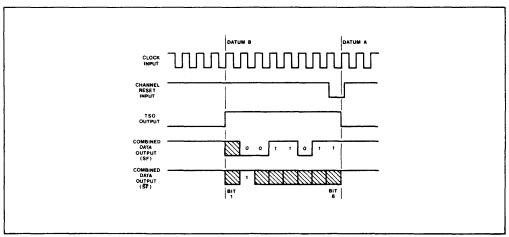

Fig.3 Data timing

#### **FUNCTIONAL DESCRIPTION**

#### Functions Listed by pin number

#### 1, 2, 5, 7, 13, 14. Bits 3 to 8

Parallel data on these inputs is asynchronously loaded into bits 3 to 8 of the PISO shift register for transmission during Time slot 0 of non-sync. frames.

#### 3. Channel Reset

A low going pulse at this input synchronises the MJ1444 with the other devices at the transmit end of the PCM link. It may be applied as a start pulse or repeated at the same instant in successive frames.

#### 4. Clock

System clock input (2.048 MHz for a 2 Mbit PCM system).

#### 6. TS16

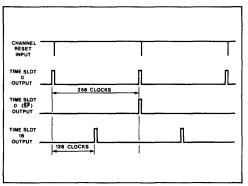

This output provides a positive pulse equivalent to 8 clock periods during time slot 16 of every 30 + 2 channel PCM frame.

#### 8. GND

Zero volts.

#### 9. TSO SF

This output provides a positive pulse equivalent to 8 clock periods during time slot 0 of non-sync. frames.

Fig.4 Sync. timing

#### 10. Combined data

This 'open collector' output injects the contents of the PISO shift register onto the PCM data highway during time slot 0 in successive frames. The contents of the PISO shift register are defined as follows:

|                 | Bit 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|-----------------|-------|---|---|---|---|---|---|---|

| Sync. Frame     | X     | 0 | 0 | 1 | 1 | 0 | 1 | 1 |

| Non-sync. frame | Х     | 1 | Х | X | Х | X | Х | Х |

X-indicates that these bits may be set according to the parallel data inputs.

#### 11. Bit 1 SF

Data on this input is asynchronously loaded into bit 1 of the PISO shift register for transmission during time slot 0 of sync. frames.

#### 12. Bit 1 SF

Data on this input is asynchronously loaded into bit 1 of the PISO shift register for transmission during time slot 0 of non-sync. frames.

#### 15. TS0

This output provides a positive pulse equivalent to 8 clock period during time slot 0 of every 30 channel PCM frame.

16.  $V_{cc}$ Positive supply, 5V ±5%.

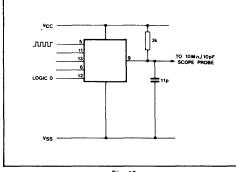

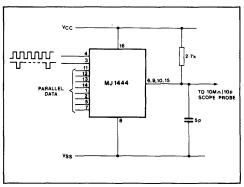

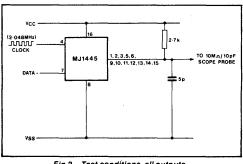

Fig.5 Test conditions (all outputs)

Fig.6 Timing definitions

### PCM SYNCHRONISING WORD RECEIVER

### MJ1445 2 MBIT PCM SIGNALLING CIRCUIT

The 2.048 Mbit PCM signalling circuits comprise a group of circuits which will perform the common signalling and error detection functions for a 2.048 MBit 30 channel PCM transmission link operating to the appropriate CCITT recommendations. The circuits are fabricated in N-channel metal gate MOS and operate from a single 5volt supply. Relevant inputs and outputs are TTL compatible.

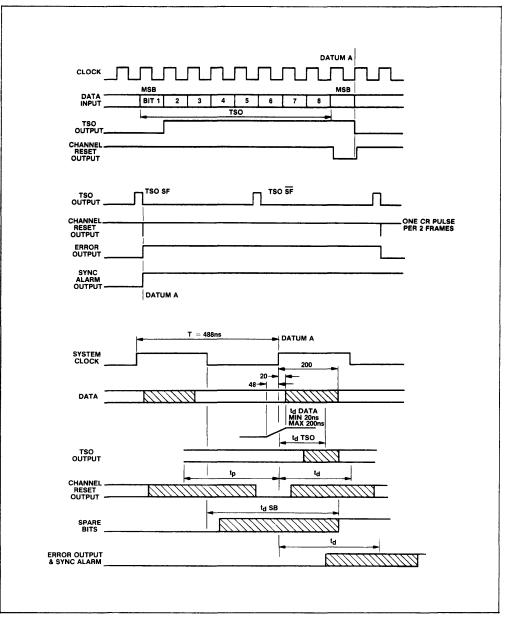

The MJ1445 establishes synchronisation by detecting the synchronising word when it is received at the remote end of the transmission system. The MJ1444 has been designed to generate this synchronisation word at the sending end of the system in accordance with CCITT recommendation G732.

Corruption of individual synchronisation words is signified by an 'Error' output, loss of synchronisation is indicated by a 'Sync Alarm' output and follows CCITT G732 in that loss of synchronism is assumed when 3 consecutive synchronisation words have been received with errors.

The 'Channel Reset' output goes low for the first period of the clock after time slot 0 in sync frames whenever the MJ1445 has established that the receiver terminal is in synchronisation in order that the rest of the receiver terminal may be reset.

The 'TSO' output is high for a period of 8 bits starting from the end of the first bit of the synchronising word. The spare data bits from the synchronising word are provided as parallel outputs.

#### **ABSOLUTE MAXIMUM RATINGS**

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded.

#### Electrical Ratings

| +Vcc    | 7V                    |

|---------|-----------------------|

| Inputs  | Vcc + 0.5V Gnd - 0.3V |

| Outputs | Vcc, Gnd –0.3V        |

|         |                       |

#### Thermal Ratings

| Max Junction Temperature 175°C   |              |

|----------------------------------|--------------|

| Thermal Resistance: Chip to Case | Chip to Amb. |

| 35°C/Watt                        | 120°C/Watt   |

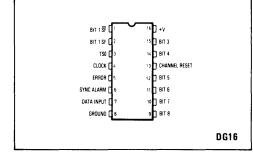

Fig.1 Pin connections

#### FEATURES

5V ± 5% Supply – 20 mA Typical.

- Conforms to CCITT Recommendation G732

- Synchronising Word Error Monitor

- Out of Sync. Alarm

- All Inputs and Outputs are TTL Compatible

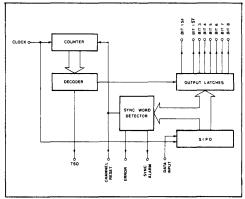

Fig.2 Block diagram MJ1445

#### **ELECTRICAL CHARACTERISTICS**

#### Test conditions (unless otherwise stated):

Supply voltage,  $V_{CC}$  = 5V  $\pm$  0.25V Ambient temperature,  $T_{amb}$  =  $-10^\circ C$  to  $+70^\circ C$

#### **Static Characteristics**

| Characteristic                              | C                                  | 01                                           |              | Value |      | Units | O an diki an a                                          |

|---------------------------------------------|------------------------------------|----------------------------------------------|--------------|-------|------|-------|---------------------------------------------------------|

|                                             | Symbol                             | Pins                                         | Min. Typ. Ma |       | Max. | Units | Conditions                                              |

| Low level input voltage                     | VIL                                | 4,7                                          | -0.3         |       | 0.8  | v     |                                                         |

| Low level input current                     | I <sub>IN</sub>                    | 4, 7                                         |              | 1     | 50   | μA    |                                                         |

| High level input voltage                    | ViH                                | 4, 7                                         | 2.4          |       | Vcc  | v     |                                                         |

| Low level output voltage                    | V <sub>ol</sub>                    | 1, 2, 3, 5, 6<br>9, 10, 11, 12<br>13, 14, 15 |              |       | 0.5  | v     | I <sub>sink</sub> =2mA                                  |

| High level output voltage<br>Supply current | V <sub>он</sub><br>I <sub>сс</sub> |                                              | 2.8          | 20    | 40   | mA    | I <sub>source</sub> = 200μ/<br>V <sub>CC</sub> = 5.25 V |

#### **Dynamic Characteristics**

| Characteristic                                                                | Symbol Value  |      |       | Units      | Conditions |                   |

|-------------------------------------------------------------------------------|---------------|------|-------|------------|------------|-------------------|

|                                                                               | Min. Typ. Max | Max. | Units | Conditions |            |                   |

| Max. clock frequency                                                          | fmax          | 2.2  |       |            | MHz        |                   |

| Input delay of data input                                                     | td data       | 20   |       | 200        | ns         | fclock = 2.048MHz |

| Propagation delay, clock to TS0 output                                        | ta TSO        | 40   |       | 200        | ns         | Fig.3             |

| Propagation delay clock to error output, sync alarm and CH. Reset output high | ta            | 50   |       | 400        | ns         | Fig.3             |

| Propagation delay, clock to CH.<br>Reset output low $(T - t_P)$               | tp            | 100  |       | 450        | ns         | Fig.3             |

| Propagation delay clock to spare bits                                         | td SB         | 50   |       | 300        | ns         | Fig.3             |

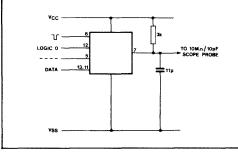

Fig.3 Test conditions, all outputs

#### **FUNCTIONAL DESCRIPTION**

#### Functions listed by pin number

#### 1. Bit 1 ŠF

This output is set to the level of data bit 1 during time slot 0 of non sync frames. The data becomes true on the first falling edge of the clock during TS1.

#### 2. Bit 1 SF

This output is set to the level of data bit 1 during time slot 0 of sync frames. The data becomes true on the first falling edge of the clock during TS1.

#### 3. TS0

This output provides a positive pulse of 8 clock periods in every frame starting from the end of the first bit of the synchronising word of the received data.

#### 4. Clock

System clock input (2.048 MHz for a 2MBit PCM system).

#### 5.Error

This output goes high at the end of time slot 0 in the 2nd sync frame following the frame with sync word errors. If consecutive sync words occur with errors this output will remain high. If a sync alarm is generated this output will remain high until sync is regained.

#### 6. Sync Alarm

This output goes high at the end of time slot 0 output in the 3rd consecutive sync frame containing sync word errors. It returns low at the end of TS0 output in the 3rd consecutive frame received correctly (sync and non sync).

#### 7. Data input

Serial data (2MBit/s) at this input is clocked through the SIPO shift register and examined by the sync word detector.

#### 8. GND

Zero volts

#### 9, 10, 11, 12, 14, 15. Bits 3 to 8

These parallel outputs are set to the level of the spare data bits (3 to 8) of time slot 0 of non sync frames. The data becomes true on the first falling edge of the clock during TS1.

#### 13. Channel reset

This output goes low for the first period of the clock after time slot 0 of the received data as long as synchronisation has been established. This pulse can be used to reset the rest of the receiver terminal.

#### 16. V<sub>cc</sub>

Positive supply 5V ±5%.

Fig.4 Timing diagram and output waveforms

## 2 MBIT PCM SIGNALLING CIRCUIT **MJ1446** TIME SLOT 16 RECEIVER AND TRANSMITTER

The 2.048 Mbit PCM signalling circuits comprise a group of circuits which will perform the common signalling and error detection functions for a 2.048 Mbit 30 channel PCM transmission link operating to the appropriate CCITT recommendations. The circuits are fabricated in N-channel metal gate MOS and operate from a single 5volt supply. Relevant inputs and outputs are TTL compatible.

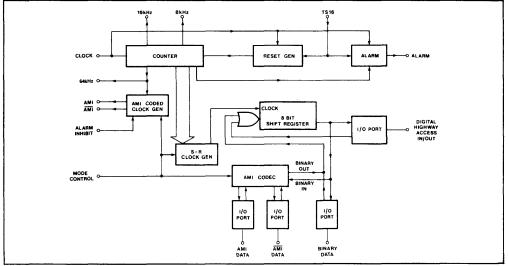

The MJ1446 has two modes of operation dependent on the state of the mode control input. With the mode control high the device is in the transmit mode and with the mode control low the device is in the receive mode.

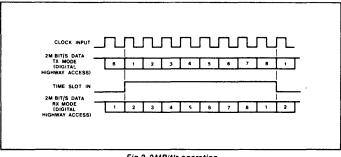

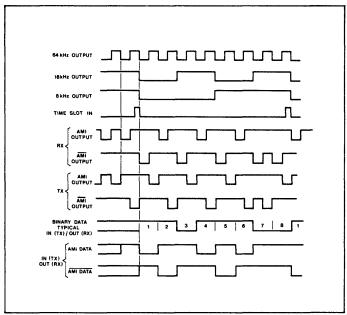

In the transmit mode the device accepts 64k bits/sec signalling information in either binary or AMI format and outputs it at 2Mbits/sec on to the digital highway during time slot 16.

In the receive mode the device accepts 2Mbit/sec information from the digital highway, during time slot 16 and output is at 64kbits/sec in both binary and AMI format.

In both receive and transmit mode there is an AMI coded clock output, AMI output and AMI output which conforms to CCITT recommendation no G372 for a 64k bits/sec contradirectional interface. The alarm inhibit input causes the 8kHz timing signal to be removed from the AMI clock output.

The device is reset in both modes by a time slot 16 channel pulse and the alarm output provides an indication that the internal counter is operating correctly.

Also provided are 64 kHz, 16 kHz and 8 kHz clock outputs.

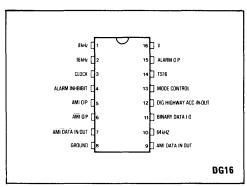

Fig.1 Pin connections

#### FEATURES

5V ±5% Supply --- 20 mA Typical

Conforms to CCITT Recommendations

Provides Both AMI and Binary Format Data Outputs

Single Chip Receive or Transmit

All Inputs and Outputs are TTL Compatible.

Fig.2 Block diagram

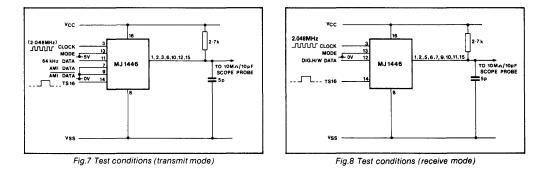

#### **ELECTRICAL CHARACTERISTICS**

#### Test conditions (unless otherwise stated):

Supply voltage  $V_{CC} = 5V \pm 0.25V$ Ambient temperature  $T_{amb} = -10^{\circ}C$  to  $+70^{\circ}C$

#### **Static Characteristics**

| Observatoriatio                                     | Gumbal                             | Pins                                  | Value       |    |                 | Units    | 0                                                  |  |

|-----------------------------------------------------|------------------------------------|---------------------------------------|-------------|----|-----------------|----------|----------------------------------------------------|--|

| Characteristic                                      | Symbol                             | PINS                                  | Min. Typ. I |    | Max.            | Units    | Conditions                                         |  |

| Low level input voltage                             | VIL                                | 3, 4, 7, 9, 11,<br>12, 13, 14         | - 0.3       |    | 0.8             | v        |                                                    |  |

| Low level input current<br>High level input current | I <sub>IN</sub>                    | 11                                    |             | 1  | 50              | μA       |                                                    |  |

| High level input voltage                            | V <sub>1H</sub>                    | 11                                    | 2.4         |    | V <sub>cc</sub> | v        |                                                    |  |

| Low level output                                    | V <sub>OL</sub>                    | 1, 2, 5, 6, 7,<br>9, 10, 11, 15<br>12 |             |    | 0.5<br>0.5      | v<br>v   | I <sub>sink</sub> = 2mA<br>I <sub>sink</sub> = 5mA |  |

| High level output voltage                           | V <sub>он</sub>                    | 1, 2, 10, 5, 6,<br>15                 | 2.8         |    |                 | v        | I <sub>source</sub> = 200µA                        |  |

| High level output leakage current<br>Supply current | I <sub>сн</sub><br>I <sub>сс</sub> | 7, 9, 11, 12                          |             | 20 | 20              | μA<br>mA | $V_{OUT} = V_{CC}$<br>$V_{CC} = 5.25 V$            |  |

#### Dynamic Characteristics (f<sub>clock</sub> = 2.048 MHz)

| Characteristic                                             | Symbol              |      | Value |      | Units | Conditions |

|------------------------------------------------------------|---------------------|------|-------|------|-------|------------|

|                                                            | Symbol              | Min. | Тур.  | Max. | Units | Conditions |

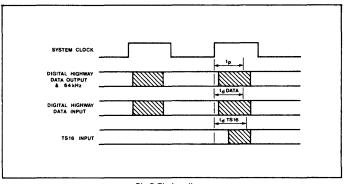

| Propogation delay clock to data out to digital highway     | t <sub>o</sub>      | 20   |       | 200  | ns    | Fig.7      |

| Propogation delay clock to 64 kHz out                      | t <sub>p</sub>      | 20   |       | 200  | ns    | Fig.7      |

| Input delay, clock to digital highway access               | t <sub>d DATA</sub> | 20   |       | 200  | ns    |            |

| Input delay, clock to time slot 16                         | t <sub>d TS16</sub> | 80   |       | 200  | ns    |            |

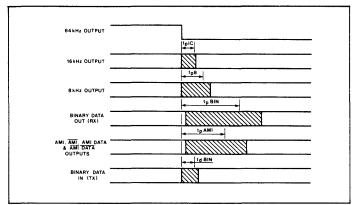

| Output delay 64 kHz to 16 kHz output                       | t <sub>p 16</sub>   |      |       | 70   | ns    | Fig.7      |

| Output delay, 64 kHz to 8 kHz output                       | t <sub>p 8</sub>    |      |       | 170  | ns    | Fig.7      |

| Output delay, 64 kHz to binary data output (64 kHz)        | t <sub>p BIN</sub>  | 20   |       | 450  | ns    | Fig.8      |

| Output delay 64 kHz to AMI, AMI, AMI data & AMI data o/p's | t <sub>p AMI</sub>  | 20   |       | 400  | ns    | Fig.8      |

| Input delay, 64kHz to binary data in (64kHz)               | t <sub>d BIN</sub>  |      |       | 100  | ns    |            |

#### **FUNCTIONAL DESCRIPTION**

#### Functions listed by pin number

#### 1.8 kHz

- 8kHz square wave output.

- 2. 16 kHz

16 kHz square wave output.

3. Clock

System clock input (2.048 MHz for a 2 Mbit PCM system) 4. Alarm inhibit

A high level on this input inhibits the 8kHz timing signal on the AMI clock outputs.

#### 5. AMI output

Alternative Mark Inversion coded 64 kHz.

#### 6. AMI output

#### 7. AMI Data in/out

In the transmit mode 64kHz signalling data in AMI format is accepted at these inputs for output to PCM highway during time slot 16.

#### 8. GND

Zero volts.

#### 9. AMI Data in/out

In the receive mode data accepted from the PCM highway during time slot 16 appears on these outputs at 64 kbits/sec in AMI format.

#### 10. 64 kHz

64 kHz square wave output.

#### 11. Binary data in/out

In the transmit mode 64k bit/sec signalling data in binary form is accepted at this input for output to the PCM data highway during time slot 16. In the receive mode data is accepted from the PCM highway during TS16 and appears at this output at 64k bits/sec in binary format.

#### 12. Digital Highway access in/out

In the receive mode 2Mbit/sec signalling data is accepted at this input during time slot 16 from the PCM digital highway. In the transmit mode signalling data is output to the PCM digital highway during time slot 16 at 2Mbits/sec.

#### 13. Mode control

A high level on this input causes the MJ1446 to operate in the transmit mode while a low level causes it to operate in the receive mode.

#### 14. TS16

This input should be connected to time slot 16 channel pulse of the PCM system to synchronise the MJ1446 with the rest of the system.

#### 15. Alarm output

A high level on this output indicates that the internal counter has stopped or is out of synchronisation with the time slot 16 channel pulse.

### 16 V<sub>cc</sub>

Positive supply 5V ±5%.

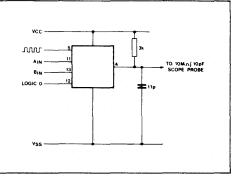

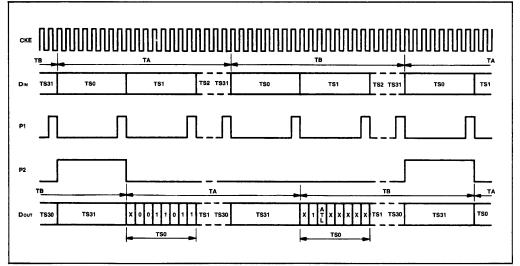

Fig.3 2MBit/s operation

#### Fig.4 64kBit/s operation

Fig.5 Timing diagram

Fig.6 Timing diagram

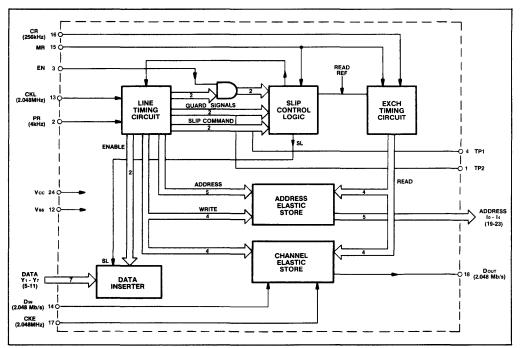

## 2 MBIT PCM SIGNALLING CIRCUIT MJ1471 HDB3 OR AMI ENCODER/DECODER

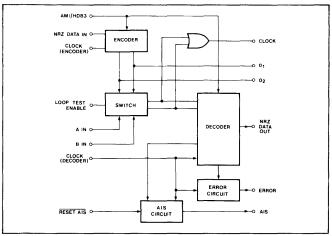

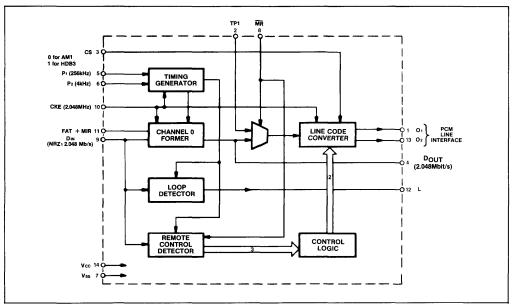

The MJ1471 is an encoder/decoder for pseudo-ternary transmission codes. The codes are true Alternate Mark Inversion (AMI) or AMI modified according to HDB3 rules (CCITT Orange Book Vol 111-2, Annex to Rec.G703). The device encodes and decodes simultaneously and asynchronously. Error monitoring functions are provided to detect violations of HDB3 coding and all ones detection (AIS). In addition a loop test function is provided for terminal testing.

#### FUNCTIONS

- 5V ± 5% Supply --- 40 mA Max.

- AMI or HDB3 Operation ---- TTL Selectable

- Loop Back Facility

- 'All Ones' Error Monitor to Detect Loss of Synchronising Word (Time Slot Zero)

- Error Monitor of HDB3 Incoming Code

- Decoded Data in NRZ Form

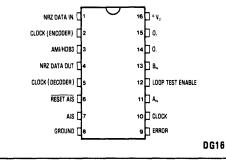

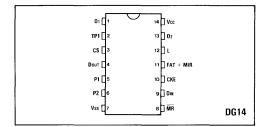

Fig.1 Pin connections

#### FUNCTIONAL DESCRIPTION

#### Functions listed by pin number

#### 1. NRZ data in

Input data for encoding into ternary form. The data is clocked by the negative-going edge of the Clock (Encoder).

#### 2. Clock (Encoder)

Clock for encoding data on pin 1.

#### 3. AMI/HDB3

MJ1471 operates in HDB3 if pin 3 is at logic '1'. AMI if pin 3 is at logic '0'.

#### 4. NRZ Data out

Decoded data from ternary inputs Ain, Bin.

#### 5. Clock (Decoder)

Clock for decoding ternary data A in, B in.

#### 6, 7. Reset AIS, AIS

Logic '0' on Reset AIS resets a decoded zero counter and either resets AIS outputs to zero provided 3 or more zeroes have been decoded in the preceding Reset AIS = 1 period or sets AIS to '1' if less than 3 zeroes have been decoded in the preceding two Reset AIS = 1 periods.

Logic '1' on Reset AIS enables the internal decoded zero counter.

#### 8. Ground

Zero volts.

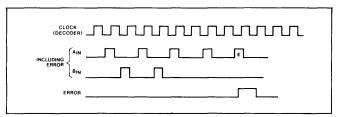

#### 9. Error

A logic '1' indicates that a violation of the HDB3 encoding law has been decoded i.e. 3 '1's of the same polarity.

#### 10. Clock

OR function of  $A_{in}$ ,  $B_{in}$  for clock regeneration when pin 12 = '0', OR function of O<sub>1</sub> O<sub>2</sub> when pin 12 = '1'.

#### 11, 13. A., B.

Inputs representing the received ternary PCM signal.  $A_{in}$  = '1' represents a positive going '1',  $B_{in}$  = '1' represents a negative going '1'.  $A_{in}$  and  $B_{in}$  are sampled by the positive going edge of the clock decoder.  $A_{in}$  and  $B_{in}$  may be interchanged.

#### 12. Loop test enable

TTL input to select normal or loop back operation. Pin  $12 = 0^{\circ}$  selects normal operation, encode and decode are independent and asynchronous.

When pin  $12 = 1^{1} O_1$  is connected internally to A<sub>in</sub> and O<sub>2</sub> to B<sub>in</sub>. Clock becomes the OR function of O<sub>1</sub> O<sub>2</sub>. **N.B.** a decode clock has to be supplied. The delay from NRZ in to NRZ out is  $7\frac{1}{2}$  clock periods in loop back.

#### 14,15,0,,02

Outputs representing the ternary encoded PCM AMI/HDB3 signal for line transmission. O, and O<sub>2</sub> are in Return to zero form and are clocked out on the positive going edge of the encode clock. The length of O, and O<sub>2</sub> pulses is set by the positive clock pulse length.

#### 16. + V<sub>cc</sub>

Positive  $5V \pm 5\%$  supply.

#### **ELECTRICAL CHARACTERISTICS**

## Test conditions (unless otherwise stated): Supply voltage $V_{CC} = 5V \pm 0.25V$ Ambient temperature $T_{amb} = 0^{\circ}C$ to +70°C

#### **Static Characteristics**

| Characteristic                                                                                                                                             | Symbol                                                                          | Pins                                                                  | Pine                     |    |                                                 | Units                                       | Conditions                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------|----|-------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

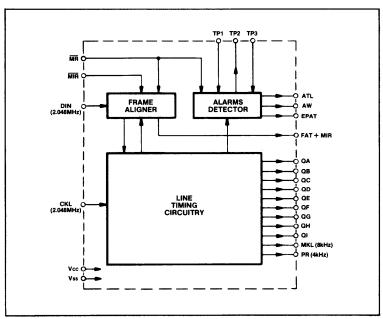

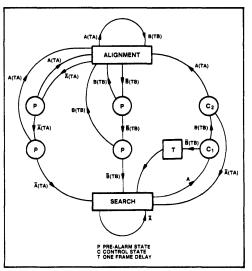

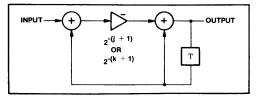

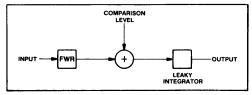

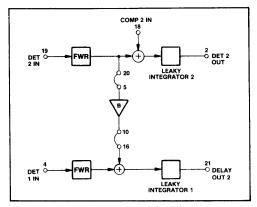

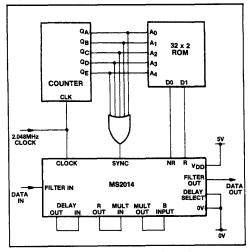

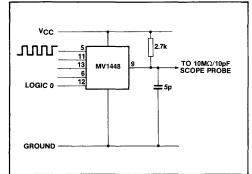

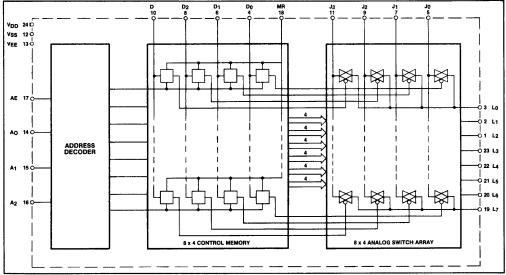

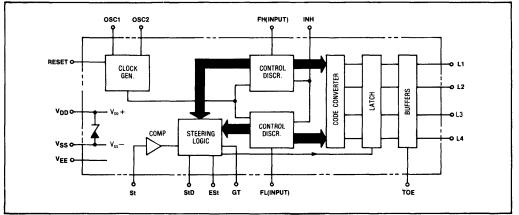

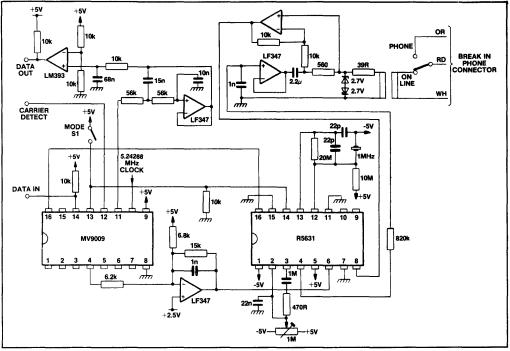

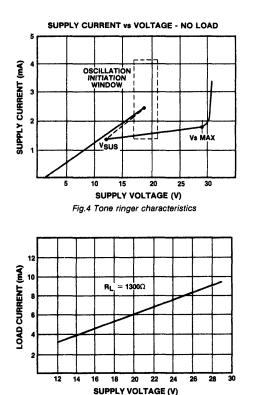

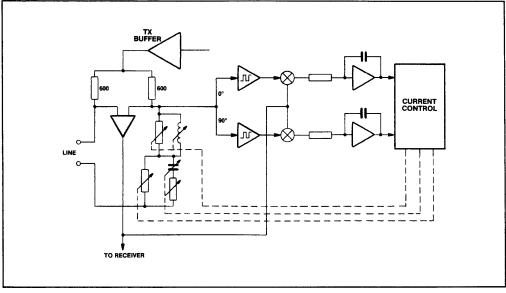

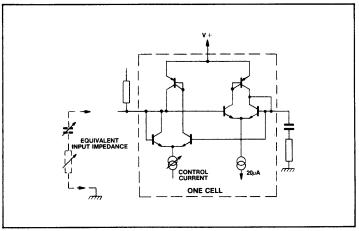

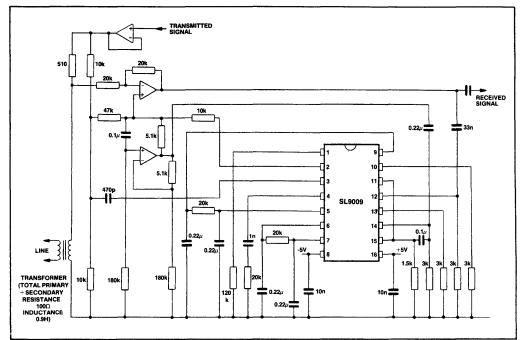

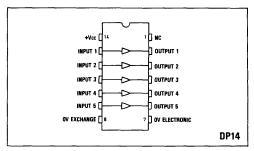

| Characteristic                                                                                                                                             | Symbol                                                                          | L II 19                                                               | Min                      |    |                                                 | Units                                       | Concisions                                                                                                                                                            |