Integrated Circuit Databook

# digital integrated circuits

|                                                                                                                      |                                                                                                     | •                                                                                |                                                                                                    |                                               |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------|

|                                                                                                                      |                                                                                                     |                                                                                  |                                                                                                    |                                               |

|                                                                                                                      |                                                                                                     |                                                                                  |                                                                                                    |                                               |

| This publication is issued the contrary by the Compregarded as a representation to alter without notice the service. | to provide outline inf<br>pany in writing) is r<br>on relating to the prod<br>specification, design | formation only and and to form part of ducts or services con, price or condition | (unless specifically ag<br>any order or contrac<br>ncerned. We reserve t<br>s of supply of any pro | greed to<br>ct or be<br>the right<br>oduct or |

| •                                                                                                                    |                                                                                                     |                                                                                  |                                                                                                    |                                               |

# contents

|                                   | Page      |

|-----------------------------------|-----------|

| Product Index                     | 5 – 7     |

| Technical Data                    |           |

| ECL 10000                         | 11 — 27   |

| ECL III                           | 28 - 74   |

| Sub-nanosecond logic              | 75        |

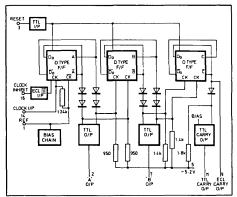

| SP8000 series high speed dividers | 79 — 196  |

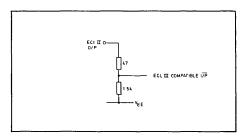

| ECL II                            | 197 — 204 |

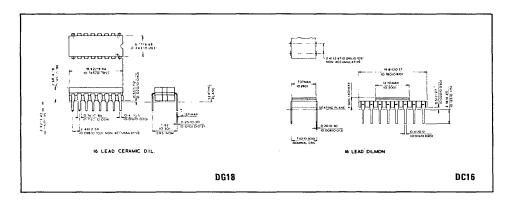

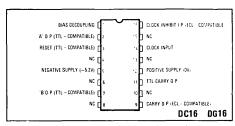

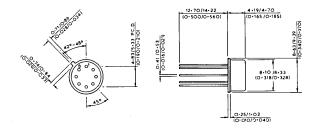

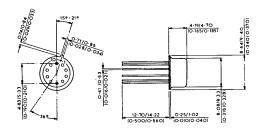

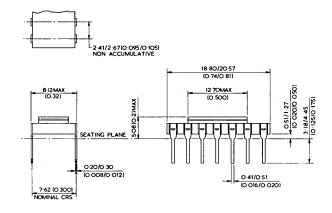

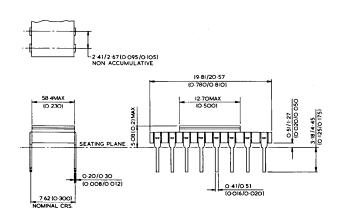

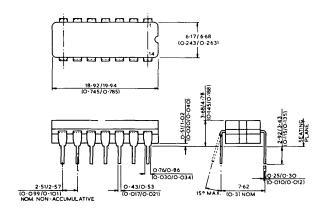

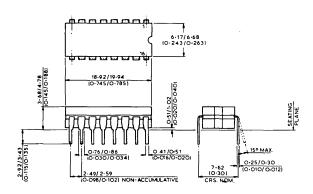

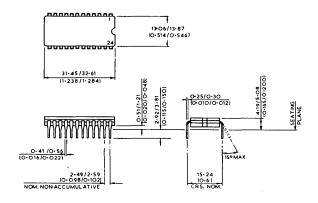

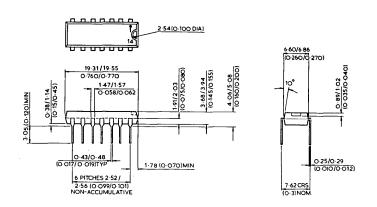

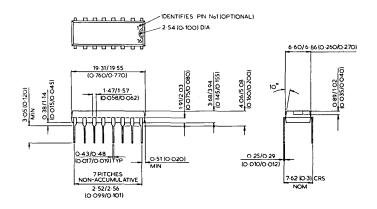

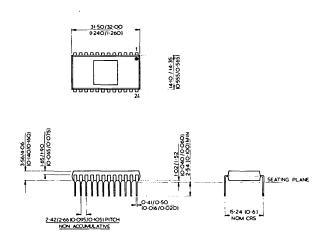

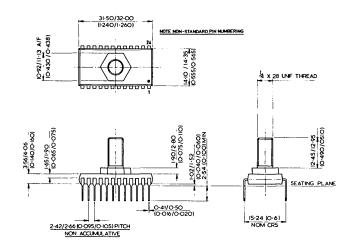

| Package Outlines                  | 207 — 212 |

| Ordering Information              | 215       |

| Plessey Semiconductors World-Wide |           |

| Sales Representatives             | 218       |

| Sales offices                     | 219       |

| Agents                            | 220       |

| Distributors                      | 221       |

### product index

#### **DEVICE TYPE**

| ECL 10 K LOGI<br>SP10,000 series | C CIRCUITS                           | 11 – 27 |

|----------------------------------|--------------------------------------|---------|

| ECLIII LOGIC (                   | CIRCUITS                             |         |

| SP1648                           | Voltage controlled oscillator        | 29      |

| SP1650                           | Dual A/D comparator, Hi-Z            | 35      |

| SP1651                           | Dual A/D comparator, Lo-Z            | 35      |

| SP1658                           | Voltage controlled multivibrator     | 37      |

| SP1660                           | Dual 4-I/P OR/NOR gate Hi-Z          | 41      |

| SP1661                           | Dual 4-I/P OR/NOR gate Lo-Z          | 41      |

| SP1662                           | Quad 2-I/P NOR gate Hi-Z             | 45      |

| SP1663                           | Quad 2-I/P NOR gate Lo-Z             | 45      |

| SP1664                           | Quad 2-I/P OR gate Hi-Z              | 47.     |

| SP1665                           | Quad 2-I/P OR gate Lo-Z              | 47      |

| SP1666                           | Dual clocked R-S Flip-Flop Hi-Z      | 49      |

| SP1667                           | Dual clocked R-S Flip-Flop Lo-Z      | 49      |

| SP1668                           | Dual clock latch Hi-Z                | 53      |

| SP1669                           | Dual clock latch Lo-Z                | 53      |

| SP1670                           | Master-slave D Flip-Flop Hi-Z        | 57      |

| SP1671                           | Master-slave D Flip-Flop Lo-Z        | 57      |

| SP1672                           | Triple 2-I/P exclusive OR gate Hi-Z  | 63      |

| SP1673                           | Triple 2-I/P exclusive OR gate Lo-Z  | 63      |

| SP1674                           | Triple 2-I/P exclusive NOR gate Hi-Z | 65      |

| SP1675                           | Triple 2-I/P exclusive NOR gate Lo-Z | 65      |

| SP1690                           | UHF prescaler type D Flip-Flop       | 67      |

| SP1692                           | Quad line receiver                   | 73      |

| SUB-NANOSEC                      | OND LOGIC                            |         |

| SP 16 F60                        | Dual 4-I/P OR/NOR Gate               | 75      |

| SP8000 SERIES Prescalers         | HIGH SPEED DIVIDERS                  |         |

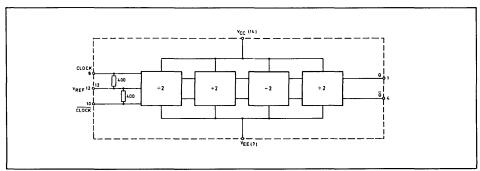

| SP8600A, B&M                     | 250MHz ÷ 4                           | 79      |

| •                                | 150HMz ÷ 4                           | 83      |

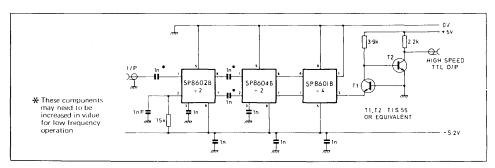

| SP8602A, B&M                     | 500MHz ÷ 2                           | 87      |

| J. JUGHT 17 DUITE                |                                      | 0,      |

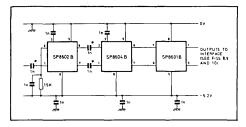

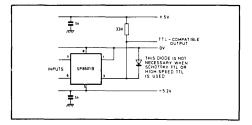

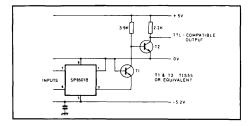

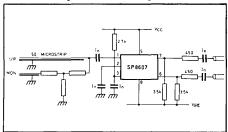

#### SP8000 SERIES HIGH SPEED DIVIDERS continued . . . **Prescalers** SP8603A, B&M 400MHz ÷ 2 87 SP8604A, B&M 300MHz ÷ 2 87 SP8607A, B&M 600MHz ÷ 2 91 SP8613B&M 700MHz ÷ 4 93 800MHz ÷ 4 SP8614B&M 93 900MHz ÷ 4 SP8615B&M 93 1 GHz ÷ 4 SP8616B 93 1.3GHz ÷ 4 SP8617B 97 SP8619B 1.5GHz ÷ 4 97 SP8620A, B&M 400MHz ÷ 5 101 SP8621A, B&M 300MHz ÷ 5 101 SP8622A, B&M 200MHz ÷ 5 101 SP8630A, B&M 600MHz ÷ 10 103 SP8631A, B&M 500MHz ÷ 10 103 SP8632A, B&M 400MHz ÷ 10 103 SP8634B 700MHz ÷ 10 (BCD O/P) 107 SP8635B 600MHz ÷ 10 (BCD O/P) 107 SP8636B 500MHz ÷ 10 (BCD O/P) 107 SP8637B 400MHz ÷ 10 (BCD O/P) 1.07 SP8650A, B&M 600MHz ÷ 16 115 SP8651A, B&M 500MHz ÷ 16 115 SP8652A, B&M 400MHz ÷ 16 115 **SP8655A**, **B&M** 200MHz ÷ 32 Low power (50mW) 119 200MHz ÷ 20 Low power (50mW) SP8657A, B&M 119 SP8659A, B&M 200MHz ÷ 16 Low power (50mW) 119 SP8660A, B&M 200MHz ÷ 10 Low power (50mW) 121 SP8665B 1 GHz ÷ 10 123 1.1GHz ÷ 10 SP8666B 123 1.2GHz ÷ 10 SP8667B 123 SP8670A, B&M 600MHz ÷ 8 125 500MHz ÷ 8 SP8671A. B&M 125 SP8672A, B&M 400MHz ÷ 8 125 SP8675B&M 1 GHz ÷ 8 129 SP8676B&M 1.1GHz ÷ 8 129 SP8677B&M 1.2GHz ÷ 8 129 SP8735B 600MHz ÷ 8 with binary O/Ps 149 SP8736B 500MHz ÷ 8 with binary O/Ps 149 SP8750B&M 1 GHz ÷ 64 177 SP8751B&M 1.1GHz ÷ 64 177 SP8752B 1.2GHz ÷ 64 177 SP8770B 1 GHz ÷ 256 181 SP8771B 1.1GHz ÷ 256 181 SP8772B 1.2GHz ÷ 256 181

| Two-modulus Pro | ogrammable Dividers                                |         |

|-----------------|----------------------------------------------------|---------|

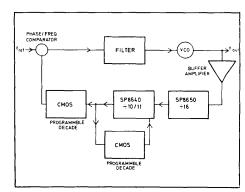

| SP8640A, B&M    | 200MHz ÷ 10/11 (ECL O/P)                           | 111     |

| SP8641A, B&M    | 250MHz ÷ 10/11 (ECL O/P)                           | 111     |

| SP8642A, B&M    | 300MHz ÷ 10/11 (ECL O/P)                           | 111     |

| SP8643A, B&M    | 350MHz ÷ 10/11 (ECL O/P)                           | 111     |

| SP8646A, B&M    | 200MHz ÷ 10/11 (TTL O/P)                           | 111     |

| SP8647A, B&M    | 250MHz ÷ 10/11 (TTL O/P)                           | 111     |

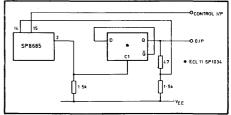

| SP8685A, B&M    | 500MHz ÷ 10/11 (ECL)                               | 131     |

| SP8690A, B&M    | 200MHz ÷ 10/11 Low power TTL O/P (70mW)            |         |

|                 | AC coupled I/P                                     | 133     |

| SP8695A, B&M    | 200MHz ÷ 10/11 Low power TTL O/P (70mW)            |         |

|                 | DC coupled I/P                                     | 137     |

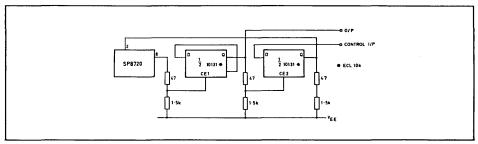

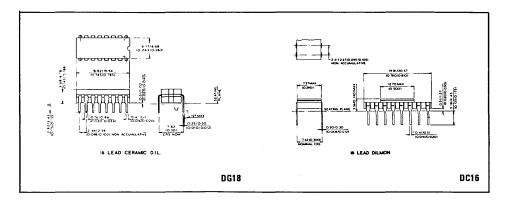

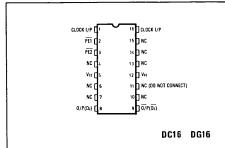

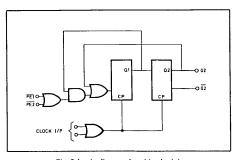

| SP8720A, B&M    | 300MHz ÷ 3/4                                       | 141     |

| SP8725A, B&M    | 300MHz ÷ 3/4                                       | 145     |

| SP8740A, B&M    | 300MHz ÷ 5/6 AC coupled I/P                        | 153     |

| SP8741A, B&M    | 300MHz ÷ 6/7 AC coupled I/P                        | 157     |

| SP8743B&M       | 500MHz ÷ 8/9 AC coupled I/P                        | 161     |

| SP8745A, B&M    | 300MHz ÷ 5/6 DC coupled I/P                        | 165     |

| SP8746A, B&M    | 300MHz ÷ 6/7 DC coupled I/P                        | 169     |

| SP8748B&M       | 300MHz ÷ 8/9 DC coupled I/P                        | 173     |

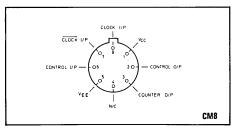

| Modulus Extende | ers                                                |         |

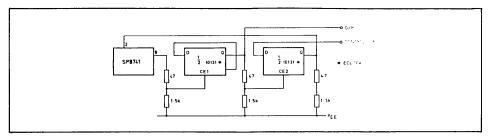

| SP8790A, B&M    | LP ÷ 4 control for all programmable devices (40mW) | ) 189   |

| SP8794A, B&M    | LP ÷ 8 control for all programmable devices (40mW  | ) 193   |

| SP8760B&M       | General purpose synthesiser circuit                | 185     |

| ECL II LOGIC C  | IRCUITS                                            |         |

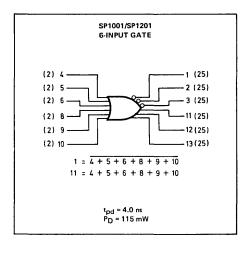

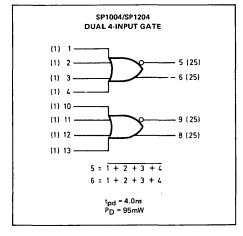

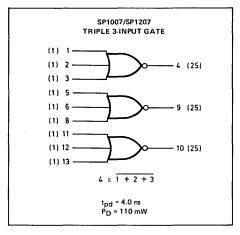

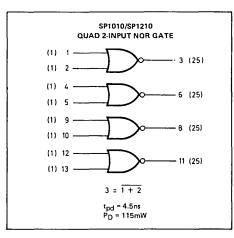

| SP1000/1200 ser |                                                    | 197-204 |

# technical data

#### **SP10,000 SERIES**

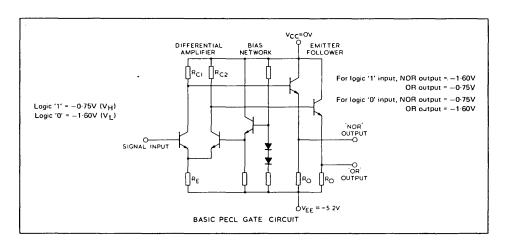

ECL 10,000

ECL 10,000 has an excellent speed-power product, has relatively low rise and fall times, and transmission-line capability. The combination of varsatile logic functions and the 2.0ns propagation delay make ECL 10,000 a versatile family for data handling and processing systems.

Circuit design with ECL 10,000 is unusually

convenient. The differential amplifier input and emitterfollower output permit high fanout, the wired-OR option, and complementary outputs. ECL III is directly compatible with ECL 10,000 and can be used to extend the speed capability of the ECL 10,000 series.

The SP 10,000 series are a direct second source for the Motorola MC 10,000 and MCM 10,000 series.

#### FUNCTIONS AND CHARACTERISTICS @ Vcc=0, Vee=-5.2V, TA=+25°C

| Function                                       | Туре               | Propagation Delay ns typ.                 | Power Dissipation*<br>mW typ/pkg |

|------------------------------------------------|--------------------|-------------------------------------------|----------------------------------|

| Quad 2-I/P NOR gate with strobe                | SP10100            | 2.0                                       | 100                              |

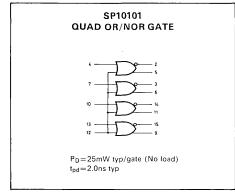

| Quad QR/NOR gate                               | SP10101            | 2.0                                       | 100                              |

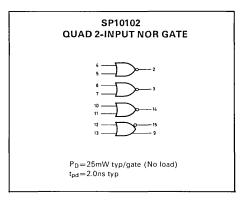

| Quad 2-I/P NOR gate                            | SP10102            | 2.0                                       | 100                              |

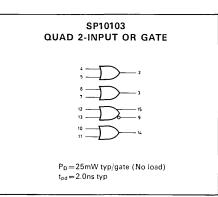

| Quad 2-1/P NOR gate                            | SP10102<br>SP10103 | 2.0                                       | 100                              |

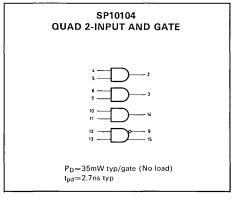

| Quad 2-I/P ON gate Quad 2-I/P AND gate         | SP10103<br>SP10104 | 2.7                                       | 140                              |

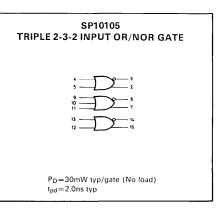

|                                                |                    | 2.7                                       | 90                               |

| Triple 2-3-2-I/P OR/NOR gate                   | SP10105            |                                           |                                  |

| Triple 4-3-3-I/P NOR gate                      | SP10106            | 2.0                                       | 90                               |

| Triple 2-I/P exclusive OR/exclusive NOR        | SP10107            | 2.5                                       | 110                              |

| Dual 4-5-I/P OR/NOR gate                       | SP10109            | 2.0                                       | 60                               |

| Dual 3-I/P 3-O/P OR gate                       | SP10110            | 2.4                                       | . 160                            |

| Dual 3-I/P 3-O/P NOR gate                      | SP10111            | 2.4                                       | 160                              |

| Dual 3-I/P 3-O/P OR/NOR gate                   | SP10112            | 2.4                                       | 160                              |

| Quad exclusive OR gate                         | SP10113            | 2.5                                       | 175                              |

| Triple line receiver                           | SP10114            | 2.4                                       | 145                              |

| Quad line receiver                             | SP10115            | 2.0                                       | 110                              |

| Triple line receiver                           | SP10116            | 2.0                                       | 85                               |

| Dual 2-wide 2-3-1/P OR-AND/OR-AND              |                    |                                           |                                  |

| Invert gate                                    | SP10117            | 2.3                                       | 100                              |

| Dual 2-wide 3-I/P OR/AND gate                  | SP10118            | 2.3                                       | 100                              |

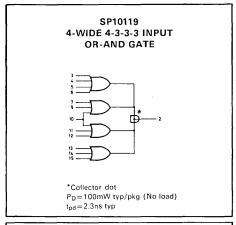

| 4-wide 4-3-3-3-I/P OR/AND gate                 | SP10119            | 2.3                                       | 100                              |

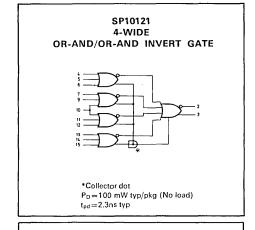

| 4-wide OR-AND/OR-AND Invert gate               | SP10121            | 2.3                                       | 100                              |

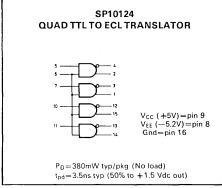

| Quad TTL to ECL translator                     | SP10124            | 3.5                                       | 380                              |

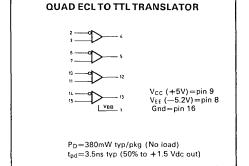

| Quad ECL to TTL translator                     | SP10125            | 4.5                                       | 380                              |

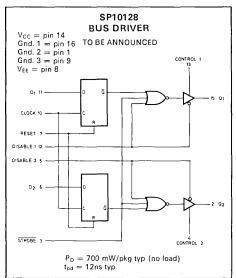

| Bus driver                                     | SP10128            | 12                                        | 700                              |

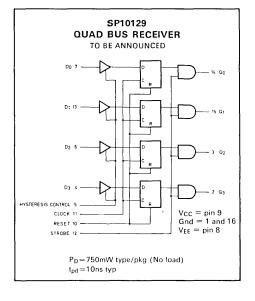

| Quad bus receiver                              | SP10129            | 10.0                                      | 750                              |

| Dual latch                                     | SP10130            | 2.5                                       | 155                              |

| Dual type D master slave flip-flop             | SP10131            | f=160MHz                                  | 235                              |

| Multiplexer with latch                         | SP10134            | 3.0                                       | 225                              |

| Dual J-K master-slave flip-flop                | SP10135            | f=140MHz                                  | 280                              |

| Universal hexadecimal counter                  | SP10136            | f=150MHz                                  | 625                              |

| Universal decade counter                       | SP10137            | f=150MHz                                  | 625                              |

| Bi-quinary counter                             | SP10138            | f=150MHz                                  | 370                              |

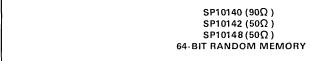

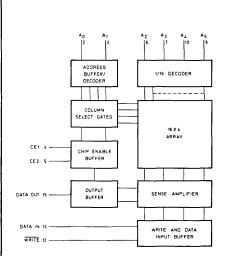

| 64-bit random access memory                    | SP10140            | t <sub>access</sub> =15ns (max)           | 420                              |

| Four-bit universal shift register              | SP10141            | f=200MHz                                  | 425                              |

| 64-bit random access memory                    | SP10142            | t <sub>access</sub> =10ns (max)           | 420                              |

| 256-bit random access memory                   | SP10144            | t <sub>access</sub> =30ns (max)           | 420                              |

| 64-bit register file (RAM)                     | SP10145            | taccess=30ns (max)<br>taccess=10ns (typ)  | 625                              |

| 1024-bit random access memory                  | SP10146            | laccess - 10113 (typ)                     | 025                              |

| 64-bit random access memory                    | SP10148            | t <sub>access</sub> =15ns (max)           | 420                              |

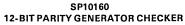

| 12-bit parity generator checker                | SP10140            | 1 <sub>access</sub> —15115 (111ax)<br>5.0 | 320                              |

| Binary to 1 out of 8 decoder (low)             | SP10161            | 4.0                                       | 315                              |

| Binary to 1 out of 8 decoder (low)             | SP10161            | 4.0                                       | 315                              |

| 8-line multiplexer                             | SP10164            | 3.0                                       | 310                              |

| 8-input priority encoder                       | SP10164<br>SP10165 | 7.0                                       | 545                              |

| Dual binary to 1 out of 4 decoder (low)        | SP10103<br>SP10171 | 4.0                                       | 325                              |

| Dual binary to 1 out of 4 decoder (low)        | SP10171<br>SP10172 | 4.0                                       | 325<br>325                       |

| Quad 2-I/P multiplexer/latch                   | SP10172<br>SP10173 | 4.0<br>2.5                                |                                  |

| Dual 4 to 1 multiplexer                        | SP10173<br>SP10174 | 2.5<br>3.5                                | 275                              |

| Quint latch                                    |                    |                                           | 305                              |

| Hex D master-slave flip-flop                   | SP10175            | 2.5                                       | 400                              |

| Binary counter                                 | SP10176            | f=250MHz                                  | 460                              |

|                                                | SP10178            | f=150MHz                                  | 370                              |

| Look-ahead carry block                         | SP10179            | 3.0 (Cn,P) 4.0 (G)                        | 300                              |

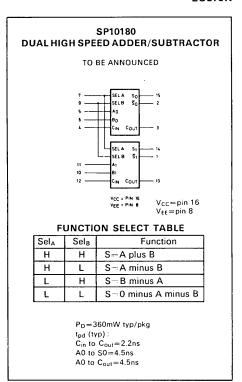

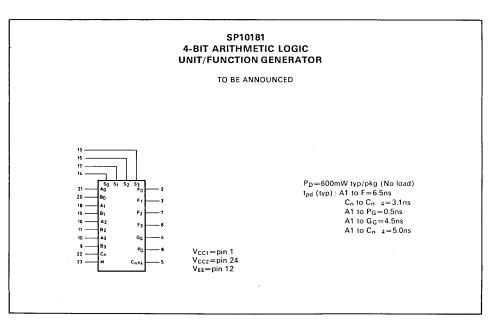

| Dual high speed adder/subtractor               | SP10180            | 4.5                                       | 360                              |

| 4-bit arithmetic logic unit/function generator | SP10181            | See logic diag.                           | 600                              |

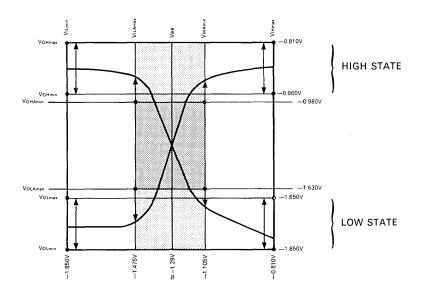

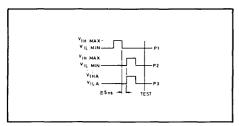

#### TYPICAL TRANSFER CHARACTERISTICS OF ECL10100 FAMILY

Test conditions:  $T_A = +25\,$  C,  $V_{EE} = -5.2V$ ,  $50\Omega$  matched inputs and outputs.

| PARAMETER | —30 C   | +25 °C  | +85 °C  |

|-----------|---------|---------|---------|

| VIHmax    | -0.890V | 0.810V  | -0.700V |

| VILmin    | —1.890V | —1.850V | 1.825V  |

| VIHAmin   | —1.205V | —1.105V | 1.035V  |

| VILAmax   | —1.500V | —1.475V | 1.440V  |

| VoHmax    | -0.890V | -0.810V | 0.700V  |

| Vol.min   | —1.890V | —1.850V | 1.825V  |

| VoHmin    | —1.060V | -0.960V | 0.890V  |

| Volmax    | —1.675V | —1.650V | —1.615V |

| VOHAmin   | —1.080V | -0.980V | -0.910V |

| VOLAmax   | 1.655V  | —1.630V | —1.595V |

#### **ABSOLUTE MAXIMUM RATINGS**

A. Limits beyond which device life may be impaired:

| Power supply voltage, V                       | $V_{EE} (V_{CC} = 0)$       | 8V to 0V              |

|-----------------------------------------------|-----------------------------|-----------------------|

| Base input voltage, $V_{in}$ ( $V_{CC} = 0$ ) |                             | OV to V <sub>EE</sub> |

| Output source current, I                      | 0:-                         |                       |

|                                               | Continuous                  | <50mA                 |

|                                               | Surge                       | <100mA                |

| Storage temperature, Tst                      |                             | 55 °C to 150 °C       |

| *Junction operating temp                      | perature, T <sub>j</sub> :- |                       |

|                                               | Plastic package             | <150 °C               |

|                                               | Ceramic package             | <165 °C               |

|                                               |                             |                       |

B. Limits beyond which performance may be degraded:

—30 °C to +85 °C DC fan-out <70  $\pm 10\%$ Power supply regulation

<sup>\*</sup>Tcase must be<150 C

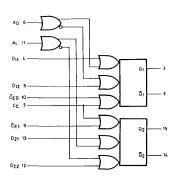

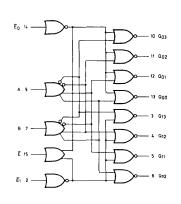

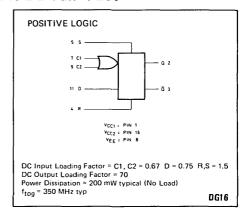

#### LOGIC DIAGRAMS

Positive logic is used throughout.

Power supply connections:

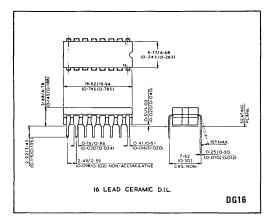

Vcc:==pin 1, Vcc2=pin 16, VEE=pin 8, except where otherwise stated.

#

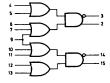

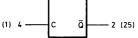

#### SP10106 TRIPLE 4-3-3 INPUT NOR GATE

$P_D=30$ mW typ/gate (No load)  $t_{pd}=2.0$ ns typ

# SP10107 TRIPLE 2-INPUT EXCLUSIVE OR/EXCLUSIVE NOR

$P_D=110$ mW typ/pkg (No load)  $t_{pd}=2.5$ ns typ

#### SP10109 DUAL 4-5-INPUT OR/NOR GATE

$P_D=30$ mW typ/gate (No load)  $t_{pd}=2.0$ ns typ

#### SP10110 DUAL 3-INPUT 3-OUTPUT OR GATE

$V_{CC1} = pins 1 and 15$   $V_{CC2} = pin 16$  $V_{EE} = pin 8$

$P_D = 160 \text{mW typ/pkg (No load)}$  $t_{pd} = 2.4 \text{ns typ}$

#### SP10111 DUAL 3-INPUT 3-OUTPUT NOR GATE

$V_{CC1} = pins 1 and 15$   $V_{CC2} = pin 16$  $V_{EE} = pin 8$

$P_D=160$ mW typ/pkg (No load)  $t_{pd}=24$ ns typ

#### SP10112 DUAL 3-INPUT 3 OUTPUT OR/NOR GATE

$P_D = 160 \text{mW typ/pkg (No load)}$  $t_{pd} = 2.4 \text{ns typ}$

#### SP10113 QUAD EXCLUSIVE OR GATE

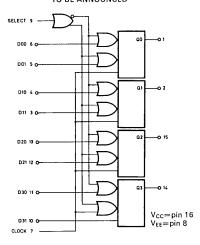

TO BE ANNOUNCED

$P_D = 175m \text{ typ/pkg (No load)}$  $t_{pd} = 2.5ns \text{ typ}$

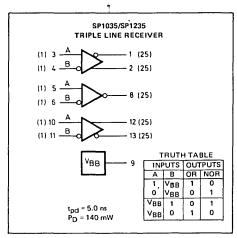

# SP10114 TRIPLE LINE RECEIVER TO BE ANNOUNCED

$t_{pd}$ =2.4ns typ (Single ended input)  $t_{pd}$ =2.0ns (Differential input)  $P_D$ =145mW typ/pkg (No load)

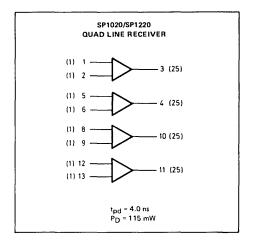

#### SP10115 QUAD LINE RECEIVER

$P_D=110$ mW typ/pkg (No load)  $t_{pd}=2.0$ ns typ

# SP10116 TRIPLE LINE RECEIVER TO BE ANNOUNCED

$P_D=85mW \text{ typ/pkg (No load)}$  $t_{pd}=2.0ns \text{ typ}$

# SP10117 DUAL 2-WIDE 2-3-INPUT OR-AND/OR-AND-INVERT GATE

$P_D=100$ mW typ/pkg (No load)  $t_{pd}=2.3$ ns typ

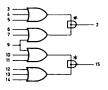

#### SP10118 DUAL 2-WIDE 3-INPUT OR-AND GATE

\*Collector dot  $P_D=100$ mW typ/pkg (No load)  $t_{pd}=2.3$ ns typ

SP10125

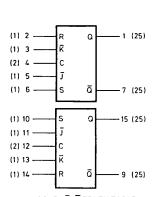

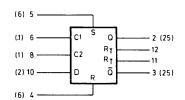

#### SP10130 DUAL LATCH

$P_D=155mW \text{ typ/pkg}$  $t_{pd}=2.5\text{ns typ}$

#### TRUTH TABLE

| D | C | СE | Q <sub>n</sub> +1 |

|---|---|----|-------------------|

| L | L | L  |                   |

| Н | L | L  | Н                 |

| ø | L | н  | Q <sub>n</sub>    |

| ø | Н | L  | $Q_n$             |

| ø | н | Н  | Qn                |

ø = Don't Care

#### SP10134 DUAL MULTIPLEXER WITH LATCH

TO BE ANNOUNCED

$P_D = 225 \text{mW typ/pkg (No load)}$  $t_{pd} = 3.0 \text{ns typ}$

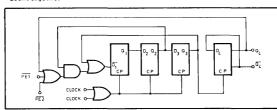

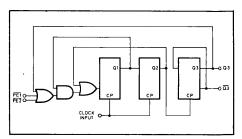

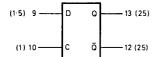

#### SP10131 DUAL TYPE D MASTER SLAVE FLIP-FLOP

P<sub>D</sub>=235mW typ/pkg (No load) f=160MHz typ

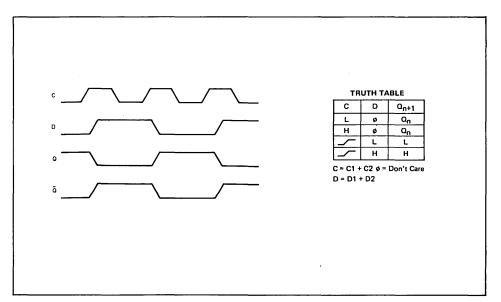

#### **CLOCKED TRUTH TABLE**

| С | D | Q <sub>n</sub> -1 |

|---|---|-------------------|

| L | Ø | Qn                |

| H | L | L                 |

| н | Н | Н                 |

A clock H is a clock transition from a low to a high state.

#### R-S TRUTH TABLE

| R | S | $Q_n - 1$ |

|---|---|-----------|

| L | L | Qn        |

| L | н | н         |

| Н | L | l_        |

| н | Н | N.D.      |

#### TRUTH TABLE

| С | A0 | D11 | D12 | Q <sub>n</sub> +1 |

|---|----|-----|-----|-------------------|

| L | L  | L   | Ø   | L                 |

| L | L  | н   | ø   | н                 |

| L | Н  | ø   | L   | L                 |

| L | Н  | ø   | н   | Н                 |

| Н | Ø  | Ø   | Ø   | Qn                |

$\emptyset = \underline{\underline{Don't}} Care$   $C = \overline{CE} + C_C$

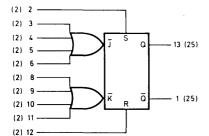

#### SP10135 DUAL J-K MASTER-SLAVE FLIP-FLOP

TO BE ANNOUNCED

$P_D=280$ mW typ/pkg (No load)  $f_{tog}=140$ MHz typ

#### **R-S TRUTH TABLE**

| R | S | $Q_n + 1$ |

|---|---|-----------|

| L | L | Qn        |

| L | Н | Н         |

| н | L | L         |

| Н | H | N.D.      |

N.D. - Not Defined

#### **CLOCK J-K TRUTH TABLE\***

| J | K | $Q_n + 1$ |

|---|---|-----------|

| L | L | Qn        |

| Н | L | L         |

| L | Н | Н         |

| Н | Н | Qn        |

<sup>\*</sup>Output states change on positive transition of clock for J-K input condition present.

#### SP10136 UNIVERSAL HEXADECIMAL COUNTER

# 10 — C<sub>IN</sub> O<sub>0</sub> — 14 13 — C 12 — O<sub>0</sub> O<sub>1</sub> — 15 11 — O<sub>1</sub> 6 — O<sub>2</sub> O<sub>2</sub> — 2 5 — O<sub>3</sub> O<sub>3</sub> — 3 9 — S<sub>1</sub> 7 — S<sub>2</sub> C<sub>OUT</sub> — 4

P<sub>D</sub>=425mW typ/pkg f<sub>shift</sub>=200MHz typ

#### **SEQUENTIAL TRUTH TABLE\***

|    |     |    | INF | UTS |    |       |       |    | Ol | JTPU | TS |       |

|----|-----|----|-----|-----|----|-------|-------|----|----|------|----|-------|

|    |     |    |     |     |    | Carry | Clock |    |    |      |    | Carry |

| S1 | \$2 | D0 | D1  | D2  | D3 | In    | **    | σo | Q1 | 02   | ØЗ | Out   |

| L  | L   | L  | L   | Н   | Н  | Ø     | Н     | L  | L  | Н    | Н  | L     |

| L  | н   | Ø  | Ø   | Ø   | Ø  | L     | н     | н  | L. | н    | н  | Н     |

| L  | Н   | Ø  | Ø   | Ø   | ø  | L     | н     | L  | н  | Н    | н  | н     |

| L  | н   | Ø  | Ø   | ø   | ø  | L     | H     | н  | н  | Н    | H. | L     |

| L  | н   | Ø  | ø   | Ø   | ø  | Н     | L     | н  | Н  | н    | н  | н     |

| L  | н   | Ø  | ø   | Ø   | Ø  | Н     | Н     | Н  | н  | Н    | Н  | н     |

| Н  | Н   | ø  | Ø   | ø   | ø  | Ø     | н     | Н  | Н  | Н    | н  | н     |

| L  | L   | н  | н   | L   | L  | Ø     | н     | н  | н  | L    | L  | L     |

| Н  | L   | Ø  | Ø   | ø   | ø  | L     | н     | L  | Н  | L    | L  | Н     |

| Н  | L   | ø  | ø   | ø   | Ø  | L     | Н     | Н  | L  | L    | L  | н     |

| н  | L   | ø  | ø   | ø   | Ø  | L     | Н     | L  | L  | L    | L  | ᅵᅵᅵ   |

| н  | L   | ø  | Ø   | Ø   | Ø  | L     | Н     | Н  | Н  | Н    | Н  | н     |

#### **FUNCTION SELECT TABLE**

| S1 | S2 | Operating Mode         |

|----|----|------------------------|

| L  | L  | Preset (Program)       |

| L  | Н  | Increment (Count Up)   |

| Н  | L  | Decrement (Count Down) |

| Н  | Н  | Hold (Stop Count)      |

ø=Don't care.

- \*Truth table shows logic states assuming inputs vary in sequence shown from top to bottom.

- \*\*A clock H is defined as a clock input transition from a low to a high logic level.

#### SP10137 **UNIVERSAL DECADE COUNTER**

PD=625mW typ/pkg (No load) f<sub>count</sub>=150MHz typ

#### **FUNCTION SELECT TABLE**

| S1 | S2 | Operating Mode         |

|----|----|------------------------|

| L  | L  | Preset (Program)       |

| L  | Н  | Increment (Count Up)   |

| Н  | L  | Decrement (Count Down) |

| Н  | Н  | Hold (Stop Count)      |

#### SEQUENTIAL TRUTH TABLE\*

|    | SEGGERAL MOTH TABLE |    |    |    |    |       |       |      |      |    |            |       |

|----|---------------------|----|----|----|----|-------|-------|------|------|----|------------|-------|

|    | INPUTS              |    |    |    |    |       | - (   | OUTF | PUTS |    |            |       |

|    |                     |    |    |    |    | Carry | Clock |      |      |    |            | Carry |

| S1 | S2                  | D0 | D1 | D2 | D3 | In    | **    | 00   | Q1   | Q2 | <b>Q</b> 3 | Out   |

| L  | L                   | Н  | Н  | Н  | L  | Ø     | Н     | Н    | Н    | Н  | L          | Н     |

| L  | н                   | ø  | ø  | ø  | ø  | L     | н     | L    | L    | L  | Н          | н     |

| L  | Н                   | ø  | ø  | Ø  | ø  | L     | н     | н    | L    | L  | Н          | L     |

| L  | н                   | ø  | ø  | Ø  | ø  | L     | н     | L    | L    | L  | L          | н     |

| L  | Н                   | ø  | ø  | Ø  | ø  | L     | Н     | Н    | L    | L  | L          | н     |

| L  | Н                   | Ø  | Ø  | Ø  | ø  | н     | н     | Н    | L    | L  | L          | н     |

| L  | Н                   | ø  | ø  | Ø  | ø  | H.    | н     | Н    | L    | L  | L          | н     |

| н  | Н                   | ø  | ø  | Ø  | ø  | ø     | Н     | н    | L    | L  | L          | Н     |

| L  | L                   | Н  | н  | L  | L  | Ø     | Н     | н    | Н    | L  | L          | Н     |

| н  | L                   | Ø  | Ø  | ø  | ø  | L     | Н     | L    | Н    | L  | L          | Н     |

| н  | L                   | ø  | ø  | Ø  | ø  | L     | Н     | Н    | L    | L  | L          | Н     |

| н  | L                   | Ø  | ø  | ø  | ø  | L     | Н     | L    | L    | L  | L          | L     |

| α: | ø=- Don't care.     |    |    |    |    |       |       |      |      |    |            |       |

- \* Truth table shows logic states assuming inputs vary in sequence shown from top to bottom.

- \*\*A clock H is defined as a clock input transition from a low to a high logic level.

#### SP10138 **BI-QUINARY COUNTER**

TO BE ANNOUNCED

$$\begin{split} P_D &= 370 \text{ mW typ/pkg (no load)} \\ f_{tog} &= 150 \text{ MHz typ} \end{split}$$

#### **COUNTER TRUTH TABLES**

COUNT

00

#### **BI-QUINARY**

| COUNT | Q1 | Ω2 | Q3 | Ω0 |

|-------|----|----|----|----|

| 0     | L  | L  | L  | L  |

| 1     | Н  | L  | L  | L  |

| 2     | L  | н  | L  | L  |

| 3     | Н  | Н  | L  | L  |

| 4     | L  | L  | Н  | L  |

| 5     | L  | L  | L  | H  |

| 6     | Н  | L  | L  | Н  |

| 7     | L  | н  | L  | Н  |

| 8     | Н  | Н  | L  | Н  |

| 9     | L  | L  | Н  | Н  |

(Clock connected to C2 and  $\overline{\Omega 3}$  connected to C1)

| COCIVI | <u> </u> | 41 |    | 43 |

|--------|----------|----|----|----|

| 0      | L        | L  | L  | L  |

| 1      | н        | L  | L  | L  |

| 2      | L        | н  | L  | L  |

| 3      | н        | Н  | L  | L  |

| 4      | L        | L  | Н  | L  |

| 5      | н        | L  | Н  | L  |

| 6      | L        | н  | Н  | L  |

| 7      | Н        | н  | н  | L  |

| 8      | L        | L  | L  | Н  |

| 9      | н        | L  | L. | н  |

BCD

01

Ω2

(Clock connected to C1 and  $\overline{QQ}$  connected to C2) 03

TO BE ANNOUNCED

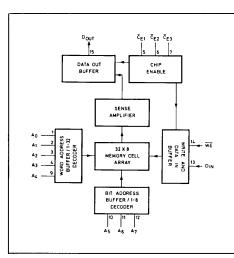

$\begin{array}{l} P_D = 420 \text{ mW typ /pkg} \\ t_{access} = 15 \text{ns (max) SP10140, SP10148} \\ = 10 \text{ns (max) SP10142} \end{array}$

#### TRUTH TABLE

|           | 1111 | <del></del> | 70     |      |

|-----------|------|-------------|--------|------|

| MODE      |      | INPUT       | OUTPUT |      |

|           | CE   | WE          | Din    | Dout |

| Write "0" | L    | L           | L      | L    |

| Write "1" | L    | L           | Н      | L    |

| Read      | L    | Н           | ø      | Q    |

| Disabled  | Н    | Ø           | Ø      | L    |

ø=Don't Care

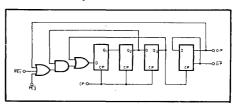

#### SP10141 FOUR-BIT UNIVERSAL SHIFT REGISTER

TO BE ANNOUNCED

$P_D=425mW \text{ typ/pkg}$  $f_{shift}=200MHz \text{ typ}$

#### TRUTH TABLE

| SEL | ECT | OPERATING      |                    | OUTP               | UTS             |                     |

|-----|-----|----------------|--------------------|--------------------|-----------------|---------------------|

| S1  | S2  | MODE           | Q0 <sub>n</sub> +1 | Q1 <sub>n</sub> +1 | $Q2_n + 1$      | Q3 <sub>n</sub> - 1 |

| L   | L   | Parallel Entry | D0                 | D1                 | D2              | D3                  |

| L   | Н   | Shift Right*   | Q1 <sub>n</sub>    | Q2 <sub>n</sub>    | Q3 <sub>n</sub> | DR                  |

| Н   | L   | Shift Left*    | DL                 | Q0 <sub>n</sub>    | Q1 <sub>n</sub> | Q2 <sub>n</sub>     |

| Н   | Н   | Stop Shift     | Q0 <sub>n</sub>    | Q1 <sub>n</sub>    | Q2 <sub>n</sub> | Q3 <sub>n</sub>     |

\*Outputs as exist after pulse appears at "C" input with input conditions as shown. (Pulse—Positive transition of clock input).

#### SP10144 256-BIT RANDOM ACCESS MEMORY

TO BE ANNOUNCED

taccess=30ns (max) (Address inputs)

#### TRUTH TABLE

| MODE      |    | INPUT | OUTPUT |      |

|-----------|----|-------|--------|------|

|           | CE | WE    | Din    | Dout |

| Write "0" | L  | L     | L      | L    |

| Write "1" | L  | L     | Н      | L    |

| Read      | L  | Н     | 0      | Q    |

| Disabled  | Н  | ø     | Ø      | L    |

ø = Don't Care

$P_D = 625$  mW typ. pkg. (no load)  $t_{access} = 10$ ns typ

#### SP10145 64-BIT REGISTER FILE (RAM)

TO BE ANNOUNCED

#### TRUTH TABLE

| MODE      |    | OUTPUT |   |   |

|-----------|----|--------|---|---|

|           | CE | WE     | D | Q |

| Write "0" | L  | L      | L | L |

| Write "1" | L  | L      | н | L |

| Read      | L  | Н      | ø | Q |

| Disabled  | Н  | ø      | ø | L |

$\phi = Don't Care.$

#### SP10146 1024 BIT RANDOM ACCESS MEMORY

TO BE ANNOUNCED

V<sub>CC</sub>=pin 16 V<sub>EE</sub>=pin 8

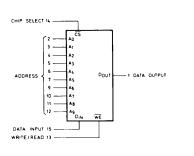

TO BE ANNOUNCED

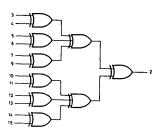

| P <sub>D</sub> =320mW typ,<br>t <sub>pd</sub> =5.0ns typ | /pkg (No load) |

|----------------------------------------------------------|----------------|

|                                                          |                |

| INPUT      | OUTPUT |

|------------|--------|

| Sum of     |        |

| High Level | Pin 2  |

| Inputs     |        |

| Even       | Low    |

| Odd        | High   |

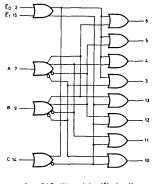

#### SP10161 BINARY TO 1 OUT OF 8 DECODER (LOW)

$P_D=315$ mW typ/pkg (No load)  $t_{pd}=4.0$ ns typ

|    | TRUTH TABLE  |   |    |     |            |         |    |    |    |    |    |    |

|----|--------------|---|----|-----|------------|---------|----|----|----|----|----|----|

|    | ABLE<br>PUTS |   | Pι | ITS |            | OUTPUTS |    |    |    |    |    |    |

| E1 | ĒΘ           | С | В  | Α   | <b>α</b> 0 | Q1      | Q2 | ØЗ | Q4 | Q5 | Q6 | Ω7 |

| L  | L            | L | L  | L   | L          | Н       | Н  | Н  | Н  | Н  | Н  | Н  |

| L  | և            | L | L  | н   | н          | L       | Н  | Н  | Н  | Н  | Н  | Н  |

| L  | L            | L | Н  | L   | н          | Н       | L  | Н  | Н  | Н  | Н  | Н  |

| L  | L            | L | Н  | н   | [н         | н       | н  | L  | Н  | н  | н  | Н  |

| L  | L            | Н | L  | L   | н          | н       | н  | н  | L  | н  | н  | н  |

| L  | L            | н | L  | Н   | Н          | Н       | Н  | н  | Н  | L  | H  | н  |

| L  | L            | н | Н  | L   | Н          | н       | н  | н  | н  | н  | L. | н  |

| L  | L            | Н | Н  | н   | н          | н       | н  | н  | Н  | н  | н  | L  |

| Н  | ø            | ø | ø  | ø   | н          | Н       | н  | Н  | н  | Н  | н  | Н  |

| ø  | Н            | ø | ø  | ø   | Н          | Н       | Н  | Н  | Н  | н  | Н  | Н  |

ø=Don't Care

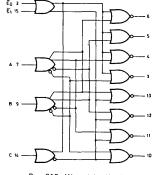

#### SP10162 BINARY TO 1 OUT OF 8 DECODER (HIGH)

$P_D=315$ mW typ/pkg (No load)  $t_{pd}=4.0$ ns typ

|    | TRUTH TABLE |     |   |   |    |         |    |    |    |    |            |    |

|----|-------------|-----|---|---|----|---------|----|----|----|----|------------|----|

|    | INI         | זטי | S |   |    | OUTPUTS |    |    |    |    |            |    |

| ΕŌ | Ē1          | С   | В | Α | σo | Q1      | Q2 | Ω3 | Q4 | Q5 | <b>Q</b> 6 | Ω7 |

| L  | L           | L   | L | L | ٦  | H       | L  | L  | L  | L  | L          | L  |

| L  | L           | L   | L | н | L  | Н       | L  | L  | L  | L  | L          | L  |

| L  | L           | L   | Н | L | L  | L       | н  | L. | L  | L  | L          | L  |

| L  | L           | L   | Н | Н | L  | L       | L  | н  | L  | L  | L          | L  |

| L  | L           | н   | L | L | L  | L       | L  | L  | н  | L  | L          | L  |

| L  | L           | Н   | L | Н | L  | L       | L  | L  | L  | н  | L          | L  |

| L  | L           | н   | Н | L | L  | L       | L  | L  | L  | L  | Н          | L  |

| L, | L           | Н   | Н | Н | L  | L       | L  | L  | L  | L  | L          | Н  |

| H  | ø           | ø   | ø | ø | L  | L       | L  | L  | L  | L  | L          | L  |

| Ø  | Н           | Ø   | ø | ø | Ł  | L       | L  | L  | L  | L  | L          | L_ |

ø=Don't Care

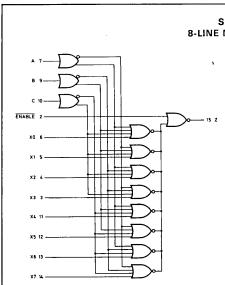

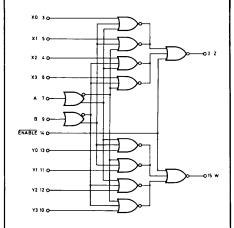

#### SP10164 **8-LINE MULTIPLEXER**

PD=310mW typ/pkg (No load)  $t_{pd} = 3.0$ ns typ

TRUTH TABLE

|        | ADDRESS INPUTS |   |   |    |  |  |  |

|--------|----------------|---|---|----|--|--|--|

| NABLE  | С              | В | Α | Z  |  |  |  |

| L      | L              | L | L | X0 |  |  |  |

| L      | L              | L | н | X1 |  |  |  |

| L      | Ĺ              | Н | L | X2 |  |  |  |

| L      | L              | Н | Н | Х3 |  |  |  |

| L      | Н              | L | ٦ | X4 |  |  |  |

| L      | Н              | L | Н | X5 |  |  |  |

| L      | Н              | н | L | Х6 |  |  |  |

| L      | Н              | Ι | Н | X7 |  |  |  |

| Н      | Ø              | Ø | Ø | L  |  |  |  |

| L<br>H | Н              | н |   |    |  |  |  |

ø=Don't Care

DATA INPUTS

#### SP10165 8-INPUT PRIORITY ENCODER

TO BE ANNOUNCED

$P_D = 545 \text{mW typ/pkg}$ t<sub>pd</sub>=7.0ns typ (Data to output)

| 571171 1111 010 |              |    |    |    |    |    |    |    |    |    |    |

|-----------------|--------------|----|----|----|----|----|----|----|----|----|----|

| D0              | D1           | D2 | D3 | D4 | D5 | D6 | D7 | 03 | Q2 | Q1 | σo |

| Н               | Ø            | Ø. | ø  | Ø  | Ø  | Ø  | Ø  | Н  | L  | L  | L  |

| L               | н            | Ø  | ø  | ø  | ø  | Ø  | Ø  | н  | L  | L  | н  |

| L               | L            | н  | ø  | ø  | ø  | ø  | ø  | Н  | L  | Н  | L  |

| L               | L            | L  | н  | ø  | ø  | ø  | ø  | Н  | L  | Н  | н  |

| L               | L            | L  | L  | н  | Ø  | ø  | ø  | Н  | Н  | L  | L  |

| L               | L            | L  | L  | L  | Н  | ø  | ø  | Н  | н  | L  | н  |

| L               | L            | L  | L  | L  | L  | н  | ø  | н  | н  | Н  | L  |

| L               | L            | L  | L  | L  | L  | L  | н  | н  | Н  | Н  | н  |

| L               | L            | L  | L  | L  | L  | L  | L  | L  | L  | L  | L  |

| Ø               | ø=Don't Care |    |    |    |    |    |    |    |    |    |    |

TRUTH TABLE

**OUTPUTS**

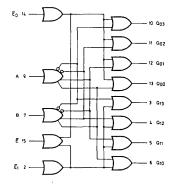

#### SP10171 **DUAL BINARY TO 1 OUT OF 4 DECODER** (LOW)

PD=325mW typ/pkg (No load)  $t_{pd} = 4.0$ ns typ

| TRUTH TABLE |            |    |     |     |          |               |     |     |     |     |     |     |

|-------------|------------|----|-----|-----|----------|---------------|-----|-----|-----|-----|-----|-----|

|             | NAB<br>NPU |    | INP | UTS | оит      |               |     |     | UTS |     |     |     |

| Ē           | ĒΟ         | Ē1 | Α   | В   | Q10      | Q11           | Q12 | Q13 | 000 | Q01 | Q02 | O03 |

| L,          | L          | L  | L   | L   | L        | Н             | Н   | Н   | L   | Н   | Н   | Н   |

| L           | L          | ٦  | L   | Н   | Н        | L             | Н   | Н   | Н   | L   | Н   | Н   |

| L           | L          | L  | Н   | L   | Н        | Н             | L   | Н   | Ħ   | Н   | L   | Н   |

| L           | L          | L. | Н   | Н   | Н        | Н             | Н   | L   | Н   | H   | L   | Н   |

| L           | L          | Н  | L   | L   | Н        | Н             | Н   | Н   | L.  | Н   | Н   | Н   |

| L           | Н          | L  | L   | L   | LHHHHHHH |               |     |     |     |     | H   |     |

| Н           | ø          | Ø  | Ø   | Ø   | Н        | н н н н н н н |     |     |     |     |     |     |

|             | _          |    |     |     |          |               |     |     |     |     |     |     |

ø=Don't Care

#### SP10172 **DUAL BINARY TO 1 OUT OF 4 DECODER** (HIGH)

PD=325mW typ/pkg (No load)  $t_{pd} = 4.0$ ns typ

|    | TRUTH TABLE |       |    |   |     |     |     |     |     |     |     |     |

|----|-------------|-------|----|---|-----|-----|-----|-----|-----|-----|-----|-----|

| Ē  | Ē1          | ĒΘ    | Α  | В | Q10 | 011 | Q12 | Q13 | 000 | Q01 | Q02 | G03 |

| L  | Н           | Н     | L  | L | Н   | L   | L   | L   | Н   | L   | L   | L   |

| L  | Н           | H     | Ĺ  | Н | L   | Н   | L   |     | L   | Н   | L   | L   |

| L  | Н           | Н     | Н  | L | L   | L   | Н   | L   | L   | L   | H   | Ĺ   |

| L  | Н           | Н     | Н  | Н | L   | L   | L   | Н   | L   | L   | L   | Н   |

| L  | L           | Н     | L  | L | L   | L   | L   | L   | H   | L   | L   | L   |

| L  | Н           | L     | L  | L | Н   | L   | L   | L,  |     | L   | L   | L   |

| Н  | Ø           | Ø     | Ø  | Ø | L   | L   | L   | L   | L   | ٦   | L   | L   |

| Ø: | = Dor       | 't Ca | re |   |     |     |     |     |     |     |     |     |

# SP10173 QUAD 2-INPUT MULTIPLEXER/LATCH TO BE ANNOUNCED

$P_D=275$ mW typ/pkg (No load)  $t_{pd}=2.5$ ns typ

#### TRUTH TABLE

|   |        | UIN IAD | LC                 |

|---|--------|---------|--------------------|

| 1 | SELECT | CLOCK   | Q0 <sub>n</sub> +1 |

|   | H      | L       | D00                |

|   | L      | L       | D01                |

|   | ø      | Н       | Q0 <sub>n</sub>    |

ø=Don't Care

#### SP10174 DUAL 4 TO 1 MULTIPLEXER

TO BE ANNOUNCED

$P_D=155mW \text{ typ/pkg}$  $t_{pd}=2.5ns \text{ typ}$

#### TRUTH TABLE

| ENABLE  | ADDRES | S INPUTS | OUT | PUTS |

|---------|--------|----------|-----|------|

| Ē       | В      | Α        | Z   | W    |

| Н       | Ø      | Ø        | L   | L    |

| L       | L      | L        | X0  | Y0   |

| L       | L      | Н -      | X1  | Y1   |

| L       | Н      | L        | X2  | Y2   |

| L       | Н      | Н        | Х3  | Y3   |

| ø=Don't | Care   |          |     |      |

#### SP10175 QUINT LATCH

TO BE ANNOUNCED

$P_D=400$ mW typ/pkg (No load)  $t_{pd}=2.5$ ns typ

#### TRUTH TABLE

| D | CO | C1 | Reset | $Q_n - 1$      |

|---|----|----|-------|----------------|

| L | L  | L  | L     | L              |

| Н | L  | L  | L     | Н              |

| ø | H  | Ø  | L     | Qn             |

| ø | Ø  | Н  | L     | Q <sub>n</sub> |

| ø | н  | ø  | н     | L              |

| ø | Ø  | Н  | н     | L              |

ø-Don't Care

#### SP10176 HEX D MASTER-SLAVE FLIP-FLOP

TO BE ANNOUNCED

$P_D = 460 \text{mW typ/pkg (No load)}$  $f_{log} = 150 \text{MHz}$

#### **CLOCKED TRUTH TABLE**

| С  | D | $Q_n + 1$      |

|----|---|----------------|

| L  | Ø | Q <sub>n</sub> |

| H* | L | L              |

| H* | Н | н              |

ø Don't Care

\*A clock H is a clock transition from a low to a high state.

#### TRUTH TABLE

|   |    |    | INPU | OUTPUTS |    |    |    |       |      |    |

|---|----|----|------|---------|----|----|----|-------|------|----|

| R | S0 | S1 | S2   | S3      | C1 | C2 | Ω0 | Q1    | Q2   | Q3 |

| Н | L  | L  | L    | L       | ø  | ø  | ٦  | L     | L    | L  |

| L | Н  | Н  | н    | Н       | ø  | ø  | н  | н     | Н    | Н  |

| L | L  | L  | L    | L       | Н  | ø  | ı  | Vo co | ount |    |

| L | L  | L  | L    | L       | ø  | Н  | ,  | No co | ount |    |

| L | L  | L  | L    | L       |    | •  | L  | L     | L    | L  |

| L | L  | L  | L    | L       |    |    | Н  | L     | L    | L  |

| L | L  | L  | L    | L       |    | •  | L  | Н     | L    | L  |

| L | L  | L  | L    | L       |    | •  | н  | Н     | L    | L  |

| L | L  | L  | L    | L       |    | •  | L  | L     | Н    | L  |

| L | L  | L  | L    | L       |    | •  | н  | L     | Н    | L  |

| L | L  | L  | L    | L       |    | •  | L  | Н     | Н    | L  |

| L | L  | L  | L    | L       |    | *  | Н  | н     | Н    | L  |

| L | L  | L  | L    | L       |    | •  | L  | L     | L    | H  |

| L | L  | L  | L    | L       |    | •  | н  | L     | L    | Н  |

| L | L  | L  | Ł    | L       |    | •  | L  | Н     | L    | Н  |

| L | L  | L  | L    | L       |    | *  | Н  | Н     | L    | ·H |

| L | L  | L  | L    | L       |    | •  | L  | L     | Н    | Н  |

| L | L  | L  | L    | L       |    | •  | н  | L     | Н    | Н  |

| L | L  | L  | L    | L       |    | •  | L  | Н     | Н    | н  |

| L | L  | L  | L    | L       |    | *  | Н  | Н     | н    | Н  |

Ø Don't Care

Clock transition from VIL to VIH may be applied to C1 or C2 or both for same effect.

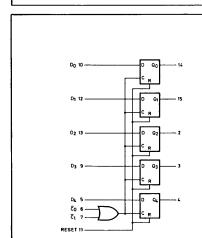

#### SP10178 BINARY COUNTER

TO BE ANNOUNCED

$P_D = 370$  mW typ/pkg (no load)  $f_{tog} = 150$  MHz typ

# SP10179 LOOK-AHEAD CARRY BLOCK TO BE ANNOUNCED G1 5 P3 13 G2 9 P2 12 Cn 11 F1 10 G0 4 PD = 300mW typ/pkg tpd = 3.0ns typ (Carry, Propagate) 4.0ns typ (Generate)

#### **IMPORTANT!**

#### **ECLIII Temperature Range**

Since the SP1600 series datasheets were prepared, the operating temperature range of all these ECLIII products has been uprated to  $-30^{\circ}$ C to  $+85^{\circ}$ C, and not  $0^{\circ}$ C to  $+75^{\circ}$ C as stated in the individual datasheets.

# SP1600 SERIES

#### **SP1648B**

#### **VOLTAGE-CONTROLLED OSCILLATOR**

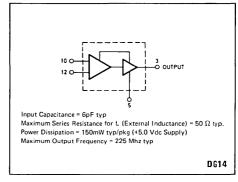

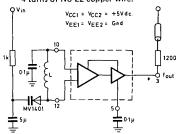

The SP1648 is an emitter-coupled oscillator, constructed on a single monolithic silicon chip. Output levels are compatible with PECL III logic levels. The oscillator requires an external parallel tank circuit consisting of the inductor (L) and capacitor (C).

A varactor diode may be incorporated into the tank circuit to provide a voltage variable input for the oscillator (VCO). The device may also be used in phase locked loops and many other applications requiring a fixed or variable frequency clock source of high spectral purity.

The SP1648 may be operated from a +5.0 Vdc supply or a -5.2 Vdc supply, depending upon system requirements.

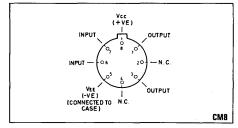

| SUPPLY VOLTAGE | GND PINS | SUPPLY PINS |

|----------------|----------|-------------|

| +5.0 Vdc       | 7, 8     | 1, 14       |

| -5,2 Vdc       | 1, 14    | 7, 8        |

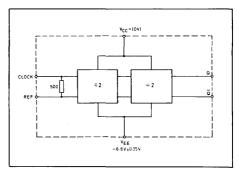

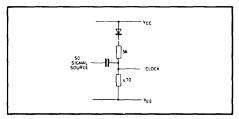

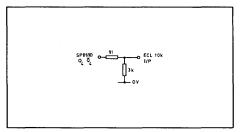

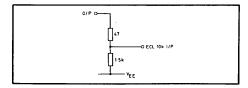

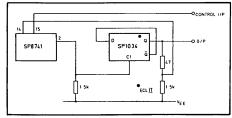

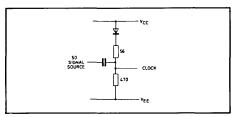

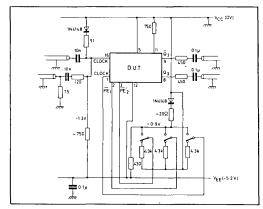

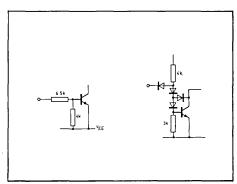

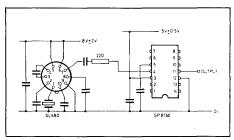

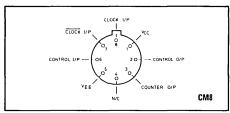

Fig. 1 Block diagram of SP1648

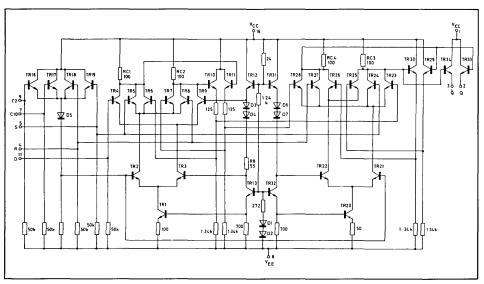

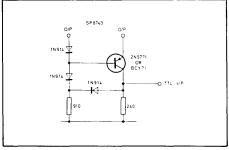

Fig. 2 Circuit diagram of SP1648

#### SP1648

#### **ELECTRICAL CHARACTERISTICS**

| Supply Voltage = +5.0 volts |                     |              |      |         |      |       |          |                                 |       |      |      |          | TEST VOLTAGE/CURRENT VALUES (Volts) mAdc |         |       |       |       |

|-----------------------------|---------------------|--------------|------|---------|------|-------|----------|---------------------------------|-------|------|------|----------|------------------------------------------|---------|-------|-------|-------|

| @ Test                      |                     |              |      |         |      |       |          |                                 |       |      |      |          |                                          | mAdc    | 1     |       |       |

|                             |                     |              |      |         |      |       |          |                                 |       |      |      | perature | V <sub>IH max</sub>                      | VIL min | Vcc   | Ti.   |       |

|                             |                     |              |      |         |      |       |          |                                 |       |      |      | o^c      | +1.900                                   | +1.400  | 5.0   | ~ 5.0 | 1     |

|                             |                     |              |      |         |      |       |          |                                 |       |      |      | +25°C    | +1.800                                   | +1.300  | 5.0   | -5.0  | 1     |

|                             |                     |              |      |         |      |       |          |                                 |       |      |      | +75°C    | +1.700                                   | +1.200  | 5.0   | 5.0   | 1     |

|                             |                     |              |      |         |      |       | SP1648 1 | TEST VOLTAGE/CURRENT APPLIED TO |       |      |      | VEE      |                                          |         |       |       |       |

| Characteristic S            | -                   | Pin<br>Under | 0°C  |         |      | +25°C |          |                                 | +75°C |      | T    |          | PINS LISTED BELOW                        |         |       |       |       |

|                             | Symbol              | Test         | Min  |         | Max  | Min   |          | Max                             | Min   |      | Max  | Unit     | VIH max                                  | VIL min | Vcc   | 1L    | (Gnd) |

| Power Supply Drain Current  | ŀΕ                  | 8            | _    |         |      | -     |          | 35                              | -     |      | -    | mAdc     |                                          |         | 1, 14 |       | 7, 8  |

| Logic "1"<br>Output Voltage | VOH                 | 3            | 4.00 |         | 4.16 | 4.04  |          | 4.19                            | 4.10  |      | 4.28 | Vdc      |                                          | 12      | 1, 14 | 3     | 7, 8  |

| Logic "0"<br>Output Voltage | VOL                 | 3            | 3.18 | 18 3.42 |      | 3.20  | ·        | 3.43                            | 3.22  | 3.46 |      | Vdc      | 12                                       | T       | 1, 14 | 3     | 7, 8  |

| Bias Voltage                | V <sub>Bias</sub> * | 10           | 1.45 |         | 1.8  | 1.4   |          | 1.7                             | 1.3   |      | 1.6  | Vdc      | -                                        | -       | 1, 14 | -     | 7, 8  |

|                             | T                   |              | Min  | Тур     | Max  | Min   | Тур      | Max                             | Min   | Тур  | Max  |          |                                          |         | 1     |       |       |

| Peak-to-Peak Tank Voltage   | Vp-p                | 12           | -    | -       | -    | -     | 500      | -                               | -     | -    | -    | m∨       | See Figure 4                             | -       | 1, 14 | 3     | 7,8   |

| Output Duty Cycle           | VDC                 | 3            | -    |         | -    | -     | 50       | -                               |       | -    | -    | %        | See Figure 4                             | -       | 1,14  | 3     | 7,8   |

| Oscillation Frequency       | I                   |              |      |         | _    | 105   | 225      |                                 | _     |      |      | MHz      | See Figure 4                             |         | 1 14  | 1 3   | 7.8   |

<sup>\*</sup> This measurement guarantees the dc potential at the bias for purposes of incorporating a varactor diode at this point

#### **ELECTRICAL CHARACTERISTICS**

| Supply Voltage = -          | 5.2 vol             | ts           |        |          |        |       |        |             |       |                       |        |       | TEST VO                         | LTAGE/CUF | RENT V | LUES | Γ.    |

|-----------------------------|---------------------|--------------|--------|----------|--------|-------|--------|-------------|-------|-----------------------|--------|-------|---------------------------------|-----------|--------|------|-------|

| .,,                         |                     |              |        |          |        |       |        |             |       |                       |        |       |                                 | mAde      | 1      |      |       |

|                             |                     |              |        |          |        |       |        |             |       | © Test<br>Temperature |        |       |                                 | VIL min   | VEE    | IL.  | 1     |

|                             |                     |              |        |          |        |       |        |             |       |                       |        | 0°C   | -3.300                          | -3.800    | -5.2   | -5.0 | 1     |

|                             |                     |              |        |          |        |       |        |             |       |                       |        | +25°C | -3.400                          | -3.900    | -5.2   | -5.0 | 1     |

|                             |                     |              |        |          |        |       |        |             |       |                       |        | +75°C | -3.500                          | -4.000    | -5.2   | -5.0 | 1     |

|                             |                     |              |        |          |        |       | SP1648 | Test Limits |       | ~~~                   |        |       | TEST VOLTAGE/CURRENT APPLIED TO |           |        |      | 7     |

| Cheracteristic              | ]                   | Pin<br>Under | 0°C    |          |        | +25°C |        |             | +75°C |                       |        | I     | PINS LISTED BELOW               |           |        |      |       |

|                             | Symbol              | Test         | Min    |          | Mex    | Min   |        | Mex         | Min   | I                     | Mex    | Unit  | VIH max VIL min                 |           | VEE    | 14   | - VCC |

| Power Supply Drain Current  | IE.                 | 8            | -      | $\neg$   |        | _     |        | 36          | -     | $\neg$                |        | mAdc  | -                               | -         | 7,8    | -    | 1, 1  |

| Logic "1"<br>Output Voltage | VOH                 | 3            | -1.000 |          | -0.840 | -0.96 | ю      | -0.810      | -0.90 | 10                    | -0.720 | Vdc   | -                               | 12        | 7, 8   | 3    | 1, 14 |

| Logic "0"<br>Output Voltage | VOL                 | 3            | -1.87  | -1.870 - |        | -1.85 | 0      | -1.620      | -1.83 | 30 -1.595             | Vdc    | 12    | -                               | 7,8       | 3      | 1, 1 |       |

| Bies Voltage                | V <sub>Bias</sub> * | 10           | -3.75  | 0        | -3.400 | -3.80 | 0      | -3.500      | -3.90 | 90                    | -3.600 | Vdc   | -                               | -         | 7, 8   | -    | 1, 1  |

|                             |                     |              | Min    | Тур      | Max    | Min   | Тур    | Max         | Min   | Тур                   | Mex    |       |                                 |           |        |      |       |

| Peak-to-Peak Voltage        | Vp-p                | 12           | -      | -        | T -    | -     | 500    | _           | _     | -                     | T -    | mv    | See Figure 4                    | _         | 7,8    | 3    | 1, 14 |

| Our- ut Duty Cycle          | VDC                 | 3            | -      | -        | -      | _     | 50     | -           | -     | -                     | -      | *     | See Figure 4                    | -         | 7,8    | 3    | 1, 1  |

| Oscillation Frequency       | fmex                | _            | -      | -        | _      | 195   | 225    | 1 -         |       | _                     | 1 -    | MHz   | See Figure 4                    |           | 7, 8   | 3    | 1, 14 |

<sup>\*</sup> This measurement guarantees the dc potential at the bias point for purposes of incorporating a varactor tuning diode at this point.

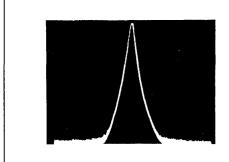

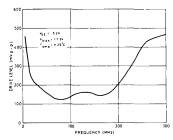

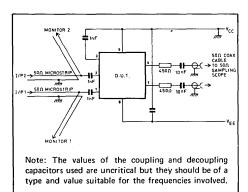

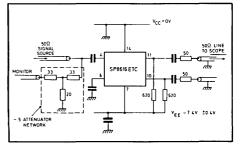

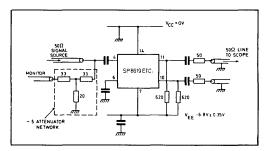

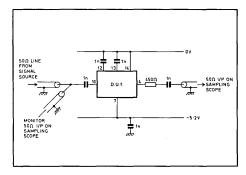

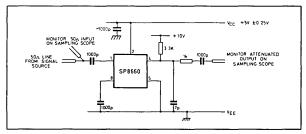

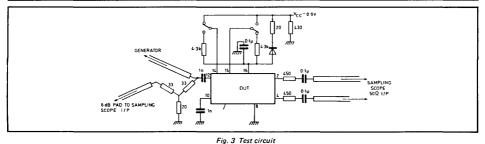

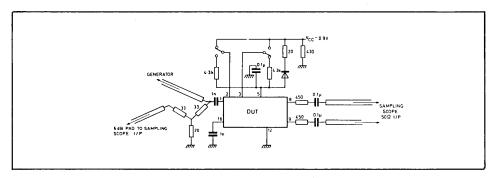

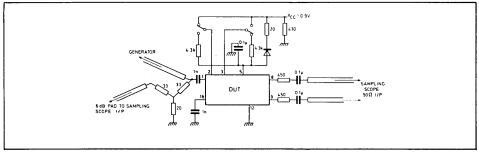

B.W. = 10kHz Scan Width = 50kHz/div Center Frequency = 100MHz Vertical Scale = 10db/div L: Micro Metal torroid #T20.13, 8 turns #30 Enameled Copper wire.

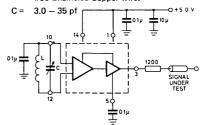

\* The 1200 ohm resistor and the scope termination impedance constitute a 25:1 attenuator probe. Coax shall be CT-070-50 or equivalent.

Fig. 3 Spectral purity of signal at output

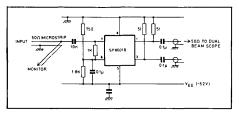

Fig. 4 Test circuit and waveforms

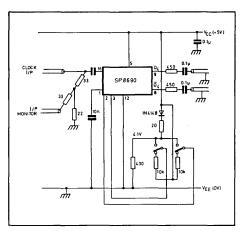

#### **OPERATING CHARACTERISTICS**

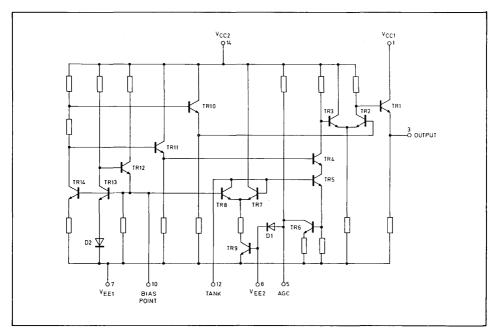

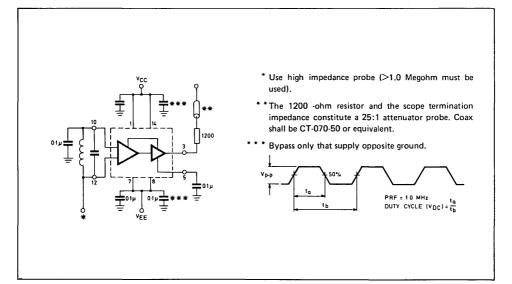

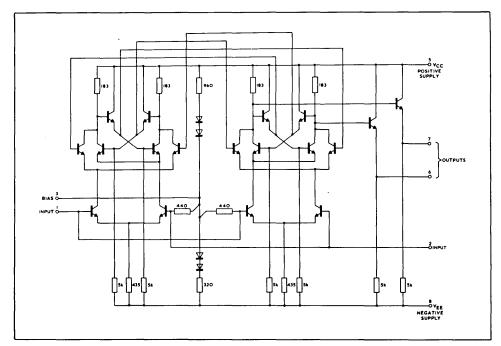

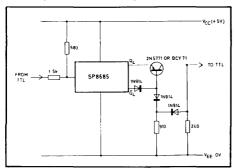

Figure 1 illustrates the circuit schematic for the SP1648. The oscillator incorporates positive feedback by coupling the base of transistor TR7 to the collector of TR8. An automatic gain control (AGC) is incorporated to limit the current through the emitter-coupled pair of transistors (TR7 and TR8) and allow optimum frequency response of the oscillator.

In order to maintain the high Q of the oscillator, and provide high spectral purity at the output, a cascode transistor (TR4) is used to translate from the emitter follower (TR5) to the output differential pair TR2 and TR3. TR2 and TR3, in conjunction with output transistor TR1, provide a highly buffered output which produces a square wave. Transistors TR10 thru TR14 provide this bias drive for the oscillator and output buffer. Figure 3 indicates the high spectral purity of the oscillator output (pin 3).

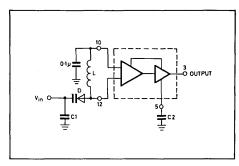

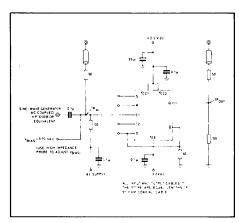

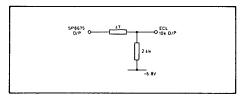

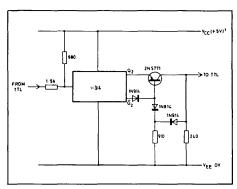

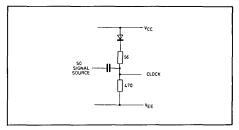

When operating the oscillator in the voltage controlled mode (Figure 5), it should be noted that the cathode of the varactor diode (D) should be biased at least 2  $V_{BE}$  above  $V_{EE}$  ( $\approx$  1.4 V for positive supply operation).

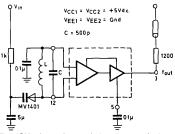

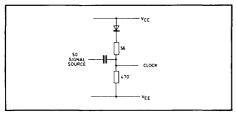

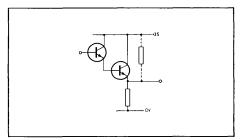

Fig. 5 The SP1648 operating in the voltage-controlled mode

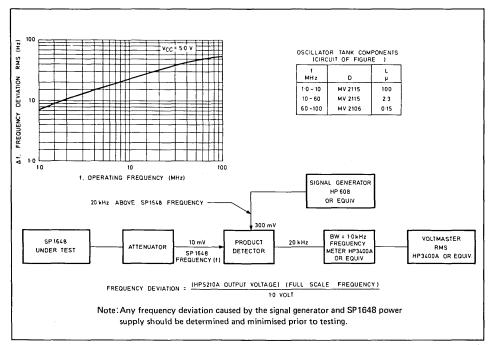

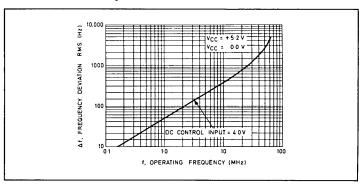

When the SP1648 is used with a constant dc voltage to the varactor diode, the output frequency will vary slightly because of internal noise. This variation is plotted versus operating frequency in Figure 6.

Fig. 6 Frequency deviation test circuit

L: Micro Metal Toroidal Core #T44-10, 4 turns of No 22 copper wire.

The 1200 ohm resistor and the scope termination impedance constitute a 25:1 attenuator probe. Coax shall be CT-070-50 or equivalent.

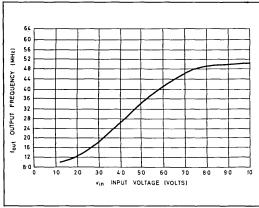

Fig. 7

L: Micro Metal Toroidal Core #44-10, 4 turns of No. 22 copper wire.

The 1200 ohm resistor and the scope termination impedance consitute a 25:1 attenuator probe. Coax shall be CT-070-50 or equivalent.

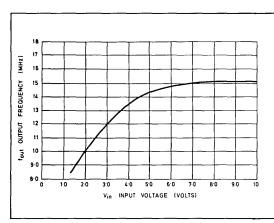

Fig. 8

L: Micro Metal Torodial Core #T30-13, 5 turns of No. 20 copper wire.

The 1200 ohm resistor and the scope termination impedance constitute a 25:1 attenuator probe. Coax shall be CT-070-50 or equivalent.

Fig. 9

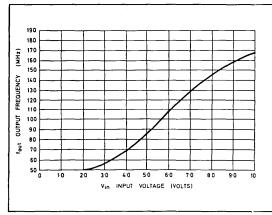

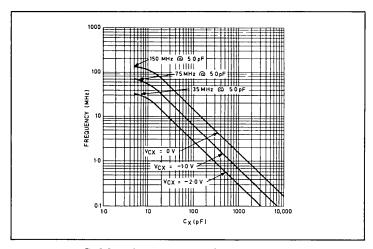

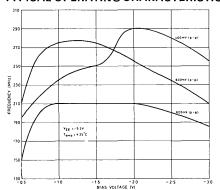

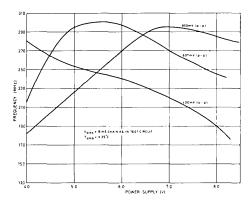

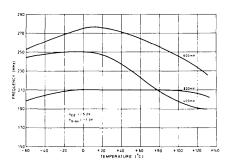

Typical transfer characteristics for the oscillator in the voltage controlled mode are shown in Figures 7, 8, and 9. Figures 7 and 9 show transfer characteristics employing only the capacitance of the varactor diode (plus the input capacitance of of the oscillator, 6pF typical). Figure 8 illustrates the oscillator operating in a voltage controlled mode with the output frequency range limited. This is achieved by adding a capacitor in parallel with the tank circuit as shown. The 1  $k\Omega$  resistor in Figures 7 and 8 is used to protect the varactor diode during testing. It is not necessary as long as the dc input voltage does not cause the diode to become forward biased. The larger-valued resistor (51  $k\Omega$ ) in Figure 9 is required to provide isolation for the high-impedance junctions of the two varactor diodes.

The tuning range of the oscillator in the voltage controlled mode may be calculated as:

$$\frac{f_{max}}{f_{min}} = \frac{\sqrt{C_D(max) + C_S}}{\sqrt{C_D(min) + C_S}}$$

where

$$f_{min} = \frac{1}{2^{\pi} \sqrt{L (C_D (max) + C_S)}}$$

Cs = shunt capacitance (input plus external capacitance).

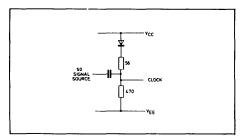

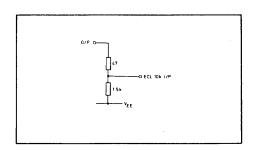

C<sub>D</sub> = varactor capacitance as a function of bias voltage. Good RF and low-frequency by-passing is necessary on the power supply pins (see Figure 3).

Capacitors (C1 and C2 of Figure 5) should be used to bypass the AGC point and the VCO input (varactor diode), guaranteeing only dc levels at these points.

For output frequency operation between 1 MHz and 50 MHz a  $0.1\mu F$  capacitor is sufficient for C1 and C2. At higher frequencies, smaller values of capacitance should be used; at lower frequencies, larger values of capacitance. At higher frequencies the value of bypass capacitors depends directly upon the physical layout of the system. All bypassing should be as close to the package pins as possible to minimize unwanted lead inductance.

The peak-to-peak swing of the tank circuit is set internally by the AGC circuitry. Since voltage swing of the tank circuit provides the drive for the output buffer, the AGC potential directly affects the output waveform. If it is desired to have a sine wave at the output of the SP1648, a series resistor is tied from the AGC point to the most negative power potential (ground if +5.0 volt supply is used). —5.2 volts if a negative supply is used).

At frequencies above 100 MHz typ, it may be necessary to increase the tank circuit peak-to-peak voltage in order to maintain a square wave at the output of the SP1648. This is accomplished by tying a series resistor (1  $k\Omega$  minimum) from the AGC to the most positive power potential (+5.0 volts if a +5.0 volt supply is used, ground if a -5.2 volt supply is used).

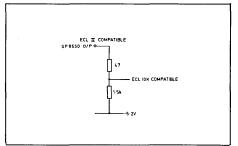

ECL III

## SP1650B (HIGH Z) SP1651B (LOW Z)

## **DUAL A/D COMPARATOR**

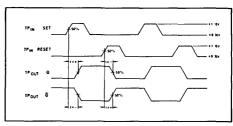

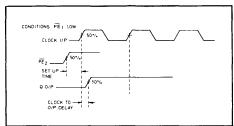

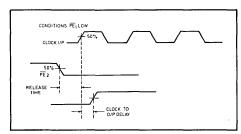

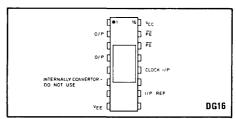

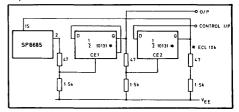

The SP1650 and the SP1651 are very high speed comparators utilizing differential amplifier inputs to sense analog signals above or below a reference level. An output latch provides a unique sample-hold feature. The SP1650 provides high impedance Darlington inputs, while the SP1651 is a lower impedance option, with higher input slew rate and higher speed capability.

Complementary outputs permit maximum utility for applications in high speed test equipment, frequency measurement, sample and hold, peak voltage detection and transmitters, receivers, memory translation and more.

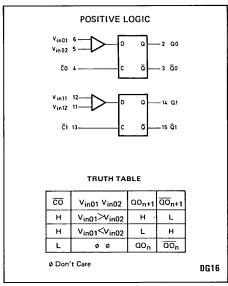

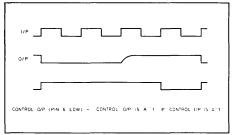

The clock inputs  $(\overline{C0} \text{ and } \overline{C1})$  operate from PECL III or PECL 10,000 digital levels. When  $\overline{C0}$  is at a logic high level, Q0 will be at a logic high level provided that  $V_{in01} > V_{in02}$  ( $V_{in01}$  is more positive than  $V_{in02}$ ).  $\overline{Q0}$  is the logic complement of Q0. When the clock input goes to a low logic level, the outputs are latched in their present state.

## **FEATURES**

- $P_D = 275 \text{ mW typ/pkg (No Load)}$

- Very High Speed − 3.5 ns Delay (SP1650)

− 2.5 ns Delay (SP1651)

- High Input Slew Rate − 350 V/µs (SP1651)

- Positive Transition Region Input Hysterisis.

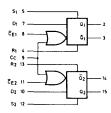

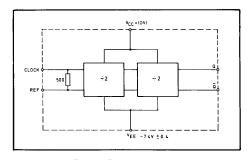

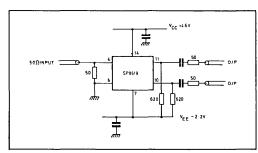

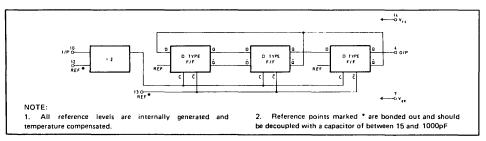

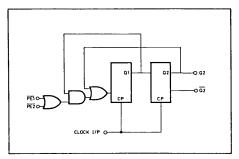

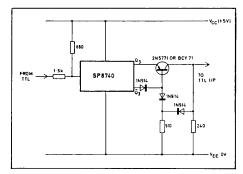

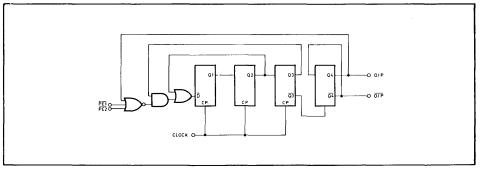

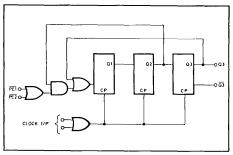

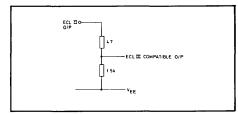

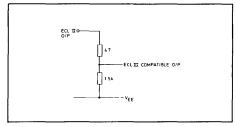

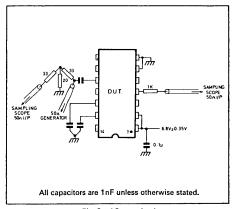

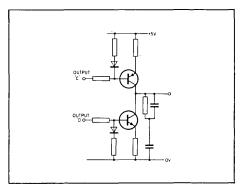

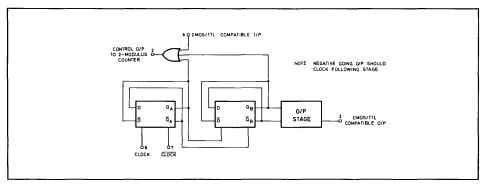

Fig. 1 Logic diagram of SP1651

**ECL III**

## **SP1658**

## VOLTAGE-CONTROLLED MULTIVIBRATOR

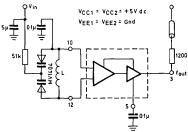

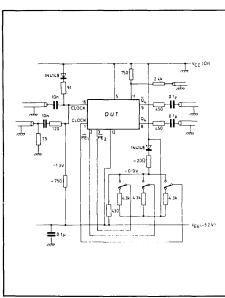

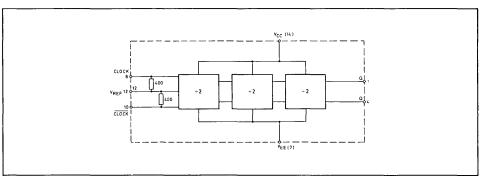

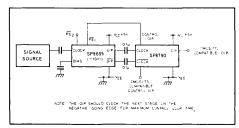

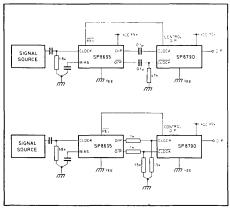

The SP1658 is a voltage-controlled multivibrator which provides appropriate level shifting to produce an output compatible with PECL III and PECL 10,000 logic levels. Frequency control is accomplished through the use of voltage-variable current sources which control the slew rate of a single external capacitor.

The bias filter may be used to help eliminate ripple on the output voltage levels at high frequencies and the input filter may be used to decouple noise from the analog input signal.

The PECL1658 is useful in phase-locked loops, frequency synthesizer and clock signal generation applications for instrumentation, communication, and computer systems.

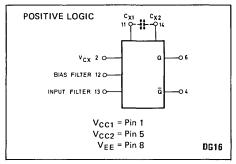

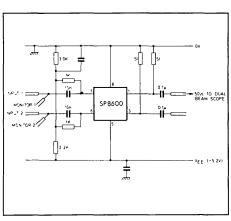

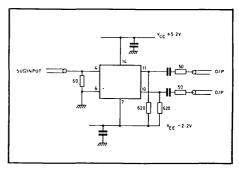

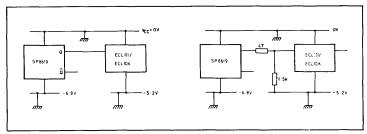

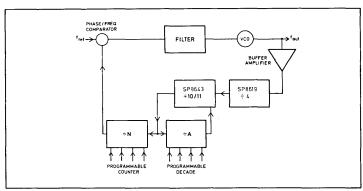

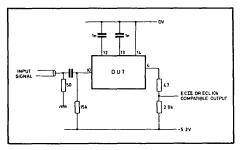

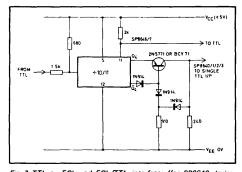

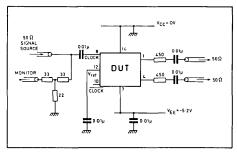

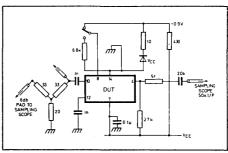

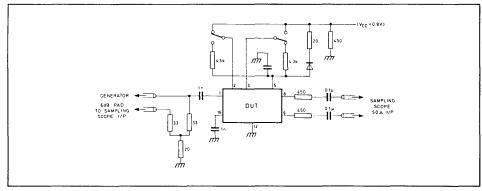

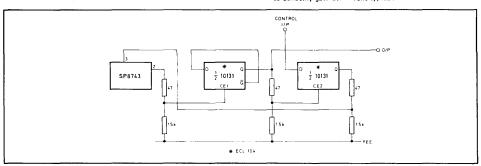

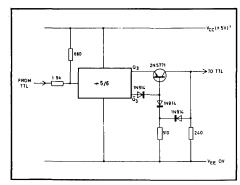

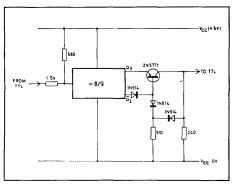

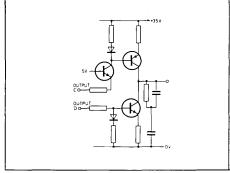

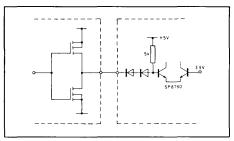

Fig. 1 Block diagram of SP1658

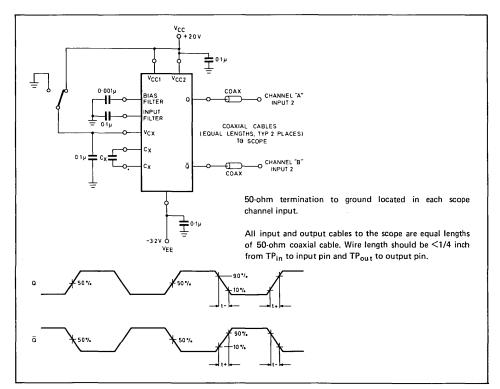

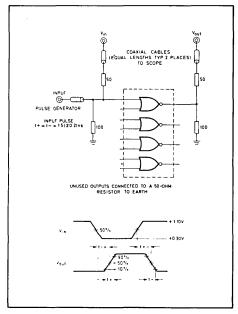

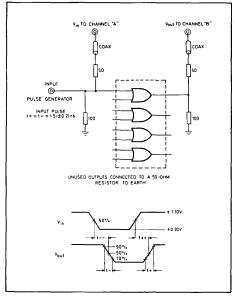

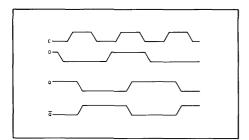

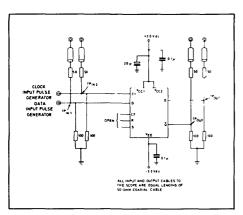

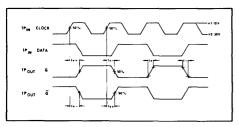

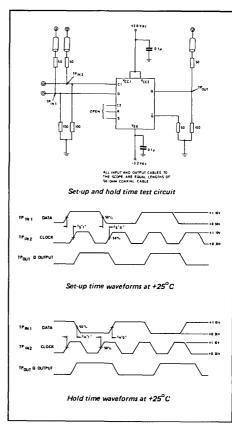

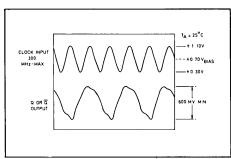

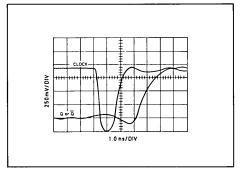

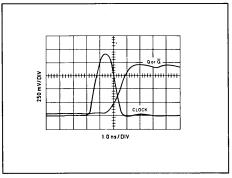

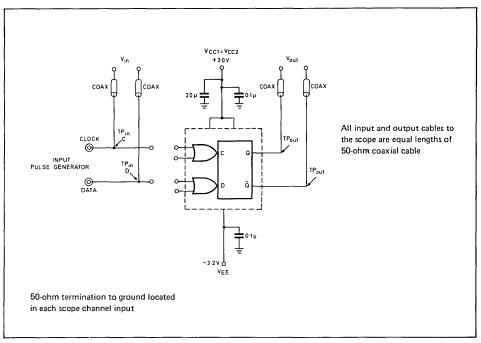

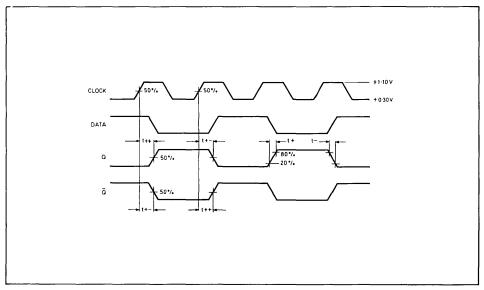

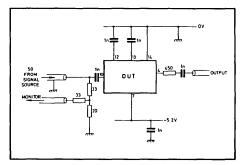

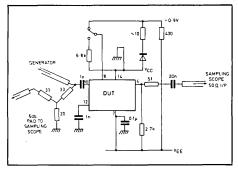

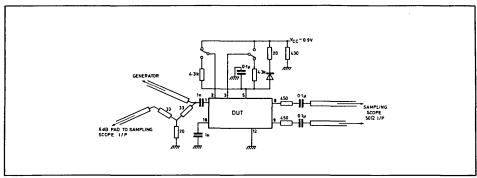

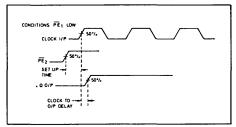

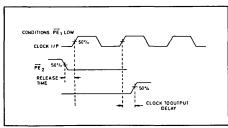

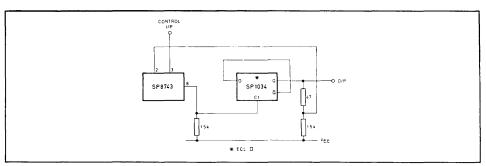

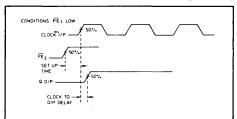

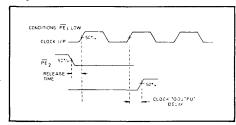

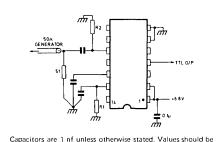

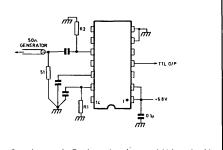

Fig. 2 AC test circuit and waveforms

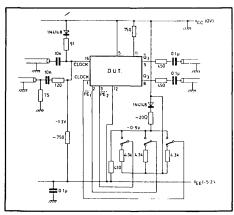

This PECL III circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 linear fpm is maintained. Outputs are terminated through a 50-ohm resistor to -- 2.0 volts.

> **TEST VOLTAGE VALUES** Vdc ± 1% @ Test VIH ٧3 Temperature VIL VIHA VEE -0.0-2.0-1.0+2.0 -5.2 +25°C +2.0 -5.2-0.0-2.0-1.0+75°C -0.0 -2.0 +2.0 -5.2 -1.0

|                                                                                 |               |              |                  |                          |                  |                          |                          |                  |                          |              | 0.0             | -2.0            | - 1.0       |               |               | 1 0.2                    |                          |

|---------------------------------------------------------------------------------|---------------|--------------|------------------|--------------------------|------------------|--------------------------|--------------------------|------------------|--------------------------|--------------|-----------------|-----------------|-------------|---------------|---------------|--------------------------|--------------------------|

|                                                                                 |               |              |                  | SP1658 Test Limits       |                  |                          |                          |                  |                          |              | VOLTA           | AGE APPL        | IED TO F    | INS LI        | STED          | BELOW                    |                          |

|                                                                                 | 1             | Pin<br>Under | 0                | °c                       |                  | +25°C                    | ;                        | +7               | 5°C                      |              | }               | 1               | Γ           | 1             | <del></del>   |                          | {                        |

| Characteristic                                                                  | Symbol        | Test         | Min              | Max                      | Min              | Тур                      | Max                      | Min              | Max                      | Unit         | VIH             | VIL             | V3          | VII           | HA            | VEE                      | Gnd                      |

| Power Supply Drain Current                                                      | 1E            | 8**          | -                | _                        | _                | -                        | 32<br>32                 | =                | =                        | mAdc<br>mAdc | 2 2             | - =             | _           | -             | -             | 8<br>8                   | 1,5<br>1,5               |

| Input Current                                                                   | linH          | 2 *          | <b>-</b>         | -                        |                  | _                        | 350                      | _                | -                        | μAdc         | 2               | _               |             |               | -             | 8                        | 1,5                      |

| Input Leakage Current                                                           | linL          | 2 *          |                  | _                        | -0.5             | -                        | _                        | _                | -                        | μAdc         | -               | 2               |             | 1 -           |               | 8                        | 1,5                      |

| "Q" High<br>Output Voltage                                                      | Voн           | 4 *<br>6 * * | -1.000<br>-1.000 | -0.840<br>-0.840         | -0.960<br>-0.960 |                          | -0.810<br>-0.810         | -0.900<br>-0.900 | -0.720<br>-0.720         | Vdc<br>Vdc   | =               | =               | 2 2         |               | -             | 8<br>8                   | 1,5<br>1,5               |

| "Q" Low<br>Output Voltage                                                       | VoL           | 6**          | -1.870<br>-1.870 | -1.620<br>-1.620         | -1.850<br>-1.850 | =                        | -1.620<br>-1.620         | -1.850<br>-1.850 | -1.595<br>-1.595         | Vdc<br>Vdc   | =               | =               | 2 2         |               | -             | 8                        | 1,5<br>1,5               |

| AC Characteristics (Figure 2) (Tests shown for one output, but checked on both) |               |              |                  |                          |                  |                          |                          |                  |                          |              | c <sub>X1</sub> | c <sub>X2</sub> | Gnd         | VILA<br>+1.0V | VIHA<br>+2.0V | V <sub>EE</sub><br>-3.2V | V <sub>CC</sub><br>+2.0V |

| checked on bothy                                                                | t†<br>t<br>t+ | 6<br>6<br>6  | _<br>            | 2.5<br>2.5<br>4.6<br>4.2 | -<br>-<br>-      | 1.6<br>1.4<br>3.7<br>2.4 | 2.5<br>2.5<br>4.6<br>4.2 | _<br>_<br>_      | 2.7<br>2.7<br>4.8<br>4.4 | ns<br>       | -<br>-<br>-     | 11,14           | _<br>_<br>_ | -<br>2<br>2   | 2 -           | 8                        | 1,5                      |

| Rise Time (10% to 90%)<br>Fall Time (10% to 90%)                                | t+<br>t-      | 6            | =                | 8.5<br>8.5               | _                | 5.7<br>5.9               | 8.5<br>8.5               |                  | 8.7<br>8.7               |              | =               | <b>│</b>        | 2 2         |               | =             |                          |                          |

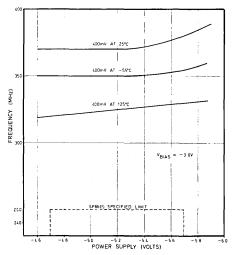

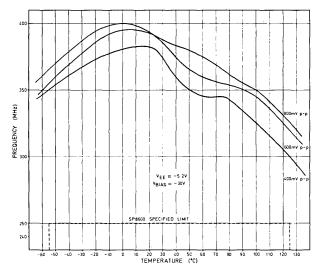

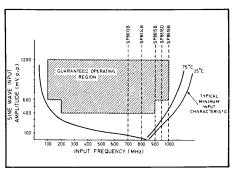

| Oscillator Frequency                                                            | fosc1         | -            | 130              | -                        | 130              | 155                      | 175                      | 110              | _                        | MHz          | -               | 11,14           | _           | -             | 2             | 8                        | 1,5                      |

|                                                                                 | fosc2         |              | -                |                          | 78               | 90                       | 100                      |                  |                          | MHz          | 11,14           | -               |             | -             | 2             | 8                        | 1,5                      |

| Tuning Ratio Test †                                                             | TR            |              | _                | _                        | 3.1              | 4.5                      |                          | _                | _                        |              | 11.14           |                 | _           | T =           | 1 - 1         | 8                        | 1,5                      |

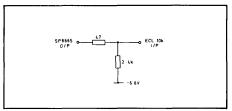

<sup>\*</sup> Germanium diode (0.4 drop) forward biased from 11 to 14 (11 — 14).

\* Germanium diode (0.4 drop) forward biased from 14 to 11 (11 — 14).

\* Gutput frequency at V<sub>CX</sub> = Gnd

Output frequency at V<sub>CX</sub> = -2.0 V

C1 = 0.01  $\mu$ F connected from pin 12 to Gnd. C2 = 0.001  $\mu$ F connected from pin 13 to Gnd. C $\chi$ 1 = 10 pF connected from pin 11 to pin 14. C $\chi$ 2 = 5 pF connected from pin 11 to pin 14.

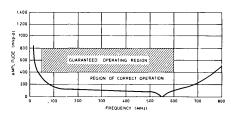

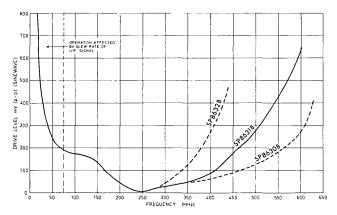

Fig. 3 Output frequency v capacitance for three values of input voltage

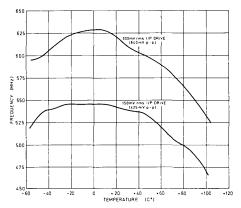

Fig. 4 RMS noise deviation v operating frequency

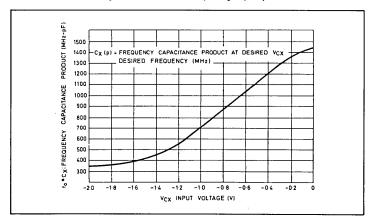

Fig. 5 Frequency-capacitance product v control voltage VCX

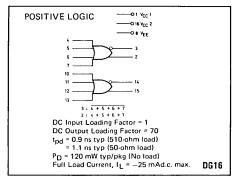

# SP1660B (HIGH Z) SP1661B (LOW Z) DUAL 4-INPUT OR/NOR GATE

SP1660B provides simultaneous OR-NOR output functions with the capability of driving  $50\Omega$  lines. This device contains an internal bias reference voltage, ensuring that the threshold point is always in the centre of the transition region over the temperature range (0°C to +75°C). The input pulldown resistors eliminate the need to tie unused inputs to  $V_{\rm FE}$ .

#### **FEATURES**

- Gate Switching Speed Ins Typ.

- MECL/PECL II and MECL 10000 Compatible

- 50Ω Line Driving Capability

- Operation With Unused I/Ps Open Circuit

- Low Supply Noise Generation

#### APPLICATIONS

- Data Communications

- Instrumentation

- PCM Transmission Systems

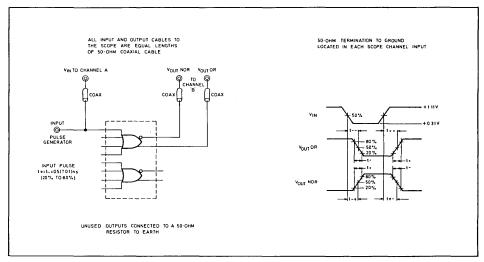

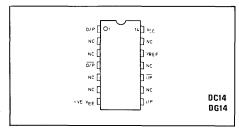

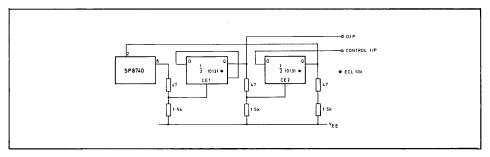

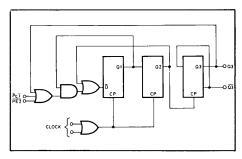

Fig. 1 Logic diagram

## **ABSOLUTE MAXIMUM RATINGS**

Power supply voltage |V<sub>CC</sub> -V<sub>EE</sub>| 8V

Base input voltage 0V to V<sub>E</sub>

O/P source current <40mA

Storage temperature 55°C to +150°C

Junction operating temp. <+125°C

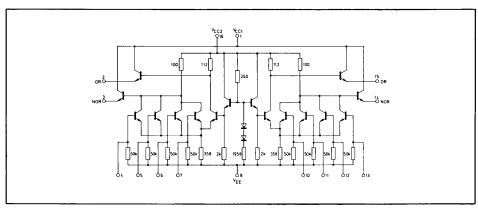

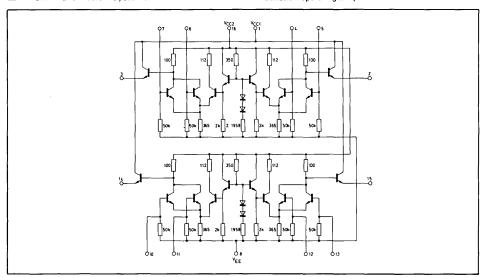

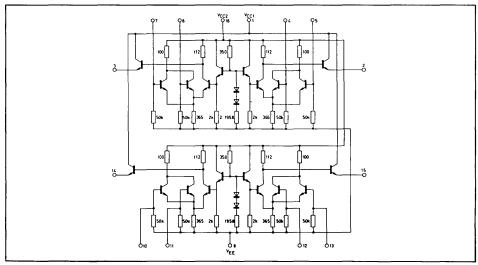

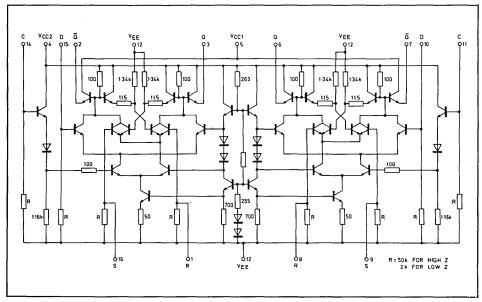

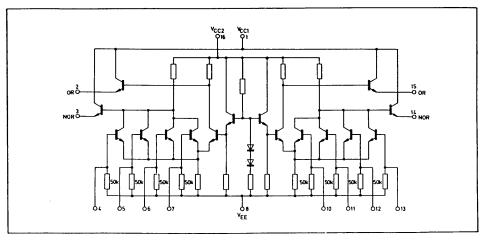

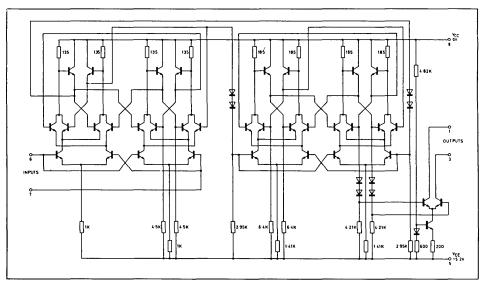

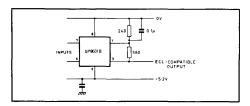

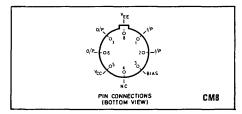

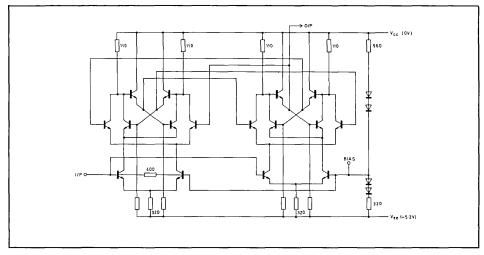

Fig. 2 Circuit diagram

## SP1660/1

## **ELECTRICAL CHARACTERISTICS**

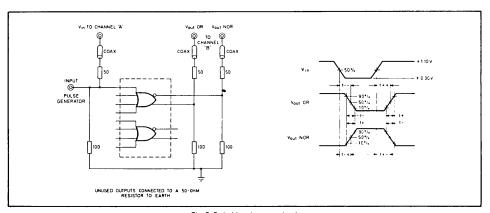

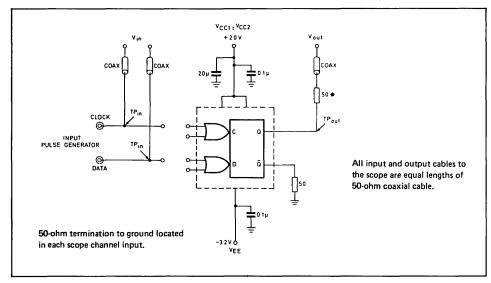

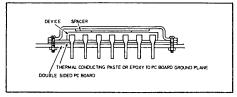

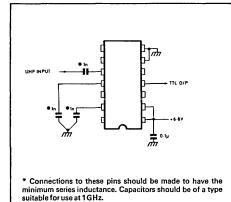

This PECL III circuit has been designed to meet the d.c. specifications shown in the characteristics table, after thermal equilibrium has been established. The package should be housed in a suitable heat sink (IERC 14A2CB or equivalent) or a transverse air flow greater than 500 linear ft/min should be maintained while the circuit is in either a test socket or is mounted on a printed circuit board. Test procedures are shown for only one gate. The other gates are tested in the same manner. Outputs are tested with a  $50\Omega$  resistor to -2.0 Vd.c.

|                                  |                   |          |        |            |               |              |            |            |                         | ļ                             | TEST VO                       | DLTAGE VA            | LUES (V)         |                  |              |

|----------------------------------|-------------------|----------|--------|------------|---------------|--------------|------------|------------|-------------------------|-------------------------------|-------------------------------|----------------------|------------------|------------------|--------------|

|                                  |                   |          |        |            |               |              |            |            | Test<br>perature<br>0°C | V <sub>IH max</sub><br>-0.840 | V <sub>IL min</sub><br>-1.870 | V <sub>IHA min</sub> | VILA mex         | V <sub>E E</sub> |              |

|                                  |                   |          |        |            |               |              |            |            | +25°C                   | -0.810                        | -1.850                        | -1.095               | -1.485           | -5.2             | 1            |

|                                  |                   |          |        |            |               |              |            |            | +75°C                   | -0.720                        | -1.830                        | -1.035               | -1.460           | -5.2             | 1            |

|                                  |                   | Pin      |        |            | SP166         | OB Test      | Limits     |            |                         | TEST                          | OLTAGE AR                     | PI IEO TO PI         | INS LISTED B     | ELOW:            | 1            |

| Characteristic                   | Symbol            | Under    | 0      | 'c         | +2            | 5°C          | +7         | 5°C        | ]                       |                               | OLIAGE AI                     | 1 212 1071           | 1 2 2 13 1 2 2 2 | LEOII.           |              |

|                                  | •                 | Test     | Min    | Max        | Min           | Max          | Min        | Max        | Units                   | VIH max                       | V <sub>IL min</sub>           | VIHA min             | VILA max         | VEE              | ov           |

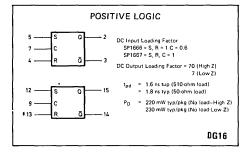

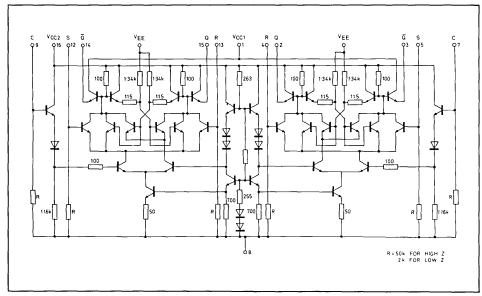

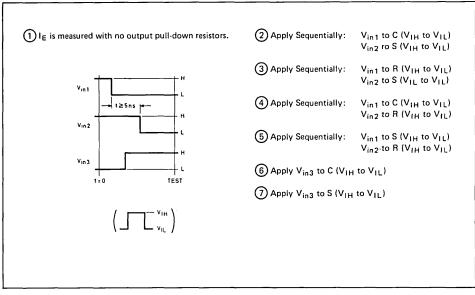

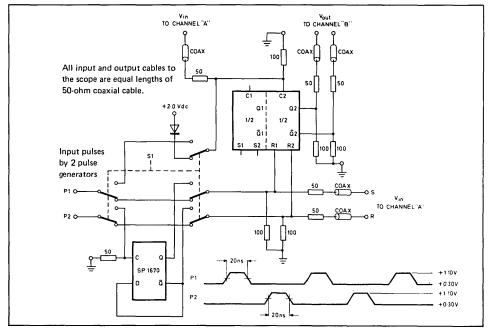

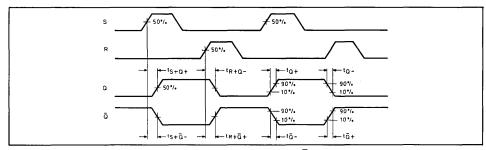

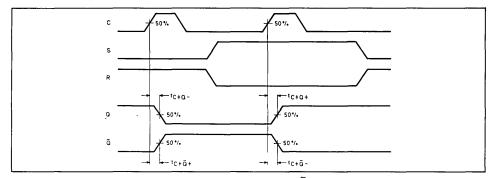

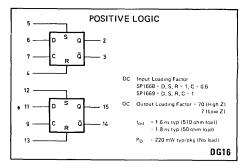

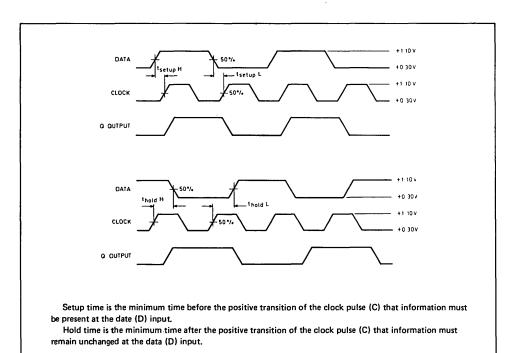

| Power Supply Drain Current       | l <sub>E</sub>    | 8        | -      | -          | -             | 28           | -          | -          | mA                      | -                             |                               | -                    | -                | 8                | 1,16         |