**Preliminary Data Book**

# FEATURES

- Optimized three-chip PCI system controller for Intel Pentium<sup>®</sup> processor-based portable computers

- Supports all Pentium<sup>®</sup> and 5-class 3.3-V processors

- Supports processor bus speeds of 50-, 60-, and 66-MHz

- Universal support for AMD<sup>®</sup> K5 and Cyrix<sup>®</sup> 6x86<sup>™</sup> processors

- Supports both toggle and linear burst sequences

- Supports SmartDock<sup>™</sup> technology

- Supports PCI hot-docking and secondary ISA bus in the docking station

- Enables desktop capabilities in a portable system

- Supports distributed DMA to provide a direct memory access on the PCI Bus

Supports level-1 write-back or write-through cache protocols

Integrated 64-bit write-through level-2 cache controller

- Supports cacheless configurations as well as cache sizes of 256 Kbytes to 1 Mbyte with 32-byte line size

- Supports synchronous burst, pipelined synchronous, and asynchronous 3.3-V SRAM

- Two less wait-states for read lead-off cycle with pipelining

#### State-of-the-art DRAM controller

- 3.3- and 5-V DRAM support

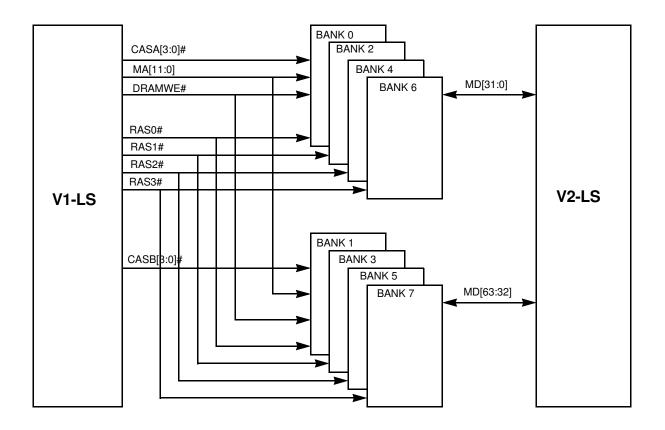

- Supports up to 256 Mbytes of system memory in four banks of 64-bit DRAM or eight banks of 32-bit DRAM

- Supports 256 Kbit, 512 Kbit, 1 Mbit, 2 Mbit, 4 Mbit, and 16 Mbit DRAM

- Supports both symmetric and asymmetric DRAM

- Supports mixed FPM (fast page mode), EDO (extended data output), and Burst EDO DRAM

- Slow and self refresh support, including hidden, staggered, CAS-before-RAS refresh or RAS-only refresh

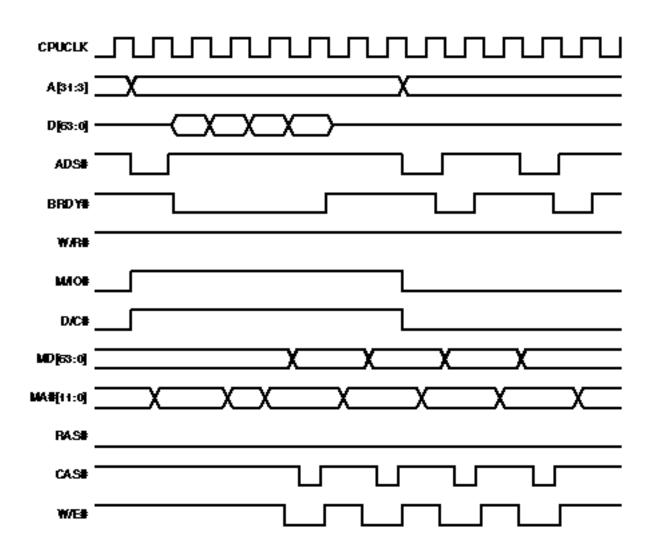

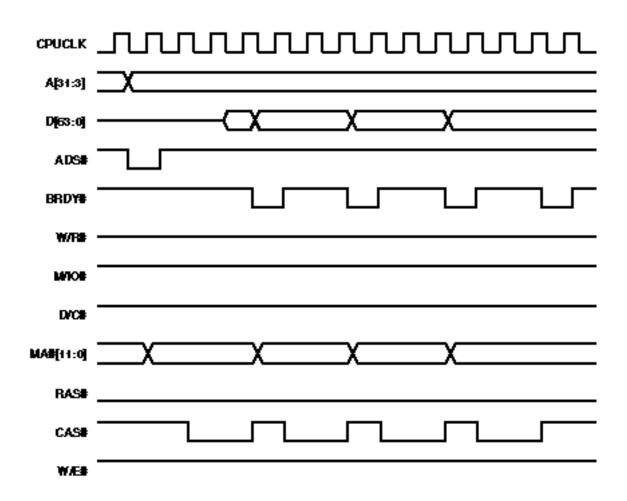

- 5-2-2-2 burst read cycles with 60-ns EDO DRAM at 66 MHz

- 5-3-3-3 page-hit and 10-3-3-3 page-miss burst-read cycles with 60-ns standard DRAM at 66 MHz

- Two less wait-states in the lead-off cycle for pipeline access

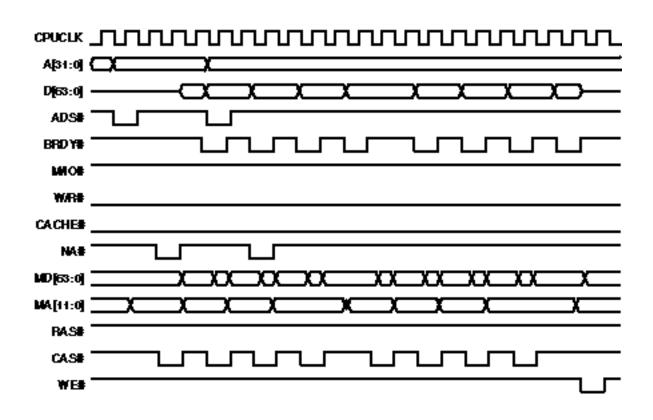

- Supports 2-1-1-1 burst write

- Supports read reordering and ROM shadowing

- Supports ROM shadowing

- Supports SMM RAM size from 32 Kbyte to 128 Kbyte with easy SMI code copying to SMM RAM in normal memory mode

(cont.)

# 5-Class Processor PCI System Controller with Power Management

# OVERVIEW

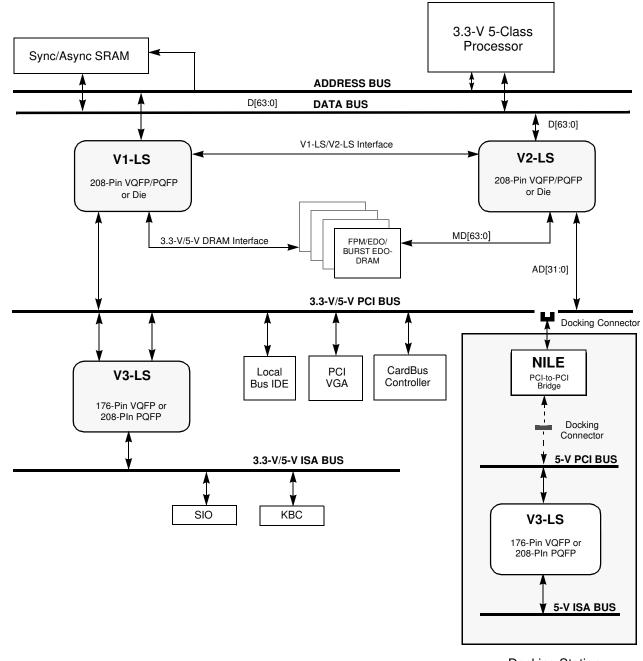

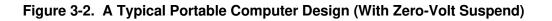

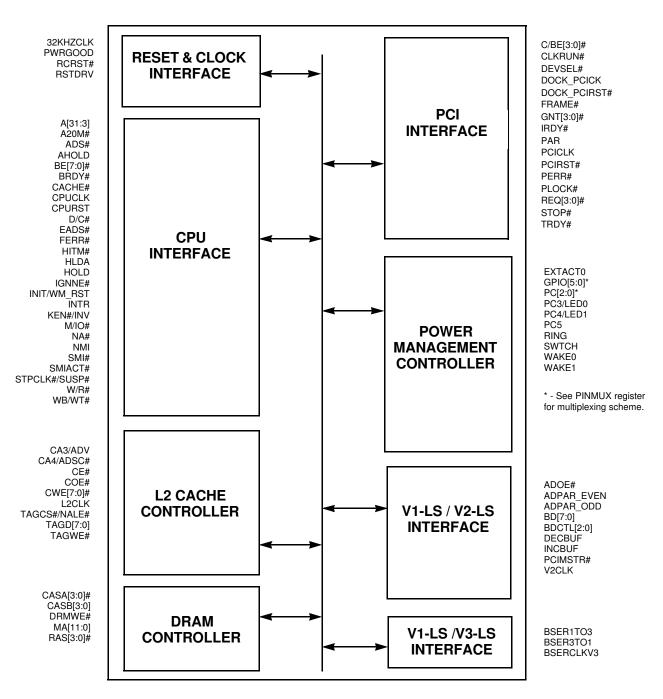

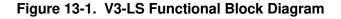

A high-performance, highly integrated system controller for Microsoft<sup>®</sup> Windows<sup>®</sup> -compatible computers, the VESUVIUS-LS supports Intel's 3.3-V Pentium<sup>®</sup> processor and comparable 5-class processors. The PCI-based VESUVIUS-LS solution is optimized for portable systems with stringent formfactor and power consumption requirements.

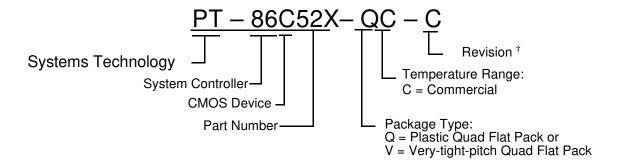

VESUVIUS-LS consists of three chips: V1-LS, V2-LS, and V3-LS. A 0.5µm CMOS device, VESU-VIUS-LS is available in a choice of PQFPand VQFP packages. For space-critical designs, VESUVIUS-LS is also available as a die product.

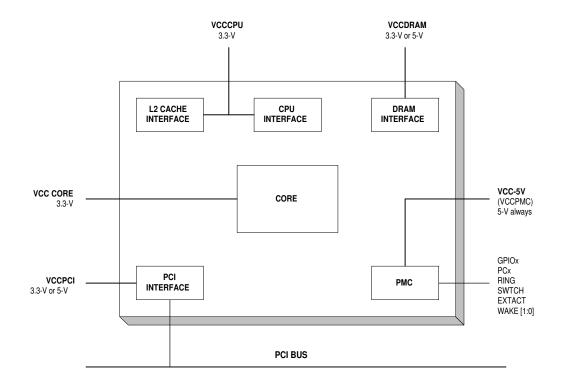

The V1-LS chip integrates the following functions

- CPU bus to the PCI Bus interface controller and arbiter

- L2 cache controller

- DRAM controller

- Power management controller

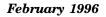

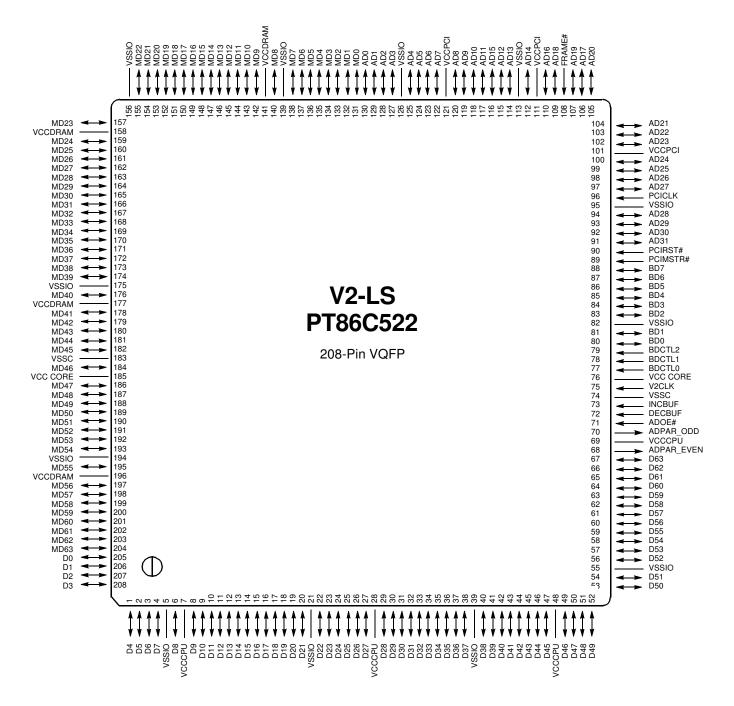

The V2-LS serves as a data path controller, providing a 32- or 64-bit data path between the CPU and the main memory; a 32-bit data path between the CPU bus and the PCI Local Bus, and a 32-bit data path between the PCI Local Bus and the main memory.

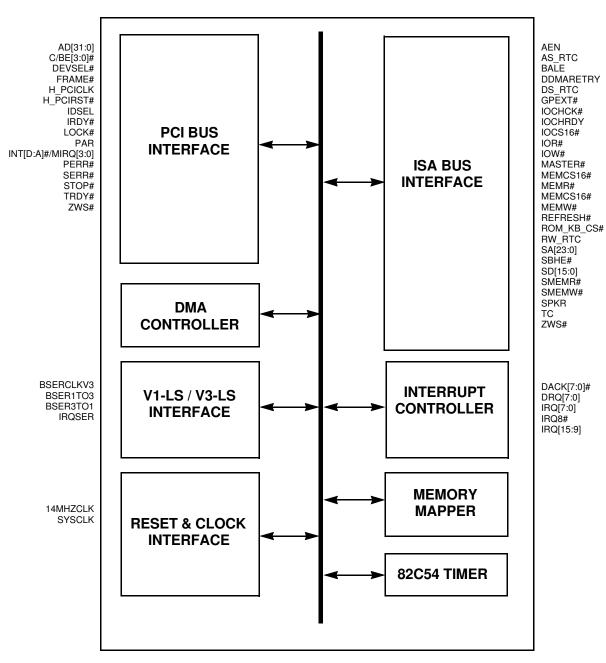

The V3-LS chip completes the VESUVIUS-LS solution by providing a bridge between the PCI and ISA buses; it has the logic to support master and slave cycles on both PCI and ISA buses.

The VESUVIUS-LS supports 3.3-V Pentiun® and other 5-class processors with speeds up to 166 MHz. It connects the 5-class processor bus to the PCI Local Bus and provides a bridge between the PCI and ISA buses to support ISA bus peripherals.

# FEATURES (cont.)

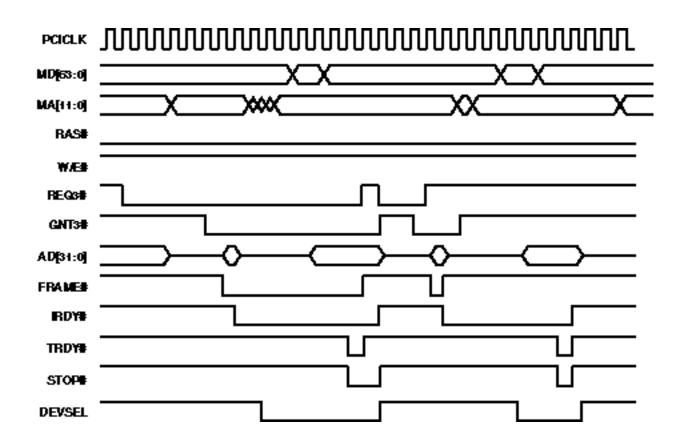

#### PCI Local Bus architecture

- Supports 25- to 33-MHz PCI bus speeds

- Supports 3.3- or 5-V 32-bit PCI Local Bus

- Synchronous interface between the CPU bus and the PCI Bus

- PCI Local Bus revision 2.0 compliant

- Supports Mobile PCI specification

- Supports PCI burst cycles

- Supports up to five PCI masters and ten PCI loads

- Integrated PCI Bus arbiter with rotating priority

- PCI parity and system error support

- Eight-level write buffers for CPU-to-PCI writes

- PCI interrupt steering

- Intelligent power management through clock scaling

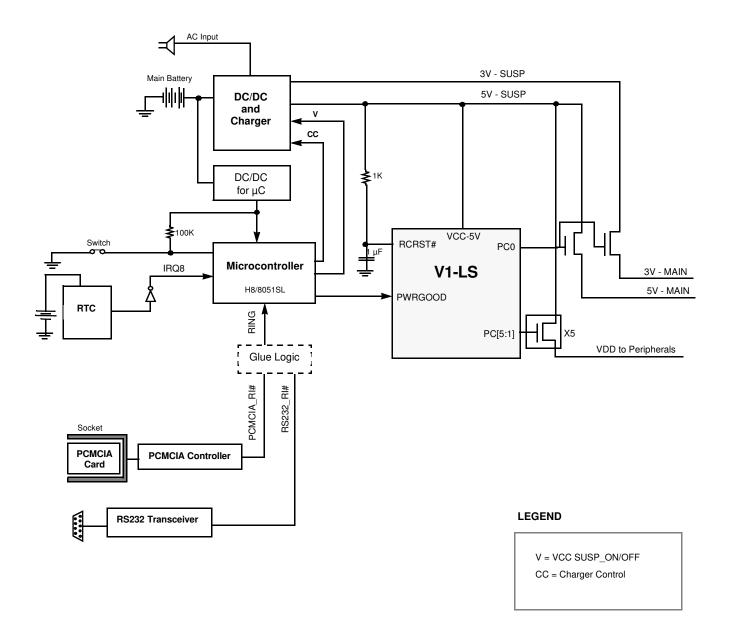

#### Best-in-class power and thermal management

- Supports SMM (system management mode), SMI (system management interrupt), Stop Clock, and AutoHalt

- Flexible hybrid voltage implementation

- Optional thermal control with thermal clock throttling

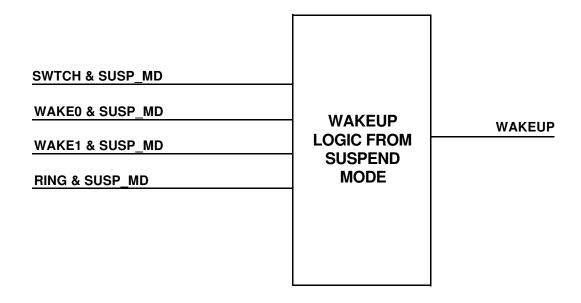

- Supports wakeup control, interrupt-as-wakeup-source, and ring-input-as-wakeup source

Supports 3.3-V processor bus, 3.3-V/5-V PCI and ISA buses, 3.3-V L2 cache controller, and 3.3-V/5-V DRAM subsystem

#### Docking station support

- Proprietary hot-docking arbitration interface

- Distributed DMA support for DMA on the PCI Bus from secondary ISA in the dock

#### PCI-to-ISA bridge

- 25- to 33-MHz operation on the PCI Bus

- Master and slave interface for the PCI and the ISA bus

- PCI-to-ISA and ISA-to-PCI Bus cycle translations

- Eight-bit BIOS ROM, FLASH EPROM support

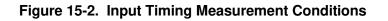

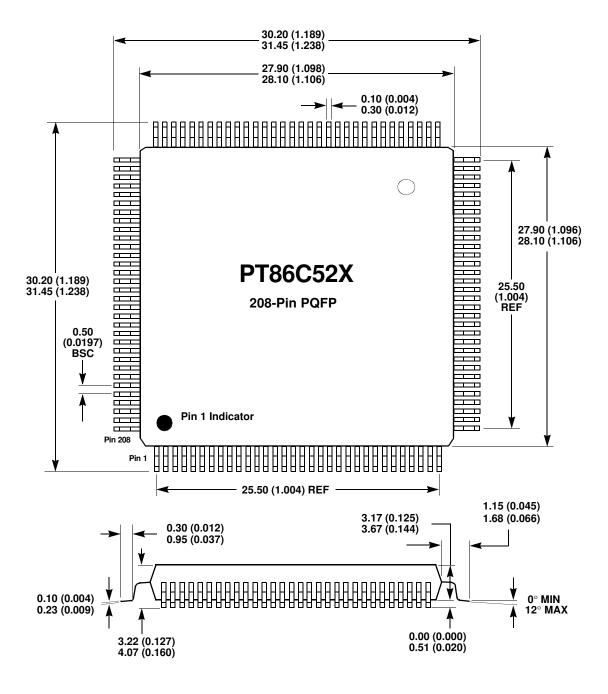

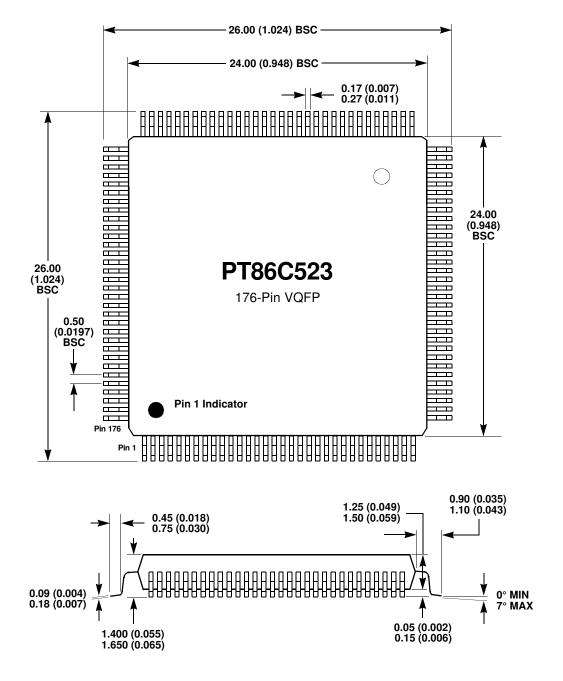

#### Available in a choice of space-efficient VQFP or PQFP packages or die

- Option one: 208-pin VQFP (V1-LS and V2-LS) and 176-pin VQFP (V3-LS) packages

- Option two: 208-pin PQFP (V1-LS, V2-LS, and V3-LS) packages

- Option three: Die (V1-LS and V2-LS) and 176-pin VQFP/208-pin PQFP (V3-LS)

# OVERVIEW (cont.)

It takes full advantage of the 5-class processor performance by supporting CPU bus frequencies of up to 66 MHz.

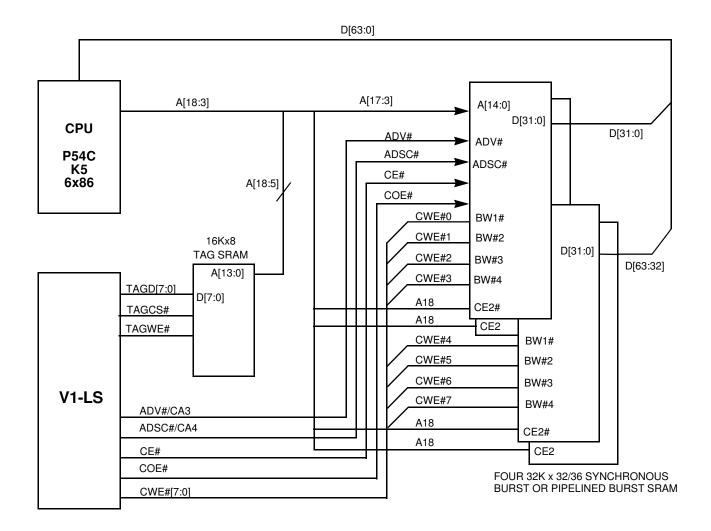

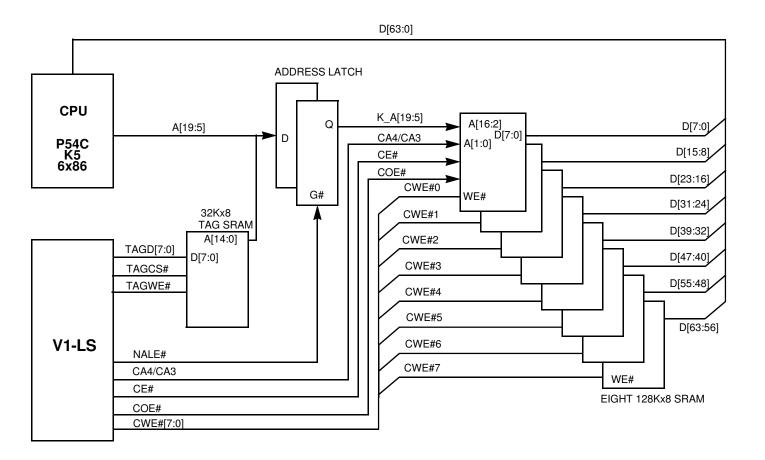

An integrated, 64-bit, direct-mapped level-2 cache controller supports synchronous burst, pipelined synchronous, and asynchronous 3.3-V SRAM. Additionally, buffered write-through cache update schemes allow further performance gains.

By providing a sophisticated DRAM ontroller which supports leading-edge DRAM technology, the VESUVIUS-LS system solutionhas been optimized for a cacheless system configuration. The DRAM controller implements the logic required to use advanced, high-speed DRAM that reduces the performance overhead of level-2 cache miss cycles. It implements a synchronous interface between the CPU and PCI buses to exploit the maximum potential of the PCI bandwidth.

VESUVIUS-LS system solution offers superior power and thermal management. It also features a thermal control mechanism that uses CPU clock throttling to efficiently control the power consumption and heat dissipation associated with the processor. An innovative programming model simplifies BIOS development without compromising any of the power management features.

To enable a full-featured docking station design, VESUVIUS-LS portable system solution provides the necessary hooks to support PCI hot- and warmdocking. By supporting a secondary ISA bus in the PCI docking station, it allows both PCI and ISA slots in the docking station.

VESUVIUS-LS implements a Distributed DMA scheme to support ISA legacy devices in the PCI docking station. It can be programmed as positive decoding (primary V3-LS in the portable system) or subtractive decoding (secondary V3-LS in the dock).

VESUVIUS-LS comes with full technical and hardware support, including samples, evaluation boards, and design examples in OrCAD<sup>®</sup>.

ii

# System Block Diagram Portable System With PCI Docking Station

iii

iv

March 1996

۷

#### SCOPE OF DOCUMENT

This document provides the system designer and programmer with comprehensivetechnical information about VESUVIUS-LS Pentium processor PCI system controller. **Information contained in this data book covers all silicon revisions up to and including Revision CC.** To assist both evaluation and system design, the material has been organized as follows:

- VESUVIUS-LS Overview

- Section 1: V1-LS PT86C521 Data Book

- Section 2: V2-LS PT86C522 Data Book

- Section 3: V3-LS PT86C523 Data Book

- Appendixes

#### **PRODUCT INFORMATION**

For information on product availability, pricing, and order status, contact your local National Semiconductor representative or the nearest sales office. A list of Direct Sales Offices can be found on the back cover of this document.

#### CONVENTIONS

This section lists conventions used in this document.

- For easy cross-referencing, the pin lists have been organized both numerically and alphabetically.

- Shading has been used to indicate changes in register information related to Revision BB and CC silicon

- Signal groups that act together as a bus are shown with the individual numbered lines grouped in brackets and separated by a colon. For example, Power Control pins 0-3 are shown as PC[3:0]

- The word "assert" refers to driving a signal true or active.

- Hexadecimal numbers are suffixed with an 'H'. For example, 00H.

#### ABBREVIATIONS

#### List of Abbreviations for Units of Measure

| Units of Measure       | Symbol Used |

|------------------------|-------------|

| megahertz              | MHz         |

| kilobyte (1,024 bytes) | Kbyte       |

| megabyte               | Mbyte       |

| microsecond            | μs          |

| nanosecond             | ns          |

The use of 'TBD' indicates values that are to be determined; 'n/a' designates 'not available', and 'NC' indicates a pin that is 'no connect'.

#### ACRONYMS

#### List of Acronyms

| Acronym | Definition                        |  |

|---------|-----------------------------------|--|

| APM     | advanced power management         |  |

| CAS     | column address strobe             |  |

| EDO     | extended data output              |  |

| FPM     | fast page mode                    |  |

| P/A     | primary activity                  |  |

| PCI     | peripheral component interconnect |  |

| PM      | power management                  |  |

| PMC     | power management controller       |  |

| PQFP    | plastic quad-flat pack            |  |

| RAS     | row address strobe                |  |

| RTC     | real-time clock                   |  |

| R/W     | read/write                        |  |

| S/A     | secondary activity                |  |

| SC      | serial clock                      |  |

| SMI     | system management interrupt       |  |

| SMM     | system management mode            |  |

| STD     | suspend-to-disk mode              |  |

| STR     | suspend-to-RAM mode               |  |

# **Table of Contents**

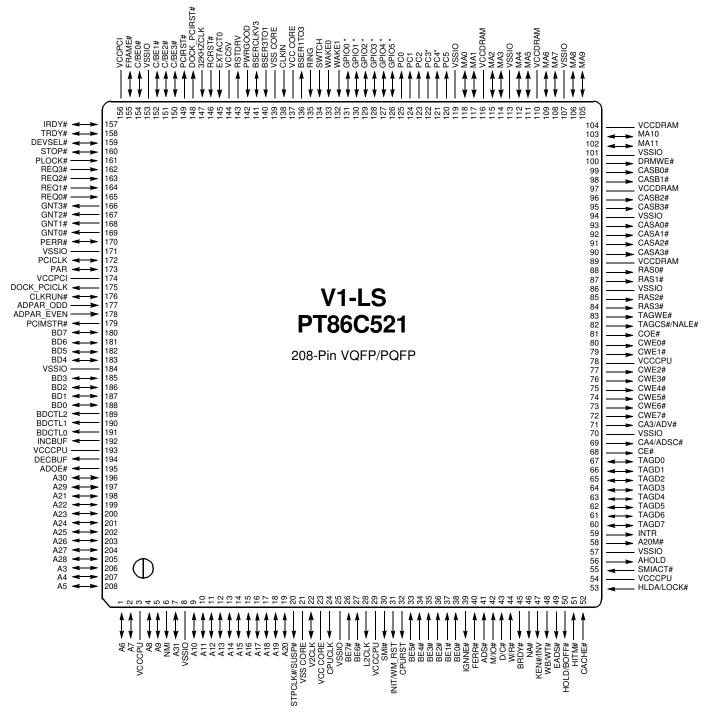

### SECTION 1: V1-LS PT86C521 DATA BOOK

| 1.         | V1-LS PIN INFORMATION                      |      |

|------------|--------------------------------------------|------|

| 1.1        | Pin Diagram                                | 1-1  |

| 1.2        | Pin Cross Reference by Pin Number          |      |

| 1.3        | Pin Cross Reference by Pin Name            |      |

| 2.         | V1-LS DETAILED PIN DESCRIPTIONS            | 1-12 |

| 2.1        | CPU Interface                              |      |

| 2.2        | DRAM Interface                             |      |

| 2.3        | L2 Cache Interface                         |      |

| 2.4        | PCI Interface                              |      |

| 2.5        | Power Management Controller Interface      |      |

| 2.6<br>2.7 | V1-LS / V2-LS Interface                    |      |

| 2.7<br>2.8 | Reset and Clock Interface                  |      |

| 2.9        | Power and Ground                           |      |

| 3.         | V1-LS FUNCTIONAL DESCRIPTION               |      |

| 3.1        | Power Plane Structure                      |      |

| 3.1.1      | Suspend-to-Disk (STD) or 0-V Suspend Mode  |      |

| 3.1.2      |                                            |      |

| 3.2        | Functional Blocks                          |      |

| 3.2.1      | Clock Interface                            |      |

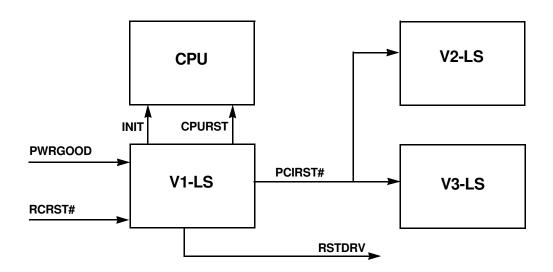

| 3.2.2      | Reset Interface                            |      |

| 3.2.3      | Power-On Configuration                     |      |

| 3.2.4      | CPU Interface                              |      |

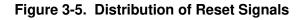

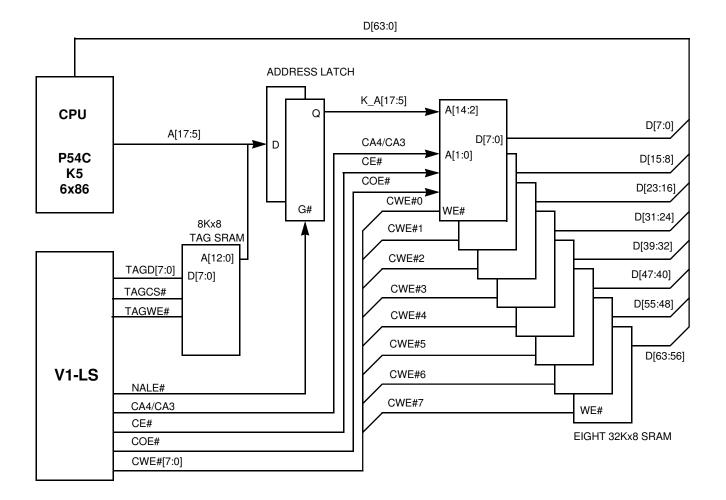

| 3.2.5      | Cache Controller                           |      |

| 3.2.6      | DRAM Controller                            |      |

| 3.2.7      | <b>j</b>                                   |      |

| 3.2.8      |                                            |      |

| 3.2.9      | Power Management Controller (PMC)          |      |

| 4.         | V1-LS REGISTER INFORMATION                 | 1-65 |

| 4.1        | Register Summary Table                     |      |

| 4.2        | Reset Sampling and Miscellaneous Registers |      |

| 4.2.1      | Revision ID Register (V1_ID)               |      |

| 4.2.2      |                                            |      |

| 4.2.3      |                                            |      |

| 4.2.4      |                                            |      |

| 4.2.5      |                                            |      |

| 4.2.6      |                                            |      |

| 4.2.7      |                                            |      |

| 4.2.8      |                                            |      |

| 4.2.9      | <b>e</b>                                   |      |

| 4.2.10     | J A A A A A A A A A A A A A A A A A A A    |      |

| 4.2.1      | 1 PCI Control Register (PCIC)              |      |

vii

| 4.2.12 | Clock Skew Adjust Register (CSA)                                   | 1-84   |

|--------|--------------------------------------------------------------------|--------|

| 4.2.13 | Bus Master and Snooping Control Register (SNOOPCTRL)               | 1-85   |

| 4.2.14 | Arbiter Control Register (ARBCTRL)                                 | 1-86   |

| 4.2.15 | Docking Control Register (DOCKC)                                   | 1-87   |

| 4.3 C  | ORAM Registers                                                     |        |

| 4.3.1  | Shadow RAM Read Enable Control Register (SHADRC)                   | 1-88   |

| 4.3.2  | Shadow RAM Write Enable Control Register (SHADWC)                  | 1-90   |

| 4.3.3  | Bank 0 Control Register (B0C)                                      | 1-92   |

| 4.3.4  | Bank 1 Control Register (B1C)                                      | 1-93   |

| 4.3.5  | Bank 0/1 Timing Control Register (B01TC)                           | 1-94   |

| 4.3.6  | Bank 2 Control Register (B2C)                                      | 1-96   |

| 4.3.7  | Bank 3 Control Register (B3C)                                      | 1-97   |

| 4.3.8  | Bank 2/3 Timing Control Register (B23TC)                           | 1-98   |

| 4.3.9  | Bank 4 Control Register (B4C)                                      | .1-100 |

| 4.3.10 | Bank 5 Control Register (B5C)                                      | .1-101 |

| 4.3.11 | Bank 4/5 Control Register (B45TC)                                  | .1-102 |

| 4.3.12 | Bank 6 Control Register (B6C)                                      |        |

| 4.3.13 | Bank 7 Control Register (B7C)                                      |        |

| 4.3.14 | Bank 6/7 Timing Control Register (B67TC)                           |        |

| 4.3.15 | DRAM Configuration Register 1(DCONF1)                              |        |

| 4.3.16 | DRAM Configuration Register 2 (DCONF2)                             |        |

| 4.3.17 | DRAM Configuration Register 3 (DCONF3)                             |        |

| 4.3.18 | DRAM Refresh Control Register (DRFSHC)                             |        |

| 4.3.19 | Burst EDO Control Register (BEDOC)                                 |        |

|        | Power Management Control Registers                                 |        |

| 4.4.1  | Clock Control Register                                             |        |

| 4.4.2  | Clock Throttling Period Control Register (CTPC)                    |        |

| 4.4.3  | Conserve Clock Throttling Ratio/Control Register (CON-CTRC)        |        |

| 4.4.4  | Heat Regulator Clock Throttling Ratio / Control Register (HR-CTRC) |        |

| 4.4.5  | Doze/Sleep Mode Clock Throttling Ratio/Control Register (DS-CTRC)  |        |

| 4.4.6  | Wake/SMI Source Register (WSS)                                     |        |

| 4.4.7  | Power Management Timer Status Register (PMTS)                      |        |

| 4.4.8  | Power Management Pin Status Register (PMPS)                        |        |

| 4.4.9  | Wake Mask Control Register (WMC)                                   |        |

| 4.4.10 | Activity Flag Register 1 (AFR1)                                    |        |

|        | Activity Flag Register 2 (AFR2)                                    |        |

|        | I/O Trap SMI Mask Register (IOTM)                                  |        |

|        | External SMI Trigger Mask Register (ESTM)                          |        |

| 4.4.14 | Internal SMI Trigger Mask Register (ISTM)                          |        |

| 4.4.15 | Software SMI Trigger Register (SST)                                |        |

| 4.4.16 | Primary Activity Option Control register (PAOC)                    |        |

| 4.4.17 | Primary Activity Mask Register 1 (PAM1)                            |        |

| 4.4.18 | Primary Activity Mask Register 2 (PAM2)                            |        |

| 4.4.19 | Secondary Activity Mask Register (SAM)                             |        |

| 4.4.20 | RING Count Control Register (RCC)                                  |        |

| 4.4.21 | Programmable Range Monitor Control Register 1 (PRM_CTRL1)          |        |

| 4.4.22 | Programmable Range Monitor Control Register 2 (PRM_CTRL2)          |        |

|        | Programmable Range Monitor 0 Address Register (PRMA0)              |        |

|        |                                                                    | /      |

| 4.4.24 |                                                                     |       |

|--------|---------------------------------------------------------------------|-------|

| 4.4.25 | -9                                                                  |       |

| 4.4.26 | Programmable Range Monitor 1 Compare Register (PRMC1)               |       |

| 4.4.27 | Programmable Range Monitor 2 Address Register (PRMA2)               |       |

| 4.4.28 | Programmable Range Monitor 2 Compare Register (PRMC2)               |       |

| 4.4.29 | Programmable Range Monitor 3 Address Register (PRMA3)               |       |

| 4.4.30 | Programmable Range Monitor 3 Compare Register (PRMC3)               |       |

| 4.4.31 | Programmable Range Monitor 4 Address Register (PRMA4)               |       |

|        | Programmable Range Monitor 4 Compare Register (PRMC4)               |       |

| 4.4.33 |                                                                     |       |

| 4.4.34 |                                                                     |       |

| 4.4.35 | Power Management Mode Register (PMM)                                |       |

| 4.4.36 |                                                                     |       |

| 4.4.37 |                                                                     |       |

| 4.4.38 |                                                                     |       |

| 4.4.39 | Doze Mode Timer Register (DZMT)                                     |       |

| 4.4.40 | Sleep Mode Timer Register (SLPMT)                                   |       |

| 4.4.41 | Suspend Mode Timer Register (SPNDMT)                                |       |

|        | Secondary Activity Timer Register (SAT)                             |       |

|        | Power on Demand Primary Activity Timer Register (POD_PAT)           |       |

| 4.4.44 |                                                                     |       |

| 4.4.45 | ······································                              |       |

| 4.4.46 | General Purpose Counter/Timer Current Value Register (GP_CNTMR_VAL) |       |

| 4.4.47 |                                                                     |       |

| 4.4.48 |                                                                     |       |

| 4.4.49 |                                                                     |       |

| 4.4.50 | Device Timer 2 Time-out Register (DTT2)                             |       |

| 4.4.51 | Device Timer 3 Time-out Register (DTT3)                             |       |

| 4.4.52 | Device Timer 4 Time-out Register (DTT4)                             |       |

| 4.4.53 |                                                                     |       |

| 4.4.54 |                                                                     |       |

| 4.4.55 | <b>ö</b>                                                            |       |

| 4.4.56 |                                                                     |       |

| 4.4.57 | - · · · ·                                                           |       |

|        | LED Indicator Control Register (LEDIC)                              |       |

| 4.4.59 | Leakage Control Register (LC)                                       |       |

| 4.4.60 | Pin Multiplexing Control Register (PINMUX)                          |       |

| 4.4.61 | Debounce Control Register (DBC)                                     |       |

|        | Edge Detect Control Register (EDC)                                  |       |

|        | Level-2 Cache Registers                                             |       |

| 4.5.1  | Level-2 Cache Configuration Register (L2C)                          |       |

| 4.5.2  | Level-2 Cache Timing Register (L2T)                                 |       |

| 4.5.3  | Level-2 Cache Miscellaneous Register (L2M)                          |       |

|        | PCI Configuration Registers                                         |       |

| 4.6.1  | Vendor ID Register (VID)                                            |       |

| 4.6.2  | Device ID Register (DID)                                            |       |

| 4.6.3  | Command Register (COMMD)                                            |       |

| 4.6.4  | Status Register (STAT)                                              | 1-207 |

ix

| 4.6.6 | Revision ID Register (RID)<br>Class Register (CLASS)<br>Latency Timer Register (LTMR) | 1-209 |

|-------|---------------------------------------------------------------------------------------|-------|

|       | V1-LS ELECTRICAL SPECIFICATIONS                                                       |       |

|       |                                                                                       |       |

| 5.1   | Absolute Maximum Ratings                                                              | 1-211 |

|       | Absolute Maximum Ratings<br>D.C. Characteristics 5.0 Volt                             |       |

| 5.2   |                                                                                       | 1-212 |

# SECTION 2: V2-LS PT86C522 DATA BOOK

| 1.  | V2-LS PIN INFORMATION                  |      |

|-----|----------------------------------------|------|

| 1.1 | Pin Diagram                            | 2-1  |

| 1.2 | Pin Cross Reference by Pin Number      |      |

| 1.3 | Pin Cross Reference by Pin Name        | 2-9  |

| 2.  | V2-LS DETAILED PIN DESCRIPTIONS        |      |

| 2.1 | CPU Interface                          | 2-12 |

| 2.2 | DRAM Interface                         | 2-12 |

| 2.3 | PCI Interface                          | 2-13 |

| 2.4 | V1-LS/V2-LS Interface                  |      |

| 2.5 | Power and Ground                       | 2-14 |

| 3.  | V2-LS FUNCTIONAL DESCRIPTION           |      |

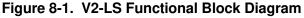

| 3.1 | Functional Block Diagram               | 2-15 |

| 4.  | V2-LS REGISTER INFORMATION             |      |

| 4.1 | Register Summary Table                 |      |

| 4.2 | Version ID Register (V2LS VID)         | 2-17 |

| 4.3 | Configuration Register (V2LS INC)      |      |

| 4.4 | V2 Miscellaneous Status Register (V2S) | 2-19 |

| 5.  | V2-LS ELECTRICAL SPECIFICATIONS        |      |

| 5.1 | Absolute Maximum Ratings               |      |

| 5.2 | DC Characteristics 5.0 Volt            |      |

| 5.3 | DC Characteristics 3.3 Volt            | 2-20 |

| 5.4 | AC Characteristics                     | 2-20 |

# SECTION 3: V3-LS PT86C523 DATA BOOK

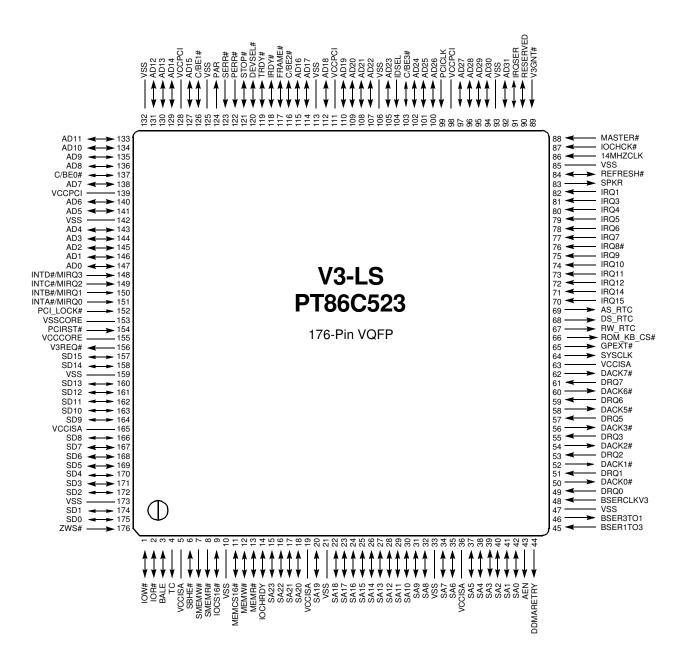

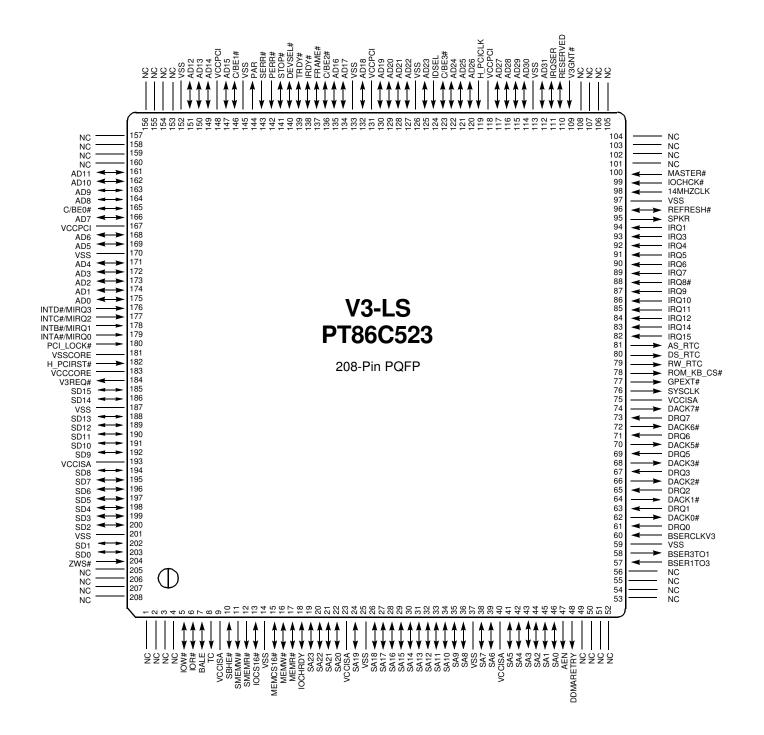

| 1.  | V3-LS PIN INFORMATION                            |  |

|-----|--------------------------------------------------|--|

|     | 176-Pin VQFP Pin Diagram                         |  |

|     | Pin Cross Reference by Pin Number (176-Pin VQFP) |  |

| 1.3 | 208-Pin PQFP Pin Diagram                         |  |

| 1.4 | Pin Cross Reference by Pin Number (208-Pin PQFP) |  |

| 1.5 | Pin Cross Reference by Pin Name                  |  |

| 2.  | V3-LS DETAILED PIN DESCRIPTIONS                  |  |

| 2.1 | ISA Interface                                    |  |

| 2.3 | Power and Ground                                 |  |

Х

| 3.     | V3-LS FUNCTIONAL DESCRIPTION                     | 3-25 |

|--------|--------------------------------------------------|------|

| 3.1    | Functional Block Diagram                         | 3-25 |

| 3.2    | Power Plane Structure                            |      |

| 3.2.1  | Power-On Configuration                           | 3-26 |

| 3.3    | Functional Blocks                                |      |

| 3.3.1  | Reset and Clock Interface                        | 3-26 |

| 3.3.2  | The V1-LS to V3-LS Interface                     |      |

| 3.3.3  | PCI Bus Interface                                |      |

| 3.3.4  | ISA Bus Interface                                |      |

| 3.3.5  | Docking Interface                                |      |

| 3.3.6  | Distributed DMA (DDMA) Support                   |      |

| 3.4    | Power Management in V3-LS                        |      |

| 3.5    | Single 8-bit BIOS ROM                            |      |

| 3.6    | Back-to-Back I/O Delay                           |      |

| 3.7    | Hidden AT Bus Refresh                            | 3-35 |

| 3.8    | General Purpose Extensions                       | 3-36 |

| 4.     | V3-LS REGISTER INFORMATION                       | 3-37 |

| 4.1    | Register Summary Table                           | 3-37 |

| 4.2    | Revision ID Register (V3REV_ID)                  | 3-39 |

| 4.3    | AT Control Registers                             | 3-40 |

| 4.3.1  | AT Control Register 1 (ATCR1)                    | 3-40 |

| 4.3.2  | AT Control Register 2 (ATCR2)                    | 3-41 |

| 4.4    | BIOS CS# Control Register (BCSC)                 |      |

| 4.5    | Port 92 Control Register (P92CNTL)               |      |

| 4.6    | GPEXT Control Registers                          |      |

| 4.6.1  | GPEXT Low Byte Register (GPEXT_LB)               | 3-44 |

| 4.6.2  | GPEXT High Byte Register (GPEXT_HB)              |      |

| 4.6.3  | Miscellaneous Configuration Register (MISC_CNFG) | 3-46 |

| 4.7    | Interrupt Mapping Registers                      |      |

| 4.7.1  | PCI Interrupt Mapping Register 1 (PCI_INTM1)     |      |

| 4.7.2  | PCI Interrupt Mapping Register 2 (PCI_INTM2)     |      |

| 4.7.3  | PCI INT# Configuration Register (PCI_INT_CFG)    | 3-49 |

| 4.7.4  | Serial IRQ Control Register (IRQSER_CNTL)        | 3-50 |

| 4.7.5  | Serial IRQ Control Register 2 (IRQSER_CNTL2)     | 3-51 |

| 4.8    | Power Management Registers                       | 3-52 |

| 4.8.1  | Power Management Control Register (PMCR)         | 3-52 |

| 4.8.2  | Primary Activity IRQ Mask Register 1 (PAIRQM1)   | 3-53 |

| 4.8.3  | Primary Activity IRQ Mask Register 2 (PAIRQM2)   | 3-54 |

| 4.8.4  | PMI Trigger IRQ Mask Register 1 (PMI_IRQM1)      | 3-55 |

| 4.8.5  | PMI Trigger IRQ Mask Register 2 (PMI_IRQM2)      | 3-56 |

| 4.8.6  | PMI Trigger Source Register 1 (PMI_IRQS1)        | 3-57 |

| 4.8.7  | PMI Trigger Source Register 2 (PMI_IRQS2)        | 3-58 |

| 4.9    | 8254/8237/8259 Shadow Registers                  | 3-59 |

|        | PCI Configuration Registers                      |      |

| 4.10.1 | Vendor ID Register (VID)                         |      |

| 4.10.2 | $\mathbf{c}$                                     |      |

|        | B Command Register (COMMD)                       |      |

|        | Status Register (STAT)                           |      |

| 4.10.5 | 5 Revision ID Register 2 (REV_ID2)               | 3-65 |

xi

|        | Class Code Register (CLASS)                                  |      |

|--------|--------------------------------------------------------------|------|

| 4.11   | PCI-DMA Configuration Registers                              | 3-67 |

| 4.11.1 | Distributed DMA Control Register (DDMA_CTRL)                 | 3-67 |

| 4.11.2 | 2 Distributed DMA Status Register (DDMA_STAT)                | 3-69 |

| 4.11.3 | 3 Slave DMAC CH0 Base Register (DDMA_CH0)                    | 3-70 |

| 4.11.4 | Slave DMAC CH1 Base Register (DDMA_CH1)                      | 3-71 |

| 4.11.5 | 5 Slave DMAC CH2 Base Register (DDMA_CH2)                    | 3-72 |

| 4.11.6 | S Slave DMAC CH3 Base Register (DDMA_CH3)                    | 3-73 |

|        | Slave DMAC CH5 Base Register (DDMA_CH5)                      |      |

|        | Slave DMAC CH6 Base Register (DDMA_CH6)                      |      |

| 4.11.9 | Slave DMAC CH7 Base Register (DDMA_CH7)                      | 3-76 |

|        | 0 PCI-to-ISA Bridge Configuration Register (ISA_BCR)         |      |

|        | 1 ISA Memory Address Positive Decode (ISAMEM_PDECODE)        |      |

|        | 2 ISA I/O Address Positive Decoder (ISAIO_PDECODE)           |      |

|        | 3 I/O Configuration Address Register (IO_CNFG)               |      |

| 4.11.1 | 4 Programmable ISA I/O Address Decoder (ISAIO_DECODE)        | 3-83 |

|        | 5 Programmable ISA Range Decoder Register 1 (ISAPR_DECODE1)  |      |

| 4.11.1 | 6 Programmable ISA Range Decoder Register 2 (ISAPR_DECODE2)  | 3-86 |

| 4.11.1 | 7 Programmable ISA Range Decoder Register 3 (ISAPR_DECODE3)  | 3-87 |

|        | 8 Programmable ISA Range Decoder Register 4 (ISAPR_DECODE4)  |      |

| 4.11.1 | 9 Programmable ISA Range Decoder Register 5 (ISAPR_DECODE5)  | 3-89 |

| 4.11.2 | 20 Programmable ISA Range Decoder Register 6 (ISAPR_DECODE6) | 3-90 |

| 4.12   | Standard AT Ports                                            | 3-91 |

| 4.12.1 | Port B                                                       | 3-92 |

| 4.12.2 | 2 Port 70H                                                   | 3-93 |

| 4.12.3 | 3 Port 92H                                                   | 3-94 |

| 5.     | V3-LS ELECTRICAL SPECIFICATIONS                              |      |

|        | Absolute Maximum Ratings                                     |      |

| 5.2    | DC Characteristics 5.0 Volt                                  | 3-96 |

|        | DC Characteristics 3.3 Volt                                  |      |

| 5.4    | AC Characteristics                                           | 3-97 |

# **APPENDICES**

| Α. | Package Specifications                              | A-1  |

|----|-----------------------------------------------------|------|

| В. | Ordering Information Example                        | A-5  |

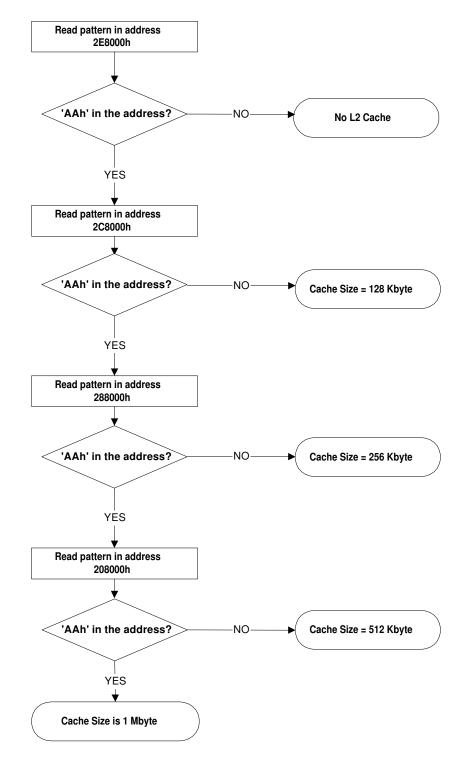

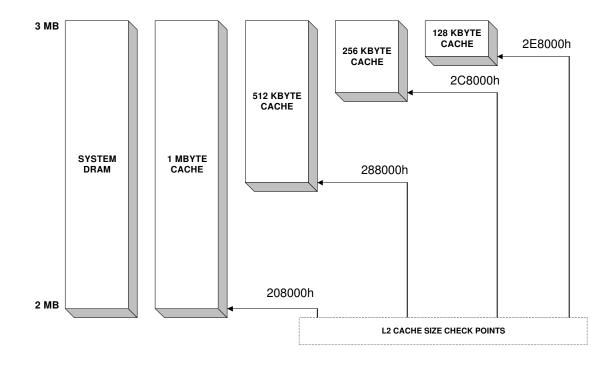

| C. | L2 Cache Auto-sizing: Sample Pseudo-Code Sequence   | A-6  |

| D. | V1-LS Leakage Control Pin Status                    | A-9  |

| Ε. | Maintaining Similar Drive Characteristics (Rev. BB) | A-17 |

| F. | Bulletin Board Service (BBS)                        | A-18 |

# V1-LS PT86C521 Data Book

# 1. V1-LS PIN INFORMATION

# 1.1 Pin Diagram

**NOTE:** Multiplexed GPIO and PC signals are shown with an asterisk (\*). Refer to Section 4.4.60 on page 1-193 for additional details on the multiplexing scheme.

### 1.2 Pin Cross Reference by Pin Number

Table 1-1. Pin Assignment Table (Arranged by Pin Number)

| PIN NO. | PIN NAME      | PIN<br>TYPE | INPUT<br>TYPE | VOLTAGE | POWER PLANE | GROUP       |

|---------|---------------|-------------|---------------|---------|-------------|-------------|

| 1       | A6            | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 2       | A7            | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 3       | VCCCPU        | PWR         |               | 3.3-V   | VCCCPU      | POWER       |

| 4       | A8            | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 5       | A9            | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 6       | NMI           | 0           |               | 3.3-V   | VCCCPU      | CPU         |

| 7       | A31           | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 8       | VSSIO         | GND         |               |         | VSSIO       | GROUND      |

| 9       | A10           | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 10      | A11           | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 11      | A12           | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 12      | A13           | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 13      | A14           | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 14      | A15           | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 15      | A16           | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 16      | A17           | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 17      | A18           | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 18      | A19           | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 19      | A20           | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 20      | STPCLK#/SUSP# | 0           |               | 3.3-V   | VCCCPU      | CPU         |

| 21      | VSS CORE      | GND         |               |         | VSSC        | GROUND      |

| 22      | V2CLK         | I/O         | Т             | 3.3-V   | VCCCPU      | V1-LS/V2-LS |

| 23      | VCC CORE      | PWR         |               | 3.3-V   | VCC CORE    | POWER       |

| 24      | CPUCLK        | 0           |               | 3.3-V   | VCCCPU      | CPU         |

| 25      | VSSIO         | GND         |               |         | VSSIO       | GROUND      |

| 26      | BE7#          | I           | Т             | 3.3-V   | VCCCPU      | CPU         |

| 27      | BE6#          | I           | Т             | 3.3-V   | VCCCPU      | CPU         |

| 28      | L2CLK         | 0           |               | 3.3-V   | VCCCPU      | L2 CACHE    |

| 29      | VCCCPU        | PWR         |               | 3.3-V   | VCCCPU      | POWER       |

I = Input-only; O = Output-only; C = CMOS-compatible; S = Schmitt-trigger; T = TTL-compatible input; PWR = Power; GND = Ground

|         |             | 1           |               |         |             |        |

|---------|-------------|-------------|---------------|---------|-------------|--------|

| PIN NO. | PIN NAME    | PIN<br>TYPE | INPUT<br>TYPE | VOLTAGE | POWER PLANE | GROUP  |

| 30      | SMI#        | 0           |               | 3.3-V   | VCCCPU      | CPU    |

| 31      | INIT/WM_RST | 0           |               | 3.3-V   | VCCCPU      | CPU    |

| 32      | CPURST      | 0           |               | 3.3-V   | VCCCPU      | CPU    |

| 33      | BE5#        | I           | Т             | 3.3-V   | VCCCPU      | CPU    |

| 34      | BE4#        | I           | Т             | 3.3-V   | VCCCPU      | CPU    |

| 35      | BE3#        | I           | Т             | 3.3-V   | VCCCPU      | CPU    |

| 36      | BE2#        | I           | Т             | 3.3-V   | VCCCPU      | CPU    |

| 37      | BE1#        | I           | Т             | 3.3-V   | VCCCPU      | CPU    |

| 38      | BE0#        | I           | Т             | 3.3-V   | VCCCPU      | CPU    |

| 39      | IGNNE#      | 0           |               | 3.3-V   | VCCCPU      | CPU    |

| 40      | FERR#       | I           | Т             | 3.3-V   | VCCCPU      | CPU    |

| 41      | ADS#        | I           | т             | 3.3-V   | VCCCPU      | CPU    |

| 42      | M/IO#       | I           | Т             | 3.3-V   | VCCCPU      | CPU    |

| 43      | D/C#        | I           | Т             | 3.3-V   | VCCCPU      | CPU    |

| 44      | W/R#        | I           | Т             | 3.3-V   | VCCCPU      | CPU    |

| 45      | BRDY#       | 0           |               | 3.3-V   | VCCCPU      | CPU    |

| 46      | NA#         | 0           |               | 3.3-V   | VCCCPU      | CPU    |

| 47      | KEN#/INV    | 0           |               | 3.3-V   | VCCCPU      | CPU    |

| 48      | WB/WT#      | 0           |               | 3.3-V   | VCCCPU      | CPU    |

| 49      | EADS#       | 0           |               | 3.3-V   | VCCCPU      | CPU    |

| 50      | HOLD/BOFF#  | 0           |               | 3.3-V   | VCCCPU      | CPU    |

| 51      | HITM#       | I           | Т             | 3.3-V   | VCCCPU      | CPU    |

| 52      | CACHE#      | I           | Т             | 3.3-V   | VCCCPU      | CPU    |

| 53      | HLDA/LOCK#  | I           | Т             | 3.3-V   | VCCCPU      | CPU    |

| 54      | VCCCPU      | PWR         |               | 3.3-V   | VCCCPU      | POWER  |

| 55      | SMIACT#     | I           | Т             | 3.3-V   | VCCCPU      | CPU    |

| 56      | AHOLD       | 0           |               | 3.3-V   | VCCCPU      | CPU    |

| 57      | VSSIO       | GND         |               |         | VSSIO       | GROUND |

| 58      | A20M#       | 0           |               | 3.3-V   | VCCCPU      | CPU    |

| 59      | INTR        | 0           |               | 3.3-V   | VCCCPU      | CPU    |

Table 1-1. Pin Assignment Table (Arranged by Pin Number) (cont.)

$\textbf{I} = \textbf{Input-only}; \ \textbf{O} = \textbf{Output-only}; \ \textbf{C} = \textbf{CMOS-compatible}; \ \textbf{S} = \textbf{Schmitt-trigger}; \ \textbf{T} = \textbf{TTL-compatible input}; \ \textbf{PWR} = \textbf{Power}; \ \textbf{GND} = \textbf{Ground}$

1-16

| PIN NO. | PIN NAME     | PIN<br>TYPE | INPUT<br>TYPE | VOLTAGE   | POWER PLANE | GROUP    |  |

|---------|--------------|-------------|---------------|-----------|-------------|----------|--|

| 60      | TAGD7        | I/O         | Т             | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 61      | TAGD6        | I/O         | Т             | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 62      | TAGD5        | I/O         | Т             | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 63      | TAGD4        | I/O         | Т             | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 64      | TAGD3        | I/O         | Т             | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 65      | TAGD2        | I/O         | Т             | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 66      | TAGD1        | I/O         | Т             | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 67      | TAGD0        | I/O         | Т             | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 68      | CE#          | 0           |               | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 69      | CA4/ADSC#    | 0           |               | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 70      | VSSIO        | GND         |               |           | VSSIO       | GROUND   |  |

| 71      | CA3/ADV#     | 0           |               | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 72      | CWE7#        | 0           |               | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 73      | CWE6#        | 0           |               | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 74      | CWE5#        | 0           |               | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 75      | CWE4#        | 0           |               | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 76      | CWE3#        | 0           |               | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 77      | CWE2#        | 0           |               | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 78      | VCCCPU       | PWR         |               | 3.3-V     | VCCCPU      | POWER    |  |

| 79      | CWE1#        | 0           |               | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 80      | CWE0#        | 0           |               | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 81      | COE#         | 0           |               | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 82      | TAGCS#/NALE# | 0           |               | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 83      | TAGWE#       | 0           |               | 3.3-V     | VCCCPU      | L2 CACHE |  |

| 84      | RAS3#        | 0           |               | 3.3-V/5-V | VCCDRAM     | DRAM     |  |

| 85      | RAS2#        | 0           |               | 3.3-V/5-V | VCCDRAM     | DRAM     |  |

| 86      | VSSIO        | GND         |               |           | VSSIO       | GROUND   |  |

| 87      | RAS1#        | 0           |               | 3.3-V/5-V | VCCDRAM     | DRAM     |  |

| 88      | RAS0#        | 0           |               | 3.3-V/5-V | VCCDRAM     | DRAM     |  |

| 89      | VCCDRAM      | PWR         |               | 3.3-V/5-V | VCCDRAM     | POWER    |  |

Table 1-1.

Pin Assignment Table (Arranged by Pin Number) (cont.)

I = Input-only; O = Output-only; C = CMOS-compatible; S = Schmitt-trigger; T = TTL-compatible input; PWR = Power; GND = Ground

| PIN NO. | PIN NAME | PIN<br>TYPE | INPUT<br>TYPE | VOLTAGE   | POWER PLANE | GROUP  |

|---------|----------|-------------|---------------|-----------|-------------|--------|

| 90      | CASA3#   | 0           |               | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 91      | CASA2#   | 0           |               | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 92      | CASA1#   | 0           |               | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 93      | CASA0#   | 0           |               | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 94      | VSSIO    | GND         |               |           | VSSIO       | GROUND |

| 95      | CASB3#   | 0           |               | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 96      | CASB2#   | 0           |               | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 97      | VCCDRAM  | PWR         |               | 3.3-V/5-V | VCCDRAM     | POWER  |

| 98      | CASB1#   | 0           |               | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 99      | CASB0#   | 0           |               | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 100     | DRMWE#   | 0           |               | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 101     | VSSIO    | GND         |               |           | VSSIO       | GROUND |

| 102     | MA11     | I/O         | Т             | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 103     | MA10     | I/O         | Т             | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 104     | VCCDRAM  | PWR         |               | 3.3-V/5-V | VCCDRAM     | POWER  |

| 105     | MA9      | I/O         | Т             | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 106     | MA8      | I/O         | Т             | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 107     | VSSIO    | GND         |               |           | VSSIO       | GROUND |

| 108     | MA7      | I/O         | Т             | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 109     | MA6      | I/O         | Т             | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 110     | VCCDRAM  | PWR         |               | 3.3-V/5-V | VCCDRAM     | POWER  |

| 111     | MA5      | I/O         | Т             | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 112     | MA4      | I/O         | Т             | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 113     | VSSIO    | GND         |               |           | VSSIO       | GROUND |

| 114     | MA3      | I/O         | Т             | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 115     | MA2      | I/O         | Т             | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 116     | VCCDRAM  | PWR         |               | 3.3-V/5-V | VCCDRAM     | POWER  |

| 117     | MA1      | I/O         | Т             | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 118     | MA0      | I/O         | т             | 3.3-V/5-V | VCCDRAM     | DRAM   |

| 119     | VSSIO    | GND         |               |           | VSSIO       | GROUND |

Table 1-1.

Pin Assignment Table (Arranged by Pin Number) (cont.)

I = Input-only; O = Output-only; C = CMOS-compatible; S = Schmitt-trigger; T = TTL-compatible input; PWR = Power; GND = Ground = Ground

| PIN NO. | PIN NAME     | PIN<br>TYPE | INPUT<br>TYPE | VOLTAGE   | POWER PLANE | GROUP       |

|---------|--------------|-------------|---------------|-----------|-------------|-------------|

| 120     | PC5          | 0           |               | 5-V       | VCC-5V      | PMC         |

| 121     | PC4*         | 0           |               | 5-V       | VCC-5V      | PMC         |

| 122     | PC3*         | 0           |               | 5-V       | VCC-5V      | PMC         |

| 123     | PC2          | 0           |               | 5-V       | VCC-5V      | PMC         |

| 124     | PC1          | 0           |               | 5-V       | VCC-5V      | PMC         |

| 125     | PC0          | 0           |               | 5-V       | VCC-5V      | PMC         |

| 126     | GPIO5*       | I/O         | Т             | 5-V       | VCC-5V      | PMC         |

| 127     | GPIO4*       | I/O         | Т             | 5-V       | VCC-5V      | PMC         |

| 128     | GPIO3*       | I/O         | Т             | 5-V       | VCC-5V      | PMC         |

| 129     | GPIO2*       | I/O         | Т             | 5-V       | VCC-5V      | PMC         |

| 130     | GPIO1*       | I/O         | Т             | 5-V       | VCC-5V      | PMC         |

| 131     | GPIO0*       | I/O         | Т             | 5-V       | VCC-5V      | PMC         |

| 132     | WAKE1        | I           | Т             | 5-V       | VCC-5V      | PMC         |

| 133     | WAKE0        | I           | Т             | 5-V       | VCC-5V      | PMC         |

| 134     | SWTCH        | I           | Т             | 5-V       | VCC-5V      | PMC         |

| 135     | RING         | I           | Т             | 5-V       | VCC-5V      | PMC         |

| 136     | BSER1TO3     | 0           |               | 5-V       | VCC-5V      | V1-LS/V3-LS |

| 137     | VCC CORE     | PWR         |               | 3.3-V     | VCC CORE    | POWER       |

| 138     | CLKIN        | I           | С             | 5-V       | VCC-5V      | CLOCK       |

| 139     | VSS CORE     | GND         |               |           | VSSC        | GROUND      |

| 140     | BSER3TO1     | I           | Т             | 5-V       | VCC-5V      | V1-LS/V3-LS |

| 141     | BSERCLKV3    | I/O         | Т             | 5-V       | VCC-5V      | V1-LS/V3-LS |

| 142     | PWRGOOD      | I           | Т             | 5-V       | VCC-5V      | RESET       |

| 143     | RSTDRV       | 0           |               | 5-V       | VCC-5V      | RESET       |

| 144     | VCC5V        | PWR         |               | 5-V       | VCC-5V      | POWER       |

| 145     | EXTACT0      | I           | Т             | 5-V       | VCC-5V      | PMC         |

| 146     | RCRST#       | I           | Т             | 5-V       | VCC-5V      | RESET       |

| 147     | 32KHZCLK     | I           | S             | 5-V       | VCC-5V      | CLOCK       |

| 148     | DOCK_PCIRST# | 0           |               | 3.3-V/5-V | VCCPCI      | PCI         |

| 149     | PCIRST#      | 0           |               | 3.3-V/5-V | VCCPCI      | PCI         |

Table 1-1.

Pin Assignment Table (Arranged by Pin Number) (cont.)

I = Input-only; O = Output-only; C = CMOS-compatible; S = Schmitt-trigger; T = TTL-compatible input; PWR = Power; GND = Ground = Ground

| PIN NO. | PIN NAME    | PIN<br>TYPE | INPUT<br>TYPE | VOLTAGE   | POWER PLANE | GROUP       |

|---------|-------------|-------------|---------------|-----------|-------------|-------------|

| 150     | C/BE3#      | I/O         | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 151     | C/BE2#      | I/O         | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 152     | C/BE1#      | I/O         | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 153     | VSSIO       | GND         |               |           | VSSIO       | GROUND      |

| 154     | C/BE0#      | I/O         | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 155     | FRAME#      | I/O         | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 156     | VCCPCI      | PWR         |               |           | VCCPCI      | POWER       |

| 157     | IRDY#       | I/O         | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 158     | TRDY#       | I/O         | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 159     | DEVSEL#     | I/O         | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 160     | STOP#       | I/O         | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 161     | PLOCK#      | I           | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 162     | REQ3#       | I           | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 163     | REQ2#       | I           | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 164     | REQ1#       | I           | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 165     | REQ0#       | I           | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 166     | GNT3#       | 0           |               | 3.3-V/5-V | VCCPCI      | PCI         |

| 167     | GNT2#       | 0           |               | 3.3-V/5-V | VCCPCI      | PCI         |

| 168     | GNT1#       | 0           |               | 3.3-V/5-V | VCCPCI      | PCI         |

| 169     | GNT0#       | 0           |               | 3.3-V/5-V | VCCPCI      | PCI         |

| 170     | PERR#       | I/O         | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 171     | VSSIO       | GND         |               |           | VSSIO       | GROUND      |

| 172     | PCICLK      | I/O         | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 173     | PAR         | I/O         | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 174     | VCCPCI      | PWR         |               |           | VCCPCI      | POWER       |

| 175     | DOCK_PCICLK | 0           |               | 3.3-V/5-V | VCCPCI      | PCI         |

| 176     | CLKRUN#     | I/O         | Т             | 3.3-V/5-V | VCCPCI      | PCI         |

| 177     | ADPAR_ODD   | I           | Т             | 3.3-V     | VCCCPU      | V1-LS/V2-LS |

| 178     | ADPAR_EVEN  | I           | Т             | 3.3-V     | VCCCPU      | V1-LS/V2-LS |

| 179     | PCIMSTR#    | 0           |               | 3.3-V     | VCCCPU      | V1-LS/V2-LS |

Table 1-1.

Pin Assignment Table (Arranged by Pin Number) (cont.)

$\textbf{I} = \textbf{Input-only}; \ \textbf{O} = \textbf{Output-only}; \ \textbf{C} = \textbf{CMOS-compatible}; \ \textbf{S} = \textbf{Schmitt-trigger}; \ \textbf{T} = \textbf{TTL-compatible input}; \ \textbf{PWR} = \textbf{Power}; \ \textbf{GND} = \textbf{Ground}$

| PIN NO. | PIN NAME | PIN<br>TYPE | INPUT<br>TYPE | VOLTAGE | POWER PLANE | GROUP       |

|---------|----------|-------------|---------------|---------|-------------|-------------|

| 180     | BD7      | I/O         | Т             | 3.3-V   | VCCCPU      | V1-LS/V2-LS |

| 181     | BD6      | I/O         | Т             | 3.3-V   | VCCCPU      | V1-LS/V2-LS |

| 182     | BD5      | I/O         | Т             | 3.3-V   | VCCCPU      | V1-LS/V2-LS |

| 183     | BD4      | I/O         | Т             | 3.3-V   | VCCCPU      | V1-LS/V2-LS |

| 184     | VSSIO    | GND         |               |         | VSSIO       | GROUND      |

| 185     | BD3      | I/O         | Т             | 3.3-V   | VCCCPU      | V1-LS/V2-LS |

| 186     | BD2      | I/O         | Т             | 3.3-V   | VCCCPU      | V1-LS/V2-LS |

| 187     | BD1      | I/O         | Т             | 3.3-V   | VCCCPU      | V1-LS/V2-LS |

| 188     | BD0      | I/O         | Т             | 3.3-V   | VCCCPU      | V1-LS/V2-LS |

| 189     | BDCTL2   | 0           |               | 3.3-V   | VCCCPU      | V1-LS/V2-LS |

| 190     | BDCTL1   | 0           |               | 3.3-V   | VCCCPU      | V1-LS/V2-LS |

| 191     | BDCTL0   | 0           |               | 3.3-V   | VCCCPU      | V1-LS/V2-LS |

| 192     | INCBUF   | 0           |               | 3.3-V   | VCCCPU      | V1-LS/V2-LS |

| 193     | VCCCPU   | PWR         |               | 3.3-V   | VCCCPU      | POWER       |

| 194     | DECBUF   | 0           |               | 3.3-V   | VCCCPU      | V1-LS/V2-LS |

| 195     | ADOE#    | 0           |               | 3.3-V   | VCCCPU      | V1-LS/V2-LS |

| 196     | A30      | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 197     | A29      | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 198     | A21      | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 199     | A22      | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 200     | A23      | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 201     | A24      | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 202     | A25      | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 203     | A26      | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 204     | A27      | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 205     | A28      | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 206     | A3       | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 207     | A4       | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

| 208     | A5       | I/O         | Т             | 3.3-V   | VCCCPU      | CPU         |

Table 1-1.

Pin Assignment Table (Arranged by Pin Number) (cont.)

I = Input-only; O = Output-only; C = CMOS-compatible; S = Schmitt-trigger; T = TTL-compatible input; PWR = Power; GND = Ground

### 1.3 Pin Cross Reference by Pin Name

| PIN NAME | PIN NO. | PIN NAME   | PIN NO. | PIN NAME  | PIN NO. |

|----------|---------|------------|---------|-----------|---------|

| 32KHZCLK | 147     | A30        | 196     | BSER3TO1  | 140     |

| A3       | 206     | A31        | 7       | C/BE0#    | 154     |

| A4       | 207     | ADOE#      | 195     | C/BE1#    | 152     |

| A5       | 208     | ADPAR_EVEN | 178     | C/BE2#    | 151     |

| A6       | 1       | ADPAR_ODD  | 177     | C/BE3#    | 150     |

| A7       | 2       | ADS#       | 41      | CA3/ADV#  | 71      |

| A8       | 4       | AHOLD      | 56      | CA4/ADSC# | 69      |

| A9       | 5       | BD0        | 188     | CACHE#    | 52      |

| A10      | 9       | BD1        | 187     | CASA0#    | 93      |

| A11      | 10      | BD2        | 186     | CASA1#    | 92      |

| A12      | 11      | BD3        | 185     | CASA2#    | 91      |

| A13      | 12      | BD4        | 183     | CASA3#    | 90      |

| A14      | 13      | BD5        | 182     | CASB0#    | 99      |

| A15      | 14      | BD6        | 181     | CASB1#    | 98      |

| A16      | 15      | BD7        | 180     | CASB2#    | 96      |

| A17      | 16      | BDCTL0     | 191     | CASB3#    | 95      |

| A18      | 17      | BDCTL1     | 190     | CE#       | 68      |

| A19      | 18      | BDCTL2     | 189     | CLKIN     | 138     |

| A20      | 19      | BE0#       | 38      | CLKRUN#   | 176     |

| A20M#    | 58      | BE1#       | 37      | COE#      | 81      |

| A21      | 198     | BE2#       | 36      | CPUCLK    | 24      |

| A22      | 199     | BE3#       | 35      | CPURST    | 32      |

| A23      | 200     | BE4#       | 34      | CWE0#     | 80      |

| A24      | 201     | BE5#       | 33      | CWE1#     | 79      |

| A25      | 202     | BE6#       | 27      | CWE2#     | 77      |

| A26      | 203     | BE7#       | 26      | CWE3#     | 76      |

| A27      | 204     | BRDY#      | 45      | CWE4#     | 75      |

| A28      | 205     | BSERCLKV3  | 141     | CWE5#     | 74      |

| A29      | 197     | BSER1TO3   | 136     | CWE6#     | 73      |

#### Table 1-2. Pin Assignment Table (Arranged by Pin Name)

| PIN NAME     | PIN NO. | PIN NAME | PIN NO. | PIN NAME      | PIN NO |

|--------------|---------|----------|---------|---------------|--------|

| CWE7#        | 72      | M/IO#    | 42      | RAS3#         | 84     |

| D/C#         | 43      | MAO      | 118     | RCRST#        | 146    |

| DECBUF       | 194     | MA1      | 117     | REQ0#         | 165    |

| DEVSEL       | 159     | MA2      | 115     | REQ1#         | 164    |

| DOCK_PCICLK  | 175     | МАЗ      | 114     | REQ2#         | 163    |

| DOCK_PCIRST# | 148     | MA4      | 112     | REQ3#         | 162    |

| DRMWE#       | 100     | MA5      | 111     | RING          | 135    |

| EADS#        | 49      | MA6      | 109     | RSTDRV        | 143    |

| EXTACT0      | 145     | MA7      | 108     | SMI#          | 30     |

| FERR#        | 40      | MA8      | 106     | SMIACT#       | 55     |

| FRAME#       | 155     | MA9      | 105     | STOP#         | 160    |

| GNT0#        | 169     | MA10     | 103     | STPCLK#/SUSP# | 20     |

| GNT1#        | 168     | MA11     | 102     | SWTCH         | 134    |

| GNT2#        | 167     | NA#      | 46      | TAGCS#/NALE#  | 82     |

| GNT3#        | 166     | NMI      | 6       | TAGD0         | 67     |

| GPIO0*       | 131     | PAR      | 173     | TAGD1         | 66     |

| GPIO1*       | 130     | PC0      | 125     | TAGD2         | 65     |

| GPIO2*       | 129     | PC1      | 124     | TAGD3         | 64     |

| GPIO3*       | 128     | PC2      | 123     | TAGD4         | 63     |

| GPIO4*       | 127     | PC3*     | 122     | TAGD5         | 62     |

| GPIO5*       | 126     | PC4*     | 121     | TAGD6         | 61     |

| HITM#        | 51      | PC5      | 120     | TAGD7         | 60     |

| HLDA/LOCK#   | 53      | PCICLK   | 172     | TAGWE#        | 83     |

| HOLD/BOFF#   | 50      | PCIMSTR# | 179     | TRDY#         | 158    |

| IGNNE#       | 39      | PCIRST#  | 149     | V2CLK         | 22     |

| INCBUF       | 192     | PERR#    | 170     | VCC5-V        | 144    |

| INIT/WM_RST  | 31      | PLOCK#   | 161     | VCC CORE      | 23     |

| INTR         | 59      | PWRGOOD  | 142     | VCC CORE      | 137    |

| IRDY#        | 157     | RAS0#    | 88      | VCCCPU        | 3      |

| KEN#/INV     | 47      | RAS1#    | 87      | VCCCPU        | 29     |

| L2CLK        | 28      | RAS2#    | 85      | VCCCPU        | 54     |

Table 1-2.

Pin Assignment Table (Arranged by Pin Name) (cont.)

| PIN NAME | PIN NO. | PIN NAME | PIN NO. | PIN NAME | PIN NO. |

|----------|---------|----------|---------|----------|---------|

| VCCCPU   | 78      | VSS CORE | 139     | VSSIO    | 113     |

| VCCCPU   | 193     | VSSIO    | 8       | VSSIO    | 119     |

| VCCDRAM  | 89      | VSSIO    | 25      | VSSIO    | 153     |

| VCCDRAM  | 97      | VSSIO    | 57      | VSSIO    | 171     |

| VCCDRAM  | 104     | VSSIO    | 70      | VSSIO    | 184     |

| VCCDRAM  | 110     | VSSIO    | 86      | W/R#     | 44      |

| VCCDRAM  | 116     | VSSIO    | 94      | WAKE0    | 133     |

| VCCPCI   | 156     | VSSIO    | 101     | WAKE1    | 132     |

| VCCPCI   | 174     | VSSIO    | 107     | WB/WT#   | 48      |

| VSS CORE | 21      |          |         |          |         |

Table 1-2.

Pin Assignment Table (Arranged by Pin Name) (cont.)

# 2. V1-LS DETAILED PIN DESCRIPTIONS

This chapter contains a detailed functional description of the pins on PT86C521. For ease of reference, the pins are arranged alphabetically within each of the following functional interface groups:

- CPU Interface (CPU)

- DRAM Interface (DRAM)

- L2 Cache Interface (L2 CACHE)

- PCI Interface (PCI)

- Power Management Interface (PMC)

- PT86C521 / V2-LS Interface (V1-LS / V2-LS)

- V1-LS / V3-LS Interface (V1-LS / V3-LS)

- Reset and Clock Interface (RESET / CLOCK)

- Power and Ground (POWER / GROUND)

The '#' symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage. Signal names without the '#' symbol indicate that the signal is active, or asserted at the high voltage level.

The '/' symbol between signal names indicates that the signals are multiplexed or have dual functionality and use the same pin for all functions.

The following conventions have been used to describe the pin type: 'I' = input-only pins; 'O' = output-only pins; 'I/O' = bi-directional pins, 'PWR' = power pins, and 'GND' = ground pins. The pin type is defined relative to the V1-LS device.

For a list of pins arranged by pin number, refer to Section 1.2 on page 1-15 For a list of pins arranged by pin name, refer to Section 1.3 on page 1-22

| Pin Name | Туре | Description                                                                                                                                                                                                                                      |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A20M#    | Ο    | <b>ADDRESS BIT 20 MASK#</b> : This output to the CPU indicates that the CPU should mask A20 in order to emulate the 8086 address wrap-<br>around.                                                                                                |

| A[31:3]  | I/O  | <b>CPU ADDRESS LINES [31:3]</b> : These are address lines that together with the byte enable signals (BE[7:0]#) make the address bus and define the physical area of memory or I/O accessed they are driven as outputs during bus master cycles. |

#### 2.1 CPU Interface

#### 2.1 CPU Interface (cont.)

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                        |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADS#     | I    | <b>ADDRESS STROBE#</b> : This input indicates the presence of a new valid bus cycle currently being driven by the CPU. ADS# is driven active in the first clock of a bus cycle and is driven inactive in the second or subsequent clocks of the cycle. ADS# is driven inactive when the bus is idle.                                                                               |

| AHOLD    | 0    | <b>ADDRESS HOLD</b> : This output is used in conjunction with EADS# for write-protecting a cacheable ROM region.                                                                                                                                                                                                                                                                   |

| BE[7:0]# | Ι    | <b>CPU BYTE ENABLE [7:0]</b> : The byte enable pins are used to determine which bytes must be written to memory, or which bytes were requested by the processor for the current cycle. They help define the physical area of the memory or I/O accessed. Byte enable pins are driven in the same clock as ADS#. They are driven with the same timing as the address lines A[31:3]. |

| BRDY#    | 0    | <b>BURST READY#:</b> This output to the Pentium processor indicates completion of the current cycle. BRDY# indicates that the V2-LS has presented valid data in response to a read, or that it has accepted the data from the Pentium processor in response to a write request.                                                                                                    |

| CACHE#   | I    | <b>CACHE#:</b> This input from the Pentium processor indicates a CPU cacheable/burstable operation.                                                                                                                                                                                                                                                                                |

| CPUCLK   | 0    | <b>CPU CLOCK OUTPUT:</b> This will be the clock output from V1-LS to the CPU.                                                                                                                                                                                                                                                                                                      |

| CPURST   | 0    | CPU RESET: This output resets the CPU.                                                                                                                                                                                                                                                                                                                                             |

| D/C#     | I    | <b>DATA_CODE#:</b> This cycle-definition input from the Pentium processor indicates whether the current cycle is a data or a code/special access. The D/C# pin is driven valid in the same clock as ADS# and the cycle address. It remains valid from the clock in which ADS# is asserted until the clock after the earlier of NA# or the last BRDY#.                              |

| EADS#    | 0    | <b>EXTERNAL ADDRESS STROBE#:</b> This output to the Pentium pro-<br>cessor indicates that a valid address has been driven onto the CPU<br>address bus for internal cache snoop cycle.                                                                                                                                                                                              |

| FERR#    | I    | <b>FLOATING-POINT ERROR#:</b> This output pin from the Pentium processor is used for floating-point error reporting.                                                                                                                                                                                                                                                               |

| HITM#    | I    | <b>HITM#:</b> This input indicates that the snoop cycle hit a modified line in the level-1 cache inside the CPU such that V1-LS should suspend the master operation, allow the CPU to evict the modified line, and then restart the master cycle.                                                                                                                                  |

### 2.1 CPU Interface (cont.)

| Pin Name    | Туре | Description                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HLDA/LOCK#  | I    | <b>HOLD ACKNOWLEDGE:</b> This input from the Pentium processor indicates a Hold Acknowledge state.                                                                                                                                                                                                                                                                                    |

|             |      | <b>LOCK#:</b> Indicates to the system that the current sequence of bus cycles should not be interrupted. <b>Note:</b> This pin applies to Revision CC only.                                                                                                                                                                                                                           |

| HOLD/BOFF#  | 0    | <b>HOLD REQUEST:</b> This output to the Pentium processor indicates a Hold Request state.                                                                                                                                                                                                                                                                                             |

|             |      | <b>BACK OFF#:</b> The back off input is used to force the Pentium processor off the bus in the next clock. <b>Note:</b> This pin applies to Revision CC only.                                                                                                                                                                                                                         |

| IGNNE#      | 0    | <b>IGNORE NUMERIC ERROR#:</b> This pin indicates that a floating-point error should be ignored.                                                                                                                                                                                                                                                                                       |

| INIT/WM_RST | 0    | <b>INIT:</b> This Pentium processor initialization input forces the Pentium processor to begin execution in a known state. The INIT/WM_RST will typically be asserted when software reset commands are written to either Port 64 or 92, or a shutdown cycle is detected.                                                                                                              |

|             |      | <b>WM_RST :</b> Cyrix 6x86 processor initialization input forces the processor to begin execution in a known state.                                                                                                                                                                                                                                                                   |

| INTR        | 0    | <b>MASKABLE INTERRUPT:</b> This pin indicates a maskable interrupt request to the Pentium processor.                                                                                                                                                                                                                                                                                  |

| INV         | 0    | See KEN#.                                                                                                                                                                                                                                                                                                                                                                             |

| KEN#/INV    | 0    | <b>CACHE ENABLE# :</b> This output to the Pentium processor indicates that the current cycle is cacheable.                                                                                                                                                                                                                                                                            |

|             |      | <b>INV:</b> This output pin indicates a request to invalidate the processor cache line during snoop cycles. If this function is not used, CPU's INV pin should either be pulled high or connected to W/R#.                                                                                                                                                                            |

| M/IO#       | I    | <b>MEMORY_INPUT &amp; OUTPUT#:</b> This cycle-definition signal is one of<br>the main pins that define the bus cycle. It distinguishes a memory<br>access from an I/O access. This signal is driven valid in the same<br>clock as ADS# and the cycle address. It remains valid from the clock<br>in which ADS# is asserted until the clock after earlier of NA# or the<br>last BRDY#. |

| NA#         | 0    | <b>NEXT ADDRESS #:</b> NA# indicates to the Pentium processor that V1-<br>LS is ready to accept a new bus cycle. This signal is used for CPU's pipelining feature.                                                                                                                                                                                                                    |

#### 2.1 CPU Interface (cont.)

| Pin Name      | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NMI           | 0    | <b>NON-MASKABLE INTERRUPT:</b> This pin indicates that an external non-maskable interrupt has been generated.                                                                                                                                                                                                                                                                                |

| SMI#          | 0    | <b>SYSTEM MANAGEMENT INTERRUPT#:</b> This output triggers a system management interrupt and is used to invoke the SMM (system management mode).                                                                                                                                                                                                                                              |

| SMIACT#       | I    | <b>SYSTEM MANAGEMENT INTERRUPT ACTIVE#:</b> This input from the Pentium processor indicates that the CPU is operating in SMM. Assertion of SMIACT# enables remapping of SMRAM to physical DRAM at 000A0000-000BFFFF region.                                                                                                                                                                  |

| STPCLK#/SUSP# | 0    | <b>STOP CLOCK#:</b> This output indicates a stop clock request to Intel's Pentium and AMD's K5 processor.                                                                                                                                                                                                                                                                                    |