National Semiconductor

#### January 1997

# PC87560 — PCI System I/O

## **1.0 General Description**

The PC87560 is a highly integrated IC that provides all of the system peripheral and power management functions (in conjunction with the PC87550 host controller) for a complete PCI based computer system. The functions include two Interrupt Controllers (8259), two DMA controllers (8237), System Timer (8254), and interfaces to an external Keyboard Controller, external ROM/FLASH ROM, and Real Time Clock for an AT compatible system. The system I/O functions include two serial ports (16550), one serial Infrared port, one Parallel port (IEEE 1284), Bus Mastering Fast IDE interface supporting two channels, Floppy Disk Controller (FDC), and OpenHCI Universal Serial Bus Controller (USB). Address re-mapping is provided for all internal functions to support Plug and Play capable systems. The PC87560 also provides additional I/O subsystem expansion via a 16-bit Fast Expansion Bus (FX Bus) giving the system designer additional I/O peripheral flexibility.

#### 1.1 Features

#### PCI Interface

- PCI 2.1 Compliant

- PCI Mobile Design Guide (revision 1.0 compliant)

- 32-bit PCI Bus

- Up to 33 MHz PCI Bus Frequency

- Positive decoding when in notebook

- Subtractive decoding when in dock

- Internal functions fully remappable via PCI configuration registers

#### Enhanced IDE

- Programmable IDE access timing per channel/drive

- 16 MBytes/sec maximum IDE data transfer rate

- 2 IDE channels supported (primary and secondary)

- Bus master support (SFF 8038 compliant)

- Multi-tasking DMA engine for channel concurrency

- 10 Double-Word write FIFOs per channel to sustain 16 MB/sec on IDE bus with burst of 8 Double-Words on the PCI Bus

- ATAPI support (SFF 8022i compliant)

- Supports ANSI ATA PIO Modes 0 through 4 and DMA modes 0 through 2

#### Universal Serial Bus (USB) Host Controller

- USB version 1.0 compliant

- OpenHCI version 1.0a compliant

- PCI Master DMA Scatter/Gather Channel

- Two Root Hub Ports

- Optimized List-Queue Manager for transfer scheduling and management

- Dynamic re-scheduling of data transfers

- Comprehensive Power Management support

- Supports real-time device attaching/detaching

- Supports transfer protocols for Full-speed (FS) and Low-Speed (LS) USB devices

- Legacy Keyboard /Mouse Emulation

- Integrated Transceivers

#### Legacy 8237 DMA Controller

- Seven 8237 compatible channels supported

- Distributed DMA Master and Slave modes

- 2 Double-Word Buffers for PCI Bus transfers

- DMA Channel routing for Plug and Play

- Support for preemption and re-arbitration per each PCI Bus transfer cycle

- ISA Compatible, Type "A", "B" and "F" timing supported

#### Floppy Disk Controller

- Software compatible with the DP8477, the 765A and the N82077

- Perpendicular Recording drive support

- Support of enhanced TDR

- Tri-mode floppy support

- 65% dynamic window margin

#### IEEE 1284 compatible Parallel Port

- All five modes supported: Compatible mode, Nibble mode, Byte mode, ECP,EPP 1.7 and 1.9.

- One Legacy DMA channel supported

#### Floppy Interface multiplexed on Parallel Port

- Two Standard Serial Ports (16550 UART)

- Second serial port configurable as serial port or IR port

- MIDI baud rate support

#### Infrared Communication Port

- IrDA (revision 1.0 compatible)

- IrDA2 (revision 1.1 compatible)

- 1.152Mb/sec and 4Mb/sec support

- Sharp support

- TV Remote Support

- Programmable pulse width of 1.6 usec or 3/16 of bit time

- Two independent DMA scatter/gather channels (one for receive and the other for transmit)

- Two Legacy 8237 DMA channels support

- Plug and Play dongle support

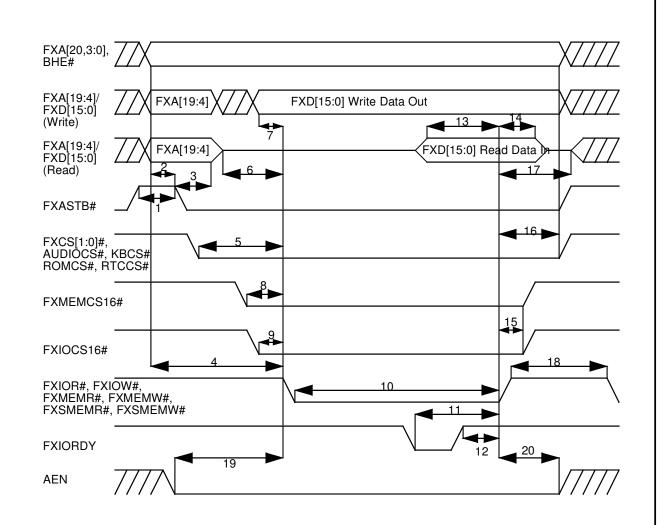

#### • FX Bus (Non- Bus Master ISA Bus)

- Programmable timing for ISA compatible peripherals

- 2 Programmable I/O range Chip selects

- One Programmable Memory Range

- One programmable, fragmented I/O window with Chip select for Sound Blaster compatibility

- IORDY support

- IOCS16 and MEMCS16 support

- DMA support (4 channels)Interrupt support (3 channels)

- Interrupt support (3 channels)

#### ROM/FLASH ROM Interface

- Supports up to 256 KBytes of ROM

- 8254 Compatible Timer

- 3 Timer Channels

#### External Keyboard Controller Interface

- Interface to 8051 or PC87570 style keyboard controller

- Keyboard Chip Select re-mappable anywhere in the 64Kbyte I/O range

#### Features Cont'd

#### External Real Time Clock Interface

- Support for DS1287 or MC146818 style RTCs

#### Interrupts

- Support for PCI native interrupts

- Two 8259 interrupt controllers

- Edge or level triggering individually programmable for each interrupt position

- Interrupt routing for Plug and Play

- PCIway Serial Interrupt support (both master and slave modes)

- Mixed Voltage Support

- 5V and 3.3V operation

#### Power Management (ACPI/Slave Mode Support)

- Advanced Configuration and Power Interface (ACPI) support (revision 1.0 compliant)

- Slave Mode: Power management control in the North-Bridge

- FDC, SP1/2, IDE 1/2 and Parallel Port access monitors

- 8 General Purpose I/Os for Power Management

- 1 System event register monitoring IRQs 15-0 and NMI

- CLKRUN# support

- Full set of shadow registers

- BSER (Burst Serial) interface to communicate power management activity to the PC87550 Host Bridge

- Other

- Each internal peripheral can be individually disabled

- Fast GateA20 and Fast Keyboard Reset support

- PCI Bus and CPU reset control

- Port 61 and Port 92 support

- Numeric coprocessor error support (Port F0)

- Back powering protection from printer, FDC and IDE

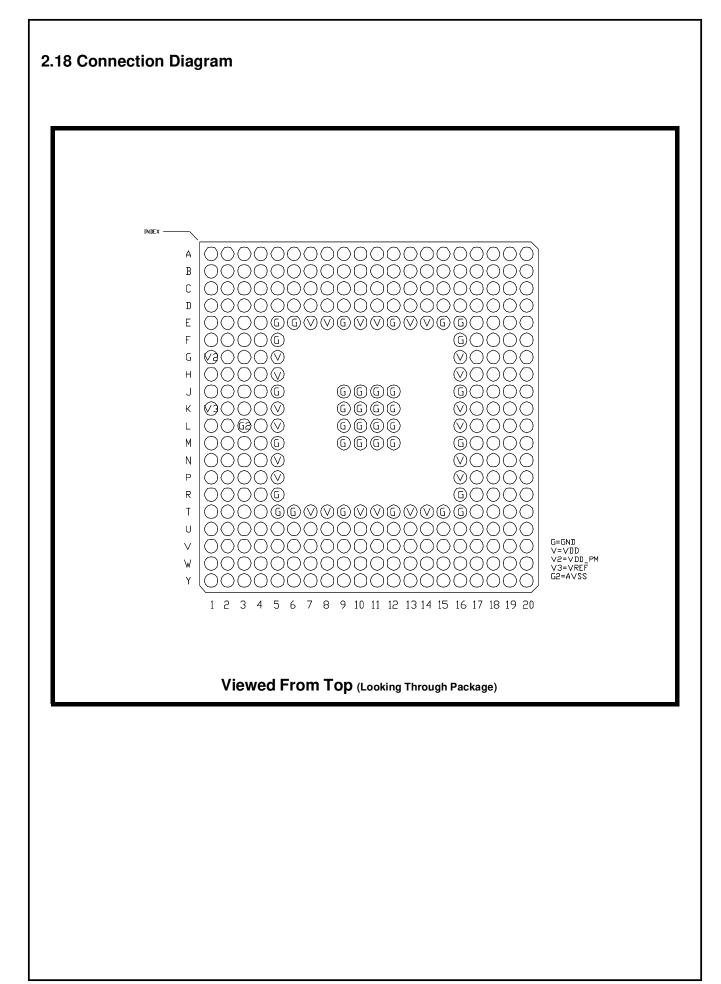

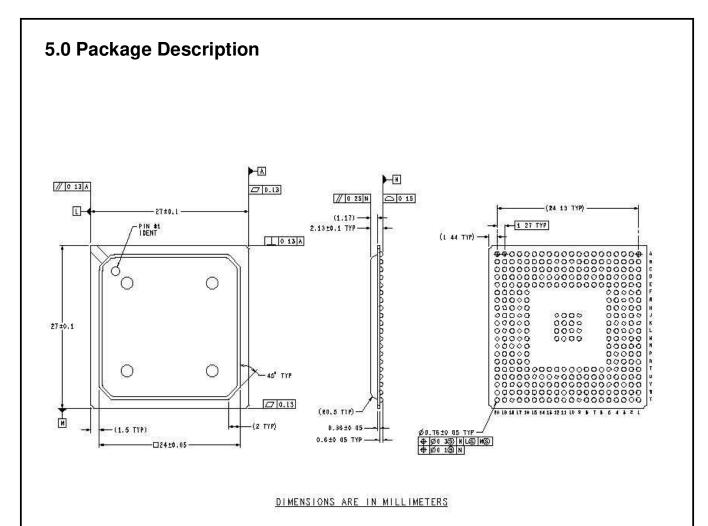

- 316 BGA package

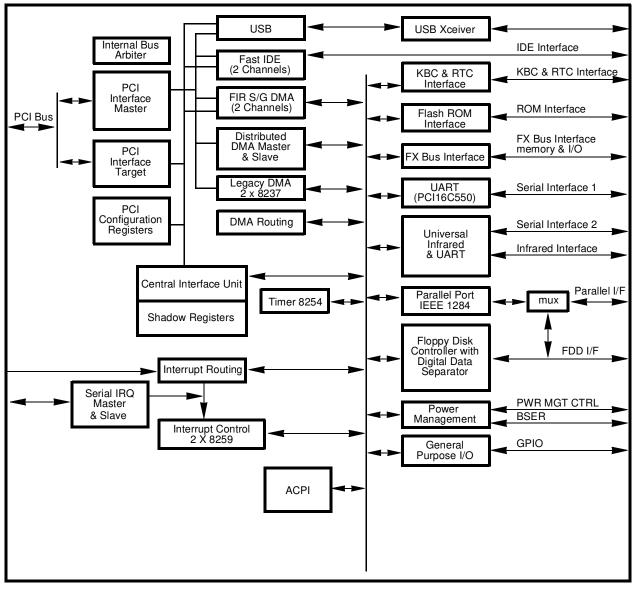

## **Block Diagram**

# 2.0 Pin Description

## 2.1 PCI Interface

| Pin                      | Name      | Voltage<br>(See Notes) | Туре | Description                                                                                                                                                                                                                                                                                                                                              |

|--------------------------|-----------|------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| See<br>Table<br>2.17     | AD[31:0]  | 3/5V                   | I/O  | Multiplexed Address and Data. The direction of these pins are defined<br>below:PhaseTargetBus MasterAddress PhaseinputoutputData PhaseReadoutputWriteinputoutput                                                                                                                                                                                         |

| G18<br>G19<br>G20<br>H17 | C/BE[3:0] | 3/5V                   | I/O  | Command/Byte Enable are multiplexed Bus command and Byte enables.                                                                                                                                                                                                                                                                                        |

| D12                      | PAR       | 3/5V                   | I/O  | <b>PAR</b> ity is even parity across AD[31:0] and C/BE[3:0]. PAR directional-<br>ity follows the AD[31:0] directionality.                                                                                                                                                                                                                                |

| B11                      | FRAME#    | 3/5V                   | I/O  | Cycle <b>FRAME</b> is driven by the initiator to indicate the beginning and duration of an access.                                                                                                                                                                                                                                                       |

| C12                      | TRDY#     | 3/5V                   | I/O  | Target ReaDY indicates that the target of the current data phase of the transaction is ready to be completed.                                                                                                                                                                                                                                            |

| B12                      | IRDY#     | 3/5V                   | I/O  | Initiator <b>R</b> ea <b>DY</b> indicates that the initiator is ready to complete the current data phase of the transaction.                                                                                                                                                                                                                             |

| C11                      | STOP#     | 3/5V                   | I/O  | <b>STOP</b> indicates that the current target is requesting the initiator to stop the current transaction.                                                                                                                                                                                                                                               |

| A11                      | LOCK#     | 3/5V                   | I    | <b>LOCK</b> indicates an atomic operation that may require multiple transactions to complete.                                                                                                                                                                                                                                                            |

| D11                      | DEVSEL#   | 3/5V                   | I/O  | <b>DEV</b> ice <b>SEL</b> ect, when driven active low, this signal indicates the driv-<br>ing device has decoded its address as the target of the current<br>access.                                                                                                                                                                                     |

| B14                      | IDSEL     | 3/5V                   | I    | Initialization <b>D</b> evice <b>SEL</b> ect is used as a chip select during configura-<br>tion read and write transactions.                                                                                                                                                                                                                             |

| A13                      | PERR#     | 3/5V                   | I/O  | Parity ERRor is used for reporting data parity errors during all PCI transactions except a Special Cycle. PERR# is an output when AD[31:0] and PAR are inputs and is an input when AD[31:0] and PAR are outputs.                                                                                                                                         |

| A12                      | SERR#     | 3/5V                   | I/O  | System <b>ERR</b> or is used for reporting address parity errors, data parity errors on the Special Cycle command, or any other system error where the result will be catastrophic. When reporting address parity errors, SERR# is an output. As an input to the PC87560, any PCI device can pulse the SERR# to indicate a catastrophic error condition. |

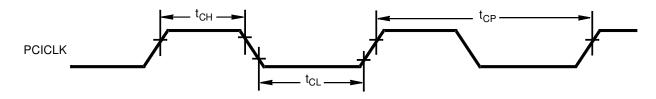

| A14                      | PCICLK    | 3/5V                   | I    | <b>PCI CL</b> ocK. The PCI clock input can be any frequency from 0-33MHz.                                                                                                                                                                                                                                                                                |

| D13                      | PCIRST#   | 3/5V                   | 0    | <b>PCI ReSeT.</b> PCIRST# is used to reset PCI bus devices and is asserted following RESET_IN#. PCIRST# will be deasserted a minimum of 1ms after RESET_IN# is deasserted.                                                                                                                                                                               |

# 2.2 Arbitration Signals

| Pin | Name    | Voltage<br>(See Notes) | Туре | Description                                                                                                                               |

|-----|---------|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| C13 | SIOGNT# | 3/5V                   | I    | PCI System I/O GraNT. This is signal is asserted from the host bridge allowing the PC87560 to become the PCI bus master.                  |

| B13 | SIOREQ# | 3/5V                   | 0    | PCI System I/O REQuest. This signal is asserted this signal to request the host controller to allow the PC87560 to become PCI bus Master. |

# 2.3 PCI Interrupts

| Pin                     | Name                                | Voltage<br>(See Notes) | Туре | Description                                                                                                                                                                                        |

|-------------------------|-------------------------------------|------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A9<br>D10<br>C10<br>B10 | INTA#,<br>INTB#,<br>INTC#,<br>INTD# | 3/5V                   | Ι    | PCI <b>INT</b> errupt Request <b>A</b> , <b>B</b> , <b>C</b> and <b>D</b> . These four active-low, share-<br>able interrupt requests may be used by PCI devices to make an inter-<br>rupt request. |

## 2.4 IDE Interface

| Pin                  | Name     | Voltage<br>(See Notes) | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------|----------|------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| See<br>Table<br>2.17 | DD[15:0] | 3/5VT                  | I/O  | IDE <b>D</b> rive <b>D</b> ata Bus. When accessing the IDE drive, this is an 8- or 16-bit bi-direction data bus between the PC87560 chip and the drive. The lower 8 bits are used for non-data 8-bit transfers (such as registers, ECC bytes).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

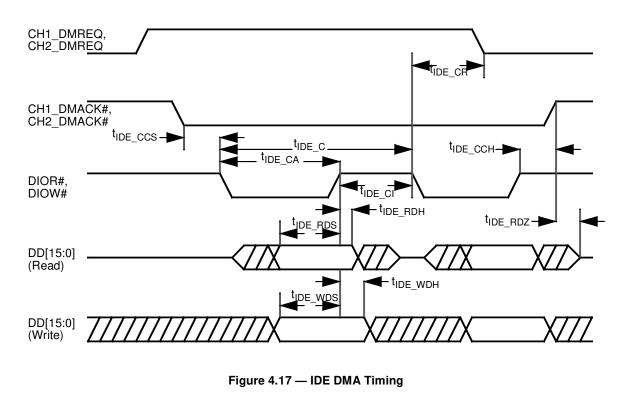

| W16,<br>V16,<br>U16  | DA[2:0]  | 3/5V                   | 0    | IDE <b>D</b> rive <b>A</b> ddress. When accessing the IDE drive, these pins are the DA[2:0] pins used to access a register or data port in the drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V11                  | DIORDY   | 3/5VT                  | I    | Drive I/O Channel ReaDY. When accessing the IDE drive, this signal<br>is negated (low) to extend a Programmable I/O (PIO) disk transfer<br>cycle of any register access (read or write) when the drive is not ready<br>to respond to a data transfer request. When an IDE drive no longer<br>desires to extend the cycle, DIORDY will be placed in TRI-STATE by<br>the IDE drive(s) and pulled high by an external pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| U11                  | DIOR#    | 3/5V                   | 0    | <b>D</b> rive <b>I/O R</b> ead. This is the read strobe signal for both channels.<br>When active low, DIOR# enables data from a register or the data port<br>of the drive onto the IDE Drive data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Y12                  | DIOW#    | 3/5V                   | 0    | <b>D</b> rive <b>I/O W</b> rite. This is the write strobe signal for both channels. The rising edge of DIOW# clocks data from the IDE Drive data bus into the register or the data port of the drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Y8                   | DRST#    | 3/5V                   | 0    | Drive ReSeT. This signal from the IDE Controller is asserted active<br>low during power up or under software control. DRST# will remain<br>active low as long as the PCI Reset signal (PCIRST#) is asserted low<br>or as long as the drive reset bit in the IDE Controller is set to one.<br>NOTE: This signal will be driven active low for a maximum of 2 msec.<br>following the rising edge of RESET_IN#. It is the system<br>designer's responsibility to guarantee that no accesses are<br>made to any IDE drive device during this period of time, if the<br>IDE drive devices use this signal as reset and the PC87560's<br>PCIRST# is not used as the PCI Bus reset. In such a case the<br>PC87560 cannot guarantee that a PCI Bus Cycle will not<br>occur while DRST# remains active low. If the PC87560's<br>PCIRST# is used as the PCI Bus reset, no accesses until<br>DRST# is de-asserted high are guaranteed. |

| U9<br>V9   | CH1_CS1#,<br>CH1_CS3# | 3/5V  | 0 | <b>CH</b> annel <b>1 C</b> hip <b>S</b> elect <b>1</b> and <b>3</b> . CH1_CS1# is the chip select signal to select the Command Block Registers. CH1_CS3# is the chip select signal to select the Control Block Registers of channel 1.                                                                                          |

|------------|-----------------------|-------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V10<br>W10 | CH2_CS1#,<br>CH2_CS3# | 3/5V  | 0 | <b>CH</b> annel <b>2</b> Chip Select <b>1</b> and <b>3</b> . CH2_CS1# is the chip select signal to select the Command Block Registers. CH2_CS3# is the chip select signal to select the Control Block Registers of channel 2.                                                                                                   |

| W9<br>Y10  | CH1_INT<br>CH2_INT    | 3/5VT | I | <b>CH</b> annel <b>1</b> and <b>CH</b> annel <b>2</b> Drive <b>INT</b> errupts. These signals are used to interrupt the host system. CH1_INT is asserted when the drive(s) on channel 1 have a pending interrupt. CH2_INT is asserted when the drive(s) on channel 2 have a pending interrupt.                                  |

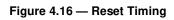

| Y9         | CH1_<br>DMREQ         | 3/5VT | I | <b>CH</b> annel <b>1 DM</b> A <b>REQ</b> uest. This signal is used when the device is configured to use the pseudo DMA handshake mode or when using the internal DMA controller. When asserted, this signals the PC87560 that the selected drive on channel 1 is ready to transfer data.                                        |

| Y11        | CH2_<br>DMREQ         | 3/5VT | I | <b>CH</b> annel <b>2 DM</b> A <b>REQ</b> uest. This signal is used when the device is configured to use the pseudo DMA handshake mode or when using the internal DMA controller. When asserted, this signals the PC87560 that the selected drive on channel 2 is ready to transfer data.                                        |

| U10        | CH1_<br>DMACK#        | 3/5V  | 0 | <b>CH</b> annel <b>1 DM</b> A <b>ACK</b> nowledge. This signal is used when the PC87560's IDE Controller is configured to use the pseudo DMA hand-shake mode or when using the internal DMA controller. This signal indicates to the selected drive on channel 1 that data has either been accepted, or that data is available. |

| W11        | CH2_<br>DMACK#        | 3/5V  | 0 | <b>CH</b> annel <b>2 DM</b> A <b>ACK</b> nowledge. This signal is used when the PC87560's IDE Controller is configured to use the pseudo DMA hand-shake mode or when using the internal DMA controller. This signal indicates to the selected drive on channel 2 that data has either been accepted, or that data is available. |

## 2.5 FX Bus Interface

| Pin                         | Name                    | Voltage<br>(See Notes) | Туре | Description                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------|-------------------------|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Y17                         | FXA[20]                 | 3/5V                   | 0    | <b>FX</b> Address 20. This is the most significant address bit on the FX Bus. It will always be driven by the PC87560 and is never multiplexed with any data.                                                                                                                                                                                                                |

| See<br>Table<br>2.17        | FXA[19:4]/<br>FXD[15:0] | 3/5VT                  | I/O  | <b>FX</b> Address19-4/FX <b>D</b> ata Bus 15-0. This is the multiplexed FX address/data bus. During FX Bus address phases, the appropriate address will be driven onto these pins by the PC87560. During FX Bus data phases, the PC87560 will drive out the appropriate data during write cycles and will TRI-STATE these signals during read cycles, thus acting as inputs. |

| R17,<br>R18,<br>R19,<br>R29 | FXA[3:0]                | 3/5VT                  | 0    | <b>FX</b> Address 3-0. These four signals are the least significant address bits on the FX Bus. They will always be driven by the PC87560 and are not multiplexed with data.                                                                                                                                                                                                 |

| P20                         | FXASTB#                 | 3/5V                   | 0    | <b>FX</b> Address <b>ST</b> ro <b>Be</b> . During the FX Bus address phase, the falling edge of FXASTB# is used to latch the address FXA[19:4] off of the multiplexed FXA[19:4]/FXD[15:0] pins.                                                                                                                                                                              |

| N17                         | FXIOR#                  | 3/5VT                  | 0    | <b>FX I/O R</b> ead. This is the FX bus I/O read strobe. The pulse width of this signal is programmable.                                                                                                                                                                                                                                                                     |

| N18                         | FXIOW#                  | 3/5VT                  | 0    | <b>FX I/O W</b> rite. This is the FX bus I/O write strobe. The pulse width of this signal is programmable.                                                                                                                                                                                                                                                                   |

| M19                         | FXMEMR#                 | 3/5V                   | 0    | <b>FX MEM</b> ory <b>R</b> ead. This is the FX bus Memory read strobe. This signal will strobe active for every memory read cycle on the FX Bus.                                                                                                                                                                                                                             |

| M20                         | FXMEMW#                 | 3/5V                   | 0    | <b>FX MEM</b> ory <b>W</b> rite. This is the FX bus Memory write strobe. This signal will strobe active for every memory write cycle on the FX Bus                                                                                                                                                                                                                           |

| L17                         | FXSMEMR#           | 3/5V  | 0   | <b>FX S</b> ystem <b>MEM</b> ory <b>R</b> ead. This is the FX bus System Memory read strobe. This signal will strobe active only for memory reads on the FX Bus with addresses below 1Meg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------|--------------------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L18                         | FXSMEMW#           | 3/5V  | 0   | <b>FX S</b> ystem <b>MEM</b> ory <b>W</b> rite. This is the FX bus System Memory write strobe. This signal will strobe active only for memory writes on the FX Bus with address below 1Meg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| N19                         | FXIORDY            | 3/5VT | I/O | <b>FX I/O R</b> ea <b>DY</b> . When accessing the FX bus this signal may be negated low by the device being accessed to extend the FX bus transfer cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| N20                         | FXIOCS16#          | 3/5VT | I   | <b>FX I/O</b> Chip Select <b>16</b> Bit. This input signal is driven active low by 16-bit I/O devices when they are being addressed and this signal will be used by the PC87560's FX Bus Controller to appropriately steer data for I/O cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| M17                         | FXMEMCS16#         | 3/5VT | I   | <b>FX MEM</b> ory Chip Select <b>16</b> Bit. This input signal is driven active low by 16-bit memory devices when they are being addressed and this signal will be used by the PC87560's FX Bus Controller to appropri ately steer data for memory cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| M18                         | BHE#               | 3/5V  | 0   | Byte High Enable. This FX Bus signal is asserted low to indicate the high (odd) data byte is being transferred. Only 16-bit devices use this signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| L20,<br>K20,<br>K19,<br>K18 | DRQ[3:0]           | 3/5VT | I   | DMA ReQuests 3-0. These DMA request pins may be steered to<br>any of the internal PC87560 8237 DMA Controllers' request inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| J18                         | DACK0#/<br>DOCKEN# | 3/5VT | I/O | DMA ACKnowledge 0/DOCK ENable. During normal operation this<br>pin will act as the active-low DMA Acknowledge output signal asso-<br>ciated with the DRQ[0] input. During a power-up reset this pin will<br>become an input strapping option and is sampled on the rising<br>edge of RESET_IN#. This I/O has a weak pull-down resistor, thus<br>will default low unless an external pull-up resistor is used. If this<br>pin is sampled low, the PC87560 will indicate that it is in a Docking<br>Station (Its Function 1 Device ID will be 000Eh). If this pin is sam-<br>pled high, then the PC87560 will indicate that it is in the Notebook<br>Motherboard (Its Function 1 Device ID will be 0011h). |

| J19                         | DACK1#/<br>FENCFG  | 3/5VT | 1/0 | DMA ACKnowledge 1/Function ENable ConFiGuration. During nor<br>mal operation this pin will act as the active-low DMA Acknowledge<br>output signal associated with the DRQ[1] input. During a power-up<br>reset this pin will become an input strapping option and is sampled<br>on the rising edge of RESET_IN#. This I/O has a weak pull-down<br>resistor, thus will default low unless an external pull-up resistor is<br>used. If this pin is sampled low, all of the PC87560 functions are<br>disabled. If this pin is sampled high, then the PC87560 functions<br>will operate normally as defined.                                                                                                 |

| J20                         | DACK2#/<br>FGA20EN | 3/5VT | 1/0 | DMA ACKnowledge 2/Fast Gate A20 ENable. During normal oper-<br>ation this pin will act as the active-low DMA Acknowledge output<br>signal associated with the DRQ[2] input. During a power-up reset<br>this pin will become an input strapping option and is sampled on the<br>rising edge of RESET_IN#. This I/O has a weak pull-down resistor,<br>thus will default low unless an external pull-up resistor is used. If<br>this pin is sampled low, the Fast GateA20 and the Fast Keyboard<br>Reset logic will be disabled. If this pin is sampled high, the Fast<br>GateA20 and the Fast Keyboard Reset logic will be enabled.                                                                        |

| K17                 | DACK3#/<br>SIRQMST | 3/5VT | I/O | DMA ACKnowledge 3/Seral Interrupt ReQuest MaSTer Mode<br>Enabled. During normal operation this pin will act as the active-low<br>DMA Acknowledge output signal associated with the DRQ[3] input.<br>During a power-up reset this pin will become an input strapping<br>option and is sampled on the rising edge of RESET_IN#. This I/O<br>has a weak pull-down resistor, thus will default low unless an exter-<br>nal pull-up resistor is used. If this pin is sampled low, the Serial<br>Interrupt interface logic will be operate as a Slave. If this pin is sam-<br>pled high, the Serial Interrupt interface logic will operate as the<br>Master.                                                                                                                                                                                                                                                                                          |

|---------------------|--------------------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J17                 | TC/<br>MRTRYD#     | 3/5VT | I/O | Terminal Count/Memory ReTRY Disable. During normal operation<br>this pin will act as the Terminal Count (TC) of a compatible 8237<br>DMA Controller. During a power-up reset this pin will become an<br>input strapping option and is sampled on the rising edge of<br>RESET_IN#. This I/O has a weak pull-down resistor, thus will<br>default low unless an external pull-up resistor is used. If it is sam-<br>pled low, memory reads from the ROM BIOS will not be retried on<br>the PCI Bus. If this pin is sampled high, memory reads from the<br>ROM BIOS will be retried on the PCI Bus.<br>NOTE: If the reads from the ROM BIOS are not retried, it<br>would tend to violate the standard 16 PCI clock Target<br>Initial Latency requirement. As long as the purpose of<br>these read cycles is to perform a POST Code copy of<br>the ROM image to memory, this will be compliant with<br>the PCI Local Bus specification Revision 2.1. |

| H20,<br>H19,<br>H18 | FXIRQ[2:0]         | 3/5VT | I   | <b>FX</b> Bus Interrupt <b>ReQ</b> uest <b>2-0</b> . These are general purpose interrupts that are internally routed (configurable) to the interrupt lines of the 8259s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P17,<br>P18         | FXCS[1:0]#         | 3/5V  | 0   | <b>FX</b> Chip Select <b>0</b> and <b>1</b> . These two active-low signals are programmable I/O address range chip selects to select external devices on the FX bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P19                 | AUDIOCS#           | 3/5V  | 0   | AUDIO Chip Select. This active-low output chip select provides support for a compatible, fragmented Sound Blaster I/O map.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## 2.6 External KBC and RTC Interface

| Pin | Name             | Voltage<br>(See Notes) | Туре | Description                                                                                                                                                                                                                                                                                                                            |

|-----|------------------|------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B8  | KBCS#            | 3/5V                   | 0    | KeyBoard Controller Chip Select. This pin is asserted during read or write accesses to the keyboard's programmable I/O locations.                                                                                                                                                                                                      |

| C8  | KBGA20           | 3/5VT                  | I    | KeyBoard GAteA20 input. Gate A20 from an external keyboard con-<br>troller.                                                                                                                                                                                                                                                            |

| C9  | KBINT            | 3/5VT                  | I    | KeyBoard INTerrupt. Keyboard interrupt request from an external keyboard controller.                                                                                                                                                                                                                                                   |

| D8  | KBRST#           | 3/5VT                  | Ι    | KeyBoard ReSeT input. Keyboard Reset from an external keyboard controller.                                                                                                                                                                                                                                                             |

| D9  | MINT             | 3/5VT                  | I    | Mouse INTerrupt. Mouse interrupt request from an external keyboard controller.                                                                                                                                                                                                                                                         |

| A7  | RTCALE/<br>PMCS# | 3/5V                   | 0    | Real Time Clock Address Latch Enable or Power Management Chip<br>Select. When this pin is programmed as the RTCALE pin, then this<br>pin is asserted during an I/O write to port 70h. When this pin is config-<br>ured as the PMCS# pin, then this pin is asserted during an I/O read/<br>write to addresses KBCBAR+2h, and KBCBAR+6h. |

| A8  | RTCCS#           | 3/5V                   | 0    | <b>R</b> eal <b>T</b> ime <b>C</b> lock <b>C</b> hip <b>S</b> elect. This pin is asserted during I/O read or write accesses to the RTC location 71h. When VMKBC is selected (Function1, Reg. 5Ch, bit 4="1"), this pin is asserted during I/O read or write accesses to locations 70h and 71h.                                         |

| J4  | RTCINT#          | 3/5VT_PM               | I    | Real Time Clock INTerrupt. Active-low Real Time Clock interrupt.                                                                                                                                                                                                                                                                       |

| 2.7 ROM Interface |        |                        |      |                                                                                                                                                |

|-------------------|--------|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin               | Name   | Voltage<br>(See Notes) | Туре | Description                                                                                                                                    |

| L19               | ROMCS# | 3/5V                   | 0    | <b>ROM C</b> hip <b>S</b> elect. This signal will be active low any time there is a memory access to the (configurable) ROM BIOS memory range. |

#### 2.8 Universal Serial Bus Interface

| Pin      | Name                | Voltage<br>(See Notes) | Туре | Description                                                                                                                                                                                                           |

|----------|---------------------|------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L4       | OC_SENSE1           | 3/5VT                  | I    | USB Root Hub <b>O</b> ver- <b>C</b> urrent <b>SENSE</b> PORT <b>1</b> input. Used in conjunction with an external bus power regulator to indicate to the host controller when a bus overcurrent shutdown has occured. |

| M1       | OC_SENSE2           | 3/5VT                  | I    | USB Root Hub <b>O</b> ver- <b>C</b> urrent <b>SENSE</b> PORT <b>2</b> input. Used in conjunction with an external bus power regulator to indicate to the host controller when a bus overcurrent shutdown has occured. |

| K3<br>K2 | PORT1D+,<br>PORT1D- | 3/5V_PM                | I/O  | USB Root Hub <b>PORT 1 D</b> ifferential Signal Pair.                                                                                                                                                                 |

| L1<br>L2 | PORT2D+,<br>PORT2D- | 3/5V_PM                | I/O  | USB Root Hub <b>PORT 2 D</b> ifferential Signal Pair.                                                                                                                                                                 |

| M2       | PWRCTL1#            | 3/5V                   | 0    | USB Root Hub <b>PoWeR ConT</b> roL PORT <b>1</b> output. Used in conjunction with an external USB bus power regulator to enable or disable bus power.                                                                 |

| M3       | PWRCTL2#            | 3/5V                   | 0    | USB Root Hub <b>PoWeR ConTroL</b> PORT <b>2</b> output. Used in con-<br>junction with an external USB bus power regulator to enable or<br>disable bus power.                                                          |

| K4       | USB_ACT             | 3/5V_PM                | 0    | <b>USB ACT</b> ivity. When active high this output indicates that there has been activity on the USB ports. This output is used to support ACPI wake-up via activity on the USB ports.                                |

## 2.9 Floppy Disk Controller Interface

| Pin   | Name       | Voltage<br>(See Notes) | Туре | Description            |

|-------|------------|------------------------|------|------------------------|

| G3,G4 | MSEN[1:0]  | 3/5VT                  | I    | Media SENse 0 and 1    |

| D2,D3 | DENSL[1:0] | 3/5V                   | 0    | DENsity Select 0 and 1 |

| E3,E2 | DS[1:0]#   | 3/5V                   | 0    | Drive Select 0 and 1   |

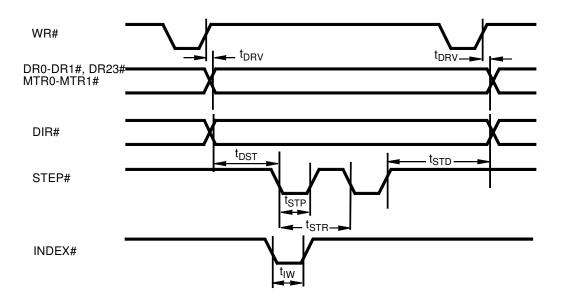

| D1,E4 | MTR[1:0]#  | 3/5V                   | 0    | MoToR Select 0 and 1   |

| E1    | DIR#       | 3/5V                   | 0    | DIRection              |

| G2    | INDEX#     | 3/5VT                  | I    | INDEX                  |

| F4    | STEP#      | 3/5V                   | 0    | STEP                   |

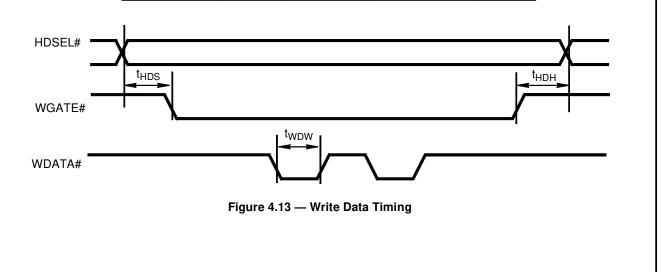

| F3    | WDATA#     | 3/5V                   | 0    | Write DATA             |

| F2    | WGATE#     | 3/5V                   | 0    | Write GATE             |

| M4    | TRK0#      | 3/5VT                  | I    | TRacK 0                |

| N1    | WP#        | 3/5VT                  | I    | Write Protect          |

| N2    | RDATA#     | 3/5VT                  | I    | Read DATA              |

| F1    | HDSEL#     | 3/5V                   | 0    | HeaD SELect            |

| N3    | DSKCHG#    | 3/5VT                  | I    | DiSK CHanGe            |

## 2.10 Serial Port 1 and 2

| Pin   | Name      | Voltage<br>(See Notes) | Туре | Description                                  |

|-------|-----------|------------------------|------|----------------------------------------------|

| Y6,U4 | DCD[1:0]# | 3/5VT                  | I    | Data Carrier Detect for Serial Port 1 and 2. |

| U7,W3 | DSR[1:0]# | 3/5VT                  | I    | Data Set Ready for Serial Port 1 and 2.      |

| V7,Y3 | SIN[1:0]  | 3/5VT                  | I    | Serial Data IN for Serial Port 1 and 2.      |

| W7,V4 | RTS[1:0]# | 3/5V                   | 0    | RequesT to Send for Serial Port 1 and 2.     |

| Y7,W4 | SOUT[1:0] | 3/5V                   | 0    | Serial Data OUTput for Serial Port 1 and 2.  |

| U8,Y4 | CTS[1:0]# | 3/5VT                  | I    | Clear To Send for Serial Port 1 and 2.       |

| V8,U5 | DTR[1:0]# | 3/5V                   | 0    | Data Terminal Ready for Serial Port 1 and 2. |

| W8,V5 | RI[1:0]#  | 3/5VT                  | I    | Ring Indicator for Serial Port 1 and 2.      |

## 2.11 Serial Infrared Interface

| Pin   | Name                   | Voltage<br>(See Notes) | Туре | Description                                                                   |

|-------|------------------------|------------------------|------|-------------------------------------------------------------------------------|

| W5    | IRTX                   | 3/5V                   | 0    | InfraRed Transmit Data                                                        |

| Y5    | IRRX                   | 3/5VT                  | I    | InfraRed Receive Data                                                         |

| U6    | IRSEL0/<br>IRRX2/ID[0] | 3/5VT                  | I/O  | InfraRed SELect 0 or InfraRed Receive Data 2 or ID0 for plug and play support |

| W6,V6 | IRSEL[2:1]/<br>ID[2:1] | 3/5VT                  | I/O  | InfraRed SELect 2-1 or ID[2:1] for plug and play support                      |

## 2.12 Parallel Port/Floppy Interface

| Pin | Name                      | Voltage<br>(See Notes) | Туре | Description                                                                                                               |  |  |  |

|-----|---------------------------|------------------------|------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|

| P2  | STB#/<br>WRITE#           | 3/5VT                  | 0    | Data <b>ST</b> ro <b>B</b> e in compatibility Parallel Port mode, <b>WRITE</b> strobe in ECP mode                         |  |  |  |

| P3  | PD0/<br>INDEX#            | 3/5VT                  | I/O  | Data 0 in Parallel Port mode or INDEX# in floppy mode.                                                                    |  |  |  |

| P4  | PD1/TRK0#                 | 3/5VT                  | I/O  | Data 1 in Parallel Port mode or TRacK 0 in floppy mode.                                                                   |  |  |  |

| R1  | PD2/WP#                   | 3/5VT                  | I/O  | Data 2 in Parallel Port mode or Write Protect in floppy mode.                                                             |  |  |  |

| R2  | PD3/<br>RDATA#            | 3/5VT                  | I/O  | Data 3 in Parallel Port mode or Read DATA in floppy mode.                                                                 |  |  |  |

| R3  | PD4/<br>DSKCHG#           | 3/5VT                  | I/O  | Data 4 in Parallel Port mode or DiSK CHanGe in floppy mode.                                                               |  |  |  |

| R4  | PD5/<br>MSEN0             | 3/5VT                  | I/O  | Data 5 in Parallel Port mode or Media SENse 0 in floppy mode.                                                             |  |  |  |

| T2  | PD6/<br>DENSL1            | 3/5VT                  | I/O  | Data 6 in Parallel Port mode or DENsity SeLect1 in floppy mode.                                                           |  |  |  |

| T1  | PD7/MSEN1                 | 3/5VT                  | I/O  | Data 7 in Parallel Port mode or Media SENse 1 in floppy mode.                                                             |  |  |  |

| Т3  | ACK#/DS1#                 | 3/5VT                  | I/O  | ACKnowledge in Parallel Port mode or Drive Select 1 in floppy mode.                                                       |  |  |  |

| Τ4  | BUSY#/<br>WAIT#/<br>MTR1# | 3/5VT                  | I/O  | <b>BUSY</b> in compatibility parallel port mode, <b>WAIT</b> in ECP mode and <b>MoToR</b> Select <b>1</b> in floppy mode. |  |  |  |

| U1  | PE/<br>WDATA#             | 3/5VT                  | I/O  | Paper End in Parallel Port mode or Write DATA in floppy mode.                                                             |  |  |  |

| U2  | SLCT/<br>WGATE#           | 3/5VT                  | I/O  | SeLeCT in parallel port mode or Write GATE in floppy mode.                                                                |  |  |  |

| U3 | SLIN#/<br>ASTB#/<br>STEP#  | 3/5V  | 0   | SeLect INput in compatibility Parallel Port mode, STroBe in ECP mode and STEP in floppy mode.                                                                                                                                                                                                                                                                                                                                       |

|----|----------------------------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V1 | INIT#/DIR#                 | 3/5V  | 0   | <b>INIT</b> ialize in Parallel Port mode or <b>DIR</b> ection in floppy mode.                                                                                                                                                                                                                                                                                                                                                       |

| V2 | ERR#/<br>HDSEL#            | 3/5VT | I/O | ERRor in Parallel Port mode or HeaD SELect in floppy mode.                                                                                                                                                                                                                                                                                                                                                                          |

| V3 | AFD#/<br>DSTRB#/<br>DENSL0 | 3/5V  | 0   | Automatic FeeD XT in compatibility Parallel Port mode, DataS-<br>TRoBe# in ECP mode and DENsity SeLect0 in floppy mode.                                                                                                                                                                                                                                                                                                             |

| N4 | PNF                        | 3/5VT | I   | <b>P</b> rinter <b>Not F</b> loppy. This input is disabled when the PNF Select bit (Bit 0 of the System I/O Configuration Register at offset 5Ch) is a zero. When this input is a zero and the PNF Select bit is a one, the FDC signals are multiplexed onto the Parallel Port/Floppy pins. When this input is a one and the PNF Select bit is a one, the Parallel Port signals are multiplexed onto the Parallel Port/Floppy pins. |

Note: DENSL1 is a 14ma push-pull output

## 2.13 Power Management Interface

| Pin | Name                 | Voltage<br>(See Notes) | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|----------------------|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A10 | CLKRUN#              | 3/5V                   | I/O  | <b>CL</b> oc <b>K RUN</b> is used to request starting or stopping the PCI clock as well as indicating the clock status. The PC87560 can request the Central Resource, to start or maintain the interface clock by assertion of CLKRUN#. The Central Resource is responsible for maintaining CLKRUN# asserted, and for driving it high to the deasserted state. CLKRUN# defaults low (active) upon deassertion of reset. CLKRUN# is a sustained TRI-STATE I/O signal.                                                                                        |

| H3  | SLPEN#               | 3/5V_PM                | 0    | <b>SL</b> eep <b>EN</b> able. This signal indicates a request for the ACPI Embedded Controller to enter an ACPI sleep mode.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| J3  | EVENT1/<br>EX_PME_EC | 3/5VT_PM               | I/O  | <b>EVENT 1</b> or <b>EX</b> ternal <b>P</b> ower <b>M</b> anagement <b>E</b> vent input from the<br><b>E</b> mbedded <b>C</b> ontroller. When power management is configured in<br>slave mode, EVENT1 is an output and will be asserted whenever<br>one of the system events occurs in the System Events 1 Register.<br>This pin can be connected to the EXTACT0 pin of the PC87550<br>Host Controller. When this signal functions as EX_PME_EC, it<br>operates as the ACPI External Power Management Event input sig-<br>nal from the Embedded Controller. |

| J1  | SMI_SB               | 3V_PM                  | 0    | System Management Interrupt. This signal is asserted high when-<br>ever an I/O trap occurs, a system event occurred, an SMI occurred<br>through the Serial Interrupt bus, or when an ACPI SMI is gener-<br>ated. SMI_SB is an active high output to a PCI Bus Host Controller<br>and will remain asserted until software clears the condition causing<br>the SMI.                                                                                                                                                                                           |

| D7  | BSERCLK3             | 3/5VT                  | I    | Burst SERial CLocK. This pin is the serial bus clock for the serial system and power management bus (BSER1TO3/BSER3TO1).                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| C7  | BSER3TO1             | 3/5V                   | 0    | Burst SERial 3TO1. Communicates system and power management information from the PC87560 to the PC87550.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B7  | BSER1TO3             | 3/5VT                  | I    | Burst SERial 1TO3. Communicates system and power management information from the PC87550 to the PC87560.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| H1  | SUSPEND#             | 3/5VT_PM               | I    | <b>SUSPEND#</b> . This pin is asserted by the ACPI Embedded Controller to acknowledge entering an ACPI sleep state. When the Embedded Controller de-asserts this signal high, it indicates that the Embedded ded Controller is waking-up the system.                                                                                                                                                                                                                                                                                                        |

| C3 | GPIO0/AEN          | 3/5VT    | I/O | General Purpose I/O 0 or FX Bus Address ENable. When this pin is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----|--------------------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                    |          |     | configured as a General Purpose I/O, this pin is accessed through<br>the General Purpose I/O register Bit 0. When this pin is configured<br>as the AEN signal, it will function as the FX Bus Address ENable<br>signal for FX Bus cycles.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| B3 | GPIO1/ID3          | 3/5VT    | I/O | General Purpose I/O 1 or Infrared ID3 input. When this pin is con-<br>figured as a General Purpose I/O, this pin is accessed through the<br>General Purpose I/O register Bit 1. When this pin is configured to<br>operate as the ID3 pin, it will act as the ID3 Infrared input signal to<br>the UIR module.<br>NOTE: When configured as a General Purpose I/O, the value<br>driven will continue to be driven to the UIR module as the<br>ID3 Infrared input signal. It is the responsibility of the hard-<br>ware and software system design to avoid any conflicts<br>between the configuration of this pin and the associated (if<br>any) Infrared Driver software. |

| A3 | GPIO2              | 3/5VT    | I/O | <b>G</b> eneral <b>P</b> urpose <b>I/O 2</b> . This pin is accessed through the General Purpose I/O register Bit 2. It may be configured to operate as either a Totem-Pole driver (default) or as an Open-Drain driver (to support a bit-bang $I^2C$ interface).                                                                                                                                                                                                                                                                                                                                                                                                        |

| C4 | GPIO3              | 3/5VT    | I/O | General Purpose I/O 3. This pin is accessed through the General Purpose I/O register Bit 3. It may be configured to operate as either a Totem-Pole driver (default) or as an Open-Drain driver (to support a bit-bang I <sup>2</sup> C interface).                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B4 | GPIO4/<br>IDE_INT1 | 3/5VT    | I/O | General Purpose I/O 4 or IDE INTerrupt 1 output. When this pin is configured as a GP I/O pin, this pin is accessed through the General Purpose I/O register Bit 4. When configured as the IDE_INT1 pin, it will be the output of the IDE Channel 1 Interrupt Request.                                                                                                                                                                                                                                                                                                                                                                                                   |

| A4 | GPIO5/<br>IDE_INT2 | 3/5VT    | I/O | General Purpose I/O 5 or IDE INTerrupt 2 output. When this pin is configured as a GP I/O pin, this pin is accessed through the General Purpose I/O register Bit 5. When configured as the IDE_INT2 pin, it will be the output of the IDE Channel 2 Interrupt Request.                                                                                                                                                                                                                                                                                                                                                                                                   |

| D5 | GPIO6/<br>USB_INT  | 3/5VT    | I/O | General Purpose I/O 6 or USB INTerrupt output. When this pin is configured as a GP I/O pin, this pin is accessed through the General Purpose I/O register Bit 6. When this pin is configured as the USB_INT pin, it will be the output of the USB Host Controller's Interrupt Request.                                                                                                                                                                                                                                                                                                                                                                                  |

| J2 | GPIO7/<br>EX_PME   | 3/5VT_PM | I/O | General Purpose I/O 7 or EXternal Power Management Event<br>input. When used as a General Purpose I/O pin, this pin is<br>accessed through the General Purpose I/O register Bit 7. When this<br>pin is configured as EX_PME, this input will signal an External<br>Power Management Event to the ACPI logic.                                                                                                                                                                                                                                                                                                                                                            |

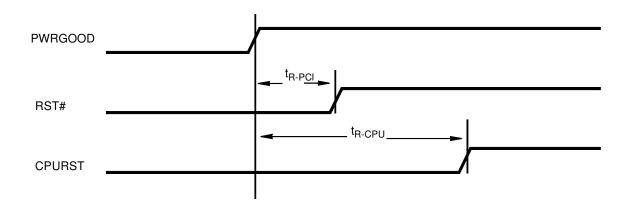

#### 2.14 CPU Interface and Miscellaneous Voltage (See Notes) Pin Name Type Description B5 FGA20 Ο Fast Gate A20. This signal with a pull-up resistor can be used to Opendrive the CPU A20M# pin. If the USB Legacy Keyboard Support Drain function is enabled, it will be the source for this output. Otherwise, if the Fast GateA20 strapping option is enabled this would be the source of this signal. If both the USB Legacy Keyboard Support function and the Fast Gate A20 strapping option are disabled, then the Keyboard GateA20 input (KBGA20) will drive this signal. A5 CPURST Open-Ο **CPU ReSeT**. This signal with a pull-up resistor can be used to drive the CPU Reset signal of the CPU. The PC87560 releases CPURST Drain during power-up (PWRGOOD negated). CPURST is driven inactive low a minimum of 2ms after RESET IN# is driven inactive to allow the CPU's clock and VCC to stablize. CPURST is driven inactive low synchronously to the rising edge of PCICLK. D6 CPUINIT 0 CPU INITialization. This signal with a pull-up resistor can be used to Opendrive the CPU's INIT pin during power-up (PWRGOOD negated) or Drain when the PC87560 detects a shutdown special cycle on the PCI bus. CPUINIT will also be active if a soft reset is initiated via Port 92, or a snooped Fast Reset (if Fast Reset is enabled) or KBRST# is asserted (if Fast Reset is disabled). 3/5VT PM L **RESET IN**put. When de-asserted high, RESET IN# is an indication to H<sub>2</sub> **RESET IN#** the PC87560 that power and PCICLK have been stable for at least 1ms, and can be driven asynchronously. When RESET IN# is asserted low, the PC87560 resets all functions powered by VDD and asserts CPURST, CPUINIT and PCIRST#. H4 PM PWRG I Power Management PoWeR GOOD. When PM PWRGOOD is 3/5VT PM OOD asserted high, it indicates that the VDD PM power is on and valid. When PM PWRGOOD is de-asserted low, it will reset all PC87560 functions that are powered by VDD PM. C5 CPUINT Open-Ο CPU INTerrupt. This signal with a pull-up resistor can be used to drive the CPU INT pin. Drain FERR# 3/5V L Numeric Coprocessor ERRor input from the CPU. C6 0 B6 **IGNNE#** Open-IGNore Numeric Error. This signal wit ha pull-up resistor may be used to drive the CPU IGNNE pin. Drain B9 SINT 3/5V I/O Serial INTerrupt I/O for Docking Interface SPKR C2 3/5V Ο SPeaKeR Output. A6 NMI Open-0 Non Maskable Interrupt. This signal with a pull-up resistor may be used to drive the CPU's NMI signal. This signal is active high when a Drain PCI System Error occurs. A2 TEST# L TEST. This input has a weak pull-up resistor and in normal operation 3/5VT should be a No Connect.

## 2.15 Clocks

| Pin | Name      | Voltage<br>(See Notes) | Туре | Description                               |

|-----|-----------|------------------------|------|-------------------------------------------|

| C1  | 14.318CLK | 3/5VT                  | I    | 14.318 Mhz CLocK Oscillator Input         |

| P1  | 48CLK     | 3/5VT                  | I    | 48Mhz CLocK input For Super I/O Functions |

| 2.16 Power and G                                                                                                                                              | iround |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|