PHILIPS

**Bipolar ICs for video equipment**

d'

11 . M. man

## Bipolar ICs for video equipment

22 01-84

Electronic components and materials for professional, industrial and consumer uses from the world-wide Philips Group of Companies

Argentina: PHILIPS ARGENTINA S.A., Div. Elcoma, Vedia 3892, 1430 BUENOS AIRES, Tel. 541-7141/7242/7343/7444/7545. Australia: PHILIPS INDUSTRIES HOLDINGS LTD., Elcoma Division, 67 Mars Road, LANE COVE, 2066, N.S.W., Tel. 427 08 88. Austria: ÖSTERREICHISCHE PHILIPS BAUELEMENTE Industrie G.m.b.H., Triester Str. 64, A-1101 WIEN, Tel. 62 91 11. Belgium: N.V. PHILIPS & MBLE ASSOCIATED, 9, rue du Pavillon, B-1030 BRUXELLES, Tel. (02) 242 74 00. Brazil: IBRAPE, Caixa Postal 7383, Av. Brigadeiro Faria Lima, 1735 SAO PAULO, SP, Tel. (011) 211-2600. Canada: PHILIPS ELECTRONICS LTD., Electron Devices Div., 601 Milner Ave., SCARBOROUGH, Ontario, M1B 1M8, Tel. 292-5161. Chile: PHILIPS CHILENA S.A., Av. Santa Maria 0760, SANTIAGO, Tel. 39-4001. Colombia: SADAPE S.A., P.O. Box 9805, Calle 13, No. 51 + 39, BOGOTA D.E. 1., Tel. 600 600. Denmark: MINIWATT A/S, Strandlodsvej 2, P.O. Box 1919, DK 2300 COPENHAGEN S, Tel. (01) 54 11 33. Finland: OY PHILIPS AB, Elcoma Division, Kaivokatu 8, SF-00100 HELSINKI 10, Tel. 1 72 71. France: R.T.C. LA RADIOTECHNIQUE-COMPELEC, 130 Avenue Ledru Rollin, F-75540 PARIS 11, Tel. 355-44-99. Germany: VALVO, UB Bauelemente der Philips G.m.b.H., Valvo Haus, Burchardstrasse 19, D-2 HAMBURG 1, Tel. (040) 3296-0. Greece: PHILIPS S.A. HELLENIQUE, Elcoma Division, 52, Av. Syngrou, ATHENS, Tel. 9215111 Hong Kong: PHILIPS HONG KONG LTD., Elcoma Div., 15/F Philips Ind. Bldg., 24-28 Kung Yip St., KWAI CHUNG, Tel. (0)-245121. India: PEICO ELECTRONICS & ELECTRICALS LTD., Elcoma Div., Ramon House, 169 Backbay Reclamation, BOMBAY 400020, Tel. 295144. Indonesia: P.T. PHILIPS-RALIN ELECTRONICS, Elcoma Div., Panim Bank Building, 2nd Fl., Jl. Jend. Sudirman, P.O. Box 223, JAKARTA, Tel. 716 131. Ireland: PHILIPS ELECTRICAL (IRELAND) LTD., Newstead, Clonskeagh, DUBLIN 14, Tel. 69 33 55. Italy: PHILIPS S.p.A., Sezione Elcoma, Piazza IV Novembre 3, I-20124 MILANO, Tel. 2-6752.1. Japan: NIHON PHILIPS CORP., Shuwa Shinagawa Bldg., 26-33 Takanawa 3-chome, Minato-ku, TOKYO (108), Tel. 448-5611. (IC Products) SIGNETICS JAPAN LTD., 8-7 Sanbancho Chiyoda-ku, TOKYO 102, Tel. (03)230-1521. Korea: PHILIPS ELECTRONICS (KOREA) LTD., Elcoma Div., Philips House, 260-199 Itaewon-dong, Yongsan-ku, C.P.O. Box 3680, SEOUL, Tel. 794-4202. Malaysia: PHILIPS MALAYSIA SDN. BERHAD, No. 4 Persiaran Barat, Petaling Jaya, P.O.B. 2163, KUALA LUMPUR, Selangor, Tel. 77 44 11. Mexico: ELECTRONICA, S.A. de C.V., Carr. Mexico-Toluca km. 62.5, TOLUCA, Edo. de Mexico 50140, Tel. Toluca 91(721)613-00. Netherlands: PHILIPS NEDERLAND, Marktgroep Elonco, Postbus 90050, 5600 PB EINDHOVEN, Tel. (040) 79 33 33. New Zealand: PHILIPS ELECTRICAL IND. LTD., Elcoma Division, 110 Mt. Eden Road, C.P.O. Box 1041, AUCKLAND, Tel. 605-914. Norway: NORSK A/S PHILIPS, Electronica Dept., Sandstuveien 70, OSLO 6, Tel. 68 02 00. Peru: CADESA, Av. Alfonso Ugarte 1268 , LIMA 5, Tel. 326070. Philippines: PHILIPS INDUSTRIAL DEV. INC., 2246 Pasong Tamo, P.O. Box 911, Makati Comm. Centre, MAKATI-RIZAL 3116, Tel. 86-89-51 to 59. Portugal: PHILIPS PORTUEGESA S.A.R.L., Av. Eng. Duarte Pacheco 6, LISBOA 1, Tel. 68 31 21. Singapore: PHILIPS PROJECT DEV. ISingapore) PTE LTD., Elcoma Div., Lorong 1, Toa Payoh, SINGAPORE 1231, Tel. 25 38 811. South Africa: EDAC (Pty.) Ltd., 3rd Floor Rainer House, Upper Railway Rd. & Ove St., New Doornfontein, JOHANNESBURG 2001, Tel. 614-2362/9. Spain: MINIWATT S.A., Balmes 22, BARCELONA 7, Tel. 301 63 12. Sweden: PHILIPS KOMPONENTER A.B., Lidingövägen 50, S-11584 STOCKHOLM 27, Tel. 08/7821000. Switzerland: PHILIPS A.G., Elcoma Dept., Allmendstrasse 140-142, CH-8027 ZÜRICH, Tel. 01-488 22 11 Taiwan: PHILIPS TAIWAN LTD., 3rd Fl., San Min Building, 57-1, Chung Shan N. Rd, Section 2, P.O. Box 22978, TAIPEI, Tel. (02)-5631717. Thailand: PHILIPS ELECTRICAL CO. OF THAILAND LTD., 283 Silom Road, P.O. Box 961, BANGKOK, Tel. 233-6330-9. Transmot, FITLER PELECTRICAL CO. OF TRATEARD ET D., 263 SIMIN TO 26, 75, 20 SI, DANOUC, Tal. 2000 S. T. Turkey: TURK PHILIPS TICARET A.S., FMET Department, Inonu Cad. No. 78-80, ISTANBUL, Tel. 43 59 10. United Kingdom: MULLARD LTD., Mullard House, Torrington Place, LONDON WCTE 7HD, Tel. 01-580 6633. United States: (Active Devices & Materials) AMPEREX SALES CORP., Providence Pike, SLATERSVILLE, R.I. 02876, Tel. (401) 762-9000. (Passive Devices) MEPCO/ELECTRA INC., Columbia Rd., MORRISTOWN, N.J. 07960, Tel. (201)539-2000. (Passive Devices & Electromechanical Devices) CENTRALAB INC., 5855 N. Glen Park Rd., MILWAUKEE, WI 53201, Tel. (414)228-7380. (IC Products) SIGNETICS CORPORATION, 811 East Argues Avenue, SUNNYVALE, California 94086, Tel. (408) 739-7700. Uruguay: LUZILECTRON S.A., Avda Uruguay 1287, P.O. Box 907, MONTEVIDEO, Tel. 914321. Venezuela: IND. VENEZOLANAS PHILIPS S.A., Elcoma Dept., A. Ppal de los Ruices, Edif. Centro Colgate, CARACAS, Tel. 36 05 11. For all other countries apply to: Philips Electronic Components and Materials Division, International Business Relations, Building BAE-3, P.O. Box 218, 5600 MD EINDHOVEN, The Netherlands, Tel. +31 40 72 33 04, Telex 35000 phtc nl/nl be vec.

A35

#### © 1984 Philips Export B.V.

This information is furnished for guidance, and with no guarantee as to its accuracy or completeness; its publication conveys no licence under any patent or other right, nor does the publisher assume liability for any consequence of its use; specifications and availability of goods mentioned in it are subject to change without notice; it is not to be reproduced in any way, in whole or in part, without the written consent of the publisher

## **INTEGRATED CIRCUITS**

PART 2 - JANUARY 1984

**BIPOLAR ICs FOR VIDEO EQUIPMENT**

#### FUNCTIONAL AND NUMERICAL INDEX MAINTENANCE TYPE LIST

GENERAL

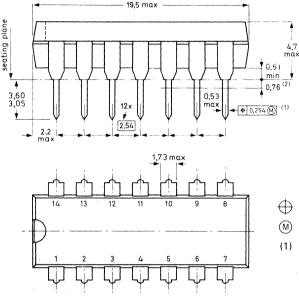

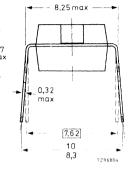

PACKAGE OUTLINES

DEVICE DATA

### DATA HANDBOOK SYSTEM

Our Data Handbook System is a comprehensive source of information on electronic components, subassemblies and materials; it is made up of four series of handbooks each comprising several parts.

| ELECTRON TUBES           | BLUE   |

|--------------------------|--------|

| SEMICONDUCTORS           | RED    |

| INTEGRATED CIRCUITS      | PURPLE |

| COMPONENTS AND MATERIALS | GREEN  |

The several parts contain all pertinent data available at the time of publication, and each is revised and reissued periodically.

Where ratings or specifications differ from those published in the preceding edition they are pointed out by arrows. Where application information is given it is advisory and does not form part of the product specification.

If you need confirmation that the published data about any of our products are the latest available, please contact our representative. He is at your service and will be glad to answer your inquiries.

This information is furnished for guidance, and with no guarantee as to its accuracy or completeness; its publication conveys no licence under any patent or other right, nor does the publisher assume liability for any consequence of its use; specifications and availability of goods mentioned in it are subject to change without notice; it is not to be reproduced in any way, in whole or in part without the written consent of the publisher.

### ELECTRON TUBES (BLUE SERIES)

The blue series of data handbooks is comprised of the following parts:

- T1 Tubes for r.f. heating

- T2a Transmitting tubes for communications, glass types

- T2b Transmitting tubes for communications, ceramic types

- T3 Klystrons, travelling-wave tubes, microwave diodes

- ET3 Special Quality tubes, miscellaneous devices (will not be reprinted)

- T4 Magnetrons

- T5 Cathode-ray tubes Instrument tubes, monitor and display tubes, C.R. tubes for special applications

- T6 Geiger-Müller tubes

#### T7 Gas-filled tubes

Segment indicator tubes, indicator tubes, dry reed contact units, thyratrons, industrial rectifying tubes, ignitrons, high-voltage rectifying tubes, associated accessories

#### T8 Picture tubes and components

Colour TV picture tubes, black and white TV picture tubes, colour monitor tubes for data graphic display, monochrome monitor tubes for data graphic display, components for colour television, components for black and white television and monochrome data graphic display

#### T9 Photo and electron multipliers

Photomultiplier tubes, phototubes, single channel electron multipliers, channel electron multiplier plates

- T10 Camera tubes and accessories, image intensifiers

- T11 Microwave semiconductors and components

### SEMICONDUCTORS (RED SERIES)

The red series of data handbooks is comprised of the following parts:

#### S1 Diodes

Small-signal germanium diodes, small-signal silicon diodes, voltage regulator diodes(< 1,5 W), voltage reference diodes, tuner diodes, rectifier diodes

- S2 Power diodes, thyristors, triacs Rectifier diodes, voltage regulator diodes (> 1,5 W), rectifier stacks, thyristors, triacs

- S3 Small-signal transistors

- S4a Low-frequency power transistors and hybrid modules

- S4b High-voltage and switching power transistors

- S5 Field-effect transistors

- S6 R.F. power transistors and modules

- S7 Microminiature semiconductors for hybrid circuits

- S8 Devices for optoelectronics Photosensitive diodes and transistors, light-emitting diodes, displays, photocouplers, infrared sensitive devices, photoconductive devices.

- S9 Power MOS transistors

- S10 Wideband transistors and wideband hybrid IC modules

### INTEGRATED CIRCUITS (PURPLE SERIES)

The purple series of data handbooks is comprised of the following parts:

- IC1 Bipolar ICs for radio and audio equipment

- IC2 Bipolar ICs for video equipment

- IC3 ICs for digital systems in radio, audio and video equipment

- IC4 Digital integrated circuits CMOS HE4000B family

- IC5 Digital integrated circuits ECL ECL10 000 (GX family), ECL100 000 (HX family), dedicated designs

- IC6 Professional analogue integrated circuits

- IC7 Signetics bipolar memories

- IC8 Signetics analogue circuits

- IC9 Signetics TTL logic

- IC10 Signetics Integrated Fuse Logic (IFL)

- IC11 Microprocessors, microcomputers and peripheral circuitry

vi

### COMPONENTS AND MATERIALS (GREEN SERIES)

The green series of data handbooks is comprised of the following parts:

- C1 Assemblies for industrial use PLC modules, PC20 modules, HNIL FZ/30 series, NORbits 60-, 61-, 90-series, input devices, hybrid ICs

- C2 Television tuners, video modulators, surface acoustic wave filters

- C3 Loudspeakers

- C4 Ferroxcube potcores, square cores and cross cores

- C5 Ferroxcube for power, audio/video and accelerators

- C6 Electric motors and accessories Permanent magnet synchronous motors, stepping motors, direct current motors

- C7 Variable capacitors

- C8 Variable mains transformers

- C9 Piezoelectric quartz devices Quartz crystal units, temperature compensated crystal oscillators, compact integrated oscillators, quartz crystal cuts for temperature measurements

- C10 Connectors

#### C11 Non-linear resistors

Voltage dependent resistors (VDR), light dependent resistors (LDR), negative temperature coefficient thermistors (NTC), positive temperature coefficient thermistors (PTC)

- C12 Variable resistors and test switches

- C13 Fixed resistors

- C14 Electrolytic and solid capacitors

- C15 Film capacitors, ceramic capacitors

- C16 Piezoelectric ceramics, permanent magnet materials

#### FUNCTIONAL AND NUMERICAL INDEX MAINTENANCE TYPE LIST

### SELECTION GUIDE BY FUNCTION

| type number                                            | description                                                                                                                                                                                                                                                        | package code                                   | pins                       |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------|

| Vision i.f. circui                                     | ts                                                                                                                                                                                                                                                                 |                                                |                            |

| Economical circ                                        | uits                                                                                                                                                                                                                                                               |                                                |                            |

| TDA2540<br>TDA2540Q                                    | i.f. amplifier and demodulator; n-p-n tuners<br>i.f. amplifier and demodulator; n-p-n tuners                                                                                                                                                                       | SOT-38<br>SOT-58                               | 16<br>16                   |

| TDA2541<br>TDA2541Q<br>TDA2542                         | i.f. amplifier and demodulator; p-n-p tuners<br>i.f. amplifier and demodulator; p-n-p tuners<br>i.f. amplifier and demodulator; for E and L standards;                                                                                                             | SOT-38<br>SOT-58                               | 16<br>16                   |

| TD 4 05 400                                            | p-n-p tuners                                                                                                                                                                                                                                                       | SOT-38                                         | 16                         |

| TDA2542Q<br>TDA2544<br>TDA2544Q<br>TDA2548<br>TDA2548Q | i.f. amplifier and demodulator; for E and L standards;<br>p-n-p tuners<br>i.f. amplifier and demodulator; MOS tuners<br>i.f. amplifier and demodulator; MOS tuners<br>i.f. amplifier and demodulator; p-n-p tuners<br>i.f. amplifier and demodulator; p-n-p tuners | SOT-58<br>SOT-38<br>SOT-58<br>SOT-38<br>SOT-58 | 16<br>16<br>16<br>16<br>16 |

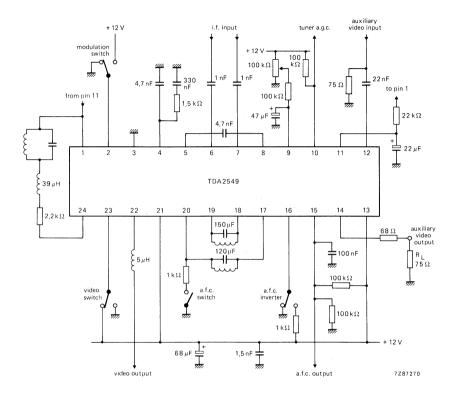

| TDA2549                                                | i.f. amplifier and demodulator; for multistandard<br>TV receivers                                                                                                                                                                                                  | SOT-101A                                       | 24                         |

| High-performant                                        | ce circuits                                                                                                                                                                                                                                                        |                                                |                            |

| TDA3540<br>TDA3540Q<br>TDA3541<br>TDA3541Q             | i.f. amplifier and demodulator; n-p-n tuners<br>i.f. amplifier and demodulator; n-p-n tuners<br>i.f. amplifier and demodulator; p-n-p tuners<br>i.f. amplifier and demodulator; p-n-p tuners                                                                       | SOT-38<br>SOT-58<br>SOT-38<br>SOT-58           | 16<br>16<br>16<br>16       |

| Colour decoding                                        | circuits                                                                                                                                                                                                                                                           |                                                |                            |

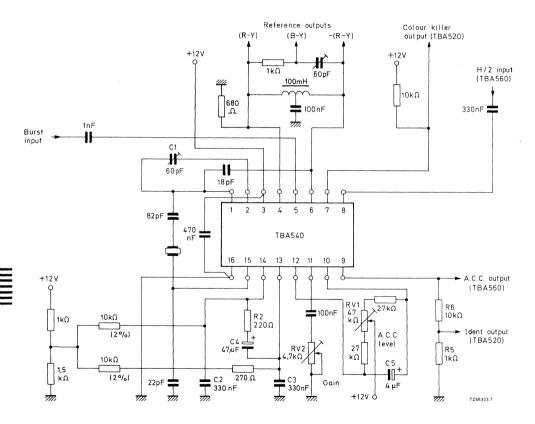

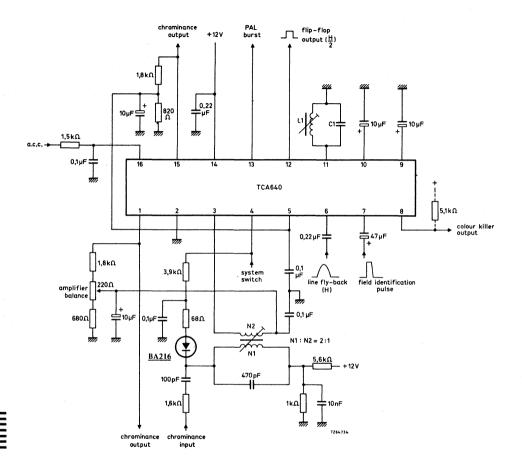

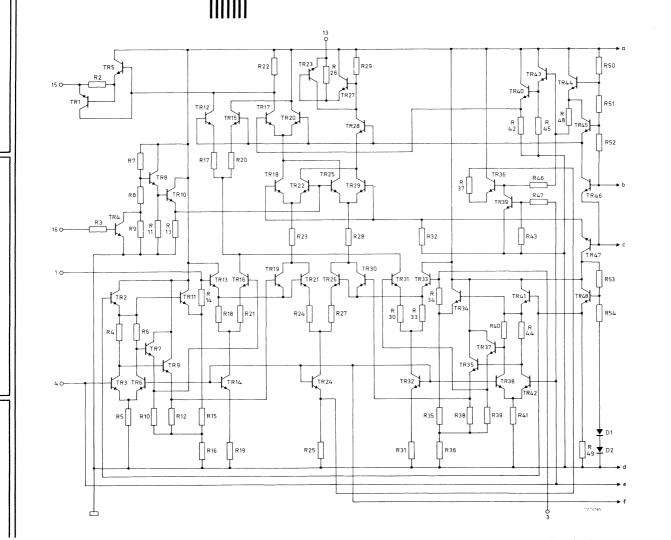

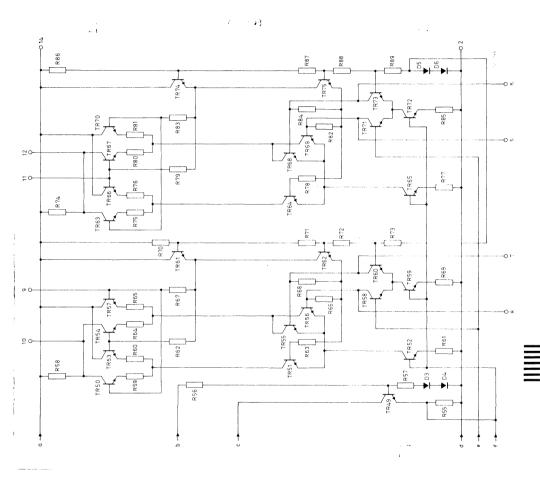

| TBA540<br>TBA540Q<br>TCA640                            | reference combination<br>reference combination<br>chrominance amplifier for SECAM or                                                                                                                                                                               | SOT-38<br>SOT-58                               | 16<br>16                   |

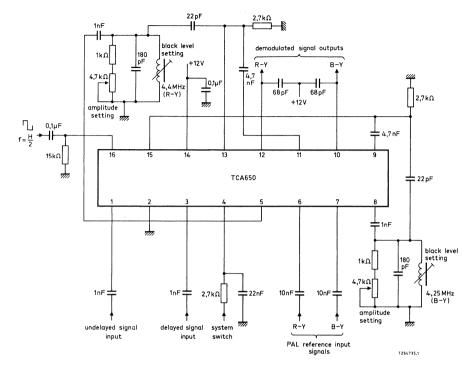

| TCA650                                                 | PAL/SECAM decoders<br>chrominance demodulator for SECAM or                                                                                                                                                                                                         | SOT-38                                         | 16                         |

| TCA660B                                                | PAL/SECAM decoders<br>contrast, saturation and brightness control                                                                                                                                                                                                  | SOT-38                                         | 16                         |

| TD 4 2500                                              | circuit for colour difference and luminance signals                                                                                                                                                                                                                | SOT-38                                         | 16                         |

| TDA3500<br>TDA3501<br>TDA3505                          | video control combination<br>video control combination<br>video control combination with automatic                                                                                                                                                                 | SOT-117<br>SOT-117                             | 28<br>28                   |

| TDA3510<br>TDA3560                                     | cut-off control<br>PAL decoder<br>PAL decoder                                                                                                                                                                                                                      | SOT-117<br>SOT-101A<br>SOT-117                 | 28<br>24<br>28             |

### SELECTION GUIDE BY FUNCTION (continued)

| cuits (continued)<br>AL decoder<br>AL/NTSC decoder<br>FSC decoder<br>FSC decoder<br>FSC decoder<br>FSC decoder<br>FSC decoder                 | SOT-117<br>SOT-117<br>SOT-117<br>SOT-101A, B<br>–                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28<br>28<br>28<br>24<br>28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AL/NTSC decoder<br>FSC decoder<br>FSC decoder<br>FSC decoder                                                                                  | SOT-117<br>SOT-117<br>SOT-101A, B<br>—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28<br>28<br>24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CAM processor circuit                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CAM processor circuit (improved TDA3590)<br>CAM processor circuit<br>L decoder<br>CAM decoder                                                 | SOT-101B<br>SOT-101B<br>SOT-101B<br>SOT-38<br>SOT-102A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 24<br>24<br>24<br>16<br>18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Iltistandard decoder<br>Iour transient improvement circuit                                                                                    | SOT-117<br>SOT-102CS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28<br>18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ircuits                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| rtical deflection circuit; PIL-S4; 30AX<br>rtical deflection circuit; monochrome, 110 <sup>0</sup> ;                                          | SOT-141B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| iy-vision colour, 90 <sup>0</sup><br>rtical deflection circuit; colour and                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| onochrome, 90º<br>rtical deflection circuit<br>rtical delfection circuit                                                                      | SOT-150<br>SOT-141B<br>SOT-110B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12<br>13<br>9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| rtical deflection circuit<br>rtical deflection circuit<br>rtical deflection circuit<br>rtical deflection circuit<br>rtical deflection circuit | SOT-131B<br>SOT-157B<br>SOT-131B<br>SOT-157B<br>SOT-110B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9<br>9<br>9<br>9<br>9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| i rrrrrrrrr                                                                                                                                   | CAM decoder<br>It istandard decoder<br>our transient improvement circuit<br>ircuits<br>tical deflection circuit; PIL-S4; 30AX<br>tical deflection circuit; PIL-S4; 30AX<br>tical deflection circuit; PIL-S4; 30AX<br>tical deflection circuit; colour and<br>onochrome, 90°<br>tical deflection circuit<br>tical deflection circuit | CAM decoderSOT-102AItistandard decoderSOT-117our transient improvement circuitSOT-102CSincuitsSOT-102CStical deflection circuit; PIL-S4; 30AXSOT-141Btical deflection circuit; monochrome, 110°;<br>y-vision colour, 90°SOT-110Btical deflection circuit; colour and<br>onochrome, 90°SOT-150tical deflection circuitSOT-141Btical deflection circuitSOT-141Btical deflection circuitSOT-150tical deflection circuitSOT-110Btical deflection circuitSOT-131Btical deflection circuitSOT-157Btical deflection circuitSOT-131Btical deflection circuitSOT-131Btical deflection circuitSOT-157Btical deflection circuitSOT-157Btical deflection circuitSOT-157Btical deflection circuitSOT-157Btical deflection circuitSOT-110B |

| type number                                                        | description                                                                                                                                                                                      | package code                                              | pins                      |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------|

| Sync processors                                                    | ; horizontal; vertical                                                                                                                                                                           |                                                           |                           |

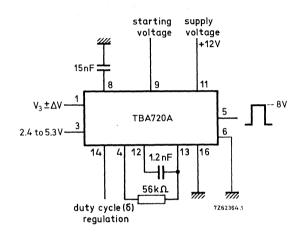

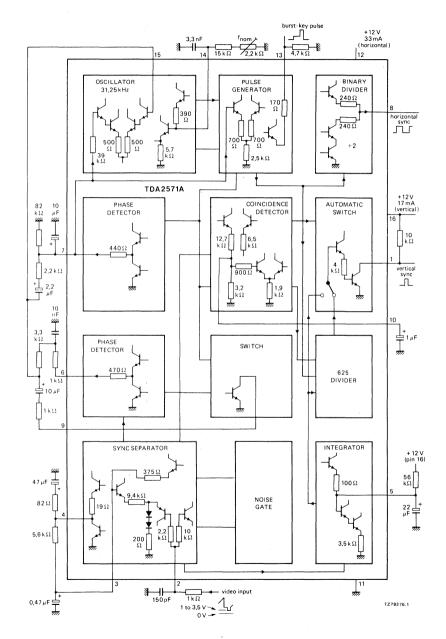

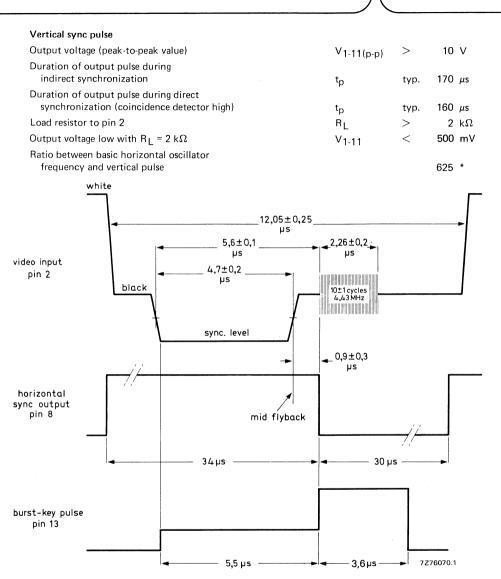

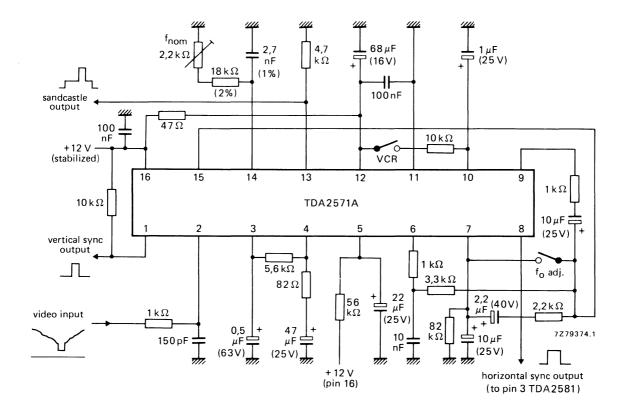

| TBA720A<br>TBA720AQ<br>TBA890<br>TBA890Q<br>TDA2571A               | horizontal oscillator circuit<br>horizontal oscillator circuit<br>signal processing circuit<br>signal processing circuit<br>horizontal synchronization and vertical                              | SOT-38<br>SOT-58<br>SOT-38<br>SOT-58                      | 16<br>16<br>16<br>16      |

| TDA2571AQ                                                          | 625 divider system<br>horizontal synchronization and vertical                                                                                                                                    | SOT-38                                                    | 16                        |

| TDA2575A                                                           | 625 divider system<br>horizontal synchronization and vertical                                                                                                                                    | SOT-58                                                    | 16                        |

| TDA2575AQ                                                          | 625 divider system<br>horizontal synchronization and vertical                                                                                                                                    | SOT-38                                                    | 16                        |

| TDA2576A                                                           | 625 divider system                                                                                                                                                                               | SOT-58                                                    | 16                        |

| TDA2576A                                                           | horizontal oscillator combination with<br>vertical 625 divider system<br>synchronization circuit with vertical                                                                                   | SOT-38                                                    | 16                        |

|                                                                    | oscillator and driver stages                                                                                                                                                                     | SOT-102HE                                                 | 18                        |

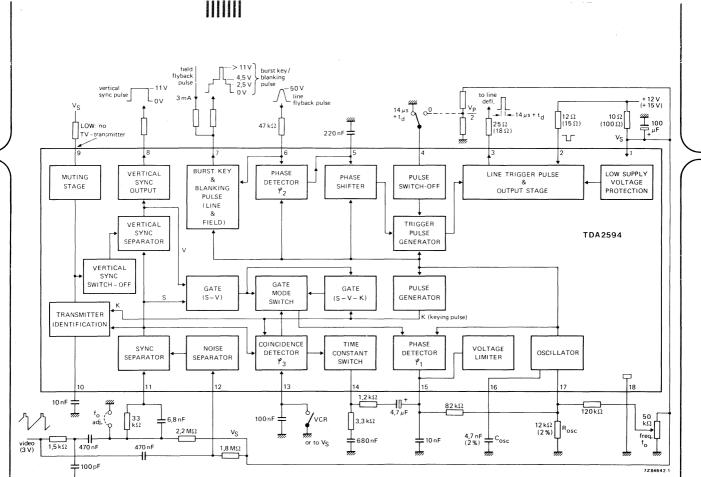

| TDA2578A<br>TDA2593<br>TDA2594                                     | synchronization circuit with vertical<br>oscillator and driver stages<br>horizontal combination<br>horizontal combination with transmitter                                                       | SOT-102HE<br>SOT-38                                       | 18<br>16                  |

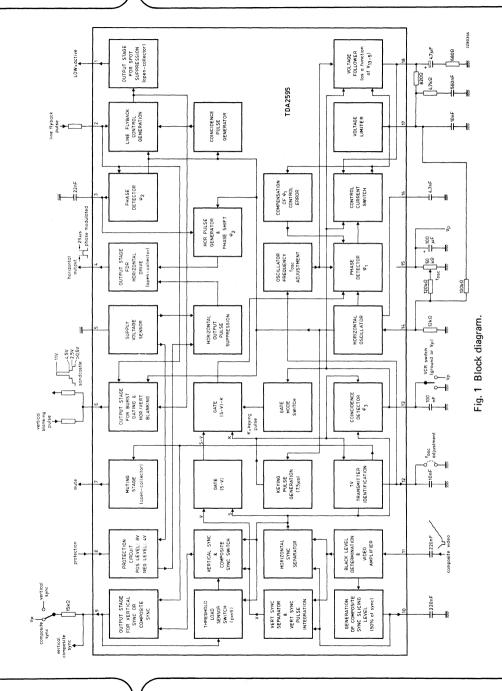

| TDA2595                                                            | identification<br>horizontal combination with transmitter                                                                                                                                        | SOT-102DS                                                 | 18                        |

| TDA3571B                                                           | identification and protection circuits<br>sync combination with transmitter identification<br>and vertical 625 divider system                                                                    | SOT-102CS<br>SOT-102A                                     | 18<br>18                  |

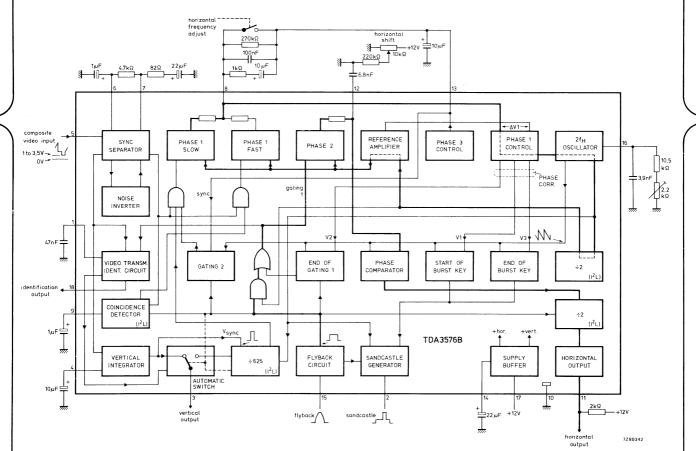

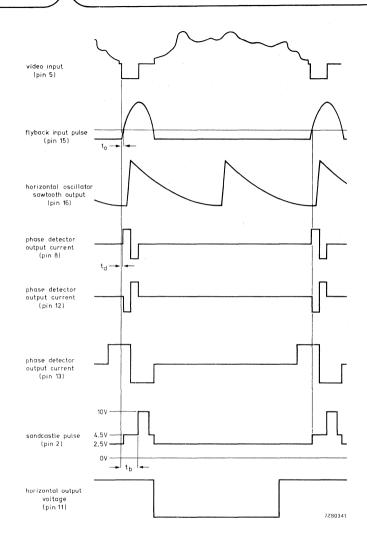

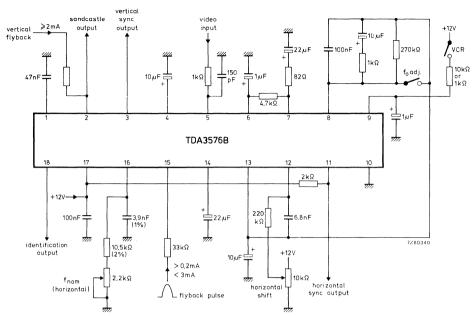

| TDA3576B                                                           | sync combination with transmitter identification and vertical 625 divider system                                                                                                                 | SOT-102HE                                                 | 18                        |

| Sound circuits                                                     |                                                                                                                                                                                                  |                                                           |                           |

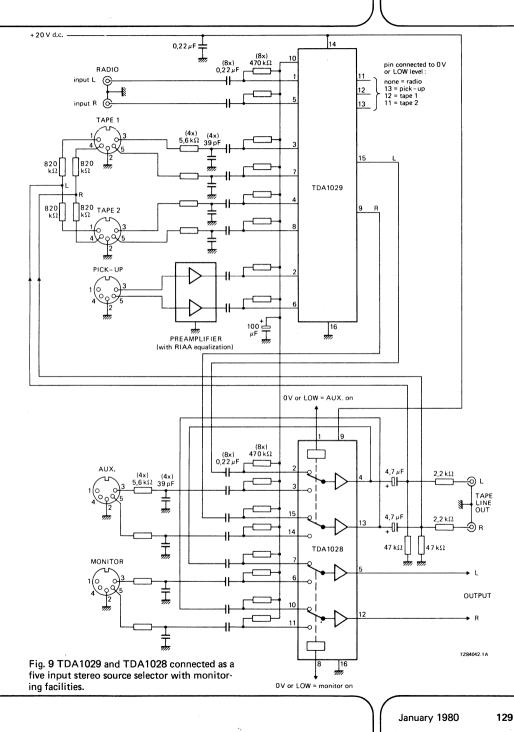

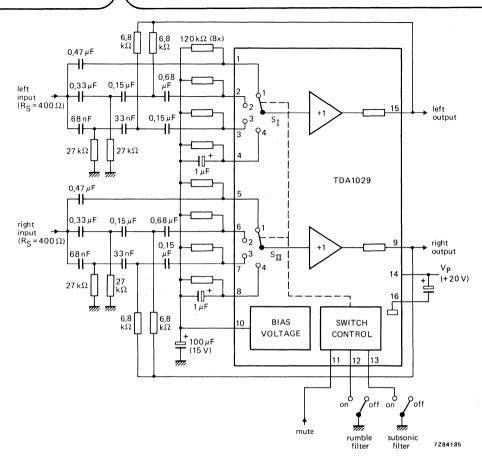

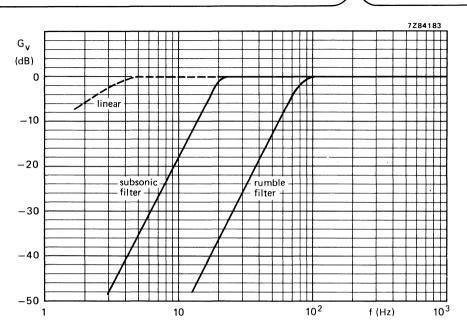

| TBA120U<br>TBA750C<br>TBA750CQ<br>TDA1029<br>TDA1512               | sound i.f. amplifier/demodulator for TV<br>limiter/amplifier<br>limiter/amplifier<br>signal sources switch (4 x two channels)<br>12 to 20 W hi-fi audio power amplifier                          | SOT-27K,M,T<br>SOT-38<br>SOT-58<br>SOT-38<br>SOT-131B     | 14<br>16<br>16<br>16<br>9 |

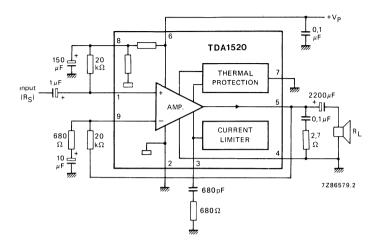

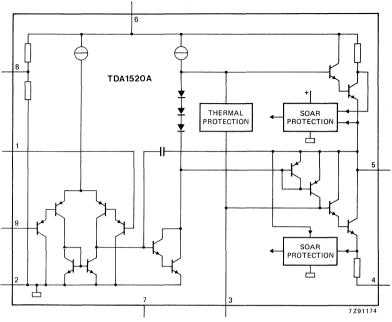

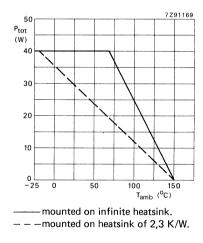

| TDA 1512Q<br>TDA 1520<br>TDA 1520Q<br>TDA 1520A<br>TDA 1520AQ      | 12 to 20 W hi-fi audio power amplifier<br>20 W hi-fi audio power amplifier           | SOT-157B<br>SOT-131A<br>SOT-157A<br>SOT-131A<br>SOT-157A  | 9<br>9<br>9<br>9<br>9     |

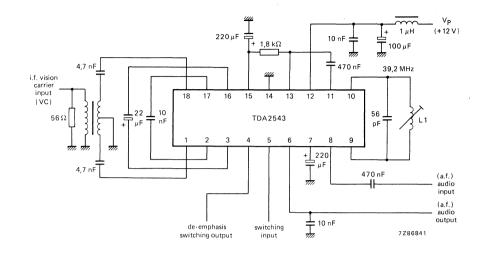

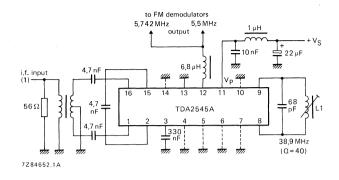

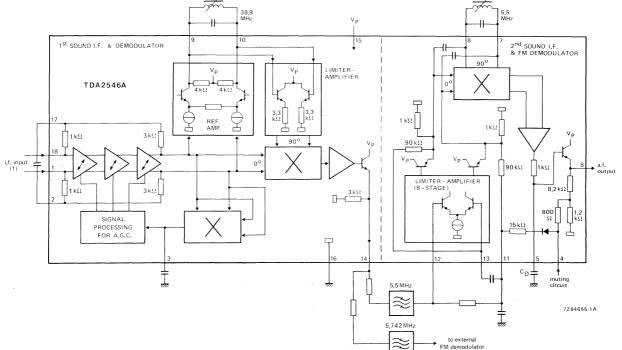

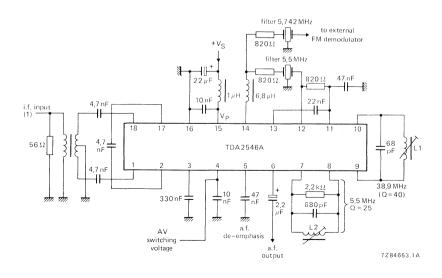

| TDA1524<br>TDA2543<br>TDA2545A<br>TDA2546A<br>TDA2546A<br>TDA2611A | stereo-tone/volume control circuit<br>AM sound i.f. circuit for French standard<br>quasi-split-sound circuit<br>quasi-split-sound circuit with 5,5 MHz demodulation<br>5 W audio power amplifier | SOT-102CS<br>SOT-102CS<br>SOT-38<br>SOT-102CS<br>SOT-110B | 18<br>18<br>16<br>18<br>9 |

### SELECTION GUIDE BY FUNCTION (continued)

| Sound circuits (continued)         TDA2791       TV sound combination; volume, treble, bass       SOT-38         TDA2795       TV stereo/dual sound identification decoder       SOT-10         TDA3800S       stereo/dual TV sound processing circuit       SOT-11         TDA3800AS       stereo/dual TV sound processing circuit       SOT-11         TDA3800G       stereo/dual TV sound processing circuit       SOT-11         TDA3800G       stereo/dual TV sound processing circuit       SOT-11         TDA3800GS       stereo/dual TV sound processing circuit       SOT-11         TDA3810       spatial, stereo and pseudo-stereo sound circuit       SOT-10 | 02DS<br>17<br>17<br>17<br>17 | 16<br>18<br>28<br>28<br>28<br>28<br>28<br>28<br>28 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------------------------|

| TDA2795TV stereo/dual sound identification decoderSOT-10TDA3800Sstereo/dual TV sound processing circuitSOT-11TDA3800ASstereo/dual TV sound processing circuitSOT-11TDA3800Gstereo/dual TV sound processing circuitSOT-11TDA3800Gstereo/dual TV sound processing circuitSOT-11TDA3800GSstereo/dual TV sound processing circuitSOT-11                                                                                                                                                                                                                                                                                                                                      | 02DS<br>17<br>17<br>17<br>17 | 18<br>28<br>28<br>28<br>28<br>28                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                              |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                              | . –                                                |

| Video recorder circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |                                                    |

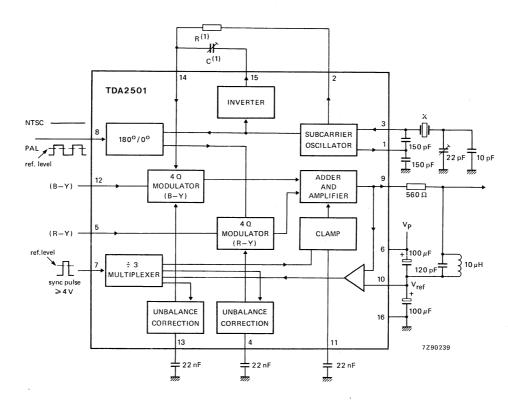

| TDA2501     PAL-NTSC encoder     SOT-38       TDA2502     tacho motor speed controller     SOT-10       TDA2503     track sensing amplifier for video recorders     SOT-38       TDA2730     FM limiter/demodulator (video recorders)     SOT-38       TDA2740     amplifier and drop-out identification circuit<br>(video recorders)     SOT-38                                                                                                                                                                                                                                                                                                                         | )2HE<br>3WE-2<br>3           | 16<br>18<br>16<br>16<br>16                         |

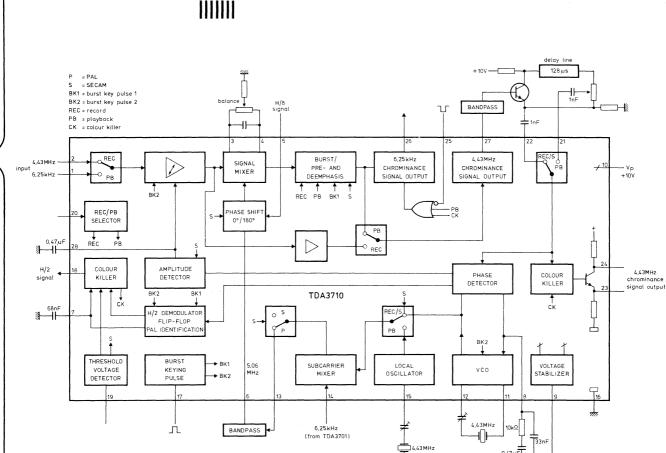

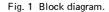

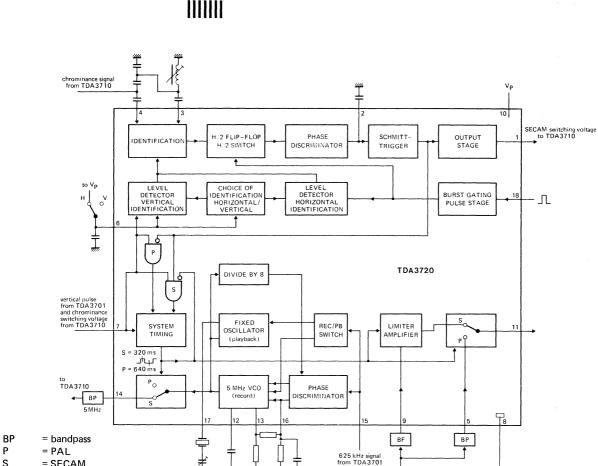

| TDA3701       PAL synchronization processor for video         recorders       SOT-11         TDA3710       chrominance signal/mixer (video recorders)       SOT-11         TDA3720       SECAM processor for video recorders       SOT-10         TDA3730       frequency demodulator and drop out       SOT-11                                                                                                                                                                                                                                                                                                                                                          | 17<br>)2HE                   | 28<br>28<br>18                                     |

| compensator for video recorders SOT-11<br>TDA3771 video processor (video recorders) SOT-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                              | 28<br>18                                           |

| TDA3780frequency modulator (video recorders)SOT-10TDA3791band selector and window detectorSOT-38TDA5010VCR tape end detectorSOT-38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BWE-2                        | 18<br>16<br>16                                     |

| Miscellaneous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |                                                    |

| SAA5030     videotex/video processor     SOT-10       TDA0820T     double balanced modulator/demodulator     SOT-10       TDA1082     east-west correction driver circuit     SOT-38       TDA2579     synchronization circuit with synchronized vertical divider system and output stages     SOT-10                                                                                                                                                                                                                                                                                                                                                                    | 08A (SO-14)<br>3             | 24<br>14<br>16<br>18                               |

| TDA2581 control circuit for SMPS SOT-38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3                            | 16                                                 |

| TDA2581Qcontrol circuit for SMPSSOT-58TDA2582control circuit for PPSSOT-38TDA2582Qcontrol circuit for PPSSOT-58TDA3047infrared receiverSOT-38TDA3048infrared receiverSOT-38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3<br>3<br>3                  | 16<br>16<br>16<br>16<br>16                         |

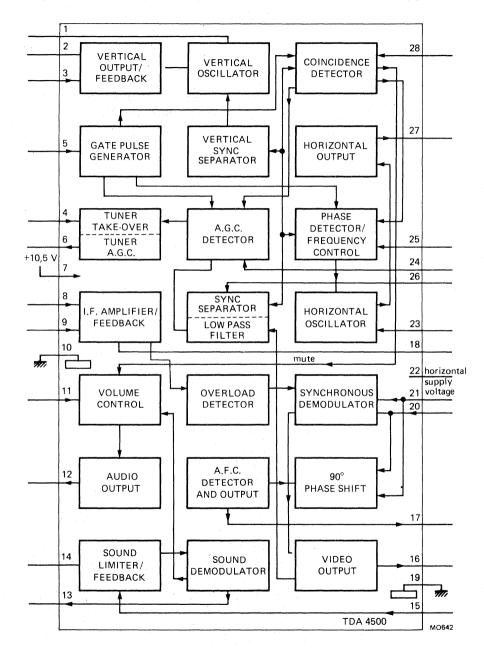

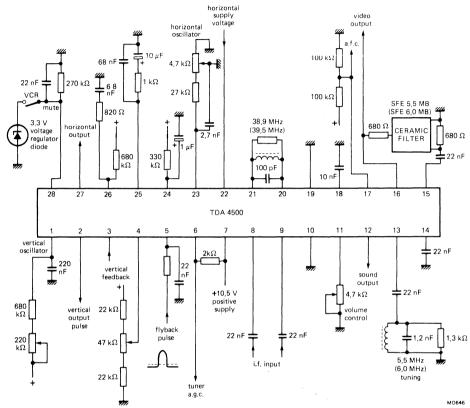

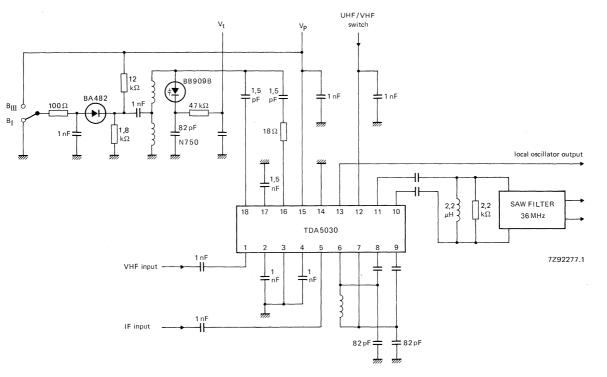

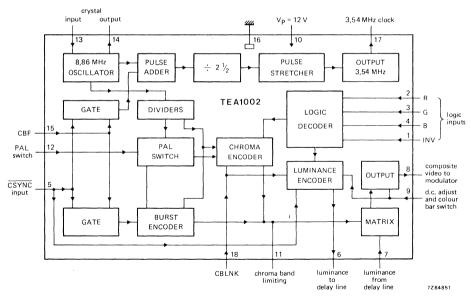

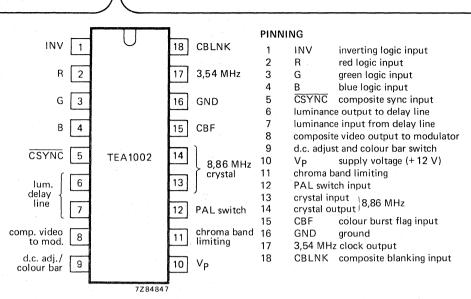

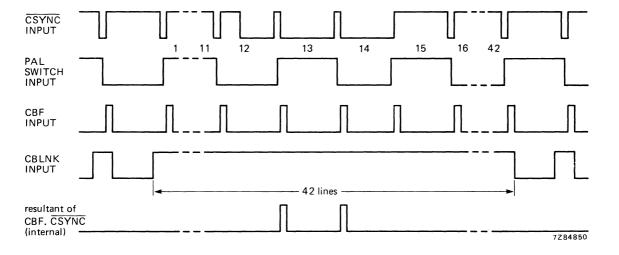

| TDA4500small signal combination IC for<br>monochrome TVSOT-11TDA5030VHF mixer/oscillator circuitSOT-10TEA1002PAL colour encoder and video summerSOT-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D2HE                         | 28<br>18<br>18                                     |

### NUMERICAL INDEX

| type number                                                      | description package code                                                                                                                                                                                                                                                 |                                                                  | pins                         |  |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------|--|

| SAA5030<br>TBA120U<br>TBA540<br>TBA540Q<br>TBA720A               | videotex/video processor<br>sound i.f. amplifier/demodulator for TV<br>reference combination<br>reference combination<br>horizontal oscillator circuit                                                                                                                   | SOT-101A<br>SOT-27K,M,T<br>SOT-38<br>SOT-58<br>SOT-38            | 24<br>14<br>16<br>16<br>16   |  |

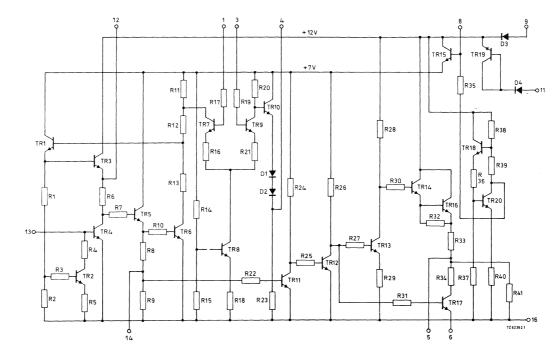

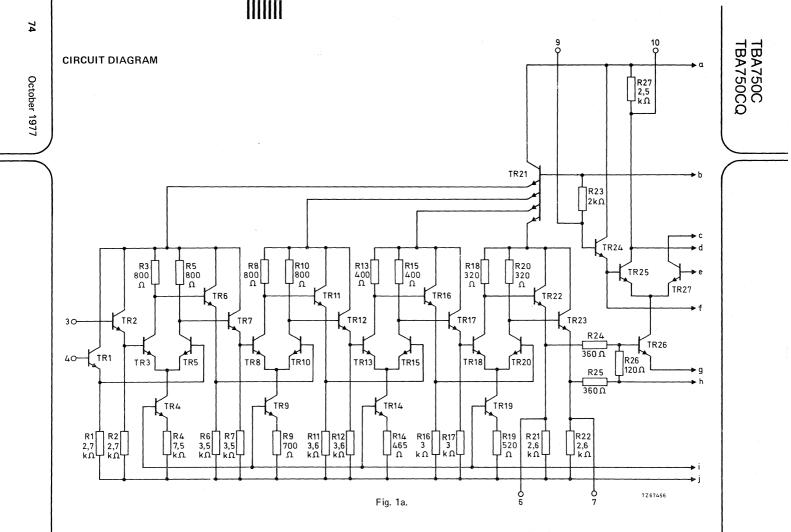

| TBA720AQ<br>TBA750C<br>TBA750CQ<br>TBA890<br>TBA890Q             | horizontal oscillator circuit<br>limiter/amplifier<br>limiter/amplifier<br>signal processing circuit<br>signal processing circuit                                                                                                                                        | SOT-58<br>SOT-38<br>SOT-58<br>SOT-38<br>SOT-58                   | 16<br>16<br>16<br>16<br>16   |  |

| TCA640<br>TCA650<br>TCA660B<br>TDA0820T                          | chrominance amplifier for SECAM or<br>PAL/SECAM decoders<br>chrominance demodulator for SECAM or<br>PAL/SECAM decoders<br>contrast, saturation and brightness control<br>circuit for colour difference and<br>luminance signals<br>double balanced modulator/demodulator | SOT-38<br>SOT-38<br>SOT-38<br>SOT-108A (SO-14)                   |                              |  |

| TDA1029<br>TDA1082<br>TDA1512<br>TDA1512Q<br>TDA1520<br>TDA1520Q | signal sources switch (4 x two channels)<br>east-west correction driver circuit<br>12 to 20 W hi-fi audio power amplifier<br>12 to 20 W hi-fi audio power amplifier<br>20 W hi-fi audio power amplifier<br>20 W hi-fi audio power amplifier                              | SOT-38<br>SOT-38<br>SOT-131B<br>SOT-157B<br>SOT-131A<br>SOT-157A | 16<br>16<br>9<br>9<br>9<br>9 |  |

| TDA1520A<br>TDA1520AQ<br>TDA1524<br>TDA2501<br>TDA2502           | 20 W hi-fi audio power amplifier<br>20 W hi-fi audio power amplifier<br>stereo-tone volume control circuit<br>PAL/NTSC encoder<br>tacho motor speed controller                                                                                                           | SOT-131A<br>SOT-157A<br>SOT-102CS<br>SOT-38WE-2<br>SOT-102HE     | 9<br>9<br>18<br>16<br>18     |  |

| TDA2503<br>TDA2540<br>TDA2540Q<br>TDA2541<br>TDA2541Q            | track sensing amplifier for video recorders<br>i.f. amplifier and demodulator; n-p-n tuners<br>i.f. amplifier and demodulator; n-p-n tuners<br>i.f. amplifier and demodulator; p-n-p tuners<br>i.f. amplifier and demodulator; p-n-p tuners                              | SOT-38WE-2<br>SOT-38<br>SOT-58<br>SOT-38<br>SOT-38<br>SOT-58     | 16<br>16<br>16<br>16<br>16   |  |

| TDA2542<br>TDA2542Q                                              | i.f. amplifier and demodulator; for E and<br>L standards; p-n-p tuners<br>i.f. amplifier and demodulator; for E and                                                                                                                                                      | SOT-38                                                           | 16                           |  |

| TDA2543<br>TDA2544<br>TDA2544Q                                   | L standards; p-n-p tuners<br>AM sound i.f. circuit for French standard<br>i.f. amplifier and demodulator; MOS tuners<br>i.f. amplifier and demodulator; MOS tuners                                                                                                       | SOT-58<br>SOT-102CS<br>SOT-38<br>SOT-58                          | 16<br>18<br>16<br>16         |  |

#### NUMERICAL INDEX (continued)

| type number  | description                                         | package code | pins |

|--------------|-----------------------------------------------------|--------------|------|

| TDA2545A     | quasi-split-sound circuit                           | SOT-38       | 16   |

| TDA2546A     | quasi-split-sound circuit with 5,5 MHz demodulation | SOT-102CS    | 18   |

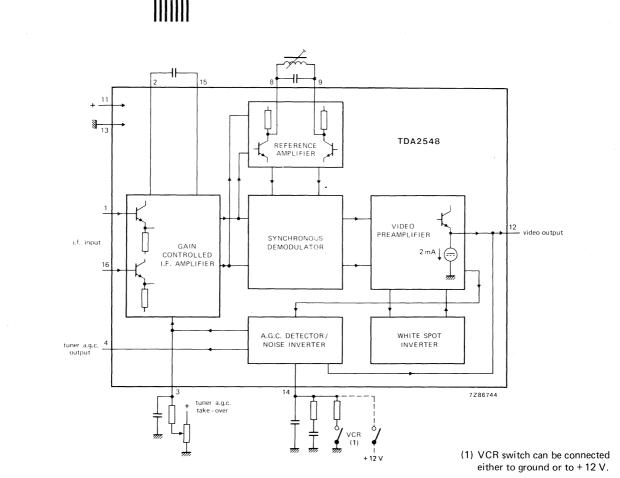

| TDA2548      | i.f. amplifier and demodulator; p-n-p tuners        | SOT-38       | 16   |

| TDA2548Q     | i.f. amplifier and demodulator; p-n-p tuners        | SOT-58       | 16   |

| TDA2549      | i.f. amplifier and demodulator;                     |              |      |

|              | for multistandard TV receivers                      | SOT-101A     | 24   |

| TDA2571A     | horizontal synchronization and vertical             |              |      |

| 10/120/1/1   | 625 divider system                                  | SOT-38       | 16   |

| TDA2571AQ    | horizontal synchronization and vertical             | 00100        |      |

|              | 625 divider system                                  | SOT-58       | 16   |

| TDA2575A     | horizontal synchronization and vertical             |              |      |

|              | 625 divider system                                  | SOT-38       | 16   |

| TDA2575AQ    | horizontal synchronization and vertical             | 00100        | 10   |

| 10/120/0/14  | 625 divider system                                  | SOT-58       | 16   |

| TDA2576A     | horizontal oscillator combination with              | 001 00       | 10   |

| 10/(20/0/(   | vertical 625 divider system                         | SOT-38       | 16   |

| TD 4 05 77 4 |                                                     | 301-30       | 10   |

| TDA2577A     | synchronization circuit with vertical               |              |      |

|              | oscillator and driver stages                        | SOT-102HE    | 18   |

| TDA2578A     | synchronization circuit with vertical               |              |      |

| TD 4 05 70   | oscillator and driver stages                        | SOT-102HE    | 18   |

| TDA2579      | synchronization circuit with synchronized           | 007 400/15   | 4.0  |

| TD 10504     | vertical divider system and output stages           | SOT-102HE    | 18   |

| TDA2581      | control circuit for SMPS                            | SOT-38       | 16   |

| TDA25810     | control circuit for SMPS                            | SOT-58       | 16   |

| TDA2582      | control circuit for PPS                             | SOT-38       | 16   |

| TDA25820     | control circuit for PPS                             | SOT-58       | 16   |

| TDA2593      | horizontal combination                              | SOT-38       | 16   |

| TDA2594      | horizontal combination with transmitter             |              |      |

|              | identification                                      | SOT-102DS    | 18   |

| TDA2595      | horizontal combination with transmitter             |              |      |

|              | identification and protection circuits              | SOT-102CS    | 18   |

| TDA2611A     | 5 W audio power amplifier                           | SOT-110B     | 9    |

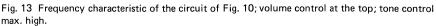

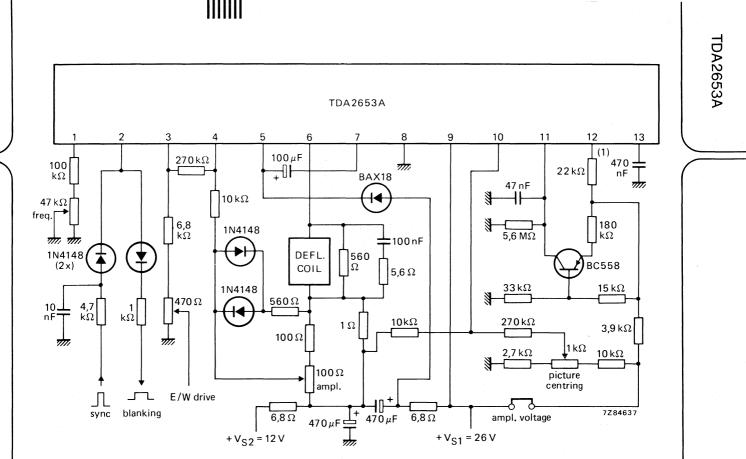

| TDA2653A     | vertical deflection circuit; PIL-S4; 30 AX          | SOT-141B     | 13   |

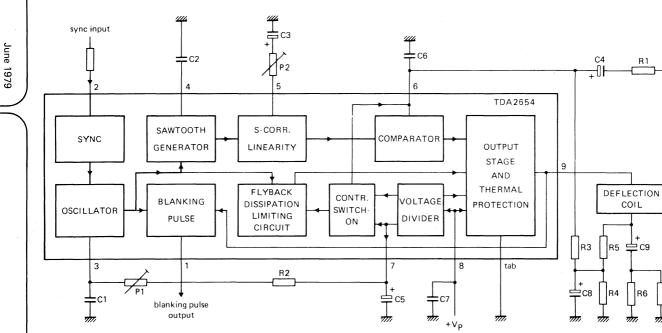

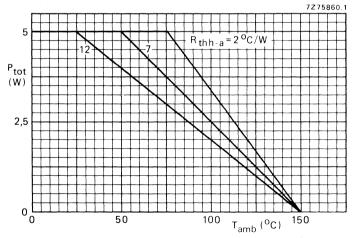

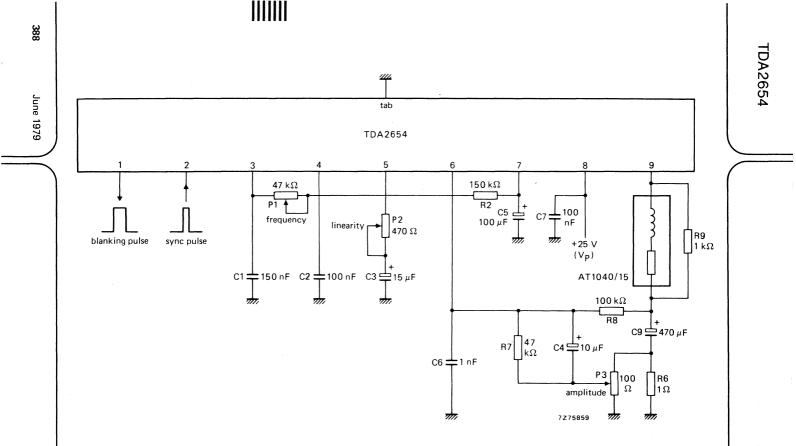

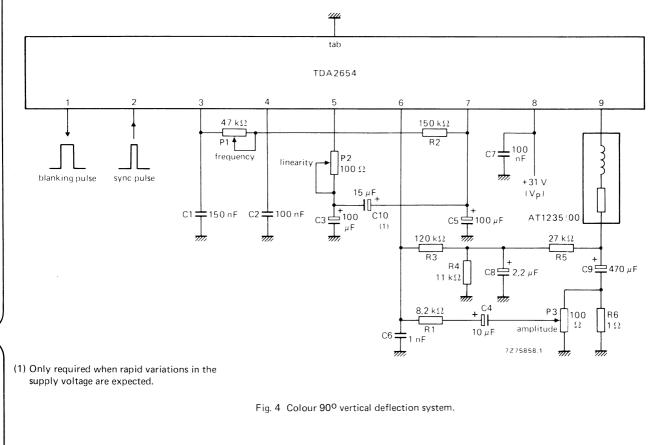

| TDA2654      | vertical deflection circuit; monochrome, 110°;      |              |      |

|              | tiny-vision colour, 90 <sup>0</sup>                 | SOT-110B     | 9    |

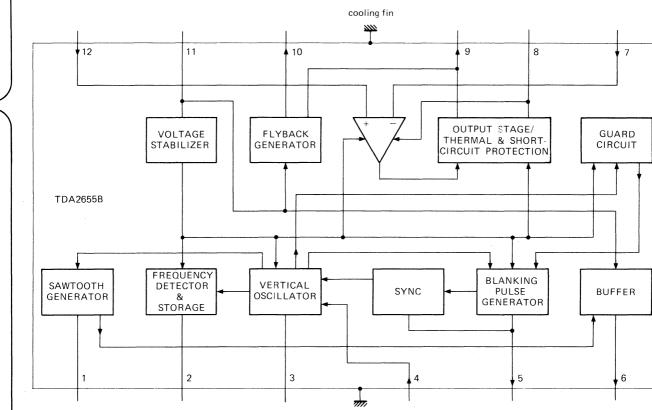

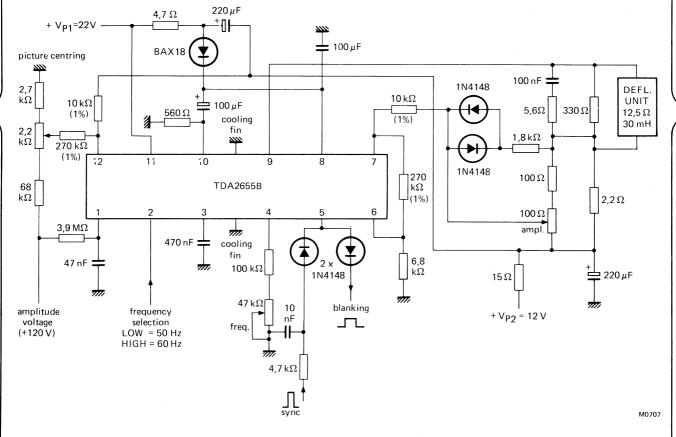

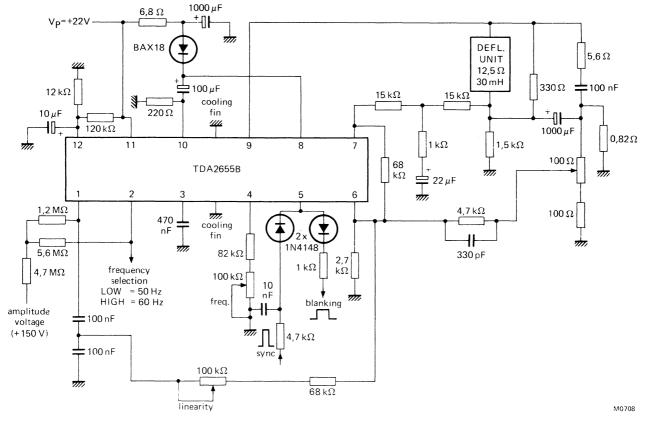

| TDA2655B     | vertical deflection circuit; colour and             |              |      |

|              | monochrome, 90 <sup>0</sup>                         | SOT-150      | 12   |

| TDA2730      | FM limiter/demodulator (video recorders)            | SOT-38       | 16   |

| TDA2740      | amplifier and drop-out identification               |              |      |

|              | circuit (video recorders)                           | SOT-38       | 16   |

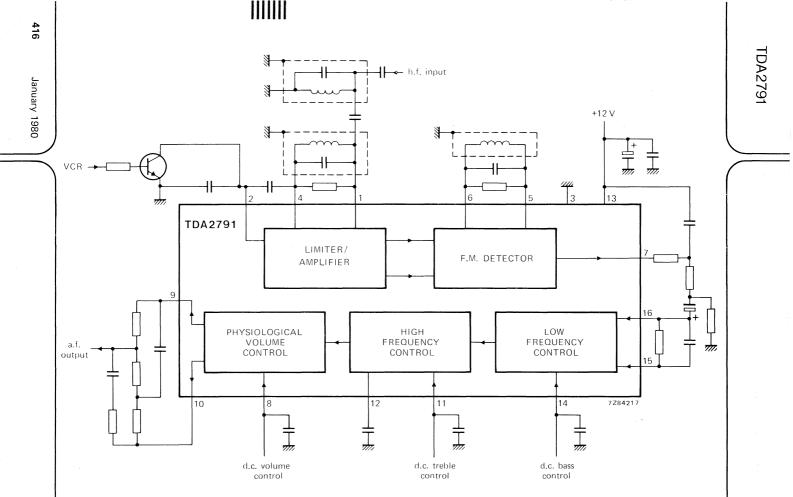

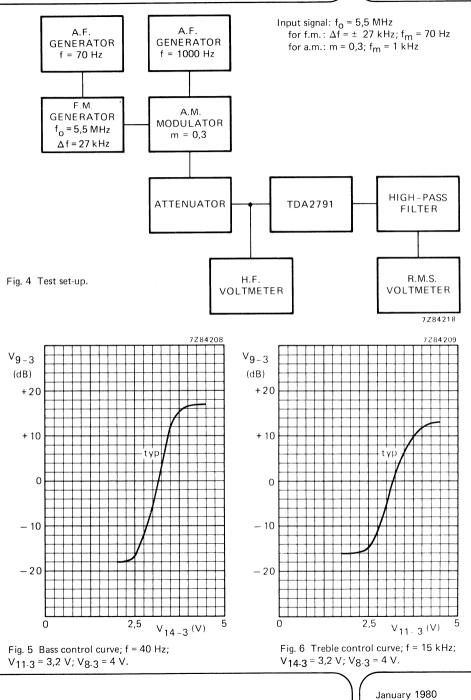

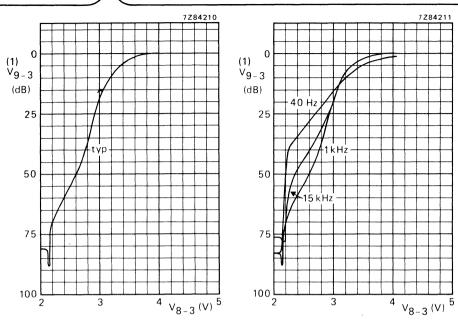

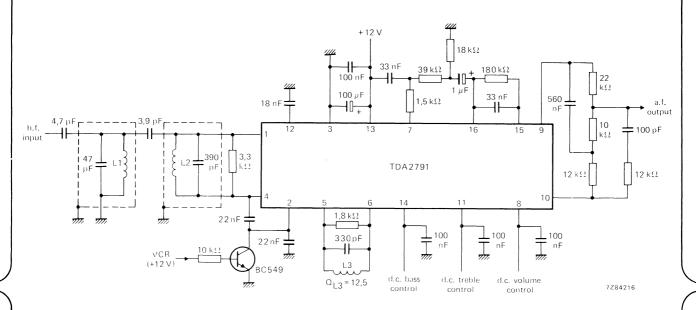

| TDA2791      | TV sound combination; volume, treble, bass          | SOT-38       | 16   |

| TDA2795      | TV stereo/dual sound identification decoder         | SOT-102DS    | 18   |

| TDA3047      | infrared receiver                                   | SOT-38       | 16   |

| TDA3048      | infrared receiver                                   | SOT-38       | 16   |

| , 0, 100-10  |                                                     | 001-00       | 10   |

|              |                                                     |              |      |

| type number                                             | description                                                                                                                                                                                                            | package code                                              | pins                       |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------|

| TDA3500<br>TDA3501<br>TDA3505                           | video control combination<br>video control combination<br>video control combination with automatic                                                                                                                     | SOT-117<br>SOT-117                                        | 28<br>28                   |

| TDA3510<br>TDA3540                                      | cut-off control<br>PAL decoder<br>i.f. amplifier and demodulator; n-p-n tuners                                                                                                                                         | SOT-117<br>SOT-101A<br>SOT-38                             | 28<br>24<br>16             |

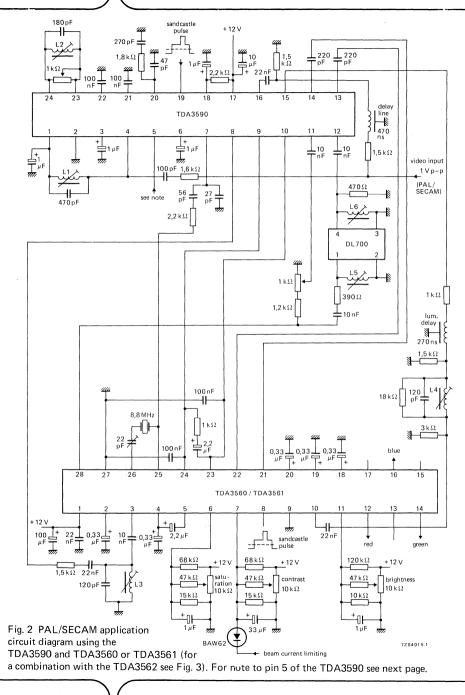

| TDA3540Q<br>TDA3541<br>TDA3541Q<br>TDA3560<br>TDA3561A  | i.f. amplifier and demodulator; n-p-n tuners<br>i.f. amplifier and demodulator; p-n-p tuners<br>i.f. amplifier and demodulator; p-n-p tuners<br>PAL decoder<br>PAL decoder                                             | SOT-58<br>SOT-38<br>SOT-58<br>SOT-117<br>SOT-117          | 16<br>16<br>16<br>28<br>28 |

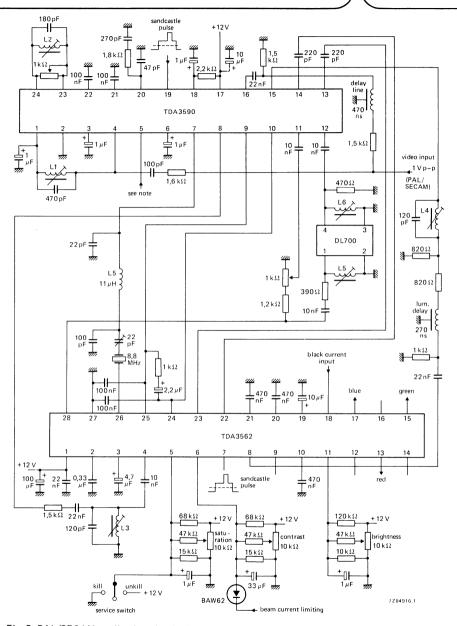

| TDA3562A<br>TDA3563<br>TDA3564<br>TDA3570<br>TDA3571B   | PAL/NTSC decoder<br>NTSC decoder<br>NTSC decoder<br>NTSC decoder<br>sync combination with transmitter identification<br>and vertical 625 divider system                                                                | SOT-117<br>SOT-117<br>SOT-101A,B<br>—<br>SOT-102A         | 28<br>28<br>24<br>28<br>18 |

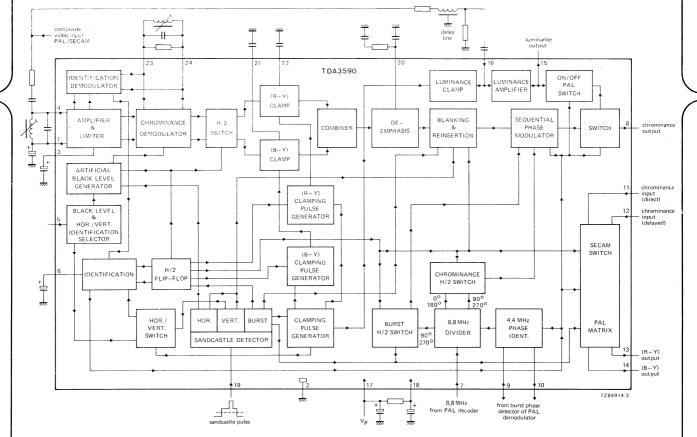

| TDA3576B<br>TDA3590<br>TDA3590A<br>TDA3591<br>TDA3650   | sync combination with transmitter identification<br>and vertical 625 divider system<br>SECAM processor circuit<br>SECAM processor circuit (improved TDA3590)<br>SECAM processor circuit<br>vertical deflection circuit | SOT-102HE<br>SOT-101B<br>SOT-101B<br>SOT-101B<br>SOT-141B | 18<br>24<br>24<br>24<br>13 |

| TDA3651<br>TDA3651A<br>TDA3651AQ<br>TDA3652<br>TDA3652Q | vertical deflection circuit<br>vertical deflection circuit<br>vertical deflection circuit<br>vertical deflection circuit<br>vertical deflection circuit                                                                | SOT-110B<br>SOT-131B<br>SOT-157B<br>SOT-131B<br>SOT-157B  | 9<br>9<br>9<br>9           |

| TDA3653<br>TDA3653A<br>TDA3701                          | vertical deflection circuit<br>vertical deflection circuit<br>PAL synchronization processor for video                                                                                                                  | SOT-110B<br>SOT-131B                                      | 9<br>9                     |

| TDA3710<br>TDA3720                                      | recorders<br>chrominance signal/mixer (video recorders)<br>SECAM processor for video recorders                                                                                                                         | SOT-117<br>SOT-117<br>SOT-102HE                           | 28<br>28<br>18             |

#### NUMERICAL INDEX (continued)

| type number | description                                     | package code | pins |

|-------------|-------------------------------------------------|--------------|------|

|             |                                                 |              |      |

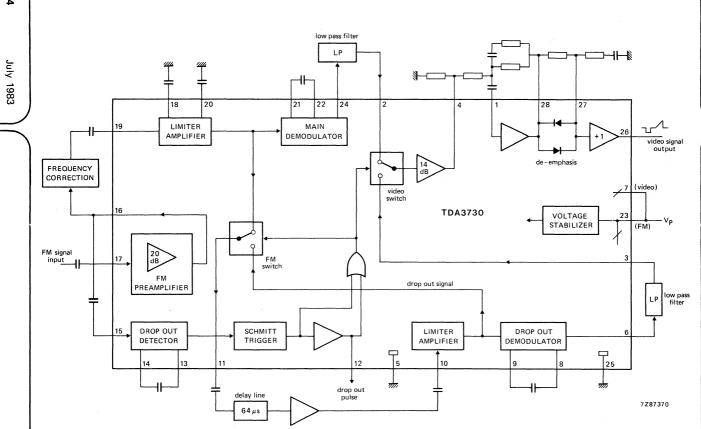

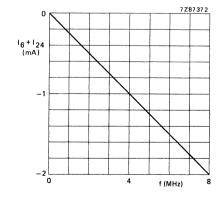

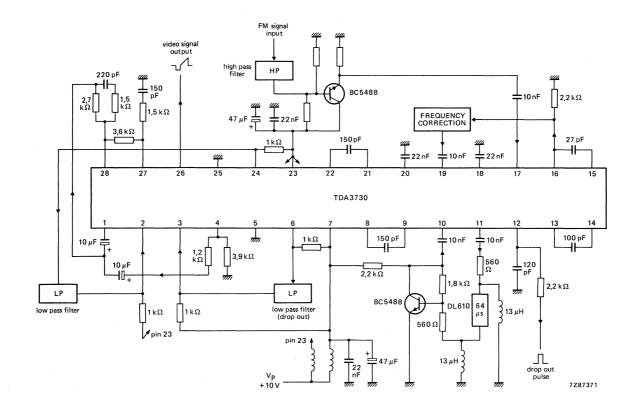

| TDA3730     | frequency demodulator and drop out              |              |      |

|             | compensator for video recorders                 | SOT-117      | 28   |

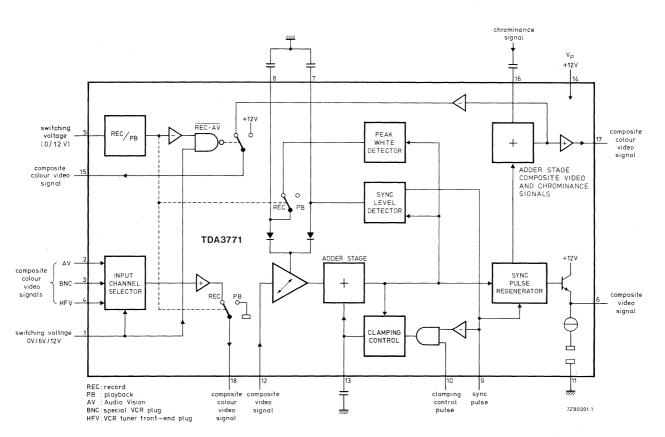

| TDA3771     | video processor (video recorders)               | SOT-102CS    | 18   |

| TDA3780     | frequency modulator (video recorders)           | SOT-102CS    | 18   |

| TDA3791     | band selector and window detector               | SOT-38WE-2   | 16   |

| TDA3800G    | stereo/dual TV sound processing circuit         | SOT-117      | 28   |

| TDA3800GS   | stereo/dual TV sound processing circuit         | SOT-117      | 28   |

| TDA3800S    | stereo/dual TV sound processing circuit         | SOT-117      | 28   |

| TDA3800AS   | stereo/dual TV sound processing circuit         | SOT-117      | 28   |

| TDA3810     | spatial, stereo and pseudo-stereo sound circuit | SOT-102CS    | 18   |

| TDA4500     | small signal combination IC for monochrome TV   | SOT-117      | 28   |

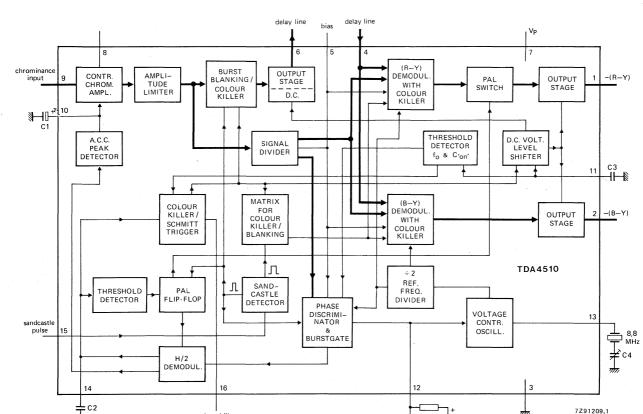

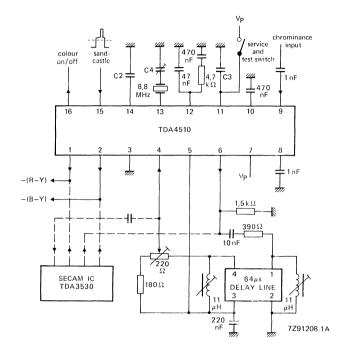

| TDA4510     | PAL decoder                                     | SOT-38       | 16   |

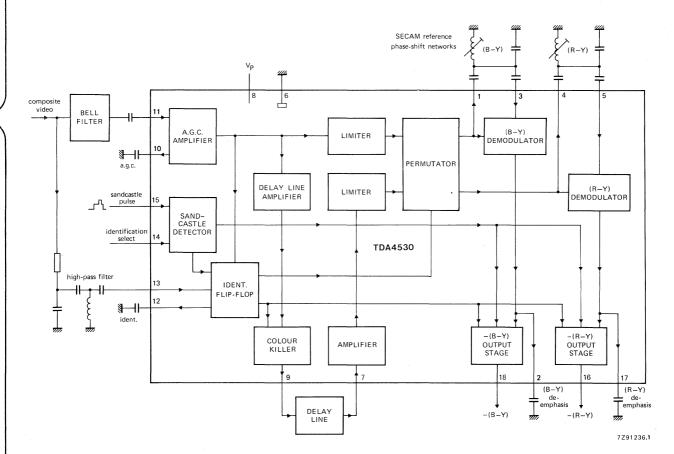

| TDA4530     | SECAM decoder                                   | SOT-102A     | 18   |

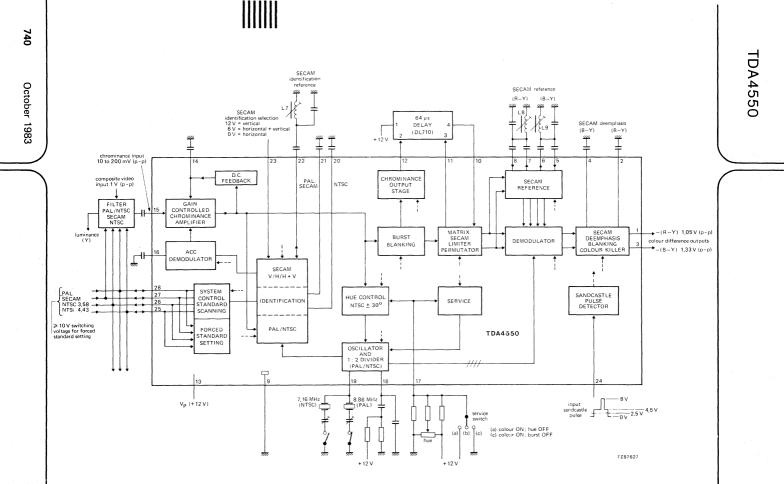

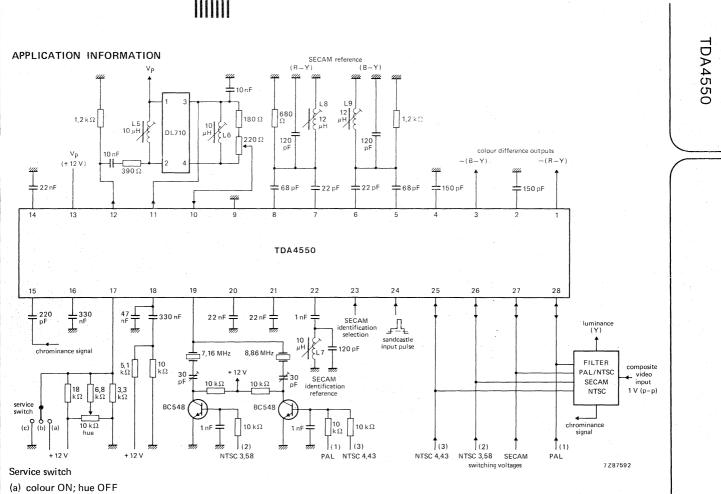

| TDA4550     | multistandard decoder                           | SOT-117      | 28   |

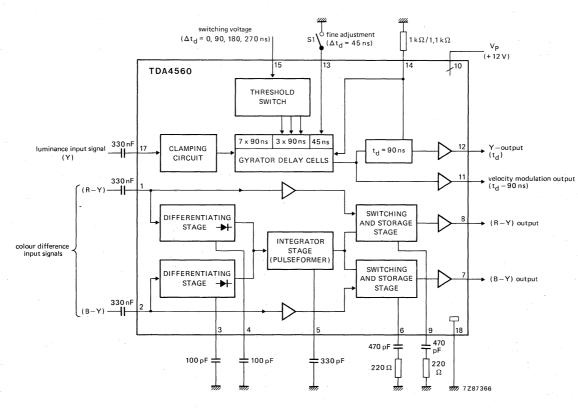

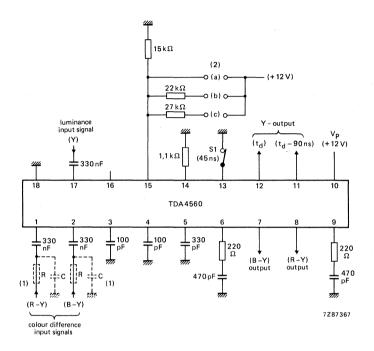

| TDA4560     | colour transient improvement circuit            | SOT-102CS    | 18   |

| TDA5010     | VCR tape end detector                           | SOT-38       | 16   |

| TDA5030     | VHF mixer/oscillator circuit                    | SOT-102HE    | 18   |

| TEA1002     | PAL colour encoder and video summer             | SOT-102CS    | 18   |

|             |                                                 |              |      |

### MAINTENANCE TYPE LIST

| TBA920<br>TBA9200<br>TBA920S<br>TDA1028<br>TDA2510     | horizontal combination<br>horizontal combination<br>horizontal combination<br>signal sources switch (2 x four channels)<br>chrominance combination                                 |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDA2510Q<br>TDA2520<br>TDA2520Q<br>TDA2522<br>TDA2522Q | chrominance combination<br>colour demodulator combination<br>colour demodulator combination<br>colour demodulator combination<br>colour demodulator combination                    |

| TDA2523<br>TDA2523Q<br>TDA2524<br>TDA2525<br>TDA2530   | colour demodulator combination<br>colour demodulator combination<br>colour demodulator combination<br>colour demodulator combination<br>RGB matrix preamplifier                    |

| TDA2530Q<br>TDA2532<br>TDA2532Q<br>TDA2545             | RGB matrix preamplifier<br>RGB matrix preamplifier<br>RGB matrix preamplifier<br>quasi-split-sound circuit<br>(successor type: TDA2545A)                                           |

| TDA2546                                                | quasi-split-sound circuit with 5,5 MHz<br>demodulation<br>(successor type TDA2546A)                                                                                                |

| TDA2560                                                | luminance and chrominance control combination                                                                                                                                      |

| TDA2560Q                                               | luminance and chrominance control combination                                                                                                                                      |

| TDA2640                                                | SMPS drive circuit                                                                                                                                                                 |

| TDA2640Q<br>TDA2652                                    | SMPS drive circuit<br>vertical deflection circuit: 20AX: 30AX                                                                                                                      |

| TDA2653<br>TDA2655A<br>TDA2721<br>TDA3520              | vertical deflection circuit; PIL-S4; 30AX<br>vertical deflection circuit; colour, 90 <sup>o</sup><br>colour sub-carrier oscillator and mixer<br>(video recorders)<br>SECAM decoder |

| TDA3700A                                               | PAL synchronization processor<br>(video recorders)                                                                                                                                 |

| TDA3800                                                | stereo/dual TV sound processing circuit (successor type: TDA3800G)                                                                                                                 |

GENERAL

Type designation Rating systems

### PRO ELECTRON TYPE DESIGNATION CODE FOR INTEGRATED CIRCUITS

This type nomenclature applies to semiconductor monolithic, semiconductor multi-chip, thin-film, thick-film and hybrid integrated circuits.

A basic number consists of:

THREE LETTERS FOLLOWED BY A SERIAL NUMBER

#### FIRST AND SECOND LETTER

1. DIGITAL FAMILY CIRCUITS

The FIRST TWO LETTERS identify the FAMILY (see note 1).

#### 2. SOLITARY CIRCUITS

The FIRST LETTER divides the solitary circuits into:

- S: Solitary digital circuits

- T : Analogue circuits

- U: Mixed analogue/digital circuits

The SECOND LETTER is a serial letter without any further significance except 'H' which stands for hybrid circuits.

3. MICROPROCESSORS

The FIRST TWO LETTERS identify microprocessors and correlated circuits as follows:

- MA : { Microcomputer

- Central processing unit

- MB : Slice processor (see note 2)

- MD : Correlated memories

- ME : Other correlated circuits (interface, clock, peripheral controller, etc.)

#### 4. CHARGE-TRANSFER DEVICES AND SWITCHED CAPACITORS

The FIRST TWO LETTERS identify the following:

- NH : Hybrid circuits

- NL : Logic circuits

- NM : Memories

- NS : Analogue signal processing, using switched capacitors

- NT : Analogue signal processing, using CTDs

- NX : Imaging devices

- NY : Other correlated circuits

#### Notes

- A logic family is an assembly of digital circuits designed to be interconnected and defined by its basic electrical characteristics (such as: supply voltage, power consumption, propagation delay, noise immunity).

- 2. By 'slice processor' is meant: a functional slice of microprocessor.

# DESIGNATION

YPF

#### THIRD LETTER

It indicates the operating ambient temperature range. The letters A to G give information about the temperature:

- A : temperature range not specified

- B : 0 to + 70 °C

- C : -55 to + 125 °C

- D: -25 to + 70 °C

- E : -25 to + 85 °C

- F : -40 to + 85 oC

- G : -55 to +85 °C

If a circuit is published for another temperature range, the letter indicating a narrower temperature range may be used or the letter 'A'.

Example: the range 0 to +75 °C can be indicated by 'B' or 'A'.

#### SERIAL NUMBER

This may be either a 4-digit number assigned by Pro Electron, or the serial number (which may be a combination of figures and letters) of an existing company type designation of the manufacturer.

To the basic type number may be added:

#### A VERSION LETTER

Indicates a minor variant of the basic type or the package. Except for 'Z', which means customized wiring, the letter has no fixed meaning. The following letters are recommended for package variants:

- C : for cylindrical

- D: for ceramic DIL

- F: for flat pack

- L : for chip on tape

- P : for plastic DIL

- Q: for QIL

- T : for miniature plastic (mini-pack)

- U: for uncased chip

Alternatively a TWO LETTER SUFFIX may be used instead of a single package version letter, if the manufacturer (sponsor) wishes to give more information.

#### FIRST LETTER: General shape

- C : Cylindrical

- D : Dual-in-line (DIL)

- E : Power DIL (with external heatsink)

- F : Flat (leads on 2 sides)

- G : Flat (leads on 4 sides)

- K : Diamond (TO-3 family)

- M: Multiple-in-line (except Dual-, Triple-, Quadruple-in-line)

- Q: Quadruple-in-line (QIL)

- R: Power QIL (with external heatsink)

- S : Single-in-line

- T : Triple-in-line

A hyphen precedes the suffix to avoid confusion with a version letter.

#### SECOND LETTER: Material

- C : Metal-ceramic

- G : Glass-ceramic (cerdip)

- M: Metal

- P : Plastic

#### RATING SYSTEMS

### RATING SYSTEMS

The rating systems described are those recommended by the International Electrotechnical Commission (IEC) in its Publication 134.

#### DEFINITIONS OF TERMS USED

Electronic device. An electronic tube or valve, transistor or other semiconductor device.

Note

This definition excludes inductors, capacitors, resistors and similar components.

*Characteristic.* A characteristic is an inherent and measurable property of a device. Such a property may be electrical, mechanical, thermal, hydraulic, electro-magnetic, or nuclear, and can be expressed as a value for stated or recognized conditions. A characteristic may also be a set of related values, usually shown in graphical form.

*Bogey electronic device.* An electronic device whose characteristics have the published nominal values for the type. A bogey electronic device for any particular application can be obtained by considering only those characteristics which are directly related to the application.

*Rating.* A value which establishes either a limiting capability or a limiting condition for an electronic device. It is determined for specified values of environment and operation, and may be stated in any suitable terms.

Note

Limiting conditions may be either maxima or minima.

*Rating system.* The set of principles upon which ratings are established and which determine their interpretation.

Note

The rating system indicates the division of responsibility between the device manufacturer and the circuit designer, with the object of ensuring that the working conditions do not exceed the ratings.

#### ABSOLUTE MAXIMUM RATING SYSTEM

Absolute maximum ratings are limiting values of operating and environmental conditions applicable to any electronic device of a specified type as defined by its published data, which should not be exceeded under the worst probable conditions.

These values are chosen by the device manufacturer to provide acceptable serviceability of the device, taking no responsibility for equipment variations, environmental variations, and the effects of changes in operating conditions due to variations in the characteristics of the device under consideration and of all other electronic devices in the equipment.

The equipment manufacturer should design so that, initially and throughout life, no absolute maximum value for the intended service is exceeded with any device under the worst probable operating conditions with respect to supply voltage variation, equipment component variation, equipment control adjustment, load variations, signal variation, environmental conditions, and variations in characteristics of the device under consideration and of all other electronic devices in the equipment.

#### DESIGN MAXIMUM RATING SYSTEM

Design maximum ratings are limiting values of operating and environmental conditions applicable to a bogey electronic device of a specified type as defined by its published data, and should not be exceeded under the worst probable conditions.

These values are chosen by the device manufacturer to provide acceptable serviceability of the device, taking responsibility for the effects of changes in operating conditions due to variations in the characteristics of the electronic device under consideration.

The equipment manufacturer should design so that, initially and throughout life, no design maximum value for the intended service is exceeded with a bogey device under the worst probable operating conditions with respect to supply voltage variation, equipment component variation, variation in characteristics of all other devices in the equipment, equipment control adjustment, load variation, signal variation and environmental conditions.

#### DESIGN CENTRE RATING SYSTEM

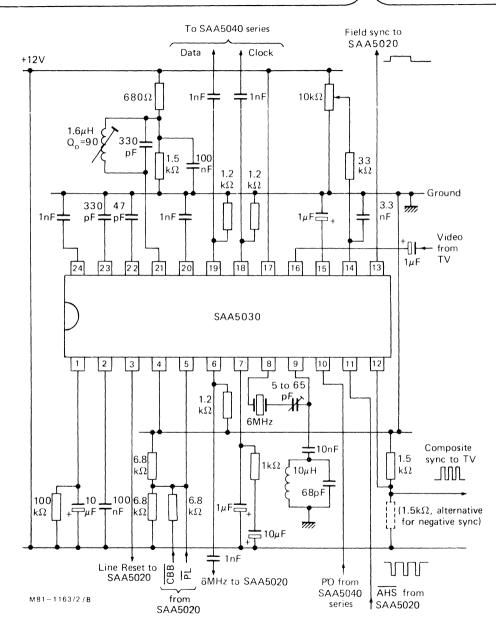

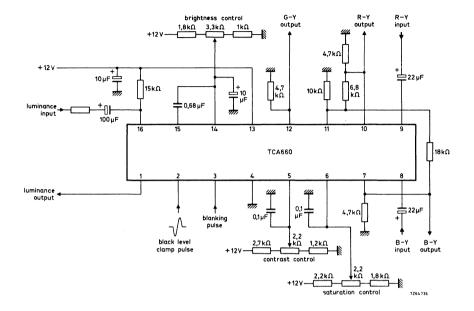

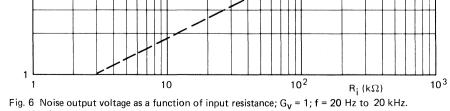

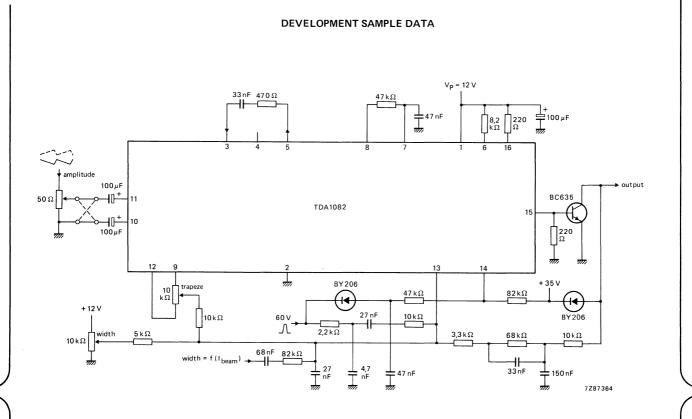

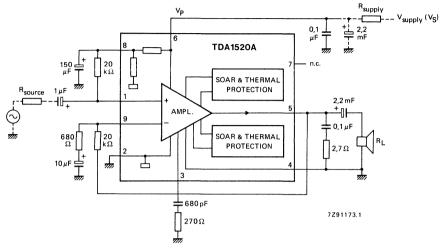

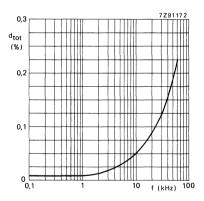

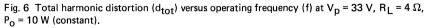

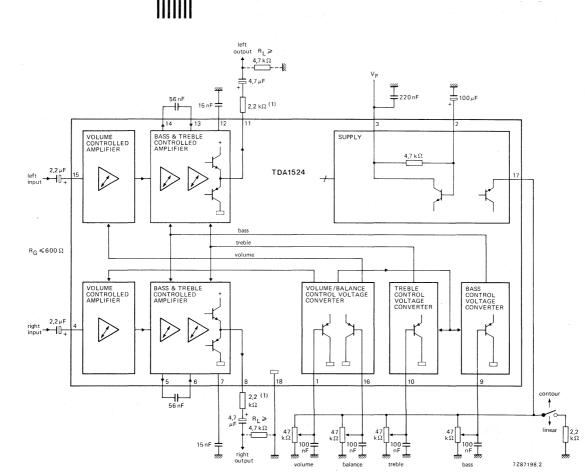

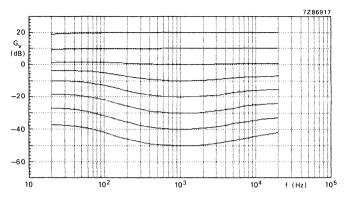

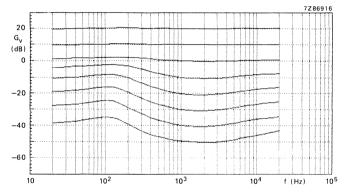

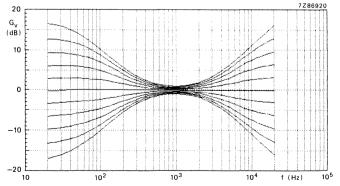

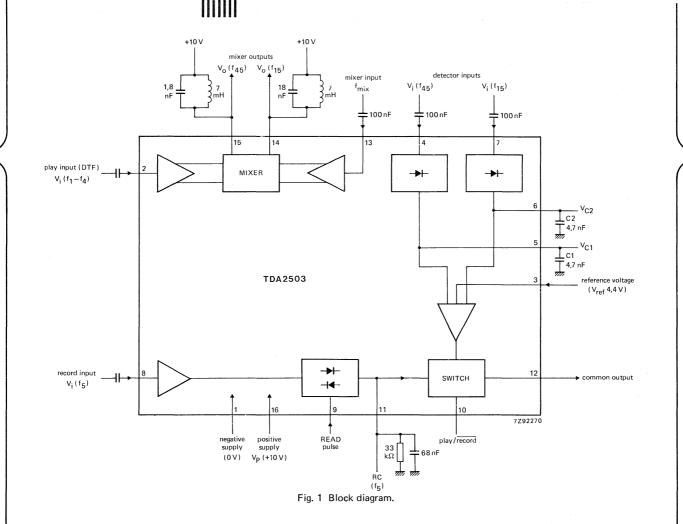

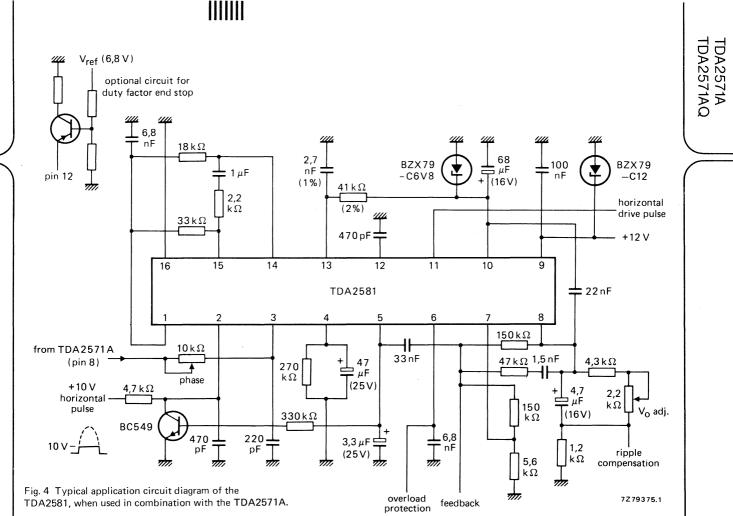

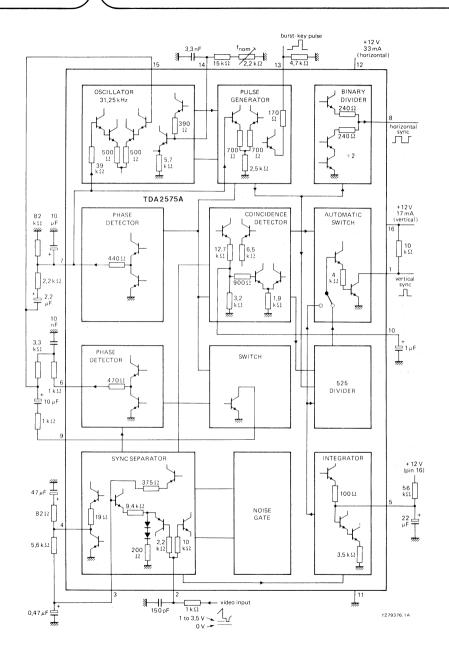

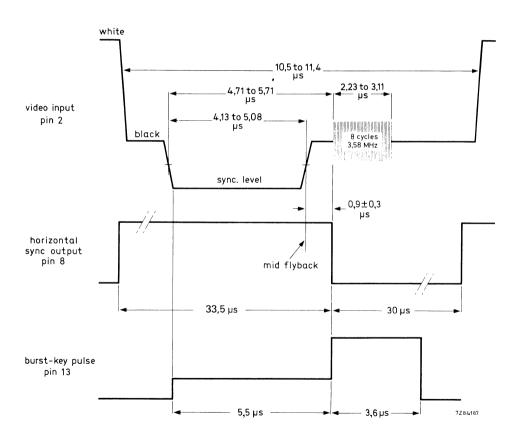

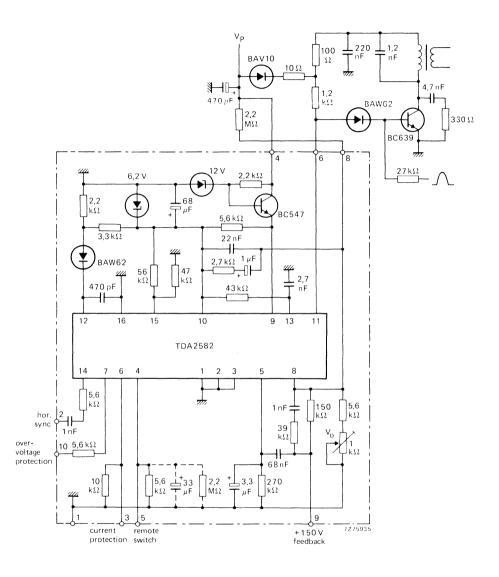

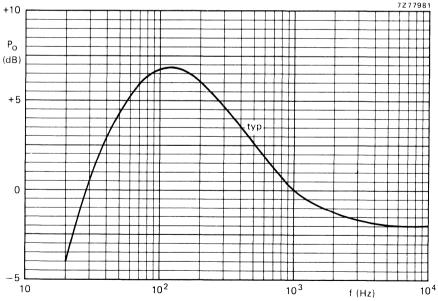

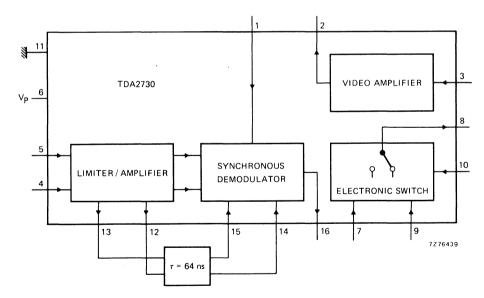

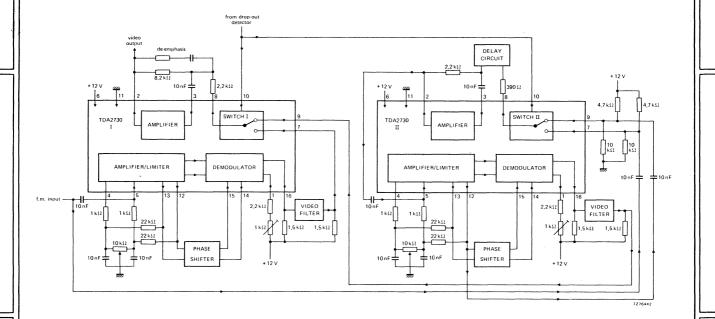

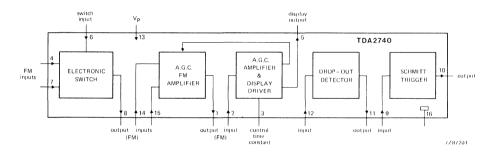

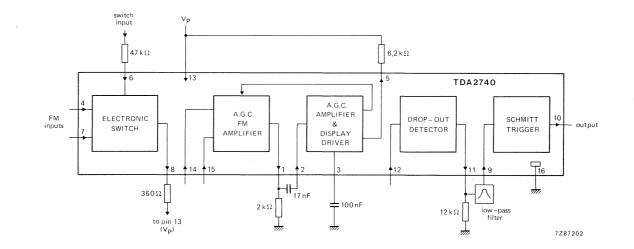

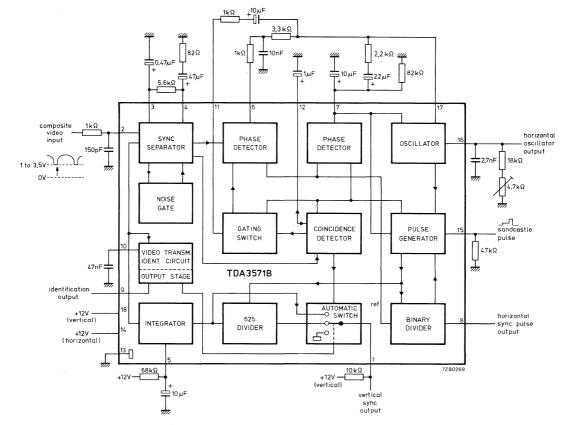

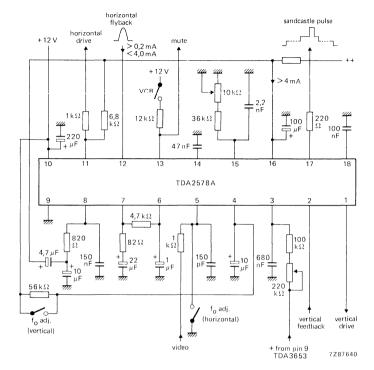

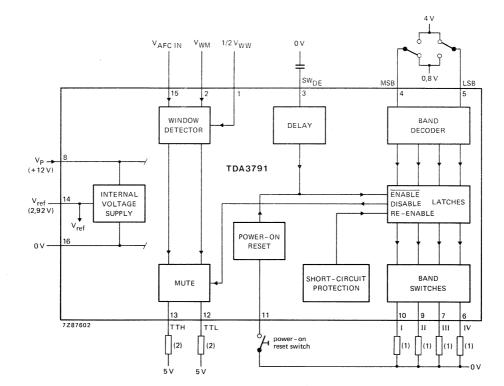

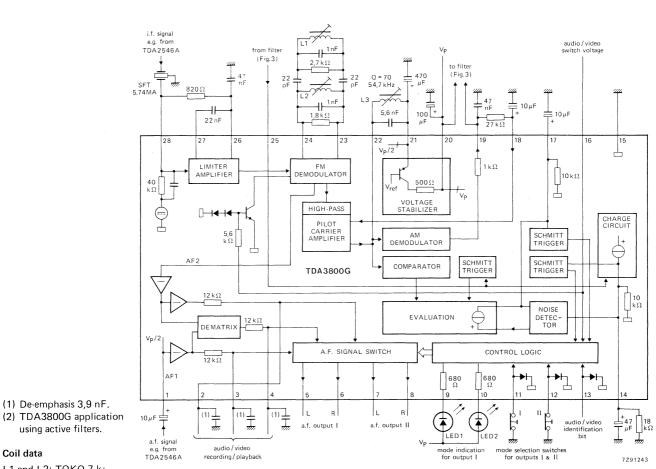

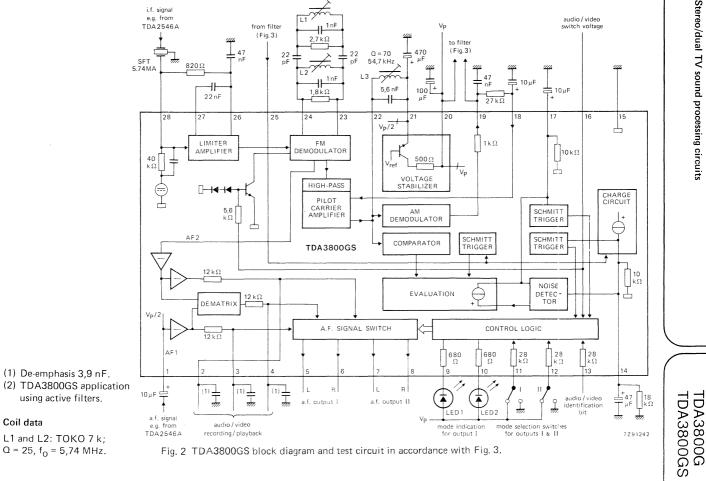

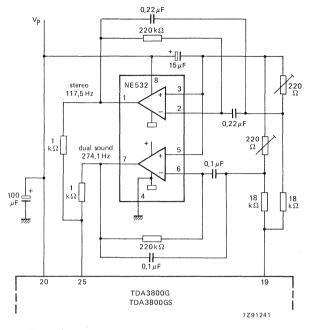

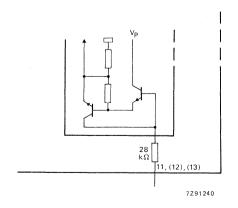

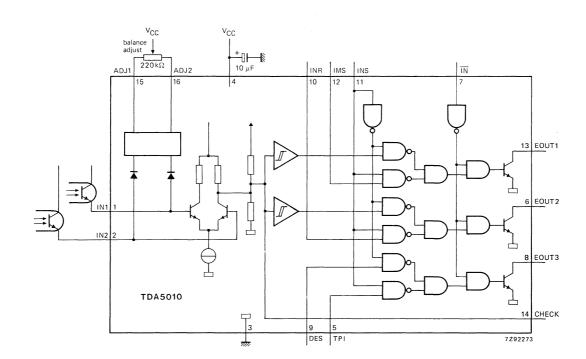

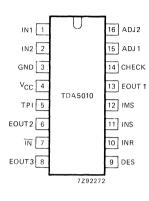

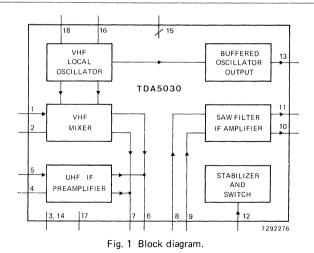

Design centre ratings are limiting values of operating and environmental conditions applicable to a bogey electronic device of a specified type as defined by its published data, and should not be exceeded under normal conditions.