R

National Semiconductor

# National SCAN Databook

*IEEE 1149.1 Products Design For Test With Boundary Scan*

# **SCAN** DATABOOK

1996 Edition

Design for Test Solutions with Boundary Scan

**Description of Boundary Scan**

**Device Description and Characteristics**

Loading Specifications, Waveforms, Quality and Reliability

**Characterization Data**

**Boundary Scan Design Support**

**Application Notes**

i

SCAN CMOS Test Access Logic Datasheets

SCAN ABT Test Access Logic Datasheets

System Test Support Datasheets Ordering Information and Physical Dimensions

#### TRADEMARKS

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

**ABiCTM** Abuseable™ AirShare™ Anadig™ APPSTM ARI1TM **ASPECT™** AT/LANTIC™ Auto-Chem Deflasher™ ВСРТМ BI-FET™ BI-FET II™ BI-LINE™ BIPLAN™ **BLCTM BLXTM** ВМАС™ Boomer® Brite-Lite™ **BSI™** BSI-2™ CDDTM CDL<sup>TM</sup> CGS™ СІМ™ **CIMBUS™ CLASIC™** COMBO® COMBO I™ COMBO IITM CompactRISC™ CompactSPEECH™ COPS™ microcontrollers COP8™ **CRDTM** CROSSVOLT™ **CSNI™ CTI™ CYCLONE™** DA4™ **DENSPAKTM** DIBTM **DISCERNTM** DISTILL™ DNR® **DPVMTM** E<sup>2</sup>CMOS™

ELSTAR™ Embedded System ProcessorTM EPTM. E-Z-LINK™ **FACT™** FACT Quiet Series™ **FAIRCAD™** Fairtech™ **FAST®** FastLock™ FASTr™ **GENIX™ GNX™ GTO™** HEX 3000™ HiSeC™ НРС™ HvBal™ 13í ® **ICM™** Integral (SE™ Intelisplay™ Inter-LERIC™ Inter-RIC™ **ISETM** ISE/06™ ISE/08™ ISE/16™ ISE32™ **ISOPLANAR™** ISOPLANAR-Z™ LERIC<sup>TM</sup> LMCMOS™ M<sup>2</sup>CMOS™ Macrobus™ Macrocomponent<sup>™</sup> MACSITM MAPLTM MAXI-ROM® Microbus™ data bus MICRO-DAC™ μPot™ µtalker™ Microtalker™ **MICROWIRETM**

MICROWIRE/PLUS™ **MOLETM** MPATM MST™ Naked-8™ National® National Semiconductor® National Semiconductor Corp.® NAX 800™ NeuFuz™ Nitride Plus™ Nitride Plus Oxide™ **NML™** NOBUS™ NS486™ NSC800™ NSCISE™ NSX-16™ NS-XC-16™ **NTERCOM™ NURAMTM OPAL™** Overture™ **OXISS™** P<sup>2</sup>CMOS™ Perfect Watch™ **PLANTM PLANARTM PLAYER™** PLAYER + ™ PLLatinum™ Plus-2TM Polycraft™ POPTM Power + Control™ POWERplanar™ **QS™** QUAD3000™ Quiet Series™ **QUIKLOOK™ BATTM RIC™ RICKIT™** RTX16™ **SCENIC™**

SCXTM SERIES/800™ Series 32000® SIMPLE SWITCHER® SNITM **SNIC™** SofChek™ **SONIC™** SpeechPro™ SPiKe™ **SPIRE™** Staggered Refresh™ **STĂR™** Starlink™ **STARPLEX™** ST-NIC™ SuperAT™ Super-Block™ SuperChip™ SuperScript™ Switchers Made Simple® SYS32™ TapePak® TDS™ TeleGate™ The National Anthem® TinyPak™ TLĆ™ Trapezoidal™ TRI-CODE™ TRI-POLY™ TRI-SAFE™ **TRI-STATE® TROPICTM** Tropic Pele'™ Tropic Reef™ **TURBOTRANSCEIVER™** TWISTER™ VIPTM VR32TM WATCHDOG™ XMOS™ **XPUTM** Z STAR™ 883B/RETS™ 883S/RETS™

29K™ and AM29200™ are trademarks of Advanced Micro Devices, Inc. AMD® and MACH®465 are registered trademarks of Advanced Micro Devices, Inc. BTPG™ is a trademark of JTAG Technologies. IBM® and PC® are registered trademarks of International Business Machines Corp.

VICTORY<sup>TM</sup> is a trademark of Teradyne, Inc.

Windows® is a registered trademark of Microsoft Corporation.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive, P.O. Box 58090, Santa Clara, California 95052-8090 1-800-272-9959 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

ii

# **Table of Contents**

National Semiconductor's SCAN Data Book offers Design for Test Solutions to improve R&D development cycle time, reduce test development and manufacturing cost and improve a customer's end system uptime. Designers, test engineers and engineering management using concurrent engineering practices will see life-cycle cost of ownership go down for systems designed with boundary scan.

The SCAN Family of IEEE 1149.1 (JTAG) compliant devices simplify integration of design and test.

### **SCAN Data Book**

### **Product Index and Selection Guide**

The Product Index is a numerical list of all device types contained in this book. The Selection Guide groups the products by function and by family.

### Section 1 Design for Test Solutions with Boundary

Describes DFT and boundary scan and why it affects the lifecycle cost of ownership of complex systems. Describes failure modes identified with boundary scan in board and system level implementations as well as embedded, on-board test.

### Section 2 Description of Boundary Scan ......2-1

Describes boundary scan architecture: Test Access Port, TAP controller, and TDI, TDO, TMS, TCK signals; registers and state diagram; mode of operation.

###

CMOS and BiCMOS characteristics of SCAN ABT and SCAN CMOS 18-bit Test Access Logic are described, including design architecture and performance attributes.

### Section 4 Loading Specifications, Waveforms, Quality and Reliability ......4-1

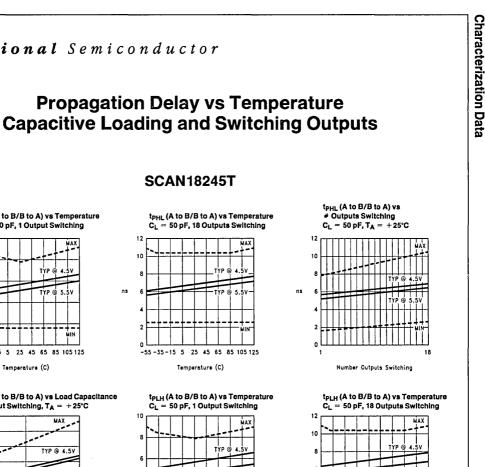

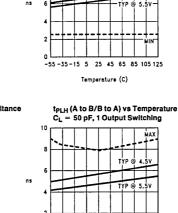

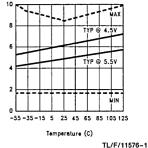

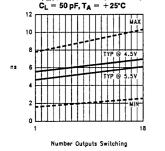

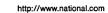

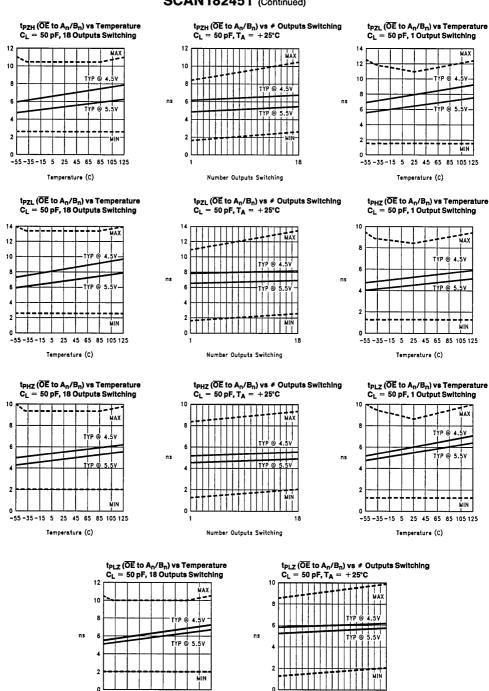

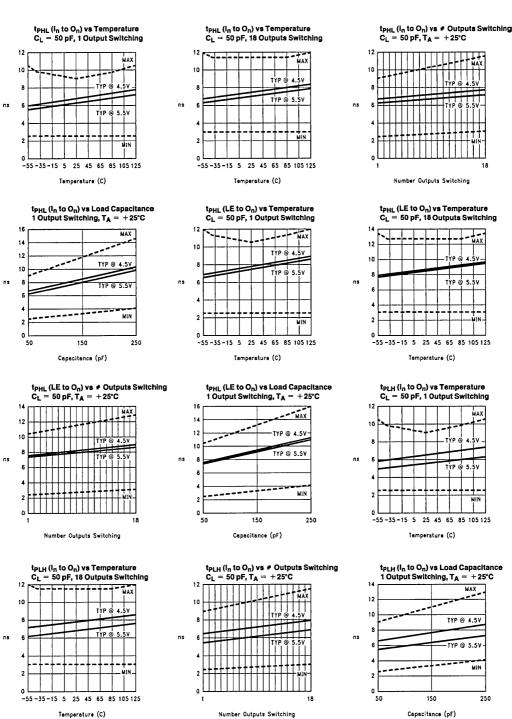

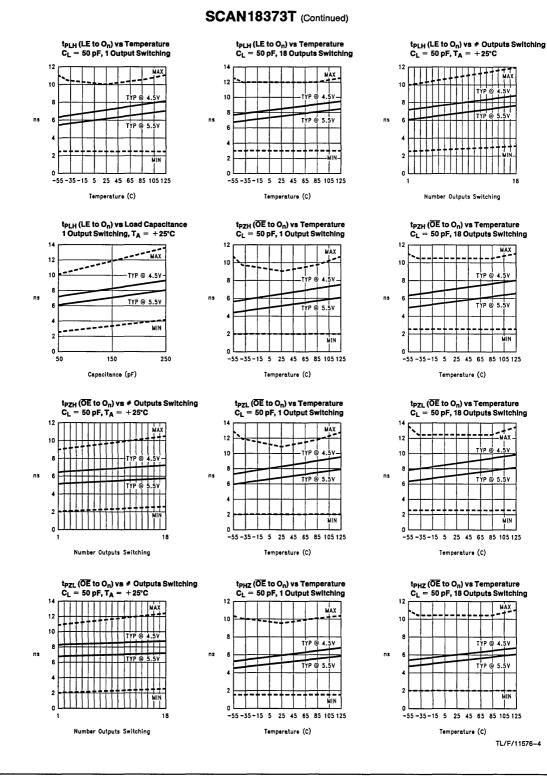

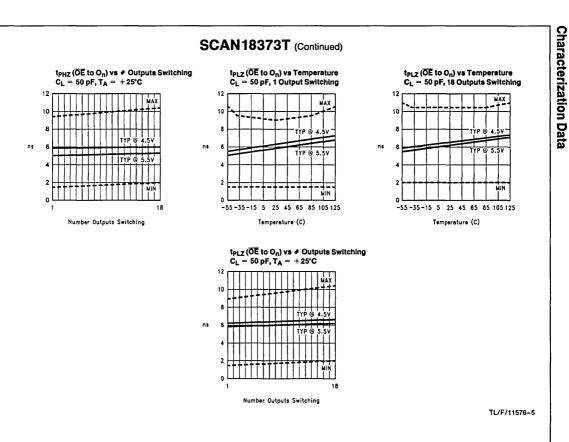

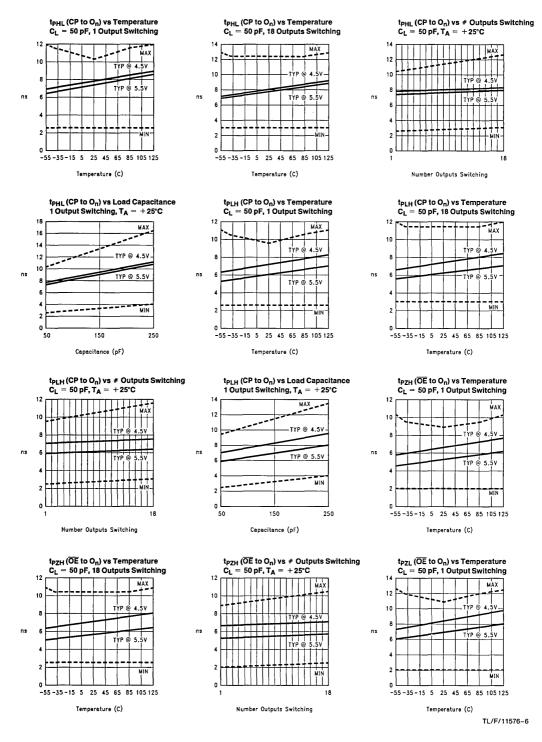

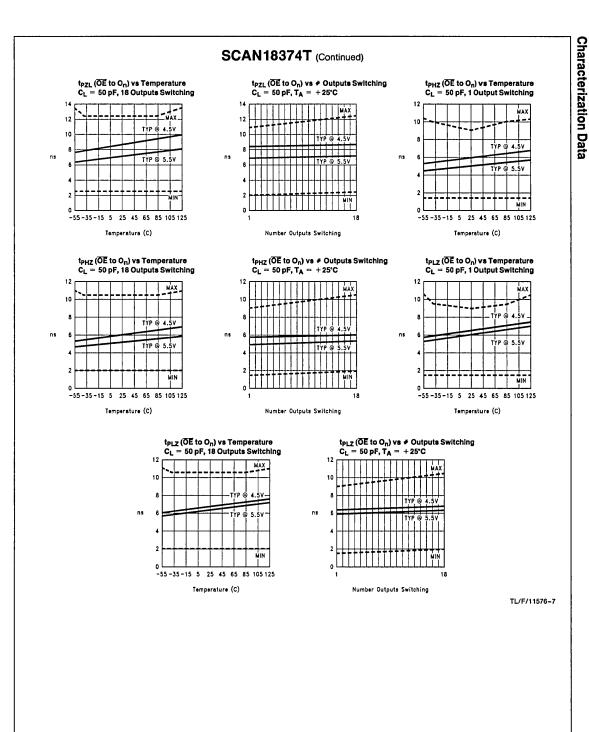

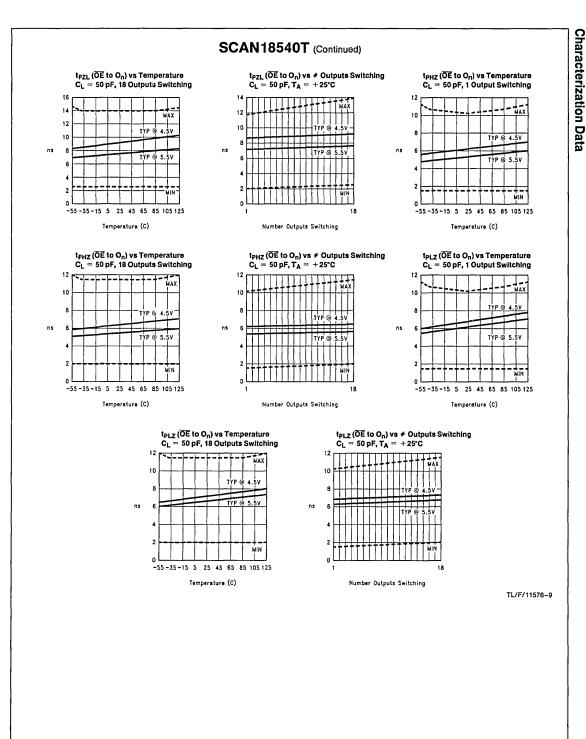

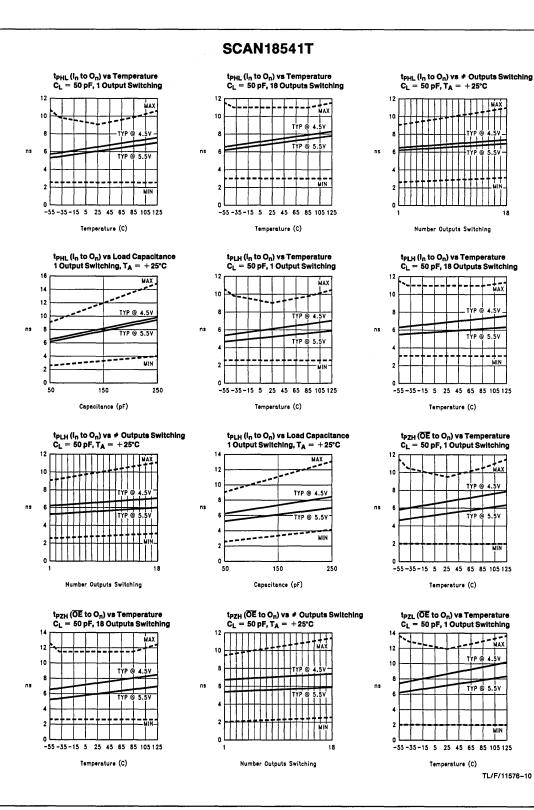

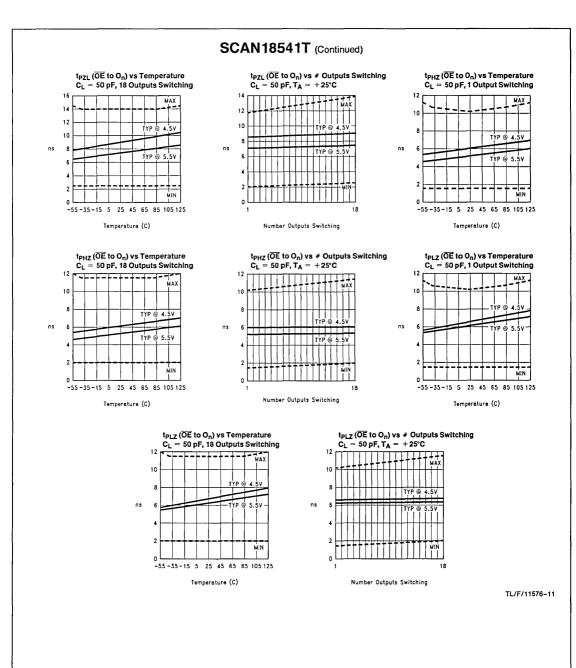

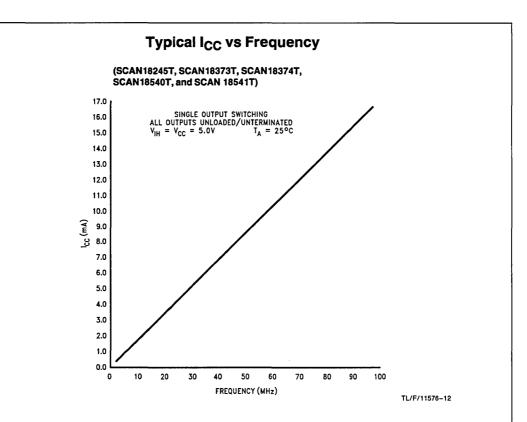

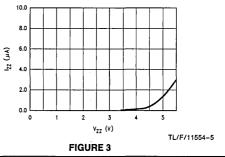

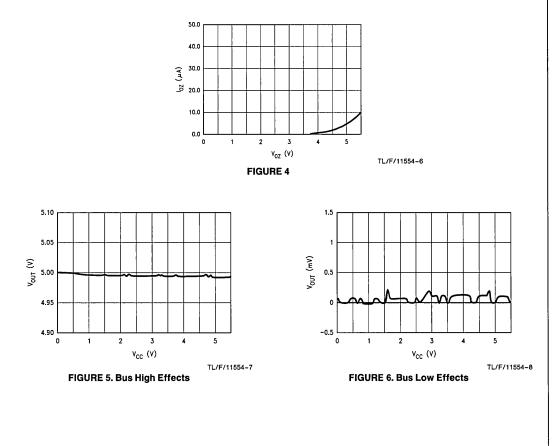

Section 5 Characterization Data ......5-1 Graphs depicting the propagation performance of the SCAN CMOS buffers and transceivers.

Section 6 Boundary Scan Design Support......6-1 How to obtain BSDL models and other simulation models. Sources of information.

### Section 7 Application Notes ......7-1

###

Datasheets for 18-bit CMOS devices feature low power consumption, -48 mA/64 mA drivers used for surrounding clusters of non-1149.1 compliant devices in order to make a board fully 1149.1 compliant.

###

Datasheets for 18-bit BiCMOS devices. They are used along the card edge going into a backplane to provide live insertion/removal capability. Their  $25\Omega$  series resistors on the output eliminate an external damping resistor and reduce ringing (noise).

###

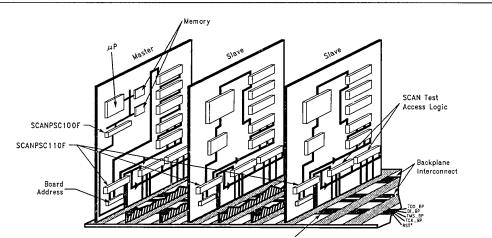

These are true "system support" products. These devices extend boundary scan features from the single board environment to several boards.

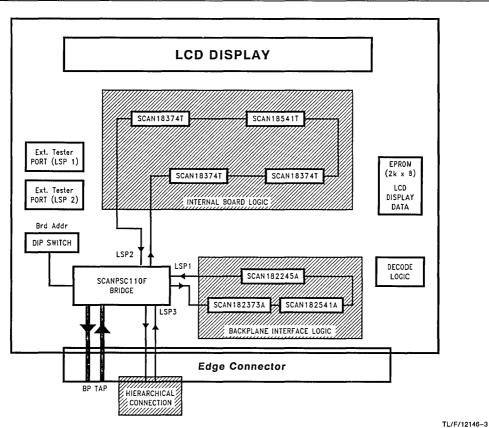

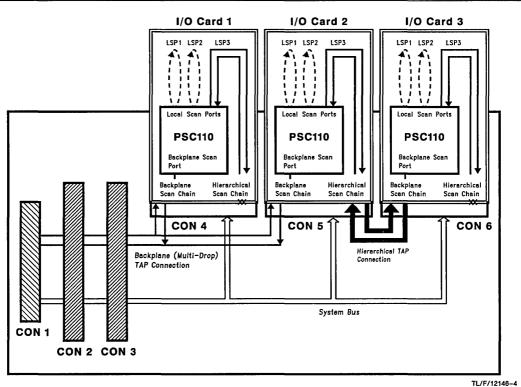

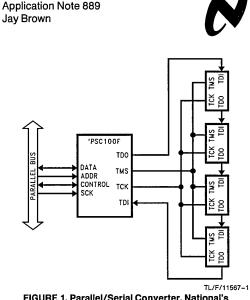

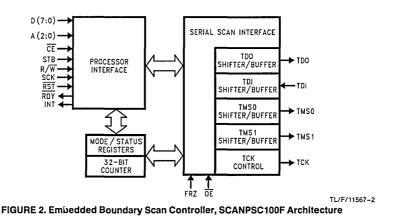

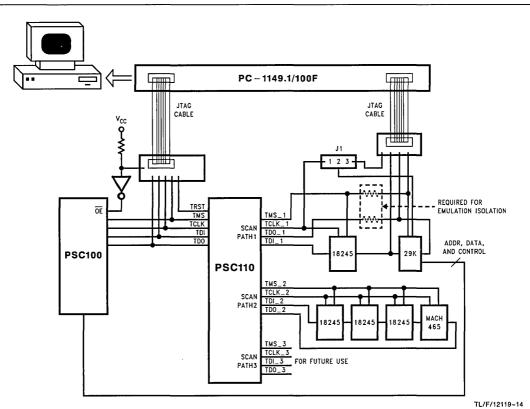

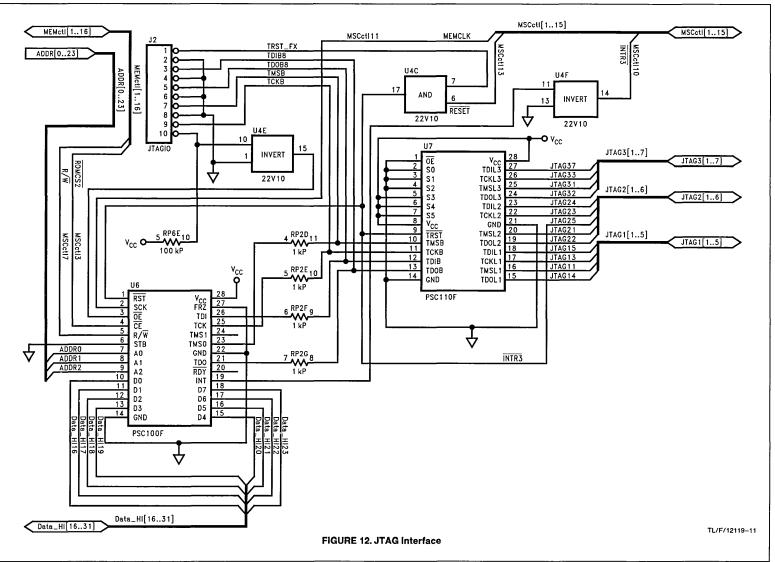

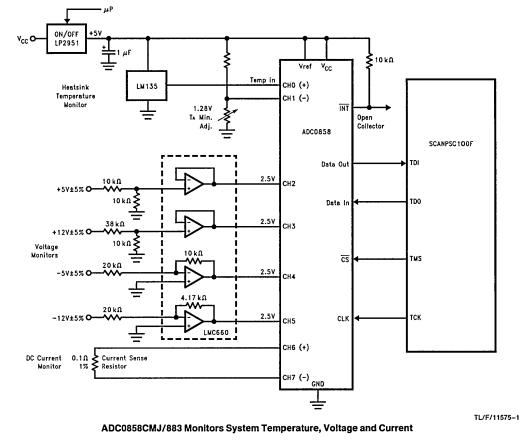

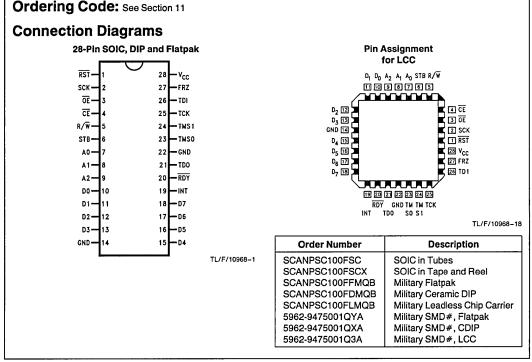

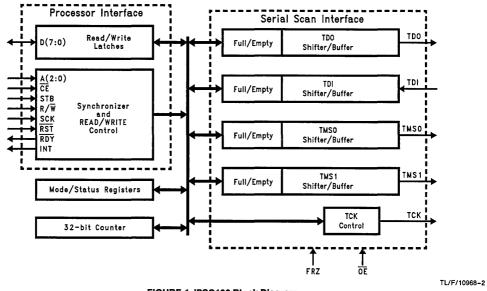

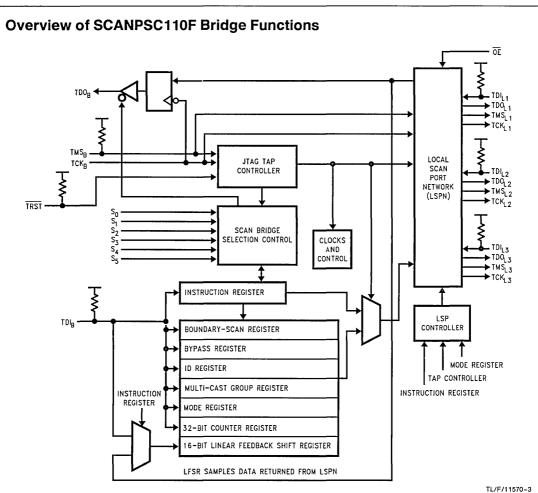

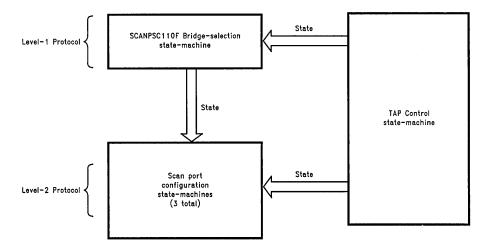

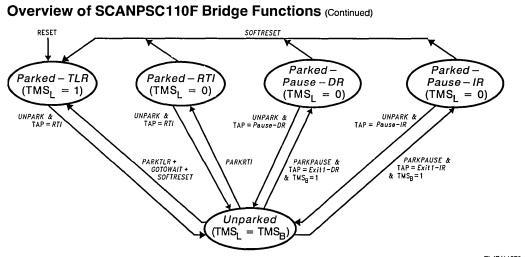

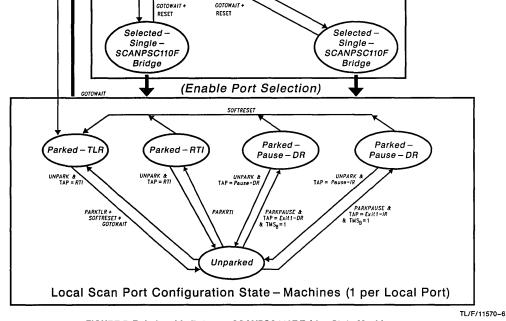

The Embedded Boundary Scan Controller, SCANPSC100F, allows creation of an on-board embedded test environment. It provides the interface from a target system's microprocessor and memory to the IEEE 1149.1 Test Access Port. The Hierarchical and Multidrop Addressable JTAG Port, SCANPSC110F Bridge, provides access to multiple boards within a system for simultaneous testing of like boards as well as system partitioning to better isolate test faults. SCAN EASE in a suite of software tools that enables test vectors to be embedded within an 1149.1 system; compiles and compresses vectors; controls and applies tests; reports failures; and includes a graphical user interface.

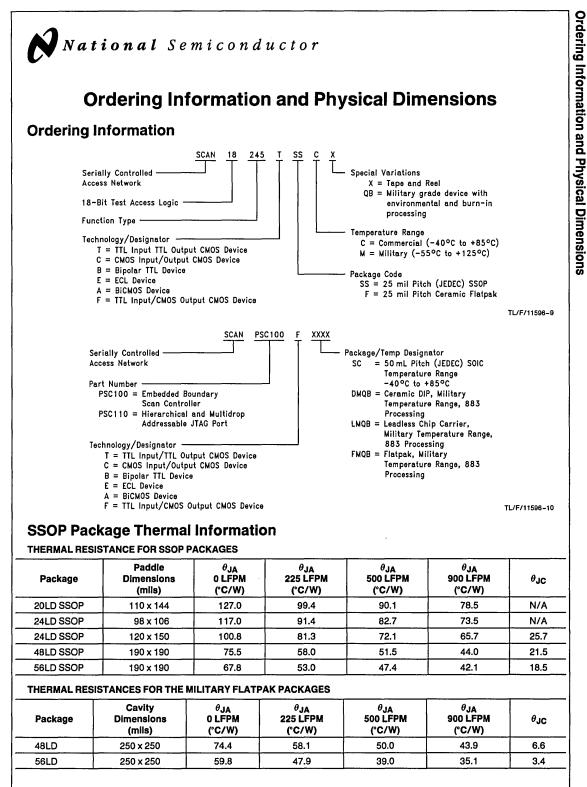

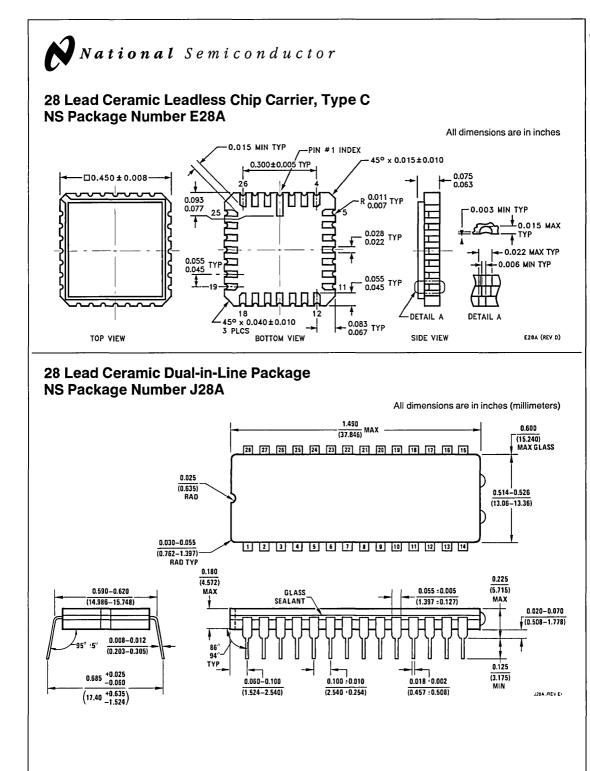

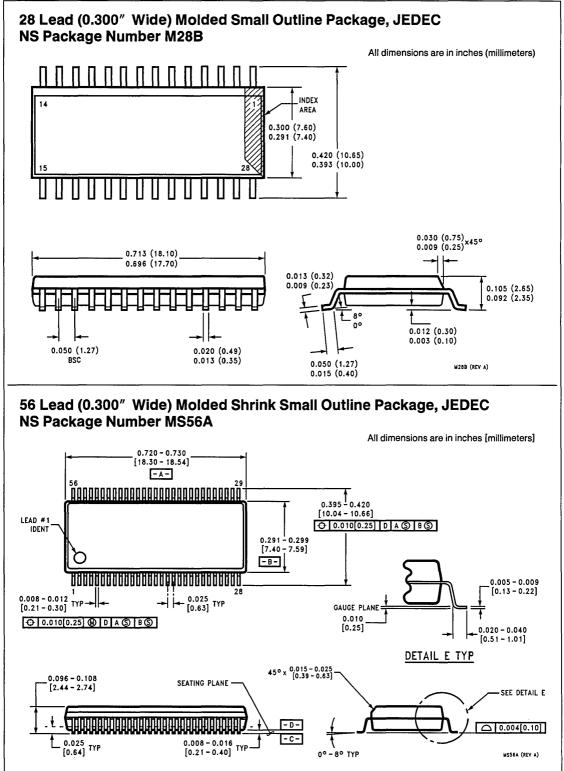

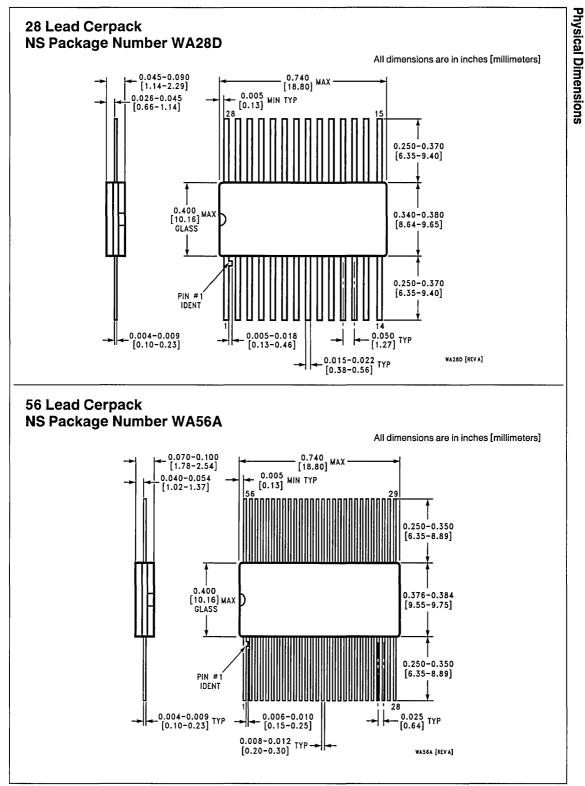

### Section 11 Ordering information and Physical Dimensions......11-1

Functional description of the ordering codes, package outlines,  $\theta_{JA}$  information and Dry Pack handling procedures.

National Semiconductor

# **Product Status Definitions**

### **Definition of Terms**

| Data Sheet Identification                     | Product Status            | Definition This data sheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                                                                  |  |  |

|-----------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advance Information                           | Formative or<br>In Design |                                                                                                                                                                                                                                                                                 |  |  |

| Preliminary<br>First Production               |                           | This data sheet contains preliminary data, and supplementary data will<br>be published at a later date. National Semiconductor Corporation<br>reserves the right to make changes at any time without notice in order<br>to improve design and supply the best possible product. |  |  |

| No Full<br>Identification Production<br>Noted |                           | This data sheet contains final specifications. National Semiconductor<br>Corporation reserves the right to make changes at any time without<br>notice in order to improve design and supply the best possible product.                                                          |  |  |

| Obsolete                                      | Not In Production         | This data sheet contains specifications on a product that has been<br>discontinued by National Semiconductor Corporation. The data sheet<br>is printed for reference information only.                                                                                          |  |  |

National Semiconductor Corporation reserves the right to make changes without further notice to any products herein to improve reliability, function or design. National does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

# Alpha-Numeric Index

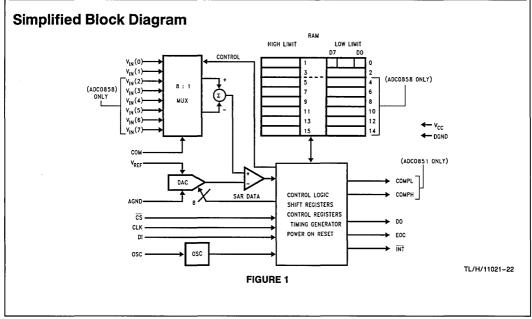

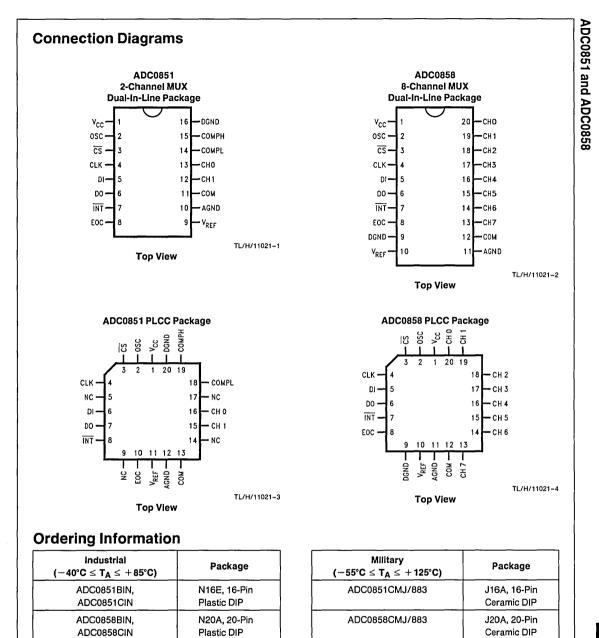

| ADC0851 8-Bit Analog Data Acquisition and Monitoring System                      |       |

|----------------------------------------------------------------------------------|-------|

| ADC0858 8-Bit Analog Data Acquisition and Monitoring System                      |       |

| AN-881 Design Considerations for Fault Tolerant Backplanes                       |       |

| AN-889 Design of a Parallel Bus-to-Scan Test Port Converter                      |       |

| AN-891 Non-Contact Test Access for Surface Mount Technology                      |       |

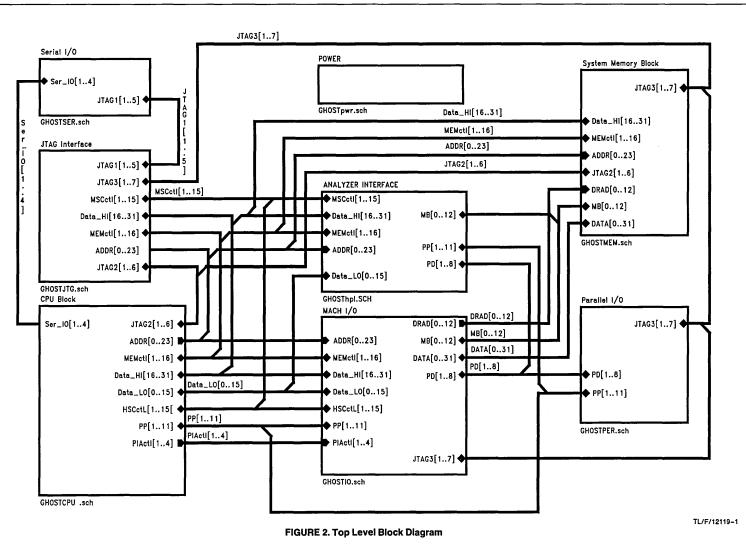

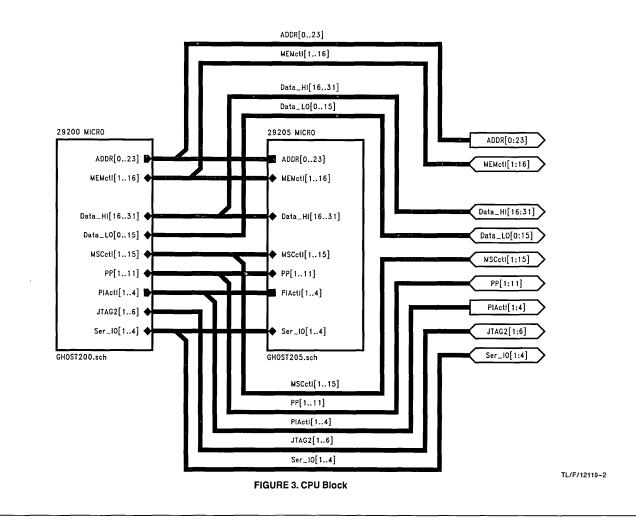

| AN-1003 G.Host JTAG Interface for Graphics Host Reference Design                 |       |

| AN-1022 Boundary Scan Silicon and Software Enable System Level Embedded Test     |       |

| AN-1023 Structural System Test via IEEE Std. 1149.1 with SCANPSC110F Hierarchica |       |

| Multidrop Addressable JTAG Port                                                  |       |

| AN-1037 Embedded IEEE 1149.1 Test Application Example                            |       |

| SCAN EASE SCAN Embedded Application Software Enabler                             |       |

| SCAN18245T Non-Inverting Transceiver with TRI-STATE Outputs                      |       |

| SCAN18373T Transparent Latch with TRI-STATE Outputs                              |       |

| SCAN18374T D Flip-Flop with TRI-STATE Outputs                                    |       |

| SCAN18540T Inverting Line Driver with TRI-STATE Outputs                          | 8-41  |

| SCAN18541T Non-Inverting Line Driver with TRI-STATE Outputs                      |       |

| SCAN182245A Non-Inverting Transceiver with 25Ω Series Resistor Outputs           |       |

| SCAN182373A Transparent Latch with 25Ω Series Resistor Outputs                   |       |

| SCAN182374A D Flip-Flop with $25\Omega$ Series Resistor Outputs                  |       |

| SCAN182541A Non-Inverting Line Driver with $25\Omega$ Series Resistor Outputs    |       |

| SCANPSC100F Embedded Boundary Scan Controller (IEEE 1149.1 Support)              |       |

| SCANPSC110F SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port         |       |

| (IEEE 1149.1 System Test Support)                                                | 10-26 |

|                                                                                  |       |

National Semiconductor

# **SCAN Products Selection Guide**

| Function      | Device      | Bit-<br>Width | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------|-------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRANSCEIVER   | IS          |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Non-Inverting | SCAN18245T  | 18-bit        | <ul> <li>Dual Output Enable Control Signals</li> <li>IEEE 1149.1 (JTAG) Compliant</li> <li>Includes CLAMP and HIGHZ Instructions</li> <li>9-Bit Data Busses for Parity Applications</li> <li>TRI-STATE® Outputs for Bus-Oriented Applications</li> <li>Reduced-Swing Outputs source 32 mA/sink 64 mA (Comm), and source 24 mA/sink 48 mA (Military)</li> <li>Guaranteed to Drive 50Ω Transmission Line to TTL Input Levels of 0.8V and 2.0V</li> <li>TTL Compatible Inputs</li> <li>25 mil Pitch SSOP (Shrink Small Outline Package)</li> </ul>    |

| Non-Inverting | SCAN182245A | 18-bit        | <ul> <li>High performance BiCMOS technology (t<sub>PD</sub> &lt; 4 ns, typ)</li> <li>25Ω series resistors in outputs eliminate the need for external terminating resistors</li> <li>Dual output enable control signals</li> <li>TRI-STATE outputs for bus-oriented applications</li> <li>25 mil pitch SSOP (Shrink Small Outline Package)</li> <li>IEEE 1149.1 (JTAG) Compliant</li> <li>Includes CLAMP, IDCODE and HIGHZ instructions</li> </ul>                                                                                                  |

| FLIP-FLOPS    |             |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| D             | SCAN18374T  | 18-bit        | <ul> <li>Buffered Positive Edge-Triggered Clock</li> <li>IEEE 1149.1 (JTAG) Compliant</li> <li>Includes CLAMP and HIGHZ Instructions</li> <li>9-Bit Data Busses for Parity Applications</li> <li>TRI-STATE Outputs for Bus-Oriented Applications</li> <li>Reduced-Swing Outputs source 32 mA/sink 64 mA (Comm), and source 24 mA/sink 48 mA (Military)</li> <li>Guaranteed to Drive 50Ω Transmission Line to TTL Input Levels of 0.8V and 2.0V</li> <li>TTL Compatible Inputs</li> <li>25 mil Pitch SSOP (Shrink Small Outline Package)</li> </ul> |

| D             | SCAN182374A | 18-bit        | <ul> <li>High performance BiCMOS technology (T<sub>PD</sub> &lt; 4 ns, typical)</li> <li>25Ω series resistor outputs eliminate need for external terminating resistors</li> <li>Buffered positive edge-triggered clock</li> <li>TRI-STATE outputs for bus-oriented applications</li> <li>25 mil pitch SSOP (Shrink Small Outline Package)</li> <li>IEEE 1149.1 (JTAG) Compliant</li> <li>Includes CLAMP, IDCODE and HIGHZ instructions</li> </ul>                                                                                                  |

| LATCHES       | Device      | Bit-<br>Width | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|-------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LATORICO      |             |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Transparent   | SCAN18373T  | 18-bit        | <ul> <li>Buffered Active-Low Latch Enable</li> <li>IEEE 1149.1 (JTAG) Compliant</li> <li>Includes CLAMP and HIGHZ Instructions</li> <li>9-Bit Data Busses for Parity Applications</li> <li>TRI-STATE Outputs for Bus-Oriented Applications</li> <li>Reduced-Swing Outputs source 32 mA/sink 64 mA (Comm), and source 24 mA/sink 48 mA (Military)</li> <li>Guaranteed to Drive 50Ω Transmission Line to TTL Input Levels of 0.8V and 2.0V</li> <li>TTL Compatible Inputs</li> <li>25 mil Pitch SSOP (Shrink Small Outline Package)</li> </ul>    |

| Transparent   | SCAN182373A | 18-bit        | <ul> <li>High performance BiCMOS technology (T<sub>PD</sub> &lt; 4 ns, typical)</li> <li>25Ω series resistor outputs eliminate need for external terminating resistors</li> <li>Buffered active-low latch enable</li> <li>TRI-STATE outputs for bus-oriented applications</li> <li>25 mil pitch SSOP (Shrink Small Outline Package)</li> <li>IEEE 1149.1 (JTAG) Compliant</li> <li>Includes CLAMP, IDCODE and HIGHZ instructions</li> </ul>                                                                                                     |

| LINE DRIVERS  | Ş           |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Inverting     | SCAN18540T  | 18-bit        | (Same Features of the SCAN18541T)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Non-Inverting | SCAN18541T  | 18-bit        | <ul> <li>Dual output enable signals per byte</li> <li>IEEE 1149.1 (JTAG) Compliant</li> <li>Includes CLAMP and HIGHZ Instructions</li> <li>9-Bit Data Busses for Parity Applications</li> <li>TRI-STATE Outputs for Bus-Oriented Applications</li> <li>Reduced-Swing Outputs source 32 mA/sink 64 mA (Comm), and source 24 mA/sink 48 mA (Military)</li> <li>Guaranteed to Drive 50Ω Transmission Line to TTL Input Levels of 0.8V and 2.0V</li> <li>TTL Compatible Inputs</li> <li>25 mil Pitch SSOP (Shrink Small Outline Package)</li> </ul> |

| Non-Inverting | SCAN182541A | 18-bit        | <ul> <li>High performance BiCMOS technology (T<sub>PD</sub> &lt; 4 ns, typical)</li> <li>25Ω series resistor outputs eliminate need for external terminating resistors</li> <li>Dual output enable signals per byte</li> <li>TRI-STATE outputs for bus-oriented applications</li> <li>25 mil pitch SSOP (Shrink Small Outline Package)</li> <li>IEEE 1149.1 (JTAG) Compliant</li> <li>Includes CLAMP, IDCODE and HIGHZ instructions</li> </ul>                                                                                                  |

**SCAN Products Selection Guide**

| Function                                                  | Device      | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-----------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SYSTEM SUPPORT                                            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Embedded<br>Boundary<br>Scan<br>Controller                | SCANPSC100F | <ul> <li>Compatible with the IEEE Std. 1149.1 (JTAG) Test Access Port and Boundary Scan Architecture</li> <li>Interfaces up to Two 1149.1 Scan Rings</li> <li>Fabricated in FACTTM 1.5μ CMOS Process</li> <li>Generic Parallel Interface Synchronizes Processor Signals with the SCANPSC100F Operation Clock, SCK</li> <li>16-Bit Serial Signature Compaction (SSC) at the Test Data in (TDI) Port</li> <li>Automatically produces Pseudo-Random Patterns at the Test Data Out (TDO) Port</li> <li>25 MHz Operation</li> <li>TTL Compatible Inputs, Outputs are Full-Swing CMOS with 24 mA Source/Sink Capability</li> </ul>     |  |  |  |

| Hierarchical<br>and Multidrop<br>Addressable<br>JTAG Port | SCANPSC110F | <ul> <li>True IEEE1149.1 Hierarchical and Multidrop Addressable Capability</li> <li>The 6 Slot Inputs Support Up to 59 Unique Addresses, a Broadcast Address, and 4 Multi-cast Group Addresses</li> <li>3 IEEE 1149.1-Compatible Configurable Local Scan Ports</li> <li>Mode Register Allows Local TAPs to be Bypassed, Selected for Insertion into the Scan Chain Individually, or Serially in Groups of Two or Three</li> <li>32-bit TCK Counter</li> <li>16-bit LFSR Signature Compactor</li> <li>Local TAPs Can Be TRI-STATE Via the OE Input to Allow an Alternate Test Master to Take Control of the Local TAPs</li> </ul> |  |  |  |

| SCAN<br>Embedded                                          | SCAN EASE   | <ul> <li>Processor independent—runs on big/little endian and memory- and I/O-mapped<br/>architectures</li> <li>Compatible with Teradyne VICTORYTM ATPG and JTAG Technology BTPGTM tools (others</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Application                                               |             | <ul> <li>supported upon request)</li> <li>Provides automated translation, application and evaluation of ATPG-generated tests in an embedded system environment</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Software                                                  |             | <ul> <li>Includes a Scan Function Library and National's Embedded Boundary Scan Controller<br/>SCANPSC100F device driver to support custom or non-ATPG generated vector applications</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Enabler                                                   |             | <ul> <li>Supports embedded test data log for diagnostic processing</li> <li>Includes Microsoft Windows GUI and serial communication tool for system administration and remote testing</li> <li>Supports SCANPSC110F Hierarchical and Multidrop JTAG Addressable Port architecture</li> </ul>                                                                                                                                                                                                                                                                                                                                     |  |  |  |

.

# Section 1 Design for Test Solutions with Boundary Scan

### **Section 1 Contents**

| What is DFT?                                   | 1-3  |

|------------------------------------------------|------|

| Board Development                              | 1-3  |

| Board Manufacturing                            | 1-4  |

| Field Service                                  | 1-4  |

| The Economics of Design for Test               | 1-5  |

| Where the Failures Are                         | 1-5  |

| Boundary Scan Fundamentals                     | 1-7  |

| System Test                                    | 1-9  |

| System-Level Embedded Test                     | 1-10 |

| The Impact of PC and Communications Technology | 1-11 |

National Semiconductor

### **Design for Test Solutions** with Boundary Scan

### What is DFT?

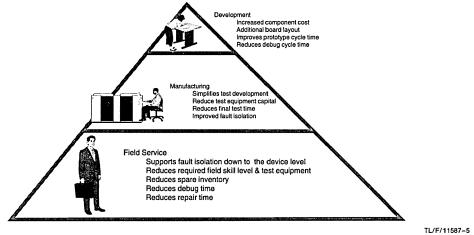

Design for Test, or DFT, is being used by many companies to lower the overall cost of development, manufacturing, test and field service. Some companies call it "Concurrent Engineering" and it replaces the "Over-the-wall" method of product development. In each stage of the product life-cycle, a consideration for testing is made in the earliest stages of design.

National employs boundary scan technology to enable not just chip testing, but also board testing, system testing, and in-field service testing.

What is the standard? For most purposes the following terms are used interchangeably:

IEEE 1149.1 1149.1 JTAG Dot 1 Boundary Scan SCAN

IEEE 1149.1 is a set of standards for board test protocol. Newer standards are being developed by different IEEE working groups for system test and analog test protocol. IEEE 1149.1 is a 4-wire standard which allows compliant silicon to perform interconnect testing. It supports BIST (Built In Self-Test), and provides an alternative or supplement to Bed of Nails testing and functional testing.

Adding boundary scan to a board does add cost and time to the design cycle due to the increased cost of boundary scan compliant components and initial time investment required to understand the boundary scan architecture and tools. However, these costs are easily justified when viewing the benefits and cost savings boundary scan provides at every stage of a product's life cycle. What was originally developed as a manufacturing test tool offers benefits before, during and after manufacturing.

### **Board Development**

A designer uses boundary scan to save time during the prototyping and design debug stage. With boundary scan, non design-related, structural faults can be detected and then eliminated at both the board level and component level. This allows designers to effectively locate and resolve design related problems. Additionally, designers use boundary scan to partition a board, load seed values for devices with BIST and/or load internal values into device registers (e.g. internal scan, LSSD, etc.) to isolate logic errors. With boundary scan, many of the vectors developed and used during the design phase can be passed on to manufacturing to provide an additional cost and time savings.

FIGURE 1. Boundary Scan Benefits Entire Product Life Cycle

### **Board Manufacturing**

The key benefits at the manufacturing phase are test development time savings; improved fault coverage and diagnosis; and improved test throughput through reduced test times. As with the design phase, boundary scan provides the additional advantage of applying many of the vectors used for manufacturing to be later applied during field debug and diagnosis.

### Field Service

Field failures are often due to structural failures which surface due to the stress-temperature, humidity, vibrationthat the boards are exposed to in the field environment. Using boundary scan, field technicians have the ability to quickly test for structural faults down to the component level without the burden of probing or returning the board to the factory. Eliminating these tasks allows for more efficient diagnosis and repair which reduces cost and system downtime.

The advantage of boundary scan become even more apparent when boundary scan is extended from the board level to the system level test.

### 80386 Conventional ICT Patterns

| Study Part            | 1 Weeks               |

|-----------------------|-----------------------|

| Develop Test Patterns | 4 Weeks               |

| Verify on ATE         | 2 Weeks               |

| Total Time            | 7 Weeks<br>(\$14,000) |

Often, the objection to the use of boundary scan include:

- 1. Performance (speed) decreases due to the extra delay added by the boundary scan multiplexer in the data path.

- 2. Cost increases due to additional silicon and TAP pins on the device package-as well as design time.

- 3. Delay to market due to additional circuit design time.

However, the manufacturing benefits as well as product development cycle time improvements easily outweigh the initial added efforts.

Using boundary scan on their 80486 design, Intel realized two orders of magnitude improvement in time to develop circuit test-patterns with significant cost reduction, too. See Figure 2.

Boundary scan provides cost savings over the life cycle of a system in the testing of boards, systems, and in field maintenance.

### 80486 with VICTORY/1149.1 ICT Patterns

| Study Part            | 1 Weeks               | Generate/Verify BSDL   | 8 Hours             |              |

|-----------------------|-----------------------|------------------------|---------------------|--------------|

| Develop Test Patterns | 4 Weeks               | Generate Test Patterns |                     |              |

| Verify on ATE         | 2 Weeks               | Verify Patterns        | 2 Hours             |              |

| Total Time            | 7 Weeks<br>(\$14,000) | Total Time             | 10 Hours<br>(\$500) |              |

|                       |                       |                        |                     | TL/F/11587-6 |

FIGURE 2. Intel Reduced Test Development Time and Test Cycle Time

### The Economics of Design for Test

Many of the perceived costs of a DFT strategy fall upon the design organization, while many of the benefits reward the manufacturing and test organizations. This adversarial position can be eliminated by meeting the needs of all organizations involved in DFT.

#### EFFECT OF DFT BY DEPARTMENT

| Design | Die Area<br>Design Cycle Time<br>Performance Impact<br>EDA Tools                             | Increased Cost<br>Lowered Cost<br>Increased Cost<br>Increased Cost |

|--------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Test   | Fault Simulation<br>Simplified Debug & Diagnostics<br>Fewer Design Changes<br>Lower ATE Cost | Lowered Cost<br>Lowered Cost<br>Lowered Cost<br>Lowered Cost       |

### IMPACT OF DFT VARIABLES BY DEPARTMENT

| <b>Profit Factor</b> | Department                   | Impact                                                                                    |

|----------------------|------------------------------|-------------------------------------------------------------------------------------------|

| Units Sold           | Design                       | New product feature,<br>faster design cycle time                                          |

|                      | Marketing                    | Lower selling price<br>through cost reduction                                             |

|                      | Sales                        | Lower selling price                                                                       |

| Selling Price        | Design<br>Marketing<br>Sales | New product features of higher quality                                                    |

| Variable Cost        | Marketing<br>Sales           | Higher cost of silicon, lower overall                                                     |

|                      | Manufacturing<br>Design      | manufacturing costs                                                                       |

| Fixed Cost           | Manufacturing                | Lower cost ATE, more<br>productive ATE (higher<br>throughput), improved<br>fault coverage |

|                      | Field Service                | Less field spare<br>inventory, faster debug<br>and diagnosis                              |

| Total Profit         | Management                   | Overall investment<br>strategy, capital<br>utilization, ROA, cost<br>calculation methods  |

Boundary scan also provides cost savings which can be measured directly in production and can reduce the time to market. This method fits within a concurrent engineering environment in various ways:

- · Reduces test time and costs

- · Reduces test preparation time and costs

- Increases the time available for test programs for production

- · Allows simpler, less costly testers

- Shortens diagnostic times

- · Provides a commonality of tester interface

- Allows the continued test of high density/poor-access boards

### Where the Failures Are

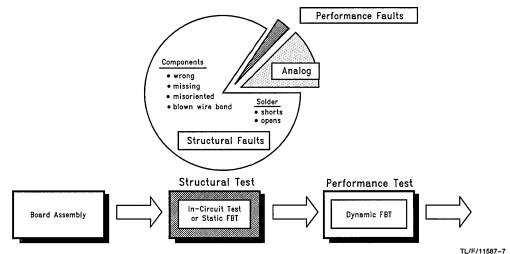

PCB test failures can result from either structural faults (opens, stuck-ats, bridging, missing/wrong components, etc.), analog failures (faulty or incorrect passive components) or performance faults (timing problems or board/ component design errors). However, structural faults account for the overwhelming majority of board failures during manufacturing test. In fact, data from Teradyne, a leader in the test industry, suggests that greater than 80% of the board level test manufacturing failures are structural in nature. See *Figure 3*.

### Where the Failures Are (Continued)

A number of methods have been implemented to provide a means of detecting structural failures. These methods range from use of functional board testers (FBT) to in-circuit testers (ICT) and combinational (ICT and FBT) testers. Boundary scan was created to provide an improved technique for screening structural faults through reduced test programming time and improved fault coverage.

It should be noted that boundary scan is not a technique for detecting at-speed, dynamic performance faults. Performance fault testing requires the use of an at-speed functional board tester. With very thorough debug and simulation during board development and pre-assembly test of board components, the need for performance fault testing during manufacturing is up to the discretion of the board manufacturer and its customers. Even if at-speed functional testing is required, the use of structural testing prior to functional testing will help eliminate manufacturing defects and ease the diagnosis of performance or functional failures.

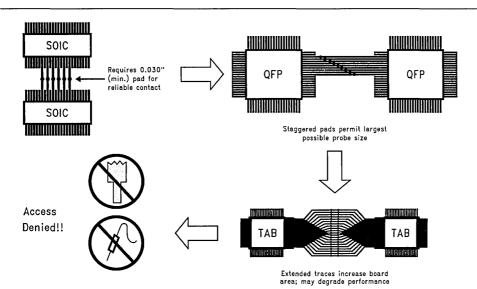

For the cases where access is possible, the access occurs at a price. Even if it is possible to add test pads, pads consume board area—contrary to the goal of saving board area—and can present performance degradation. Additionally, the cost increases substantially for test point fixtures, the fine tip probes or clam shell probes for double sided boards. See *Figure 4*.

For the case of MCMs (multi-chip modules) and inaccessible board nodes (nodes under a mezzanine card, blocked by a component or other hardware, etc.), access is not possible and the only option other than boundary scan is cluster testing: using bed of nails to apply stimulus on MCM or board cluster inputs and measure values at outputs of the MCM or board cluster. This creates the same burdens as when using a FBT, where creating test vectors requires knowledge of the entire MCM or board cluster functionality which increases test development, diagnostics and test time.

The existence of inaccessible nodes in manufacturing are passed on to the field service engineer attempting to use manual probing as a vital step in debugging a board failure. This leads to increased field service time and costs and, longer system down time for your customer.

FIGURE 3. The Majority of Printed Circuit Board (PCB) Manufacturing Failures Are a Result of Structural Faults

TL/F/11587-8

FIGURE 4. Device Packaging Density Makes Physical Access Expensive, Unreliable, or Impossible

### **Boundary Scan Fundamentals**

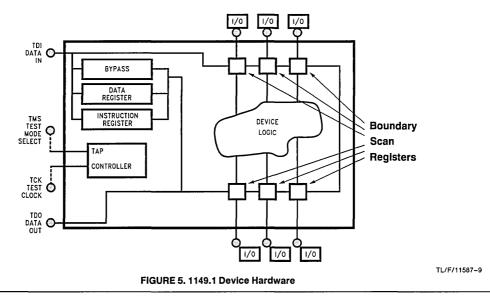

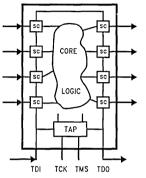

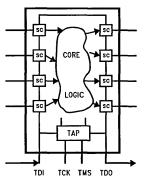

The IEEE 1149.1 standard defines a 4 pin TAP (Test Access Port) which allows electrical access around the "boundary" of compliant devices. The TAP pins are:

- TDI Test Data In

- TDO Test Data Out

- TMS Test Mode Select

- TCK Test Clock

It also defines a 16 state TAP Controller and several registers used to control the test data.

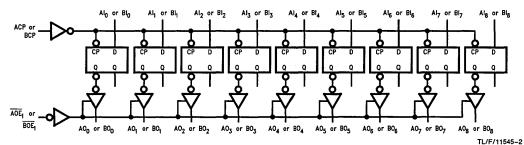

Boundary scan registers are placed at all I/O pins, and they are interconnected to form a serial chain around the core functionality of the device.

With the addition of the boundary scan registers at the I/O of a component, interconnect testing with boundary scan devices can be performed with no dependence on device functionality. IEEE 1149.1 compliant automatic test program generation (ATPG) tools are available from a number of vendors to automatically generate interconnect tests using a board netlist and BSDL files for each 1149.1 compliant device on the board as inputs. BSDL files provide a description of the specific implementation of boundary scan features within each compliant component.

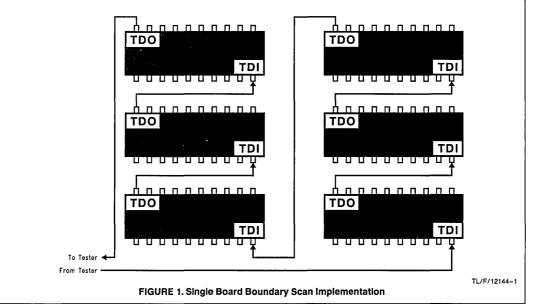

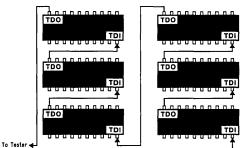

In like fashion as the chip, the boundary scan chain is extended to the board in a serial scan chain. Boards in systems can also be linked in a scan chain.

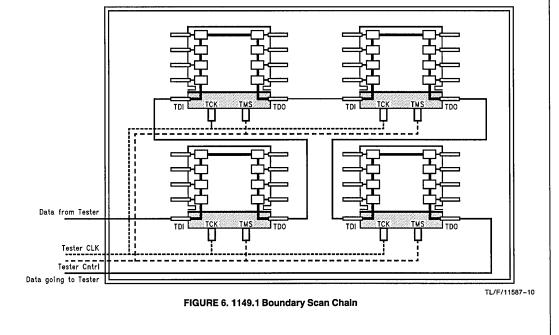

When placed on a printed circuit board, each 1149.1 component is connected together to form a chain of boundary scan devices. In *Figure 6*, note the scan chain connections:

- TDI/TDO: The tester's serial test data out pin is connected to the first device's TDI. The test data is passed from the first device to the second device via the TDO pin which connects to the second device's TDI pin. This chain formation continues until the last device's TDO pin is connected back to the tester. Therefore, shifting data into a device's instruction or data registers requires that the data passes through every JTAG device which is connected ahead of the device in the scan chain. Additionally, as the data is shifted into the device, the data previously stored in the selected instruction or data register is shifted out of the chain. The tester software either reads and evaluates the returning data or masks it out. The Bypass register is included to shorten the chain when shifting data through devices which are not participating in a given scan operation.

- TCK/TMS: All devices in the chain are connected in parallel to the TCK and TMS signals. This means that all the devices' TAP controllers are in the exact same state and transition simultaneously. The instruction register allows each device to include different data registers in the scan chain and perform different scan operations.

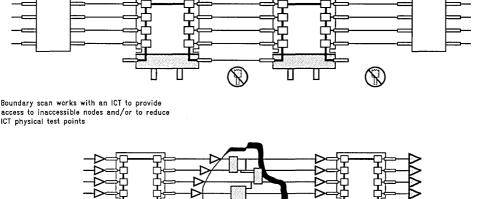

Implementing boundary scan on every component on the board provides the maximum benefit in terms of reduced tester cost, test development times and concurrent engineering. However, boundary scan can also complement an ICT in testing structural faults. See Figure 7. This was fully recognized by ICT tester companies when they developed their ICT systems and most ICT's now have a connector dedicated for boundary scan testing. Additionally, these tester companies included the option of mixing boundary scan and ICT in their ATPG tools by using ICT component libraries for non-scan products and BSDL for scan products. For example, vectors can be automatically generated to drive signals with boundary scan and compare results using physical test probes. Many companies have already invested millions of dollars in ICTs and may want to use boundary scan only where required for inaccessible nodes, non-library parts, etc. or as a means of cutting ICT fixture costs.

For smaller companies or companies in the process of purchasing new ICT equipment, implementing boundary scan may provide a way to reduce the required ICT features like number of channels providing a tremendous reduction in the tester cost where cost ranges from \$200K up to \$1M.

Figure 7 shows two examples of ICT and boundary scan working together. The lower of the two graphics shows cluster testing. Cluster testing is the testing of a group of devices by applying data to the inputs of the group or cluster and evaluating the results on the output of the group or cluster. Cluster testing can vary from testing the interconnects between the components in the cluster to testing the internal nodes of each component within the cluster.

### System Test

National supports the needs of the system design architect by:

- · Acknowledging the need for live insertion on the backplane

- Fully complying to IEEE 1149.1 (board test)

- · Addressing the 1149.5 standard (system test)

While boundary scan diagnostics are particularly useful for telecommunications and workstations, their benefits also extend to board manufacturers that want to reduce the timeto-market of their products.

For small companies, we provide the option to expensive \$1 million test equipment. With help from our software and hardware partners (such as Corelis and JTAG Technologies), National can support total system test solutions with PC-based boundary scan devices, software, and hardware solutions.

access to inaccessible nodes and/or to reduce ICT physical test points

FIGURE 7. Boundary Scan and ICT Can Work Together

TL/F/11587-11

#### HOW IT WORKS

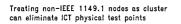

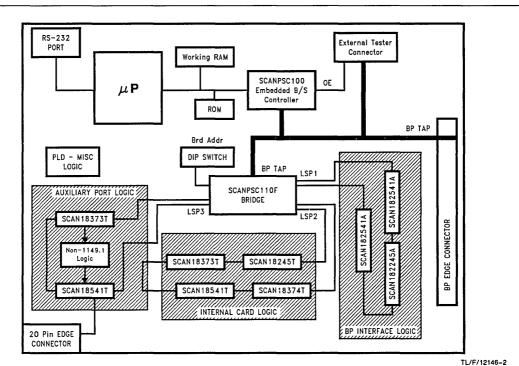

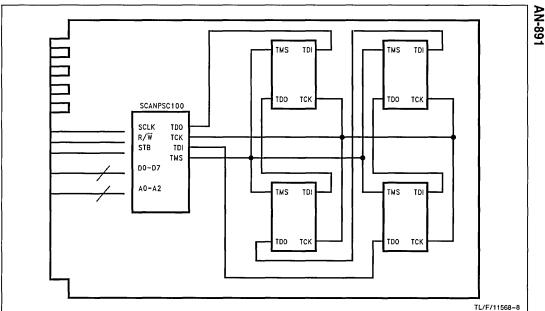

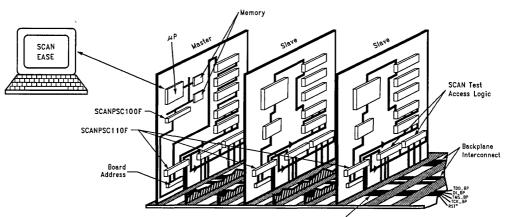

For system test and diagnostics, start with the Embedded Boundary Scan Controller, SCANPSC100F and your choice of microprocessor and memory to create an embedded test master, freeing up external test equipment.

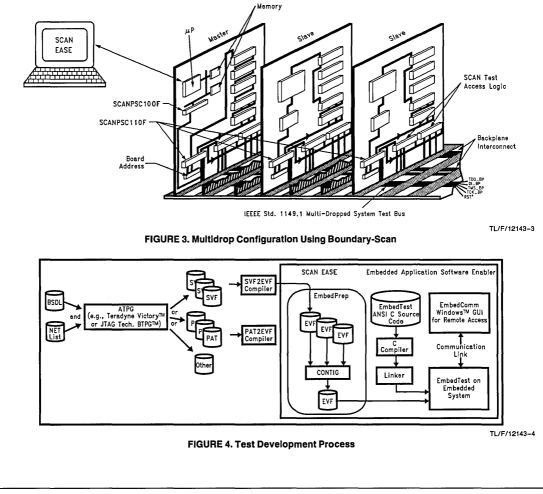

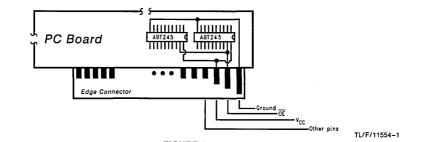

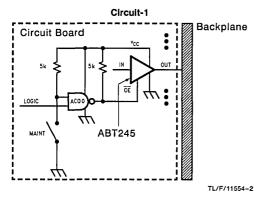

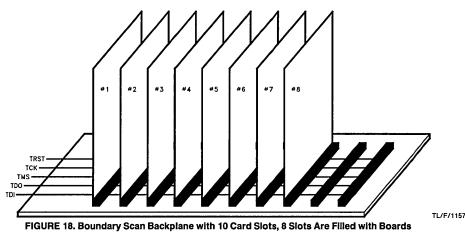

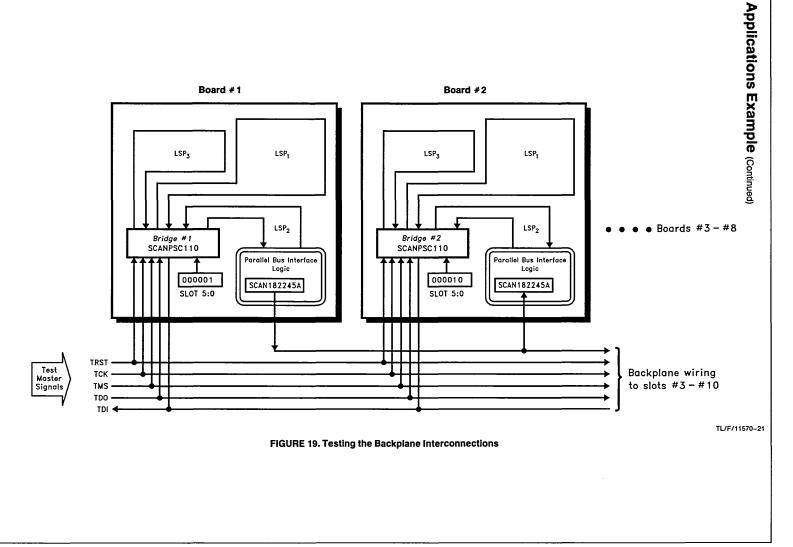

Add the Hierarchical and Multidrop Addressable JTAG Port, SCANPSC110F Bridge to each board in the multidrop or hierarchical backplane to address any number of boards, selectively or in groups, for board test as well as backplane interconnect failures. If a board is off-line or removed, the scan chains remain unbroken. But what if a board is removed while powered up? Then add SCAN ABT Test Access Logic along the back-plane card edge to provide fault-tolerant power-up and power-down live insertion. Now backplane interconnect checks can be performed and boards inserted/removed through controlled power-up/power-down sequences. The  $25\Omega$  series resistors on SCAN ABT outputs also eliminates the need for an external damping resistor.

- · SCAN EASE Compatible with 1149.1 hardware and existing test board vectors

- SCANPSC100F creates embedded test master

- SCANPSC110F enables individual board addressing, multiple and hierarchical boards for testing "like" boards simultaneously

- SCAN ABT live insertion

#### **FIGURE 8. Creating Embedded System Test**

### System-Level Embedded Test

Developing hardware and software to implement embedded test capability can be significant in terms of both time and expense. To reduce our customers' in-house software development efforts, National offers SCAN EASE to apply, control, and evaluate tests within an 1149.1-compliant embedded system. For more examples refer to AN-1022, Boundary-Scan, An Enabling Technology for System Level Embedded Test.

#### SCAN EASE TOOLS

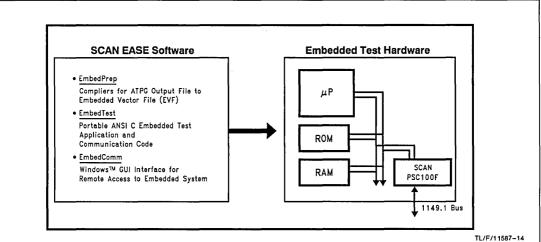

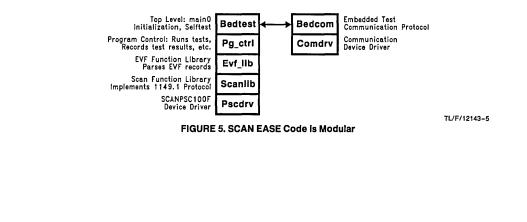

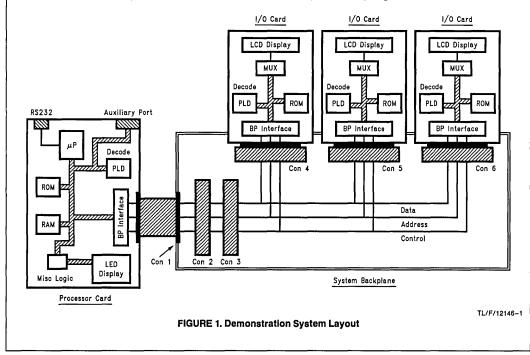

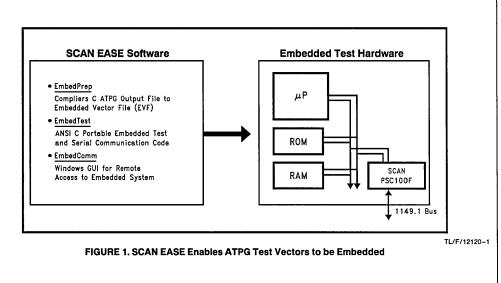

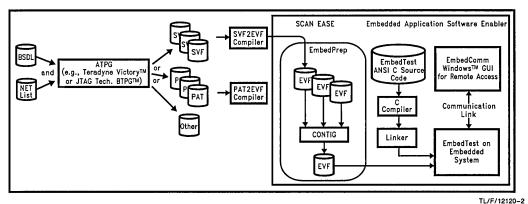

SCAN EASE (Embedded Applications Software Enabler) is a suite of software tools that enables ATPG (Automatic Test Program Generation) or custom-generated test vectors to be embedded within an IEEE 1149.1 compatible system. See *Figure 9*. SCAN EASE includes three groups of tools:

- EmbedPrep

- EmbedTest

- EmbedComm

#### **TEST DEVELOPMENT PROCESS**

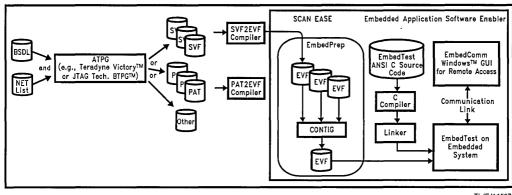

The test development process for embedded system test begins with generating tests using an off-the-shelf ATPG tool. See *Figure 10*. Separate tests are created for each board type in the system during manufacturing test development. These tests can be re-used for embedded test. National's SCAN EASE includes tools to compile test vectors

stored in Serial Vector Format (SVF) or Pattern Format (PAT) into Embedded Vector Format (EVF) for use with EmbedTest. EVF is a compact binary vector format suitable for embedded applications. Several of the board-level EVF files can be concatenated to create a system-level test. Partitioning tests enables EmbedTest to isolate and report pass/fail information to the partition level (board, module, etc.) without running diagnostic software. EVF test files can be located in ROM for power-up self test or down loaded to RAM.

TL/F/11587-16

EmbedTest provides a set of functions that enable communication between the embedded system and a serial interface to a system administrator or remote computer. Embed-Test commands—such as configuration, reporting test results, downloading new tests, and uploading data logs—are performed over this interface.

Note that SCAN EASE is also included in our SCAN Developer/Demo Kit. This kit demonstrates system board check, interconnect testing, and backplane testing (see *Figure 8*). Included are:

- Embedded Boundary Scan Controller—SCANPSC100F works with customer's choice of microprocessor

- Multidrop and Hierarchical Addressable JTAG Port SCANPSC100F SCAN Bridge for system test—addresses any number of boards in the backplane

- SCAN ABT Test Access Logic—provides live insertion capability for boards along the backplane

FIGURE 9. SCAN EASE Enables ATPG Test Vectors to be Embedded

TL/F/11587-15

FIGURE 10. SCAN EASE Reuses Existing Test Vectors, Compiles them for your Target Microprocessors and Compresses them for Storage in Memory

### The Impact of PC and Communications Technology

The market is ripe for the valuable services provided by PCbased and in-system testing. Having a system perform its own self-test upon power-up frees up design engineers to add more features to an end system, as opposed to spending money on testing a system. With advances in PCs, the capability of remote testing now exists. It is possible to dial up a modem service, connect to a remote system in the field and perform maintenance, improving the end-system uptime. Once the target site is on-line, the system performs self-testing and reports back failures.

There are many factors associated with improving end-system uptime including systems that require high reliability, systems that perform services for large groups of people or customers that need to stay on-line all the time. Initially SCAN EASE will diagnose the problem for the purpose of repair. Since vectors are stored in ROM, it will be easy to download system upgrades and new system configurations in the near future. Recent applications have arisen to extend the use of IEEE 1149.1 boundary scan all the way to system integration and field service. This new arena boasts additional leverage for the re-use of test vectors, improved time to break-even for products and increased value to end-users.

What products will result from this technology? A tester on a chip will go into simple machines that give people trouble like printers, copiers, facsimile machines, and give them the intelligence to do power-on self-test, diagnosis and repair. The machine will be able to call the home office through advanced communications capabilities, communicate with the home office, literally saying, "This is what is wrong with me." Remote verification of the diagnosis as well as repair can then take place.

On an even wider scale, telecommunications equipment buried in remote locations will be accessible. Board will be tested, brought off-line, and others brought on-line to replace them—electronically and remotely. Design for Test Solutions with Boundary Scan

·

# Section 2 Description of Boundary Scan

2

### **Section 2 Contents**

| Boundary-Scan Circuitry | 2-3 |

|-------------------------|-----|

| Boundary-Scan Registers | 2-4 |

| Boundary Scan Overview  | 2-5 |

National Semiconductor

# **Description of Boundary-Scan**

### **Boundary-Scan Circuitry**

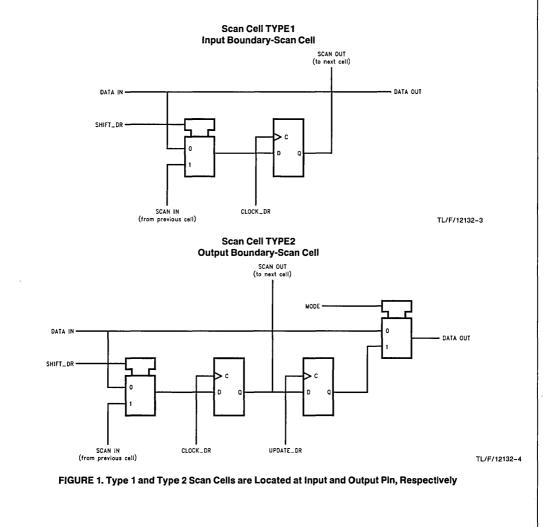

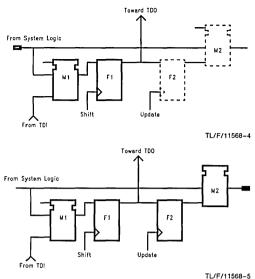

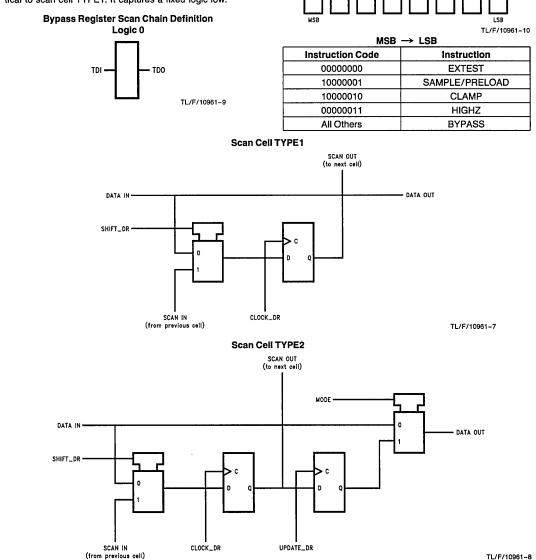

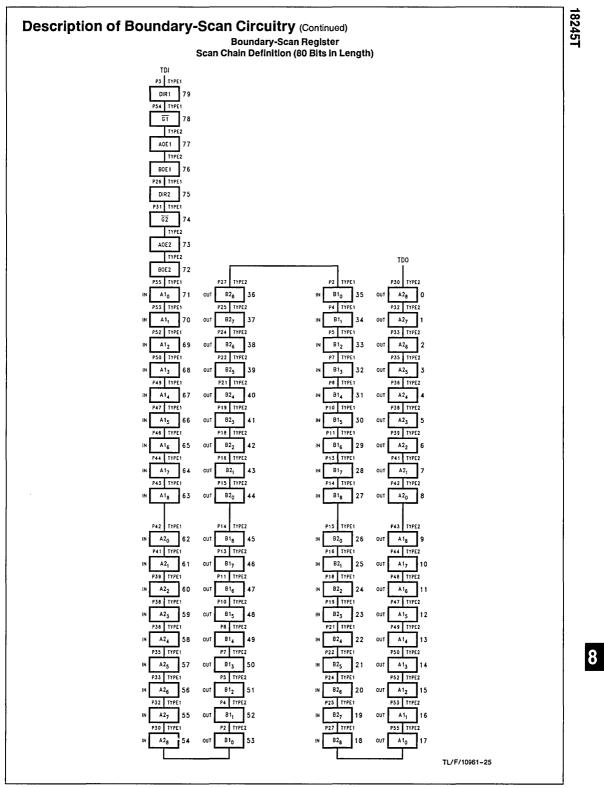

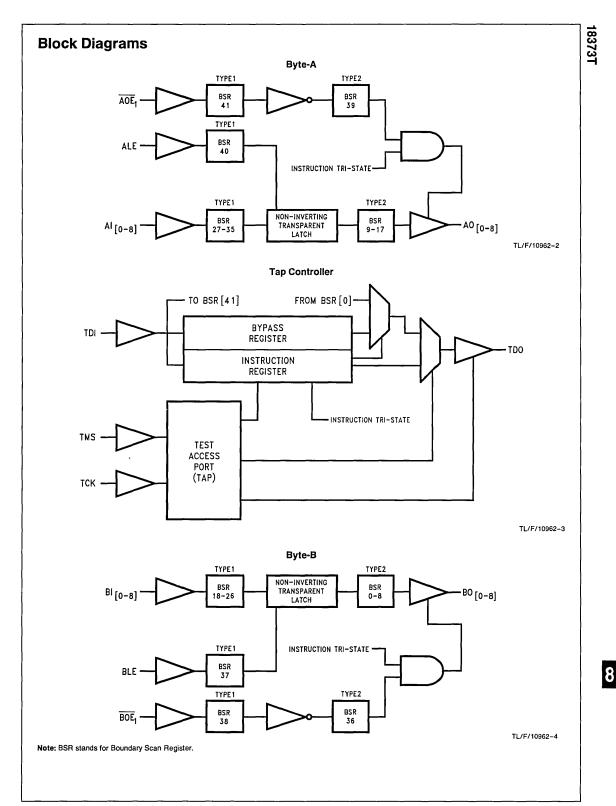

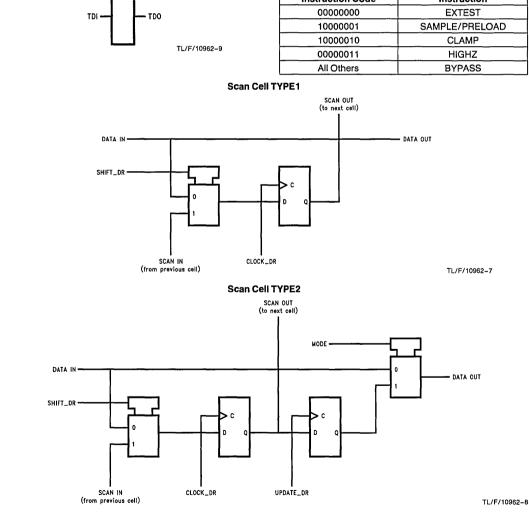

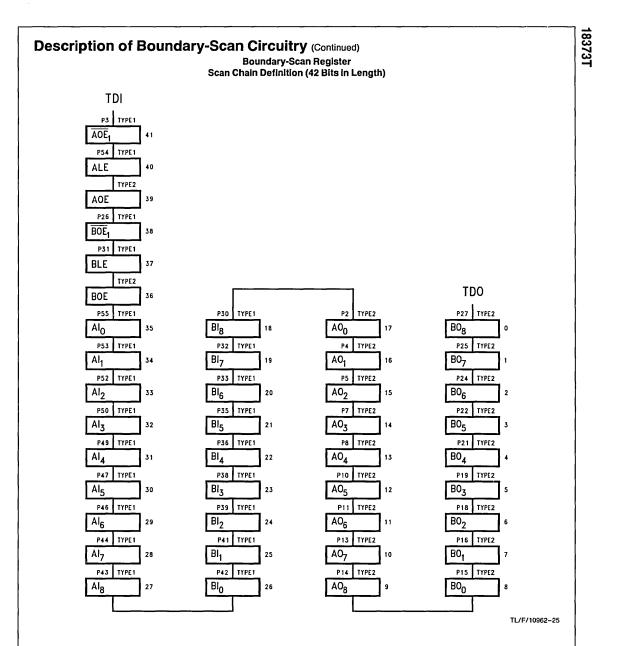

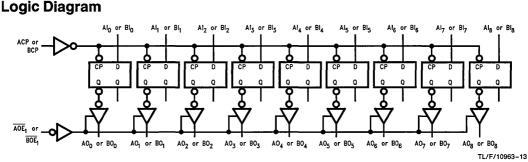

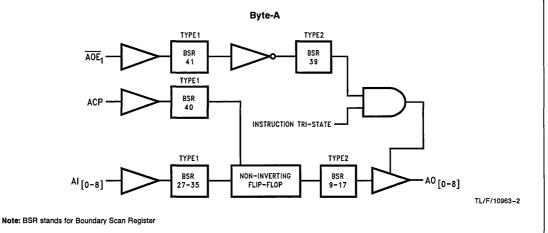

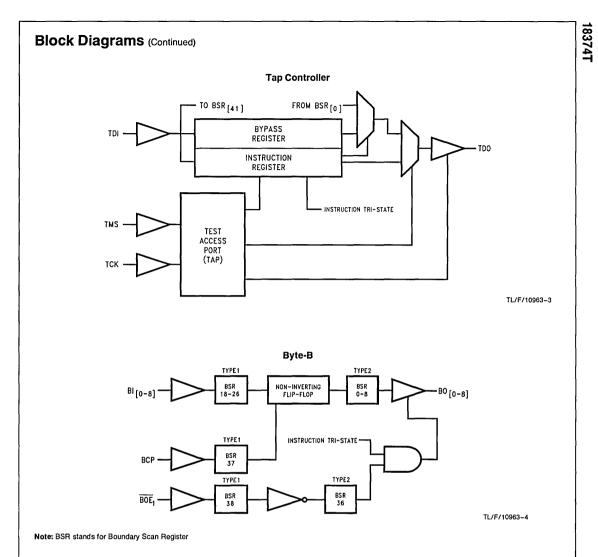

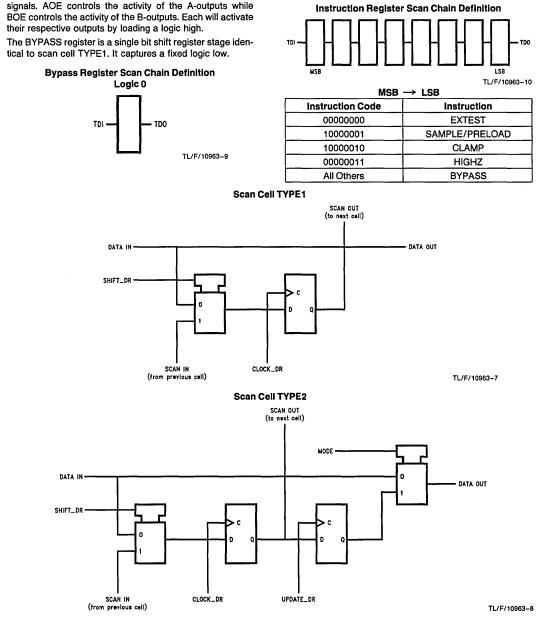

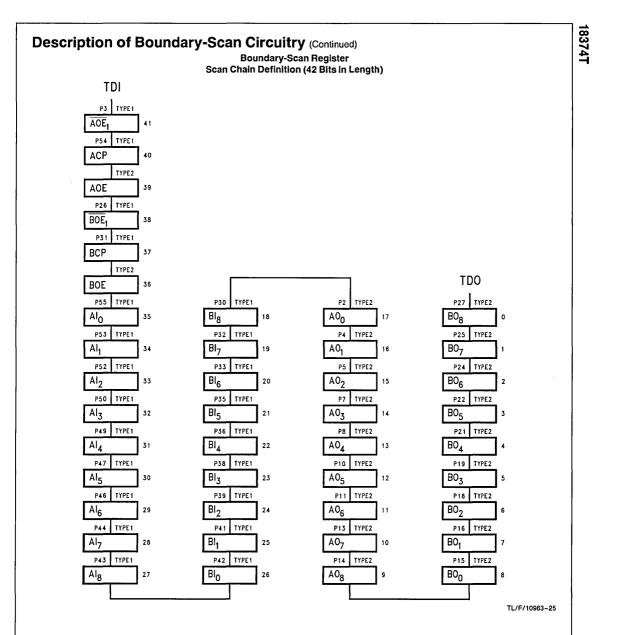

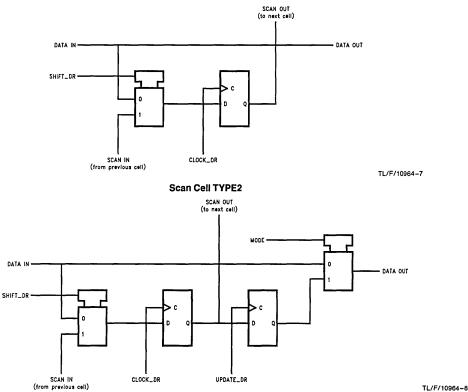

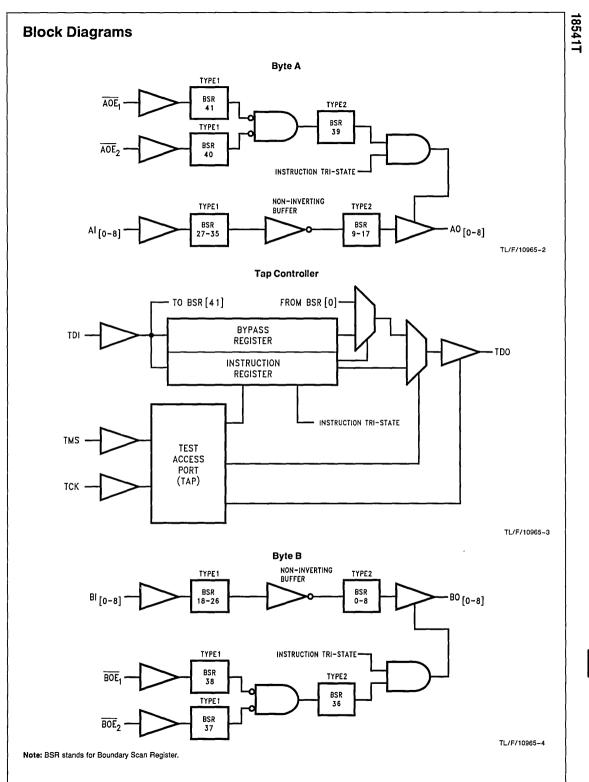

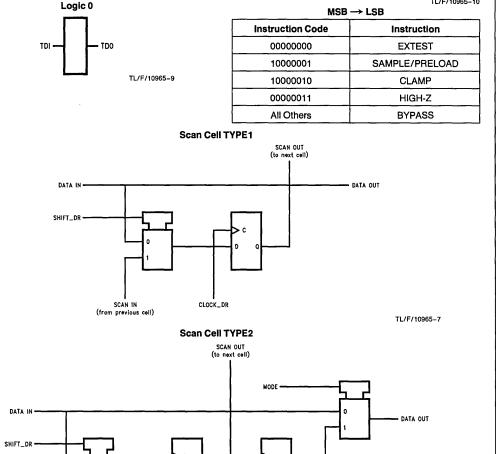

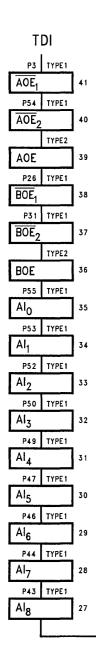

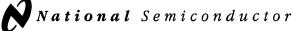

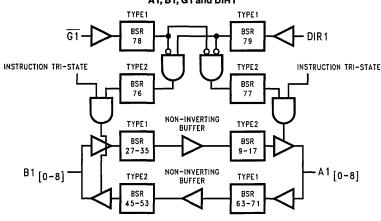

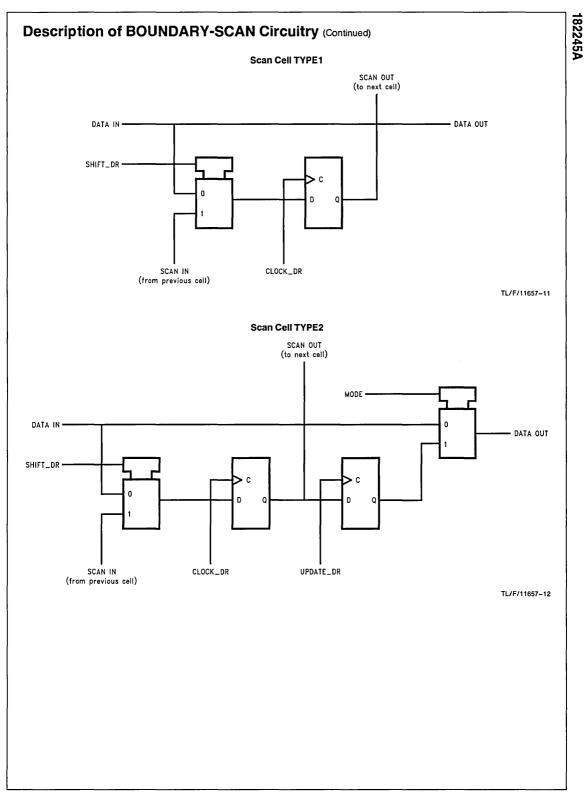

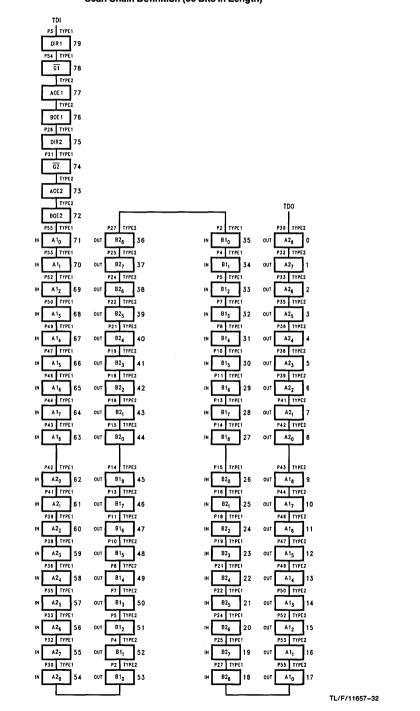

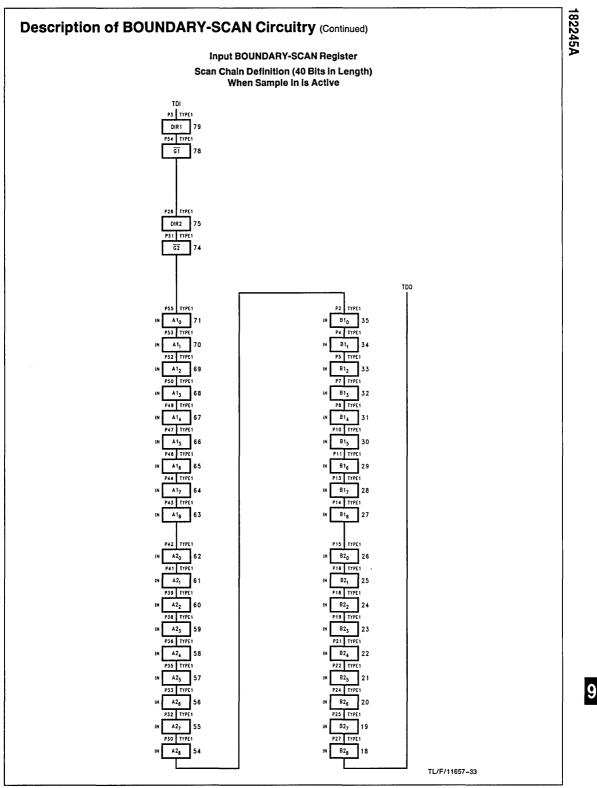

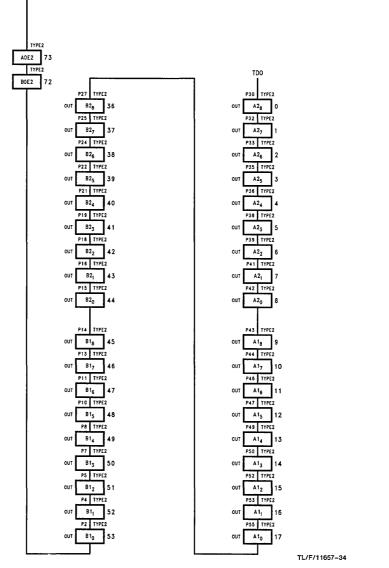

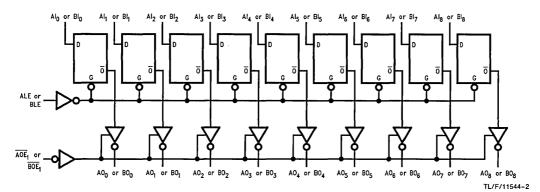

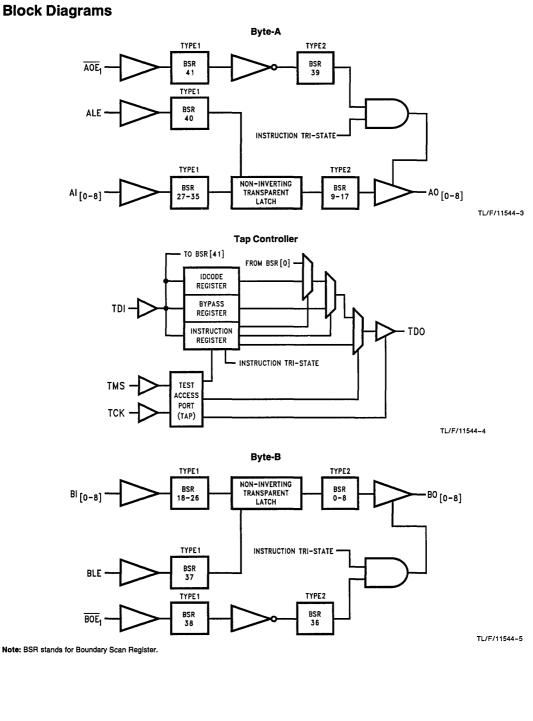

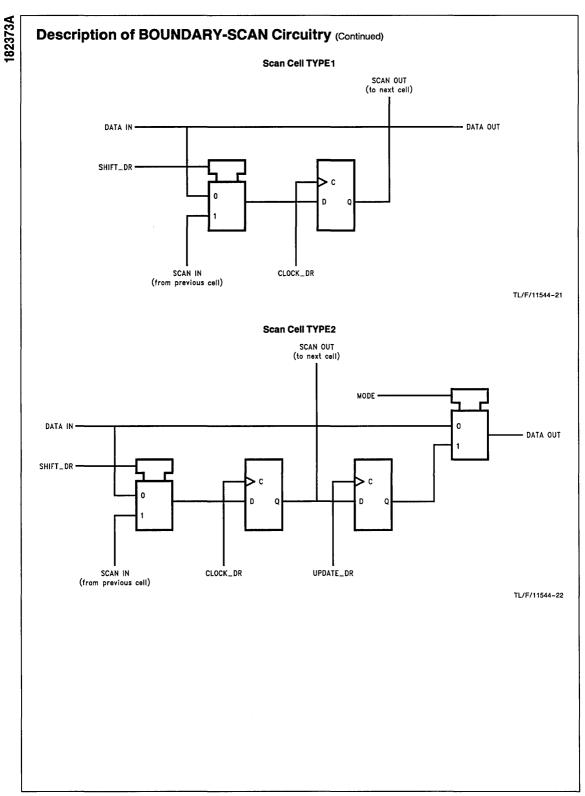

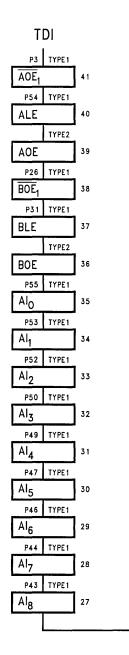

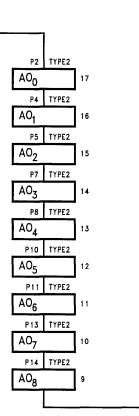

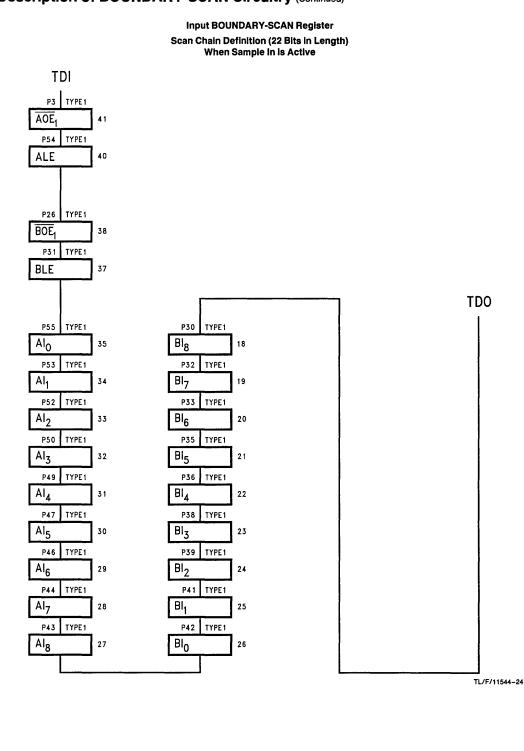

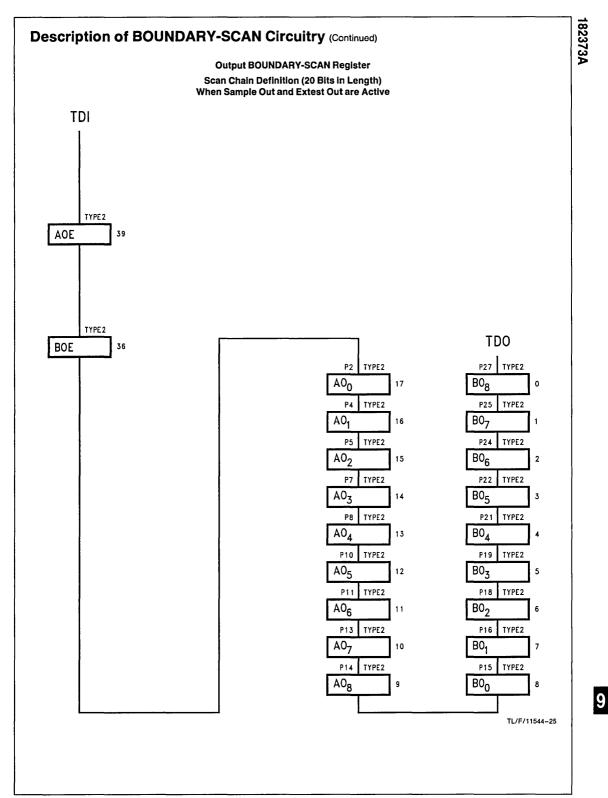

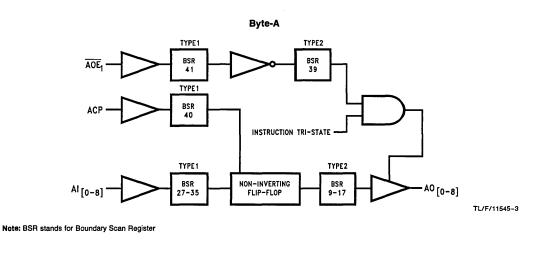

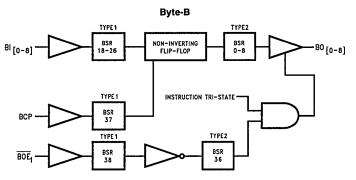

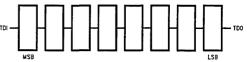

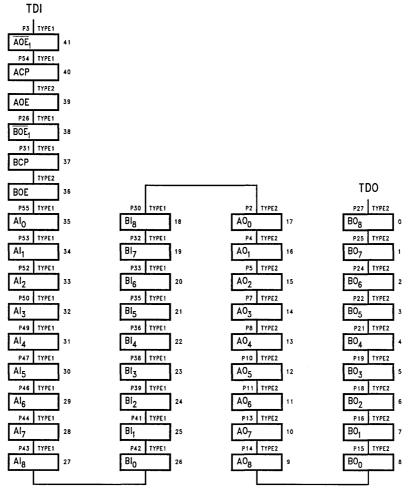

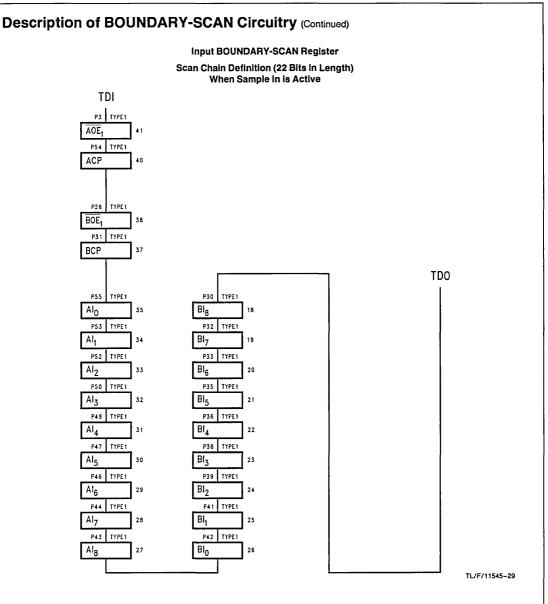

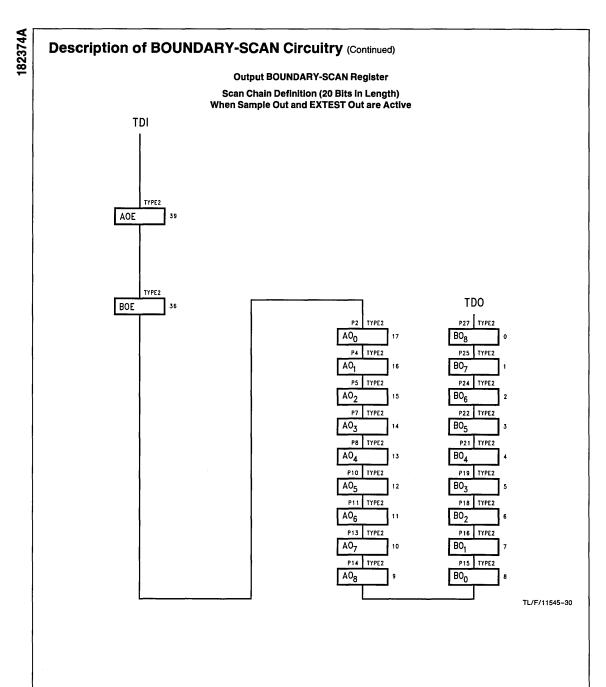

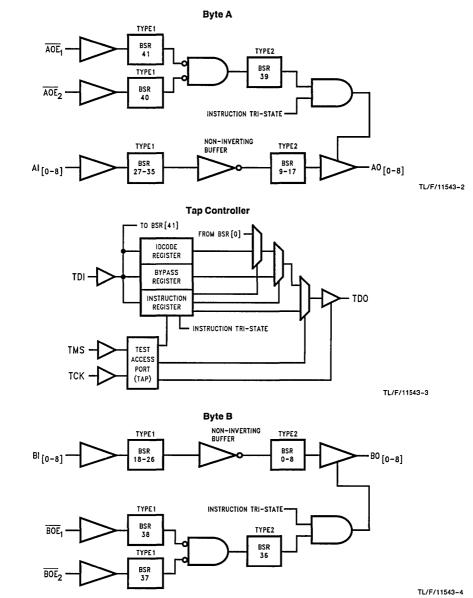

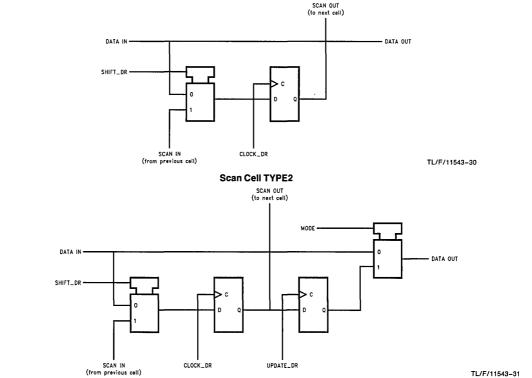

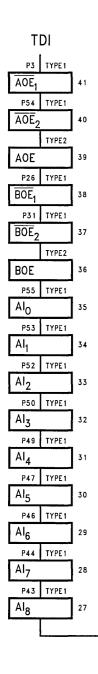

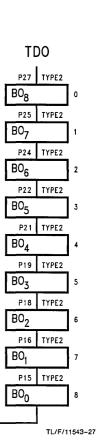

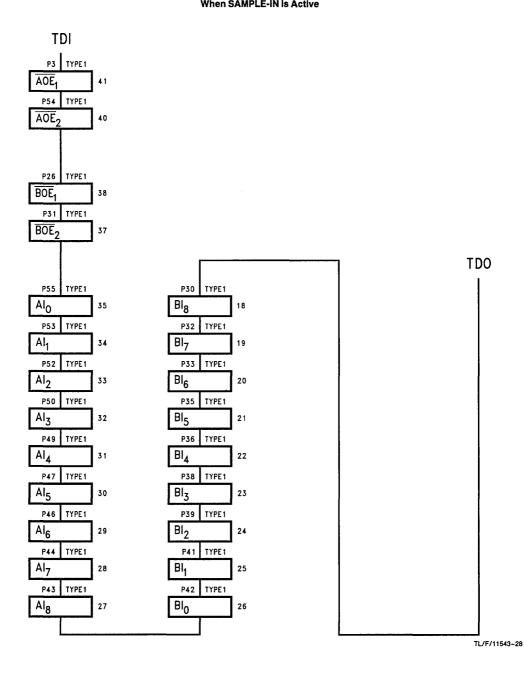

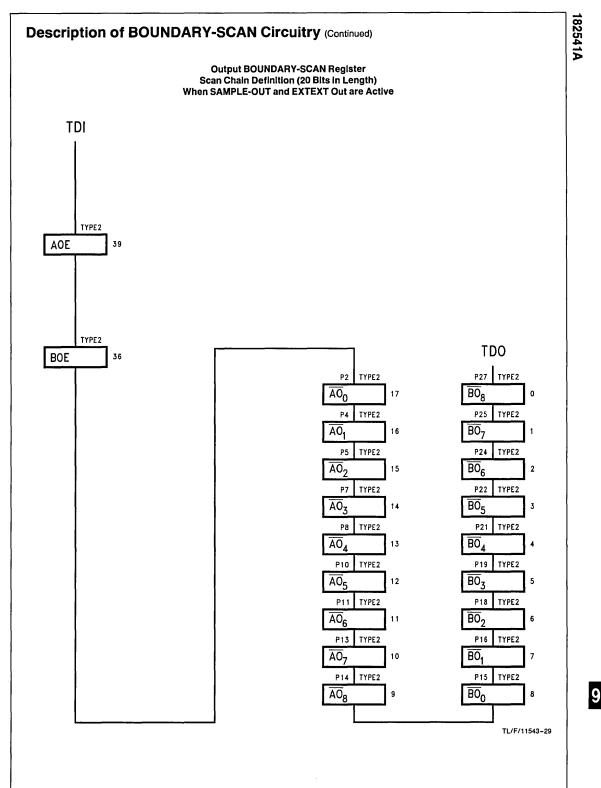

The scan cells used in the Boundary-Scan register are one of the following two types depending upon their location. Scan cell TYPE1 is intended to solely observe system data, while TYPE2 has the additional ability to control system data. (See IEEE Standard 1149.1 *Figure 10–11* for a further description of scan cell TYPE1 and *Figure 10–12* for a further the description of scan cell TYPE2.)

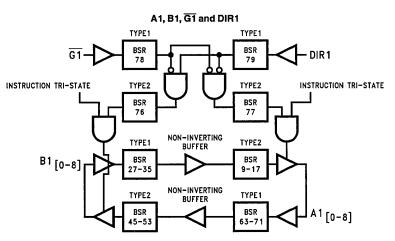

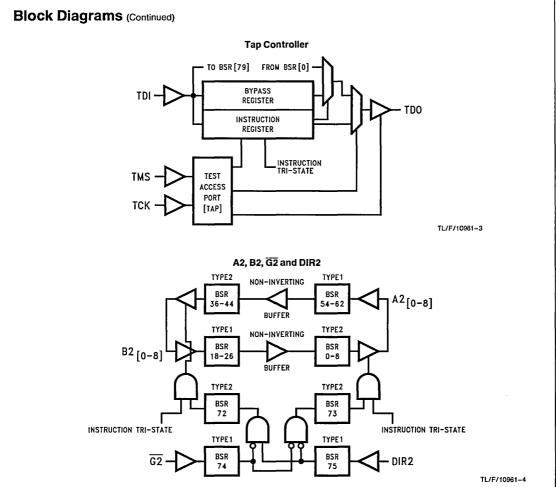

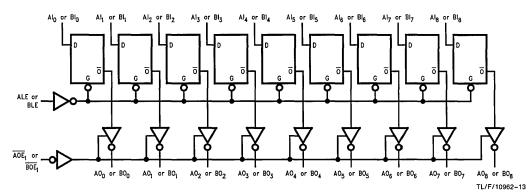

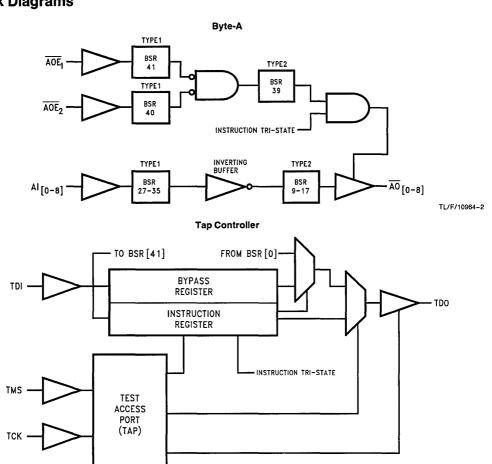

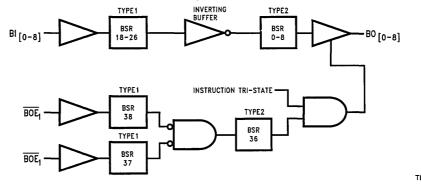

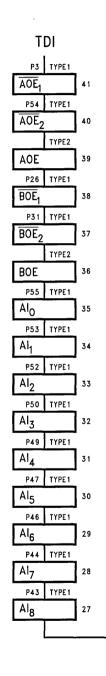

Scan cell TYPE1 is located on each system input pin while scan cell TYPE2 is located at each system output pin as well as at each of the two internal active-high output enable signals see *Figure 1*. AOE controls the activity of the A-outputs while BOE controls the activity of the B-outputs. Each will activate their respective outputs by loading a logic high.

### **Boundary-Scan Registers**

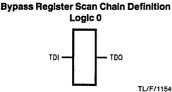

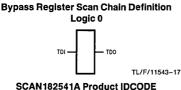

The BYPASS register is a single bit shift register stage identical to scan cell TYPE1. It captures a fixed logic low.

TL/F/12132-1 **FIGURE 2. Bypass Register Scan Chain Definition**

#### **TABLE Ia. Scan ABT Product IDCODE** (32-Bit Code per IEEE 1149.1)

| Device      | Version | Entity | Part<br>Number | Manufacturer<br>ID | Required by<br>1149.1 |

|-------------|---------|--------|----------------|--------------------|-----------------------|

| SCAN182245A | 0000    | 111111 | 0000000000     | 00000001111        | 1                     |

| SCAN182373A | 0000    | 111111 | 0000001000     | 00000001111        | 1                     |

| SCAN182374A | 0000    | 111111 | 0000000111     | 00000001111        | 1                     |

| SCAN182541A | 0000    | 111111 | 0000001001     | 00000001111        | 1                     |

| MSB         |         |        |                |                    | LSB                   |

#### MSB

#### TABLE Ib. SCAN CMOS Device Identification (8-Bit Code Described in Device BSDL)

| Device     | 8-Bit Code |  |

|------------|------------|--|

| SCAN18245T | 00111101   |  |

| SCAN18373T | 00101101   |  |

| SCAN18374T | 00011101   |  |

| SCAN18540T | 01001101   |  |

| SCAN18541T | 10111101   |  |

Scan ABT devices include the 32-bit 1149.1-compliant IDCODE as shown in Table Ia. Scan CMOS devices do not include the IDCODE, however they do have an 8-bit device identification code which is described in its device BSDL model and shown in Table lb.

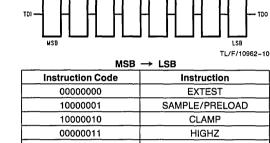

Tables IIa, IIb and IV show which instructions are included for SCAN ABT and SCAN CMOS.

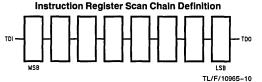

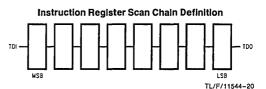

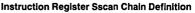

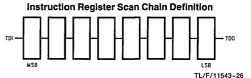

The INSTRUCTION register Figure 3 is an 8-bit register which, for SCAN ABT, captures the default value of 10000001 (SAMPLE/PRELOAD, Table IIa) during the CAPTURE-IR instruction command. The benefit of capturing SAMPLE/PRELOAD as the default instruction during CAPTURE-IR is that the user is not required to shift in the 8-bit instruction for SAMPLE/PRELOAD. The sequence of: CAPTURE-IR → EXIT1-IR → UPDATE-IR will update the SAMPLE/PRELOAD instruction.

In the case of SCAN CMOS, the 8-bit INSTRUCTION register captures the device's 8-bit identification code in Table lb. For more information refer to the section on instruction definitions.

#### **TABLE IIa. SCAN ABT Instruction Registers**

| Instruction Code | Instruction    |  |

|------------------|----------------|--|

| 0000000          | EXTEST         |  |

| 1000001          | SAMPLE/PRELOAD |  |

| 10000010         | CLAMP          |  |

| 00000011         | HIGH-Z         |  |

| 01000001         | SAMPLE-IN      |  |

| 01000010         | SAMPLE-OUT     |  |

| 00100010         | EXTEST-OUT     |  |

| 10101010         | IDCODE         |  |

| 1111111          | BYPASS         |  |

| All Others       | BYPASS         |  |

#### **TABLE IIb. SCAN CMOS Instruction Register**

| Instruction Code | Instruction    |

|------------------|----------------|

| 0000000          | EXTEST         |

| 1000001          | SAMPLE/PRELOAD |

| 10000010         | CLAMP          |

| 00000011         | HIGH-Z         |

| All Others       | BYPASS         |

### **Boundary Scan Overview**

This document is a supplement to the National Semiconductor SCAN Test Access Logic products datasheets. It provides an overview of the IEEE 1149.1 (boundary scan) circuit features included on the National's SCAN devices. The IEEE 1149.1 Std. document should be consulted for more detailed information about the IEEE 1149.1 standard requirements.

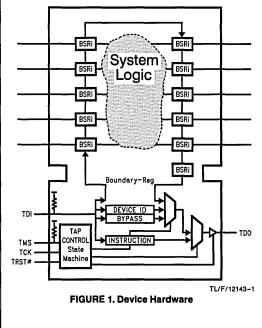

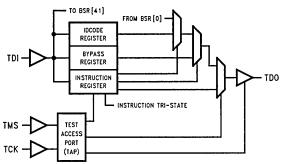

The IEEE 1149.1 boundary scan standard circuitry is comprised of 3 functional blocks—a test access port (TAP), a TAP controller and a set of registers.

#### I. TEST ACCESS PORT (TAP)

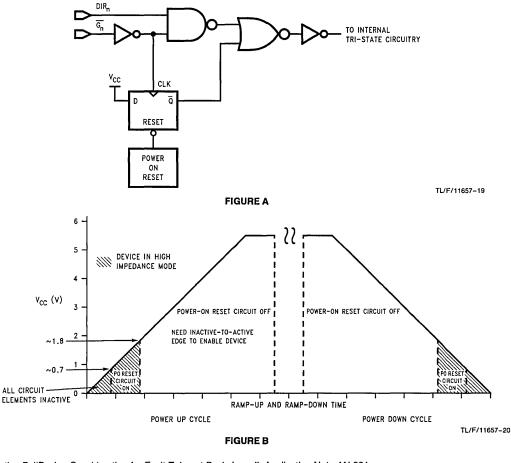

The Test Access Port (TAP) consists of four pins dedicated solely to the operation of the test logic. The four pins include TMS (Test Mode Select), TDI (Test Data In), TDO (Test Data Out), and TCK (Test Clock). These products contain a power-up reset function in lieu of adding the TRST pin. The motivation of this option is to save package size and hence customer board space, thus making the decision to implement 1149.1 less costly to the system designer.

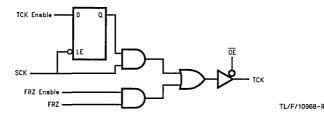

TCK: This input provides the test clock for the test logic defined by the IEEE 1149.1 Standard. In accordance with the standard requirements, all test logic will retain its state indefinitely upon stopping TCK at a logic low, or 0. Additionally, the same retention may occur upon stopping TCK at a logic high, or 1, which is a permission granted by the standard. The motivation for TCK to be a dedicated test input is 1) to insure that it can be used independently of system clocks running at different frequencies, 2) that it permits shifting of test data without altering any system logic state when undertaking on-line system monitoring tasks, and 3) that it can be used to test all board interconnect even when that interconnect transfers clock signals from one device to another.

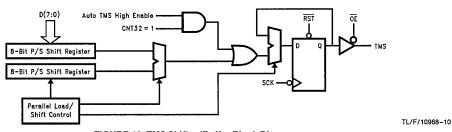

TMS: This input is the command signal to control system operation modes. Its value is accepted into the test logic upon the rising edge of TCK. This input has a pull-up resistor to implement a logic high for an undriven input. The requirement that an unforced TMS input produce a logic high is to ensure that the normal operation of the design can continue without interference from the test logic by guaranteeing that an undriven TMS input can put the TAP Controller into the Test Logic Reset state.

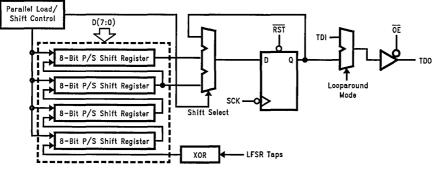

TDI: This signal provides the serial data input of test instructions and data to the test logic. Its value is accepted into the test logic upon the rising edge of TCK. This input has a pullup resistor to implement a logic high for an undriven input. Test data will arrive at TDO without inversion after the appropriate number of clock cycles as determined by the length of the register currently connected between TDI and TDO. The requirement that an unforced TDI input produce a logic high is to assist in the determination of manufacturing defects in the test scan chain interconnect. A consistent where a break in the scan chain interconnect occurred.

**TDO:** This signal provides the serial data output of test instructions and data from the test logic. Changes in the logic state and drive activity for this output occur upon the falling edge of TCK. This is to avoid a race condition when TDO is connected to TDI of the next chip in the scan chain which is sampled on the rising edge. This output shall remain inactive except when the scanning of data is in progress. This is to permit the ability to multiplex scan chains on the board without causing signal contention between multiple TDO outputs connected together to form parallel scan chains.

### **II. TAP CONTROLLER**

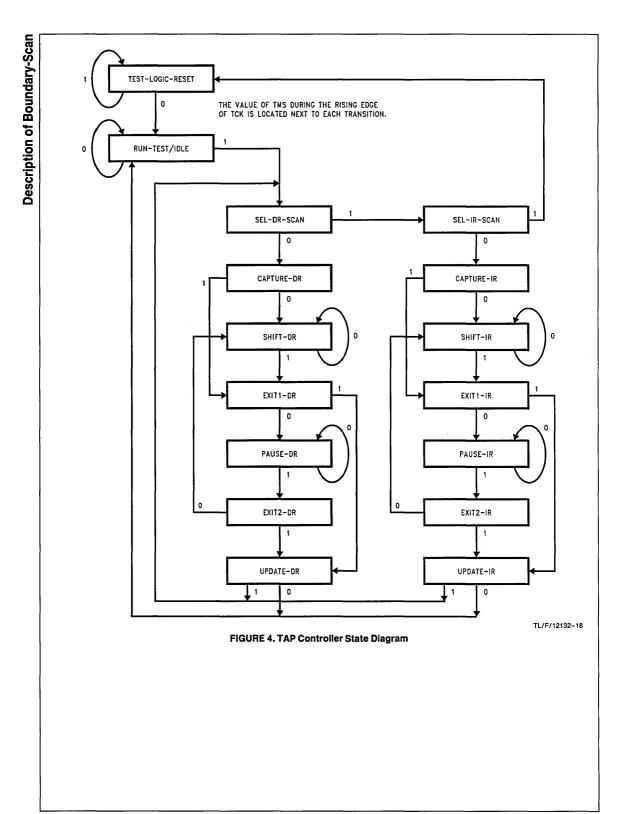

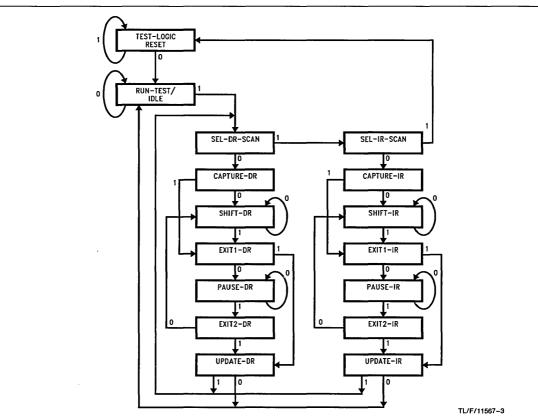

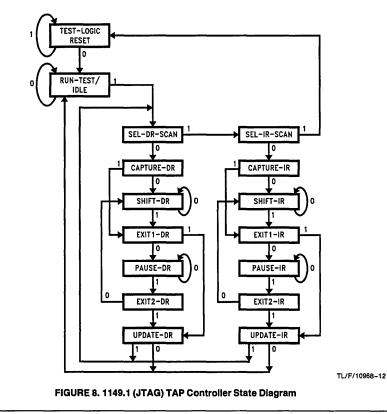

The TAP controller is a 16 state finite state machine which controls the insertion of the data and instruction registers (described later in this document) between TDI and TDO pins, and controls the flow of data through these registers.

Changes in the state of the TAP Controller (see *Figure 4*) are solely a response to the value of TMS upon the rising edge of TCK, or upon power-up (or the application of a logic low to the optional TRST input which is not included in the products referring to this document). In any given state actions of the test logic taken in that state occur on the falling or rising edge of TCK following the rising edge of TCK which caused the TAP Controller to enter the state initially.

Note: It may happen that actions to occur in one state happen on the same rising edge of TCK that cause the TAP Controller to enter the next state.

Test Logic Reset: In this state, the boundary scan test logic is disabled to allow the device to function normally. All boundary scan registers are reset to their default states. This state is entered by at most, five TCK cycles while holding TMS high or asynchronously by pulling TRST low (if TRST pin is included). The IEEE 1149.1 standard requires that an internal pull-up be included on the TMS pin to assure the TAP will return and remain in test logic reset if TMS is floating.

Run Test/Idle: This state provides a dual purpose depending on the active instruction. It is included to allow for optional or user defined tests, including BIST, to be performed. For the required IEEE 1149.1 instructions, all test data registers retain their current state (i.e., remain idle).

**SELECT-DR Scan:** This is a temporary state in which all test data registers retain their previous values.

**Capture-DR:** In this controller state data may be parallel loaded into the data register selected by the current instruction; otherwise, it retains its previous values.

SHIFT-DR: In this state the test data register selected between TDI and TDO by the current instruction will shift one stage at each rising edge of TCK. TDO is active during this state. Test data registers not selected by the current instruction maintain their previous values.

**Exit1-DR:** This is a temporary state in which all test data registers retain their previous values.

PAUSE-DR: This is a temporary state in which all data registers retain their previous values. This state is intended to temporarily halt the shifting of test data into the data register selected while retaining the ability to keep TCK running; TCK may be a free-running clock. This state is often used to load additional test vectors from external memory.

**Exit2-DR:** This is a temporary state in which all test data registers retain their previous values.

**UPDATE-DR:** The parallel output register of the selected test data register may be updated on the falling edge of TCK in this state, provided the test data register has such a parallel output register. The intent of the parallel output register is to provide the ability to apply the contents of the test data registers to the test logic simultaneously rather than applying it as it is being shifted in. All test data registers not selected by the current instruction retain their previous values.

http://www.national.com

SELECT-IR Scan: This is a temporary state in which the INSTRUCTION register retains its previous value.

**Capture-IR:** In this controller state, a fixed value must be parallel loaded into the INSTRUCTION register. The only restriction on what that data may be is that its least significant bit must be a logic high, or 1, and its second least significant bit must be a logic low, or 0. These opposite state bits can be used to check the correct operation of the scan chain on the board by forcing a bit toggle when the instructions are shifted.

SHIFT-IR: In this state the INSTRUCTION register selected between TDI and TDO will shift one stage at each rising edge of TCK. TDO is active during this state.

**Exit1-IR:** This is a temporary state in which the INSTRUC-TION register retains its previous value.

**PAUSE-IR:** This is a temporary state in which the INSTRUC-TION register retains its previous value. This state is intended to temporarily halt the shifting of test data into the IN-STRUCTION register while retaining the ability to keep TCK running. This state is often used to load additional test vectors from external memory.

**Exit2-IR:** This is a temporary state in which the INSTRUC-TION register retains its previous value.

**UPDATE-IR:** The parallel output register of the INSTRUC-TION register will be updated on the falling edge of TCK in this state. The intent of the parallel output register is to provide the ability to apply the contents of the INSTRUCTION register to the test logic simultaneously rather than applying it as it is being shifted in.

#### TDO OUTPUT ACTIVITY

Control of the TDO output buffer follows Table III.

| Controller<br>State | Register Selected<br>between<br>TDI and TDO | TDO<br>Driver |  |

|---------------------|---------------------------------------------|---------------|--|

| Test Logic Reset    | BYPASS                                      | Inactive      |  |

| Run Test/Idle       | BYPASS                                      | Inactive      |  |

| SELECT-DR Scan      | **                                          | Inactive      |  |

| SELECT-IR Scan      | INSTRUCTION                                 | Inactive      |  |

| Capture-IR          | INSTRUCTION                                 | Inactive      |  |

| SHIFT-IR            | INSTRUCTION                                 | ACTIVE        |  |

| Exit1-IR            | INSTRUCTION                                 | Inactive      |  |

| PAUSE-IR            | INSTRUCTION                                 | Inactive      |  |

| Exit2-IR            | INSTRUCTION                                 | Inactive      |  |

| UPDATE-IR           | INSTRUCTION                                 | Inactive      |  |

| Capture-DR          | **                                          | Inactive      |  |

| SHIFT-DR            | TEST DATA                                   | ACTIVE        |  |

| Exit1-DR            | **                                          | Inactive      |  |

| PAUSE-DR            | **                                          | Inactive      |  |

| Exit2-DR            | **                                          | Inactive      |  |

| UPDATE-DR           | **                                          | Inactive      |  |

TABLE III. TDO Output Buffer Control

Note: \*\* = Data register selected depends on currently active instruction.

#### FEATURES OF THE TAP CONTROLLER

The TAP Controller will not be initialized by the operation of any system pin such as a system reset. The TAP Controller will be initialized into the Test Logic Reset state upon power-up. This requirement is intended to avoid bus signal contention upon system power-up by disabling the test logic which allows the system logic to operate normally and hence be controlled to avoid any contention. (The TAP Controller will return to the Test Logic Reset state after, at most, five clock cycles of TCK with TMS high; but the time required to enact that operation may not be sufficient to avoid contention.)

Note that the TAP Controller has been defined such that six of the sixteen states have the ability to maintain their state provided that TMS remains at the same value it had when entering the state. Those states include Test Logic Reset to hold off the test logic during normal system operation, Run Test/Idle to undertake multi-cycle self tests, SHIFT-DR and SHIFT-IR to maintain the data shifting process for an extended period, and PAUSE-DR and PAUSE-IR to halt the shifting process while some other activity is performed such as retrieving test data from additional memory. This feature is available in any/all states where multiple clock cycles may be required to achieve the desired outcome or where activity is to be halted but still provide the ability to make TCK a free-running clock.

#### **III. BOUNDARY SCAN REGISTERS**

#### INSTRUCTION REGISTER

The INSTRUCTION register permits specific commands to be shifted into the design to select a particular test data register and/or a specific test function. Additionally, the capture sequence of the INSTRUCTION register permits design specific data to be examined.

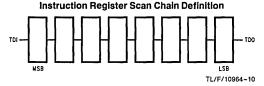

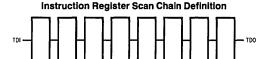

The INSTRUCTION register must be at least two bits long, the specific INSTRUCTION register included into the devices which reference this document is eight bits long, and the two least significant bits must capture the value "01". The significance of the two bit minimum length is two fold. First it permits the ability to supply unique codes for at least each of the three mandatory instructions required by the standard. Secondly, the bit value "01" in the least significant locations can be used to check the connectivity of the scan chain by forcing a bit toggle at each instruction during a scan of the INSTRUCTION registers. This technique not only assists in determining the correct connectivity of the scan chain about the board, but also assists in pin-pointing the location of any break in the scan chain.

All of National's SCAN Test Access Logic devices utilize an 8-bit instruction register. For the SCAN CMOS Test Access Logic devices, the 6 most significant bits which are loaded into the instruction register during the CAPTURE-IR state are used to provide a "pseudo ID code". The different codes captured into the INSTRUCTION register is a means of distinguishing the products in order to supply a method of evaluating the correct board placement of the products when an interrogation is performed through the scan chain only.

The captured "pseudo ID code" value is provided in each of the SCAN CMOS Test Access logic datasheets.

The SCAN ABT Test Access Logic devices include the IEEE 1149.1 optional ID CODE register and each device captures the same fixed value. This fixed value is the opcode for the SAMPLE/PRELOAD instruction, 1000001.

The order of scan through the INSTRUCTION register must be least-to-most; that is, the least significant bit is closest to TDO for a loaded instruction. During the SHIFT-IR state the instruction shifts one bit between TDI and TDO upon each rising edge of TCK and appears without inversion at TDO following the appropriate number of TCK cycles depending on the fixed length of the INSTRUCTION register. A latched parallel output register accompanies each bit of the IN-STRUCTION register such that the instruction can be updated or applied to the test logic simultaneously, rather than during the shift sequence. This latched parallel output changes upon the falling edge of TCK in the Update-IR state as well as upon the falling edge of TCK during the Test Logic Reset state. (It changes asynchronously upon the low assertion of the TRST input or upon power-up.)

Each instruction will identify a particular test data register to be connected between TDI and TDO when in the Shift-DR state along with defining any particular test actions to occur to that test data register and/or any others.

#### INSTRUCTION DEFINITIONS

The required instructions (see Table IV) include the BYPASS, EXTEST, and SAMPLE/PRELOAD instructions with optional instructions of HIGH-Z and CLAMP; and, for SCAN ABT only, the IDCODE. The additional instructions SAMPLE-IN, SAMPLE-OUT and EXTEST-OUT have also been incorporated into the SCAN ABT devices. The optional INTEST instruction was not incorporated because it adds a delay penalty to the system logic from gating that logic in order to provide controllability as well as observability. In the following descriptions each instruction will identify the test data register to be connected between TDI and TDO during the SHIFT-DR state, any restrictions on the binary codes used to implement the instruction, and what test data register same used in undertaking the actions of the instruction.

1. EXTEST. This instruction allows circuitry external to the component package, typically the board interconnect, to be tested. Boundary-Scan register cells at the output pins are used to apply test stimuli, while those at the input pins capture test results. When this instruction is selected, the states of all signals on the system input pins will be loaded into the Boundary-Scan register upon the rising edge of TCK in the Capture-DR state and the contents of the Boundary-Scan register will solely define the state of the system outputs upon the falling edge of TCK in the UP-DATE-DR state. This instruction is mandatory under the guidelines of IEEE Standard 1149.1. The 000. . .0 instruction binary code must invoke the EXTEST instruction. During this instruction the Boundary-Scan register is connected between TDI and TDO in the SHIFT-DR state. Additional binary codes for this instruction are permitted.

2. SAMPLE/PRELOAD. This instruction allows a "snapshot" of the normal operation of the component to be taken and examined. It also allows data values to be loaded onto the latched parallel outputs of the Boundary-Scan SHIFT register prior to selection of another Boundary-Scan test instruction. During this instruction the Boundary-Scan register is connected between TDI and TDO in the SHIFT-DR state. When this instruction is selected, the states of all signals on the system pins will be loaded into the Boundary-Scan register upon the rising edge of TCK in the CAPTURE-DR state and the contents of the Boundary-Scan register will be loaded into the parallel output register included with the Boundary-Scan register bits upon the falling edge of TCK in the UPDATE-DR state.

Note that by interfacing these two actions through the Exit1-DR state, the current state of the system pins can be captured into the Boundary-Scan register and stored into its parallel output registers for later application back onto those same pins. When the SAMPLE/PRELOAD instruction is selected, the test logic shall have no impact upon the system logic in performing its system function. This instruction is mandatory under the guidelines of IEEE Standard 1149.1, but the binary code may be device specific.

3. BYPASS. This instruction allows rapid movement of test data to and from other components on a board that are required to perform test operations by selecting the BYPASS register, a single-bit shift-register stage, between TDI and TDO in the SHIFT-DR state to provide a minimum-length serial scan path. This instruction is mandatory under the guidelines of IEEE Standard 1149.1. The 111...1 instruction binary code must invoke the BYPASS instruction. This specific opcode, along with the requirement that an undriven TDI input produce a logic high value, is intended to load the BYPASS instruction during an instruction-scan cycle if the scan chain is broken. In such a case all instructions following the break in the scan chain will be loaded with the BYPASS instruction and hence have no impact upon the system's normal functional operation. Additional binary codes for this instruction are permitted. When the BYPASS instruction is selected, the test logic shall have no impact upon the system logic in performing its system function. When the optional IDCODE register is not included, this instruction is loaded into the INSTRUCTION register in the Test Logic Reset state.

| IEEE 1149.1 | SCAN ABT                    | SCAN CMOS   |  |

|-------------|-----------------------------|-------------|--|

| Required    | BYPASS                      | BYPASS      |  |

| Required    | EXTEST                      | EXTEST      |  |

| Required    | SAMPLE/PRELOAD SAMPLE/PRELO |             |  |

| Optional    | HIGH-Z                      | HIGH-Z      |  |

| Optional    | CLAMP                       | CLAMP CLAMP |  |

| Optional    | IDCODE                      |             |  |

| Optional    | SAMPLE-IN                   |             |  |

| Optional    | SAMPLE-OUT                  |             |  |

| Optional    | EXTEST-OUT                  |             |  |

#### TABLE IV. Required and Optional Instructions Included

- 4. CLAMP. This instruction allows fixed guarding values to be placed on signals that control the operation of logic not involved in the test, but does not require that the Boundary-Scan register be part of the serial scan path as in the EXTEST instruction. The contents of the Boundary-Scan register will solely define the state of the system outputs upon the falling edge of TCK in the UPDATE-IR state for this instruction. The BYPASS register is connected between TDI and TDO in the SHIFT-DR state. This instruction is optional under the guidelines of IEEE Standard 1149.1 and therefore the binary code/s may be device specific.

- 5. HIGH-Z. This instruction allows all of a components system outputs to be placed in an inactive drive state to permit its outputs to be safely backdriven during testing of other integrated circuits on the printed circuit board. All outputs of the device will become inactive even if during their normal system function they are two-state outputs. The BYPASS register is connected between TDI and TDO in the SHIFT-DR state. This instruction is optional under the guidelines of IEEE Standard 1149.1 and therefore the binary code/s may be device specific.

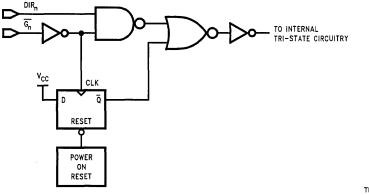

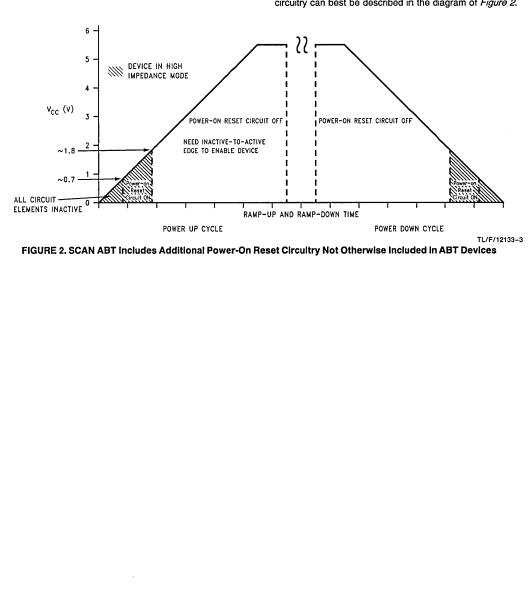

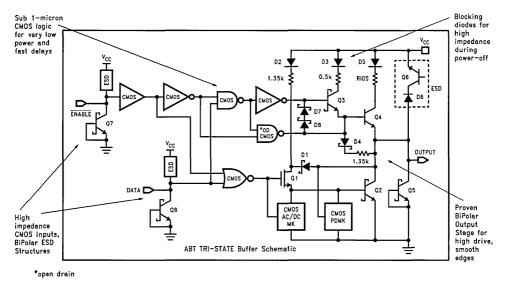

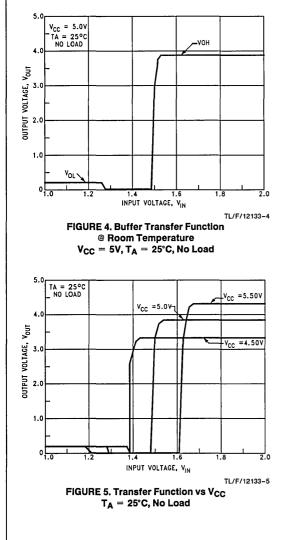

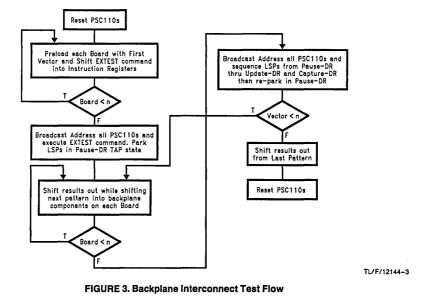

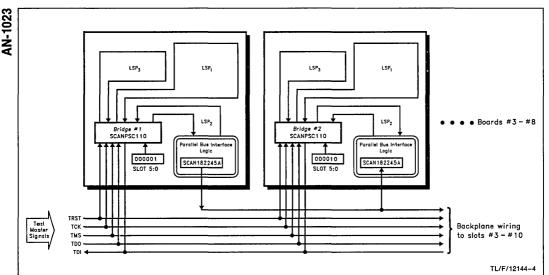

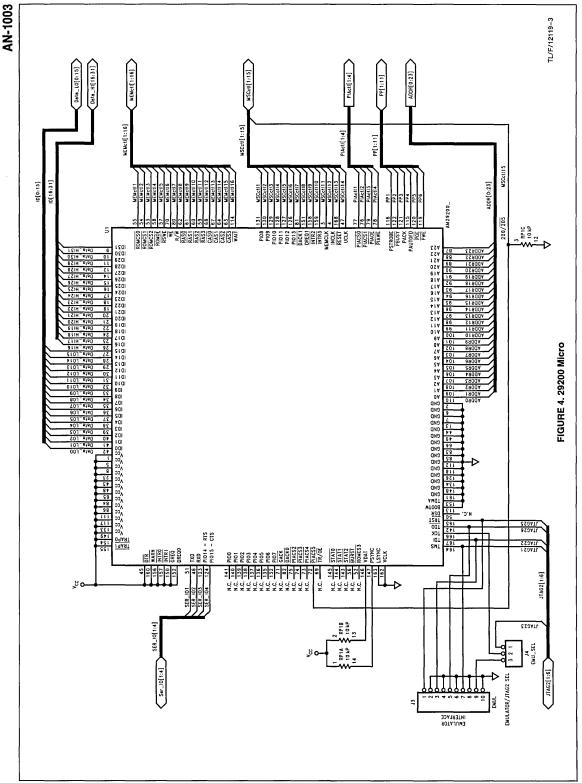

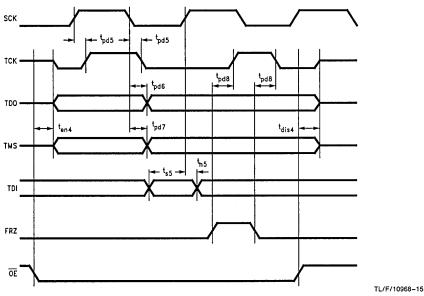

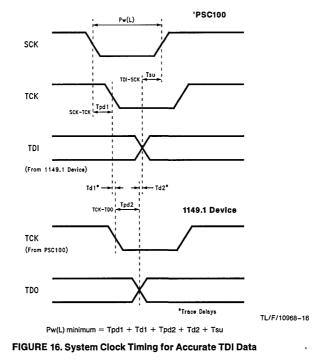

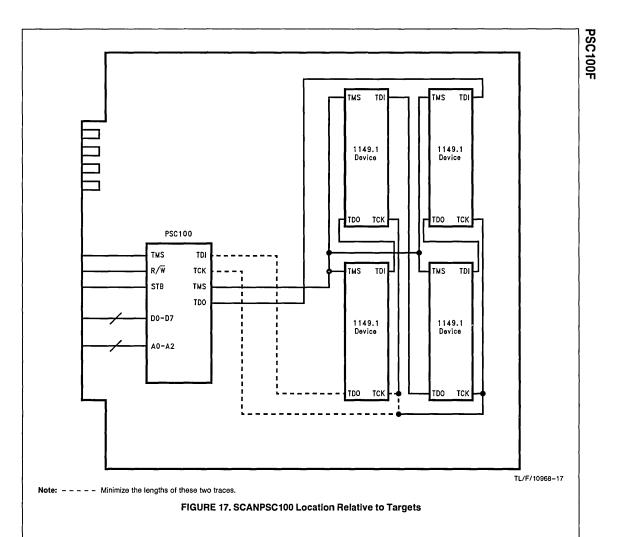

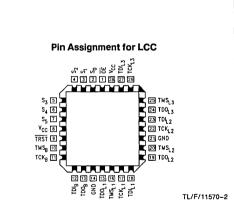

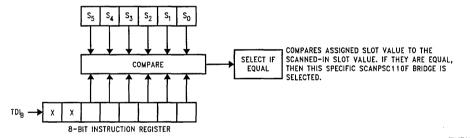

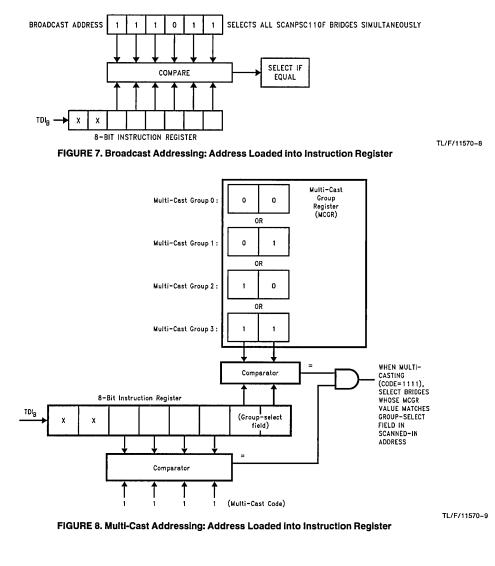

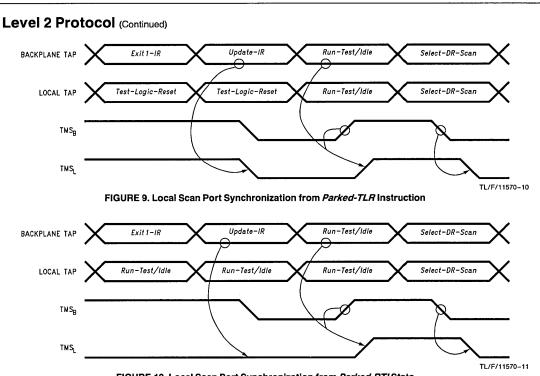

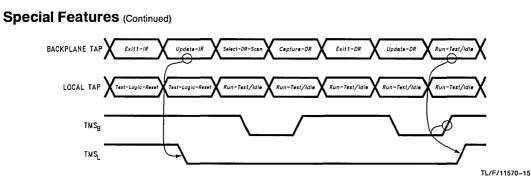

- IDCODE. (SCAN ABT and PSC110F only.) This instruction allows a blind interrogation of an identification code that is unique to this device type. During this instruction the IDCODE Register is connected between TDI and TDO in the SHIFT-DR state.