basic family user's manual

COP8

COP8 Basic Family User's Manual

Literature Number 620895-002 June 1996

# REVISION RECORD

| REVISION | RELEASE DATE | SUMMARY OF CHANGE                                                                                                                                                                                                                                          |

|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A        | 04/87        | First Release.<br>COPS™ COP820C/COP840C<br>User's Manual<br>NSC Publication Number 420410703-001.                                                                                                                                                          |

| В        | 10/88        | Modified the program store memory section, corrected the hex and binary information for the load B pointer and the return from subroutine, and modified the description of subtract with carry. Incorporated new documentation standards where applicable. |

| B1       | 03/89        | Name change. MOLE changed to microcontroller development system within text.                                                                                                                                                                               |

| C        | 05/92        | Reformatted and updated entire manual.                                                                                                                                                                                                                     |

| D        | 02/95        | Updated Appendices A and B.                                                                                                                                                                                                                                |

| -001     | 05/95        | Modified to incorporate information on the COP912C/912CH and the COP840CJ/842CJ/940CJ/942CH micorcontrollers.                                                                                                                                              |

| -002     | 06/96        | Modified to delete obsoleted parts.                                                                                                                                                                                                                        |

### PREFACE

The  $COP8^{\text{TM}}$  family of 8-bit microcontrollers is ideally suited to embedded control applications such as keyboard interfaces, electronic cordless telephones, home applications, and ABS systems. The design of this family takes advantage of National Semiconductor's  $M^2CMOS^{\text{TM}}$  manufacturing technology, providing a useful combination of high performance, low power consumption, and reasonable cost. The rich instruction set and flexible addressing modes of the COP8 controllers contribute to their high performance and code efficiency.

This manual describes the features, architecture, instruction set, and usage of the COP8 microcontrollers. The first eight chapters describe the general features found in all family members. Later chapters describe the individual family members and their specific features. The following specific devices are covered:

- COP912/820/840/880

- COP820C/840CJ

Chapter 1, OVERVIEW, provides a general overview of COP8 family with specific feature comparisons.

Chapter 2, ARCHITECTURE, describes the overall architecture of the COP8 microcontroller, including the CPU core, registers, memory organization, reset operation, and clock options.

Chapter 3, INTERRUPTS, describes the device interrupts.

Chapter 4, TIMER, describes the on-chip timer and its various operating modes.

Chapter 5, MICROWIRE/PLUS, describes the microcontroller's MICROWIRE/PLUS serial interface and its operating modes.

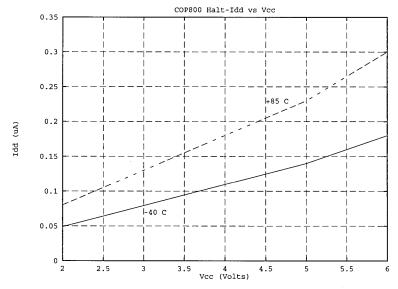

Chapter 6, POWER SAVE MODE, describes an operating mode in which the microcontroller is halted, reducing power consumption almost to zero while maintaining the processor status and all register contents.

Chapter 7, INPUT/OUTPUT, describes the input/output ports of the microcontroller and how they are used.

Chapter 8, INSTRUCTION SET, describes the instruction set of the COP8 microcontrollers, including detailed descriptions of each instruction.

Chapters 9, and 10 describe the specific features of the COP912/COP820/840/880, and COP820CJ/COP840CJ respectively.

COP8, MICROWIRE/PLUS and MICROWIRE are trademarks of National Semiconductor Corporation. TRI-STATE is a registered trademark of National Semiconductor Corporation.

Appendix A, APPLICATION HINTS, contains COP8 application information.

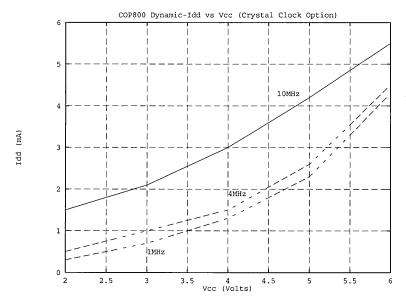

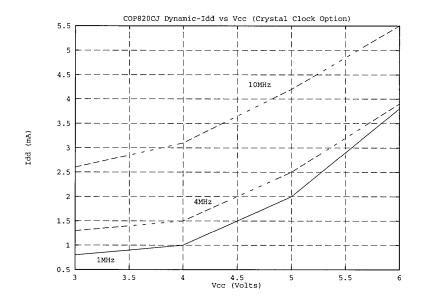

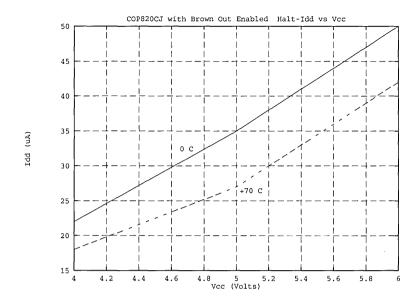

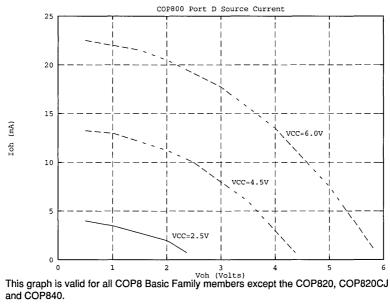

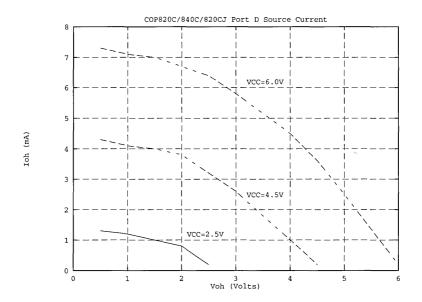

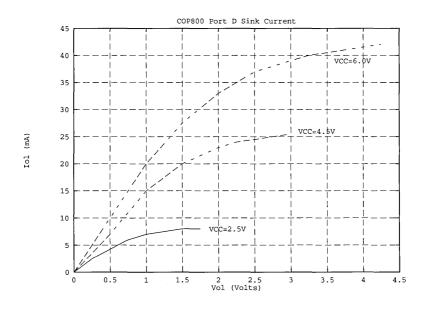

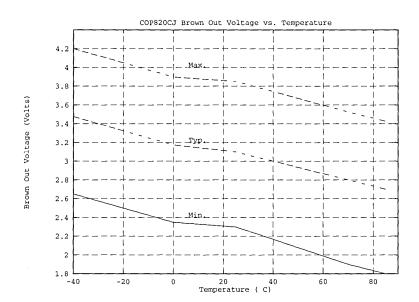

Appendix B covers device electrical characterization data.

Additional information on individual COP8 family members is available from their respective data sheets.

The information contained in this manual is for reference only and is subject to change without notice.

No part of this document may be reproduced in any form or by any means without the prior written consent of National Semiconductor Corporation.

| Chapter 1  | OVERVIEW                                      |

|------------|-----------------------------------------------|

| 1.1        | INTRODUCTION                                  |

| 1.2        | BASIC FEATURES                                |

| 1.3        | DEVICE SPECIFIC FEATURES. 1-2                 |

| _,,        |                                               |

| Chapter 2  | ARCHITECTURE                                  |

| 2.1        | INTRODUCTION                                  |

| 2.2        | BLOCK DIAGRAM2-1                              |

| 2.3        | MEMORY ORGANIZATION                           |

|            | 2.3.1 Program Memory                          |

|            | 2.3.2 Data Memory                             |

|            | 2.3.3 Memory Mapped I/O Registers             |

| 2.4        | CORE REGISTERS                                |

|            | 2.4.1 Accumulator                             |

|            | 2.4.2 Program Counter                         |

|            | 2.4.3 Control Registers                       |

|            | 2.4.4 Data Registers                          |

|            | 2.4.5 MICROWIRE/PLUS Register 2-9             |

|            | 2.4.6 Timer Registers                         |

| 2.5        | CPU OPERATION                                 |

|            | 2.5.1 Memory Fetches                          |

|            | 2.5.2 Instruction Decoding and Execution      |

|            | 2.5.3 Interrupt and Error Handling2-16        |

| 2.6        | RESET2-17                                     |

| 2.7        | CLOCK OPTIONS                                 |

|            | 2.7.1 Crystal Oscillator                      |

|            | 2.7.2 RC Oscillator                           |

|            | 2.7.3 RC Oscillator for the COP840CJ Only2-19 |

|            | 2.7.4 External Oscillator                     |

| Chapter 3  | INTERRUPTS                                    |

| 3.1        |                                               |

| 3.1        | INTRODUCTION                                  |

| 3.2<br>3.3 | MASKABLE INTERRUPTS3-1                        |

| ა.ა        |                                               |

|            | 3.3.1 Timer 1 Interrupt                       |

| 3.4        | 3.3.2 External Interrupt                      |

| 3.4        | SOFTWARE TRAP3-4                              |

| Chapter 4  | TIMER                                         |

| 4.1        | INTRODUCTION                                  |

| 4.2        | TIMER/COUNTER BLOCK                           |

| 4.3        | TIMER CONTROL BITS                            |

| 4.4        | TIMER OPERATING MODES4-3                      |

|            | 4.4.1 PWM Mode                                |

|            | 4.4.2 External Event Counter Mode             |

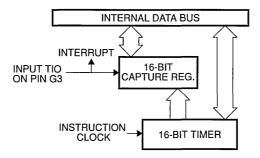

|           | 4.4.3  | Input Capture Mode                         | . 4-5 |

|-----------|--------|--------------------------------------------|-------|

| Chapter 5 | MIC    | ROWIRE/PLUS                                |       |

| 5.1       | INTROD | OUCTION                                    | . 5-1 |

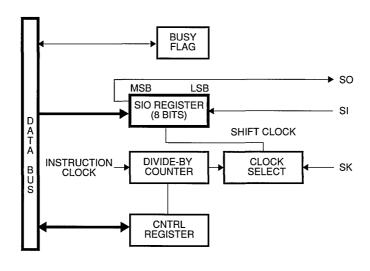

| 5.2       |        | Y OF OPERATION                             |       |

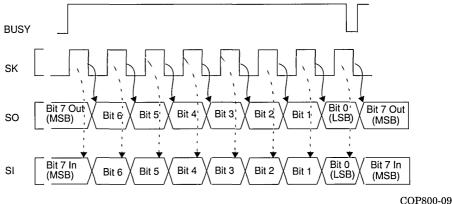

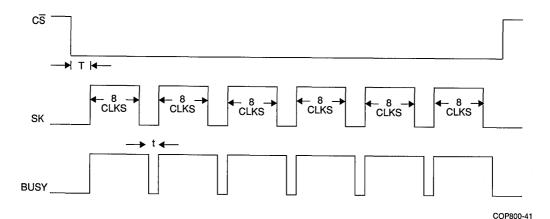

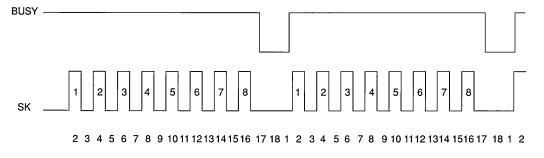

| 0.2       | 5.2.1  | Timing                                     |       |

|           | 5.2.2  | Port G Configuration                       |       |

|           | 5.2.3  | SK Clock Operation                         |       |

|           | 5.2.4  | Busy Flag                                  |       |

| 5.3       |        | R MODE OPERATION EXAMPLE                   |       |

| 5.4       |        | MODE OPERATION EXAMPLE                     |       |

| 0.4       | DLAVE  | WODE OF ERRITOR EXAMILEE                   | . 0-0 |

| Chapter 6 |        | VER SAVE MODE                              |       |

| 6.1       | INTROD | OUCTION                                    | . 6-1 |

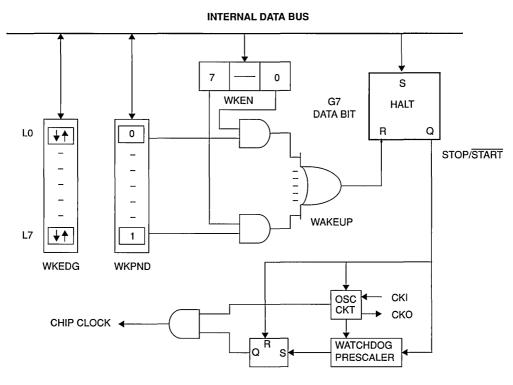

| 6.2       | CLOCK- | STOPPING METHOD                            | . 6-1 |

| 6.3       | PORT G | METHOD                                     | . 6-2 |

| Chapter 7 | INP    | UT/OUTPUT                                  |       |

| 7.1       |        | OUCTION                                    | 7 1   |

| 7.1 $7.2$ |        | COLOR                                      |       |

| 7.2 $7.3$ |        |                                            |       |

| 7.3       |        |                                            |       |

|           |        |                                            |       |

| 7.5       |        |                                            |       |

| 7.6       |        | NATE PORT FUNCTIONS                        |       |

| 7.7       | ALTERN | NATE PORT FUNCTIONS                        | . 1-3 |

| Chapter 8 | INS    | TRUCTION SET                               |       |

| 8.1       | INTROD | OUCTION                                    | . 8-1 |

| 8.2       | FEATUR | RES                                        | . 8-1 |

| 8.3       | ADDRES | SSING MODES                                | . 8-1 |

|           | 8.3.1  | Operand Addressing Modes                   | . 8-2 |

|           | 8.3.2  | Transfer-of-Control Addressing Modes       | . 8-4 |

| 8.4       | INSTRU | CTION TYPES                                | . 8-6 |

| 8.5       | INSTRU | CTION DESCRIPTIONS                         | . 8-9 |

|           | 8.5.1  | ADC— Add with Carry                        | 8-11  |

|           | 8.5.2  | ADD — Add                                  |       |

|           | 8.5.3  | AND — And                                  | 8-13  |

|           | 8.5.4  | CLR — Clear Accumulator                    |       |

|           | 8.5.5  | DCOR — Decimal Correct                     | 8-15  |

|           | 8.5.6  | DEC — Decrement Accumulator                |       |

|           | 8.5.7  | DRSZ REG# — Decrement Register and Skip if |       |

|           |        | Result is Zero                             | 8-17  |

|           | 8.5.8  | IFBIT — Test Memory Bit                    |       |

|           | 8.5.9  | IFBNE # — If B Pointer Not Equal           |       |

|           | 8.5.10 | IFC — Test if Carry                        |       |

|           | 8.5.11 | IFEQ — Test if Equal                       |       |

|           | 8.5.12 | IFGT — Test if Greater Than                |       |

|           | 8.5.13 | IFNC — Test if No Carry                    |       |

|           | 8.5.14 | INC — Increment Accumulator                |       |

|           | J.J    |                                            |       |

| 8.5.16 JID — Jump Indirect  8.5.17 JMP — Jump Absolute  8.5.18 JMPL — Jump Absolute Long  8.5.19 JP — Jump Relative  8.5.20 JSR — Jump Subroutine  8.5.21 JSRL — Jump Subroutine Long  8.5.22 LAID — Load Accumulator Indirect  8.5.23 LD — Load B Pointer  8.5.24 LD — Load B Pointer  8.5.25 LD — Load Register  8.5.26 LD — Load Register  8.5.27 NOP — No Operation  8.5.28 OR — Or  8.5.29 RBIT — Reset Memory Bit  8.5.30 RC — Reset Carry  8.5.31 RET — Return from Subroutine  8.5.32 RETI — Return from Interrupt  8.5.33 RETSK — Return and Skip  8.5.34 RRC — Rotate Accumulator Right Throug  8.5.35 SBIT — Set Memory Bit  8.5.36 SC — Set Carry  8.5.37 SUBC — Subtract with Carry  8.5.38 SWAP — Swap Nibbles of Accumulator  8.5.39 X — Exchange Memory with Accumulator  8.5.40 XOR — Exclusive Or  8.61 Instruction Operations Summary                                                                                                                                                                                                                                            | 8-28 8-29 8-30 8-31 8-32 8-33 8-34 8-36 8-36 8-40 8-41 8-42 8-45 8-46 8-46 8-47 8-46 8-46 8-47 8-46                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 8.5.18       JMPL — Jump Relative         8.5.19       JP — Jump Relative         8.5.20       JSR — Jump Subroutine         8.5.21       JSRL — Jump Subroutine Long         8.5.22       LAID — Load Accumulator Indirect         8.5.23       LD — Load Accumulator         8.5.24       LD — Load B Pointer         8.5.25       LD — Load Memory         8.5.26       LD — Load Register         8.5.27       NOP — No Operation         8.5.28       OR — Or         8.5.29       RBIT — Reset Memory Bit         8.5.30       RC — Reset Carry         8.5.31       RET — Return from Subroutine         8.5.32       RETI — Return from Interrupt         8.5.33       RETSK — Return and Skip         8.5.34       RRC — Rotate Accumulator Right Throught         8.5.35       SBIT — Set Memory Bit         8.5.36       SC — Set Carry         8.5.37       SUBC — Subtract with Carry         8.5.38       SWAP — Swap Nibbles of Accumulator         8.5.39       X — Exchange Memory with Accumulator         8.5.40       XOR — Exclusive Or         INSTRUCTION SET SUMMARY TABLES | 8-29 8-30 8-31 8-32 8-34 8-36 8-36 8-36 8-36 8-40 8-41 8-42 8-45 8-46 8-46 8-47 8-46 8-46 8-46 8-46 8-46 8-46 8-46 8-46 |

| 8.5.19       JP — Jump Relative         8.5.20       JSR — Jump Subroutine         8.5.21       JSRL — Jump Subroutine Long         8.5.22       LAID — Load Accumulator Indirect         8.5.23       LD — Load Recumulator         8.5.24       LD — Load B Pointer         8.5.25       LD — Load Memory         8.5.26       LD — Load Register         8.5.27       NOP — No Operation         8.5.28       OR — Or         8.5.29       RBIT — Reset Memory Bit         8.5.30       RC — Reset Carry         8.5.31       RET — Return from Subroutine         8.5.32       RETI — Return from Interrupt         8.5.33       RETSK — Return and Skip         8.5.34       RRC — Rotate Accumulator Right Throught         8.5.35       SBIT — Set Memory Bit         8.5.36       SC — Set Carry         8.5.37       SUBC — Subtract with Carry         8.5.38       SWAP — Swap Nibbles of Accumulator         8.5.39       X — Exchange Memory with Accumulator         8.5.40       XOR — Exclusive Or         1NSTRUCTION SET SUMMARY TABLES                                           | 8-30 8-31 8-32 8-33 8-34 8-36 8-38 8-38 8-38 8-40 8-41 8-42 8-45 8-46 8-46 8-47 8-46 8-46 8-46 8-46 8-46 8-46 8-46 8-46 |

| 8.5.20 JSR — Jump Subroutine Long 8.5.21 JSRL — Jump Subroutine Long 8.5.22 LAID — Load Accumulator Indirect 8.5.23 LD — Load Accumulator 8.5.24 LD — Load B Pointer 8.5.25 LD — Load Memory 8.5.26 LD — Load Register 8.5.27 NOP — No Operation 8.5.28 OR — Or 8.5.29 RBIT — Reset Memory Bit 8.5.30 RC — Reset Carry 8.5.31 RET — Return from Subroutine 8.5.32 RETI — Return from Interrupt 8.5.33 RETSK — Return and Skip 8.5.34 RRC — Rotate Accumulator Right Throug 8.5.35 SBIT — Set Memory Bit 8.5.36 SC — Set Carry 8.5.37 SUBC — Subtract with Carry 8.5.38 SWAP — Swap Nibbles of Accumulator 8.5.39 X — Exchange Memory with Accumulator 8.5.40 XOR — Exclusive Or 1NSTRUCTION SET SUMMARY TABLES                                                                                                                                                                                                                                                                                                                                                                                      | 8-31 8-32 8-34 8-34 8-36 8-37 8-38 8-38 8-40 8-41 8-45 8-45 8-46 8-46 8-47 8-46 8-46 8-47 8-46 8-46 8-46 8-47 8-46      |

| 8.5.21       JSRL — Jump Subroutine Long         8.5.22       LAID — Load Accumulator Indirect         8.5.23       LD — Load B Pointer         8.5.24       LD — Load B Pointer         8.5.25       LD — Load Memory         8.5.26       LD — Load Register         8.5.27       NOP — No Operation         8.5.28       OR — Or         8.5.29       RBIT — Reset Memory Bit         8.5.30       RC — Reset Carry         8.5.31       RET — Return from Subroutine         8.5.32       RETI — Return from Interrupt         8.5.33       RETSK — Return and Skip         8.5.34       RRC — Rotate Accumulator Right Through         8.5.35       SBIT — Set Memory Bit         8.5.36       SC — Set Carry         8.5.37       SUBC — Subtract with Carry         8.5.38       SWAP — Swap Nibbles of Accumulator         8.5.39       X — Exchange Memory with Accumulator         8.5.40       XOR — Exclusive Or         8.6       INSTRUCTION SET SUMMARY TABLES                                                                                                                       | 8-32 8-36 8-36 8-36 8-37 8-38 8-38 8-38 8-40 8-41 8-42 8-45 8-45 8-46 8-46 8-47 8-46 8-46 8-46 8-47 8-46                |

| 8.5.22 LAID — Load Accumulator Indirect 8.5.23 LD — Load Accumulator 8.5.24 LD — Load B Pointer 8.5.25 LD — Load Memory 8.5.26 LD — Load Register 8.5.27 NOP — No Operation 8.5.28 OR — Or 8.5.29 RBIT — Reset Memory Bit 8.5.30 RC — Reset Carry 8.5.31 RET — Return from Subroutine 8.5.32 RETI — Return from Interrupt 8.5.33 RETSK — Return and Skip 8.5.34 RRC — Rotate Accumulator Right Throug 8.5.35 SBIT — Set Memory Bit 8.5.36 SC — Set Carry 8.5.37 SUBC — Subtract with Carry 8.5.38 SWAP — Swap Nibbles of Accumulator 8.5.39 X — Exchange Memory with Accumulator 8.5.40 XOR — Exclusive Or  INSTRUCTION SET SUMMARY TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8-36 8-36 8-36 8-36 8-37 8-38 8-38 8-40 8-41 8-42 8-45 8-45 8-46 8-46 8-47 8-46 8-46 8-46 8-47 8-46                     |

| 8.5.23 LD — Load Accumulator  8.5.24 LD — Load B Pointer  8.5.25 LD — Load Memory  8.5.26 LD — Load Register  8.5.27 NOP — No Operation  8.5.28 OR — Or  8.5.29 RBIT — Reset Memory Bit  8.5.30 RC — Reset Carry  8.5.31 RET — Return from Subroutine  8.5.32 RETI — Return from Interrupt  8.5.33 RETSK — Return and Skip  8.5.34 RRC — Rotate Accumulator Right Throug  8.5.35 SBIT — Set Memory Bit  8.5.36 SC — Set Carry  8.5.37 SUBC — Subtract with Carry  8.5.38 SWAP — Swap Nibbles of Accumulator  8.5.39 X — Exchange Memory with Accumulator  8.5.40 XOR — Exclusive Or  INSTRUCTION SET SUMMARY TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8-34 8-36 8-37 8-38 8-38 8-39 8-40 8-41 8-42 8-45 8-45 8-46 8-46 8-47 8-46 8-46 8-47 8-46 8-46 8-47                     |

| 8.5.24 LD — Load B Pointer  8.5.25 LD — Load Memory  8.5.26 LD — Load Register  8.5.27 NOP — No Operation  8.5.28 OR — Or  8.5.29 RBIT — Reset Memory Bit  8.5.30 RC — Reset Carry  8.5.31 RET — Return from Subroutine  8.5.32 RETI — Return from Interrupt  8.5.33 RETSK — Return and Skip  8.5.34 RRC — Rotate Accumulator Right Throug  8.5.35 SBIT — Set Memory Bit  8.5.36 SC — Set Carry  8.5.37 SUBC — Subtract with Carry  8.5.38 SWAP — Swap Nibbles of Accumulator  8.5.39 X — Exchange Memory with Accumulator  8.5.40 XOR — Exclusive Or  INSTRUCTION SET SUMMARY TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8-36 8-37 8-38 8-38 8-40 8-41 8-42 8-44 8-44 8-46 8-46 8-46 8-47 8-46 8-46 8-46                                         |

| 8.5.25       LD — Load Memory         8.5.26       LD — Load Register         8.5.27       NOP — No Operation         8.5.28       OR — Or         8.5.29       RBIT — Reset Memory Bit         8.5.30       RC — Reset Carry         8.5.31       RET — Return from Subroutine         8.5.32       RETI — Return from Interrupt         8.5.33       RETSK — Return and Skip         8.5.34       RRC — Rotate Accumulator Right Throught         8.5.35       SBIT — Set Memory Bit         8.5.36       SC — Set Carry         8.5.37       SUBC — Subtract with Carry         8.5.38       SWAP — Swap Nibbles of Accumulator         8.5.39       X — Exchange Memory with Accumulator         8.5.40       XOR — Exclusive Or         8.6       INSTRUCTION SET SUMMARY TABLES                                                                                                                                                                                                                                                                                                               | 8-37 8-38 8-38 8-40 8-41 8-42 8-42 8-46 8-46 8-46 8-46 8-46 8-46 8-46 8-46                                              |

| 8.5.26 LD — Load Register  8.5.27 NOP — No Operation  8.5.28 OR — Or  8.5.29 RBIT — Reset Memory Bit  8.5.30 RC — Reset Carry  8.5.31 RET — Return from Subroutine  8.5.32 RETI — Return from Interrupt  8.5.33 RETSK — Return and Skip  8.5.34 RRC — Rotate Accumulator Right Throug  8.5.35 SBIT — Set Memory Bit  8.5.36 SC — Set Carry  8.5.37 SUBC — Subtract with Carry  8.5.38 SWAP — Swap Nibbles of Accumulator  8.5.39 X — Exchange Memory with Accumulator  8.5.40 XOR — Exclusive Or  INSTRUCTION SET SUMMARY TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8-38 8-39 8-40 8-41 8-42 8-45 8-46 8-46 8-46 8-46 8-46 8-46 8-46 8-46                                                   |

| 8.5.27 NOP — No Operation  8.5.28 OR — Or  8.5.29 RBIT — Reset Memory Bit  8.5.30 RC — Reset Carry  8.5.31 RET — Return from Subroutine  8.5.32 RETI — Return from Interrupt  8.5.33 RETSK — Return and Skip  8.5.34 RRC — Rotate Accumulator Right Throug  8.5.35 SBIT — Set Memory Bit  8.5.36 SC — Set Carry  8.5.37 SUBC — Subtract with Carry  8.5.38 SWAP — Swap Nibbles of Accumulator  8.5.39 X — Exchange Memory with Accumulator  8.5.40 XOR — Exclusive Or  INSTRUCTION SET SUMMARY TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8-39 8-40 8-41 8-42 8-45 8-46 8-47 8-47 8-46 8-46 8-46 8-46 8-46 8-46 8-46 8-46                                         |

| 8.5.28 OR — Or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8-40<br>8-41<br>8-42<br>8-45<br>8-46<br>8-47<br>8-47<br>8-48<br>8-49<br>8-50<br>8-50                                    |

| 8.5.29 RBIT — Reset Memory Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8-41<br>8-42<br>8-43<br>8-44<br>8-44<br>8-47<br>8-48<br>8-49<br>8-50<br>8-51                                            |

| 8.5.30 RC — Reset Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-42<br>8-44<br>8-44<br>gh Carry 8-46<br>8-48<br>8-49<br>8-50                                                           |

| 8.5.31 RET — Return from Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8-45<br>8-44<br>8-45<br>gh Carry 8-46<br>8-47<br>8-48<br>8-49<br>8-50                                                   |

| 8.5.31 RET — Return from Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8-45<br>8-44<br>8-45<br>gh Carry 8-46<br>8-47<br>8-48<br>8-49<br>8-50                                                   |

| 8.5.33 RETSK — Return and Skip  8.5.34 RRC — Rotate Accumulator Right Throug  8.5.35 SBIT — Set Memory Bit  8.5.36 SC — Set Carry  8.5.37 SUBC — Subtract with Carry  8.5.38 SWAP — Swap Nibbles of Accumulator  8.5.39 X — Exchange Memory with Accumulator  8.5.40 XOR — Exclusive Or  INSTRUCTION SET SUMMARY TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-48 gh Carry 8-46 8-47 8-48 8-48 8-49 8-50 8-50                                                                        |

| 8.5.34 RRC — Rotate Accumulator Right Throug 8.5.35 SBIT — Set Memory Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | gh Carry 8-46 8-47 8-47 8-48 8-49 8-50 8-50                                                                             |

| 8.5.35 SBIT — Set Memory Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8-47<br>8-48<br>8-49<br>8-50<br>8-51                                                                                    |

| 8.5.35 SBIT — Set Memory Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8-47<br>8-48<br>8-49<br>8-50<br>8-51                                                                                    |

| 8.5.37 SUBC — Subtract with Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                         |

| 8.5.38 SWAP — Swap Nibbles of Accumulator . 8.5.39 X — Exchange Memory with Accumulator . 8.5.40 XOR — Exclusive Or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                         |

| 8.5.39 X — Exchange Memory with Accumulator<br>8.5.40 XOR — Exclusive Or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | c 8-51                                                                                                                  |

| 8.5.40 XOR — Exclusive Or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                         |

| 8.6 INSTRUCTION SET SUMMARY TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8-5?                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                         |

| 8.6.1 Instruction Operations Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                         |

| 8.6.2 Bytes and Cycles Per Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8-55                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                         |

| Chapter 9 COP912C/COP820C/COP840C/COP880C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                         |

| 9.1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9-1                                                                                                                     |

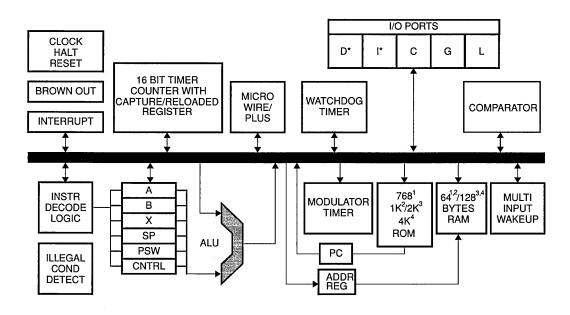

| 9.2 BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9-1                                                                                                                     |

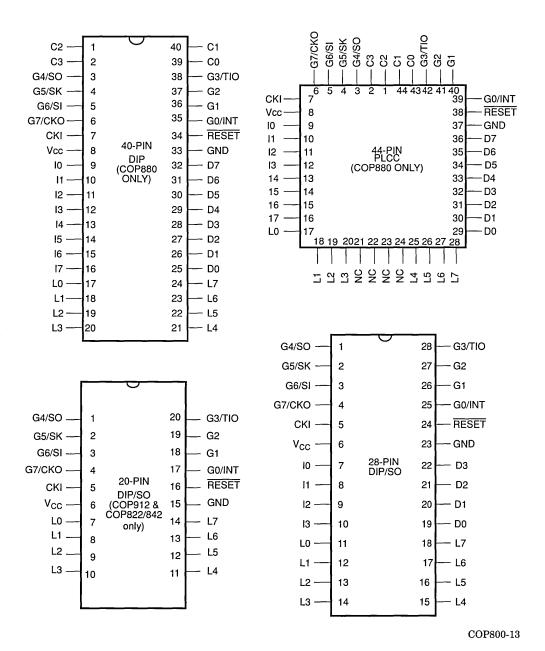

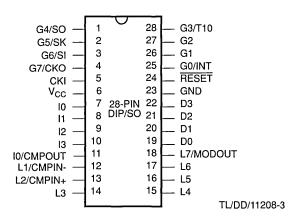

| 9.3 DEVICE PINOUT/PACKAGES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                         |

| 9.4 PIN DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                         |

| 9.5 INPUT/OUTPUT PORTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                         |

| 9.6 PROGRAM MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                         |

| 9.7 DATA MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-6                                                                                                                     |

| 9.8 REGISTER BIT MAPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                         |

| 9.9 MEMORY MAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                         |

| 9.10 RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                         |

| 9.11 MASK OPTION(S)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                         |

| 9.11.1 COP912                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                         |

| 9.11.2 COP820C/COP840C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9-10                                                                                                                    |

| 9.11.3 COP880                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                         |

| Chapter 10 COP820CJ/COP840CJ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                         |

| 10.1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10-1                                                                                                                    |

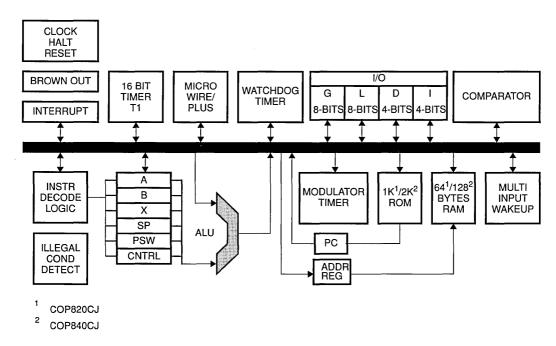

| 10.2 BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                         |

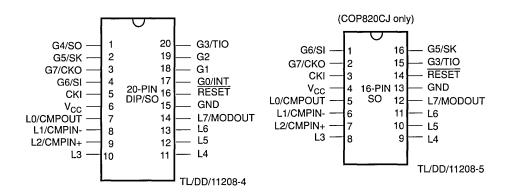

| 10.3             |            | E PINOUT/PACKAGES                                     |         |

|------------------|------------|-------------------------------------------------------|---------|

| 10.4             |            | ESCRIPTIONS                                           |         |

| 10.5             |            | YOUTPUT PORTS                                         |         |

| 10.6             |            | RAM MEMORY                                            |         |

| 10.7             |            | MEMORY                                                |         |

| 10.8             |            | TER BIT MAPS                                          |         |

| 10.9             |            | PRY MAP                                               |         |

| 10.10            |            | 1                                                     |         |

|                  | 10.10.1    |                                                       |         |

|                  | 10.10.2    |                                                       |         |

|                  | 10.10.3    |                                                       |         |

|                  | 10.10.4    |                                                       |         |

|                  | 10.10.5    |                                                       |         |

|                  | 10.10.6    |                                                       |         |

| 10.11            | 10.10.7    |                                                       |         |

| 10.11            |            | N OUT PROTECTION                                      |         |

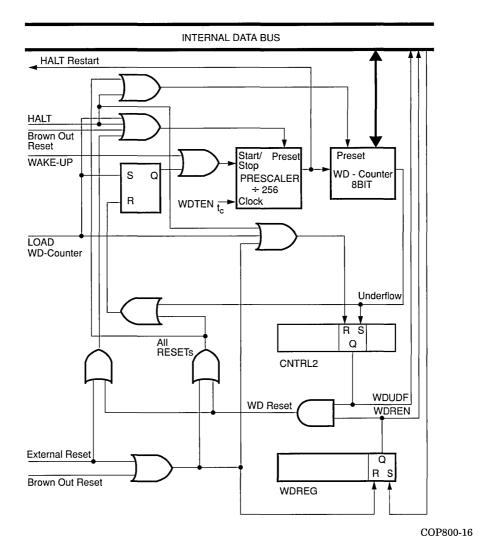

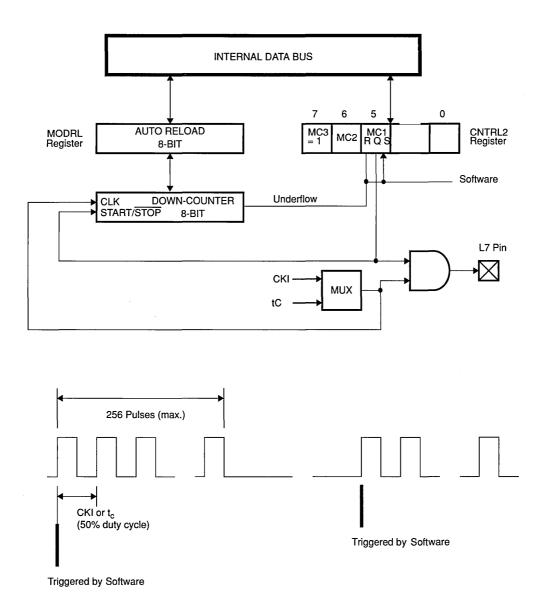

| $10.12 \\ 10.13$ |            | HDOG<br>LATOR/TIMER                                   |         |

|                  |            |                                                       |         |

| $10.14 \\ 10.15$ |            | ARATOR                                                |         |

| 10.15 $10.16$    |            | OPTIONS                                               |         |

| 10.16            | MASK       | OPTIONS                                               | . 10-25 |

| Appendix         | <b>A</b> A | APPLICATION HINTS                                     |         |

| A.1              |            | DUCTION                                               |         |

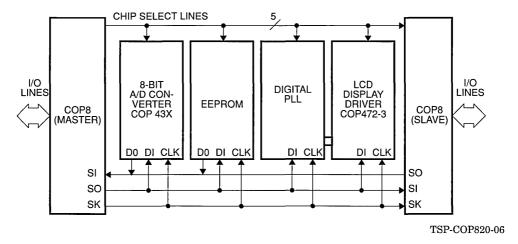

| <b>A.</b> 2      | MICRO      | OWIRE/PLUS INTERFACE                                  |         |

|                  | A.2.1      | MICROWIRE/PLUS Master/Slave Protocol                  |         |

|                  | A.2.2      | MICROWIRE/PLUS Continuous Mode                        |         |

|                  | A.2.3      | MICROWIRE/PLUS Fast Burst Output                      |         |

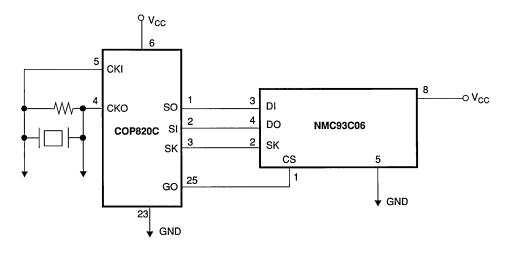

|                  | A.2.4      | NMC93C06-COP820C Interface                            |         |

| <b>A</b> .3      |            | R APPLICATIONS                                        |         |

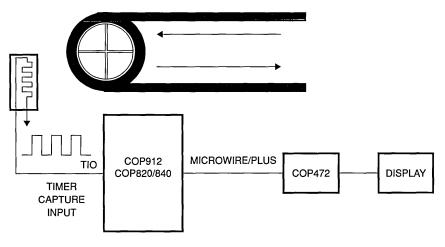

|                  | A.3.1      | Timer Capture Example                                 |         |

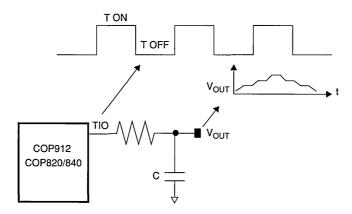

|                  | A.3.2      | Timer PWM Example                                     |         |

|                  | A.3.3      | External Event Counter Example                        |         |

| A.4              |            | CONTROL                                               |         |

| A.5              |            | 0CJ/COP840CJ APPLICATION HINTS                        |         |

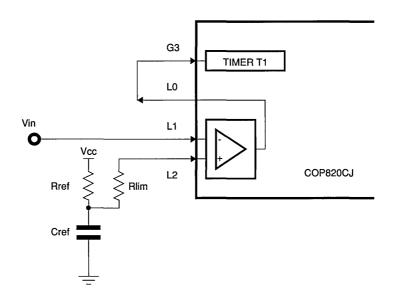

|                  | A.5.1      | Analog To Digital Conversion Using On-chip Comparator | A-18    |

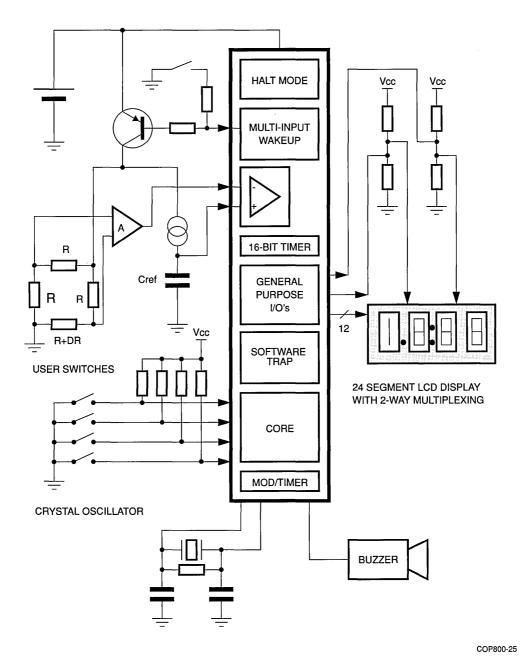

|                  | A.5.2      | Application Example: Battery-Powered Weight           | 4.01    |

|                  |            | Measurement                                           | A-21    |

|                  | A.5.3      | Zero Cross Detection                                  |         |

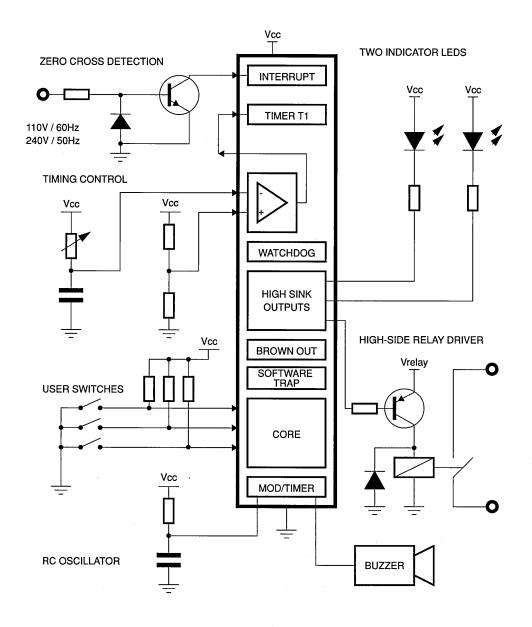

|                  | A.5.4      | Application Example: Industrial Timer                 |         |

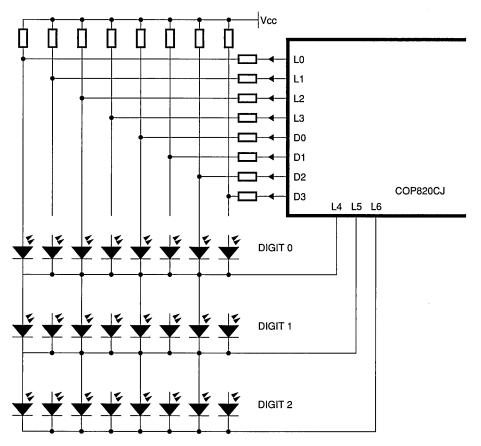

|                  | A.5.5      | LED Drive Using the COP820CJ                          |         |

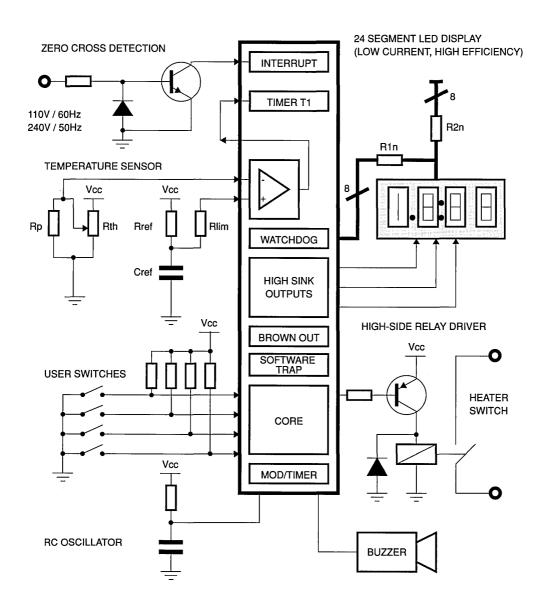

|                  | A.5.6      | Application Example: Temperature Control              |         |

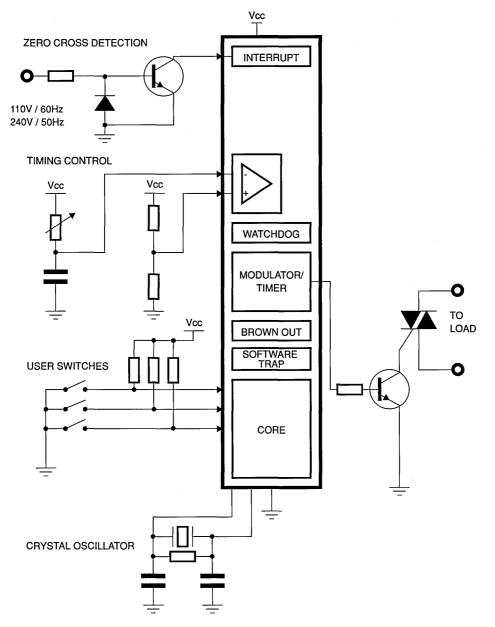

|                  | A.5.7      | Phase Control of an AC Load                           | A-29    |

| A C              | A.5.8      | Application Example: Remote Control Unit              |         |

| A.6              |            | RAMMING EXAMPLES                                      |         |

|                  | A.6.1      | Clear RAM                                             |         |

|                  | A.6.2      | Binary/BCD Arithmetic Operations                      |         |

|                  | A.6.3      | Binary Multiplication                                 |         |

|                  | A.6.4      | Binary Division                                       | A-38    |

| A.7  | DAIL-A | -HELPER SERVICE               |

|------|--------|-------------------------------|

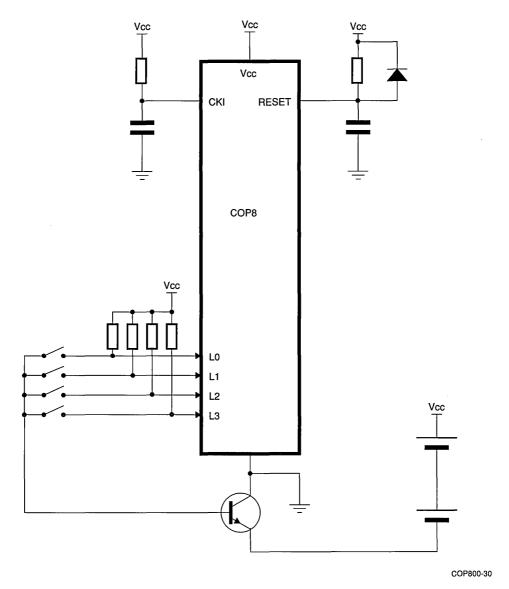

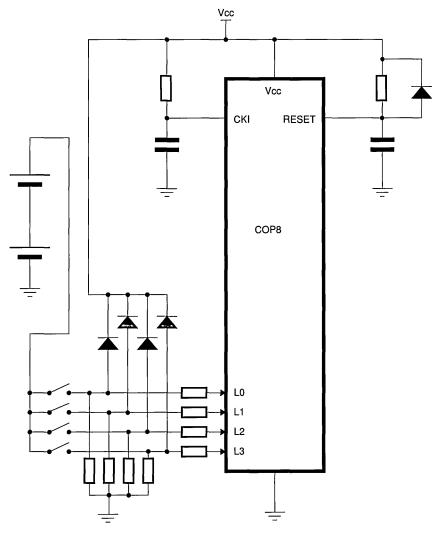

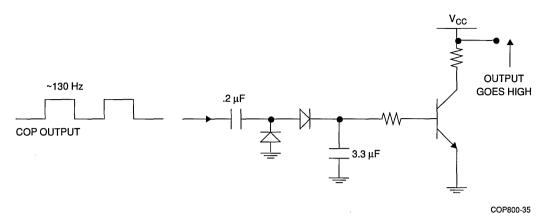

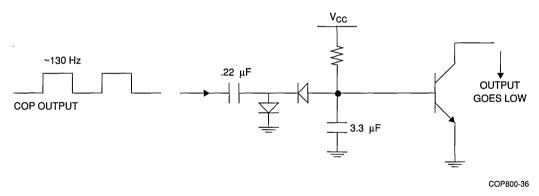

| A.8  | EXTER  | NAL POWER WAKEUP CIRCUIT      |

| A.9  | EXTER  | NAL WATCHDOG CIRCUIT          |

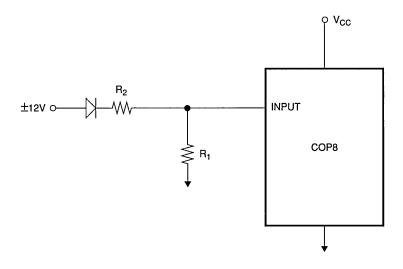

| A.10 | INPUT  | PROTECTION ON COP8 PINS       |

| A.11 | ELECT  | ROMAGNETIC INTERFERENCE (EMI) |

|      | CONSII | DERATIONS                     |

|      | A.11.1 | Introduction                  |

|      | A.11.2 | Emission Predictions          |

|      | A.11.3 | Board Layout                  |

|      | A.11.4 | Decoupling                    |

|      | A.11.5 | Output Series Resistance      |

|      | A.11.6 | Oscillator Control            |

|      | A.11.7 | Mechanical Shielding          |

|      | A 11 8 | Conclusion A-51               |

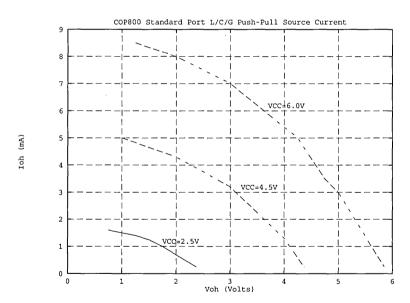

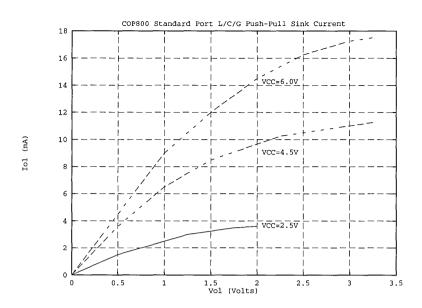

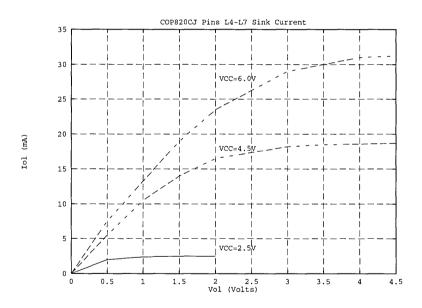

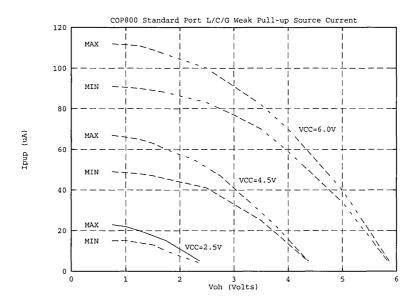

## Appendix B ELECTRICAL CHARACTERIZATION DATA

## Index

| Figures     |                                                       |       |

|-------------|-------------------------------------------------------|-------|

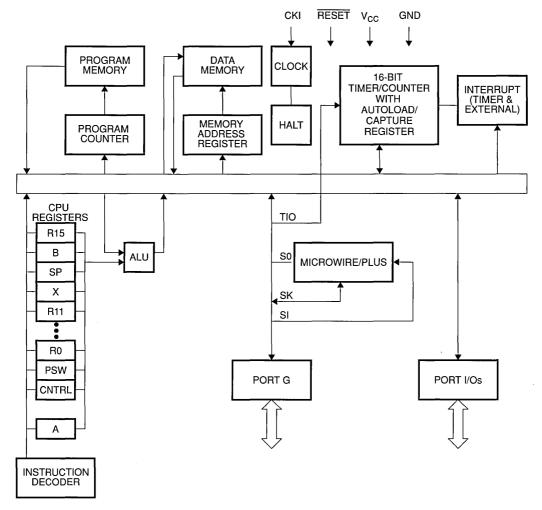

| Figure 2-1  | COP8 Basic Family Block Diagram                       | 2-2   |

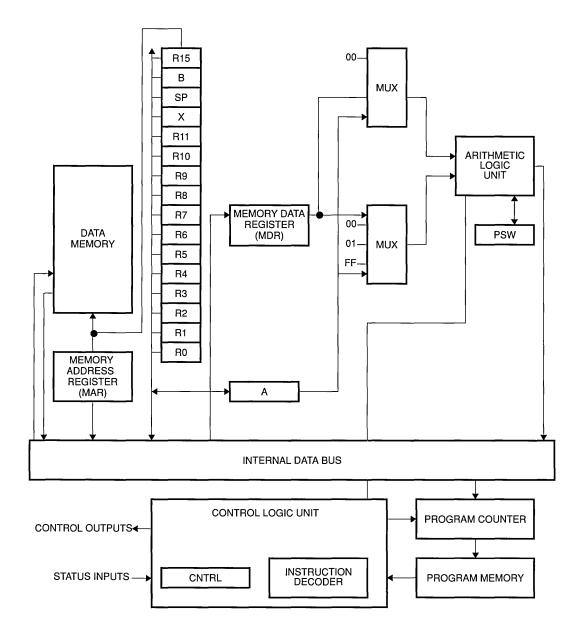

| Figure 2-2  | COP8 CPU Interface                                    | 2-10  |

| Figure 2-3  | Crystal Oscillator Circuit                            | 2-18  |

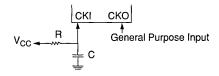

| Figure 2-4  | RC Oscillator Circuit                                 |       |

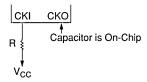

| Figure 2-5  | RC Oscillator Circuit for COP840CJ Only               | 2-19  |

| Figure 2-6  | External Oscillator Circuit                           |       |

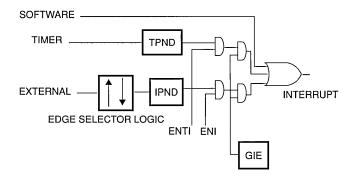

| Figure 3-1  | Interrupt Block Diagram                               | 3-1   |

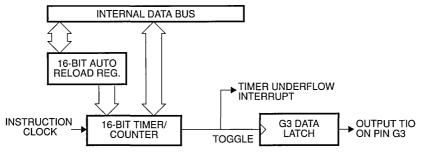

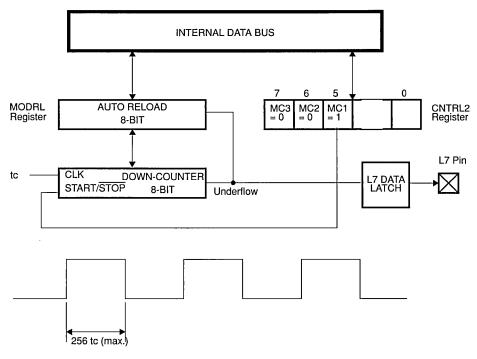

| Figure 4-1  | Timer in PWM Mode                                     |       |

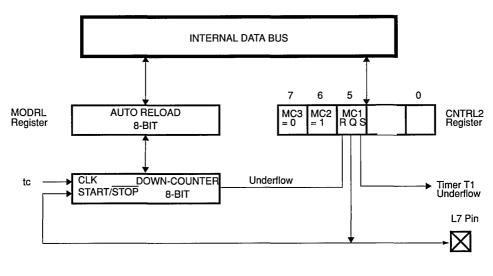

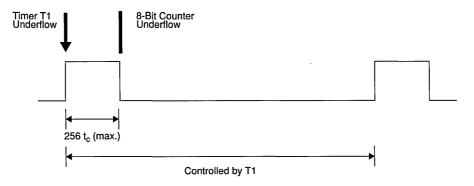

| Figure 4-2  | Timer in External Event Counter Mode                  | 4-5   |

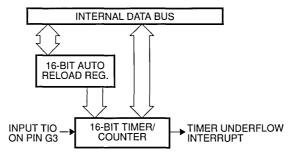

| Figure 4-3  | Timer in Input Capture Mode                           | 4-6   |

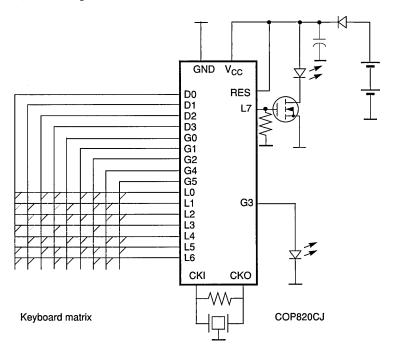

| Figure 5-1  | MICROWIRE/PLUS Example                                |       |

| Figure 5-2  | MICROWIRE/PLUS Circuit Block Diagram                  | 5-2   |

| Figure 5-3  | MICROWIRE/PLUS Interface Timing                       | 5-3   |

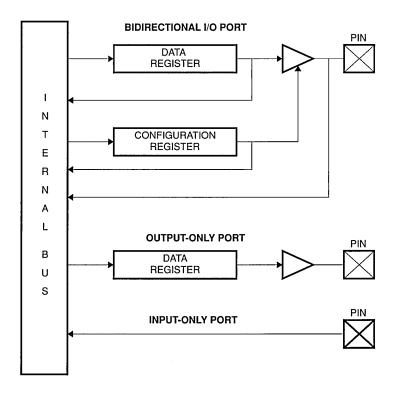

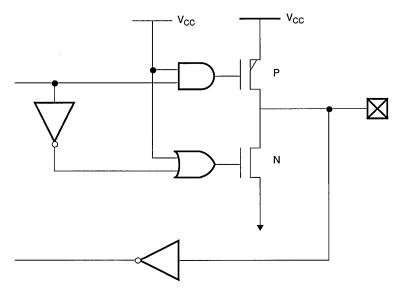

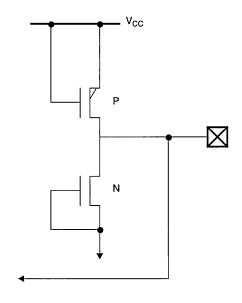

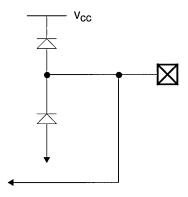

| Figure 7-1  | COP8 Basic Family Port Structure                      | 7-1   |

| Figure 9-1  | COP912/820/840/880 Block Diagram                      | 9-2   |

| Figure 9-2  | Device Package Pinouts                                | 9-3   |

| Figure 10-1 | COP820CJ/840CJBlock Diagram                           | 10-2  |

| Figure 10-2 | Device Package Pinouts                                | 10-3  |