# INTERFACE: Data Transmission Databook

Special Interface LVDS Technology Line Drivers and Receivers

## INTERFACE: DATA TRANSMISSION DATABOOK

1994 Edition

TIA/EIA-232 (RS-232) TIA/EIA-422 and 423 TIA/EIA-485 Low Voltage Differential Signaling Special Interface General Purpose Line Drivers General Purpose Receivers Application Notes Military Interface

**Appendices and Physical Dimensions**

i

#### TRADEMARKS

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

АВіС™ Abuseable<sup>™</sup> Anadig™ APPSTM ARi1™ **ASPECT™** AT/LANTIC™ Auto-Chem Deflasher™ ВСРТМ BI-FET™ BI-FET II™ BI-LINE™ **BIPLANTM BLCTM** BLXTM **ВМАСТМ** Brite-Lite™ **BSITM** BSI-2™ CDDTM **CDLTM** CGSTM СІМ™ **CIMBUSTM CLASIC™** COMBO® COMBO ITM COMBO IITM COPS™ microcontrollers CRD™ **CSNI™ CTITM CYCLONE™** DA4™ **DENSPAKTM** DIBTM **DISCERN™** DISTILL™ DNR® **DPVMTM** E<sup>2</sup>CMOS™ **ELSTARTM**

Embedded System ProcessorTM ЕРТМ E-Z-LINK™ **FACT™** FACT Quiet Series™ **FAIRCADTM** Fairtech™ **FAST® FASTr™ Flash™ GENIX™ GNX™ GTOTM HEX 3000TM HPC™** HyBal™ |3Ĺ® ІСМ™ Integral ISE™ Intelisplav<sup>TM</sup> Inter-LERIC™ Inter-RIC™ **ISETM** ISE/06™ ISE/08™ ISE/16™ ISE32™ **ISOPLANAR™** ISOPLANAR-Z™ **LERIC™** LMCMOSTM M<sup>2</sup>CMOS™ Macrobus™ Macrocomponent<sup>™</sup> **MACSITM** MAPLTM MAXI-ROM® Microbus™ data bus MICRO-DAC™ µtalker™ Microtalker<sup>TM</sup> **MICROWIRETM**

MICROWIRE/PLUS™ **MOLETM МРА**ТМ MST™ Naked-8™ National<sup>®</sup> National Semiconductor® National Semiconductor Corp.® NAX 800™ Nitride Plus™ Nitride Plus Oxide™ **NMLTM NOBUSTM** NSC800TM **NSCISE™** NSX-16™ NS-XC-16™ **NTERCOM™ NURAMTM OPALTM OXISS™** P<sup>2</sup>CMOS™ Perfect Watch™ **PLANTM PLANARTM PLAYER™** PLAYER + ™ Plus-2™ Polycraft™ POPTM. Power + Control™ POWERplanar™ QS™. QUAD3000TM Quiet Series™ **QUIKLOOK™ RAT™ RIC™ RICKIT™** RTX16™ **SCANTM** SCXTM

SERIES/800™ Series 32000® SIMPLE SWITCHER™ **SNITM SNIC™** SofChek™ **SONICTM SPiKe™** SPIRETM Staggered Refresh™ **STARTM** Starlink™ **STARPLEX™** ST-NIC™ SuperAT<sup>TM</sup> Super-Block™ SuperChip™ SuperI/O™ SuperScript<sup>™</sup> SYS32™ TapePak® TDSTM TeleGate™ The National Anthem® TLCTM Trapezoidal™ TRI-CODE™ TRI-POLY™ TRI-SAFE™ TRI-STATE® **TROPIC™** Tropic Pele'™ Tropic Reef™ **TURBOTRANSCEIVER™** VIРтм VR32™ WATCHDOG™ XMOS™ **XPUTM** Z STAR™ 883B/RETS™ 883S/RFTS™

IBM®, PC®, PC-AT®, PC-XT® and PS/2® are registered trademarks of International Business Machines Corp. KYNAR® is a registered trademark of Elf Atochem. Lap-Link® is a registered trademark of Traveling Software. LocalTalk™ and QuickRing™ are trademarks of Apple Computer, Inc. PolyClamp® is a registered trademark of Electromer Corp.

Teflon® is a registered trademark of E.I. DuPont de Nemours Co.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive, P.O. Box 58090, Santa Clara, California 95052-8090 1-800-272-9959 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

ii

## Introduction

Since its creation in 1973, National Semiconductor's Interface design and production teams have continuously produced technically advanced products unparalleled in the semiconductor industry.

Growing from a line of early drivers and receivers, which pioneered the introduction of the TRI-STATE® function, National Semiconductor's Data Transmission product line today is the most comprehensive available—with over 150 devices in a variety of product categories. These Interface devices support and complement National's VLSI product families.

Based on its advance design and process capabilities, National's Data Transmission product line includes:

- The industry's first CMOS TIA/EIA-232 (RS-232) Drivers and Receivers

- The industry's first CMOS TIA/EIA-422 (RS-422) Drivers and Receivers

- The industry's widest selection of TIA/EIA-485 (RS-485) Drivers, Receivers, Transceivers, and Repeaters

- The industry's first TIA/EIA-485 (RS-485) type Military Qualified (883) Transceivers, Drivers and Receivers

- The industry's first TIA/EIA-485 (RS-485) Quad Transceiver

- The industry's first TIA/EIA-485 (RS-485) BiCMOS Hex Transceiver

- The industry's first 3.3V powered RS-232 3 Driver X 5 Receiver Device for Laptop and Notebook Applications

- The industry's first LVDS—Low Voltage Differential Signaling Quad Drivers and Receivers for applications requiring ultra low power dissipation and switching rates exceeding 65 MHz

In addition to the detailed data transmission product datasheets, this databook includes the following documents to speed component selection and for technical reference: Selection Guides, Cross References, Package Drawings, and over 25 application notes devoted solely to the topic of Data Transmission.

For applications support or product information on National Semiconductor's Interface: Data Transmission Products, please contact the:

#### Customer Support Center at 1-800-272-9959 (USA)

or your local National Sales Office or distributor (listed on the back cover of this book).

### National Semiconductor

## **Product Status Definitions**

### **Definition of Terms**

| Data Sheet Identification     | Product Status            | Definition                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|-------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Advance Information           | Formative or<br>In Design | This data sheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                                                                             |  |  |  |  |  |

| Preliminary                   | First<br>Production       | This data sheet contains preliminary data, and supplementary data will<br>be published at a later date. National Semiconductor Corporation<br>reserves the right to make changes at any time without notice in order<br>to improve design and supply the best possible product. |  |  |  |  |  |

| No<br>Identification<br>Noted | Full<br>Production        | This data sheet contains final specifications. National Semiconductor<br>Corporation reserves the right to make changes at any time without<br>notice in order to improve design and supply the best possible product.                                                          |  |  |  |  |  |

| Obsolete                      | Not In Production         | This data sheet contains specifications on a product that has been discontinued by National Semiconductor Corporation. The data sheet is printed for reference information only.                                                                                                |  |  |  |  |  |

National Semiconductor Corporation reserves the right to make changes without further notice to any products herein to improve reliability, function or design. National does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

## **Table of Contents**

| Alphanumeric Index                                                       | ix           |

|--------------------------------------------------------------------------|--------------|

| Line Drivers and Receivers Selection Guide                               | xiii         |

| Line Drivers and Receivers Cross Reference Guide                         | xxiii        |

| Extended Temperature Range Devices                                       | XXVIII       |

| New Additions to the Interface: Data Transmission Databook               | xxix         |

|                                                                          |              |

| Application Note-Selection Guide                                         | XXX          |

| Cross Reference for Related Products                                     | xxxii        |

| Section 1 TIA/EIA-232 (RS-232)                                           |              |

| DRIVER/RECEIVER COMBINATIONS                                             |              |

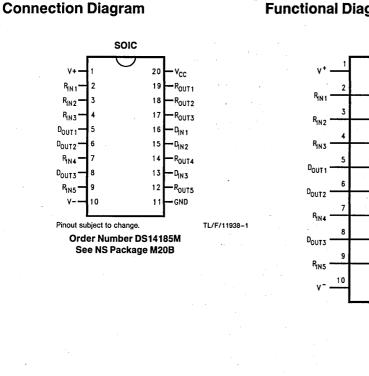

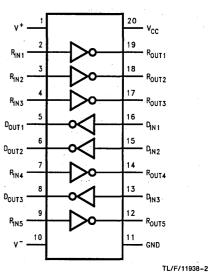

| DS14185 TIA/EIA-232 3 x 5 Driver/Receiver                                | 1-3          |

| DS14C232C/DS14C232T Low Power + 5V Powered TIA/EIA-232 Dual              | 1.           |

| Drivers/Receivers                                                        | - 1-8        |

| DS14C237 Single Supply TIA/EIA-232 5 x 3 Driver/Receiver                 | 1-17         |

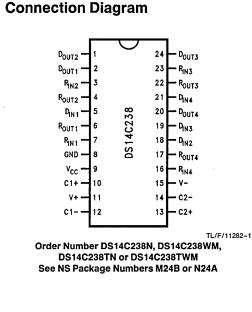

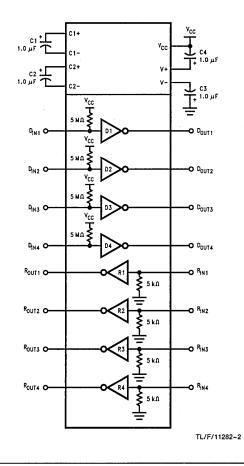

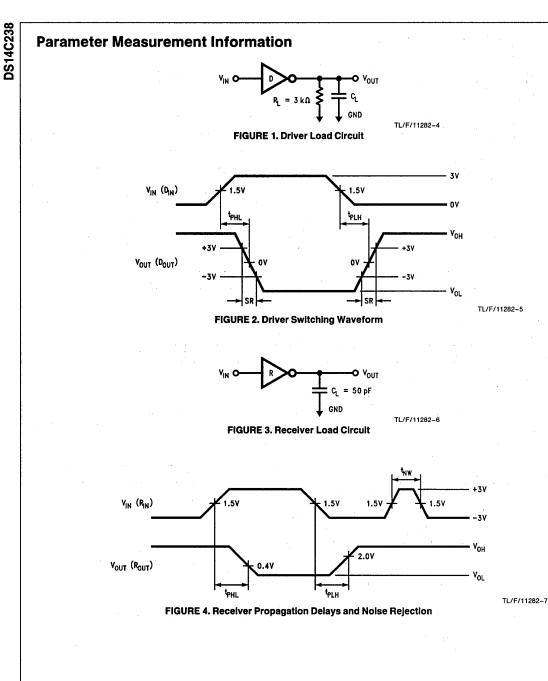

| DS14C238 Single Supply TIA/EIA-232 4 x 4 Driver/Receiver                 | 1-21         |

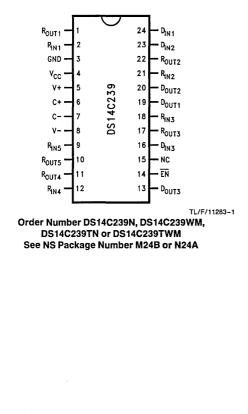

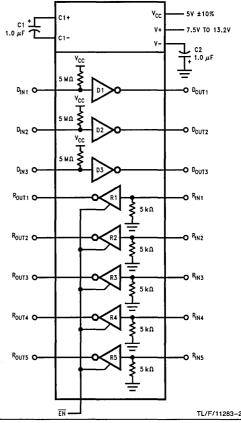

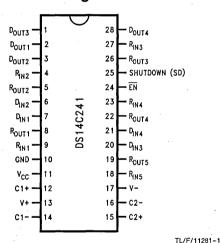

| DS14C239 Dual Supply TIA/EIA-232 3 x 5 Driver/Receiver                   | 1-26         |

| DS14C241 Single Supply TIA/EIA-232 4 x 5 Driver/Receiver                 | 1-31         |

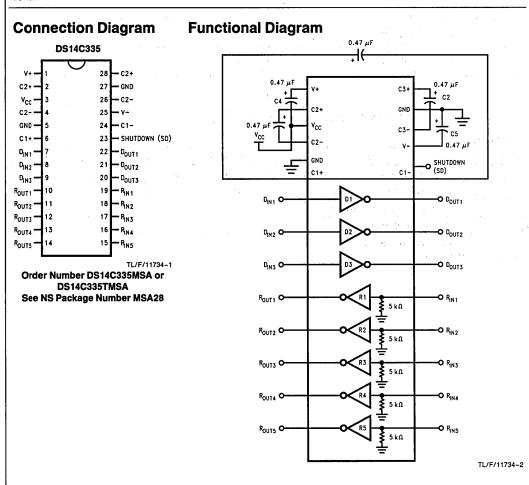

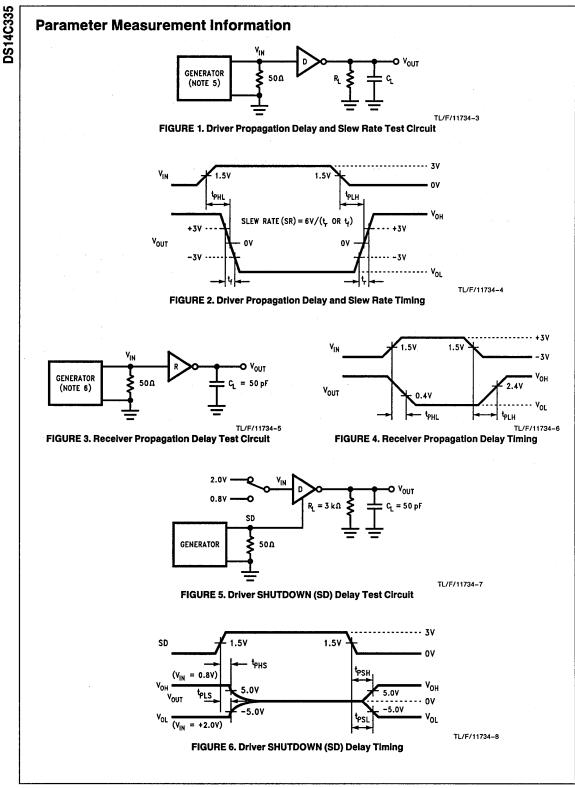

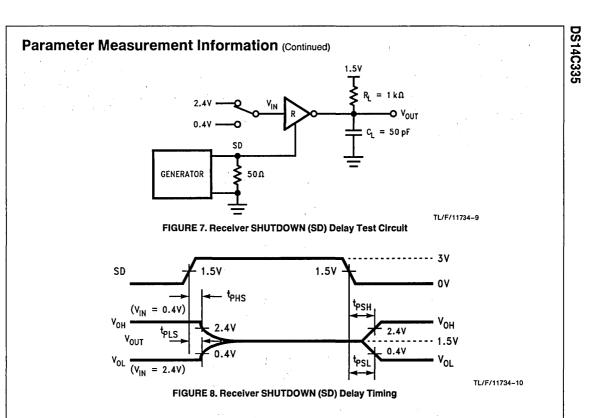

| DS14C335 + 5V Supply TIA/EIA-232 3 x 5 Driver/Receiver                   | 1-38         |

| DS14C535 + 3V Supply TIA/EIA-232 3 x 5 Driver/Receiver                   | 1-47         |

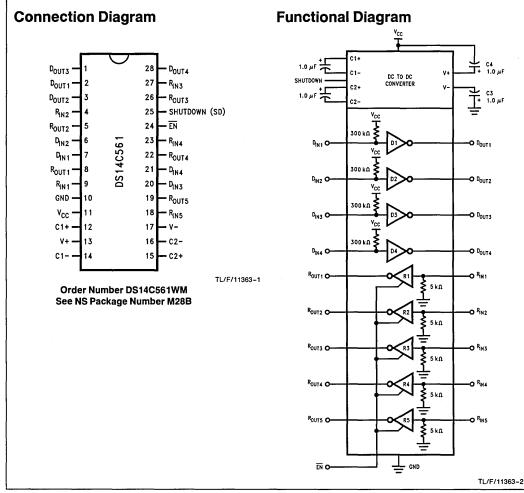

| DS14C561 + 3.3V-Powered 4 x 5 Driver/Receiver                            | 1-54         |

| DRIVERS OR RECEIVERS                                                     |              |

| DS14C88/DS14C88T Quad CMOS Line Drivers                                  | 1-59         |

| DS1488 Quad Line Driver                                                  | 1-63         |

| DS14C89A/DS14C89AT Quad CMOS Receivers                                   | 1-67         |

| DS1489/DS1489A Quad Line Receivers                                       | 1-70         |

| DS75150 Dual Line Driver                                                 | 1-74         |

| DS75154 Quad Line Receiver                                               | 1-78         |

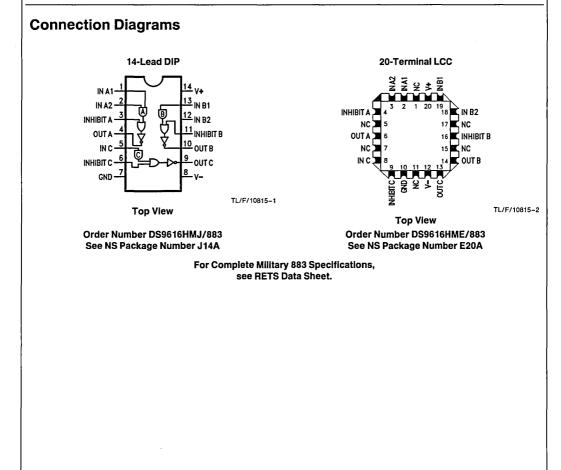

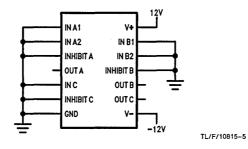

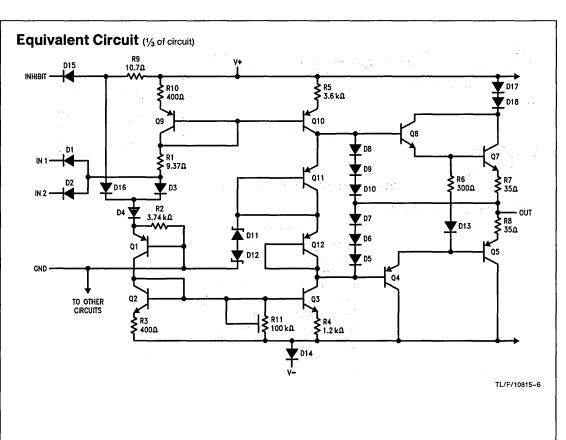

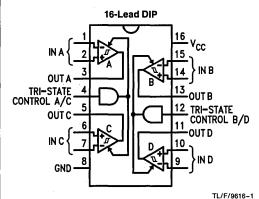

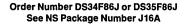

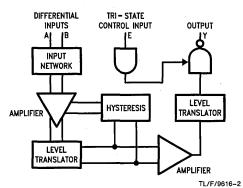

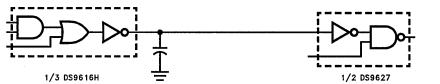

| DS9616H Triple Line Driver                                               | 1-83         |

| DS9627 Dual Line Receiver                                                | 1-87         |

|                                                                          | 1-07         |

| Section 2 TIA/EIA 422 & 423 Line Drivers and Receivers                   |              |

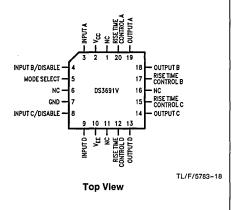

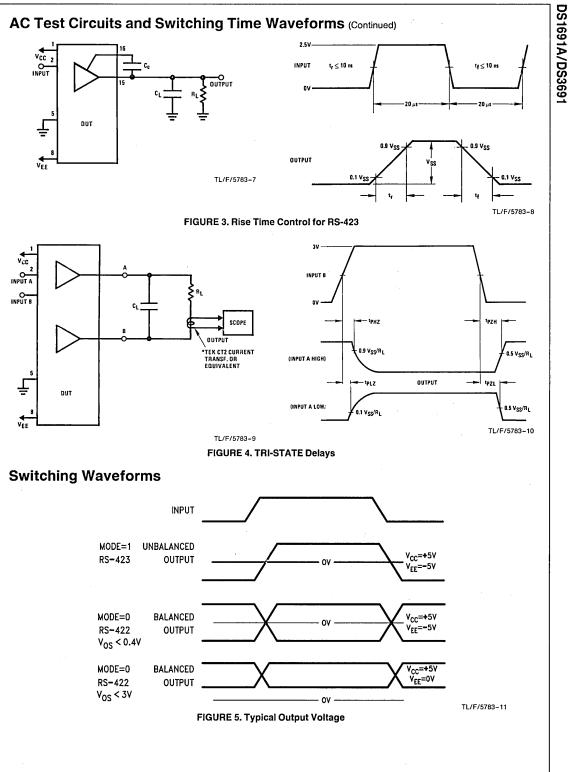

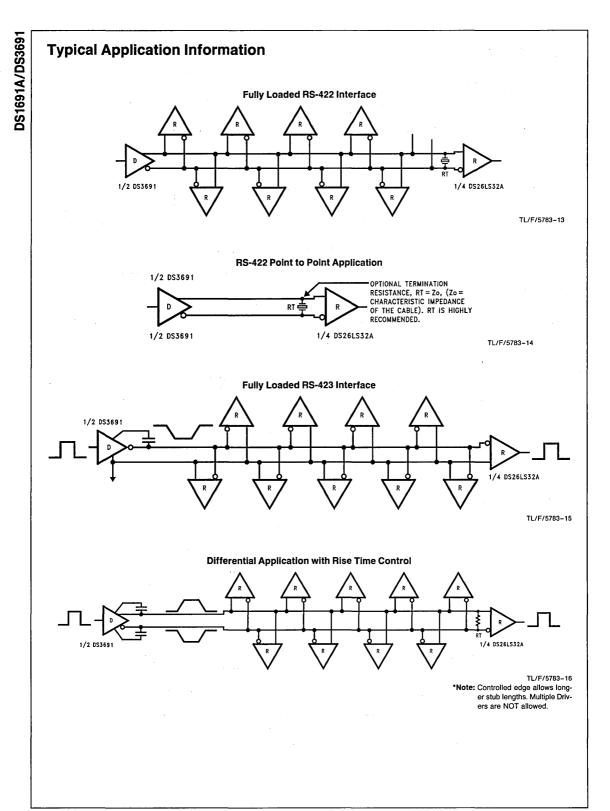

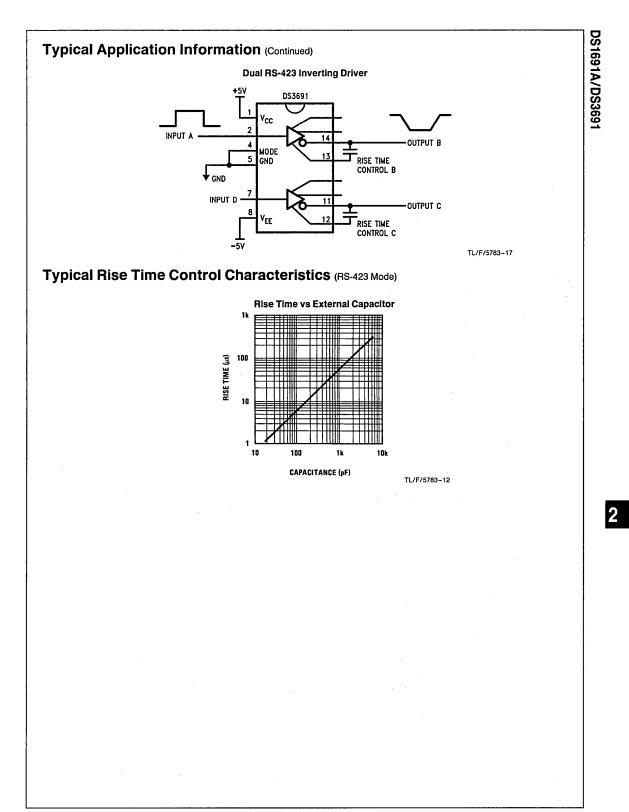

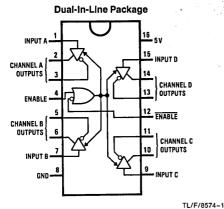

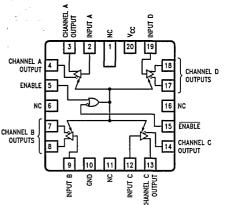

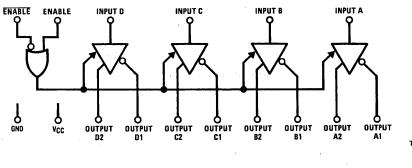

| DS1691A/DS3691 RS-422/RS-423 Line Drivers with TRI-STATE Outputs         | 2-3          |

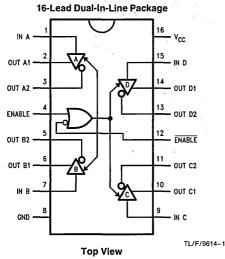

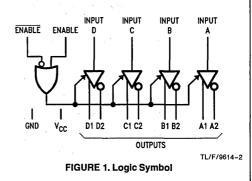

| DS26C31T/DS26C31M CMOS Quad TRI-STATE Differential Line Driver           | 2-10         |

|                                                                          | 2-18         |

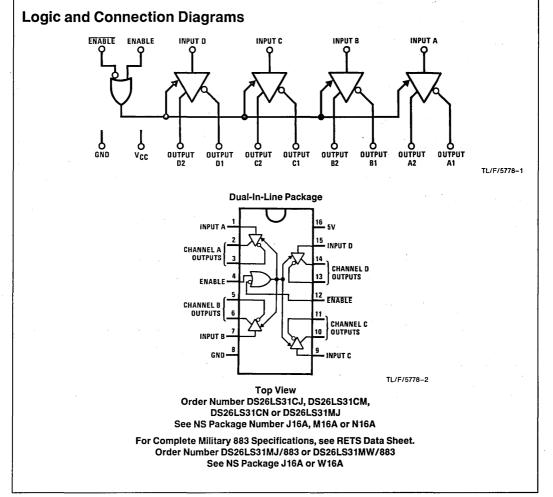

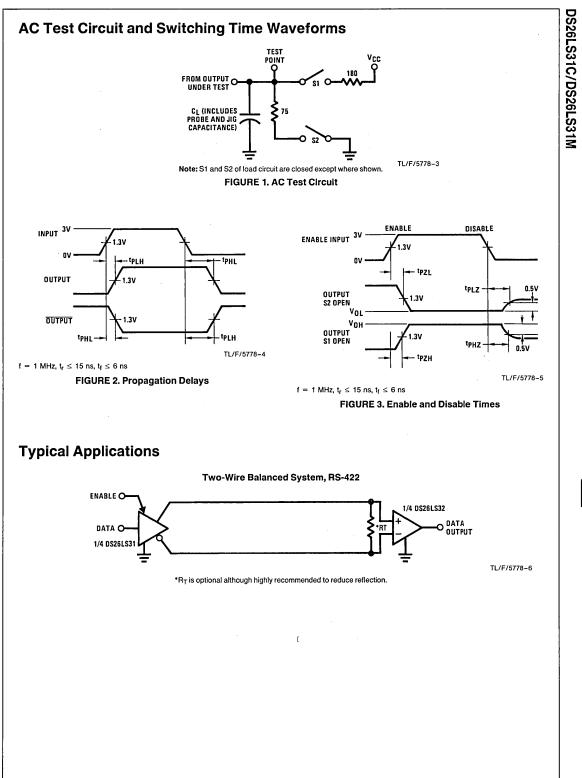

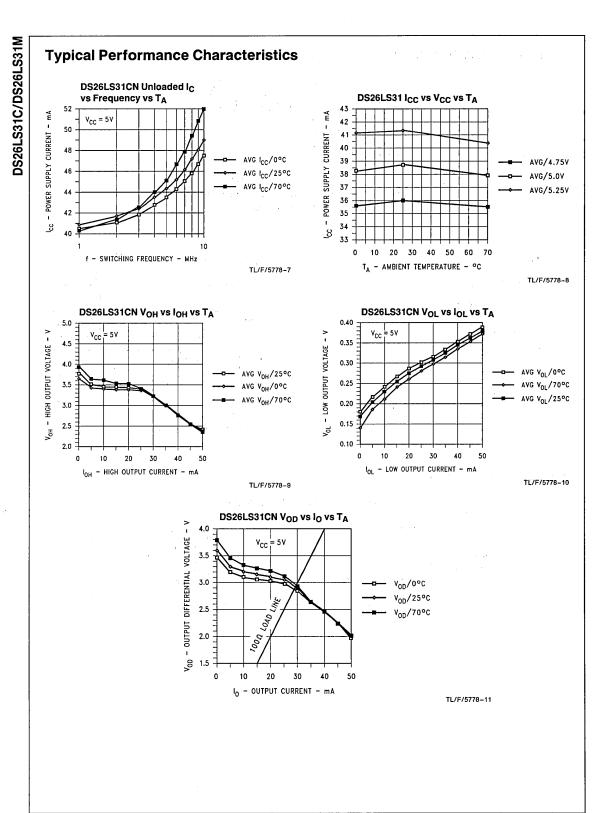

| DS26LS31C/DS26LS31M Quad High Speed Differential Line Driver             | 2-21         |

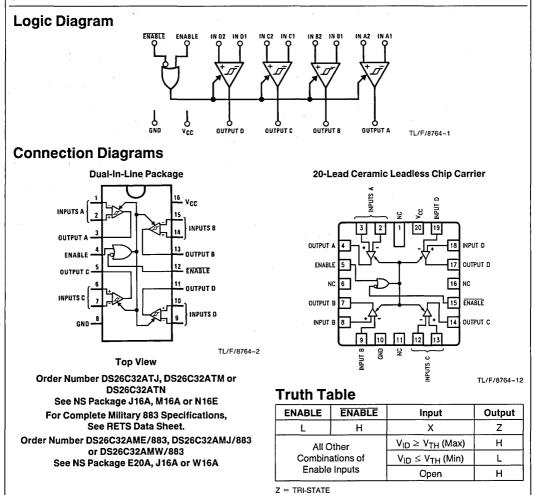

| DS26C32AT/DS26C32AM CMOS Quad Differential Line Receiver                 | 2-25         |

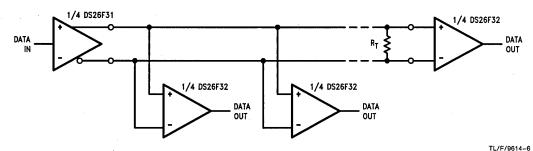

| DS26F32C/DS26F32M Quad Differential Line Receiver                        | 2-32         |

| DS26LS32C/DS26LS32M/DS26LS32AC/DS26LS33C/DS26LS33M/DS26LS33AC            | 11.1         |

| Quad Differential Line Receivers                                         | 2-36         |

| DS34C86T Quad CMOS Differential Line Receiver                            | 2-39         |

| DS35F86/DS34F86 RS-422/RS-423 Quad Line Receivers with TRI-STATE Outputs | 2-44         |

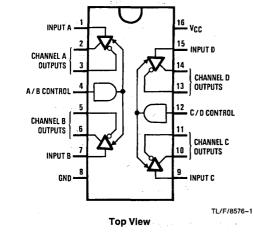

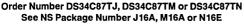

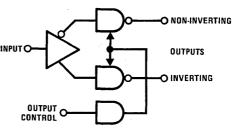

| DS3486 Quad RS-422/RS-423 Line Receiver                                  | 2-48         |

| DS34C87T CMOS Quad TRI-STATE Differential Line Driver                    | 2-52         |

| DS35F87/DS34F87 RS-422 Quad Line Driver with TRI-STATE Outputs           | 2-57         |

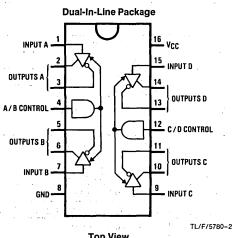

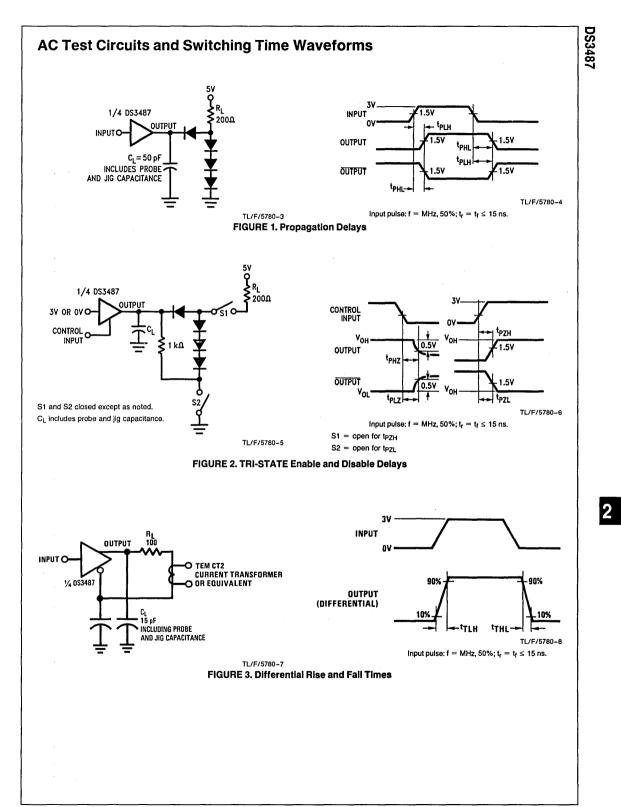

| DS3487 Quad TRI-STATE Line Driver                                        | 2-61         |

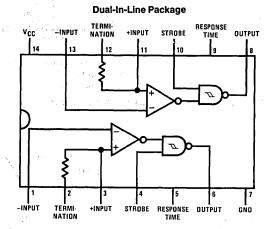

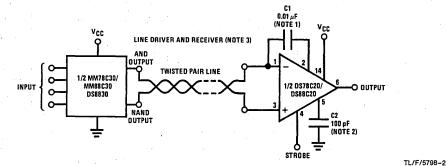

| DS78C20/DS88C20 Dual CMOS Compatible Differential Line Receiver          | 2-64         |

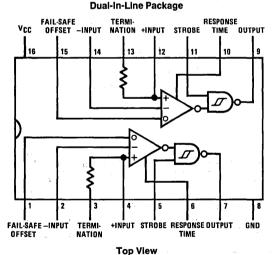

| DS78C120/DS88C120 Dual CMOS Compatible Differential Line Receiver        | 2-68         |

| DS78LS120/DS88LS120 Dual Differential Line Receiver (Noise Filtering and |              |

| Fail Safe)                                                               | 2-76         |

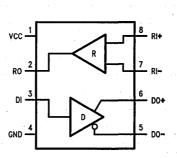

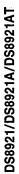

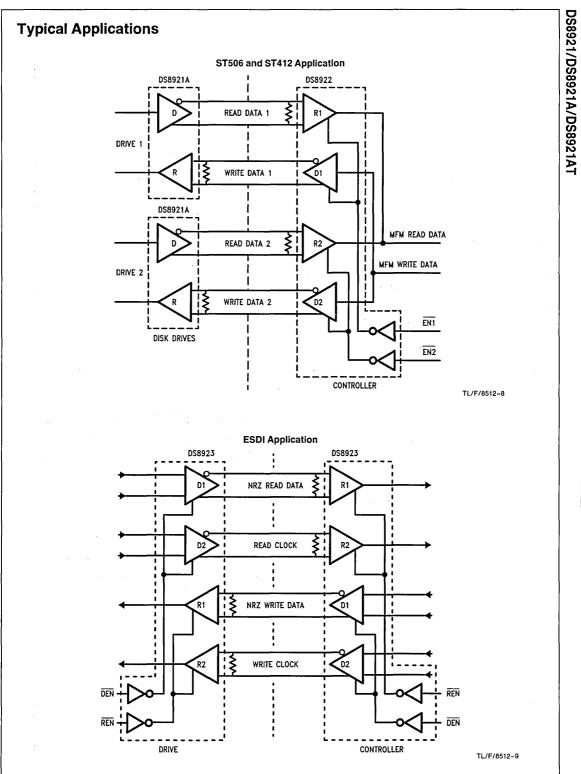

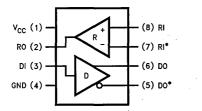

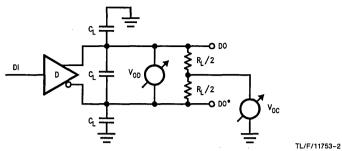

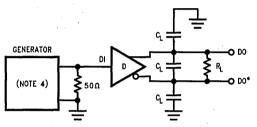

| DS8921/DS8921A/DS8921AT Differential Line Driver and Receiver Pair       | 2-70         |

| DS89217 DS89217 DS69217 Differential CMOS Line Driver and Receiver Pair  | 2-83<br>2-88 |

| DS8922/DS8922A/DS8923/DS8923A TRI-STATE RS-422 Dual Differential Line    | 2-00         |

|                                                                          | 2 02         |

| Driver and Receiver Pairs                                                | 2-93         |

## Table of Contents (Continued)

| Section 2 TIA/EIA 422 & 423 Line Drivers and Receivers (Continued)            |                   |

|-------------------------------------------------------------------------------|-------------------|

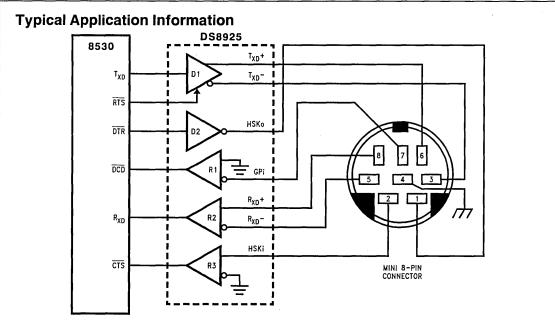

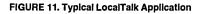

| DS8925 Local Talk Dual Driver/Triple Receiver                                 | 2-103             |

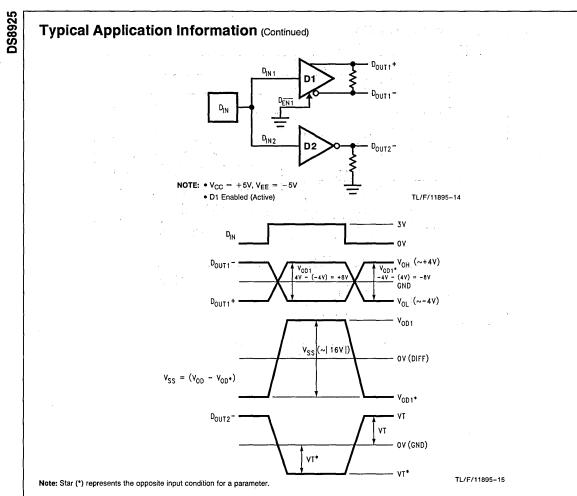

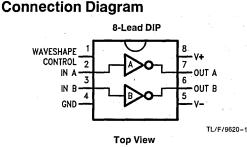

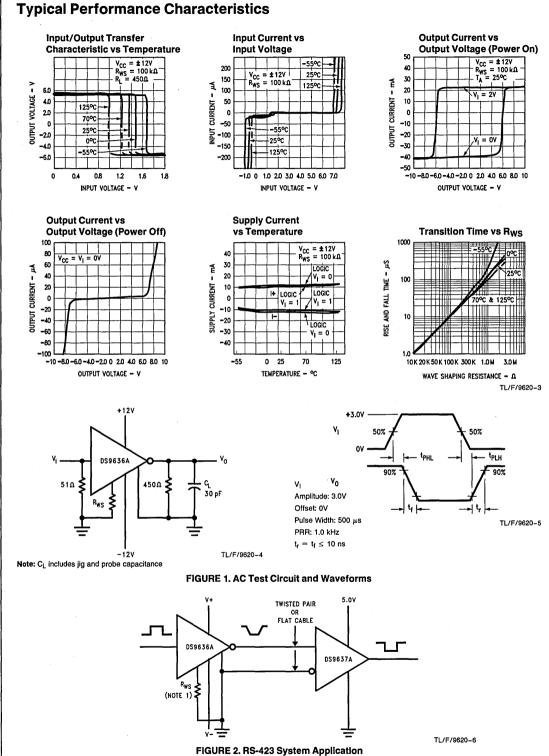

| DS9636A RS-423 Dual Programmable Slew Rate Line Driver                        | 2-111             |

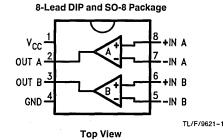

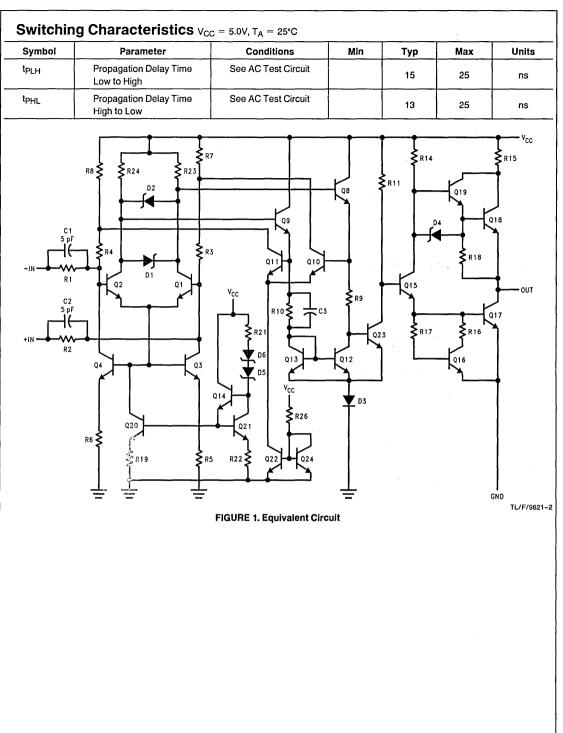

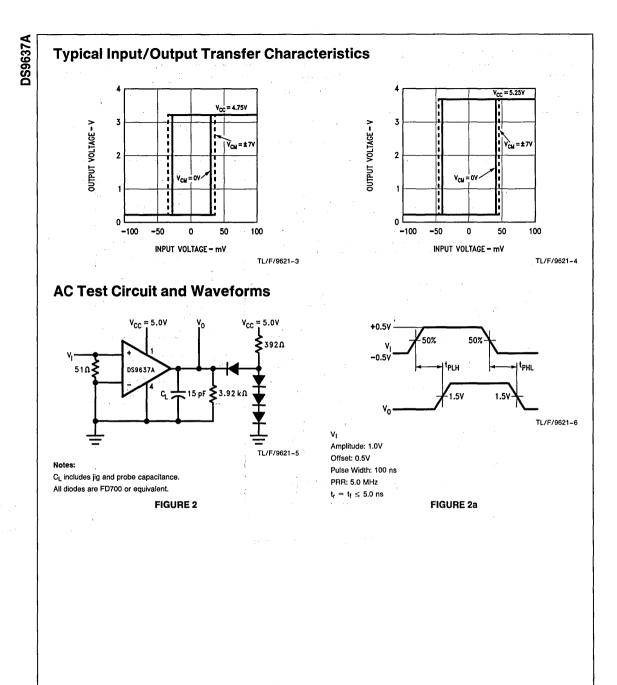

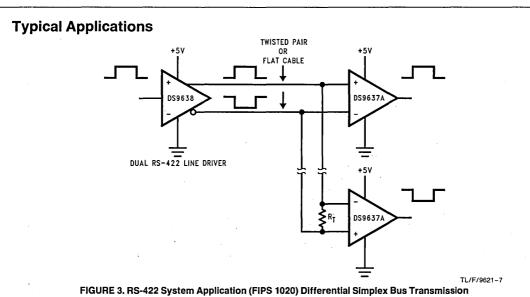

| DS9637A Dual Differential Line Receiver                                       | 2-115             |

| DS9638 RS-422 Dual High Speed Differential Line Driver                        |                   |

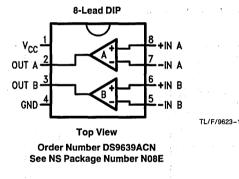

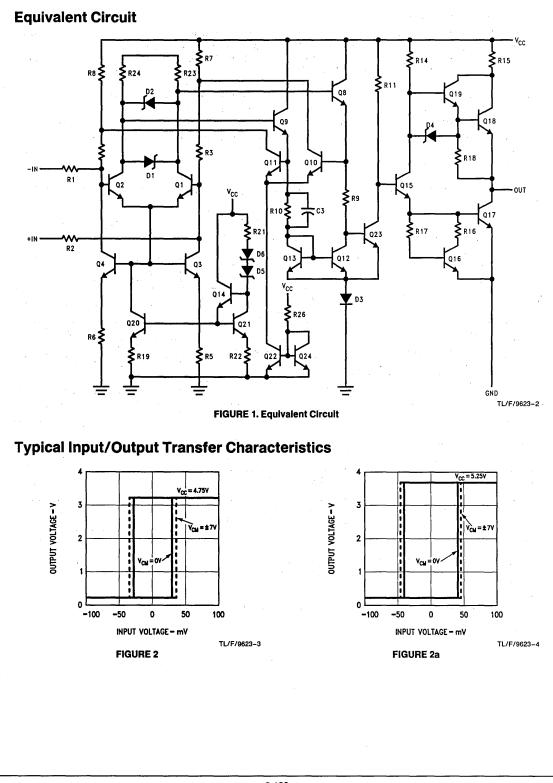

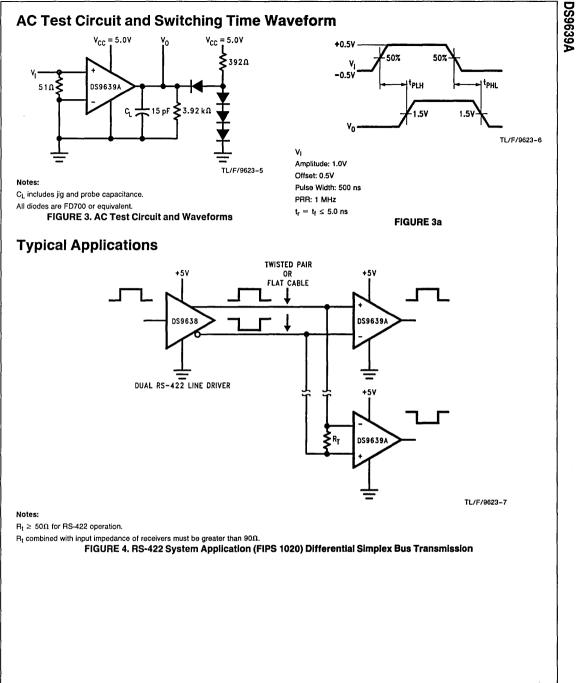

| DS9639A Dual Differential Line Receiver                                       | 2-124             |

| Section 3 TIA/EIA-485 Line Drivers, Receivers, Repeaters and Transceivers     | · · · · ·         |

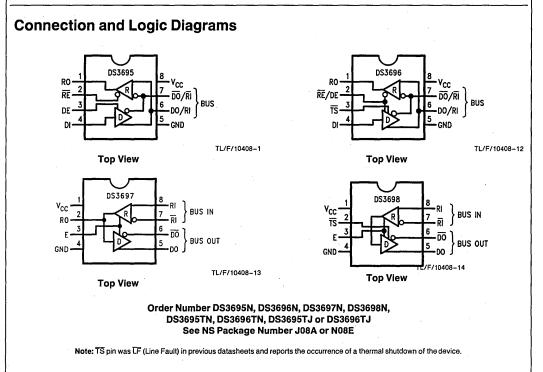

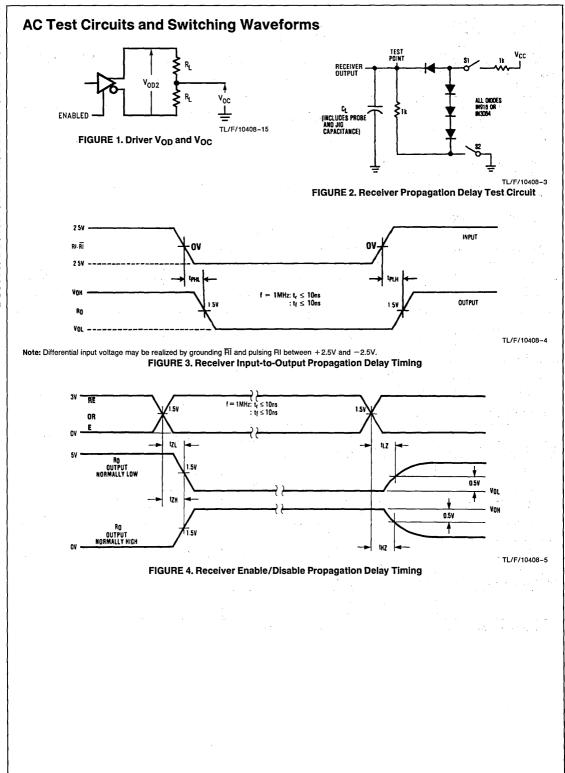

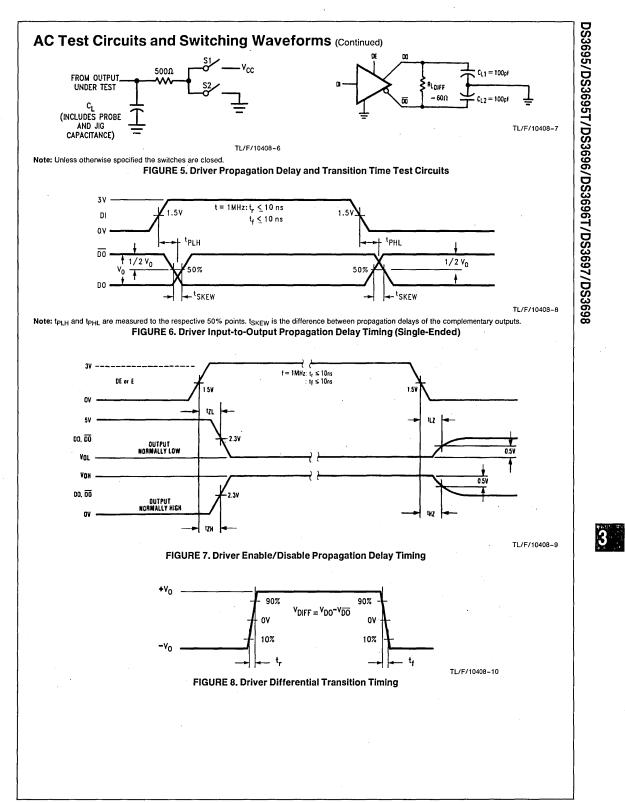

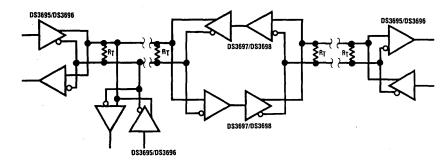

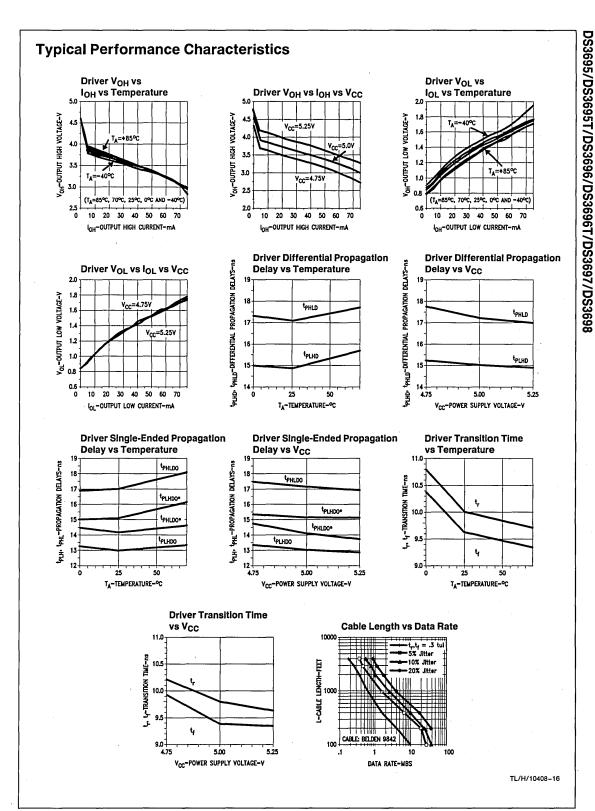

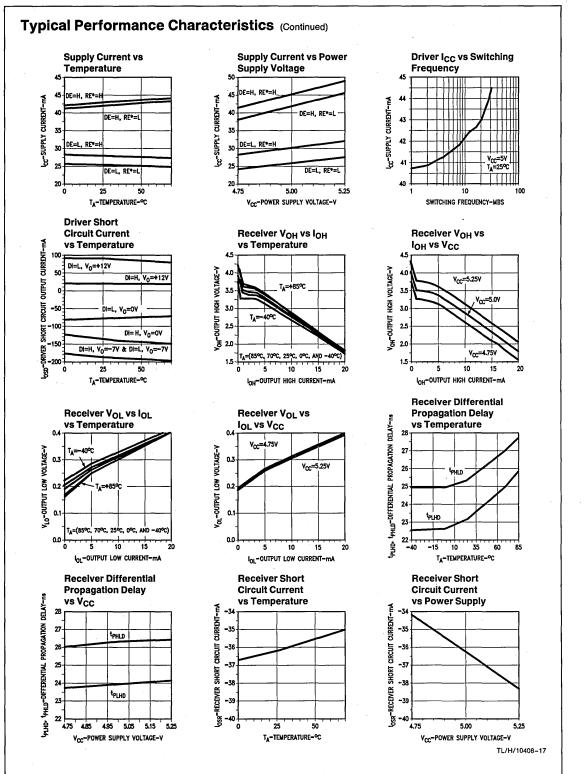

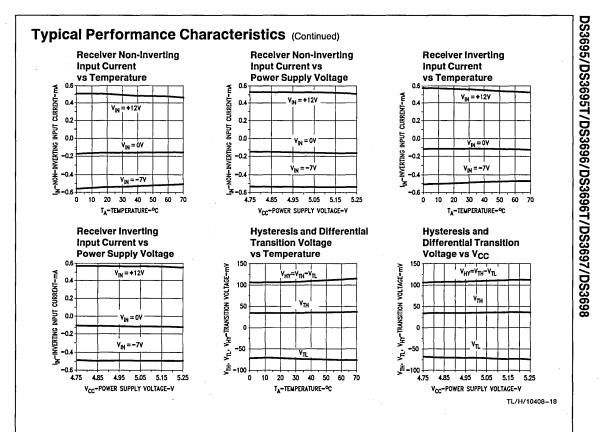

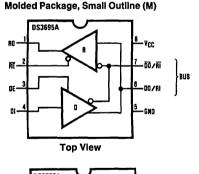

| DS3695/DS3695T/DS3696/DS3696T/DS3697/DS3698 Multipoint RS-485/RS-422          | 5 - S             |

| Transceivers/Repeaters                                                        | 3-3               |

| DS3695A/DS3695AT/DS3696A Multipoint RS-485/RS-422 Transceivers                | 3-12              |

| DS16F95/DS36F95 EIA-485/EIA-422A Differential Bus Transceivers                | 3-18              |

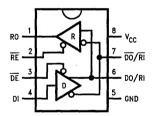

| DS36276 Failsafe Multipoint Transceiver                                       | 3-28              |

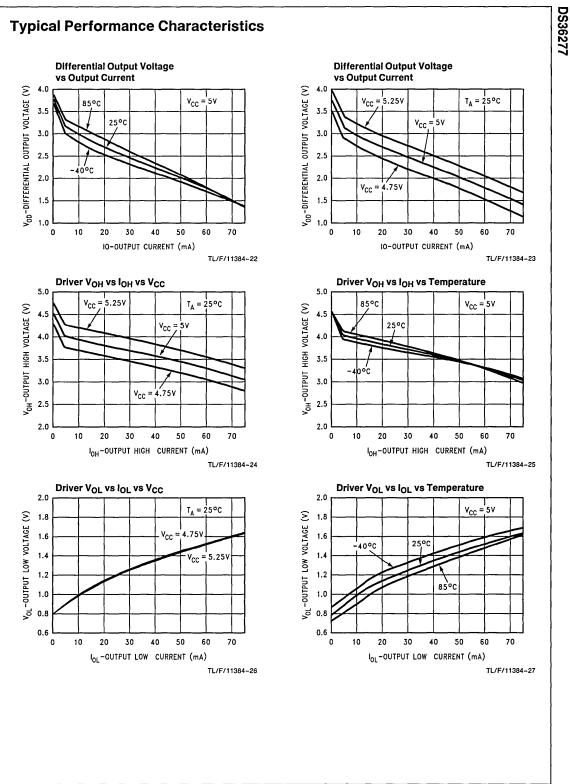

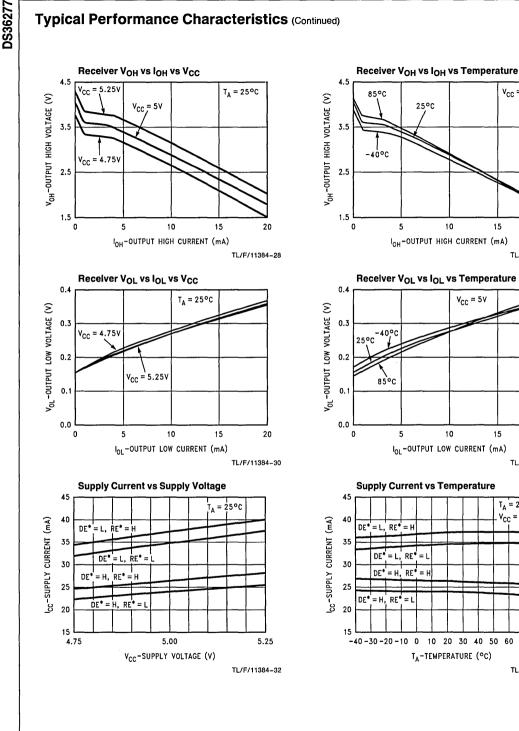

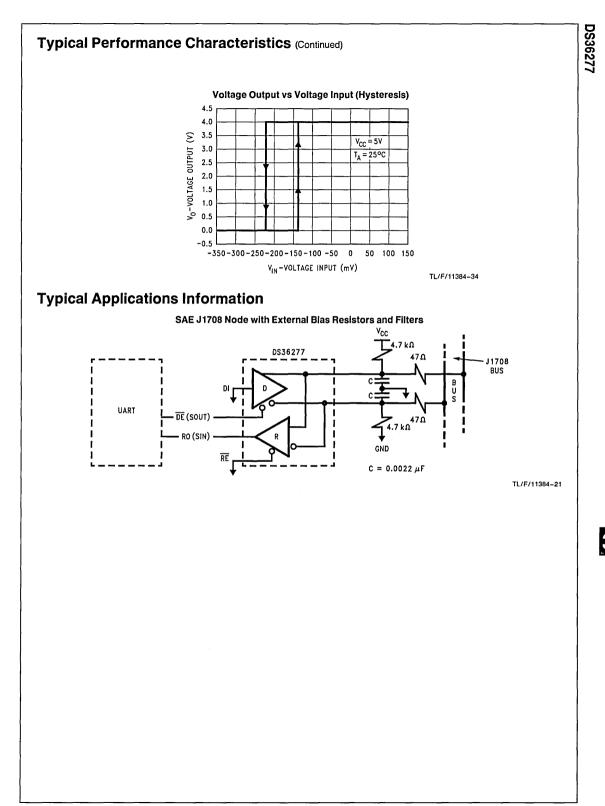

| DS36277 Dominant Mode Multipoint Transceiver                                  | 3-40              |

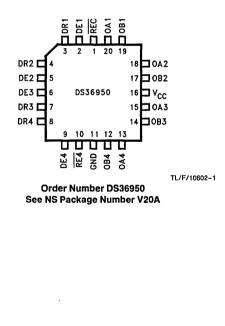

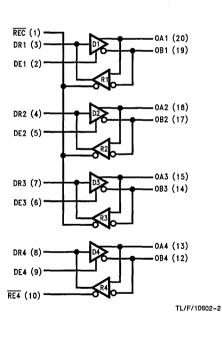

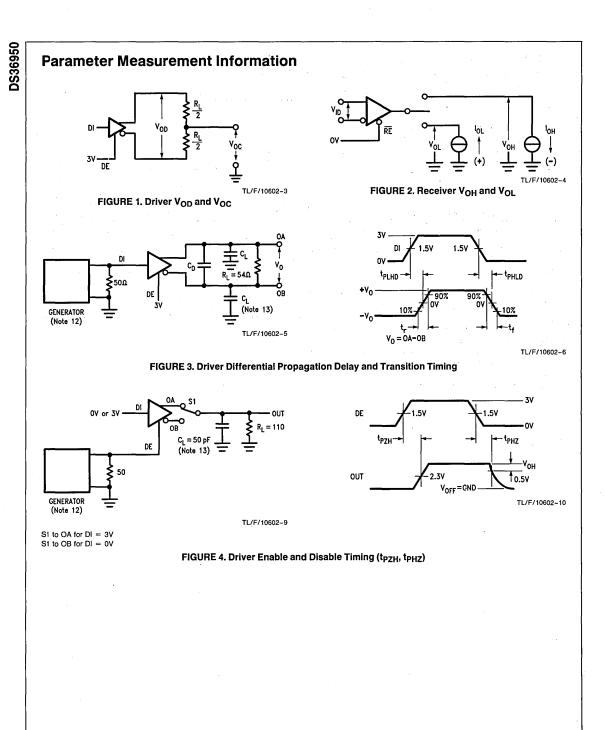

| DS36950 Quad Differential Bus Transceiver                                     | 3-52              |

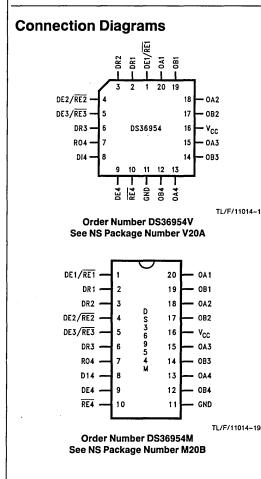

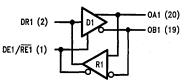

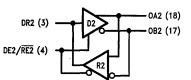

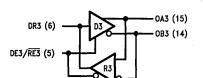

| DS36954 Quad Differential Bus Transceiver                                     | 3-61              |

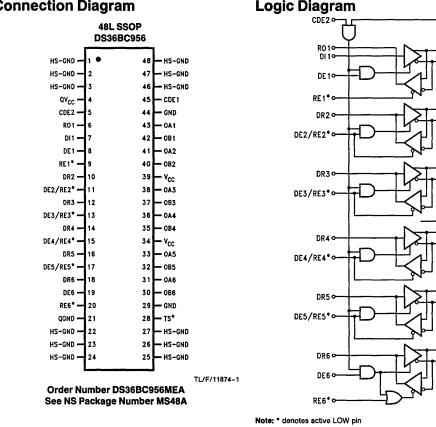

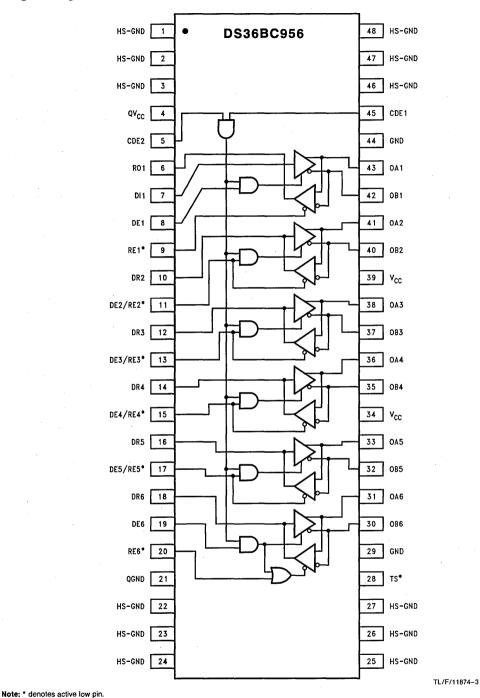

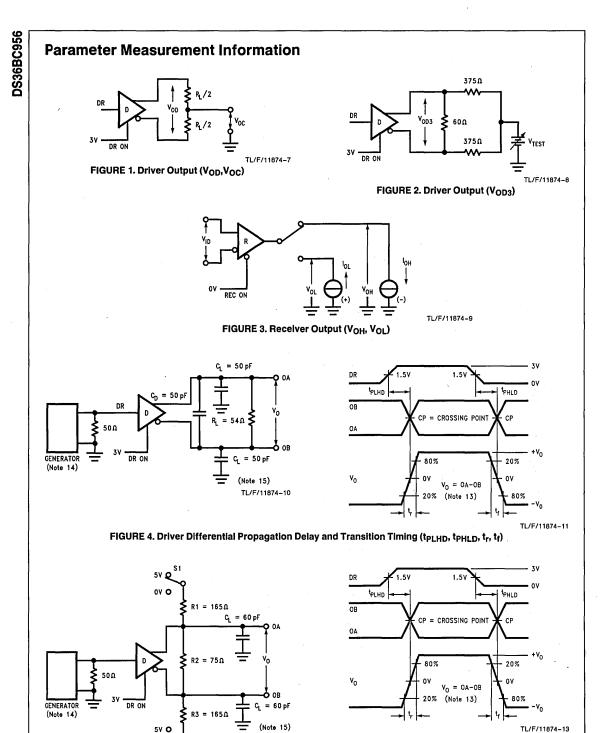

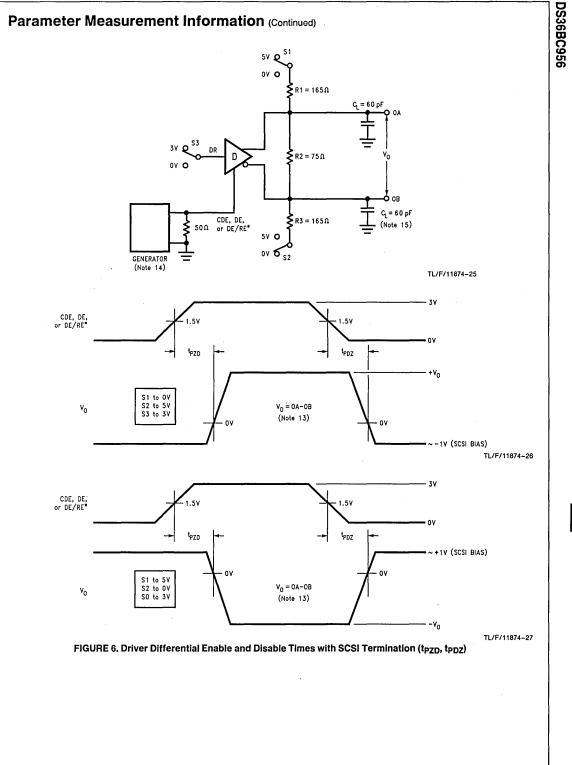

| DS36BC956 Low Power BiCMOS Hex Differential Bus Transceiver                   | 3-68              |

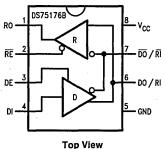

| DS75176B/DS75176BT Multipoint RS-485/RS-422 Transceivers                      | 3-79              |

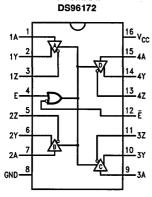

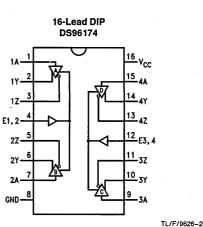

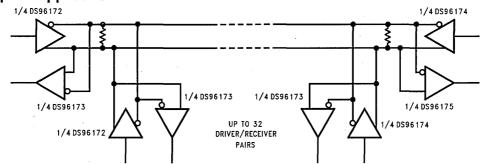

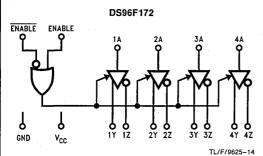

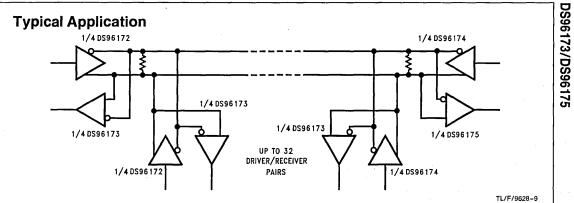

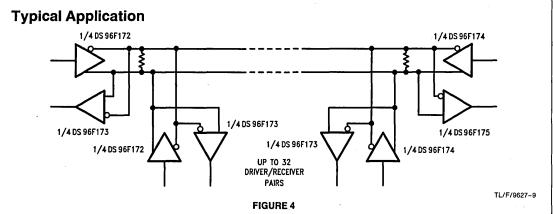

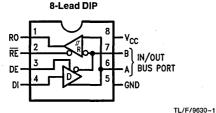

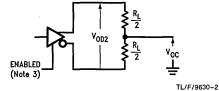

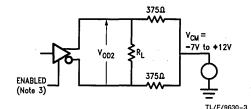

| DS96172/DS96174 RS-485/RS-422 Quad Differential Line Drivers                  | 3-84              |

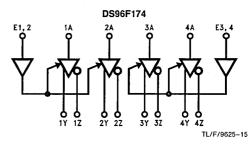

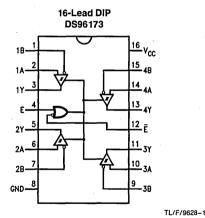

| DS96F172C/DS96F172M/DS96F174C/DS96F174M EIA-485/EIA-422A Quad                 | 0.00              |

| Differential Drivers                                                          | 3-89<br>3-97      |

|                                                                               | 3-97              |

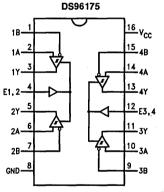

| DS96F173C/DS96F173M/DS96F175C/DS96F175M EIA-485/EIA-422 Quad                  | 3-102             |

| Differential Receivers                                                        | 3-102             |

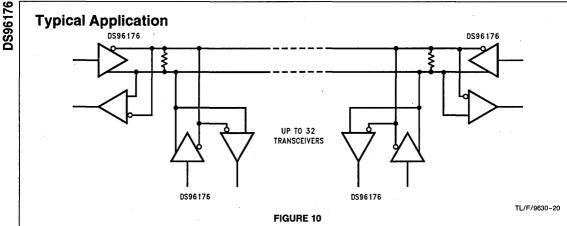

| DS96176 RS-485/RS-422 Differential Bus Repeater                               | 3-110             |

| ·                                                                             | 3-120             |

| ootaan 1700 Ion tanago Dinaran aginamig                                       | 4.0               |

| LVDS Introduction                                                             | 4-3<br><b>4-4</b> |

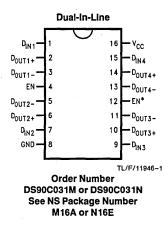

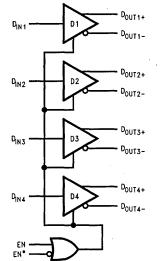

| DS90C031 LVDS Quad CMOS Differential Line Driver                              | 4-4<br>4-8        |

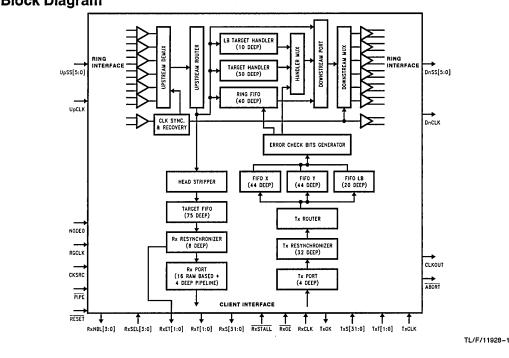

| QR0001 QuickRing Datastream Controller                                        | 4-0<br>4-11       |

|                                                                               | 4-11              |

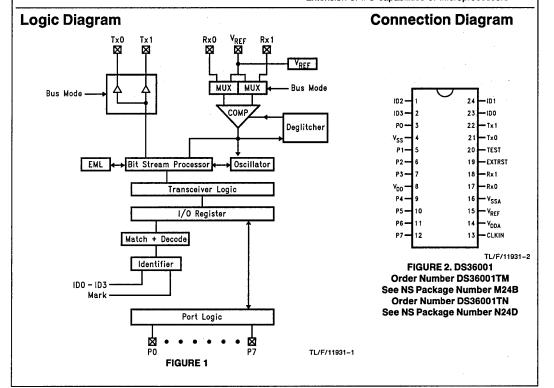

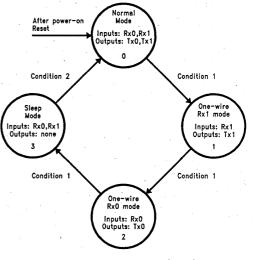

| Section 5 Special Interface<br>DS36001 SLIO1 Serial Link Input/Output Device  | 5-3               |

| SUPER I/O                                                                     | 5-3               |

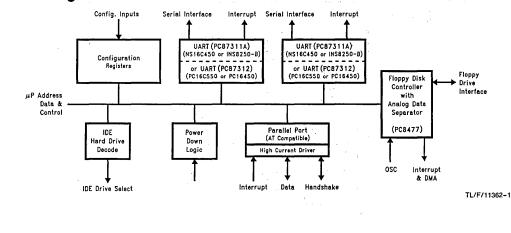

| PC87310 (Super I/OTM) Dual UART with Floppy Disk Controller and Parallel Port | 5-20              |

| PC87310 (Super I/O™) Dual OART with Ploppy Disk Controller with Dual UARTs,   | 0-20              |

| Parallel Port and IDE Interface                                               | 5-21              |

| PC I/O COMMUNICATIONS                                                         | J-21              |

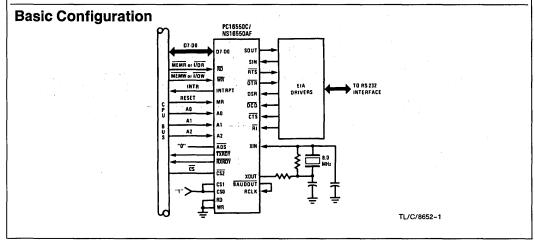

| PC16550C/NS16550AF Universal Asynchronous Receiver/Transmitter with FIFOs     | 5-22              |

| Section 6 General Purpose Line Drivers                                        | • <u></u>         |

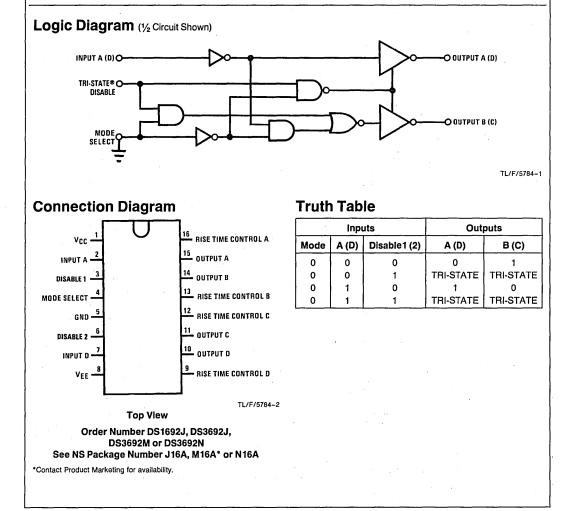

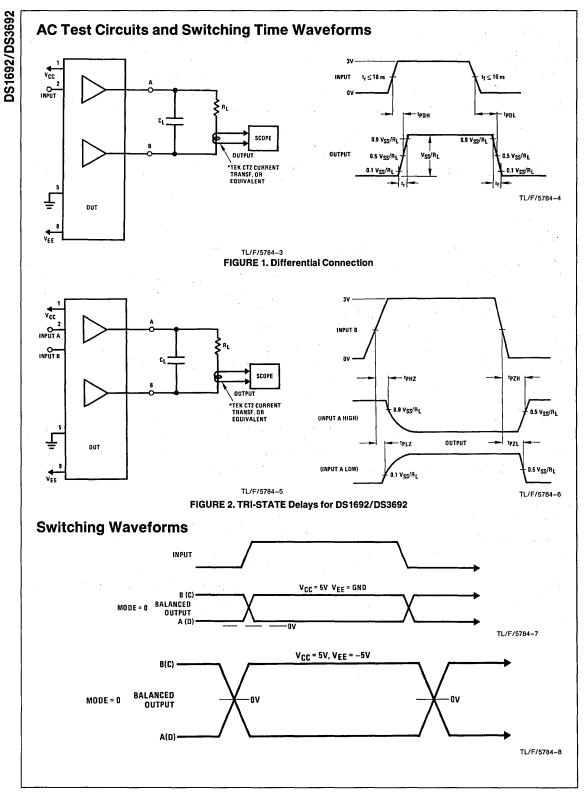

| DS1692/DS3692 TRI-STATE Differential Line Drivers                             | 6-3               |

| DS55110A/DS75110A Dual Line Drivers                                           | 6-7               |

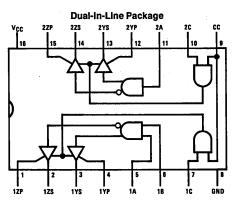

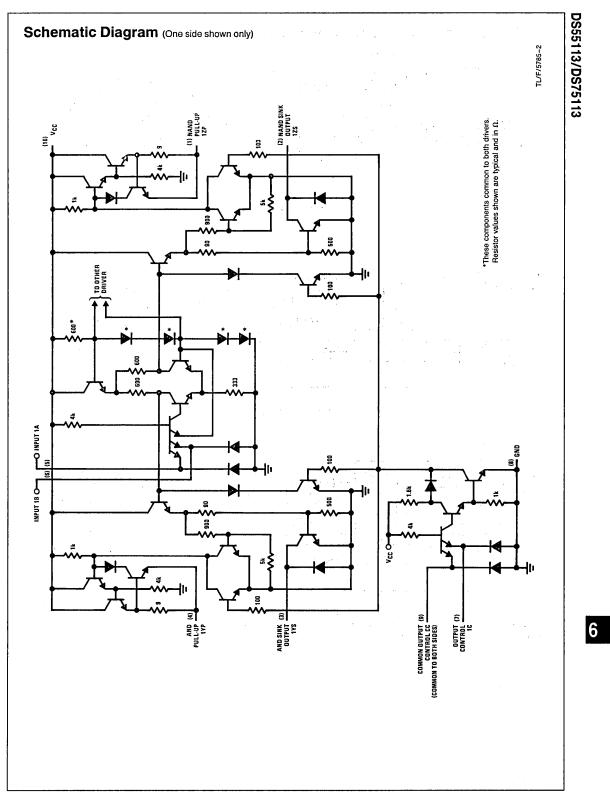

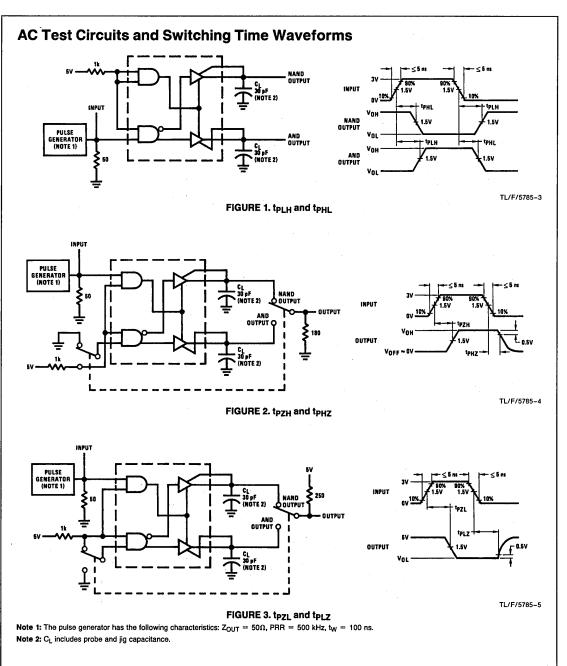

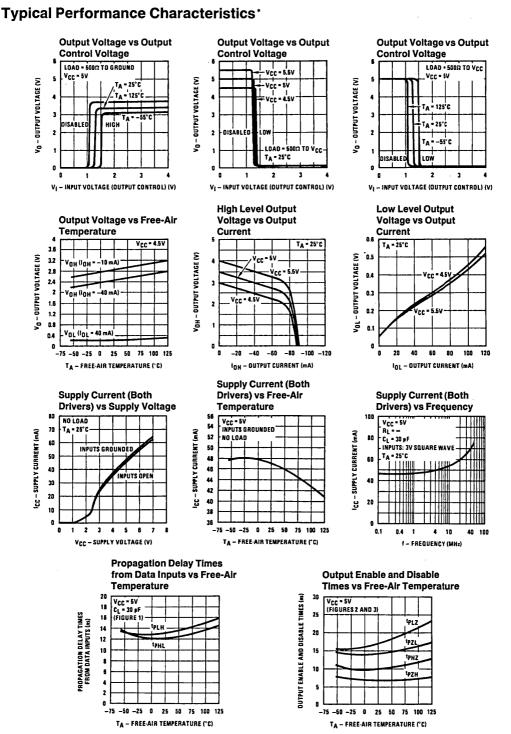

| DS55113/DS75113 Dual TRI-STATE Differential Line Drivers                      | 6-12              |

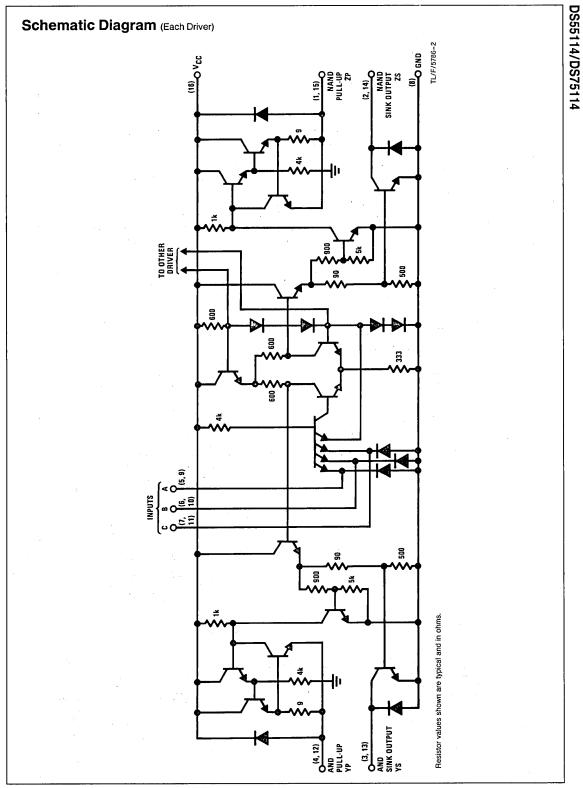

| DS55114/DS75114 Dual Differential Line Drivers                                | 6-19              |

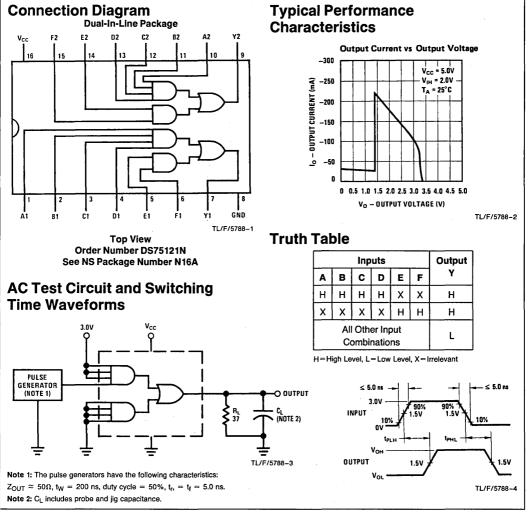

| DS75121 Dual Line Driver                                                      | 6-24              |

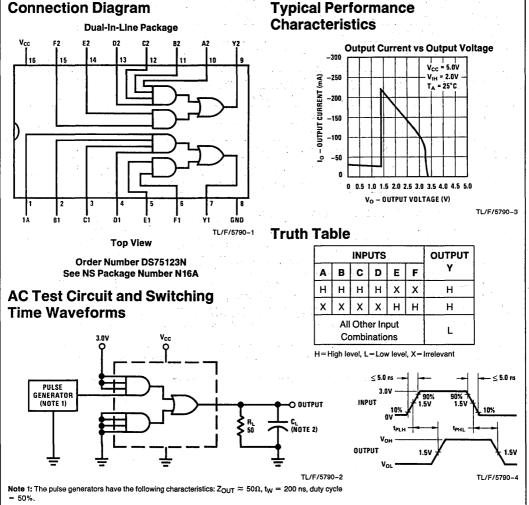

| DS75123 Dual Line Driver                                                      | 6-26              |

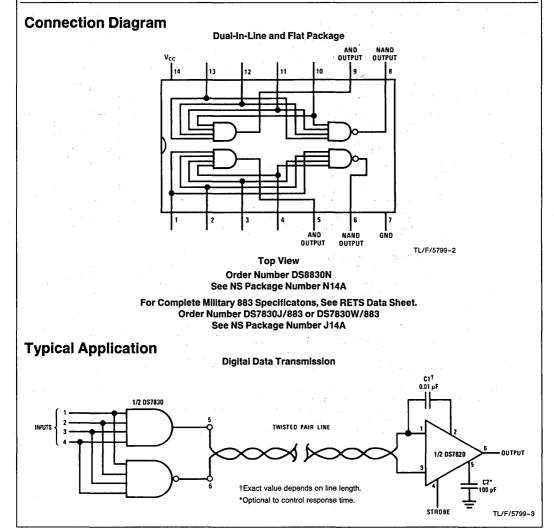

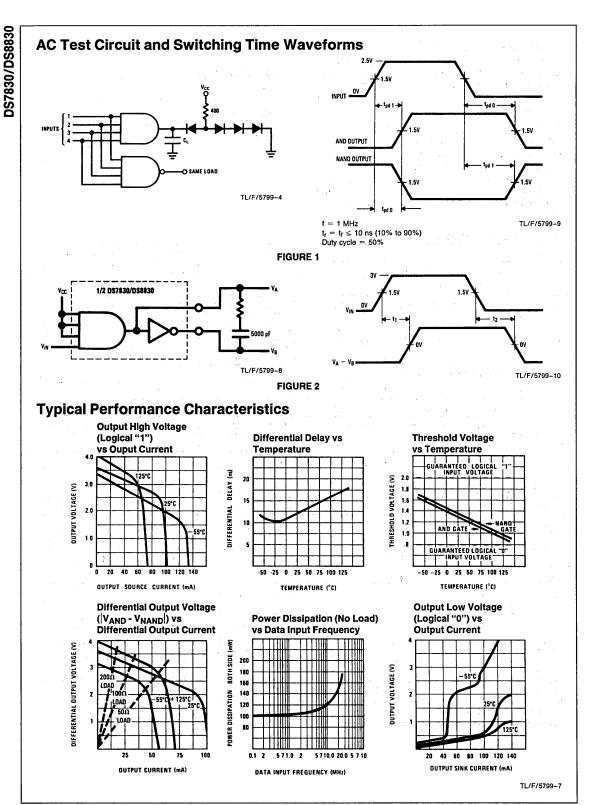

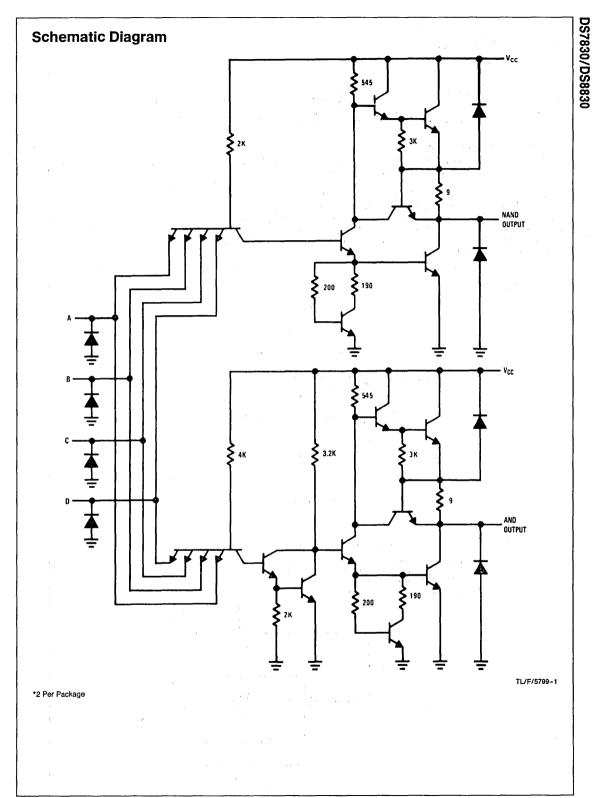

| DS7830/DS8830 Dual Differential Line Driver                                   | 6-28              |

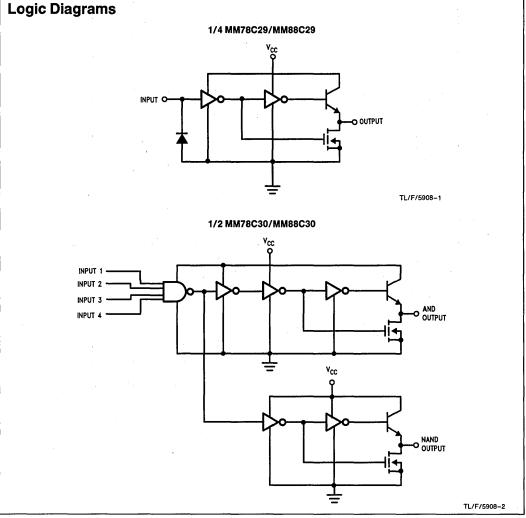

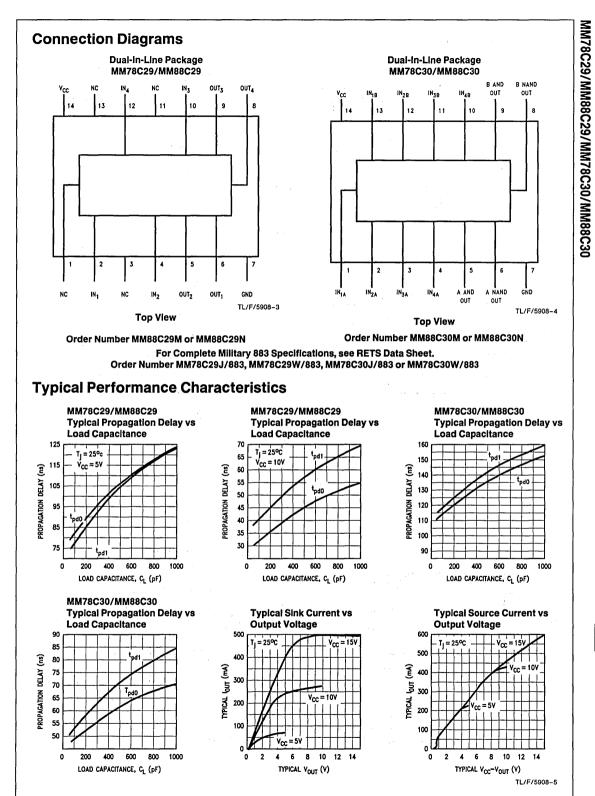

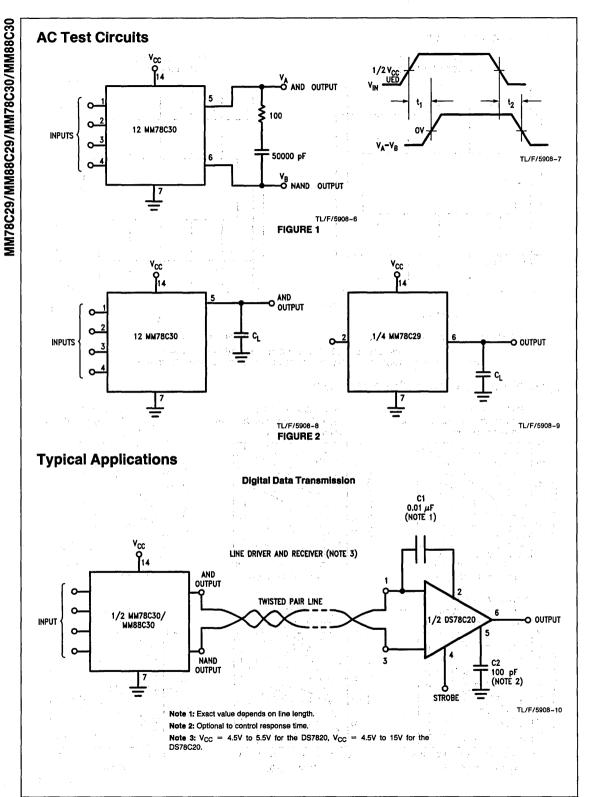

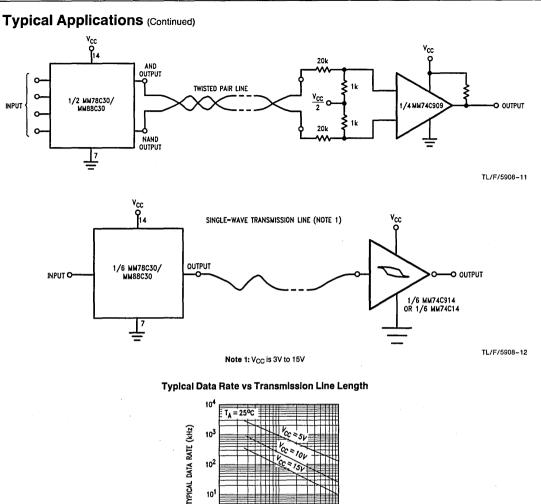

| MM78C29/MM88C29 Quad Single-Ended Line Drivers                                | 6-32              |

| MM78C30/MM88C30 Dual Differential Line Drivers                                | 6-32              |

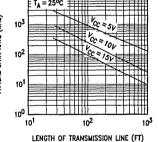

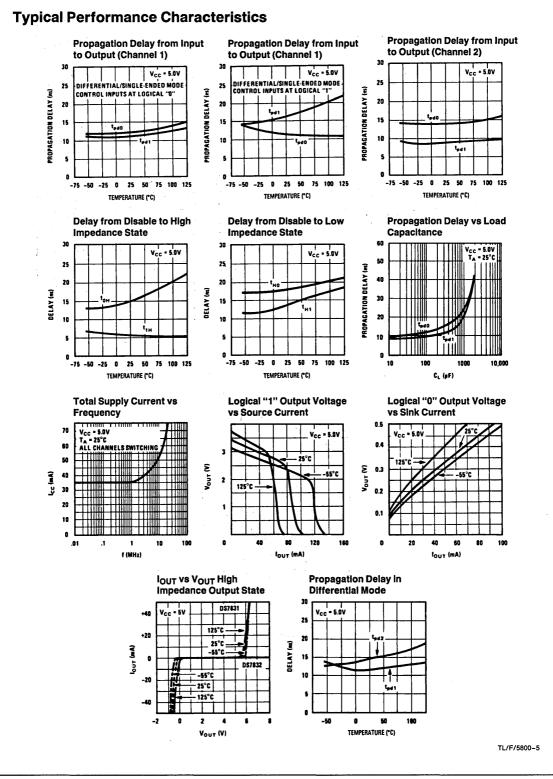

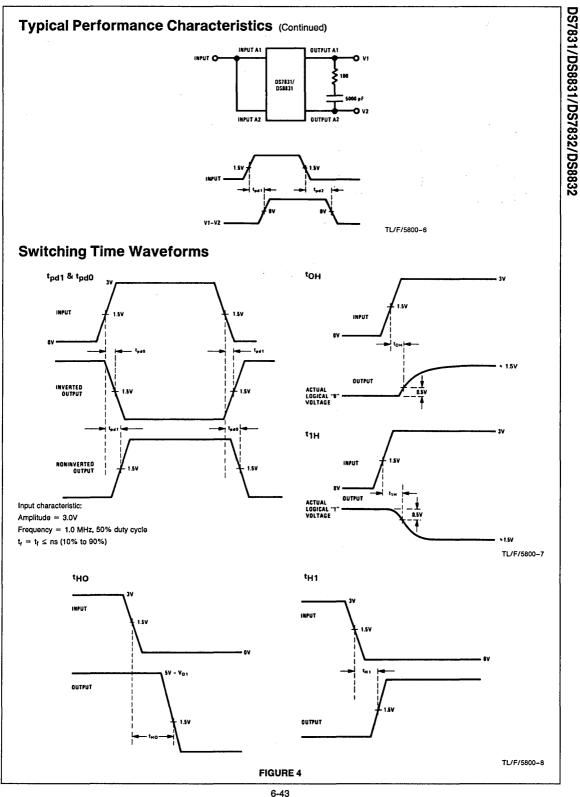

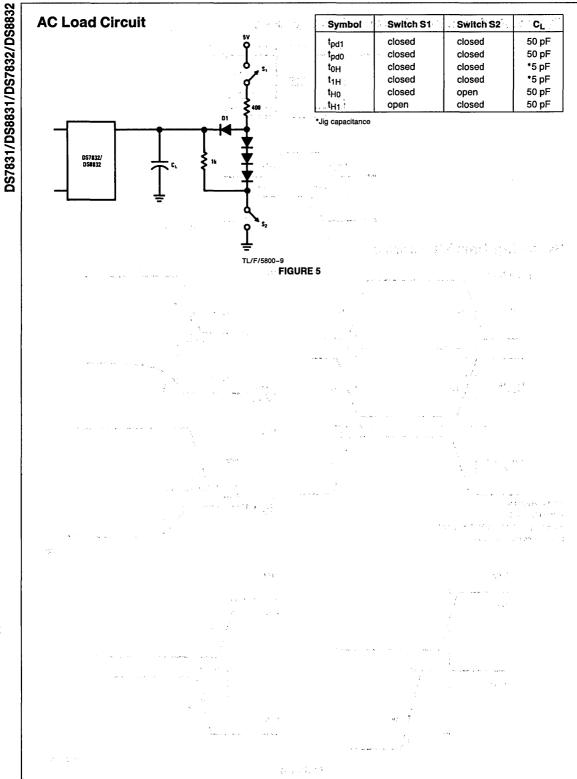

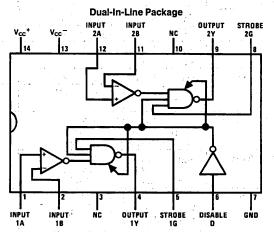

| DS7831/DS8831/DS7832/DS8832 Dual TRI-STATE Line Drivers                       | 6-38              |

| Section 7 General Purnose Receivers                                           |                   |

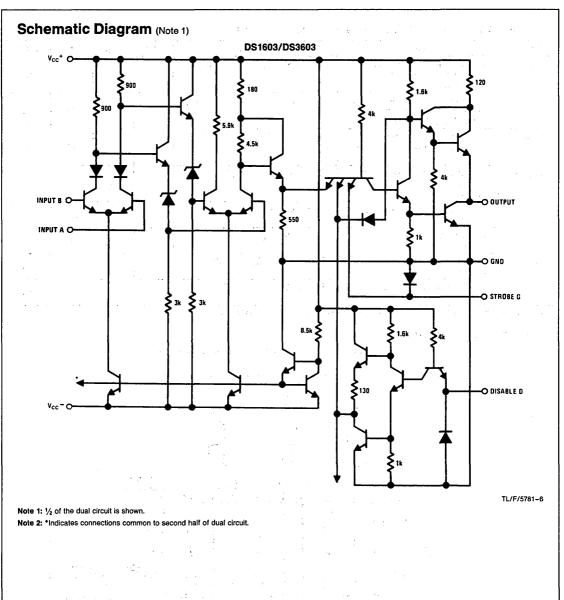

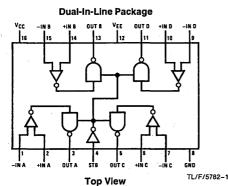

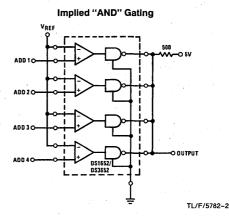

| DS1603/DS3603 TRI-STATE Dual Receivers                                        | 7-3               |

|                                                                               |                   |

## Table of Contents (Continued)

| Section 7 General Purpose Receivers (Continued)                                                                   |       |

|-------------------------------------------------------------------------------------------------------------------|-------|

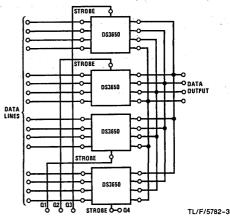

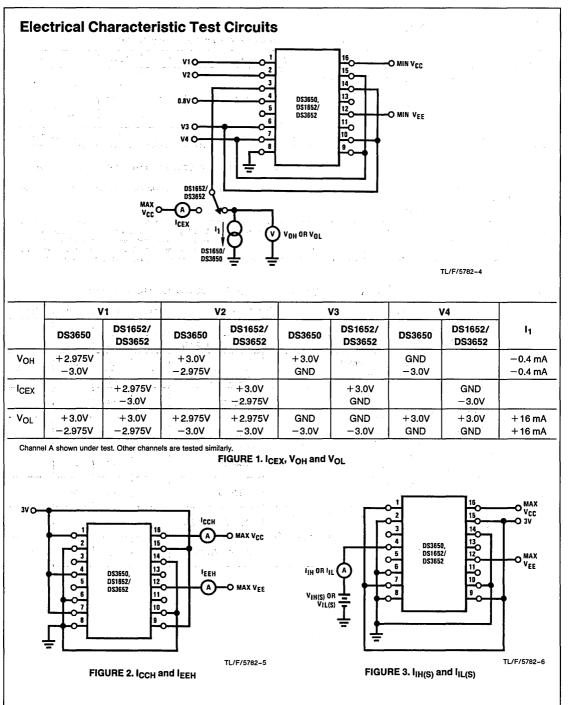

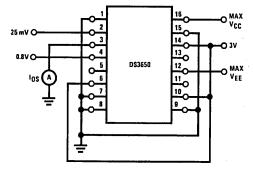

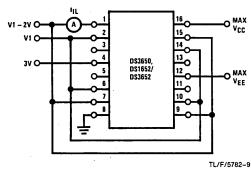

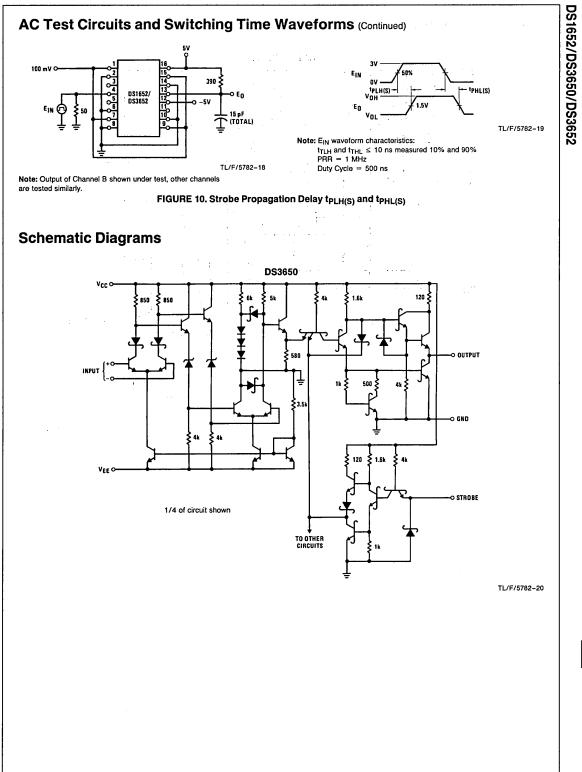

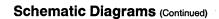

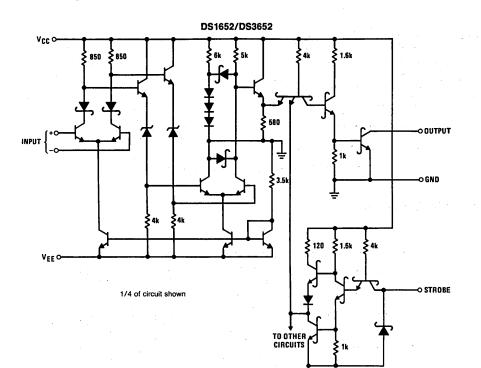

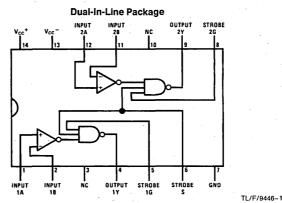

| DS1652/DS3650/DS3652 Quad Differential Line Receivers                                                             | 7-7   |

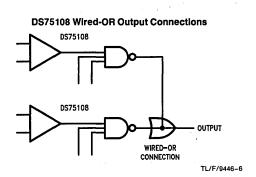

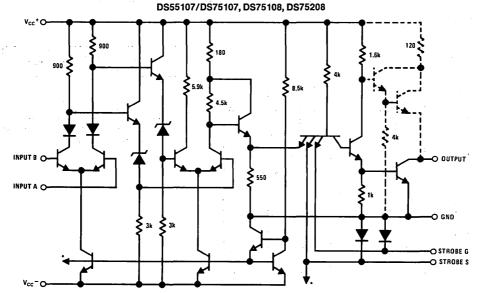

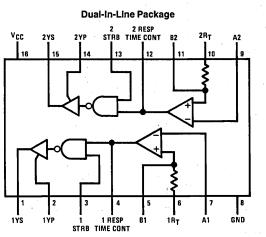

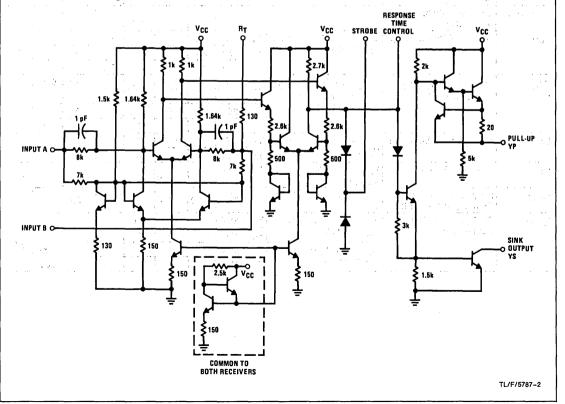

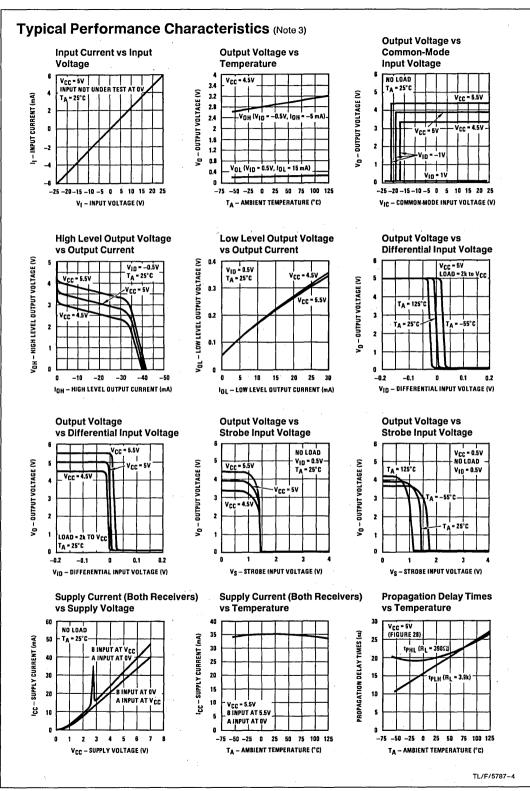

| DS55107/DS75107/DS75108/DS75208 Dual Line Receivers                                                               | 7-15  |

| DS55115/DS75115 Dual Differential Line Receivers                                                                  | 7-22  |

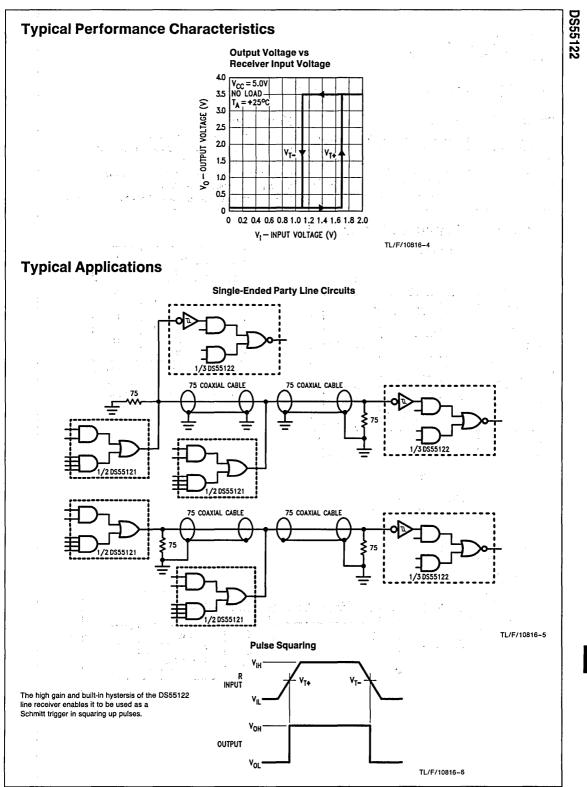

| DS55122 Triple Line Receiver                                                                                      | 7-27  |

| DS75124 Triple Line Receiver                                                                                      | 7-30  |

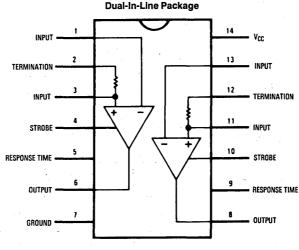

| DS75129 Eight-Channel Line Receiver                                                                               | 7-33  |

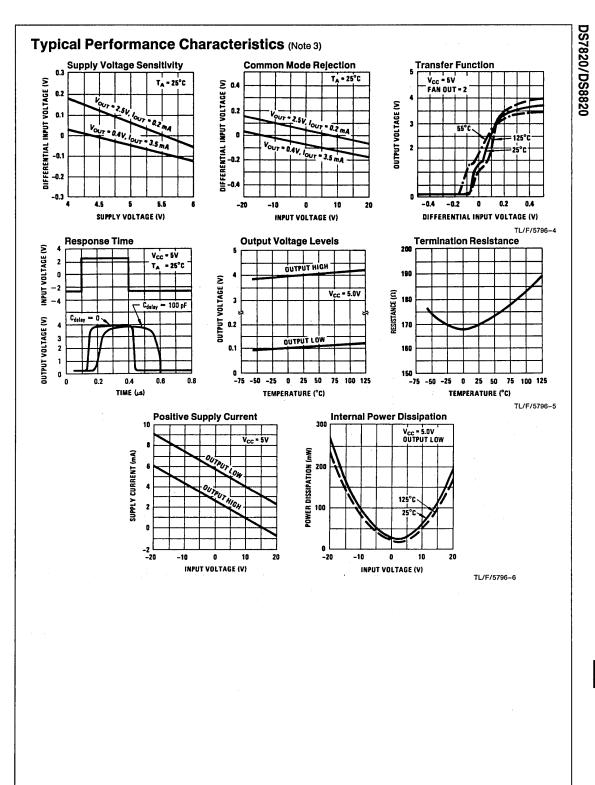

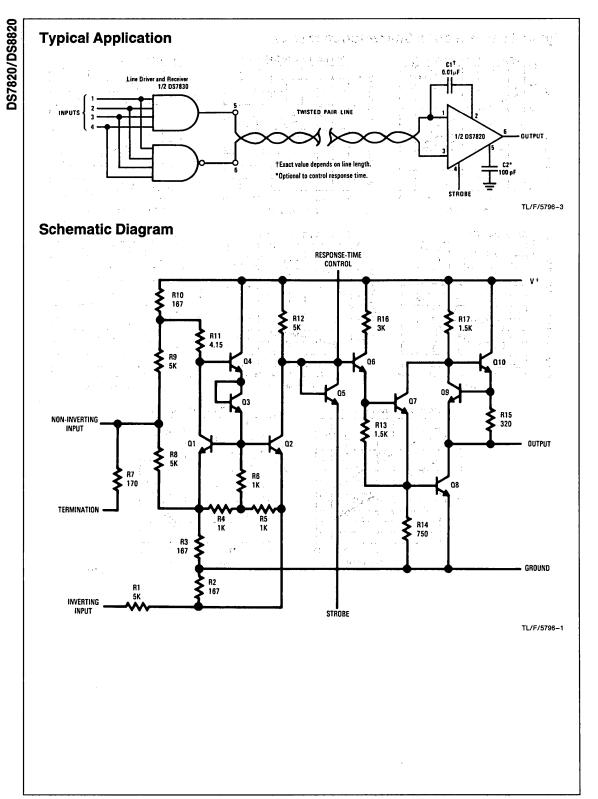

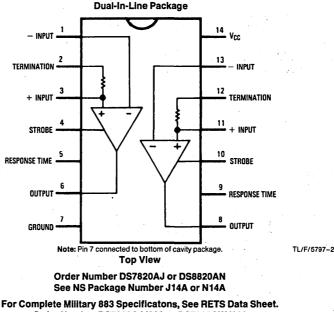

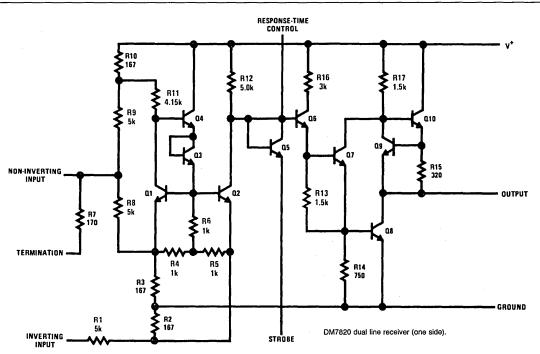

| DS7820/DS8820 Dual Line Receivers                                                                                 | 7-37  |

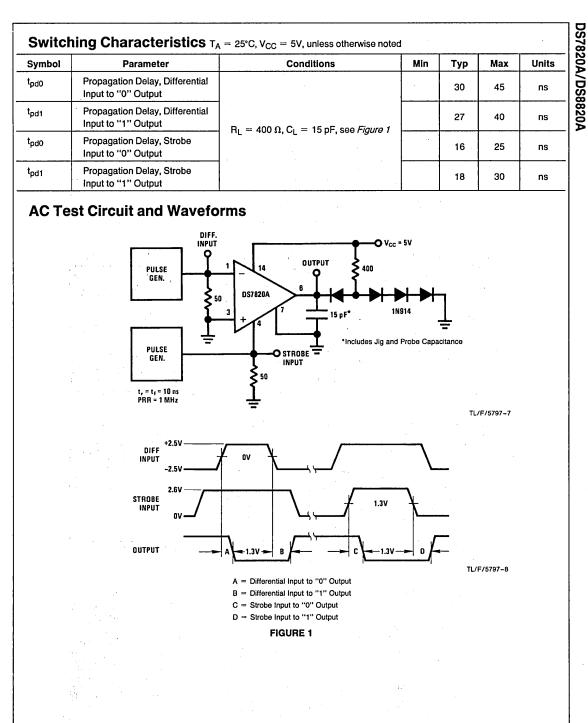

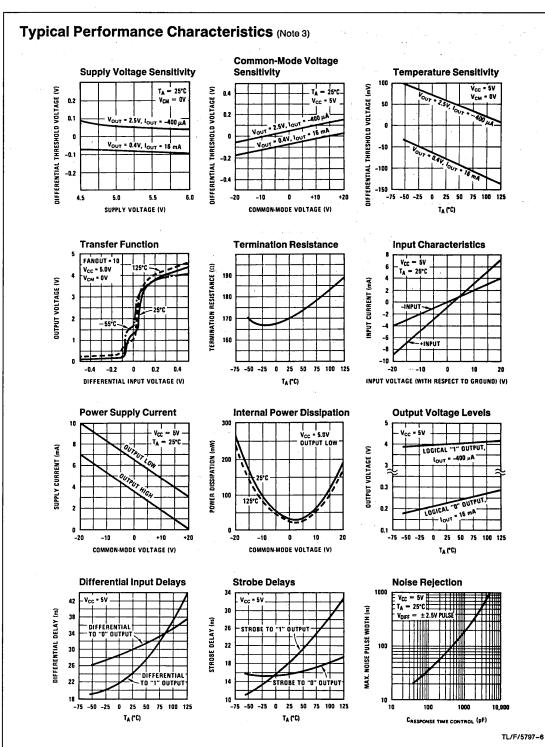

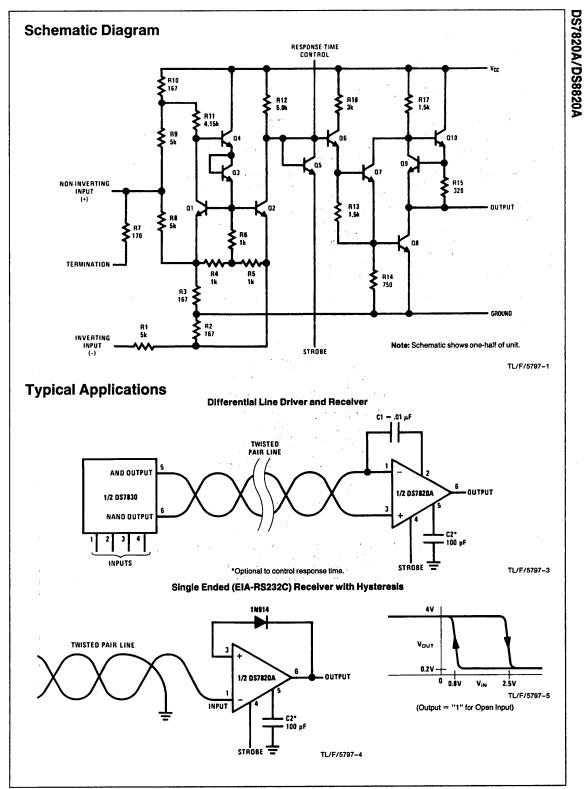

| DS7820A/DS8820A Dual Line Receivers                                                                               | 7-41  |

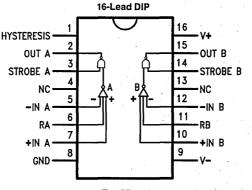

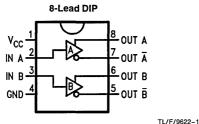

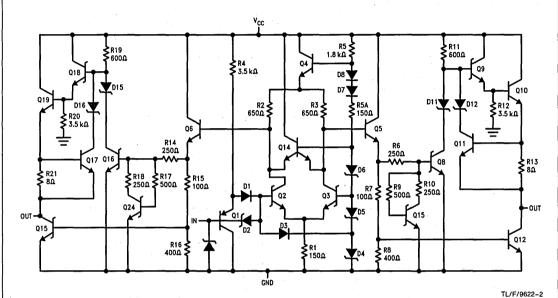

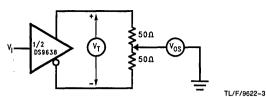

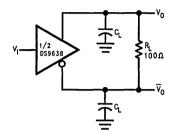

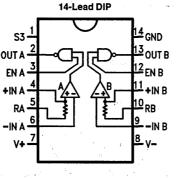

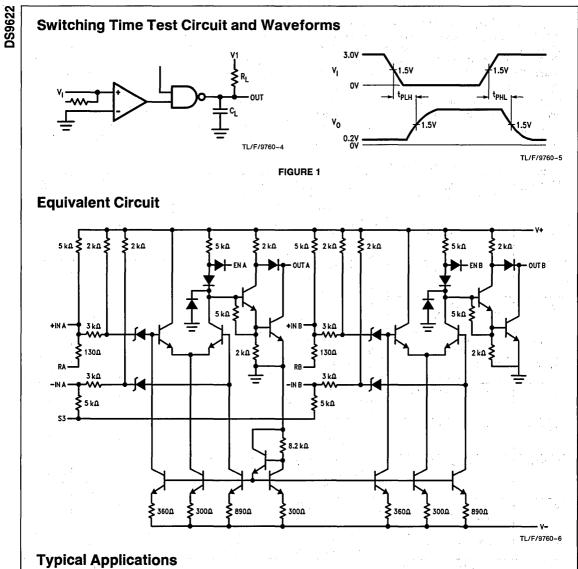

| DS9622 Dual Line Receiver                                                                                         | 7-46  |

| Section 8 Application Notes                                                                                       |       |

| Application Note-Selection Guide                                                                                  | 8-3   |

| AN-22 Integrated Circuits for Digital Data Transmission                                                           | 8-5   |

| AN-108 Transmission Line Characteristics                                                                          | 8-19  |

| AN-214 Transmission Line Drivers and Receivers for TIA/EIA Standards RS-422 and                                   | • • • |

| RS-423                                                                                                            | 8-25  |

| AN-216 Summary of Well Known Interface Standards                                                                  | 8-35  |

| AN-409 Transceivers and Repeaters Meeting the EIA RS-485 Interface Standard                                       | 8-45  |

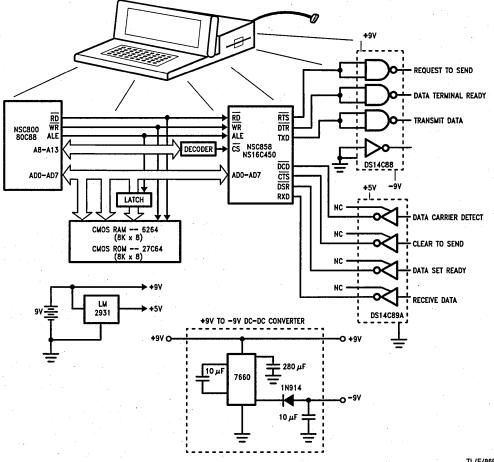

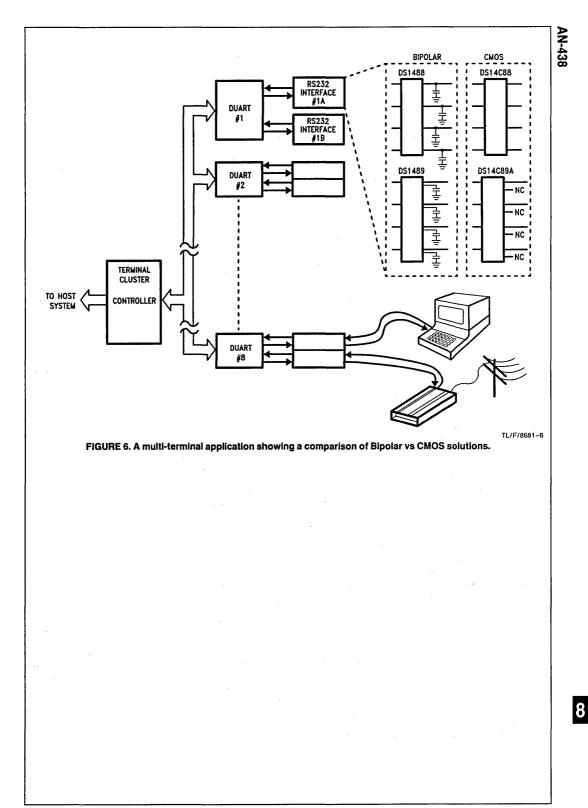

| AN-438 Low Power RS-232C Driver and Receiver in CMOS                                                              | 8-52  |

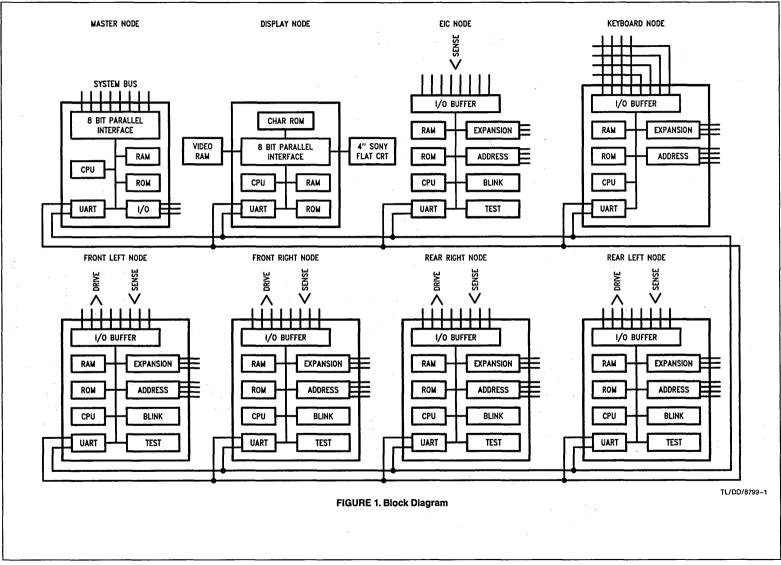

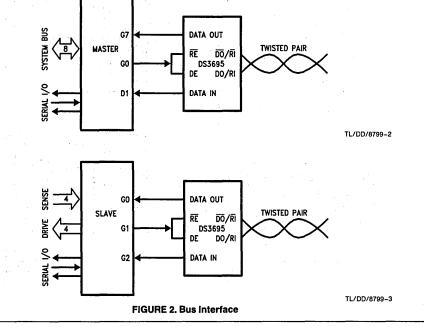

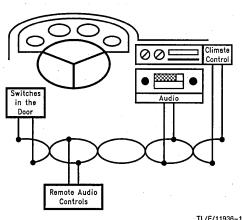

| AN-454 Automotive Multiplex Wiring                                                                                | 8-56  |

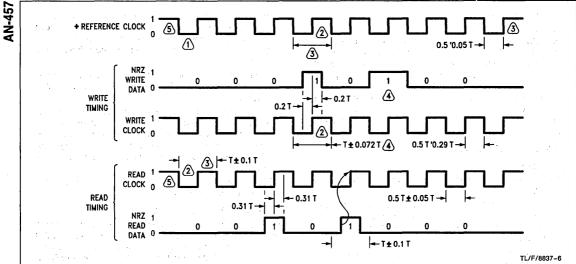

| AN-457 High Speed, Low Skew RS-422 Drivers and Receivers Solve Critical System                                    |       |

| Timing Problems                                                                                                   | 8-60  |

| AN-643 EMI/RFI Board Design                                                                                       | 8-64  |

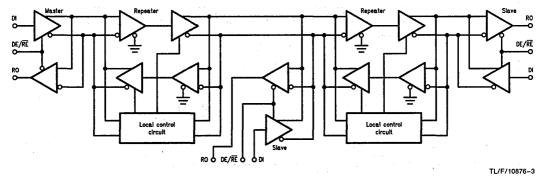

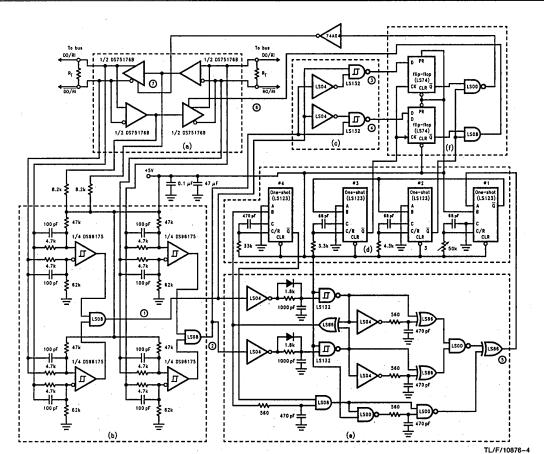

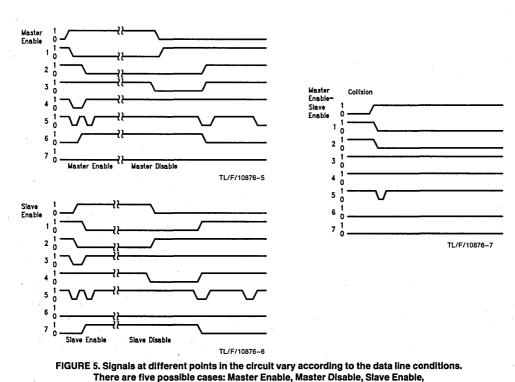

| AN-702 Build a Directional-Sensing Bidirectional Repeater                                                         | 8-81  |

| AN-759 Comparing EIA-485 and EIA-422-A Line Drivers and Receivers in Multipoint                                   | 001   |

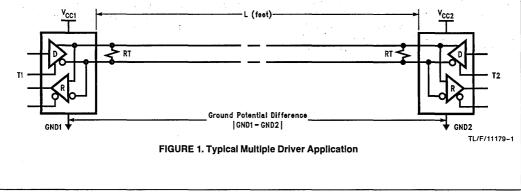

| Applications                                                                                                      | 8-86  |

| AN-805 Calculating Power Dissipation for Differential Line Drivers                                                | 8-89  |

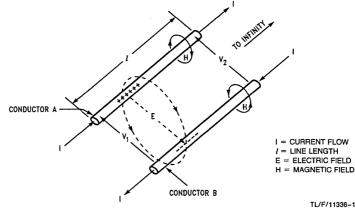

| AN-806 Data Transmission Lines and Their Characteristics                                                          | 8-96  |

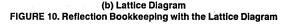

| AN-807 Reflections: Computations and Waveforms                                                                    | 8-102 |

| AN-808 Long Transmission Lines and Data Signal Quality                                                            | 8-126 |

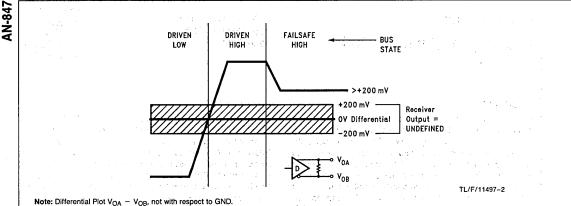

| AN-847 Failsafe Biasing of Differential Buses                                                                     | 8-145 |

| AN-876 Inter-Operation of the DS14C335 with + 5V UARTs                                                            | 8-151 |

| AN-878 Increasing System ESD Tolerance for Line Drivers and Receivers Used                                        | 0 101 |

| in RS-232 Interfaces                                                                                              | 8-154 |

| AN-903 A Comparison of Differential Termination Techniques                                                        | 8-157 |

| AN-904 An Introduction to the Differential SCSI Interface                                                         | 8-165 |

| AN-914 Understanding Power Requirements in RS-232 Applications                                                    | 8-173 |

| AN-915 Automotive Physical Layer SAE J1708 and the DS36277                                                        | 8-179 |

| AN-916 A Practical Guide to Cable Selection                                                                       | 8-182 |

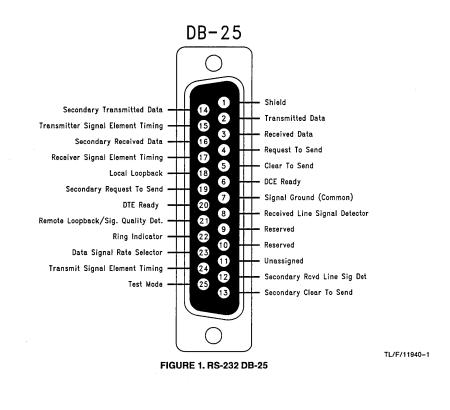

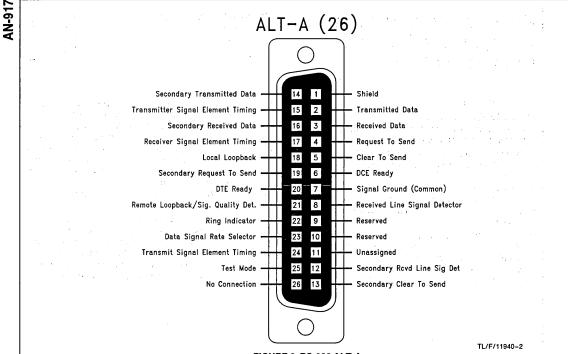

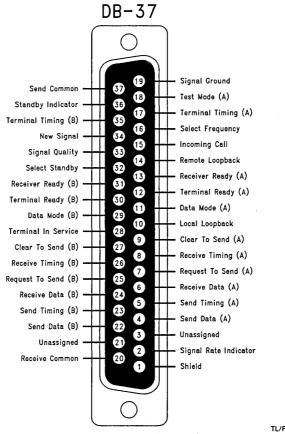

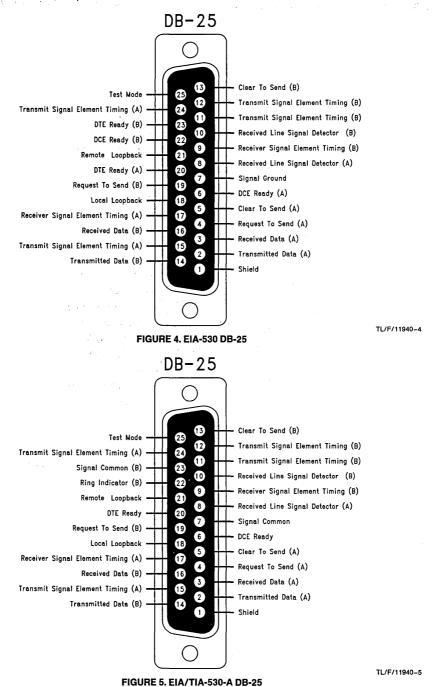

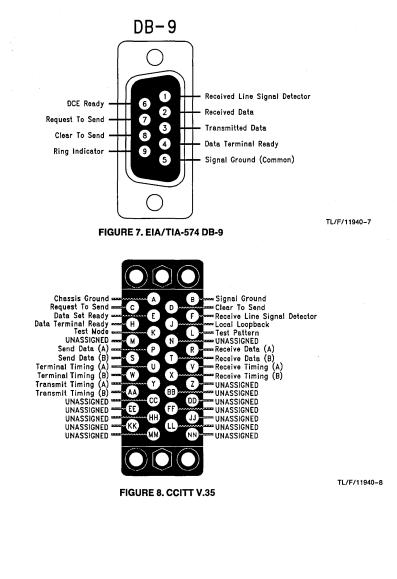

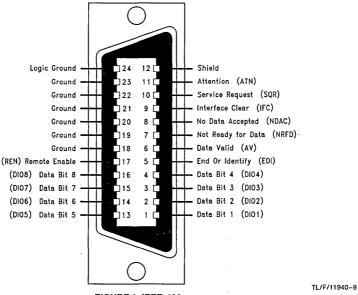

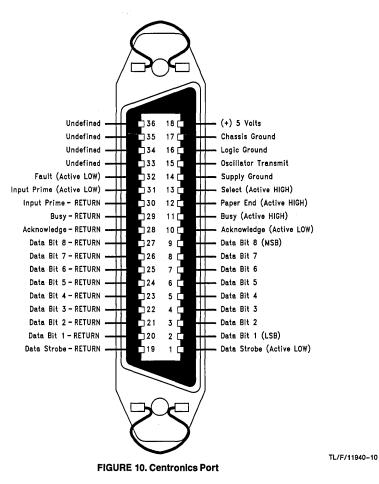

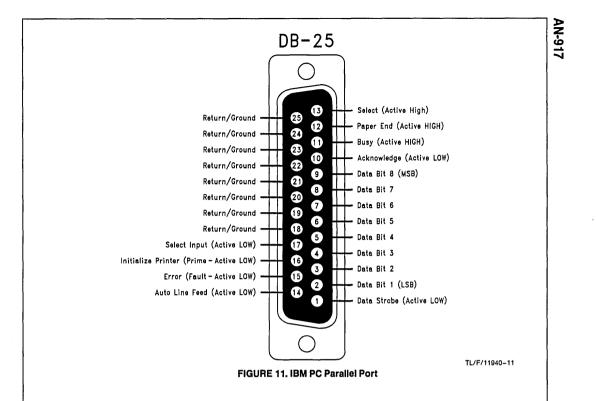

| AN-917 Popular Connector Pin Assignments for Data Communications                                                  | 8-191 |

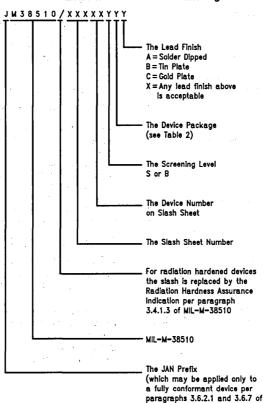

| Section 9 Military Interface                                                                                      |       |

| Line Drivers and Receivers Military Products—Selection Guide                                                      | 9-3   |

| Military/Aerospace Programs from National Semiconductor                                                           | 9-4   |

|                                                                                                                   | 04    |

| Section 10 Appendices and Physical Dimensions<br>Appendix A: AN-912 Common Data Transmission Parameters and Their |       |

| Definitions                                                                                                       | 10-3  |

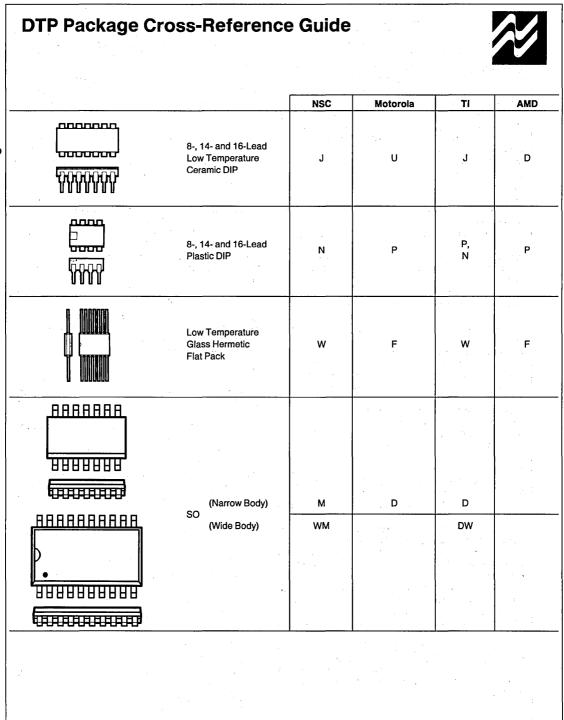

| Appendix B: DTP Package Cross Reference Guide                                                                     | 10-3  |

| PACKAGING APPLICATION NOTES                                                                                       | 10-0  |

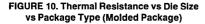

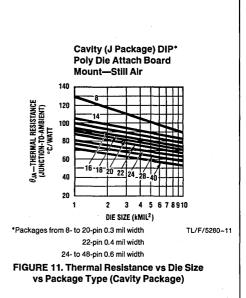

| Appendix B: AN-336 Understanding Integrated Circuit Package Power Capabilities                                    | 10-10 |

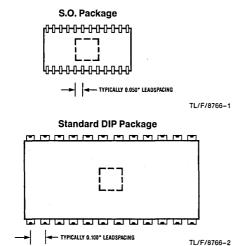

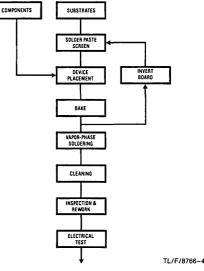

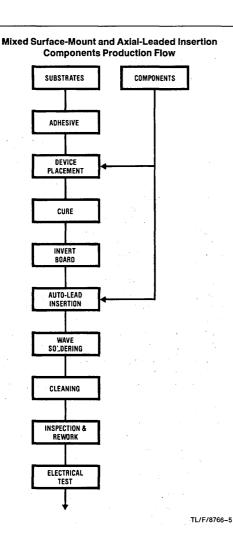

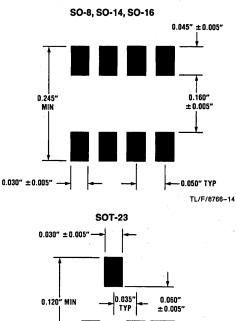

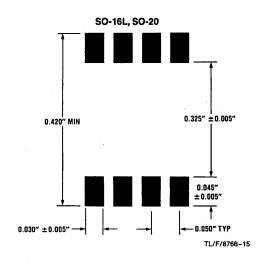

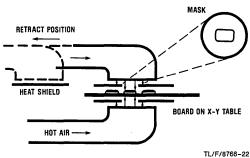

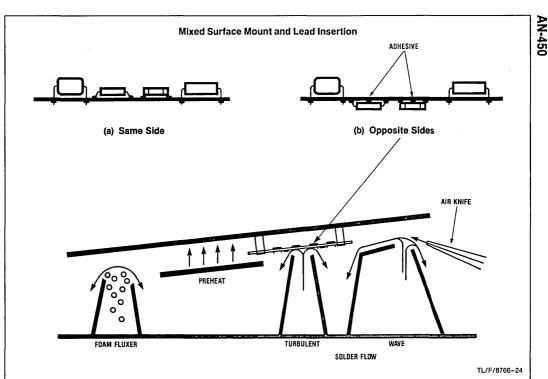

| Appendix B: AN-350 Small Outline (S.O.) Package Surface Mounting Methods—                                         | 10-10 |

| Parameters and Their Effect on Product Reliability                                                                | 10-15 |

|                                                                                                                   | 10-10 |

.

## Table of Contents (Continued)

| Section 10 Appendices and Physical Dimens<br>Appendix C: Data Transmission Products Nom<br>Cross Reference Guide | enclature Revisions and Obsolescence |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Appendix C: National's A + Program                                                                               |                                      |

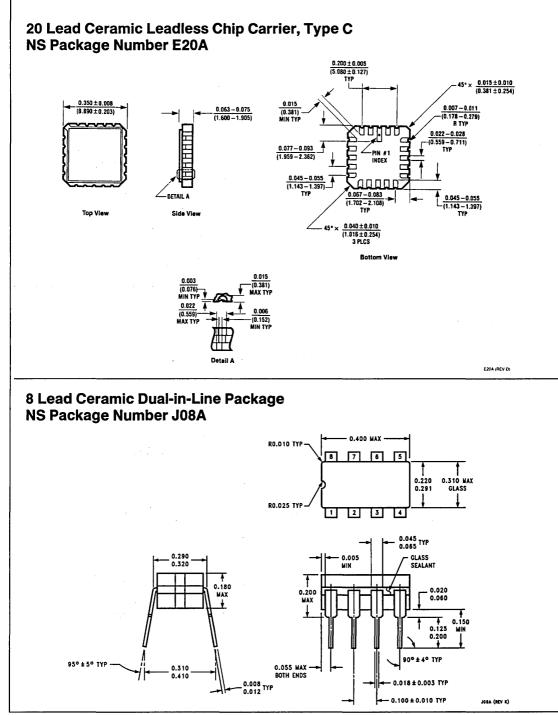

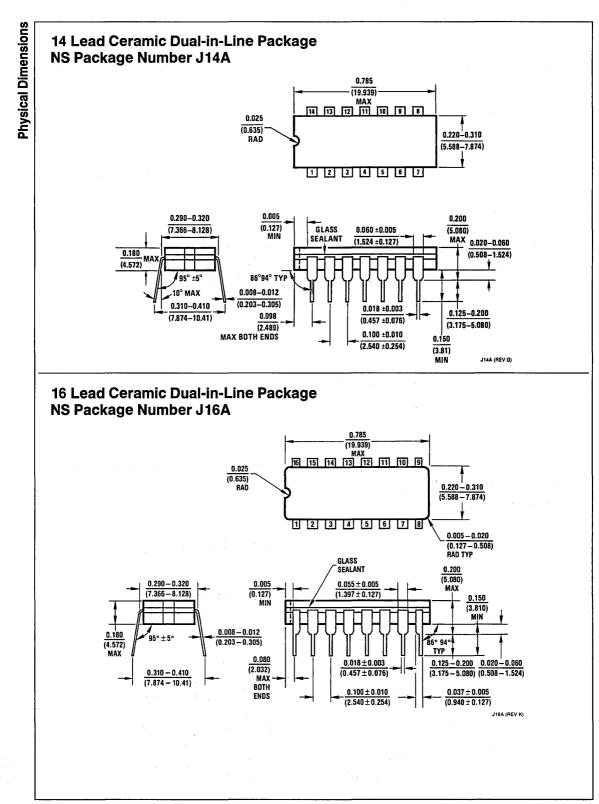

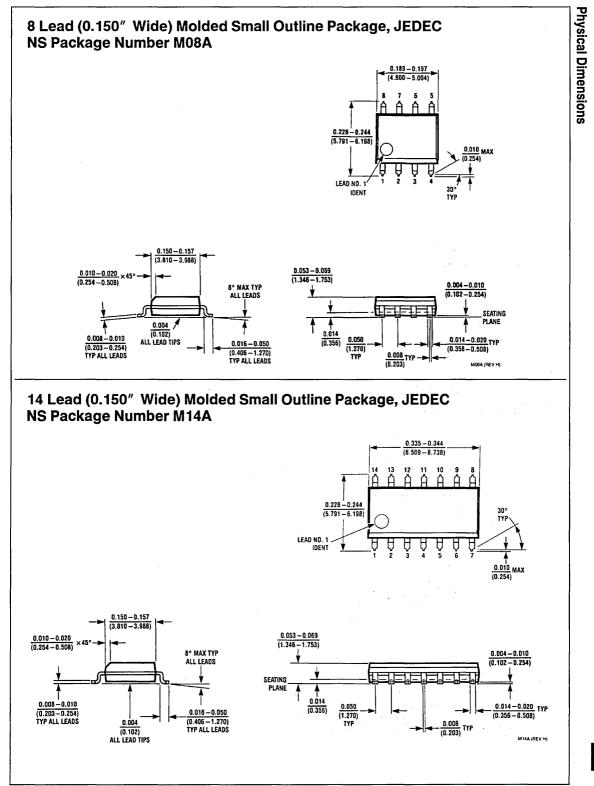

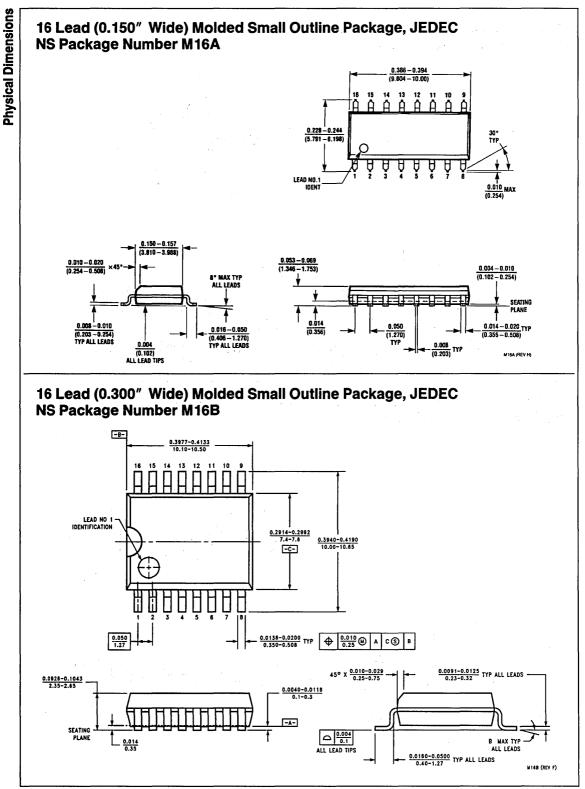

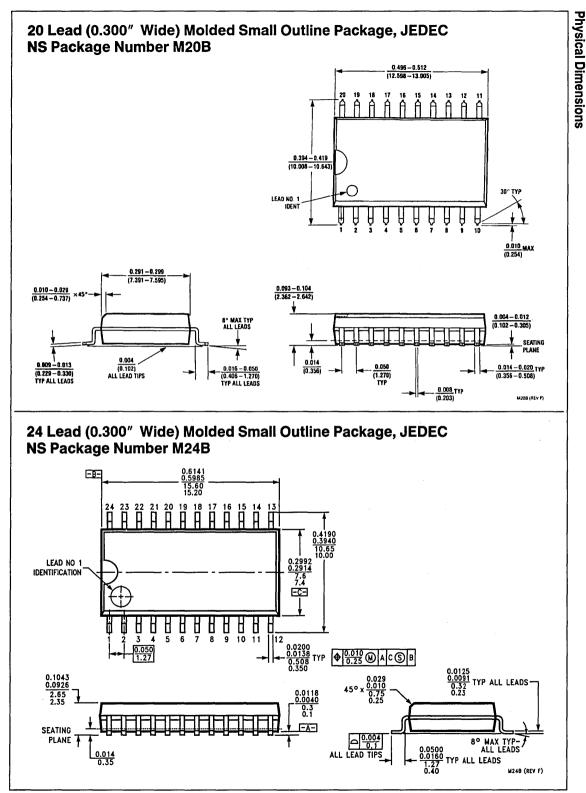

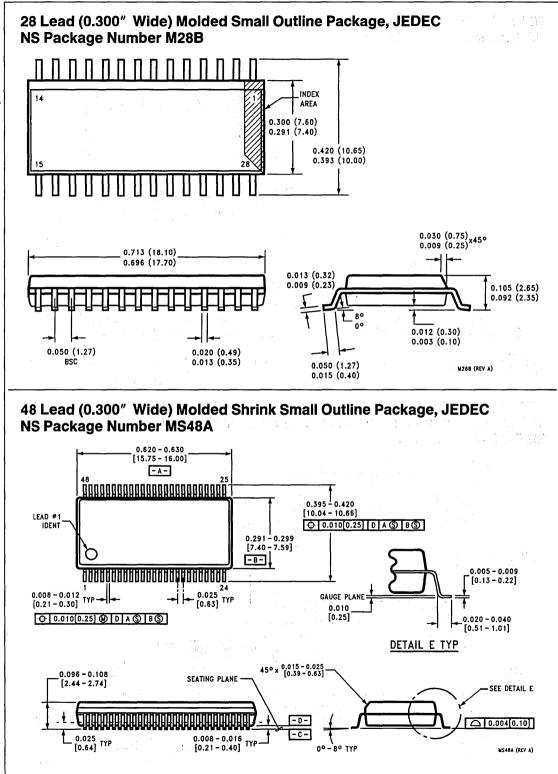

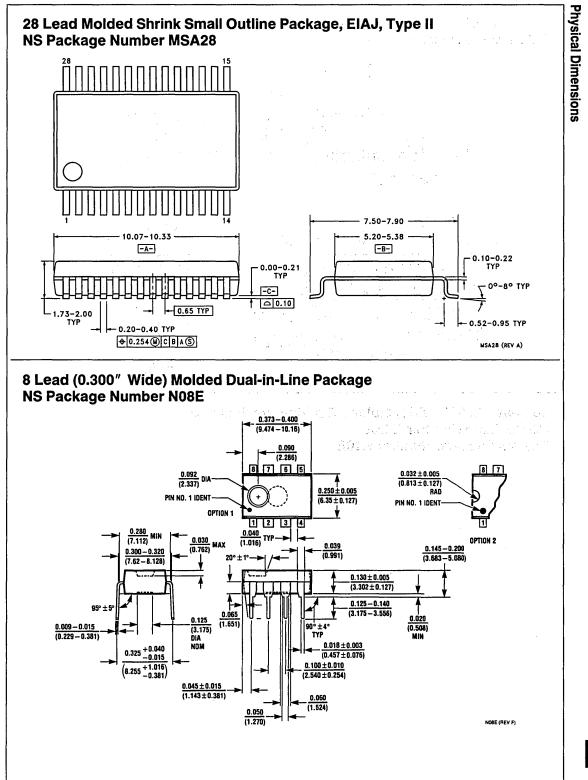

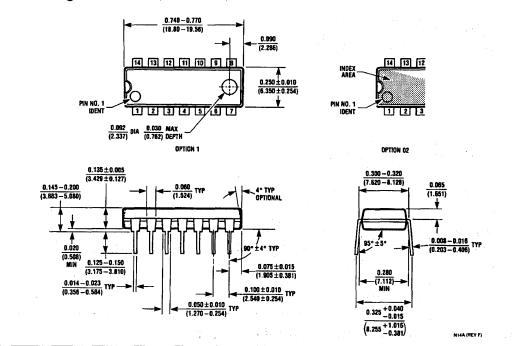

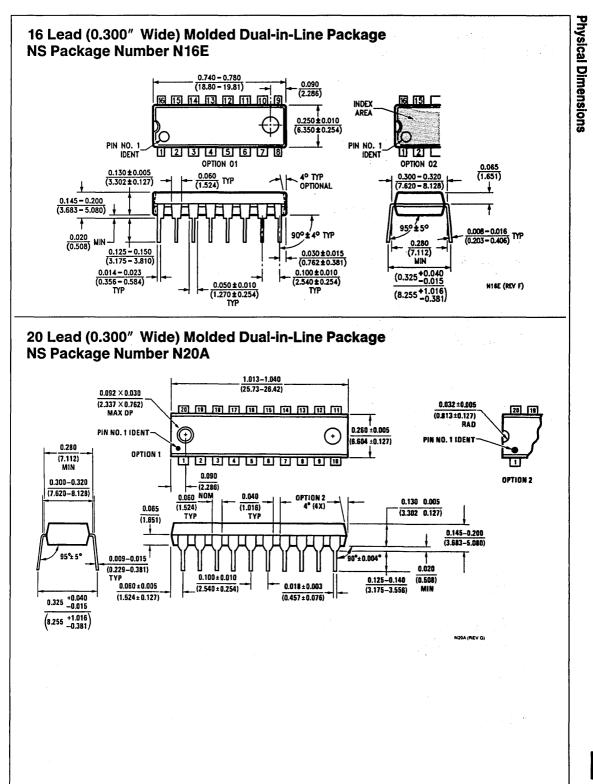

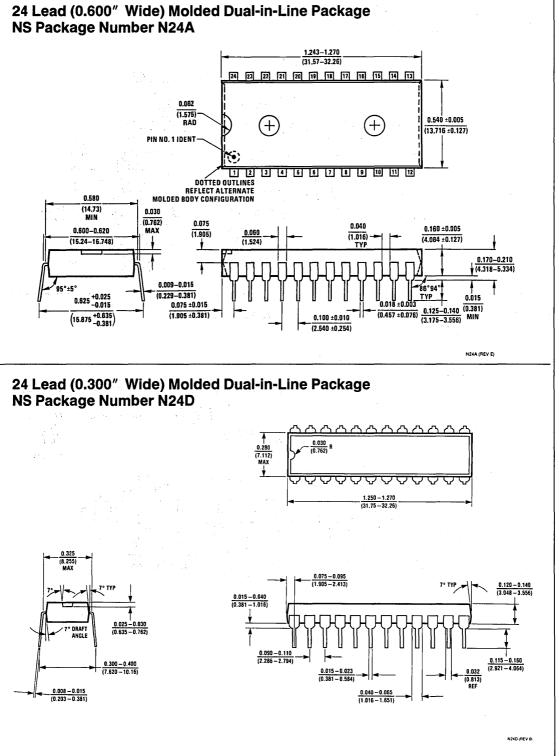

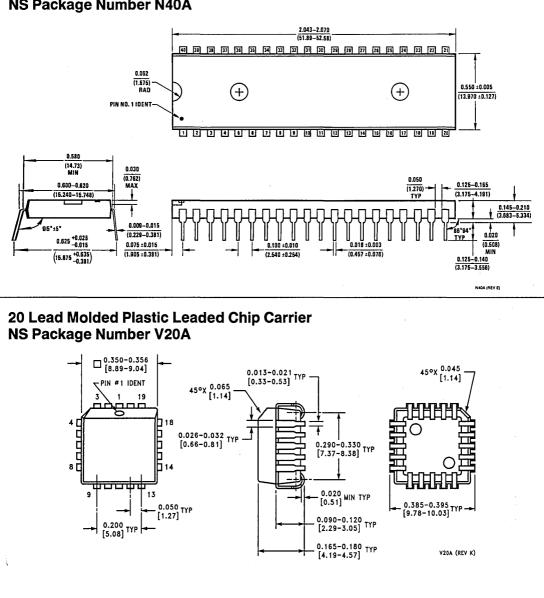

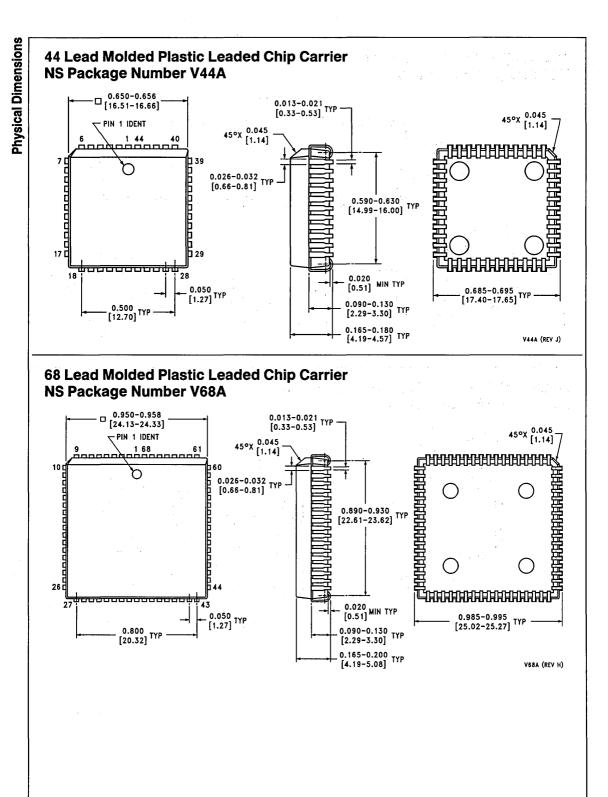

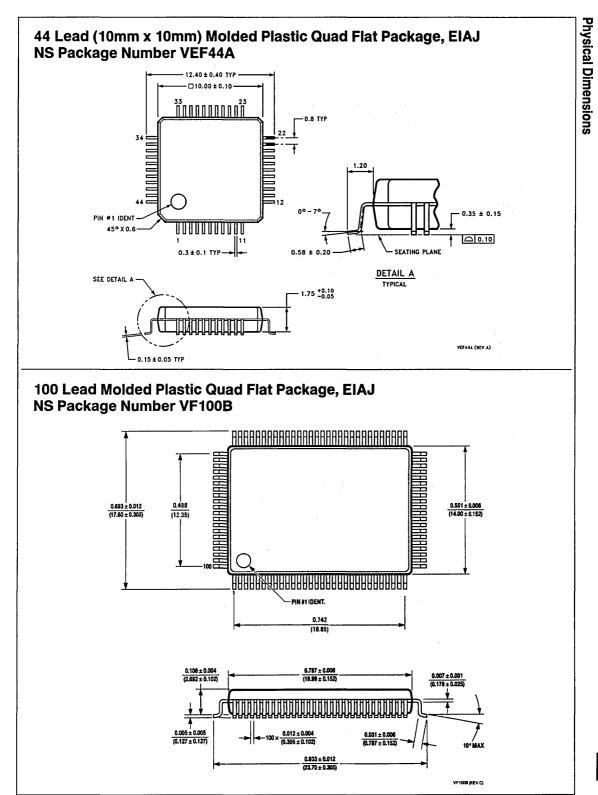

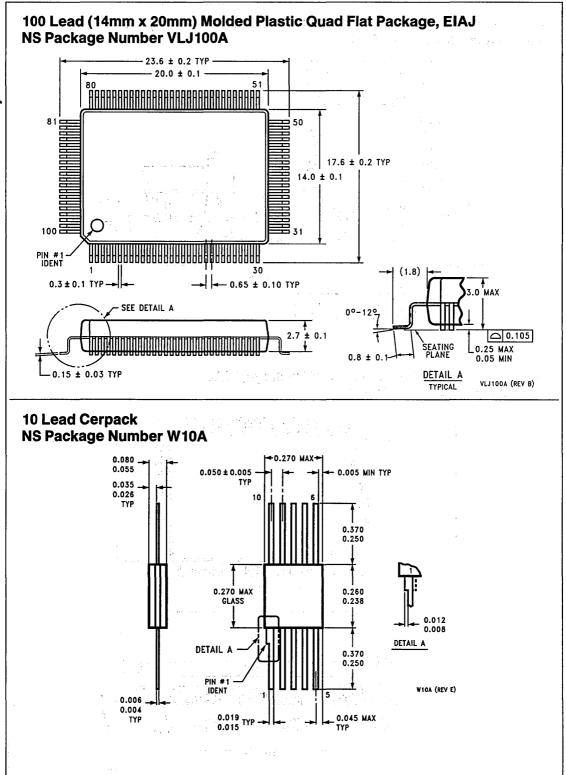

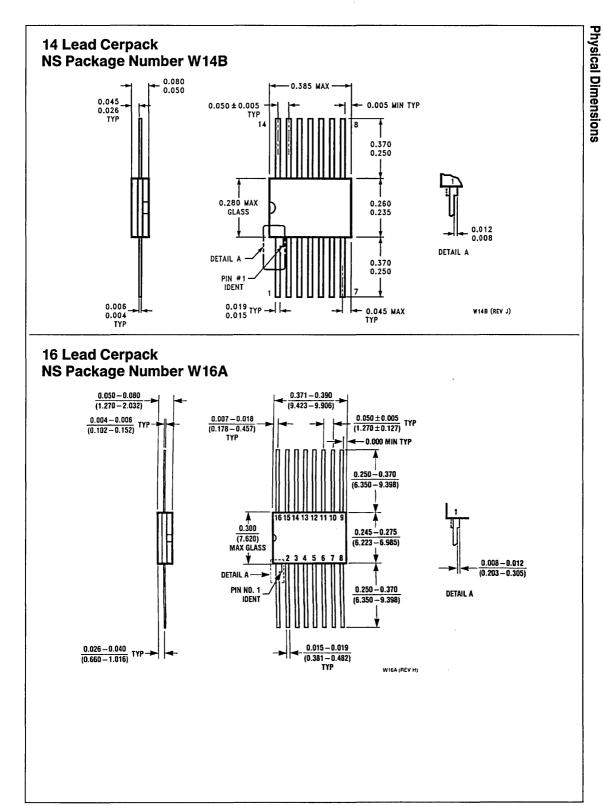

| Physical Dimensions                                                                                              |                                      |

| Bookshelf<br>Distributors                                                                                        |                                      |

5 A.J.

the starts

#### \*Boldface denotes new product Introduction and Application Notes.

## Alpha-Numeric Index

| AN-22      | Integrated Circuits for Digital Data Transmission                                                              |

|------------|----------------------------------------------------------------------------------------------------------------|

| AN-108     | Transmission Line Characteristics                                                                              |

| AN-214     | Transmission Line Drivers and Receivers for TIA/EIA Standards RS-422 and RS-423 .8-25                          |

| AN-216     | Summary of Well Known Interface Standards8-35                                                                  |

| AN-409     | Transceivers and Repeaters Meeting the EIA RS-485 Interface Standard                                           |

| AN-438     | Low Power RS-232C Driver and Receiver in CMOS                                                                  |

| AN-454     | Automotive Multiplex Wiring8-56                                                                                |

| AN-457     | High Speed, Low Skew RS-422 Drivers and Receivers Solve Critical System           Timing Problems         8-60 |

| AN-643     | EMI/RFI Board Design                                                                                           |

| AN-702     | Build a Directional-Sensing Bidirectional Repeater                                                             |

| AN-759     | Comparing EIA-485 and EIA-422-A Line Drivers and Receivers in Multipoint<br>Applications                       |

| AN-805     | Calculating Power Dissipation for Differential Line Drivers                                                    |

| AN-806     | Data Transmission Lines and Their Characteristics                                                              |

| AN-807     | Reflections: Computations and Waveforms                                                                        |

| AN-808     | Long Transmission Lines and Data Signal Quality                                                                |

| AN-847     | Failsafe Biasing of Differential Buses                                                                         |

| AN-876     | Inter-Operation of the DS14C335 with +5V UARTs                                                                 |

| AN-878     | Increasing System ESD Tolerance for Line Drivers and Receivers Used in                                         |

|            | RS-232 Interfaces                                                                                              |

| AN-903     | A Comparison of Differential Termination Techniques                                                            |

| AN-904     | An Introduction to the Differential SCSI Interface                                                             |

| AN-914     | Understanding Power Requirements in RS-232 Applications                                                        |

| AN-915     | Automotive Physical Layer SAE J1708 and the DS36277                                                            |

| AN-916     | A Practical Guide to Cable Selection                                                                           |

| AN-917     | Popular Connector Pin Assignments for Data Communications                                                      |

| Appendix A | AN-912 Common Data Transmission Parameters and Their Definitions                                               |

| Appendix B | AN-336 Understanding Integrated Circuit Package Power Capabilities                                             |

| Appendix B | AN-450 Small Outline (S.O.) Package Surface Mounting Methods—Parameters                                        |

|            | and Their Effect on Product Reliability10-15                                                                   |

| Appendix B | DTP Package Cross Reference Guide10-8                                                                          |

| Appendix C | Data Transmission Products Nomenclature Revisions and Obsolescence<br>Cross Reference Guide                    |

| Appendix C | National's A + Program                                                                                         |

| pperion. e | Application Note-Selection Guide                                                                               |

| DS14C88    | Quad CMOS Line Driver                                                                                          |

| DS14C88T   | Quad CMOS Line Driver                                                                                          |

| DS14C89A   | Quad CMOS Receiver                                                                                             |

| DS14C89AT  | Quad CMOS Receiver                                                                                             |

| DS14C232C  | Low Power + 5V Powered TIA/EIA-232 Dual Driver/Receiver1-8                                                     |

| DS14C232T  | Low Power + 5V Powered TIA/EIA-232 Dual Driver/Receiver1-8                                                     |

| DS14C237   | Single Supply TIA/EIA-232 5 x 3 Driver/Receiver1-17                                                            |

| DS14C238   | Single Supply TIA/EIA-232 4 x 4 Driver/Receiver1-21                                                            |

| DS14C239   | Dual Supply TIA/EIA-232 3 x 5 Driver/Receiver                                                                  |

| DS14C241   | Single Supply TIA/EIA-232 4 x 5 Driver/Receiver                                                                |

| DS14C335   | + 5V Supply TIA/EIA-232 3 x 5 Driver/Receiver                                                                  |

| DS14C535   | + 3V Supply TIA/EIA-232 3 x 5 Driver/Receiver1-47                                                              |

| DS14C561   | + 3.3V-Powered 4 x 5 Driver/Receiver1-54                                                                       |

| DS16F95    | EIA-485/EIA-422A Differential Bus Transceiver                                                                  |

| DS26C31M   | CMOS Quad TRI-STATE Differential Line Driver2-10                                                               |

## Alpha-Numeric Index (Continued)

| DOGOOAT          |                                                                 |

|------------------|-----------------------------------------------------------------|

| DS26C31T         | CMOS Quad TRI-STATE Differential Line Driver                    |

| DS26C32AM        | CMOS Quad Differential Line Receiver                            |

| DS26C32AT        | CMOS Quad Differential Line Receiver                            |

| DS26F31C         | Quad High Speed Differential Line Driver                        |

| DS26F31M         | Quad High Speed Differential Line Driver         2-18           |

| DS26F32C         | Quad Differential Line Receiver                                 |

| DS26F32M         | Quad Differential Line Receiver   2-32                          |

| DS26LS31C        | Quad High Speed Differential Line Driver    2-21                |

| DS26LS31M        | Quad High Speed Differential Line Driver                        |

| DS26LS32AC       | Quad Differential Line Receiver2-36                             |

| DS26LS32C        | Quad Differential Line Receiver    2-36                         |

| DS26LS32M        | Quad Differential Line Receiver    2-36                         |

| DS26LS33AC       | Quad Differential Line Receiver    2-36                         |

| DS26LS33C        | Quad Differential Line Receiver    2-36                         |

| DS26LS33M        | Quad Differential Line Receiver    2-36                         |

| DS34C86T         | Quad CMOS Differential Line Receiver         2-39               |

| DS34C87T         | CMOS Quad TRI-STATE Differential Line Driver2-52                |

| DS34F86          | RS-422/RS-423 Quad Line Receiver with TRI-STATE Outputs         |

| DS34F87          | RS-422 Quad Line Driver with TRI-STATE Outputs2-57              |

| DS35F86          | RS-422/RS-423 Quad Line Receiver with TRI-STATE Outputs         |

| DS35F87          | RS-422 Quad Line Driver with TRI-STATE Outputs2-57              |

| DS36BC956        | Low Power BiCMOS Hex Differential Bus Transceiver               |

| DS36F95          | EIA-485/EIA-422A Differential Bus Transceiver                   |

| DS78C20          | Dual CMOS Compatible Differential Line Receiver         2-64    |

| DS78C120         | Dual CMOS Compatible Differential Line Receiver         2-68    |

| DS78LS120        | Dual Differential Line Receiver (Noise Filtering and Fail Safe) |

| DS88C20          | Dual CMOS Compatible Differential Line Receiver                 |

| DS88C120         | Dual CMOS Compatible Differential Line Receiver         2-68    |

| DS88LS120        | Dual Differential Line Receiver (Noise Filtering and Fail Safe) |

| DS89C21          | Differential CMOS Line Driver and Receiver Pair                 |

| DS90C031         | LVDS Quad CMOS Differential Line Driver                         |

| DS90C032         | LVDS Quad CMOS Differential Line Receiver                       |

| DS96F172C        | EIA-485/EIA-422A Quad Differential Driver                       |

| DS96F172M        | EIA-485/EIA-422A Quad Differential Driver                       |

| DS96F173C        | EIA-485/EIA-422 Quad Differential Receiver                      |

| DS96F173M        | EIA-485/EIA-422 Quad Differential Receiver                      |

| DS96F174C        | EIA-485/EIA-422A Quad Differential Driver                       |

| DS96F174M        | EIA-485/EIA-422A Quad Differential Driver                       |

| DS96F175C        | EIA-485/EIA-422 Quad Differential Receiver                      |

| DS96F175M        | EIA-485/EIA-422 Quad Differential Receiver                      |

| DS1488           | Quad Line Driver                                                |

| DS1489           | Quad Line Receiver                                              |

| DS1489A          | Quad Line Receiver 1-70                                         |

|                  | TRI-STATE Dual Receiver                                         |

| DS1652           | Quad Differential Line Receiver                                 |

| DS1691A          | RS-422/RS-423 Line Driver with TRI-STATE Outputs2-3             |

| DS1692           | TRI-STATE Differential Line Driver                              |

| DS3486           | Quad RS-422/RS-423 Line Receiver                                |

| DS3480           | Quad TRI-STATE Line Driver                                      |

| DS3487<br>DS3603 | TRI-STATE Dual Receiver                                         |

| DS3650           | Quad Differential Line Receiver                                 |

| 00000            |                                                                 |

## Alpha-Numeric Index (Continued)

| DS3652                                                                                                                                                                                                                                                        | Quad Differential Line Receiver7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| DS3691                                                                                                                                                                                                                                                        | RS-422/RS-423 Line Driver with TRI-STATE Outputs2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-3                                                                              |

| DS3692                                                                                                                                                                                                                                                        | TRI-STATE Differential Line Driver6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-3                                                                              |

| DS3695                                                                                                                                                                                                                                                        | Multipoint RS-485/RS-422 Transceiver/Repeater                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9-3                                                                              |

| DS3695A                                                                                                                                                                                                                                                       | Multipoint RS-485/RS-422 Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| DS3695AT                                                                                                                                                                                                                                                      | Multipoint RS-485/RS-422 Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| DS3695T                                                                                                                                                                                                                                                       | Multipoint RS-485/RS-422 Transceiver/Repeater                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| DS3696                                                                                                                                                                                                                                                        | Multipoint RS-485/RS-422 Transceiver/Repeater                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| DS3696A                                                                                                                                                                                                                                                       | Multipoint RS-485/RS-422 Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| DS3696A<br>DS3696T                                                                                                                                                                                                                                            | Multipoint RS-485/RS-422 Transceiver/Repeater                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

|                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| DS3697                                                                                                                                                                                                                                                        | Multipoint RS-485/RS-422 Transceiver/Repeater                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -3                                                                               |

| DS3698                                                                                                                                                                                                                                                        | Multipoint RS-485/RS-422 Transceiver/Repeater                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| DS7820                                                                                                                                                                                                                                                        | Dual Line Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| DS7820A                                                                                                                                                                                                                                                       | Dual Line Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| DS7830                                                                                                                                                                                                                                                        | Dual Differential Line Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| DS7831                                                                                                                                                                                                                                                        | Dual TRI-STATE Line Driver6-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 38                                                                               |

| DS7832                                                                                                                                                                                                                                                        | Dual TRI-STATE Line Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38                                                                               |

| DS8820                                                                                                                                                                                                                                                        | Dual Line Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37                                                                               |

| DS8820A                                                                                                                                                                                                                                                       | Dual Line Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| DS8830                                                                                                                                                                                                                                                        | Dual Differential Line Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28                                                                               |

| DS8831                                                                                                                                                                                                                                                        | Dual TRI-STATE Line Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

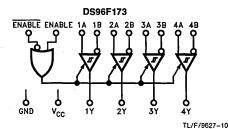

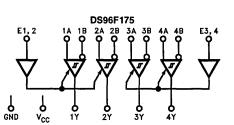

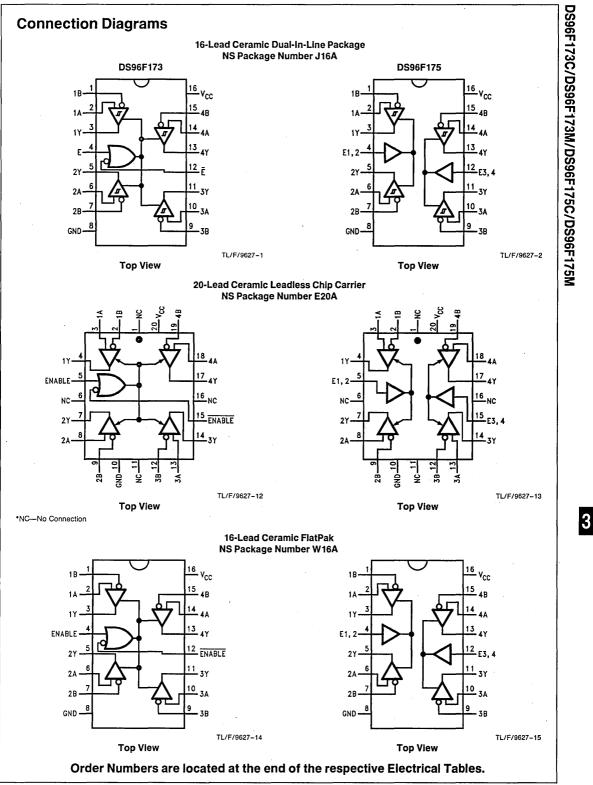

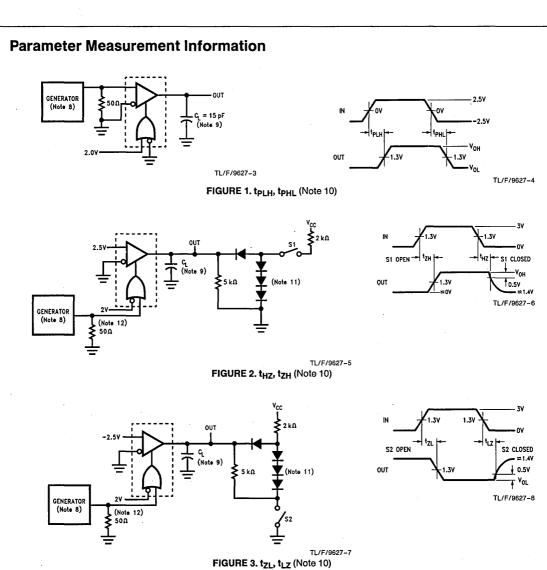

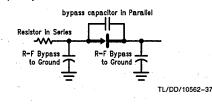

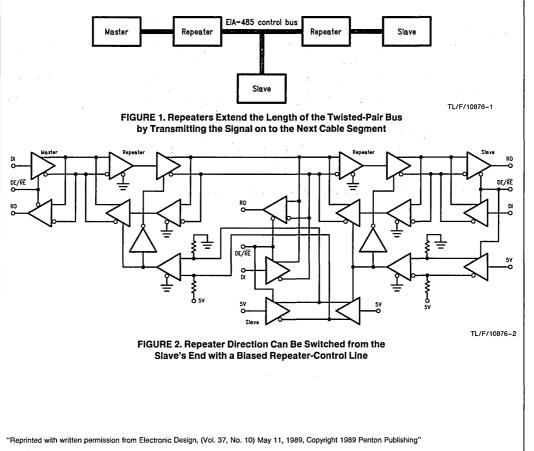

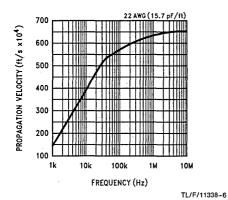

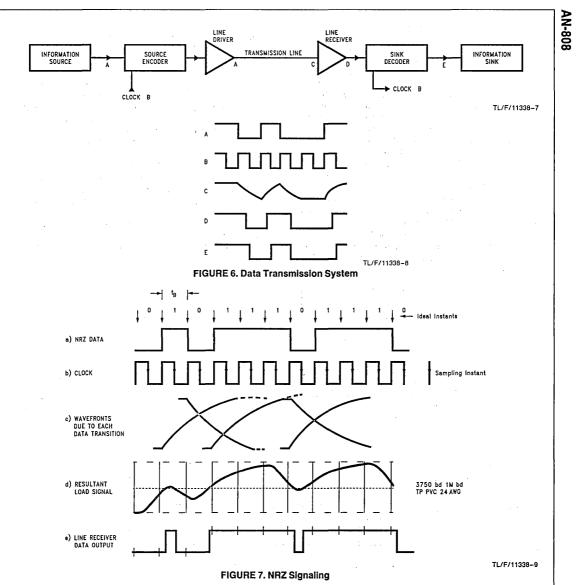

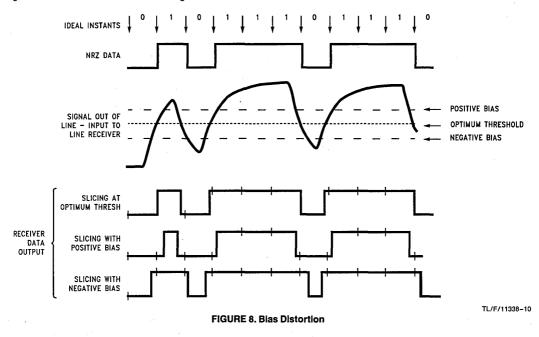

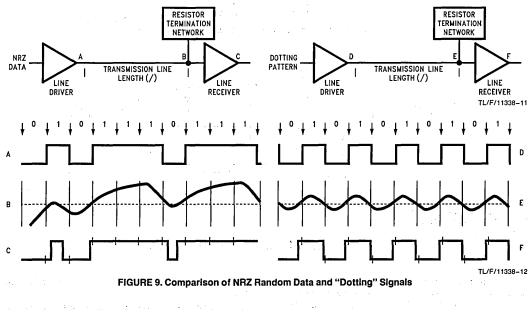

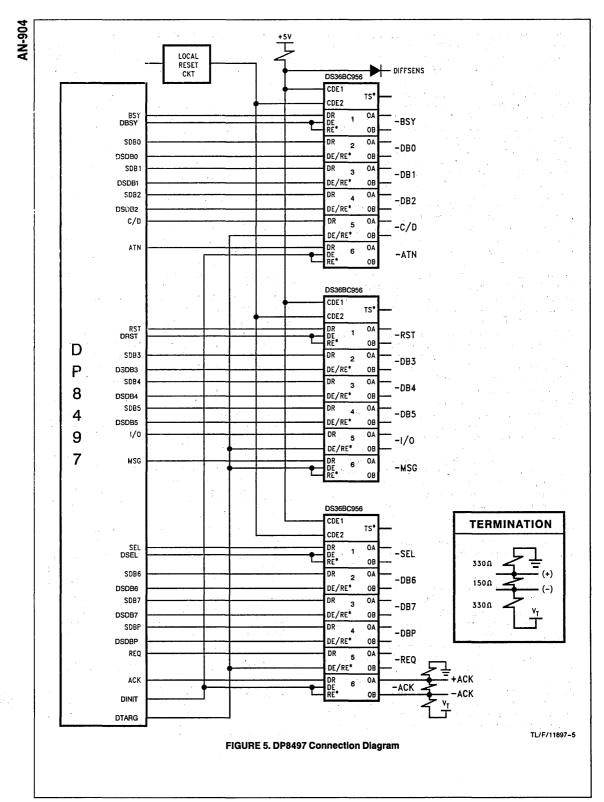

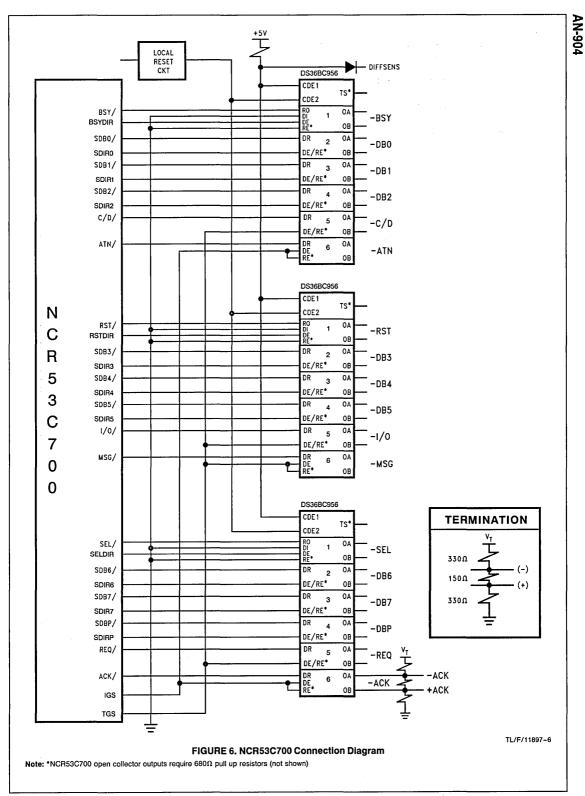

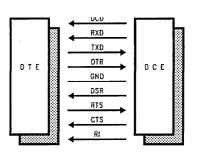

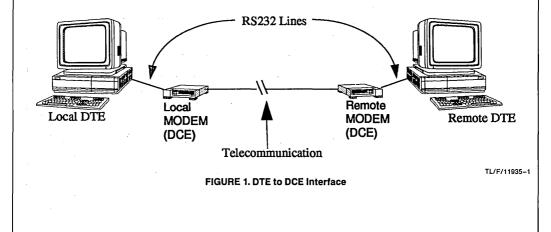

| DS8832                                                                                                                                                                                                                                                        | Dual TRI-STATE Line Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |