# MEMORY DATABOOK

1992 Edition

CMOS EPROMs CMOS EEPROMs PROMs Application Notes Quality and Reliability

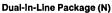

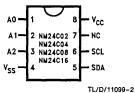

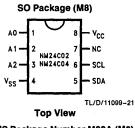

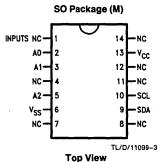

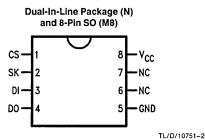

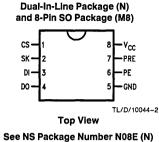

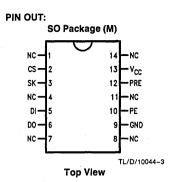

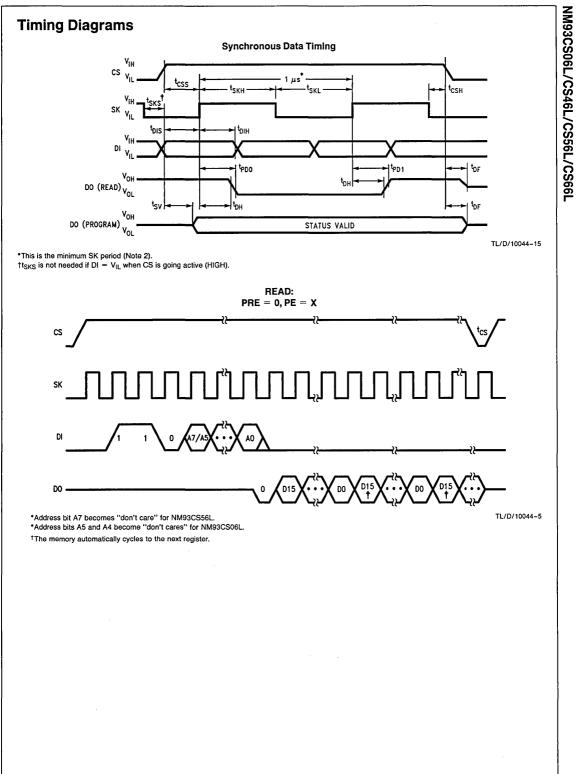

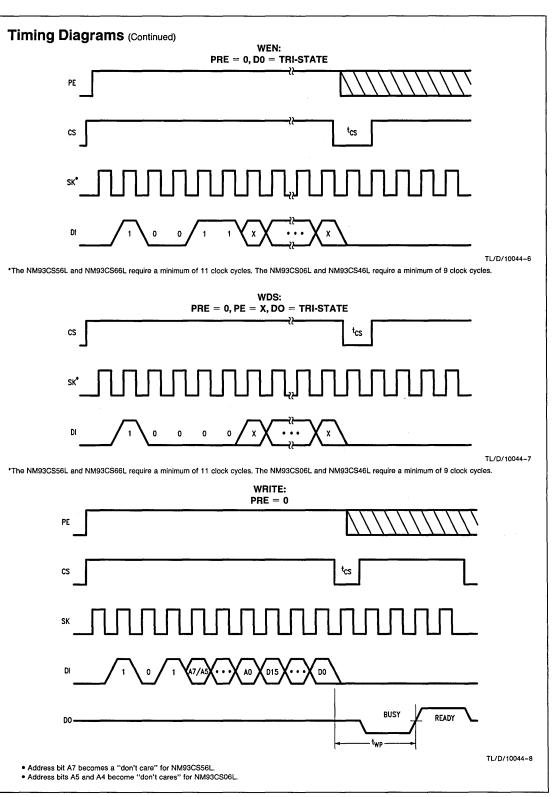

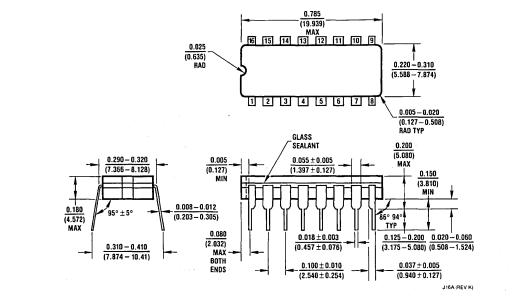

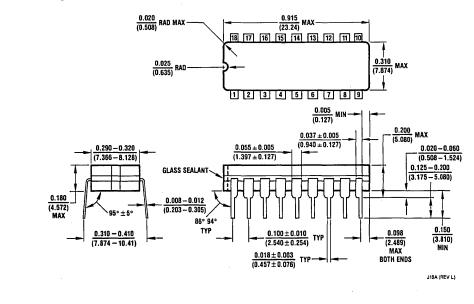

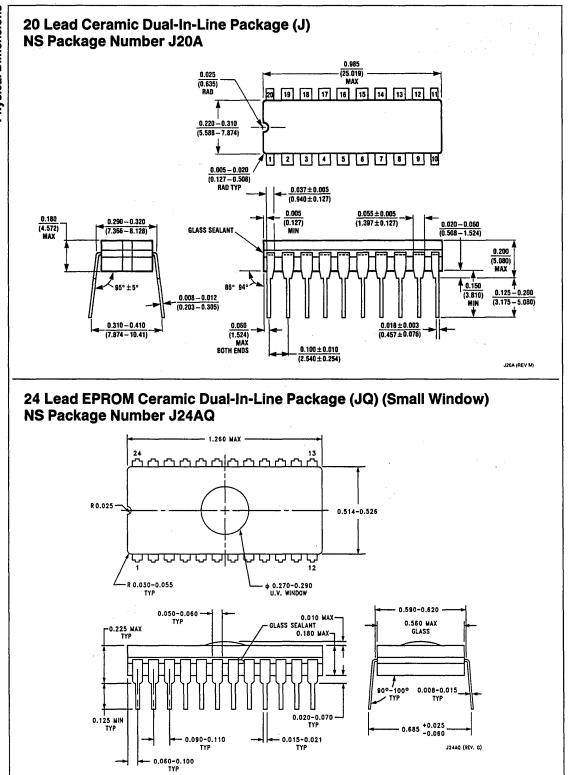

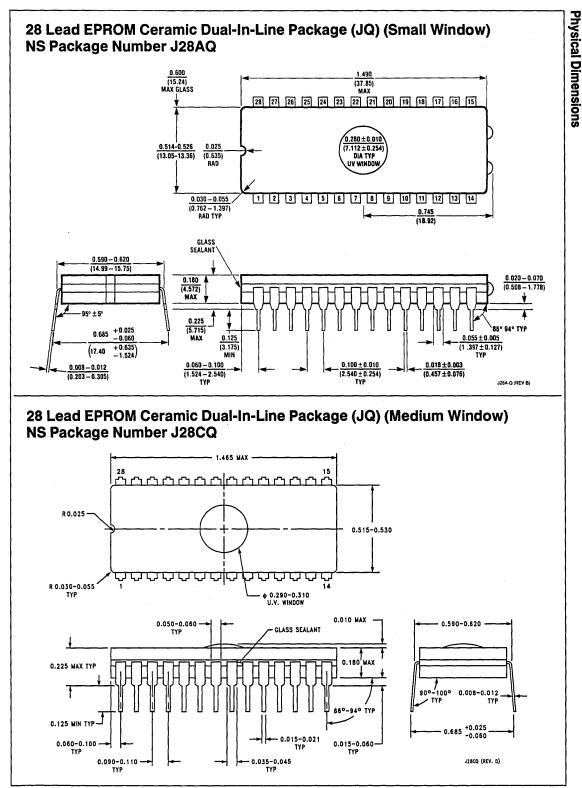

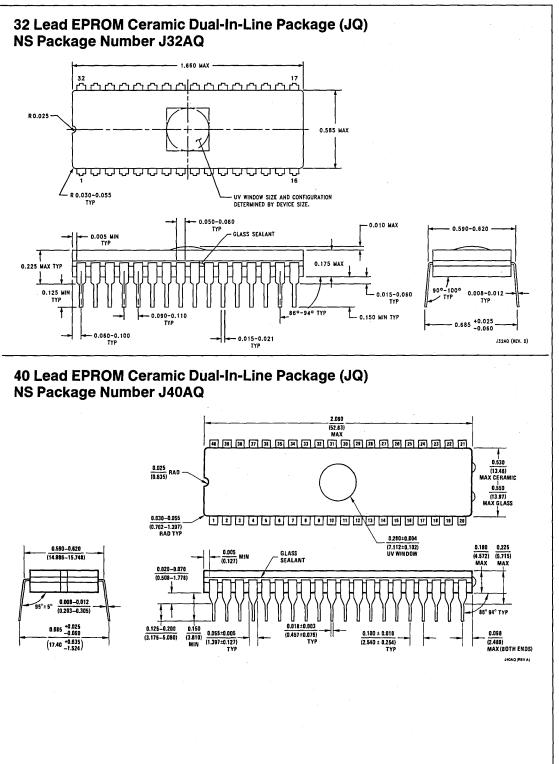

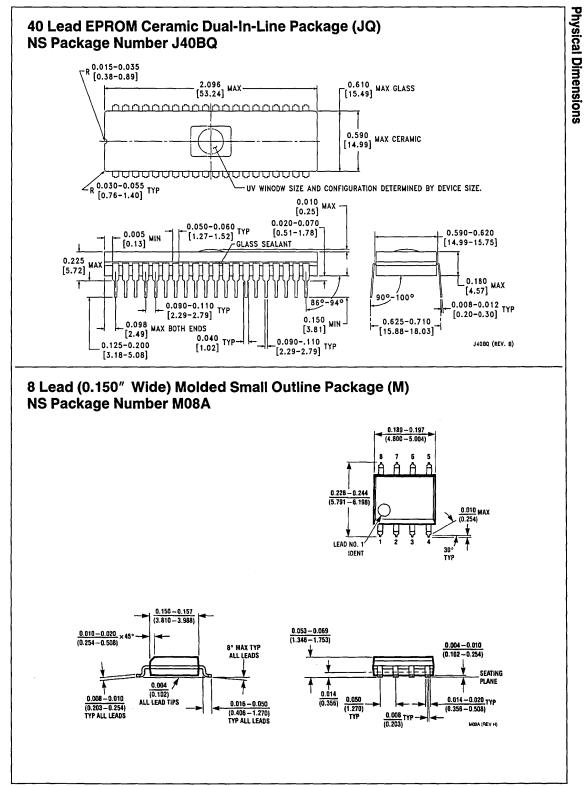

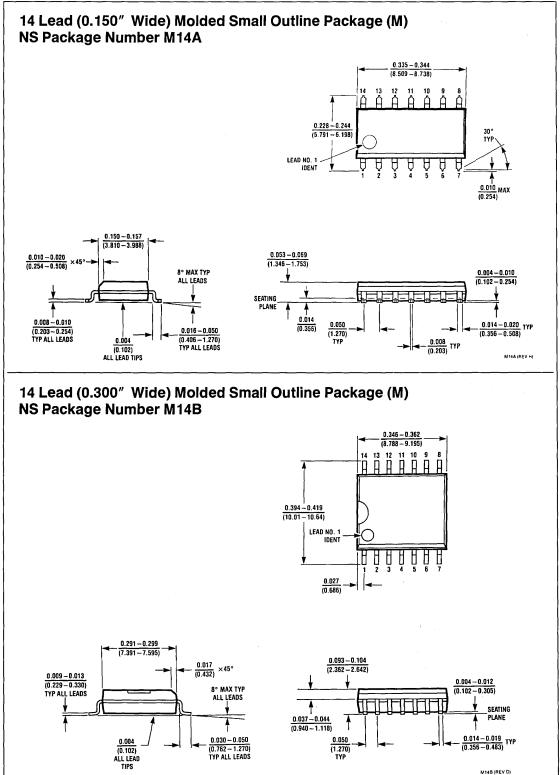

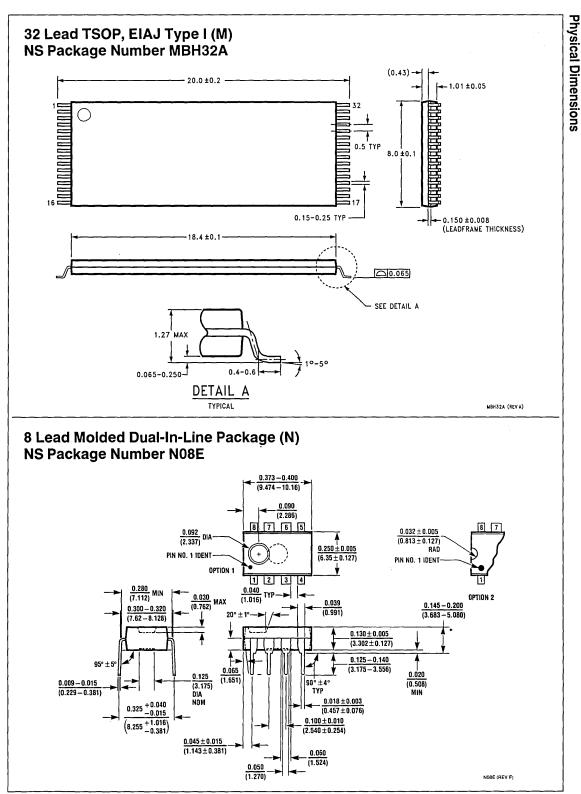

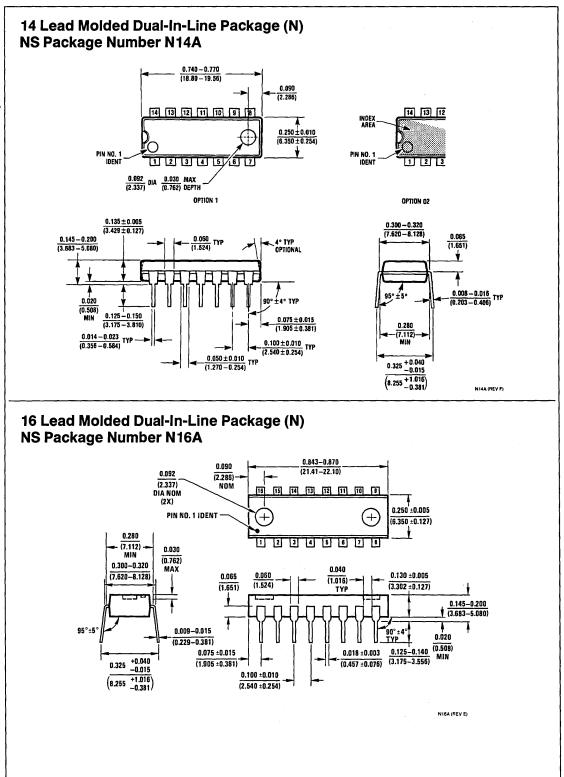

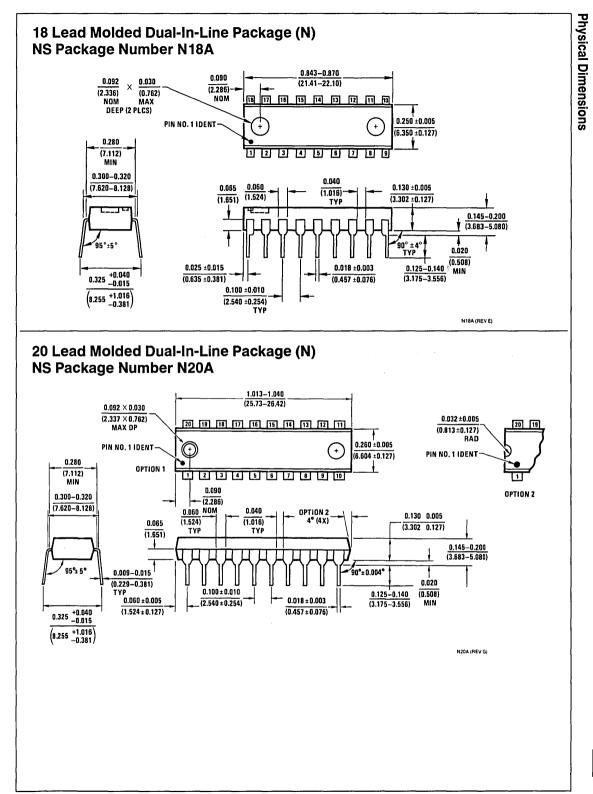

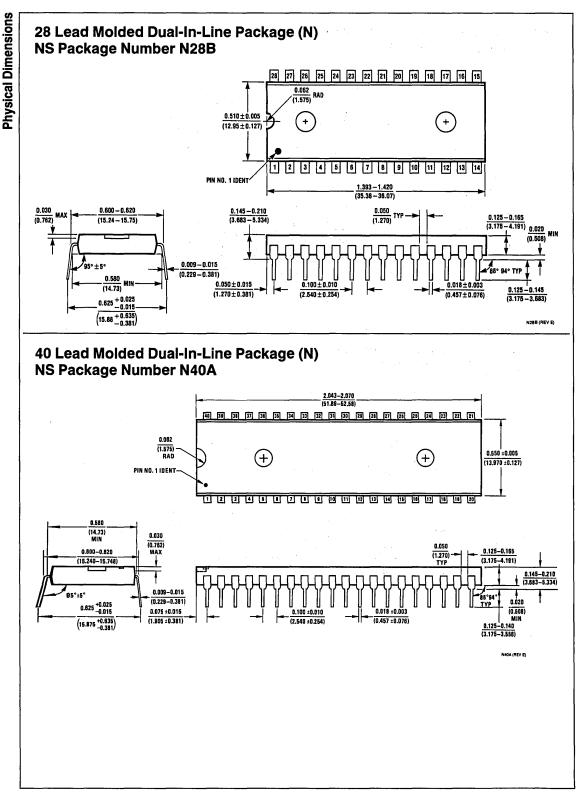

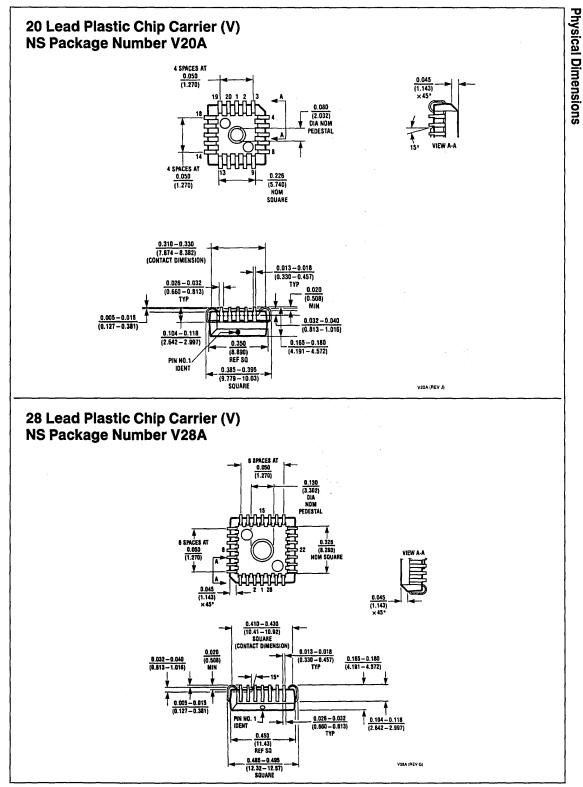

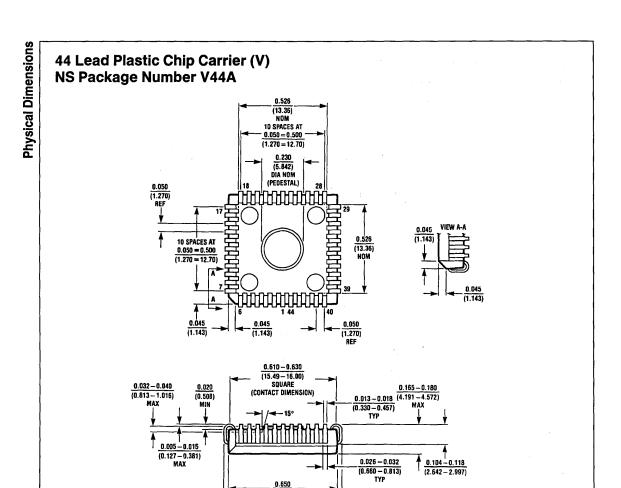

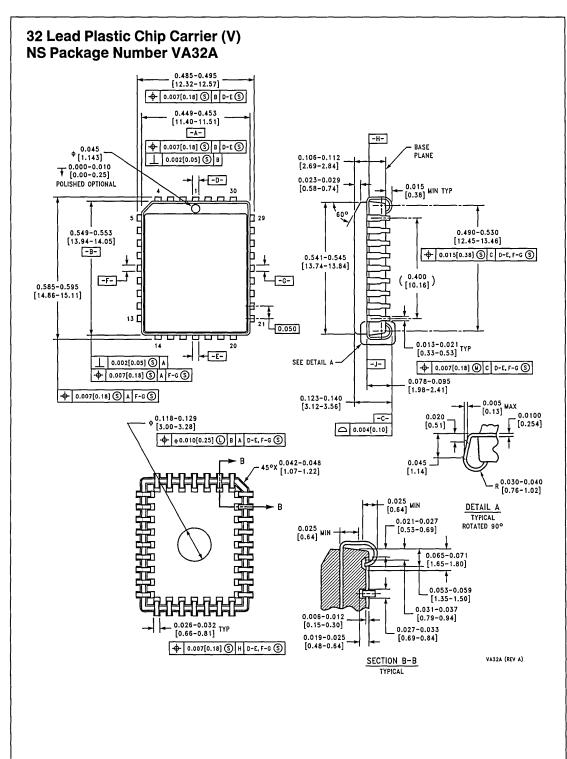

**Physical Dimensions**

#### TRADEMARKS

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

ABICTM Abuseable™ Anadia™ ANS-R-TRAN™ APPSTM **ASPECT™** Auto-Chem Deflasher™ ВСРтм BI-FET™ BI-FET II™ BI-LINE™ **BIPLANTM BLCTM** BLXTM **ВМАСТМ** Brite-Lite™ BSI™ BSI-2™ **CDDTM** CheckTrack™ СІМ™ **CIMBUS™ CLASIC™** Clock // Chek™ COMBO® COMBO I™ COMBO II™ COPS™ microcontrollers **CRDTM** DA4™ Datachecker® **DENSPAKTM** DIBTM **DISCERN™** DISTILL™ DNR® **DPVMTM** E<sup>2</sup>CMOS™ ELSTAR™ Embedded System Processor™ ЕРТМ E-Z-LINK™ **FACT™**

FACT Quiet Series™ **FAIRCADTM** Fairtech™ **FAST®** FASTr™ 5-Star Service™ Flash™ GENIX™ **GNXTM GTO™** HAMRTM HandiScan™ HEX 3000™ НРС™ HyBal™ |3Ľ® ICM™ **INFOCHEX™** Integral ISE™ Intelisplay™ Inter-LERIC™ Inter-RIC™ **ISE™** ISE/06TM ISE/08™ ISE/16™ ISE32™ **ISOPLANAR™ ISOPLANAR-Z™** KeyScan™ LERICTM LMCMOS™ M<sup>2</sup>CMOS™ Macrobus™ Macrocomponent<sup>™</sup> MAPLTM MAXI-ROM® Meatr Chek™ MenuMaster™ Microbus™ data bus MICRO-DAC™ µtalker™ Microtalker™

**MICROWIRE™** MICROWIRE/PLUS™ **MOLE™ MPATM MSTTM** Naked-8™ National® National Semiconductor® National Semiconductor Corp.® NAX 800™ Nitride Plus™ Nitride Plus Oxide™ **NMLTM** NOBUS™ NSC800™ **NSCISE™** NSX-16™ NS-XC-16™ **NTERCOM™ NURAM™ OPALTM OXISS™** P<sup>2</sup>CMOS™ PC Master™ Perfect Watch™ Pharma/ChekTM **PLAN™ PLANARTM PLAYER™** Plus-2TM Polycraft™ POSilink™ POSitalker™ Power + Control™ POWERplanar™ QUAD3000TM **QUIKLOOK™** RAT™ **RICTM** RTX16™ **SABR™ SCAN™**

Script/Chek™ SCX™ SERIES/800™ Series 900™ Series 3000™ Series 32000® Shelf ChekTM Simple Switcher™ SofChek™ **SONIC™ SPIRE™** Staggered Refresh™ STARTM Starlink™ STARPLEX™ ST-NIC™ SuperAT™ Super-Block™ SuperChip™ SuperScript™ SYS32™ TapePak® TDSTM TeleGate™ The National Anthem® Time⊮Chek™ **TINATM** TLC™ Trapezoidal™ TRI-CODE™ TRI-POLYTM TRI-SAFE™ **TRI-STATE® TROPIC™ TURBOTRANSCEIVER™ VIPTM** VR32™ **WATCHDOG™** XMOS™ **XPUTM** Z STAR™ 883B/RETS™ 883S/RETS™

ABEL™ is a trademark of Data I/O Corporation.

Ethernet® is a registered trademark of Xerox Corporation.

GAL® is a registered trademark of Lattice Semiconductor Corporation.

PAL® is a registered trademark of and used under license from Advanced Micro Devices, Inc.

PC-AT® is a registered trademark of International Business Machines Corporation.

SPI™ is a trademark of Motorola Corporation.

TouchTone™ is a trademark of Western Electric Co., Inc.

Z80® is a registered trademark of Zilog Corporation.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life suppor device or system whose failure to perform can be reasc ably expected to cause the failure of the life support r vice or system, or to affect its safety or effectivenes

National Semiconductor Corporation 2900 Semiconductor Drive, P.O. Box 58090, Santa Clara, California 95052-8090 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reservithout notice, to change said circuitry or specifications.

## **New Products for 1992**

## **EPROMs**

#### 68040 Compatible EPROM

Brlef Description: This device can interface directly with Motorola's 68040 Microprocessor to allow for speed maximization while reducing the number of glue logic devices, thus reducing system cost.

#### Low Voltage EPROMs

Brief Description: These devices operate at 3V for low power consumption, and have JEDEC standard pinouts. These devices are ideal for handheld applications.

#### 2 Megabyte EPROM

Brief Description: This device is a high performance device that possesses two megabytes of NV memory, and has JEDEC standard pinout.

#### **EEPROMs**

#### **16K MICROWIRE™ EEPROM**

Brief Description: The NM93C86A can be configured either x8 or x16 and offers 16K of NV memory. This device will be offered in an 8-pin small-outline (SO) package for minimal space usage.

#### **16K MICROWIRE EEPROM**

Brlef Description: The NM59C16 can be configured either x8 or x16, can be monitored for programming status by monitoring the RDY/BUSY pin and offers 16K of NV memory. This device will be offered in an 8-pin small-outline (SO) package for minimal space usage.

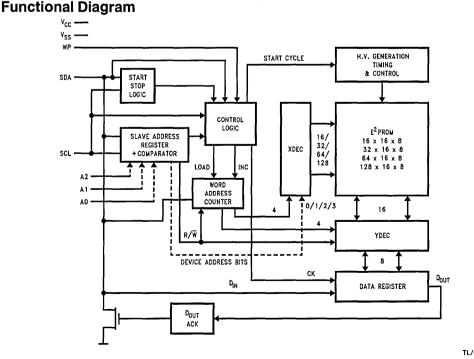

#### 2K/4K Extended Low Voltage I<sup>2</sup>C EEPROM

Brief Description: These devices operate on an I<sup>2</sup>C 2-wire bus and operate in an extended voltage range of 2.5V to 5.5V.

#### 4K SPI™ EEPROM

Brlef Description: These devices are designed for data storage in applications requiring both non-volatile memory and in-system data updates.

Note: For device status and availability, contact your local sales office.

K

## Memory Databook Introduction

National Semiconductor's Memory Databook is a comprehensive collection of information on advanced memory products intended to meet the needs of virtually every electronic system. We are committed to designing and providing stateof-the-art non-volatile EPROM and EEPROM solutions. National's EPROM families—Standard Products, Processor Oriented ePROMs, 5V Low Current and Low Voltage (3V), along with our EEPROM families—MICROWIRE™ and I<sup>2</sup>C, are designed to do just that.

National Semiconductor's EPROM families are suited to meet a variety of customer needs. The Standard Product EPROMs are industry compliant JEDEC parts. Yet, a standard EPROM does not meet the needs of every electronic system. To meet these needs, National provides other families such as the Low Current 5V family which has low I<sub>CC</sub> for power sensitive applications, Low Voltage EPROMs for new-ly emerging portable hand-held markets, and Processor Oriented ePROMs (POPTM) which are designed to fully utilize microprocessor features which increase data throughput.

National Semiconductor's EEPROM families are also suited to provide any solution in serial EEPROM. Different microcontrollers provide various serial interfaces. National, the industry leader, is setting the standard again! The MICRO-WIRE interface is the industry standard. We have expanded our offering to also include the I<sup>2</sup>C interface for consumer electronics, and SPITM for automotive and telecommunication.

National Semiconductor is committed to excellence in design, manufacturing, reliability, and service to our customers through the continuing development of new products and technologies. As new information and devices become available, individual new datasheets will be issued. For the most current information, please contact your local National Semiconductor sales office or distributor.

Look to National for long term support for your memory needs!

## National Semiconductor

# **Product Status Definitions**

## **Definition of Terms**

| Data Sheet Identification     | Product Status            | Definition                                                                                                                                                                                                                                                                      |

|-------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance information           | Formative or<br>In Design | This data sheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                                                                             |

| Preliminary                   | First<br>Production       | This data sheet contains preliminary data, and supplementary data will<br>be published at a later date. National Semiconductor Corporation<br>reserves the right to make changes at any time without notice in order<br>to improve design and supply the best possible product. |

| No<br>Identification<br>Noted | Full<br>Production        | This data sheet contains final specifications. National Semiconductor<br>Corporation reserves the right to make changes at any time without<br>notice in order to improve design and supply the best possible product.                                                          |

National Semiconductor Corporation reserves the right to make changes without further notice to any products herein to improve reliability, function or design. National does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

# **Table of Contents**

| Alphanumeric Index                                                                  | viii  |

|-------------------------------------------------------------------------------------|-------|

| Section 1 CMOS EPROMS                                                               |       |

| STANDARD PRODUCT EPROMS                                                             |       |

| CMOS EPROM Selection Guide                                                          | 1-3   |

| NMC27C16B 16,384-Bit (2048 x 8) CMOS EPROM                                          | 1-4   |

| NMC27C32B 32,768-Bit (4096 x 8) CMOS EPROM                                          | 1-13  |

| NMC27C64 65,536-Bit (8192 x 8) CMOS EPROM                                           | 1-22  |

| NM27C128 131,072-Bit (16K x 8) High Performance CMOS EPROM                          | 1-31  |

| NM27C256 262,144-Bit (32K x 8) High Performance CMOS EPROM                          | 1-41  |

| NM27C512 524,288-Bit (64K x 8) High Performance CMOS EPROM                          | 1-51  |

| NM27C010 1,048,576-Bit (128K x 8) High Performance CMOS EPROM                       | 1-61  |

| NM27C210 1,048,576-Bit (64K x 16) High Performance CMOS EPROM                       | 1-69  |

| NM27C040 4,194,304-Bit (512K x 8) High Performance CMOS EPROM                       | 1-78  |

| PROCESSOR ORIENTED EPROMS                                                           | 1-70  |

| Processor Oriented EPROM Selection Guide                                            | 1-88  |

| NM27P512 524,288-Bit (64K x 8) Processor Oriented CMOS EPROM                        |       |

|                                                                                     | 1-89  |

| NM27P210 1,048,576-Bit (64K x 16) Processor Oriented CMOS EPROM                     | 1-99  |

| NM27P040 4,194,304-Bit (512K x 8) Processor Oriented CMOS EPROM                     | 1-108 |

| NMC87C257 262,144-Bit (32K x 8) CMOS EPROM with On-Chip Address Latches             | 1-117 |

| 5V LOW CURRENT EPROMS                                                               |       |

| NM27LC256 262,144-Bit (32K x 8) Low Current CMOS EPROM                              | 1-127 |

| NM27LC512 524,288-Bit (64K x 8) Low Current CMOS EPROM                              | 1-136 |

| LOW VOLTAGE EPROMS                                                                  |       |

| NM27LV512 524,288-Bit (64K x 8) Low Voltage EPROM                                   | 1-146 |

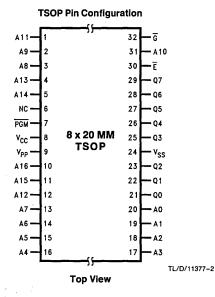

| NM27LV010 1,048,576-Bit (128K x 8) Low Voltage EPROM                                | 1-147 |

| NM27LV210 1,048,576-Bit (64K x 16) Low Voltage EPROM                                | 1-155 |

| Section 2 CMOS EEPROMS                                                              |       |

| I <sup>2</sup> C CMOS EEPROM Selection Guide                                        | 2-3   |

| MICROWIRE CMOS EEPROM Selection Guide                                               | 2-4   |

| Specialty Products CMOS EEPROM Selection Guide                                      | 2-5   |

| I <sup>2</sup> C SYNCHRONOUS 2-WIRE BUS                                             | 20    |

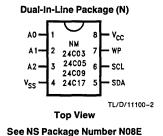

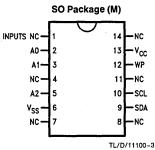

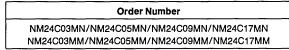

| NM24C02/C04/C08/C16 2K-/4K-/8K-/16K-Bit Serial EEPROM (I <sup>2</sup> C Synchronous |       |

| 2-Wire Bus)                                                                         | 2-6   |

| NM24C03/C05/C09/C17 2K-/4K-/8K-/16K-Bit Serial EEPROM with Write Protect            | 2-0   |

| (I <sup>2</sup> C Synchronous 2-Wire Bus)                                           | 2-17  |

| NM24C02L/C04L 2K-/4K-Bit Serial EEPROM with Extended Voltage (I <sup>2</sup> C      | 2-17  |

|                                                                                     | 0.07  |

| Synchronous 2-Wire Bus).                                                            | 2-27  |

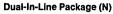

| NM24C03L/C05L 2K-/4K-Bit Serial EEPROM with Write Protect and Extended              |       |

| Voltage (I <sup>2</sup> C Synchronous 2-Wire Bus)                                   | 2-39  |

| MICROWIRE SERIAL EEPROMS                                                            |       |

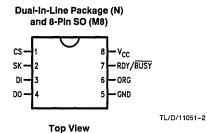

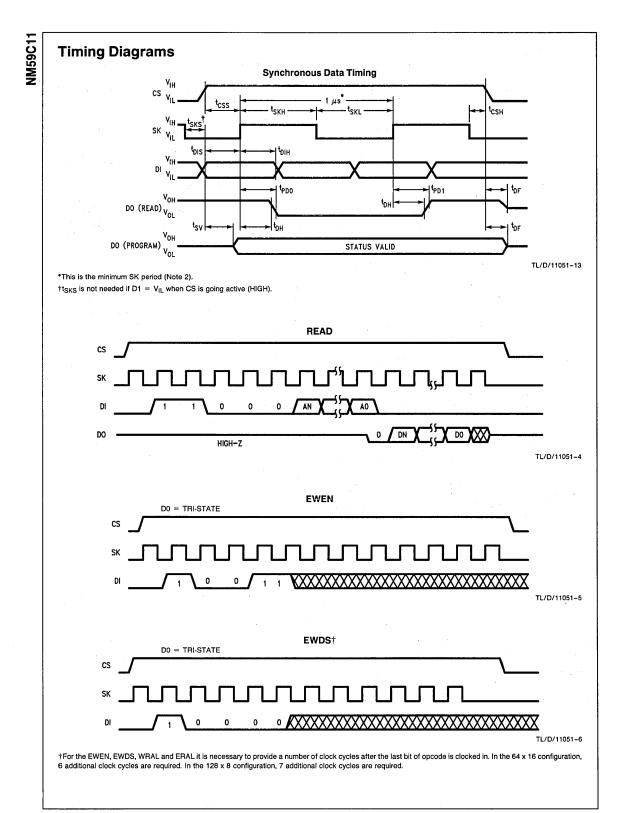

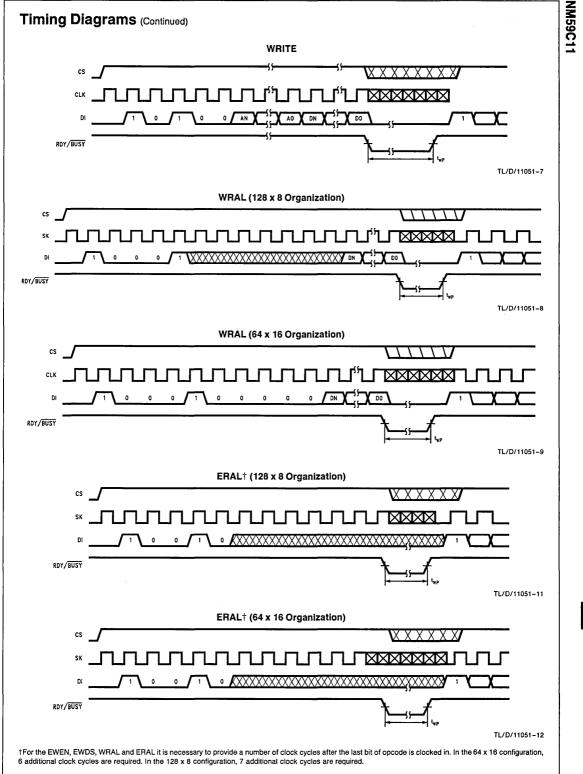

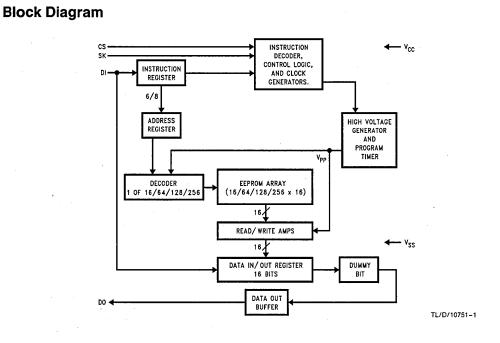

| NM59C11 1024-Bit Serial EEPROM 64 x 16-Bit or 128 x 8-Bit Configurable with         |       |

| Programming Status                                                                  | 2-51  |

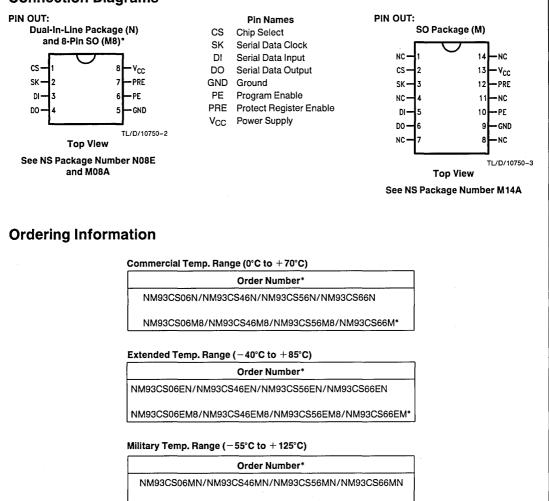

| NM93C06/C46/C56/C66 256-/1024-/2048-/4096-Bit Serial EEPROM                         |       |

| (MICROWIRE)                                                                         | 2-58  |

| NM93CS06/CS46/CS56/CS66 256-/1024-/2048-/4096-Bit Serial EEPROM with Data           |       |

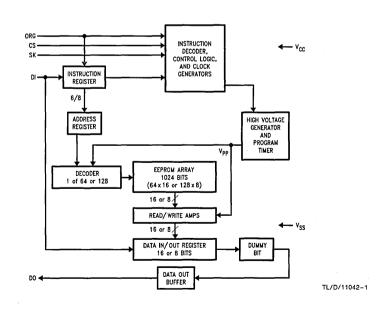

| Protect and Sequential Read                                                         | 2-66  |

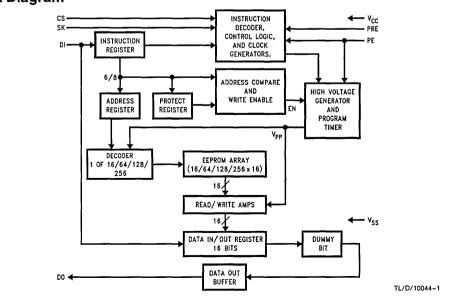

| NM93C06L/C46L/C56L/C66L 256-/1024-/2048-/4096-Bit Serial EEPROM with                |       |

| Extended Voltage (2.0V to 5.5V)                                                     | 2-77  |

| NM93CS06L/CS46L/CS56L/CS66L 256-/1024-/2048-/4096-Bit Serial EEPROM with            |       |

| Extended Voltage (2.0V to 5.5V) and Data Protect                                    | 2-87  |

| NM93C46A 1024-Bit Serial EEPROM 64 x 16-Bit or 128 x 8-Bit Configurable             | 2-100 |

|                                                                                     |       |

# Table of Contents (Continued)

| Section 2 CMOS EEPROMS (Continued)                                                                     |              |

|--------------------------------------------------------------------------------------------------------|--------------|

| NM93C46AL 1024-Bit Serial EEPROM 64 x 16-Bit or 128 x 8-Bit Configurable                               | 2-108        |

| APPLICATION SPECIFIC EEPROM                                                                            |              |

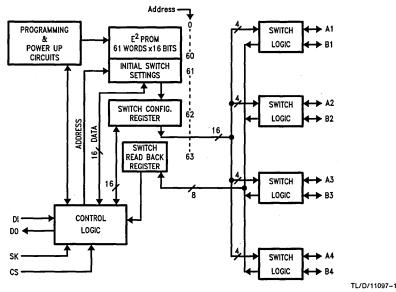

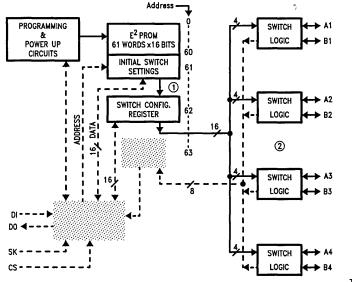

| NM95C12 1K-Bit CMOS EEPROM with Programmable Switches                                                  | 2-118        |

| Section 3 PROMS                                                                                        |              |

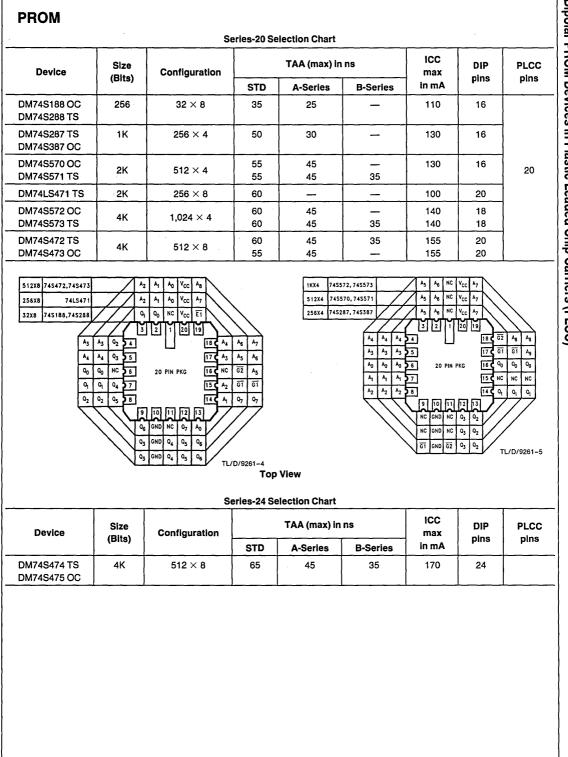

| Bipolar PROM Selection Guide                                                                           | 3-3          |

| NON-REGISTERED BIPOLAR PROMS                                                                           |              |

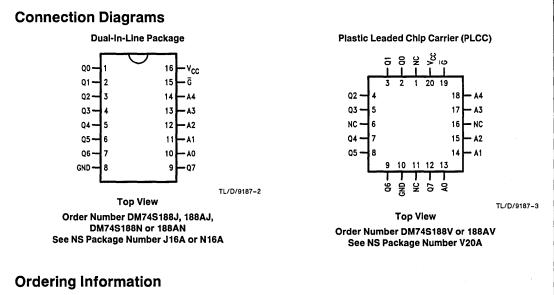

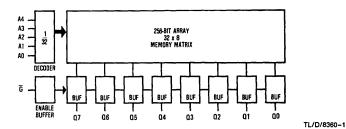

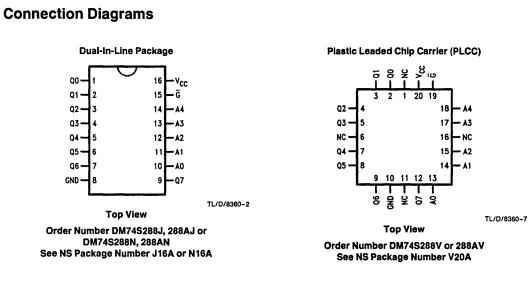

| DM74S188 (32 x 8) 256-Bit TTL PROM                                                                     | 3-4          |

| DM74S288 (32 x 8) 256-Bit TTL PROM                                                                     | 3-8          |

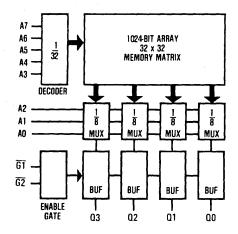

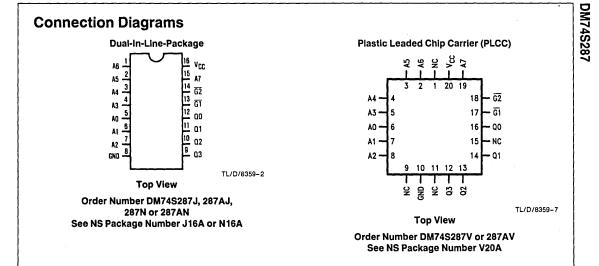

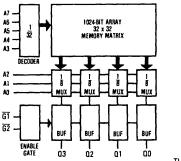

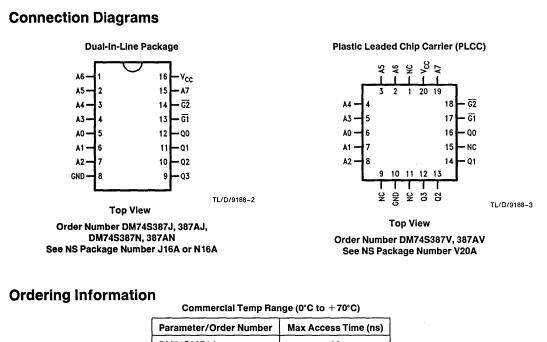

| DM74S287 (256 x 4) 1024-Bit TTL PROM                                                                   | 3-12         |

| DM74S387 (256 x 4) 1024-Bit TTL PROM                                                                   | 3-16         |

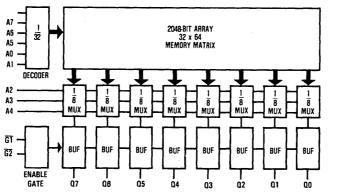

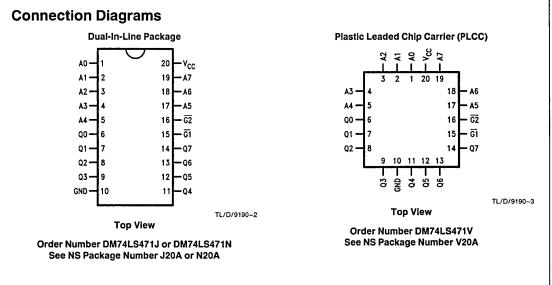

| DM74LS471 (256 x 8) 2048-Bit TTL PROM                                                                  | 3-20         |

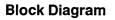

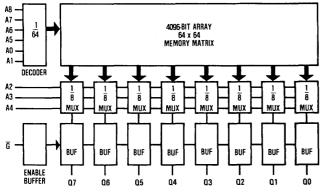

| DM74S472 (512 x 8) 4096-Bit TTL PROM.                                                                  | 3-24         |

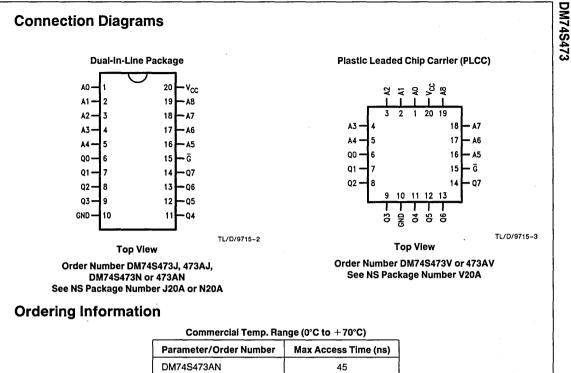

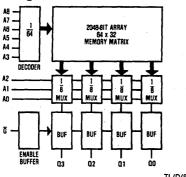

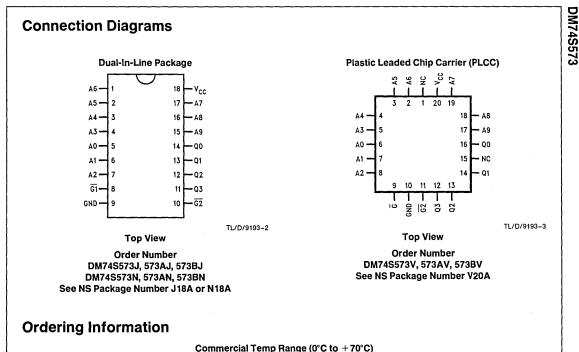

| DM74S473 (512 x 8) 4096-Bit TTL PROM                                                                   | 3-28         |

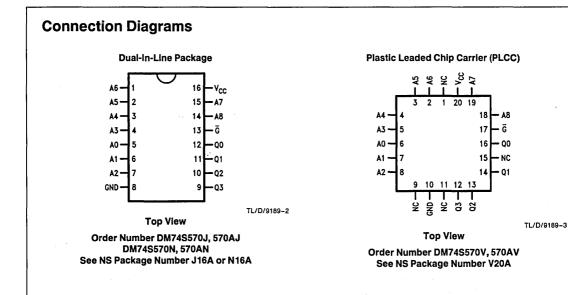

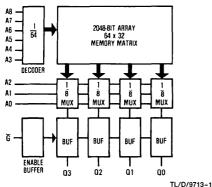

| DM74S570 (512 x 4) 2048-Bit TTL PROM.                                                                  | 3-32         |

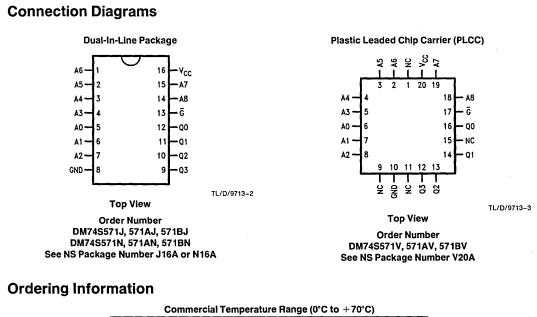

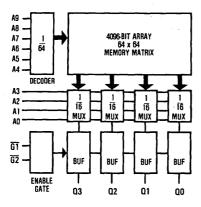

| DM74S571 (512 x 4) 2048-Bit TTL PROM.                                                                  | 3-36         |

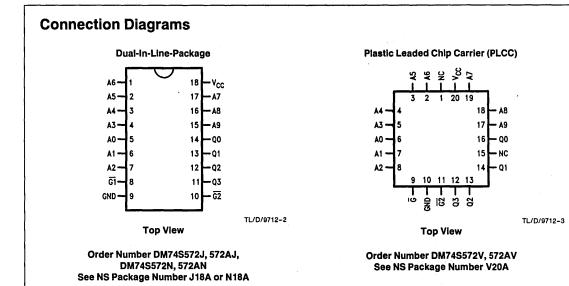

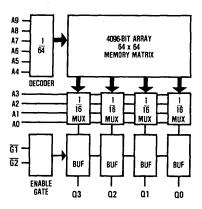

| DM74S572 (1024 x 4) 4096-Bit TTL PROM                                                                  | 3-40         |

| DM74S573 (1024 x 4) 4096-Bit TTL PROM                                                                  | 3-44         |

| APPLICATIONS INFORMATION                                                                               | 3-48         |

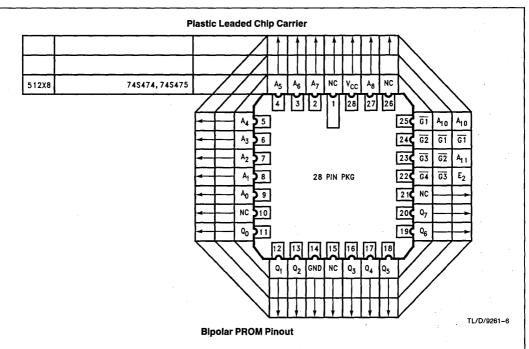

| Bipolar PROM Devices in Plastic Leaded Chip Carriers                                                   | 3-48<br>3-51 |

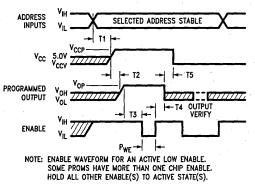

| Non-Registered PROM Programming Procedure                                                              | 3-51         |

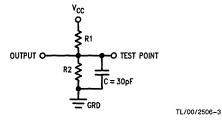

| Standard Test Load                                                                                     | 3-52         |

| Approved Programmers/Quality Enhancement                                                               | 3-53         |

|                                                                                                        | 3-55         |

| Section 4 Application Notes                                                                            | 4.0          |

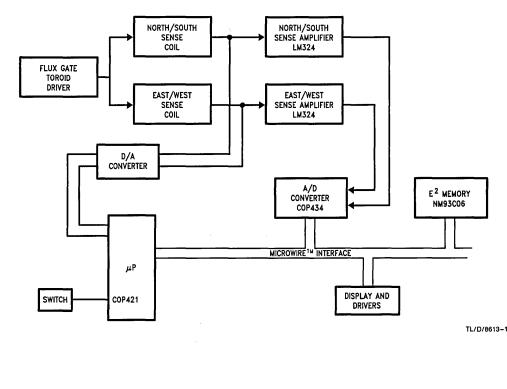

| AB-15 Protecting Data in Serial EEPROMs<br>AB-18 Electronic Compass Calibration Made Easy with EEPROMs | 4-3<br>4-5   |

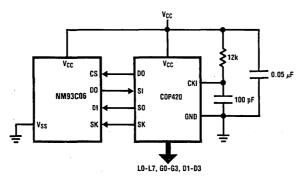

| AN-338 Designing with the NM93C06 A Versatile Simple to Use EEPROM                                     | 4-5<br>4-6   |

| AN-338 Designing with the NM93C06 A Versatile Simple to Use EEPROM                                     | 4-0<br>4-12  |

| AN-425 The NM95C40—All Allazing Device                                                                 | 4-12         |

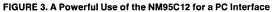

| AN-716 Using the NM93CS EEPROM Family Features                                                         | 4-13         |

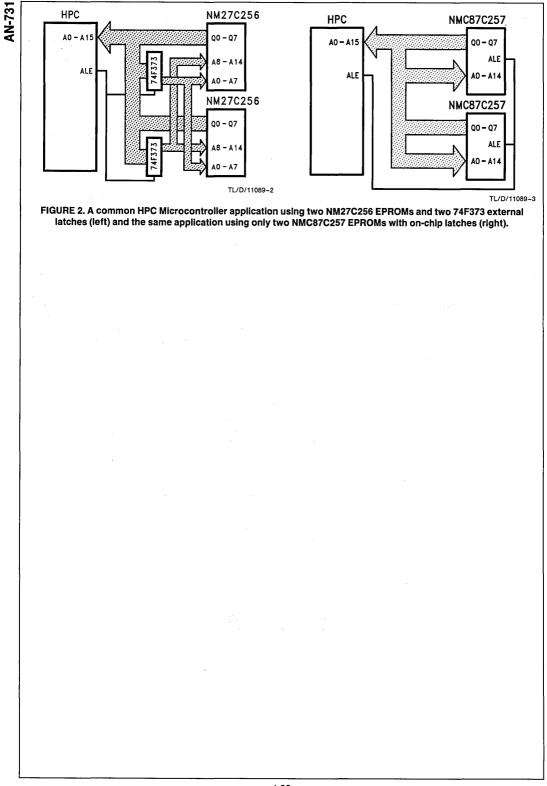

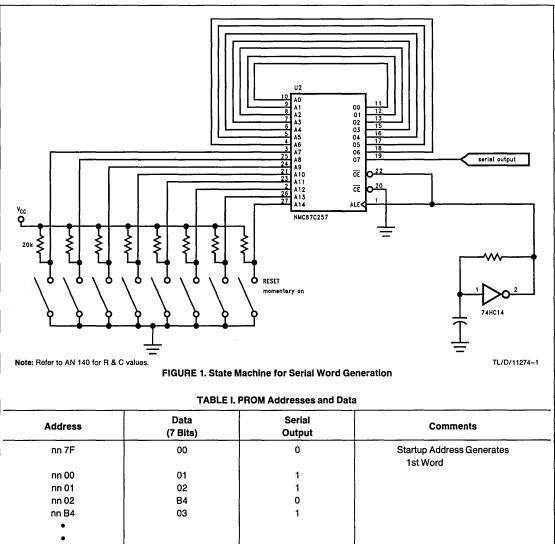

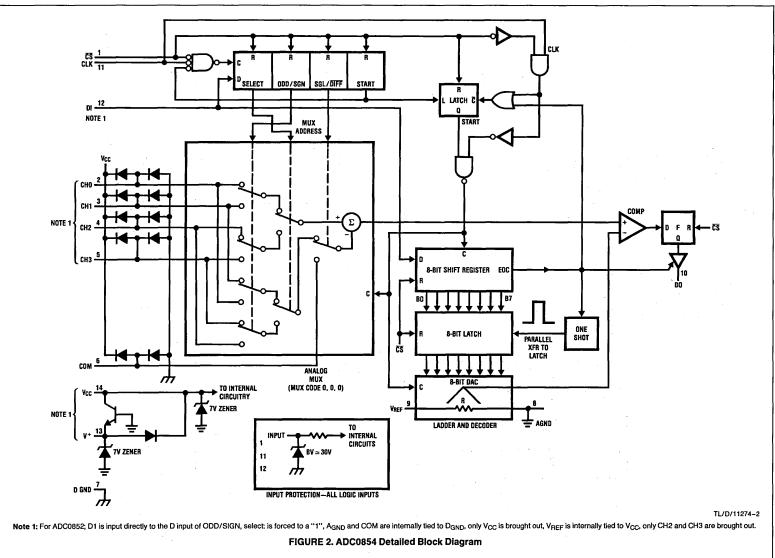

| AN-731 Using National's NMC87C257 256K EPROM with On-Chip Latches                                      | 4-23         |

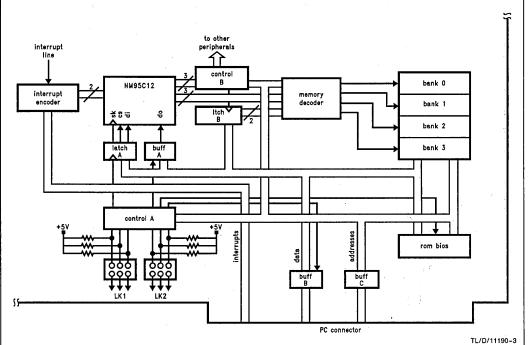

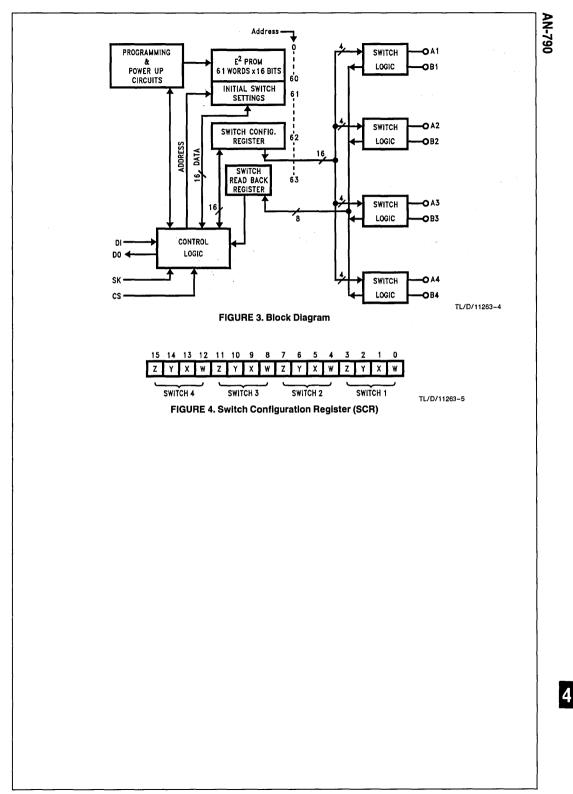

| AN-735 Understanding National's NM95C12 EEPROM with Programmable Switches .                            | 4-33         |

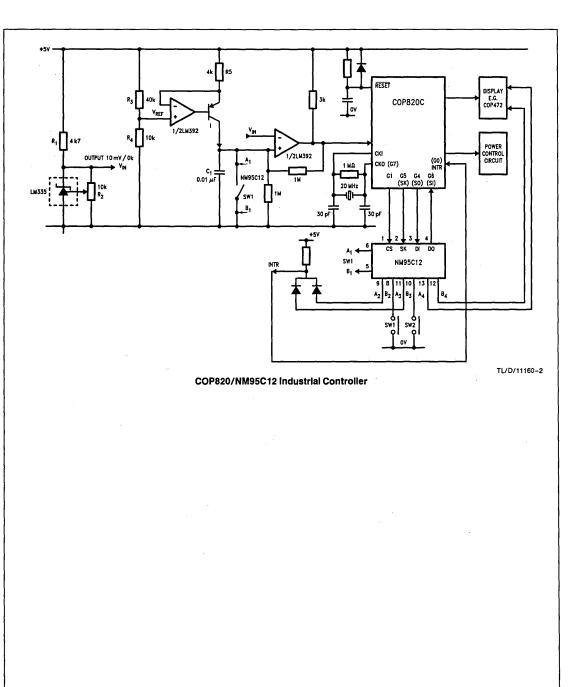

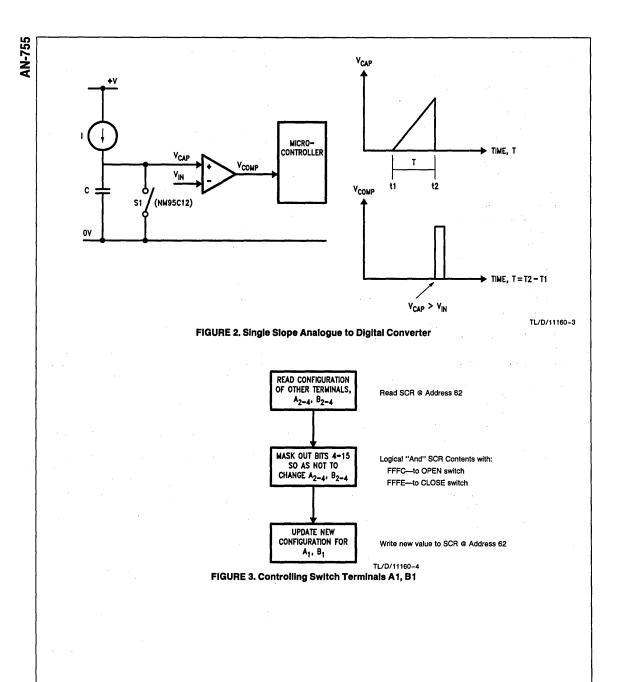

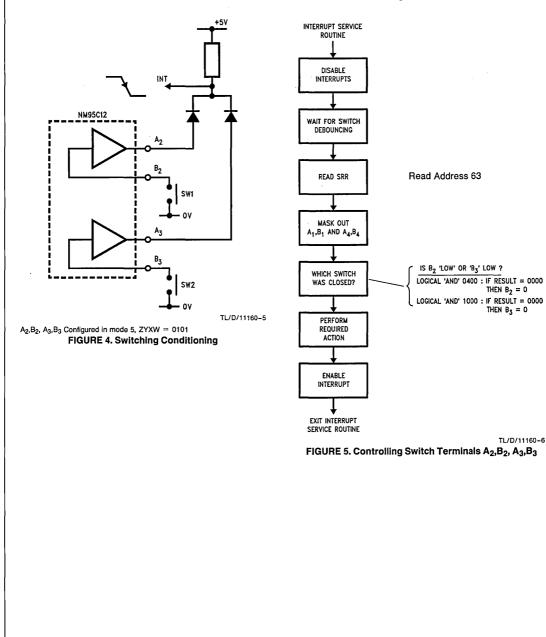

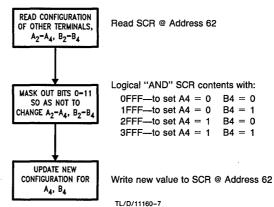

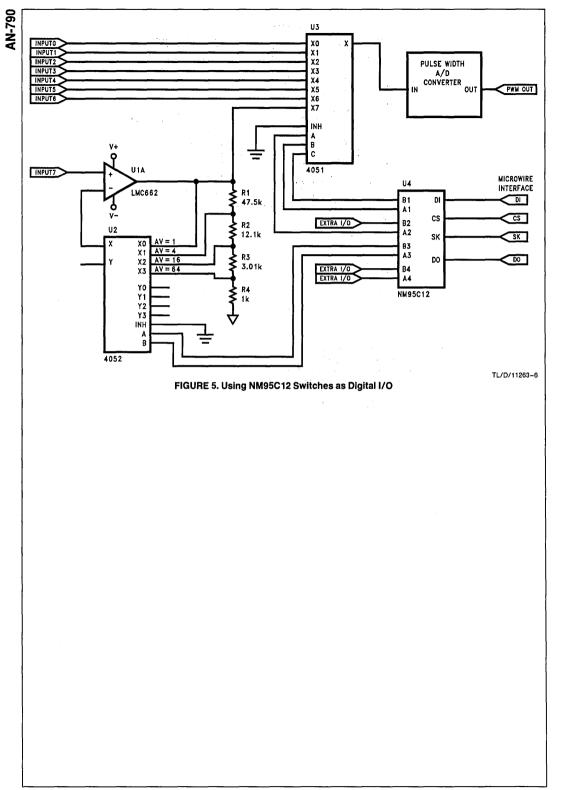

| AN-755 NM95C12 Flexibility in Industrial Control Applications                                          | 4-39         |

| AN-756 Using the NM95C12 to Solve Common Manufacturing Problems                                        | 4-50         |

| AN-758 Using National's MICROWIRE EEPROM                                                               | 4-62         |

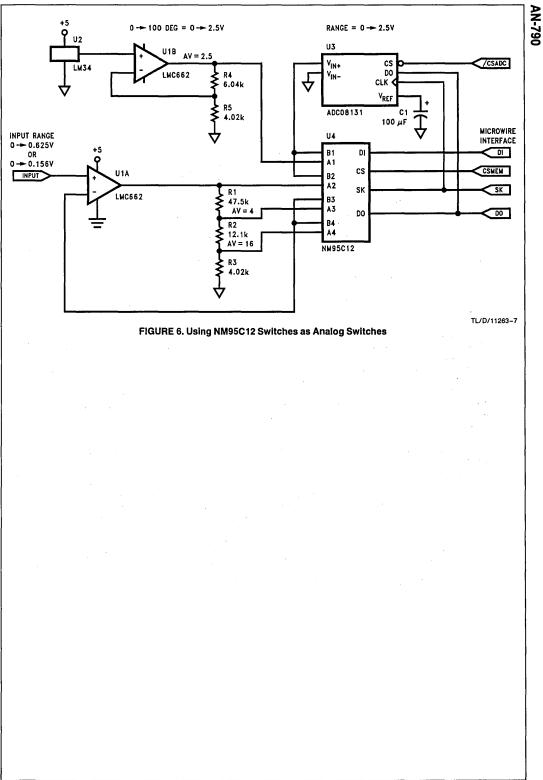

| AN-765 Using the NM95C12 CMOS EEPROM with Programmable Switches for Analog                             |              |

| Applications                                                                                           | 4-73         |

| AN-766 Using the NM95C12 in a Stand Alone Metering Device                                              | 4-80         |

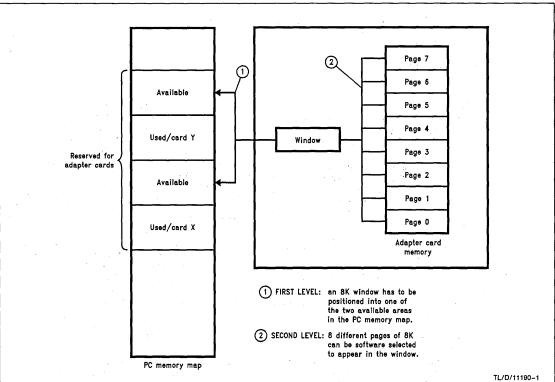

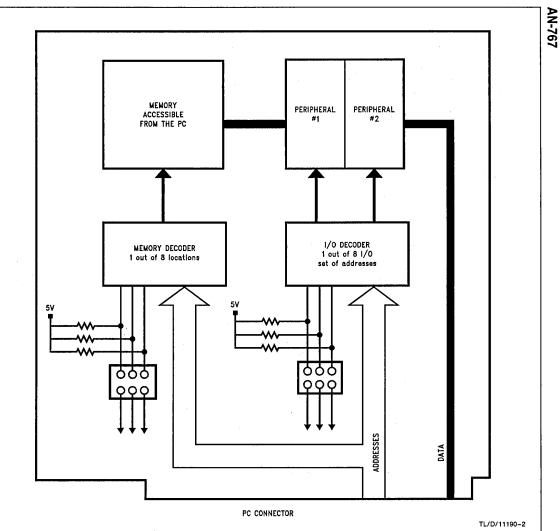

| AN-767 NM95C12 Memory Mapping Solution for PC® Applications                                            | 4-89         |

| AN-789 Integrated Manufacturing Control—NM95C12                                                        | 4-93         |

| AN-790 NM95C12 EEPROM Controls Amplifier Gain                                                          | 4-96         |

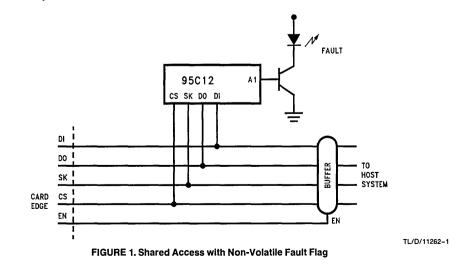

| AN-791 Stand Alone Control of MICROWIRE Peripherals Using the NMC87C257                                | 4-102        |

| AN-792 NM95C12 Applications in a PC-AT Ethernet Adapter                                                | 4-123        |

| AN-794 Using an EEPROM-I <sup>2</sup> C Interface NM24C02/03/04/05/08/09/16/17                         | 4-127        |

| Section 5 Quality and Reliability                                                                      |              |

| EPROM and EEPROM Reliability Information                                                               | 5-3          |

| Section 6 Physical Dimensions                                                                          |              |

| Physical Dimensions                                                                                    | 6-3          |

| Bookshelf                                                                                              |              |

| Distributors                                                                                           |              |

# Alpha-Numeric Index

| AB-15 Protecting Data in Serial EEPROMs 4-3                                                         |

|-----------------------------------------------------------------------------------------------------|

| AB-18 Electronic Compass Calibration Made Easy with EEPROMs 4-5                                     |

| AN-338 Designing with the NM93C06 A Versatile Simple to Use EEPROM                                  |

| AN-423 The NM93C46—An Amazing Device                                                                |

| AN-507 Using the NM93CSXX Family of Electrically Erasable Programmable Memory 4-15                  |

| AN-716 Using the NM93CS EEPROM Family Features                                                      |

| AN-731 Using National's NMC87C257 256K EPROM with On-Chip Latches                                   |

| AN-735 Understanding National's NM95C12 EEPROM with Programmable Switches                           |

| AN-755 NM95C12 Flexibility in Industrial Control Applications                                       |

| AN-756 Using the NM95C12 to Solve Common Manufacturing Problems                                     |

| AN-758 Using National's MICROWIRE EEPROM                                                            |

| AN-765 Using the NM95C12 CMOS EEPROM with Programmable Switches for Analog                          |

| Applications                                                                                        |

| AN-766 Using the NM95C12 in a Stand Alone Metering Device                                           |

| AN-767 NM95C12 Memory Mapping Solution for PC® Applications                                         |

| AN-789 Integrated Manufacturing Control—NM95C12                                                     |

|                                                                                                     |

| AN-790 NM95C12 EEPROM Controls Amplifier Gain                                                       |

| AN-791 Stand Alone Control of MICROWIRE Peripherals Using the NMC87C257                             |

| AN-792 NM95C12 Applications in a PC-AT Ethernet Adapter                                             |

| AN-794 Using an EEPROM-I <sup>2</sup> C Interface NM24C02/03/04/05/08/09/16/17 4-127                |

| DM74LS471 (256 x 8) 2048-Bit TTL PROM                                                               |

| DM74S188 (32 x 8) 256-Bit TTL PROM                                                                  |

| DM74S287 (256 x 4) 1024-Bit TTL PROM                                                                |

| DM74S288 (32 x 8) 256-Bit TTL PROM                                                                  |

| DM74S387 (256 x 4) 1024-Bit TTL PROM                                                                |

| DM74S472 (512 x 8) 4096-Bit TTL PROM                                                                |

| DM74S473 (512 x 8) 4096-Bit TTL PROM                                                                |

| DM74S570 (512 x 4) 2048-Bit TTL PROM                                                                |

| DM74S571 (512 x 4) 2048-Bit TTL PROM                                                                |

| DM74S572 (1024 x 4) 4096-Bit TTL PROM                                                               |

| DM74S573 (1024 x 4) 4096-Bit TTL PROM                                                               |

| NM24C02 2K-Bit Serial EEPROM (I <sup>2</sup> C Synchronous 2-Wire Bus)                              |

| NM24C02L 2K-Bit Serial EEPROM with Extended Voltage (I <sup>2</sup> C Synchronous 2-Wire Bus)       |

| NM24C03 2K-Bit Serial EEPROM with Write Protect (I <sup>2</sup> C Synchronous 2-Wire Bus)           |

| NM24C03L 2K-Bit Serial EEPROM with Write Protect and Extended Voltage (I <sup>2</sup> C Synchronous |

| 2-Wire Bus)                                                                                         |

| NM24C04 4K-Bit Serial EEPROM (I <sup>2</sup> C Synchronous 2-Wire Bus)                              |

| NM24C04L 4K-Bit Serial EEPROM with Extended Voltage (I <sup>2</sup> C Synchronous 2-Wire Bus)       |

|                                                                                                     |

| NM24C05 4K-Bit Serial EEPROM with Write Protect (I <sup>2</sup> C Synchronous 2-Wire Bus)           |

| NM24C05L 4K-Bit Serial EEPROM with Write Protect and Extended Voltage (I <sup>2</sup> C Synchronous |

| 2-Wire Bus)                                                                                         |

| NM24C08 8K-Bit Serial EEPROM (I <sup>2</sup> C Synchronous 2-Wire Bus)                              |

| NM24C09 8K-Bit Serial EEPROM with Write Protect (I <sup>2</sup> C Synchronous 2-Wire Bus)           |

| NM24C16 16K-Bit Serial EEPROM (I <sup>2</sup> C Synchronous 2-Wire Bus)                             |

| NM24C17 16K-Bit Serial EEPROM with Write Protect (I <sup>2</sup> C Synchronous 2-Wire Bus) 2-17     |

| NM27C010 1,048,576-Bit (128K x 8) High Performance CMOS EPROM 1-61                                  |

| NM27C040 4,194,304-Bit (512K x 8) High Performance CMOS EPROM 1-78                                  |

| NM27C128 131,072-Bit (16K x 8) High Performance CMOS EPROM1-31                                      |

| NM27C210 1,048,576-Bit (64K x 16) High Performance CMOS EPROM                                       |

| NM27C256 262,144-Bit (32K x 8) High Performance CMOS EPROM                                          |

| NM27C512 524,288-Bit (64K x 8) High Performance CMOS EPROM                                          |

|                                                                                                     |

# Alpha-Numeric Index (Continued)

| NM27LC256 262,144-Bit (32K x 8) Low Current CMOS EPROM       1-127         NM27LC512 524,288-Bit (64K x 8) Low Current CMOS EPROM       1-136         NM27LV010 1,048,576-Bit (128K x 8) Low Voltage EPROM       1-147         NM27LV210 1,048,576-Bit (64K x 16) Low Voltage EPROM       1-155         NM27LV512 524,288-Bit (64K x 8) Low Voltage EPROM       1-146         NM27P040 4,194,304-Bit (512K x 8) Processor Oriented CMOS EPROM       1-108         NM27P210 1,048,576-Bit (64K x 16) Processor Oriented CMOS EPROM       1-99         NM27P512 524,288-Bit (64K x 8) Processor Oriented CMOS EPROM       1-99         NM27P512 524,288-Bit (64K x 8) Processor Oriented CMOS EPROM       1-89 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NM59C11 1024-Bit Serial EEPROM 64 x 16-Bit or 128 x 8-Bit Configurable with Programming<br>Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| NM93C06 256-Bit Serial EEPROM (MICROWIRE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| NM93C06L 256-Bit Serial EEPROM with Extended Voltage (2.0V to 5.5V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| NM93C46 1024-Bit Serial EEPROM (MICROWIRE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| NM93C46A 1024-Bit Serial EEPROM 64 x 16-Bit or 128 x 8-Bit Configurable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NM93C46AL 1024-Bit Serial EEPROM 64 x 16-Bit or 128 x 8-Bit Configurable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| NM93C46L 1024-Bit Serial EEPROM with Extended Voltage (2.0V to 5.5V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| NM93C56 2048-Bit Serial EEPROM (MICROWIRE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| NM93C56L 2048-Bit Serial EEPROM with Extended Voltage (2.0V to 5.5V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| NM93C66 4096-Bit Serial EEPROM (MICROWIRE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| NM93C66L 4096-Bit Serial EEPROM with Extended Voltage (2.0V to 5.5V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| NM93CS06 256-Bit Serial EEPROM with Data Protect and Sequential Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| NM93CS06L 256-Bit Serial EEPROM with Extended Voltage (2.0V to 5.5V) and Data Protect 2-87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| NM93CS46 1024-Bit Serial EEPROM with Data Protect and Sequential Read2-66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| NM93CS46L 1024-Bit Serial EEPROM with Extended Voltage (2.0V to 5.5V) and Data Protect 2-87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| NM93CS56 2048-Bit Serial EEPROM with Data Protect and Sequential Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NM93CS56L 2048-Bit Serial EEPROM with Extended Voltage (2.0V to 5.5V) and Data Protect 2-87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| NM93CS66 4096-Bit Serial EEPROM with Data Protect and Sequential Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NM93CS66L 4096-Bit Serial EEPROM with Extended Voltage (2.0V to 5.5V) and Data Protect 2-87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| NM95C12 1K-Bit CMOS EEPROM with Programmable Switches 2-118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| NMC27C16B 16,384-Bit (2048 x 8) CMOS EPROM1-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NMC27C32B 32,768-Bit (4096 x 8) CMOS EPROM 1-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NMC27C64 65,536-Bit (8192 x 8) CMOS EPROM 1-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| NMC87C257 262,144-Bit (32K x 8) CMOS EPROM with On-Chip Address Latches 1-117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## Section 1 CMOS EPROMs

## **Section 1 Contents**

| STANDARD PRODUCT EPROMS                                                 |       |

|-------------------------------------------------------------------------|-------|

| CMOS EPROM Selection Guide                                              | 1-3   |

| NMC27C16B 16,384-Bit (2048 x 8) CMOS EPROM                              | 1-4   |

| NMC27C32B 32,768-Bit (4096 x 8) CMOS EPROM                              | 1-13  |

| NMC27C64 65,536-Bit (8192 x 8) CMOS EPROM                               | 1-22  |

| NM27C128 131,072-Bit (16K x 8) High Performance CMOS EPROM              | 1-31  |

| NM27C256 262,144-Bit (32K x 8) High Performance CMOS EPROM              | 1-41  |

| NM27C512 524,288-Bit (64K x 8) High Performance CMOS EPROM              | 1-51  |

| NM27C010 1,048,576-Bit (128K x 8) High Performance CMOS EPROM           | 1-61  |

| NM27C210 1,048,576-Bit (64K x 16) High Performance CMOS EPROM           | 1-69  |

| NM27C040 4,194,304-Bit (512K x 8) High Performance CMOS EPROM           | 1-78  |

| PROCESSOR ORIENTED EPROMS                                               |       |

| Processor Oriented EPROM Selection Guide                                | 1-88  |

| NM27P512 524,288-Bit (64K x 8) Processor Oriented CMOS EPROM            | 1-89  |

| NM27P210 1,048,576-Bit (64K x 16) Processor Oriented CMOS EPROM         | 1-99  |

| NM27P040 4,194,304-Bit (512K x 8) Processor Oriented CMOS EPROM         | 1-108 |

| NMC87C257 262,144-Bit (32K x 8) CMOS EPROM with On-Chip Address Latches | 1-117 |

| 5V LOW CURRENT EPROMS                                                   |       |

| NM27LC256 262,144-Bit (32K x 8) Low Current CMOS EPROM                  | 1-127 |

| NM27LC512 524,288-Bit (64K x 8) Low Current CMOS EPROM                  | 1-136 |

| LOW VOLTAGE EPROMS                                                      |       |

| NM27LV512 524,288-Bit (64K x 8) Low Voltage EPROM                       | 1-146 |

| NM27LV010 1,048,576-Bit (128K x 8) Low Voltage EPROM                    | 1-147 |

| NM27LV210 1,048,576-Bit (64K x 16) Low Voltage EPROM                    | 1-155 |

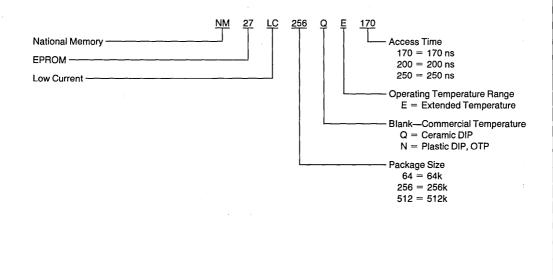

## CMOS EPROM Selection Guide Standard Products

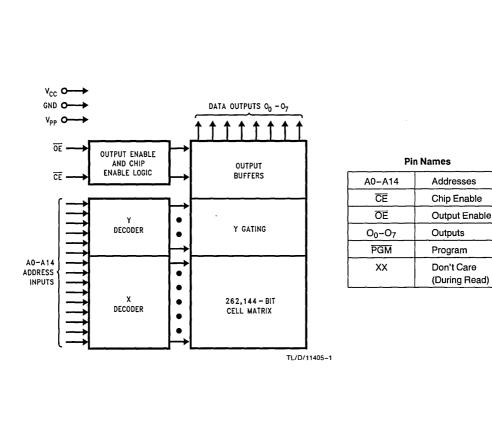

## **General Description**

National Semiconductor's family of high performance CMOS EPROMs offer the following shared features: pin compatibility with byte-wide JEDEC EPROMs; "Don't Care" feature during read operations; high speed operation with high performance CPUs such as the 80186, 68020, 80386; single chip solutions for the code storage requirements of 100% firmware based equipment.

A feature not shared by all family members is found in the NMC87C257—address latches for direct interfacing with address/data multiplexed microprocessors. Other differences are memory size, speed, packaging and operating temperature range.

## **Features**

- High performance CMOS — 100 ns access time

- Fast programming

- EPI processing

- Latch-up immunity to 200 mA

- ESD protection exceeds 2000V

- Compatible with JEDEC EPROM configurations

- Simplified upgrade path

V<sub>PP</sub> and PGM are "Don't Care" during normal read operation

- Single 5V power supply

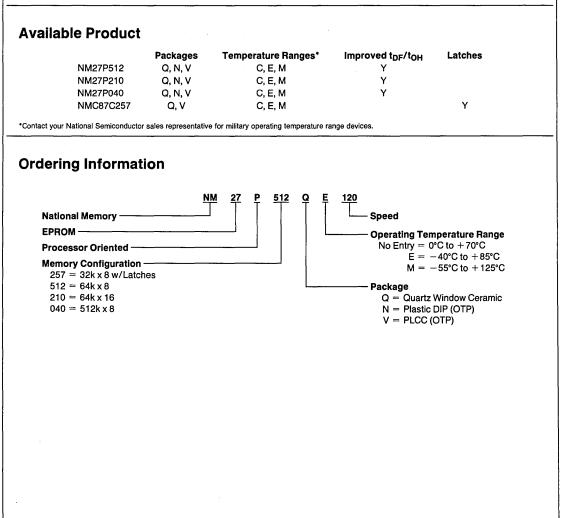

## **Available Product**

|           | Packages | <b>Temperature Ranges</b> | Speed                          |

|-----------|----------|---------------------------|--------------------------------|

| NMC27C16B | Q        | C, E                      | 15 <b>0 ns, 2</b> 00 ns        |

| NMC27C32B | Q        | C, E                      | 20 <b>0 ns</b>                 |

| NMC27C64  | Q, N     | C, E, M*                  | 15 <b>0 ns, 2</b> 00 ns        |

| NM27C128  | Q, N     | C, E                      | 20 <b>0 ns, 2</b> 50 ns        |

| NM27C256  | Q, V, N  | C, E                      | 100 ns, 120 ns, 150 ns, 200 ns |

| NM27C512  | Q, V, N  | C, E                      | 120 ns, 150 ns, 200 ns         |

| NM27C010  | Q, V, N  | C, E                      | 120 ns, 150 ns, 200 ns         |

| NM27C210  | Q, V     | C, E                      | 120 ns, 150 ns, 200 ns         |

| NM27C040  | Q        | C, E                      | 150 ns, 170 ns, 200 ns         |

|           |          |                           |                                |

\*N package available only in commercial temperature range (0°C to +70°C).

Note: All products will operate at speeds slower than those listed.

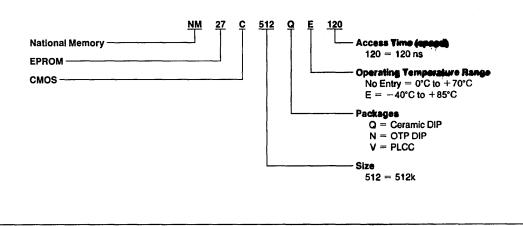

## **Ordering Information**

## National Semiconductor

# NMC27C16B 16,384-Bit (2048 x 8) CMOS EPROM

## **General Description**

The NMC27C16B is a high performance 16K UV erasable and electrically reprogrammable CMOS EPROM, ideally suited for applications where fast turnaround, pattern experimentation and low power consumption are important requirements.

The NMC27C16B is packaged in a 24-pin dual-in-line package with a quartz window. The quartz window allows the user to expose the chip to ultraviolet light to erase the bit pattern. A new pattern can then be written into the device by following the programming procedure.

This EPROM is fabricated with National's proprietary, time proven CMOS double-poly silicon gate technology which combines high performance and high density with low power consumption and excellent reliability.

## Features

- Low CMOS power consumption Active power: 55 mW max Standby power: 0.55 mW max (99% savings)

- Optimal EPROM for total CMOS systems

- Extended temperature range available, -40°C to +85°C

- Fast and reliable programming (100 µs for most bytes)

- TTL compatible inputs/outputs

- TRI-STATE® output

- Manufacturer's identification code for automatic programming equipment

- High current CMOS level output drivers

- Upgrade for NMOS 2716

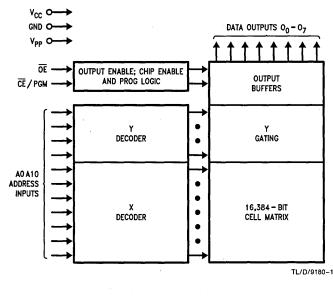

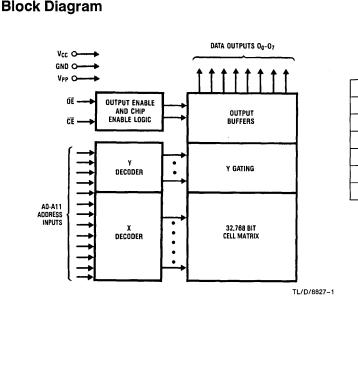

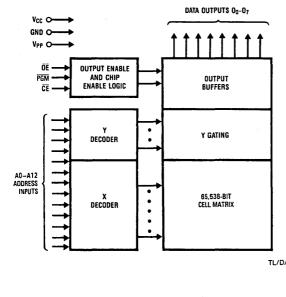

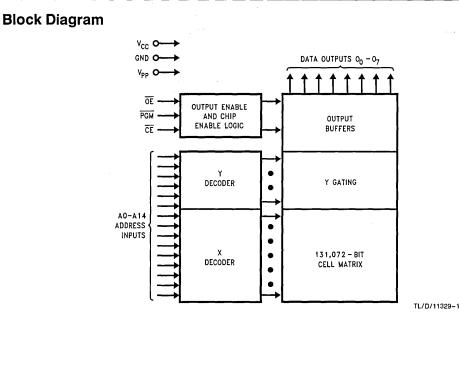

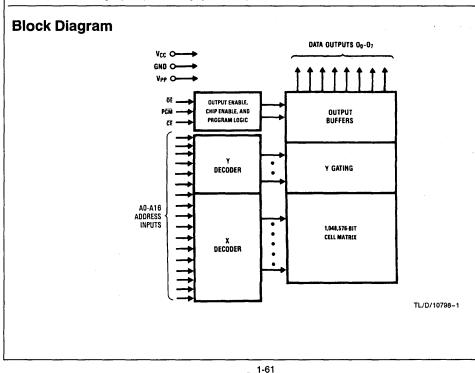

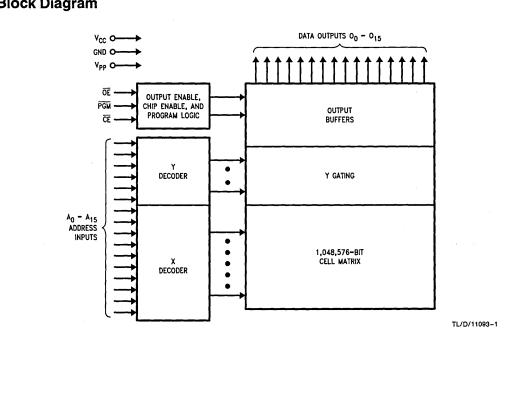

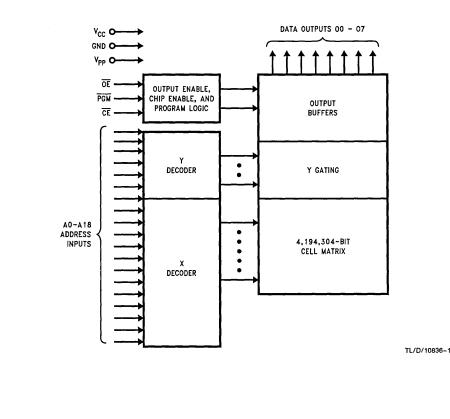

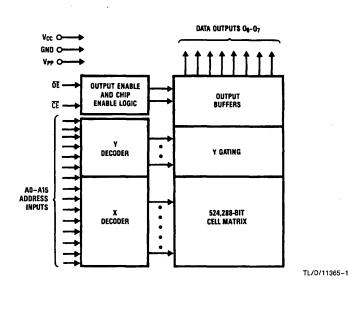

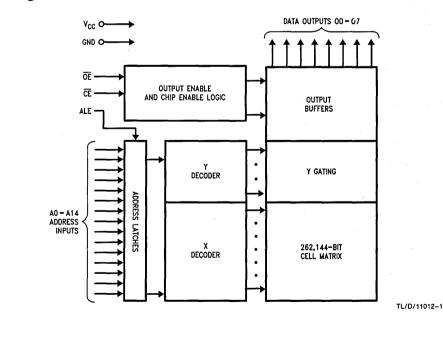

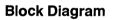

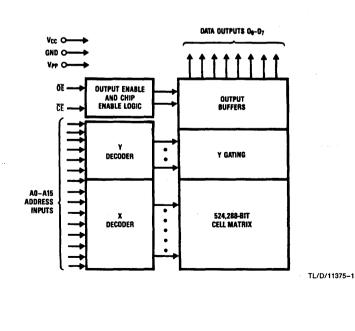

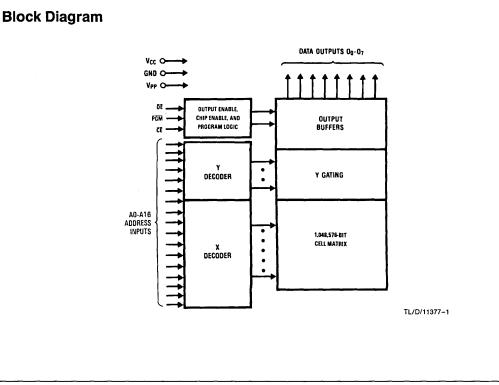

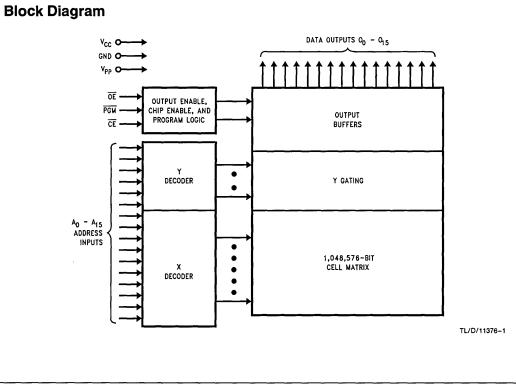

## **Block Diagram**

| Pin Names                      |               |  |

|--------------------------------|---------------|--|

| A0-A10 Addresses               |               |  |

| CE                             | Chip Enable   |  |

| ŌĒ                             | Output Enable |  |

| O <sub>0</sub> -O <sub>7</sub> | Outputs       |  |

| PGM                            | Program       |  |

| NC                             | No Connect    |  |

NMC27C16B

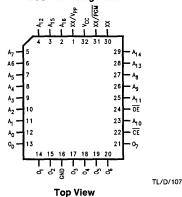

| Connection | Diagram |

|------------|---------|

|------------|---------|

| 27C256<br>27256 | 27C128<br>27128 | 27C64<br>2764   | 27C32<br>2732 |

|-----------------|-----------------|-----------------|---------------|

| V <sub>PP</sub> | Vpp             | V <sub>PP</sub> |               |

| A12             | A12             | A12             | [             |

| A7              | A7              | A7              | A7            |

| A6              | A6              | A6              | A6            |

| A5              | A5              | A5              | A5            |

| A4              | A4              | A4              | A4            |

| A3              | A3              | A3              | A3            |

| A2              | A2              | A2              | A2            |

| A1              | A1              | A1              | A1            |

| A0              | A0              | A0              | AO            |

| O0              | 00              | 00              | 00            |

| O <sub>1</sub>  | 01              | 01              | 01            |

| O2              | O <sub>2</sub>  | 02              | 02            |

| GND             | GND             | GND             | GND           |

| 27C32<br>2732      | 27C64<br>2764   | 27C128<br>27128 | 27C256<br>27256 |

|--------------------|-----------------|-----------------|-----------------|

|                    | V <sub>CC</sub> | Vcc             | V <sub>CC</sub> |

|                    | PGM             | PGM             | A14             |

| Vcc                | NC              | A13             | A13             |

| A8                 | A8              | A8              | A8              |

| A9                 | A9              | A9              | A9              |

| A11                | A11             | A11             | A11             |

| OE/V <sub>PP</sub> | OE              | ŌĒ              | ŌĒ              |

| A10                | A10             | A10             | A10             |

| CE                 | CE              | ĈĒ              | CE              |

| 07                 | 07              | 07              | 07              |

| O <sub>6</sub>     | O <sub>6</sub>  | 0 <sub>6</sub>  | 0 <sub>6</sub>  |

| O <sub>5</sub>     | O5              | O <sub>5</sub>  | O <sub>5</sub>  |

| 04                 | 04              | 04              | 04              |

| O <sub>3</sub>     | O3              | O3              | O <sub>3</sub>  |

TL/D/9180-2

Top View Note: Socket compatible EPROM pin configurations are shown in the blocks adjacent to the NMC27C16B pins.

#### Order Number NMC27C16BQ See NS Package Number J24AQ

#### Commercial Temp. Range (0°C to 70°C) $V_{CC} = 5V \pm 10\%$

| Parameter/Order Number | Access Time (ns) |

|------------------------|------------------|

| NMC27C16BQ150          | 150              |

| NMC27C16BQ200          | 200              |

#### Extended Temp. Range ( $-40^{\circ}$ C to $+85^{\circ}$ C) V<sub>CC</sub> = 5V $\pm 10\%$

| Parameter/Order Number | Access Time (ns) |

|------------------------|------------------|

| NMC27C16BQE150         | 150              |

| NMC27C16BQE200         | 200              |

# **NMC27C16B**

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Temperature Under Bias                                           |                 |

|------------------------------------------------------------------|-----------------|

| Commercial Parts                                                 | -10°C to +80°C  |

| Extended Temp. Parts                                             | -40°C to +85°C  |

| Storage Temperature                                              | -65°C to +150°C |

| V <sub>CC</sub> Supply with<br>Respect to Ground                 | +7.0V to -0.6V  |

| All Input Voltages except A9 with<br>Respect to Ground (Note 10) | +6.5V to -0.6V  |

| All Output Voltages with<br>Respect to Ground (Note 10)         | V <sub>CC</sub> + 1.0V to GND - 0.6V |

|-----------------------------------------------------------------|--------------------------------------|

| V <sub>PP</sub> Supply and A9 Voltage<br>with Respect to Ground | + 14.0V to -0.6V                     |

| Power Dissipation                                               | 1.0W                                 |

| Lead Temp. (Soldering, 10 sec.)                                 | 300°C                                |

## Operating Conditions (Note 8)

| Temperature Range            |                |

|------------------------------|----------------|

| NMC27C16BQ150, 200           | 0°C to +70°C   |

| NMC27C16BQE150, 200          | -40°C to +85°C |

| V <sub>CC</sub> Power Supply | +5V ±10%       |

## **READ OPERATION**

## **DC Electrical Characteristics**

| Symbol                       | Parameter                                        | Conditions                                                                                 | Min                  | Typ<br>(Note 11) | Max                 | Units |

|------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------|------------------|---------------------|-------|

| lu                           | Input Load Current                               | V <sub>IN</sub> = V <sub>CC</sub> or GND                                                   |                      | 0.1              | 1                   | μA    |

| ILO                          | Output Leakage Current                           | $V_{OUT} = V_{CC} \text{ or GND, } \overline{CE} = V_{IH}$                                 |                      | 0.1              | 1                   | μΑ    |

| I <sub>CC1</sub><br>(Note 3) | V <sub>CC</sub> Current (Active)<br>TTL Inputs   | $\overline{CE} = V_{IL}, f = 5 \text{ MHz}$<br>Inputs = $V_{IH}$ or $V_{IL}$<br>I/O = 0 mA |                      | 5                | 20                  | mA    |

| I <sub>CC2</sub><br>(Note 3) | V <sub>CC</sub> Current (Active)<br>CMOS Inputs  | $\overline{CE} = GND, f = 5 MHz$ Inputs = $V_{CC}$ or GND, I/O = 0 mA                      |                      | 3                | 10                  | mA    |

| ICCSB1                       | V <sub>CC</sub> Current (Standby)<br>TTL Inputs  | $\overline{CE} = V_{IH}$                                                                   |                      | 0.1              | 1                   | mA    |

| ICCSB2                       | V <sub>CC</sub> Current (Standby)<br>CMOS Inputs | $\overline{CE} = V_{CC}$                                                                   |                      | 0.5              | 100                 | μΑ    |

| lpp                          | VPP Load Current                                 | V <sub>PP</sub> = 5.5V                                                                     |                      |                  | 10                  | μΑ    |

| VIL                          | Input Low Voltage                                |                                                                                            | -0.2                 |                  | 0.8                 | v     |

| VIH                          | Input High Voltage                               |                                                                                            | 2.0                  |                  | V <sub>CC</sub> + 1 | v     |

| V <sub>OL1</sub>             | Output Low Voltage                               | l <sub>OL</sub> = 2.1 mA                                                                   |                      |                  | 0.45                | v     |

| V <sub>OH1</sub>             | Output High Voltage                              | I <sub>OH</sub> = -400 mA                                                                  | 2.4                  |                  |                     | v     |

| V <sub>OL2</sub>             | Output Low Voltage                               | l <sub>OL</sub> = 10 μA                                                                    |                      |                  | 0.1                 | v     |

| V <sub>OH2</sub>             | Output High Voltage                              | $I_{OH} = -10 \mu A$                                                                       | V <sub>CC</sub> -0.1 |                  |                     | v     |

## **AC Electrical Characteristics**

|                 |                                                                   |                                          |             | NMC27C16BQ |             |     |       |  |

|-----------------|-------------------------------------------------------------------|------------------------------------------|-------------|------------|-------------|-----|-------|--|

| Symbol ,        | Parameter                                                         | Conditions                               | Q150, QE150 |            | Q200, QE200 |     | Units |  |

|                 |                                                                   |                                          | Min         | Max        | Min         | Max |       |  |

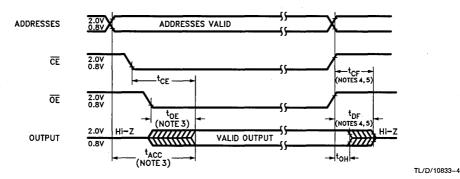

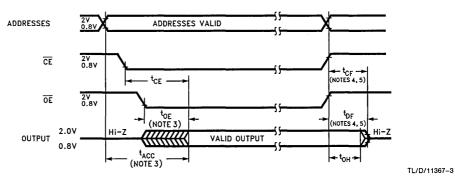

| tACC            | Address to Output Delay                                           | $\overline{CE} = \overline{OE} = V_{IL}$ |             | 150        |             | 200 | ns    |  |

| t <sub>CE</sub> | CE to Output Delay                                                | $\overline{OE} = V_{IL}$                 |             | 150        |             | 200 | ns    |  |

| t <sub>OE</sub> | OE to Output Delay                                                | $\overline{CE} = V_{IL}$                 |             | 60         |             | 60  | ns    |  |

| t <sub>DF</sub> | OE High to Output Float                                           | $\overline{CE} = V_{IL}$                 | 0           | 50         | 0           | 60  | ns    |  |

| <sup>t</sup> CF | CE High to Output Float                                           | $\overline{OE} = V_{IL}$                 | 0           | 50         | 0           | 60  | ns    |  |

| t <sub>OH</sub> | Output Hold from Addresses,<br>CE or OE, Whichever Occurred First | $\overline{OE} = \overline{OE} = V_{ L}$ | 0           |            | 0           |     | ns    |  |

## Capacitance $T_A = +25^{\circ}C$ , f = 1 MHz (Note 4)

| Symbol          | Parameter          | Conditions           | Тур | Max | Units |

|-----------------|--------------------|----------------------|-----|-----|-------|

| C <sub>IN</sub> | Input Capacitance  | V <sub>IN</sub> = 0V | 6   | 12  | pF    |

| COUT            | Output Capacitance | $V_{OUT} = 0V$       | 9   | 12  | pF    |

## **AC Test Conditions**

| Output Load (Note 12)     | 1 TTL Gate and $C_L = 100  pF$ |

|---------------------------|--------------------------------|

| Input Rise and Fall Times | ≤ 5 ns                         |

| Input Pulse Levels        | 0.45V to 2.4V                  |

| Timing Measurement Reference Lev | el |

|----------------------------------|----|

| Inputs                           |    |

| Outputs                          |    |

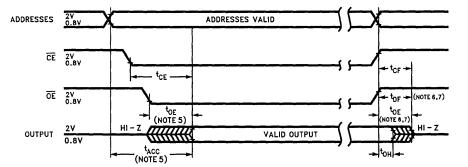

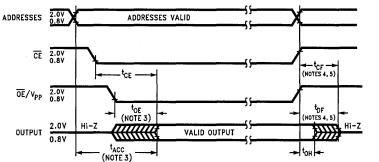

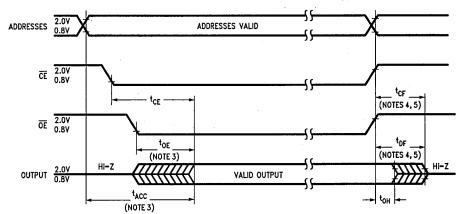

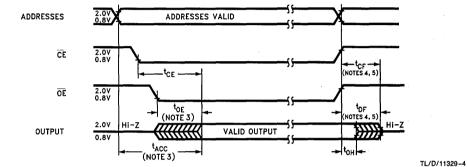

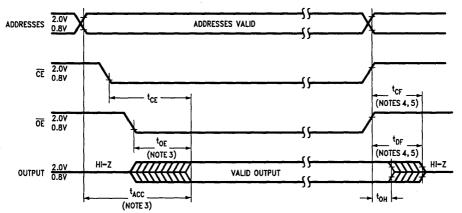

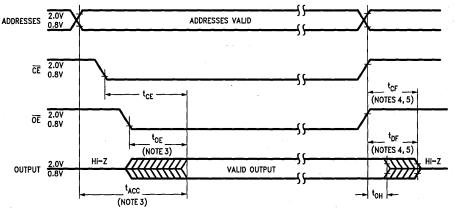

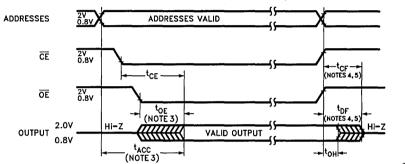

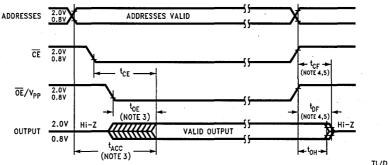

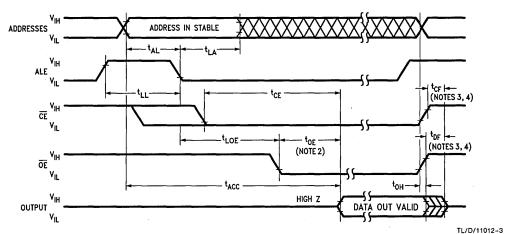

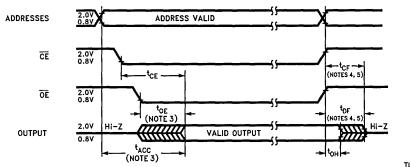

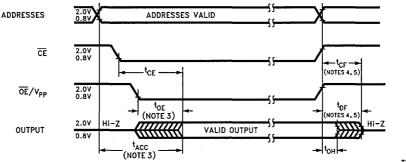

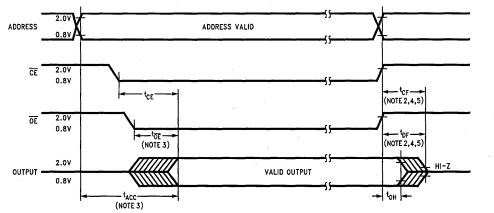

## AC Waveforms (Notes 2 & 9)

TL/D/9180-3

0.8V and 2V 0.8V and 2V

Note 1: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2: V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

Note 3: Vpp may be connected to V<sub>CC</sub> except during programming.  $I_{CC1} \le$  the sum of the I<sub>CC</sub> active and I<sub>PP</sub> read currents.

Note 4: This parameter is only sampled and is not 100% tested.

Note 5:  $\overrightarrow{OE}$  may be delayed up to  $t_{ACC} - t_{OE}$  after the falling edge of  $\overrightarrow{CE}$  without impact on  $t_{ACC}$ .

Note 6: The  $t_{DF}$  and  $t_{CF}$  compare level is determined as follows:

High to TRI-STATE, the measured  $V_{OH1}$  (DC) - 0.10V;

Low to TRI-STATE, the measured  $V_{OL1}$  (DC) + 0.10V.

Note 7: TRI-STATE may be attained using  $\overrightarrow{\text{OE}}$  or  $\overrightarrow{\text{CE}}$ .

Note 8: The power switching characteristics of EPROMs require careful device decoupling. It is recommended that a 0.1 µF ceramic capacitor be used on every device between V<sub>CC</sub> and GND.

Note 9: The outputs must be restricted to V<sub>CC</sub> + 1.0V to avoid latch-up and device damage.

Note 10: Inputs and outputs can undershoot to -2.0V for 20 ns maximum.

Note 11: Typical values are for  $T_A = 25^{\circ}C$  and nominal supply voltages.

Note 12: 1 TTL Gate:  $I_{DL} = 1.6$  mA,  $I_{OH} = 400 \ \mu$ A.

CL: 100 pF inlcudes fixture capacitance.

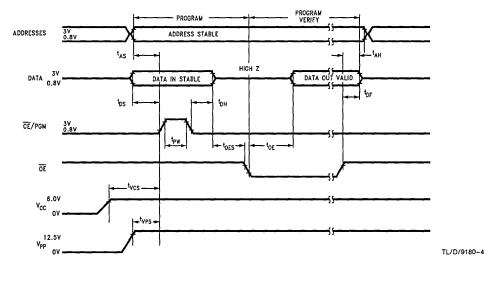

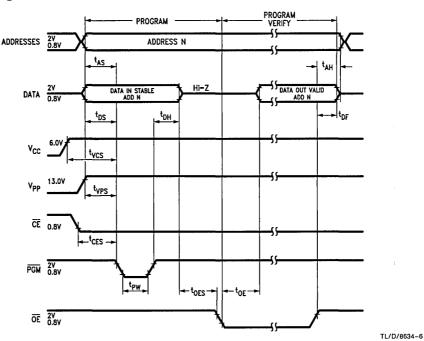

| Symbol           | Parameter                                                  | Conditions                                                              | Min  | Тур                                   | Max  | Units |

|------------------|------------------------------------------------------------|-------------------------------------------------------------------------|------|---------------------------------------|------|-------|

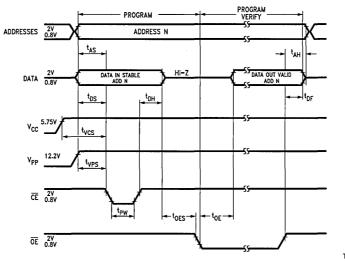

| t <sub>AS</sub>  | Address Setup Time                                         |                                                                         | 1    |                                       |      | μs    |

| tOES             | OE Setup Time                                              |                                                                         | 1.   |                                       |      | μs    |

| t <sub>DS</sub>  | Data Setup Time                                            |                                                                         | 1    |                                       |      | μs    |

| tvcs             | V <sub>CC</sub> Setup Time                                 |                                                                         | 1    |                                       |      | μs    |

| t <sub>VPS</sub> | V <sub>PP</sub> Setup Time                                 |                                                                         | 1    |                                       |      | μs    |

| t <sub>AH</sub>  | Address Hold Time                                          |                                                                         | 0    |                                       |      | μs    |

| t <sub>DH</sub>  | Data Hold Time                                             |                                                                         | 1    |                                       |      | μs    |

| t <sub>DF</sub>  | Output Enable to Output Float Delay                        | $\overline{CE}/PGM = V_{IL}$                                            | 0    |                                       | 60   | ns    |

| t <sub>PW</sub>  | Program Pulse Width                                        |                                                                         | 95   | 100                                   | 105  | μs    |

| tOE              | Data Valid from OE                                         | $\overline{CE}/PGM = V_{IL}$                                            |      |                                       | 150  | ns    |

| Ipp              | V <sub>PP</sub> Supply Current During<br>Programming Pulse | $\frac{\overline{CE}}{\overline{OE}} = V_{IH}$ $\overline{OE} = V_{IH}$ |      |                                       | 30   | mA    |

| lcc              | V <sub>CC</sub> Supply Current                             |                                                                         |      |                                       | 10   | mA    |

| T <sub>A</sub>   | Temperature Ambient                                        |                                                                         | 20   | 25                                    | 30   | °C    |

| Vcc              | Power Supply Voltage                                       |                                                                         | 6.0  | 6.25                                  | 6.5  | V     |

| VPP              | Programming Supply Voltage                                 |                                                                         | 12.5 | 12.75                                 | 13.0 | V     |

| t <sub>FR</sub>  | Input Rise, Fall Time                                      |                                                                         | 5    |                                       |      | ns    |

| VIL              | Input Low Voltage                                          |                                                                         |      | 0.0                                   | 0.45 | v     |

| VIH              | Input High Voltage                                         |                                                                         | 3.0  | 4.0                                   |      | V     |

| t <sub>IN</sub>  | Input Timing Reference Voltage                             |                                                                         | 0.8  | · · · · · · · · · · · · · · · · · · · | 2.0  | v     |

| tOUT             | Output Timing Reference Voltage                            |                                                                         | 0.8  |                                       | 2.0  | V     |

Note 1: National's standard product warranty applies only to devices programmed to specifications described herein.

Note 2: V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>. The EPROM must not be inserted into or removed from a board with voltage applied to V<sub>PP</sub> or V<sub>CC</sub>.

Note 3: The maximum absolute allowable voltage which may be applied to the V<sub>PP</sub> pin during programming is 14V. Care must be taken when switching the V<sub>PP</sub> supply to prevent any overshoot from exceeding this 14V maximum specification. At least a 0.1 µF capacitor is required across V<sub>PP</sub>, V<sub>CC</sub> to GND to suppress spurious voltage transients which may damage the device.

Note 4: Programming and program verify are tested with the fast Program Algorithm, at typical power supply voltages and timings. The Min and Max Limit Parameters are Design parameters, not Tested or guaranteed.

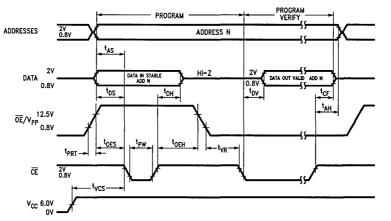

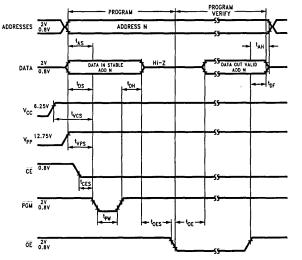

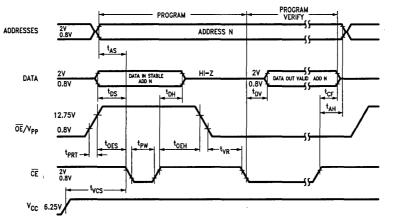

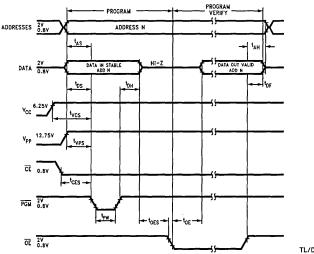

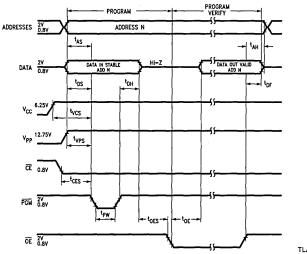

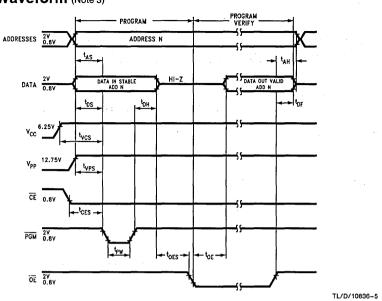

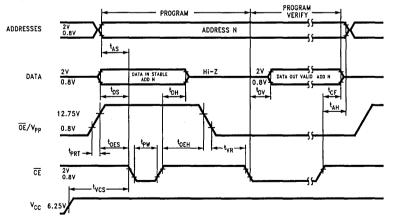

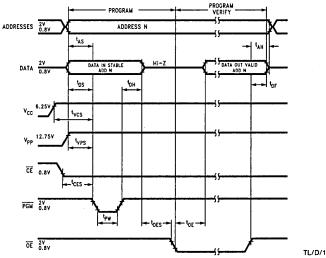

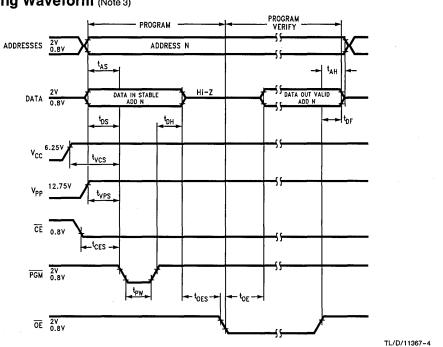

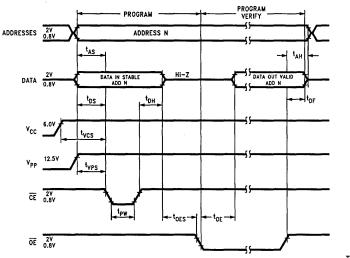

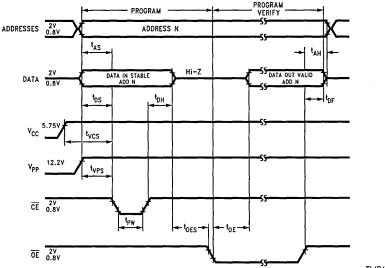

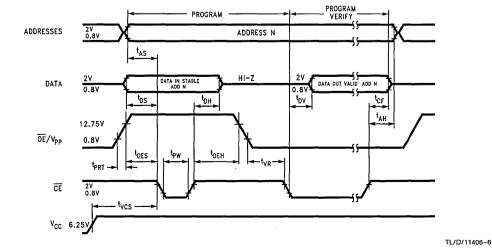

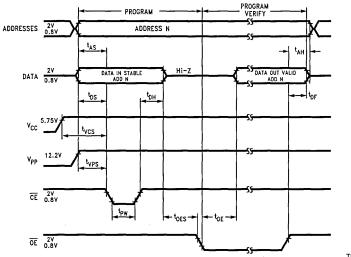

## **Programming Waveforms**

1-10

## **Functional Description**

#### DEVICE OPERATION

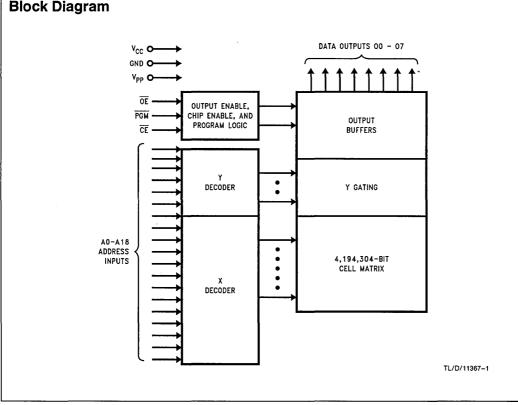

The six modes of operation of the NMC27C16B are listed in Table I. It should be noted that all inputs for the six modes are at TTL levels. The power supplies required are V<sub>CC</sub> and V<sub>PP</sub>. The V<sub>PP</sub> power supply must be at 12.75V during the three programming modes, and must be at V<sub>CC</sub> in the other modes. The V<sub>CC</sub> power supply must be at 6.25V during the three programming modes, and at 5V in the other modes.

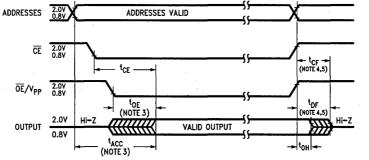

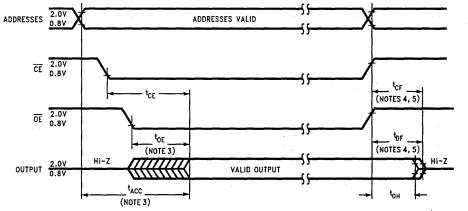

#### Read Mode

The NMC27C16B has two control functions, both of which must be logically active in order to obtain data at the outputs. Chip Enable ( $\overline{CE}$ ) is the power control and should be used for device selection. Output Enable ( $\overline{OE}$ ) is the output control and should be used to gate data to the output pins, independent of device selection. Assuming that addresses are stable, address access time ( $t_{ACC}$ ) is equal to the delay from  $\overline{CE}$  to output ( $t_{CE}$ ). Data is available at the outputs  $t_{OE}$  after the falling edge of  $\overline{OE}$ , assuming that  $\overline{CE}$  has been low and addresses have been stable for at least  $t_{ACC} - t_{OE}$ .

The sense amps are clocked for fast access time.  $V_{CC}$  should therefore be maintained at operating voltage during read and verify. If  $V_{CC}$  temporarily drops below the spec. voltage (but not to ground) an address transition must be performed after the drop to insure proper output data.

#### Standby Mode

The NMC27C16B has a standby mode which reduces the active power dissipation by 99%, from 55 mW to 0.55 mW. The NMC27C16B is placed in the standby mode by applying a CMOS high signal to the  $\overline{CE}$  input. When in standby mode, the outputs are in a high impedance state, independent of the  $\overline{OE}$  input.

#### **Output OR-Tying**

Because NMC27C16Bs are usually used in larger memory arrays, National has provided a 2-line control function that accommodates this use of multiple memory connections. The 2-line control function allows for:

- a) the lowest possible memory power dissipation, and

- b) complete assurance that output bus contention will not occur.

To most efficiently use these two control lines, it is recommended that  $\overline{CE}$  (pin 18) be decoded and used as the pri-

mary device selecting function, while  $\overline{OE}$  (pin 20) be made a common connection to all devices in the array and connected to the READ line from the system control bus. This assures that all deselected memory devices are in their low power standby modes and that the output pins are active only when data is desired from a particular memory device.

#### Programming

CAUTION: Exceeding 14V on pin 21 (V\_PP) will damage the NMC27C16B.

Initially, and after each erasure, all bits of the NMC27C16B are in the "1" state. Data is introduced by selectively programming "0s" into the desired bit locations. Although only "0s" will be programmed, both "1s" and "0s" can be presented in the data word. The only way to change a "0" to a "1" is by ultraviolet light erasure.

The NMC27C16B is in the programming mode when the V<sub>PP</sub> power supply is at 12.75V and  $\overline{OE}$  is at V<sub>IH</sub>. It is required that at least a 0.1  $\mu F$  capacitor be placed across V<sub>PP</sub>, V<sub>CC</sub> to ground to suppress spurious voltage transients which may damage the device. The data to be programmed is applied 8 bits in parallel to the data output pins.

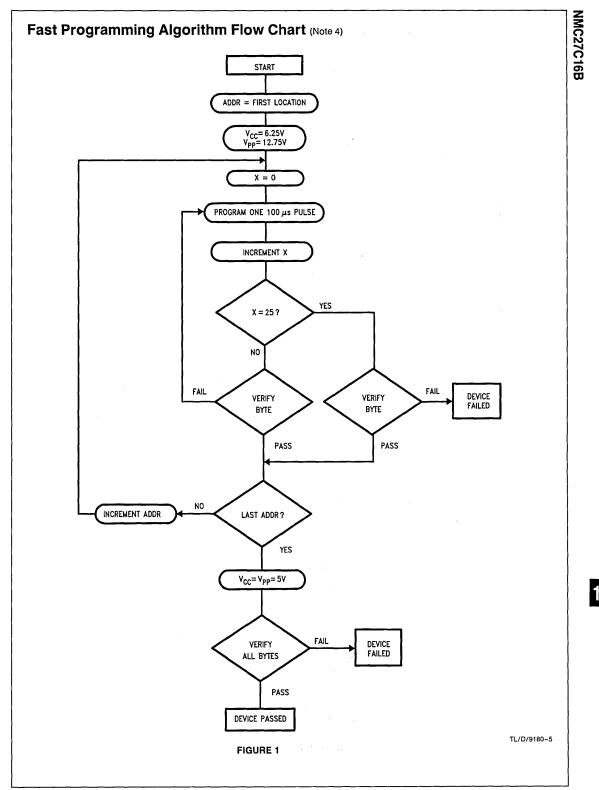

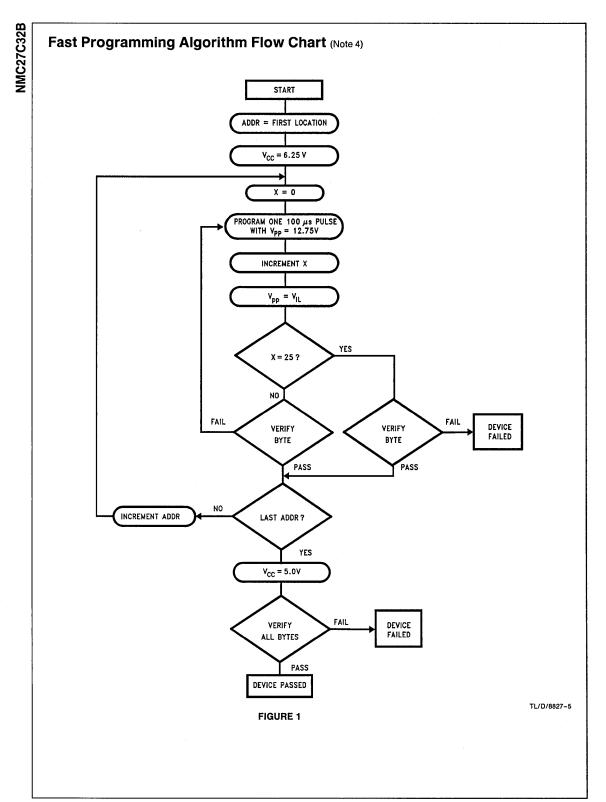

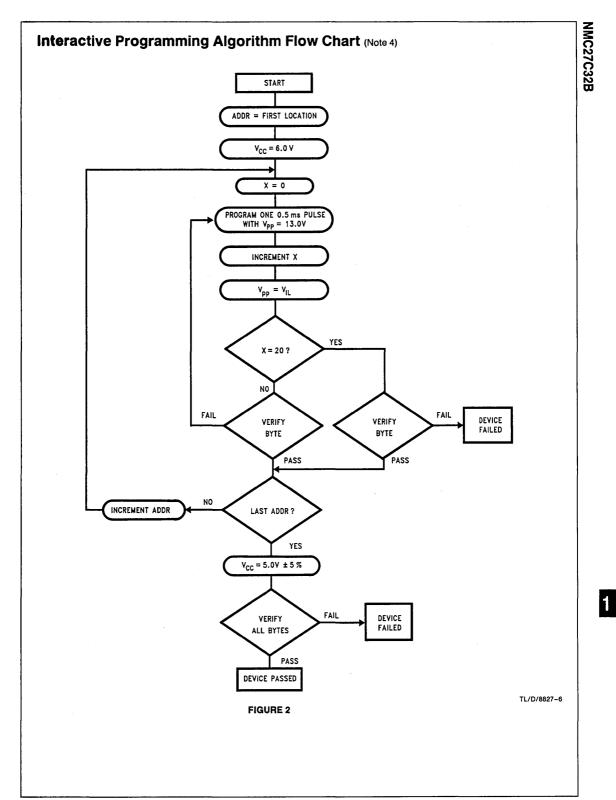

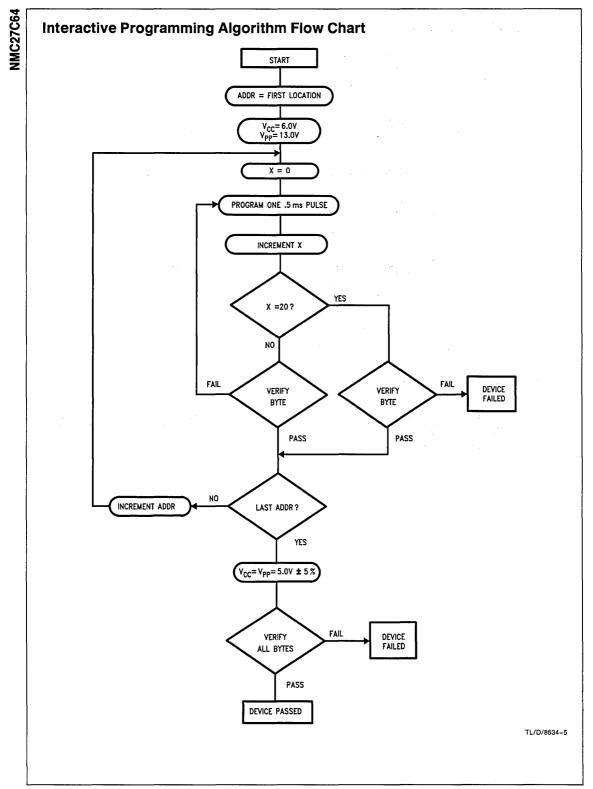

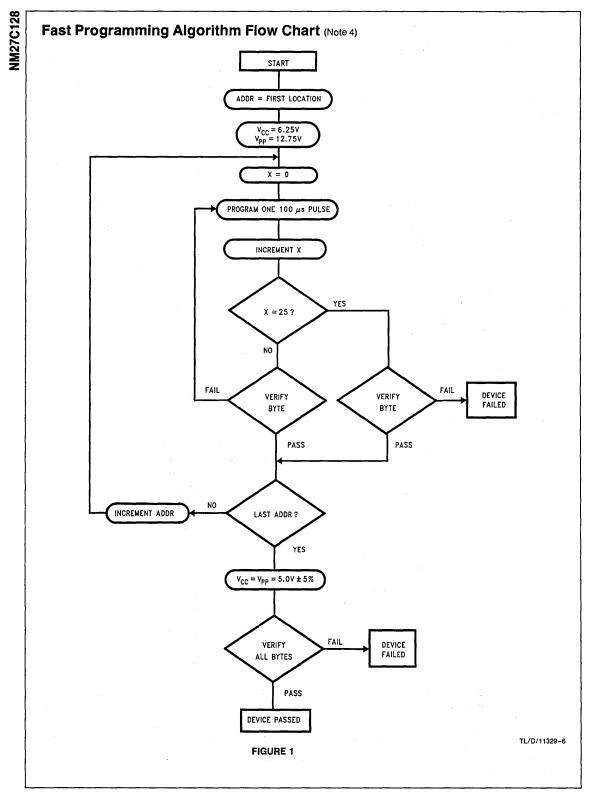

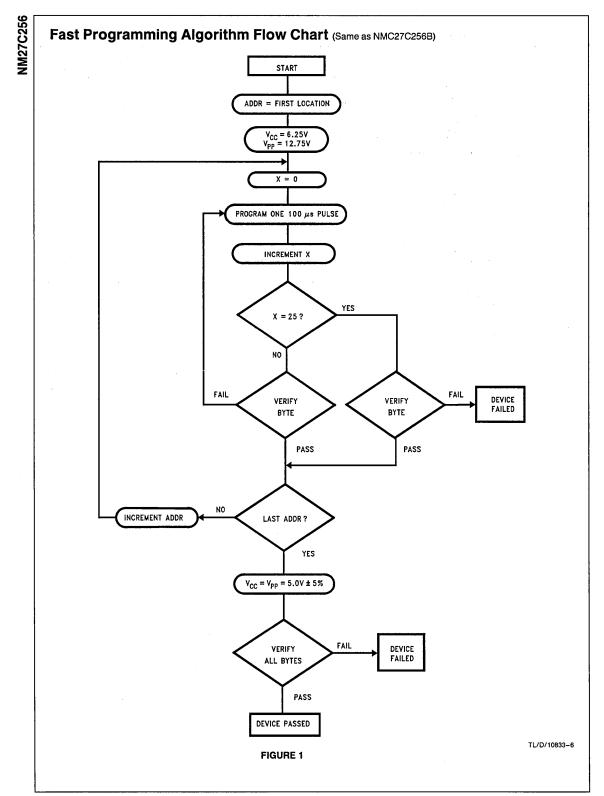

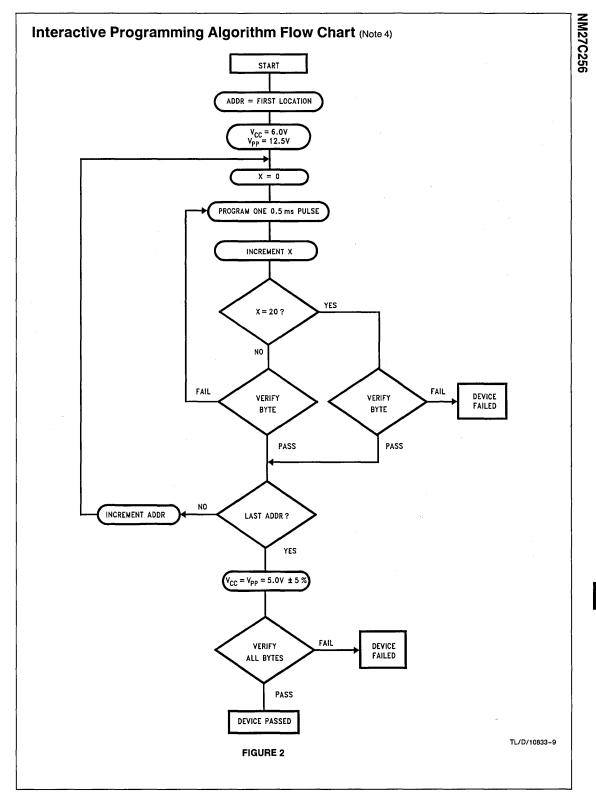

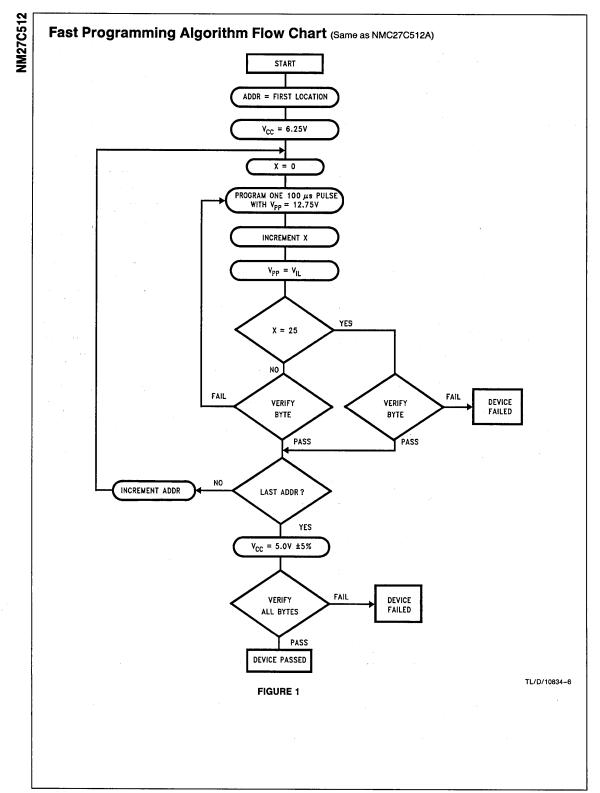

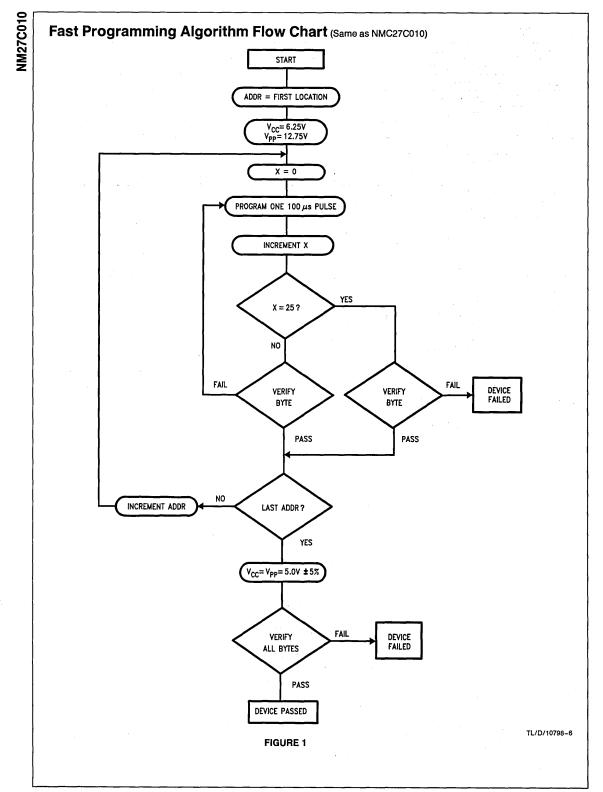

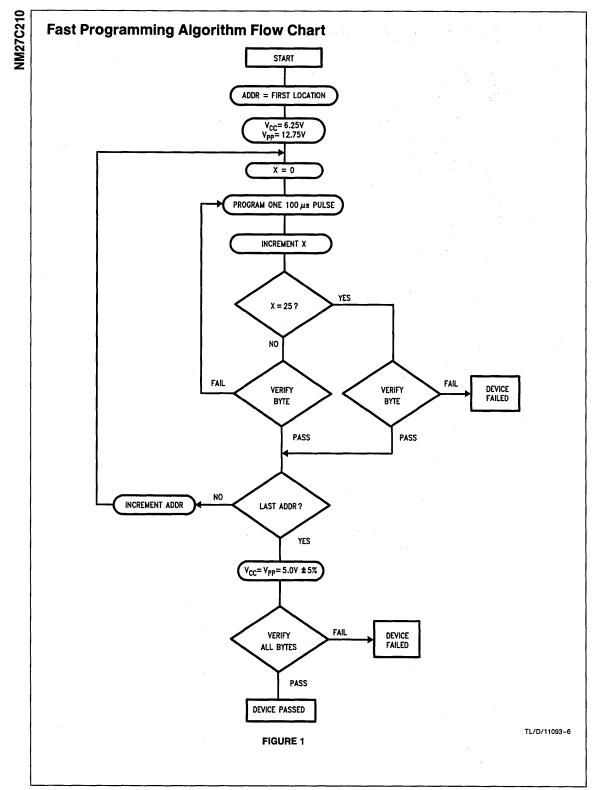

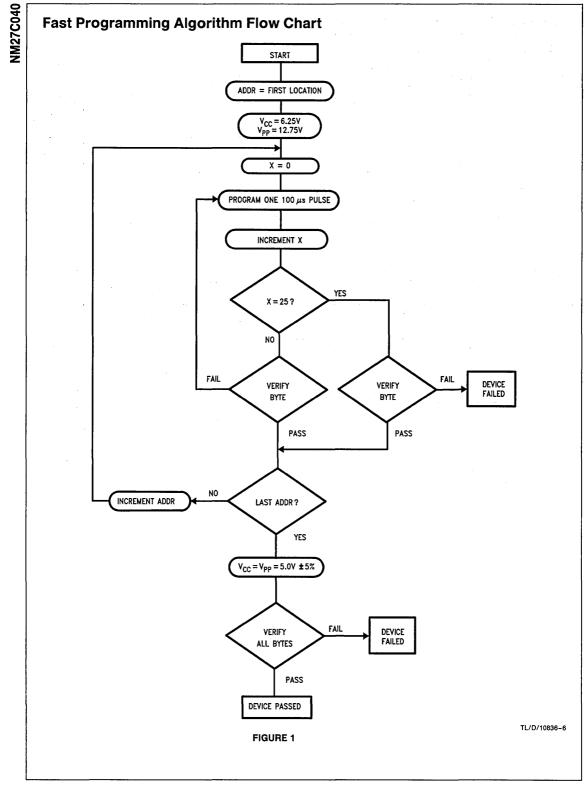

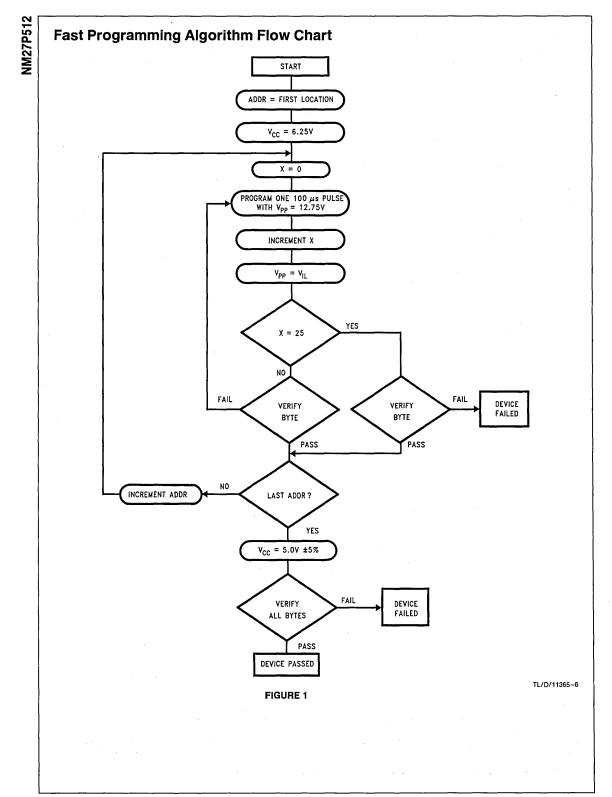

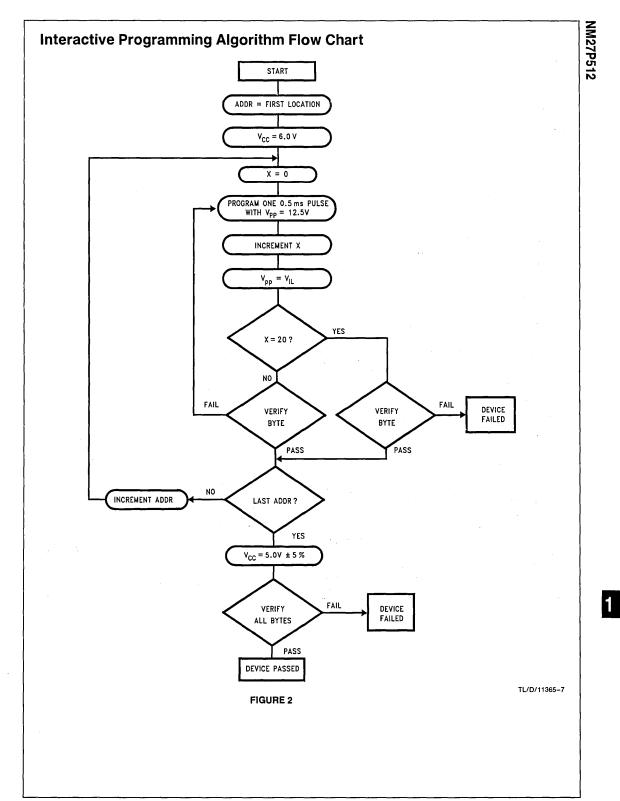

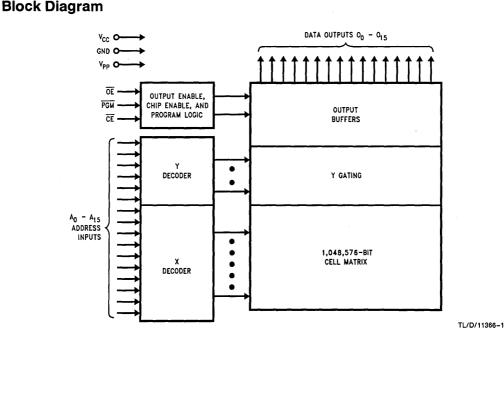

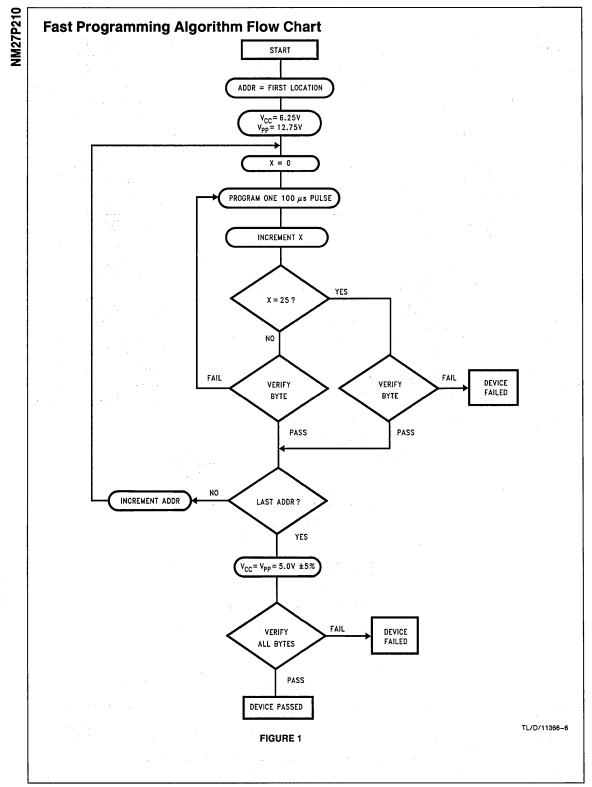

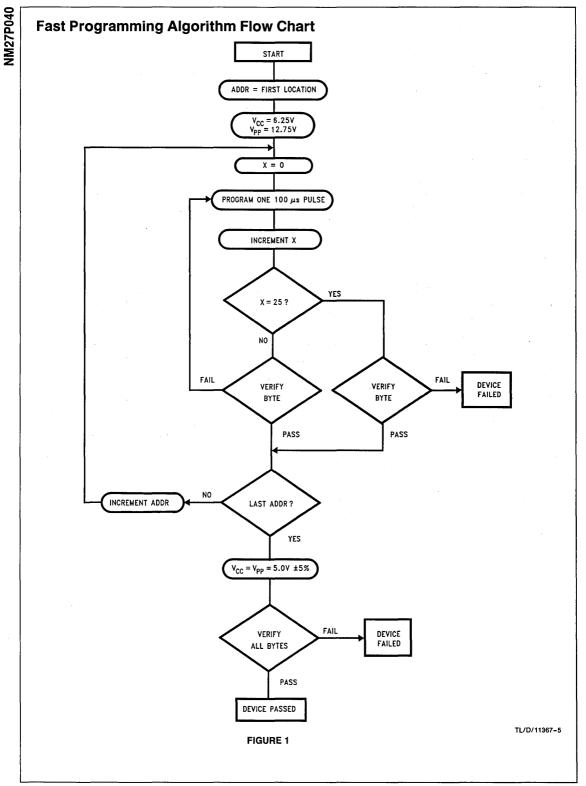

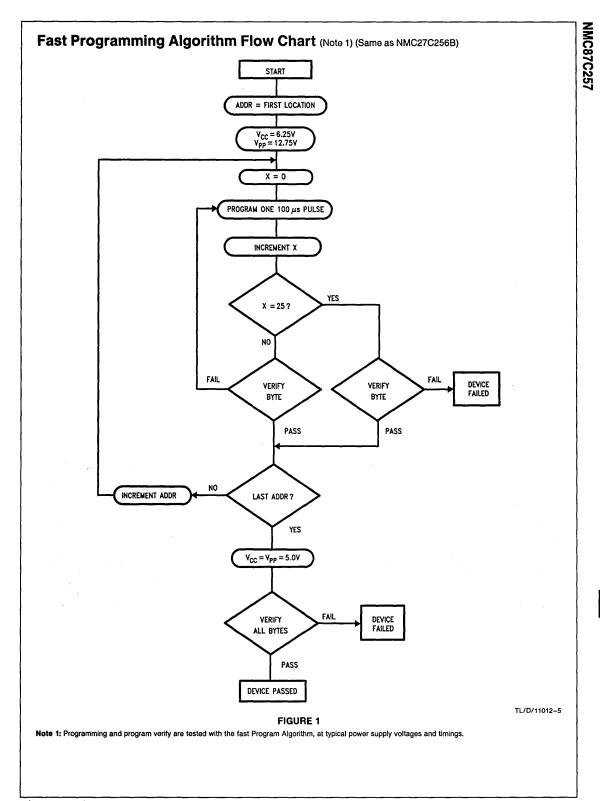

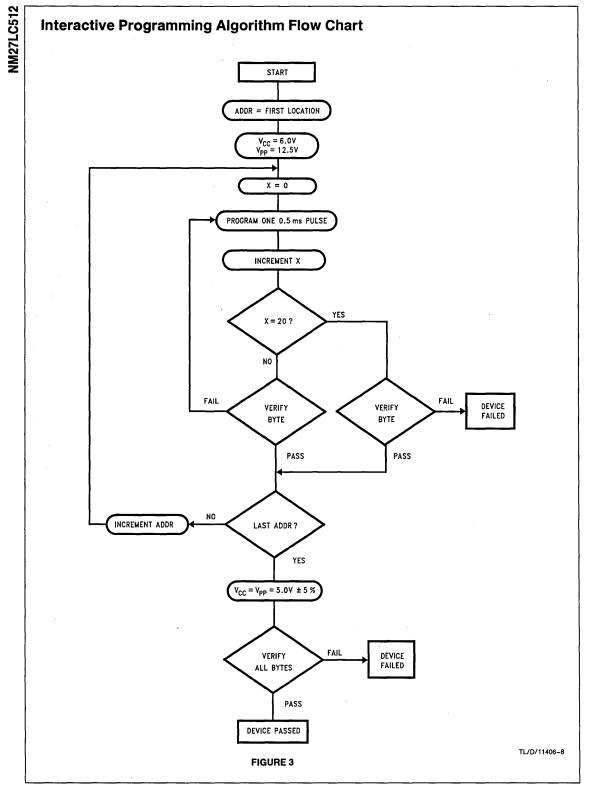

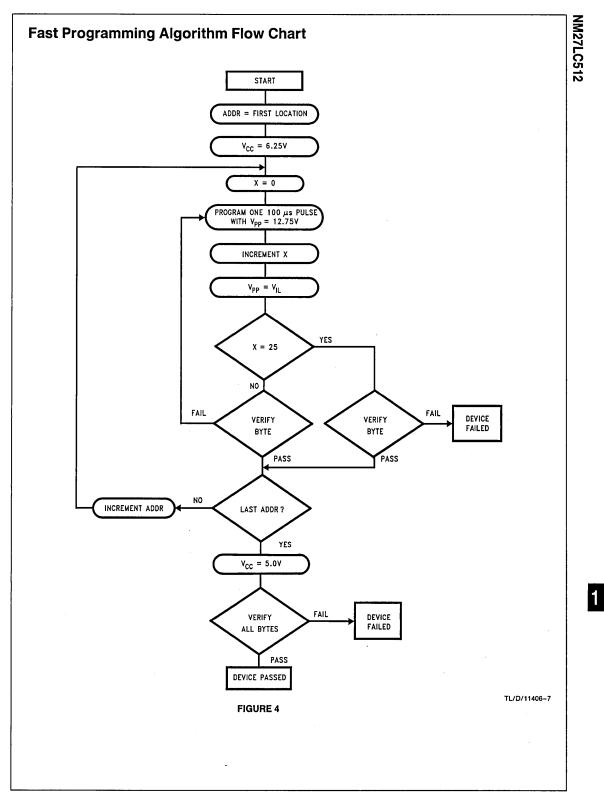

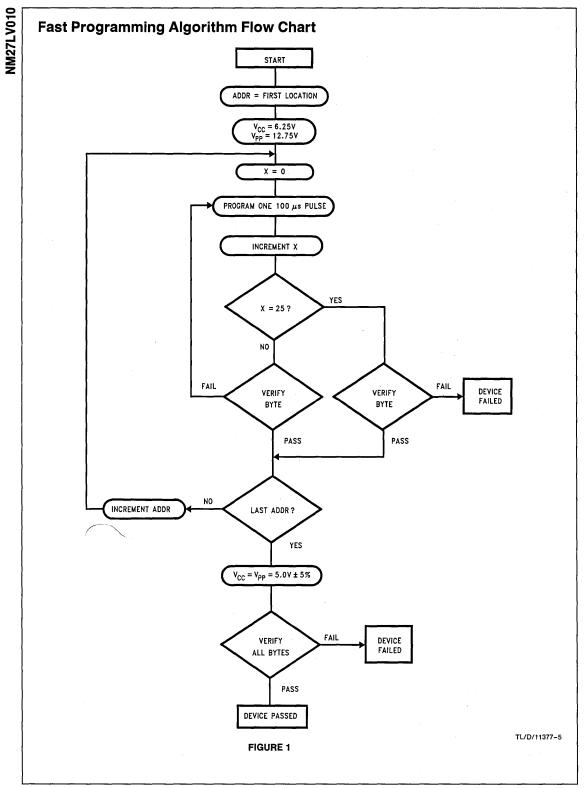

When the address and data are stable, an active high, TTL program pulse is applied to the  $\overline{CE/PGM}$  input. A program pulse must be applied at each address location to be programmed. The NMC27C16B is programmed with the Fast Programming Algorithm shown in *Figure 1*. Each Address is programmed with a series of 100  $\mu$ s pulses until it verifies good, up to a maximum of 25 pulses. Most memory cells will program with a single 100  $\mu$ s pulse.

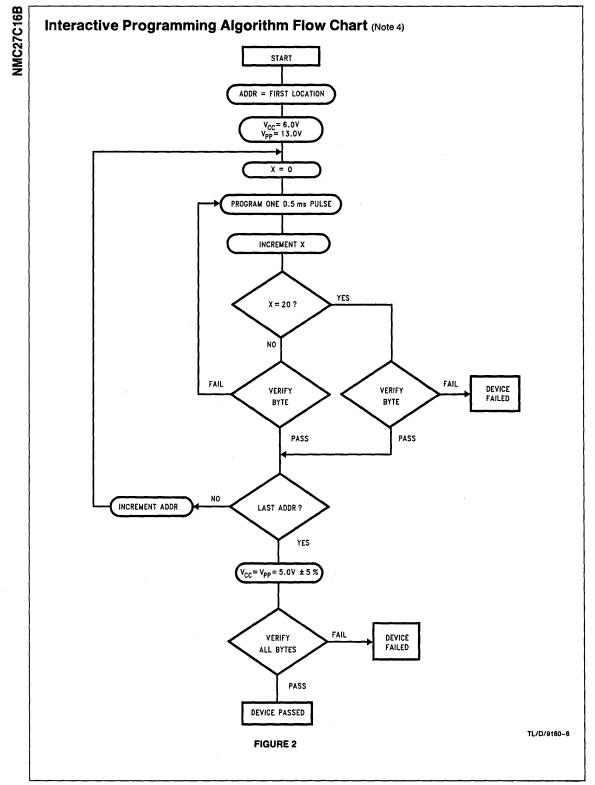

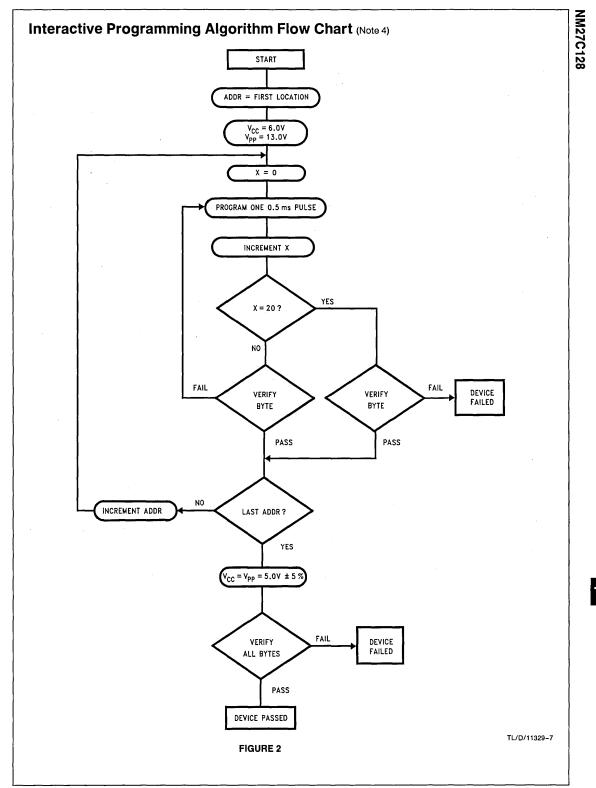

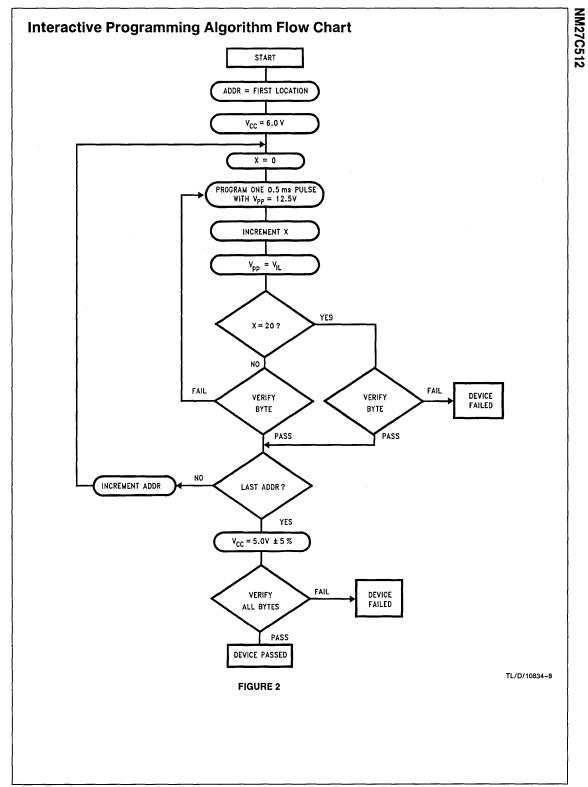

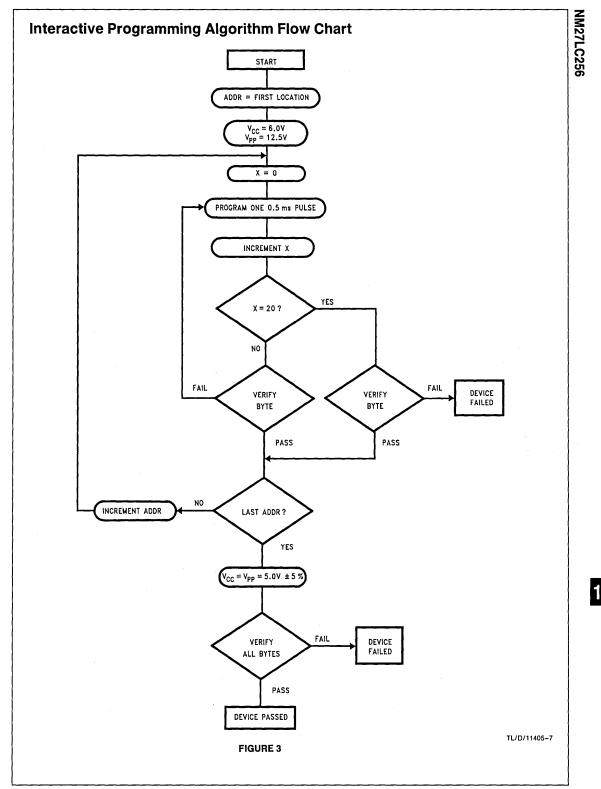

Note: Some programmer manufacturers due to equipment limitation may offer interactive program Algorithm (shown in *Figure 2*).

The NMC27C16B must not be programmed with a DC signal applied to the  $\overline{\text{CE}}/\text{PGM}$  input.

Programming multiple NMC27C16Bs in parallel with the same data can be easily accomplished due to the simplicity of the programming requirements. Like inputs of the paralleled NMC27C16Bs may be connected together when they are programmed with the same data. A high level TTL pulse applied to the  $\overline{\text{CE}}/\text{PGM}$  input programs the paralleled NMC27C16Bs.

| Pins<br>Mode    | CE/PGM<br>(18) | ÖE<br>(20) | V <sub>PP</sub><br>(21) | V <sub>CC</sub><br>(24) | Outputs<br>(9-11), (13-17 |

|-----------------|----------------|------------|-------------------------|-------------------------|---------------------------|

| Read            | VIL            | VIL        | V <sub>CC</sub>         | 5                       | D <sub>OUT</sub>          |

| Standby         | VIH            | Don't Care | V <sub>CC</sub>         | 5                       | Hi-Z                      |

| Output Disable  | Don't Care     | VIH        | V <sub>CC</sub>         | 5                       | Hi-Z                      |

| Program         | VIH            | VIH        | 12.75V                  | 6.25                    | D <sub>IN</sub>           |

| Program Verify  | VIL            | VIL        | 12.75V                  | 6.25                    | Dout                      |

| Program Inhibit | VIL            | VIH        | 12.75V                  | 6.25                    | Hi-Z                      |

#### TABLE I. Mode Selection

## Functional Description (Continued)

#### Program Inhibit

Programming multiple NMC27C16Bs in parallel with different data is also easily accomplished. Except for  $\overline{CE}/PGM$  all like inputs (including  $\overline{OE}$ ) of the parallel NMC27C16Bs may be common. A TTL high level program pulse applied to an NMC27C16B's  $\overline{CE}/PGM$  input with V<sub>PP</sub> at 12.75V will program that NMC27C16B. A TTL low level  $\overline{CE}/PGM$  input inhibits the other NMC27C16Bs from being programmed.

#### **Program Verify**

A verify should be performed on the programmed bits to determine whether they were correctly programmed. The verify may be performed with  $V_{PP}$  at 12.75V. Except during programming and program verify,  $V_{PP}$  must be at  $V_{CC}$ .

#### MANUFACTURER'S IDENTIFICATION CODE

The NMC27C16B has a manufacturer's identification code to aid in programming. The code, shown in Table III, is two bytes wide and is stored in a ROM configuration on the chip. It identifies the manufacturer and the device type. The code for the NMC27C16B is, "8F80", where "8F" designates that it is made by National Semiconductor, and "60" designates a 16k part.