# F100K ECL 300 Series Databook and Design Guide

# F100K ECL DATABOOK

1992 Edition

**Family Overview**

F100K 200 and 300 Series Datasheets

F100K 100 Series Datasheets

**11C Datasheets**

i

F100K ECL Design Guide and Application Notes Ordering Information and Physical Dimensions

#### TRADEMARKS

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

АВіС™ Abuseable<sup>™</sup> Anadig™ APPSTM **ASPECT™** Auto-Chem Deflasher™ ВСРТМ BI-FET™ BI-FET II™ BI-LINE™ **BIPLANTM BLCTM BLXTM** ВМАС™ Brite-Lite™ **BSITM** BSI-2™ CDDTM СІМ™ **CIMBUS™ CLASIC™** COMBO® COMBO I™ COMBO IITM COPS™ microcontrollers **CRDTM** DA4™ **DENSPAKTM** DIB™ **DISCERNTM** DISTILL™ DNR® **DPVM**TM E<sup>2</sup>CMOS™ ELSTAR™ Embedded System Processor™ EPTM

E-Z-LINK™ **FACTTM** FACT Quiet Series™ FAIRCAD™ Fairtech™ **FAST®** FASTr™ Flash™ GENIX™ **GNXTM GTO™** HEX 3000™ **HPC™** HvBal™ I3L® **ICM**TM Integral ISE™ Intelisplay™ Inter-LERIC™ Inter-RIC™ **ISETM** ISE/06™ ISE/08™ ISE/16™ ISE32™ **ISOPLANAR™ ISOPLANAR-Z™ LERIC™** LMCMOS™ M<sup>2</sup>CMOSTM Macrobus™ Macrocomponent<sup>™</sup> **MAPLTM** MAXI-ROM® Microbus™ data bus MICRO-DAC™ utalker™

**MICROWIRE™** MICROWIRE/PLUSTM **MOLE™ МРАТМ MST™** Naked-8™ National® National Semiconductor® National Semiconductor Corp.® NAX 800™ Nitride Plus™ Nitride Plus Oxide™ **NML™ NOBUS™** NSC800™ **NSCISE™** NSX-16™ NS-XC-16™ **NTERCOM™ NURAM™ OPALTM OXISS™** P2CMOSTM Perfect Watch™ **PLANTM PLANARTM** PLAYERTM Plus-2™ Polvcraft™ Power + Control™ POWERplanar™ QUAD3000™ **QUIKLOOKTM** RATTM **RIC™** RTX16™

SERIES/800™ Series 32000® Simple Switcher™ SofChek™ **SONIC™ SPIRE™** Staggered Refresh™ **STAR™** Starlink™ STARPI EXTM ST-NIC™ SuperAT™ Super-Block™ SuperChip™ SuperScript™ SYS32TM TapePak® **TDS™** TeleGate™ The National Anthem® **TLC™** Trapezoidal™ TRI-CODE™ TRI-POLY™ TRI-SAFE™ TRI-STATE® **TROPICTM** Tropic Pele'™ Tropic Reef™ TURBOTRANSCEIVER™ VIPTM VR32™ **WATCHDOG™** XMOS™ **XPUTM** Z STAR™ 883B/RETS™ 883S/RETS™

MECL™ is a trademark of Motorola, Inc.

Multiwire® is a registered trademark of Multiwire Corporation.

Mylar<sup>®</sup> and Teflon<sup>®</sup> are registered trademarks of E.I. DuPont de Nemours Company. Sentry<sup>®</sup> is a registered trademark of Schlumberger Limited.

. Microtalker™

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR COR-PORATION. As used herein:

SCXTM

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive, P.O. Box 58090, Santa Clara, California 95052-8090 1-800-272-9959 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

### Introduction

National Semiconductor's F100K 300 Series ECL Databook has been prepared to assist the experienced ECL designer as well as the first time ECL designer in everything from selecting the right logic function to using the proper termination technique in your design.

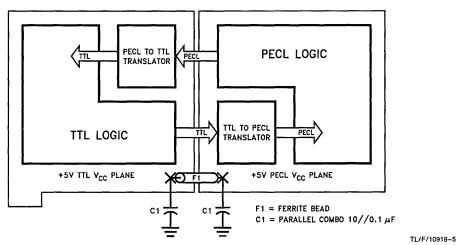

The 300 Series is designed to be an affordable highperformance logic family ideal for applications operating at frequencies above 50 MHz. F100K is still the favorite ECL technology for most high-end computer, telecommunication and test applications. The 300 Series is a much needed upgrade for these users. New users are also reaping the many benefits of the 300 Series. This family is designed to interface easily with other technologies as the types of systems mixing TTL, CMOS, and ECL expands. To assist designers with this multiple technology interface, the 300 Series offers a wide selection of translators, the ease and convenience of operation from +5V, and the availability of smaller, inexpensive, plastic packaging.

This Databook is designed to be an easy to use reference guide. Included are complete DC and AC characteristics for all package types (PCC, SOIC, PDIP, CDIP and CERPAK) and temperature ranges (commercial, industrial and military) with AC accuracy down to 10 ps. Device selection guides, circuit design basics, transmission line concepts, power distribution, thermal considerations and testing techniques are all discussed in detail to help in designing with ECL. A qualification guide is also included to aid in qualifying the 300 Series for use in your application.

A number of application notes, covering a wide range of subjects is included in this Handbook. These application notes cover such subjects as ECL backplanes and operating ECL from a positive +5V power supply. For more specific application assistance, please contact our applications staff at 1-800-341-0392.

### F100K Data Book

#### **Product Index and Selection Guide**

The Product Index is a numerical list of all device types contained in this book. The Selection Guide groups the products by function and by family.

#### Section 2 F100K 200 and 300 Series Datasheets......2-1

Contains individual datasheets for the F100K 300 Series family devices. Also included is a datasheet on the first single-gate 200 Series device, the 100201.

#### Section 3 F100K 100 Series Datasheets . . 3-1

The F100K 100 Series family of devices have been obsoleted. This section contains "reference only" individual data sheets for those F100K 100 Series devices that were not redesigned as part of the 300 Series family. For example, a 100101 was redesigned as a 100301; therefore the 100101 datasheet will not appear in this databook. On the other hand, the 100118 was not redesigned and has been obsoleted. It's datasheet is printed in this section to be referred to in the event the device is currently being used in a system. The devices in this section will be unavailable for future purchases.

#### Section 4 11C Datasheets ...... 4-1

The 11C family of devices have been obsoleted. This section contains "reference only" individual datasheets to be referred to in the event the devices are currently being used in a system. The devices in this section will be unavailable for future purchases.

### F100K Design Guide and Application Notes—Section 5

Chapter 1 Circuit Basics ......5-3 Discusses internal circuitry and logic function formation. Also, a sample analysis of noise margins is outlined.

### Chapter 2 Logic Design ..... 5-9

Features brief applications of F100K logic arranged according to function.

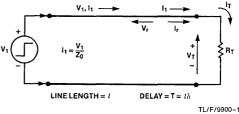

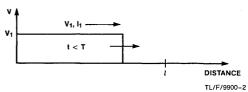

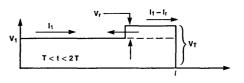

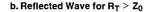

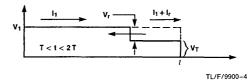

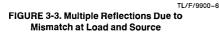

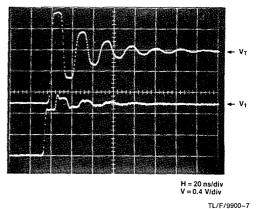

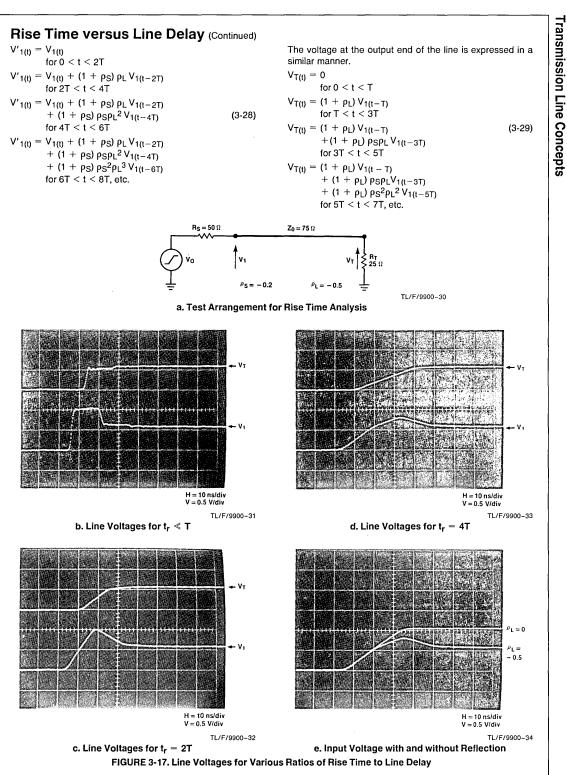

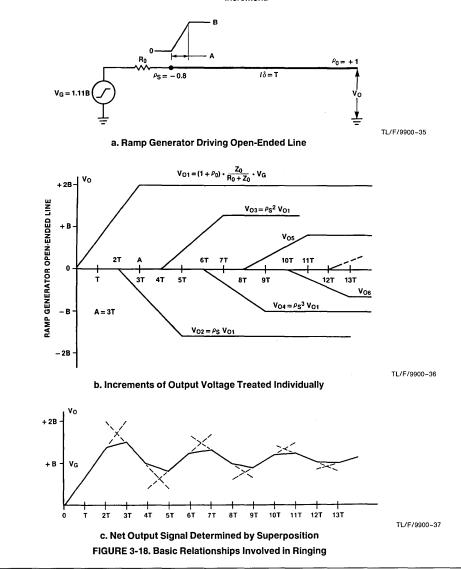

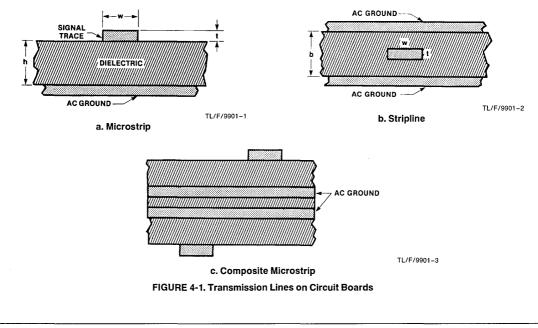

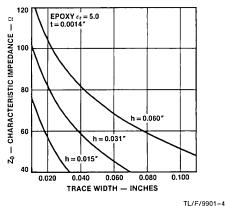

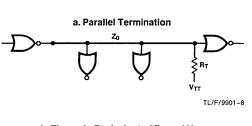

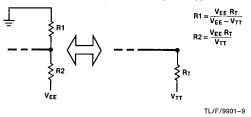

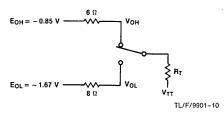

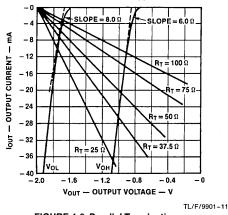

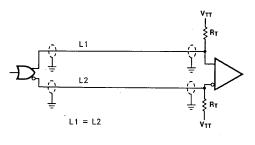

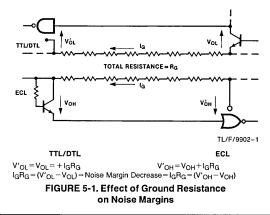

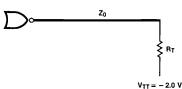

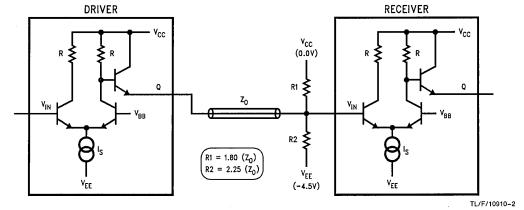

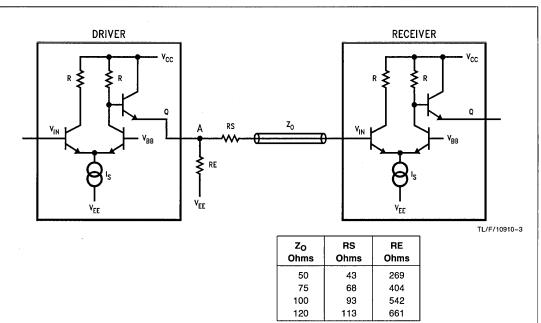

#### Chapter 3 Transmission Line Concepts . 5-19

Reviews the concepts of characteristic impedance and propagation delay and discusses termination, mismatch, reflections and associated waveforms.

#### Chapter 4 System Considerations ...... 5-32

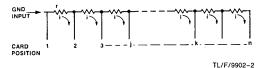

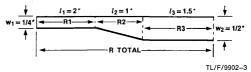

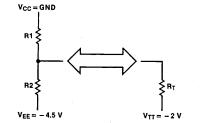

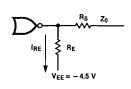

Extends the transmission line approach to the specific configurations, signal levels and parameter values of ECL. Various methods of driving and terminating signal lines are discussed.

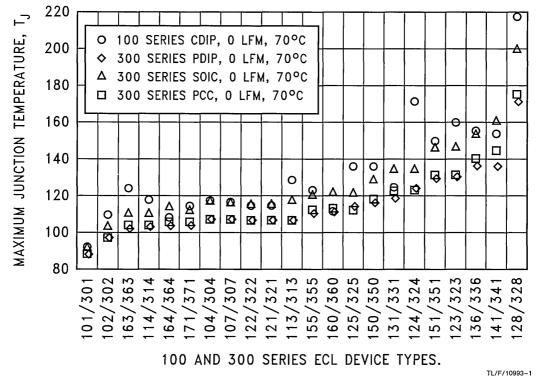

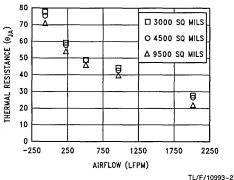

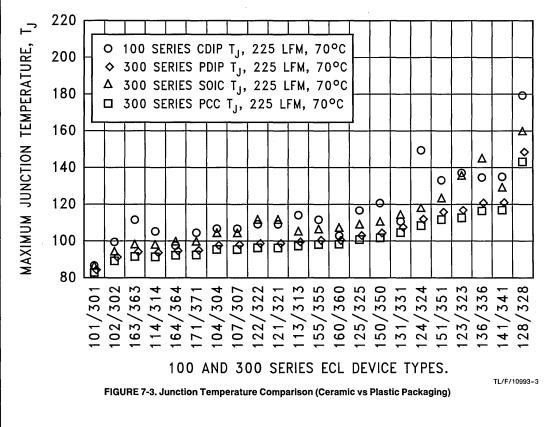

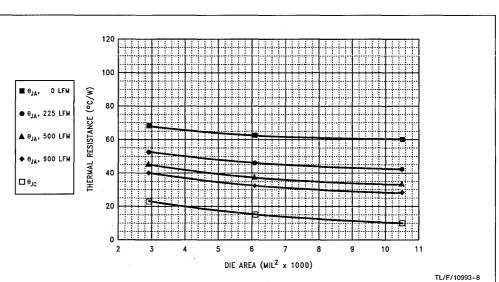

#### Chapter 5 Power Distribution and Thermal Considerations .....5-45

Discusses power supply, decoupling and system cooling requirements.

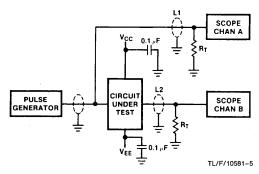

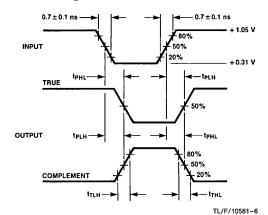

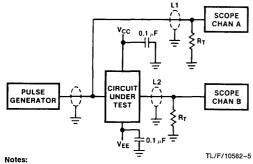

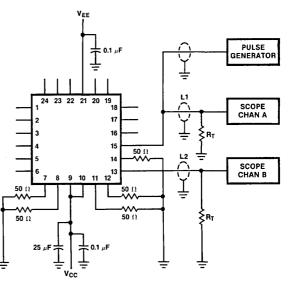

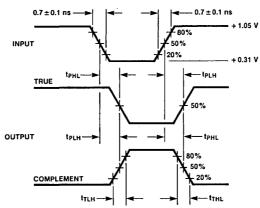

Chapter 6 Testing Techniques ......5-51

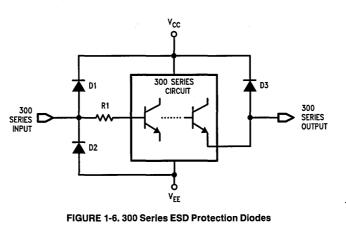

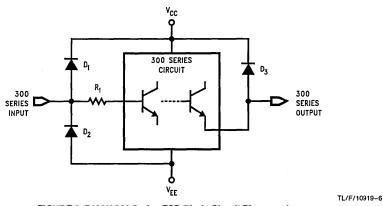

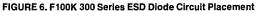

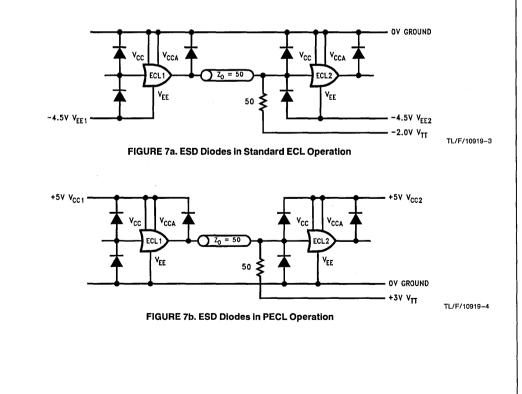

Discusses various methods and techniques used in testing ECL devices (intended for those concerned with customer incoming inspection). Also includes a section on Electrostatic Discharge, what is ESD and how we perform our ESD Classification testing.

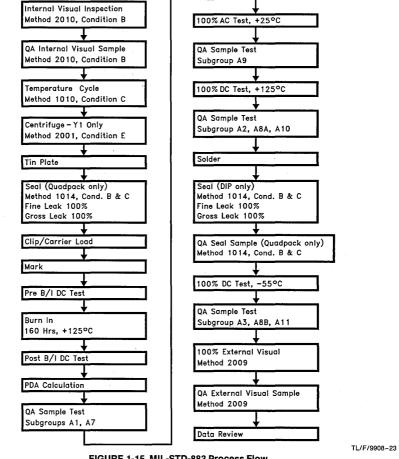

#### Chapter 7 300 Series Package Qualification ......5-58

Discusses the details of the 300 Series family package qualification. Describes the process used in qualifying the family along with supplying the summarized data.

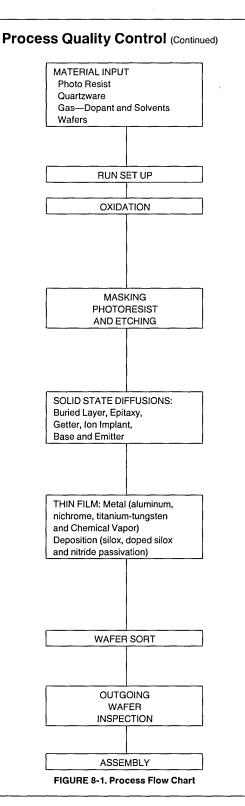

#### Chapter 8 Quality Assurance and Reliability.....5-70

Reviews the quality and reliability programs currently in use.

####

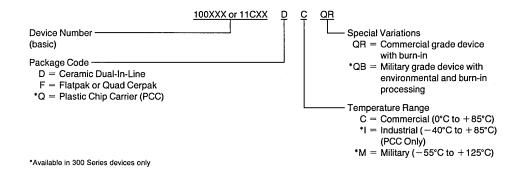

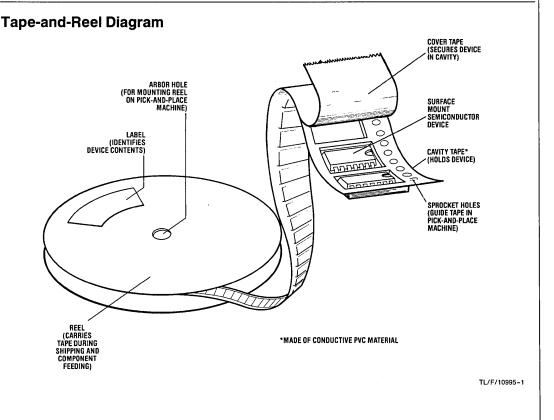

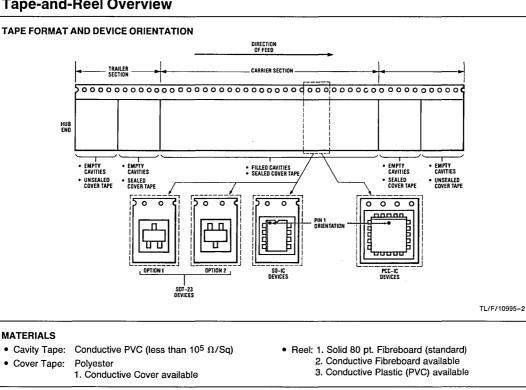

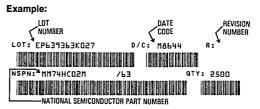

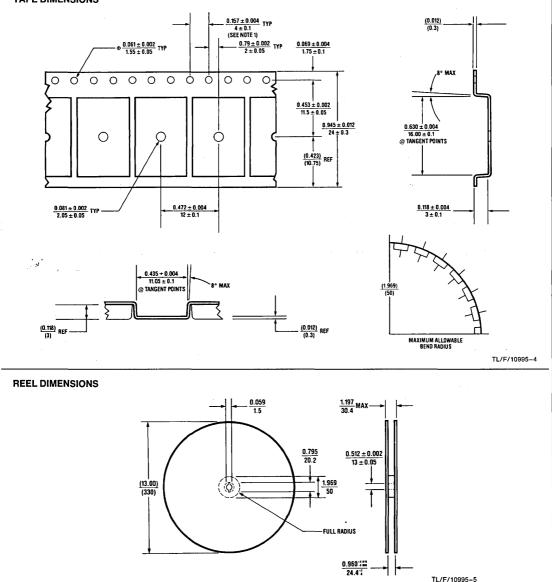

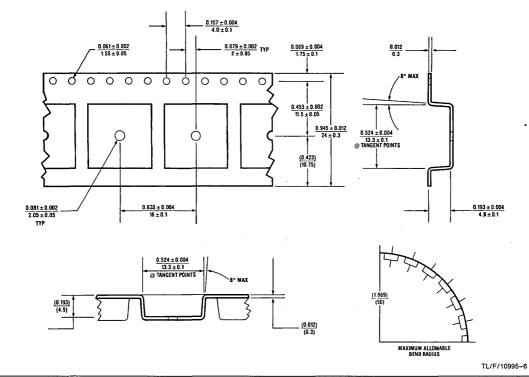

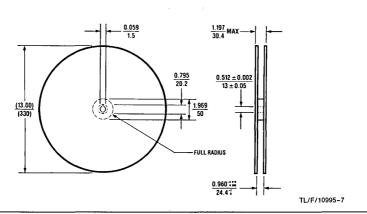

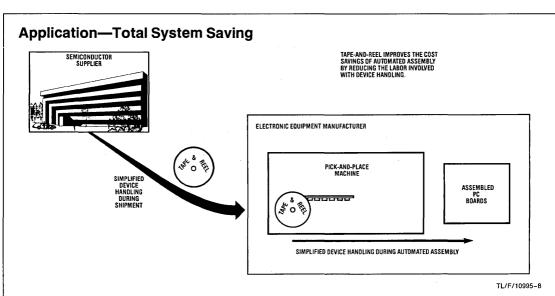

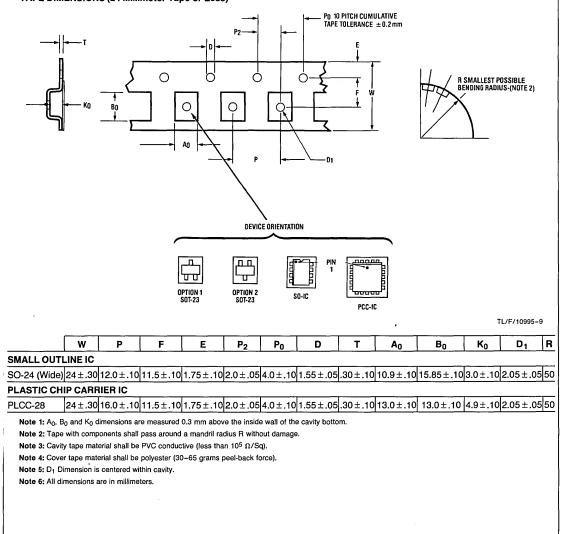

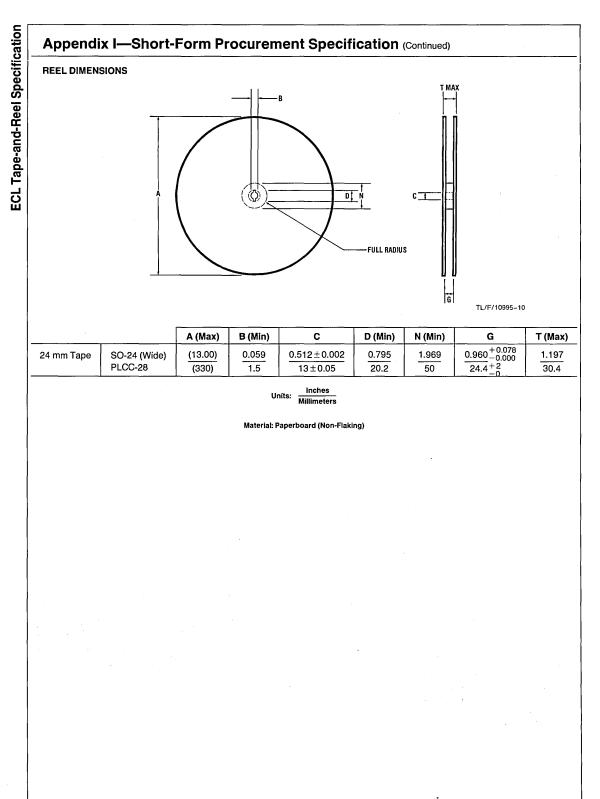

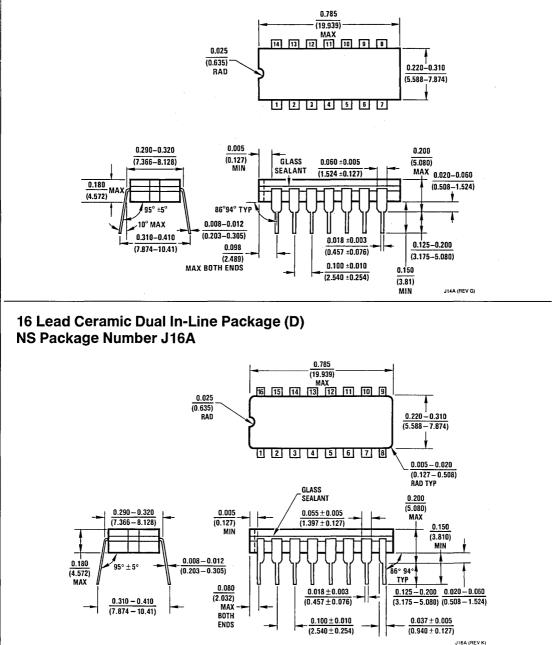

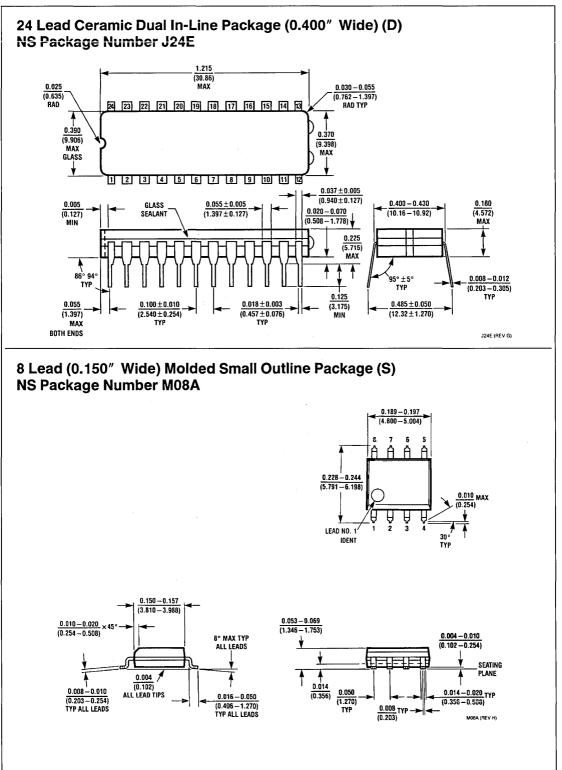

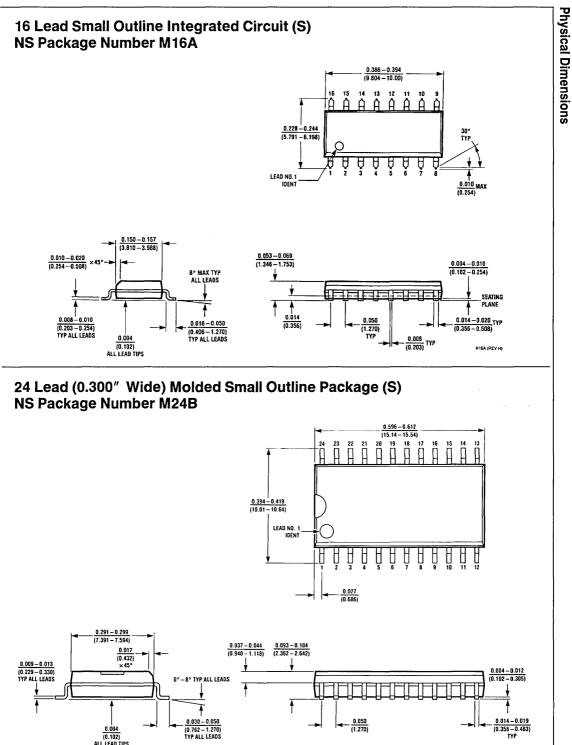

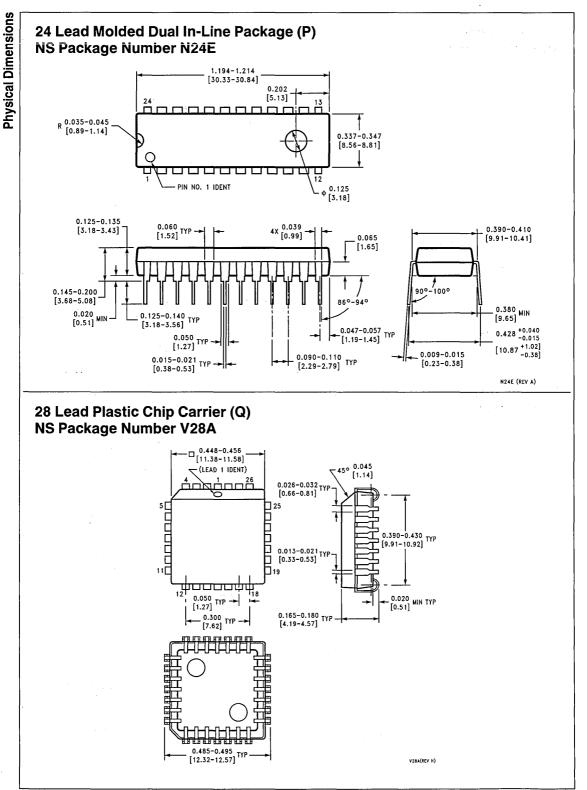

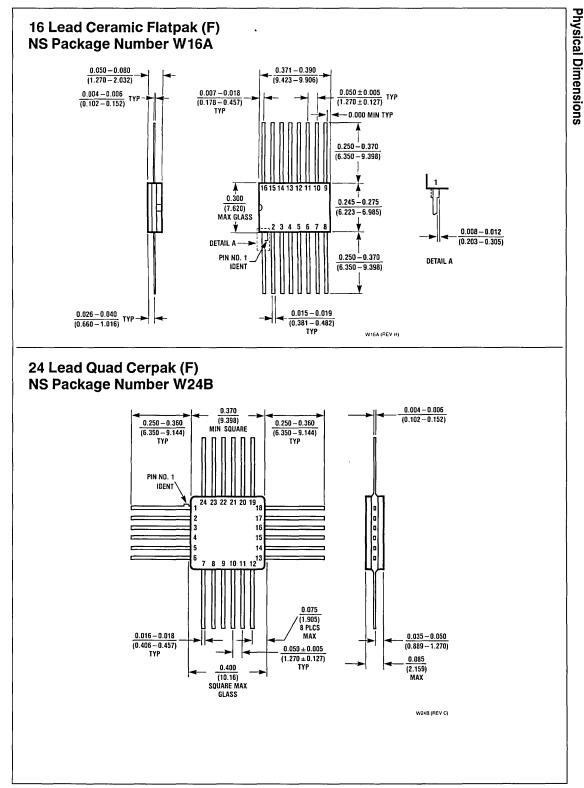

Functional description of the ordering codes. Package outlines of all the options available to the 300 Series family. Tape and reel dimensions and specifications for the plastic packages (PCC and SOIC).

# Alpha-Numeric Index

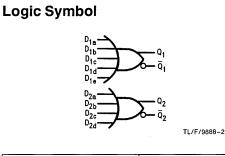

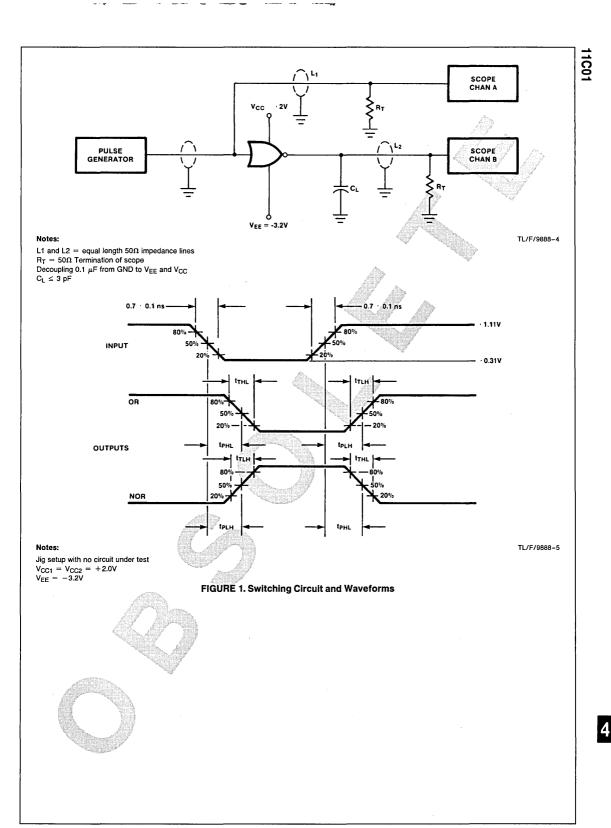

| 11C01 Dual Input OR/NOR Gate                                          |

|-----------------------------------------------------------------------|

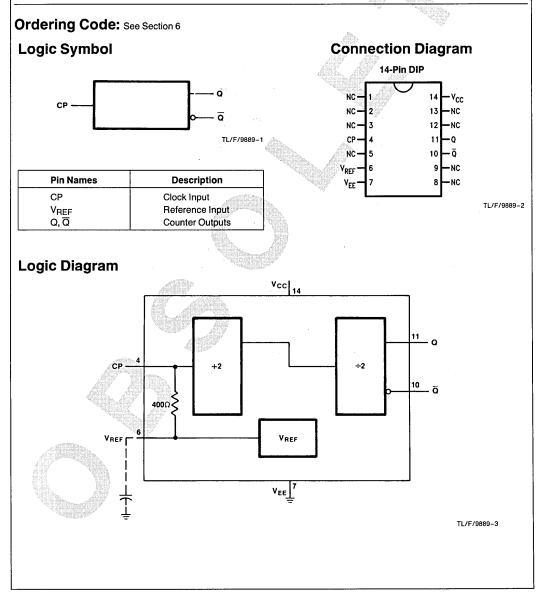

| 11C05 1 GHz Divide-by-Four Counter                                    |

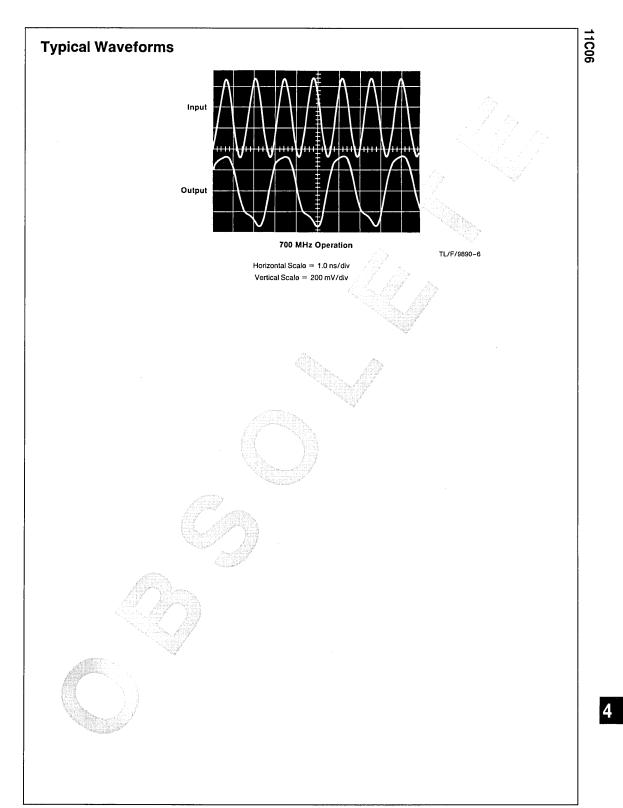

| 11C06 750 MHz D-Type Flip-Flop                                        |

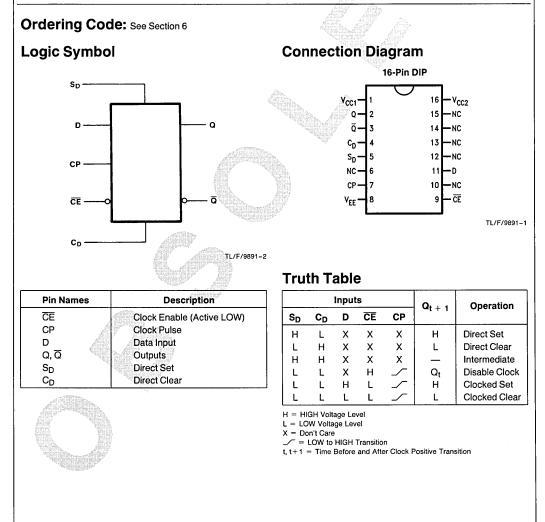

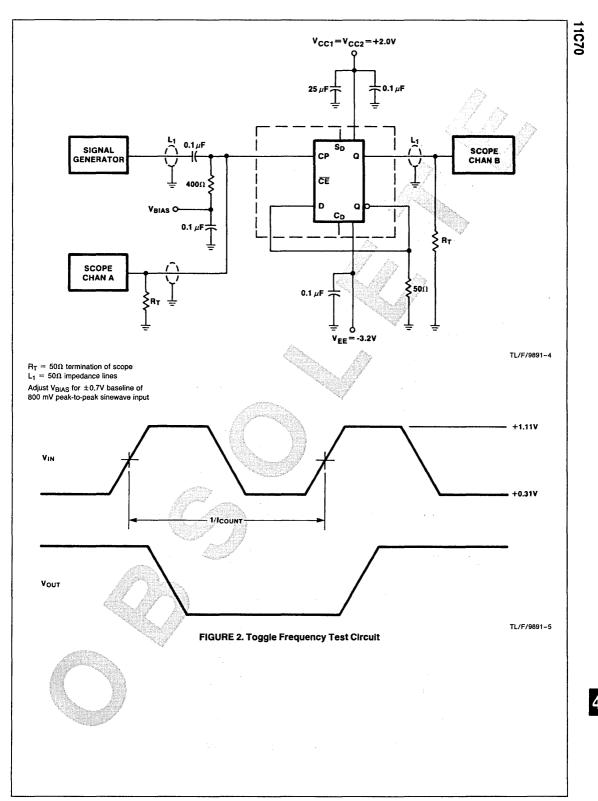

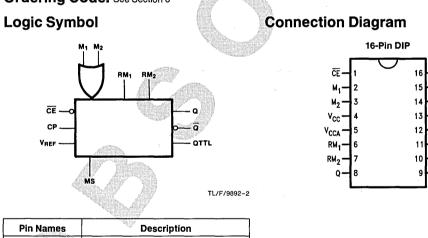

| 11C70 Master-Slave D-Type Flip-Flop                                   |

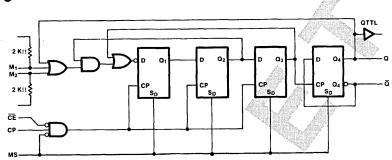

| 11C90 650 MHz Prescaler                                               |

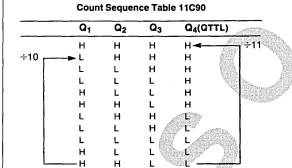

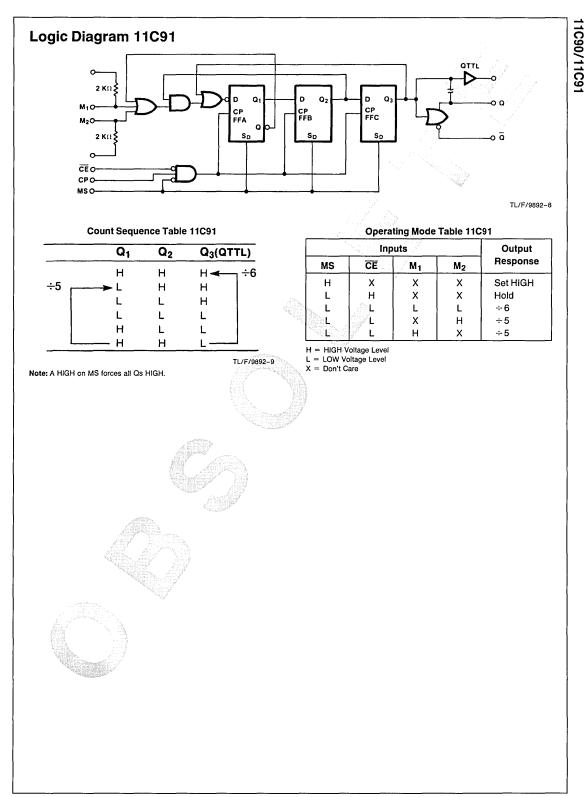

| 11C91 650 MHz Prescaler                                               |

| 100117 Triple 2-Wide OA/OAI Gate                                      |

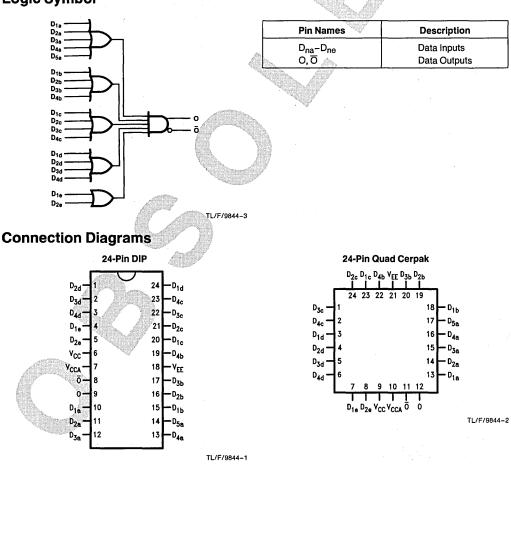

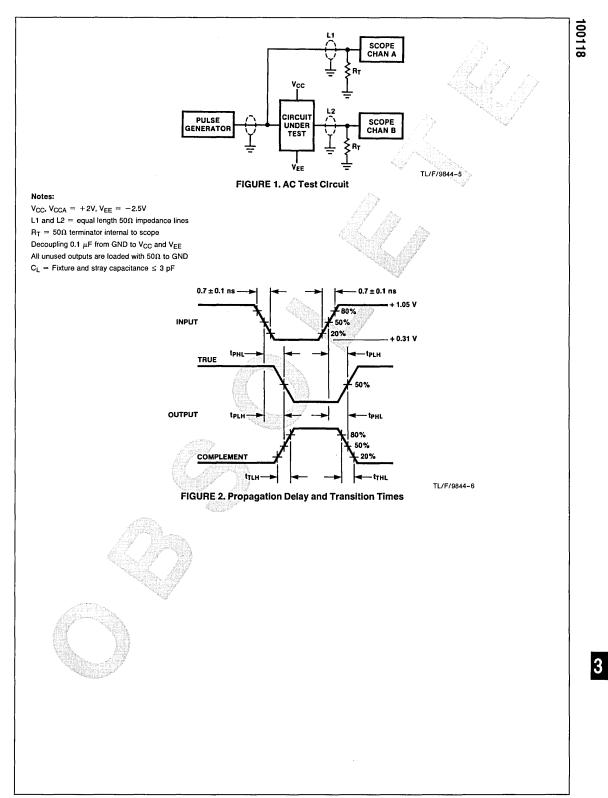

| 100118 5-Wide 5-4-4-4-2 OA/OAI Gate                                   |

| 100126 9-Bit Backplane Driver                                         |

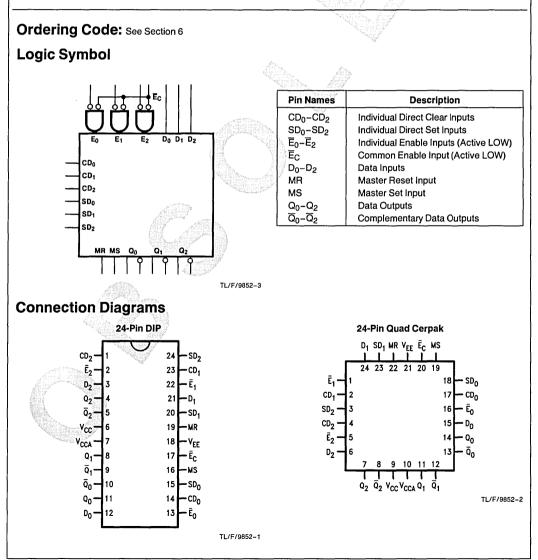

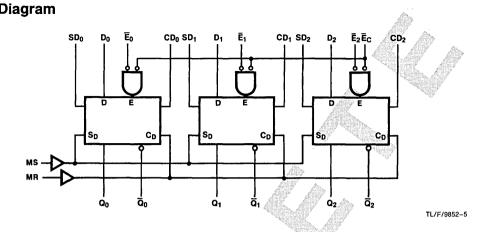

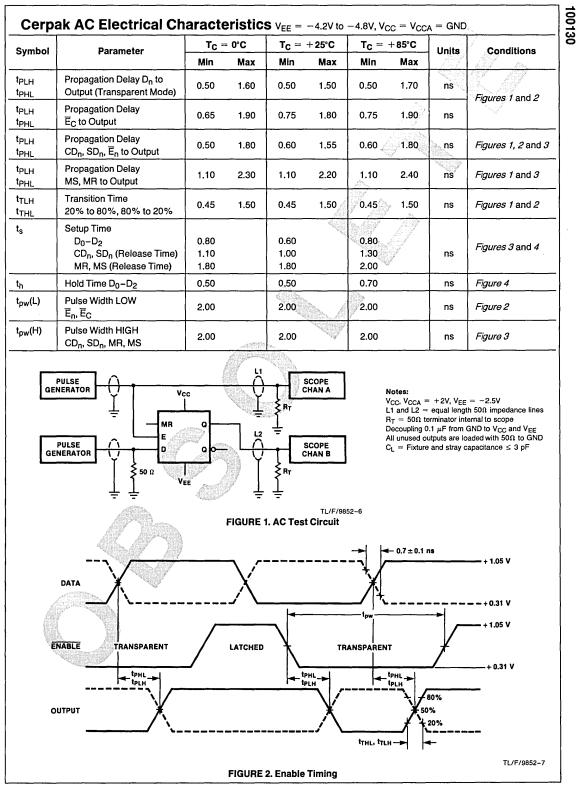

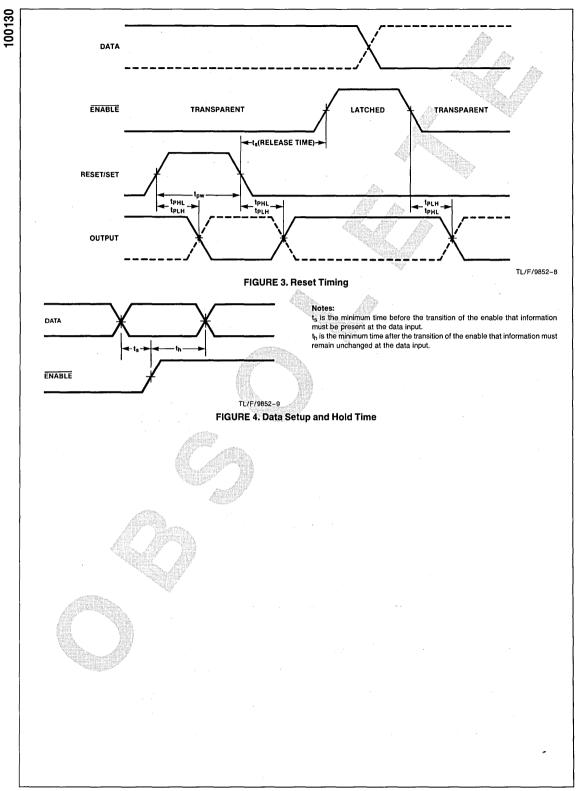

| 100130 Triple D Latch                                                 |

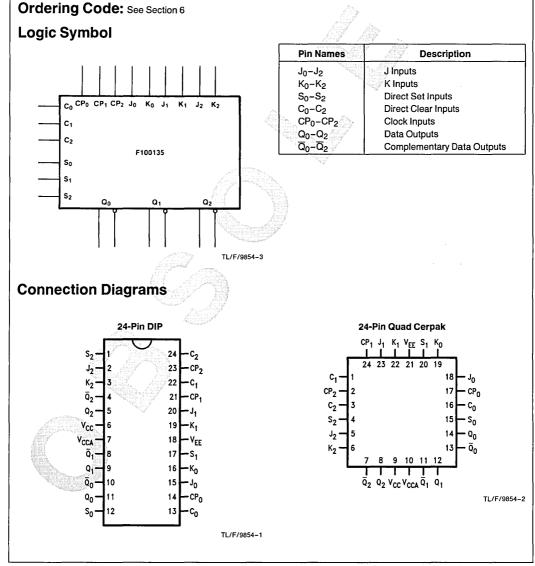

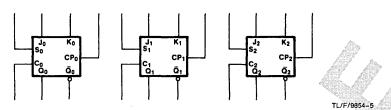

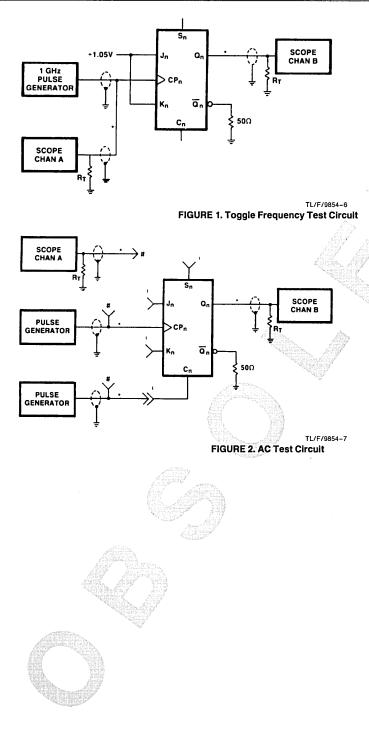

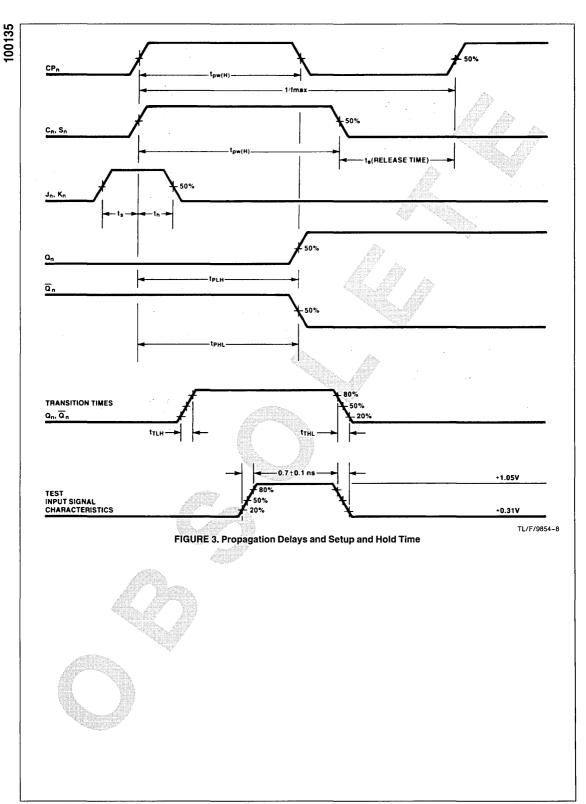

| 100135 Triple JK Flip-Flop                                            |

| 100142 4 x 4 Content Addressable Memory                               |

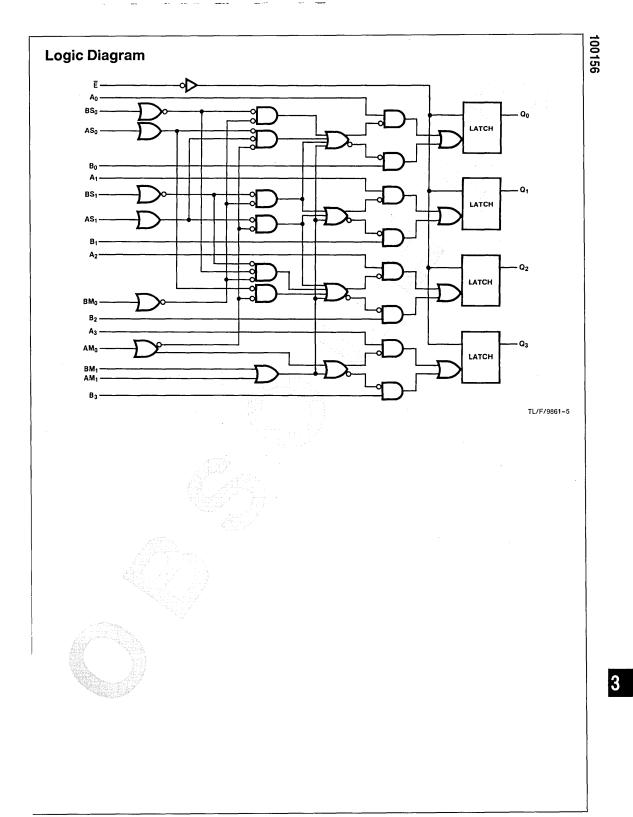

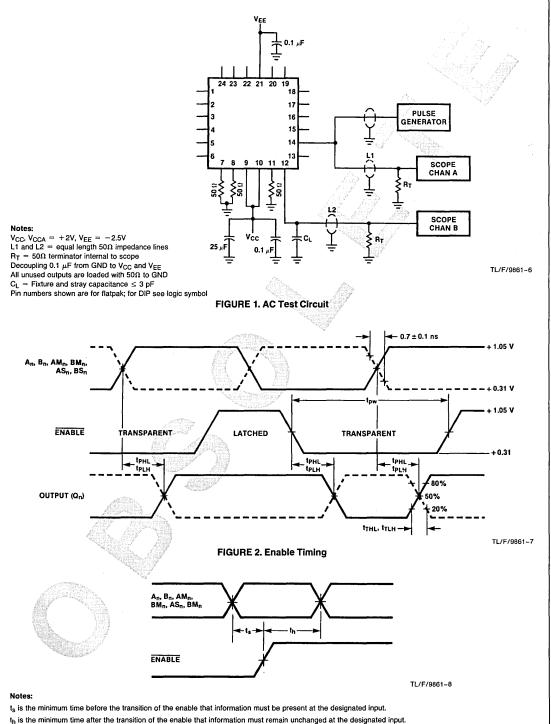

| 100156 Mask/Merge Latch                                               |

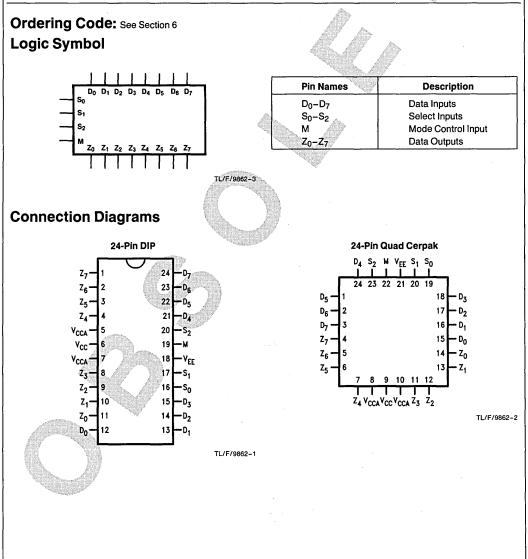

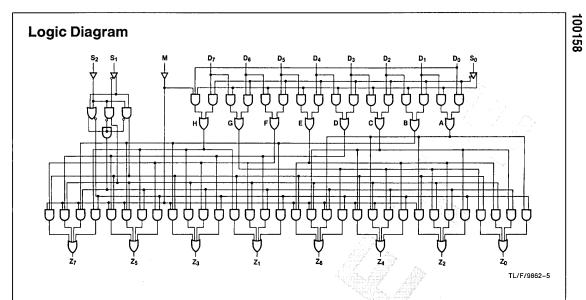

| 100158 8-Bit Shift Matrix                                             |

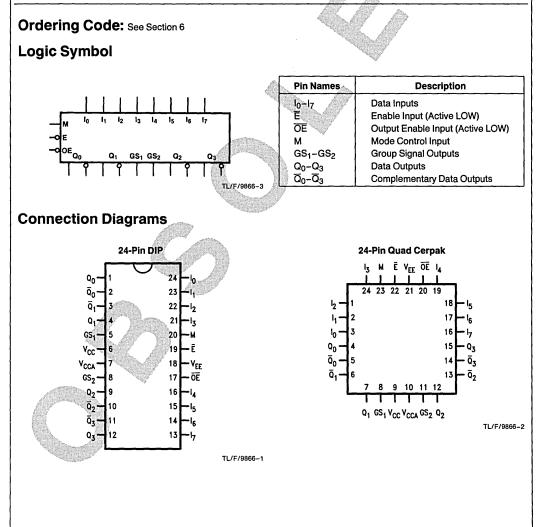

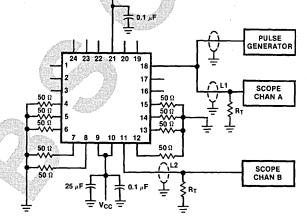

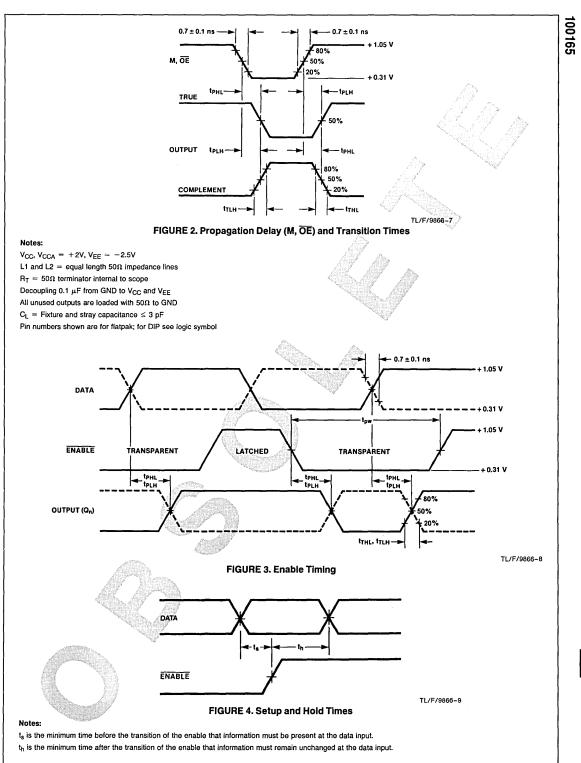

| 100165 Universal Priority Encoder                                     |

|                                                                       |

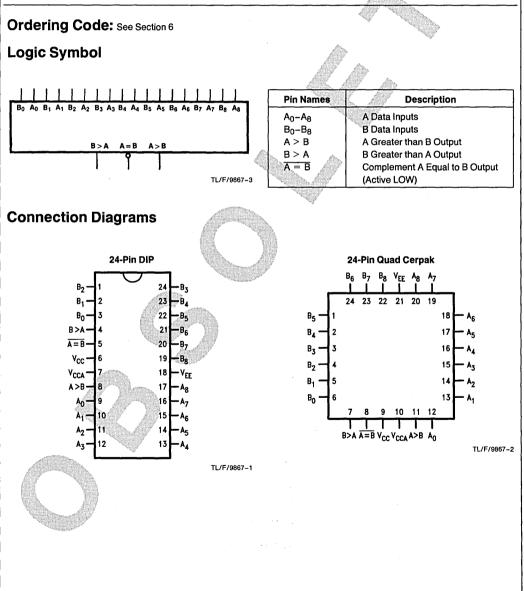

| 100166 9-Bit Comparator                                               |

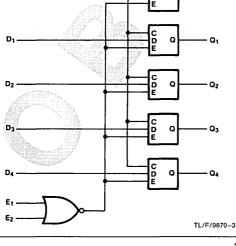

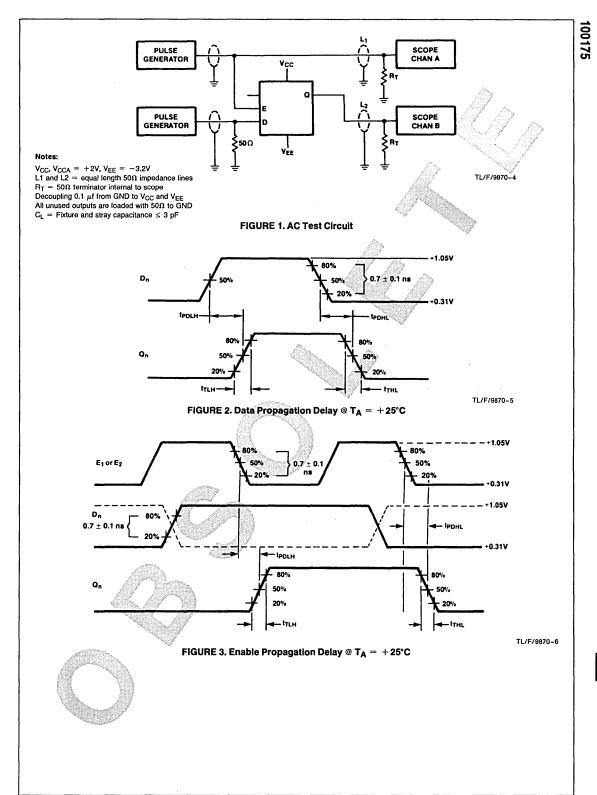

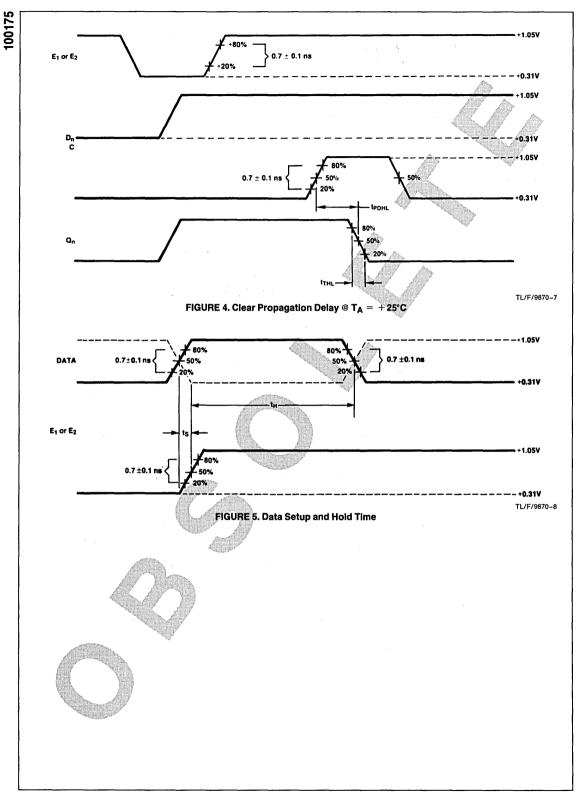

| 100175 Quint 100K-to-10K Latch                                        |

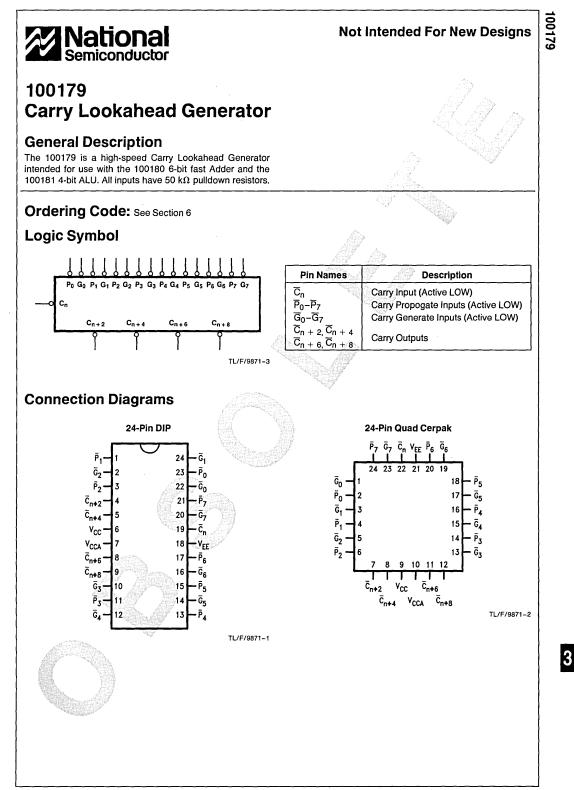

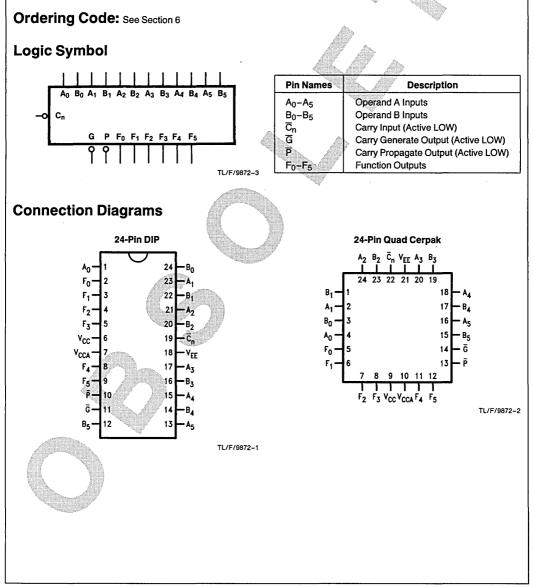

| 100179 Carry Lookahead Generator                                      |

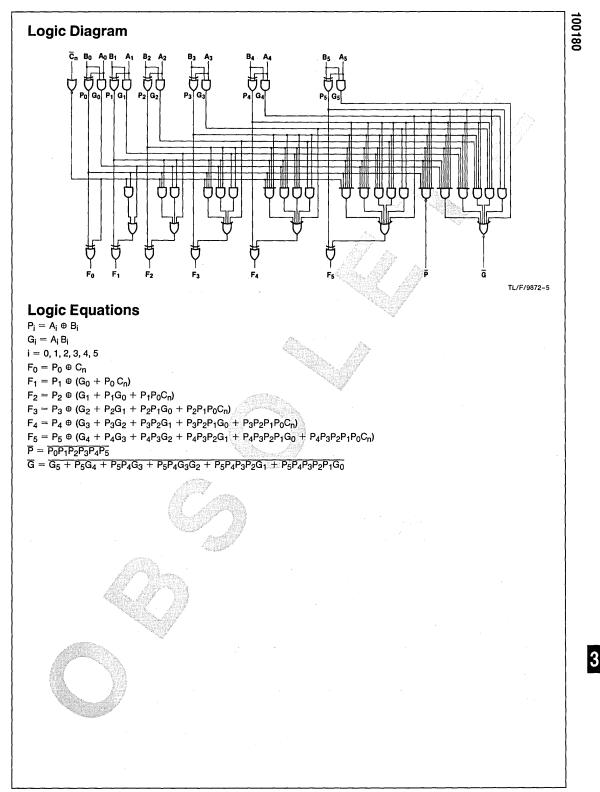

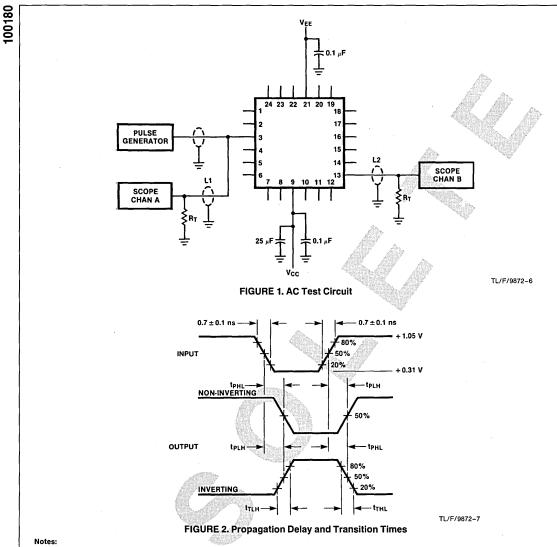

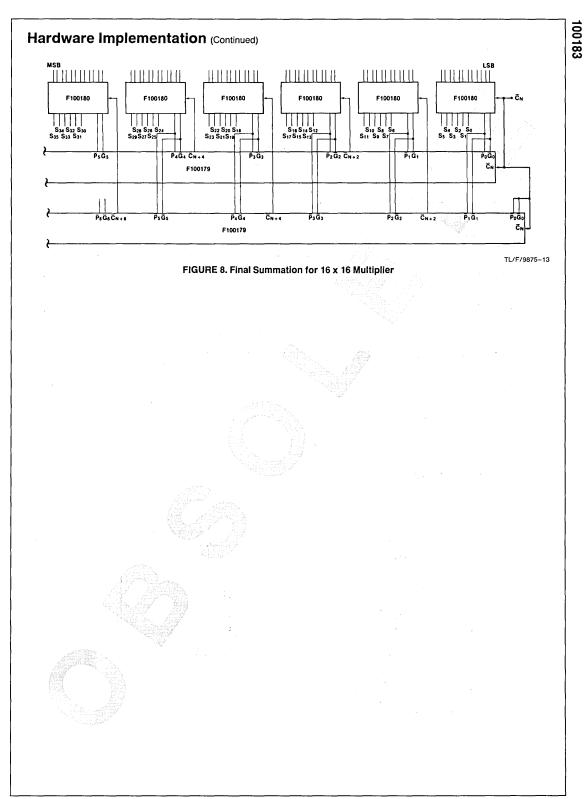

| 100180 High-Speed 6-Bit Adder                                         |

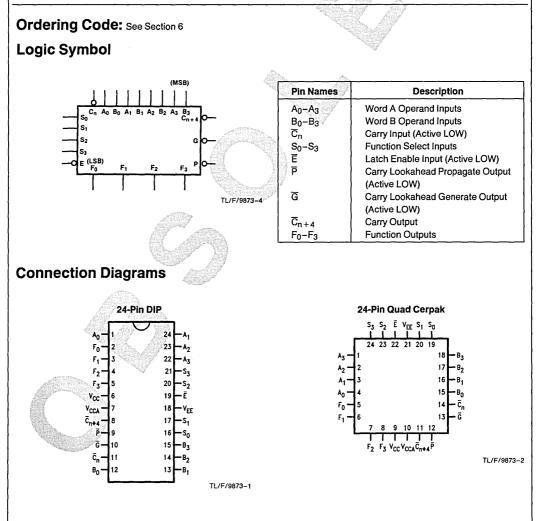

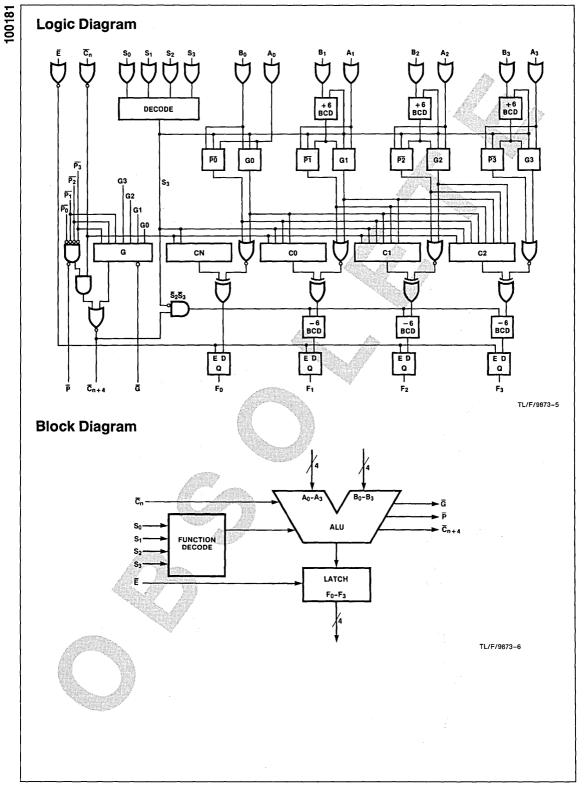

| 100181 4-Bit Binary/BCD ALU                                           |

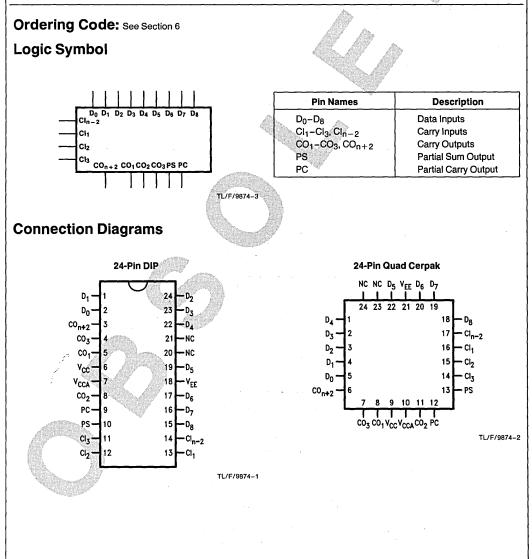

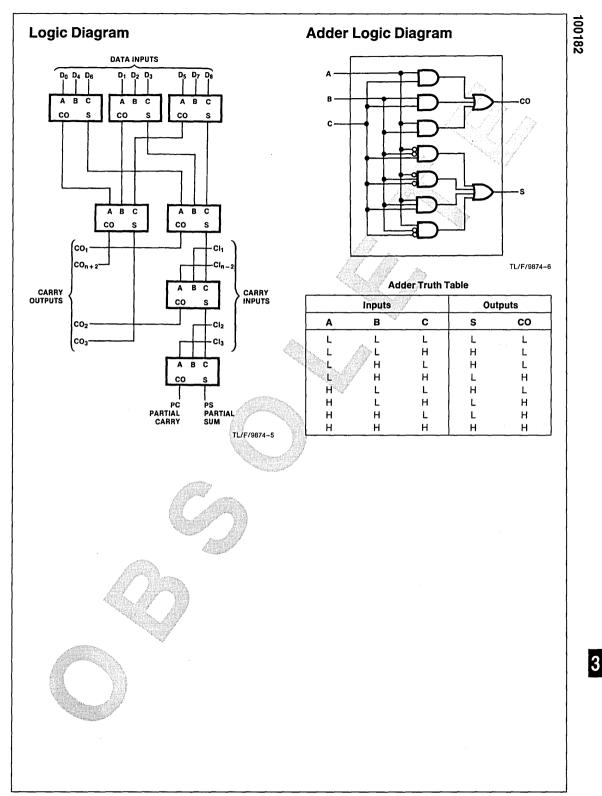

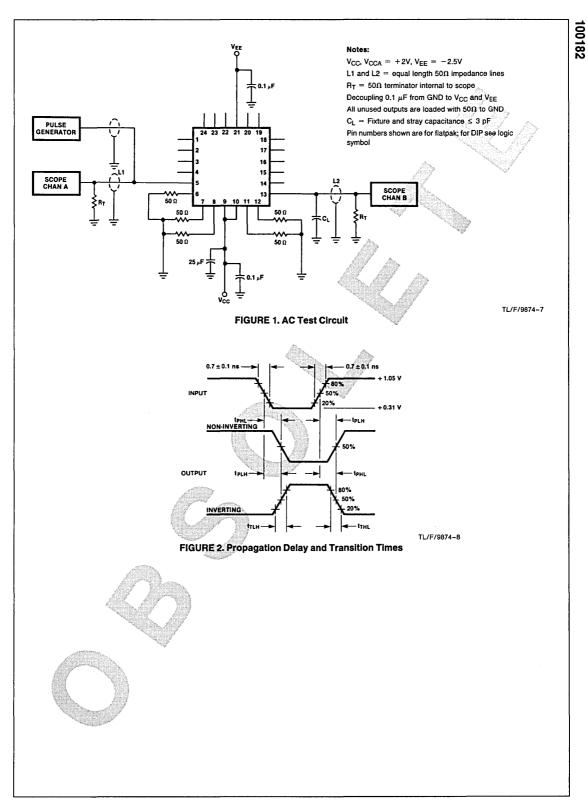

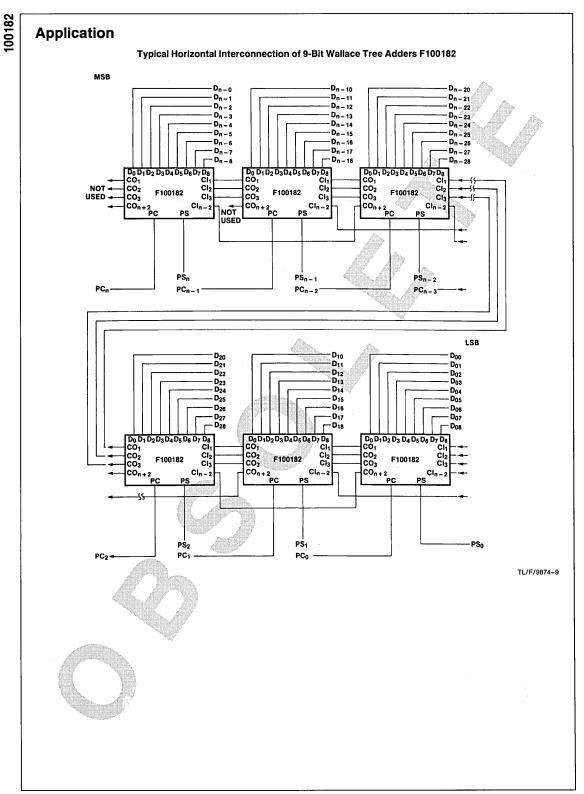

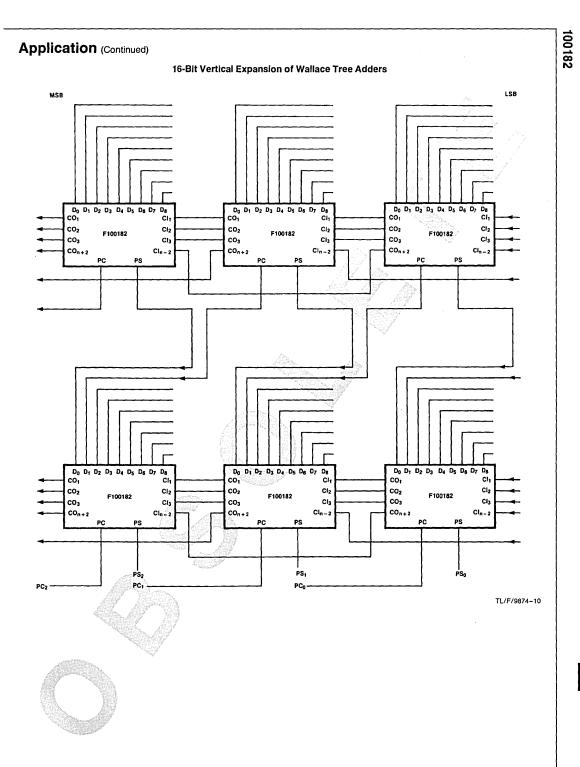

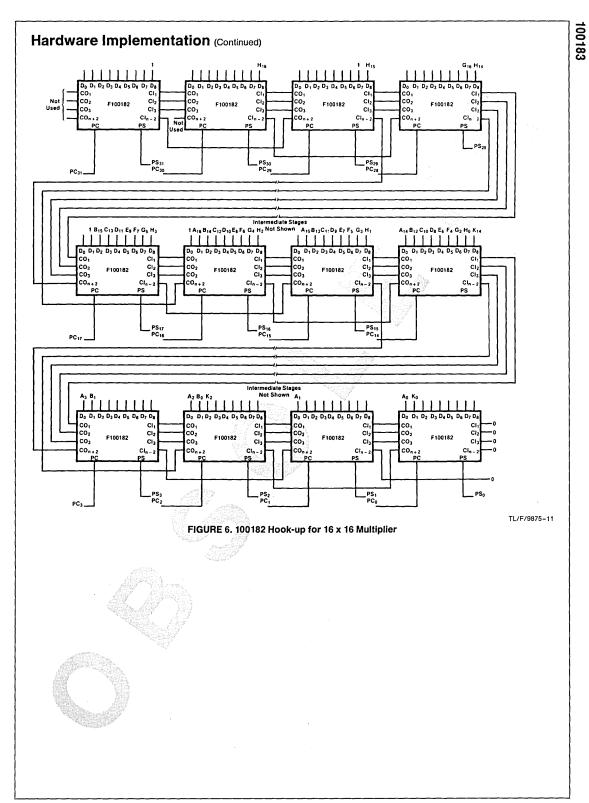

| 100182 9-Bit Wallace Tree Adder                                       |

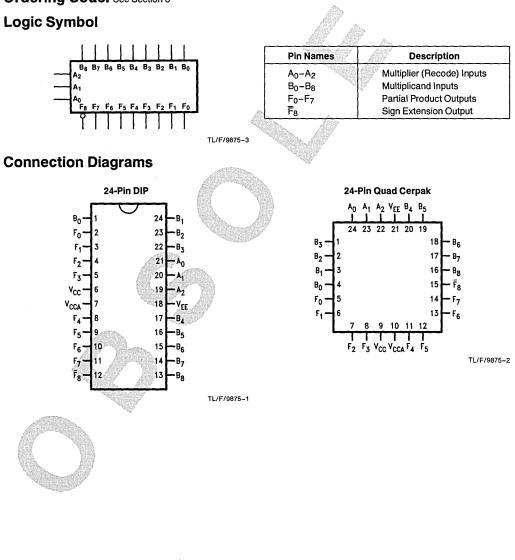

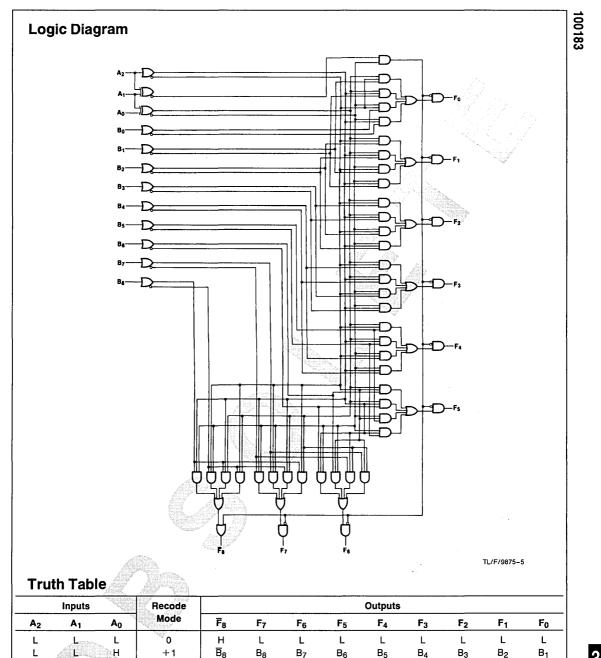

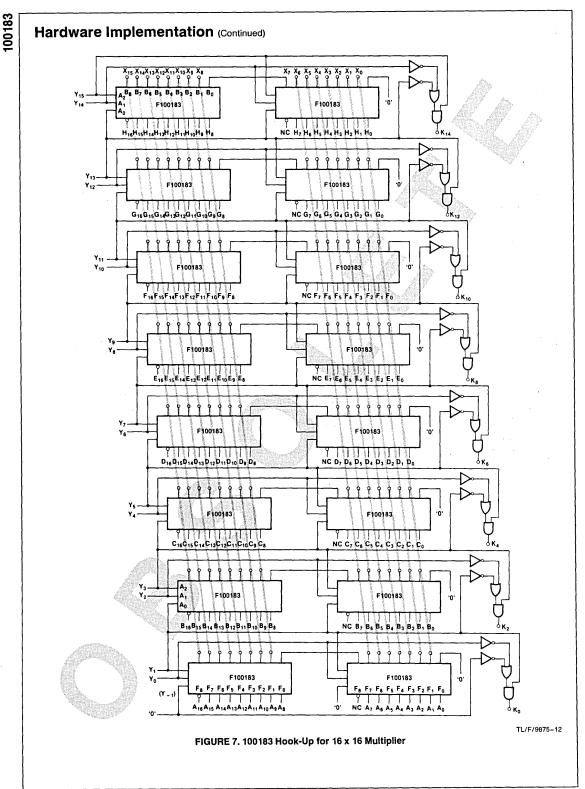

| 100183 2 x 8-Bit Recode Multiplier                                    |

| 100201 Low Power 2-Input OR/NOR Gate/Inverter                         |

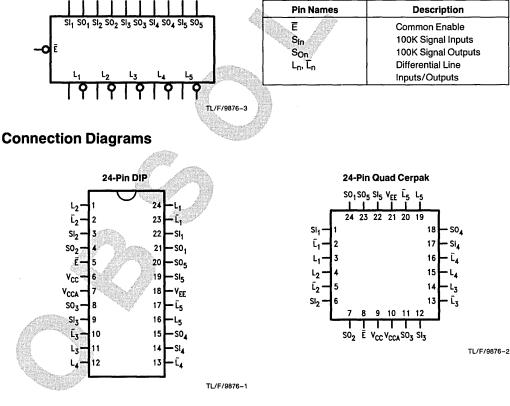

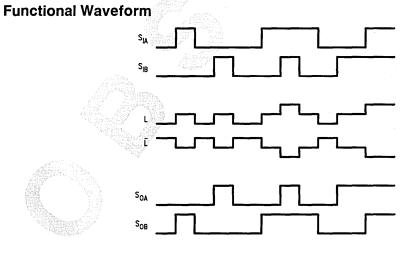

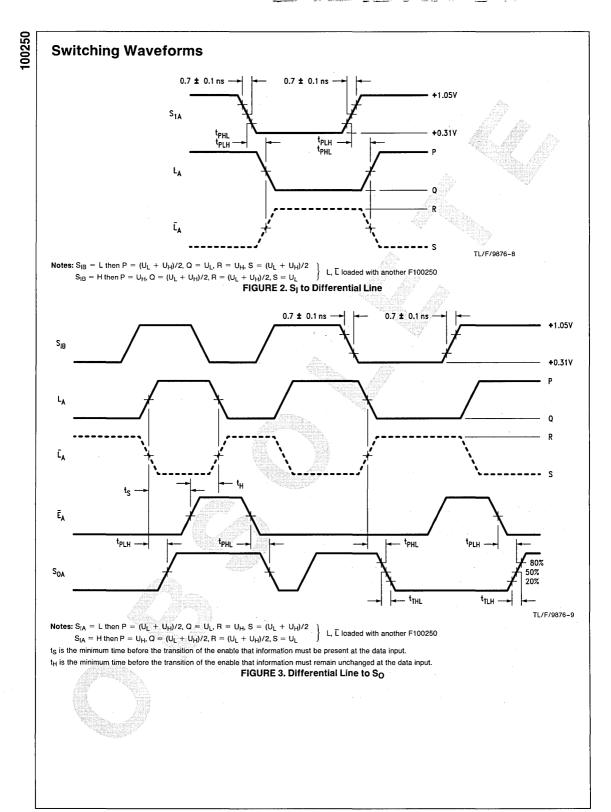

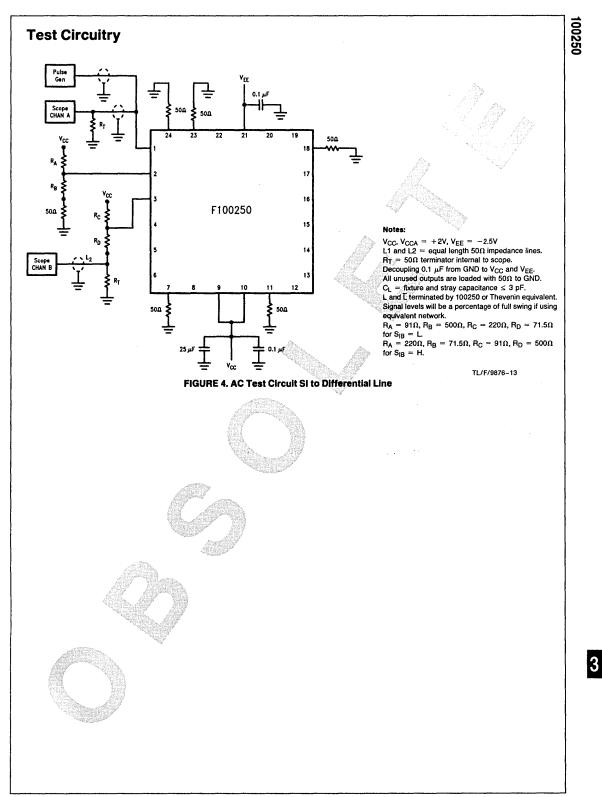

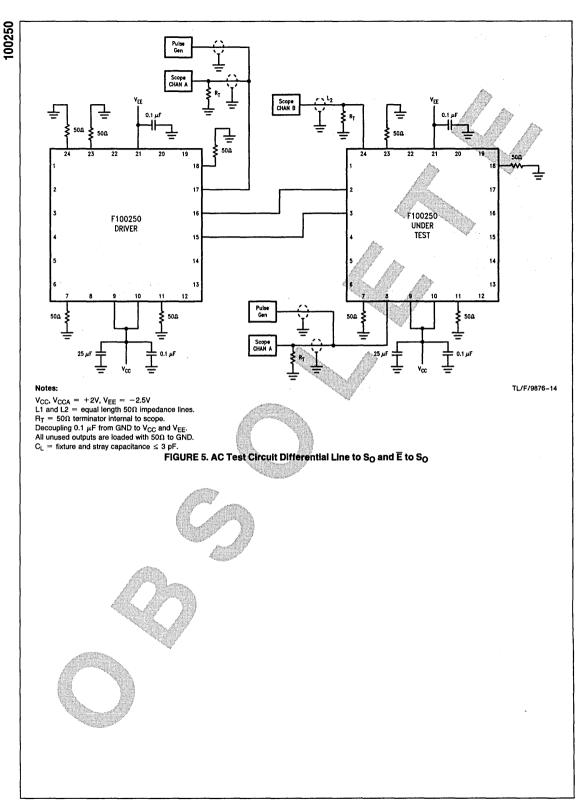

| 100250 Quint Full Duplex Line Transceiver                             |

| 100301 Low Power Triple 5-Input OR/NOR Gate                           |

| 100302 Low Power Quint 2-Input OR/NOR Gate                            |

| 100304 Low Power Quint AND/NAND Gate                                  |

| 100307 Low Power Quint Exclusive OR/NOR Gate                          |

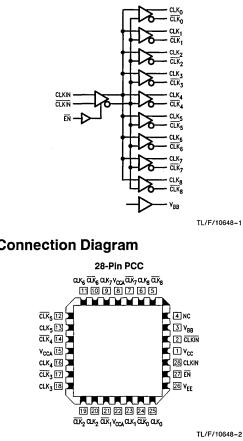

| 100310 Low Skew 2:8 Differential Clock Driver                         |

| 100311 Low Skew 9-Bit Clock Driver                                    |

| 100313 Low Power Quad Driver                                          |

| 100314 Low Power Quint Differential Line Receiver                     |

| 100315 Low Skew Quad Clock Driver                                     |

| 100316 Low Power Quad Differential Line Driver with Cut-Off           |

| 100319 Low Power Hex Line Driver with Cut-Off                         |

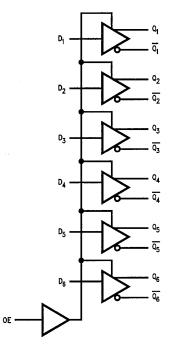

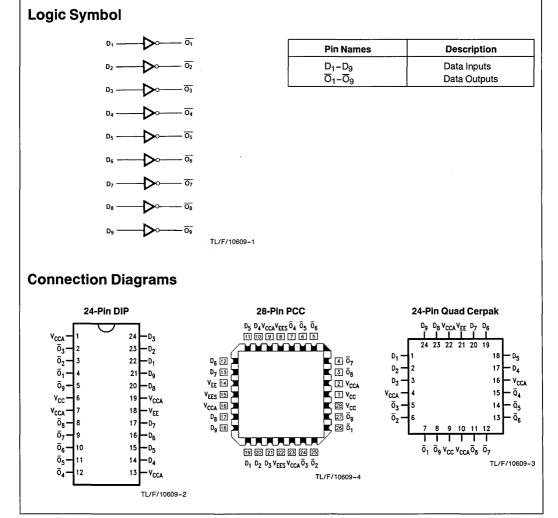

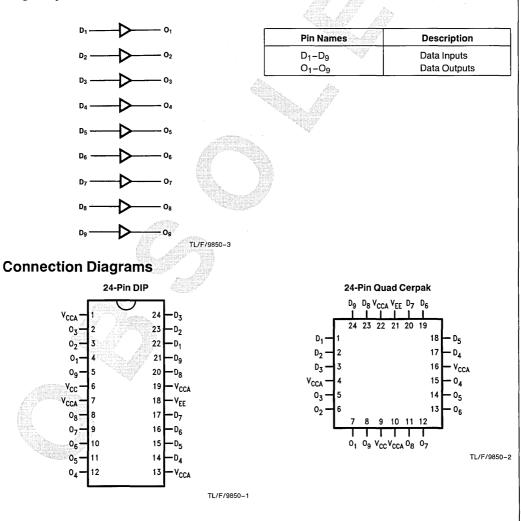

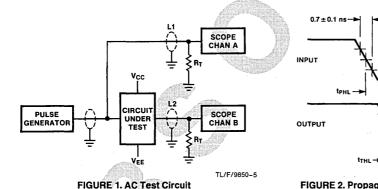

| 100321 Low Power 9-Bit Inverter                                       |

| 100322 Low Power 9-Bit Buffer                                         |

| 100323 Low Power Hex Bus Driver                                       |

| 100324 Low Power Hex TTL-to-ECL Translator                            |

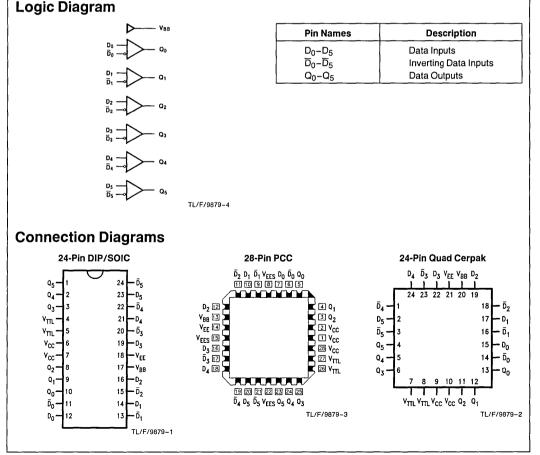

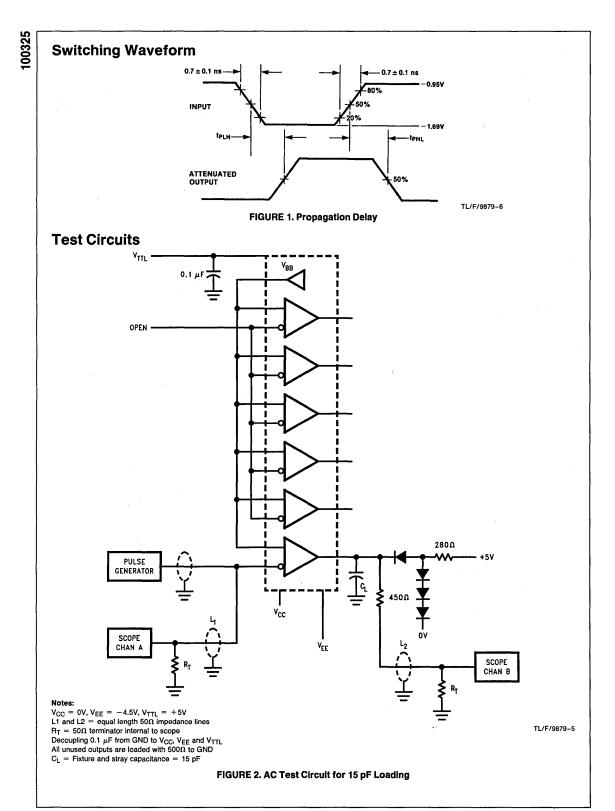

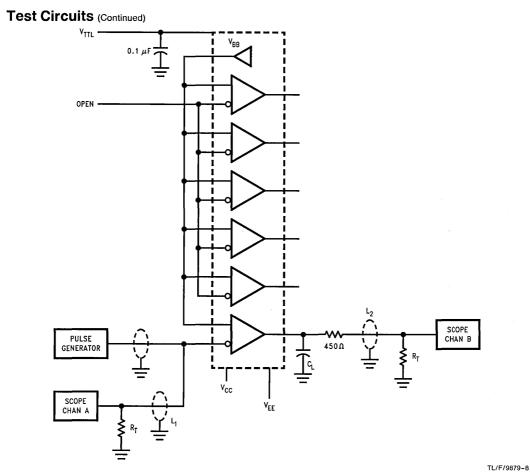

| 100325 Low Power Hex ECL-to-TTL Translator                            |

| 100328 Low Power Octal ECL/TTL Bidirectional Translator with Latch    |

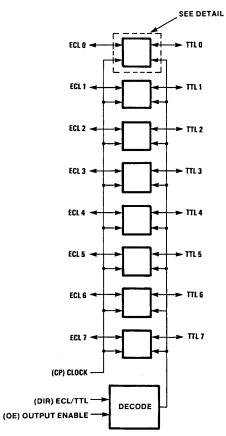

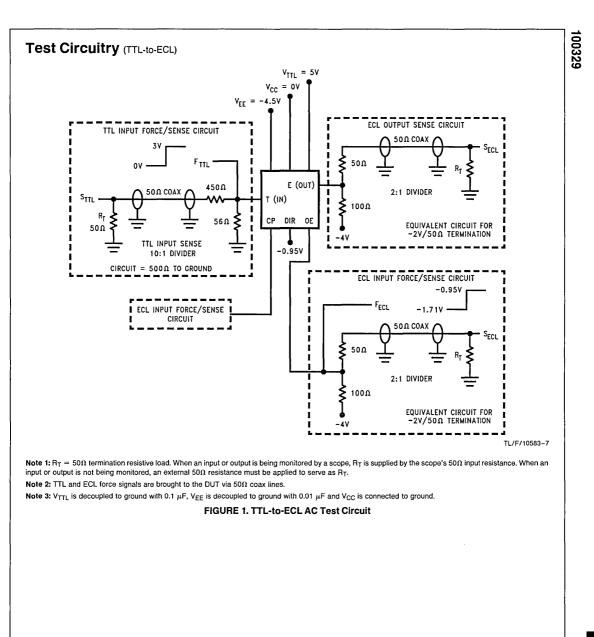

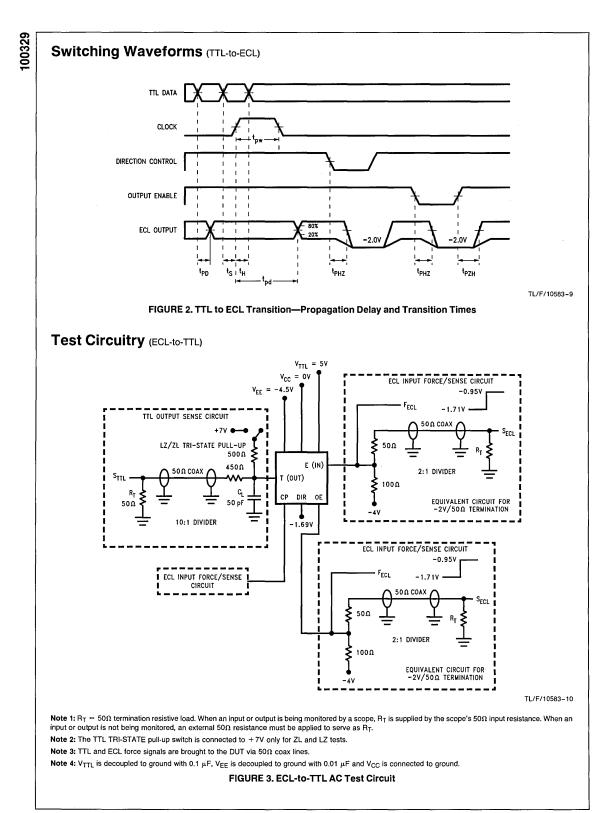

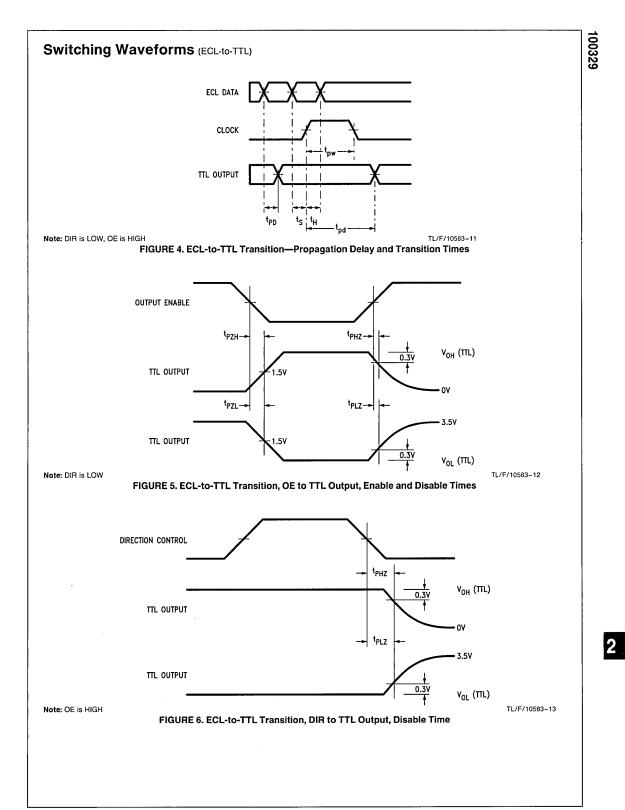

| 100329 Low Power Octal ECL/TTL Bidirectional Translator with Register |

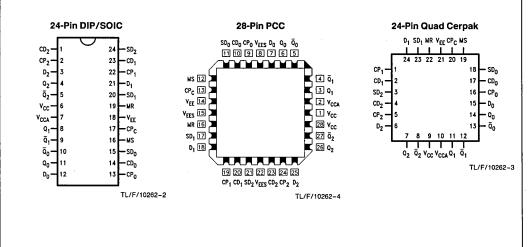

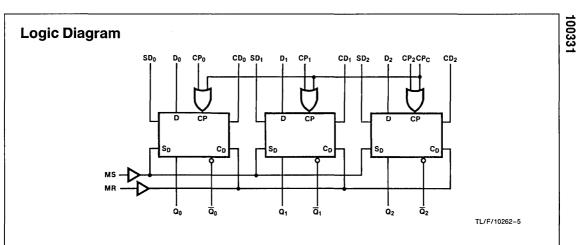

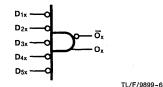

| 100331 Low Power Triple D Flip-Flop                                   |

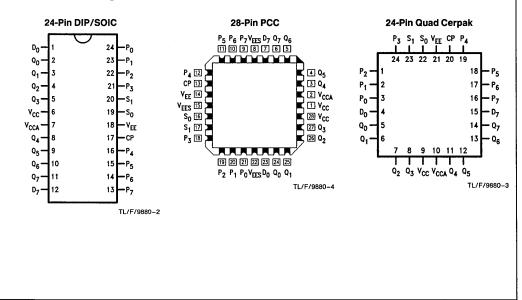

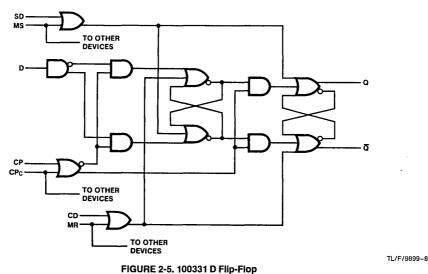

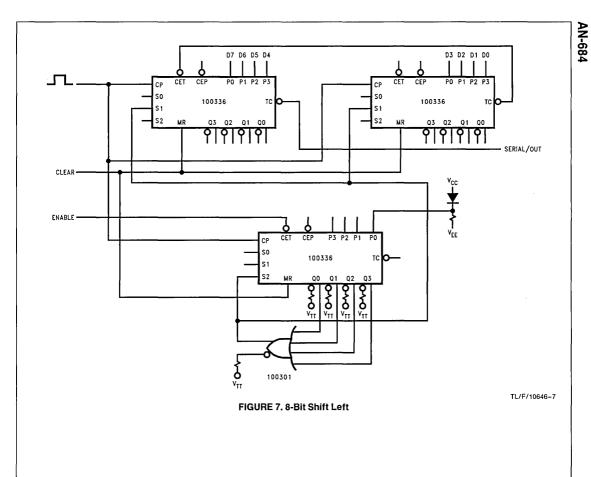

| 100336 Low Power 4-Stage Counter/Shift Register 2-136                 |

| 100341 Low Power 8-Bit Shift Register                                 |

| 100343 Low Power Octal Register                                       |

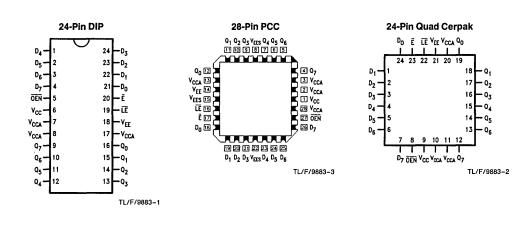

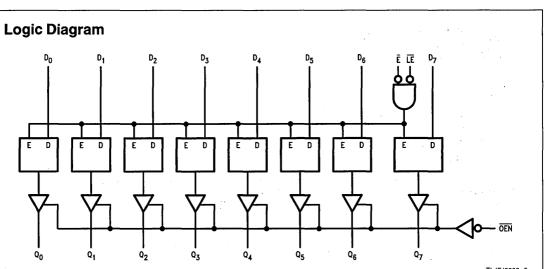

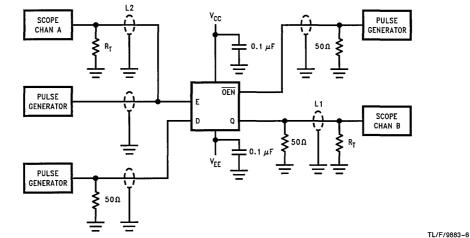

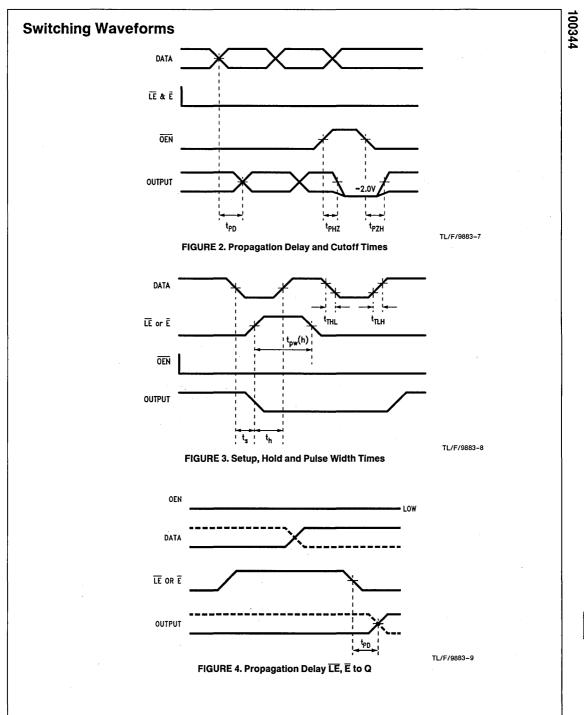

| 100344 Low Power Octal Latch with Cutoff Drivers                      |

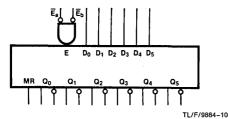

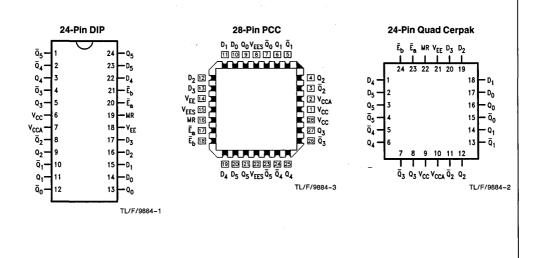

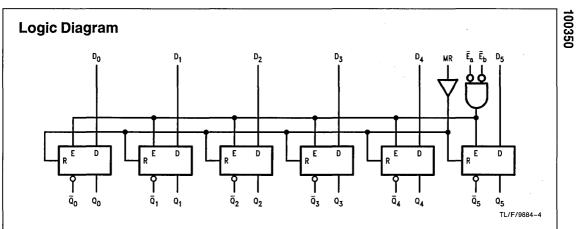

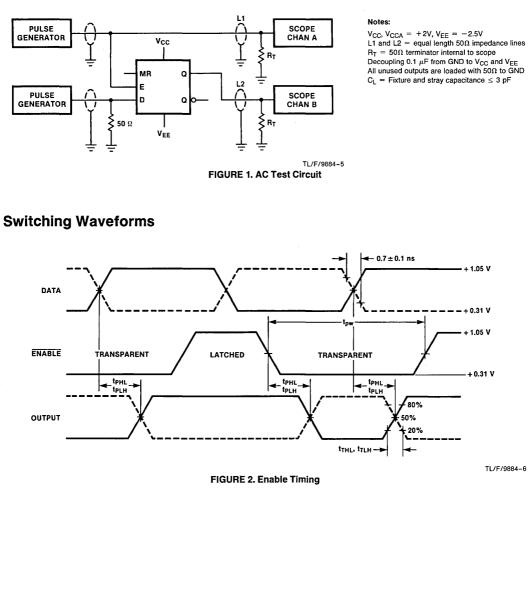

| 100350 Low Power Hex D Latch                                          |

| 100351 Low Power Hex D Flip-Flop                                      |

| 100352 Low Power Octal Buffer with Cutoff Drivers                     |

| 100353 Low Power Octal Latch                                          |

| 100354 Low Power Octal Register with Cutoff Drivers                   |

|                                                                       |

# Alpha-Numeric Index (Continued)

| 00355 Low Power Quad Multiplexer/Latch                              | 3 |

|---------------------------------------------------------------------|---|

| 00360 Low Power Dual Parity Checker/Generator                       |   |

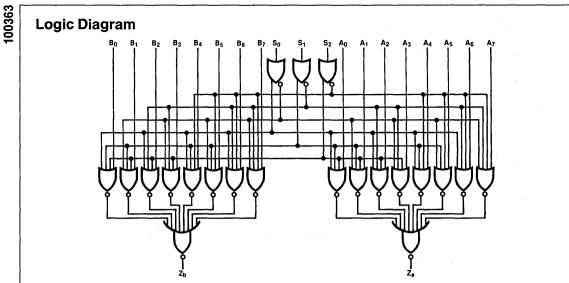

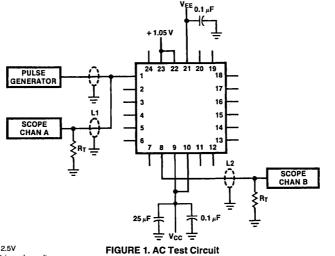

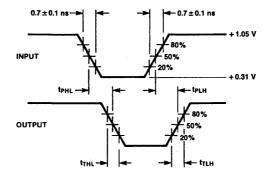

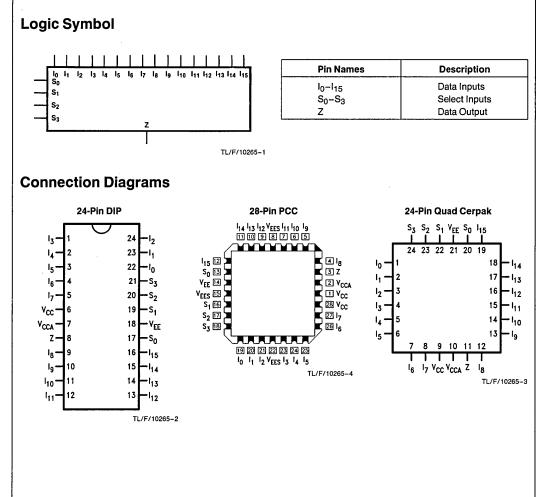

| 00363 Low Power Dual 8-Input Multiplexer                            |   |

| 00364 Low Power 16-Input Multiplexer 2-241                          |   |

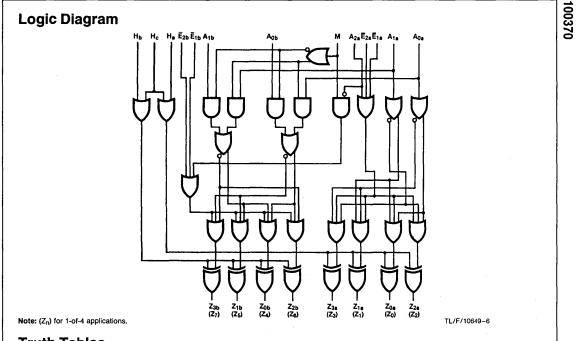

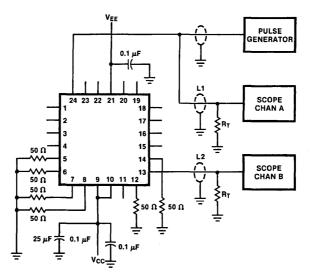

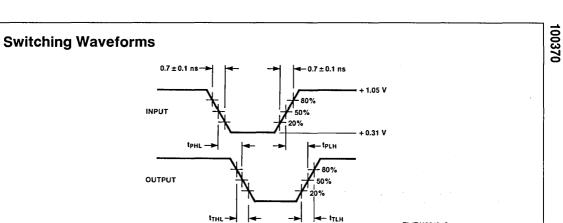

| 00370 Low Power Universal Demultiplexer/Decoder                     |   |

| 00371 Low Power Triple 4-Input Multiplexer 2-256                    |   |

| 00389 Single Supply Hex CMOS-to-ECL Translator with Cutoff Drivers  |   |

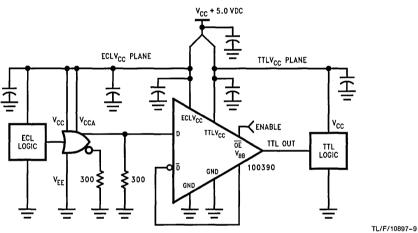

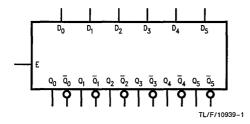

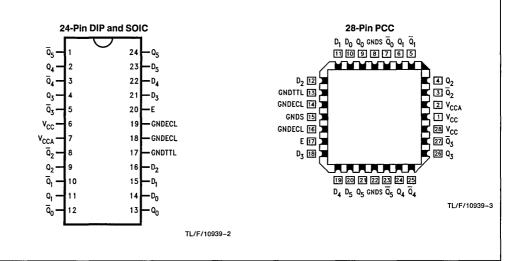

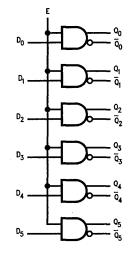

| 00390 Low Power Single Supply Hex ECL-to-TTL Translator             |   |

| 00391 Single Supply Hex TTL-to-ECL Translator                       |   |

| 00392 Single Supply Quint TTL-to-ECL Translator with Cutoff Drivers |   |

| 00393 Low Power 9-Bit ECL-to-TTL Translator with Latch              | Э |

| 00395 Low Power 9-Bit ECL-to-TTL Translator with Register           | 4 |

| 00397 Quad Differential ECL/TTL Translating Transceiver with Latch  | Э |

| 00398 Quad Differential ECL/TTL Translating Transceiver with Latch  | 3 |

| N-682 Terminating F100K ECL Inputs                                  | 5 |

| N-683 300 MHz Dual Eight-Way Multiplexer/Demultiplexer              | 7 |

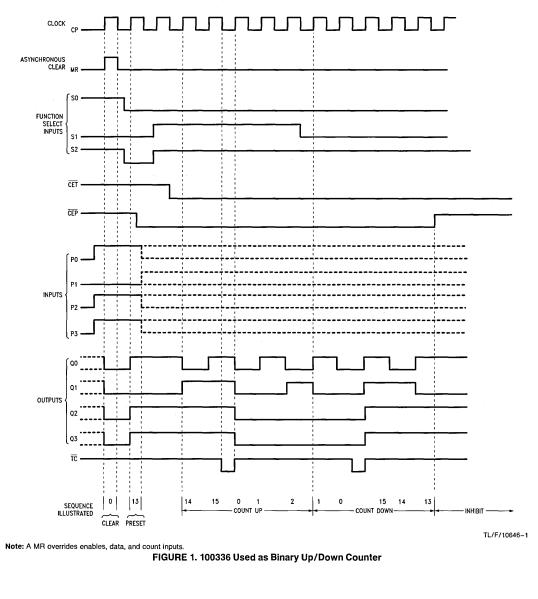

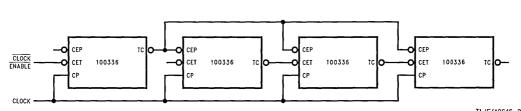

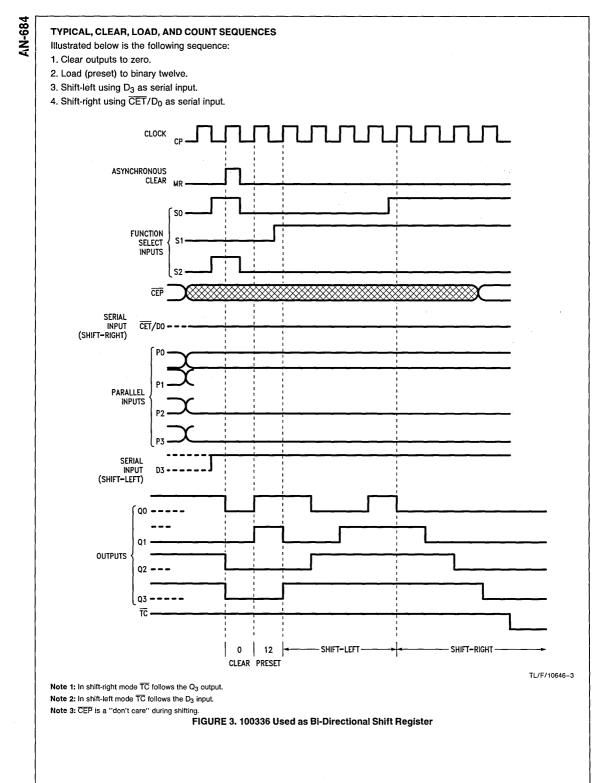

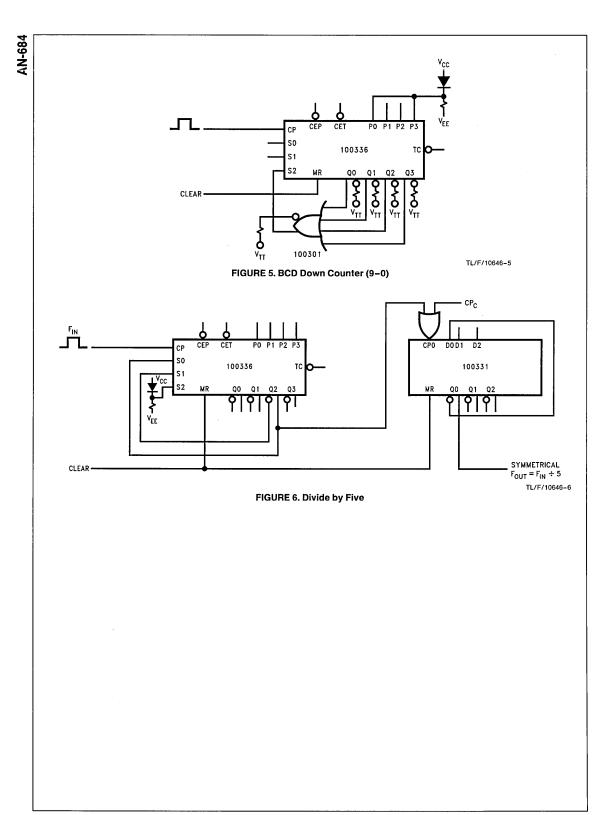

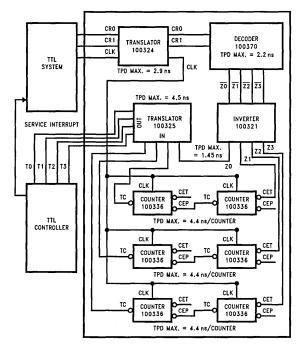

| N-684 F100336 Four Stage Counter/Shift Register                     | Э |

| N-768 ECL Backplane Design                                          | 3 |

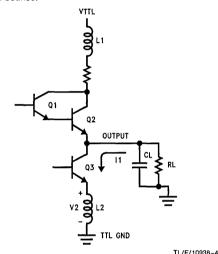

| N-780 Operating ECL From a Single Positive Supply5-94               | 4 |

| N-784 F100K ECL Dual Rail Translators                               |   |

| N-817 ECL Clock Drivers                                             | 7 |

### **ECL Product Selection Guide**

### Gates

| Function                               | Device | Inputs/<br>Gate | No. of<br>Gates |  |

|----------------------------------------|--------|-----------------|-----------------|--|

| OR/NOR Exclusive OR/NOR                |        |                 |                 |  |

| Low Power 2-Input OR/NOR Gate/Inverter | 100201 | 2/1             | 2               |  |

| Low Power Triple 5-Input OR/NOR        | 100301 | 5               | 3               |  |

| Low Power Quint 2-Input OR/NOR         | 100302 | 2               | 5               |  |

| Low Power Quint Exclusive OR/NOR       | 100307 | 2               | 5               |  |

| AND/NAND                               |        |                 |                 |  |

| Low Power Quint 2-Input AND/NAND       | 100304 | 2               | 5               |  |

### **Flip-Flops**

| Function                     | Device | Clock<br>Edge           | Direct<br>Set | Direct<br>Clear | Outputs      |

|------------------------------|--------|-------------------------|---------------|-----------------|--------------|

| Low Power Triple D Flip-Flop | 100331 | $\langle \cdot \rangle$ | Yes           | Yes             | Differential |

| Low Power Hex D Flip-Flop    | 100351 |                         | No            | Yes             | Differential |

### Latches

| Function                         | Device | Enable<br>Inputs | inputs       | Outputs      | Direct<br>Set | Direct<br>Clear |

|----------------------------------|--------|------------------|--------------|--------------|---------------|-----------------|

| Low Power Hex D Latch            | 100350 | 2(L)             | Single-ended | Differential | Yes           | Yes             |

| Low Power Quad 2-Input Mux/Latch | 100355 | 2(L)             | Single-ended | Differential | Yes           | Yes             |

| Low Power 8-Bit Latch            | 100343 | 2(L)             | Single-ended | Single-ended | No            | No              |

| Low Power 8-Bit Latch w/Cutoff   | 100344 | 3(L)             | Single-ended | Single-ended | No            | No              |

| Drivers and $25\Omega$ Drive     |        |                  | -            | -            |               |                 |

### Multiplexers/Demultiplexers/Decoders

| Function                             | Device | Enable<br>Inputs | Inputs       | Outputs      |

|--------------------------------------|--------|------------------|--------------|--------------|

| Multiplexers/Decoders/Demultiplexers |        |                  |              |              |

| Low Power Quad 2-Input Mux/Latch     | 100355 | 2(L)             | Single-ended | Differential |

| Low Power Dual 8-Input               | 100363 |                  | Single-ended | Single-ended |

| Low Power 16-Input                   | 100364 |                  | Single-ended | Single-ended |

| Low Power Triple 4-Input             | 100371 | 1(L)             | Single-ended | Differential |

| Decoders/Demultiplexers              |        |                  |              |              |

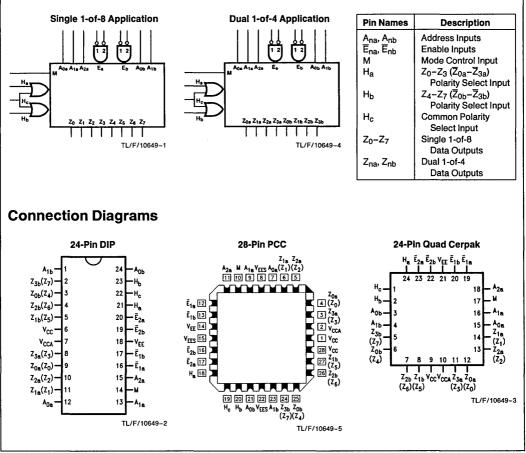

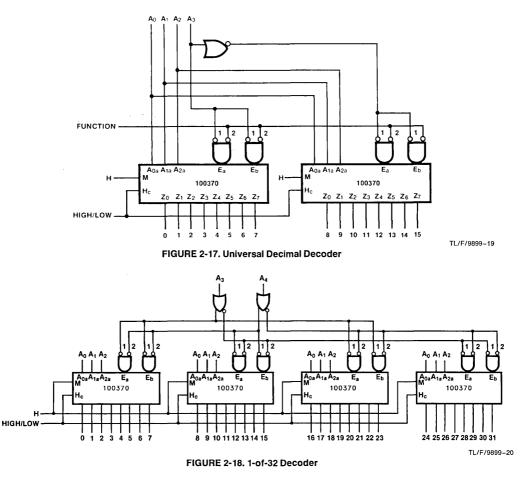

| Low Power Dual 1-of-4/Single 1-of-8  | 100370 | 2(L) & 2(L)      | Single-ended | Single-ended |

### intoro/Shift Dogistoro

| Registers/Shift Registers                    |        |                 |              |              |

|----------------------------------------------|--------|-----------------|--------------|--------------|

| Function                                     | Device | Clock<br>Inputs | Inputs       | Outputs      |

| Registers                                    |        |                 |              |              |

| Low Power 8-Bit Register                     | 100353 | ~               | Single-ended | Single-ended |

| Low Power 8-Bit Register w/Cutoff            | 100354 | · _             | Single-ended | Single-ended |

| Drivers and 25 $\Omega$ Drive                |        |                 |              |              |

| Shift Registers                              |        |                 |              |              |

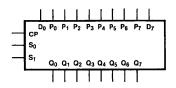

| Low Power 4-Bit Bidirectional Shift Register | 100336 | ~               | Single-ended | Differential |

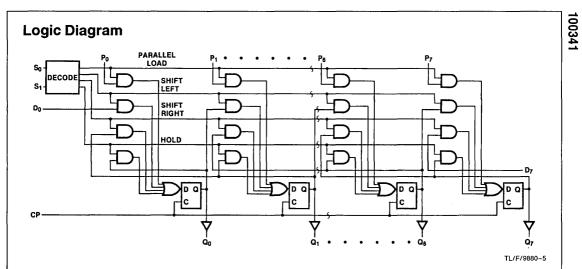

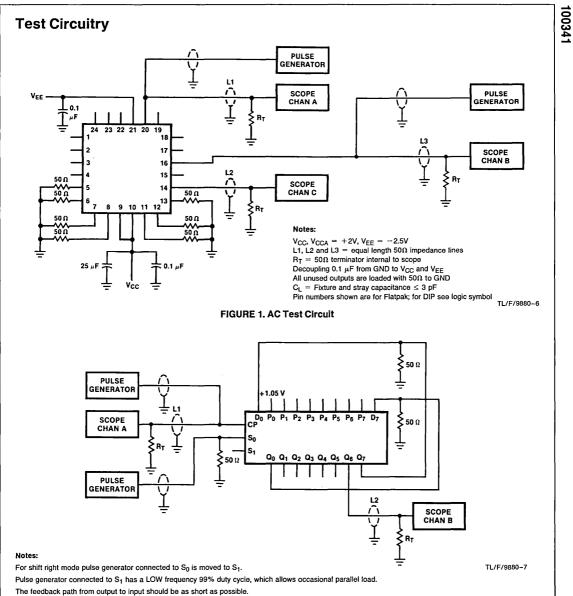

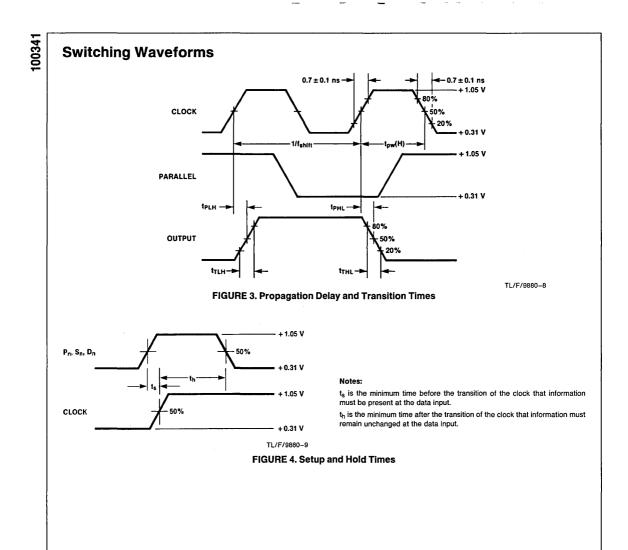

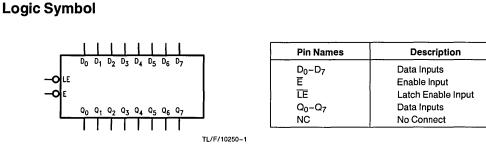

| Low Power 8-Bit Shift Register               | 100341 | <u>~</u>        | Single-ended | Single-ended |

### **Buffers/Drivers/Receivers**

| Function                                   | Device | Inputs       | Outputs      | 25Ω<br>Drive | Output<br>Cut-off |

|--------------------------------------------|--------|--------------|--------------|--------------|-------------------|

| Buffers/Inverters                          |        |              |              |              |                   |

| Low Power 9-Bit Inverter                   | 100321 | Single-ended | Single-ended | No           | No                |

| Low Power 9-Bit Buffer                     | 100322 | Single-ended | Single-ended | No           | No                |

| Low Power 8-Bit Buffer                     | 100352 | Single-ended | Single-ended | Yes          | Yes               |

| Drivers/Bus Drivers                        |        |              |              |              |                   |

| Low Power Quad Line Driver                 | 100313 | Single-ended | Differential | No           | No                |

| Low Power Hex Bus Driver                   | 100323 | Single-ended | Single-ended | Yes          | Yes               |

| Low Power Quad Line Driver                 | 100316 | Single-ended | Differential | Yes          | Yes               |

| Low Power Hex Line Driver                  | 100319 | Differential | Differential | Yes          | Yes               |

| Receivers/Transceivers                     |        |              |              |              |                   |

| Low Power Quint Differential Line Receiver | 100314 | Differential | Differential | No           | No                |

### Counter

| Function                       | Device | Parallel<br>Entry | Reset      | Up/Down |

|--------------------------------|--------|-------------------|------------|---------|

| Low Power 4-Bit Binary Counter | 100336 | Sync              | Sync/Async | Yes     |

### **Arithmetic Operator**

| Function                                      | Device | Features   |

|-----------------------------------------------|--------|------------|

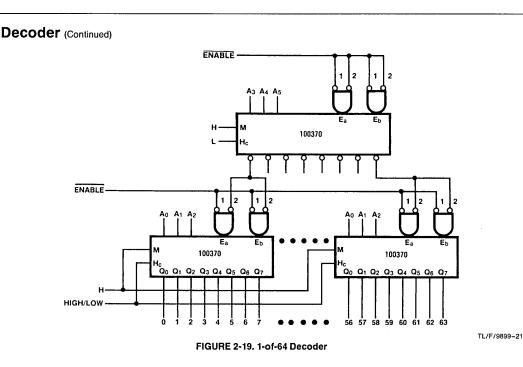

| Low Power Dual 9-Bit Parity Checker/Generator | 100360 | Expandable |

### **Clock Drivers**

| Function                      | Device | Clock<br>Inputs | Single-ended<br>Clock | Differential<br>Clock |

|-------------------------------|--------|-----------------|-----------------------|-----------------------|

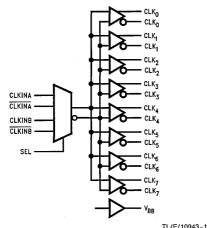

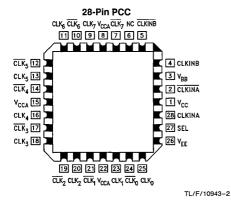

| Low Power 2 to 8 Clock Driver | 100310 | 2               |                       | 2                     |

| Low Skew 1 to 9 Clock Driver  | 100311 | 1               |                       | 1                     |

| Low Skew Quad Clock Driver    | 100315 | 2               | 1                     | 1                     |

| Features                                                  | 100324 | 100325 | 100328 | 100329 | 100393 | 100395 | 100397 | 100398 |

|-----------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| Data Bits                                                 | 6      | 6      | 8      | 8      | 9      | 9      | 4      | 4      |

| ECL-to-TTL                                                |        | х      | Х      | х      | x      | x      | x      | x      |

| TTL-to-ECL                                                | х      |        | х      | X      |        |        | X      | x      |

| Flow-Thru                                                 | X      | х      |        |        |        |        |        |        |

| Latched                                                   |        |        | х      |        | X      |        | X      | х      |

| Registered                                                |        |        |        | X      |        | х      |        |        |

| ECL Differential Input                                    |        | X1     |        |        |        |        | Х      | Х      |

| ECL Differential Output                                   | X      |        |        |        |        |        | X      | х      |

| ECL Output Drive (Ω)                                      | 50     |        | 50     | 50     |        |        | 25     | 25     |

| ECL Cutoff (Hi Z)                                         |        |        | X      | X      |        |        | X      | х      |

| TTL Output Drive (mA) (I <sub>OL</sub> /I <sub>OH</sub> ) |        | 20/-2  | 23/-3  | 24/-3  | 64/-15 | 64/-15 | 64/-15 | 64/-15 |

| TTL TRI-STATE®                                            |        |        | Х      | X      | X      | x      | X      | x      |

| ECL Control Pins                                          |        |        | X      | X      | X      | Х      | X      |        |

| TTL Control Pins                                          | Х      |        |        |        | X      |        |        | х      |

| TPD E to T (ns Max)                                       |        | 4.8    | 5.9    | 7.7    | 5.3    | 6.4    | 5.8    | 5.8    |

| TPD T to E (ns Max)                                       | 3.0    |        | 3.8    | 3.9    |        |        | 2.4    | 2.2    |

| I <sub>EE</sub> (mA Max)                                  | -70    | -37    | - 169  | - 199  | -39    | -67    | -99    | 99     |

| I <sub>EE</sub> (mA Max) (Cutoff)                         |        |        | -169   | - 199  |        |        | - 159  | - 159  |

| I <sub>CC</sub> (mA Max)                                  | 38     | 65     | 74     | 74     | 65     | 65     | 36     | 45     |

$^1\mathrm{V}_{\mathrm{BB}}$  provided for Single-ended Operation

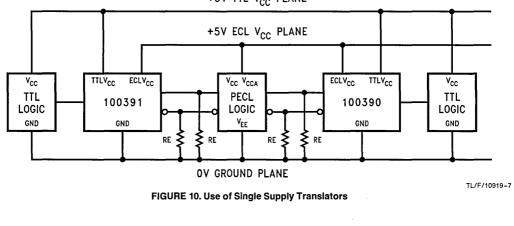

### Single Supply Translators

| Features                          | 100390 | 100391 | 100392 | 100389 |

|-----------------------------------|--------|--------|--------|--------|

| Data Bits                         | 6      | 6      | 5      | 6      |

| ECL-to-TTL                        | x      |        |        |        |

| TTL-to-ECL                        |        | X      |        |        |

| CMOS-to-ECL                       |        |        | X      | x      |

| ECL Differential Input            | χ2     |        |        |        |

| ECL Differential Output           | 1      | x      | х      | x      |

| ECL Output Drive $(\Omega)$       |        | 50     | 25     | 50     |

| ECL Cutoff (Hi Z)                 | ]      |        | . X    |        |

| TTL Output Drive (mA) (IOL/IOH)   | 24/-3  |        |        |        |

| TTL TRI-STATE®                    | x x    |        |        |        |

| TTL Control Pins                  | x      | x      |        |        |

| CMOS Control Pins                 |        |        | х      | x      |

| TPD E to T (ns Max)               | 6.4    |        |        |        |

| TPD T to E (ns Max)               | }      | 1.7    |        |        |

| TPD C to E (ns Max)               |        |        | TBD    | TBD    |

| I <sub>EE</sub> (mA Max) (Cutoff) |        |        | TBD    |        |

| I <sub>CC</sub> (mA Max)          | 48     | 60     | TBD    | TBD    |

$^{2}\mathrm{V}_{BB}$  provided for Single-ended Operation

ix

| CDIP<br>X<br>X<br>X<br>X<br>X | PDIP<br>X<br>X<br>X<br>X<br>X | QFP<br>X<br>X<br>X<br>X<br>X                                                                                                                                                                                                                                                                                                                           | SOIC<br>X<br>X                                                                                                                               | PCC<br>X<br>X<br>X                                                                                                                                        | SOIC                                                                                                                                                                          |

|-------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| x<br>x                        | x<br>x                        | x<br>x                                                                                                                                                                                                                                                                                                                                                 | x                                                                                                                                            | х                                                                                                                                                         |                                                                                                                                                                               |

| x                             | x                             | х                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

|                               | ~                             | ~                                                                                                                                                                                                                                                                                                                                                      | Х                                                                                                                                            | x                                                                                                                                                         | 1                                                                                                                                                                             |

|                               | 1                             |                                                                                                                                                                                                                                                                                                                                                        | ^                                                                                                                                            | x                                                                                                                                                         | 1                                                                                                                                                                             |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              | x                                                                                                                                                         | · ·                                                                                                                                                                           |

| x                             | x                             | x                                                                                                                                                                                                                                                                                                                                                      | x                                                                                                                                            | x                                                                                                                                                         |                                                                                                                                                                               |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

| ^                             | ^                             | ^                                                                                                                                                                                                                                                                                                                                                      | <b>^</b>                                                                                                                                     | ^                                                                                                                                                         |                                                                                                                                                                               |

| ~                             | v                             |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              | v                                                                                                                                                         | X                                                                                                                                                                             |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

|                               |                               | <b>V</b>                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           | · ·                                                                                                                                                                           |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           | }                                                                                                                                                                             |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        | X                                                                                                                                            |                                                                                                                                                           | 1                                                                                                                                                                             |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

|                               |                               | х                                                                                                                                                                                                                                                                                                                                                      | х                                                                                                                                            | x                                                                                                                                                         |                                                                                                                                                                               |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        | Х                                                                                                                                            |                                                                                                                                                           |                                                                                                                                                                               |

| x                             | x                             | х                                                                                                                                                                                                                                                                                                                                                      | · · ·                                                                                                                                        | <b>X</b> .                                                                                                                                                |                                                                                                                                                                               |

| x                             | x                             | х                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                              | Х                                                                                                                                                         | · ·                                                                                                                                                                           |

| X                             |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           | ]                                                                                                                                                                             |

| x                             |                               |                                                                                                                                                                                                                                                                                                                                                        | х                                                                                                                                            |                                                                                                                                                           |                                                                                                                                                                               |

| x                             |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           | d                                                                                                                                                                             |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           | ]                                                                                                                                                                             |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           | 1                                                                                                                                                                             |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

| x                             |                               | x                                                                                                                                                                                                                                                                                                                                                      | x                                                                                                                                            |                                                                                                                                                           |                                                                                                                                                                               |

| ^                             |                               | ~                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

| ×                             |                               | x                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

|                               |                               | ~                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                              |                                                                                                                                                           | í .                                                                                                                                                                           |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        | <u>^</u>                                                                                                                                     |                                                                                                                                                           | 1                                                                                                                                                                             |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           | 1                                                                                                                                                                             |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

|                               | v                             |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                               |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |                                                                                                                                                           | 1                                                                                                                                                                             |

|                               |                               |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              | ^                                                                                                                                                         | l                                                                                                                                                                             |

|                               | X sol                         | X X X<br>X X X X X<br>X X X X X<br>X X X X X X<br>X X X X X X X X X X X X X X X X X X X X | XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX | XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX | XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX |

# **Product Status Definitions**

### **Definition of Terms**

| Data Sheet Identification                     | Product Status            | Definition                                                                                                                                                                                                                                                                      |  |  |  |

|-----------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Advance Information                           | Formative or<br>In Design | This data sheet contains the design specifications for product development. Specifications may change in any manner without notice                                                                                                                                              |  |  |  |

| Preliminary                                   | First<br>Production       | This data sheet contains preliminary data, and supplementary data will<br>be published at a later date. National Semiconductor Corporation<br>reserves the right to make changes at any time without notice in order<br>to improve design and supply the best possible product. |  |  |  |

| No Full<br>Identification Production<br>Noted |                           | This data sheet contains final specifications. National Semiconductor<br>Corporation reserves the right to make changes at any time without<br>notice in order to improve design and supply the best possible produ-                                                            |  |  |  |

| Obsolete                                      | Not In Production         | This data sheet contains specifications on a product that has been<br>discontinued by National Semiconductor Corporation. The data sheet<br>is printed for reference information only.                                                                                          |  |  |  |

National Semiconductor Corporation reserves the right to make changes without further notice to any products herein to improve reliability, function or design. National does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

.

N

# Section 1 Family Overview

### **Section 1 Contents**

| Family Overview                           | 1-3  |

|-------------------------------------------|------|

| Introduction                              | 1-3  |

| F100K Design Philosophy                   | 1-3  |

| 300 Series Design Philosophy              | 1-4  |

| Process Technology                        | 1-7  |

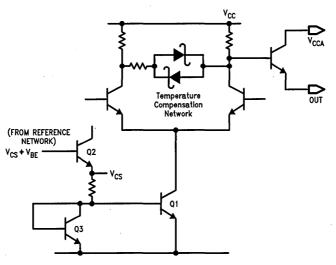

| Compensation Network                      | 1-7  |

| Characteristics                           | 1-8  |

| Features                                  | 1-9  |

| System Benefits                           | 1-10 |

| Packaging                                 | 1-11 |

| Industrial Applications                   | 1-11 |

| Military Applications                     | 1-11 |

| Definitions of Symbols and Terms          | 1-13 |

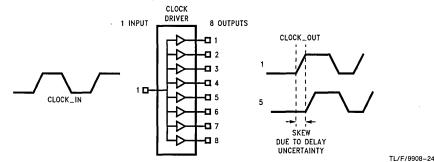

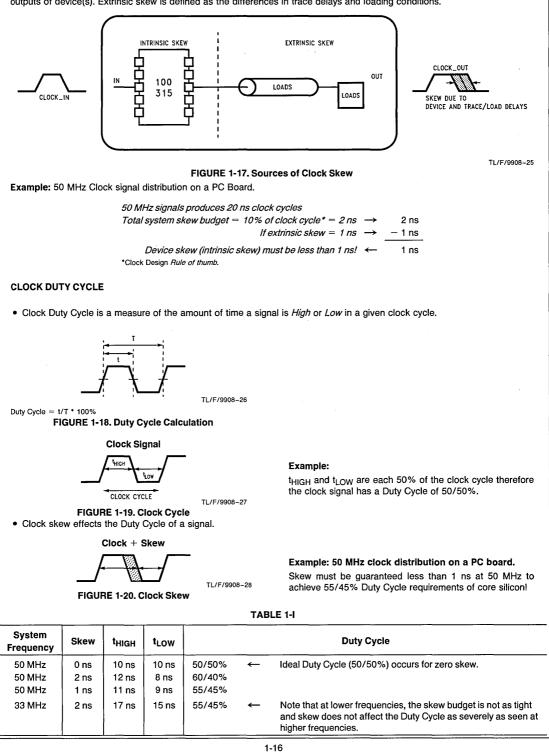

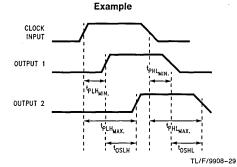

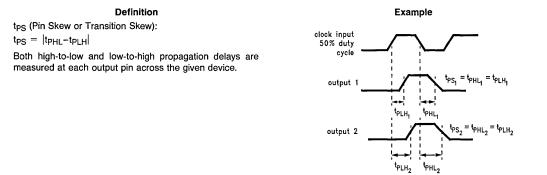

| Definitions of Output Skew Specifications | 1-15 |

### **Family Overview**

### Introduction

Precious few alternatives available offer the performance of ECL. Most designers recognize the advantages offered by ECL in high speed systems extend beyond just quick switching times. However, the use of ECL has been somewhat limited to those applications concerned with high speed and often little more. These applications usually had extravagant cooling systems and massive power sources to keep the signal moving. Rapid advancements in microprocessors and high resolution video equipment are now beginning to push preferred TTL and CMOS technologies to their limits. The need for functions with ECL-like speeds without ECL-like power for use in smaller but increasingly powerful systems is growing rapidly.

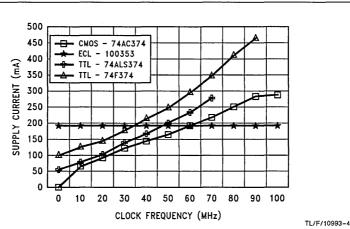

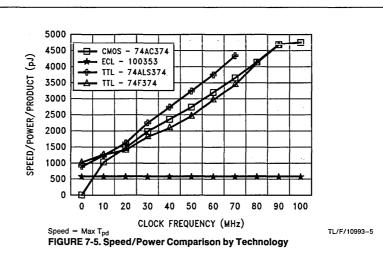

The problems with working with high speed systems are beginning to migrate downward from supercomputers to workstations as the performance of workstations moves upward. The benefits of using ECL in high-end applications have long been recognized by those designers familiar with it. Low propagation delays with moderate edge rates, negligible noise and ground bounce, constant power consumption over frequency and the ability to drive low impedance transmission lines have combined to make ECL the preferred technology for designers who have had previous experience with it. However, the majority of designers never had to consider ECL, until now. The increasing availability of high speed microprocessors is driving the need for faster busses and more accurate clocking.

ECL still has its drawbacks, but recent technological advances have made ECL a much more appealing and usable technology. With the growing need for high speed signal distribution, ECL is beginning to move more into high performance backplanes. Designers like and require the high speed, differential outputs, low impedance drive and transmission line-like characteristics of ECL. ECL is also being used increasingly in clock distribution trees because of its speed and inherently low skew. High resolution video graphics terminals with a display resolution of 1024 x 1024 pixels require a bandwidth of over 80 MHz, not an easy task for CMOS or TTL but well within the range of ECL. Broadband communication systems are also using a great deal of ECL as fiber optic data transfer moves into greater utilization.

National Semiconductor introduced the F100K 300 Series to allow ECL to be more usable in today's high performance systems. In developing this new family, much emphasis was placed on power, space and cost reductions. The 300 Series was designed to interact with other technologies, not to replace them. Many new designs are attempting to optimize the most efficient mix of speed, power and price with ECL, CMOS and TTL all working together. ECL will handle the speed critical applications, CMOS functions would keep the overall system power low and TTL would be included to keep costs down. The performance, power, packaging

and functionality of the 300 Series make this family ideal for those applications operating above 50 MHz.

Much of what the 300 Series has evolved into, is a compilation of inputs received from designers who could not use the older F100K 100 Series for various reasons. This resulted in parts with lower operating power, significantly improved ESD protection, plastic surface mount packaging, additional AC testing including skew, easy interface with other technologies and increased functionality. This section will go into much greater detail about ECL and the evolution of the 300 Series.

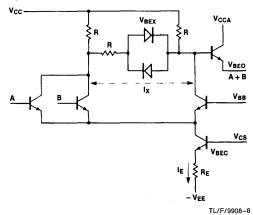

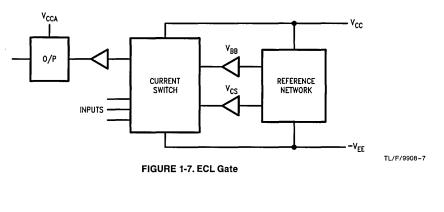

### F100K Design Philosophy

F100K was designed to meet four key requirements: high speed at reduced power, high level of on-chip integration, flexible logic functions, and optimum I/O pin assignment.

#### Subnanosecond Gate Delays

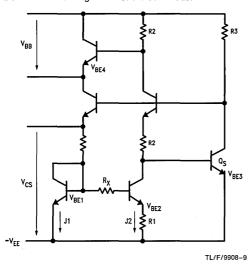

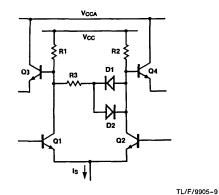

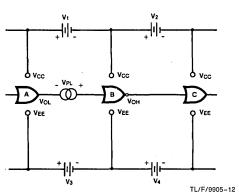

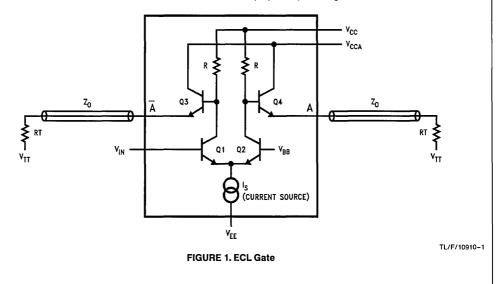

The subnanosecond internal gate delays of F100K 100 Series were obtained by the use of ECL design techniques and the advanced Isoplanar-Z process. Many circuit approaches were carefully considered prior to selecting the optimum gate configuation for the F100K family. The emitter-follower current-switch (E<sup>2</sup>CL) and current-mode logic (CML) gates were eliminated mainly because of poor capacitive drive and lack of output wired-OR capability; the CML gate has low noise margins. The 2-½D, EFL, DCTTL and hysteresis gates were eliminated due to the lack of simultaneous complementary outputs along with difficult temperature and voltage compensation characteristics that lead to the loss of system noise immunity.

The choice narrowed down to the current-switch emitter-follower ECL gate which offers the following characteristics:

- High fan-out capability

- · Simultaneous complementary outputs

- · Excellent AC characteristics

- · Compatibility with existing ECL logic and memories

- · Internal series gating capability

- · Good noise immunity

- Amenable full compensation and extended temperature characteristics

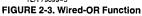

- · External wired-OR capability

In order to ease drive requirements all circuit inputs were designed to have similar loading characteristics; i.e., buffers are incorporated where an input pin would normally drive more than one on-chip gate. The on-chip delay incurred by buffering is less than the system delay caused by an output which drives a capacitance of higher than three unit loads. Full compensation was selected for the F100K Family to provide improved switching characteristics. Full compensation results in relatively constant signal levels and thresh-

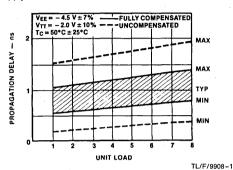

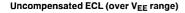

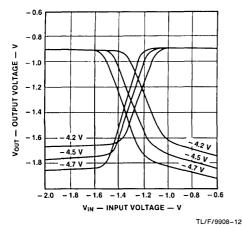

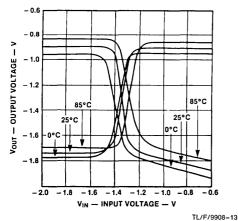

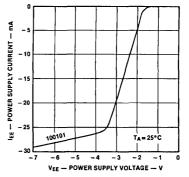

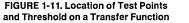

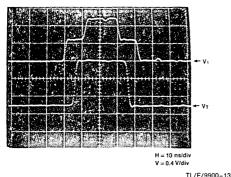

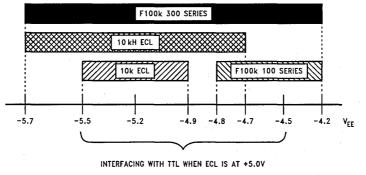

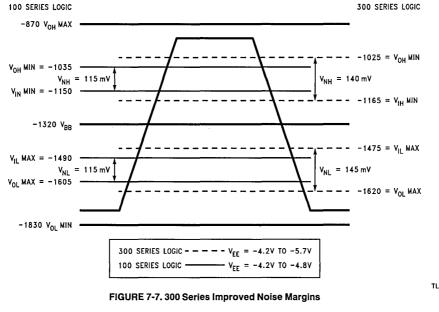

olds and in improved noise margins over temperature and voltage variations from chip to chip, and thus a tighter AC window in the system environment. A comparison of fully compensated ECL to conventional ECL shows a 2:1 improvement in system AC performance due solely to full compensation (*Figure 1-1*). And, the improved speed has been achieved at reduced power. Power reduction is accomplished by the use of advanced process technology that reduces parasitic capacitances and improves tolerances, by optimum circuit designs using series gating and collector and emitter dotting, and by designing for the use of a -4.5V V<sub>EE</sub> power supply. F100K 100 Series is specified at a V<sub>EE</sub> power supply of -4.2V to -4.8V, but a  $-5.2V \pm 10\%$  power supply can be used to interface with 2 ns ECL families.

#### **High On-Chip Integration**

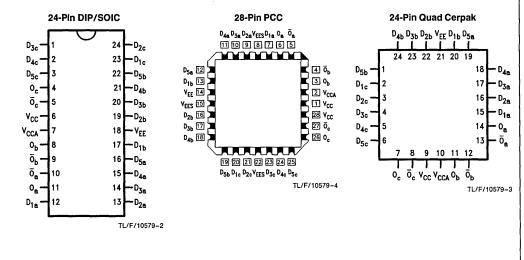

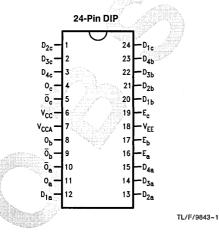

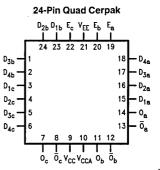

Higher on-chip integration is made possible by using the 24pin package to increase the number of signal pins by 62% over the conventional 16-pin package. The emphasis in F100K is to minimize the number of SSI functions and maximize the use of MSI and LSI to reduce wiring delays and thus make more efficient use of the fast on-chip switching technology. Only 10 SSI functions are needed to serve the system needs presently requiring 25 functions in the ECL 10K family.

#### **Flexibility and Pin Assignment**

F100K was planned to minimize to total number of logic functions by increasing the flexibility of each function and by making use of more I/O pins. Since next-generation system performance and ease of system designs are major F100K goals, pin assignment is important and was planned to minimize crosstalk, noise coupling and feedthrough, to facilitate OR-ties and to ease power-bus routing. Some of the key considerations in selecting the F100K pin assignments were:

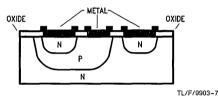

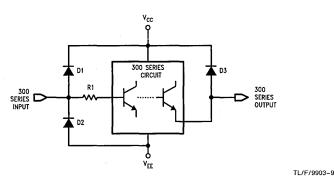

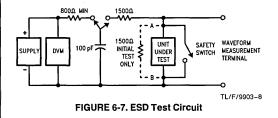

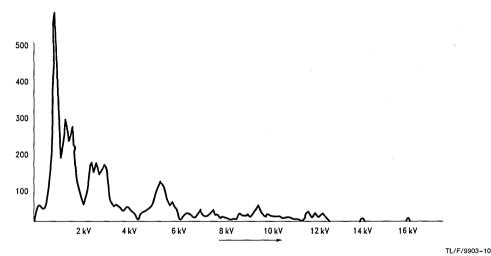

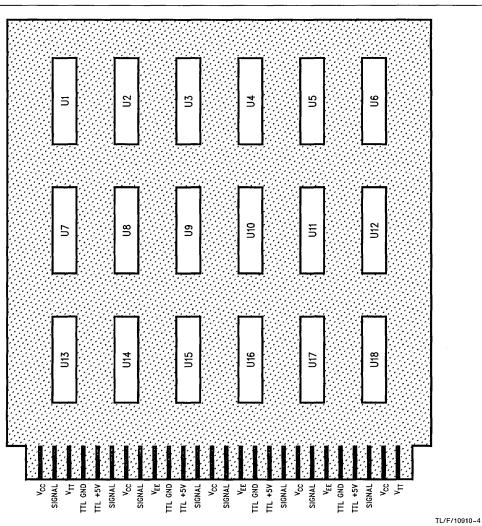

- Locate power pins in the center on opposite sides of the DIP package to ease system design and to provide lowinductance connections to the chip.