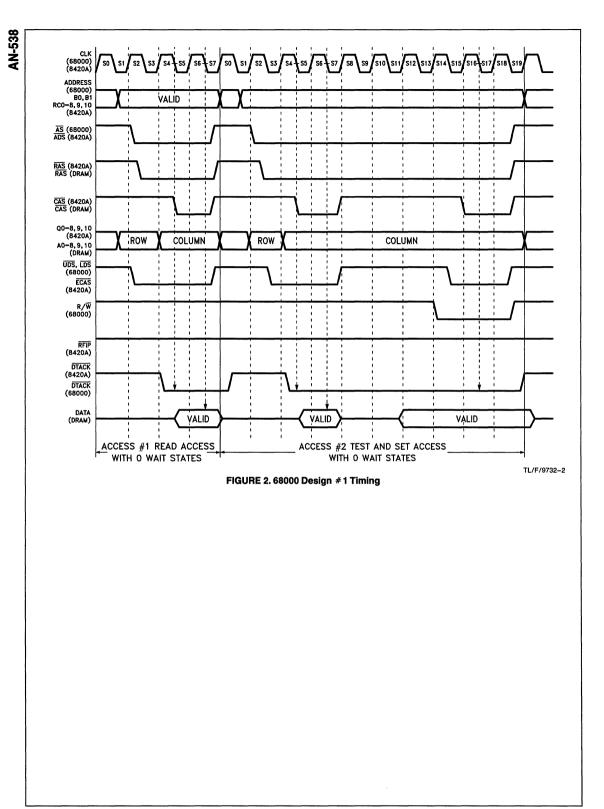

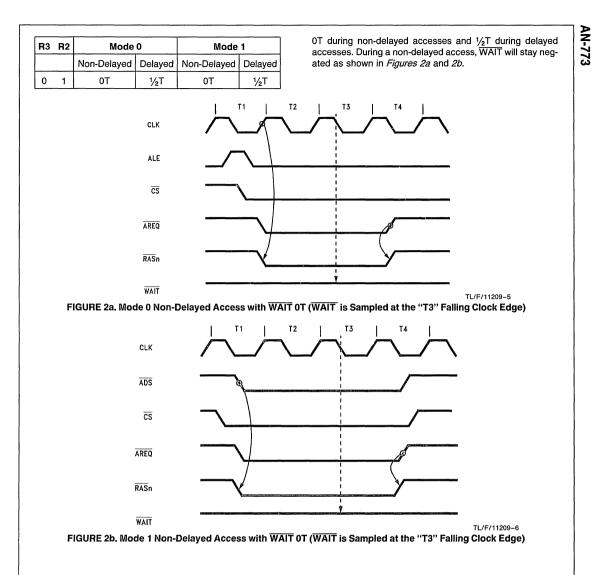

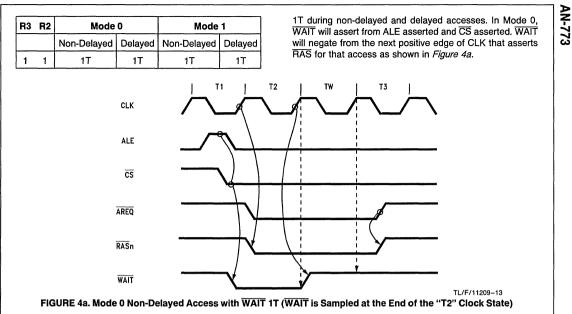

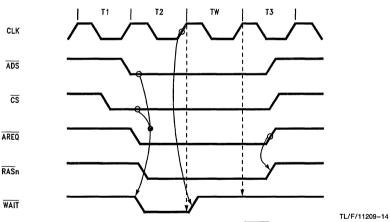

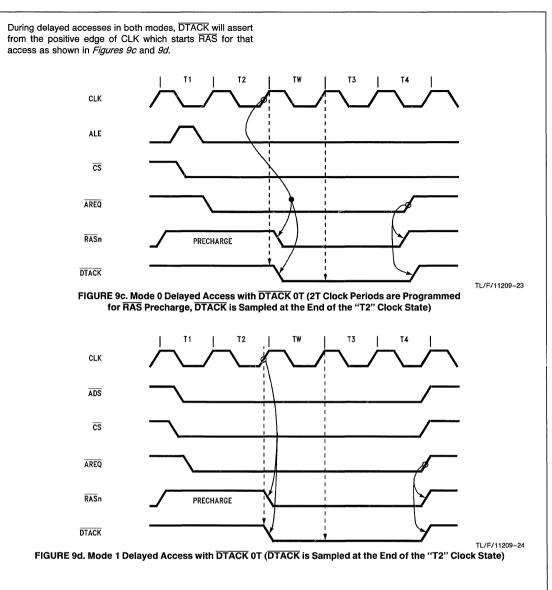

# DRAM Management Handbook

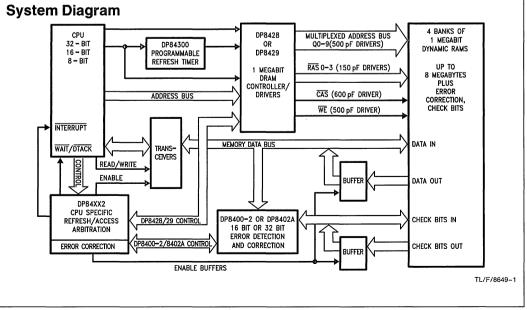

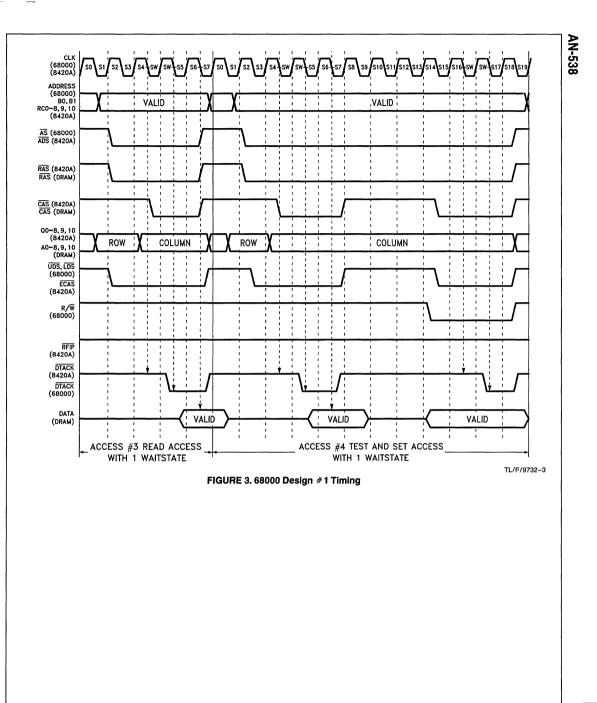

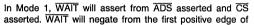

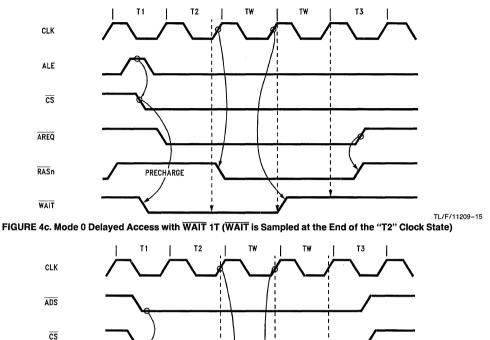

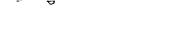

Dynamic Memory Control Error Detection And Correction Application Support

# **DRAM MANAGEMENT**

**1991 Edition**

**Dynamic Memory Control**

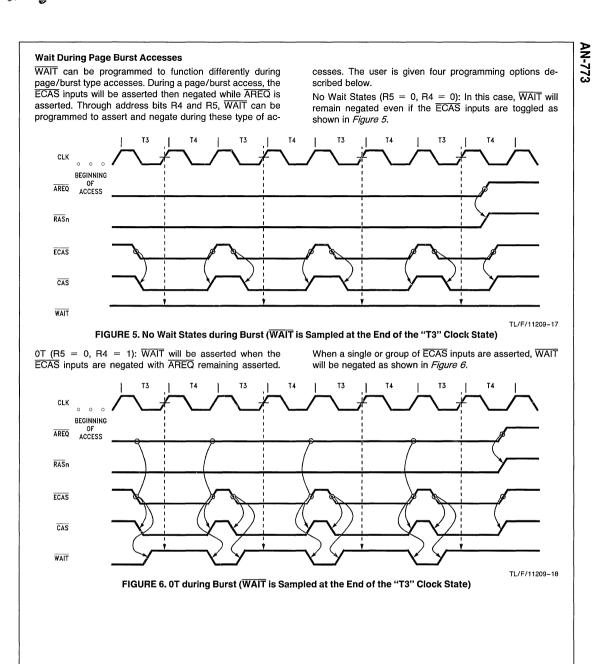

Error Detection and Correction Microprocessor Applications for the DP8408A/09A/17/18/19/28/29

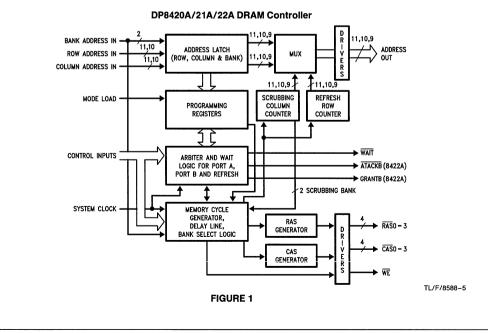

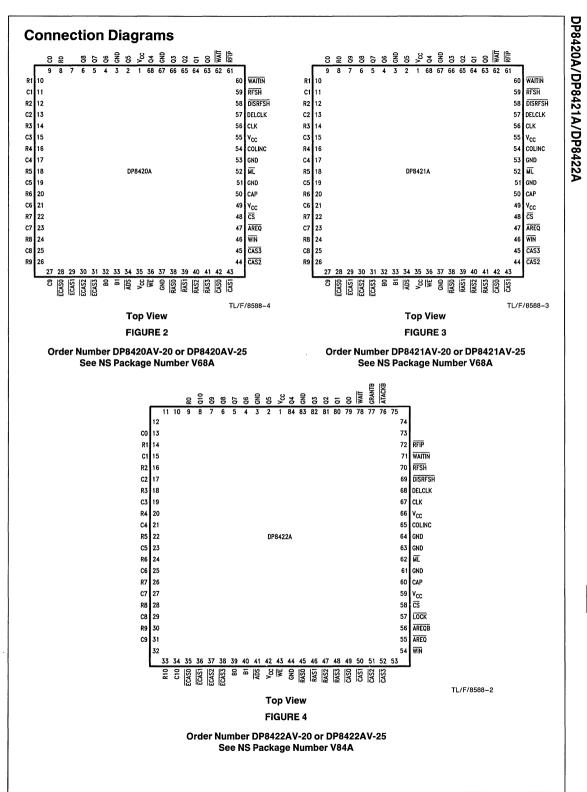

Microprocessor Applications for the DP8420A/21A/22A

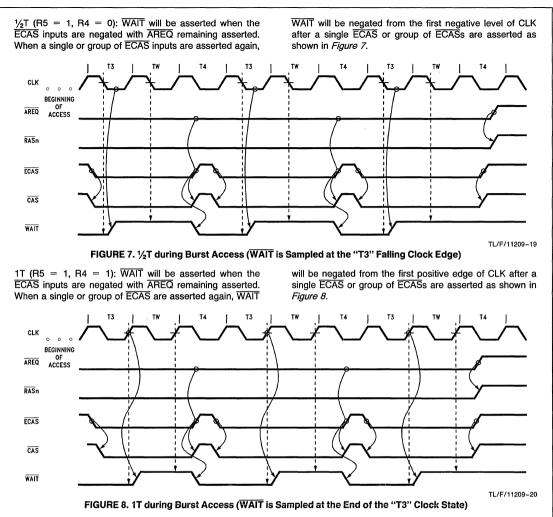

Microprocessor Application for the NS32CG821

**Physical Dimensions/Appendices**

#### TRADEMARKS

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

| Following is the most current     | list of National Semiconductor    | Corporation's trademarks and reg | jistered trademarks.  |  |

|-----------------------------------|-----------------------------------|----------------------------------|-----------------------|--|

| ABICTM                            | FACT™                             | MICROWIRE/PLUS™                  | SCXTM                 |  |

| Abuseable™                        | FACT Quiet Series™                | MOLE™                            | SERIES/800™           |  |

| Anadig™                           | FAIRCAD™                          | МРАтм                            | Series 900™           |  |

| ANS-R-TRAN™                       | Fairtech™                         | MST™                             | Series 3000™          |  |

| APPS™                             | FAST®                             | Naked-8™                         | Series 32000®         |  |

| ASPECT™                           | FASTr™                            | National <sup>®</sup>            | Shelf <b>//</b> Chek™ |  |

| Auto-Chem Deflasher™              | 5-Star Service™                   | National Semiconductor®          | Simple Switcher™      |  |

| BCPTM                             | Flash™                            | National Semiconductor           | SofChek™              |  |

| BI-FET™                           | GENIX™                            | Corp.®                           | SONICTM               |  |

| BI-FET II™                        | GNX™                              | NAX 800™                         | SPIRE™                |  |

| BI-LINE™                          | GTO™                              | Nitride Plus™                    | Staggered Refresh™    |  |

| BIPLAN™                           | HAMR™                             | Nitride Plus Oxide™              | STAR™                 |  |

| BLC™                              | HandiScan™                        | NML™                             | Starlink™             |  |

| BLX™                              | HEX 3000™                         | NOBUS™                           | STARPLEX™             |  |

| BMAC™                             | HPC™                              | NSC800™                          | Super-Block™          |  |

| Brite-Lite™                       | 3 <b>_</b> ®                      | NSCISE™                          | SuperChip™            |  |

| BSI™                              | ICM™                              | NSX-16™                          | SuperScript™          |  |

| CDD™                              | INFOCHEX™                         | NS-XC-16™                        | SYS32™                |  |

| CheckTrack™                       | Integral ISE™                     | NTERCOM™                         | TapePak®              |  |

| CIM™                              | Intelisplay™                      | NURAM™                           | TDS™                  |  |

| CIMBUS™                           | ISE™                              | OPAL™                            | TeleGate™             |  |

| CLASIC™                           | ISE/06™                           | OXISS™                           | The National Anthem®  |  |

| Clock⊮Chek™                       | ISE/08™                           | P <sup>2</sup> CMOS™             | TimerChek™            |  |

| COMBO®                            | ISE/16™                           | PC Master™                       | TINA™                 |  |

| COMBO ITM                         | ISE32™                            | Perfect Watch™                   | TLC™                  |  |

| COMBO II™                         | ISOPLANAR™                        | PharmarChek™                     | Trapezoidal™          |  |

| COPS™ microcontrollers            | ISOPLANAR-Z™                      | PLAN™                            | TRI-CODE™             |  |

| CRD™                              | KeyScan™                          | PLANAR™                          | TRI-POLY™             |  |

| DA4 <sup>TM</sup>                 | LMCMOS™                           | PLAYER™                          | TRI-SAFE™             |  |

| Datachecker <sup>®</sup>          | M <sup>2</sup> CMOS <sup>TM</sup> | Plus-2™                          | TRI-STATE®            |  |

| DENSPAK™                          | Macrobus™                         | Polycraft™                       | TURBOTRANSCEIVER™     |  |

| DIB™                              | Macrocomponent™                   | POSilink™                        | VIPTM                 |  |

| DISCERN™                          | MAPLTM                            | POSitalker™                      | VR32™                 |  |

| DISTILL™                          | MAXI-ROM®                         | Power + Control™                 | WATCHDOG™             |  |

| DNR®                              | Meat⊮Chek™                        | POWERplanar™                     | XMOS™                 |  |

| DPVMTM                            | MenuMaster™                       | QUAD3000TM                       | XPU™                  |  |

| E <sup>2</sup> CMOS <sup>TM</sup> | Microbus™ data bus                | QUIKLOOK™                        | Z STAR™               |  |

| ELSTAR™                           | MICRO-DAC™                        | RAT™                             | 883B/RETS™            |  |

| Embedded System                   | µtalker™                          | RTX16™                           | 883S/RETS™            |  |

| Processor™                        | Microtalker™                      | SABR™                            |                       |  |

| E-Z-LINK™                         | MICROWIRE™                        | Script <mark>⊮</mark> Chek™      |                       |  |

PAL® and PALASM™ are trademarks of and are used under license from Advanced Micro Devices, Inc.

Z80® and Z80A® are registered trademarks of Zilog Corporation.

Z8000™ is a trademark of Zilog Corporation.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive, P.O. Box 58090, Santa Clara, California 95052-8090 1-800-272-9959 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

# **DRAM Management Introduction**

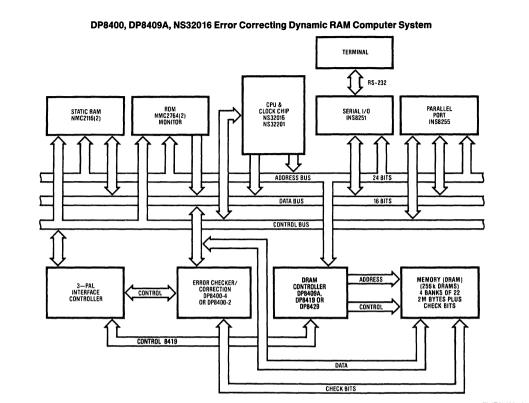

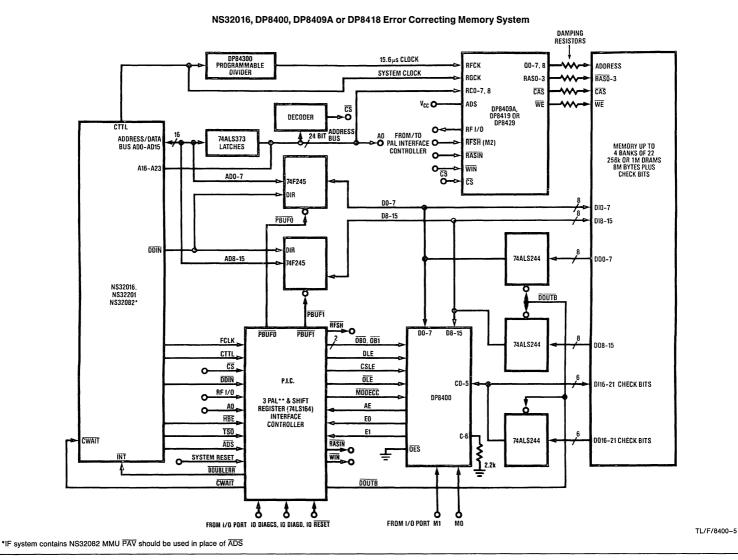

Today's large Dynamic Random Access Memory (DRAM) arrays require sophisticated high performance devices to provide timing access arbitration on board drive and control. National Semiconductor offers the broadest range of DRAM controllers with the highest "No-waitstate" performance available on the market. Controllers are available in Junction Isolated LS, Oxide Isolated ALS, and double metal CMOS for DRAMs from 64k bit through 4M bit devices, supporting memory arrays up to 64 Mbyte in size with only one LSI/VLSI device. For critical applications, National Semiconductor has developed several 16- and 32-bit Error Checking and Correction (ECC) devices to provide maximum data integrity.

The DRAM Management Handbook contains complete product information. This includes the largest number and most complete set of DRAM control and ECC products, peripheral support devices and application notes detailing complete DRAM memory system design.

# National Semiconductor

# Introduction to VLSI Products

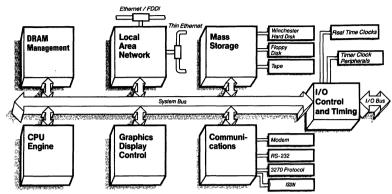

National Semiconductor VLSI products include complex peripheral circuits designed to serve a variety of applications. The VLSI products are especially well suited for microcomputer and microprocessor systems such as graphics workstations, personal computers, and many others. National Semiconductor VLSI devices are fully described in a series of databooks and handbooks.

Among the books are the following titles:

#### MASS STORAGE

The National Semiconductor family of mass storage interface products offers the industry's highest performance and broadest range of products for Winchester hard disks, high performance ESDI and SCSI hard disks and floppy disks. Combined with CLASICTM, analog and high performance microcontroller devices, these products offer unparalleled solutions for integration.

#### DRAM MANAGEMENT

National Semiconductor offers the broadest range of DRAM controllers with the highest "No-waitstate" performance available on the market. For critical applications, National Semiconductor has developed several 16- and 32-bit Error Checking and Correction (ECC) devices to provide maximum data integrity.

#### MICROCONTROLLER

As one of the broadest cost/performance product offerings in the industry today, National's microcontrollers provide the intelligence required for high performance applications such as laser printers, ISDN terminal adapters, floppy disks and SCSI hard disks. Complete support tools are available, including applications specific software, Designer's Kits, emulators, simulators, and development systems. Whether the application demands 4-, 8- or 16-bit performance, National has the right embedded control solution.

# LOCAL AREA NETWORKS, DATA COMMUNICATIONS, UARTS

National Semiconductor provides a complete three-chip solution for an entire IEEE 802.3 standard for Ethernet/Thin Ethernet LANs. National Semiconductor offers a completely integrated solution for the IBM 370 class mainframes, System 3X and AS/400 systems for physical layer front end and processing of the IBM 3270/3299 "coaxial" and 5250 "twinaxial" protocols. National's family of UARTs provides high performance, low power serial data input/output interface.

TL/XX/0058-1

#### INTERFACE

To drive the communications lines, National Semiconductor has drivers and receivers designed to meet all the major standards such as RS-232, RS-422, and RS-485.

#### REAL TIME CLOCKS

The RTC family provides a simple  $\mu$ P bus compatible interface to any system requiring accurate, reliable, on-going real time and calender functions. Certain products in this family also include power fail management and peripheral timers on board.

#### EMBEDDED SYSTEMS PROCESSORS

National's Embedded System Processor™ family offers the most complete solution to 32-bit embedded processor needs via CPUs, slave processors, system peripherals, evaluation/development tools and software.

Our total product system solution approach includes the hardware, software, and development support products necessary for your design. Evaluation board, in-system emulator, software development tools, and third party software are available now.

# **Product Status Definitions**

# **Definition of Terms**

| Data Sheet Identification     | Product Status            | Definition                                                                                                                                                                                                                                                                      |

|-------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information           | Formative or<br>In Design | This data sheet contains the design specifications for product<br>development. Specifications may change in any manner without notice.                                                                                                                                          |

| Preliminary                   | First<br>Production       | This data sheet contains preliminary data, and supplementary data will<br>be published at a later date. National Semiconductor Corporation<br>reserves the right to make changes at any time without notice in order<br>to improve design and supply the best possible product. |

| No<br>Identification<br>Noted | Full<br>Production        | This data sheet contains final specifications. National Semiconductor<br>Corporation reserves the right to make changes at any time without<br>notice in order to improve design and supply the best possible product.                                                          |

National Semiconductor Corporation reserves the right to make changes without further notice to any products herein to improve reliability, function or design. National does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

# **Table of Contents**

| Alphanumeric Index                                                               | x       |

|----------------------------------------------------------------------------------|---------|

| Section 1 Dynamic Memory Control                                                 |         |

| DRAM Controller Master Selection Guide                                           | 1-3     |

| DP8408A Dynamic RAM Controller/Driver                                            | 1-4     |

| DP8409A Multi-Mode Dynamic RAM Controller/Driver                                 | 1-22    |

| DP8417/NS32817/DP8418/NS32818/DP8419/NS32819/DP8419X/NS32819X 64k,               |         |

| 256k Dynamic RAM Controller/Drivers                                              | 1-44    |

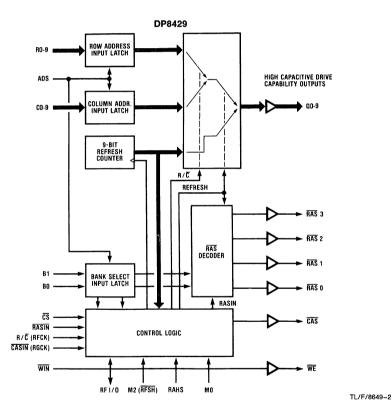

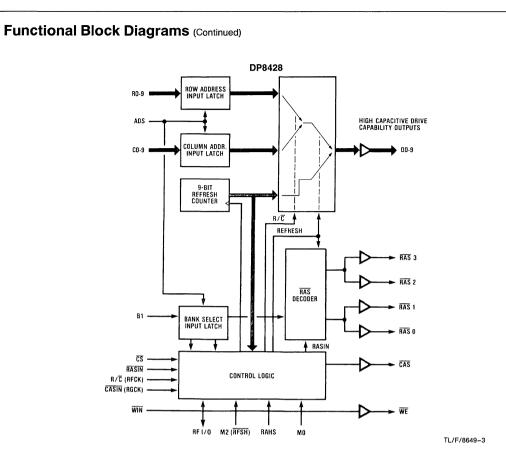

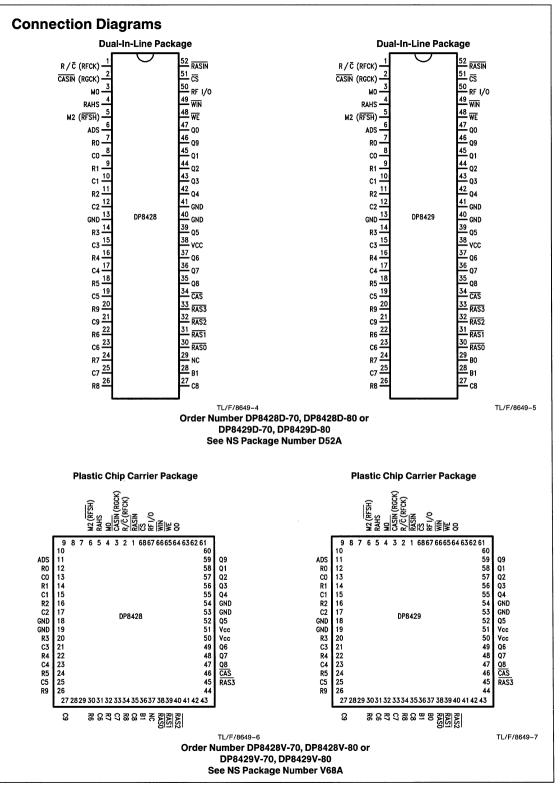

| DP8428/NS32828/DP8429/NS32829 1 Megabit High Speed Dynamic RAM                   |         |

| Controller/Drivers                                                               | 1-69    |

| DP8420A/DP8421A/DP8422A microCMOS Programmable 256k/1M/4M Dynamic                |         |

| RAM Controller/Drivers                                                           | 1-92    |

| DP8420V-33/DP8421V-33/DP8422V-33, DP84T22-25 microCMOS Programmable              |         |

| 256k/1M/4M Dynamic RAM Controller/Drivers                                        | 1-149   |

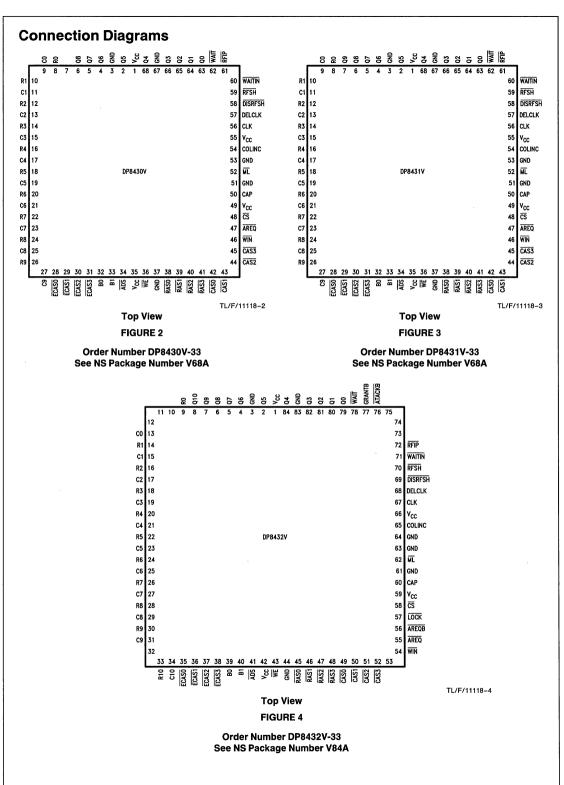

| DP8430V-33/DP8431V-33/DP8432V-33 microCMOS Programmable 256k/1M/4M               | 4 007   |

| Dynamic RAM Controller/Drivers                                                   | 1-207   |

| NS32CG821A microCMOS Programmable 1M Dynamic RAM Controller/Driver               | 1-261   |

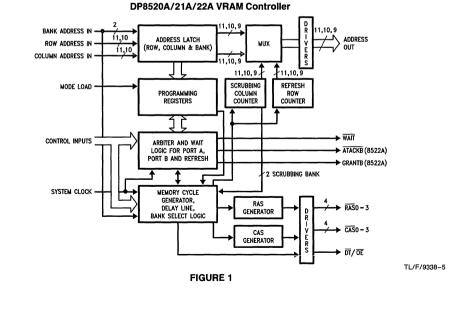

| DP8520A/DP8521A/DP8522A microCMOS Programmable 256k/1M/4M Video RAM              | 4 000   |

| Controller/Drivers                                                               | 1-298   |

| 29F68 256 Kbit Dynamic RAM Controller                                            | 1-367   |

| 54F/74F968 1 Mbit Dynamic RAM Controller                                         | 1-378   |

| AN-305 Precautions to Take When Driving Memories                                 | 1-391   |

| AB-1 DP8408A/DP8409A/DP8417/DP8418/DP8419/DP8428/DP8429 Application              | 1 005   |

| HintsAB-9 DP8408A/DP8409A Fastest DRAM Access Mode                               | 1-395   |

|                                                                                  | 1-396   |

| Section 2 Error Detection and Correction                                         |         |

| 54F/74F420 Parallel Check Bit/Syndrome Bit Generator                             | 2-3     |

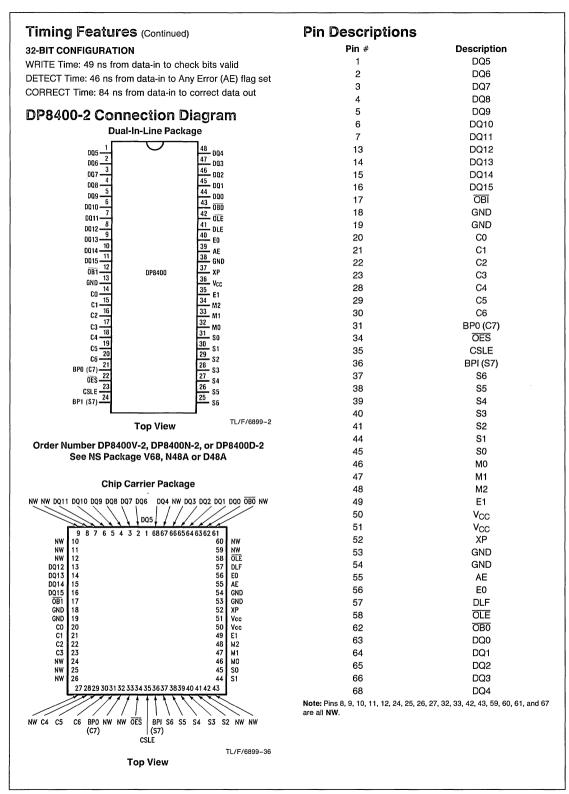

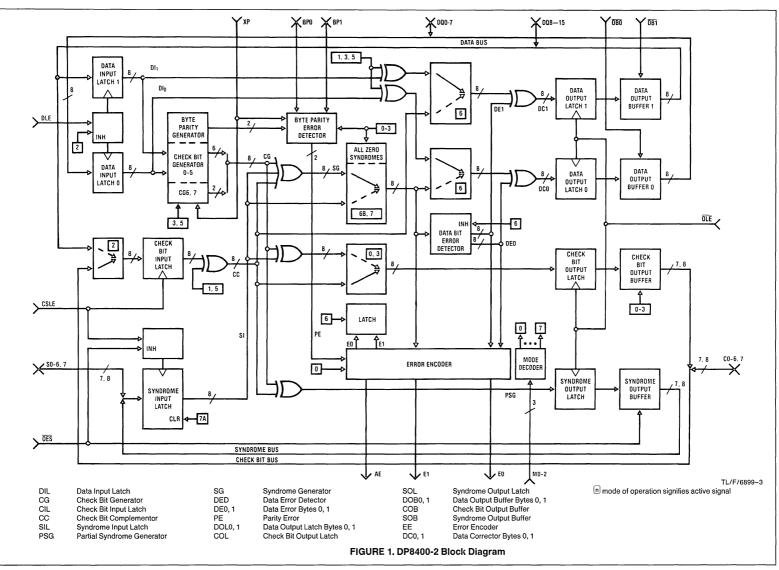

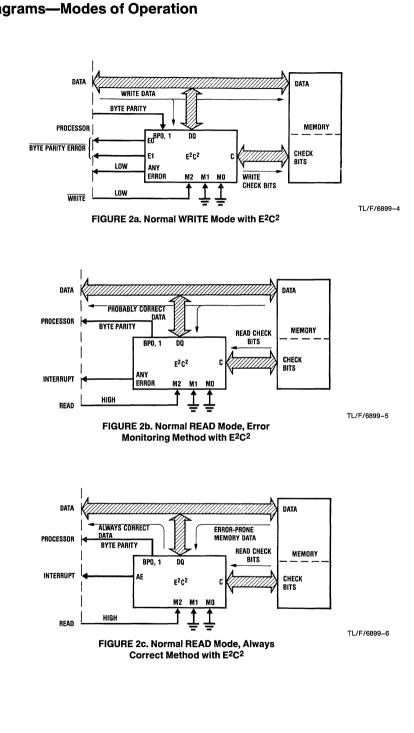

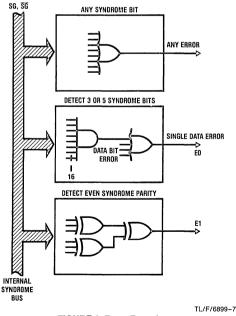

| DP8400-2—E <sup>2</sup> C <sup>2</sup> Expandable Error Checker/Corrector        | 2-8     |

| DP8402A/DP8403/DP8404/DP8405 32-Bit Parallel Error Detection and Correction      |         |

| Circuits (EDAC's)                                                                | 2-42    |

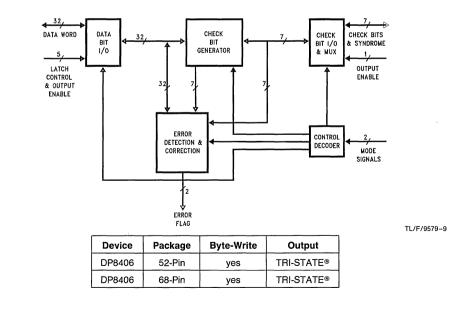

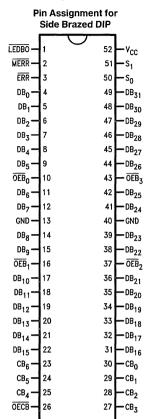

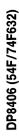

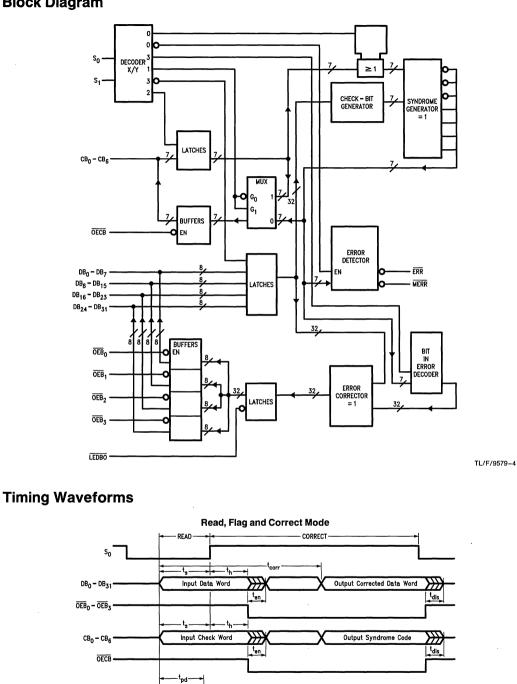

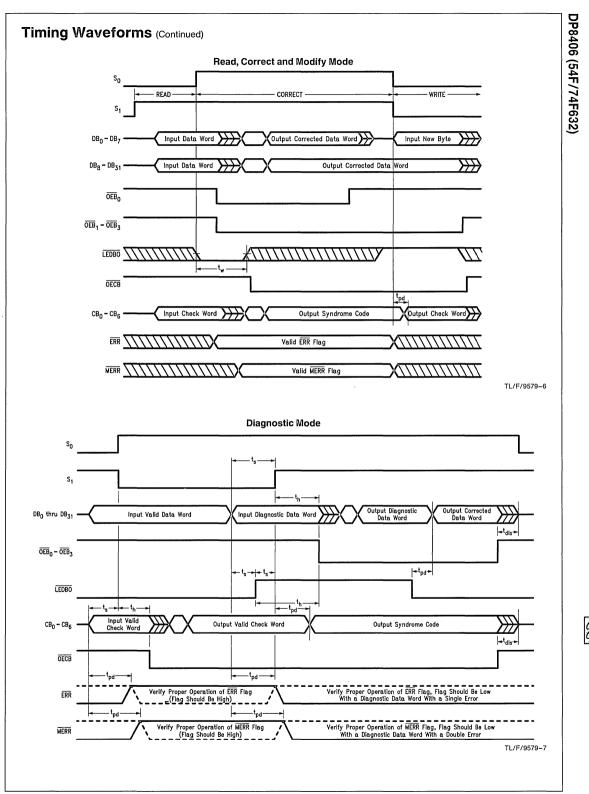

| DP8406 (54F/74F632) 32-Bit Parallel Error Detection and Correction Circuit       | 2-59    |

| AN-306 Expanding the Versatility of the DP8400                                   | 2-71    |

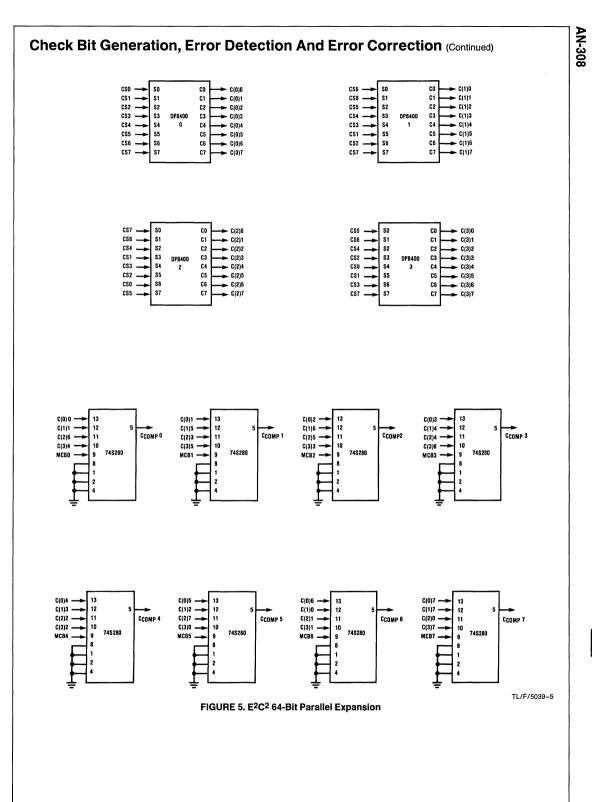

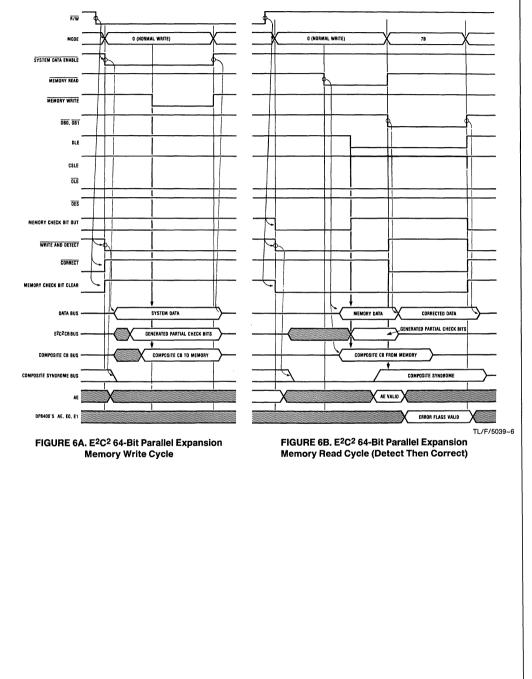

| AN-308 DP8400s in 64-Bit Expansion                                               | 2-83    |

| Section 3 Microprocessor Applications for the DP8408A/09A/17/18/19/28/29         |         |

| Microprocessor to DP8409A/17/18/19/28/29 Interface Selection Guide               | 3-3     |

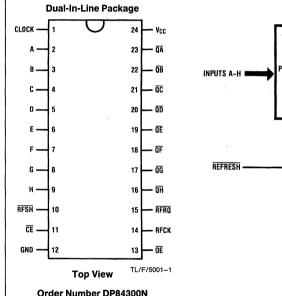

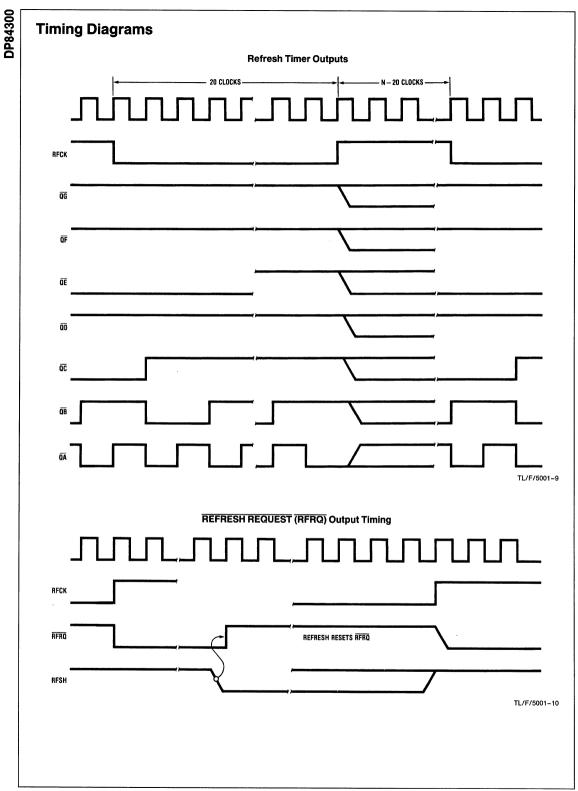

| DP84300 Programmable Refresh Timer                                               | 3-4     |

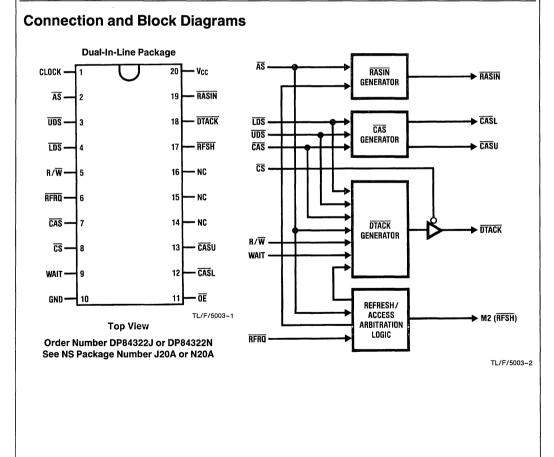

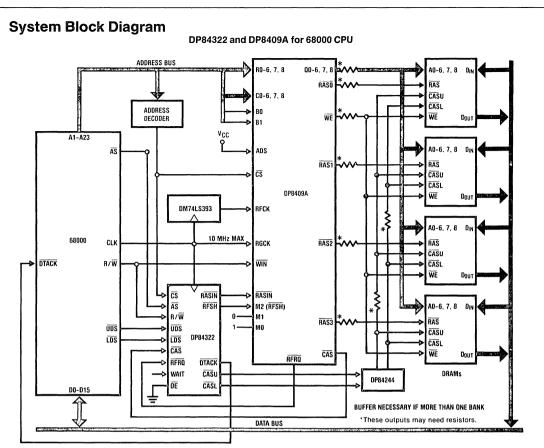

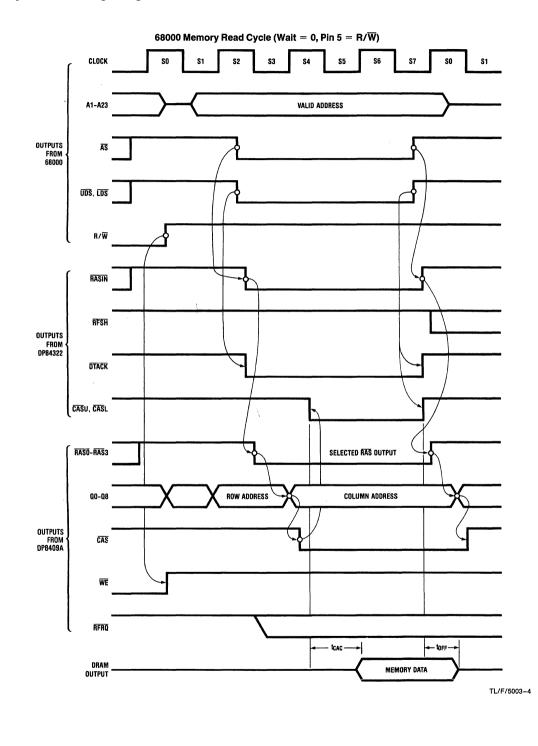

| DP84322 Dynamic RAM Controller Interface Circuit for the 68000 CPU               | 3-9     |

| DP84412 Dynamic RAM Controller Interface Series Circuit for the Series 32000 CPU | 3-24    |

| DP84422 Dynamic RAM Controller Interface Circuit for the 68000/008/010 CPUs      | 3-37    |

| DP84432 Dynamic RAM Controller Interface Circuit for the 8086/8088/80186/80188   |         |

| CPU's.                                                                           | 3-51    |

| DP84512 Dynamic RAM Controller Interface Circuit for the NS32332                 | 3-64    |

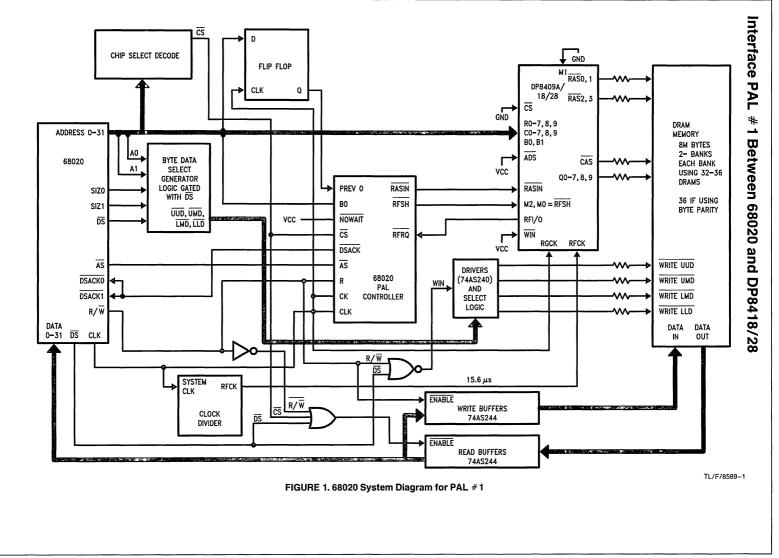

| DP84522 Dynamic RAM Controller Interface Circuit for the 68020 CPU               | 3-65    |

| DP84532 Dynamic RAM Controller Interface Circuit for the iAPX 286 CPU            | 3-81    |

| AN-309 Interfacing the DP8408A/DP8409A To Various Microprocessors                | 3-93    |

| AN-387 DP8400/DP8419 Error Correcting Dynamic RAM Memory System for the          | 0 407   |

| Series 32000                                                                     | 3-107   |

| AN-411 Determining the Speed of the Dynamic RAM Needed When Interfacing the      | 0 4 0 0 |

| DP8419-80 to Most Major Microprocessors                                          | 3-122   |

| AN-436 Dual Port Interface for the DP8417/DP8418/DP8419/DP8428/DP8429            | 0 100   |

| DRAM Controller                                                                  | 3-129   |

# Table of Contents (Continued)

-----

~

| Section 4 Microprocessor Applications for the DP8420A/21A/22A                    |       |

|----------------------------------------------------------------------------------|-------|

| AB-36 Explanation of National Semiconductor "PLAN" Software for Programming      |       |

| PALs                                                                             | 4-3   |

| AN-542 Interfacing the DP8420A/DP8421A/DP8422A to the                            |       |

| NS32008/NS32016/NS32C016/NS32032 and NS32132                                     | 4-4   |

| AN-543 Interfacing the DP8420A/DP8421A/DP8422A to the National Semiconductor     |       |

| NS32332                                                                          | 4-11  |

| AN-541 Interfacing the DP8420A/DP8421A/DP8422A to the National Semiconductor     |       |

| NS32532                                                                          | 4-24  |

| AN-540 A Dual Access NS32532 Error Detecting and Correcting Memory System        | 4-34  |

| AN-538 Interfacing the DP8420A/DP8421A/DP8422A to the 68000/008/010              | 4-40  |

| AN-615 Interfacing the DP8422A to the 68000-16 (Zero Wait State Burst Mode       |       |

| Access)                                                                          | 4-56  |

| AN-539 Interfacing the DP8420A/DP8421A/DP8422A to the 68020                      | 4-61  |

| AN-616 Interfacing the DP8422A to the 68020 (Zero Wait State Burst Mode Access)  | 4-82  |

| AN-617 Interfacing the DP8422A to an Asynchronous Port B in a Dual 68020 System. | 4-86  |

| AN-537 Interfacing the DP8420A/DP8421A/DP8422A to the 68030 Microprocessor       | 4-90  |

| AN-535 A PAL Interface for a Dual Access DP8422A/68030/74F632 Error Detecting    |       |

| and Correcting Memory System                                                     | 4-98  |

| AN-544 Interfacing the DP8420A/DP8421A/DP8422A to the 8086/186/88/188            |       |

| Microprocessor                                                                   | 4-114 |

| AN-545 Interfacing the DP8420A/DP8421A/DP8422A to the 80286                      | 4-118 |

| AN-618 A PAL Interface for a 25 MHz and above No-Wait State DP8422A/80286 Burst  |       |

| Mode DRAM Memory System                                                          | 4-130 |

| AN-536 Interfacing the DP8420A/DP8421A/DP8422A to the 80386                      | 4-139 |

| AN-619 Interfacing the DP8420A/DP8421A/DP8422A to the 80386 (Zero Wait State     |       |

| Burst Mode Access)                                                               | 4-156 |

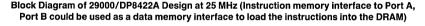

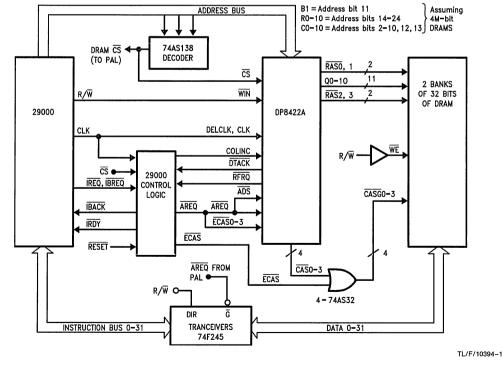

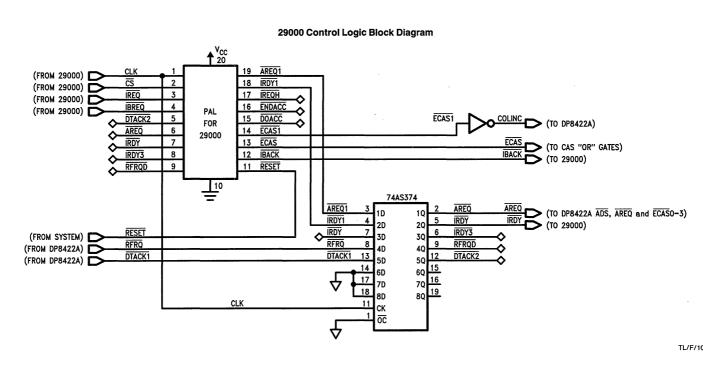

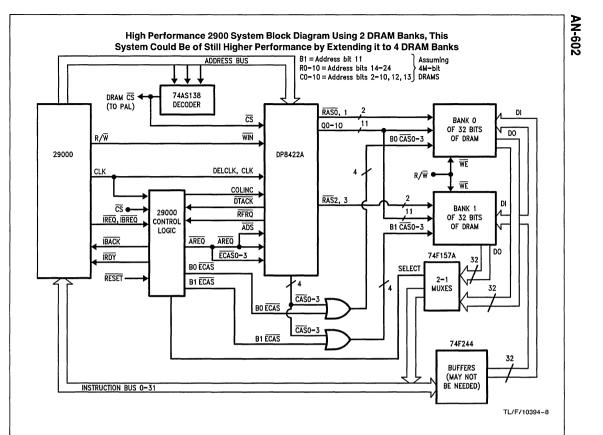

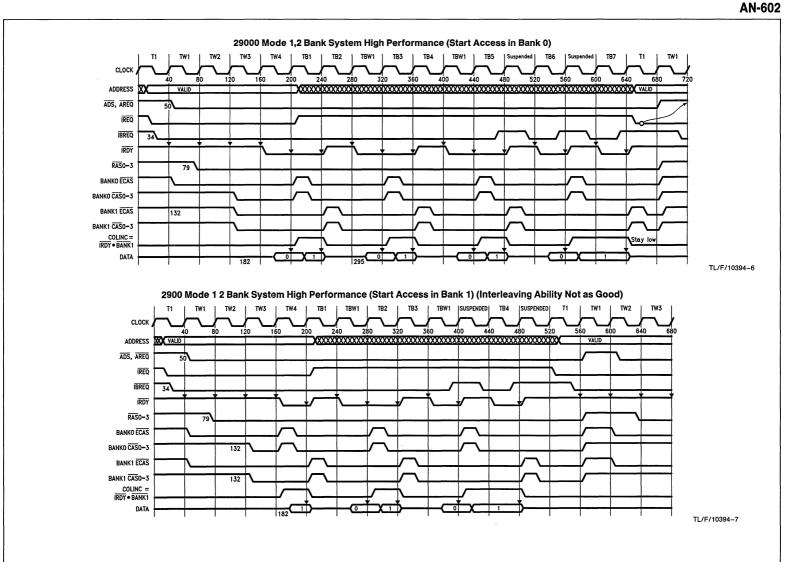

| AN-602 Interfacing the DP8420A/DP8421A/DP8422A to the 29000 Utilizing the Burst  |       |

| Access Mode                                                                      | 4-172 |

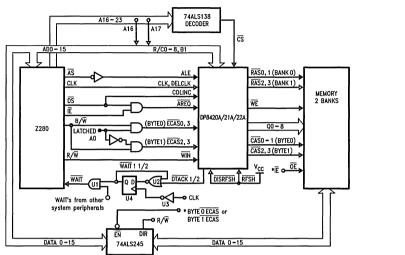

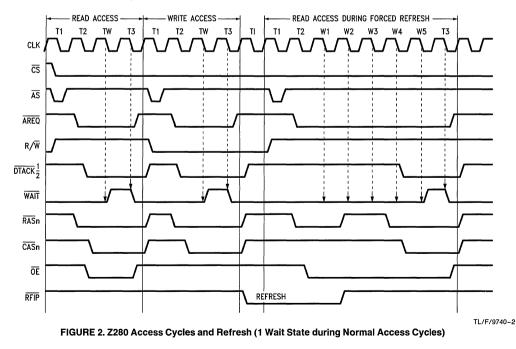

| AN-546 Interfacing the DP8420A/DP8421A/DP8422A to the Z280/Z80000/Z8000          |       |

| Microprocessor                                                                   | 4-185 |

| AN-642 Interfacing the Dual Port DP8422A to the TMS320C30 and the VME Bus        | 4-189 |

| AN-773 Port A Wait Support for the DP8420A/21A/22A, DP8420V/21V/22V,             |       |

| DP84T22V, DP8430V/31V/32V, DP8520A/21A/22A and NS32CG821A DRAM                   |       |

| Controllers                                                                      | 4-192 |

| Section 5 Microprocessor Application for the NS32CG821                           |       |

| AN-576 Interfacing the NS32CG821 to the NS32CG16                                 | 5-3   |

| Section 6 Physical Dimensions/Appendices                                         |       |

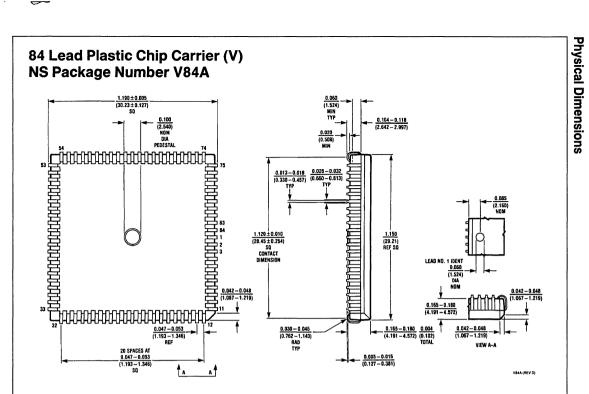

| Physical Dimensions                                                              | 6-3   |

| Bookshelf                                                                        |       |

| Distributors                                                                     |       |

# Alpha-Numeric Index

| 29F68 256 Kbit Dynamic RAM Controller 1                                                   | -367    |

|-------------------------------------------------------------------------------------------|---------|

| 54F420 Parallel Check Bit/Syndrome Bit Generator                                          | . 2-3   |

| 54F632 32-Bit Parallel Error Detection and Correction Circuit                             | 2-59    |

| 54F968 1 Mbit Dynamic RAM Controller 1                                                    | -378    |

| 74F420 Parallel Check Bit/Syndrome Bit Generator                                          | . 2-3   |

| 74F632 32-Bit Parallel Error Detection and Correction Circuit                             |         |

| 74F968 1 Mbit Dynamic RAM Controller 1                                                    |         |

| AB-1 DP8408A/DP8409A/DP8417/DP8418/DP8419/DP8428/DP8429 Application Hints 1               | -395    |

| AB-9 DP8408A/DP8409A Fastest DRAM Access Mode1                                            |         |

| AB-36 Explanation of National Semiconductor "PLAN" Software for Programming PALs          |         |

| AN-305 Precautions to Take When Driving Memories                                          |         |

| AN-306 Expanding the Versatility of the DP8400                                            |         |

| AN-308 DP8400s in 64-Bit Expansion                                                        |         |

| AN-309 Interfacing the DP8408A/DP8409A To Various Microprocessors                         |         |

| AN-387 DP8400/DP8419 Error Correcting Dynamic RAM Memory System for the Series 32000 3    |         |

| AN-411 Determining the Speed of the Dynamic RAM Needed When Interfacing the               |         |

| DP8419-80 to Most Major Microprocessors                                                   | -122    |

| AN-436 Dual Port Interface for the DP8417/DP8418/DP8419/DP8428/DP8429 DRAM Controller . 3 |         |

| AN-535 A PAL Interface for a Dual Access DP8422A/68030/74F632 Error Detecting and         |         |

| Correcting Memory System                                                                  | 4-98    |

| AN-536 Interfacing the DP8420A/DP8421A/DP8422A to the 80386                               |         |

| AN-537 Interfacing the DP8420A/DP8421A/DP8422A to the 68030 Microprocessor                |         |

| AN-538 Interfacing the DP8420A/DP8421A/DP8422A to the 68000/008/010                       |         |

| AN-539 Interfacing the DP8420A/DP8421A/DP8422A to the 68020                               |         |

| AN-540 A Dual Access NS32532 Error Detecting and Correcting Memory System                 |         |

| AN-541 Interfacing the DP8420A/DP8421A/DP8422A to the National Semiconductor NS32532      |         |

| AN-542 Interfacing the DP8420A/DP8421A/DP8422A to the                                     | 7 67    |

| NS32008/NS32016/NS32C016/NS32C32 and NS32132                                              | 1-1     |

| AN-543 Interfacing the DP8420A/DP8421A/DP8422A to the National Semiconductor NS32332      |         |

| AN-544 Interfacing the DP8420A/DP8421A/DP8422A to the 8086/186/88/188 Microprocessor 4    |         |

| AN-545 Interfacing the DP8420A/DP8421A/DP8422A to the 80286                               |         |

| AN-546 Interfacing the DP8420A/DP8421A/DP8422A to the 00200                               | -110    |

| Microprocessor                                                                            | -185    |

| AN-576 Interfacing the NS32CG821 to the NS32CG16                                          |         |

| AN-602 Interfacing the DP8420A/DP8421A/DP8422A to the 29000 Utilizing the Burst Access    | . 5-5   |

| Mode                                                                                      | 1 1 7 0 |

| AN-615 Interfacing the DP8422A to the 68000-16 (Zero Wait State Burst Mode Access)        |         |

| AN-615 Interfacing the DP6422A to the 68020 (Zero Wait State Burst Mode Access)           |         |

| AN-617 Interfacing the DP6422A to an Asynchronous Port B in a Dual 68020 System           |         |

| AN-617 Interfacing the DP6422A to an Asynchronous Port B in a Duar 66020 System           | 4-00    |

|                                                                                           | 1 100   |

| DRAM Memory System                                                                        | -130    |

|                                                                                           |         |

| ···/, ·····                                                                               | 1-156   |

| AN-642 Interfacing the Dual Port DP8422A to the TMS320C30 and the VME Bus                 | 1-189   |

| AN-773 Port A Wait Support for the DP8420A/21A/22A, DP8420V/21V/22V, DP84T22V,            |         |

| DP8430V/31V/32V, DP8520A/21A/22A and NS32CG821A DRAM Controllers                          |         |

| DP84T22-25 microCMOS Programmable 4M Dynamic RAM Controller/Driver                        |         |

| DP8400-2—E <sup>2</sup> C <sup>2</sup> Expandable Error Checker/Corrector                 |         |

| DP8402A 32-Bit Parallel Error Detection and Correction Circuits (EDAC's)                  |         |

| DP8403 32-Bit Parallel Error Detection and Correction Circuits (EDAC's)                   |         |

| DP8404 32-Bit Parallel Error Detection and Correction Circuits (EDAC's)                   | 2-42    |

# Alpha-Numeric Index (Continued)

| DP8405 32-Bit Parallel Error Detection and Correction Circuits (EDAC's)                   |

|-------------------------------------------------------------------------------------------|

| DP8406 32-Bit Parallel Error Detection and Correction Circuit                             |

| DP8408A Dynamic RAM Controller/Driver                                                     |

| DP8409A Multi-Mode Dynamic RAM Controller/Driver                                          |

| DP8417 64k Dynamic RAM Controller/Driver1-44                                              |

| DP8418 64k Dynamic RAM Controller/Driver 1-44                                             |

| DP8419 256k Dynamic RAM Controller/Driver1-44                                             |

| DP8419X 256k Dynamic RAM Controller/Driver                                                |

| DP8420A microCMOS Programmable 256k Dynamic RAM Controller/Driver                         |

| DP8420V-33 microCMOS Programmable 256k Dynamic RAM Controller/Driver                      |

| DP8421A microCMOS Programmable 1M Dynamic RAM Controller/Driver                           |

| DP8421V-33 microCMOS Programmable 1M Dynamic RAM Controller/Driver                        |

| DP8422A microCMOS Programmable 4M Dynamic RAM Controller/Driver                           |

| DP8422V-33 microCMOS Programmable 4M Dynamic RAM Controller/Driver                        |

| DP8428 1 Megabit High Speed Dynamic RAM Controller/Driver                                 |

| DP8429 1 Megabit High Speed Dynamic RAM Controller/Driver                                 |

| DP8430V-33 microCMOS Programmable 256k Dynamic RAM Controller/Driver                      |

| DP8431V-33 microCMOS Programmable 1M Dynamic RAM Controller/Driver                        |

| DP8432V-33 microCMOS Programmable 4M Dynamic RAM Controller/Driver                        |

| DP8520A microCMOS Programmable 256k Video RAM Controller/Driver                           |

| DP8521A microCMOS Programmable 1M Video RAM Controller/Driver                             |

| DP8522A microCMOS Programmable 4M Video RAM Controller/Driver 1-298                       |

| DP84300 Programmable Refresh Timer                                                        |

| DP84322 Dynamic RAM Controller Interface Circuit for the 68000 CPU                        |

| DP84412 Dynamic RAM Controller Interface Series Circuit for the Series 32000 CPU 3-24     |

| DP84422 Dynamic RAM Controller Interface Circuit for the 68000/008/010 CPUs               |

| DP84432 Dynamic RAM Controller Interface Circuit for the 8086/8088/80186/80188 CPU's 3-51 |

| DP84512 Dynamic RAM Controller Interface Circuit for the NS32332                          |

| DP84522 Dynamic RAM Controller Interface Circuit for the 68020 CPU                        |

| DP84532 Dynamic RAM Controller Interface Circuit for the iAPX 286 CPU                     |

| NS32CG821A microCMOS Programmable 1M Dynamic RAM Controller/Driver 1-261                  |

| NS32817 64k Dynamic RAM Controller/Driver 1-44                                            |

| NS32818 64k Dynamic RAM Controller/Driver 1-44                                            |

| NS32819 256k Dynamic RAM Controller/Driver 1-44                                           |

| NS32819X 256k Dynamic RAM Controller/Driver 1-44                                          |

| NS32828 1 Megabit High Speed Dynamic RAM Controller/Driver 1-69                           |

| NS32829 1 Megabit High Speed Dynamic RAM Controller/Driver 1-69                           |

# Section 1 Dynamic Memory Control

# **Section 1 Contents**

| DRAM Controller Master Selection Guide                                     | 1-3   |

|----------------------------------------------------------------------------|-------|

| DP8408A Dynamic RAM Controller/Driver                                      | 1-4   |

| DP8409A Multi-Mode Dynamic RAM Controller/Driver                           | 1-22  |

| DP8417/NS32817/DP8418/NS32818/DP8419/NS32819/DP8419X/NS32819X 64k, 256k    |       |

| Dynamic RAM Controller/Drivers                                             | 1-44  |

| DP8428/NS32828/DP8429/NS32829 1 Megabit High Speed Dynamic RAM             |       |

| Controller/Drivers                                                         | 1-69  |

| DP8420A/DP8421A/DP8422A microCMOS Programmable 256k/1M/4M Dynamic RAM      |       |

| Controller/Drivers                                                         | 1-92  |

| DP8420V-33/DP8421V-33/DP8422V-33, DP84T22-25 microCMOS Programmable        |       |

| 256k/1M/4M Dynamic RAM Controller/Drivers                                  | 1-149 |

| DP8430V-33/DP8431V-33/DP8432V-33 microCMOS Programmable 256k/1M/4M Dynamic |       |

| RAM Controller/Drivers                                                     | 1-207 |

| NS32CG821A microCMOS Programmable 1M Dynamic RAM Controller/Driver         | 1-261 |

| DP8520A/DP8521A/DP8522A microCMOS Programmable 256k/1M/4M Video RAM        |       |

| Controller/Drivers                                                         | 1-298 |

| 29F68 256 Kbit Dynamic RAM Controller                                      | 1-367 |

| 54F/74F968 1 Mbit Dynamic RAM Controller                                   | 1-378 |

| AN-305 Precautions to Take When Driving Memories                           | 1-391 |

| AB-1 DP8408A/DP8409A/DP8417/DP8418/DP8419/DP8428/DP8429 Application Hints  | 1-395 |

| AB-9 DP8408A/DP8409A Fastest DRAM Access Mode                              | 1-396 |

|                                                                            |       |

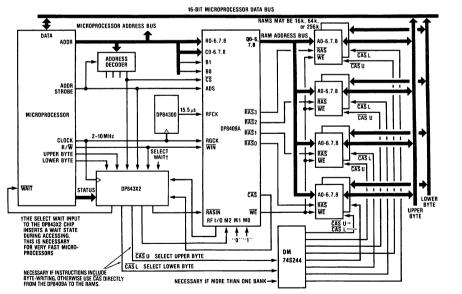

## **DRAM Controller Master Selection Guide**

The data below is intended to highlight the key differentiable features of each DRAM Controller/Driver offered by National Semiconductor. All NSC DRAM controllers integrate onboard delay line timing, high capacitive drive, row/column muxing logic, refresh counter, row and column input latches, memory bank select logic. As a result of the family feature commonality, most devices offer pin for pin up/downward compatibility. Beyond this however, the process and design differences between the devices result in a broad selection of feature and performance options for the best system fit.

| Device # &<br>Speed Options                                | DRAMS<br>Supported                         | Process                     | Тур<br>Ісс | A.C. Specified<br>Word Width                  | Max RAS<br>to CAS Out<br>*Fast Slow<br>Mode Mode | Guaranteed Row<br>Address Hold<br>*Fast Slow<br>Mode Mode | v <sub>cc</sub> | Operating<br>Temp Range                                                                                              | Package            | Page<br>No.            |

|------------------------------------------------------------|--------------------------------------------|-----------------------------|------------|-----------------------------------------------|--------------------------------------------------|-----------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------|--------------------|------------------------|

| DP8408A<br>A-2<br>A-3                                      | 16, 64k                                    | Junction<br>Isolated<br>(S) | 210 mA     | 4 Banks of<br>16 Bit Data w/<br>6 Bit ECC ea. | 105 ns/125 ns<br>85 ns/100 ns<br>120 ns/145 ns   | 20 ns/30 ns<br>12 ns/20 ns<br>20 ns/30 ns                 | +5V ±5%         | 0°-70°C<br>0°-85°C                                                                                                   | 48N<br>48D         | 1-4                    |

| DP8409A<br>A-2<br>A-3                                      | 16, 64, 256k                               | Junction<br>Isolated<br>(S) | 210 mA     | 4 Banks of<br>16 Bit Data w/<br>6 Bit ECC ea. | 105 ns/125 ns<br>85 ns/100 ns<br>120 ns/145 ns   | 20 ns/30 ns<br>12 ns/20 ns<br>20 ns/30 ns                 | +5V ±5%         | 0°-70°C<br>0°-85°C                                                                                                   | 48N<br>48D<br>68V  | 1-22                   |

| DP8417-80<br>-70                                           | 16, 64, 256k                               | Oxide<br>Isolated<br>(ALS)  | 150 mA     | 4 Banks of<br>16 Bit Data w/<br>6 Bit ECC ea. | 63 ns/80 ns<br>50 ns/72 ns                       | 15 ns/25 ns<br>15 ns/25 ns                                | +5V ±10%        | 0°-70°C<br>-40°-+85°C<br>-55°-+125°C                                                                                 | 48 N<br>48D<br>68V | 1-44                   |

| DP8418-80<br>-70                                           | 16, 64, 256k                               | Oxide<br>Isolated<br>(ALS)  | 150 mA     | 2 Banks of<br>32 Bit Data w/<br>7 Bit ECC ea. | 63 ns/80 ns<br>50 ns/72 ns                       | 15 ns/25 ns<br>15 ns/25 ns                                | +5V ±10%        | 0°-70°C<br>-40°-+85°C<br>-55°-+125°C                                                                                 | 48 N<br>48D<br>68V | 1-44                   |

| DP8419-80<br>-70                                           | 16, 64, 256k                               | Oxide<br>Isolated<br>(ALS)  | 150 mA     | 4 Banks of<br>16 Bit Data w/<br>6 Bit ECC ea. | 63 ns/80 ns<br>50 ns/72 ns                       | 15 ns/25 ns<br>15 ns/25 ns                                | +5V ±10%        | $\begin{bmatrix} 0^{\circ} - 70^{\circ}C \\ -40^{\circ} - +85^{\circ}C \\ -55^{\circ} - +125^{\circ}C \end{bmatrix}$ | 48 N<br>48D<br>68V | 1-44                   |

| DP8420A/21A/22A<br>DP8420V/21V/22V/T22V<br>DP8430V/31V/32V | 16, 64, 256k,<br>1 Mega Bit,<br>4 Mega Bit | 2μ CMOS                     | 5 mA       | 2 Banks of<br>32 Bit Data w/<br>7 Bit ECC ea. | 53 ns/63 ns<br>47 ns/56 ns                       | 15 ns/25 ns<br>15 ns/25 ns                                | +5V ±10%        | $\begin{bmatrix} 0^{\circ} - 70^{\circ}C \\ -40^{\circ} - +85^{\circ}C \\ -55^{\circ} - +125^{\circ}C \end{bmatrix}$ | 68V<br>84V         | 1-92<br>1-149<br>1-207 |

| DP8428-80<br>-70                                           | 16, 64, 256k<br>& 1 Mega Bit               | Oxide<br>Isolated<br>(ALS)  | 150 mA     | 2 Banks of<br>32 Bit Data w/<br>7 Bit ECC ea. | 63 ns/80 ns<br>50 ns/72 ns                       | 15 ns/25 ns<br>15 ns/25 ns                                | +5V ±10%        | $\begin{bmatrix} 0^{\circ} - 70^{\circ}C \\ -40^{\circ} - +85^{\circ}C \\ -55^{\circ} - +125^{\circ}C \end{bmatrix}$ | 52D<br>68V         | 1-69                   |

| DP8429-80<br>-70                                           | 16, 64, 256k<br>& 1 Mega Bit               | Oxide<br>Isolated<br>(ALS)  | 150 mA     | 4 Banks of<br>16 Bit Data w/<br>6 Bit ECC ea. | 63 ns/80 ns<br>50 ns/72 ns                       | 15 ns/25 ns<br>15 ns/25 ns                                | +5V ±10%        | 0°-70°C<br>-40°-+85°C<br>-55°-+125°C                                                                                 | 52D<br>68V         | 1-69                   |

\*All AC valves shown factor in worst case loading (including all ouputs switching simultaneously), operating temperature, and V<sub>CC</sub> supply variables. All delays assume the use of National's on-board automatic timing and delay line logic although external delay line control timing is allowed and supported.

#### **DRAM Controller Master Selection Guide**

# **DP8408A Dynamic RAM Controller/Driver**

## **General Description**

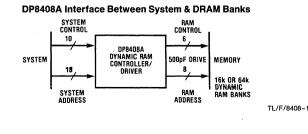

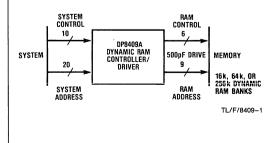

Dynamic memory system designs, which formerly required several support chips to drive the memory array, can now be implemented with a single IC . . . the DP8408A Dynamic RAM Controller/Driver. The DP8408A is capable of driving all 16k and 64k Dynamic RAMs (DRAMs). Since the DP8408A is a one-chip solution (including capacitive-load drivers), it minimizes propagation delay skews, the major performance disadvantage of multiple-chip memory drive and control.

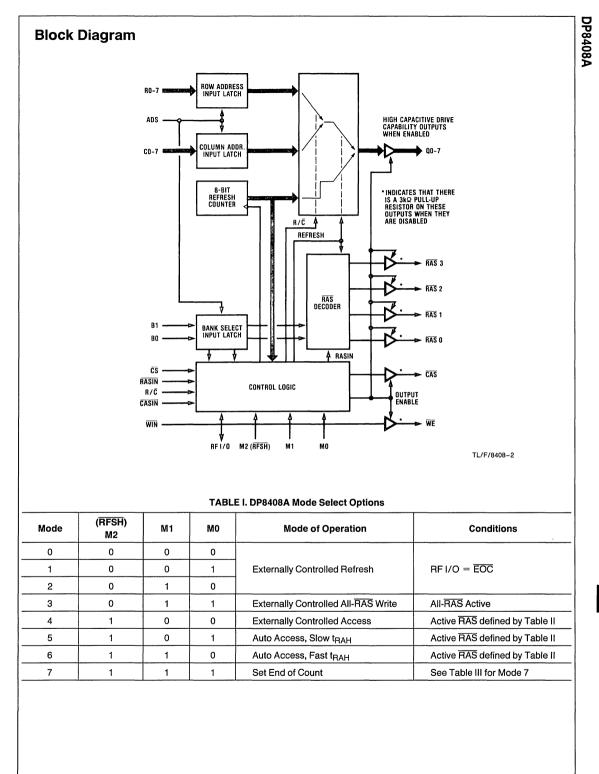

The DP8408A's 6 modes of operation offer a wide selection of DRAM control capabilities. Memory access may be controlled externally or on-chip automatically; an on-chip refresh counter makes refreshing less complicated.

The DP8408A is a 48-pin DRAM Controller/Driver with 8 multiplexed address outputs and control signals. It consists of two 8-bit address latches, an 8-bit refresh counter, and control logic. All output drivers are capable of driving 500 pF loads with propagation delays of 25 ns. The DP8408A timing parameters are specified driving the typical load capacitance of 88 DRAMs, including trace capacitance.

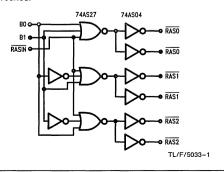

The DP8408A has 3 mode-control pins: M2, M1, and M0, where M2 is in general REFRESH. These 3 pins select 6 modes of operation. Inputs B1 and B0 in the memory access modes (M2 = 1), are select inputs which select one of four RAS outputs. During normal access, the 8 address outputs can be selected from the Row Address Latch or the Column Address Latch. During refresh, the 8-bit on-chip refresh counter is enabled onto the address bus and in this mode all RAS outputs are selected, while CAS is inhibited.

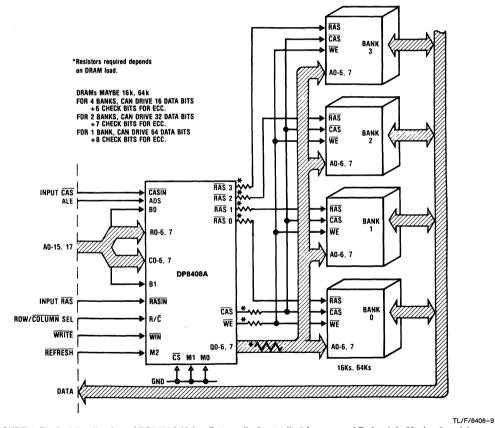

The DP8408A can drive up to 4 banks of DRAMs, with each bank comprised of 16k's, or 64k's. Control signal outputs RAS, CAS, and WE are provided with the same drive capability. Each RAS output drives one bank of DRAMs so that the four RAS outputs are used to select the banks, while CAS, WE, and the multiplexed addresses can be connected to all of the banks of DRAMs. This leaves the non-selected banks in the standby mode (less than one tenth of the operating power) with the data outputs in TRI-STATE®. Only the bank with its associated RAS low will be written to or read from.

## **Operational Features**

- All DRAM drive functions on one chip—minimizes skew on outputs, maximizes AC performance

- On-chip capacitive-load drives (specified to drive up to 88 DRAMs)

- Drive directly all 16k and 64k DRAMs

- Capable of addressing 64k and 256k words

- Propagation delays of 25 ns typical at 500 pF load

- CAS goes low automatically after column addresses are valid if desired

- Auto Access mode provides RAS, Row to Column, select, then CAS automatically and fast

- WE follows WIN unconditionally—offering READ, WRITE or READ-MODIFY-WRITE cycles

- On-chip 8-bit refresh counter with selectable End-of-Count (127 or 255)

- End-of-Count indicated by RF I/O pin going low at 127 or 255

- Low input on RF I/O resets 8-bit refresh counter

- CAS inhibited during refresh cycle

- Fall-through latches on address inputs controlled by ADS

- TRI-STATE outputs allow multi-controller addressing of memory

- Control output signals go high-impedance logic "1" when disabled for memory sharing

- Power-up: counter reset, control signals high, address outputs TRI-STATE, and End-of-Count set to 127

### Mode Features

- 6 modes of operation: 3 access, 1 refresh, and 2 set-up

- 2 externally controlled modes: 1 access (Mode 4) and 1 refresh (Modes 0, 1, 2)

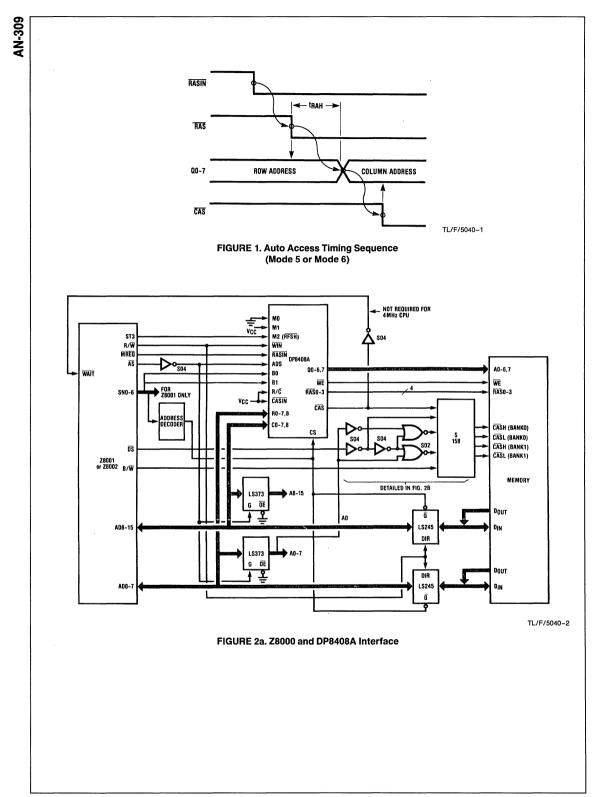

- 2 auto-access modes  $\overline{RAS} \rightarrow R/\overline{C} \rightarrow \overline{CAS}$  automatic, with  $t_{RAH} = 20$  or 30 ns minimum (Modes 5, 6)

- Externally controlled All-RAS Access modes for memory initialization (Mode 3)

- End-of-Count value of Refresh Counter set by B1 and B0 (Mode 7)

1-5

Ц

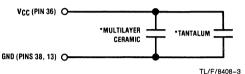

## **Pin Definitions**

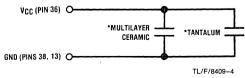

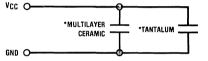

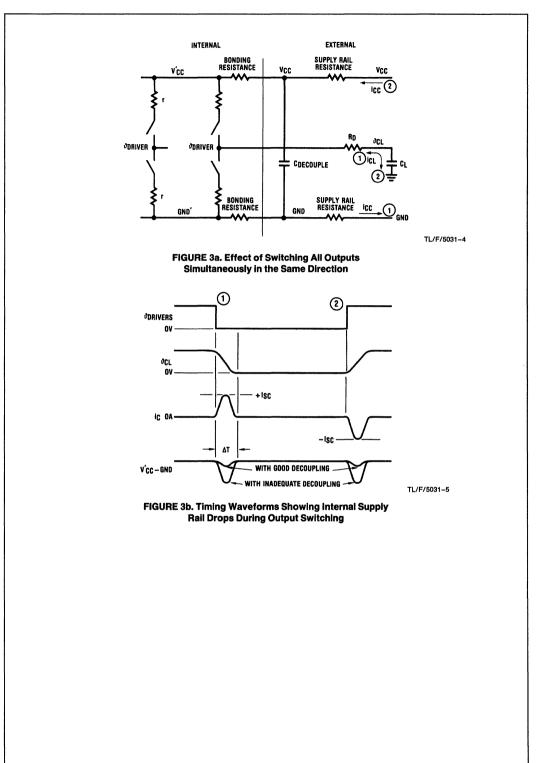

$V_{CC}$ , GND, GND— $V_{CC}=5V\pm5\%$ . The three supply pins have been assigned to the center of the package to reduce voltage drops, both DC and AC. There are also two ground pins to reduce the low level noise. The second ground pin is located two pins from V\_{CC}, so that decoupling capacitors can be inserted directly next to these pins. It is important to adequately decouple this device, due to the high switching currents that will occur when all 8 address bits change in the same direction simultaneously. A recommended solution would be a 1  $\mu$ F multilayer ceramic capacitor in parallel with a low-voltage tantalum capacitor, both connected as close as possible to pins 36 and 38 to reduce lead inductance. See *Figure* below.

\*Capacitor values should be chosen depending on the particular application.

R0-R7: Row Address Inputs.

C0-C7: Column Address Inputs.

Q0-Q7: Multiplexed Address Outputs—Selected from the Row Address Input Latch, the Column Address Input Latch, or the Refresh Counter.\*

**RASIN: Row Address Strobe Input**—Enables selected  $RAS_n$  output when M2 (RFSH) is high, or all  $RAS_n$  outputs when RFSH is low.

**R/C: Row/Column Select Input**—Selects either the row or column address input latch onto the output bus.

**CASIN: Column Address Strobe Input**—Inhibits CAS output when high in Modes 4 and 3. In Mode 6 it can be used to prolong CAS output.

**ADS: Address (Latch) Strobe Input**—Row Address, Column Address, and Bank Select Latches are fall-through with ADS high; Latches on high-to-low transition.

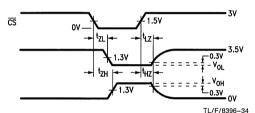

**CS:** Chip Select Input—TRI-STATE the Address Outputs and puts the control signal into a high-impedance logic "1" state when high (except in Mode 0); enables all outputs when low.

**M0, M1, M2: Mode Control Inputs**—These 3 control pins determine the 6 major modes of operation of the DP8408A as depicted in Table I.

**RF I/O**—The I/O pin functions as a Reset Counter Input when set low from an external open-collector gate, or as a flag output. The flag goes active-low when M2 = 0 and the End-of-Count output is at 127 or 255 (see Table III).

#### WIN: Write Enable Input.

WE: Write Enable Output—Buffered output from WIN.\*

**CAS:** Column Address Strobe Output—In Modes 5 and 6, CAS goes low following valid column address. In Modes 3 and 4, it transitions low after  $R/\overline{C}$  goes low, or follows CASIN going low if  $R/\overline{C}$  is already low. CAS is high during refresh.\*

**RAS 0–3: Row Address Strobe Outputs**—Selects a memory bank decoded from B1 and B0 (see Table II), if RFSH is high. If RFSH is low, all banks are selected.\*

**B0, B1: Bank Select Inputs**—Strobed by ADS. Decoded to enable one of the RAS outputs when RASIN goes low. Also used to define End-of-Count in Mode 7 (Table III).

\*These outputs may need damping resistors to prevent overshoot, undershoot. See AN-305 "Precautions to Take When Driving Memories."

| TABLE | II. Memory | / Bank | Decode |

|-------|------------|--------|--------|

|       |            |        |        |

|    | Select<br>I by ADS) | Enabled RAS <sub>n</sub> |  |  |

|----|---------------------|--------------------------|--|--|

| B1 | BO                  |                          |  |  |

| 0  | 0                   | RAS <sub>0</sub>         |  |  |

| 0  | 1                   | RAS <sub>1</sub>         |  |  |

| 1  | 0                   | RAS <sub>2</sub>         |  |  |

| 1  | 1                   | RAS <sub>3</sub>         |  |  |

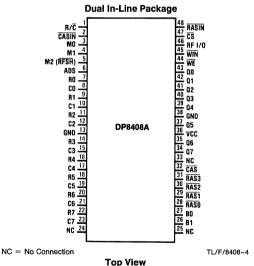

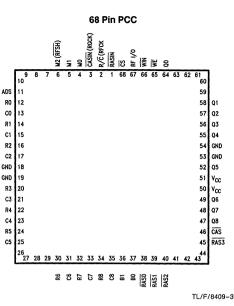

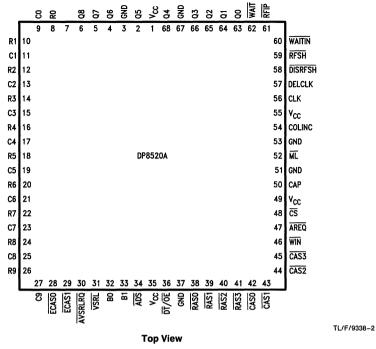

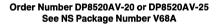

# **Connection Diagram**

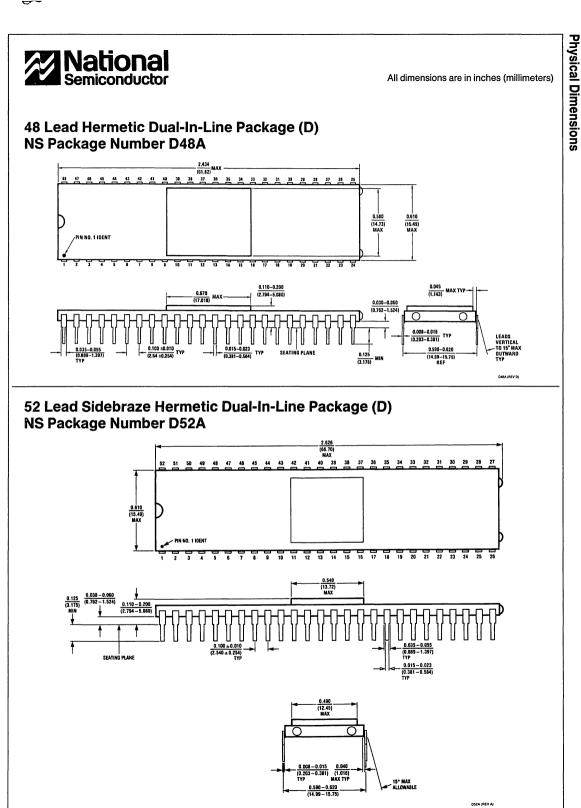

Order Number DP8408AD, DP8408AN or DP8408AN-3 See NS Package Number D48A or N48A

# **Conditions for all Modes**

#### INPUT ADDRESSING

The address block consists of a row-address latch, a columnaddress latch, and a resettable refresh counter. The address latches are fall-through when ADS is high and latch when ADS goes low. If the address bus contains valid addresses until after the valid address time, ADS can be permanently high. Otherwise ADS must go low while the addresses are still valid.

In normal memory access operation,  $\overline{\text{RASIN}}$  and R/C are initially high. When the address inputs are enabled into the address latches, the row addresses appear on the Q outputs. The address strobe also inputs the bank-select address, (B0 and B1). If  $\overline{\text{CS}}$  is low, all outputs are enabled. When  $\overline{\text{CS}}$  is transitioned high, the address outputs go TRI-STATE and the control outputs first go high through a low impedance, and then are held by an on-chip high impedance. This allows output paralleling with other DP8408As for multi-addressing. All outputs go active about 50 ns after the chip is selected again. If  $\overline{\text{CS}}$  is high, and a refresh cycle begins, all the outputs become active until the end of the refresh cycle.

#### DRIVE CAPABILITY

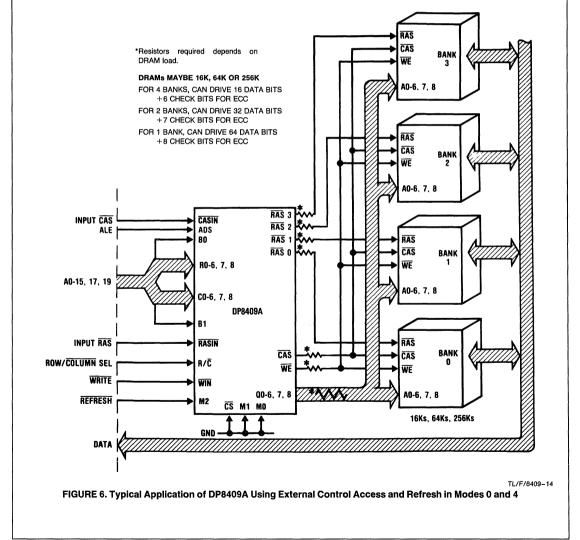

The DP8408A has timing parameters that are specified with up to 600 pF loads. In a typical memory system this is equivalent to about 88, 5V-only DRAMs, with trace lengths kept to a minimum. Therefore, the chip can drive four banks each of 16 or 22 bits, or two banks of 32 or 39 bits, or one bank of 64 or 72 bits.

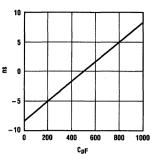

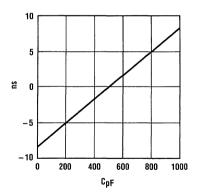

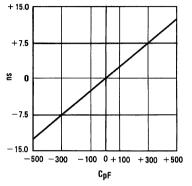

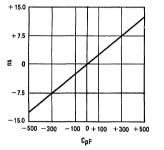

Less loading will slightly reduce the timing parameters, and more loading will increase the timing parameters, according to the graph of *Figure 6*. The AC performance parameters are specified with the typical load capacitance of 88 DRAMs. This graph can be used to extrapolate the variations expected with other loading.

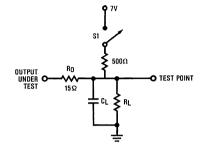

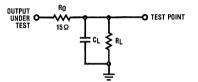

Because of distributed trace capacitance and inductance and DRAM input capacitance, current spikes can be created, causing overshoots and undershoots at the DRAM inputs that can change the contents of the DRAMs or even destroy them. To remove these spikes, a damping resistor (low inductance, carbon) can be inserted between the DP8408A driver outputs and the DRAMs, as close as possible to the DP8408A. The values of the damping resistors may differ between the different control outputs; RAS's CAS, Q's and WE. The damping resistors should be determined by the first prototypes (not wire-wrapped due to larger distributed capacitance and inductance). The best values for the damping resistors are the critical values giving a critically damped transition on the control outputs. Typical values for the damping resistors will be between  $15\Omega$  and 100 $\Omega$ , the lower the loading the higher the value. (For more information, see AN-305 "Precautions to Take When Driving Memories.")

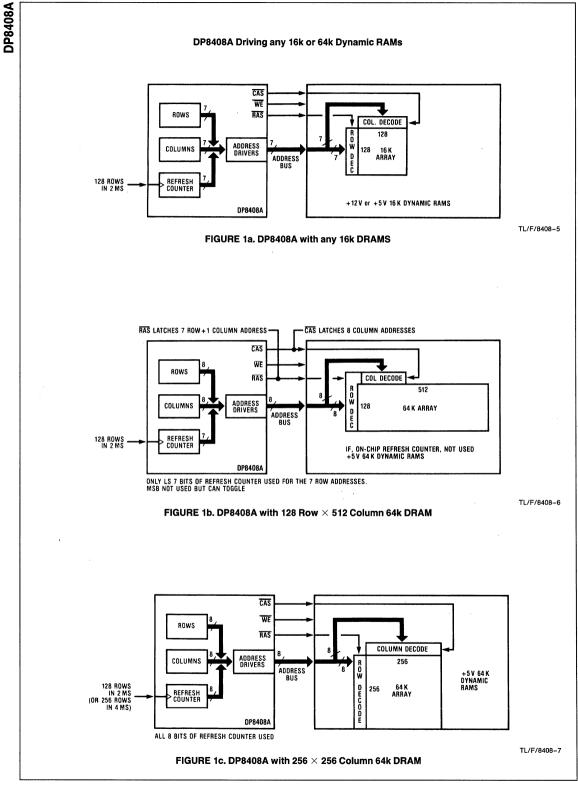

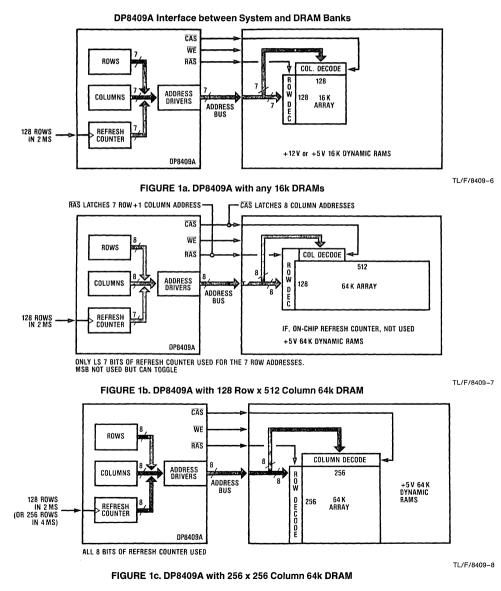

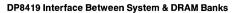

#### DP8408A DRIVING ANY 16K OR 64K DRAMS

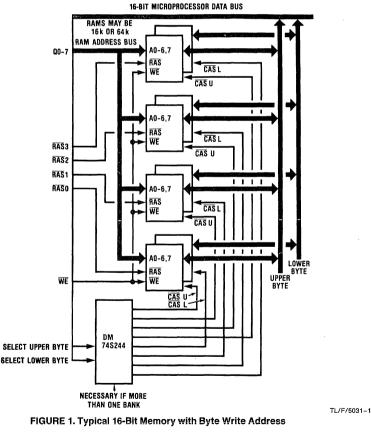

The DP8408A can drive any 16k or 64k DRAMs. All 16k DRAMs are basically the same configuration, including the newer 5V-only version. Hence, in most applications, different manufacturers' DRAMs are interchangeable (for the same supply-rail chips), and the DP8408A can drive all 16k DRAMS (see *Figure 1a*).

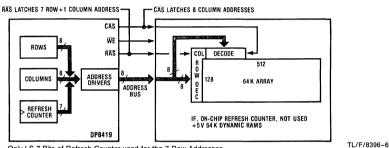

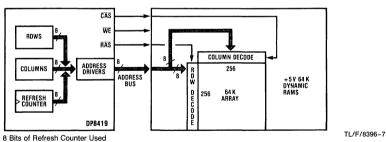

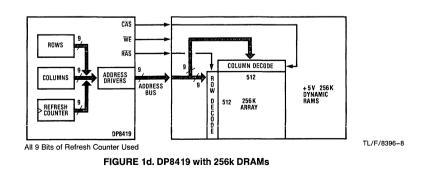

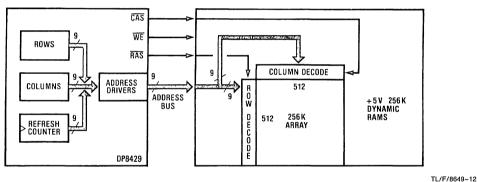

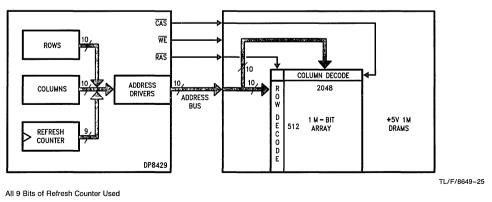

There are three basic configurations for the 5V-only 64k DRAMs: a 128-row by 512-column array with an on-RAM refresh counter, a 128-row by 512-column array with no on-RAM refresh counter, and a 256-row by 256-column array with no on-RAM refresh counter. The DP8408A can drive all three configurations, and at the same time allows them all to be interchangeable (as shown in *Figure 1b* and *1c*), providing maximum flexibility in the choice of DRAMs. Since the 8-bit on-chip refresh counter can be used as a 7-bit refresh counter for the 128-row configuration, or as an 8-bit refresh counter (if present) is never used. As long as 128 rows are refreshed every 2 ms (i.e. 256 rows in 4 ms) all DRAM types are correctly refreshed.

When the DP8408A is in a refresh mode, the RF I/O pin indicates that the on-chip refresh counter has reached its end-of-count. This end-of-count is selectable as 127 or 255 to accommodate 16k or 64k DRAMs, respectively. Although the end-of-count may be chosen to be either of these values, the counter is not reset and always counts to 255 before rolling over to zero.

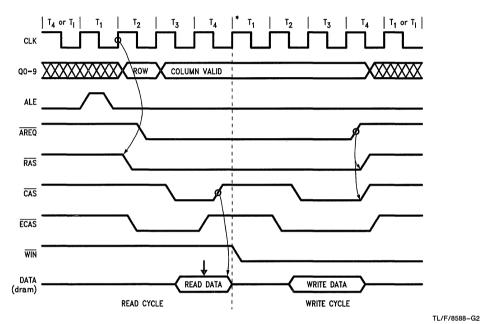

#### READ, WRITE AND READ-MODIFY-WRITE CYCLES

The output signal,  $\overline{WE}$ , determines what type of memory access cycle the memory will perform. If  $\overline{WE}$  is kept high while  $\overline{CAS}$  goes low, a read cycle occurs. If  $\overline{WE}$  goes low before  $\overline{CAS}$  goes low, a write cycle occurs and data at DI (DRAM input data) is written into the DRAM as  $\overline{CAS}$  goes low. If  $\overline{WE}$  goes low later than t<sub>CWD</sub> after  $\overline{CAS}$  goes low, first a read occurs and DO (DRAM output data) becomes valid; then data DI is written into the same address in the DRAM when  $\overline{WE}$  goes low. In this read-modify-write case, DI and DO cannot be linked together. The type of cycle is therefore controlled by  $\overline{WE}$ , which follows  $\overline{WIN}$ .

#### **POWER-UP INITIALIZE**

When V<sub>CC</sub> is first applied to the DP8408A, an initialize pulse clears the refresh counter, the internal control flip-flops, and sets the End-of-Count of the refresh counter to 127 (which may be changed via Mode 7). As V<sub>CC</sub> increases to about 2.3V, it holds the output control signals at a level of one Schottky diode-drop below V<sub>CC</sub>, and the output address to TRI-STATE. As V<sub>CC</sub> increases above 2.3V, control of these outputs is granted to the system.

# **Functional Mode Descriptions**

Note: All delay parameters stated in text refer to the DP8408A. Substitute the respective delay numbers for the DP8408-2 or DP8408-3 when using these devices.

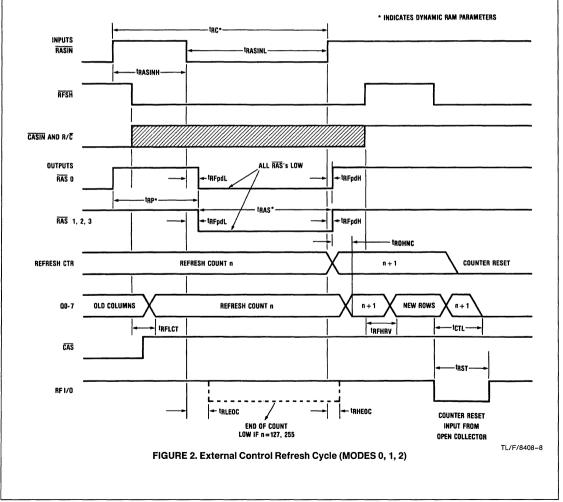

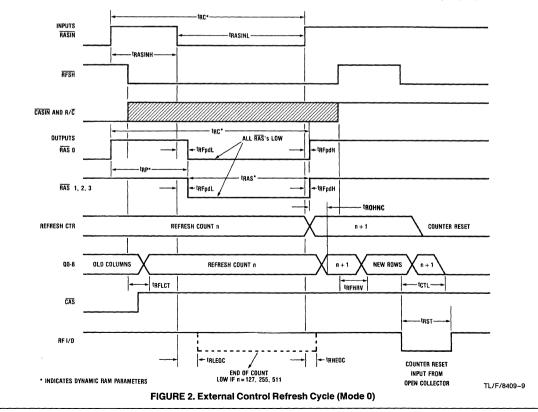

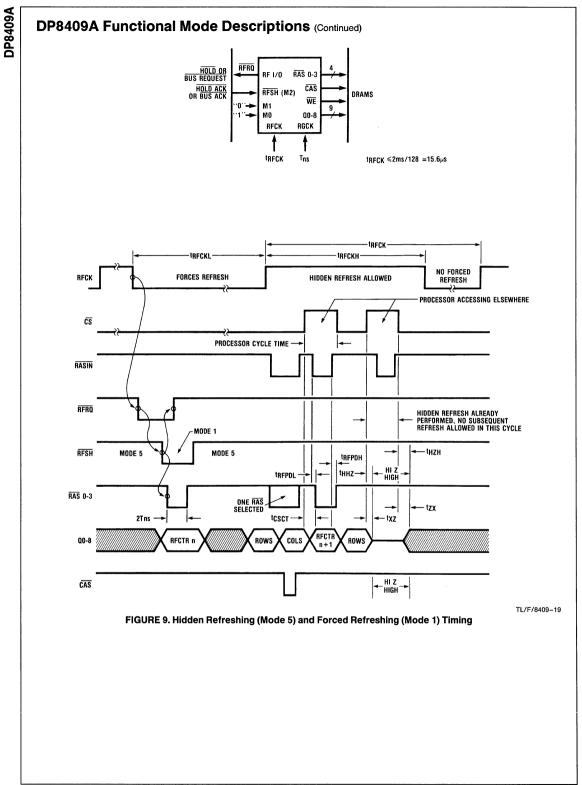

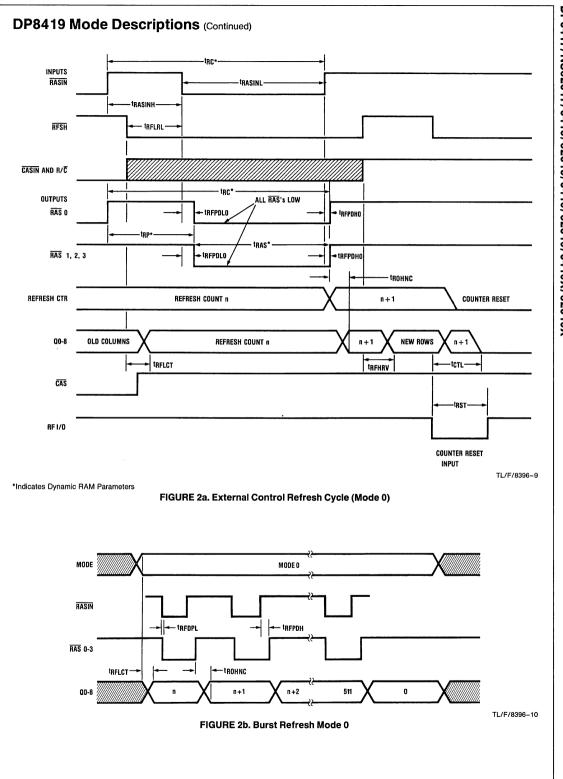

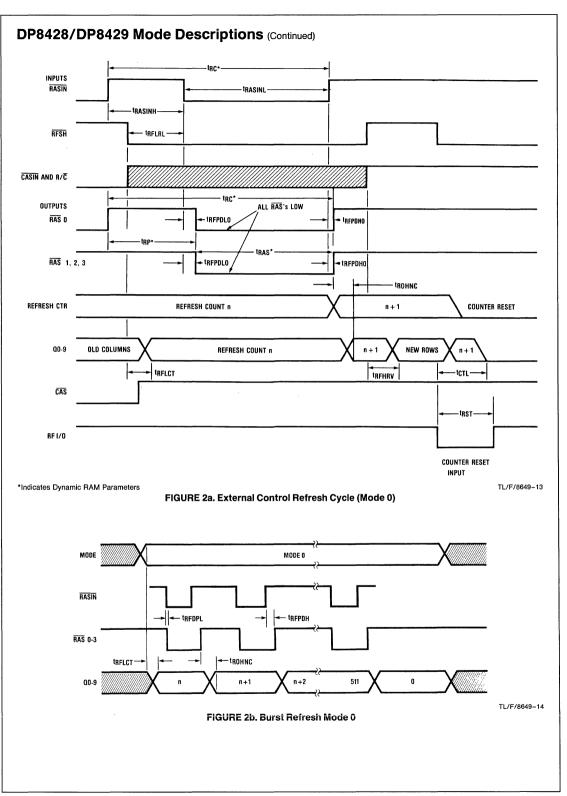

#### MODES 0, 1, 2 — EXTERNALLY CONTROLLED REFRESH

In this mode, the input address latches are disabled from the address outputs and the refresh counter is enabled. When  $\overline{\text{RAS}}$  occurs, the enabled row in the DRAM is refreshed. In the Externally Controlled Refresh mode, all  $\overline{\text{RAS}}$  outputs are enabled following  $\overline{\text{RASIN}}$ , and  $\overline{\text{CAS}}$  is inhibited. This refreshes the same row in all four banks. The refresh counter increments when either  $\overline{\text{RASIN}}$  or  $\overline{\text{RFSH}}$  goes low-to-high after a refresh. RF I/O goes low when the count is 127 or 255, as set by End-of-Count (see Table III), with  $\overline{\text{RASIN}}$  and  $\overline{\text{RFSH}}$  goes. RF I/O is set low through an external open-collector driver.

During refresh,  $\overrightarrow{RASIN}$  and RFSH must be skewed transitioning low such that the refresh address is valid on the address outputs of the controller before the  $\overrightarrow{RAS}$  outputs go low. The amount of time that RFSH should go low before  $\overrightarrow{RASIN}$  does depends on the capacitive loading of the address and  $\overline{\text{RAS}}$  lines. For the load specified in the switching characteristics of this data sheet, 10 ns is sufficient. Refer to *Figure 2*.

To perform externally controlled burst refresh, RASIN is toggled while RFSH is held low. The refresh counter increments with RASIN going low to high, so that the DRAM rows are refreshed in succession by RASIN going high to low.

#### MODE 3 — EXTERNALLY CONTROLLED ALL-RAS WRITE

This mode is useful at system initialization. The memory address is provided by the processor, which also performs the incrementing. All four TAS outputs follow TASIN (supplied by the processor), strobing the row address into the DRAMs. R/C can now go low, while CASIN may be used to control CAS (as in the Externally Controlled Access mode), so that CAS strobes the column address contents into the DRAMs. At this time WE should be low, causing the data to be written into all four banks of DRAMs. At the end of the write cycle, the input address is incremented and latched by the DP8408A for the next write cycle.

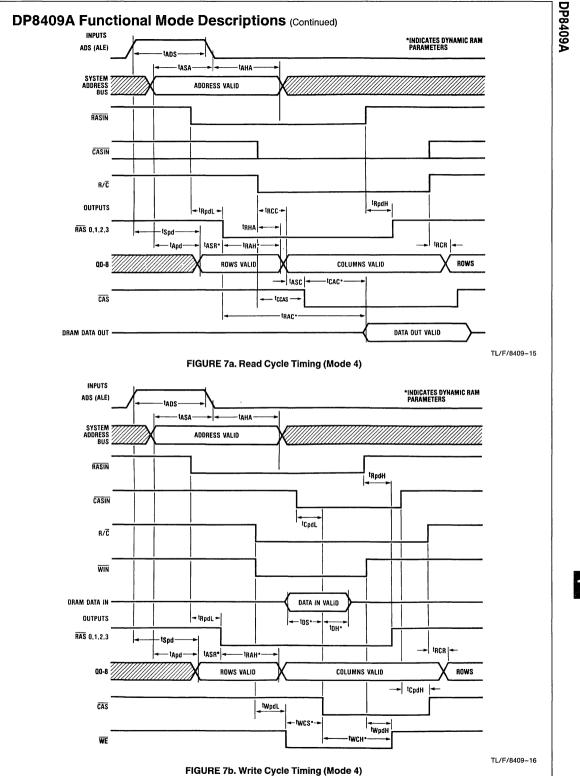

#### MODE 4 -- EXTERNALLY CONTROLLED ACCESS

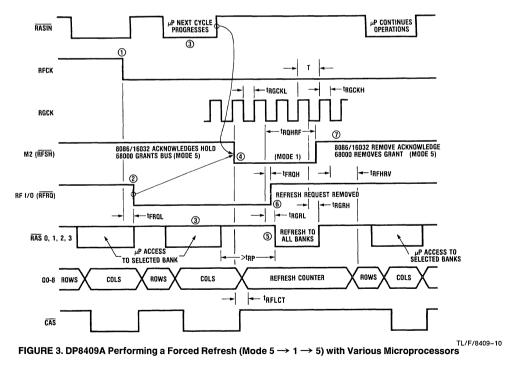

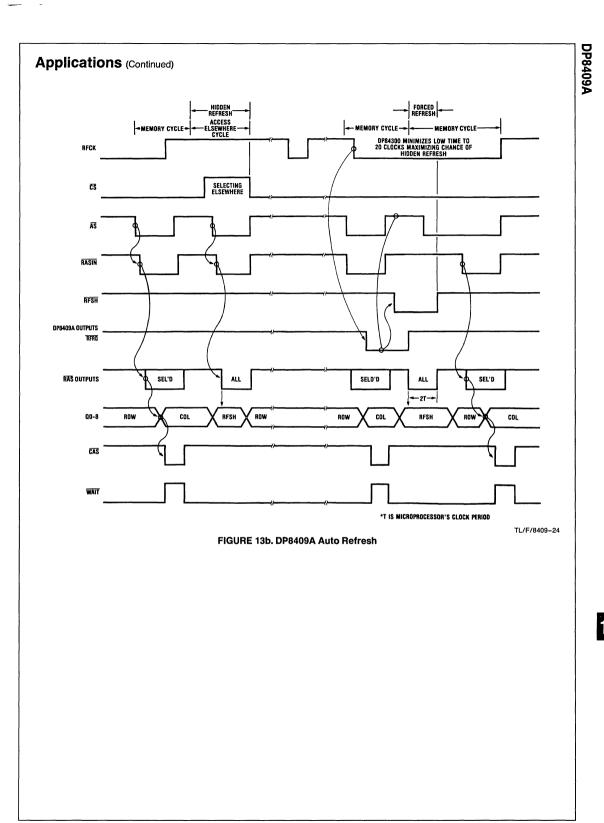

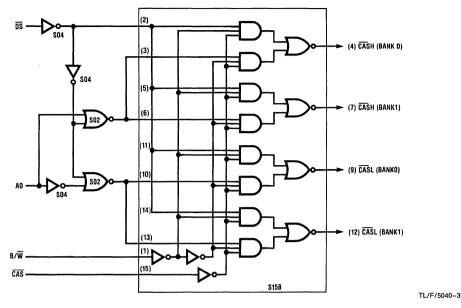

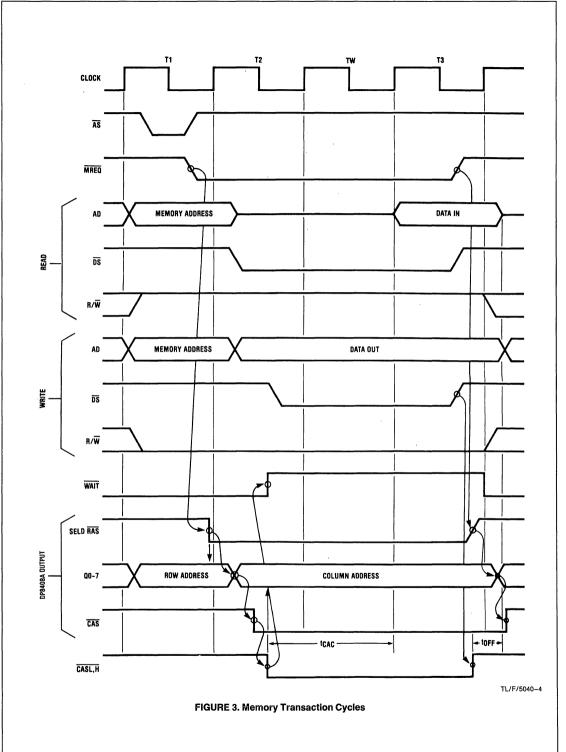

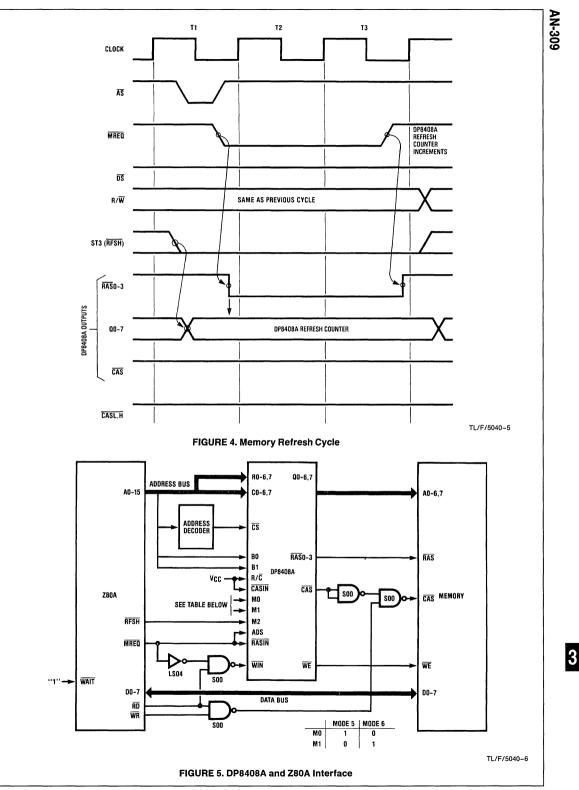

This mode facilitates externally controlling all access-timing parameters associated with the DRAMs. The application of modes 0 and 4 are shown in *Figure 3*.

#### **Output Address Selection**

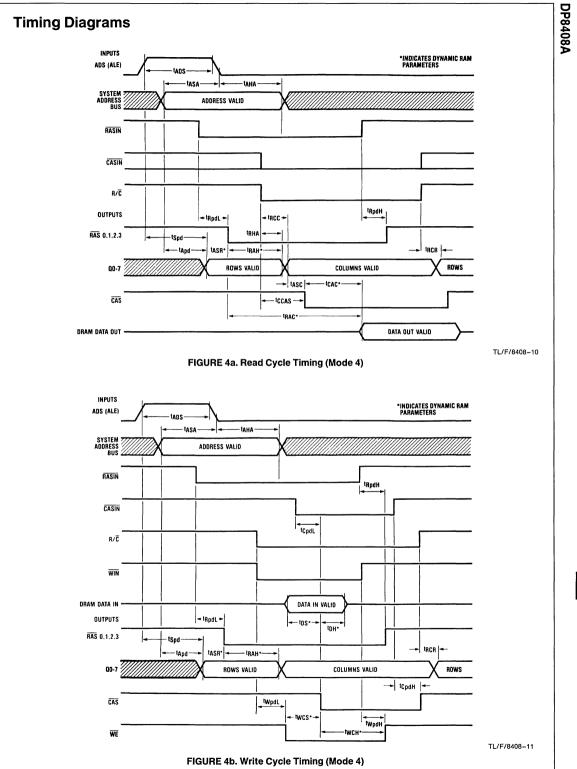

Refer to *Figure 4a.* With M2 (RFSH) and R/ $\overline{C}$  high, the row address latch contents are transferred to the multiplexed address bus output Q0–Q7, provided  $\overline{CS}$  is set low. The column address latch contents are output after R/ $\overline{C}$  goes low. RASIN can go low after the row addresses have been set up on Q0–Q7. This selects one of the RAS outputs, strobing the row address on the Q outputs into the desired bank of memory. After the row-address hold-time of the DRAMS, R/ $\overline{C}$  can go low so that about 40 ns later column addresses appear on the Q outputs.

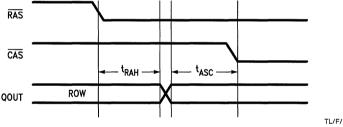

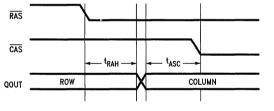

#### Automatic CAS Generation

In a normal memory access cycle  $\overline{CAS}$  can be derived from inputs  $\overline{CASIN}$  or R/ $\overline{C}$ . If  $\overline{CASIN}$  is high, then R/ $\overline{C}$  going low switches the address output drivers from rows to columns.  $\overline{CASIN}$  then going low causes  $\overline{CAS}$  to go low approximately 40 ns later, allowing  $\overline{CAS}$  to occur at a predictable time (see *Figure 4b*). If  $\overline{CASIN}$  is low when R/ $\overline{C}$  goes low,  $\overline{CAS}$  will be automatically generated, following the row to column transition by about 20 ns (see *Figure 4a*). Most DRAMs have a column address set-up time before  $\overline{CAS}$  (t<sub>ASC</sub>) of 0 ns or -10 ns. In other words, a t<sub>ASC</sub> greater than 0 ns is safe. This feature reduces timing-skew problems, thereby improving access time of the system.

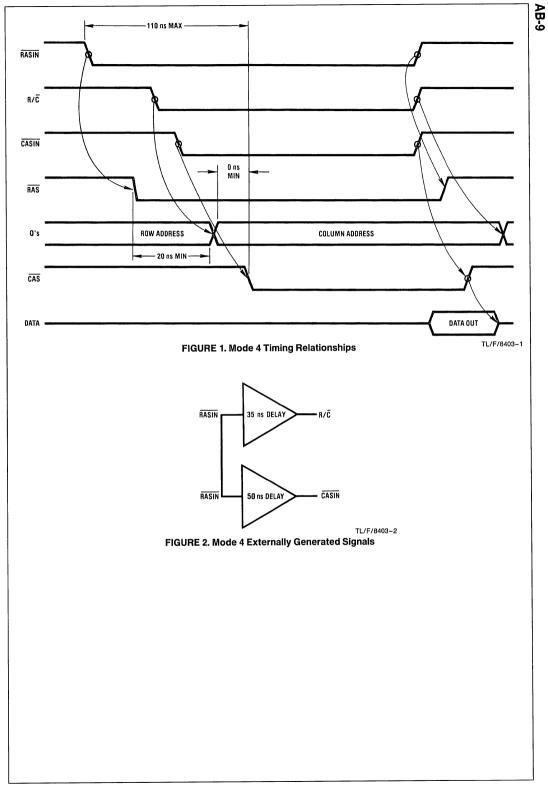

#### Fast Memory Access

AC parameters  $t_{DIF1}$ ,  $t_{DIF2}$  may be used to determine the minimum delays required between  $\overline{RASIN}$ ,  $R/\overline{C}$ , and  $\overline{CASIN}$  (see Application Brief 9; "Fastest DRAM Access Mode").

FIGURE 3. Typical Application of DP8408A Using Externally Controlled Access and Refresh in Modes 0 and 4

1

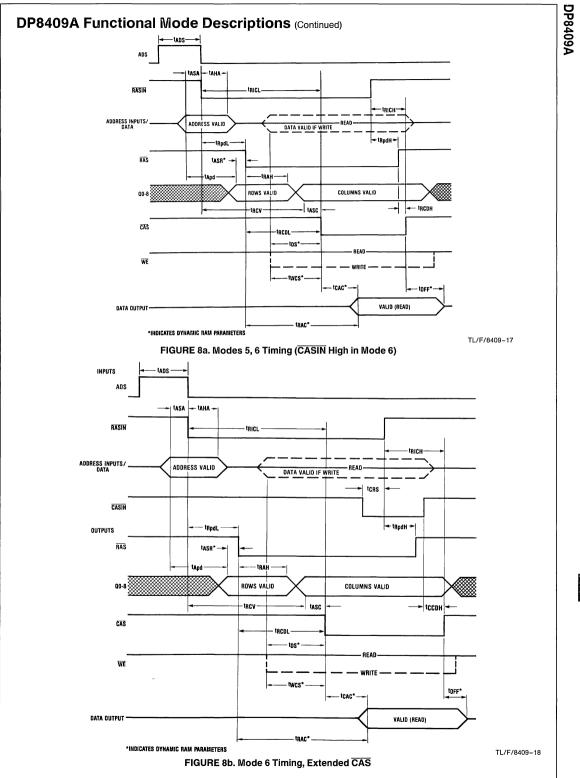

#### MODE 5-AUTOMATIC ACCESS

The Auto Access mode has two advantages over the Externally Controlled Access mode, due to the fact that all outputs except WE are initiated from RASIN. First, inputs R/ $\overline{C}$ and  $\overline{CASIN}$  are unnecessary. Secondly, because the output control signals are derived internally from one input signal (RASIN), timing-skew problems are reduced, thereby reducing memory access time substantially or allowing use of slower DRAMs. The automatic access features of Mode 5 (and Mode 6) of the DP8408A make DRAM accessing appear essentially "static".

#### AUTOMATIC ACCESS CONTROL

The major disadvantage of DRAMs compared to static RAMs is the complex timing involved. First, a RAS must occur with the row address previously set up on the multiplexed address bus. After the row address has been held for  $t_{RAH}$ , (the Row-Address hold-time of the DRAM), the column address is set up and then  $\overline{CAS}$  occurs. This is all performed automatically by the DP8408A in this mode.

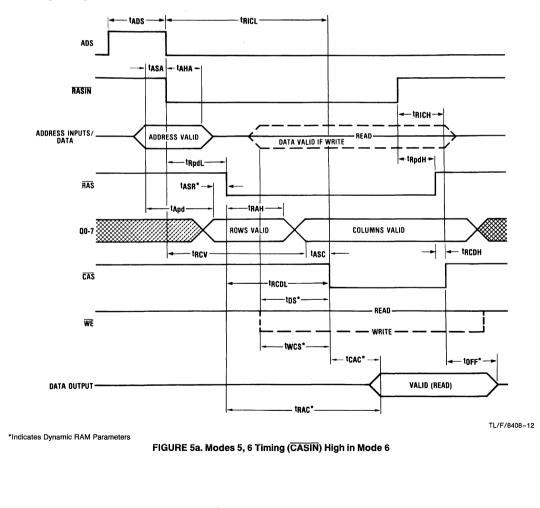

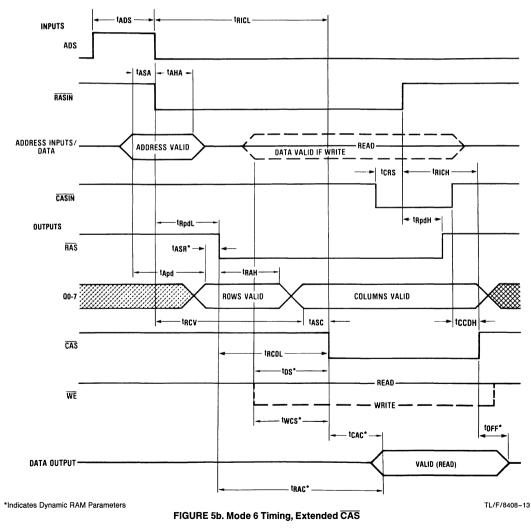

Provided the input address is valid as ADS goes low,  $\overrightarrow{RASIN}$  can go low any time after ADS. This is because the selected  $\overrightarrow{RAS}$  occurs typically 27 ns later, by which time the row address is already valid on the address output of the DP8408A. The Address Setup-Up time ( $t_{ASR}$ ), is 0 ns on most DRAMs. The DP8408A in this mode (with ADS and  $\overrightarrow{RASIN}$  edges simultaneously applied) produces a minimum  $t_{ASR}$  of 0 ns. This is true provided the input address was valid  $t_{ASA}$  before ADS went low (see *Figure 5a*).

Next, the row address is disabled after  $t_{RAH}$  (30 ns minimum); in most DRAMs,  $t_{RAH}$  minimum is less than 30 ns. The column address is then set up and  $t_{ASC}$  later,  $\overline{CAS}$

# **Timing Diagram**

occurs. The only other control input required is  $\overline{\text{WIN}}$ . When a write cycle is required,  $\overline{\text{WIN}}$  must go low at least 30 ns before  $\overline{\text{CAS}}$  is output low.

This gives a total typical delay from: input address valid to  $\overline{\text{RASIN}}$  (15 ns); to  $\overline{\text{RAS}}$  (27 ns); to rows held (50 ns); to columns valid (25 ns); to  $\overline{\text{CAS}}$  (23 ns) = 140 ns (that is, 125 ns from  $\overline{\text{RASIN}}$ . All of these typical figures are for heavy capacitive loading, of approximately 88 DRAMs. This mode is therefore extremely fast. The external timing is greatly simplified for the memory system designer: the only system signal required is  $\overline{\text{RASIN}}$ .

#### MODE 6—FAST AUTOMATIC ACCESS

The Fast Access mode is similar to Mode 5, but has a faster  $t_{\hbox{\scriptsize RAH}}$  of 20 ns, minimum. It therefore can only be used with

fast 16k or 64k DRAMs (which have a  $t_{RAH}$  of 10 ns to 15 ns) in applications requiring fast access times; RASIN to CAS is typically 105 ns.

In this mode, the  $R/\overline{C}$  pin is not used, but  $\overline{CASIN}$  is used to allow an extended  $\overline{CAS}$  after  $\overline{RAS}$  has already terminated. Refer to *Figure 5b*. This is desirable with fast cycle-times where  $\overline{RAS}$  has to be terminated as soon as possible before the next  $\overline{RAS}$  begins (to meet the precharge time, or  $t_{RP}$ , requirements of the DRAM).  $\overline{CAS}$  may then be held low by  $\overline{CASIN}$  to extend the data output valid time from the DRAM to allow the system to read the data.  $\overline{CASIN}$  subsequently going high ends  $\overline{CAS}$ . If this extended  $\overline{CAS}$  is not required,  $\overline{CASIN}$  should be set high in Mode 6.

# **Timing Diagram**

#### MODE 7-SET END-OF-COUNT

The End-of-Count can be externally selected in Mode 7, using ADS to strobe in the respective value of B1 and B0 (see Table III). With B1 and B0 the same EOC is 127; with B1=0 and B0=1, EOC is 255; and with B1=1 and B0=0, EOC is 127. This selected value of EOC will be used until the next Mode 7 selection. At power-up the EOC is automatically set to 127 (B1 and B0 set to 11).

| TABLE III. Mode 7 |                     |                          |  |  |  |

|-------------------|---------------------|--------------------------|--|--|--|

|                   | Select<br>d by ADS) | End of Count<br>Selected |  |  |  |

| B1                | B0                  | Celebieu                 |  |  |  |

| 0                 | 0                   | 127                      |  |  |  |

| 0                 | 1                   | 255                      |  |  |  |

| 1                 | 0                   | 127                      |  |  |  |

| 1                 | 1                   | 127                      |  |  |  |

TL/F/8408-14

# Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage, V <sub>CC</sub>                                      | 7.0V                  |

|----------------------------------------------------------------------|-----------------------|

| Storage Temperature Range                                            | -65°C to +150°C       |

| Input Voltage                                                        | 5.5V                  |

| Output Current                                                       | 150 mA                |

| Lead Temperature (Soldering, 10 sec)                                 | 300°C                 |

| *Derate cavity package 23.6 mW/°C above 25°C, 22.7 mW/°C above 25°C. | derate molded package |

| Maximum Power Dissipation* at 25°C |         |

|------------------------------------|---------|

| Cavity Package                     | 3542 mW |

| Molded Package                     | 2833 mW |

# **Operating Conditions**

|                 |                     | Min  | Мах  | Units |  |

|-----------------|---------------------|------|------|-------|--|

| V <sub>CC</sub> | Supply Voltage      | 4.75 | 5.25 | v     |  |

| TA              | Ambient Temperature | 0    | +70  | °C    |  |

## **Electrical Characteristics** $V_{CC} = 5.0V \pm 5\%$ , 0°C $\leq T_A \leq 70$ °C (unless otherwise noted) (Notes 2, 6)

| Symbol             | Parameter                                         | Conditions                                                                                                      | Min | Тур   | Max  | Units |

|--------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|-------|------|-------|

| V <sub>C</sub>     | Input Clamp Voltage                               | $V_{CC} = Min., I_C = -12 mA$                                                                                   |     | -0.8  | -1.2 | v     |

| l <sub>IH1</sub>   | Input High Current for ADS, $R/\overline{C}$ only | $V_{IN} = 2.5V$                                                                                                 |     | 2.0   | 100  | μA    |

| I <sub>IH2</sub>   | Input High Current for All Other Inputs*          | $V_{IN} = 2.5V$                                                                                                 |     | 1.0   | 50   | μΑ    |

| I <sub>I</sub> RSI | Output Load Current for RF I/O                    | V <sub>IN</sub> = 0.5V, Output High                                                                             |     | -1.5  | -2.5 | mA    |

| II CTL             | Output Load Current for RAS, CAS, WE              | V <sub>IN</sub> = 0.5V, Chip Deselect                                                                           |     | -1.5  | -2.5 | mA    |

| l <sub>IL1</sub>   | Input Low Current for ADS, R/C only               | $V_{IN} = 0.5V$                                                                                                 | -   | -0.1  | -1.0 | mA    |

| I <sub>IL2</sub>   | Input Low Current for All Other Inputs*           | V <sub>IN</sub> = 0.5V                                                                                          |     | -0.05 | -0.5 | mA    |

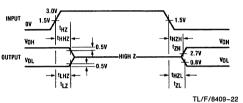

| VIL                | Input Low Threshold                               |                                                                                                                 |     |       | 0.8  | V     |

| VIH                | Input High Threshold                              |                                                                                                                 | 2.0 |       |      | V     |

| V <sub>OL1</sub>   | Output Low Voltage*                               | $I_{OL} = 20 \text{ mA}$                                                                                        |     | 0.3   | 0.5  | v     |

| V <sub>OL2</sub>   | Output Low Voltage for RF I/O                     | $I_{OL} = 10 \text{ mA}$                                                                                        |     | 0.3   | 0.5  | V     |

| V <sub>OH1</sub>   | Output High Voltage*                              | $I_{OH} = -1 \text{ mA}$                                                                                        | 2.4 | 3.5   |      | V     |

| V <sub>OH2</sub>   | Output High Voltage for RF I/O                    | I <sub>OH</sub> = - 100 μA                                                                                      | 2.4 | 3.5   |      | v     |

| I <sub>1D</sub>    | Output High Drive Current*                        | V <sub>OUT</sub> = 0.8V (Note 3)                                                                                |     | -200  |      | mA    |

| loD                | Output Low Drive Current*                         | V <sub>OUT</sub> = 2.7V (Note 3)                                                                                |     | 200   |      | mA    |

| I <sub>OZ</sub>    | TRI-STATE Output Current<br>(Address Outputs)     | $\begin{array}{l} 0.4 V \leq V_{OUT} \leq 2.7 V, \\ \overline{\mathrm{CS}} = 2.0 V,  \text{Mode 4} \end{array}$ | -50 | 1.0   | 50   | μΑ    |

| lcc                | Supply Current                                    | V <sub>CC</sub> = Max.                                                                                          |     | 210   | 285  | mA    |

# Switching Characteristic DP8408A/DP8408-3

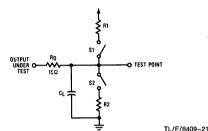

$V_{CC} = 5.0V \pm 5\%$ , 0°C  $\leq T_A \leq 70$ °C unless otherwise noted (Notes 2, 4, 5). The output load capacitance is typical for 4 banks of 22 DRAMs each of 88 DRAMs including trace capacitance. These values are: Q0–Q7, C<sub>L</sub> = 500 pF; RAS0–RAS3, C<sub>L</sub> = 150 pF; WE, C<sub>L</sub> = 500 pF; CAS, C<sub>L</sub> = 600 pF, unless otherwise noted. See *Figure 7* for test load. Switches S1 and S2 are closed unless otherwise noted, and R1 and R2 are 4.7 k $\Omega$  unless otherwise noted. Maximum propagation delays are specified with all outputs switching.

| Symbol            | Access Parameter                                                                                    | Conditions             |    | 8408A | ·   |     | 8408-3 | 3   | Units  |

|-------------------|-----------------------------------------------------------------------------------------------------|------------------------|----|-------|-----|-----|--------|-----|--------|

| Cymbol            | Access rarameter                                                                                    | N                      |    | Тур   | Max | Min | Тур    | Max | Office |

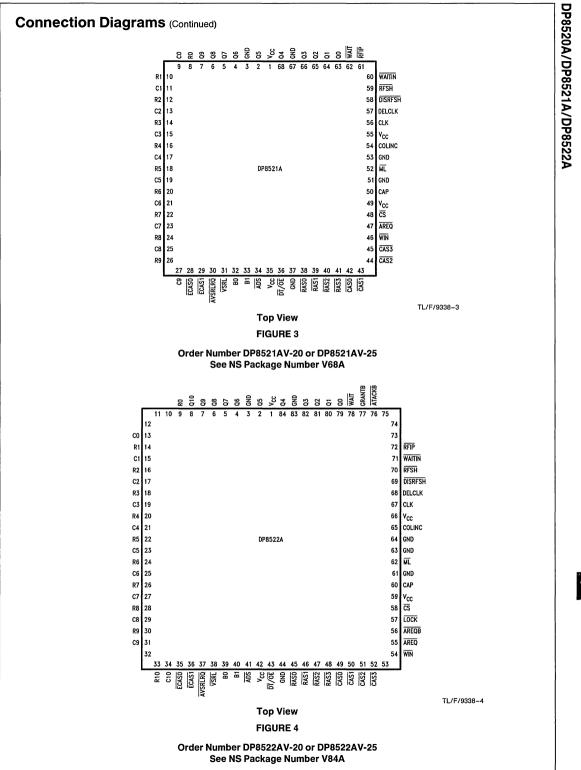

| t <sub>RICL</sub> | RASIN to CAS Output Delay (Mode 5)                                                                  | Figure 5a              | 95 | 125   | 160 | 95  | 125    | 185 | ns     |

| t <sub>RICL</sub> | RASIN to CAS Output Delay (Mode 6)                                                                  | Figures 5a, 5b         | 80 | 105   | 140 | 80  | 105    | 160 | ns     |

| t <sub>RICH</sub> | RASIN to CAS Output Delay (Mode 5)                                                                  | Figure 5a              | 40 | 48    | 60  | 40  | 48     | 70  | ns     |

| t <sub>RICH</sub> | RASIN to CAS Output Delay (Mode 6)                                                                  | Figures 5a, 5b         | 50 | 63    | 80  | 50  | 63     | 95  | ns     |

| t <sub>RCDL</sub> | RAS to CAS Output Delay (Mode 5)                                                                    | Figure 5a              |    | 98    | 125 |     | 98     | 145 | ns     |

| t <sub>RCDL</sub> | RAS to CAS Output Delay (Mode 6)                                                                    | Figures 5a, 5b         |    | 78    | 105 |     | 78     | 120 | ns     |

| t <sub>RCDH</sub> | RAS to CAS Output Delay (Mode 5)                                                                    | Figure 5a              |    | 27    | 40  |     | 27     | 40  | ns     |

| t <sub>RCDH</sub> | RAS to CAS Output Delay (Mode 6)                                                                    | Figure 5a              |    | 40    | 65  |     | 40     | 65  | ns     |

| t <sub>CCDH</sub> | CASIN to CAS Output Delay (Mode 6)                                                                  | Figure 5b              | 40 | 54    | 70  | 40  | 54     | 80  | ns     |

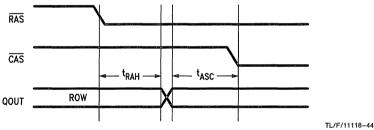

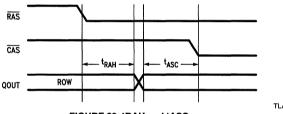

| t <sub>RAH</sub>  | Row Address Hold Time (Mode 5)                                                                      | Figure 5a              | 30 |       |     | 30  |        |     | ns     |

| t <sub>RAH</sub>  | Row Address Hold Time (Mode 6)                                                                      | Figures 5a, 5b         | 20 |       |     | 20  |        |     | ns     |

| t <sub>ASC</sub>  | Column Address Setup Time (Mode 5)                                                                  | Figure 5a              | 8  |       |     | 8   |        |     | ns     |

| t <sub>ASC</sub>  | Column Address Setup Time (Mode 6)                                                                  | Figures 5a, 5b         | 6  |       |     | 6   |        |     | ns     |

| t <sub>RCV</sub>  | RASIN to Column Address Valid (Mode 5)                                                              | Figure 5a              |    | 90    | 120 |     | 90     | 140 | ns     |

| t <sub>RCV</sub>  | RASIN to Column Address Valid (Mode 6)                                                              | Figures 5a, 5b         |    | 75    | 105 |     | 75     | 120 | ns     |

| t <sub>RPDL</sub> | RASIN to RAS Delay                                                                                  | Figures 4a, 4b, 5a, 5b | 20 | 27    | 35  | 20  | 27     | 40  | ns     |

| t <sub>RPDH</sub> | RASIN to RAS Delay                                                                                  | Figures 4a, 4b, 5a, 5b | 15 | 23    | 32  | 15  | 23     | 37  | ns     |

| t <sub>APDL</sub> | Address Input to Output Low Delay                                                                   | Figures 4a, 4b, 5a, 5b |    | 25    | 40  |     | 25     | 46  | ns     |

| t <sub>APDH</sub> | Address Input to Output High Delay                                                                  | Figures 4a, 4b, 5a, 5b |    | 25    | 40  |     | 25     | 46  | ns     |

| tSPDL             | Address Strobe to Address Output Low                                                                | Figures 4a, 4b         |    | 40    | 60  |     | 40     | 70  | ns     |

| tSPDH             | Address Strobe to Address Output High                                                               | Figures 4a, 4b         |    | 40    | 60  |     | 40     | 70  | ns     |

| t <sub>ASA</sub>  | Address Setup Time to ADS                                                                           | Figures 4a, 4b, 5a, 5b | 15 |       |     | 15  |        |     | ns     |

| t <sub>AHA</sub>  | Address Hold Time from ADS                                                                          | Figures 4a, 4b, 5a, 5b | 15 |       |     | 15  |        |     | ns     |

| t <sub>ADS</sub>  | Address Strobe Pulse Width                                                                          | Figures 4a, 4b, 5a, 5b | 30 |       |     | 30  |        |     | ns     |

| twPDL             | WIN to WE Output Delay                                                                              | Figure 4b              | 15 | 25    | 30  | 15  | 25     | 35  | ns     |

| twpdh             | WIN to WE Output Delay                                                                              | Figure 4b              | 15 | 30    | 60  | 15  | 30     | 70  | ns     |

| t <sub>CRS</sub>  | CASIN Setup Time to RASIN High (Mode 6)                                                             | Figure 5b              | 35 |       |     | 35  |        |     | ns     |

| t <sub>CPDL</sub> | $\overline{\text{CASIN}}$ to $\overline{\text{CAS}}$ Delay (R/ $\overline{\text{C}}$ low in Mode 4) | Figure 4b              | 32 | 41    | 68  | 32  | 41     | 77  | ns     |

| t <sub>CPDH</sub> | CASIN to CAS Delay                                                                                  | Figure 4b              | 25 | 39    | 50  | 25  | 39     | 60  | ns     |

| t <sub>RCC</sub>  | Column Select to Column Address Valid                                                               | Figure 4a              |    | 40    | 58  |     | 40     | 67  | ns     |

| t <sub>RCR</sub>  | Row Select to Row Address Valid                                                                     | Figures 4a, 4b         |    | 40    | 58  |     | 40     | 67  | ns     |

| t <sub>RHA</sub>  | Row Address Held from Column Select                                                                 | Figure 4a              | 10 |       |     | 10  |        |     | ns     |

| t <sub>CCAS</sub> | $R/\overline{C}$ Low to $\overline{CAS}$ Low (Mode 4 Auto $\overline{CAS}$ )                        | Figure 7a              |    | 65    | 90  |     |        |     | ns     |

# Switching Characteristics DP8408A/DP8408-3 (Continued)

$V_{CC} = 5.0V \pm 5\%$ , 0°C  $\leq T_A \leq 70$ °C unless otherwise noted (Notes 2, 4, 5). The output load capacitance is typical for 4 banks of 22 DRAMs each of 88 DRAMs including trace capacitance. These values are: Q0–Q7,  $C_L = 500 \text{ pF}$ ;  $\overline{RAS0}$ – $\overline{RAS3}$ ,  $C_L = 150 \text{ pF}$ ;  $\overline{WE}$ ,  $C_L = 500 \text{ pF}$ ;  $\overline{CAS}$ ,  $C_L = 600 \text{ pF}$ , unless otherwise noted. See *Figure 7* for test load. Switches S1 and S2 are closed unless otherwise noted, and R1 and R2 are 4.7 k $\Omega$  unless otherwise noted. Maximum propagation delays are specified with all outputs switching.

| Symbol                  | Access Parameter                                | Conditions                                                      | 8408A |       |     |     | Units |     |       |

|-------------------------|-------------------------------------------------|-----------------------------------------------------------------|-------|-------|-----|-----|-------|-----|-------|

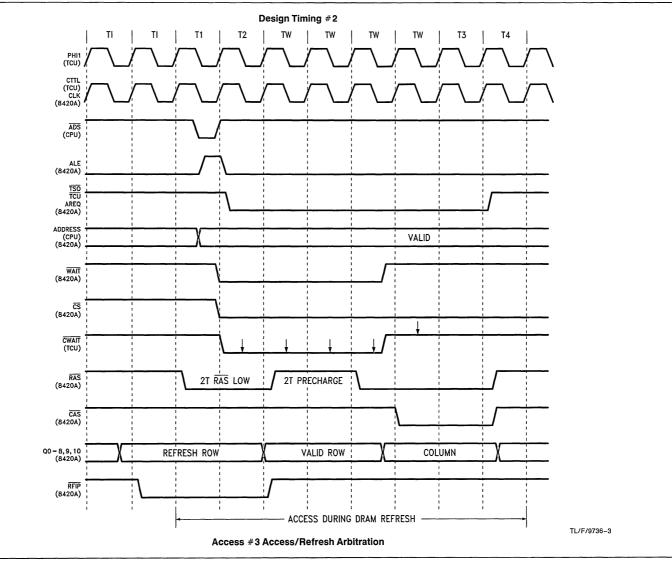

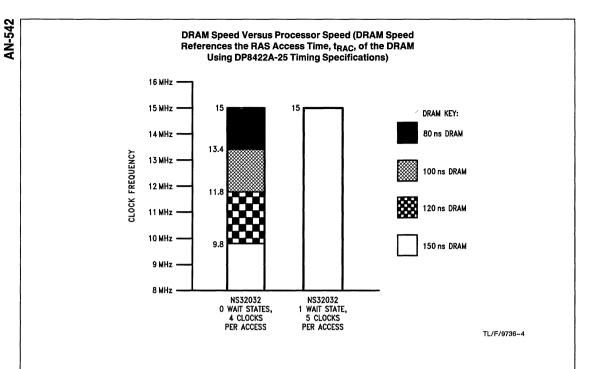

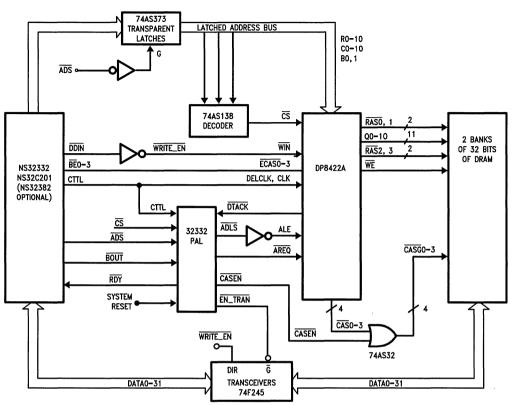

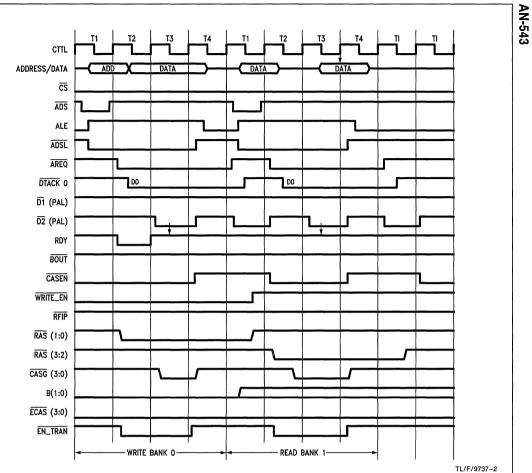

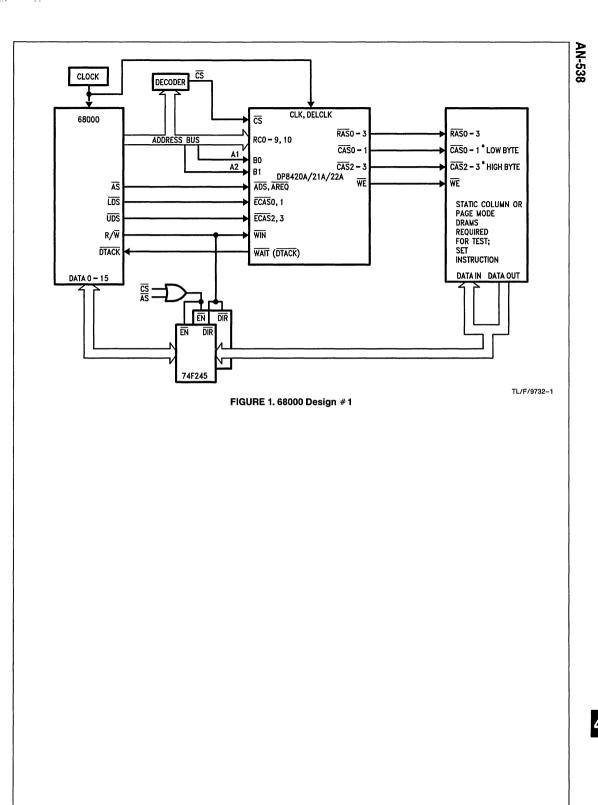

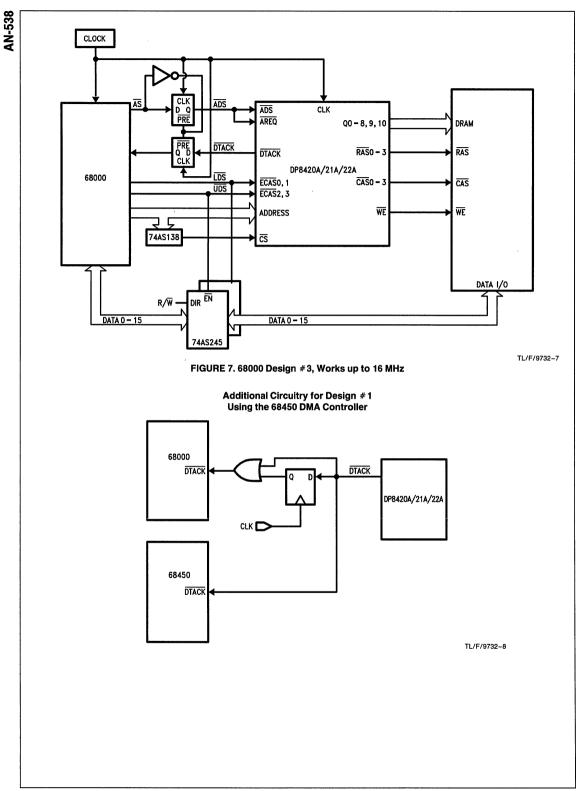

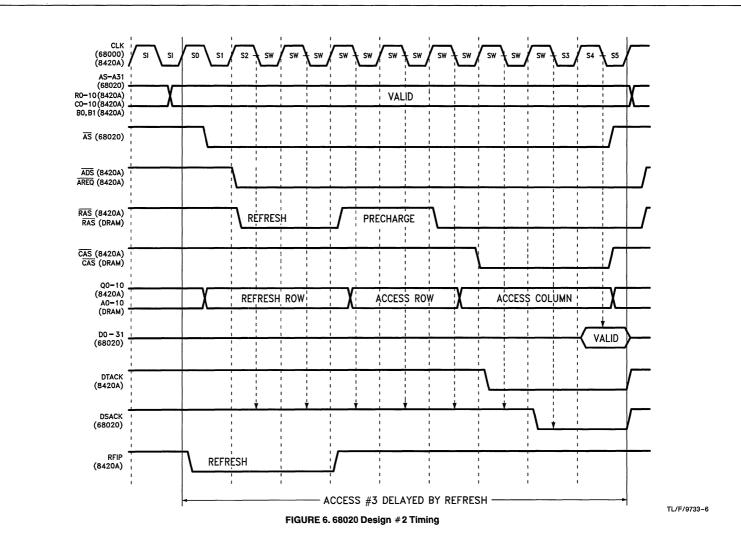

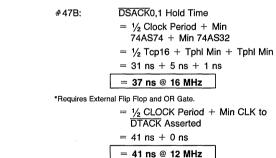

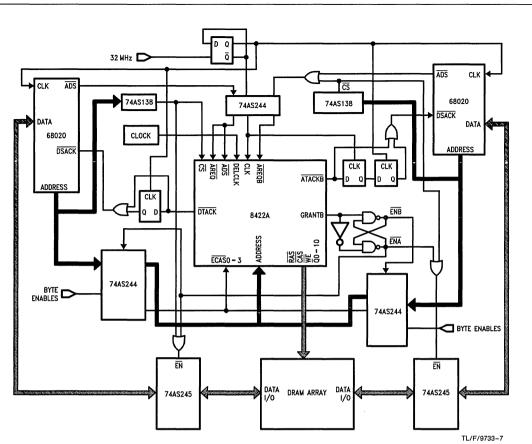

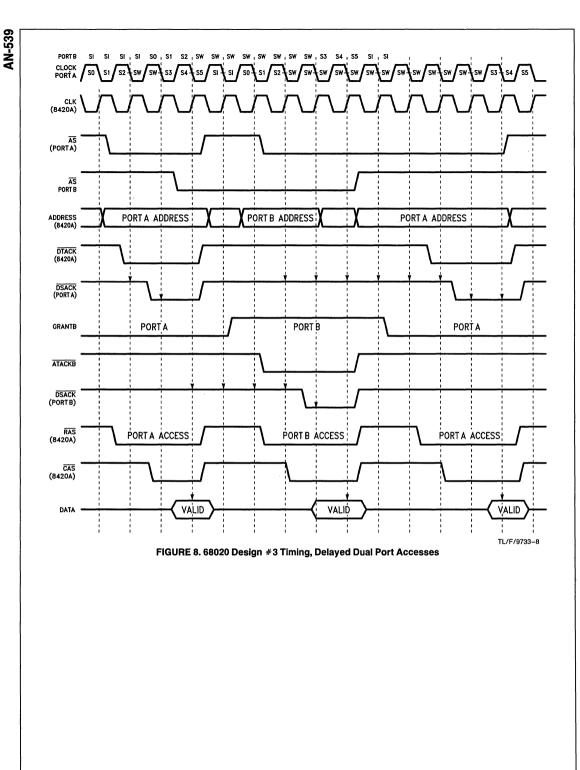

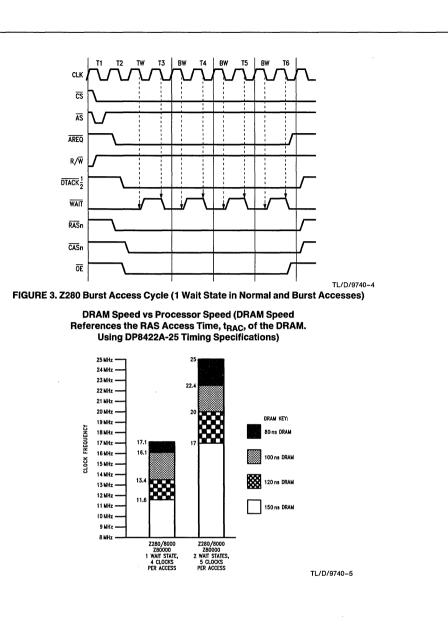

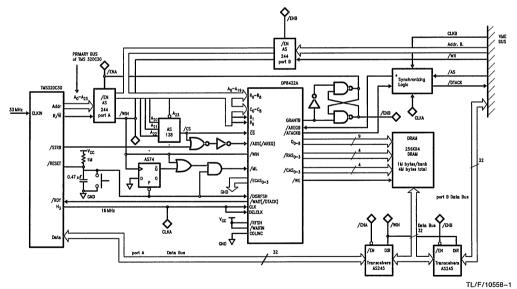

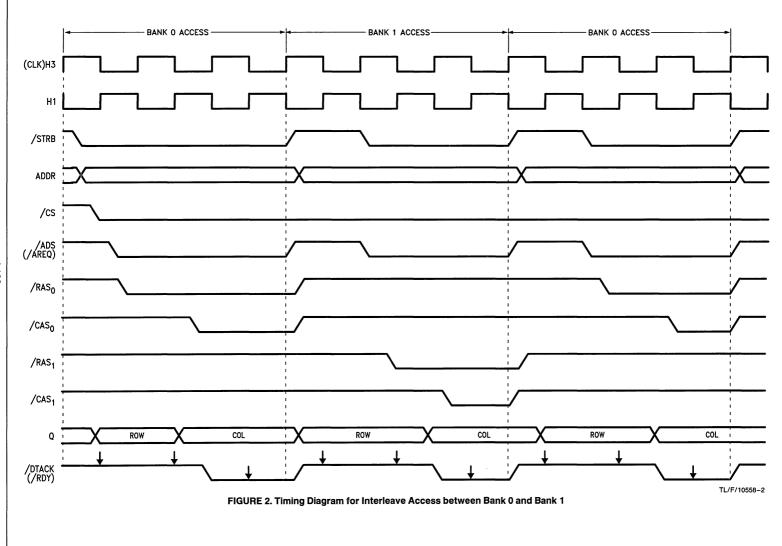

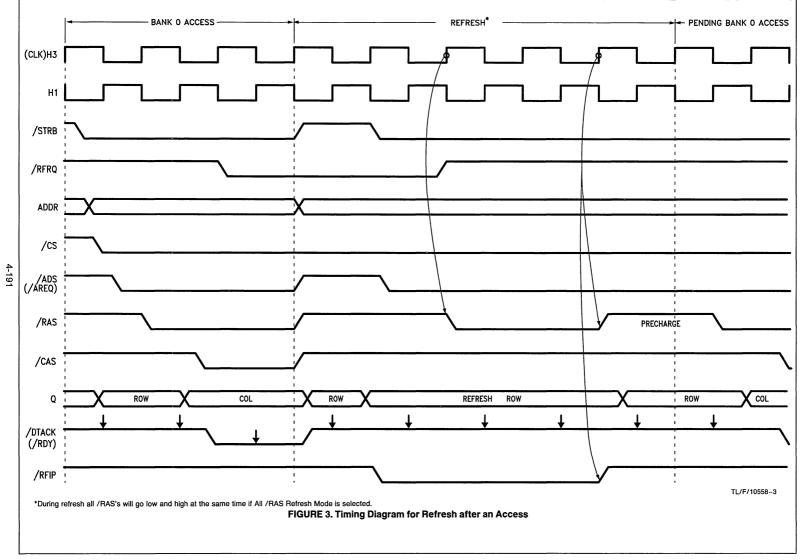

| Symbol                  | Access Farameter                                | Conditions                                                      | Min   | Тур   | Max | Min | Тур   | Max | Units |