# FACT™ Advanced CMOS Logic Databook

Includes New Product Information.

## **FACT**DATABOOK

1990 Edition

**Descriptions and Family Characteristics**

Ratings, Specifications, and Waveforms Design Considerations and Application Notes

**Advanced CMOS Datasheets**

**Quiet Series Datasheets**

**FCT Series Datasheets**

FCT A and B Series Datasheets Ordering Information and Physical Dimensions

J.

b

7

8

#### **TRADEMARKS**

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

Embedded System Microtalker™ SABRTM Abuseable<sup>TM</sup> Processor<sup>TM</sup> MICROWIRE™ Script/Chek™ E-Z-LINKTM Anadig<sup>TM</sup> MICROWIRE/PLUSTM SCXTM ANS-R-TRAN™ **FACTTM** MOLETM SERIES/800™ APPSTM FACT Quiet Series™ **МРАТМ** Series 900™ **ASPECT™ FAIRCADTM MSTTM** Series 3000TM Auto-Chem Deflasher™ Fairtech<sup>TM</sup> Naked-8™ Series 32000® ВСРТМ **FAST®** National® Shelf ChekTM National Semiconductor® Simple Switcher™ BI-FETTM 5-Star Service™ BI-FET II™ FlashTM SofChekTM National Semiconductor SONICTM BI-LINETM **GENIXTM** Corp.® **BIPLANTM GNXTM** NAX 800TM SPIRETM **BLCTM GTOTM** Nitride Plus™

Staggered Refresh<sup>TM</sup> **HAMRTM BLXTM** Nitride Plus Oxide™ STARTM ВМАСТМ HandiScan™ **NMLTM** Starlink<sup>TM</sup> Brite-Lite™ HEX 3000™ **NOBUSTM** STARPLEXTM **BSITM НРСТМ** NSC800™ Super-Block™ BTLTM 131 ® **NSCISETM** SuperChip™ CDDTM **ICMTM** NSX-16TM SuperScript<sup>TM</sup> CheckTrackTM INFOCHEX™ NS-XC-16™ SYS32TM **CIMTM** Integral ISETM NTERCOM<sup>TM</sup> TapePak® **CIMBUSTM** TDSTM Intelisplay™ NURAM™ CLASICTM ISETM OXISSTM TeleGate<sup>TM</sup> Clock**/**Chek™ ISE/06TM P2CMOSTM The National Anthem®

COMBO® ISE/08TM PC Master™ Time Chek™ COMBO ITM ISE/16TM Perfect Watch™ TINATM COMBO IITM TLCTM ISE32™ Pharma ✓ Chek™ COPS™ microcontrollers **ISOPLANARTM** PLANTM TrapezoidalTM

**CRDTM** ISOPLANAR-ZTM **PLANARTM** TRI-CODE™ DA4TM KevScan™ **PLAYERTM** TRI-POLYTM Datachecker® **LMCMOSTM** Plus-2TM TRI-SAFE™ DENSPAKTM M2CMOSTM Polycraft™ TRI-STATE® DIBTM Macrobus<sup>TM</sup> POSilink<sup>TM</sup>

DIB<sup>TM</sup> Macrobus<sup>TM</sup> POSilink<sup>TM</sup> TURBOTRANSCEIVER<sup>TM</sup>

Digitalker® Macrocomponent<sup>TM</sup> POSitalker<sup>TM</sup> VIP<sup>TM</sup>

**DISCERNTM** Power + Control<sup>TM</sup> MAXI-ROM® VR32TM **DISTILLTM** Meat ✓ Chek™ POWERplanar<sup>TM</sup> WATCHDOG™ DNR® MenuMaster™ QUAD3000TM **XMOSTM DPVMTM** Microbus™ data bus QUIKLOOKTM **XPUTM** E2CMOSTM MICRO-DACTM RATTM Z STARTM **ELSTARTM** μtalker<sup>TM</sup> RTX16™ 883B/RETSTM

MULTIBUS® is a registered trademark of Intel Corporation.

VMEbus™ is a trademark of Motorola Incorporated.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

883S/RETSTM

National Semiconductor Corporation 2900 Semiconductor Drive, P.O. Box 58090, Santa Clara, California 95052-8090 (408) 721-5000 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

#### Introduction

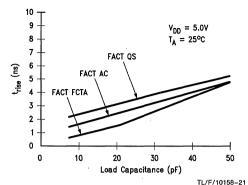

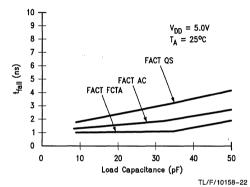

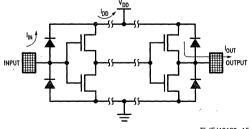

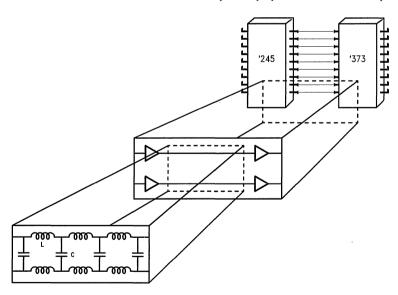

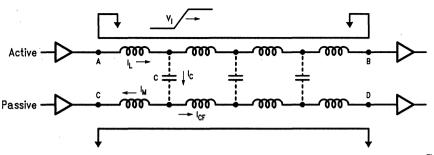

FACT<sup>TM</sup> (Fairchild Advanced CMOS Technology) is a very high-speed, low power CMOS Logic family utilizing a 1.3 μM Isoplanar silicon gate CMOS process. FACT logic functions can attain speeds similar to that of Advanced Low Power Schottky while retaining the advantages of CMOS logic: Ultra low static power and high noise immunity. FACT offers the system designer the added benefit of superior line driving characteristics and excellent ESD and Latch-up immunity.

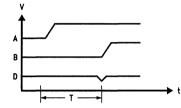

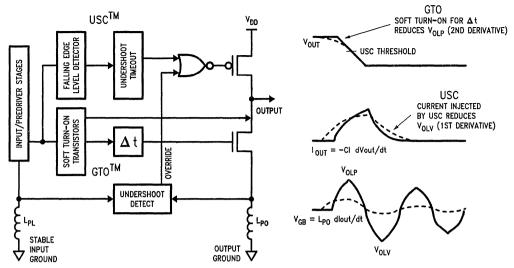

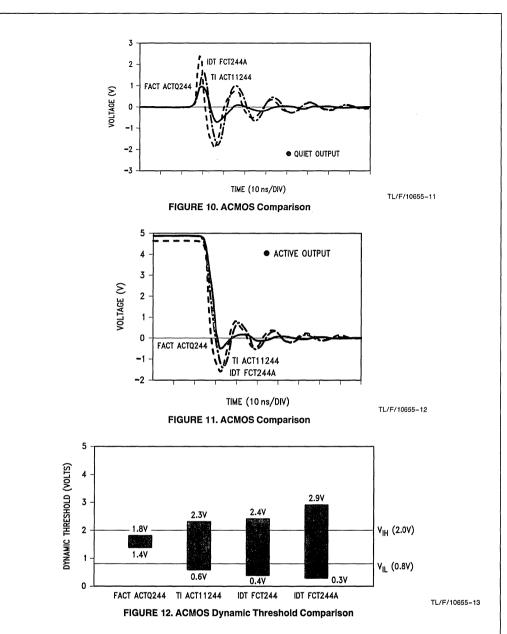

FACT Quiet Series, an extension of the FACT family, is a high speed, low power CMOS family IDEAL for ACMOS applications requiring increased noise margins. Utilizing NSC Quiet Series Technology, FACT QS features GTO™ outputs control, undershoot corrector and a split ground bus for superior ACMOS performance. In addition, FACT QS features improved AC specifications, specifies maximum pin-to-pin output skew and provides enhanced ESD immunity and latch-up protection.

FACT FCT, an extension of the FACT family, features 7 ns propagation delays and 64/48 mA output drive. The series incorporates National's Quiet Series Technology to provide the lowest noise performance of any FCT logic family. FACT FCTA is the high speed, high drive extension of the FACT family featuring 5 ns maximum propagation delays and 64/48 mA output drive. In addition, FACT FCTA features quiet circuitry to provide increased noise margins.

The FACT/FACT QS families consist of devices in two categories:

- AC/ACQ—standard logic functions with CMOS compatible inputs and TTL and MOS compatible outputs;

- 2. ACT/ACTQ—standard logic functions with TTL compatible inputs and TTL and MOS compatible outputs.

#### **Product Index and Selection Guide**

Lists FACT, FACT QS, FACT FCT, and FACT FCTA circuits currently available, in design or planned. The selection guide groups the circuits by function.

| Section 1    | Descrip   | otions   | and Family  |           |             |

|--------------|-----------|----------|-------------|-----------|-------------|

|              | Charac    | teristic | s           |           | <b>1-</b> 1 |

| Basic inforn | nation on | FACT     | performance | including | technol-    |

Basic information on FACT performance including technologies.

### Section 2 Ratings, Specifications and Waveforms.....2-1

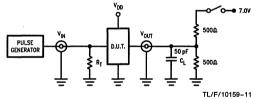

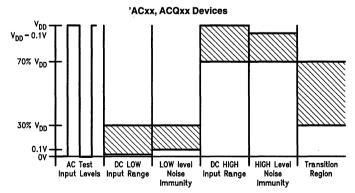

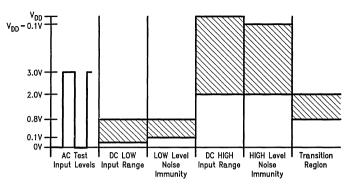

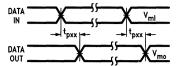

Contains common ratings and specifications for FACT devices, as well as AC test loads and waveforms.

| Section 3 Design Considerations                                                                                            |    |

|----------------------------------------------------------------------------------------------------------------------------|----|

| Section 4 Advanced CMOS Datasheets 4 Contains datasheets for currently available ar pending new FACT products.             |    |

| Section 5 Quiet Series Datasheets 5 Contains datasheets for currently available ar pending new FACT Quiet Series products. | •  |

| Section 6 FCT Series Datasheets                                                                                            | -  |

| Section 7 FCT A and B Series Datasheets                                                                                    |    |

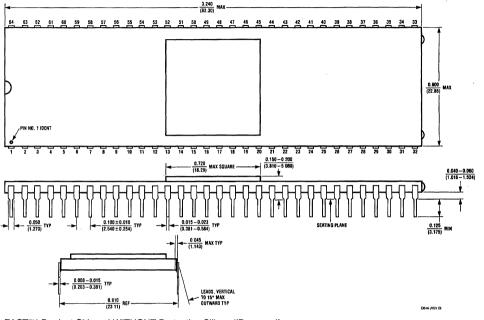

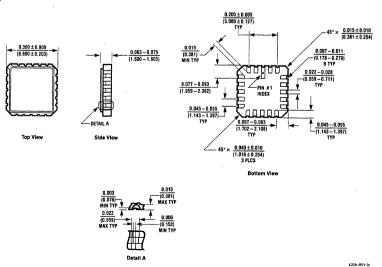

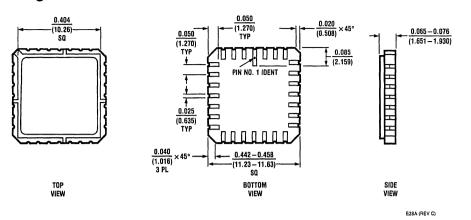

| Section 8 Ordering Information and Physical Dimensions                                                                     | -1 |

#### **Product Status Definitions**

#### **Definition of Terms**

| Data Sheet Identification     | Product Status            | Definition                                                                                                                                                                                                                                                             |

|-------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information           | Formative or<br>In Design | This data sheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                                                                    |

| Preliminary                   | First<br>Production       | This data sheet contains preliminary data, and supplementary data will be published at a later date. National Semiconductor Corporation reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

| No<br>Identification<br>Noted | Full<br>Production        | This data sheet contains final specifications. National Semiconductor Corporation reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                       |

National Semiconductor Corporation reserves the right to make changes without further notice to any products herein to improve reliability, function or design. National does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

## Alpha-Numeric Index

| 54AC/74AC00 Quad 2-Input NAND Gate                                                                    |       |

|-------------------------------------------------------------------------------------------------------|-------|

| 54AC/74AC02 Quad 2-Input NOR Gate                                                                     |       |

| 54AC/74AC04 Hex Inverter                                                                              |       |

| 54AC/74AC08 Quad 2-Input AND Gate                                                                     | 4-17  |

| 54AC/74AC10 Triple 3-Input NAND Gate                                                                  | 4-21  |

| 54AC/74AC11 Triple 3-Input AND Gate                                                                   | 4-25  |

| 54AC/74AC14 Hex Inverter with Schmitt Trigger Input                                                   |       |

| 54AC/74AC20 Dual 4-Input NAND Gate                                                                    |       |

| 54AC/74AC32 Quad 2-Input OR Gate                                                                      |       |

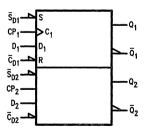

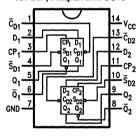

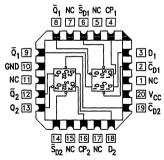

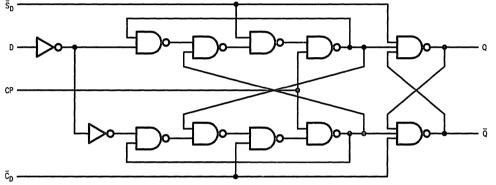

| 54AC/74AC74 Dual D Positive Edge-Triggered Flip-Flop                                                  |       |

| 54AC/74AC86 Quad 2-Input Exclusive-OR Gate                                                            |       |

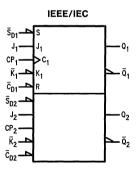

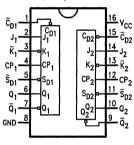

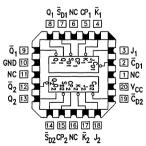

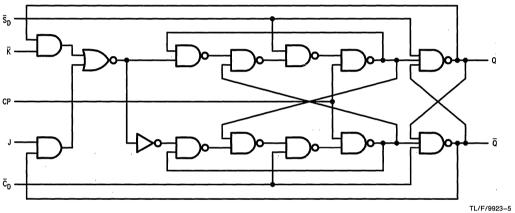

| 54AC/74AC109 Dual JK Positive Edge-Triggered Flip-Flop                                                |       |

| 54AC/74AC125 Quad TRI-STATE Buffer                                                                    | 4-53  |

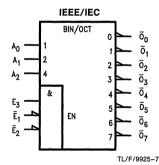

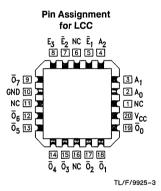

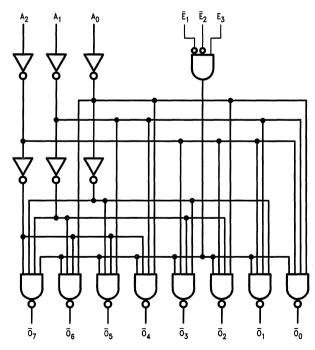

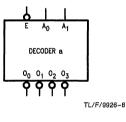

| 54AC/74AC138 1-of-8 Decoder/Demultiplexer                                                             | 4-57  |

| 54AC/74AC139 Dual 1-of-4 Decoder/Demultiplexer                                                        |       |

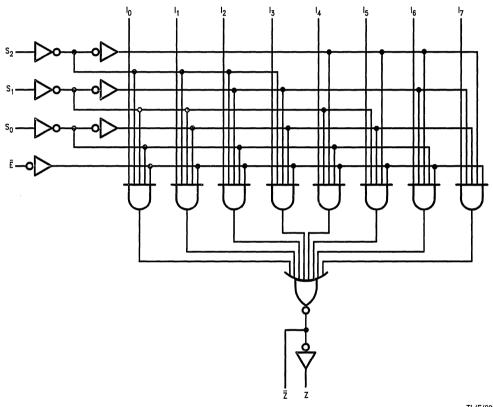

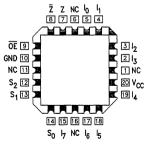

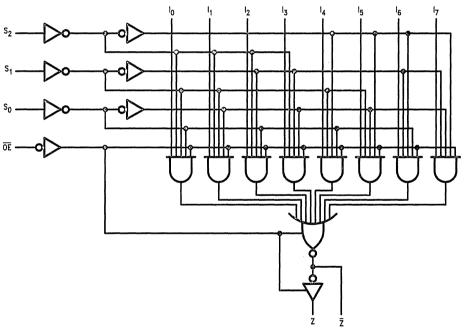

| 54AC/74AC151 8-Input Multiplexer                                                                      |       |

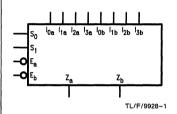

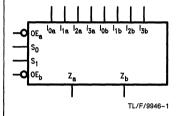

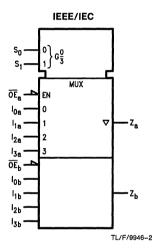

| 54AC/74AC153 Dual 4-Input Multiplexer                                                                 | 4-74  |

| 54AC/74AC157 Quad 2-Input Multiplexer                                                                 |       |

| 54AC/74AC158 Quad 2-Input Multiplexer                                                                 |       |

| 54AC/74AC133 Quad 2-input Multiplexer 54AC/74AC161 Synchronous Presettable Binary Counter             |       |

| 54AC/74AC163 Synchronous Presettable Binary Counter                                                   |       |

| 54AC/74AC169 4-Stage Synchronous Bidirectional Counter                                                |       |

| 54AC/74AC179 4-Stage Synchronous Bidirectional Counter 54AC/74AC174 Hex D Flip-Flop with Master Reset | 4 110 |

| 54AC/74AC174 Flex D Flip-Flop with Master Reset.                                                      | 4 110 |

| 54AC/74AC175 Quad D Filip-Flop                                                                        |       |

|                                                                                                       |       |

| 54AC/74AC240 Octal Buffer/Line Driver with TRI-STATE Outputs                                          |       |

| 54AC/74AC241 Octal Buffer/Line Driver with TRI-STATE Outputs                                          |       |

| 54AC/74AC244 Octal Buffer/Line Driver with TRI-STATE Outputs                                          |       |

| 54AC/74AC245 Octal Bidirectional Transceiver with TRI-STATE Inputs/Outputs                            | 4-144 |

| 54AC/74AC251 8-Input Multiplexer with TRI-STATE Output                                                | 4-148 |

| 54AC/74AC253 Dual 4-Input Multiplexer with TRI-STATE Outputs                                          | 4-154 |

| 54AC/74AC257 Quad 2-Input Multiplexer with TRI-STATE Outputs                                          |       |

| 54AC/74AC258 Quad 2-Input Multiplexer with TRI-STATE Outputs                                          |       |

| 54AC/74AC273 Octal D Flip-Flop                                                                        |       |

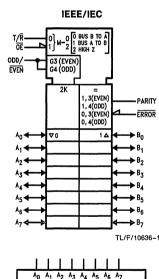

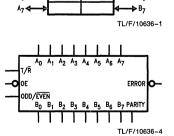

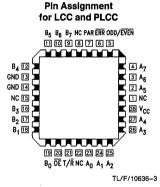

| 54AC/74AC280 9-Bit Parity Generator/Checker                                                           | 4-175 |

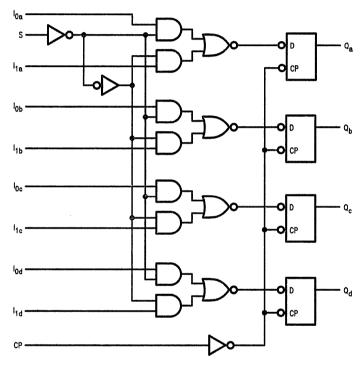

| 54AC/74AC299 8-Input Universal Shift/Storage Register with Common Parallel I/O Pins                   | 4-179 |

| 54AC/74AC367 Hex TRI-STATE Buffer                                                                     |       |

| 54AC/74AC373 Octal Transparent Latch with TRI-STATE Outputs                                           |       |

| 54AC/74AC374 Octal D Flip-Flop with TRI-STATE Outputs                                                 |       |

| 54AC/74AC377 Octal D Flip-Flop with Clock Enable                                                      |       |

| 54AC/74AC378 Parallel D Register with Enable                                                          | 4-215 |

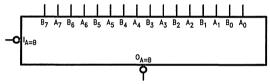

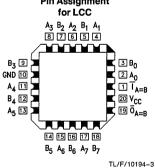

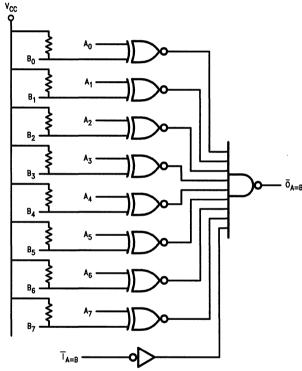

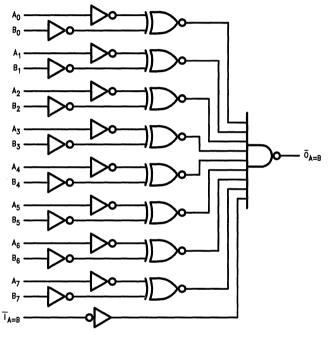

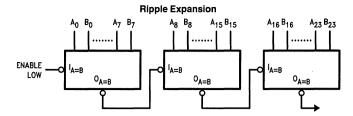

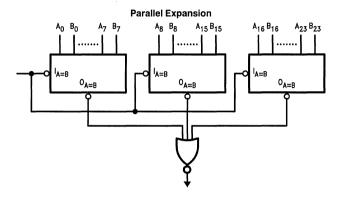

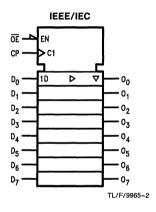

| 54AC/74AC520 8-Bit Identity Comparator                                                                |       |

| 54AC/74AC521 8-Bit Identity Comparator                                                                | 4-229 |

| 54AC/74AC540 Octal Buffer/Line Driver with TRI-STATE Outputs                                          | 4-240 |

| 54AC/74AC541 Octal Buffer/Line Driver with TRI-STATE Outputs                                          |       |

| 54AC/74AC574 Octal D Flip-Flop with TRI-STATE Outputs                                                 | 4-259 |

| 54AC/74AC646 Octal Transceiver/Register with TRI-STATE Outputs                                        |       |

| 54AC/74AC648 Octal Transceiver/Register with TRI-STATE Outputs                                        |       |

| 54AC/74AC821 10-Bit D Flip-Flop with TRI-STATE Outputs                                                | 4-294 |

| 54AC/74AC843 9-Bit Transparent Latch                                                                  |       |

| 54AC/74AC899 9-Bit Latchable Transceiver Register with Parity Generator/Checker                       |       |

| · · · · · · · · · · · · · · · · · · ·                                                                 |       |

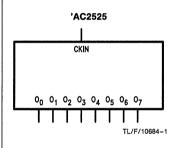

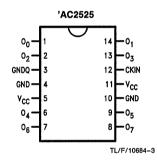

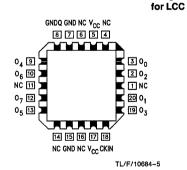

| 54AC/74AC2525 Minimum Skew Clock Driver                                                 | 4-338  |

|-----------------------------------------------------------------------------------------|--------|

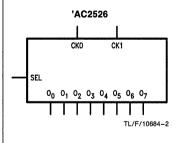

| 54AC/74AC2526 Minimum Skew Clock Driver with Multiplexed Clock Input                    | 4-338  |

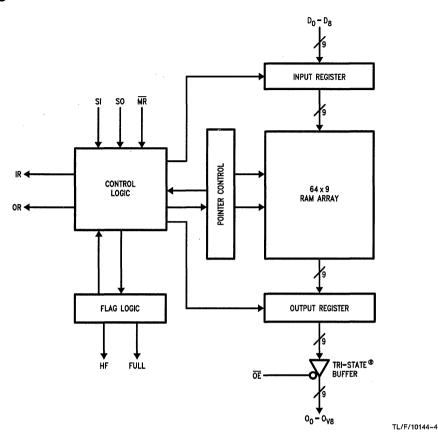

| 54AC/74AC2708 64 x 9 First-In, First-Out Memory                                         |        |

| 54ACQ/74ACQ240 Quiet Series Octal Buffer/Line Driver with TRI-STATE Outputs             | 5-7    |

| 54ACQ/74ACQ241 Quiet Series Octal Buffer/Line Driver with TRI-STATE Outputs             |        |

| 54ACQ/74ACQ244 Quiet Series Octal Buffer/Line Driver with TRI-STATE Outputs             |        |

| 54ACQ/74ACQ245 Quiet Series Octal Bidirectional Transceiver with TRI STATE Outputs      |        |

| 54ACQ/74ACQ273 Quiet Series Octal D Flip-Flop                                           |        |

| 54ACQ/74ACQ373 Quiet Series Octal Transparent Latch with TRI-STATE Outputs              | 5-32   |

| 54ACQ/74ACQ374 Quiet Series Octal D Flip-Flop with TRI-STATE Outputs                    |        |

| 54ACQ/74ACQ377 Quiet Series Octal D Flip-Flop with Clock Enable                         |        |

| 54ACQ/74ACQ533 Quiet Series Octal Latch with TRI-STATE Outputs                          |        |

| 54ACQ/74ACQ534 Quiet Series Octal D Flip-Flop with TRI-STATE Outputs                    | 5-51   |

| 54ACQ/74ACQ543 Quiet Series Octal Registered Transceiver with TRI-STATE Outputs         |        |

| 54ACQ/74ACQ544 Quiet Series Octal Registered Transceiver with TRI-STATE Outputs         |        |

| 54ACQ/74ACQ563 Quiet Series Octal Latch with TRI-STATE Outputs                          |        |

| 54ACQ/74ACQ564 Quiet Series Octal D Flip-Flop with TRI-STATE Outputs                    |        |

| 54ACQ/74ACQ573 Quiet Series Octal Latch with TRI-STATE Outputs                          |        |

| 54ACQ/74ACQ574 Quiet Series Octal D Flip-Flop with TRI-STATE Outputs                    |        |

| 54ACQ/74ACQ821 Quiet Series 10-Bit D Flip-Flop with TRI-STATE Outputs                   |        |

| 54ACT/74ACT00 Quad 2-Input NAND Gate                                                    |        |

| 54ACT/74ACT02 Quad 2-Input NAND Gate                                                    | 4.0    |

| 54ACT/74ACT02 Quau 2-input NOA Gate                                                     | 4 10   |

| 54ACT/74ACT04 Hex Inverter 54ACT/74ACT08 Quad 2-Input AND Gate                          |        |

| 54ACT/74ACT10 Triple 3-Input NAND Gate                                                  | . 4-17 |

|                                                                                         |        |

| 54ACT/74ACT32 Quad 2-Input OR Gate                                                      |        |

|                                                                                         |        |

| 54ACT/74ACT109 Dual JK Positive Edge-Triggered Flip-Flop                                |        |

|                                                                                         |        |

| 54ACT/74ACT138 1-of-8 Decoder/Demultiplexer                                             |        |

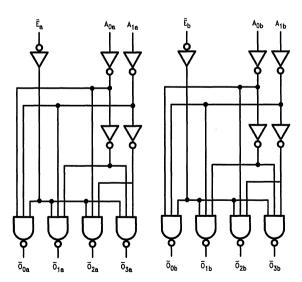

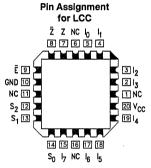

| 54ACT/74ACT139 Dual 1-of-4 Decoder/Demultiplexer                                        |        |

| 54ACT/74ACT151 6-Input Multiplexer                                                      |        |

|                                                                                         |        |

| 54ACT/74ACT157 Quad 2-Input Multiplexer                                                 |        |

| 54ACT/74ACT158 Quad 2-Input Multiplexer                                                 |        |

|                                                                                         |        |

| 54ACT/74ACT163 Synchronous Presettable Binary Counter                                   |        |

| 54ACT/74ACT174 Hex D Flip-Flop with Master Reset                                        |        |

| 54ACT/74ACT174 Hex D Flip-Flop with Master Heset                                        |        |

|                                                                                         |        |

| 54ACT/74ACT240 Octal Buffer/Line Driver with TRI-STATE Outputs                          |        |

|                                                                                         |        |

| 54ACT/74ACT244 Octal Buffer/Line Driver with TRI-STATE Outputs                          |        |

| 54ACT/74ACT245 Octal Bidirectional Transceiver with TRI-STATE Inputs/Outputs            |        |

| 54ACT/74ACT251 8-Input Multiplexer with TRI-STATE Output                                |        |

| 54ACT/74ACT253 Dual 4-Input Multiplexer with TRI-STATE Outputs                          |        |

| 54ACT/74ACT257 Quad 2-Input Multiplexer with TRI-STATE Outputs                          |        |

| 54ACT/74ACT258 Quad 2-Input Multiplexer with TRI-STATE Outputs                          |        |

| 54ACT/74ACT299 8-Input Universal Shift/Storage Register with Common Parallel I/O Pins   | 4-1/9  |

| 54ACT/74ACT323 8-Bit Universal Shift/Storage Register with Synchronous Reset and Common | 4 400  |

| I/O Pins                                                                                | 4-186  |

| 54ACT/74ACT368 Hex TRI-STATE Inverting Buffer                                        |       |

|--------------------------------------------------------------------------------------|-------|

| 54ACT/74ACT373 Octal Transparent Latch with TRI-STATE Outputs                        | 4-197 |

| 54ACT/74ACT374 Octal D Flip-Flop with TRI-STATE Outputs                              |       |

| 54ACT/74ACT377 Octal D Flip-Flop with Clock Enable                                   | 4-209 |

| 54ACT/74ACT399 Quad 2-Port Register                                                  | 4-219 |

| 54ACT/74ACT520 8-Bit Identity Comparator                                             | 4-223 |

| 54ACT/74ACT521 8-Bit Identity Comparator                                             | 4-229 |

| 54ACT/74ACT534 Octal D Flip-Flop with TRI-STATE Outputs                              | 4-235 |

| 54ACT/74ACT563 Octal Latch with TRI-STATE Outputs                                    | 4-246 |

| 54ACT/74ACT564 Octal D Flip-Flop with TRI-STATE Outputs                              | 4-251 |

| 54ACT/74ACT573 Octal Latch with TRI-STATE Outputs                                    |       |

| 54ACT/74ACT574 Octal D Flip-Flop with TRI-STATE Outputs                              | 4-259 |

| 54ACT/74ACT646 Octal Transceiver/Register with TRI-STATE Outputs                     | 4-265 |

| 54ACT/74ACT705 Arithmetic Logic Unit for Digital Signal Processing Applications      | 4-278 |

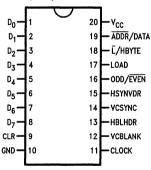

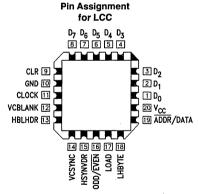

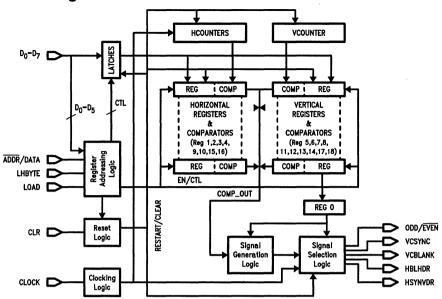

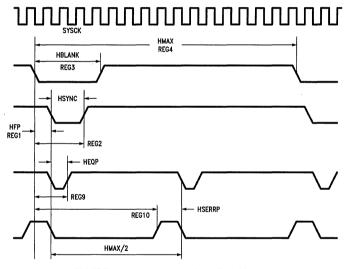

| 54ACT/74ACT715 Programmable Video Sync Generator                                     | 4-279 |

| 54ACT/74ACT818 8-Bit Diagnostic Register                                             |       |

| 54ACT/74ACT821 10-Bit D Flip-Flop with TRI-STATE Outputs                             |       |

| 54ACT/74ACT823 9-Bit D Flip-Flop                                                     |       |

| 54ACT/74ACT825 8-Bit D Flip-Flop                                                     | 4-304 |

| 54ACT/74ACT841 10-Bit Transparent Latch with TRI-STATE Outputs                       |       |

| 54ACT/74ACT843 9-Bit Transparent Latch                                               |       |

| 54ACT/74ACT845 8-Bit Transparent Latch with TRI-STATE Outputs                        |       |

| 54ACT/74ACT899 9-Bit Latchable Transceiver Register with Parity Generator/Checker    |       |

| 54ACT/74ACT2708 64 x 9 First-In, First-Out Memory                                    |       |

| 54ACT/74ACT2725 512 x 9 First In, First Out Memory (FIFO)                            | 4-355 |

| 54ACT/74ACT2726 512 x 9 Bidirectional First-In, First-Out Memory (BiFIFO)            | 4-356 |

| 54ACTQ/74ACTQ153 Dual 4-Input Multiplexer                                            | 5-3   |

| 54ACTQ/74ACTQ240 Quiet Series Octal Buffer/Line Driver with TRI-STATE Outputs        |       |

| 54ACTQ/74ACTQ241 Quiet Series Octal Buffer/Line Driver with TRI-STATE Outputs        |       |

| 54ACTQ/74ACTQ244 Quiet Series Octal Buffer/Line Driver with TRI-STATE Outputs        |       |

| 54ACTQ/74ACTQ245 Quiet Series Octal Bidirectional Transceiver with TRI-STATE Outputs |       |

| 54ACTQ/74ACTQ273 Quiet Series Octal D Flip-Flop                                      |       |

| 54ACTQ/74ACTQ373 Quiet Series Octal Transparent Latch with TRI-STATE Outputs         | 5-32  |

| 54ACTQ/74ACTQ374 Quiet Series Octal D Flip-Flop with TRI-STATE Outputs               |       |

| 54ACTQ/74ACTQ377 Quiet Series Octal D Flip-Flop with Clock Enable                    |       |

| 54ACTQ/74ACTQ533 Quiet Series Octal Latch with TRI-STATE Outputs                     |       |

| 54ACTQ/74ACTQ534 Quiet Series Octal D Flip-Flop with TRI-STATE Outputs               |       |

| 54ACTQ/74ACTQ543 Quiet Series Octal Registered Transceiver with TRI-STATE Outputs    | 5-57  |

| 54ACTQ/74ACTQ544 Quiet Series Octal Registered Transceiver with TRI-STATE Outputs    |       |

| 54ACTQ/74ACTQ563 Quiet Series Octal Latch with TRI-STATE Outputs                     |       |

| 54ACTQ/74ACTQ564 Quiet Series Octal D Flip-Flop with TRI-STATE Outputs               | 5-66  |

| 54ACTQ/74ACTQ573 Quiet Series Octal Latch with TRI-STATE Outputs                     |       |

| 54ACTQ/74ACTQ574 Quiet Series Octal D Flip-Flop with TRI-STATE Outputs               |       |

| 54ACTQ/74ACTQ646 Quiet Series Octal Transceiver/Register with TRI-STATE Outputs      | 5-85  |

| 54ACTQ/74ACTQ657 Quiet Series Octal Bidirectional Transceiver with 8-Bit Parity      |       |

| Generator/Checker and TRI-STATE Outputs                                              | 5-86  |

| 54ACTQ/74ACTQ827 Quiet Series 10-Bit Buffer/Line Driver with TRI-STATE Outputs       |       |

| 54ACTQ/74ACTQ841 Quiet Series 10-Bit Transparent Latch with TRI-STATE Outputs        |       |

| 54ACTQ/74ACTQ843 Quiet Series 9-Bit Transparent Latch with TRI-STATE Outputs         |       |

| 54FCT540 Inverting Octal Buffer/Line Driver with TRI-STATE Outputs                   |       |

| 54FCT541 Non-Inverting Octal Buffer/Line Driver with TRI-STATE Outputs               |       |

|                                                                                      |       |

| 54FCT/74FCT138 1-to-8 Multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 54FCT/74FCT138A 1-to-8 Multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

| 54FCT/74FCT240 Octal Buffer/Line Driver with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                      |

| 54FCT/74FCT240A Octal Buffer/Line Driver with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 7-4                                                                                                                                                                |

| 54FCT/74FCT241 Octal Buffer/Line Driver with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 6-8                                                                                                                                                                |

| 54FCT/74FCT241A Octal Buffer/Line Driver with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 7-8                                                                                                                                                                |

| 54FCT/74FCT244 Octal Buffer/Line Driver with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6-12                                                                                                                                                                 |

| 54FCT/74FCT244A Octal Buffer/Line Driver with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                      |

| 54FCT/74FCT245 Octal Buffer/Line Driver with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                      |

| 54FCT/74FCT245A Octal Buffer/Line Driver with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                      |

| 54FCT/74FCT273 Octal D Flip-Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                      |

| 54FCT/74FCT273A Octal D Flip-Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-20                                                                                                                                                                 |

| 54FCT/74FCT373 Octal Transparent Latch with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                      |

| 54FCT/74FCT373A Octal Transparent Latch with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                      |

| 54FCT/74FCT374 Octal D Flip-Flop with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

| 54FCT/74FCT374A Octal D Flip-Flop with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

| 54FCT/74FCT377 Octal D Flip-Flop with Clock Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

| 54FCT/74FCT377A Octal D Flip-Flop with Clock Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |

| 54FCT/74FCT521 8-Bit Identity Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

| 54FCT/74FCT521A 8-Bit Identity Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                      |

| 54FCT/74FCT533 Octal Transparent Latch with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                      |

| 54FCT/74FCT533A Octal Transparent Latch with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                      |

| 54FCT/74FCT534 Octal D Flip-Flop with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

| 54FCT/74FCT534A Octal D Flip-Flop with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

| 54FCT/74FCT543 Octal Registered Transceiver with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                      |

| 54FCT/74FCT543A Octal Registered Transceiver with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-43                                                                                                                                                                 |

| 54FCT/74FCT543A Octal Registered Transceiver with TRI-STATE Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |