**Graphics Handbook**

1989

# Advanced Peripherals

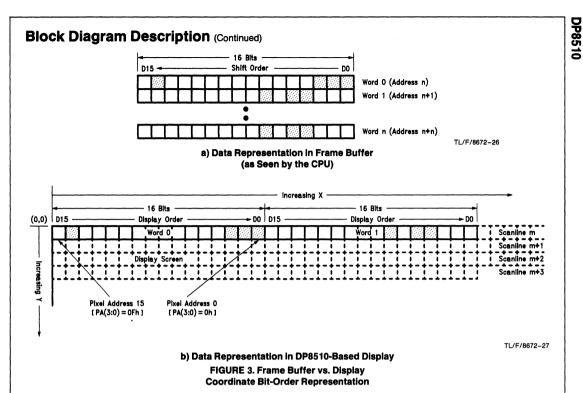

1

# Graphics Handbook

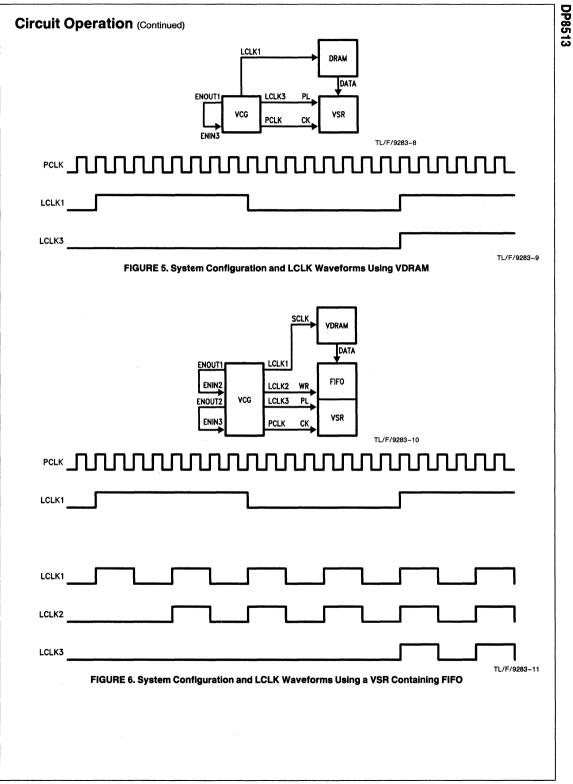

# A Corporate Dedication to Quality and Reliability

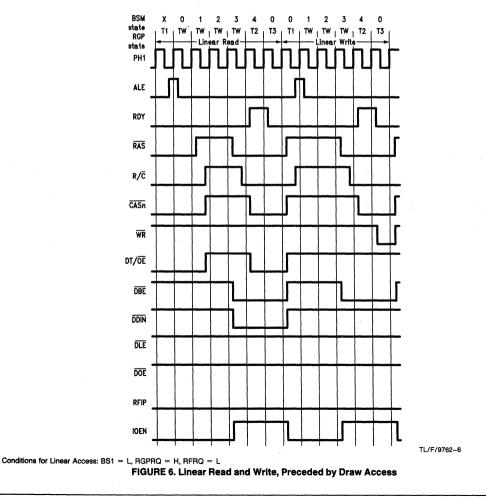

National Semiconductor is an industry leader in the manufacture of high quality, high reliability integrated circuits. We have been the leading proponent of driving down IC defects and extending product lifetimes. From raw material through product design, manufacturing and shipping, our quality and reliability is second to none.

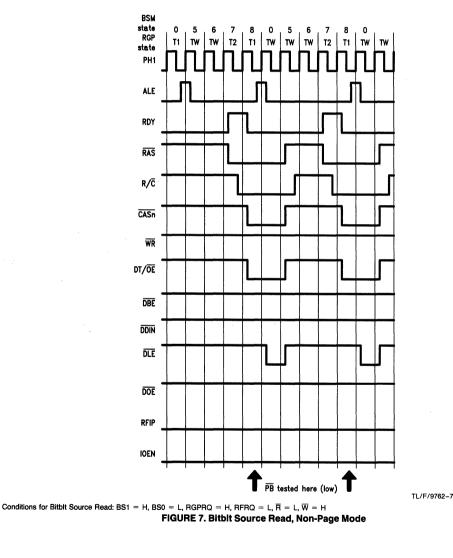

We are proud of our success . . . it sets a standard for others to achieve. Yet, our quest for perfection is ongoing so that you, our customer, can continue to rely on National Semiconductor Corporation to produce high quality products for your design systems.

antic horn

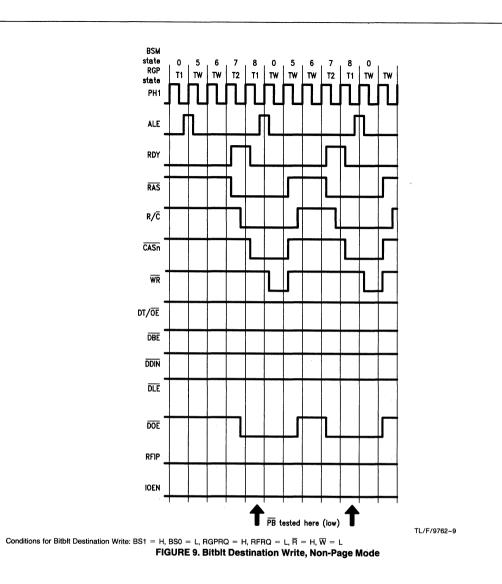

Charles E. Sporck President, Chief Executive Officer National Semiconductor Corporation

#### Wir fühlen uns zu Qualität und Zuverlässigkeit verpflichtet

National Semiconductor Corporation ist führend bei der Herstellung von integrierten Schaltungen hoher Qualität und hoher Zuverlässigkeit. National Semiconductor war schon immer Vorreiter, wenn es galt, die Zahl von IC Ausfällen zu verringern und die Lebensdauern von Produkten zu verbessern. Vom Rohmaterial über Entwurf und Herstellung bis zur Auslieferung, die Qualität und die Zuverlässigkeit der Produkte von National Semiconductor sind unübertroffen.

Wir sind stolz auf unseren Erfolg, der Standards setzt, die für andere erstrebenswert sind. Auch ihre Ansprüche steigen ständig. Sie als unser Kunde können sich auch weiterhin auf National Semiconductor verlassen.

#### La Qualité et La Fiabilité:

Une Vocation Commune Chez National Semiconductor Corporation

National Semiconductor Corporation est un des leaders industriels qui fabrique des circuits intégrés d'une très grande qualité et d'une fiabilité exceptionelle. National a été le premier à vouloir faire chuter le nombre de circuits intégrés défectueux et a augmenter la durée de vie des produits. Depuis les matières premières, en passant par la conception du produit sa fabrication et son expédition, partout la qualité et la fiabilité chez National sont sans équivalents.

Nous sommes fiers de notre succès et le standard ainsi défini devrait devenir l'objectif à atteindre par les autres sociétés. Et nous continuons à vouloir faire progresser notre recherche de la perfection; il en résulte que vous, qui êtes notre client, pouvez toujours faire confiance à National Semiconductor Corporation, en produisànt des systèmes d'une très grande qualité standard.

#### Un Impegno Societario di Qualità e Affidabilità

National Semiconductor Corporation è un'industria al vertice nella costruzione di circuiti integrati di altà qualità ed affidabilità. National è stata il principale promotore per l'abbattimento della difettosità dei circuiti integrati e per l'allungamento della vita dei prodotti. Dal materiale grezzo attraverso tutte le fasi di progettazione, costruzione e spedizione, la qualità e affidabilità National non è seconda a nessuno.

Noi siamo orgogliosi del nostro successo che fissa per gli altri un traguardo da raggiungere. Il nostro desiderio di perfezione è d'altra parte illimitato e pertanto tu, nostro cliente, puoi continuare ad affidarti a National Semiconductor Corporation per la produzione dei tuoi sistemi con elevati livelli di qualità.

Charlie Sponk

Charles E. Sporck President, Chief Executive Officer National Semiconductor Corporation

ii

# **GRAPHICS** HANDBOOK

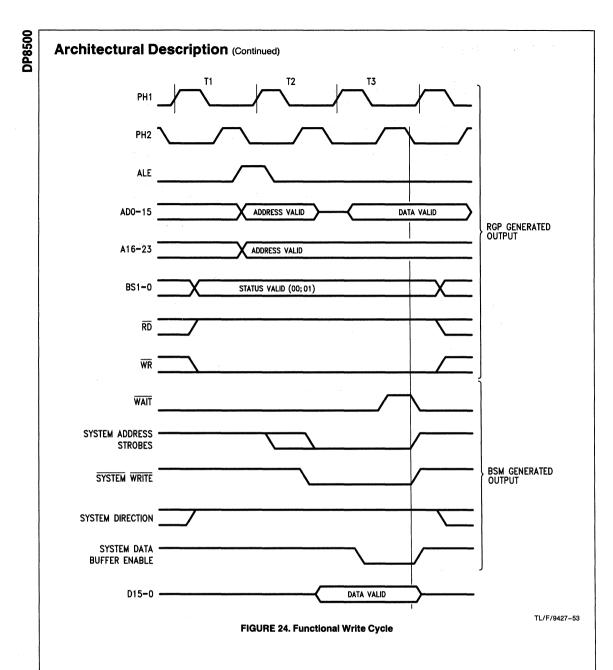

1989 Edition

**Advanced Graphics Chipset**

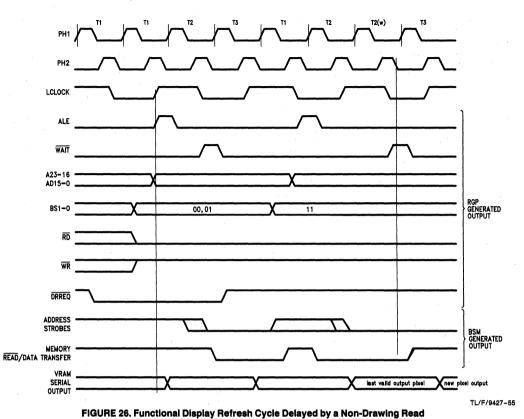

**DP8500 Development Tools**

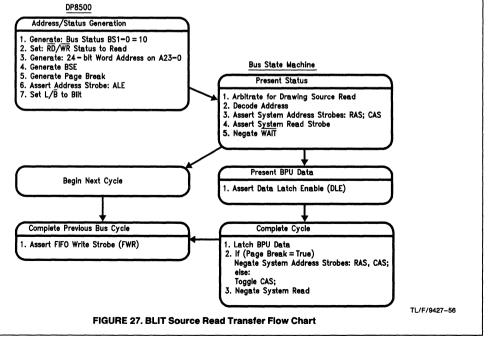

**Application Notes**

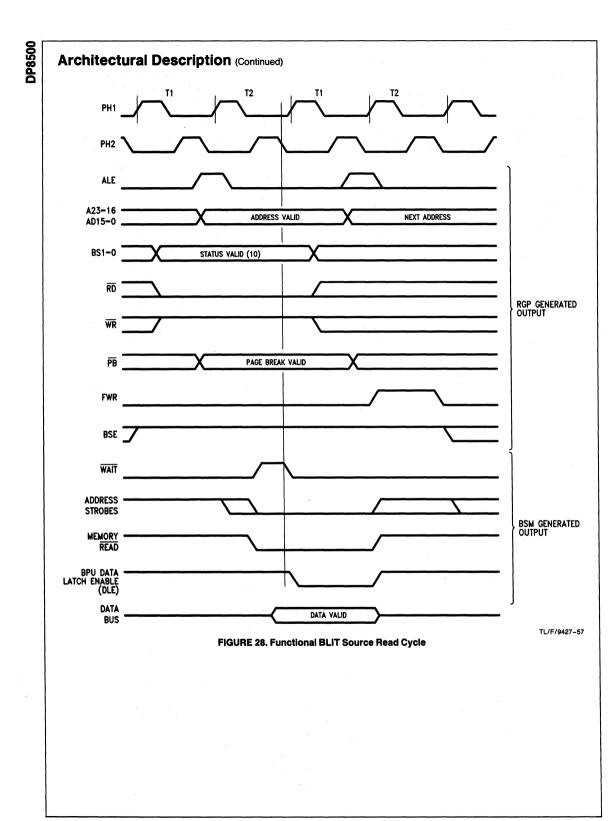

**Physical Dimensions/Appendices**

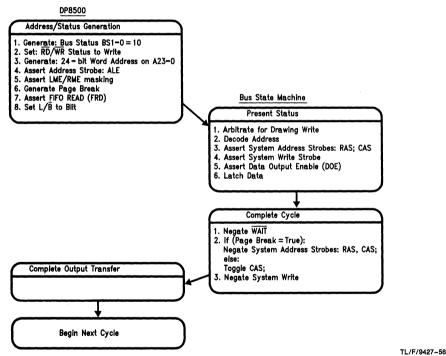

#### TRADEMARKS

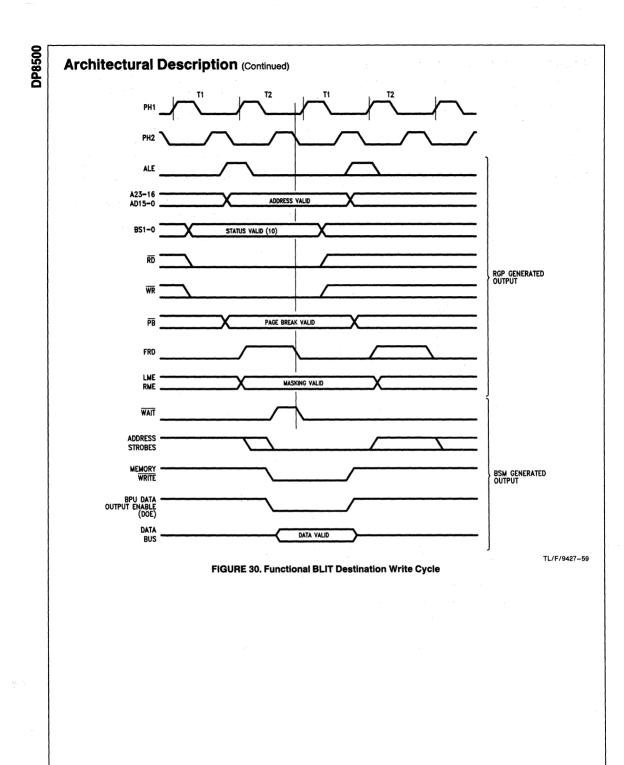

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

Abuseable™ **FAIRCADTM** Anadia™ Fairtech™ ANS-R-TRAN™ **FAST® APPSTM** 5-Star Service™ **ASPECT™ GENIX™** Auto-Chem Deflasher™ **GNXTM** ВСРТМ HAMBTM BI-FET™ HandiScan™ BI-FET II™ HEX 3000™ НРС™ **BI-LINE™** |3L® **BIPLANTM BLCTM ICM™ BLXTM INFOCHEX™** Brite-Lite™ Integral ISE™ **BTLTM** Intelisplav<sup>TM</sup> CheckTrack™ **ISETM** СІМ™ ISE/06™ ISE/08™ **CIMBUS™ CLASIC™** ISE/16™ Clock Chek™ ISE32™ **СОМВО™ ISOPLANAR™** COMBO ITM **ISOPLANAR-Z™** COMBO IITM KeyScan™ COPS™ microcontrollers LMCMOSTM Datachecker® M<sup>2</sup>CMOS™ **DENSPAKTM** Macrobus™ DIB<sup>TM</sup> Macrocomponent<sup>™</sup> Digitalker® MAXI-ROM® **DISCERNTM** Meatr Chek™ DISTILL™ MenuMaster™ DNR® Microbus™ data bus **DPVMTM** MICRO-DAC™ ELSTAR™ utalker™ Embedded System Microtalker™ Processor™ **MICROWIRE™** E-Z-LINK™ MICROWIRE/PLUS™ **FACTTM MOLETM**

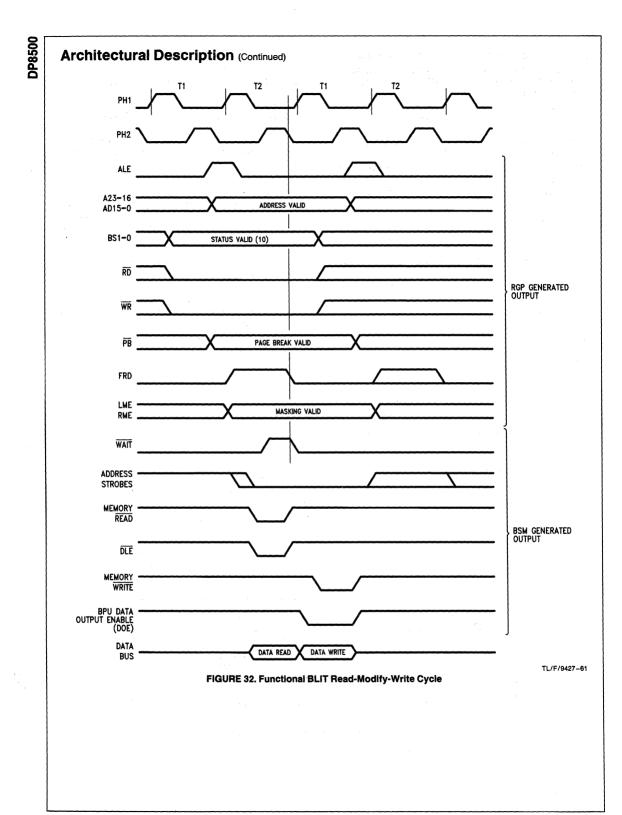

MSTTM Naked-8TM National® National Semiconductor® National Semiconductor Corp.® **NAX 800TM** Nitride Plus™ Nitride Plus Oxide™ **NMLTM NOBUS™** NSC800™ **NSCISE™** NSX-16™ NS-XC-16™ **NTERCOMTM NURAM™ OXISS™** P<sup>2</sup>CMOS<sup>™</sup> PC Master™ Perfect Watch™ Pharma/ChekTM **PLANTM PLANAR<sup>TM</sup>** Plus-2™ Polycraft™ **POSilink™ POSitalker™** Power + Control™ **POWERplanar™** QUAD3000™ **QUIKLOOKTM RATTM** RTX16™ SABR™ Script/Chek™

SCXTM SERIES/800TM Series 900TM Series 3000™ Series 32000® Shelf//Chek™ SofChek™ SPIRETM **STARTM** Starlink™ **STARPLEX™** Super-Block™ SuperChip™ SuperScript™ SYS32™ TapePak® TDSTM TeleGate™ The National Anthem® Time⊮Chek™ TINATM TLCTM Trapezoidal™ TRI-CODE™ TRI-POLY™ **TRI-SAFE™** TRI-STATE® **TURBOTRANSCEIVER™** VIPTM VR32™ WATCHDOG™ XMOSTM **XPUTM** Z STAR™ 883B/RETS™ 883S/RETS™

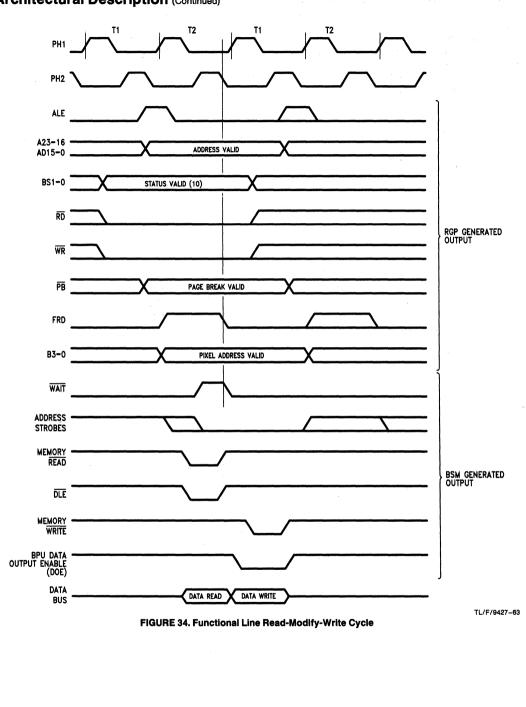

GAL® is a registered trademark of Lattice Semiconductor.

PAL® is a registered trademark of and is used under license from Monolithic Memories, Inc.

UNIX® is a registered trademark of AT & T.

DEC<sup>™</sup> and Ultrix<sup>™</sup> are trademarks of Digital Equipment Corp.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive, P.O. Box 58090, Santa Clara, California 95052-8090 (408) 721-5000 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

# Introduction

# National Semiconductor

# Introduction

National Semiconductor's graphics and imaging products include complex VLSI peripheral circuits designed to serve a variety of applications. These products are especially well suited for microcomputer and microprocessor systems such as workstations, terminals, personal computers, and many others.

#### GRAPHICS

Sophisticated human interface is the mark of the newest computer systems. Today's personal computer may have better graphics display capability than engineering workstations of a few years ago. National Semiconductor has developed a new family of Advanced Graphics products to provide extremely high performance, high resolution monochrome or color graphics displays. The graphics chip set is designed to provide the highest level of performance without placing constraints on the overall system design or performance. Flexibility is as important as is overall performance. That flexibility is provided by the partitioned functionality, modular building block approach, open architecture, programmability of all components and the ability to address the frame buffer in a planar (parallel) mode or in a pixel-wise mode. The graphics system may be expanded to any number of color planes with virtually unlimited resolution. The Graphics Databook provides all of the details to make display system design easy.

# National Semiconductor

# **Introduction Advanced Peripherals**

Winchest teal Time Clock DRAM I cool Mass Hard Diel Storage Area Manacement Flopp) Disk Network Timer Cloc Perinheral Tane 1/0 System Bus Control and Timing CPU Graphics Communi-Modem Engine Display cations Control RS-232 3270 Protocol

National Semiconductor Advanced Peripherals products include complex VLSI peripheral circuits designed to serve a variety of applications. The Advanced Peripherals products are especially well suited for microcomputer and microprocessor systems such as graphics workstations, personal computers, and many others. National Semiconductor Advanced Peripherals devices are fully described in a series of databooks and handbooks.

Among the Advanced Peripherals books are the following titles:

#### MASS STORAGE

The National Semiconductor family of mass storage interface products offers the industry's highest performance and broadest range of products for Winchester hard disks and floppy disks. The Mass Storage Handbook includes complete product information and datasheets as well as a comprehensive design guide for disk controller systems.

#### DRAM MANAGEMENT

Today's large Dynamic Random Access Memory (DRAM) arrays require sophisticated high performance devices to provide timing access arbitration on board drive and control. National Semiconductor offers the broadest range of DRAM controllers with the highest "No-waitstate" performance available on the market. Controllers are available in Junction Isolated LS, Oxide Isolated ALS, and double metal CMOS for DRAMs from 64k bit through 4M bit devices, supporting memory arrays up to 64 Mbyte in size with only one LSI/VLSI device. For critical applications, National Semiconductor has developed several 16- and 32-bit Error Checking and Correction (ECC) devices to provide maximum data integrity. The Memory Support Handbook contains complete product information and several application notes detailing complete memory system design.

#### LOCAL AREA NETWORKS AND DATA COMMUNICATIONS

Today's computer systems have created a huge demand for data communications and Local Area Networks (LANs).

TL/XX/0058-1

National Semiconductor provides a complete three-chip solution for an entire IEEE 802.3 standard for Ethernet/ Cheapernet LANs. National Semiconductor offers a completely integrated solution for the IBM 370 class mainframes, System 3X and AS/400 systems for physical layer front end and processing of the IBM 3270/3299 "coaxial" and 5250 "twinaxial" protocols. To drive the communications lines, National Semiconductor has drivers and receivers designed to meet all the major standards such as RS-232, RS-422, and RS-485. Datasheets and applications information for all these products are in the LAN/DATA COMM Handbook.

#### GRAPHICS

Sophisticated human interface is a mark of the newest computer systems designs. Today's personal computer may have better graphics display capability than engineering workstations of a few years ago. National Semiconductor has developed a new family of Advanced Graphics products to provide extremely high performance, high resolution color graphics displays. The graphics chip set is designed to provide the highest level of performance with minimum demands and loading on the system CPU. The graphics system may be expanded to any number of color planes with virtually unlimited resolution. The Graphics Databook lays it all out and makes the display system design easy.

#### **REAL TIME CLOCKS**

National offers a family of Real Time Clocks (RTCs) and advanced Timer Clock Peripherals (TCPs). The RTC family provides a simple  $\mu$ P bus compatible interface to any system requiring accurate, reliable, on-going real time and calender functions. The TCP family offers the RTC, RAM and two 16-bit programmable timers with fast  $\mu$ P bus handshake controls for chip select, read and write. The Real Time Clock handbook includes complete product information and datasheets as well as applications information.

# **Product Status Definitions**

### **Definition of Terms**

| Data Sheet Identification     | Product Status            | Definition                                                                                                                                                                                                                                                                      |  |  |

|-------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advance Information           | Formative or<br>In Design | This data sheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                                                                             |  |  |

| Proliminary                   | First<br>Production       | This data sheet contains preliminary data, and supplementary data will<br>be published at a later date. National Semiconductor Corporation<br>reserves the right to make changes at any time without notice in order<br>to improve design and supply the best possible product. |  |  |

| No<br>Identification<br>Noted | Full<br>Production        | This data sheet contains final specifications. National Semiconductor<br>Corporation reserves the right to make changes at any time without<br>notice in order to improve design and supply the best possible product.                                                          |  |  |

National Semiconductor Corporation reserves the right to make changes without further notice to any products herein to improve reliability, function or design. National does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

# **Table of Contents**

| Alphanumeric Index                                                                  | ix    |

|-------------------------------------------------------------------------------------|-------|

| Section 1 Advanced Graphics Chipset                                                 |       |

| DP8500 Raster Graphics Processor                                                    | 1-3   |

| NS32CG16-10, NS32CG16-15 High-Performance Printer/Display Processor                 | 1-62  |

| DP8510 BITBLT Processing Unit                                                       | 1-63  |

| DP8511 BITBLT Processing Unit (BPU)                                                 | 1-84  |

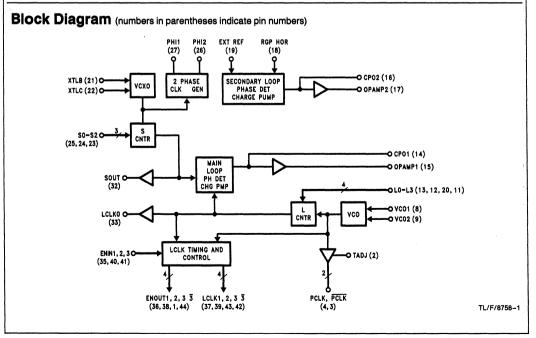

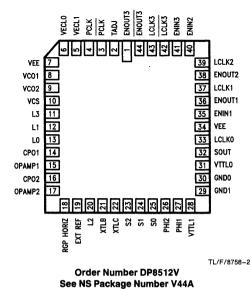

| DP8512 Video Clock Generator                                                        | 1-120 |

| DP8513 Multi-Board Video Clock Generator                                            | 1-135 |

| DP8514 Crystal Clock Generator                                                      | 1-153 |

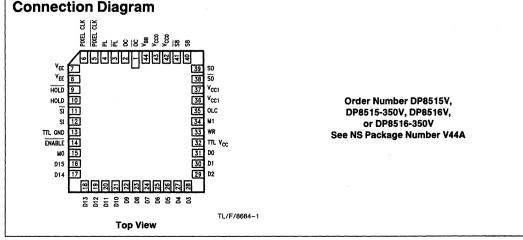

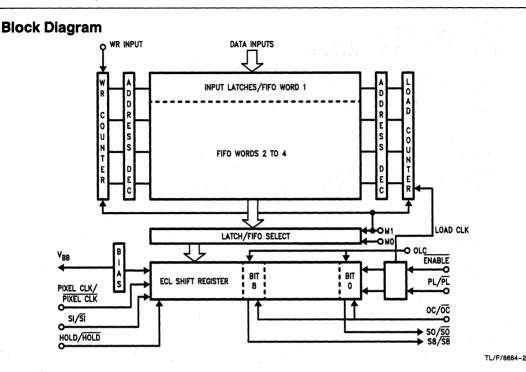

| DP8515/DP8515-350/DP8516/DP8516-350 Video Shift Register (VSR)                      | 1-159 |

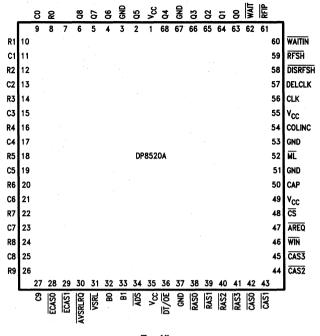

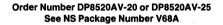

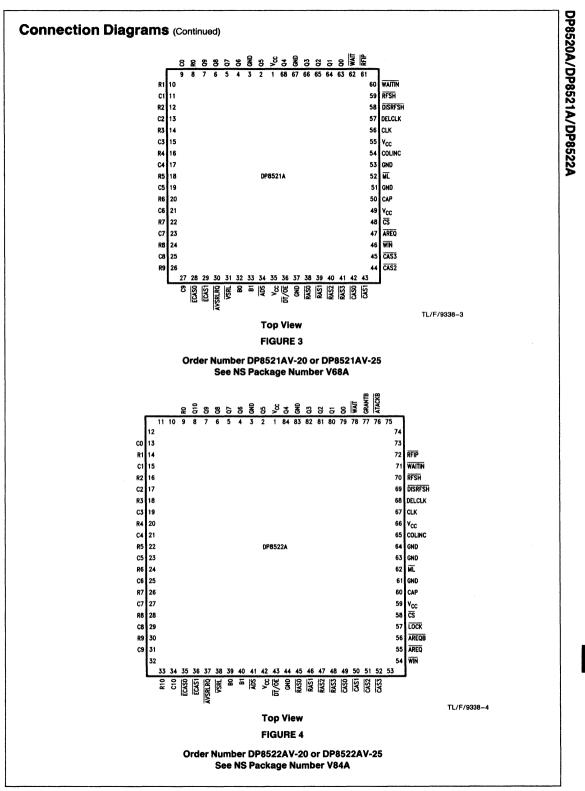

| DP8520A/DP8521A/DP8522A microCMOS Programmable 256k/1M/4M Video RAM                 |       |

| Controller/Driver                                                                   | 1-174 |

| DP8530 Clock Generator                                                              | 1-262 |

| Section 2 DP8500 Development Tools                                                  |       |

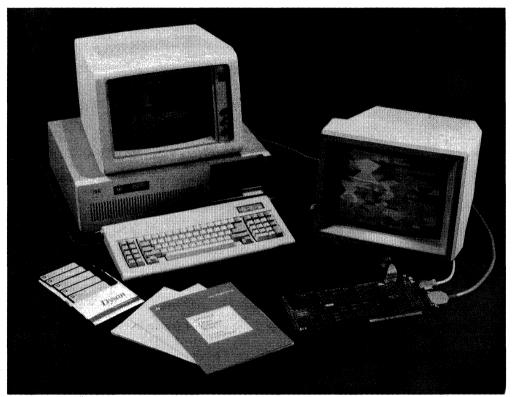

| DP850EB Raster Graphics Processor (RGP) 4-Plane Evaluation System                   | 2-3   |

| DP850DB8 Raster Graphics Processor (RGP) 8-Plane Development System                 | 2-4   |

| DP8500 Raster Graphics Processor Software Tools                                     | 2-5   |

| Section 3 Application Notes                                                         |       |

| AN-451 An Architectural Solution for High Performance Graphics                      | 3-3   |

| AN-547 Interfacing the DP8500 Raster Graphics Processor                             | 3-11  |

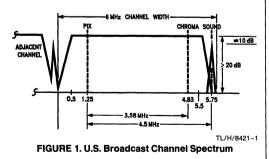

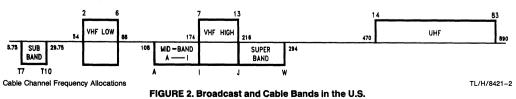

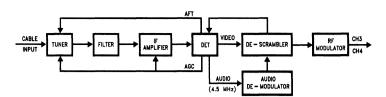

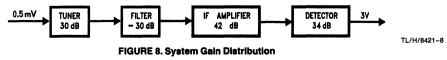

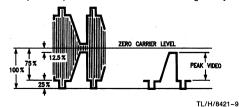

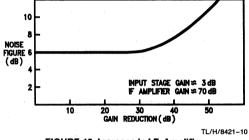

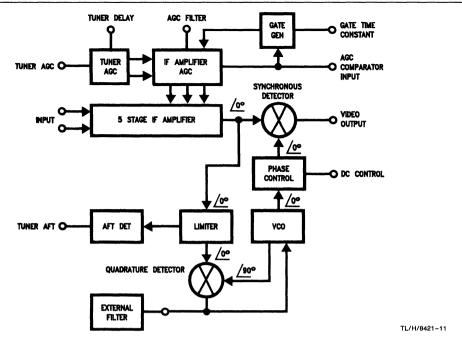

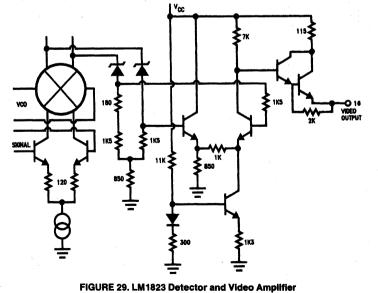

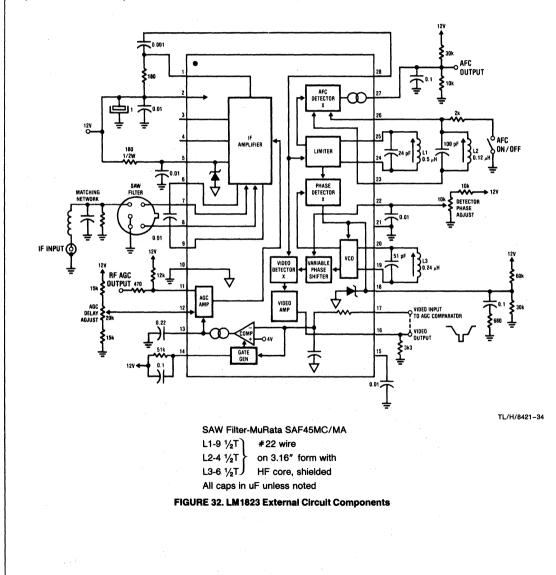

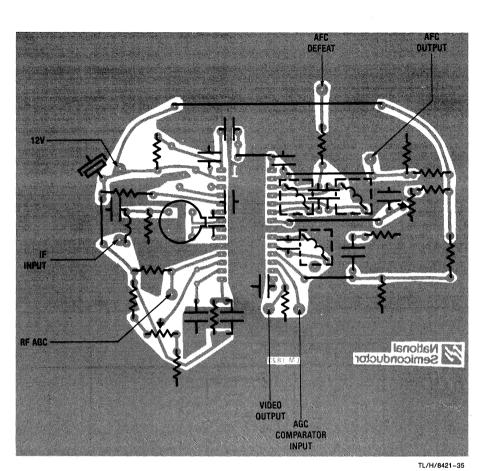

| AN-391 The LM1823 A High Quality TV Video IF Amplifier and Synchronous Detector     |       |

| for Cable Receivers                                                                 | 3-26  |

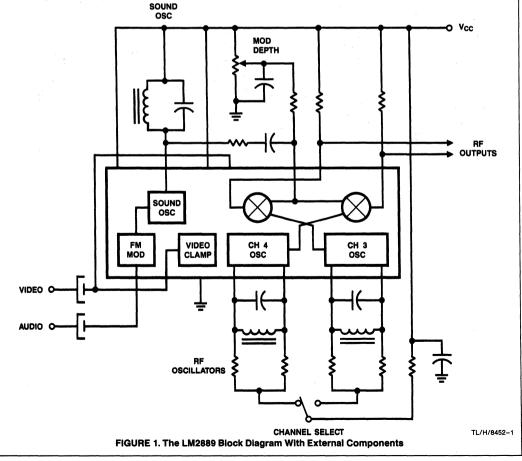

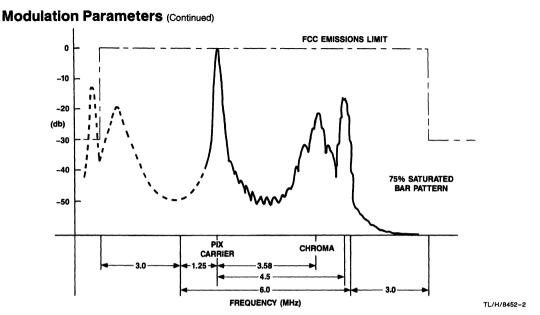

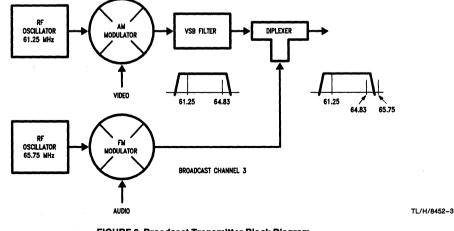

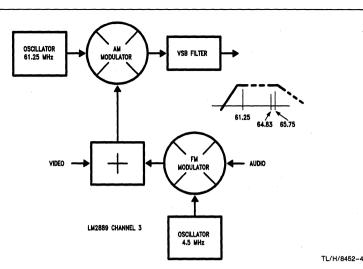

| AN-402 LM2889 R.F. Modulator                                                        | 3-42  |

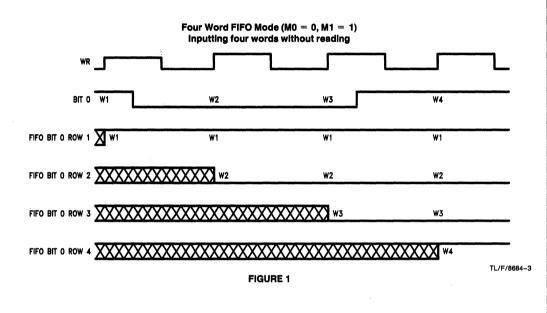

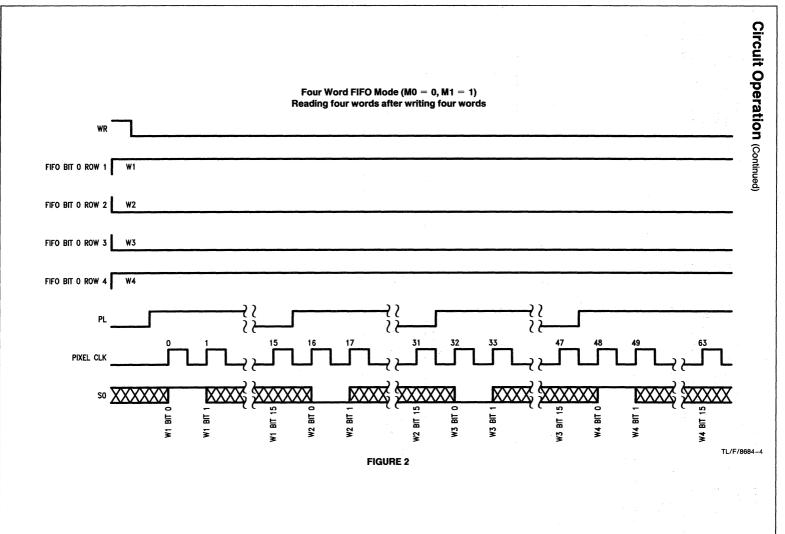

| AN-580 A 16-Bit Video Shift Register with On-Board FIFO Operates at Rates Up to 350 |       |

| Million Pixels per Second                                                           | 3-53  |

| AN-553 Mid-Scan-Line Load Techniques Using the DP8500 Raster Graphics               |       |

| Processor                                                                           | 3-60  |

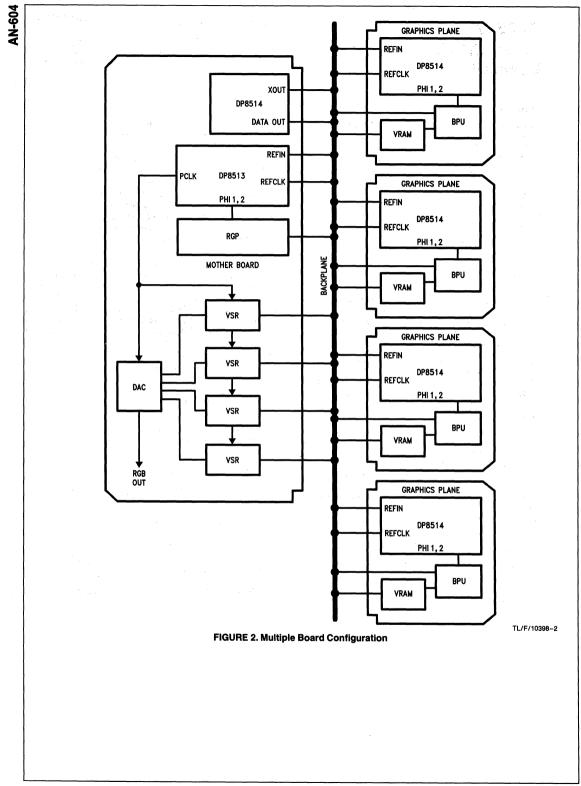

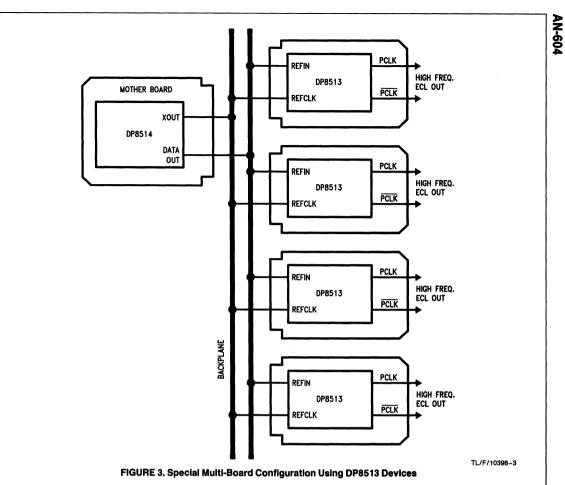

| AN-554 Accurate Timing for Multi-Board Graphics Systems                             | 3-65  |

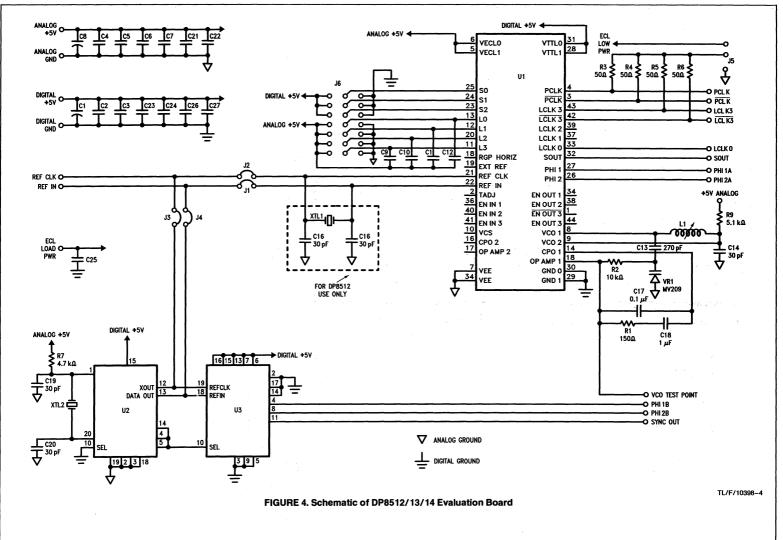

| AN-604 DP8512, DP8513, DP8514 Video Clock Generator Evaluation Board                | 3-69  |

| AN-609 A Graphics Acceleration Card for the AT Using the Advanced Graphics Chip     |       |

| Set                                                                                 | 3-82  |

| Section 4 Physical Dimensions/Appendices                                            |       |

| Appendix A: Related Datasheets                                                      | 4-3   |

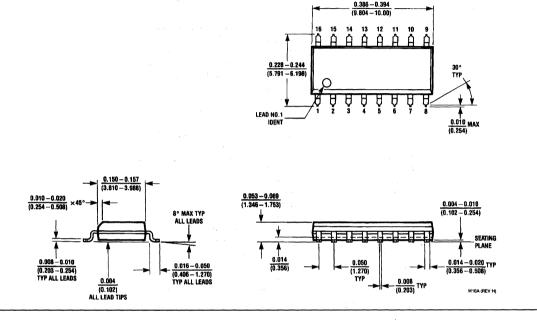

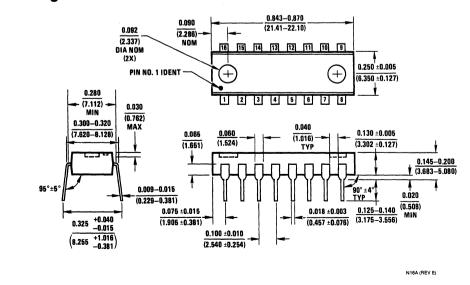

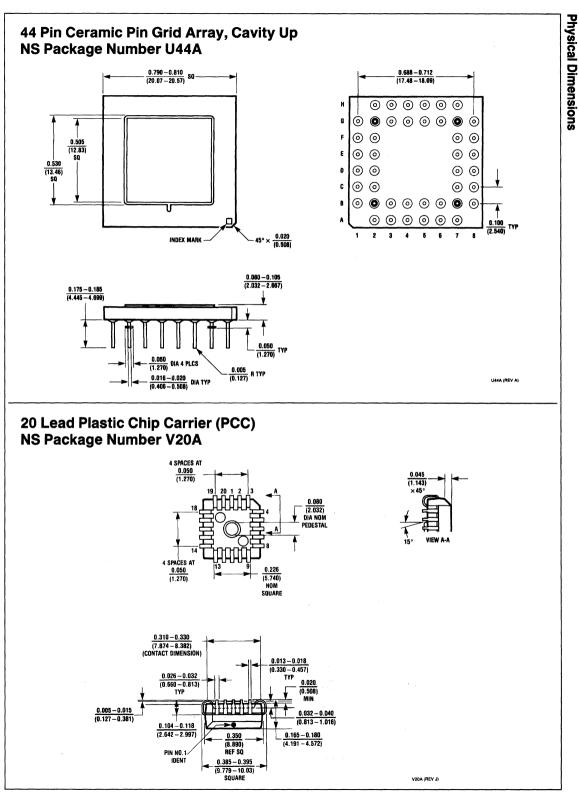

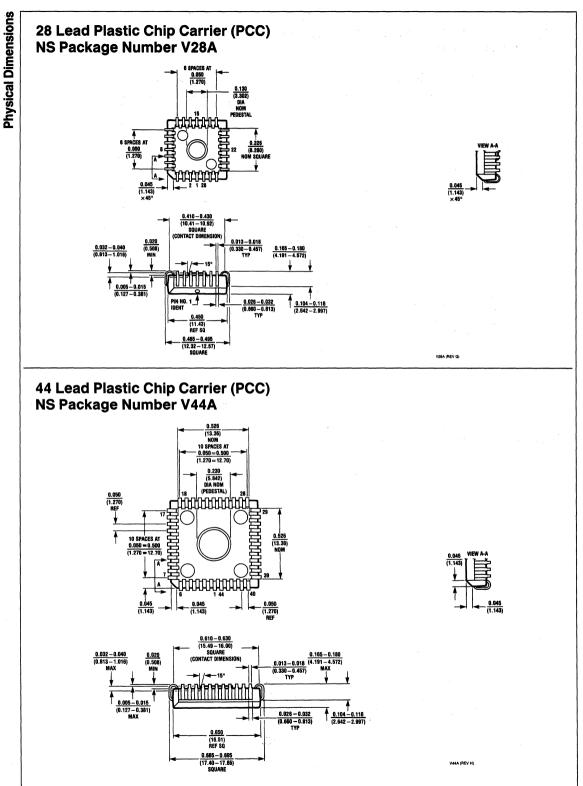

| Physical Dimensions                                                                 | 4-4   |

| Bookshelf                                                                           |       |

| Distributors                                                                        |       |

# Alpha-Numeric Index

The formation of the format

(a) A set of the se

# Section 1 Advanced Graphics Chipset

### Section 1 Contents

| DP8500 Raster Graphics Processor                                    | 1-3   |

|---------------------------------------------------------------------|-------|

| NS32CG16-10, NS32CG16-15 High-Performance Printer/Display Processor | 1-62  |

| DP8510 BITBLT Processing Unit                                       | 1-63  |

| DP8511 BITBLT Processing Unit (BPU)                                 | 1-84  |

| DP8512 Video Clock Generator                                        | 1-120 |

| DP8513 Multi-Board Video Clock Generator                            | 1-135 |

| DP8514 Crystal Clock Generator                                      | 1-153 |

| DP8515/DP8515-350/DP8516/DP8516-350 Video Shift Register (VSR)      | 1-159 |

| DP8520A/DP8521A/DP8522A microCMOS Programmable 256k/1M/4M Video RAM |       |

| Controller/Driver                                                   | 1-174 |

| DP8530 Clock Generator                                              | 1-262 |

# National Semiconductor

# **DP8500 Raster Graphics Processor**

### **General Description**

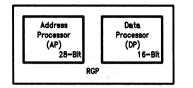

National's DP8500 Raster Graphics Processor (RGP) is a microprocessor specifically tuned for graphics applications. A member of the Advanced Graphics Chip Set, it provides the set of functions required for display buffer update and video refresh in mid-to-high-performance color or monochrome raster graphics systems employing both graphics primitives and text. The RGP combines the following elements: a general-purpose microcoded microprocessor, a programmable video refresh generator, a vector generator, a BITBLT controller and a rectangular clipper. As such, it may be used in standalone applications or as a dedicated graphics engine in conjunction with any general-purpose microprocessor.

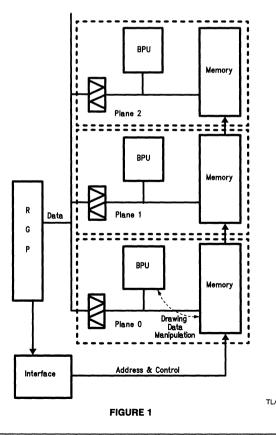

The RGP supports a system architecture that features constant drawing speed, measured in pixels/second, independent of the depth (number of bits) of the pixel. This key feature arises from the RGP's use of an external data path device, the BITBLT Processing Unit (BPU), for all drawing functions. By employing a BPU on each plane of memory, the traditional "bottleneck" is removed from the data manipulation path. In effect, the data bus width (for drawing purposes) is made proportional to the pixel depth, thus preserving the drawing speed as pixel depth is increased from one bit to any number of bits.

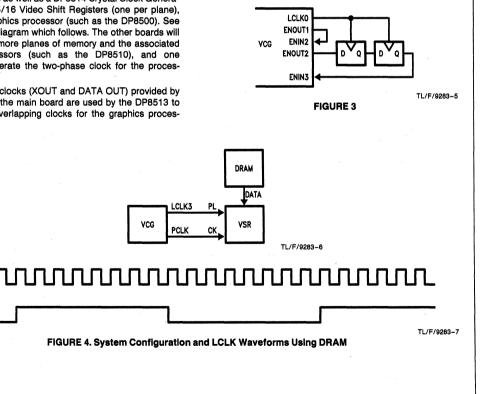

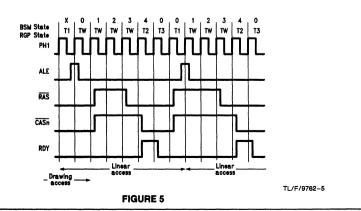

During video refresh, the RGP produces all synchronization and blanking signals for CRT displays and generates memory cycles, appropriate for the type of memory used, on behalf of the video shift registers. Any type of memory may be used: SRAM, DRAM or video RAM. In addition, the RGP supports the use of fast access modes in dynamic RAMS, such as page mode or static column mode.

#### **Features**

- 20 MHz operation

- Fully programmable

- Large, uniform address space

- 28-bit bit (pixel) address

- 24-bit word address

- 16-bit data bus

- Program, data, and display memories can reside anywhere

- Flexible bus interface

- Processor independent

- Conventional HOLD/HLDA mechanism

- Large drawing space

- Up to 16384 by 16384 pixels per bitmap

- Pixels of any depth

- Dedicated graphics hardware

- --- Vector generator

- Line pattern generator

- BITBLT controller

- Rectangular clipper

- Efficient text support

- Multiple fonts/sizes

- Proportional spacing

- Programmable video refresh

- Can be disabled for laser printer applications

- Pixel rates to 250 MHz and beyond

- Display formats to 65536 pixels by 4096 scan lines

- Interlaced or non-interlaced

- Genlock support

- microCMOS technology

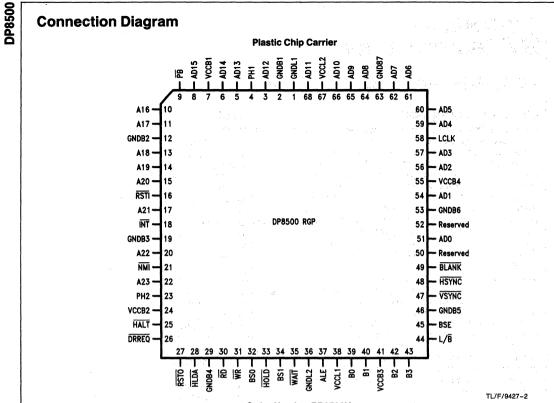

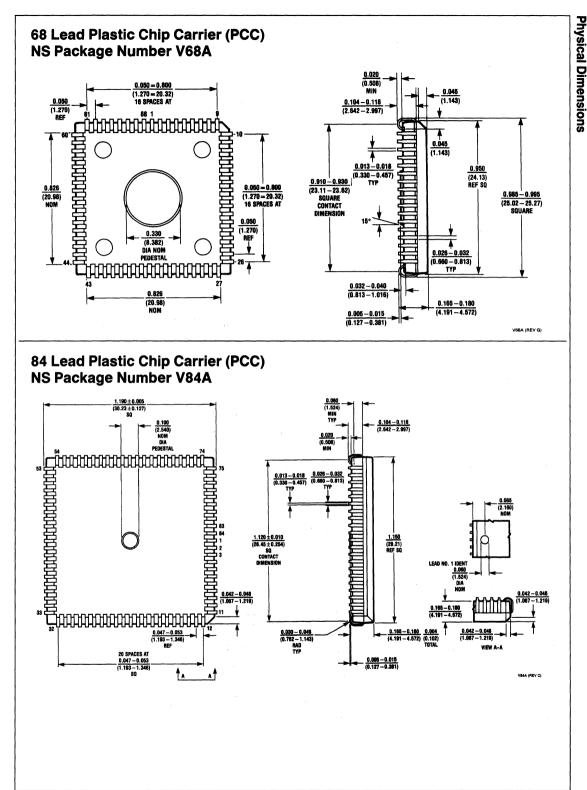

- 68-lead PLCC package

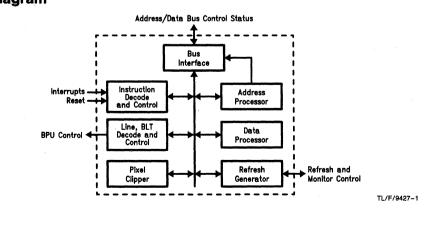

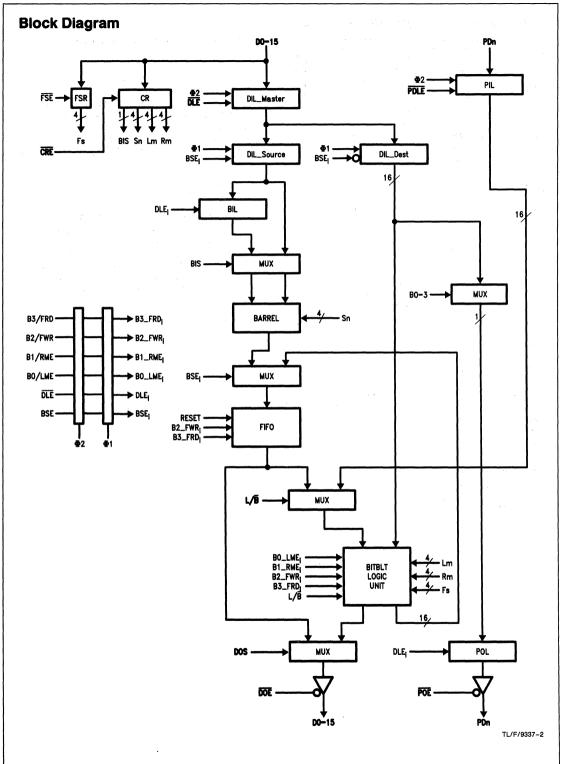

#### **Block Diagram**

DP8500

Order Number DP8500V See NS Package Number V68A

# **Pin Descriptions**

| Pin             | Description                                                                                                        |

|-----------------|--------------------------------------------------------------------------------------------------------------------|

| SUPPLIES        | <b>i</b>                                                                                                           |

| VCCL1-<br>VCCL2 | Positive supply for internal logic: 5 Vdc $\pm$ 10%.                                                               |

| GNDL1-<br>GNDL2 | Ground for internal logic.                                                                                         |

| VCCB1-<br>VCCB4 | Positive supply for on-chip buffers: 5Vdc $\pm$ 10%.                                                               |

| GNDB1-<br>GNDB7 | Ground for on-chip buffers.                                                                                        |

| INPUTS          |                                                                                                                    |

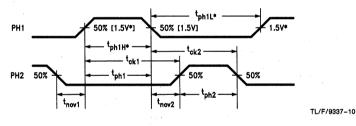

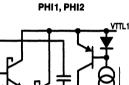

| PH1             | Phase 1. PH1 is an MOS-level clock normally<br>provided by the VCG. It must have no overlap with<br>the PH2 clock. |

| PH2             | Phase 2. PH2 is an MOS-level clock normally<br>provided by the VCG. It must have no overlap with<br>the PH1 clock. |

| Pin    | Description                                                                                                                                                                                                                                                             |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| INPUTS | (Continued)                                                                                                                                                                                                                                                             |  |  |

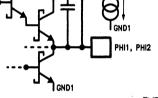

| LCLK   | Load Clock. LCLK is a TTL-compatible clock<br>normally supplied by the VCG's LCLK0. It provides<br>the basic time unit used in the registers that<br>specify digitally the video refresh functions: sync,<br>blanking and display-refresh bus cycles.                   |  |  |

| RSTI   | Reset In (active low) RSTI is used to place the<br>RGP into the reset state; this is typically done at<br>power-up.                                                                                                                                                     |  |  |

| WAIT   | Wait (active low). WAIT is used to cause the RGP to insert one or more wait states into the current bus cycle. This mechanism can be used to accommodate the RGP to relatively slow memory devices; it can also serve as a bus-not-ready indication from a bus arbiter. |  |  |

# Pin Descriptions (Continued)

| Pin         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| INPUTS (Cor | ntinued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| HOLD        | Hold Request (active low). HOLD serves as a request from another master for the RGP's bus. In response, the RGP will complete the current bus cycle (if any), TRI-STATE® only the address and data buses and assert Hold Acknowledge.                                                                                                                                                                                                                                                   |  |  |

| INT         | Interrupt Request (active low). INT causes the<br>RGP to suspend normal processing after<br>completion of the current instruction (if any), to<br>save the Program Counter and Processor<br>Status Register on the stack and to enter the<br>user's interrupt service routine. This function<br>can be disabled via the Processor Status<br>Register.                                                                                                                                   |  |  |

| NMI         | Non-Maskable Interrupt Request (negative<br>edge triggered). NMI causes the RGP to<br>suspend normal processing after the<br>completion of the current instruction (if any), to<br>save the Program Counter and Processor<br>Status Register on the stack and to enter the<br>user's non-maskable interrupt service routine.<br>This function is disabled upon Reset, and is<br>enabled upon the first store operation to the<br>PSR register.                                          |  |  |

| RESERVED    | Reserved for NSC testing. Must be tied to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| OUTPUTS     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| A16-A23     | Address Lines. A16–A23 provide the most<br>significant eight bits of memory addresses<br>during bus cycles. A23 is the most significant.<br>A16–A23 are at TRI-STATE whenever HLDA<br>is asserted by the RGP. Addresses are<br>guaranteed to be valid at the falling edge of<br>ALE.                                                                                                                                                                                                    |  |  |

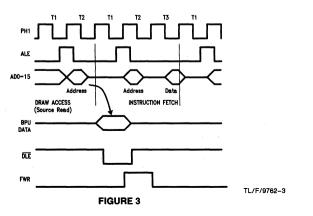

| BS0-BS1     | Bus Status Lines. BS0–BS1 are used to<br>indicate the type of bus cycle to be performed<br>by the RGP. (See Table I.) BS0–BS1 become<br>valid during the first T-STATE of a bus cycle<br>(before the rising edge of ALE) and remain<br>valid through the end of the last T-state of that<br>cycle.                                                                                                                                                                                      |  |  |

| RD          | Read (active low status). $\overline{RD}$ indicates that<br>the current cycle will cause memory to be<br>read. $\overline{RD}$ becomes valid during the first T-<br>state of a bus cycle (before the rising edge<br>of ALE) and remains valid through the end of<br>the last T-state of that cycle. Both $\overline{RD}$ and<br>$\overline{WR}$ may be asserted in the same cycle. This<br>indicates that the RGP is requesting a read-<br>modify-write operation in the current cycle. |  |  |

| Pin Description |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| OUTPUT          | S (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| WR              | Write (active low status). $\overline{WR}$ indicates that the current cycle will cause memory to be written.<br>$\overline{WR}$ becomes valid during the first T-state of a bus cycle (before the rising edge of ALE) and remains valid through the end of the last T-state of that cycle. Both $\overline{WR}$ and $\overline{RD}$ may be asserted in the same cycle. This indicates that the RGP is requesting a read-modify-write operation in the current cycle.                                                                                                         |  |  |

| ALE             | Address Latch Enable. ALE indicates the beginning of a bus cycle. Its rising edge indicates that bus status, consisting of BS1–0, $\overline{\text{ND}}$ and $\overline{\text{WR}}$ are valid. Its falling edge indicates that the $\overline{\text{PB}}$ and the address, consisting of AD0–15, A16–23 and (if used in this cycle) B0–3, are valid.                                                                                                                                                                                                                         |  |  |

| PB              | Page Break (active low status). $\overline{PB}$ indicates that<br>the 16 most significant address bits (AD8–15<br>and A16–23) of the RGP's current bus cycle are<br>not equal to the 16 most significant address bits<br>generated by the RGP in the previous bus cycle.<br>$\overline{PB}$ can be used by the system's memory<br>controller to allow it to generate page-mode<br>accesses to memory, resulting in shorter access<br>times. Since the eight least significant bits of<br>addresses are ignored in the above comparison<br>the page size is always 256 words. |  |  |

| HLDA            | Hold Acknowledge (active low). <u>HLDA</u> indicates<br>that the RGP has put the address and data<br>buses at TRI-STATE and has entered an<br>internal <i>hold</i> condition. The RGP will not exit the<br>hold condition until the <u>HOLD</u> input has been<br>removed.                                                                                                                                                                                                                                                                                                   |  |  |

| HSYNC           | Horizontal Synchronization (active low). HSYNC<br>indicates to the CRT monitor that the horizontal<br>sweep should begin its retrace. The RGP can be<br>programmed to use this output as <i>composite</i><br><i>sync</i> , that is, the exclusive-NOR of HSYNC and<br>VSYNC. This option is selected via the RGP's<br>Video Control Register.                                                                                                                                                                                                                                |  |  |

| BLANK           | Composite Blanking (active low). BLANK is the result of ORing the internal vertical and horizontal blanking signals. BLANK indicates to the CRT monitor that the screen should be blanked.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| DRREQ           | Display Refresh Request (active low). DRREQ<br>starts generation of a Video Refresh bus cycle.<br>DRREQ can be used by an external bus arbiter<br>as a high-priority bus request. It can also be<br>used for precise control of video DRAM transfer<br>cycles, e.g., when performing mid-scanline<br>transfers.                                                                                                                                                                                                                                                              |  |  |

DP8500

### Pin Descriptions (Continued)

| Pin    | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUTPUT | S (Continued)                                                                                                                                                                                                                                                                                                                                                                                                       |

| L/B    | Linedraw/BITBLT mode. $L/\overline{B}$ sets the operating<br>mode of the BPU during drawing operations.<br>$L/\overline{B}$ is high to place the BPU into line-drawing<br>mode, low to place the BPU into BITBLT mode.<br>$L/\overline{B}$ is asserted throughout execution of any<br>drawing instruction that uses the BPU, starting<br>prior to the generation of any bus cycles within<br>that instruction.      |

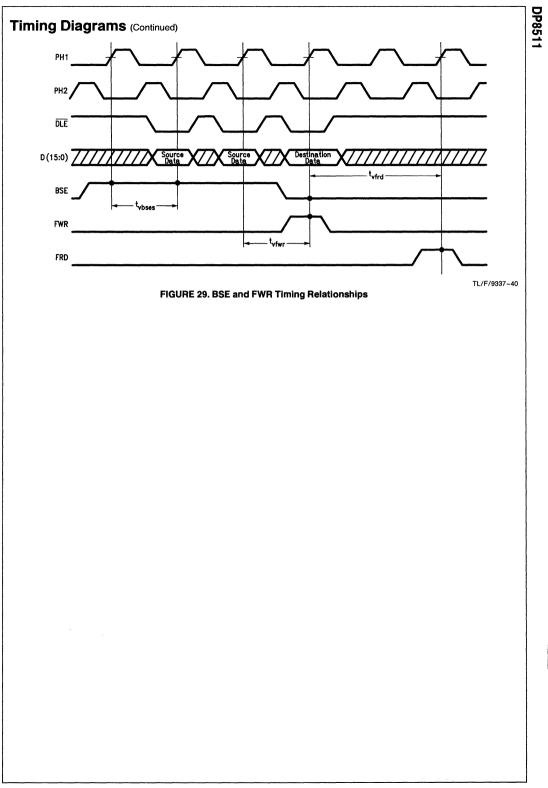

| BSE    | BITBLT Source Enable. BSE directs the flow of<br>data within the BPU. When high, BSE indicates<br>to the BPU that the current bus cycle is<br>associated with BITBLT data in the source<br>rectangle. BSE is low during BITBLT destination<br>data bus cycles and during non-BITBLT cycles.<br>It is valid on the rising edge of ALE and remains<br>valid throughout the bus cycle.                                 |

| B0/LME | Bit Select 0 or Left Mask Enable. This output to the BPU serves two purposes. When $L/\overline{B}$ is high it functions as B0 (see below). When $L/\overline{B}$ is low it functions as LME, which serves to enable the left mask. LME is valid at the falling edge of ALE and remains valid throughout the bus cycle.                                                                                             |

| B1/RME | Bit Select 1 or Right Mask Enable. This output to<br>the BPU serves two purposes. When $L/\overline{B}$ is high<br>it functions as B1 (see below). When $L/\overline{B}$ is low<br>it functions as RME, which serves to enable the<br>right mask. RME is valid at the falling edge of<br>ALE and remains valid throughout the bus cycle.                                                                            |

| B2/FWR | Bit Select 2 or FIFO Write. This output to the<br>BPU serves two purposes. When $L/\overline{B}$ is high it<br>functions as B2 (see below). When $L/\overline{B}$ is low it<br>functions as FWR, which causes the BPU's<br>barrel-shifter output to be written to the BPU's<br>FIFO. FWR is valid on the rising edge of PH1,<br>two clock periods after WAIT is sampled high<br>during the next T2-state bus cycle. |

| B3/FRD | Bit Select 3 or FIFO Read. This output to the BPU serves two purposes. When $L/\overline{B}$ is high it functions as B3 (see below). When $L/\overline{B}$ is low it functions as FRD, which causes the BPU's FIFO output to be read into the BPU's logic unit. FRD is valid at the rising edge of a PH1 during the fetch of the corresponding destination data word.                                               |

| B0-B3  | Bit Select. When $L/\overline{B}$ is low, these four outputs<br>have other functions (see above). When $L/\overline{B}$ is<br>high, B0–3 select a specific bit within the word<br>addressed by AD0–15 and A16–23. B0–3<br>become valid prior to the falling edge of ALE<br>and remain valid throughout the bus cycle.                                                                                               |

| Pin          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUTPU        | TS (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| HALT         | Halt (active low). HALT indicates that the RGP<br>has executed a HALT instruction and entered<br>the <i>halt</i> state, a state in which no instructions<br>are processed, but video refresh functions<br>continue. The halt state can be exited via an<br>interrupt or reset.                                                                                                                                                                                                                                                                                           |

| RSTO         | Reset Out (active low). <u>RSTO</u> is driven low<br>whenever <u>RSTI</u> is driven low. It is also driven low<br>(for two clock cycles) at the end of execution of<br>FILLA or FILLT instructions. The INITB<br>instruction drives <u>RSTO</u> low for two clocks.<br><u>RSTO</u> is normally connected to the BPU's<br><u>RESET</u> input.                                                                                                                                                                                                                             |

| INPUT/       | OUTPUTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AD0-<br>AD15 | Multiplexed Address and Data lines. AD0–15<br>serve as outputs early in a bus cycle, providing<br>the 16 least significant memory address bits.<br>Later in the bus cycle they serve as the data<br>bus. AD0 is the least significant bit of data or<br>address. As a data bus, these lines can be<br>inputs (during reads), outputs (during writes) or<br>can be ignored by the RGP (e.g., during<br>BITBLTs). These lines are at TRI-STATE<br>whenever Hold Acknowledge is asserted by the<br>RGP. Addresses are guaranteed to be valid at<br>the falling edge of ALE. |

| VSYNC        | Vertical Synchronization (active low). <u>VSYNC</u><br>can serve as an input or an output. As an output,<br>it indicates to the CRT monitor that the vertical<br>sweep should begin its retrace. As an input, it<br>clears the internal counters associated with<br>vertical sync generation within the RGP. As<br>such, it allows the RGP to synchronize itself with<br>an external video source (this assumes the use<br>of horizontal synchronization features of the<br>VCG). This option is selected via the RGP's<br>Video Control Register.                       |

| Bus Status<br>(BS1, BS0) | Cycle Type<br>(Function)     |

|--------------------------|------------------------------|

| 0, 0                     | Operand Read or Write        |

| 0, 1                     | Instruction Fetch            |

| 1, 0                     | BITBLT/Draw (Address Only)   |

| 1, 1                     | Video Refresh (Address Only) |

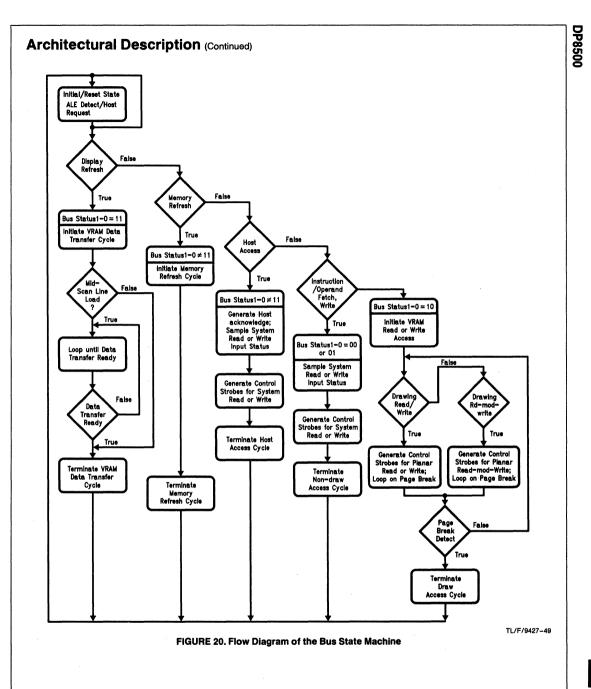

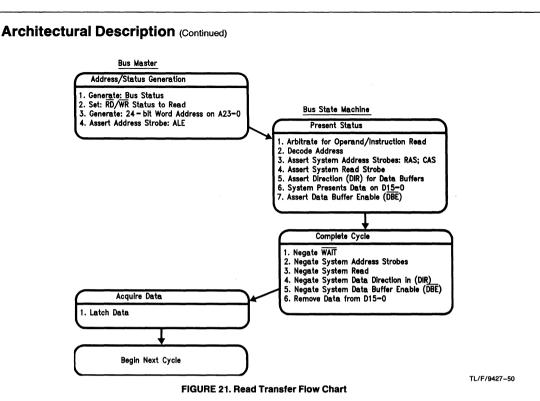

### **Architectural Description**

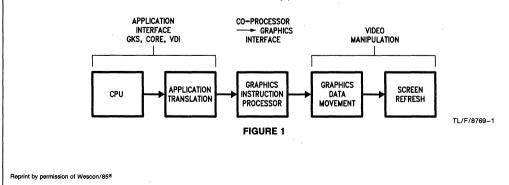

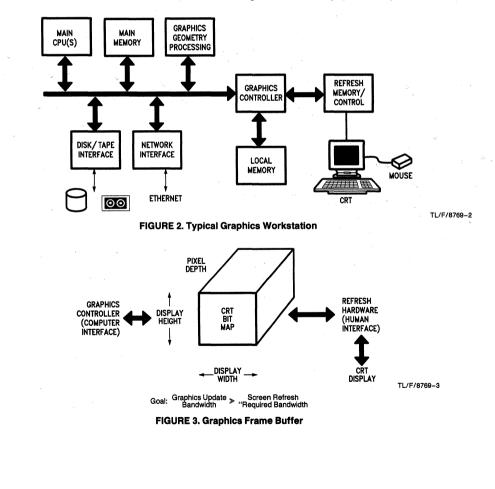

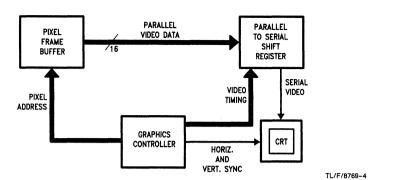

#### AGCS OVERVIEW

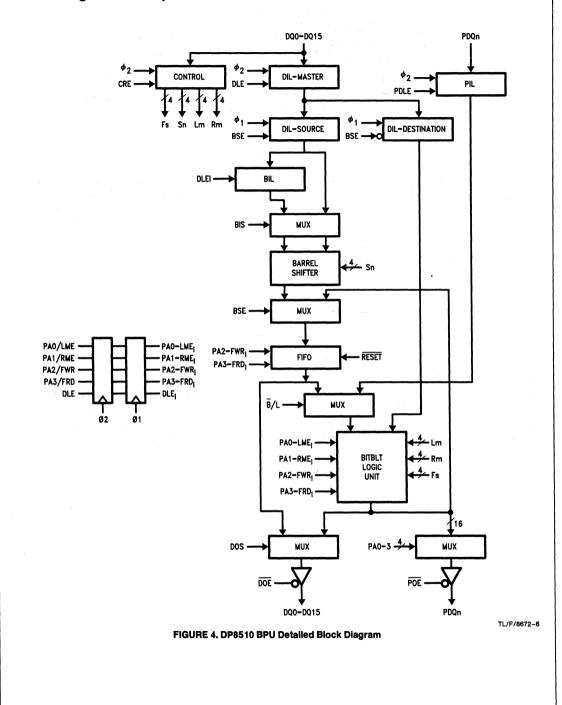

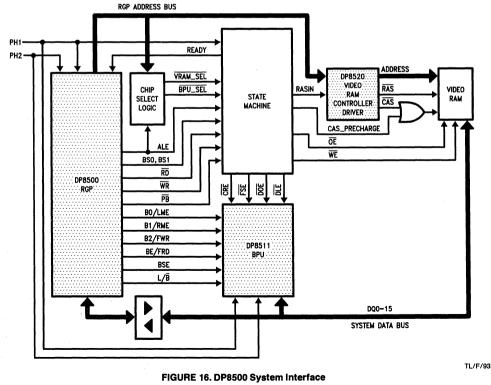

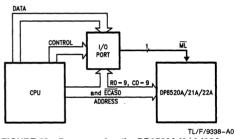

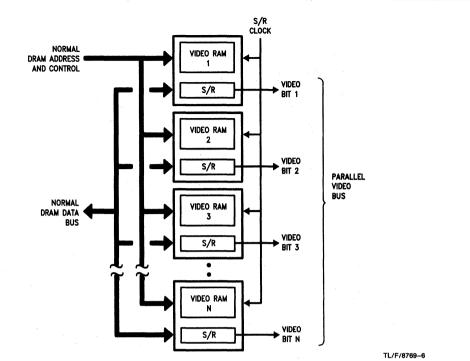

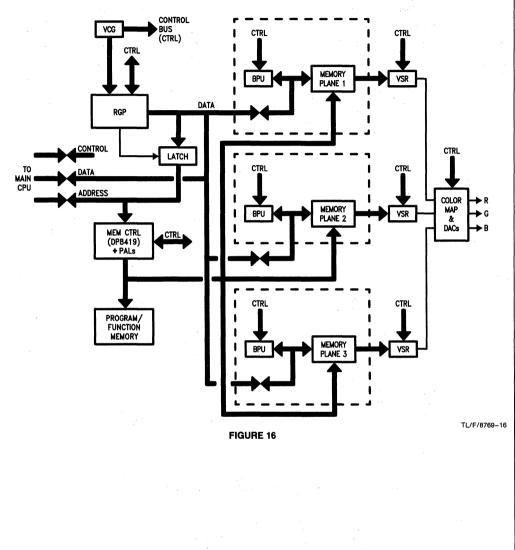

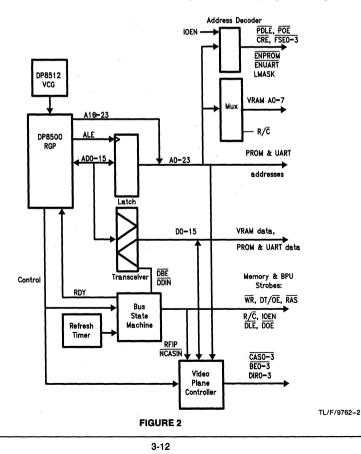

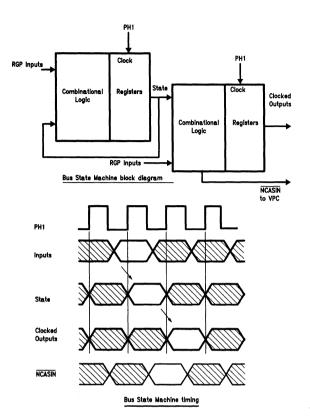

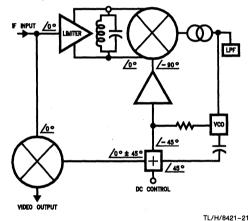

The RGP, serving as the core of a bitmapped graphics system, is designed to work in concert with the other members of the Advanced Graphics Chip Set (AGCS). Other components of the chip set include the DP8512 Video Clock Generator (VCG), the DP8515/16 Video Shift Register (VSR) and the DP8511 BITBLT Processing Unit (BPU). Additional functions required for system implementation are provided by National through such components as the DP8520/22 Video DRAM Controller and the Bus State Machine (BSM).

The components that comprise the Advanced Graphics Chip Set are fabricated in a variety of technologies, each appropriate to the function performed by that component. Both CMOS and bipolar technologies are used in the family. As a result, the family exhibits both VLSI functionality and 250 MHz operation.

The Advanced Graphics Chip Set supports a high-performance architecture without imposing a particular bus protocol, timing or memory type upon the system designer. As a result, AGCS-based systems can be realized with a range of solutions to the cost/performance tradeoff. Advances in memory technology can be capitalized upon in future systems while retaining software compatibility. A major feature of the system architecture is the support of simultaneous data manipulation (during drawing) at each of the bitplanes. This allows the system to retain its drawing speed (in pixels per second) as pixel depth increases from one to any number of bits.

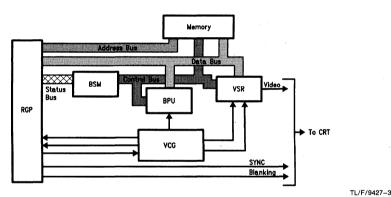

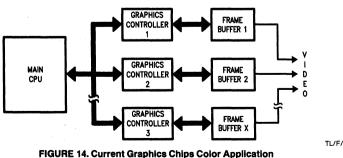

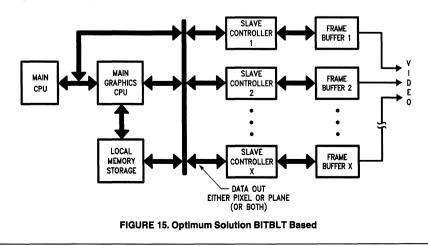

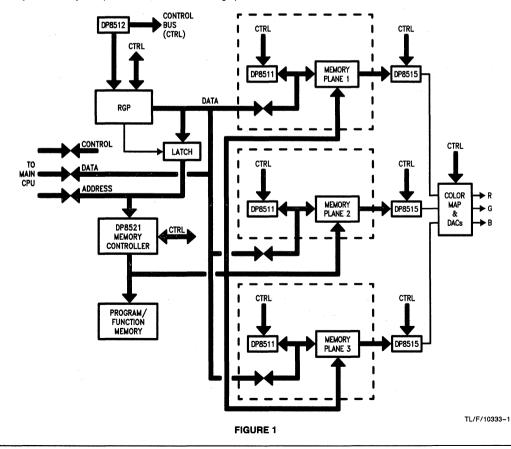

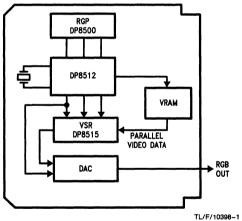

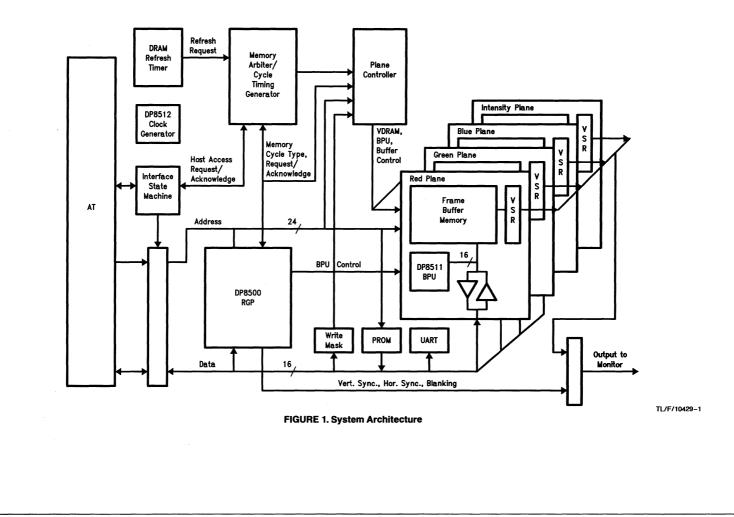

The functional interconnection of these components is illustrated in *Figure 1*, which represents a minimal bitmapped graphics system. In this system, the intensity of each pixel is described by a single bit, i.e., each pixel is either on or off. The roles of the various components are described below, as are design considerations for color systems.

#### **DP8500 Raster Graphics Processor (RGP)**

The RGP is designed to be the overall control mechanism in graphics systems. It draws graphics objects in the display buffer, refreshes the video display, and performs general purpose computing tasks.

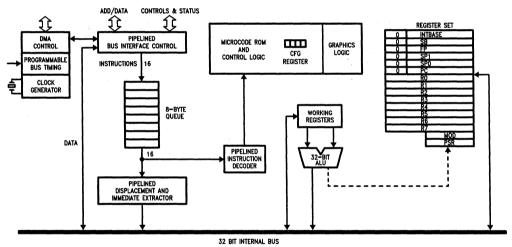

The implementation of the RGP reflects these functions (see *Figure 2*). A general purpose microcoded microprocessor core is augmented by dedicated hardware for the setup and execution of graphics primitives. In addition, a programmable state machine handles all video synchronization functions and produces addresses for video refresh. Internal bus arbitration logic controls access to the external bus.

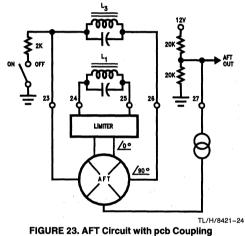

FIGURE 1. Minimal Bit-Mapped Graphics System

Address General Processo Data Bus I/F Status/ Clocks Controller Control Tevt and Processo Bus Arbiter Control Drawing Video SYNC and Refresh BITBLT Blanking Processo RGP BPU Control TL/F/9427-4 FIGURE 2. RGP Organization Diagram

1

#### DP8511 BITBLT Processing Unit (BPU)

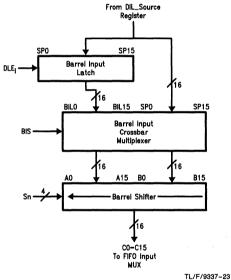

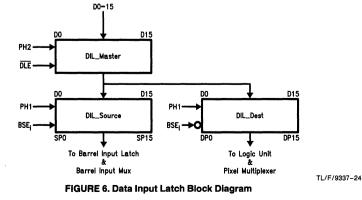

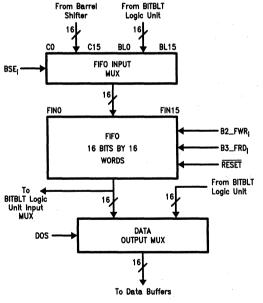

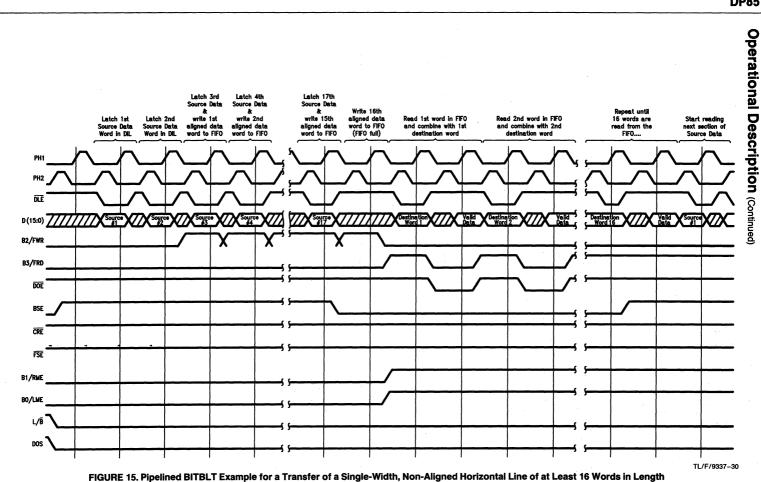

The DP8511 BPU provides a data path for changing the contents of the frame buffer. The drawing functions of the RGP, e.g., line drawing and polygon filling, rely on the BPU to accept data from memory, modify it, and return it to memory. The general scheme underlying these operations is BITBLT (BIT boundary BLock Transfer). During BITBLT, the RGP serves as an address generator to initiate the appropriate memory cycles and as a strobe generator to control the BPU's operation.

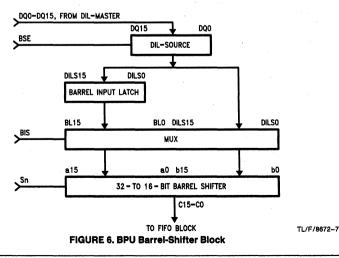

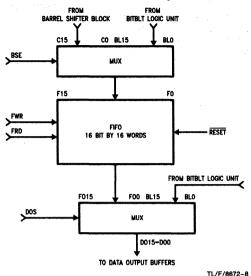

The BPU is a microCMOS device intended to provide hardware support for BITBLT. It includes a barrel shifter, used to shift source data into bit alignment with the destination and a FIFO to contain a series of shifted source words. A 16function logic unit allows all possible bitwise combinations between the source and destination data. The BPU has hardware to support pixel operations and line drawing. In particular, it can address a single bit within the current word and read and write the selected bit. Details of BPU operation can be obtained from the BPU data sheet.

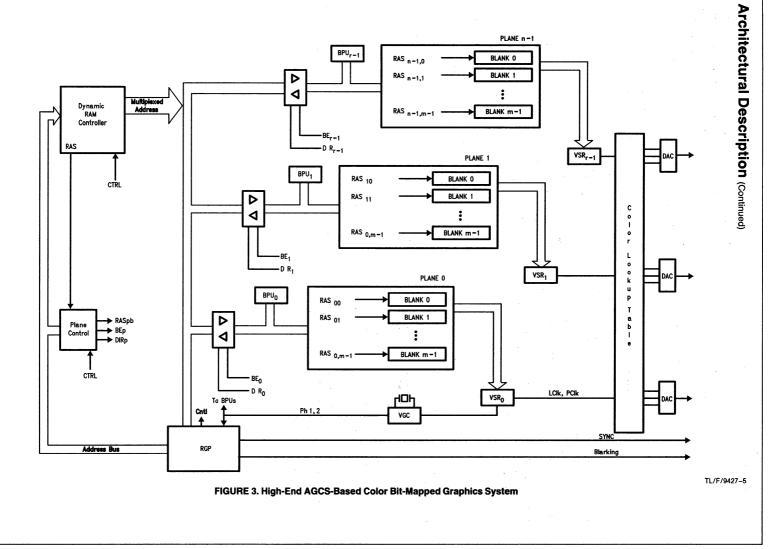

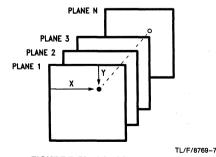

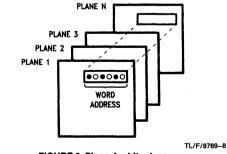

The use of BITBLT as the underlying mechanism for all drawing operations promotes a common method for handling both simple systems, as shown in Figure 1, and more complex, high performance systems, as shown in Figure 3. This latter figure illustrates a multi-plane system, i.e., one in which several bits (one from each plane) describe the value of a pixel. This might be used to describe the intensity (in monochrome) or the hue (in color) of the pixel. The use of a BPU per plane, permitting simultaneous update of all planes, leads to the highest performance. Alternatively, a cost-performance trade-off might be made by sharing one or more BPUs across two or more planes. At one extreme (single BPU) updates are done serially to each plane. At the other extreme (a BPU per plane) updates are performed in a purely parallel manner. A middle ground could be implemented, updating the planes in a serial-parallel manner. The mechanism of implementing the data path function in the BPU, rather than the RGP, produces this design flexibility.

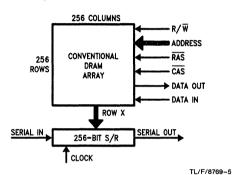

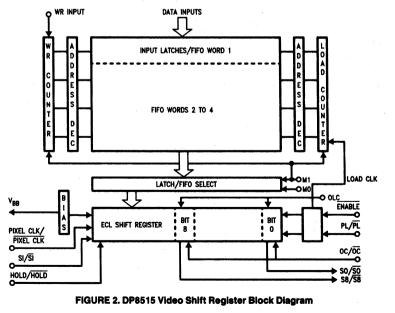

#### DP8515/16 Video Shift Register (VSR)

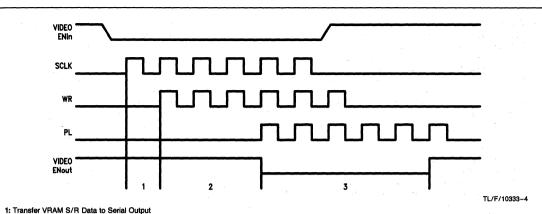

The DP8515/16 VSR shifts pixel information at the data rate required by the CRT. It is implemented in National's

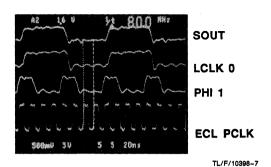

Bipolar-CMOS process. It combines CMOS control logic and a CMOS input FIFO with an ECL shifter. As a result, it provides the system designer additional timing flexibility in the load path coupled with up to 350 MHz shift capability without excessive current consumption. The DP8515 provides ECL 10k compatible outputs, while the DP8516 is ECL 100k compatible. Parallel loading of the VSR is initiated by the RGP and assisted by the VCG.

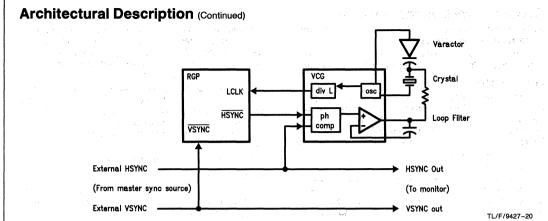

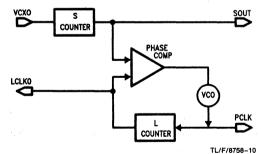

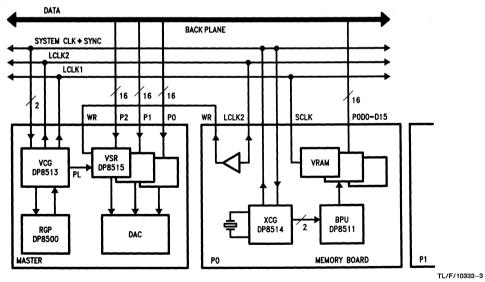

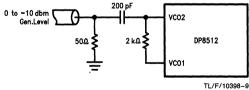

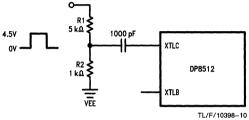

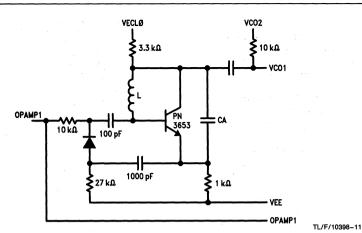

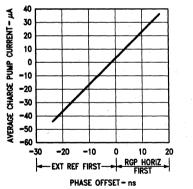

#### DP8512 Video Clock Generator (VCG)

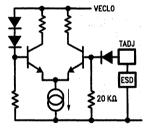

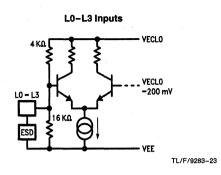

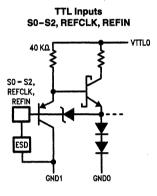

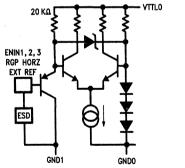

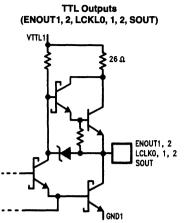

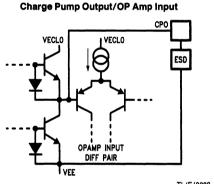

The DP8512 VCG, implemented in National's oxide-isolated bipolar process, provides all clocks in the system. It generates all clocks from a relatively low frequency (less than 20 MHz) crystal or external clock, simplifying system design and reducing system cost.

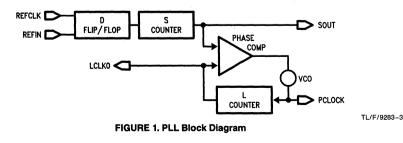

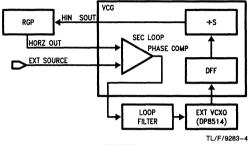

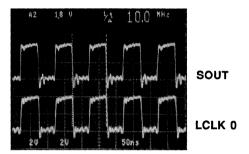

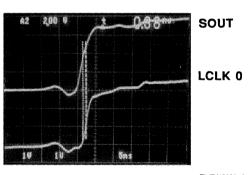

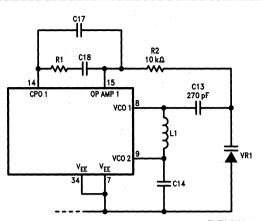

A two-phase MOS processor clock is supplied to the RGP and BPU; TTL clocks are generated for the RGP video refresh logic and for the VSR's FIFO control functions. The VSR's load and shift functions are controlled by ECL clocks generated by the VCG. An on-chip phase-locked loop (PLL) multiplies the reference crystal/clock in order to generate a pixel clock as high as 225 MHz. The VCG also includes another PLL for synchronizing the horizontal sync (generated by the RGP) to an external source.

#### **PROGRAMMING MODEL**

The RGP is a microprocessor combined with a concurrent video-refresh machine. This section will discuss the programmer-visible aspects of both the microprocessor and the video-refresh machine. For additional information, refer to the DP8500 RGP Programmer's Reference Manual (PRM).

The processor section of the RGP is a general purpose microprocessor with an instruction set expanded to include graphics operations. While the processor is microcode driven, certain graphics operations, notably BITBLT, line drawing and clipping, are implemented via dedicated hardware for increased throughput.

The organization of the processor, shown in *Figure 4*, reflects the duality, present in raster-graphics systems, of

1-9

**DP8500**

DP8500

#### Architectural Description (Continued)

TL/F/9427-6

#### FIGURE 4. RGP Dual-Processor Configuration

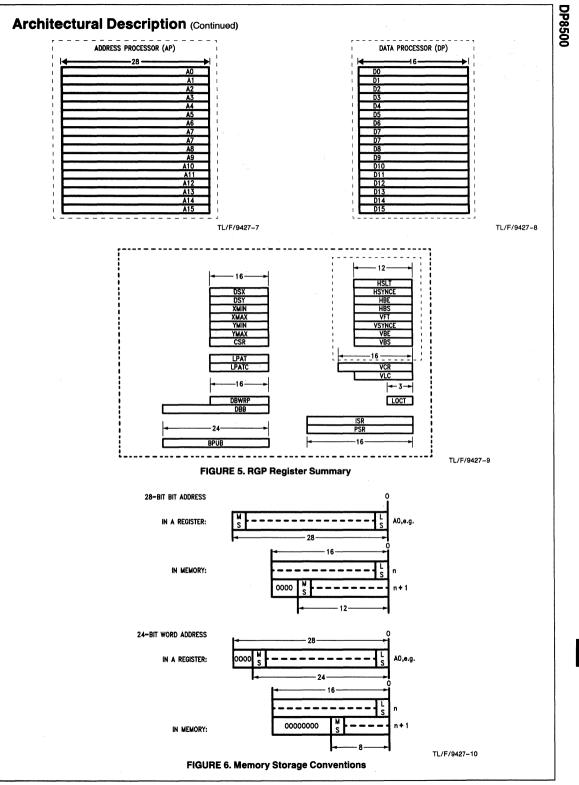

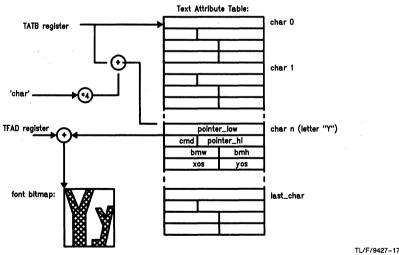

a virtual (Cartesian, x-y) drawing space and a physical (memory address) space. That is, the RGP's processor section actually consists of two processors, the Address Processor (AP) and the Data Processor (DP), operating concurrently, driven by common microcode. The RGP's register complement, described below, is shown in *Figure 5*.

The AP consists of a 28-bit Arithmetic and Logic Unit (ALU), having a relatively simple instruction set, and a private bank of sixteen 28-bit registers. The DP is composed of a 16-bit ALU, having a relatively rich instruction set, and a bank of sixteen 16-bit registers. These instruction sets operate register-to-register only and then only within their respective register banks.

The remaining registers of the RGP have dedicated functions in support of the graphics environment or the video refresh mechanism. Examples include the registers of the Clipper and the Display Buffer Base Address register (DBB).

A single stream of instructions, fetched from external memory, serves both processors via microcode control. This includes the register-to-register instructions of both the AP and DP and the instructions for data transfers between RGP registers and memory. Additional RGP instructions, not belonging exclusively to the AP or DP, use both processors and, often, additional on-chip resources; this is typical of all of the drawing instructions. An example of this is the DRLN (draw line) instruction, which uses both processors, the clipper, the line drawing controller, the line-pattern generator and the BITBLT controller. While simple instructions like ADD and MOV leave unmodified any registers not specified in their encodings as being operands, the more complex drawing instructions like DRLN use certain registers of the AP and DP as implicit arguments or as temporary storage. These *side effects* of RGP drawing instructions are detailed in the Programmer's Reference Manual PRM.

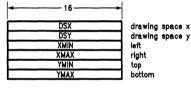

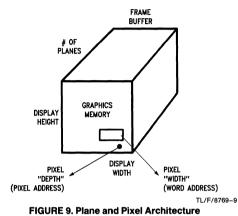

#### **Memory Organization and Data Types**

The RGP supports uniform 24-bit addressing; the unit of storage in memory is the word. That is, the memory space of the RGP consists of 224 16-bit words. Parts of the memory space can be designated by the user as Program, Data, Stack, Display Buffer, etc., at the user's discretion; the RGP imposes no restrictions upon these allocations.

For purposes of drawing, the RGP views the memory as being bit addressable (see Memory Addressing Section). In this case, the address is a 28-bit quantity, called a Bit Address, which consists of a 24-bit Word Address, left-shifted four bits and added to a 4-bit bit-selection field.

Data elements treated by the RGP vary in length (number of bits) from 3 to 28 bits according to their function. However, they are always stored right justified (that is, justified toward bit 0) in registers or in memory (see *Figure 6*). Further, when stored in memory, multiple-word quantities are always stored with the least significant word at the lowest storage address. Supporting what is known as "Little-Endian" architecture. The address of a memory-resident quantity is the address of its least significant word.

The following data element lengths are used by the RGP:

| word         | 16 bits or less |

|--------------|-----------------|

| word address | 24 bits         |

| bit address  | 28 bits         |

If an element is written from memory to a register that is shorter than the element, the more significant portion of the element is truncated to allow the less significant portion to fit into the register. If an element is written from a register to memory, the element is right justified in the memory location and unused bits are set to zero.

#### Address Processor Registers

The registers of the Address Processor (*Figure 7*) are 28 bits in length. They are used to hold operands for the Address Processor or to hold Word Addresses or Bit Addresses. Registers A0, A1 and A2 are not subject to side effects of RGP drawing instructions.

| A0  | an<br>an    |

|-----|-------------|

| A1  |             |

| A2  |             |

| A3  | FILL/TNXC   |

| A4  | MICRO/TTCH  |

| A5  | MICRO/TTHWB |

| A6  | BSAD        |

| A7  | BSWRP/MICRO |

| A8  | DSAD        |

| A9  | DSWRP       |

| A10 | TCDB/LDA1   |

| A11 | LDA2/TFAD   |

| A12 | INTB        |

| A13 | SP          |

| A14 | PC          |

| A15 | MICRO       |

| 4   | 28          |

| - RESERVED FOR USER                                                                                                                                                                                                                                                       |           |                                           |         |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------|---------|------|

| - RESERVED FOR USER                                                                                                                                                                                                                                                       | 197 - E   |                                           |         |      |

| - RESERVED FOR USER                                                                                                                                                                                                                                                       | 20 Mar    |                                           |         |      |

| - POLYGON FILL/CHARACTER NEXT                                                                                                                                                                                                                                             |           |                                           |         |      |

| FONT ADDRESS                                                                                                                                                                                                                                                              |           |                                           |         |      |

| - MICROCODE USAGE/CHARACTER                                                                                                                                                                                                                                               |           | 1999 - 1999<br>1999 - 1999<br>1999 - 1999 |         |      |

| TRAP VALUE                                                                                                                                                                                                                                                                |           |                                           |         | 1.14 |

| - MICROCODE USAGE/CHARACTER<br>TRAP PARAMETER VALUES                                                                                                                                                                                                                      |           | 14                                        |         |      |

| BITBLT SOURCE ADDRESS                                                                                                                                                                                                                                                     |           |                                           |         |      |

| - BITBLT SOURCE WARP/MICRO                                                                                                                                                                                                                                                |           |                                           |         |      |

| CODE USAGE                                                                                                                                                                                                                                                                |           | - <u>-</u>                                | e       |      |

| - BITBLT DESTINATION ADDRESS                                                                                                                                                                                                                                              | 1.5       |                                           |         |      |

| <ul> <li>DRAWING SPACE WARP</li> <li>CHARACTER DESCRIPTOR TABLE/BRESI<br/>ADDRESS INCREMENT</li> <li>BRESSINHAM BIT ADDRESS INCREMENT,<br/>BITMAP</li> <li>INTERRUPT VECTOR TABLE BAS</li> <li>STACK POINTER</li> <li>PROGRAM COUNTER</li> <li>MICROCODE USAGE</li> </ul> | /text fon |                                           |         |      |

|                                                                                                                                                                                                                                                                           |           | т                                         | L/F/942 | 7-11 |

#### FIGURE 7. Address Processor Registers

#### **Data Processor Registers**

The registers of the Data Processor (Figure 8) are 16 bits in length. All of these registers are subject to side effects of RGP drawing instructions, but D0-5 are preserved through execution of all RGP instructions except those used for polygon filling.

| DO . | DSXT       |   |

|------|------------|---|

| D1   | LOCTT      |   |

| D2   | LLENT      |   |

| D3   | LDE1T      |   |

| D4   | LDE2T      |   |

| D5   | LERRT      |   |

| D6   | FX/MICRO   |   |

| D7   | FXT/MICRO  |   |

| D8   | MICRO      |   |

| D9   | LLEN       |   |

| D10  | LDE1       |   |

| D11  | MICRO/LDE2 |   |

| D12  | MICRO/LERR |   |

| D13  | BWD/MICRO  |   |

| D14  | BHT/MICRO  |   |

| D15  | MICRO      |   |

|      |            |   |

|      | 16         | ļ |

|   | RESERVED |     |       |

|---|----------|-----|-------|

|   | RESERVED |     |       |

| - | RESERVED | FOR | USER* |

- RESERVED FOR USER\*

- RESERVED FOR USER\*

- RESERVED FOR USER\*

- RESERVED FOR POLGON FILL

- RESERVED FOR LINE LENGTH

- BRESENHAM ERROR INCREMENT1

- BRESENHAM ERROR INCREMENT2

- BRESENHAM ERROR

- BITBLT WIDTH

- BITBLT HEIGHT

- RESERVED FOR MICROCODE

except during FILL instructions

FIGURE 8. Data Processor Registers

TL/F/9427-12

#### Status/Control Registers

The following registers indicate or control instruction or interrupt status of the RGP. They are each 16 bits in length.

The Processor Status Register (PSR, see *Figure 9*) indicates the status returned as a result of instruction execution. It also controls the enabling of maskable interrupts and the enabling of the clipper. The individual bits are defined as follows (all fields are asserted when set to one, negated when set to zero):

- Z: Data Processor Zero bit

- C: Data Processor Carry bit

- N: Data Processor Negative bit

- V: Data Processor Overflow bit

- AZ: Address Processor Zero bit

- AC: Address Processor Carry bit

- K: An undrawn character code is present in register TNXC.

- W: The current x,y is within the bounds of the clipper.

- EIP: External Maskable Interrupt Pending

- VIP: Video Interrupt Pending

- CLE: Enable Clipper (1 to enable)

- PTE: Enable Pick Trap

- EIE: Enable External Maskable Interrupt

- VIE: Enable Video Interrupt

See the PRM for more information

|     | ••• |     |     |     | ••• | 98       | - | - | -  |    | - | - | • | • |

|-----|-----|-----|-----|-----|-----|----------|---|---|----|----|---|---|---|---|

| VIE | EIE | PTE | CLE | VIP | EIP | Reserved | w | к | AC | ΑZ | ۷ | N | С | z |

#### **FIGURE 9. Processor Status Register**

#### **Clipper Registers**

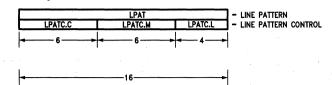

All drawing operations executed by the RGP are subject to the action of a rectangular clipper, when the clipper is enabled. The action of the clipper is to suppress the drawing of pixels outside its boundary. Clipping always takes place to bit resolution independently of the nature of the graphics primitive/operation. That is, all lines, polygons, BITBLTs and text primitives are clipped exactly to the coordinate values defined in the clipper.

The clipper consists of six 16-bit coordinate registers and a 16-bit clipper status register, as follows:

- XMIN The x-coordinate of the left boundary of the clipper

- XMAX The x-coordinate of the right boundary of the clipper

- YMIN The y-coordinate of the top boundary of the clipper

- YMAX The y-coordinate of the bottom boundary of the clipper

- DSX The x-coordinate of the current drawing point

- DSY The y-coordinate of the current drawing point

- CSR The 16-bit Clipper Status Register

When enabled, the clipper is invoked by the RGP for all drawing instructions. The clipper may also be utilized by drawing routines written by the user. The organization of the CSR (*Figure 10*) facilitates this use of the clipper. The CSR contains the results of the four meaningful comparisons between the clipper boundary registers and the current point registers. These results are expressed in "outcode" format in the four least significant bits of the CSR.

15 4 3 2 1 0 RESERVED x>=x<=y>= y<= CSR

TL/F/9427-13

FIGURE 10. Clipper Registers

FIGURE 11. Line Style Generator

Line Style Registers

Those graphics primitives which are drawn by the RGP one pixel at a time, i.e., points, lines and polylines, are drawn subject to the action of a line pattern generator within the RGP. This mechanism produces a pattern along the length of a (presumed) line by suppressing the memory cycles associated with drawing certain points along the line, according to values contained in the registers of the line pattern generator. The line pattern generator includes a mechanism for pattern magnification. The registers of the line pattern generator (*Figure 11*) are defined as follows:

- LPAT 16-bit Pattern Register

- LPATC 16-bit Pattern Control Register, contains three fields:

- LEN Pattern Length (4 bits)

- MAG Pattern Magnification (6 bits)

- CTR Pattern Counter (6 bits)

During pointwise drawing operations, the RGP examines the least significant bit of the LPAT register to determine whether or not to produce a memory cycle to draw the current point. A one in this position will enable drawing; a zero will inhibit drawing. At this point the memory cycle associated with drawing the current point will be executed if appropriate.

The least significant bit of LPAT remains in place for the number of points specified in the MAG field of LPATC; then a circular right shift is performed on the n least significant bits of LPAT, where n is the value specified by the LEN field of LPATC. The CTR field of LPATC serves as a counter used by the RGP to implement magnification. See the PRM for more information.

Since the length of the LPAT register is 16 bits, the maximum pattern length (assuming a magnification of one, i.e., no magnification) is 16 bits. However, shorter patterns can be implemented by setting the LEN field to an appropriate value. The length of the pattern is the number of least significant bits of LPAT that participate in the circular shift. LEN, MAG and CTR all have biases of +1. That is, values of 0 in these fields will program the line pattern generator for a pattern of length 1 and a magnification of 1.

The registers LPAT and LPATC are never reinitialized implicitly by RGP instructions. Once set, a pattern persists through all subsequent points, lines or polylines drawn.

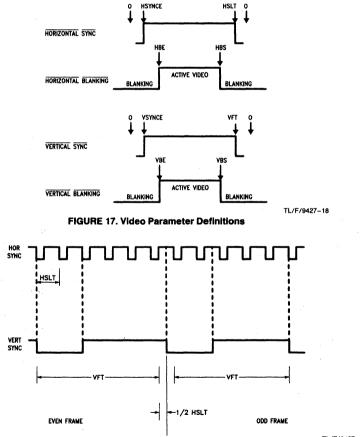

#### Video Refresh Registers

The video refresh registers (*Figures 12* and *13*) contain the parameters for the programmable video refresh machine. They are of two types, distinguished by the mode of accessing them.

TL/F/9427-14

The first type is composed of eight registers that share a common register address (VIDEO); these can be accessed serially by successive MOV instructions. A 3-bit circular pointer (the VRX field of the VCR register) advances after each MOV and can be set to point to any of the eight registers.

The second type consists of 3 registers with separate addresses. The video refresh registers and their interpretations are detailed below. The eight serially addressable registers are shown first, in order. HSLT corresponds to a VRX value of 0, VBS to a value of 7.

- HSLT Horizontal Scan Line Time (12 bits)

- HSE Horizontal Sync End (12 bits)

- HBE Horizontal Blanking End (12 bits)

- HBS Horizontal Blanking Start (12 bits)

- VFT Vertical Frame Time (12 bits)

- VSE Vertical Sync End (12 bits)

- VBE Vertical Blanking End (12 bits)

- VBS Vertical Blanking Start (12 bits)

| ← 12 → |                           |

|--------|---------------------------|

| HSLT   | HORIZONTAL SCAN LINE TIME |

| HSYNCE | HORIZONTAL SYNC END       |

| HBE    | HORIZONTAL BLANK END      |

| HBS    | HORIZONTAL BLANK START    |

| VFT    | VERTICAL FRAME TIME       |

| VSYNCE | VERTICAL SYNC END         |

| VBE    | VERTICAL BLANK END        |

| VBS    | VERTICAL BLANK START      |

FIGURE 12. Video Refresh Parameter Block

FIGURE 13. Video Control Register

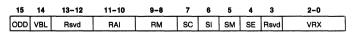

- VCR Video Control Register (16 bits), composed of the following fields:

- VRX Video Register Index (3 bits)

- SE Scan Enable (1 bit)

- SM Master Sync (1 bit)

- SI Interlaced Mode (1 bit)

- SC Composite Sync Mode (1 bit)

- RM Video Refresh Mode (2 bits)

- RAI Video Refresh Address Increment (2 bits)

- VBL The Vertical Blanking Flag

- ODD The Odd Video Field Flag

- DBB Display Buffer Starting Address (24 bits)

- DBWRP Display Buffer Warp (16 bits)

#### THE GRAPHICS ENVIRONMENT

This section discusses the conventions adopted by the RGP and the resultant environment within which all graphics operations take place.

#### **Memory Addressing**

For operations, such as instruction and operand fetching, stack operations and interrupt service, the RGP accesses memory as a uniform space of 2<sup>24</sup> 16-bit words, starting at address 0 and extending to address FFFFFF hex. Bytes are not directly addressable by the RGP.

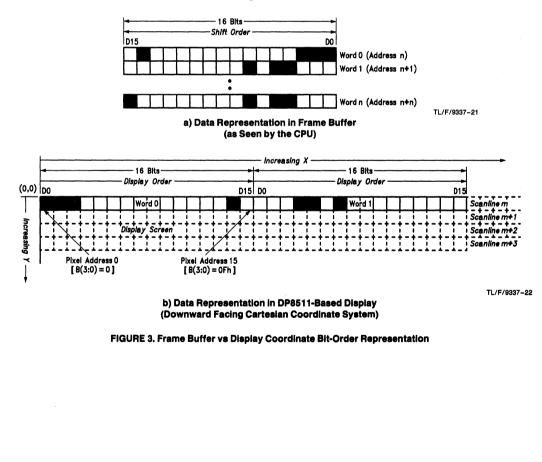

During drawing operations, the RGP can access individual bits in memory by means of a 28-bit quantity called a bit address. The correspondence between a bit address and the physical bit in memory is as follows: the 24 most significant bits of the bit address provide the address of the word in memory containing the addressed bit, while the four least-significant bits of the bit address select a bit within that word. If the four LSBs are zero, bit zero (i.e., the memory bit corresponding to the AD0 pin of the RGP) is addressed. Thus, the bit-addressed memory starts at Bit 0 of Word 0 and extends linearly to Bit 15 of Word  $2^{24} - 1$ .

In practice, the RGP does not read and write individual memory bits directly. When it generates a 28-bit bit address, the most-significant 24 bits are used to access a 16-bit word in the linear address space, while the 4 least significant bits go to the BPU as B0-3. The BPU contains hardware to read

BIT ADDRESS

and write exactly one bit in the current word. In color systems with one BPU per plane, all BPUs operate in parallel, reading and/or writing the corresponding bit in each plane (that is, all the bits of a pixel). As a result, the 28-bit quantity can be viewed as a pixel address as well as a bit address, though this interpretation is system hardware dependent and may in fact be operation-dependent. This is discussed more fully in the Multiple-Bit Pixels Section.

#### **Cartesian Drawing Space**

Drawing operations performed by the RGP execute in a logical drawing space which is Cartesian. This x-y space is defined as having the origin in the upper left. Movement to the right increases the x-coordinate; movement downward increases the y-coordinate. Each axis may be a maximum of  $2^{16}$  bits in length. Therefore, each coordinate may take on any integer value in the range of 0 to  $2^{16} - 1$ . Note that while the coordinate space can range from 0 to  $2^{16} - 1$ , vector drawing instructions (such as DRLN and DRPLN) have the requirement that a vector length not exceed  $2^{14} - 1$  pixels.

A flexible mechanism controls the correspondence between the logical (x-y) location and the physical (bit) address in memory. Once the correspondence has been initialized by the user, the RGP maintains it throughout all drawing operations. The correspondence can be changed explicitly at any time.

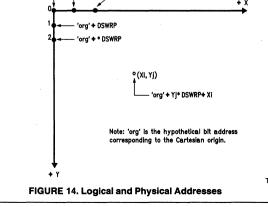

The correspondence is shown in *Figure 14*. The Cartesian origin (x=y=0) corresponds to the hypothetical bit address **org**. Incrementing the logical x-coordinate increments the bit address. Incrementing the y-coordinate adds the contents of the DSWRP register (the *warp* of the drawing space) to the bit address. The current bit address is maintained in the DSAD register. Thus,

$DASD = org + DSY \times DSWRP + DSX$

The correspondence between Cartesian coordinates and bit addresses is established by explicitly loading the registers DSX, DSY and DSAD. This correspondence is maintained by the RGP during the execution of all instructions if DSWRP contains a value appropriate for the current drawing space. Note that the drawing space can coincide with or overlap the display buffer or can be entirely distinct from it, and the two spaces can have separate warps.

'ora' + 2

TL/F/9427-15

#### Dot/Line/Polyline/Polygon Drawing Operations

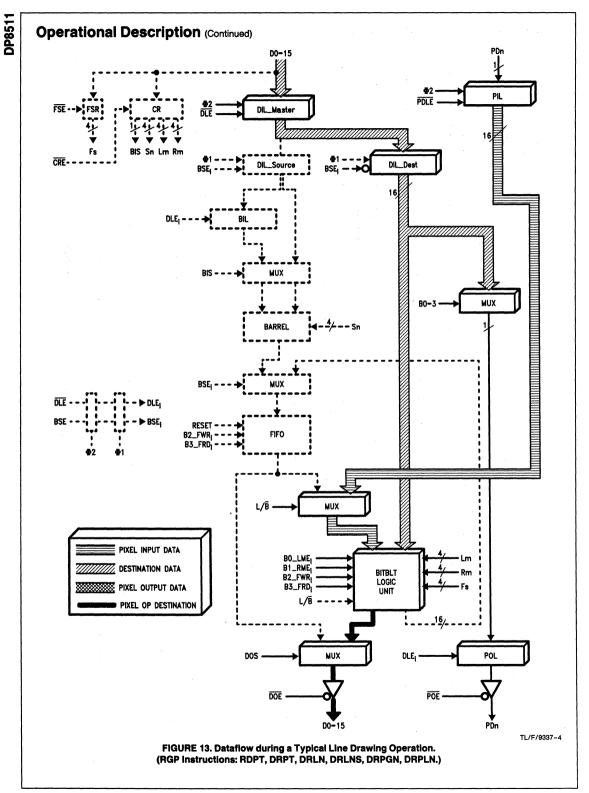

During the execution of the RGP's drawing instructions, the flow of data is between the memory and its associated BPU. The RGP's drawing operations can be divided into two classes, based upon the operating mode of the BPU: BITBLT or LINE, according to the state of the  $L/\overline{B}$  line of the RGP and BPU(s). LINE mode is used for all pointwise drawing operations; BITBLT mode is used for all wordwise drawing operations.

Pointwise drawing operations include reading and writing individual bits (RDPT, DRPT), drawing lines (DRLN), drawing polylines (DRPLN) and drawing polygons (DRPGN). During all pointwise operations, the line pattern generator is active. The clipper (if enabled), is also active.

The clipper performs its function by suppressing the memory cycle associated with drawing the current point if that point is outside the clipper.

The line pattern generator operates in a continuous fashion within and between these instructions; it is not forced to a given state at the beginning of a pointwise drawing instruction. Therefore, a line pattern will continue around the vertices of a polyline. Also, a curve drawn with a series of DRPT instructions will be subject to the line pattern generator. Since the line pattern generator cannot be disabled, it must be loaded with a solid (all ones) pattern if a solid line (no pattern) is desired. Similarly, a pattern of all zeros will suppress all pointwise drawing.

The RDPT instruction is not affected by the clipper or line pattern generator, nor does it affect them.

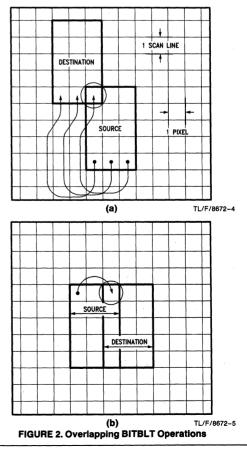

#### **BITBLT Operations**

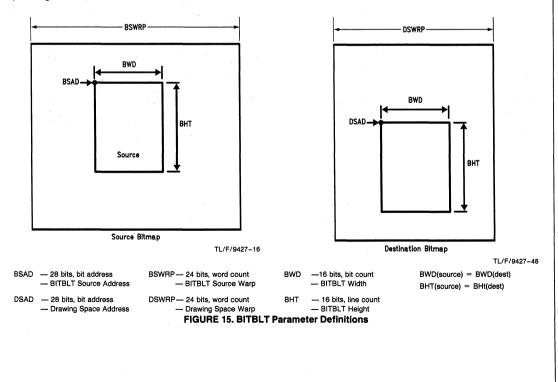

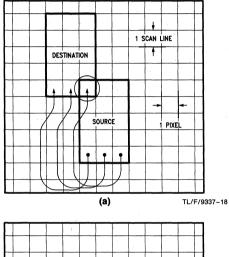

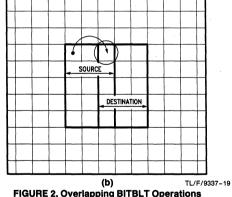

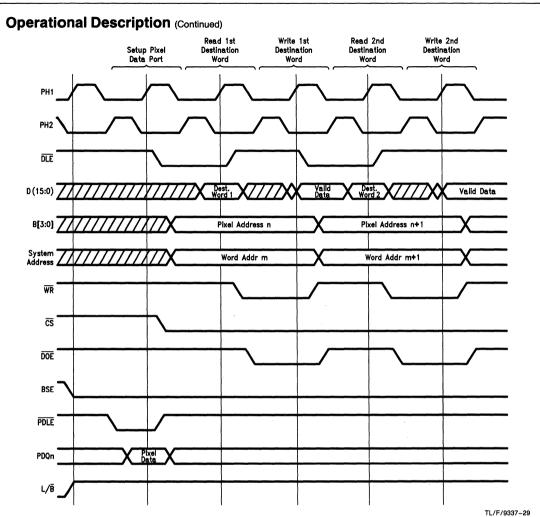

Bit Boundary Block Transfer (BITBLT) operations are carried out by the RGP with the BPU(s) in BITBLT mode. BITBLT is the performance of sixteen specific bitwise logical operations between two rectangular arrays of bits, each having the same height and width and an arbitrary bit alignment (see *Figure 15*). In RGP-based color graphics systems, each DP8511 BPU participating in the BITBLT operation can be programmed to perform its logical operation independently of the others. This permits such effects as transparency and foreground-background color rendering.

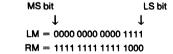

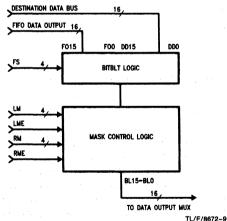

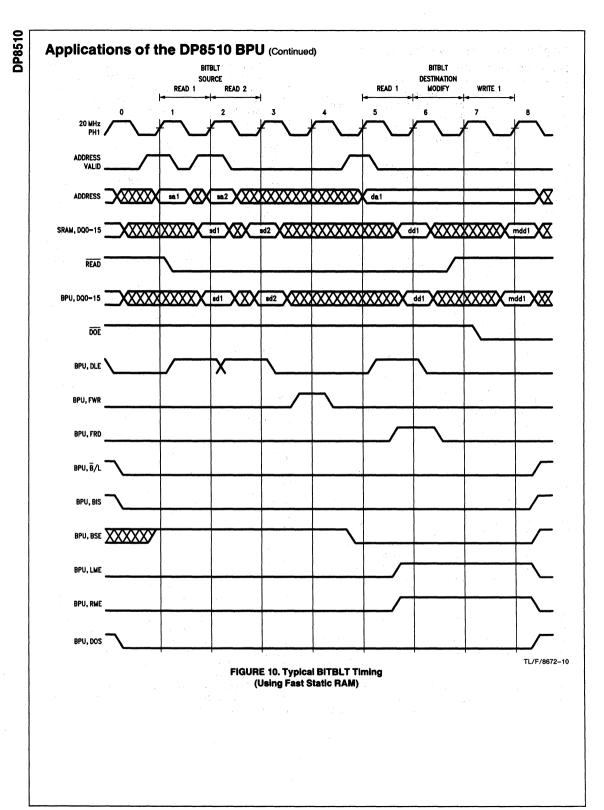

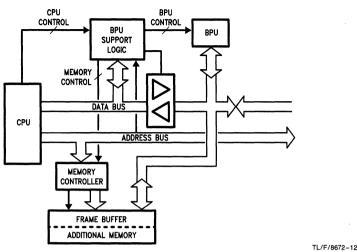

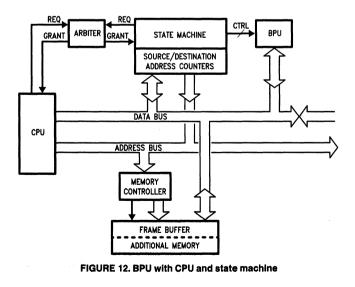

During BITBLT, the RGP produces all memory (word) addresses and the set of BPU control signals necessary to control the FIFO and masking functions. The BPU is responsible for assembling and shifting source words, storing them in the FIFO, receiving destination words, logically combining them with the corresponding shifted source words, (masking any destination bits necessary) and returning the result to the destination.

As during pointwise operations, the clipper is active and clips the destination to pixel resolution. In the process, the BITBLT left and right masks may change from those predicted by the destination alignment alone. Thus, the minimum number of memory cycles required, considering the clipper, is always performed.

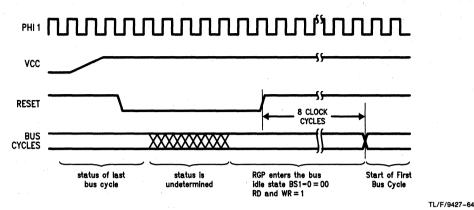

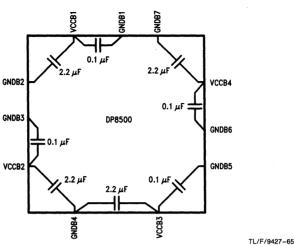

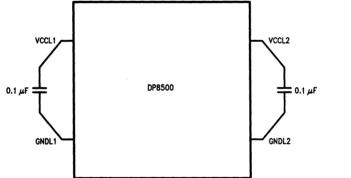

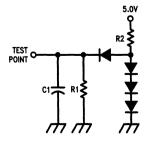

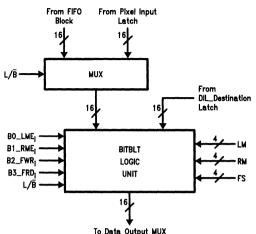

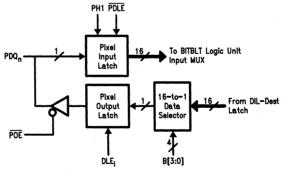

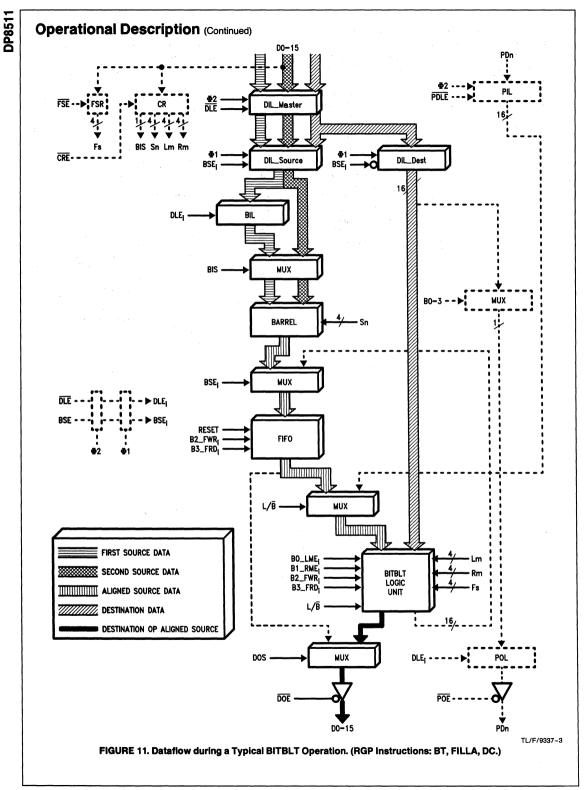

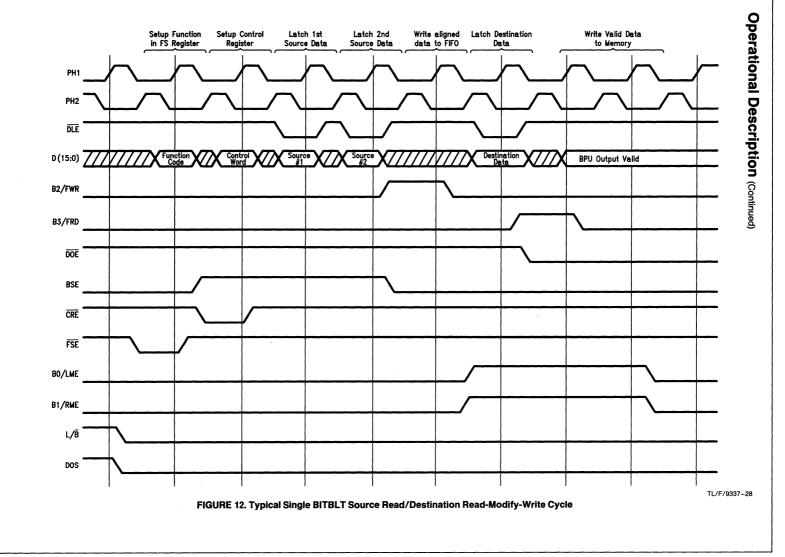

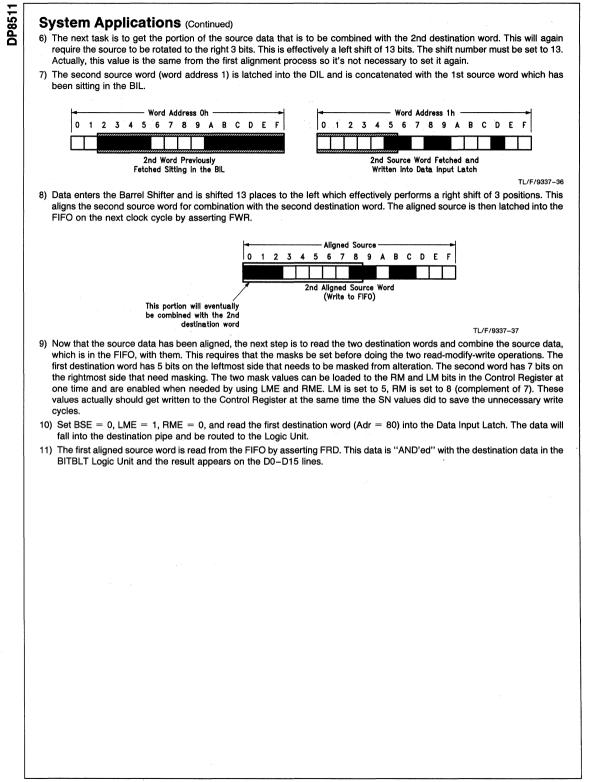

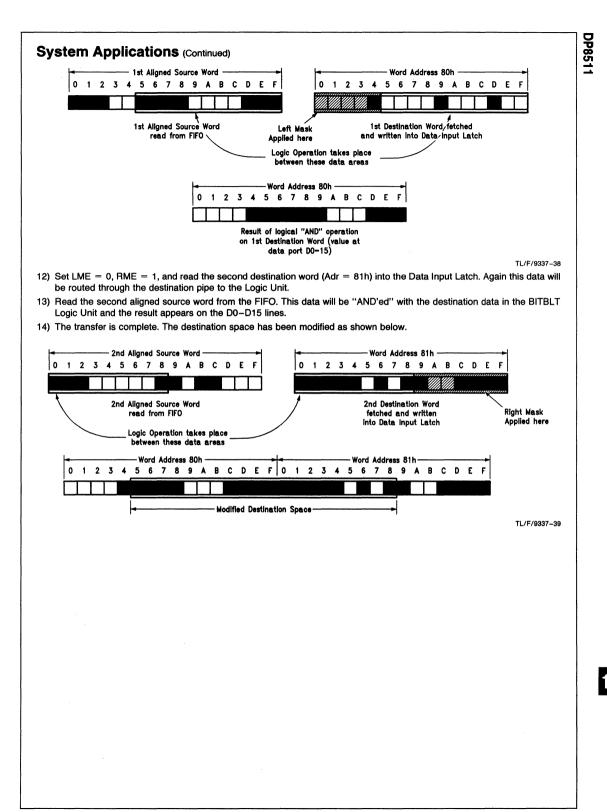

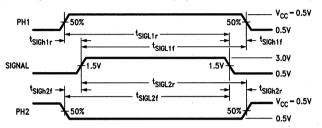

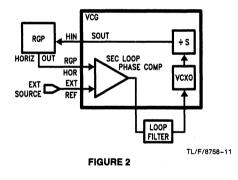

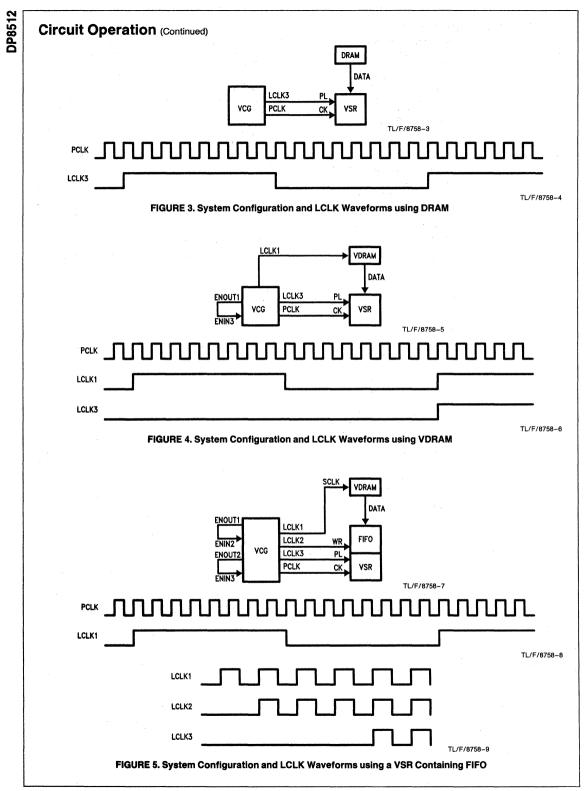

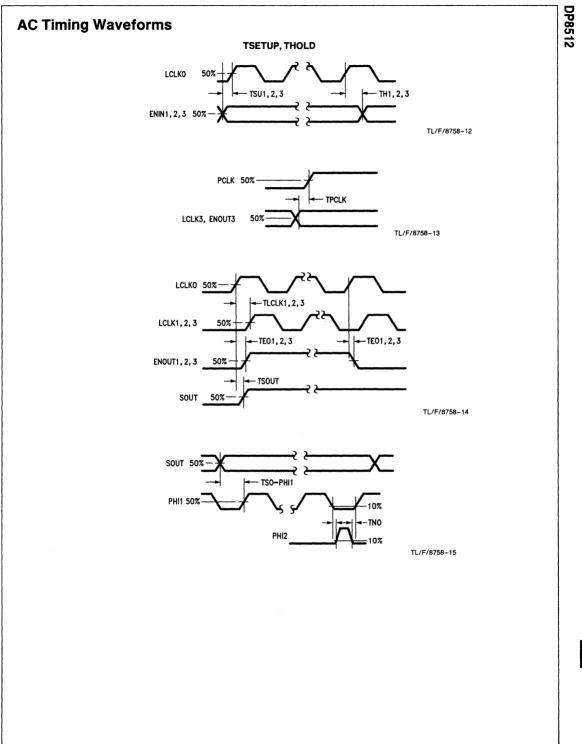

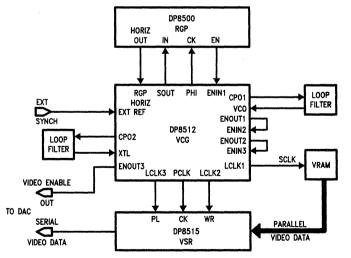

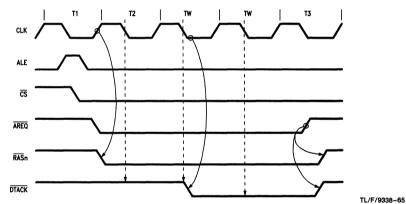

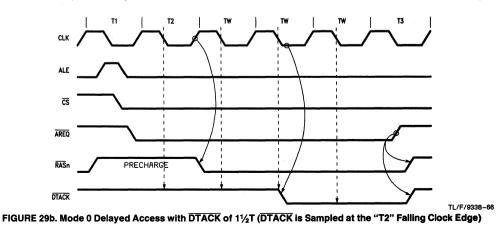

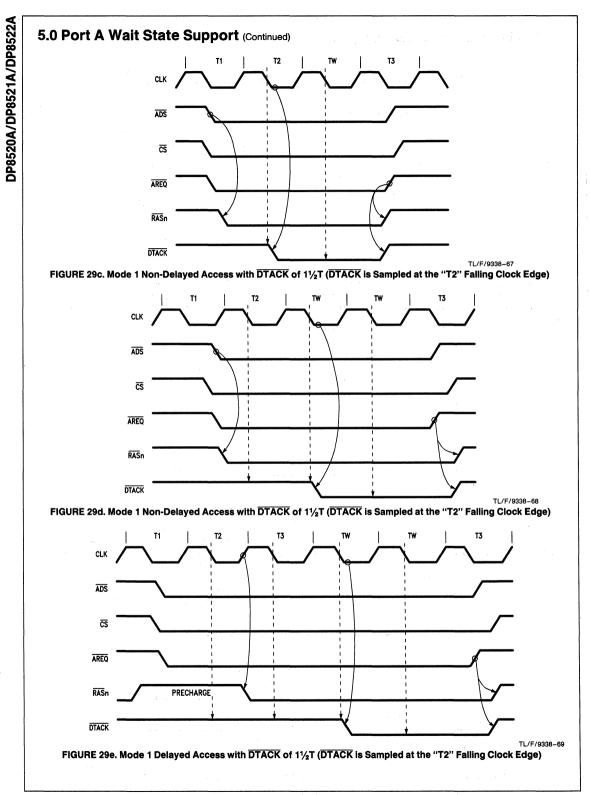

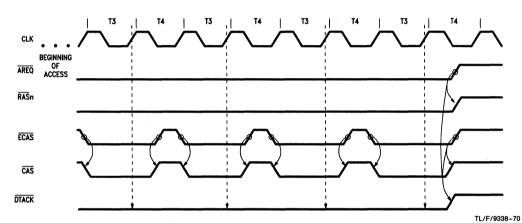

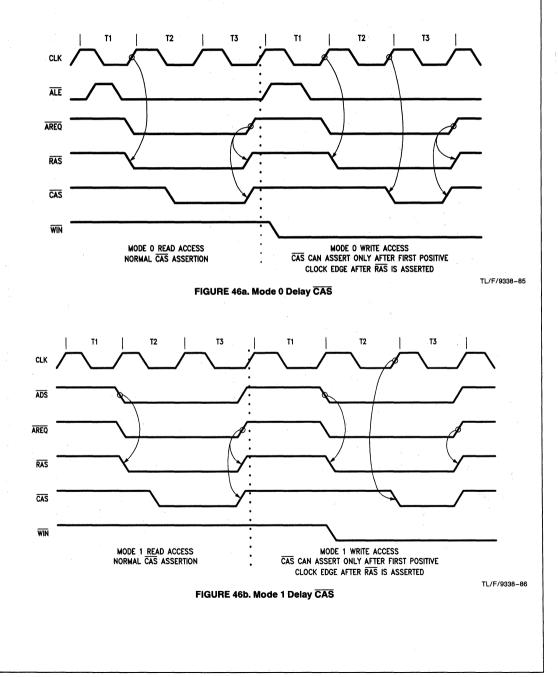

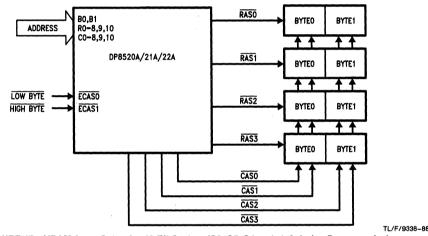

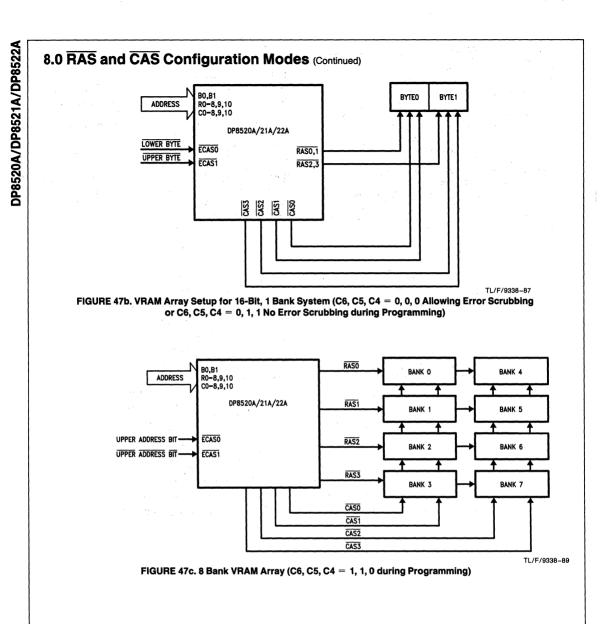

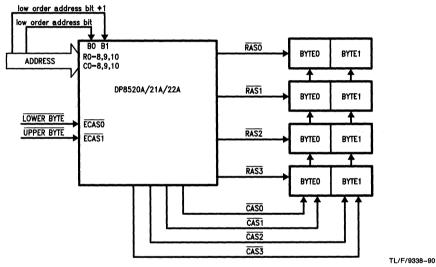

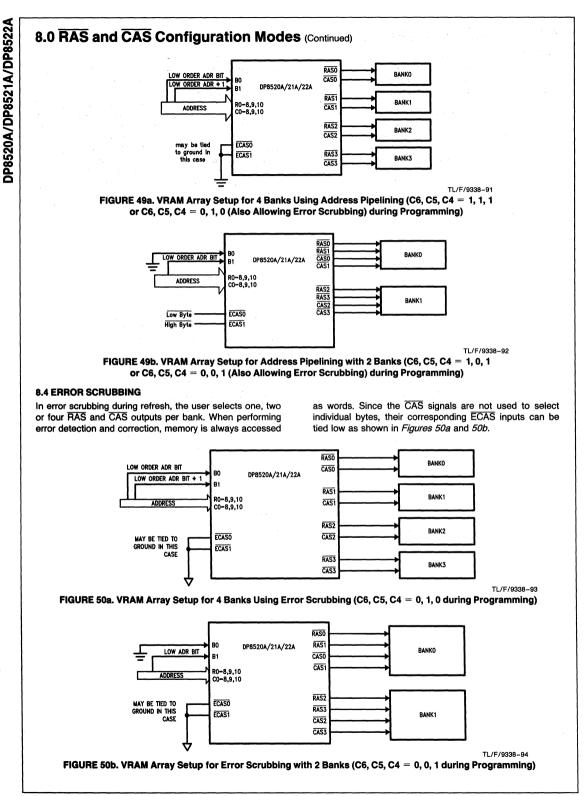

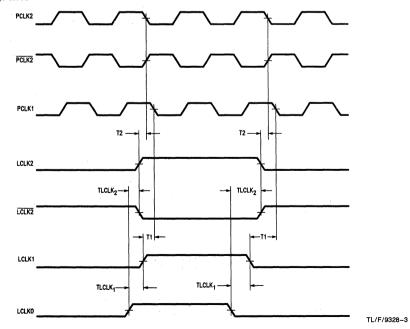

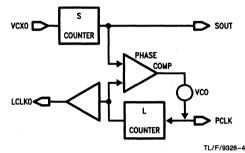

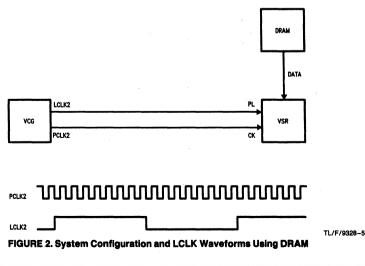

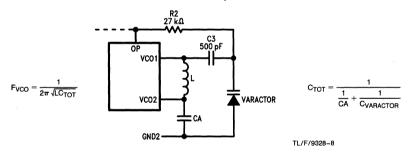

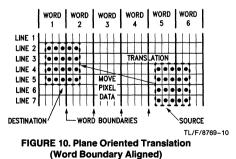

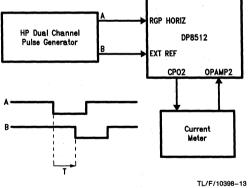

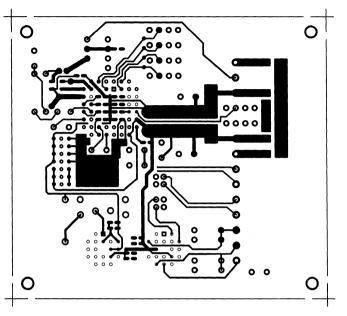

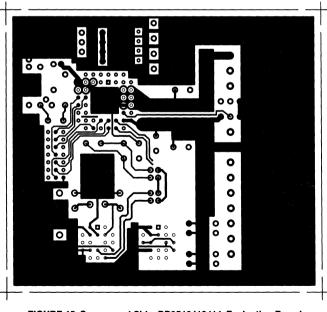

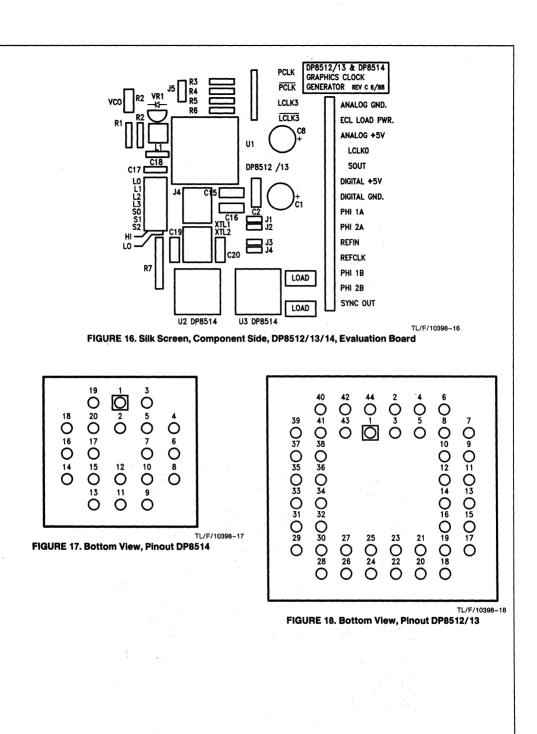

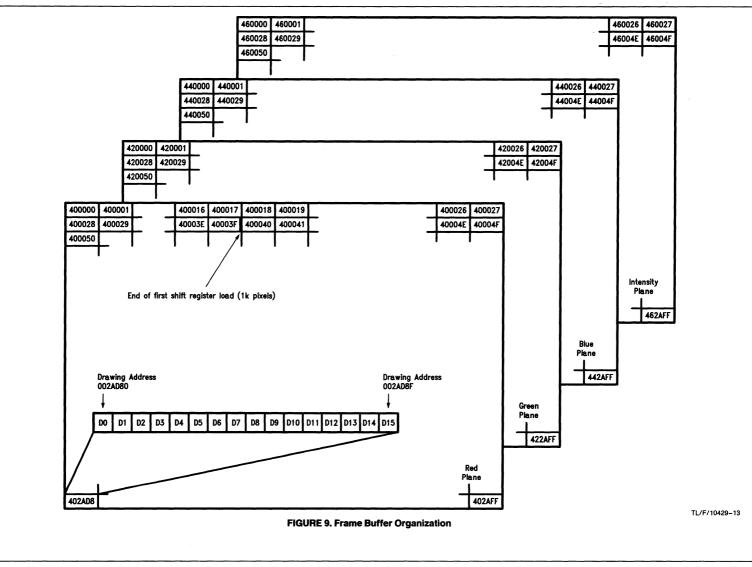

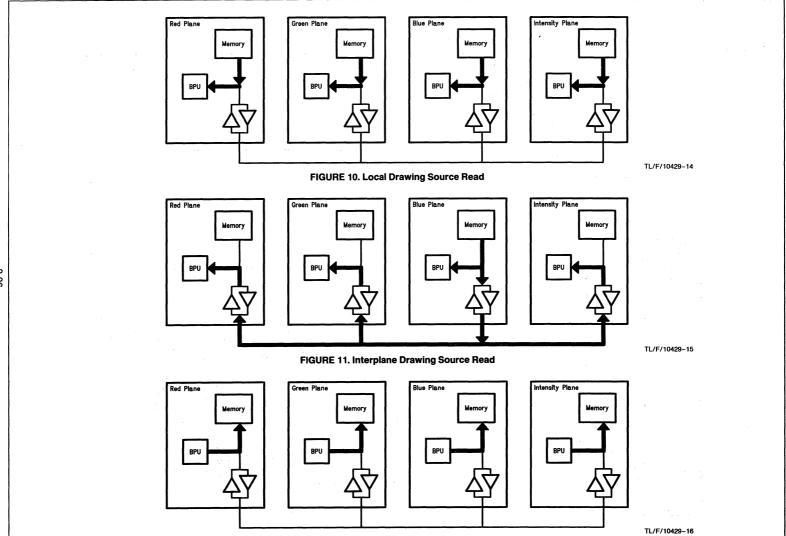

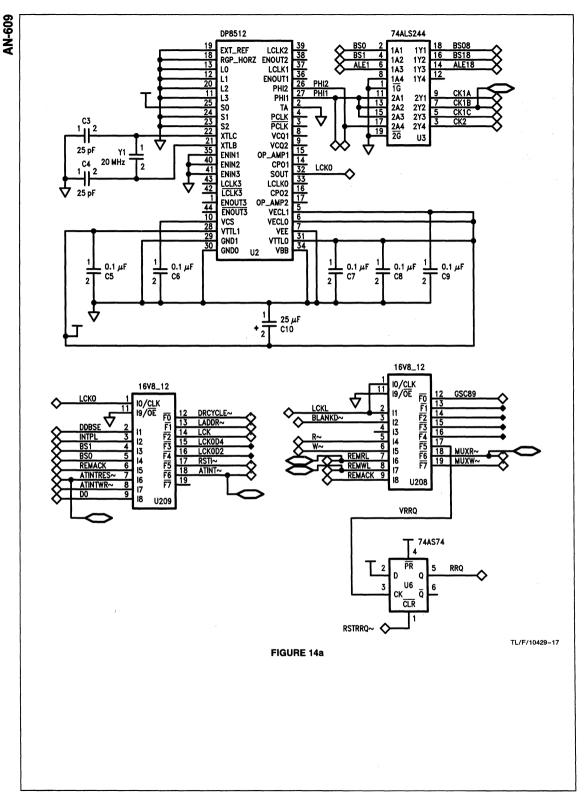

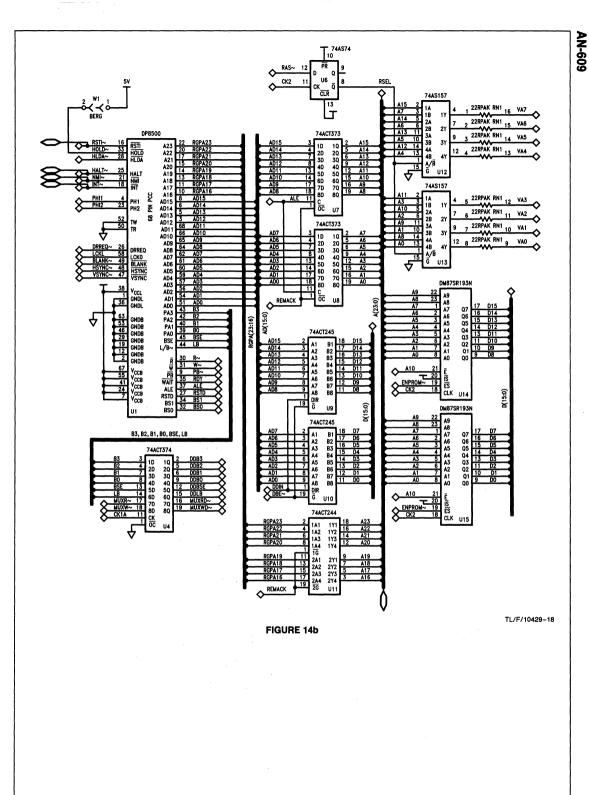

The two directions of execution of BITBLTs can be specified independently: right to left (versus left to right) and bottom to top (versus top to bottom).