# Microcontrollers Databook

### A Corporate Dedication to Quality and Reliability

National Semiconductor is an industry leader in the manufacture of high quality, high reliability integrated circuits. We have been the leading proponent of driving down IC defects and extending product lifetimes. From raw material through product design, manufacturing and shipping, our quality and reliability is second to none.

We are proud of our success . . . it sets a standard for others to achieve. Yet, our quest for perfection is ongoing so that you, our customer, can continue to rely on National Semiconductor Corporation to produce high quality products for your design systems.

Charles E. Sporck

President, Chief Executive Officer National Semiconductor Corporation

# Wir fühlen uns zu Qualität und Zuverlässigkeit verpflichtet

National Semiconductor Corporation ist führend bei der Herstellung von integrierten Schaltungen hoher Qualität und hoher Zuverlässigkeit. National Semiconductor war schon immer Vorreiter, wenn es galt, die Zahl von IC Ausfällen zu verringern und die Lebensdauern von Produkten zu verbesern. Vom Rohmaterial über Entwurf und Herstellung bis zur Auslieferung, die Qualität und die Zuverlässigkeit der Produkte von National Semiconductor sind unübertroffen.

Wir sind stolz auf unseren Erfolg, der Standards setzt, die für andere erstrebenswert sind. Auch ihre Ansprüche steigen ständig. Sie als unser Kunde können sich auch weiterhin auf National Semiconductor verlassen.

#### La Qualité et La Fiabilité:

Une Vocation Commune Chez National Semiconductor Corporation

National Semiconductor Corporation est un des leaders industriels qui fabrique des circuits intégrés d'une très grande qualité et d'une fiabilité exceptionelle. National a été le premier à vouloir faire chuter le nombre de circuits intégrés défectueux et a augmenter la durée de vie des produits. Depuis les matières premières, en passant par la conception du produit sa fabrication et son expédition, partout la qualité et la fiabilité chez National sont sans équivalents.

Nous sommes fiers de notre succès et le standard ainsi défini devrait devenir l'objectif à atteindre par les autres sociétés. Et nous continuons à vouloir faire progresser notre recherche de la perfection; il en résulte que vous, qui êtes notre client, pouvez toujours faire confiance à National Semiconductor Corporation, en produisant des systèmes d'une très grande qualité standard.

#### Un Impegno Societario di Qualità e Affidabilità

National Semiconductor Corporation è un'industria al vertice nella costruzione di circuiti integrati di altà qualità ed affidabilità. National è stata il principale promotore per l'abbattimento della difettosità dei circuiti integrati e per l'allungamento della vita dei prodotti. Dal materiale grezzo attraverso tutte le fasi di progettazione, costruzione e spedizione, la qualità e affidabilità National non è seconda a nessuno.

Noi siamo orgogliosi del nostro successo che fissa per gli altri un traguardo da raggiungere. Il nostro desiderio di perfezione è d'altra parte illimitato e pertanto tu, nostro cliente, puoi continuare ad affidarti a National Semiconductor Corporation per la produzione dei tuoi sistemi con elevati livelli di qualità.

Charles E. Sporck

President, Chief Executive Officer National Semiconductor Corporation

Charlie Jonk

# **MICROCONTROLLER**

### DATABOOK

1988 Edition

**COP400 Family**

**COP800 Family**

**COPS Applications**

**HPC™** Family

**HPC Applications**

MICROWIRE™ and MICROWIRE/PLUS™ Peripherals

Display/Terminal Management Processor (TMP)

**Microcontroller Development Support**

**Appendices/Physical Dimensions**

#### **TRADEMARKS**

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

Abuseable<sup>TM</sup> E-Z-LINK™ Anadig™ **FACTTM** ANS-R-TRANTM **FASTTM APPSTM** 5-Star Service™ Auto-Chem Deflasher™ GAL® ВСРТМ **GENIXTM** BI-FETTM **GNXTM** BI-FET IITM HEX 3000™ BI-LINETM **НРСТМ BIPLANTM ICMTM BLCTM** INFOCHEX™ **BLXTM** Integral ISETM Brite-Lite™ Intelisplay™ **BTLTM ISETM** CheckTrackTM ISE/06TM **CIMTM** ISE/08TM **CIMBUSTM** ISE/16™ Clock**/** Chek™ ISE32TM **СОМВОТМ** KeyScan<sup>TM</sup> COMBO ITM **LMCMOSTM** COMBO IITM M2CMOSTM COPS™ microcontrollers Macrobus™ Datachecker® **DENSPAKTM** Meat ✓ Chek™

Clock Chek™

COMBO™

COMBO™

COMBO ITM

COMBO IITM

COMBO IITM

COPS™

COPS™ microcontrollers

Datachecker®

DENSPAK™

DIB™

Microbus™

M

**MSTTM** Naked-8TM National® NAX 800TM Nitride Plus™ Nitride Plus Oxide™ **NMLTM NOBUSTM** NSC800TM NSX-16™ NS-XC-16™ **NURAM™** OXISSTM . P2CMOSTM Perfect Watch™ Pharma ✓ Chek™ **PLANTM** РМРТМ Polycraft™

Pharmar ChekTM

PLANTM

PMPTM

POlycraftTM

POSitalkerTM

Power & ControlTM

QUAD3000TM

QUIKLOOKTM

RATTM

RTX16TM

SABRTM

Scriptr ChekTM

SCXTM

SERIES/800TM

Series 3000TM

Series 32000®

Shelf ChekTM

SPIRETM

STARTM

StarlinkTM

STARPLEXTM

STARPLEX IITM

SuperChipTM

SuperScriptTM

SYS32TM

TapePak®

TDSTM

TeleGateTM

The National Anthem®

The National Anti TimerChekTM TINATM TLCTM TrapezoidalTM TRI-CODETM TRI-POLYTM TRI-SAFETM TRI-STATES

TURBOTRANSCEIVERTM

VIPTM

VR32TM

WATCHDOGTM

XMOSTM

XPUTM

Z STARTM

883B/RETSTM

883S/RETS™

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive, P.O. Box 58090, Santa Clara, California 95052-8090 (408) 721-5000 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

### **Microcontroller Introduction**

#### **Practical Solutions to Real Problems**

Microcontrollers have always been driven by customer need rather than technological capability.

They were designed to meet specific needs with specific performance in specific applications with specific cost.

That also meant, however, that your choices were limited to what was available on the market—which meant possibly having to compromise your design objectives because you couldn't get exactly the microcontroller you needed.

No more

Now you can get a microcontroller from National that spans a wide range of system solutions—to go almost anywhere your design imagination takes you.

Whether you need a low-cost 4-bit workhorse or a 16-bit 30 MHz powerhouse, whether you want ½ kbyte of ROM or over 64 kbytes, whether you're building a simple singing greeting card or a complex telecommunications network, we have a microcontroller for the job.

With on-board CPU, memory, internal logic, and I/Os, National microcontrollers are helping more and more designers lower system costs and shrink system size.

And as technology brings more peripheral functions onto the chip, including user-programmable memory, fast SRAM, timers, UARTs, comparators, A/D converters, and LAN interfaces, the microcontroller will become the cost-efficient choice for even such real-time "microprocessor" applications as laser printers, ISDN, and digital signal processing.

That's why National continues to lead the industry in the development of microcontroller technology.

That's why we're including our 8-bit and 16-bit controller cores in our standard-cell library.

That's why we're scaling our common M<sup>2</sup>CMOS<sup>TM</sup> process for submicron feature sizes, hypermegahertz frequencies, and unparalleled performance levels.

That's why we offer you "Hot-Line" applications support and a 24-hour-a-day digital information service.

That's why we offer you IBM®-PC and DECTM- VAXTM-based development tools and high-level-language (C) compilers

And that's why we've committed the full resources of our company to provide you with the most complete, most reliable, most cost-effective systems solution for all your needs.

This databook is a reflection of that committment.

It will give you an overview of microcontrollers in general and of National's microcontrollers in particular.

It will help you evaluate your microcontroller options from both a business perspective and an engineering perspective.

It will help you make reasoned judgements about selecting the best microcontroller for your needs.

And it will show you what the microcontroller future holds in store for all of us.

If you'd like more information, or you'd like to find out how to put a microcontroller to work in your own application, just contact your local National Semiconductor Sales Office.

#### **How to Select a Microcontroller**

Microcontrollers have evolved far beyond their origins as control chips in calculators.

Today, microcontrollers can be the perfect solution for simplifying a wide range of designs. And for giving those designs a clear competitive advantage in the marketplace.

Whether used for simple logic replacement or as an integral part of a high performance system, a microcontroller can reduce system costs, shrink system size, and shorten system design cycles. And yet deliver performance often superior to "traditional" digital solutions.

Still, all microcontrollers are not created equal. And it's important to consider a number of factors before committing to a particular device:

- 1. Is the microcontroller optimized for your specific application in terms of speed, performance, features, and cost?

- 2. Is it code-efficient, and based on a true microcontroller architecture for the highest performance and efficiency?

- 3. Is it fabricated in the most advanced CMOS process technology, and is it fully scalable to maintain its performance edge in the future?

- 4. Is it supported by a comprehensive family of development tools that run on standard platforms such as the IBM-PC and DEC VAX?

- 5. Is it backed by a dedicated team of professionals who are available not only to provide expert training for new users, to get them on-line quickly and efficiently, but also to provide technical guidance for even the most experienced user?

- 6. Is it designed for the future, with the capability of on-chip gate arrays and with the planned implementation of the controller core as a standard-cell functional block?

If you answered "yes" to all these questions, then you already know that there's only one company with the product depth and technology capability to provide you with a microcontroller optimized for your specific application.

National Semiconductor.

You'll find National Microcontrollers in:

Laser Printers

Disc Controllers

Telecommunications Systems

Keyboards

Airplane Multiplex Systems

Car Radios

**Engine Control Systems**

Anti-Skid Brake Systems

Armaments

**Factory Automation**

Medical Equipment

**Fuses**

Scales

Refrigerators

Security Systems

Garage Door Openers

Camera Aperture Controls

Office Copiers

Cable TV Converters

Televisions

Video Recorders

Solar Heating Controls

Thermostats

Climate Control Systems

Intelligent Toys

Kitchen Timers

### Why Select a National Microcontroller

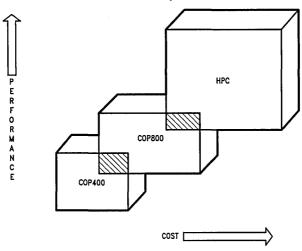

National has created the most complete selection of 4-, 8-, and 16-bit microcontrollers of any company in the industry.

Which means that no matter what the specific needs of your application are, you can find a National microcontroller to meet them.

Our COP400 family offers the lowest-cost, 4-bit solutions for timing, counting, and control functions.

Our COP800 family offers low-cost, feature-rich, 8-bit solutions

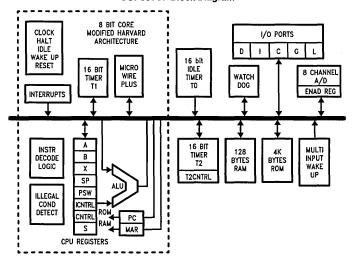

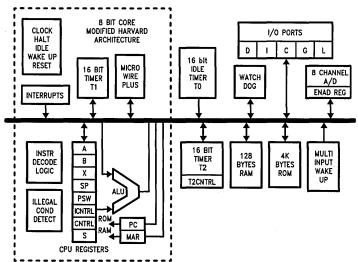

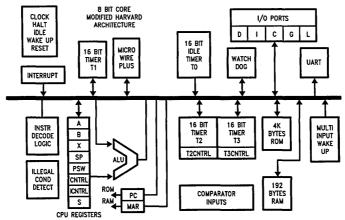

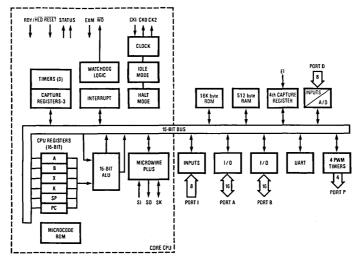

And our High Performance microController (HPCTM) family offers the highest performance with the world's fastest 16-bit CMOS solution.

#### **Microcontroller Family of Products**

With a full range of performance- and feature-options, National's microcontroller families can be customized to meet the needs of your specific application.

#### 1.0 COMMON FEATURES FOR A CUSTOM FIT

All our microcontrollers are designed to provide not just a one-time-only solution, but a continuum of solutions to meet the changing demands of your product and the market-place.

Our COP400 family, for example, which consists of over 60 devices, is designed with a common instruction set, so you can migrate from one member of the family to others without having to recode, so you can take efficient advantage of the application-specific flexibility of the COP400 family's programmable I/O options.

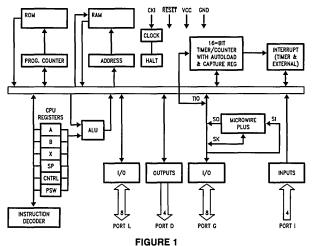

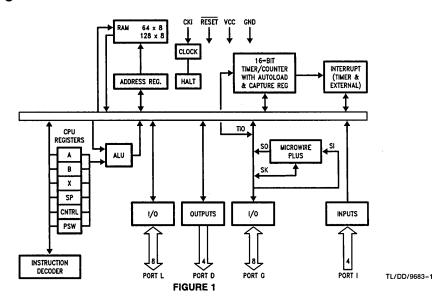

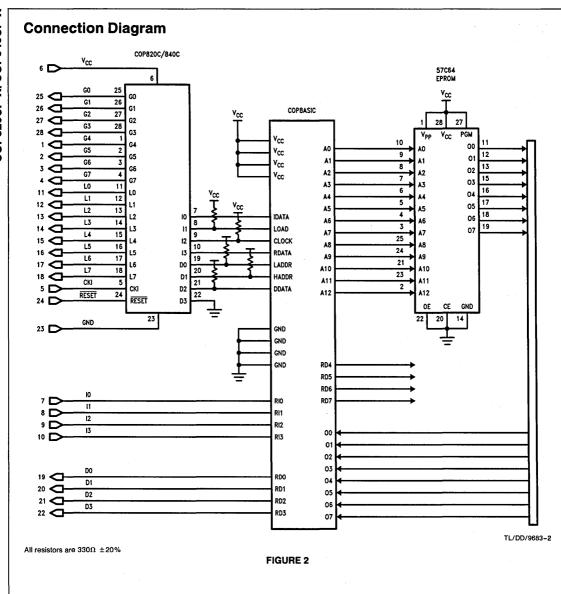

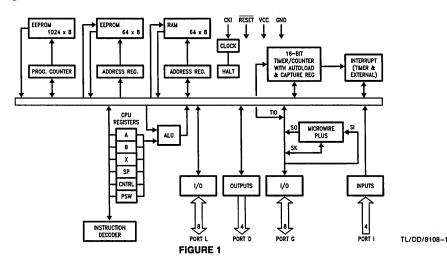

Our COP800 and HPC families, on the other hand, are each designed around a common CPU core that then can be surrounded by a variety of standard functional building blocks such as RAM, ROM, user programmable memory, fast SRAM, DMA, UART, comparator, A/D, HDLC, and I/O.

This unique core approach allows us to offer you a microcontroller with the exact combination of CPU power and peripheral function you need for your specific application. So you don't have to compromise your design parameters by using an inappropriate device, and you don't have to compromise your cost parameters by paying for performance and features you don't need.

TL/XX/0071-1

This core concept also allows us to bring new microcontroller products to market fast and at a lower cost to help you keep pace with the rapidly changing conditions in your own market

And it allows us to implement both the COP800 and the HPC cores as standard cells, for the highest levels of integration and flexibility in your own proprietary design.

#### 2.0 TRUE MICROCONTROLLER ARCHITECTURE

Our microcontrollers are designed as true controllers, not modified microprocessors.

The COP400 family is designed with a two-bus Harvard architecture; the COP800 family with a memory-mapped, modified Harvard architecture, and the HPC family with a memory-mapped, von Neumann architecture.

All three control-oriented families, however, are optimized for high code efficiency. Most instructions are only 1 byte long—yet each can typically execute several functions. This "function-dense" code provides a substantial increase in memory efficiency and processing speed.

## 3.0 ADVANCED PROCESS AND PACKAGING TECHNOLOGIES

National offers you not only the right microcontroller for your needs, but also the right process technology for your microcontroller.

COP400 devices are available in both high-speed NMOS and low-power CMOS fabrications, while the higher-performance COP800 and HPC families are both fabricated in National's advanced M<sup>2</sup>CMOS process.

M²CMOS. This double-metal CMOS process offers significant design advantages. It combines the speed of NMOS, the ruggedness of bipolar, and the low power consumption of bulk CMOS to produce fast, dense, highly efficient, highly scalable devices for a wide variety of integrated-circuit designs.

It's for these reasons that M2CMOS has become the standard process technology for all of National's advanced-

technology LSI and VLSI products, including microprocessors, gate arrays, standard cells, telecommunications devices. linear devices and, of course, microcontrollers.

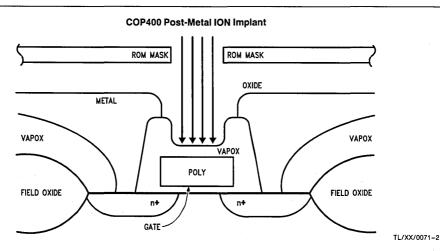

**Post-Metal Programming (PMP).** This is a new process technology available from no other semiconductor manufacturer in the world. It offers the fastest, guaranteed prototype programmed-ROM turn-time in the industry.

PMP is a high-energy implantation process that allows microcontroller ROM to be programmed **after** final metallization.

This is a true innovation, because ROM is usually implemented in the second die layer, with nine or ten other layers then added on top. And that means the ROM pattern must be specified early in the production process, and completed prototype devices won't be available typically for six weeks. With PMP, however, dice can be fully manufactured through metallization and electrical tests (only the passivation layers need to be added), and held in inventory. Which means ROM can be programmed late in the production cycle, making prototypes available in only two weeks!

And production parts can follow in as little as four weeks.

PMP allows you to adapt to fast-changing market conditions and to take maximum advantage of narrow windows of opportunity.

And shorter production lead times can simplify your inventory control and reduce safety stock by up to 20%, giving you significant cost reductions.

Currently, Post-Metal Programming is available for selected members of the COP400 family, and will be expanded to the COP800 and HPC familes in the near future.

**Military versions.** All National microcontrollers have CMOS parts available in the full military temperature range ( $-55^{\circ}$ C to  $+125^{\circ}$ C).

In addition, parts are available that have been certified under MIL-STD-883, Rev. C, the most rigorous non-JAN screening flow in the electronics industry.

Packaging. One major reason that National microcontrollers demonstrate such consistently high levels of reliability is that we've developed special advanced packaging processes to protect the die.

For example, we've designed a unique leadframe with "locking holes" that helps block any penetrating moisture from reaching the die itself.

And the leadframes themselves are made of an unusual high-strength copper alloy that has a lower thermal resistance ( $\theta_{JA}$ ) than typical Alloy 42-leadframes.

We've also employed a unique low-stress, high-purity epoxy molding compound for our packages, which gives them a coefficient of expansion that nearly matches that of the leadframes. As a result, many of our microcontrollers are also offered in plastic packages for military-temperature-range operation.

Reliability is built-in at the die level as well. Our M<sup>2</sup>CMOS microcontrollers are fabricated on dedicated lines at our world-class, six-inch wafer-fab facility in Arlington, Texas. With its Class-10 clean rooms and automated-handling system, Arlington has set a standard of reliability equalled by few other companies in the industry.

And this reliability is available to you in a wide variety of microcontroller packages, ranging in size from 20 to 84 pins. Package types include plastic and ceramic DIPs, small outline (S.O.) surface mounts, plastic and ceramic leaded chip carriers, and pin grid arrays.

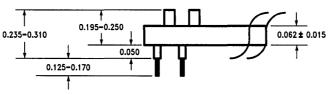

Or, you can select the world's most advanced, high-density packaging option, TapePak<sup>TM</sup>.

TapePak comines the advantages of an automated tapeand-reel-type delivery system with built-in testing pads for reliability and a unique plastic package carrier. The result is a surface-mounted package that can be as small as  $\frac{1}{10}$  the size of conventional surface mounts, with lead spacings of 20 mils

#### **4.0 FULL DEVELOPMENT SUPPORT**

Even the right microcontroller, of course, is useless without the right development tool to put that controller to work in your application.

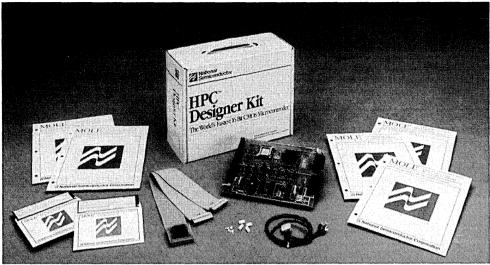

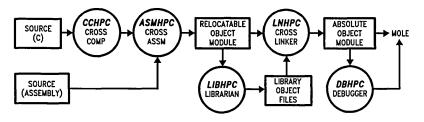

That's why National offers you a full range of development support. Ready-to-run evaluation boards. Emulators. Software. Prototyping devices. Training and seminars for beginning and advanced users. Everything you need to take your design from concept to reality.

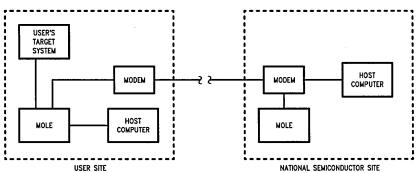

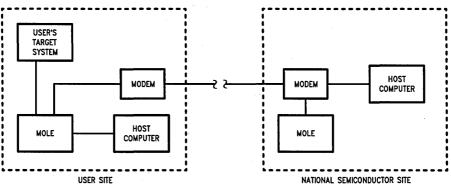

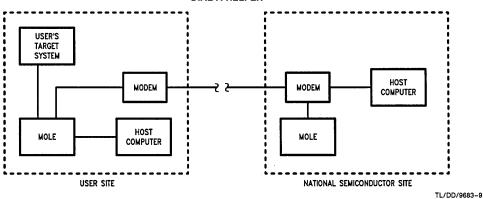

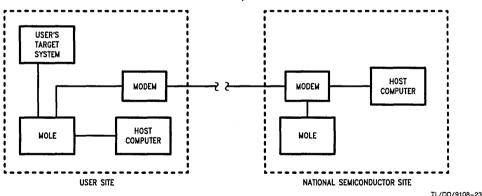

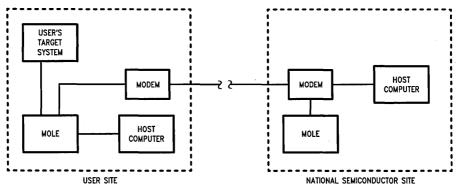

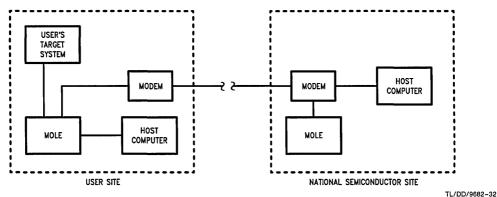

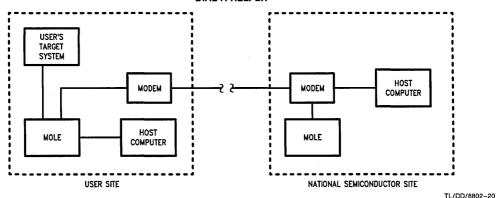

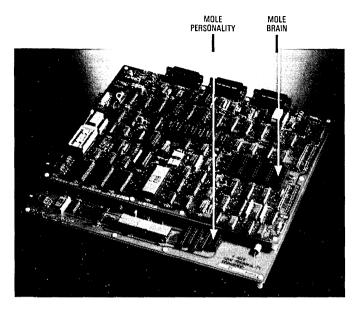

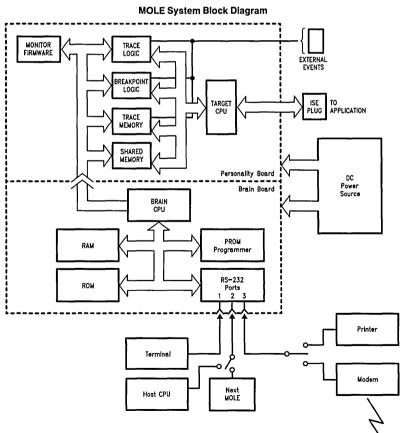

And you don't need an expensive development environment to do it. With our exclusive Microcontroller On-Line Emulator (MOLE<sup>TM</sup>), a standard IBM PC or DEC VAX becomes a full-featured platform.

And with our comprehensive library of prewritten routines, from keyboard scanners to Fast Fourier Transforms, you can reduce software programming to a minimum. This "user-friendly" service can help you bring your design to market quickly and cost-effectively.

#### **5.0 FULL APPLICATIONS SUPPORT**

At National, we believe that applications support should be immediate and "hands-on".

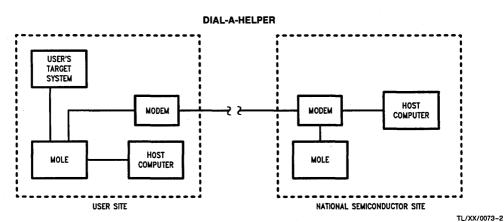

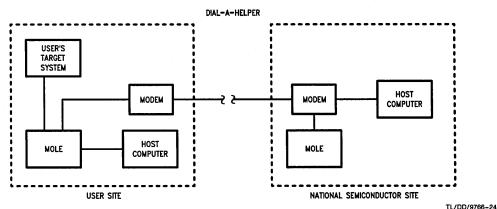

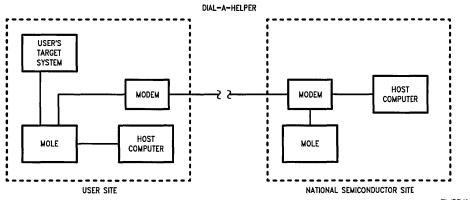

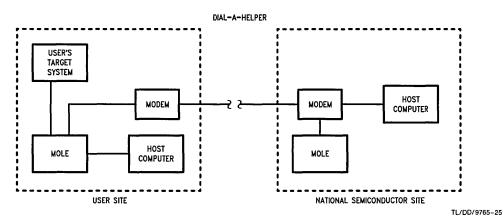

That's why we established the unique Dial-A-Helper program.

With a computer, modem, and telephone, you can tie directly into our Microcontroller Applications Group for fast, direct assistance in developing your design.

You can leave messages on our electronic bulletin board for our Applications Engineers, who will respond to you directly. You can access applications files.

You can download those files for later reference.

Or, if you're having a real problem, you can actually turn the control of your Microcontroller On-Line Emulator development system over to our engineering staff, who can perform remote diagnostic routines to locate and eliminate any bugs.

The point is, when you buy a microcontroller from National, you're buying more than silicon—you're buying the commitment of an entire company of dedicated professionals who share a single goal: to help you put that silicon to work.

#### Systems in the Future—Integration Path

TL/XX/0071-3

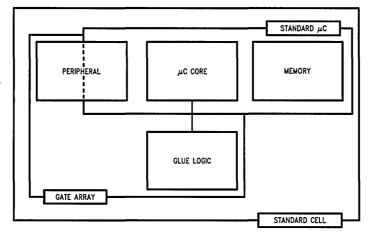

#### **6.0 THE ASIC FUTURE**

National's microcontrollers were designed to meet two objectives: to adapt to your evolving needs, and to adapt to evolving technology.

Both "evolutions," however, are leading to the same goal: the complete "system-on-chip" solution. Already, the glue logic that ties a microcontroller to its peripheral functions can be replaced with a gate array. And soon, all three functions (microcontroller "core", logic, and peripherals) will be available as a single standard-cell functional block.

The key to achieving this goal, of course, is a common, advanced, scalable process technology.

That's why both the COP800 and HPC families are fabricated in our high-performance double-metal CMOS process. This is a highly scalable technology that can accommodate die shrinks to submicron feature sizes, increasing performance and cutting power consumption with each step.

Moreover, because M2CMOS is now the standard process technology for all new National LSI and VLSI devices, the

COP800 and HPC cores will not only be available as part of our standard-cell library, but will also be able to support one of the broadest range of functional blocks available from any semiconductor manufacturer—all aligned on the same set of design rules.

So you can standardize your designs on just one or two core processors, and, as we introduce new technologies and functions, you can maintain that design knowledge base while taking advantage of these new, higher levels of functional integration.

And because National (and only National) gives you the option of using standard parts or designing your own customized solutions—both supported by common design tools and a common process—you can create highly competitive, highly secure, highly optimized solutions in minimal space at minimal cost in minimal time.

And that's the name of the game.

# **Table of Contents**

| COP400.         1-3           ROM*d Devices         COP210C/COP211C Single-Chip CMOS Microcontrollers         1-8           COP224C/COP225C/COP226C/COP244C/COP245C Single-Chip 1k and 2k CMOS         Microcontrollers         1-20           COP210C/COP211C/COP310L/COP311C Single-Chip CMOS Microcontrollers         1-37           COP410C/COP411L/COP310L/COP311L Single-Chip N-Channel Microcontrollers         1-52           COP413L/COP313Single Chip Microcontrollers         1-52           COP413L/COP314Single-Chip N-Channel Microcontrollers         1-70           COP413C/COP413CH/COP313C/COP313C/COP313CH Single-Chip CMOS Microcontrollers         1-70           COP412C/COP421C/COP422C/COP320/COP321/COP322 Single-Chip N-Channel Microcontrollers         1-11           COP42D/COP425C/COP428C/COP320L/COP325C/COP326C/ and COP444C/COP445C/COP426C/OP426C/OP345C Single-Chip 1k and 2k CMOS Microcontrollers         1-161           COP44D/COP441/COP442/COP340C Single-Chip 1k and 2k CMOS Microcontrollers         1-161           COP44D/COP444L/COP442/COP340C Single-Chip N-Channel Microcontrollers         1-181           COP401L ROMIess N-Channel Microcontroller         1-227           COP401L ROMIess N-Channel Microcontroller         1-227           COP401L ROMIess N-Channel Microcontrollers         1-241           COP402COP402M ROMIess N-Channel Microcontroller         1-227           COP404C ROMIess N-Channel Microcontroller         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Section 1 COP400 Family                                                |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------|

| 1-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | COP400                                                                 | 1-3   |

| COP24C/COP225C/COP226C/COP244C/COP24SC Single-Chip 1k and 2k CMOS Microcontrollers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                        |       |

| Microcontrollers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                        | 1-8   |

| COP410C/COP411C/COP310C/COP311C Single-Chip N-Channel Microcontrollers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                        |       |

| COP410L/COP411L/COP310L/COP311L Single-Chip N-Channel Microcontrollers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                        | 1-20  |

| COP413L/COP313L Single Chip Microcontrollers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                        | 1-37  |

| COP413C/COP413CH/Ö0P313C/COP313CH Single-Chip CMOS Microcontrollers         1-83           COP414L/COP314L Single-Chip N-Channel Microcontrollers         1-97           COP420/COP421L/COP422L/COP320/COP321/COP322 Single-Chip N-Channel Microcontrollers         1-112           COP420L/COP421L/COP422L/COP320L/COP321L/COP322L Single-Chip N-Channel Microcontrollers         1-135           COP442C/COP425C/COP428C/COP324C/COP325C/COP326C/ and COP444C/COP445C/COP344C/COP345C Single-Chip 1k and 2k CMOS Microcontrollers         1-161           COP444C/COP344C/COP345C Single-Chip 1k and 2k CMOS Microcontrollers         1-181           COP444L/COP442L/COP344C/COP341/COP342 Single-Chip N-Channel Microcontrollers         1-204           ROMIess Devices         1-204           ROMIess Devices         2-204           COP401L ROMIess N-Channel Microcontroller         1-227           COP401L ROMIess N-Channel Microcontrollers         1-224           COP402C/COP404M ROMIess N-Channel Microcontrollers         1-254           COP404 ROMIess N-Channel Microcontroller         1-272           COP404 ROMIess N-Channel Microcontroller         1-272           COP404 ROMIess N-Channel Microcontroller         1-276           COP404 ROMIess N-Channel Microcontroller         1-276           COP404 ROMIess N-Channel Microcontroller         1-276           COP404 ROMIess R-Channel Microcontroller         2-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |       |

| COP414L/COP314L Single-Chip N-Channel Microcontrollers 1-97 COP420/COP421/COP322/COP320/COP321/COP322 Single-Chip N-Channel Microcontrollers 1-112 COP420L/COP421L/COP422L/COP320L/COP321L/COP322L Single-Chip N-Channel Microcontrollers 1-135 COP4226/COP426C/COP426C/COP326C/COP326C/ and COP44C/COP445C/COP426C/COP345C Single-Chip 1k and 2k CMOS Microcontrollers 1-161 COP445C/COP441/COP442/COP345C Single-Chip 1k and 2k CMOS Microcontrollers 1-161 COP440/COP441/COP442/COP340/COP341/COP342 Single-Chip N-Channel Microcontrollers 1-204 ROMIess Devices 1-204 ROMIess Devices 1-204 COP401L ROMIess N-Channel Microcontroller 1-227 COP401L ROMIess N-Channel Microcontroller 1-227 COP4041L ROMIess N-Channel Microcontroller 1-254 COP404 ROMIess N-Channel Microcontroller 1-254 COP404 ROMIess N-Channel Microcontroller 1-272 COP404C ROMIess CMOS Microcontroller 1-279 COP404C ROMIess CMOS Microcontroller 1-279 COP404LSN-5 ROMIess N-Channel Microcontroller 1-279 COP404LSN-5 ROMIess N-Channel Microcontroller 1-279 COP404C ROMIess CMOS Microcontroller 1-279 COP404C ROMIess N-Channel Microcontroller 1-270 COP800C 2-30 COP80C 3-30 COP |                                                                        | 1-70  |

| COP420/COP421/COP422/COP320/COP321/COP322 Single-Chip N-Channel Microcontrollers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                        | 1-83  |

| Microcontrollers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                        | 1-97  |

| COP420L/COP421L/COP422L/COP320L/COP321L/COP322L Single-Chip N-Channel Microcontrollers . 1-135 COP424C/COP425C/COP426C/COP324C/COP325C/COP326C/ and COP444C/COP445C/COP345C Single-Chip 1k and 2k CMOS Microcontrollers . 1-161 COP440/COP441/COP442/COP340/COP341/COP342 Single-Chip N-Channel Microcontrollers . 1-204 Microcontrollers . 1-204 ROMless Devices COP401L ROMless N-Channel Microcontroller . 1-227 COP401L-X13/COP401L-R13 ROMless N-Channel Microcontrollers . 1-241 COP402/COP402M ROMless N-Channel Microcontroller . 1-272 COP404 ROMless N-Channel Microcontroller . 1-272 COP404C ROMless N-Channel Microcontroller . 1-272 COP404C ROMless N-Channel Microcontroller . 1-279 COP404LSN-5 ROMless N-Channel Microcontroller . 1-279 COP404LSN-5 ROMless N-Channel Microcontroller . 1-296 COP420P/COP444CP/COP444LP Piggyback EEPROM Microcontrollers . 1-310 Section 2 COP800 Family COP800C . 2-3 COP820C/COP821C/COP822C/COP840C/COP841C/COP842C/COP620C/COP621C/COP622C/COP640C/COP641C/COP642C Single-Chip microCMOS Microcontrollers . 2-36 COP820CP-X/COP8721C/COP8722C Single-Chip microCMOS Microcontroller . 2-26 COP888CF Single-Chip microCMOS Microcontroller . 2-36 COP Brief 2 Easy Logarithms for COP400 Microcontroller . 3-33 COP Brief 3 Foftware and Opcode Differences in the COP444L Instruction Set . 3-15 COP Brief 5 Software and Opcode Differences in the COP444L Instruction Set . 3-15 COP Brief 5 RAM Keep-Alive . 3-16 COP Note 1 Analog to Digital Conversion Techniques with COPS Family Microcontrollers . 3-49 COP Note 5 Oscillator Characteristics of COPS Microcontroller Family . 3-71 COP Note 7 Testing of COPS Chips . 3-79 AB-3 Current Consumption in NMOS COPS Microcontrollers | COP420/COP421/COP422/COP320/COP321/COP322 Single-Chip N-Channel        |       |

| Channel Microcontrollers . 1-135 COP42C/COP42EC/COP42EC/COP324C/COP32EC/COP32EC/ and COP444C/ COP445C/COP44C/COP345C Single-Chip 1k and 2k CMOS Microcontrollers . 1-161 COP440/COP441/COP442/COP340/COP341/COP342 Single-Chip N-Channel Microcontrollers . 1-181 COP44L/COP445L/COP344L/COP345L Single-Chip N-Channel Microcontrollers . 1-204 ROMless Devices COP401L ROMless N-Channel Microcontroller . 1-227 COP401L ROMless N-Channel Microcontroller . 1-227 COP401L-X13/COP401L-R13 ROMless N-Channel Microcontrollers . 1-241 COP402/COP402M ROMless N-Channel Microcontroller . 1-272 COP404 ROMless N-Channel Microcontroller . 1-272 COP404 ROMless N-Channel Microcontroller . 1-272 COP404 ROMless N-Channel Microcontroller . 1-279 COP404LSN-5 ROMless N-Channel Microcontroller . 1-279 COP40P4CP/COP444LP Piggyback EEPROM Microcontrollers . 1-296 COP420P/COP444CP/COP444LP Piggyback EEPROM Microcontrollers . 1-296 COP420P/COP44CP/COP444LP Piggyback EEPROM Microcontrollers . 2-3 COP820C/COP821C/COP822C/COP840C/COP841C/COP842C/COP620C/ COP621C/COP622C/COP640C/COP641C/COP642C Single-Chip microCMOS Microcontrollers . 2-7 COP820CP-X/COP840CP-X Piggyback EPROM Microcontroller . 2-27 COP8720C/COP8721C/COP8722C Single-Chip microCMOS Microcontroller . 2-26 COP888CF Single-Chip microCMOS Microcontroller . 2-26 COP898CF Single-Chip microCMOS Microcontroller . 3-15 COP Brief 5 RAM Keep-Alive . 3-16 COP Note 1 Analog to Digital Conversion Techniques with COPS Family Microcontrollers . 3-16 COP Note 5 Trac Control Using the COP400 Microcontroller Family . 3-71 COP Note  |                                                                        | 1-112 |

| COP424C/COP425C/COP426C/COP324C/COP325C/COP326C/ and COP444C/ COP44SC/COP344C/COP345C Single-Chip 1k and 2k CMOS Microcontrollers . 1-161 COP449C/COP441/COP442/COP340/COP341/COP342 Single-Chip N-Channel Microcontrollers . 1-181 COP444L/COP445L/COP344L/COP345L Single-Chip N-Channel Microcontrollers . 1-204 ROMless Devices . 1-204 ROMless Devices . 1-227 COP401L ROMless N-Channel Microcontroller . 1-227 COP401L ROMless N-Channel Microcontroller . 1-227 COP402L ROMless N-Channel Microcontrollers . 1-241 COP402/COP402M ROMless N-Channel Microcontrollers . 1-254 COP404 ROMless N-Channel Microcontroller . 1-279 COP404G ROMless CMOS Microcontroller . 1-279 COP404LSN-5 ROMless N-Channel Microcontroller . 1-279 COP404LSN-5 ROMless N-Channel Microcontroller . 1-296 COP420P/COP444CP/COP444LP Piggyback EEPROM Microcontrollers . 1-310 Section 2 COP800 Family COP800C . 2-3 COP820C/COP821C/COP822C/COP840C/COP841C/COP842C/COP620C/ COP621C/COP622C/COP640C/COP641C/COP642C Single-Chip microCMOS Microcontrollers . 2-27 COP8720C/COP8721C/COP8722C Single-Chip microCMOS Microcontroller . 2-27 COP880CP-X/COP840CP-X Piggyback EPROM Microcontroller . 2-27 COP880CP-X/COP8721C/COP8722C Single-Chip microCMOS Microcontroller . 2-25 COP888CG Single-Chip microCMOS Microcontroller . 2-26 COP Brief 2 Easy Logarithms for COP400 . 3-3 COP Brief 5 Software and Opcode Differences in the COP444L Instruction Set . 3-15 COP Brief 6 RAM Keep-Alive . 3-16 COP Note 1 Analog to Digital Conversion Techniques with COPS Family Microcontrollers . 3-16 COP Note 5 Triac Control Using the COP400 Microcontroller Family . 3-71 COP Note 6 Triac Control Using the COP400 Microcontroller Family . 3-71 COP Note 7 Testing of COPS Chips . 3-88                                                                                                                                                                             |                                                                        |       |

| COP445C/COP344C/COP345C Single-Chip 1k and 2k CMOS Microcontrollers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                        | 1-135 |

| COP440/COP441/COP442/COP340/OOP341/COP342 Single-Chip N-Channel Microcontrollers   1-181 COP444L/COP445L/COP344L/COP345L Single-Chip N-Channel Microcontrollers   1-204 ROMIess Devices   1-204 ROMIess Devices   1-227 COP401L ROMIess N-Channel Microcontroller   1-227 COP401L ROMIess N-Channel Microcontrollers   1-247 COP402L ROMIess N-Channel Microcontrollers   1-254 COP404 ROMIess N-Channel Microcontrollers   1-254 COP404 ROMIess N-Channel Microcontroller   1-272 COP404 ROMIess N-Channel Microcontroller   1-279 COP404 ROMIess N-Channel Microcontroller   1-279 COP404 ROMIess CMOS Microcontroller   1-279 COP404LSN-5 ROMIess N-Channel Microcontroller   1-279 COP404LSN-5 ROMIess N-Channel Microcontroller   1-279 COP40P40P/COP444LP Piggyback EEPROM Microcontrollers   1-310 Section 2 COP800 Family   2-30 COP820C/COP821C/COP822C/COP840C/COP841C/COP842C/COP820C/COP820C/COP821C/COP822C/COP840C/COP841C/COP842C/COP820C/COP820C/COP822C/COP840C/COP841C/COP842C/COP820C/COP820C/COP822C/COP8640C/COP841C/COP842C/COP820C/COP820C/COP8720C/COP8722C/Single-Chip microCMOS Microcontroller   2-27 COP8720C/COP8721C/COP8722C Single-Chip microCMOS Microcontroller   2-36 COP888CF Single-Chip microCMOS Microcontroller   2-36 COP886CF Single-Chi   |                                                                        |       |

| Microcontrollers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                        | 1-161 |

| COP444L/COP445L/COP344L/COP345L Single-Chip N-Channel Microcontrollers  COP401L ROMless N-Channel Microcontroller  COP401L-X13/COP401L-R13 ROMless N-Channel Microcontrollers  1-227 COP401L-X13/COP401L-R13 ROMless N-Channel Microcontrollers  1-254 COP404 ROMless N-Channel Microcontroller  1-272 COP404 ROMless CMOS Microcontroller  1-279 COP404LSN-5 ROMless N-Channel Microcontroller  1-279 COP404LSN-5 ROMless N-Channel Microcontroller  1-296 COP420P/COP444CP/COP444LP Piggyback EEPROM Microcontrollers  1-310 Section 2 COP800 Family  COP800C  COP621C/COP622C/COP640C/COP641C/COP642C Single-Chip microCMOS Microcontrollers  COP621C/COP622C/COP640C/COP641C/COP642C Single-Chip microCMOS Microcontrollers  2-7 COP820CP-X/COP840CP-X Piggyback EPROM Microcontroller  2-27 COP8720C/COP8721C/COP8722C Single-Chip microCMOS Microcontrollers  2-36 COP888CL Single-Chip microCMOS Microcontroller  2-56 COP888CS Single-Chip microCMOS Microcontroller  2-56 COP888CG Single-Chip microCMOS Microcontroller  2-85 COP888CG Single-Chip microCMOS Microcontroller  2-85 COP888CG Single-Chip microCMOS Microcontroller  3-31 COP Brief 2 Easy Logarithms for COP400  3-3 COP Brief 2 Easy Logarithms for COP400  3-3 COP Brief 5 RAM Keep-Alive  3-16 COP Note 1 Analog to Digital Conversion Techniques with COPS Family  Microcontrollers  3-17 COP Note 4 The COP444L Evaluation Device 444L-EVAL  3-49 COP Note 5 Oscillator Characteristics of COPS Microcontroller Family  3-79 AB-3 Current Consumption in NMOS COPS Microcontroller Family  3-88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | COP440/COP441/COP442/COP340/COP341/COP342 Single-Chip N-Channel        |       |

| ROMless Devices         COP401L ROMless N-Channel Microcontroller         1-227           COP401L-X13/COP401L-R13 ROMless N-Channel Microcontrollers         1-241           COP402/COP402M ROMless N-Channel Microcontrollers         1-254           COP404 ROMless N-Channel Microcontroller         1-272           COP404 ROMless CMOS Microcontroller         1-279           COP404LSN-5 ROMless N-Channel Microcontroller         1-296           COP420P/COP444CP/COP444LP Piggyback EEPROM Microcontrollers         1-310           Section 2 COP800 Family         2-3           COP800C         2-3           COP800C COP821C/COP822C/COP840C/COP841C/COP842C/COP620C/COP621C/COP622C/COP622C/COP640C/COP641C/COP642C Single-Chip microCMOS Microcontroller         2-7           COP820CP-X/COP840CP-X Piggyback EPROM Microcontroller         2-27           COP820CP-X/COP840CP-X Piggyback EPROM Microcontroller         2-36           COP838CL Single-Chip microCMOS Microcontroller         2-36           COP888CL Single-Chip microCMOS Microcontroller         2-36           COP888CG Single-Chip microCMOS Microcontroller         2-85           COP888CG Single-Chip microCMOS Microcontroller         2-116           Section 3 COPS Applications         3-3           COP Brief 2 Easy Logarithms for COP400         3-3           COP Brief 6 RAM Keep-Alive         3-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Microcontrollers                                                       | 1-181 |

| COP401L ROMIess N-Channel Microcontroller         1-227           COP401L-X13/COP401L-R13 ROMIess N-Channel Microcontrollers         1-241           COP402/COP402M ROMIess N-Channel Microcontrollers         1-254           COP404 ROMIess N-Channel Microcontroller         1-272           COP404C ROMIess CMOS Microcontroller         1-279           COP404LSN-5 ROMIess N-Channel Microcontroller         1-296           COP420P/COP444CP/COP444LP Piggyback EEPROM Microcontrollers         1-310           Section 2 COP800 Family           COP820C/COP821C/COP822C/COP840C/COP841C/COP842C/COP620C/COP821C/COP822C/COP640C/COP641C/COP642C Single-Chip microCMOS           Microcontrollers         2-7           COP820CP-X/COP840CP-X Piggyback EPROM Microcontroller         2-36           COP8721C/COP8721C/COP8722C Single-Chip microCMOS Microcontroller         2-36           COP888CL Single-Chip microCMOS Microcontroller         2-36           COP888CF Single-Chip microCMOS Microcontroller         2-36           COP888CG Single-Chip microCMOS Microcontroller         2-85           COP888CG Single-Chip microCMOS Microcontroller         2-85           COP888CG Single-Chip microCMOS Microcontroller         3-3           COP Brief 2 Easy Logarithms for COP400         3-3           COP Brief 5 Software and Opcode Differences in the COP444L Instruction Set         3-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | COP444L/COP445L/COP344L/COP345L Single-Chip N-Channel Microcontrollers | 1-204 |

| COP401L-X13/COP401L-R13 ROMIess N-Channel Microcontrollers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ROMIess Devices                                                        |       |

| COP402/COP402M ROMless N-Channel Microcontrollers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | COP401L ROMIess N-Channel Microcontroller                              | 1-227 |

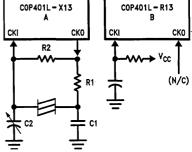

| COP404 ROMless N-Channel Microcontroller         1-272           COP404C ROMless CMOS Microcontroller         1-279           COP404LSN-5 ROMless N-Channel Microcontroller         1-296           COP420P/COP444CP/COP444LP Piggyback EEPROM Microcontrollers         1-310           Section 2 COP800 Family         2-3           COP820C/COP821C/COP842C/COP840C/COP841C/COP842C/COP620C/COP621C/COP622C/COP640C/COP641C/COP642C Single-Chip microCMOS         2-7           COP820CP-X/COP840CP-X Piggyback EPROM Microcontroller         2-7           COP820CP-X/COP8721C/COP8722C Single-Chip microCMOS Microcontrollers         2-36           COP888CL Single-Chip microCMOS Microcontroller         2-56           COP888CF Single-Chip microCMOS Microcontroller         2-85           COP888CG Single-Chip microCMOS Microcontroller         2-16           Section 3 COPS Applications         3-3           COP Brief 2 Easy Logarithms for COP400         3-3           COP Brief 4 L-Bus Considerations         3-14           COP Brief 5 Software and Opcode Differences in the COP444L Instruction Set         3-15           COP Note 1 Analog to Digital Conversion Techniques with COPS Family Microcontrollers         3-16           COP Note 4 The COP444L Evaluation Device 444L-EVAL         3-49           COP Note 5 Oscillator Characteristics of COPS Microcontrollers         3-54           COP Note 6 Triac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | COP401L-X13/COP401L-R13 ROMless N-Channel Microcontrollers             | 1-241 |

| COP404C ROMIess CMOS Microcontroller         1-279           COP404LSN-5 ROMIess N-Channel Microcontroller         1-296           COP420P/COP444CP/COP444LP Piggyback EEPROM Microcontrollers         1-310           Section 2 COP800 Family         2-3           COP820C/COP821C/COP822C/COP840C/COP841C/COP842C/COP620C/<br>COP621C/COP622C/COP640C/COP641C/COP642C Single-Chip microCMOS         2-7           COP820CP-X/COP840CP-X Piggyback EPROM Microcontroller         2-7           COP820CP-X/COP8721C/COP8722C Single-Chip microCMOS Microcontrollers         2-36           COP888CL Single-Chip microCMOS Microcontroller         2-56           COP888CF Single-Chip microCMOS Microcontroller         2-85           COP888CG Single-Chip microCMOS Microcontroller         2-116           Section 3 COPS Applications         3-3           COP Brief 2 Easy Logarithms for COP400         3-3           COP Brief 3 Software and Opcode Differences in the COP444L Instruction Set         3-15           COP Brief 6 RAM Keep-Alive         3-16           COP Note 1 Analog to Digital Conversion Techniques with COPS Family         3-17           COP Note 5 Oscillator Characteristics of COPS Microcontrollers         3-49           COP Note 6 Triac Control Using the COP400 Microcontroller Family         3-79           AB-3 Current Consumption in NMOS COPS Microcontrollers         3-88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | COP402/COP402M ROMIess N-Channel Microcontrollers                      | 1-254 |

| COP404LSN-5 ROMless N-Channel Microcontroller 1-296 COP420P/COP444CP/COP444LP Piggyback EEPROM Microcontrollers 1-310  Section 2 COP800 Family  COP800C 2-3 COP820C/COP821C/COP822C/COP840C/COP841C/COP842C/COP620C/ COP621C/COP622C/COP640C/COP641C/COP642C Single-Chip microCMOS Microcontrollers 2-7 COP820CP-X/COP840CP-X Piggyback EPROM Microcontroller 2-27 COP8720C/COP8721C/COP8722C Single-Chip microCMOS Microcontrollers 2-36 COP888CL Single-Chip microCMOS Microcontroller 2-56 COP888CC Single-Chip microCMOS Microcontroller 2-85 COP888CG Single-Chip microCMOS Microcontroller 2-116  Section 3 COPS Applications COP Brief 2 Easy Logarithms for COP400 3-3 COP Brief 4 L-Bus Considerations 3-14 COP Brief 5 Software and Opcode Differences in the COP444L Instruction Set 3-15 COP Brief 6 RAM Keep-Alive 3-16 COP Note 1 Analog to Digital Conversion Techniques with COPS Family Microcontrollers 3-17 COP Note 4 The COP444L Evaluation Device 444L-EVAL 3-49 COP Note 5 Oscillator Characteristics of COPS Microcontroller Family 3-71 COP Note 7 Testing of COPS Chips 3-79 AB-3 Current Consumption in NMOS COPS Microcontrollers 3-88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | COP404 ROMless N-Channel Microcontroller                               | 1-272 |

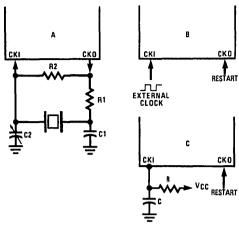

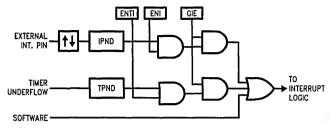

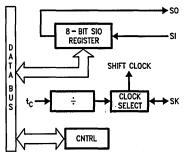

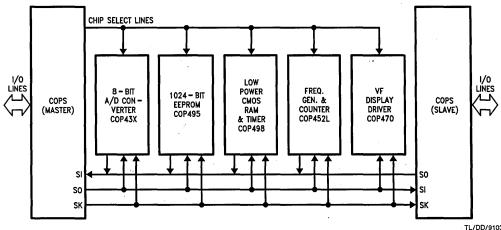

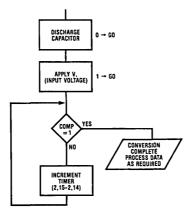

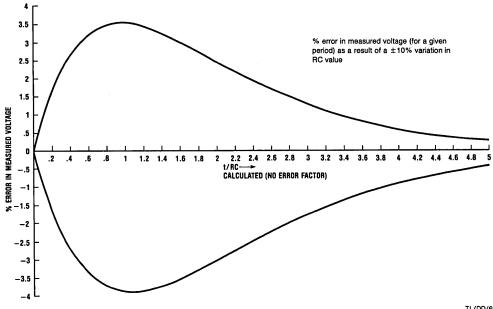

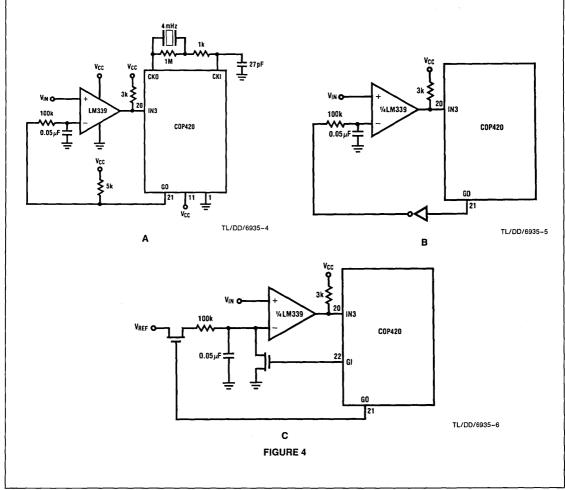

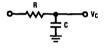

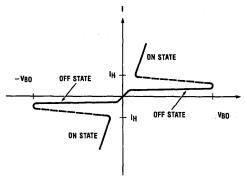

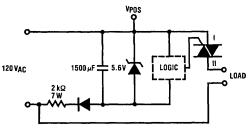

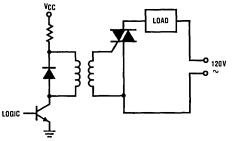

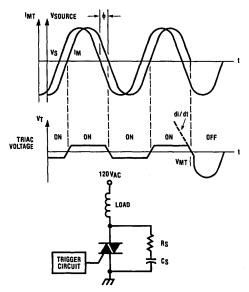

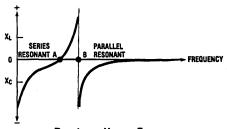

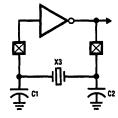

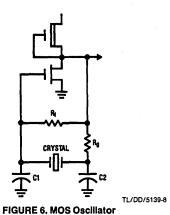

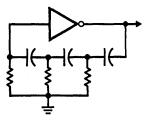

| COP420P/COP444CP/COP444LP Piggyback EEPROM Microcontrollers 1-310  Section 2 COP800 Family  COP800C 2-3  COP820C/COP821C/COP822C/COP840C/COP841C/COP842C/COP620C/ COP621C/COP622C/COP640C/COP641C/COP642C Single-Chip microCMOS  Microcontrollers 2-7  COP820CP-X/COP840CP-X Piggyback EPROM Microcontroller 2-27  COP8720C/COP8721C/COP8722C Single-Chip microCMOS Microcontrollers 2-36  COP888CL Single-Chip microCMOS Microcontroller 2-56  COP888CF Single-Chip microCMOS Microcontroller 2-85  COP888CG Single-Chip microCMOS Microcontroller 2-85  COP888CG Single-Chip microCMOS Microcontroller 2-116  Section 3 COPS Applications  COP Brief 2 Easy Logarithms for COP400 3-3  COP Brief 4 L-Bus Considerations 3-14  COP Brief 5 Software and Opcode Differences in the COP444L Instruction Set 3-15  COP Brief 6 RAM Keep-Alive 3-16  COP Note 1 Analog to Digital Conversion Techniques with COPS Family  Microcontrollers 3-17  COP Note 4 The COP444L Evaluation Device 444L-EVAL 3-49  COP Note 5 Oscillator Characteristics of COPS Microcontrollers 3-54  COP Note 6 Triac Control Using the COP400 Microcontroller Family 3-71  COP Note 7 Testing of COPS Chips 3-79  AB-3 Current Consumption in NMOS COPS Microcontrollers 3-88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | COP404C ROMIess CMOS Microcontroller                                   | 1-279 |