# Programmable Logic Design Guide

2 National Semiconductor Corporation

Literature Order Number 320100-001

# A Corporate Dedication to Quality and Reliability

National Semiconductor is an industry leader in the manufacture of high quality, high reliability integrated circuits. We have been the leading proponent of driving down IC defects and extending product lifetimes. From raw material through product design, manufacturing and shipping, our quality and reliability is second to none.

We are proud of our success . . . it sets a standard for others to achieve. Yet, our quest for perfection is ongoing so that you, our customer, can continue to rely on National Semiconductor Corporation to produce high quality products for your design systems.

1. Shore

Charles E. Sporck President, Chief Executive Officer National Semiconductor Corporation

i

# Wir fühlen uns zu Qualität und Zuverlässigkeit verpflichtet

National Semiconductor Corporation ist führend bei der Harstellung von integrierten Schaltungen hoher Qualität und hoher Zuverlässigkeit. National Semiconductor war schon immer Vorreiter, wenn es galt, die Zahl von IC Ausfällen zu verringern und die Lebensdauern von Produkten zu verbessern. Vom Rohmaterial Über Entwurf und Herstellung bis zur Auslieferung die Qualität und die Zuverlässigkeit der Produkte von National Semiconductor sind unübertroffen.

Wir sind stolz auf unseren Erfolg, der Standards setzt, die für andere erstrebenswert sind. Auch ihre Ansprüche steigen ständig, Sie als unser Kunde können sich auch weiterhin auf National Semiconductor verlassen.

### La Qualité et La Fiabilité:

Une Vocation Commune Chez National Semiconductor Corporation

National Semiconductor Corporation c'est l'un des leaders industriels qui fabrique des circuits intégrés d'une très grande qualité et d'une fiabilité exceptionelle. National a été le premier à vouloir faire chuter le nombre de circuits intégrés defectueux et a augmenter la durée de vie des produits. Depuis les matières premières, en passant par la conception du produit sa fabrication et son expédition, partout la qualité et la fiabilité chez National sont sans équivalents.

Nous sommes fiers de notre succès et le standard ainsi défini devrait devenir l'objectif à atteindre par les autres sociétés. Et nous continuons à vouloir faire progresser notre recherche de la perfection; il en résulte que vous, qui êtes notre client, pouvez toujours faire confiance à National Semiconductor Corporation, en produisànt des systèmes d'une très grande qualité standard.

## Un Impegno Societario di Qualità e Affidabilità

National Semiconductor Corporation è un'industria al vertice nella costruzione di circuiti integrati di altà qualità ed affidabilità. National è stata il principale promotore per l'abbattimento della difettosità dei circuiti integrati e per l'allungamento della vita dei prodotti. Dal materiale grezzo attraverso tutte le fasi di progettazione, costruzione e spedizione, la qualità e affidabilità National non è seconda a nessuno.

Noi siamo orgogliosi del nostro successo che fissa per gli altri un traguardo da raggiungere. Il nostro desiderio di perfezione è d'altra parte illimitato e pertanto tu, nostro cliente, puoi continuare ad affidarti a National Semiconductor Corporation per la produzione dei tuoi sistemi con elevati livelli di gualità.

Charlie ponk

Charles E. Sporck President, Chief Executive Officer National Semiconductor Corporation

# Programmable Logic Design Guide

Bipolar Memory National Semiconductor Corporation Santa Clara, California

#### TRADEMARKS

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

| Abuseable™             | DPVMTM                      | MSTTM                      | SPIRE™                  |

|------------------------|-----------------------------|----------------------------|-------------------------|

| Anadig™                | <b>ELSTAR™</b>              | National®                  | STAR™                   |

| ANS-R-TRAN™            | E-Z-LINK™                   | NAX 800TM                  | Starlink™               |

| Auto-Chem Deflasher™   | GENIXTM                     | Nitride Plus <sup>TM</sup> | STARPLEXTM              |

| BI-FETTM               | HEX 3000TM                  | Nitride Plus Oxide™        | STARPLEX IITM           |

| BI-FET II™             | INFOCHEXTM                  | NMLTM                      | SuperChip™              |

| BI-LINE™               | Integral ISETM              | NOBUSTM                    | SYS32TM                 |

| BIPLAN™                | Intelisplay™                | NSC800™                    | TAPE-PAK™               |

| BLC™                   | ISETM                       | NSX-16™                    | TDSTM                   |

| BLXTM                  | ISE/06™                     | NS-XC-16™                  | TeleGate™               |

| Brite-Lite™            | ISE/08™                     | NURAM™                     | The National Anthem®    |

| BTL™                   | ISE/16™                     | OXISS™                     | Time Chek <sup>TM</sup> |

| CIMTM                  | ISE32™                      | Perfect Watch™             | TLCTM                   |

| CIMBUS™                | Macrobus™                   | Pharmar Chek™              | Trapezoidal™            |

| Clock → Chek™          | Macrocomponent <sup>™</sup> | PLAN™                      | TRI-CODE™               |

| COMBOTM                | Meat-Chek™                  | Polycraft™                 | TRI-POLY <sup>TM</sup>  |

| COPS™ microcontrollers | Microbus™ data bus          | POSitalker <sup>™</sup>    | TRI-SAFE™               |

| DATACHECKER®           | (adjective)                 | QUAD3000TM                 | TRI-STATE®              |

| DENSPAKTM              | MICRO-DACTM                 | RATM                       | XMOS™                   |

| DIBTM                  | µtalker™                    | RTX16™                     | XPUTM                   |

| Digitalker®            | Microtalker™                | Script-ChekTM              | Z STAR™                 |

| DISCERNTM              | MICROWIRE™                  | Shelf-Chek™                | 883B/RETS™              |

| DISTILL™               | MICROWIRE/PLUS™             | SERIES/800TM               | 883S/RETS™              |

| DNR™                   | MOLETM                      | Series 32000™              |                         |

|                        |                             |                            |                         |

PAL® is a registered trademark of Monolithic Memories, Inc.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive, P.O. Box 58090, Santa Clara, California 95052-8090 (408) 721-5000 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

# Preface

### The CLASS<sup>™</sup> Revolution

The nature of logic design is changing and National Semiconductor is leading this change into software-based logic and systems design through the use of structured programmable logic arrays. We welcome you to join us in the CLASS revolution. CLASS stands for Complete Logic And Software Solutions, and it exemplifies National's commitment to the design, development and support of programmable logic devices, and to the software-based design tools that can make the logic and system designer's task easier.

# **Table of Contents**

# 1.0 Introduction

2.0

3.0

| 1.1   | Purpose of this Design Guide                                 |

|-------|--------------------------------------------------------------|

| 1.2   | Overview of Programmable Logic1                              |

| 1.3   | National Semiconductor, The Leader                           |

| Prog  | cammable Logic Basics                                        |

| 2.1   | What is Programmable Logic                                   |

| 2.2   | User Benefits of Programmable Logic 4                        |

|       | Reduced Board Space                                          |

|       | Fast Systems Design                                          |

|       | Design Flexibility                                           |

|       | Multi-level Logic Reduction                                  |

|       | Cost Reduction                                               |

|       | Example to Illustrate Lower Component Costs                  |

|       | Example of Cost Reduction Through Reliability Improvements 8 |

|       | Small Inventory                                              |

| 2.3   | Elements of Programmable Logic 10                            |

|       | The PROM                                                     |

|       | The FPLA                                                     |

|       | The PAL (Programmable Array Logic) Device                    |

|       | Comparison                                                   |

| 2.4   | Programmable Logic Versus Other LSI, Semicustom and Custom   |

|       | Alternatives                                                 |

|       | Standardized LSI                                             |

|       | Full Custom ICs                                              |

|       | Gate Arrays                                                  |

| Boole | ean Logic Review                                             |

| 3.1   | Basic Operators and Theorems                                 |

| 3.2   | Derivation of a Boolean Expression                           |

| 3.3 | Minimization                | 24 |

|-----|-----------------------------|----|

| 3.4 | K-map Method                | 25 |

| 3.5 | Sequential Circuit Elements | 31 |

| 3.6 | State Machine Fundamentals  | 34 |

# viii Programmable Logic Design Guide

| 4.0 | The I   | Programmable Logic Family                                   |

|-----|---------|-------------------------------------------------------------|

|     | 4.1     | Basic Groups                                                |

|     | 4.2     | The PAL Family                                              |

|     |         | PAL Devices for Every Task                                  |

|     |         | Gates                                                       |

|     |         | Register Options With Feedback                              |

|     |         | Programmable I/O                                            |

|     |         | PAL Device — Speed/Power Groups                             |

|     | 1.0     | PAL Device Logic Symbols                                    |

|     | 4.3     | The Prom Family                                             |

|     | 4.4     | Logic Diagrams                                              |

| 5.0 | How     | to Design With Programmable Logic                           |

|     | 5.1     | Problem Definition                                          |

|     | 5.2     | Device Selection                                            |

|     | 5.3     | Writing Logic Equations                                     |

|     | 5.4     | Programming the Device                                      |

|     | 5.5     | Testing the Device                                          |

|     | 5.6     | Programmer Vendor List                                      |

|     | 5.7     | Examples                                                    |

|     |         | Example 1: Replace Existing Logic                           |

|     |         | Example 2: Design a Multiplexer                             |

|     |         | Example 3: Design a 3-bit Counter 100                       |

| '   |         | Example 4: Design a Video-Telephone Sync Pulse Detector 102 |

| 6.0 | Softw   | vare Support                                                |

|     | 6.1     | Advantages of Software-Based Programmable Logic Design 107  |

|     | 6.2     | Programmable Logic Analysis by National (PLAN) 108          |

|     |         | Boolean Entry                                               |

|     |         | File Editing and Documentation 110                          |

|     | ÷       | Programming and Testing 110                                 |

|     | 6.3     | Other Software                                              |

|     |         | CUPL                                                        |

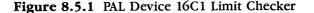

|     |         | PALASM                                                      |

|     | <i></i> | ABEL                                                        |

|     | 6.4     | Software for Testing Programmable Logic                     |

|     | 6.5     | Software Vendor List                                        |

| 7.0 | Testi   | ng and Reliability                                          |

|     | 7.1     | National Factory Testing                                    |

|     | 7.2     | Logic Verifications                                         |

|     | 7.3     | Customer's Responsibilities                                 |

|     | 7.4     | Reliability Data                                            |

|     | /       |                                                             |

|     | 7.5     | PAL Device Functional Testing                               |

# Table of Contents ix

|        |       | Combinational and Sequential Circuits                    |

|--------|-------|----------------------------------------------------------|

|        |       | Description of PAL (Programmable Array Logic) Device 128 |

|        |       | PAL Device Design Procedures 128                         |

|        |       | Description of Functional Table                          |

|        |       | How to Generate Test Vectors and the Function Table      |

|        |       | From Logic Equations                                     |

|        | 7.6   | Example of Testing                                       |

|        |       | Example 1: Combinational PAL12H6 136                     |

|        |       | Description                                              |

|        |       | Example 2: Sequential PAL16R4 143                        |

|        |       | Description                                              |

|        |       |                                                          |

| 8.0    | Appli | cations                                                  |

|        | 8.1   | Basic Gates                                              |

|        | 8.2   | Basic Clocked Flip-Flops 162                             |

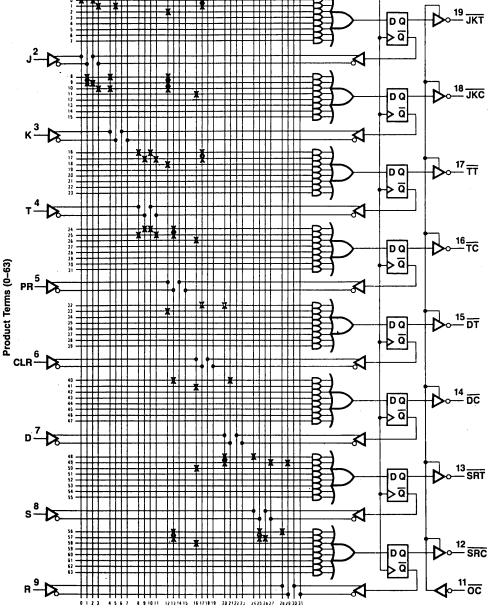

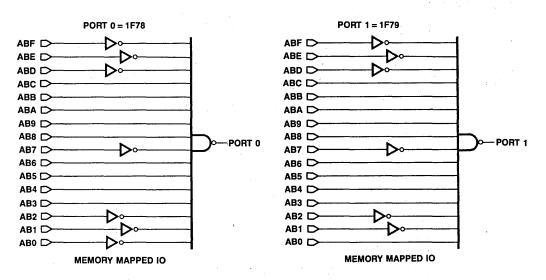

|        | 8.3   | Memory-Mapped I/O (Address Decoder)                      |

|        |       | Functional Description                                   |

|        | 8.4   | Hexadecimal Decoder/Lamp Driver                          |

|        |       | Functional Description                                   |

|        |       | General Description                                      |

|        |       | PAL Device Implementation                                |

| · .    | 8.5   | Between Limits Comparator/Logic 178                      |

|        | 8.6   | Quadruple 3-Line/1-Line Data Selector Multiplexer        |

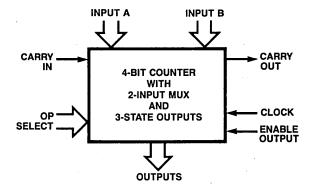

|        | 8.7   | 4-bit Counter with 2-Input Multiplexer                   |

|        | 8.8   | 8-bit Synchronous Counter                                |

|        | 8.9   | 6-bit Shift Register with Three-state Outputs            |

|        | 8.10  | Portion of Random Control Logic for 8086 CPU Board 194   |

|        | 8.11  | DP84312 Dynamic RAM Controller                           |

|        |       | Interface Circuit for the NS32032, CPU 197               |

|        |       | General Description                                      |

|        |       | Features                                                 |

|        |       | Mnemonic Description                                     |

|        |       | Functional Description                                   |

|        | 8.12  | DP84322 Dynamic RAM Controller Interface Circuit         |

| ÷      |       | for the 68000 CPU                                        |

|        |       | General Description                                      |

| ,<br>, |       | Features                                                 |

|        |       | Mnemonic Description                                     |

|        |       | Functional Description                                   |

|        | 8.13  | DP84332 Dynamic RAM Controller Interface Circuit         |

| 1.00   |       | for the 8086 and 8088 CPUs 227                           |

|        |       | General Description                                      |

|        |       | Features                                                 |

|        |       | Mnemonic Description                                     |

|        |       |                                                          |

| ж    | Progra | mmable Logic Design Guide                                                                                                                                                                                                                             |            |

|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

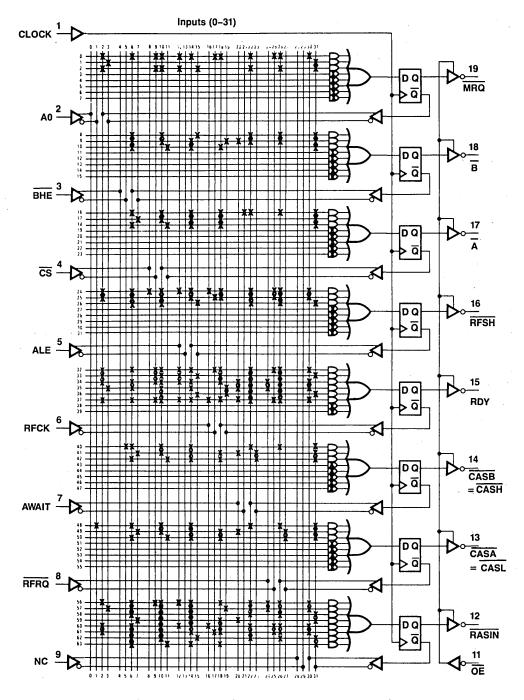

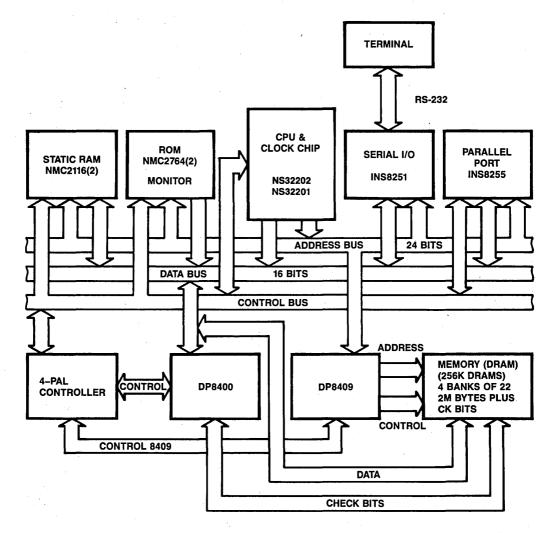

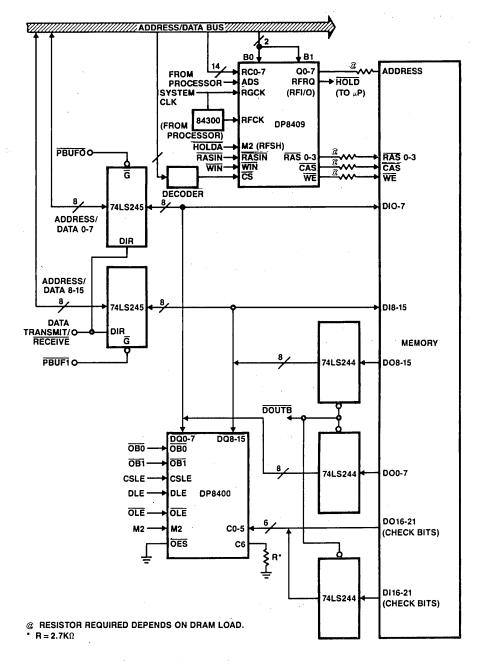

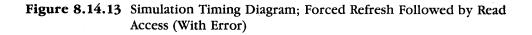

|      | 8.14   | Functional Description<br>System Description<br>Refresh Request Logic<br>A PAL Device Interface Between the National Semiconductor<br>NS32032 Microprocessor, DP8409 Dynamic RAM Controller,<br>and the DP8400 Expandable Error Checker and Corrector | 231<br>233 |

| 9.0  | Natio  | nal Masked Logic (NML)                                                                                                                                                                                                                                |            |

|      | 9.1    | NML Procedure                                                                                                                                                                                                                                         | 269        |

|      | 9.2    | NML Guidelines                                                                                                                                                                                                                                        |            |

| 10.0 | Advar  | ntages of National's Programmable Logic Family                                                                                                                                                                                                        |            |

|      | 10.1   | Technology                                                                                                                                                                                                                                            | 271        |

|      | 10.2   | Broad Product Line                                                                                                                                                                                                                                    | 271        |

| •    | 10.3   | Customer Service and Support                                                                                                                                                                                                                          | 272        |

| 11.0 | Data S | Sheets                                                                                                                                                                                                                                                |            |

|      | 11.1   | PAL Device Data Sheets                                                                                                                                                                                                                                | 273        |

|      |        | Description                                                                                                                                                                                                                                           |            |

|      |        | Features                                                                                                                                                                                                                                              |            |

|      |        | 20-Pin, Standard, Small PAL Devices                                                                                                                                                                                                                   |            |

|      |        | 20-Pin, Standard, Medium PAL Devices                                                                                                                                                                                                                  |            |

|      |        | 20-Pin, Fast, Small PAL Devices                                                                                                                                                                                                                       |            |

|      |        | 20-Pin, Fast, Medium PAL Devices                                                                                                                                                                                                                      |            |

|      |        | 20-Pin, Ultra High-Speed, Medium PAL Devices                                                                                                                                                                                                          |            |

|      | 20-Pin | , Fast, Half-Power, Small PAL Devices                                                                                                                                                                                                                 |            |

|      |        | , Fast, Half-Power, Medium PAL Devices                                                                                                                                                                                                                |            |

|      |        | I, Ultra High-Speed, Half-Power, Medium PAL Devices                                                                                                                                                                                                   |            |

|      |        | , Standard PAL Devices                                                                                                                                                                                                                                |            |

|      |        | , Fast PAL Devices                                                                                                                                                                                                                                    |            |

|      | 11.2   | Programming/Verifying Procedure—20 Pin PAL Devices                                                                                                                                                                                                    |            |

|      | 11.2   | Pre-verification                                                                                                                                                                                                                                      |            |

|      |        | Programming Algorithm                                                                                                                                                                                                                                 |            |

|      |        | Programming the Security Fuses                                                                                                                                                                                                                        |            |

|      | 11.3   | Programming/Verifying Procedure—24 Pin PAL Devices                                                                                                                                                                                                    |            |

|      | 11.5   | Pre-Verification                                                                                                                                                                                                                                      |            |

|      |        | Programming Algorithm                                                                                                                                                                                                                                 |            |

|      |        | Programming the Security Fuses                                                                                                                                                                                                                        |            |

|      | 11 6   |                                                                                                                                                                                                                                                       |            |

|      | 11.4   | Logic PROM Data Sheets                                                                                                                                                                                                                                |            |

|      |        | Descriptions                                                                                                                                                                                                                                          |            |

|      |        | Testability                                                                                                                                                                                                                                           |            |

|      | 11 -   | Reliability                                                                                                                                                                                                                                           |            |

|      | 11.5   | DM54/74S188, DM54/74S288 ( $32 \times 8$ ) 256-bit TTL PROMs                                                                                                                                                                                          |            |

| 1.1  | 11.6   | PL77/87X288 (32 + 8) 256-bit TTL PROM                                                                                                                                                                                                                 |            |

## Table of Contents xi

|      | 11.7       | DM54/74LS471 (256 + 8) 2K-bit TTL PROM               | 311        |

|------|------------|------------------------------------------------------|------------|

|      | 11.8       | DM54/74S473, DM54/74S472, DM54/74S473A, DM54/74S472A |            |

|      |            | DM54/74S472B (512 × 8) 4K-bit TTL PROMS              |            |

|      |            | General Description                                  |            |

|      |            | Features                                             | . 313      |

|      | 11.9       | DM54/74S475, DM54/74S474, DM54/74S475A, DM54/74S474A | 21/        |

|      |            | DM54/74S474B (512 × 8) 4K-bit TTL PROMS              |            |

|      |            | General Description                                  |            |

|      | 11 10      | Features                                             | . 510      |

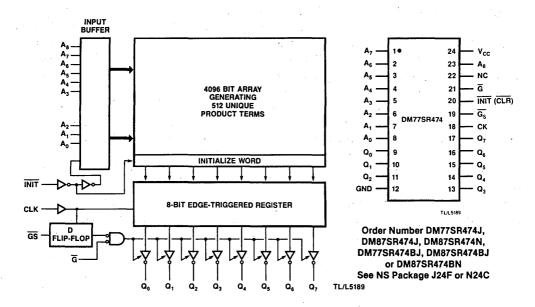

|      | 11.10      | DM77/87SR474, DM77/87SR474B (512 × 8) 4K-bit         | 210        |

|      |            | Registered TTL PROMs                                 | . 319      |

|      |            | Resistered TTL PROMs                                 | 210        |

|      |            | General Description                                  |            |

|      | 11.11      | Features                                             |            |

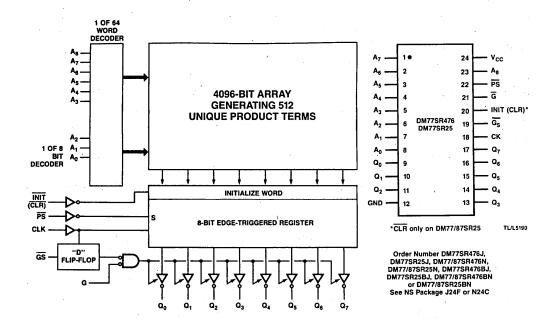

|      | 11.11      | DM77/87SR476, DM77/87SR25, DM77/87SR476B, DM77/87S   |            |

|      |            | (512 × 8) 4K-bit Registered TTL PROMs                |            |

|      |            | Features                                             |            |

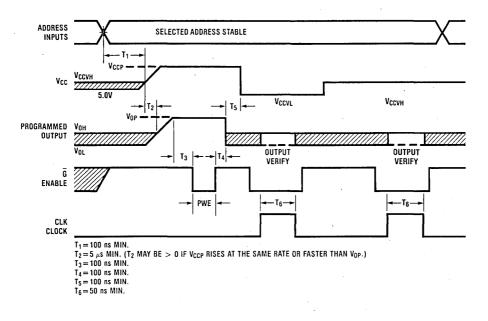

|      | 11.12      | Registered PROM Programming Procedure                |            |

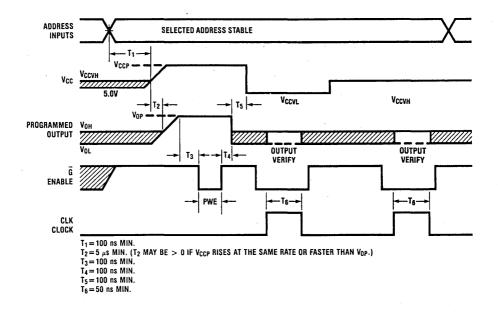

|      | 11.12      | Non-Registered PROM Programming Procedure            |            |

|      | 11.15      | Quality Enhancement Programs                         |            |

| 12.0 |            | age Outlines                                         |            |

| 13.0 |            | inology                                              |            |

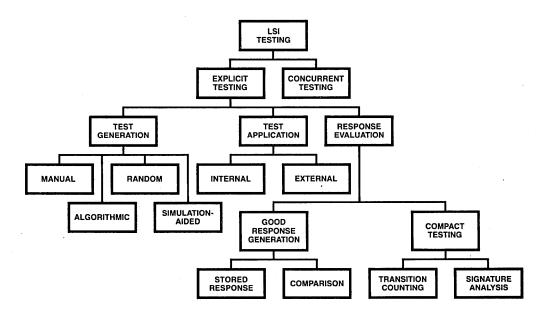

| •    |            | An Overview of LSI Testing Techniques                | 341<br>347 |

| лррс | A.1        | Testing Methods                                      |            |

|      | <b>A.1</b> | Concurrent Testing                                   |            |

|      |            | Explicit Testing                                     |            |

|      | A.2        | Test Generation Techniques                           |            |

|      | 1 1. 24    | NP-Complete Problems                                 |            |

|      |            | Manual Test Generation                               |            |

|      |            | Path Sensitization and the D-Algorithm               |            |

|      |            | Algorithmic Test Generation                          |            |

|      |            | The Thatte-Abraham Technique                         |            |

|      |            | The Abadir-Reghbati Technique                        |            |

|      |            | Simulation-Aided Test Generation                     |            |

|      |            | Binary Decision Diagrams                             | 365        |

|      |            | Random Test Generation                               |            |

|      | A.3        | Response Evaluation Techniques                       | 368        |

|      |            | Good Response Generation                             |            |

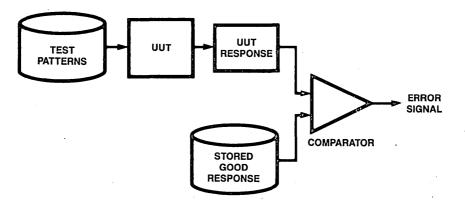

|      |            | Stored Response Testing                              | 368        |

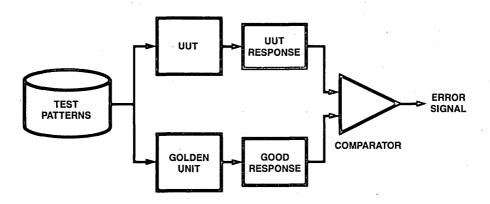

|      |            | Comparison Testing                                   | 370        |

|      |            | Compact Testing                                      |            |

|      |            | Transition Counting                                  |            |

|      |            | Signature Analysis                                   | 373        |

. . .

# List of Illustrations

## Figure No.

# Page No.

| 2.1.1  | Conventional Representation                               | 3  |

|--------|-----------------------------------------------------------|----|

| 2.1.2  | Programmable Logic Representation                         | 4  |

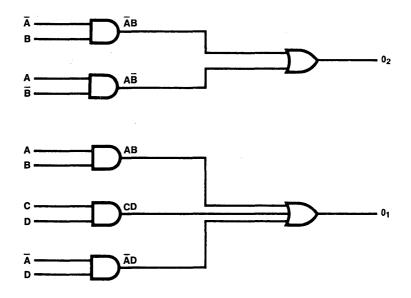

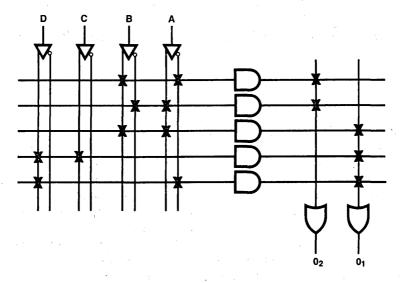

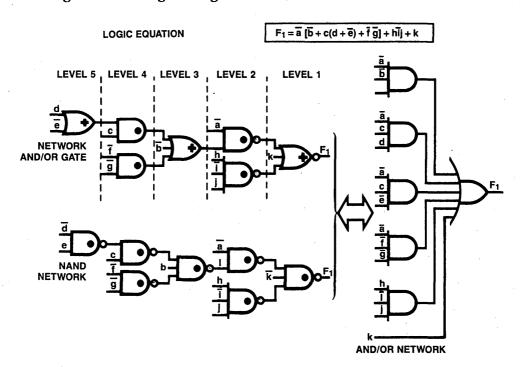

| 2.2.1  | Multilevel Logic Reduction                                | 6  |

| 2.3.1  | Diode OR Matrix                                           | 10 |

| 2.3.2  | $4 \times 4$ Bit PROM                                     | 11 |

| 2.3.3  | PROM Having 16 Words × 4 Bits                             | 12 |

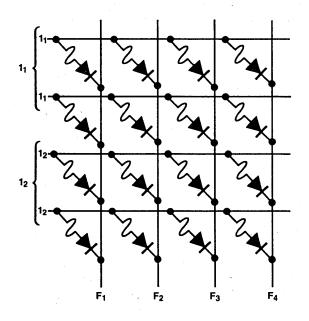

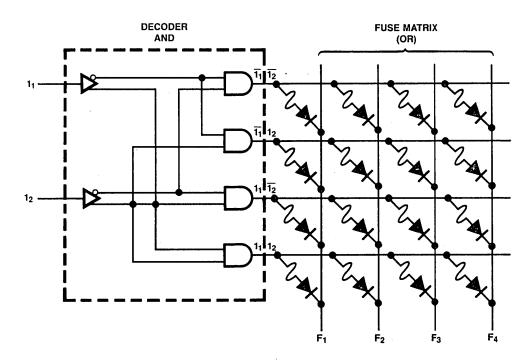

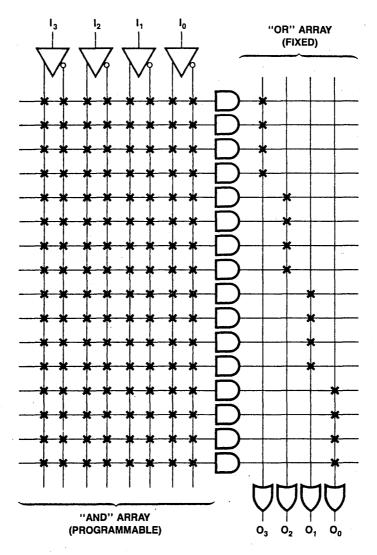

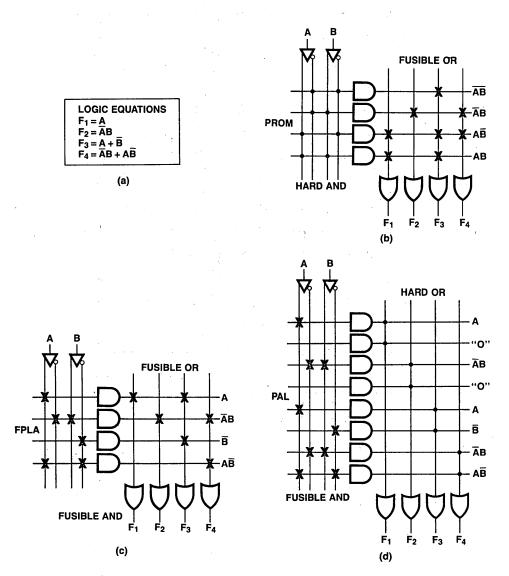

| 2.3.4  | FPLA Having 4 Inputs, 4 Outputs, and 16 Products          | 13 |

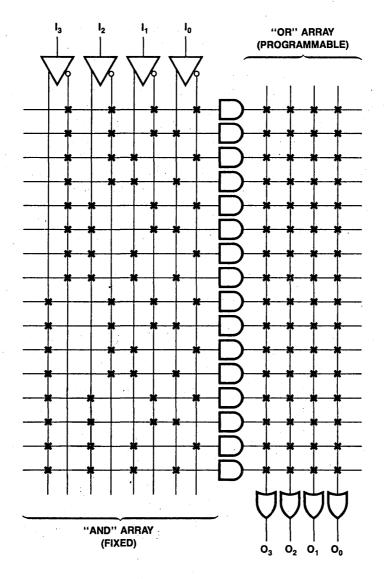

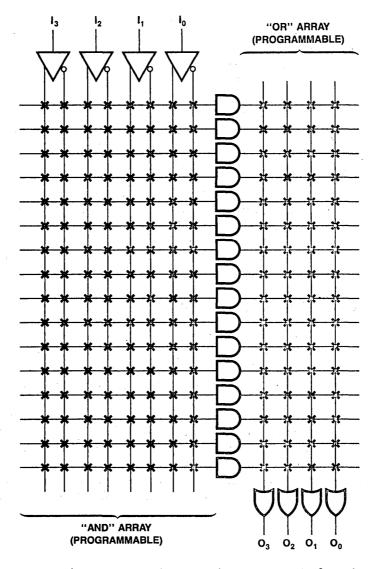

| 2.3.5  | PAL Device Having 4 Inputs, 4 Outputs, and 16 Products    | 15 |

| 2.3.6  | (a) Logic Equation, (b) PROM Solution, (c) FPLA Solution, |    |

|        | (d) PAL Device Solution                                   | 16 |

|        |                                                           |    |

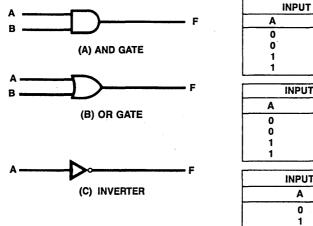

| 3.1.1  | Basic Gates                                               | 19 |

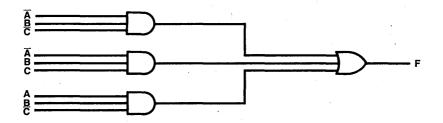

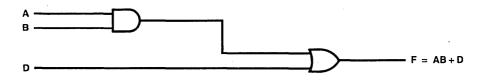

| 3.2.1  | Logic Circuits of Eq. 3.2.1                               | 23 |

| 3.2.2  | Logic Circuits of Eq. 3.2.2                               | 23 |

| 3.2.3  | Simplified Logic Circuits                                 | 24 |

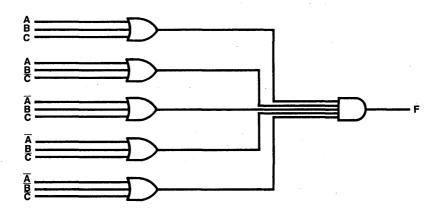

| 3.3.1  | A Random Logic Circuit                                    | 24 |

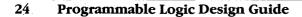

| 3.3.2  | Minimied Logic Circuit                                    | 25 |

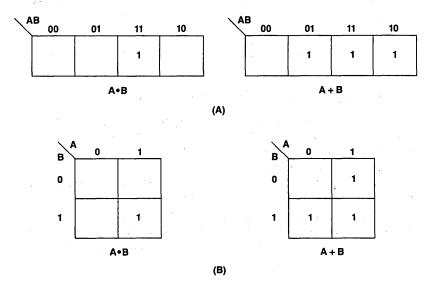

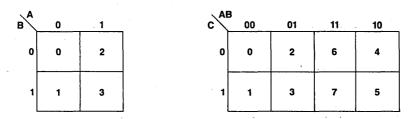

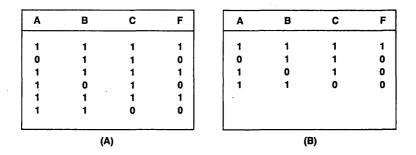

| 3.4.1  | Truth Tables for AND and OR                               | 26 |

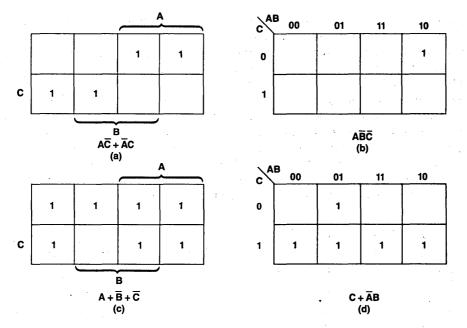

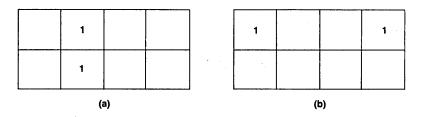

| 3.4.2  | K-maps for AND and OR                                     | 26 |

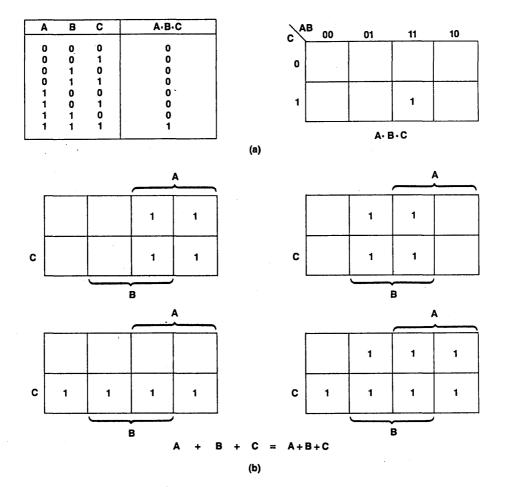

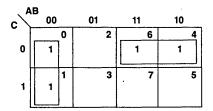

| 3.4.3  | K-maps for 3-Variables AND and OR                         | 27 |

| 3.4.4  | Sample 3-Variable K-maps                                  | 28 |

| 3.4.5  | K-maps for Two and Three Variables                        | 28 |

| 3.4.6  |                                                           |    |

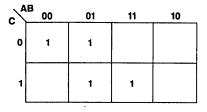

| 3.4.7  | K-map of M (0, 1, 5, 6)                                   |    |

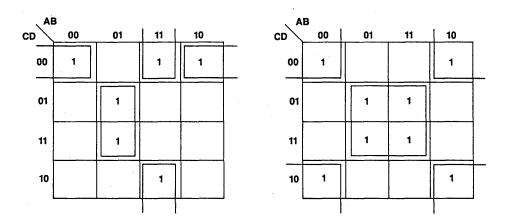

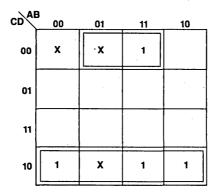

| 3.4.8  | Adjacent Minterms on a K-map                              | 29 |

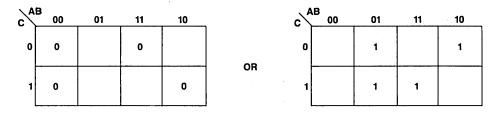

| 3.4.9  | Minimization                                              | 30 |

| 3.4.10 | Minimization                                              | 30 |

| 3.4.11 | Minimization                                              | 31 |

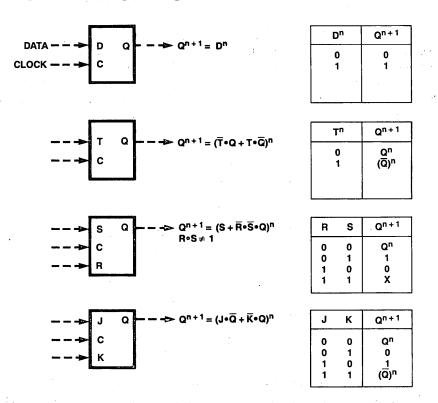

| 3.5.1  | Basic Flip-Flops                                          | 32 |

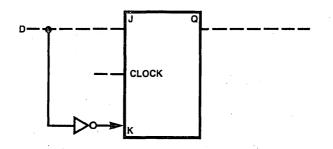

| 3.5.2  |                                                           |    |

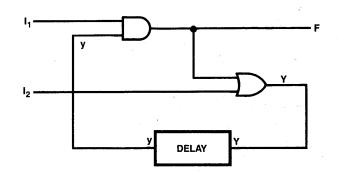

| 3.6.1  |                                                           |    |

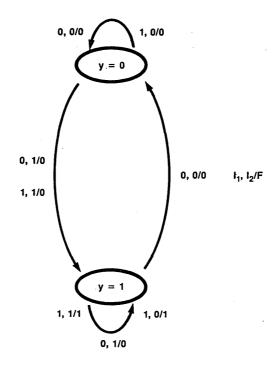

| 3.6.2  | State Diagram                                             |    |

| 3.6.3  | Example of Hazard Circuit                                 | 36 |

# xiv Programmable Logic Design Guide

| 3.6.4  | Example of Unstable Circuit                                  | 36 |

|--------|--------------------------------------------------------------|----|

| 3.6.5  | Example fo Circuit With Unpredictable Output States          | 37 |

|        |                                                              |    |

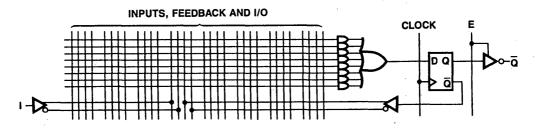

| 4.2.1  | PAL Device Output Register Circuit, Simplified Logic Diagram | 41 |

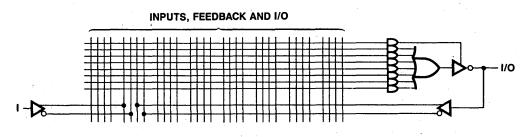

| 4.2.2  | PAL Device Bidirectional Circuit, Logic Diagram              | 42 |

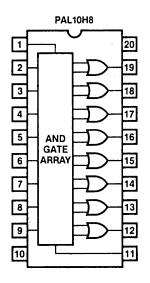

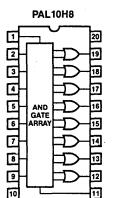

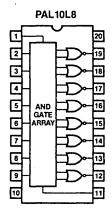

| 4.2.3  | Logic Symbol. DMPAL10H8                                      | 43 |

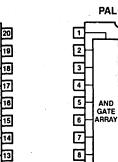

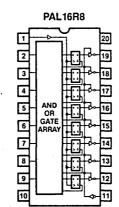

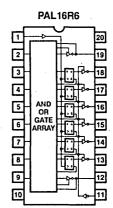

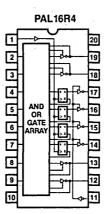

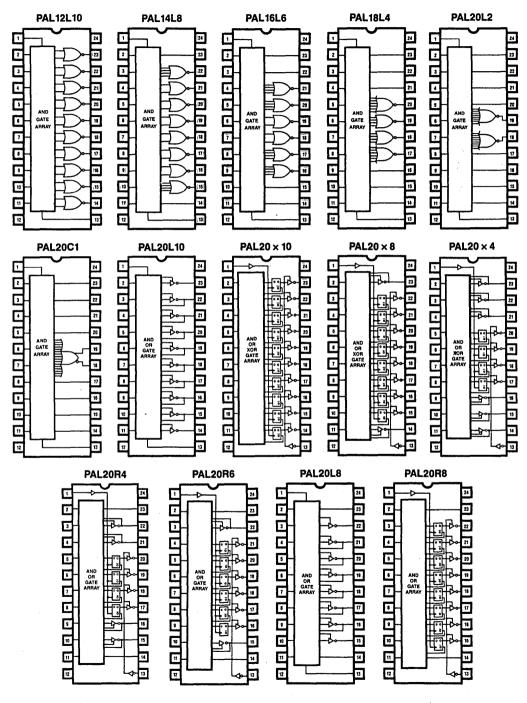

| 4.2.4  | PAL Device Logic Symbols — Series 20                         | 44 |

| 4.2.5  | PAL Device Logic Symbols — Series 24                         | 46 |

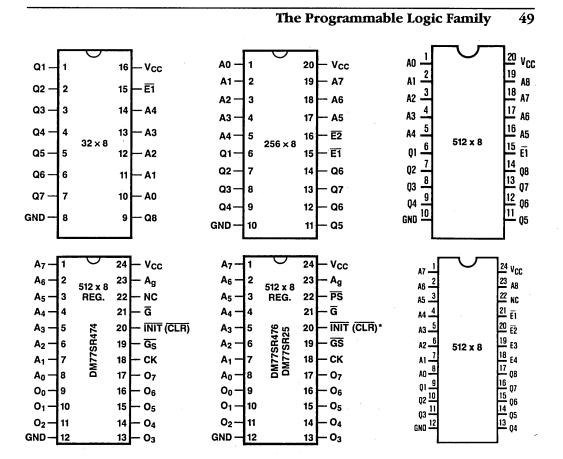

| 4.3.1  | PROM Logic Symbols                                           | 49 |

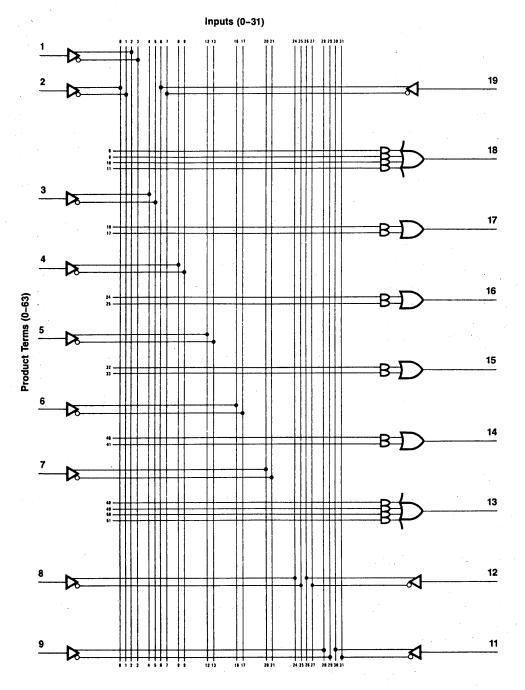

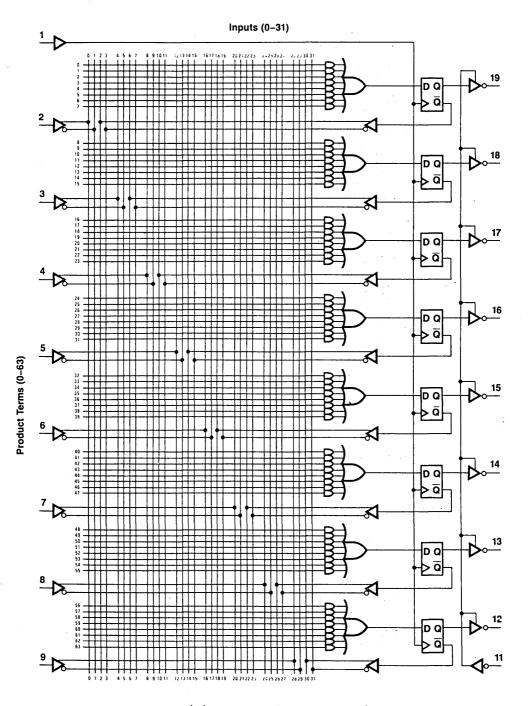

| 4.4.1  | Logic Diagram PAL10H8                                        | 50 |

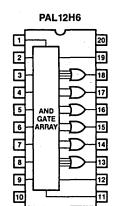

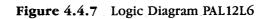

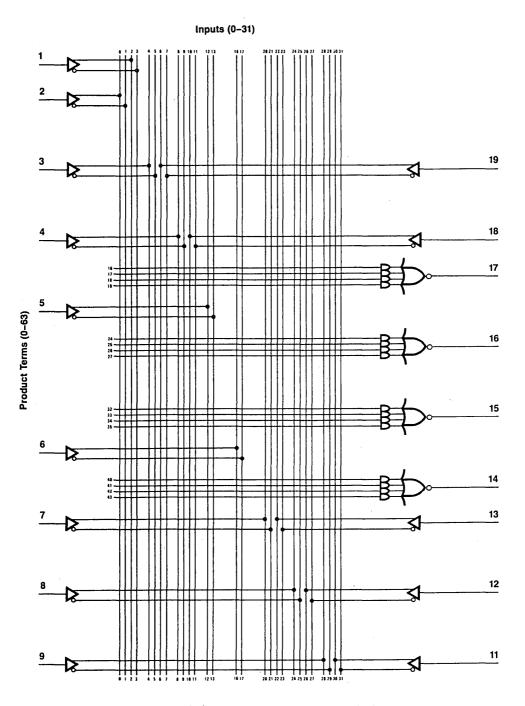

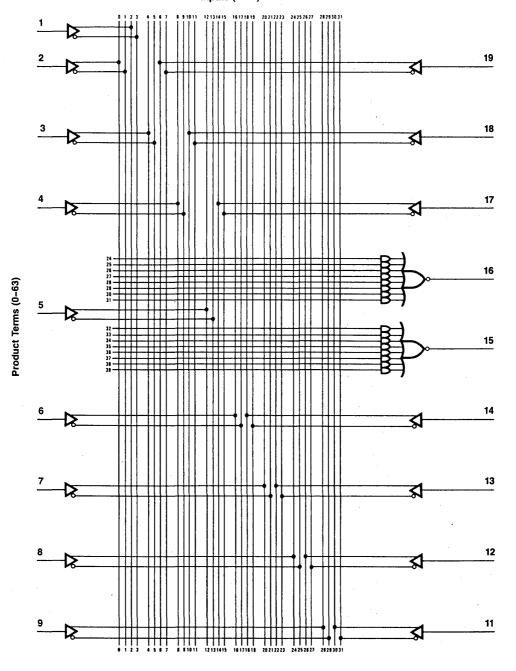

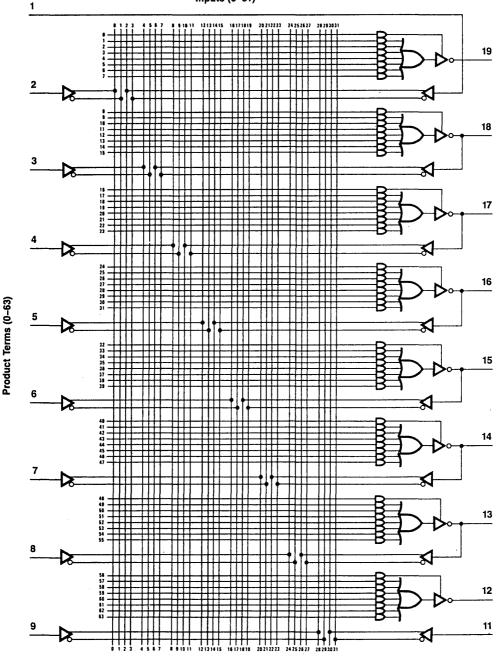

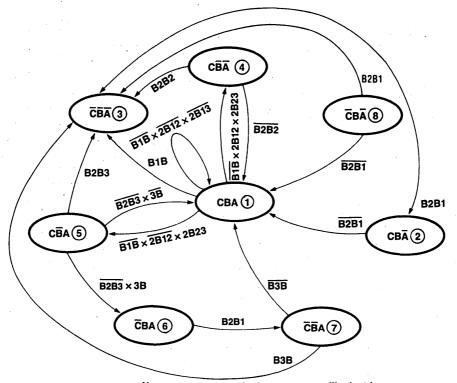

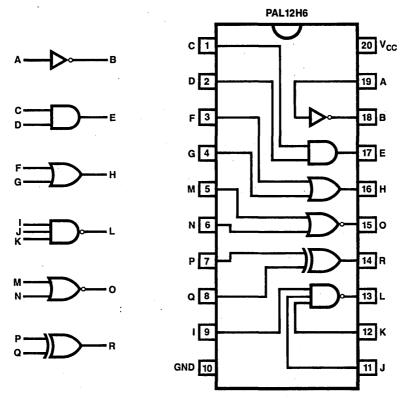

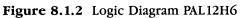

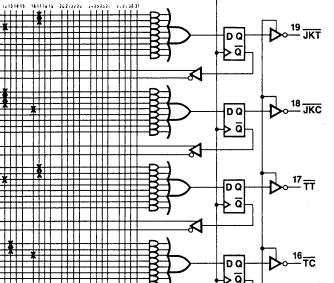

| 4.4.2  | Logic Diagram PAL12H6                                        | 51 |

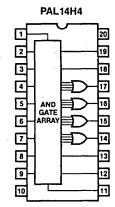

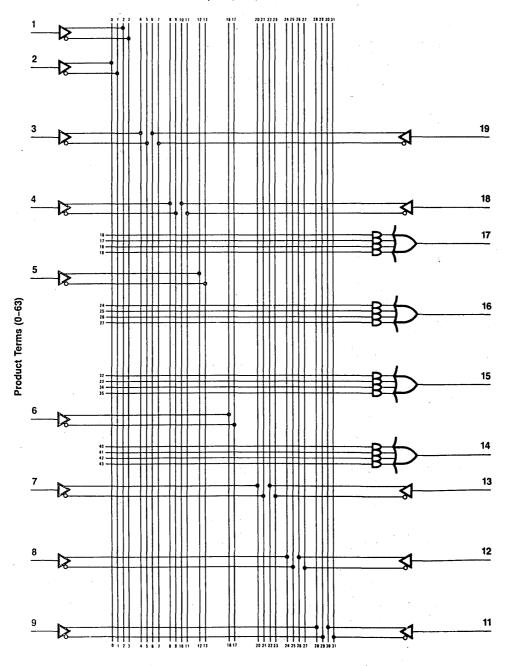

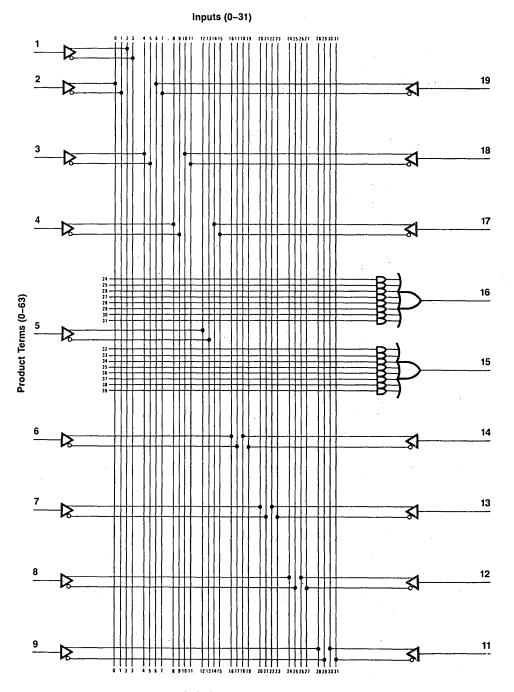

| 4.4.3  | Logic Diagram PAL14H4                                        | 52 |

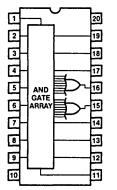

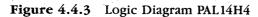

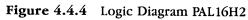

| 4.4.4  | Logic Diagram PAL16H2                                        | 53 |

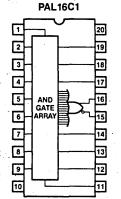

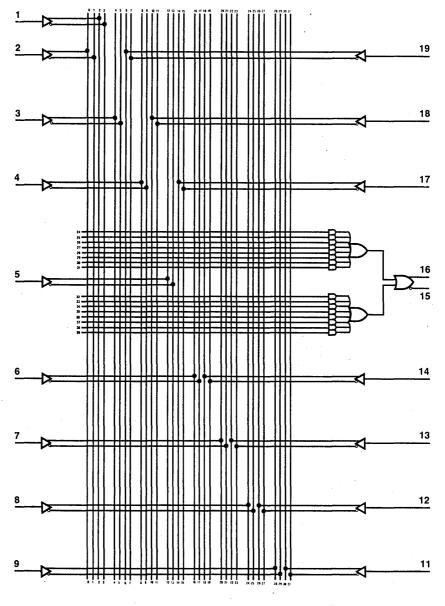

| 4.4.5  | Logic Diagram PAL16C1                                        | 54 |

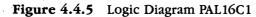

| 4.4.6  | Logic Diagram PAL10L8                                        | 55 |

| 4.4.7  | Logic Diagram PAL12L6                                        | 56 |

| 4.4.8  | Logic Diagram PAL14L4                                        | 57 |

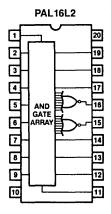

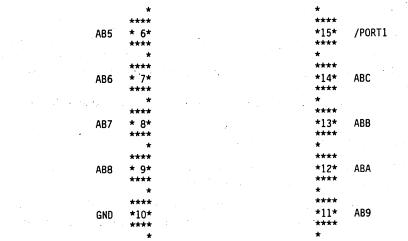

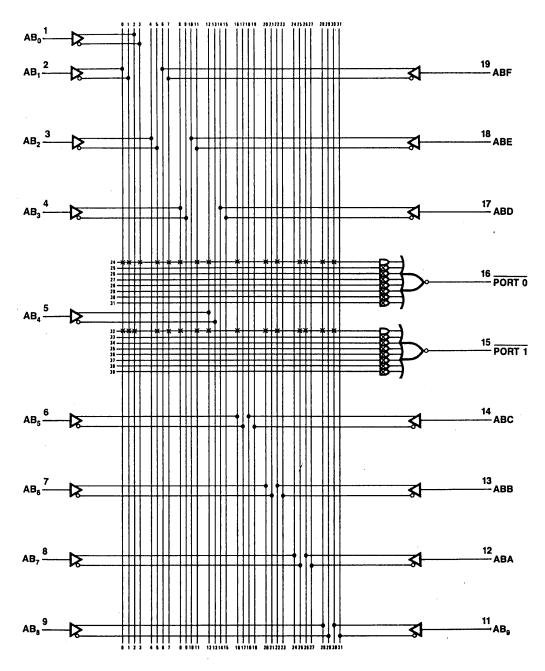

| 4.4.9  | Logic Diagram PAL16L2                                        | 58 |

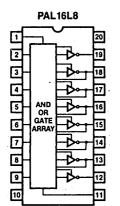

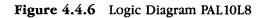

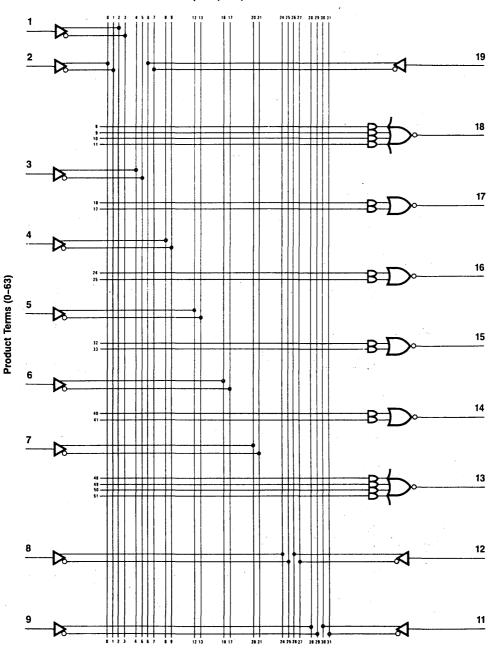

| 4.4.10 | Logic Diagram PAL16L8                                        | 59 |

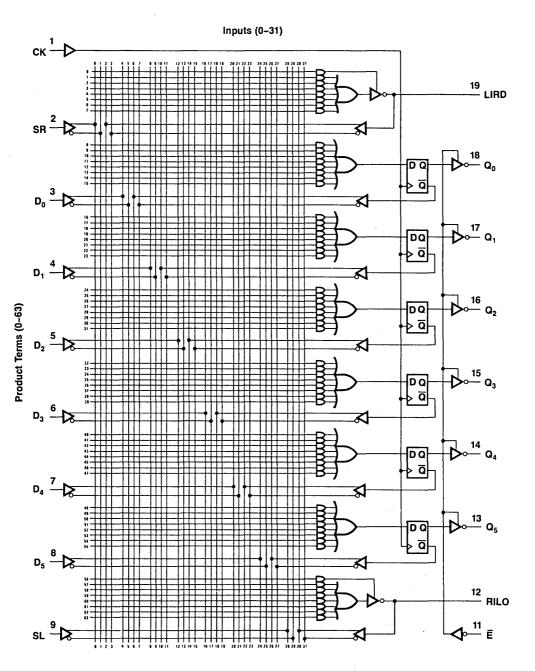

| 4.4.11 | Logic Diagram PAL16R8                                        | 60 |

| 4.4.12 | Logic Diagram PAL16R6                                        | 61 |

| 4.4.13 | Logic Diagram PAL16L4                                        | 62 |

| 4.4.14 | Logic Diagram PAL12L10                                       | 63 |

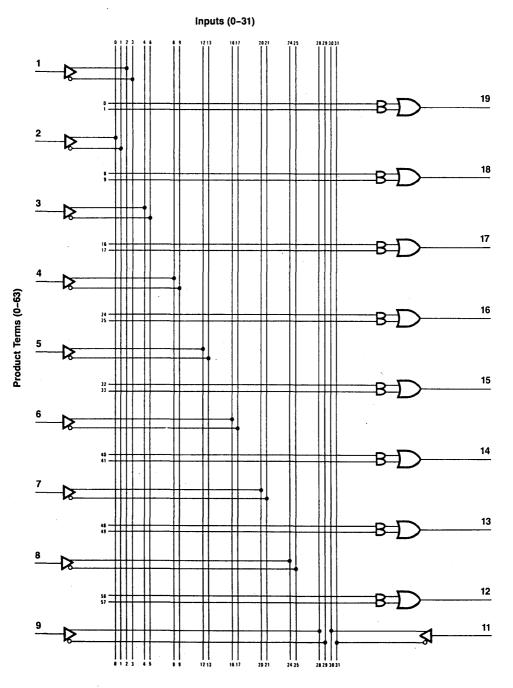

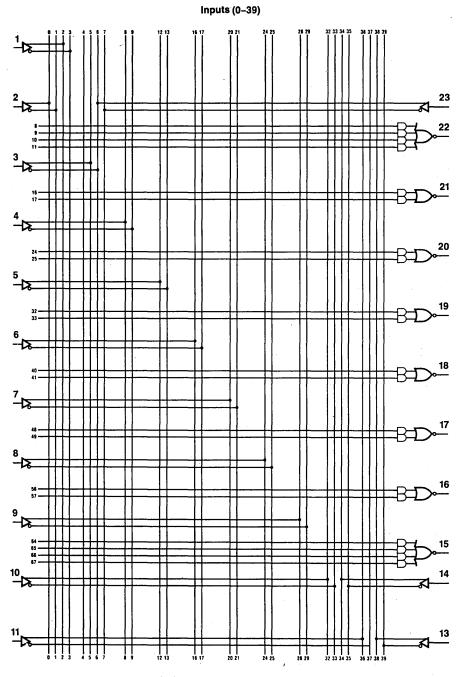

| 4.4.15 | Logic Diagram PAL14L8                                        | 64 |

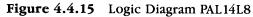

| 4.4.16 | Logic Diagram PAL16L6                                        | 65 |

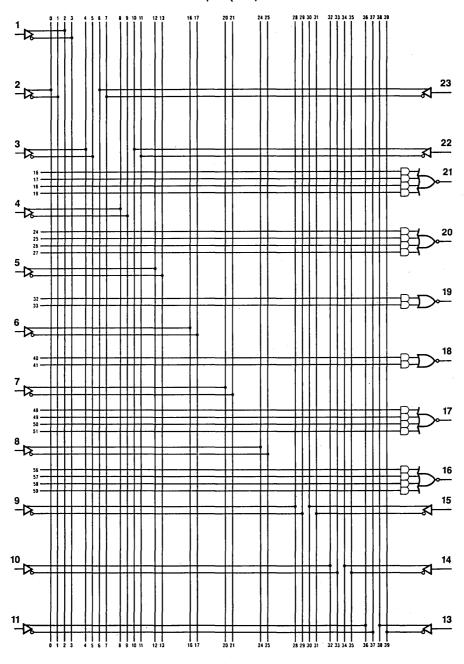

| 4.4.17 | Logic Diagram PAL18L4                                        | 66 |

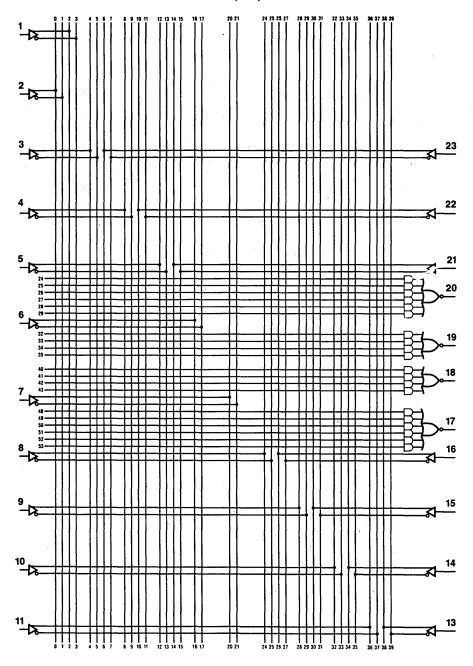

| 4.4.18 | Logic Diagram PAL20L2                                        | 67 |

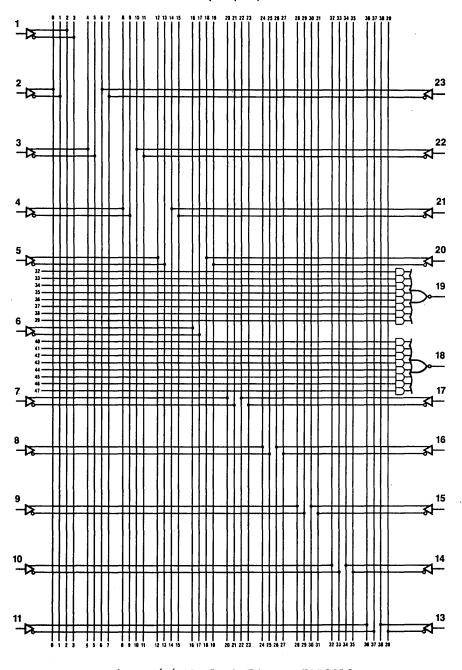

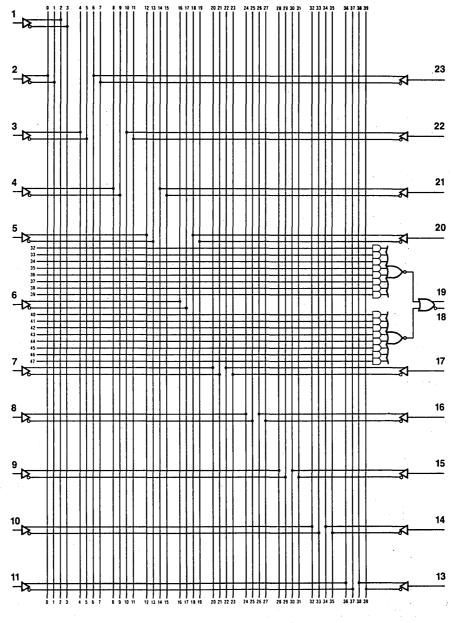

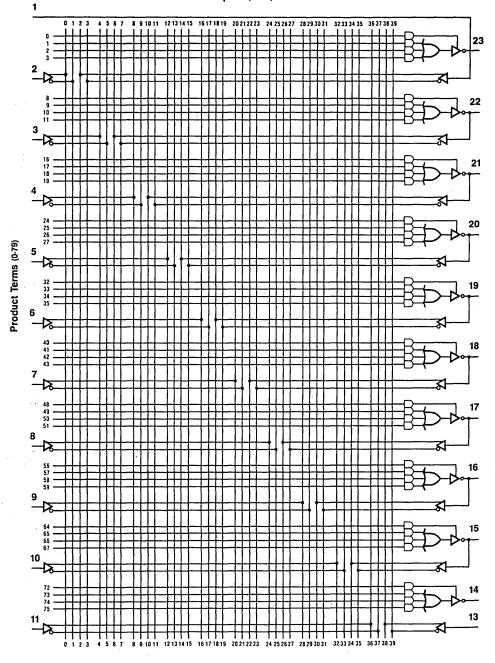

| 4.4.19 | Logic Diagram PAL20C1                                        | 68 |

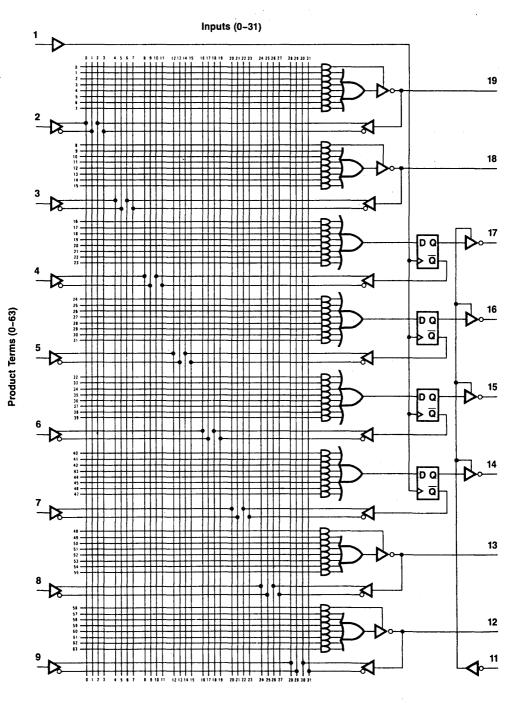

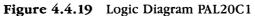

| 4.4.20 | Logic Diagram PAL20L10                                       | 69 |

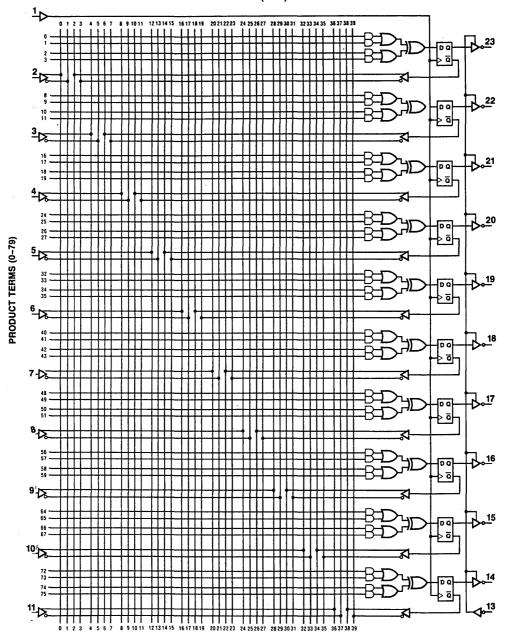

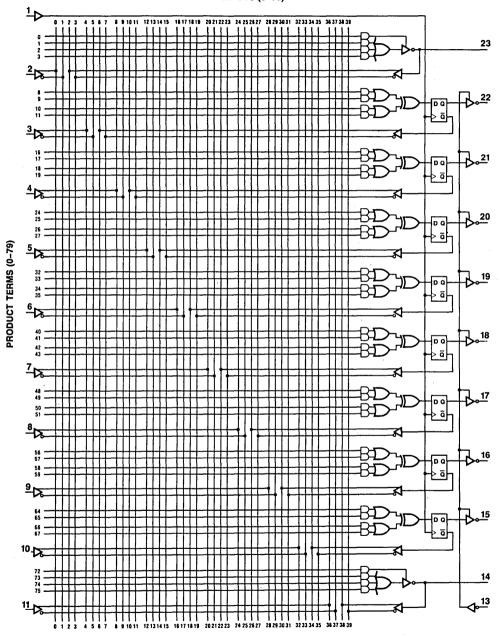

| 4.4.21 | Logic Diagram PAL20X10                                       | 70 |

| 4.4.22 | Logic Diagram PAL20X8                                        | 71 |

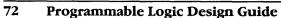

| 4.4.23 | Logic Diagram PAL20X4                                        | 72 |

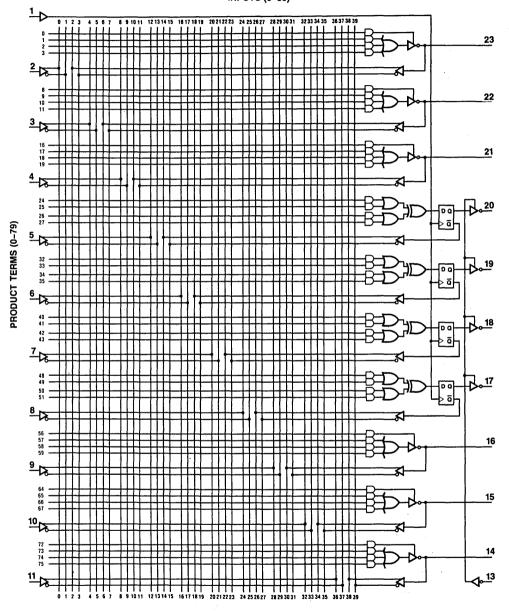

| 4.4.24 | Logic Diagram PAL20L8                                        | 73 |

| 4.4.25 | Logic Diagram PAL20R8                                        | 74 |

| 4.4.26 | Logic Diagram PAL20R6                                        | 75 |

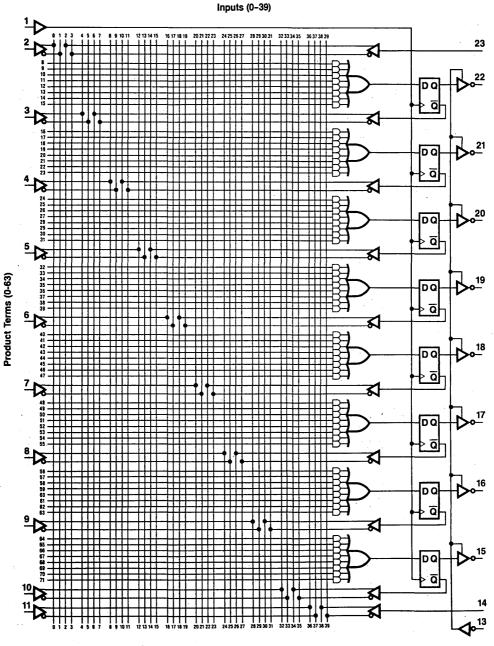

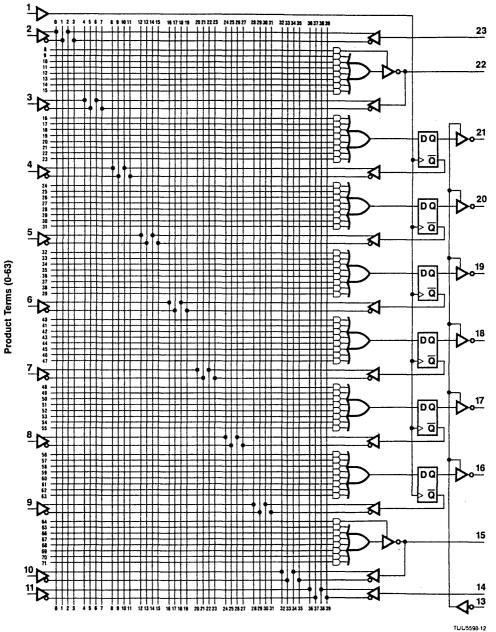

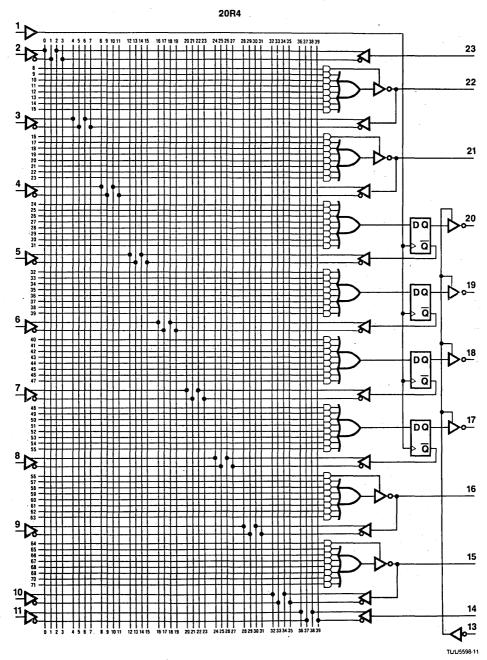

| 4.4.27 | Logic Diagram PAL20R4                                        | 76 |

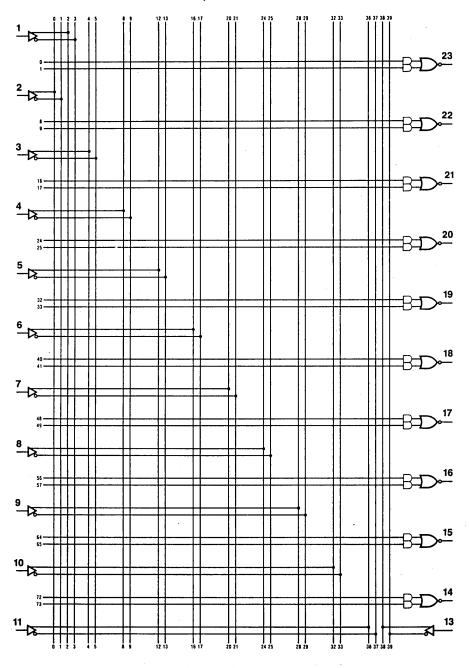

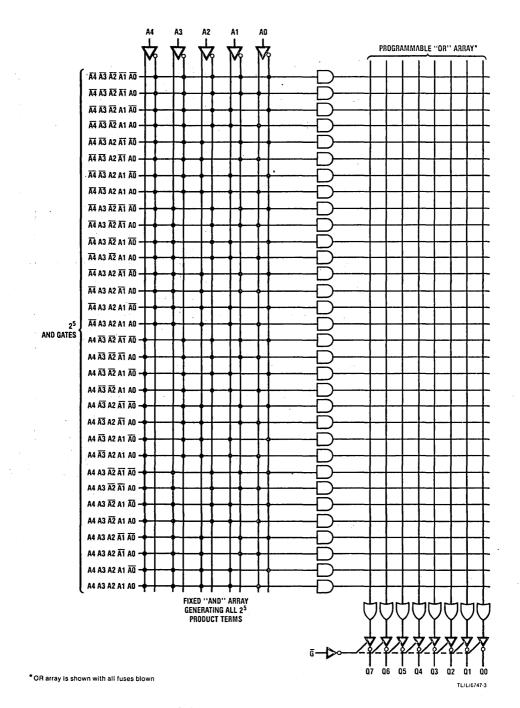

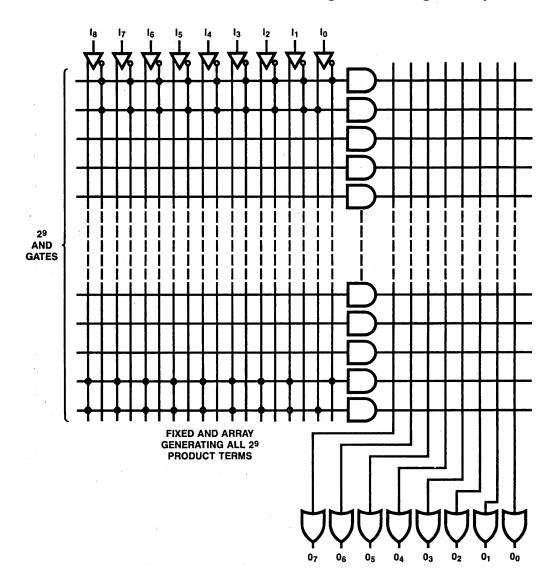

| 4.4.28 | 32 × 8 PROM Logic Diagram                                    | 77 |

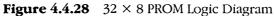

| 4.4.29 | 256 × 8 PROM Logic Diagram                                   | 78 |

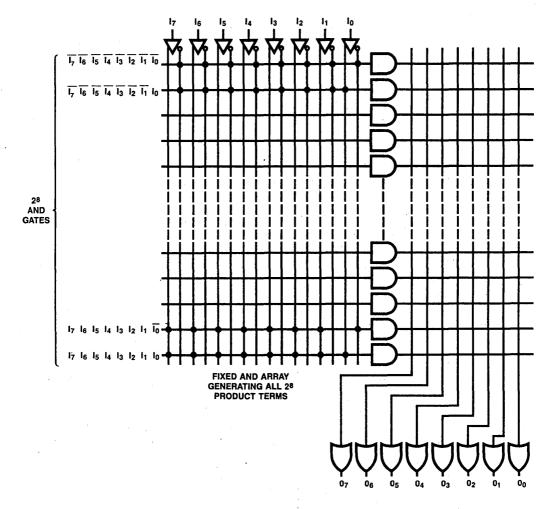

| 4.4.30 | 512 × 8 PROM Logic Diagram                                   | 79 |

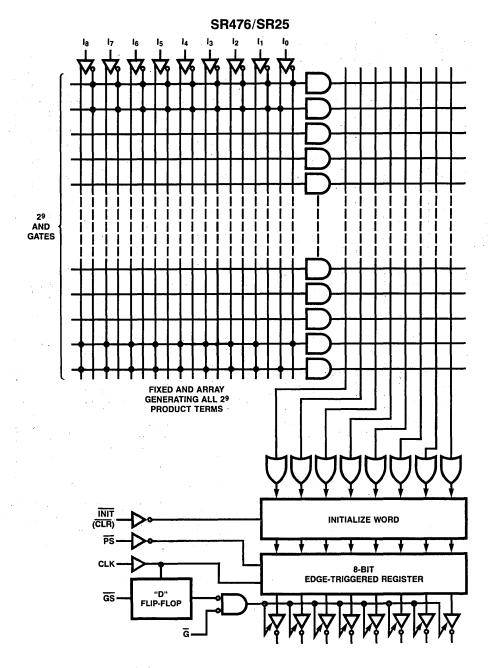

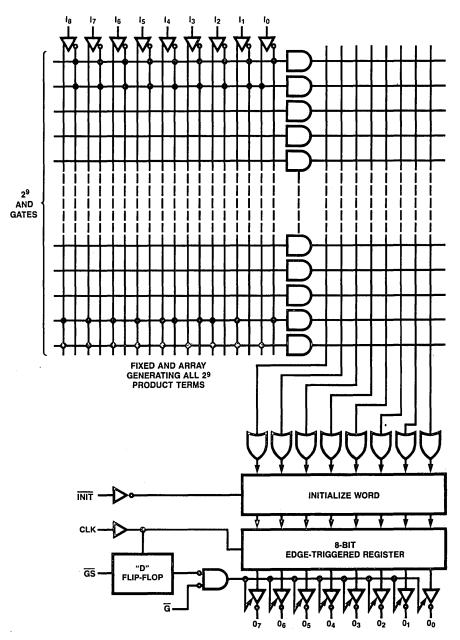

| 4.4.31 | 512 × 8 PROM Logic Diagram, SR476/SR25                       | 80 |

| 4.4.32 | 512 × 8 Register PROM Logic Diagram                          | 81 |

# List of Illustrations xv

# Figure No.

# Page No.

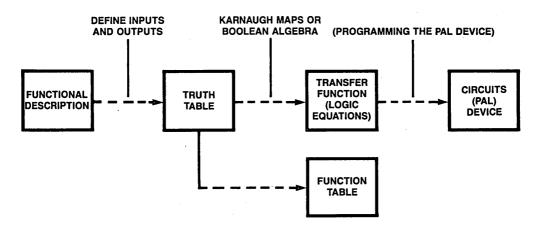

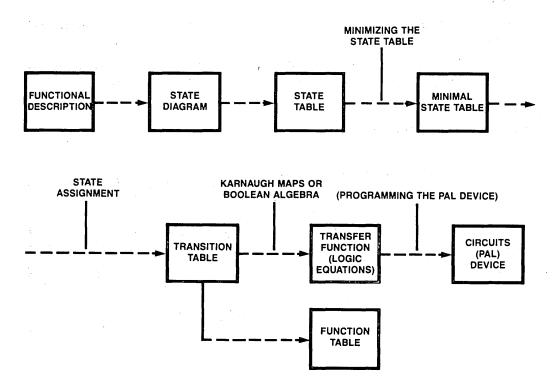

| 5.1.1         | Design Sequence of the Programmable Logic Device   | 83  |

|---------------|----------------------------------------------------|-----|

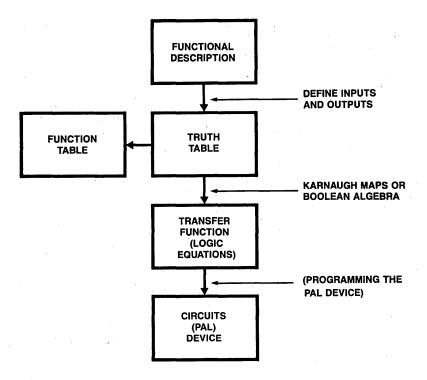

| 5.3.1         | Combinational PAL Device Design Steps              | 87  |

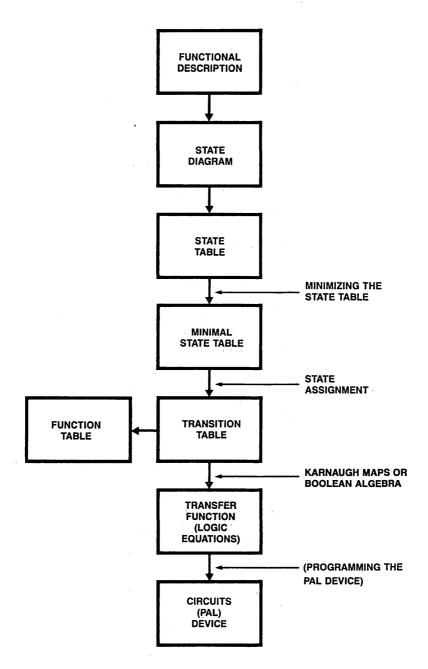

| 5.3.2         | Sequential PAL Device Design Steps                 | 88  |

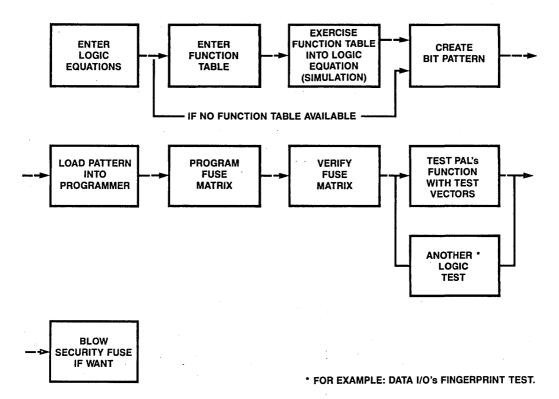

| 5.4.1         | PAL Device Programming Procedures                  | 89  |

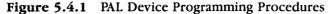

| 5.5.1         | Test Vectors Creating Steps                        | 90  |

| 5.7.1         | Design Example, Logic Diagram                      | 92  |

| 5.7.2         | Example of PALASM Program Input                    | 93  |

| <b>5.7.3</b>  | PALASM Operators                                   | 94  |

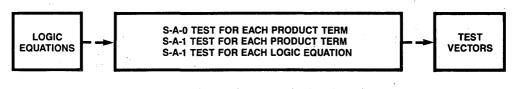

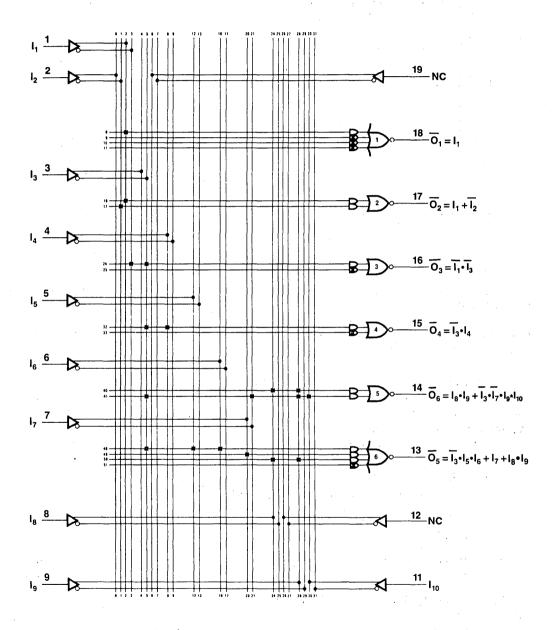

| 5.7.4         | Logic Diagram of the National Type 12L6 PAL Device | 96  |

| 5.7.5         | PAL Device Legend                                  | 97  |

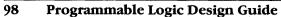

| 5.7.6         | Block Diagram of a Multiplexer                     | 98  |

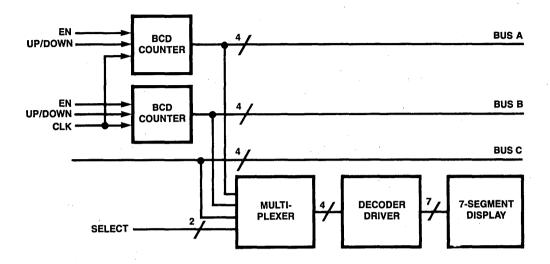

| 5.7.7         | Logic Diagram of the National Type 14H4 PAL Device | 99  |

| 5.7.8         | 3-Bit Counter                                      | 100 |

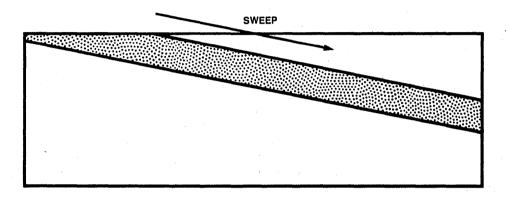

| 5.7.9         | К-тар                                              | 101 |

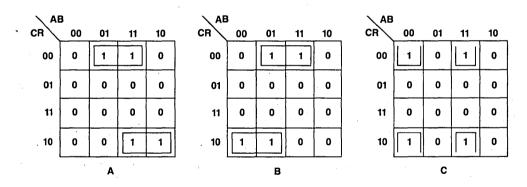

| 5.7.10        | Sweep Generation                                   | 102 |

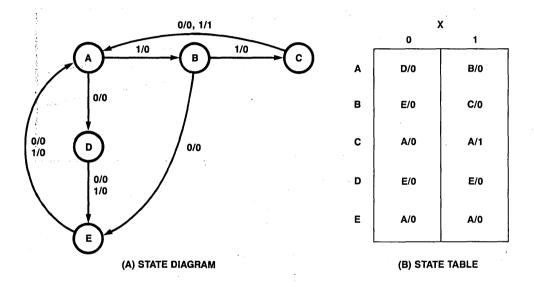

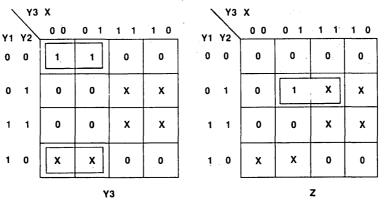

| 5.7.11        | (a) State Diagram, (b) State Table                 | 103 |

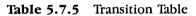

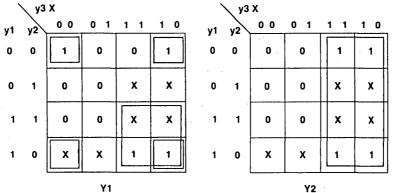

| 5.7.12        | К-тар                                              | 105 |

|               |                                                    |     |

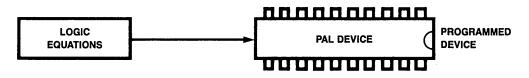

| 6.1.1         | Early Role of Software                             | 107 |

| 6.1.2         | Expanded Role of Software                          | 108 |

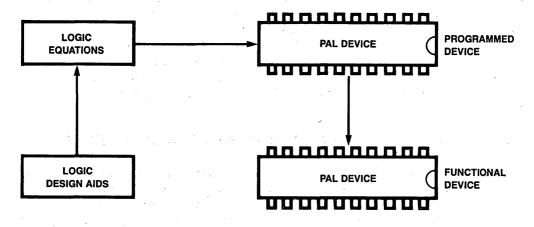

| 6.2.2         | Plan File Information                              | 110 |

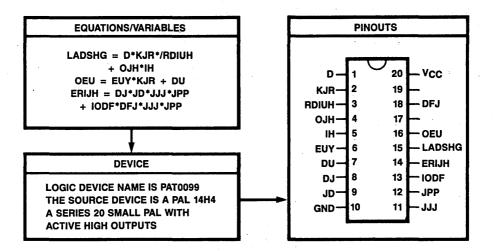

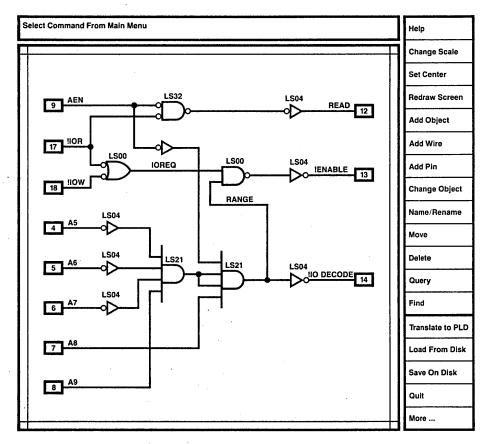

| 6.2.2         | Fuse Map Display from Plan                         | 111 |

| 6.3.1         | CUPL-GTS Screen Display Example                    | 115 |

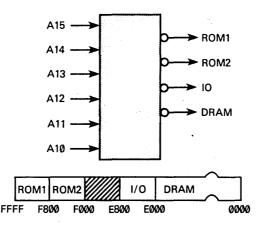

| 6.3.2         | Block Diagram: 6809 Memory Address Decoder         | 117 |

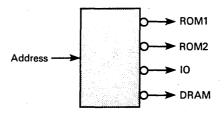

| 6.3.3         | Simplified Block Diagram                           | 118 |

| 6.3.4         | Source File: 6809 Memory Address Decoder           | 119 |

|               |                                                    |     |

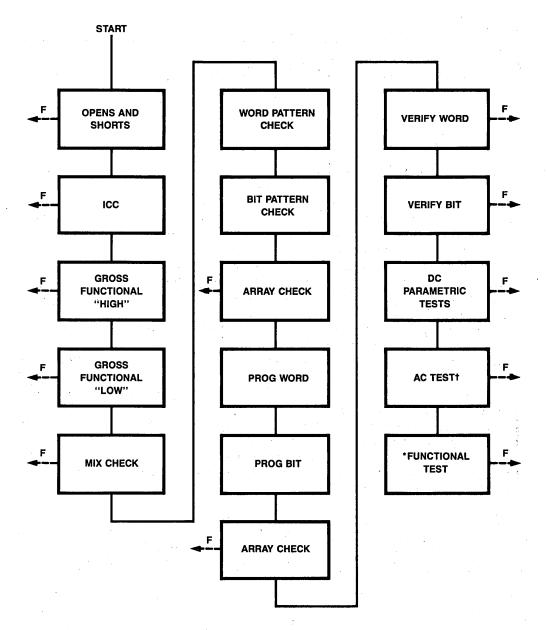

| 7.1.1         | PAL Device Test Flow                               | 122 |

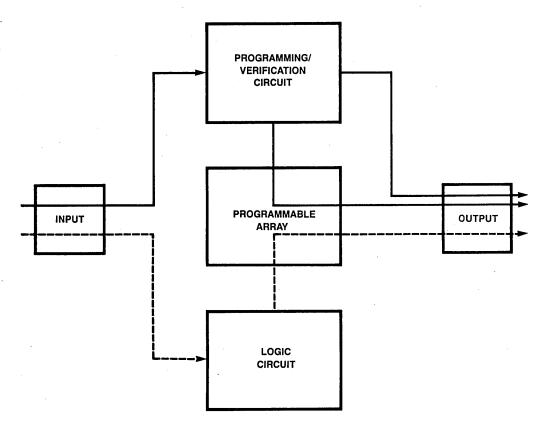

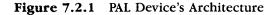

| 7.2.1         | PAL Devices Architecture                           | 123 |

| 7.2.2         | Function of Test Vector                            | 124 |

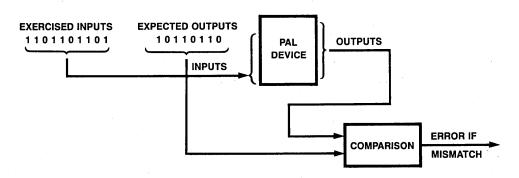

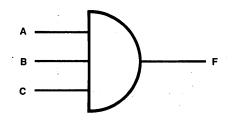

| 7.2.3         | 3-Input and Gate                                   | 124 |

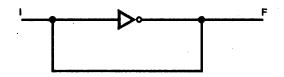

| 7.5.1         | Combinational Circuit                              | 126 |

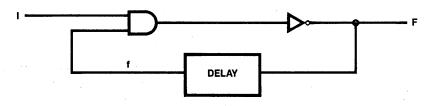

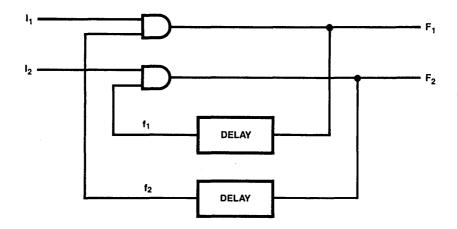

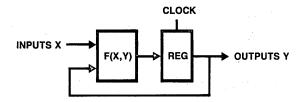

| 7.5.2         | Sequential Circuit                                 | 128 |

| 7.5.3         | Combinational PAL Device Design Steps              | 130 |

| 7.5.4         | Sequential PAL Device Design Steps                 | 131 |

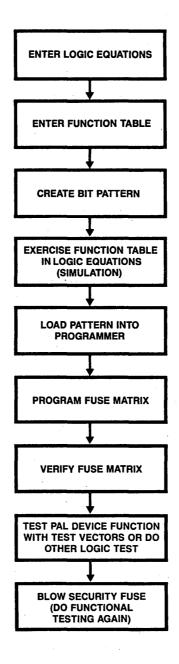

| 7.5.5         | PAL Device Programming Procedures                  | 132 |

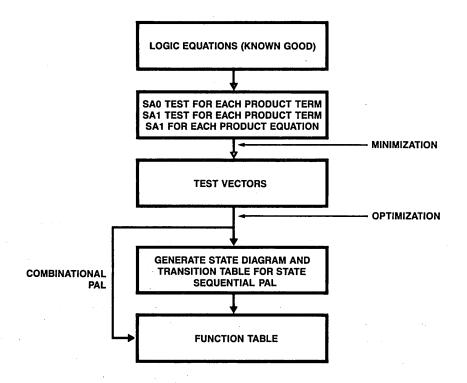

| 7.5.6         | Test Vector and Function Table Creating Steps      | 133 |

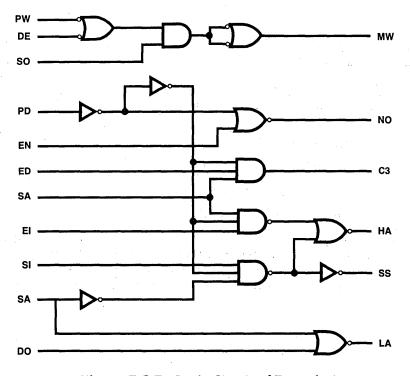

| 7.5.7         | Logic Circuit of Example #1                        | 136 |

| 7 <b>.5.8</b> | State Diagram                                      | 152 |

# xvi Programmable Logic Design Guide

| 8.1.1   | Basic Gates                                                 | 157 |

|---------|-------------------------------------------------------------|-----|

| 8.1.2   | Logic Diagram PAL12H6                                       | 160 |

| 8.2.1   | Logic Diagram PAL16R8                                       | 167 |

| 8.3.1   | Memory Mapped I/O Logic Diagram                             | 168 |

| 8.3.2   | Logic Diagram PAL16L2                                       | 171 |

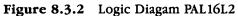

| 8.4.1   | Hex Display Decoder-Driver, Combinational Logic Diagram     | 173 |

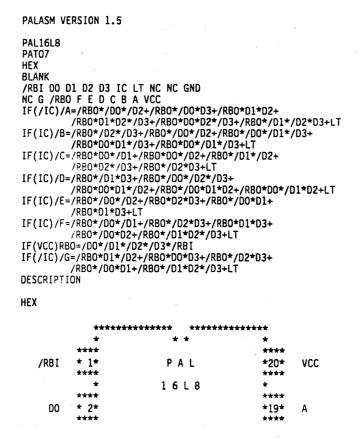

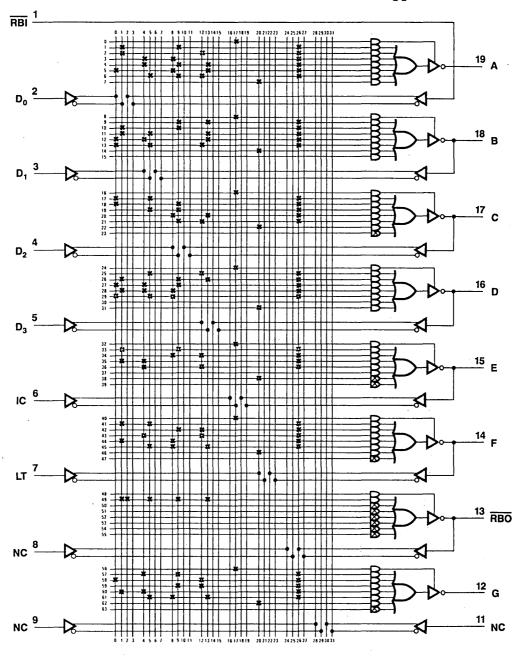

| 8.4.2   | Logic Diagram PAL16L8                                       | 177 |

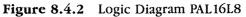

| 8.5.1   | PAL Device 16C1 Limit Checker                               | 178 |

| 8.5.2   | Logic Diagram PAL16C1                                       | 180 |

| 8.6.1   | Logic Diagram PAL14H4                                       | 182 |

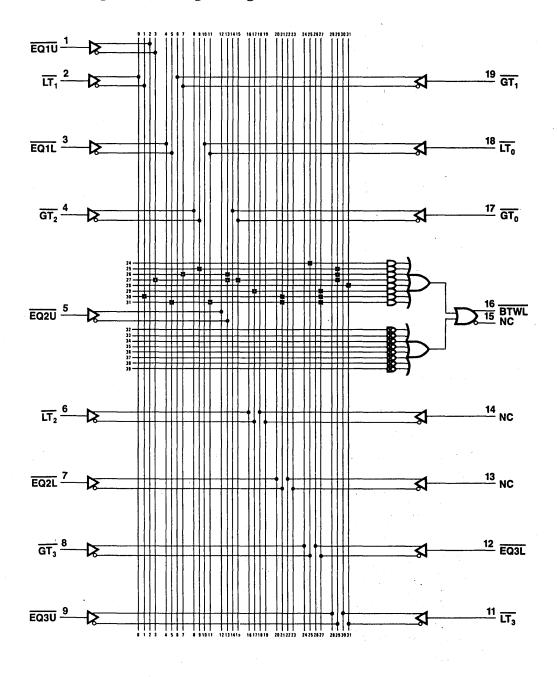

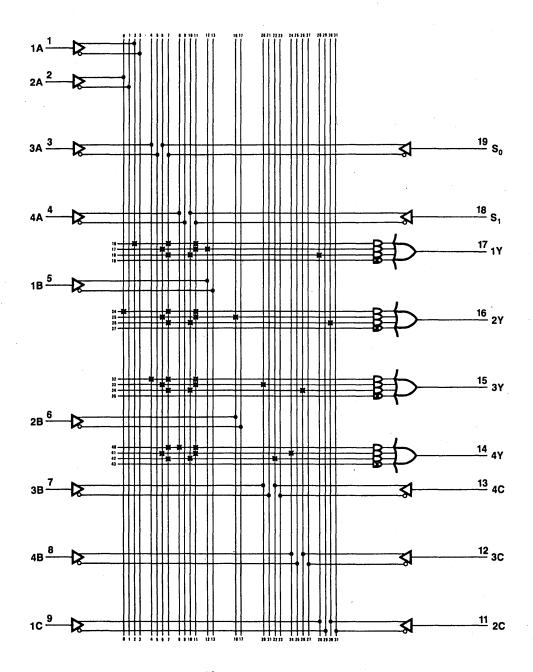

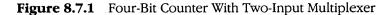

| 8.7.1   | Four-Bit Counter With Two-Input Multiplexer                 | 183 |

| 8.7.2   | 0 0                                                         | 186 |

| 8.9.1   |                                                             | 193 |

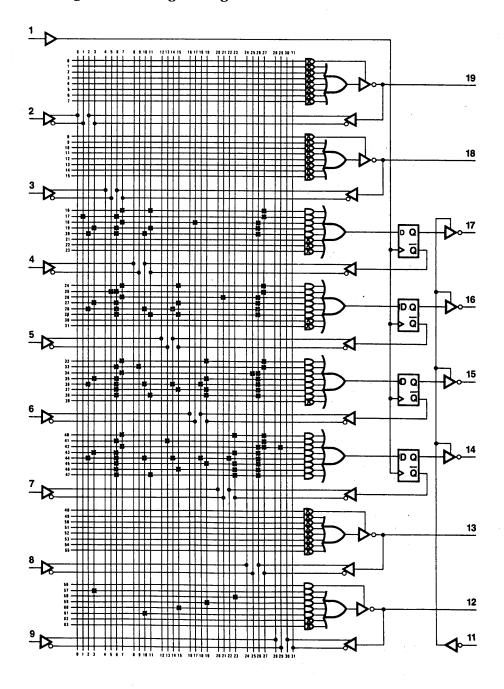

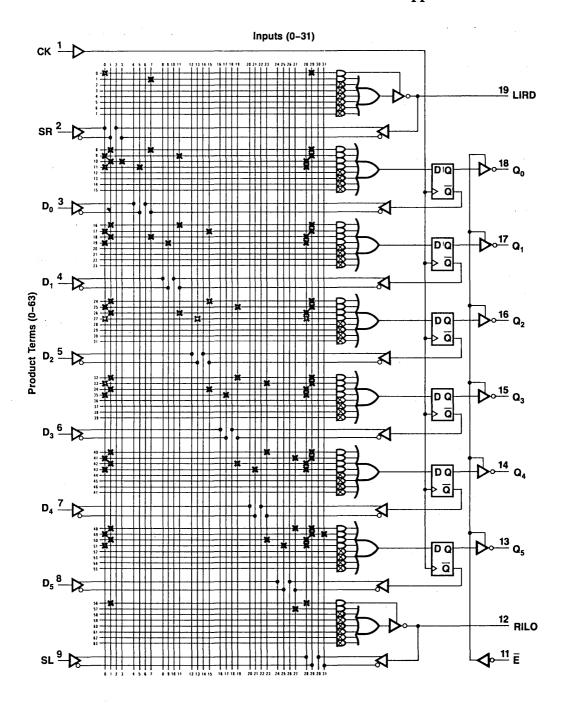

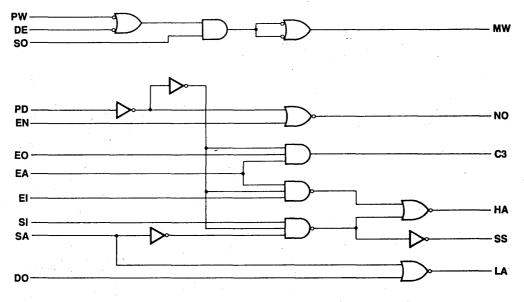

| 8.10.1  | Control Logic for 8086 CPU Board                            | 194 |

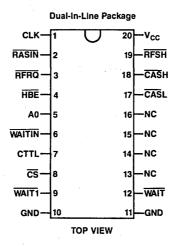

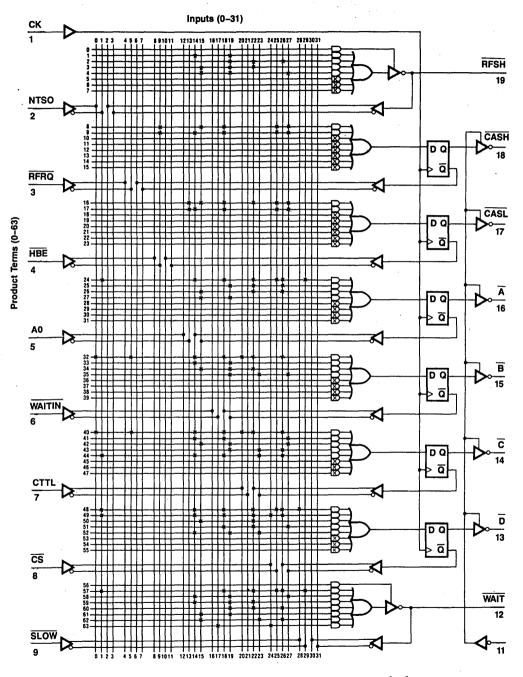

| 8.11.1  | Connection Diagram                                          | 197 |

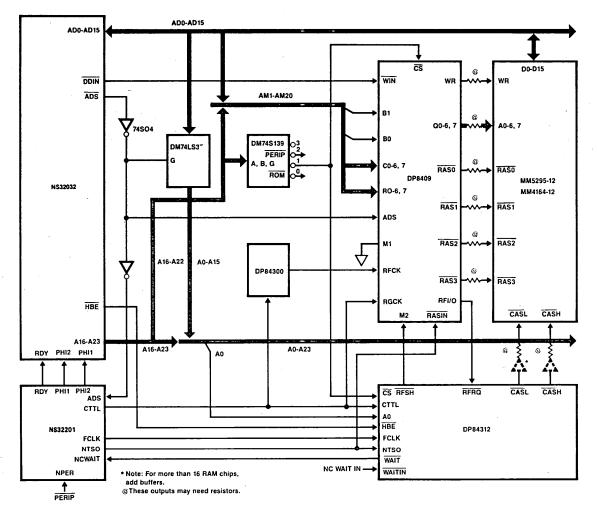

| 8.11.2  | System Block Diagram                                        | 199 |

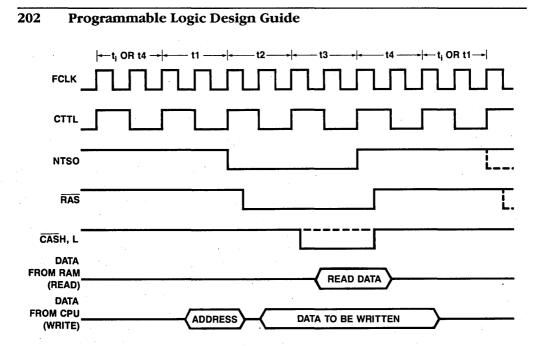

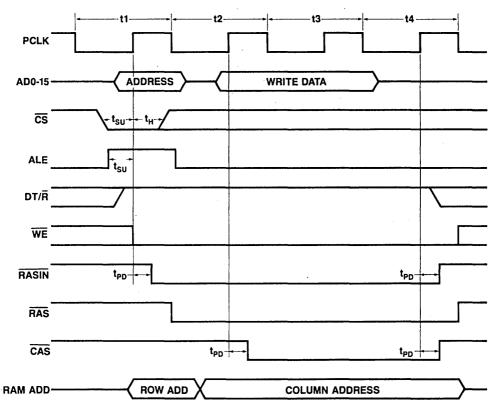

| 8.11.3  | Timing Diagram; Read, Write or Hidden Refresh Memory        | ÷   |

| :       | Cycle for the NS16032-DP8409 Interface                      | 202 |

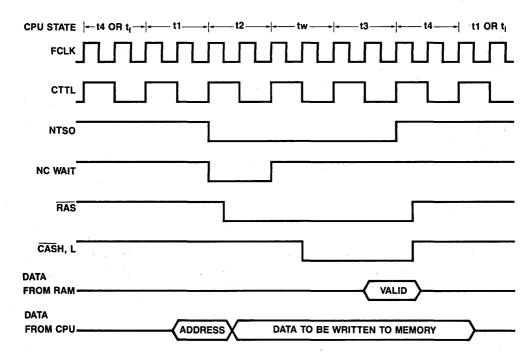

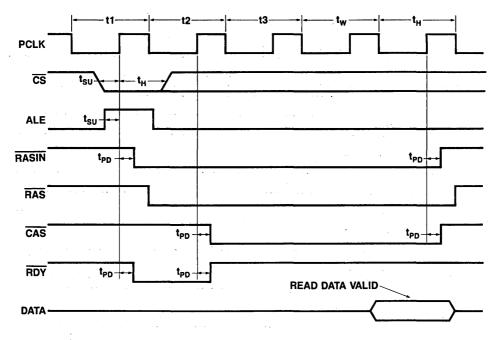

| 8.11.4  | Timing Diagram; Read, or Write Memory Cycle With One Wait   | 202 |

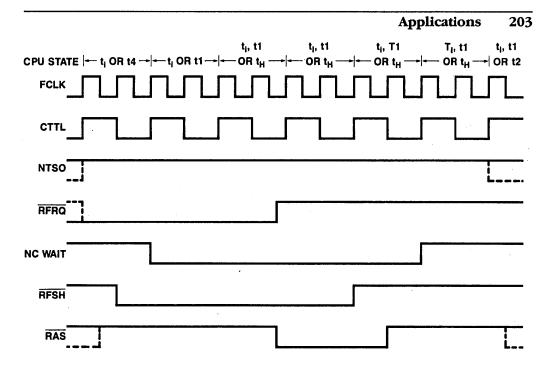

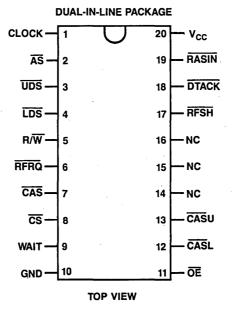

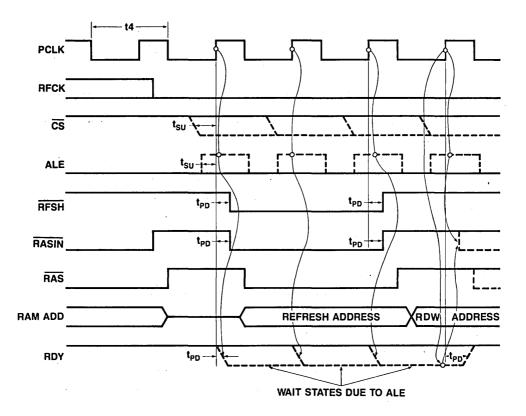

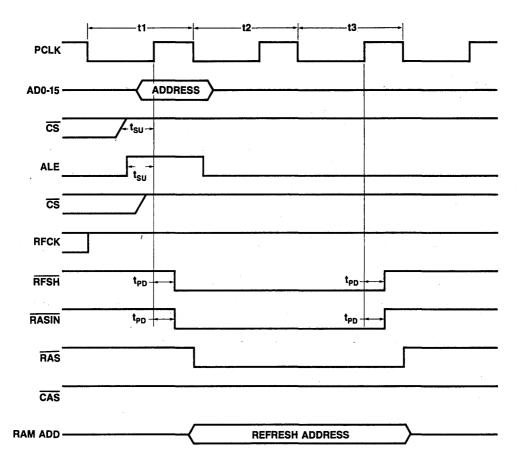

| 8.11.5  | Timing Diagram; Forced Refresh cycle                        | 203 |

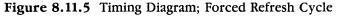

| 8.11.6  | DP84312 Logic Diagram PAL16R6                               | 206 |

| 8.12.1  | Connection Diagram                                          | 207 |

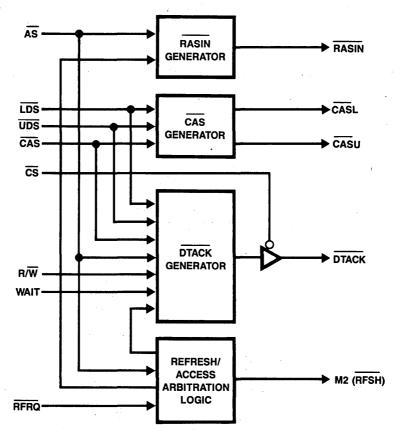

| 8.12.2  | Block Diagram                                               | 208 |

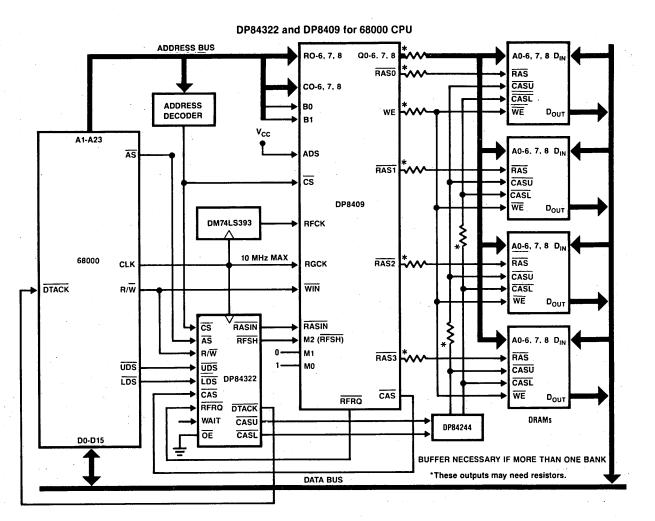

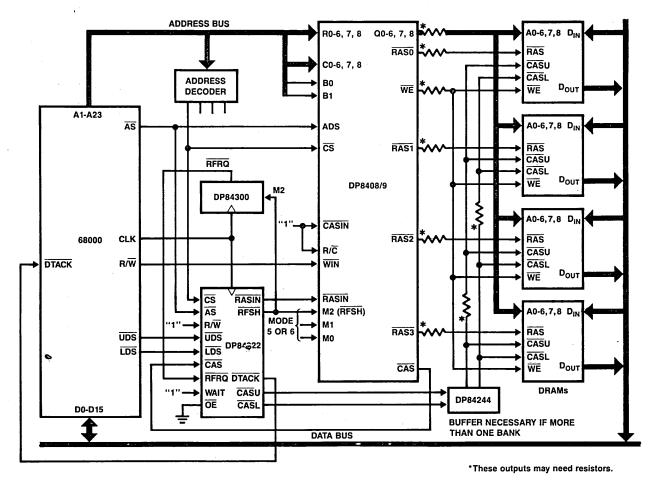

| 8.12.3  | System Block Diagram                                        | 210 |

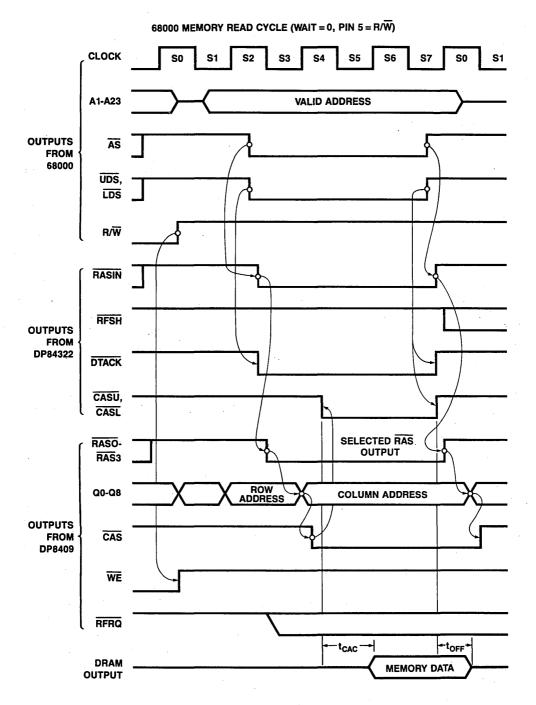

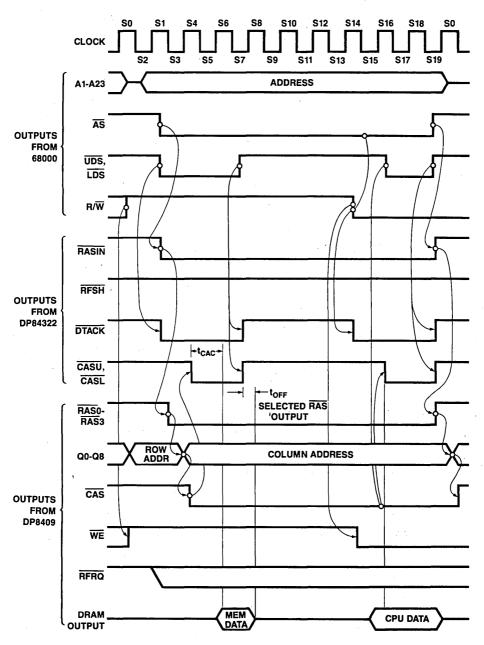

| 8.12.4  | Timing Diagram; 68000 Memory Read Cycle                     | 216 |

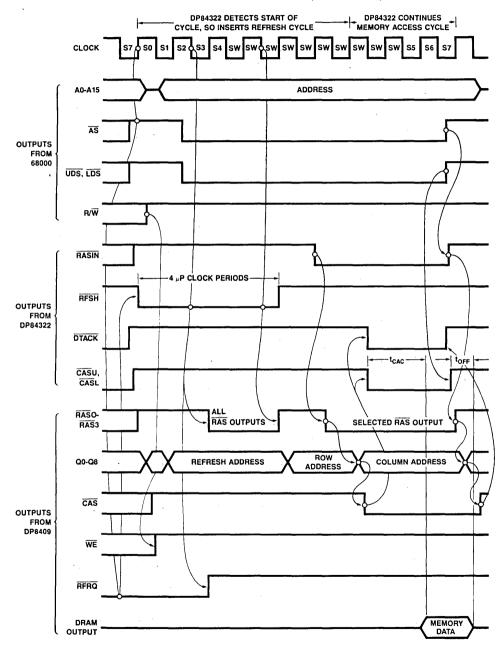

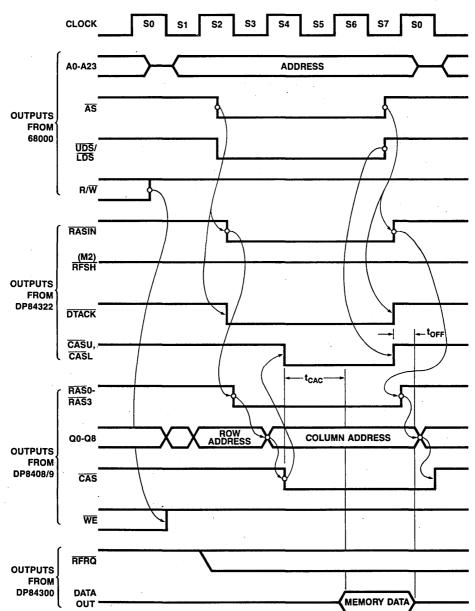

| 8.12.5  | Timing Diagram; 68000 Memory Read Cycle and Forced Refresh  | 217 |

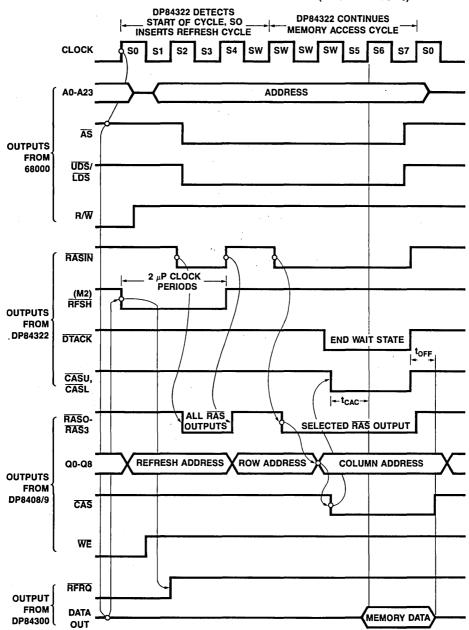

| 8.12.6  | Timing Diagram; TAS Instruction Cycle                       | 218 |

| 8.12.7  | Timing Diagram; Memory Read Cycle                           | 219 |

| 8.12.8  | Timing Diagram; Memory Read Cycle and Forced Refresh        | 220 |

| 8.12.9  | Modified System Block Diagram                               | 221 |

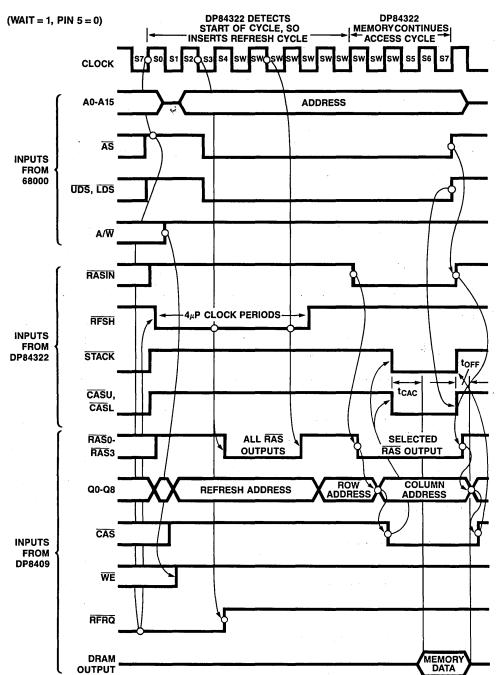

| 8.12.10 | Timing Diagram 68000 Memory Read Cycle                      | 222 |

| 8.12.11 | Timing Diagram 68000 Memory Read Cycle and Memory Refresh . | 223 |

| 8.12.12 | DP84322 Logic Diagram PAL Device 16R4                       |     |

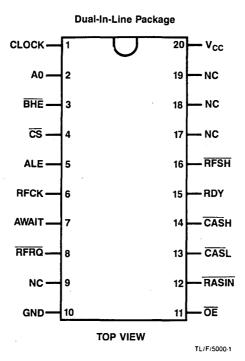

| 8.13.1  | Connection Diagram                                          | 227 |

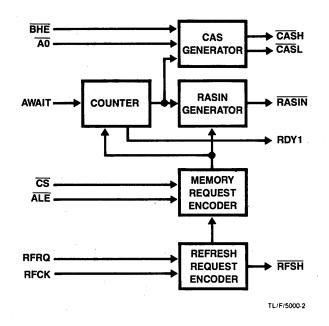

| 8.13.2  | Block Diagram                                               | 228 |

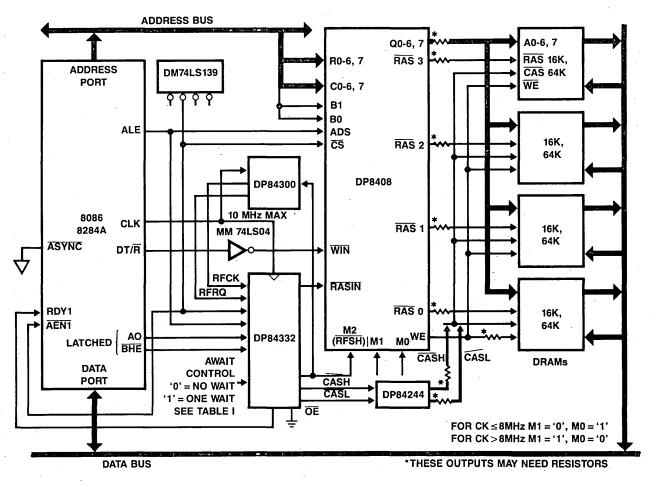

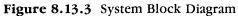

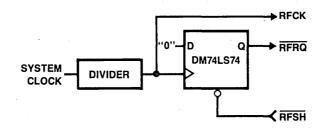

| 8.13.3  | System Block Diagram                                        | 232 |

| 8.13.4  | Using a Flip-Flop and a Counter for Refresh Request Logic   | 233 |

| 8.13.5  | Using the DP84300 Refresh Counter for Refresh Logic         | 233 |

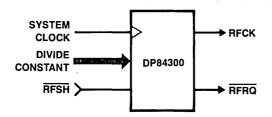

| 8.13.6  | Timing Diagram; Read Timing                                 | 234 |

| 8.13.7  | Timing Diagram; Write Timing                                | 235 |

| 8.13.8  | Timing Diagram; Memory Cycle With 1 Wait State              | 236 |

#### Lis i

| st of Illustrations | xvii    |

|---------------------|---------|

| Р                   | age No. |

| 8.13.9  | Timing Diagram; Forced Refresh                             | 237 |  |  |  |  |  |

|---------|------------------------------------------------------------|-----|--|--|--|--|--|

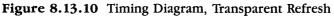

| 8.13.10 | Timing Diagram, Transparent Refresh                        |     |  |  |  |  |  |

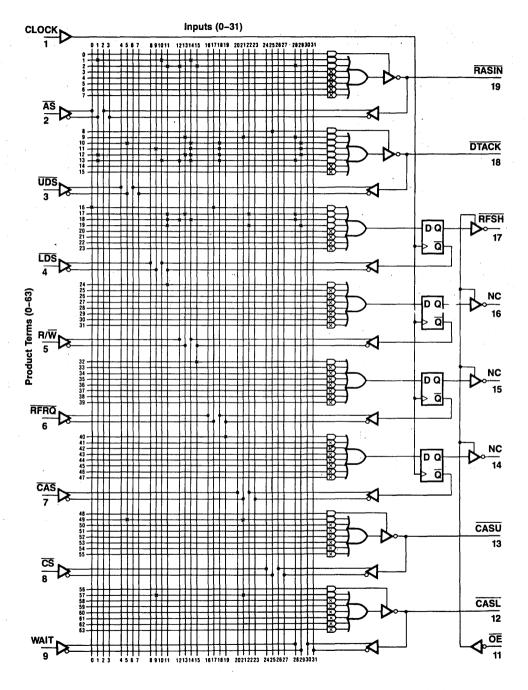

| 8.13.11 | 84332 Logic Diagram PAL16R8 24                             |     |  |  |  |  |  |

| 8.14.1  | DP8400, DP8409, NS16032 6 MHz Computer System 24           |     |  |  |  |  |  |

| 8.14.2  | DP8400/8409 System Interface Block Diagram 24              |     |  |  |  |  |  |

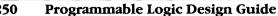

| 8.14.3  | Timing Diagram; Read Cycle and Write Cycle 2               |     |  |  |  |  |  |

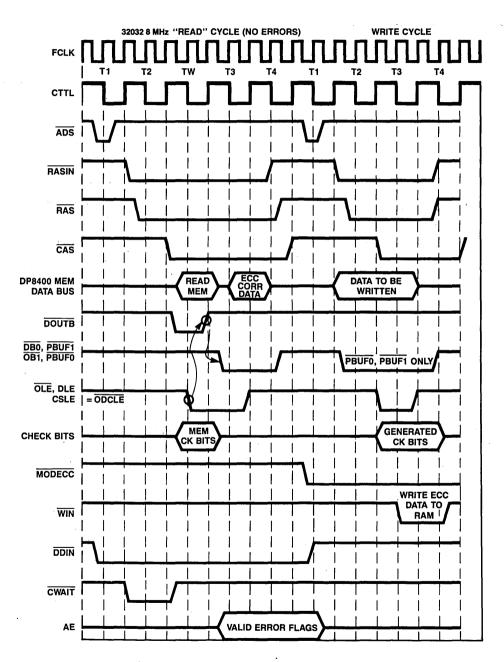

| 8.14.4  | Timing Diagram; Read Cycle With Simple Bit Error 2         |     |  |  |  |  |  |

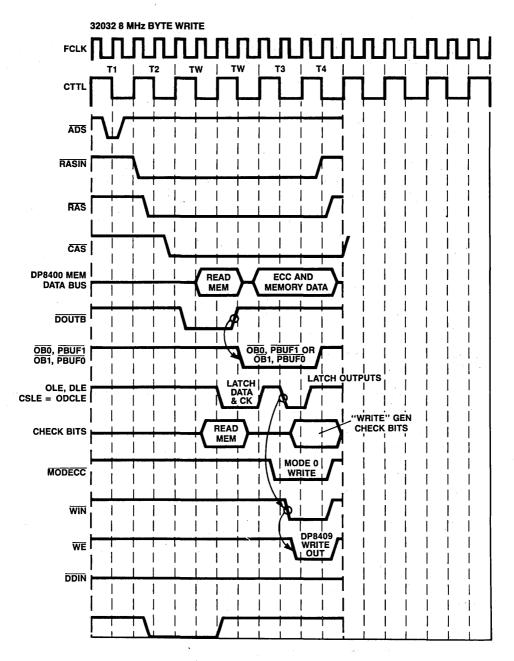

| 8.14.5  | Timing Diagram; Byte Write                                 |     |  |  |  |  |  |

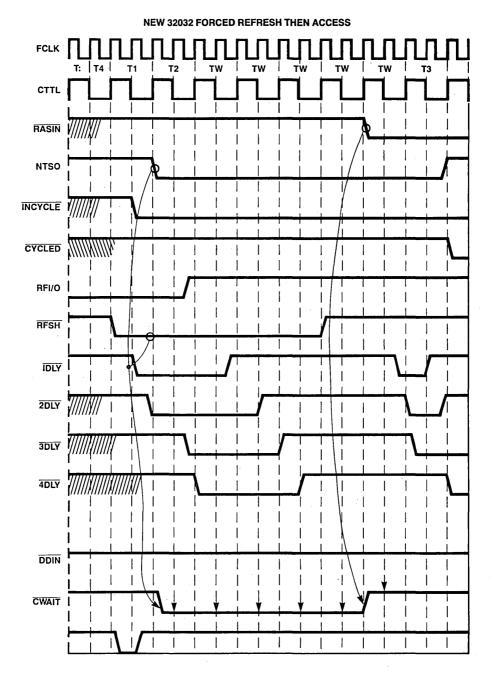

| 8.14.6  | Timing Diagram; Forced Refresh Then Access                 | 253 |  |  |  |  |  |

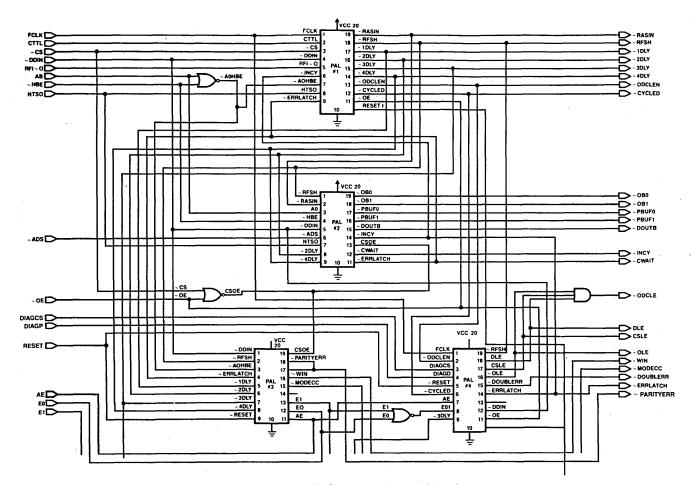

| 8.14.7  | Simulation Circuit                                         |     |  |  |  |  |  |

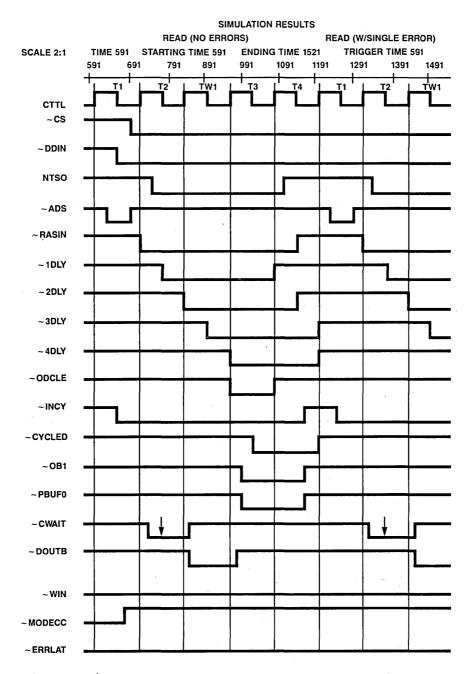

| 8.14.8  | Simulation Timing Diagram; Read/Wrtie Without Errors       | 255 |  |  |  |  |  |

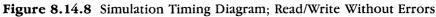

| 8.14.9  | Simulation Timing Diagram; Read With Error and Write Cycle | 256 |  |  |  |  |  |

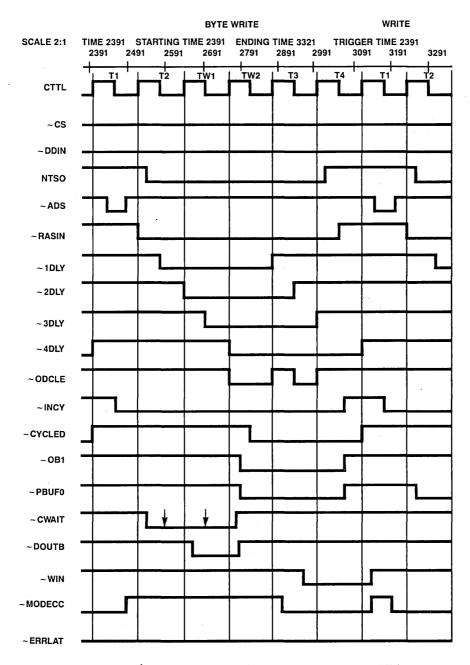

| 8.14.10 | Simulation Timing Diagram; Byte Write                      | 257 |  |  |  |  |  |

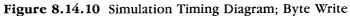

| 8.14.11 | Simulation Timing Diagram; Forced Refresh Then Access      | 258 |  |  |  |  |  |

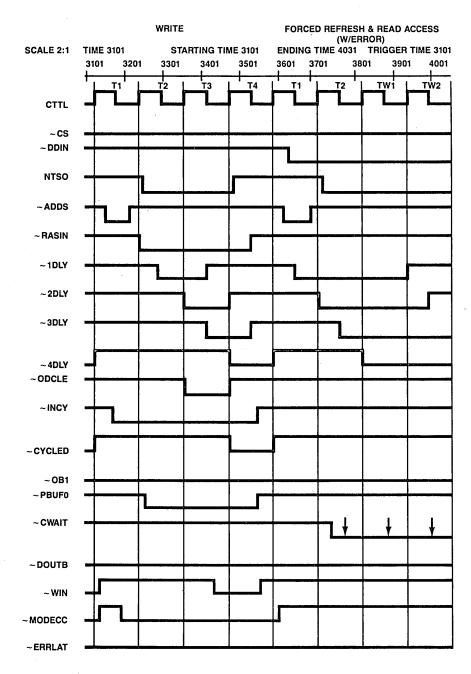

| 8.14.12 | Simulation Timing Diagram; Write, Forced Refresh and       |     |  |  |  |  |  |

|         | Read Access                                                | 259 |  |  |  |  |  |

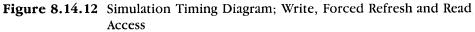

| 8.14.13 | Simulation Timing Diagram; Forced Refresh Followed by      |     |  |  |  |  |  |

|         | Read Access (With Error)                                   | 260 |  |  |  |  |  |

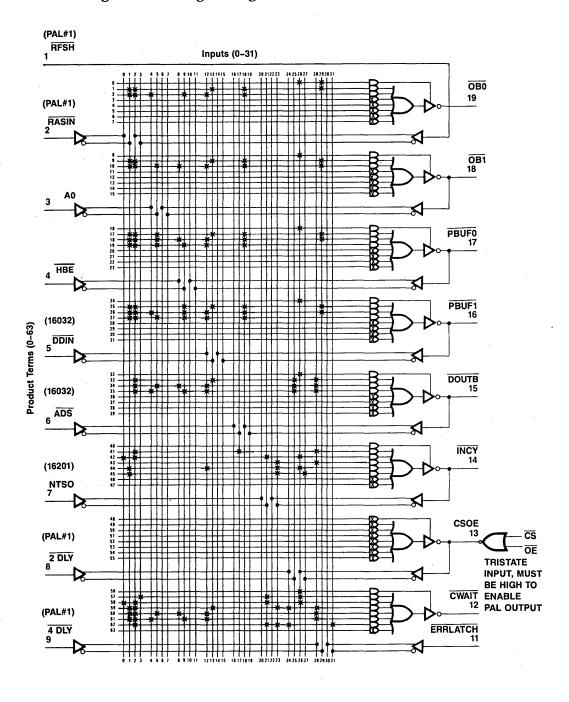

| 8.14.14 | Logic Diagram of PAL Device #1                             | 265 |  |  |  |  |  |

| 8.14.15 | Logic Diagram of PAL Device #2                             | 266 |  |  |  |  |  |

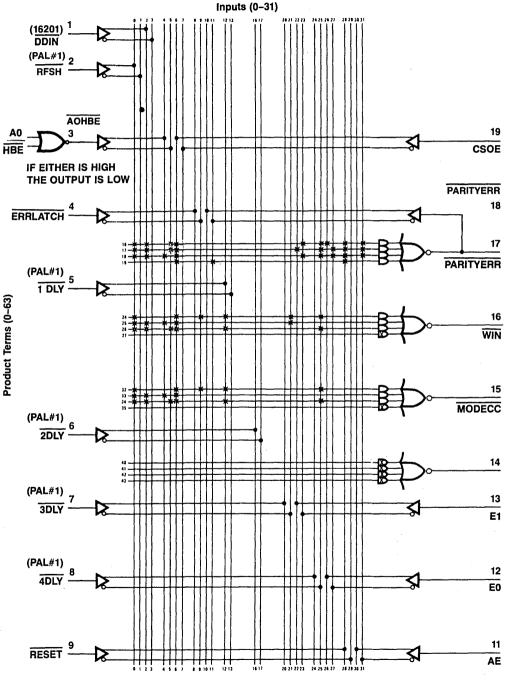

| 8.14.16 | Logic Diagram of PAL Device #3                             | 267 |  |  |  |  |  |

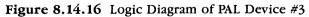

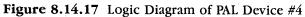

| 8.14.17 | Logic Diagram of PAL Device #4                             | 268 |  |  |  |  |  |

|         |                                                            |     |  |  |  |  |  |

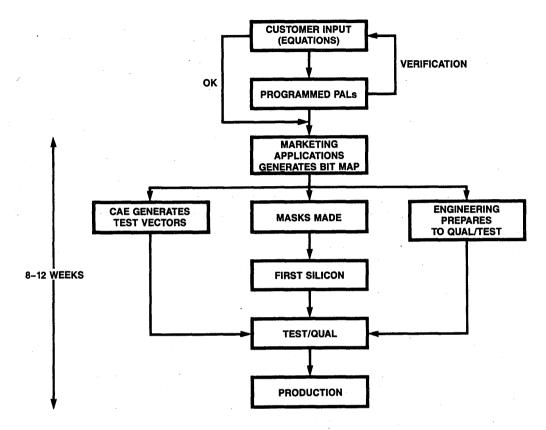

| 9.1.1   | NML Procedure                                              | 270 |  |  |  |  |  |

|         |                                                            |     |  |  |  |  |  |

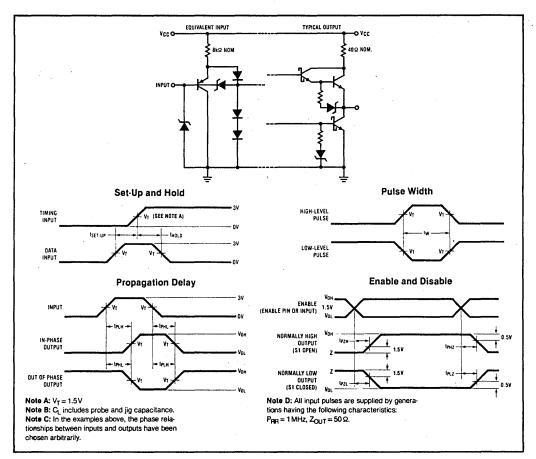

| 11.1.1  | Test Waveforms and Schematics of Inputs and Outputs        | 275 |  |  |  |  |  |

| 11.2.1  | Pin Assignment for Programming                             | 294 |  |  |  |  |  |

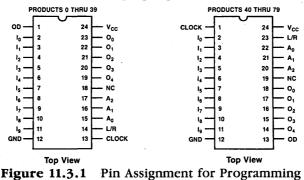

| 11.3.1  | Pin Assignment for Programming                             | 298 |  |  |  |  |  |

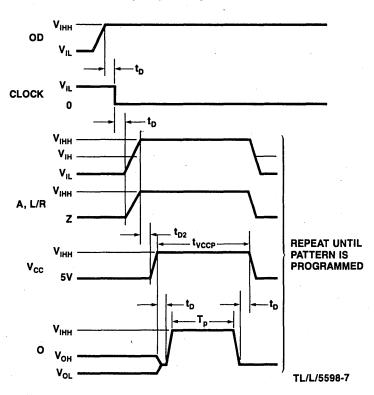

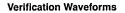

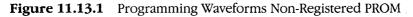

| 11.3.2  | Programming Waveforms                                      | 302 |  |  |  |  |  |

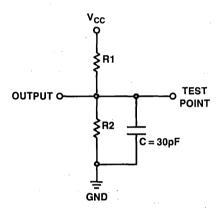

| 11.4.1  | Standard Test Load                                         | 305 |  |  |  |  |  |

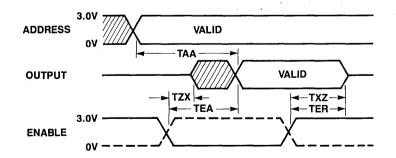

| 11.4.2  | Switching Time Waveforms Non-Registered PROMs              | 305 |  |  |  |  |  |

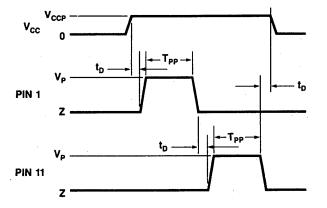

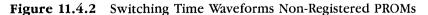

| 11.4.3  | Switching Waveforms, Registered PROM                       | 306 |  |  |  |  |  |

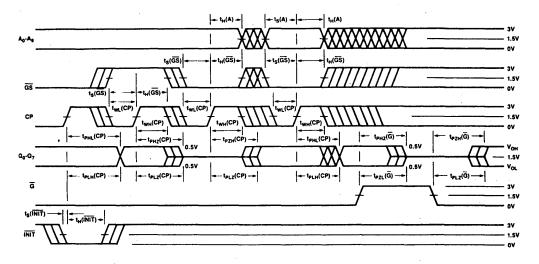

| 11.4.4  | Key to Timing Diagram                                      | 306 |  |  |  |  |  |

| 11.5.1  | Block and Connection Diagram                               | 307 |  |  |  |  |  |

| 11.6.1  | Block and Connection Diagram                               | 309 |  |  |  |  |  |

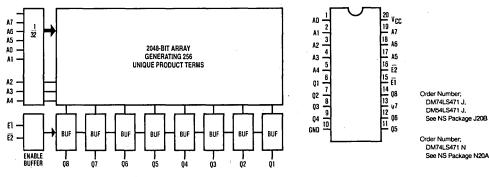

| 11.7.1  | Block and Connection Diagram                               | 311 |  |  |  |  |  |

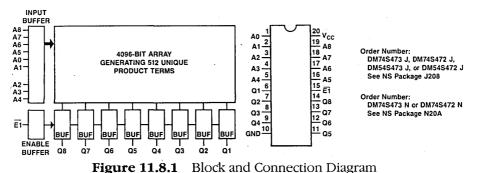

| 11.8.1  | Block and Connection Diagram                               | 313 |  |  |  |  |  |

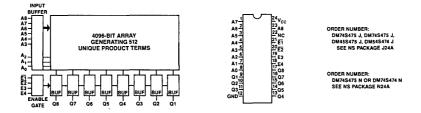

| 11.9.1  | Block and Connection Diagram                               | 316 |  |  |  |  |  |

| 11.10.1 | Block and Connection Diagram                               | 320 |  |  |  |  |  |

| 11.11.1 | Block and Connection Diagram                               | 324 |  |  |  |  |  |

| 11.12.1 | Programming Waveforms, Registered PROM                     | 329 |  |  |  |  |  |

| 11.13.1 | Programming Waveforms, Non-Registered PROM                 | 331 |  |  |  |  |  |

# xviii Programmable Logic Design Guide

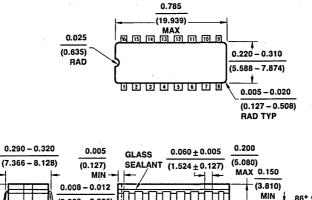

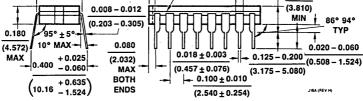

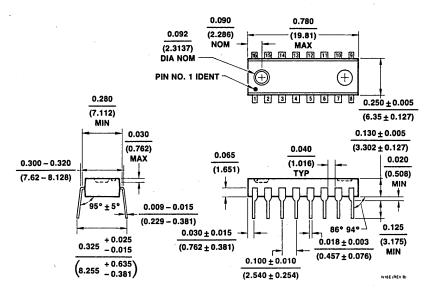

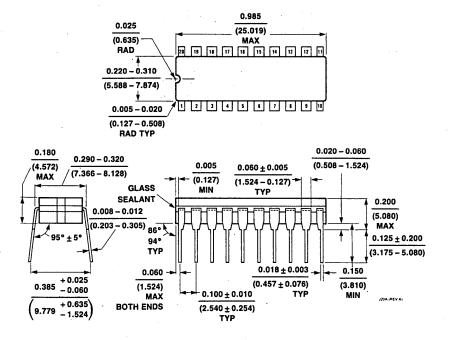

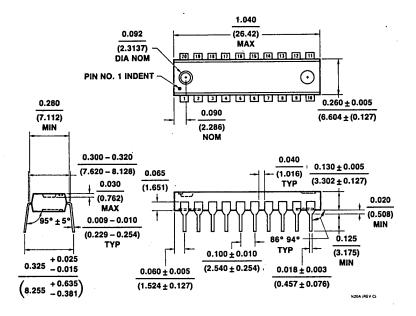

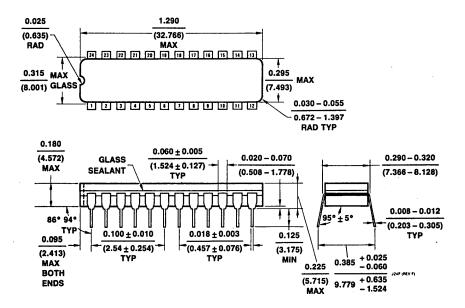

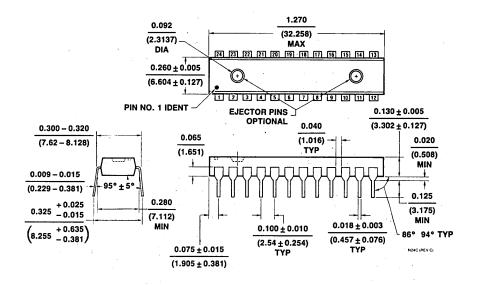

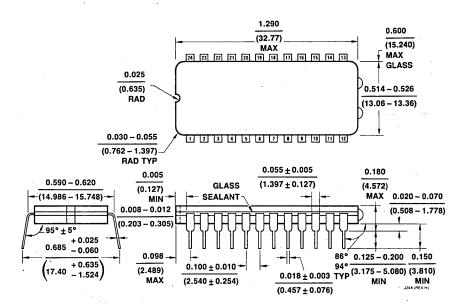

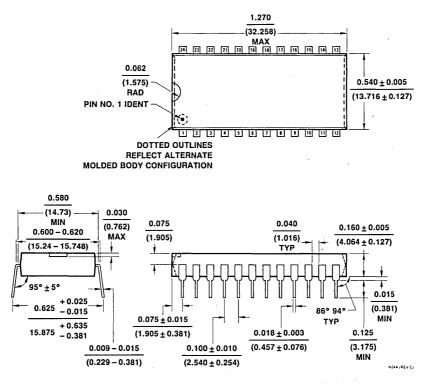

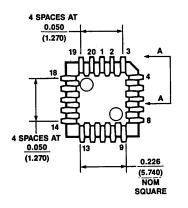

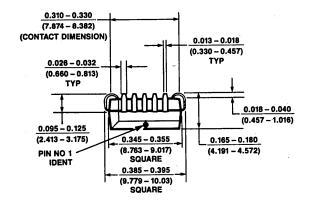

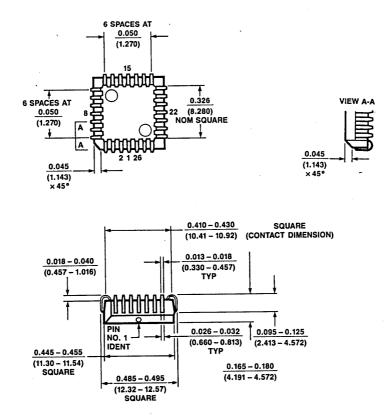

| 12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7<br>12.8<br>12.9 | NS Package N16E, 16-Lead Molded DIP (N) (Substitute for N16A)<br>NS Package J20A, 20-Lead Cavity DIP (J)<br>NS Package N20A, 20-Lead Molded DIP (N)<br>NS Package J24F, 24-Lead Cavity DIP (J)<br>NS Package N24C, 24-Lead Molded DIP (N)<br>NS Package J24A, 24-Lead Cavity DIP (J)<br>NS Package N24A, 24-Lead Molded DIP (N) | 333<br>334<br>334<br>335<br>335<br>336<br>336<br>336<br>337<br>338 |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 12.10                                                                |                                                                                                                                                                                                                                                                                                                                 | 339                                                                |

| A.1.1                                                                | LSI Test Technology                                                                                                                                                                                                                                                                                                             | 350                                                                |

| A.2.1(a)                                                             |                                                                                                                                                                                                                                                                                                                                 | 353                                                                |

| A.2.1(b)                                                             |                                                                                                                                                                                                                                                                                                                                 | 353                                                                |

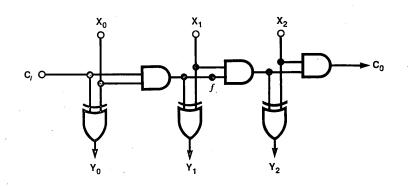

| A.2.2                                                                | Gate-Level Description of a Three-Bit Incrementer                                                                                                                                                                                                                                                                               |                                                                    |

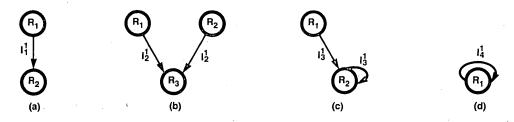

| A.2.3(a)                                                             |                                                                                                                                                                                                                                                                                                                                 | 361                                                                |

| A.2.3(b)                                                             |                                                                                                                                                                                                                                                                                                                                 | 361                                                                |

| A.2.3(c)                                                             |                                                                                                                                                                                                                                                                                                                                 | 361                                                                |

| A.2.3(d)                                                             | -                                                                                                                                                                                                                                                                                                                               | 361                                                                |

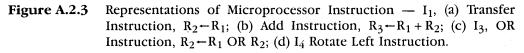

| A.2.4(a)                                                             |                                                                                                                                                                                                                                                                                                                                 | 365                                                                |

| A.2.4(b)                                                             |                                                                                                                                                                                                                                                                                                                                 | 365                                                                |

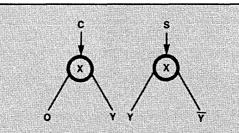

| A.2.4(c)                                                             | Binary Decision Diagram for $S = X + Y(c)$                                                                                                                                                                                                                                                                                      | 365                                                                |

| A.2.5                                                                |                                                                                                                                                                                                                                                                                                                                 | 366                                                                |

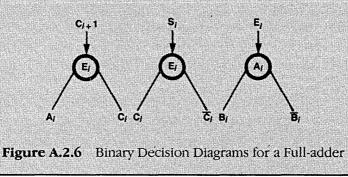

| A.2.6                                                                | Binary Decision Diagrams for a Full-Adder                                                                                                                                                                                                                                                                                       | 366                                                                |

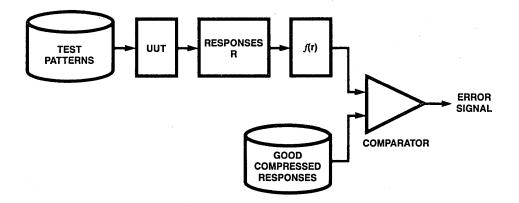

| A.3.1                                                                |                                                                                                                                                                                                                                                                                                                                 | 369                                                                |

| A.3.2                                                                | Comparison Testing                                                                                                                                                                                                                                                                                                              | 369                                                                |

| A.3.3                                                                | Compact Testing                                                                                                                                                                                                                                                                                                                 | 371                                                                |

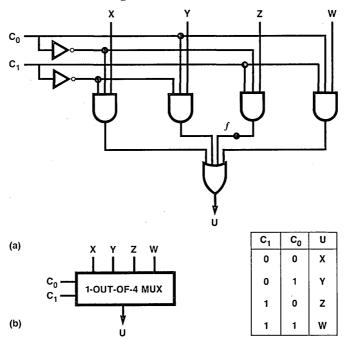

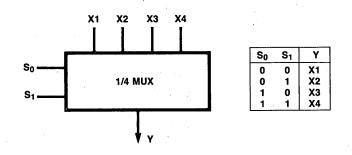

| A.3.4                                                                | One-Out-of-Four Multiplexer                                                                                                                                                                                                                                                                                                     | 372                                                                |

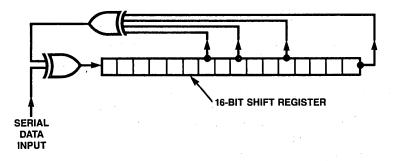

| A.3.5                                                                | The 16-Bit Linear Feedback SR Used in Signature Analysis                                                                                                                                                                                                                                                                        | 373                                                                |

# List of Tables

## Table No.

## Page No.

| 2.2.1                                                                                                    | Typical Component Cost Structure                                                                                                                                                                                           | 7                                                           |

|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

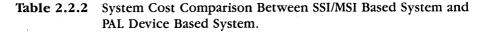

| 2.2.2                                                                                                    | System Cost Comparison Between SSI/MSI Based System and<br>PAL Device Based System                                                                                                                                         | 8                                                           |

| 3.2.1<br>3.6.1                                                                                           | Truth Table of Eq. 3.2.1 and 3.2.2                                                                                                                                                                                         | 22<br>34                                                    |

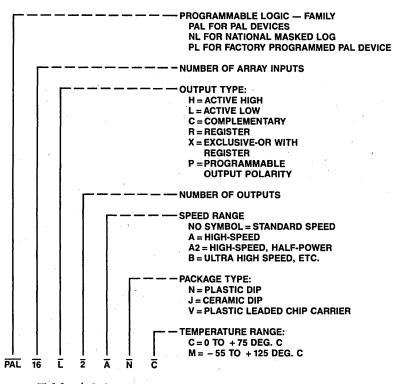

| 4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.3.1<br>4.3.2                                              | Members of the 20-Pin PAL Device FamilyMembers of the 24-Pin PAL Device FamilyPAL Device Part Number Interpretation20-Pin PAL Device Speed/Power Groups24-Pin Speed/Power GroupsPROM ConfigurationsPROM Products for Logic | 39<br>40<br>40<br>42<br>43<br>47<br>48                      |

| 5.1.1<br>5.2.1<br>5.2.2<br>5.6.1<br>5.6.2<br>5.7.1<br>5.7.2<br>5.7.3<br>5.7.4<br>5.7.5<br>5.7.6<br>5.7.7 | Typical PAL Circuits                                                                                                                                                                                                       | 84<br>85<br>90<br>91<br>95<br>98<br>98<br>100<br>101<br>104 |

| 6.2.1<br>6.2.2<br>6.2.3<br>6.3.1<br>6.3.2                                                                | Boolean Operators<br>Macro Entry With PLAN<br>Fuse Map File Formats in PLAN<br>Address Ranges for 6809 Controller<br>PALASM Operators                                                                                      | 109<br>109<br>111<br>118<br>116                             |

# xx Programmable Logic Design Guide

## Table No.

| 7.1.1<br>7.2.1<br>7.2.2<br>7.5.1 | Test Fuses<br>Test Vectors Generated by the Exhaustive Method<br>Test Vectors Generated by Fault Modeling<br>National's PAL Device Family | 121<br>125<br>125<br>129 |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 7.5.2                            | Test Vectors                                                                                                                              | 138                      |

| 7.5.3                            | Test Vectors                                                                                                                              | 139                      |

| 7. <b>5.</b> 4                   | Final Test Vectors                                                                                                                        | 139                      |

| 7.5.5                            | Final Function Table                                                                                                                      | 140                      |

| 7.5.6                            | Test Vectors                                                                                                                              | 145                      |

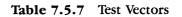

| 7.5.7                            | Test Vectors                                                                                                                              | 148                      |

| 7.5.8                            | Test Vectors                                                                                                                              | 149                      |

| 7.5.9                            | State Assignment                                                                                                                          | 150                      |

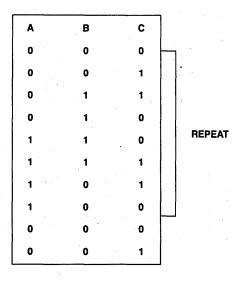

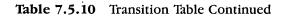

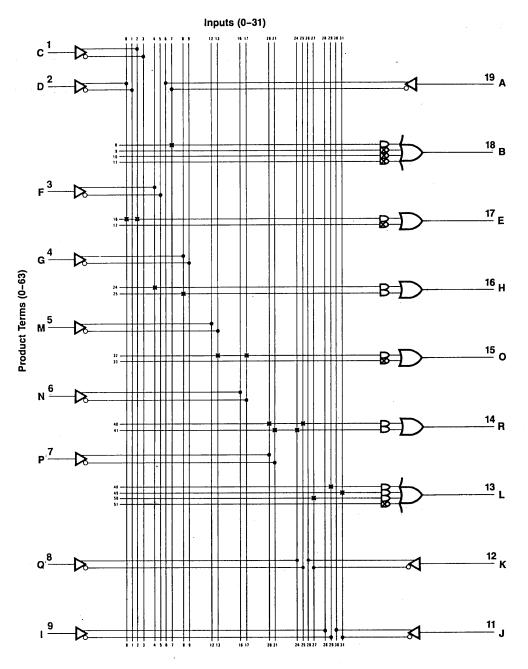

| 7.5.10                           | Transition Table                                                                                                                          | 150                      |

| 7.5.11                           | Final Function Table                                                                                                                      | 151                      |

| /                                |                                                                                                                                           | 1)1                      |

| 8.4.1                            | Function Description                                                                                                                      | 172                      |

| 8.11.1                           | Recommended Operating Conditions                                                                                                          | 198                      |

| 8.11.2                           | Electrical Characteristics                                                                                                                | 198                      |

| 8.11.3                           | Switching Characteristics                                                                                                                 | 198                      |

| 8.11.4                           | Function Table                                                                                                                            | 205                      |

| 8.12.1                           | Recommended Operating Conditions                                                                                                          | 209                      |

| 8.12.2                           | Electrical Characteristics                                                                                                                | 209                      |

| 8.12.3                           | Switching Characteristics                                                                                                                 | 209                      |

| 8.12.4                           | Memory Speed                                                                                                                              | 213                      |

| 8.12.5                           | Memory Speed of 68000                                                                                                                     | 214                      |

| 8.12.6                           | Function Table                                                                                                                            | 225                      |

| 8.13.1                           | Recommended Operating Conditions                                                                                                          | 229                      |

| 8.13.2                           | Electrical Characteristics                                                                                                                | 229                      |

| 8.13.3                           | 0                                                                                                                                         | 229                      |

| 8.13.4                           | Memory Speed Requirements                                                                                                                 | 231                      |

| 8.13.5                           | Function Table                                                                                                                            | 240                      |

|                                  |                                                                                                                                           | •.•                      |

| 11.1.1                           | 20-Pin PAL Devices                                                                                                                        | 274                      |

| 11.1.2                           | 24-Pin PAL Devices                                                                                                                        | 274                      |

| 11.1.3                           | Absolute Maximum Ratings                                                                                                                  | 275                      |

| 11.1.4                           | Standard Test Load                                                                                                                        | 275                      |

| 11.1.5                           | AC and DC Specifications for 20-Pin, Standard, Small PAL Devices .                                                                        | 276                      |

| 11.1.6                           | AC and DC Specifications for 20-Pin, Standard, Medium                                                                                     |                          |

|                                  | PAL Devices                                                                                                                               | 277                      |

| 11.1.7                           | AC and DC Specifications for 20-Pin, Fast, Small PAL Devices                                                                              | 279                      |

| <b>11.1.8</b>                    | AC and DC Specifications for 20-Pin, Fast, Medium PAL Devices                                                                             | 280                      |

#### List of Tables xxi

| Table No. | Page                                                                         | No.          |

|-----------|------------------------------------------------------------------------------|--------------|

| 11.1.9    | AC and DC Specifications for 20-Pin, Ultra High-Speed,                       |              |

|           | Medium PAL Devices                                                           | 282          |

| 11.1.10   | AC and DC Specifications for 20-Pin, Fast, Half-Power, Small                 | <b>a</b> a ( |

|           | PAL Devices                                                                  | 284          |

| 11.1.11   | AC and DC Specifications for 20-Pin, Fast, Half-Power, Medium                | 201          |

|           | PAL Devices                                                                  | 286          |

| 11.1.12   | AC and DC Specifications for 20-Pin, Ultra High-Speed,                       | 200          |

|           | Half-Power, Medium PAL Devices                                               | 288          |

| 11.1.13   | AC and DC Specifications for 24-Pin, Standard PAL Devices                    | 290          |

| 11.1.14   | AC and DC Specifications for 24-Pin, Fast PAL Devices                        | 292          |

| 11.2.1    | Input Line Select                                                            | 295          |

| 11.2.2    | Input Line Select                                                            | 295          |

| 11.3.1    | Input Line Select                                                            | 299          |

| 11.3.2    | Product Line Select                                                          | 299          |

| 11.3.3    | Programming Parameters                                                       | 301          |

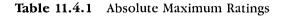

| 11.4.1    | Absolute Maximum Ratings                                                     | 305          |

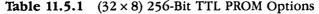

| 11.5.1    | (32 × 8) 256-Bit TTL PROM Options                                            | 307          |

| 11.5.2    | AC and DC Specifications for $(32 \times 8)$ 256-Bit TTL PROMs               | 308          |

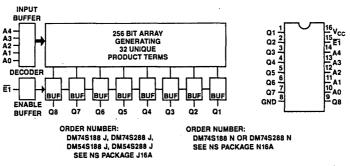

| 11.6.1    | $(32 \times 8)$ 256-Bit TTL PROM Options                                     | 309          |

| 11.6.2    | AC and DC Specifications for $(32 \times 8)$ 256-Bit TTL                     | 210          |

| 11 9 1    | Logic PROMs                                                                  | 310          |

| 11.7.1    | $(256 \times 8)$ 2048-Bit TTL PROM Options                                   | 311          |

| 11.7.2    | AC and DC Specifications for $(256 \times 8)$ 2048-Bit TTL PROMS             | 312          |

| 11.8.1    | $(512 \times 8)$ 4096-Bit TTL PROM Options                                   | 313          |

| 11.8.2    | AC and DC Specifications for (512) 4096-Bit TTL PROM                         | 314          |

| 11.9.1    | $(512 \times 8)$ 4096-Bit TTL PROM                                           | 316          |

| 11.9.2    | AC and DC Specifications for $(512 \times 8)$ 4096-Bit TTL                   | 217          |

| 11 10 1   | High-Speed PROM                                                              | 317          |

| 11.10.1   | AC and DC Specifications for $(512 \times 8)$ 4K-Bit Registered<br>TTL PROMs | 221          |

| 11.11.1   | TTL PROMs                                                                    | 321          |

| 11.11.1   |                                                                              | 325          |

| 11.12.1   | TTL PROMs<br>Programming Parameters Do Not Test or You May Program           | 525          |

| 11.12.1   | the Device                                                                   | 328          |

| 11.13.1   | Programming Parameters Do Not Test or You May Program                        | 540          |

| 11.15.1   | the Device                                                                   | 331          |

| 11.13.2   | Approved Programmers for NSC PROMs                                           | 332          |

| 11.13.2   | Quality Enhancement Program for Bipolar Memory                               | 332          |

| 11.14.1   | Quanty Emiancement riogram for Dipolar Memory                                | 554          |

| A.3.1     | The eight test patterns used for testing the multiplexer                     |              |

|           | of Figure A.4.4                                                              | 373          |

| A.3.2     | A different sequence of the eight multiplexer test patterns                  | 373          |

. .

# Programmable Logic Design Guide

1

# Introduction

## 1.1 PURPOSE OF THIS DESIGN GUIDE

This book was conceived to fill the need for a comprehensive Design Guide about Field-Programmable Logic Devices. The Guide is organized to serve both the experienced programmable logic user and the uninitiated. The primary objective of this guide is to introduce the uninitiated logic designer to programmable logic and to take the designer through a step-by-step approach to logic design by using programmable logic devices. The Guide is comprehensive in that it covers all aspects of design, including: Boolean logic basics, sequential and combinational circuit basics, testing, and applications. Every effort has been made to clearly illustrate points with examples. National Semiconductor invites comments and suggestions from our users on improving this Design Guide.

## 1.2 OVERVIEW OF PROGRAMMABLE LOGIC

Programmable Logic has been used for many years as the means of customizing logic design. The early devices were primarily mask-programmed and were developed by computer manufacturers for in-house use while the vast majority of other logic users were relegated to the world of standard SSI/MSI devices. Then, in the mid to late seventies, along came fuse-programmable logic. The logic devices could actually be customized by the designer who used external pulses generated by simple programmer equipment. Now logic designers had devices that could be customized instantly and that offered higher integration than standard logic. Field-programmable logic devices became the first, true semicustom logic that was widely available for both the small and the larger user.

Today, the user can choose from a variety of speeds, power, packages, logic features and vendors.