EEPROM DATABOOK

NATIONAL SEMICONDUCTOR CORPORATION

**JULY 1985**

## A Corporate Dedication to Quality and Reliability

National Semiconductor is an industry leader in the manufacture of high quality, high reliability integrated circuits. We have been the leading proponent of driving down IC defects and extending product lifetimes. From raw material through product design, manufacturing and shipping, our quality and reliability is second to none.

We are proud of our success . . . it sets a standard for others to achieve. Yet, our quest for perfection is ongoing so that you, our customer, can continue to rely on National Semiconductor Corporation to produce high quality products for your design systems.

whice horn

Charles E. Sporck President, Chief Executive Officer National Semiconductor Corporation

i

# Wir fühlen uns zu Qualität und Zuverlässigkeit verpflichtet

National Semiconductor Corporation ist führend bei der Herstellung von integrierten Schaltungen von hoher Qualität und hoher Zuverlässigkeit. National Semiconductor war schon immer Vorreiter, wenn es galt, die Zahl von IC Ausfällen zu verringern und die Lebensdauer von Produkten zu verbessern. Vom Rohmaterial über Entwurf und Herstellung bis zur Auslieferung sind die Qualität und die Zuverlässigkeit der Produkte von National Semiconductor sind unübertroffen.

Wir sind stolz auf unseren Erfolg, der Standards setzt, die für andere erstrebenswert sind. Auch ihre Ansprüche steigen ständig. Sie als unser Kunde können sich auch weiterhin auf National Semiconductor verlassen.

#### La Qualité et La Fiabilité:

Une Vocation Commune Chez National Semiconductor Corporation

National Semiconductor Corporation est un des leaders industriels qui fabrique des circuits intégrés d'une très grande qualité et d'une fiabilité exceptionelle. National a été le premier à vouloir faire chuter le nombre de circuits intégrés défectueux et à augmenter la durée de vie des produits. Depuis les matières premières, en passant par la conception du produit sa fabrication et son expédition, partout la qualité et la fiabilité chez National sont sans équivalents.

Nous sommes fiers de notre succès et le standard ainsi défini devrait devenir l'objectif à atteindre par les autres sociétés. Et nous continuons à vouloir faire progresser notre recherche de la perfection; il en résulte que vous, qui êtes notre client, pouvez toujours faire confiance à National Semiconductor Corporation, en produisant des systèmes d'une très grande qualité standard.

## Un Impegno Societario di Qualità e Affidabilità

National Semiconductor Corporation è un'industria al vertice nella costruzione di circuiti integrati di altà qualità ed affidabilità. National è stata il principale promotore per l'abbattimento della difettosità dei circuiti integrati e per l'allungamento della vita dei prodotti. Dal materiale grezzo attraverso tutte le fasi di progettazione, costruzione e spedizione, la qualità e affidabilità National non è seconda a nessuno.

Noi siamo orgogliosi del nostro successo che fissa per gli altri un traguardo da raggiungere. Il nostro desiderio di perfezione è d'altra parte illimitato e pertanto tu, nostro cliente, puoi continuare ad affidarti a National Semiconductor Corporation per la produzione dei tuoi sistemi con elevati livelli di qualità.

Charlie Sporth

Charles E. Sporck President, Chief Executive Officer National Semiconductor Corporation

# EEPROM DATABOOK

Datasheets

**Application Notes**

**Reliability Information**

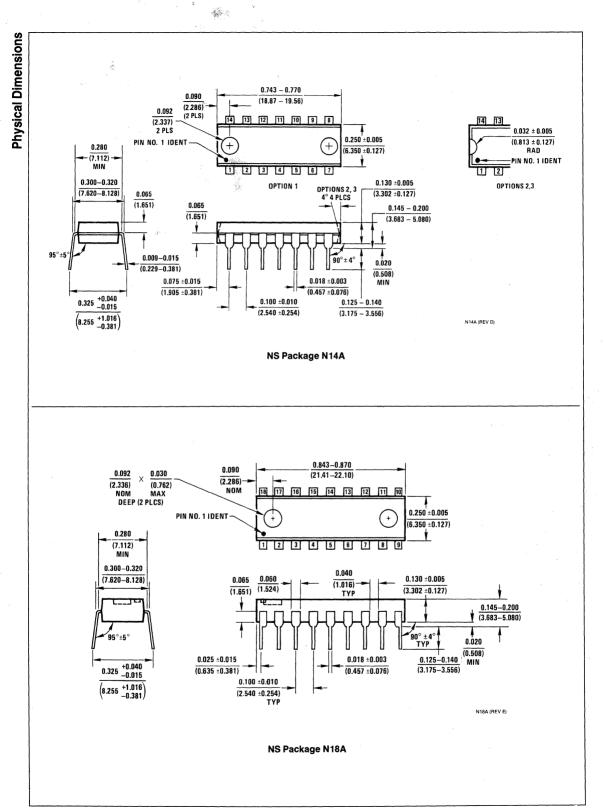

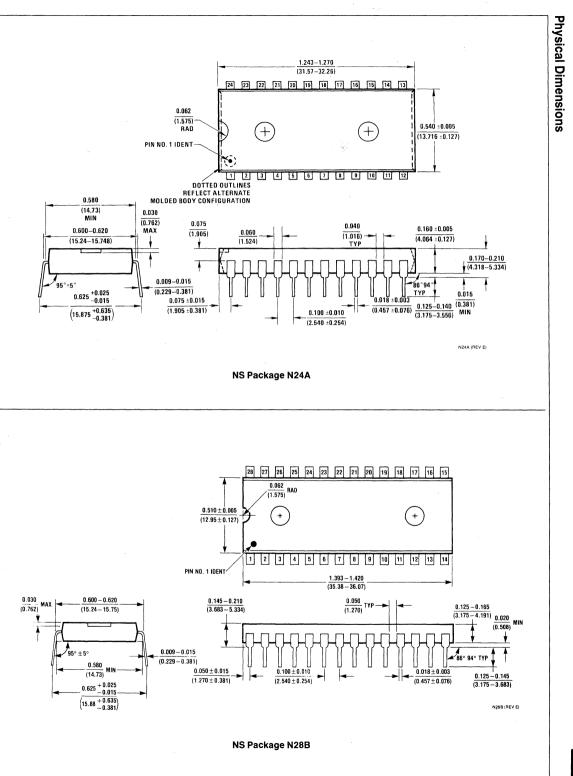

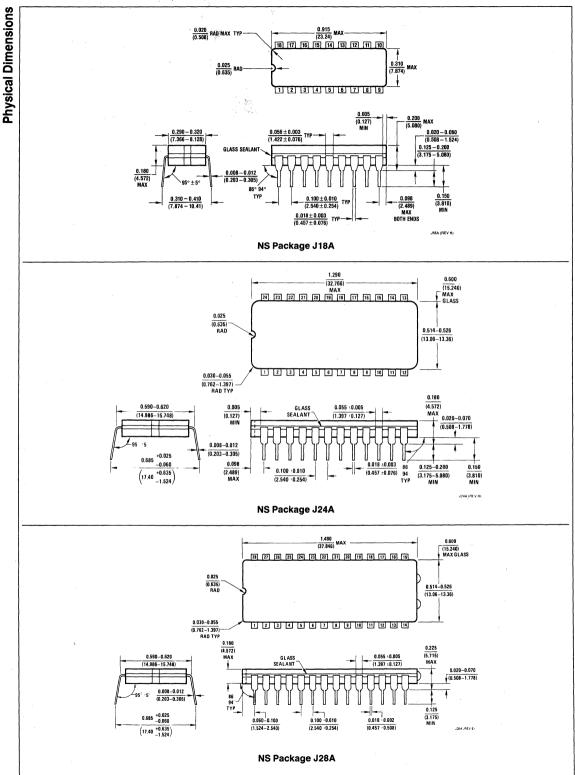

**Physical Dimensions**

#### TRADEMARKS

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

AbuseableTM Anadia™ ANS-R-TRAN™ Auto-Chem Deflasher™ BI-FETTM BI-FET II™ BI-LINE™ **BIPLANTM BLCTM BLXTM** Brite-Lite™ СІМ™ **CIMBUS™** Clock ← Chek™ СОМВО™ COPS™ microcontrollers **DATACHECKER®** DENSPAK™ DIB™ Digitalker® **DISCERNTM** DISTILLTM DNRTM **DPVMTM**

FI STARTM E-Z-LINK™ **GENIX™** HEX 3000™ **INFOCHEXTM** Integral ISE™ Intelisplay™ **ISE™** ISE/06™ ISE/08™ ISE/16™ ISE32™ Macrobus™ Macrocomponent<sup>™</sup> Meatr/Chek™ Microbus™ data bus (adjective) MICRO-DAC™ µtalker™ Microtalker™ **MICROWIRETM** MICROWIRE/PLUS™ **MOLETM**

MSTIM National® NAX 800™ Nitride Plus™ Nitride Plus Oxide™ NMLTM **NOBUS™** NSC800™ NSX-16™ NS-XC-16™ NURAM™ OXISS™ Perfect Watch™ Pharma/Chek™ **PLANTM** Polvcraft™ POSitalker<sup>™</sup> QUAD3000™ **BATTM** RTX16™ Script/Chek™ Shelf-Chek™ SERIES/800™

Series 32000™ **SPIRE™ STAR™** Starlink™ **STARPLEX™** STARPLEX IITM SuperChip™ SYS32™ **TAPE-PAK™** TDSTM ToloGatoTM The National Anthem® Time⊮Chek™ **TLCTM** Trapezoidal™ TRI-CODE™ TRI-POLY™ TRI-SAFE™ TRI-STATE® XMOS™ **XPUTM** Z STAR™ 883B/RETS™ 883\$/RETS™

TouchTone™ is a trademark of Western Electric. Z80<sup>®</sup> is a registered trademark of Zilog Corp.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR COR-PORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive, P. O. Box 58090, Santa Clara, California 95052-8090 (408) 721-5000 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

## **EEPROM Databook**

#### Introduction

v

National Semiconductor Corporation's EEPROM Databook is a comprehensive collection of information on advanced, non-volatile memory products covering the spectrum of this mainstream semiconductor component category.

Virtually every electronic system being designed today requires some level of storage capacity. National is committed to designing and supplying high-performance programmable non-volatile EPROMs and EEPROMs which are currently finding increasing usage in a wide range of microprocessorbased systems.

National is committed to technical excellence in design, manufacturing, reliability and service to our customers through the continuing development of new devices. If you don't find the memory products you need in this book, please contact your local National Semiconductor sales office or distributor.

# **Table of Contents**

| DATASHEETS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NMC9306/COP494 256-Bit Serial Electrically Erasable Programmable Memory 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NMC9306E/COP494E 256-Bit Serial Electrically Erasable Programmable Memory 1-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NMC9307E 256-Bit Serial Electrically Erasable Programmable Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| NMC9345/COP495 1024-Bit Serial Electrically Erasable Programmable Memory (5V Only)1-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| NMC9346/COP495 1024-Bit Serial Electrically Erasable Programmable Memory (5V Only) 1-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| NMC9346E/COP395 1024-Bit Serial Electrically Erasable Programmable Memory (5V Only) . 1-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

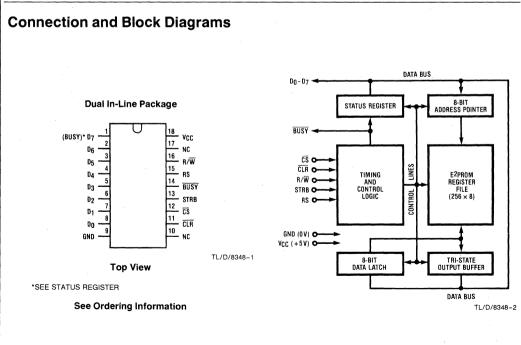

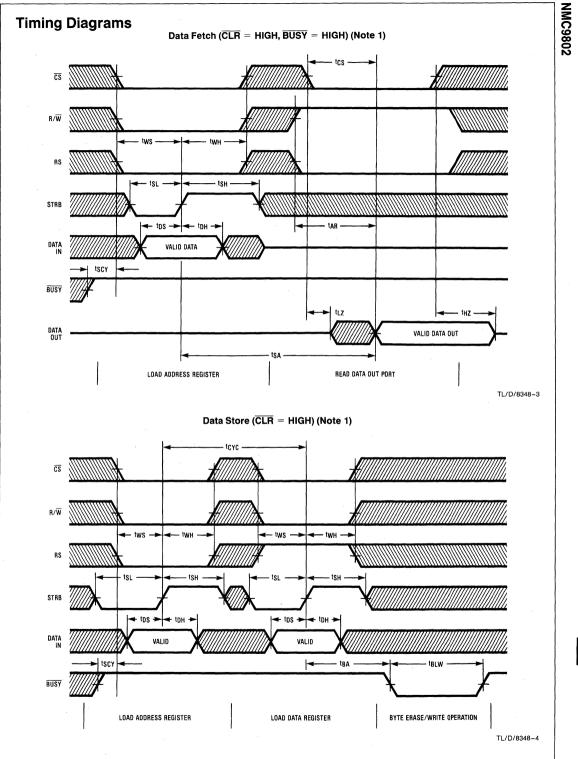

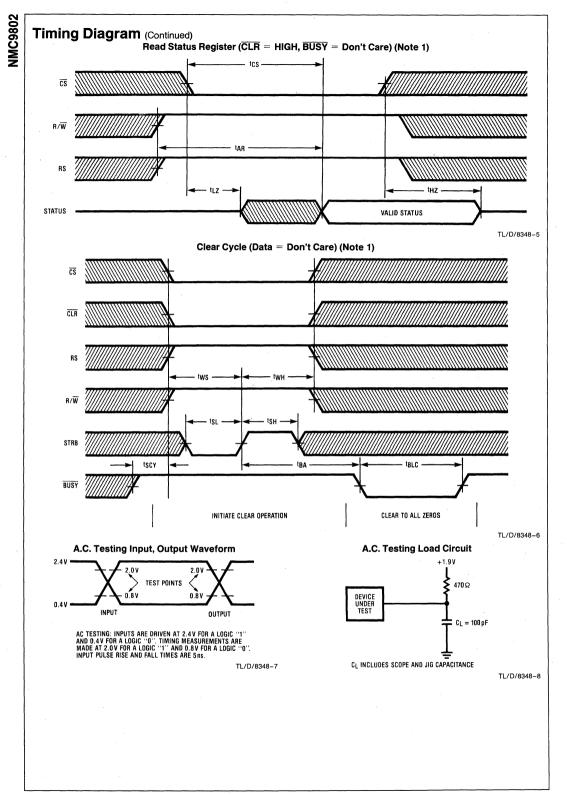

| NMC9802 2048-Bit Parallel (256 x 8) Electrically Erasable Programmable ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

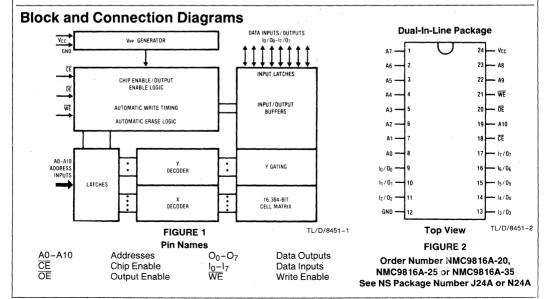

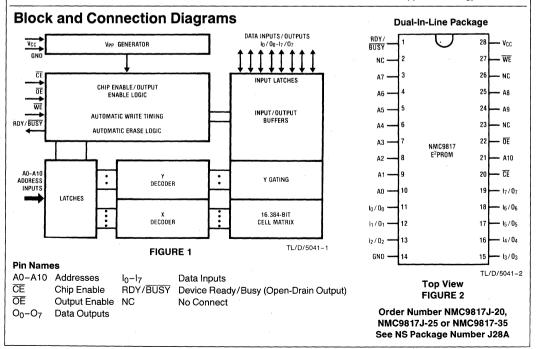

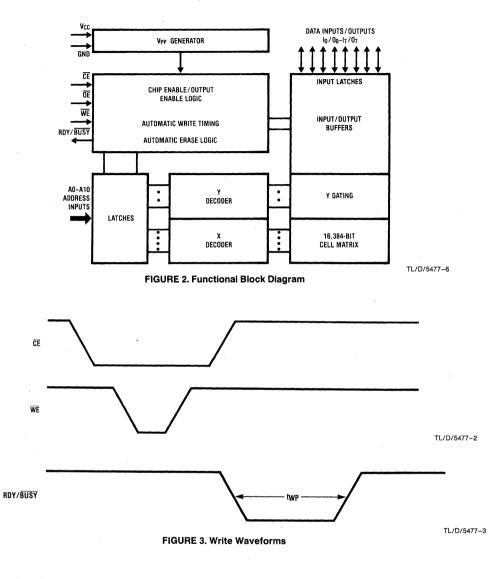

| NMC9816A 16,384-Bit (2k x 8) EEPROM1-39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

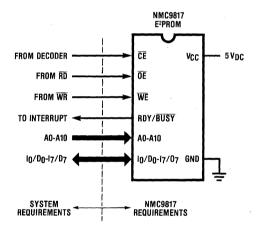

| NMC9817 16,384-Bit (2k x 8) EEPROM1-45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

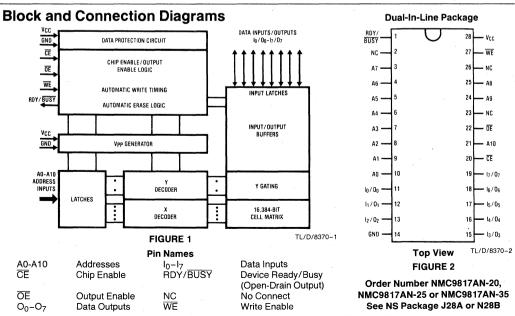

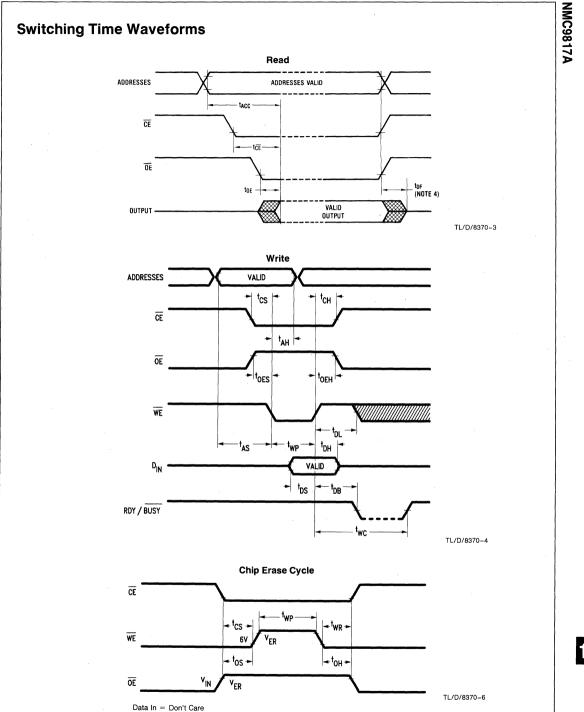

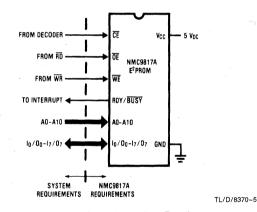

| NMC9817A 16,384-Bit (2k x 8) EEPROM1-50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

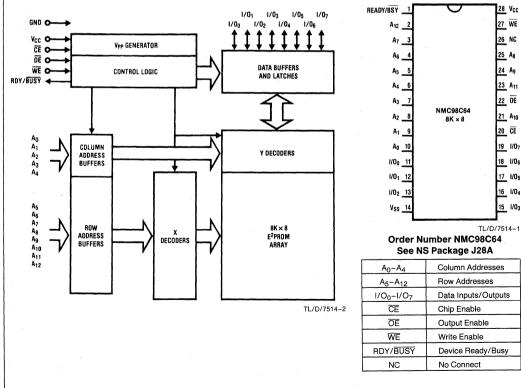

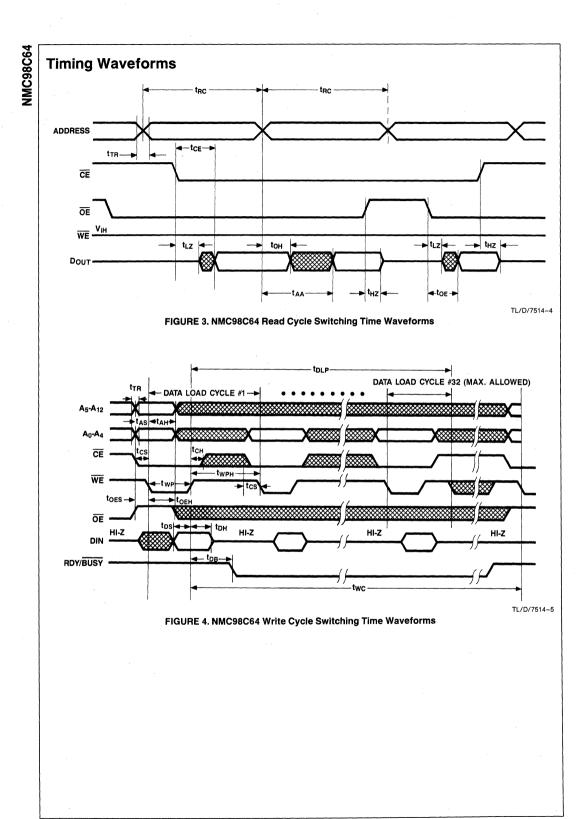

| NMC98C64A 8k x 8 CMOS Electrically Erasable PROM1-56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| APPLICATION NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AB-13 Avoiding Problems Caused by Capacitive Coupling Between Input Signal Lines or 21-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AB-13 Avoiding Problems Caused by Capacitive Coupling Between Input Signal Lines or 21-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

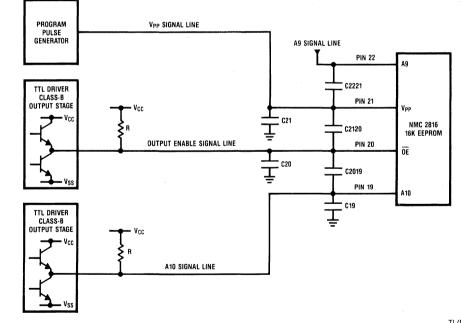

| AB-13 Avoiding Problems Caused by Capacitive Coupling Between Input Signal Lines or 21-<br>Volt EEPROMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AB-13 Avoiding Problems Caused by Capacitive Coupling Between Input Signal Lines or 21-<br>Volt EEPROMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

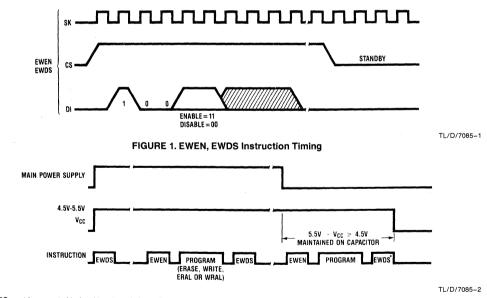

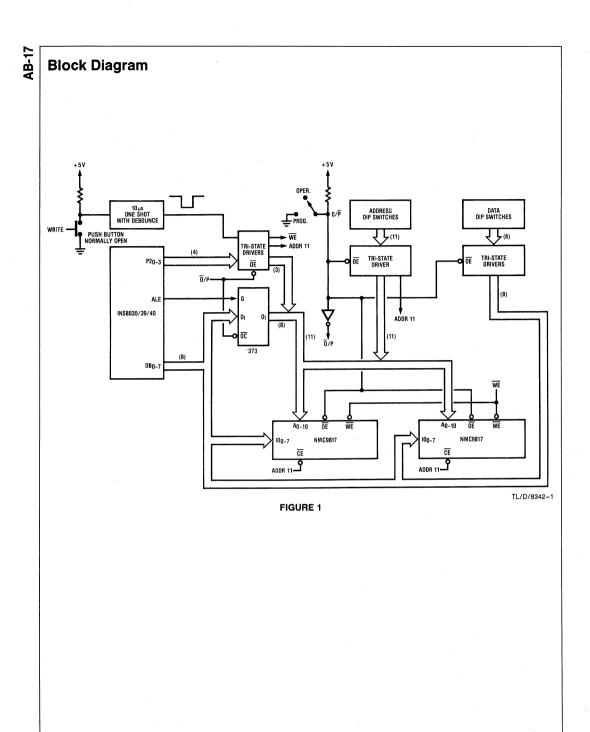

| AB-13 Avoiding Problems Caused by Capacitive Coupling Between Input Signal Lines or 21-       2-3         Volt EEPROMs       2-3         AB-15 Protecting Data in the NMC9306/COP494 and NMC9346/COP495 Serial EEPROMs       2-5         AB-17 Using EEPROMs with ROMIess Single Chip Microcontroller       2-7         AN-328 EEPROM Application Note V <sub>PP</sub> Generation on Board       2-9                                                                                                                                                                                                                       |

| AB-13 Avoiding Problems Caused by Capacitive Coupling Between Input Signal Lines or 21-         Volt EEPROMs       2-3         AB-15 Protecting Data in the NMC9306/COP494 and NMC9346/COP495 Serial EEPROMs       2-5         AB-17 Using EEPROMs with ROMIess Single Chip Microcontroller       2-7                                                                                                                                                                                                                                                                                                                      |

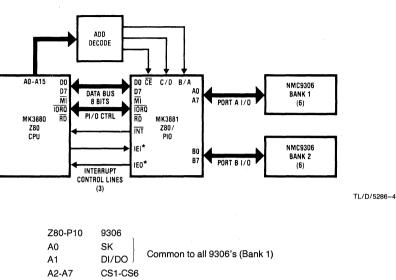

| AB-13 Avoiding Problems Caused by Capacitive Coupling Between Input Signal Lines or 21-         Volt EEPROMs       2-3         AB-15 Protecting Data in the NMC9306/COP494 and NMC9346/COP495 Serial EEPROMs       2-5         AB-17 Using EEPROMs with ROMIess Single Chip Microcontroller       2-7         AN-328 EEPROM Application Note V <sub>PP</sub> Generation on Board       2-9         AN-338 Designing with the NMC9306/COP494, a Versatile Simple to Use EEPROM       2-15                                                                                                                                   |

| AB-13 Avoiding Problems Caused by Capacitive Coupling Between Input Signal Lines or 21-<br>Volt EEPROMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AB-13 Avoiding Problems Caused by Capacitive Coupling Between Input Signal Lines or 21-<br>Volt EEPROMs       2-3         AB-15 Protecting Data in the NMC9306/COP494 and NMC9346/COP495 Serial EEPROMs       2-5         AB-17 Using EEPROMs with ROMless Single Chip Microcontroller       2-7         AN-328 EEPROM Application Note V <sub>PP</sub> Generation on Board       2-9         AN-338 Designing with the NMC9306/COP494, a Versatile Simple to Use EEPROM       2-15         AN-342 Designing with the NMC9817, a 2nd Generation EEPROM       2-22                                                          |

| AB-13 Avoiding Problems Caused by Capacitive Coupling Between Input Signal Lines or 21-       2-3         Volt EEPROMs       2-3         AB-15 Protecting Data in the NMC9306/COP494 and NMC9346/COP495 Serial EEPROMs       2-5         AB-17 Using EEPROMs with ROMless Single Chip Microcontroller       2-7         AN-328 EEPROM Application Note V <sub>PP</sub> Generation on Board       2-9         AN-338 Designing with the NMC9306/COP494, a Versatile Simple to Use EEPROM       2-15         AN-342 Designing with the NMC9817, a 2nd Generation EEPROM       2-22         RELIABILITY INFORMATION       3-3 |

# Alpha-Numerical Index

| AB-13 Avoiding Problems Caused by Capacitive Coupling Between Input Signal Lines on        |

|--------------------------------------------------------------------------------------------|

| 21-Volt EEPROMs                                                                            |

| AB-15 Protecting Data in the NMC9306/COP494 and NMC9346/COP495 Serial EEPROMs . 2-5        |

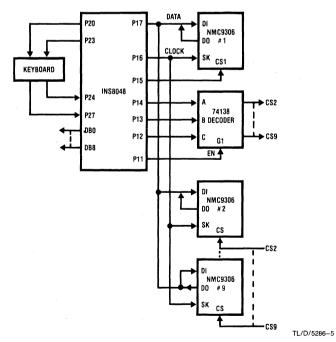

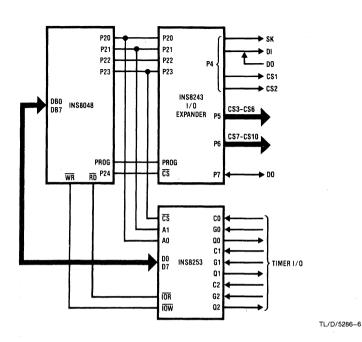

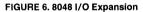

| AB-17 Using EEPROMs with ROMless Single Chip Microcontroller 2-7                           |

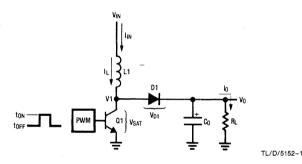

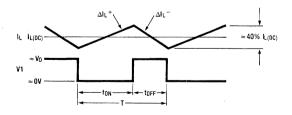

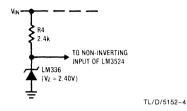

| AN-328 EEPROM Application Note VPP Generation on Board 2-9                                 |

| AN-338 Designing with the NMC9306/COP494, a Versatile, Simple to Use EEPROM 2-15           |

| AN-342 Designing with the NMC9817, a 2nd Generation EEPROM                                 |

| NMC9306/COP494 256-Bit Serial Electrically Erasable Programmable Memory 1-3                |

| NMC9306E/COP494E 256-Bit Serial Electrically Erasable Programmable Memory 1-8              |

| NMC9307E 256-Bit Serial Electrically Erasable Programmable Memory                          |

| NMC9345/COP495 1024-Bit Serial Electrically Erasable Programmable Memory (5V Only)1-18     |

| NMC9346/COP495 1024-Bit Serial Electrically Erasable Programmable Memory (5V Only)1-23     |

| NMC9346E/COP395 1024-Bit Serial Electrically Erasable Programmable Memory (5V Only) . 1-28 |

| NMC9802 2048-Bit Parallel (256 x 8) Electrically Erasable Programmable ROM 1-33            |

| NMC9816A 16,384-Bit (2k x 8) EEPROM                                                        |

| NMC9817 16,384-Bit (2k x 8) EEPROM1-45                                                     |

| NMC9817A 16,384-Bit (2k x 8) EEPROM1-50                                                    |

| NMC98C64A 8k x 8 CMOS Electrically Erasable PROM1-56                                       |

| Reliability Qualification Procedure for All EEPROM Products 3-5                            |

| The A+ Reliability Enhancement Program 3-3                                                 |

# Section 1

# Datasheets

# National Semiconductor

# NMC9306/COP494 256-Bit Serial Electrically Erasable **Programmable Memory**

## **General Description**

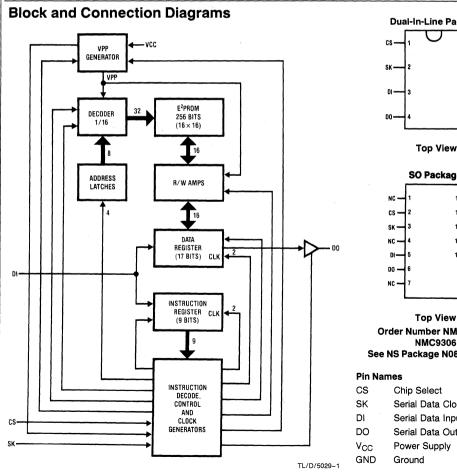

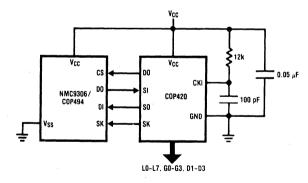

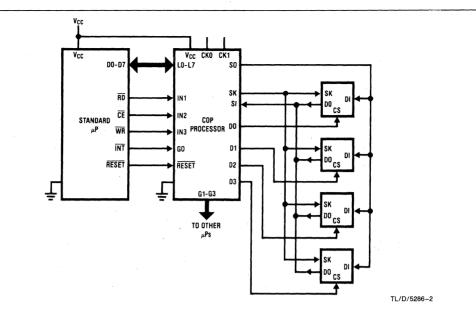

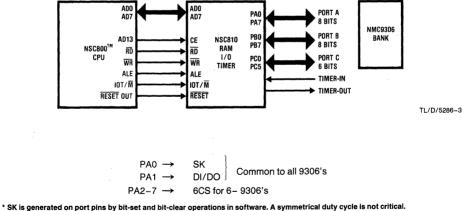

The NMC9306/COP494 is a 256-bit non-volatile sequential access memory fabricated using advanced floating gate N-channel E<sup>2</sup>PROM technology. It is a peripheral memory designed for data storage and/or timing and is accessed via the simple MICROWIRE™ serial interface. The device contains 256 bits of read/write memory divided into 16 registers of 16 bits each. Each register can be serially read or written by a COP400 series controller. Written information is stored in a floating gate cell with at least 10 years data retention and can be updated by an erase-write cycle. The NMC9306/COP494 has been designed to meet applications requiring up to  $1 \times 10^4$  erase/write cycles per register. A power down mode reduces power consumption by 70 percent.

#### Features

- Low cost

- Single supply operation (5V±10%)

- TTL compatible

- 16×16 serial read/write memory

- MICROWIRE compatible serial I/O

- Compatible with COP400 processors

- Low standby power

- Non-volatile erase and write

- Reliable floating gate technology

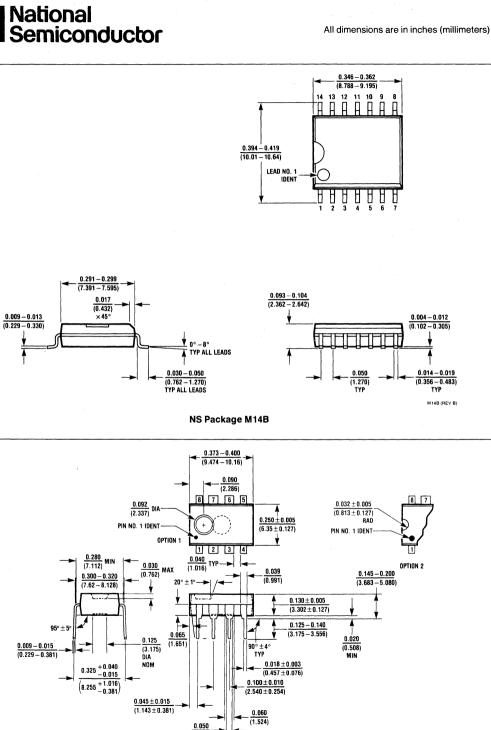

Order Number NMC9306N. NMC9306 See NS Package N08E or M14B

Chip Select Serial Data Clock Serial Data Input Serial Data Output Power Supply

## Absolute Maximum Ratings

| Voltage Relative to GND             | +6V to -0.3V    |

|-------------------------------------|-----------------|

| Ambient Operating Temperature       |                 |

| NMC9306/COP494                      | 0°C to +70°C    |

| Ambient Storage Temperature         |                 |

| with Data Retention                 | -65°C to +125°C |

| Lead Temperature (Soldering, 10 sec | onds) 300°C     |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## $Electrical \ Characteristics \ {}_{0}\circ C \leq TA \leq \ 70\circ C, \ V_{CC} = 5V \pm 10\% \ unless \ otherwise \ specified$

| Parameter                                                                                                         | Conditions                                                                              | Min                    | Тур | Max                       | Units                |

|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------|-----|---------------------------|----------------------|

| Operating Voltage (V <sub>CC</sub> )                                                                              |                                                                                         | 4.5                    |     | 5.5                       | v                    |

| Operating Current (I <sub>CC1</sub> )                                                                             | $V_{CC} = 5.5V, CS = 1$                                                                 |                        |     | 10                        | mA                   |

| Standby Current (I <sub>CC2)</sub>                                                                                | $V_{CC} = 5.5V, CS = 0$                                                                 |                        |     | 3                         | mA                   |

| Input Voltage Levels<br>ViL<br>ViH                                                                                |                                                                                         | -0.1<br>2.0            |     | 0.8<br>V <sub>CC</sub> +1 | v<br>v               |

| Output Voltage Levels<br>V <sub>OL</sub><br>V <sub>OH</sub>                                                       | I <sub>OL</sub> =2.1 mA<br>I <sub>OH</sub> = -400 μA                                    | 2.4                    |     | 0.4                       | v<br>v               |

| Input Leakage Current                                                                                             | V <sub>IN</sub> =5.5V                                                                   |                        |     | 10                        | μΑ                   |

| Output Leakage Current                                                                                            | V <sub>OUT</sub> =5.5V, CS=0                                                            |                        |     | 10                        | μA                   |

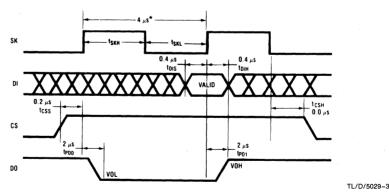

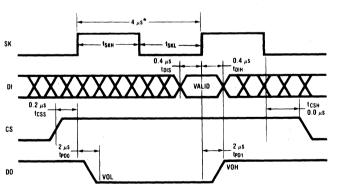

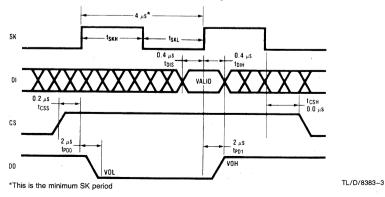

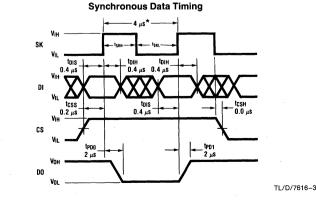

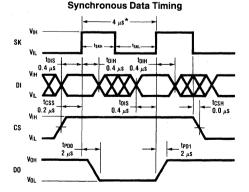

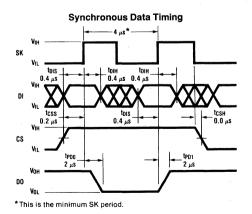

| SK Frequency<br>SK HIGH TIME t <sub>SKH</sub> (Note 2)<br>SK LOW TIME t <sub>SKL</sub> (Note 2)                   |                                                                                         | 0 ·<br>1<br>1          |     | 250                       | kHz<br>μs<br>μs      |

| Input Set-Up and Hold Times<br>CS t <sub>CSS</sub><br>t <sub>CSH</sub><br>DI t <sub>DIS</sub><br>t <sub>DIH</sub> |                                                                                         | 0.2<br>0<br>0.4<br>0.4 |     |                           | μs<br>μs<br>μs<br>μs |

| Output Delay<br>DO t <sub>PD1</sub><br>t <sub>PD0</sub>                                                           | $CL = 100 \text{ pF} \\ V_{OL} = 0.8V, V_{OH} = 2.0V \\ V_{IL} = 0.45V, V_{IH} = 2.40V$ |                        |     | 2<br>2                    | μs<br>μs             |

| Erase/Write Pulse Width ( $t_{E/W}$ ) (Note 1)                                                                    |                                                                                         | 10                     |     | 30                        | ms                   |

| CS Low Time (t <sub>CS</sub> ) (Note 3)                                                                           |                                                                                         | 1                      |     |                           | μs                   |

Note 1: tE/W measured to rising edge of SK or CS, whichever occurs last.

Note 2: The SK frequency spec. specifies a minimum SK clock period of 4  $\mu$ s, therefore in an SK clock cycle,  $t_{SKH} + t_{SKL}$  must be greater than or equal to 4  $\mu$ s. e.g. if  $t_{SKL} = 1 \mu$ s then the minimum  $t_{SKH} = 3 \mu$ s in order to meet the SK frequency specification.

Note 3: CS must be brought low for a minimum of 1  $\mu$ s (t<sub>CS</sub>) between consecutive instruction cycles.

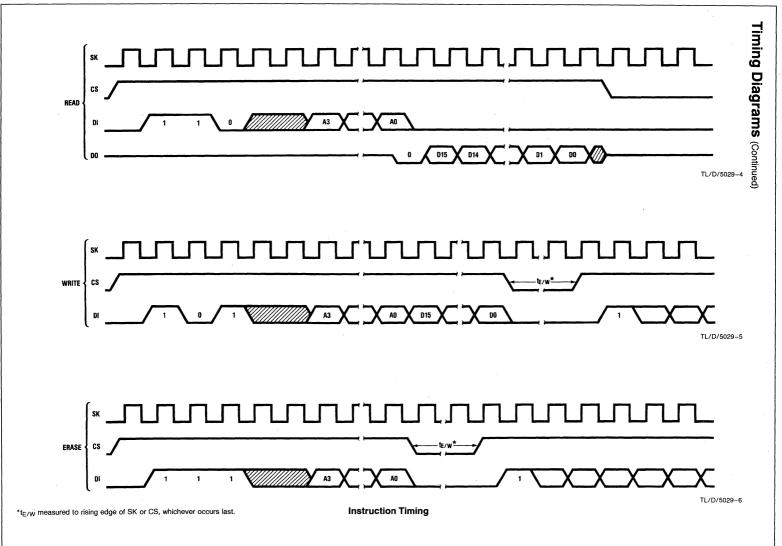

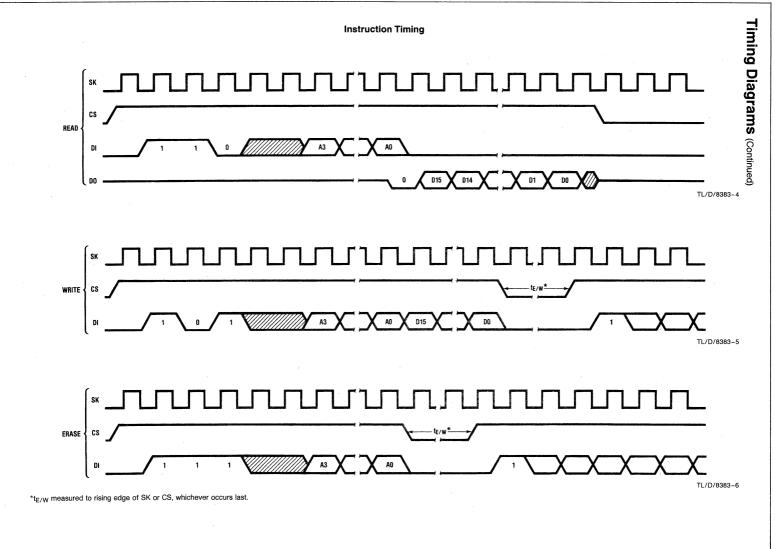

## **Instruction Set**

| Instruction | SB | Op Code | Address  | Data   | Comments                |  |

|-------------|----|---------|----------|--------|-------------------------|--|

| READ        | 1  | 10xx    | A3A2A1A0 |        | Read register A3A2A1A0  |  |

| WRITE       | 1  | 01xx    | A3A2A1A0 | D15-D0 | Write register A3A2A1A0 |  |

| ERASE       | 1  | 11xx    | A3A2A1A0 |        | Erase register A3A2A1A0 |  |

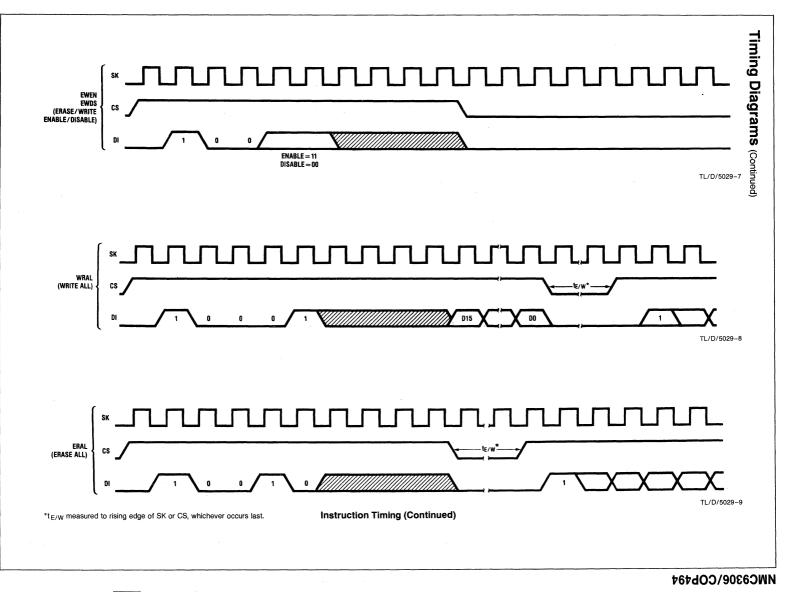

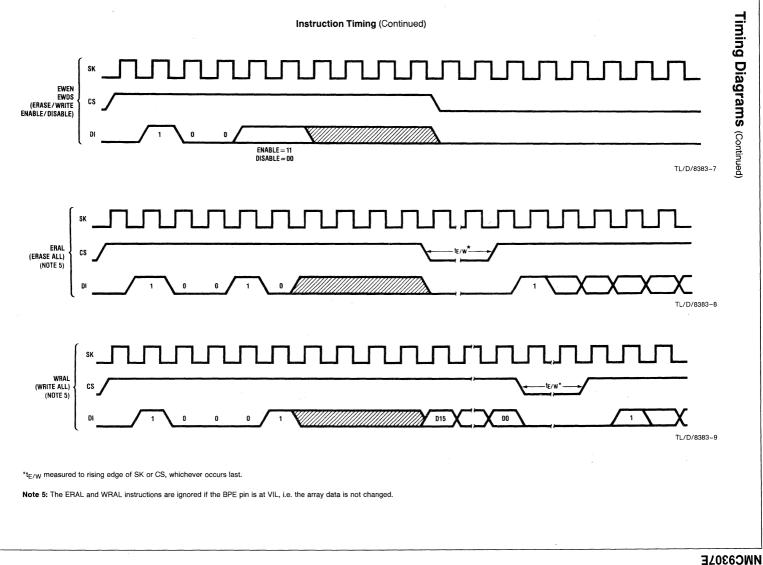

| EWEN        | 1  | 0011    | XXXX     |        | Erase/write enable      |  |

| EWDS        | 1  | 0000    | XXXX     |        | Erase/write disable     |  |

| ERAL        | 1  | 0010    | XXXX     |        | Erase all registers     |  |

| WRAL        | 1  | 0001    | хххх     | D15-D0 | Write all registers     |  |

NMC9306/COP494 has 7 instructions as shown. Note that MSB of any given instruction is a "1" and is viewed as a start bit in the interface sequence. The next 8 bits carry the op code and the 4-bit address for 1 of 16, 16-bit registers. X is a don't care state.

## **Functional Description**

The NMC9306/COP494 is a small peripheral memory intended for use with COPS™ controllers and other non-volatile memory applications. Its organization is sixteen registers and each register is sixteen bits wide. The input and output pins are controlled by separate serial formats. Seven 9-bit instructions can be executed. The instruction format has a logical '1' as a start bit, four bits as an op code, and four bits of address. SK clock cycle is necessary after CS equals logical "1" before the instruction can be loaded. The onchip programming-voltage generator allows the user to use a single power supply (V<sub>CC</sub>). Only during the read mode is the serial output (DO) pin valid. During all other modes the DO pin is in TRI-STATE®, eliminating bus contention.

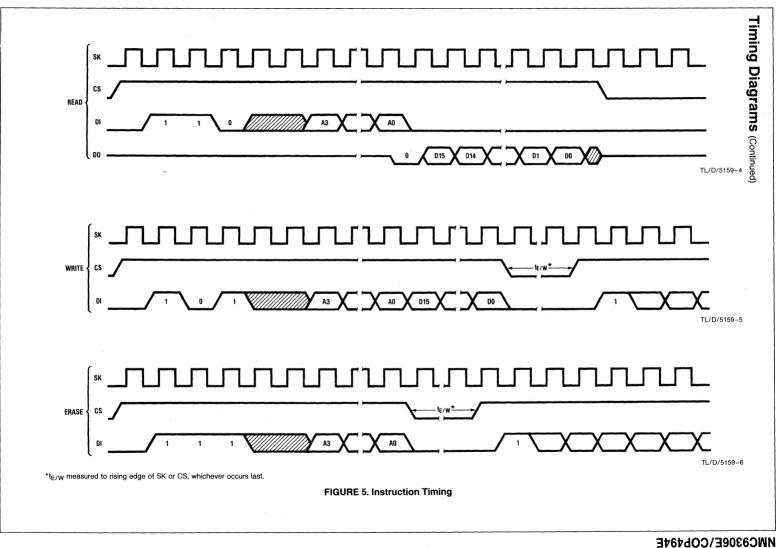

#### READ

The read instruction is the only instruction which outputs serial data on the DO pin. after a READ instruction is received, the instruction and address are decoded, followed by data transfer from the memory register into a 16-bit serial-out shift register. A dummy bit (logical '0') precedes the 16-bit data output string. Output data changes are initiated by a low to high transition of the SK clock.

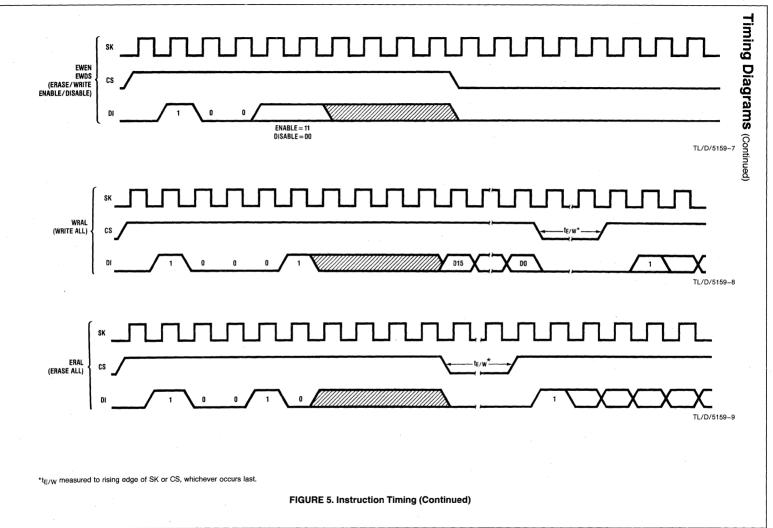

#### ERASE/WRITE ENABLE AND DISABLE

Programming must be preceded once by a programming enable (EWEN) instruction. Programming remains enabled until a programming disable (EWDS) instruction is executed. The programming disable instruction is provided to protect against accidental data disturb. Execution of a READ instruction is independent of both EWEN and EWDS instructions.

#### ERASE (Note 4)

Like most E<sup>2</sup>PROMS, the register must first be erased (all bits set to 1s) before the register can be written (certain bits

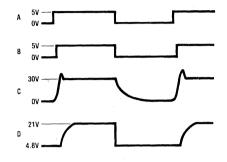

## **Timing Diagrams**

set to 0s). After an ERASE instruction is input, CS is dropped low. This falling edge of CS determines the start of programming. The register at the address specified in the instruction is then set entirely to 1s. When the erase/write programming time ( $t_{E/W}$ ) constraint has been satisfied, CS is brought up for at least one SK period. A new instruction may then be input, or a low-power standby state may be achieved by dropping CS low.

#### WRITE (Note 4)

The WRITE instruction is followed by 16 bits of data which are written into the specified address. This register must have been previously erased. Like any programming mode, erase/write time is determined by the low state of CS following the instruction. The on-chip high voltage section only generates high voltage during these programming modes, which prevents spurious programming during other modes. When CS rises to V<sub>IH</sub>, the programming cycle ends. All programming modes should be ended with CS high for one SK period, or followed by another instruction.

#### CHIP ERASE (Note 4)

Entire chip erasing is provided for ease of programming. Erasing the chip means that all registers in the memory array have each bit set to a 1. Each register is then ready for a WRITE instruction.

#### CHIP WRITE (Note 4)

All registers must be erased before a chip write operation. The chip write cycle is identical to the write cycle, except for the different op code. All registers are simultaneously written with the data pattern specified in the instruction.

Note 4: During a programming mode (write, erase, chip erase, chip write), SK clock is only needed while the actual instruction, i.e., start bit, op code, address and data, is being input. It can remain deactivated during the Erase/ Write pulse width ( $t_{E,W}$ ).

\*This is the minimum SK period

Synchronous Data Timing

1

#### NMC9306/COP494

# National Semiconductor

# NMC9306E/COP494E 256-Bit Serial Electrically Erasable **Programmable Memory**

## **General Description**

The NMC9306E/COP494E is a 256-bit non-volatile sequential access memory fabricated using advanced floating gate N-channel E<sup>2</sup>PROM technology. It is a peripheral memory designed for data storage and/or timing and is accessed via the simple MICROWIRETM serial interface. The device contains 256 bits of read/write memory divided into 16 registers of 16 bits each. Each register can be serially read or written by a COP400 series controller. Written information is stored in a floating gate cell with at least 10 years data retention and can be updated by an erase-write cycle. The NMC9306E/COP494E has been designed to meet applications requiring up to 1 imes 10<sup>4</sup> erase/write cycles per register. A power down mode reduces power consumption by 70 percent.

#### Features

- . Low cost

- Single supply operation (5V ±10%)

- . TTL compatible

- -16 x 16 serial read/write memory

- MICROWIRE compatible serial I/O

- Compatible with COP400 processors -

- Low standby power

- Non-volatile erase and write

- Reliable floating gate technology

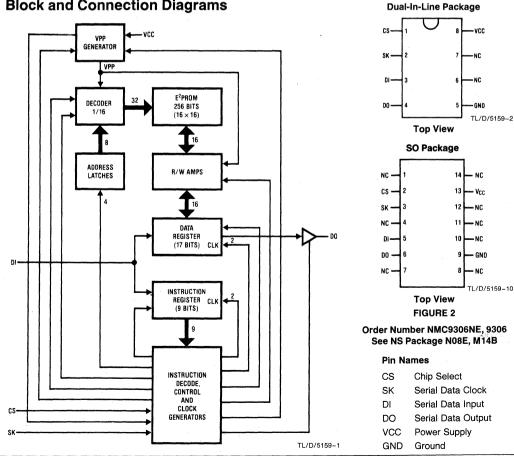

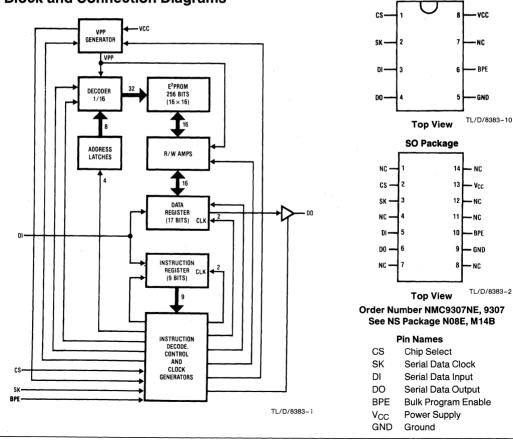

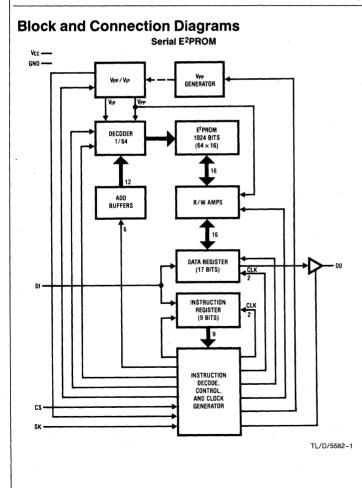

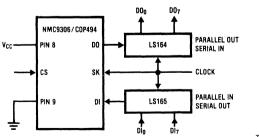

## **Block and Connection Diagrams**

## **Absolute Maximum Ratings**

| Voltage Relative to GND                            | +6V to -0.3V    |

|----------------------------------------------------|-----------------|

| Ambient Operating Temperature<br>NMC9306E/COP494E  | -40°C to +85°C  |

| Ambient Storage Temperature<br>with Data Retention | -65°C to +125°C |

| Lead Temp. (Soldering, 10 seconds)                 | 300°C           |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Electrical Characteristics** $-40^{\circ}C \le TA \le +85^{\circ}C$ , VCC = 5V $\pm 10\%$ unless otherwise specified

| Parameter                                                                                                         | Conditions                                                                                                                                             | Min                    | Тур | Max          | Units                |

|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|--------------|----------------------|

| Operating Voltage (VCC)                                                                                           |                                                                                                                                                        | 4.5                    |     | 5.5          | V                    |

| Operating Current (ICC1)                                                                                          | VCC=5.5V, CS=1                                                                                                                                         |                        |     | 10           | mA                   |

| Standby Current (ICC2)                                                                                            | VCC=5.5V, CS=0                                                                                                                                         |                        |     | 3            | mA                   |

| Input Voltage Levels<br>VIL<br>VIH                                                                                |                                                                                                                                                        | - 0.1<br>2.0           |     | 0.8<br>VCC+1 | V<br>V               |

| Output Voltage Levels<br>VOL<br>VOH                                                                               | IOL = 2.1  mA<br>$IOH = -400 \mu \text{A}$                                                                                                             | 2.4                    |     | 0.4          | V<br>V               |

| Input Leakage Current                                                                                             | VIN = 5.5V                                                                                                                                             |                        |     | 10           | μΑ                   |

| Output Leakage Current                                                                                            | VOUT=5.5V, CS=0                                                                                                                                        |                        |     | 10           | μΑ                   |

| SK Frequency<br>SK HIGH TIME t <sub>SKH</sub> (Note 2)<br>SK LOW TIME T <sub>SKL</sub> (Note 2)                   |                                                                                                                                                        | 0<br>1<br>1            |     | 250          | kHz<br>μs<br>μs      |

| Input Set-up and Hold Times<br>CS T <sub>CSS</sub><br>t <sub>CSH</sub><br>DI t <sub>DIS</sub><br>t <sub>DIH</sub> |                                                                                                                                                        | 0.2<br>0<br>0.4<br>0.4 |     |              | μs<br>μs<br>μs<br>μs |

| Output Delay<br>DO t <sub>PD1</sub><br>t <sub>PD0</sub>                                                           | $\begin{array}{l} C_L = 100 \ \text{pF} \\ V_{OL} = 0.8 \text{V}, V_{OH} = 2.0 \text{V} \\ V_{IL} = 0.45 \text{V}, V_{IH} = 2.40 \text{V} \end{array}$ |                        |     | 2<br>2       | μs<br>μs             |

| Erase/Write Pulse Width (t <sub>E/W</sub> ) (Note 1)                                                              |                                                                                                                                                        | 10                     |     | 30           | ms                   |

| CS Low Time (t <sub>CS</sub> ) (Note 3)                                                                           |                                                                                                                                                        | 1                      |     |              | μs                   |

Note 1: tE/W measured to rising edge of SK or CS, whichever occurs last.

Note 2: The SK frequency spec. specifies a minimum SK clock period of 4  $\mu$ s, therefore in an SK clock cycle, t<sub>SKH</sub> + t<sub>SKL</sub> must be greater than or equal to 4  $\mu$ s. e.g. if t<sub>SKL</sub> = 1  $\mu$ s then the minimum t<sub>SKH</sub> = 3  $\mu$ s in order to meet the SK frequency specification.

Note 3: CS must be brought low for a minimum of 1  $\mu s$  (t<sub>CS</sub>) between consecutive instruction cycles.

## Instruction Set

| Instruction | SB | Op Code | Address  | Data   | Comments                |  |

|-------------|----|---------|----------|--------|-------------------------|--|

| READ        | 1  | 10xx    | A3A2A1A0 |        | Read register A3A2A1A0  |  |

| WRITE       | 1  | 01xx    | A3A2A1A0 | D15-D0 | Write register A3A2A1A0 |  |

| ERASE       | 1  | 11xx    | A3A2A1A0 |        | Erase register A3A2A1A0 |  |

| EWEN        | 1  | 0011    | хххх     |        | Erase/write enable      |  |

| EWDS        | 1  | 0000    | хххх     |        | Erase/write disable     |  |

| ERAL        | 1  | 0010    | xxxx     |        | Erase all registers     |  |

| WRAL        | 1  | 0001    | XXXX     | D15-D0 | Write all registers     |  |

NMC9306E/COP494E has 7 instructions as shown. Note that MSB of any given instruction is a "1" and is viewed as a start bit in the interface sequence. The next 8 bits carry the op code and the 4-bit address for 1 of 16, 16-bit registers.

X is a don't care state.

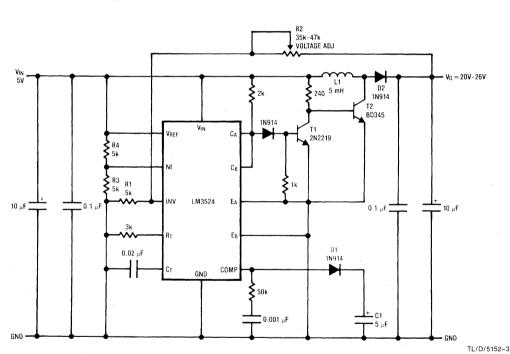

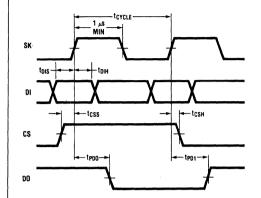

FIGURE 3

## **Functional Description**

The NMC9306E/COP494E is a small peripheral memory intended for use with COPS™ controllers and other non-volatile memory applications. Its organization is sixteen registers and each register is sixteen bits wide. The input and output pins are controlled by separate serial formats. Seven 9-bit instructions can be executed. The instruction format has a logical '1' as a start bit, four bits as an op code, and four bits of address. SK clock cycle is necessary after CS equals logical "1" before the instruction can be loaded. The onchip programming-voltage generator allows the user to use a single power supply (VCC). Only during the read mode is the serial output (DO) pin valid. During all other modes the DO pin is in TRI-STATE®, eliminating bus contention.

#### READ

The read instruction is the only instruction which outputs serial data on the DO pin. After a READ instruction is received, the instruction and address are decoded, followed by data transfer from the memory register into a 16-bit serial-out shift register. A dummy bit (logical '0') precedes the 16-bit data output string. Output data changes are initiated by a low to high transition of the SK clock.

#### ERASE/WRITE ENABLE AND DISABLE

Programming must be preceded once by a programming enable (EWEN) instruction. Programming remains enabled until a programming disable (EWDS) instruction is executed. The programming disable instruction is provided to protect against accidental data disturb. Execution of a READ instruction is independent of both EWEN and EWDS instructions.

#### ERASE (Note 4)

Like most E<sup>2</sup>PROMS, the register must first be erased (all bits set to 1s) before the register can be written (certain bits

set to 0s). After an ERASE instruction is input, CS is dropped low. This falling edge of CS determines the start of programming. The register at the address specified in the instruction is then set entirely to 1s. When the erase/write programming time ( $t_{E/W}$ ) constraint has been satisfied, CS is brought up for at least one SK period. A new instruction may then be input, or a low-power standby state may be achieved by dropping CS low.

#### WRITE (Note 4)

The WRITE instruction is followed by 16 bits of data which are written into the specified address. This register must have been previously erased. Like any programming mode, erase/write time is determined by the low state of CS following the instruction. The on-chip high voltage section only generates high voltage during these programming modes, which prevents spurious programming during other modes. When CS rises to VIH, the programming cycle ends. All programming modes should be ended with CS high for one SK period, or followed by another instruction.

#### CHIP ERASE (Note 4)

Entire chip erasing is provided for ease of programming. Erasing the chip means that all registers in the memory array have each bit set to a 1. Each register is then ready for a WRITE instruction.

#### CHIP WRITE (Note 4)

All registers must be erased before a chip write operation. The chip write cycle is identical to the write cycle, except for the different op code. All registers are simultaneously written with the data pattern specified in the instruction.

Note 4: During a programming mode (write, erase, chip erase, chip write), SK clock is only needed while the actual instruction. i.e. start bit, op code, address and data, is being input. It can remain deactivated during the Erase/ Write pulse width (t<sub>EW</sub>).

TI /D/5159-3

## Timing Diagrams

\* This is the minimum SK period

#### NMC9306E/COP494E

# National Semiconductor

# NMC9307E 256-Bit Serial Electrically Erasable **Programmable Memory**

## **General Description**

The NMC9307E is a 256-bit non-volatile sequential access memory fabricated using advanced floating gate N-channel E<sup>2</sup>PROM technology. It is a peripheral memory designed for data storage and/or timing and is accessed via the simple MICROWIRE™ serial interface. The device contains 256 bits of read/write memory divided into 16 registers of 16 bits each. Each register can be serially read or written by a COP400 series controller. Bulk programming instructions (chip erase, chip write) can be enabled or disabled by the user for enhanced data protection. Written information is stored in a floating gate cell with at least 10 years data retention and can be updated by an erase-write cycle. The NMC9307E has been designed to meet applications requiring up to 1×10<sup>4</sup> erase/write cycles per register. A power down mode reduces power consumption by 70 percent.

#### Features

- Low cost

- Single supply operation (5V ± 10%)

- TTL compatible

- 16 x 16 serial read/write memory

- . MICROWIRE compatible serial I/O

- . Compatible with COP400 processors

- Low standby power

- Non-volatile erase and write

- Reliable floating gate technology

- Bulk programming enable/disable for enhanced data protection

**Dual-In-Line Package**

## Absolute Maximum Ratings

| Voltage Relative to GND            | +6V to -0.3V    |

|------------------------------------|-----------------|

| Ambient Operating Temperature      |                 |

| NMC9307E                           | -40°C to +85°C  |

| Ambient Storage Temperature        | -65°C to +125°C |

| Lead Temp. (Soldering, 10 seconds) | 300°C           |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Electrical Characteristics** $-40^{\circ}$ C $\leq$ TA $\leq$ $+85^{\circ}$ C, V<sub>CC</sub> = 5V $\pm$ 10% unless otherwise specified

| Parameter                                                                                                         | Conditions                                                                                                                           | Min                    | Тур | Max                        | Units                |

|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|----------------------------|----------------------|

| Operating Voltage (V <sub>CC</sub> )                                                                              |                                                                                                                                      | 4.5                    |     | 5.5                        | V                    |

| Operating Current (I <sub>CC1</sub> )                                                                             | $V_{\rm CC} = 5.5 V, C_{\rm S} = 1$                                                                                                  |                        |     | 10                         | mA                   |

| Standby Current (I <sub>CC2</sub> )                                                                               | $V_{CC} = 5.5 V, C_{S} = 0$                                                                                                          |                        |     | 3                          | mA                   |

| Input Voltage Levels<br>V <sub>IL</sub><br>VIH                                                                    |                                                                                                                                      | -0.1<br>2.0            |     | 0.8<br>V <sub>CC</sub> + 1 | v<br>v               |

| Output Voltage Levels<br>V <sub>OL</sub><br>V <sub>OH</sub>                                                       | $I_{OL} = 2.1 \text{ mA}$<br>$I_{OH} = -400 \ \mu\text{A}$                                                                           | 2.4                    |     | 0.4                        | v<br>v               |

| Input Leakage Current<br>PINS 1, 2, 3<br>PIN 6                                                                    | $V_{IN} = 0$ to 5.5V                                                                                                                 |                        |     | ±10<br>±50                 | μΑ<br>μΑ             |

| Output Leakage Current                                                                                            | $V_{OUT} = 5.5V, CS = 0$                                                                                                             |                        |     | 10                         | μΑ                   |

| SK Frequency<br>SK HIGH TIME t <sub>SKH</sub> (Note 2)<br>SK LOW TIME t <sub>SKL</sub> (Note 2)                   |                                                                                                                                      | 0<br>1<br>1            |     | 250                        | kHz<br>μs<br>μs      |

| Input Set-Up and Hold Times<br>CS t <sub>CSS</sub><br>t <sub>CSH</sub><br>DI t <sub>DIS</sub><br>t <sub>DIH</sub> |                                                                                                                                      | 0.2<br>0<br>0.4<br>0.4 |     |                            | μs<br>μs<br>μs<br>μs |

| Output Delay<br>DO t <sub>PD1</sub><br>t <sub>PD0</sub>                                                           | $\begin{array}{l} CL = \ 100 \ _{p} F \\ V_{OL} = \ 0.8 V, \ V_{OH} = \ 2.0 V \\ V_{IL} = \ 0.45 V, \ V_{IH} = \ 2.40 V \end{array}$ |                        |     | 2<br>2                     | μs<br>μs             |

| Erase/Write Pulse Width ( $t_{E/W}$ ) (Note 1)                                                                    |                                                                                                                                      | 10                     |     | 30                         | ms                   |

| CS Low Time (t <sub>CS</sub> ) (Note 3)                                                                           |                                                                                                                                      | 1                      |     |                            | μs                   |

Note 1:  $t_{E/W}$  measured to rising edge of SK or CS, whichever occurs last.

Note 2: The SK frequency spec. specifies a minimum SK clock period of 4  $\mu$ s, therefore in an SK clock cycle, t<sub>SKH</sub> + t<sub>SKL</sub> must be greater than or equal to 4  $\mu$ s. e.g. if t<sub>SKL</sub> = 1  $\mu$ s then the minimum t<sub>SKH</sub> = 3  $\mu$ s in order to meet the SK frequency specification.

Note 3: CS must be brought low for a minimum of 1 µs (tcs) between consecutive instruction cycles.

## **Instruction Set**

| Instruction   | SB | Op Code | Address  | Data   | BPE                   | Comments                |

|---------------|----|---------|----------|--------|-----------------------|-------------------------|

| READ          | 1  | 10XX    | A3A2A1A0 |        | Х                     | Read register A3A2A1A0  |

| WRITE         | 1  | 01XX    | A3A2A1A0 | D15-D0 | Х                     | Write register A3A2A1A0 |

| ERASE         | 1  | 11XX    | A3A2A1A0 |        | Х                     | Erase register A3A2A1A0 |

| EWEN          | 1  | 0011    | XXXX     |        | Х                     | Erase/write enable      |

| EWDS          | 1  | 0000    | XXXX     |        | X                     | Erase/write disable     |

| ERAL (Note 5) | 1  | 0010    | XXXX     |        | V <sub>IH</sub> /OPEN | Erase all registers     |

| WRAL (Note 5) | 1  | 0001    | XXXX     | D15-D0 | V <sub>IH</sub> /OPEN | Write all registers     |

NMC9307E has 7 instructions as shown. Note that MSB of any given instruction is a "1" and is viewed as a start bit in the interface sequence. The next 8 bits carry the op code and the 4-bit address of 1 of 16, 16-bit registers.

## **Functional Description**

The NMC9307E is a small peripheral memory intended for use with COPSTM controllers and other non-volatile memory applications. Its organization is sixteen registers and each register is sixteen bits wide. The input and output pins are controlled by separate serial formats. Seven 9-bit instructions can be executed. The instruction format has a logical '1' as a start bit, four bits as an op code, and four bits of address. SK clock cycle is necessary after CS equals logical '1' before the instruction can be loaded. The on-chip programming-voltage generator allows the user to use a single power supply (V<sub>CC</sub>). Only during the read mode is the serial output (DO) pin valid. During all other modes he DO pin is in TRI-STATE®, eliminating bus contention.

The bulk programming instructions (ERAL, WRAL) are enabled or disabled by the PBE pin. The BPE pin at V<sub>IH</sub> enables execution of these instructions. The BPE pin at V<sub>IL</sub> causes these instructions to be ignored. If the BPE pin is not connected, it is pulled up to V<sub>CC</sub> by an on-chip pull-up and the bulk programming instructions are enabled. Execution of the EWEN, EWDS, READ and byte programming instructions (ERASE, WRITE) are independent of the state of the BPE pin.

#### READ

The read instruction is the only instruction which outputs serial data on the DO pin. After a READ instruction is received, the instruction and address are decoded, followed by data transfer from the memory register into a 16-bit serial-out shift register. A dummy bit (logical '0') precedes the 16-bit data output string. Output data changes are initiated by the low to high transition of the SK clock.

#### ERASE/WRITE ENABLE AND DISABLE

Programming must be preceded once by a programming enable (EWEN) instruction. Programming remains enabled until a programming disable (EWDS) instruction is executed. The programming disable instruction is provided to protect against accidental data disturb. Execution of a READ instruction is independent of both EWEN and EWDS instructions.

#### ERASE (Note 4)

Like most E<sup>2</sup>PROMS, the register must first be erased (all bits set to 1s) before the register can be written (certain bits

set to 0s). After an ERASE instruction is input, CS is dropped low. This falling edge of CS determines the start of programming. The register at the address specified in the instruction is then set entirely to 1s. When the erase/write programming time ( $t_{E/W}$ ) constraint has been satisfied, CS is brought up for at least one SK period. A new instruction may then be input, or a low-power standby state may be achieved by dropping CS low.

#### WRITE (Note 4)

The WRITE instruction is followed by 16 bits of data which are written into the specified address. This register must have been previously erased. Like any programming mode, erase/write time is determined by the low state of CS following the instruction. The on-chip high voltage section only generates high voltage during these programming modes, which prevents spurious programming during other modes. When CS rises to V<sub>IH</sub>, the programming cycle ends. All programming modes should be ended with CS high for one SK period, or followed by another instruction.

#### CHIP ERASE (Note 4)

Entire chip erasing is provided for ease of programming. Erasing the chip means that all registers in the memory array have each bit set to a 1. Each register is then ready for a WRITE instruction. The chip erase (ERAL) instruction is ignored if the BPE pin is at  $V_{IL}$ , i.e. the array data is not changed.

#### CHIP WRITE (Note 4)

All registers must be erased before a chip write operation. The chip write cycle is identical to the write cycle except for the different op code. All registers are simultaneously written with the data pattern specified in the instruction. The chip write (WRAL) instruction is ignored if the BPE pin is at  $V_{\rm IL}$ , i.e. the array data is not changed.

- Note 4: During a programming mode (write, erase, chip erase, chip write), SK clock is only needed while the actual instruction, i.e. start bit, op code, address and data, is being input. It can remain deactivated during the Erase/Write pulse width (t<sub>E/W</sub>).

- Note 5: The ERAL and WRAL instructions are ignored if the BPE pin is at  $V_{IL}$  i.e. the array data is not changed.

## Timing Diagrams

1-15

\_\_\_\_\_

#### NMC9307E

# National Semiconductor

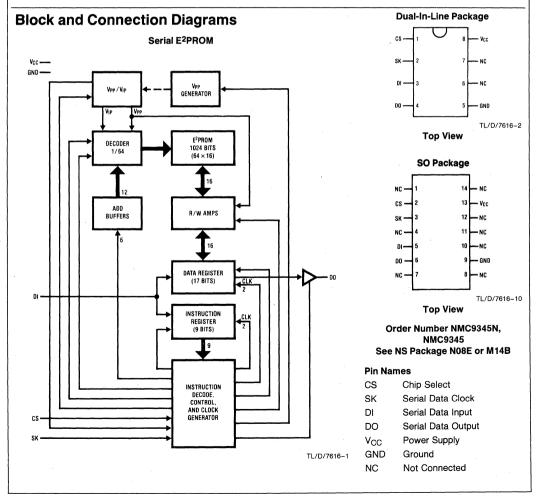

# NMC9345/COP495 1024-Bit Serial Electrically Erasable Programmable Memory (5V Only)

## **General Description**

The NMC9345/COP495 is a 1024-bit non-volatile, sequential E<sup>2</sup>PROM, fabricated using advanced N-channel E<sup>2</sup>PROM technology. It is an external memory with the 1024 bits of read/write memory divided into 64 registers of 16 bits each. Each register can be serially read or written by a COP400 controller, or a standard microprocessor. Written information is stored in a floating gate cell until updated by an erase and write cycle. The NMC9345 has been designed for applications requiring up to 10<sup>4</sup> erase/write cycles per register. A power-down mode is provided by CS to reduce power consumption by 75 percent.

#### **Features**

- Low cost

- Single supply read/write/erase operations (5V±10%)

- TTL compatible

- 64×16 serial read/write memory

- MICROWIRE™ compatible serial I/O

- Simple interfacing

- Low standby power

- Non-volatile erase and write

- Reliable floating gate technology

- Self-timed programming cycle

- Device status signal during programming

#### Absolute Maximum Ratings (Note 1)

Ambient Storage Temperature Lead Temp. (Soldering, 10 seconds) -65°C to +125°C 300°C

## DC and AC Electrical Characteristics NMC9345: $0^{\circ}C \le T_A \le 70^{\circ}C$ , $V_{CC} = 5V \pm 10\%$ unless specified

| Symbol                                 | Parameter                                          | Conditions                                                                                                                      | Min                    | Max                       | Units                |  |

|----------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------|----------------------|--|

| V <sub>CC</sub>                        | Operating Voltage                                  |                                                                                                                                 | 4.5                    | 5.5                       | V                    |  |

| I <sub>CC1</sub>                       | Operating Current<br>Erase/Write Operating Current | $V_{CC} = 5.5V, CS = 1, SK = 1$<br>$V_{CC} = 5.5V$                                                                              |                        | 12<br>12                  | mA<br>mA             |  |

| I <sub>CC2</sub>                       | Standby Current                                    | $V_{CC} = 5.5V, CS = 0$                                                                                                         |                        | 3                         | mA                   |  |

| V <sub>IL</sub><br>V <sub>IH</sub>     | Input Voltage Levels                               |                                                                                                                                 | -0.1<br>2.0            | 0.8<br>V <sub>CC</sub> +1 | v<br>v               |  |

| V <sub>OL</sub><br>V <sub>OH</sub>     | Output Voltage Levels                              | I <sub>OL</sub> =2.1 mA<br>I <sub>OH</sub> =-400 μA                                                                             | 2.4                    | 0.4                       | v<br>v               |  |

| ILI                                    | Input Leakage Current                              | V <sub>IN</sub> =5.5V                                                                                                           |                        | 10                        | μΑ                   |  |

| LO                                     | Output Leakage Current                             | $V_{OUT} = 5.5V, CS = 0$                                                                                                        |                        | 10                        | μΑ                   |  |

| tskh<br>tskl                           | SK Frequency<br>SK High Time<br>SK Low Time        |                                                                                                                                 | 0<br>2<br>1            | 250                       | kHz<br>μs<br>μs      |  |

| tcss<br>tcsн<br>tDIS<br>tDIH           | Inputs<br>CS<br>DI                                 |                                                                                                                                 | 0.2<br>0<br>0.4<br>0.4 |                           | μS<br>μS<br>μS<br>μS |  |

| t <sub>pd</sub> 1<br>t <sub>pd</sub> 0 | Output<br>DO                                       | $\begin{array}{c} C_L\!=\!100 \text{ pF} \\ V_{OL}\!=\!0.8V, V_{OH}\!=\!2.0V \\ V_{IL}\!=\!0.45V, V_{IH}\!=\!2.40V \end{array}$ |                        | 2<br>2                    | μS<br>μS             |  |

| t <sub>E/W</sub>                       | Self-Timed Program<br>Cycle                        |                                                                                                                                 |                        | 10                        | ms                   |  |

| t <sub>CS</sub>                        | Min CS Low Time (Note 3)                           |                                                                                                                                 | 1                      |                           | μS                   |  |

| t <sub>SV</sub>                        | Rising Edge of CS to<br>Status Valid               | C <sub>L</sub> =100 pF                                                                                                          |                        | 1                         | μS                   |  |

| t <sub>OH,</sub> t <sub>1H</sub>       | Falling Edge of CS<br>to DO TRI-STATE®             |                                                                                                                                 |                        | 0.4                       | μS                   |  |

Note 1: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2: The SK frequency spec. specifies a minimum SK clock period of 4  $\mu$ s, therefore in an SK clock cycle t<sub>SKH</sub> + t<sub>SKL</sub> must be greater than or equal to 4  $\mu$ s. e.g. if t<sub>SKL</sub> = 1  $\mu$ s then the minimum t<sub>SKH</sub> = 3  $\mu$ s in order to meet the SK frequency specification.

Note 3: CS must be brought low for a minimum of  $1\mu S$  (t<sub>CS</sub>) between consecutive instruction cycles.

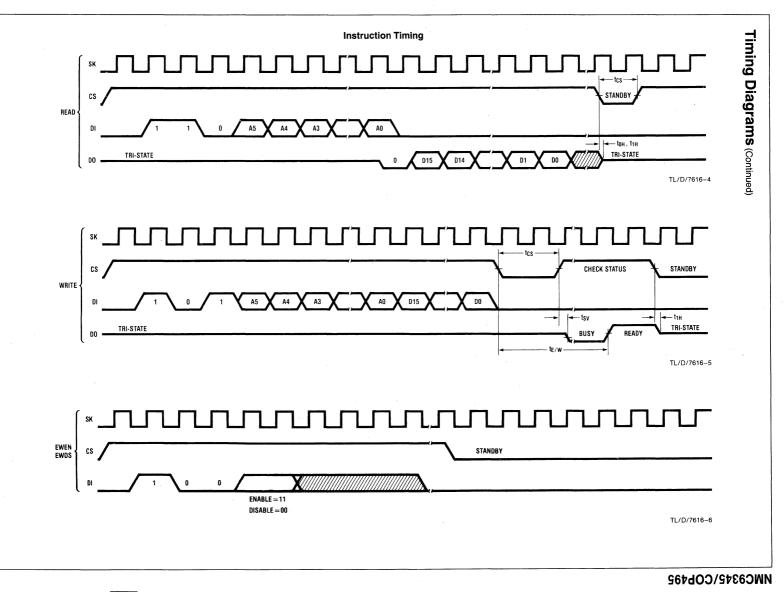

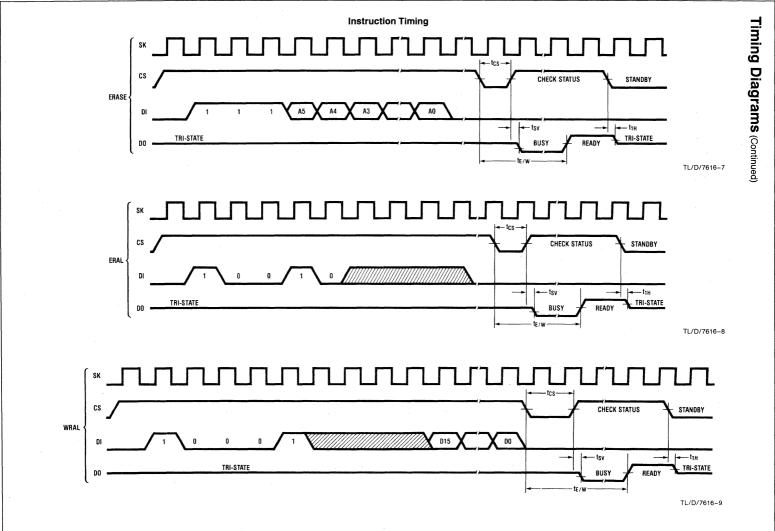

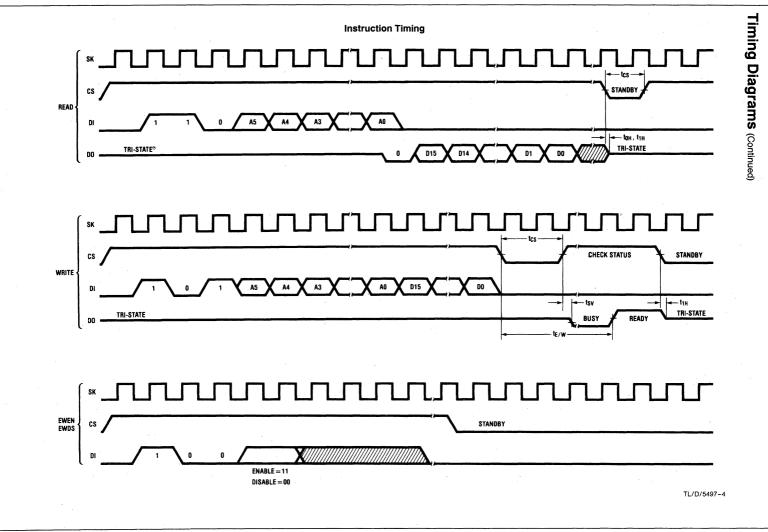

## **Functional Description**

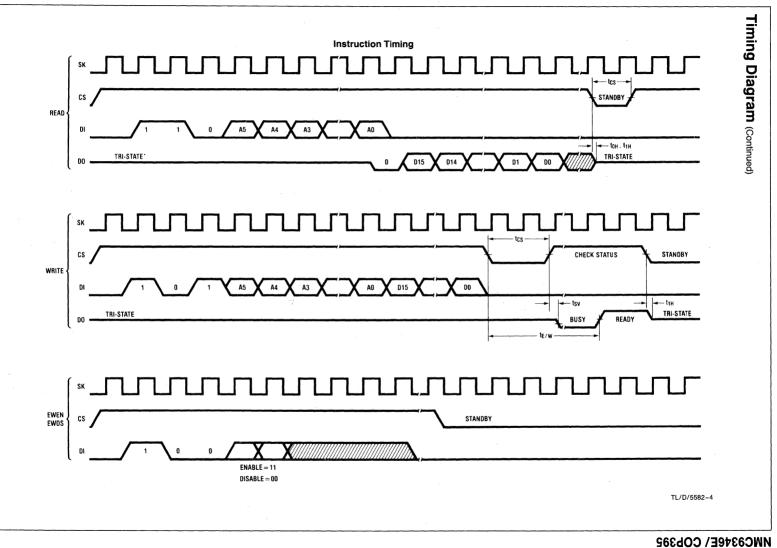

The NMC9345/COP495 is a small peripheral memory intended for use with COPS™ controllers and other non-volatile memory applications. Its organization is sixty-four registers and each register is sixteen bits wide. The input and output pins are controlled by separate serial formats. Seven 9-bit instructions can be executed. The instruction format has a logical '1' as a start bit, two bits as an op code, and six bits of address. The programming cycle is self-timed, with the data out (DO) pin indicating the read/busy status of the chip.

The on-chip programming voltage generator allows the user to use a single power supply (V<sub>CC</sub>). It only generates high voltage during the programming modes (write, erase, chip erase, chip write) to prevent spurious programming during other modes. The DO pin is valid as data out during the read mode, and if initiated, as a ready/busy status indicator during a programming cycle. During all other modes the DO pin is in TRI-STATE, eliminating bus contention.

## Functional Description (Continued)

#### READ

The read instruction is the only instruction which outputs serial data on the DO pin. After a read instruction is received, the instruction and address are decoded, followed by data transfer from the memory register into a 16-bit serial-out shift register. A dummy bit (logical '0') precedes the 16-bit data output string. Output data changes are initiated by a low to high transition of the SK clock.

#### ERASE/WRITE ENABLE AND DISABLE

When  $V_{CC}$  is applied to the part it powers up in the programming disable (EWDS) state, programming must be preceded by a programming enable (EWEN) instruction. Programming remains enabled until a programming disable (EWDS) instruction is executed or  $V_{CC}$  is removed from the part. The programming disable instruction is provided to protect against accidental data disturb. Execution of a read instruction is independent of both EWEN and EWDS instructions.

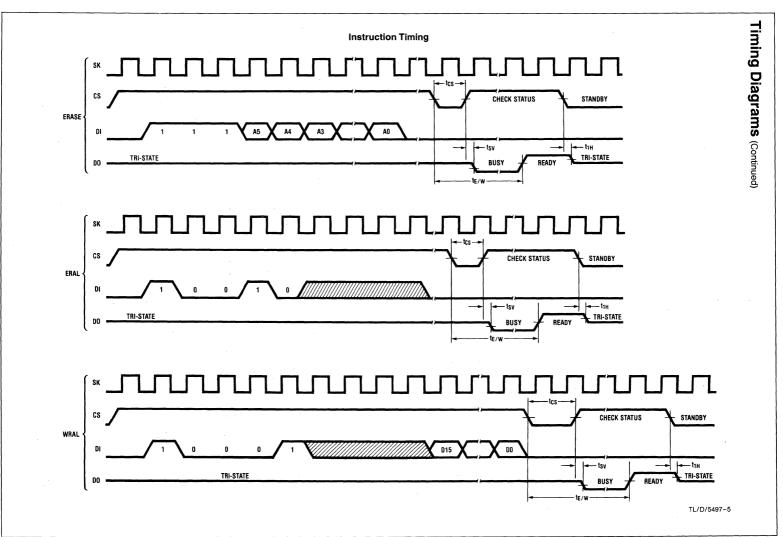

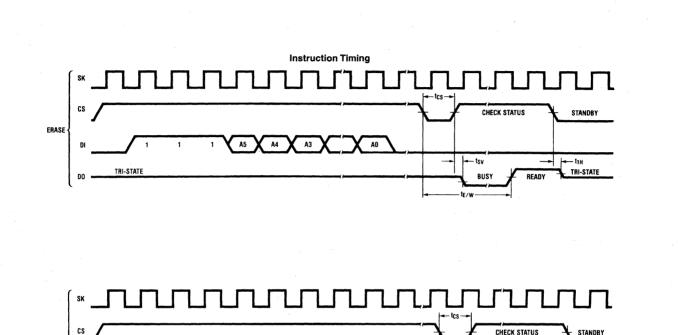

#### ERASE (Note 4)

Like most E<sup>2</sup>PROMs, the register must first be erased (all bits set to logical '1') before the register can be written (certain bits set to logical '0'). After an erase instruction is input, CS is dropped low. This falling edge of CS determines the start of the self-timed programming cycle. If CS is brought high subsequently (after observing the  $t_{CS}$  specification), the DO pin will indicate the ready/busy status of the chip. The DO pin will go low if the chip is still programming. The DO pin will go high when all bits of the register at the address specified in the instruction have been set to a logical '1'. The part is now ready for the next instruction sequence.

#### WRITE (Note 4)

The write instruction is followed by 16 bits of data to be written into the specified address. After the last bit of data (D0) is put on the data in (DI) pin CS must be brought low before the next rising edge of the SK clock. This falling edge of CS initiates the self-timed programming cycle. Like all programming modes, DO indicates the ready/busy status of the chip if CS is brought high after a minimum of 1  $\mu$ S (t<sub>CS</sub>). DO=logical '0' indicates that programming is still in progress. DO= logical '1' indicates that the register at the address specified in the instruction has been written with the data pattern specified in the instruction and the part is ready for another instruction. The register to be written into must have been previously erased.

#### CHIP ERASE (Note 4)

Entire chip erasing is provided for ease of programming. Erasing the chip means that all registers in the memory array have each bit set to a logical '1'. Each register is then ready for a write instruction. The chip erase cycle is identical to the erase cycle except for the different op code.

#### CHIP WRITE (Note 4)

All registers must be erased before a chip write operation. The chip write cycle is identical to the write cycle except for the different op code. All registers are simultaneously written with the data pattern specified in the instruction.

Note 4: During a programming mode (write, erase, chip erase, chip write), SK clock is only needed while the actual instruction, i.e., start bit, op code, address and data, is being input. It can remain deactivated during the selftimed programming cycle and status check.

| Instruction | SB | Opcode | Address      | Data   | Comments                    |

|-------------|----|--------|--------------|--------|-----------------------------|

| READ        | 1  | 10     | A5A4A3A2A1A0 |        | Read register A5A4A3A2A1A0  |

| WRITE       | 1  | 01     | A5A4A3A2A1A0 | D15-D0 | Write register A5A4A3A2A1A0 |

| ERASE       | 1  | 11     | A5A4A3A2A1A0 |        | Erase register A5A4A3A2A1A0 |

| EWEN        | 1  | 00     | 11xxxx       |        | Erase/Write enable          |

| EWDS        | 1  | 00     | 00xxxx       |        | Erase/Write disable         |

| ERAL        | 1  | 00     | 10xxxx       |        | Erase all registers         |

| WRAL        | 1  | 00     | 01xxxx       | D15-D0 | Write all registers         |

NMC9345/COP495 has 7 instructions as shown. Note that the MSB of any given instruction is a "1" and is viewed as a start bit in the interface sequence. The next 8 bits carry the op code and the 6-bit address for 1 of 64, 16-bit registers.

## **Timing Diagrams**

\*This is the minimum SK period.

months has writed for a non-station

Carlo Ba

#### NMC9345/COP495

# National Semiconductor

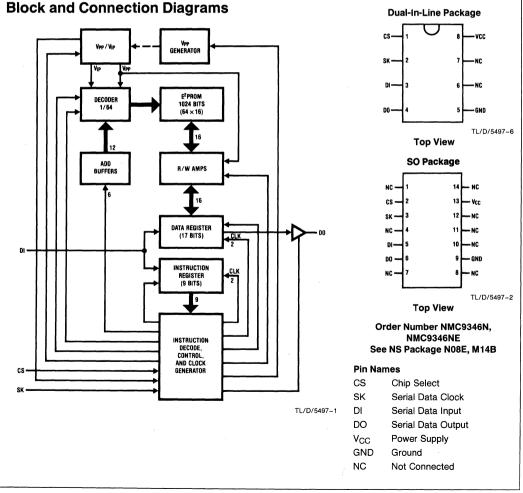

## NMC9346/COP495 1024-Bit Serial Electrically Erasable Programmable Memory (5V Only)

## **General Description**

The NMC9346/COP495 is a 1024-bit non-volatile, sequential E<sup>2</sup>PROM, fabricated using advanced N-channel E<sup>2</sup>PROM technology. It is an external memory with the 1024 bits of read/write memory divided into 64 registers of 16 bits each. Each register can be serially read or written by a COP400 controller, or a standard microprocessor. Written information is stored in a floating gate cell until updated by an erase and write cycle. The NMC9346/COP495 has been designed for applications requiring up to 104 erase/write cycles per register. A power-down mode is provided by CS to reduce power consumption by 75 percent.

#### **Features**

- Low cost

- Single supply read/write/erase operations (5V±10%)

- TTL compatible

- 64 x 16 serial read/write memory

- MICROWIRE™ compatible serial I/O

- Simple interfacing

- Low standby power

- Non-volatile erase and write

- Reliable floating gate technology

- Self-timed programming cycle

- Device status signal during programming

| •                                      | rating Temperature 0°C t                                      | to -0.3V Ambient Storage T<br>to +70°C Lead Temperature                                        | (Soldering, 10         | ) seconds)                | to + 125°<br>300°    |

|----------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------|---------------------------|----------------------|

| DC and                                 | AC Electrical Characte                                        | <b>Pristics</b> $0^{\circ}C \le T_A \le 70^{\circ}C$ , $V_{CC} = 5$<br>Conditions              | V±10% unles            | T                         |                      |

|                                        |                                                               | Conditions                                                                                     |                        | Max                       | Units                |

| V <sub>CC</sub>                        | Operating Voltage                                             |                                                                                                | 4.5                    | 5.5                       | V                    |

| ICC1                                   | Operating Current<br>Erase/Write Operating Current            | $V_{CC} = 5.5V, CS = 1, SK = 1$<br>$V_{CC} = 5.5V$                                             |                        | 12<br>12                  | mA<br>mA             |

| I <sub>CC2</sub>                       | Standby Current                                               | $V_{CC} = 5.5V, CS = 0$                                                                        |                        | 3                         | mA                   |

| V <sub>IL</sub><br>VIH                 | Input Voltage Levels                                          |                                                                                                | -0.1<br>2.0            | 0.8<br>V <sub>CC</sub> +1 | V<br>V               |

| V <sub>OL</sub><br>V <sub>OH</sub>     | Output Voltage Levels                                         | I <sub>OL</sub> =2.1 mA<br>I <sub>OH</sub> = -400 μA                                           | 2.4                    | 0.4                       | v<br>v               |