SERIES 8000 MICROPROCESSOR FAMILY HANDBOOK

# NATIONAL SEMICONDUCTOR

National Semiconductor

1978

# SERIES 8000 MICROPROCESSOR FAMILY HANDBOOK

# NATIONAL SEMICONDUCTOR

## **Edge Index**

## National Semiconductor

**Table of Contents**

Introduction

The MICROBUS

The Series 8000 Microprocessor Family CPU Group Designing Series 8000 Microprocessor Family Systems

ing cenes bood meroprocessor ranny bystems

**Memory Components**

MAXI-ROMs

Input/Output Components

**Peripheral Control Components**

**Communications Components**

**Development Support**

Programming

**MICROBUS Electrical Specifications**

Series 8000 Microprocessor Family Design Example

**Additional Information Sources**

**Data Sheets**

**CPU Group**

Digital I/O Components

Peripheral Control Components

**Communications Components**

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry.

DATA

SHEETS

APPENDICES

n in destructions in the second se The second sec The second se

This handbook replaces the N8080 System Design Manual. The Series 8000 Microprocessor Family encompasses not only the INS8080A, but also many peripheral control components as well. The title change reflects this increased emphasis on peripherals. This handbook provides design information pertaining to the National Semiconductor Series 8000 Microprocessor Family. The material contained in this handbook is presented at a level-of-detail sufficient for use in the design and development of microprocessor systems using the proven INS8080A CPU and support components. The material is up-to-date at the time of publication and is subject to change without notice.

Copies of this publication and other National Semiconductor publications may be obtained from the National Semiconductor sales office or distributor serving your locality.

Available data sheets are included in appendix D. Related National Semiconductor Publications:

- National's 8080A Microprocessor Family Quick Reference

- Pace Resident Macro Assemblers Manual (for UDS based 8080 cross assembler)

- Universal Development System Users Manual

- Universal Development System Editor Users Manual

- Universal Development System PROM Programmer Users Manual

- LLL Basic Interpreter Users Manual

- Microprocessor Family Product Guide

- National's Spectrum of IC Components for Terminals

- Microprocessor System Design Training

- Microprocessor Applications in Business, Science and Industry

## **Data Sheet Index**

The Series 8000 Microprocessor Family Data Sheets available at time of publication are listed below and included in appendix D in the order shown (for memory data sheets refer to National's Memory Databook):

#### D.1 CPU GROUP

Page

| INS8080A     | 8-Bit Microprocessor D- 3             |  |

|--------------|---------------------------------------|--|

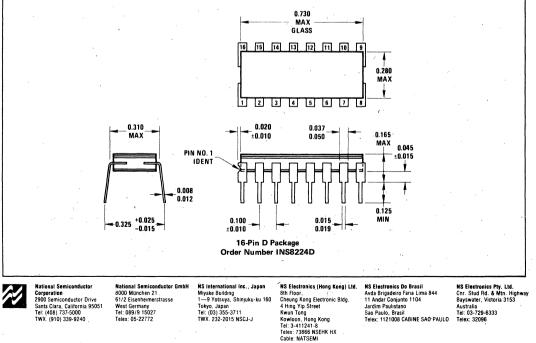

| INS8224      | Clock Generator and Driver D-13       |  |

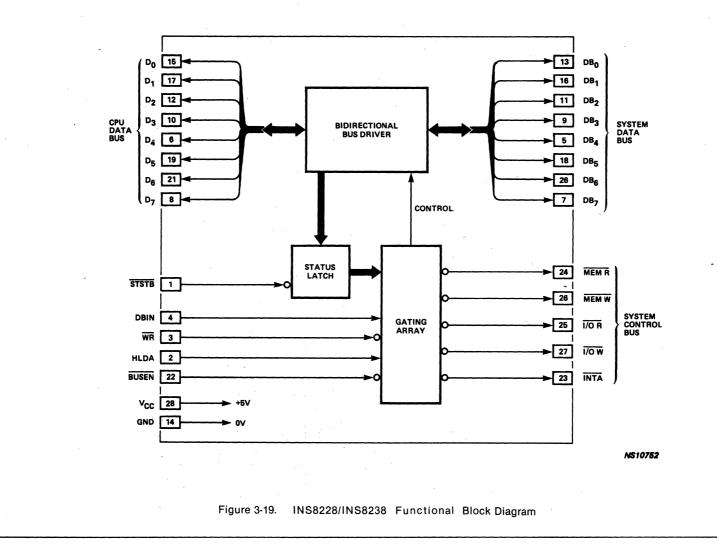

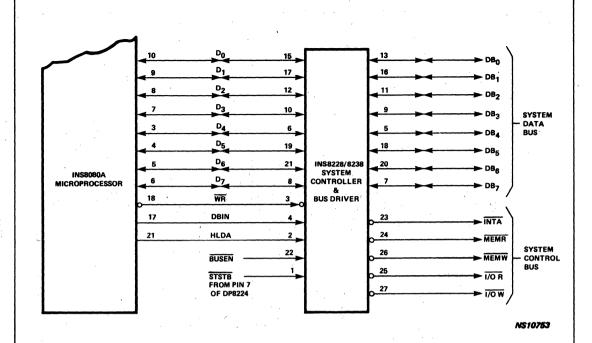

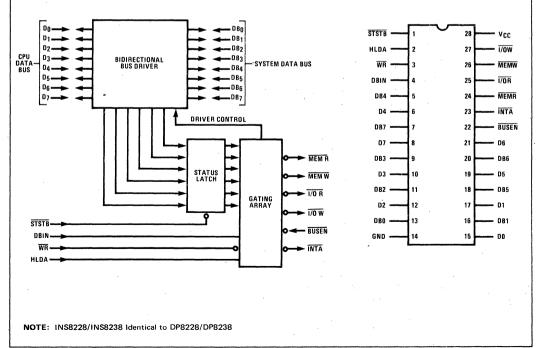

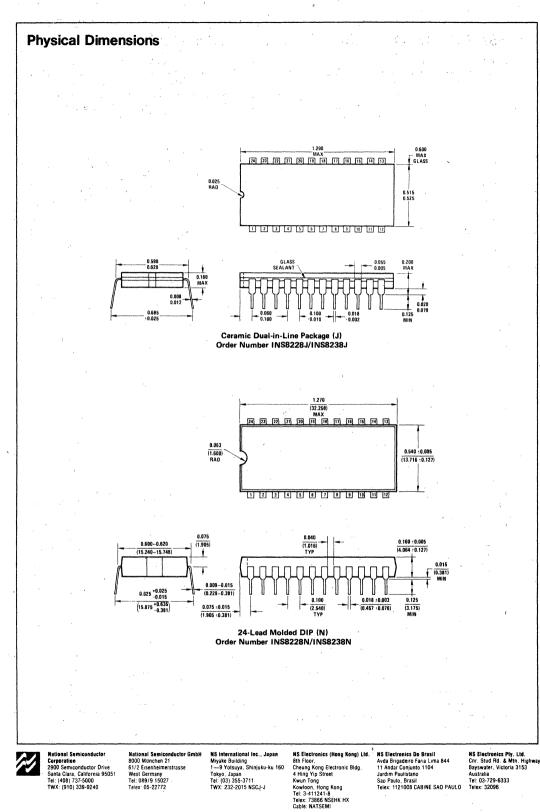

| INS8228/8238 | System Controller and Bus Driver D-19 |  |

#### D.2 DIGITAL I/O COMPONENTS

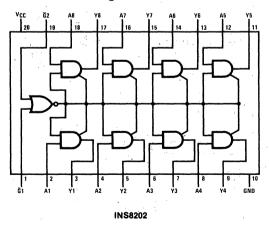

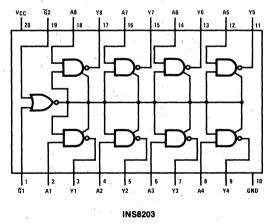

| INS8202 | TRI-STATE® 8-Bit Bus Driver D-2            | 5 |

|---------|--------------------------------------------|---|

| INS8203 | TRI-STATE 8-Bit Bus Driver (Inverting) D-2 | 5 |

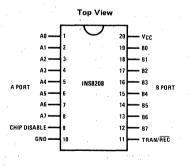

| INS8208 | 8-Bit Bidirectional Bus Driver D-2         | 9 |

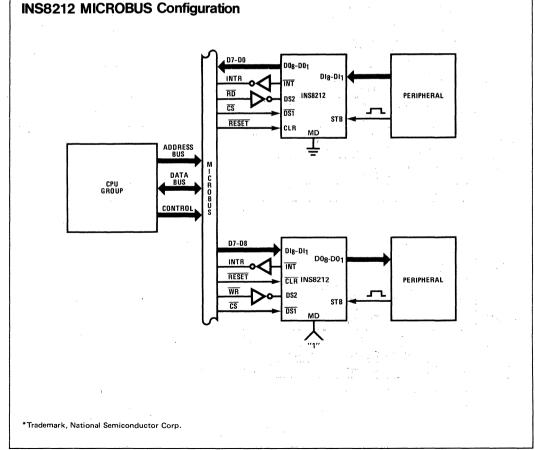

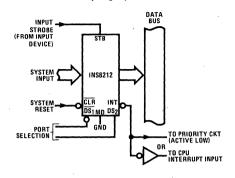

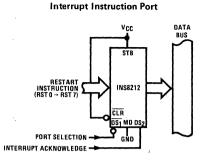

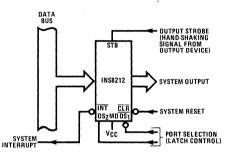

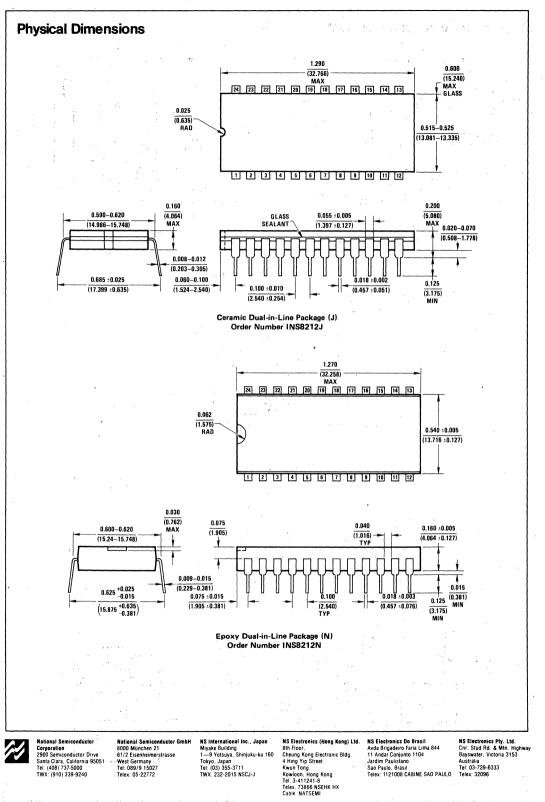

| INS8212 | 8-Bit I/O Port                             | 5 |

| INS8216 | 4-Bit Bidirectional Bus Driver D-4         | 3 |

| INS8226 | 4-Bit Bidirectional Bus Driver             |   |

|         | (Inverting)                                | 3 |

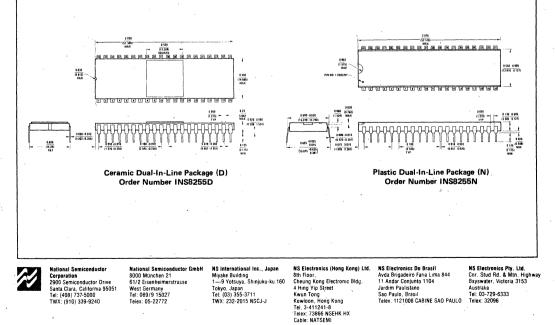

| INS8255 | Programmable Peripheral InterfaceD-4       | 7 |

### D.3 PERIPHERAL CONTROL COMPONENTS

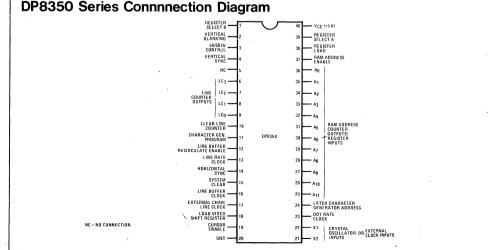

| DP8350    | Series Programmable CRT Controller      |

|-----------|-----------------------------------------|

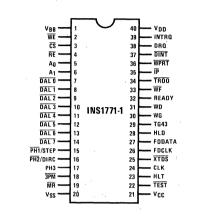

| INS1771-1 | Floppy Disk Formatter/Controller        |

| INS8253   | Programmable Timer D-91                 |

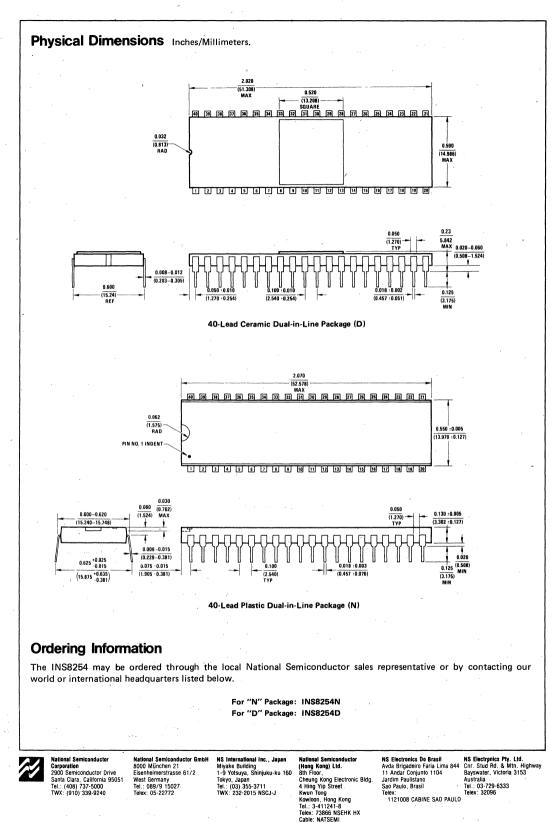

| INS8254   | Programmable 16-Bit Addressable         |

|           | Peripheral InterfaceD-101               |

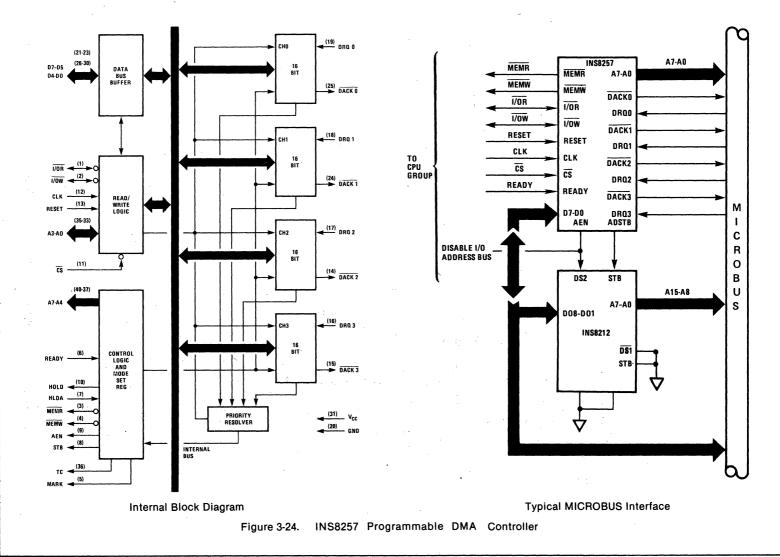

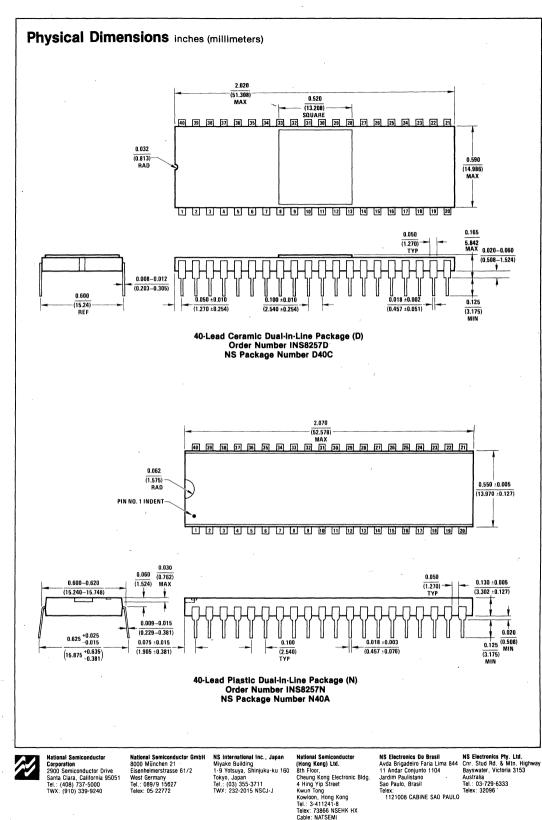

| INS8257   | Programmable DMA Controller D-115       |

| INS8259   | Programmable Interrupt Controller D-127 |

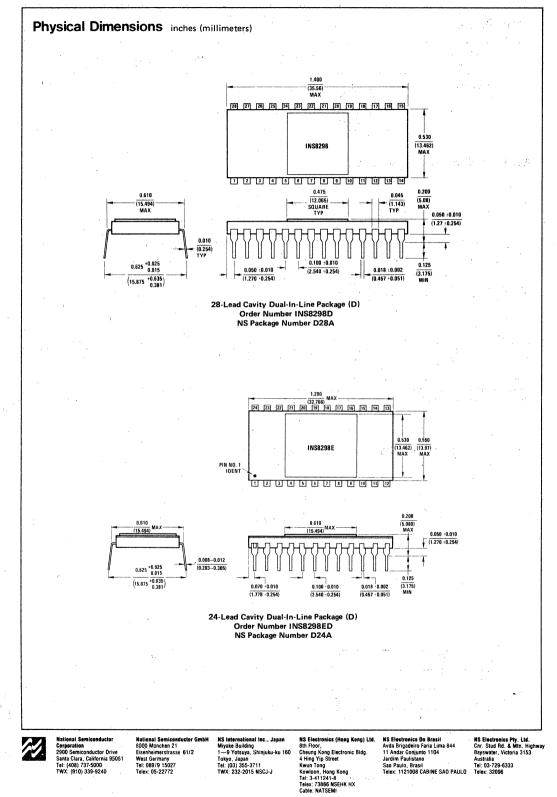

| INS8298E* | LLL BASIC Interpreter D-139             |

### **D.4 COMMUNICATIONS COMPONENTS**

| INS1671 | ASTRO Communications Interface            | . D-145 |

|---------|-------------------------------------------|---------|

| INS8250 | Asynchronous Communications Element (ACE) | . D-157 |

| INS8251 | Programmable Communications Interface     | . D-173 |

\*NOTE: For the following devices, contact National's Microprocessor Marketing regarding availability of devices and data sheets:

| INS9298E | LLL BASIC Interpreter                  |

|----------|----------------------------------------|

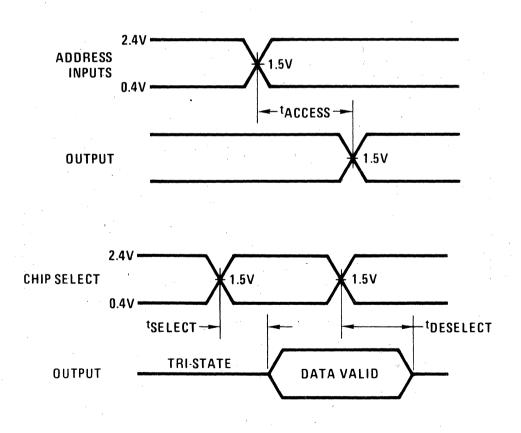

| INS8316  | (same as MM52116) 16K bit (2K x 8) ROM |

| INS8332  | (same as MM52132) 32K bit (4K x 8) ROM |

| INS8364  | (same as MM52164) 64K bit (8K x 8) ROM |

## **Table of Contents**

### **Chapter 1 INTRODUCTION**

National Semiconductor

| 1.1 GENERAL DESCRIPTION                                   | 1-1 |

|-----------------------------------------------------------|-----|

| 1.2 HANDBOOK ORGANIZATION                                 | 1-3 |

| 1.2.1 Introduction                                        |     |

| 1.2.2 The MICROBUS                                        |     |

| 1.2.3 The Series 8000 Microprocessor Family CPU Group     | 1-3 |

| 1.2.4 Designing Series 8000 Microprocessor Family Systems |     |

| 1.2.5 Memory Components                                   |     |

| 1.2.6 MAXI-ROMs                                           |     |

| 1.2.7 Input/Output Components                             | 1-4 |

| 1.2.8 Peripheral Control Components                       |     |

| 1.2.9 Communications Components                           | 1-4 |

| 1.2.10 Development Support                                | 1-4 |

| 1.2.11 Programming                                        | 1-4 |

| 1.2.12 Appendices                                         | 1-4 |

| A MICROBUS Electrical Specifications                      |     |

| B Series 8000 Microprocessor Family Design Example        |     |

| C Additional Information Sources                          |     |

| D Data Sheets                                             |     |

.

## Chapter 2 THE MICROBUS

| 2-1 INTRODUCTION                                   | 1 |

|----------------------------------------------------|---|

| 2-2 GENERAL DESCRIPTION                            | 1 |

| 2.2.1 Basic MICROBUS Interface                     | 1 |

| 2.2.1.1 Data Bus (D <sub>7</sub> -D <sub>0</sub> ) | 1 |

| 2.2.1.2 Chip Select (CS)                           |   |

| 2.2.1.3 Read Strobe (RD)                           | 3 |

| 2.2.1.4 Write Strobe(WR)                           |   |

| 2.2.1.5 Reset (RESET)                              |   |

| 2.2.1.6 Ground (GND)                               | 3 |

| 2.2.2 Addressing Techniques                        | 3 |

| 2.2.2.1 Input Case                                 |   |

| 2.2.2.2 Address/Chip Select Relationship           | 4 |

| 2.2.2.3 Bidirectional Addresses                    |   |

| 2.2.3 Interrupt Convention                         |   |

| 2.2.4 Direct Memory Access (DMA) Transfers         | 4 |

| 2.2.5 Ready Signal                                 | 5 |

| 2.2.6 The Basic Interface Model                    | 5 |

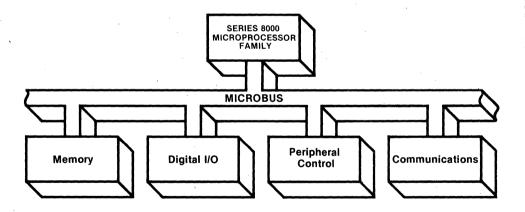

### Chapter 3 THE SERIES 8000 MICROPROCESSOR FAMILY CPU GROUP

| 3.1 INTRODUCTION                             | 3-1          |

|----------------------------------------------|--------------|

| 3.2 INS8080A MICROPROCESSOR                  | 3-2          |

| 3.2.1 Architecture of the INS8080A           | 3-2          |

| 3.2.1.1 Register Array and Address Logic     | 3-2          |

| 3.2.1.2 ALU and Registers                    | 3-2          |

| 3.2.1.3 Instruction Register and Decoder     | <i>,</i> 3-6 |

| 3.2.1.4 Timing and Control Unit              | 3-6          |

| 3.2.1.5 Data Bus Buffer/Latch                | 3-6          |

| 3.2.2 Operating Cycle                        | 3-6          |

| 3.2.2.1 Instruction Cycle and Related Timing | 3-6          |

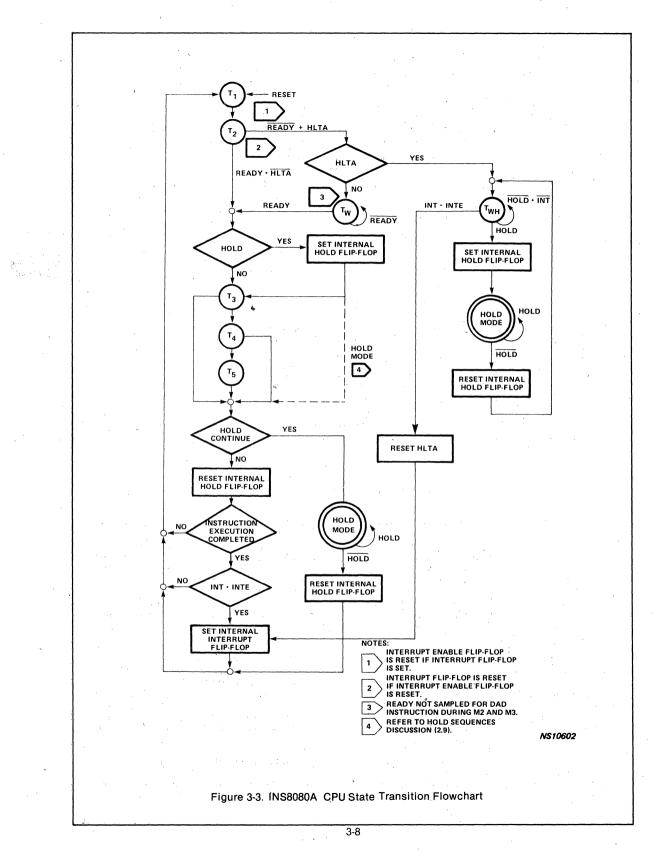

| 3.2.2.2 State Transition Sequence            | 3-7          |

V

## Table of Contents (Continued)

| 3.2.3 Data and Instruction Representation         |  |

|---------------------------------------------------|--|

| 3.2.4 Status Information                          |  |

| 3.2.5 Addressing Capabilities                     |  |

| 3.2.5.1 Immediate Addressing                      |  |

| 3.2.5.2 Direct Addressing                         |  |

| 3.2.5.3 Register Addressing                       |  |

| 3.2.5.4 Register Indirect Addressing              |  |

| 3.2.6 Input/Output Operation and Control          |  |

| 3.2.6.1 Data Input Operations                     |  |

| 3.2.6.2 Data Output Operations                    |  |

| 3.2.7 Interrupts                                  |  |

| 3.2.8 Hold Operations                             |  |

| 3.2:9 Microprocessor Halt                         |  |

| 3.2.10 Initialization                             |  |

| 3.3 INS8224 CLOCK GENERATOR AND DRIVER            |  |

| 3.4 INS8228/8238 SYSTEM CONTROLLER AND BUS DRIVER |  |

| 3.5 CPU CHIP SET                                  |  |

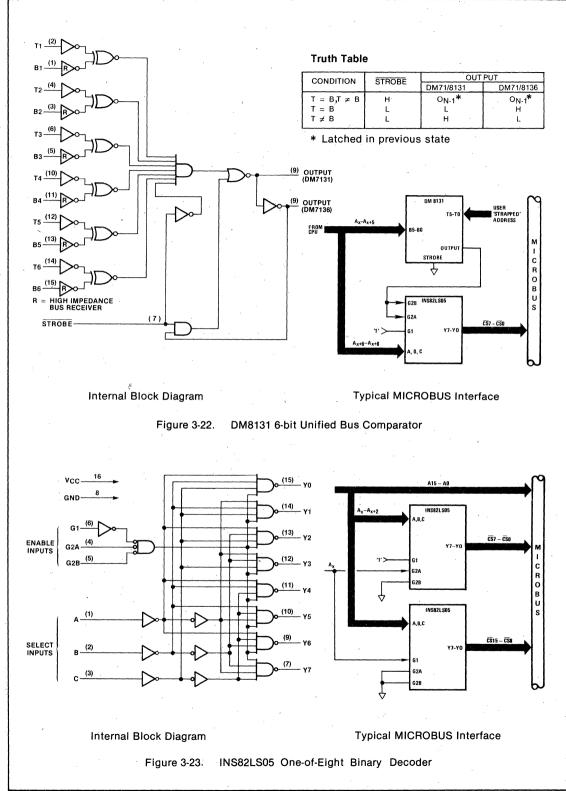

| 3.5.1 DM8131 6-Bit Unified Bus Comparator         |  |

| 3.5.2 INS82LS05One -of-Eight Binary Decoder       |  |

| 3.5.3 INS8257 Programmable DMA Controller         |  |

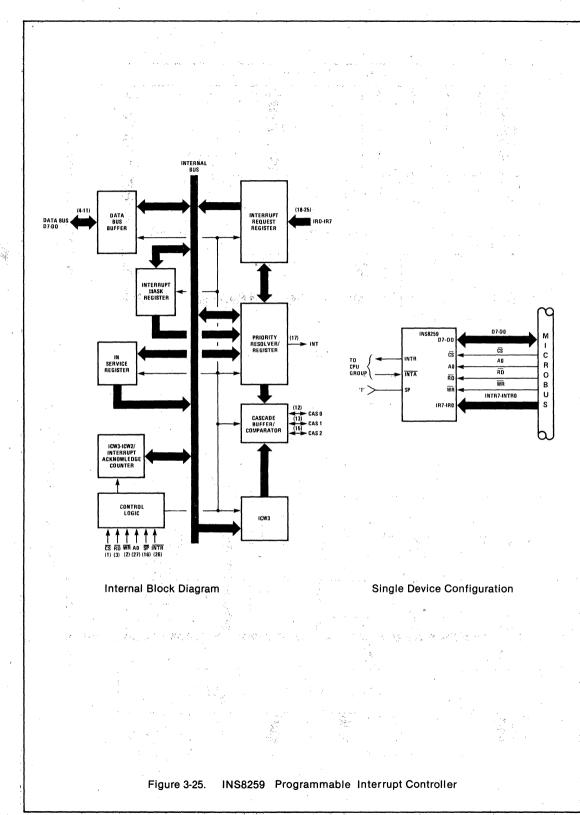

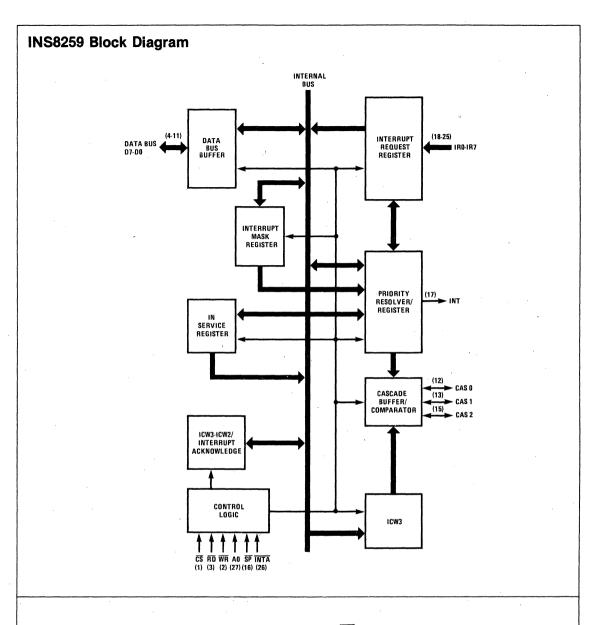

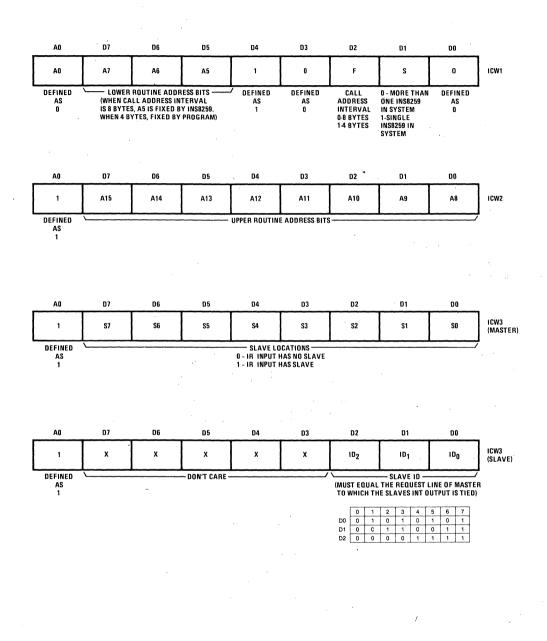

| 3.5.4 INS8259 Programmable Interrupt Controller   |  |

|                                                   |  |

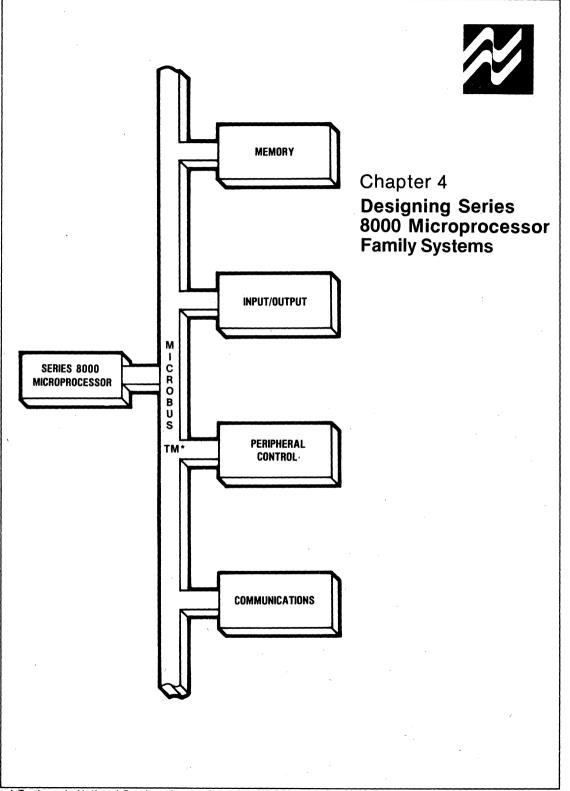

## Chapter 4 DESIGNING SERIES 8000 MICROPROCESSOR FAMILY SYSTEMS

| 4.1 INTRODUCTION                              | . 4-1 |

|-----------------------------------------------|-------|

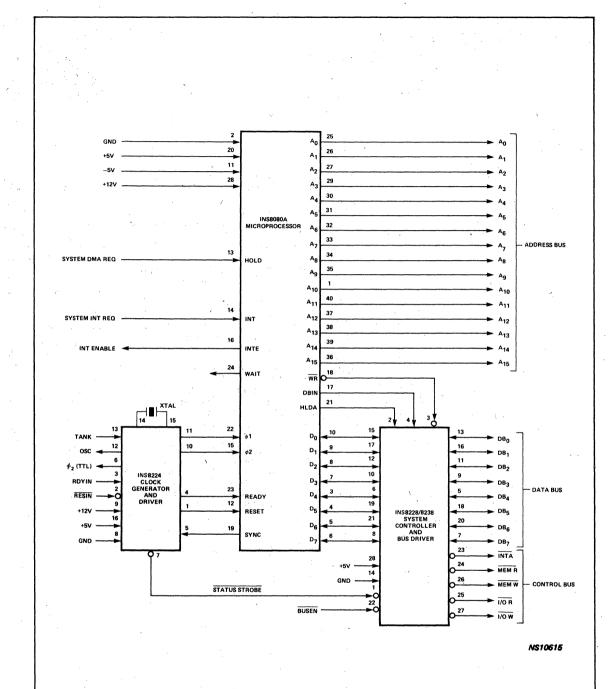

| 4.2 CPU GROUP DESIGN                          | . 4-1 |

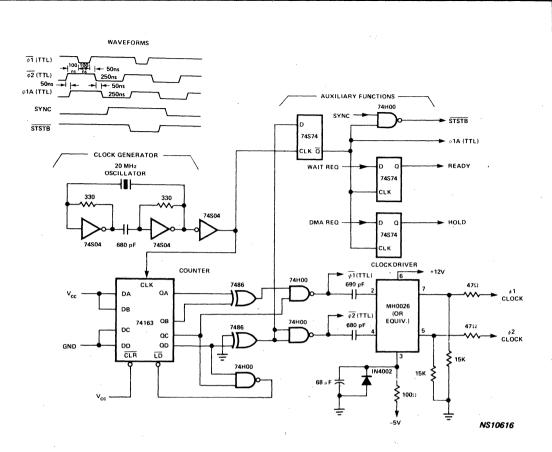

| 4.2.1 Clock Generator and Driver Design       | . 4-1 |

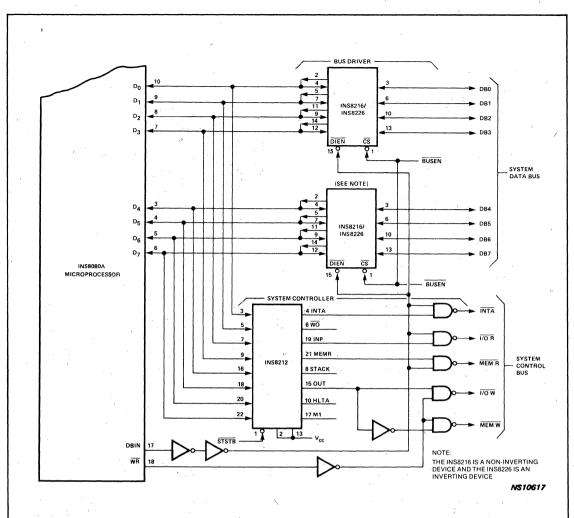

| 4.2.2 System Controller and Bus Driver Design | . 4-1 |

| 4.3 ADDRESSING CONSIDERATIONS AND TECHNIQUES  | . 4-3 |

| 4.4 INTERFACING TO MEMORY                     | . 4-6 |

| 4.5 DYNAMIC MEMORY                            |       |

| 4.5.1 Introduction                            | . 4-8 |

| 4.5.2 RAM Chip Characteristics                | . 4-8 |

| 4.5.3 Memory Subsystem Design Considerations  | . 4-9 |

| 4.5.4 Summary                                 | 4-11  |

| 4.6 INTERFACING TO INPUT/OUTPUT DEVICES       | 4-11  |

| 4.6.1 Input/Output Addressing                 | 4-12  |

| 4.6.2 Interfacing 8-Bit Peripherals           | 4-14  |

| 4.6.3 Interfacing Serial Devices              | 4-14  |

| 4.7 EXPANDING INTERRUPTS                      |       |

| 4.8 USE OF INS8080A SUPPORT CHIPS             | 4-15  |

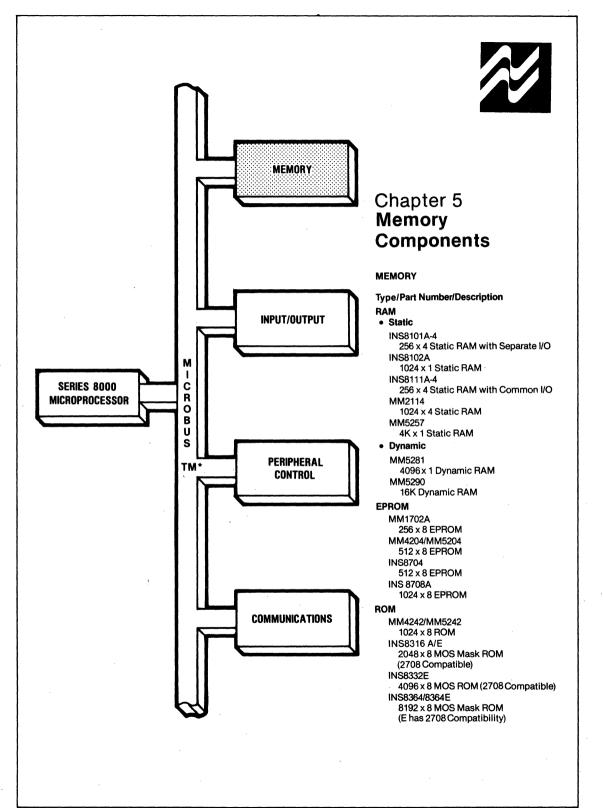

## Chapter 5 MEMORY COMPONENTS

| 5.1 GENE  | ERAL DESCRIPTION                                   |                                       |

|-----------|----------------------------------------------------|---------------------------------------|

| 5.2 ADDF  | RESSING CONSIDERATIONS                             |                                       |

| 5.3 INTER | RFACING TO MEMORY                                  |                                       |

| 5.4 DYNA  | AMIC MEMORY                                        |                                       |

|           | 154 128-by-8 Bit RAM I/O                           |                                       |

| 5.6 OTHE  | ER MEMORY COMPONENTS (DATA SHEETS IN APPENDIX D)   |                                       |

| RAM       | M                                                  | · · · · · · · · · · · · · · · · · · · |

| - S1      | STATIC                                             |                                       |

|           | 1K                                                 |                                       |

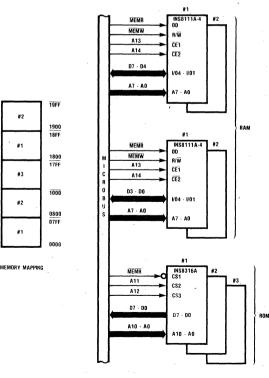

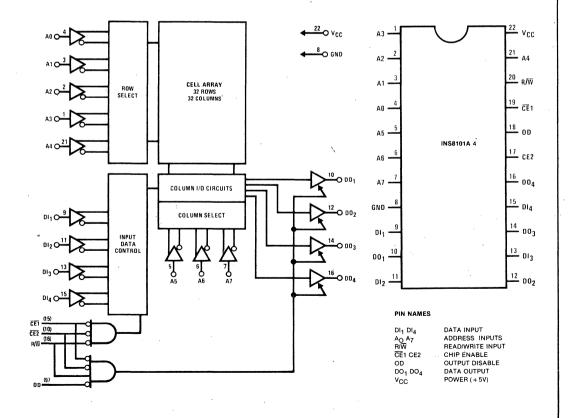

| 5.6.1     | INS8101A-4 1K (256x4) Static RAM With Separate I/O |                                       |

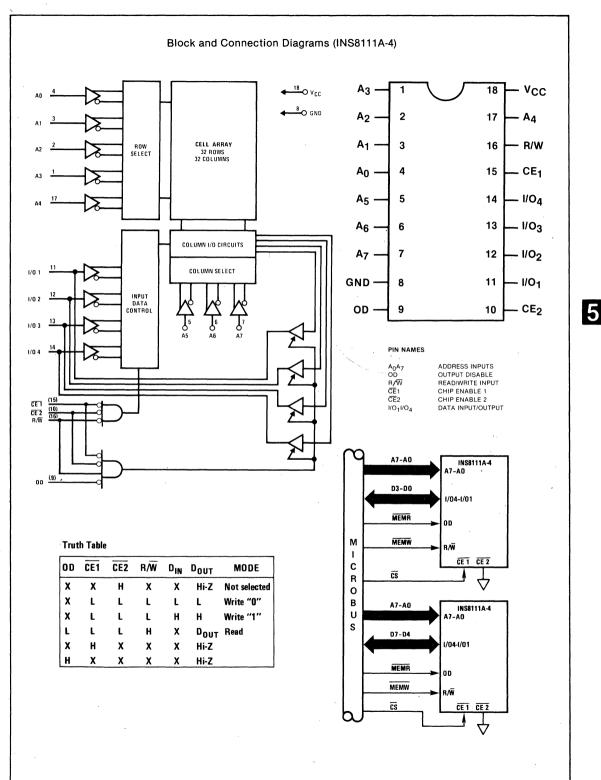

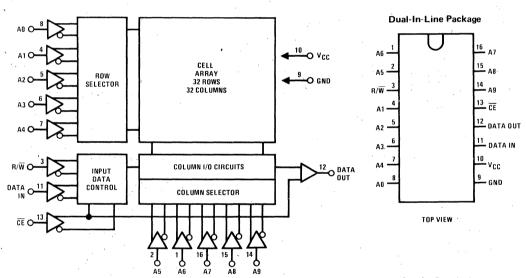

| 5.6.2     | INS8111A-4 1K (256x4) RAM With Common I/O          |                                       |

| 5.6.3     | INS8102A 1K (1024x1) Static RAM                    |                                       |

|           | 4K                                                 |                                       |

| 5.6.4     | MM2114 4K (1024x4) Static RAM                      |                                       |

|           |                                                    | A                                     |

### Table of Contents (Continued)

V

| 5.6.5 MM5257 4K (4096x1) Static RAM                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------|

| 5.6.6 MM5281 4K (4096x1) Dynamic RAM                                                                                     |

| 5.6.7 MM5290 16K (16,384x1) Dynamic RAM                                                                                  |

| 5.6.8 MM1702A (256x8) EPROM                                                                                              |

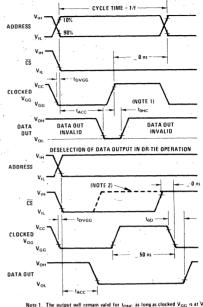

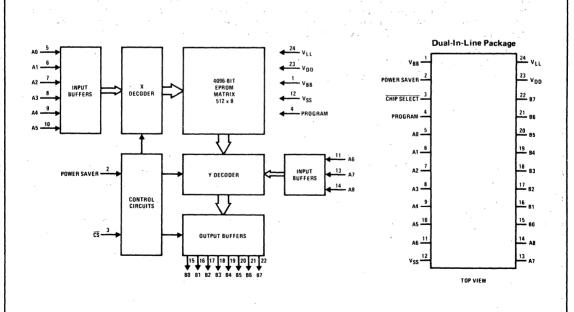

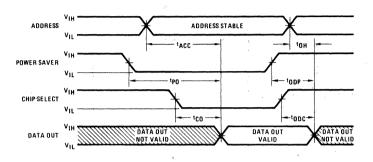

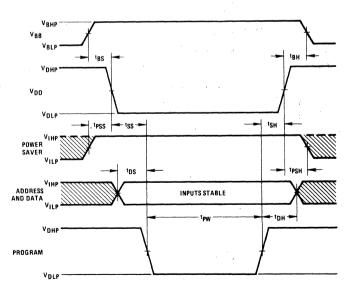

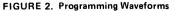

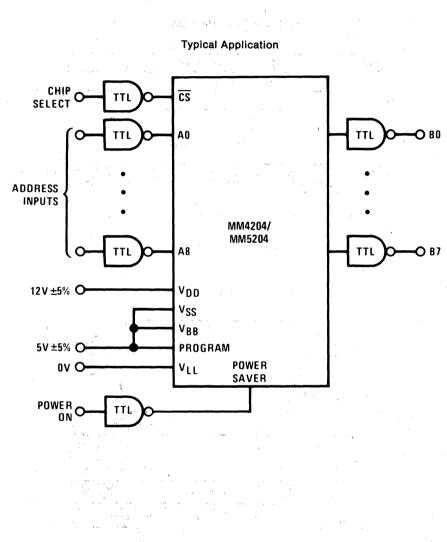

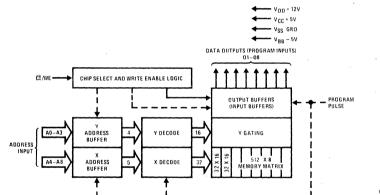

| 5.6.9         MM4204/MM5204 4K (512x8) EPROM         5-25           5.6.10         INS8704 4K (512x8) EPROM         5-29 |

| 5.6.11 INS8708A 8K (1024x8) EPROM                                                                                        |

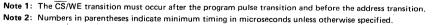

| ROM<br>5.6.12 MM4242/MM5242 8K (1024x8) ROM                                                                              |

| 5.6.12 MM4242/MM5242 8K (1024x8) ROM                                                                                     |

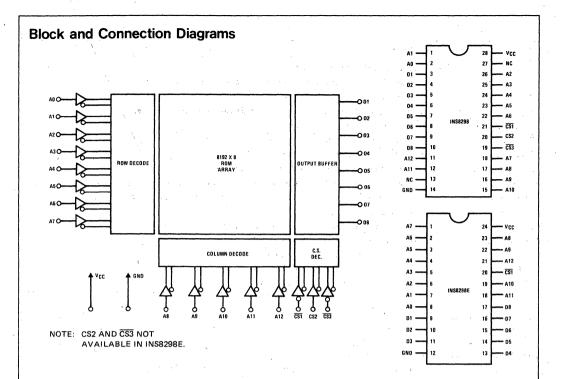

| 5.6.14         INS8332E/MM52132 MAXI-ROM 32,768 Bit Read Only Memory (2708 Compatible)                                   |

| (Also Available as 8298, See Chapter 6, MAXI-ROMs)                                                                       |

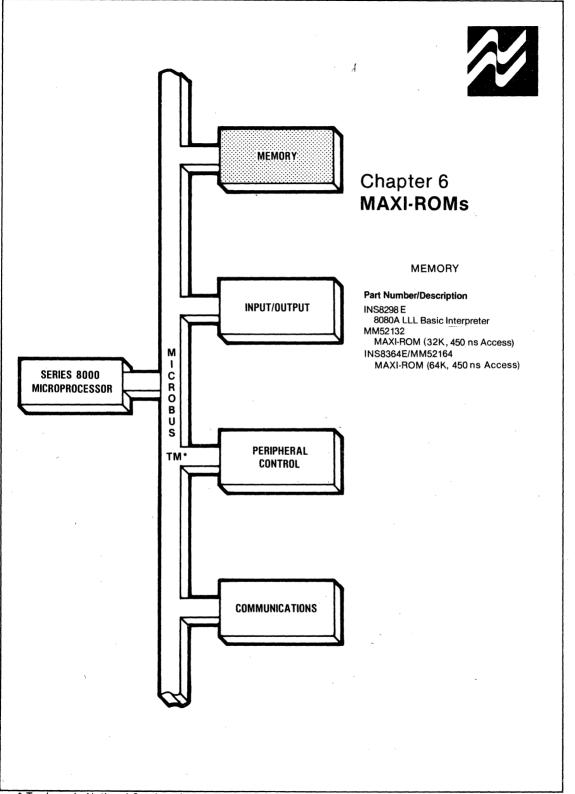

| Chapter 6 MAXI-ROMs                                                                                                      |

| 6.1 GENERAL DESCRIPTION                                                                                                  |

| 6.2 INTERFACING TO MEMORY                                                                                                |

| 6.3 UNPROGRAMMED MAXI-ROMS                                                                                               |

| Operation                                                                                                                |

| System Configuration                                                                                                     |

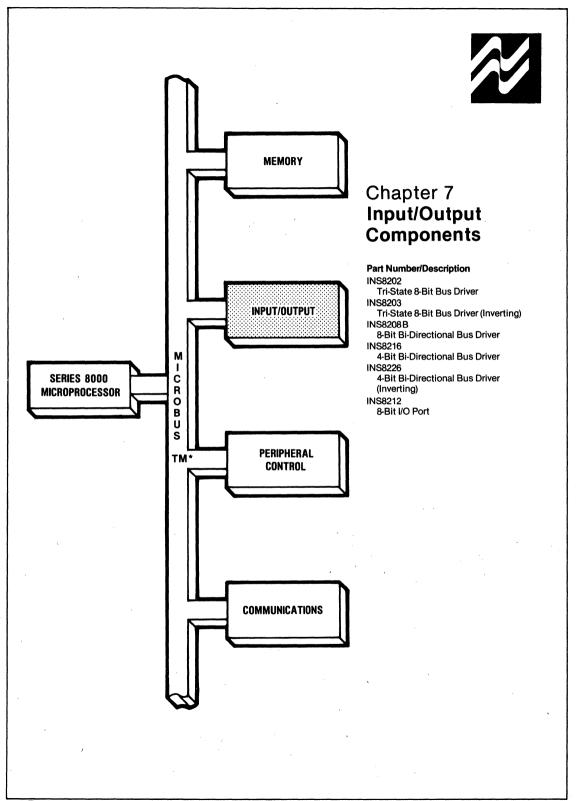

| Chapter 7 INPUT/OUTPUT COMPONENTS                                                                                        |

| 7.1 GENERAL DESCRIPTION                                                                                                  |

| 7.2 INTERFACING I/O COMPONENTS                                                                                           |

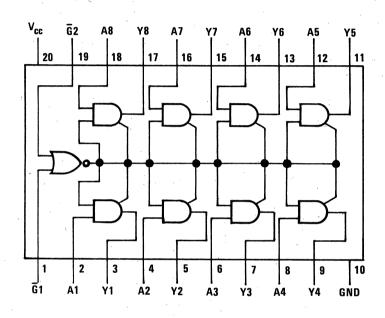

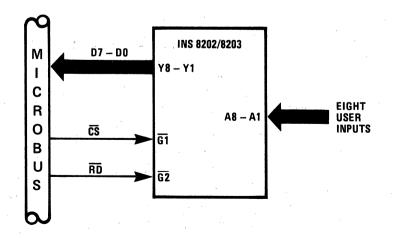

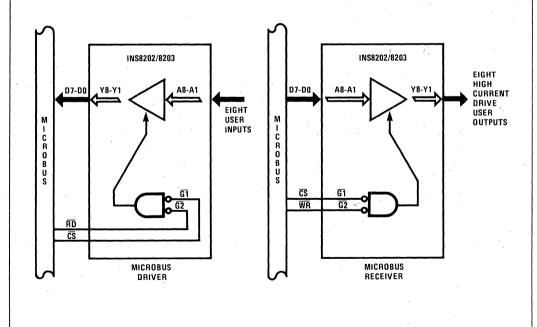

| 7.4 INS8202/INS8203 TRI-STATE OCTAL BUFFERS                                                                              |

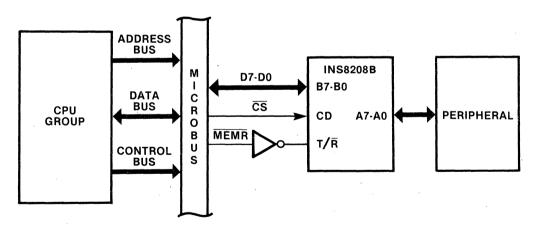

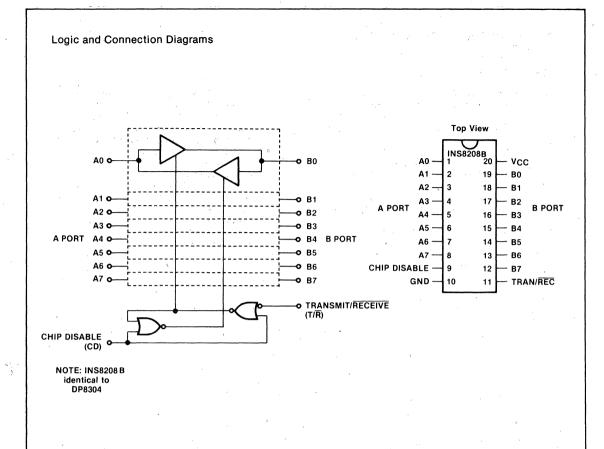

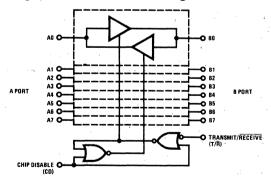

| 7.5 INS8208B 8-BIT BIDIRECTIONAL BUS DRIVER                                                                              |

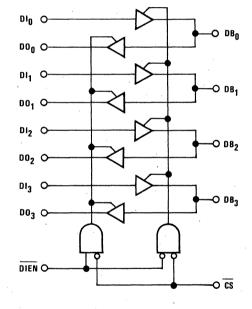

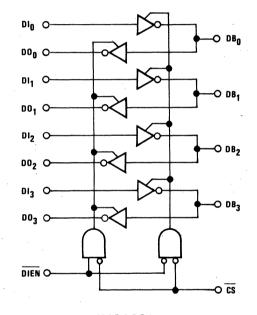

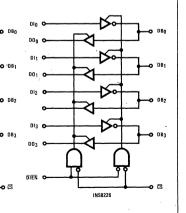

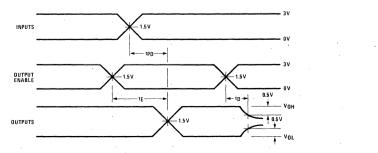

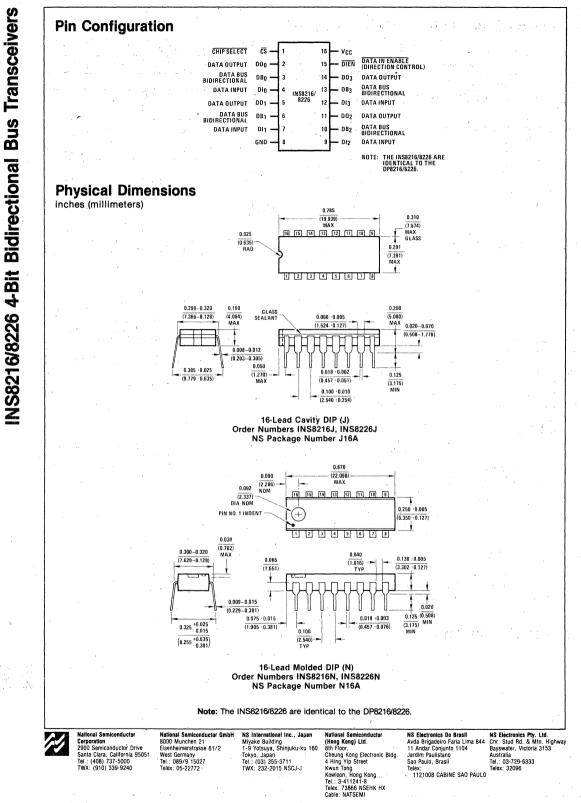

| 7.6 INS8216/INS8226 4-BIT BIDIRECTIONAL BUS DRIVER                                                                       |

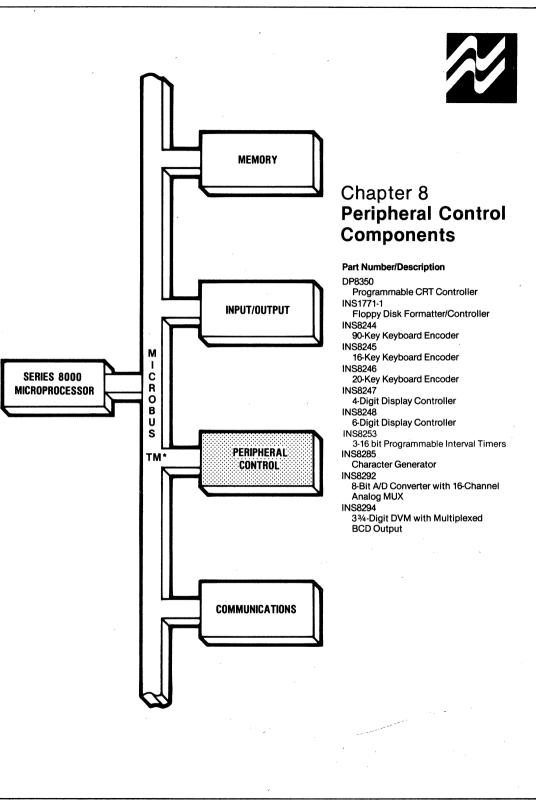

| Chapter 8 PERIPHERAL CONTROL COMPONENTS                                                                                  |

| 8.1 GENERAL DESCRIPTION                                                                                                  |

| 8.2 INTERFACING THE PERIPHERAL CONTROL COMPONENTS                                                                        |

| 8.3 KEYBOARD ENCODERS/DISPLAY CONTROLLERS                                                                                |

| 8.3.2 INS8245/INS8246 Keyboard Encoders                                                                                  |

| 8.3.3 INS8247/INS8248 Display Controller                                                                                 |

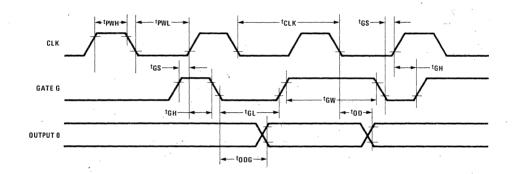

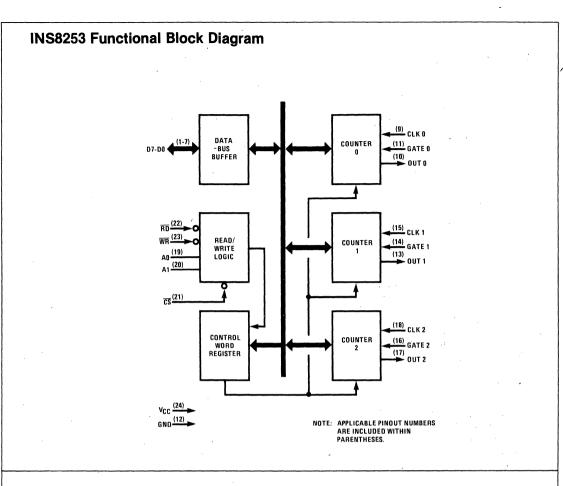

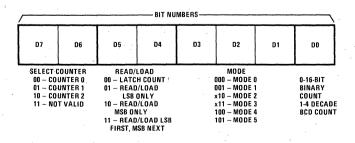

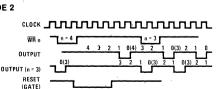

| 8.4 PROGRAMMABLE INTERVAL TIMER (INS8253)                                                                                |

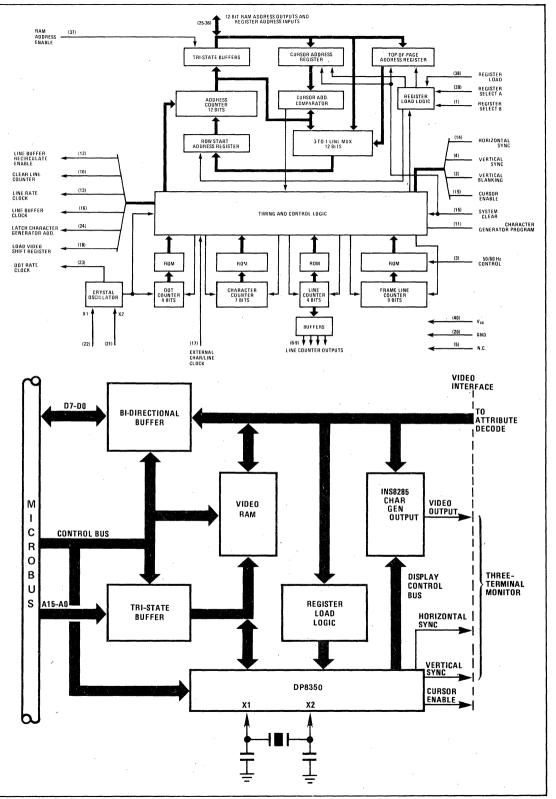

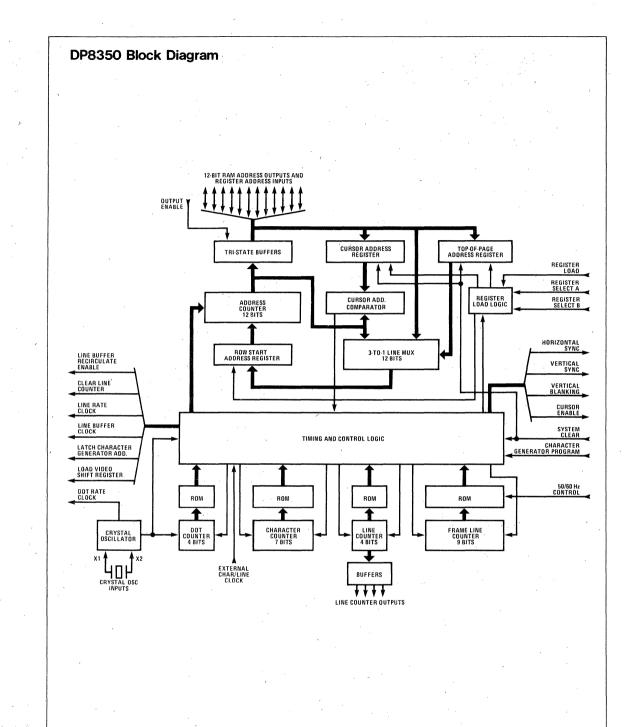

| 8.6 PROGRAMMABLE CRT CONTROLLER (DP8350)                                                                                 |

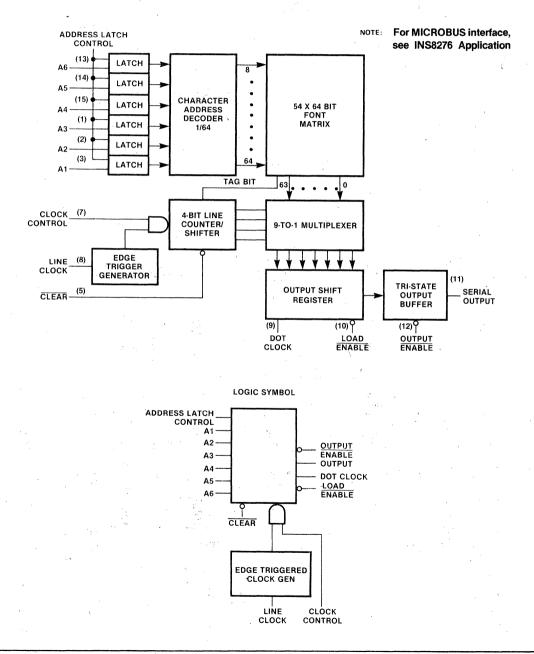

| 8.7 CHARACTER GENERATOR (INS8285)                                                                                        |

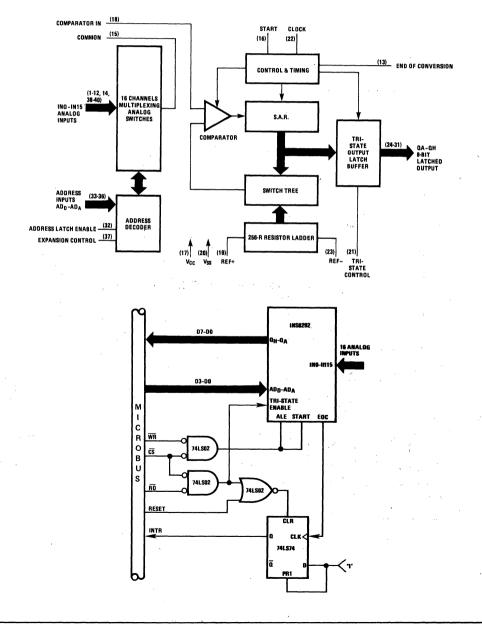

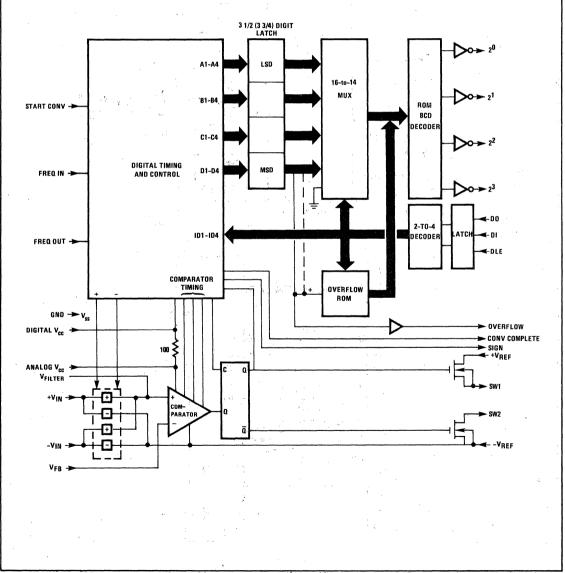

| 8.9 3-3/4 DIGIT DIGITAL VOLTMETER (INS8294) (MICROPROCESSOR COMPATIBLE)                                                  |

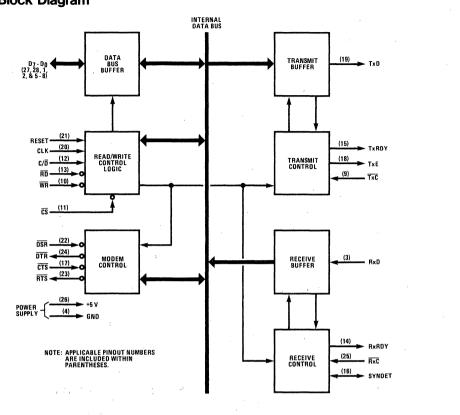

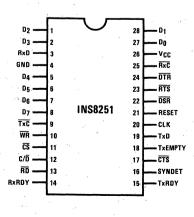

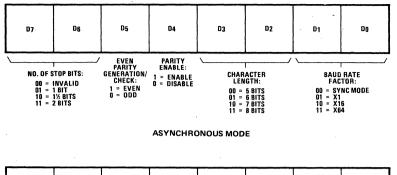

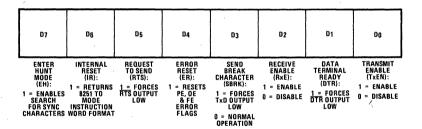

| Chapter 9 COMMUNICATIONS COMPONENTS                                                                                      |

| 9.1 GENERAL DESCRIPTION                                                                                                  |

| 9.2 INTERFACING THE COMMUNICATIONS COMPONENTS                                                                            |

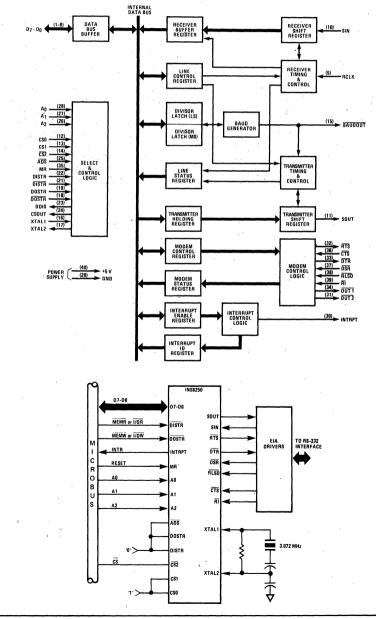

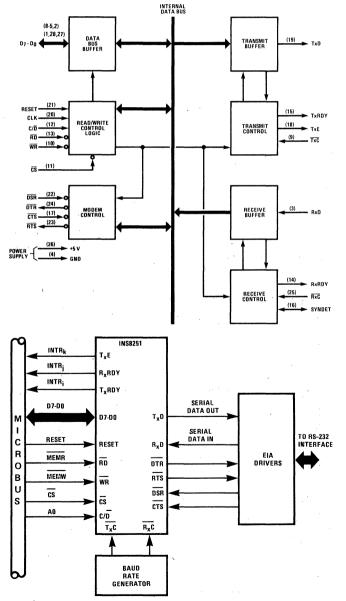

| 9.3 INS8250 ASYNCHRONOUS COMMUNICATIONS ELEMENT (ACE)                                                                    |

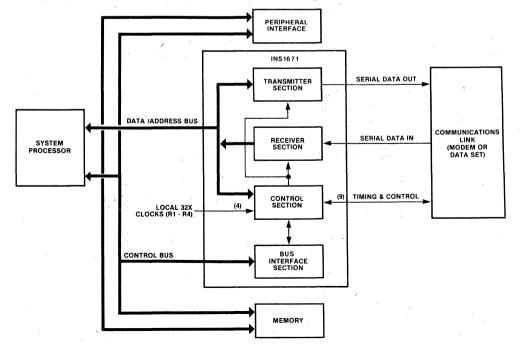

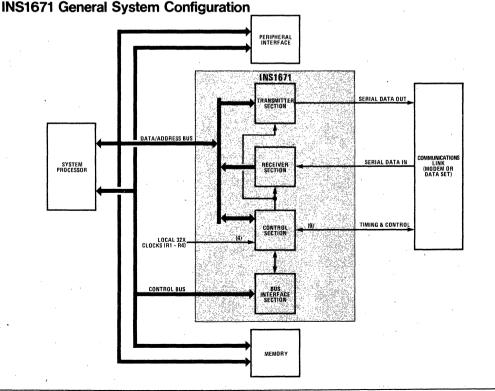

| 9.5 INS1671 ASYNCHRONOUS/SYNCHRONOUS TRANSMITTER/RECEIVER                                                                |

|                                                                                                                          |

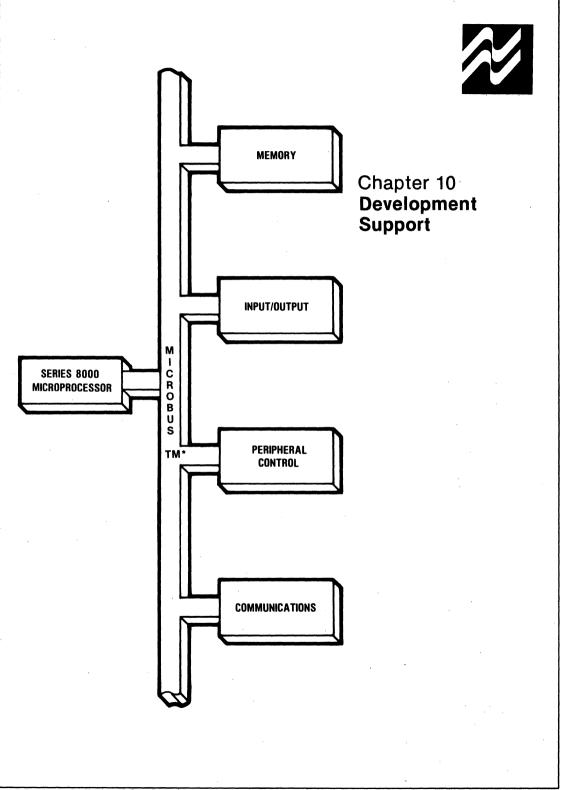

### Chapter 10 DEVELOPMENT SUPPORT

| 10.1 GENERAL DESCRIPTION                                            |       |

|---------------------------------------------------------------------|-------|

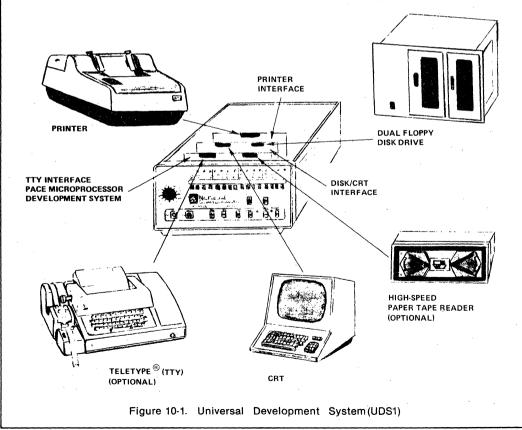

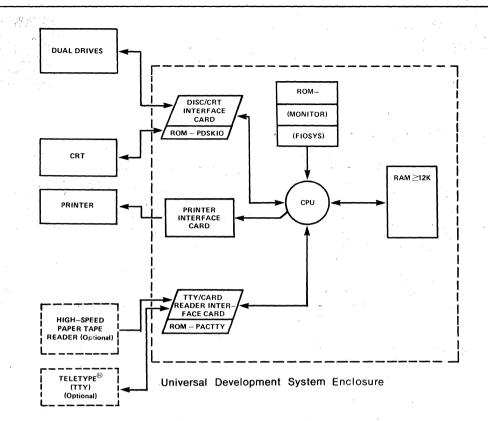

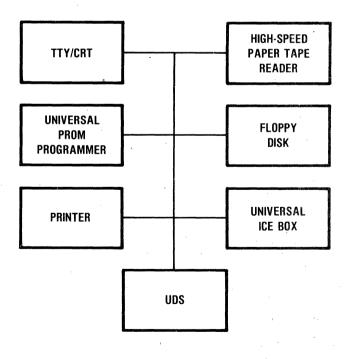

| 10.2 UNIVERSAL DEVELOPMENT SYSTEM (UDS1)                            | 10-1  |

| 10.2.1 Hardware Support                                             | 10-3  |

| 10.2.1.1 Dual Diskette Drives                                       | 10-3  |

| 10.2.1.2Disk/CRT Interface Card                                     | 10-3  |

| 10.2.1.3 Universal Development System                               | 10-3  |

| 10.2.1.4 Peripherals                                                |       |

| 10.2.2 Software Support                                             | 10-3  |

| 10.2.2.1 Monitor System (MONITOR)                                   | 10-5  |

| 10.2.2.2 File Input/Output Subsystem (FIOSYS)                       | 10-5  |

| 10.2.2.3 File Manager Program (PACFM)                               | 10-5  |

| 10.2.2.4 Supporting System Software                                 | 10-5  |

| 10.2.2.5 PACE 12K Resident Assembler (PAC12ASM)                     | 10-5  |

| 10.2.2.6 Cross Assemblers for 8060, 8070, and 8080                  | 10-5  |

| 10.2.2.7 UDS1 Editor (EDITOR)                                       | 10-5  |

| 10.2.2.8 Linkage Editor (LINKEDIT)                                  | 10-5  |

| 10.2.2.9 Diskette Diagnostic Program (PFDDIA)                       | 10-5  |

| 10.2.2.10 UDS1 Utility Programs                                     | 10-5  |

| 10.3 INS8080A CROSS ASSEMBLER                                       |       |

| 10.4 PROM PROGRAMMING                                               |       |

| 10.4.1 UDS1 PROM Programmer (Peripheral)                            |       |

| 10.4.2 UDS1 Serial Link Card                                        |       |

| 10.5 SERIES/80 FAMILY INCLUDING UNIVERSAL PROTOTYPE BOARD (BLC 905) |       |

| 10.5.1 Series/80 System Design Aids                                 | 10-10 |

| 10.5.2 Board-Level Computers                                        | 10-10 |

| 10.5.3 OEM Rack Mountable Computers                                 |       |

| 10.5.4 Memory Boards                                                | 10-10 |

| 10.5.5 Input/Output and Memory Expansion Boards                     | 10-10 |

| 10.5.6 BLC 604 System Chassis and BLC 614 Expansion Board Cage      | 10-10 |

| 10.5.7 RMC 660 System Chassis                                       | 10-11 |

| 10.5.8 BLC 635 Power Supply                                         | 10-11 |

| 10.5.9 BLC 665 Heavy Duty Power Supply                              | 10-11 |

| 10.6 PUBLICATIONS                                                   | 10-11 |

| 10.7 TRAINING                                                       |       |

| 10.8 NATIONAL'S MICROPROCESSOR USERS GROUP                          | 10-12 |

| 10.9 Technical Support Programs                                     |       |

| 10.10 MICRO+ PROGRAM (Quality Control and Testing Process)          | 10-13 |

|                                                                     |       |

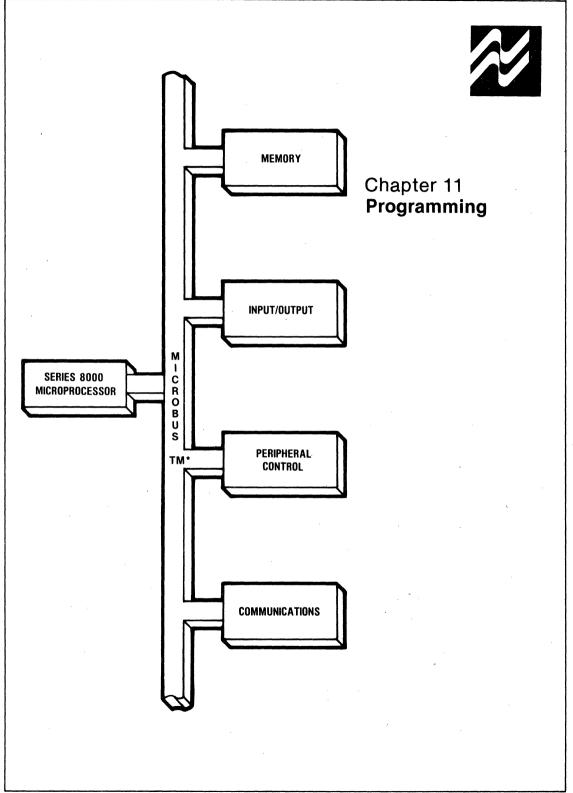

### Chapter 11 PROGRAMMING

| 11.1 INS8080A INSTRUCTION SET       |  |

|-------------------------------------|--|

| 11.1.1 Instruction and Data Formats |  |

| 11.1.2 Addressing Modes             |  |

| 11.1.3 Condition Flags              |  |

| 11.1.4 Presentation Format          |  |

| 11.1.5 Data Transfer Group          |  |

| 11.1.6 Arithmetic Group             |  |

| 11.1.7 Logical Group                |  |

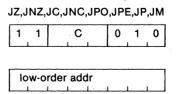

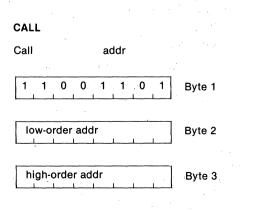

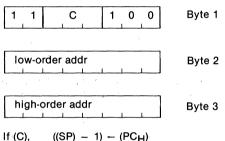

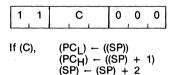

| 11.1.8 Branch Group                 |  |

#### APPENDICES

### Appendix A MICROBUS ELECTRICAL SPECIFICATIONS

| A.1 GENERAL DESCRIPTION                        | Λ <b>1</b> |

|------------------------------------------------|------------|

| All GENERAL DESORIT HON                        |            |

| A.2 LOGICAL AND ELECTRICAL STATE RELATIONSHIPS | A -1       |

| A.2 LOGICAL AND ELECTRICAL STATE RELATIONSHIPS |            |

|                                                |            |

| A.3 DRIVER REQUIREMENTS                                                                                        | A-2 |

|----------------------------------------------------------------------------------------------------------------|-----|

| A.4 RECEIVER REQUIREMENTS                                                                                      |     |

| A.4.1 Receiver Specifications, Standard                                                                        | A-2 |

| A.5 BIDIRECTIONAL SIGNALS                                                                                      |     |

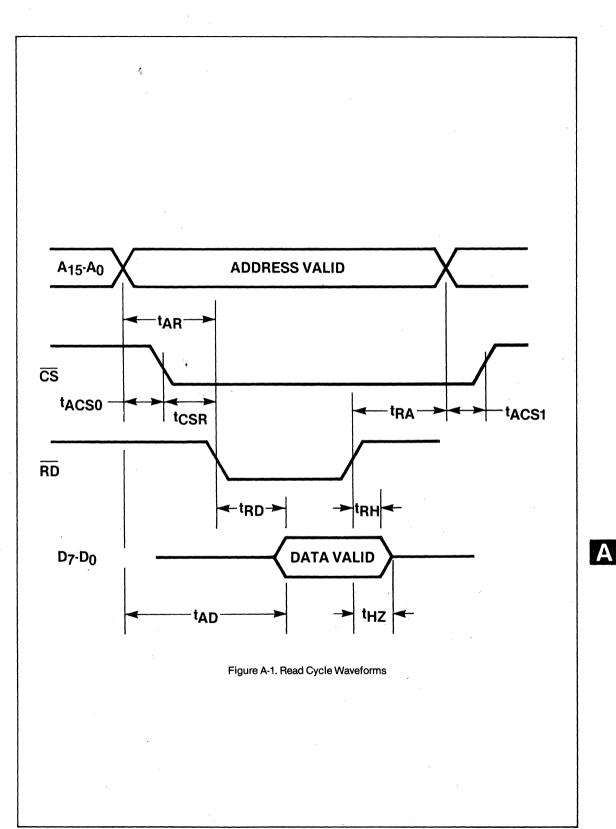

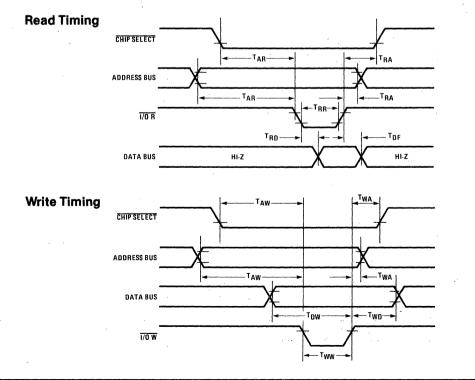

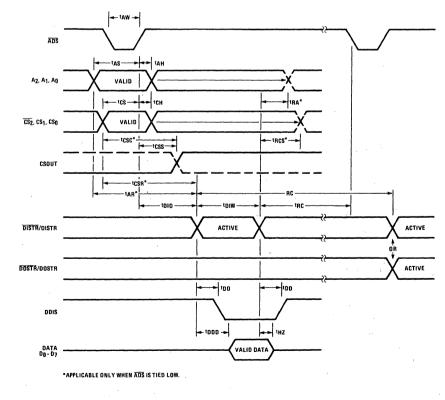

| A.6 READ CYCLE TIMING                                                                                          | A-2 |

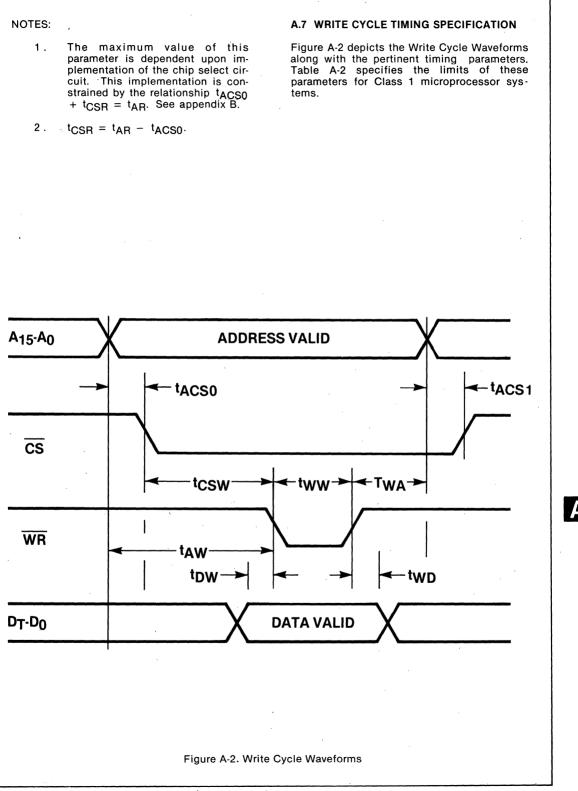

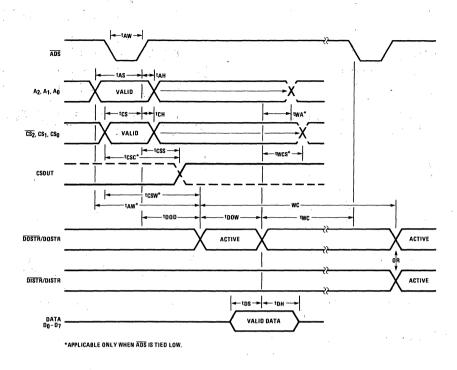

| A.7 WRITE CYCLE TIMING                                                                                         |     |

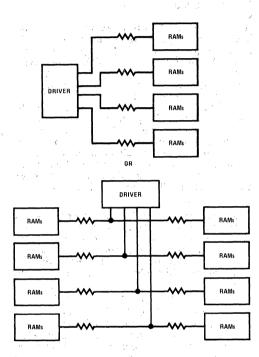

| A.8 MICROBUS AND DEVICES                                                                                       | A-6 |

| N CONTRACTOR OF CONTRACTOR |     |

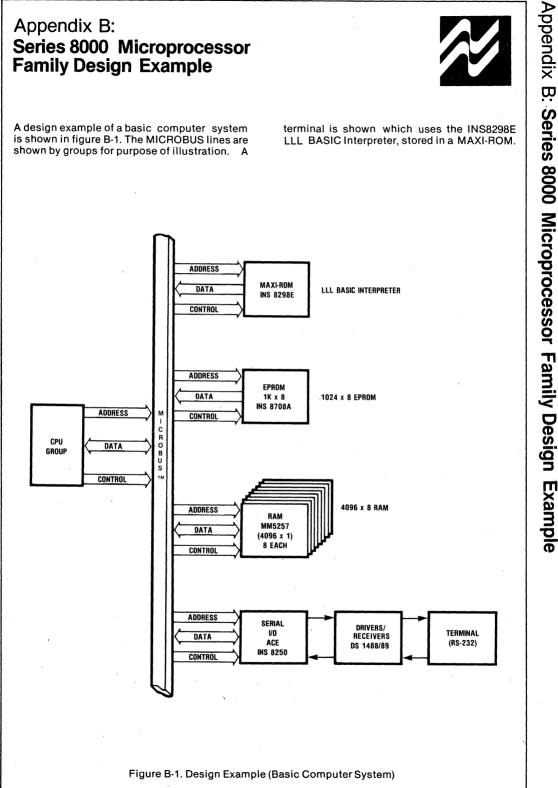

| Appendix B SERIES 8000 MICROPROCESSOR FAMILY DESIGN EXAMPLE                                                    | B-1 |

| Appendix C ADDITIONAL INFORMATION SOURCES                                                                      | C-1 |

## Appendix D DATA SHEETS

| D.1 CPU GROUP                     | D-3   |

|-----------------------------------|-------|

| D.2 DIGITAL I/O COMPONENTS        | D-25  |

| D.3 PERIPHERAL CONTROL COMPONENTS | D-59  |

| D.4 COMMUNICATIONS COMPONENTS     | D-145 |

### List of Illustrations

| Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Title                                                                                    | Page                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| <ul> <li>1-1 National Semiconductor Series 80<br/>INS8080A CPU Group)</li> <li>1-2 Series 8000 Microprocessor Family.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                 |                                                                                          |                                                             |

| 2-1 Read Cycle - Fundamental Timing R<br>2-2 Write Cycle - Fundamental Timing R<br>2-3 Interrupt Service - Interface Device V<br>2-4 Single Cycle DMA Transfer from an I<br>2-5 Relationship of READY to CS, WR, a<br>2-6 INS8080A S; 3 tem Model for the Bas<br>2-7 INS8080 Family CPU Group to MICR<br>2-8 INS8060 System Model                                                                                                                                                                | elationships<br>Vaveforms<br>nterface Device to Memory<br>nd RD<br>ic MICROBUS Interface | 2-1<br>2-4<br>2-5<br>2-5<br>2-5<br>2-6<br>2-7<br>2-7<br>2-8 |

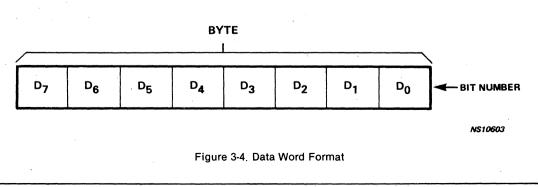

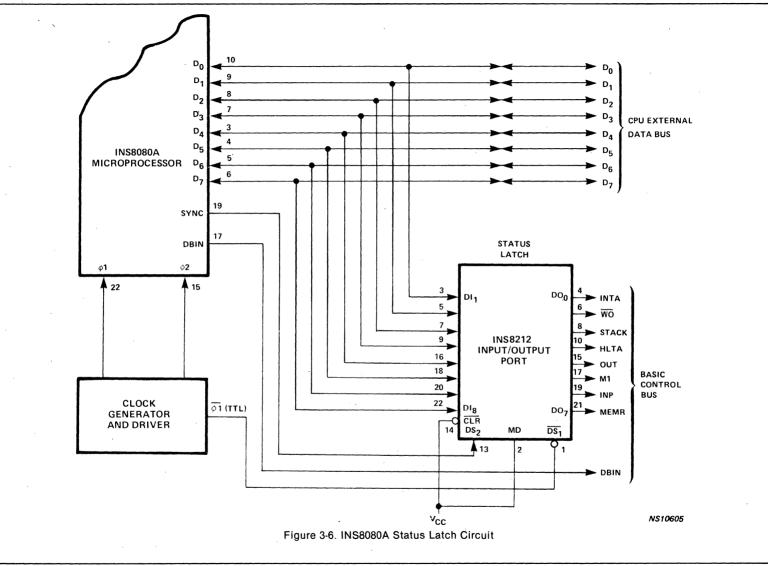

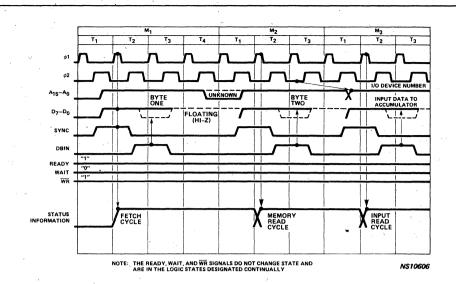

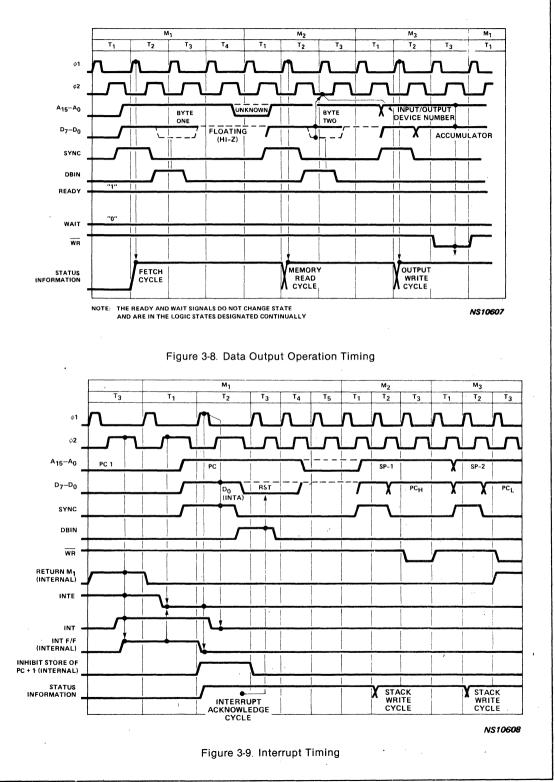

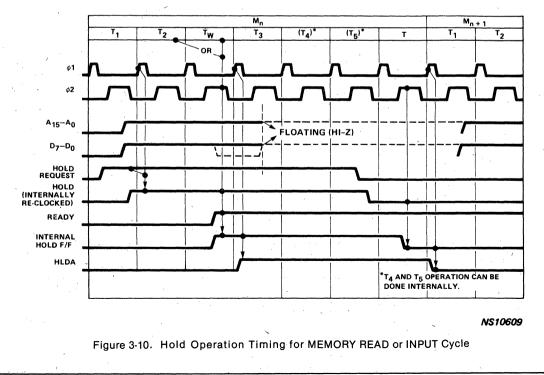

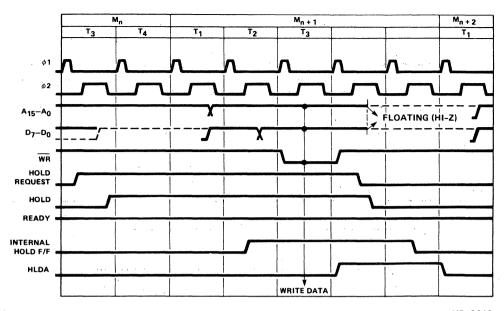

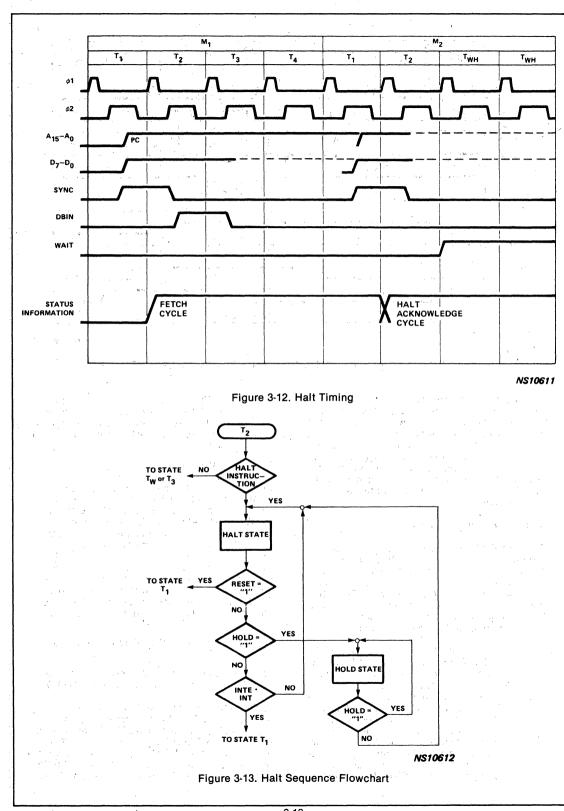

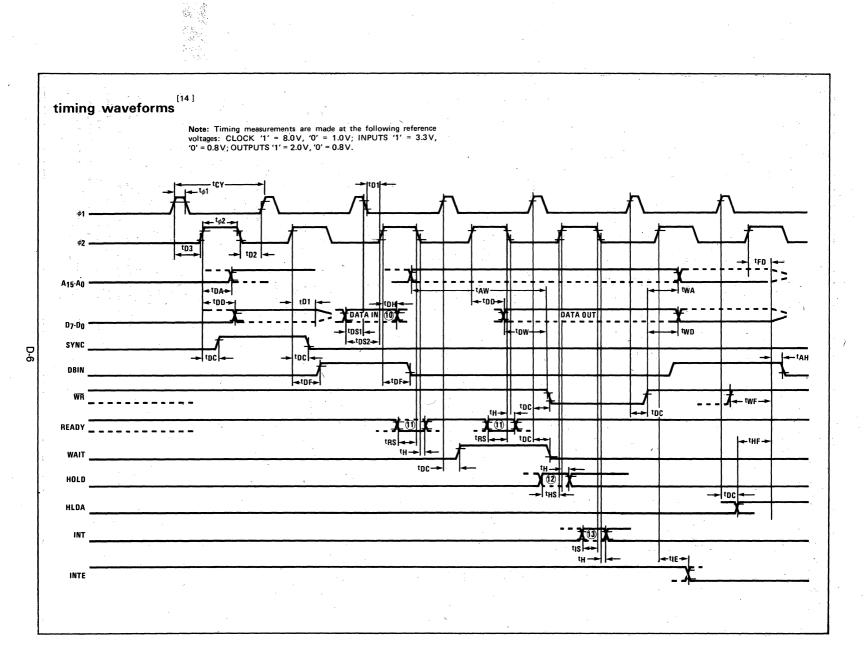

| <ul> <li>3-1 CPU Architecture and Pinouts of IN</li> <li>3-2 Basic Instruction Cycle</li> <li>3-3 INS8080A CPU State Transition Flow</li> <li>3-4 Data Word Format</li> <li>3-5 Instruction Formats</li> <li>3-6 INS8080A Status Latch Circuit</li> <li>3-7 Data Input Operation Timing</li> <li>3-8 Data Output Operation Timing</li> <li>3-9 Interrupt Timing</li> <li>3-10 Hold Operation Timing for MEMOR</li> <li>3-11 Hold Operation Timing for MEMOR</li> <li>3-12 Halt Timing</li> </ul> | WChart<br>Y READ or INPUT Cycle<br>Y WRITE or OUTPUT Cycle                               |                                                             |

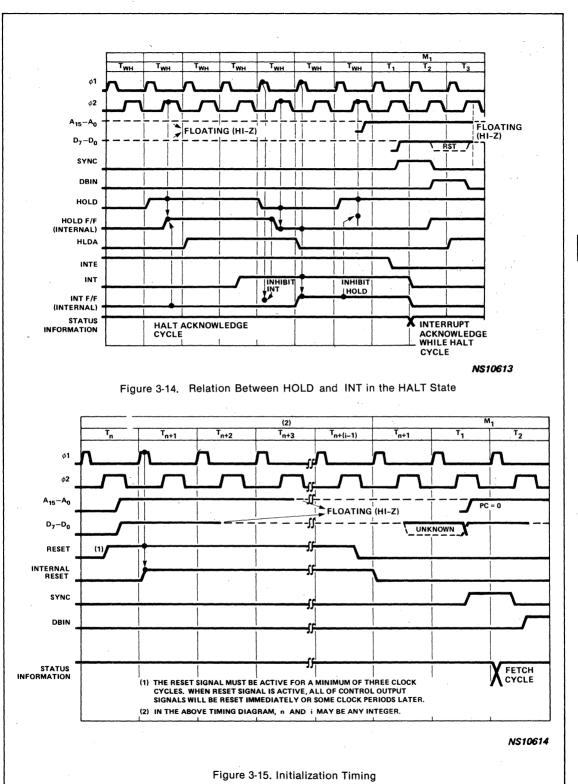

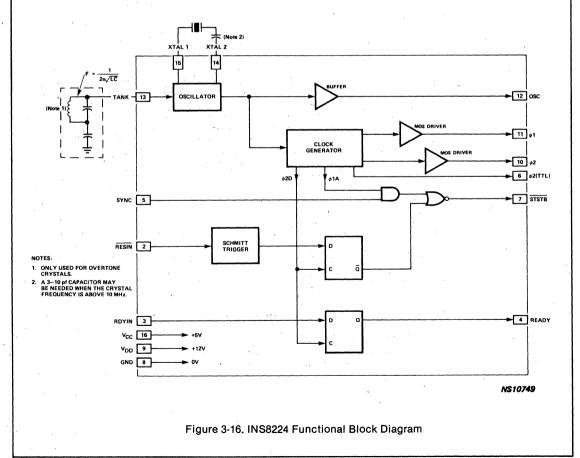

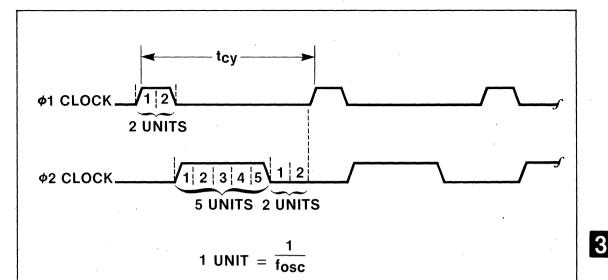

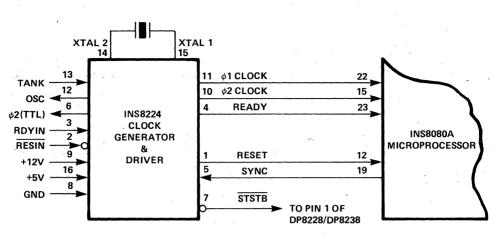

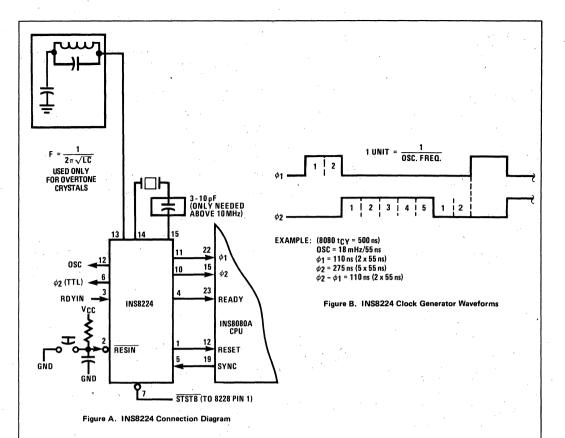

| 3-13 Halt Sequence Flowchart<br>3-14 Relationship Between HOLD and II<br>3-15 Initialization Timing<br>3-16 INS8224 Functional Block Diagram<br>3-17 Relative Timing of INS8224 Clock C<br>3-18 INS8224 to INS8080A Interconnect<br>3-19 INS8228/INS8238 Functional Block<br>3-20 INS8228/INS8238 to INS8080A Inte<br>3-21 Preferred Method of CPU Group Im                                                                                                                                      | NT in the HALT State<br>Dutput Waveforms<br>ion<br>Diagram<br>prconnection               |                                                             |

## V

| 3-22 DM8131 6-Bit Unified Bus Comparator                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| 3-23 INS82LS05 One-of-Eight Binary Decoder                                                                                                 |

| 3-24 INS8257 Programmable DMA Controller       3-27         3-25 INS8259 Programmable Interrupt Controller       3-28                      |

|                                                                                                                                            |

| 4-1 Preferred Method of CPU Group Implementation                                                                                           |

| 4-2 System Clock Generator and Driver Using Discrete Components                                                                            |

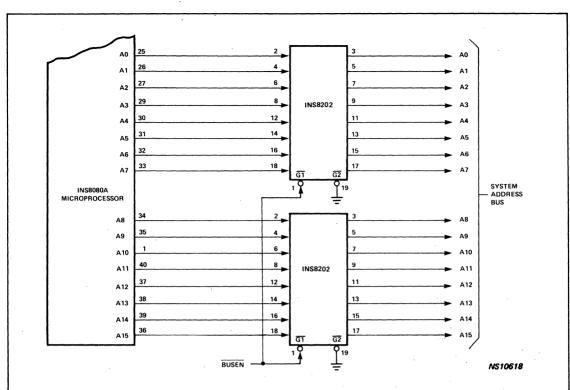

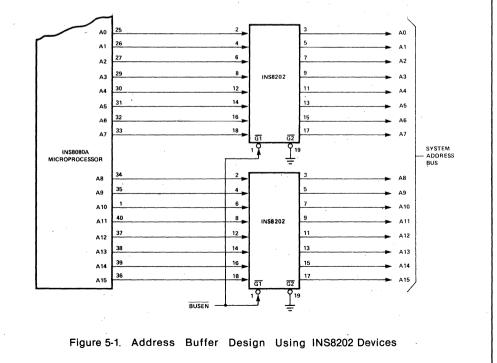

| 4-3 System Controller and Bus Driver Using Discrete Components       4-4         4-4 Address Buffer Design Using INS8202 Devices       4-5 |

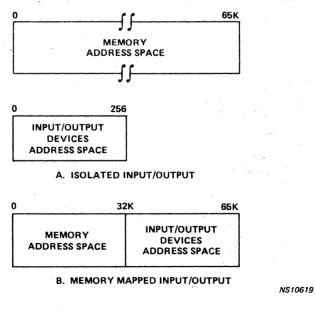

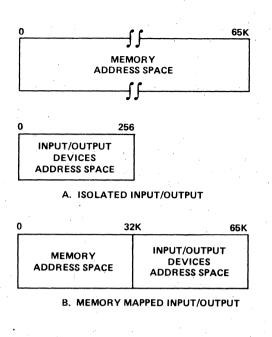

| 4-5 Mapping for Isolated Input/Output and Memory mapped Input/Output Techniques                                                            |

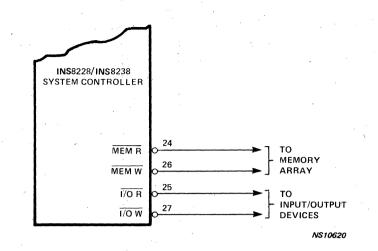

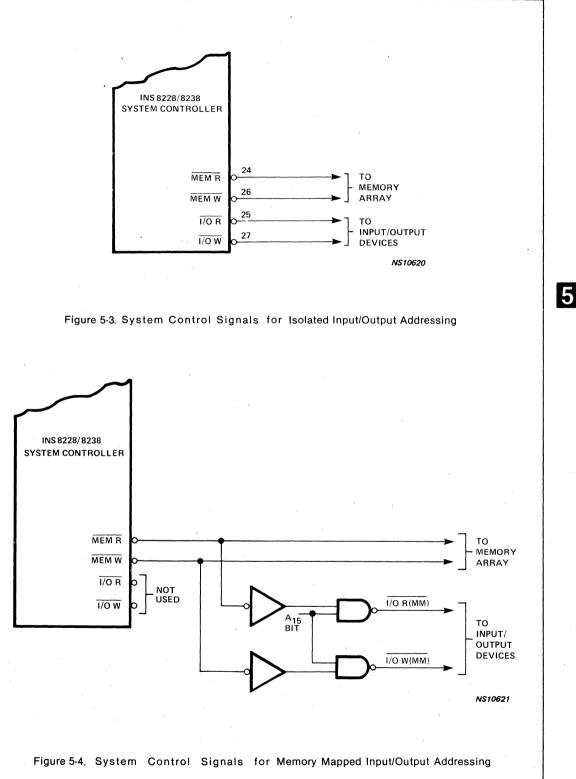

| 4-6 System Control Signals for Isolated Input/Output Addressing                                                                            |

| 4-7 System Control Signals for Memory Mapped Input/Output Addressing                                                                       |

| 4-8 Typical Memory Interface                                                                                                               |

| 4-9 Cell Comparison         4-8           4-10 IDD Current Waveform         4-9                                                            |

| 4-10 DD Current Waveronn                                                                                                                   |

| 4-12 Typical Input/Output Interface                                                                                                        |

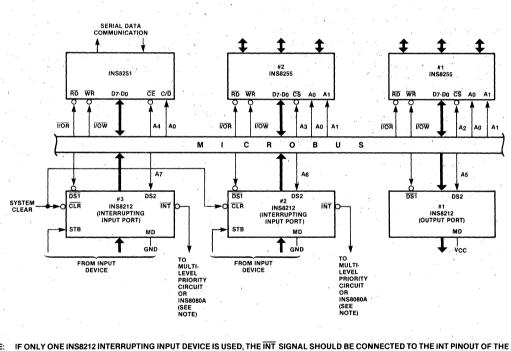

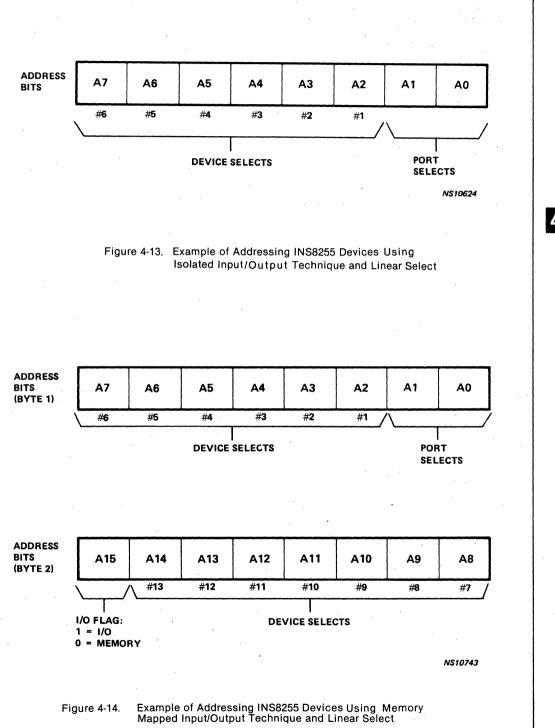

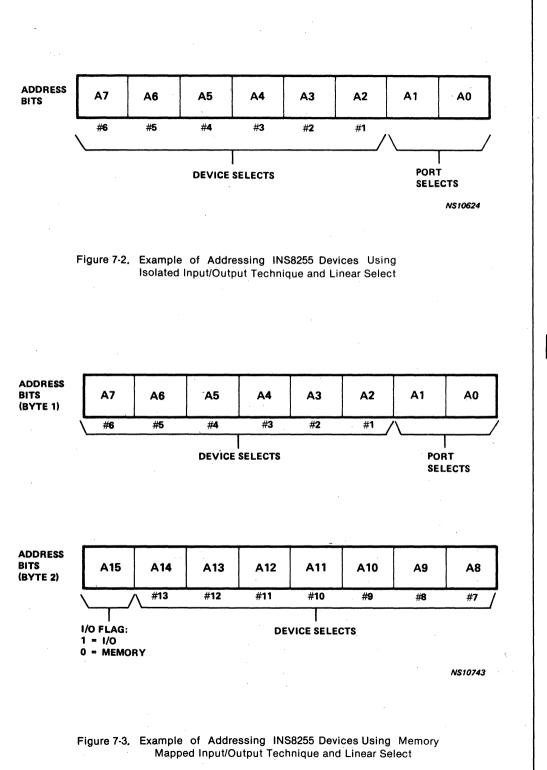

| 4-13 Example of Addressing INS8255 Devices Using Isolated Input/Output Technique and Linear Select . 4-13                                  |

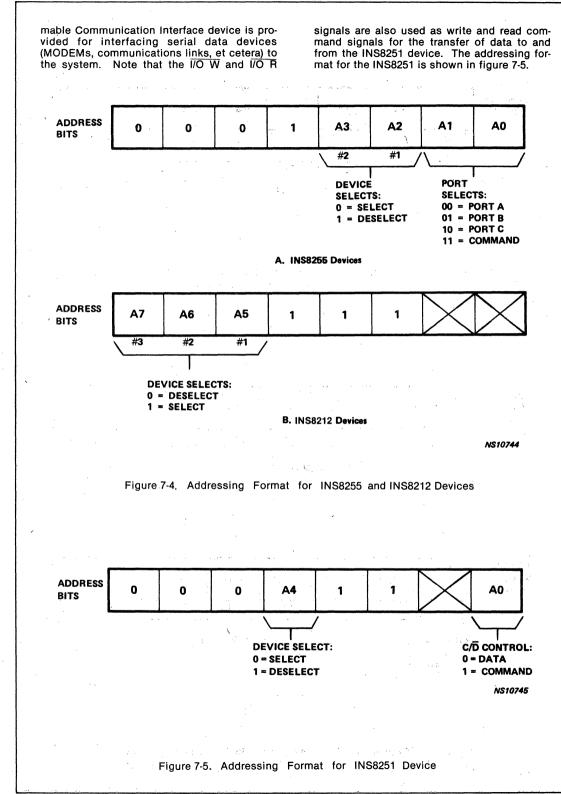

| 4-14 Example of Addressing INS8255 Devices Using Memory Mapped Input/Output Technique and                                                  |

| Linear Select                                                                                                                              |

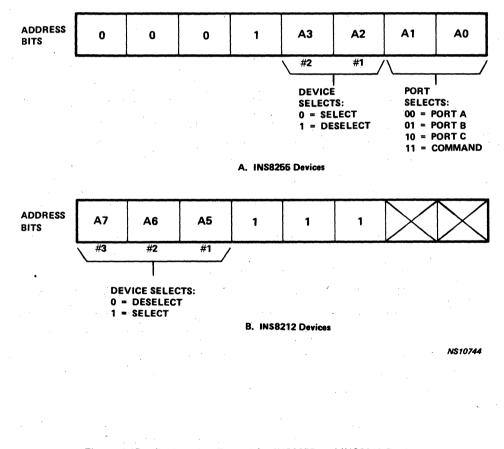

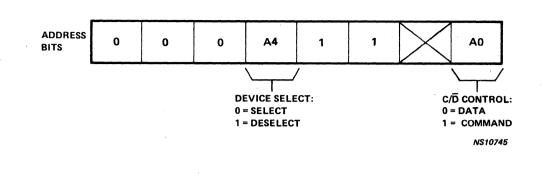

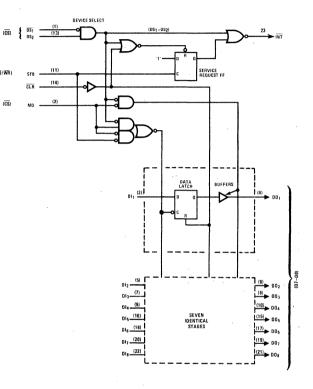

| 4-15 Addressing Format for INS8255 and INS8212 Devices       4-14         4-16 Addressing Format for INS8251 Device       4-15             |

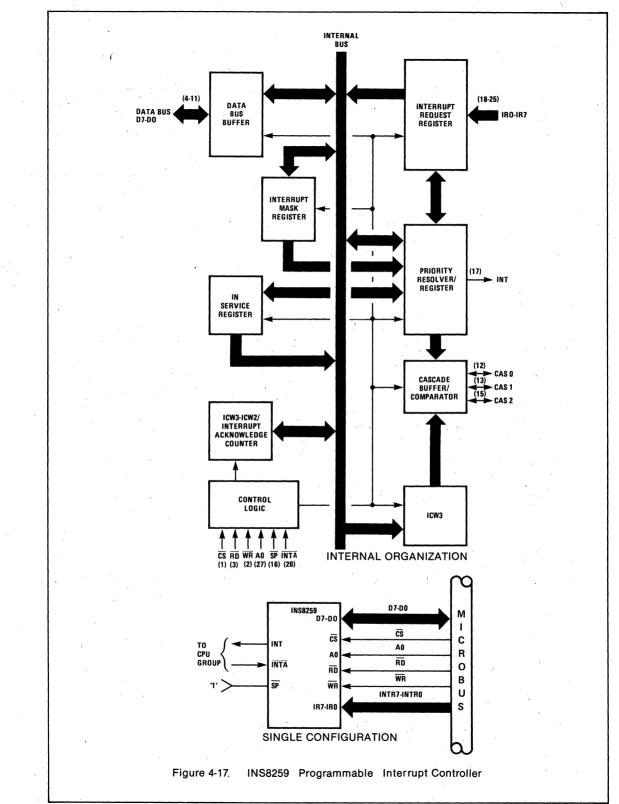

| 4-17 INS8259 Programmable Interrupt Controller                                                                                             |

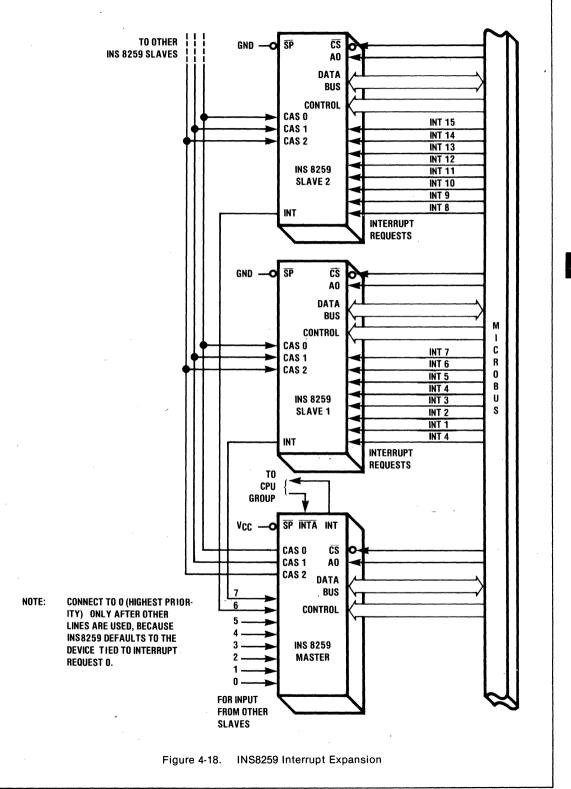

| 4-18 INS8259 Interrupt Expansion                                                                                                           |

| 5-1 Address Buffer Design Using INS8202 Devices                                                                                            |

| 5-1 Address Buffer Design Using INS8202 Devices                                                                                            |

| 5-2 Mapping for Isolated Input/Output and Memory Mapped Input/Output Techniques                                                            |

| 5-4 System Control Signals for Memory Mapped Input/Output Addressing                                                                       |

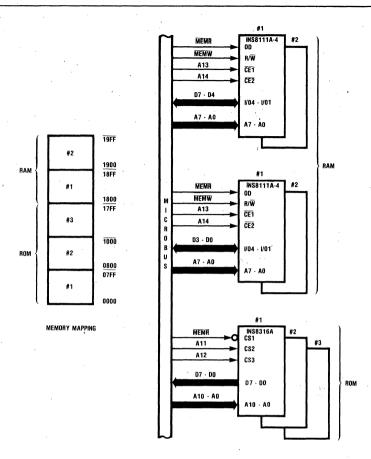

| 5-5 Typical Memory Interface                                                                                                               |

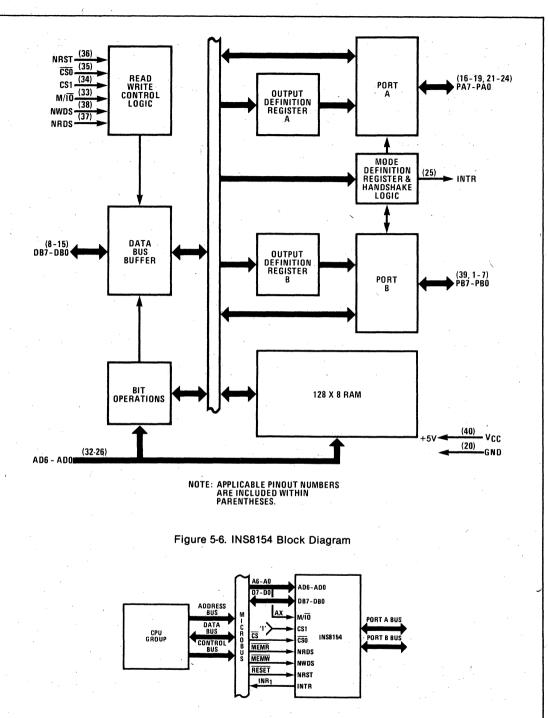

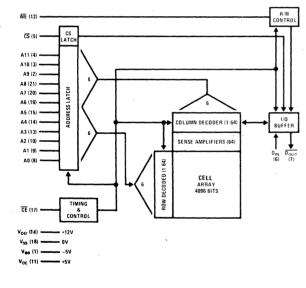

| 5-6 INS8154 Block Diagram                                                                                                                  |

| 5-7 INS8154 MICROBUS Connection                                                                                                            |

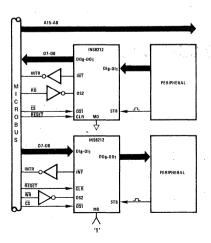

| 7-1 Typical Input/Output Interface                                                                                                         |

| 7-2 Example of Addressing INS8255 Devices Using Isolated Input/Output Technique and Linear Select 7-3                                      |

| 7-3 Example of Addressing INS8255 Devices Using Memory Mapped Input/Output Technique and Linear                                            |

| Select                                                                                                                                     |

| 7-4 Addressing Format for INS8255 and INS8212 Devices                                                                                      |

|                                                                                                                                            |

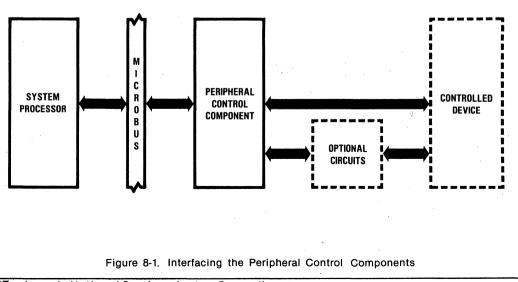

| 8-1 Interfacing the Peripheral Control Components                                                                                          |

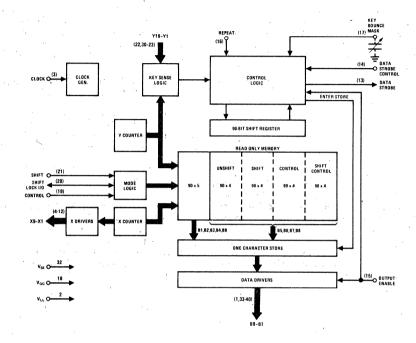

| 8-2 INS8244 Internal Block Diagram                                                                                                         |

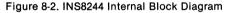

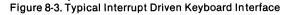

| 8-3 Typical Interrupt Driven Keyboard Interface                                                                                            |

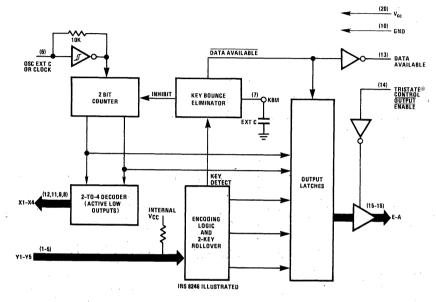

| 8-4 INS8246 Block Diagram                                                                                                                  |

| 8-5 Typical MICROBUS Connection                                                                                                            |

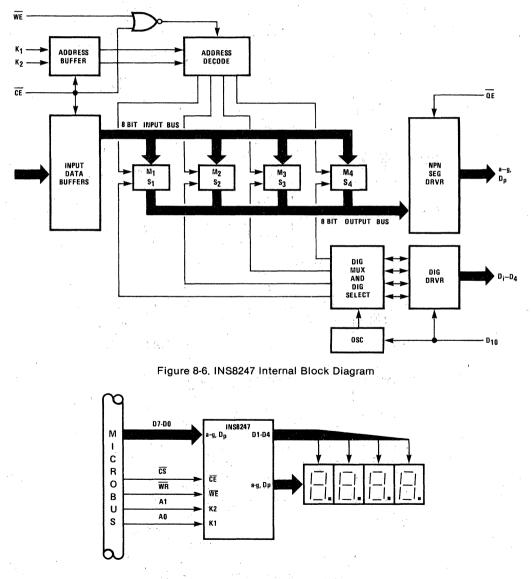

| 8-7 INS8247 MICROBUS Interface                                                                                                             |

| 8-8 INS8253 Internal Block Diagram                                                                                                         |

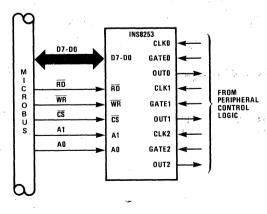

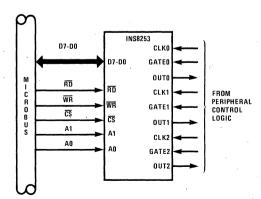

| 8-9 INS8253 MICROBUS Connection                                                                                                            |

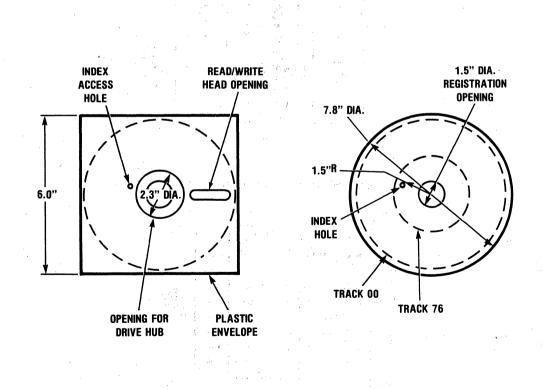

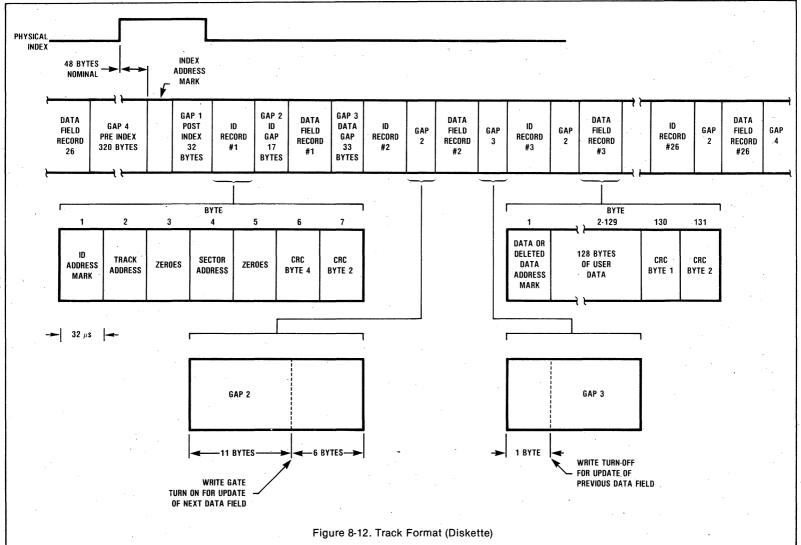

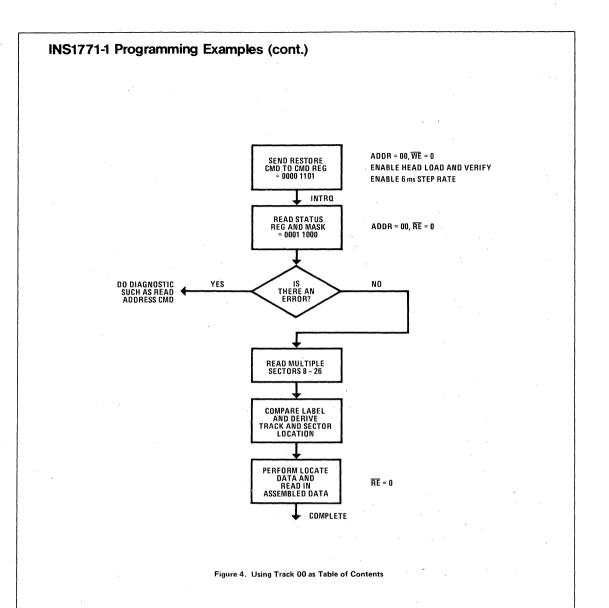

| 8-10 Diskette Layout (Example)                                                                                                             |

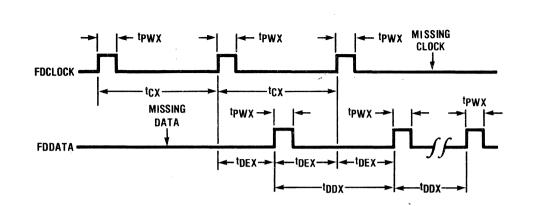

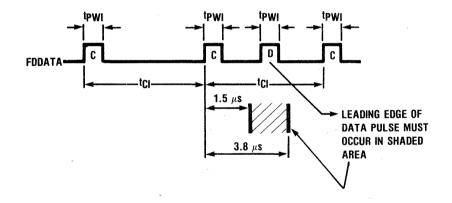

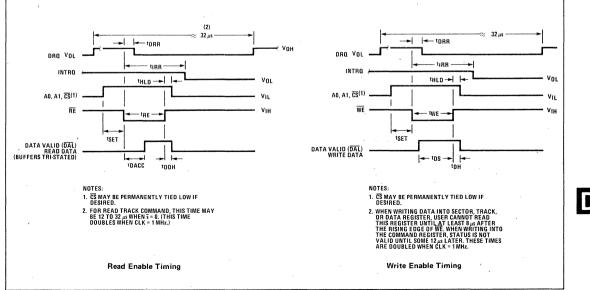

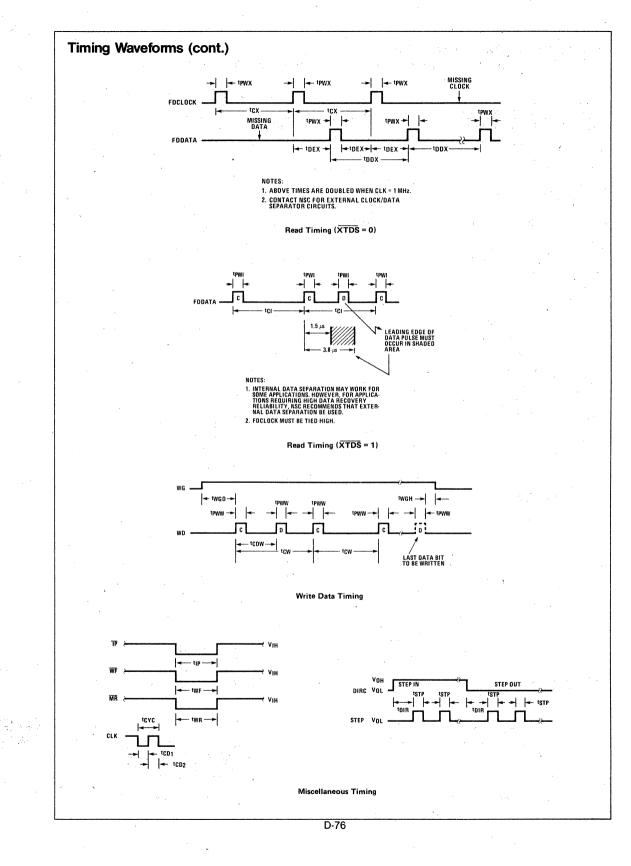

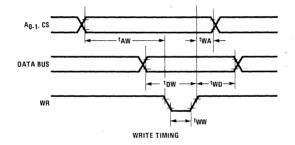

| 8-11 Read Timing                                                                                                                           |

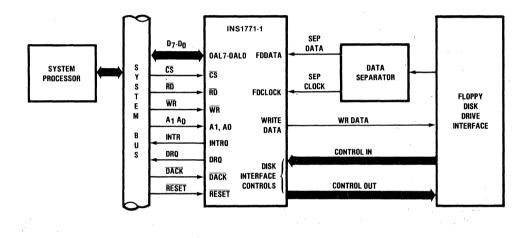

| 8-13 Interface to System Bus                                                                                                               |

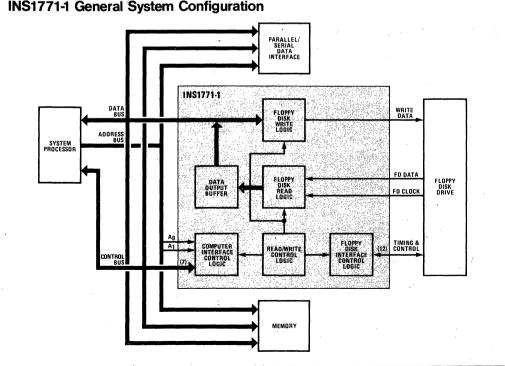

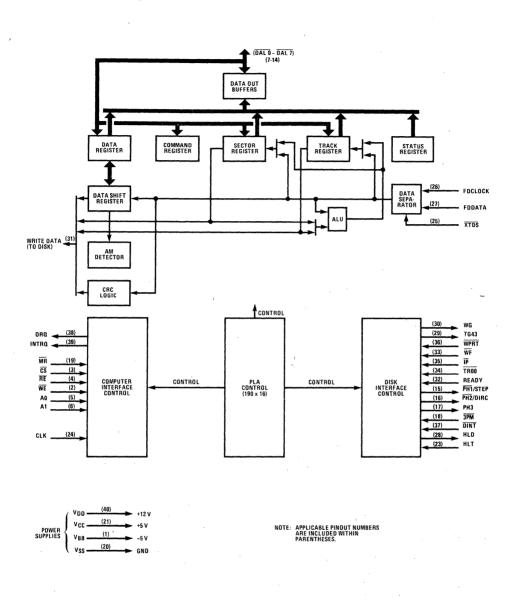

| 8-14 INS1771-1 Block Diagram                                                                                                               |

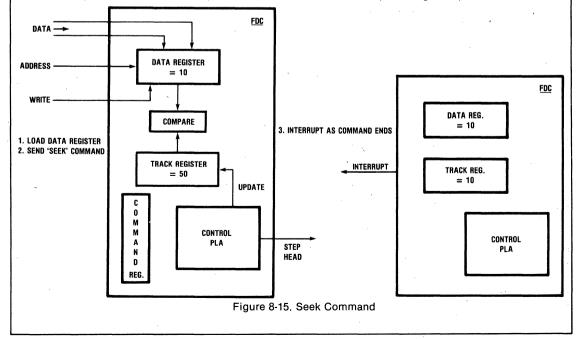

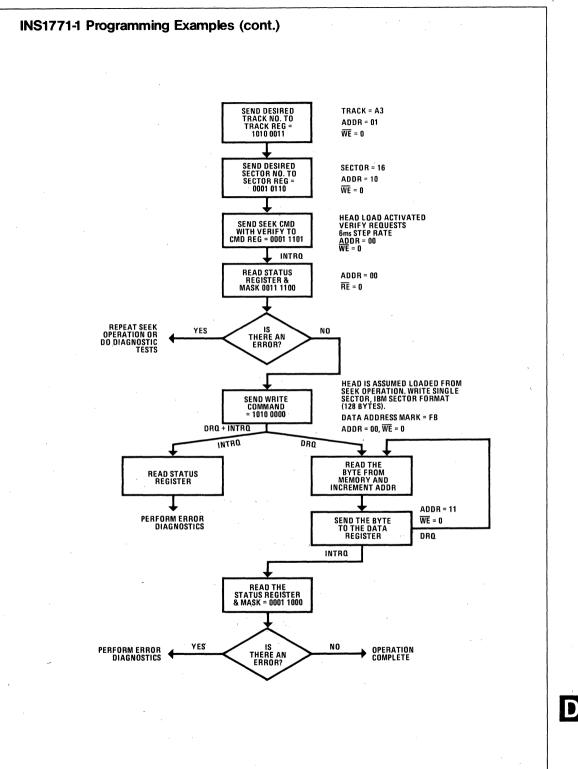

| 8-15 Seek Command                                                                                                                          |

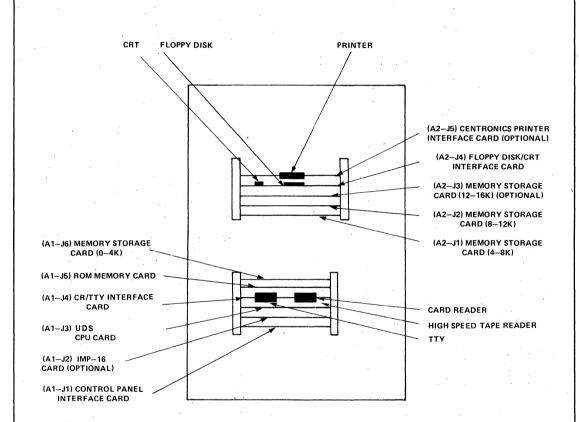

| 10-1 Universal Development System (UDS1)                                                                                                   |

| 10-2 UDS1 Block Diagram         10-2           10-3 Top Internal View of Universal Development System         10-4                         |

| igo rop internal view of oniversal development system                                                                                      |

х

List of Illustrations (Continued)

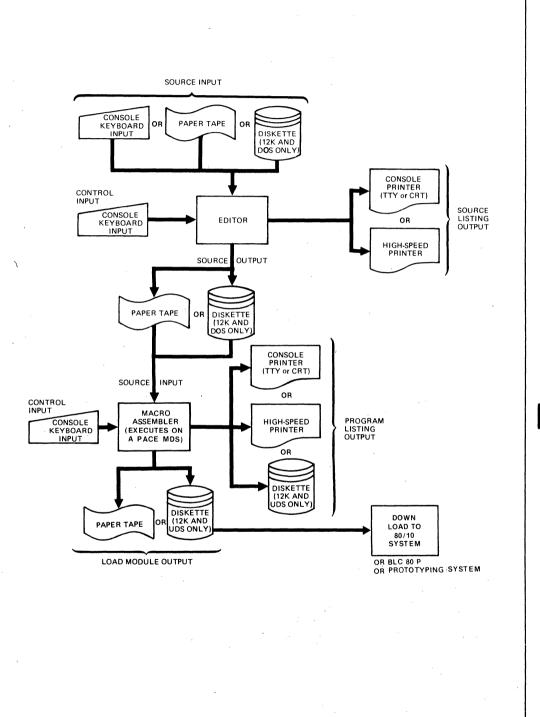

| 10-4 Operational Sequence of the UDS1 Editor and Assemblers         10-5 Universal Development System Configuration |            |

|---------------------------------------------------------------------------------------------------------------------|------------|

| 11-1 Presentation Format                                                                                            |            |

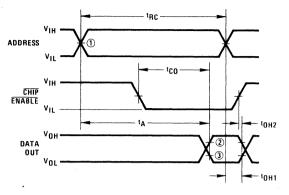

| A-1 Read Cycle Waveforms                                                                                            | A-3<br>A-5 |

| B-1 Design Example (Basic Computer System)                                                                          | . B-1      |

## List of Tables

| Table                                                                                                                                                                           | Title | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| 2-1 Signal Lines (Referenced to the Interface Devic                                                                                                                             | ;e)   | 2-2  |

| <ul> <li>3-1 Input/Output Signal Descriptions</li> <li>3-2 Status Information Distribution and Definition</li> <li>3-3 Status Bit Outputs for Each Type of Machine C</li> </ul> |       | 3-12 |

| 8-1 INS1771-1 Register Selection<br>8-2 Commands Summary                                                                                                                        |       |      |

| 10-1 Assembler Peripheral Options                                                                                                                                               |       | 10-6 |

| 11-1 Symbols and Notations                                                                                                                                                      | ·     |      |

| A-1 Class 1 Read Cycle Timing Specifications<br>A-2 Class 1 Write Cycle Timing Specifications                                                                                   |       |      |

## V

**\$**;

## Introduction

#### **1.1 GENERAL DESCRIPTION**

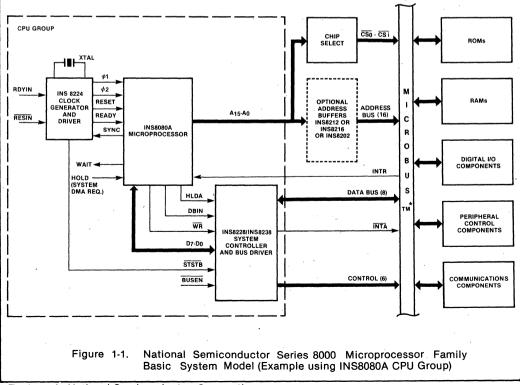

The National Semiconductor Series 8000 Microprocessor Family covers the broad general-purpose segment of microprocessor applications (see figure 1-1 for INS8080A example). Included in the Series 8000 Microprocessor Family are the proven INS8080A CPU and components of proprietary designs as well as a wide range of multiple source devices. The Series 8000 microprocessor family finds use in 8-bit microprocessor system designs ranging from complex controls to highly sophisticated communications applications. Some of the user benefits are listed below:

- Family approach to system design

- Complete CPU group

- Programmable input/output concepts

- Multiple source availability

- Complete line of support components

- Total product support

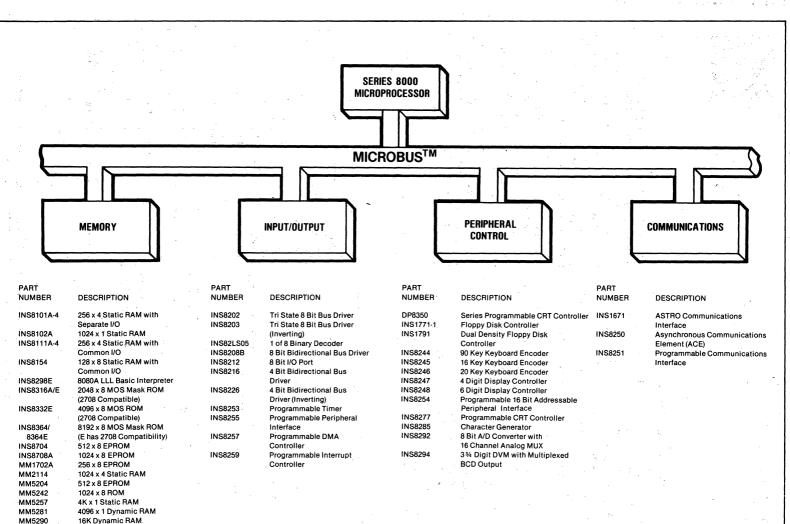

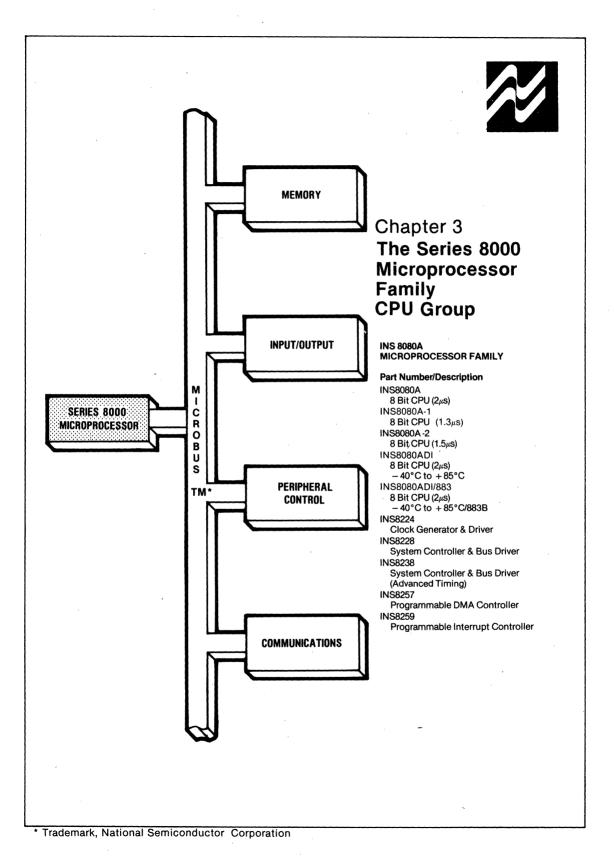

Most components of the Series 8000 Microprocessor Family are shown in figure 1-2. (For a more nearly complete list, see chapter 10 references and specific publications such as National's Memory Databook). Components are discussed by type (see 1.2). Representative of the type of CPU that can be used with the Series 8000 Microprocessor Family is the INS-8080A, an 8-bit CPU chip that may be used interchangeably with the Intel 8080A. The Series 8000 Microprocessor Family can be used in systems that range from a few family components to designs that utilize the extensive capabilities available. The INS8080A falls between the cost-effective 8-bit INS8060 chip and the highly versatile 16-bit INS8900 chip in National Semiconductor's microprocessor spectrum. Any of these three microprocessors can be used with Series 8000 peripheral components.

The designer can satisfy memory requirements

Trademark, National Semiconductor Corporation 1-1

Figure 1-2. Series 8000 Microprocessor Family

Ň

from the wide range of National Semiconductor's RAM, ROM, PROM, and MAXI-ROM<sup>TM\*</sup> components. Programmable input/output and peripheral functions enable the system designer to configure and adapt interface lines to his own requirements. Data communications may be accomplished by using a variety of Series 8000 Communications Peripherals.

The Series 8000 Microprocessor Family is supported by industry standard design kits, easyto-use development systems, and a full complement of cross and resident assemblers. Various components and software also are available to support the Series 8000 Microprocessor family from experimentation to final production (see chapter 10, Development Support).

#### **1.2 HANDBOOK ORGANIZATION**

The major portions of the Series 8000 Microprocessor Family Handbook are as follows:

- Introduction

- The MICROBUS

- The Series 8000 Microprocessor Family CPU Group

- Designing Series 8000 Microprocessor Family Systems

- Memory Components

- MAXI-ROMs

- Input/Output Components

- Peripheral Control Components

- Communications Components

- Development Support

- Programming

- Appendices

The handbook takes the approach of introducing the system concept of the MICROBUS first, since this is the System Bus used to interconnect the various Component Device Groups.An example of a CPU group is discussed next to form a base for discussing the various sizes of systems that follow. With this base of information, the chapter on designing Series 8000 Microprocessor Family Systems is presented next followed by detailed discussion of other device types, so that the designer can pick the chapters of interest that follow and skip the rest. Chapters 5 and 6 discuss memory components including MAXI-ROMs, and their use in storing large programs in ROM. Having covered the various memory options, it is possible to examine how Input/Output is included in the system. This is treated in two chapters (7 and 8) so that individual Input/Output Components can be selected more easily.

The communications components allow data transfer to remote locations, and are covered in chapter 9. We next turn our attention to

Development Support, covering how the designer is aided, and then programming. Appendices are included next which give reference data such as MICROBUS specifications, additional sources of information and complete the manual with the available Data Sheets for the devices referenced.

#### 1.2.1. Introduction

Chapter 1, Introduction, gives a general view of the Series 8000 Microprocessor Family and discusses the plan of the Handbook. It identifies the key concepts that are used throughout the Handbook such as the MICROBUS, and discusses the relationship of the various chapters to each other.

#### 1.2.2 The MICROBUS

The MICROBUS chapter describes the use of the system bus and its conventions. The bus concept is developed, indicating bus usage for various size systems, recognizing that most systems will not need the entire MICROBUS capability.

#### 1.2.3 The Series 8000 Microprocessor Family CPU Group

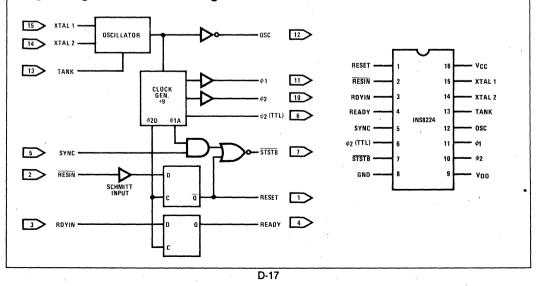

The discussion of the CPU Group includes as an example, the INS8080A Microprocessor, the INS8224 Clock Generator and Driver and the INS8228/INS8238 System Controller and Bus Driver. The architecture of the INS8080A is discussed along with the operating cycle, data and instruction representation. Other key topics such as addressing capabilities, Input/Output operation and control, and interrupts are examined in this chapter and then referenced in following chapters. In particular the next chapter on Designing Series 8000 Microprocessor Family Systems relies heavily on an understanding of the CPU Group as discussed in this chapter.

#### 1.2.4 Designing Series 8000 Microprocessor Family Systems

The handbook is organized so that a designer might start with this chapter and refer to each of the other chapters as needed, while considering the design requirements of the system being designed for a particular application. For example, a particular system might need powerful input/output capability and therefore chapters 7 and 8 might be reviewed while considering approaches for the design of a system with that capability.

#### 1.2.5 Memory Components

The diversity of Memory options range from small RAM to the mask programmable MAXI-ROM.

#### 1.2.6 MAXI-ROMs

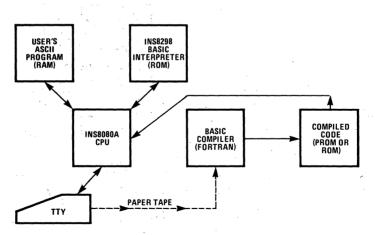

Mask programmable MAXI-ROMs may contain complete programs. As an example of the possibilities, the 8298 LLL (Lawrence Livermore Laboratory) BASIC interpreter for the INS8080A is discussed. This program resides in an INS-8298E, (65,536 bit) static mask-programmable ROM.

#### 1.2.7 Input/Output Components

These devices receive a somewhat lighter discussion than the Peripheral Control Components because of their simplicity. The devices of a more complex nature (i.e. Peripheral Control Components), are given a more extensive treatment to make it easier for a designer to feel comfortable in designing with the devices. It is assumed that the designer has considerable background in the use of similar I/O devices and other Component Groups of concern in his design. The next two chapters are companions to this one and are intended to be used with it.

#### 1.2.8 Peripheral Control Components

The discussion of these devices is somewhat grouped because of their typical use together, although no rigid division is implied by chapter divisions or order of discussion of devices. The statement that the only limitation is the imagination of the designer applies perhaps stronger with the I/O, than any other area of design, for here is the interface capability to other devices, equipment, and systems in the outside world. The treatment in the two Input/Output chapters (7 and 8) and the communications chapter (9), is intended to get the imagination going, and emphasize the range of devices available, rather than give cook book solutions to particular problems. (See appendix C for additional information sources.)

#### **1.2.9 Communication Components**

Various communications devices are covered in this chapter.

#### 1.2.10 Development Support

This chapter identifies items of general support, such as the 8080 cross assembler, PROM Programmer and the Universal Development System (UDS), training and technical support. (Also see appendix C for additional information sources.)

#### 1.2.11 Programming

In this chapter, programming topics are covered from machine language through high level languages. Reference is also made to related programmable devices, such as Programmable Peripheral Control Components.

#### 1.2.12 Appendices

In addition to general reference data, additional information sources are identified in appendix C.

Available data sheets for the referenced devices are grouped in Appendix D. Notice that they are grouped by area of concern (i.e., CPU group, Memory components, Digital I/O Components, Peripheral Control Components, and Communication Components).

-

## MICROBUS™

#### 2.1 INTRODUCTION

MICROBUS, the National Semiconductor Standard for Microprocessor Interfaces, deals with systems that use 8-bit parallel means to transfer digital data between MOS/LSI microprocessor CPUs and interfacing devices. The interface system described herein allows proximate components to communicate over a unified bus system.

This standard applies to relatively small systems representative of users' end products. Typically, these are systems where fewer than ten integrated circuits are interconnected to a common system bus, with buffering kept to a minimum.

Application of this standard will provide the user with a broad line of support devices which can be effectively "plugged" into systems without regard to complex timing or electrical analysis, thereby making interfacing easy for the system designer.

#### 2.2 GENERAL DESCRIPTION

This standard applies to interface systems used to interconnect electronic devices with MOS/LSI microprocessor systems. Devices should have the following characteristics:

- Data exchanged among the interconnecting devices is digital (as distinct from analog).

- Total transmission path among interconnecting devices is electrically short. That is, transmission line considerations are negligible.

- Number of devices interconnected on the system bus is small (ten or fewer).

This standard defines the most general system. The large majority of interfacing devices employ only a subset of the signals. Signal Lines are described in table 2-1. For details contact National Semiconductor.

#### 2.2.1 Basic MICROBUS Interface

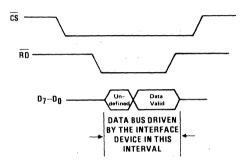

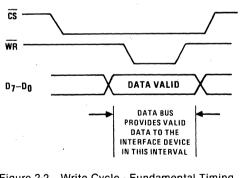

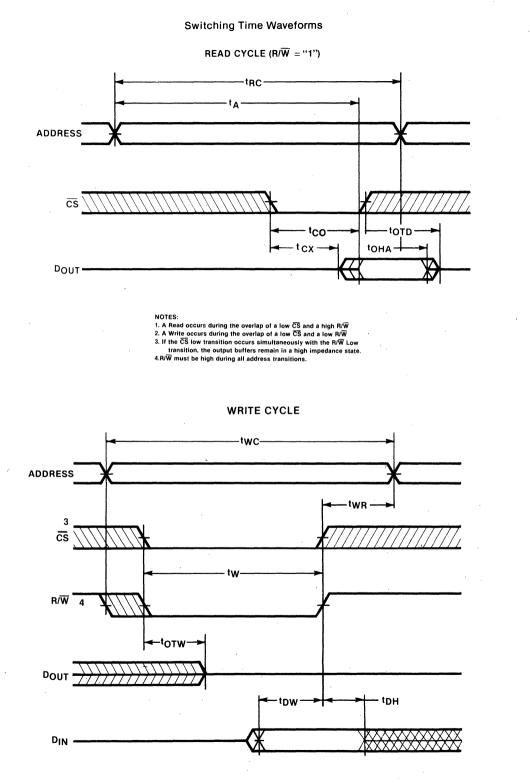

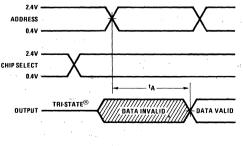

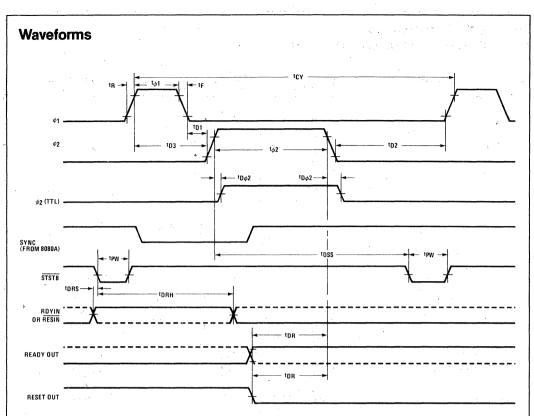

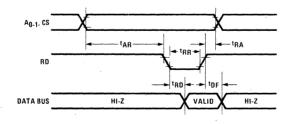

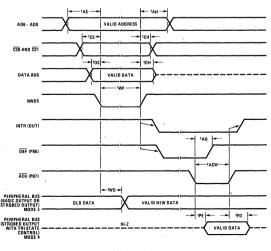

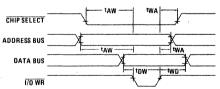

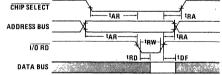

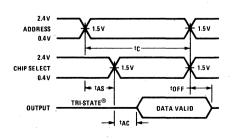

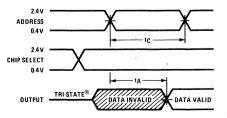

The following paragraphs define the Basic MICROBUS Interface Signals. Figures 2-1 and 2-2 illustrate the fundamental read and write cycle timing.

The Basic MICROBUS Interface defines generalized read and write strobes - RD and WR. In actual systems there may be both memory

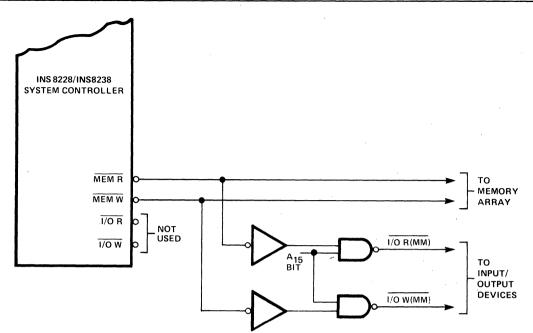

strobes and peripheral device (I/O) strobes. Because it is actually the option of the system designer whether he implements both sets of strobes, only the generalized strobes are discussed in detail. The mnemonics to be used for the memory strobes are MEMR and MEMW. The mnemonics for peripheral strobes are I/OR and I/OW. (Refer to Section 4.3 for discussion of mapping peripherals in memory vs. I/O addressing space.)

Figure 2-1. Read Cycle - Fundamental Timing Relationships

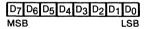

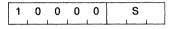

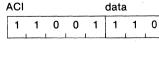

#### 2.2.1.1 Data Bus (D7-D0)

These signal lines carry bit-parallel data information, typically, implemented as eight TRI-STATE input/output lines. In such a typical application status, control and data information is transferred. In most applications, eight bits are implemented.

| FUNCTION                 | MNEMONIC            | NUMBER      | TYPE          |

|--------------------------|---------------------|-------------|---------------|

| Data                     | D7-D0               | 8           | Bidirectional |

| Generalized Read Strobe  | RD                  | 1           | Input         |

| Generalized Write Strobe | WR                  | 1           | Input         |

| Memory Read Strobe       | MEMR                | 1           | Input         |

| Memory Write Strobe      | MEMW                | 1           | Input         |

| I/O Read Strobe          | I/OR                | 1           | Input         |

| I/O Write Strobe         | I/OW                | 1           | Input         |

| Device (Chip) Select     | CS                  | 1           | Input         |

| Reset                    | RESET               | 1           | Input         |

| Ground                   | GND                 | 1           | Power Supply  |

| Address                  | A <sub>15</sub> -A0 | 16          | Input         |

| Interrupt                | INTR                | <u> </u>    | Output        |

| DMA Request              | DRQ                 |             | Output        |

| DMA Acknowledge          | DACK                | <del></del> | Input         |

| Terminal Count           | тс                  | 1           | Input         |

| Ready                    | READY               | 1           | O.C. Output   |

| Early Write Strobe       | EWR                 | 1           | Input         |

| Data Buffer Enable       | DBE                 | 1           | Output        |

| Data Buffer Out          | DBO                 | 1           | Output        |

| Address Buffer Enable    | ABE                 | í Í         | Output        |

| Address Buffer Out       | ABO                 | 1           | Output        |

|                          |                     |             |               |

## <sup>7</sup> Table 2-1. SIGNAL LINES (Referenced to the Interface Device)

2-2

In simpler, dedicated, interface applications, these signal lines may be unidirectional. Examples are, simple interface latches, keyboard controllers, and display controllers.

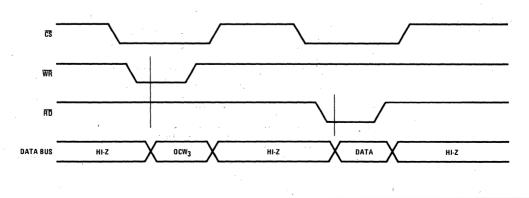

#### 2.2.1.2 Chip Select (CS)

This input pin enables communication between the interface device and the system. This signal is a combinational active low state indicator that the device is being addressed by the system. The user/designer must accommodate transients on this signal during changes in the address bus. Therefore, this signal should be used as a combinational enable function, i.e., level sensitive applications are O.K., edge sensitive are not.

In a data transfer, the  $\overline{\text{CS}}$  signal will envelope the  $\overline{\text{RD}}$  or  $\overline{\text{WR}}$  signals.

#### 2.2.1.3 Read Strobe (RD)

A low state on this input pin enables the interface device to send information to the system via the data bus. This signal is the indicator to the interface device to provide data to the MICROBUS whenever  $\overline{CS}$  is also active (low). Otherwise, the interface device data bus drivers should be in the high impedance state.

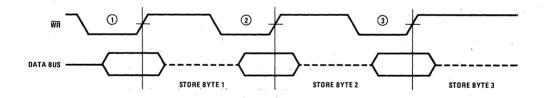

#### 2.2.1.4 Write Strobe (WR)

A low on this input signal in combination with a low on the  $\overline{CS}$  input signal enables the transfer of information from the MICROBUS to the interface device.

The data bus  $(D_7-D_0)$  will be valid to the interface device before the high to low transition of WR and will remain valid until after the low to high transition of WR.

Designers of new interface devices should not rely upon data being valid on the leading edge of the write strobe because some existing and future microprocessors do not provide data valid at this time.

#### 2.2.1.5 Reset (RESET)

The RESET signal is supplied by the system to all interfacing devices at power on time and typically by a manual (pushbutton) operation. Devices are to be reset whenever the RESET signal is in the low voltage state.

The reset signal should place all interfacing devices into a known initial state. It is desirable that every sequential storage element within an interface device be initialized by this signal. For example, when a floppy disk interface device is reset, it should restore the head to track zero. A mag tape device, however, should terminate tape movement operations. Each electromechanical device must be considered separately when determining what effect the RESET input will have on its controlling states.

Whenever the RESET signal is applied, the interface device shall place its data bus and other TRI-STATE system outputs into the high impedance state. The device designer may assume that the RESET input will be low for a minimum of 100  $\mu$ sec.

Many MOS/LSI interface devices require an active high voltage RESET signal while most existing TTL devices use RESET. For this reason, most systems will require both RESET and RESET. Either reset signal is acceptable for this standard. Future interface devices should standardize on the RESET convention.

#### 2.2.1.6 Ground (GND)

This signal provides 0v reference to the interface device. All signals and voltages are referenced to GND.

#### 2.2.2 Addressing Techniques

The first extension of complexity beyond the Basic MICROBUS is the addition of addressing capability. The addition of address signals to the interface device provides a binary encoded selection of device internal registers or memory locations.

#### 2.2.2.1 Input Case

These input signals, in conjunction with the  $\overline{CS}$  and  $\overline{RD}$  or  $\overline{WR}$  inputs, control the selection of data, control, or status information transfer between the MICROBUS and the interfacing device.

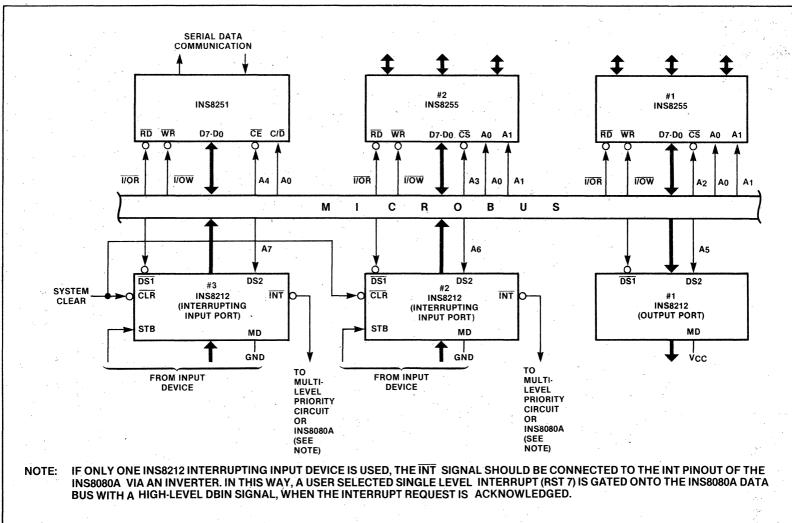

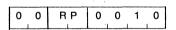

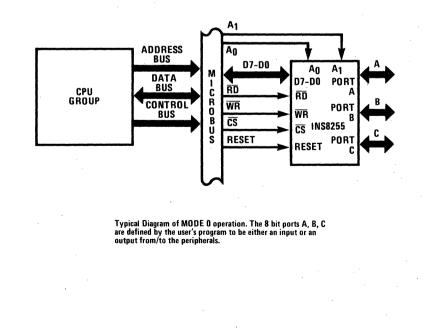

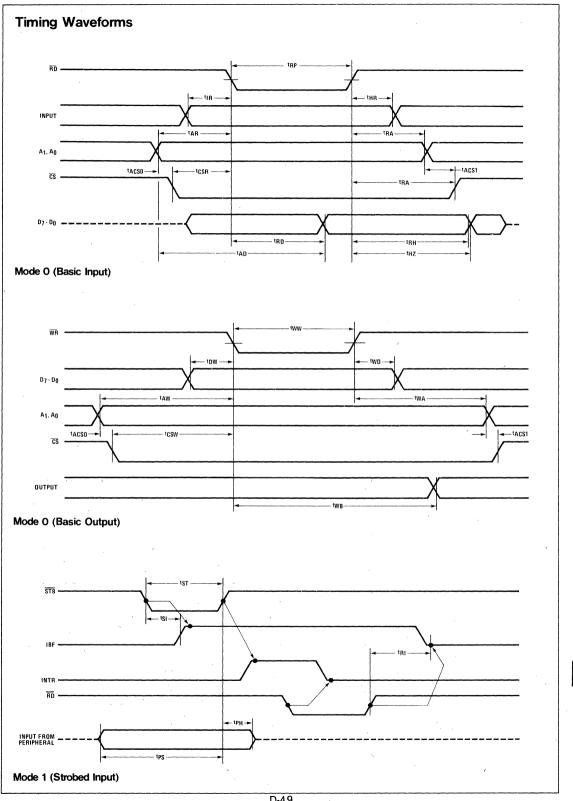

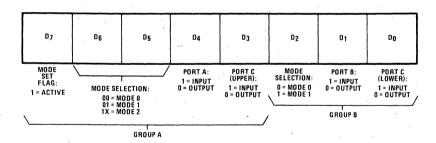

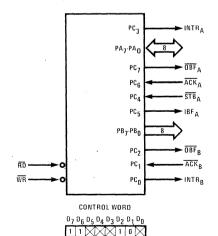

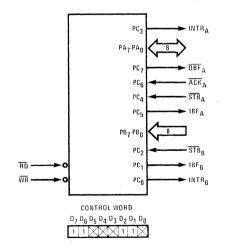

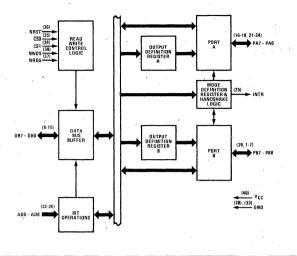

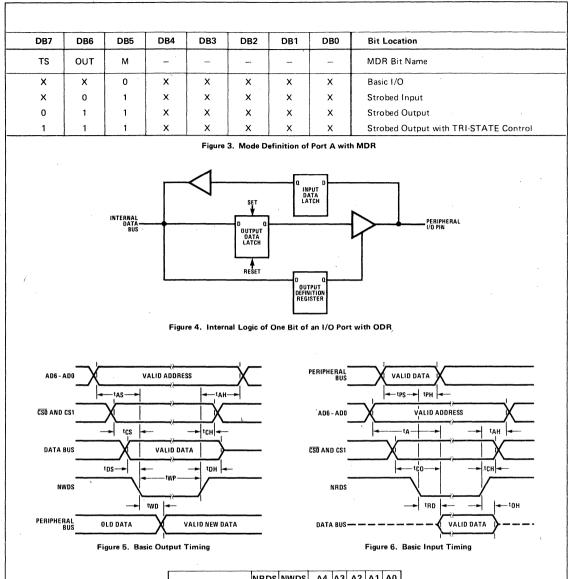

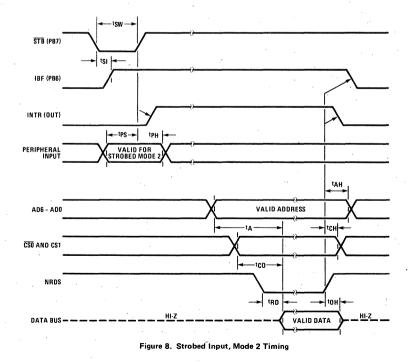

A common example is the 8255 Programmable Peripheral Interface. This device has two address inputs ( $A_1$  and  $A_0$ ). Internal to the device, there are three data ports - A, B, and C; a status register; and a control register. The A, B, and C data ports may be read or written and are specified by the address inputs during the time RD or WR is low. In this case, port A, B, or C is specified when the  $A_1A_0$  inputs are 00, 01, or 10 respectively. When the address inputs are 11 and a read operation is performed, the 8255 provides information from its status register to the data bus. When the address inputs are 11 and a write is performed, the 8255 command register is loaded from the data bus.

In this example, a write only and a read only register share a common address. This is not a preferred practice as it adds complexity to the controlling software. Data written to write only control or data registers must often be duplicated in RAM when independent bit operations are to be performed on the register.

#### 2.2.2.2 Address/Chip Select Relationship

It is implied that the chip select signal,  $\overline{CS}$  (2.2.2) is a combinational function of the system address bus. Because of this relationship, transitions of  $\overline{CS}$  are delayed from changes in the address bus. The timing specifications for the  $\overline{CS}$  signal are derived from the typical implementation presented in appendix B.

#### 2.2.2.3 Bidirectional Addresses

In the future, interface devices will provide their own address information during direct memory access (DMA) transfers. In this class of interface device the address lines are outputs during DMA transfers and inputs during conventional, programmed I/O transfers as described in section 4.3. Special control signals are required to control external TRI-STATE address buffers and latches needed for this type of device. These signals control the direction of data through the TRI-STATE buffer and the TRI-STATE enable. They are named Address Buffer Out (ABO) and Address Buffer Enable (ÅBE) respectively.

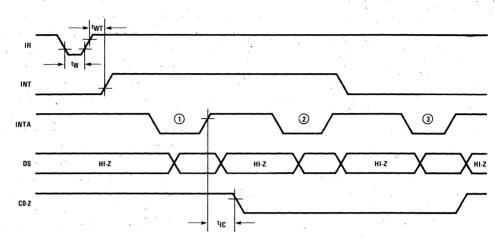

#### 2.2.3 Interrupt Convention

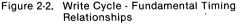

Interface devices often provide interrupts to the system to request the initiation or indicate the completion of a task.

In the standard bus environment, interface devices may provide one or more interrupt signals. In the singular case, this signal is named INTR. It is an active high signal that is asserted in the high voltage state to request a Program interruption.

Once asserted high by the interface device, the interrupt signal must remain high until it is serviced by the system. Typically, interrupts may be serviced by the system taking action to either identify or service the condition which caused the interrupt. In all cases, this must beimplemented by a programmed I/O transfer between the system and the device. The particular protocol for removal of the interrupt is dependent upon the type of device producing it.

The interrupt signal may be asserted asynchronously with respect to other signals in the system. See figure 2-3. It must be removed by the completion of the appropriate RD or WR strobe when the CS and address inputs are active.

An example of implementation is an A/D converter designed to interface to the MICROBUS. The device designer who wishes to make his A/D converter compatible with the MICROBUS will modify the classical control and timing logic to replace the END OF CONVERSION signal with an interrupt output (INTR). The START CONVERSION input is replaced or supplemented by a programmed I/O operation.

#### Figure 2-3. Interrupt Service - Interface Device Waveforms

In the simplest case, the INTR output is set high at END OF CONVERSION. The system responds to the interrupt by reading the A/D output buffer which sets the INTR Iow and simultaneously starts a new conversion. The reader will notice that the START CONVERSION input is not required. In practice it is desirable to implement control and status registers to allow the system to select how the interrupt and start conversion systems will function.

In an 8080 system, the interrupt feature may be implemented by adding an 8259. The interrupt controller is added to the CPU group to provide the MICROBUS interrupt inputs for interfacing devices.

#### 2.2.4 Direct Memory Access (DMA) Transfers

Systems that provide DMA capability interface to devices via two dedicated and one common signal. Each DMA device controls its own DMA request signal (DRQ). The system responds to DRQ with a dedicated DMA acknowledge signal (DACK). The third special signal for DMA is the terminal count (TC) indicator provided by the system to the device to indicate that the present DMA cycle should be the last cycle for this data block.

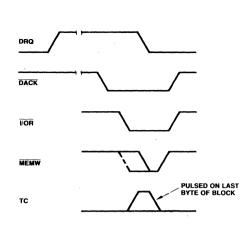

Figure 2-4 illustrates a typical DMA cycle in which the device is providing data to the system. In this type of DMA channel, a simultaneous read peripheral (I/OR) and write memory operation (MEMR) is performed.

The interface device designer should consider the DACK signal to be equivalent to a special chip select signal with equivalent timing relationships to the read and write strobes and TRI-STATE enables of the MICROBUS.

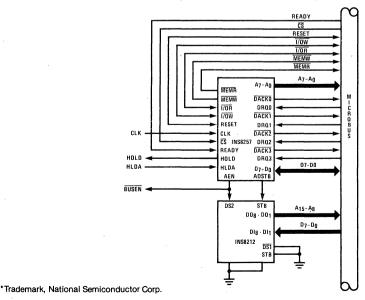

Refer to manufacturer's literature for the standard 8257 DMA Controller for further detailed discussion of the various modes and relationships possible for DMA interface devices.

In an 8080 system, DMA capability may be implemented by adding an 8257 DMA controller and an 8212-8-Bit I/O Latch to the basic system model.

From a device designer's viewpoint, this addition may be implied as part of the MICROBUS.

#### 2.2.5 Ready Signal

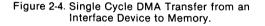

The <u>READY</u> signal is used to extend the period of a RD or WR strobe. It is a system input that may be driven by any number of interfacing devices. Interfacing devices that cannot otherwise meet the access time requirements of the system should provide a READY output to the system. This output should not have an active or passive connection to V<sub>CC</sub>(+5V). It should be open-collector (open drain if n-channel). The system will provide a common resistive pull-up device for the READY signal. Typically, use of the READY signal requires complex electrical design and timing analysis.

Figure 2-5 illustrates timing relationships for the READY signal. In this example, the system initiates a read or write cycle to the device by activating its RD or WR and CS inputs. If the interface device cannot respond within the system access time requirements, it may assert the READY signal low indefinitely until it has had time to stabilize the data bus in a read operation or accept the data in a write operation.

The device designer is cautioned to use the READY feature only for access time extension and not for synchronization because it may severely impact system throughout.

Figure 2-5. Relationship of READY to CS, WR, and RD.

#### 2.2.6 The Basic Interface Model

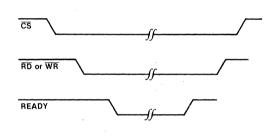

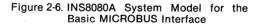

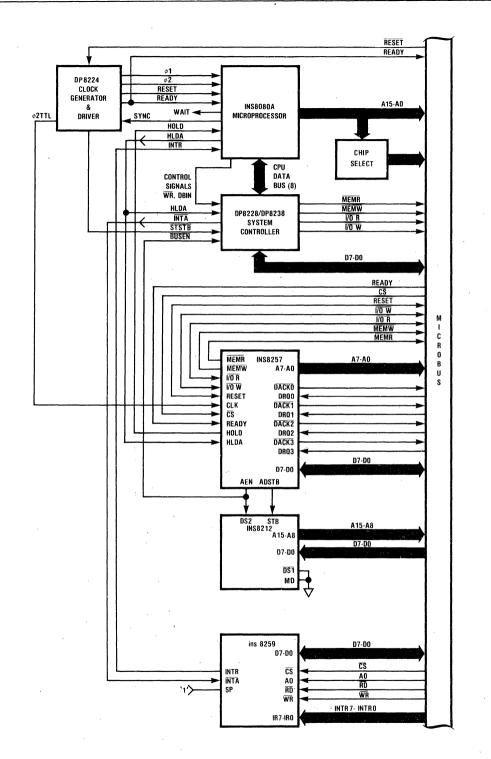

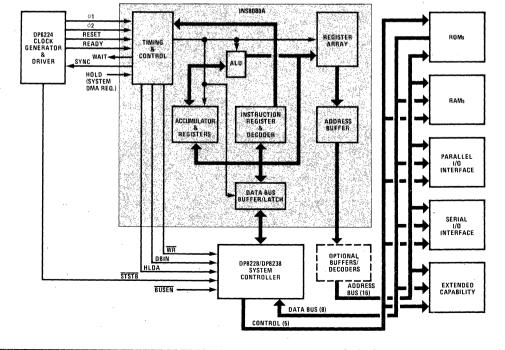

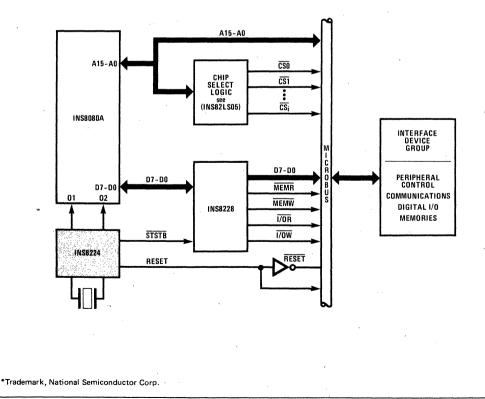

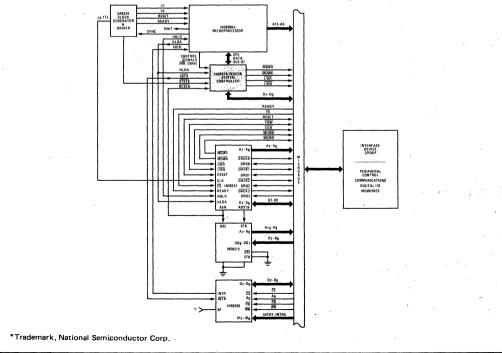

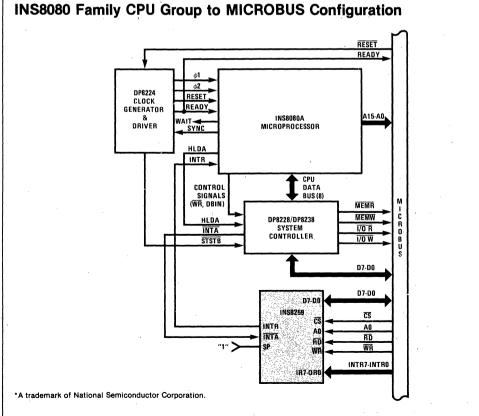

The specific implementation and model for the Basic MICROBUS Interface (Class 1) is the combination of the INS8080A CPU, 8224 Clock Generator, 8228 System Bus Controller, and Chip Select Logic. This system model is depicted in Figure 2-7. The expanded CPU Group is shown in Figure 2-8. Note the use of the INS8259 at the bottom of the figure to expand interrupts. See section 4.7 for expansion using INS8259.

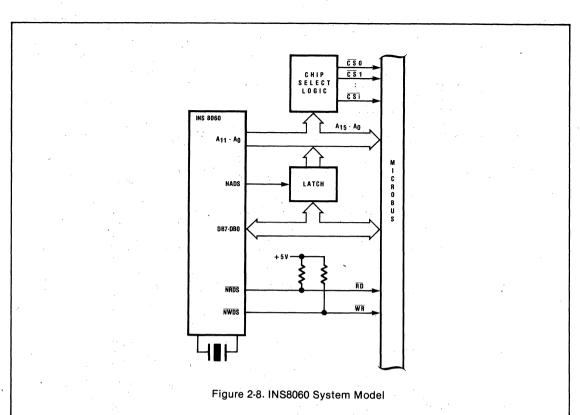

Class 1 devices will also interface directly with the INS8060 (SC/MP II) microprocessor system model depicted in Figure 2-9. INS8070 system model is shown in Figure 2-10.

2-5

#### For purposes of clarification:

- Class 0 devices are those which may require special conditioning of their interface to successfully function with microprocessor systems.

- Class 1 devices perform with the following microprocessor CPUs when other bus loading is within the D.C. and capacitive

load limits: INS8060, INS8070, INS8080A.

• Class 2 devices are tailored for nextgeneration microprocessors. The specification will be available in the future.

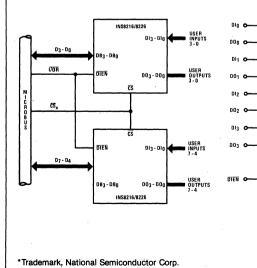

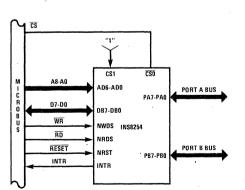

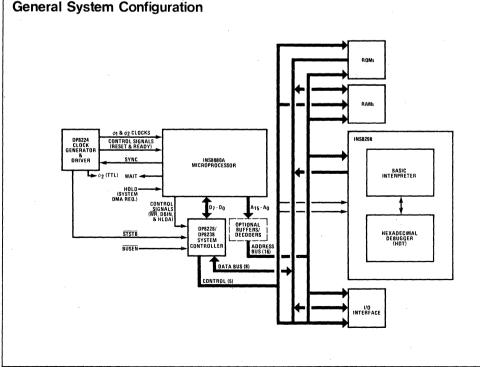

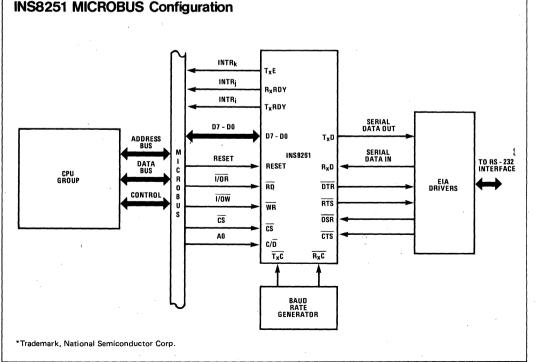

Figure 2-7. INS8080 Family CPU Group to MICROBUS Configuration

2-7

2

2-8

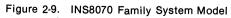

## The Series 8000 Microprocessor Family CPU Group

#### 3.1 INTRODUCTION

This chapter provides detailed information on the Series 8000 Microprocessor family of support chips that comprise the INS8080A CPU Group. The information within this chapter is intended to assist the Series 8000 designer by providing both descriptions of the operating characteristics of the devices and typical interconnection diagrams. Detailed parametric information on each of the CPU Group devices is contained in appendix D, Device Data Sheets.

National Semiconductor offers the broadest line of microprocessors of any semiconductor manufacturer in the world. National has expanded its microprocessor base so any microprocessor application can be designed and produced using its products. From the simplest electronic toy or control mechanism to large control arrays, point-of-sale systems, and large data-processing systems, National can supply your needs. Some of the features and benefits of dealing with National follow.

- Micro-Plus testing, special reliability and quality program

- Full development system support all the way from the high-powered PACE development system (with numerous software packages and a DOS) to lowcost development systems (for PACE and SC/MP) to do-it-yourself PACE and SC/MP kits

National Semiconductor also offers the most extensive line of CPU-to-peripheral support products - for digital input/output, communications, peripheral control, and memory. And National Semiconductor is expanding the support lines, so you can expect to see even more!

#### National's INS8080A Family

Positioned between the cost-effective INS8060 and the highly versatile 16-bit INS8900, Na-

- Cost effectiveness because of our variety, our microprocessors afford designs that can be tailored to a multitude of applications

- Broad product family of microprocessors and peripherals

- 16-Bit COMPUTATION microprocessors for precision control functions

- 8-Bit BYTE HANDLING microprocessors for terminals

- 4/8-Bit LOW-COST CONTROL microprocessors for industrial controllers

- Second sourced families

- Ready availability off-the-shelf shopping

tional's INS8080A can be used in systems which range from a few family components to designs which utilize its full capabilities. National offers the broadest line of peripheral circuits and memories to complement the basic INS8080A CPU. National's INS8080A features and benefits:

- Family approach to system design

- Complete CPU group

- Programmable input/output concepts

- Multiple source availability

- Complete line of support components

- Total product support

National's INS8080A family is supported by industry-standard design kits, easy-to-use development systems, and a full complement of cross and resident assemblers. Various components and software also are available to support the INS8080A family from experimentation to final production.

#### 3.2 INS8080A MICROPROCESSOR

The basic INS8080A CPU Group consists of three components:

- The INS8080A Microprocessor

- The INS8224 Clock Generator and Driver

- The INS8228 System Controller

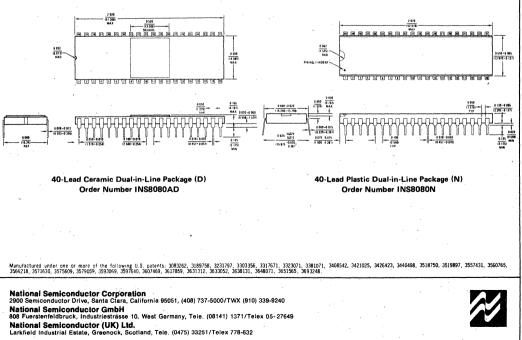

The INS8080A is an 8-bit microprocessor housed in a standard 40-pin dual in-line package. The chip is fabricated using N-channel silicon-gate technology. The INS8080A has a 16-bit address bus capable of addressing up to 65k bytes of memory, 256 input/output devices. Data is transmitted on a separate bidirectional 8-bit TRI-STATE bus. The INS8080A directly provides signals to control the interface to memory and I/O ports. The INS8080A has:

- 74 Instructions Variable Length

- 6 General Purpose Registers plus an accumulator

- Variable Length Stack

- Addresses 256 Input and 256 Output Ports

- Multiple Addressing Modes

The INS8080A is an 8-bit CPU chip that may be used interchangeably with the Intel 8080A. It can be used in systems that range from a few family components to designs that utilize its full capabilities.

Detailed descriptions of both the INS8080A Instruction Set and the INS8080A parametric information is contained in the INS8080A Data Sheet in appendix D.

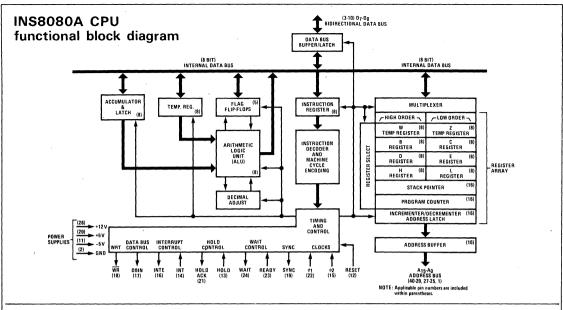

#### 3.2.1 Architecture of the INS8080A

Figure 3-1 illustrates CPU architecture and the pinouts of the chip. (Refer to table 3-1 for descriptions of the INS8080A chip pinouts.) The INS8080A consists of the following major functional units: (1) Register Array and Address Logic, (2) Arithmetic and Logic Unit (ALU) and Registers, (3) Instruction Register and Decoder, (4) Timing and Control, and (5) Data Bus Buffer/Latch. Each of the major functional units and its logic units are briefly discussed below.

#### 3.2.1.1 Register Array and Address Logic

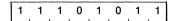

This functional section of the CPU chip comprises a static RAM Register array, and Incrementer/Decrementer, an Address Latch, and a Register-Select Multiplexer. The Register array is organized into six 16-bit registers as follows.

- A Program Counter

- A Stack Pointer

- Three register pairs (BC, DE, and HL) composed of six 8-bit general-purpose registers.

- A register pair (W and Z) composed of two 8-bit temporary registers.

The Program Counter (PC) is a special-purpose register that contains the address of the instruction being executed; the PC is incremented during each instruction fetch. The Stack Pointer (SP) is also a special-purpose register and contains the address of the next available stack location in the external read/write memory (RAM). Using the SP register, any area of the external memory may be reserved as a last-in-first-out (LIFO) external stack. The stack is used primarily for temporary storage of the contents of the PC and all general-purpose registers (including the Accumulator) during subroutine execution and Interrupt Service Routine execution. The Stack Pointer is decremented when data are "pushed" onto the stack and incremented when data are "popped" off the stack. In other words, the stack is filled from top to bottom.

General-purpose registers B, C, D, E, H, and L can be used by the programmer as either single 8-bit secondary accumulators or as 16-bit register pairs that function as data counters. The HL register pair is the primary data counter and provides the indirect memory address for most memory-reference instructions (refer to 3.2.5). The BC and DE register pairs are used as data counters for a limited number of memoryreference instructions (for example: STAX B, STAX D, LDAX B, AND LDAX D). Temporary registers W and Z, which are not under software control, are only used as a 16-bit register pair for the internal execution of instructions.

The Register-Select Multiplexer enables 8-bit data transfers between the Internal Data Bus and the Register Array. Sixteen-bit transfers occur between the Register Array and either the Address Latch or the Incrementer/Decrementer. Any of the three register pairs (BC, DE, or HL) routes its 16-bit data output to the Address Latch, which in turn drives both the 16-bit  $A_{15}$ -A<sub>0</sub> Address Bus (via the associated 16-bit unidirectional TRI-STATE Address Buffer) and the Incrementer/Decrementer. The data output of the Incrementer/Decrementer is routed to the Register Array. The 16-bit data may be either incremented, decremented, or merely transferred between registers.

#### 3.2.1.2 ALU and Registers

This functional section of the CPU chip includes the Arithmetic Logic Unit (ALU), an 8-bit

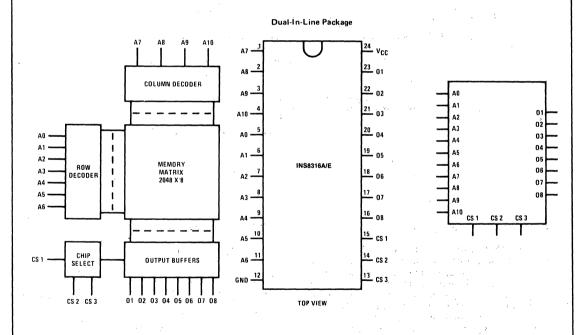

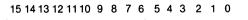

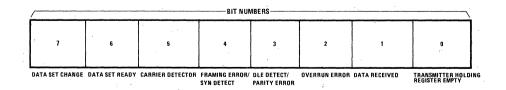

(3-10) D7-D0 EXTERNAL DATA BUS DATA BUS BUFFER/LATCH (8-BIT) (8-BIT) INTERNAL DATA BUS INTERNAL DATA BUS ALU INSTRUCTION REGISTER ARRAY REGISTER REGISTERS AND AND DECODER REGISTER-SELECT MULTIPLEXER ADDRESS TEMP ACCUMULATOR FLAG LOGIC AND LATCH (ACC & ACT) REGISTER REGISTER INSTRUCTION (TMP) – HIGH ORDER – - LOW ORDER REGISTER **a** i w TEMP RÉGISTER TEMP REGISTER 8 С REGISTER REGISTER D E REGISTER REGISTER REGISTER ARRAY ABITHMETIC н L LOGIC UNIT REGISTER REGISTER (ALU) INSTRUCTION DECODER AND MACHINE CYCLE STACK POINTER (SP) 1 ENCODING PROGRAM COUNTER (PC) INCREMENTER/DECREMENTER DECIMAL ADJUST AND ADDRESS LATCH (28)► +12V TIMING AND CONTROL UNIT (20) +5∨ ADDRESS BUFFER POWER (11) -5V DATA BUS INTERRUPT HOLD CONTROL SUPPLIES WAIT WBT CONTROL CONTROL CONTROL SYNC CLOCKS (2) GND A15-A0 ADDRESS BUS (40-29, 27-25, 1) WR (18) DBIN INTE INT HOLD HOLD WAIT READY SYNC 01 φ2 RESET (17) (16) (14) ACK (21) (13) (24) (23)(15) (19) (22) (12) NOTE: APPLICABLE PINOUT NUMBERS ARE INCLUDED WITHIN PARENTHESES. NS10600

Figure 3-1. CPU Architecture and Pinouts of INS8080A

1

ယ ယ

## Table 3-1. Input/Output Signal Descriptions

| SIGNAL MNEMONIC/<br>PIN DESIGNATION | FUNCTIONAL NAME                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|-------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| READY (Input)                       | Memory or I/O<br>Synchronization | When high (logic 1), indicates that valid memory<br>or input data are available to the CPU on the<br>INS8080A External Data Bus. The READY signal<br>is used to synchronize the CPU with slower memory<br>or input/output devices. If the INS8080A does not<br>receive a high READY input after sending out an<br>address to memory or an input/output device, the<br>INS8080A enters a WAIT mode for as long as the<br>READY input remains low (logic 0). The CPU may<br>also be single stepped by the use of the READY<br>signal.                                                                                                                        |  |  |  |  |  |  |

| HOLD (Input)                        | Hold or DMA<br>Operations        | <ul> <li>When high, requests that the CPU enter the HOLD mode. When the CPU is in HOLD mode, the CPU address and data buses both are in the high-impedance state. The HOLD mode allows an external device to gain control of the INS8080A address and data buses immediately following the completion of the current machine cycle by the CPU. The CPU acknowledges the HOLD mode via the HOLD ACKNOWLEDGE (HLDA) output line. The HOLD request is recognized under the following conditions: <ul> <li>The CPU is in the HALT mode.</li> <li>The READY signal is active and the CPU is in the T<sub>2</sub> or T<sub>W</sub> state.</li> </ul> </li> </ul> |  |  |  |  |  |  |

| INT (Input)                         | Interrupt Request                | When high, the CPU recognizes an interrupt re-<br>quest on this line after completing the current<br>instruction or while in the HALT mode. An inter-<br>rupt request is not honored if the CPU is in the<br>HOLD mode (HLDA = logic 1) or the Interrupt<br>Enable Flip-flop is reset (INTE = logic 0).                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| RESET (Input)                       | Reset                            | When activated (high) for a minimum of three clock<br>periods, the content of the Program Counter is<br>cleared and the internal Interrupt Enable and Hold<br>Acknowledge Flip-flops are reset. Following a<br>RESET, program execution starts at memory loca-<br>tion O. It should be noted that the Status Flags,<br>Accumulator, Stack Pointer, and other registers are<br>not cleared during the RESET sequence.                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| SYNC (Output)                       | Synchronizing Signal             | When activated (high), the beginning of a new machine cycle is indicated and the status word information is outputted on the External Data Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| WAIT (Output)                       | Wait Mode                        | When high, acknowedges that the CPU is in the WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| WR (Output)                         | Write                            | When low, the data on the External Data Bus are stable for WRITE memory or OUTPUT operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

## Table 3-1. Input/Output Signal Descriptions (Continued)

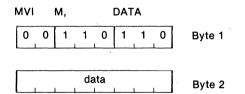

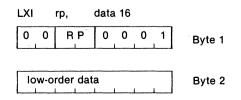

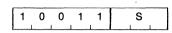

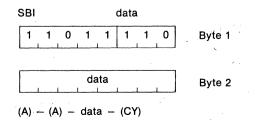

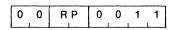

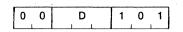

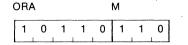

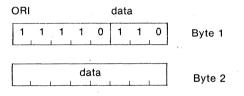

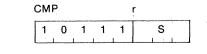

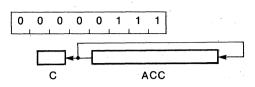

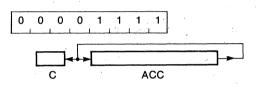

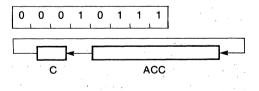

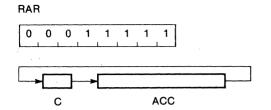

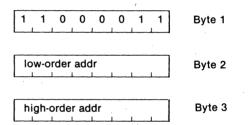

3