## MOS INTEGRATED CIRCUITS

FEBRUARY 1972

• . •

February 1972

**National Semiconductor Corporation**

2900 Semiconductor Drive, Santa Clara, California 95051 (408) 732-5000 / TWX (910) 339-9240

·····

### Introduction

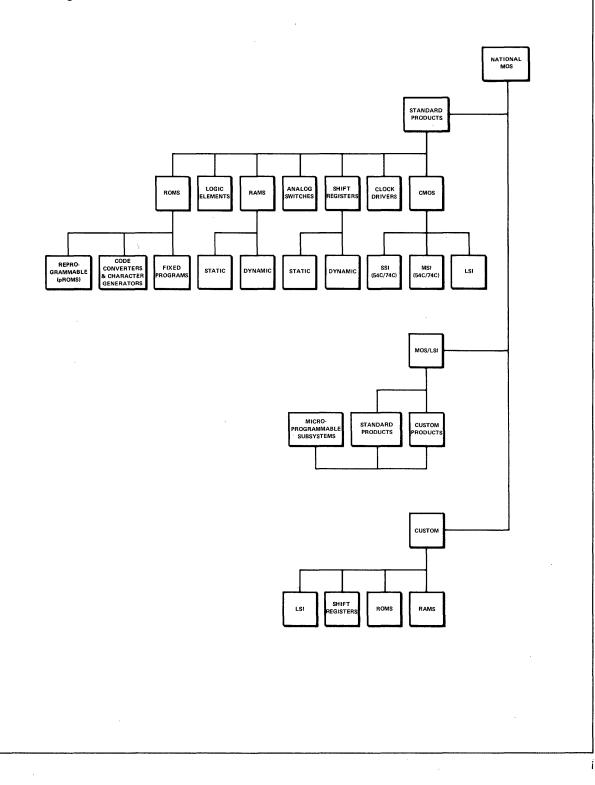

Here is National's newest handbook on MOS products. Extra copies of this handbook, <sup>6</sup>plus those on our other major product lines – digital, linear and transistors – are also available. To receive our handbooks, contact a National sales office, representative or distributor; to keep current on our growing product lines ask to be placed on our mailing list.

### **Table of Contents**

| MOS Selection Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | vi                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| MAPS (Microprogrammable Arithmetic Processor System)         MM5704AA MOS/LSI Keyboard Interface Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1<br>3                                                                                                                             |

| MM1403A 1024-Bit Dynamic Shift Register         MM1404A 1024-Bit Dynamic Shift Register         MM4001A/MM5001A Dual 64-Bit Dynamic Shift Register         MM4006A/MM5006A Dual 100-Bit Shift Register         MM4007/MM5007 Dual 100-Bit Programmable Shift Register         MM4010A/MM5010A Dual 64-Bit Accumulator         MM4012/MM5012 Dual 256-Bit Dynamic Shift Register         MM4013/MM5013 1024-Bit Dynamic Shift Register/Accumulator                                                                                                                                                | 9<br>9<br>9<br>9<br>9<br>12<br>12<br>15<br>18<br>15<br>12<br>25<br>28                                                              |

| MM4016/MM5016 512-Bit Dynamic Shift Register         MM4017/MM5017 Dual 512-Bit Dynamic Shift Register         MM4018/MM5018 Triple 64-Bit Dynamic Shift Register         MM4019/MM5019 Dual 256-Bit Mask Programmable Shift Register         MM4020/MM5020 Quad 80-Bit Dynamic Shift Register         MM4021/MM5021 Triple 80-Bit Dynamic Shift Register         MM4021/MM5021 Triple 80-Bit Dynamic Shift Register         MM5024A 1024-Bit Dynamic Shift Register         MM5081 10-Bit Serial In-Parallel Out Lamp Driver/Register         MM4104/MM5104 Multi-Length Dynamic Shift Register | <ol> <li>31</li> <li>34</li> <li>37</li> <li>18</li> <li>40</li> <li>40</li> <li>12</li> <li>43</li> <li>45</li> <li>48</li> </ol> |

| MM405/MM505 Dual 32-Bit Static Shift Register         MM4040/MM5040 Dual 16-Bit Static Shift Register         MM4050A/MM5050A Dual 32-Bit Static Shift Register         MM4051A/MM5051A Dual 32-Bit Static Shift Register-Split Clock         MM4052/MM5052 Dual 80-Bit Static Shift Register         MM4053/MM5053 Dual 100-Bit Static Shift Register                                                                                                                                                                                                                                           | 51<br>54<br>57<br>57<br>60<br>60<br>63                                                                                             |

| MM4210/MM52101024-Bit Static Read-Only MemoryMM4211/MM52111024-Bit Static Read-Only MemoryMM4213/MM52131024-Bit Read-Only MemoryMM4220/MM52201024-Bit Static Read-Only MemoryMM4221/MM52211024-Bit Static Read-Only MemoryMM4230/MM52302048-Bit Static Read-Only MemoryMM4231/MM52312048-Bit Static Read-Only MemoryMM4231/MM52312048-Bit Static Read-Only MemoryMM4232/MM52324096-Bit Static Read-Only Memory                                                                                                                                                                                   | 67<br>71<br>75<br>8A<br>79<br>83<br>87<br>91<br>95<br>99                                                                           |

| RAMs107MM1101 256-Bit Fully Decoded Static Random-Access Memory107MM11011 256-Bit Fully Decoded Static Random-Access Memory107MM1101A 256-Bit Fully Decoded Static Random-Access Memory107MM1101A1 256-Bit Fully Decoded Static Random-Access Memory107MM1101A2 256-Bit Fully Decoded Static Random-Access Memory107MM1101A2 256-Bit Fully Decoded Static Random-Access Memory107MM1101A2 256-Bit Fully Decoded Static Random-Access Memory107MM1103 1024-Bit Fully Decoded Dynamic Random-Access Memory111MM5260 1024-Bit Fully Decoded Dynamic Random-Access Memory114MM5262 2048-Bit Fully Decoded Dynamic Random-Access MemoryTBA                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

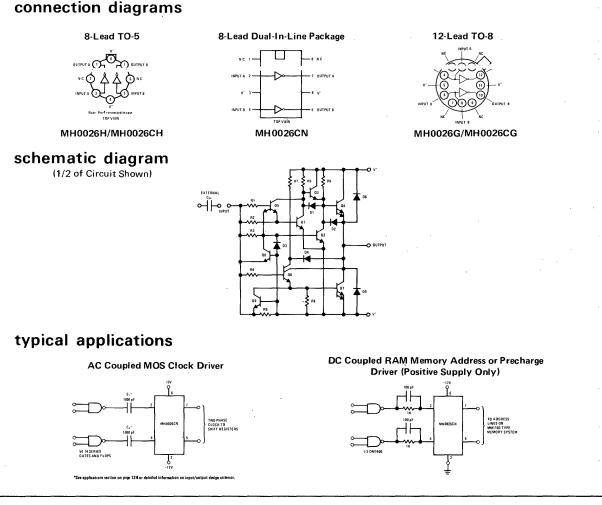

| Clock DriversMH0007/MH0007C Single Phase MOS Clock Driver117MH0009/MH0009C Two Phase MOS Clock Driver119MH0012/MH0012C High Speed MOS Clock Driver121MH0013/MH0013C Two Phase MOS Clock Driver123MH0025/MH0025C Two Phase MOS Clock Driver127MH0026/MH0026C 5 MHz Two Phase MOS Clock Driver130MH0027C Dual High Speed MOS Interface Driver138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

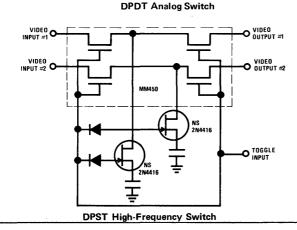

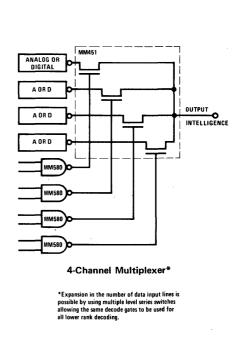

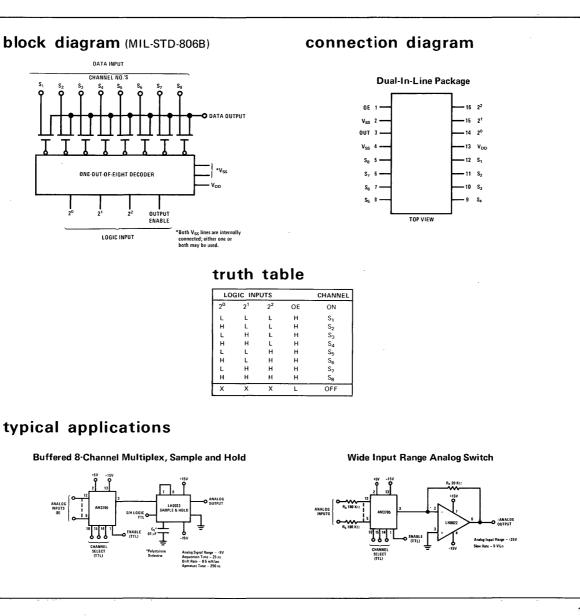

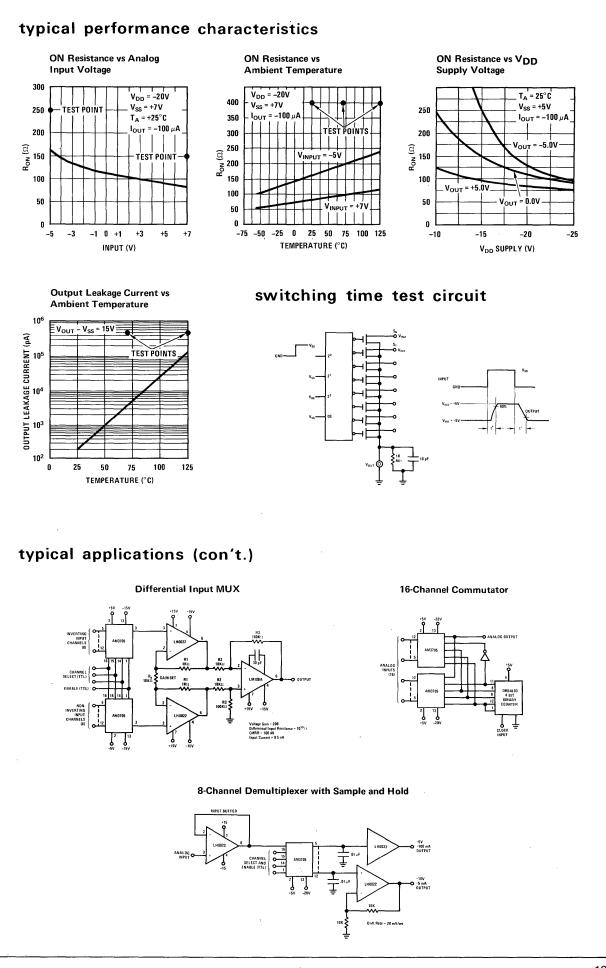

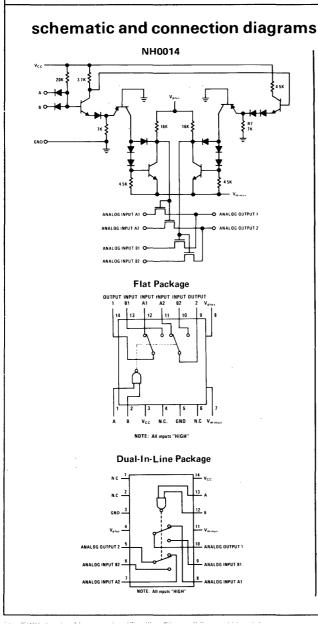

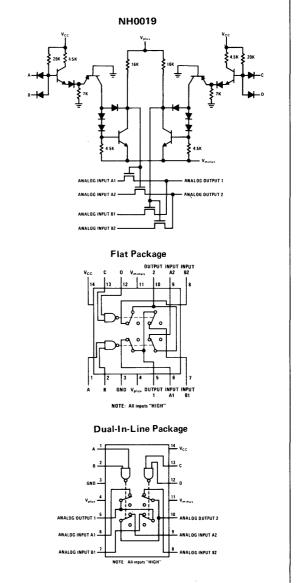

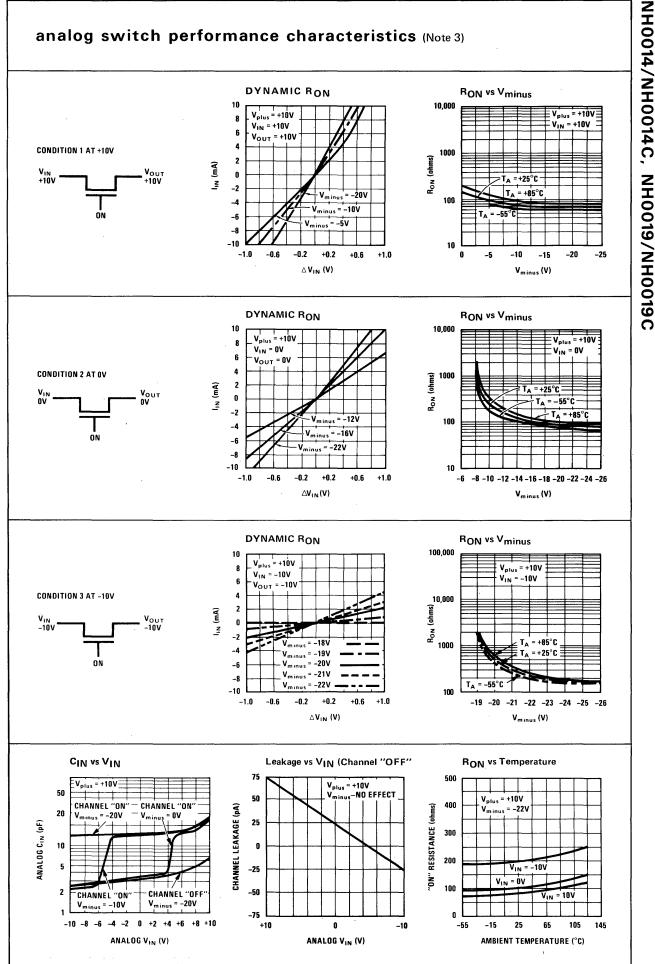

| Analog SwitchesMM450/MM550 Dual Differential Analog Switch141MM451/MM551 Four-Channel Analog Switch141MM452/MM552 Four MOS Transistor Package141MM454/MM554 Four-Channel Commutator145MM455/MM555 Three MOS Transistor Package141AH0120 Series High Level Analog Switches148AH0130 Series High Level Analog Switches148AH0140 Series High Level Analog Switches148AH0150 Medium Level Analog Switches148AH0160 Series High Level Analog Switches148AH0160 Medium Level Analog Switches148AH0160 Medium Level Analog Switch157AM1000 Silicon N-Channel High Speed Analog Switch157AM1002 Silicon N-Channel High Speed Analog Switch157AM1002 Silicon N-Channel High Speed Analog Switch157AM3705/AM3705C & Channel MOS Analog Multiplexer159NH0014/NH0014C DTL/TTL Compatible DPDT Analog Switch163NH0015/NH0015C Quad Analog Switch163NH0019/NH0019C (MH453/MH533) DTL/TTL Compatible Dual DPST Analog Switch163 |

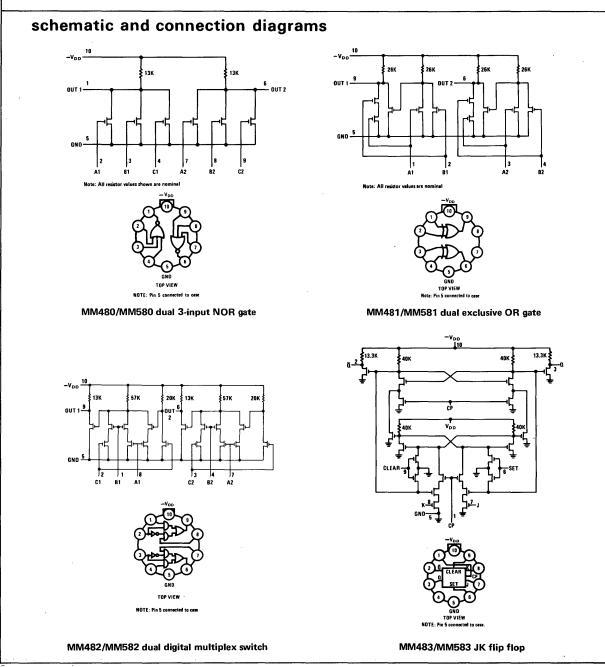

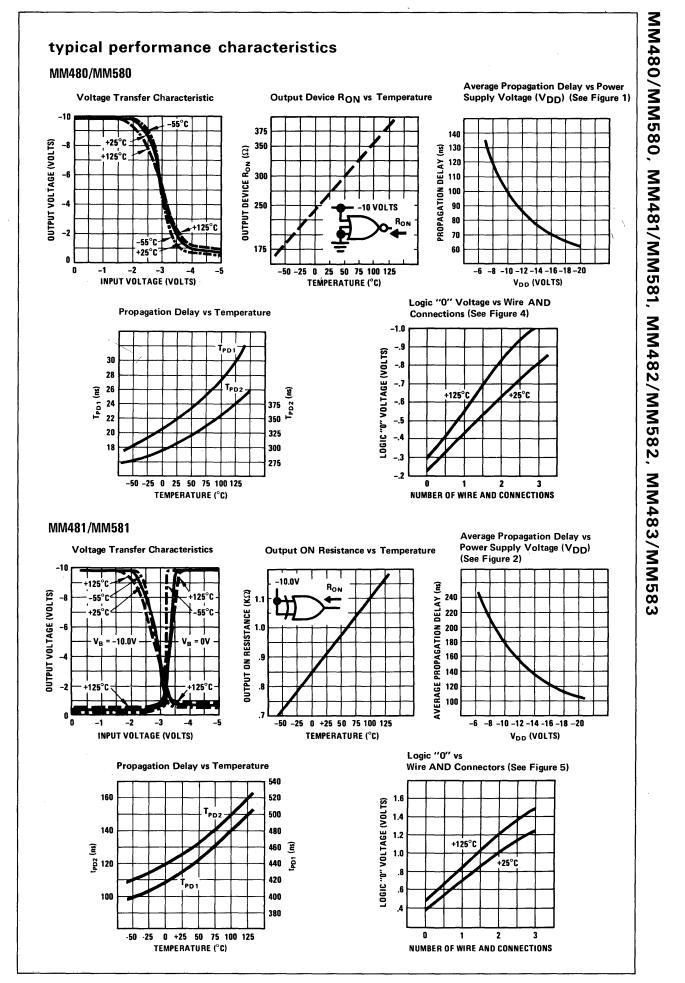

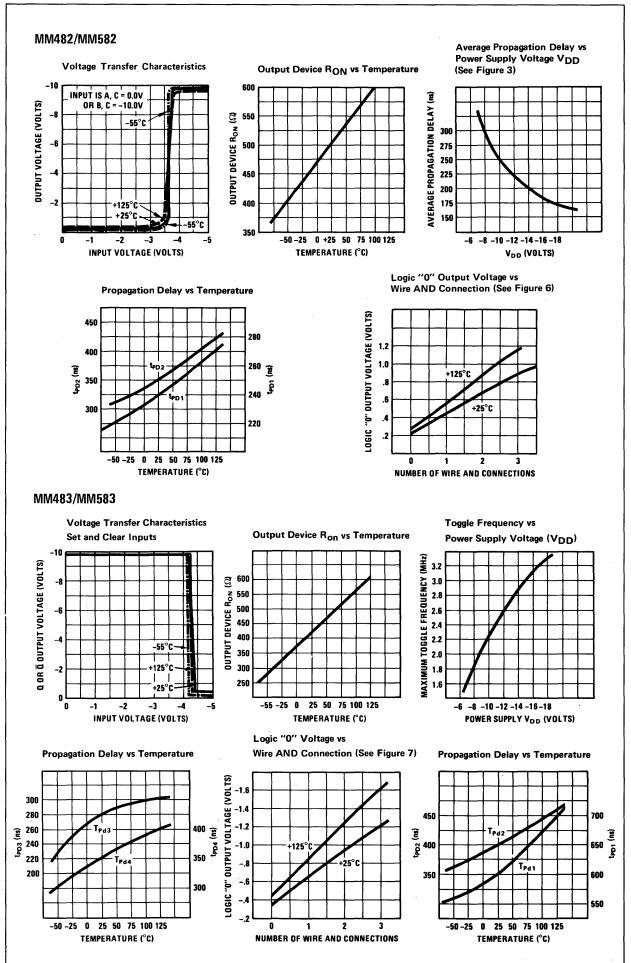

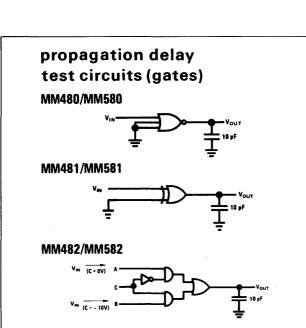

| Logic Elements         167           MM480/MM580 Dual 3-Input NOR Gate         167           MM481/MM581 Dual Exclusive OR Gate         167           MM482/MM582 Dual Digital Multiplex Switch         167           MM483/MM583 JK Flip Flop         167                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

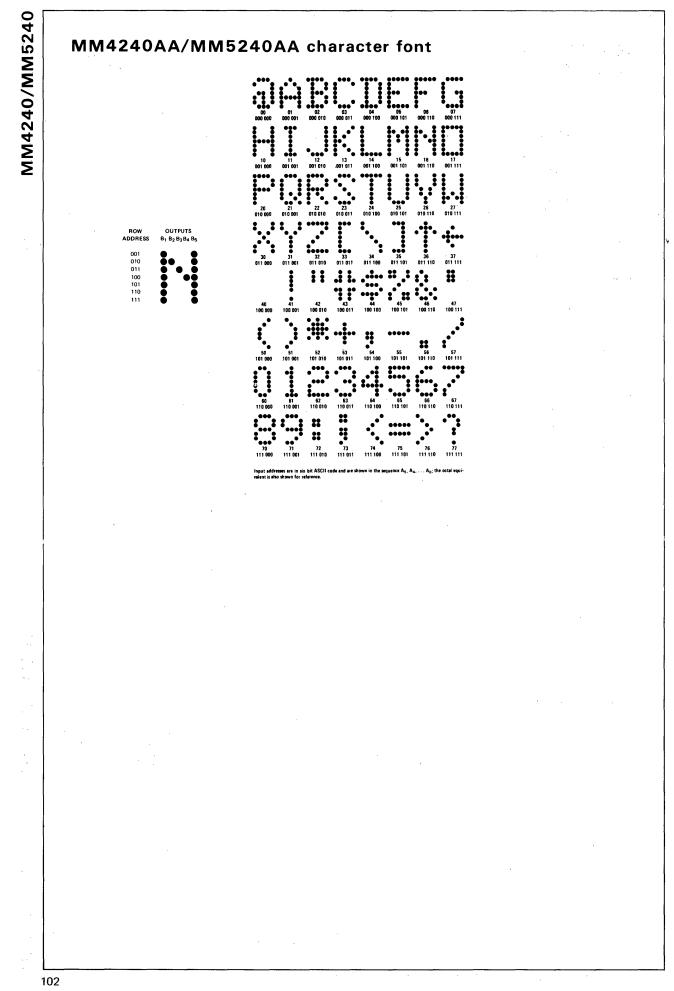

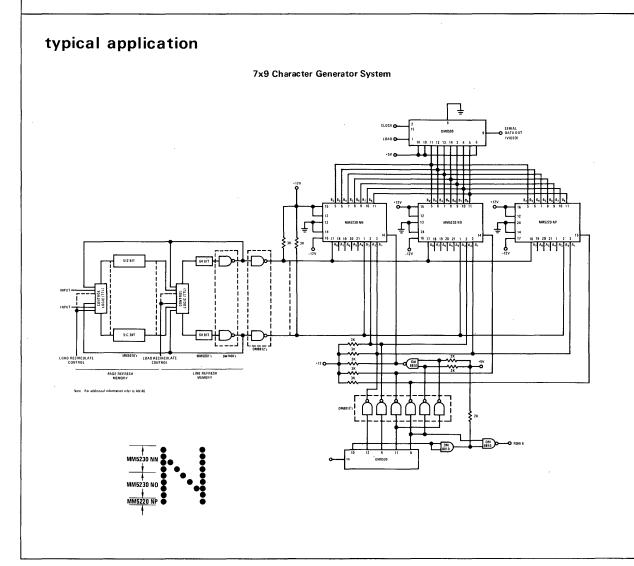

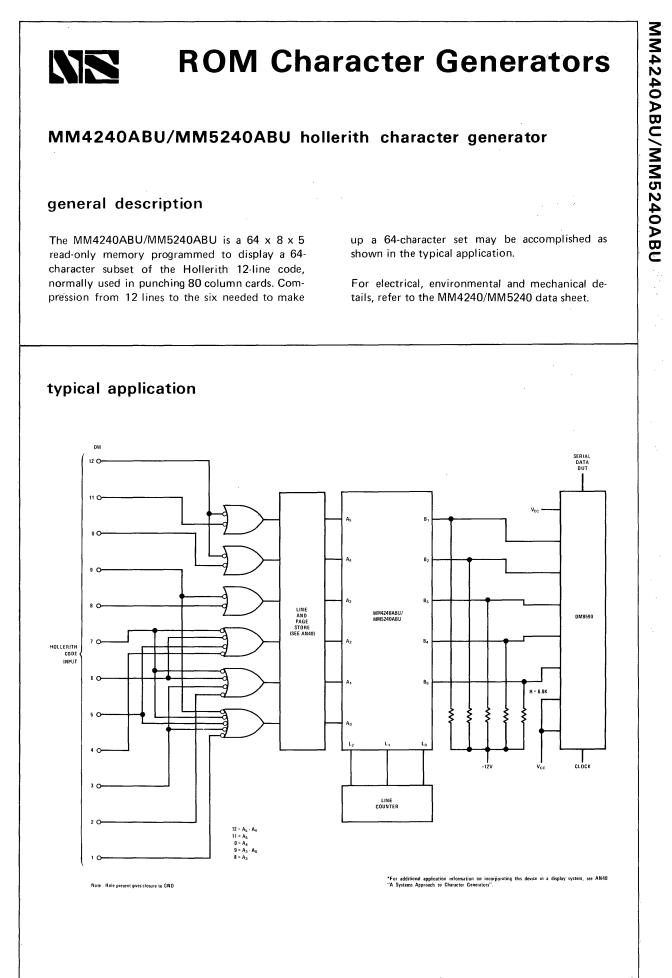

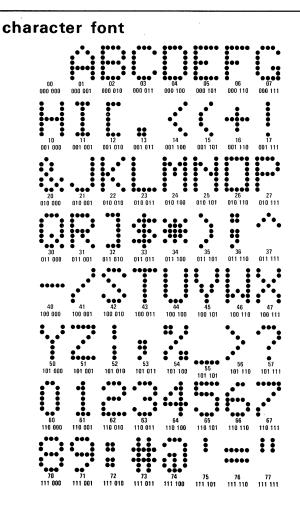

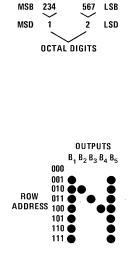

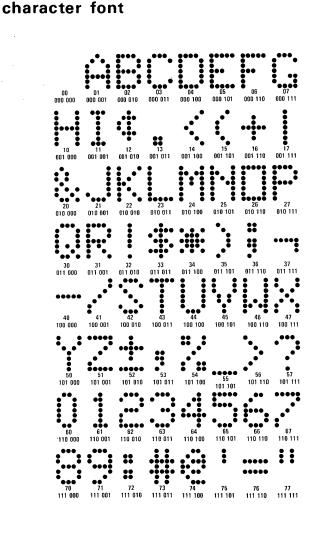

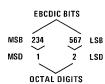

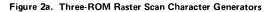

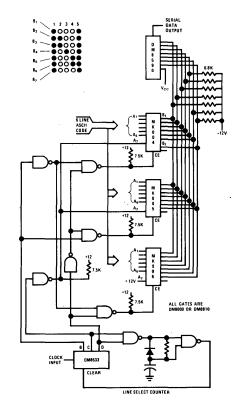

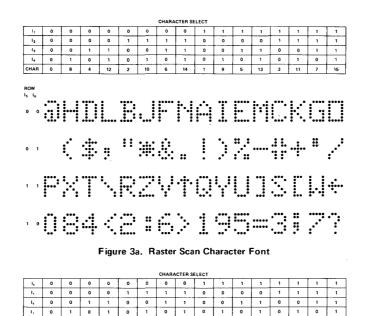

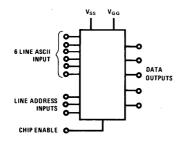

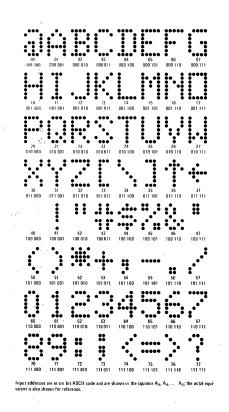

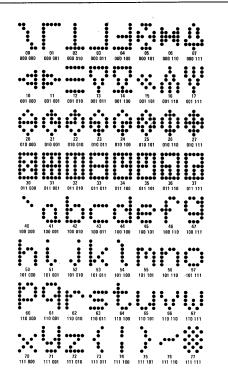

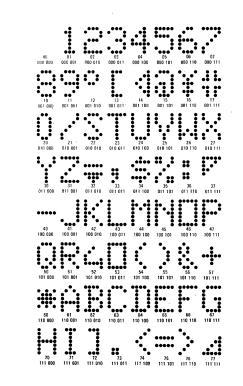

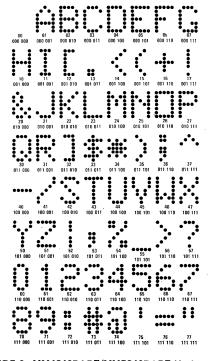

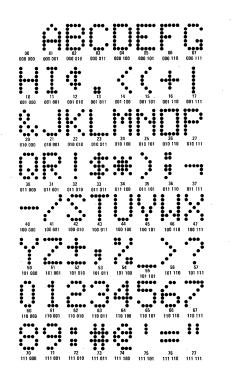

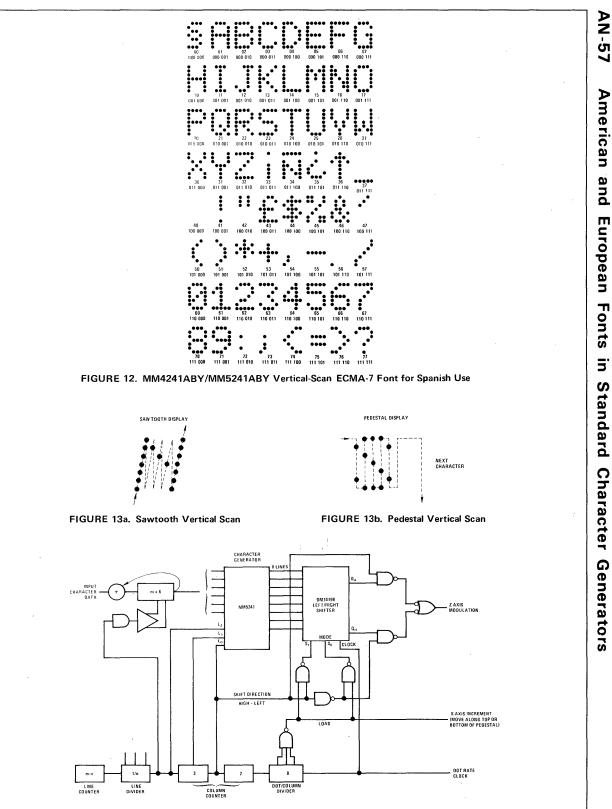

| ROM Character GeneratorsMM4220NP/MM5220NP 7x9 Horizontal Scan Display Character Generator173MM4230NN/MM5230NN 7x9 Horizontal Scan Display Character Generator173MM4230NO/MM5230NO 7x9 Horizontal Scan Display Character Generator173MM4240AA/MM5240AA 7x5 Horizontal Scan ASCII-7 Character Generator99, 267MM4240AE/MM5240AE ASCII-7 and Lower Case Character Generator267MM4240ABU/MM5240ABU Hollerith Character Generator175, 267MM4240ABZ/MM5240ABZ EBCDIC-8 Character Generator177, 267MM4240ACA/MM5240ACA EBCDIC Character Generator178, 267MM4240ACA/MM5241ABL Vertical Scan ASCII-7 Character Generator267MM4241ABV/MM5241ABV Vertical Scan ECMA-7 (Scandinavian) Character Generator267MM4241ABX/MM5241ABX Vertical Scan ECMA-7 (French, British, Italian) Character Generator267MM4241ABY/MM5241ABY Vertical Scan ECMA-7 (Spanish) Character Generator267MM4241ABY/MM5241ABY Vertical Scan ECMA-7 (Spanish) Character Generator267MM4241ABY/MM5241ABY Vertical Scan ECMA-7 (Spanish) Character Generator267                                                    |

For information on the following character generators contact National, Santa Clara: MM4240AD/MM5240AD Katakana Alphabet Character Generator MM4240AF/MM5240AF 5x7 ASCII-6 with Low True Outputs Character Generator MM4240AH/MM5240AH 5x7 ASCII-6 with High True Outputs Character Generator MM4240AK/MM5240AK 5x7 ECMA-6 (French, British, Italian) Character Generator MM4241AAN/MM5241AAN ASCII Vertical Scan Character Generator

| ROM Code Converters                                                                            |      |

|------------------------------------------------------------------------------------------------|------|

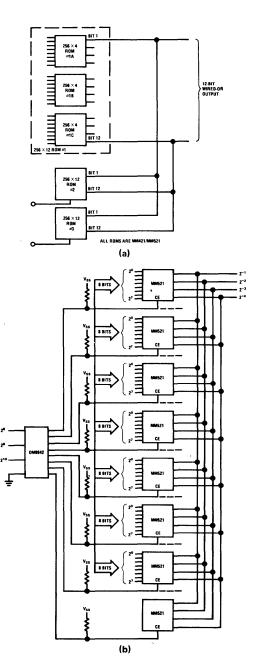

| SK0003 Sine/Cosine Look-Up Table Kit                                                           | 179  |

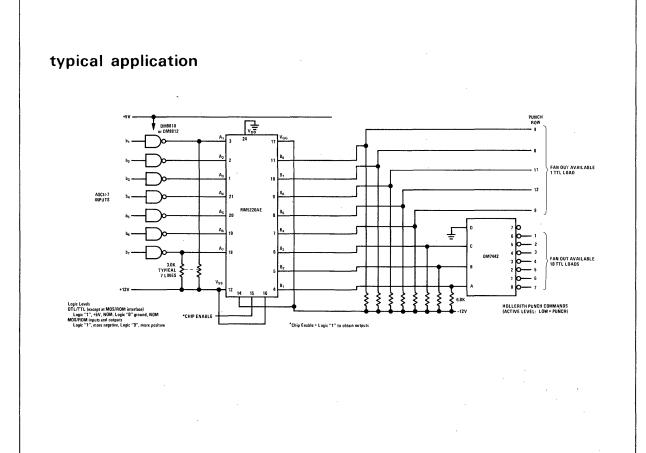

| MM4220AE/MM5220AE ASCII-7 to Hollerith Code Converter                                          | 181  |

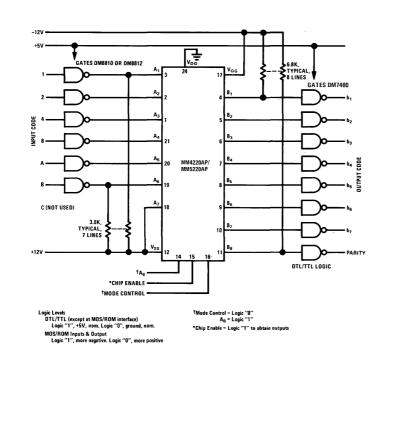

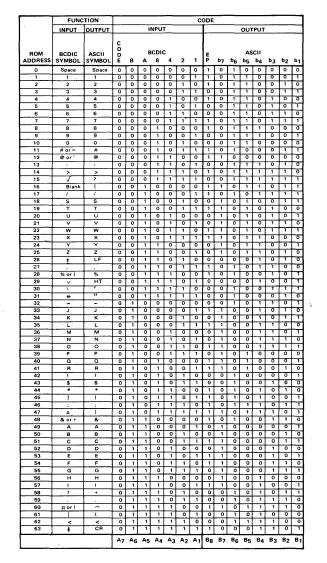

| MM4220AP/MM4220AP BCDIC to ASCII Code Converter                                                | 183  |

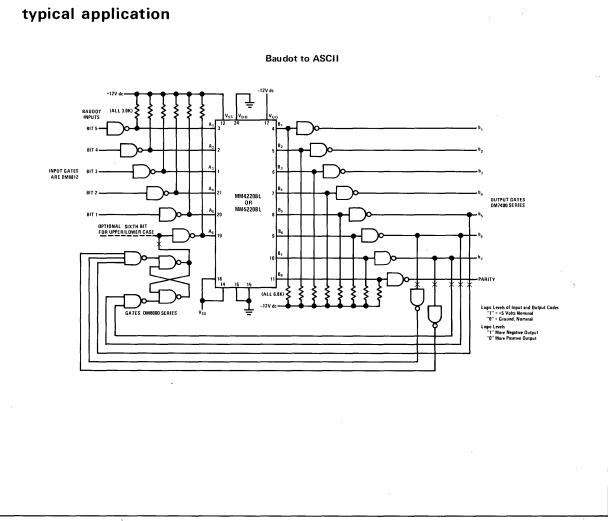

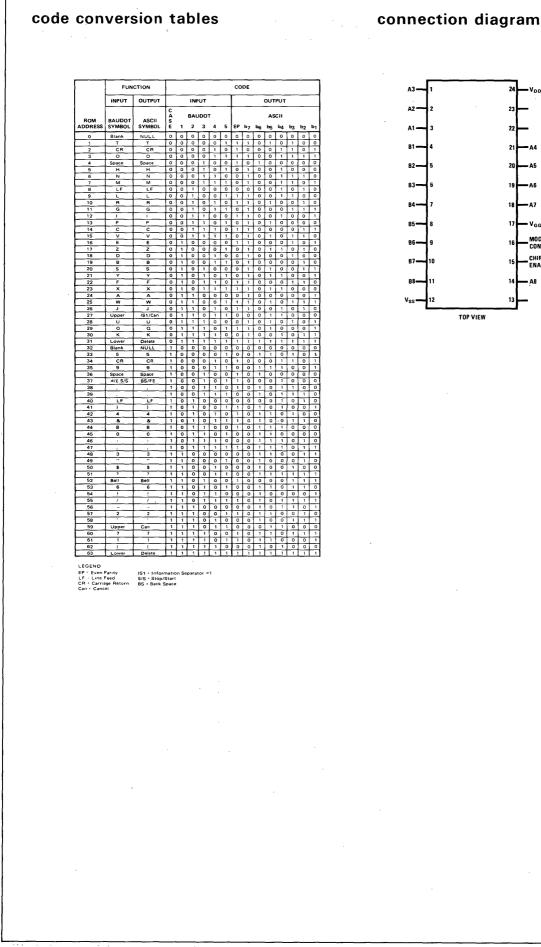

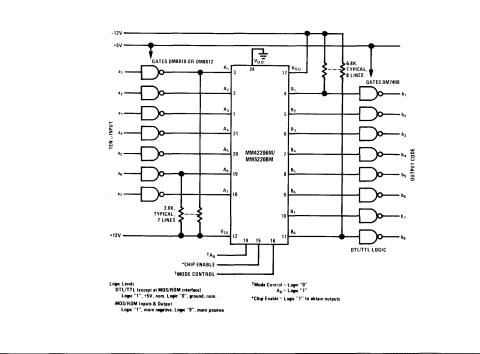

| MM4220BL/MM5220BL Baudot to ASCII Code Converter                                               | 185  |

| MM4220BM/MM5220BM Sine Look-Up Table                                                           | 187  |

| MM4220BN/MM5220BN Arctangent Look-Up Table                                                     |      |

| MM4220DF/MM5220DF "Quick Brown Fox" Generator                                                  |      |

| MM4220EK/MM5220EK BCDIC to EBCDIC and ASCII to EBCDIC Code Converter                           |      |

| MM4220LR/MM5220LR BCDIC to ASCII-7, ASCII-7 to BCDIC Code Converter                            |      |

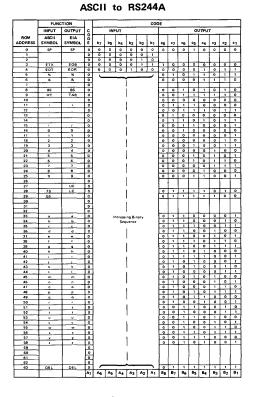

| MM4221RQ/MM5221RQ ASCII-7 to EIA RS244A, EIA RS244A to ASCII-7 Code Converter                  |      |

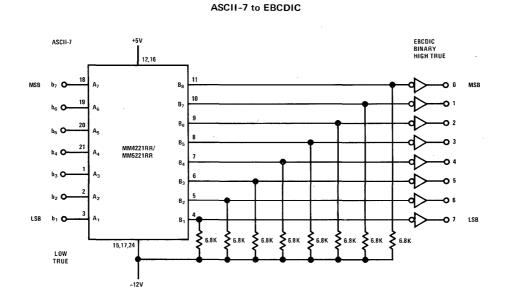

| MM4221RR/MM5221RR ASCII-7 to EBCDIC Code Converter                                             |      |

| MM4230BO/MM5230BO Hollerith to ASCII Code Converter                                            |      |

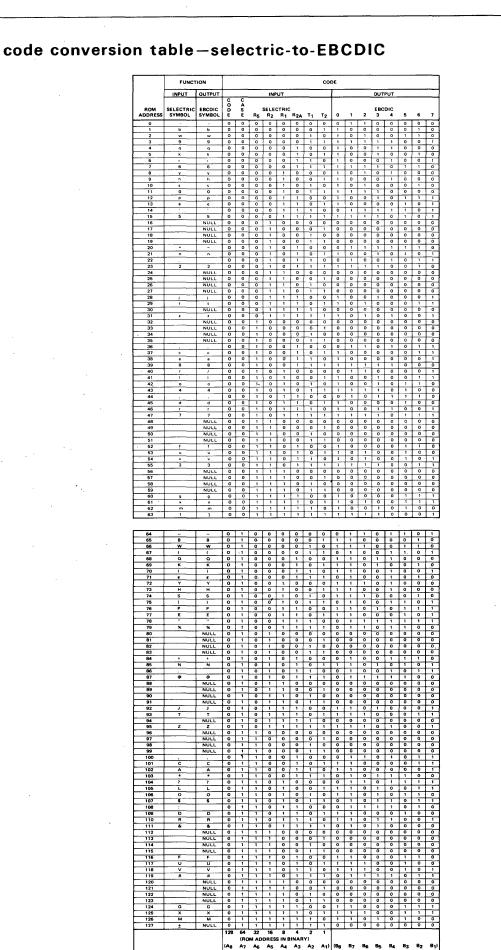

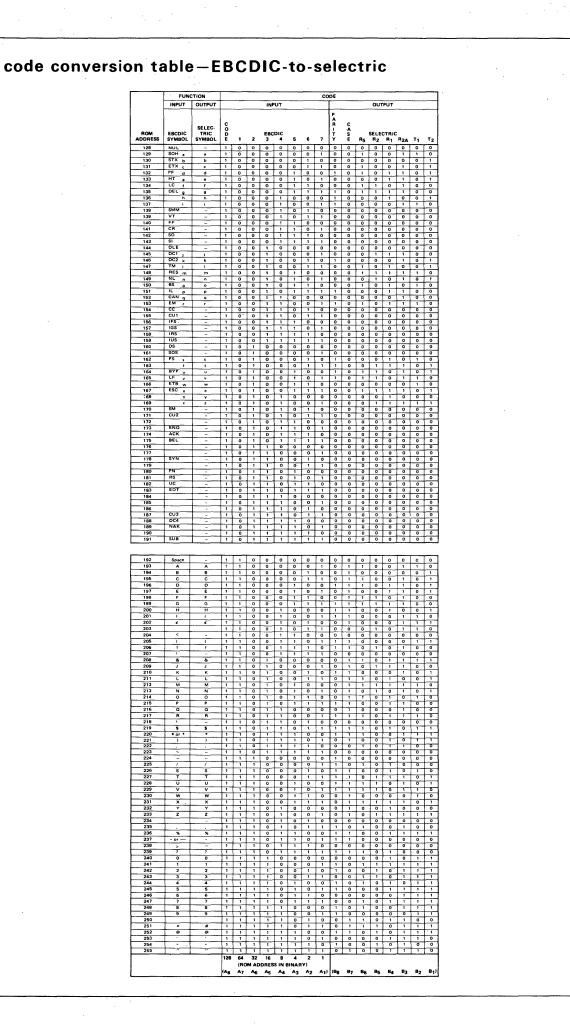

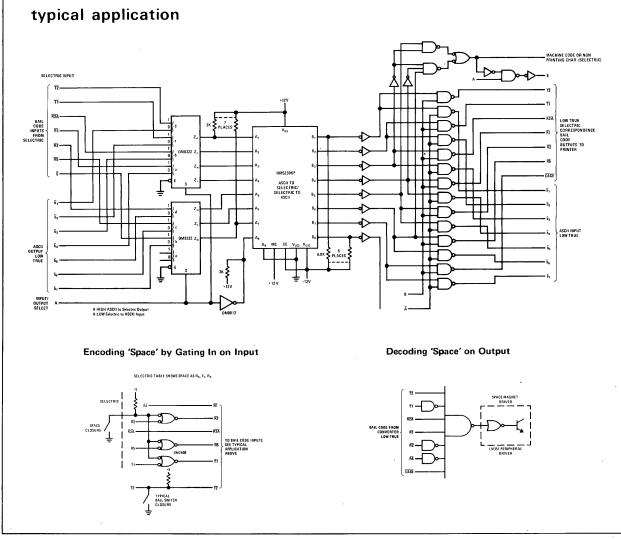

| MM4230FE/MM5230FE Selectric to EBCDIC, EBCDIC to Selectric Code Converter                      |      |

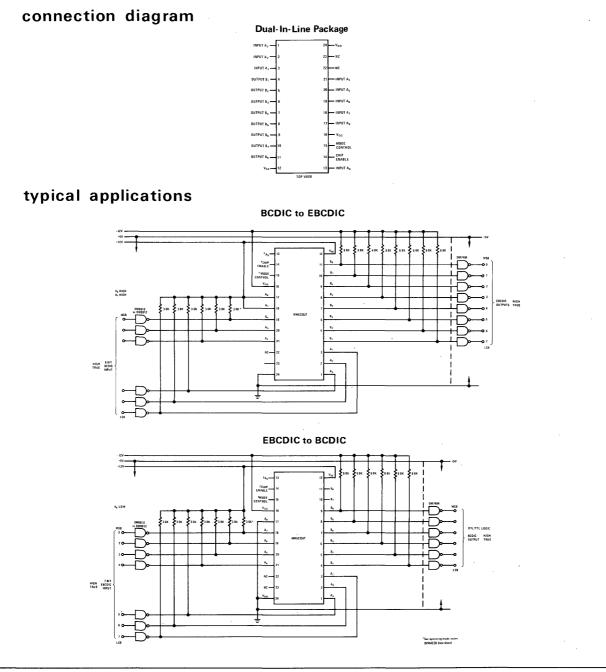

| MM4230JT/MM5230JT BCDIC to EBCDIC, EBCDIC to BCDIC Code Converter                              |      |

|                                                                                                |      |

| MM4230KP/MM5230KP ASCII-7 to Selectric Code Converter                                          |      |

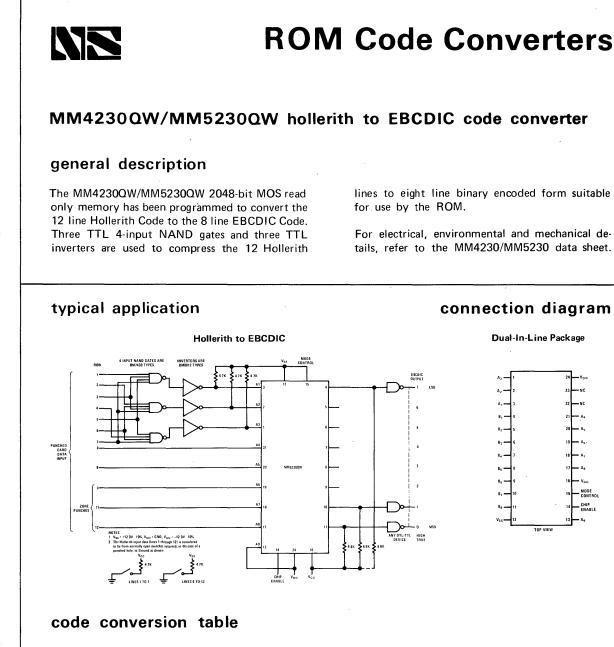

| MM4230QW/MM5230QW Hollerith to EBCDIC Code Converter                                           |      |

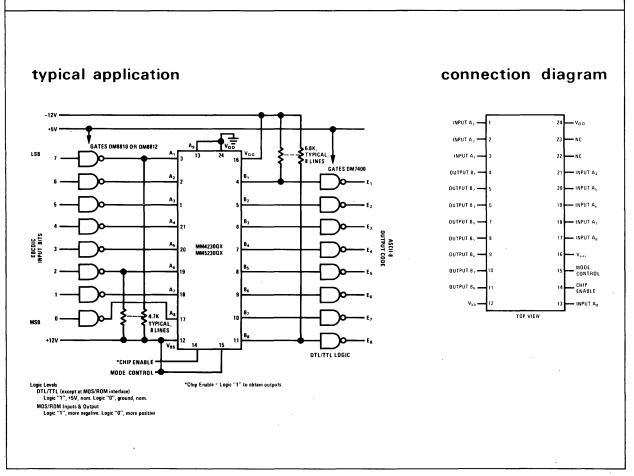

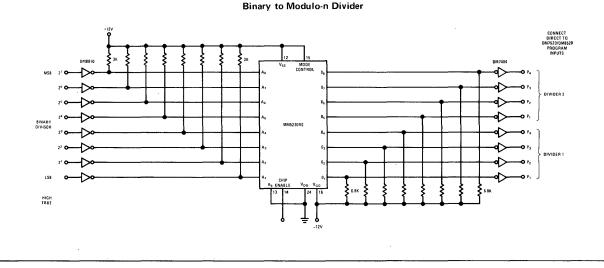

| MM4230QX/MM5230QX EBCDIC-8 to ASCII-8 Code Converter.                                          |      |

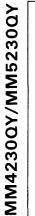

| MM4230QY/MM5230QY ASCII-8 to EBCDIC-8 Code Converter                                           |      |

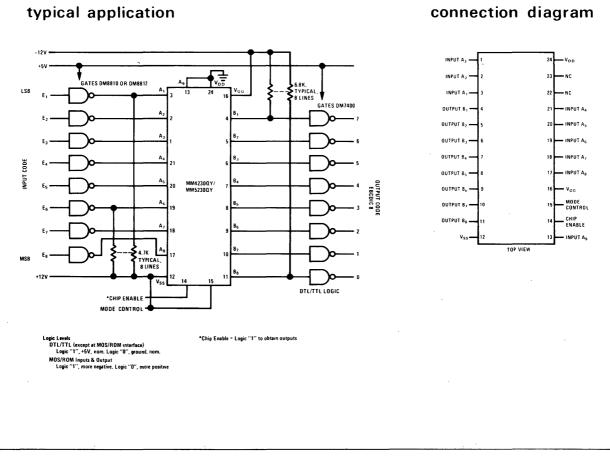

| MM5230RS Binary to Modulo-n Divider Code Converter                                             |      |

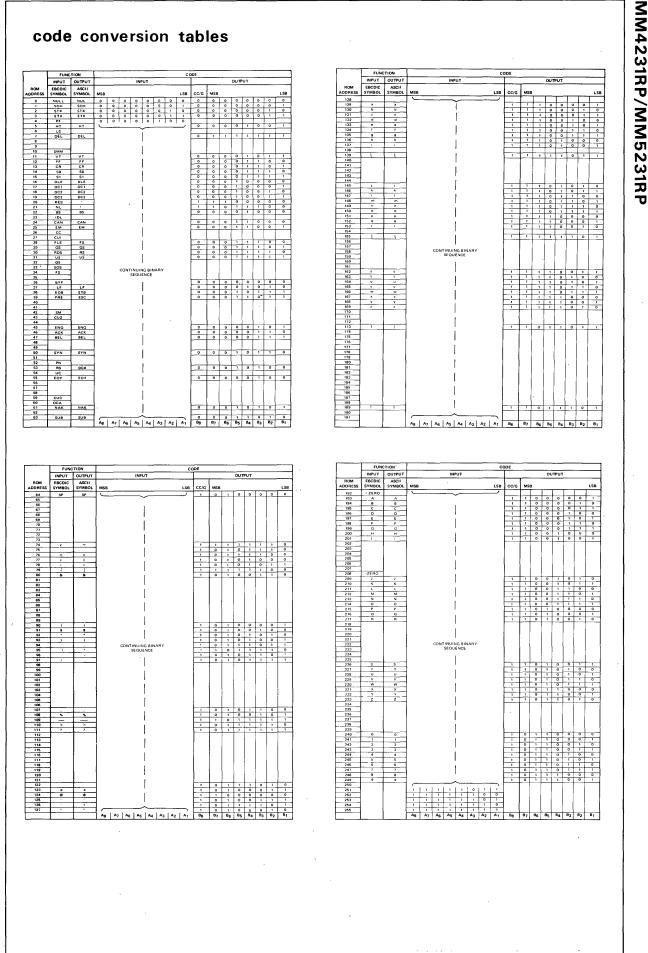

| MM4231RP/MM5231RP IBM 1130 EBCDIC to ASCII-7 Code Converter                                    |      |

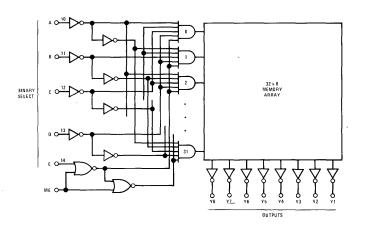

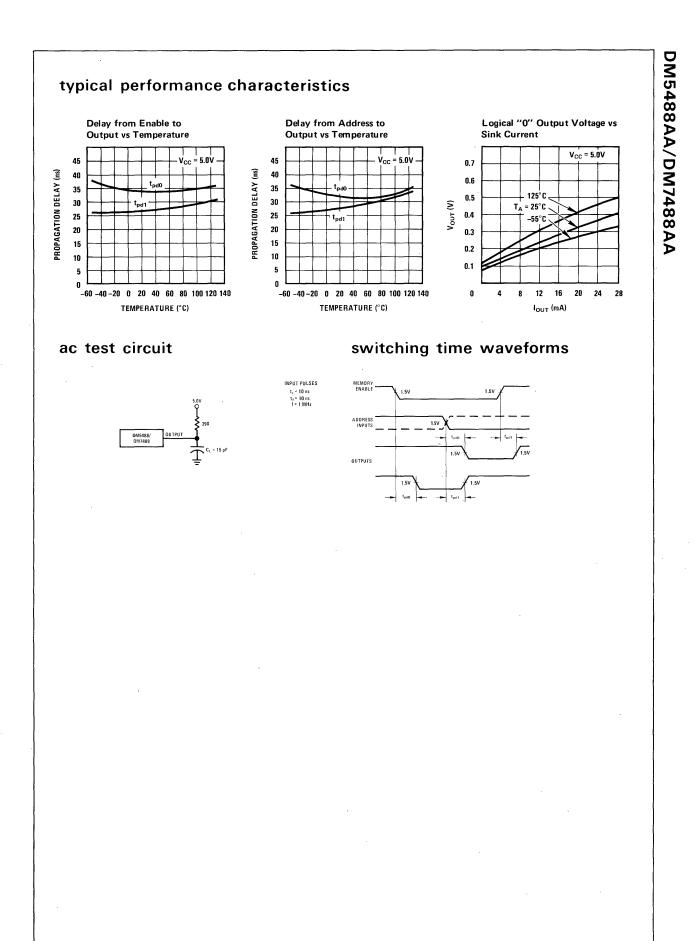

| DM5488AA/DM7488AA (SN5488/SN7488) 256-Bit Sine Look-Up Table Read-Only Memory                  |      |

| DM7598AA/DM8598AA TRI-STATE <sup>TM</sup> 256-Bit Sine Look-Up Table Read-Only Memory $\ldots$ | 222  |

| For information on the following code converters contact National, Santa Clara:                |      |

| MM3501TL ASCII to Baudot, Baudot to ASCII Code Converter                                       |      |

| MM4213UW/MM5213UW EBCDIC-8 to Hollerith Code Converter                                         |      |

| MM4221TM/MM5221TM ASCII to Baudot, Baudot to ASCII Code Converter                              |      |

| MM4230JC/MM5230JC ASCII to Hollerith Code Converter*                                           | ,    |

| MM4230JP/MM5230JP ASCII to MDS Code Converter                                                  |      |

| MM4230JQ/MM5230JQ Hollerith to EBCDIC Code Converter*                                          |      |

| MM4230JR/MM5230JR Selectric to EBCDIC Code Converter*                                          |      |

| MM4230JS/MM5230JS EBCDIC to Selectric Code Converter*                                          |      |

| MM4230SQ/MM5230SQ ASCII-8 to Hollerith Code Converter                                          |      |

|                                                                                                |      |

| Custom MOS/LSI                                                                                 | 225  |

|                                                                                                |      |

|                                                                                                |      |

| Application Notes                                                                              |      |

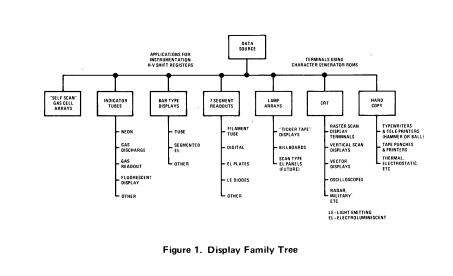

| AN-40 The Systems Approach to Character Generators                                             |      |

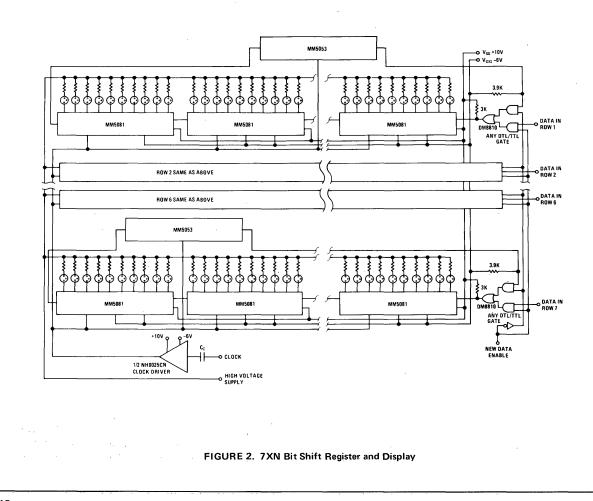

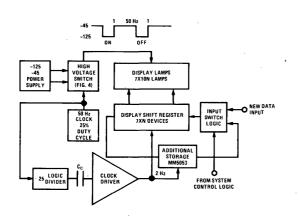

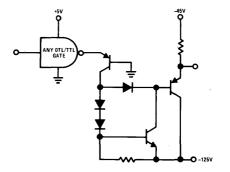

| AN-44 High Voltage Shift Registers Move Displays                                               |      |

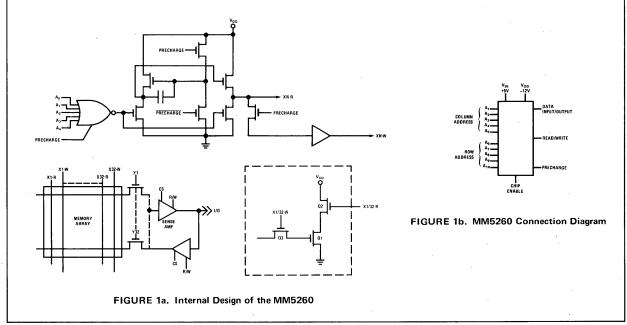

| AN-50 Dynamic MOS Random Access Memories System                                                |      |

| · · · · · · · · · · · · · · · · · · ·                                                          |      |

| AN-55 Low Frequency Operation with Dynamic Shift Registers                                     |      |

| AN-57 American and European Fonts in Standard Character Generators                             | 267  |

|                                                                                                |      |

| MOS Briefs                                                                                     |      |

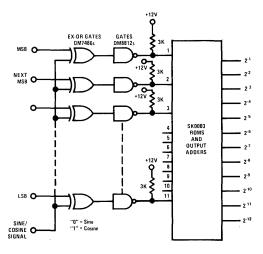

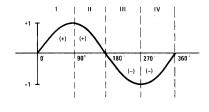

| MOS Brief 10 Trig Function Generators                                                          | 273  |

| MOS Brief 14 Mask Programming Specializes MOS Shift Register Designs.                          |      |

|                                                                                                |      |

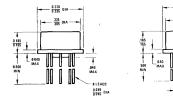

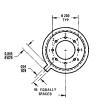

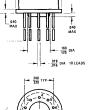

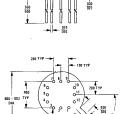

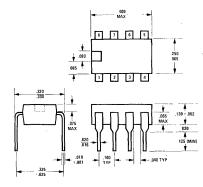

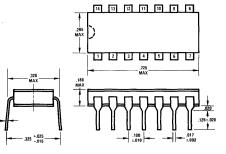

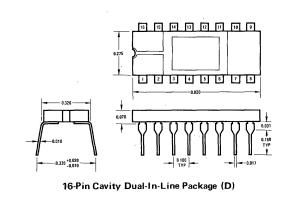

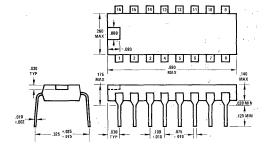

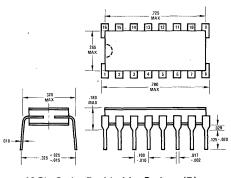

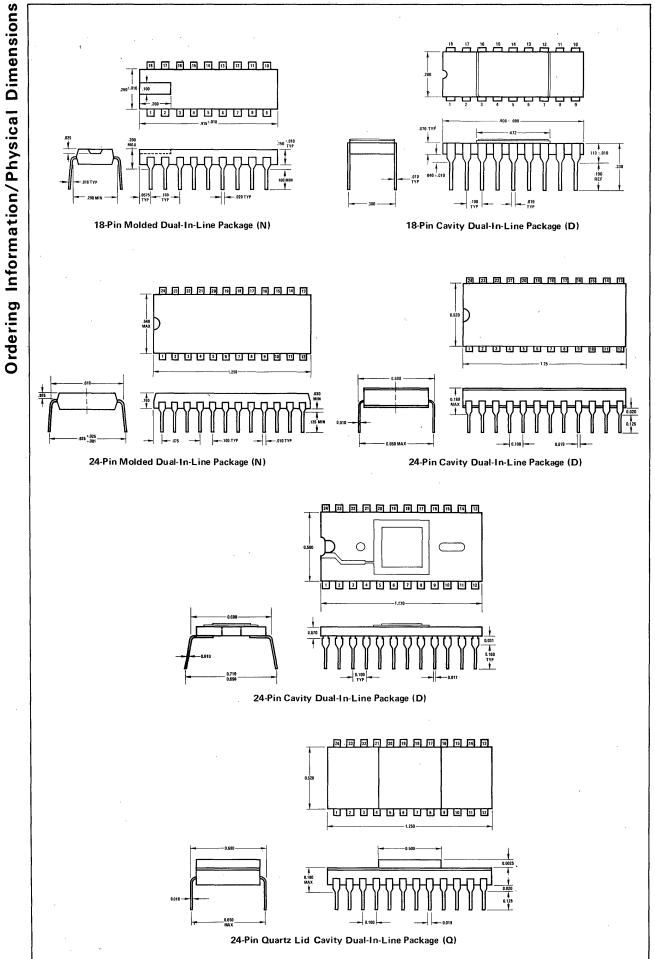

| Ordering Information and Physical Dimensions                                                   | 277  |

|                                                                                                |      |

|                                                                                                |      |

| Definition of Terms                                                                            | 2/9  |

|                                                                                                | 2.12 |

| *Not recommended for new designs. TBA – To Be Announced                                        |      |

v

**MOS Selection Guide**

### **MOS Selection Guide**

|            | PRODUCT TYPE NO.<br>MIL/COM                                                                                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                               | MAX FREQ<br>OR MIN<br>ACCESS TIME                                                                           | v <sub>SS</sub>                                                         | V <sub>DD</sub>                                 | V <sub>DD2</sub><br>OR<br>V <sub>GG</sub>                       | CLOCK<br>SWING                                                     |

|------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|

|            | MM400/MM500                                                                                                                        | Dual 25 Bit                                                                                                                                                                                                                                                                                                                                                               | 1.0 MHz                                                                                                     | +10                                                                     | GND                                             | None                                                            | 16                                                                 |

|            | MM401/MM501                                                                                                                        | Dual 25 Bit                                                                                                                                                                                                                                                                                                                                                               | 1.0 MHz                                                                                                     | +10                                                                     | GND                                             | None                                                            | 16                                                                 |

|            | MM402/MM502                                                                                                                        | Dual 50 Bit                                                                                                                                                                                                                                                                                                                                                               | 1.0 MHz                                                                                                     | +10                                                                     | GND                                             | None                                                            | 16                                                                 |

|            | MM403/MM503                                                                                                                        | Dual 50 Bit                                                                                                                                                                                                                                                                                                                                                               | 1.0 MHz                                                                                                     | +10                                                                     | GND                                             | None                                                            | 16                                                                 |

|            | MM406/MM506                                                                                                                        | Dual 100 Bit                                                                                                                                                                                                                                                                                                                                                              | 1.0 MHz                                                                                                     | +10                                                                     | GND                                             | None                                                            | 16                                                                 |

|            | MM407/MM507                                                                                                                        | Dual 100 Bit                                                                                                                                                                                                                                                                                                                                                              | 1.0 MHz                                                                                                     | +10                                                                     | GND                                             | None                                                            | 16                                                                 |

|            | MM4001A/MM5001A                                                                                                                    | Dual 64 Bit Split Clock                                                                                                                                                                                                                                                                                                                                                   | 2.5 MHz                                                                                                     | +5                                                                      | None                                            | -12                                                             | 17                                                                 |

|            | MM4006A/MM5006A                                                                                                                    | Dual 100 Bit                                                                                                                                                                                                                                                                                                                                                              | 2.5 MHz                                                                                                     | +5                                                                      | None                                            | -12                                                             | 17                                                                 |

|            | MM4008A/MM5008A<br>MM4007/MM5007                                                                                                   | Dual 100 Bit Mask Programmable                                                                                                                                                                                                                                                                                                                                            | 2.5 MHz                                                                                                     | +5                                                                      | None                                            | -12                                                             | 17                                                                 |

|            |                                                                                                                                    | Dual 64 Bit Accumulator                                                                                                                                                                                                                                                                                                                                                   | 2.5 MHz                                                                                                     | +5                                                                      | None                                            | -12                                                             | 17                                                                 |

|            | MM4010A/MM5010A                                                                                                                    | Dual 64 Bit Common Clock                                                                                                                                                                                                                                                                                                                                                  | 2.5 MHz                                                                                                     | +5                                                                      | None                                            | -12                                                             | 17                                                                 |

|            | MM4011A/MM5011A                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                             |                                                                         |                                                 | -12                                                             |                                                                    |

| <u>ب</u>   | MM4012/MM5012                                                                                                                      | Dual 256 Bit Accumulator                                                                                                                                                                                                                                                                                                                                                  | 2.5 MHz                                                                                                     | +5                                                                      | None                                            |                                                                 | 17                                                                 |

| Ś          | MM4013/MM5013                                                                                                                      | 1024 Bit Accumulator                                                                                                                                                                                                                                                                                                                                                      | 2.5 MHz                                                                                                     | +5                                                                      | None                                            | -12                                                             | 17                                                                 |

| Dynamic S/ | MM4015A/MM5015A                                                                                                                    | Triple 60 + 4 Accumulator                                                                                                                                                                                                                                                                                                                                                 | 2.5 MHz                                                                                                     | +5                                                                      | None                                            | -12                                                             | 17                                                                 |

| nar        | MM4016/MM5016                                                                                                                      | 500/512 Bit                                                                                                                                                                                                                                                                                                                                                               | 2.5 MHz                                                                                                     | +5                                                                      | None                                            | -12                                                             | 17                                                                 |

| ā          | MM4017/MM5017                                                                                                                      | Dual 500/512 Bit                                                                                                                                                                                                                                                                                                                                                          | 2.5 MHz                                                                                                     | +5                                                                      | None                                            | -12                                                             | 17                                                                 |

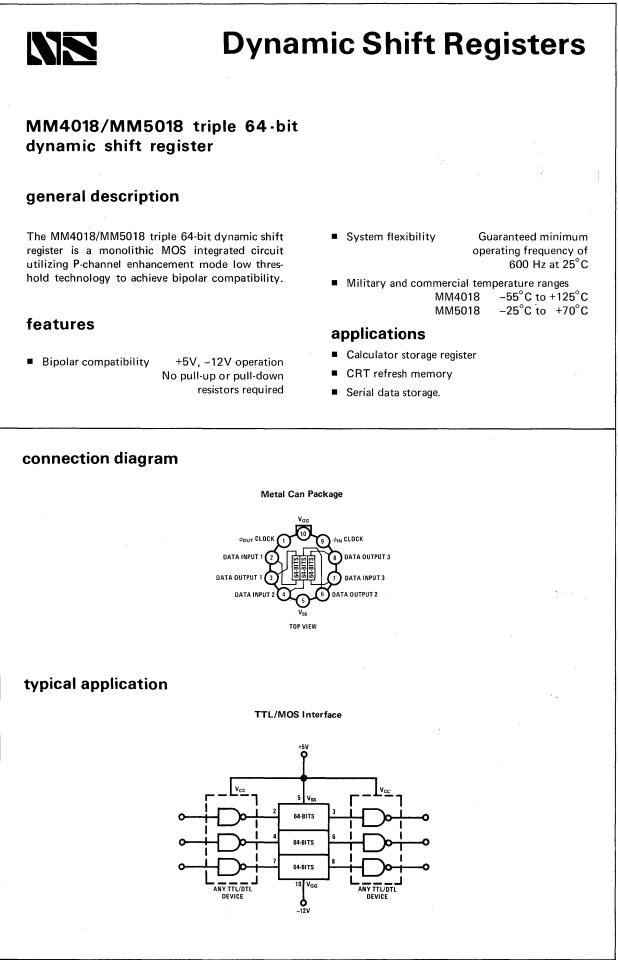

|            | MM4018/MM5018                                                                                                                      | Triple 64 Bit                                                                                                                                                                                                                                                                                                                                                             | 2.5 MHz                                                                                                     | +5                                                                      | None                                            | -12                                                             | 17                                                                 |

|            | MM4019/MM5019                                                                                                                      | Dual 256 Mask Programmable                                                                                                                                                                                                                                                                                                                                                | 2.5 MHz                                                                                                     | +5                                                                      | None                                            | -12                                                             | 17                                                                 |

|            | MM4020/MM5020                                                                                                                      | Quad 80 Bit                                                                                                                                                                                                                                                                                                                                                               | 2.5 MHz                                                                                                     | +5                                                                      | None                                            | -12                                                             | 17                                                                 |

|            | MM4021/MM5021                                                                                                                      | Triple 80 Bit                                                                                                                                                                                                                                                                                                                                                             | 2.5 MHz                                                                                                     | +5                                                                      | None                                            | -12                                                             | 17                                                                 |

|            | MM4100/MM5100                                                                                                                      | 144/156 Bit                                                                                                                                                                                                                                                                                                                                                               | 1.0 MHz                                                                                                     | +5                                                                      | None                                            | -12                                                             | 17                                                                 |

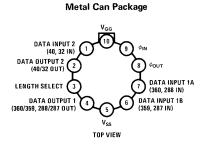

|            | MM4104/MM5104                                                                                                                      | 360/359 + 288/287, 40/32 Bit                                                                                                                                                                                                                                                                                                                                              | 2.5 MHz                                                                                                     | +5                                                                      | None                                            | -12                                                             | 17                                                                 |

|            | MM4105/MM5105                                                                                                                      | Quad 64 Accumulator                                                                                                                                                                                                                                                                                                                                                       | 2.2 MHz                                                                                                     | +5                                                                      | None                                            | -12                                                             | 17                                                                 |

|            | MM1402A                                                                                                                            | Quad 256 Bit                                                                                                                                                                                                                                                                                                                                                              |                                                                                                             | +5                                                                      | -9                                              | None                                                            | 14                                                                 |

|            |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                           | 5.0 MHz                                                                                                     |                                                                         | -9<br>-9                                        | -                                                               |                                                                    |

|            | MM1403A                                                                                                                            | Dual 512 Bit                                                                                                                                                                                                                                                                                                                                                              | 5.0 MHz                                                                                                     | +5                                                                      | -                                               | None                                                            | 14                                                                 |

|            | MM1404A                                                                                                                            | Single 1024 Bit                                                                                                                                                                                                                                                                                                                                                           | 5.0 MHz                                                                                                     | +5                                                                      | 9                                               | None                                                            | 14                                                                 |

|            | MM5024A                                                                                                                            | Single 1024 Bit with<br>Internal Pullup Resistor                                                                                                                                                                                                                                                                                                                          | 5.0 MHz                                                                                                     | +5                                                                      | 9                                               | None                                                            | 14                                                                 |

|            | MM404/MM504                                                                                                                        | Dual 16 Bit                                                                                                                                                                                                                                                                                                                                                               | 1.0 MHz                                                                                                     | +10                                                                     | GND                                             | 6                                                               | 16                                                                 |

|            | MM405/MM505                                                                                                                        | Dual 32 Bit                                                                                                                                                                                                                                                                                                                                                               | 1.0 MHz                                                                                                     | +10                                                                     | GND                                             | 6                                                               | 16                                                                 |

|            | 4                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                           | 2.2.MHz                                                                                                     | +5                                                                      | GND                                             | -12                                                             | 17                                                                 |

| Æ          | MM4040/MM5040                                                                                                                      | Dual 16 Bit                                                                                                                                                                                                                                                                                                                                                               |                                                                                                             | -                                                                       |                                                 |                                                                 |                                                                    |

| Ś          | MM4050/MM5050                                                                                                                      | Dual 32 Bit Common Clock                                                                                                                                                                                                                                                                                                                                                  | 1.6 MHz                                                                                                     | +5                                                                      | GND                                             | -12                                                             | 1.7                                                                |

| Static S/R | MM4051/MM5051                                                                                                                      | Dual 32 Bit Split Clock                                                                                                                                                                                                                                                                                                                                                   | 1.6 MHz                                                                                                     | +5                                                                      | GND                                             | -12                                                             | 17                                                                 |

| Sté        | MM4052/MM5052                                                                                                                      | Dual 80 Bit                                                                                                                                                                                                                                                                                                                                                               | 1.6 MHz                                                                                                     | +5                                                                      | GND                                             | -12                                                             | 17                                                                 |

|            | MM4053/MM5053                                                                                                                      | Dual 100 Bit                                                                                                                                                                                                                                                                                                                                                              | 1.6 MHz                                                                                                     | +5                                                                      | GND                                             | -12                                                             | 17                                                                 |

|            | MM4054/MM5054                                                                                                                      | Dual 64/72/80 On Chip Clock                                                                                                                                                                                                                                                                                                                                               | 2.2 MHz                                                                                                     | +5                                                                      | GND                                             | -12                                                             | TTL                                                                |

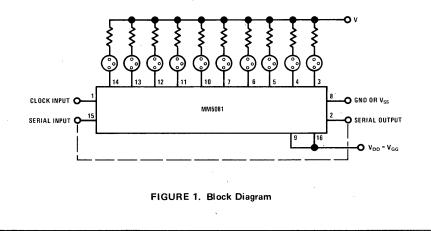

| _          | MM5081                                                                                                                             | High Voltage (VL=-55V) MM413                                                                                                                                                                                                                                                                                                                                              | 250 kHz                                                                                                     | GND                                                                     | -20                                             | -20                                                             | -20                                                                |

| _          | MM4203/MM5203                                                                                                                      | 2048 Bit ROM (Pin Compatible<br>MM4213) TSL                                                                                                                                                                                                                                                                                                                               | 1.0 μs                                                                                                      | +5                                                                      | -12                                             | -12                                                             | None                                                               |

|            | MM4210/MM5210                                                                                                                      | 1024 Bit (256 × 4)                                                                                                                                                                                                                                                                                                                                                        | 650 ns                                                                                                      | +12                                                                     | -12                                             | -12                                                             | None                                                               |

|            | MM4210/MM5210                                                                                                                      | 1024 Bit (256 x 4)                                                                                                                                                                                                                                                                                                                                                        | 950 ns                                                                                                      | +12                                                                     | -12                                             | -12                                                             | None                                                               |

|            |                                                                                                                                    | 2048 Bit ROM (Pin Compatible                                                                                                                                                                                                                                                                                                                                              | 300 HS                                                                                                      | + <b>U</b>                                                              | -12                                             | -12                                                             | NOTE                                                               |

|            | MM4213/MM5213                                                                                                                      | MM4203) TSL                                                                                                                                                                                                                                                                                                                                                               | 750 ns                                                                                                      | +5                                                                      | -12                                             | -12                                                             | None                                                               |

|            | MM4220/MM5220                                                                                                                      | 1024 Bit (256×4 or 128×8)                                                                                                                                                                                                                                                                                                                                                 | 650 ns                                                                                                      | +12                                                                     | -12                                             | -12                                                             | None                                                               |

| Ms         | MM4220/MM5220<br>MM4221/MM5221                                                                                                     | 1024 Bit (256x4 of 128x8)                                                                                                                                                                                                                                                                                                                                                 | 950 ns                                                                                                      | +5                                                                      | -12                                             | -12                                                             | None                                                               |

| ROMs       | MM4230/MM5230                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                           | 725 ns                                                                                                      | +5<br>+12                                                               | -12                                             | -12                                                             | None                                                               |

| Ľ.         |                                                                                                                                    | 2048 Bit (512x4 or 256x8)                                                                                                                                                                                                                                                                                                                                                 |                                                                                                             |                                                                         |                                                 |                                                                 |                                                                    |

|            | MM4231/MM5231                                                                                                                      | 2048 Bit (512x4 or 256x8)                                                                                                                                                                                                                                                                                                                                                 | 950 ns                                                                                                      | +5<br>+5                                                                | -12                                             | -12                                                             | None                                                               |

|            | MM4232/MM5232                                                                                                                      | 4096 Bit (1024x4 or 512x8) TSL<br>2560 Bit Character Generator                                                                                                                                                                                                                                                                                                            | 1.0 μs                                                                                                      | +5                                                                      | -12                                             | -12                                                             | None                                                               |

|            |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                           | 600 ns                                                                                                      | +12                                                                     | -12                                             | -12                                                             | None                                                               |

|            | MM4240/MM5240                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                             |                                                                         |                                                 | -12                                                             | None                                                               |

|            | MM4240/MM5240<br>MM4241/MM5241                                                                                                     | 3072 Bit Character Generator                                                                                                                                                                                                                                                                                                                                              | 900 ns                                                                                                      | +5                                                                      | -12                                             |                                                                 | N                                                                  |

|            | MM4240/MM5240                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                             | +5<br>+12                                                               | -12                                             | -12                                                             | None                                                               |

|            | MM4240/MM5240<br>MM4241/MM5241                                                                                                     | 3072 Bit Character Generator                                                                                                                                                                                                                                                                                                                                              | 900 ns                                                                                                      | +12<br>+5                                                               | -12<br>-7                                       | -12<br>-10                                                      | None                                                               |

|            | MM4240/MM5240<br>MM4241/MM5241<br>SK0003                                                                                           | 3072 Bit Character Generator<br>Sine Look-Up Table                                                                                                                                                                                                                                                                                                                        | 900 ns<br>1.0 MHz                                                                                           | +12                                                                     | -12                                             | -12                                                             |                                                                    |

|            | MM4240/MM5240<br>MM4241/MM5241<br>SK0003<br>MM1101                                                                                 | 3072 Bit Character Generator<br>Sine Look-Up Table<br>256 Bit Static (256 x 1)                                                                                                                                                                                                                                                                                            | 900 ns<br>1.0 MHz<br>1.5 μs                                                                                 | +12<br>+5                                                               | -12<br>-7                                       | -12<br>-10                                                      | None                                                               |

|            | MM4240/MM5240<br>MM4241/MM5241<br>SK0003<br>MM1101<br>MM11011                                                                      | 3072 Bit Character Generator<br>Sine Look-Up Table<br>256 Bit Static (256 × 1)<br>256 Bit Static (256 × 1)                                                                                                                                                                                                                                                                | 900 ns<br>1.0 MHz<br>1.5 μs<br>1.0 μs                                                                       | +12<br>+5<br>+5                                                         | 12<br>7<br>7                                    | -12<br>-10<br>-10                                               | None<br>None                                                       |

| Ns         | MM4240/MM5240<br>MM4241/MM5241<br>SK0003<br>MM1101<br>MM11011<br>MM1101A                                                           | 3072 Bit Character Generator<br>Sine Look-Up Table<br>256 Bit Static (256 × 1)<br>256 Bit Static (256 × 1)<br>256 Bit Static (256 × 1)                                                                                                                                                                                                                                    | 900 ns<br>1.0 MHz<br>1.5 μs<br>1.0 μs<br>1.5 μs                                                             | +12<br>+5<br>+5<br>+5                                                   | -12<br>-7<br>-7<br>-9                           | -12<br>-10<br>-10<br>-9                                         | None<br>None<br>None                                               |

| tAMs       | MM4240/MM5240<br>MM4241/MM5241<br>SK0003<br>MM1101<br>MM11011<br>MM1101A<br>MM1101A1                                               | 3072 Bit Character Generator<br>Sine Look-Up Table<br>256 Bit Static (256 × 1)<br>256 Bit Static (256 × 1)<br>256 Bit Static (256 × 1)<br>256 Bit Static (256 × 1)                                                                                                                                                                                                        | 900 ns<br>1.0 MHz<br>1.5 μs<br>1.0 μs<br>1.5 μs<br>1.0 μs                                                   | +12<br>+5<br>+5<br>+5<br>+5<br>+5                                       | 12<br>7<br>7<br>9<br>9                          | -12<br>10<br>10<br>9<br>-9                                      | None<br>None<br>None<br>None                                       |

| RAMs       | MM4240/MM5240<br>MM4241/MM5241<br>SK0003<br>MM1101<br>MM11011<br>MM1101A<br>MM1101A1<br>MM1101A2                                   | 3072 Bit Character Generator<br>Sine Look-Up Table<br>256 Bit Static (256 × 1)<br>256 Bit Static (256 × 1)                                                                                                                                                                            | 900 ns<br>1.0 MHz<br>1.5 μs<br>1.0 μs<br>1.5 μs<br>1.0 μs<br>500 ns                                         | +12<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5                                 | 12<br>7<br>7<br>9<br>9                          | -12<br>-10<br>-9<br>-9<br>-9                                    | None<br>None<br>None<br>None<br>None                               |

| RAMs       | MM4240/MM5240<br>MM4241/MM5241<br>SK0003<br>MM1101<br>MM11011<br>MM1101A<br>MM1101A1<br>MM1101A2<br>MM5260                         | 3072 Bit Character Generator<br>Sine Look-Up Table<br>256 Bit Static (256 × 1)<br>256 Bit Static (256 × 1)<br>1024 Bit Dynamic (1024×1)                                                                                                                                               | 900 ns<br>1.0 MHz<br>1.5 μs<br>1.0 μs<br>1.5 μs<br>1.0 μs<br>500 ns<br>350 ns                               | +12<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5                           | 12<br>7<br>7<br>9<br>9                          | -12<br>10<br>9<br>-9<br>-9<br>-12                               | None<br>None<br>None<br>None<br>15                                 |

| RAMs       | MM4240/MM5240<br>MM4241/MM5241<br>SK0003<br>MM1101<br>MM1101A<br>MM1101A1<br>MM1101A2<br>MM5260<br>MM5262                          | 3072 Bit Character Generator<br>Sine Look-Up Table<br>256 Bit Static (256 x 1)<br>256 Bit Static (256 x 1)<br>1024 Bit Dynamic (1024x1)<br>2048 Bit Dynamic (2048x1)<br>2048 Bit Dynamic with                                                                                         | 900 ns<br>1.0 MHz<br>1.5 μs<br>1.0 μs<br>1.5 μs<br>1.0 μs<br>500 ns<br>350 ns                               | +12<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5                           | 12<br>7<br>7<br>9<br>9                          | -12<br>10<br>9<br>-9<br>-9<br>-12                               | None<br>None<br>None<br>None<br>15                                 |

| RAMs       | MM4240/MM5240<br>MM4241/MM5241<br>SK0003<br>MM1101<br>MM1101A<br>MM1101A1<br>MM1101A2<br>MM5260<br>MM5262                          | 3072 Bit Character Generator<br>Sine Look-Up Table<br>256 Bit Static (256 × 1)<br>256 Bit Static (256 × 1)<br>1024 Bit Dynamic (1024×1)<br>2048 Bit Dynamic (2048×1)                                                                                                                  | 900 ns<br>1.0 MHz<br>1.5 μs<br>1.0 μs<br>1.5 μs<br>1.0 μs<br>500 ns<br>350 ns<br>360 ns                     | +12<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5                     | 12<br>7<br>7<br>9<br>9                          | -12<br>-10<br>-9<br>-9<br>-9<br>-12<br>-15                      | None<br>None<br>None<br>None<br>15<br>18                           |

| RAMs       | MM4240/MM5240<br>MM4241/MM5241<br>SK0003<br>MM1101<br>MM1101A<br>MM1101A1<br>MM1101A2<br>MM5260<br>MM5263                          | 3072 Bit Character Generator<br>Sine Look-Up Table<br>256 Bit Static (256 x 1)<br>256 Bit Static (256 x 1)<br>1024 Bit Dynamic (1024x1)<br>2048 Bit Dynamic (2048x1)<br>2048 Bit Dynamic (with<br>TSL Output (On Chip Sense Amp)                                                      | 900 ns<br>1.0 MHz<br>1.5 μs<br>1.0 μs<br>1.5 μs<br>1.0 μs<br>500 ns<br>350 ns<br>360 ns                     | +12<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5               | -12<br>-7<br>-9<br>-9<br>-9                     | -12<br>-10<br>-9<br>-9<br>-9<br>-12<br>-15<br>-15               | None<br>None<br>None<br>None<br>15<br>18                           |

|            | MM4240/MM5240<br>MM4241/MM5241<br>SK0003<br>MM1101<br>MM1101A<br>MM1101A1<br>MM1101A2<br>MM5260<br>MM5263<br>MM1103<br>MM480/MM580 | 3072 Bit Character Generator<br>Sine Look-Up Table<br>256 Bit Static (256 x 1)<br>256 Bit Static (256 x 1)<br>1024 Bit Dynamic (1024x1)<br>2048 Bit Dynamic (2048x1)<br>2048 Bit Dynamic with<br>TSL Output (On Chip Sense Amp)<br>1024 Bit Dynamic (1024x1)<br>Dual 3 Input NOR Gate | 900 ns<br>1.0 MHz<br>1.5 μs<br>1.0 μs<br>1.5 μs<br>1.0 μs<br>500 ns<br>350 ns<br>360 ns<br>390 ns<br>200 ns | +12<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5<br>+16<br>+10 | -12<br>-7<br>-9<br>-9<br>-9<br>-9<br>GND<br>GND | -12<br>-10<br>-9<br>-9<br>-9<br>-12<br>-15<br>-15<br>12<br>None | None<br>None<br>None<br>None<br>15<br>18<br>18<br>18               |

| Logic RAMs | MM4240/MM5240<br>MM4241/MM5241<br>SK0003<br>MM1101<br>MM1101A<br>MM1101A1<br>MM1101A2<br>MM5260<br>MM5262<br>MM5263<br>MM1103      | 3072 Bit Character Generator<br>Sine Look-Up Table<br>256 Bit Static (256 x 1)<br>256 Bit Static (256 x 1)<br>1024 Bit Dynamic (1024x1)<br>2048 Bit Dynamic (2048x1)<br>2048 Bit Dynamic with<br>TSL Output (On Chip Sense Amp)<br>1024 Bit Dynamic (1024x1)                          | 900 ns<br>1.0 MHz<br>1.5 μs<br>1.0 μs<br>1.5 μs<br>1.0 μs<br>500 ns<br>350 ns<br>360 ns<br>390 ns           | +12<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5<br>+5<br>+16              | -12<br>-7<br>-9<br>-9<br>-9<br>-9               | -12<br>-10<br>-9<br>-9<br>-9<br>-12<br>-15<br>-15<br>12         | None<br>None<br>None<br>None<br>15<br>18<br>18<br>18<br>19<br>None |

vi

MAPS

### microprogrammable arithmetic processor system

### general description

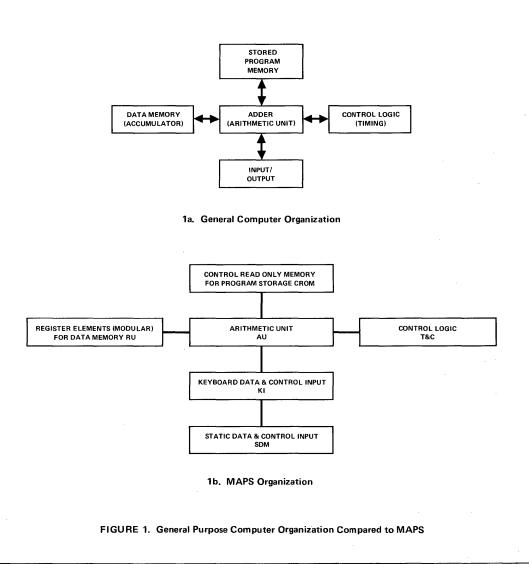

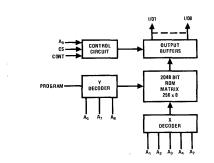

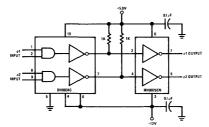

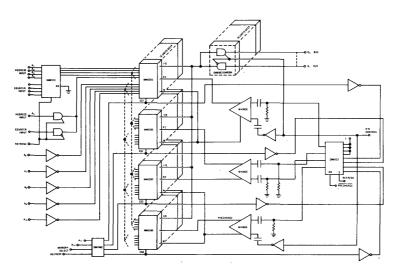

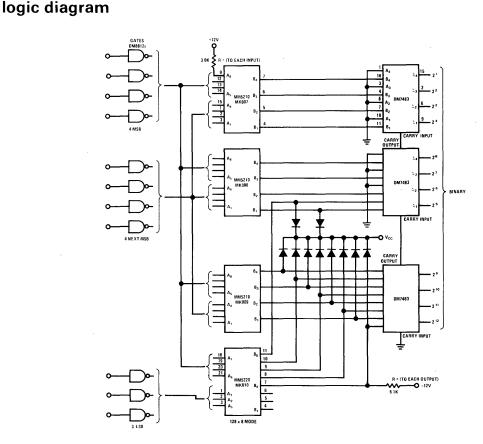

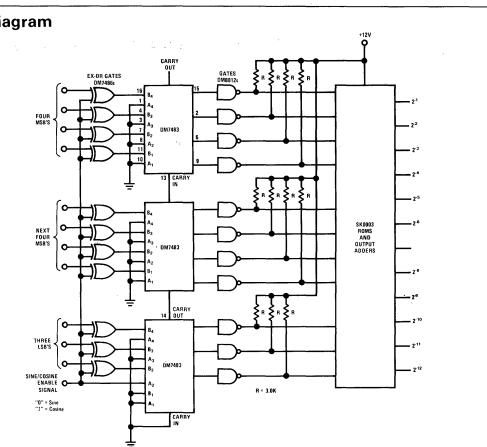

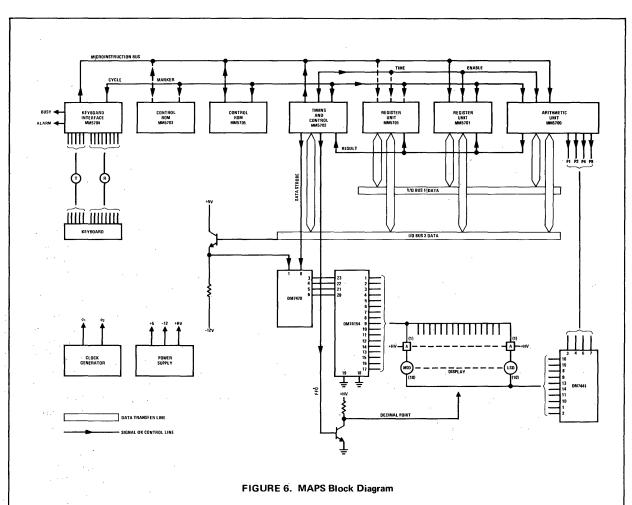

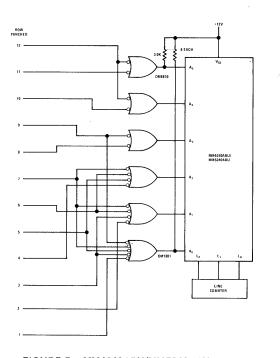

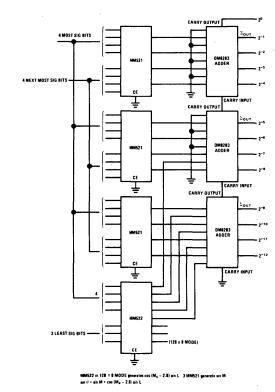

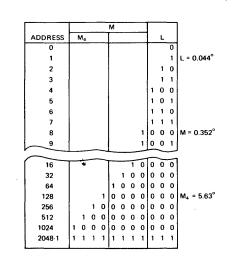

Microprogrammable Arithmetic Processor System devices (MAPS) are MOS/LSI elements that represents a general purpose serial data processor (see Figure 1). The system can be programmed to operate in binary or BCD up to a 76 bit one cycle data word. The system provides a wide variety of data word formating and is applicable to any serial arithmetic control system from machine and process control to business machines.

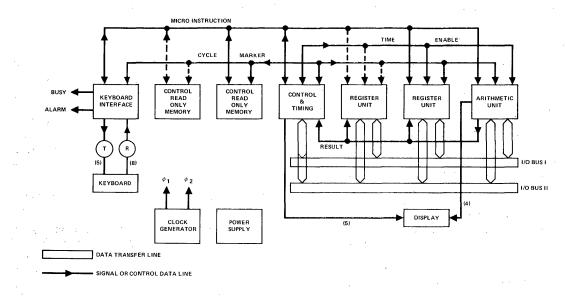

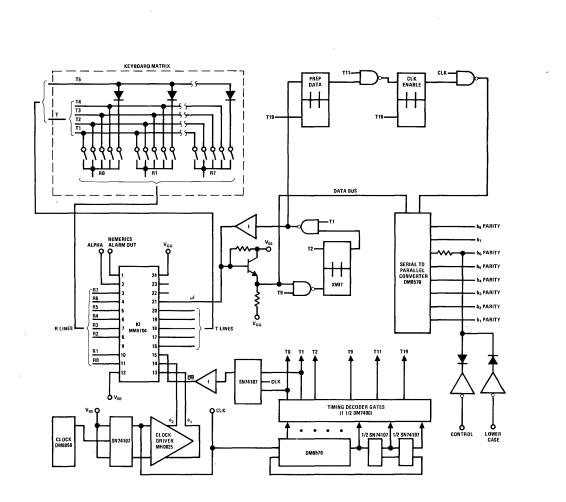

The basic system is comprised of five MOS/LSI sub-system elements:

MM5700 Arithmetic Unit

- MM5701 Register Unit

- MM5702 Timing and Control Unit

- MM5704 Keyboard Interface Unit

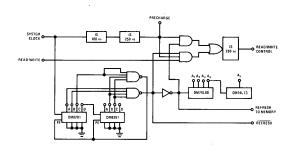

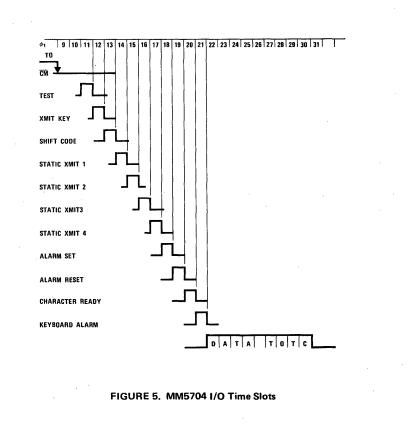

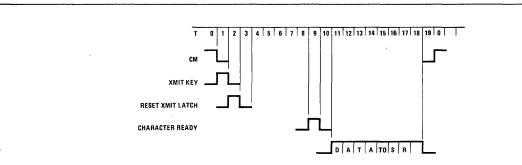

- MM5705 Control Read Only Memory