Art, Science, and Personalities

Edited by Jim Williams

## **Analog Circuit Design**

# Analog Circuit Design

## **Art, Science, and Personalities**

Edited by Jim Williams

Butterworth-Heinemann

Boston London Oxford Singapore Sydney Toronto Wellington

Copyright © 1991 by Butterworth-Heinemann, a division of Reed Publishing (USA) Inc. All rights reserved.

Paperback reprint 1994

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

Recognizing the importance of preserving what has been written, it is the policy of Butterworth-Heinemann to have the books it publishes printed on acid-free paper, and we exert our best efforts to that end.

Library of Congress Cataloging-in-Publication Data

Analog circuit design: art, science, and personalities / edited by Jim Williams p. cm. — (The EDN series for design engineers)

Includes bibliographical references and index. ISBN 0-7506-9166-2 (hard: acid-free) \$44.95 ISBN 0-7506-9640-0 (softcover) 1. Linear integrated circuits—Maintenance and repair. 2. Electronic circuit design. I. Williams, Jim, 1948–. II. Series TK7874.A548 1991 91-9930 621.381'5—dc20 CIP

British Library Cataloguing in Publication Data

Analogue circuits, Design

Williams, Jim 1948— II. Series 621.3815

ISBN 0-7506-9166-2

ISBN 0-7506-9640-0 (softcover)

Butterworth-Heinemann 313 Washington Street Newton, MA 02158-1626

Linacre House, Jordan Hill Oxford OX2 8DP United Kingdom

109876 Printed in the United States of America

Editorial, design, and production services provided by HighText Publications, Inc. Solana Beach, California.

For Celia, Michael, and Bonillas. These are my friends, and this is what we do.

Bob Widlar's contributions, albeit not received for this book, are acknowledged by all.

## Contents

Preface xi Contributors xiii

### **One Introduction**

| •••••• | ****************** | <br>••••• |

|--------|--------------------|-----------|

- 1. Barometers and Analog Design 3 Alexander Calandra

- Analogs Yesterday, Today, and Tomorrow, or Metaphors of the Continuum 5 George A. Philbrick

- 3. It's An Analog World—Or Is it? 15 Dan Sheingold

- 4. Is Analog Circuit Design Dead? 17 Jim Williams

### Two What Is Analog Design?

.....

- 5. On Being the Machine 23 Bernard Gordon

- 6. Reflections of a Dinosaur 31 Samuel Wilensky

- 7. Max Wien, Mr. Hewlett, and a Rainy Sunday Afternoon 43 Jim Williams

### Three The Making of an Analog Engineer

.....

- 8. True Analog Circuit Design 59 Tom Hornak

- The Story of the P2 (The First Successful Solid-State Operational Amplifier With Picoampere Input Currents) 67 Bob Pease

- 10. Propagation of the Race (of Analog Circuit Designers) 79 Jim Roberge

- 11. The Process of Analog Design 89 Rod Russell

- 12. Analog Design Discipline: A Tale of Three Diodes 93 Milton Wilcox

- 13. Should Ohm's Law Be Repealed? 99 Jim Williams

### Four Intuitions and Insights

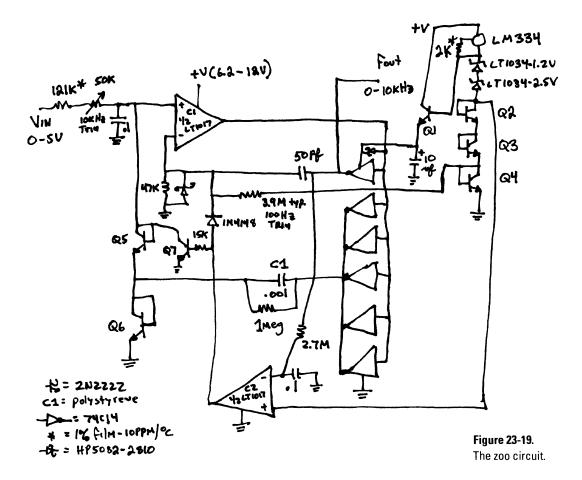

14. Good Engineering and Fast Vertical Amplifiers 107 John Addis 15. Understanding Why Things Don't Work 123 **Bob Blauschild** 16. Building Blocks for the Linear IC Designer: Linear Synthesis for Monolithic Circuits 127 A. Paul Brokaw 17. How to Design Analog Circuits Without a Computer or a Lot of Paper 149 Richard S. Burwen 18. Starting to Like Electronics in Your Twenties 169 George Erdi 19. Where Do Little Circuits Come From? 177 Barrie Gilbert 20. The Process of Analog Design 1**87** Garry Gillette 21. The Art of Good Analog Circuit Design—Some Basic Problems and Possible Solutions 193 **Barry Hilton** 22. My Approach to Feedback Loop Design 199 Phil Perkins 23. The Zoo Circuit: History, Mistakes, and Some Monkeys Design a Circuit 215 Jim Williams

### 24. Reality-Driven Analog Integrated Circuit Design 233 Derek F. Bowers 25. Current-Feedback Amplifiers 261 Sergio Franco 26. Analog Extensions of Digital Time and Frequency Generation 277 Garry Gillette 27. Some Practical Aspects of SPICE Modeling for Analog Circuits 299 E. J. Kennedy 28. Design of Crystal Oscillator Circuits 333 Robert J. Matthys 29. A Tale of Voltage-to-Frequency Converters (Ancient History) 349 **Bob** Pease 30. Op Amps and Their Characteristics 361 Dan Sheingold

Five Techniques, Tips, and Applications

Index 387

This is a weird book. When I was asked to write it I refused, because I didn't believe anybody could, or should, try to explain how to do analog design. Later, I decided the book might be possible, but only if it was written by many authors, each with their own style, topic, and opinions. There should be an absolute minimum of editing, no subject or style requirements, no planned page count, no outline, no nothing! I wanted the book's construction to reflect its subject. What I asked for was essentially a mandate for chaos. To my utter astonishment the publisher agreed and we lurched hopefully forward.

A meeting at my home in February 1989 was well-attended by potential participants. What we concluded went something like this: everyone would go off and write about anything that could remotely be construed as relevant to analog design. Additionally, no author would tell any other author what they were writing about. The hope was that the reader would see many different styles and approaches to analog design, along with some commonalities. Hopefully, this would lend courage to someone seeking to do analog work. There are many very different ways to proceed, and every designer has to find a way that feels right.

This evolution of a style, of getting to know oneself, is critical to doing good design. The single greatest asset a designer has is self-knowledge. Knowing when your thinking feels right, and when you're trying to fool yourself. Recognizing when the design is where you want it to be, and when you're pretending it is because you're only human. Knowing your strengths and weaknesses, prowesses and prejudices. Learning to recognize when to ask questions and when to believe your answers.

Formal training can augment all this, but cannot replace it or obviate its necessity. I think that factor is responsible for some of the mystique associated with analog design. Further, I think that someone approaching the field needs to see that there are lots of ways to do this stuff. They should be made to feel comfortable experimenting and evolving their own methods.

The risk in this book, that it will come across as an exercise in discord, is also its promise. As it went together, I began to feel less nervous. People wrote about all kinds of things in all kinds of ways. They had some very different views of the world. But also detectable were commonalities many found essential. It is our hope that readers will see this somewhat discordant book as a reflection of the analog design process. Take what you like, cook it any way you want to, and leave the rest.

Things wouldn't be complete without a special thanks to Carol Lewis and Harry Helms at HighText Publications, and John Martindale at Butterworth-Heinemann Publishers. They took on a book with an amorphous charter and no rudder and made it work. A midstream change of publishers didn't bother Carol and Harry, and John didn't seem to get nervous over a pretty risky approach to book writing.

I hope this book is as interesting and fun to read as it was to put together. Have a good time.

## Contributors

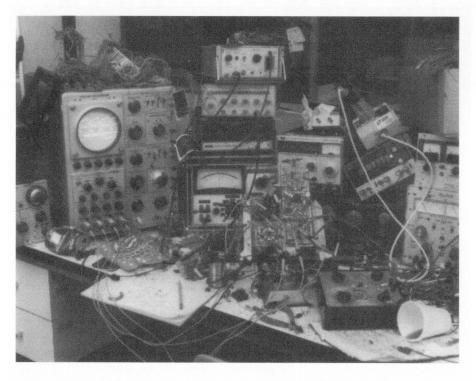

**JIM WILLIAMS** is the editor-in-chief of this book. In this role, Jim developed the basic concept of the book, identified, contacted, and cajoled potential contributors, and served as the "guiding light" of the entire project. Jim was at the Massachusetts Institute of Technology from 1969 to 1979, concentrating exclusively on analog circuit design. His teaching and research interests involved application of analog circuit techniques to biochemical and biomedical problems. Concurrently, he consulted U.S. and foreign concerns and governments, specializing in analog circuits. In 1979, he moved to National Semiconductor Corp., continuing work in the analog area with the Linear Integrated Circuits Group. In 1983, he joined Linear Technology Corp. as staff scientist, where he is presently employed. Interests include product definition, development, and support. Jim has authored over 250 publications relating to analog circuit design. His spare time interests include sports cars, collecting antique scientific instruments, art, and restoring and using old Tektronix oscilloscopes. He lives in Belmont, California, with his wife Celia, son Michael, a dog named Bonillas and 14 Tektronix oscilloscopes.

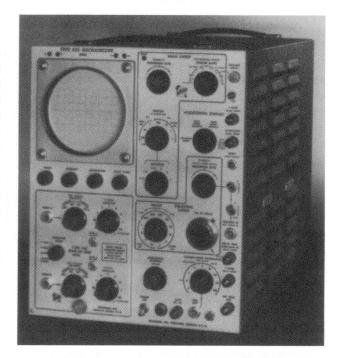

**JOHN ADDIS** received his B.S.E.E. from the Massachusetts Institute of Technology in 1963 and joined Tektronix that same year. His career at Tektronix has been spent in the design of various vertical amplifiers and pulse sources. The products John has engineered include the 1A7, 10A2A, 7A11, 485 vertical preamplifier, 7A29, and the analog paths of the 11A32, 11A34, and 11A52. He holds 14 U.S. patents, and was formerly responsible for analog integrated circuit design for high-speed oscilloscopes at Tektronix. He is now a consultant on analog design. John has traveled widely, including three trips to the Soviet Union and two to South America.

**BOB BLAUSCHILD** received his B.S.E.E. from Columbia University in 1971 and his M.S.E.E. from the University of California at Berkeley in 1973. He is also proud of his diploma from Ridgefield Memorial High School in New Jersey. Bob is currently manager of advanced analog development for Signetics, and has previously been an independent design consultant. He holds 12 patents in the area of analog circuit design, served ten years on the program committee for the International Solid State Circuits Conference, and is the author of numerous technical papers. His hobbies include running, visiting with old friends, coaching in the Special Olympics, and daydreaming of retirement on a warm beach.

**DEREK F. BOWERS** was born in Maesteg, Wales in 1954 and received a B.Sc. in physics and mathematics from the University of Sheffield in 1976. His first positions were with the University Space Physics Group and Triad Computing Systems. In 1978, he joined Precision Monolithics, Inc.'s U.K. division. In 1980, he transferred to Santa Clara as a senior design engineer. Since then he has held various positions within the company and is currently staff vice president, design. He has over thirty integrated circuit designs in volume production, including op amps, instrumentation amplifiers, audio products, and data conversion circuits. Derek has authored 35 technical articles and publications and holds ten patents. He is also a

### Contributors

senior member of the IEEE and a member of the Audio Engineering Society. In his spare time, he enjoys music and regards himself as a connoisseur of beer and exorbitantly spicy food.

**A. PAUL BROKAW** spent his early years investigating flashlight workings and disemboweling toasters. After obtaining his B.S. in physics from Oklahoma State University, he developed electronics for scientific satellites with Labko Scientific, Inc. He also worked with Arthur D. Little, Inc., as a circuit design consultant. In 1971, he joined Nova Devices, which eventually became the semiconductor division of Analog Devices. He has held several positions at Analog, generally related to design, and is now an Analog Fellow. He holds over 50 U.S. patents in such areas as analog-to-digital and digital-to-analog converters, references, amplifiers, and application-specific integrated circuits. He has published technical papers in several IEEE journals, and is an IEEE Fellow.

**RICHARD S. BURWEN** received a S.B. (cum laude) in physics in 1949 and an A.M. in engineering sciences and applied physics in 1950 from Harvard. He was one of the three founders of Analog Devices and worked as a consultant to the company, designing several of the circuits for its initial product lines. Other companies with which he was associated in their beginning phases have included Mark Levinson Audio Systems, Cello Ltd., and Novametrix Medical Systems. He became a founder of Copley Controls in 1984 and has designed many of the company's products. In the case of all companies he has helped start, Richard maintains his independence by working as a consultant from his own laboratory. His home in Lexington, Massachusetts is designed around his 20,000-watt, 169-speaker recording and reproducing studio. He continues independent research in digital audio.

**GEORGE ERDI** has been designing linear integrated circuits for a quarter-century. In the 1960s, he designed the first precision op amp and and codesigned the first monolithic digital-to-analog converter while at Fairchild Semiconductor. In 1969, he cofounded Precision Monolithics, Inc., and created such industry standards as the OP-07 and REF-01 analog circuits. In 1981, George was a cofounder of Linear Technology where he designed 30 new circuits, including the popular LT1012, LT1013, LT1028, and LT1078. He has also presented six papers at the International Solid-State Circuits Conference. In September 1988, *Electronic Engineering Times* cited George as one of the "thirty who made a difference" in the history of integrated circuits.

**SERGIO FRANCO** is a professor of electrical engineering at San Francisco State University, where he teaches microelectronics courses and acts as an industry consultant. Prior to assuming his current professorship, Sergio was employed at Zeltron, Zanussi's Electronics Institute (Udine, Italy). He received a B.S. in physics from the University of Rome, a M.S. in physics from Clark University, and a Ph.D. in computer science from the University of Illinois. Sergio is a member of the IEEE, and in his spare time enjoys classical music, gardening, and mountain hiking.

**BARRIE GILBERT** has spent most of his life designing analog circuits, beginning with four-pin vacuum tubes in the late 1940s. Work on speech encoding and synthesis at the Signals Research and Development Establishment in Britain began a love affair with the bipolar transistor that shows no signs of cooling off. Barrie joined Analog Devices in 1972, where he is now a Division Fellow working on a

wide variety of IC products and processes while managing the Northwest Labs in Beaverton, Oregon. He has published over 40 technical papers and been awarded 20 patents. Barrie received the IEEE Outstanding Achievement Award in 1970, was named an IEEE Fellow in 1984, and received the IEEE Solid-State Circuits Council Outstanding Development Award in 1986. For recreation, Barrie used to climb mountains, but nowadays stays home and tries to write music in a classical style for performance on a cluster of eight computer-controlled synthesizers and other toys.

**GARRY GILLETTE** received a B.S.E.E. from Stanford in 1961 and a M.S.E.E. from the University of California–Irvine in 1968. While a student at Stanford, his summer employment at Electro-Instruments Corp. in San Diego exposed him to a group of pioneer transistor circuit designers, leaving him with an indelible respect for intellectual honesty, highest technical standards, lightning empiricism, and the fun of creating something efficient and elegant. Since 1974, he has been employed by the Semiconductor Test Division of Teradyne, Inc., and is currently their manager of advanced technology. Garry holds several patents.

**BERNARD GORDON** is president and chairman of the board of Analogic Corporation, a high technology company specializing in the design and development of precision measuring instrumentation and high-speed computing equipment. He is the holder of over 200 patents worldwide in such fields as data converters, array processing computers, industrial controllers, diagnostic imaging, and automated test equipment. An IEEE Fellow, Bernard received the National Medal of Technology in 1986. He is also the founder of The Gordon Institute to enhance the leadership potential of engineers.

**BARRY HILTON** was born and educated in Britain and received a Higher National Certificate in Applied Physics from Kingston College of Advanced Technology. Early in his career, he was employed by Solartron Ltd. as a designer of digital voltmeters. In 1969, Analog Devices hired him to help design the first converter modules in Boston, and in 1973 Barry became director of engineering for Analog Devices. In 1975, he decided to establish his own design consulting company, A.I.M., Inc. Since that time, Analog Devices has kept him very busy as a consultant designing hybrid converters and numerous integrated circuits. In 1989, Barry established a second company, Acculin Inc., for the design and manufacture of very high speed analog integrated circuits. In his leisure time, Barry enjoys golf, swimming, traveling, and classical music.

**Tom Hornak** was born in Bratislava, Czechoslovakia. He received his Dipl.Ing. degree from the Bratislava Technical University and his Ph.D. from the Prague Technical University, both in electrical engineering. From 1947 to 1961 he worked in Prague at the Tesla Corp.'s Radio Research Laboratory and from 1962 to 1968 in the Prague Computer Research Institute. His work in Czechoslovakia involved development of television cameras, ferrite and thin film memories, high-speed pulse generators, and sampling oscilloscopes. In 1968, Tom joined Hewlett-Packard's Corporate Research Laboratory and is presently head of their high-speed electronics department. He is responsible for applied research of high-speed data communication circuits, high-speed analog/digital interfaces, and electronic instrumentation utilizing advanced Si and GaAs IC processes. Tom has published 50 papers and holds 40 patents. He has served as guest and associate editor of the *IEEE Journal of Solid State Circuits* and as chairman of the IEEE Solid State Circuits and Technology Committee. Tom has been named an IEEE Fellow.

### Contributors

**E. J. (ED) KENNEDY** received his Ph.D. in electrical engineering in 1967 from the University of Tennessee at Knoxville. Before joining the faculty of the University of Tennessee, he held positions at the Arnold Engineering Development Center and the Oak Ridge National Laboratory. Ed's research interests include nuclear instrumentation, strapdown gyroscope rebalance electronics, hybrid thick-film electronics, switching regulators, and analog integrated circuits. He was appointed Fulton Professor of Electrical Engineering in 1983, has been a Ford Foundation Teaching Fellow, and has received the NASA Commendation Award. Ed's books include *Operational Amplifier Circuits* (1988) and the forthcoming *Semiconductor Devices and Circuits*. He is married, has three daughters, and enjoys tennis, gardening, and growing roses.

**ROBERT J. MATTHYS** retired from Honeywell's Systems & Research Center in Minneapolis, Minnesota as a research engineer, and is still associated with the Center on a part-time basis. He has over 38 years of experience in optical, mechanical, and electronic design. He has written a book on crystal oscillator circuits, holds five patents (with two pending), and has published 17 technical papers. Among his other achievements of which he is proud are seven children and four grandchildren. His interest in crystal oscillators began when he was asked to design one, and found the reference articles disagreed with each other and some were even obviously wrong.

**PHIL PERKINS** is a Fellow of LTX Corp. in Westwood, Massachusetts. His work includes analog instrumentation and system design for the LTX semiconductor test systems. Most recently, he has developed test heads for the Synchromaster line of mixed-signal semiconductor test systems. Prior to co-founding LTX, Phil worked eight years at Teradyne, Inc. in Boston. He received his degrees in electrical engineering from the Massachusetts Institute of Technology. Phil's interests include local and national activities in the United Methodist Church, home computer hobbying plus consulting for friends, vegetable gardening, and bicycling. He lives in Needham, Massachusetts, with his lovely wife Laurie.

**BOB PEASE** graduated from the Massachusetts Institute of Technology in 1961 with a B.S.E.E. He was employed at George A. Philbrick Researches from 1961 to 1975, where he designed many operational amplifiers, analog computing modules, and voltage-to-frequency converters. Bob joined National Semiconductor in 1976. Since then, he has designed several ICs, including regulators, references, voltageto-frequency converters, temperature sensors, and amplifiers. He has written about 60 magazine articles and holds eight patents. Bob has been the self-declared Czar of Bandgaps since 1986, and enjoys hiking, backpacking, and following abandoned railroad roadbeds. He also designs voltage-to-frequency converters in his spare time. Bob wrote an award-winning series of articles on troubleshooting analog circuits which appeared in *EDN* Magazine in 1989, and which will be expanded into a book to be published by Butterworth-Heinemann. Bob currently writes a column about analog circuits which appears in *Electronic Design* Magazine.

**JIM K. ROBERGE** has been at the Massachusetts Institute of Technology since 1956, initially as a freshman and currently as professor of electrical engineering. In between, he received the S.B., S.M., and Sc.D. degrees in electrical engineering and held various research and academic staff appointments. His teaching and research interests are in the areas of electronic circuits and system design. Much of his research is conducted at M.I.T. Lincoln Laboratory and is involved with communications satellites. He is the author of *Operational Amplifiers: Theory and Practice*

and co-author of *Electronic Components and Measurements*. He has made a twenty-lecture video course entitled *Electronic Feedback Systems*. He has served as consultant to more than 90 organizations, and has eight patents awarded or in process. For recreation, he plays with his toys, which include a large collection of Lionel electric trains and a 1973 E-type Jaguar roadster.

**ROD RUSSELL** is president of Custom Linear Corp. He got turned on to analog electronics while serving in the U.S. Navy, where he repaired and maintained VHF and UHF transceivers. During his last semester at New Mexico State University, a professor fleetingly mentioned that an operational amplifier had just been fabricated in silicon. After obtaining his B.S., he joined Motorola Semiconductor and also obtained his M.S.E.E. from Arizona State University. He says the vast number of possibilities (some are called problems) in analog electronics is what makes it interesting.

**DAN SHEINGOLD** received his B.S. with distinction from Worcester Polytechnic Institute in 1948 and a M.S.E.E. from Columbia University in 1949. He then joined George A. Philbrick Researches as their second engineer (the other being George A. Philbrick). Dan eventually became vice president for marketing, and was present at the development of the world's first commercial differential plug-in operational amplifier, the vacuum tube K2-W. He also served as editor of *The Lightning Empiricist* while at Philbrick. In 1969, Dan joined Analog Devices as manager of technical marketing. He's currently involved in the writing and editing of their popular *Analog Dialogue* magazine, and has developed an extensive list of tutorial books on Analog's technologies and products, including such classics as *Analog-Digital Conversion Handbook* and the *Transducer Interfacing Handbook*. He was elected an IEEE Fellow in 1990. He and his wife Ann have two children, Mark (an engineer) and Laura (a physician). Dan enjoys music, walking, running, crosscountry skiing, and has an airplane pilot's license.

**MILTON WILCOX** has been interested in electronics since high school. He received his B.S.E.E. in 1968 and his M.S.E.E. in 1971 from Arizona State University. From 1968 to 1975 he was employed by Motorola as an analog design engineer designing consumer linear integrated circuits. In 1975, Milt moved to National Semiconductor where he was section head of an RF and video IC design group for over 14 years. He currently heads a small group designing new power control ICs at Linear Technology Corporation. Milt holds 25 patents, has authored seven technical papers, and continues to actively design.

**SAMUEL WILENSKY** was first exposed to Ohm's Law at the Massachusetts Institute of Technology, where he received his B.S.E.E. He did graduate work at the M.I.T. department of nuclear engineering, where his thesis project was the measurement of non-elastic neutron cross-sections using a pulsed neutron source (i.e., the Rockefeller Accelerator). Samuel was one of the founders of Hybrid Systems, now Sypex. During the early years of Hybrid Systems, he became—of necessity—an analog designer. His main efforts have been in the design of data conversion devices, with detours into consumer products. He recently used his nuclear training to study the effects of nuclear radiation on data conversion products. He enjoys playing pick-up basketball, sailing, coaching youth soccer, being embarrassed by his son and daughter on ski slopes, and supplying muscle for his wife's gardening.

## Introduction

Most books have a single introduction. This one has four. Why?

Analog circuit design is a very "personalized" discipline. To be sure, everyone's bound by the same physics and mathematics, but there's no single "right way" for those tools to be applied to solve a problem. Practitioners of analog design are noted for their individuality. Three of the four introductions that follow are by acknowl-edged masters of the analog art and deal with analog's place in a world that seems overwhelmed by digital electronics. Each of those three authors gives a highly personal viewpoint that can't be objectively proven "right" or "wrong," but that's the way it is in many aspects of analog design. The remaining introduction, which appears first, doesn't directly deal with analog electronics at all. However, it does illustrate the "matrix of thought" that so many successful analog designers bring to their efforts.

Analog design is often less a collection of specific techniques and methods than it is a way of looking at things. Dr. Calandra's thoughts originally appeared in the January, 1970 issue of "The Lightning Empiricist," then published by Teledyne Philbrick Nexus, and is reprinted by permission of Teledyne Corporation. We don't know if the student described ever became interested in analog electronics, but he clearly had all the necessary attributes of a good analog design engineer.

The name of George Philbrick will be invoked several times in this book, and in each instance some awe and reverence is noticeable. This is because if contemporary analog design has a founding father, it would have to be George Philbrick. Many of the top names in the field today either worked under or were influenced by him. Although he passed away several years ago, his wisdom is still relevant to many current situations. Here's a sample from the October 1963 issue of "The Lightning Empiricist," published by the company he founded, Teledyne Philbrick. We're grateful for the company's kind permission to reprint the following, since it's difficult to imagine a *real* guide to analog design without George Philbrick!

Let's face it: analog electronics isn't very sexy these days. The announcement of a new microprocessor or high-capacity DRAM is what makes headlines in the industry and business press; no one seems to care about new precision op amps or voltage-to-frequency converters. Sometimes it seems if digital electronics is the only place in electronics where anything's going on. Not so, says Jim Williams, as he tells why analog electronics is more than still important—it's unavoidable.

Dan Sheingold's essay originated as a letter to the editor of *Electronic Engineering Times*. In its original form (with a slightly different message), it appeared on December 4, 1989. Often electronics engineers draw clear distinctions between "analog electronics" and "digital electronics," implying clear barriers between the two disciplines that only the very brave (or very foolish) dare cross. However, as Dan points out, the differences between them might not be quite what we think.

Introductions are normally read before the rest of the book, and so should these. But you might want to return and read them again after you've finished this book. It's likely that you might have a different reaction to them then than the one you'll have now.

## 1. Barometers and Analog Design

Some time ago I received a call from a colleague, who asked if I would be the referee on the grading of an examination question. He was about to give a student a zero for his answer to a physics question, while the student claimed he should receive a perfect score and would if the system were not set up against the student. The instructor and the student agreed to an impartial arbiter, and I was selected. I went to my colleague's office and read the examination question: "Show how it is possible to determine the height of a tall building with the aid of a barometer."

The student had answered: "Take the barometer to the top of the building, attach a long rope to it, lower the barometer to the street, and then bring it up, measuring the length of the rope. The length of the rope is the height of the building."

I pointed out that the student really had a strong case for full credit since he had really answered the question completely and correctly. On the other hand, if full credit were given, it could well contribute to a high grade in his physics course. A high grade is supposed to certify competence in physics, but the answer did not confirm this. I suggested that the student have another try at answering the question. I was not surprised that my colleague agreed, but I was surprised that the student did.

I gave the student six minutes to answer the question with the warning that the answer should show some knowledge of physics. At the end of five minutes, he had not written anything. I asked if he wished to give up, but he said no. He had many answers to this problem; he was just thinking of the best one. I excused myself for interrupting him and asked him to please go on. In the next minute he dashed off his answer which read:

"Take the barometer to the top of the building and lean over the edge of the roof. Drop the barometer, timing its fall with a stopwatch. Then using the formula  $S = 0.5 at^2$ , calculate the height of the building."

At this point, I asked my colleague if he would give up. He conceded, and gave the student almost full credit.

In leaving my colleague's office, I recalled that the student had said he had other answers to the problem, so I asked him what they were. "Oh, yes," said the student. "There are many ways of getting the height of a tall building with the aid of a barometer. For example, you could take the barometer out on a sunny day and measure the height of the barometer, the length of its shadow, and the length of the shadow of the building, and by the use of simple proportion, determine the height of the building."

"Fine," I said, "and the others?"

"Yes," said the student. "There is a very basic measurement method you will like. In this method, you take the barometer and begin to walk up the stairs. As you

Reprinted with permission of Teledyne Components.

climb the stairs, you mark off the length of the barometer along the wall. You then count the number of marks, and this will give you the height of the building in barometer units. A very direct method.

"Of course, if you want a more sophisticated method, you can tie the barometer to the end of a string, swing it as a pendulum, and determine the value of g at the street level and at the top of the building. From the difference between the two values of g, the height of the building, in principle, can be calculated.

"Finally," he concluded, "there are many other ways of solving the problem. Probably the best," he said, "is to take the barometer to the basement and knock on the superintendent's door. When the superintendent answers, you speak to him as follows: 'Mr. Superintendent, here I have a fine barometer. If you will tell me the height of this building, I will give you this barometer.'"

At this point, I asked the student if he really did not know the conventional answer to this question. He admitted that he did, but said that he was fed up with high school and college instructors trying to teach him how to think, to use the "scientific method," and to explore the deep inner logic of the subject in a pedantic way, as is often done in the new mathematics, rather than teaching him the structure of the subject. With this in mind, he decided to revive scholasticism as an academic lark to challenge the Sputnik-panicked classrooms of America.

# 2. Analogs Yesterday, Today, and Tomorrow, or Metaphors of the Continuum

It was naturally pleasurable for me to have been approached by the Simulation Councillors to write an article, substantially under the above super-title, for their new magazine. This euphoria persists even now, when my performance has in fact begun, and is only moderately tempered by the haunting suspicion of what their real reason might have been for so honoring me. It certainly could not be because my views on analog computing and simulation are somewhat eccentric in relation to much of the contemporary doctrine, although I accept and actually relish this characterization. It could conceivably be in recognition of my relatively early start in the field of electronic analog technology; this again is not denied by me, but here we may have found the clue. The fact that I began a long time ago in this sort of activity doesn't mean at all that I am either oracle or authority in it. The truth of the matter is subtler still: it only means that I am getting old. So we have it out at last. They are showing respect for the aged. Here then, steeped in mellow nostalgia, are the musing of a well-meaning and harmless Old Timer.

Since truth will out, I might as well admit immediately that I do not claim to be the original inventor of the operational amplifier. It is true, however, that I did build some of them more than four years before hearing of anyone else's, and that their purpose was truly simulative. These amplifiers were indeed DC feedback units, used to perform mathematical operations in an analog structure, but the very first such amplifier *itself* began as a model builder, even at that stage, loomed larger than my possible role as an inventor, and I have been dealing continually with models and analogs ever since. Hereafter in this context I shall not speak of what I may have invented or originated, and in fact shall not much longer continue in the first person singular. By the same token I shall make no pretense in this article of assigning credit to other individuals or to other institutions. There are far too many of both, hundreds and thousands, stretching from this point back into history, to give any accurate and fair account of the brainpower and perspiration which have made analog computing what it is today, without leaving out many who have put vital links in the chain.

While electronic analog equipment, using this phrase in the modern sense, certainly existed in the thirties, and in the forties became available on the open market in several forms, its roots really went still further back in time. It is doubted that a completely exhaustive chronology of the contributory precursor technologies could ever be produced, let alone by one amateur historian. Nothing even approximating such a feat will be attempted, but it is hoped that an outline of the tools and techniques which were on hand in the previous era will show that the ingredients were already there, and that the modern analog machine was almost inevitable. As is usual in such surges of progress, several fields of science and engineering over-

Reprinted with permission of Teledyne Components.

lapped to breathe life into this department. Among others were Physics and Scientific Instruments, Communications and Electronics, Controls and Servomechanisms, Mathematics, and Aeronautical plus Electrical plus Mechanical Engineering. It is recognized that these fields are not mutually exclusive, and that each realm constitutes a multidimensional cross-section which has interpenetrated the other realms enumerated.

There is one thread, come to think of it, which appears to run through the whole background of the analog doctrine, and which may be said to belong to it more intrinsically that it does to the other major branch of computation; that thread is *feedback*. It will appear again frequently in what follows.

The clearest anticipation of analog machines was in the differential analyzer. This primarily mechanical device could handle total differential equations at least as well as we can now, and in some ways better. One such analyzer afforded automatic establishment of its interconnections and parameters, tape storage of these data, and automatic readout: both numerical and graphical. Although slower than newer electronic equivalents, nonetheless for a 19-integrator problem which was run on it in 1945, a thoroughly non-linear problem by the way, the analyzer time scale was only twice as slow as the real scale for the remotely controlled glide vehicle which was being simulated. The disc integrators of this machine were things of beauty, with accuracies approaching, and resolution exceeding, 5 decimals. They could integrate with respect to dependent variables, thus enabling multiplication with only two integrators, logarithms without approximation, and so on. Integrators of this same general type were also applied in astronomical and military computing devices, in which less elaborate but still legitimate differential equations were embodied and solved. This sort of equipment inspired many of the electronic analog devices which followed, as well as the digital differential analyzers which have come much later. Although the electronic integrators of analog equipment prefer time as the direct variable of integration, they have shown extreme flexibility of operating speed. One imagines the mechanical discs of the older analyzers running at millions of rpm trying to keep up with their progeny!

The disc integrators of the differential analyzer worked without feedback, as did its other basic parts. Where then did feedback appear in these analyzers? In the differential equations acted out within it. Any equation requiring solution involves at least one causal loop. But for feedback in its more exuberant forms we nominate the next discipline to be considered, namely automatic controls.

Regulatory mechanisms such as those which are found in industrial control systems have been around for a long time. Roughly in historical sequence, they have been mechanical, hydraulic, pneumatic, electric, and electronic. Translating as they do from the unbalance or error in a controlled condition to the manipulation which is intended to reduce that unbalance, they close a feedback loop which includes some sort of plant. In typical cases these mechanisms have embodied mathematical laws with continuous fidelity, and in order to attain fidelity they have resorted to internal feedbacks precisely analogous to those employed in a modern amplifier. It may not be widely known, particularly among the younger computing set, that this sort of local feedback was applied in standard controller mechanisms of the twenties and even earlier. These antecedent regulatory devices qualify as DC feedback and even null-seeking at two distinct levels, and with mathematical capabilities, it is not difficult to trace the logical paths of evolution from these devices to analog computing as it is now enjoyed. Furthermore it is not uncommon in the thirties to build simulators embodying convenient models of plants, into which the real regulatory mechanism could be connected. Both developmental and educational purposes were served by these structures, just as with simulators today. The next stage, in which the real control mechanisms were replaced by models, permitted the whole loop to be electronic and hence vastly more flexible and greatly accelerated. In simulators of this sort, several plants might be interconnected under control, so that the newer stability problems thus encountered could be studied conveniently. Again, plants with multiple inputs and outputs having internally interacting paths were included, and regulatory loops in hierarchies where master controls manipulated the desired conditions of subordinate controls, all could be simulated in an analog. Note the ascending succession of feedback loops, which are most dramatically represented in control systems of this sort: within amplifiers to attain promptness and stability; locally around amplifiers to give the desired mathematical performance for regulatory mechanisms; in control loops to promote the minimum difference between desired and existing conditions; in more comprehensive control loops which include complete but subordinate loops in cascade; in still more comprehensive loops for supervisory or evaluative purposes; and finally in the experimental design and optimizing operations, using models or computational structures to evolve most effective system operation.

Servomechanisms are also part of the lore which preceded and inspired the modern analog machines. Though not as old as the governors, pressure regulators, and controllers of temperature, flow, level, etcetera of the last paragraph, servos as positional followers were functionally similar as regards control philosophy and feedback loops. Further, being more modern, they benefited from the increasingly mathematical technologies of development and design. Perhaps most relevant was the simultaneity and parallelism between servo theory and that of feedback amplifiers in communications. Stability criteria for the latter were seen as applicable to the former, at least in the linear realm. Analysis in the frequency domain, a natural procedure for linear communications equipment, was carried over rather directly to servomechanisms. This debt has since been partially repaid, as servomechanisms have helped to furnish nonlinear analog elements and other items in computing equipment for the study of nonlinear phenomena, generally in the time domain, as they occur in communications and elsewhere. Thus do the various doctrines and practical disciplines feed on each other to mutual benefit, and (if you will forgive the liberty) feedback sideways as well as back and forth.

We pick up servomechanisms again, much further back along the trail, and usually in relatively low-performance embodiments. Though scientific instruments do practically everything today, including computation, synthesis, manipulation, and regulation, on every scale, they were once used principally for measurement, in the laboratory or the observatory. For accurate measurement it was found that feedback methods, when possible, were surpassingly effective. While the underlying philosophical reasons for this circumstance are of vital importance, we shall take them here on faith. Note, however, that the observation of balance in a measurement, and the manipulation which may be made to achieve balance, is still a feedback process even if done by a human agency. The slave can be the experimenter himself. Precise weighing with a beam balance may stand as a clear example of this procedure, but a myriad of others may readily be spread forth. Succinctly, the process is reduced by feedback to dependency on only one or a few reliable elements. Automation of the loop-closing, null-seeking action merely replaces one slave by another. In this light the venerable self-balancing slidewire potentiometer recorder stands with the latest feedback operational amplifier, and so we see yet another plausible path from then to now.

Antedating but partly anticipating the development of active analogs was the use

### Analogs Yesterday, Today, and Tomorrow

of models which depended much more directly on the analogies between phenomena as they appear in widely differing physical media. Of main concern here are those cases in which the modelling medium has been electric, but quite accurate and articulate models have also been mechanical and hydraulic, and many of these are hoary with age indeed. Ever since accurate and dependable circuit elements have been available, and this has been for many decades, notably for resistors and capacitors, highly successful passive models have been built for the study and solution of such problems as those which occur in heat conduction. Dynamic as well as steady state phenomena may be handled, often in the same model. Again, vibrations have been studied with direct models having all three kinds of circuit element, plus transformers. Furthermore very large and complete simulative structures, called network analyzers and based heavily on passive elements, were used in particular forthough not limited to-AC power distribution and communication lines. Even today one finds such continuous conductive models as electrolytic tanks still in use and under development. Many of these tools have specialized capabilities which are hard to match with the more familiar sort of modern apparatus. The similitude conditions and principles which accompanied and abetted the application of such models have been carried over to, and guided the users of, the newer computing means. It should be added that the very demanding doctrines of "lumping," which must take place when continuous systems are represented by separate but connected analog operations, are substantially unchanged as compared to those in passive models. Here is another branch of knowledge and effort, then, to which we own recognition as contributing to present day simulation and computing.

From a different direction, in terms of need and application, came another practical model-building technique which is woven into the analog fabric which surrounds us today. This one is straight down the simulation highway; we refer to trainers of the sort used for many years to indoctrinate pilots of aircraft. These trainers modelled just about everything except nonangular spatial accelerations. They presented, to a human operator, a simulated environment resembling the real one in many important ways, as regards his manipulations and the responses returned to him as a consequence thereof. Of course the later counterparts of the first training aids have become tremendously more refined, and similar structures have been adapted to other man-machine collaborations, but the inspiration to analog enthusiasts on a broader scale seems rather obvious. Here was an operative model, in real time and undelayed, where to the sensory and motor periphery of the trainee the real environment was presented in a safe and pedagogically corrective atmosphere. Now it is true that training devices for physical skills are even more numerous today, and analog simulative equipment finds important applications in these, but a somewhat extended simile might be in order. For system design in its larger implications we are all trainees; analog simulation to teach us how a proposed system might work when at least part of it is new, to guarantee safety if we try out a poor idea, and to offer peripheral communication at the deliberative level, projects the trainer concept to an advanced modern setting. The task of simulating the trained pilot and even the learning pilot, or other human operators, provided a challenge which has been partly met, and which is still relevant. Simulating the system designer, as a logical extension, leads as far as you might care to travel.

### Overlook

Things are looking up all over for the analog profession. Substantially every branch of engineering now applies analog computing equipment: in theory, experiment,

### **George A. Philbrick**

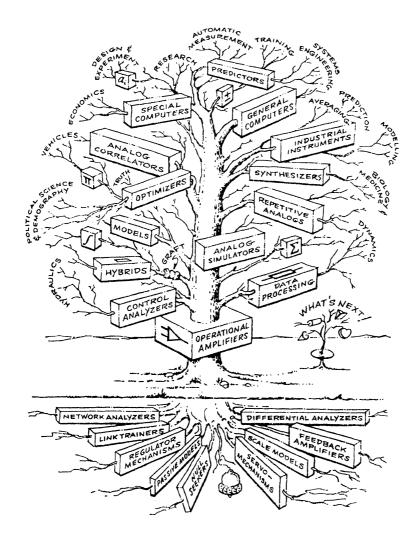

#### Figure 2-1.

This was George's vision of the mighty analog tree. It remains relevant almost three decades later. Courtesy of Teledyne Components.

design, manufacture, and test. Applications are even on the increase for scientific research, where in a sense such equipment began. We shall not try to list the many embodiments and applications in this text, but have included some of them in a figure to be found nearby, which has been prepared to bear out the morphology of our burgeoning field.

Analog representation in terms of modern apparatus is a far cry from scale models, but the model concepts still seem incomparably fruitful. In direct models, which retain the physical medium of their prototypes, scaling is the biggest part of the game. Similitude conditions must be faithfully adhered to, and an appreciation of these conditions imparts a feeling for models which is never lost. Actually the use of direct scale models has not decreased, and is still a powerful technique in such areas as hydraulics and structures: natural and man-made. Much ingenuity has been lavished on such models; they must by no means be looked down upon by the users and designers of more fashionable modelling items.

In a scale model the transformation of dimensions is typically direct and simple, especially if shape is preserved. Even when the scaling involves distortions of shape, such as relative compression and bending, the transformations generally carry distance into distance, velocity into velocity, and so on, with only numerical

scale factors relating them in pairs. Basic parameters, when the scale ratios are properly assigned, turn out to be numerical, and apply equally to model and to prototype. This doctrine, whereby characteristic system parameters are dimensionless, is applicable to all modelling procedures. The transformation concept, so clear and concise for scale models, carries over with little confusion to modelling in which the physical form is changed, and ultimately to electronic analogs where transformation includes transmogrification. The scale ratios in general, however, are no longer numbers, but the basic parameters may be. This sort of introduction is recommended for physicists and applied mathematicians who may be coming suddenly into modern analog contacts, since it utilizes some of the ideas and precepts, however badly expressed here, of the more classical fields.

Another sort who is momentarily taken aback by the liberties permitted in analog models is typified by an engineer who has been too long away from the time domain. Often brought up, pedagogically, on linear systems and frequency analysis, he (or she) may even be suspicious of a mechanism which gives solutions as functions of time, perhaps not realizing that it will provide amplitude and phase spectra as well if one merely applies a different stimulus to the same model structure. It is frequently worthwhile, in these cases, to introduce the analog from the viewpoint of the frequency domain, shifting later from the familiar to the strange and magical. Oddly enough, the most confirmed practical and the most profoundly theoretical of engineers will both be found to favor the time domain, with or without computing equipment. In the former case this is by virtue of convenience in handling real equipment, and in the latter it is since—among other reasons—he finds it better to approach nonlinear problems in the time domain than in the frequency domain.

Analog engines have not always been as respected as they are now becoming. Analogy itself we have been warned against, in proverb and in folklore, as being dangerous and requiring proof. Parenthetically, this is good advice. Simulation has had connotations of deceit, empiricism of quackery. It was stylish, even recently, to say that the only good electronics is that which says Yes or No. There is nothing to be gained in disputing these allegations, least of all by excited rejoinder. The continuous active analog is in its infancy, and time is (literally) running in its favor.

Time as an independent variable, given at low cost by Nature, has the advantage of nearly, if not actually, infinite resolution. This continuity, coupled with the continuity of voltage and charge, leads to the ability to close loops at very high frequency, or with short time intervals. As a consequence one may approach the ideals of differentiability which are inherent in the infinitesimal calculus, which postulates the existence of a continuum. While most contemporary analog apparatus does not press these limits, it is comforting to know that there is room left to maneuver in.

In modest applications to on-line measurement and data-processing, it is quite generally conceded that the advantages of continuous analog apparatus make it irresistible. This is partly owing to the simplicity and speed which its continuity makes possible, and partly to the fact that almost every input transducer is also "analog" in character, that is to say continuous in excursion and time. Storage and sampling, for example are frequently unnecessary in such applications, as in many others. When we turn from simpler to more involved data processing, to ambitious simulation, or when in general we pass from modest to more pretentious computations, there has been some feeling that digital means should automatically be substituted, especially if funds are available. In this connection we should like to quote, on the other side of the argument, no less a figure than Dr. Simon Ramo, writing on Systems Engineering in a collected volume called *Parts and Wholes* (edited by Daniel Lerner; Macmillan, New York, 1963). The following is admittedly taken out of context:

Digital computers, however, cannot be used conveniently or efficiently to obtain answers to all of the problems. In some cases, even they cannot solve the equations in any reasonable time, and in other cases the problems are not understood well enough for satisfactory mathematical formulation. Under these circumstances we can often turn to analog, real-time, simulation devices to predict the behaviour of the system. No engineering computing center is well equipped without such devices.

One should certainly be happy to settle for this, even though the text continues in a discussion of other kinds of equipment than analog with which the latter may be associated. Only the most hard-shelled of analog champions would suggest that all simulative and computational equipment be undiluted by numerical or logical adjuncts. Certainly many of the best known individuals and organizations in the analog field are now willing and able to talk about hybrids. This term, by the way, is too broad to have much meaning at this stage of the game. Is an analog apparatus hybridized by adding a digital voltmeter? The possibilities are far too numerous. The present treatment does not even contemplate giving a complete account of analog computing machines themselves, let alone the combination they may form with other machines. A large and growing library of good books cover these areas quite completely. Many of these are written by officials of the Simulation Councils, who typically have the sort of university connections which should give them appropriately unbiased viewpoints: viewpoints which a mere company man can only envy. Perhaps, however, an example or two might be appended here which will amuse and even edify.

At a large Eastern university, under the guidance of a well-known and gifted computationalist, a successful project has been reported on whereby the scaling for an analog installation is done entirely by rote on a digital machine. No guessing or trial runs at all are involved. Straight from the equations, the digital solution dictates the analog settings which will bring the maximum excursion of every variable analog voltage to within 20% of the limiting value. Local wags thus proclaim the discovery at last of a practical contribution by the digital apparatus. Seriously, they enjoy the ability to "get at" the solutions of the analog during operation.

Some analog men, perhaps over-fond and defensive as regards continuous functions, really believe that analog operations are generalizations of digital ones, or that conversely digital operations are special cases of analog ones. What can be done with such people? They depreciate the importance of the fact that discrete measurescales approach continuity in the limit, alleging that infinite processes are already tacit and available, without passing to the limit, in an analog variable. Pointing for example to analog selector circuits which can pick out and transmit whichever of a set of variables is algebraically the greatest of the least, they cite this capability as broader than the logical sum or the logical product, amounting in fact to infinitelymany-valued logic. Selectors followed, for example, by bounding operations serve directly in the rudimentary case of two-valued logic. On the basis of such reasoning it is surprising, the argument runs, that analog apparatus is not permitted to make decisions for itself. It is hard to answer these arguments, especially when dealing with confirmed analog partisans. When cornered on some point of superior digital accomplishment, they simply claim the whole digital province as part of their analogs.

Predictions are scheduled for the Tomorrow part of this article, but one such properly belongs here. While it is agreed that analog and digital techniques will increasingly cross-fertilize and inter-relate, it is predicted that the controversy between their camps will rage on, good natured but unabated, for years to come in spite of hybrid attachments. The serious issue of reliability has recently arisen as

between the two ideologies referring for example to instruments for interplanetary exploration. It is preferred here to avoid an opinion of judgment on this very important issue, but it is suggested that others similarly withhold judgment. At all costs we must not go down the wrong road. There are quite powerful and rational and experienced brains in which the reliability vote would be cast for analog, or at least against the exclusion of continuous variability. We must cooperate in a dispassionate but devoted study to determine the likeliest facts and fancies in this affair. If one believes that Nature is ahead in reliability, and there would appear to be justification for this belief in recognition of the redundancy, repairability, and adaptability of animal organisms, then conclusions may follow which are based on how one views such organisms. It has been standard practice to view the details of animal nervous systems as evidence that they are digital, but there are major reasons to question this.<sup>1</sup> The central nervous system itself seems digital to digital men, and analog to analog men. If it is both, then it is more intimately and profoundly intermingled hybrid than any of the artificial structures which have come to light. One thing is pretty sure, and that is that the brain builds models. We are in good company.

Back on reliability, at least in the sense of predictability, there is a duality to be noted in the relation between analog and digital techniques. If one must predictably manipulate an imperfectly accessible entity, he may proceed by arranging a discrete set of states for that entity, then transmit a prearranged number of command signals to it. Alternatively, with a nonquantitized feedback indicating the state of the entity, one commands changes outwardly by whatever means until the desired state is shown to have been attained. What one achieves by quantitizing, the other does by feedback. This is oversimplified, and does not immediately enable an evaluation of reliability. For the moment, it is only a point in (practical) philosophy, but as with many other continuous/discrete instrumental relations it is reminiscent of the wave–particle dualism.

### Auguries

It has been predicted above that the analog-digital struggle will persist, and this will mean some wear and tear as the proponents contend, but on balance such contention will probably be beneficial since it will assure that the maximum potential of each technique will be realized. As to some mixtures, all the obvious ones will soon be seen somewhere. More intimate mixtures, which might offer something approaching universal applicability, will depend on the appearance of new instrumental tools. But also note that urgent needs provide as potent a force for development as does the availability of new and startling techniques. Hasty prediction from either angle would be hazardous; certainly anything specific on our part would be irresponsible as well as foolhardy. There do seem to be possibilities, however, in recognition of the ability of continuous analog instruments to operate quickly and smoothly in closing feedback loops, plus the abitrary accuracy and permanency of discrete processes. Graphical computation may give a clue of sorts here, since anyone who deals with geometrical plots is prone to appeal alternately to continuous criteria and to numerical coincidences in calibration. Coordinates in general may have both of these meanings simultaneously. Are they any better than we are?

As to analogs themselves, it is evident that some forms of instrument, though not all, will become progressively smaller and handier in solid state incarnations. It is

<sup>1.</sup> R.W. Jones, Science 140, 3566 (1963). See also the companion article by J. S. Gray.

also evident that optimizing and search operations will be made increasingly automatic, as the deliberative functions of the user are encroached on more and more by deliberately imposed autonomous controls. But one of the principal lessons from the past is that substantially all the earlier techniques will continue to be used, and will grow and improve horizontally. Possibly you have a slide rule in your pocket, though admittedly you may have turned in your abacus for a desk calculator. All the older apparatus of the above section on origins are in current usage, and will continue so. As an example may we consider passive models?

It would be a big surprise if passive electric models do not expand in application and in technical excellence. More adept peripheral instruments, to drive and to measure them, are either in the cards or on the table. Passive circuit elements, adjustable as well as fixed, are gradually but surely improving as to accuracy, bandwidth, and stability. In this category are included not only resistors and capacitors, and less insistently inductors and transformers, but also certain nonlinear elements. A combination of compensation and regulation can cut the parametric effects of temperature down to size, especially with the advent of flexible devices for thermoelectric heat pumping. Relatively little work has been done on passive networks for model building, even for linear systems, compared to that expended for communications. The challenges introduced in the nonlinear cases are considerable, but with newer analytical techniques and instrumental tools it would be unwise to put limits on what might be accomplished. Part of the lure is that many biological structures appear to have been designed along these lines, though not of course without active adjuncts.

Another trend which is evident, and which will probably gain in momentum, is that of the unification of assorted instrumental techniques based on analog feedback operations. When it is considered how fundamental is the function of the operational amplifier, and how its benefits are continually being rediscovered in new fields of technology, it seems likely that multipurpose modular structures will perform the tasks of a number of specialized measuring and manipulative instruments. Beyond its classical and celebrated mathematical operations, comprising addition, algebraic and functional inversion, linear combination, differentiation, integration, etcetera, are the abilities to store and to isolate, among a number of others which are less well known. Since it is well known, on the other hand, where information of this kind is available, there is no need or propriety to elaborate here on the application of this basic tool. However, the philosophy of this sort of amplifier as an electrical nullseeking or balancing agent carries its own impact once it is understood. When basically similar methods and equipment are found to be effective in each, such fields as computing, data processing, testing, regulation, and model building will not be kept separate, but will diffuse and perhaps ultimately fuse with one another. One key to the future appears to lie in the quasi-paradox of special-purpose instrumental assemblages based on general-purpose analog modules.

Systems engineers are coming along now in greater numbers and of higher average caliber, and they are not now so brutally divided into disparate camps of practical and theoretical people. More mutual respect, at least seems to obtain between these two sides of the track. Analog models will be increasingly resorted to by both groups in studying the formidable problems of system engineering they must attack. It is getting around generally that the modelling approach may best be taken in stages. Not only should subsystems be separately modelled and carefully confirmed, but a given model need not represent all the aspects of a given subsystem or system at once. Linear approximations usually represent only a crude beginning, but may be confirmed by relatively simple analysis. Nonlinear models are harder to build but much harder to analyze, so that frequently the approach to nonlinear structures

### Analogs Yesterday, Today, and Tomorrow

should begin with drastic approximations to the nonlinear features, which are refined in stages as the project develops. Each step should be simple and well defined, with continual checking of the assumptions, and of those portions which are assumed to be complete, before forging ahead. Of course the parallel development of rudimentary overall models is in order if it is understood that they should be taken with a grain of salt: they may impart some idea of the flavor of the final concoction. Aspects of a system suitable for separate analog study will depend on the nature of the system; this is the age of broadness of system definition, extending even to all of Society. Taking such a case, one might study population density, political stability, wealth and commerce, considering these somewhat independently before they are all joined in one model. Again, the study in each case might be from the viewpoints of transients, or cycles, or statistics (possibly introducing random perturbations from independent sources). Still further, the item of interest might be tolerance to parametric changes, transitions from one regime to another, extrapolations backward and forward in time, and so on. But my prognostications have turned into a ramble.

As an offshoot of specialized training applications, analogs should find growing applications to pedagogy of a more general kind. This is partly owing to the personal experience which the subject may be afforded, but also to the interest which is induced by living analogies. The speed at which dynamic models may be operated is another factor in maintaining interest, and in saving time as well. If fast repetitive operations are employed, an introductory step may involve slower demonstrations, better to enable the mental transformation of time scale. Block diagrams or signal flow graphs become immediately more meaningful if tangible analog apparatus is made available to fulfill them. The innate property of causality, for example, is given memorable and dramatic emphasis. Feedback is of course the big thrill to the innocent in its general framework, along with its embodiment in differential equations, automatic controls including servomechanisms, and vibrations.

Models and analogs, even as concepts, are powerful teaching means in any case. Symbols themselves are rudimentary analogs, striving close to reality in mathematical operators. Words and languages are analogs right down to the ground. Physicists think and talk in models, the very best of them saying that models are their most powerful tools. Similitude conditions apply equally to all physical phenomena, along with dimensional analysis, so called. The unification of a set of properties in one structure, suggestive of an underlying organization and beauty, gives power and appeal to the model concept in the education of students: and students we all should remain, every one. So we close with a student's recollection.

Emerging many years ago from the old Jefferson Physical Laboratory at Harvard, one could read on the Music Building opposite, cut into the stone under the eaves, an inscription which should still be there:

To charm, to strengthen, and to teach, These are the three great chords of truth.

## 3. It's an Analog World—Or Is It?

Back in the 1950s, I once heard George Philbrick say, "Digital is a special case of analog." He was a passionate believer in the analog nature of the world. (He was also skeptical about frequency, though he understood transform theory—Laplace, Fourier, and especially Heaviside—better than most. But that's a matter for another essay.)

Now that we've had a few more decades to reflect on nature, to observe convergences between organisms and computer programs, and to see ways of simulating electrical behavior of organisms with computers (e.g., neural nets), it's possible to make some definite statements about what's analog and what's digital.

First of all, though, we have to dispose of *nonlinearity* and *discontinuity* in nature as arguments for digital.

*Linearity* of real-world phenomena has nothing to do with the analog versus digital question. The real (analog) world is full of nonlinearities. My employer and others manufacture a number of purposely, predictably, and accurately nonlinear devices—for example, devices with natural logarithmic or trigonometric (instead of linear) responses. They are all *analog* devices.

Second, *discreteness* and *discontinuity* really have little to do with the analog versus digital question. You don't have to go to microscopic phenomena to find discrete analog devices. My employer also manufactures analog switches and comparators. They are discontinuous (hence discrete) devices. The switches are fundamental digital to analog converters: the comparators are fundamental analog to digital converters. But voltage or current, *representing digital quantities*, operates the switches; and the outputs of the comparators are voltages, *representing the choice of a digital 1 or 0*. Thus, these basic data converters are *analog to analog* devices.

Perhaps nature is *discrete* at the limits; current could, in a sense, be counted as a flow of discrete charge carriers; time could be counted as ticks of a clock. And noise limits the resolution of continuous measurements, which some might use to argue against the continuous case. But these arguments also work against the discrete case. The uncertainty principle says we can't locate a charge carrier and at the same time say accurately how fast it's going. So we *measure* current as the *average* number of charge carriers that flow in a circuit and call the individual carriers *noise*. Similarly, a clock that ticked with every event would be useless because it would tick irregularly, so again we choose a clock that *averages* the basic ticks, and call the basic ticks *jitter*.

Perhaps it's useful to accept the *duality* of discrete and continuous in the analog real world, even as most people accept that natural phenomena are both particles (discrete) and waves (continuous).

*The important point is that "digital" is irrelevant to all that.* Digital in the quantitative sense applied to physical phenomena is a human concept; it didn't exist

before people, while voltages did (e.g., lightning, which fixed nitrogen, thus fertilizing plants without human intervention). Digital as a quantitative idea first occurred when people learned how to count—using their God-given *digits*. Digital as a computational idea is the human-invented number system. Digital is the numbers marked on an *analog* meter. Except for the natural phenomena shaped to embody it, digital is everything having to do with logic, microprocessors, computers, and so on. But such natural phenomena, and the quantitative equations governing them, are *analog* in nature, because they are analogs for one another.

As a clincher, note that Voyager II's information was digitally encoded; but to find the "digital" signal you had to resort to analog processes, such as amplification, demodulation, and filtering, to recover some sort of pulses representing the noisy information before sophisticated digital signal-processing could be employed to actually pry the information out of the noise. The pulses carrying the digital information were analog quantities. The hardware to do all that (the DSP, too) used real-world analog quantities like voltage and current. The *software* was truly digital.

Have you now been convinced that everything in the world, except for human creations, is analog? Well, I'm not! Apart from logic and number systems, there's another feature of digital that we have to consider: the ability to encode and decode, to program, to store in memory, and to execute.

That ability existed in nature long before humankind. It exists in the genes of all living beings, the strings and interconnections of DNA elements A, G, C, and T that encode, remember, and carry the program for the nature and development of life. They permit biochemical processes to differentiate between flora and fauna and, within these, all the many phyla, species, and individuals.

So perhaps, if we are to generalize, we might say that the vibrant world of life is based on digital phenomena; the physical world is analog and basically noncreative, except as its random, chaotic, and analog-programmed behaviors act on—and are acted upon by—living creatures.

## 4. Is Analog Circuit Design Dead?

Rumor has it that analog circuit design is dead. Indeed, it is widely reported and accepted that *rigor mortis* has set in. Precious filters, integrators, and the like seem to have been buried beneath an avalanche of microprocessors, ROMs, RAMs, and bits and bytes. As some analog people see it (peering out from behind their barricades), a digital monster has been turned loose, destroying the elegance of continuous functions with a blitzing array of flipping and flopping waveforms. The introduction of a "computerized" oscilloscope—the most analog of all instruments—with *no knobs* would seem to be the *coup de grâce*.

These events have produced some bizarre behavior. It has been kindly suggested, for instance, that the few remaining analog types be rounded up and protected as an endangered species. Colleges and universities offer few analog design courses. And some localities have defined copies of Korn and Korn publications, the *Philbrick Applications Manual*, and the *Linear Applications Handbook* as pornographic material, to be kept away from engineering students' innocent and impressionable minds. Sadly, a few well-known practitioners of the art are slipping across the border (James E. Solomon has stated, for example, that "all classical analog techniques are dead"), while more principled ones are simply leaving town.

Can all this be happening? Is it really so? Is analog dead? Or has the hysteria of the moment given rise to exaggeration and distorted judgment?

To answer these questions with any degree of intelligence and sensitivity, it is necessary to consult history. And to start this process, we must examine the patient's body.

Analog circuit design is described using such terms as subtractor, integrator, differentiator, and summing junction. These mathematical operations are performed by that pillar of analoggery, the operational amplifier. The use of an amplifier as a computing tool is not entirely obvious and was first investigated before World War II. Practical "computing amplifiers" found their first real niche inside electronic analog computers (as opposed to mechanical analog computers such as the Norden bombsight or Bush's Differential Analyzer), which were developed in the late 1940s and 1950s. These machines were, by current standards, monstrous assemblages made up of large numbers of amplifiers that could be programmed to integrate, sum, differentiate, and perform a host of mathematical operations. Individual amplifiers performed singular functions, but complex operations were performed when all the amplifiers were interconnected in any desired configuration.

The analog computer's forte was its ability to model or simulate events. Analog computers did not die out because analog simulations are no longer useful or do not approximate truth; rather, the rise of digital machines made it enticingly easy to use digital fakery to *simulate the simulations*.

Adapted from the July 22, 1991, issue of EDN Magazine.

As digital systems came on line in the late 1950s and early 1960s, a protracted and brutally partisan dispute (some recall it as more of a war) arose between the analog and digital camps. Digital methods offered high precision at the cost of circuit complexity. The analog way achieved sophisticated results at lower accuracy and with comparatively simple circuit configurations. One good op amp (eight transistors) could do the work of 100 digitally configured 2N404s. It seemed that digital circuitry was an accurate but inelegant and overcomplex albatross. Digital types insisted that analog techniques could never achieve any significant accuracy, regardless of how adept they were at modeling and simulating real systems.

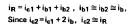

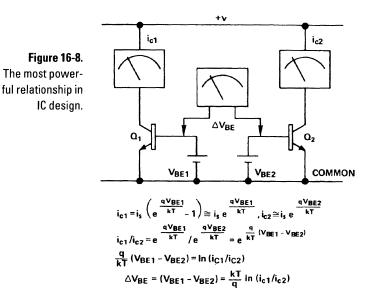

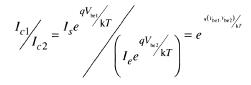

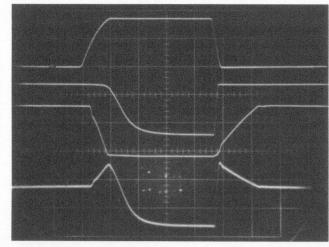

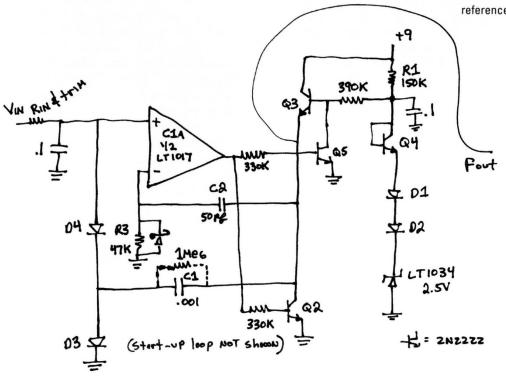

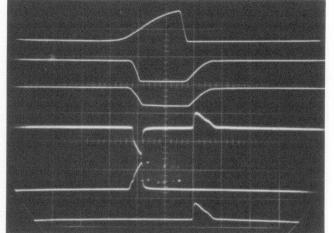

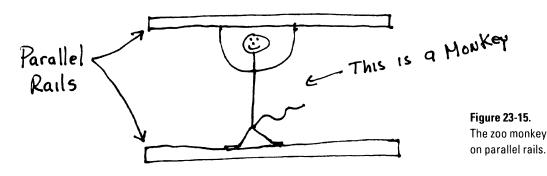

This battle was not without its editorializing. One eloquent speaker was George A. Philbrick, a decided analog man, who wrote in 1963 (in *The Lightning Empiricist*, Volume II, No. 4, October, "Analogs Yesterday, Today, and Tomorrow," pp. 3-8), "In modest applications to on-line measurement and data processing, it is quite generally conceded that the advantage of continuous analog apparatus make it irresistible. This is partly owing to the simplicity and speed which its continuity makes possible, and partly to the fact that almost every input transducer is also 'analog' in character, that is to say, continuous in excursion and time."