Peripheral Components

Chip Sets

PC I/O Peripherals.

Memory Controllers

UPI: Keyboard Controllers

Support Peripherals

inte

intel<sub>®</sub>

# PERIPHERAL COMPONENTS

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

MDS is an ordering code only and is not used as a product name or trademark of Intel Corporation.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

\*Other brands and names are the property of their respective owners.

Additional copies of this document or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641 or call 1-800-879-4683

©INTEL CORPORATION, 1993

#### **CUSTOMER SUPPORT**

#### **FAXBACK SYSTEM**

Order documents by phone for prompt delivery to your fax machine. You can rely on FaxBACK for the following types of information.

- Product Literature

- Tools and technical support material

- Application articles

- New product announcements

- Design recommendations

- Stepping and errata notification

Just dial 1-800-628-2283 or 916-356-3105 and the userfriendly system will prompt you along. Just have your fax number ready. Available 24 hours a day.

#### APPLICATIONS SUPPORT HOTLINE

The Technical Hotline is manned by applications personnel during normal business hours. You can leave a message during off hours or when applications personnel are already handling calls. The number (U.S. and Canada) is 1-800-628-8686. Assistance is also available through your local distributor or sales office.

# INTEL'S APPLICATION BULLETIN BOARD SYSTEM

Key into our centralized Intel Applications Bulletin Board System and pull up all the latest information in Intel's product line. The BBS can provide you with the following type of information:

- software drivers

- documentation

- new products

- tools information

- firmware upgrades

- presentations

- revised software

Intel's Application Bulletin Board System enables file retrieval and message/file exchange with our System Operator (Sysop) and File Operators (Fileops).

Just dial 916-356-3600 on your modem, and the user-friendly system will prompt you along.

For new users, the first log-in allows you to register with the system operator by entering your name and location. To access files on the BBS, log in again 24 hours later.

For immediate file access, call 1-800-628-8686 or 916-356-3104. For a listing of files available on the BBS, call FaxBACK at 1-800-628-2283 or 916-356-3105, order catalog #6.

- Settings: 9600 baud, N, 8, 1

- Auto configuration supports 1200 through 9600 baud MODEMs

### **DATA SHEET DESIGNATIONS**

Intel uses various data sheet markings to designate each phase of the document as it relates to the product. The marking appears in the upper, right-hand corner of the data sheet. The following is the definition of these markings:

| Data Sheet Marking   | Description                                                                                                                                                                                    |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Preview      | Contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product becomes available. |

| Advanced Information | Contains information on products being sampled or in the initial production phase of development.*                                                                                             |

| Preliminary          | Contains preliminary information on new products in production.*                                                                                                                               |

| No Marking           | Contains information on products in full production.*                                                                                                                                          |

<sup>\*</sup>Specifications within these data sheets are subject to change without notice. Verify with your local Intel sales office that you have the latest data sheet before finalizing a design.

# intel<sub>®</sub>

| Chip Sets                |  |

|--------------------------|--|

| PC I/O Peripherals       |  |

| Memory Controllers       |  |

| UPI Keyboard Controllers |  |

|                          |  |

Support Peripherals

# **Table of Contents**

| Alphanumeric Index                                                       | χi             |

|--------------------------------------------------------------------------|----------------|

| Data-On-Demand Literature                                                | xii            |

| CHAPTER 1                                                                | -              |

| Chip Sets                                                                |                |

| PCIsets                                                                  |                |

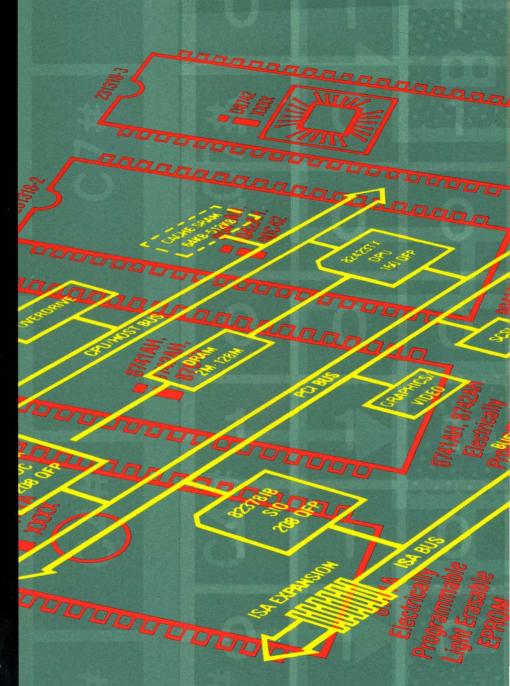

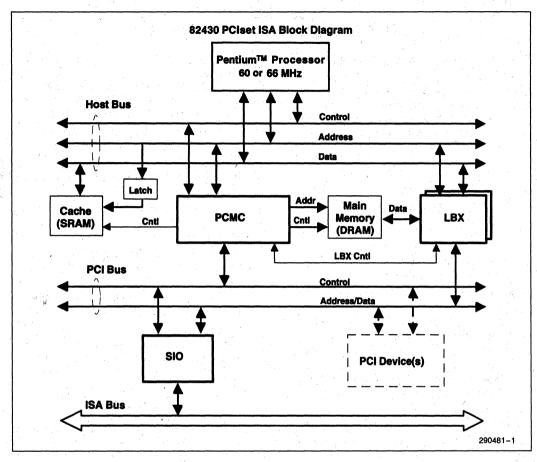

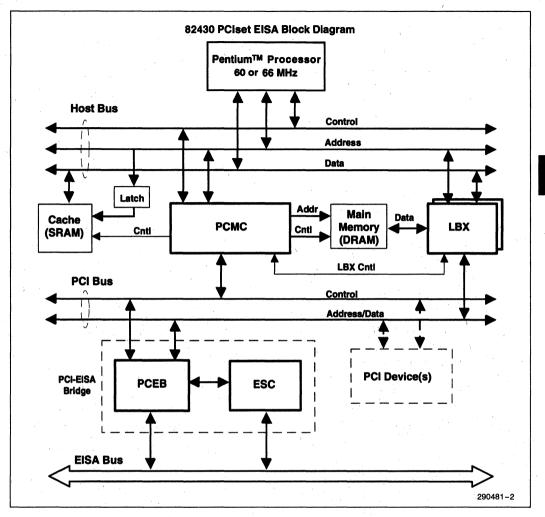

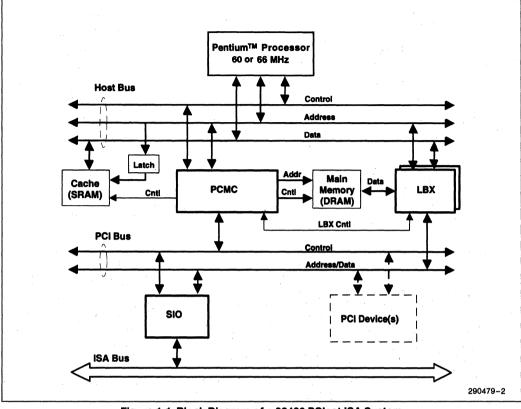

| 82430 PCIset for the Pentium™ Processor                                  | 1-1            |

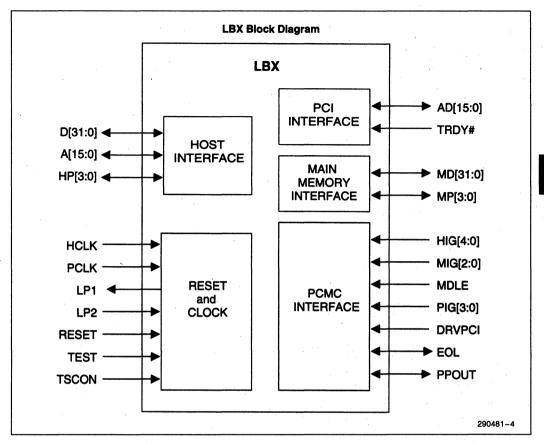

| 82433LX Local Bus Accelerator (LBX)                                      | 1-14           |

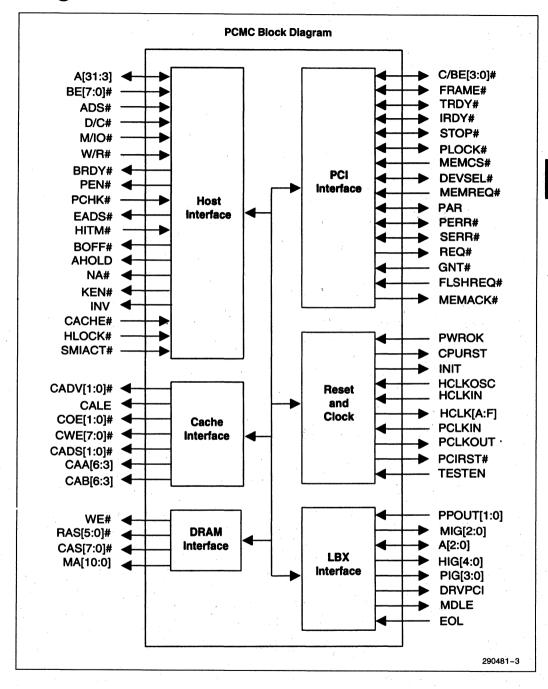

| 82434LX PCI, Cache and Memory Controller (PCMC)                          | 1-58           |

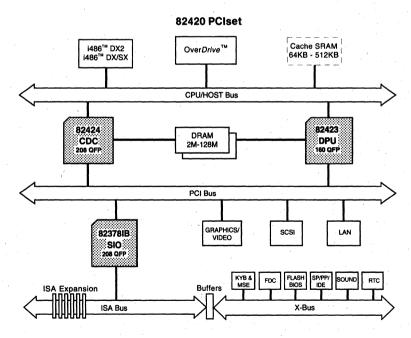

| 82420 PCIset                                                             | 1-203          |

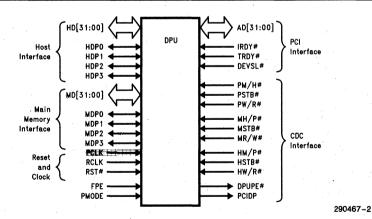

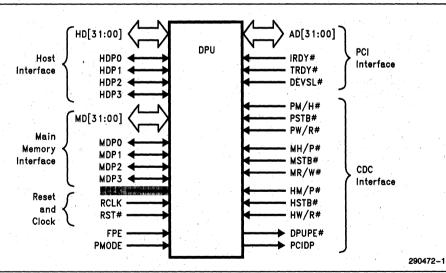

| 82423 Data Path Unit (DPU)                                               | 1-214          |

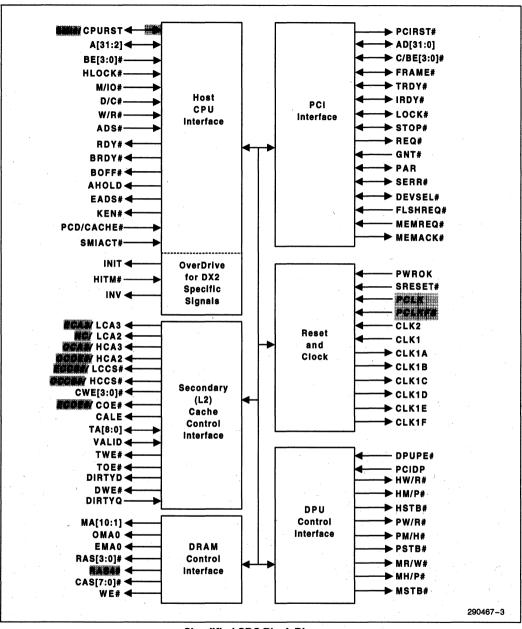

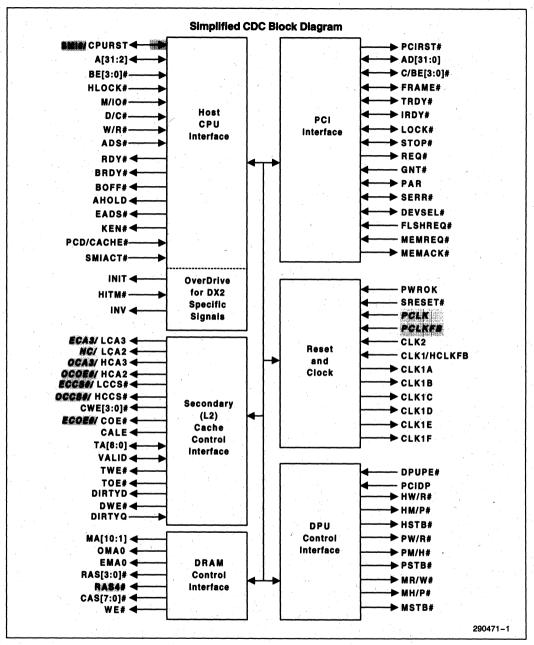

| 82424 Cache and DRAM Controller (CDC)                                    | 1-215<br>1-217 |

| 82420/82430 PCIset Bridge Component                                      | 1-217          |

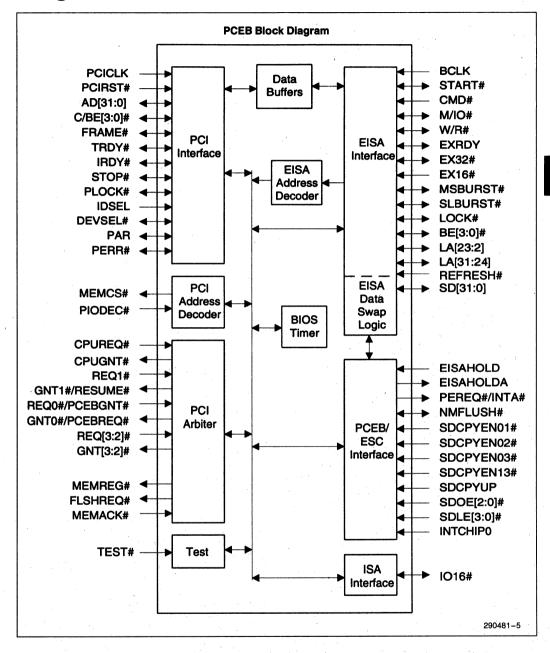

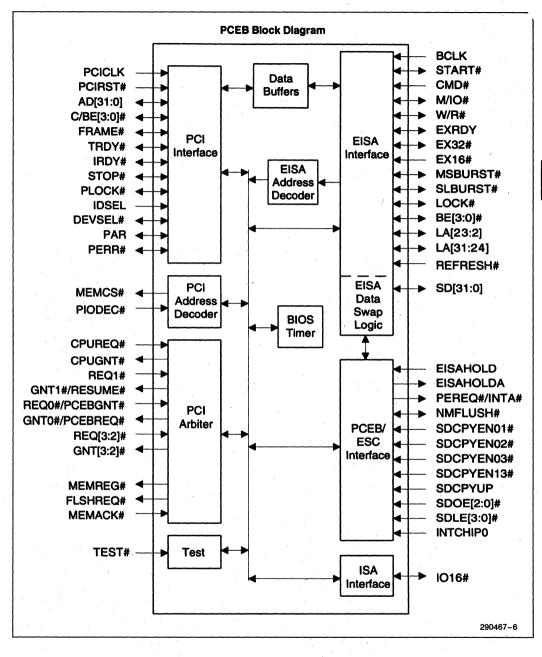

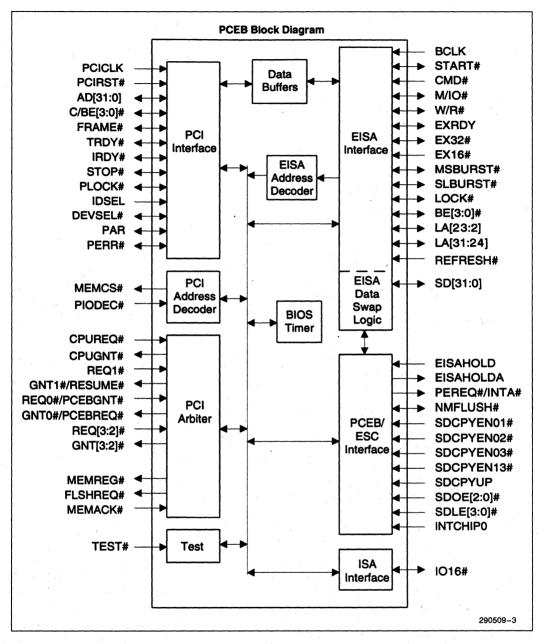

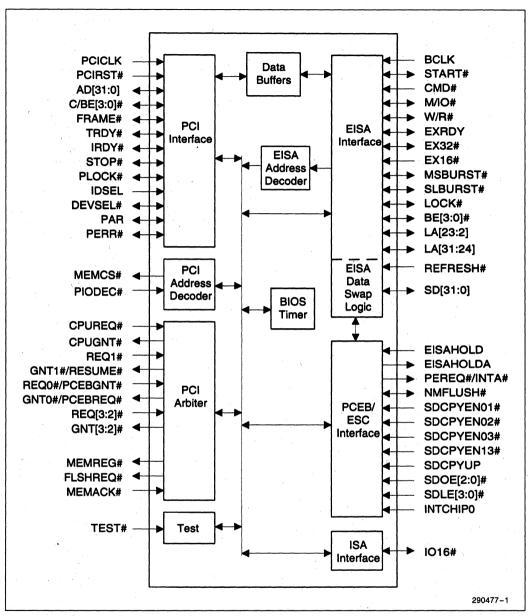

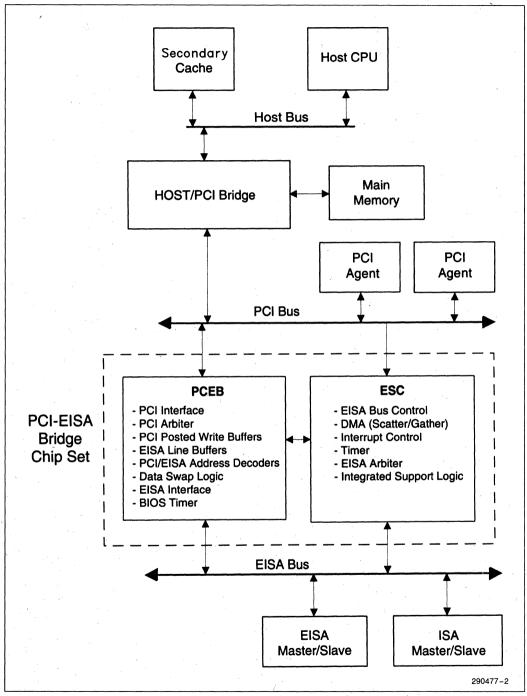

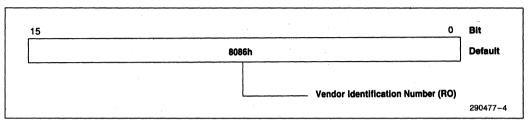

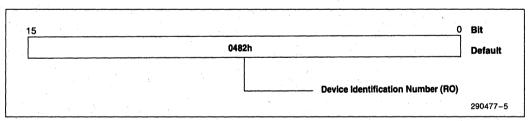

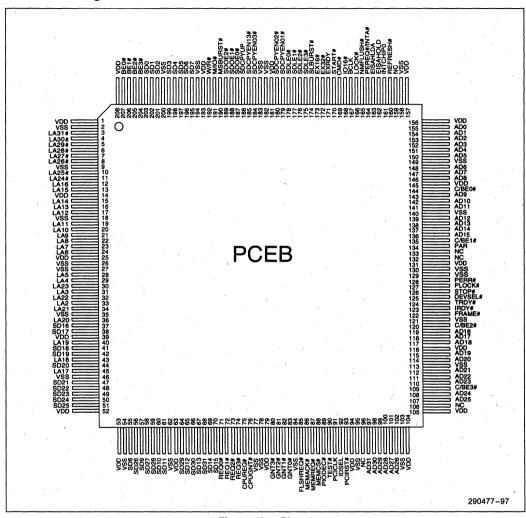

| 82375EB PCI-EISA Bridge (PCEB)                                           | 1-224          |

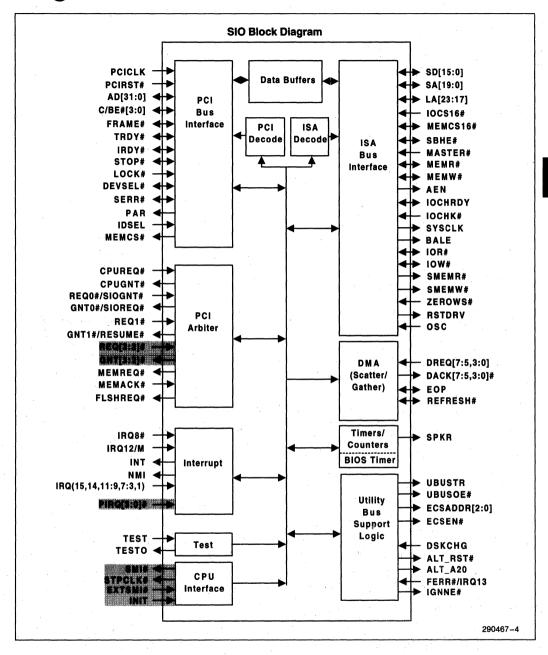

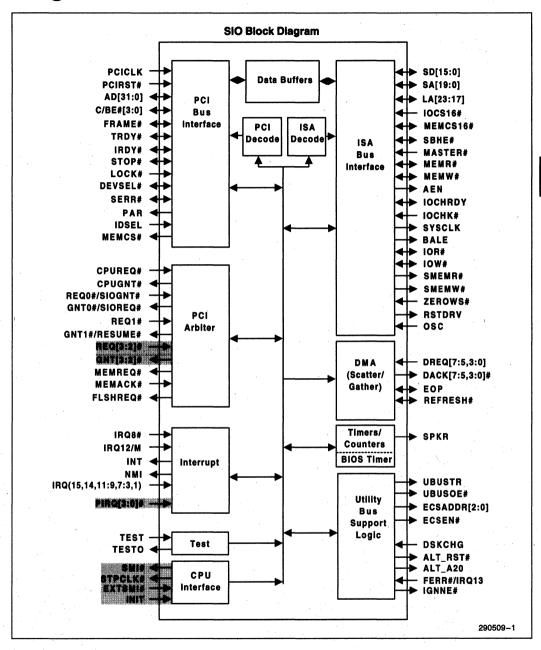

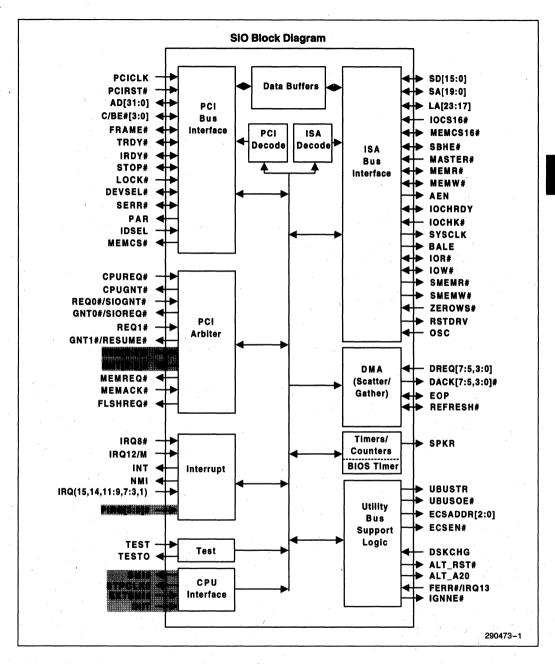

| 82378 System I/O (SIO)                                                   | 1-558          |

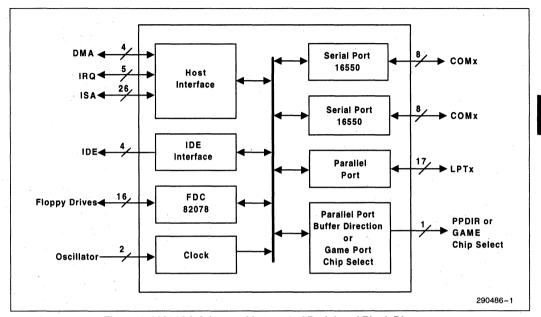

| 82091AA Advanced Integrated Peripheral (AIP)                             | 1-560          |

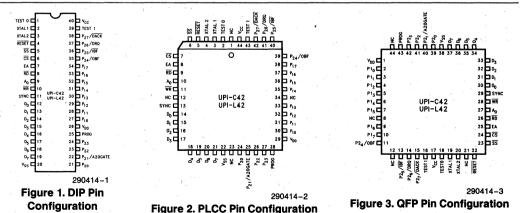

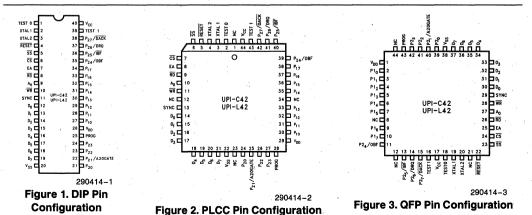

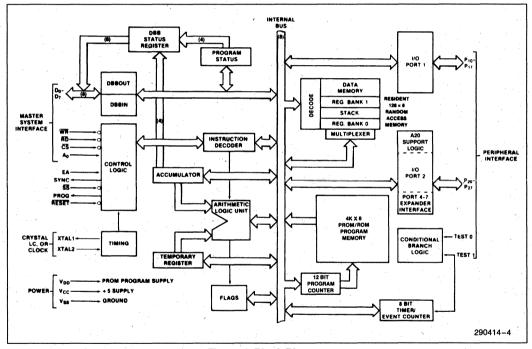

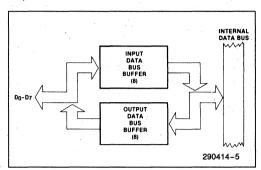

| UPI-C42/UPI-L42 Universal Peripheral Interface CHMOS 8-Bit Slave         | . 555          |

| Microcontroller                                                          | 1-562          |

| EISA CHIP SETS                                                           | •              |

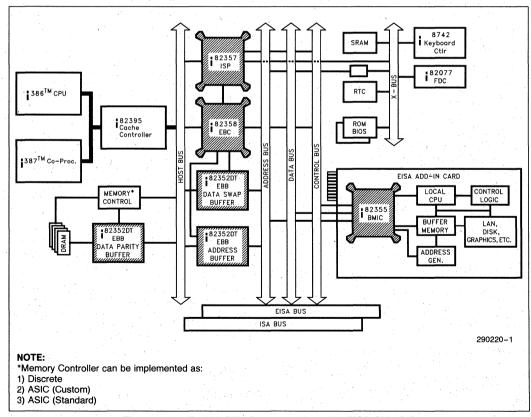

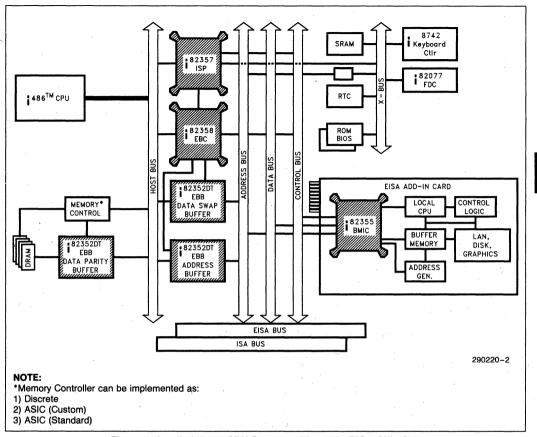

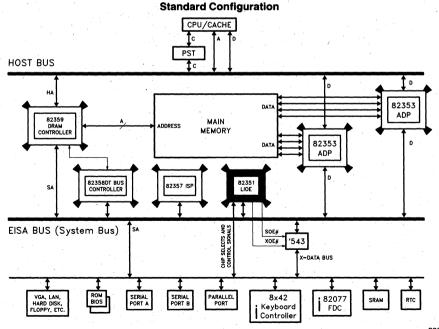

| 82350 EISA Chip Set                                                      | 1-563          |

| 82351 Local I/O EISA Support Peripheral (LIO.E)                          | 1-572          |

| 82352DT EISA Bus Buffer (EBB)                                            | 1-573          |

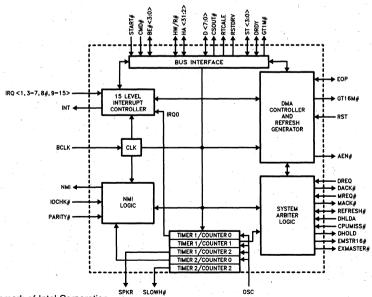

| 82357 Integrated System Peripheral (ISP)                                 | 1-574          |

| 82358DT EISA Bus Controller (EBCDT)                                      | 1-575          |

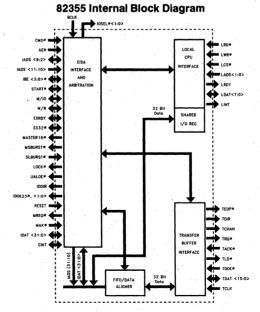

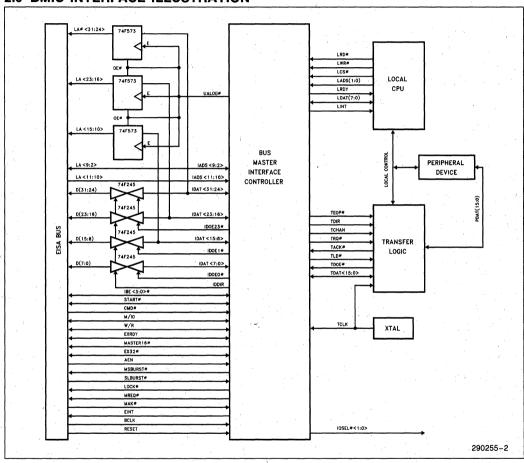

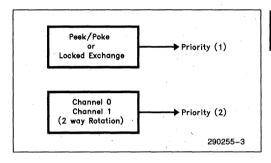

| 82355 Bus Master Interface Controller (BMIC)                             | 1-576          |

| CHAPTER 2                                                                |                |

| PC I/O Peripherals                                                       |                |

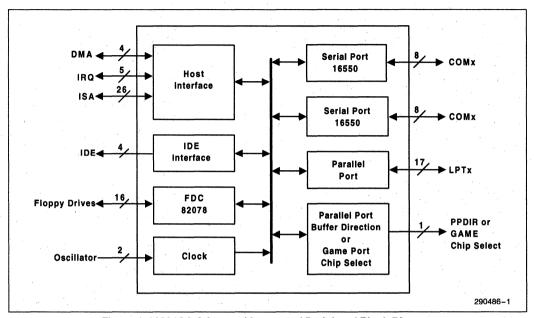

| 82091AA Advanced Integrated Peripheral (AIP)                             | 2-1            |

| 82092AA PCI to PCMCIA/Enhanced IDE Controller (PPEC)                     | 2-3            |

| FLOPPY DISK CONTROLLER DATA SHEETS                                       |                |

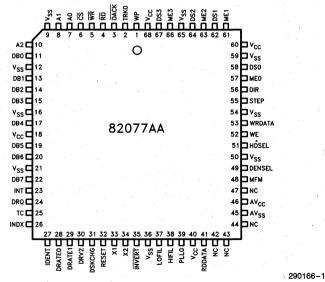

| 82077AA CHMOS Single-Chip Floppy Disk Controller                         | 2-4            |

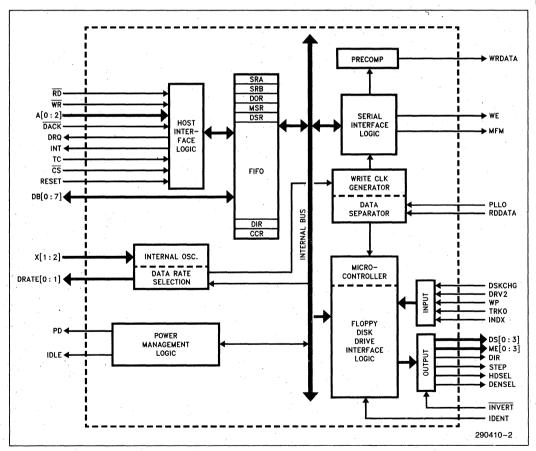

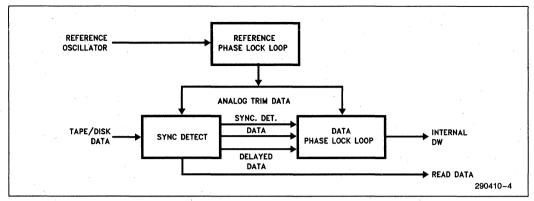

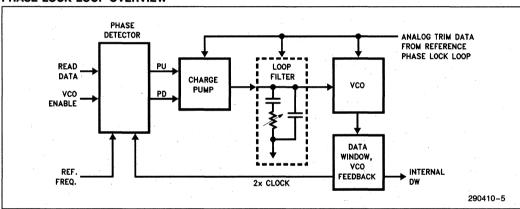

| 82077SL CHMOS Single-Chip Floppy Disk Controller                         | 2-5            |

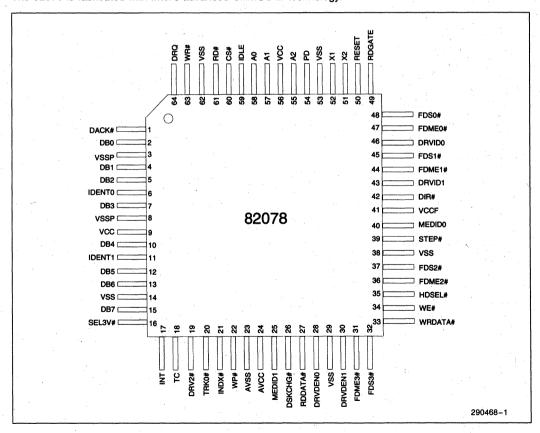

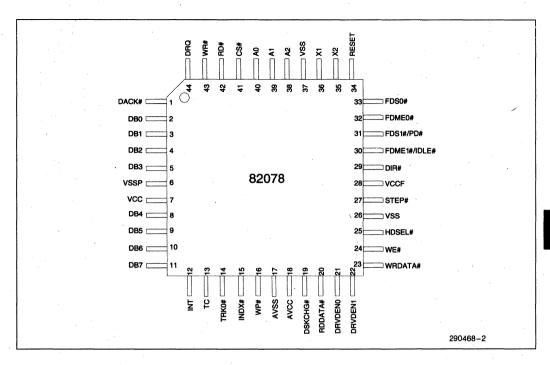

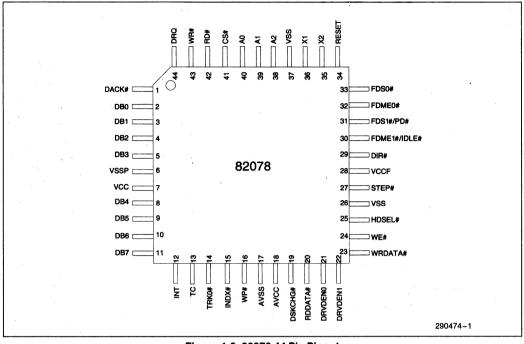

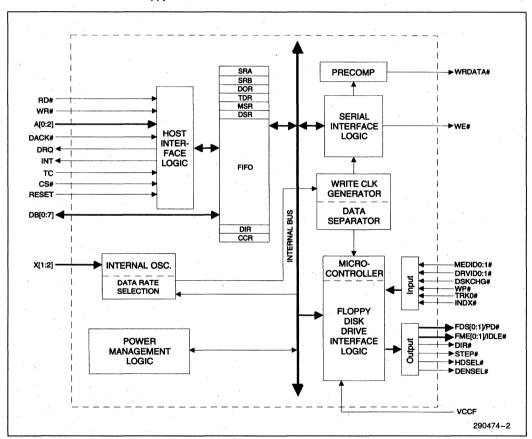

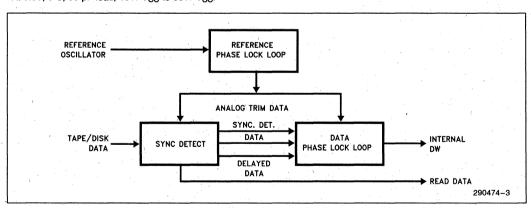

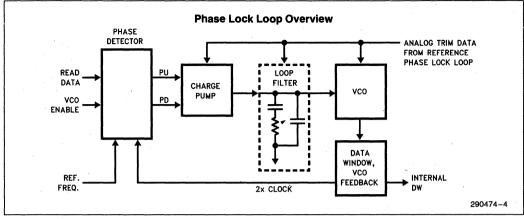

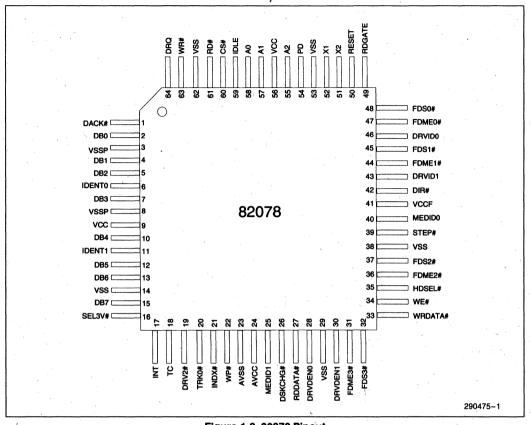

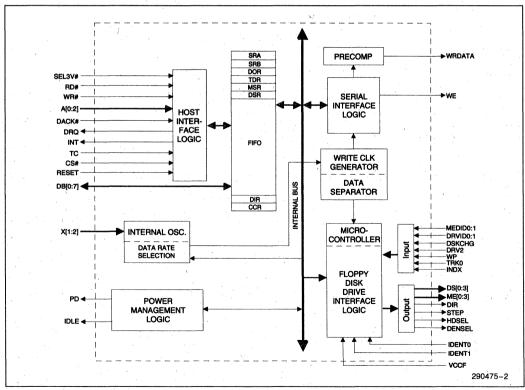

| 82078 CHMOS Single-Chip Floppy Disk Controller                           | 2-75           |

| 82078 44 Pin CHMOS Single-Chip Floppy Disk Controller                    | 2-78           |

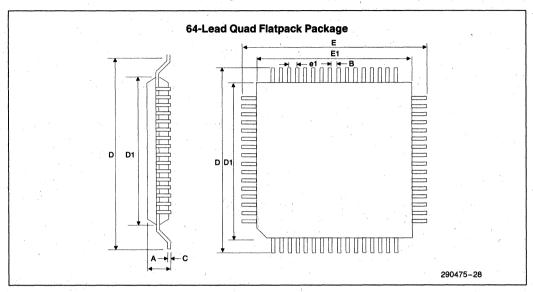

| 82078 64 Pin CHMOS Single-Chip Floppy Disk Controller                    | 2-149          |

| APPLICATION NOTE AP-358 Intel 82077SL for Super Dense Floppies           | 0 007          |

|                                                                          | 2-221          |

| CHAPTER 3                                                                |                |

| Memory Controllers                                                       | 1              |

| DATA SHEETS                                                              |                |

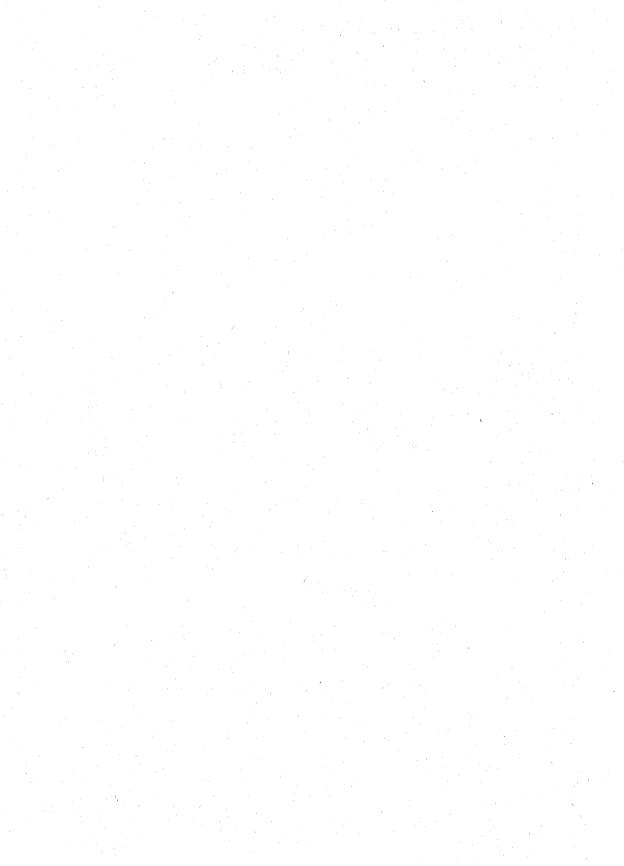

| 8206 Error Detection and Correction Unit                                 | 3-1            |

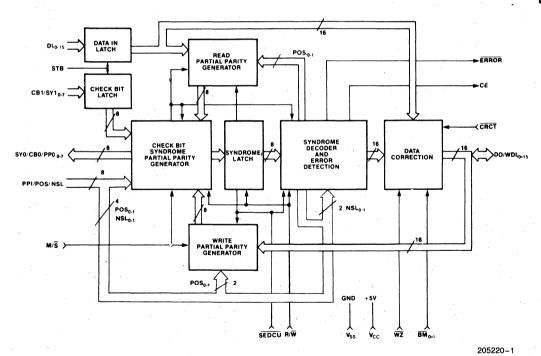

| 8207 Dual-Port Dynamic RAM Controller                                    | 3-2            |

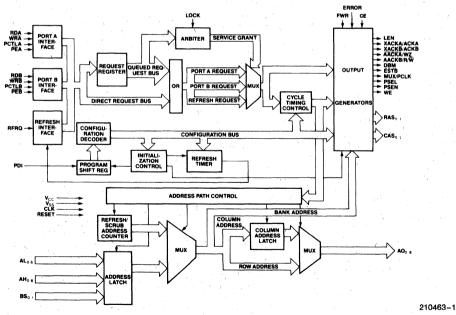

| 82C08 CHMOS Dynamic RAM Controller                                       | 3-3            |

| CHAPTER 4                                                                |                |

| UPI Keyboard Controllers                                                 |                |

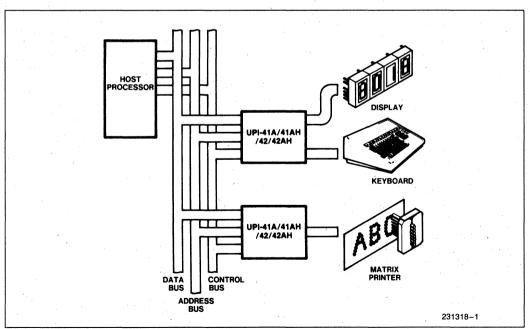

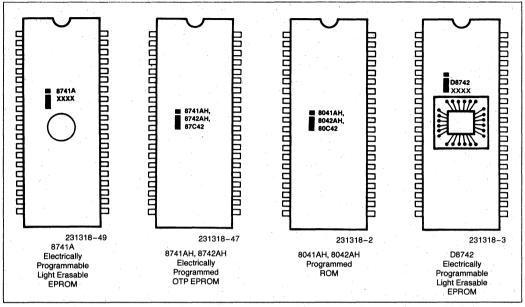

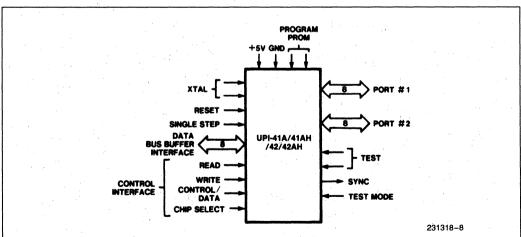

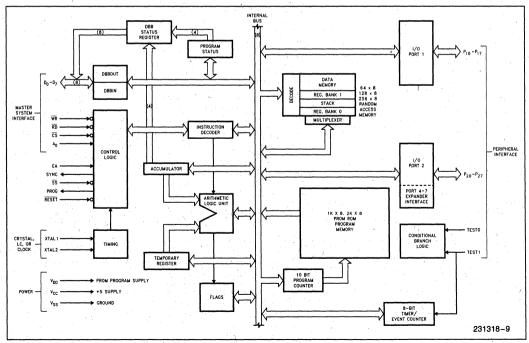

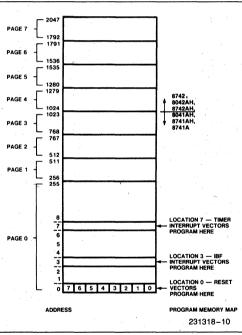

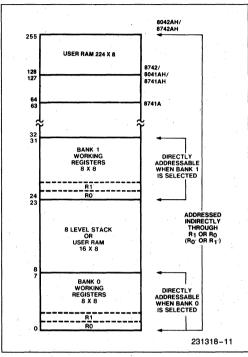

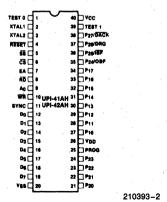

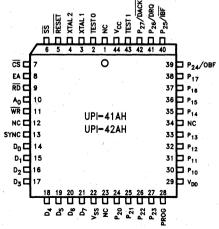

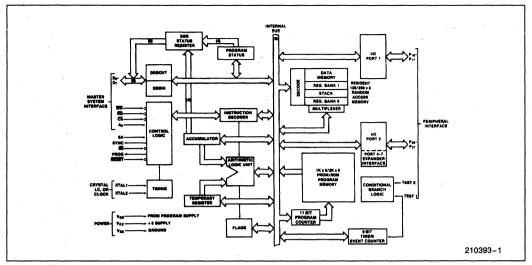

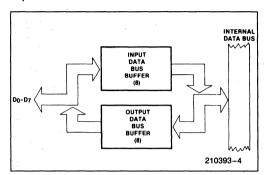

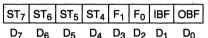

| Microprocessor Peripherals UPI-41A/41AH/42/42AH User's Manual            | 4-1            |

| DATA SHEETS                                                              |                |

| UPI-41AH/42AH Universal Peripheral Interface 8-Bit Slave Microcontroller | 4-68           |

| 8741A Universal Peripheral Interface 8-Bit Microcomputer                 | 4-88           |

| 8742 Universal Peripheral Interface 8-Bit Slave Microcontroller          | 4-100          |

| UPI-C42/UPI-L42 Universal Peripheral Interface CHMOS 8-Bit Slave         | 4 4 4 4 4      |

| Microcontroller                                                          | 4-112          |

# Table of Contents (Continued)

| C | H | A | Ρ. | TE | F | 15 |

|---|---|---|----|----|---|----|

| Support Peripherals DATA SHEETS UPI-452 CHMOS Programmable I/O Processor 8231A Arithmetic Processing Unit |      |

|-----------------------------------------------------------------------------------------------------------|------|

| DATA SHEETS UPI-452 CHMOS Programmable I/O Processor                                                      |      |

| UPI-452 CHMOS Programmable I/O Processor                                                                  |      |

| 8231A Arithmetic Processing Unit                                                                          |      |

|                                                                                                           | 5-2  |

| 8237A High Performance Programmable DMA Controller (8237A-5)                                              | 5-3  |

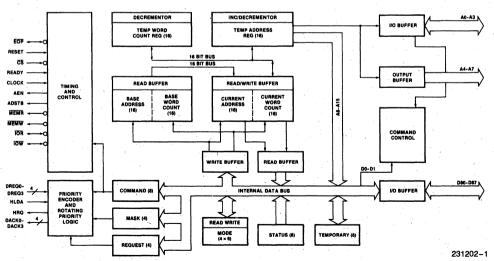

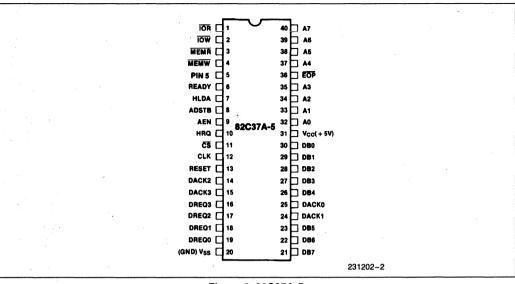

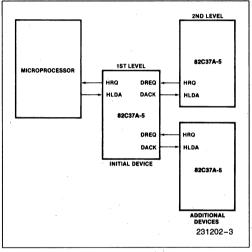

| 82C37A-5 CHMOS High Performance Programmable DMA Controller                                               |      |

| 8253/8253-5 Programmable Interval Timer                                                                   |      |

| 8254 Programmable Interval Timer                                                                          |      |

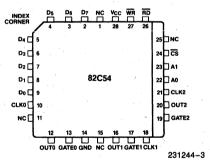

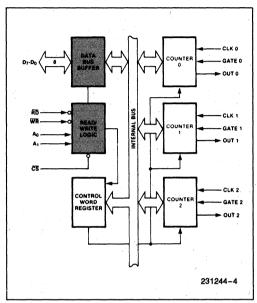

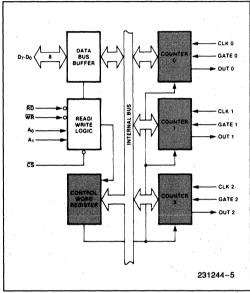

| 82C54 CHMOS Programmable Interval Timer                                                                   | 5-24 |

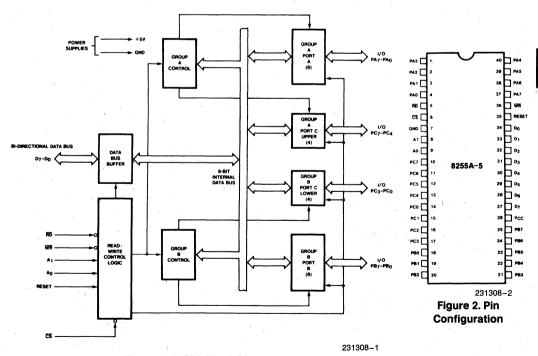

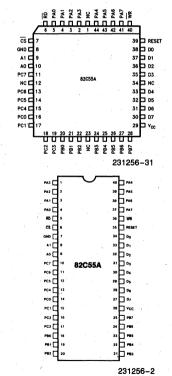

| 8255A-5 Programmable Peripheral Interface                                                                 |      |

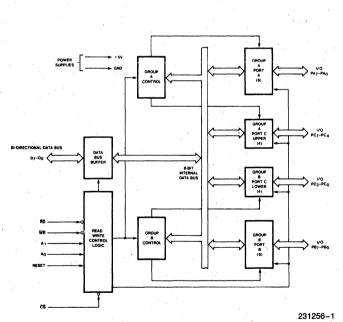

| 82C55A CHMOS Programmable Peripheral Interface                                                            |      |

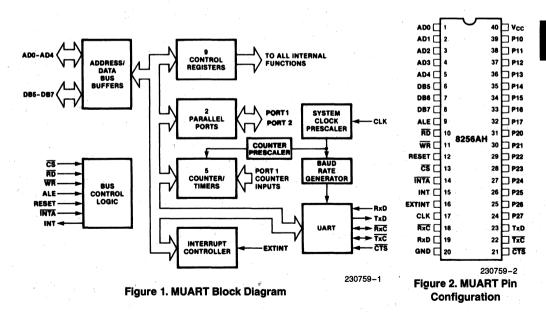

| 8256AH Multifunction Microprocessor Support Controller                                                    |      |

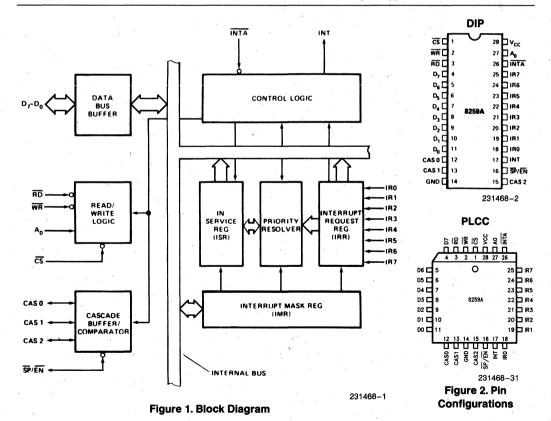

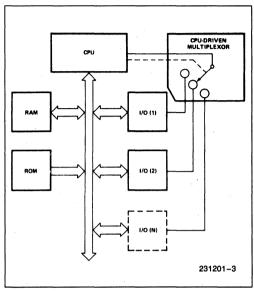

| 8259A Programmable Interrupt Controller (8259A/8259A-2)                                                   |      |

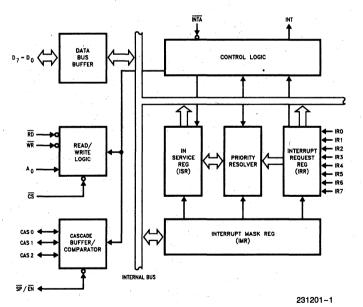

| 82C59A-2 CHMOS Programmable Interrupt Controller                                                          |      |

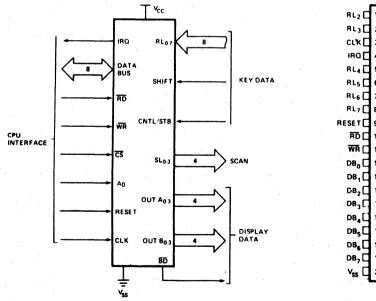

| 8279/8279-5 Programmable Keyboard/Display Interface                                                       |      |

| 82389 Message Passing Coprocessor A MULTIBUS II Bus Interface Controller                                  | 5-66 |

# Alphanumeric Index

| 8206 Error Detection and Correction Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-1   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 8207 Dual-Port Dynamic RAM Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-2   |

| 82077AA CHMOS Single-Chip Floppy Disk Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-4   |

| 82077SL CHMOS Single-Chip Floppy Disk Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-5   |

| 82078 44 Pin CHMOS Single-Chip Floppy Disk Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-78  |

| 82078 64 Pin CHMOS Single-Chip Floppy Disk Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-149 |

| 82078 CHMOS Single-Chip Floppy Disk Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-75  |

| 82091AA Advanced Integrated Peripheral (AIP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-1   |

| 82092AA PCI to PCMCIA/Enhanced IDE Controller (PPEC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-3   |

| 8231A Arithmetic Processing Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-2   |

| 82350 EISA Chip Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1-563 |

| 82351 Local I/O EISA Support Peripheral (LIO.E)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-572 |

| 82352DT EISA Bus Buffer (EBB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-572 |

| 82355 Bus Master Interface Controller (BMIC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1-576 |

| 82357 Integrated System Peripheral (ISP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-574 |

| 02057 Integrated dysterir Feriphera (ISF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-574 |

| 82358DT EISA Bus Controller (EBCDT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

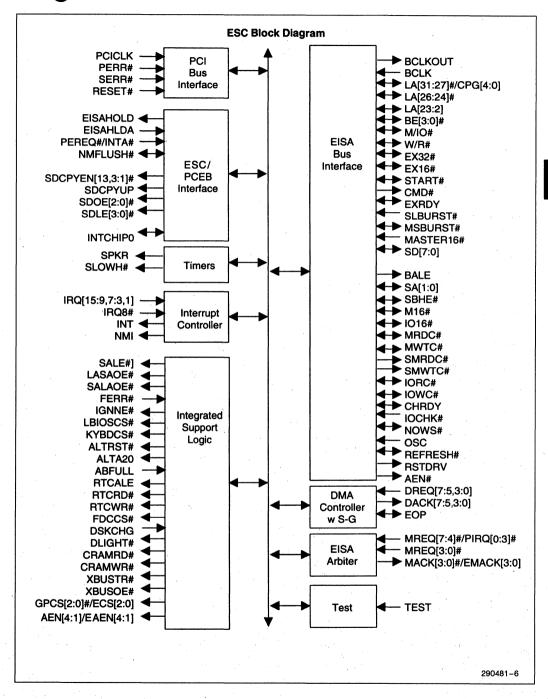

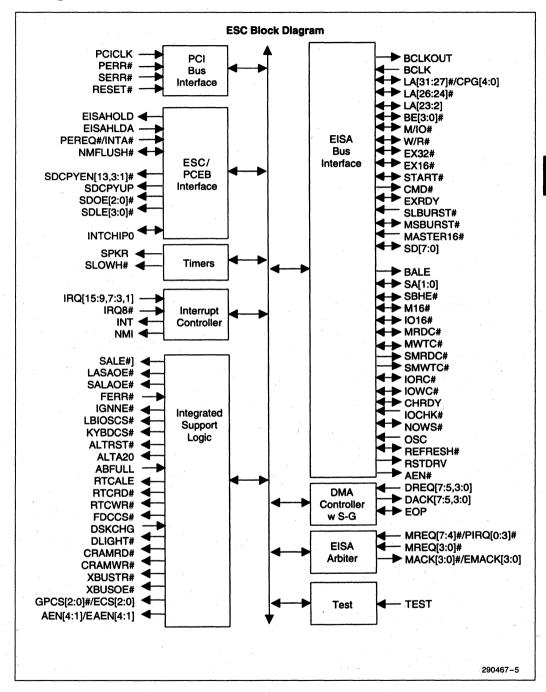

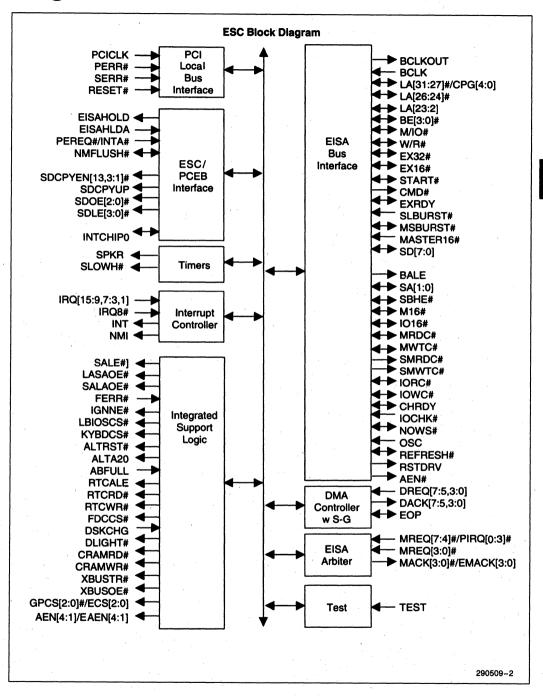

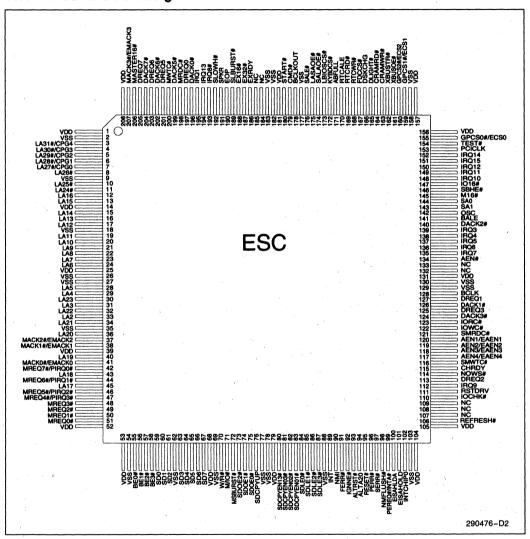

| 82374EB EISA System Component (ESC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1-224 |

| 82375EB PCI-EISA Bridge (PCEB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-419 |

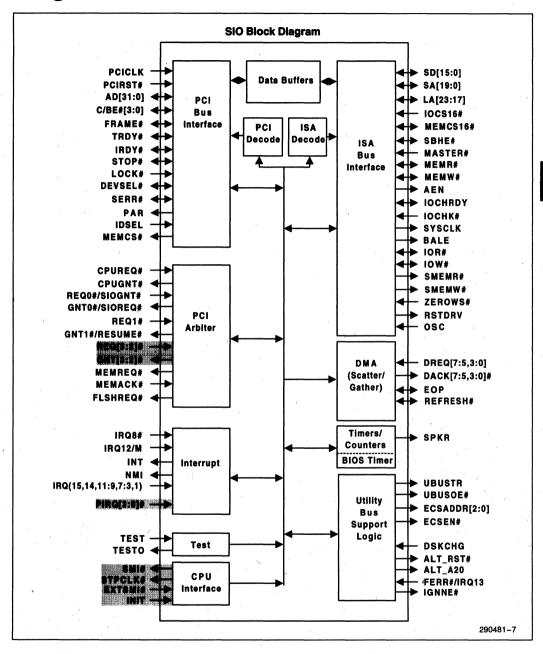

| 82378 System I/O (SIO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-558 |

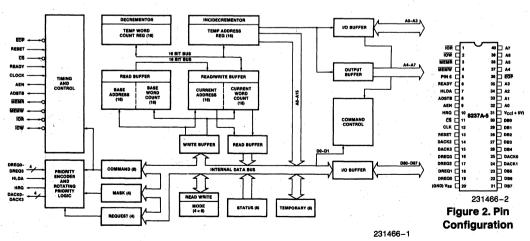

| 8237A High Performance Programmable DMA Controller (8237A-5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-3   |

| 82389 Message Passing Coprocessor A MULTIBUS II Bus Interface Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-66  |

| 82420 PCIset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1-203 |

| 82420/82430 PCIset Bridge Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1-217 |

| 82423 Data Path Unit (DPU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-214 |

| 82424 Cache and DRAM Controller (CDC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-215 |

| 82430 PCIset for the Pentium™ Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-1   |

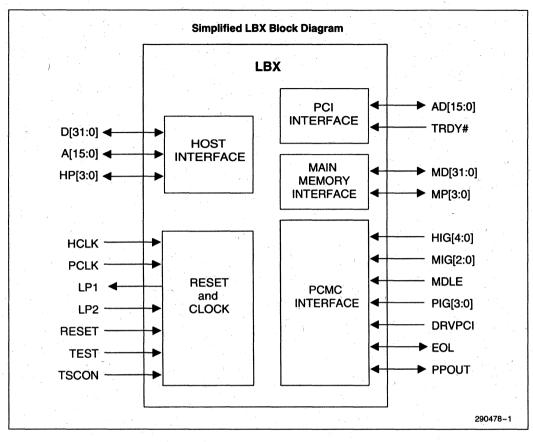

| 82433LX Local Bus Accelerator (LBX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1-14  |

| 82434LX PCI, Cache and Memory Controller (PCMC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-58  |

| 8253/8253-5 Programmable Interval Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-22  |

| 8254 Programmable Interval Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-23  |