September 1988

**Product Description**

# SPARC™ MB86901 (S-25) High Performance 32-Bit RISC Processor

|            | SPARC™<br>MB86901 (S–25)<br>High Performance<br>–32-Bit RISC Processor ——                                                                                                                                                                                                                                                                                                                 |                        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| •          |                                                                                                                                                                                                                                                                                                                                                                                           | Product<br>Description |

|            |                                                                                                                                                                                                                                                                                                                                                                                           |                        |

| All so and |                                                                                                                                                                                                                                                                                                                                                                                           |                        |

|            | Fujitsu Limited                                                                                                                                                                                                                                                                                                                                                                           |                        |

|            | Fujitsu Microelectronics, Inc.                                                                                                                                                                                                                                                                                                                                                            |                        |

|            | Fujitsu Mikroelektronik GmbH<br>Fujitsu Microelectronics Pacific Asia Ltd.                                                                                                                                                                                                                                                                                                                |                        |

|            | Copyright © 1988 Fujitsu Limited and Fujitsu Microelectronics, Inc.<br>This publication contains information considered proprietary by Fujitsu<br>Limited and Fujitsu Microelectronics, Inc. No part of this document may be<br>copied or reproduced in any form or by any means or transferred to any third<br>party without the prior written consent of Fujitsu Microelectronics, Inc. |                        |

|            | SPARC is a trademark of Sun Microsystems, Inc.                                                                                                                                                                                                                                                                                                                                            |                        |

Copyright © 1988 Fujitsu Limited and Fujitsu Microelectronics, Inc.

All rights reserved.

Circuit diagrams utilizing Fujitsu products are included as a means of illustrating typical semiconductor applications. Consequently, complete information sufficient for construction purposes is not necessarily given.

The information contained in this document has been carefully checked and is believed to be entirely accurate. However, Fujitsu Limited and Fujitsu Microelectronics, Inc. assume no responsibility for inaccuracies.

The information contained in this document does not convey any license under the copyrights, patent rights or trademarks claimed and owned by Fujitsu Limited or its subsidiaries.

Fujitsu Limited and its subsidiaries reserve the right to change products or specifications without notice.

This document is published by the marketing department of Fujitsu Microelectronics, Inc.'s Advanced Products Division, 50 Rio Robles, Bldg. 3, San Jose, California, U.S.A. 95134-1804

Printed in the U.S.A.

SPARC is a trademark of Sun Microsystems, Inc. VAX is a trademark of Digital Equipment Corp.

### **Table of Contents**

| 2. CPU       2         2.1. Instruction Pipeline       2         2.1.1. Fetch Stage       2         2.1.2. Decode Stage       2         2.1.3. Execute Stage       4         2.1.4. Write Stage       4         2.1.5. Pipeline Examples       4         2.1.6. Delayed Control Transfers       5         2.2. Execution Unit       7         2.3. Address Generation Unit       7         2.4. Address Space Organization       10         2.4.1. Processor Data Types       11         2.4.2. Addressing Conventions       11         2.5. Registers       12         2.5.1. Window Selection       14         2.5.2. Special Purpose Registers       16         2.5.2. Special Purpose Register (PSR)       16         2.5.2. Window Invalid Mask Register (WIM)       18         2.5.2. A Y Register       18         2.5.3. Program Counters       18         3. Instruction Set       19         3.1. Data Transfer Instructions       23         3.2.1. Add and Subtract       23         3.2.2. Tagged Add and Subtract       24         3.2.3. Multiply Step Instructions       25         3.2.4. Sigical Instruction       26         3                                                                                                          | 1. Introduction2                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 2.1.1. Fetch Stage       2         2.1.2. Decode Stage       2         2.1.3. Execute Stage       2         2.1.3. Execute Stage       4         2.1.4. Write Stage       4         2.1.5. Pipeline Examples       4         2.1.6. Delayed Control Transfers       5         2.2. Execution Unit       7         2.3. Address Generation Unit       7         2.4. Address Space Organization       10         2.4.1. Processor Data Types       11         2.4.2. Addressing Conventions       11         2.5. Registers       12         2.5.1. Register File       12         2.5.1. Register Window Use       15         2.5.2. Special Purpose Registers       16         2.5.2. Special Purpose Register (PSR)       16         2.5.2. Window Invalid Mask Register (WIM)       18         2.5.2. Window Invalid Mask Register (WIM)       18         2.5.2. Vindow Invalid Mask Register (WIM)       18         2.5.2. Special Purpose Support Instructions       23         3.1. Data Transfer Instructions       22         3.1.1. Multiprocessor Support Instructions       23         3.2.2. Tagged Add and Subtract       24         3.2.3. Multiply Step Instructions       25                                                               | 2. CPU                                          |

| 2.1.2. Decode Stage       2         2.1.3. Execute Stage       4         2.1.4. Write Stage       4         2.1.5. Pipeline Examples       4         2.1.6. Delayed Control Transfers       5         2.2. Execution Unit       7         2.3. Address Generation Unit       7         2.4. Address Generation Unit       7         2.4. Address Generation Unit       7         2.4. Address or Data Types       11         2.4. Addressing Conventions       11         2.5. Registers       12         2.5.1. Register File       12         2.5.1. Register Window Use       15         2.5.2. Special Purpose Registers       16         2.5.2. Window Invalid Mask Register (WIM)       18         2.5.2. Window Invalid Mask Register (WIM)       18         2.5.2. Trap Base Register (TBR)       18         2.5.2.4. Y Register       18         2.5.3. Program Counters       18         3. Instruction Set       19         3.1. Data Transfer Instructions       23         3.2.1. Add and Subtract       24         3.2.3. Multiply Step Instructions       25         3.2.4. Shift Instructions       25         3.2.5. Shift Instructions       26                                                                                          |                                                 |

| 2.1.3. Execute Stage       4         2.1.4. Write Stage       4         2.1.5. Pipeline Examples       4         2.1.6. Delayed Control Transfers       5         2.2. Execution Unit       7         2.3. Address Generation Unit       7         2.4. Address Space Organization       10         2.4.1. Processor Data Types       11         2.4.2. Addressing Conventions       11         2.5. Registers       12         2.5.1. Register File       12         2.5.1. Window Selection       14         2.5.2. Special Purpose Registers       16         2.5.2. Special Purpose Register (PSR)       16         2.5.2.3. Trap Base Register (TBR)       18         2.5.2.4. Y Register       18         2.5.3. Program Counters       18         2.5.4. Y Register       19         3.1. Data Transfer Instructions       22         3.1.1. Multiprocessor Support Instructions       23         3.2.2. Tagged Add and Subtract       24         3.2.3. Multiply Step Instruction       24         3.2.4. Logical Instructions       25         3.2.5. Shift Instructions       26         3.2.7. SETHI Instruction       26         3.2.7. SETHI Instruction <td< td=""><td></td></td<>                                                           |                                                 |

| 2.1.4. Write Stage       4         2.1.5. Pipeline Examples       4         2.1.6. Delayed Control Transfers       5         2.2. Execution Unit       7         2.3. Address Generation Unit       7         2.4. Address Space Organization       10         2.4.1. Processor Data Types       11         2.4.2. Addressing Conventions       11         2.5.8 Registers       12         2.5.1. Register File       12         2.5.1.1. Window Selection       14         2.5.2. Special Purpose Registers       16         2.5.2. Special Purpose Register (PSR)       16         2.5.2. Supecial Purpose Register (PSR)       16         2.5.2. Supecial Purpose Register (PSR)       16         2.5.2. Window Invalid Mask Register (WIM)       18         2.5.2. Window Invalid Mask Register (WIM)       18         2.5.2. Window Invalid Mask Register (WIM)       18         2.5.3. Trap Base Register (TBR)       18         2.5.4. Y Register       18         2.5.3. Program Counters       18         3. Instruction Set       19         3.1. Data Transfer Instructions       23         3.2. Arithmetic/Logical/Shift Instructions       23         3.2.1. Add and Subtract       24                                                      |                                                 |

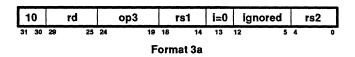

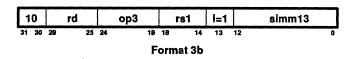

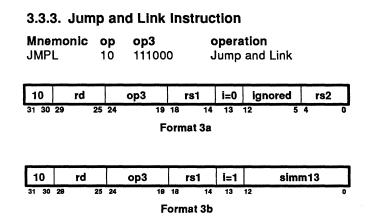

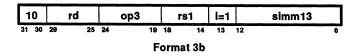

| 2.1.5. Pipeline Examples42.1.6. Delayed Control Transfers52.2. Execution Unit72.3. Address Generation Unit72.4. Address Space Organization102.4.1. Processor Data Types112.4.2. Addressing Conventions112.5. Registers122.5.1. Register File122.5.1. Register File122.5.1. Register Window Use152.5.2. Special Purpose Registers162.5.2. Window Invalid Mask Register (WIM)182.5.2. Window Invalid Mask Register (WIM)182.5.2. Trap Base Register (TBR)182.5.3. Trap Base Register (TBR)182.5.4. Y Register193.1. Data Transfer Instructions233.2. Arithmetic/Logical/Shift Instructions233.2.1. Add and Subtract243.2.3. Multiply Step Instruction243.2.4. Logical Instructions253.2.5. Shift Instructions263.2.7. SETHI Instructions263.2.7. SETHI Instruction273.3.2. CALL Instruction273.3.3. Jump and Link Instruction273.3.4. Trap on Integer Condition Instructions273.3.5. Return from Trap Instruction293.4. Trap on Integer Condition Codes293.4. Trap on Integer Condition Codes                                                                                                        | 2.1.3. Execute Stage                            |

| 2.1.6. Delayed Control Transfers52.2. Execution Unit72.3. Address Generation Unit72.4. Address Space Organization102.4.1. Processor Data Types112.4.2. Addressing Conventions112.5. Registers122.5.1. Register File122.5.1. Register File122.5.1. Register Window Use152.5.2. Special Purpose Registers162.5.2. Special Purpose Registers162.5.2. Special Purpose Register (PSR)162.5.2.3. Trap Base Register (TBR)182.5.3. Program Counters183. Instruction Set193.1. Data Transfer Instructions233.2.1. Add and Subtract233.2.2. Tagged Add and Subtract243.2.3. Multiply Step Instructions253.2.4. Logical Instructions253.2.5. Shift Instructions263.3.1. Branch on Integer Condition Instructions273.3.2. CALL Instruction273.3.3. Jump and Link Instruction273.4. Trap on Integer Condition Instructions293.4. Trap on Integer Condition Codes293.4.1. Read State Register Instructions303.4.1. Read State Register Instructions30                                                                                                                                                                                                                                                                                                                   | 2.1.4. Write Stage                              |

| 2.2. Execution Unit72.3. Address Generation Unit72.4. Address Space Organization102.4.1. Processor Data Types112.4.2. Addressing Conventions112.5. Registers122.5.1. Register File122.5.1. Register File122.5.1. Register Window Use152.5.2. Special Purpose Registers162.5.2.1. Processor State Register (PSR)162.5.2.3. Trap Base Register (TBR)182.5.3. Program Counters183. Instruction Set193.1. Data Transfer Instructions223.1.1. Multiprocessor Support Instructions233.2.2. Tagged Add and Subtract243.2.3. Multiply Step Instruction243.2.4. Logical Instructions253.2.5. Shift Instructions253.2.6. Save and Restore Instructions263.3.1. Branch on Integer Condition Instructions 27263.3.2. CALL Instruction273.3.3. Jump and Link Instruction273.4. Trap on Integer Condition Codes293.5. Return from Trap Instruction293.4. Trap on Integer Condition Codes293.4.1. Read State Register Instructions303.4.1. Read State Register Instructions30                                                                                                                                                                                                                                                                                             |                                                 |

| 2.3. Address Generation Unit72.4. Address Space Organization102.4.1. Processor Data Types112.4.2. Addressing Conventions112.5. Registers122.5.1. Register File122.5.1. Register File122.5.1. Window Selection142.5.1.2. Register Window Use152.5.2. Special Purpose Registers162.5.2.1. Processor State Register (PSR)162.5.2.2. Window Invalid Mask Register (WIM)182.5.2.3. Trap Base Register (TBR)182.5.3. Program Counters183. Instruction Set193.1. Data Transfer Instructions223.1.1. Multiprocessor Support Instructions233.2.2. Tagged Add and Subtract243.2.3. Multiply Step Instruction243.2.4. Logical Instructions253.2.5. Shift Instructions253.2.6. Save and Restore Instructions263.3.1. Branch on Integer Condition Instructions 273.3.2. CALL Instruction273.3.3. Jump and Link Instruction293.4. Trap on Integer Condition Codes293.5. Return from Trap Instruction293.4. Trap on Integer Condition Codes293.4. Trap on Integer Instructions303.4.1. Read State Register Instructions303.4.1. Read State Register Instructions30                                                                                                                                                                                                        |                                                 |

| 2.4. Address Space Organization102.4.1. Processor Data Types112.4.2. Addressing Conventions112.5. Registers122.5.1. Register File122.5.1. Register File122.5.1.1. Window Selection142.5.1.2. Register Window Use152.5.2. Special Purpose Registers162.5.2.1. Processor State Register (PSR)162.5.2.3. Trap Base Register (TBR)182.5.3. Trap Base Register (TBR)182.5.3. Program Counters183. Instruction Set193.1. Data Transfer Instructions223.1.1. Multiprocessor Support Instructions233.2.2. Tagged Add and Subtract243.2.3. Multiply Step Instruction243.2.4. Logical Instructions253.2.5. Shift Instructions253.2.6. Save and Restore Instructions263.3.1. Branch on Integer Condition Instructions 273.3.2. CALL Instruction273.3.3. Jump and Link Instruction293.4. Trap on Integer Condition Codes293.5. Return from Trap Instruction293.4. Trap on Integer Condition Codes293.4. Read/Write Control Register Instructions303.4.1. Read State Register Instructions30                                                                                                                                                                                                                                                                            |                                                 |

| 2.4.1. Processor Data Types       11         2.4.2. Addressing Conventions       11         2.5. Registers       12         2.5.1. Register File       12         2.5.1. Window Selection       14         2.5.1.2. Register Window Use       15         2.5.2. Special Purpose Registers       16         2.5.2.1. Processor State Register (PSR)       16         2.5.2.2. Window Invalid Mask Register (WIM)       18         2.5.2.3. Trap Base Register (TBR)       18         2.5.2.4. Y Register       18         2.5.3. Program Counters       18         3. Instruction Set       19         3.1. Data Transfer Instructions       22         3.1.1. Multiprocessor Support Instructions       23         3.2.1. Add and Subtract       23         3.2.2. Tagged Add and Subtract       24         3.2.3. Multiply Step Instruction       24         3.2.4. Logical Instructions       25         3.2.5. Shift Instructions       26         3.2.7. SETHI Instruction       26         3.3.1. Branch on Integer Condition Instructions 27       3.3.2. CALL Instruction         3.3.3. Jump and Link Instruction       29         3.4. Trap on Integer Condition Codes       29         3.4. Trap on Integer C                                    |                                                 |

| 2.4.2. Addressing Conventions       11         2.5. Registers       12         2.5.1. Register File       12         2.5.1. Window Selection       14         2.5.1.2. Register Window Use       15         2.5.2. Special Purpose Registers       16         2.5.2. Special Purpose Register (PSR)       16         2.5.2.1. Processor State Register (PSR)       16         2.5.2.2. Window Invalid Mask Register (WIM)       18         2.5.2.3. Trap Base Register (TBR)       18         2.5.2.4. Y Register       18         2.5.3. Program Counters       18         2.5.3. Program Counters       18         3. Instruction Set       19         3.1. Data Transfer Instructions       22         3.1.1. Multiprocessor Support Instructions       23         3.2.1. Add and Subtract       23         3.2.2. Tagged Add and Subtract       24         3.2.3. Multiply Step Instruction       24         3.2.4. Logical Instructions       25         3.2.5. Shift Instructions       26         3.2.7. SETHI Instruction       26         3.3.1. Branch on Integer Condition Instructions 27       3.3.2. CALL Instruction         3.3.3. Jump and Link Instruction       29         3.4. Trap on Integer Cond                                    |                                                 |

| 2.5. Registers122.5.1. Register File122.5.1. Window Selection142.5.1.2. Register Window Use152.5.2. Special Purpose Registers162.5.2.1. Processor State Register (PSR)162.5.2.2. Window Invalid Mask Register (WIM)182.5.2.3. Trap Base Register (TBR)182.5.2.4. Y Register182.5.3. Program Counters183. Instruction Set193.1. Data Transfer Instructions223.1.1. Multiprocessor Support Instructions233.2.2. Tagged Add and Subtract233.2.3. Multiply Step Instructions243.2.4. Logical Instructions253.2.5. Shift Instructions253.2.6. Save and Restore Instructions263.3.1. Branch on Integer Condition Instructions 27273.3.3. Jump and Link Instruction273.3.4. Trap on Integer Condition Codes293.3.5. Return from Trap Instruction293.4. Read/Write Control Register Instructions303.4.1. Read State Register Instructions30                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                 |

| 2.5.1. Register File       12         2.5.1.1. Window Selection       14         2.5.1.2. Register Window Use       15         2.5.2. Special Purpose Registers       16         2.5.2. Special Purpose Register (PSR)       16         2.5.2.1. Processor State Register (PSR)       16         2.5.2.2. Window Invalid Mask Register (WIM)       18         2.5.2.3. Trap Base Register (TBR)       18         2.5.2.4. Y Register       18         2.5.3. Program Counters       18         3. Instruction Set       19         3.1. Data Transfer Instructions       22         3.1.1. Multiprocessor Support Instructions       23         3.2.2. Tagged Add and Subtract       24         3.2.3. Multiply Step Instruction       24         3.2.4. Logical Instructions       25         3.2.5. Shift Instructions       25         3.2.6. Save and Restore Instructions       26         3.3.1. Branch on Integer Condition Instructions 27       3.3.2. CALL Instruction         3.3.1. Branch on Integer Condition Codes       29         3.3.4. Trap on Integer Condition Codes       29         3.3.5. Return from Trap Instruction       29         3.4. Trap on Integer Condition Codes       29         3.4. Read/Write Control Register Ins |                                                 |

| 2.5.1.1. Window Selection       14         2.5.1.2. Register Window Use       15         2.5.2. Special Purpose Registers       16         2.5.2. Special Purpose Register (PSR)       16         2.5.2.1. Processor State Register (PSR)       16         2.5.2.2. Window Invalid Mask Register (WIM)       18         2.5.2.3. Trap Base Register (TBR)       18         2.5.2.4. Y Register       18         2.5.3. Program Counters       18         3. Instruction Set       19         3.1. Data Transfer Instructions       22         3.1.1. Multiprocessor Support Instructions       23         3.2. Arithmetic/Logical/Shift Instructions       23         3.2.1. Add and Subtract       24         3.2.3. Multiply Step Instruction       24         3.2.4. Logical Instructions       25         3.2.5. Shift Instructions       25         3.2.6. Save and Restore Instructions       26         3.3. Control Transfer Instructions       26         3.3.1. Branch on Integer Condition Instructions 27       3.3.2. CALL Instruction         3.3.2. CALL Instruction       27         3.3.3. Jump and Link Instruction       29         3.4. Trap on Integer Condition Codes       29         3.4. Trap on Integer Condition Codes          |                                                 |

| 2.5.1.2. Register Window Use152.5.2. Special Purpose Registers162.5.2.1. Processor State Register (PSR)162.5.2.2. Window Invalid Mask Register (WIM)182.5.2.3. Trap Base Register (TBR)182.5.2.4. Y Register182.5.3. Program Counters183. Instruction Set193.1. Data Transfer Instructions223.1.1. Multiprocessor Support Instructions233.2.2. Tagged Add and Subtract243.2.3. Multiply Step Instruction243.2.4. Logical Instructions253.2.5. Shift Instructions253.2.6. Save and Restore Instructions263.3.1. Branch on Integer Condition Instructions 27273.3.2. CALL Instruction273.3.3. Jump and Link Instruction293.4. Trap on Integer Condition Codes293.4. Read/Write Control Register Instructions303.4.1. Read State Register Instructions30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                 |

| 2.5.2. Special Purpose Registers162.5.2.1. Processor State Register (PSR)162.5.2.2. Window Invalid Mask Register (WIM)182.5.2.3. Trap Base Register (TBR)182.5.2.4. Y Register182.5.3. Program Counters183. Instruction Set193.1. Data Transfer Instructions223.1.1. Multiprocessor Support Instructions233.2.2. Arithmetic/Logical/Shift Instructions233.2.1. Add and Subtract233.2.2. Tagged Add and Subtract243.2.3. Multiply Step Instruction243.2.4. Logical Instructions253.2.5. Shift Instructions253.2.6. Save and Restore Instructions263.7. SETHI Instruction263.8. Control Transfer Instructions263.9. CALL Instruction273.3.1. Branch on Integer Condition Instructions273.3.3. Jump and Link Instruction293.4. Trap on Integer Condition Codes293.5. Return from Trap Instruction293.4. Trap on Integer Condition Codes293.4. Read/Write Control Register Instructions303.4.1. Read State Register Instructions30                                                                                                                                                                                                                                                                                                                             |                                                 |

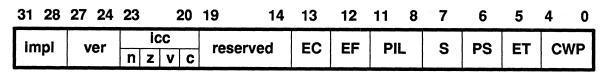

| 2.5.2.1. Processor State Register (PSR)162.5.2.2. Window Invalid Mask Register (WIM)182.5.2.3. Trap Base Register (TBR)182.5.2.4. Y Register182.5.3. Program Counters183. Instruction Set193.1. Data Transfer Instructions223.1.1. Multiprocessor Support Instructions233.2. Arithmetic/Logical/Shift Instructions233.2.1. Add and Subtract243.2.2. Tagged Add and Subtract243.2.3. Multiply Step Instruction243.2.4. Logical Instructions253.2.5. Shift Instructions253.2.6. Save and Restore Instructions263.3. Control Transfer Instructions263.3. Instruction273.3. Jump and Link Instruction273.4. Trap on Integer Condition Codes293.4. Read/Write Control Register Instructions303.4.1. Read State Register Instructions30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                 |

| 2.5.2.2. Window Invalid Mask Register (WIM).182.5.2.3. Trap Base Register (TBR).182.5.2.4. Y Register.182.5.3. Program Counters.183. Instruction Set.193.1. Data Transfer Instructions.223.1.1. Multiprocessor Support Instructions.233.2. Arithmetic/Logical/Shift Instructions.233.2.1. Add and Subtract.233.2.2. Tagged Add and Subtract.243.2.3. Multiply Step Instruction.243.2.4. Logical Instructions.253.2.5. Shift Instructions.253.2.6. Save and Restore Instructions.263.3. Control Transfer Instructions.263.3. Linstruction.263.3. Linstruction.273.3. Jump and Link Instruction.273.4. Trap on Integer Condition Codes.293.4. Trap on Integer Condition Codes.293.4. Read/Write Control Register Instructions.303.4.1. Read State Register Instructions.30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                 |

| 2.5.2.3. Trap Base Register (TBR)182.5.2.4. Y Register182.5.3. Program Counters183. Instruction Set193.1. Data Transfer Instructions223.1.1. Multiprocessor Support Instructions233.2. Arithmetic/Logical/Shift Instructions233.2.1. Add and Subtract233.2.2. Tagged Add and Subtract243.2.3. Multiply Step Instruction243.2.4. Logical Instructions253.2.5. Shift Instructions253.2.6. Save and Restore Instructions263.2.7. SETHI Instruction263.3. Control Transfer Instructions263.3.1. Branch on Integer Condition Instructions 27273.3.3. Jump and Link Instruction293.4. Trap on Integer Condition Codes293.4. Trap on Integer Condition Codes293.4. Read/Write Control Register Instructions303.4.1. Read State Register Instructions30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.5.2.2. Window Invalid Mask Register (WIM) .18 |

| 2.5.3. Program Counters.183. Instruction Set.193.1. Data Transfer Instructions.223.1.1. Multiprocessor Support Instructions.233.2. Arithmetic/Logical/Shift Instructions.233.2.1. Add and Subtract.233.2.2. Tagged Add and Subtract.243.2.3. Multiply Step Instruction.243.2.4. Logical Instructions.253.2.5. Shift Instructions.253.2.6. Save and Restore Instructions.263.7. SETHI Instruction.263.8. Control Transfer Instructions.263.9. CALL Instruction.273.3.1. Branch on Integer Condition Instructions 273.3.2. CALL Instruction.273.3.4. Trap on Integer Condition Codes.293.4. Trap on Integer Condition Codes.293.4. Read/Write Control Register Instructions.303.4.1. Read State Register Instructions.30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                 |

| 3. Instruction Set193.1. Data Transfer Instructions223.1.1. Multiprocessor Support Instructions233.2. Arithmetic/Logical/Shift Instructions233.2.1. Add and Subtract233.2.2. Tagged Add and Subtract243.2.3. Multiply Step Instruction243.2.4. Logical Instructions253.2.5. Shift Instructions253.2.6. Save and Restore Instructions263.2.7. SETHI Instruction263.3. Control Transfer Instructions263.3.1. Branch on Integer Condition Instructions 27273.3.3. Jump and Link Instruction293.4. Trap on Integer Condition Codes293.4. Read/Write Control Register Instructions303.4.1. Read State Register Instructions30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                 |

| 3.1. Data Transfer Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.5.3. Program Counters                         |

| 3.1.1. Multiprocessor Support Instructions.233.2. Arithmetic/Logical/Shift Instructions.233.2.1. Add and Subtract.233.2.2. Tagged Add and Subtract.243.2.3. Multiply Step Instruction.243.2.4. Logical Instructions.253.2.5. Shift Instructions.253.2.6. Save and Restore Instructions.263.2.7. SETHI Instruction.263.3. Control Transfer Instructions.263.3.1. Branch on Integer Condition Instructions 273.3.2. CALL Instruction.273.3.3. Jump and Link Instruction.293.4. Trap on Integer Condition Codes.293.4. Read/Write Control Register Instructions.303.4.1. Read State Register Instructions.30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3. Instruction Set19                            |

| 3.1.1. Multiprocessor Support Instructions.233.2. Arithmetic/Logical/Shift Instructions.233.2.1. Add and Subtract.233.2.2. Tagged Add and Subtract.243.2.3. Multiply Step Instruction.243.2.4. Logical Instructions.253.2.5. Shift Instructions.253.2.6. Save and Restore Instructions.263.2.7. SETHI Instruction.263.3. Control Transfer Instructions.263.3.1. Branch on Integer Condition Instructions 273.3.2. CALL Instruction.273.3.3. Jump and Link Instruction.293.4. Trap on Integer Condition Codes.293.4. Read/Write Control Register Instructions.303.4.1. Read State Register Instructions.30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.1. Data Transfer Instructions                 |

| 3.2.1. Add and Subtract233.2.2. Tagged Add and Subtract243.2.3. Multiply Step Instruction243.2.4. Logical Instructions253.2.5. Shift Instructions253.2.6. Save and Restore Instructions263.2.7. SETHI Instruction263.3. Control Transfer Instructions263.3.1. Branch on Integer Condition Instructions 273.3.2. CALL Instruction273.3.3. Jump and Link Instruction293.4. Trap on Integer Condition Codes293.4. Read/Write Control Register Instructions303.4.1. Read State Register Instructions30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                 |

| 3.2.2. Tagged Add and Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.2. Arithmetic/Logical/Shift Instructions23    |

| 3.2.3. Multiply Step Instruction.243.2.4. Logical Instructions.253.2.5. Shift Instructions.253.2.6. Save and Restore Instructions.263.2.7. SETHI Instruction.263.3. Control Transfer Instructions.263.3.1. Branch on Integer Condition Instructions 273.3.2. CALL Instruction.273.3.3. Jump and Link Instruction.293.4. Trap on Integer Condition Codes.293.4. Read/Write Control Register Instructions.303.4.1. Read State Register Instructions.30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.2.1. Add and Subtract                         |

| 3.2.4. Logical Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                 |

| 3.2.5. Shift Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                 |

| 3.2.6. Save and Restore Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                 |

| 3.2.7. SETHI Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                 |

| 3.3. Control Transfer Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                 |

| <ul> <li>3.3.1. Branch on Integer Condition Instructions 27</li> <li>3.3.2. CALL Instruction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                 |

| 3.3.2. CALL Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                 |

| <ul> <li>3.3.3. Jump and Link Instruction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                 |

| <ul> <li>3.3.4. Trap on Integer Condition Codes</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                 |

| 3.3.5. Return from Trap Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •                                               |

| 3.4. Read/Write Control Register Instructions .30<br>3.4.1. Read State Register Instructions30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                 |

| 3.4.1. Read State Register Instructions30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                 |

| 4. Floating Point Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _                                               |

| 5. Trap and Exception Handling            |

|-------------------------------------------|

| 5.1. Synchronous Traps                    |

| 5.2. Floating Point Traps                 |

| 5.3. Asynchronous Traps                   |

| 5.4. Trap Addressing                      |

| 5.5. Trap Priorities                      |

| 5.6. Trap Processing                      |

| 5.7. Interrupt Detection                  |

| 5.8. Trap Definitions                     |

| 6. Reset                                  |

|                                           |

| 7. Bus Signals                            |

| 7.1. System Interface40                   |

| 7.1.1. Basic Timing                       |

| 7.1.2. Basic Data Transfer Timing         |

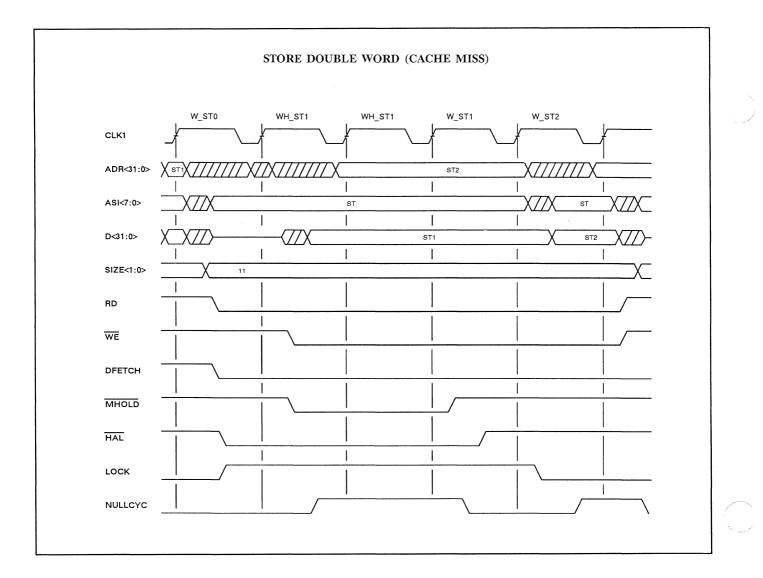

| 7.1.3. Cache Miss Timing                  |

| 7.1.4. Memory Exception Timing            |

| 7.1.5. Special Timing                     |

| 7.2. Floating Point Interface             |

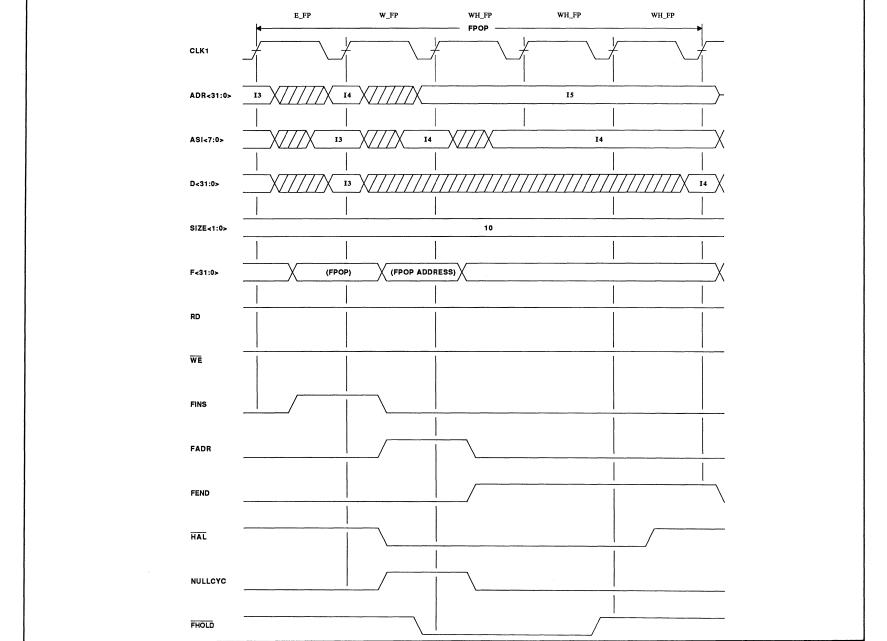

| 7.2.1. FPOP Instruction Transfer Timing62 |

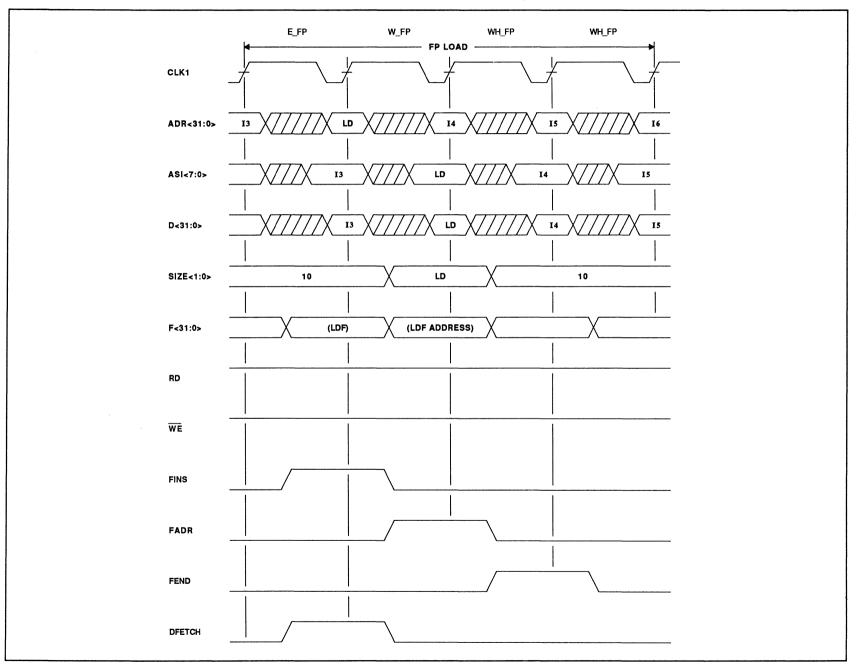

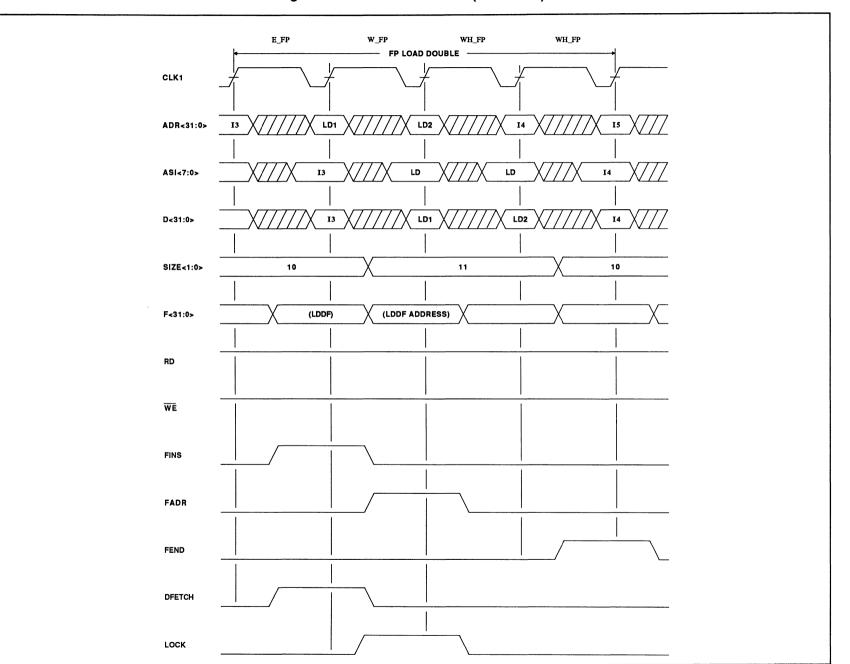

| 7.2.2. FP Load And Store Timing           |

| 7.2.3. Cache Miss and Exception Timing62  |

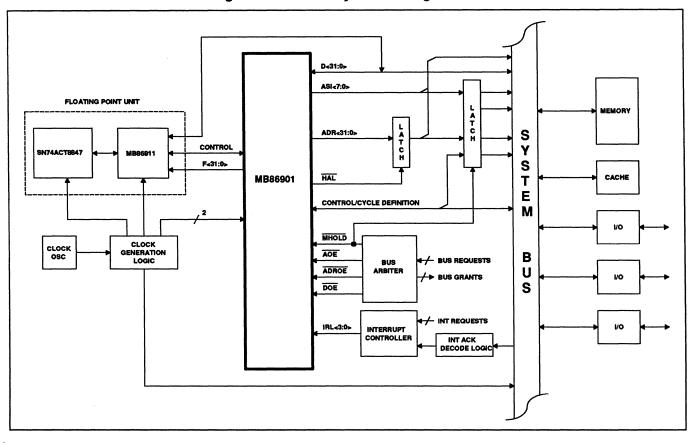

| 7.3. System Configuration                 |

| 8. System Design Considerations           |

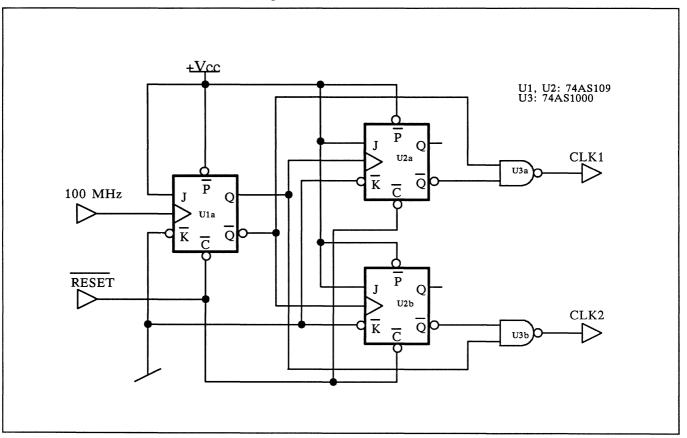

| 8.1. Clock Generator                      |

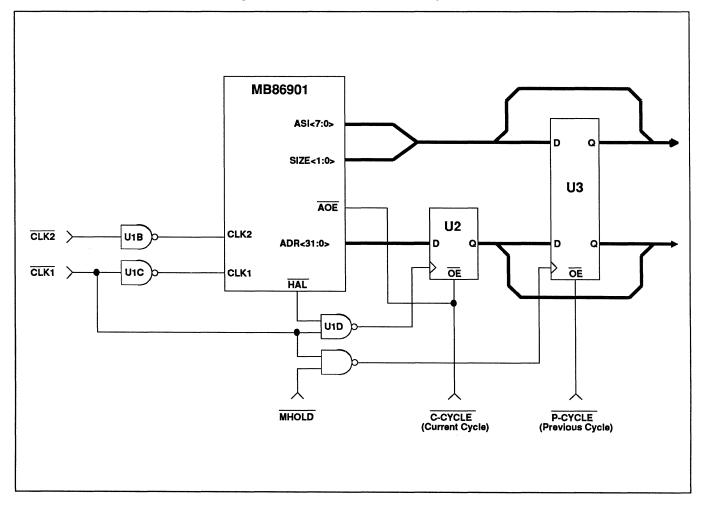

| 8.2. External Address Pipeline            |

| 9. Processor Specifications80             |

| 10. Errata94                              |

# FUJITSU

FUJITSU M

List of Figures

# MB86901

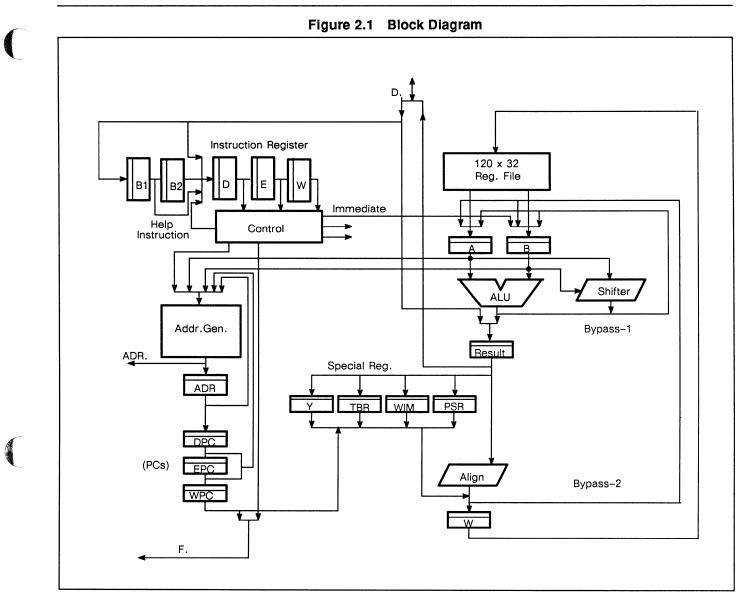

| Figure 2.1    | Block Diagram                                                  |

|---------------|----------------------------------------------------------------|

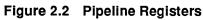

| Figure 2.2    | Pipeline Registers                                             |

| Figure 2.3    | Single-cycle Instruction Pipeline<br>Progression4              |

| Figure 2.4    | Two-cycle Instruction Pipeline                                 |

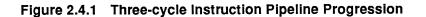

| Figure 2.4.1  | Progression5<br>Three-cycle Instruction Pipeline               |

| -             | Progression6                                                   |

| Figure 2.4.2  | Illustration of Register Interlock6                            |

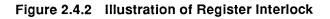

| Figure 2.4.3a | Delay Instruction Executed                                     |

| Figure 2.4.3b | During Branch Taken (a=0)8<br>Delay Instruction Annulled (a=1) |

|               | During Branch Not Taken8                                       |

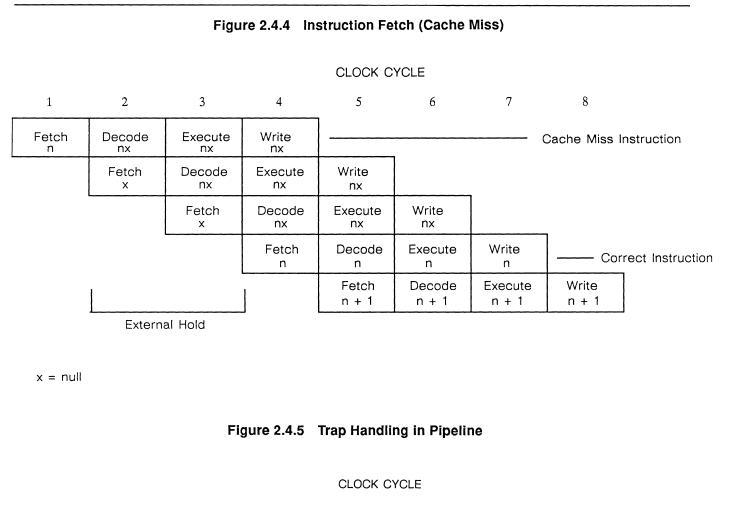

| Figure 2.4.4  | Instruction Fetch<br>(Cache Miss)9                             |

| Figure 2.4.5  | Trap Handling in Pipeline9                                     |

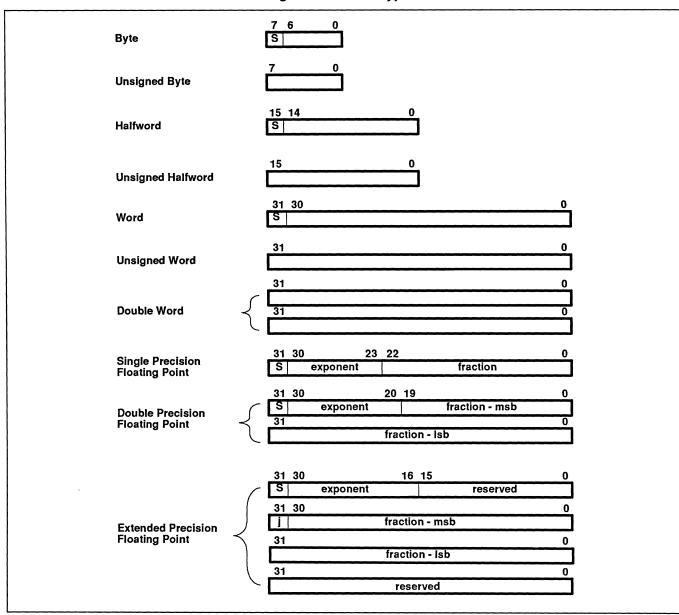

| Figure 2.5    | Data Types                                                     |

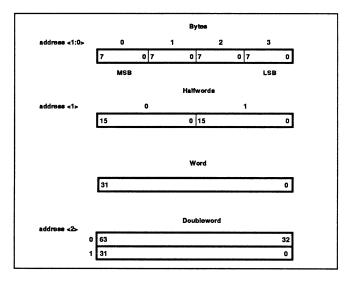

| Figure 2.5.1  | Addressing Conventions                                         |

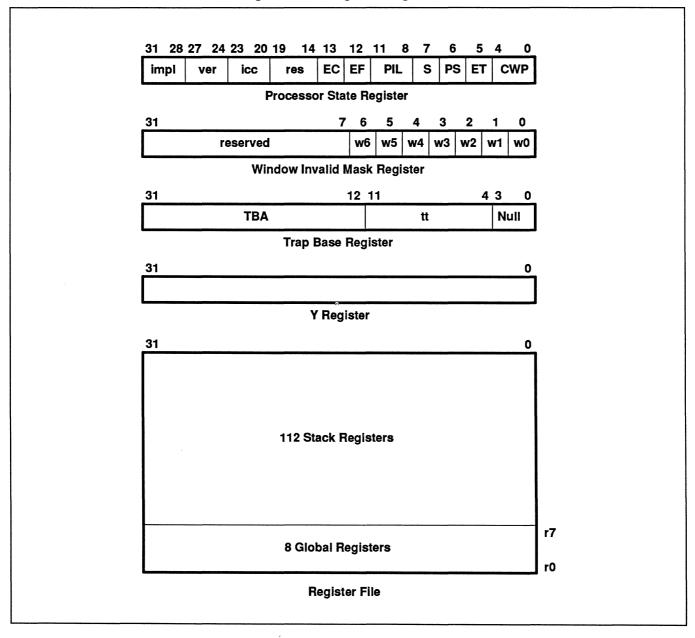

| Figure 2.6    | Programming Model                                              |

|               |                                                                |

| Figure 2.7    | Register File with Windows13                                   |

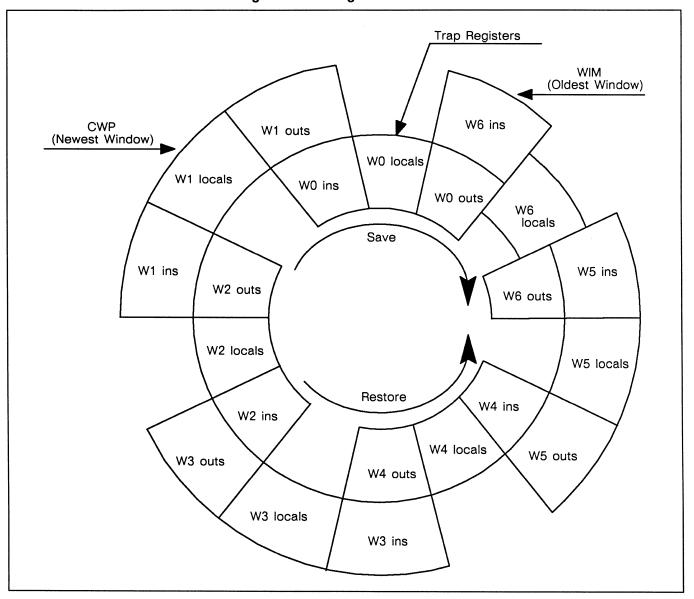

| Figure 2.7.1  | Register Windows                                               |

| Figure 2.8    | Program Counter Sequencing 18                                  |

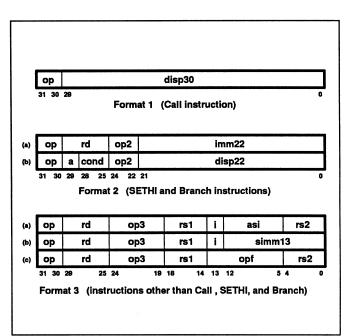

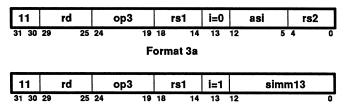

| Figure 3.1    | Instruction Formats                                            |

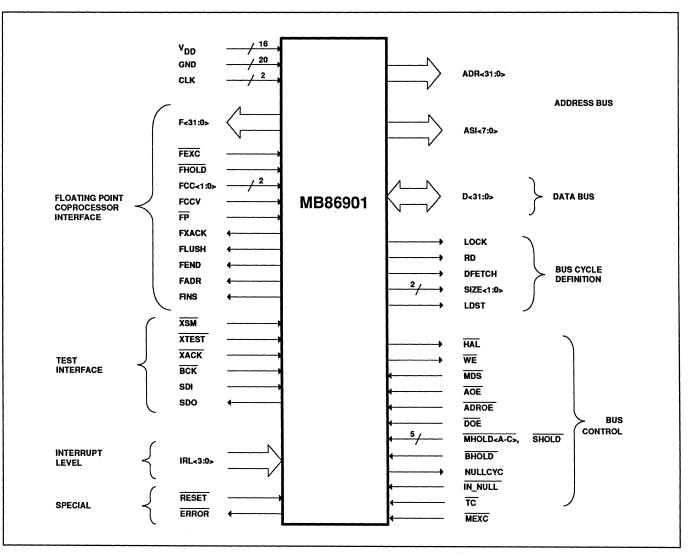

| Figure 7.1    | Processor Signals                                              |

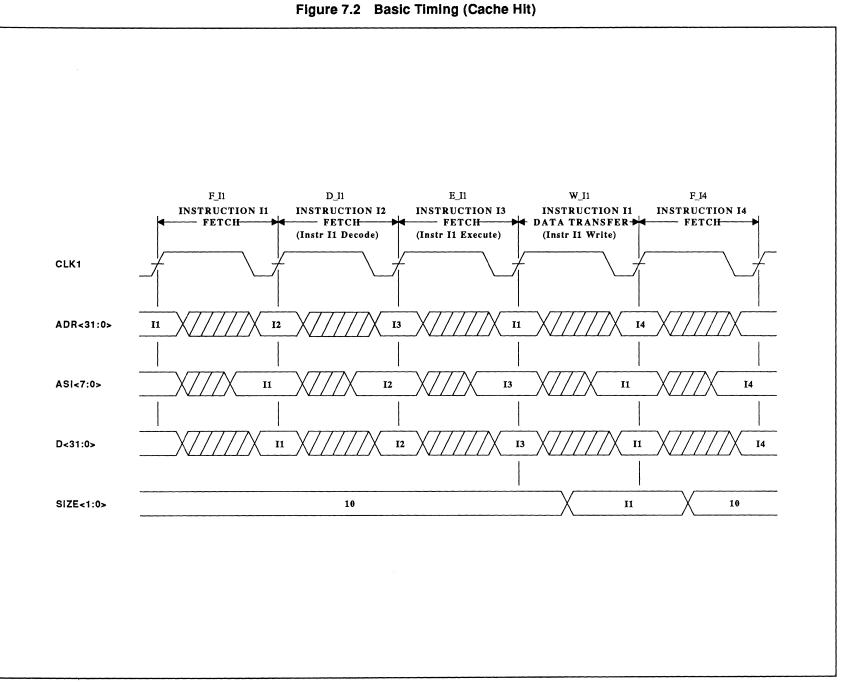

| Figure 7.2    | Basic Timing (Cache Hit)43                                     |

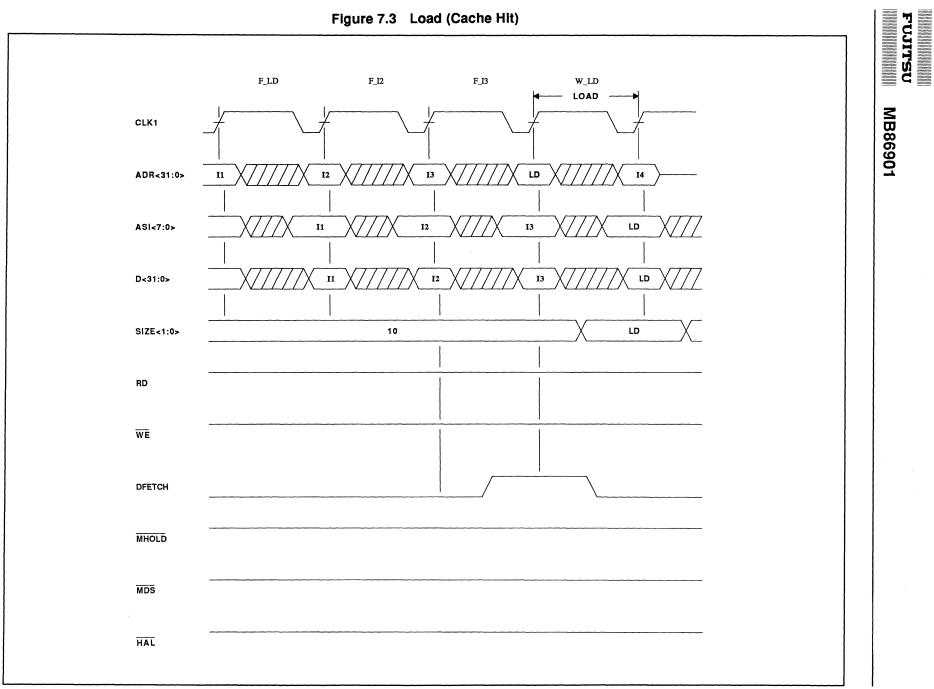

| Figure 7.3    | Load (Cache Hit)                                               |

| Figure 7.4    | Store (Cache Hit)                                              |

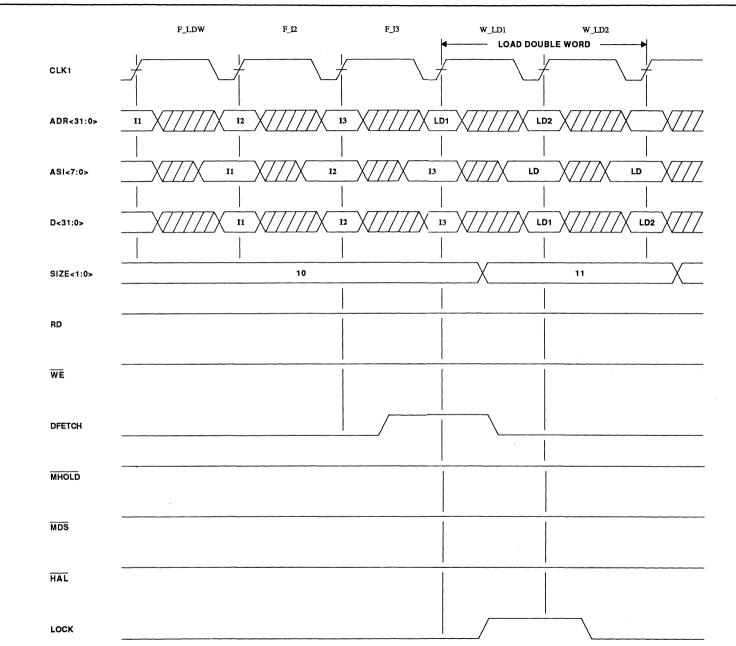

| Figure 7.5    | Load Double Word (Cache Hit)46                                 |

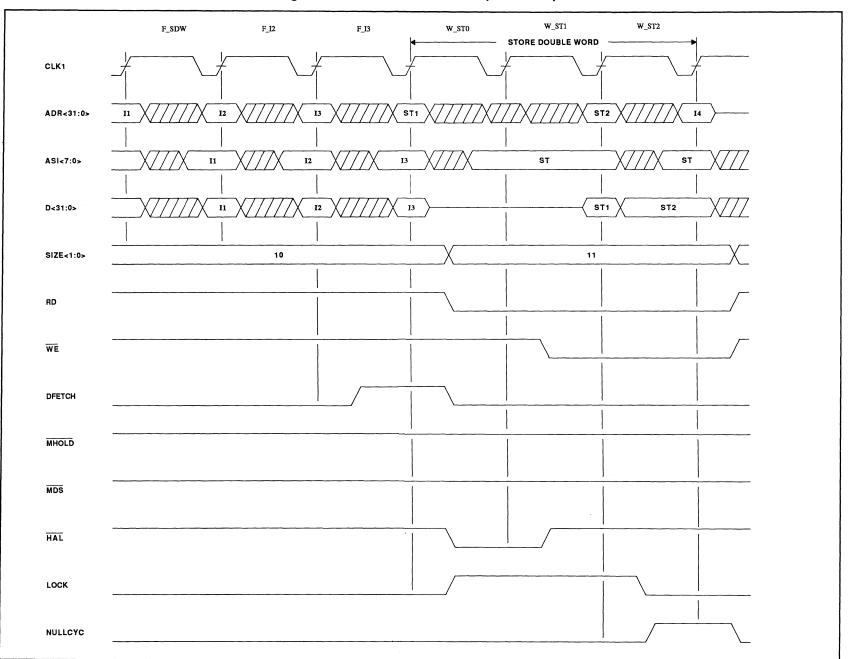

| Figure 7.6    | Store Double Word (Cache Hit)47                                |

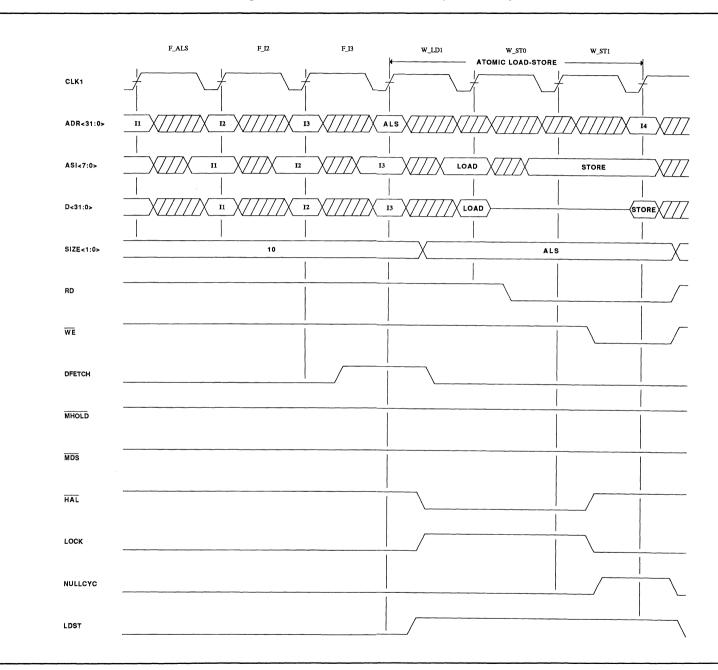

| Figure 7.7    | Atomic Load-Store (Cache Hit)48                                |

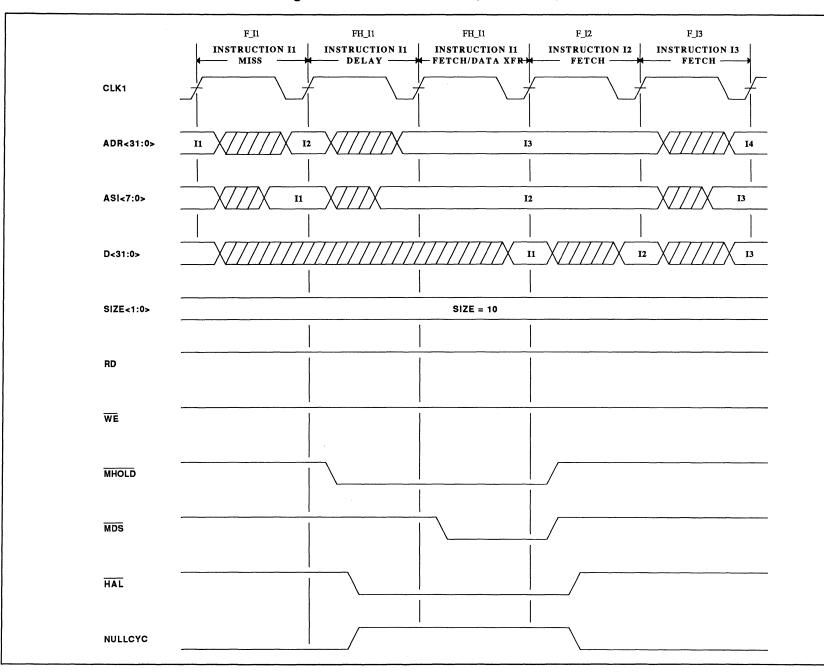

| Figure 7.8    | Instruction Fetch (Cache Miss)50                               |

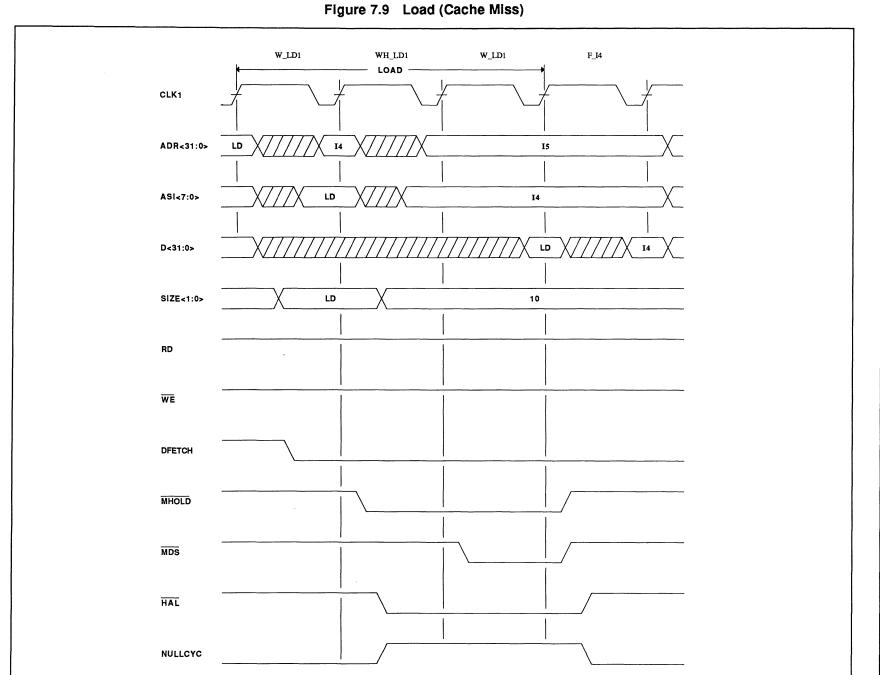

| Figure 7.9    | Load (Cache Miss)                                              |

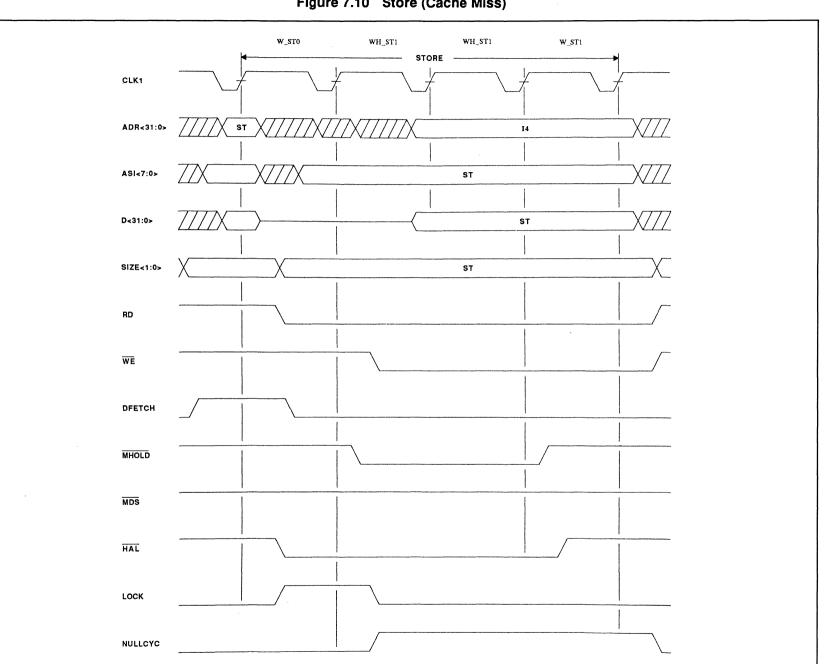

| Figure 7.10   | Store (Cache Miss)                                             |

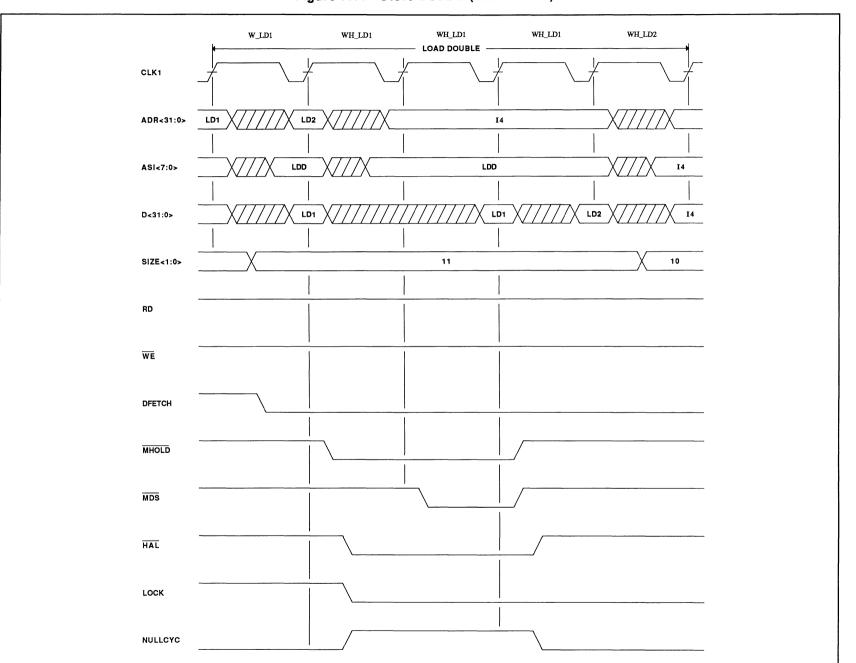

| Figure 7.11   | Load Double (Cache Miss) 53 (94)                               |

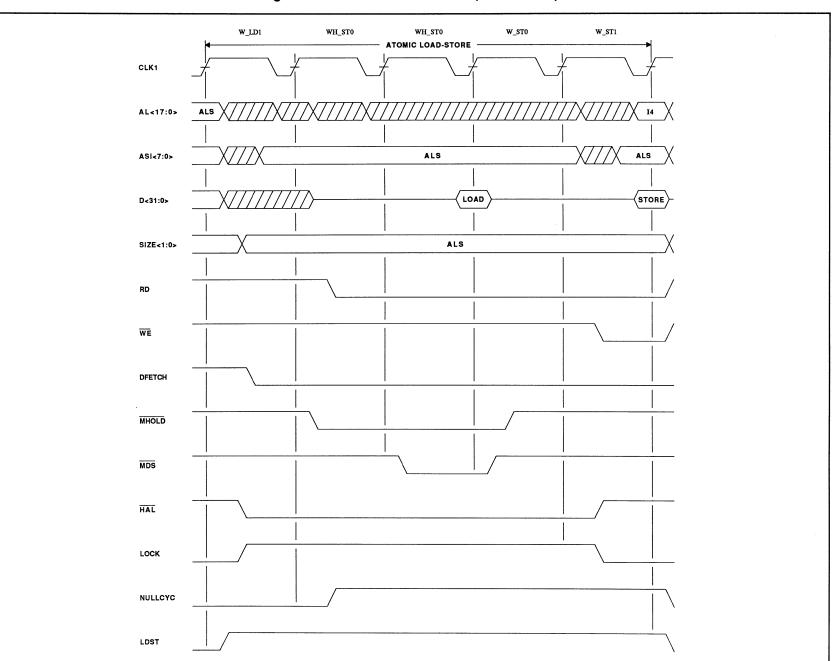

| Figure 7.12   | Atomic Load-Store<br>(Cache Miss)54                            |

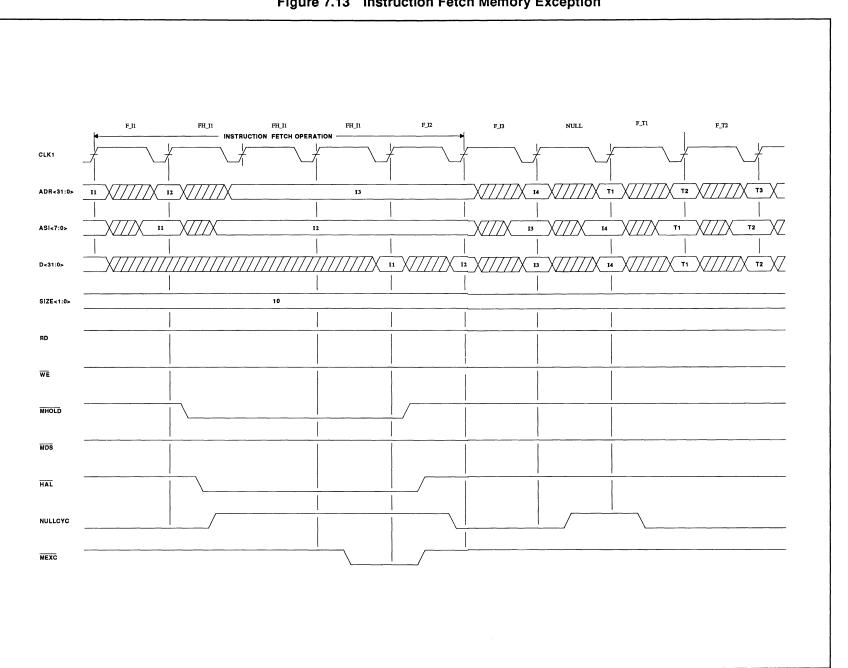

| Figure 7.13   | Instruction Fetch Memory                                       |

| 5             | Exception                                                      |

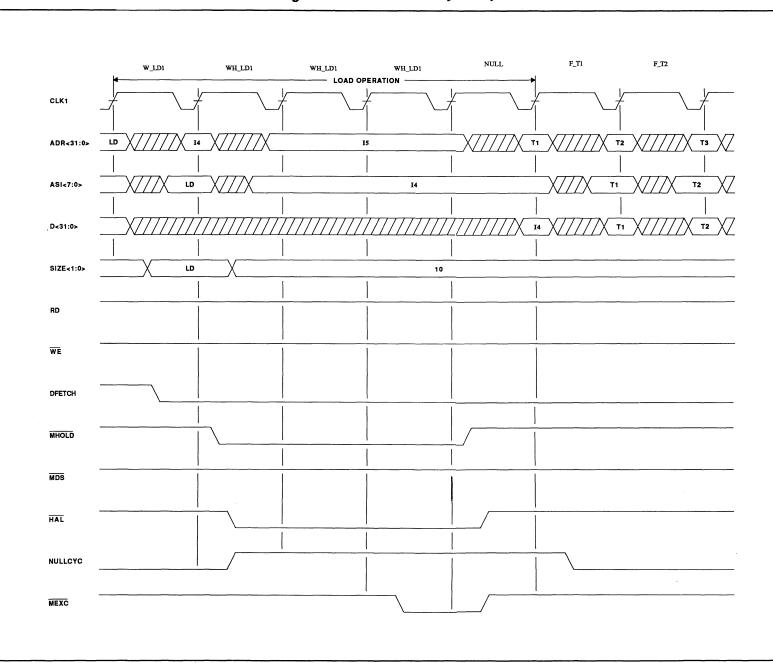

| Figure 7.14   | Load Memory Exception                                          |

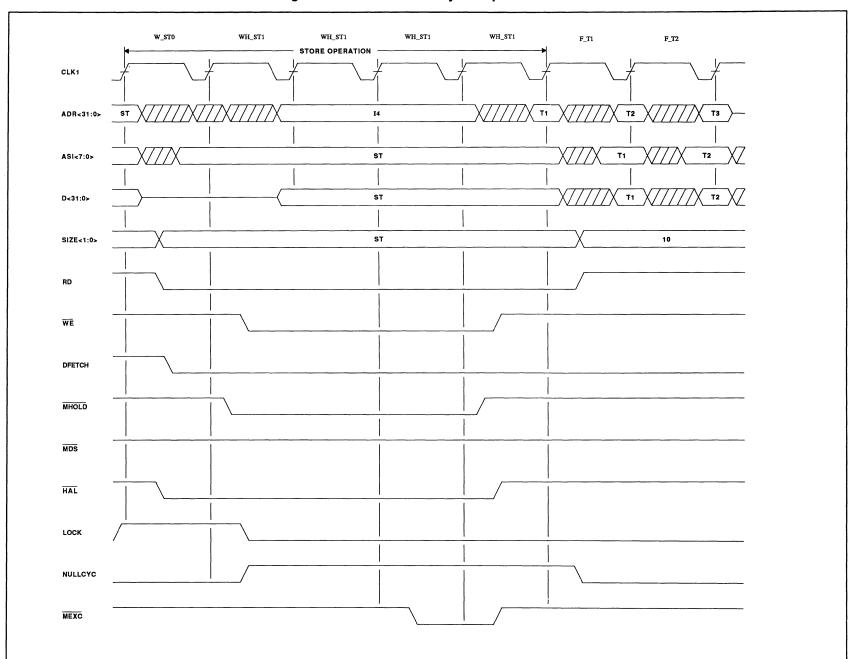

| Figure 7.15   | Store Memory Exception                                         |

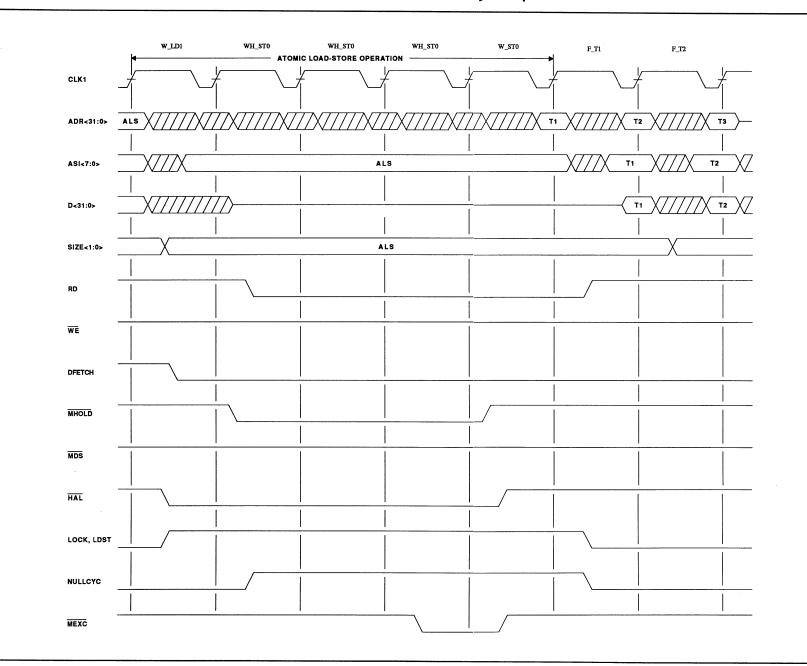

| Figure 7.16   | Atomic Load-Store Memory                                       |

|               | Exception                                                      |

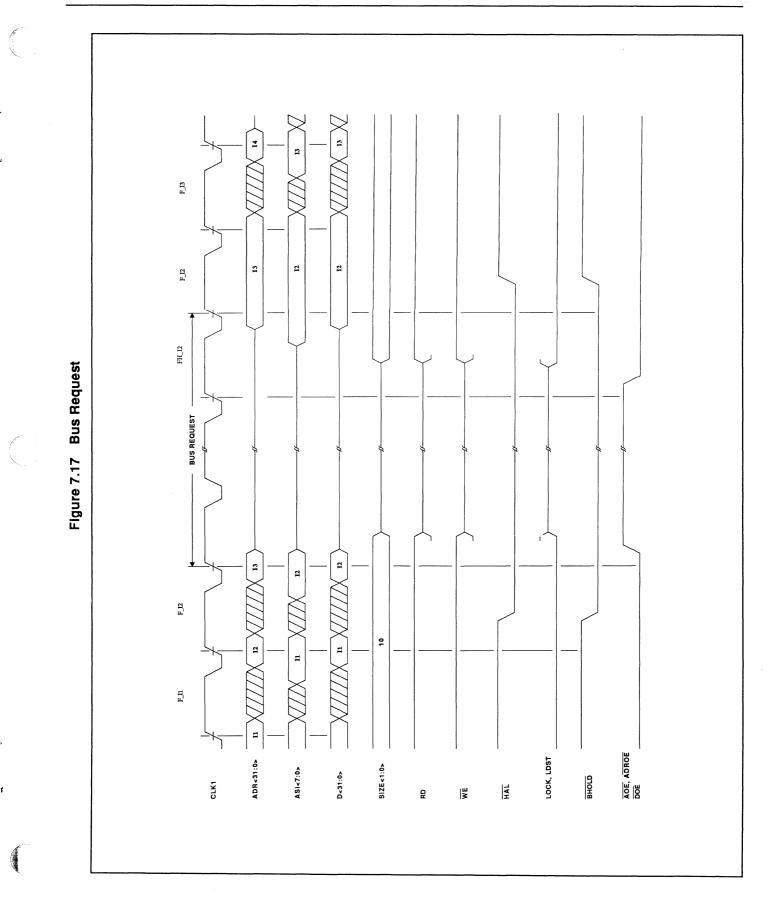

| Figure 7.17   | Bus Request                                                    |

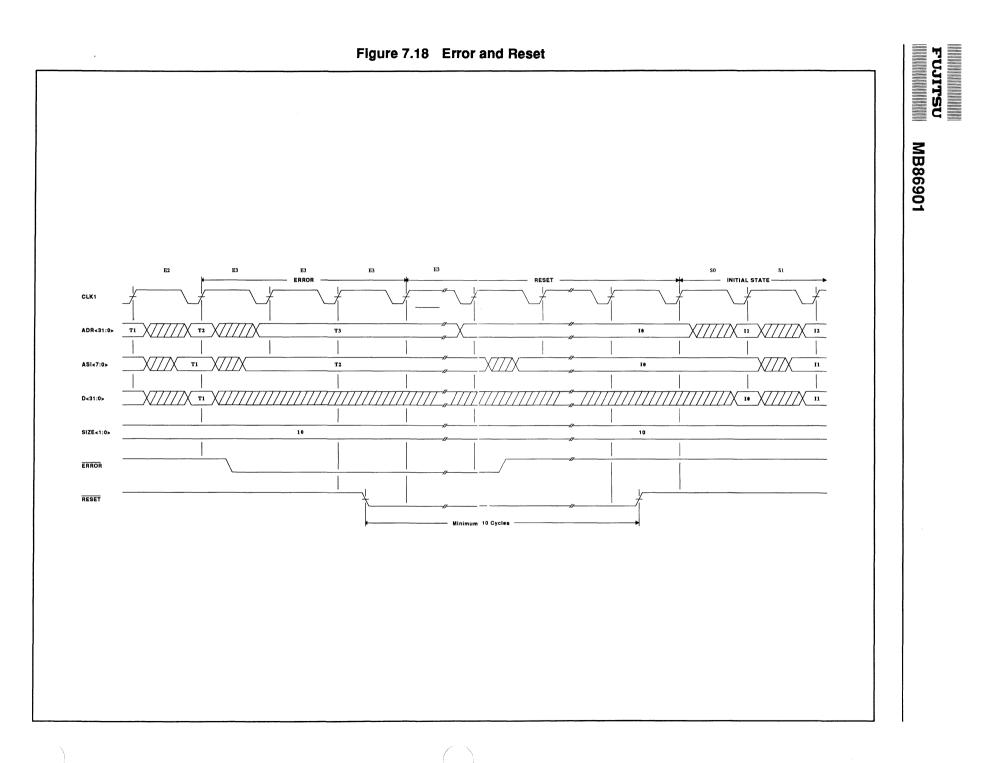

| Figure 7.18   | Error and Reset60                                              |

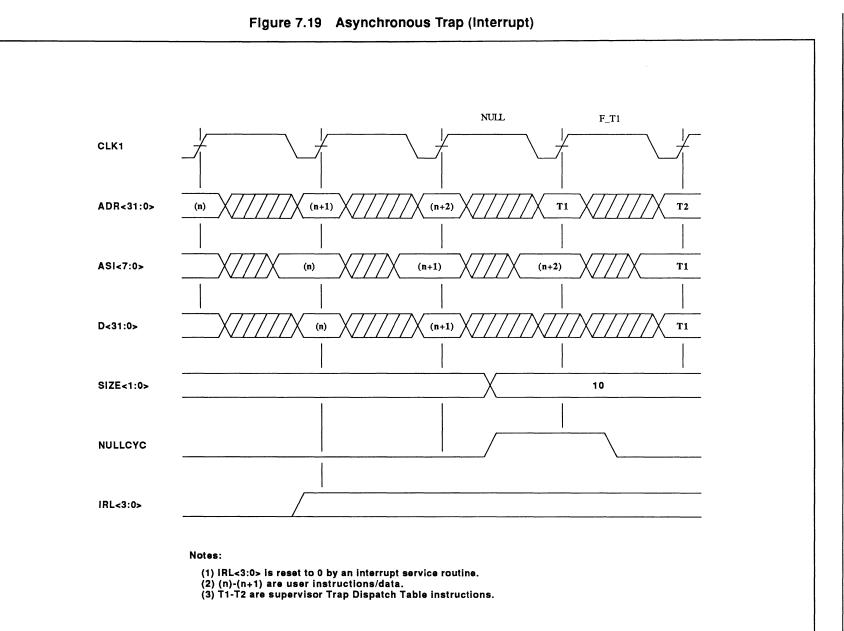

| Figure 7.19   | Asynchronous Trap (Interrupt)61                                |

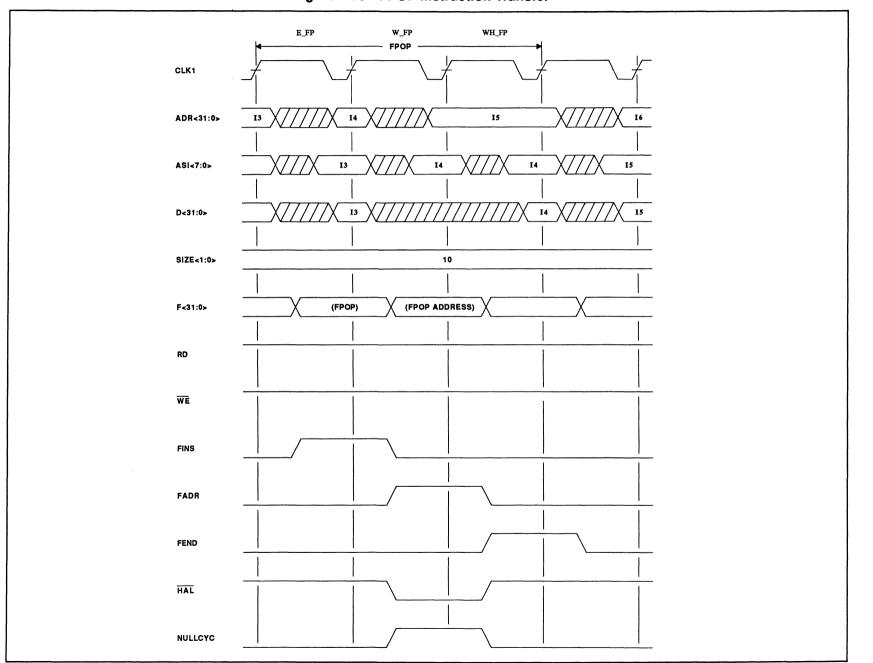

| Figure 7.20   | FPOP Instruction Transfer63                                    |

| Figure 7.21   | FPOP Instruction Hold64                                        |

| Figure 7.22   | FP Load (Cache Hit)65                                          |

| Figure 7.23   | FP Store (Cache Hit)66                                         |

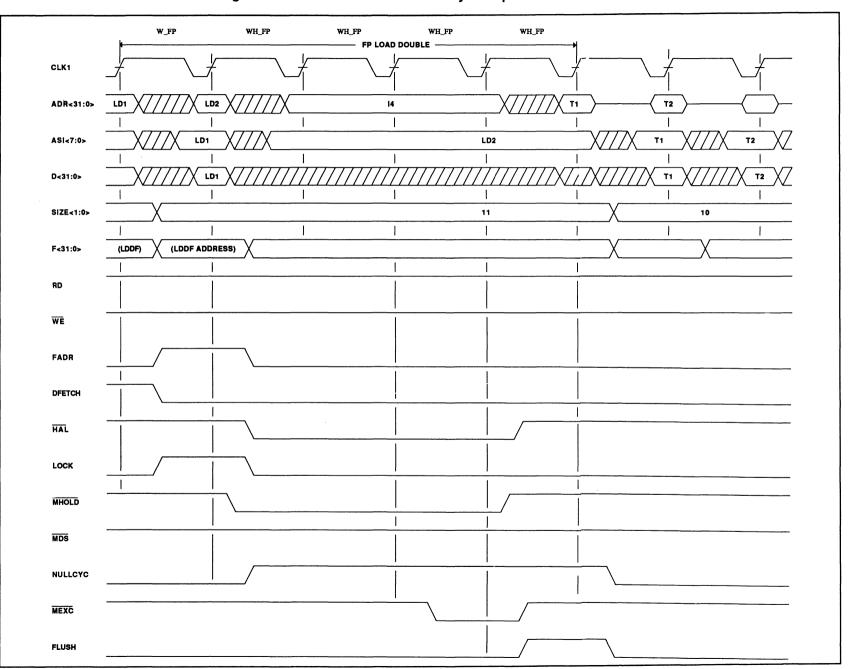

| Figure 7.24   | FP Load Double (Cache Hit)67                                   |

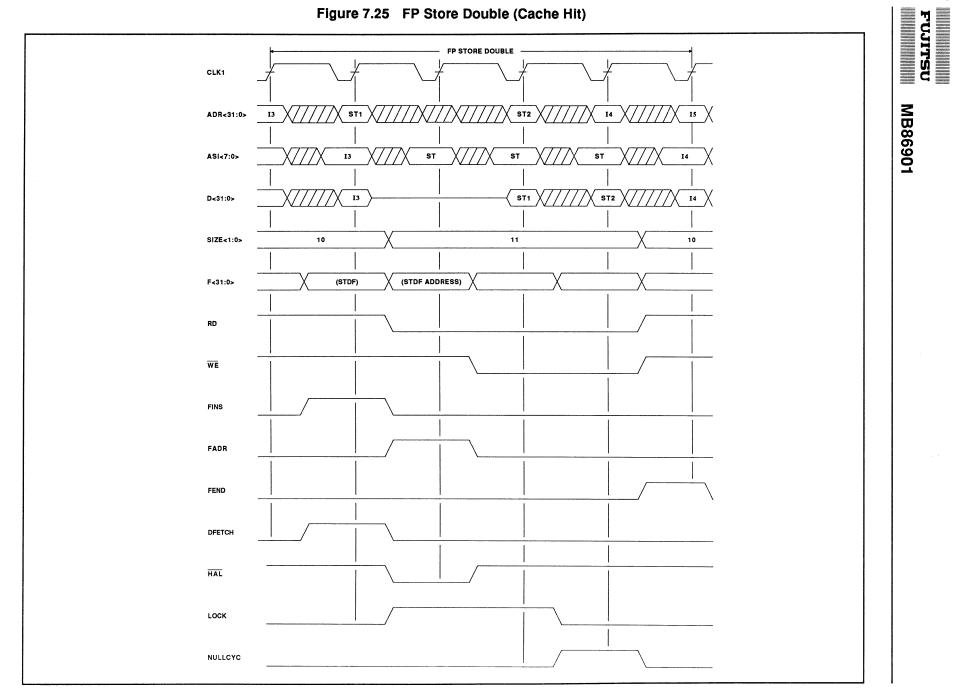

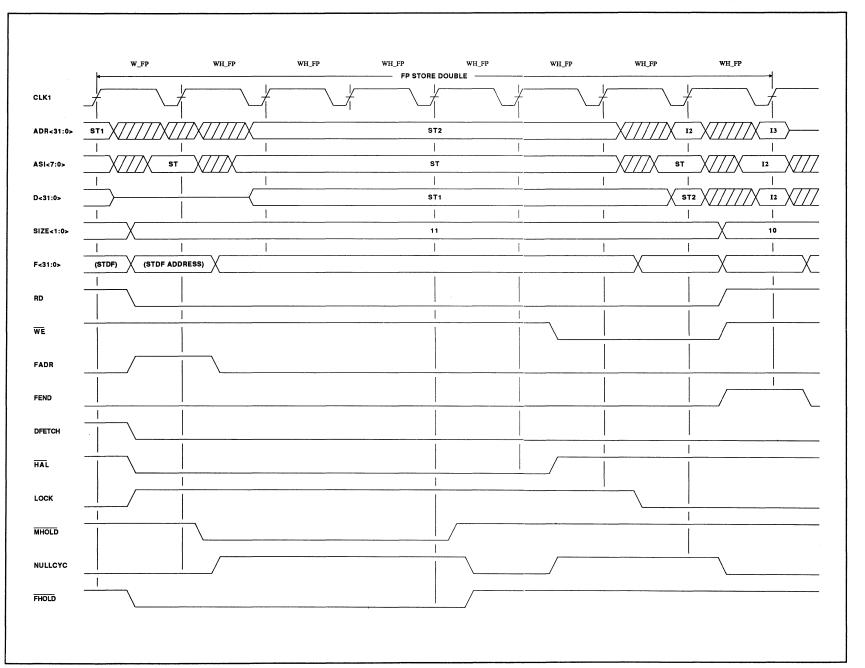

| Figure 7.25   | FP Store Double (Cache Hit)68                                  |

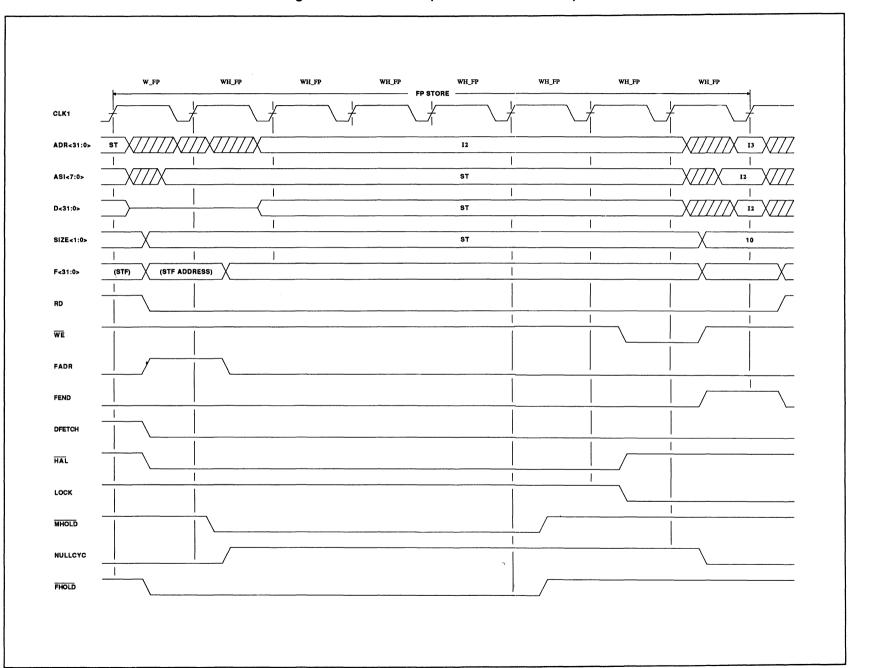

| Figure 7.26   | FP Store (Hold and Cache Miss)69                               |

| -             | · · · · · ·                                                    |

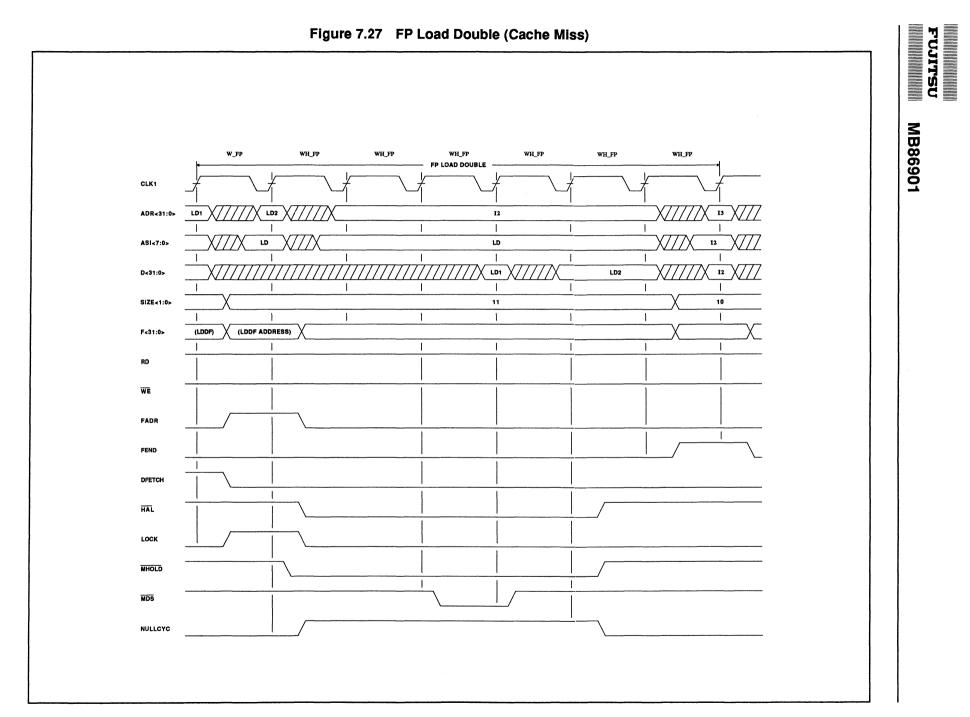

| Figure 7.28FP Store Double (Cache Miss)71Figure 7.29FP Store Double (Hold and<br>Cache Miss)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Figure 7.27 | FP Load Double (Cache Miss)70  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------|

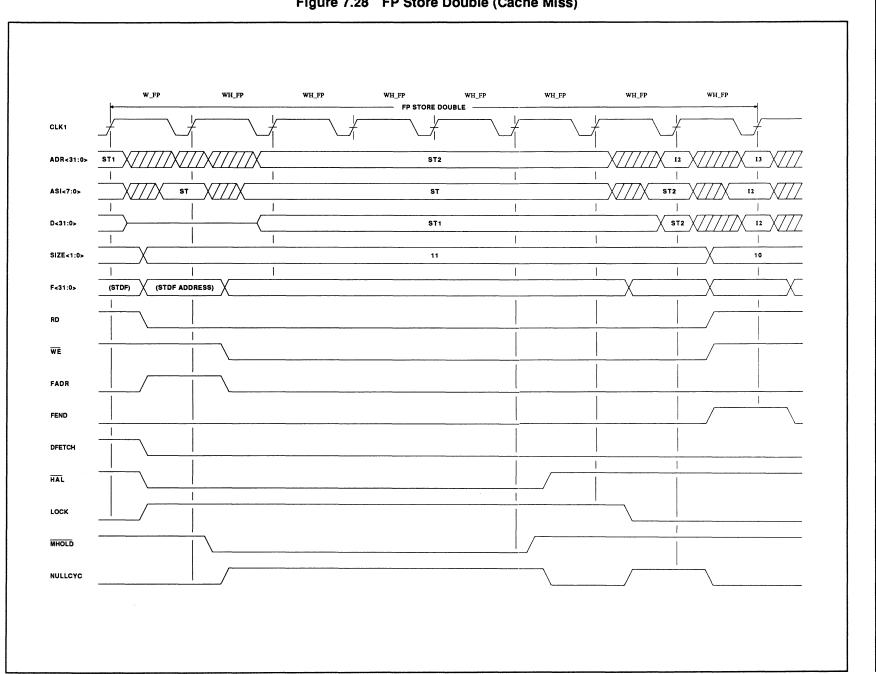

| Cache Miss).72Figure 7.30FP Load Exceptions.73Figure 7.31FP Store Exceptions.74Figure 7.32FP Load Double MemoryExceptionException                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 7.28 | FP Store Double (Cache Miss)71 |

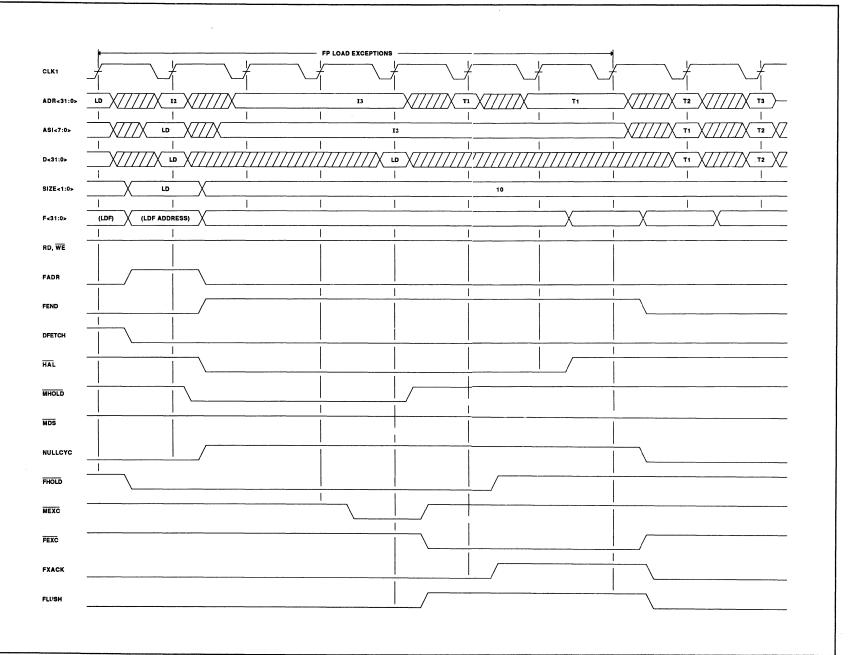

| Figure 7.30FP Load Exceptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Figure 7.29 | FP Store Double (Hold and      |

| Figure 7.30FP Load Exceptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -           |                                |

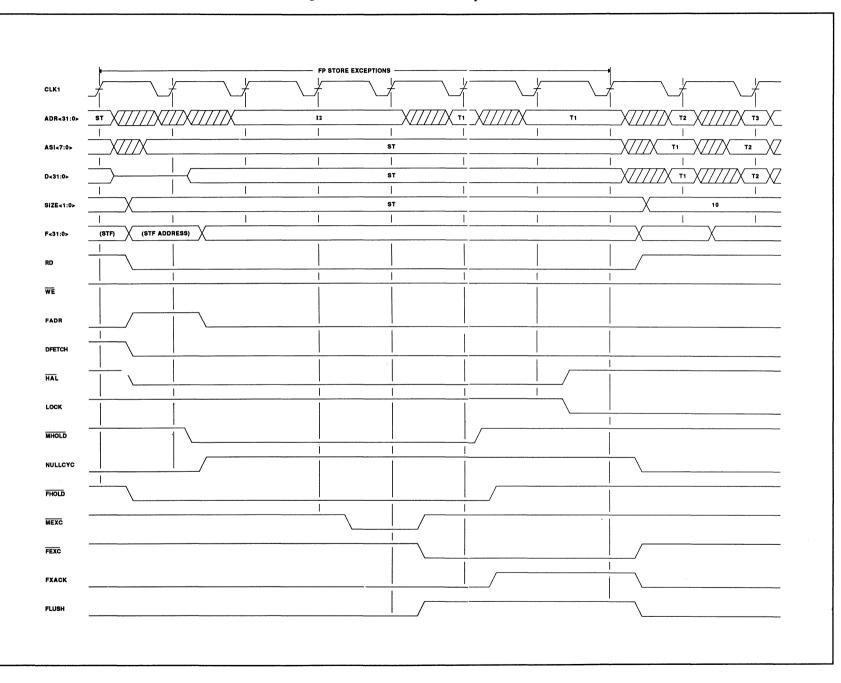

| Figure 7.31FP Store Exceptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 7.30 |                                |

| Figure 7.32FP Load Double Memory<br>Exception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |                                |

| Exception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •           |                                |

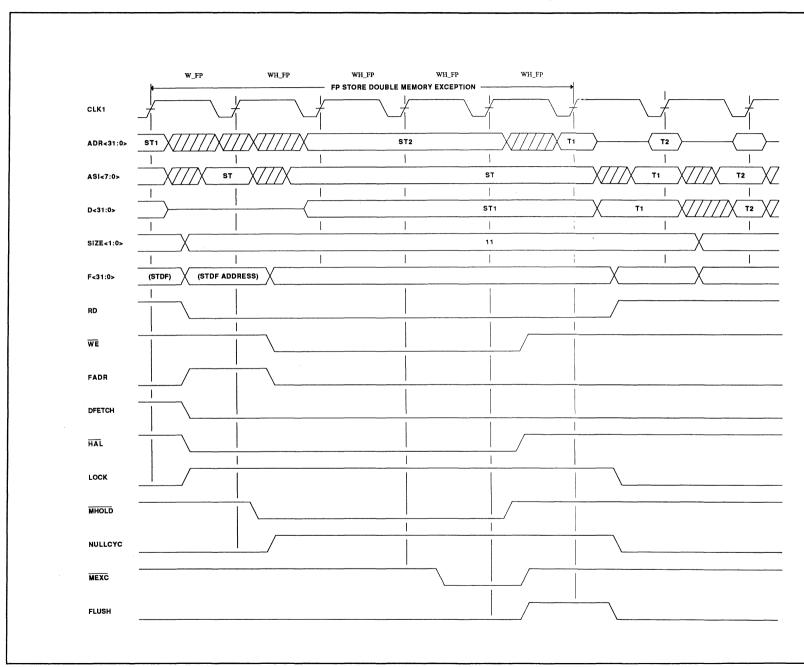

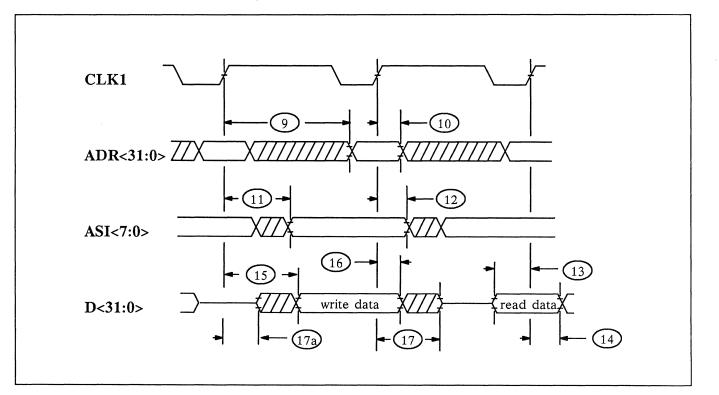

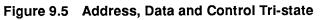

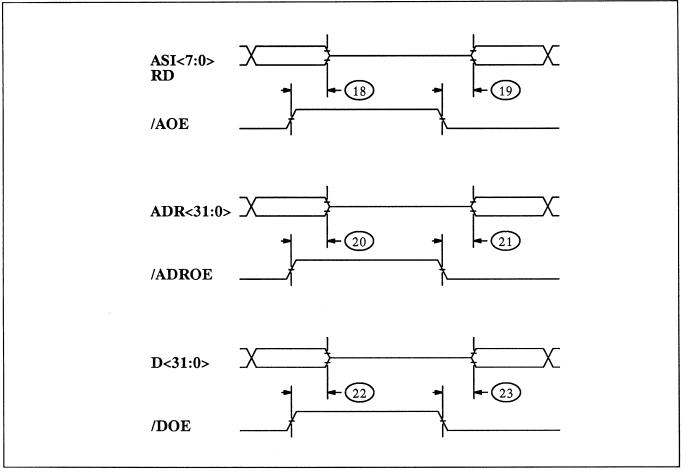

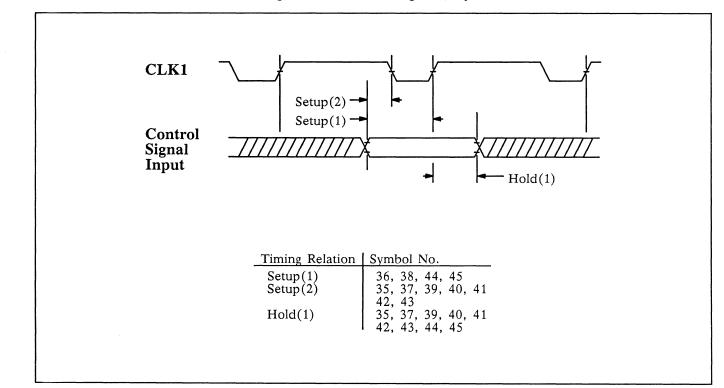

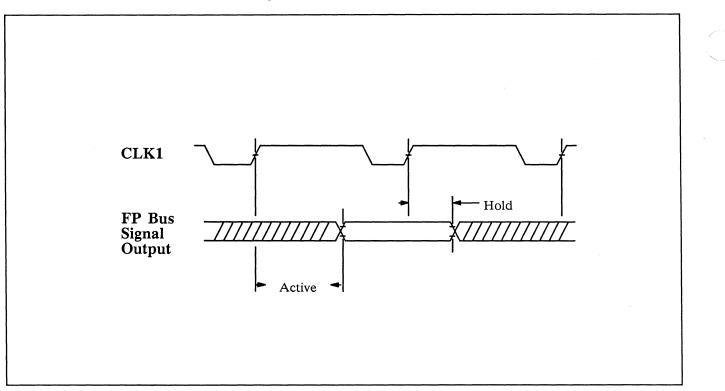

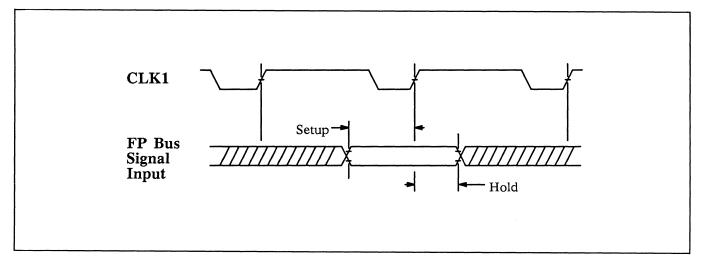

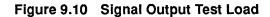

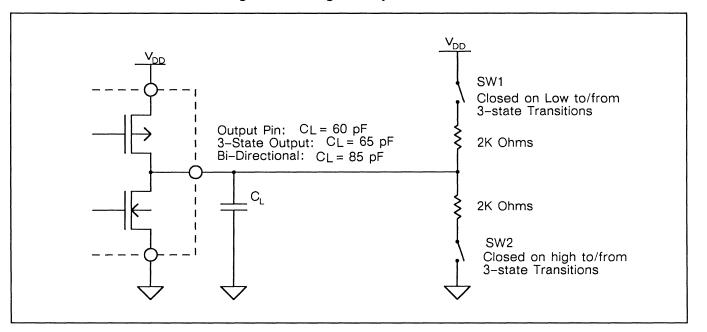

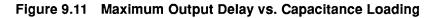

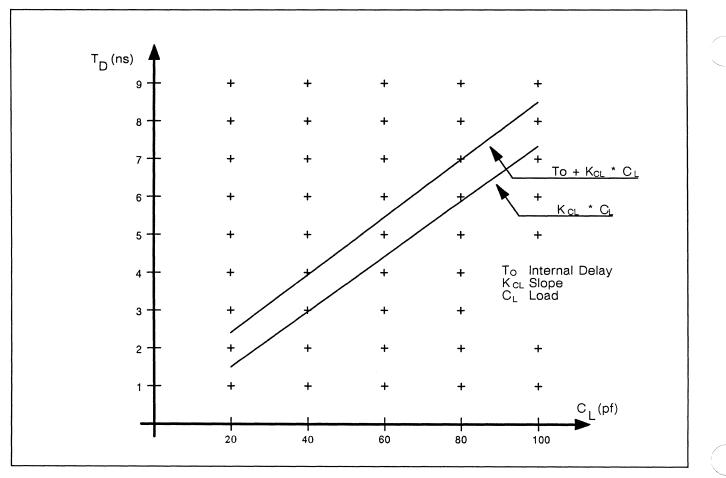

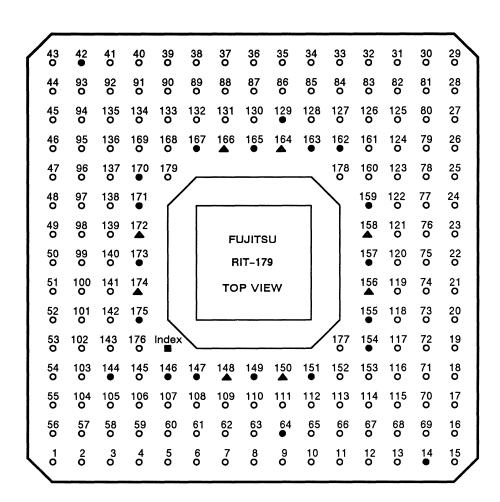

| Figure 7.33FP Store Double Memory<br>Exception76Figure 7.34FPOP Floating Point Exception77Figure 7.35Basic System Configuration78Figure 8.1Clock Circuit79Figure 8.2External Address Pipeline80Figure 9.1Signal AC Measurement Points82Figure 9.2Clock AC Measurement Points82Figure 9.3Clocks Timing Diagram83Figure 9.4Address and Data Bus84Figure 9.5Address, Data and Control85Figure 9.6Control Signals, Output86Figure 9.7Control Signals, Input87Figure 9.8FP Bus, Output88Figure 9.9FP Bus, Input89Figure 9.10Signal Output Test Load90Figure 9.11Maximum Output Delay vs.<br>Capacitance Loading90Figure 9.12179-Lead Plastic Pin Grid Array<br>Package91 | 0           |                                |

| Exception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure 7.33 | FP Store Double Memory         |

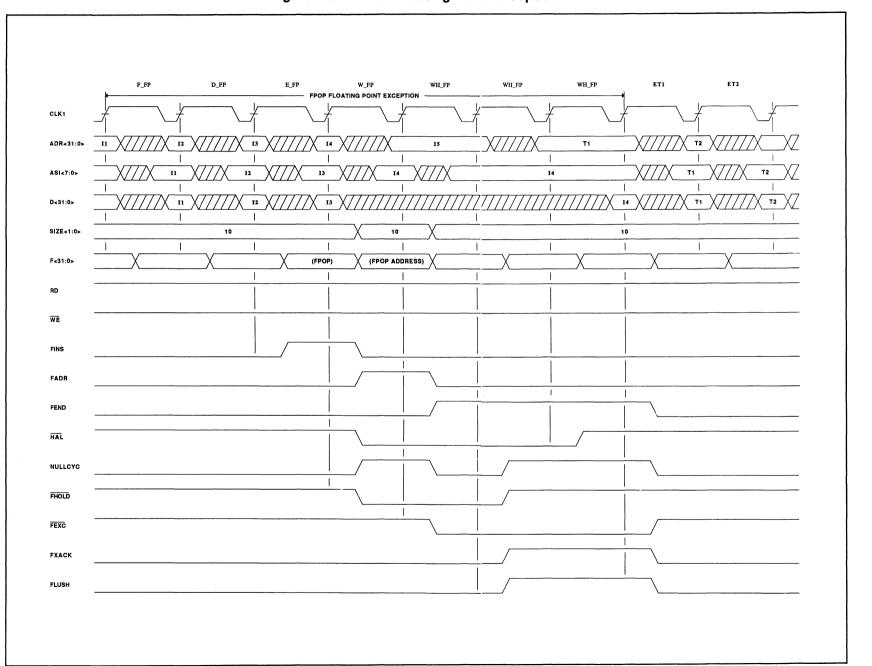

| Figure 7.34FPOP Floating Point Exception77Figure 7.35Basic System Configuration78Figure 8.1Clock Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ·           |                                |

| Figure 7.35Basic System Configuration.78Figure 8.1Clock Circuit.79Figure 8.2External Address Pipeline.80Figure 9.1Signal AC Measurement Points.82Figure 9.2Clock AC Measurement Points.82Figure 9.3Clocks Timing Diagram.83Figure 9.4Address and Data Bus.84Figure 9.5Address, Data and ControlTri-state.85Figure 9.6Control Signals, Output.86Figure 9.7Control Signals, Input.87Figure 9.8FP Bus, Output.88Figure 9.9FP Bus, Input.89Figure 9.10Signal Output Test Load.90Figure 9.11Maximum Output Delay vs.<br>Capacitance Loading.90Figure 9.12179-Lead Plastic Pin Grid Array<br>Package.91                                                                   | Figure 7.34 |                                |

| Figure 8.1Clock Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Figure 7.35 |                                |

| Figure 8.2External Address Pipeline80Figure 9.1Signal AC Measurement Points82Figure 9.2Clock AC Measurement Points82Figure 9.3Clocks Timing Diagram83Figure 9.4Address and Data Bus84Figure 9.5Address, Data and Control85Figure 9.6Control Signals, Output86Figure 9.7Control Signals, Input87Figure 9.8FP Bus, Output88Figure 9.9FP Bus, Input89Figure 9.10Signal Output Test Load90Figure 9.11Maximum Output Delay vs.<br>Capacitance Loading90Figure 9.12179-Lead Plastic Pin Grid Array<br>Package91                                                                                                                                                           |             |                                |

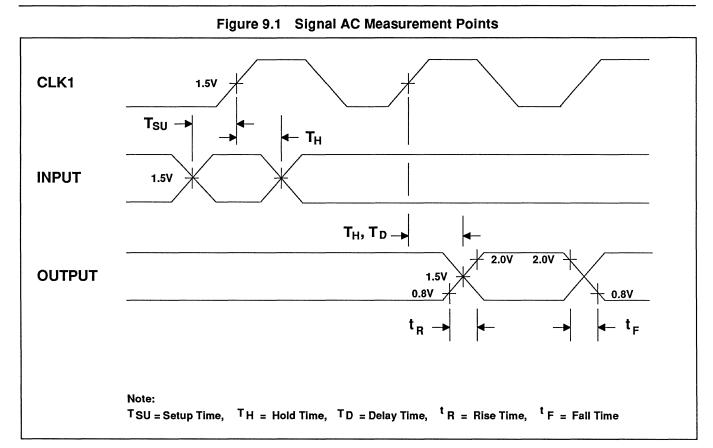

| Figure 9.1Signal AC Measurement Points82Figure 9.2Clock AC Measurement Points82Figure 9.3Clocks Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             | External Address Pipeline      |

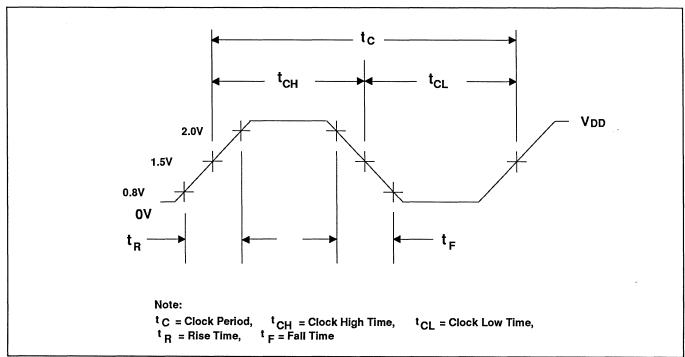

| Figure 9.2Clock AC Measurement Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                                |

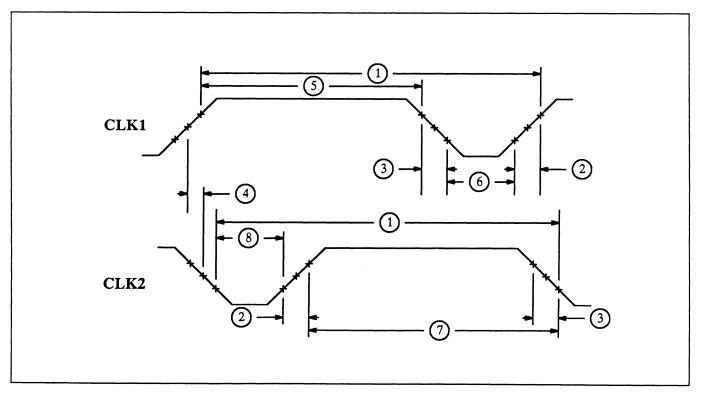

| Figure 9.3Clocks Timing Diagram83Figure 9.4Address and Data Bus84Figure 9.5Address, Data and Control77Tri-state7885Figure 9.6Control Signals, Output86Figure 9.7Control Signals, Input87Figure 9.8FP Bus, Output88Figure 9.9FP Bus, Input89Figure 9.10Signal Output Test Load90Figure 9.11Maximum Output Delay vs.<br>Capacitance Loading90Figure 9.12179-Lead Plastic Pin Grid Array<br>Package91                                                                                                                                                                                                                                                                  | Figure 9.2  |                                |

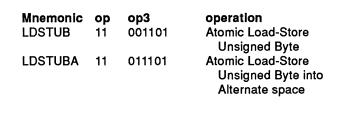

| Figure 9.4Address and Data Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •           |                                |