# Fairchild Advanced CMOS Technology Logic Data Book

# Fairchild Advanced CMOS Technology Logic Data Book

© 1987 Fairchild Semiconductor Corporation, Digital and Analog Unit 333 Western Avenue, South Portland, Maine 04106 207-775-8700 • TWX 710-221-1980

### FAIRCHILD

# Introduction

This data book presents advanced information on Fairchild's very high-speed, low-power CMOS logic family, fabricated with Fairchild's state-of-the-art CMOS process.

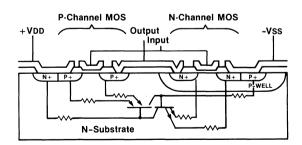

FACT (Fairchild Advanced CMOS Technology) utilizes Fairchild's 1.3  $\mu$ m Isoplanar silicon gate CMOS process to attain speeds similar to that of Advanced Low Power Schottky while retaining the advantages of CMOS logic, namely, ultra low power and high noise immunity. As an added benefit, FACT offers the system designer superior line driving characteristics and excellent ESD and latch-up immunity.

The FACT family consists of devices in two categories:

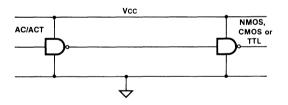

- AC, standard logic functions with CMOS compatible inputs and TTL and MOS compatible outputs;

- 2. ACT, standard logic functions with TTL compatible inputs and TTL and MOS compatible outputs.

#### Section 1 Literature Classification, Product Index and Selection Guide

Tabulation of device numbers to assist in locating appropriate technical data.

#### Section 2 FACT Descriptions and Family Characteristics

Basic information on FACT performance including technologies.

# Section 3 Ratings, Specifications and Waveforms

#### Section 4 Design Considerations

Information to assist both TTL and CMOS designers to get the most out of Fairchild's FACT family.

- Section 5 Data Sheets

- Section 6 Package Outlines and Ordering Information

- Section 7 CMOS Gate Array Family FGC Series

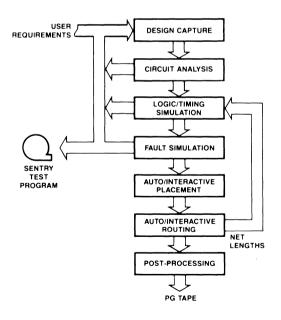

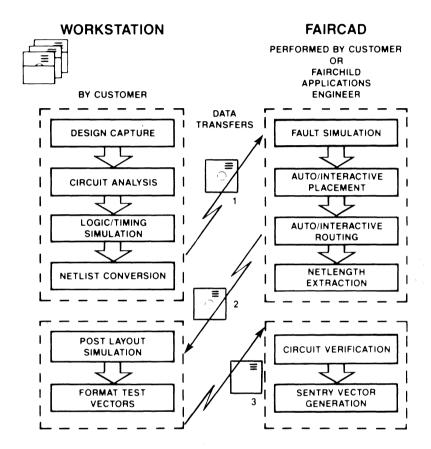

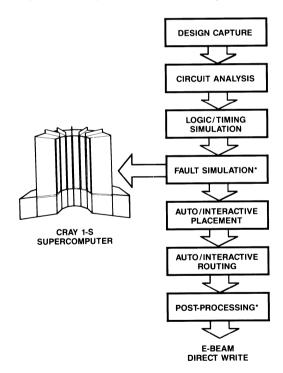

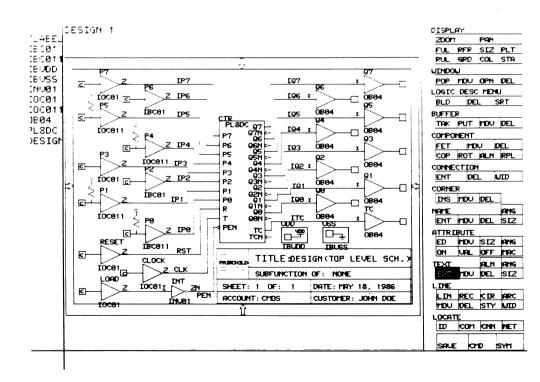

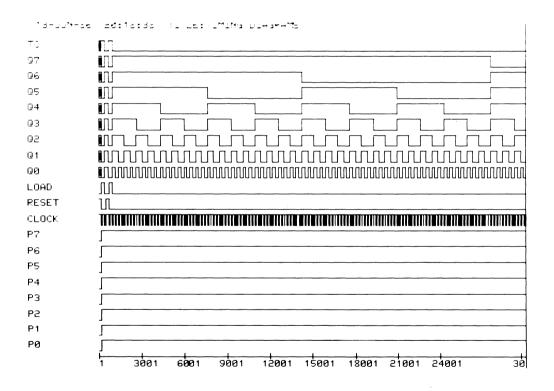

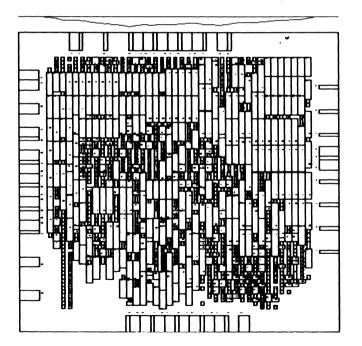

Section 8 CMOS Gate Array Computer Aided Design Tools

Section 9 CMOS Gate Array Packaging

#### Section 10 Field Sales Offices and Distributor Locations

### FAIRCHILD

## **Table of Contents**

#### Section 1 Literature Classification, Product Index and Selection Guide

| Literature Classification            | 1-2  |

|--------------------------------------|------|

| Product Index                        | 1-3  |

| Selection Guide                      | 1-7  |

| Gates                                | 1-7  |

| Registers                            | 1-7  |

| Flip-Flops                           | 1-8  |

| Latches                              | 1-9  |

| Counters                             | 1-9  |

| Buffers/Line Drivers                 | 1-10 |

| FIFOs                                | 1-10 |

| Decoders/Demultiplexers              | 1-10 |

| Arithmetic Functions                 | 1-10 |

| Shift Registers                      | 1-11 |

| Multiplexers                         | 1-11 |

| Comparators                          | 1-11 |

| Transceivers/Registered Transceivers | 1-12 |

|                                      |      |

# Section 2 FACT Descriptions and Family Characteristics

| Family Characteristics       | 2-3  |

|------------------------------|------|

| Logic Family Characteristics | 2-8  |

| Circuit Characteristics      | 2-10 |

| Section 3 | Ratings, Specifications and |     |

|-----------|-----------------------------|-----|

|           | Waveforms                   | 3-3 |

#### Section 4 Design Considerations

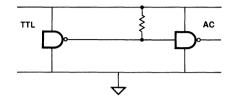

| Interfacing                              | 4-3  |

|------------------------------------------|------|

| Line Driving                             | 4-5  |

| CMOS Bus Loading                         | 4-7  |

| Crosstalk                                | 4-7  |

| Ground Bounce                            | 4-9  |

| Decoupling Requirements                  | 4-10 |

| TTL-Compatible CMOS Designs Require      |      |

| Delta ICC Consideration                  | 4-13 |

| Testing Advanced CMOS Devices with       |      |

| I/O Pins                                 | 4-14 |

| Testing Disable Times of 3-State Outputs |      |

| in a Transmission Line Environment       | 4-16 |

| Section 5 Data Sheets                    | 5-3  |

#### Section 6 Package Outlines and Ordering Information

| Ordering Info | ormation                                          | 6-3  |

|---------------|---------------------------------------------------|------|

| Package Out   | llines                                            | 6-4  |

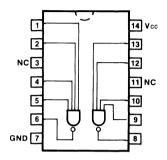

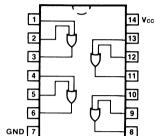

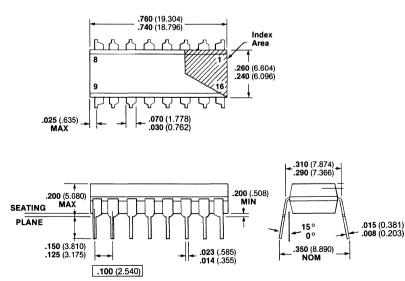

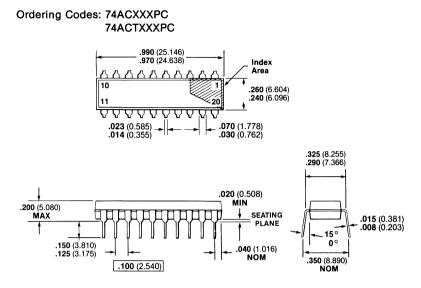

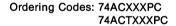

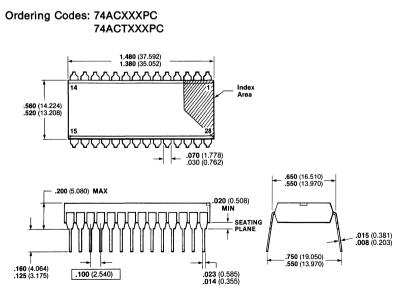

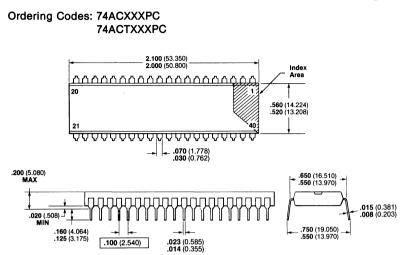

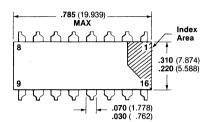

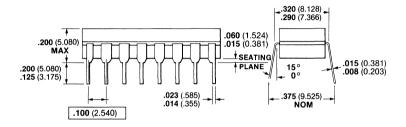

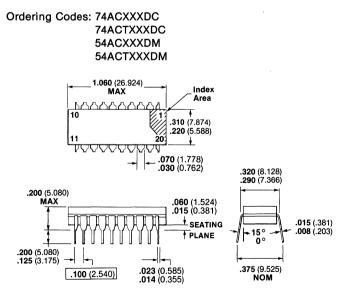

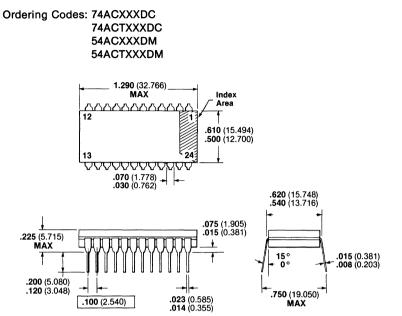

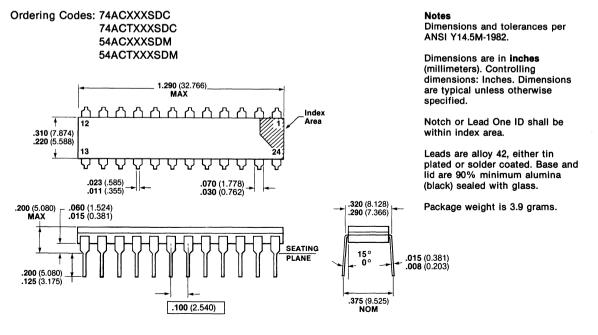

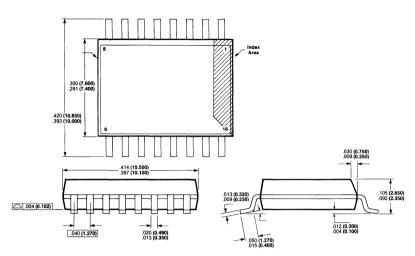

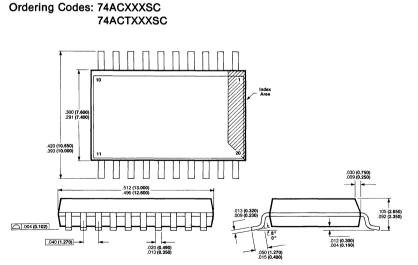

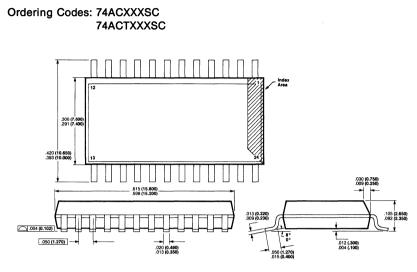

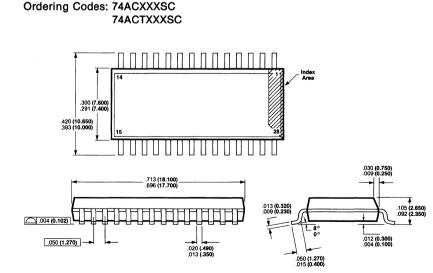

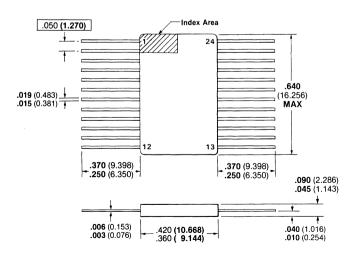

| Plastic I     | Dual In-Line                                      | 6-4  |

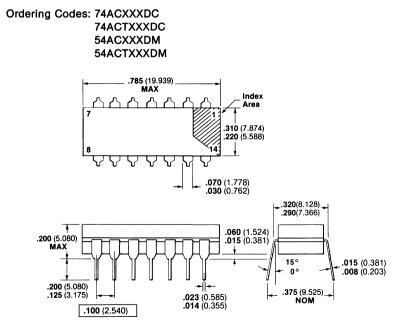

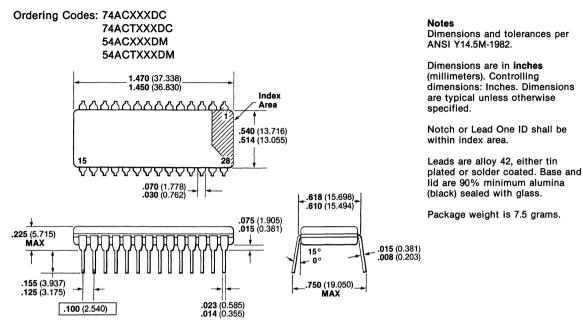

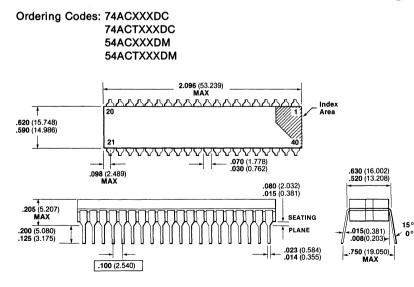

| Ceramic       | : Dual In-Line                                    | 6-7  |

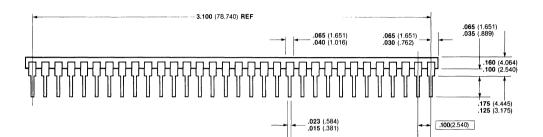

| Side Bra      | azed Dual In-Line                                 | 6-11 |

| Small O       | utline Integrated Circuit                         | 6-12 |

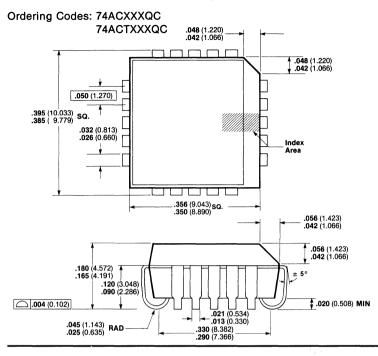

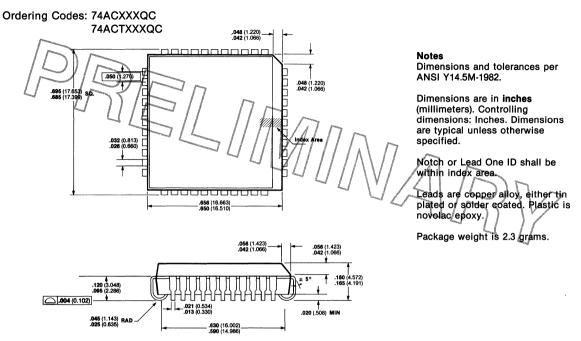

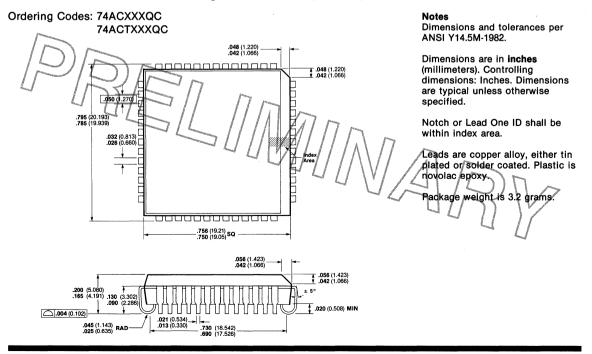

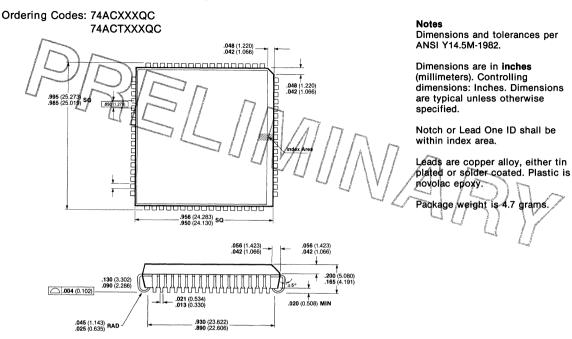

| Plastic (     | Chip Carrier                                      | 6-15 |

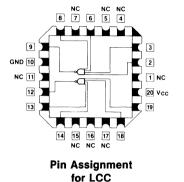

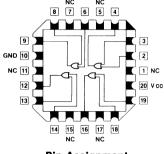

| Ceramic       | : Leadless Chip Carrier                           | 6-18 |

| Ceramic       | : Flatpak                                         | 6-19 |

| Section 7     | FGC Series Advanced<br>2-Micron Gate Array Family | 7-3  |

| Section 8     | FAIRCAD <sup>™</sup> Semicustom<br>Design System  | 8-3  |

| Section 9     | CMOS Arrays Packaging<br>Guide                    | 9-3  |

| Section 10    | Field Sales Offices and<br>Distributor Locations  | 10-3 |

.

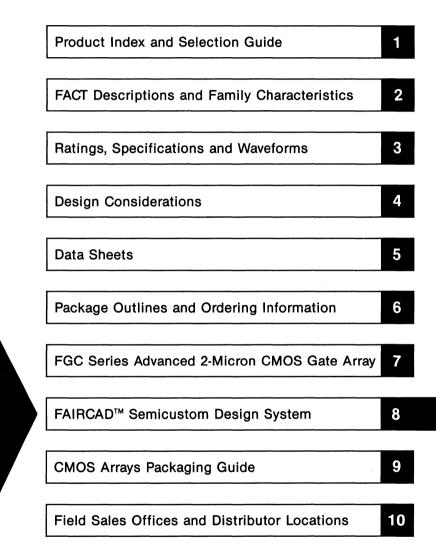

| , | Product Index and Selection Guide             | 1  |

|---|-----------------------------------------------|----|

|   |                                               |    |

|   | FACT Descriptions and Family Characteristics  | 2  |

|   | ,                                             |    |

|   | Ratings, Specifications and Waveforms         | 3  |

|   |                                               |    |

|   | Design Considerations                         | 4  |

|   |                                               |    |

|   | Data Sheets                                   | 5  |

|   |                                               |    |

|   | Package Outlines and Ordering Information     | 6  |

|   |                                               |    |

|   | FGC Series Advanced 2-Micron CMOS Gate Array  | 7  |

|   |                                               |    |

|   | FAIRCAD <sup>™</sup> Semicustom Design System | 8  |

|   |                                               |    |

|   | CMOS Arrays Packaging Guide                   | 9  |

|   |                                               |    |

|   | Field Sales Offices and Distributor Locations | 10 |

|   |                                               |    |

# **Literature Classification**

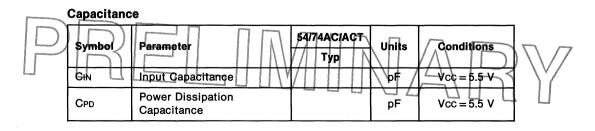

**Preliminary:** This product is in sampling or preproduction stage. This document contains advanced information and specifications that are subject to change without notice. Fairchild reserves the right to make changes at any time in order to improve design and provide the best product possible.

### FAIRCHILD

# Product Index and Selection Guide

| Product Index       |                                           |          |

|---------------------|-------------------------------------------|----------|

| 'ACXX Devices — CMC | DS Input Levels                           |          |

| Device No.          | Description                               | Page No. |

| 54AC/74AC00         | Quad 2-Input NAND Gate                    | 5-3      |

| 54AC/74AC02         | Quad 2-Input NOR Gate                     | 5-5      |

| 54AC/74AC04         | Hex Inverter                              | 5-7      |

| 54AC/74AC08         | Quad 2-Input AND Gate                     | 5-9      |

| 54AC/74AC10         | Triple 3-Input NAND Gate                  | 5-11     |

| 54AC/74AC11         | Triple 3-Input AND Gate                   | 5-13     |

| 54AC/74AC14         | Hex Inverter Schmitt Trigger              | 5-15     |

| 54AC/74AC20         | Dual 4-Input NAND Gate                    | 5-18     |

| 54AC/74AC32         | Quad 2-Input OR Gate                      | 5-20     |

| 54AC/74AC74         | Dual D Flip-Flop                          | 5-22     |

| 54AC/74AC86         | Quad 2-Input Exclusive-OR Gate            | 5-27     |

| 54AC/74AC109        | Dual JK Positive Edge-Triggered Flip-Flop | 5-29     |

| 54AC/74AC138        | 1-of-8 Decoder/Demultiplexer              | 5-34     |

| 54AC/74AC139        | Dual 1-of-4 Decoder/Demultiplexer         | 5-39     |

| 54AC/74AC151        | 8-Input Multiplexer                       | 5-43     |

| 54AC/74AC153        | Dual 4-Input Multiplexer                  | 5-47     |

| 54AC/74AC157        | Quad 2-Input Multiplexer                  | 5-51     |

| 54AC/74AC158        | Quad 2-Input Multiplexer                  | 5-55     |

| 54AC/74AC160        | BCD Decade Counter, Asynchronous Reset    | 5-59     |

| 54AC/74AC161        | 4-Bit Binary Counter, Asynchronous Reset  | 5-66     |

| 54AC/74AC162        | BCD Decade Counter, Synchronous Reset     | 5-59     |

| 54AC/74AC163        | 4-Bit Binary Counter, Synchronous Reset   | 5-66     |

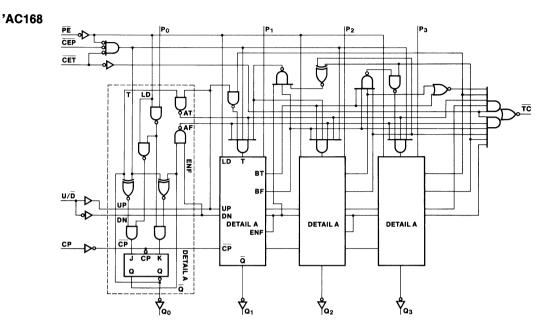

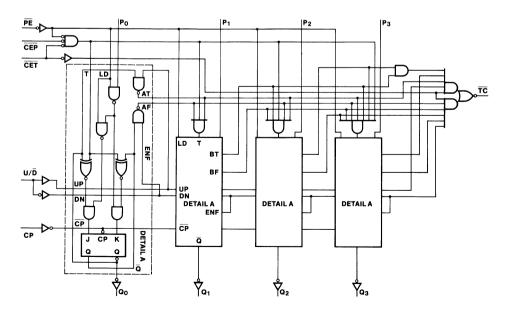

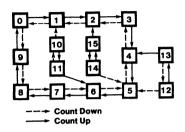

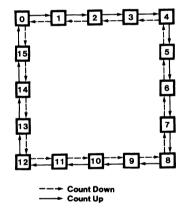

| 54AC/74AC168        | 4-Bit Bidirectional Binary Counter        | 5-77     |

| 54AC/74AC169        | 4-Bit Bidirectional Binary Counter        | 5-77     |

| 54AC/74AC174        | Hex D Flip-Flop with Master Reset         | 5-85     |

| 54AC/74AC175        | Quad D Flip-Flop with Master Reset        | 5-89     |

| 54AC/74AC190        | Up/Down Decade Counter                    | 5-94     |

| 54AC/74AC191        | Up/Down Binary Counter                    | 5-94     |

| 54AC/74AC192        | Up/Down Decade Counter                    | 5-102    |

| 54AC/74AC193        | Up/Down Binary Counter                    | 5-102    |

| 54AC/74AC240        | Octal Buffer/Line Driver                  | 5-109    |

| 54AC/74AC241        | Octal Buffer/Line Driver                  | 5-112    |

| 54AC/74AC244        | Octal Buffer/Line Driver                  | 5-115    |

| 54AC/74AC245        | Octal Bidirectional Transceiver           | 5-118    |

| 54AC/74AC251        | 8-Input Multiplexer                       | 5-121    |

| 54AC/74AC253        | Dual 4-Input Multiplexer                  | 5-125    |

|                     |                                           | 0.25     |

| Device No.   | Description                                      | Page No. |

|--------------|--------------------------------------------------|----------|

| 54AC/74AC257 | Quad 2-Input Multiplexer                         | 5-129    |

| 54AC/74AC258 | Quad 2-Input Multiplexer                         | 5-133    |

| 54AC/74AC273 | Octal D Flip-Flop                                | 5-137    |

| 54AC/74AC299 | Octal Shift/Storage Register                     | 5-142    |

| 54AC/74AC323 | Octal Shift/Storage Register                     | 5-149    |

| 54AC/74AC352 | Dual 4-Input Multiplexer                         | 5-156    |

| 54AC/74AC353 | Dual 4-Input Multiplexer                         | 5-161    |

| 54AC/74AC373 | Octal D Latch                                    | 5-165    |

| 54AC/74AC374 | Octal D Flip-Flop                                | 5-170    |

| 54AC/74AC377 | Octal D Flip-Flop with Clock Enable              | 5-175    |

| 54AC/74AC378 | Parallel D Register with Enable                  | 5-180    |

| 54AC/74AC379 | Quad D Flip-Flop with Enable                     | 5-185    |

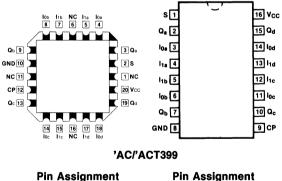

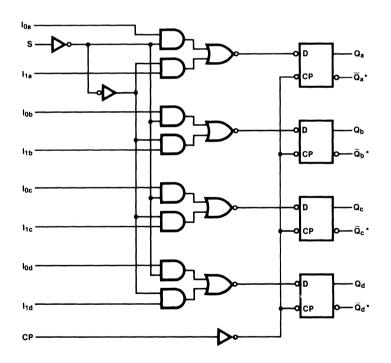

| 54AC/74AC398 | Quad 2-Port Register                             | 5-190    |

| 54AC/74AC399 | Quad 2-Port Register                             | 5-190    |

| 54AC/74AC520 | 8-Bit Identity Comparator with Pull-Up Resistors | 5-223    |

| 54AC/74AC521 | 8-Bit Identity Comparator                        | 5-223    |

| 54AC/74AC533 | Octal Transparent Latch                          | 5-228    |

| 54AC/74AC534 | Octal D Flip-Flop                                | 5-233    |

| 54AC/74AC540 | Octal Buffer/Line Driver                         | 5-238    |

| 54AC/74AC541 | Octal Buffer/Line Driver                         | 5-238    |

| 54AC/74AC563 | Octal D Latch                                    | 5-241    |

| 54AC/74AC564 | Octal D Flip-Flop                                | 5-246    |

| 54AC/74AC568 | 4-Bit Bidirectional Decade Counter               | 5-251    |

| 54AC/74AC569 | 4-Bit Bidirectional Binary Counter               | 5-251    |

| 54AC/74AC573 | Octal D Latch                                    | 5-260    |

| 54AC/74AC574 | Octal D Flip-Flop                                | 5-265    |

| 54AC/74AC640 | Octal Transceiver                                | 5-270    |

| 54AC/74AC643 | Octal Transceiver                                | 5-273    |

| 54AC/74AC646 | Octal Bus Transceiver and Register               | 5-276    |

| 54AC/74AC648 | Octal Bus Transceiver and Register               | 5-280    |

| 54AC/74AC705 | DSP ALU                                          | 5-284    |

| 54AC/74AC708 | 64 x 9 FIFO Memory                               | 5-296    |

| 54AC/74AC723 | 64 x 9 FIFO                                      | 5-314    |

| 54AC/74AC725 | 512 x 9 FIFO                                     | 5-330    |

| 54AC/74AC818 | Diagnostic and Pipeline Register                 | 5-346    |

| 54AC/74AC821 | 10-Bit D Flip-Flop                               | 5-354    |

| 54AC/74AC822 | 10-Bit D Flip-Flop                               | 5-354    |

| 54AC/74AC823 | 9-Bit D Flip-Flop                                | 5-359    |

| 54AC/74AC824 | 9-Bit D Flip-Flop                                | 5-359    |

| 54AC/74AC825 | 8-Bit D Flip-Flop                                | 5-366    |

| Device No.                       | Description                                   | Page No. |

|----------------------------------|-----------------------------------------------|----------|

| 54AC/74AC826                     | 8-Bit D Flip-Flop                             | 5-366    |

| 54AC/74AC841                     | 10-Bit Transparent Latch                      | 5-373    |

| 54AC/74AC842                     | 10-Bit Transparent Latch                      | 5-373    |

| 54AC/74AC843                     | 9-Bit Transparent Latch                       | 5-378    |

| 54AC/74AC844                     | 9-Bit Transparent Latch                       | 5-378    |

| 54AC/74AC845                     | 8-Bit Transparent Latch                       | 5-385    |

| 54AC/74AC846                     | 8-Bit Transparent Latch                       | 5-385    |

| 54AC/74AC1010                    | 16 x 16 Multiplier/Accumulator                | 5-392    |

| 54AC/74AC1016                    | 16 x 16 Parallel Multiplier                   | 5-402    |

| 54AC/74AC1017                    | 16 x 16 Parallel Multiplier with Common Clock | 5-413    |

| 'ACTXX Devices — TTL Input       | Levels                                        |          |

| 54ACT/74ACT00                    | Quad 2-Input NAND Gate                        | 5-3      |

| 54ACT/74ACT04                    | Hex Inverter                                  | 5-7      |

| 54ACT/74ACT08                    | Quad 2-Input AND Gate                         | 5-9      |

| 54ACT/74ACT14                    | Hex Inverter Schmitt Trigger                  | 5-15     |

| 54ACT/74ACT32                    | Quad 2-Input OR Gate                          | 5-20     |

| 54ACT/74ACT74                    | Dual D Flip-Flop                              | 5-22     |

| 54ACT/74ACT109                   | Dual JK Positive Edge-Triggered Flip-Flop     | 5-29     |

| 54ACT/74ACT138                   | 1-of-8 Decoder/Demultiplexer                  | 5-34     |

| 54ACT/74ACT139                   | Dual 1-of-4 Decoder/Demultiplexer             | 5-39     |

| 54ACT/74ACT151                   | 8-Input Multiplexer                           | 5-43     |

| 54ACT/74ACT153                   | Dual 4-Input Multiplexer                      | 5-47     |

| 54ACT/74ACT157                   | Quad 2-Input Multiplexer                      | 5-51     |

| 54ACT/74ACT158                   | Quad 2-Input Multiplexer                      | 5-55     |

| 54ACT/74ACT160                   | BCD Decade Counter, Asynchronous Reset        | 5-59     |

| 54ACT/74ACT161                   | 4-Bit Binary Counter, Asynchronous Reset      | 5-66     |

| 54ACT/74ACT162                   | BCD Decade Counter, Synchronous Reset         | 5-59     |

| 54ACT/74ACT163                   | 4-Bit Binary Counter, Synchronous Reset       | 5-66     |

| 54ACT/74ACT174                   | Hex D Flip-Flop with Master Reset             | 5-85     |

| 54ACT/74ACT175                   | Quad D Flip-Flop                              | 5-89     |

| 54ACT/74ACT240                   | Octal Buffer/Line Driver                      | 5-109    |

| 54ACT/74ACT241                   | Octal Buffer/Line Driver                      | 5-112    |

| 54ACT/74ACT244                   | Octal Buffer/Line Driver                      | 5-115    |

| 54ACT/74ACT245                   | Octal Bidirectional Transceiver               | 5-118    |

| 54ACT/74ACT251                   | 8-Input Multiplexer                           | 5-121    |

| 54ACT/74ACT253                   | Dual 4-Bit Multiplexer                        | 5-125    |

| 54ACT/74ACT257                   | Quad 2-Input Multiplexer                      | 5-129    |

| 54ACT/74ACT258<br>54ACT/74ACT273 | Quad 2-Input Multiplexer                      | 5-133    |

| J4AU1/14AU1213                   | Octal D Flip-Flop                             | 5-137    |

1

| SACT/74ACT299<br>SACT/74ACT323Octal Shift/Storage Register5-142<br>5-142SACT/74ACT323Octal Shift/Storage Register5-142<br>5-145SACT/74ACT323Dual 4-Input Multiplexer5-165SACT/74ACT323Dual 4-Input Multiplexer5-161SACT/74ACT373Octal D Elip-Flop5-170SACT/74ACT374Octal D Flip-Flop with Clock Enable5-175SACT/74ACT378Parallel D Flip-Flop with Clock Enable5-180SACT/74ACT379Quad D Flip-Flop with Enable5-180SACT/74ACT398Quad 2-Port Register5-190SACT/74ACT398Quad 2-Port Register5-190SACT/74ACT398Quad 2-Port Register5-190SACT/74ACT398Quad 2-Port Register5-190SACT/74ACT5208-Bit Identity Comparator with Puli-Up Resistors5-223SACT/74ACT533Octal D Flip-Flop5-233SACT/74ACT534Octal D Flip-Flop5-238SACT/74ACT540Octal Buffer/Line Driver5-238SACT/74ACT541Octal D Latch5-246SACT/74ACT543Octal D Latch5-246SACT/74ACT544Octal D Latch5-246SACT/74ACT545DSP ALU5-246SACT/74ACT544Octal D Latch5-233SACT/74ACT545DSP ALU5-246SACT/74ACT544Octal D Flip-Flop5-330SACT/74ACT545DSP ALU5-246SACT/74ACT545DSP ALU5-284SACT/74ACT6454Delit D Flip-Flop5-354SACT/74ACT6454Delit D Flip-Flop5-354<                                                                                                                                                                                                                             | Device No.             | Description                                   | Page No. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------|----------|

| 54ACT/7ACT323Octal ShiftStorage Register5-14954ACT/7ACT352Dual 4-Input Multiplexer5-15654ACT/7ACT353Dual 4-Input Multiplexer5-16154ACT/7ACT353Dotal D Latch5-16554ACT/7ACT374Octal D Flip-Flop with Clock Enable5-17554ACT/7ACT378Parallel D Register with Enable5-18054ACT/7ACT379Quad D Flip-Flop with Clock Enable5-18054ACT/7ACT378Quad D Polip-Flop with Enable5-18554ACT/7ACT379Quad D Polip-Flop with Enable5-18554ACT/7ACT398Quad 2-Port Register5-19054ACT/7ACT399Quad 2-Port Register5-19054ACT/7ACT488General Purpose Interface Bus (GPIB) Circuit5-19554ACT/7ACT5208-Bit Identity Comparator with Puli-Up Resistors5-22354ACT/7AACT531Octal Buffer/Line Driver5-23854ACT/7AACT540Octal Buffer/Line Driver5-23854ACT/7AACT541Octal Buffer/Line Driver5-23854ACT/7AACT543Octal D Elip-Flop5-24654ACT/7AACT544Octal D Latch5-24654ACT/7AACT545DSP ALU5-24654ACT/7AACT544Octal D Latch5-27354ACT/7AACT545DSP ALU5-24654ACT/7AACT544Octal D Flip-Flop5-33054ACT/7AACT545DSP ALU5-24654ACT/7AACT544Octal D Flip-Flop5-35454ACT/7AACT545DSP ALU5-24654ACT/7AACT545DSP ALU5-24654ACT/7AACT545Deshit D Flip-Flop5                                                                                                                                                                                                                | 5 4 A OT /2 4 A OT 000 |                                               | •        |

| 54ACT/74ACT352Dual 4-Input Multiplexer5-16554ACT/74ACT353Dual 4-Input Multiplexer5-16154ACT/74ACT353Octal D Latch5-16554ACT/74ACT374Octal D Flip-Flop with Clock Enable5-17554ACT/74ACT377Octal D Flip-Flop with Clock Enable5-17554ACT/74ACT378Parallel D Register with Enable5-18054ACT/74ACT379Quad 2 Port Register5-18054ACT/74ACT399Quad 2 Port Register5-19054ACT/74ACT5208-Bit Identity Comparator with Pull-Up Resistors5-22354ACT/74ACT5218-Bit Identity Comparator5-23354ACT/74ACT533Octal D Flip-Flop5-23354ACT/74ACT534Octal D Enip-Flop5-23354ACT/74ACT535Octal D Enip-Flop5-23854ACT/74ACT540Octal Buffer/Line Driver5-23854ACT/74ACT541Octal D Latch5-24654ACT/74ACT543Octal D Latch5-24654ACT/74ACT544Octal D Latch5-27054ACT/74ACT573Octal D Latch5-27054ACT/74ACT574Octal D Flip-Flop5-28054ACT/74ACT573Octal D Latch5-27054ACT/74ACT644Octal D Flip-Flop5-33054ACT/74ACT645Diagnostic and Pipeline Register5-36454ACT/74ACT643Octal D Flip-Flop5-33954ACT/74ACT644Oetal D Flip-Flop5-33954ACT/74ACT645Dist D Flip-Flop5-33954ACT/74ACT644Oetal D Flip-Flop5-33954ACT/74ACT645Dist D Flip-Flop5-36                                                                                                                                                                                                                |                        |                                               |          |

| 54ACT/74ACT353Dual 4-Input Multiplexer5-16154ACT/74ACT373Octal D Latch5-18554ACT/75ACT374Octal D Filp-Flop with Clock Enable5-17554ACT775ACT377Octal D Filp-Flop with Enable5-18054ACT77AACT378Parallel D Register with Enable5-18054ACT77AACT379Quad 2-Port Register5-18054ACT77AACT389Quad 2-Port Register5-19054ACT77AACT5208-Bit Identity Comparator with Pull-Up Resistors5-22354ACT77AACT5218-Bit Intransparent Comparator5-23354ACT77AACT5218-Bit Intransparent Latch5-22854ACT77AACT540Octal D Filp-Flop5-23354ACT77AACT540Octal D Utfer/Line Driver5-23854ACT77AACT540Octal D Latch5-24154ACT77AACT540Octal D Latch5-24654ACT77AACT540Octal D Latch5-24554ACT77AACT540Octal D Latch5-22054ACT77AACT540Octal D Latch5-22054ACT77AACT541Octal D Filp-Flop5-23354ACT77AACT542DSP ALU5-24154ACT77AACT543Octal D Latch5-29654ACT77AACT544Octal D Filp-Flop5-33054ACT77AACT545DSP ALU5-28454ACT77AACT545DSP ALU5-28454ACT77AACT545DSP ALU5-33054ACT77AACT545DSP ALU5-33054ACT77AACT545DSP ALU5-33054ACT77AACT545DSP ALU5-33054ACT77AACT545DSP ALU5-33654ACT                                                                                                                                                                                                                                                                      |                        |                                               |          |

| SAACT/74ACT373Octal D Latch5-165SAACT/74ACT374Octal D Filp-Flop with Clock Enable5-175SAACT/74ACT377Octal D Filp-Flop with Clock Enable5-175SAACT/74ACT378Parallel D Register with Enable5-180SAACT/74ACT379Quad D Filp-Flop with Clock Enable5-185SAACT/74ACT378Quad 2-Port Register5-190SAACT/74ACT388Quad 2-Port Register5-190SAACT/74ACT488General Purpose Interface Bus (GPIB) Circuit5-195SAACT/74ACT5208-Bit Identity Comparator with Pull-Up Resistors5-223SAACT/74ACT533Octal Transparent Latch5-228SAACT/74ACT534Octal D Hilp-Flop5-233S4ACT/74ACT534Octal D Latch5-246SAACT/74ACT540Octal D Filp-Flop5-246SAACT/74ACT541Octal D Filp-Flop5-246SAACT/74ACT543Octal D Latch5-226SAACT/74ACT544Octal D Filp-Flop5-273SAACT/74ACT557Octal D SP ALU5-224SAACT/74ACT545DSP ALU5-284SAACT/74ACT55S12 x 9 FIFO5-334SAACT/74ACT52S12 x 9 FIFO5-336SAACT/74ACT52S12 x 9 FIFO5-334SAACT/74ACT52S11 D Filp-Flop5-334SAACT/74ACT52S11 D Filp-Flop5-336SAACT/74ACT52S12 x 9 FIFO5-336SAACT/74ACT52S11 D Filp-Flop5-336SAACT/74ACT52S12 x 9 FIFO5-336SAACT/74ACT52S12 x 9 FIFO5-336SAACT/74ACT52<                                                                                                                                                                                                                                       |                        | • •                                           |          |

| 54ACT/74ACT374Octal D Flip-Flop5-17054ACT/74ACT378Parallel D Rejister with Enable5-17554ACT/74ACT378Parallel D Rejister with Enable5-18554ACT/74ACT378Quad 2-Port Register5-18054ACT/74ACT389Quad 2-Port Register5-19054ACT/74ACT389Quad 2-Port Register5-19054ACT/74ACT389General Purpose Interface Bus (GPIB) Circuit5-19554ACT/74ACT5208-Bit Identity Comparator with Pull-Up Resistors5-22354ACT/74ACT5319-Bit Transparent Comparator5-22354ACT/74ACT5320-Ctal Buffer/Line Driver5-23354ACT/74ACT540Octal Buffer/Line Driver5-23854ACT/74ACT563Octal D Flip-Flop5-23854ACT/74ACT564Octal D Latch5-24154ACT/74ACT574Octal D Flip-Flop5-27354ACT/74ACT564Octal D Flip-Flop5-27354ACT/74ACT575DSP ALU5-28454ACT/74ACT705DSP ALU5-28454ACT/74ACT705DSP ALU5-28454ACT/74ACT725512 x 9 FIFO5-33454ACT/74ACT725512 x 9 FIFO5-34654ACT/74ACT725512 x 9 FIFO5-34654ACT/74ACT7259-Bit D Flip-Flop5-36654ACT/74ACT8249-Bit D Flip-Flop5-36654ACT/74ACT8249-Bit D Flip-Flop5-36654ACT/74ACT8249-Bit D Flip-Flop5-36654ACT/74ACT8249-Bit D Flip-Flop5-36654ACT/74ACT8249-Bit D Flip-Flop5-36654ACT/74ACT824                                                                                                                                                                                                                                  | 54ACT/74ACT353         | Dual 4-Input Multiplexer                      | 5-161    |

| 54ACT/74ACT378Octal D Flip-Flop with Clock Enable5-17554ACT/74ACT378Parallel D Register with Enable5-18054ACT/74ACT379Quad D Flip-Flop with Enable5-18054ACT/74ACT398Quad 2-Port Register5-19054ACT/74ACT488General Purpose Interface Bus (GPIB) Circuit5-19554ACT/74ACT5208-Bit Identity Comparator with Pull-Up Resistors5-22354ACT/74ACT5218-Bit Transparent Comparator522354ACT/74ACT5248-Bit Transparent Comparator5-22354ACT/74ACT534Octal D Flip-Flop5-23354ACT/74ACT541Octal Buffer/Line Driver5-23854ACT/74ACT543Octal D Latch5-24654ACT/74ACT544Octal D Latch5-24654ACT/74ACT543Octal D Flip-Flop5-26554ACT/74ACT544Octal D Flip-Flop5-26554ACT/74ACT543Octal D Flip-Flop5-26554ACT/74ACT544Octal D Flip-Flop5-26654ACT/74ACT543Octal D Flip-Flop5-26654ACT/74ACT544Octal D Flip-Flop5-26554ACT/74ACT545DSP ALU5-22454ACT/74ACT640Octal Transceiver5-27354ACT/74ACT643Octal D Flip-Flop5-33054ACT/74ACT643Octal Transceiver5-27354ACT/74ACT643Diagnostic and Pipeline Register5-34654ACT/74ACT725512 × 9 FIFO5-33654ACT/74ACT8249-Bit D Flip-Flop5-35654ACT/74ACT8249-Bit D Flip-Flop5-36654ACT/74ACT8249-Bit D Fli                                                                                                                                                                                                       | 54ACT/74ACT373         | Octal D Latch                                 | 5-165    |

| 54ACT/74ACT378Parallel D Register with Enable5-18054ACT/74ACT379Quad D Flip-Flop with Enable5-18554ACT/74ACT388Quad 2-Port Register5-19054ACT774ACT388Quad 2-Port Register5-19054ACT774ACT488General Purpose Interface Bus (GPIB) Circuit5-19554ACT774ACT5208-Bit Identity Comparator with Pull-Up Resistors5-22354ACT774ACT5218-Bit Transparent Comparator5-22354ACT774ACT533Octal Transparent Latch5-22854ACT774ACT540Octal Buffer/Line Driver5-23854ACT774ACT541Octal D Latch5-24154ACT774ACT563Octal D Latch5-24654ACT774ACT573Octal D Latch5-27054ACT774ACT540Octal Transceiver5-27354ACT774ACT573Octal D Latch5-28054ACT774ACT574Octal Transceiver5-27354ACT774ACT573Octal D Latch5-28054ACT774ACT643Octal Transceiver5-27354ACT774ACT643Octal Transceiver5-27354ACT774ACT705DSP ALU5-28454ACT774ACT72364 x 9 FIFO5-33454ACT774ACT7239-Bit D Flip-Flop5-35654ACT774ACT8249-Bit D Flip-Flop5-35654ACT774ACT8258-Bit D Flip-Flop5-35654ACT774ACT8249-Bit D Flip-Flop5-35654ACT774ACT8249-Bit D Flip-Flop5-35654ACT774ACT8249-Bit D Flip-Flop5-35654ACT774ACT8249-Bit Transparent Latch5-37354A                                                                                                                                                                                                                                  | 54ACT/74ACT374         | Octal D Flip-Flop                             | 5-170    |

| S4ACT/74ACT379Quad D Flip-Flop with Enable5-185S4ACT/74ACT398Quad 2-Port Register5-190S4ACT/74ACT399Quad 2-Port Register5-190S4ACT/74ACT488General Purpose Interface Bus (GPIB) Circuit5-195S4ACT/74ACT5208-Bit Identity Comparator with Pull-Up Resistors5-223S4ACT/74ACT5310-Cital D Flip-Flop5-233S4ACT/74ACT540Octal D Flip-Flop5-233S4ACT/74ACT541Octal D Flip-Flop5-238S4ACT/74ACT543Octal D Flip-Flop5-238S4ACT/74ACT544Octal D Hip-Flop5-238S4ACT/74ACT545Octal D Latch5-241S4ACT/74ACT573Octal D Latch5-246S4ACT/74ACT574Octal D Flip-Flop5-265S4ACT/74ACT573Octal D Latch5-265S4ACT/74ACT640Octal Transceiver5-273S4ACT/74ACT643Octal Transceiver5-273S4ACT/74ACT643Octal Transceiver5-273S4ACT/74ACT643Octal Transceiver5-334S4ACT/74ACT643Octal Transceiver5-330S4ACT/74ACT82D-Bit D Flip-Flop5-354S4ACT/74ACT8210-Bit D Flip-Flop5-354S4ACT/74ACT8249-Bit D Flip-Flop5-354S4ACT/74ACT8249-Bit D Flip-Flop5-356S4ACT/74ACT8249-Bit D Flip-Flop5-356S4ACT/74ACT8249-Bit D Flip-Flop5-356S4ACT/74ACT8249-Bit D Flip-Flop5-356S4ACT/74ACT8258-Bit D Flip-Flop5-356S4ACT/74ACT826                                                                                                                                                                                                                                           | 54ACT/75ACT377         | Octal D Flip-Flop with Clock Enable           | 5-175    |

| 54ACT/74ACT388Quad 2-Port Register5-19054ACT/74ACT389General Purpols Interface Bus (GPIB) Circuit5-19054ACT774ACT5208-Bit Identity Comparator with Pull-Up Resistors5-22354ACT74ACT5218-Bit Transparent Comparator5-22354ACT74ACT533Octal Transparent Latch5-22354ACT74ACT540Octal D Flip-Flop5-23354ACT74ACT541Octal D Latch5-23354ACT74ACT543Octal D Latch5-23454ACT74ACT544Octal D Latch5-23454ACT74ACT573Octal D Latch5-24654ACT74ACT574Octal D Latch5-26554ACT74ACT574Octal D Latch5-26554ACT74ACT574Octal D Latch5-26554ACT74ACT574Octal D Latch5-27354ACT74ACT574Octal D Transceiver5-27354ACT74ACT575DSP ALU5-28454ACT74ACT705DSP ALU5-28454ACT74ACT705DSP ALU5-28454ACT74ACT725512 x 9 FIFO5-33054ACT74ACT818Diagnostic and Pipeline Register5-34654ACT74ACT8249-Bit D Flip-Flop5-35454ACT74ACT8258-Bit D Flip-Flop5-35654ACT74ACT8249-Bit D Flip-Flop5-35654ACT74ACT8258-Bit D Flip-Flop5-35654ACT74ACT8249-Bit D Flip-Flop5-35654ACT74ACT8258-Bit D Flip-Flop5-35654ACT74ACT8268-Bit D Flip-Flop5-35654ACT74ACT8268-Bit Transparent Latch5-37854ACT                                                                                                                                                                                                                                                                      | 54ACT/74ACT378         | Parallel D Register with Enable               | 5-180    |

| 54ACT/74ACT388<br>54ACT/74ACT389Quad 2-Port Register<br>Quad 2-Port Register5-19054ACT/74ACT389General Purgister dentrace Bus (GPIB) Circuit5-19054ACT74ACT5208-Bit Identity Comparator with Pull-Up Resistors5-22354ACT74ACT5218-Bit Transparent Comparator5-22354ACT74ACT533Octal Transparent Latch5-22354ACT74ACT540Octal D Flip-Flop5-23354ACT74ACT541Octal D Latch5-23354ACT74ACT553Octal D Latch5-23454ACT74ACT564Octal D Latch5-24654ACT74ACT573Octal D Latch5-24654ACT74ACT574Octal D Latch5-26554ACT74ACT574Octal D Latch5-26554ACT74ACT574Octal D Latch5-27354ACT74ACT574Octal D Latch5-27354ACT74ACT574Octal D Transceiver5-27354ACT74ACT575DSP ALU5-28454ACT74ACT705DSP ALU5-28454ACT74ACT705DSP ALU5-28454ACT74ACT725512 x 9 FIFO5-33054ACT74ACT818Diagnostic and Pipeline Register5-36654ACT74ACT8249-Bit D Flip-Flop5-35454ACT74ACT8258-Bit D Flip-Flop5-35654ACT74ACT8249-Bit D Flip-Flop5-35654ACT74ACT8249-Bit D Flip-Flop5-35654ACT74ACT8258-Bit D Flip-Flop5-35654ACT74ACT8249-Bit D Flip-Flop5-35654ACT74ACT8258-Bit Transparent Latch5-37854ACT74ACT8449-Bit Tran                                                                                                                                                                                                                                             | 54ACT/74ACT379         | Quad D Flip-Flop with Enable                  | 5-185    |

| 54ACT/74ACT399Quad 2-Port Register5-19054ACT/74ACT488General Purpose Interface Bus (GPIB) Circuit5-19554ACT74ACT5208-Bit Identity Comparator with Pull-Up Resistors5-22354ACT74ACT5218-Bit Transparent Comparator5-22354ACT74ACT533Octal D Flip-Flop5-23354ACT74ACT540Octal Buffer/Line Driver5-23854ACT74ACT541Octal Buffer/Line Driver5-23854ACT74ACT543Octal D Latch5-24654ACT74ACT544Octal D Latch5-24654ACT74ACT573Octal D Latch5-26554ACT74ACT574Octal D Latch5-26554ACT74ACT574Octal D Latch5-27054ACT74ACT574Octal D Latch5-27054ACT74ACT574Octal Transceiver5-27054ACT74ACT574Octal Transceiver5-27054ACT74ACT574Octal Transceiver5-27054ACT74ACT574Octal Transceiver5-27054ACT74ACT705DSP ALU5-28654ACT74ACT706DSP ALU5-28654ACT74ACT72364 x 9 FIFO5-31454ACT74ACT724512 x 9 FIFO5-33054ACT74ACT82110-Bit D Flip-Flop5-35454ACT74ACT8239-Bit D Flip-Flop5-35454ACT74ACT8249-Bit D Flip-Flop5-35654ACT74ACT8258-Bit D Flip-Flop5-36654ACT74ACT8259-Bit D Flip-Flop5-36654ACT74ACT8269-Bit D Flip-Flop5-36654ACT74ACT8269-Bit Transparent Latch5-37354                                                                                                                                                                                                                                                                      | 54ACT/74ACT398         |                                               | 5-190    |

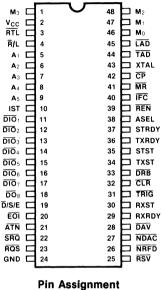

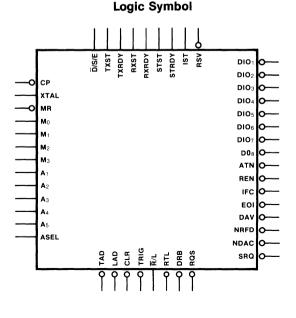

| 54ACT/74ACT488General Purpose Interface Bus (GPIB) Circuit5-19554ACT/74ACT5208-Bit Identity Comparator with Pull-Up Resistors5-22354ACT/74ACT5218-Bit Transparent Comparator5-22354ACT/74ACT533Octal Transparent Latch5-22354ACT/74ACT540Octal Buffer/Line Driver5-23354ACT/74ACT541Octal Buffer/Line Driver5-23354ACT/74ACT543Octal D Filp-Flop5-24554ACT/74ACT544Octal D Latch5-24154ACT/74ACT573Octal D Latch5-26554ACT/74ACT574Octal D Filp-Flop5-26554ACT/74ACT574Octal D Filp-Flop5-26554ACT/74ACT640Octal Transceiver5-27054ACT/74ACT643Octal Transceiver5-27054ACT/74ACT705DSP ALU5-28454ACT/74ACT725512 x 9 FIFO5-31454ACT/74ACT725512 x 9 FIFO5-33654ACT/74ACT82110-Bit D Filp-Flop5-35454ACT/74ACT8239-Bit D Filp-Flop5-35454ACT/74ACT8239-Bit D Filp-Flop5-35454ACT/74ACT8249-Bit D Filp-Flop5-35454ACT/74ACT8258-Bit D Filp-Flop5-35454ACT/74ACT8249-Bit D Filp-Flop5-35654ACT/74ACT8258-Bit D Filp-Flop5-35654ACT/74ACT84110-Bit Transparent Latch5-37354ACT/74ACT8458-Bit Transparent Latch5-37354ACT/74ACT8468-Bit Transparent Latch5-37654ACT/74ACT8468-Bit Transparent Latch5-378 <td< td=""><td></td><td></td><td></td></td<>                                                                                                                                                                                    |                        |                                               |          |

| 54ACT/74ACT5208-Bit Identity Comparator with Pull-Up Resistors5-22354ACT/74ACT5218-Bit Transparent Latch5-22354ACT/74ACT533Octal D Flip-Flop5-23354ACT/74ACT540Octal Buffer/Line Driver5-23854ACT/74ACT541Octal Buffer/Line Driver5-23854ACT/74ACT541Octal Buffer/Line Driver5-23854ACT7/4ACT541Octal D Latch5-24154ACT/74ACT573Octal D Latch5-24654ACT/74ACT574Octal D Flip-Flop5-26654ACT/74ACT573Octal D Latch5-26754ACT/74ACT574Octal D Flip-Flop5-26554ACT/74ACT573Octal D Flip-Flop5-26554ACT/74ACT574Octal Transceiver5-27354ACT/74ACT643Octal Transceiver5-27354ACT/74ACT705DSP ALU5-28454ACT/74ACT72364 x 9 FIFO5-33054ACT/74ACT725Diagnostic and Pipeline Register5-34654ACT/74ACT818Diagnostic and Pipeline Register5-34654ACT/74ACT8239-Bit D Flip-Flop5-35954ACT/74ACT8249-Bit D Flip-Flop5-35954ACT/74ACT8258-Bit D Flip-Flop5-36654ACT/74ACT84110-Bit Transparent Latch5-37354ACT/74ACT84210-Bit Transparent Latch5-37354ACT/74ACT8439-Bit Transparent Latch5-37854ACT/74ACT8458-Bit Transparent Latch5-37854ACT/74ACT8468-Bit Transparent Latch5-37854ACT/74ACT8468-Bit Transparent Latch5-385<                                                                                                                                                                                                                     |                        |                                               |          |

| 54ACT/74ACT521         Bit Transparent Comparator         5-223           54ACT/74ACT533         Octal D Filp-Flop         5-233           54ACT/74ACT540         Octal Buffer/Line Driver         5-233           54ACT/74ACT541         Octal Buffer/Line Driver         5-238           54ACT/74ACT563         Octal D Latch         5-246           54ACT/74ACT564         Octal D Latch         5-246           54ACT/74ACT573         Octal D Latch         5-265           54ACT/74ACT574         Octal D Filp-Flop         5-265           54ACT/74ACT573         Octal D Latch         5-266           54ACT/74ACT544         Octal Transceiver         5-270           54ACT/74ACT640         Octal Transceiver         5-270           54ACT/74ACT705         DSP ALU         5-284           54ACT/74ACT725         512 x 9 FIFO         5-314           54ACT/74ACT725         512 x 9 FIFO         5-330           54ACT/74ACT818         Diagnostic and Pipeline Register         5-346           54ACT/74ACT821         10-Bit D Flip-Flop         5-354           54ACT/74ACT823         9-Bit D Flip-Flop         5-354           54ACT/74ACT824         9-Bit D Flip-Flop         5-356           54ACT/74ACT824         9-Bit D Flip-Flop                                                                       |                        | deneral Pulpose interface bus (dr ib) oncur   | 5-185    |

| 54ACT/74ACT533         Octal Transparent Latch         5-228           54ACT/74ACT534         Octal D Flip-Flop         5-233           54ACT/74ACT540         Octal Buffer/Line Driver         5-238           54ACT/74ACT561         Octal Buffer/Line Driver         5-238           54ACT7/4ACT563         Octal D Latch         5-246           54ACT7/4ACT564         Octal D Latch         5-246           54ACT7/4ACT573         Octal D Latch         5-260           54ACT/74ACT574         Octal D Flip-Flop         5-265           54ACT/74ACT574         Octal Transcelver         5-273           54ACT/74ACT643         Octal Transcelver         5-273           54ACT/74ACT655         DSP ALU         5-284           54ACT/74ACT705         DSP ALU         5-286           54ACT/74ACT723         64 x 9 FIFO         5-330           54ACT/74ACT725         512 x 9 FIFO         5-330           54ACT/74ACT818         Diagnostic and Pipeline Register         5-346           54ACT/74ACT82         10-Bit D Flip-Flop         5-354           54ACT/74ACT82         9-Bit D Flip-Flop         5-356           54ACT/74ACT82         9-Bit D Flip-Flop         5-356           54ACT/74ACT824         9-Bit D Flip-Flop         5-36                                                                       |                        |                                               |          |

| 54ACT/74ACT534         Octal D Flip-Flop         5-233           54ACT/74ACT540         Octal Buffer/Line Driver         5-238           54ACT/74ACT541         Octal Buffer/Line Driver         5-238           54ACT/74ACT563         Octal D Latch         5-246           54ACT/74ACT564         Octal D Flip-Flop         5-266           54ACT/74ACT573         Octal D Latch         5-266           54ACT/74ACT574         Octal D Flip-Flop         5-265           54ACT/74ACT540         Octal Transcelver         5-273           54ACT/74ACT643         Octal Transcelver         5-273           54ACT/74ACT705         DSP ALU         5-284           54ACT/74ACT708         64 x 9 FIFO Memory         5-286           54ACT/74ACT723         64 x 9 FIFO         5-330           54ACT/74ACT818         Diagnostic and Pipeline Register         5-346           54ACT/74ACT82         10-Bit D Flip-Flop         5-354           54ACT/74ACT823         9-Bit D Flip-Flop         5-356           54ACT/74ACT824         9-Bit D Flip-Flop         5-356           54ACT/74ACT825         8-Bit D Flip-Flop         5-356           54ACT/74ACT824         9-Bit D Flip-Flop         5-356           54ACT/74ACT825         8-Bit D Flip-Flop                                                                    |                        |                                               |          |

| 54ACT/74ACT540         Octal Buffer/Line Driver         5-238           54ACT/74ACT541         Octal Buffer/Line Driver         5-238           54ACT/74ACT563         Octal D Latch         5-241           54ACT/74ACT564         Octal D Flip-Flop         5-246           54ACT/74ACT573         Octal D Latch         5-266           54ACT/74ACT574         Octal D Flip-Flop         5-266           54ACT/74ACT574         Octal D Transceiver         5-273           54ACT/74ACT643         Octal Transceiver         5-273           54ACT/74ACT643         Octal Transceiver         5-273           54ACT/74ACT643         Octal Transceiver         5-273           54ACT/74ACT705         DSP ALU         5-284           54ACT/74ACT723         64 × 9 FIFO Memory         5-296           54ACT/74ACT725         512 × 9 FIFO         5-330           54ACT/74ACT818         Diagnostic and Pipeline Register         5-354           54ACT/74ACT82         10-Bit D Flip-Flop         5-354           54ACT/74ACT82         9-Bit D Flip-Flop         5-359           54ACT/74ACT824         9-Bit D Flip-Flop         5-366           54ACT/74ACT825         8-Bit D Flip-Flop         5-366           54ACT/74ACT844         9-Bit Transparent Lat                                                              |                        |                                               |          |

| SAACT/74ACT541         Octal Buffer/Line Driver         5-238           SAACT/74ACT563         Octal D Latch         5-241           S4ACT/74ACT564         Octal D Flip-Flop         5-246           S4ACT/74ACT573         Octal D Latch         5-260           S4ACT/74ACT574         Octal D Latch         5-260           S4ACT/74ACT574         Octal Transceiver         5-265           S4ACT/74ACT643         Octal Transceiver         5-273           S4ACT/74ACT643         Octal Transceiver         5-273           S4ACT/74ACT643         Octal Transceiver         5-284           S4ACT/74ACT705         DSP ALU         5-284           S4ACT/74ACT725         DSP ALU         5-284           S4ACT/74ACT725         DSP ALU         5-284           S4ACT/74ACT725         DSP ALU         5-284           S4ACT/74ACT725         DSP ALU         5-284           S4ACT/74ACT821         10-Bit D Flip-Flop         5-314           S4ACT/74ACT821         10-Bit D Flip-Flop         5-354           S4ACT/74ACT823         9-Bit D Flip-Flop         5-356           S4ACT/74ACT824         9-Bit D Flip-Flop         5-366           S4ACT/74ACT825         8-Bit D Flip-Flop         5-366           S4ACT                                                                                                 | 54ACT/74ACT534         | Octal D Flip-Flop                             | 5-233    |

| 54ACT/74ACT563         Octal D Latch         5-241           54ACT/74ACT564         Octal D Flip-Flop         5-246           54ACT/74ACT573         Octal D Latch         5-260           54ACT/74ACT574         Octal D Latch         5-265           54ACT/74ACT640         Octal Transceiver         5-270           54ACT/74ACT643         Octal Transceiver         5-273           54ACT/74ACT643         Octal Transceiver         5-284           54ACT/74ACT705         DSP ALU         5-284           54ACT/74ACT723         64 x 9 FIFO         5-314           54ACT/74ACT725         512 x 9 FIFO         5-330           54ACT/74ACT818         Diagnostic and Pipeline Register         5-346           54ACT/74ACT821         10-Bit D Flip-Flop         5-354           54ACT/74ACT822         10-Bit D Flip-Flop         5-354           54ACT/74ACT823         9-Bit D Flip-Flop         5-356           54ACT/74ACT824         9-Bit D Flip-Flop         5-366           54ACT/74ACT825         8-Bit D Flip-Flop         5-366           54ACT/74ACT824         9-Bit D Flip-Flop         5-366           54ACT/74ACT824         9-Bit D Flip-Flop         5-366           54ACT/74ACT845         8-Bit Transparent Latch         5-37                                                                       | 54ACT/74ACT540         | Octal Buffer/Line Driver                      | 5-238    |

| 54ACT/74ACT564         Octal D Flip-Flop         5-246           54ACT/74ACT573         Octal D Latch         5-260           54ACT/74ACT574         Octal D Flip-Flop         5-265           54ACT/74ACT640         Octal Transceiver         5-270           54ACT/74ACT643         Octal Transceiver         5-273           54ACT/74ACT643         Octal Transceiver         5-273           54ACT/74ACT705         DSP ALU         5-284           54ACT/74ACT708         64 x 9 FIFO         5-284           54ACT/74ACT723         64 x 9 FIFO         5-314           54ACT/74ACT725         512 x 9 FIFO         5-330           54ACT/74ACT818         Diagnostic and Pipeline Register         5-346           54ACT/74ACT821         10-Bit D Flip-Flop         5-354           54ACT/74ACT823         9-Bit D Flip-Flop         5-359           54ACT/74ACT824         9-Bit D Flip-Flop         5-356           54ACT/74ACT825         8-Bit D Flip-Flop         5-366           54ACT/74ACT824         9-Bit D Flip-Flop         5-366           54ACT/74ACT825         8-Bit D Flip-Flop         5-366           54ACT/74ACT841         10-Bit Transparent Latch         5-373           54ACT/74ACT843         9-Bit Transparent Latch                                                                            | 54ACT/74ACT541         | Octal Buffer/Line Driver                      | 5-238    |

| 54ACT/74ACT573         Octal D Latch         5-260           54ACT/74ACT574         Octal Transceiver         5-265           54ACT/74ACT640         Octal Transceiver         5-273           54ACT/74ACT643         Octal Transceiver         5-273           54ACT/74ACT643         Octal Transceiver         5-273           54ACT/74ACT705         DSP ALU         5-284           54ACT/74ACT705         DSP ALU         5-284           54ACT/74ACT723         64 x 9 FIFO         5-314           54ACT/74ACT725         512 x 9 FIFO         5-330           54ACT/74ACT818         Diagnostic and Pipeline Register         5-346           54ACT/74ACT821         10-Bit D Flip-Flop         5-354           54ACT/74ACT823         9-Bit D Flip-Flop         5-359           54ACT/74ACT824         9-Bit D Flip-Flop         5-359           54ACT/74ACT825         8-Bit D Flip-Flop         5-359           54ACT/74ACT824         9-Bit D Flip-Flop         5-359           54ACT/74ACT825         8-Bit D Flip-Flop         5-366           54ACT/74ACT841         10-Bit Transparent Latch         5-373           54ACT/74ACT841         10-Bit Transparent Latch         5-373           54ACT/74ACT843         9-Bit Transparent Latch                                                                         | 54ACT/74ACT563         | Octal D Latch                                 | 5-241    |

| 54ACT/74ACT574         Octal D Flip-Flop         5-265           54ACT/74ACT640         Octal Transceiver         5-270           54ACT/74ACT643         Octal Transceiver         5-273           54ACT/74ACT643         Octal Transceiver         5-273           54ACT/74ACT705         DSP ALU         5-284           54ACT/74ACT708         64 x 9 FIFO         5-296           54ACT/74ACT723         64 x 9 FIFO         5-314           54ACT/74ACT725         512 x 9 FIFO         5-330           54ACT/74ACT818         Diagnostic and Pipeline Register         5-346           54ACT/74ACT821         10-Bit D Flip-Flop         5-354           54ACT/74ACT823         9-Bit D Flip-Flop         5-359           54ACT/74ACT824         9-Bit D Flip-Flop         5-359           54ACT/74ACT825         8-Bit D Flip-Flop         5-366           54ACT/74ACT824         9-Bit D Flip-Flop         5-366           54ACT/74ACT825         8-Bit D Flip-Flop         5-366           54ACT/74ACT824         9-Bit D Flip-Flop         5-366           54ACT/74ACT825         8-Bit D Flip-Flop         5-366           54ACT/74ACT844         9-Bit Transparent Latch         5-373           54ACT/74ACT845         9-Bit Transparent Latch                                                                         | 54ACT/74ACT564         | Octal D Flip-Flop                             | 5-246    |

| 54ACT/74ACT574         Octal D Flip-Flop         5-265           54ACT/74ACT640         Octal Transceiver         5-270           54ACT/74ACT643         Octal Transceiver         5-273           54ACT/74ACT643         Octal Transceiver         5-273           54ACT/74ACT705         DSP ALU         5-284           54ACT/74ACT708         64 x 9 FIFO         5-296           54ACT/74ACT723         64 x 9 FIFO         5-314           54ACT/74ACT725         512 x 9 FIFO         5-330           54ACT/74ACT818         Diagnostic and Pipeline Register         5-346           54ACT/74ACT821         10-Bit D Flip-Flop         5-354           54ACT/74ACT823         9-Bit D Flip-Flop         5-359           54ACT/74ACT824         9-Bit D Flip-Flop         5-359           54ACT/74ACT824         9-Bit D Flip-Flop         5-366           54ACT/74ACT844         9-Bit Transparent Latch         5-373           54ACT/74ACT842         10-Bit Transparent Latch                                                                        | 54ACT/74ACT573         | Octal D Latch                                 | 5-260    |

| 54ACT/74ACT640         Octal Transceiver         5-270           54ACT/74ACT643         Octal Transceiver         5-273           54ACT/74ACT643         Octal Transceiver         5-273           54ACT/74ACT643         OSP ALU         5-284           54ACT/74ACT705         DSP ALU         5-284           54ACT/74ACT708         64 x 9 FIFO Memory         5-296           54ACT/74ACT723         64 x 9 FIFO         5-314           54ACT/74ACT725         512 x 9 FIFO         5-330           54ACT/74ACT818         Diagnostic and Pipeline Register         5-346           54ACT/74ACT821         10-Bit D Flip-Flop         5-354           54ACT/74ACT822         10-Bit D Flip-Flop         5-359           54ACT/74ACT823         9-Bit D Flip-Flop         5-359           54ACT/74ACT824         9-Bit D Flip-Flop         5-359           54ACT/74ACT825         8-Bit D Flip-Flop         5-366           54ACT/74ACT841         10-Bit Transparent Latch         5-373           54ACT/74ACT842         10-Bit Transparent Latch         5-373           54ACT/74ACT843         9-Bit Transparent Latch         5-378           54ACT/74ACT844         9-Bit Transparent Latch         5-378           54ACT/74ACT845         8-Bit Transparen                                                              |                        |                                               |          |

| 54ACT/74ACT643         Octal Transceiver         5-273           54ACT/74ACT705         DSP ALU         5-284           54ACT/74ACT708         64 x 9 FIFO         5-296           54ACT/74ACT708         64 x 9 FIFO         5-314           54ACT/74ACT725         512 x 9 FIFO         5-330           54ACT/74ACT818         Diagnostic and Pipeline Register         5-346           54ACT/74ACT821         10-Bit D Flip-Flop         5-354           54ACT/74ACT822         10-Bit D Flip-Flop         5-354           54ACT/74ACT823         9-Bit D Flip-Flop         5-359           54ACT/74ACT824         9-Bit D Flip-Flop         5-359           54ACT/74ACT825         8-Bit D Flip-Flop         5-359           54ACT/74ACT826         8-Bit D Flip-Flop         5-366           54ACT/74ACT826         8-Bit D Flip-Flop         5-366           54ACT/74ACT841         10-Bit Transparent Latch         5-373           54ACT/74ACT842         10-Bit Transparent Latch         5-378           54ACT/74ACT845         8-Bit Transparent Latch         5-378           54ACT/74ACT845         8-Bit Transparent Latch         5-385           54ACT/74ACT845         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit T                                                              |                        |                                               |          |

| 54ACT/74ACT708         64 x 9 FIFO Memory         5-296           54ACT/74ACT723         64 x 9 FIFO         5-314           54ACT/74ACT725         512 x 9 FIFO         5-330           54ACT/74ACT818         Diagnostic and Pipeline Register         5-346           54ACT/74ACT821         10-Bit D Flip-Flop         5-354           54ACT/74ACT822         10-Bit D Flip-Flop         5-354           54ACT/74ACT823         9-Bit D Flip-Flop         5-354           54ACT/74ACT823         9-Bit D Flip-Flop         5-359           54ACT/74ACT824         9-Bit D Flip-Flop         5-359           54ACT/74ACT825         8-Bit D Flip-Flop         5-359           54ACT/74ACT826         8-Bit D Flip-Flop         5-366           54ACT/74ACT825         8-Bit D Flip-Flop         5-366           54ACT/74ACT841         10-Bit Transparent Latch         5-373           54ACT/74ACT842         10-Bit Transparent Latch         5-378           54ACT/74ACT843         9-Bit Transparent Latch         5-378           54ACT/74ACT845         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT846 </td <td></td> <td></td> <td></td>                    |                        |                                               |          |

| 54ACT/74ACT708         64 x 9 FIFO Memory         5-296           54ACT/74ACT723         64 x 9 FIFO         5-314           54ACT/74ACT725         512 x 9 FIFO         5-330           54ACT/74ACT818         Diagnostic and Pipeline Register         5-346           54ACT/74ACT821         10-Bit D Flip-Flop         5-354           54ACT/74ACT822         10-Bit D Flip-Flop         5-354           54ACT/74ACT823         9-Bit D Flip-Flop         5-354           54ACT/74ACT823         9-Bit D Flip-Flop         5-359           54ACT/74ACT824         9-Bit D Flip-Flop         5-359           54ACT/74ACT825         8-Bit D Flip-Flop         5-359           54ACT/74ACT826         8-Bit D Flip-Flop         5-356           54ACT/74ACT825         8-Bit D Flip-Flop         5-366           54ACT/74ACT841         10-Bit Transparent Latch         5-373           54ACT/74ACT842         10-Bit Transparent Latch         5-378           54ACT/74ACT843         9-Bit Transparent Latch         5-378           54ACT/74ACT845         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT846 </td <td>54ACT/74ACT705</td> <td></td> <td>5-284</td> | 54ACT/74ACT705         |                                               | 5-284    |

| 54ACT/74ACT723       64 x 9 FIFO       5-314         54ACT/74ACT725       512 x 9 FIFO       5-330         54ACT/74ACT818       Diagnostic and Pipeline Register       5-346         54ACT/74ACT818       Diagnostic and Pipeline Register       5-346         54ACT/74ACT821       10-Bit D Flip-Flop       5-354         54ACT/74ACT822       10-Bit D Flip-Flop       5-354         54ACT/74ACT823       9-Bit D Flip-Flop       5-359         54ACT/74ACT824       9-Bit D Flip-Flop       5-359         54ACT/74ACT825       8-Bit D Flip-Flop       5-366         54ACT/74ACT826       8-Bit D Flip-Flop       5-366         54ACT/74ACT841       10-Bit Transparent Latch       5-373         54ACT/74ACT842       10-Bit Transparent Latch       5-378         54ACT/74ACT845       8-Bit Transparent Latch       5-385         54ACT/74ACT846       8-Bit Transparent Latch       5-385         54ACT/74ACT846       8-Bit Transparent Latch       5-385         54ACT/74ACT846       8-Bit Transparent Latch       5-385 <td< td=""><td></td><td></td><td></td></td<>                                                                    |                        |                                               |          |

| 54ACT/74ACT725         512 x 9 FIFO         5-330           54ACT/74ACT818         Diagnostic and Pipeline Register         5-346           54ACT/74ACT821         10-Bit D Flip-Flop         5-354           54ACT/74ACT822         10-Bit D Flip-Flop         5-354           54ACT/74ACT823         9-Bit D Flip-Flop         5-359           54ACT/74ACT823         9-Bit D Flip-Flop         5-359           54ACT/74ACT824         9-Bit D Flip-Flop         5-366           54ACT/74ACT825         8-Bit D Flip-Flop         5-366           54ACT/74ACT826         8-Bit D Flip-Flop         5-366           54ACT/74ACT826         8-Bit D Flip-Flop         5-366           54ACT/74ACT826         8-Bit D Flip-Flop         5-366           54ACT/74ACT841         10-Bit Transparent Latch         5-373           54ACT/74ACT842         10-Bit Transparent Latch         5-378           54ACT/74ACT843         9-Bit Transparent Latch         5-378           54ACT/74ACT845         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT                                                     |                        | •                                             |          |

| 54ACT/74ACT818         Diagnostic and Pipeline Register         5-346           54ACT/74ACT821         10-Bit D Flip-Flop         5-354           54ACT/74ACT822         10-Bit D Flip-Flop         5-354           54ACT/74ACT822         10-Bit D Flip-Flop         5-354           54ACT/74ACT823         9-Bit D Flip-Flop         5-359           54ACT/74ACT824         9-Bit D Flip-Flop         5-359           54ACT/74ACT825         8-Bit D Flip-Flop         5-366           54ACT/74ACT826         8-Bit Transparent Latch         5-373           54ACT/74ACT842         10-Bit Transparent Latch         5-378           54ACT/74ACT843         9-Bit Transparent Latch         5-378           54ACT/74ACT844         9-Bit Transparent Latch         5-378           54ACT/74ACT845         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385                                                          |                        |                                               |          |

| 54ACT/74ACT821       10-Bit D Flip-Flop       5-354         54ACT/74ACT822       10-Bit D Flip-Flop       5-354         54ACT/74ACT823       9-Bit D Flip-Flop       5-359         54ACT/74ACT823       9-Bit D Flip-Flop       5-359         54ACT/74ACT823       9-Bit D Flip-Flop       5-359         54ACT/74ACT824       9-Bit D Flip-Flop       5-366         54ACT/74ACT825       8-Bit D Flip-Flop       5-366         54ACT/74ACT826       8-Bit D Flip-Flop       5-366         54ACT/74ACT841       10-Bit Transparent Latch       5-373         54ACT/74ACT842       10-Bit Transparent Latch       5-378         54ACT/74ACT843       9-Bit Transparent Latch       5-378         54ACT/74ACT844       9-Bit Transparent Latch       5-378         54ACT/74ACT845       8-Bit Transparent Latch       5-378         54ACT/74ACT845       8-Bit Transparent Latch       5-385         54ACT/74ACT846       8-Bit Transparent Latch       5-385 <tr< td=""><td>54AC1//4AC1/25</td><td>512 X 9 FIFO</td><td>5-330</td></tr<>                          | 54AC1//4AC1/25         | 512 X 9 FIFO                                  | 5-330    |

| 54ACT/74ACT822       10-Bit D Flip-Flop       5-354         54ACT/74ACT823       9-Bit D Flip-Flop       5-359         54ACT/74ACT823       9-Bit D Flip-Flop       5-359         54ACT/74ACT824       9-Bit D Flip-Flop       5-359         54ACT/74ACT825       8-Bit D Flip-Flop       5-366         54ACT/74ACT826       8-Bit D Flip-Flop       5-366         54ACT/74ACT826       8-Bit D Flip-Flop       5-366         54ACT/74ACT841       10-Bit Transparent Latch       5-373         54ACT/74ACT842       10-Bit Transparent Latch       5-378         54ACT/74ACT843       9-Bit Transparent Latch       5-378         54ACT/74ACT844       9-Bit Transparent Latch       5-378         54ACT/74ACT845       8-Bit Transparent Latch       5-378         54ACT/74ACT845       8-Bit Transparent Latch       5-385         54ACT/74ACT846       8-Bit Transparent Latch       5-392                                                                                                 |                        |                                               |          |

| 54ACT/74ACT823       9-Bit D Flip-Flop       5-359         54ACT/74ACT824       9-Bit D Flip-Flop       5-359         54ACT/74ACT825       8-Bit D Flip-Flop       5-366         54ACT/74ACT826       8-Bit D Flip-Flop       5-366         54ACT/74ACT826       8-Bit D Flip-Flop       5-366         54ACT/74ACT826       8-Bit D Flip-Flop       5-366         54ACT/74ACT841       10-Bit Transparent Latch       5-373         54ACT/74ACT842       10-Bit Transparent Latch       5-378         54ACT/74ACT843       9-Bit Transparent Latch       5-378         54ACT/74ACT844       9-Bit Transparent Latch       5-378         54ACT/74ACT845       8-Bit Transparent Latch       5-378         54ACT/74ACT845       8-Bit Transparent Latch       5-385         54ACT/74ACT846       8-Bit Transparent Latch       5-385         54ACT/74ACT1010       16 x 16 Multiplier/Accumulator       5-392                                                                                    |                        | • •                                           |          |

| 54ACT/74ACT824       9-Bit D Flip-Flop       5-359         54ACT/74ACT825       8-Bit D Flip-Flop       5-366         54ACT/74ACT826       8-Bit D Flip-Flop       5-366         54ACT/74ACT826       8-Bit D Flip-Flop       5-366         54ACT/74ACT841       10-Bit Transparent Latch       5-373         54ACT/74ACT842       10-Bit Transparent Latch       5-373         54ACT/74ACT843       9-Bit Transparent Latch       5-378         54ACT/74ACT844       9-Bit Transparent Latch       5-378         54ACT/74ACT845       8-Bit Transparent Latch       5-378         54ACT/74ACT846       8-Bit Transparent Latch       5-385         54ACT/74ACT1010       16 x 16 Multiplier/Accumulator       5-392         54ACT/74ACT1016       16 x 16 Parallel Multiplier       5-402 <td>54ACT/74ACT822</td> <td>10-Bit D Flip-Flop</td> <td>5-354</td>                                                                 | 54ACT/74ACT822         | 10-Bit D Flip-Flop                            | 5-354    |

| 54ACT/74ACT825       8-Bit D Flip-Flop       5-366         54ACT/74ACT826       8-Bit D Flip-Flop       5-366         54ACT/74ACT841       10-Bit Transparent Latch       5-373         54ACT/74ACT842       10-Bit Transparent Latch       5-373         54ACT/74ACT843       9-Bit Transparent Latch       5-378         54ACT/74ACT844       9-Bit Transparent Latch       5-378         54ACT/74ACT844       9-Bit Transparent Latch       5-378         54ACT/74ACT845       8-Bit Transparent Latch       5-378         54ACT/74ACT845       8-Bit Transparent Latch       5-385         54ACT/74ACT846       8-Bit Transparent Latch       5-385         54ACT/74ACT1010       16 x 16 Multiplier/Accumulator       5-392         54ACT/74ACT1016       16 x 16 Parallel Multiplier       5-402                                                                                                                                                                                                                                                                                                                           | 54ACT/74ACT823         | 9-Bit D Flip-Flop                             | 5-359    |

| 54ACT/74ACT826       8-Bit D Flip-Flop       5-366         54ACT/74ACT841       10-Bit Transparent Latch       5-373         54ACT/74ACT842       10-Bit Transparent Latch       5-373         54ACT/74ACT842       10-Bit Transparent Latch       5-373         54ACT/74ACT843       9-Bit Transparent Latch       5-378         54ACT/74ACT844       9-Bit Transparent Latch       5-378         54ACT/74ACT845       8-Bit Transparent Latch       5-378         54ACT/74ACT845       8-Bit Transparent Latch       5-385         54ACT/74ACT846       8-Bit Transparent Latch       5-385         54ACT/74ACT846       8-Bit Transparent Latch       5-385         54ACT/74ACT846       8-Bit Transparent Latch       5-385         54ACT/74ACT1010       16 x 16 Multiplier/Accumulator       5-392         54ACT/74ACT1016       16 x 16 Parallel Multiplier       5-402                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 54ACT/74ACT824         | 9-Bit D Flip-Flop                             | 5-359    |

| 54ACT/74ACT826         8-Bit D Flip-Flop         5-366           54ACT/74ACT841         10-Bit Transparent Latch         5-373           54ACT/74ACT842         10-Bit Transparent Latch         5-373           54ACT/74ACT842         10-Bit Transparent Latch         5-373           54ACT/74ACT843         9-Bit Transparent Latch         5-378           54ACT/74ACT844         9-Bit Transparent Latch         5-378           54ACT/74ACT845         8-Bit Transparent Latch         5-378           54ACT/74ACT845         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT1010         16 x 16 Multiplier/Accumulator         5-392           54ACT/74ACT1016         16 x 16 Parallel Multiplier         5-402                                                                                                                                                                                                                                                                                                   | 54ACT/74ACT825         | 8-Bit D Flip-Flop                             | 5-366    |

| 54ACT/74ACT841       10-Bit Transparent Latch       5-373         54ACT/74ACT842       10-Bit Transparent Latch       5-373         54ACT/74ACT842       10-Bit Transparent Latch       5-373         54ACT/74ACT843       9-Bit Transparent Latch       5-378         54ACT/74ACT844       9-Bit Transparent Latch       5-378         54ACT/74ACT845       8-Bit Transparent Latch       5-378         54ACT/74ACT845       8-Bit Transparent Latch       5-385         54ACT/74ACT846       8-Bit Transparent Latch       5-385         54ACT/74ACT846       8-Bit Transparent Latch       5-385         54ACT/74ACT1010       16 x 16 Multiplier/Accumulator       5-392         54ACT/74ACT1016       16 x 16 Parallel Multiplier       5-402                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54ACT/74ACT826         |                                               | 5-366    |

| 54ACT/74ACT843         9-Bit Transparent Latch         5-378           54ACT/74ACT844         9-Bit Transparent Latch         5-378           54ACT/74ACT845         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT1010         16 x 16 Multiplier/Accumulator         5-392           54ACT/74ACT1016         16 x 16 Parallel Multiplier         5-402                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        | • •                                           |          |

| 54ACT/74ACT843         9-Bit Transparent Latch         5-378           54ACT/74ACT844         9-Bit Transparent Latch         5-378           54ACT/74ACT845         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT1010         16 x 16 Multiplier/Accumulator         5-392           54ACT/74ACT1016         16 x 16 Parallel Multiplier         5-402                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 54ACT/74ACT842         | 10-Bit Transparent Latch                      | 5-373    |

| 54ACT/74ACT8449-Bit Transparent Latch5-37854ACT/74ACT8458-Bit Transparent Latch5-38554ACT/74ACT8468-Bit Transparent Latch5-38554ACT/74ACT101016 x 16 Multiplier/Accumulator5-39254ACT/74ACT101616 x 16 Parallel Multiplier5-402                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |                                               |          |

| 54ACT/74ACT845         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT1010         16 x 16 Multiplier/Accumulator         5-392           54ACT/74ACT1016         16 x 16 Parallel Multiplier         5-402                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        |                                               |          |

| 54ACT/74ACT846         8-Bit Transparent Latch         5-385           54ACT/74ACT1010         16 x 16 Multiplier/Accumulator         5-392           54ACT/74ACT1016         16 x 16 Parallel Multiplier         5-402                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |                                               |          |

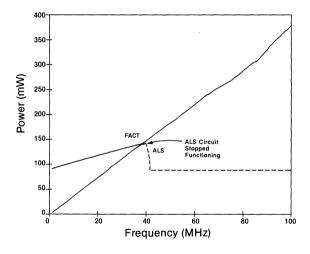

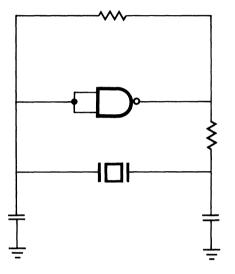

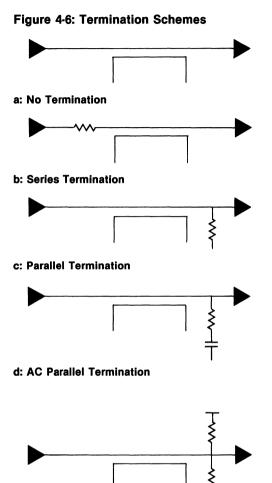

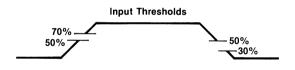

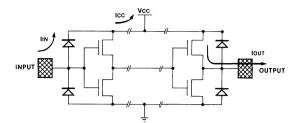

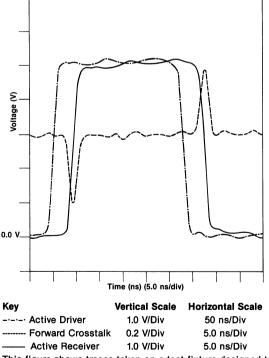

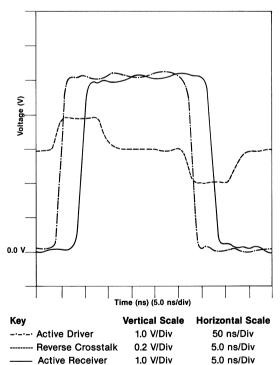

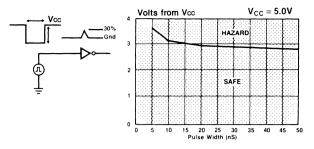

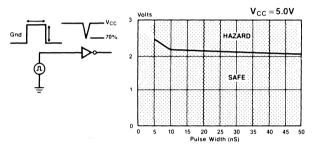

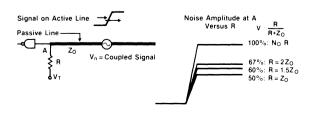

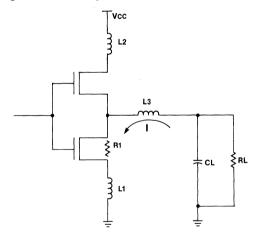

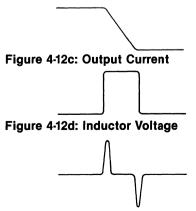

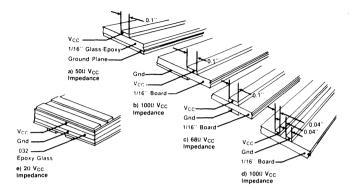

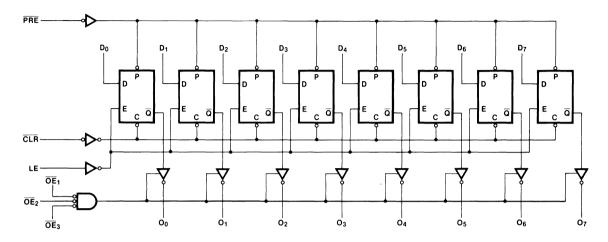

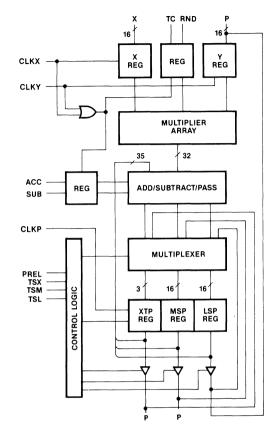

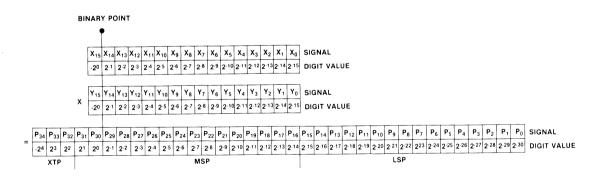

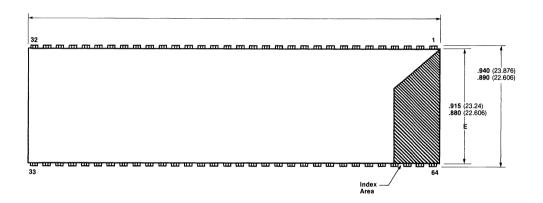

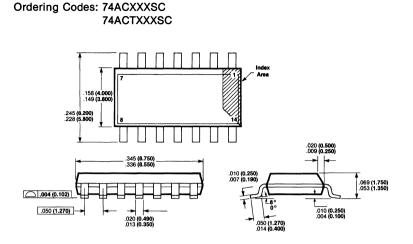

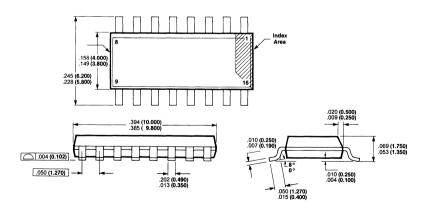

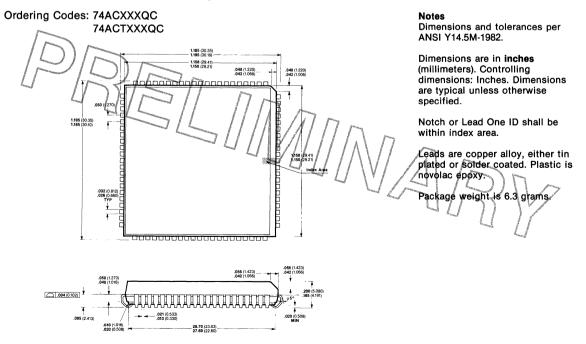

| 54ACT/74ACT1010         16 x 16 Multiplier/Accumulator         5-392           54ACT/74ACT1016         16 x 16 Parallel Multiplier         5-402                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54AU1//4AU1040         | o-Dit mansparent Laton                        | 0-300    |