A Schlumberger Company

## Memory Data Book

Memory Data Book

Memory and High Speed Logic

\$4.95

©1986 Fairchild Semiconductor Corporation Memory and High Speed Logic P.O. Box 5000 M/S 2C17 Puyallup, WA 98373-0900 206/841-6000 TWX 510 101 0846 .,

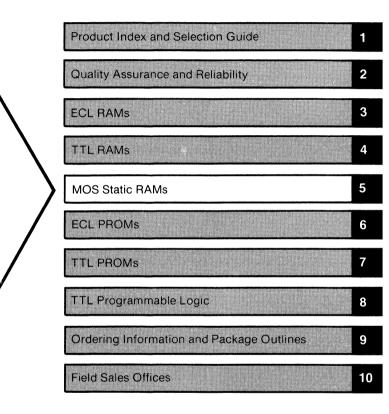

## **Table of Contents**

| Chapter 1   | Product Index, Selection<br>Guide, and Cross Reference |      |

|-------------|--------------------------------------------------------|------|

| Numerical I | ndex                                                   | 1-2  |

| Selection G | auide                                                  | 1-4  |

| Cross Refe  | rence                                                  | 1-6  |

| Chapter 2   | Quality Assurance and<br>Reliability                   |      |

| Introductio | n                                                      | 2-5  |

| Incoming C  | Quality Inspection                                     | 2-5  |

| Process Qu  | uality Control                                         | 2-5  |

| Quality Ass | surance                                                | 2-8  |

| Reliability |                                                        | 2-9  |

| Chapter 3   | ECL RAMs                                               | 3-3  |

| Chapter 4   | TTL RAMs                                               | 4-3  |

| Chapter 5   | MOS STATIC RAMS                                        | 5-3  |

| Chapter 6   | ECL PROMs                                              | 6-3  |

| Chapter 7   | TTL PROMs                                              |      |

| Data Sheet  | s                                                      | 7-4  |

| Isoplanar-Z |                                                        | 7-18 |

|             | -<br>Z Programming                                     | 7-20 |

| Chapter 8   | TTL Programmable Logic                                 | 8-3  |

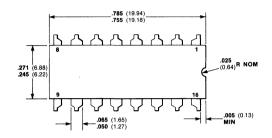

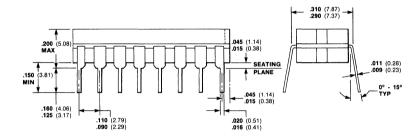

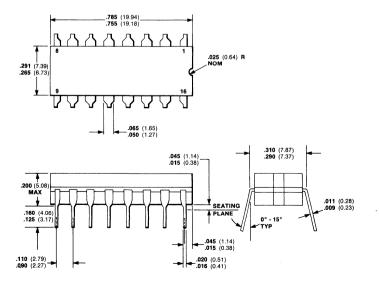

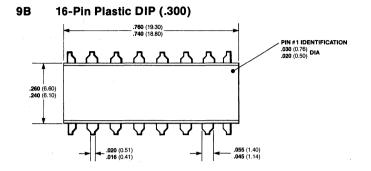

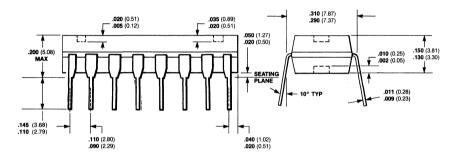

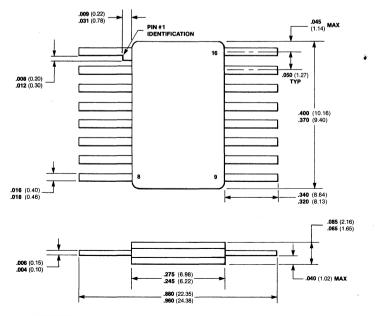

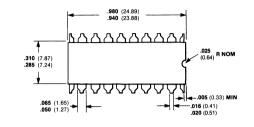

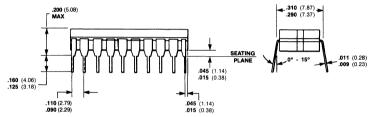

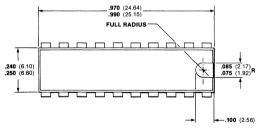

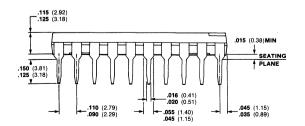

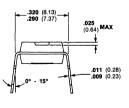

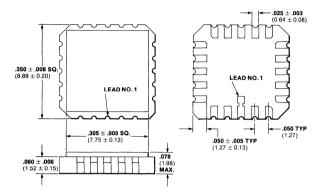

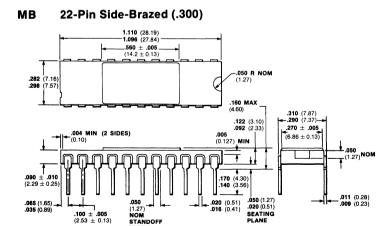

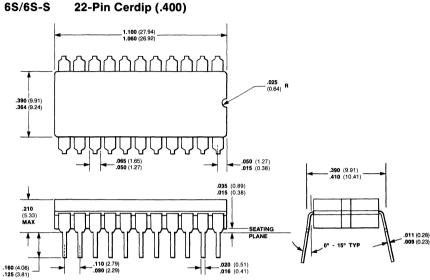

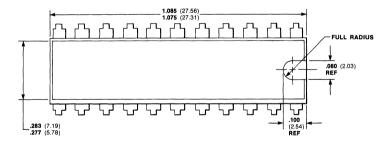

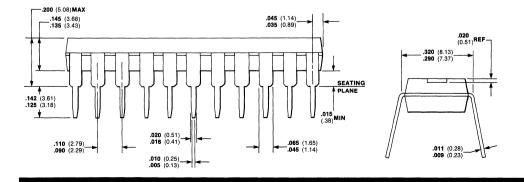

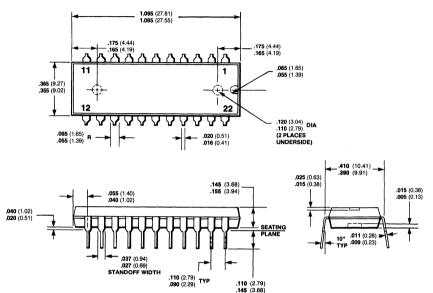

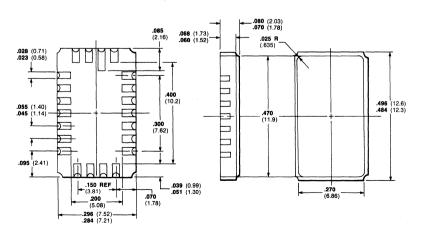

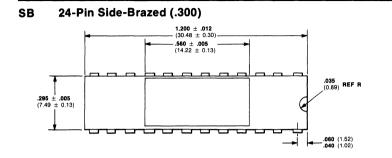

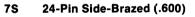

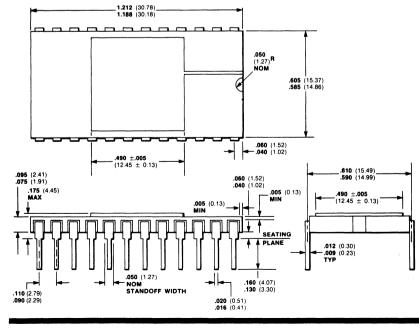

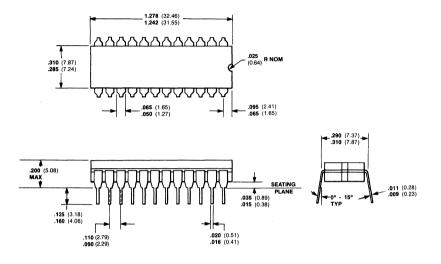

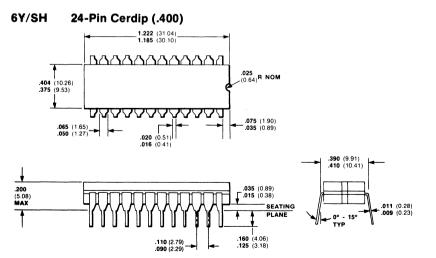

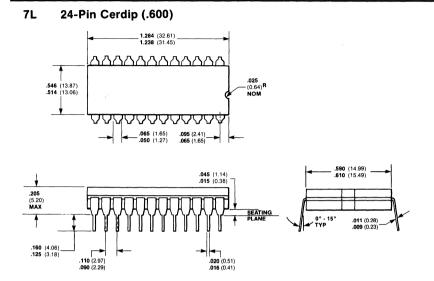

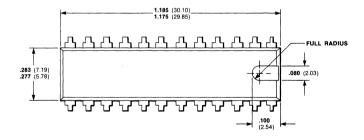

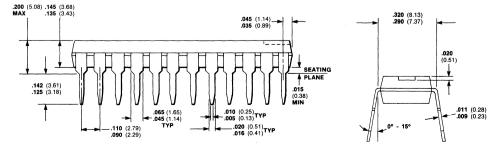

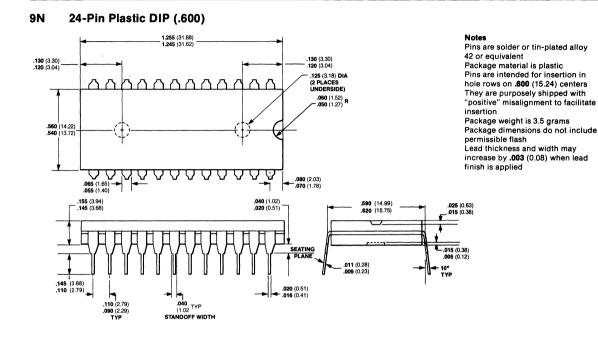

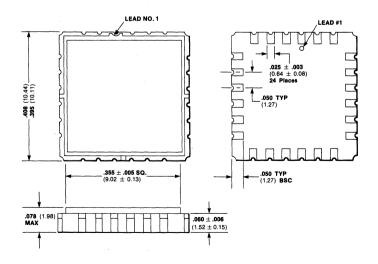

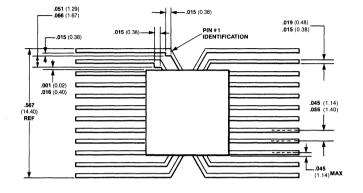

| Chapter 9   | Package Outlines                                       | 9-3  |

| Chapter 10  | Field Sales Offices and<br>Distributor Locations       | 10-3 |

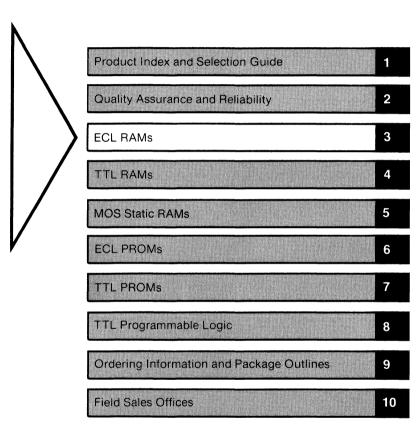

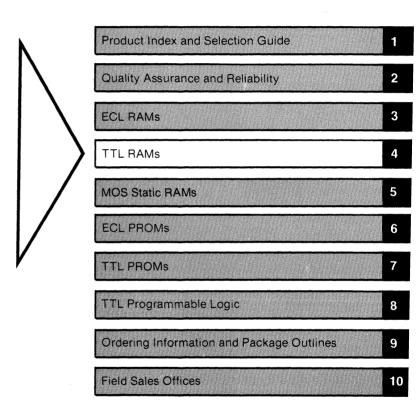

| Product Index and Selection Guide         | 1  |

|-------------------------------------------|----|

| Quality Assurance and Reliability         | 2  |

| ECL RAMs                                  | 3  |

| TTL RAMs                                  | 4  |

| MOS Static RAMs                           | 5  |

| ECL PROMs                                 | 6  |

| TTL PROMS                                 | 7  |

| TTL Programmable Logic                    | 8  |

| Ordering Information and Package Outlines | 9  |

| Field Sales Offices                       | 10 |

# Numerical Index of Devices

| F100K Serie  |                                                      |          |

|--------------|------------------------------------------------------|----------|

| DC Family    | Electrical Specifications                            | 3-3, 6-3 |

| F100145      | 16 × 4-Bit Register File (RAM)                       | 3-6      |

| F100402      | 16 × 4-Bit Register File (RAM)                       | 3-12     |

| F100415      | 1024 × 1-Bit Static RAM                              | 3-16     |

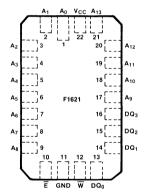

| F100Z416     | 256 × 4-Bit PROM — Isoplanar-Z Fuse                  | 6-6      |

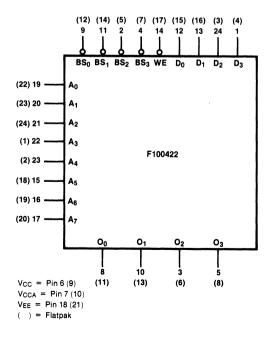

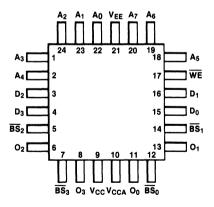

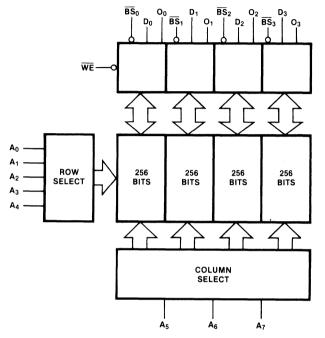

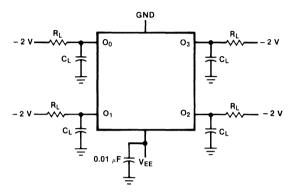

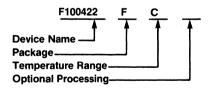

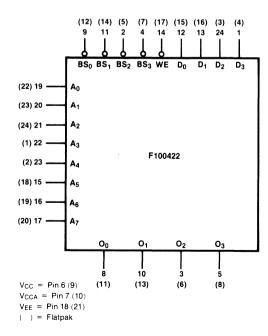

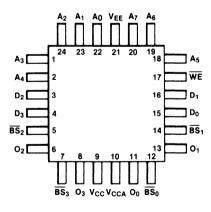

| F100422      | 256 × 4-Bit Static RAM                               | 3-22     |

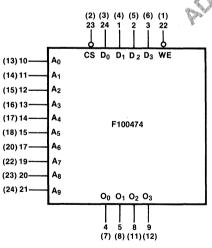

| F100474      | 1024 × 4-Bit Static RAM                              | 3-28     |

| F10K Series  |                                                      |          |

| DC Family    | Electrical Specifications                            | 3-5. 6-5 |

| F10145A      | 16 × 4-Bit Register File (RAM)                       | 3-30     |

| F10402       | 16 × 4-Bit Register File (RAM)                       | 3-34     |

| F10415       | 1024 × 1-Bit Static RAM                              | 3-38     |

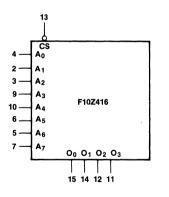

| F10Z416      | 256 × 4-Bit PROM — Isoplanar-Z Fuse                  | 6-8      |

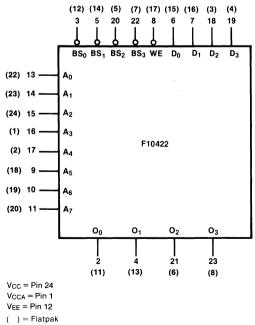

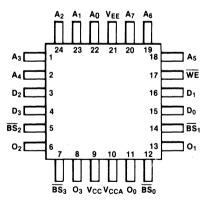

| F10422       | 256 × 4-Bit Static RAM                               | 3-44     |

| F10474       | 1024 × 4-Bit Static RAM                              | 3-50     |

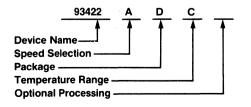

| 93xxx Series | TTL                                                  |          |

| TTL Family   | Electrical Specifications                            | 4-3, 7-3 |

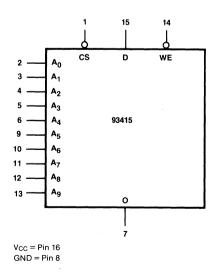

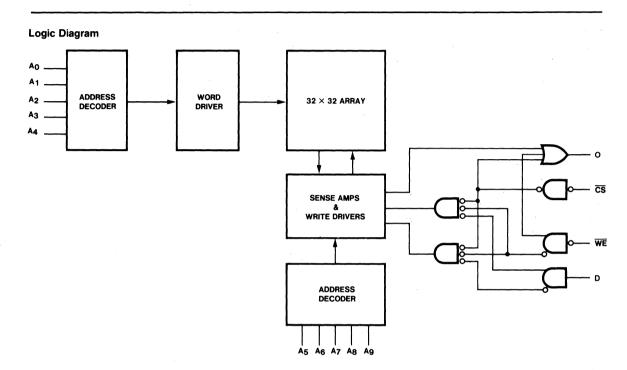

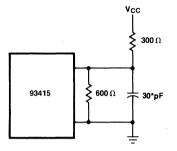

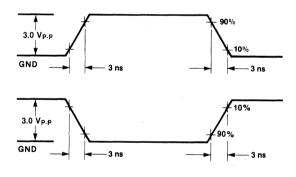

| 93415        | 1024 × 1-Bit Static RAM — Open Collector             | 4-5      |

| 93L415       | 1024 × 1-Bit Static RAM — Low Power, Open Collector  | 4-5      |

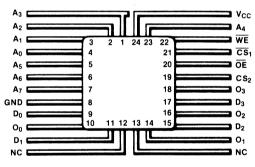

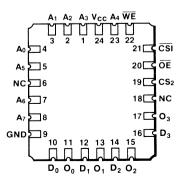

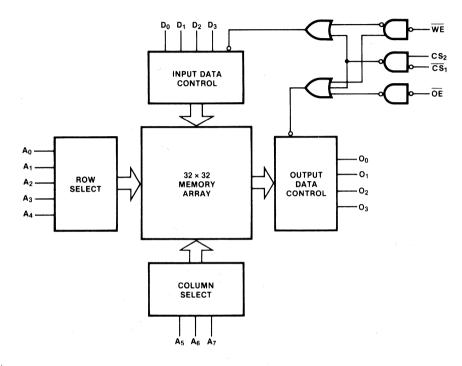

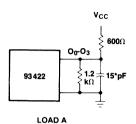

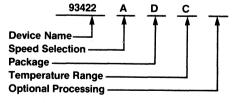

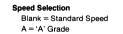

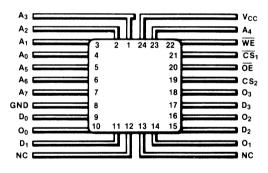

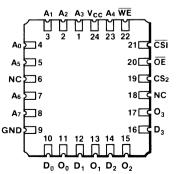

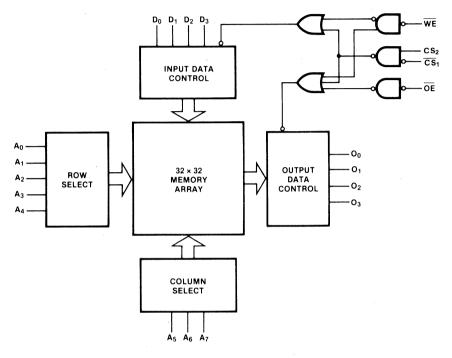

| 93422        | 256 × 4-Bit Static RAM — Three State                 | 4-13     |

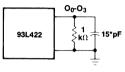

| 93L422       | 256 × 4-Bit Static RAM — Low Power, Three State      | 4-19     |

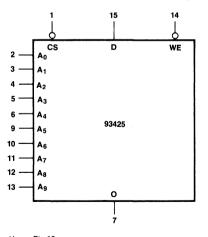

| 93425        | 1024 × 1-Bit Static RAM — Three State                | 4-25     |

| 93L425       | 1024 × 1-Bit Static RAM — Low Power, Three State     | 4-25     |

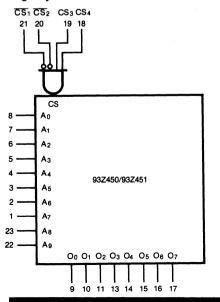

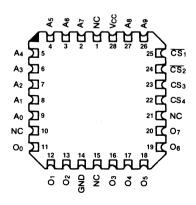

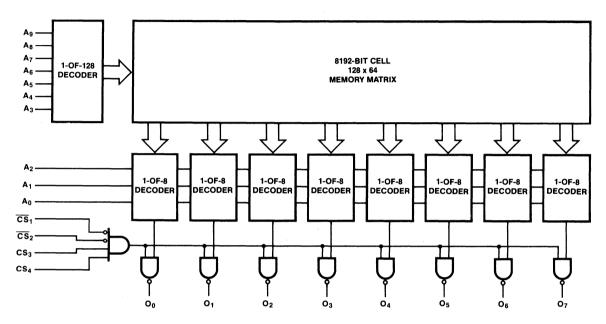

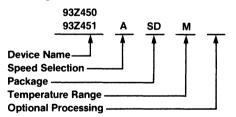

| 93Z450       | 1024 × 8-Bit PROM — Isoplanar-Z Fuse, Open Collector | 7-4      |

| 93Z451       | 1024 × 8-Bit PROM — Isoplanar-Z Fuse, Three State    | 7-4      |

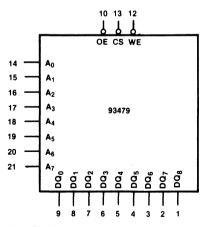

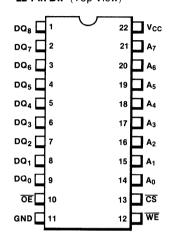

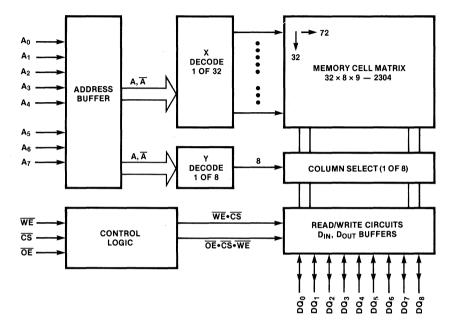

| 93479        | 256 × 9-Bit Static RAM — Three State                 | 4-33     |

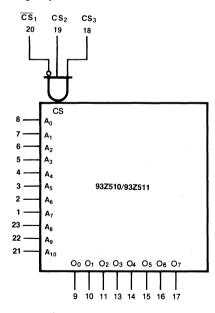

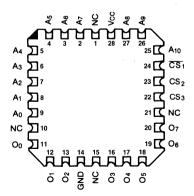

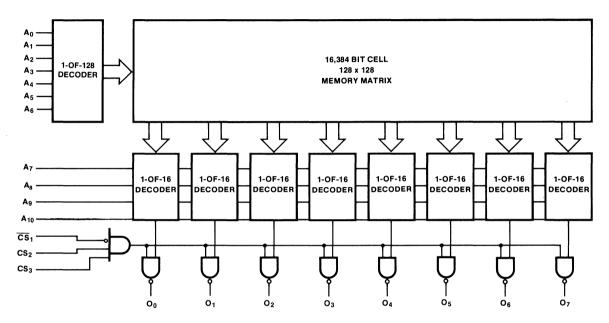

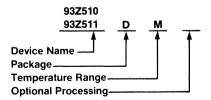

| 93Z510       | 2048 × 8-Bit PROM — Isoplanar-Z Fuse, Open Collector | 7-8      |

| 93Z511       | 2048 × 8-Bit PROM — Isoplanar-Z Fuze, Three State    | 7-8      |

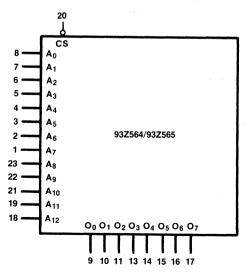

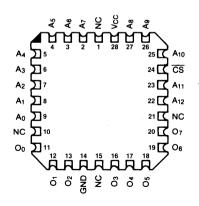

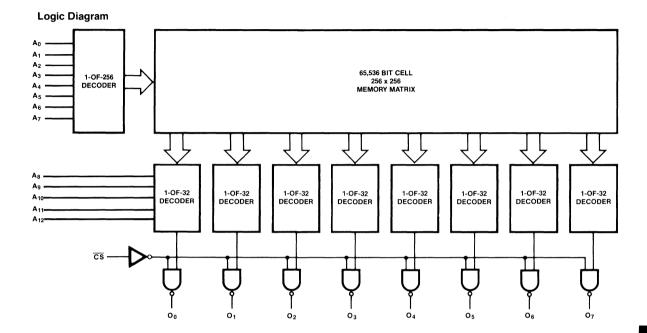

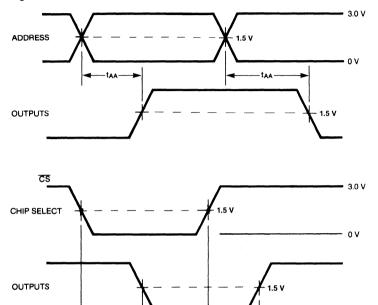

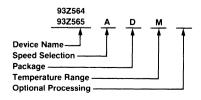

| 93Z564       | 8192 × 8-Bit PROM — Isoplanar-Z Fuse, Open Collector | 7-12     |

| 93Z565       | 8192 × 8-Bit PROM — Isoplanar-Z Fuse, Three State    | 7-12     |

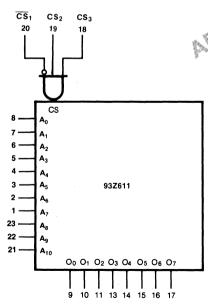

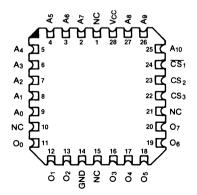

| 93Z611       | 2048 × 8-Bit PROM — Fast-Z Fuse, Three State         | 7-16     |

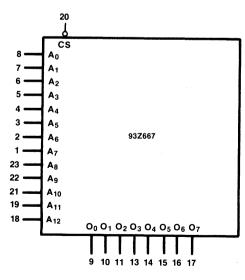

| 93Z667       | 8192 × 8-Bit PROM — Fast-Z Fuse. Three State         | 7-17     |

## Numerical Index of Devices (Cont'd)

1

| MOS Static  | RAM                                                                           |      |

|-------------|-------------------------------------------------------------------------------|------|

| F1600       | 65,536 × 1-Bit Static RAM                                                     | 5-3  |

| F1600       | 65,536 × 1-Bit Static RAM, Military Temperature Range                         | 5-10 |

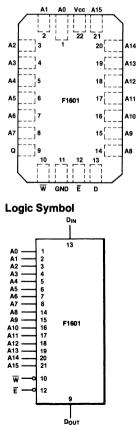

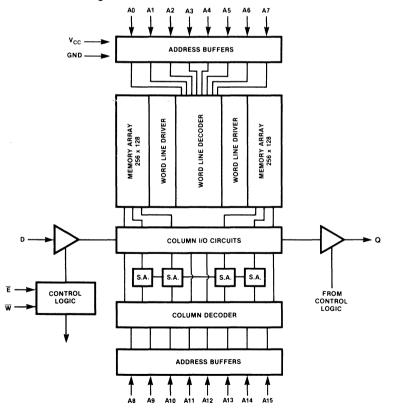

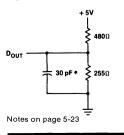

| F1601       | 65,536 × 1-Bit Static RAM, Data Retention Version                             | 5-17 |

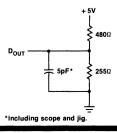

| F1601       | 65,536 × 1-Bit Static RAM, Data Retention Version, Military Temperature Range | 5-25 |

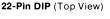

| F1620       | 16,384 × 4-Bit Static RAM                                                     | 5-33 |

| F1621       | 16,384 × 4-Bit Static RAM, Data Retention Version                             | 5-34 |

| F1622       | 16,384 × 4-Bit Static RAM                                                     | 5-35 |

| F1623       | 16,384 × 4-Bit Static RAM, Data Retention Version                             | 5-36 |

| TTL Prograu | mmable Logic                                                                  |      |

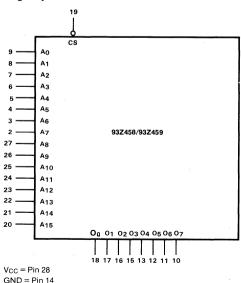

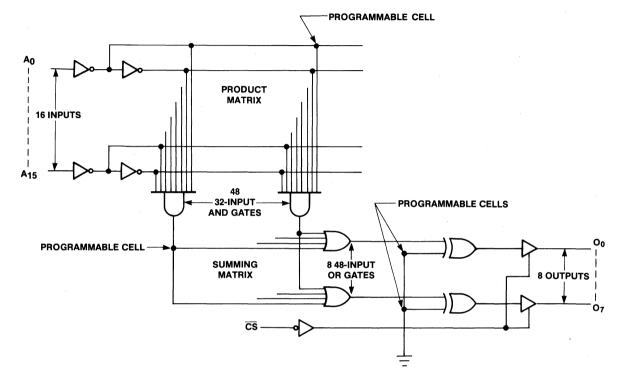

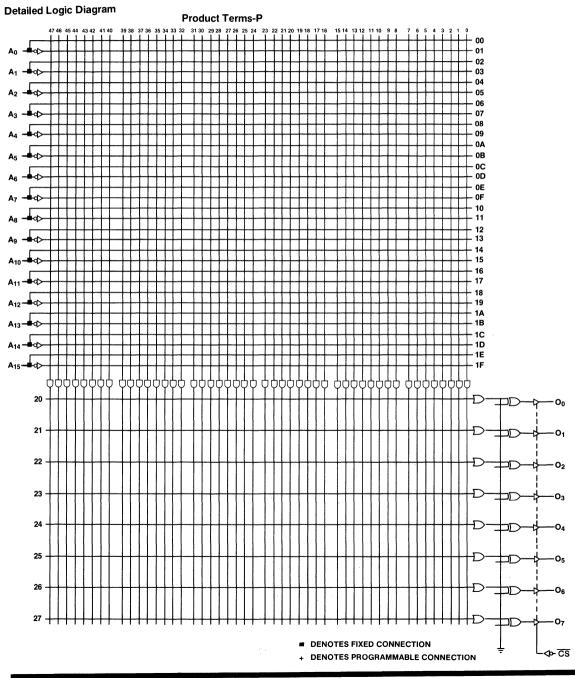

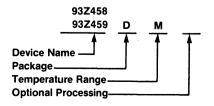

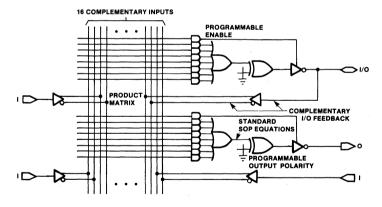

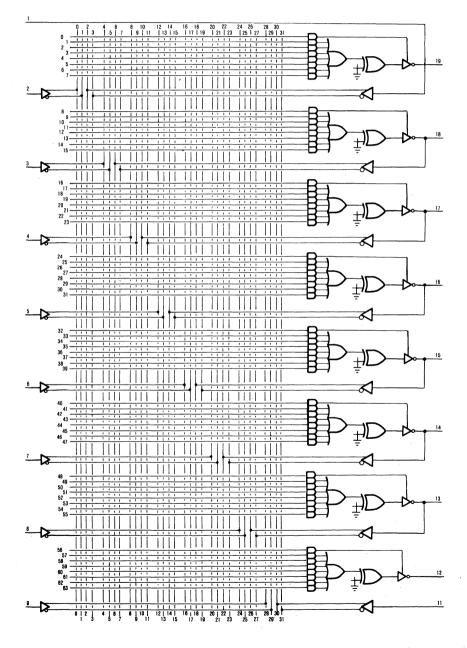

| 93Z458      | 16 × 48 × 8 FPLA — Isoplanar-Z Fuse, Open Collector                           | 8-3  |

| 93Z459      | 16 × 48 × 8 FPLA — Isoplanar-Z Fuse, Three State                              | 8-3  |

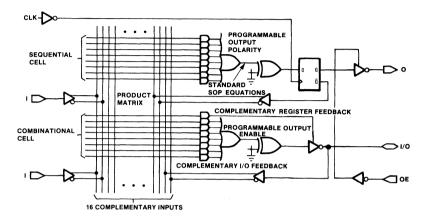

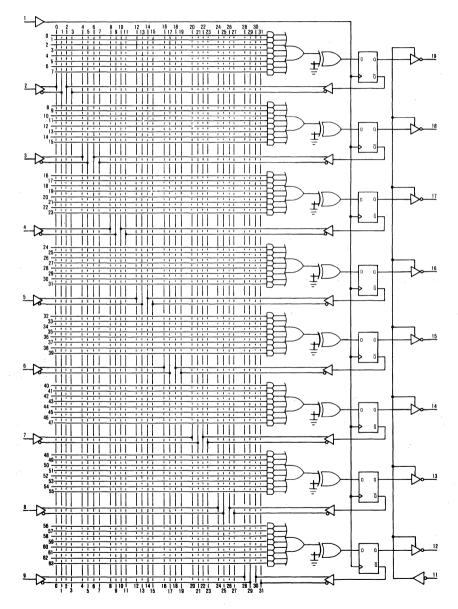

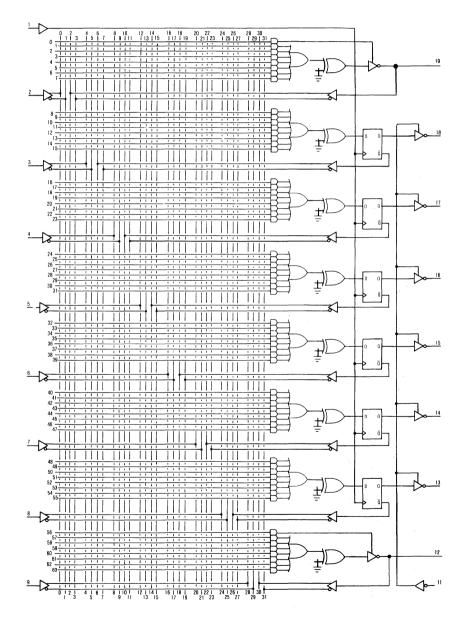

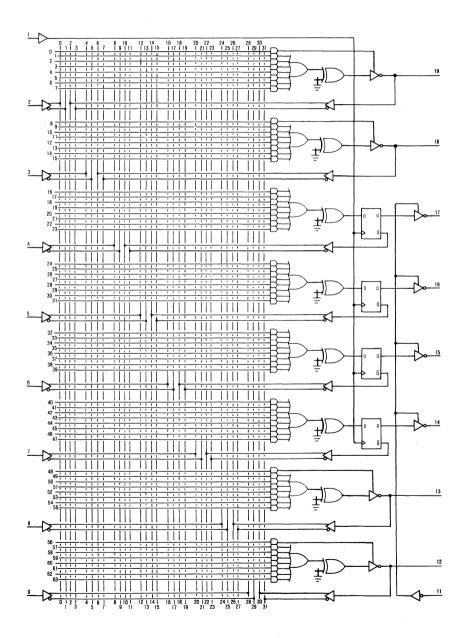

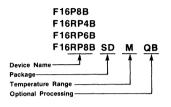

| 16P8B       | Programmable Logic Array                                                      | 8-16 |

| 16RP8B      | Programmable Logic Array                                                      | 8-16 |

| 16RP6B      | Programmable Logic Array                                                      | 8-16 |

| 16RP4B      | Programmable Logic Array                                                      | 8-16 |

## **Selection Guide**

|                                                                               | Device   | Page |

|-------------------------------------------------------------------------------|----------|------|

| F100K RAMs                                                                    |          |      |

| 16 × 4-Bit Register File (RAM)                                                | F100145  | 3-6  |

| 16 × 4-Bit Register File (RAM)                                                | F100402  | 3-12 |

| 1024 × 1-Bit RAM                                                              | F100415  | 3-16 |

| 256 × 4-Bit RAM                                                               | F100422  | 3-22 |

| 1024 × 4-Bit RAM                                                              | F100474  | 3-28 |

| F10K RAMs                                                                     |          |      |

| 16 × 4-Bit Register File (RAM)                                                | F10145A  | 3-30 |

| 16 × 4-Bit Register File (RAM)                                                | F10402   | 3-35 |

| 1024 × 1-Bit RAM                                                              | F10415   | 3-38 |

| 256 × 4-Bit RAM                                                               | F10422   | 3-44 |

| 1024 × 4-Bit RAM                                                              | F10474   | 3-50 |

| TTL RAMs                                                                      |          |      |

| 1024 × 1-Bit RAM — Open Collector                                             | 93415    | 4-5  |

| 1024 × 1-Bit RAM — Low Power, Open Collector                                  | 93L415   | 4-5  |

| 256 × 4-Bit RAM — Three State                                                 | 93422    | 4-13 |

| 256 × 4-Bit RAM — Low Power, Three State                                      | 43L422   | 4-19 |

| 1024 × 1-Bit RAM — Three State                                                | 93425    | 4-25 |

| 2014 × 1-Bit RAM — Low Power, Three State                                     | 93L425   | 4-25 |

| 256 × 9-Bit RAM — Three State                                                 | 93479    | 4-33 |

| MOS Static RAM                                                                |          |      |

| 65,536 × 1-Bit Static RAM                                                     | F1600    | 5-3  |

| 63,536 × 1-Bit Static RAM, Military Temperature Range                         | F1600    | 5-10 |

| 65,536 × 1-Bit Static RAM, Data Retention Version                             | F1601    | 5-17 |

| 65,536 × 1-Bit Static RAM, Data Retention Version, Military Temperature Range | F1601    | 5-25 |

| 16,384 × 4-Bit Static RAM                                                     | F1620    | 5-33 |

| 16,384 × 4-Bit Static RAM, Data Retention Version                             | F1621    | 5-34 |

| 16,384 × 4-Bit Static RAM                                                     | F1622    | 5-35 |

| 16,384 × 4-Bit Static RAM, Data Retention Version                             | F1623    | 5-36 |

| F100K PROM                                                                    |          |      |

| 256 × 4-Bit PROM — Isoplanar-Z Fuse                                           | F100Z416 | 6-6  |

| F10K PROM                                                                     |          |      |

| 256 × 4-Bit PROM — Isoplanar-Z Fuse                                           | F10Z416  | 6-8  |

## Selection Guide (Cont'd)

#### TTL PROMs

| 1024 × 8-Bit PROM — Open Collector                            | 93Z450 | 7-4  |

|---------------------------------------------------------------|--------|------|

| 1024 × 8-Bit PROM — Three State                               | 93Z451 | 7-4  |

| 2048 × 8-Bit PROM — Open Collector                            | 93Z510 | 7-8  |

| 2048 × 8-Bit PROM — Three State                               | 93Z511 | 7-8  |

| 8192 × 8-Bit PROM — Open Collector                            | 93Z564 | 7-12 |

| 8192 × 8-Bit PROM — Three State                               | 93Z565 | 7-12 |

| 2048 × 8-Bit PROM — Three State                               | 93Z611 | 7-16 |

| 8192 × 8-Bit PROM — Three State                               | 93Z667 | 7-17 |

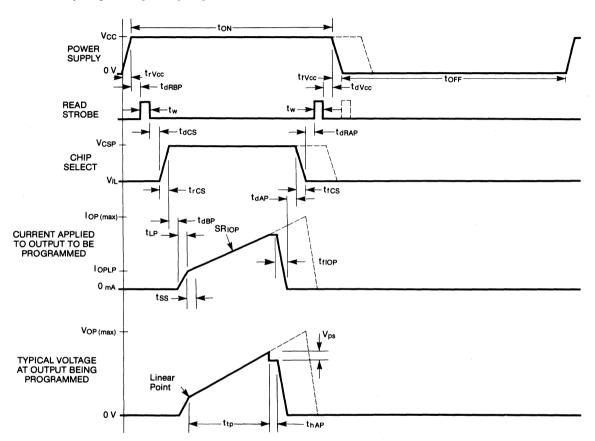

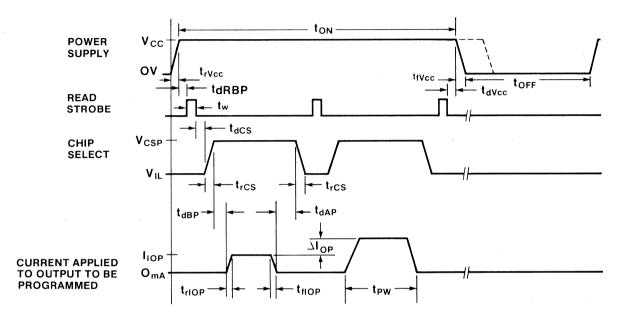

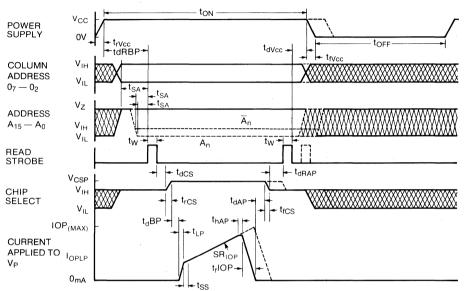

| Isoplanar-Z Junction Fuse Principles and Programming          |        | 7-18 |

| Isoplanar-Z TTL PROM Current-Ramp Programming Specifications  |        | 7-20 |

| Isoplanar-Z TTL PROM Current-Pulse Programming Specifications |        | 7-22 |

| TTL Programmable Logic                                        |        |      |

| 16 × 48 × 8 FPLA — Open Collector                             | 93Z458 | 8-3  |

| 16 × 48 × 8 FPLA — Three State                                | 93Z459 | 8-3  |

| Programmable Logic Array                                      | 16P8B  | 8-16 |

| Programmable Logic Array                                      | 16RP8B | 8-16 |

| Programmable Logic Array                                      | 16RP6B | 8-16 |

| Programmable Logic Array                                      | 168P48 | 8-16 |

## ECL/TTL/CMOS RAMs and PROMs Cross Reference Guide

| FSC P/N | Org   | Output | T <sub>AA</sub> | Pkg Pins | Other Features | AMD      | Harris  | Hitachi   | INMOS   |

|---------|-------|--------|-----------------|----------|----------------|----------|---------|-----------|---------|

| 10145A  | 16x4  | ECL    | 9               | 24       | REG FILE       |          |         | HD10145   |         |

| 100145  | 16x4  | ECL    | 9               | 24       | REG FILE       |          |         | HD100145  |         |

| 10402   | 16x4  | ECL    | 6               | 16       | REG FILE       |          |         |           |         |

| 100402  | 16x4  | ECL    | 6               | 16       | REG FILE       |          |         |           |         |

| 10415   | 1Kx1  | ECL    | 10              | 16       |                | AM10415  |         | HM2110/12 |         |

| 100415  | 1Kx1  | ECL    | 10              | 16       |                | AM100415 |         | HD100415  |         |

| 10422   | 256x4 | ECL    | 10              | 24       |                | AM10422  |         | HD10422   |         |

| 100422  | 256x4 | ECL    | 10              | 24       |                | AM100422 |         | HD100422  |         |

| 93415   | 1Kx1  | oc     | 30/25           | 16       |                | AM93415  |         |           |         |

| 93L415  | 1Kx1  | OC     | 45/35           | 16       |                |          |         |           |         |

| 93425   | 1Kx1  | TS     | 30/25           | 16       |                | AM93425  |         |           |         |

| 93L425  | 1Kx1  | TS     | 45/35           | 16       |                |          |         |           |         |

| 93419   | 64x9  | OC     | 45/35           | 28       |                |          |         |           |         |

| 93422   | 256x4 | TS     | 45/35           | 22       |                | AM93422  |         |           |         |

| 93L422  | 256x4 | TS     | 60/45           | 22       |                | AM93L422 |         |           |         |

| 93479   | 256×9 | TS     | 45/35           | 22       |                |          |         |           |         |

| 10Z416  | 256x4 | ECL    | 20              | 16       |                |          |         |           |         |

| 100Z416 | 256x4 | ECL    | 20              | 16       |                |          |         |           |         |

| 93Z450  | 1Kx8  | oc     | 40/35           | 24       |                | AM27S180 | HM7680  | HN25088   |         |

| 93Z450  | 1Kx8  | OC     | 40/35           | 24       | SLIMLINE       | AM27S280 |         |           |         |

| 93Z451  | 1Kx8  | TS     | 40/35           | 24       |                | AM27S181 | HM7681  | HN25089   |         |

| 93Z451  | 1Kx8  | TS     | 40/35           | 24       | SLIMLINE       | AM27S281 |         |           |         |

| 93Z510  | 2Kx8  | oc     | 45              | 24       |                | AM27S190 |         | HN25168   |         |

| 93Z510  | 2Kx8  | OC     | 45              | 24       | SLIMLINE       | AM27S290 |         |           |         |

| 93Z511  | 2Kx8  | TS     | 45              | 24       |                | AM27S191 | HM76161 | HN25169   |         |

| 93Z511  | 2Kx8  | TS     | 45              | 24       | SLIMLINE       | AM27S291 |         |           |         |

| 93Z564  | 8Kx8  | OC     | 55/45           | 24       |                |          |         |           |         |

| 93Z565  | 8Kx8  | TS     | 55/45           | 24       |                | AM27S49  | HM76641 |           |         |

| F1600   | 64Kx1 | SMOS   | 70/55/45        | 22       |                |          |         | HN6287    | IMS1600 |

| Fujitsu               | MMI     | Motorola  | Naťl                 | NEC     | Raytheon | Signetics       | ті                    |

|-----------------------|---------|-----------|----------------------|---------|----------|-----------------|-----------------------|

|                       |         | MCM10145  |                      |         |          | 10145           |                       |

|                       |         | MCM10H145 |                      |         |          |                 |                       |

| MBM10415              |         |           | DM10415              |         |          | 10415           |                       |

| MBM100415<br>MBM10422 |         |           | DM10422              |         |          | 100415<br>10422 |                       |

| MBM10422<br>MBM100422 |         |           | DIVI10422            |         |          | 10422           |                       |

|                       |         | MCM93415  |                      |         |          |                 |                       |

|                       |         | MCM93425  |                      |         |          |                 |                       |

|                       |         |           |                      |         |          |                 |                       |

|                       |         | MCM93422  |                      |         |          |                 |                       |

|                       |         | MCM93L422 |                      |         |          |                 |                       |

|                       |         |           |                      |         |          | S82S212         |                       |

|                       |         | MCM10149  |                      |         |          | 10149<br>100149 |                       |

| MB7131<br>MB7131SK    | 53/6380 | MCM7680   | DM87S180<br>DM87S280 | uBP409  | 29630    | N82S180         | TBP28SA86<br>TBP28S86 |

| MB7132<br>MB7132SK    | 53/6381 | MCM7681   | DM87S181<br>DM87S281 | uBP417  | 29631    | N82S181         | TBP28S86<br>TBP28S86  |

| MB7137                |         | MCM76160  | DM87S190             | uBP409  | 29680    | N82S190         | TBP28SA166            |

| MB7137SK              |         |           | DM87S290             |         |          | N82S190         | TBP28S166             |

| MB7138                | 63S1681 | MCM76161  | DM87S191             | uBP429  | 29681    | N82S191         |                       |

| MB7138SK              |         |           | DM87S291             |         |          | N82S191         |                       |

| MB7143                |         |           |                      |         |          |                 |                       |

| MB7144                |         |           |                      |         |          |                 |                       |

|                       |         |           |                      | uBP4361 |          |                 |                       |

#### Fairchild Memory Products Listed on Military Jan Qualified Products List (QPL) — 38510<sup>3</sup>

#### Jan Part Numbering System

| J                | M38510/     | 231         | 02      | В          | Е       | В                  |

|------------------|-------------|-------------|---------|------------|---------|--------------------|

| Jan Designator   | General     | Refers to   | Defines | Processing | Defines | Lead Finish        |

| Cannot be Marked | Procurement | Slash Sheet | Device  | Level      | Package | A Hot Solder Dip   |

| "J" Unless       | Spec        |             | Туре    | S          | Туре    | B Tin Plate        |

| Qualified by     | •           |             |         | В          | Per     | C Gold Plate       |

| DESC-EQM         |             |             |         |            | Slash   | X Lead Finish A,B, |

|                  |             |             |         |            | Sheet   | or C               |

#### TTL RAMs

| Fairchild<br>Generic P/N <sup>1</sup> | Jan Slash No. <sup>2</sup> | Jan QPL Part | Organization  | Access Time<br>(T <sub>AA</sub> ) |

|---------------------------------------|----------------------------|--------------|---------------|-----------------------------------|

| 93422DMQB                             | 23110BWA                   | 11           | 256X4, TS     | 60 ns                             |

| FMQB                                  | 23110BXA                   | 11           | 256X4, TS     | 60 ns                             |

| LMQB                                  | 23110BYC                   | 11           | 256X4, TS     | 60 ns                             |

| 93422ADMQB                            | 23114BWA                   | 11           | 256X4, TS     | 45 ns                             |

| AFMQB                                 | 23114BXA                   | 11           | 256X4, TS     | 45 ns                             |

| ALMQB                                 | 23114BYC                   | 11           | 256X4, TS     | 45 ns                             |

| 93L422DMQB                            | 23112BWA                   | 1            | 256X4, TS, LP | 75 ns                             |

| FMQB                                  | 23112BXA                   | 1            | 256X4, TS, LP | 75 ns                             |

| LMQB                                  | 23112BYC                   | 1            | 256X4, TS, LP | 75 ns                             |

| 93L422ADMQB                           | 23115BWA                   | 1            | 256X4, TS, LP | 55 ns                             |

| AFMQB                                 | 23115BXA                   | 1 .          | 256X4, TS, LP | 55 ns                             |

| ALMQB                                 | 23115BYC                   | 1            | 256X4, TS, LP | 55 ns                             |

| 93L415DMQB                            | 23103BEA                   | I            | 1KX1, OC      | 70 ns                             |

| FMQB                                  | 23103BFA                   | 1            | 1KX1, OC      | 70 ns                             |

| 93425DMQB                             | 23102BEA                   | I            | 1KX1, TS      | 60 ns                             |

|                                       |                            |              |               | (TWSA=15, TWHD=5)                 |

|                                       | 23106BEA                   | 1            | 1KX1, TS      | 60 ns                             |

|                                       |                            |              |               | (TWSA=10, TWHD=10                 |

| FMQB                                  | 23102BFA                   | 1            | 1KX1, TS      | 60 ns                             |

|                                       |                            |              |               | (TWSA=15, TWHD=5)                 |

|                                       | 23106BFA                   |              | 1KX1, TS      | 60 ns                             |

|                                       |                            |              |               | (TWSA=10, TWHD=10                 |

| 93425ADMQB                            | 23108BEA                   | ł            | 1KX1, TS      | 45 ns                             |

| FMQB                                  | 23108BFA                   | I            | 1KX1, TS      | 45 ns                             |

| 93L425DMQB                            | 23104BEA                   | I            | 1KX1, TS, LP  | 70 ns                             |

| FMQB                                  | 23104BFA                   | 1            | 1KX1, TS, LP  | 70 ns                             |

| 93L425ADMQB                           | 23113BEA                   | I            | 1KX1, TS, LP  | 50 ns                             |

| FMQB                                  | 23113BFA                   | I            | 1KX1, TS, LP  | 50 ns                             |

| TTL PROMs                             |                            |              |              |                                   |  |  |

|---------------------------------------|----------------------------|--------------|--------------|-----------------------------------|--|--|

| Fairchild<br>Generic P/N <sup>1</sup> | Jan Slash No. <sup>2</sup> | Jan QPL Part | Organization | Access Time<br>(T <sub>AA</sub> ) |  |  |

| 93Z511DMQB                            | 21002BJA                   | I            | 2KX8, TS     | 100 ns                            |  |  |

|                                       | 21004BJA                   | I            | 2KX8, TS     | 55 ns                             |  |  |

#### Notes

<sup>1</sup>Fairchild HI-REL generic QB product is processed to Hi-Rel level QB flow (in full compliance with MIL-STD-883) of Figure 2-2 and tested to the limits specified in individual data sheets under DC, AC, and functional (FN) performance characteristics.

<sup>2</sup>Fairchild JAN product is processed to HI-REL JAN flow per MIL-M38510 and MIL-STD-883 and tested per the DC, AC, and FN performance characteristics of the respective military slash sheet.

<sup>3</sup>Check Qualified Product List (QPL) — 38510 for current JAN listings.

$\label{eq:state} \begin{array}{l} \mbox{Legend} \\ TS = Three-State \\ A = Highspeed Version \\ OC = Open Collector \\ LP = Low Power Version \end{array}$

## Notes

# Quality Assurance and Reliability

#### Introduction

All Fairchild Memory and High Speed Logic Products are manufactured to strict quality and reliability standards. Product conformance to these standards is insured by careful monitoring of the following functions: (1) incoming quality inspection, (2) process quality control, (3) quality assurance, and (4) reliability.

#### **Incoming Quality Inspection**

Purchased piece parts and raw materials must conform to purchase specifications. Major monitoring programs are the inspection of package piece parts, inspection of raw silicon wafers, and inspection of bulk chemicals and materials. Two other important functions of incoming quality inspection are to provide real-time feedback to vendors and in-house engineering, and to define and initiate quality improvement programs.

#### Package Piece Parts Inspection

Each shipment of package piece parts is inspected and accepted or rejected based on AQL sampling plans. Inspection tests include both inherent characteristics and functional use tests. Inherent characteristics include physical dimensions, color, plating quality, material purity, and material density. Functional use tests for various package piece parts include die attach, bond pull, seal, lid torque, salt atmosphere, lead fatigue, solderability, and mechanical strength. In these tests, the piece parts are sent through process steps that simulate package assembly. The units are then destructively tested to determine whether or not they meet the required quality and reliability levels.

#### Silicon Wafer Inspection

Each shipment of raw silicon wafers is accepted or rejected based on AQL sampling plans. Raw silicon wafers are subjected to non-destructive and destructive tests. Included in the testing are flatness, physical dimensions, resistivity, oxygen and carbon content, and defect densities. The test results are used to accept or reject the lot.

#### Bulk Chemical and material Inspection

Bulk chemicals and materials play an important role in any semiconductor process. To insure that the bulk chemicals and materials used in processing Fairchild wafers are the highest quality, they are stringently tested for trace impurities and particulate or organic contamination. Mixtures are also analyzed to verify their chemical make-up. Incoming inspection is only the first step in determining the acceptability of bulk chemicals and materials. After acceptance, detailed documentation is maintained to correlate process results to various vendors and to any variations found in mixture consistency.

#### **Process Quality Control**

Process quality is maintained by establishing and maintaining effective controls for monitoring the wafer fabrication process, reporting the results of the monitors, and initiating valid measurement techniques for improving quality and reliability levels.

#### Methods of Control

The process quality control program utilizes the following methods of control: (1) process audits, (2) environmental monitors, (3) process monitors, (4) lot acceptance inspections, (5) process qualifications, and (6) process integrity audits. These methods of control, defined below, characterize visually and electrically the wafer fabrication operation.

Process Audit — Audits concerning manufacturing operator conformance to specification. These are performed on all operations critical to product quality and reliability.

Environmental Monitor-Monitors concerning the process environment, *i.e.*, water purity, air temperature/ humidity, and particulate count.

Process Monitor — Periodic inspection at designated process steps for verification of manufacturing inspection and maintenance of process average. These inspections provide both attribute and variables data.

Lot Acceptance — Lot by lot sampling. This sampling method is reserved for those operations deemed as critical and, as such, requiring special attention.

Process Qualification — Complete distributional analysis is run to specified tolerance averages and standard deviations. These qualifications are typically conducted on deposition and evaporation processes, *i.e.*, epi, aluminum, vapox, and backside gold.

Process Integrity Audit — Special audits conducted on oxidation and metal evaporation processes (CV drift — oxidation; SEM evaluation — metal evaporation).

## Quality Assurance and Reliability

#### Data Reporting

Process quality control data is recorded on an attribute or variable basis as required; control charts are maintained on a regular basis. This data is reviewed at periodic intervals and serves as the basis for judging the acceptability of specific processes. Summary data from the various process quality control operations are relayed to cognizant line, engineering and management

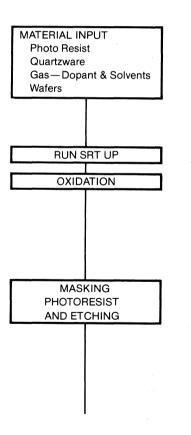

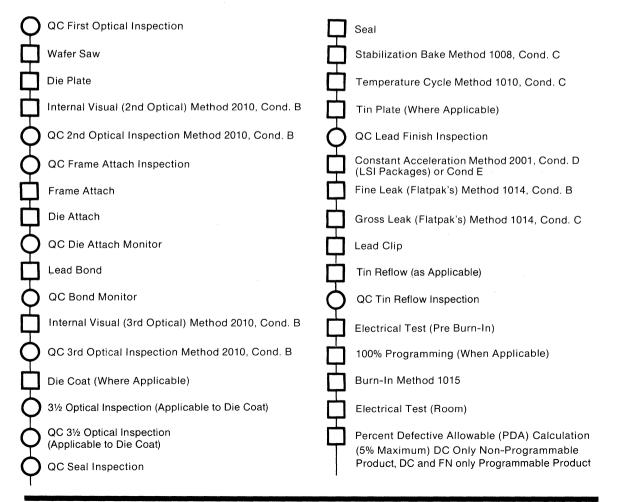

#### Fig. 2-1 Process Flow Chart

personnel in real time so that, if appropriate, the necessary corrective actions can be immediately taken.

#### Process Flow

*Figure 2-1* shows the integration of the various methods of control into the wafer fabrication process flow. The process flow chart contains examples of the process quality controls and inspections utilized in the manufacturing operation.

#### Process Controls (Examples)

- A. Environmental

- B. Chemical supplies

- C. Substrate exam. (resistivity, flatness, thickness, crystal perfection, etc.)

- D. Photoresist evaluation

- E. Mask inspections

- A. Process audit

- A. Process audit/qualification

- B. Environmental

- C. Process monitors (thickness, pinhole and crack measurements)

- E. C V Plotting

- F. Calibration

- A. Process audits

- B. Environmental

- C. Visual examinations

- Photoresist evaluation (preparation, storage, application, baking, development and removal).

- E. Etchant controls

- F. Exposure controls (intensity, uniformity)

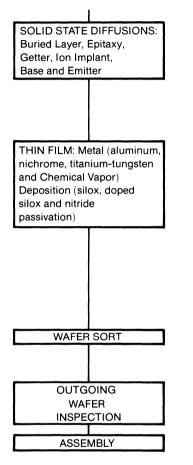

#### Fig. 2-1 Process Flow Chart (cont'd.)

- A. Process audits/qualification

- B. Environmental

- C. Temperature profiling

- D. Quartz cleaning

- E. Calibration

- F. Electrical tests (resistivity, breakdown voltages, etc.)

- A. Process audits/qualification

- B. Environmental

- C. Visual examinations

- D. Epitaxy controls (thickness, resistivity cleaning, visual examination)

- E. Metallization controls (thickness, temperature cleaning, SEM, C V plotting)

- F. Glassivation controls (thickness, dopant concentraton, pinhole and crack measurements)

- A. Process audit

- B. Environments

- C. Visual examinations

- A. Process audit

- B. Inspection

## Quality Assurance and Reliability

#### Quality Assurance

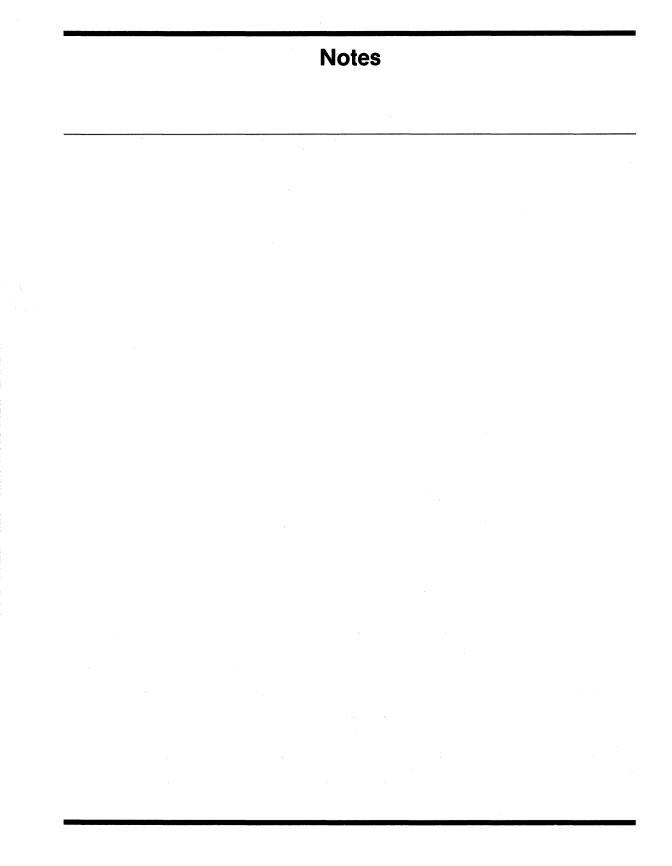

To assure that all product shipped meets both internal Fairchild specifications for standard product and customer specifications in the case of negotiated specs, a number of QA inspections throughout the assembly process flow (*Figure 2-2*) are required.

The Hi-Rel and Standard Rel Assembly and Test Flows are shown below to provide a clearer understanding of

#### Fig. 2-2 HI-REL (Level B) Assembly and Test Flow (per MIL-STD-883, Methods 5004, 5005)

the operations performed. Flows, much more detailed than the flows in Figures 2-2 and 2-3, govern the assembly and test of devices to Fairchild's specifications.

The Product built to the Hi-Rel Level B Assembly and Test Flow meet the requirements of MIL-STD-883 (Test Methods and Procedures for Microcircuits).

QC External Visual Inspection QC PDA Verification QC Fine & Gross Leak Methods 1014. QC Group A Electrical Test (Room) Cond. B & Method 1014, Cond. C (Subgroup B-7) Electrical Test (Cold) DC Electrical Screen of QC Seal Test Samples External Visual of QC Seal Test Samples, QC Group A Electrical Test (Cold) Method 2009 QC Internal Visual/Mechanical Method 2014 Solder Finish (Where Applicable) (Subgroup B-4) QC Solder Lead Finish Inspection QC Solderability Method 2003 (Subgroup B-3) (Where Applicable) Fine Leak (DIP's & LCC's) Method 1014, QC Bond Strength Method 2011 (Subgroup B-5) Cond. B QC Resistance to Solvents Methods 2015 Gross Leak (DIP's & LCC's) Method 1041, (Subgroup B-2) Cond. C QC Physical Dimensions Method 2016 Mark (Subgroup B-1) Electrical Test (Hot) Pack Quality Conformance Inspection (QCI) QC Group A, Electrical Test (Hot) Method 5005 (Group C & D) Programmability Sample (When Applicable) QC Data Check Electrical Test (Hot) of Programmed Samples (When Applicable) Shipping Clearance Electrical Test (Cold) of Programmed Samples (When Applicable) QA Plant Clearance/Buy-Off Electrical Test (Room) of Programmed Samples

#### NOTE

The sequence of Operations Between Pre Burn-in Electrical Test and Hot Electrical Test May Differ Slightly for some products.

External Visual Inspection, Method 2009

(When Applicable)

2-7

#### Fig. 2-3 STD

| 3 STD-REL Assembly and Test Flow |                |                                     |

|----------------------------------|----------------|-------------------------------------|

| QC First Optical Inspection      |                | Burn-In (QR Product Only)           |

| Wafer Saw                        | $\Box$         | Electrical Test (Room-QR Product)   |

| Die Plate                        |                | Fine Leak (DIP's & LCC's)           |

| QC Frame Attach Inspection       | 白              | Gross Leak (DIP's & LCC's)          |

| Frame Attach                     | 白              | Electrical Test (Hot)               |

| Die Attach                       | Ó              | QC Resistance To Solvents           |

| QC Die Attach Monitor            | Ó              | QC Solderability                    |

| Lead Bond                        | <b></b>        | Customer Finish & Visual/Mechancial |

| QC Bond Strength Monitor         | <b></b>        | QC Fine & Gross Leak                |

| Internal Visual (3rd Optical)    | <b></b>        | QC Visual/Mechanical                |

| QC 3rd Optical Inspection        | <b></b>        | QC Electrical Inspection            |

| QC Torque Test Monitor           | 口              | Pack                                |

| Seal                             | <b></b>        | QC Box Stock Buy-In                 |

| External Visual (4th Optical)    | $\diamondsuit$ | QC Plant Clearance/Buy-Off          |

| QC 4th Optical Inspection        | $\nabla$       | Shipping Clearance                  |

| Temperature Cycle                |                |                                     |

|                                  |                |                                     |

NOTE

The Sequence Of Operations Between Mark and Hot Electrical Test May Differ Slightly For Some Products.

Electrical Test (Room)

Tin Plate (Where Applicable)

QC Lead Finish Inspection

Fine Leak (Flatpak's)

Lead Clip

Mark

Gross Leak (Flatpak's)

#### Quality Assurance and Reliability

#### Reliability

A number of programs, among them qualification testing, reliability monitoring, failure analysis, and reliability data collection and presentation, are maintained.

#### Qualification Programs

All products receive reliability qualification prior to the product being released for shipment. Qualification is required for (1) new product designs, (2) new fabrication processes or (3) new packages or assembly processes. Stress tests are run in accordance to test methods described in MIL-STD-883. Test results are evaluated against existing reliability levels, and must be better than or equal to current product for the new product to receive qualification.

New Product Designs — Receive, as a minimum, +125° C operating life tests. Readouts are normally scheduled at 168 hours, 500 hours, 1000 hours and 2000 hours. The samples stressed are electrically good units from initial wafer runs. Additional life testing, consisting of high-temperature operating life test, 85/85 humidity bias tests, bias pressure pot (BPTH) tests, mechanical series or thermal series may be run as deemed necessary. Redesigns of existing device layouts are considered to be new product designs, and full qualification is necessary.

New Fabrication Processes - Qualifications are designed to evaluate the new process against the current process. Stress tests consist of operating life test, hightemperature operating life test, 85/85 humidity bias test and/or biased pressure pot (BPTH) test. In addition, package environment tests may be performed, such as Thermal Series or Mechanical Series. Evaluations are performed on various products throughout the development stages of the new process. Units stressed are generally from split wafer runs. All processing is performed as a single wafer lot up to the new process steps, where the lot is split for the new and the current process steps. Then the wafers are recombined, and again processed as a single wafer lot. This allows for controlled evaluation of the new process against the standard process. Both significant modifications to existing process and transferring existing products to new fabrication plants are treated as a new process.

New Packages or Assembly Processes — Qualifications are performed for new package designs, changes to existing piece parts, changes in piece part vendors, and

significant modification to assembly process methods. In general, samples from three assembly runs are stressed to a matrix in accordance to MIL-STD-883, Method 5005, group B, group C, subgroup 2, and group D (*Table 2-1*). In addition, +100°C operating life tests, 85/85 humidity bias tests, biased pressure pot (BPTH) tests and unbiased pressure pot tests are performed for plastic packages.

#### **Reliability Monitors**

Reliability testing of mature products is performed to establish device failure rates, and to identify problems occuring in production. Samples are obtained on a regular basis from production. These units are stressed with operating life tests or package environmental tests. The results of these tests are summarized and reported. When a problem is identified, the respective engineering group is notified, impact on the customer is reviewed and a corrective action plan is implemented.

Current testing levels are in excess of 14,000 units per year stressed with operating life tests, and 23,000 units per year stressed with package environmental tests.

#### Failure Analysis

Failure analysis is performed on all units failing reliability stress tests. Failure analysis is offered as a service to support manufacturing and engineering, and to support customer returns and customer requested failure studies. The failure analysis procedure used has been established to provide a technique of sequential analysis. This technique is based on the premise that each step of analysis will provide information of the failure without destroying information to be obtained from subsequent steps. The ultimate purpose is to uncover all underlying failure mechanisms through complete, in-depth, defect analysis. The procedure places great emphasis on electrical analysis, both external before decapsulation, and internal micro-probing. Visual examinations with high magnification microscopes or SEM analysis are used to confirm failure mechanisms. Results of the failure analysis are recorded and, if abnormalities are found, reported to engineering and/or manufacturing for corrective action.

#### Data Collection and Presentation

Product reliability is controlled by first stressing the product, and then feeding back results to manufacturing and engineering. This feedback takes two forms. There is a formal monthly Reliability Summary distributed to all groups. The summary shows current product failure rates, highlights problem areas, and shows the status of qualification and corrective action programs. Less formal feedback is obtained by including reliability personnel at

all product meetings, which gives high visibility to the reliability aspects of various products. As a customer service, product reliability data is compiled and made available upon request.

|                                                                                                                                                                    | MIL-STD-883          |                                                                                                                                                                                                                                                                           |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Test                                                                                                                                                               | Method               | Condition                                                                                                                                                                                                                                                                 |  |  |  |

| Group B<br>Subgroup 1<br>Physical dimensions                                                                                                                       | 2016                 |                                                                                                                                                                                                                                                                           |  |  |  |

| Subgroup 2<br>Resistance to solvents                                                                                                                               | 2015                 |                                                                                                                                                                                                                                                                           |  |  |  |

| Subgroup 3<br>Solderability                                                                                                                                        | 2003                 | Soldering temperature +245 $\pm$ 5°C, +260 $\pm$ 5°C (L <sub>CC</sub> only)                                                                                                                                                                                               |  |  |  |

| Subgroup 5<br>Bond strength<br>(1) Thermocompression<br>(2) Ultrasonic or wedge                                                                                    | 2011                 | <ul> <li>(1) Test condition C or D</li> <li>(2) Test condition C or D</li> </ul>                                                                                                                                                                                          |  |  |  |

| Group C<br>Subgroup 2<br>Temperature cycling<br>Constant acceleration<br>Seal<br>(a) Fine<br>(b) Gross<br>Visual examination<br>End-point electrical<br>parameters | 1010<br>2001<br>1014 | Test condition C ( $-65^{\circ}$ C to $+150^{\circ}$ C)<br>Test condition E (30Kg), Y <sub>1</sub> orientation and X <sub>1</sub> orientation<br>(where available)<br>Test condition D (20K g) for packages over 5 gram weight or with<br>seal ring greater than 2 inches |  |  |  |

| Group D<br>Subgroup 2<br>Lead integrity<br>Seal<br>(a) Fine<br>(b) Gross                                                                                           | 2004<br>1014         | Test condition B2 (lead fatigue)<br>As applicable                                                                                                                                                                                                                         |  |  |  |

#### Table 2-1 Package Environmental Stress Matrix (cont'd.)

|                                                                                                                                                                                          |                              | MIL-STD-883                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------|

| Test                                                                                                                                                                                     | Method                       | Condition                                                                                                     |

| Subgroup 3<br>Thermal shock<br>Temperature cycling<br>Moisture resistance<br>Seal<br>(a) Fine<br>(b) Gross<br>Visual examination<br>End-point electrical<br>parameters                   | 1011<br>1010<br>1004<br>1014 | Test condition B (-55°C to +125°C) 15 cycles minimum<br>Test condition C (-65°C to +150°C) 100 cycles minimum |

| Subgroup 4<br>Mechanical shock<br>Vibration, variable<br>frequency<br>Constant acceleration<br>Seal<br>(a) Fine<br>(b) Gross<br>Visual examination<br>End-point electrical<br>parameters | 2002<br>2007<br>2001<br>1014 | Test condition B (1500G, 0.5 ms)<br>Test condition A (20G)<br>Same as group C, subgroup 2                     |

| Subgroup 5<br>Salt atmosphere<br>Seal<br>(a) Fine<br>(b) Gross<br>Visual examination                                                                                                     | 1009<br>1014                 | Test condition A minimum (24 hours)<br>As applicable                                                          |

| Subgroup 6<br>Internal water-vapor<br>content                                                                                                                                            | 1018                         |                                                                                                               |

| Subgroup 7<br>Adhesion of lead finish                                                                                                                                                    | 2025                         |                                                                                                               |

| Subgroup 8<br>Lid Torque                                                                                                                                                                 | 2024                         | As applicable (prior to 883C, this test was part of Subgroup D-7)                                             |

| Die Shear   | 2019 |                                              |

|-------------|------|----------------------------------------------|

| Radiography | 2012 | (Prior to 1984, this test was not performed) |

### F100K DC Family Specifications

DC characteristics for the F100K series family parametric limits listed below are guaranteed for the entire F100K ECL family unless specified on the individual data sheet.

- -

| <b>j</b>                                                                                                                                                                               | which the useful<br>ay be impaired <sup>1</sup>                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Storage Temperature<br>Maximum Junction Temperature (T <sub>J</sub> )<br>Supply Voltage Range<br>Input Voltage (dc)<br>Output Current (dc Output HIGH)<br>Operating Range <sup>2</sup> | -65° C to +150° C<br>+175° C<br>-7.0 V to +0.5 V<br>V <sub>EE</sub> to +0.5 V<br>-50 mA<br>-5.7 V to -4.2 V |

| Lead Temperature (Soldering 10 sec)                                                                                                                                                    | 300° C                                                                                                      |

#### **DC Characteristics:** $V_{EE} = -4.5 \text{ V}$ , $V_{CC} = V_{CCA} = \text{GND}$ , $T_C = 0^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ , Note 3

| Symbol | Characteristic      | Min   | Max   | Unit | Conditions                               |  |

|--------|---------------------|-------|-------|------|------------------------------------------|--|

| Vон    | Output HIGH Voltage | -1025 | -880  | mV   | $V_{IN} = V_{IH(max)}$                   |  |

| Vol    | Output LOW Voltage  | -1810 | -1620 | mV   | or VIL (min) Loading with                |  |

| Vонс   | Output HIGH Voltage | -1035 |       | mv   | $V_{\rm IN} = V_{\rm IH(min)}$           |  |

| Volc   | Output LOW Voltage  |       | -1610 | mV   | or VIL (max)                             |  |

| VIH    | Input HIGH Voltage  | -1165 | -880  | mV   | Guaranteed HIGH Signal<br>for All Inputs |  |

| VIL    | Input LOW Voltage   | -1810 | -1475 | mV   | Guaranteed LOW Signal for All Inputs     |  |

| ЦĽ     | Input LOW Current   | 0.50  |       | μA   | $V_{IN} = V_{IL}(min)$                   |  |

1. Unless specified otherwise on individual data sheet.

2. Parametric values specfied at -4.8 V to -4.2 V.

3. The specified limits represent the "worst case" value for the parameter. Since these "worst case" values normally occur at the temperature extremes, additional noise immunity and guard banding can be achieved by decreasing the allowable system operating ranges.

All ECL RAM products (except for Register File RAMs) in ceramic packages: dual-in-line, and flatpak are polyimide die-coated to decrease sensitivity to alpha particles emitted primarily by the seal glass and ceramic of the package.

### F100K DC Family Specifications

| Symbol | Characteristic      | Min   | Max   | Unit | Conditions                            |                       |  |

|--------|---------------------|-------|-------|------|---------------------------------------|-----------------------|--|

| Vон    | Output HIGH Voltage | -1020 | -870  | mV   | VIN = VIH(max)                        |                       |  |

| Vol    | Output LOW Voltage  | -1810 | -1605 | mV   | or VIL (min)                          | Loading with          |  |

| Vонс   | Output HIGH Voltage | -1030 |       | mv   | $V_{IN} = V_{IH(min)}$                | 50 $\Omega$ to -2.0 V |  |

| Volc   | Output LOW Voltage  |       | -1595 | mV   | or VIL (max)                          |                       |  |

| Viн    | Input HIGH Voltage  | -1150 | -880  | mV   | Guaranteed HIGH Signal for All Inputs |                       |  |

| VIL    | Input LOW Voltage   | -1810 | -1475 | mV   | Guaranteed LO<br>for All Inputs       | W Signal              |  |

| h      | Input LOW Current   | 0.50  |       | μA   | VIN = VIL (min)                       |                       |  |

DC Characteristics:  $V_{EE} = -4.8 \text{ V}$ ,  $V_{CC} = V_{CCA} = GND$ ,  $T_C = 0^{\circ}C$  to  $+85^{\circ}C$ , Note 3

| Symbol | Characteristic      | Min   | Max   | Unit | Conditions                               |  |

|--------|---------------------|-------|-------|------|------------------------------------------|--|

| Vон    | Output HIGH Voltage | -1035 | -880  | mV   | VIN = VIH (max)                          |  |

| Vol    | Output LOW Voltage  | -1830 | -1620 | mV   | or VIL(min)                              |  |

| Vонс   | Output HIGH Voltage | -1045 |       | mv   | $V_{\rm IN} = V_{\rm IH(min)}$           |  |

| Volc   | Output LOW Voltage  |       | -1610 | mV   | or VIL (max)                             |  |

| Viн    | Input HIGH Voltage  | -1165 | -880  | mV   | Guaranteed HIGH Signal<br>for All Inputs |  |

| VIL    | Input LOW Voltage   | -1810 | -1490 | mV   | Guaranteed LOW Signal for All Inputs     |  |

| կլ     | Input LOW Current   | 0.50  |       | μA   | VIN = VIL (min)                          |  |

Notes on preceding page

# F10K DC Family Specifications

DC characteristics for the F10K series memories. Parametric limits listed below are guaranteed for all F10K memories, except where noted on individual data sheets.

| Absolute Maximum Ratings:                                                                       | Above which the useful life may be impaired <sup>2</sup> |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Storage Temperature<br>Maximum Junction Temperatu<br>V <sub>EE</sub> Pin Potential to Ground Pi |                                                          |

| Input Voltage (dc)                                                                              | V <sub>EE</sub> to +0.5 V                                |

| Output Current (dc Output HIC                                                                   | GH) $-30 \text{ mA to} +0.1 \text{ mA}$                  |

| Lead Temperature (Soldering                                                                     | 10 sec) 300° C                                           |

| Guaranteed | Operating | Ranges |

|------------|-----------|--------|

|------------|-----------|--------|

| Suppl   | ly Voltage | Case Temperature |                   |

|---------|------------|------------------|-------------------|

| Min     | Min Typ    |                  | (T <sub>c</sub> ) |

| -5.46 V | -5.2 V     | -4.94 V          | 0°C to +75°C      |

| <b>DC Characteristics</b> | $V_{EE} = -5.2 V_{,}$ | $V_{CC} = V_{CCA} =$ | GND, $T_C = 0^\circ$ | C to + 75° C <sup>1</sup> |

|---------------------------|-----------------------|----------------------|----------------------|---------------------------|

|---------------------------|-----------------------|----------------------|----------------------|---------------------------|

| Symbol | Characteristic      | Min                     | Max                     | Unit | т <sub>с</sub>        | Conditions <sup>2</sup>                     |                              |  |

|--------|---------------------|-------------------------|-------------------------|------|-----------------------|---------------------------------------------|------------------------------|--|

| Vон    | Output HIGH Voltage | -1000<br>-960<br>-900   | -840<br>-810<br>-720    | mV   | 0°C<br>+25°C<br>+75°C | VIN = VIH (max)                             | Loading is<br>50 Ω to −2.0 V |  |

| Vol    | Output LOW Voltage  | -1870<br>-1850<br>-1830 | -1665<br>-1650<br>-1625 | mV   | 0°C<br>+25°C<br>+75°C | or VIL (min)                                |                              |  |

| Vонс   | Output HIGH Voltage | -1020<br>-980<br>-920   |                         | mv   | 0°C<br>+25°C<br>+75°C | 1 4                                         |                              |  |

| Volc   | Output LOW Voltage  |                         | -1645<br>-1630<br>-1605 | mV   | 0°C<br>+25°C<br>+75°C | or VIL (max)                                |                              |  |

| VIH    | Input HIGH Voltage  | -1145<br>-1105<br>-1045 | -840<br>-810<br>-720    | mV   | 0°C<br>+25°C<br>+75°C | Guaranteed Input<br>for All Inputs          | Voltage HIGH                 |  |

| VIL    | Input LOW Voltage   | -1870<br>-1850<br>-1830 | -1490<br>-1475<br>-1450 | mV   | 0°C<br>+25°C<br>+75°C | Guaranteed Input Voltage LOW for All Inputs |                              |  |

| h      | Input LOW Current   | 0.5                     | 170                     | μA   | +25°C                 | VIN = VIL (min)                             |                              |  |

1. The specified limits represent the "worst case" value for the parameter. Since these "worst case" values normally occur at the temperature extremes, additional noise immunity and guard banding can be achieved by decreasing the allowable system operating ranges.

2. Unless specified otherwise on individual data sheet.

#### FAIRCHILD

A Schlumberger Company

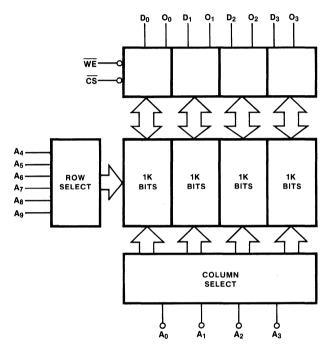

#### Description

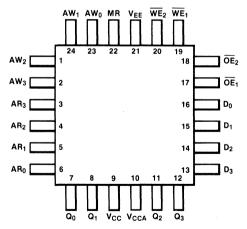

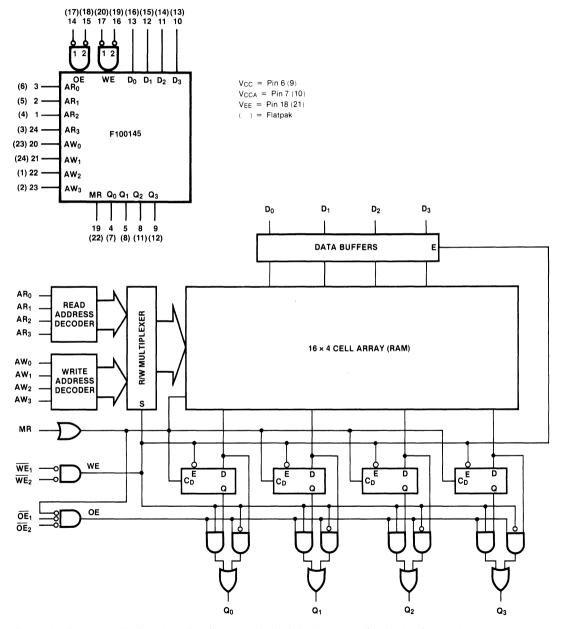

The F100145 is a 64-bit register file organized as 16 words of four bits each. Separate address inputs for Read (AR<sub>n</sub>) and Write (AW<sub>n</sub>) operations reduce overall cycle time by allowing one address to be setting up while the other is being executed. Operating speed is also enhanced by four output latches which store data from the previous read operation while writing is in progress. When both Write Enable ( $\overline{WE}$ ) inputs are LOW, the circuit is in the Write mode and the latches are in a Hold mode. When either WE input is HIGH, the circuit is in the Read mode, but the outputs can be forced LOW by a HIGH signal on either of the Output Enable  $\overline{(OE)}$ inputs. This makes it possible to tie one WE input and one OE input together to serve as an active-LOW Chip Select (CS) input. When this wired CS input is HIGH. reading will still take place internally and the resulting data will enter the latches and become available as soon as the  $\overline{CS}$  signal goes LOW, provided that the other  $\overline{OE}$ input is LOW. A HIGH signal on the Master Reset (MR) input overrides all other inputs, clears all cells in the memory, resets the output latches, and forces the outputs LOW.

#### Pin Names

| AR0-AR3       | Read Address Inputs               |

|---------------|-----------------------------------|

| $AW_0 - AW_3$ | Write Address Inputs              |

| WE1, WE2      | Read Enable Inputs (Active LOW)   |

| OE1, OE2      | Output Enable Inputs (Active LOW) |

| D0-D3         | Data Inputs                       |

| MR            | Master Reset Input                |

| Q0-Q3         | Data Outputs                      |

## F100145 16 x 4-Bit Register File (RAM)

Memory and High Speed Logic

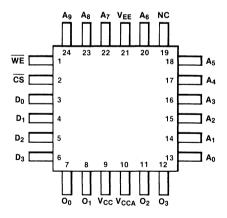

#### **Connection Diagrams**

24-Pin DIP (Top View)

24-Pin Flatpak (Top View)

F100145

Logic Symbol and Logic Diagram

Note that this diagram is provided for understanding of logic operation only. It should not be used for evaluation of propagation delays as many internal functions are achieved more efficiently than indicated.

3-7

3

#### F100145

**DC Characteristics:**  $V_{EE} = -4.2 \text{ V}$  to -4.8 V unless otherwise specified,  $V_{CC} = V_{CCA} = \text{ GND}$ ,  $T_C = 0^{\circ}\text{C}$  to  $+85^{\circ}\text{C}^{\star}$

| Symbol | Characteristic                   | Min  | Тур  | Мах | Unit | Condition      |

|--------|----------------------------------|------|------|-----|------|----------------|

| Ιн     | Input HIGH Current<br>All Inputs |      |      | 240 | μΑ   | VIN = VIH(max) |

| IEE    | Power Supply Current             | -247 | -170 |     | mA   | Inputs Open    |

\*See Family Characteristics for other dc specifications.

### AC Characteristics: $V_{EE} = -4.2$ V to -4.8 V, $V_{CC} = V_{CCA} = GND$

|                                    |                                                                                                    | $T_{C} = 0^{\circ}C$ $T_{C} = +25^{\circ}C$ $T_{C} = +85^{\circ}C$ |                      |                                      |                      |                                      |                      |                            |                                      |

|------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------|--------------------------------------|----------------------|--------------------------------------|----------------------|----------------------------|--------------------------------------|

| Symbol                             | Characteristic                                                                                     | Min                                                                | Max                  | Min                                  | Мах                  | Min                                  | Max                  | Unit                       | Condition                            |

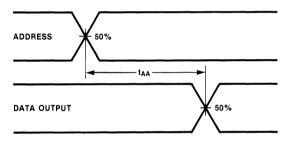

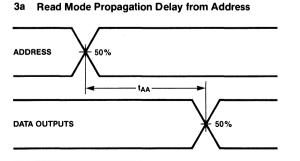

| taa<br>tor<br>tod                  | Access/Recovery Timing<br>Address Access <sup>1</sup><br>Output Recovery<br>Output Disable         | 2.20<br>1.00<br>1.00                                               | 7.40<br>2.90<br>2.90 | 2.20<br>1.10<br>1.10                 | 7.40<br>2.90<br>2.90 | 2.20<br>1.10<br>1.10                 | 7.60<br>3.20<br>3.20 | ns<br>ns<br>ns             | Figures 1 and 3a<br>Figures 1 and 3e |

| trsa1<br>tweq                      | <b>Read Timing</b><br>Address Setup<br>Output Delay                                                | 1.10<br>2.00                                                       | 5.00                 | 1.10<br>2.00                         | 5.00                 | 1.10<br>2.00                         | 5.50                 | ns<br>ns                   | Figures 1 and 3b                     |

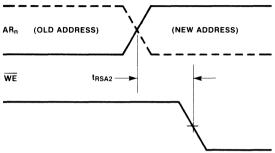

| trsa2<br>trha                      | Output Latch Timing<br>Address Setup<br>Address Hold                                               | 4.10<br>0.10                                                       |                      | 4.10<br>0.10                         |                      | 5.60<br>0.10                         |                      | ns<br>ns                   | Figures 1 and 3c<br>Figures 1 and 3d |

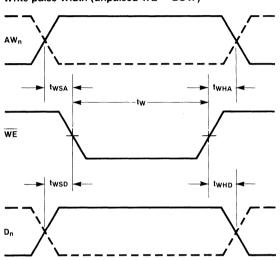

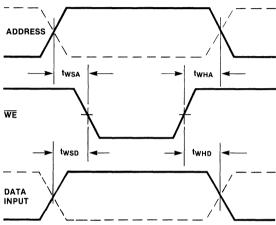

| twsa<br>twha<br>twsd<br>twhd<br>tw | Write Timing<br>Address Setup<br>Address Hold<br>Data Setup<br>Data Hold<br>Write Pulse Width, LOW | 0.10<br>1.10<br>1.10<br>1.10<br>4.60                               |                      | 0.10<br>1.60<br>1.60<br>1.60<br>5.00 |                      | 0.10<br>1.60<br>1.90<br>1.90<br>5.50 |                      | ns<br>ns<br>ns<br>ns<br>ns | tw = 6.0 ns<br>Figures 1 and 4       |

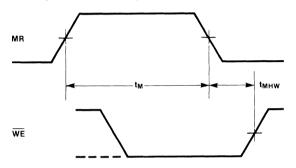

| tм<br>tмнw                         | Master Reset Timing<br>Reset Pulse Width, LOW<br>WE Hold to Write                                  | 4.50<br>6.30                                                       |                      | 4.50<br>7.10                         |                      | 5.00<br>10.50                        |                      | ns<br>ns                   | Figures 1 and 5a                     |

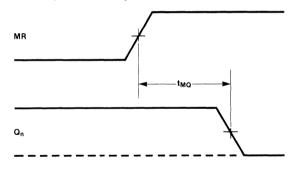

| tMQ                                | Output Disable                                                                                     | 2.80                                                               |                      | 2.80                                 |                      | 3.20                                 |                      | ns                         | Figures 1 and 5b                     |

| tт∟н<br>tтн∟                       | Transition Time<br>20% to 80%, 80% to 20%                                                          | 0.50                                                               | 2.30                 | 0.50                                 | 2.30                 | 0.50                                 | 2.30                 | ns                         |                                      |

1. The maximum address access time is guaranteed to be the worst case bit in memory using a pseudo random testing pattern.

#### F100145

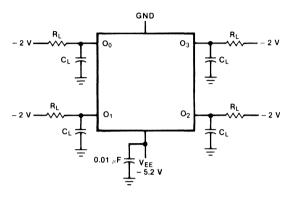

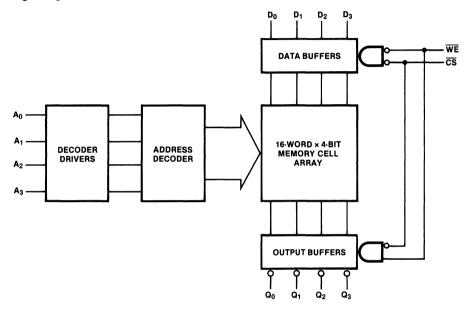

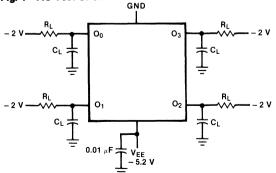

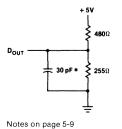

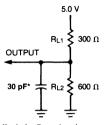

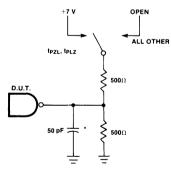

#### Fig. 1 AC Test Circuit

#### Notes

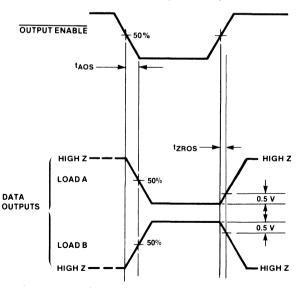

All Timing Measurements Referenced to 50% of Input Levels  $C^{}_L$  = 3 pF including Fixture and Stray Capacitance  $R^{}_L$  = 50  $\Omega$  to -2.0 V

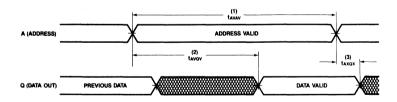

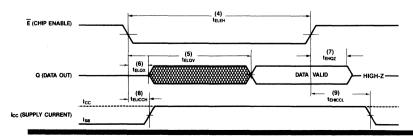

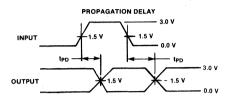

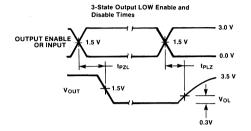

Fig. 3 Read Timing 3a Address Access Time ( $\overline{WE_1}$  or  $\overline{WE_2}$  = HIGH;  $\overline{OE_1} = \overline{OE_2} = LOW$ (OLD ADDRESS) ARn ARn WE tAA Qn 3b Address Setup Time before WE, to Ensure Minimum Delay (unpulsed  $\overline{WE} = \overline{OE}_1 =$  $\overline{OE_2} = LOW$ (OLD ADDRESS) ARn ARn tRSA1 -WE WE 3e tweQ ŌĒ (FROM ARRAY) (DATA FROM LATCHES) Qn tor

3c Address Setup Time to Ensure Latching Data from New Address (unpulsed WE = LOW)

3d Address Hold Time to Ensure Latching Data from Old Address (unpulsed  $\overline{WE} = LOW$ )

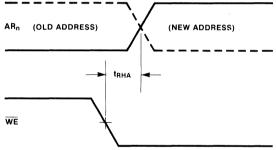

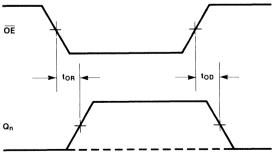

3e Output Recovery/Disable Times,  $\overline{OE}$  to Q<sub>n</sub> (unpulsed  $\overline{OE}$  = LOW)

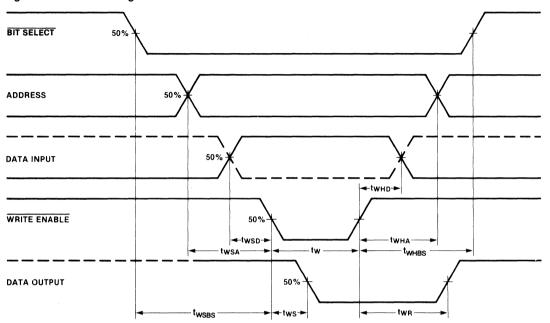

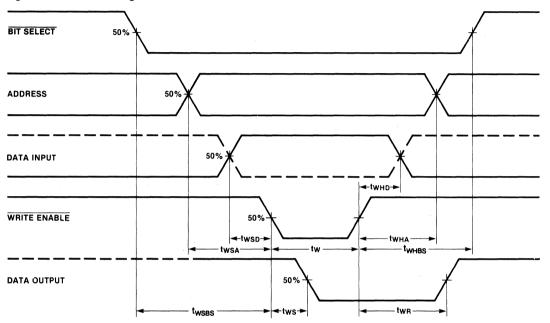

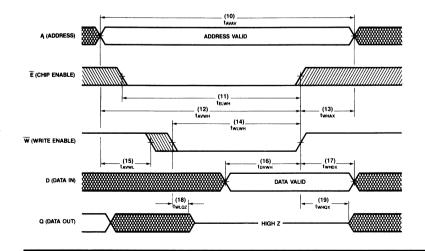

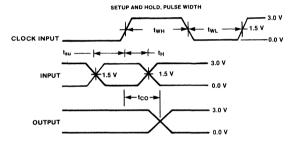

### Fig. 4 Write Timing

Address and Data Setup and Hold Times; Write pulse Width (unpulsed  $\overline{WE} = LOW$ )

- Fig 5 Master Reset Timing

- 5a Reset Pulse Width; WE Hold Time for Subsequent Writing (address already setup, unpulsed WE = LOW)

5b Output Reset Delay, MR to Qn

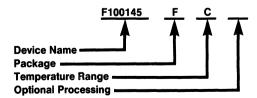

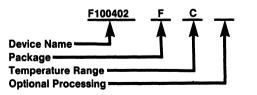

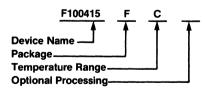

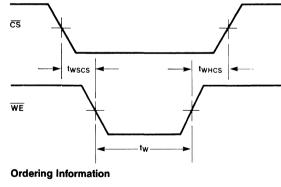

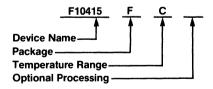

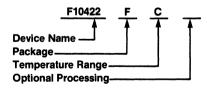

### **Ordering Information**

- Packages and Outlines (See Section 9) D = Ceramic DIP F = Flatpak

- Temperature Ranges  $C = 0^{\circ}C$  to +85°C. Case

- Optional Processing QR = 160 Hour Burn in

# FAIRCHILD

A Schlumberger Company

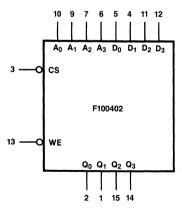

# F100402 16 x 4-Bit Register File (RAM)

Memory and High Speed Logic

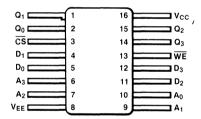

#### Description

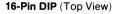

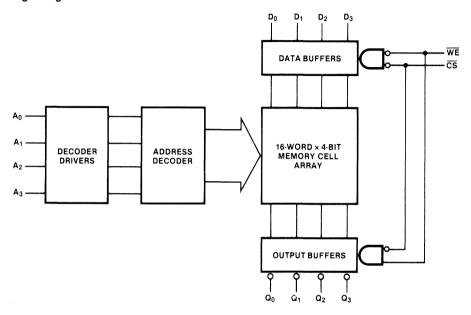

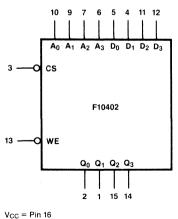

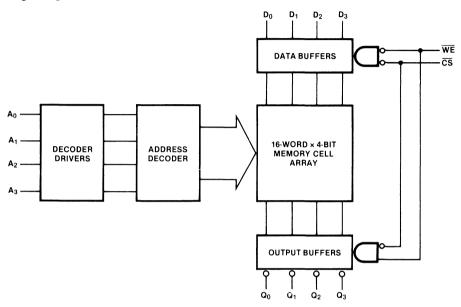

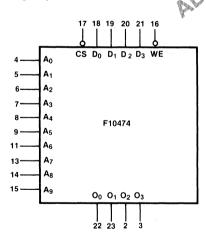

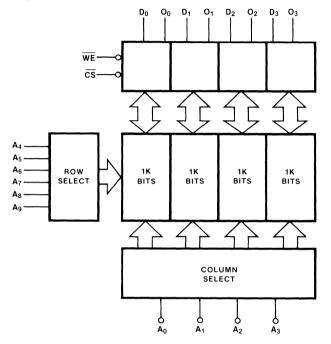

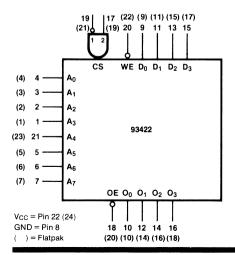

The F100402 is a high-speed 64-bit Random Access Memory (RAM) organized as a 16-word by 4-bit array. External logic requirements are minimized by internal address decoding, while memory expansion and data busing are facilitated by the output disabling features of the Chip Select  $\overline{(CS)}$  and Write Enable  $\overline{(WE)}$  inputs.

A HIGH signal on  $\overline{CS}$  prevents read and write operations and forces the outputs to the LOW state. When  $\overline{CS}$  is LOW, the  $\overline{WE}$  input controls chip operations. A HIGH signal on  $\overline{WE}$  disables the Data input (D<sub>n</sub>) buffers and enables readout from the memory location determined by the Address (A<sub>n</sub>) inputs. A LOW signal on  $\overline{WE}$  forces the Q<sub>n</sub> outputs LOW and allows data on the D<sub>n</sub> inputs to be stored in the addressed location. Data exists in the same logical sense as presented at the data inputs, *i.e.*, the memory is non-inverting.

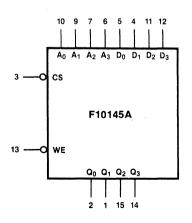

#### Pin Names

| CS          | Chip Select Input  |

|-------------|--------------------|

| $A_0 - A_3$ | Address Inputs     |

| D0-D3       | Data Inputs        |

| WE          | Write Enable Input |

| Q0-Q3       | Data Outputs       |

#### Logic Symbol

### **Connection Diagrams**

#### 16-Pin Flatpak (Top View)

| Q1             | 1 | 16 Vc             | с |

|----------------|---|-------------------|---|

| Q <sub>0</sub> | 2 | 15 Q2             |   |

| cs             | 3 | 14 Q <sub>3</sub> |   |

| D1             | 4 | 13 WE             |   |

| Do             | 5 | 12 D3             |   |

| A3             | 6 | 11 D2             |   |

| A <sub>2</sub> | 7 | 10 A <sub>0</sub> |   |

|                | 8 | 9 A1              |   |

Logic Diagram

| DC Characteristics: VEE = -4.2 V to -4.8 V unless otherwise specified | l, Vcc = | = GND, $T_C = 0^{\circ}C$ to +85°C* |

|-----------------------------------------------------------------------|----------|-------------------------------------|

|-----------------------------------------------------------------------|----------|-------------------------------------|

| Symbol | Characteristic                   | Min  | Тур  | Max | Unit | Condition      |

|--------|----------------------------------|------|------|-----|------|----------------|

| Ін     | Input HIGH Current<br>All Inputs |      |      | 300 | μA   | VIN = VIH(max) |

| IEE    | Power Supply Current             | -170 | -110 |     | mA   | Inputs Open    |

\*See Family Characteristics for other dc specifications.

|                                                |                                                                                                               | T <sub>C</sub> =                             | = 0°C        | T <sub>C</sub> = ·                           | +25°C        | T <sub>C</sub> = -                           | +85°C        |                                  |                              |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------|----------------------------------------------|--------------|----------------------------------------------|--------------|----------------------------------|------------------------------|

| Symbol                                         | Characteristic                                                                                                | Min                                          | Max          | Min                                          | Max          | Min                                          | Мах          | Unit                             | Condition                    |

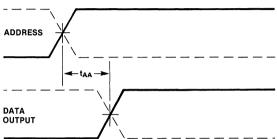

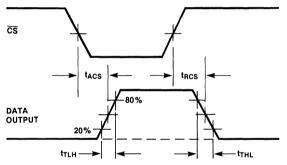

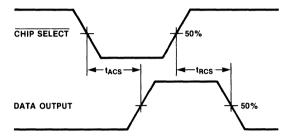

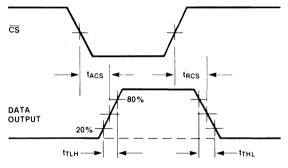

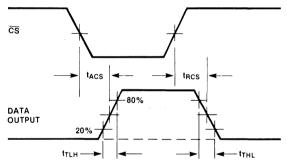

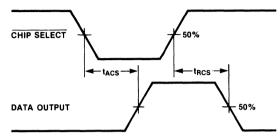

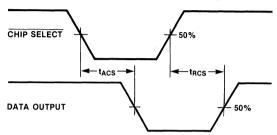

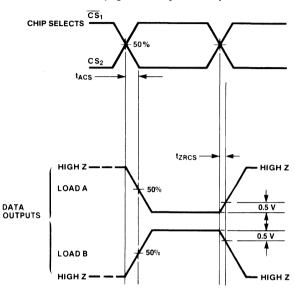

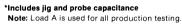

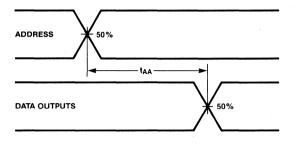

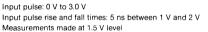

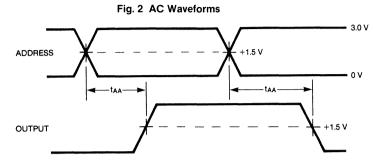

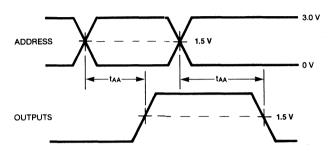

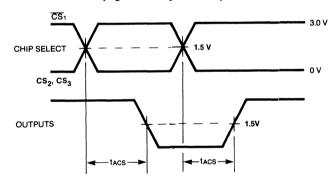

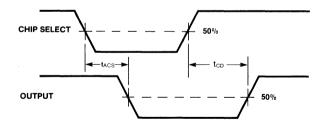

| tacs<br>trcs                                   | Access/Recovery Timing<br>Chip Select Access<br>Chip Select Recovery                                          |                                              | 3.30<br>3.30 |                                              | 3.50<br>3.50 |                                              | 3.80<br>3.80 | ns<br>ns                         | Figures 1 and 4              |

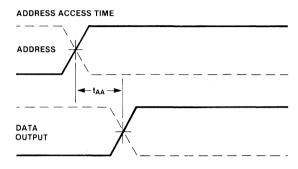

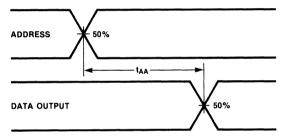

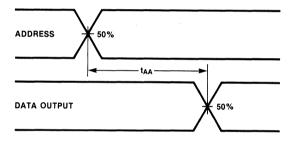

| tAA                                            | Address Access <sup>1</sup>                                                                                   |                                              | 5.00         |                                              | 5.30         |                                              | 6.00         | ns                               |                              |

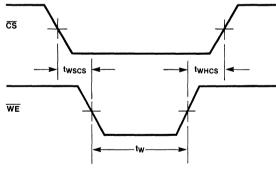

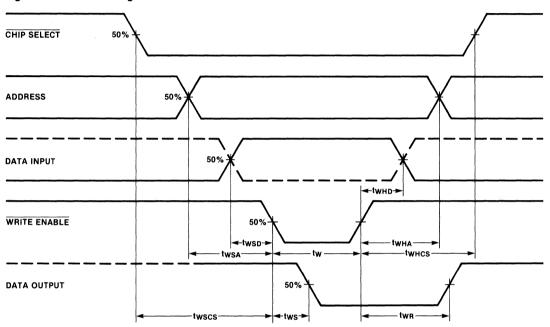

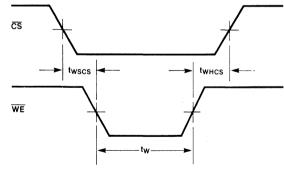

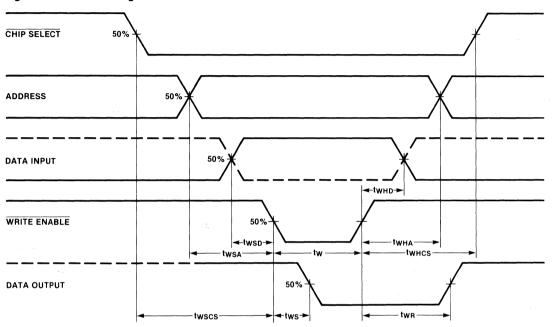

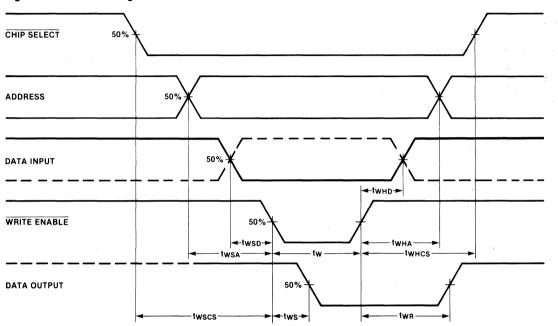

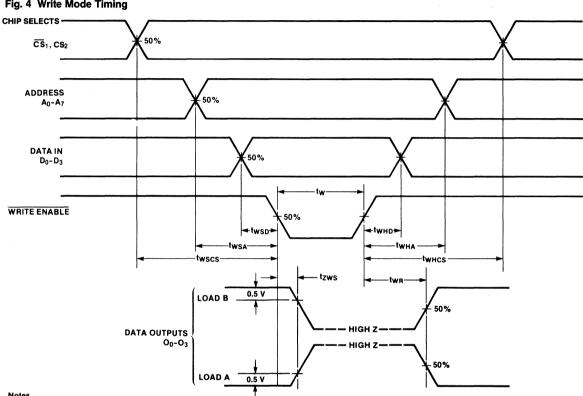

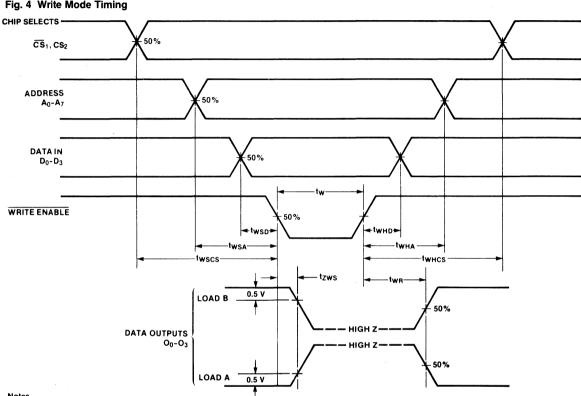

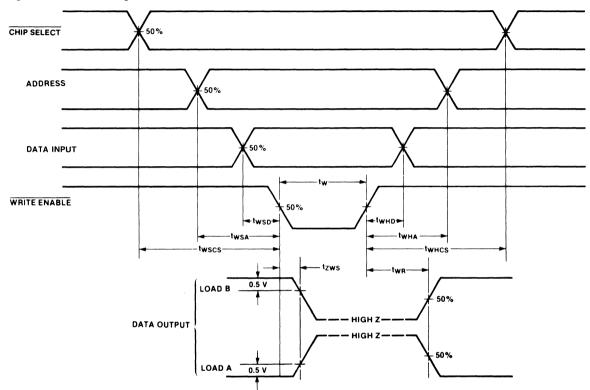

| twsD<br>twscs<br>twsA<br>twHD<br>twHCs<br>twHA | Write Timing, Setup<br>Data<br>Chip Select<br>Address<br>Write Timing, Hold<br>Data<br>Chip Select<br>Address | 0.50<br>1.50<br>1.00<br>0.50<br>0.50<br>2.50 |              | 0.50<br>1.50<br>1.00<br>0.50<br>0.50<br>2.50 |              | 0.80<br>1.50<br>1.00<br>0.50<br>0.50<br>2.50 |              | ns<br>ns<br>ns<br>ns<br>ns<br>ns | Figures 1 and 3<br>tw = 6 ns |

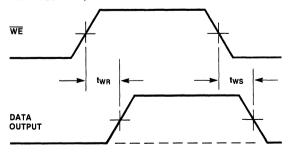

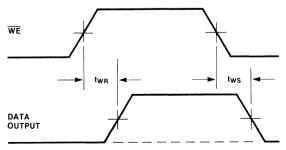

| twr<br>tws                                     | Write Recovery Time<br>Write Disable Time                                                                     | 4.00<br>3.00                                 |              | 4.00<br>3.00                                 |              | 4.50<br>3.50                                 |              | ns<br>ns                         | Figures 1 and 4              |

| tw                                             | Write Pulse Width, (LOW)                                                                                      | 2.50                                         |              | 2.50                                         |              | 3.00                                         |              | ns                               |                              |

| tcs                                            | Chip Select Pulse<br>Width, (LOW)                                                                             | 2.50                                         |              | 2.50                                         |              | 3.00                                         |              | ns                               | Figures 1 and 3              |

| t⊤∟H<br>t⊤н∟                                   | Transition Time<br>20% to 80%, 80% to 20%                                                                     | 0.50                                         | 1.70         | 0.50                                         | 1.70         | 0.50                                         | 1.70         | ns                               | Figures 1 and 4              |

### AC Characteristics: VEE = -4.2 V to -4.8 V, V<sub>CC</sub> = GND, Applies to Flatpak and DIP Packages

1. The maximum address access time is guaranteed to be the worst case bit in memory using a pseudo random testing pattern.

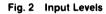

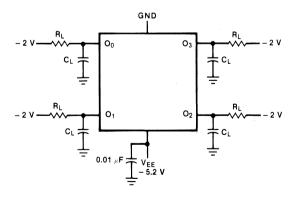

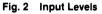

#### Fig. 1 AC Test Circuit

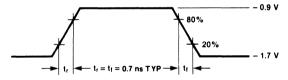

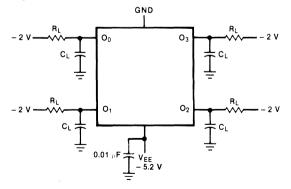

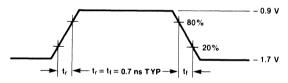

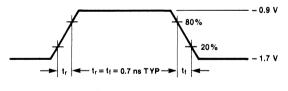

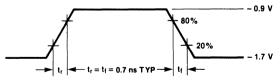

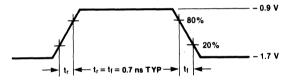

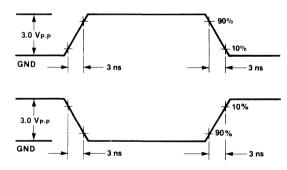

Fig. 2 Input Levels

#### Notes

All Timing Measurements Referenced to 50% of Input Levels  $C_L$  = 3 pF including Fixture and Stray Capacitance  $R_L$  = 50  $\Omega$  to -2.0 V

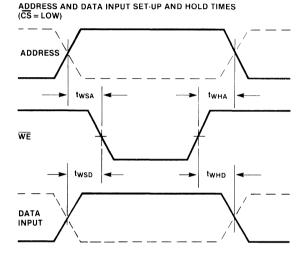

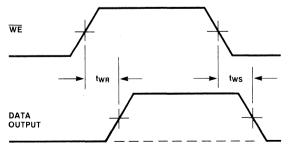

#### Fig. 3 Write Modes

#### Write Enable Strobe

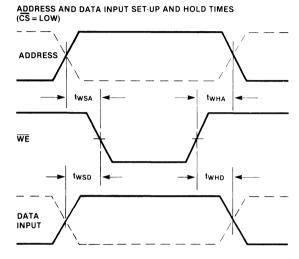

ADDRESS AND DATA INPUT SET UP AND HOLD TIMES (CS = LOW)

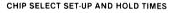

#### CHIP SELECT SET-UP AND HOLD TIMES

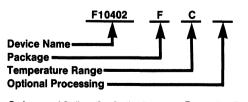

**Ordering Information**

Packages and Outlines (See Section 9) D = Ceramic DIP F = Flatpak Temperature Ranges C = 0°C to +85°C. Case

**Optional Processing** QR = 160 Hour Burn in

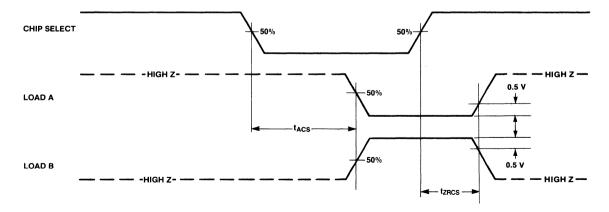

### Fig. 4 Read Modes

Address Input to Data Output ( $\overline{WE} = HIGH, \overline{CS} = LOW$ )

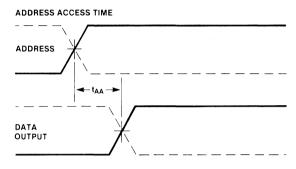

ADDRESS ACCESS TIME

### Chip Select Input to Data Output (WE = HIGH)

CHIP SELECT ACCESS AND RECOVERY TIMES

Write Enable Input to Data Output (CS = LOW) WRITE RECOVERY, DISABLE TIMES

FAIRCHILD

A Schlumberger Company

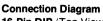

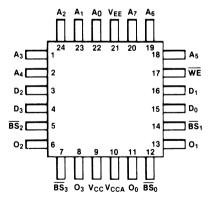

# F100415 1024 x 1-Bit Static Random Access Memory

Memory and High Speed Logic

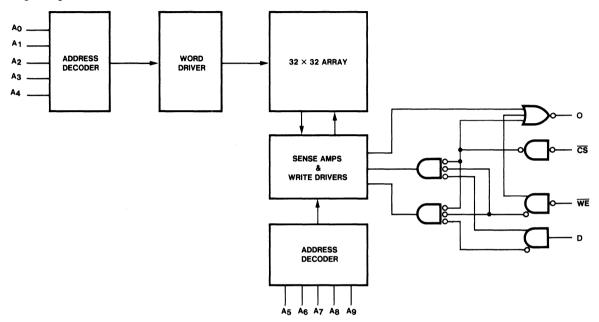

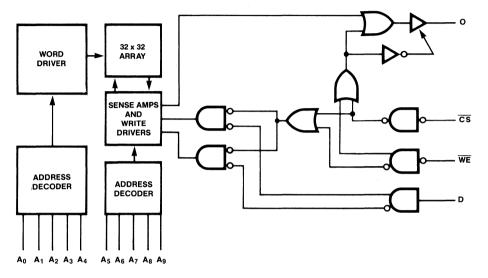

#### Description

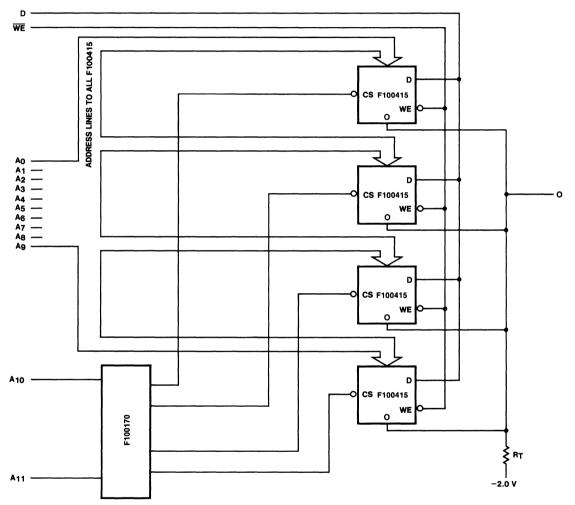

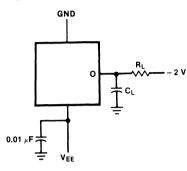

The F100415 is a 1024-bit read/write Random Access Memory (RAM), organized as 1024 words by one bit per word and designed for high-speed scratchpad, control and buffer storage applications. The device includes full on-chip address decoding, separate Data Input and non-inverting Data Output lines, as well as an active-LOW Chip Select line.

- Address Access Time 10 ns Max

- Chip Select Access Time 5.0 ns Max

- Open-emitter Output for Easy Memory Expansion

- Power Dissipation 0.79 mW/Bit Typ

- Power Dissipation Decreases with Increasing

Temperature

- Polyimide Die Coat for Alpha Immunity

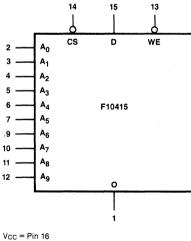

#### **Pin Names**

| WE    | Write Enable Input (Active LOW) |

|-------|---------------------------------|

| CS    | Chip Select Input (Active LOW)  |

| A0-A9 | Address Inputs                  |

| D     | Data Input                      |

| 0     | Data Output                     |

#### Logic Symbol

16-Pin DIP (Top View)

#### Note

The 16-pin Flatpak version has the same pinouts (Connection Diagram) as the Dual In-line Package

Logic Diagram

#### **Functional Description**

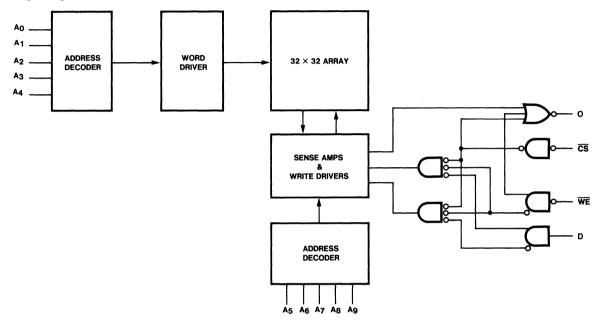

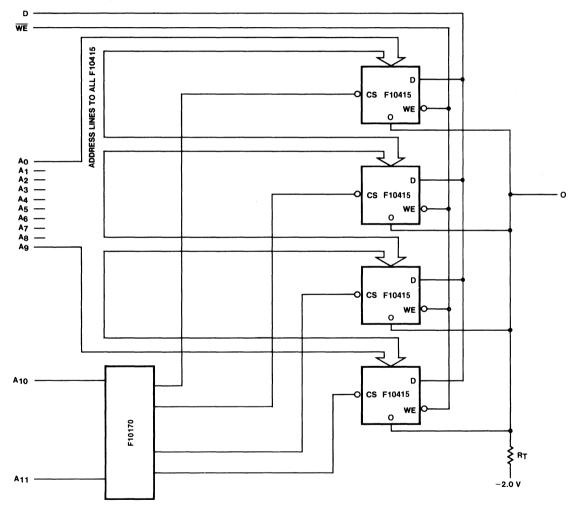

The F100415 is a fully decoded 1024-bit read/write random access memory, organized 1024 words by one bit. Bit selection is achieved by means of a 10-bit address,  $A_0$  through  $A_9$ .

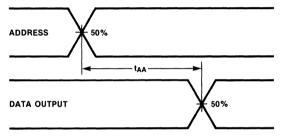

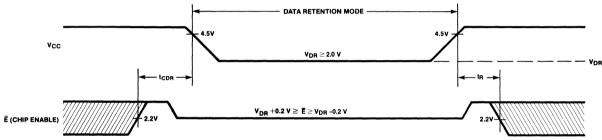

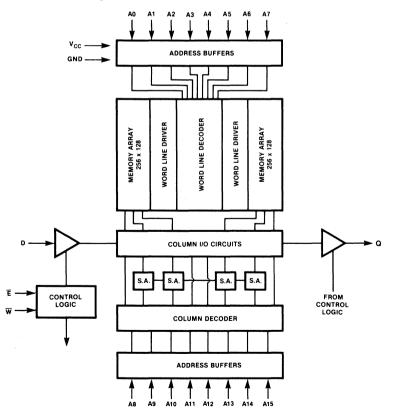

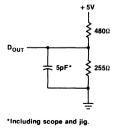

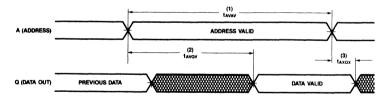

One Chip Select input is provided for memory array expansion up to 2048 words without the need for external decoding. For larger memories, the fast chip select time permits the decoding of Chip Select,  $(\overline{CS})$  from the address without affecting system performance.