# MICROPROCESSOR PRODUCTS DATA BOOK

# PRODUCTS OCESSOR Ō MICROPR( DATA BOC

© 1982 Fairchild 3420 Central Expressway Santa Clara CA 95051

.

The Advance Product Information designation on a Fairchild publication indicates that the product described is not characterized. The specifications presented are based on design goals or preliminary part evaluation and, as they are subject to change, are not guaranteed. Fairchild Microprocessor Division should be contacted for current information on these products.

The information furnished in this publication is believed to be accurate and reliable. However, Fairchild cannot assume responsibility for its use, or for use of any circuitry described, other than circuitry entirely embodied in a Fairchild product. No license is granted or implied under any Fairchild patents, patents, or trademarks.

Fairchild reserves the right to make changes in the circuitry or specifications presented in this publication at any time and without notice.

iv

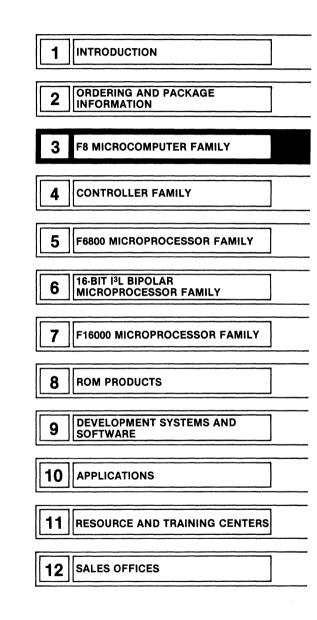

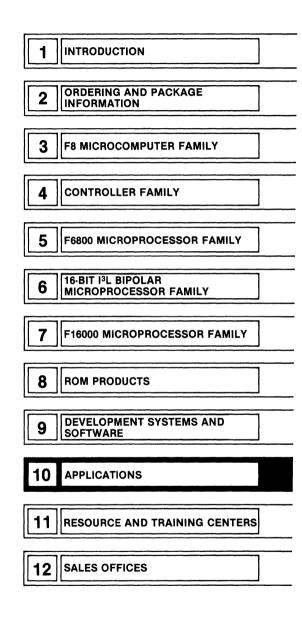

| Section 1 Introduction                                       |  |

|--------------------------------------------------------------|--|

| General                                                      |  |

| Product Line                                                 |  |

| Data Book                                                    |  |

| Section 2 Ordering and Package Information                   |  |

| General                                                      |  |

| Temperature Range                                            |  |

| Package Types and Outlines                                   |  |

| Section 3 F8 Microcomputer Family                            |  |

| General                                                      |  |

| Memory Interface Devices                                     |  |

| Input/Output Devices                                         |  |

| Bus Structure                                                |  |

| Instruction Set                                              |  |

| F3850 Central Processing Unit.                               |  |

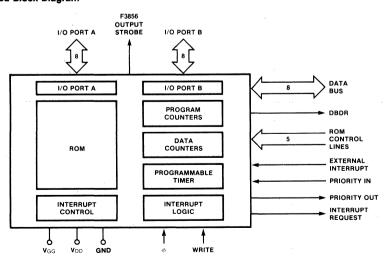

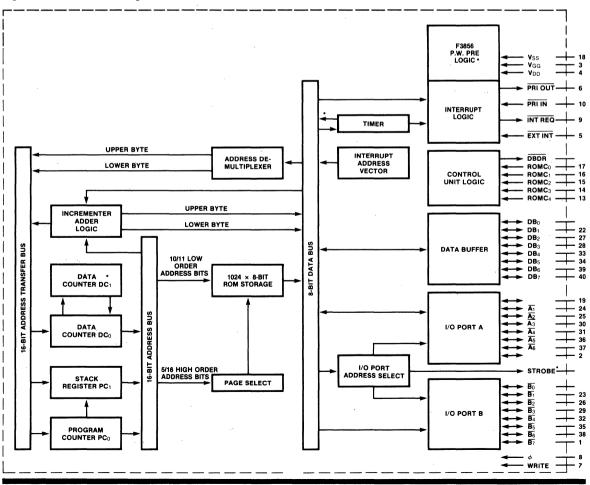

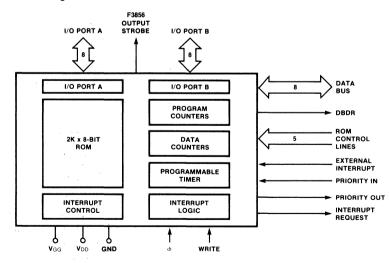

| F3851/F3856 Program Storage Unit                             |  |

| F3852 Dynamic Memory Interface/F3853 Static Memory Interface |  |

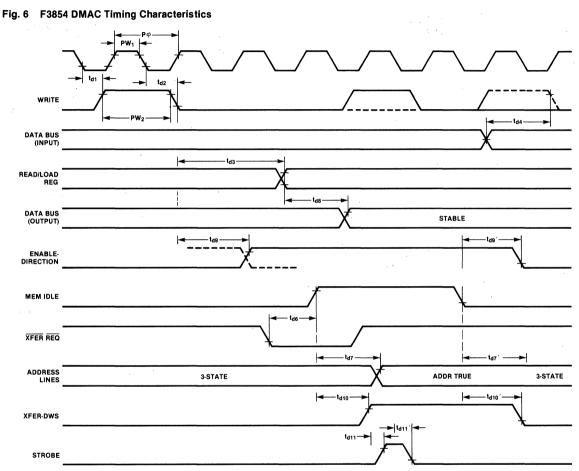

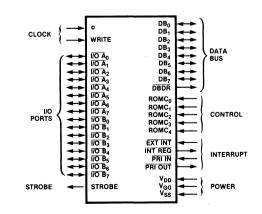

| F3854 Direct Memory Access Controller                        |  |

| F38T56 Program Storage Unit.                                 |  |

| F3861 Peripheral Input/Output                                |  |

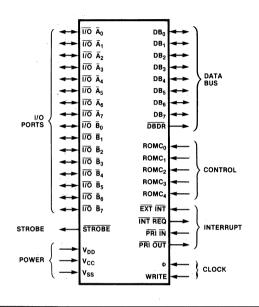

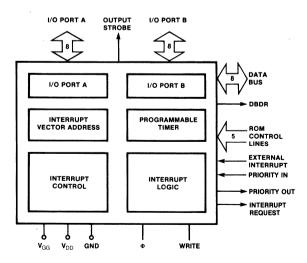

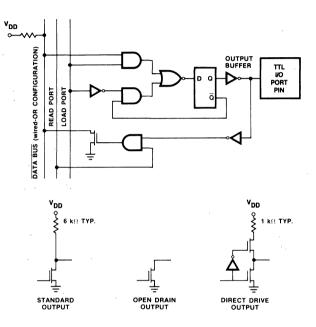

| F3871 Peripheral Input/Output                                |  |

| Section 4 Controller Family                                  |  |

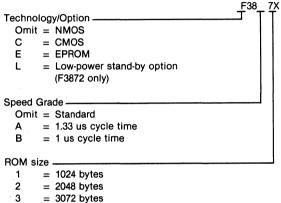

| F387X Family                                                 |  |

| F3870X Family                                                |  |

| Part Numbers                                                 |  |

| Descriptions                                                 |  |

| F3870 Single-Chip Microcomputer                              |  |

| F3870A/F3870B High-Speed Single-Chip Microcomputer           |  |

| F38C70 Single-Chip Microcomputer.                            |  |

| F38E70 Single-Chip Microcomputer                             |  |

| F3872/F38L72 Single-Chip Microcomputer                       |  |

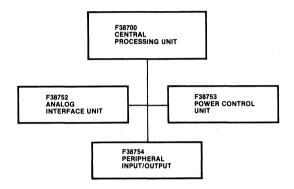

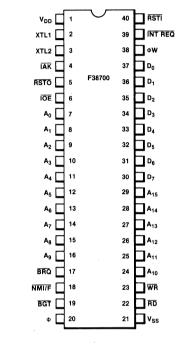

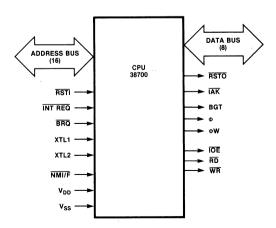

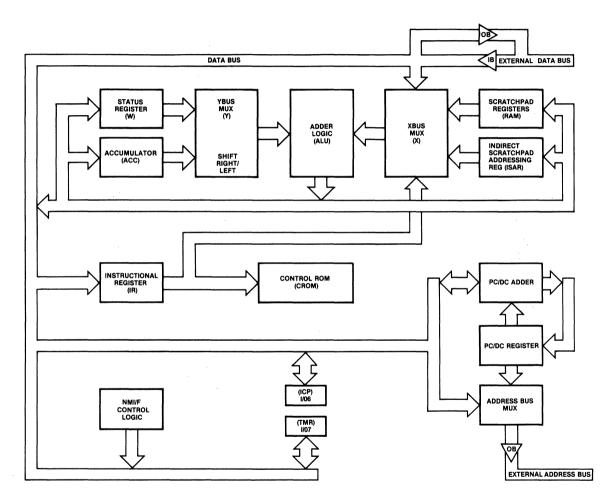

| F38700 Central Processing Unit.                              |  |

| F38701 Single-Chip Microcomputer.                            |  |

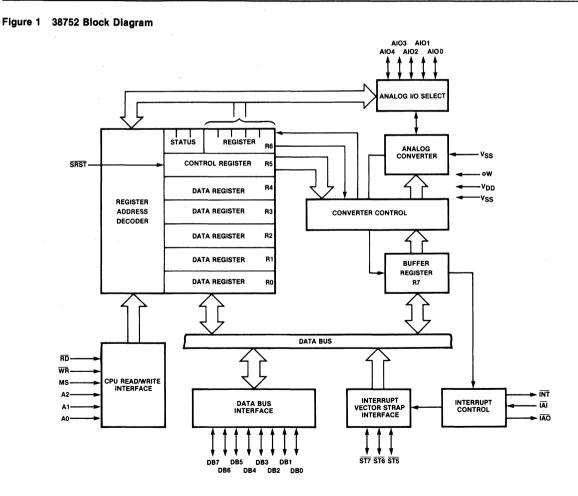

| F38752 Analog Interface Unit                                 |  |

| F38753 Power Control Unit                                    |  |

| F38754 Peripheral Input/Output                               |  |

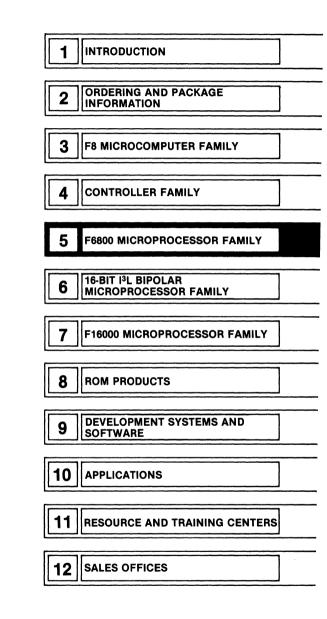

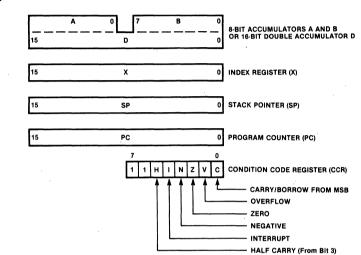

| Section 5 F6800 Microprocessor Family                             |       |

|-------------------------------------------------------------------|-------|

| General                                                           | 5-3   |

| Instruction Set                                                   | 5-3   |

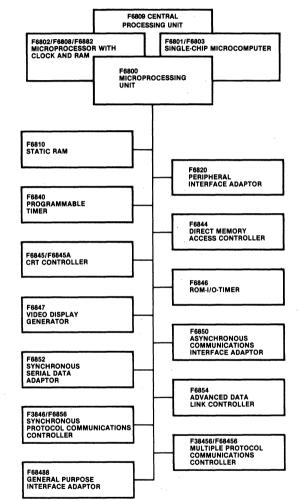

| F6800/F68B00 8-Bit Microprocessing Unit.                          | 5-11  |

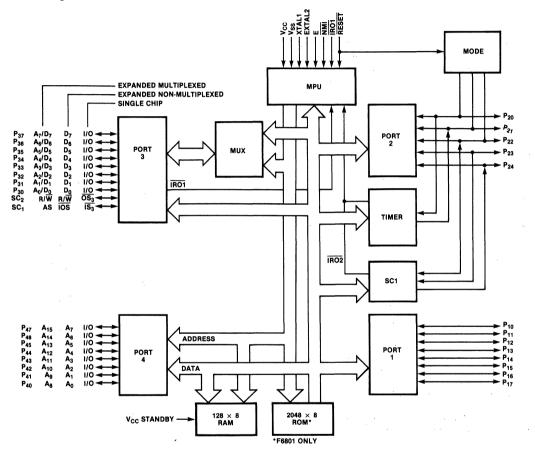

| F6801/F6803 Single-Chip Microcomputer.                            | 5-51  |

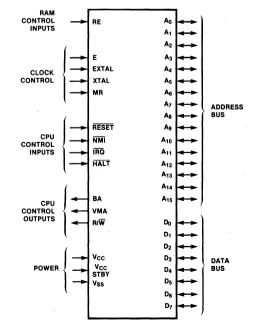

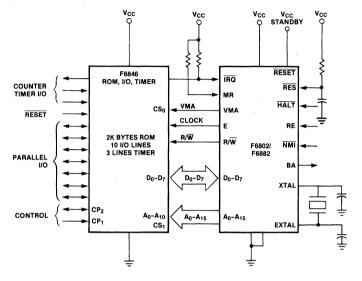

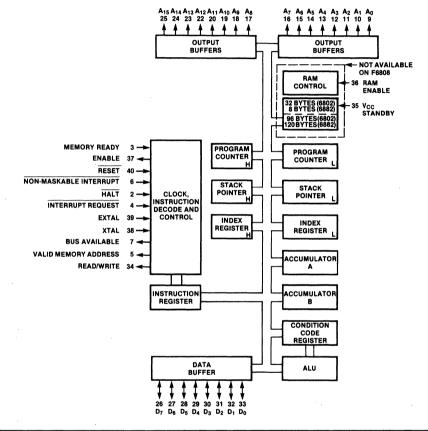

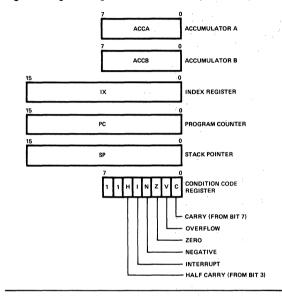

| F6802/F6882/F6808 Microprocessor With Clock and RAM.              | 5-57  |

| F6809 Central Processing Unit.                                    | 5-81  |

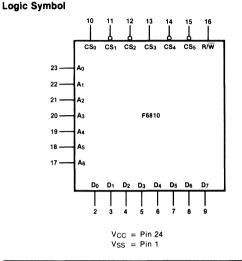

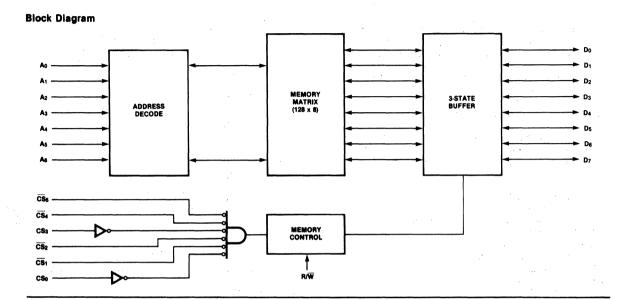

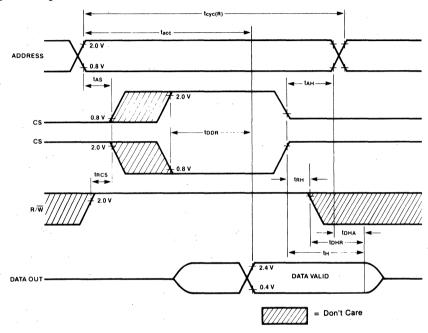

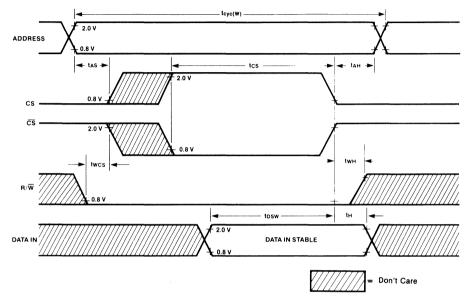

| F6810/F68A10/F68B10 128 × 8-Bit Static RAM                        | 5-83  |

| F6820 Peripheral Interface Adaptor.                               |       |

| F6821/F68A21/F68B21 Peripheral Interface Adaptor.                 |       |

| F6840/F68A40/F68B40 Programmable Timer                            |       |

| F6844 Direct Memory Access Controller.                            |       |

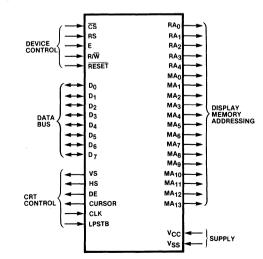

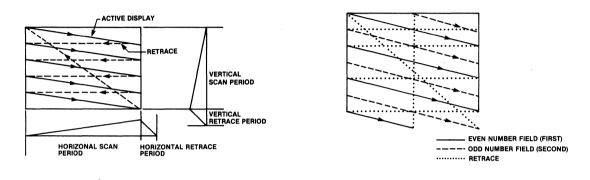

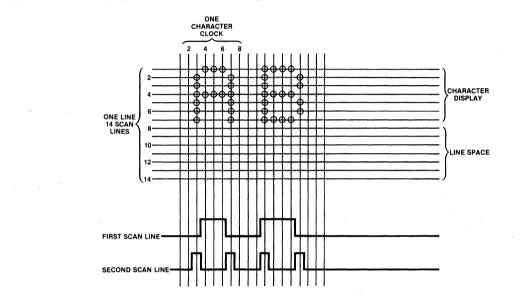

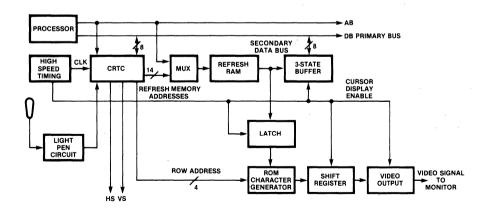

| F6845/F6845A CRT Controller.                                      |       |

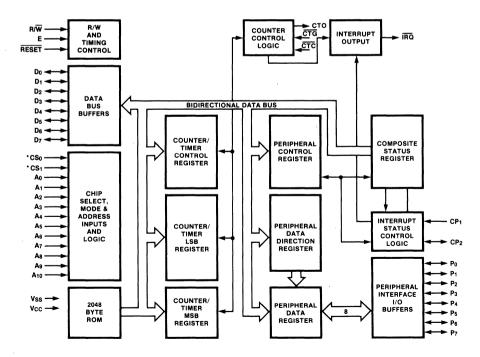

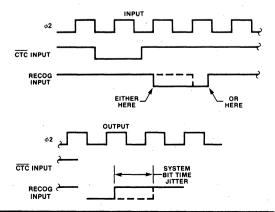

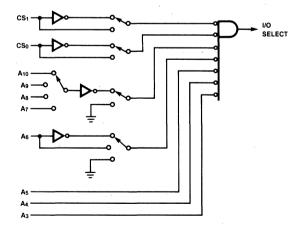

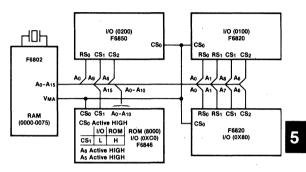

| F6846 ROM-I/O-Timer                                               | 5-175 |

| F6847 Video Display Generator.                                    |       |

| F6850/F68A50/F68B50 Asynchronous Communications Interface Adaptor |       |

| F6852/F68A52/F68B52 Synchronous Serial Data Adaptor.              |       |

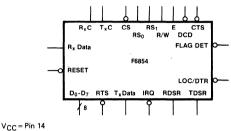

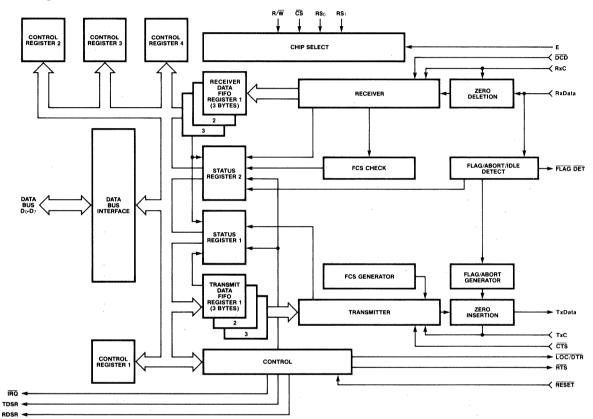

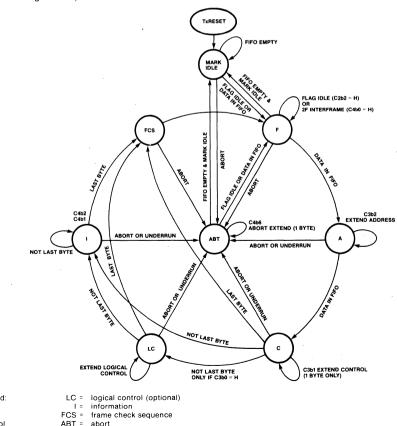

| F6854/F68A54/F68B54 Advanced Data Link Controller.                |       |

| F3846/F6856 Synchronous Protocol Communications Controller        |       |

| F38456/F68456 Multiple Protocol Communications Controller.        |       |

| F68488 General Purpose Interface Adaptor.                         | 5-297 |

|                                                                   |       |

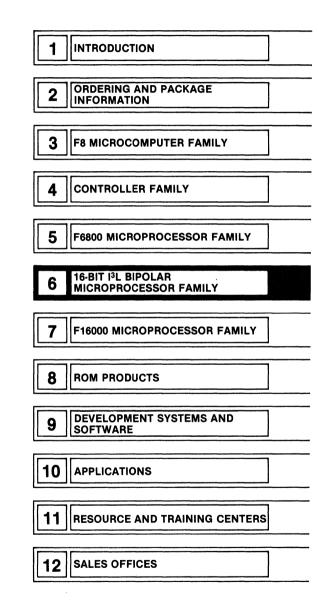

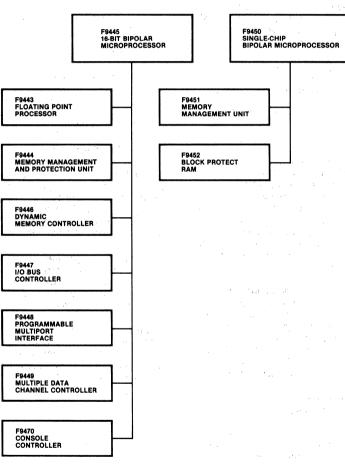

| Section 6 16-Bit I <sup>3</sup> L Bipolar Microprocessor Family   |       |

| General                                                           |       |

| Instruction Set                                                   |       |

| F9443 Floating Point Processor.                                   |       |

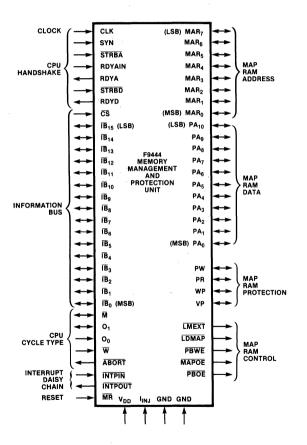

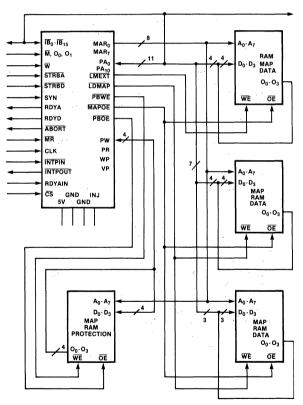

| F9444 Memory Management and Protection Unit.                      |       |

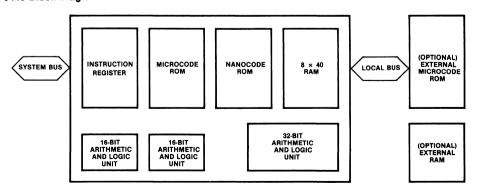

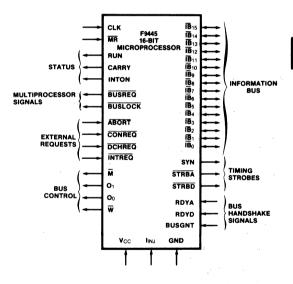

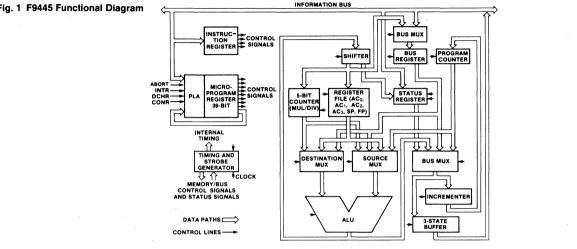

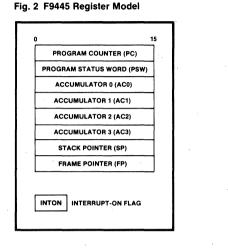

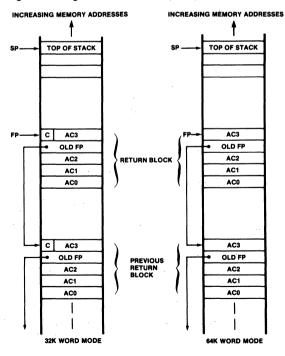

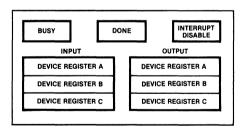

| F9445 16-Bit Bipolar Microprocessor.                              |       |

| F9446 Dynamic Memory Controller.                                  |       |

| F9447 I/O Bus Controller.                                         |       |

| F9448 Programmable Multiport Interface.                           |       |

| F9449 Multiple Data Channel Controller.                           |       |

| F9450 Single-Chip Microprocessor.                                 |       |

| F9451 Memory Management Unit.                                     |       |

| F9452 Block Protect RAM.                                          |       |

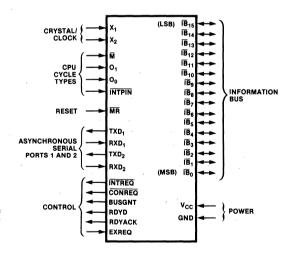

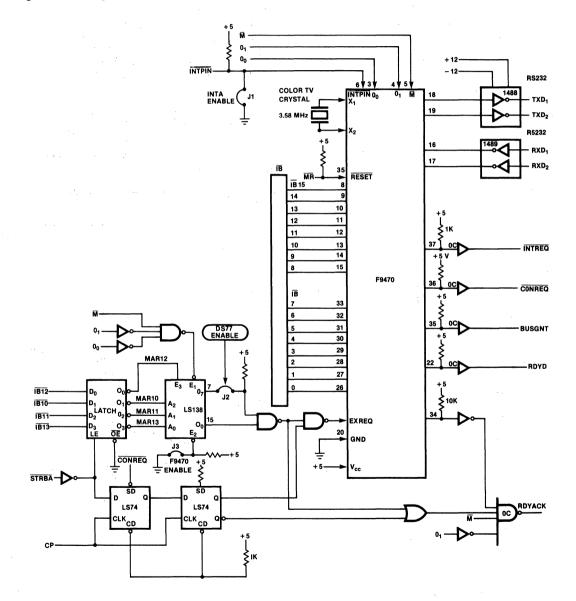

| F9470 Console Controller                                          | 6-81  |

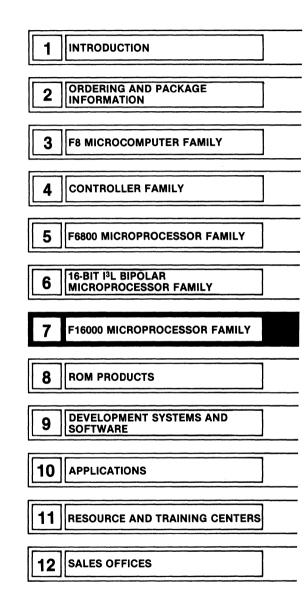

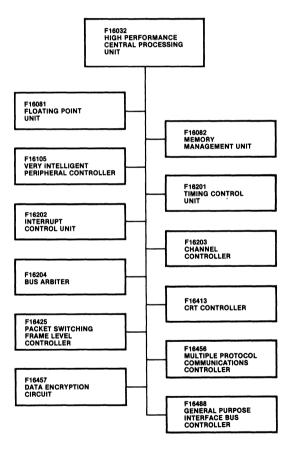

| Section 7 F16000 Microprocessor Family              |      |

|-----------------------------------------------------|------|

| General                                             | 7-3  |

| Addressing                                          |      |

| Virtual Memory                                      | 7-3  |

| Symmetry                                            | 7-3  |

| High-Level Language Support.                        | 7-4  |

| Modularity                                          | 7-4  |

| Slave Processors                                    | 7-4  |

| System Protection                                   | 7-4  |

| Future Expansion.                                   | 7-4  |

| F16032 High Performance Central Processing Unit.    | 7-7  |

| F16081 Floating Point Unit                          | 7-13 |

| F16082 Memory Management Unit.                      | 7-15 |

| F16105 Very Intelligent Peripheral Controller       |      |

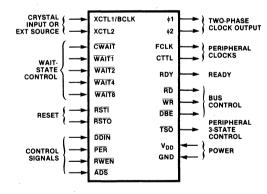

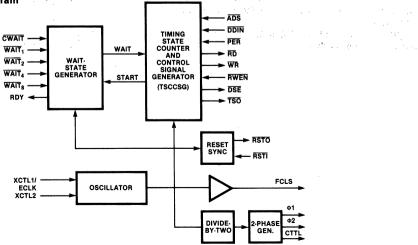

| F16201 Timing Control Unit                          | 7-19 |

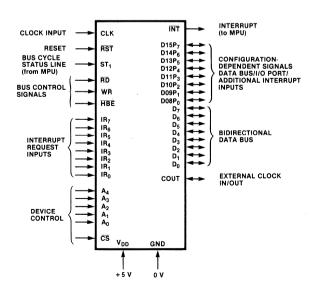

| F16202 Interrupt Control Unit.                      | 7-21 |

| F16203 Channel Controller                           |      |

| F16204 Bus Arbiter                                  | 7-25 |

| F16413 CRT Controller                               |      |

| F16425 Packet Switching Frame Level Controller      | 7-31 |

| F16456 Multiple Protocol Communications Controller. |      |

| F16457 Data Encryption Circuit.                     | 7-39 |

| F16488 GPIB Controller                              | 7-41 |

|                                                     |      |

| Section 8                                           | ,    |

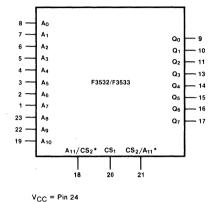

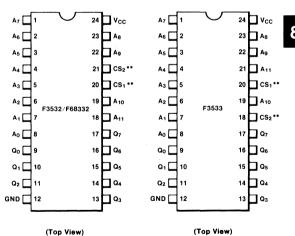

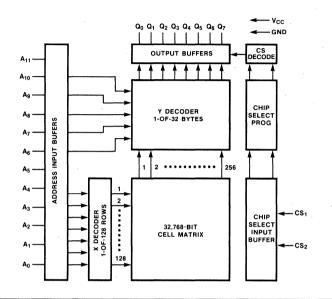

| F3532/F68332/F3533 32K ROM                          |      |

| F3564 64K ROM                                       |      |

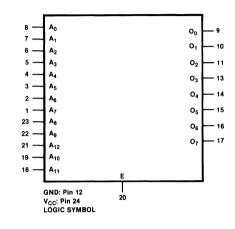

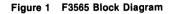

| F3565 64K ROM                                       |      |

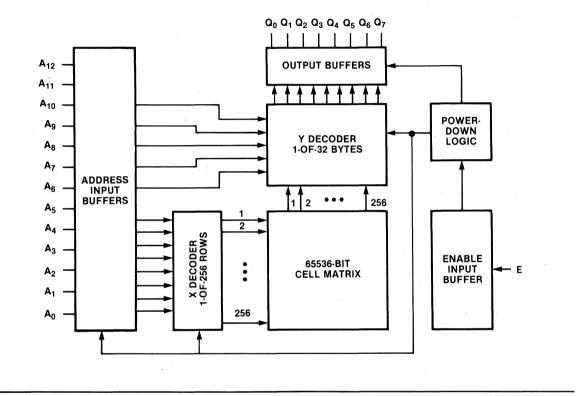

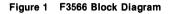

| F3566 64K ROM                                       |      |

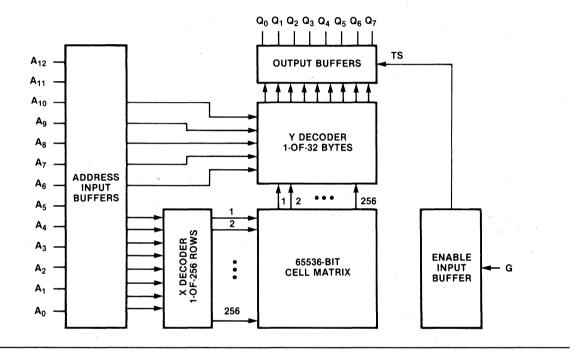

| F3568 64K ROM                                       |      |

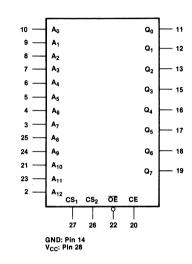

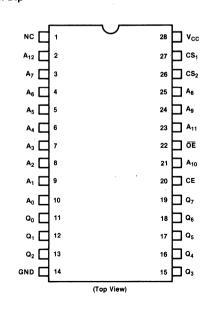

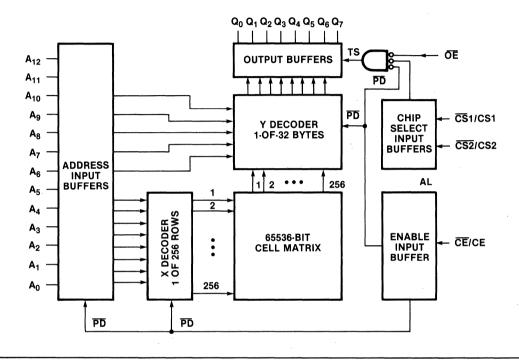

| F3569 64K ROM                                       |      |

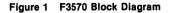

| F3570 64K ROM                                       |      |

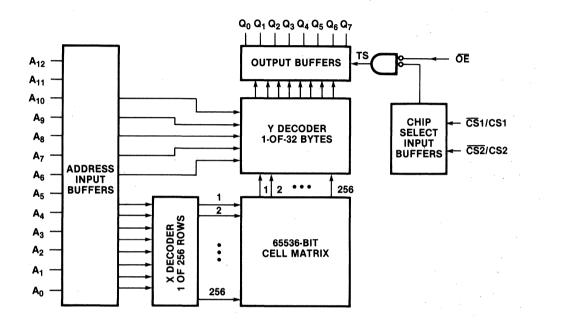

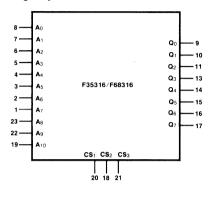

| F35316/F68316 16K ROM                               | 8-23 |

|                                                     |      |

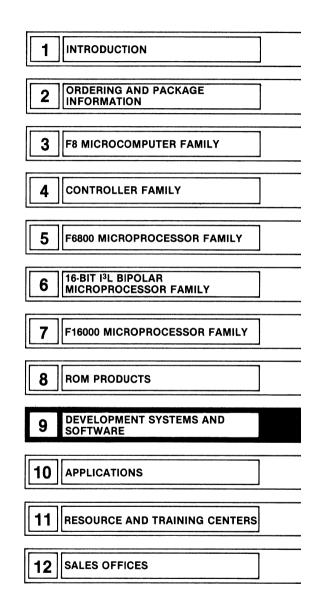

| Section 9 Development Systems and Software          |      |

| EMUTRAC                                             |      |

| Formulator.                                         |      |

| FS-1                                                |      |

| PEP-45                                              |      |

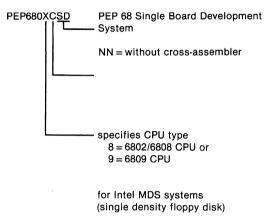

| PEP-68                                              |      |

| PEP-387X                                            |      |

| Software                                            | 9-27 |

| Section 10 Applications |        |

|-------------------------|--------|

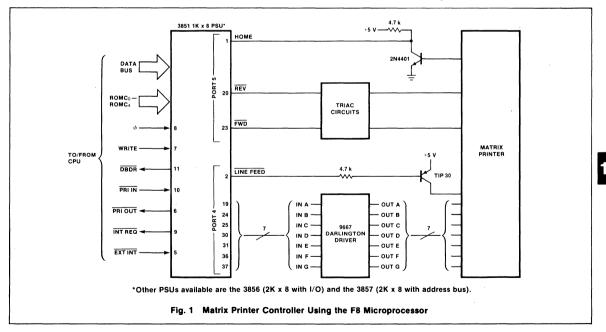

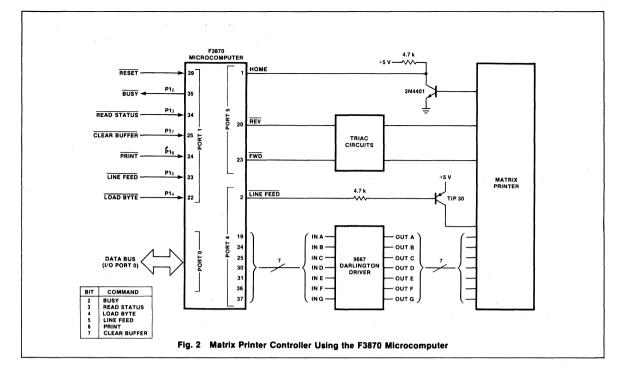

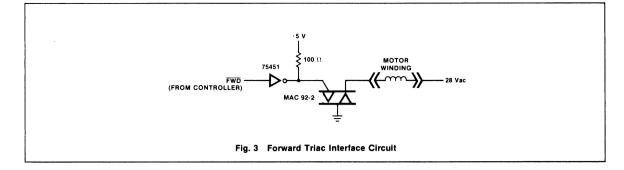

| Matrix Printer          | . 10-5 |

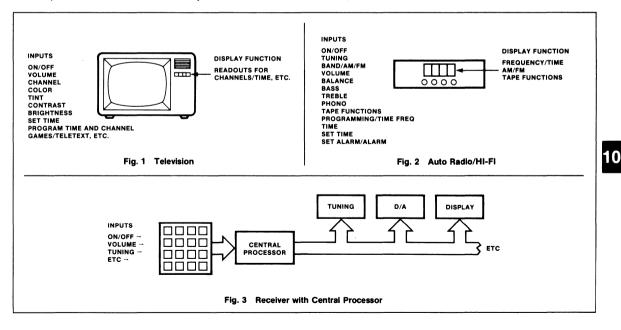

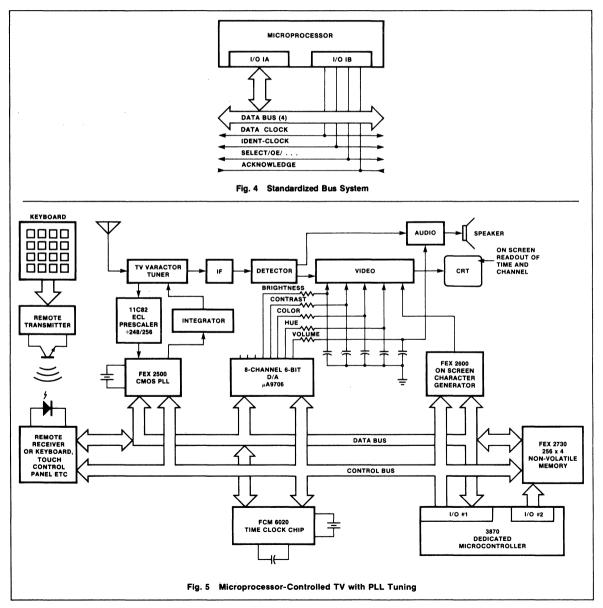

| PLL System.             | 10-19  |

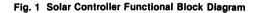

| Solar Controller        | 10-31  |

# Section 11 Resource and Training Centers

Section 12 Sales Offices

.

# Section 1

# Introduction

# General

A microprocessor is essentially an integrated circuit logic replacement device that performs the functions of the central processing unit (CPU) of a computer system. The overall task of the microprocessor is to receive digital data and store it for later processing, to perform arithmetic and logic operations on the data in accordance with instructions contained in a stored program, and to present the results of these operations to the user through some form of output mechanism.

The program is a definable and non-varying specification for any given application. It normally resides in a read only memory (ROM) or program storage unit (PSU). Variable data that is to be operated upon by the microprocessor is normally stored in a random access memory (RAM) or other transient data storage element.

Although architectural details vary depending upon manufacturer and technology, a typical microprocessor comprises the following functional areas:

- 1. Instruction decoding to interpret program instructions.

- An arithmetic and logic unit (ALU) to perform binary addition, subtraction, etc., and Boolean logic operations.

- Registers to temporarily store frequently manipulated data.

- 4. Address buffers to provide the next program instruction address.

- 5. Input/output (I/O) buffers to read information into or write information out of the microprocessor.

Microprocessors are generally used in conjunction with support devices that perform timing, program and transient data memory, I/O signal interface, and other functions. A wide range of configurations is possible with a microprocessor and its related devices; each configuration represents a full microcomputer system.

A single-chip microcomputer incorporates CPU, memory, I/O, control, and other functions into one integrated circuit. Typically, such devices have facilities for enhancement of

capabilities by interconnection with external devices.

The Fairchild Microprocessor Division product line encompasses microprocessors and their support devices, singleand multi-chip microcomputers, and systems to emulate and develop hardware and software.

# **Product Line**

The Microprocessor Division product line includes a wide range of devices to meet the specific needs of four broad application areas:

- 1. 8-bit microprocessors

- 2. 8-bit single-chip microcomputers

- 3. 16-bit microprocessors

- 4. Development aids

Within these areas, the Division offers a blend of innovative, state-of-the-art devices and proven, wellestablished devices. For example, the members of the F6800 family, and of the F8 family, can be configured to create a variety of 8-bit computer systems that have a wide range of capabilities. Similarly, the F9445 family components can create extremely fast 16-bit computer systems that are exceptionally resistant to harsh environments, and the F16000 family members can be used in configurations that are ideally suited to communications applications. (The F16000 has a 16-bit I/O structure and a 32-bit internal architecture.)

To the user, the Microprocessor Division line represents a single source of cost-effective solutions to the full spectrum of application problems.

# Data Book

This data book presents a complete technical description of the Fairchild Microprocessor Division product line. Where devices have been characterized, specific information is presented in the form of data sheets. Information on partially characterized devices, and on devices currently under development, is in the form of advance product information sheets. More complete data can be obtained from the Product Marketing Department.

# Introduction

# General

Specific ordering codes, as well as the temperature ranges and package types available, are included in each data sheet of sections 3 through 8.

# **Temperature Range**

The basic temperature ranges typically available are:

- C Commercial (0°C to 75°C)

- L Automotive (-40°C to 85°C)

- M Military (- 55°C to 125°C)

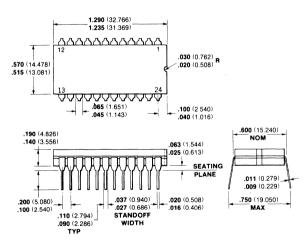

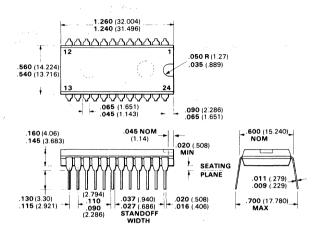

# 24-Pin Ceramic Dual-In-Line

# Package Types and Outlines

The basic package type of a device, such as dual-in-line plastic or dual-in-line ceramic, is indicated by the ordering code for that device. To accommodate various die sizes and pin numbers, different package forms exist within each package type.

The package forms indicated by device ordering codes are illustrated in the following detailed outline drawings.

# NOTES:

All dimensions are in inches **bold** and millimeters (parentheses). Pin material is nickel gold-plated kovar. Cap is kovar. Base is ceramic. Package weight is 6.5 grams.

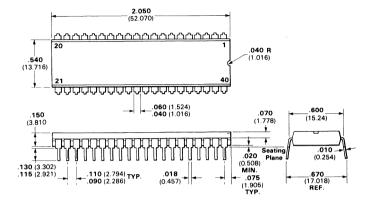

#### 24-Pin Plastic DIP

NOTES:

All dimensions are in inches **bold** and millimeters (parentheses). Pins are tin-plated kovar. Package material is plastic.

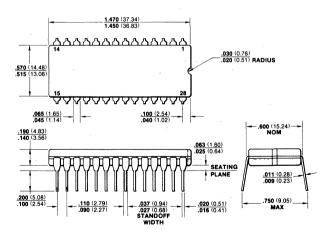

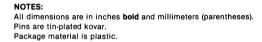

# 28-Pin Ceramic Dual-In-Line

NOTES: All dimensions are in inches **bold** and millimeters (parentheses). Pin material is nickel gold-plated kovar. Cap is kovar. Base is ceramic. Package weight is 6.5 grams.

# 28-Pin Plastic Dual-In-Line

NOTES:

All dimensions are in inches **bold** and millimeters (parentheses). Pins are tin-plated kovar. Package material is plastic.

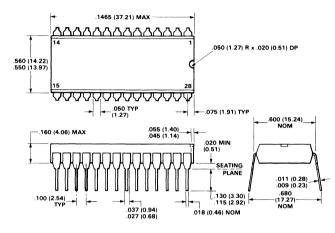

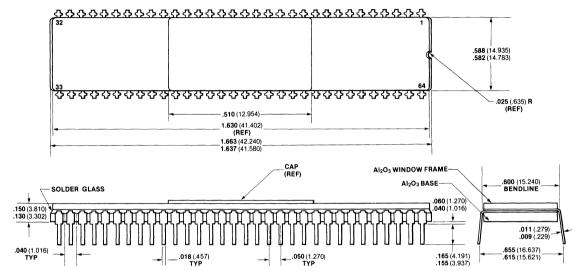

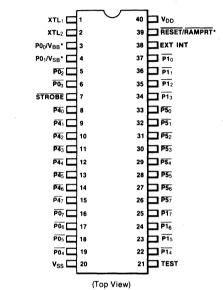

# 40-Pin Ceramic Dual-In-Line

#### NOTES: All dimensions are in inches **bold** and millimeters (parentheses). Pin material is nickel gold-plated kovar.

Pin material is nickel gold-plated kovar. Cap is kovar. Base is ceramic. Package weight is 6.5 grams.

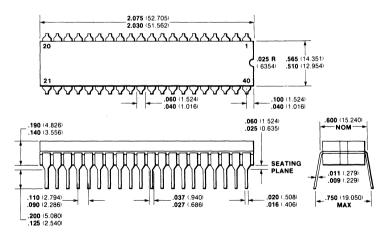

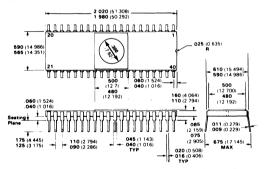

# 40-Pin Plastic Dual-In-Line

40-Pin Ceramic Dual-In-Line (EPROM)

#### NOTES:

All dimensions are in inches **bold** and millimeters (parentheses). Pin material is nickel gold-plated kovar. Cap is kovar. Base is ceramic. Package weight is 6.5 grams.

NOTES: All dimensions are in inches **bold** and millimeters (parentheses). Pin material is nickel gold-plated kovar. Cap is kovar. Base is ceramic. Package weight is 6.5 grams.

2-7

2

2-8

.

. .

.

# **Section 3**

# F8 Microcomputer Family

# General

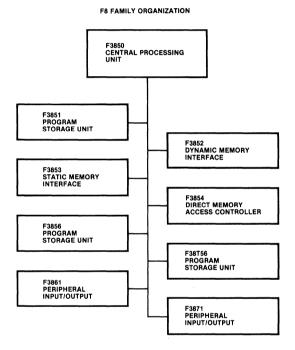

The distribution of logic among the various elements of a microcomputer system is one of the most variable features of such systems. The traditional division of logic corresponds to the requirements of a computer; e.g., one device serving as CPU, one as memory, and one as I/O. In the F8 microcomputer family, logic is implemented in devices in terms of application complexity rather than in terms of computer function. Thus, for example, two F8 devices implement all of the basic functions of a small microcomputer.

To accomplish this, the design of the F8 family includes a number of non-traditional function assignment features:

- 1. A small amount of RAM is implemented within the CPU as a scratchpad memory.

- 2. Memory addressing logic is implemented in the memory devices rather than in the CPU.

- The I/O ports are implemented in the CPU and memory devices rather than in discrete I/O devices.

Every F8 configuration must contain an F3850 CPU, at least one F3851 Program Storage Unit (PSU) or memory interface device, and standard ROM or PROM (see figure 3-1). The memory-oriented devices may be used singly or together in the same system; when necessary, multiple units of the same type may be used. For example, an F3850 and two F3851s may comprise a system requiring 2K words of ROM, 64 bytes of RAM, and six I/O ports.

# **Memory Interface Devices**

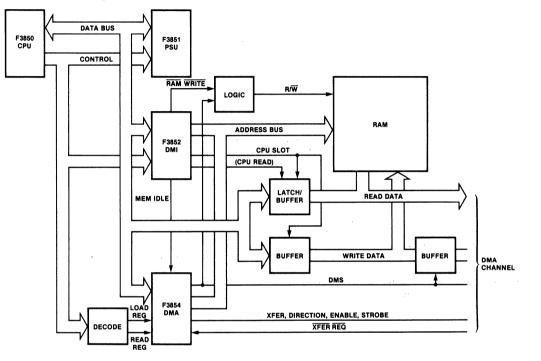

When required by the application, the F3851 PSU may be replaced by an F3852 Dynamic Memory Interface (DMI) or F3853 Static Memory Interface (SMI). Both of these devices interpret control signals output by the F3850 and generate the standard address and control signals required by off-the-shelf dynamic and static memory devices.

The F3854 Direct Memory Interface (DMA) device is used in

conjunction with the F3852 DMI. It generates the address and control signals needed to perform data transfers between memory and external logic. These transfers occur in parallel with normal operation within the F8 system.

#### Input/Output Devices

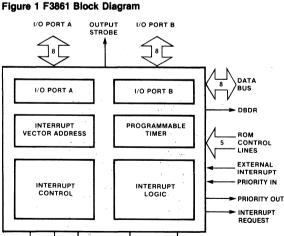

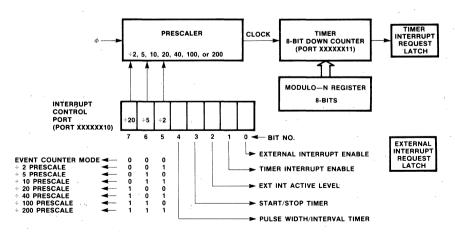

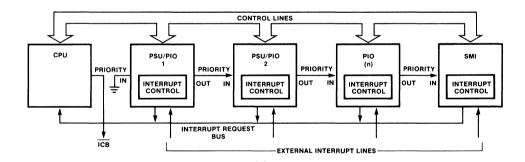

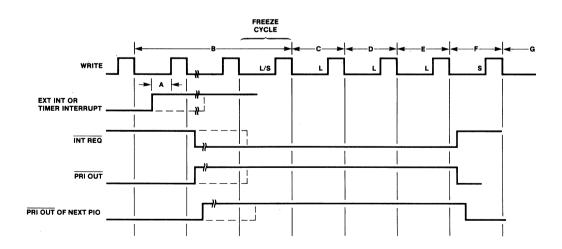

Applications that require additional I/O and interrupt capabilities but do not require the PSU storage capacity can make use of the F3861 Peripheral Input/Output (PIO) device. The PIO, which also contains interrupt logic and a programmable timer, interprets CPU control signals to drive two 8-bit I/O ports.

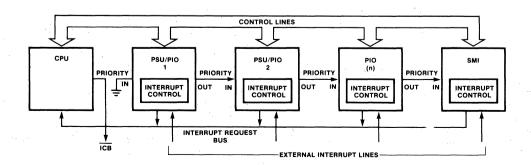

# **Bus Structure**

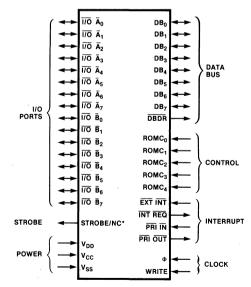

The F8 microcomputer components are interconnected by means of a system bus structure that is composed of the following elements:

- 1. Eight data bus lines (DB<sub>0</sub> DB<sub>7</sub>)

- 2. Five control lines ( $ROMC_0 ROMC_4$ )

- 3. Two clock lines (Φ, WRITE)

- 4. Three interrupt lines (PRI IN, PRI OUT, INT REQ)

# Instruction Set

The instruction set of a microprocessor or microcomputer is the software tool used to shape the device or system for a particular application. The F8 instruction set is divided into four functional groups:

- 1. Input/Output

- 2. Arithmetic/Logical

- 3. Address Register Control

- 4. Indirect Scratchpad Address Register (ISAR) and Status Control

The F8 instruction set is presented in table 3-1.

# F8 Microcomputer Family

# Table 3-1 F8 Instruction Set

| Instruction | Description                         | Instruction | Description                               |

|-------------|-------------------------------------|-------------|-------------------------------------------|

| ADC         | Add Accumulator to Data Counter     |             |                                           |

| AL          | Add Immediate to Accumulator        | JMP         | Branch Immediate                          |

| AM          | Add (Binary) Memory to Accumulator  |             |                                           |

| AMD         | Add (Decimal) Memory to Accumulator | LI          | Load Immediate                            |

| AS          | Add (Binary) Scratchpad Memory      | LIS         | Load Immediate Short                      |

|             | to Accumulator                      | LISL        | Load Lower Octal Digit of ISAR            |

| ASD         | Add (Decimal) Scratchpad Memory     | LISU        | Load Upper Octal Digit of ISAR            |

|             | to Accumulator                      | LM          | Load Accumulator from Memory              |

|             |                                     | LNK         | Link Carry to Accumulator                 |

| BC          | Branch on Carry                     | LR          | Load Register                             |

| BF          | Branch on false                     | • • •       | · · · · · · · · · · · · · · · · · · ·     |

| BM          | Branch on Negative                  | NI          | AND Immediate                             |

| BNC         | Branch if No Carry                  | NM          | Logical AND from Memory                   |

| BNO         | Branch if No Overflow               | NOP         | No Operation                              |

| BNZ         | Branch if Not Zero                  | NS          | Logical AND from Scratchpad Memory        |

| BP          | Branch if Positive                  |             |                                           |

| BR          | Unconditional Branch                | OI          | OR Immediate                              |

| BR7         | Branch on ISAR                      | OM          | Logical OR from Memory                    |

| BT          | Branch on True                      | OUT         | Output Long Address                       |

| BZ          | Branch on Zero                      | OUTS        | Output Short Address                      |

| CI          | Compare Immediate                   | PI          | Call to Subroutine Immediate              |

| CLR         | Clear Accumulator                   | PK          | Call to Subroutine Direct and Return from |

|             |                                     |             | Subroutine Direct                         |

| СОМ         | Complement                          | POP         | Return from Subroutine                    |

| DCI         | Load Data Counter Immediate         | SL          | Shift Left                                |

| DI          | Disable Interrupt                   | SR          | Shift Right                               |

| DS          | Dessement Scratchpad Memory Content | ST          | Store to Memory                           |

| EI.         | Enable Interrupt                    | XDC         | Exchange Data Counters                    |

|             | Enable menupt                       | XI          | Ekxclusive-OR Immediate                   |

| IN          | Input Long Address                  | XM          | Exclusive-OR from Memory                  |

| INC         | Increment Accumulator               | XS          | Exclusive-OR from Scratchpad Memory       |

| INS         | Input Short Address                 |             |                                           |

|             | input onort Address                 |             |                                           |

F8 Microcomputer Family

# Descriptions

Following is data that describes the members of the F8 microcomputer system family.

3

F8 Microcomputer Family

# F3850

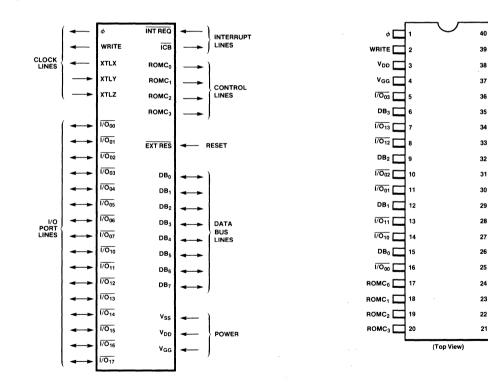

# **Central Processing Unit (CPU)**

Microprocessor Product

# Description

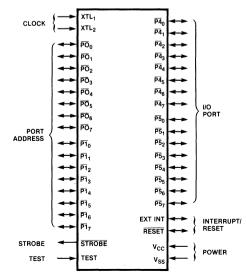

The Fairchild F3850 is the Central Processing Unit (CPU) for the F8 8-Bit Microprocessor family. The F3850 contains more than 70 instructions in its instruction set and operates on 8-bit units of information.

- N-channel Isoplanar MOS Technology

- 2 µs Cycle Time

- 64-Byte Scratchpad on the CPU Chip

- Two Bidirectional, 8-Bit I/O Ports, with Output Latches

- 8-Bit Arithmetic and Logic Unit, Supporting Both Binary and Decimal Arithmetic

- Interrupt Control Logic

- Power-on Reset Logic

- Clock Generation Logic Within the CPU Chip, With Crystal and External Clock Generation

XTLZ

XTLZ

EXT RES

1/004

1/014

1/015

DB5

1/005

1/006

DB6

1/016

1/017

DB7

1/007

V<sub>ss</sub>

ісв

INT REQ

- More Than 70 Instructions

- +5 V and +12 V Power Supplies

- Low Power Dissipation (Typically Less Than 330 mW)

# **Signal Functions**

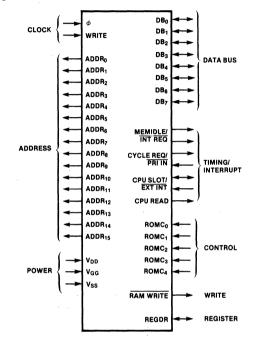

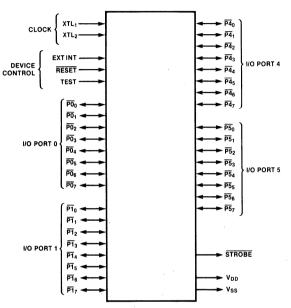

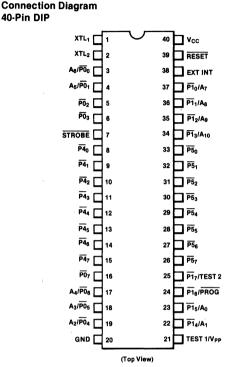

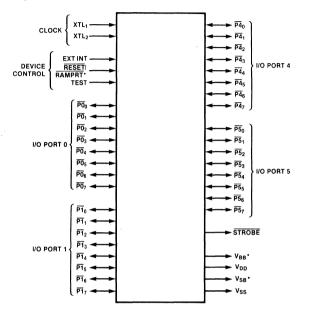

Connection Diagram

3-7

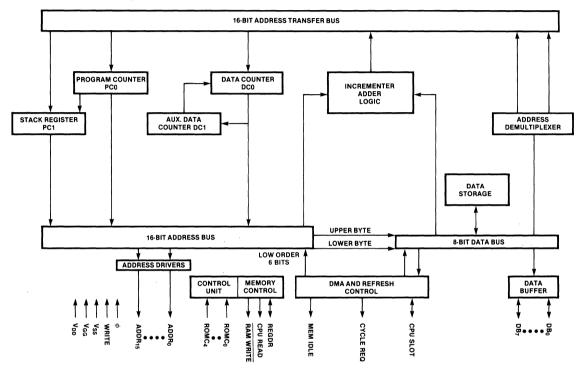

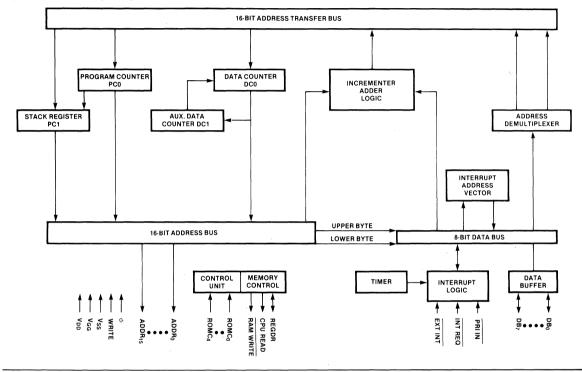

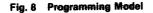

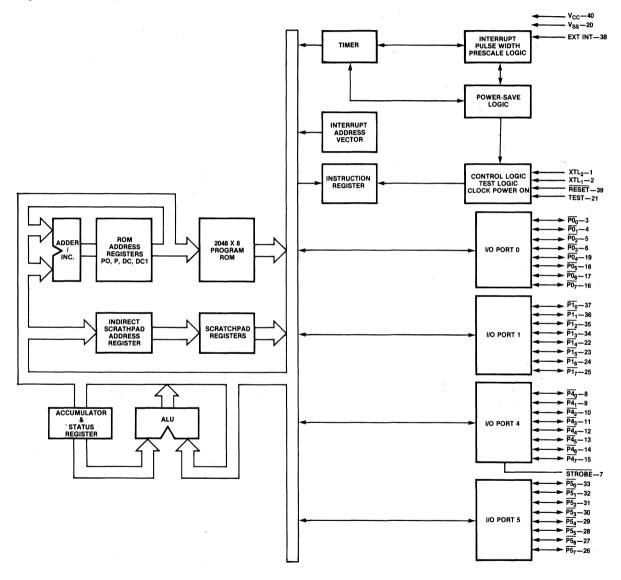

# **Device Organization**

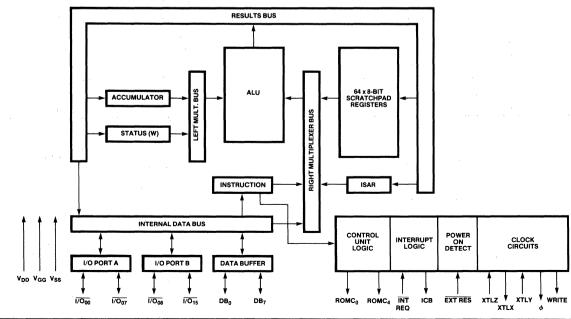

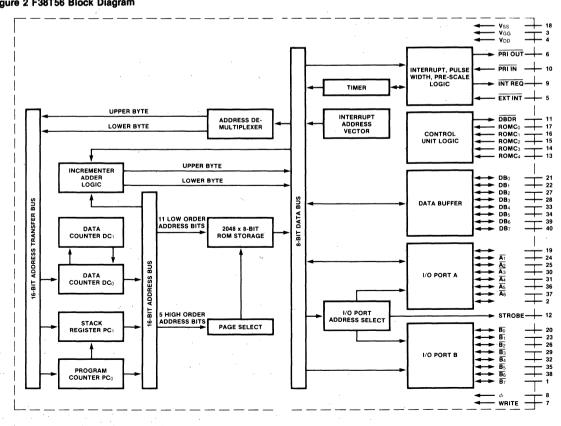

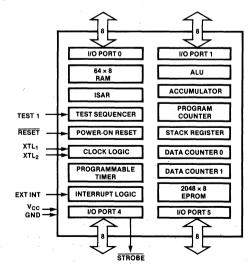

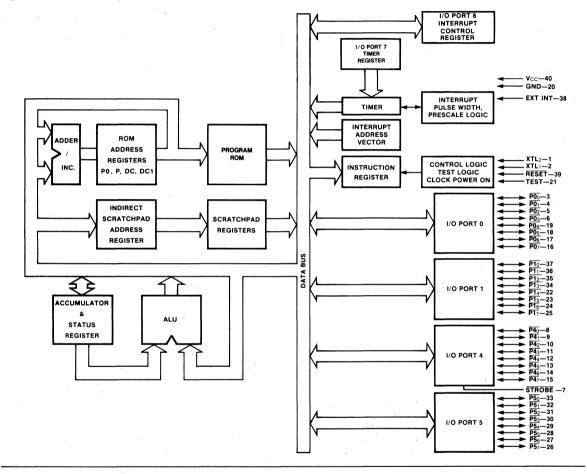

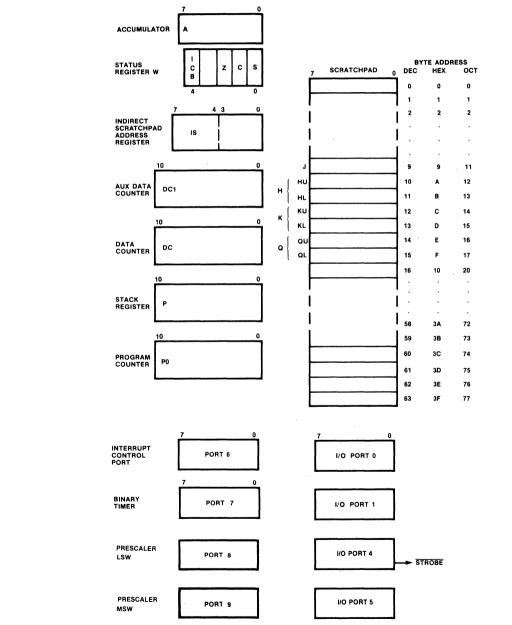

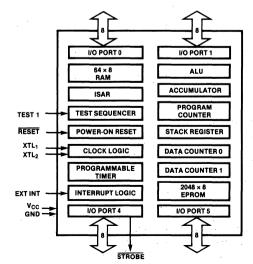

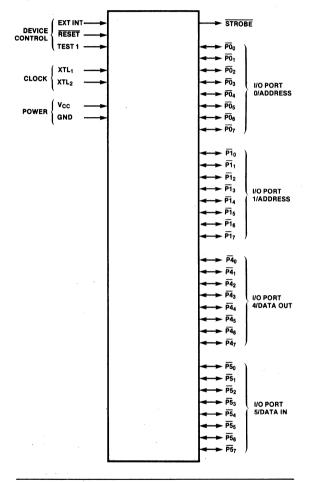

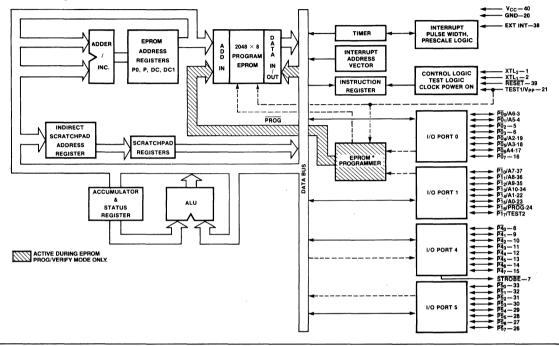

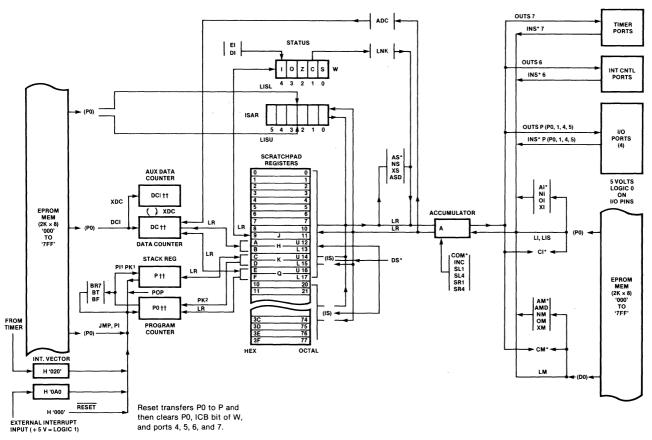

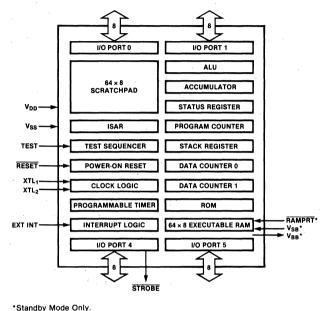

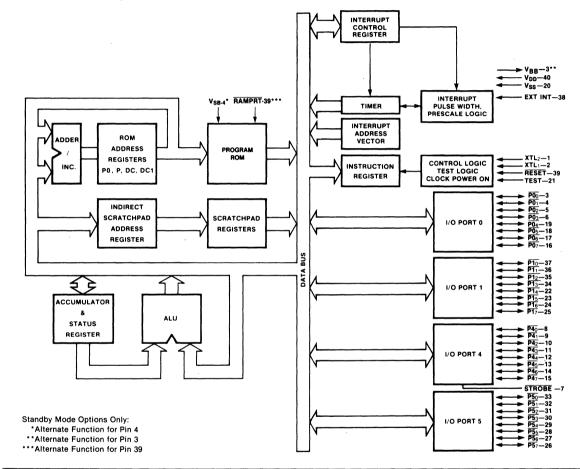

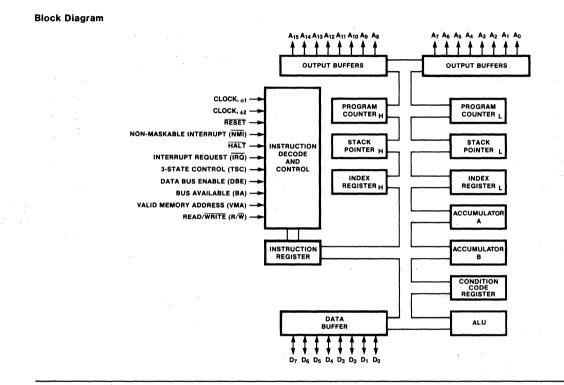

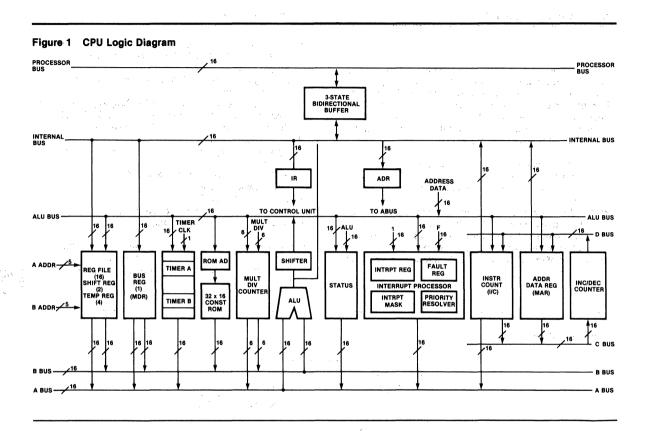

The logical organization and pins for the F3850 CPU are illustrated in *Figure 1*.

# Arithmetic and Logic Unit

The arithmetic and logic unit (ALU) provides all data manipulating logic for the F3850. It contains logic that operates on a single 8-bit source data word or combines two 8-bit words of source data to generate a single 8-bit result. Additional information is reported in status flags, where appropriate.

Operations performed on two units of source data include addition, compare, and the Boolean operations (AND, OR, Exclusive-OR). The two sources are input to the ALU through the left and right multiplexer buses; the result is placed on the result bus.

Operations performed on a single 8-bit unit of source data include complement, increment, decrement, shift right, shift left, and clear. The source is input to the ALU through either the left or right multiplexer bus; the result is placed on the result bus.

# Instruction Register

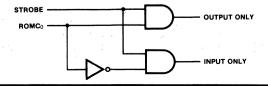

The CPU contains registers for storing various types of data. The instruction register holds an 8-bit code, which defines the operations to be performed by the CPU. The contents of the instruction register are decoded by control unit logic, which generates signals to enable specific sequences of logic operations within the CPU chip. In response to the contents of the instruction register, the control unit also generates five signals, ROMC<sub>0</sub> through ROMC<sub>4</sub>, that control operations throughout the microprocessor system.

#### Accumulator

The accumulator is a general-purpose 8-bit data register, which is the most common data source and results destination for the ALU.

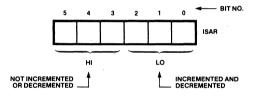

#### Scratchpad and ISAR

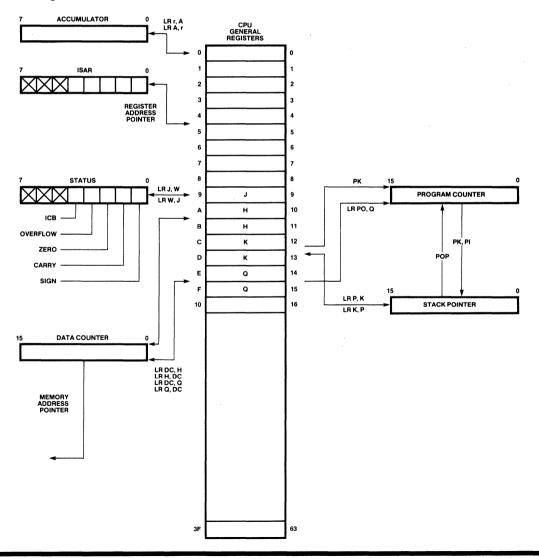

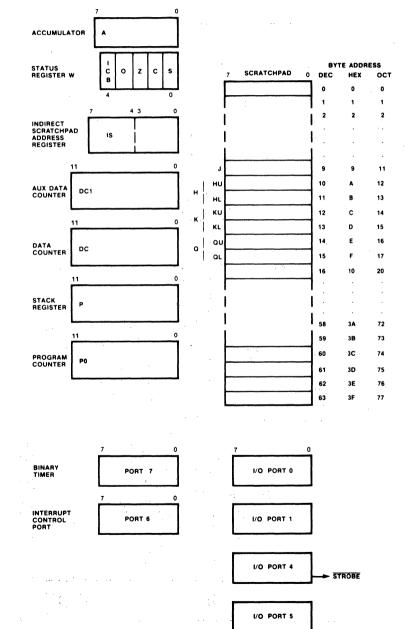

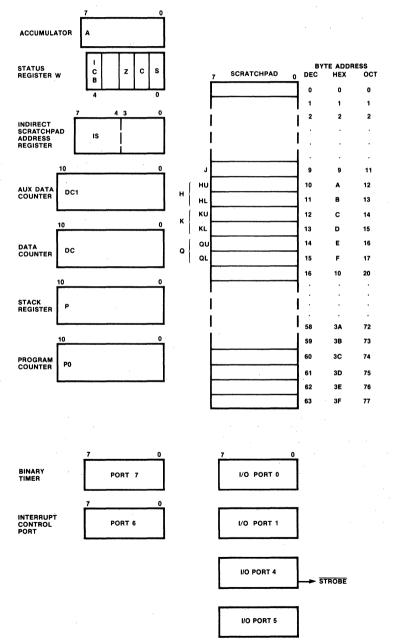

The scratchpad provides 64 8-bit registers that may be used as general-purpose RAM memory (see *Figure 2*).

# Figure 2 F8 Programming Model

# Figure 1 F3850 CPU Logical Organization

The indirect scratchpad address register (ISAR) is a 6-bit register used to address the 64 scratchpad registers.

The first 16 scratchpad bytes can be identified either by instructions without using the ISAR or referenced through the ISAR. The remaining scratchpad bytes are referenced through the ISAR; i.e., the ISAR is assumed to hold the address of the scratchpad byte that is to be referenced.

The ISAR may be visualized as holding two octal digits, HI and LO, as illustrated in *Figure 3*. This division of the ISAR is important, since a number of instructions increment or decrement the con-

#### Figure 3 ISAR Register

tents of the ISAR, when referencing scratchpad bytes through the ISAR. This makes it easy to reference a buffer consisting of contiguous scratchpad bytes. However, only the low-order octal digit (LO) is incremented or decremented; thus ISAR is incremented from O'27'\* to O'20', not to O'30'. Similarly, ISAR is decremented from O'20' to O'27', not to O'17'. This feature of the ISAR is very useful in that it greatly simplifies many program sequences.

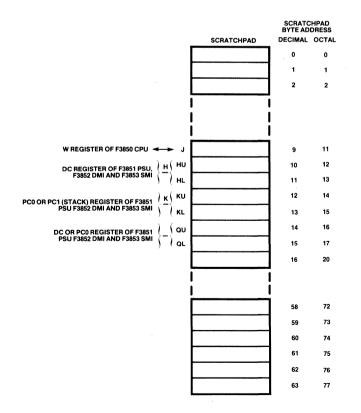

Selected scratchpad registers are reserved for direct communication with other registers within the F8 system, as illustrated in *Figure 4.*

Scratchpad register 9 (O'11') is used as temporary storage for the CPU status register (W register). Scratchpad registers 10 through 15 (O'12' through O'17') communicate directly with data

\*The notation O'nn' represents an octal number.

and program memory address registers that are maintained on the F3851, F3852, and F3853 chips. *Figure 4* identifies the data transfers that can be implemented by executing a single F8 instruction. For example, the illustration:

#### W register of F3850 CPU ↔ J

means that a single instruction can move the contents of the W (or status) register to scratchpad register 9 (J register). Another single instruction can move data in the opposite direction.

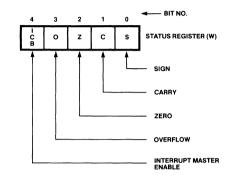

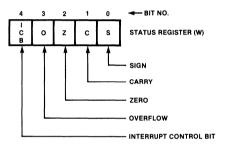

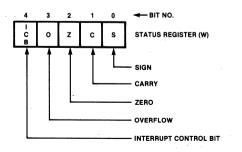

# **Status Registers**

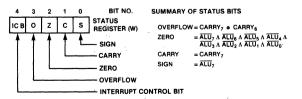

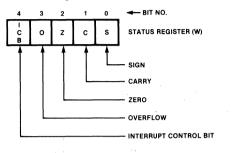

The status (W) register holds five status flags. *Table 1* summarizes the way each flag is used. Note that status flags are selectively modified following execution of different instructions. See the "Instruction Execution" section for a discussion of the way individual F8 instructions modify status flags.

# Figure 4 F3850 CPU Scratchpad Registers

F3850

**Sign (S Bit)**—When the results of an ALU operation are being interpreted as a signed binary number, the high-order bit (bit 7) represents the sign of the number. At the conclusion of instructions that may modify the accumulator bit 7, the S bit is set to the complement of the accumulator bit 7.

# Table 1 Summary of Status Bits

| OVERFLOW | $= CARRY_7 + CARRY_6$                                                                                                                                                                   |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZERO     | $= \overline{\text{ALU}}_7 \ \overline{\text{ALU}}_6 \ \overline{\text{ALU}}_5 \ \overline{\text{ALU}}_4 \ \overline{\text{ALU}}_3 \ \overline{\text{ALU}}_2 \ \overline{\text{ALU}}_1$ |

|          | ALU <sub>0</sub>                                                                                                                                                                        |

| CARRY    | = CARRY <sub>7</sub>                                                                                                                                                                    |

| SIGN     | $= \overline{ALU}_7$                                                                                                                                                                    |

**Carry (C Bit)**—The C bit may be visualized as an extension of an 8-bit data unit; i.e., the ninth of a 9-bit data unit. When two bytes are added, and the sum is greater than 255, then the carry out of the high-order bit appears in the C bit; e.g.:

|                                 | C76543210 ← Bit Number |

|---------------------------------|------------------------|

| Accumulator contents:           | 01100101               |

| Value added:                    | 01110110               |

| Sum:                            | 0 11011011             |

| There is no carry, so C is res  | set to 0.              |

|                                 | C76543210 ← Bit Number |

| Accumulator contents:           | 10011101               |

| Value added:                    | 11010001               |

| Sum:                            | 1 01101110             |

| There is a carry, so C is set t | o 1.                   |

Zero (Z bit)—The Z bit is set whenever an arithmetic or logical operation generates a zero result. The Z bit is reset to 0 when an arithmetic or logical operation could have generated a zero result but did not. **Overflow (O Bit)**—When the results of an ALU operation are being interpreted as a signed binary number, since the high-order bit (bit 7) represents the sign of the number, some method must be provided for indicating a carry out of the highest numeric bit (bit 6). This is done using the O bit. After arithmetic operations, the O bit is set to the Exclusive-OR of a carry out of bits 6 and 7. The simplification of signed binary arithmetic is described in the *F8 and F3870 Guide to Programming*; examples are presented below:

|                       | 76543210 ← Bit Number |

|-----------------------|-----------------------|

| Accumulator contents: | 10110011              |

| Value added:          | 01110001              |

| Sum:                  | 11100100              |

There is a carry out of bit 6 and a carry out of bit 7, so the O bit is reset to 0  $(1 \oplus 1 = 0)$ . The C bit is set to 1.

|                       | 76543210 ← Bit Number |

|-----------------------|-----------------------|

| Accumulator contents: | 01100111              |

| Value added:          | 00100100              |

| Sum:                  | 10001011              |

There is a carry out of bit 6, but no carry out of bit 7; the O bit is set to 1  $(1 \oplus 0 = 1)$ . The C bit is reset to 0.

Interrupts (ICB Bit)—External logic can alter program execution sequence within the CPU by interrupting ongoing operations. However, interrupts are allowed only when the ICB is set to 1; interrupts are disallowed when the ICB is reset to 0.

#### **Control Unit**

The control unit decodes the contents of the instruction register and generates two sets of control signals. These signals are transparent to the user.

Five control signals ( $ROMC_0$  through  $ROMC_4$ ) are output by the control unit to identify operations that other chips of the F8 family must perform. These signals are described in the "ROMC Signals" section.

# Interrupt Logic

This logic handles the interrupt requests. For a complete description refer to the "Interrupt" discussion within the "Instruction Execution" section.

# **Power on Detect**

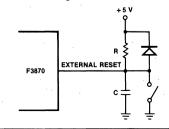

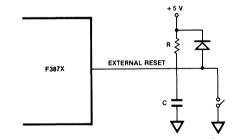

When the External Reset (EXT RES) signal is pulled low and then returned high, or when power is turned on, the power on detect logic sets the PC registers to 0, causing a program originating at memory location 0 to be executed. Also, the interrupt control status bit is set low, inhibiting interrupt acknowledgement. The system is locked in an idle state while EXT RES is held low.

F3850

# Signal Descriptions

The F3850 input and output signals are described in Table 2.

# Table 2 F3850 Signal Descriptions

| Mnemonic                                 | Pin No.                       | Name                                  | Description                                                                                                                                                                                                                                                        |

|------------------------------------------|-------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock                                    |                               |                                       |                                                                                                                                                                                                                                                                    |

| φ<br>WRITE                               | 1<br>2                        | Clock<br>Write                        | These output signals drive all other devices in the F8 family.                                                                                                                                                                                                     |

| XTLX                                     | 39                            | Crystal Clock                         | The XTLX output signal is used when generating the system clock<br>in the crystal mode (with the XTLY and XTLZ signals).                                                                                                                                           |

| XTLY                                     | 38                            | External Clock                        | The XTLY input signal is used with the XTLX signal when generating the system clock in the crystal mode, and is also used for operating in the external clock mode.                                                                                                |

| XTLZ                                     | 40                            | Crystal Clock                         | This input signal must be grounded for crystal clock or external clock.                                                                                                                                                                                            |

| I/O Port                                 |                               |                                       |                                                                                                                                                                                                                                                                    |

| 1/O 00-1/O 07                            | 16, 11, 10, 5, 36, 31, 30, 25 | I/O Port Zero                         | These bidirectional signals are ports through which the CPU<br>communicates with logic external to the microprocessor system.                                                                                                                                      |

| 1/0 <sub>10</sub> -1/0 <sub>17</sub>     | 14, 13, 8, 7, 34, 33, 28, 27  | I/O Port One                          |                                                                                                                                                                                                                                                                    |

| Interrupt                                |                               |                                       |                                                                                                                                                                                                                                                                    |

| ICB                                      | 22                            | Interrupt Control<br>Bit              | The ICB output signal indicates whether or not the CPU is currently ignoring the INT REQ line. If the ICB signal is low, the CPU responds to interrupt requests; if the ICB signal is high, the CPU ignores interrupt requests.                                    |

| INT REQ                                  | 23                            | Interrupt Request                     | This input line is used to signal the CPU that an interrupt is being requested. The F3851 PSU, F3861 and F3871 PIOs, and F3853 SMI devices contain logic to initiate interrupt requests by pulling the INT REQ signal low. The CPU acknowledges interrupt requests |

| Control                                  |                               |                                       | by outputting the appropriate ROMC signals.                                                                                                                                                                                                                        |

| ROMC <sub>0</sub> -<br>ROMC <sub>4</sub> | 17—21                         | Control                               | The ROMC output signals control logic operations for other devices in the F8 family. These signals assume a state early in each machine cycle and hold that state for the duration of the cycle. Refer to the "Instruction Execution" section for further          |

|                                          |                               | · · · · · · · · · · · · · · · · · · · | discussion and a summary table of the ROMC interpretation by CPU logic.                                                                                                                                                                                            |

| Mnemonic                                              | Pin No.                      | Name                                   | Description                                                                                                                                                                           |

|-------------------------------------------------------|------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset                                                 |                              |                                        |                                                                                                                                                                                       |

| EXT RES                                               | 37                           | External Reset                         | This input signal can be used to externally reset the system.<br>When the line is pulled low, a program originating at memory<br>address 0 is executed.                               |

| Data Bus                                              |                              |                                        |                                                                                                                                                                                       |

| DB <sub>0</sub> -DB <sub>7</sub>                      | 15, 12, 9, 6, 35, 32, 29, 26 | Data Bus                               | These eight bidirectional signals are data bus lines that link the F3850 CPU with all other F8 devices in the system. They are multiplexed lines used to transfer data and addresses. |

| Power                                                 |                              |                                        |                                                                                                                                                                                       |

| V <sub>DD</sub><br>V <sub>GG</sub><br>V <sub>SS</sub> | 3<br>4<br>24                 | Power Supply<br>Power Supply<br>Ground | Nominal +5 Vdc<br>Nominal +12 Vdc<br>Common power and signal return                                                                                                                   |

# Table 2 F3850 Signal Descriptions (Continued)

# Clock Circuits

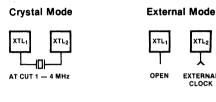

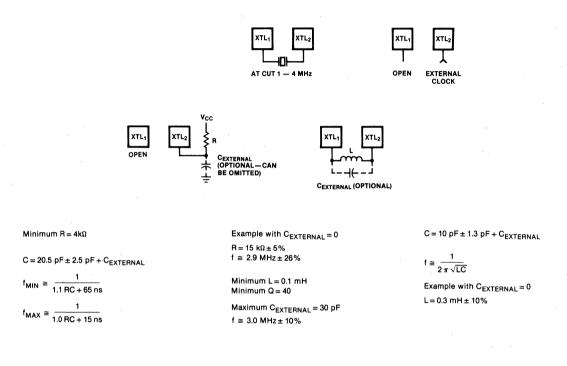

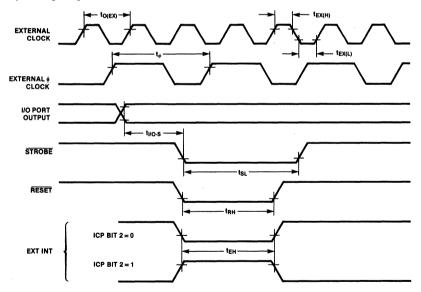

A unique feature of the F8 microprocessor is that clock logic forms an integral part of the F3850 CPU chip. The F3850 CPU offers two methods of generating a system clock: crystal mode and external mode.

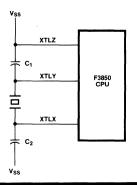

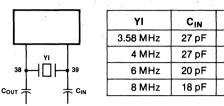

# **Crystal Mode**

Figure 5 shows the pin configuration for clock generation using the crystal mode. A crystal in the 1- to 2-MHz range is placed across the XTLX and XTLY pins, along with two capacitors (C<sub>1</sub> and C<sub>2</sub>), to provide a highly precise clock frequency. The external crystal (and capacitors) together with internal circuitry combine to form a parallel resonant crystal oscillator. Capacitors C<sub>1</sub> and C<sub>2</sub> should be approximately 15 pF. The characteristics of the crystal

# Figure 5 Crystal Mode Clock Generation

used in this mode of clock generation are summarized as:

$\label{eq:started} \begin{array}{l} \mbox{Frequency: 1 to 2 MHz, typical AT cut} \\ \mbox{Mode of Oscillation: Fundamental} \\ \mbox{Operating Temp. Range: 0°C to +70°C} \\ \mbox{Drive Level: 10 mW} \\ \mbox{Frequency Tolerance: } f_0 = 1 \mbox{ or 2 MHz} \pm 1000 \mbox{ ppm } @\mbox{ C}_L \\ = 20 \mbox{ pF} \end{array}$

# **External Mode**

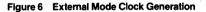

For F8 applications where synchronization with an external system clock is desired, the external clock mode may be used as shown in *Figure 6*. For example, a slave F3850 CPU may receive its timing from a master F3850 CPU by having the master  $\phi$  output drive the slave XTLY input.

# F3850

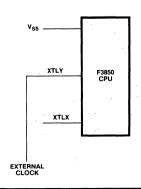

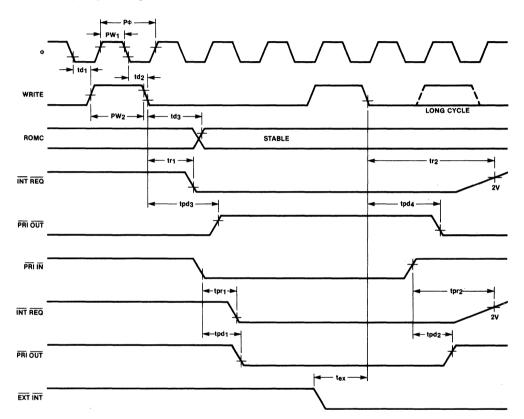

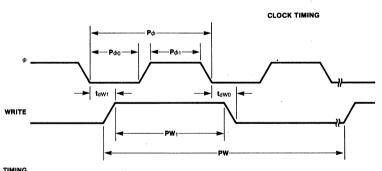

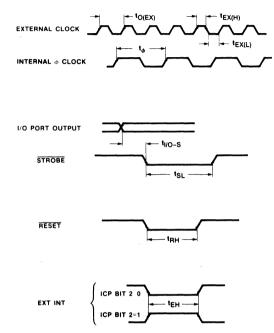

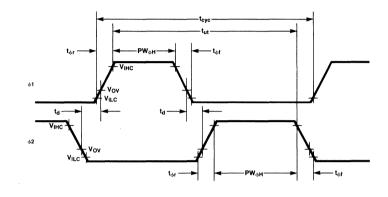

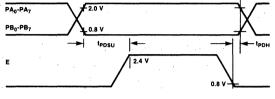

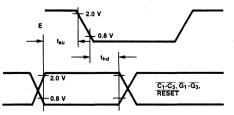

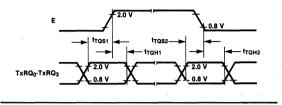

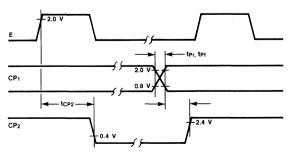

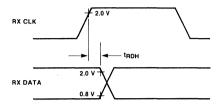

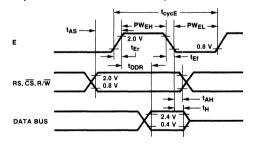

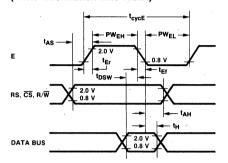

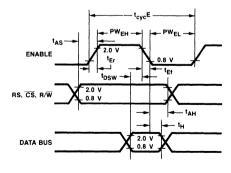

Figure 7 illustrates the timing characteristics of the clock signal needed for external mode clock generation and the timing characteristics of the  $\phi$  and WRITE signals generated by the CPU.

# **Timing Signal Outputs**

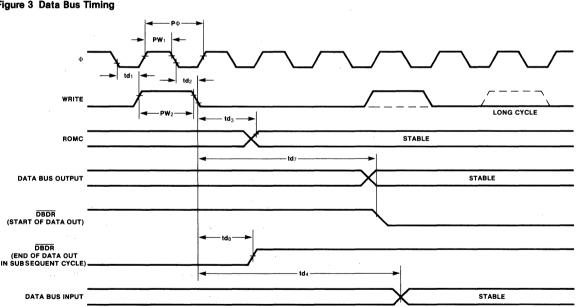

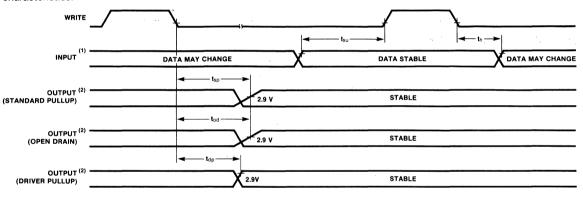

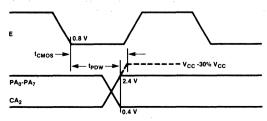

In response to the three clock mode inputs, the F3850 CPU outputs two timing signals: clock signal  $\phi$  and instruction cycle control signal WRITE. As shown in *Figure 7*,  $\phi$  is the signal used to synchronize the entire microprocessor system. The WRITE signal defines the duration of each machine cycle. Refer to the "Instruction Execution" section. Parameters and specifications for the timing signals are detailed in the "Timing Characteristics" section.

#### Instruction Execution

The F3850 CPU logic controls instruction execution through the  $\phi$  and WRITE timing signals, plus the five ROMC control lines. Devices external to the F3850 CPU must respond directly to these signals.

# Instruction Cycle

All instructions are executed in cycles that are timed by the trailing edge of WRITE.

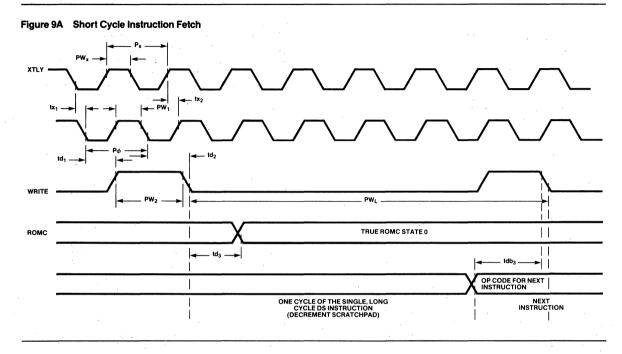

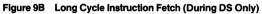

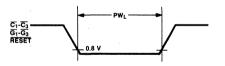

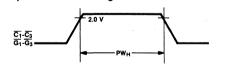

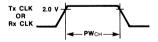

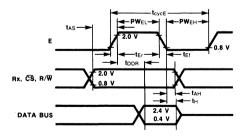

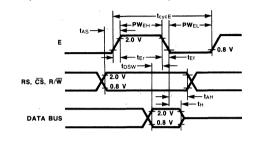

There are two types of instruction cycle: the short cycle, which is four  $\phi$  periods long, and the long cycle, which is six  $\phi$  periods long. The long cycle is sometimes referred to as 1.5 cycles. *Figure 7* illustrates the short cycle (PW<sub>S</sub>) and the long cycle (PW<sub>L</sub>). Note that WRITE high appears only at the end of an instruction cycle.

The simplest instructions of the F8 instruction set execute in one short cycle. The most complex instruction (PI) requires two short cycles plus three long cycles.

#### **ROMC Signals**

The CPU logic uses the five ROMC signals to identify operations that devices must perform during any instruction cycle. The 32 possible ROMC states are described in the "ROMC Signal Functions" section. The state of the ROMC signals and the operation they identify last through one instruction cycle.

The general distribution of logic among devices of the F8 family and general data movements associated with instruction execution are given in the F8 and F3870 Guide to Programming.

Memory addressing logic is located on the F3851 Program Storage Unit (PSU), the F3852 Dynamic Memory Interface (DMI), and the F3853 Static Memory Interface (SMI) devices. Each of these devices contains registers to address programs (PC0 and PC1) or data (DC0 or DC1). The F3851 PSU does not have a DC1 register.

Unlike other microprocessors, the F3850 CPU does not output addresses at the start of memory access sequences; a simple command to access the memory location addressed by PC0 or DC0 is sufficient, since the device receiving the memory access command contains PC0 and DC0 registers. (The PC1 and DC1 are buffer registers for PC0 and DC0.)

Moving memory addressing logic from the CPU to memory (and memory interface) devices simplifies CPU logic; however, it creates the potential for devices to compete when responding to memory access commands.

There will be as many PC0 and DC0 registers in a microcomputer system as there are PSU, DMI, and SMI devices; the ambiguity of which unit will respond to a memory read or write command is resolved by ensuring that all PC0 and DC0 registers contain the same information at all times. Every PSU, DMI, and SMI device

#### Figure 7 Clock Generation Timing Signals

has a unique address space, i.e., a unique block of memory addresses within which it responds to memory access commands.

For example, an F3851 PSU may have an address space of H'0000' through H'03FF'; an F3852 DMI may have an address space of H'0400' through H'07FF'. If a microcomputer system has these two memory devices and no others, then the F3851 PSU will respond to memory access commands when the PC0 or DC0 registers (whichever are identified as the address source) contain a value between H'0000' and H'03FF'; the F3852 DMI will respond to addresses in the range H'0400' through H'07FF'. No device will respond to addresses beyond H'07FF', even though such addresses may exist in PC0 and/or DC0.

Each device compares its address space with the contents of PC0 and DC0, whichever is identified as the address source, and only responds to a memory access command if the contents of PC0 or DC0 is within the device's address space.

If all memory address registers (PC0, PC1, DC0, and DC1) are to contain the same information, then ROMC states that require any of these registers' contents to be modified must be acted upon by all devices containing any of these four registers. If devices are not to compete when an ROMC state specifies that a memory access must be performed, then only a device whose address space includes the identified memory address must respond to the ROMC state.

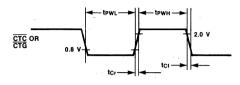

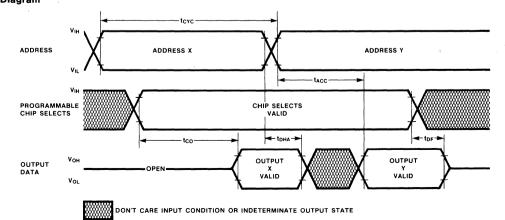

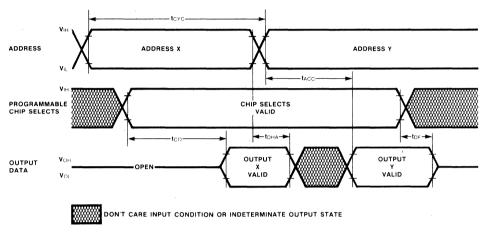

As illustrated in *Figure 8*, the five ROMC signals that define the ROMC state are output early in the instruction cycle and are maintained stable for the duration of the instruction cycle; i.e., only one ROMC state can be specified per instruction cycle. Therefore, devices can only be called upon to perform one instruction execution related operation per one instruction cycle. As referenced in the "ROMC Signal Functions" section, each ROMC state is identified by individual signal line states (1 for high, 0 for low), and by a two-digit hexadecimal code. The hexadecimal code is used to identify ROMC states throughout this data sheet. Also given in the "ROMC Signal Functions" section is the instruction cycle length (short or long) implied by each code, plus the way in which codes must be interpreted by the other F8 devices.

# Instruction Execution Sequence

Every instruction execution sequence ends with an instruction code being fetched from memory to identify the next instruction cycle. The instruction code is loaded into the CPU instruction register, out of which it is decoded by the CPU control unit logic. An instruction fetch is executed during the last instruction cycle of the previous instruction, as illustrated in *Figure 9.*

There is a group of F8 instructions that cause operations to occur entirely within the F3850 CPU. These instructions do not use the data bus, therefore can execute in one cycle. Since one-cycle instructions do not use the data bus, no ROMC state needs to be generated for the one-cycle instruction being executed; therefore, as illustrated in *Figure 9*, ROMC state 0 is specified, causing the instruction fetch of the next instruction.

Multi-cycle instructions must end with a cycle that does not use the data bus; ROMC state 0 is specified at the beginning of this last instruction cycle, causing the next instruction to be fetched.

Following an instruction fetch, CPU logic decodes the fetched instruction code and executes the specified instruction. There are Five types of instruction cycles that can follow.

Operations may all be internal to the CPU. This will be the last or the only cycle for an instruction, and will specify ROMC state 0, as illustrated in *Figure 9.*

Figure 8 ROMC Timing Signals Output by F3850 CPU

3-17

- 2. Data may be transferred between the F3850 CPU and memory devices. See the "Referencing Memory" section.

- 3. Data may be transferred from one memory device to all memory devices. The CPU is not the transmitter or the receiver of data in this transfer. See the "Memory-to-Memory Data Transfers" section.

- 4. Data may be transferred to or from an I/O port, as described in the "Input/Output Interfacing" section.

- 5. An interrupt may be acknowledged, as described in the "Interrupts" section.

Every F8 instruction is executed as one, or a sequence of, standard instruction cycles. Timing for the standard instruction cycles is illustrated in Figures 9, 10, 11 and 12.

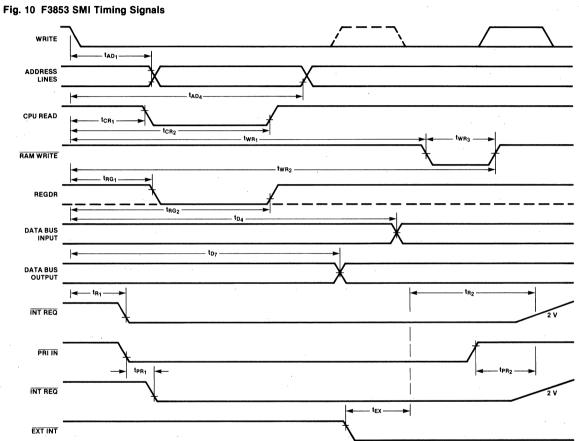

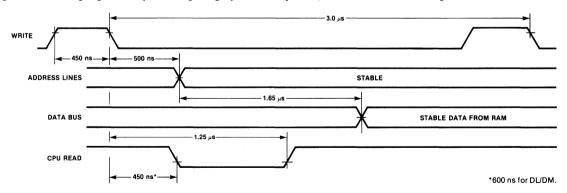

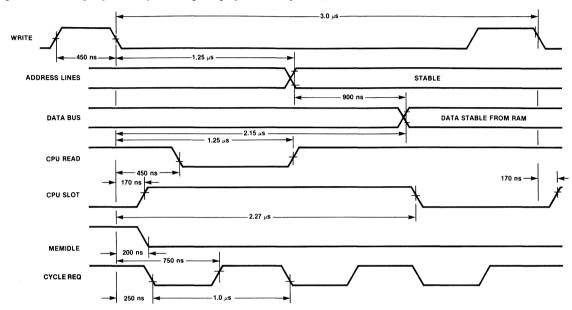

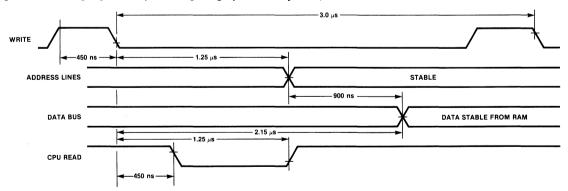

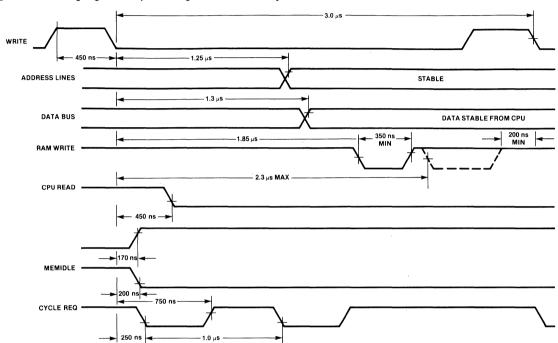

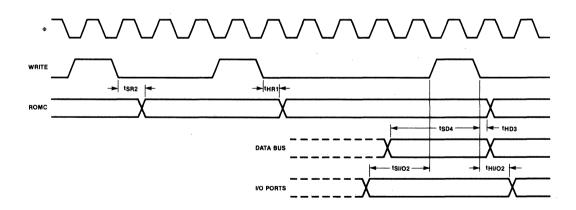

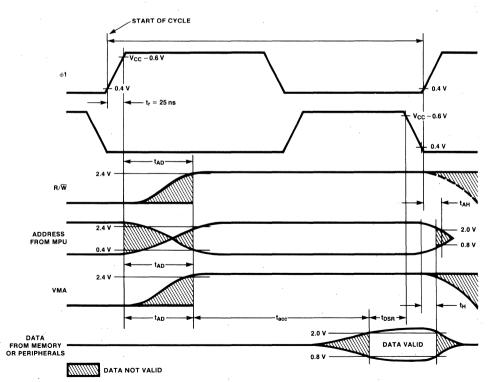

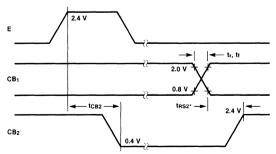

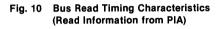

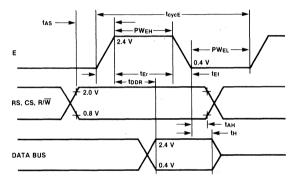

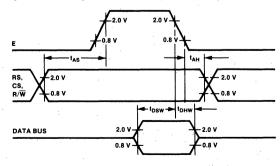

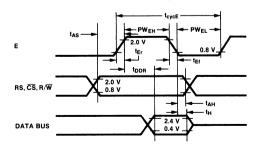

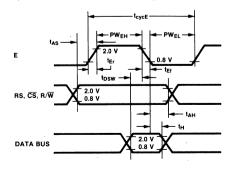

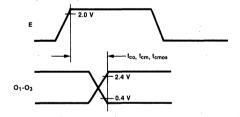

Figure 10 Memory Reference Timing

Refer to the "Instruction Cycle Execution and Timing" section for a list of the instruction cycles and their associated ROMC state.

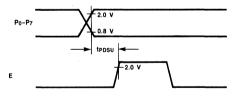

#### **Referencing Memory**

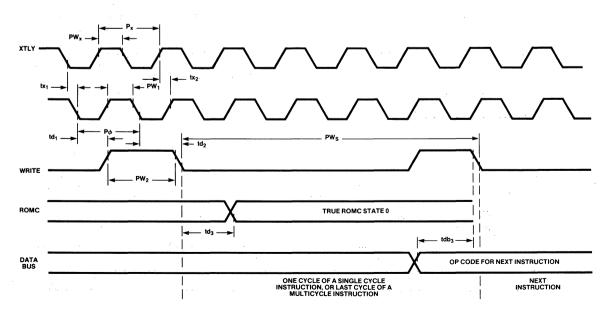

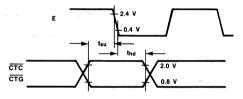

Memory may be referenced during an instruction cycle either to transfer the data from the CPU to a memory word or to transfer data from a memory word to the CPU. A memory reference occurs as shown in Figure 10.

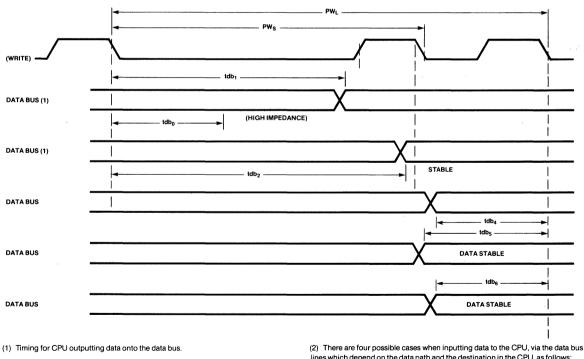

If data is being output by the CPU, then the delay before data output is stable will be tdb1 when data comes from the accumulator; the instruction cycle will be long. The delay before data output is stable will be tdb<sub>2</sub> when data comes from the scratchpad; the instruction cycle in this case will also be long.

Delay tdb1 is the delay when data is coming from the accumulator.

Delay tdb<sub>2</sub> is the delay when data is coming from the scratchpad (or from a memory device).

Delay tdb<sub>0</sub> is the delay for the CPU to stop driving the data bus.

lines which depend on the data path and the destination in the CPU, as follows:

tdb<sub>3</sub>: Destination - IR (instruction Fetch)

- tdb<sub>4</sub>: Destination Accumulator (with ALU operation AM)

- tdb<sub>5</sub>: Destination Scratchpad (LR K,P etc.)

tdb<sub>6</sub>: Destination — Accumulator (no ALU operation — LM)

In each case a stable data hold time of 50 ns from the WRITE reference point is required.

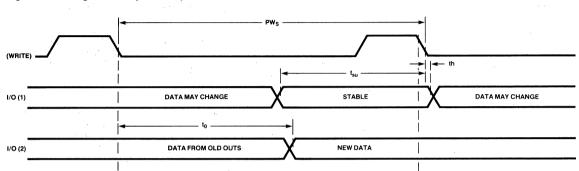

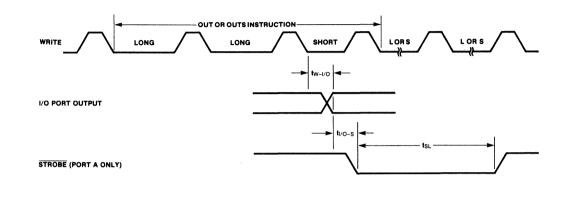

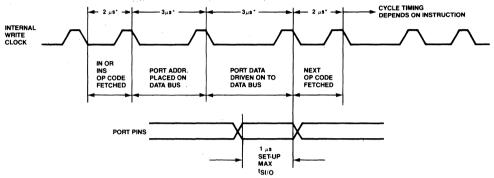

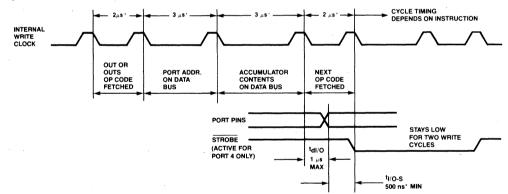

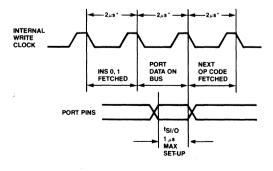

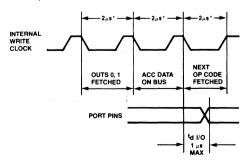

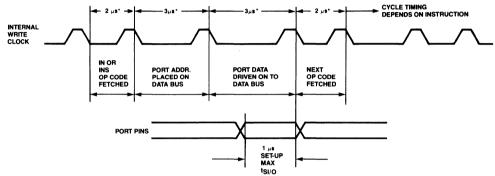

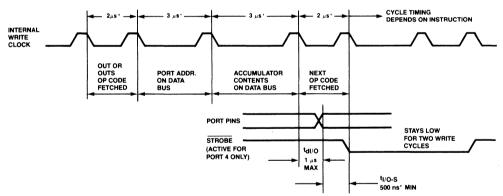

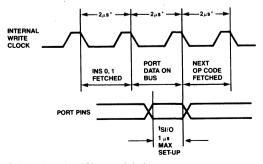

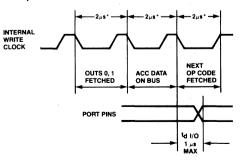

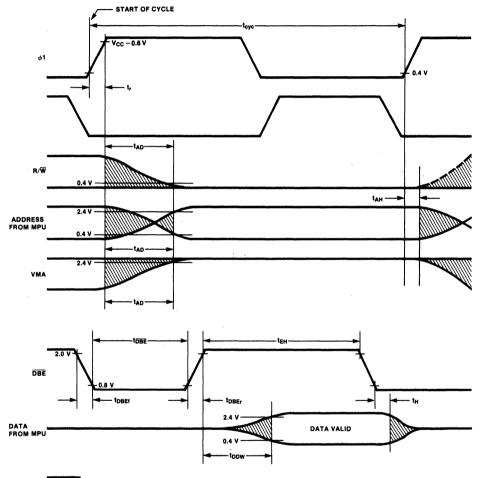

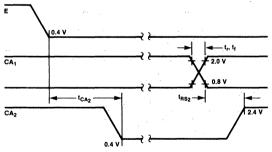

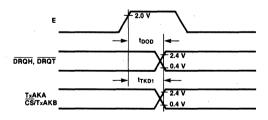

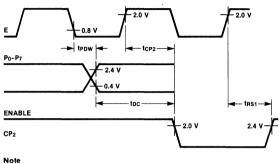

# Figure 11 Timing for Data Input or Output at I/O Port Pins

(1) This represents the timing for data at the I/O pin during the execution of the INS instruction, i.e., the CPU is inputting.

(2) This represents the timing for data being output by the CPU at the I/O pin.

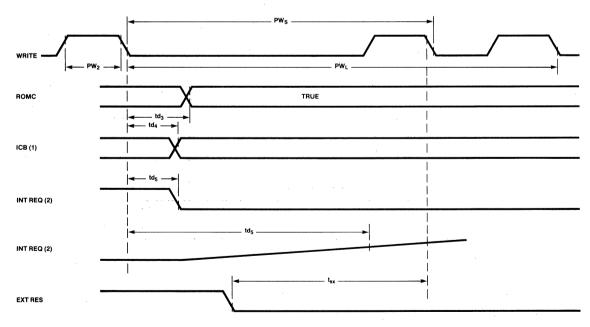

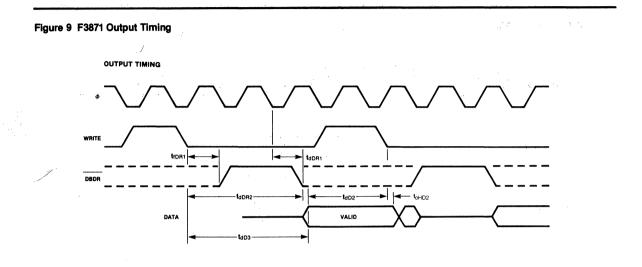

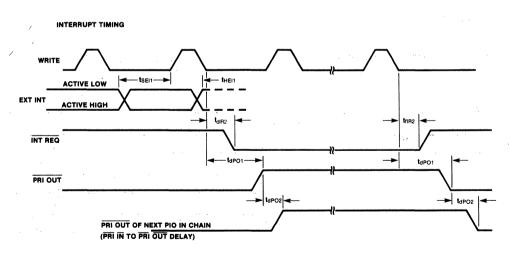

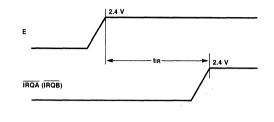

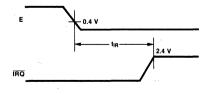

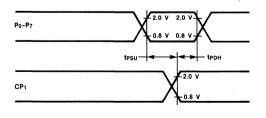

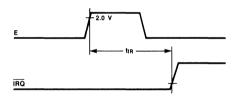

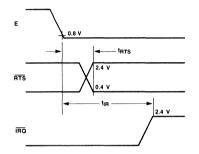

# Figure 12 Interrupt Signals Timing

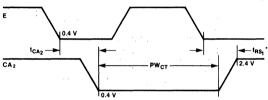

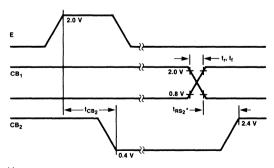

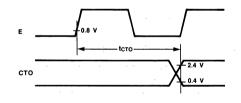

(1) The ICB signal will go from a 1 to a 0 following the execution of the E1 instruction and will go from a 0 to a 1 following either the execution of the D1 instruction or the CPU's acknowledgement of an interrupt. (2) This is an input to the CPU chip and is generated by a PSU or F3853 M1 chip The open drain outputs of these chips are all wire—ANDed together on this line with the pull-up being located on the CPU chip. For a 0 to 1 transition the delay is measured to 2.0 V. If data is being input to the CPU, then the delay before incoming data must be stable depends on the destination of the data, as illustrated in *Figure 10*.

The type of data transfer is identified by the ROMC state that is output at the beginning of the instruction cycle.

The instruction fetch may also be viewed as a memory reference operation where the destination is the instruction register. Timing for this case is illustrated in *Figure 9.*

#### Memory-to-Memory Data Transfers

In response to appropriate ROMC states, data can be transferred from one memory device to all memory devices during one instruction cycle. For example, data can be transferred from a memory byte within (or controlled by) one memory device, to one byte of an address register (PC0 or DC0) within all memory devices.

Three ROMC states (C, E, and 11) specify operations of this type, and *Figure 10* illustrates timing for the data transfer. In *Figure 10*, tdb<sub>2</sub> is the delay until data from memory or a memory address register is stable on the data bus.

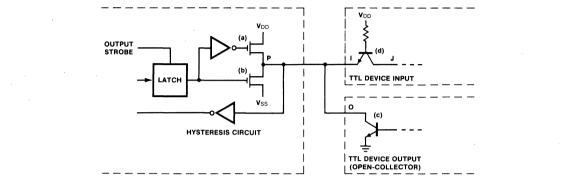

#### Input/Output Interfacing

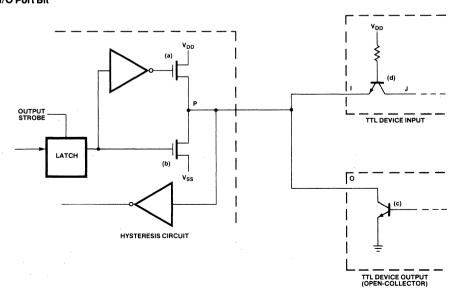

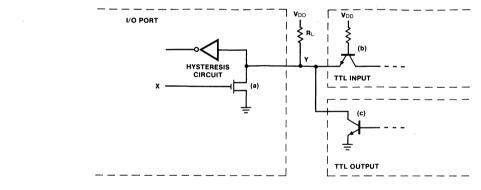

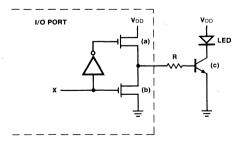

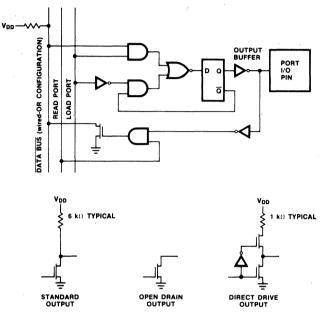

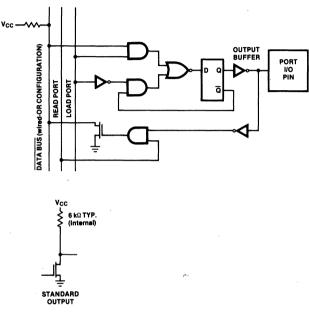

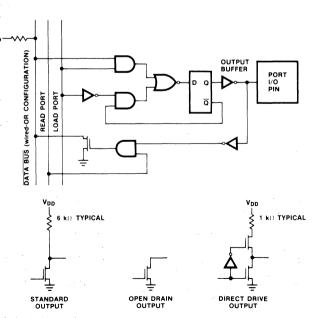

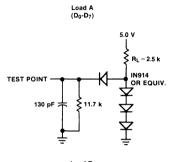

Programmed I/O in the F8 microcomputer system is influenced by the design of the I/O port pins. As illustrated in *Figure 13*, each I/O port pin is a "wire-AND" structure between an internal latch and an external signal, if any. The latch is always loaded directly from the accumulator.

Each F8 I/O pin can be set high or low under program control. If a 1 (high) is presented at the latch, then gate (b) turns on and gate (a) turns off, so that P is at V<sub>SS</sub> (low). If a 0 (low) is presented at the latch, then gate (a) turns on and gate (b) turns off, so that P is at V<sub>DD</sub> (high).

When outputting data through an I/O port, the pin can be connected directly to a TTL gate input ("TTL Device Input" in *Figure 13*). Data is input to the pin from a "TTL Device Output" in *Figure 13*.

In normal operation, high or low levels at P drive the external TTL device input transistor (d). If a low level is set at P, transistor (d) conducts current through the path J, 1, P, and FET(b). This is transferred as a low level to the rest of the circuits in the TTL device and results in a high or low level at the output of the device, depending on its characteristics. If the level at P is set high, transistor (d) does not conduct current, and a high level is transferred by (d).

When data is input to the I/O pin, high or low levels at 0 drive the hysteresis circuit in the port and result in logic ones or zeros being transferred to the accumulator.

# Figure 13 F8 I/O Port Bit

Since the I/O pin and the TTL device output at 0 are wire-ANDed, it is possible for the state of one to affect the transfer of data out from the I/O pin or in from the TTL device output. For example, if the latch in the I/O port is set so that the pin is clamped low by (b), then the level at 0 cannot pull P high. Conversely, if P is clamped to a low level by (c), setting the latch for a high level has no effect.

All I/O port bits should be set for a high level, before data input, to prevent incoming logic zeros from being "masked" by logic ones present at the port from previous outputs. In some instances, the ability to mask bits of a port to logic 1 is useful. (Note that logic 1 becomes a 0 V electrical level at the I/O pin; logic 0 corresponds to a high electrical level.)

The F8 CPU can execute two types of programmed I/O operation:

- 1) I/O via the two CPU ports (0 and 1)

- 2) I/O via ports on the other devices

Input/Output operations that use the two CPU I/O ports execute in two instruction cycles. During the first cycle, the fetched instruction is decoded; the data bus is unused. In this cycle data is either sent from the accumulator to the I/O latch or enabled from the I/O pin to the accumulator, depending on whether the instruction is an output or an input. At the falling edge of the WRITE signal (marking the end of the first cycle and beginning of the second cycle), the data is strobed into either the latch (OUTS) or the accumulator (INS), respectively. The second cycle is then used by the CPU for its next instruction fetch. *Figure 11* illustrates I/O timing.

Note that for the data input (INS) the setup and hold times specified are with respect to the WRITE pulse occurring at the end of the first cycle in the two-cycle instruction. For output data (OUTS) the delay is specified with respect to the falling edge of the WRITE signal marking the beginning of the second cycle in the two-cycle instruction.

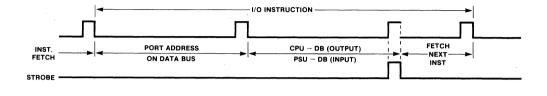

Input/Output instructions that address I/O ports with an I/O port address greater than H'OF' occupy two bytes; the first byte specifies an IN or OUT instruction, while the second byte provides the I/O port address. Required timing at I/O port pins is given in the section of this data sheet that describes the device containing the addressed I/O port.

#### Interrupts

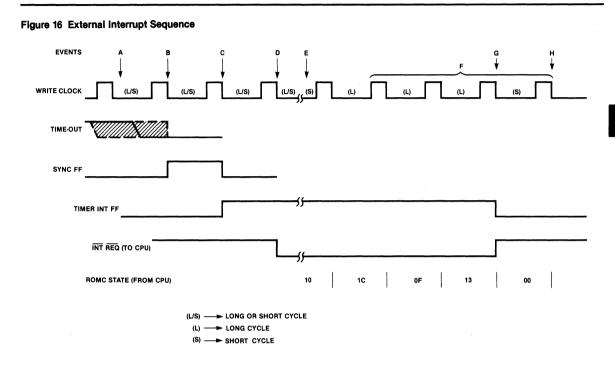

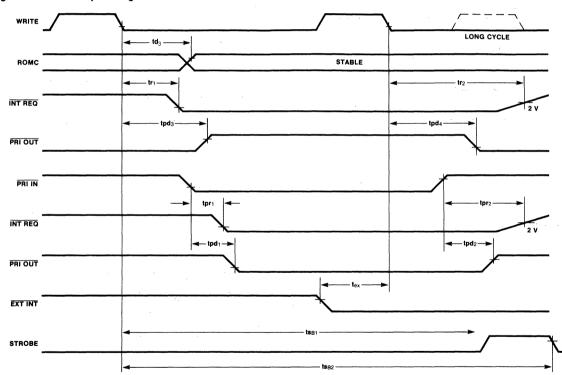

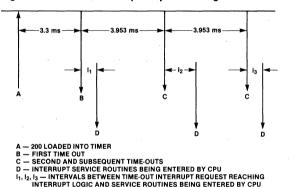

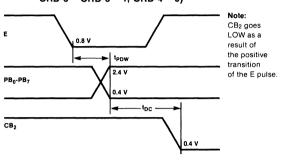

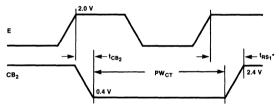

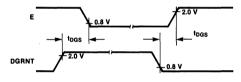

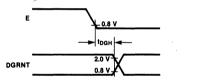

There are three CPU signals with interrupt processing; timing for all signals is illustrated in *Figure 12*.

An interrupt sequence is initiated by pulling either the  $\overline{INT}$  REQ signal or the  $\overline{EXT}$  RES signal low. In the case of the  $\overline{INT}$  REQ signal nothing happens unless the  $\overline{ICB}$  signal is low. Also,

nothing happens until the next interruptable instruction comes to the end of execution. In the case of the  $\overline{\text{EXT}}$   $\overline{\text{RES}}$  signal, execution of the interrupt routine begins in the machine cycle immediately following that in which the signal goes low, provided that the setup time specified in *Figure 12* has been met. The  $\overline{\text{EXT}}$   $\overline{\text{RES}}$  signal response logic ignores the  $\overline{\text{ICB}}$  signal.

In response to the INT REQ signal being low, when the CPU acknowledges the interrupt, it forces the ICB signal high and initiates instruction cycles with ROMC states 1C, 0F, 13, and 00, in that order. This causes program execution to branch to the interrupting device's address vector.

In response to the EXT RES signal being low, when the CPU acknowledges the interrupt, it forces the ICB signal high, then initiates instruction cycles with ROMC states 1C, 08, and 00, in that order. This causes program execution to branch to memory location 0.

The ICB signal is pulled low by the E1 instruction and is returned high by the D1 instruction.

#### Instruction Set Summary

The F3850 CPU instruction set is summarized in *Table 3*. This section does not attempt to give complete directions for programming the F8 microcomputer system; it explains signals and timing associated with the execution of every instruction. Refer to *F8 and F3870 Guide to Programming* for programming details. The columns used in *Table 3* are described below.

**Op Code**—The Op Code is the instruction mnemonic that appears in the mnemonic field of an assembly language instruction and identifies the instruction.

**Operand (s)**—If the instruction contains any information in the operand field of the assembly language source code, the information is shown in this column. Arrows identify the portion of object code that represents the operand field. Any portion of object code that does not represent the operand field must represent the memonic field. *Table 4* explains symbology used in the operand field.

**Object Code**—This is the hexadecimal representation of the instruction's object code. The first byte of object code, or in some cases the first hexadecimal digit of object code, represents the Op Code. The operand is represented by the second and third bytes of object code, if present, or in some cases by the second hexadecimal digit of the first object code byte. Refer to *Table 4* for symbology used in the object code field.

**Cycle**—This column identifies each instruction cycle for every instruction. Every cycle is listed on a separate horizontal line and is identified by the letter S for a short (four clock period) cycle or

the letter L for a long (six clock period) cycle. Thus, the entry

s

represents an instruction that executes in one short cycle. The entry

S L S

represents an instruction that executes in three cycles: the first is a short cycle; the second is a long cycle; the third (and last) is a short cycle.

**ROMC State**—This is the state, as identified in the "ROMC Signal Functions" section, that is output by the F3850 CPU in the early stages of the instruction cycle.

**Timing**—Timing for all instructions, except INS and OUTS accessing I/O ports 0 and 1, can be created out of *Figures 9* and *10*. For the exceptions, *Figure 11* is required.

The ROMC lines are always set after a delay of  $td_3$ , as shown in *Figure 9*. The only timing variations for each instruction cycle are data bus timing variations. Therefore, data bus timing is defined using the delays  $tdb_1$  through  $tdb_6$ . With the exception of  $tdb_3$ , these time delays are unambiguous in that they are keyed to either the leading edge or the trailing edge of the WRITE signal high, for a long or short instruction cycle, as illustrated in *Figure 10*. There are two cases for  $tdb_3$ , however, as illustrated in *Figure 9B*;  $tdb_1$  through  $tdb_6$  are otherwise identified by the numbers 1 through 6.

Cycles that do not use the data bus are identified by 0 in the timing column; *Figure 8* illustrates timing in this case.

# Cycle Represents

- 1 tdb<sub>1</sub> in *Figure 10* 2 tdb<sub>2</sub> in *Figure 10*

- 2 tdb<sub>2</sub> in *Figure 10* 3S tdb<sub>3</sub> in *Figure 9A*

- 3L tdb<sub>3</sub> in *Figure 9B*

- 4 tdb₄ in *Figure 10*

- 5 tdb<sub>5</sub> in *Figure 10*

- 6 tdb<sub>6</sub> in *Figure 10*

Status Flags-Status flags are identified as follows:

- O-Overflow

- Z-Zero

- C-Carry

- S-Sign

Within each column, symbology is used as follows:

- Status not affected

- 0 Status set to 0

- I/O Status set to either 1 or 0, depending on the results of the instruction's execution

Interrupt—An "x" in this column identifies an instruction that disallows interrupts at the end of the instruction's execution. A "y" identifies cycles in which the ICB is reset to 0 (cleared).

**Function**—The effect of each instruction cycle is described in this column using symbology given in *Table 4*.

#### Instruction Cycle Execution and Timing

Table 3 lists the instruction cycles, plus the ROMC state associated with each cycle, for every F8 instruction. Note that instructions are described in the table by order of ascending instruction (first byte) object code. Table 4 lists the symbology used in Table 3.

| Op   |            | Object |       | ROMC  |        |   | Stat | tus Flaç | js |           |           |

|------|------------|--------|-------|-------|--------|---|------|----------|----|-----------|-----------|

| Code | Operand(s) | Code   | Cycle | State | Timing | 0 | z    | С        | S  | Interrupt | Function  |

| LR   | A, KU      | 00     | s     | 0     | 3S     | _ | _    | _        |    |           | A ← (r12) |

| LR   | A, KL      | 01     | s     | 0     | 35     | - |      |          | _  |           | A ← (r13) |

| LR   | A, QU      | 02     | s     | 0     | 35     |   | _    | —        | _  |           | A ← (r14) |

| LR   | A, QL      | 03     | s     | 0     | 35     | - | —    |          | —  |           | A ← (r15) |

| LR   | KU, A      | 04     | s     | 0     | 35     |   | —    |          |    |           | r12 ← (A) |

| LR   | KL, A      | 05     | s     | 0     | 35     | _ | ·    |          | —  |           | r13 - (A) |

| LR   | QU, A      | 06     | s     | 0     | 35     |   |      | —        | —  |           | r14 — (A) |

| LR   | QL, A      | 07     | s     | 0     | 35     | - |      | -        |    |           | r15 ← (A) |

#### Table 3 Instruction Cycle Execution and Timing

| Ор       |                | Object   |          | ROMC     |          |     | Status  | Flags |             |           |                                                  |

|----------|----------------|----------|----------|----------|----------|-----|---------|-------|-------------|-----------|--------------------------------------------------|

| Code     | Operand(s)     | Code     | Cycle    | State    | Timing   | 0   | z       | С     | S           | Interrupt | Function                                         |

| LR       | K, P           | 08       | L        | 7        | 5        | —   | _       | _     |             |           | r12 ← (PC1U)                                     |

|          |                |          |          | В        | 5        | -   |         | -     | —           |           | r13 ← (PC1L)                                     |

| LR       | P, K           | 09       | S<br>L   | 0<br>15  | 3S<br>2  |     | _       |       | _           |           | PC1U ← (r12)                                     |

|          | .,             |          | L        | 18       | 2        | _   | _       | _     | _           |           | PC1L ← (r13)                                     |

|          |                |          | S        | 0        | 3S       | —   | —       | -     | -           |           |                                                  |

| LR<br>LR | A, IS<br>IS, A | 0A<br>0B | S<br>S   | 0        | 3S<br>3S |     | _       | -     | _           |           | A ← (ISAR)<br>ISAR ← (A)                         |

| PK       | 10, 7          |          | L        | 12       | 2        |     | _       |       | _           |           | $PC1 \leftarrow (PC0);$                          |

|          |                |          | L        | 14       | 2        | —   | —       |       | _           |           | PC0L ← (r13)                                     |

|          | <b>PD 0</b>    | 00       | S        | 0        | 35       | —   | _       | -     | _           |           | PC0U ← (r12)                                     |

| LR       | P0, Q          | 0D       | L        | 17<br>14 | 2<br>2   | _   | _       |       | _           | x         | PC0L ← (r15)                                     |

|          |                |          | s        | 0        | 35       | —   | _       |       |             |           | PC0U ← (r14)                                     |

| LR       | Q, DC          | 0E       | L        | 6        | 3        | —   |         | -     |             | 1         | r14 ← (DC0U)                                     |

|          |                |          | LS       | 9<br>0   | 5<br>3S  | _   | _       | _     | _           |           | r15 ⊷ (DC0L)                                     |

| LR       | DC,Q           | 0F       | L        | 16       | 2        | _   |         |       | _           |           | DC0U ← (r14)                                     |

|          |                |          | L        | 19       | 2        |     |         | -     | _           |           | DC0L - (r15)                                     |

|          | 50.11          |          | s        | 0        | 3S       | —   |         | -     | -           |           |                                                  |

| LR       | DC, H          | 10       | L<br>  L | 16<br>19 | 2<br>2   | _   | _       | _     | _           |           | DC0U ← (r10)<br>DC0L ← (r11)                     |

|          |                |          | S        | 0        | 35       | _   |         | _     |             |           |                                                  |

| LR       | H, DC          | 11       | L        | 6        | 5        |     |         | -     |             |           | r10 ← (DC0U)                                     |

|          |                |          | LS       | 9<br>0   | 5<br>3S  | _   | _       |       | _           |           | r11 ← (DC0L)                                     |

| SR       | 1              | 12       | s        | 0        | 35<br>35 | 0   | <br>1/0 | 0     | 1           |           | Shift (A) right one bit                          |

|          |                |          |          |          |          | -   |         |       |             |           | position (zero fill)                             |

| SL       | 1              | 13       | s        | 0        | 3S       | 0   | 1/0     | 0     | 1/0         |           | Shift (A) left one bit                           |

| SR       | 4              | 14       | s        | . 0      | 3S       | o   | 1/0     | 0     | 1           |           | position (zero fill)<br>Shift (A) right four bit |

|          |                |          |          |          |          | Ŭ   |         |       | ·           |           | positions (zero fill)                            |

| SL       | 4              | 15       | s        | 0        | 3S       | 0   | 1/0     | 0     | 1/0         |           | Shift (A) left four bit                          |

| LM       |                | 16       | L        | 2        | 6        |     | _       |       |             | ,         | positions (zero fill)<br>A ← ((DC0))             |

|          |                |          | S        | Ő        | 35       |     | _       | _     | _           |           |                                                  |

| ST       |                | 17       | L        | 5        | 1        | _   |         | - 1   | <del></del> |           | (DC) — (A)                                       |

| СОМ      |                | 18       | S<br>S   |          | 3S<br>3S |     | <br>1/0 | 0     | <br>1/0     |           |                                                  |

| CON      |                | 10       |          |          | 33       | 0   | 1/0     | 0     | 1/0         |           | A ← (A) ⊕ H'FF'<br>Complement                    |

|          |                |          |          |          |          |     |         |       |             |           | accumulator                                      |

| LNK      |                | 19       | S        | 0        | 35       | 1/0 | 1/0     | 1/0   | 1/0         |           | $A \leftarrow (A) + (C)$                         |

| DI       |                | 1A       | S<br>S   | 1C<br>0  | 0<br>3S  |     | _       | _     | _           | У         | Clear ICB                                        |

| EI       |                | 1B       | S        | 1C       | 0        | _   | _       | _     | _           |           | Set ICB                                          |

|          |                |          | s        | 0        | 3S       | -   |         | -     |             | ×         |                                                  |

| POP      |                | 1C       | S<br>S   | 4        | 0<br>3S  | -   | _       |       | _           |           | PC0 (PC1)                                        |

|          |                |          |          |          | 33       | _   | _       | _ '   | -           | ×         |                                                  |

# Table 3 Instruction Cycle Execution and Timing (Continued)

3-22

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | H'aa'<br>H'aa'<br>H'aa'<br>H'aa' |

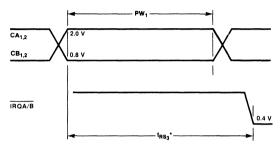

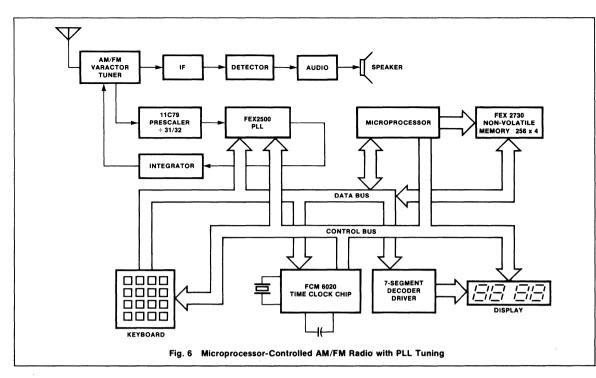

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|