© 1981 Fairchild 464 Ellis Street • Mountain View, California 94042 415/962-5011 • TWX 910-379-6435

# Introduction

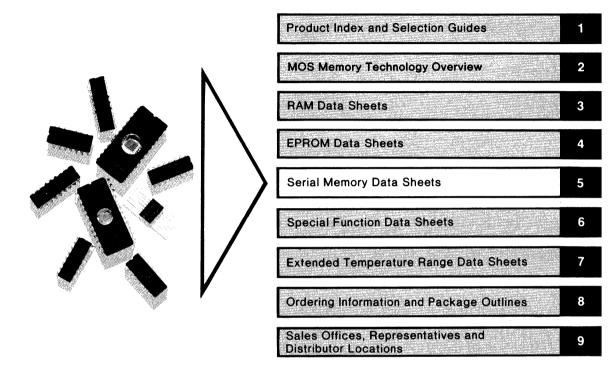

This data book presents a complete technical description of Fairchild's MOS Memory product line (excluding Read-Only Memories). The package outlines, electrical behavior, and ordering information are all included for this broad line of LSI and VLSI devices, manufactured using proven Isoplanar MOS processing techniques.

Complete technical data and ordering information on MOS ROMs can be obtained from Fairchild's Microprocessor Products Group. Section 1 Product Index and Selection Guides Handy tabulation of device numbers to assist in locating appropriate technical data.

Section 2 MOS Memory Technology Overview Basic treatise covering the nature and history of MOS technology.

#### Section 3 RAM Data Sheets

Complete technical data on static and dynamic random access memories.

#### Section 4 EPROM Data Sheets

Complete technical data on UV EPROMs.

#### Section 5 Serial Memory Data Sheets

Complete technical data on static shift registers (including FIFOs).

#### Section 6 Special Function Data Sheets

Complete technical data on several useful random logic devices.

## Section 7 Extended Temperature Range Data Sheets

Complete technical data for extended temperature range operation of selected MOS devices.

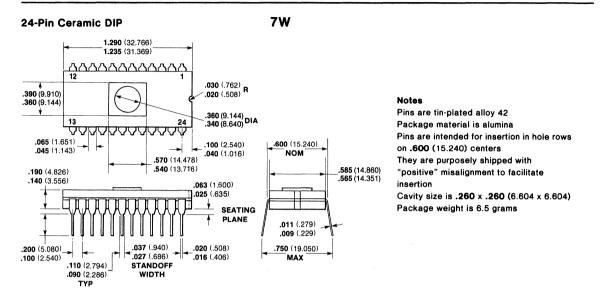

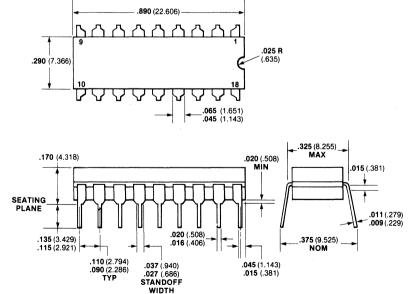

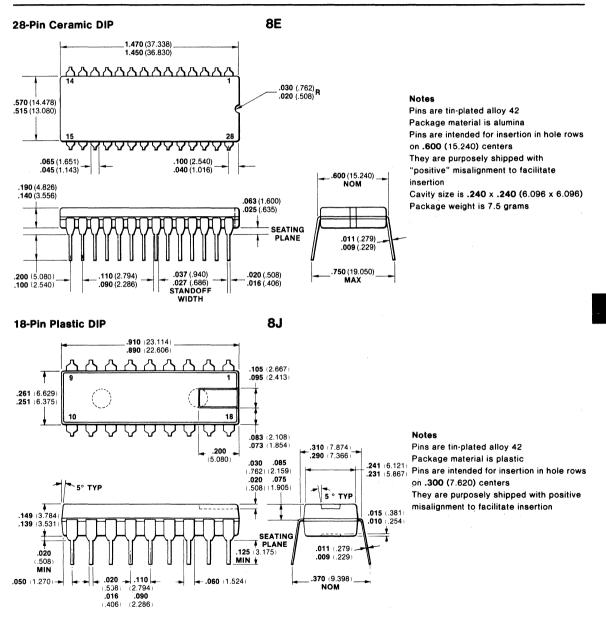

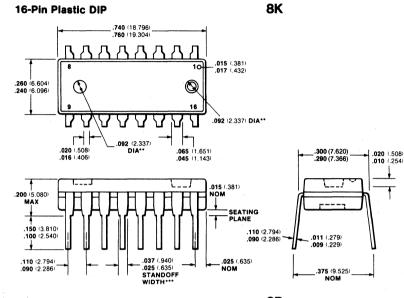

#### Section 8 Ordering Information and Package Outlines

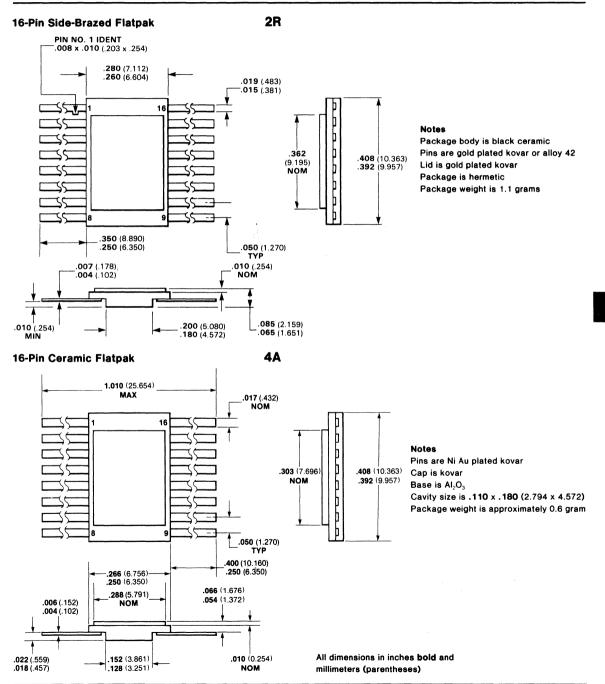

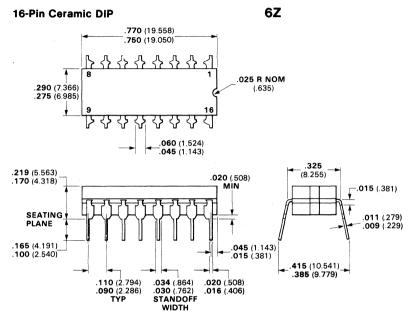

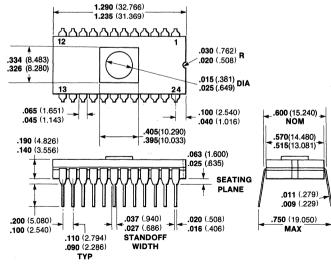

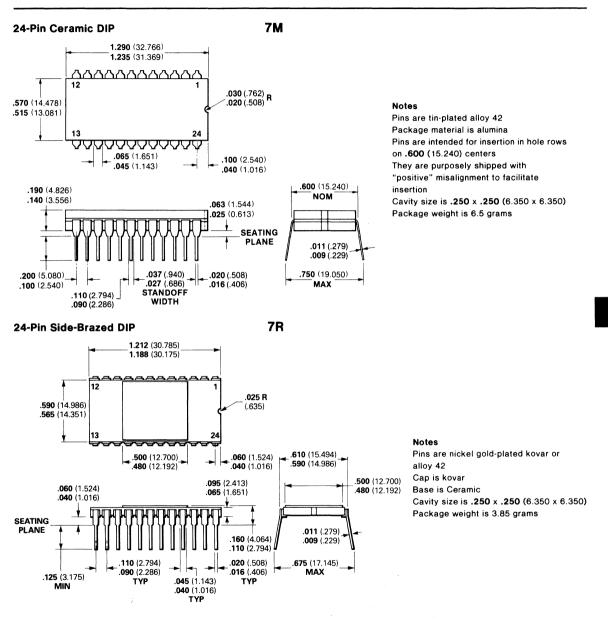

Detailed package drawings and ordering code information for standard parts, as well as Matrix VI and Unique 38510.

# Section 9 Sales Offices, Representatives and Distributor Locations

# Table of Contents

| Section 1 Product Index and Selection Guides                       |   |

|--------------------------------------------------------------------|---|

| Product Index                                                      |   |

| Random Access Memories                                             |   |

| UV Erasable Programmable Read Only Memories1-5                     |   |

| Serial Memories                                                    |   |

| Special Function Memories                                          |   |

| Section 2 MOS Memory Technology Overview                           |   |

| Introduction                                                       | , |

| Transistor Operations                                              |   |

| Memory-cell Design                                                 |   |

| RAM Architecture                                                   |   |

| 64K DRAM Architecture                                              |   |

| The Future of MOS Memory                                           |   |

| Section 3 RAM Data Sheets                                          |   |

| 2102/2102L/21L02                                                   |   |

| F2114/F2114L 3-8                                                   |   |

| F3528                                                              |   |

| F3567                                                              |   |

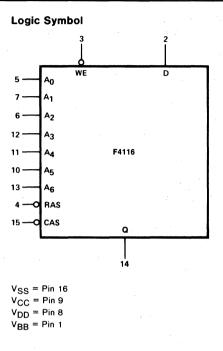

| F4116                                                              |   |

| F4164                                                              |   |

| Section 4 EPROM Data Sheets                                        |   |

| F2708                                                              |   |

| F2732                                                              |   |

| F2764                                                              |   |

| Section 5 Serial Memory Data Sheets                                |   |

| 3341/3341A                                                         |   |

| 3342                                                               |   |

| 3348/3349                                                          |   |

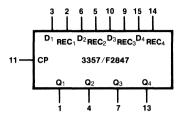

| 3357 / F2847                                                       |   |

|                                                                    |   |

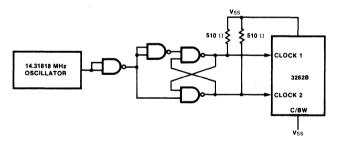

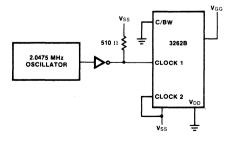

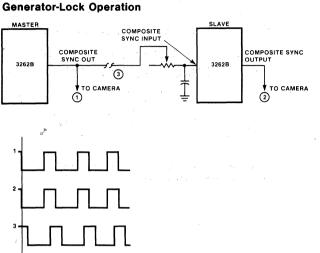

| Section 6 Special Function Data Sheets 3262A                       |   |

| 3262B                                                              |   |

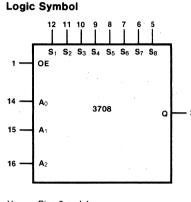

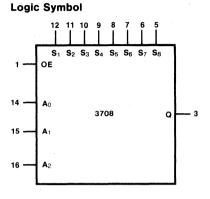

| 3708                                                               |   |

|                                                                    |   |

| Section 7 Extended Temperature Range Data Sheets<br>2102/2102L 7-3 |   |

| F2114/F2114L                                                       |   |

| 3341/3341A                                                         |   |

| 3351                                                               |   |

| 3357/F2847                                                         | j |

| 3708                                                               |   |

| F4116                                                              | ł |

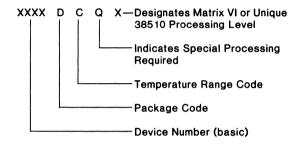

| Section 8 Ordering Information and Package Outlines                |   |

| General Ordering Information                                       |   |

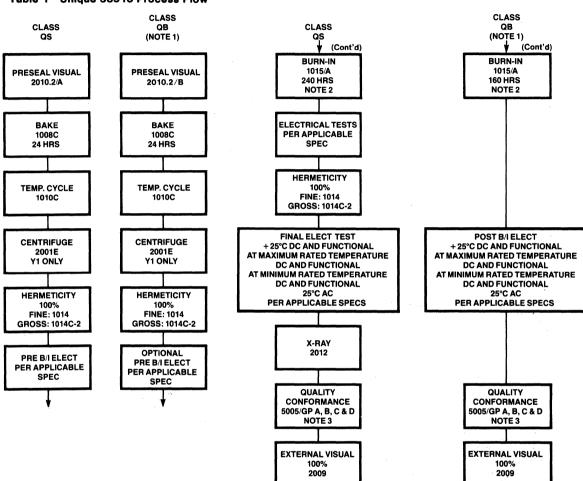

| Unique 38510 Ordering Information                                  |   |

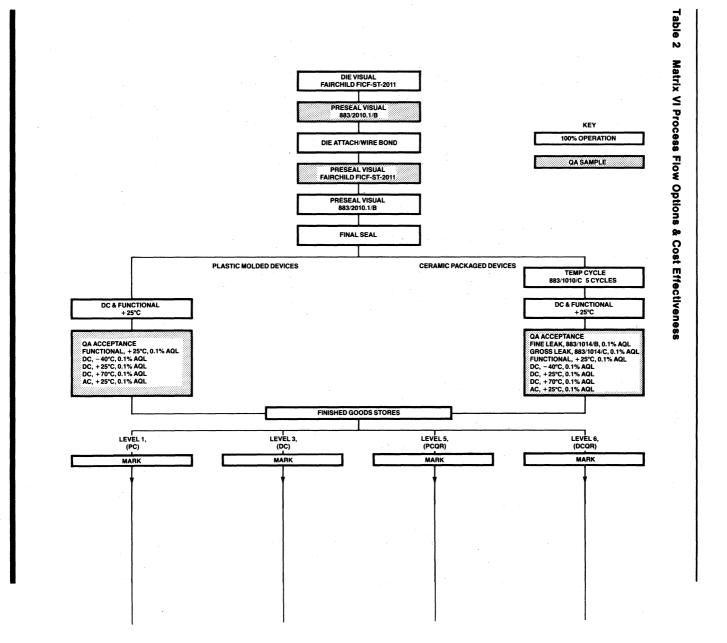

| Matrix VI Ordering Information                                     |   |

| Package Outlines8-8                                                | 2 |

| Section 9 Sales Offices, Representatives and Distributor Locations | ; |

| Product Index and Selection Guides                          | 1 |

|-------------------------------------------------------------|---|

| MOS Memory Technology Overview                              | 2 |

| RAM Data Sheets                                             | 3 |

| EPROM Data Sheets                                           | 4 |

| Serial Memory Data Sheets                                   | 5 |

| Special Function Data Sheets                                | 6 |

| Extended Temperature Range Data Sheets                      | 7 |

| Ordering Information and Package Outlines                   | 8 |

| Sales Offices, Representatives and<br>Distributor Locations | 9 |

ĵ<sup>e</sup>

# Section 1 Product Index and Selection Guides

| Device No. | Description                          | Page No.   |

|------------|--------------------------------------|------------|

| 2102       | 1024 x 1 Static RAM                  | 3-3, 7-3   |

| 2102L      | 1024 x 1 Static RAM                  | 3-3, 7-3   |

| 21L02      | 1024 x 1 Static RAM                  | 3-3        |

| F2114      | 1024 x 4 Static RAM                  | 3-8, 7-6   |

| F2114L     | 1024 x 4 Static RAM                  | 3-8, 7-6   |

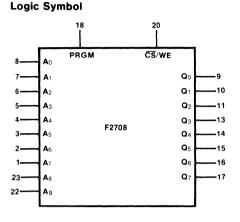

| F2708      | 1024 x 8 UV Erasable PROM            | 4-3        |

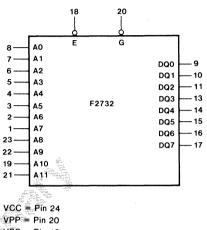

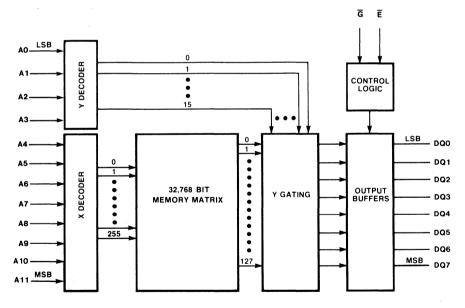

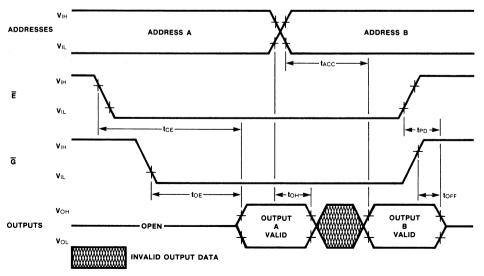

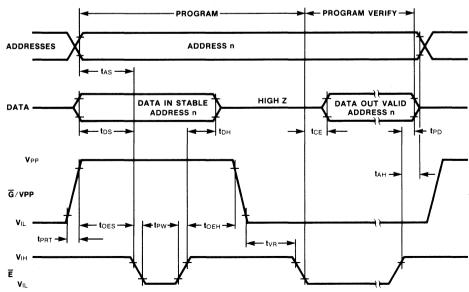

| F2732      | 4K x 8 UV Erasable PROM              | 4-10       |

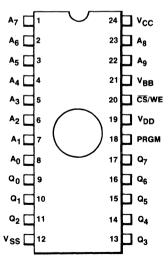

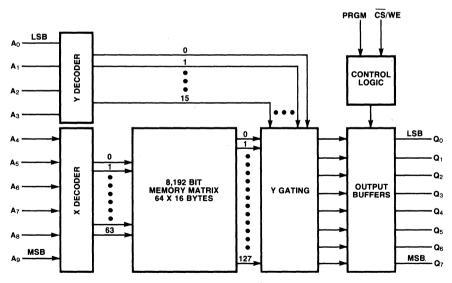

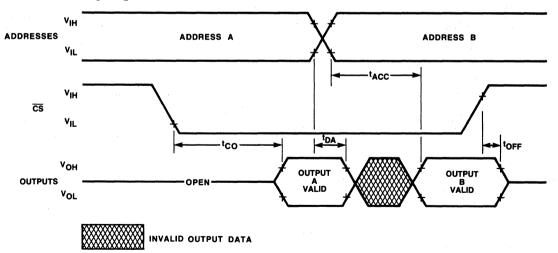

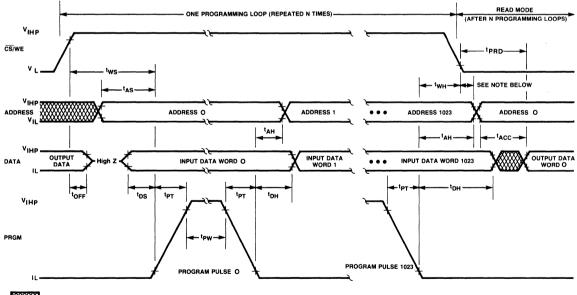

| F2764      | 8192 x 8 UV Erasable PROM            | 4-16       |

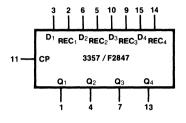

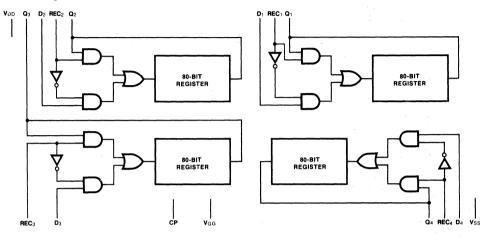

| F2847      | Quad 80-Bit Static Shift Register    | 5-25, 7-15 |

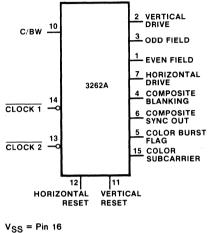

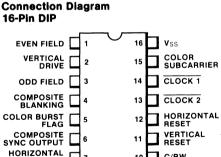

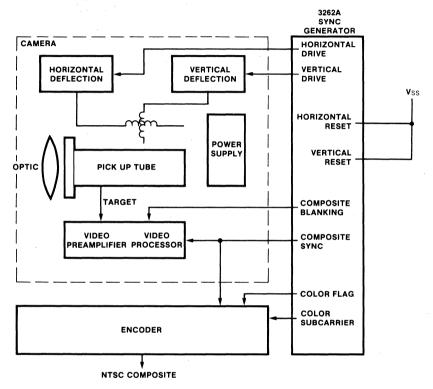

| 3262A      | TV Sync Generator                    | 6-3        |

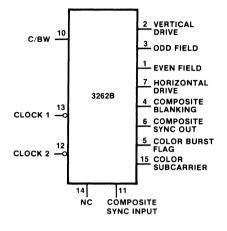

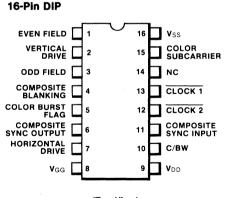

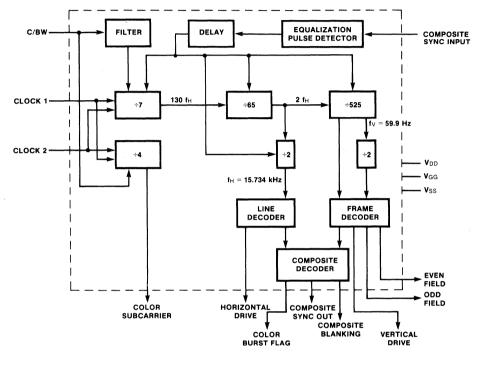

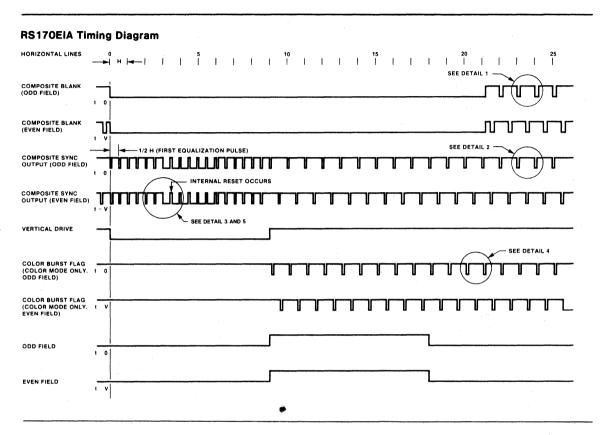

| 3262B      | TV Sync Generator for Generator Lock | 6-9        |

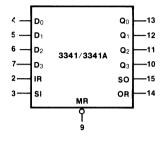

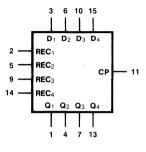

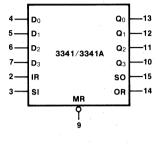

| 3341       | 64 x 4 FIFO Serial Memory            | 5-3, 7-8   |

| 3341A      | 64 x 4 FIFO Serial Memory            | 5-3, 7-8   |

| 3342       | Quad 64-Bit Static Shift Register    | 5-9        |

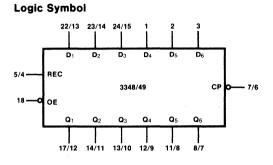

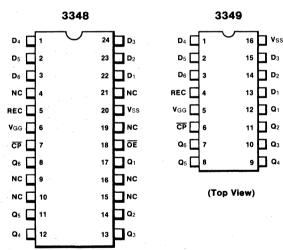

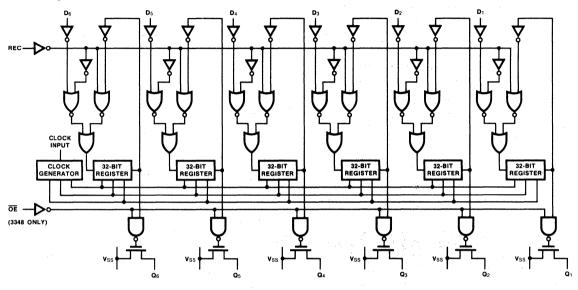

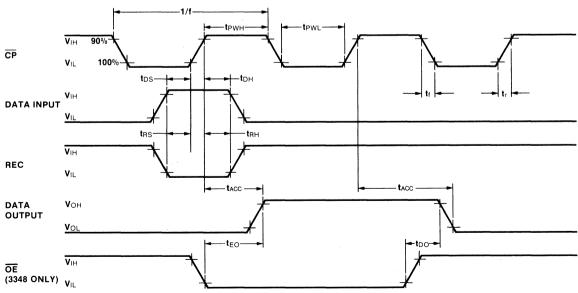

| 3348       | Hex 32-Bit Static Shift Register     | 5-13       |

| 3349       | Hex 32-Bit Static Shift Register     | 5-13       |

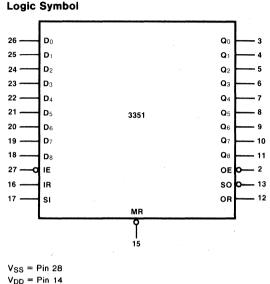

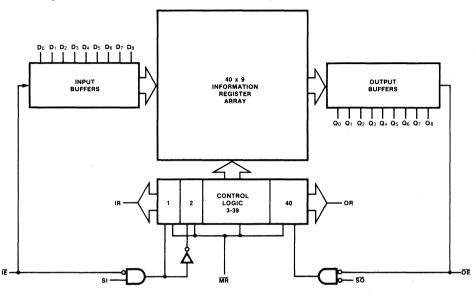

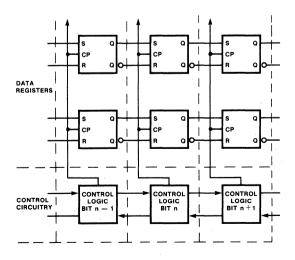

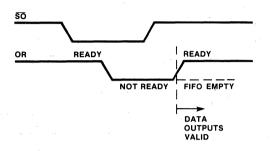

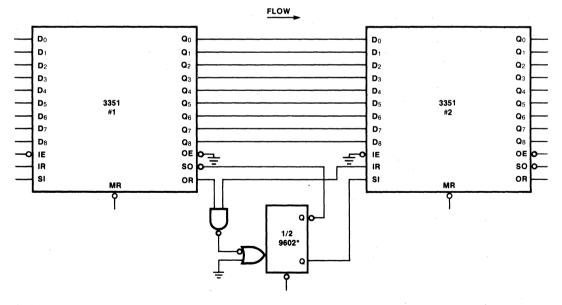

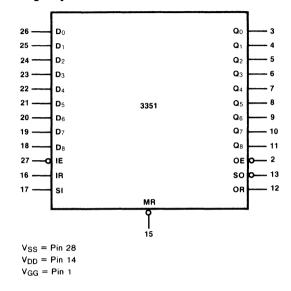

| 3351       | 40 x 9 FIFO Serial Memory            | 5-16, 7-11 |

| 3357       | Quad 80-Bit Static Shift Register    | 5-25, 7-15 |

| 3528       | 2048 x 8 Static RAM                  | 3-12       |

| F3567      | 16,384 x 1 Static RAM                | 3-14       |

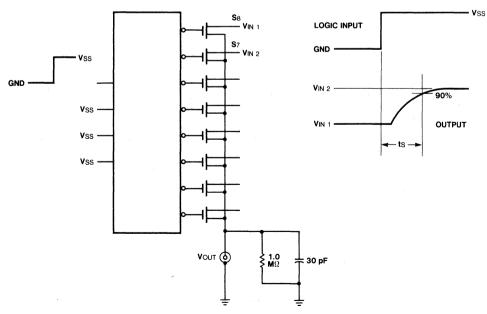

| 3708       | 8-Channel Multiplex Switch           | 6-15, 7-18 |

| F4116      | 16,384 x 1 Dynamic RAM               | 3-15, 7-20 |

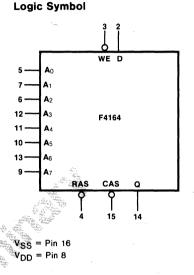

| F4164      | 65,536 x 1 Dynamic RAM               | 3-37       |

1

### **Product Index and Selection Guides**

| Organization | Part No. | Description                    | Access<br>Time<br>(ns) | Max<br>Power<br>Dissi-<br>pation<br>(mW) | Power<br>Supply<br>(V) | No.<br>of<br>Pins | Tech-<br>nology | Temper-<br>ature<br>Range<br>(Note 1) | Package<br>(Note 2) | Page No.   |

|--------------|----------|--------------------------------|------------------------|------------------------------------------|------------------------|-------------------|-----------------|---------------------------------------|---------------------|------------|

|              | 2102-H   |                                | 250                    |                                          |                        |                   |                 |                                       |                     | 3-3, 7-3   |

|              | 2102-F   |                                | 350                    |                                          |                        |                   |                 |                                       |                     | 3-3, 7-3   |

|              | 2102-1   | 1K Static RAM                  | 450                    | 290                                      | +5                     | 16                | NMOS            | C,L,M                                 | D,P,F               | 3-3, 7-3   |

|              | 2102-2   |                                | 650                    |                                          |                        |                   |                 |                                       |                     | 3-3, 7-3   |

|              | 2102L-H  |                                | 250                    |                                          |                        |                   |                 |                                       |                     | 3-3, 7-3   |

|              | 2102L-F  | 1K Low-power                   | 350                    |                                          |                        |                   |                 |                                       |                     | 3-3, 7-3   |

| 1024 x 1     | 2102L-1  | Static RAM                     | 450                    | 160                                      | +5                     | 16                | NMOS            | C,L,M                                 | D,P,F               | 3-3, 7-3   |

|              | 2102L-2  |                                | 650                    |                                          |                        |                   |                 |                                       |                     | 3-3, 7-3   |

|              | 21L02-H  |                                | 250                    |                                          | +5                     | 16                | NMOS            | C, L                                  | D,P,F               | 3-3        |

|              | 21L02-F  | 1K Static RAM<br>w/Power Down  | 350                    | 160/25                                   |                        |                   |                 |                                       |                     | 3-3        |

|              | 21L02-1  |                                | 450                    |                                          |                        |                   |                 |                                       |                     | 3-3        |

|              | 21L02-2  |                                | 650                    |                                          |                        |                   |                 |                                       |                     | 3-3        |

|              | F2114-2  | 4K Static RAM                  | 200                    | 530                                      | +5                     | 18                | NMOS            | С,М                                   | D,P                 | 3-8, 7-6   |

|              | F2114-3  |                                | 300                    |                                          |                        |                   |                 |                                       |                     | 3-8, 7-6   |

| 1004         | F2114    |                                | 450                    |                                          |                        |                   |                 |                                       |                     | 3-8, 7-6   |

| 1024 x 4     | F2114L-2 |                                | 200                    | 265                                      | +5                     | 18                | NMOS            | С,М                                   | D,P                 | 3-8, 7-6   |

|              | F2114L-3 | 4K Low-power<br>Static RAM     | 300                    |                                          |                        |                   |                 |                                       |                     | 3-8, 7-6   |

|              | F2114L   |                                | 450                    |                                          |                        |                   |                 |                                       |                     | 3-8, 7-6   |

| 00400        | F3528-25 | 16K Static RAM                 | 250                    | 450/100                                  | 1.5                    |                   | 1               | 0                                     | <b>_</b>            | 3-12       |

| 2048 x 8     | F3528-35 | w/Power Down                   | 350                    | 450/100                                  | +5                     | 24                | lso-H           | С                                     | D                   | 3-12       |

| 16,384 x 1   | F3567-55 | 16K Static RAM<br>w/Power Down | 55                     | 700/170                                  | +5                     | 20                | lso-H           | с                                     | D                   | 3-14       |

|              | F4116-2  |                                | 150                    |                                          | 1.10                   |                   |                 |                                       |                     | 3-15, 7-20 |

| 16,384 x 1   | F4116-3  | 16K Dynamic<br>RAM             | 200                    | 465/25                                   | +12,                   | 16                | NMOS            | C,L,M*                                | D,P,F,L             | 3-15, 7-20 |

|              | F4116-4  |                                | 250                    |                                          | ±5                     |                   |                 |                                       |                     | 3-15, 7-20 |

|              | F4164-1  |                                | 120                    |                                          | 1                      | 16                | lso-H           | с                                     |                     | 3-37       |

| 65,536 x 1   | F4164-2  | 64K Dynamic<br>RAM             | 150                    | 250/20                                   | +5                     |                   |                 |                                       | D                   | 3-37       |

|              | F4164-3  |                                | 200                    | 1                                        |                        |                   |                 |                                       |                     | 3-37       |

Notes

Commercial (T<sub>A</sub> = 0°C to +70°C) Limited Military (T<sub>A</sub> = -55°C to +85°C) 1. C =

L =

Military (T<sub>A</sub> =  $-55^{\circ}$ C to  $+125^{\circ}$ C) м =

M\* = Special Military (T<sub>Case</sub> = -55°C to +110°C)

Plastic DIP 2. P = Ceramic DIP D =

Flatpak F =

L = Leadless Chip Carrier

# Product Index and Selection Guides

### UV Erasable Programmable Read Only Memories

| Organization | Part No. | Description | Access<br>Time<br>(ns) | Max<br>Power<br>Dissi-<br>pation<br>(mW) | Power<br>Supply<br>(V) |      |       | Temper-<br>ature<br>Range<br>(Note 1) | Package<br>(Note 2) | Page No. |     |

|--------------|----------|-------------|------------------------|------------------------------------------|------------------------|------|-------|---------------------------------------|---------------------|----------|-----|

| 1004 - 0     | F2708-1  | 8K EPROM    | 350                    | 800                                      | +12,                   | +12, | 24    | NMOS                                  | С                   | <b>D</b> | 4-3 |

| 1024 x 8     | F2708    |             | 450                    | 800                                      | ±5                     | 24   | NM05  | С                                     | טן                  | 4-3      |     |

| 4096 x 8     | F2732    | 32K EPROM   | 450                    | 790/160                                  | +5                     | 24   | NMOS  | С                                     | D                   | 4-10     |     |

| 8192 x 8     | F2764    | 64K EPROM   | 200                    | 750                                      | +5                     | 28   | lso-H | С                                     | D                   | 4-16     |     |

#### **Serial Memories**

| Function                 | Organization | Part No. | Fre-<br>quency<br>Range<br>(MHz) | Max<br>Power<br>Dissi-<br>pation<br>(mW) | Power<br>Supply<br>(V) | of | Temper-<br>ature<br>Range<br>(Note 1) | Tech-<br>nology | Package<br>(Note 2) | Page No.   |

|--------------------------|--------------|----------|----------------------------------|------------------------------------------|------------------------|----|---------------------------------------|-----------------|---------------------|------------|

|                          | 00 0         | 3348     |                                  | 500                                      | -12,                   | 24 | 6                                     | DUOS            | D                   | 5-13       |

|                          | 32 x 6       | 3349     | dc to 1.0                        | 500                                      | +5                     | 16 | С                                     | PMOS            | D,P                 | 5-13       |

|                          | 64 x 4       | 3342     | dc to 1.5                        | 380                                      | -12,<br>+5             | 16 | с                                     | PMOS            | D,P                 | 5-9        |

| Static Shift             |              | 3357-1   | dc to 4.0                        | 375                                      |                        |    | C,L,M                                 | PMOS            | D,P                 | 5-25, 7-15 |

| Register                 |              | F2847    | dc to 3.0                        | 455                                      | -12,<br>+5             |    | С                                     |                 | D,P                 | 5-25       |

|                          | 80 x 4       | F2847    | dc to 2.5                        | 600                                      |                        | 16 | L,M                                   |                 | D                   | 7-15       |

|                          |              | 3357-2   | dc to 2.0                        | 285                                      |                        |    | С                                     |                 | D,P                 | 5-25       |

| Low Power                |              | F2847L   | dc to 3.0                        | 320                                      |                        |    | С                                     |                 | D,P                 | 5-25       |

| Static<br>Shift Register |              | F2847L   | dc to 2.5                        | 410                                      |                        |    | L,M                                   |                 | D                   | 7-15       |

|                          | 04 4         | 3341A    | dc to 1.0                        | 450                                      | -12,                   |    | 16 C,L,M                              | PMOS            | _                   | 5-3, 7-8   |

|                          | 64 x 4       | 3341     | dc to 0.7                        | 450                                      | +5                     | 10 |                                       |                 | D                   | 5-3, 7-8   |

| First-in<br>First-out    |              | 3351-1   | dc to 2.0                        | 520                                      |                        |    |                                       |                 |                     | 5-16, 7-11 |

|                          | 40 x 9       | 3351-3   | dc to 1.5                        | 420                                      | -12,<br>+5             | 28 | C,L,M                                 | PMOS            | D,P                 | 5-16, 7-11 |

|                          |              | 3351-2   | dc to 1.0                        | 420                                      |                        |    |                                       |                 |                     | 5-16, 7-11 |

#### **Special Function Products**

| Function                        | Part No. |            | Max<br>Power<br>Dissi-<br>pation<br>(mW) | Temper-<br>ature | of | Tech-<br>nology | Package | Page No.   |

|---------------------------------|----------|------------|------------------------------------------|------------------|----|-----------------|---------|------------|

| TV Sync Generator               | 3262A    | -12, +5    | 575                                      | С                | 16 | PMOS            | D       | 6-3        |

| TV Sync Generator with Gen-Lock | 3262B    | -12, +5    | 575                                      | С                | 16 | PMOS            | D       | 6-9        |

| 8-Channel Multiplex Switch      | 3708     | - 19, +5.5 | 175                                      | C,L,M            | 16 | PMOS            | D       | 6-15, 7-18 |

Notes on previous page.

and the second second

and the second second

| Product Index and Selection Guides                          | 1   |

|-------------------------------------------------------------|-----|

| MOS Memory Technology Overview                              | 2   |

| RAM Data Sheets                                             | 3   |

| EPROM Data Sheets                                           | - 4 |

| Serial Memory Data Sheets                                   | 5   |

| Special Function Data Sheets                                | 6   |

| Extended Temperature Range Data Sheets                      | 7   |

| Ordering Information and Package Outlines                   | 8   |

| Sales Offices, Representatives and<br>Distributor Locations | 9   |

# Section 2 **MOS Memory Technology Overview**

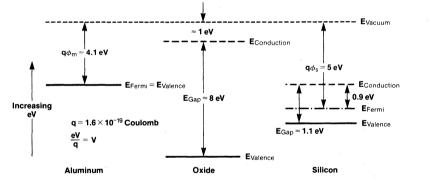

To understand MOS circuitry, it is first necessary to become familiar with some of the physical characteristics of the metal-oxide-semiconductor structure. The MOS process involves the separation of a metal or other gate-material electrode from a semiconductor substrate by a thin insulator of silicon dioxide (oxide). The stand-alone band structures of the materials are pictured in Figure 1. The Fermi level. stated simply, is a reference energy level at which the probability of finding an electron is 1/2. The bands below it are mostly full, and those above are generally empty. Thus, since the conduction band in the metal is full, the Fermi level is situated within the conduction band. The work function, or the amount of energy needed to remove an electron from the Fermi level to a point outside the atom, is designated  $\phi$ .

Figure 1

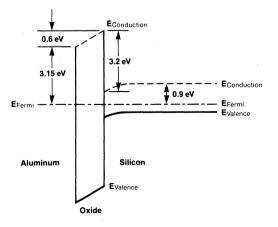

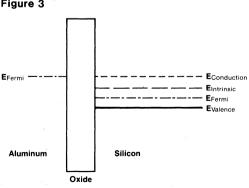

When these materials are together in an equilibrium state, electrons have been transferred from the metal to the silicon due to the lower work function of the metal. This equalizes the Fermi levels at the junctions and forms a potential across the non-conducting oxide (Figure 2). This structure, in effect, is a capacitor with charge stored on the gate and in the substrate, with a voltage equal to the difference in the work functions. In the particular case shown, if a negative voltage, with respect to the substrate, is applied to the gate, the voltage across the capacitor tends to decrease until it reaches the point shown in Figure 3. This applied voltage is then equal to the difference in work functions and is designated the *flat-band voltage* VFR. Therefore,  $V_{FB} = \phi$  metal  $-\phi$  silicon in the ideal case. This voltage is useful when computing another important parameter, the threshold voltage, discussed later.

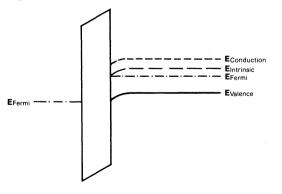

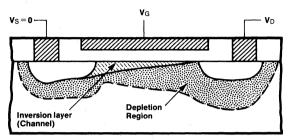

As the voltage on the gate becomes positive with respect to the substrate, it continues to repel the positive charge carriers in the surface below as well as build up a positive charge on the gate. When the substrate surface is nearly void of mobile carriers, the condition is called surface depletion (Figure 4). As the gate voltage becomes still more positive under equilibrium conditions, the Fermi level remains constant and the energy bands continue to bend downward. At the point where the actual Fermi level crosses the intrinsic (undoped) Fermi level, the substrate behaves like an n-type semiconductor. This forms a channel of n-type carriers (mobile electrons) between the source and drain called the inversion laver (Figure 5). The voltage at which this channel forms is known as the threshold voltage, and can be expressed as

$$V_{T} = V_{FB} + 2 |\phi_{p}| + \frac{1}{C'_{0x}} \sqrt{2E_{S} qN_{a} (2\phi_{p} + V_{C} - V_{B})} + V_{C} \quad (1)$$

where VFB is the positive voltage needed to neutralize the charge between the gate and the substrate, and  $2 |\phi_{\rm D}|$  is the voltage required to cause the bands to bend into the inverted condition. The third term results from the charge distribution within the substrate and depends on the permittivity of the silicon (E<sub>S</sub>), the doping level Na, the channel-to-substrate bias  $(V_C - V_B)$ , and the oxide capacitance C'<sub>ox</sub> (per square unit). V<sub>C</sub>, the last term, is the channel voltage (typically zero when referenced to the source).

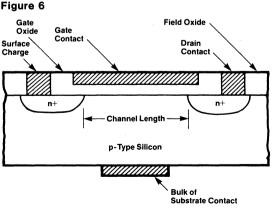

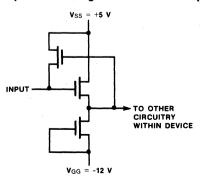

#### Figure 4

Since the channel forms because of the applied voltage, this device is said to conduct in the enhancement mode. Depletion-mode devices, on the other hand, are manufactured so that the channel exists without any external bias applied. The gate voltage must be applied to remove the channel and shut the transistor off. In fact, due to the internal positive charge contained in the oxide, an n-channel device may have an inverted substrate with no gate bias applied (Figure 6). Thus, it was not until special processing techniques were developed to reduce the oxide charge that enhancement NMOS devices became popular. Until that time, the majority of MOS devices were p-channel (PMOS). Although the previous discussion applies to NMOS technology, it is also applicable to PMOS with an n-type substrate and a negative gate-to-substrate voltage.

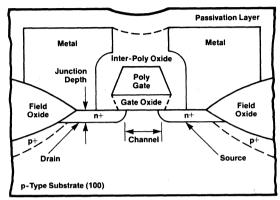

A brief history of MOS devices may prove enlightening. PMOS devices were originally constructed using <111>-oriented silicon with metal gates and had a typical threshold voltage of -4 V. Unfortunately, threshold voltages of -2 V or less were required for compatibility with TTL circuitry. This problem was solved by substituting a heavily doped, highly conductive layer of poly-crystalline silicon (poly) for the aluminum gate. This substitution brought about three major advantages. First, since the silicon gate material had a work function  $\phi$  closer to that of the substrate, VFB was reduced and VT was correspondingly smaller. Secondly, since this type of silicon was stable at high temperatures, the source and drain could be diffused after the gate, thus vielding near perfect gate-channel alignment using the gate layer as a mask. And third, since another insulating layer could be deposited over the first poly. a second layer of metal or poly interconnections could be run over the top of the first (Figure 7).

In addition to changing the gate material, it was also found that substituting <100>-oriented silicon for <111> type tended to lower threshold voltages and reduce surface state charge by a factor of three. Unfortunately, while the surface could be inverted under the gate with less voltage, it would also be inverted under the thicker field-oxide region, causing a lower field threshold VTF. This limited the operating voltage, and to some extent the density, of the device.

Fairchild addressed this low-V<sub>TF</sub> problem through the Isoplanar process. The field oxide is selectively grown to provide a thicker oxide layer where required (*Figure 7*). Since the oxide repels the p-type dopants, the substrate just below the field oxide becomes a p<sup>+</sup> or a more concentrated p region. As can be seen from *Equation 1*, the threshold voltage is higher where N<sub>a</sub> is greater. In addition to raising the V<sub>TF</sub>, this process also reduces vertical steps, making devices easier to manufacture.

Also to help overcome the V<sub>TF</sub> problem and to aid in adjusting threshold voltages, the ion-implantation process was developed. This process consists of accelerating a pure beam of ionized dopant atoms and directing them onto the surface of the silicon. Typically, these ions are used to change the doping level of the channel area to lower the threshold properties with respect to the field or to effect more precise V<sub>T</sub> control.

While the above advances are applicable to both P and NMOS, NMOS has received most of the attention due, in part, to its inherent speed advantages. Since

the mobility of carriers (electrons) is roughly two times that of holes, NMOS devices typically exhibit higher speed performance.

#### **Transistor Operations**

MOS transistors are a subset of a more general class of devices called insulated-gate field-effect transistors or IGFETs. While many of the properties discussed in the following section apply specifically to MOSFETs, most are analogous to the characteristics of other types of IGFETs. See *Figure 8* for the MOS transistor symbol and definition of terminals.

After the gate voltage exceeds V<sub>T</sub> and the channel has formed, the magnitude of the current between the source and drain depends on the drain voltage V<sub>D</sub>. Since the channel acts as a resistive element, V<sub>D</sub> and V<sub>T</sub> are typically specified with respect to the source.

Thus when the channel first begins to form,  $V_T = V_G - V_S$ . As  $V_D$  continues to increase positively, the current increases linearly to a saturated condition (*Figure 9*), where further increases in  $V_D$  do not produce appreciable changes in drain current I<sub>D</sub>. At this point,

$$V_{\rm D(SAT)} = V_{\rm G} - V_{\rm T} \tag{2}$$

١

#### Figure 9

When operated in the linear region, below  $V_{D(SAT)}$ , the MOSFET looks very much like a voltage-controlled resistor. MOSFET gain is typically measured by its transconductance, the rate of change of drain current with respect to gate voltage. The transconductance in the saturation region is given by

$$g_{msat} = \mu_n C'_{ox} W/L (V_G - V_S - V_T)$$

(3)

where  $\mu_{\rm II}$  is the mobility of electrons,  $\dot{C}_{\rm OX}$  is the oxide capacitance (per unit area), and W/L is the channel width-to-length ratio, which will be discussed in greater detail later.

In a typical MOS integrated circuit, the substrate is common to many transistors. The substrate voltage can be varied with respect to the source and will affect the threshold voltage as indicated by *Equation 4.* In general, the change in  $V_T$  with substrate bias  $V_B$  is given by

$$V_{\rm T} = K \sqrt{V_{\rm S} - V_{\rm B}} \tag{4}$$

where K is an empirical constant usually between 0.5 and 0.75.

In an MOS integrated circuit the source-substrate junction must be reverse biased to isolate the transistors from each other. Thus, the substrate voltage can be no greater than 0.6 V relative to the source. The negative voltage limit is the reverse breakdown voltage of this junction. Due to the charge distribution within the bulk, making V<sub>B</sub> more negative causes V<sub>T</sub> to become more positive. This effect is used in some devices to adjust V<sub>T</sub>.

Threshold voltage  $V_T$  is a very important parameter since it affects input and output levels (noise margin), power-supply tolerance, power dissipation, speed, and output-drive current. Also, if the device design must allow for large variations in  $V_T$ , the speed-power product cannot be maximized. A substrate-bias generator can be used on-chip to control V<sub>T</sub> such as in the case of the F4164 and F3528. This circuit compares the on-chip threshold voltages against a reference that is a fixed percentage of V<sub>CC</sub>. The generator senses V<sub>T</sub> variations and, using a *chargepump* technique, adjusts the substrate bias to compensate. In addition to improving design, the bias generator eliminates the need for an external V<sub>BB</sub> supply.

#### **Memory-cell Design**

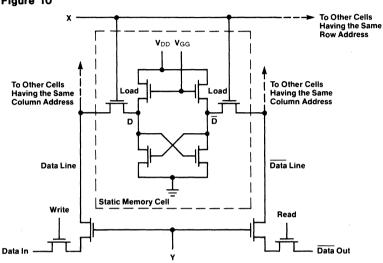

The basic static read-write random access memory (RAM) cell (Figure 10) consists of two cross-coupled inverters used to latch the data as a '1' or '0'. The X (word) lines and the Y (bit) lines service other similar cells. Various types of cell pull-up devices have been employed, with the depletion-mode transistor shown or the poly resistor the most popular. These types are favored over enhancement-mode loads because the VT drop required in an enhancement device lowers the cell's output-HIGH voltage below acceptable levels. Poly resistors have gained popularity over diffused resistors because of smaller size and higher resistance values. While fairly simple in structure, static cells have two main drawbacks-relatively large size and high power consumption, both critical parameters for high-density memories.

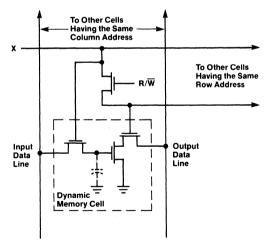

To overcome these limitations, the dynamic memory cell was devised. The most popular cells initially were the three-transistor types. Two major types were produced, differing mainly in the number of interconnections. The method of storage was the same, however.

Since the gates of MOS transistors are basically a capacitor, charge can be stored on the gate-to-source capacitance shown in Figure 11. This stored charge switches the transistor either on or off, storing the information. Unfortunately, since the charge eventually leaks off the gate, this cell needs to be refreshed at regular intervals: hence, the term dvnamic memory is applied. Peripheral circuitry senses the data and rewrites it into the cell. This increased complexity can be shared among many cells in a multiplexed fashion, reducing the cell to three transistors with no direct power path between supplies. The resulting increase in density and reduction in power have made dynamic RAMs (DRAMs) very popular. The three-transistor cell was employed in DRAMs up through the 2K-bit density level.

#### Figure 10

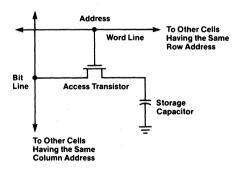

The 4K-bit DRAM generation and the following density levels (16K, 64K, etc.), incorporate the smaller onetransistor-cell design consisting of a capacitor and an access transistor (*Figure 12*). Because the onetransistor cell is much smaller than its predecessors, the amount of stored signal available for detection is also less. The one-transistor cell requires a more complex balanced sense amplifier, but the inherent density advantages make this cell viable.

#### **RAM Architecture**

The basic RAM organization can be word-wide ( $2K \times 8$ ,  $1K \times 4$ ) or bit-wide ( $1K \times 1$ ,  $16K \times 1$ ). Word-wide RAMs are generally used in applications requiring relatively small amounts of byte-organized memory, such as microprocessor-based systems. Accessing one 8-bit-wide device requires less power than enabling eight 1-bit-wide devices for the same amount of information.

In larger systems, the bit-wide device finds favor for two reasons. First, since the error-correction schemes employed in many large systems can correct single bit errors in a word, if one bit-wide device fails, the addressed word is correctable. Word-wide RAMs would be unsuitable for this application, because a general device failure would cause an uncorrectable 8- or 4-bit error in some words. Second, since output buffers required on a word-wide device are eliminated, the bit-wide memory-chip size is smaller. This is critical, for devices are necessary in cost-effective large memory systems.

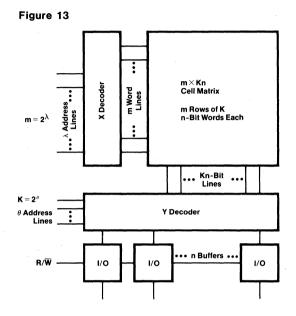

In a word-wide arrangement, some of the address lines ( $\lambda$ ) are decoded to select a row of memory cells, as in *Figure 13.* The remaining address bits ( $\theta$ ) are decoded to determine which of the K sets of n cells within the row is being accessed. The entire n-bit word is then available at the I/O circuits.

In the bit-wide case, each word is one bit wide and the decoders are used to select any of the Y bit locations within the total X number of rows. In this configuration, the data lines may be connected in parallel to a single I/O buffer. These same matrix ideas are employed on both static and dynamic RAMs, although additional peripheral complexity is required for sensing and refreshing in the DRAM.

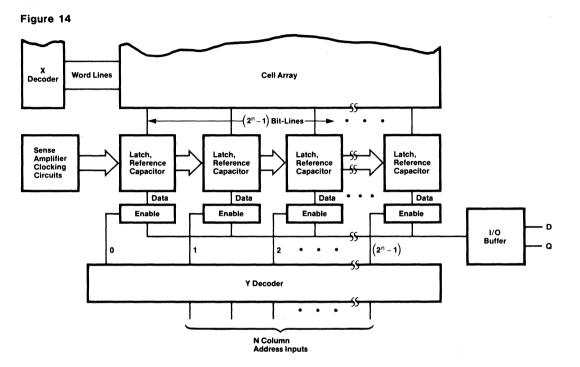

Due to the small amount of charge stored in DRAM memory cells, any loss of charge due to leakage or charge used during a read operation must be replaced by refreshing the location. Restoration is typically accomplished by the sense amp reading the information present in the cell, and then rewriting it immediately afterward. This function can be shared among all the cells in a given column. A block diagram of a sense amp and how it relates to the memory cells is shown in *Figure 14*.

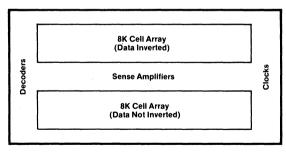

There are many configurations of the sense-amp relationship to the storage-cell array; one of the most popular DRAM architectures is shown in *Figure 15*. It was not by accident that the sense amps are in the

center of the array. Since the small amount of stored charge must drive the bit-line capacitance, which is related to the bit-line length, the bit lines should be kept as short as possible. Thus, there is a tradeoff between the number of cells serviced by any one sense amp and the signal wasted to charge the bit line. This effect, coupled with the balanced nature of the sense amps, makes the middle of the array a good compromise. In addition, because the ratio of bit-line capacitance to storage capacitance can be 10:1 or more, the bit lines are sometimes precharged with a clocking circuit before the cell is connected.

Figure 15

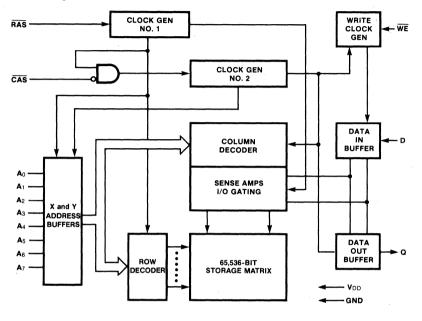

#### **64K DRAM Architecture**

With the advent of the 64K dynamic RAMs, the associated reduction in storage-cell charge has made the bit-line capacitance problem even more important. This problem is complicated for, as the array is further divided to effect shorter bit lines with less cells per line, the word lines become longer. Since layered interconnects are required and the word lines are fabricated with the less conductive polysilicon, the increased resistance adds RC time delays and slows access time. The F4164 is organized as eight 8K-bit blocks, with the word-line drivers located as shown in *Figure 16* to reduce word-line length. In addition, since the majority of the power is consumed by the sense amps, reducing the number of cells per sense amp by increasing the sense-amp count also increases the power.

Fairchild, by unique sense-amp design, has been able to double the effective service range of each sense amp of the F4164 without seriously affecting the signal available for sensing. Each of the 128 sense amps has 4 (not 2) bit lines, serving 64 cells per line. Each half bit line has an isolating transistor associated with it so only one bit-line half is connected to the desired cell.

In a balanced sense-amp design, the voltage on the bit-line half connected to the cell is compared against a reference voltage set up on another bit-line half connected to a *dummy* capacitor. Ideally, this dummy capacitor should be one half the capacitance of the storage cell. Unfortunately, if the storage capacitor is the minimum allowable size, there is obviously a problem making the dummy half that size. Fairchild

#### Figure 16

| 64 Reference Cells | 8K Cell EF<br>Array 85<br>87<br>87<br>87<br>87<br>87<br>87<br>87<br>87<br>87<br>87<br>87<br>87<br>87 |               | 1 of 128<br>E SK Cell O SK<br>a Array L A<br>U M<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 |                | 8K Cell<br>Array | 64 Sense Amps | 8K Cell<br>Array | 64 Reference Cells |  |  |

|--------------------|------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------|----------------|------------------|---------------|------------------|--------------------|--|--|

|                    |                                                                                                      |               | W                                                                                                                 | ord Line Drive | rs               |               |                  |                    |  |  |

|                    | 1 of 256 Row Decoder                                                                                 |               |                                                                                                                   |                |                  |               |                  |                    |  |  |

|                    |                                                                                                      |               | W                                                                                                                 | ord Line Drive | rs               |               |                  |                    |  |  |

| 64 Reference Cells | 8K Cell<br>Array                                                                                     | 64 Sense Amps | 8K Cell<br>Array                                                                                                  | D E C O D E R  | 8K Cell<br>Array | 64 Sense Amps | 8K Cell<br>Array | 64 Reference Cells |  |  |

has overcome this problem in the F4164 sense amp by sharing one full-size dummy capacitor between the two halves of each bit line; thus, half the charge is supplied to each to establish the reference voltage. If the memory-cell capacitor has a HIGH charge, connecting it to a half bit line will cause that half to be more positive than the reference. If the cell has a LOW charge, the opposite occurs. This difference is sensed and latched by the sense amp.

#### **Manufacturing Advances**

With the advent of the one-transistor DRAM cell, it seems unlikely that further circuit evolution will bring about dramatic reductions in cell size. Further size reductions will come from process improvements, just as process modifications have already decreased the one-transistor cell from about 1 mil<sup>2</sup> to roughly 0.3 mil<sup>2</sup>.

There are several ways to *shrink* an existing circuit without changing its basic design. A two-dimensional reduction in device geometries has already been successfully employed on several generations of MOS devices. At the transistor level, the length-to-width ratio of the channel determines its resistive properties, gain, speed performance, and relative size. Roughly, the higher the W/L, the lower the resistance, higher the gain and speed, and the larger the relative device area. Photographic size reduction can result in a smaller device that has similar properties to the original simply by keeping the W/L ratio constant.

A size reduction affecting all three dimensions is called *scaling*. Ideal scaling involves the reduction of each device dimension by a constant scale factor K. Since the field strength must generally be kept constant, the voltage at the device level is scaled by the same factor. In addition to the device area being reduced by the  $1/K^2$  factor, there are also performance improvements. Speed is increased, since the smaller device area results in reduced capacitance and transit time. Also, because the voltage after scaling is 1/K times the voltage before and the post-scaling current is reduced by a like amount, power (V x I) is scaled by  $1/K^2$ . Since both power and voltage are lower in the scaled device, reliability is enhanced.

To ensure that a scaled design can be manufactured, the ideal scaling rules must be adjusted to provide process compatibility. The process parameters involved are dopant levels, oxide thickness, junction depths, and supply voltage. Isoplanar-H is Fairchild's proprietary Isoplanar scaled-MOS process. This scaled NMOS is characterized by optical lithography,

dry (plasma) etching, arsenic junctions, sub-500  ${\rm \AA}$  oxides, and multiple levels of interconnect.

At present, scaling techniques are limited by the tolerances of existing photolithographic equipment. Contact printers with tolerances of  $\pm$ 0.75 microns, once acceptable when dealing with 10-micron line widths, are no longer useful at the 1-2 micron level. The advent of electron beam (E-beam) and step-and-repeat printers has demonstrated that this accuracy is possible for a price. The cost, just for the equipment, to set up a medium-size scaled-MOS line is around 30 million dollars.

Aside from the scaling limits imposed by equipment availability, there are physical limits as well. Reduced alpha immunity, short-channel effects, and reduced storage charge, are problems that increase significantly as device dimensions become smaller.

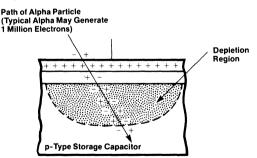

Alpha immunity is the relative resistance of a particular device to alpha-particle induced *soft errors*. Soft errors are defined as random bit errors not associated with physical defects on the chip. Alpha-induced soft errors occur when extra electron-hole pairs are generated by an alpha-particle collision with the chip, thus injecting extraneous charge that causes sensing malfunctions (*Figure 17*). The package material is the source of these alpha particles.

#### Figure 17

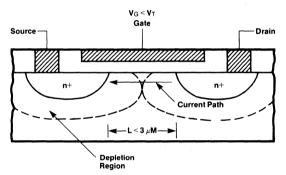

As device dimensions are further reduced, the amount of charge stored in each cell is decreased. Thus, the difference in the number of electrons sensed as a '1' and the number representing a '0' is also smaller. Therefore, since the number of electron-hole pairs produced within the silicon by an incident alpha particle is roughly constant, the probability of an error caused by this extra charge increases as device geometries and stored charge are scaled. Other factors limiting the degree to which a device can be scaled are grouped into a category called *short-channel effects.* These characteristics become most pronounced when the channel length becomes less than about 3 microns. Although threshold voltage and several other parameters are affected, the largest problem is caused by the proximity of the source and drain regions. Since these two regions are now separated by a small distance, the relatively constant depletion regions that surround them may overlap, causing an unwanted current path between the source and drain (*Figure 18*). Research is underway to minimize these difficulties by varying process techniques, but short-channel effects remain a physical consideration when scaling.

#### Figure 18

Since vertical dimensions like oxide thickness also shrink during scaling, storage capacitance per unit area for future devices will remain roughly the same as for present-day NMOS. However, since the power supply voltage must be scaled to maintain a constant electric field, the charge written into a dynamic memory cell will be reduced since it is a product of the cell capacitance and writing voltage.

This reduction is fairly critical for a DRAM, because the charge in the cell is shared with a relatively large bit-line capacitance. Therefore, the signal voltage that the sense amplifier must correctly process is scaled in the same manner as the writing voltage.

#### The Future of MOS Memory

Future advances in very large scale integration will depend heavily on the ability of manufacturers to reduce device geometries beyond the current state of the art. Present geometries used for devices like the 64K DRAM, 16K fast static RAMs and the like are based on 3-micron design rules. Thus, MOS transistor

channel lengths are drawn to a 3-micron length. The finished effective channel length is 2-2.5 microns.

Future enhancements involve further shrinking of the design rules. At channel lengths below 1.5 micron, a new lithography technique such as X-ray or electron beam will be required. Using these mask-exposure techniques, sub-micron geometries will evolve to produce 1 megabit DRAMs in the late 1980s.

VLSI geometries will encounter a silicon-material limit at about the 0.5 micron level by the end of the decade. At this point, new substrate materials such as gallium arsenide may be required to continue the trend of increased integration. Materials development programs are presently investigating refractory metalsilicide gate structures. This approach significantly reduces the delays caused by interconnect resistivity while maintaining the relatively low work-function difference between the silicon substrate and the gate material. Thus, TTL compatibility can still be realized. Decreased RC delays will reduce the DRAM speedrelated pattern sensitivities.

DRAMs will benefit from new types of materials, continued reduction of defect density, and increased automation of the production process. All of these factors will contribute to the increases in density, cost-effectiveness, reliability and performance that will appear in future generations of semiconductor memories.

| Product Index and Selection Guides                          | 1 |

|-------------------------------------------------------------|---|

| MOS Memory Technology Overview                              | 2 |

| RAM Data Sheets                                             | 3 |

| EPROM Data Sheets                                           | 4 |

| Serial Memory Data Sheets                                   | 5 |

| Special Function Data Sheets                                | 6 |

| Extended Temperature Range Data Sheets                      | 7 |

| Ordering Information and Package Outlines                   | 8 |

| Sales Offices, Representatives and<br>Distributor Locations | 9 |

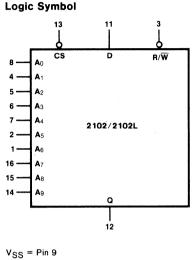

# 2102/2102L/21L02 1024 x 1 Static RAM

#### **MOS Memory Products**

#### Description

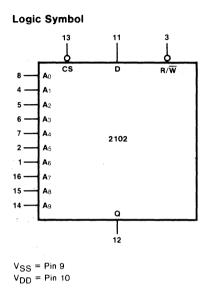

The 2102 family consists of 1024-word by 1-bit static Random Access read/write Memories (RAM) that require a single 5 V supply, have fully TTL-compatible inputs and output, and require no clocking or refresh. Chip Select (CS) permits a 3-state output allowing the outputs to be wired-OR. Special features include low power dissipation (2102L) and a power-down capability (21L02).

The 2102, 2102L and 21L02 are manufactured using the n-channel Isoplanar process and are available in a 16-pin dual in-line package or flatpak.

- FAST ACCESS-250 ns

- SINGLE +5 V SUPPLY

- TTL-COMPATIBLE INPUTS AND OUTPUT

- TOTALLY STATIC—NO CLOCKS OR REFRESH

- 3-STATE OUTPUT

- LOW POWER (2102L)

- POWER-DOWN CAPABILITY (21L02)

- FULLY EXPANDABLE

- FULLY DECODED

- 16-PIN DUAL IN-LINE PACKAGE

#### **Pin Names**

| A <sub>0</sub> -A <sub>9</sub> | Address Inputs           |

|--------------------------------|--------------------------|

| D                              | Data Input               |

| R/W                            | Read / Write             |

| CS                             | Chip Select (active LOW) |

| Q                              | Data Output              |

#### Absolute Maximum Ratings

| Voltage on Any Pin with Respect |                  |

|---------------------------------|------------------|

| to V <sub>SS</sub>              | −0.5 V to +7.0 V |

| Storage Temperature             | -55°C to +150°C  |

| Operating Temperature           | 0°C to +70°C     |

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliabiliy.

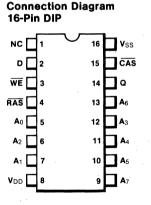

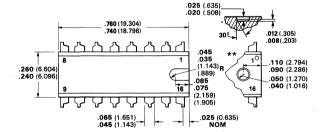

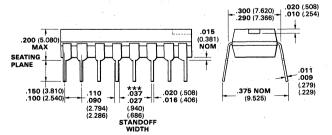

#### Connection Diagram 16-Pin DIP

#### (Top View)

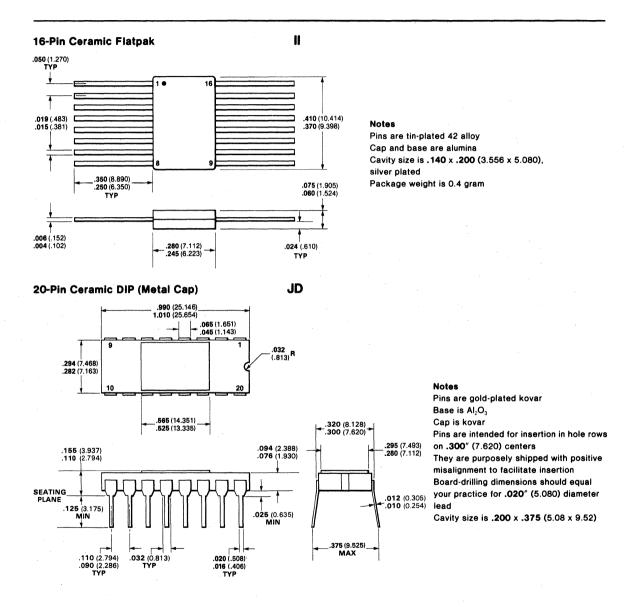

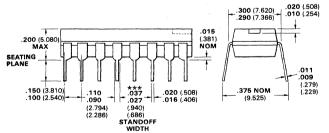

| Package     | Outline | Order<br>Code |

|-------------|---------|---------------|

| Ceramic DIP | 6Z      | D             |

| Plastic DIP | UC      | P             |

| Flatpak     | 11.     | F             |

Note

The Flatpak has the same pin number-to-function correspondence as the DIP.

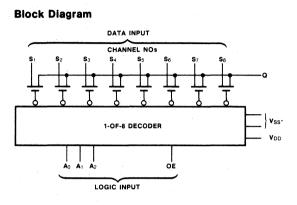

#### **Block Diagram**

#### **Truth Table**

| <u>CS</u> | R/W | D | Q  | Comments        |

|-----------|-----|---|----|-----------------|

| н         | х   | х | •  | Chip Deselected |

| L         | L   | н | н  | Write "1"†      |

| L         | L   | L | L  | Write "0"†      |

| L         | н   | Х | Dn | Read†           |

H = HIGH Voltage Level

L = LOW Voltage Level

- X = Don't Care

- = Output High Impedance State

- D<sub>n</sub> = Data at Address Location

† = Chip Selected

#### **Power/Access Time Guide**

|          | Part<br>Number | Access<br>Time | DD(MAX) |

|----------|----------------|----------------|---------|

|          | 21L02H         | 250 ns         | 30 mA   |

| Power    | 21L02F         | 350 ns         | 30 mA   |

| Down     | 21L021         | 450 ns         | 30 mA   |

|          | 21L022         | 650 ns         | 30 mA   |

|          | 2102LH         | 250 ns         | 30 mA   |

| Low      | 2102LF         | 350 ns         | 30 mA   |

| Power    | 2102L1         | 450 ns         | 30 mA   |

|          | 2102L2         | 650 ns         | 30 mA   |

|          | 2102H          | 250 ns         | 55 mA   |

| Standard | 2102F          | 350 ns         | 55 mA   |

|          | 21021          | 450 ns         | 55 mA   |

|          | 21022          | 650 ns         | 55 mA   |

#### **Functional Description**

The 2102, 2102L and 21L02 are 1024 x 1 static RAMs. When the Chip Select ( $\overline{CS}$ ) goes HIGH, the Read/Write ( $\overline{R/W}$ ) input is disabled and the Data Output (Q) is forced into a high impedance state. When  $\overline{CS}$  goes LOW, the Read/Write input is enabled.

When  $R/\overline{W}$  goes LOW, data from the Data Input (D) is written at the location specified by the Address Inputs (A<sub>n</sub>). The Data Output will be identical to the Data Input during a write command. When  $R/\overline{W}$  goes HIGH, the contents of the addressed location will appear at Q. Q is not inverted from D in the 2102. (See Truth Table).

### **DC Requirements** $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$

| Symbol                 |                         |                      | 2102,           | 2102L           | 21L02           |                 |      |           |  |

|------------------------|-------------------------|----------------------|-----------------|-----------------|-----------------|-----------------|------|-----------|--|

|                        | Characteristic, Not     | Characteristic, Note |                 | Max             | Min             | Max             | Unit | Condition |  |

| VIH Input HIGH Voltage | H,F,1                   | 2.0                  | V <sub>DD</sub> | 2.0             | V <sub>DD</sub> | V               |      |           |  |

|                        |                         | 2                    | 2.2             | V <sub>DD</sub> | 2.2             | V <sub>DD</sub> | - v  |           |  |

|                        | Input LOW Voltage       | H,F,1                | -0.5            | 0.8             | -0.5            | 0.8             | V    |           |  |

| VIL                    |                         | 2                    | -0.5            | 0.65            | -0.5            | 0.65            | - V  |           |  |

| V <sub>DD</sub>        | Power Supply<br>Voltage |                      | 4.75            | 5.25            | 4.5             | 5.5             | v    |           |  |

### DC Characteristics $~V_{DD}$ = 5.0 V $\pm$ 5%, $V_{SS}$ = 0 V, $T_{A}$ = 0°C to +70°C

| Symbol          |                                                    |                      | 2102, 210 | 2L, 21L02      |      |                                                               |  |

|-----------------|----------------------------------------------------|----------------------|-----------|----------------|------|---------------------------------------------------------------|--|

|                 | Characteristic, N                                  | Characteristic, Note |           | Max            | Unit | Condition                                                     |  |

|                 | Output HIGH                                        | H,F,1                | 2.4       |                |      | 100 4                                                         |  |

| VOH             | Voltage                                            | 2                    | 2.2       |                | V    | $I_{OH} = -100 \ \mu A$                                       |  |

| VOL             | Output LOW Volt                                    | age                  |           | 0.4            | V    | $I_{OL} = 2.1 \text{ mA}$                                     |  |

| IIN             | Input Leakage Cu                                   | urrent               |           | 10             | μA   | $V_{IN} = V_{DD}$                                             |  |

| ЮН              | Output HIGH Curr                                   | ent                  |           | 5.0            | μΑ   | $\frac{V_{OUT} = V_{OH(Min)}}{CS = V_{IH(Min)}}$              |  |

| I <sub>OL</sub> | Output LOW Curr                                    | ent                  |           | -10            | μΑ   | $\frac{V_{OUT} = V_{OL(Max)}}{CS} = V_{IH(Min)}$              |  |

| I <sub>DD</sub> | Power Supply Cu<br>2102<br>2102L<br>2102L<br>21L02 | rrent                |           | 55<br>30<br>30 | mA   | Inputs = $V_{DD(Max)}$<br>$D_{OUT}$ open,<br>$T_A = T_A(Min)$ |  |

### AC Requirements $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$

|                 |                                 | 2102H<br>2102LH<br>21L02H | 2102F<br>2102LF<br>21L02F | 21021<br>2102L1<br>21L021 | 21022<br>2102L2<br>21L022 |    |                            |

|-----------------|---------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|----|----------------------------|

| Symbol          | Characteristic Min Min Min Unit | Condition                 |                           |                           |                           |    |                            |

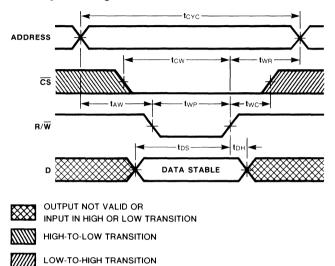

| tcyc            | Read or Write Cycle Time        | 250                       | 350                       | 450                       | 650                       | ns |                            |

| t <sub>AW</sub> | Address to Write Time           | 20                        | 20                        | 20                        | 200                       | ns |                            |

| twp             | Write Pulse Width               | 170                       | 170                       | 200                       | 350                       | ns | V <sub>SS</sub> = 0 V      |

| twR             | Write Recovery Time             | 0                         | 0                         | 0                         | 50                        | ns | See DC Requirements        |

| tDS             | Data Set-up Time                | 170                       | 170                       | 200                       | 350                       | ns | for Conditions on $V_{DD}$ |

| t <sub>DH</sub> | Data Hold Time                  | 0                         | 0                         | 0                         | 20                        | ns |                            |

| tcw             | Chip Select to Write Time       | 170                       | 170                       | 200                       | 400                       | ns | ]                          |

| twc             | Write to Chip Select Time       | 0                         | 0                         | 0                         | 50                        | ns |                            |

Note

See Power / Access Time Guide and AC Characteristics for definitions of H, F, 1 and 2 speed grades.

| AC Char | acteristics $T_A = 0^\circ C t_0$                     | o +70°(              | 0    |                   |     |                   |     |                   |     |    |                                                       |

|---------|-------------------------------------------------------|----------------------|------|-------------------|-----|-------------------|-----|-------------------|-----|----|-------------------------------------------------------|

|         |                                                       | 2102<br>2102<br>21L0 | 2LH  | 210<br>210<br>21L | 2LF | 210<br>210<br>21L | 2L1 | 210<br>210<br>21L | 2L2 |    |                                                       |

| Symbol  | Symbol Characteristic Min Max Min Max Min Max Min Max | Max                  | Unit | Condition         |     |                   |     |                   |     |    |                                                       |

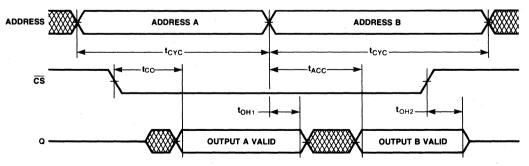

| tACC    | Read Access Time                                      |                      | 250  |                   | 350 |                   | 450 |                   | 650 | ns |                                                       |

| tco     | Chip Select LOW to<br>Output Valid Delay              |                      | 130  |                   | 170 |                   | 200 |                   | 400 | ns | V <sub>SS</sub> = 0 V                                 |

| tOH1    | Data Valid after<br>Address                           | 40                   |      | 50                |     | 50                |     | 50                |     | ns | See DC Requirements for Conditions on V <sub>DD</sub> |

| tOH2    | Previous Data Valid<br>after Chip Deselect            | 0                    |      | 0                 |     | 0                 |     | 0                 |     | ns |                                                       |

| CIN     | Input Capacitance                                     |                      | 5.0  |                   | 5.0 |                   | 5.0 |                   | 5.0 | pF | $V_{IN} = 0 V, V_{SS} = 0 V$                          |

| COUT    | Output Capacitance                                    |                      | 10   |                   | 10  |                   | 10  |                   | 10  | рF | $f = 1 MHz, T_A = 25^{\circ}C$                        |

### Power Down Characteristics (21L02 only) $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$

|                       |                         | 21L02 |     |      |                  |

|-----------------------|-------------------------|-------|-----|------|------------------|

| Symbol Characteristic | Characteristic          | Min   | Max | Unit | Condition        |

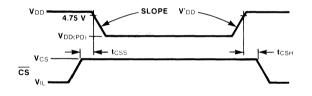

| IDD(PD)               | Power Supply Current    |       | 15  | mA   | $V_{DD} = 1.6 V$ |

| V <sub>DD(PD)</sub>   | Power Supply Voltage    | 1.6   |     | V    |                  |

| tcss                  | Chip Select Set-up Time | 100   |     | ns   | · ·              |

| tCSH                  | Chip Select Hold Time   | 100   |     | ns   |                  |

| Vcs                   | Chip Select Voltage     | 2.0   |     | V    |                  |

| V'DD                  | Power Supply Slew Rate  |       | 100 | V/µs |                  |

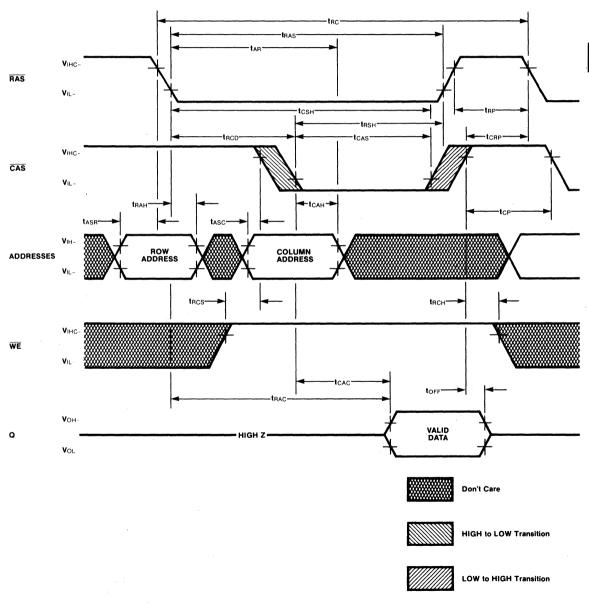

### **Timing Diagrams**

### **Read Cycle Timing**

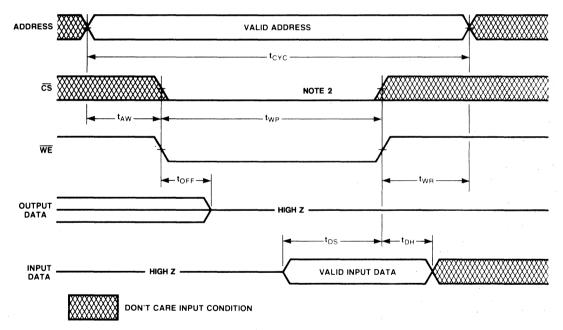

Write Cycle Timing

LOW-TO-HIGH TRANSITION

#### **AC Conditions**

3-7

Input Levels: V<sub>IL(Max)</sub> to V<sub>IH(Min)</sub> Input Rise and Fall Times: 10 ns Timing Measurement Reference Levels: Inputs: 1.5 V Output: 2.0 and 0.8 V Output Load: 1 TTL Gate + 100 pF

3

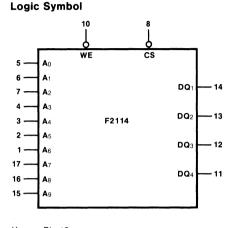

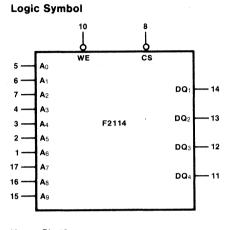

# F2114/2114L 1024 x 4 Static RAM

**MOS Memory Products**

#### Description

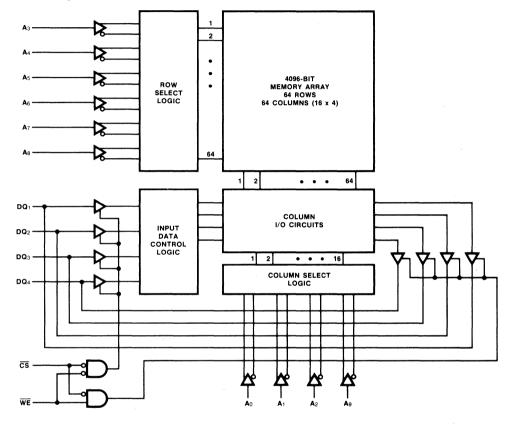

The F2114 is a 4096-bit static Random Access Memory (RAM) organized as 1024 words of four bits each. Since the operation of the F2114 is entirely static, there is no clocking or refreshing required. It operates from a single +5 V supply and is directly a TTL compatible at all inputs and outputs including the four bidirectional data I/O pins.

It is designed for memory applications in which static operation, large bit-capacity, and simple interfacing are important design considerations.

The F2114 is manufactured using Fairchild's n-channel silicon gate Isoplanar process. The innovative use of polysilicon resistors in the static memory cell permits a high bit packing density and insures low-power characteristics. It is available in a standard plastic or ceramic 18-pin dual in-line package.

- 1024 x 4-BIT ORGANIZATION

- SINGLE +5 V SUPPLY

- COMPLETELY STATIC—NO CLOCKS OR REFRESH

- TOTALLY TTL COMPATIBLE

- COMMON DATA I/O PINS WITH 3-STATE CAPABILITY

- IDENTICAL CYCLE AND ACCESS TIMES

- LOW POWER (2114L)

#### **Pin Names**

| A <sub>0</sub> -A <sub>9</sub> | Address Inputs            |

|--------------------------------|---------------------------|

| CS                             | Chip Select (Active LOW)  |

| WE                             | Write Enable (Active LOW) |

| DQ1-DQ4                        | Data Input/Output         |

| Vcc                            | +5 V Power Supply         |

| GND                            | Ground                    |

#### **Absolute Maximum Ratings**

| Voltage at Any Pin with Respect |                  |

|---------------------------------|------------------|

| to GND                          | -0.5 V to +7.0 V |

| Operating Temperature (Ambient) | 0°C to +70°C     |

| Storage Temperature (Ambient)   | -55°C to +150°C  |

| Power Dissipation               | 1 W              |

| -                               |                  |

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions exceeding those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

$V_{CC} = Pin \ 18$ GND = Pin 9

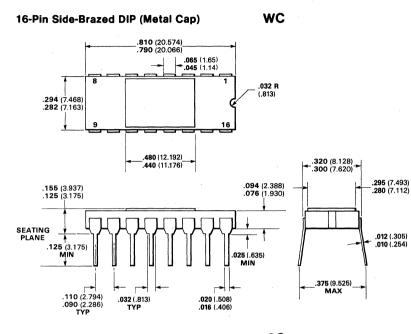

# Connection Diagram 18-Pin DIP

(Top View)

| Package     | Outline | Order<br>Code |  |

|-------------|---------|---------------|--|

| Ceramic DIP | 8D      | D             |  |

| Plastic DIP | 8J      | P             |  |

F2114/2114L

#### **Block Diagram**

#### **Functional Description**

The F2114, organized as 1024 words by four bits, is controlled by the Chip Select ( $\overline{CS}$ ), Write Enable (WE) and the ten address inputs. When  $\overline{CS}$  goes HIGH the memory becomes deselected; the bidirectional input/output pins become high impedance, and the WE input is ignored. Therefore no read or write operations may occur. This feature allows the DQ pins to be OR-tied directly to a data bus. When the memory is selected ( $\overline{CS}$  LOW), and the WE pin is in the HIGH state, the 4-bit word stored at the memory location specified by the address inputs is gated through to the DQ pins after a delay equal to the access time. If the WE is forced LOW, then the DQ pins become HIGH impedance inputs so that an externally supplied data word may be placed on them. All inputs and bidirectional DQ pins are directly TTL compatible with data always being read out in the same polarity as it was written (i.e., not inverted).

**Truth Table**

| <u>cs</u> | WE | DQ     | Comments        |

|-----------|----|--------|-----------------|

| н         | X  | High Z | Chip Deselected |

| L         | L  | н      | Write "1"       |

| L         | L  | L      | Write "O"       |

| L         | H  | Data   | Read            |

### F2114/2114L

| Symbol          | Characteristic                                                  | Min  | Тур | Max | Unit | Condition                                                               |

|-----------------|-----------------------------------------------------------------|------|-----|-----|------|-------------------------------------------------------------------------|

| VIH             | Input HIGH Voltage                                              | 2.0  |     | Vcc | V    |                                                                         |

| VIL             | Input LOW Voltage                                               | -0.5 |     | 0.8 | V    |                                                                         |

| VOH             | Output HIGH Voltage                                             | 2.4  |     | Vcc | V    | $I_{OUT} = -1.2 \text{ mA}$                                             |

| VOL             | Output LOW Voltage                                              | 0    |     | 0.4 | V    | I <sub>OUT</sub> = 3.2 mA                                               |

| los             | Output Short-Circuit<br>Current, Note 2                         |      |     | 65  | mA   | V <sub>OUT</sub> = 0 V                                                  |

| lcc             | Average V <sub>CC</sub> Supply Current F2114L2, F2114L3, F2114L |      |     | 70  | mA   | $V_{CC} = 5.25 V,$<br>$T_A = 0^{\circ}C,$                               |

|                 | Average V <sub>CC</sub> Supply Current F2114-2, F2114-3, F2114  |      |     | 100 | mA   | V <sub>IN</sub> = 5.25 V,<br>I/O current = 0 mA                         |

| IIN             | Input Leakage Current                                           |      |     | 10  | μA   | V <sub>IN</sub> = 0 to 5.25 V                                           |

| Ισα             | I/O Leakage Current                                             | -10  |     | 10  | μA   | $\overline{CS} = 2.0 V,$<br>V <sub>I/O</sub> = 0.4 V to V <sub>CC</sub> |

| C <sub>IN</sub> | Input Capacitance                                               |      |     | 5.0 | pF   | $T_{A} = 25^{\circ}C, f = 1.0 \text{ MHz}$ $V_{IN} = 0 \text{ V}$       |

| C <sub>DQ</sub> | I/O Capacitance                                                 |      |     | 5.0 | pF   | $T_A = 25^{\circ}C, f = 1.0 \text{ MHz}$<br>$V_{I/O} = 0 \text{ V}$     |

# DC Electrical Requirements and Characteristics $T_A$ = 0 to 70°C, $V_{CC}$ = 5.0 V $\pm$ 5%, all voltages are with respect to ground, Note 1

#### AC Electrical Requirements And Characteristics $T_A = 0^{\circ}C$ to 70°C, $V_{CC} = 5.0 V \pm 5\%$ , Notes 1 and 3

| Symbol          | Characteristic                          | F2114L-2<br>F2114-2 |     | F2114L-3<br>F2114-3 |     | F2114L<br>F2114 |     |      |      |

|-----------------|-----------------------------------------|---------------------|-----|---------------------|-----|-----------------|-----|------|------|

|                 |                                         | Min                 | Max | Min                 | Max | Min             | Max | Unit | Note |

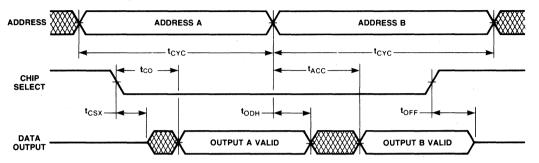

| tcyc            | Read or Write Cycle Time                | 200                 |     | 300                 |     | 450             |     | ns   |      |

| tACC            | Read Access Time                        |                     | 200 |                     | 300 |                 | 450 | ns   |      |

| tco             | CS LOW to Output Valid Delay            |                     | 70  |                     | 100 |                 | 100 | ns   |      |

| tcsx            | CS LOW to Output Active Delay           | 20                  |     | 20                  |     | 20              |     | ns   |      |

| todh            | Output Data Hold Time<br>After Address  | 50                  |     | 50                  |     | 50              |     | ns   |      |

| tOFF            | Output Buffer Turn-Off Delay<br>from CS | 0                   | 60  | 0                   | 80  | 0               | 100 | ns   |      |

| t <sub>AW</sub> | Address to Write Set-up Time            | 0                   |     | 0                   |     | 0               |     | ns   |      |

| twp             | WE Pulse Width                          | 120                 |     | 150                 |     | 200             |     | ns   |      |

| twR             | Write Recovery Time                     | 0                   |     | 0                   |     | 0               |     | ns   |      |

| t <sub>DS</sub> | Input Data Set-up Time                  | 120                 |     | 150                 |     | 200             |     | ns   | 1    |

| tDH             | Input Data Hold Time                    | 0                   |     | 0                   |     | 0               |     | ns   |      |

#### Notes

1. Test Note: The F2114 employs a self starting oscillator and a charge pump which require a start-up time of 500  $\mu s$  after V<sub>CC</sub> reaches at least 4.75 V.

3. AC Characteristic Test Conditions:

of 500 µs Input Levels Input Rise and Fall Times Input and Output Timing Levels Output Load 0.8 to 2.0 V 10 ns 1.5 V 1 TTL Gate, and CL = 100 pF

2. Duration not to exceed 30 seconds.

### F2114/2114L

#### Read Mode Timing Diagram, Note 1

#### Write Mode Timing Diagram

#### Notes

- 1. WE must remain HIGH during READ cycles.

- twp is measured from the falling edge of either CS or WE (whichever is the last to go LOW) to the rising edge of either CS or WE (whichever is the first to go HIGH).

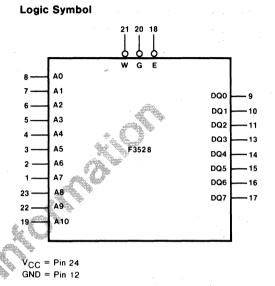

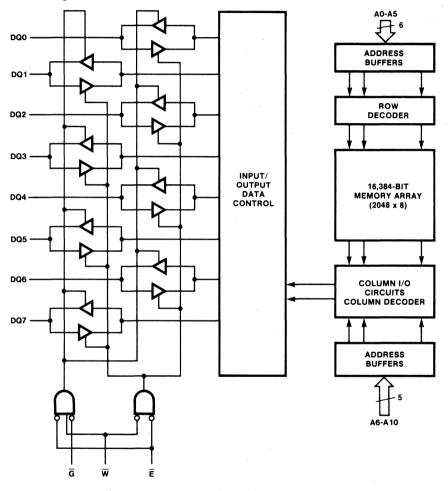

# F3528 2048 x 8 Static RAM

**MOS Memory Products**

#### Description

The F3528 is a 16,384-bit static Random Access Memory (RAM) organized as 2048 words of eight bits each. Since the operation of the F3528 is entirely static, no clocks or refresh are required. This device operates from a single +5 V supply and is directly TTL compatible at all inputs and outputs, including the eight bidirectional data DQ pins. The F3528 has an automatic power-down feature controlled by the Chip Enable function ( $\vec{E}$  = active LOW). When not enabled, the F3528 is in standby mode; this reduces power dissipation by as much as 75% with no degradation of access time.

The F3528 is designed for memory applications where static operation, low cost, large bit-capacity and simple interfacing are important design considerations. It is manufactured using Fairchild's high performance, scaled NMOS technology, Isoplanar-H<sup>™</sup>. State-of-the-art design and process techniques ensure high density, lower power dissipation and excellent speed performance.

The F3528 is available in a standard 24-pin dual in-line package in a configuration that is pin and function compatible with the 2716 ultraviolet erasable PROM.

- 2048 x 8-BIT ORGANIZATION

- COMPLETELY STATIC—NO CLOCKS OR REFRESH

- SINGLE +5 V SUPPLY

- AUTOMATIC POWER DOWN WHEN CHIP NOT ENABLED (E)

- ACCESS TIME 250 ns, 350 ns

- LOW POWER DISSIPATION 450 mW ACTIVE (MAX) 100 mW STANDBY (MAX)

- TOTALLY TTL COMPATIBLE WITH SIMPLE BUS CONTROL

- COMMON DATA I/O BUS WITH 3-STATE CAPABILITY

- PIN/FUNCTION COMPATIBLE WITH 2716

- STANDARD 24-PIN DIP

#### **Pin Names**

| A0-A10  | Address Inputs        |

|---------|-----------------------|

| W       | Write Enable Input    |

| G       | Output Enable Input   |

| Ē       | Chip Enable Input     |

| DQ0-DQ7 | Data Inputs / Outputs |

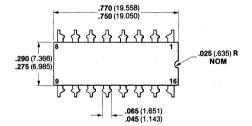

(Top View)

| Package     | Outline | Order Code |

|-------------|---------|------------|

| Ceramic DIP | 7R      | D          |

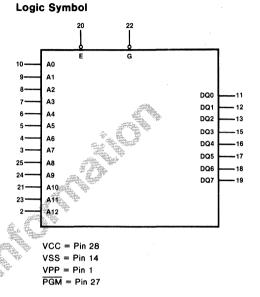

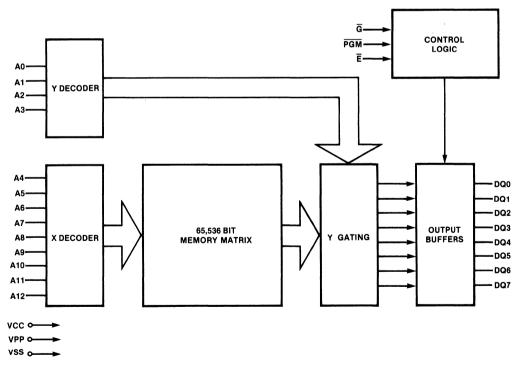

**Block Diagram**

### **Truth Table**

| G | Ē | W  | Modé               | Output | Power   |

|---|---|----|--------------------|--------|---------|

| X | н | X  | Chip Not Enabled   | High Z | Standby |

| н | L | X  | Output Not Enabled | High Z | Active  |

| L | L | H. | Read               | Data   | Active  |

| L | L | L  | Write              | High Z | Active  |

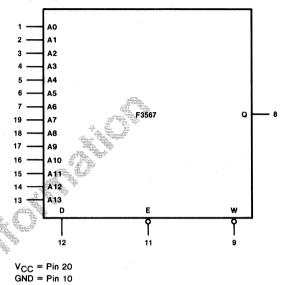

# F3567 16,384 x 1 Static RAM

#### **MOS Memory Products**

#### Description

The F3567 is a 16,384 x 1-bit Random Access Memory (RAM). Its operation is entirely static; therefore, no clocking or refreshing is required. The F3567 offers very fast access and cycle times, requires only a single +5 V power supply and is fully TTL compatible. D and Q functions are available on separate pins.