©1978 Fairchild Camera and Instrument Corporation/464 Ellis Street, Mountain View, California 94042/(415) 962-5011/TWX 910-379-6435 Fairchild reserves the right to make changes in the circuitry or specifications in this book at any time without notice. Manufactured under one of the following U.S. Patents: 2981877, 3015048, 3064167, 3108359, 3117260, other patents pending.

# INTRODUCTION

This TTL DATA BOOK is a complete reference source for all Fairchild semiconductor SSI/MSI TTL products (except Fairchild Advanced Schottky TTL, FAST, devices). It is organized into the following sections:

#### Section 1 - Product Indices and Selection Guides

The Product Indices are divided according to the numbering system used, i.e., 54/74 Family TTL, 9XXX Family TTL, etc. Each index indicates which speed versions are available for the given product number and on which page the data sheet can be found. Selection Guides within this section are divided according to the device function. SSI functions are tabulated by speed family, MSI functions by their significant parameters.

#### Section 2 - TTL Characteristics

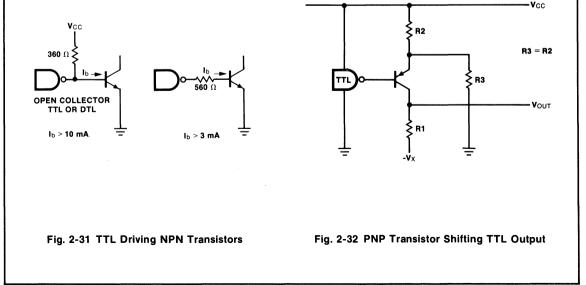

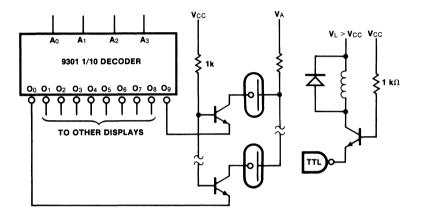

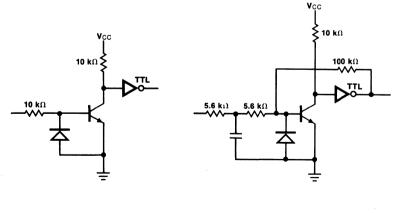

Section 2 defines the dc and ac parameter symbols used throughout this data book and discusses the general scheme for naming the various types of logic inputs and outputs. Speed/power trade-offs and basic gate schematics are compared for the different TTL circuit families. Input/output characteristics, thresholds and noise margins are discussed. Wiring, line driving and decoupling recommendations, as well as specific examples of interfacing TTL to other types of logic circuits, are included.

#### Section 3 - Loading, Specifications and Waveforms

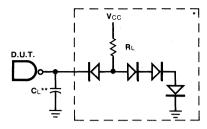

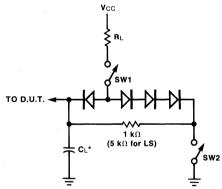

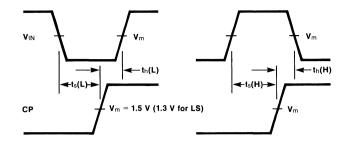

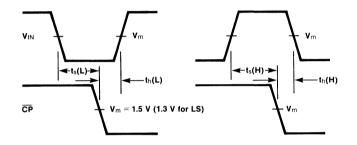

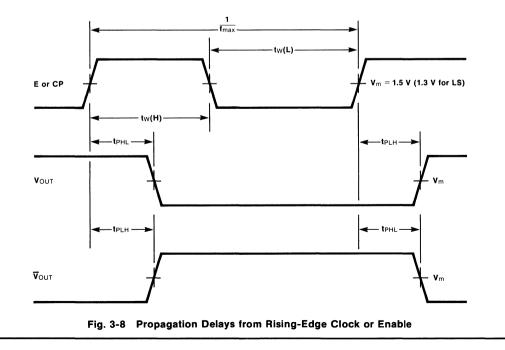

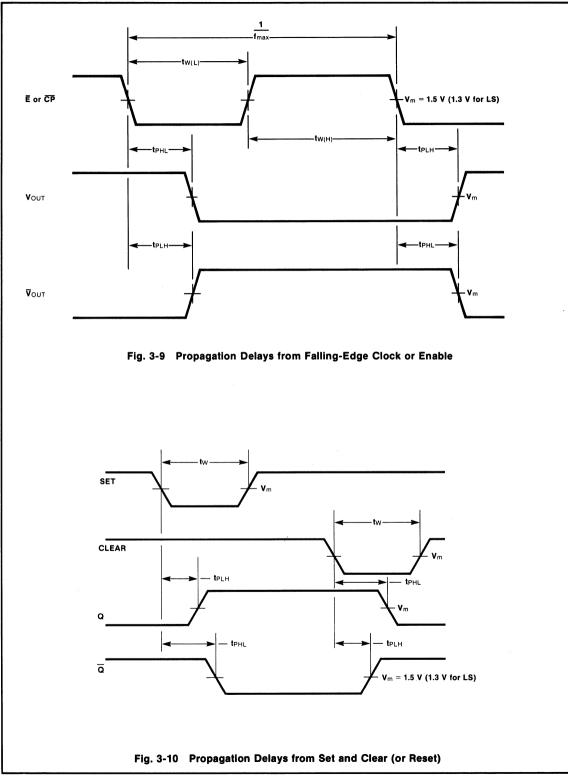

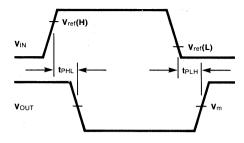

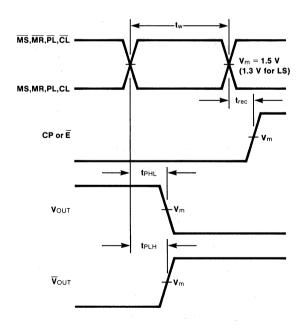

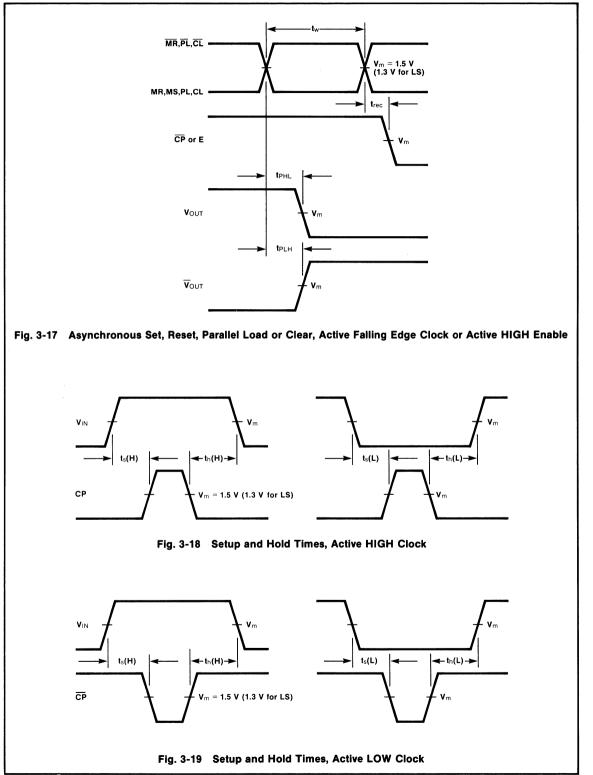

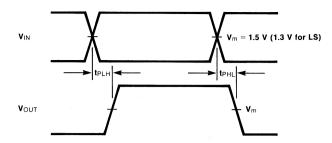

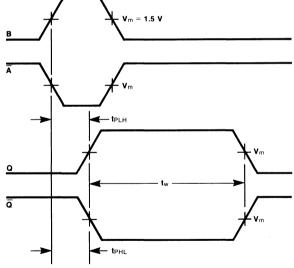

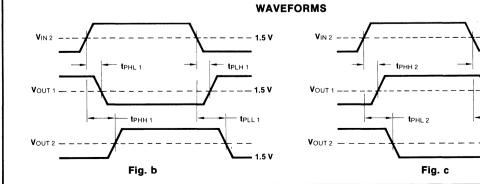

This section contains dc specifications and ratings common to all devices in each family of circuits. Included is a discussion of the unit load method of normalizing the input and output characteristics of a circuit, and how to translate the numbers given in the Input Loading/Fan-Out table of a data sheet into the actual values of  $I_{IH}$ ,  $I_{IL}$ ,  $I_{OH}$  and  $I_{OL}$  currents. The various load configurations for ac testing, a table of  $R_L$  and  $C_L$  values for SSI gates and waveforms that help to define the various ac parameters are also included.

#### Section 4 through 7 - Family Data Sheets

Individual data sheets are grouped by product family (i.e., 54/74, 9XXX TTL, etc.) and arranged in numerical order within these families. The last two digits of the device number are repeated on the outside corner of each page for the convenience of the reader.

#### Section 8 - Other Digital Products

Shortform information on older logic families (DTL, CTL, RTL) is given for reference.

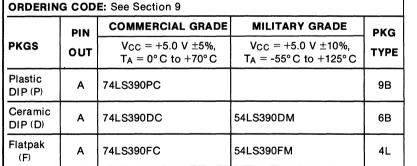

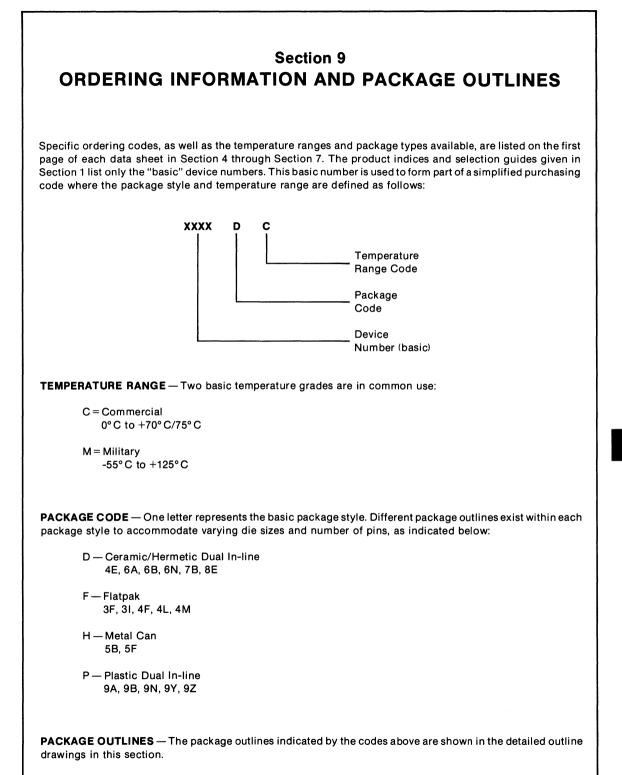

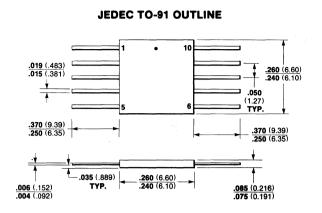

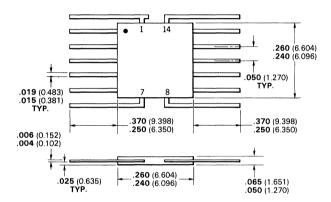

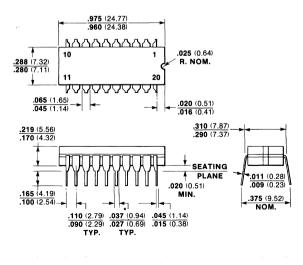

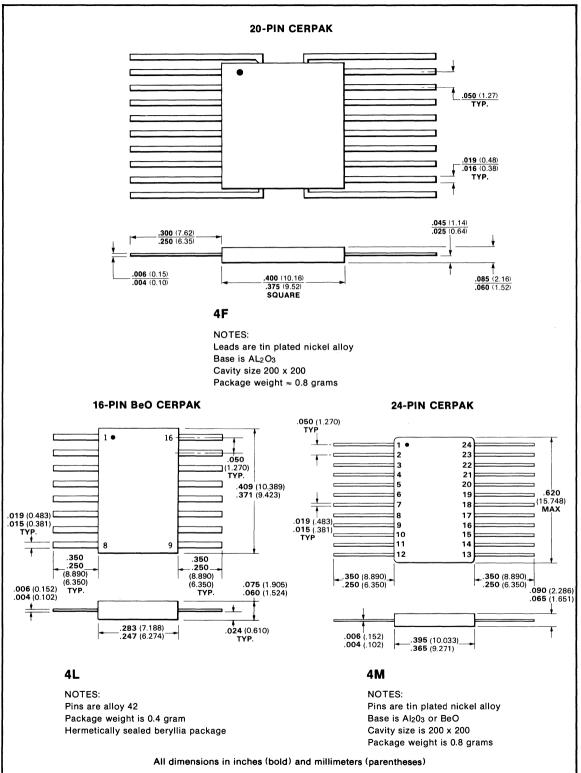

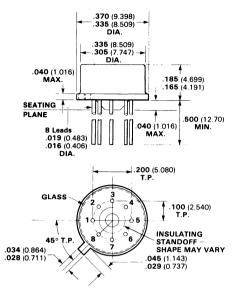

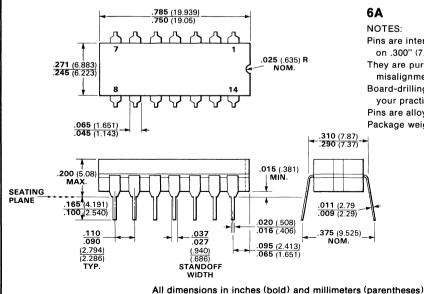

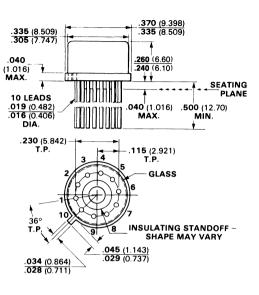

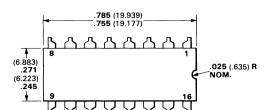

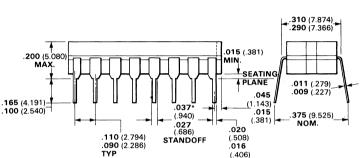

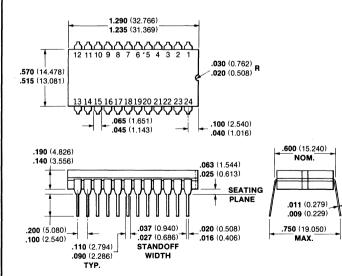

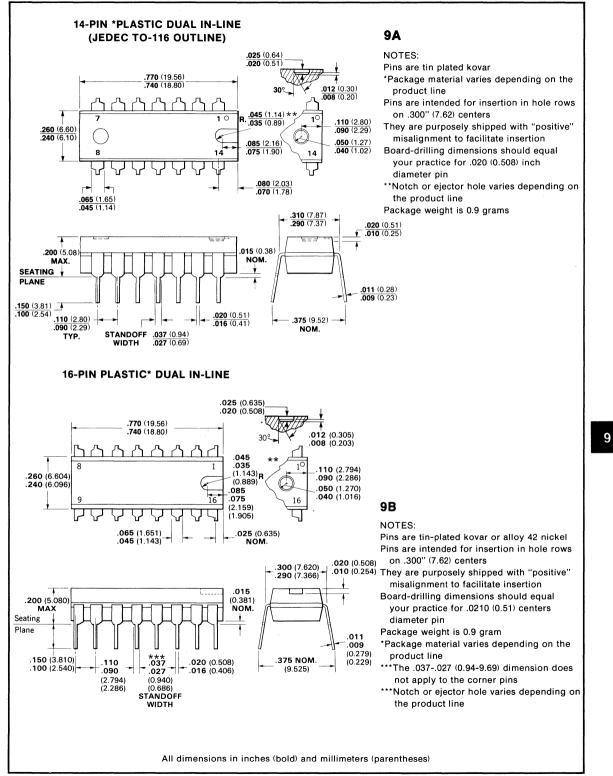

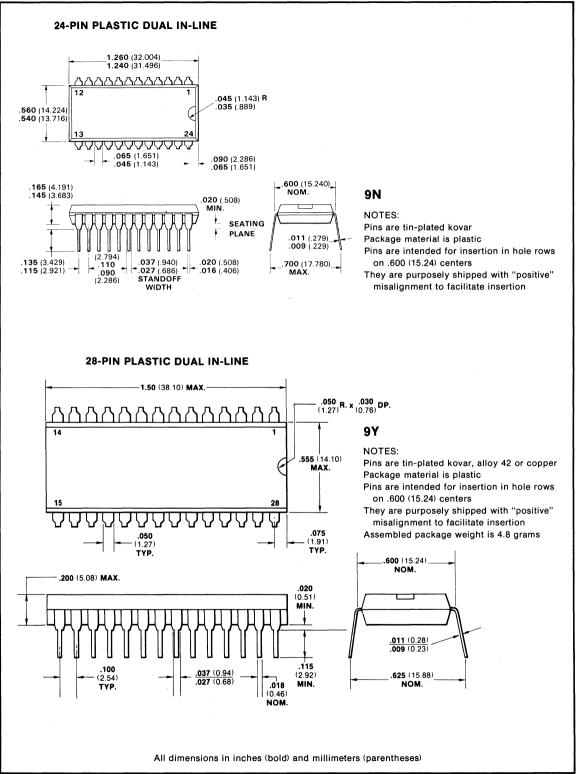

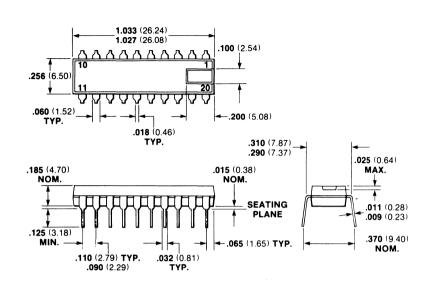

#### Section 9 – Ordering Information and Package Outlines

The simplified purchasing code which identifies not only the device type, but also the package type and temperature range, is explained. Detailed physical dimension drawings for each package are given.

Section 10 – Fairchild Field Sales Offices, Representatives and Distributors

# **TABLE OF CONTENTS**

#### SECTION 1 PRODUCT INDICES AND SELECTION GUIDES

| Indices                                     |      |

|---------------------------------------------|------|

| 54/74 Family TTL                            | 1-3  |

| 9XXX Family TTL                             | 1-10 |

| 93XX Family TTL                             |      |

| 96XX Family TTL                             |      |

| Selection Guides                            |      |

| SSI Functions                               | 1-12 |

| Single and Dual Flip-Flops                  |      |

| Latches                                     | 1-16 |

| Multiple Flip-Flops                         |      |

| Multiplexers                                |      |

| Decoders/Demultiplexers                     |      |

| Registers                                   |      |

| Counters                                    |      |

| Monostables (One-Shots)                     |      |

| Line and Bus Drivers/Transceivers/Receivers |      |

| Display Decoder/Drivers                     |      |

| Arithmetic Operators                        |      |

| Random Access Memories                      |      |

|                                             |      |

#### SECTION 2 TTL CHARACTERISTICS

| Glossary                       | ;  | 2-3 |

|--------------------------------|----|-----|

| Logic Symbols and Terminology  | ;  | 2-6 |

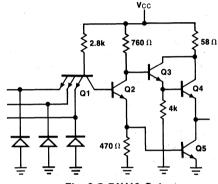

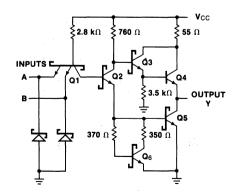

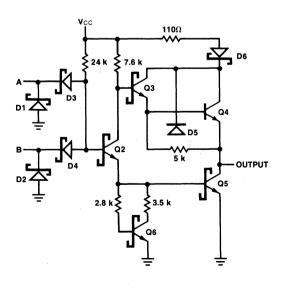

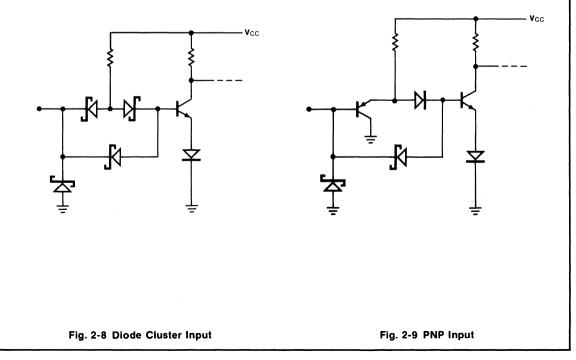

| TTL Circuit Families           | :  | 2-8 |

| Input Characteristics          | 2- | -12 |

| Unused Inputs                  | 2- | -13 |

| Output Characteristics         | 2- | -13 |

| Increasing Fan-Out             | 2- | -15 |

| 3-State Outputs                | 2. | -15 |

| Open-Collector Outputs         | 2- | -16 |

| Thresholds and Noise Margins   |    |     |

| Crosstalk                      |    |     |

| Transmission Lines             |    |     |

| Transmission Line Effects      |    |     |

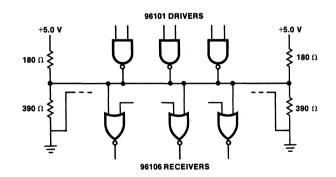

| Backplane Data Bus             |    |     |

| Decoupling                     |    |     |

| Grounds                        |    |     |

| Supply Voltage and Temperature |    |     |

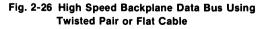

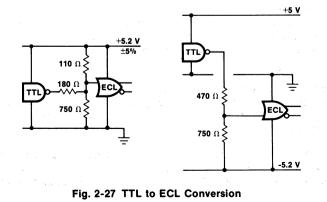

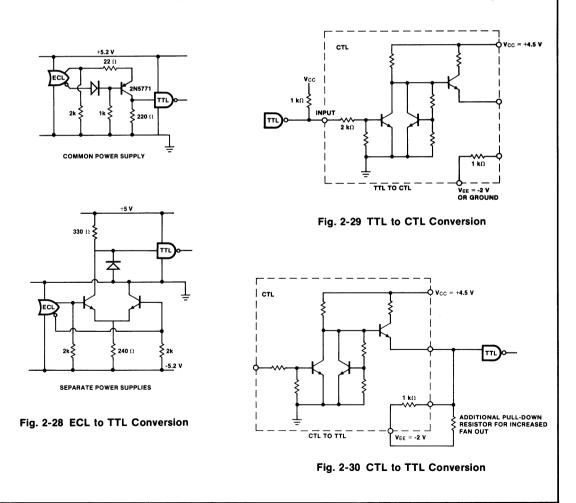

| Interfacing                    | 2. | -25 |

|                                |    |     |

#### SECTION 3 LOADING, SPECIFICATIONS AND WAVEFORMS

| Unit Loads (U.L.)                |      |

|----------------------------------|------|

| Absolute Maximum Ratings         |      |

| Recommended Operating Conditions |      |

| DC Characteristics Tables        |      |

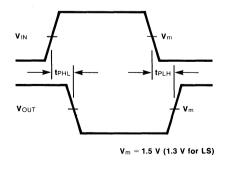

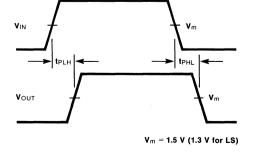

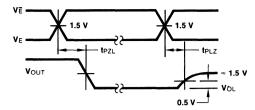

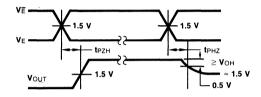

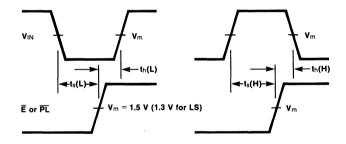

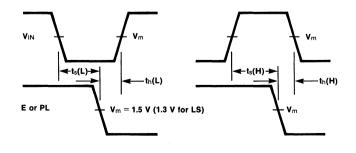

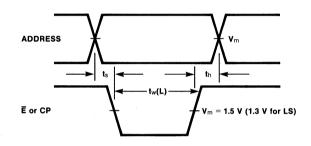

| AC Loading and Waveforms         | 3-11 |

| SECTIC | )N 4   | 54/74 FAMILY DATA SHEETS                      | 4-3  |

|--------|--------|-----------------------------------------------|------|

| SECTIC | )N 5   | 9XXX FAMILY DATA SHEETS                       | 5-3  |

| SECTIC | )N 6   | 93XX FAMILY DATA SHEETS                       | 6-3  |

| SECTIC | )N 7   | 96XX FAMILY DATA SHEETS                       | 7-3  |

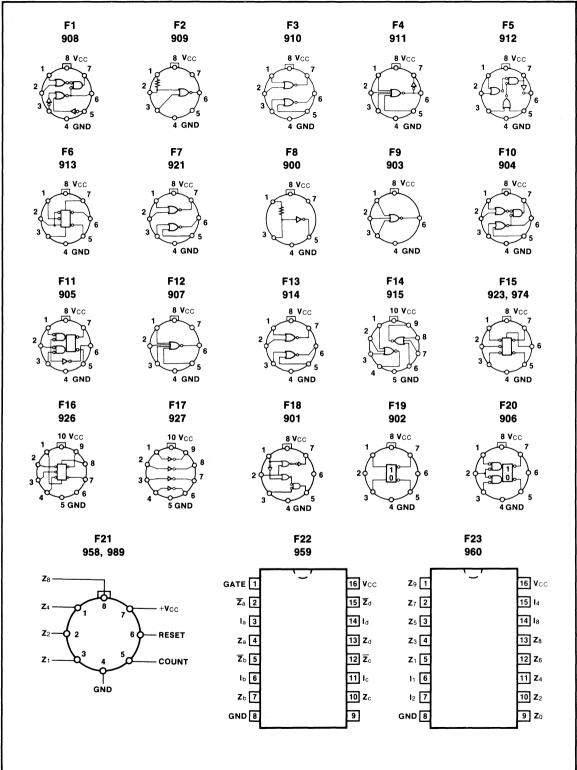

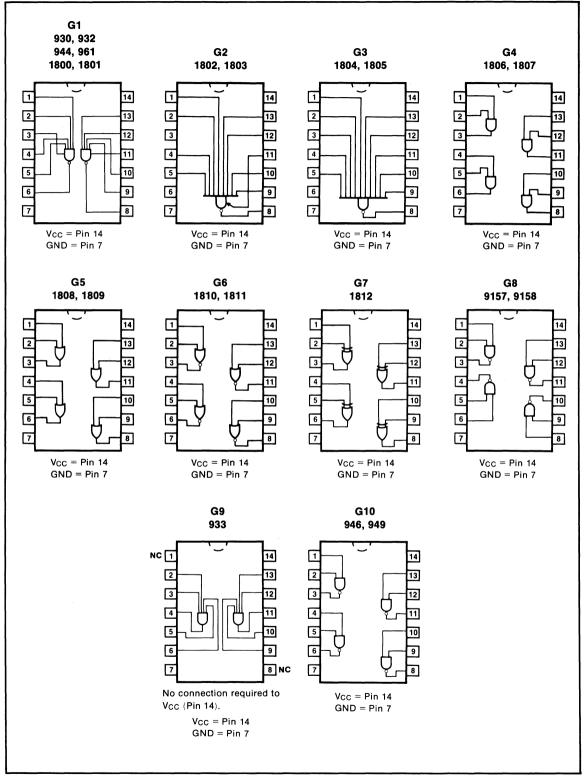

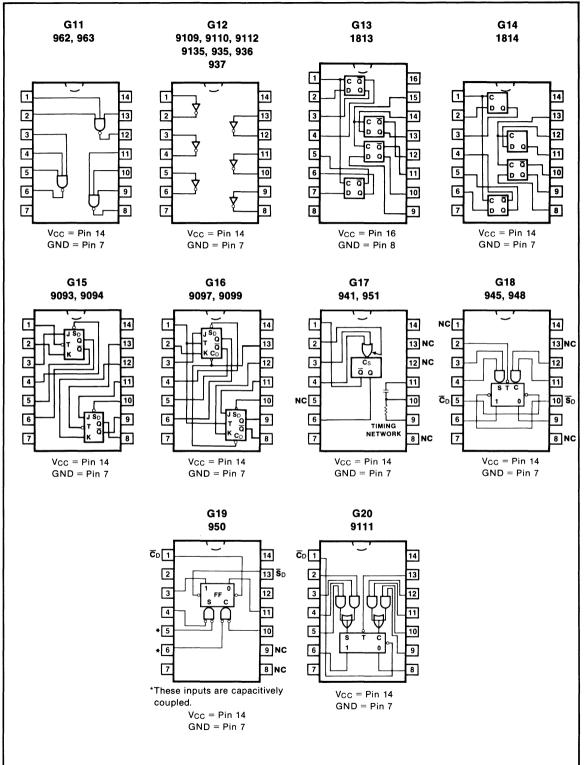

| SECTIC | N 8    | OTHER DIGITAL PRODUCTS                        |      |

| R      | TL Mi  | crologic and CTL Counting Micrologic Elements | 8-3  |

| D      | TL Mi  | crologic and CTL Counting Micrologic Elements | 8-3  |

|        |        | ORDERING INFORMATION AND PACKAGE OUTLINES     |      |

| C      | rderin | g Information                                 | 9-3  |

| P      | ackag  | e Outlines                                    | 9-4  |

| SECTIC | N 10   |                                               | 10-3 |

## PRODUCT INDICES AND 1 SELECTION GUIDES 2 TTL CHARACTERISTICS LOADING, SPECIFICATIONS AND 3 WAVEFORMS 54/74 FAMILY DATA SHEETS 4 9000 FAMILY DATA SHEETS 5 9300 FAMILY DATA SHEETS 6 9600 FAMILY DATA SHEETS 7 OTHER DIGITAL PRODUCTS 8 ORDERING INFORMATION AND 9 PACKAGE OUTLINES FAIRCHILD FIELD SALES OFFICES, REPRESENTATIVES AND DISTRIBUTORS 10

#### **SECTION 1**

- Indices

54/74 Family TTL

9XXX Family TTL

93XX Family TTL

96XX Family TTL

- Selection Guides

SSI Functions

Single and Dual Flip-Flops

Latches

Multiple Flip-Flops

Multiplexers

Decoders/Demultiplexers

Registers

Counters

Monostables (One-Shots)

Line and Bus Drivers/Transceivers/Receivers

Display Decoder/Drivers

Arithmetic Operators

Random Access Memories

# Section 1 PRODUCT INDICES AND SELECTION GUIDES

## INDICES

| DEVICE<br>NO. | DESCRIPTION                      | 54/74<br>TTL | 54H/74H<br>H-TTL | 54S/74S<br>S-TTL | 54LS/74LS<br>LS-TTL | PAGE<br>NO. |

|---------------|----------------------------------|--------------|------------------|------------------|---------------------|-------------|

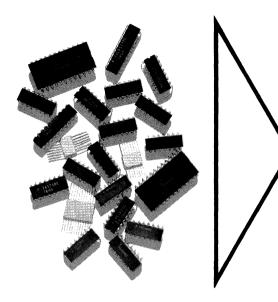

| 00            | Quad 2-Input NAND Gate           | x            | x                | х                | x                   | 4-3         |

| 01            | Quad 2-Input NAND Gate           | x            | x                |                  |                     | 4-4         |

| 02            | Quad 2-Input NOR Gate            | x            |                  | х                | X                   | 4-5         |

| 03            | Quad 2-Input NAND Gate           | x            |                  | х                | x                   | 4-6         |

| 04            | Hex Inverter                     | x            | x                | х                | x                   | 4-7         |

| 04A           | Hex Inverter                     |              |                  | х                |                     | 4-7         |

| 05            | Hex Inverter                     | x            | х                | х                | x                   | 4-8         |

| 05A           | Hex Inverter                     |              |                  | х                |                     | 4-8         |

| 06            | Hex Inverter Buffer/Driver       | x            |                  |                  |                     | 4-9         |

| 07            | Hex Buffer/Driver                | x            |                  |                  |                     | 4-10        |

| 08            | Quad 2-Input AND Gate            | x            | x                | х                | x                   | 4-11        |

| 09            | Quad 2-Input AND Gate            | x            |                  | х                | x                   | 4-12        |

| 10            | Triple 3-Input NAND Gate         | x            | x                | х                | x                   | 4-13        |

| 11            | Triple 3-Input AND Gate          | x            | X                | х                | x                   | 4-14        |

| 12            | Triple 3-Input NAND Gate         | x            |                  |                  |                     | 4-15        |

| 13            | Dual 4-Input Schmitt Trigger     | x            |                  |                  | x                   | 4-16        |

| 14            | Hex Schmitt Trigger Inverter     | x            |                  |                  | x                   | 4-17        |

| 15            | Triple 3-Input AND Gate          |              |                  | x                | x                   | 4-18        |

| 16            | Hex Inverter Buffer/Driver       | x            |                  |                  |                     | 4-19        |

| 17            | Hex Buffer/Driver                | x            |                  | \<br>\           |                     | 4-20        |

| 20            | Dual 4-Input NAND Gate           | x            | X                | x                | X                   | 4-21        |

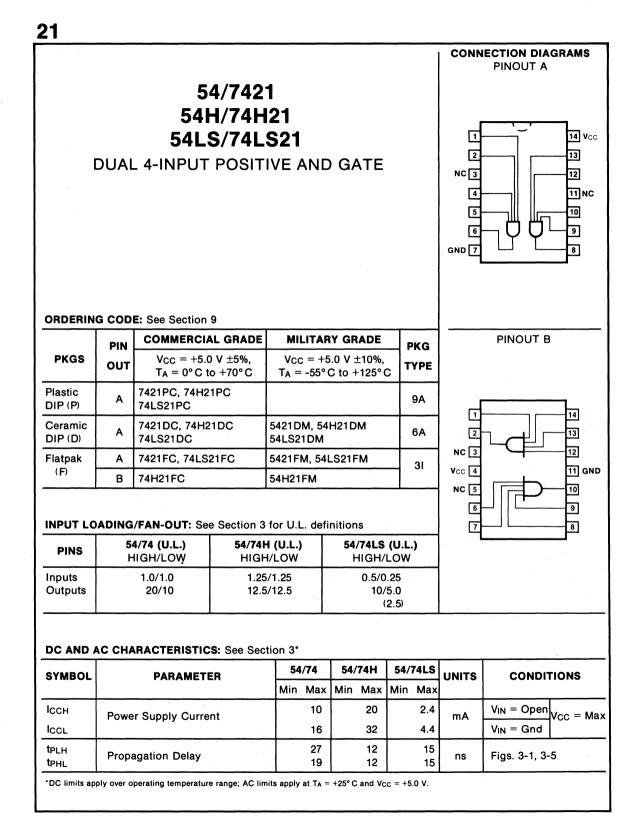

| 21            | Dual 4-Input Positive AND Gate   | x            | x                |                  | x                   | 4-22        |

| 22            | Dual 4-Input NAND Gate           | x            | X                | x                | X                   | 4-23        |

| 23            | Expandable Dual 4-Input NOR Gate | x            |                  |                  |                     | 4-24        |

| 25            | Dual 4-Input NOR Gate            | x            |                  |                  |                     | 4-26        |

| 26            | Quad 2-Input NAND Buffer         | x            |                  |                  | x                   | 4-27        |

| 27            | Triple 3-Input NOR Gate          | ×            |                  |                  | x                   | 4-28        |

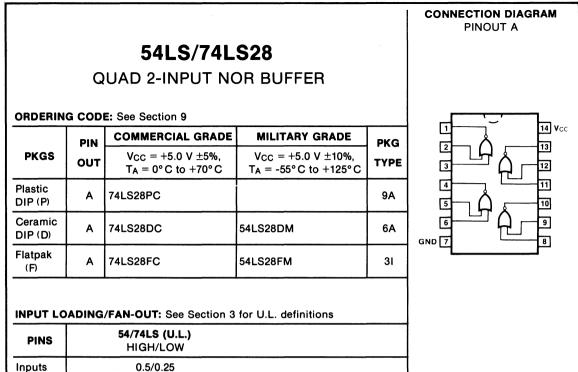

| 28            | Quad 2-Input NOR Buffer          |              |                  |                  | X                   | 4-29        |

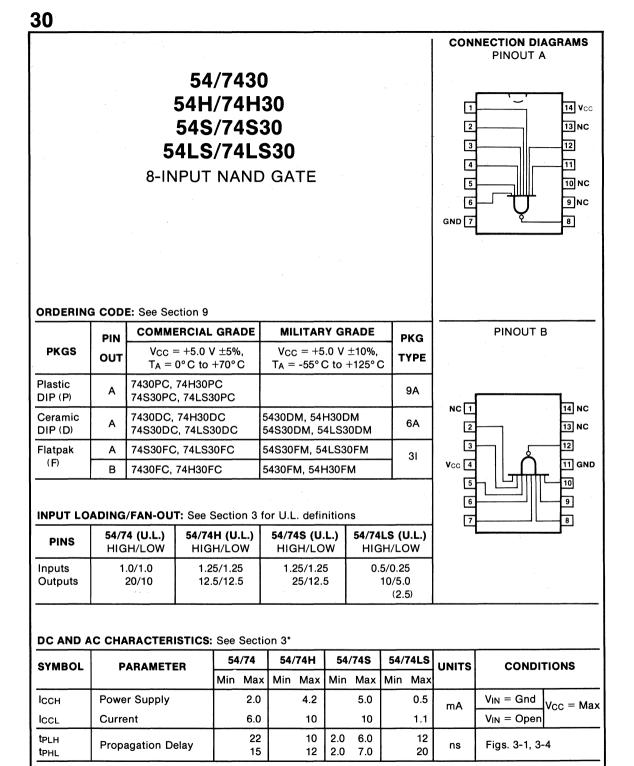

| 30            | 8-Input NAND Gate                | x            | X                | х                | x                   | 4-30        |

#### 54/74 FAMILY TTL

1

| DEVICE<br>NO. | DESCRIPTION                                           | 54/74<br>TTL | 54H/74H<br>H-TTL | 54S/74S<br>S-TTL | 54LS/74LS<br>LS-TTL | PAGE<br>NO. |

|---------------|-------------------------------------------------------|--------------|------------------|------------------|---------------------|-------------|

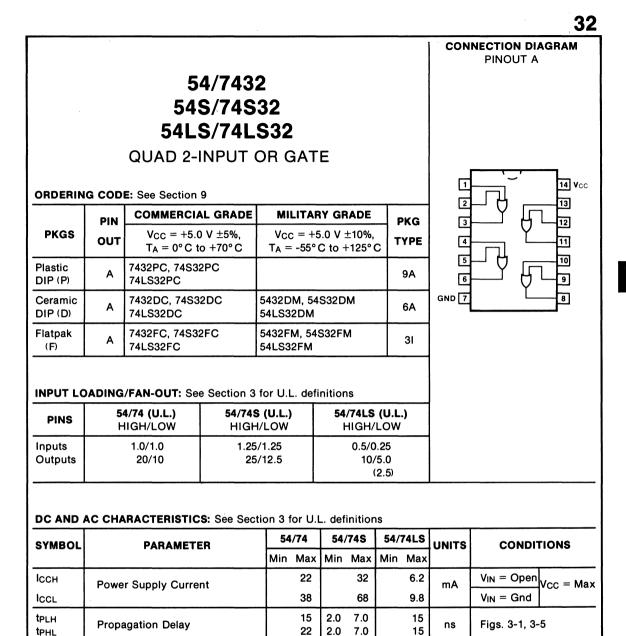

| 32            | Quad 2-Input OR Gate                                  | х            |                  | х                | x                   | 4-31        |

| 33            | Quad 2-Input NOR Buffer                               |              |                  |                  | x                   | 4-32        |

| 37            | Quad 2-Input NAND Buffer                              | х            |                  |                  | x                   | 4-33        |

| 38            | Quad 2-Input NAND Buffer                              | х            |                  |                  | x                   | 4-34        |

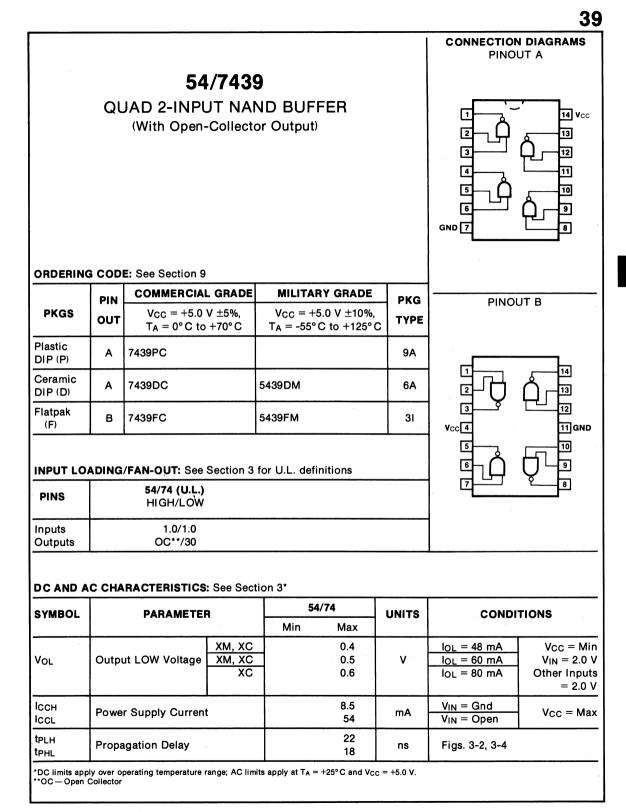

| 39            | Quad 2-Input NAND Buffer                              | х            |                  |                  |                     | 4-35        |

| 40            | Dual 4-Input NAND Buffer                              | х            | X                | х                | x                   | 4-36        |

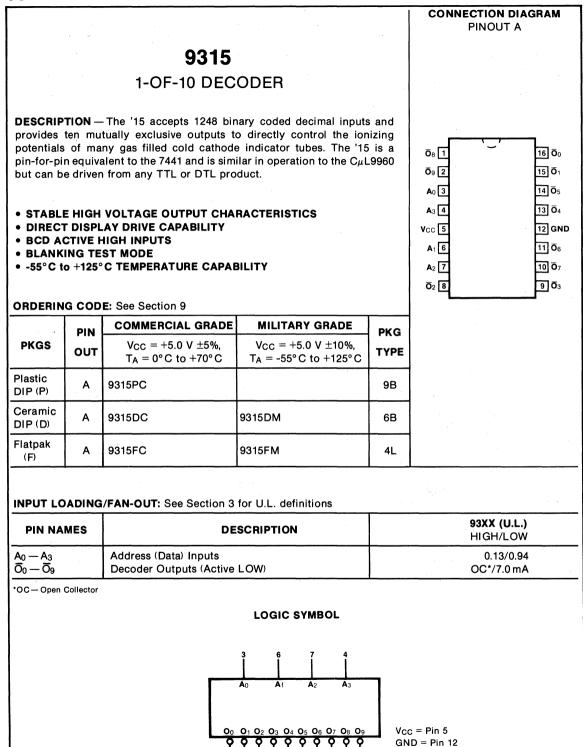

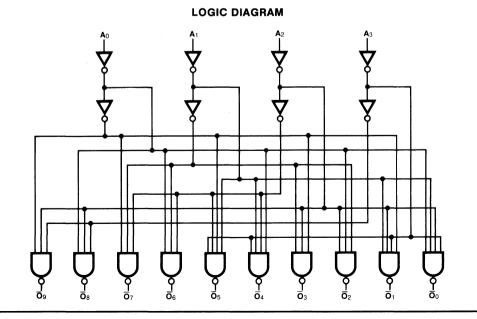

| 41            | 1-of-10 Decoder/Driver (Nixie)                        | 9315         |                  |                  |                     | 6-48        |

| 42            | 1-of-10 Decoder                                       |              |                  |                  | x                   | 4-37        |

| 42A           | 1-of-10 Decoder                                       | х            |                  |                  |                     | 4-37        |

| 43A           | 1-of-10 Decoder                                       | х            |                  |                  |                     | 4-37        |

| 44A           | 1-of-10 Decoder                                       | х            |                  |                  |                     | 4-37        |

| 45            | 1-of-10 Decoder/Driver                                | х            |                  |                  |                     | 4-41        |

| 46A           | BCD to 7-Segment Decoder/Driver                       | х            |                  |                  |                     | 4-44        |

| 47            | BCD to 7-Segment Decoder/Driver                       |              |                  |                  | x                   | 4-44        |

| 47A           | BCD to 7-Segment Decoder/Driver                       | х            |                  |                  |                     | 4-44        |

| 48            | BCD to 7-Segment Decoder                              | X            |                  |                  | x                   | 4-48        |

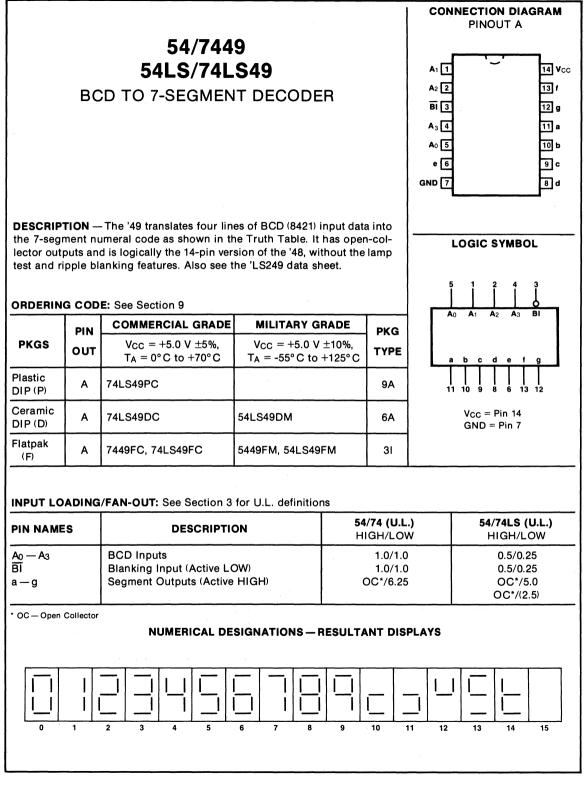

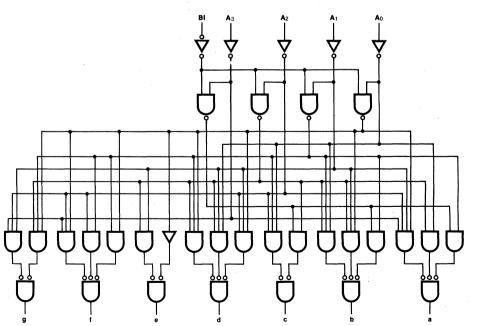

| 49            | BCD to 7-Segment Decoder                              | х            |                  |                  | x                   | 4-51        |

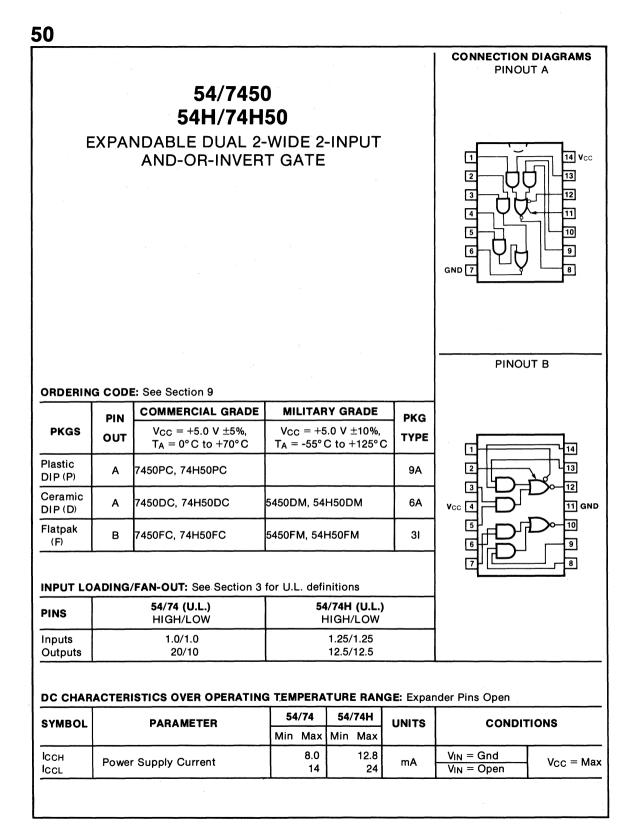

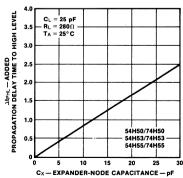

| 50            | Expandable Dual 2-Wide,<br>2-Input AND-OR-Invert Gate | х            | x                |                  |                     | 4-54        |

| 51            | Dual 2-Wide AND-OR-Invert Gate                        | х            | X                | х                | x                   | 4-56        |

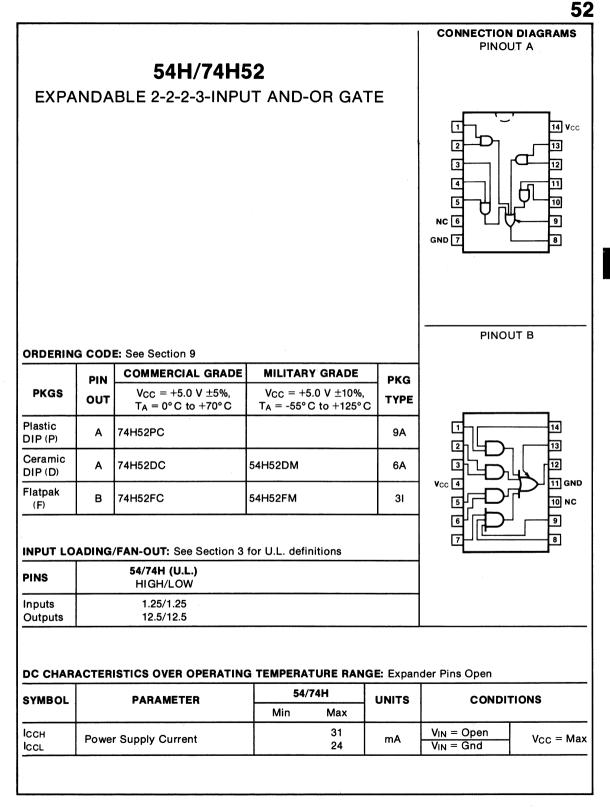

| 52            | Expandable 2-2-2-3-Input<br>AND-OR Gate               |              | x                |                  |                     | 4-57        |

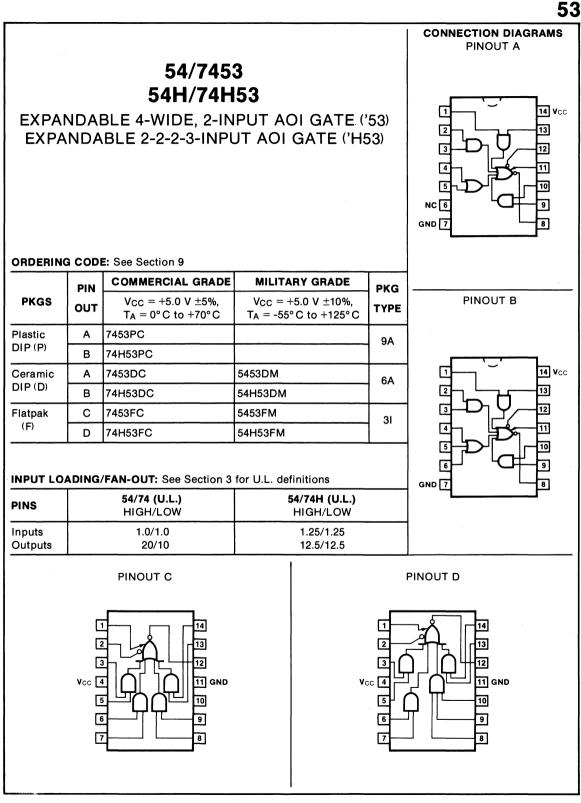

| 53            | Expandable AND-OR-Invert Gate                         | х            | x                |                  |                     | 4-59        |

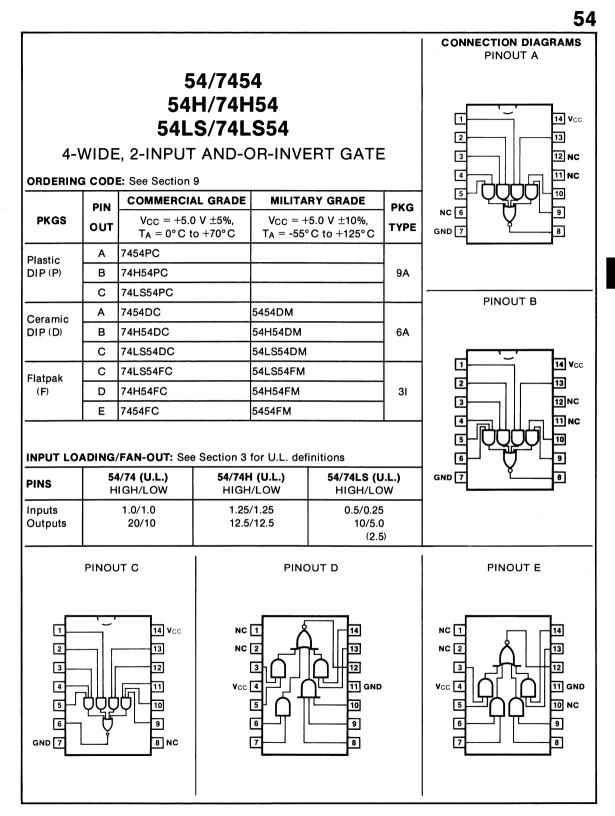

| 54            | 4-Wide, 2-Input AND-OR-Invert Gate                    | х            | x                |                  | X                   | 4-61        |

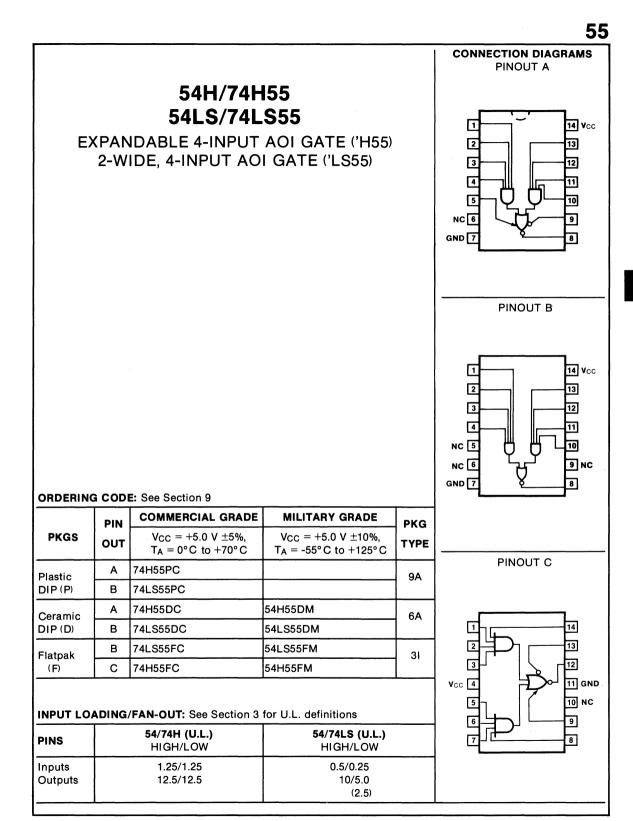

| 55            | AND-OR-Invert Gate                                    |              | x                |                  | X                   | 4-63        |

| 60            | Dual 4-Input Expander                                 | х            | x                |                  |                     | 4-64        |

| 61            | Triple 3-Input Expander                               |              | x                |                  |                     | 4-67        |

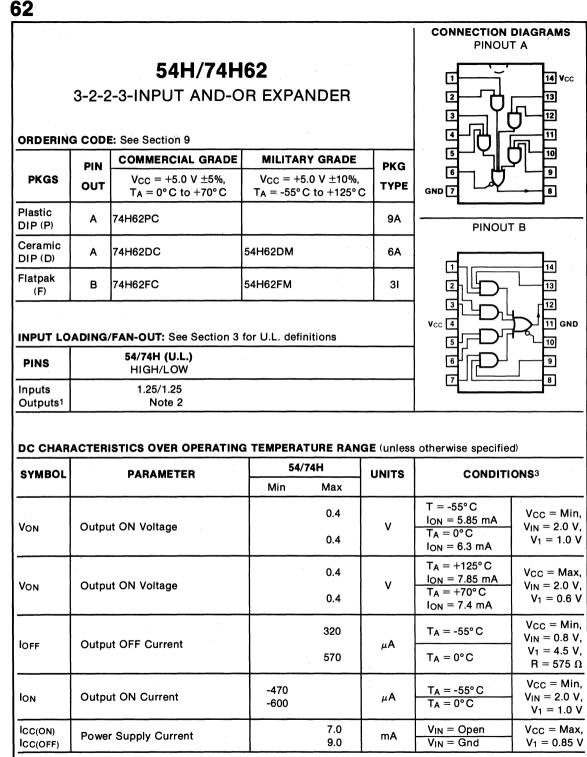

| 62            | 3-2-2-3-Input AND-OR Expander                         |              | X                |                  |                     | 4-68        |

| 64            | 4-2-3-2-Input AND-OR-Invert Gate                      |              |                  | х                |                     | 4-70        |

| 65            | 4-2-3-2-Input AND-OR-Invert Gate                      |              |                  | х                |                     | 4-71        |

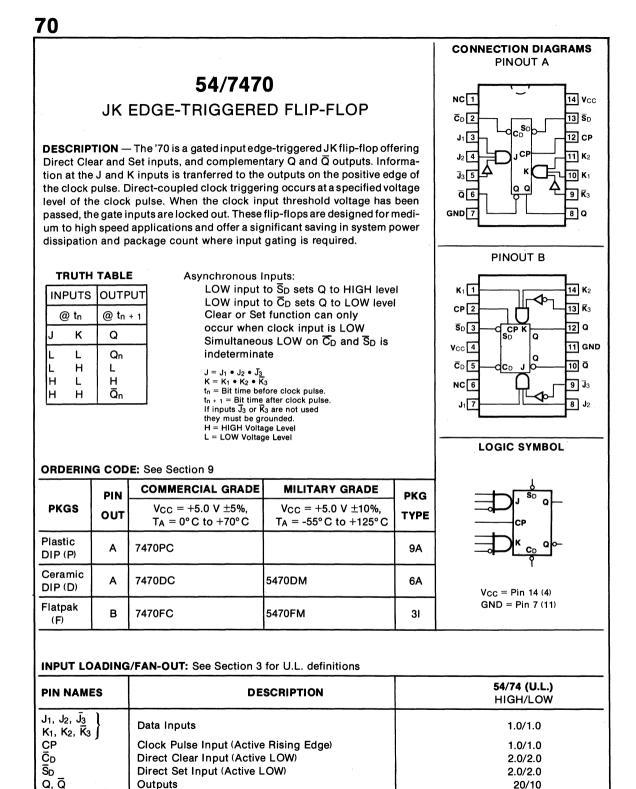

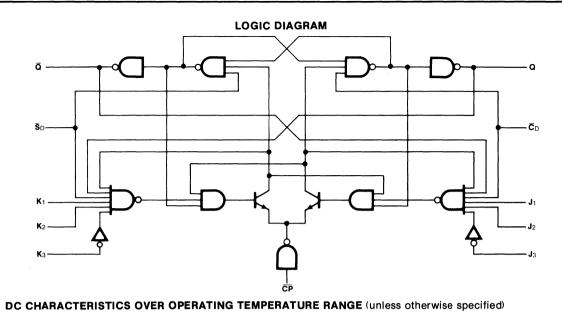

| 70            | JK Edge-Trigger Flip-Flop                             | x            |                  |                  |                     | 4-72        |

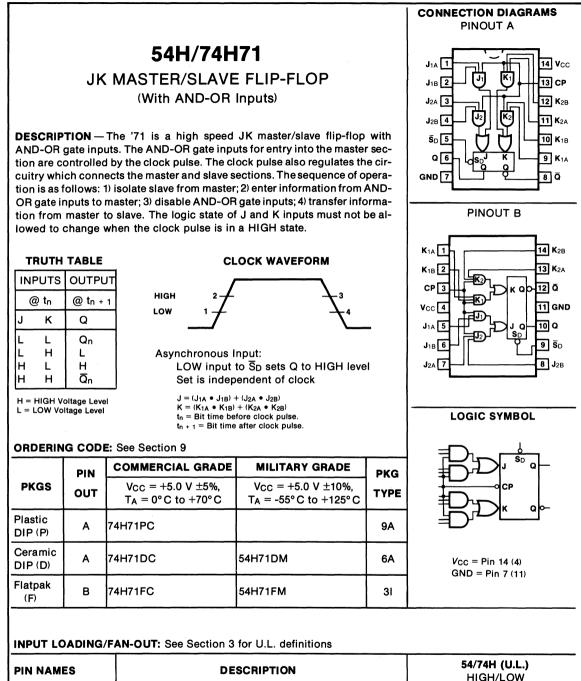

| 71            | JK Master/Slave Flip-Flop                             |              | x                |                  |                     | 4-74        |

| 72            | JK Master/Slave Flip-Flop                             | X            | X                |                  |                     | 4-76        |

| 73            | Dual JK Flip-Flop                                     | х            | X                |                  | x                   | 4-78        |

| DEVICE<br>NO. | DESCRIPTION                                      | 54/74<br>TTL | 54H/74H<br>H-TTL | 54S/74S<br>S-TTL | 54LS/74LS<br>LS-TTL | PAGE<br>NO. |

|---------------|--------------------------------------------------|--------------|------------------|------------------|---------------------|-------------|

| 74            | Dual D-Type Positive<br>Edge-Triggered Flip-Flop | x            | x                | x                | x                   | 4-81        |

| 75            | 4-Bit Bistable Latch                             | x            |                  |                  |                     | 4-84        |

| 76            | Dual JK Flip-Flop                                | x            | x                |                  | х                   | 4-86        |

| 77            | Quad D-Type Latch                                | x            |                  |                  |                     | 4-89        |

| 78            | Dual JK Flip-Flop                                |              | x                |                  | х                   | 4-90        |

| 80            | Gated Full Adder                                 | x            |                  |                  |                     | 4-93        |

| 82            | 2-Bit Full Adder                                 | x            |                  |                  |                     | 4-95        |

| 83A           | 4-Bit Binary Full Adder                          | x            |                  |                  | х                   | 4-98        |

| 85            | 4-Bit Magnitude Comparator                       | x            |                  |                  | х                   | 4-10        |

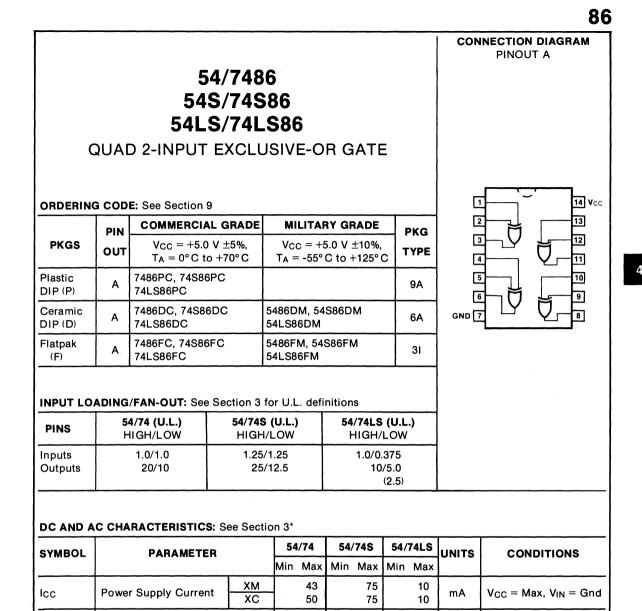

| 86            | Quad 2-Input Exclusive-OR Gate                   | x            |                  | х                | х                   | 4-10        |

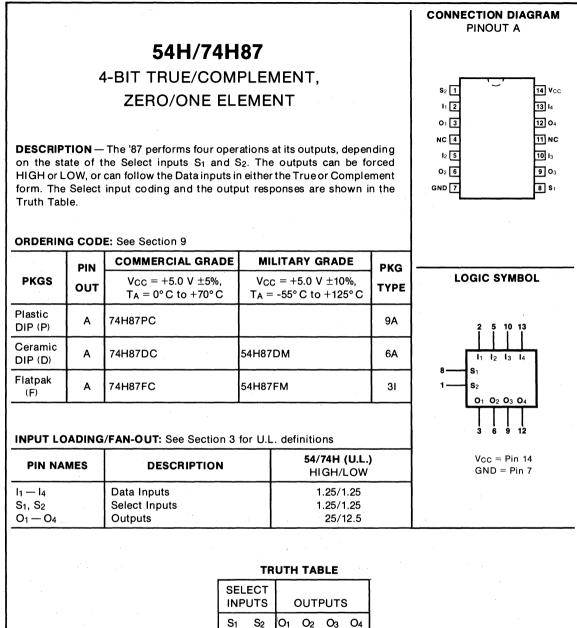

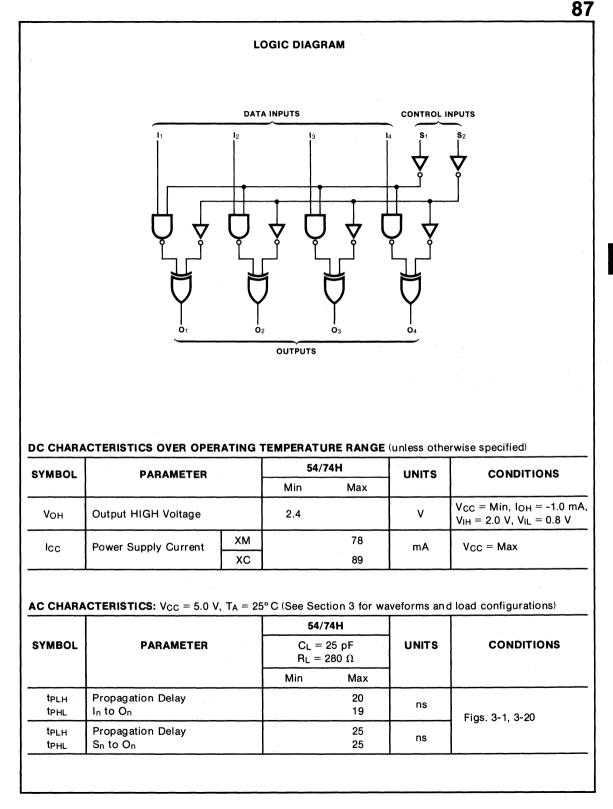

| 87            | 4-Bit True/Complement,<br>Zero/One Element       |              | x                |                  |                     | 4-10        |

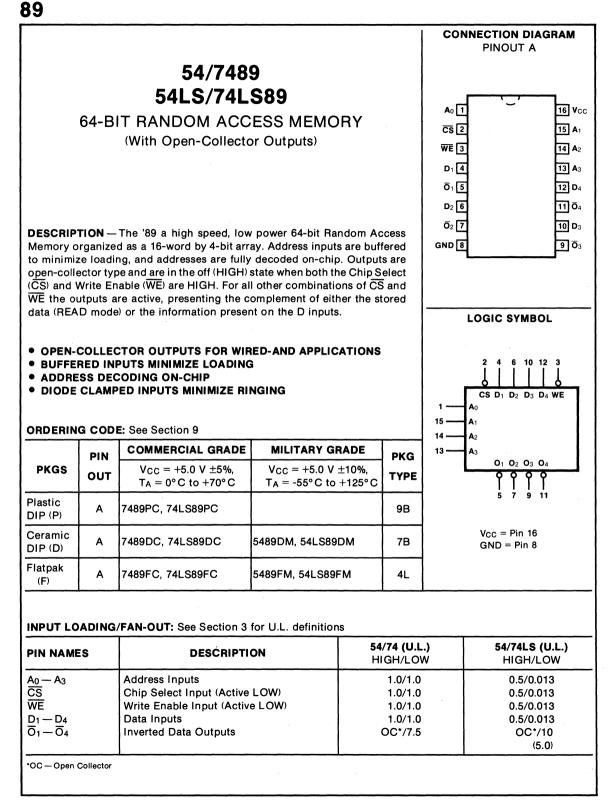

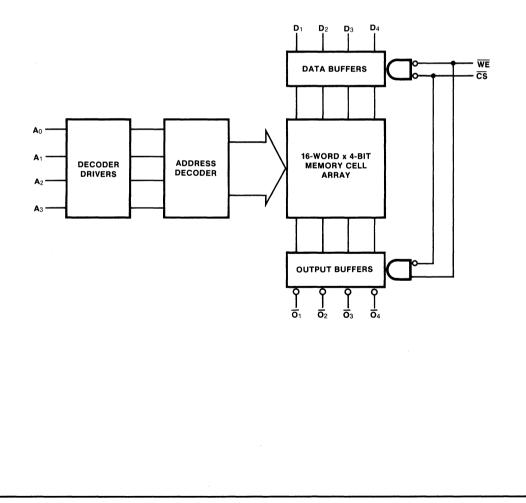

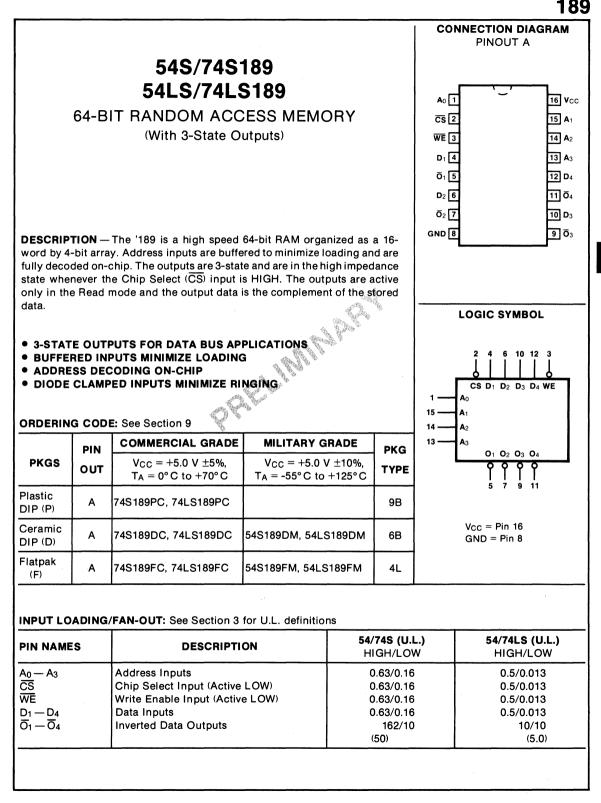

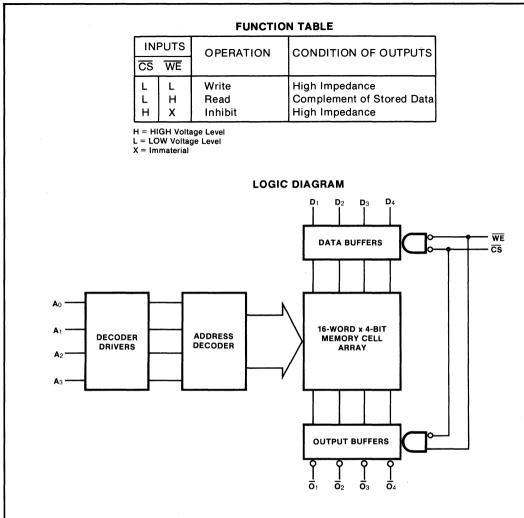

| 89            | 64-Bit Random Access Memory                      | X            |                  |                  | х                   | 4-10        |

| 90            | Decade Counter                                   |              |                  |                  | х                   | 4-11        |

| 90A           | Decade Counter                                   | x            |                  |                  |                     | 4-11        |

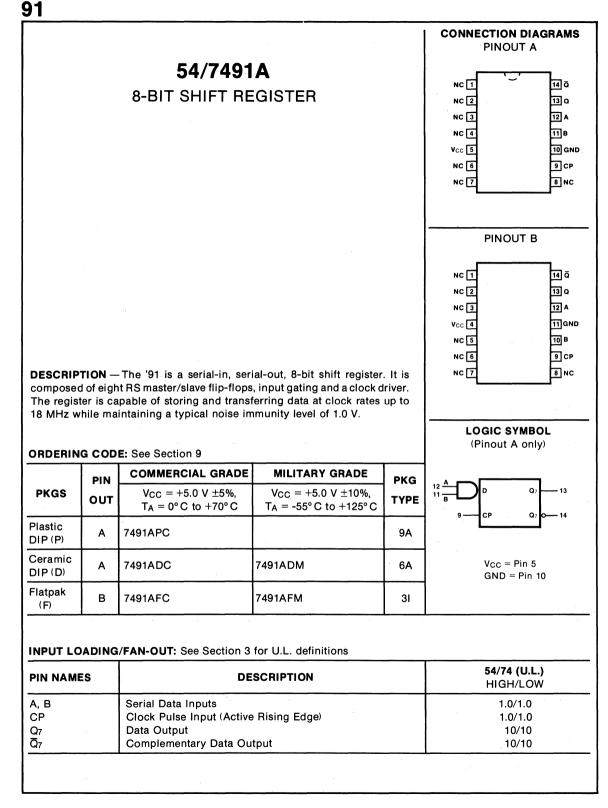

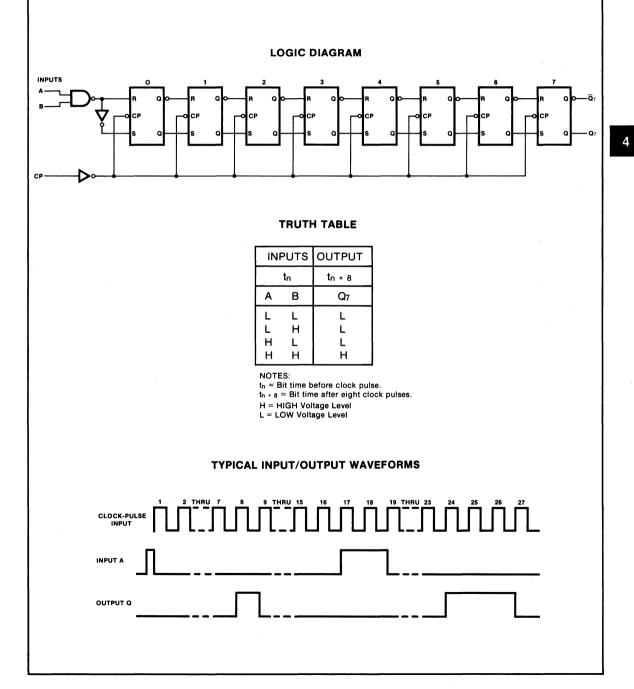

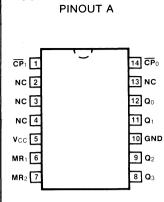

| 91A           | 8-Bit Shift Register                             | x            |                  |                  |                     | 4-11        |

| 92            | Divide-by-Twelve Counter                         |              |                  |                  | х                   | 4-11        |

| 92A           | Divide-by-Twelve Counter                         | X            |                  |                  |                     | 4-11        |

| 93            | Divide-by-Sixteen Counter                        |              |                  |                  | х                   | 4-12        |

| 93A           | Divide-by-Sixteen Counter                        | X            |                  |                  |                     | 4-12        |

| 94            | 4-Bit Shift Register                             | X            |                  |                  |                     | 4-12        |

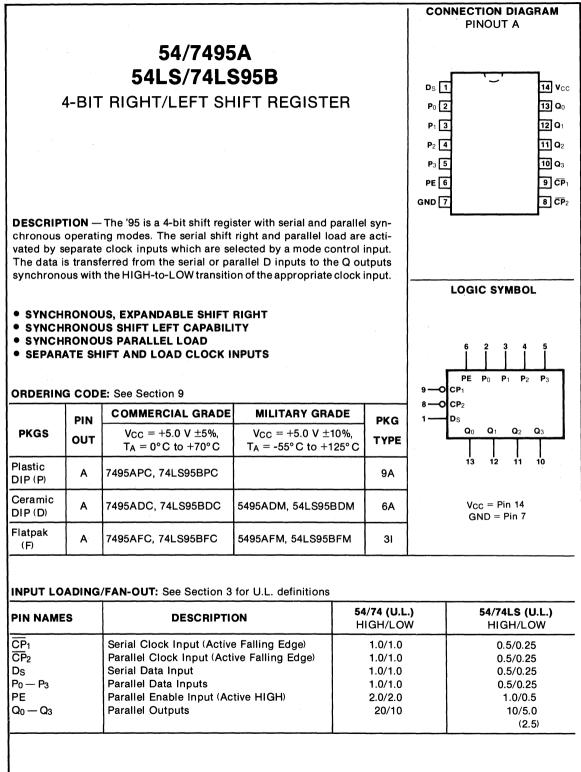

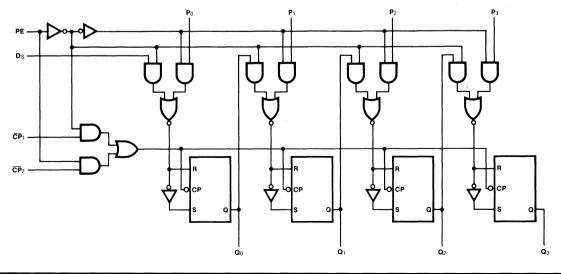

| 95A           | 4-Bit Right/Left Shift Register                  | X            |                  |                  |                     | 4-12        |

| 95B           | 4-Bit Right/Left Shift Register                  |              |                  |                  | х                   | 4-12        |

| 96            | 5-Bit Shift Register                             | X            |                  |                  |                     | 4-12        |

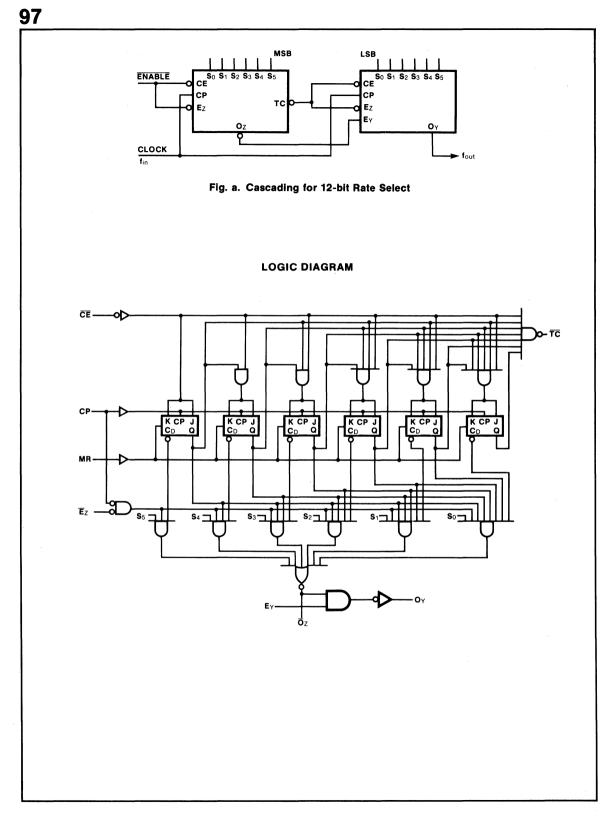

| 97            | Synchronous Modulo-64<br>Bit Rate Multiplier     | x            |                  |                  |                     | 4-13        |

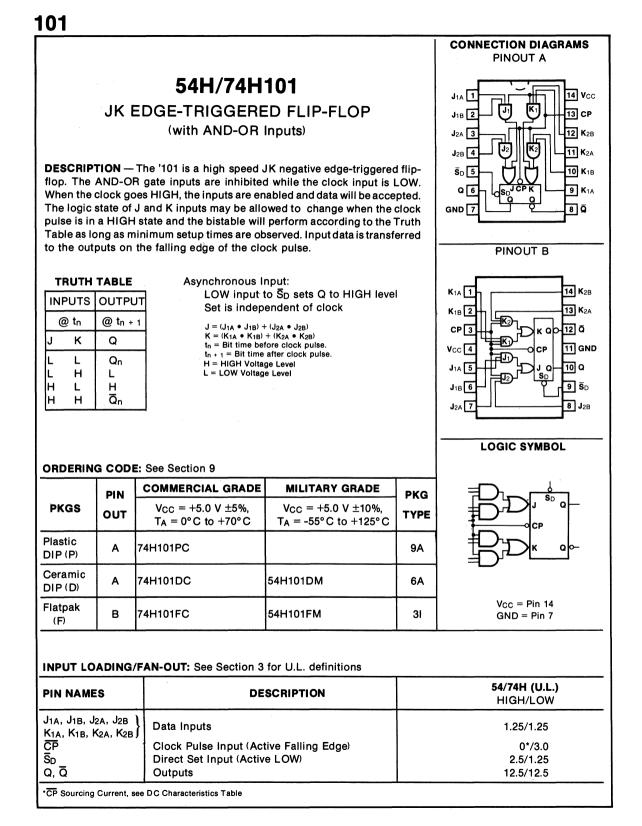

| 101           | JK Edge-Triggered Flip-Flop                      |              | x                |                  |                     | 4-13        |

| 102           | JK Edge-Triggered Flip-Flop                      |              | x                |                  |                     | 4-14        |

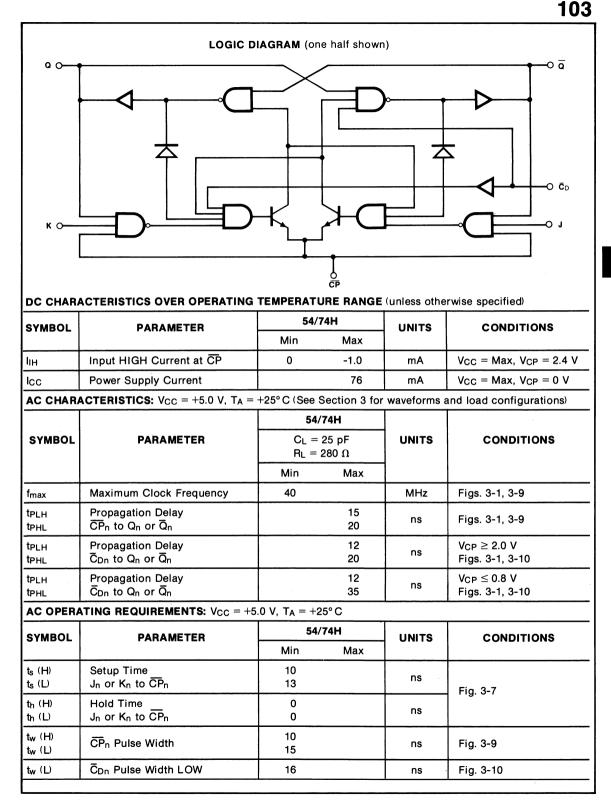

| 103           | Dual JK Edge-Triggered Flip-Flop                 |              | x                |                  |                     | 4-14        |

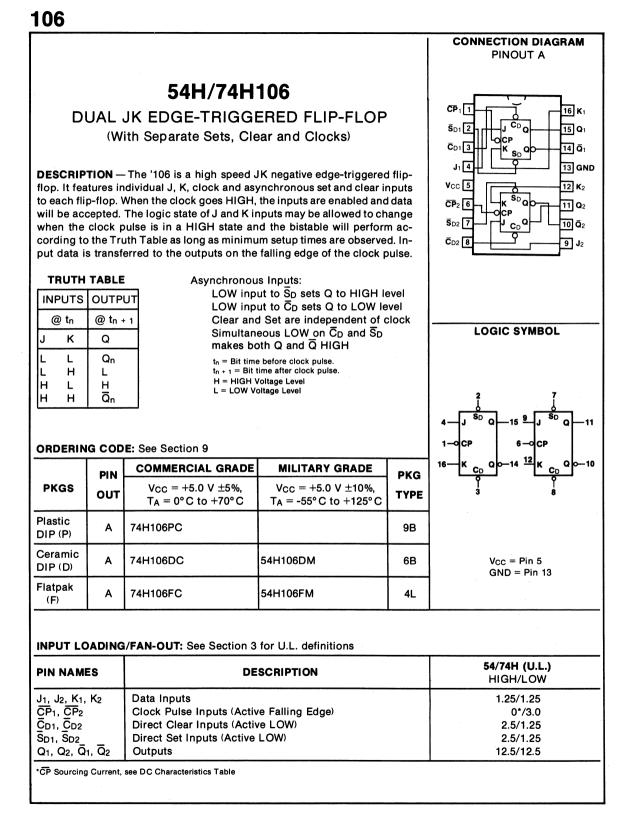

| 106           | Dual JK Edge-Triggered Flip-Flop                 |              | x                |                  |                     | 4-14        |

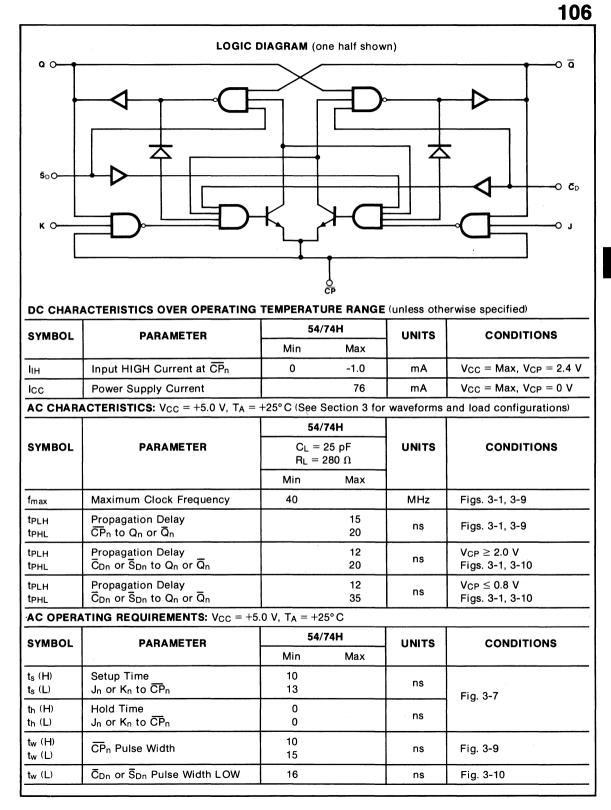

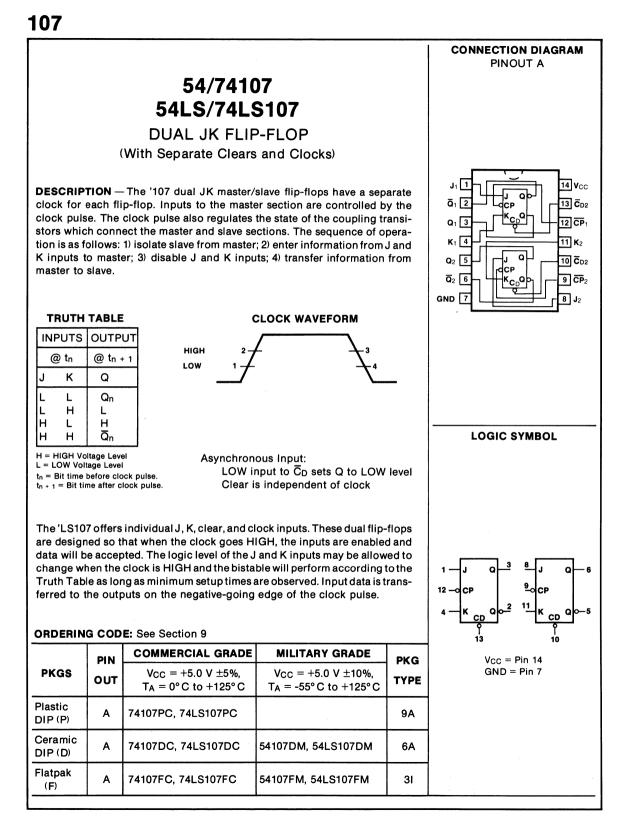

| 107           | Dual JK Flip-Flop                                | x            |                  |                  | x                   | 4-14        |

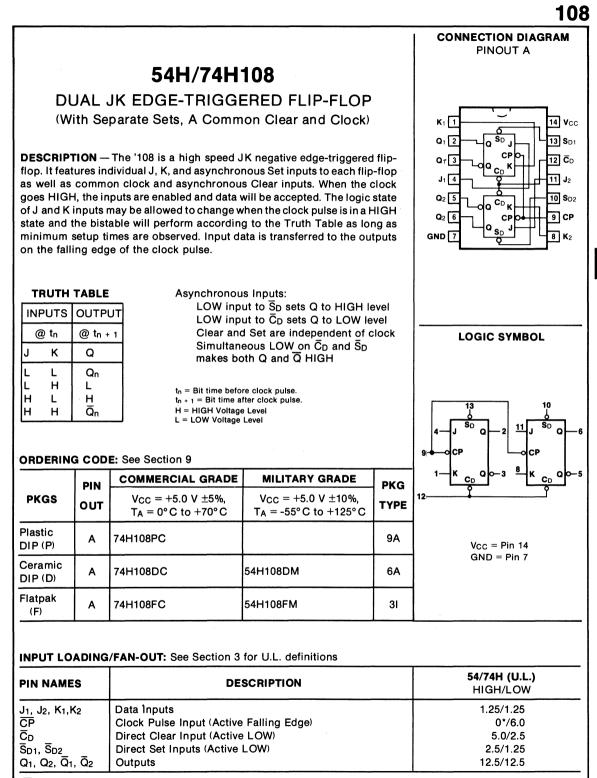

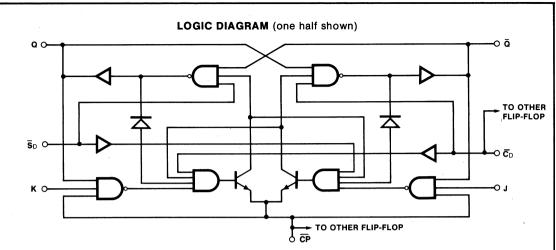

| 108           | Dual JK Edge-Triggered Flip-Flop                 |              | x                |                  |                     | 4-14        |

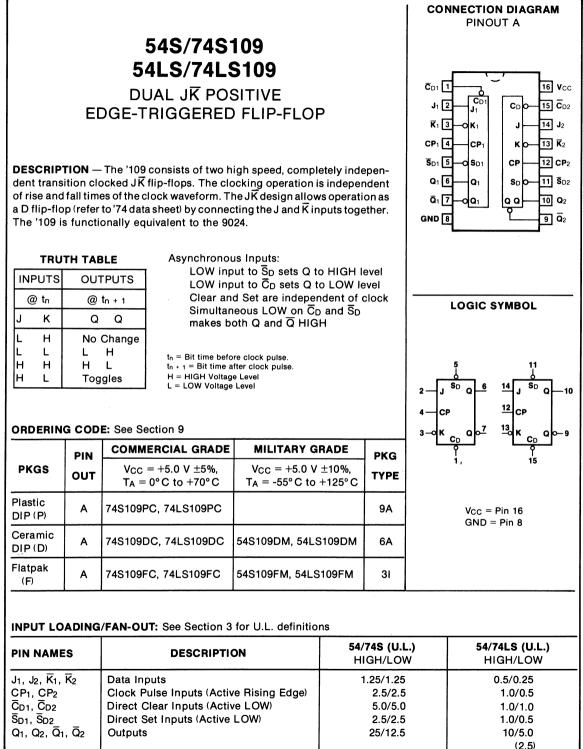

| 109           | Dual JK Positive<br>Edge-Triggered Flip-Flop     |              |                  | х                | X                   | 4-15        |

Γ

1

1

| DEVICE<br>NO. | DESCRIPTION                                    | 54/74<br>TTL | 54H/74H<br>H-TTL | 54S/74S<br>S-TTL | 54LS/74LS<br>LS-TTL | PAGE<br>NO. |

|---------------|------------------------------------------------|--------------|------------------|------------------|---------------------|-------------|

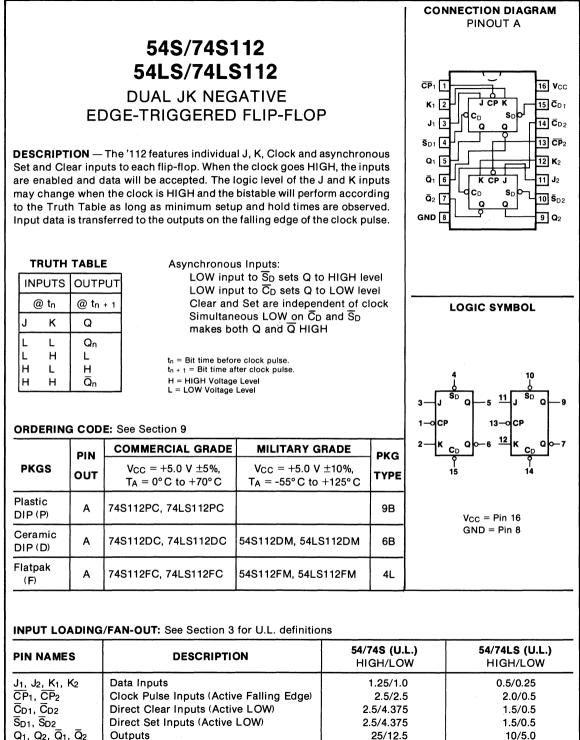

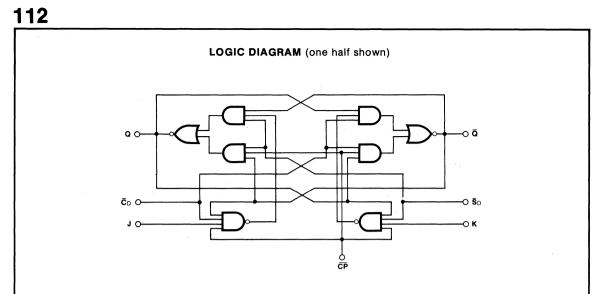

| 112           | Dual JK Negative<br>Edge-Triggered Flip-Flop   |              |                  | х                | x                   | 4-153       |

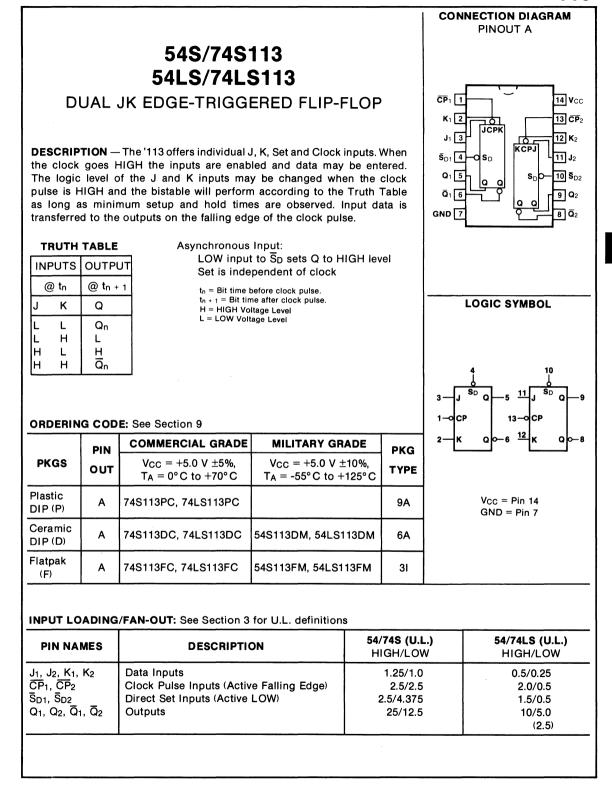

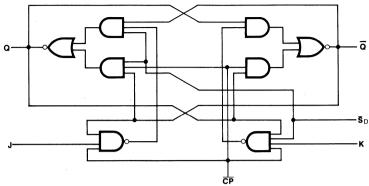

| 113           | Dual JK Edge-Triggered Flip-Flop               |              |                  | х                | x                   | 4-155       |

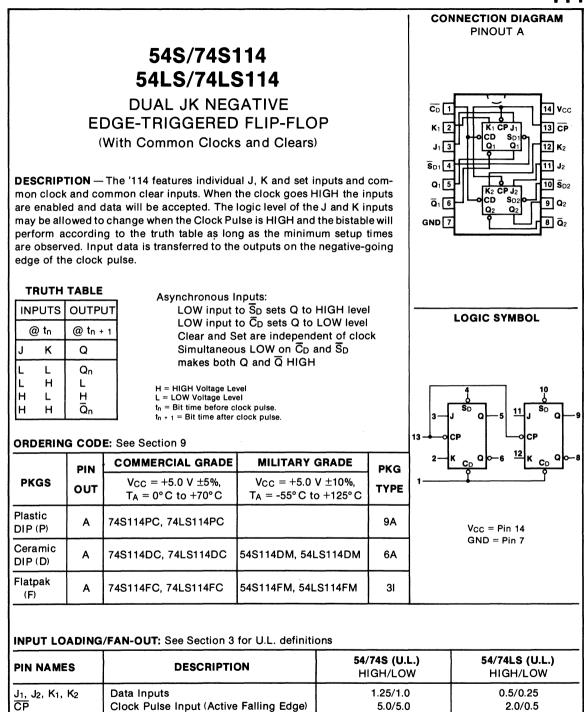

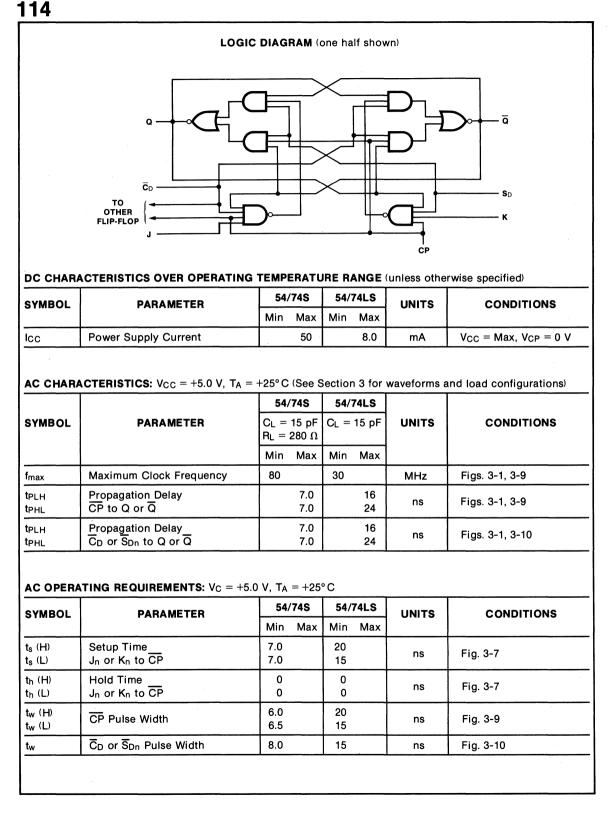

| 114           | Dual Negative<br>Edge-Triggered Flip-Flop      |              |                  | х                | X                   | 4-157       |

| 116           | Dual 4-Bit Latch                               | 9308         |                  |                  |                     | 6-24        |

| 121           | Monostable Multivibrator                       | x            |                  |                  |                     | 4-159       |

| 122           | Retriggerable Resettable Multivibrator         | х            |                  |                  |                     | 4-163       |

| 123           | Dual Retriggerable<br>Resettable Multivibrator | x            |                  |                  |                     | 4-166       |

| 125           | Quad Bus Buffer Gate                           | х            |                  |                  |                     | 4-169       |

| 125A          | Quad Bus Buffer Gate                           |              |                  |                  | х                   | 4-169       |

| 126           | Quad Bus Buffer Gate                           | х            |                  |                  | x                   | 4-17(       |

| 132           | Quad 2-Input Schmitt<br>Trigger NAND Gate      | х            |                  | x                | X                   | 4-17        |

| 133           | 13-Input NAND Gate                             |              |                  | х                | X                   | 4-17        |

| 134           | 12-Input NAND Gate                             |              |                  | х                |                     | 4-17        |

| 135           | Quad Exclusive-OR/NOR Gate                     |              |                  | x                |                     | 4-17        |

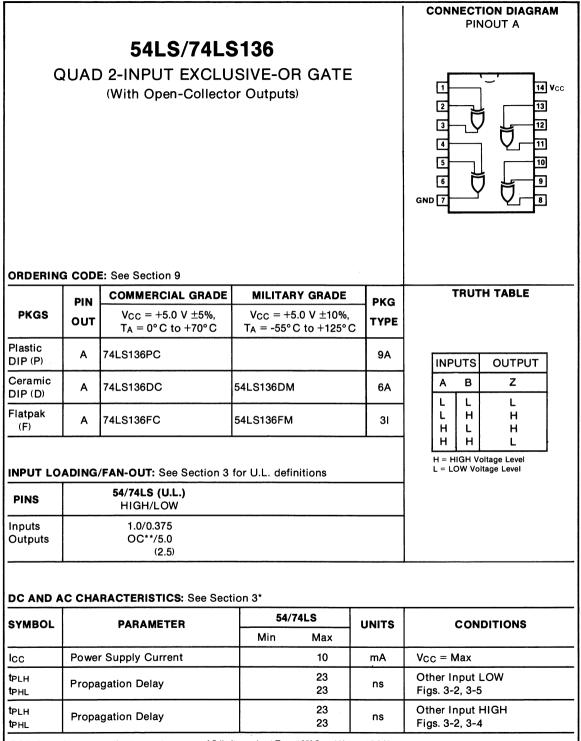

| 136           | Quad 2-Input Exclusive-OR Gate                 |              |                  |                  | x                   | 4-17        |

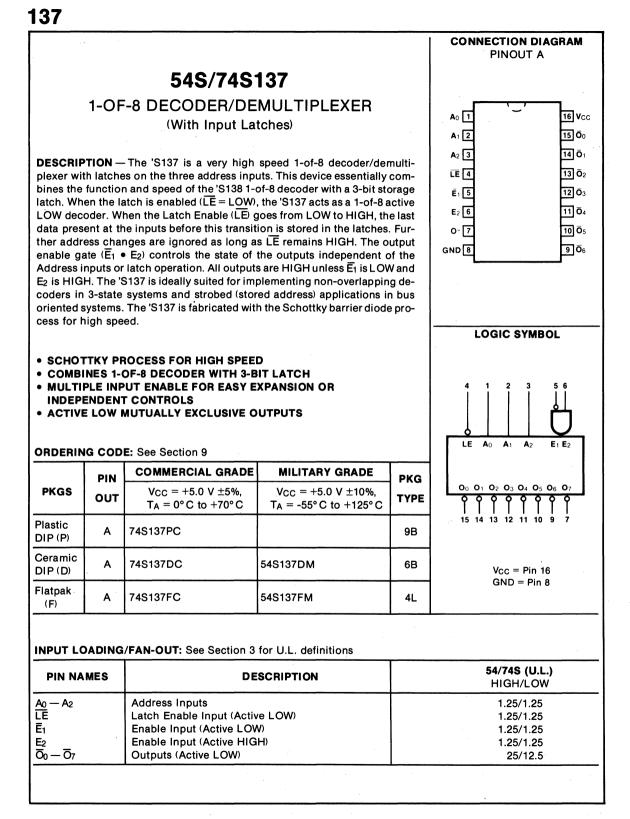

| 137           | 1-of-8 Decoder/Demultiplexer                   |              |                  | x                |                     | 4-17        |

| 138           | 1-of-8 Decoder/Demultiplexer                   |              |                  | x                | X                   | 4-18        |

| 139           | Dual 1-of-4 Decoder                            |              |                  | x                | X                   | 4-18        |

| 140           | Dual 4-Input NAND Line Driver                  |              |                  | X                |                     | 4-18        |

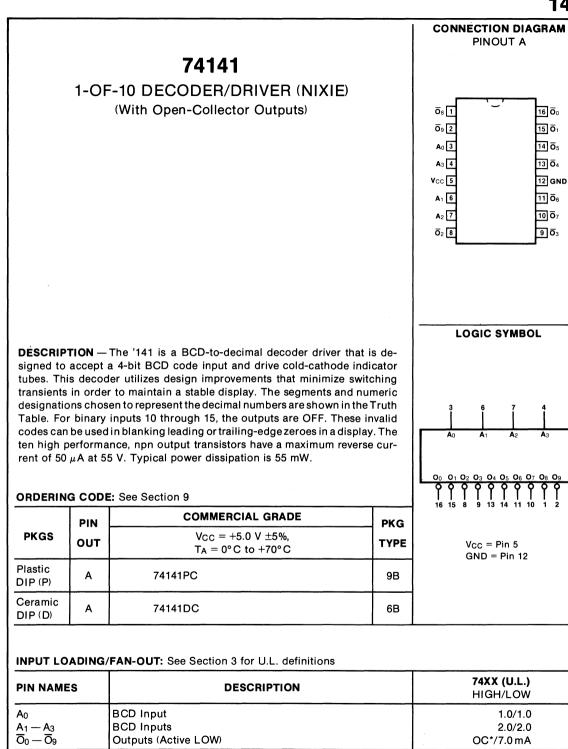

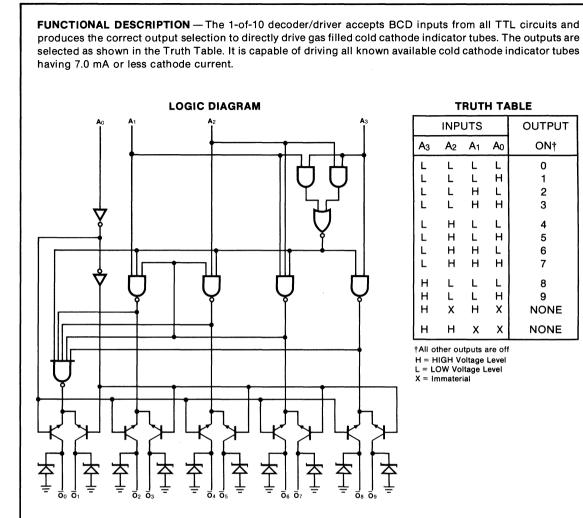

| 141           | 1-of-10 Decoder/Driver (Nixie)                 | х            |                  |                  |                     | 4-18        |

| 145           | 1-of-10 Decoder/Driver                         | х            |                  |                  |                     | 4-18        |

| 150           | 16-Input Multiplexer                           | х            |                  |                  |                     | 4-19        |

| 151           | 8-Input Multiplexer                            |              |                  | X                | x                   | 4-19        |

| 151A          | 8-Input Multiplexer                            | Х            |                  |                  |                     | 4-19        |

| 152           | 8-Input Multiplexer                            |              |                  |                  | X                   | 4-19        |

| 152A          | 8-Input Multiplexer                            | X            |                  |                  |                     | 4-19        |

| 153           | Dual 4-Input Multiplexer                       | X            |                  | x                | X                   | 4-19        |

| 154           | 1-of-16 Decoder/Demultiplexer                  | x            |                  |                  |                     | 4-20        |

| 155           | Dual 1-of-4 Decoder/Demultiplexer              | x            |                  |                  | x                   | 4-20        |

| 156           | Dual 1-of-4 Decoder/Demultiplexer              | x            |                  |                  | х                   | 4-20        |

| 157           | Quad 2-Input Multiplexer                       | х            |                  | X                | Х                   | 4-21        |

Г

| DEVICE<br>NO. | DESCRIPTION                                           | 54/74<br>TTL | 54H/74H<br>H-TTL | 54S/74S<br>S-TTL | 54LS/74LS<br>LS-TTL | PAGE<br>NO.    |

|---------------|-------------------------------------------------------|--------------|------------------|------------------|---------------------|----------------|

| 158           | Quad 2-Input Multiplexer                              |              |                  | х                | x                   | 4-213          |

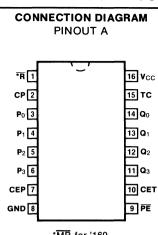

| 160           | Synchronous Presettable<br>BCD Decade Counter         | x            |                  | 93S10            | x                   | 4-215/<br>6-30 |

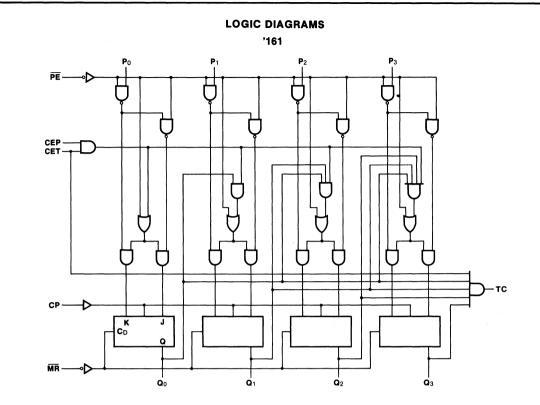

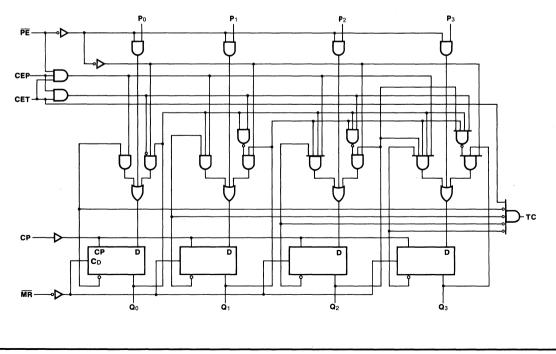

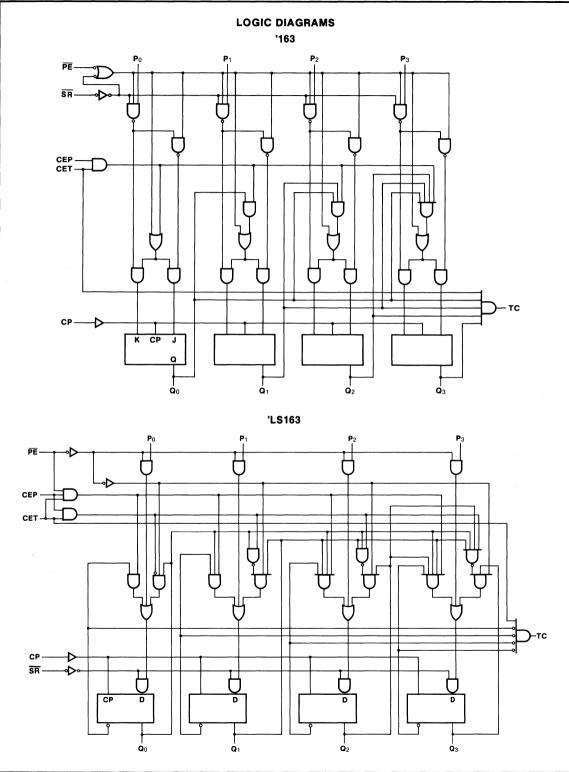

| 161           | Synchronous Presettable<br>Binary Counter             | х            |                  |                  | x                   | 4-221          |

| 162           | Synchronous Presettable<br>BCD Decade Counter         | х            |                  |                  | x                   | 4-215          |

| 163           | Synchronous Presettable<br>Binary Counter             | х            |                  |                  | x                   | 4-221          |

| 164           | Serial-In Parallel-Out Shift Register                 | х            |                  |                  | х                   | 4-224          |

| 165           | 8-Bit Parallel-to-Serial Converter                    | x            |                  |                  | х                   | 4-227          |

| 166           | 8-Bit Shift Register                                  | х            |                  |                  |                     | 4-230          |

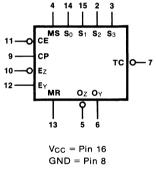

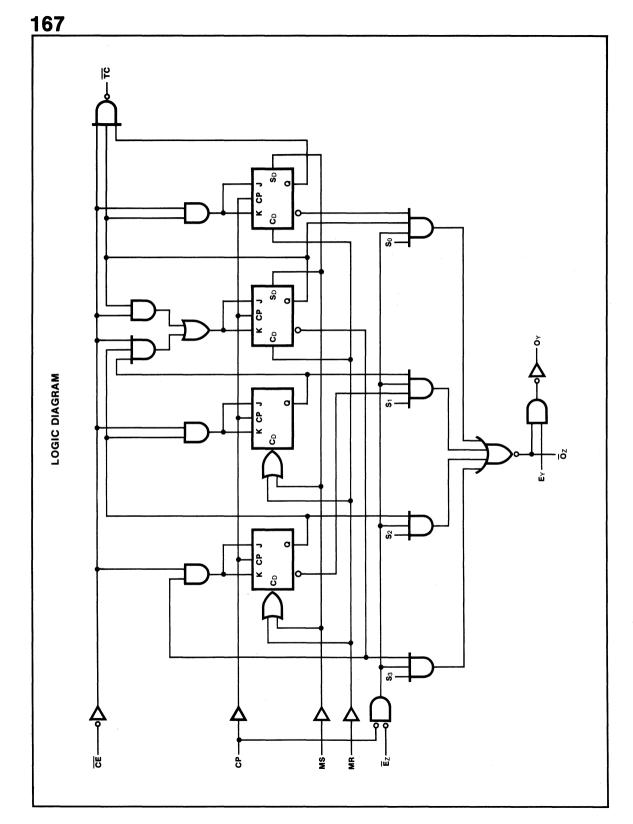

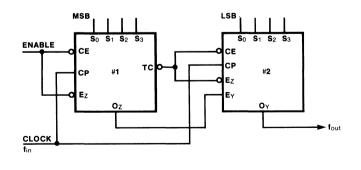

| 167           | Synchronous Decade Rate Multiplier                    | х            |                  |                  |                     | 4-232          |

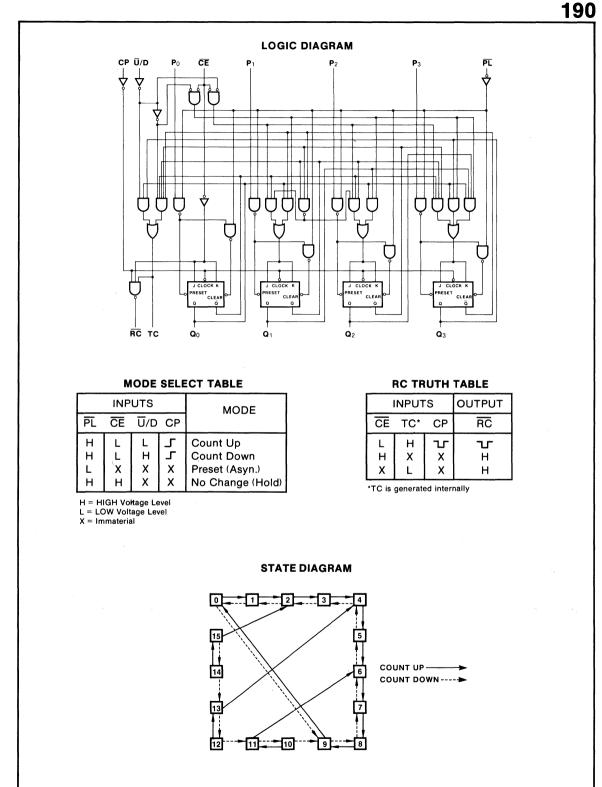

| 168           | Synchronous Bidirectional<br>BCD Decade Counter       |              |                  |                  | x                   | 4-239          |

| 169           | Synchronous Bidirectional<br>Modulo-16 Binary Counter |              |                  |                  | X                   | 4-242          |

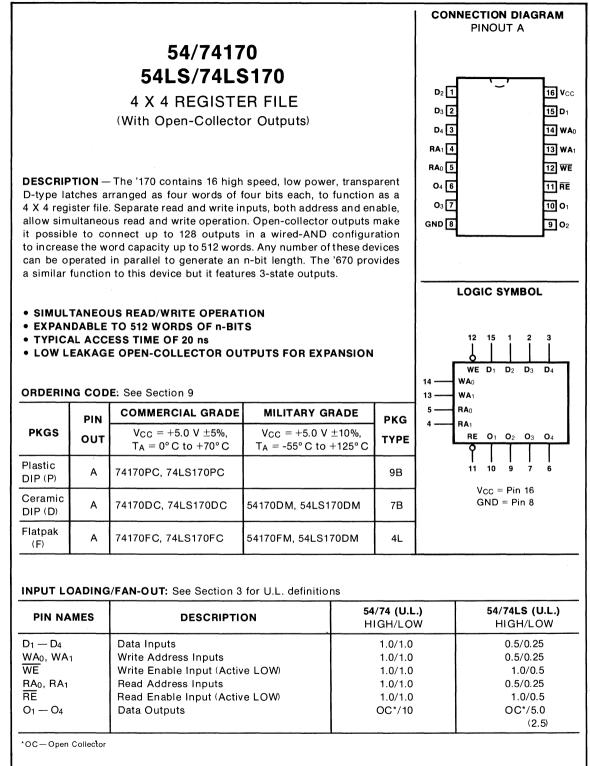

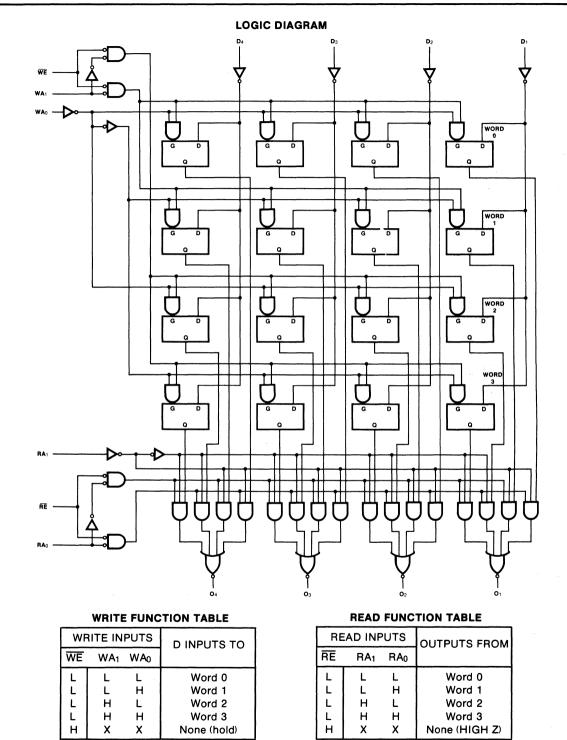

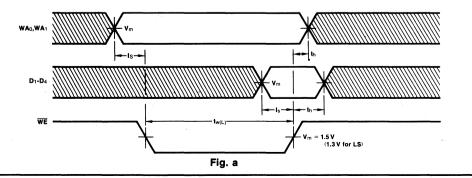

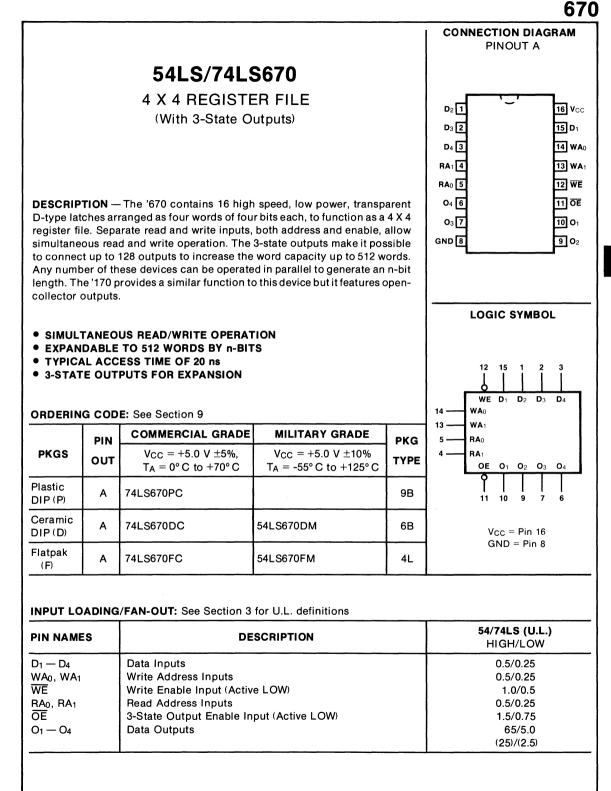

| 170           | 4 x 4 Register File                                   | х            |                  |                  | X                   | 4-244          |

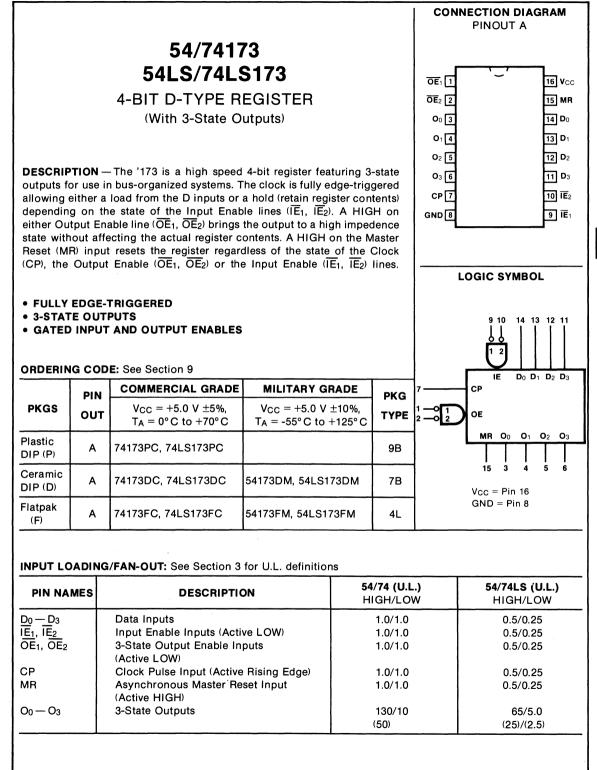

| 173           | 4-Bit D-Type Register                                 | х            |                  |                  | х                   | 4-247          |

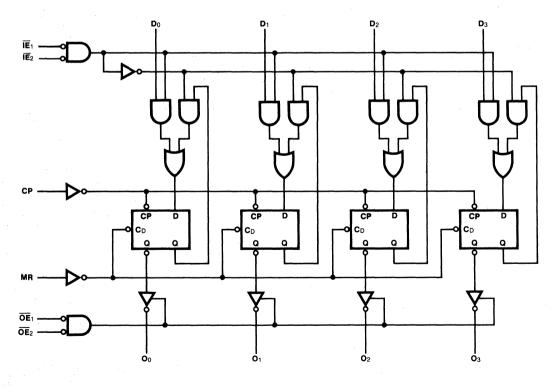

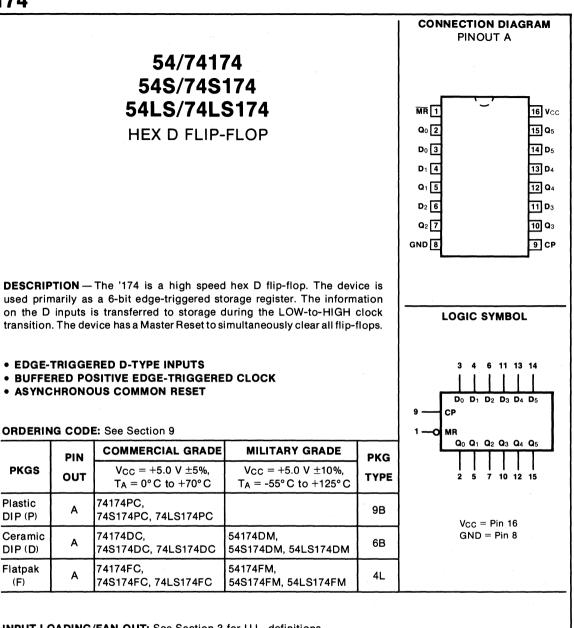

| 174           | Hex D Flip-Flop                                       | х            |                  | х                | X                   | 4-250          |

| 175           | Quad D Flip-Flop                                      | х            |                  | x                | X                   | 4-253          |

| 176           | Presettable Decade Counter                            | х            |                  |                  |                     | 4-256          |

| 177           | Presettable Binary Counter                            | х            |                  |                  |                     | 4-260          |

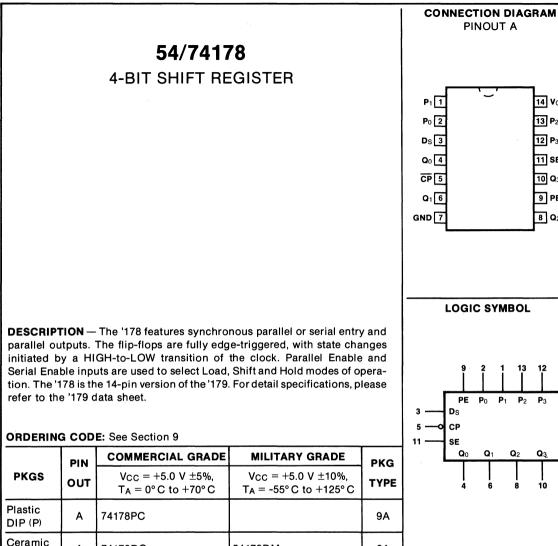

| 178           | 4-Bit Shift Register                                  | х            |                  |                  |                     | 4-262          |

| 179           | 4-Bit Shift Register                                  | х            |                  |                  |                     | 4-264          |

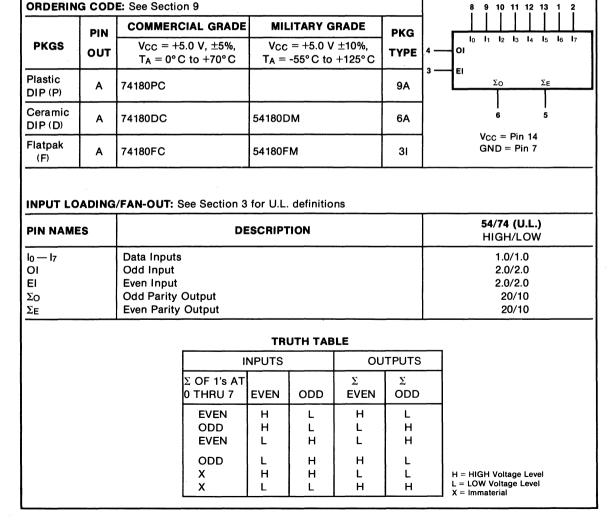

| 180           | 8-Bit Parity Generator/Checker                        | х            |                  |                  |                     | 4-267          |

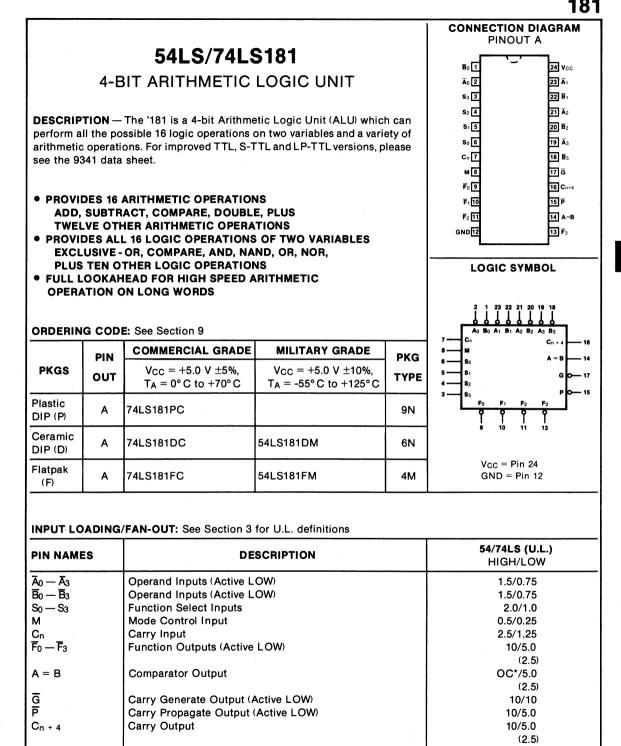

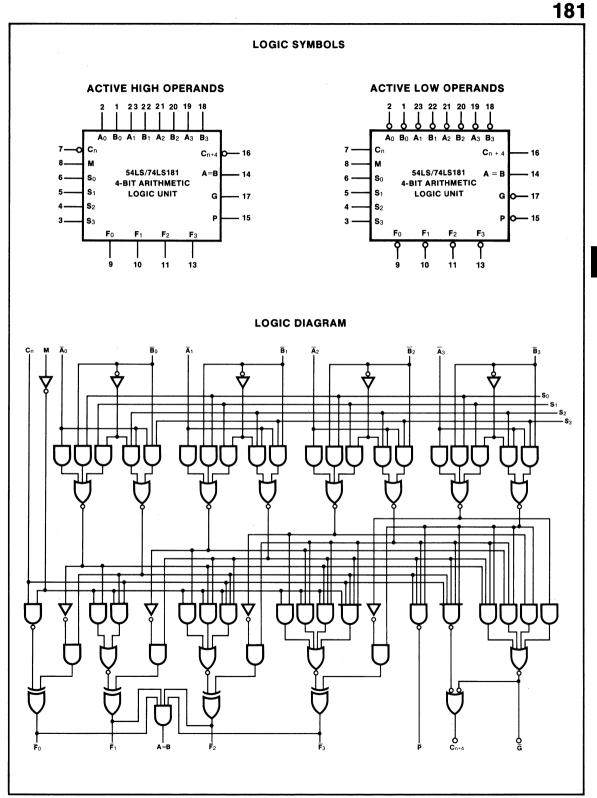

| 181           | 4-Bit Arithmetic Logic Unit                           | 9341         |                  | 93S41            | X                   | 4-269<br>6-87  |

| 182           | Carry Lookahead Generator                             | 9342         |                  | 93S42            |                     | 6-94           |

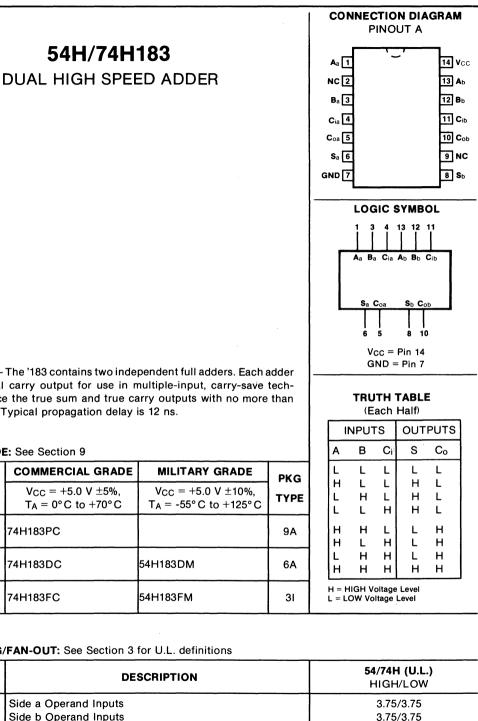

| 183           | Dual High Speed Adder                                 |              | x                |                  |                     | 4-275          |

| 189           | 64-Bit Random Access Memory                           |              |                  | х                | x                   | 4-277          |

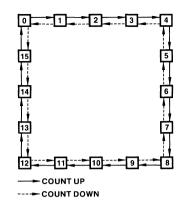

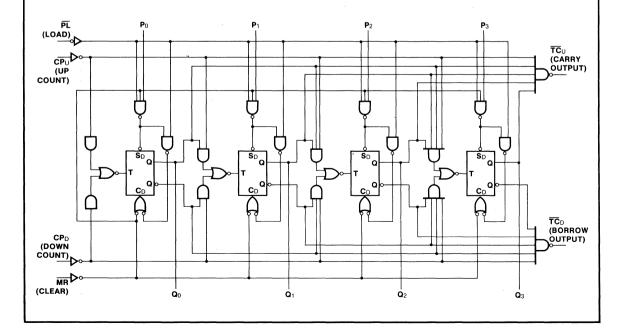

| 190           | Up/Down Decade Counter                                | х            |                  |                  | x                   | 4-280          |

| 191           | Up/Down Binary Counter                                | х            |                  |                  | x                   | 4-28           |

| 192           | Up/Down Decade Counter                                | х            |                  |                  | x                   | 4-28           |

| 193           | Up/Down Binary Counter                                | Х            |                  |                  | X                   | 4-29           |

٦

Г

| DEVICE<br>NO. | DESCRIPTION                                     | 54/74<br>TTL | 54H/74H<br>H-TTL | 54S/74S<br>S-TTL | 54LS/74LS<br>LS-TTL | PAGE<br>NO.       |

|---------------|-------------------------------------------------|--------------|------------------|------------------|---------------------|-------------------|

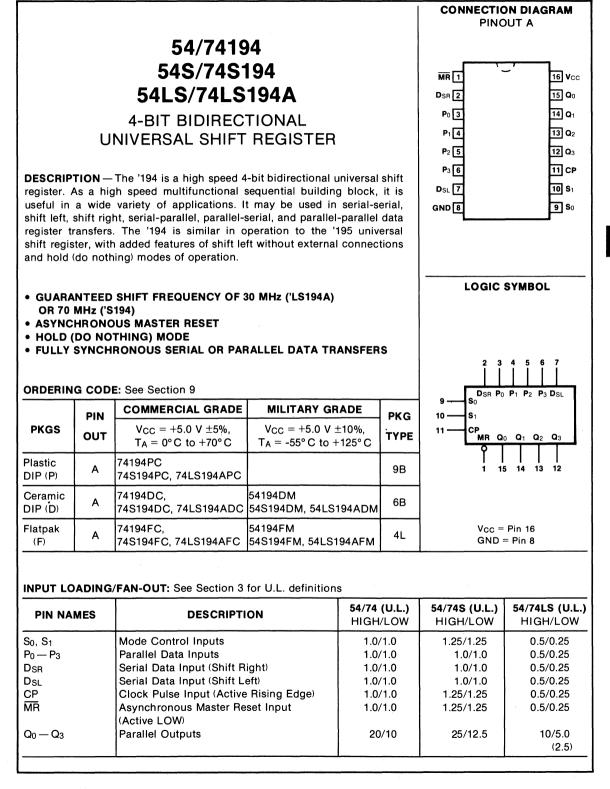

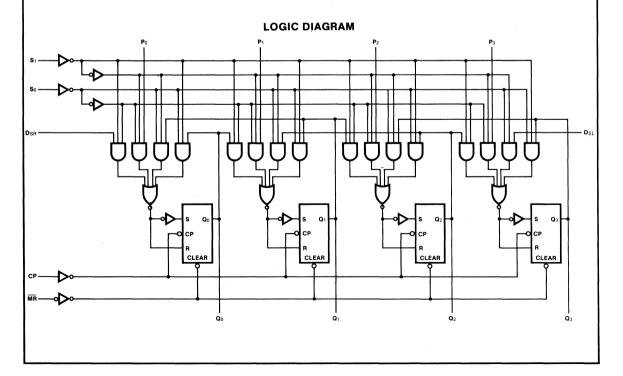

| 194           | 4-Bit Bidirectional<br>Universal Shift Register | x            |                  | x                |                     | 4-293             |

| 194A          | 4-Bit Bidirectional<br>Universal Shift Register |              |                  |                  | x                   | 4-293             |

| 195           | Universal 4-Bit Shift Register                  | x            | 93H00            | 93500            |                     | 4-296<br>6-3      |

| 195A          | Universal 4-Bit Shift Register                  |              |                  |                  | x                   | 4-296             |

| 196           | Presettable Decade Counter                      | x            |                  |                  | x                   | 4-299             |

| 197           | Presettable Binary Counter                      | x            |                  |                  | x                   | 4-303             |

| 198           | 8-Bit Right/Left Shift Register                 | x            |                  |                  |                     | 4-305             |

| 199           | 8-Bit Parallel I/O Shift Register               | x            |                  |                  |                     | 4-308             |

| 240           | Octal Buffer/Line Driver                        |              |                  | x                | x                   | 4-31              |

| 241           | Octal Buffer/Line Driver                        |              |                  | x                | X                   | 4-31 <sup>-</sup> |

| 242           | Quad Bus Transceiver                            |              |                  |                  | x                   | 4-314             |

| 243           | Quad Bus Transceiver                            |              |                  |                  | x                   | 4-31              |

| 244           | Octal Buffer/Line Driver                        |              |                  |                  | х                   | 4-31              |

| 245           | Octal Bus Transceiver                           |              |                  |                  | x                   | 4-31              |

| 247           | BCD to 7-Segment Decoder/Driver                 |              |                  |                  | х                   | 4-31              |

| 248           | BCD to 7-Segment Decoder                        |              |                  |                  | х                   | 4-31              |

| 249           | BCD to 7-Segment Decoder                        |              |                  |                  | x                   | 4-32              |

| 251           | 8-Input Multiplexer                             |              |                  | x                | X                   | 4-32              |

| 253           | Dual 4-Input Multiplexer                        |              |                  | x                | X                   | 4-32              |

| 256           | Dual 4-Bit Addressable Latch                    |              |                  |                  | x                   | 4-32              |

| 257           | Quad 2-Input Multiplexer                        |              |                  | x                | x                   | 4-33              |

| 257A          | Quad 2-Input Multiplexer                        |              |                  |                  | x                   | 4-33              |

| 258           | Quad 2-Input Multiplexer                        |              |                  | x                | Х                   | 4-33              |

| 258A          | Quad 2-Input Multiplexer                        |              |                  |                  | X                   | 4-33              |

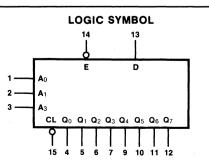

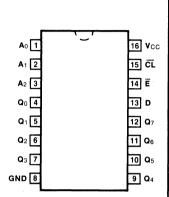

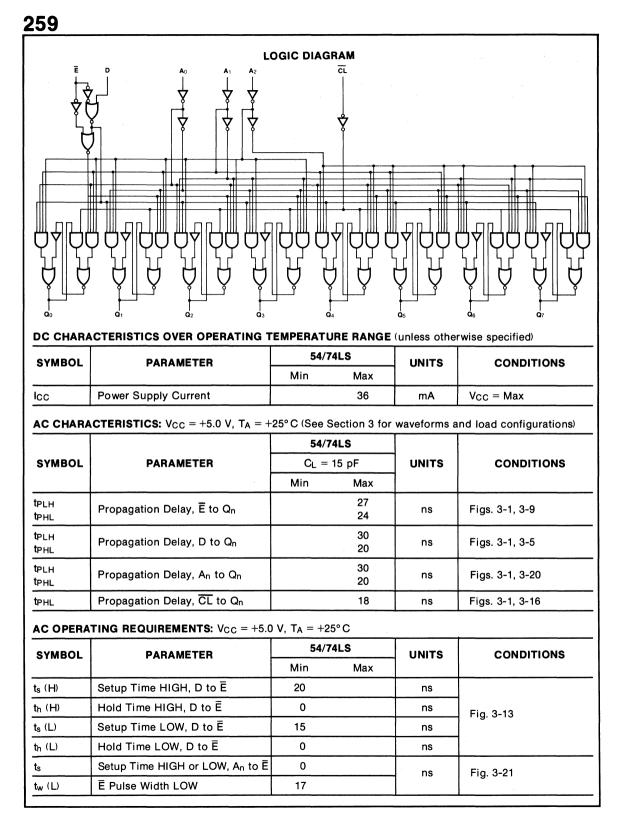

| 259           | 8-Bit Addressable Latch                         |              |                  |                  | x                   | 4-33              |

| 260           | Dual 5-Input NOR Gate                           |              |                  | x                | x                   | 4-34              |

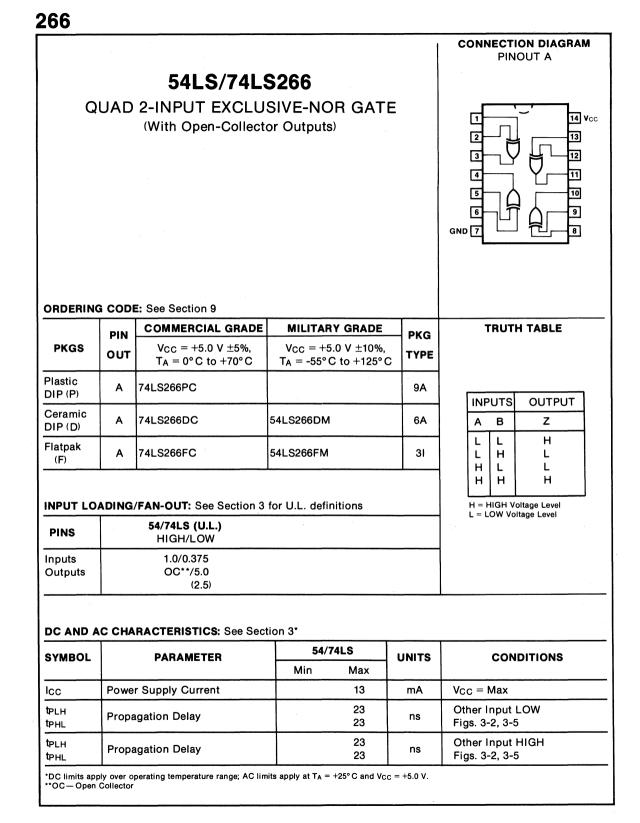

| 266           | Quad 2-Input Exclusive-NOR Gate                 |              |                  |                  | x                   | 4-34              |

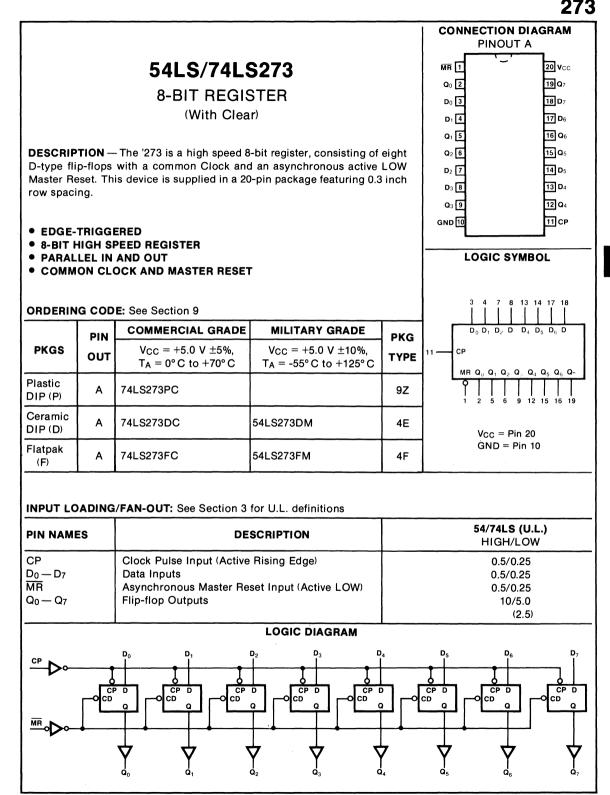

| 273           | 8-Bit Register                                  |              |                  |                  | x                   | 4-34              |

| 279           | Quad Set-Reset Latch                            | x            |                  |                  | X                   | 4-34              |

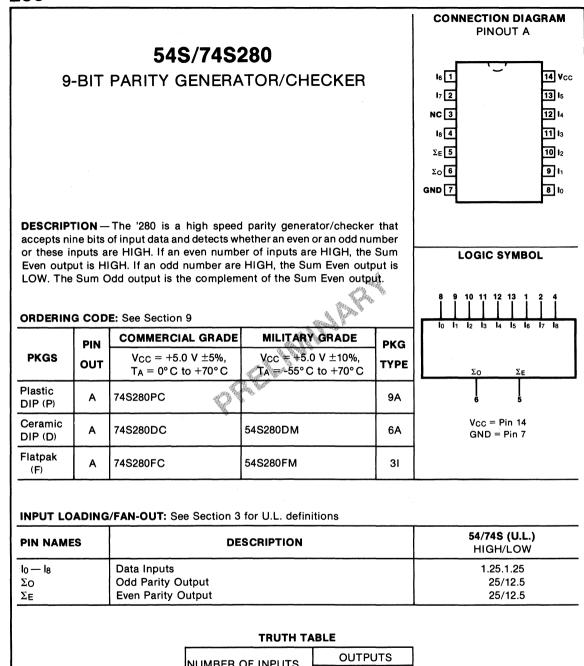

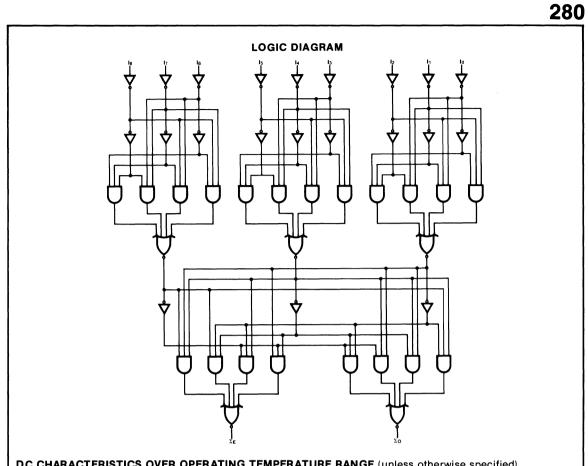

| 280           | 9-Bit Parity Generator/Checker                  |              |                  | x                |                     | 4-34              |

| 283           | 4-Bit Binary Full Adder                         | x            |                  |                  | x                   | 4-34              |

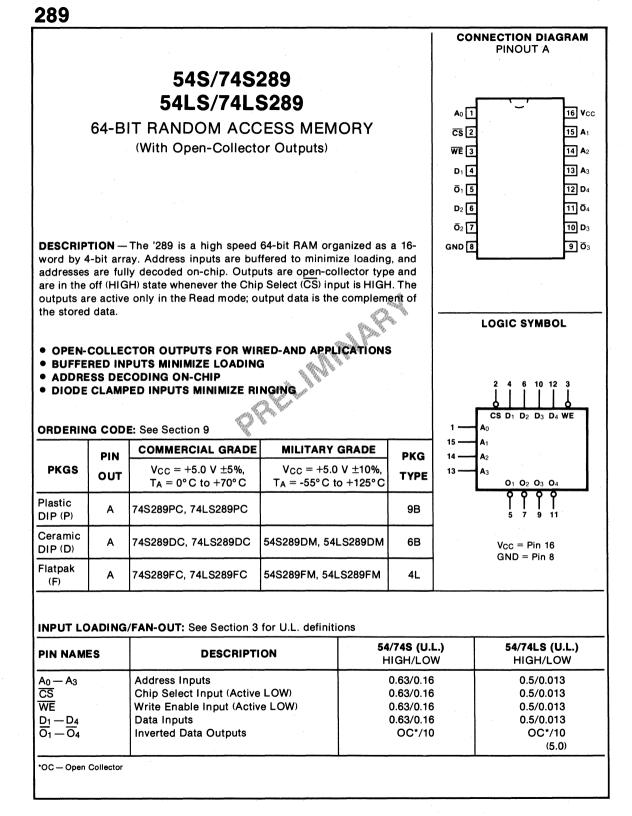

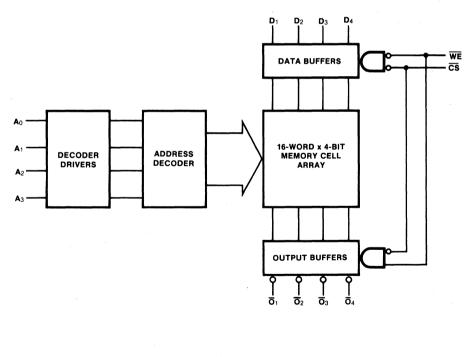

| 289           | 64-Bit Random Access Memory                     |              |                  | X                | x                   | 4-35              |

| DEVICE<br>NO. | DESCRIPTION                                         | 54/74<br>TTL | 54H/74H<br>H-TTL | 54S/74S<br>S-TTL | 54LS/74LS<br>LS-TTL | PAGE<br>NO. |

|---------------|-----------------------------------------------------|--------------|------------------|------------------|---------------------|-------------|

| 290           | BCD Decade Counter                                  | x            |                  |                  | x                   | 4-355       |

| 293           | Modulo-16 Binary Counter                            | x            |                  |                  | x                   | 4-356       |

| 295A          | 4-Bit Shift Register                                |              |                  |                  | x                   | 4-357       |

| 298           | Quad 2-Port Register                                | x            |                  |                  | х                   | 4-360       |

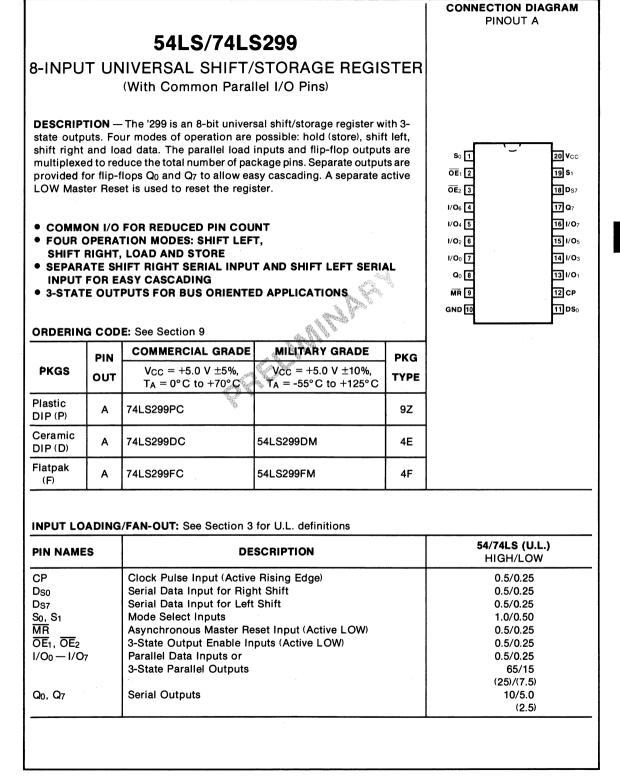

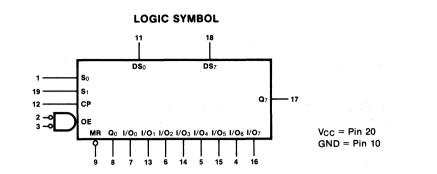

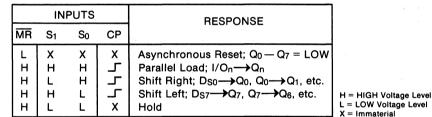

| 299           | 8-Input Universal<br>Shift/Storage Register         |              |                  |                  | x                   | 4-363       |

| 322           | 8-Bit Serial/Parallel Register                      |              |                  |                  | x                   | 4-366       |

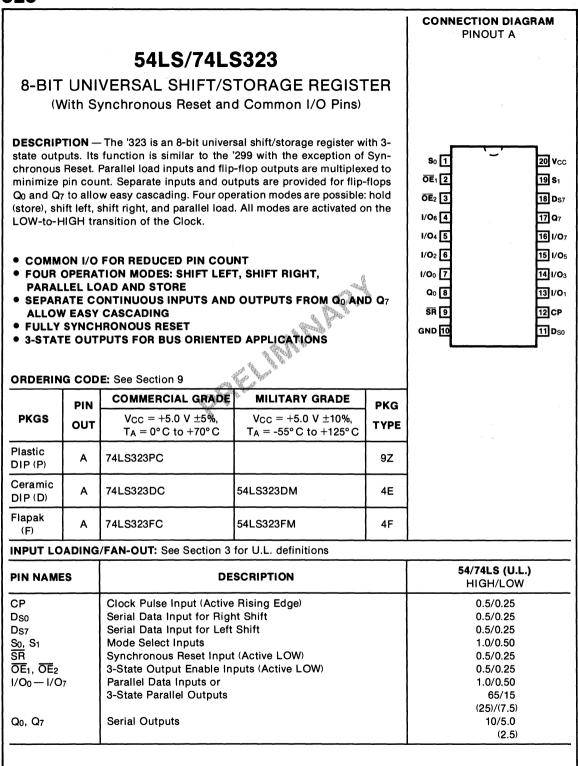

| 323           | 8-Bit Universal Shift/Storage Register              |              |                  |                  | x                   | 4-370       |

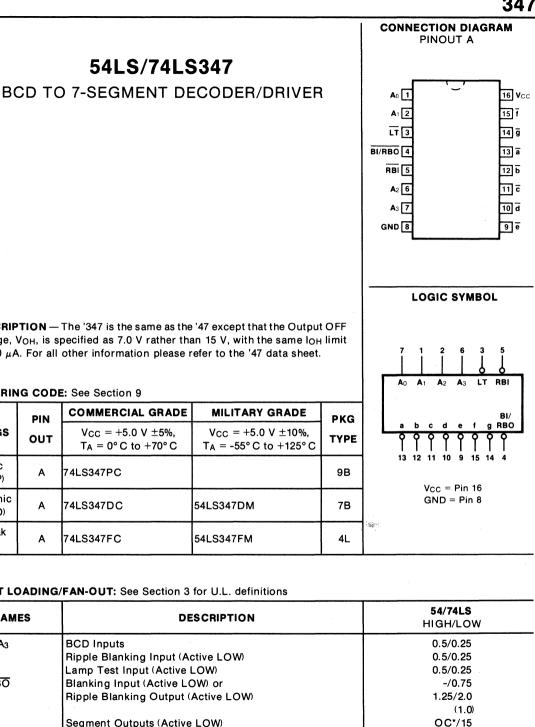

| 347           | BCD to 7-Segment Decoder                            |              |                  |                  | x                   | 4-373       |

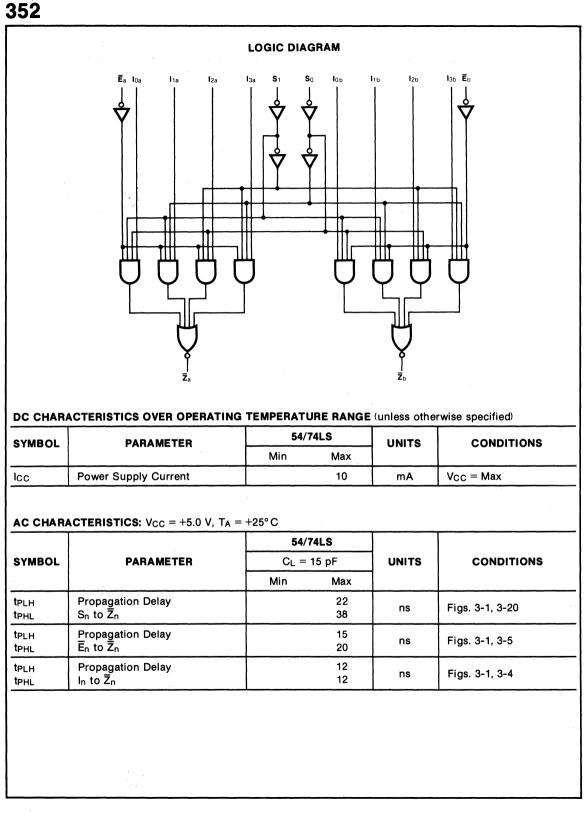

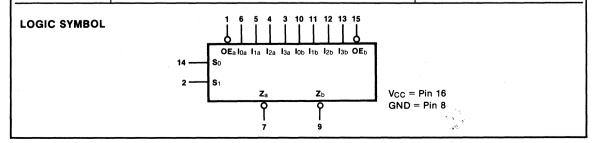

| 352           | Dual 4-Input Multiplexer                            |              |                  |                  | x                   | 4-374       |

| 353           | Dual 4-Input Multiplexer                            |              |                  |                  | x                   | 4-377       |

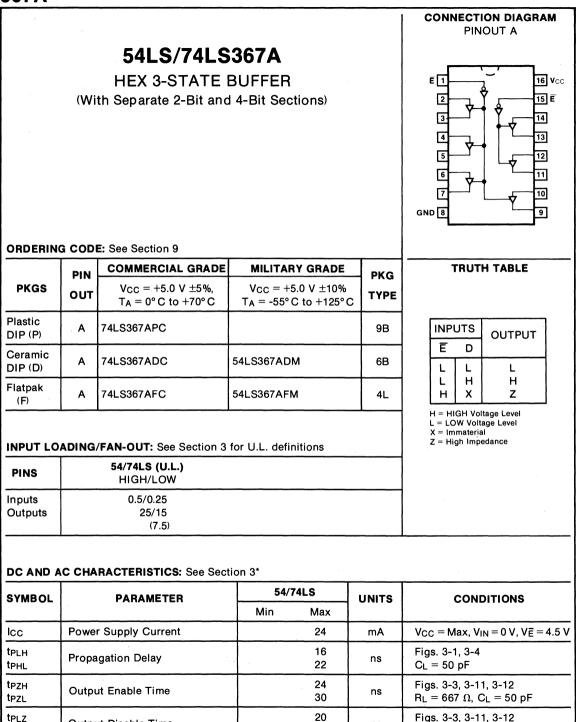

| 365A          | Hex 3-State Buffer                                  |              |                  |                  | X                   | 4-380       |

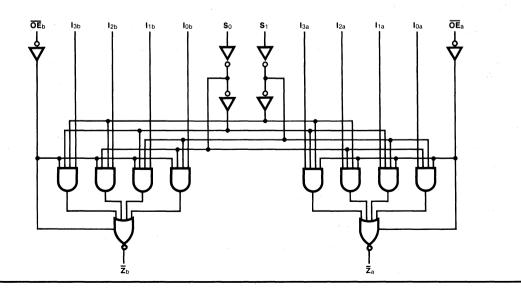

| 366A          | Hex 3-State Inverter Buffer                         |              |                  |                  | x                   | 4-38        |

| 367A          | Hex 3-State Buffer                                  |              |                  |                  | X                   | 4-382       |

| 368A          | Hex 3-State Inverter Buffer                         |              |                  |                  | x                   | 4-383       |

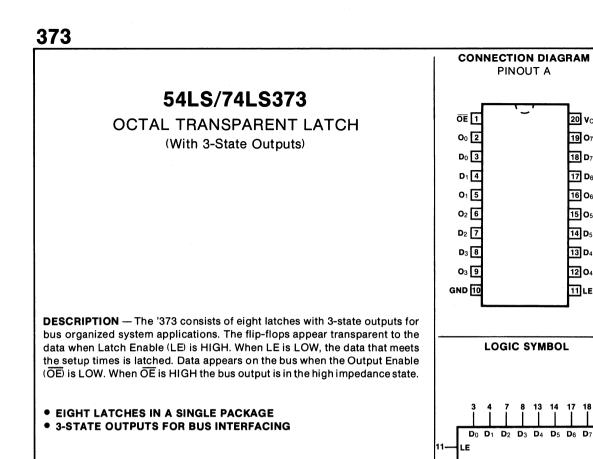

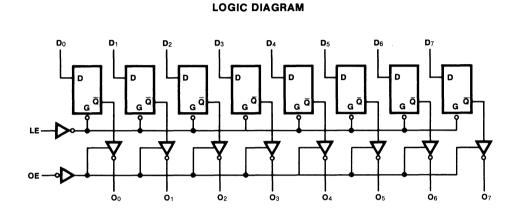

| 373           | Octal Transparent Latch                             |              |                  |                  | х                   | 4-384       |

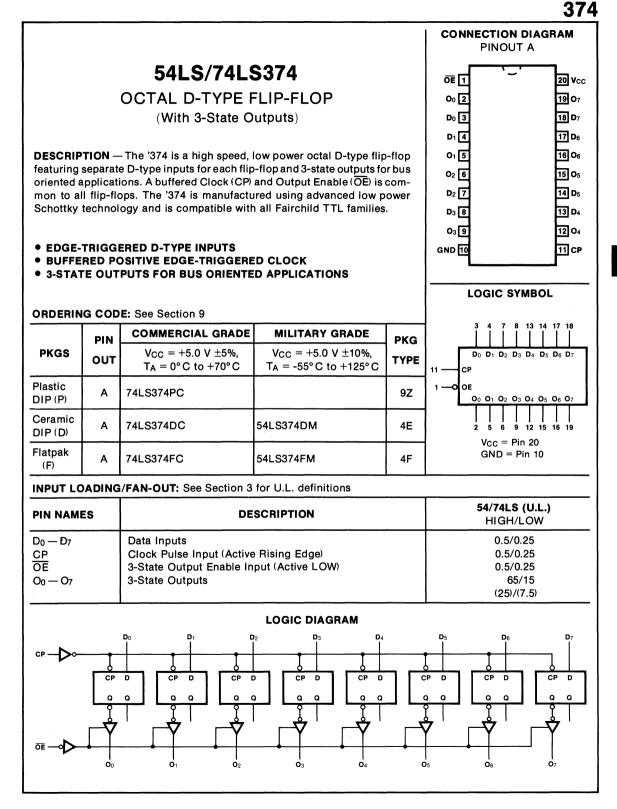

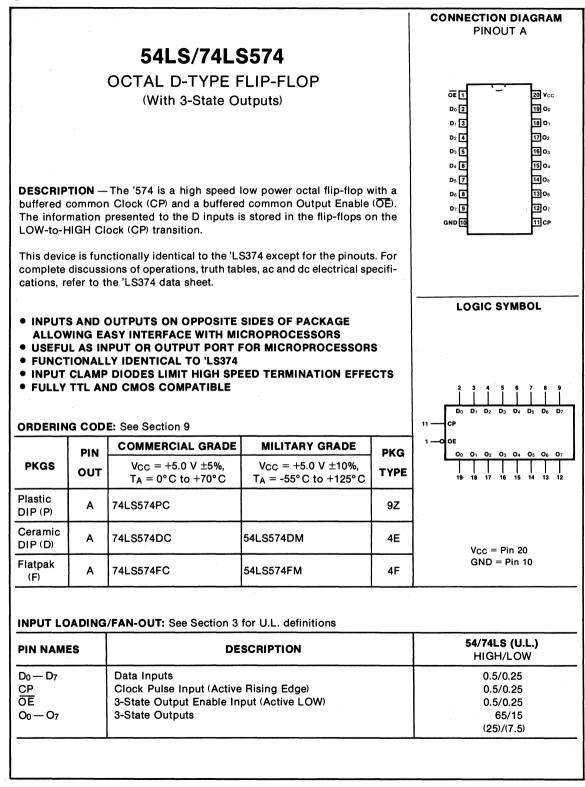

| 374           | Octal D-Type Flip-Flop                              |              |                  |                  | x                   | 4-38        |

| 375           | 4-Bit Latch                                         |              |                  |                  | X                   | 4-38        |

| 377           | Octal D Flip-Flop                                   |              | T                |                  | X                   | 4-39        |

| 378           | Parallel D Register                                 |              |                  |                  | x                   | 4-39        |

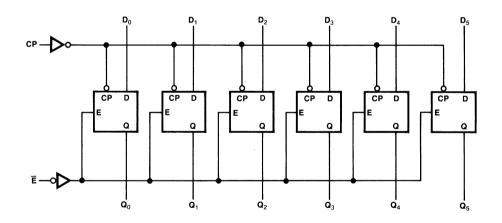

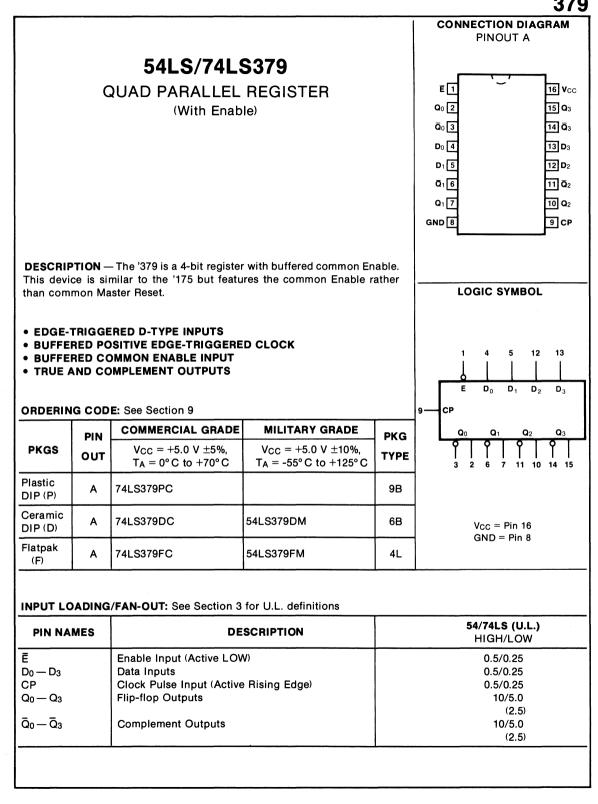

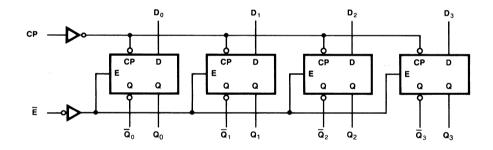

| 379           | Quad Parallel Register                              |              |                  |                  | x                   | 4-39        |

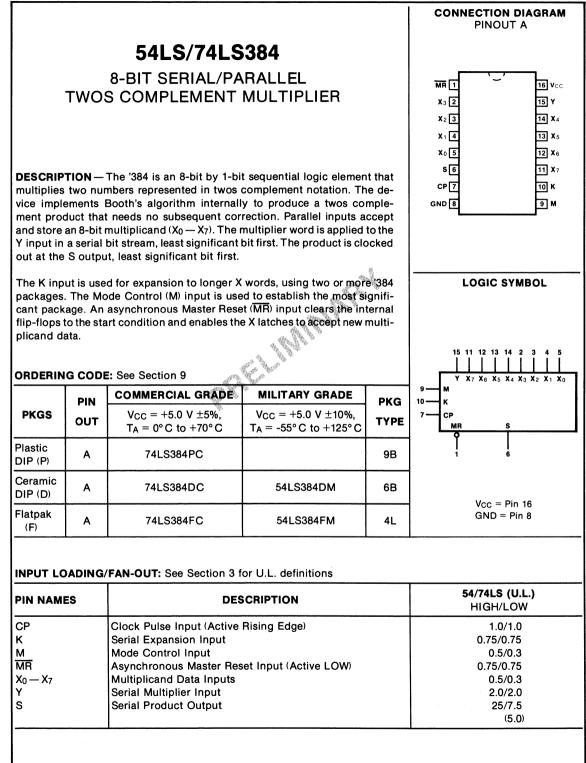

| 384           | 8-Bit Serial/Parallel<br>Twos Complement Multiplier |              |                  |                  | X                   | 4-40        |

| 390           | Dual Decade Counter                                 |              |                  |                  | - X                 | 4-40        |

| 393           | Dual Modulo-16 Counter                              |              |                  |                  | x                   | 4-40        |

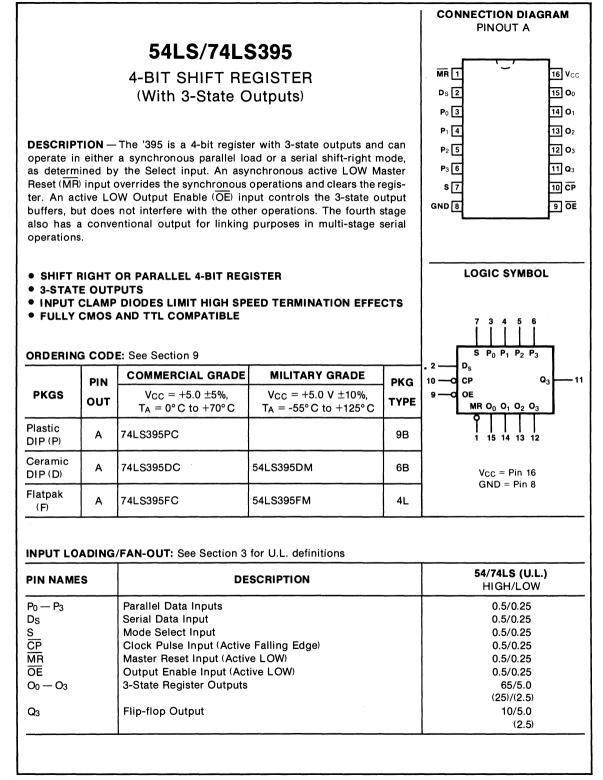

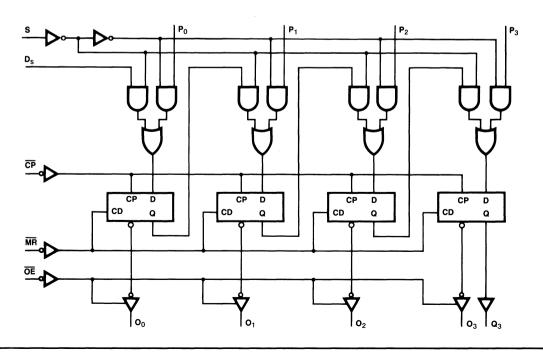

| 395           | Shift Register                                      |              |                  |                  | X                   | 4-41(       |

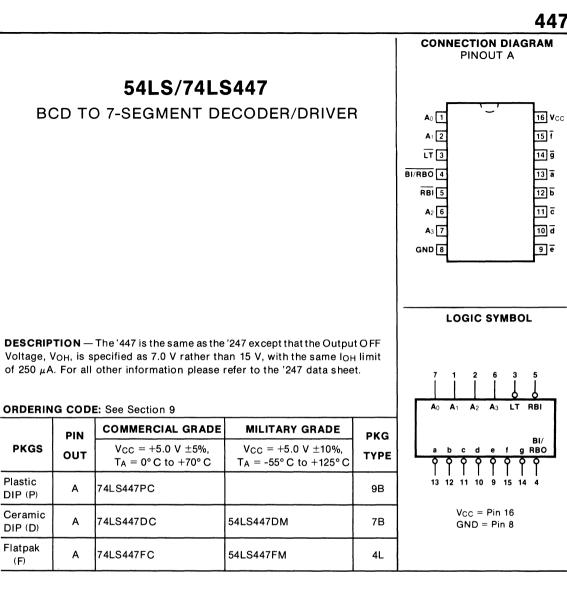

| 447           | BCD to 7-Segment Decoder                            |              |                  |                  | X                   | 4-41:       |

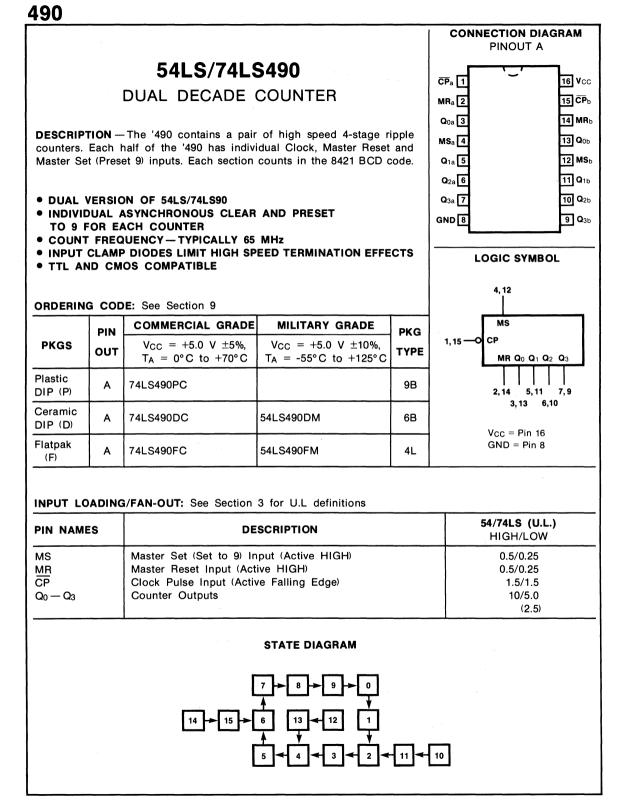

| 490           | Dual Decade Counter                                 |              |                  |                  | x                   | 4-41        |

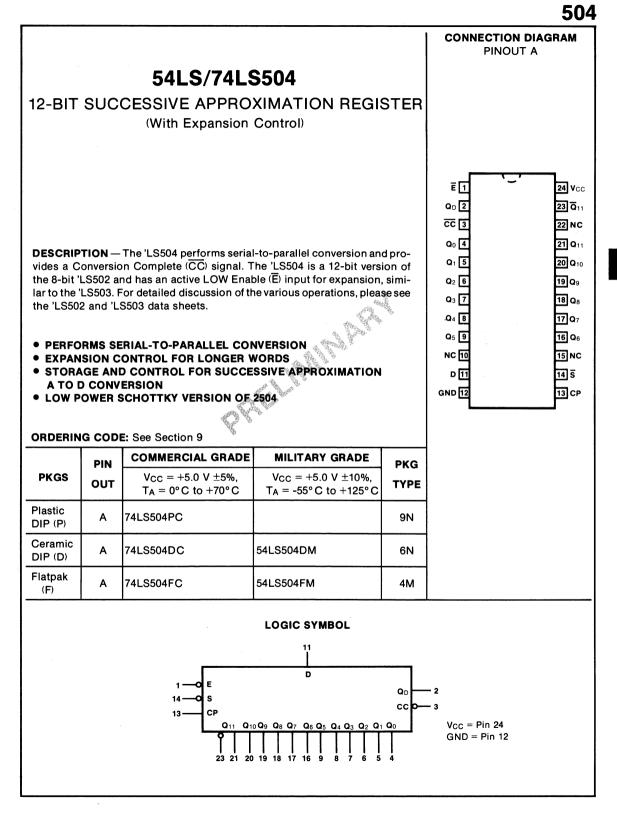

| 502           | 8-Bit Successive<br>Approximation Register          |              |                  |                  | X                   | 4-41        |

| 503           | 8-Bit Successive<br>Approximation Register          |              |                  |                  | X                   | 4-42        |

| 504           | 12-Bit Successive<br>Approximation Register         |              |                  | 1                | X                   | 4-42        |

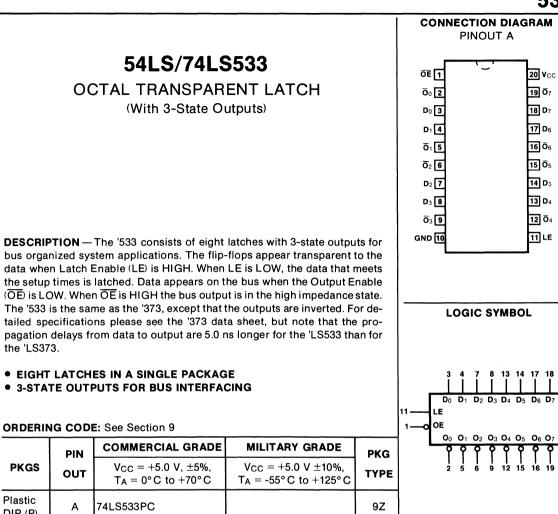

| 533           | Octal Transparent Latch                             |              |                  |                  | x                   | 4-42        |

| DEVICE<br>NO. | DESCRIPTION              | 54/74<br>TTL | 54H/74H<br>H-TTL | 54S/74S<br>S-TTL | 54LS/74LS<br>LS-TTL | PAGE<br>NO. |

|---------------|--------------------------|--------------|------------------|------------------|---------------------|-------------|

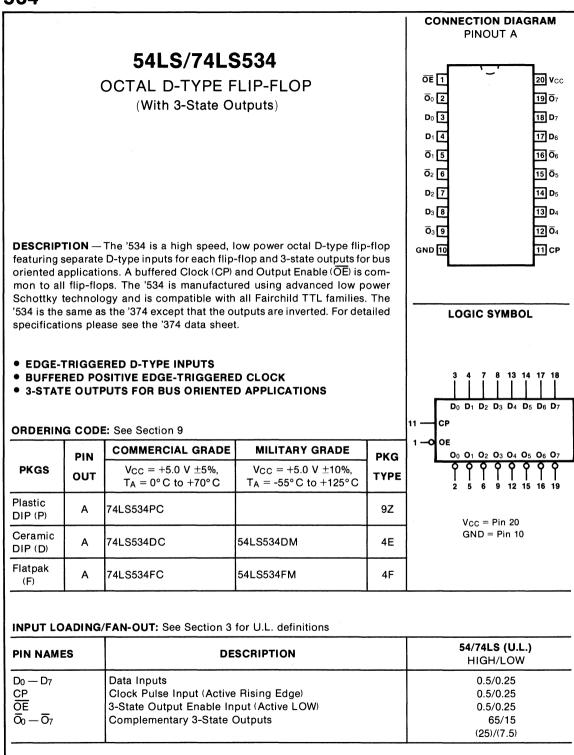

| 534           | Octal D-Type Flip-Flop   |              |                  |                  | x                   | 4-426       |

| 540           | Octal Buffer/Line Driver |              |                  |                  | x                   | 4-427       |

| 541           | Octal Buffer/Line Driver |              |                  |                  | x                   | 4-427       |

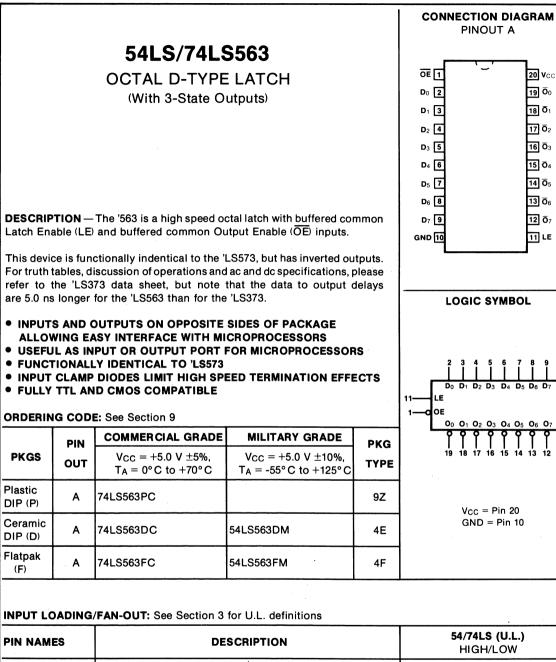

| 563           | Octal D-Type Latch       |              |                  |                  | x                   | 4-429       |

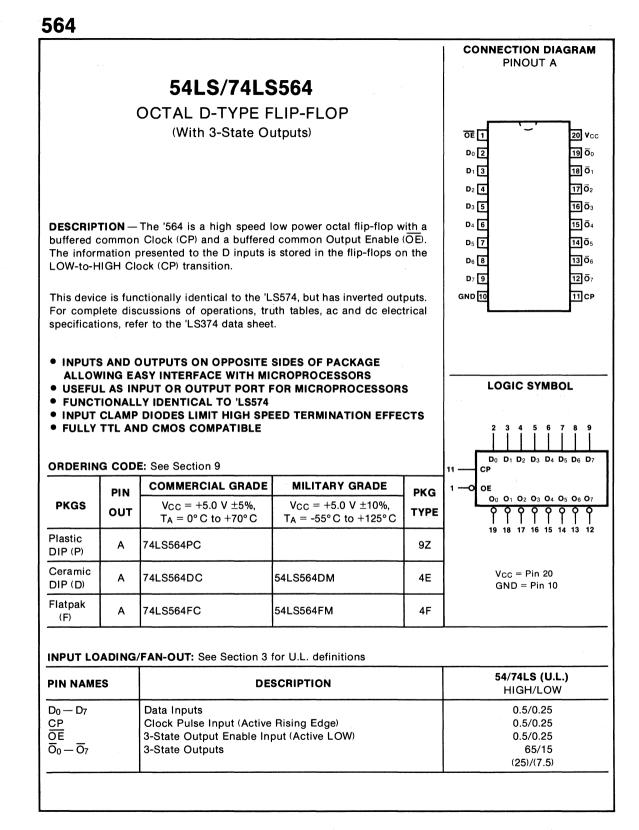

| 564           | Octal D-Type Latch       |              |                  |                  | X                   | 4-430       |

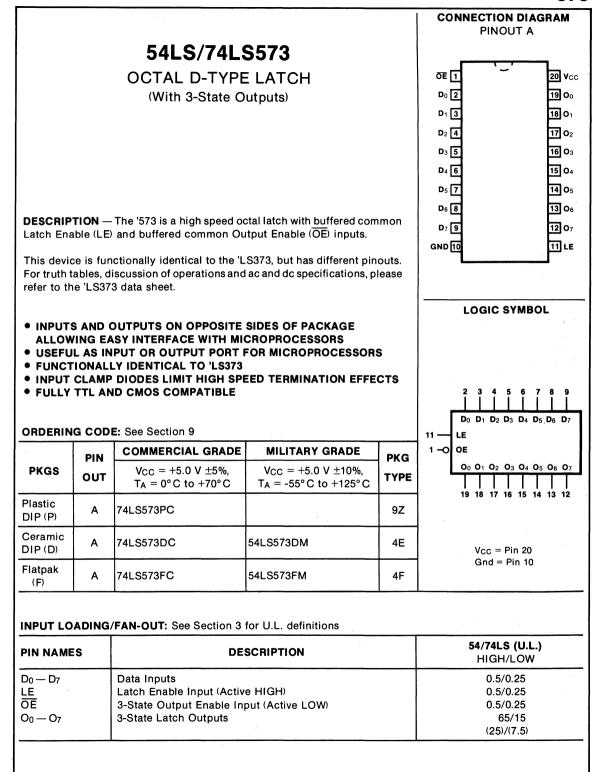

| 573           | Octal D-Type Flip-Flop   |              |                  |                  | X                   | 4-431       |

| 574           | Octal D-Type Flip-Flop   |              |                  |                  | x                   | 4-432       |

| 670           | 4 x 4 Register File      |              |                  |                  | X                   | 4-433       |

#### 9XXX FAMILY TTL

| DEVICE<br>NO. | DESCRIPTION                   | PAGE<br>NO. |      |                          | PAGE<br>NO. |

|---------------|-------------------------------|-------------|------|--------------------------|-------------|

| 9000          | JK Flip-Flop                  | 5-3         | 9009 | NAND Buffer              | 5-17        |

| 9001          | JK Flip-Flop                  | 5-3         | 9012 | NAND Gate                | 5-10        |

| 9002          | NAND Gate                     | 5-10        | 9014 | Quad Exclusive-OR Gate   | 5-19        |

| 9003          | NAND Gate                     | 5-10        | 9015 | Quad NOR Gate            | 5-22        |

| 9004          | NAND Gate                     | 5-10        | 9016 | Hex Inverter             | 5-10        |

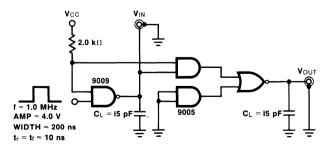

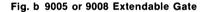

| 9005          | Extendable AND-OR-Invert Gate | 5-13        | 9017 | Hex Inverter             | 5-10        |

| 9006          | Extender                      | 5-13        | 9020 | Dual JK Flip-Flop        | 5-3         |

| 9007          | NAND Gate                     | 5-10        | 9022 | Dual JK Flip-Flop        | 5-3         |

| 9008          | Entendable AND-OR-Invert Gate | 5-13        | 9024 | Dual JK (or D) Flip-Flop | 5-24        |

### 93XX FAMILY TTL

| DEVICE<br>NO. | DESCRIPTION                    | 93XX<br>TTL | 93H<br>H-TTL | 93L<br>L-TTL | 93S<br>S-TTL | PAGE<br>NO. |

|---------------|--------------------------------|-------------|--------------|--------------|--------------|-------------|

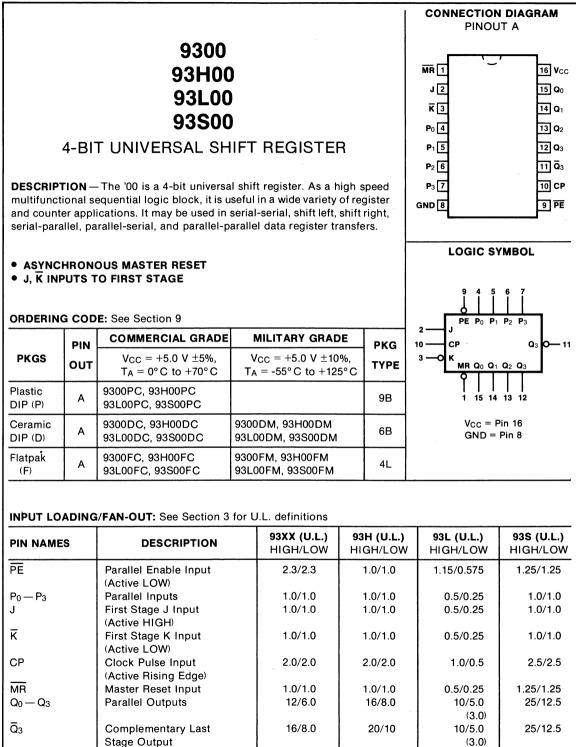

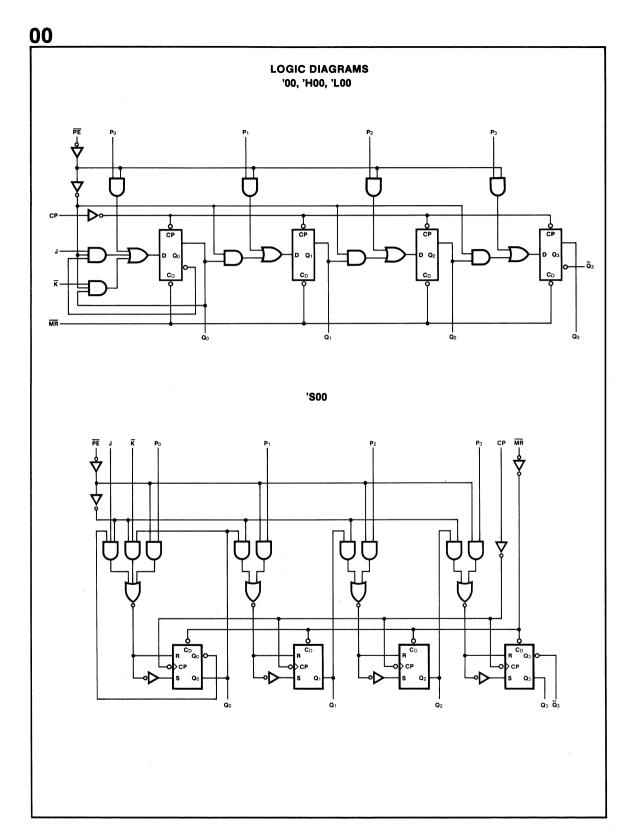

| 00            | 4-Bit Universal Shift Register | x           | х            | , <b>X</b>   | x            | 6-3         |

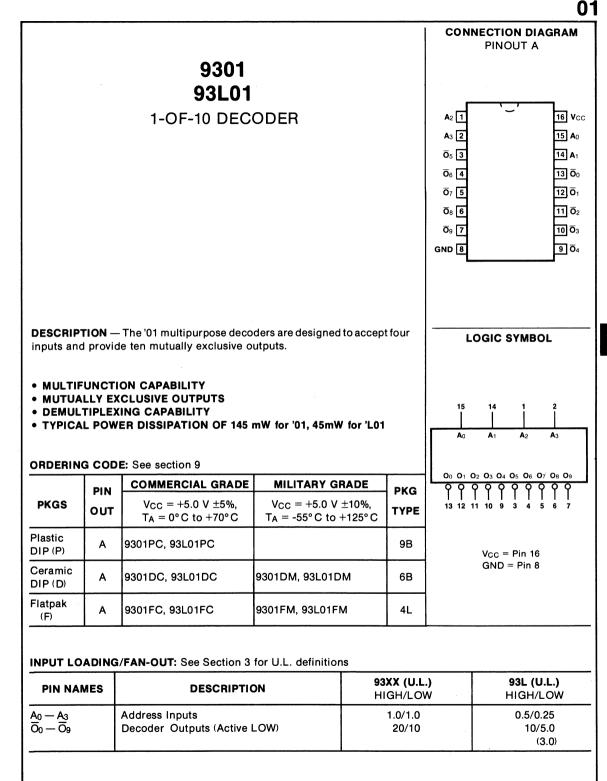

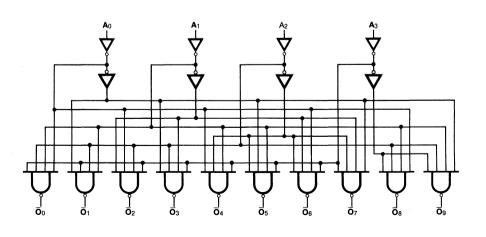

| 01            | 1-of-10 Decoder                | X           |              | х            |              | 6-7         |

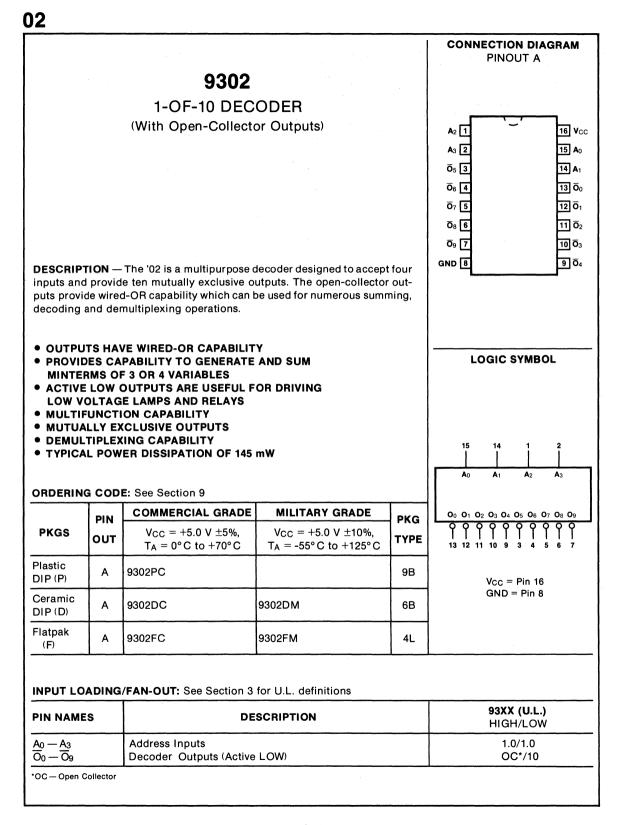

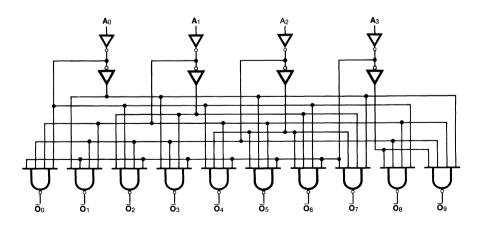

| 02            | 1-of-10 Decoder                | X           |              |              |              | 6-10        |

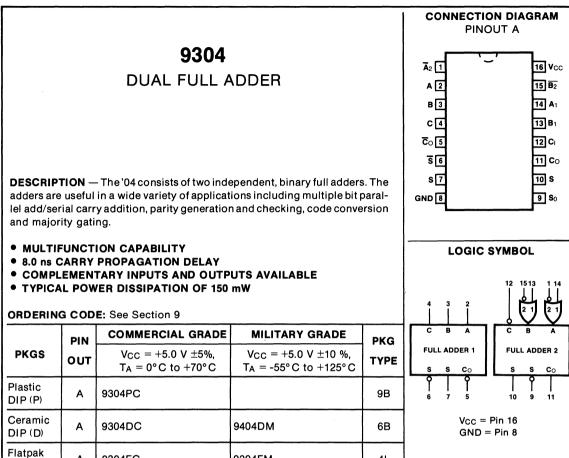

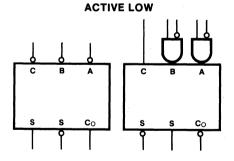

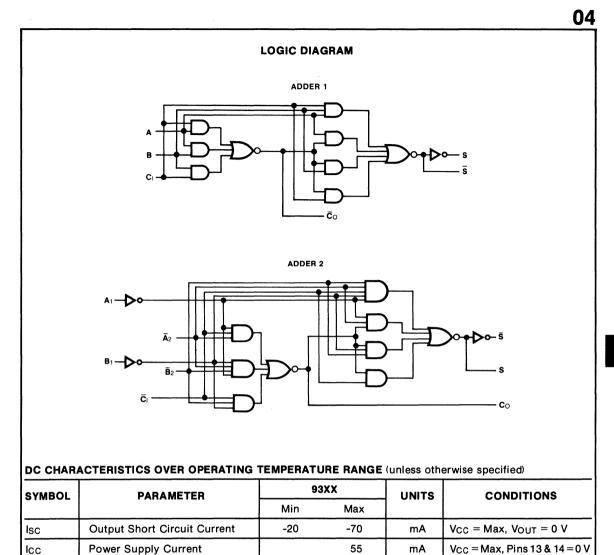

| 04            | Dual Full Adder                | X           |              |              |              | 6-13        |

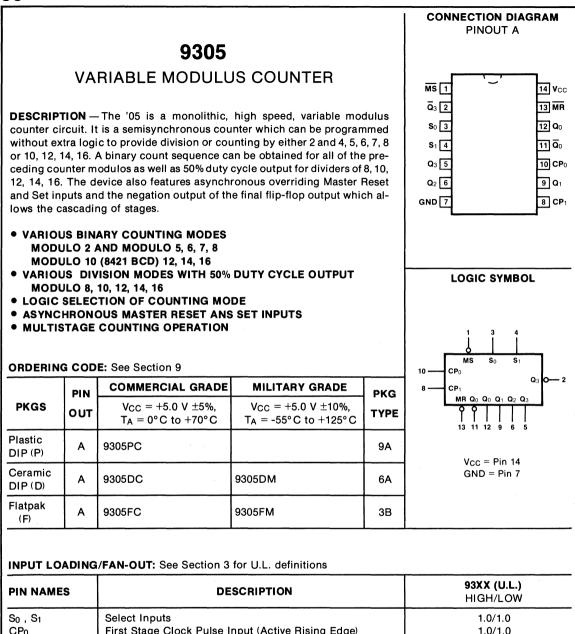

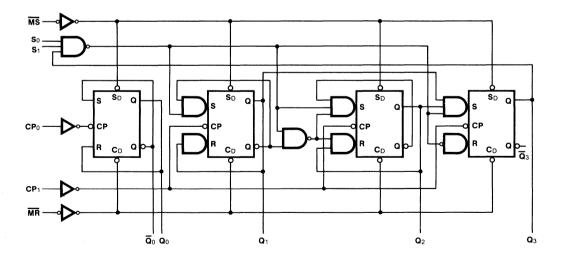

| 05            | Variable Modulus Counter       | X           |              |              |              | 6-16        |

| 07            | 7-Segment Decoder              | X           |              |              |              | 6-20        |

| 08            | Dual 4-Bit Latch               | X           |              | х            |              | 6-24        |

| 09            | Dual 4-Input Multiplexer       | x           |              | Х            |              | 6-27        |

| DEVICE<br>NO. | DESCRIPTION                                  | 93XX<br>TTL | 93H<br>H-TTL | 93L<br>L-TTL | 93S<br>S-TTL | PAGE<br>NO. |

|---------------|----------------------------------------------|-------------|--------------|--------------|--------------|-------------|

| 10            | BCD Decade Counter                           | х           |              | x            | х            | 6-30        |

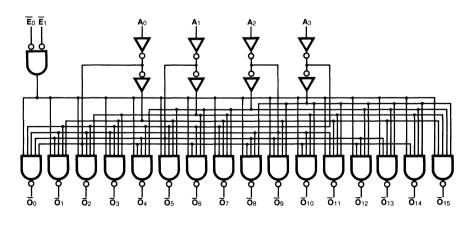

| 11            | 1-of-16 Decoder/Demultiplexer                | х           |              | х            |              | 6-36        |

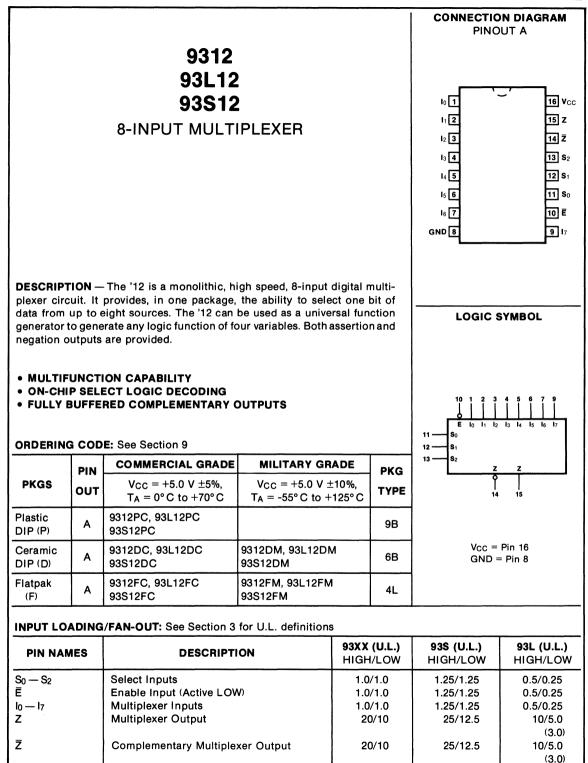

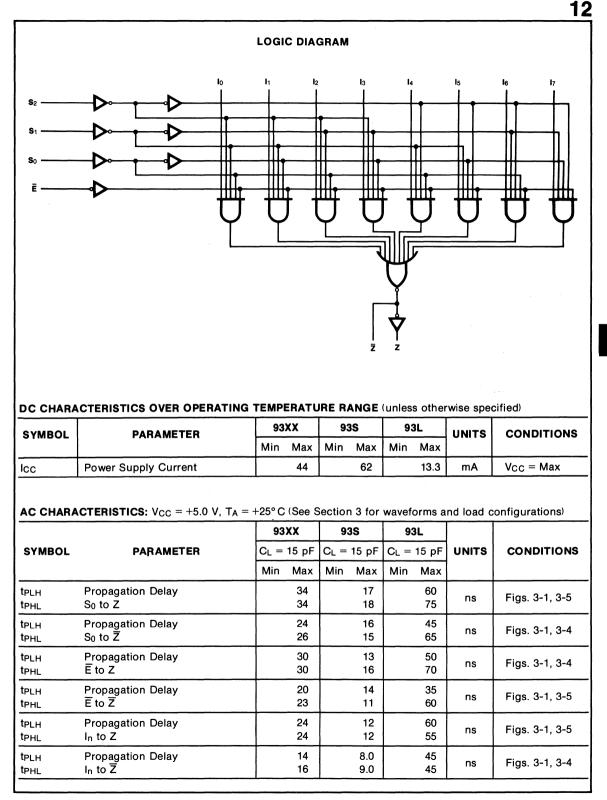

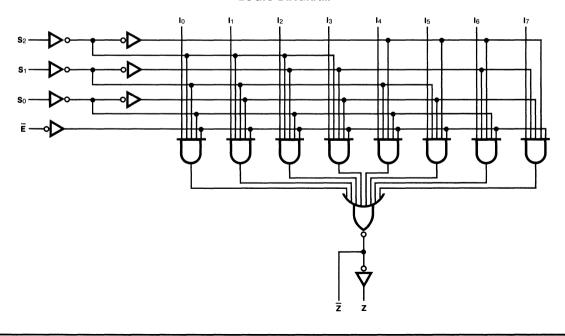

| 12            | 8-Input Multiplexer                          | х           |              | x            | х            | 6-39        |

| 13            | 8-Input Multiplexer                          | х           |              |              |              | 6-42        |

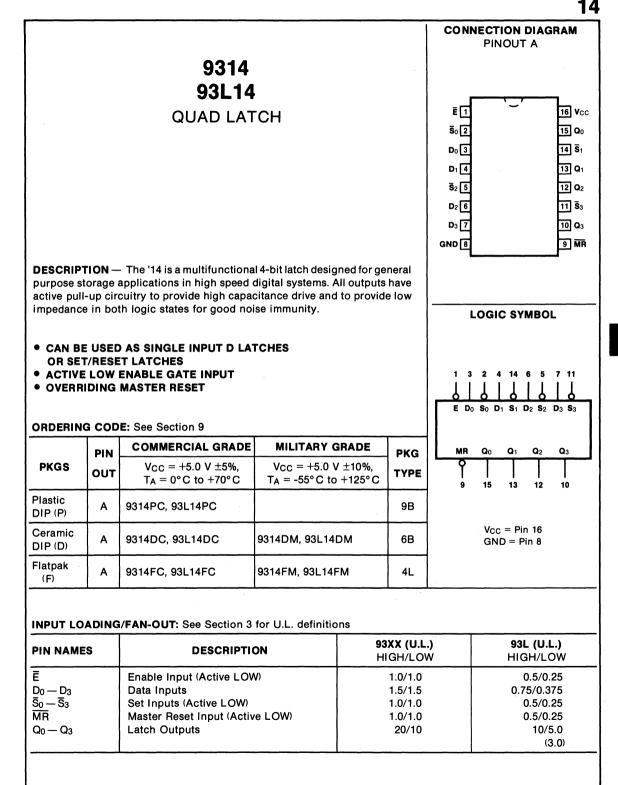

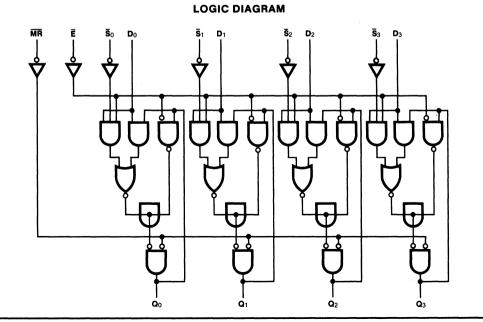

| 14            | Quad Latch                                   | х           |              | x            |              | 6-45        |

| 15            | 1-of-10 Decoder                              | х           |              |              |              | 6-48        |

| 16            | 4-Bit Binary Counter                         | х           |              | X            | х            | 6-30        |

| 17B           | 7-Segment Decoder/Driver                     | х           |              |              |              | 6-51        |

| 17C           | 7-Segment Decoder/Driver                     | х           |              |              |              | 6-51        |

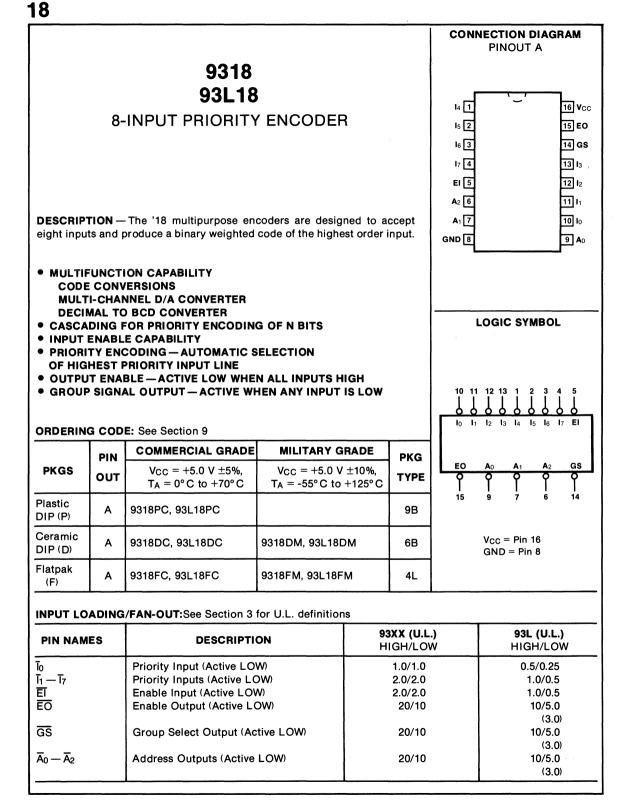

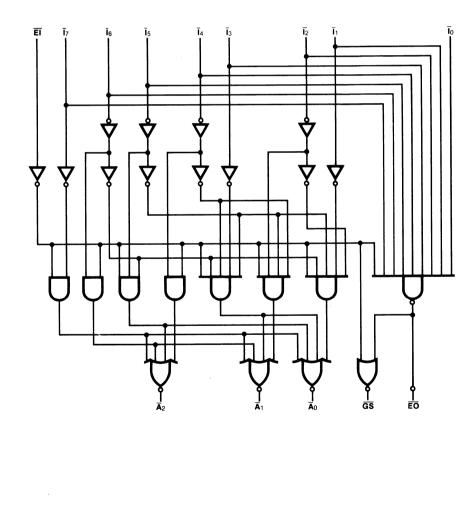

| 18            | 8-Input Priority Encoder                     | х           |              | x            |              | 6-56        |

| 19            | Decade Sequencer                             | х           |              |              |              | 6-59        |

| 20            | Decade Sequencer                             | х           |              |              |              | 6-59        |

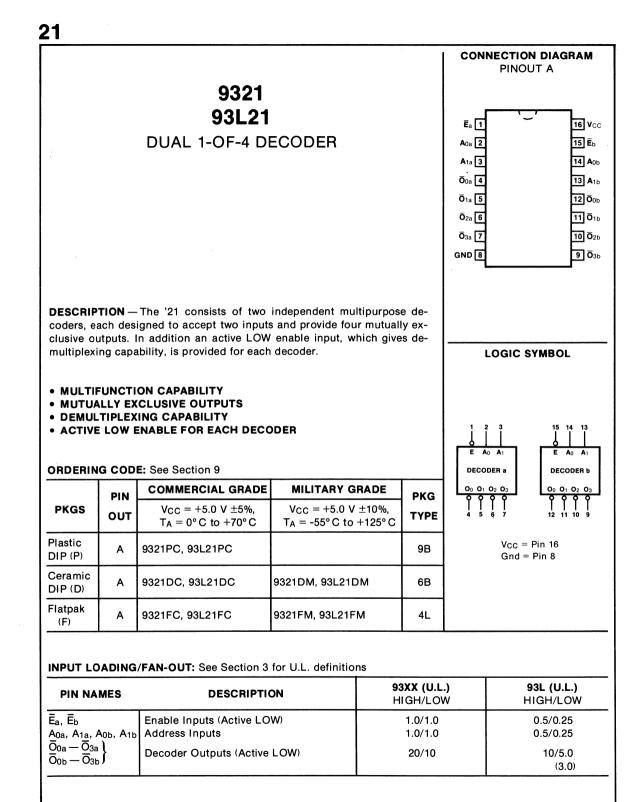

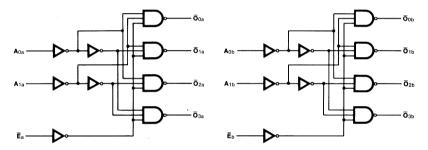

| 21            | Dual 1-of-4 Decoder                          | х           |              | x            |              | 6-64        |

| 22            | Quad 2-Input Multiplexer                     | х           |              | х            |              | 6-66        |

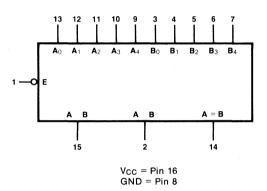

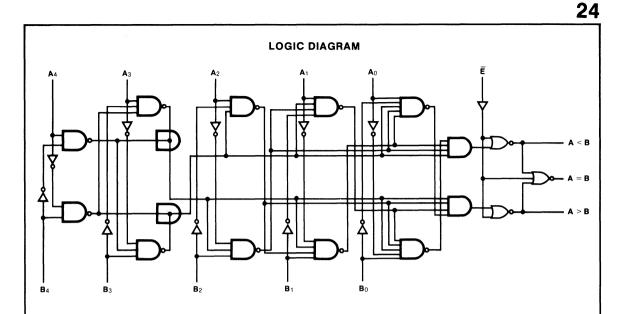

| 24            | 5-Bit Comparator                             | х           |              | x            |              | 6-69        |

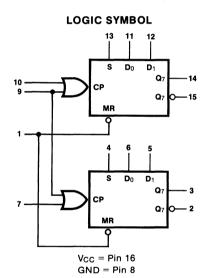

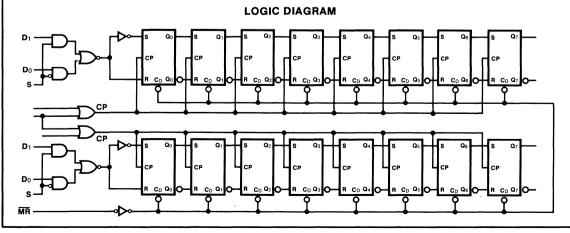

| 28            | Dual 8-Bit Shift Register                    | х           |              | x            |              | 6-72        |

| 34            | 8-Input Addressable Latch                    | х           |              | x            |              | 6-75        |

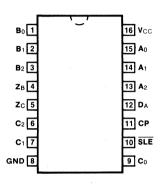

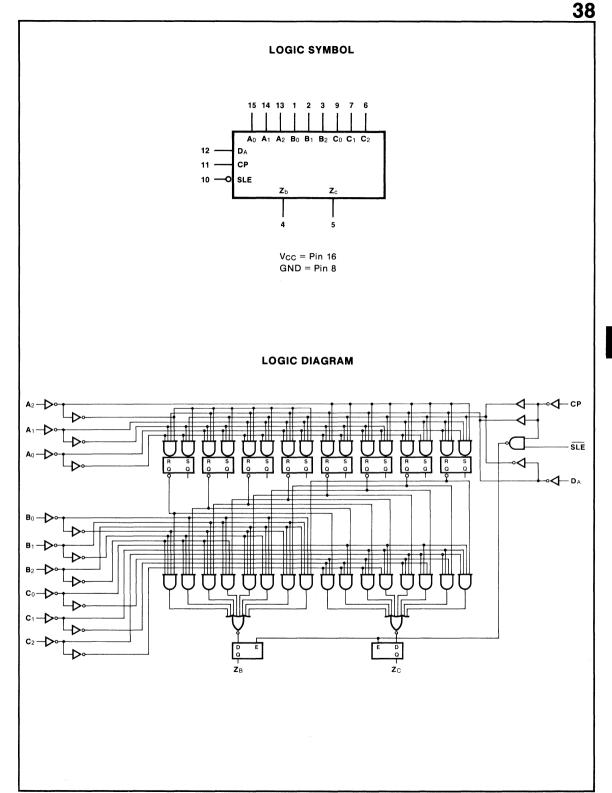

| 38            | 8-Bit Multiple Port Register                 | х           |              | x            |              | 6-78        |

| 40            | 4-Bit Arithmetic Logic Unit                  | х           |              |              |              | 6-82        |

| 41            | 4-Bit Arithmetic Logic Unit                  | х           |              | х            | x            | 6-87        |

| 42            | Carry Lookahead Generator                    | х           |              |              | х            | 6-94        |

| 43            | 4-Bit by 2-Bit Twos<br>Complement Multiplier |             |              |              | x            | 6-98        |

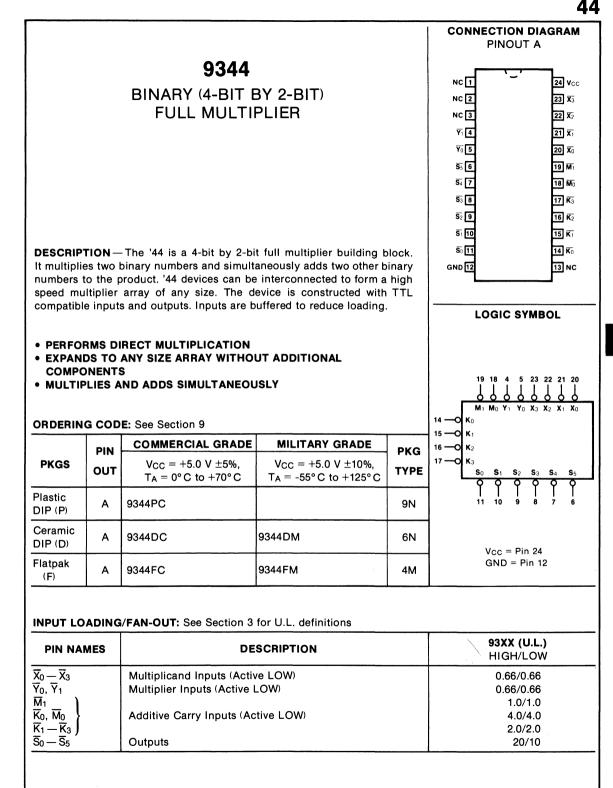

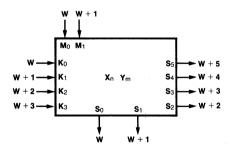

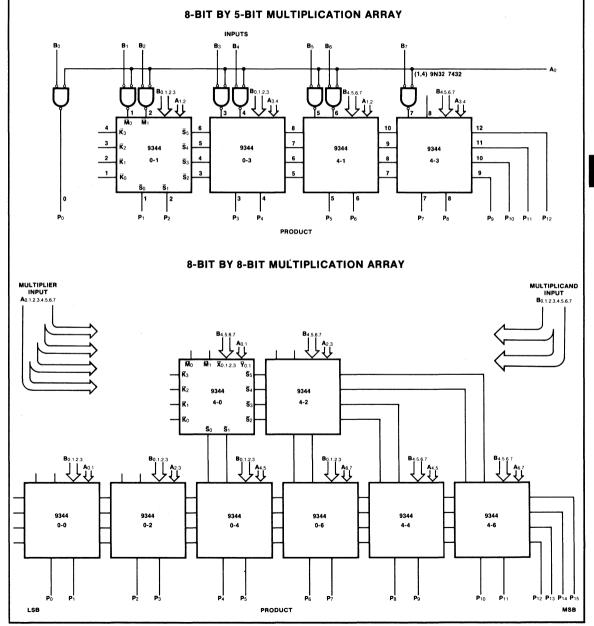

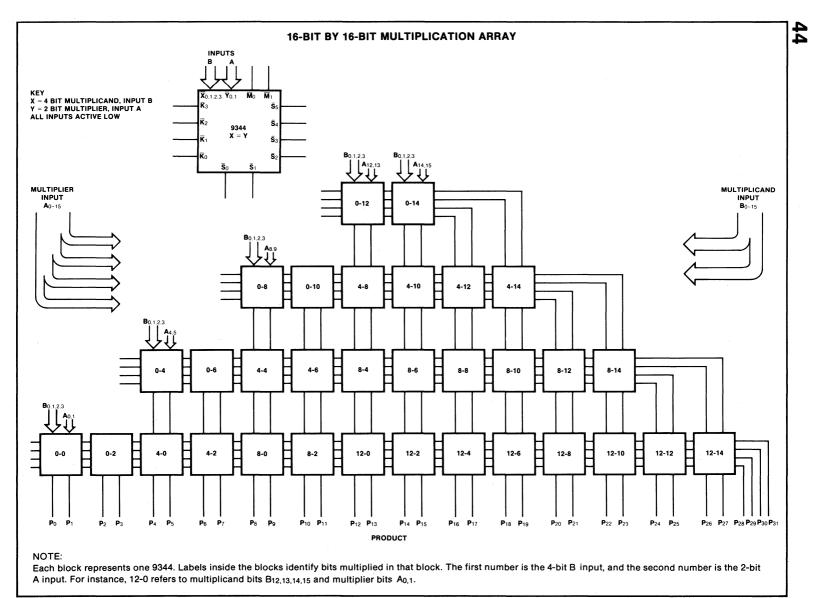

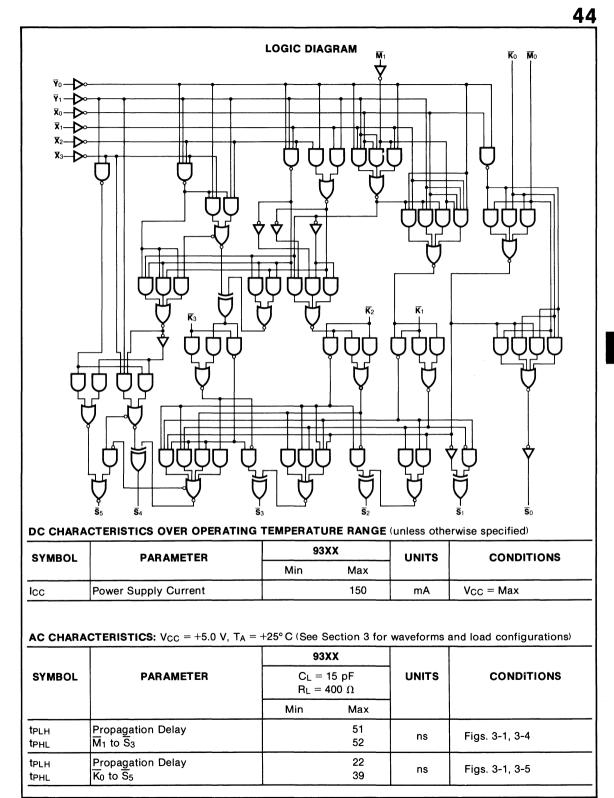

| 44            | Binary (4-Bit by 2-Bit) Full Multiplier      | х           |              |              |              | 6-10        |

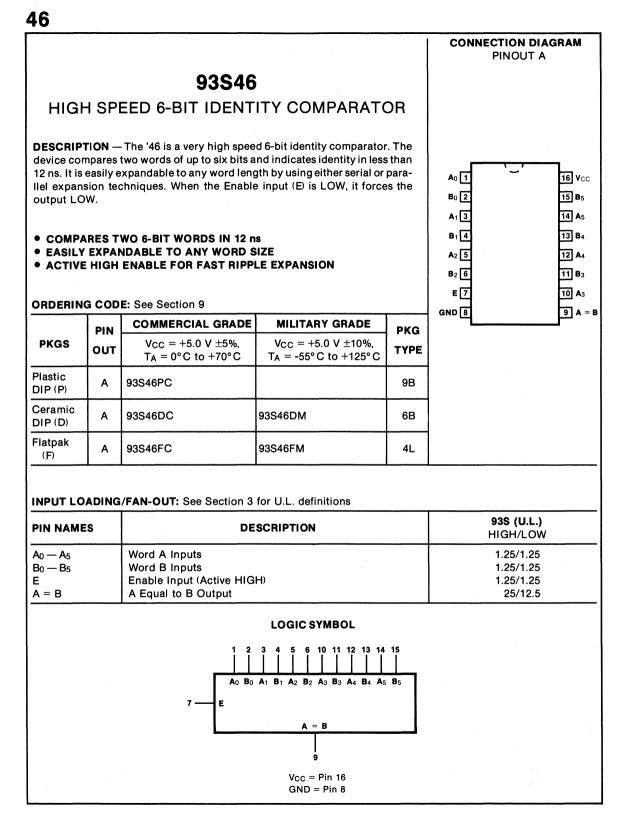

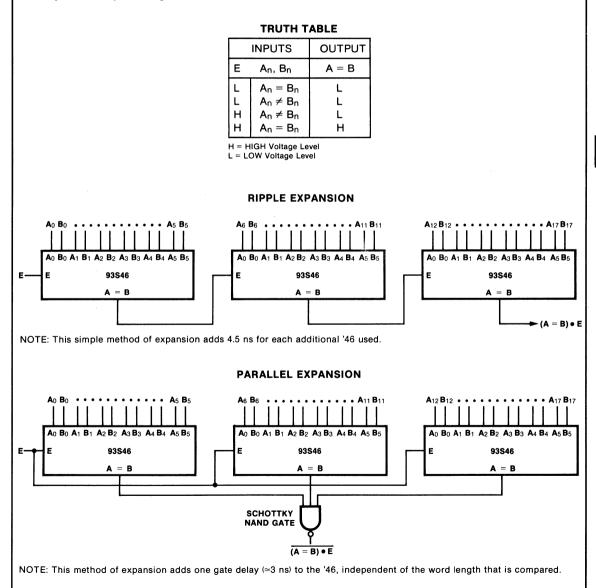

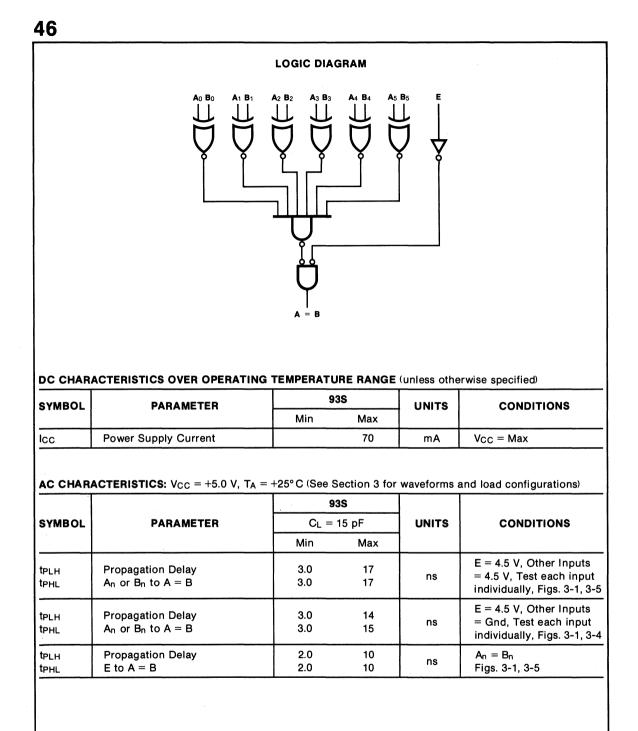

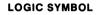

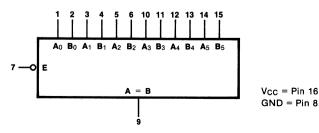

| 46            | High Speed 6-Bit Identity Comparator         |             |              |              | х            | 6-10        |

| 47            | High Speed 6-Bit Identity Comparator         |             |              |              | х            | 6-10        |

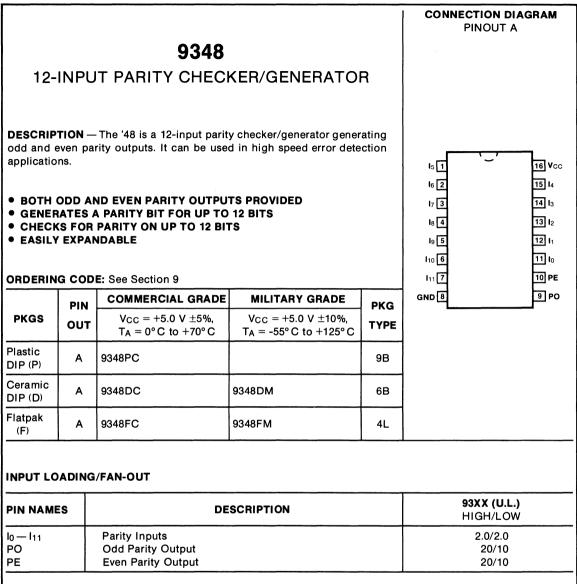

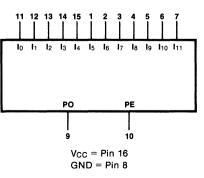

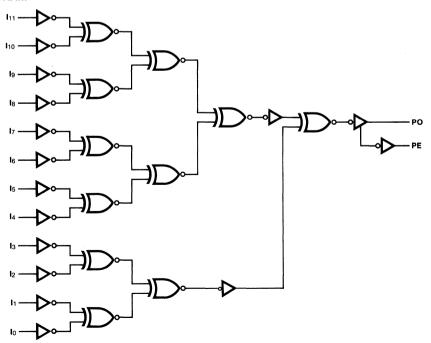

| 48            | 12-Input Parity Checker/Generator            | х           |              |              |              | 6-11        |

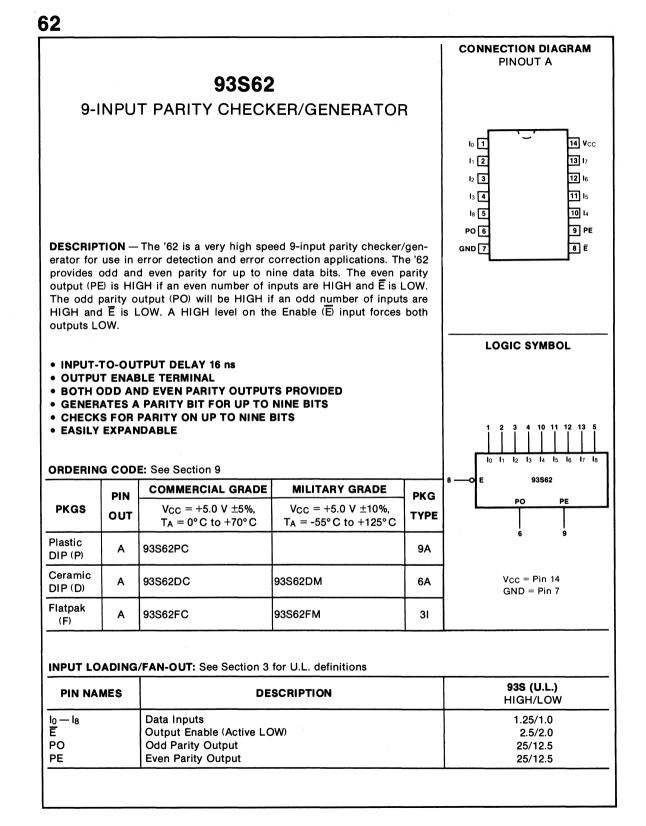

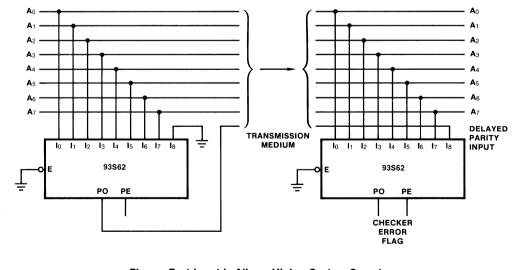

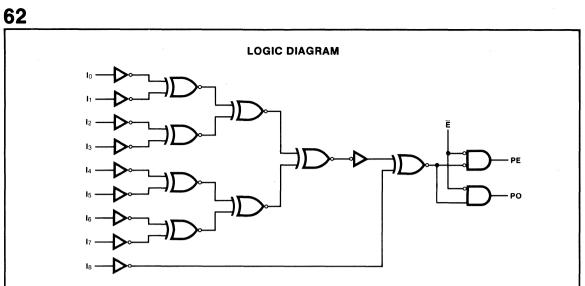

| 62            | 9-Input Parity Checker/Generator             |             |              |              | x            | 6-11        |

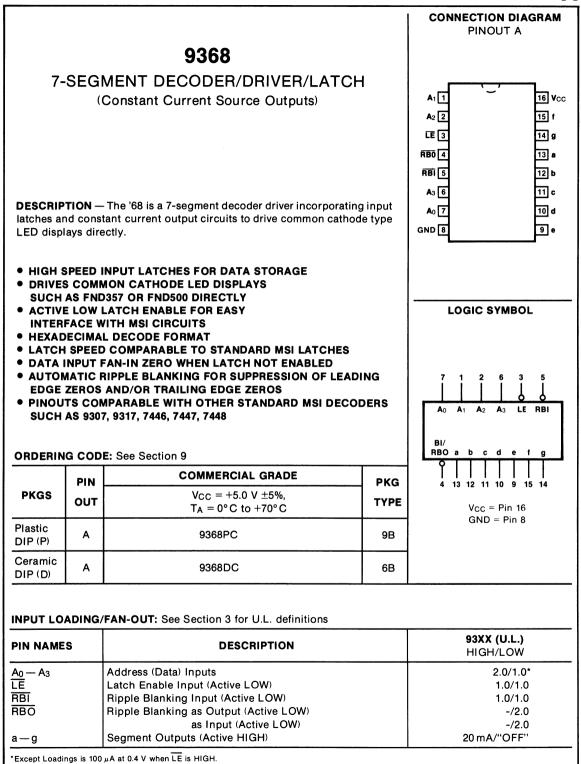

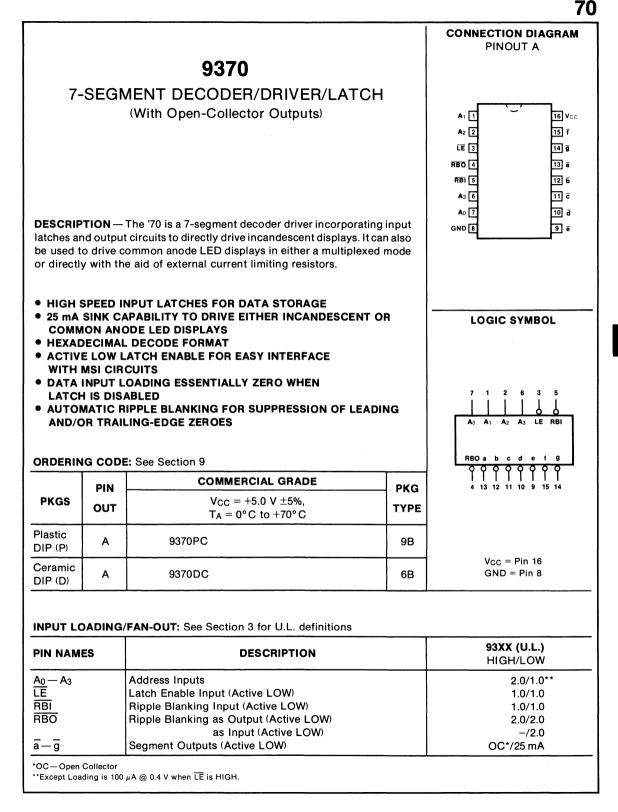

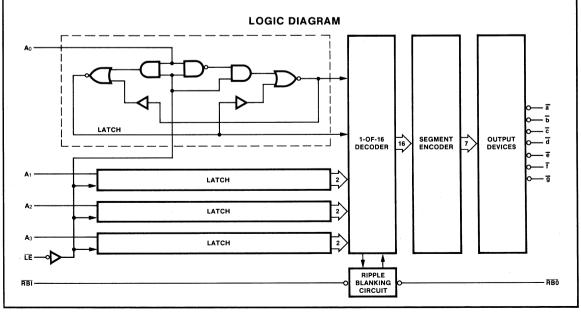

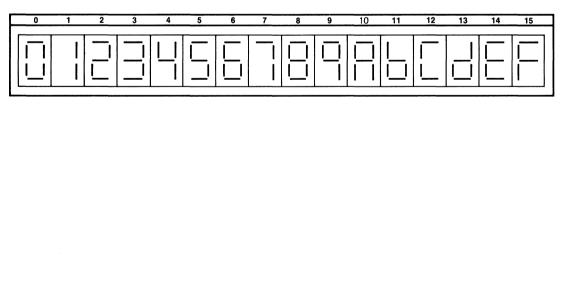

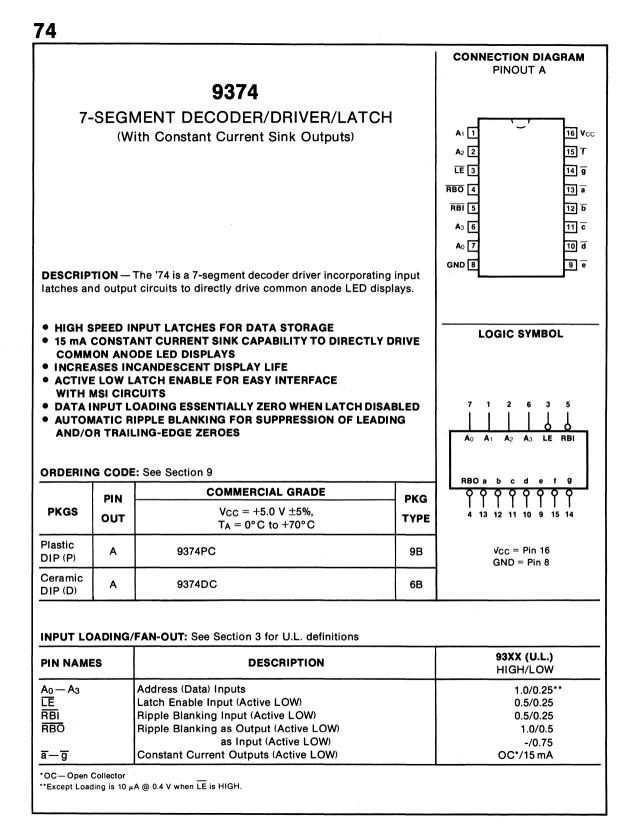

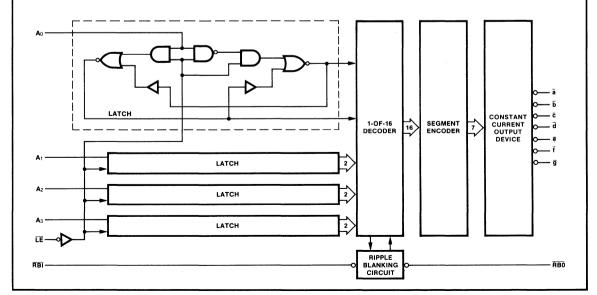

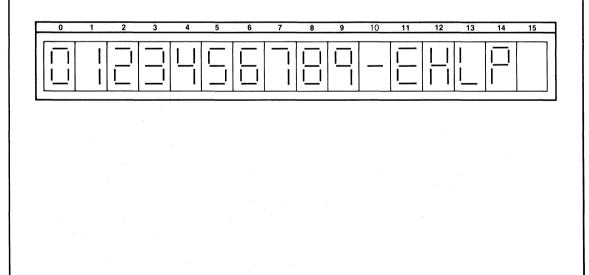

| 68            | 7-Segment Decoder/Driver/Latch               | х           |              |              |              | 6-11        |

| 70            | 7-Segment Decoder/Driver/Latch               | X           |              |              |              | 6-12        |

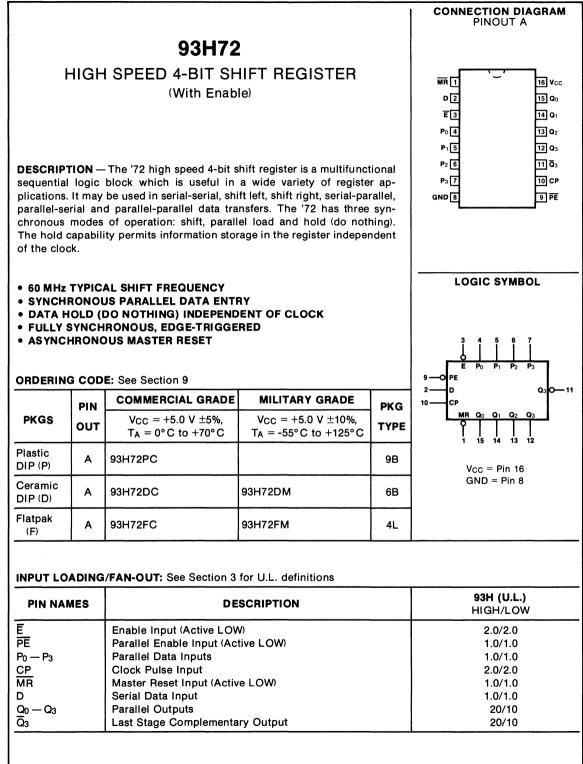

| 72            | High Speed 4-Bit Shift Register              |             | x            |              |              | 6-12        |

| 74            | 7-Segment Decoder/Driver/Latch               | x           |              |              |              | 6-13        |

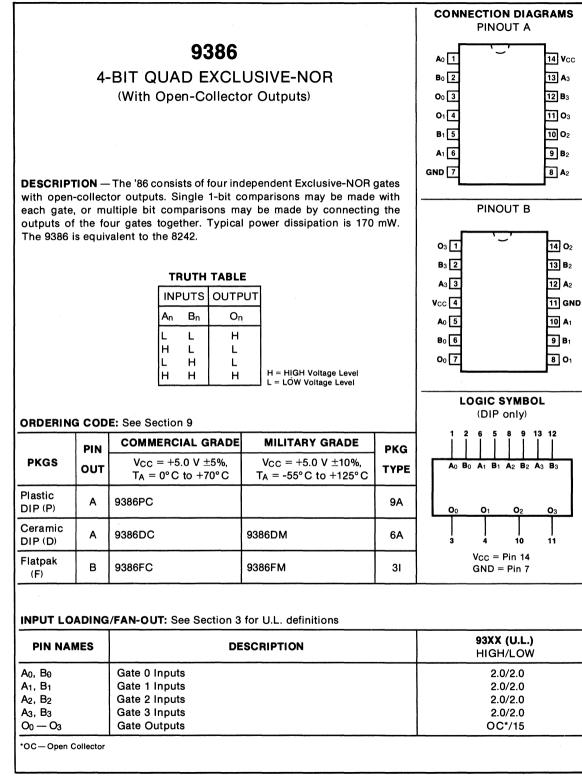

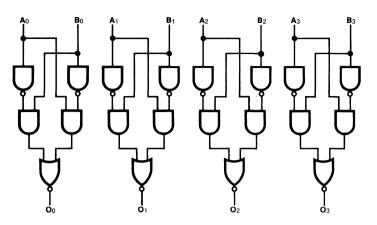

| 86            | 4-Bit Quad Exclusive-NOR                     | x           |              |              |              | 6-13        |

1

٦

| DEVICE<br>NO. | DESCRIPTION                                               | 96XX<br>TTL | 96L<br>L-TTL | 96S<br>S-TTL | 96LS<br>LS-TTL | PAGE<br>NO.   |

|---------------|-----------------------------------------------------------|-------------|--------------|--------------|----------------|---------------|

| 00            | Retriggerable Resettable<br>Monostable Multivibrator      | х           |              |              |                | 7-3           |

| 01            | Retriggerable Monostable Multivibrator                    | х           |              |              |                | 7-8           |

| 02            | Dual Retriggerable Resettable<br>Monostable Multivibrator | х           | x            | x            | x              | 7-14/<br>7-20 |

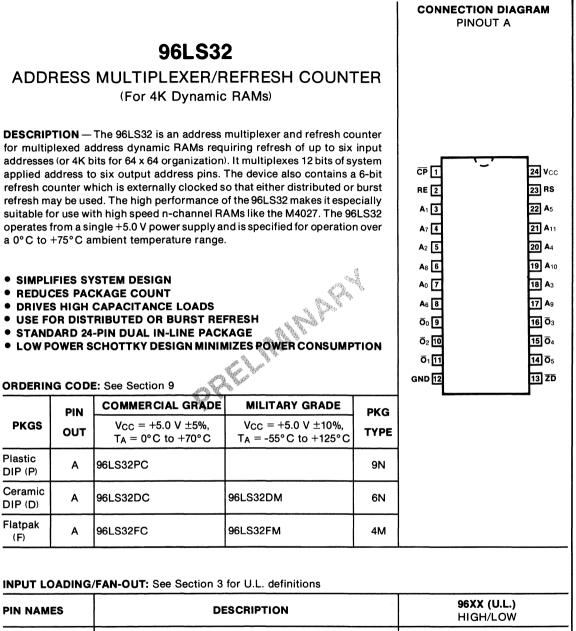

| 32            | Address Multiplexer/Refresh Counter                       |             |              |              | x              | 7-27          |

| 42            | Address Multiplexer/Refresh Counter                       | ,           |              |              | x              | 7-30          |

| 101           | Quad 2-Input Positive NAND Buffer                         | х           |              |              |                | 7-33          |

| 103           | Quad Bus Transceiver                                      | х           |              |              |                | 7-34          |

| 106           | Quad 2-Input NOR Receiver                                 | x           |              |              |                | 7-36          |

## **SELECTION GUIDES**

#### SSI FUNCTIONS

| FUNCTION            | 9XXX | 54/74   | 54H/74H   | 54S/74S                 | 54LS/74LS                              |

|---------------------|------|---------|-----------|-------------------------|----------------------------------------|

| NAND Gates          |      |         |           |                         | •••••••••••••••••••••••••••••••••••••• |

| Hex Inverters       | 9016 | 54/7404 | 54H/74H04 | 54S/74S04<br>54S/74S04A | 54LS/74LS04                            |

| Hex Inverters (OC*) | 9017 | 54/7405 | 54H/74H05 | 54S/74S05<br>54S/74S05A | 54LS/74LS05                            |

| Hex Inverter (15 V) |      | 54/7416 |           |                         |                                        |

| Hex Inverter (30 V) |      | 54/7406 |           |                         |                                        |

| Hex Schmitt Trigger |      | 54/7414 |           |                         | 54LS/74LS14                            |

| Quad 2-Input        | 9002 | 54/7400 | 54H/74H00 | 54S/74S00               | 54LS/74LS00                            |

| Quad 2-Input (OC*)  | 9012 | 54/7403 |           | 54S/74S03               | 54LS/74LS03                            |

| Quad 2-Input (OC*)  |      | 54/7401 | 54H/74H01 |                         |                                        |

| Quad 2-Input (12 V) |      | 7426    |           |                         | 54LS/74LS26                            |

| Quad 2-Input (48 V) |      | 54/7437 |           |                         | 54LS/74LS37                            |

\*OC = Open-collector; 3S = 3-State

| FUNCTION                 | 9X X X | 54/74    | 54H/74H   | 54S/74S    | 54LS/74LS    |

|--------------------------|--------|----------|-----------|------------|--------------|

| NAND Gates (Cont'd)      |        |          |           |            |              |

| Quad 2-Input (OC*/48 mA) |        | 54/7438  |           |            | 54LS/74LS38  |

| Quad 2-Input Line Driver | 96101  | 54/7439  |           |            |              |

| Quad 2-Input Schmitt     |        | 54/74132 |           | 54S/74S132 | 54LS/74LS132 |

| Triple 3-Input           | 9003   | 54/7410  | 54H/74H10 | 54S/74S10  | 54LS/74LS10  |

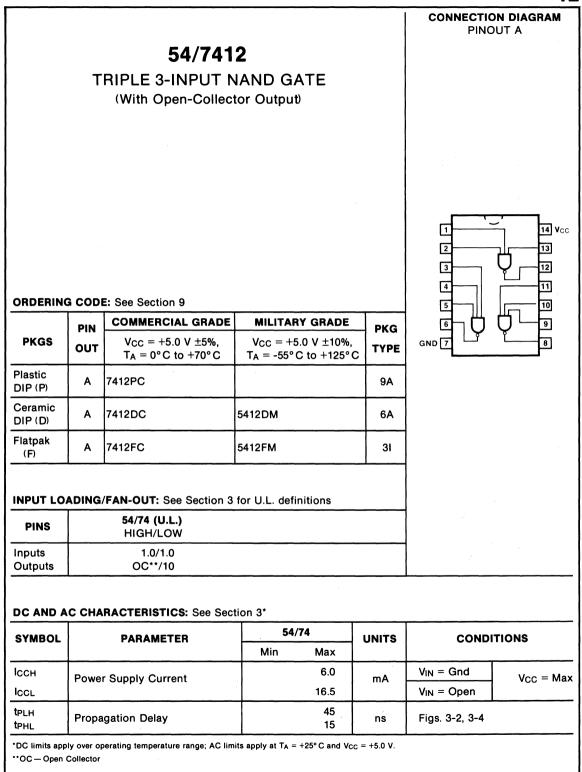

| Triple 3-Input (OC*)     |        | 54/7412  |           |            |              |

| Dual 4-Input             | 9004   | 54/7420  | 54H/74H20 | 54S/74S20  | 54LS/74LS20  |

| Dual 4-Input Schmitt     |        | 54/7413  |           |            | 54LS/74LS13  |

| Dual 4-Input (OC*)       |        | 54/7422  | 54H/74H22 | 54S/74S22  | 54LS/74LS22  |

| Dual 4-Input Buffer      | 9009   | 54/7440  | 54H/74H40 | 54S/74S40  | 54LS/74LS40  |

| Dual 4-Input Line Driver |        |          |           | 54S/74S140 |              |

| 8-Input                  | 9007   |          |           |            |              |

| 8-Input                  |        | 54/7430  | 54H/74H30 | 54S/74S30  | 54LS/74LS30  |

| 13-Input                 |        |          |           | 54S/74S133 | 54LS/74LS133 |

| 12-Input (3S*)           |        |          |           | 54S/74S134 |              |

| NOR Gates                |        |          |           |            | -            |

| Quad 2-Input             |        | 54/7402  |           | 54S/74S02  | 54LS/74LS02  |

| Quad 2-Input             | 9015   |          |           |            |              |

| Triple 3-Input           |        | 54/7427  |           |            | 54LS/74LS27  |

| Dual 4-Input w/Strobe    |        | 54/7425  |           |            |              |

| Dual 4-Input (Exp)       |        | 54/7423  |           |            |              |

| Dual 5-Input             |        |          |           | 54S/74S260 | 54LS/74LS260 |

| Quad 2-Input             |        |          |           |            | 54LS/74LS28  |

| Quad 2-Input (OC*)       |        |          |           |            | 54LS/74LS33  |

| AND Gates                |        |          |           |            |              |

| Hex Buffer (OC*/15 V)    |        | 54/7417  |           |            |              |

| Hex Buffer (OC*/30 V)    |        | 54/7407  |           |            |              |

| Quad 2-Input             |        | 54/7408  | 54H/74H08 | 54S/74S08  | 54LS/74LS08  |

| Quad 2-Input (OC*)       |        | 54/7409  |           | 54S/74S09  | 54LS/74LS09  |

| Triple 3-Input           |        | 54/7411  | 54H/74H11 | 54S/74S11  | 54LS/74LS11  |

| Triple 3-Input (OC*)     |        |          | <u></u>   | 54S/74S15  | 54LS/74LS15  |

| Dual 4-Input             |        | 54/7421  | 54H/74H21 |            | 54LS/74LS21  |

\*OC = Open-Collector; 3S = 3-State

Γ

| FUNCTION                 | 9XXX | 54/74       | 54H/74H   | 54S/74S    | 54LS/74LS     |

|--------------------------|------|-------------|-----------|------------|---------------|

| OR Gates                 |      |             |           |            |               |

| Quad 2-Input             |      | 54/7432     |           | 54S/74S32  | 54LS/74LS32   |

| Exclusive-OR Gates       |      |             | -         |            |               |

| Quad 2-Input             |      | 54/7486     |           | 54S/74S86  | 54LS/74LS86   |

| Quad 2-Input (OC*)       |      |             |           |            | 54LS/74LS136  |

| Quad 2-Input OR/NOR      | 9014 |             | -         |            |               |

| Quad 2-Input OR/NOR      |      |             |           | 54S/74S135 |               |

| Exclusive-NOR Gate       |      |             |           |            |               |

| Quad 2-Input (OC*)       |      | 9386 (8242) |           |            | 54LS/74LS266  |

| AND-OR Gates             |      |             |           |            |               |

| 2-2-2-3 Input (Exp)      |      |             | 54H/74H52 |            |               |

| AND-OR-INVERT Gates      |      |             |           |            |               |

| Dual 2-2 Input (Exp)     | 9005 | 54/7450     | 54H/74H50 |            |               |

| Dual 2-2 Input           |      | 54/7451     | 54H/74H51 | 54S/74S51  | 54LS/74LS51   |

| 2-2-2-3 Input (Exp)      | 9008 | 54/7453     | 54H/74H53 |            |               |

| 2-2-2-3 Input            |      | 54/7454     | 54H/74H54 |            |               |

| 2-2-3-3 Input            |      |             |           |            | 54LS/74LS54   |

| 2-2-3-4 Input            |      |             |           | 54S/74S64  |               |

| 2-2-3-4 Input (OC*)      |      |             |           | 54S/74S65  |               |

| 4-4 Input (Exp)          |      |             | 54H/74H55 |            |               |

| 4-4 Input                |      |             |           |            | 54LS/74LS55   |

| Gate Expanders           |      |             |           |            |               |

| Triple 3-Input           |      |             | 54H/74H61 |            |               |

| Dual 4-Input             | 9006 | 54/7460     | 54H/74H60 |            |               |

| 2-2-3-3 AND-OR           |      |             | 54H/74H62 |            |               |

| Buffer Gates and Drivers |      |             | -         |            |               |

| Quad Buffer (3S*)        |      | 54/74125    |           |            | 54LS/74LS125  |

| Quad Buffer (3S*)        |      | 54/74126    |           |            | 54LS/74LS126  |

| Hex (3S*)                |      |             |           |            | 54LS/74LS365/ |

| Hex Inverter (3S*)       |      |             |           |            | 54LS/74LS366  |

| Hex (3S*)                |      |             |           |            | 54LS/74LS367  |

| Hex Inverter (3S*)       |      |             |           |            | 54LS/74LS368/ |

\*OC = Open-Collector; 3S = 3-State

Г

| FUNCTION  | DEVICE NO.     | INPUTS                      | CLOCK<br>EDGE | DIRECT<br>SET | DIRECT<br>CLEAR | GUARANTEED<br>CLOCK FREQ<br>MHz |

|-----------|----------------|-----------------------------|---------------|---------------|-----------------|---------------------------------|

| Single JK | 9000           | 3J, 3K, JK                  | 7             | Х             | х               | 20 (Typ)                        |

| Single JK | 9001           | 2J, 2K, J, K, JK            | 7             | X             | х               | 50 (Тур)                        |

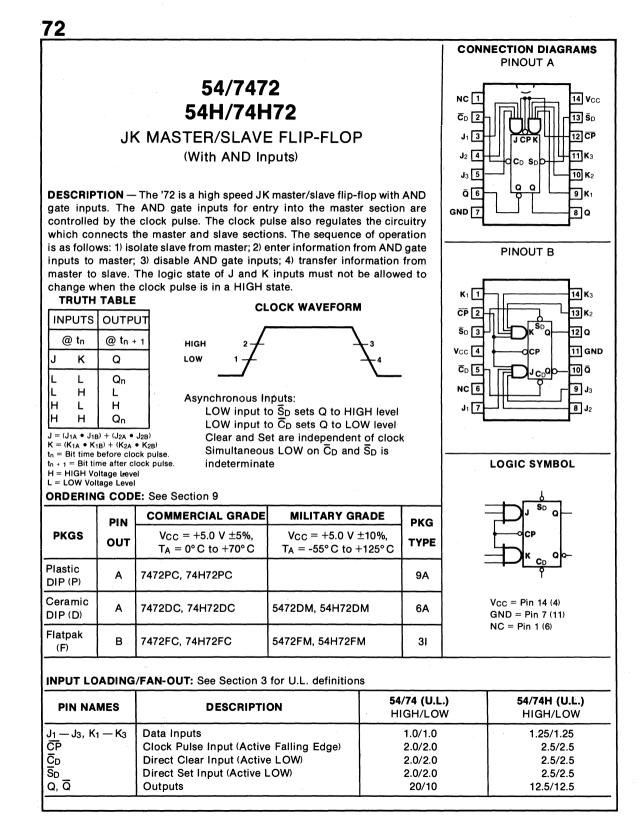

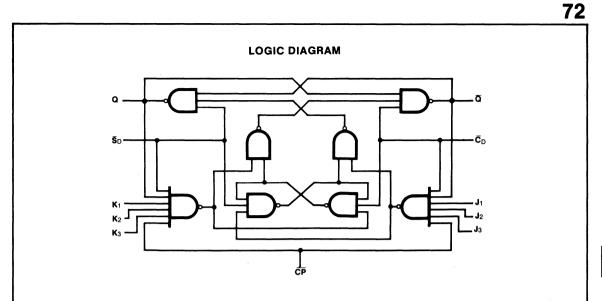

| Single JK | 54H/74H71      | (AOI)<br>(2 + 2)J, (2 + 2)K | ~             | X             |                 | 25                              |

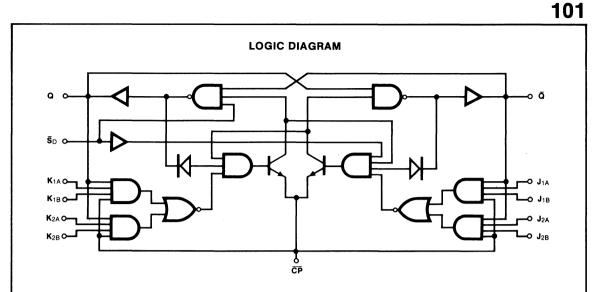

| Single JK | 54H/74H101     | (AOI)<br>(2 + 2)J, (2 + 2)K | ~             | X             |                 | 40                              |

| Single JK | 54/7472        | 3J, 3K                      | $\sim$        | Х             | х               | 15                              |

| Single JK | 54H/74H72      | 3J, 3K                      | $\sim$        | Х             | х               | 25                              |

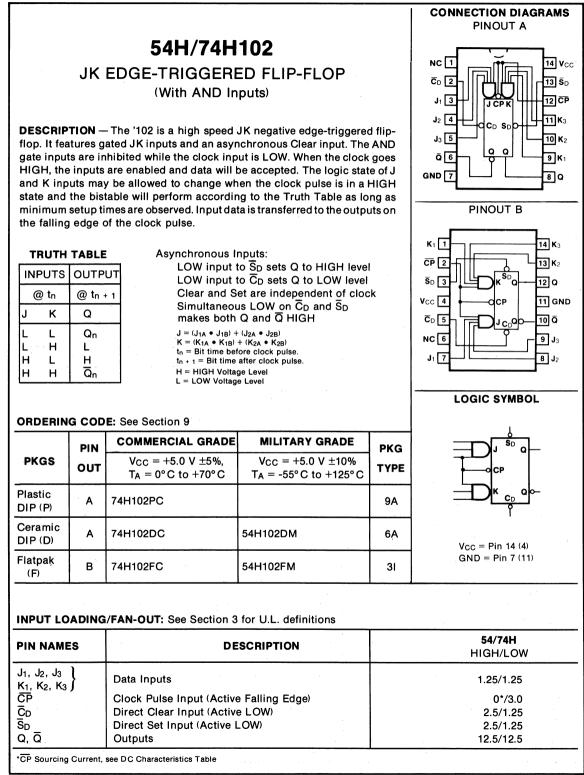

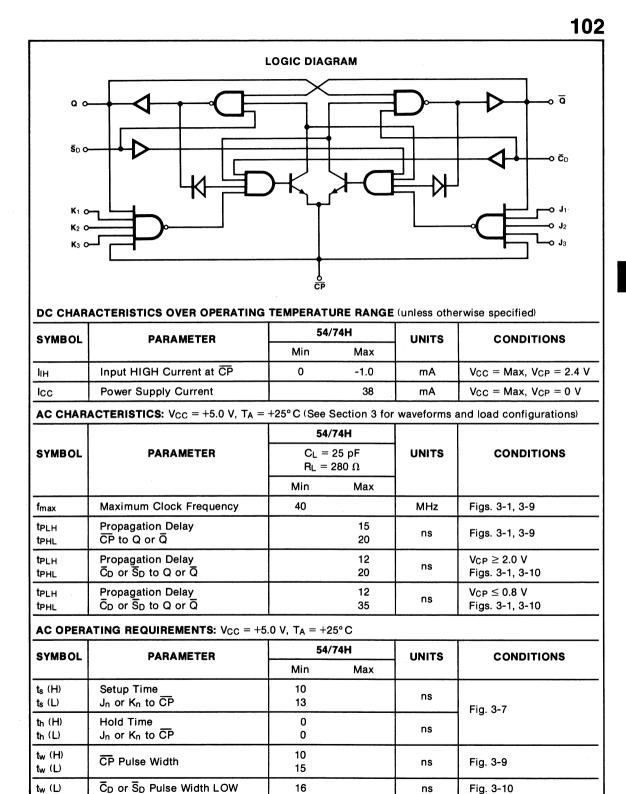

| Single JK | 54H/74H102     | 3J, 3K                      | $\sim$        | х             | х               | 40                              |

| Single JK | 54/7470        | 2J, 2K, J, K                | ~             | Х             | х               | 20                              |

| Dual D    | 54/7474        | D                           |               | х             | х               | 15                              |

| Dual D    | 54H/74H74      | D                           |               | Х             | х               | 35                              |

| Dual D    | 548/74874      | D                           | 7             | х             | X               | 75                              |

| Dual D    | 54LS/74LS74    | D                           | 7             | Х             | х               | 30                              |

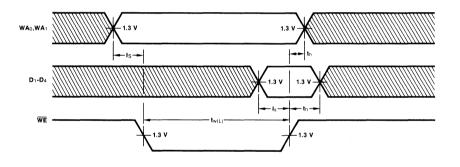

| Dual JK   | 9020           | J, K, J, K, JK              | 7             |               | х               | 50 (Typ)                        |

| Dual JK   | 9022           | J, <del>K</del> , JK        | ~             | х             | х               | 50 (Typ)                        |

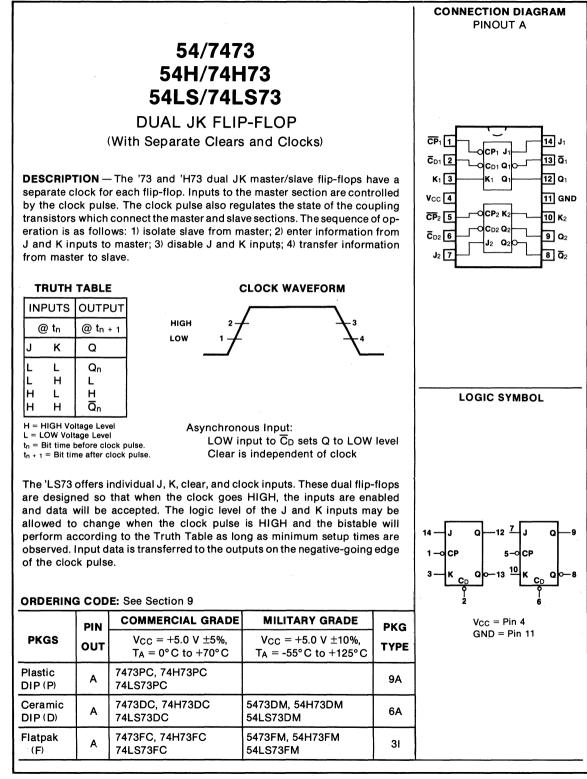

| Dual JK   | 54/7473        | J, K                        | $\sim$        |               | х               | 15                              |

| Dual JK   | 54/74107       | J, K                        | $\sim$        |               | X               | 15                              |

| Dual JK   | 54H/74H73      | J, K                        | $\sim$        |               | х               | 25                              |

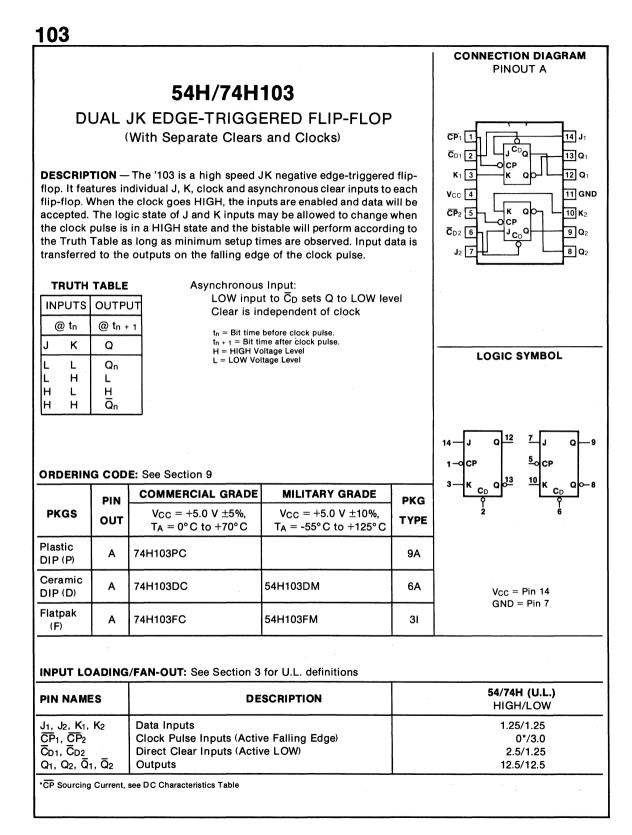

| Dual JK   | 54H/74H103     | J, K                        | $\sim$        |               | х               | 40                              |

| Dual JK   | 54S/74S113     | J, K                        | $\sim$        | х             |                 | 80                              |

| Dual JK   | 54LS/74LS113   | J, K                        | $\sim$        | х             |                 | 30                              |

| Dual JK   | 54/7476        | J, K                        | $\sim$        | х             | х               | 15                              |

| Dual JK   | 54H/74H76      | J, K                        | $\sim$        | х             | X               | 25                              |

| Dual JK   | 54H/74H106     | J, K                        | $\overline{}$ | х             | х               | 40                              |

| Dual JK   | 54S/74S112     | J, K                        | $\sim$        | Х             | х               | 80                              |

| Dual JK   | 54LS/74LS112   | J, K                        | $\sim$        | х             | X               | 30                              |

| Dual JK   | 54H/74H78      | J, K                        | $\sim$        | х             | х               | 25                              |

| Dual JK   | 54H/74H108     | J, K                        | 7             | х             | X               | 40                              |

| Dual JK   | 54LS/74LS73    | J, K                        | $\sim$        |               | х               | 30                              |

| Dual JK   | 54S/74S114     | J, K                        | $\sim$        | х             | x               | 80                              |

| Dual JK   | 54LS/74LS114   | J, K                        | $\sim$        | X             | х               | 30                              |

| Dual JK   | 9024, 54/74109 | J, K                        | 7             | х             | X               | 25                              |

2

7

х

GUARANTEED CLOCK FREQ. MHz 75 30 30

30

30

Х

х

| SINGLE AND DUAL FLIP-FLOPS (Cont'd) |              |        |               |               |        |  |  |  |  |

|-------------------------------------|--------------|--------|---------------|---------------|--------|--|--|--|--|

| FUNCTION                            | DEVICE NO.   | INPUTS | CLOCK<br>EDGE | DIRECT<br>SET | DIRECT |  |  |  |  |

| Dual JK                             | 54S/74S109   | J, K   | 7             | х             | x      |  |  |  |  |

| Dual JK                             | 54LS/74LS109 | J, K   | 5             | х             | x      |  |  |  |  |

| Dual JK                             | 54LS/74LS76  | J, K   |               | Х             | X      |  |  |  |  |

J, K

J, K

#### LATCHES

Dual JK

Dual JK

54ĽS/74LS107

54LS/74LS78

| FUNCTION                  | DEVICE NO.         | DATA<br>INPUTS                       | COMMON<br>CLEAR | ENABLE<br>INPUTS<br>(LEVEL) | MIN ENABLE<br>PULSE WIDTH<br>ns | MAX DELAY<br>ENABLE TO<br>OUTPUT-ns |

|---------------------------|--------------------|--------------------------------------|-----------------|-----------------------------|---------------------------------|-------------------------------------|

| 4-Bit RS Latch            | 9314               | 4 X (R <sub>1</sub> S <sub>1</sub> ) | L               | 1 (L)                       | 18                              | 24                                  |

| 4-Bit RS Latch            | 93L14              | 4 X (R1S1)                           | L               | 1 (L)                       | 30                              | 45                                  |

| 4-Bit D Latch             | 9314               | 4 X D                                | L               | 1 (L)                       | 18                              | 24                                  |

| 4-Bit D Latch             | 93L14              | 4 X D                                | L               | 1 (L)                       | 30                              | 45                                  |

| Dual 4-Bit D Latch        | 9308<br>(54/74116) | 8 X D                                | 2 X L           | 2 X 2 AND                   | 18                              | 30                                  |

| Dual 4-Bit D Latch        | 93L08              | 8 X D                                | 2 X L           | 2 X 2 AND                   | 30                              | 45                                  |

| 4-Bit RS Latch            | 54/74279           | 4 X (RS)                             |                 |                             |                                 |                                     |

| 4-Bit RS Latch            | 54LS/74LS279       | 4 X (RS)                             |                 |                             |                                 |                                     |

| 4-Bit D Latch             | 54/7475            | 4 X D                                |                 | 2 (H)                       | 20                              | 30                                  |

| 4-Bit D Latch             | 54/7477            | 4 X D                                |                 | 2 (H)                       | 20                              | 30                                  |

| 4-Bit D Latch             | 54LS/74LS375       | 4 X D                                |                 | 2 (H)                       | 20                              | 30                                  |

| Dual 4-Bit<br>Addr. Latch | 54LS/74LS256       | 8 X D                                | L               | 2 (L)                       | 17                              | 27                                  |

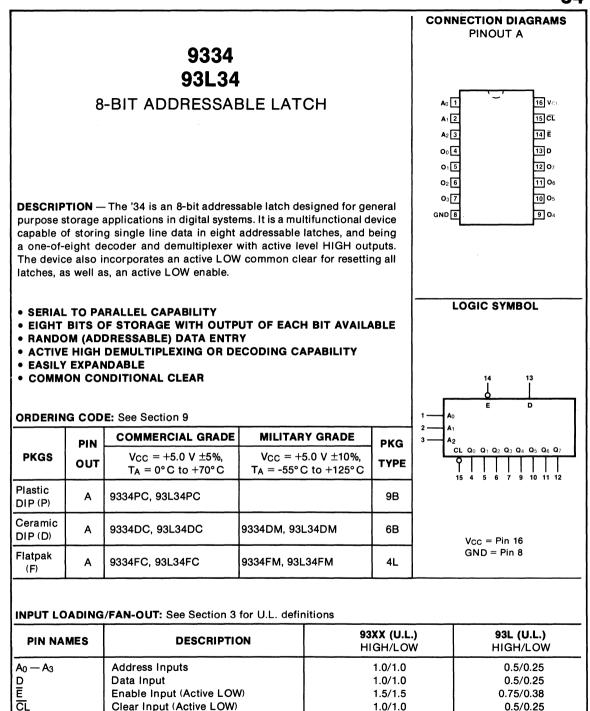

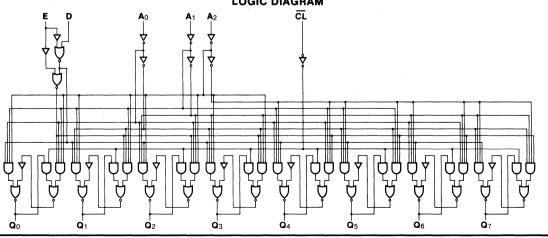

| 8-Bit Addr. Latch         | 9334               | 1 X D                                | L               | 1 (L)                       | 17                              | 24                                  |

| 8-Bit Addr. Latch         | 93L34              | 1 X D                                | L               | 1 (L)                       | 26                              | 45                                  |

| 8-Bit D Latch             | 54LS/74LS373       | 8 X D                                |                 | 1 (H)                       | 15                              | 30                                  |

| 8-Bit D Latch             | 54LS/74LS573       | 8 X D                                |                 | 1 (L)                       | 15                              | 30                                  |

| 8-Bit D Latch             | 54LS/74LS533       | 8 X D                                |                 | 1 (H)                       | 15                              | 30                                  |

| 8-Bit D Latch             | 54LS/74LS563       | 8 X D                                |                 | 1 (H)                       | 15                              | 30                                  |

| 8-Bit Addr. Latch         | 54LS/74LS259       | 1 X D                                | L               | 1 (L)                       | 17                              | 27                                  |

| 16-Bit D Latch            | 54/74170           | 4 X D                                |                 | 2                           | 25                              | 45                                  |

| 16-Bit D Latch            | 54LS/74LS170       | 4 X D                                |                 | 2                           | 25                              | 35                                  |

| 16-Bit D Latch            | 54LS/74LS670       | 4 X D                                |                 | 2                           | 25                              | 35                                  |

| 64-Bit Memory             | 54/7489            | 4 X D                                |                 | 2 (L)                       | 40                              | 70                                  |

#### LATCHES (Cont'd)

| FUNCTION      | DEVICE NO.   | DATA<br>INPUTS | COMMON<br>CLEAR | ENABLE<br>INPUTS<br>(LEVEL) | MIN ENABLE<br>PULSE WIDTH<br>ns | MAX DELAY<br>ENABLE TO<br>OUTPUT-ns |

|---------------|--------------|----------------|-----------------|-----------------------------|---------------------------------|-------------------------------------|

| 64-Bit Memory | 54LS/74LS89  | 4 X D          |                 | 2 (L)                       | 25 (Typ)                        | 30 (Typ)                            |

| 64-Bit Memory | 54S/74S189   | 4 X D          |                 | 2 (L)                       | 20                              | 40                                  |

| 64-Bit Memory | 54LS/74LS189 | 4 X D          |                 | 2 (L)                       | 25 (Typ)                        | 30 (Typ)                            |

| 64-Bit Memory | 54S/74S289   | 4 X D          |                 | 2 (L)                       | 20                              | 40                                  |

| 64-Bit Memory | 54LS/74LS289 | 4 X D          |                 | 2 (L)                       | 25 (Typ)                        | 30 (Typ)                            |

#### MULTIPLE FLIP-FLOPS

| FUNCTION                     | DEVICE NO.   | DATA<br>INPUTS | COMMON<br>CLEAR | CP INPUTS<br>(LEVEL) | GUARANTEED<br>CLOCK FREQ.<br>MHz |

|------------------------------|--------------|----------------|-----------------|----------------------|----------------------------------|

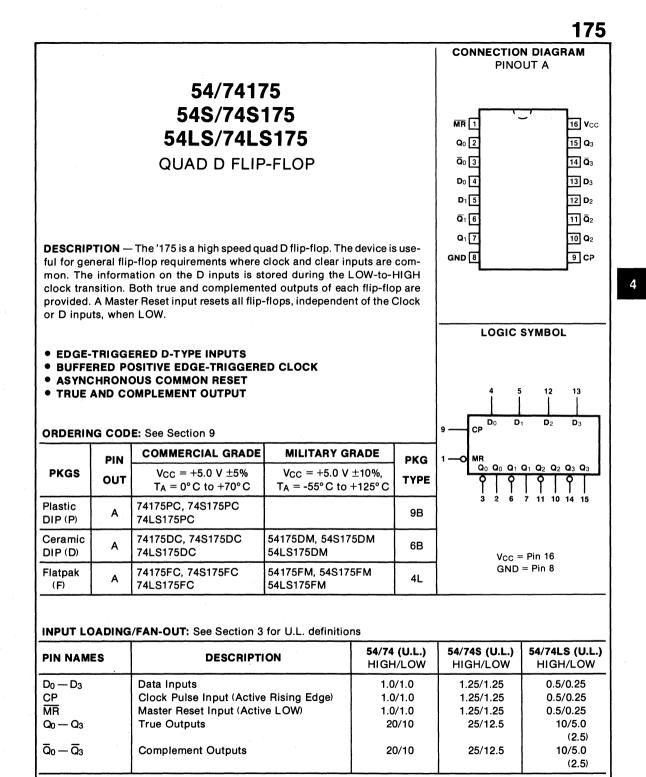

| 4-Bit D Flip-Flop            | 54/74175     | 4 X D          | L               | 1()                  | 25                               |

| 4-Bit D Flip-Flop            | 54S/74S175   | 4 X D          | L               | 1()                  | 75                               |

| 4-Bit D Flip-Flop            | 54LS/74LS175 | 4 X D          | L               | 1 ()                 | 30                               |

| 4-Bit D Flip-Flop            | 54/74298     | 2 X 4 X D      |                 | 1(乀)                 | 25                               |

| 4-Bit D Flip-Flop            | 54LS/74LS298 | 2 X 4 X D      |                 | 1 (乀)                | 25                               |

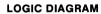

| 6-Bit D Flip-Flop            | 54/74174     | 6 X D          | L               | 1(了)                 | 25                               |

| 6-Bit D Flip-Flop            | 54S/74S174   | 6 X D          | L               | 1()                  | 75                               |

| 6-Bit D Flip-Flop            | 54LS/74LS174 | 6 X D          | L               | 1()                  | 30                               |

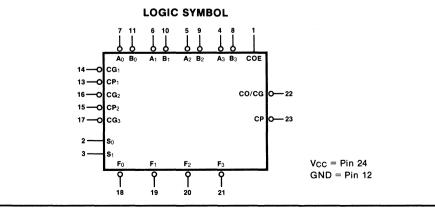

| 8-Bit Multiple Port Register | 9338         | 1 X D          |                 | 1 (L)                | 27                               |

| 8-Bit Multiple Port Register | 93L38        | 1 X D          |                 | • 1 (L)              | 14                               |

| 8-Bit D Flip-Flop            | 54LS/74LS374 | 8 X D          |                 | 1()                  | 35                               |

| 8-Bit D Flip-Flop            | 54LS/74LS534 | 8 X D          |                 | 1()                  | 35                               |

| 8-Bit D Flip-Flop            | 54LS/74LS564 | 8 X D          |                 | 1()                  | 35                               |

#### MULTIPLEXERS

| FUNCTION     | DEVICE NO.   | ENABLE<br>INPUTS |   | COMPLEMENT<br>OUTPUT |

|--------------|--------------|------------------|---|----------------------|

| Quad 2-Input | 9322         | 1                | x |                      |

| Quad 2-Input | 93L22        | 1                | X |                      |

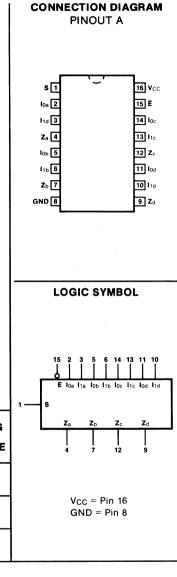

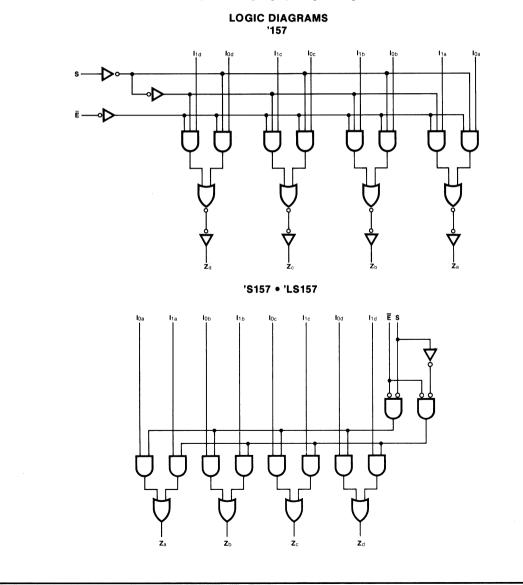

| Quad 2-Input | 54/74157     | 1                | x |                      |

| Quad 2-Input | 54S/74S157   | 1                | x |                      |

| Quad 2-Input | 54LS/74LS157 | 1                | x |                      |

| Quad 2-Input | 54S/74S158   | 1                |   | x                    |

| Quad 2-Input | 54LS/74LS158 | 1                |   | x                    |

| FUNCTION     | DEVICE NO.    | ENABLE<br>INPUTS          | TRUE<br>OUTPUT | COMPLEMENT<br>OUTPUT |

|--------------|---------------|---------------------------|----------------|----------------------|

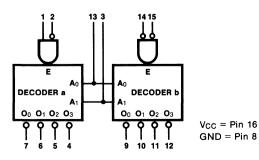

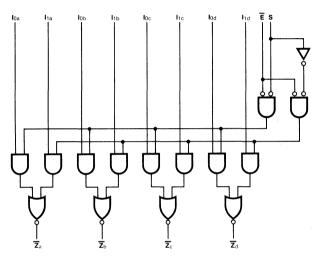

| Quad 2-Input | 54\$/74\$257  | 1                         | 3S*            |                      |