464 Ellis Street, Mountain View, California 94042

© 1978 Fairchild Camera and Instrument Corporation/464 Ellis Street, Mountain View, California 94042/(415) 962-5011/TWX 910-379-6435

# INTRODUCTION

The increase in complexity and diversity of Linear Integrated Circuits over the last few years has necessitated a change in the format of the Fairchild Linear Data Books. In this data book, Fairchild is pleased to present important technical information on one of the industries broadest and most advanced family of Linear Interface, Comparator and Data Conversion circuits. Other Fairchild Linear data books will cover Operational Amplifiers, Consumer and Regulator devices.

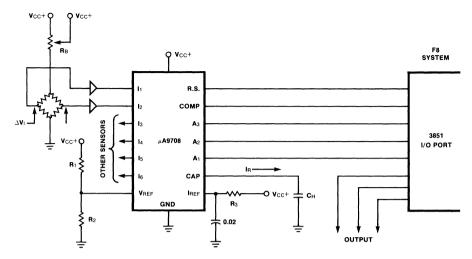

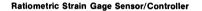

Fairchild continues to be a pioneer in Linear Interface and Data Conversion products. Today Fairchild's state-of-the-art technology is bringing forth devices like the 9643; MOS/CCD driver, 75S20 series of Schottky core memory sense amplifiers, 9634/6/7/8 series of RS422/423 compatible line circuits,  $\mu$ A9708; micro-processor based 8-bit A/D subsystem, and the CMOS processed  $\mu$ A9706; micro-processor compatible 8 channel, 6-bit D/A converter.

You'll find complete specifications on Fairchild's MOS/CCD memory interface, data transmission, peripheral driver, memory sense amplifier, display interface, data conversion, comparator and special functions. Also included is advanced information on some of Fairchild's Interface circuits to be introduced shortly.

To expedite the designer's search for the right devices to meet various system requirements, several helpful aids are provided — selection guides by function, an LIC cross reference identifying competitive devices with their Fairchild direct replacements or nearest equivalents and the numerical indexes will let you locate specific type numbers quickly. For the Hi Rel customer, Fairchild's Hi Rel processing and Matrix VI are given in a separate section.

.

# TABLE OF CONTENTS

| Chapter | 1.  | Alpha Numerical Index of Interface Devices and Selection Guides1-3   |

|---------|-----|----------------------------------------------------------------------|

| Chapter | 2.  | Linear Industry Cross Reference                                      |

| Chapter | 3.  | Quality, Reliability and Hi Rel Processing                           |

| Chapter | 4.  | Voltage Comparators4-3                                               |

| Chapter | 5.  | Data Acquisition                                                     |

| Chapter | 6.  | Line Circuits — Drivers, Receivers and Transceivers                  |

| Chapter | 7.  | Peripheral and Display Drivers7-3                                    |

| Chapter | 8.  | Memory Interface                                                     |

| Chapter | 9.  | Transistor Arrays and Special Functions9-3                           |

| Chapter | 10. | Data Transmission Information 10-3                                   |

| Chapter | 11. | Order Information, Dice Policy and Package Outlines 11-3             |

| Chapter | 12. | Fairchild Field Sales Offices, Representatives and Distributors 12-3 |

| ALPHA NUMERIC INDEX OF INTERFACE<br>DEVICES AND SELECTION GUIDES   |

|--------------------------------------------------------------------|

| LINEAR INDUSTRY<br>CROSS REFERENCE 2                               |

| QUALITY, RELIABILITY AND<br>HI REL PROCESSING                      |

| VOLTAGE COMPARATORS                                                |

| DATA ACQUISITION 5                                                 |

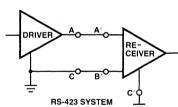

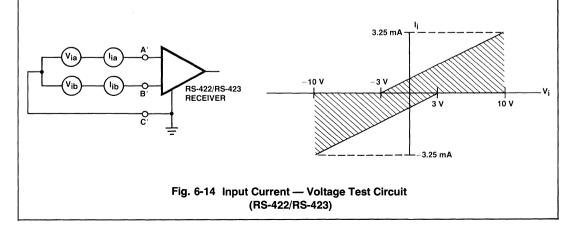

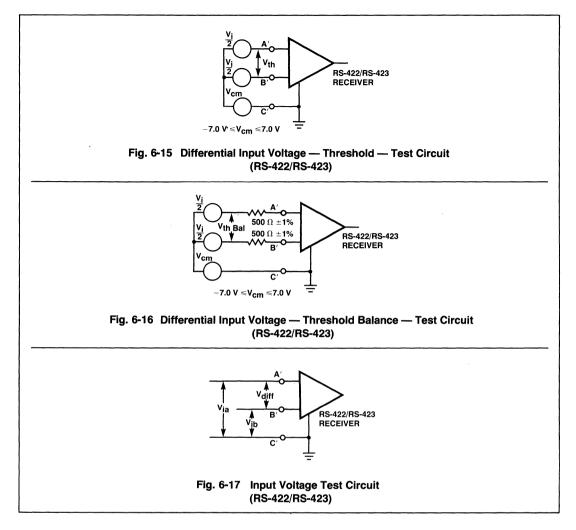

| LINE CIRCUITS – DRIVERS.<br>RECEIVERS AND TRANSCEIVERS 6           |

| PERIPHERAL AND DISPLAY DRIVERS 7                                   |

| MEMORY INTERFACE 8                                                 |

| TRANSISTOR ABRAYS AND<br>SPECIAL FUNCTIONS                         |

| DATA TRANSMISSION INFORMATION 10                                   |

| ORDER INFORMATION, DICE POLICY<br>AND PACKAGE OUTLINES             |

| FAIRCHILD FIELD SALES OFFICES,<br>REPRESENTATIVES AND DISTRIBUTORS |

.

#### ALPHA NUMERICAL INDEX OF INTERFACE DEVICES AND SELECTION GUIDES

| Alpha Numerical Inde | ex of Interface Devices | 1-3 |

|----------------------|-------------------------|-----|

| Selection Guides     |                         | 1-7 |

#### **ALPHA-NUMERICAL INDEX**

#### DEVICE

.

#### DESCRIPTION

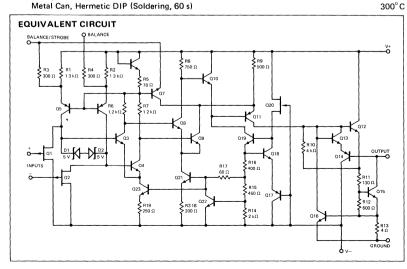

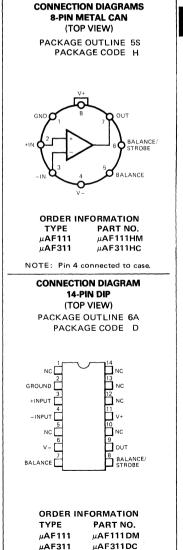

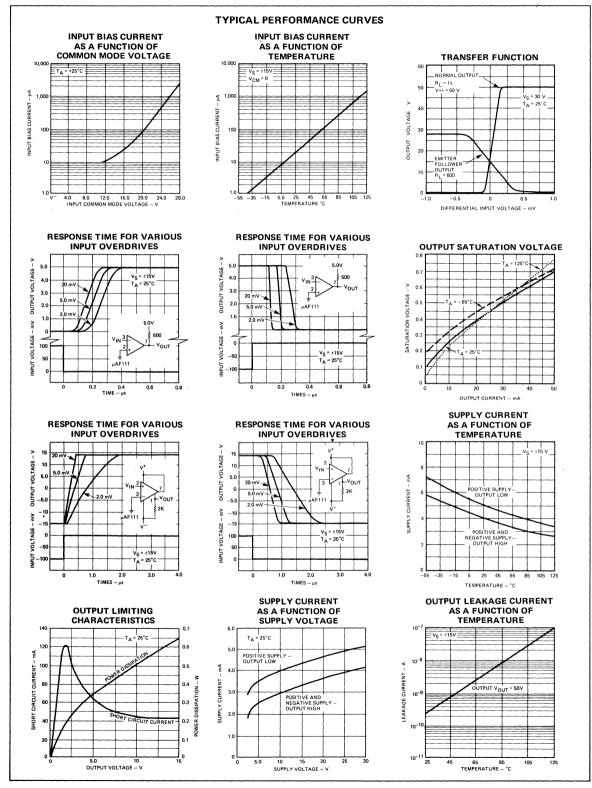

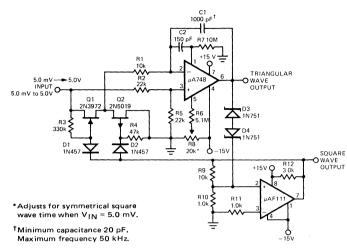

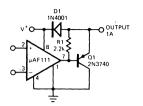

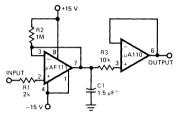

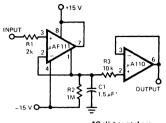

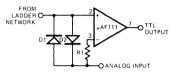

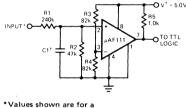

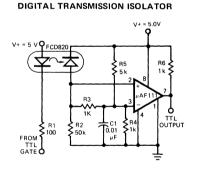

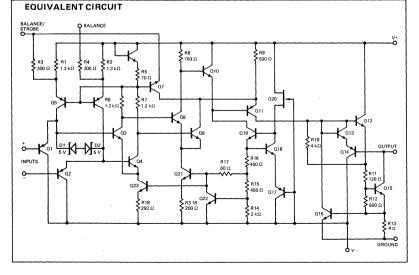

| μAF111               | FET-Input Voltage Comparator                  | 4-3  |

|----------------------|-----------------------------------------------|------|

| μAF311               | FET-Input Voltage Comparator                  |      |

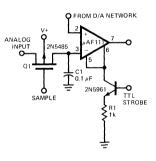

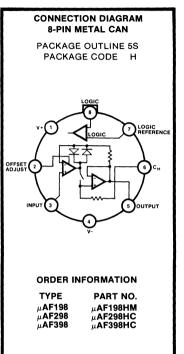

| μAF198               | Monolithic Sample and Hold                    | 5-3  |

| μAF298               | Monolithic Sample and Hold                    | 5-3  |

| μAF398               | Monolithic Sample and Hold                    |      |

| $\mu A0801 (DAC-08)$ | 8-Bit High-Speed Multiplying D/A Converter    | 5-4  |

| $\mu A0802 (MC1408)$ | 8-Bit Multiplying D/A Converter               | 5-10 |

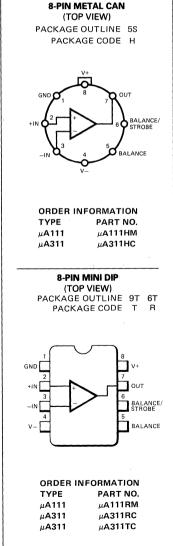

| μA111                | Voltage Comparator                            | 4-8  |

| μA311                | Voltage Comparator                            | 4-8  |

| μA139                | Low-Power, Low-Offset Quad Voltage Comparator | 4-13 |

| μA139A               | Low-Power, Low-Offset Quad Voltage Comparator | 4-13 |

| μA1488               | Quad EIA RS-232C Line Driver                  | 6-3  |

| μA1489               | Quad EIA RS-232C Line Receiver                | 6-43 |

| μA1489A              | Quad EIA RS-232C Line Receiver                | 6-43 |

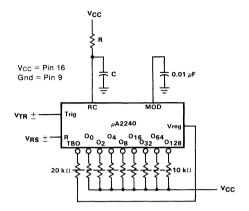

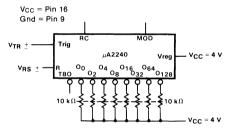

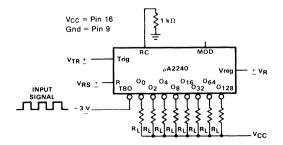

| μA2240               | Programmable Timer/Counter                    | 9-36 |

| μA239                | Low-Power, Low-Offset Quad Voltage Comparator | 4-13 |

| μA239A               | Low-Power, Low-Offset Quad Voltage Comparator | 4-13 |

| μA2901               | Low-Power, Low-Offset Quad Voltage Comparator | 4-13 |

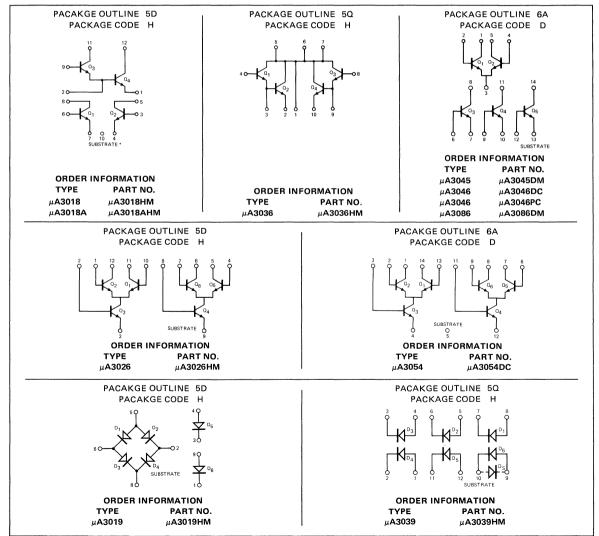

| μA3018               | Matched Monolithic Transistor Array           | 9-3  |

| μA3018A              | Matched Monolithic Transistor Array           | 9-3  |

| μA3019               | Diode Array                                   | 9-3  |

| μA3026               | Transistor Array                              | 9-3  |

| μA3036               | Transistor Array                              | 9-3  |

| μA3039               | Diode Array                                   | 9-3  |

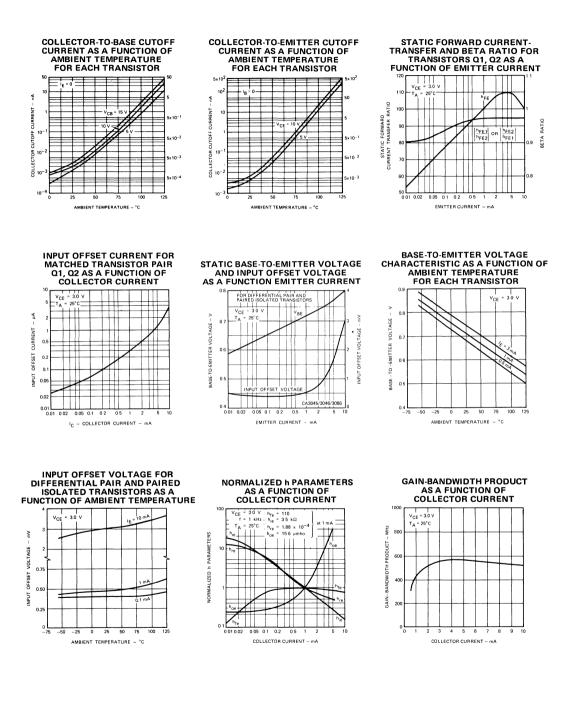

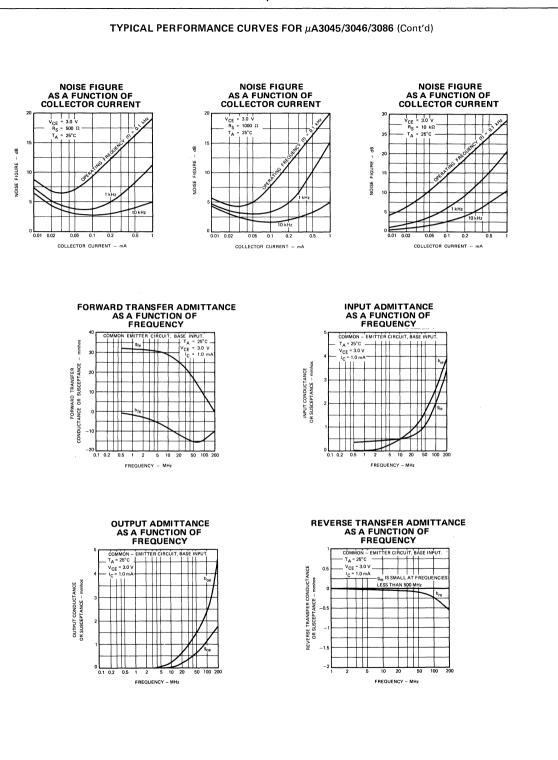

| μA3045               | Transistor Array                              | 9-3  |

| μA3046               | Transistor Array                              | 9-3  |

| μA3054               | Transistor Array                              | 9-3  |

| μA3086               | Transistor Array                              | 9-3  |

| μA3302               | Low-Power, Low-Offset Quad Voltage Comparator | 4-13 |

| μA339                | Low-Power, Low-Offset Quad Voltage Comparator | 4-13 |

| μΑ339Α               | Low-Power, Low-Offset Quad Voltage Comparator | 4-13 |

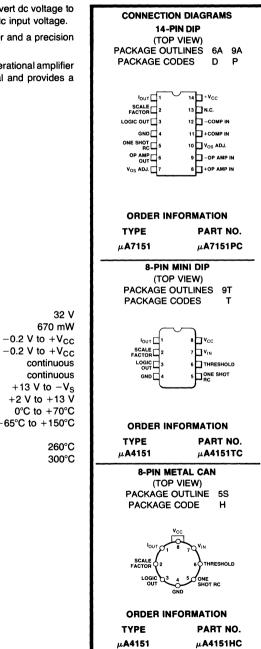

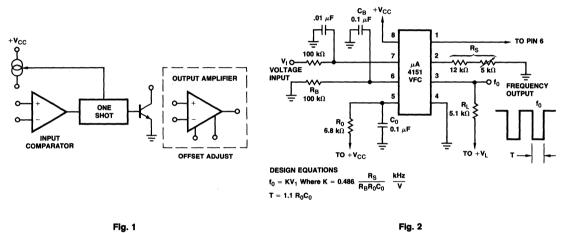

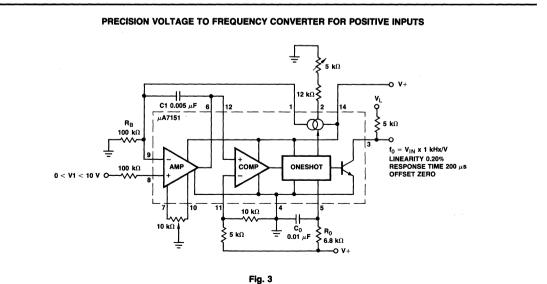

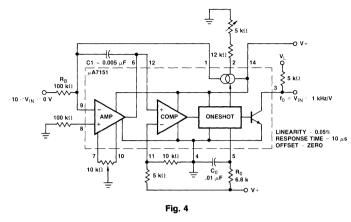

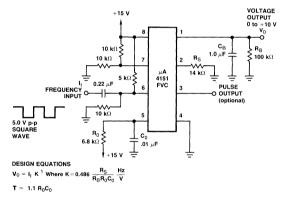

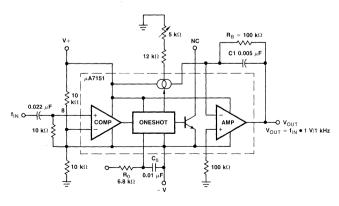

| μA4151               | Voltage-to-Frequency Converter                | 5-15 |

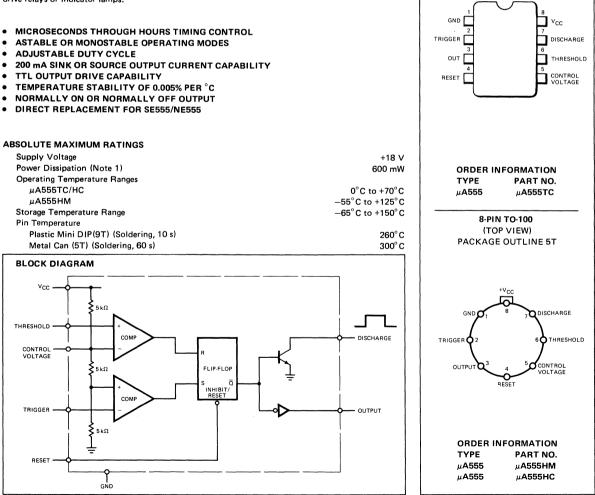

| μA555                | Single Timing Circuit                         |      |

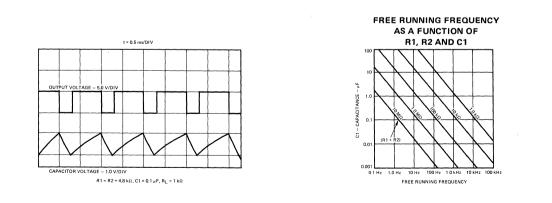

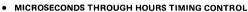

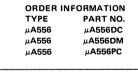

| μA556                | Dual Timing Circuit                           | 9-31 |

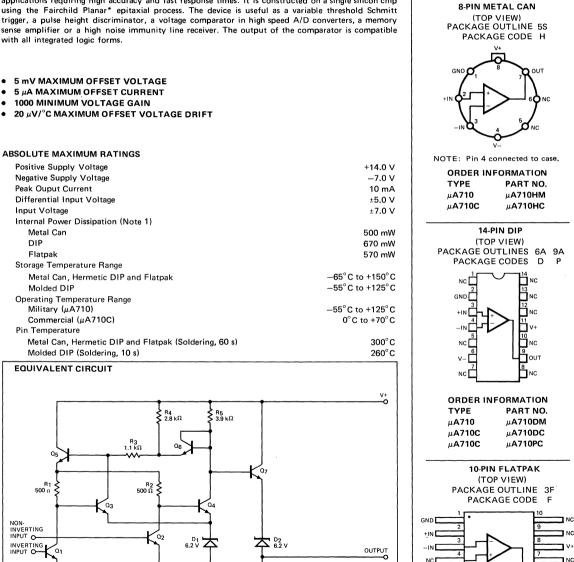

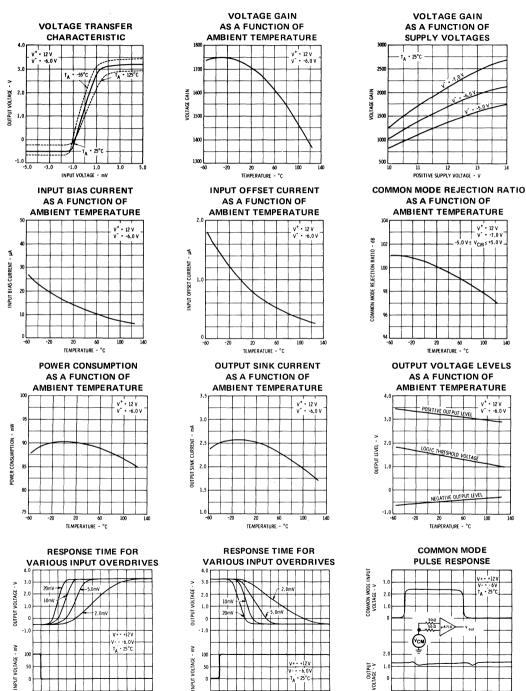

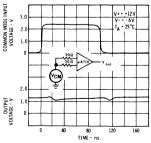

| μA710                | High-Speed Differential Comparator            | 4-21 |

| μA710C               | High-Speed Differential Comparator            | 4-21 |

| μA711                | Dual High-Speed Differential Comparator       | 4-25 |

| μA711C               | Dual High-Speed Differential Comparator       | 4-25 |

| μA7151               | Voltage-to-Frequency Converter with Op Amp    | 5-15 |

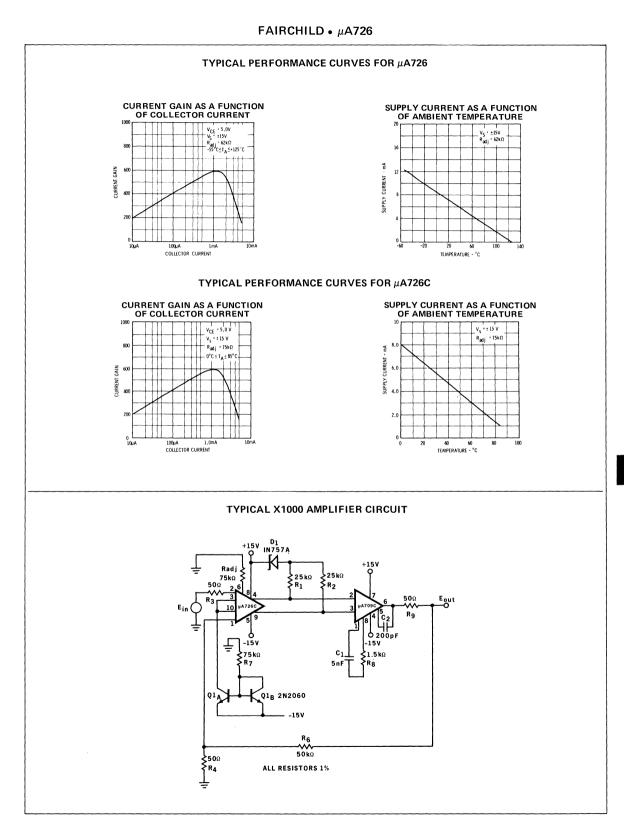

| μA726                | Temperature-Controlled Differential Pair      |      |

| μA734                | Precision Voltage Comparator                  |      |

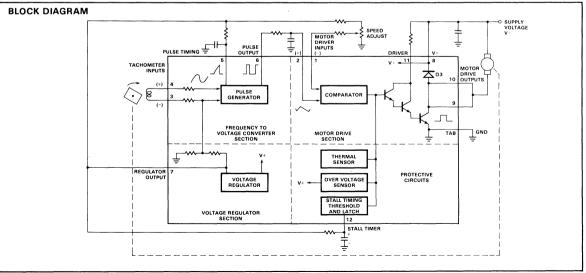

| μA7391               | DC Motor-Speed Control                        | 9-48 |

PAGE

## ALPHA-NUMERICAL INDEX (Cont.)

#### DESCRIPTION

DEVICE

| μA7392             | DC Motor-Speed Control                                                             | 0.50 |

|--------------------|------------------------------------------------------------------------------------|------|

| μA760              | High-Speed Differential Comparator                                                 |      |

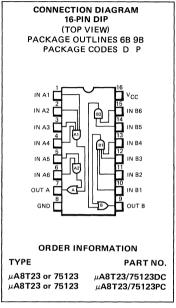

| μΑ700<br>μΑ8Τ13    | Dual Single-Ended Line Driver                                                      |      |

| μA8T14             | Triple Line Receiver                                                               |      |

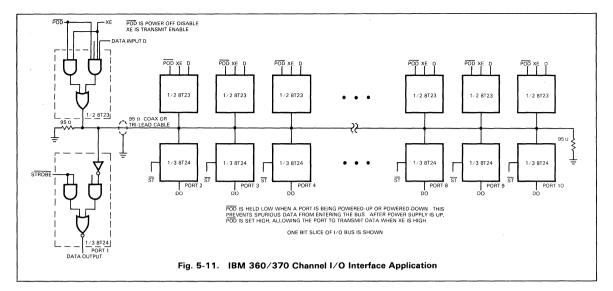

| μΑ8Τ23             | Dual IBM 360/370 I/O Single-Ended Line Driver                                      |      |

| μA8T24             | Triple IBM 360/370 I/O Line Receiver                                               |      |

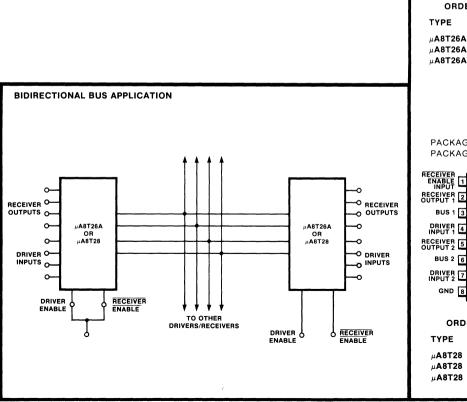

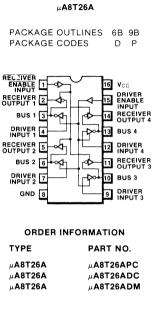

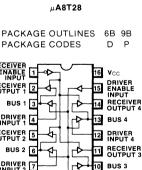

| μΑ8Τ26Α            | Quad 3-State Inverting Bus Transceiver                                             |      |

| μA0120A<br>μA8T28  | Quad 3-State Non-Inverting Bus Transceiver                                         |      |

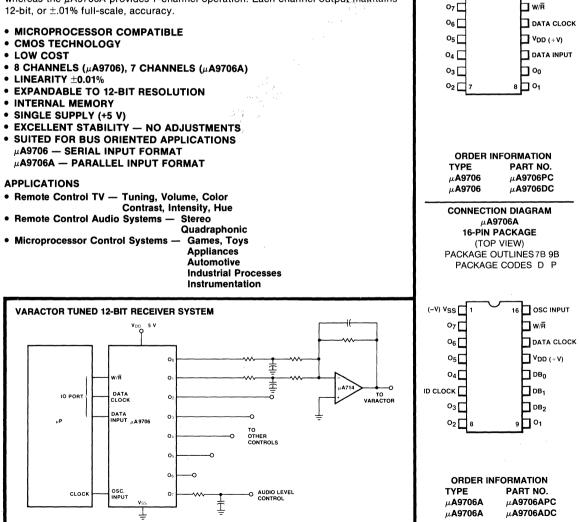

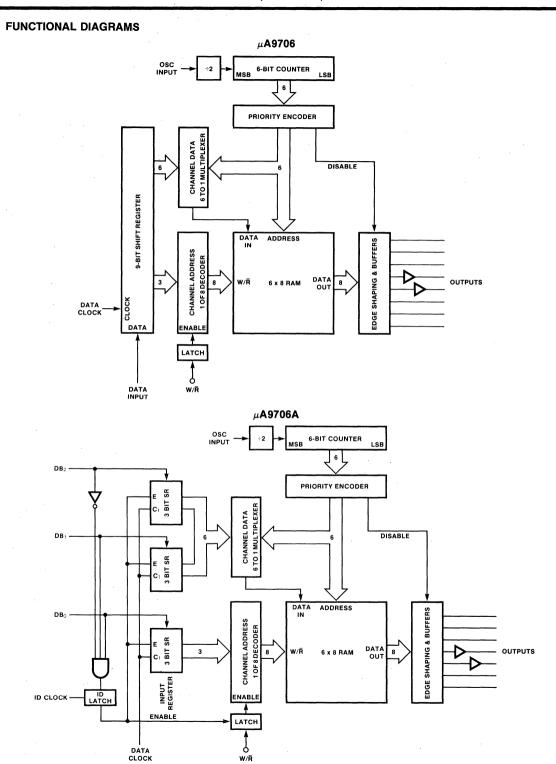

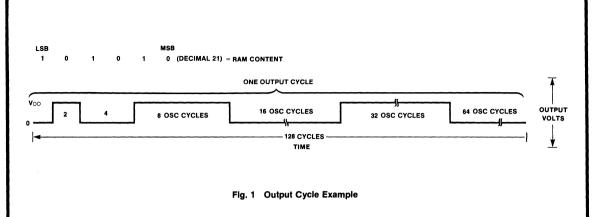

| μA9706             | 8-Channel, 12-Bit, $\mu$ P Compatible D/A Converter                                |      |

| μA9706A<br>μA9706A | 7-Channel, 12-Bit, $\mu$ P Compatible D/A Converter                                |      |

| μA9708             | 6-Channel, 8-Bit, $\mu$ P Compatible A/D Converter Subsystem                       |      |

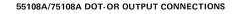

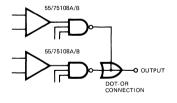

| 55107A             | Dual General-Purpose Line Receiver                                                 |      |

| 55107B             | Dual General-Purpose Line Receiver                                                 |      |

| 55108A             | Dual General-Purpose Line Receiver                                                 |      |

| 55108A             | Dual General-Purpose Line Receiver                                                 |      |

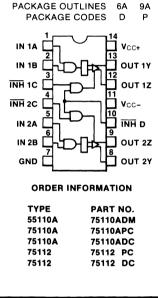

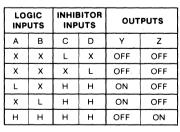

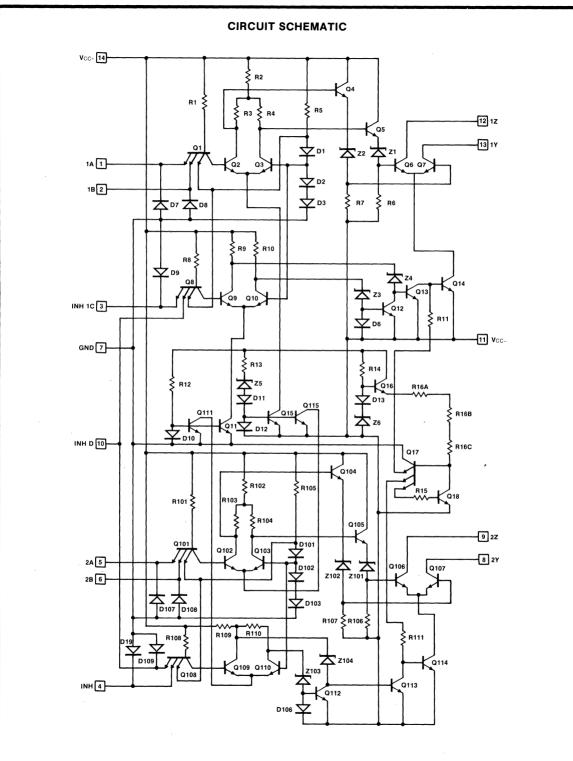

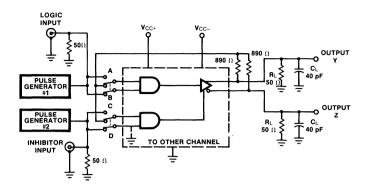

| 55110A             | Dual General-Purpose Line Driver                                                   |      |

| 55122              |                                                                                    |      |

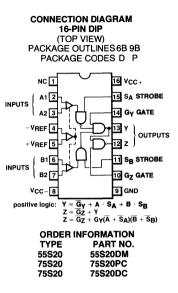

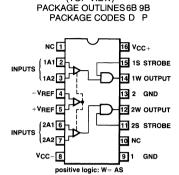

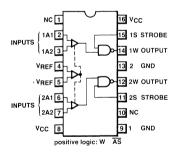

| 55S20              | Triple-Line Receiver<br>Dual Schottky ±2.5 mV Sense Amp with Complementary Outputs |      |

| 55S24              |                                                                                    |      |

| 55S234             | Dual Schottky ±2.5 mV Sense Amp                                                    |      |

| 55232              | Dual Schottky ±2.5 mV Sense Amp                                                    |      |

| 55238              | Dual Sense Amp with Open Collector Outputs                                         |      |

|                    | Dual Sense Amp with Preamplifier Test Points                                       |      |

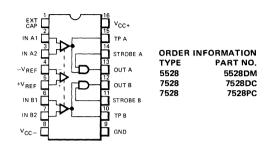

| 5528               | Dual Sense Amp with Preamplifier Test Points                                       |      |

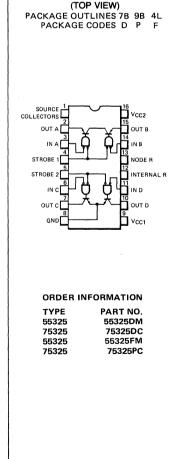

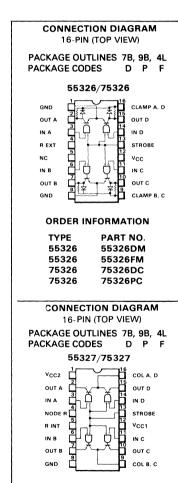

| 55325              | Dual Core Memory Drivers                                                           |      |

| 55326              | Quad Positive OR Sink Core Memory Drivers                                          |      |

| 55327              | Quad Core Memory Switches                                                          |      |

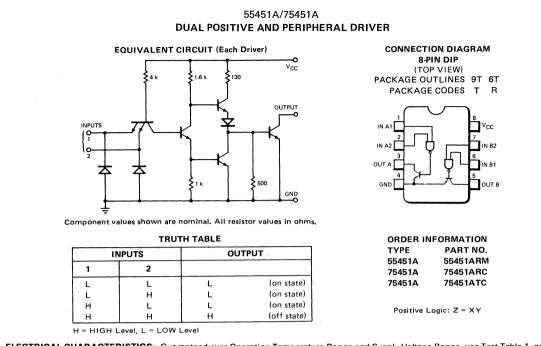

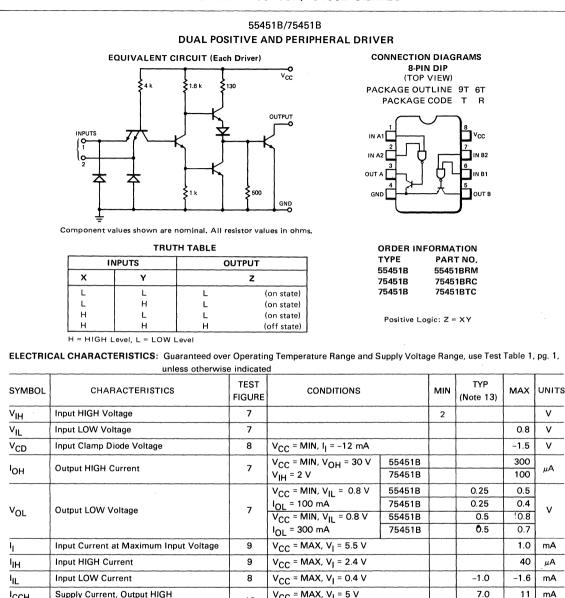

| 55450A             | Dual Positive AND Peripheral Driver                                                |      |

| 55450B             | Dual High-Speed Positive AND Peripheral Driver                                     |      |

| 55451A             | Dual Positive AND Peripheral Driver                                                |      |

| 55451B             | Dual High-Speed Positive AND Peripheral Driver                                     |      |

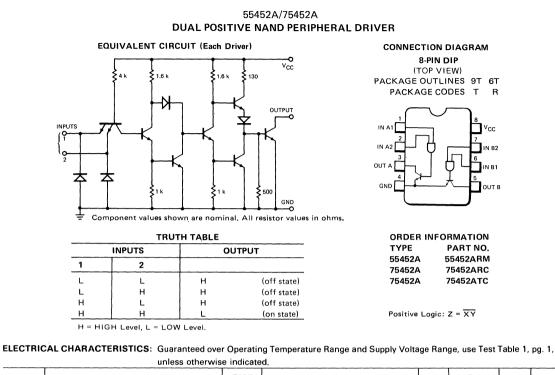

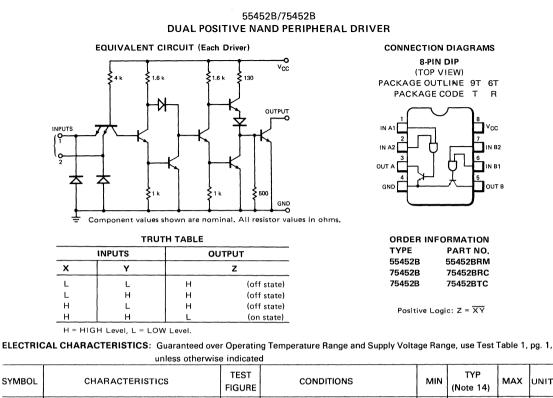

| 55452A             | Dual Positive NAND Peripheral Driver                                               |      |

| 55452B             | Dual High-Speed Positive NAND Peripheral Driver                                    |      |

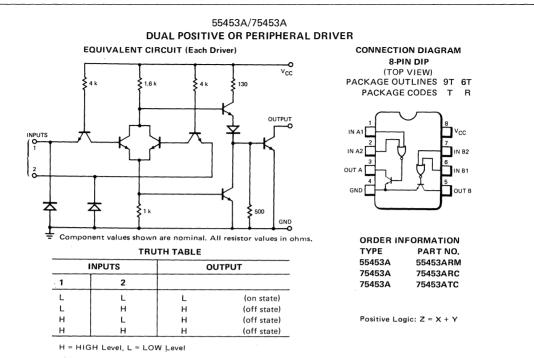

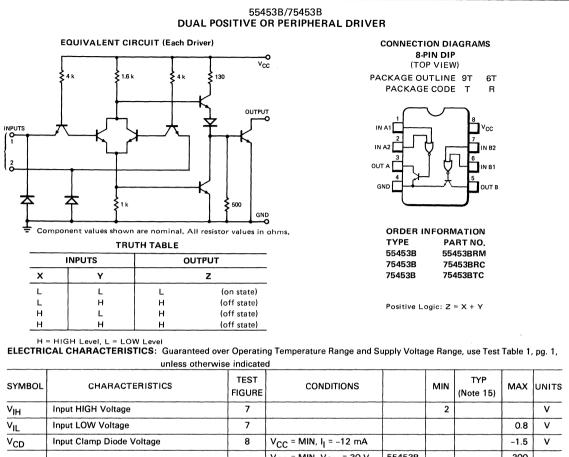

| 55453A             | Dual OR Positive Peripheral Driver                                                 |      |

| 55453B             | Dual High-Speed OR Positive Peripheral Driver                                      |      |

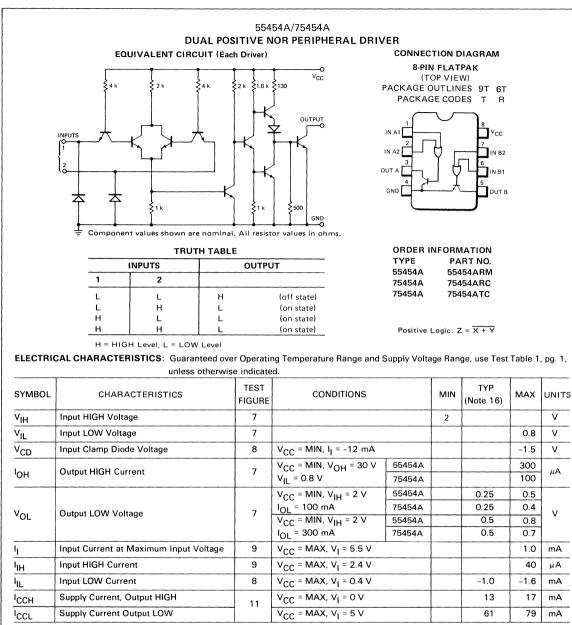

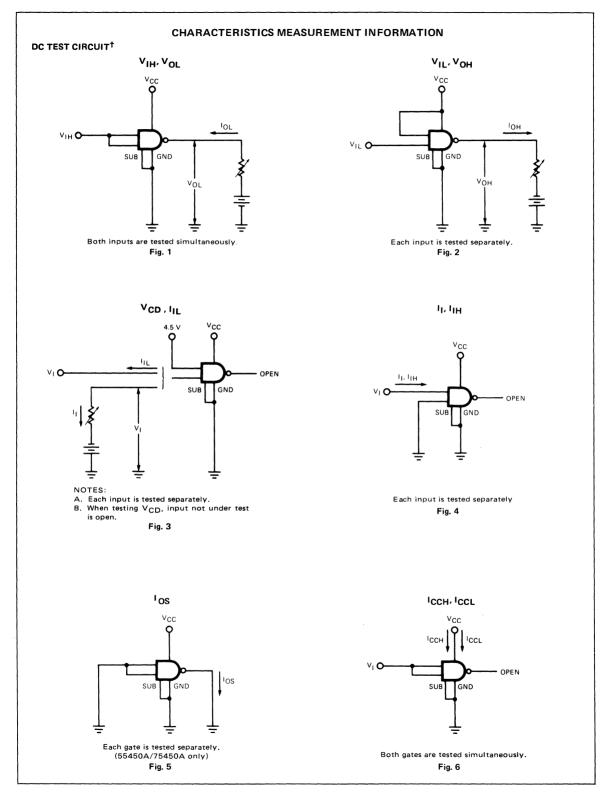

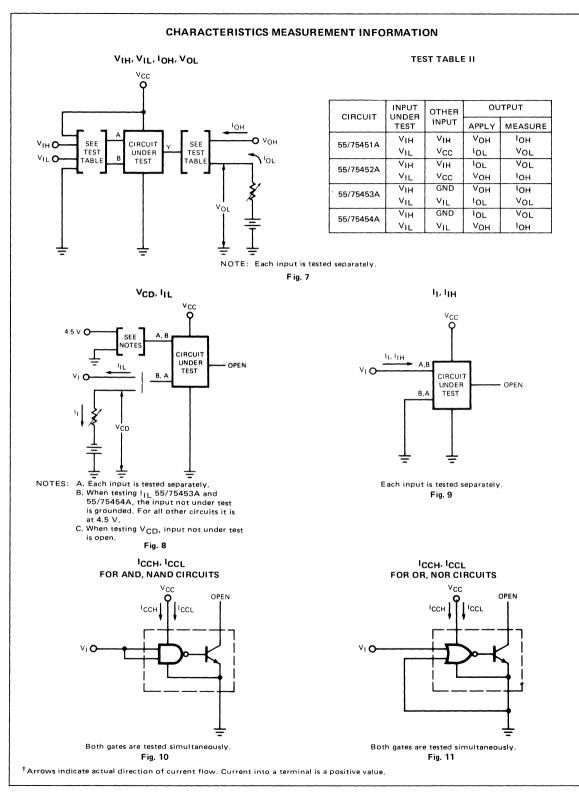

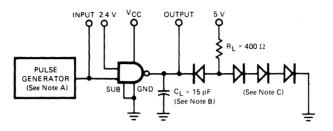

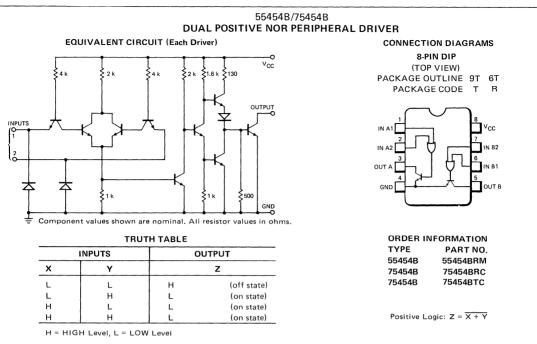

| 55454A             | Dual Positive NOR Peripheral Driver                                                |      |

| 55454B             | Dual High-Speed Positive NOR Peripheral Driver                                     |      |

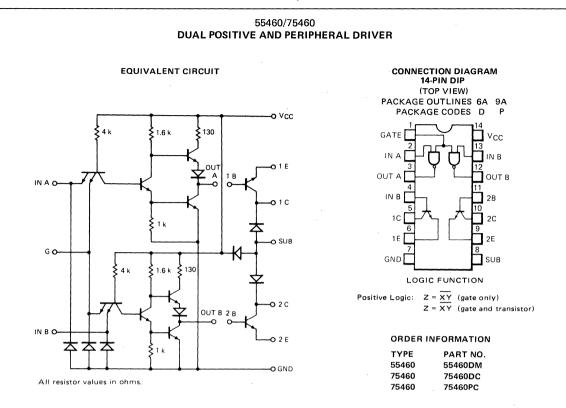

| 55460              | Dual High-Voltage Positive AND Peripheral Driver                                   |      |

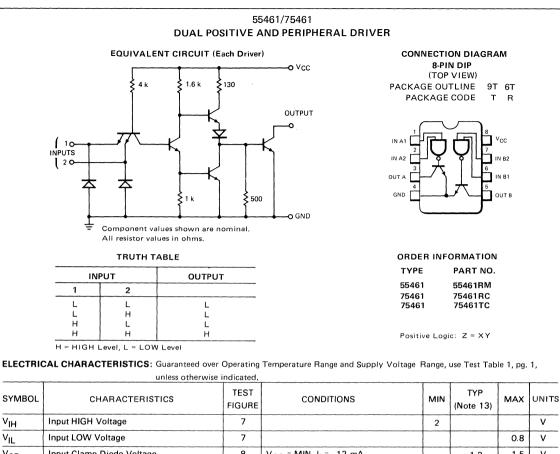

| 55461              | Dual High-Voltage Positive ANd Peripheral Driver                                   |      |

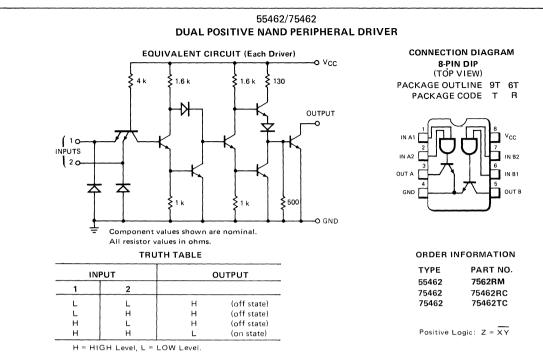

| 55462              | Dual High-Voltage Positive NAND Peripheral Driver                                  |      |

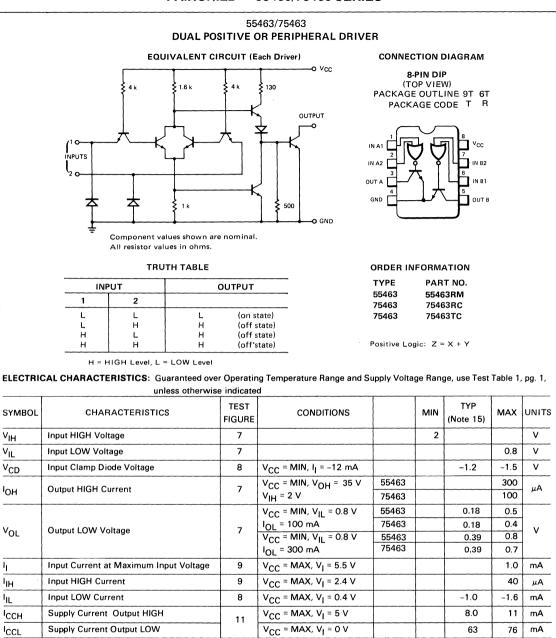

| 55463              | Dual High-Voltage Positive OR Peripheral Driver                                    | 7-31 |

#### ALPHA-NUMERICAL INDEX (Cont.)

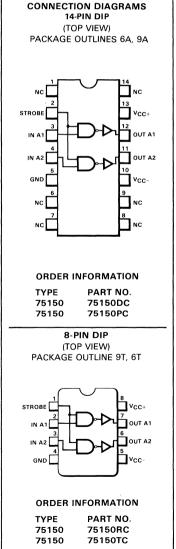

#### DEVICE DESCRIPTION PAGE 55464 55471 55472 55473 55474 55491 55491A 55492 55492A 75107A 75107B 75108A 75108B 75110A 75112 75121 75122 75123 75124 75150 75154 Quad EIA RS-232C Line Receiver ..... 6-60 75S20 Dual Schottky $\pm 2.5$ mV Sense Amp with Complementary Outputs ..... 8-20 75S24 Dual Schottky ±2.5 mV Sense Amp...... 8-20 Dual Schottky ±2.5 mV Sense Amp...... 8-20 75S234 75232 75238 7528 75325 75326 75327 75450A Dual Positive AND Peripheral Driver......7-3 75450B 75451A Dual Positive AND Peripheral Driver.....7-3 75451B 75452A Dual Positive NAND Peripheral Driver ......7-3 75452B 75453A Dual OR Positive Peripheral Driver .....7-3 75453B 75454A Dual Positive NOR Peripheral Driver......7-3 75454B 75460

# ALPHA-NUMERICAL INDEX (Cont.)

| DEVICE         | DESCRIPTION                                          | AGE  |

|----------------|------------------------------------------------------|------|

| 75461          | Dual High-Voltage Positive AND Peripheral Driver     | 7-31 |

| 75462          | Dual High-Voltage Positive NAND Peripheral Driver    | 7-31 |

| 75463          | Dual High-Voltage Positive OR Peripheral Driver      | 7-31 |

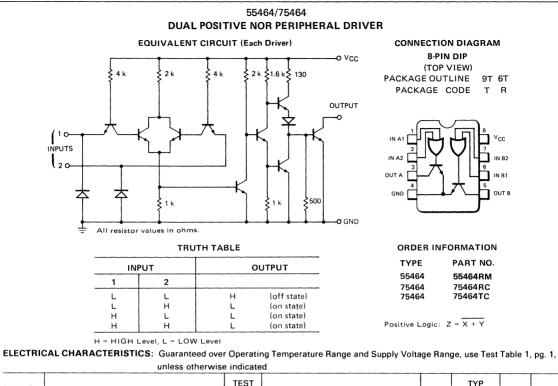

| 75464          | Dual High-Voltage Positive NOR Peripheral Driver     | 7-31 |

| 75471          | Dual High-Voltage Positive AND Peripheral Driver     | 7-42 |

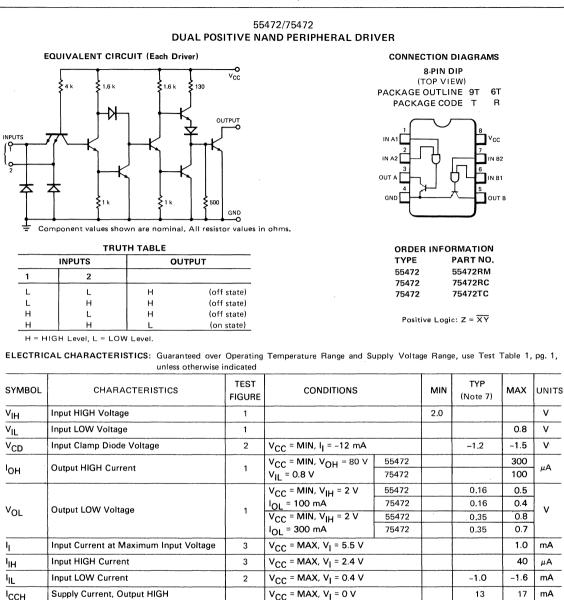

| 75472          | Dual High-Voltage Positive NAND Peripheral Driver    | 7-42 |

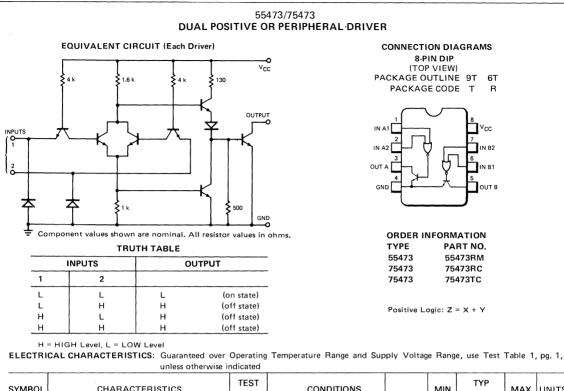

| 75473          | Dual High-Voltage Positive OR Peripheral Driver      | 7-43 |

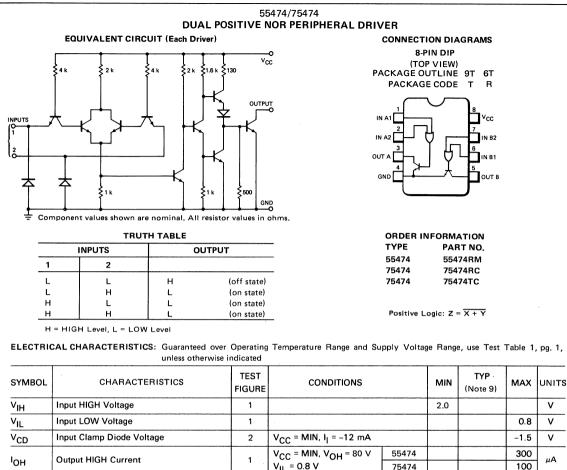

| 75474          | Dual High-Voltage Positive NOR Peripheral Driver     | 7-42 |

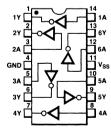

| 75491          | Quad MOS-to-LED Segment Drivers                      |      |

| 75491A         | Quad MOS-to-LED Segment Drivers                      | 7-54 |

| 75492          | HEX MOS-to-LED Digit Drivers                         |      |

| 75492A         | HEX MOS-to-LED Digit Drivers                         | 7-54 |

| 9612           | Dual Differential Line Driver                        | 6-22 |

| 9612A          | Dual Differential Line Driver                        | 6-22 |

| 9612E          | Dual Differential Line Driver                        | 6-22 |

| 9613           | Dual Differential Line Receiver                      | 6-65 |

| 9613C          | Dual Differential Line Receiver                      | 6-65 |

| 9614           | Dual Differential Line Driver                        | 6-26 |

| 9615           | Dual Differential Line Receiver                      | 6-69 |

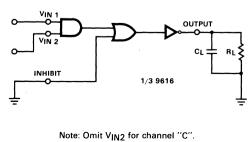

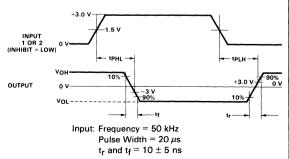

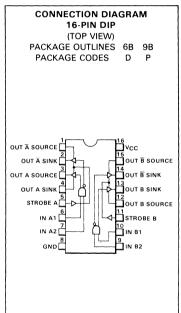

| 9616           | Triple EIA-RS-232C/MIL-STD-188C Line Driver          | 6-30 |

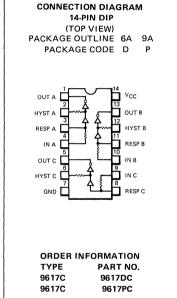

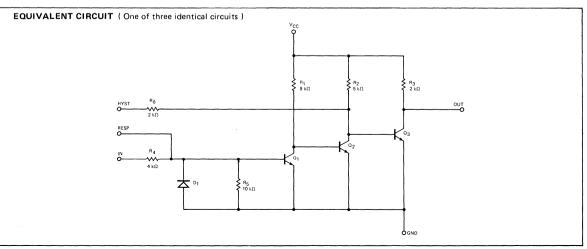

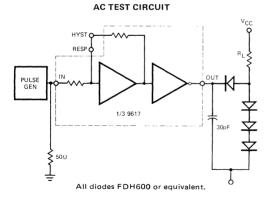

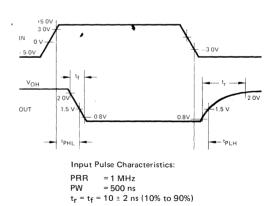

| 9617           | Triple EIA RS-232C Line Receiver                     | 6-74 |

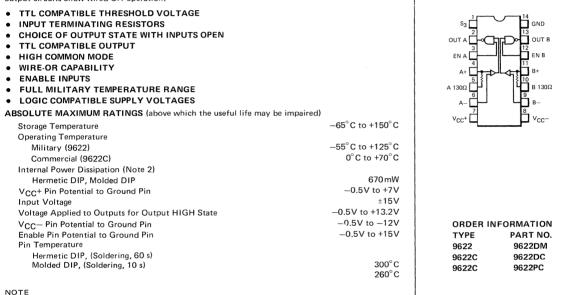

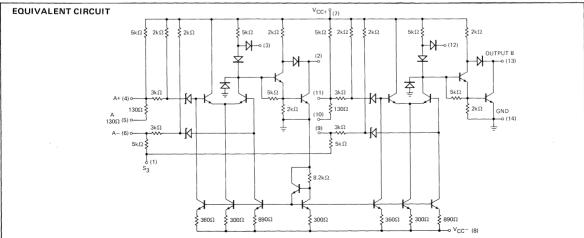

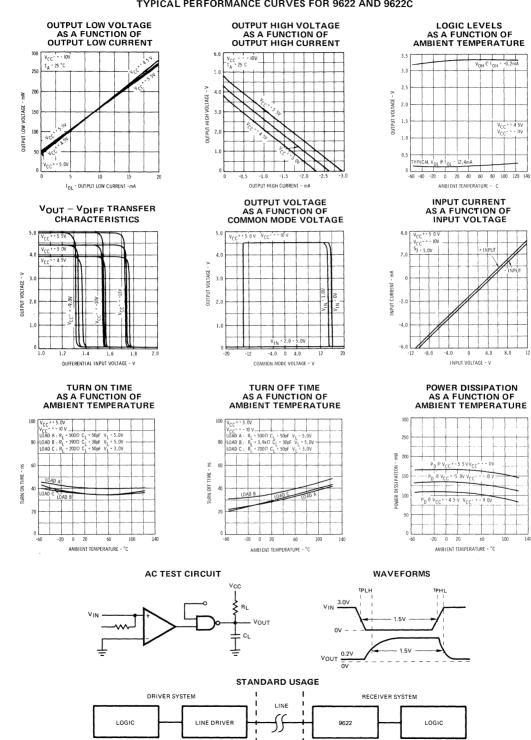

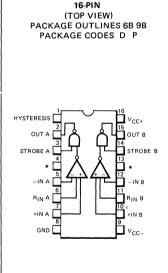

| 9622           | Dual Line Receiver                                   | 6-76 |

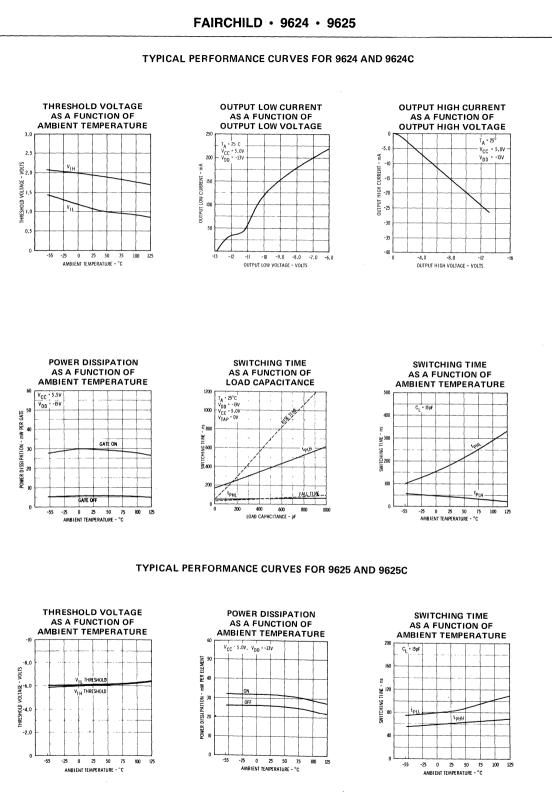

| 9624           | Dual TTL-to-MOS Interface Element                    | .8-3 |

| 9625           | Dual TTL-to-MOS Interface Element                    | .8-3 |

| 9627           | Dual EIA RS-232C/MIL-STD-188C Line Receiver          | 6-80 |

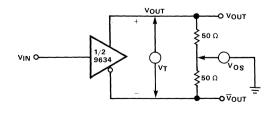

| 9634           | Dual 3-State EIA RS-422 Differential Line Driver     | 6-33 |

| 9636A          | Dual Programmable Slew Rate EIA RS-423 Line Driver   | 6-36 |

| 9637A          | Dual EIA RS-422/423 Differential Line Receiver       | 6-84 |

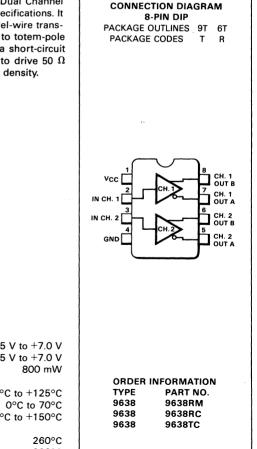

| 9638           | Dual EIA RS-422 High-Speed Differential Line Driver  | 6-40 |

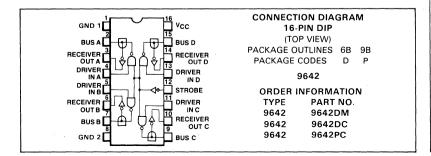

| 9640 (26S10)   | Quad General-Purpose Bus Transceiver                 | 6-94 |

| 9641 (26S11)   | Quad General-Purpose Bus Transceiver                 | 6-94 |

| 9642           | Quad General-Purpose Bus Transceiver with Hysteresis | 6-94 |

| 9643           | Dual AND TTL-to-MOS/CCD Driver                       | 8-10 |

| 9644           | Dual NAND TTL-to-MOS/CCD Driver                      | 8-10 |

| 9645 (3245)    | Quad TTL-to-MOS/CCD Driver                           | 8-13 |

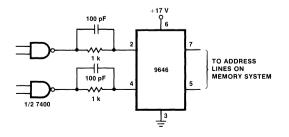

| 9646 (DS0026)  | Dual 5 MHz Two Phase MOS Clock Driver                | 8-16 |

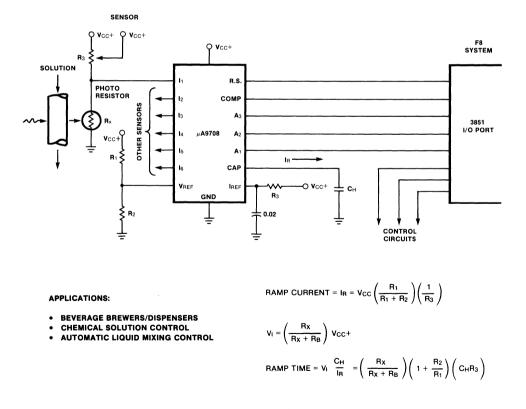

| 9650           | 4-Bit Precision Current Source                       | 5-35 |

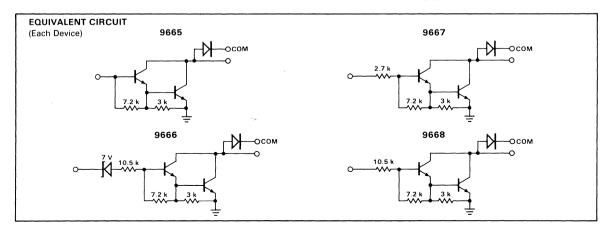

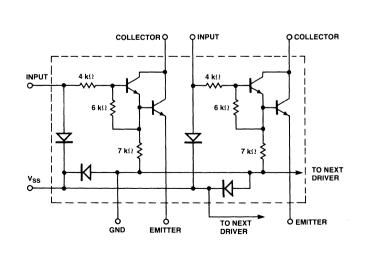

| 9665 (ULN2001) | Seven High-Voltage, High-Current Darlington Drivers  | 7-49 |

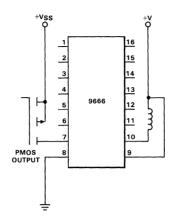

| 9666 (ULN2002) | Seven High-Voltage, High-Current Darlington Drivers  |      |

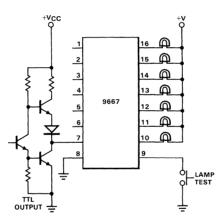

| 9667 (ULN2003) | Seven High-Voltage, High-Current Darlington Drivers  |      |

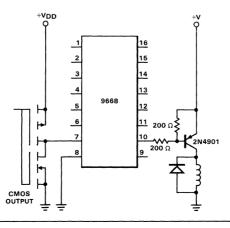

| 9668 (ULN2004) | Seven High-Voltage, High-Current Darlington Drivers  | 7-49 |

|                 | VOL                                                         | TAGE                                      | СОМРАЯ                                    | RATOR                                         | SELE                  | CTION GUI                                   | DE                        |                   |                   |                |

|-----------------|-------------------------------------------------------------|-------------------------------------------|-------------------------------------------|-----------------------------------------------|-----------------------|---------------------------------------------|---------------------------|-------------------|-------------------|----------------|

| Device No.      | Description                                                 | Input Bias<br>Current<br>μA (Max)<br>25°C | Input Offset<br>Current<br>(Max)<br>25° C | Input Offset<br>Voltage<br>mV - (Max)<br>25°C | Voltage Gain<br>(Typ) | Supply Voltage<br>V (Typ)                   | Response Time<br>ns (Typ) | DTL/TTL<br>Fanout | Temperature Range | Package(s)     |

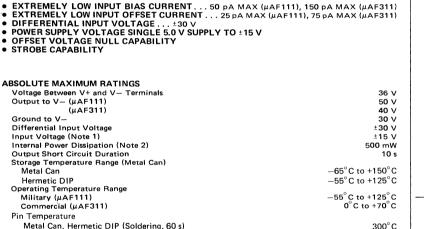

| μ <b>AF111</b>  | Fet-Input Voltage Comparator                                | 0 05                                      | 0 000025                                  | 4.0                                           | 200K                  | +36                                         | 200                       | 2                 | м                 | 5S, 6A         |

| μ <b>AF311</b>  | Fet-Input Voltage Comparator                                | 0 15                                      | 0 000075                                  | 10                                            | 200K                  | +36                                         | 200                       | 2                 | с                 | 5S, 6A         |

| μ <b>A</b> 111  | Voltage Comparator Strobed Inputs,<br>Single Supply, Low IB | 01                                        | 0 04                                      | 0.7                                           | 200K                  | ±15                                         | 200                       | 5                 | м                 | 5S             |

| μ <b>A</b> 311  | Voltage Comparator Strobed Inputs,<br>Single Supply, Low IB | 0.25                                      | 0 06                                      | 2.0                                           | 200K                  | ±15                                         | 200                       | 5                 | С                 | 5S             |

| μ <b>A139</b>   | Quad Comparator Single Supply,<br>CMRR incl. gnd            | 01                                        | 0 025                                     | 5.0                                           | 200K                  | ±1 to ±18 or from<br>2 to 36 and gnd        | 1300                      | 1                 | м                 | 6A             |

| μ <b>Α139</b> Α | Quad Comparator Single Supply,<br>CMRR incl. gnd            | 01                                        | 0 025                                     | 2.0                                           | 200K                  | ±1 to ±18 or from<br>2 to 36 and gnd        | 1300                      | 1                 | м                 | 6A             |

| μ <b>Α239</b>   | Quad Comparator Single Supply,<br>CMRR incl. gnd            | 0 25                                      | 0 05                                      | 50                                            | 200K                  | ±1 to ±18 or from<br>2 to 36 and gnd        | 1300                      | 1                 | A                 | 6A, 9A         |

| μ <b>Α239Α</b>  | Quad Comparator Single Supply,<br>CMRR incl. gnd            | 0 25                                      | 0 05                                      | 2 0                                           | 200K                  | ±1 to ±18 or from<br>2 to 36 and gnd        | 1300                      | 1                 | A                 | 6A, 9A         |

| μ <b>Α339</b>   | Quad Comparator Single Supply,<br>CMRR incl. gnd            | 0 25                                      | 0 05                                      | 5.0                                           | 200K                  | ±1 to ±18 or from<br>2 to 36 and gnd        | 1300                      | 1                 | с                 | 6A, 9A         |

| μ <b>Α339Α</b>  | Quad Comparator Single Supply,<br>CMRR incl. gnd            | 0 25                                      | 0 05                                      | 2.0                                           | 200K                  | $\pm 1$ to $\pm 18$ or from 2 to 36 and gnd | 1300                      | 1                 | с                 | 6A, 9A         |

| 4710/C          | High Speed Differential<br>Voltage Comparator               | 20/25                                     | 3 0/5 0                                   | 2 0/5.0                                       | 1 75K                 | +12, -6                                     | 40                        | 1                 | M, C              | 5S. 3F. 6A. 9A |

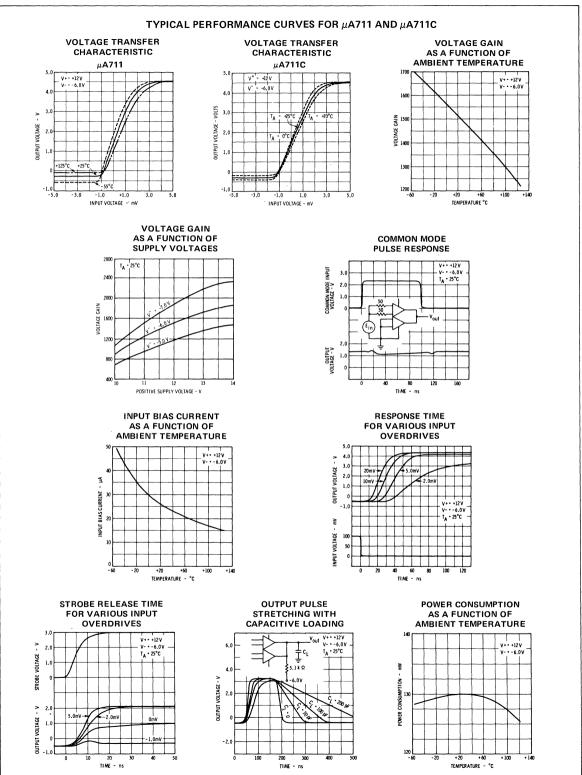

| μ <b>Α711/C</b> | Dual High Speed<br>Differential Comparator                  | 75 100                                    | 10/15                                     | 3 5/5 0                                       | 1 5K                  | +12, -6                                     | 40                        | 1                 | M, C              | 3F. 5F. 6A. 9A |

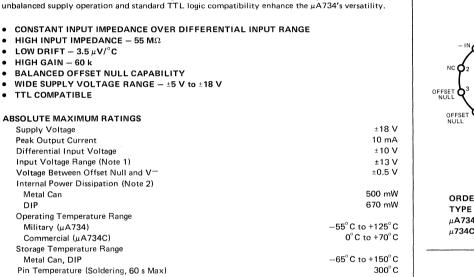

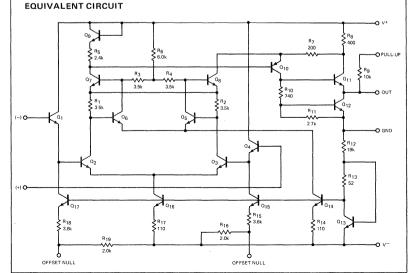

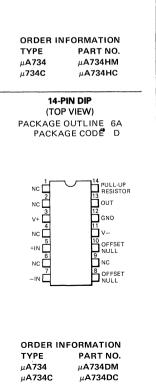

| μΑ734           | Precision Comparator<br>Low Drift −3.5 μV/°C                | 0 15                                      | 0 025/0 05                                | 5 0/3 0                                       | 25K                   | ±5 to ±15                                   | 200                       | 2                 | M, C              | 5N. 6A         |

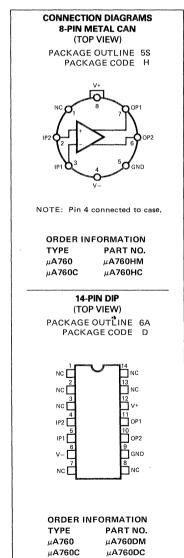

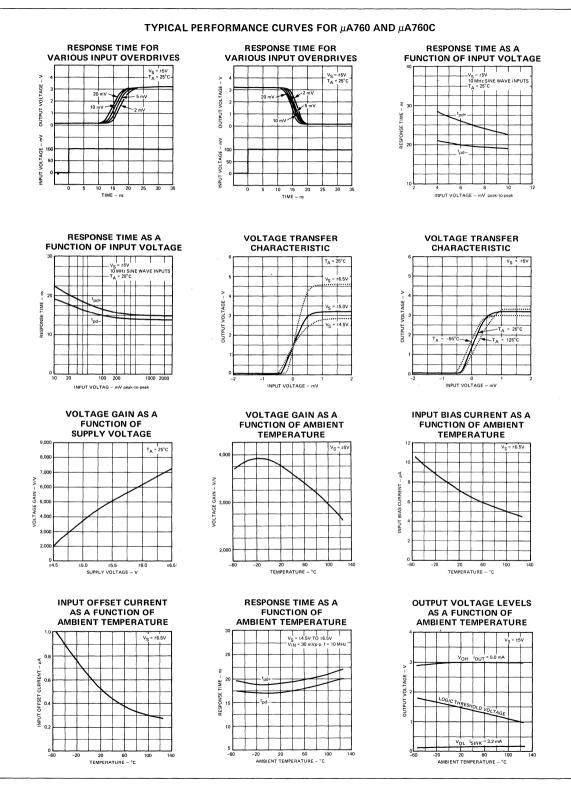

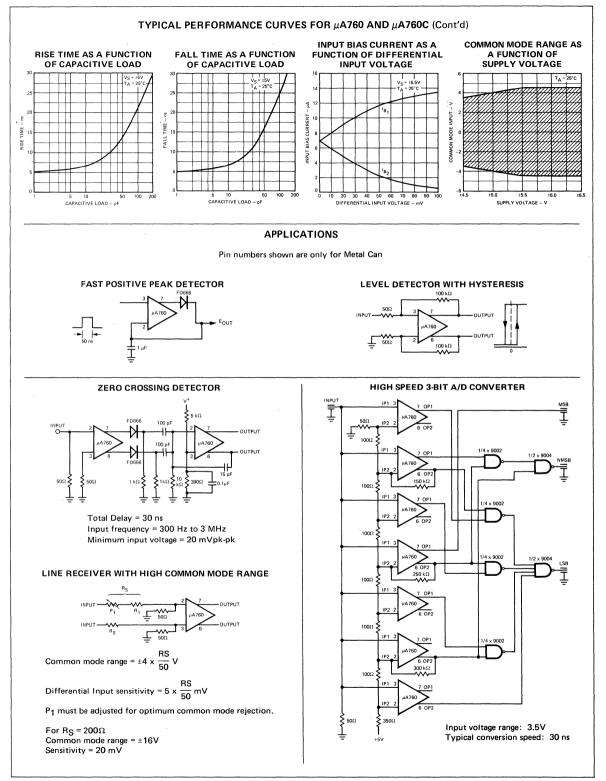

| μ <b>Α760</b>   | High Speed Differential Comparator                          | 60                                        | 75                                        | 60                                            | 5K                    | ±4.5 to ±6.5                                | 25                        | 2                 | M, C              | 5S. 6A         |

| μ <b>A2901</b>  | Quad Comparator Single Supply,<br>CMRR incl. gnd            | 0 25                                      | 0 05                                      | 70                                            | 200K                  | ±1 to μ18 or from<br>2 to 36 and gnd        | 1300                      | 1                 | A                 | 6A.9A          |

| μ <b>Α3302</b>  | Quad Comparator Single Supply,<br>CMRR incl. gnd            | 05                                        | 01                                        | 20 0                                          | 200K                  | ±1 to ±18 or from<br>2 to 36 and gnd        | 1300                      | 1                 | С                 | 6A. 9A         |

| Device Number              | Function                                         | Operating<br>Temp. Range (° C) | Maximum<br>Non-Linearity<br>(% FS) | Supply<br>Voltage<br>(V)           | Package(s)   |

|----------------------------|--------------------------------------------------|--------------------------------|------------------------------------|------------------------------------|--------------|

| μ <b>Α0801Α (DAC-08Α)</b>  |                                                  | -55/+125                       | ±0.1                               | ±15                                | 6B           |

| μ <b>A0801 (DAC-08)</b>    | 8 bit high speed                                 | -55/+125                       | <u>+</u> 0.19                      | ±15                                | 6B           |

| μ <b>Α0801Η (DAC-08Η)</b>  | multiplying D/A converter                        | 0/+70                          | ±0.1                               | ±15                                | 6B, 9B       |

| μA0801E (DAC-08E)          |                                                  | 0/+70                          | ±0.19                              | ±15                                | 6B, 9B       |

| μA0801C (DAC-08C)          |                                                  | 0/+70                          | ±0.39                              | ±15                                | 6B, 9B       |

| μ <b>Α0802 (MC1508-8)</b>  |                                                  | -55/+125                       | ±0.19                              |                                    | 6B           |

| μ <b>Α0802Α (MC1408-8)</b> | 8 bit multiplying                                | 0/+70                          | ±0.19                              | +5                                 | 6B, 9B       |

| μ <b>Α0802B (MC1408-7)</b> | D/A converter                                    | 0/+70                          | ±0.39                              | and<br>-5 to -15                   | 6B, 9B       |

| μA0802C (MC1408-6)         |                                                  | 0/+70                          | ±0.78                              | 1                                  | 6B, 9B       |

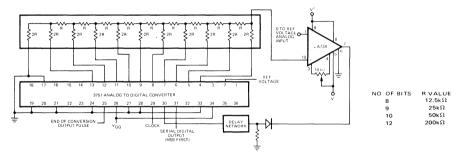

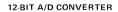

| μ <b>Α9708</b>             | 6 channel, 8 bit<br>μP compatible A/D converter  | -55/+125<br>0/+70              | ±0.2                               | +4.75 to +15                       | 7B<br>7B, 9B |

| μ <b>Α9706</b>             | 8 channel, 12 bit<br>μP compatible D/A converter | 0/+70                          | ±0.01                              | +5                                 | 6A, 9A       |

| μ <b>Α9706Α</b>            | 7 channel, 12 bit<br>μP compatible D/A converter | 0/+70                          | ±0.01                              | +5                                 | 7B, 9B       |

| μ <b>Α4151</b>             | Voltage to frequency converter                   | 0⁄/+70                         | · · · ·                            | +8 to +15                          | 5S, 6T, 9T   |

| μ <b>Α7151</b>             | Voltage to frequency converter with op amp       | 0/+70                          | ±0.5                               | +8 to +15                          | 6A, 9A       |

| μ <b>AF198</b>             | Sample and hold Amplifier                        | -55/+125                       |                                    | ±5 to ±18                          | 5S           |

| μ <b>AF398</b>             | Sample and hold Amplifier                        | 0/+70                          |                                    | ±5 to ±18                          | 5S           |

| 9650                       | 4-bit current source<br>A/D or D/A               | 0/+70                          | ±0.2 to ±0.01                      | +4.5 and -14<br>or<br>+5.5 and -16 | 6B           |

|                            | Output<br>Current  | Propagation                |                                      |                         |        | Power           | Device <sup>-</sup><br>Temperat | Type For<br>ure Range |                      | Drivers        |                        |                                    |

|----------------------------|--------------------|----------------------------|--------------------------------------|-------------------------|--------|-----------------|---------------------------------|-----------------------|----------------------|----------------|------------------------|------------------------------------|

| Description                | Capability<br>(mA) | Delay Time<br>Typical (ns) | S = Single Ended<br>D = Differential | Party Line<br>Operation | Strobe | Supplies<br>(V) | 55° C to 125° C                 | 0° C to 70° C         | Package<br>Type      | Per<br>Package | Companion<br>Receivers | Additional<br>Features             |

|                            | 300                | 20                         | S, D                                 | Yes                     | Yes    | 5               | 55450B                          | 75450B                | 6A<br>6A, 9A         | 2              | 9615<br>75122/         | And Logic                          |

|                            | 300                | 20                         | S                                    | Yes                     | Yes    | 5               | 55451B                          | 75451B                | 6Т<br>6Т, 9Т         | 2              | μA8T14                 | Function                           |

| General                    | 100                | 22                         | S                                    | Yes                     | Yes    | 5               | 55121/µA8T13                    | 75121/µA8T13          | 6B<br>6B, 9B         | 2              | 75122/<br>μA8T14       |                                    |

| Purpose<br>Drivers         | 40                 | 12                         | S, D                                 | No                      | No     | 5               | 9612A                           | 9612E                 | 6T, 5B<br>6T, 9T, 5B | 2              | 9613                   | Complimentary<br>Outputs           |

| ×                          | 40                 | 15                         | S, D                                 | Yes                     | Yes    | 5               | 9614DM                          | 9614                  | 6B<br>6B, 9B         | 2              | 9615                   | 3 Input AND/<br>NAND Function      |

| 360/370 I/O<br>Interface   | 100                | 20                         | S                                    | Yes                     | Yes    | 5               |                                 | 75123/<br>μA8T23      | 6B, 9B               | 2              | 75124/<br>μA8T24       |                                    |

|                            | 50                 | 10                         | D                                    | Yes                     | Yes    | 5               | 9634RM                          | 9634                  | 6B<br>6B, 9B         | 2              | 9637A                  | 3-State Output<br>RS-422           |

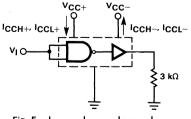

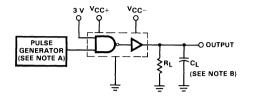

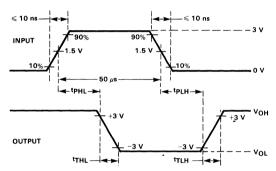

|                            | 10                 | 60                         | S                                    | No                      | Yes    | ±12             |                                 | 75150                 | 6A, 9A,<br>6T, 9T    | 2              | 75154<br>9627,9617     | RS-232C/<br>MIL-STD-188C           |

| Drivers<br>Meeting         | 10                 | 220                        | S                                    | No                      | Yes    | ±12             |                                 | μA1488                | 6A, 9A               | 4              | μA1489<br>μA1489A      | RS-232C                            |

| EIA<br>Standards           | 30                 | 320                        | S                                    | No                      | No     | ±12             | 9616DM                          | 9616C, E              | 6A<br>6A, 9A         | 3              | μA1489/A<br>9617, 9627 | RS-232C/<br>MIL-STD-188C           |

|                            | 40                 | 10                         | D                                    | No                      | No     | 5               | 9638RM                          | 9638                  | 6T<br>6T, 9T         | 2              | 9637A                  | RS-422,<br>High Speed              |

|                            | 17                 | *                          | S                                    | No                      | No     | ±12             | 9636ARM                         | 9636A                 | 6Т<br>6Т, 9Т         | 2              | 9637A                  | RS-423, Slew Rate*<br>Programmable |

|                            | 18                 | 9                          | D                                    | Yes                     | Yes    | ±5              |                                 | 75112                 | 6A, 9A               | 2              | 75107A/B               |                                    |

| Current<br>Mode<br>Drivers | 6.5                | 9                          | D ·                                  | Yes                     | Yes    | ±5              | 55110A                          | 75110A                | 6A<br>6A, 9A         | 2              | 75108A/B               | Glitchless<br>Current Outputs      |

#### LINE DRIVER SELECTION GUIDE

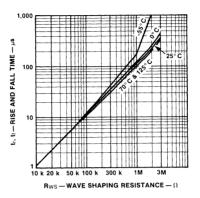

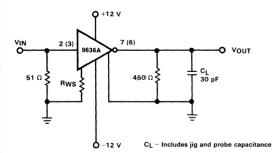

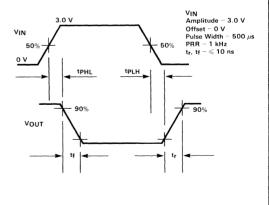

\*9636A output slew rates are jointly controlled by a single external resistor.

|                                                   | S = Single Ended | Type Of | Propagation<br>Delay Time | Party Line |        | Power<br>Supplies | Device Typ<br>Temperature | Range             | Package          | Receivers<br>Per | Companion             | Additional                                                                 |

|---------------------------------------------------|------------------|---------|---------------------------|------------|--------|-------------------|---------------------------|-------------------|------------------|------------------|-----------------------|----------------------------------------------------------------------------|

| Description                                       | D = Differential | Output* | Typical (ns)              | Operation  | Strobe | (V)               | -55° C to 125° C          | 0° C to 70° C     | Туре             | Package          | Drivers               | Features                                                                   |

|                                                   | D                | Т       | 17                        | Yes        | Yes    |                   |                           | 75207*            | 6A, 9A           | 2                |                       |                                                                            |

|                                                   | D                | 0       | 19                        | Yes        | Yes    |                   |                           | 75208*            | 6A, 9A           | 2                | 75110A,               |                                                                            |

|                                                   | D                | т       | 17                        | Yes        | Yes    | ±5                | 55107A                    | 75107A            | 6A, 3I<br>6A, 9A | 2                | 55110A                |                                                                            |

|                                                   | U                |         | 17                        | 165        | 163    | -0                | 55107B                    | 75107B            | 6A, 3I<br>6A, 9A | 2                |                       | B versions have input<br>protection diodes for<br>power off condition      |

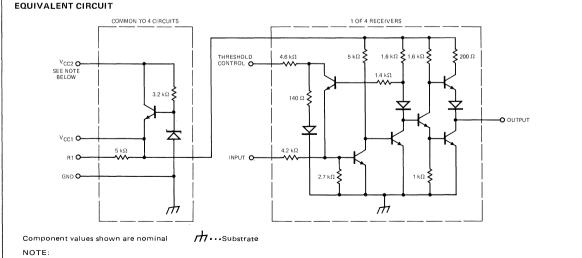

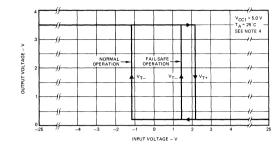

|                                                   |                  |         |                           |            |        |                   | 55108A                    | 75108A            | 6A, 3I<br>6A, 9A | 2                | 75110A,<br>75112      |                                                                            |

| General<br>Purpose<br>Receivers                   | D                | 0       | 19                        | Yes        | Yes    |                   | 55108B                    | 75108B            | 6A, 3I<br>6A, 9A | ·2               |                       |                                                                            |

|                                                   | S                | т       | 30                        | Yes        | Yes    | 5                 | 55122/µA8T14              | 75122/<br>μA8T14  | 6B<br>6B, 9B     | 3                | 75121/<br>μA8T13      | Hysteresis for improved<br>noise immunity                                  |

|                                                   | D                | O or T  | 20                        | Yes        | Yes    | × _5              | 9615DM, FM                | 9615              | 6B, 4L<br>6B, 9B | 2                | 9614                  | ±500 mV input sensitivity<br>±15 CMRR                                      |

|                                                   | D                | т       | 25                        | No         | No     | 5                 | 9613                      | 9613C             | 6Т<br>6Т, 9Т     | 2                | 9612                  | ±15V CMRR                                                                  |

|                                                   | S                | т       | 35                        | Yes        | Yes    | +5 and<br>-10     | 9622                      | 9622C             | 6A<br>6A, 9A     | 2                | 9621                  | Wire — or capability                                                       |

| Receivers<br>For 360/370<br>/O Interface          | S                | · T     | 20                        | No         | Yes    | 5                 |                           | 75124/<br>μA8T24  | 6B, 9B           | 3                | 75123/<br>μA8T13      | Hysteresis                                                                 |

|                                                   | S                | Т       | 22                        | No         | No     | +5 or +12         |                           | 75154             | 6B, 9B           | 4                | 75150                 | Hysteresis                                                                 |

| Receivers<br>Meeting EIA<br>Standard              | S                | ·R      | 25                        | No         | No     | 5                 |                           | μΑ1489<br>μΑ1489Α | 6A, 9A<br>6A, 9A | 4                | μA1488                | Response threshold<br>control, 1489A has more<br>Hysteresis than 1489      |

| RS-232-C                                          | S                | R       | 50                        | No         | No     | ±12               |                           | 9617              | 6A, 9A           | 3                | 9616                  |                                                                            |

|                                                   | D                | т       | 60                        | No         | Yes    | ±12               | 9627DM                    | 9627              | 6B, 9B<br>6B, 9B | 2                | 9616                  | Also meets MIL-STD-1880<br>Hysteresis                                      |

| Receivers<br>Meeting<br>IA Standard<br>RS-422/423 | S, D             | Ť       | 13                        | Yes        | No     | 5                 | 9637ARM                   | 9637A             | 6Т<br>6Т, 9Т     | 2                | 9634<br>9638<br>9636A | ±30mV built in Hysteresis<br>Schottky circuitry also<br>meets MIL-STD-188C |

\*T = Totem pole. O = Open collector. R = Resistor pull-up Not recommended for new designs, but Fairchild will continue to supply these devices for existing applications.

1-10

|                                                                                            | Chi                                     | Driver<br>aracteristic             | :5                     |                                    | eiver<br>teristics     |                                           | _          |                 |                                                                                                                                                       |  |

|--------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------|------------------------|------------------------------------|------------------------|-------------------------------------------|------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Common Features                                                                            | Output<br>Current<br>Capability<br>(mA) | tp <sub>D</sub><br>Typical<br>(ns) | Strobe<br>Or<br>Enable | tp <sub>D</sub><br>Typical<br>(ns) | Strobe<br>Or<br>Enable | Device T<br>Temperatu<br>-55° C to 125° C | • •        | Package<br>Type | Additional Features                                                                                                                                   |  |

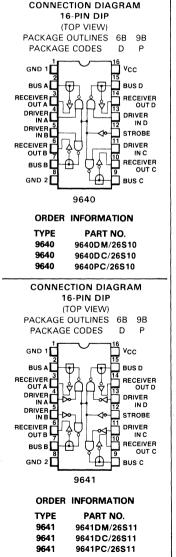

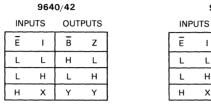

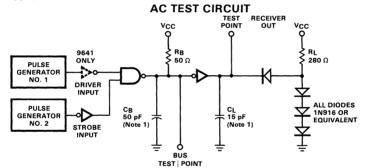

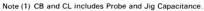

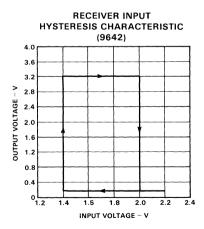

| Schottky Circuitry                                                                         | 100                                     | 10                                 | Strobe                 | 10                                 | Strobe                 | 9640DM/26S10                              | 9640/26S10 | 6B<br>6B, 9B    |                                                                                                                                                       |  |

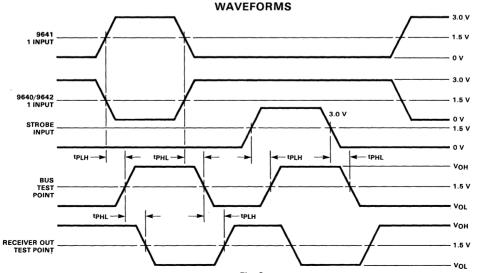

| Single 5 V Supply                                                                          | 100                                     | 12                                 | Strobe                 | 10                                 | Strobe                 | 9641DM/26S11                              | 9641/26S11 | 6B<br>6B, 9B    | <ul> <li>Inverting Bus on 9640/26S10, 9642</li> <li>Non-Inverting Bus on 9641/26S11</li> <li>600 mV Receiver Hysteresis on 9642</li> </ul>            |  |

| <ul> <li>Party Line Operation</li> <li>TTL-Compatible Driver Inputs</li> </ul>             | 100                                     | 15                                 | Strobe                 | 8                                  | Strobe                 | 9642DM                                    | 9642       | 6B<br>6B, 9B    | For Maximum System Noise Margin                                                                                                                       |  |

| <ul> <li>Totem-Pole Receiver Outputs</li> <li>Four Transceivers<br/>Per Package</li> </ul> | 48                                      | 12                                 | Enable                 | 8                                  | Enable                 | μΑ8Τ26ADM                                 | μA8T26A    | 6B<br>6B,9B     | <ul> <li>3-State Driver and Receiver Outputs</li> <li>μA8T26A - Inverting Bus</li> <li>μA8T28 - Non-Inverting Bus</li> <li>μP Bus Extender</li> </ul> |  |

| P-N-P Outputs To     Reduce Input Loading                                                  | 48                                      | 8 12 Enable                        |                        | 8 Enable                           |                        | μA8T28DM                                  | μA8T28     | 6B<br>6B, 9B    | <ul> <li>μr bus extended</li> <li>Replaces NE8T26A and NE8T28</li> </ul>                                                                              |  |

#### LED DISPLAY DRIVERS

| Description | Input<br>Compatibility | Power<br>Supplies<br>(V) | Drivers<br>Per<br>Package | Device<br>Type | Package<br>Typ <del>e</del> | Additional Features          |

|-------------|------------------------|--------------------------|---------------------------|----------------|-----------------------------|------------------------------|

| Segment     |                        | 10                       | 4                         | 75491          | 6A, 9A                      | •50mA source/sink capability |

| Drivers     | NOS                    | 20                       | 4                         | 75491A         | 6A, 9A                      | •SomA source/sink capability |

| Digit       | MOS                    | 10                       | 6                         | 75492          | 6A, 9A                      |                              |

| Drivers     |                        | 20                       | 6                         | 75492A         | 6A, 9A                      | •250mA sink capability       |

| Maximum                     | Minimum                    | Maximum                        | Typical                                  | Output   | Drivers        |                         | D              | evice Typ | e And Packa | age⁵   |                   |

|-----------------------------|----------------------------|--------------------------------|------------------------------------------|----------|----------------|-------------------------|----------------|-----------|-------------|--------|-------------------|

| Off-State<br>Voltage<br>(V) | Latch-up<br>Voltage<br>(V) | Recommended<br>Current<br>(mA) | Delay Clamp<br>Time Clamp<br>(ns) Diodes |          | Per<br>Package | Input<br>Compatibility  | -55°C to 125°C |           | 0°C to 70°C |        | Logic<br>Function |

|                             |                            |                                |                                          |          |                |                         | 55450A         | 6A        | 75450A      | 6A, 9A | And*              |

|                             |                            |                                |                                          |          |                |                         | 55451A         | 6T        | 75451A      | 6T, 9T | And               |

| 30                          | 20                         | 300                            | 25                                       | No       | 2              | TTL, DTL                | 55452A         | 6T        | 75452A      | 6T, 9T | Nand              |

|                             |                            |                                |                                          |          |                |                         | 55453A         | 6T        | 75453A      | 6T, 9T | Or                |

|                             |                            |                                |                                          |          |                |                         | 55454A         | 6T        | 75454A      | 6T, 9T | Nor               |

|                             |                            |                                |                                          |          |                |                         | 55450B         | 6A        | 75450B      | 6A, 9A | And*              |

|                             |                            |                                |                                          |          |                |                         | 55451B         | 6T        | 75451B      | 6T, 9T | And               |

| 30                          | 20                         | 300                            | 21                                       | No       | 2              | TTL, DTL                | 55452B         | 6T        | 75452B      | 6T, 9T | Nand              |

|                             |                            |                                |                                          |          |                | 55453B                  | 6T             | 75453B    | 6T, 9T      | Or     |                   |

|                             |                            |                                |                                          |          |                |                         | 55454B         | 6T        | 75454B      | 6T, 9T | Nor               |

|                             |                            |                                |                                          |          |                |                         | 55460          | 6A        | 75460       | 6A, 9A | And*              |

|                             |                            |                                |                                          |          |                | ÷                       | 55461          | 6T        | 75461       | 6T, 9T | And               |

| 35                          | 30                         | 300                            | 33                                       | No       | 2              | TTL, DTL                | 55462          | 6T        | 75462       | 6T, 9T | Nand              |

|                             |                            |                                |                                          |          |                |                         | 55463          | 6T        | 75463       | 6T, 9T | Or                |

|                             |                            |                                |                                          |          |                |                         | 55464          | 6T        | 75464       | 6T, 9T | Nor               |

|                             |                            |                                |                                          |          |                | TTL, DTL, CMOS, P-MOS   |                |           | 9665        | 6B, 9B |                   |

|                             |                            |                                |                                          | Yes      |                | 14-V to 25-V P-MOS      | 9666DM         | 6B        | 9666        | 6B, 9B | Inverting         |

| 50                          | 50                         | 350                            | 200                                      | (350 mA) | 7              | TTL and 5-V CMOS        | 9667DM         | 6B        | 9667        | 6B, 9B | Buffer            |

|                             |                            |                                |                                          |          |                | 6-V to 15-V P-MOS, CMOS | 9668DM         | 6B        | 9668        | 6B, 9B |                   |

|                             |                            |                                |                                          |          |                |                         | 55471          | 6T        | 75471       | 6T, 9T | And               |

|                             |                            |                                |                                          |          |                |                         | 55472          | 6T        | 75472       | 6T, 9T | Nand              |

| <sup>-</sup> 80             | 55                         | 300                            | 33                                       | No       | 2              | TTL, DTL                | 55473          | 6T        | 75473       | 6T, 9T | Or                |

|                             |                            |                                |                                          |          |                |                         | 55474          | 6T        | 75474       | 6T, 9T | Nor               |

#### PERIPHERAL DRIVERS

\* With output transistor base connected externally to output of gate

+ All plastic packages are on copper lead frames

| Supply<br>Voltage<br>(V)                              | Propagation<br>Delay<br>Time (Typical)<br>(ns) | V <sub>ОН</sub><br>(Min)<br>(V) | V <sub>OL</sub><br>(Max)<br>(V) | Device<br>Type   | Package<br>Type  | Drivers<br>Per<br>Package | Features                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------|------------------------------------------------|---------------------------------|---------------------------------|------------------|------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

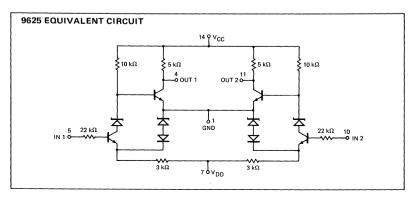

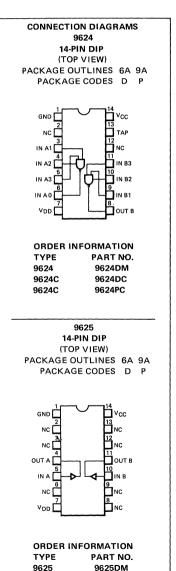

| V <sub>CC</sub> = +5<br>V <sub>DD</sub> = 0 to -30    | 50                                             | +3.5                            | 0.2                             | 9624             | 6A, 9A           | 2                         | <ul> <li>Dual MOS-to-TTL converter</li> <li>Non-inverting buffer</li> </ul>                                                                                                                                                                                                                      |

| V <sub>CC</sub> = +5<br>V <sub>DD</sub> = 0 to -30    | 50                                             | +2.6                            | 0.2                             | 9625             | 6A, 9A           | 2                         | <ul> <li>Dual MOS-to-TTL converter</li> <li>Inverting buffer</li> </ul>                                                                                                                                                                                                                          |

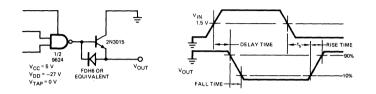

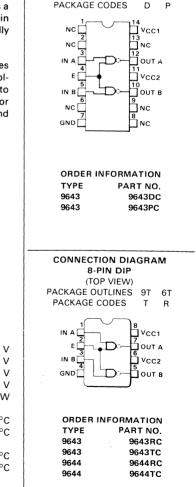

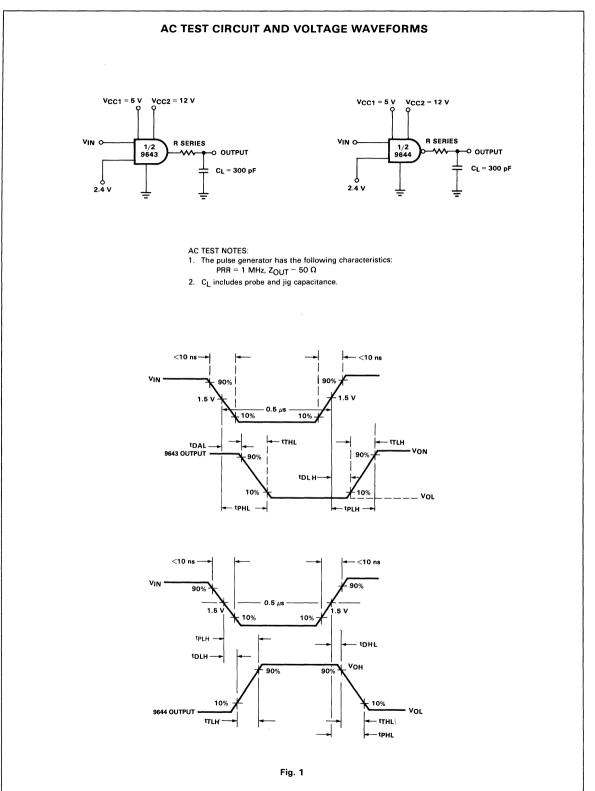

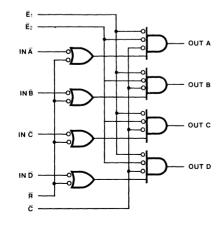

| $V_{CC1} = +5$<br>$V_{CC2} = +5$ to +12               | 9                                              | V <sub>CC2</sub> - 0.5          | 0.3                             | 9643             | 6T, 9T, 6A, 9A   | 2                         | <ul> <li>Positive AND TTL-to-MOS/CCD driver</li> <li>Replaces SN75322 and SN75363</li> <li>9643/4 does not require two external PNP</li> <li>High voltage Schottky technology</li> <li>V<sub>CC3</sub> supply is not needed</li> <li>Satisfies F464 CCD memory clock<br/>requirements</li> </ul> |

| V <sub>CC1</sub> = +5<br>V <sub>CC2</sub> = +5 to +12 | 6                                              | V <sub>CC</sub> - 0.5           | 0.3                             | 9644             | 6Т, 9Т           | 2                         | <ul> <li>Dual positive NAND TTL-to-MOS/CCD</li> <li>Same features as 9643</li> </ul>                                                                                                                                                                                                             |

| V <sub>CC</sub> = +5<br>V <sub>DD</sub> = +12         | 10                                             | V <sub>DD</sub> - 0.5           | 0.45                            | 9645<br>(3245)   | 7B, 9B           | 4                         | Quad TTL-to-MOS/CCD driver     Replaces Intel 3245     Satisfies F464 CCD memory requirements                                                                                                                                                                                                    |

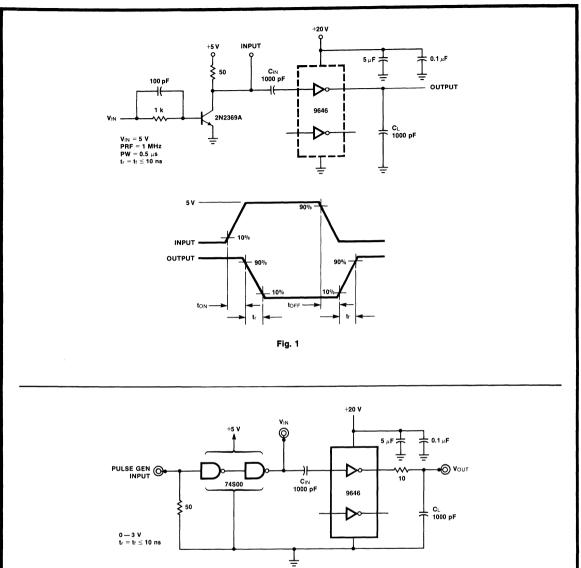

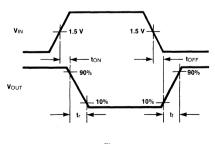

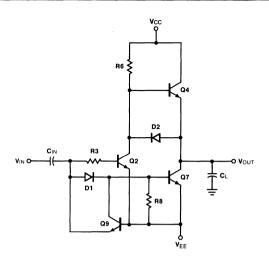

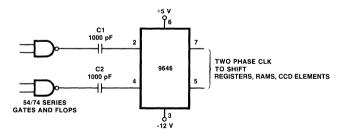

| ±V = 0 to ±20                                         | 10                                             | (+V) -1.0                       | (-V) +1.0                       | 9646<br>(DS0026) | 6A, 9A<br>6T, 9T | 2                         | <ul> <li>Dual two phase MOS clock driver</li> <li>Replaces DS0026</li> <li>±1.5 Amp output current capability</li> </ul>                                                                                                                                                                         |

| SENSE AMPLIFIERS                   |                          |               |              |               |                        |               |                  |                |                                                                                                                           |   |                                                                                                                                                       |

|------------------------------------|--------------------------|---------------|--------------|---------------|------------------------|---------------|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    |                          | Common-       | Type†        | Propagation   | Device Ty<br>Temperatu |               |                  | Units          |                                                                                                                           |   |                                                                                                                                                       |

| Description                        | Threshold<br>Sensitivity | Mode<br>Range | Of<br>Output | Delay<br>Time | -55°C to 125°C         | 0° C to 70° C | Package<br>Type  | Per<br>Package | Additional Features                                                                                                       |   |                                                                                                                                                       |

|                                    | ±2.5mV                   |               | R            | 35ns          | 55S20                  | 75S20         | 6B<br>6B, 9B     | 1              | <ul> <li>Internally compensated ref. amp</li> <li>Provides memory data register</li> <li>Complementary outputs</li> </ul> |   |                                                                                                                                                       |

|                                    | ±2.5mV                   |               | R            | 25ns          | 55S24                  | 75S24         | 6B<br>6B, 9B     | 2              | <ul> <li>Internally compensated ref. amp</li> <li>Independent strobes</li> </ul>                                          |   |                                                                                                                                                       |

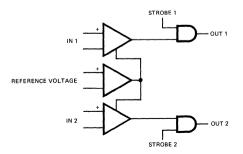

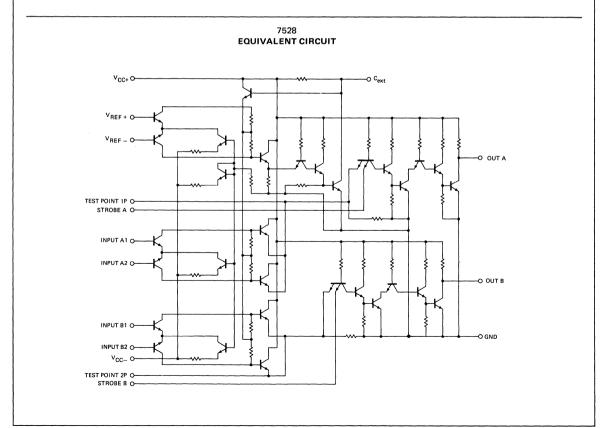

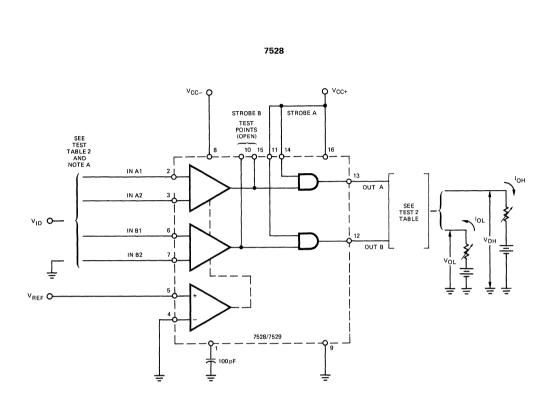

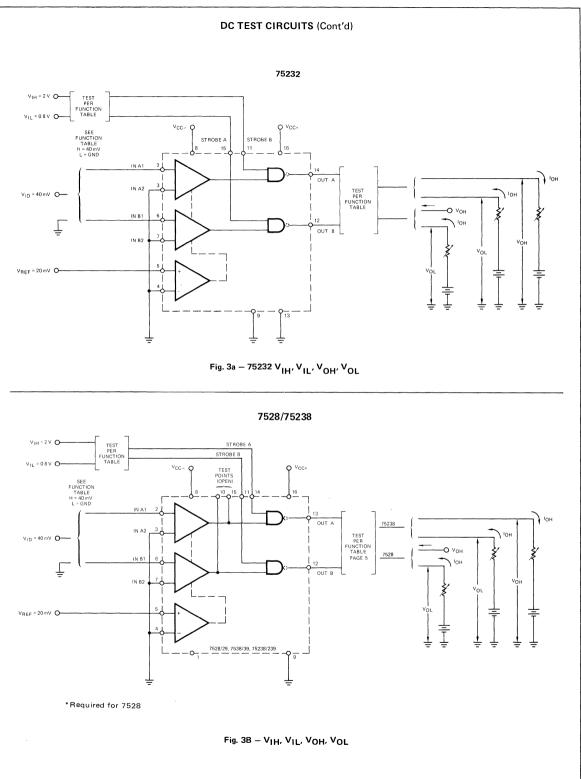

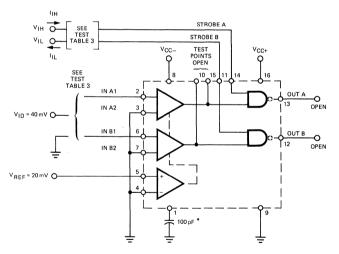

|                                    | ±4.0mV                   |               | R            | 25ns          | 5528                   | 7528          | 6B<br>6B, 9B     | 2              | <ul> <li>Independent strobes</li> <li>Test points for strobe timing adjustment</li> </ul>                                 |   |                                                                                                                                                       |

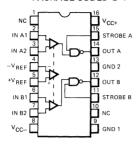

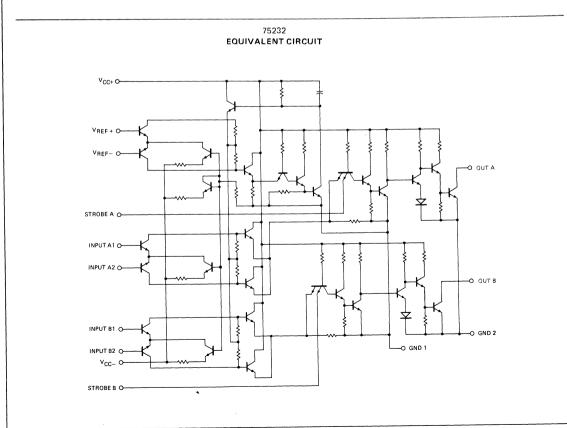

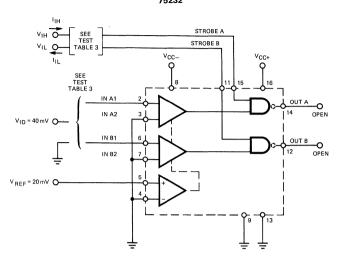

| Core Memory<br>Sense<br>Amplifiers | ±4.0mV                   | ±2.5V         | 0-C          | 25ns          | 55232                  | 75232         | 6B<br>6B, 9B     | 2              | <ul> <li>Independent strobes</li> <li>Internally compensated reference amplifier</li> </ul>                               |   |                                                                                                                                                       |

|                                    | ±2.5mV                   |               | R            | 25ns          | 55S234                 | 75S234        | 6B<br>6B, 9B     | 2              | <ul> <li>Independent strobes</li> <li>Internally compensated reference amplifier</li> </ul>                               |   |                                                                                                                                                       |

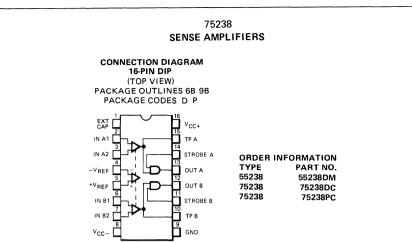

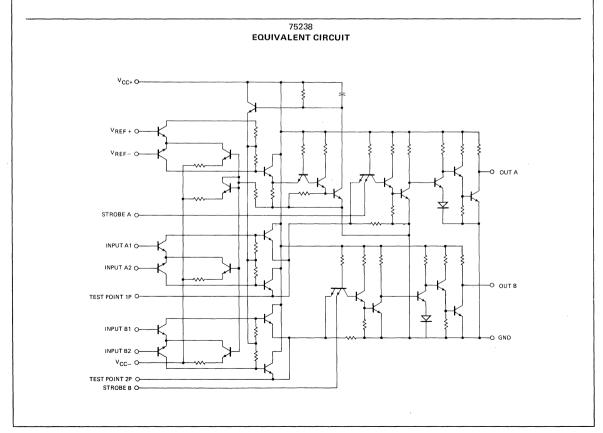

|                                    | ±4.0mV                   |               |              |               | R                      | 25ns          | 55238            | 75238          | 6B<br>6B, 9B                                                                                                              | 2 | <ul> <li>Independent strobes</li> <li>Internally compensated reference<br/>amplifier</li> <li>Test points for strobe timing<br/>adjustment</li> </ul> |

| MOS-Memory                         | ±25mV                    | ±3V           | Т-Р          | 17ns          | 55107*                 | 75107A*       | 6A, 3I<br>6A, 9A | 2              | <ul> <li>Independent strobes</li> </ul>                                                                                   |   |                                                                                                                                                       |

| MOS-memory<br>Sense<br>Amplifiers  | ±25mV                    | ±3V           | O-C          | 19ns          | 55108A*                | 75108A*       | 6A, 3I<br>6A, 9A | 2              | <ul> <li>Independent strobes</li> </ul>                                                                                   |   |                                                                                                                                                       |

|                                    | ±10mV                    | ±3V           | T-P          | 17ns          |                        | 75207*        | 6A, 9A           | 2              | <ul> <li>Independent strobes</li> </ul>                                                                                   |   |                                                                                                                                                       |

|                                    |                          | <u>_'</u> 3v  | 0-C          | 19ns          |                        | 75208*        | 6A, 9A           |                |                                                                                                                           |   |                                                                                                                                                       |

+ T-P = Totem Pole, O-C = Open Collector, R = Resistor Pull-Up

• See Line Circuit Section for details

| Description                              | Maximum<br>Output<br>Current | Propagation<br>Delay<br>Time<br>(ns) | Power<br>Supplies                                              | Device Type For<br>Temperature Range<br>-55°C to 125°C 0°C to 70°C |       | Package<br>Type  | Additional Features                                                                                                                                                                                             |  |  |

|------------------------------------------|------------------------------|--------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------|-------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

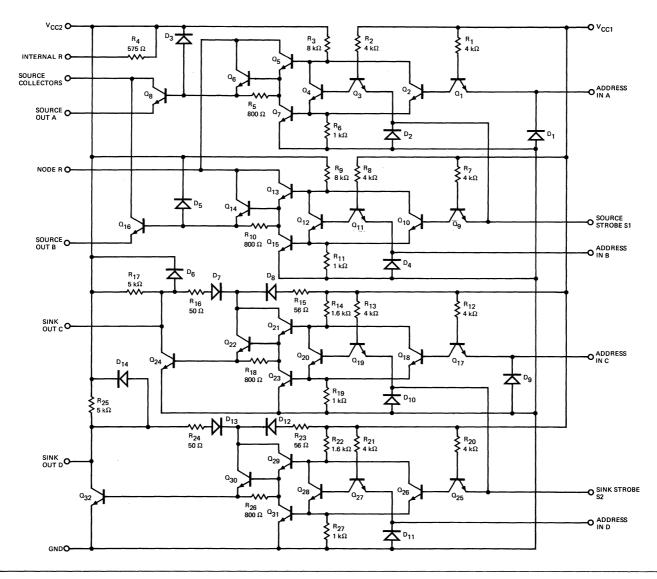

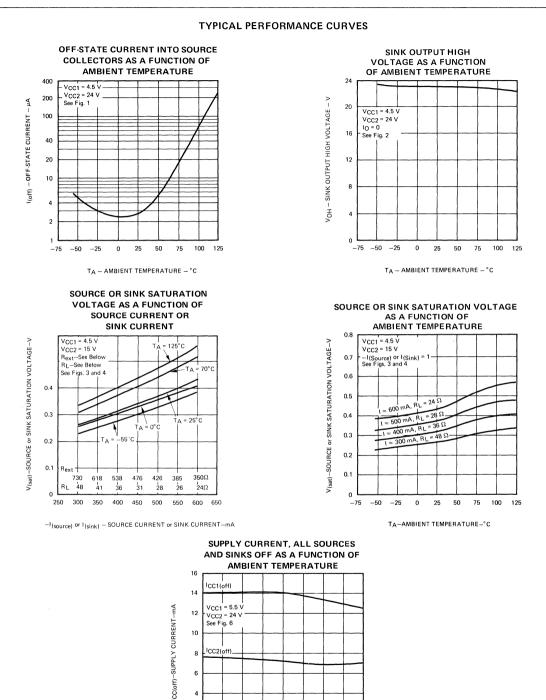

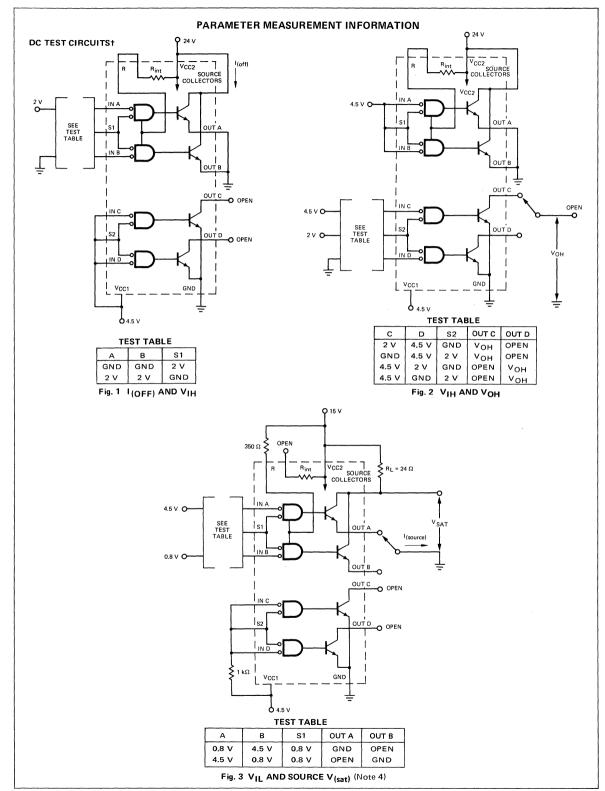

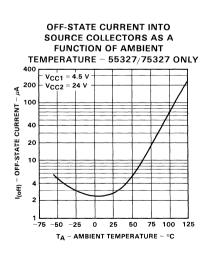

| Dual<br>Sink/Source<br>Memory<br>Drivers | ·                            | 35                                   | V <sub>CC1</sub> - 5 V<br>V <sub>CC2</sub> variable<br>to 24 V | 55325                                                              | 75325 | 7B, 4L<br>7B, 9B | <ul> <li>Also used for high-voltage, high-current<br/>driver applications</li> <li>Output transient voltage protection</li> <li>Source output terminals swing between<br/>V<sub>CC2</sub> and ground</li> </ul> |  |  |

| Quadruple<br>Sink Memory<br>Drivers      | 600mA                        | 35                                   | V <sub>CC1</sub> - 5 V<br>V <sub>CC2</sub> variable<br>to 24 V | 55327                                                              | 75327 | 7B, 4L<br>7B, 9B | <ul> <li>Also used for high speed magnetic<br/>memory applications</li> <li>Output transient voltage protection</li> <li>Output capable of swinging between<br/>V<sub>CC2</sub> and ground</li> </ul>           |  |  |

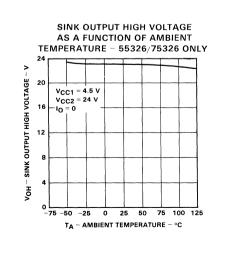

| Quadruple<br>Memory<br>Drivers           |                              | 30                                   | V <sub>CC</sub> = 5 V                                          | 55326                                                              | 75326 | 7B, 4L<br>7B, 9B | <ul> <li>Also used for high-voltage, high-current<br/>driver applications</li> <li>Output transient voltage protection</li> <li>24V output capability</li> </ul>                                                |  |  |

\*Also see MOS/CCD driver section

# SPECIAL FUNCTIONS-TIMERS AND COUNTERS

| Device<br>Number | Function                   | Time<br>Delay<br>Hours | Free Running<br>Frequency<br>(kHz) | Output<br>Compatibility | Output<br>Current<br>(mA) | Supply<br>Voltage<br>V (Max) | Timing<br>Error<br>% | Package(s)     |

|------------------|----------------------------|------------------------|------------------------------------|-------------------------|---------------------------|------------------------------|----------------------|----------------|

| μ <b>Α555</b>    | Single Timer               | 1.0                    | 100                                | TTL                     | 200                       | +18                          | 1.0                  | 5S, 6T, 9T, 6A |

| μ <b>Α556</b>    | Dual Timer                 | 1.0                    | 100                                | TTL                     | 200                       | +18                          | 1.0                  | 6A, 9A         |

| μ <b>Α2240</b>   | Programmable Timer-Counter | 120                    |                                    | TTL                     | 5.0                       | +18                          | 0.5                  | 7B, 9B         |

# MEMODY DDIVEDC\*

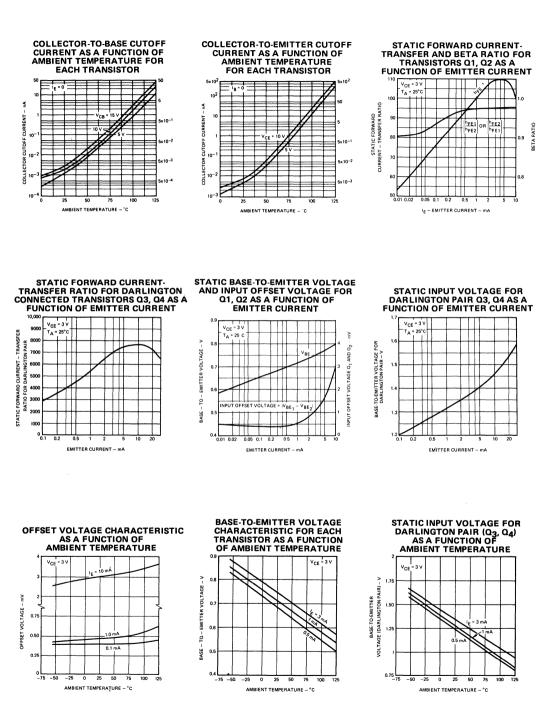

## SPECIAL FUNCTIONS-TRANSISTOR AND DIODE ARRAYS

| Device<br>Number | Function                            | Balanced<br>Input | Balanced<br>Output | Low<br>Noise | AGC<br>Capability | Multiple<br>Unit | Wideband | Switching<br>Application | <b>V</b> сво- <b>V</b> | VCEO-V | VEBO-V | IC-MA | V <sub>BE</sub> or V <sub>O</sub> | Package(s) |

|------------------|-------------------------------------|-------------------|--------------------|--------------|-------------------|------------------|----------|--------------------------|------------------------|--------|--------|-------|-----------------------------------|------------|

| μ <b>Α726*</b>   | Temp Controlled<br>Diff Pair        | •                 | •                  | •            | -                 | _                | —        | -                        | 40                     | 30     | 5.0    | 5.0   | 2.5                               | 5U         |

| μ <b>Α3018</b> * | Matched Transistor<br>Array         | •                 | •                  |              | •                 | •                | •        | —                        | 20                     | 15     | 5.0    | 50    | 5.0                               | 5D         |

| μ <b>Α3018Α*</b> | Matched Transistor<br>Array         | •                 | •                  | _            | •                 | •                | •        | _                        | 30                     | 15     | 5.0    | 50    | 2.0                               | 5D         |

| μ <b>Α3019</b> * | Quad Plus Two<br>Diode Array        | 1                 | _                  | -            |                   | _                | _        | •                        | -                      | 1      |        | -     | 5.0                               | 5Q         |

| μ <b>Α3026</b> * | Dual Diff Amp<br>Transistor Array   | _                 | _                  | _            | _                 |                  | _        | _                        | 20                     | 15     | 5.0    | 50    | 5.0                               | 5D         |

| µ <b>A3036</b> * | Dual Darlington<br>Transistor Array | •                 | •                  | •            |                   | •                | -        | _                        | 30                     | 15     | 5.0    | 50    | -                                 | 5Q         |

| μ <b>Α3039</b> * | Hex Ultra Fast<br>Diode Array       |                   | _                  | -            | _                 | -                | _        | •                        | -                      | _      | -      |       | 5.0                               | 5D         |

| µ <b>A3045</b> * | Diff Pair Plus<br>Three Transistors | •                 | •                  | -            |                   | •                | •        |                          | 20                     | 15     | 5.0    | 50    | 5.0                               | 6A         |

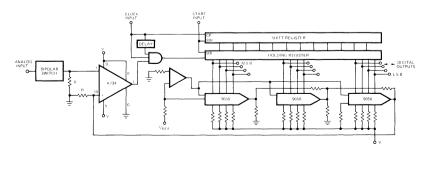

| μ <b>Α3046</b>   | Diff Pair Plus<br>Three Transistors | •                 | •                  | —            |                   | •                | •        | _                        | 20                     | 15     | 5.0    | 50    | 5.0                               | 6A, 9A     |

| μ <b>Α3054</b>   | Dual Diff Amp<br>Transistor Array   | —                 | —                  | _            | -                 | •                | —        | _                        | 20                     | 15     | 5.0    | 50    | 5.0                               | 6A, 9A     |

| μ <b>Α3086</b>   | Dual Diff Plus<br>Three Transistors | •                 | •                  |              |                   | •                | •        | _                        | 20                     | 15     | 5.0    | 50    | -                                 | 6A, 9A     |

\*Military grade available

#### ALPHA NUMERIC INDEX OF INTERFACE 1 DEVICES AND SELECTION GUIDES

| LINEAR INDUSTRY<br>CROSS REFERENCE                                 | 2 |

|--------------------------------------------------------------------|---|

| QUALITY, RELIABILITY AND<br>HI REL PROCESSING                      | 3 |

| VOLTAGE COMPARATORS                                                | 4 |

| DATA ACQUISITION                                                   | 5 |

| LINE CIRCUITS - DRIVERS,<br>RECEIVERS AND TRANSCEIVERS             | 6 |

| PERIPHERAL AND DISPLAY DRIVERS                                     | 7 |

| MEMORY INTERFACE                                                   | 8 |

| TRANSISTOR ARRAYS AND<br>SPECIAL FUNCTIONS                         | 9 |

| DATA TRANSMISSION INFORMATION                                      | 1 |

| ORDER INFORMATION, DICE POLICY<br>AND PACKAGE OUTLINES             | 1 |

| FAIRCHILD FIELD SALES OFFICES.<br>REPRESENTATIVES AND DISTRIBUTORS | 1 |

| Part<br>Number | Fairchild<br>Direct<br>Replacement | Fairchild<br>Functional<br>Equivalent | Part<br>Number | Fairchild<br>Direct<br>Replacement | Fairchild<br>Functional<br>Equivalent |

|----------------|------------------------------------|---------------------------------------|----------------|------------------------------------|---------------------------------------|

| 1458CE         | μA1458CHC                          |                                       | 741CJ          | μA741PC                            |                                       |

| 1458CP         | μA1458CTC                          |                                       | 741CP          | μΑ741TC                            |                                       |

| 1458E          | μA1458HC                           |                                       | 747BE          | μΑ747ΗΜ                            |                                       |

| 1458P          | μA1458TC                           |                                       | 747BL          | μΑ747DM                            |                                       |

| 1558E          | μA1558HM                           |                                       | 747CE          | μA747HC                            |                                       |

| 3207A          |                                    | 9645                                  | 747CJ          | μA747PC                            |                                       |

| 3245           | 9645/3245                          |                                       | 747CL          | ,<br>μΑ747DC                       |                                       |

| 527            |                                    | μA760HM                               | 748BE          | μA748HM                            |                                       |

| 532            |                                    | ,<br>μΑ798TC                          | 748BH          | _<br>μA748FM                       |                                       |

| 536            |                                    | μA740AHM                              | 748BL          | μA748DM                            |                                       |

| 556CJ          | μA556PC                            |                                       | 748CE          | μA748HC                            |                                       |

| 709AE          | μΑ709ΑΗΜ                           |                                       | 748CL          | μA748DC                            |                                       |

| 709AH          | _<br>μA709AFM                      |                                       | 748CP          | _<br>μA748TC                       |                                       |

| 709AL          | μA709ADM                           |                                       | 75S107         | 1                                  | 75107APC                              |

| 709BE          | μA709HM                            |                                       | 75S108         |                                    | 75108APC                              |

| 709BH          | μA709FM                            |                                       | 75S207         |                                    | 75207PC                               |

| 709BL          | μA709DM                            |                                       | 75S208         |                                    | 75208PC                               |

| 709CE          | μA709HC                            |                                       | 75322          | 9643DC                             |                                       |

| 709CJ          | μA709PC                            |                                       | 75361          | 9644DC                             |                                       |

| 709CL          | μA709DC                            |                                       | 75361A         |                                    | 9643DC                                |

| 710BE          | μA710HM                            |                                       | 75363          | 9643DC                             |                                       |

| 710BH          | μA710FM                            |                                       | 75450N         | 75450APC                           |                                       |

| 710BL          | μA710DM                            |                                       | 78M05BE        | μA78M05HM                          |                                       |

| 710CE          | μA710HC                            |                                       | 78M05CE        | ,<br>μΑ78Μ05HC                     |                                       |

| 710CL          | μA710DC                            |                                       | 78M06BE        | μA78M06HM                          |                                       |

| 711BE          | μA711HM                            |                                       | 78M06CE        | μΑ78M06HC                          |                                       |

| 711BH          | μA711FM                            |                                       | 78M08BE        | μA78M08HM                          |                                       |

| 711BL          | μA711DM                            |                                       | 78M08CE        | _<br>μA78M08HC                     |                                       |

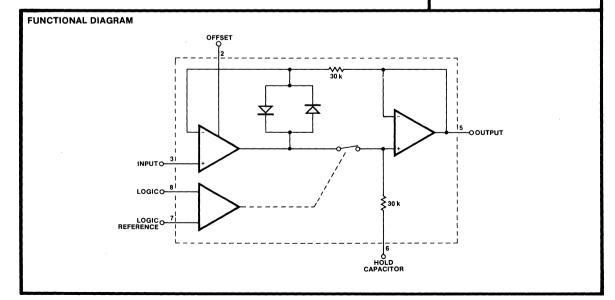

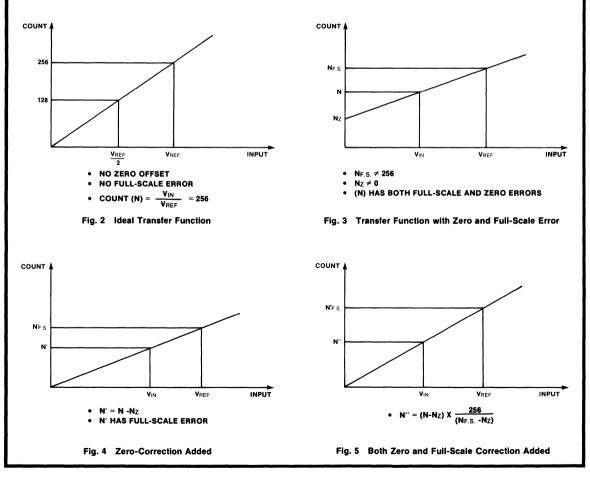

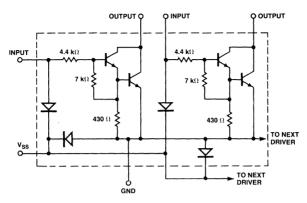

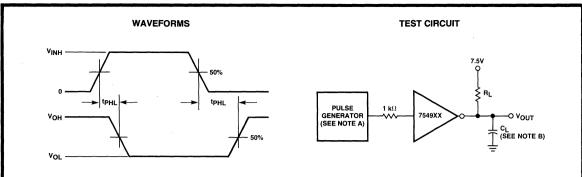

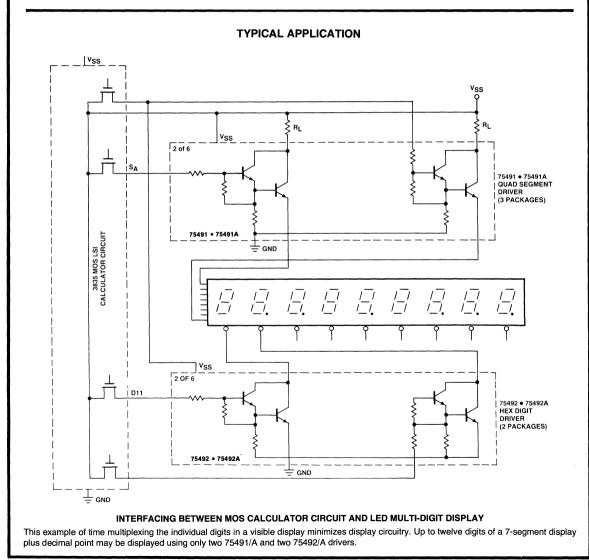

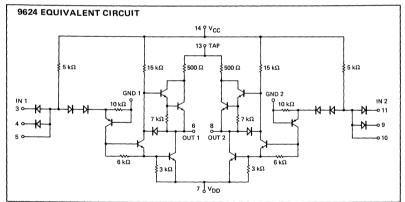

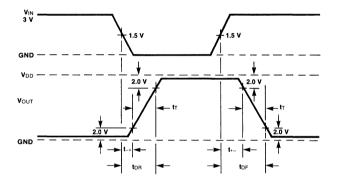

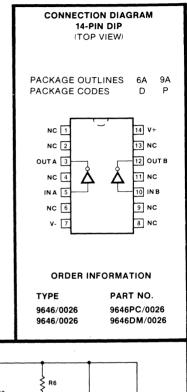

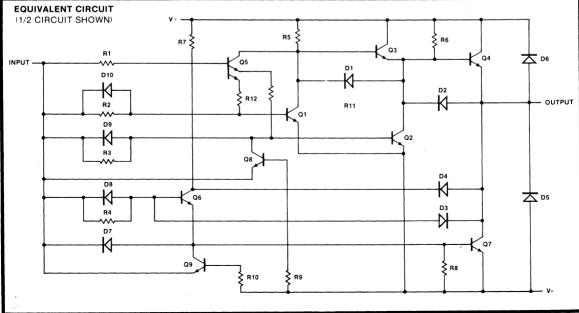

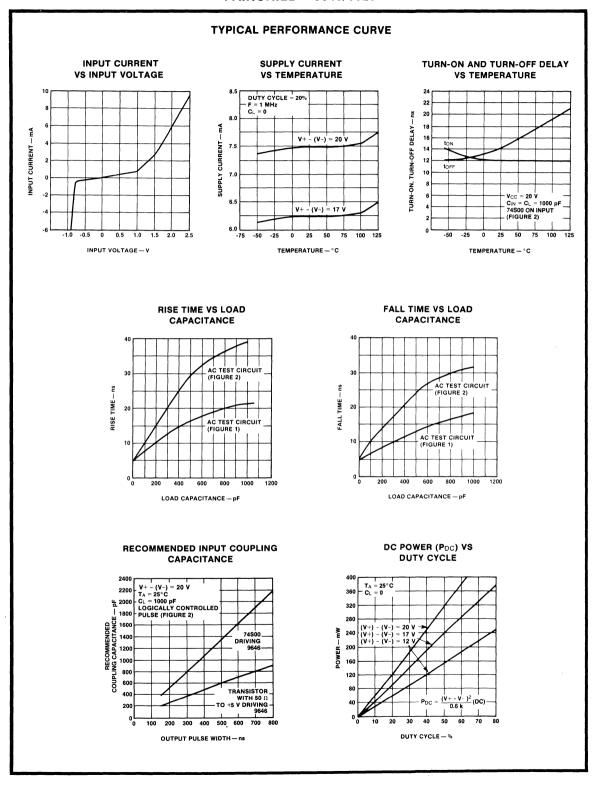

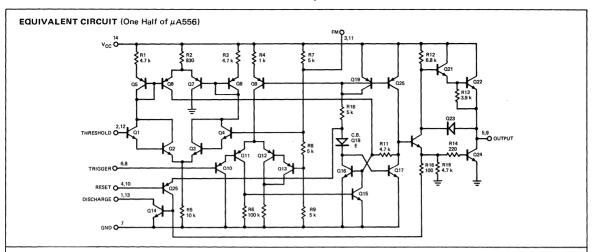

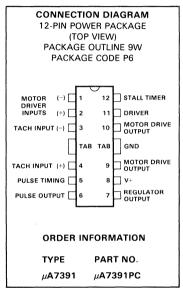

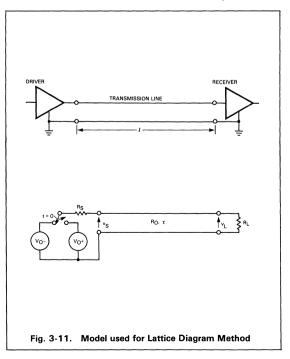

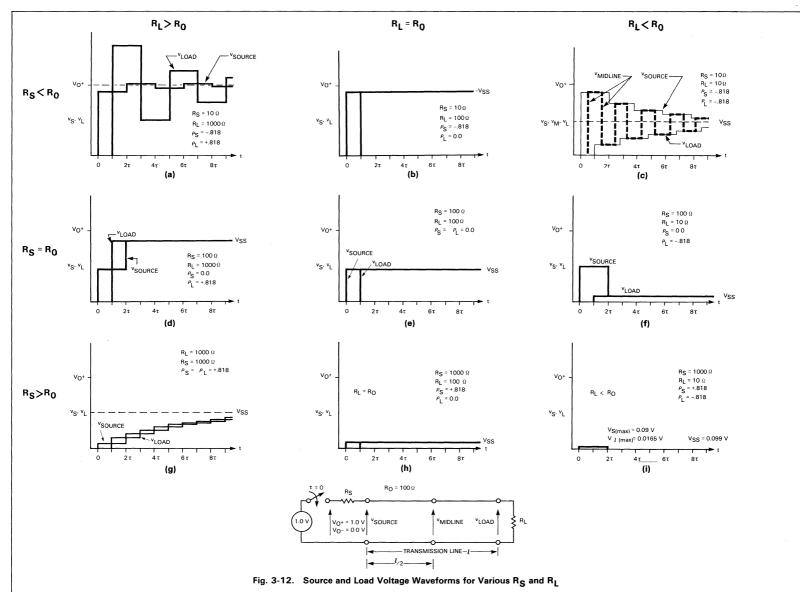

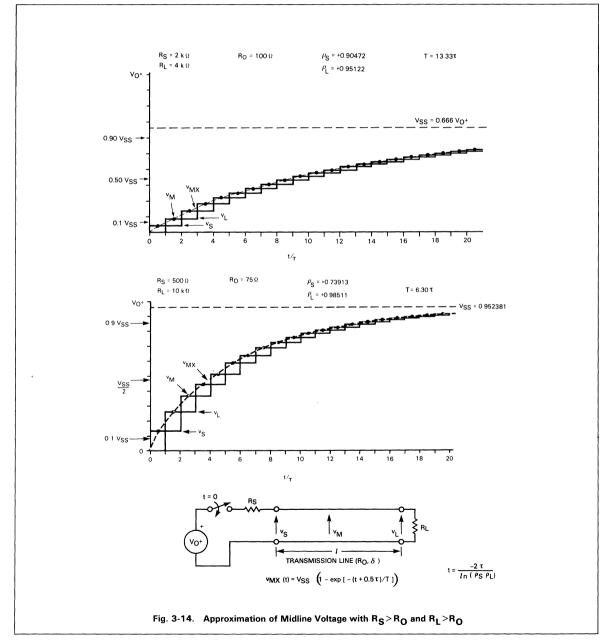

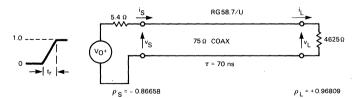

| 711CE          | μA711HC                            |                                       | 78M12BE        | μA78M12HM                          |                                       |