# FAIRCHILD SEMICONDUCTOR

SEPTEMBER 1972

## FAIRCHILD OPTIMOS

The promise of MOS/LSI is being fulfilled — inexpensive monolithic circuits can replace entire electronic assemblies today. MOS large scale integration processes can provide a subsystem of several hundred to more than a thousand gates at a cost around \$10. Such arrays are now being designed into many more types of digital signalprocessing systems than in the past because MOS circuit performance has quadrupled in the past few years.

Nevertheless, MOS/LSI presents risks as well as rewards to the equipment manufacturer. If MOS devices are applicable, all competing equipment manufacturers are virtually compelled to use them. Only the most cost-effective designs, obviously, will be successful. In every instance, since MOS/LSI is a subsystem rather than a component technology, the difference between success and failure will be the ability of the MOS manufacturer to support the cost and design goals of the system planner.

No single approach to MOS/LSI design covers all needs. Striking the right balance among standard MOS products, custom MOS development and bipolar support functions, for example, demands meticulous evaluation of MOS products, design alternatives, and development costs and timing.

This guidebook will examine those planning factors as they relate to MOS/LSI in general and to OPTIMOS in particular. OPTIMOS, a Fairchild acronym for optimum MOS in terms of capability and application is a method of exercising all major MOS cost and design options. It encompasses all Fairchild resources in standard and custom MOS development and production.

1

# Contents

| Sections   |                                                    | Page |

|------------|----------------------------------------------------|------|

| 1          | Where MOS Makes Sense Today                        | 3    |

| II         | MOS Economics: An Overview                         | 4    |

| 111        | The Critical MOS Decisions                         | 8    |

| IV         | What OPTIMOS Has To Offer                          | 12   |

| V          | OPTIMOS Facilities In Action                       | 17   |

| Appendices |                                                    | Page |

| Α          | Standard Product Data Sheets and Application Notes | 33   |

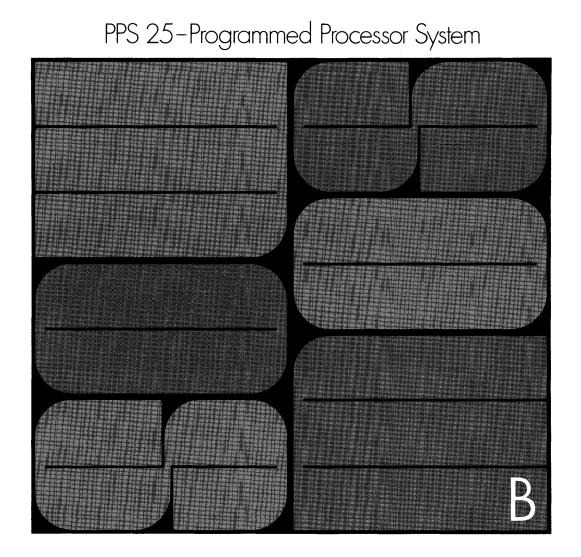

| В          | PPS 25 — Programmed Processor System               | 213  |

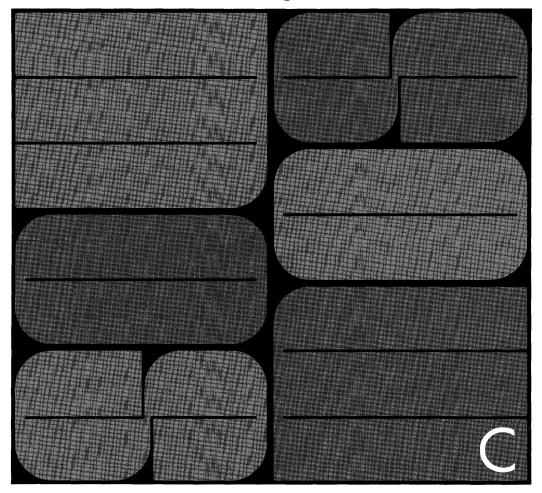

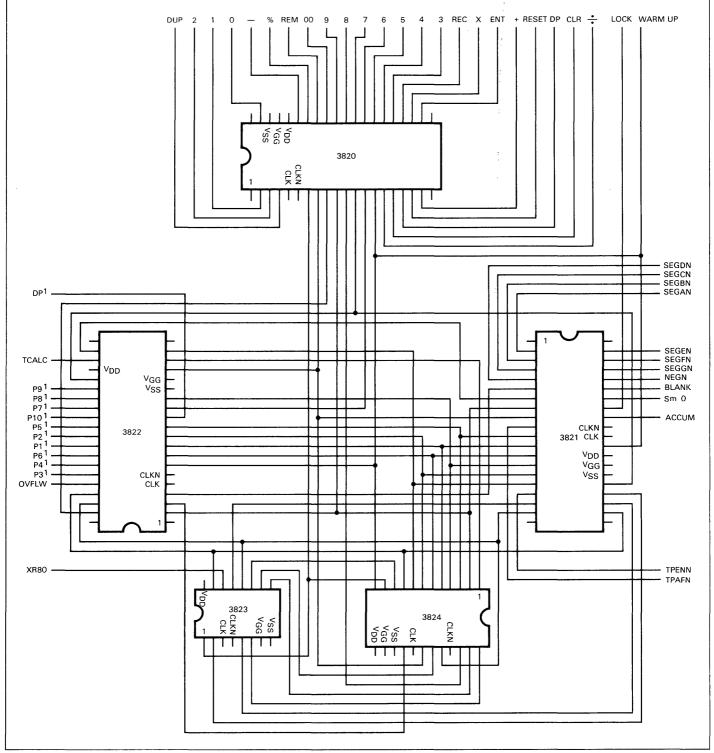

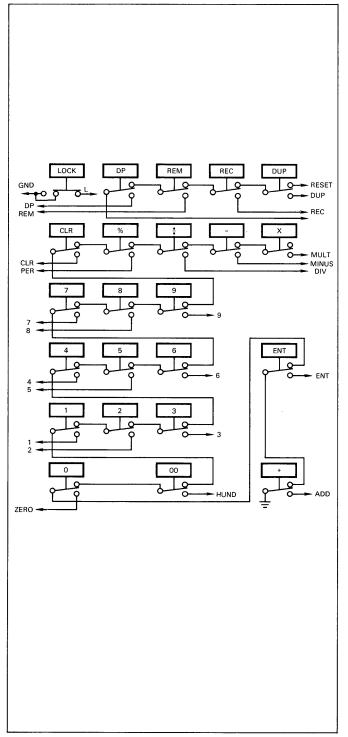

| С          | SPRINT Accounting Calculator Set                   | 221  |

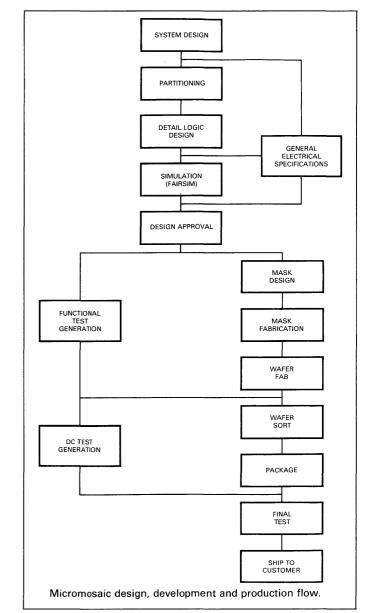

| D          | Micromosaic™ Logic Design                          | 235  |

| Е          | CAD — Computer-Aided Design                        | 281  |

| F          | Reliability, Quality Assurance and Testing         | 285  |

| G          | Silicon Gate Process                               | 291  |

| Н          | Ordering Information and Packaging                 | 297  |

The OPTIMOS process is graphically represented in the form of a flow chart at the back of this manual.

.

Fairchild Semiconductor, 464 Ellis Street, Mountain View, California 94040

## Where MOS Makes Sense Today

The equipment designer's task of choosing between MOS and bipolar circuits used to be relatively simple. MOS/LSI reigned supreme in low power applications while bipolar SSI/MSI (small-to-medium scale integration) was uncontested wherever high circuit speed was essential. As a result of advances in both MOS and bipolar processing, however, the performance attributes attainable through each have moved closer together. In fact, many systems being designed today can tolerate both MOS speeds and bipolar power requirements as well.

So it almost always makes sense to consider MOS/LSI totally or in part, where there is digital signal processing to be performed. Even where medium-to-high circuit speeds are required, the innovative implementation of MOS/LSI with bipolar SSI/MSI may provide a more economical solution than conventional bipolar designs. Now more than ever, the system planner must carefully analyze design alternatives before settling on any single semiconductor process or combination of processes.

#### **MOS/LSI Lowers Digital Signal Processing Costs**

In digital processing applications that do not require critically high circuit speeds or drive capability, MOS/LSI more than bipolar SSI/MSI can potentially lower the overall system development cost. Not only is the MOS transistor smaller than the bipolar transistor, but it is self-isolating as well. This combination of smaller transistor area and virtual elimination of isolation area is a major contributor to the cost-savings realizable through MOS because functional density per unit area on a given chip is far greater than that attainable in bipolar MSI/LSI. Moreover, MOS/LSI more readily lends itself to dynamic circuit techniques, and therefore requires fewer components per function.

MOS/LSI should thus be considered for any digital circuit design, unless the speed performance of bipolar logic is essential. Medium speed systems are sometimes produced at unnecessarily high costs with bipolar logic assemblies because the designer did not realize that in large scale arrays, silicon gate MOS/LSI can equal DTL speed.

The overall system design should be studied to determine which portions must work at bipolar speed and drive levels and which can tolerate MOS speed (up to 3 MHz for random logic and up to 8 MHz for structured logic clock rates such as shift registers). Computer peripheral interface logic and storage functions typically operate at or below MOS speed.

There is also the possibility of employing parallel processing to achieve high throughput with relatively low clock rates. This approach can be highly effective because of extremely low cost per gate of MOS/LSI.

#### The Buck Stops Here

If you are considering your first MOS/LSI system, be prepared to make some hard decisions. To get the best results from the technology may involve some pioneering and some risk.

The conservative approach is not always practical or safe. A small logic system of 300 to 500 gates can be converted to one large scale integrated circuit at a cost of about \$10 per circuit in large production quantities. Beyond that, it starts to get sticky because MOS/LSI makes its own rules about large systems and how they should be sliced.

A system partitioned along lines which have grown to be industry standards will no doubt be more economical than the same system assembled with custom packaged logic — assuming MOS is suitable for the system.

While a system that wholly or partially uses standard parts may provide economics over one designed with custom parts, there always exists the possibility that a competitive manufacturer using a totally custom approach may achieve a product of equal or superior performance at a reduced cost.

Furthermore, MOS technology is still in a state of flux. The rules are not fixed. They change from application to application and with each introduction of a new standard circuit, a new set of custom design cells, or an improvement in wafer fabrication processes.

## MOS Economics: An Overview

At one time, MOS circuits were employed in avionics and portable military equipment primarily to achieve small size and low power consumption as well as improved reliability through minimum use of failure-prone component interconnections. The early MOS/LSI circuits were expensive because of poor manufacturing yields.

Now lower manufacturing cost, due to improved yields, is the overriding factor in the phenomenal growth of MOS applications in commercial, industrial, automotive and consumer electronics equipment. User costs have dropped to considerably less than 1¢ per gate in many standard MOS products. In large production quantities, custom MOS circuits can approach standard MOS costs.

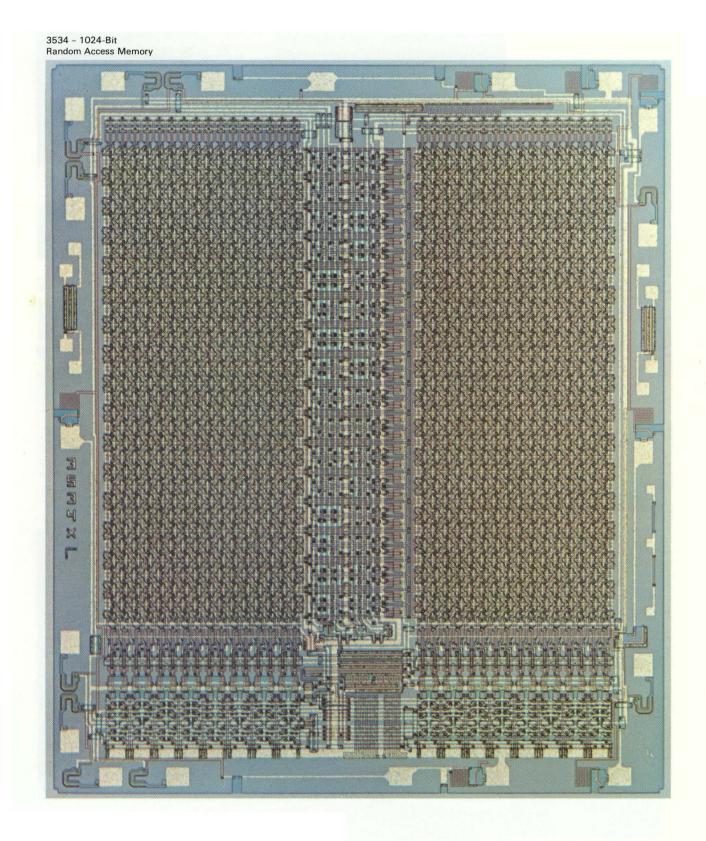

Before the prospective MOS user decides how to structure and partition his system — or which process and vendor to use — he should first understand MOS economics. The cost of using MOS typically ranges from purchasing standard products such as a 1024-bit random access memory (RAM) for under \$10 for 1000 pieces to \$100 for a custom design (including amortized design cost) for the same quantity. The user must decide where in this economic range he will derive the maximum benefit from MOS implementation.

#### **Production Volume Governs Custom Cost**

The cost of an MOS custom circuit development is governed primarily by the volume of circuits purchased. In other words, the larger the production run, the smaller the development cost per circuit. Accompanying this cost/volume relationship is the proverbial learning curve. As the production volume increases, the manufacturer becomes more familiar with the circuit. Accordingly, fewer processing errors and higher yields can be expected to further drive down the unit cost.

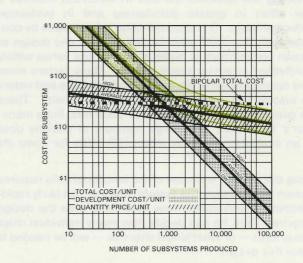

The potential economics of using custom MOS/LSI versus standard bipolar SSI/MSI can be readily demonstrated through a direct comparison. Consider, for example, a subsystem designed with 300 TTL gates. In assorted MSI and SSI functions, this represents about 30 dual in-line packages. While actual field figures show that the *indirect* cost per bipolar package averages about \$2.00, let's make a conservative comparsion and assume this cost to be only \$1.00. This indirect per package cost which covers component insertion, PC board, testing and documentation thus totals \$30 for the bipolar implemented system. To be even more conservative, let's ignore the unit cost of the bipolar devices and assume the total subsystem cost to be \$30.

Now if the same subsystem were designed with a single custom MOS circuit, the one-time development charge would be about \$20,000 and the unit cost would be about \$15 in quantities of 10,000. As shown in *Figure 1*, MOS implementation becomes a more economical approach at a production level that is greater than 2100 subsystems. At the 15,000 subsystem level, a two times advantage is held by MOS. Beneath 2100 subsystems, bipolar MSI/SSI is more economical.

The graph in *Figure 1* also depicts a cost spread on the MOS implementation representing higher and lower complexity levels than the 300 gate example. The one-time

development charges could range from \$10,000 to \$50,000. This will depend on the design effort required for logic circuit and layout implementation and test pattern generation. The unit cost could vary from \$10 to \$30 in production quantities of 10,000 depending on the size and complexity of the chip.

The higher cost for smaller quantities of custom MOS subsystems stems chiefly from the need of the MOS manufacturer to amortize custom development and manufacturing startup costs through either front-end charges to the customer or by a contractual commitment for a large volume of units. In the past, MOS manufacturers were frequently willing to underwrite much of the start-up cost as a means of winning customers. Besides, some of the start-up costs could not be distinguished from the MOS manufacturer's own investments necessary to initiate MOS development and processing.

Since these costs are now well established and the direct result of individual development projects, MOS manufacturers are generally reluctant to undertake a custom development order without a firm commitment regarding payment of costs or a production volume sufficient to amortize the costs. For these reasons, the system manufacturer is advised to make sure before making a decision to go custom that the right custom approach is started — indeed, that a custom approach is more economical for the volume of subsystems required.

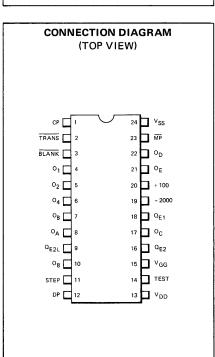

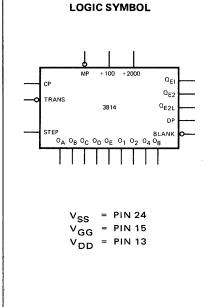

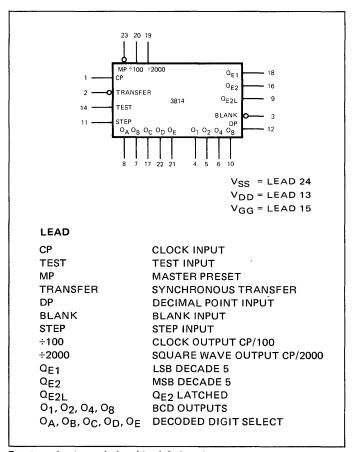

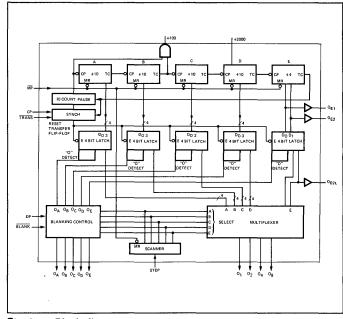

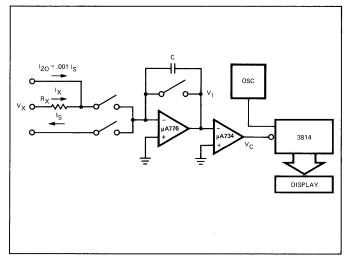

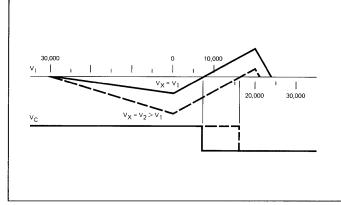

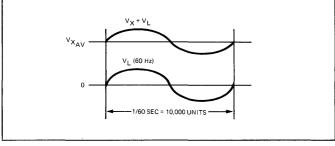

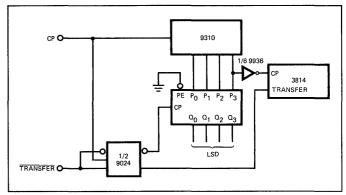

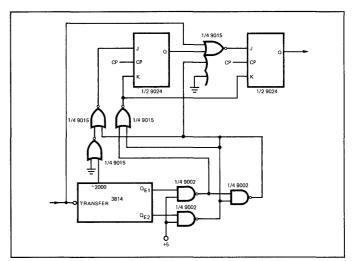

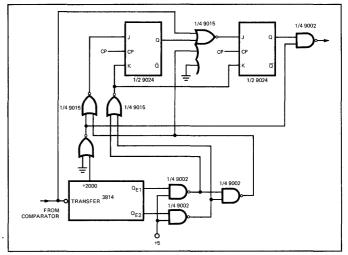

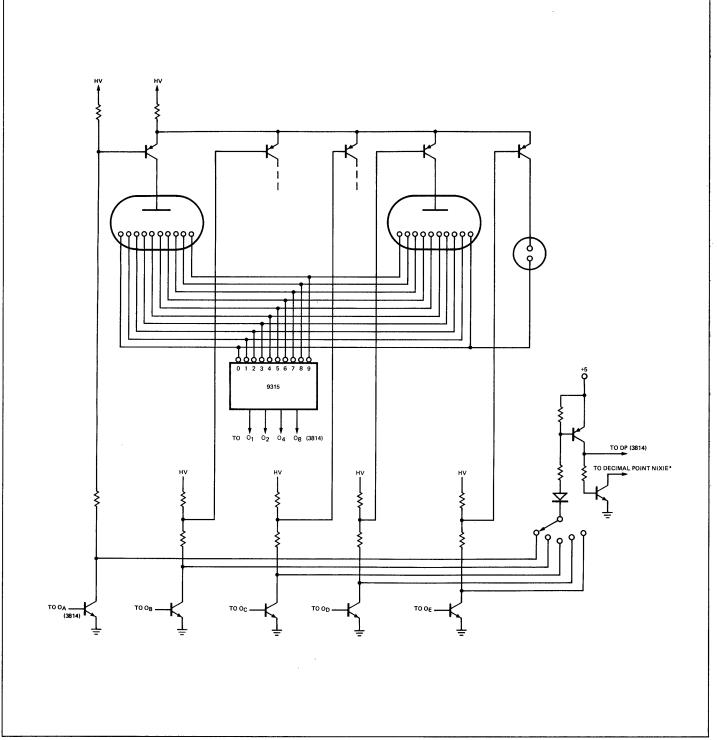

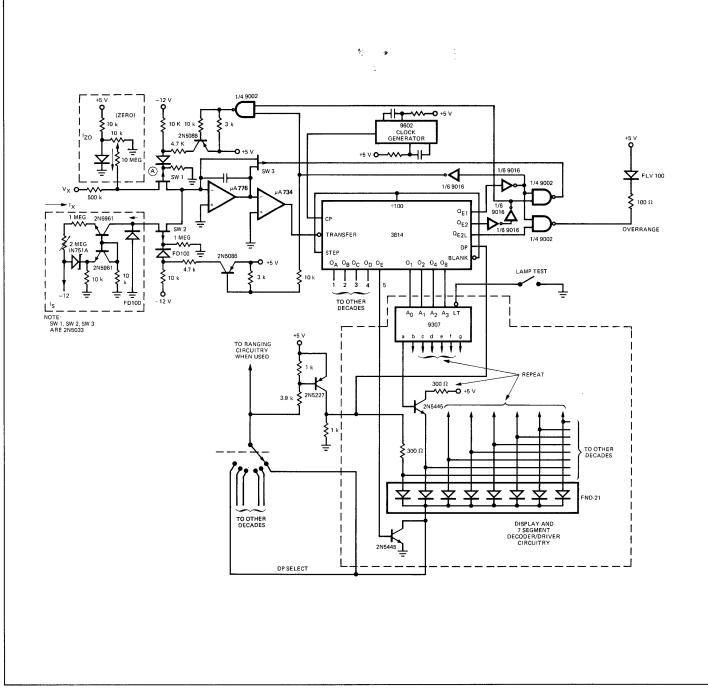

The COMPARATIVE COSTS OF A 300-GATE SUBSYSTEM are depicted for both custom MOS/LSI and standard bipolar SSI/ MSI approaches. Assuming the total cost of a bipolar implemented subsystem to be \$30, the custom MOS/LSI implementation which is assumed to have a one-time development charge of \$20,000 becomes more economical as the production volume exceeds 2100 subsystems. In an increasing number of cases, the subsystem functions can be performed with standard MOS/LSI circuits, thereby eliminating custom development cost. For example, Fairchild's Digital Voltmeter Logic (3814) is a standard MOS/LSI device that provides a complex measurement function — and yet costs less than the bipolar equivalent at *all production levels*.

Figure 1. Comparative Costs of a 300-Gate Subsystem

#### **Optimum Die Size Growing Larger**

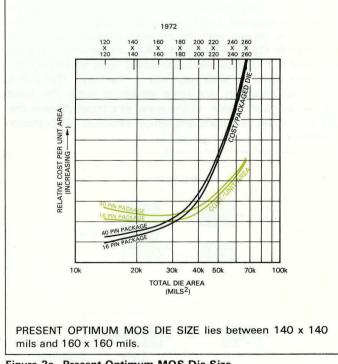

Determining the optimum die size in MOS/LSI requires a parallel effort in system partitioning and in evaluation of production costs. This determination is best made by consultation with the MOS manufacturer before any design or production commitment is made, since die size varies widely with individual customer requirements. Many factors enter into the determination of die size, such as the size and nature of the system, the process used, and circuit density. There are no general rules governing these trade offs, but a manufacturer's experience with large numbers of designs does allow an evaluation of wafer fabrication costs for given die sizes.

Knowing the number and sizes of the functional cells required for a given MOS design, the system designer can fairly rapidly determine approximately how much chip area the design will require. Thus, he can decide how many individual chips of various sizes — or what single chip size — will be needed to fabricate this design.

Consider now the equation for determining die cost:

#### Die Cost = ---

#### Wafer Fabrication Cost (Gross Dice/Wafer) (Probe Yield)

The gross dice/wafer represents the number of potentially good dice, and is dependent on wafer area and die size. The relationship of die size to the number of potentially good dice garnered from a 2-inch diameter wafer is shown below:

| Die Size<br>(Mils) | Gross Dice/<br>2" Wafer | Die Size<br>(Mils) | Gross Dice/<br>2" Wafer |

|--------------------|-------------------------|--------------------|-------------------------|

| 120 x 120          | 166                     | 200 x 200          | 47                      |

| 140 x 140          | 115                     | 220 x 220          | 36                      |

| 160 x 160          | 84                      | 240 x 240          | 28                      |

| 180 x 180          | 62                      |                    |                         |

The *probe yield* in the die cost equation is also related to die size as it is the product of two parameters:

- the percentage of semiconductor material that is processed within specifications and independent of die size (typically ranges from 60% to 80%); and

- the defect-limited functional yield that is governed by both the die size and the active area density on the die; this parameter represents the probability that a failure-causing defect will *not* occur on any given die.

Thus as die size increases, the probability that a failurecausing defect will occur on any given die also increases. Accordingly, the probe yield decreases, thereby causing the die cost to increase.

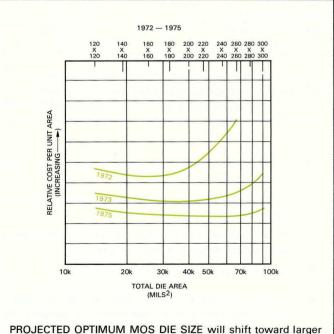

While the die cost equation is helpful in placing the range of die sizes in perspective, it only approximates the cost per function, which, in the final analysis, is the major determinant of optimum die size. *Figure 2a* graphically relates die size to cost per unit of functional area. This analysis concludes that the most functions per dollar would be derived from a die size between  $140 \times 140$  mils and  $160 \times 160$  mils. Of course the curves in *Figure 2a* will change with time; *Figure 2b* projects this change through 1975.

If a subsystem function is too large to fit on an optimum size chip, it may not necessarily be wise to partition the function to operate on two or more smaller chips. Such partitioning

Figure 2a. Present Optimum MOS Die Size

can sometimes complicate the interconnection and logic design or cause performance degradation. Moreover, if the subsystem is to be in production for several years, it is probably wise to choose a die size that is larger than the current optimum range. The optimum die size has been increasing year by year. By 1975, the optimum die size will likely be 240 x 240 mils. The increasing size of an optimum die coupled with increases in MOS circuit density may entirely eliminate the need to partition a subsystem, indeed an entire system, into two or more smaller dice. Accordingly, the MOS cost per function may drop by a factor of 7 by 1975.

PROJECTED OPTIMUM MOS DIE SIZE will shift toward larger areas, reaching 240 x 240 mils by 1975.

Figure 2b. Projected Optimum MOS Die Size

## The Critical MOS Decisions

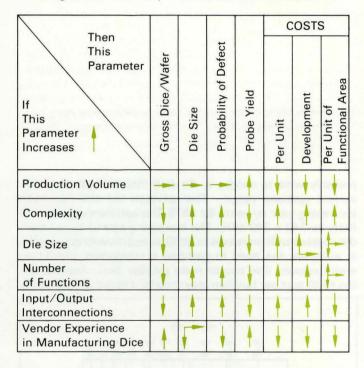

Before tackling the important judgements that must be made when pursuing MOS/LSI implementation, consider the following tabular summary of MOS economic factors.

Assuming that the evaluation of the tabular parameters, as they relate to a proposed design of a digital signal processing system, has been done and that it is concluded that MOS/LSI is economically justified, some very critical decision must be made.

- Is the system design optimally structured for MOS implementation?

- What is the proper balance between standard and custom usage?

- What kind of partitioning will avoid performance degradation while minimizing cost?

- Which MOS process is best to use?

- Which semiconductor manufacturer has the appropriate experience and capabilities to support the design and cost objectives?

Let us now consider each of these key decisions in greater detail.

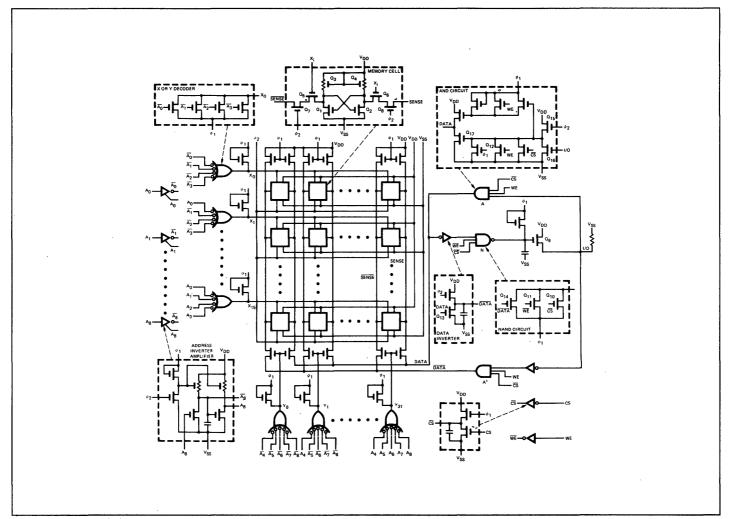

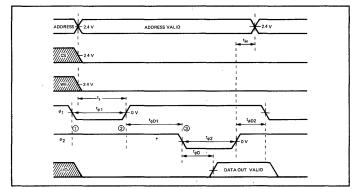

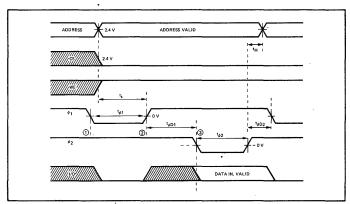

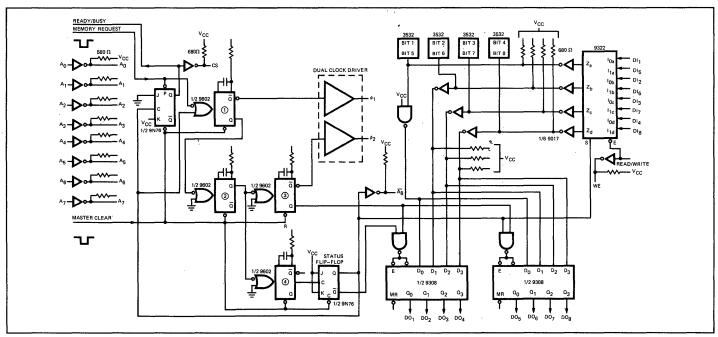

#### Structuring A System Design For MOS/LSI

To fully exploit the benefits of MOS/LSI, a system should be structured for what MOS/LSI does best, namely, *repetitive logic with few input/output lines.*

Of course, the most common repetitive logic is the memory function. More than any other approach, MOS/LSI can perform the memory function in smaller packages at lower cost. Unlike its magnetic counterpart, for example, MOS memory can be inexpensively distributed throughout the system.

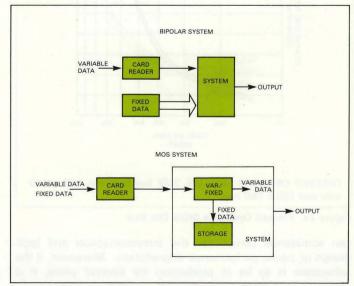

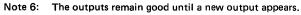

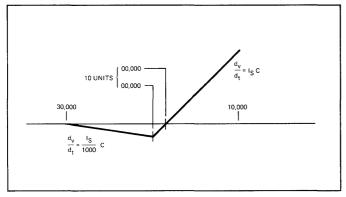

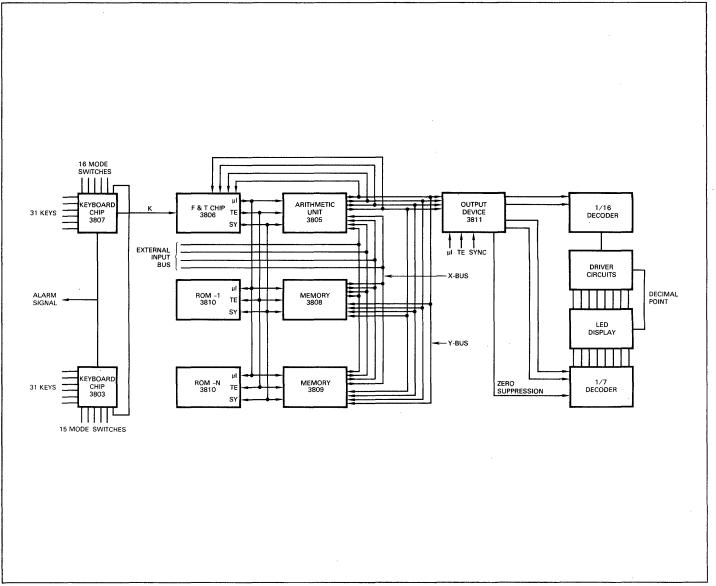

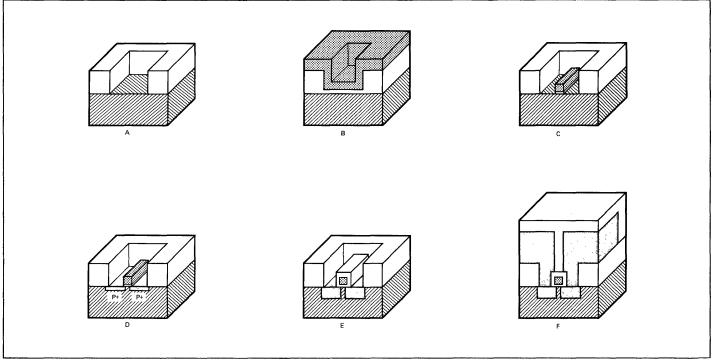

When using MOS/LSI it is possible to reduce system development cost by replacing input/output lines with distributed memory. To illustrate this cost-saving approach, consider a proposed design for a system that would first read variable data from punched cards, then process these data with other external fixed data - and then finally generate output on command. If bipolar circuits were used to implement the system, the external, fixed data would likely be stored in a diode matrix, replete with the necessary input/output lines. As shown in Figure 3 below, an MOS implemented system can avoid the expense of input/output lines by storing the fixed data either in shift registers or memory. Using this economical approach, it's quite simple to enter the fixed data via the card reader. In the event of a power failure, the fixed data could be guickly and simply reloaded when power is restored.

Figure 3. Structural Change from Bipolar to MOS

Another way to reduce the number of input/output lines is through MOS matrix techniques. In an MOS keyboard encoder circuit, for example, only 22 leads are required to determine which of 120 keys are depressed. This is accomplished with a 12 x 10 MOS scanning matrix which can also be used in any system employing switches for external data input.

Multiplexing with MOS/LSI presents yet another method for reducing input/output connections. MOS circuits facilitate the economical use of logic for interleaving both input and output signals on a single input/output line.

The ultimate structure of any proposed system design will greatly depend on the task to be performed. Wherever possible, however, an effort should be made to restructure the proposed design to make maximum use of repetitive logic while reducing the number of input/output lines. This effort will be well worth the cost savings realized.

#### The Standard Versus Custom Question

Very few system designs should be implemented with all custom or all standard circuits. The optimum approach generally combines both custom and standard circuit functions. In choosing the proper balance between custom and standard usage, the key factors to remember are:

- standard circuits are usually less expensive as their development cost has been amortized through a large production volume for many customers;

- an increasing number of standard, complex MOS circuits are being produced in large enough quantities to make them cost competitive with equivalent implementations in standard bipolar circuits;

- a proprietary total custom approach can provide a significant edge in the marketplace, but not without risks and a substantially large initial investment;

- standard circuits are immediately available while custom circuits have a long lead time, typically six months from the time the system partitioning is finalized; and

- custom circuits should be avoided if it appears that standard circuits will soon emerge to perform the required function.

Leading the list of versatile standard circuits are the memory elements — ROMs, RAMs and Registers. Through micropro-

graming these circuits can be combined with data processing logic to form a dedicated processor for applications in calculators, machine tool control, process control and instrumentation. An increasing number of standard circuits are emerging to perform very complex specialized functions; these include keyboard encoders, calculator and data processing arrays, TV sync generators, DVM logic and data rate buffers. Properly exploited, many of these new generalized standards can replace expensive specialized custom designs. They are now economical to use because the high production volume has not only amortized their development cost, but improved their yields as well. The system planner should always strive to use standard circuits when they will not compromise his competitive market posture.

As pointed out earlier in the MOS Economics section, the high cost of developing proprietary custom circuits stems from low production volume and high engineering content. While the low production volume inherently slows the improvement in yield, the high engineering content represents a substantial commitment of a MOS vendor's resources. This commitment must be matched by the customer in the form of a high initial development cost. In the maturing semiconductor industry, the MOS vendor is having to become increasingly efficient in maximizing the profitable return from his resources. Accordingly, the MOS vendor will engage in custom development contracts only when the customer is prepared to share the potential risks.

#### **Optimum Partitioning: A Moving Target**

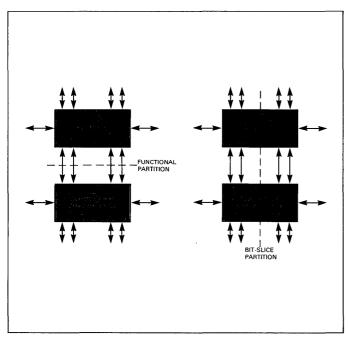

Partitioning, the task of optimally dividing a system function into sub-functions, must take into account several factors including die size, pin-to-gate ratio and operating speed. Optimum partitioning will generally result through the maximum use of standard building blocks with common designs. On a much finer scale, the goal of partitioning is basically the same as that of structuring the system design, namely low cost. In other words, the goal of partitioning is to divide the system function into sub-functions (i.e., die sizes) that are small enough to provide good yields — yet large enough to minimize the cost per integrated function. Technology is advancing so rapidly that the achievement of this objective compares to hitting a moving target.

The most favorable system partitioning will often require using die sizes that are larger than what is currently considered optimum. From the time partitioning is finalized to the time production commences, it is very likely that the optimum die size will grow larger. Moreover, a larger nonoptimum die size, in spite of its lower yield is often less costly than using two smaller optimum sized dice.

The economic advantages of minimizing the number of input/ output lines has already been discussed with regard to structuring the system design. These same advantages should be exploited when performing the partitioning task. In addition to those techniques previously discussed, the designer should consider duplicating local functions (e.g., decode, count, etc.) on each chip and using serial data transfer between chips. While serializing data flow compromises speed, other partitioning techniques can be exploited to mitigate this impact. These include minimizing the number of chips in a critical speed path to reduce speed delays in buffering interconnections as well as using on chip parallelism and bipolar MSI/ SSI for those portions requiring high speed performance. Moreover, higher power, higher speed MOS circuit elements could be used in critical paths.

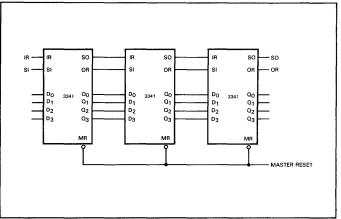

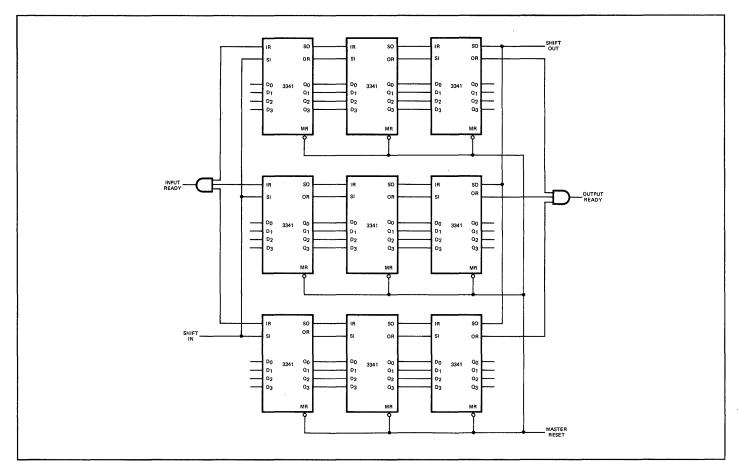

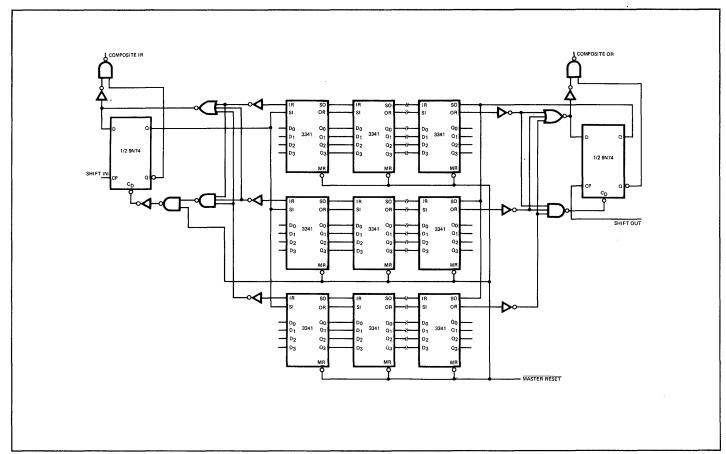

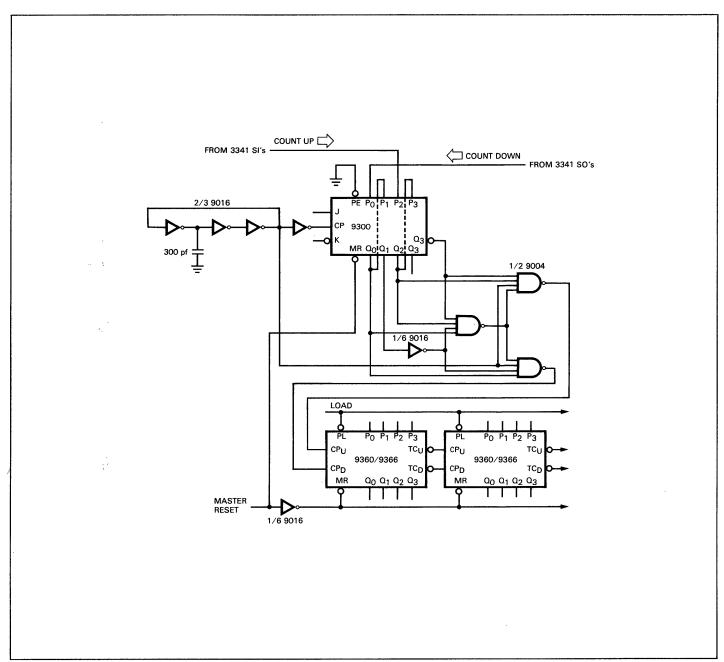

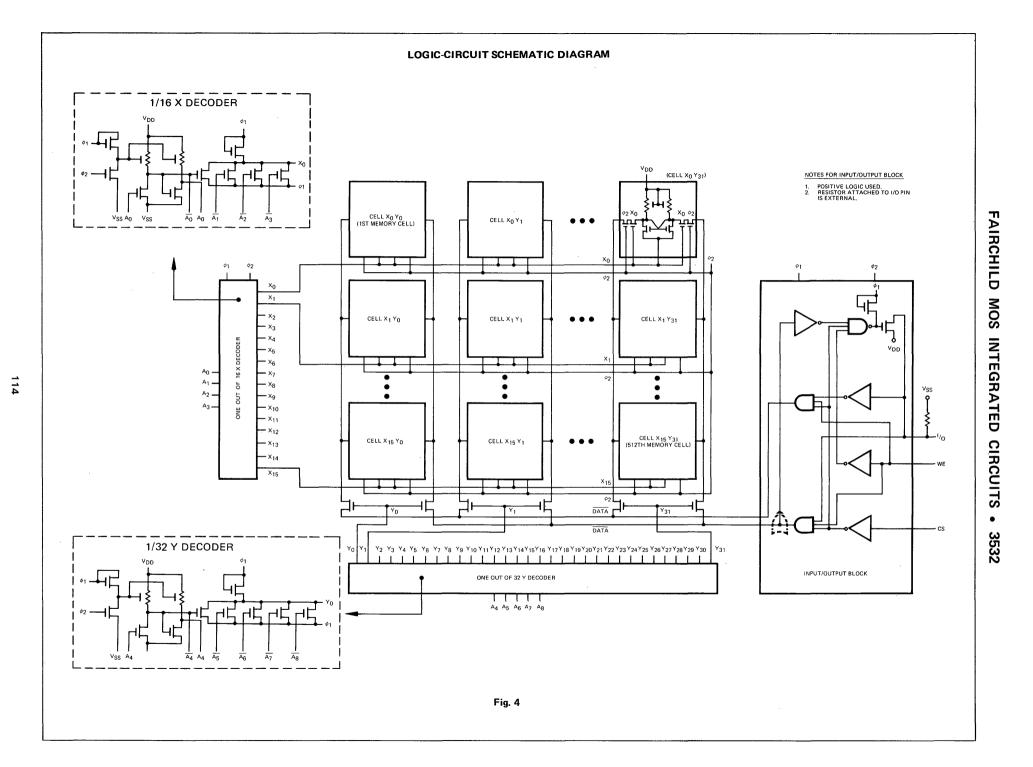

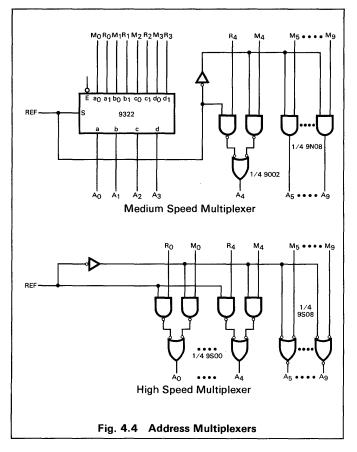

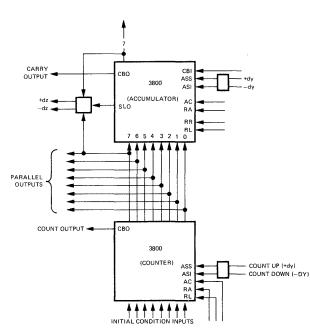

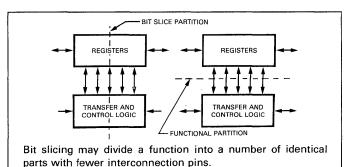

An effective partitioning technique for reducing both engineering and inventory costs is bit slicing where a system is divided into parallel paths. As shown in *Figure 4* below, this technique does not follow a functional division—but rather a division of parallel paths. The bit slice partition reduces the number of different designs and increases the production (hence yield) of a single design.

At first blush, the partitioning task appears to be rather complicated. However, the designer should be comforted by the fact that even a less-than-perfect MOS partitioning job will almost always result in a system cost that is lower than an equivalent bipolar SSI/MSI design. This assumes, of course, that the required production volume justifies the custom MOS approach in the first place.

#### **Proven Processes Better Your Odds**

As the prospective MOS user faces an increasingly wider choice of MOS processes, he must take greater care in evaluating the relation of price/performance factors to his design objective. Yesterday's P-channel metal gate MOS/LSI has been virtually eclipsed by P-channel silicon gate MOS/LSI which now boasts a far superior speed power product. However, high-threshold metal gate devices still remain uncontested where high noise immunity is a vital requirement.

Complementary MOS/LSI has emerged as a good choice for applications requiring low power—while N-channel silicon gate MOS/LSI brings the promise of high speed. Although new processes with cost and performance advantages will continually emerge, the prudent designer will stay with a proven process unless his design lead time is long enough to allow a new process to reach production maturity.

#### **Evaluating An MOS Vendor's Capabilities**

To properly evaluate an MOS vendor's capabilities, it is first necessary to fully understand the services that are required. The fold-out flow chart on the back page of this book depicts the services required from conceptual design to completed system. It is recommended that this flow chart be folded out and referred to while reading the remainder of this section.

The required services are:

LOGIC DESIGN — After the system has been partitioned as to what each chip will do in terms of its black box terminal characteristics, it is necessary to select the specific logic functions to be used on the chip itself. These logic functions can either be custom designed for the specific task or selected from a library of pre-designed function cells or a combination of both. Pre-designed cells give three advantages; reduced design time and cost and proven performance.

Figure 4. Bit Slice and Functional Partitioning

- LOGIC SIMULATION To ensure that the logic design performs the desired function, it is necessary to either breadboard the system or use some form of computer logic simulation. The advantage of computer logic simulation is time and cost. Breadboarding in some cases may be an attractive adjunct (but not a replacement) to simulation.

- PERFORMANCE SIMULATION Once you have a logic design and know that it will perform your function, you should do an analysis of speed performance, determining if this implementation is fast enough on all critical paths. As in the previous step, this can be achieved manually or with a computer program. The advantages of a computer speed simulation are time and cost.

- CHIP LAYOUT (PLACEMENT AND ROUTING) The custom designed logic functions using predesigned cells must be placed in a location related to their position on the final chip and their interconnections must be routed. This again can be accomplished manually or with a computer program. A combination of both seems to be best as a manual approach takes too long and an all-computer method is not flexible enough. A man interacting with the computer offers an optimum in speed and flexibility.

- MASK MAKING Each step in the list of services discussed so far permits the customer to perform the task himself if he so desires. However, very few equipment manufacturers have the facilities required to make masks. Here the artwork for chip layout is converted to 1:1 photographic plates that will be used in the actual production of MOS devices.

- TEST GENERATION The importance of the MOS vendor's capability in test generation cannot be overemphasized. If all input combinations and sequences were tested, a single part could take a century to test. Conversely, a part must be tested thoroughly enough to guarantee its performance. Available computer programs can generate test patterns that select those key tests which most fully check a device within a practical time frame. Often

the investment in engineering and computer time required for test pattern generation equals the chip layout investment.

- WAFER FABRICATION The photomasks are brought together with all other materials to produce a subsystem on a small square or rectangular chip of silicon.

- TESTING Testing is normally accomplished at both the wafer and packaged unit levels. The good units are selected from the entire population; testing is both parametric and functional. An MOS vendor's capital investment in test equipment should be on a par with that of wafer fabrication.

- ASSEMBLY The silicon chip is then assembled into a package to provide a form factor for incorporation into the system.

The selection of an MOS vendor should be based on how comprehensively and cost-effectively the above services can be provided. While some *low bids* turn out satisfactorily, many do not as they result in deliveries so late that any savings on parts cost is negated.

Underlying the effective MOS program is a close customer/ vendor relationship where the customer requires a reasonably high production volume — and the vendor provides a *proven, total capability.* The most successful MOS programs are based on a business arrangement which mutually commits both the customer and the vendor to share the risks as well as the rewards.

# What OPTIMOS Has To Offer

A technology as diverse as MOS/LSI is optimally used only when its diversity is properly exploited. The Fairchild program for the efficient and cost-effective exploitation of MOS/ LSI has been named OPTIMOS, an acronym for optimum MOS in terms of capability and application. OPTIMOS lives up to its name by offering prospective MOS users not only two proven MOS processes — silicon gate and metal gate, but also the flexibility to blend custom and/or standard MOS designs with bipolar SSI/MSI. Moreover, reliable packaging is tailored for unique applications.

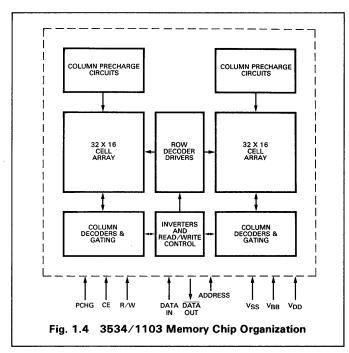

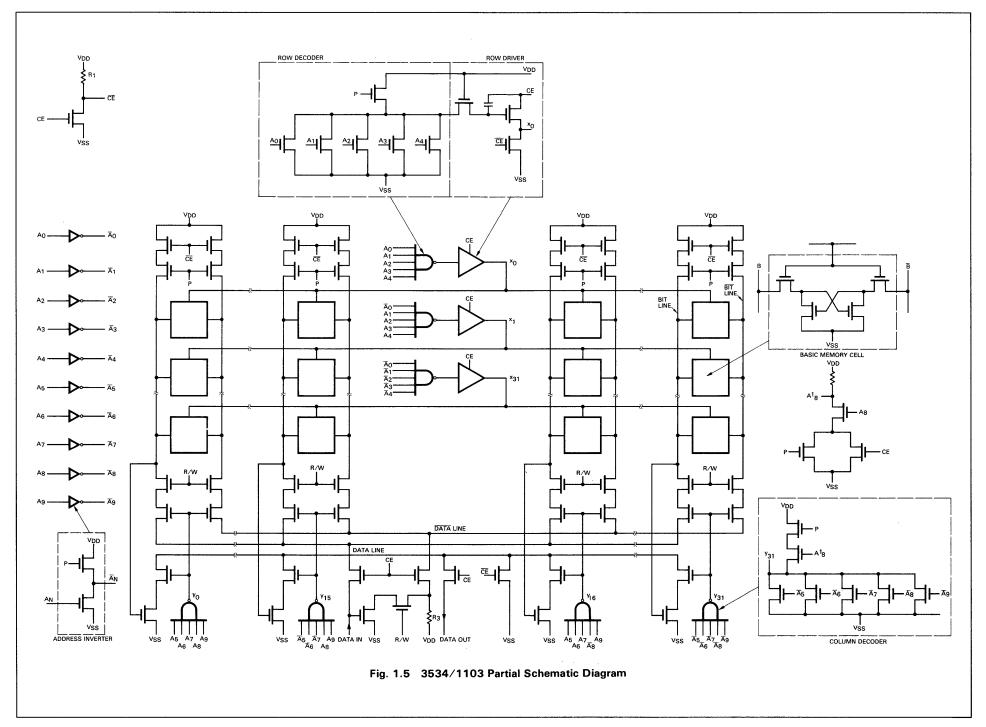

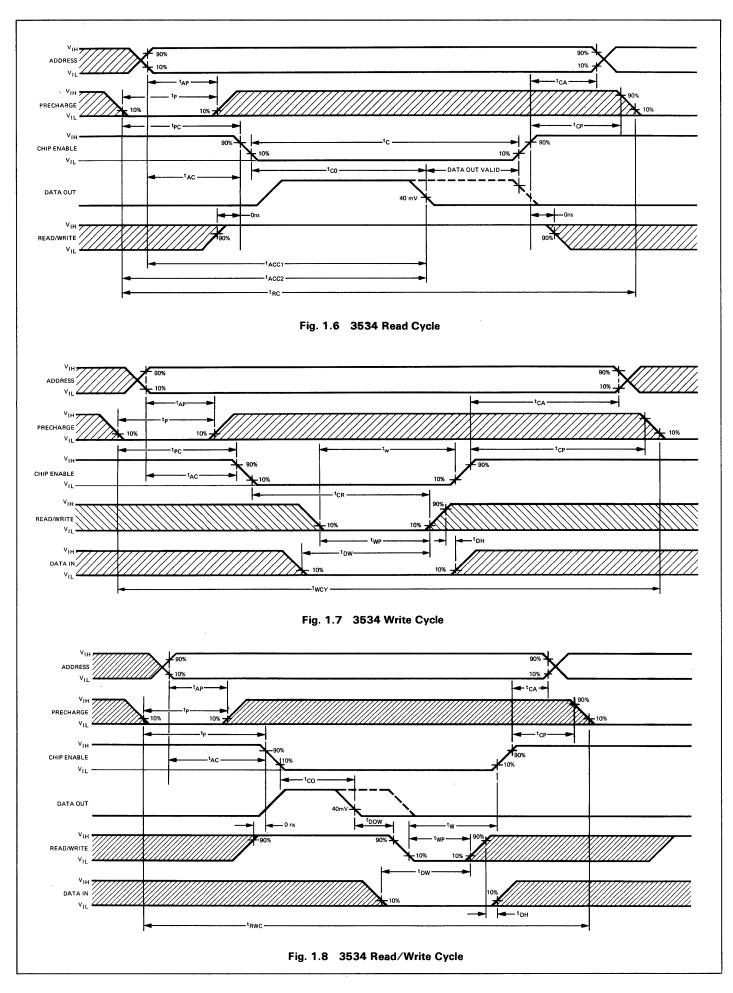

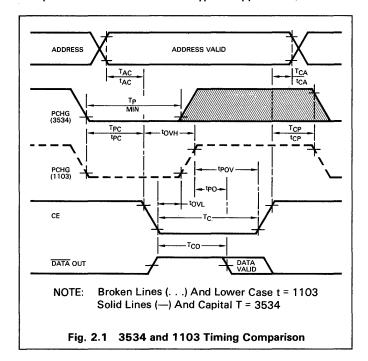

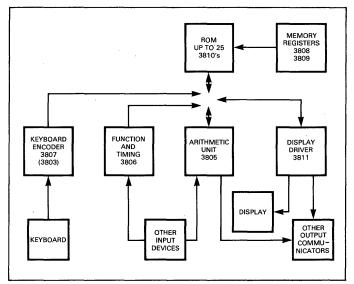

The wide and expanding selection of standard OPTIMOS circuits offers a broad range of applications. These vary from industry standards like the 3534/1103 1K RAM and the 3514 4K ROM to new areas like the 3814 Digital Voltmeter Logic and the 3261 TV Sync Generator. This manual also includes a full complement of devices which constitute a Programmable Processor System (PPS 25). They are capable of performing in scientific calculators, cash register terminals, process controls, medical instrumentation and virtually all areas that require processor control.

In performing custom design, OPTIMOS derives its efficiency from libraries of predesigned cells for each process (Micromosaic<sup>™</sup> Libraries) — and highly developed computer-aided design (CAD) software for design simulation (FAIRSIM) and corresponding test generation (FAIRGEN). The maturity of the OPTIMOS program has been well established, as even first-time MOS designers have been able to rapidly and inexpensively achieve their design objective through custom MOS/LSI.

OPTIMOS allows a completely flexible customer/vendor relationship. The customer is invited to do as much of the logic design and implementation using our standard cells as he chooses, with the commensurate benefits of higher value added and reduced vendor costs. The preliminary design can be performed with or without a computor, on or off the Fairchild premises. Fairchild has even offered to make its software available to customers who have large requirements for custom circuits and a desire to do their own logic and test sequence design.

The fold-out flow chart at the back of the book shows the major design and production steps that are involved in the OPTIMOS program. Within the past three years, Fairchild has generated 40 standard product designs and 200 custom designs. Throughput of the OPTIMOS program now averages eight to ten new designs each month.

#### **OPTIMOS: A Brief History**

The OPTIMOS methods used today stem from R & D conducted at Fairchild during the 1960's. Then, as now, the emphasis was on reducing costs, design time, and testing difficulties associated with large scale integration.

As an alternative to the "master slice" techniques popular in the 1960's, Fairchild pursued extremely microminiaturized

cellular designs as a means of retaining design flexibility while improving circuit yields. Most MOS manufacturers use this approach today. With process improvements, the technique has become very efficient.

Computer-aided design and testing systems were developed as a parallel effort. These systems have been improved through several years of increasing use and now eliminate most of the laborious, error-prone manual design and testing once required.

#### **Balancing Standard and Custom**

Only the customer can define his system and determine the correct mix of standard and custom devices. Our applications engineering staff is available to systems planners, however, for consultation and recommendations on all MOS-associated design problems. The staff should be consulted as early as possible in the planning cycle since early decisions, such as system structuring, involve parallel decisions in product and MOS process selection. Cost quotes for MOS/LSI and other system semiconductor component requirements can also be made available at this time.

In general, we follow the standard/custom product tradeoff recommendations discussed in Section III. A broad and expanding line of standard MOS/LSI is available from Fairchild as alternatives to custom design. These vary from RAMs, ROMs and registers through Digital Voltmeters, TV Sync Generators and Buffer Memories to the PPS 25 Processor Set.

The PPS 25 is a set of MOS/LSI computer building blocks and is described in Appendix B. This system of devices represents a major breakthrough in the application of MOS/LSI to minicomputers and processors. Equipment engineers have long recognized the flexibility of equipment design afforded them if a minicomputer could be employed at the heart of the system. Such a design permits microprogramming of the system function and is ready tailored to fit a specified equipment need.

In system designs where a built-in minicomputer would be desirable, but cost and size are limiting factors, the Fairchild PPS 25 Processor Set offers an order of magnitude reduction in cost and several orders of magnitude reduction in size, provided that the system design can accomodate MOS performance and speeds. Virtually all small control and calculating systems can be economically designed from this set of components.

The SPRINT Accounting Calculator Set, described in Appendix C, is a low cost memory calculator for accounting purposes. Unlike the low cost algebraic calculator sets presently on the market, the SPRINT can perform a grand total operation on the extra memory. Many business problems such as invoicing, chain discounts and payroll problems can be solved without a copy and re-enter step. Custom designs that have standard product potential offer mutual advantages to the customer and the vendor. Often, it is possible to give the customer both the economy of standard circuits and the competitive lead time of custom circuits. There remain, however, many applications for which there are no standard components. In these, a custom design is definately needed. At Fairchild, considerable investment has been made in the methods and software programs required for successful custom programs. Whether the outcome of such a program is a proprietary product or whether it eventually becomes a standard product is a decision that must be made by the customer. The basis for this decision is the potential economical advantages to all in allowing the design to become standard. The custom development charge and possibly the volume quantity cost would be lower if the product had potential as a standard to the vendor.

#### **Optimum Partitioning: A Matter of Experience**

Partitioning an MOS design is not fundamentally different from partitioning a large system assembly into modules. The designer is chiefly concerned with organization of the functions so that each unit is as complete as possible to optimize both performance and gate-to-pin ratio within the most economical number and size of chips.

If the system manufacturer is hesitant about his engineering staff's ability to partition an MOS design, he can consider interfacing with Fairchild's design group closer to the front end of the design process. (See fold-out chart in the back of this manual) The experience gained through working with Fairchild designers may allow the interface to be chosen farther down the line on the next project.

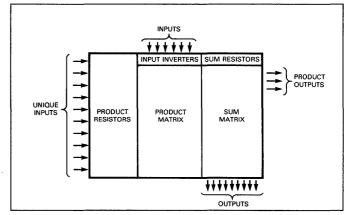

#### Micromosaic: A Better Way

Micromosaic custom design is covered in detail in Appendix D, but a few points pertinent to engineering management should be stressed here.

- The software required for Micromosaic design is comprehensive and readily understandable to any logic designer.

- Little knowledge of MOS is required.

- No computer programming knowledge is required.

- Depending upon the customer's in-house expertise, he can select the point at which the design responsibility is transferred to Fairchild. See the design interface points in the flow chart at the back of the book.

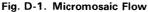

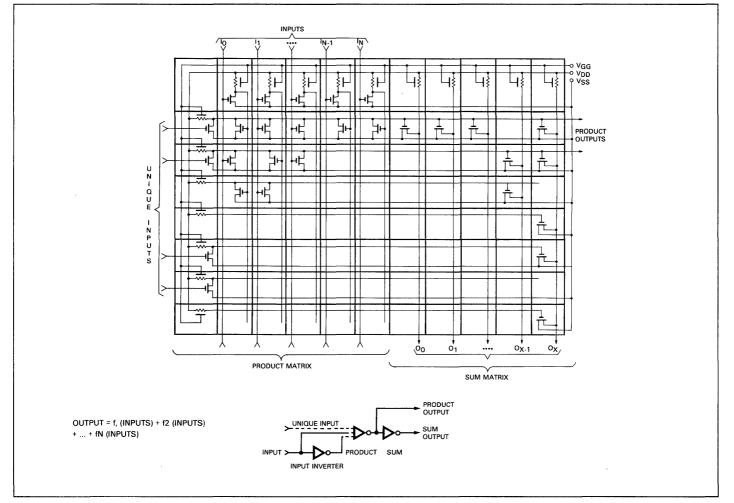

At the core of the Micromosaic System is the cell library and the powerful CAD software related to it. While the Micromosaic concept is not new, it has been greatly expanded under the OPTIMOS program. The cells, which are predesigned logic functions, are available for both silicon gate and metal gate designs. These predesigned cells are thoroughly characterized and are represented by familiar bipolar positive logic symbols. As such, they enable the designer with very little knowledge of MOS technology to easily convert his design into MOS/LSI.

Assume a conventional logic diagram has been prepared (or a TTL breadboard). The designer selects the appropriate cells from the Micromosaic set, decides which cell connections are required and calculates logic path delays using the constants in the design appendix. The cell selections and connections are then listed in a simple code. If any delay problems are anticipated, delays are adjusted by substituting low speed or high speed cells for standard speed cells. Handwork on the design computer, calls out the cell descriptions from a cell software library and the computer models the network. Then, the computer simulates circuit operation.

The cell library, which is fully specified in Appendix D, comprises all functions available in bipolar logic. These include gates and flip-flops as well as numerous other functions which can be combined to form long counter chains, sequential access memories, output buffers, clock generators and the like. In addition to these standard cells which perform specific functions, the Micromosaic library also contains composable cells which permit the designer to simulate a host of unique logic operations through a look-up table approach. In other words, the designer can specify input conditions to arrive at desired sets of output conditions. One version of a composable cell, for example, is similar to a readonly memory that is programmed to perform a unique logic operation. Thus composable cells not only provide an abundance of gates in a relatively small chip area - but they also simplify the design task by enabling the designer to work directly from truth tables.

#### CAD Weaves Cells Into Subsystem Arrays

Each of the Micromosaic cells (at this writing there are over 200 ranging in complexity from simple inverters to composable cells including both dynamic and static logic) is completely characterized in CAD software. This characterization includes a precise description of each cell's logic function, delay equations and associated photomask layout. When a cell is chosen for a design, its "vital statistics" can therefore be easily accessed and manipulated via the design computer.

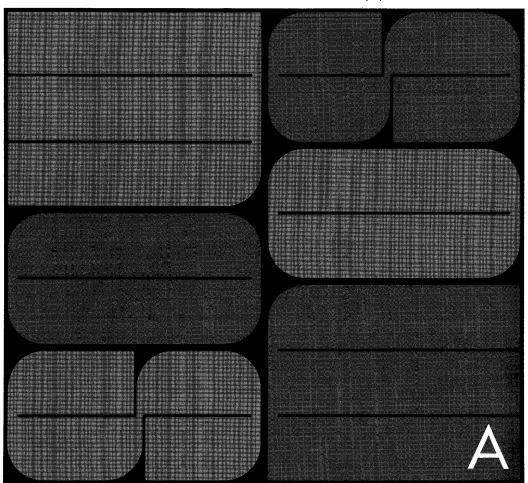

These cells have a fixed height and variable width depending on logic complexity. During layout, the cells are arranged on the chip area in rows. Then they are systematically interconnected by thin-film wiring patterns routed between the cell rows. They are powered through supply and ground lines running over the rows. With the aid of the computer, the designer may rearrange the cells until the most suitable interconnection pattern is achieved.

The height of the wiring alleys between cell rows is also flexible to accomodate different wiring densities. Output buffers, input level translators (if required) and bonding pads are then added to interface the chip with the package and the external system or another OPTIMOS circuit.

To further simplify the design process, the elements within the cells have standard geometries so that all logic cells have equivalent dc input/output transfer characteristics. Thus, signal propagation speeds within the array of cells can be automatically calculated from the nodal capacitances. These capacitances are computed using the data base of the completed computer-aided layout.

#### Interactive CAD Permits Fine Tuning

Fairchild has 12 computer-aided design programs that fit together in an integrated package to carry both standard and custom designs from concept to finished product. See flow chart at back of book.

MMAP — Transient and dc MOS circuit analysis

FAIRSIM — Logic simulation and verification

FAIRGEN — Functional test generation and verification

SENTRY — Merges parameter tests with output of FAIRSIM for Fairchild testers.

FAST — Calculates path speeds using cell and predicted interconnect capacitances

SPEED — Calculates path speeds using cell and actual interconnect capacitances

LAYOUT - Cell placement, wiring and verification

RETGEN — Converts LAYOUT output for use in reticle generator for mask making

NDRAW — Plots LAYOUT output plus general purpose plotting

V-MACRO — Hand digitizer

ROMCODE — Converts customer ROM pattern to RETGEN

PROSIM — Simulates ROM codes for PPS 25 (Programmed Processor System).

The major programs that the customer becomes directly involved with are FAIRSIM and FAIRGEN.

These CAD programs constitute a complete design system, and not just a collection of independent programs aiding in different aspects of the design process. All major components of the CAD system interface directly with one another via computer-generated data sets, thus eliminating many time consuming and error prone manual data preparation steps.

The FAIRSIM logic simulation program is used to check both silicon gate and metal gate MOS designs. The logic is exercised, within the computer, after the network assembly has been checked against the Netlist requirements. Use of the

program is not difficult to learn, so the customer may run his own simulations and performance verifications if he prefers. And as discussed earlier, Fairchild's CAD programs are interactive; the layouts implemented through FAIRSIM can therefore be easily optimized by designer inputs.

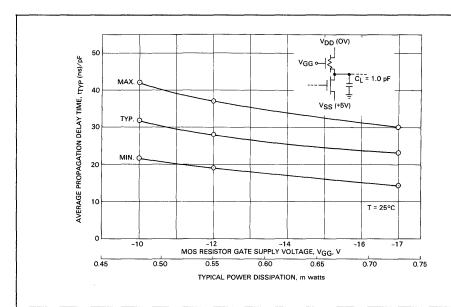

FAIRSIM includes an array speed analysis program which predicts actual propagation delays within the cell array. It is used to examine critical logic paths so that possible race conditions can be detected and avoided. Moreover, these parameters can be evaluated for the parameter spreads produced by process variations and tolerances.

In effect, the simulation phase of CAD is a first order approximation of a thorough test of a prototype array. The computer output documents become a basic part of the array performance specifications. They give the customer and Fairchild a precise, detailed analysis of the array's functional behavior. Very few arrays checked with this program have required more than minor modification when the actual prototypes were made and tested. Just recently, a series of 24 arrays were put into production without one correction required. This is not to suggest that CAD is infallible, but it has certainly proved much more effective than conventional debugging.

Proper use of the FAIRSIM program eliminates any necessity to breadboard in most cases. It will almost invariably give a more accurate picture of array performance. Furthermore, when partitioning and laying out the arrays, the designer may find it convenient to implement logic functions with different cell groupings than a 1:1 translation of a bipolar logic breadboard. Some examples of useful cell groupings are given in the applications section of the cell library (Appendix D).

FAIRGEN is a CAD program for automatically generating functional tests. It also performs verification on proposed sequences to ensure that all possible faults are detectable. Another feature of FAIRGEN is establishing initial conditions in sequential circuits. If this task requires too much testing or the circuit cannot be initialized, FAIRGEN interacts with FAIRSIM to provide extra inputs for initializing.

As a circuit is being designed, it may be necessary to modify its design to make it testable. In general, the most important requirement is that the array must be capable of initialization to a known state after a predetermined input sequence is applied. Test points are sometimes added to reduce the test length, or to force initialization, or both. The undefined output state of FAIRSIM is very useful in identifying a logic path that cannot be initialized. More detailed information on testing is available in Fairchild's FAIRSIM and FAIRGEN program manuals. Most of the programs allow a large degree of designer interaction and interaction between each other. Thus, the designers have complete flexibility to use the computer as a tool to try out new design arrangements and then verify if they work.

#### **Artwork Generation**

Fairchild maintains an automated photomask generation facility. Unless hand optimization is desirable, computer controlled plotters or a reticle generator prepare the wafer fabrication patterns from the output of the LAYOUT program. The reticle generator prepares 10X plates directly.

The mask generation program closes the computer-aided design loop by fetching the functional pattern descriptions from the cell software library. All the computer generated data that might be needed to replicate or modify the design at some future time is stored away in a universal format.

#### **Testing Sets the Pace**

Testing difficulty skyrockets between medium scale integration (MSI) and LSI. Adequate test facilities have to be assured in advance because the typical lead time of an MOS/ LSI design is shorter than the lead time for developing a computer controlled test capability.

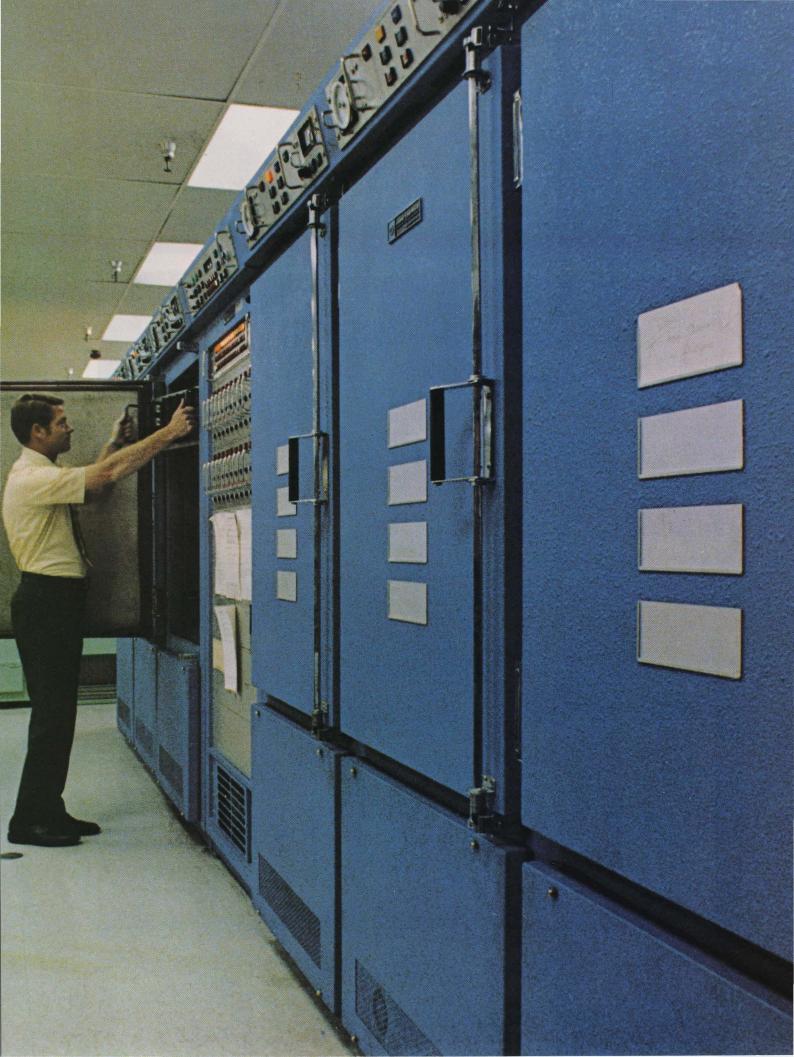

The testing — both at the wafer probe and packaged device stages — is done with Sentry 400 and Super Sentry 600 test systems. Each Sentry 400 is capable of testing four arrays simultaneously at rates up to 286,000 tests per second. The Sentry 600 tests two arrays simultaneously at rates up to 5,000,000 tests per second. FAIRGEN effectively amplifies these rates by minimizing the number of test patterns used in functional testing. Other special diagnostic equipment is on-line for engineering analysis.

Dynamic tests (ac or "speed" testing) should not be specified unless essential. These take more test system time than dc and functional tests and usually do little more than increase the total cost once a device has been simulated and the prototype thoroughly tested. With good process control, dynamic performance of devices passing the normal tests will be consistent. The dc tests verify process control (also verified independently by the Quality Control department).

#### Varible Interface: A Balance of Resources

The high complexity of large scale integration (LSI) has placed Fairchild in the business of designing and fabricating subsystems, blurring the distinction between a component supplier and a systems engineering and consulting firm. Where the customer formerly interfaced mainly with circuit and component engineers, he must now communicate with system engineers, logic designers and package engineers as well. Thus the LSI customer must be more aware of key aspects of process technology such as economic chip sizes, testing methods, etc. Since each customer has different levels of expertise and manpower, as well as varying design schedules, no single interface program will be optimum for all customers.

In general, the interface should divide and identify responsibilities as clearly and thoroughly as possible. The flow chart in the back of this manual illustrates the key steps and the interface options available. The extensive use of computeraided design lowers costs and ensures quick turnaround.

The system design phase clearly must be performed by the customer. The areas of partitioning, logic design and test generation are flexible and may be performed either by Fairchild or by the customer. Mask generation, fabrication and testing must be done by Fairchild.

Many working interface relationships are possible, each of which encompasses three basic elements: design data, design verification and customer involvement.

- A DESIGN DATA OPTIONS

- 1. *Performance Specifications:* Customer performs system design and generates performance specifications. Fairchild performs partitioning and logic design.

- 2. Performance Specification with Partitioning: The customer performs enough initial design to partition the system into arrays. Logic design is done by Fairchild.

- 3. Logic Diagram, Unpartitioned: The customer provides logic diagrams of the required function, with no partitioning. Unfortunately, it is usually impractical to perform partitioning without a thorough knowledge of the system, since the logic implementation is likely to change radically during partitioning.

- 4. *Non-Micromosaic Logic Diagram, Partitioned:* The customer provides logic diagrams of partitioned arrays. Fairchild converts the logic into Micromosaic cells with logic minimization wherever possible.

- Partitioned Micromosaic Logic Diagram: The customer provides the logic diagram of partitioned arrays, converted to Micromosaic cells. Fairchild checks logic design for minimization, testing requirements, etc.

- Design Ready for Layout: The customer provides logic diagrams and/or FAIRSIM network descriptions of partitioned arrays ready for layout without further simulation.

- **B** DESIGN VERIFICATION OR TEST DATA OPTIONS

Because of the economic incentive to get an LSI design right the first time, extensive checking of a design before mask design is mandatory.

- 1. *Performance Specification:* The customer provides complete performance specifications for the system. Fairchild simulates all arrays and accepts responsibility for the operation of the system. Fairchild also generates individual functional tests for all arrays.

- Customer Analysis of Fairchild Tests: Fairchild simulates the proposed design to its own input sequences. The customer analyzes the simulation output for correct operation. Fairchild generates production func-

tional tests for all arrays. This method is practical for arrays with an easily understood operation, such as counters, buffers, etc., but is impractical for complex control logic.

- 3. Customer Supplied Input Sequence: The customer supplies input sequences in truth table or timing diagram form. Fairchild simulates and provides simulated output for customer analysis. Fairchild generates production functional tests.

- 4. Customer Supplied Input and Output Specifications: The customer supplies input and output data in truth table or timing diagram form. This method allows Fairchild to simulate and verify a design directly. Fairchild generates production functional tests.

- Customer Supplied Functional Tests: The customer supplies input/output sequences of production test length. Fairchild uses tests to verify design and for production testing.

- 6. *Customer Supplied FAIRSIM Input:* The customer supplies input sequences in FAIRSIM format for simulation of the design. Fairchild performs simulation and presents the simulated operation to the customer for approval. Fairchild performs production functional test generation.

- 7. Customer Supplied Functional Tests in FAIRSIM: The customer provides design verification sequences and production functional test sequences in FAIRSIM format.

- C PHYSICAL INTERFACE

- Mail, Telephone, and Telecopier: All design data is communicated via mail, telephone, and/or telecopier. This interface is used primarily when little customer involvement is required, as in the case of performance specifications.

- 2. Fairchild Team at Customer's Plant: This approach is most commonly used in the initial stages of system design, when a large degree of customer involvement is anticipated. A one-day seminar is presented on partitioning and on use of the Micromosaic cell set.

- 3. Customer Team at Fairchild: This is the most common and useful interface, since it allows instant communication and on-line use of the CAD system. It is most commonly used during the detailed design and simulation phase.

Obviously, the working relationship between Fairchild and the Micromosaic customer is often complex. However, the optimum tradeoff among cost, scheduling, and design confidence can be obtained by selecting various options from each of the basic interface elements — design data, design verification and testing, and the amount of customer involvement.

#### Fairchild Uses Proven MOS Processes

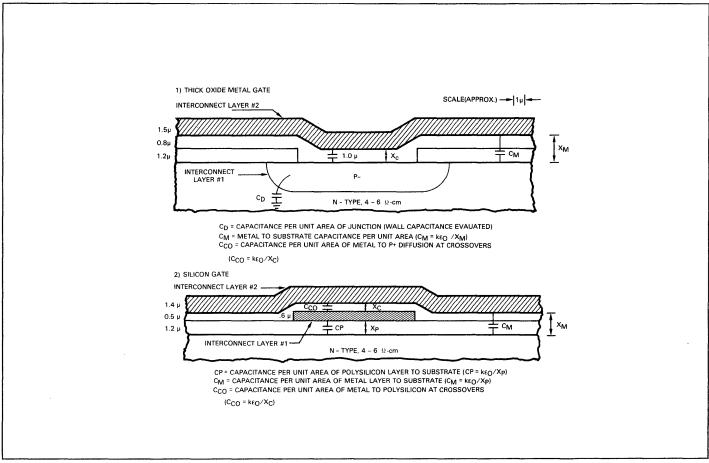

Fairchild is presently producing custom circuits with the two proven P-channel MOS processes silicon gate and high-threshold metal gate. Currently, silicon gate is being used in the majority of standard and custom MOS designs at Fairchild because of its advantages in most applications.

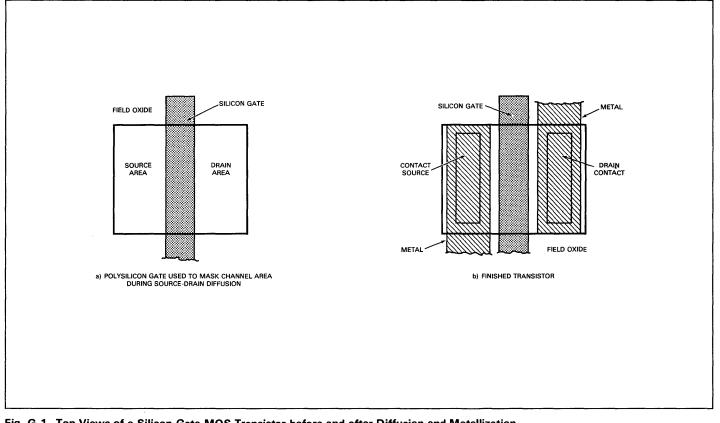

When compared to the metal gate process, the silicon gate approach is generally more economical as it provides higher circuit densities, greater operating speeds and, in many instances, requires fewer off chip components. The basic silicon gate and metal gate processes are compared in greater detail in Appendix G. The two processes are compatible and have been effectively combined in specific custom applications. Moreover, the superior noise immunity inherent in high-threshold metal gate circuits can often be a welcome adjunct to silicon gate designs.

Fairchild is continually performing research on new MOS and bipolar processes, offering them only when they have proven their viability in a production environment. Ion implantation, for example, has recently demonstrated its capability as a production process and Fairchild will soon be offering ion implanted silicon gate devices - both standard and custom. Fairchild's Isoplanar process has proven itself in the bipolar arena, and will soon be commercially applied to P-channel MOS after further refinements. With Isoplanar P-channel MOS, Fairchild carefeduce the size of silicon gate devices by about 40%. This dramatic size reduction is made possible because of two factors: the Isoplanar process moves active elements closer together by lateral oxide isolation and selfaligned contacts - and the oxide surface without steps allows a proportional improvement in interconnection density through higher resolution photomasking. The Isoplanar process combined with ion implantation will also offer higher speeds due to decreased capacitances of both cells and interconnections.

#### The Fairchild Capability in Review

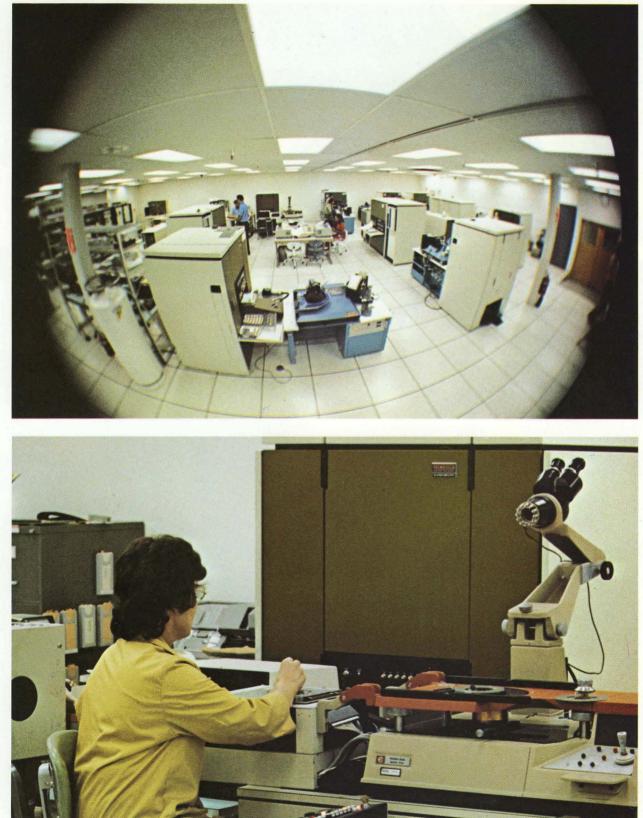

Fairchild offers strength in the areas of both standard and custom MOS/LSI. The broad selection of 51 standard circuits covers a wide range of applications. The computeraided design programs ensure the custom user of workable "first time" custom results, regardless of his level of expertise. The proven silicon gate process ensures the MOS user of a reliable economic product. The lsoplanar process offers lower cost circuits with higher performance in the future. The heavy investment in test equipment and test pattern generation programs ensures that the product is what the user wants. The photo section offers a plant tour of the Fairchild MOS facilities.

Before choosing a vendor, the wise MOS user will visit the facilities for a review of vendor capabilities. At Fairchild we invite comparison.

# **OPTIMOS** Facilities In Action

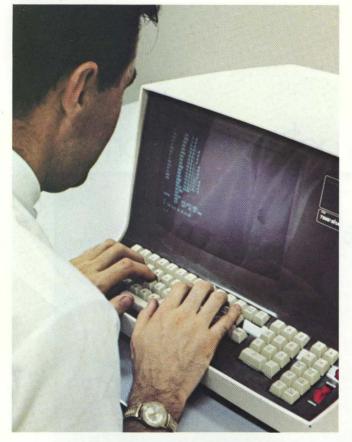

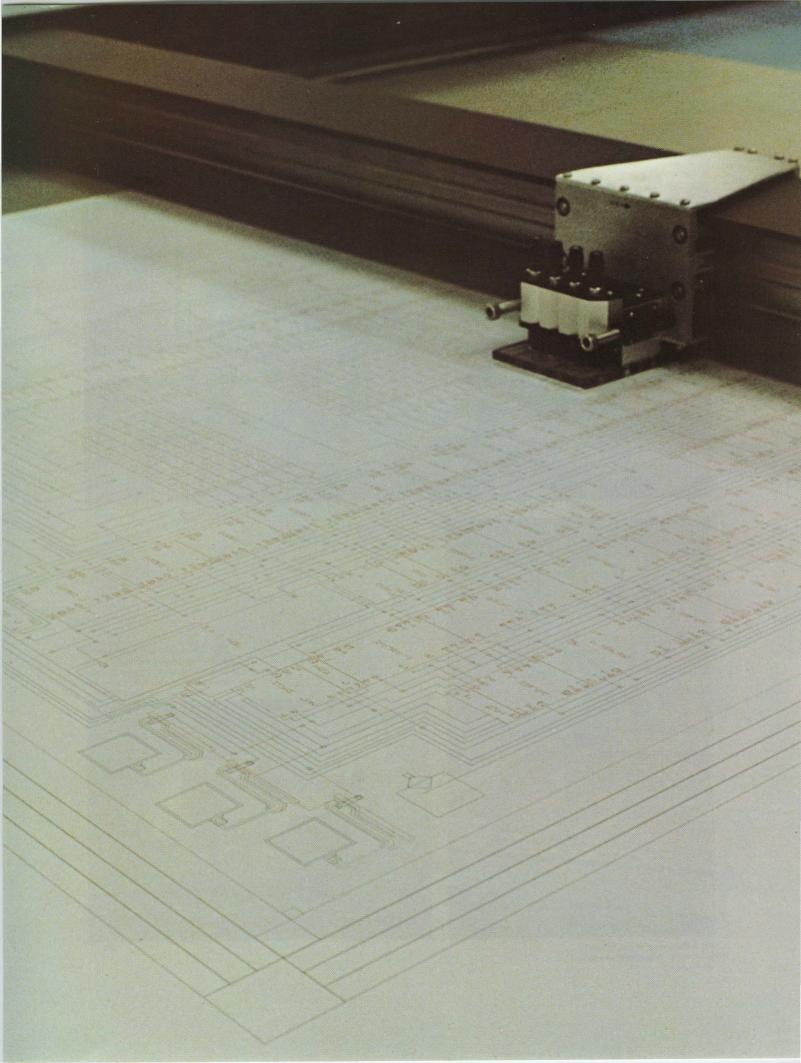

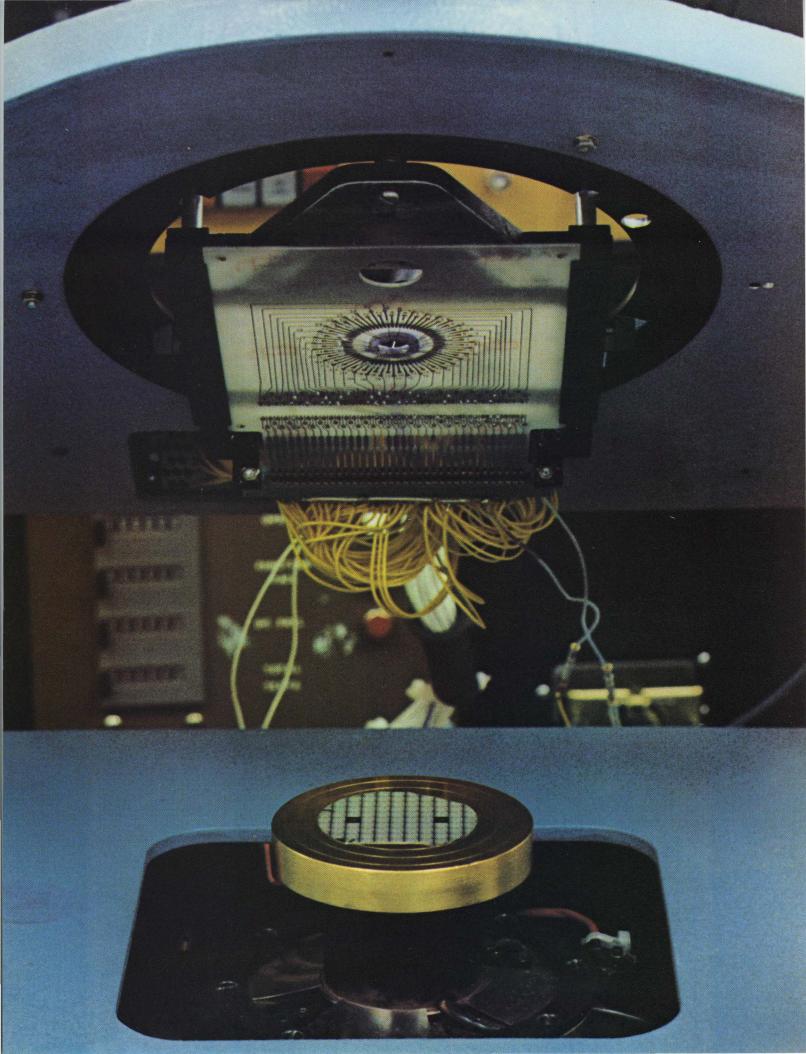

Designer interfacing with computer programs in a logic simulation problem. Calcomp stick plot of the 3261 TV Sync Generator using Micromosaic cells. The cells are shown box outlines and metal and silicon interconnects are shown as lines.

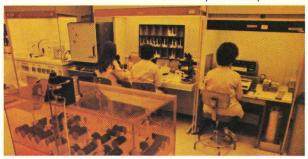

Designers checking FAIRSIM Netlist.

Customer engineer checking FAIRSIM listing.

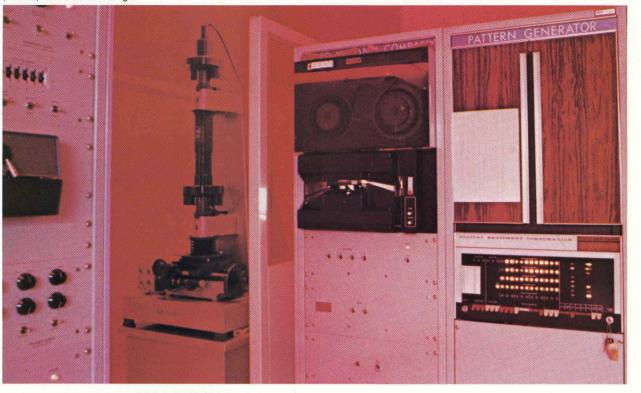

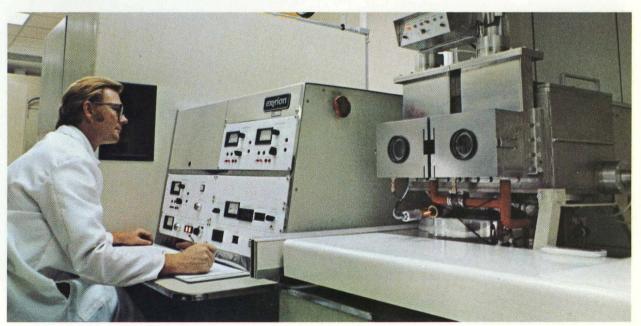

The RETGEN program converts the LAYOUT output to a David Mann Reticle Generator. This system eliminates the rubylith cut and peel step by exposing photographic plates (reticles) with a 10 to 1 image.

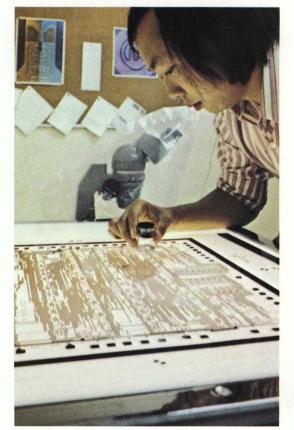

An 80X blowup of the artwork, is made for alignment and circuit verification.

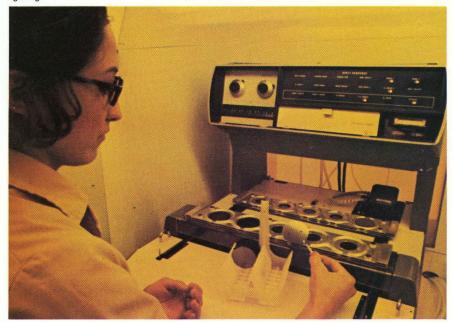

The 10X reticle is converted to a 1X master by exposing a photographic plate with repeated images in rows and columns. Working plates are made from the master plates.

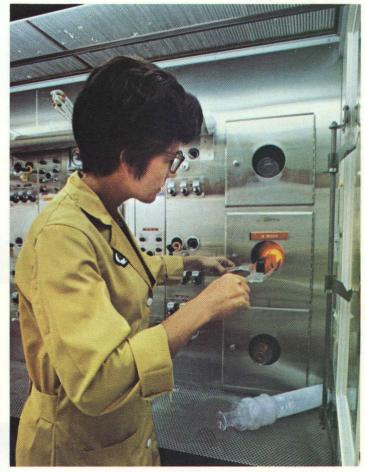

Silicon wafers become photographic plates after being coated with a layer of etch resist. The resist is then baked. These photo steps are all performed in a room with controlled lighting.

The coated wafers are stored in lightfiltered boxes prior to exposure.

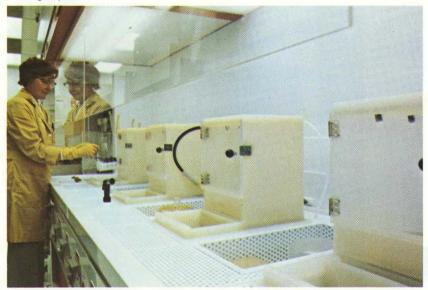

The exposed wafers are developed in the right-hand station. A rinse removes the unexposed etch resist exposing the surface for future chemical action. The center station is an in-process inspection station. The light-filtered box in the foreground stores exposed wafers until they are developed.

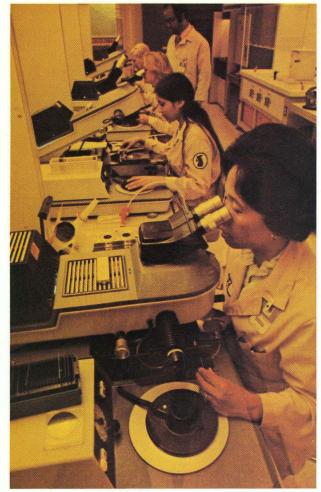

In these mask aligners, new mask patterns (from working plate) are aligned to the existing pattern on the wafer. A box of working plates is shown in foreground.

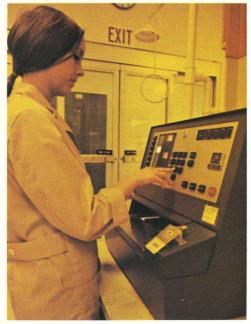

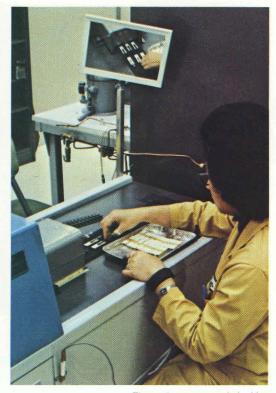

Wafer movement is recorded in a production control terminal that maintains control of all material in the production flow.

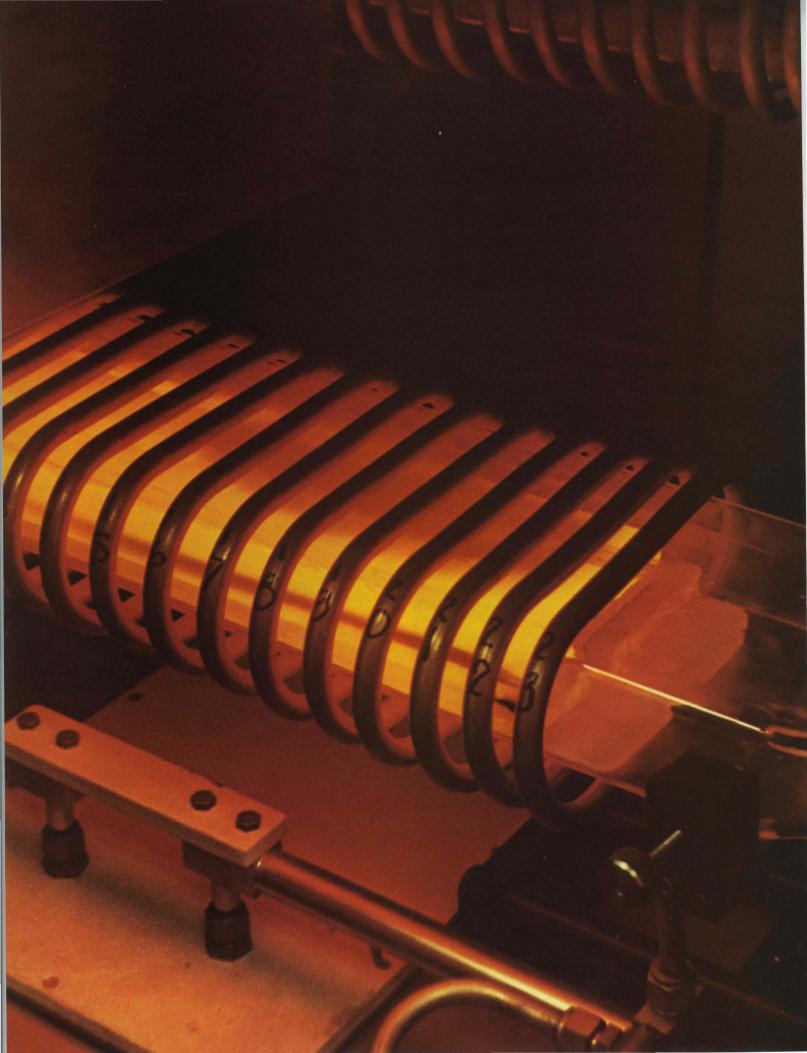

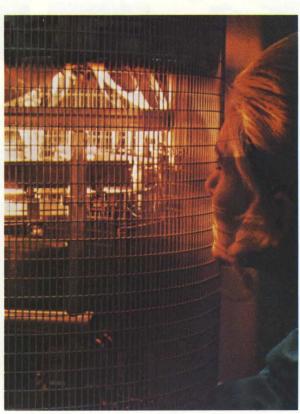

Wafers are loaded into a silicon reactor which deposits polysilicon metal in the gate and interconnection areas.

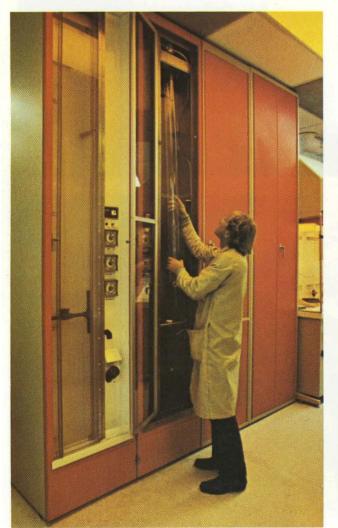

Loading a diffusion furnace.

Wafers being unloaded from silicon reactor.

Diffusion furnaces drive controlled impurities into silicon to form parts of the MOS transistors.

Rinse stations used in cleaning steps.

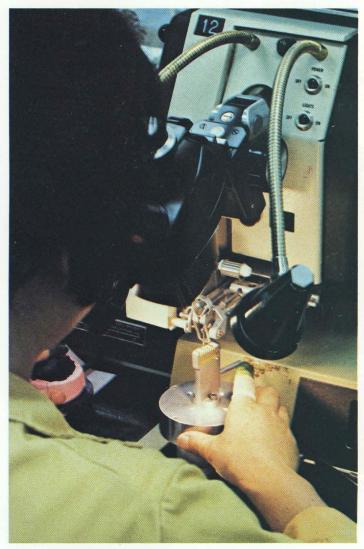

Finished wafers are functionally tested before committing a die to a package. The reject units are marked by a pen located in the middle of the probes.

Film thickness measurements are made on an interferometer. Thickness can also be monitored on an ellipsometer (see chart on wall).

The diffusion furnace tubes are regularly cleaned by flushing with HF (hydrofloric acid), rinsed with DI water and dried with N2.

Aluminum metal is deposited in vacuum chambers. A planatary gear arrangement insures that the metal forms evenly over the steps in the oxide surface.

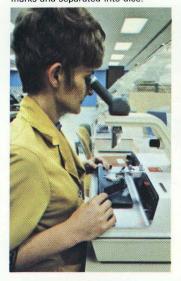

Tested wafers are scribed with a diamond scriber. The wafers are then fractured along these scribe marks and separated into dice.

Die bonding welds acceptable dice into a package for interconnection purposes.

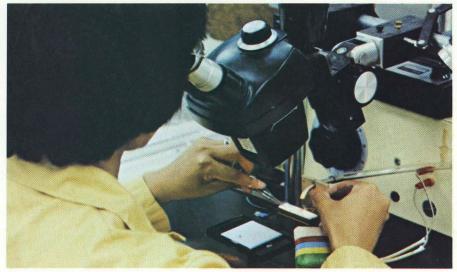

Wire bonding connects the pads on the die to the leads of the package.

The packages are sealed with a lid to provide environmental and mechanical protection to the die.

Fairchild's testing capabilities include a Super Sentry 600 and several Sentry 400 test systems. Each Sentry 400 can handle 4 stations and the Super Sentry can handle 2 stations.

Packaged unit testing on a Super Sentry station.

Production burn-in racks.

Gross leak testing ensures the quality of the seal.

R & QA environmental processing area for high reliability processing.

R & QA lab provides both routine inspections and failure analysis.

lon implantation equipment installed in production diffusion room for use with Isoplanar to provide superior density and performance.

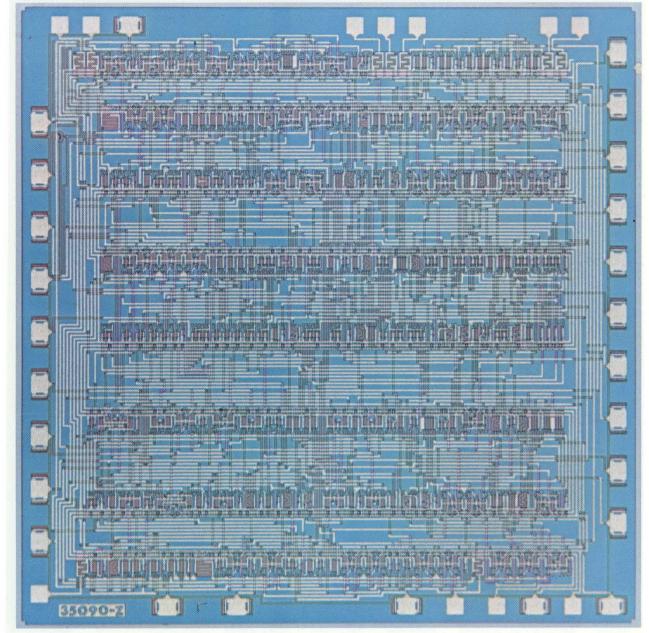

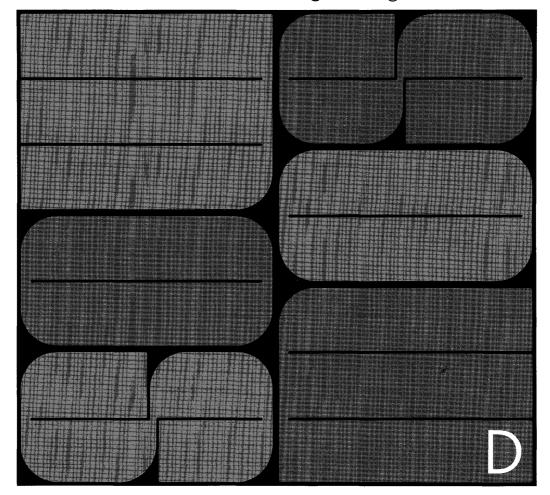

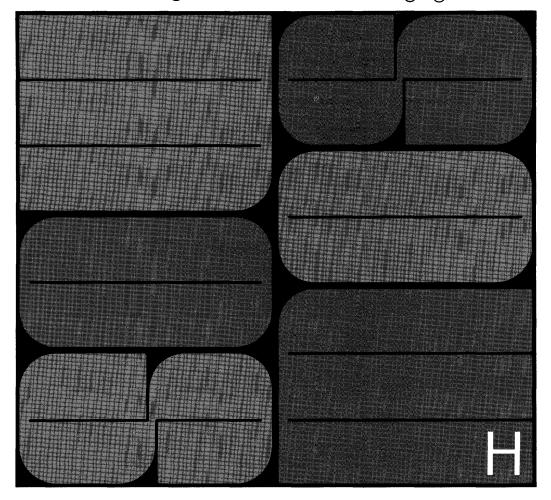

Custom Micromosaic Calculator Chip

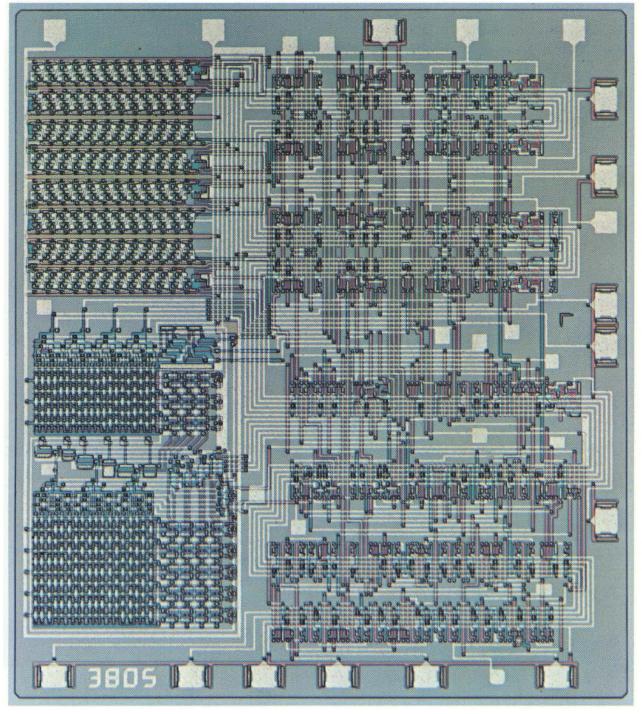

3805 - PPS 25 Arithmetic Unit

# Standard Product Data Sheets And Application Notes

#### **APPENDIX A**

### STANDARD PRODUCT DATA SHEETS AND APPLICATION NOTES

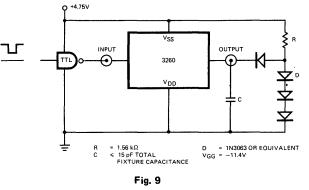

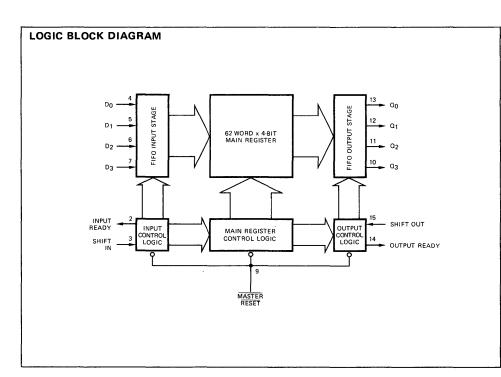

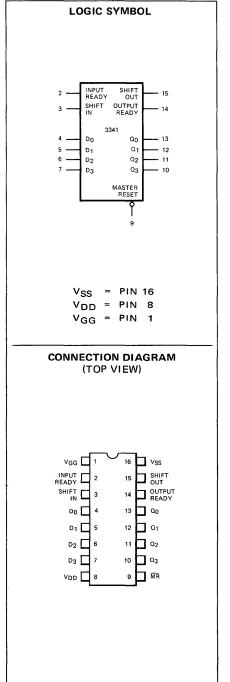

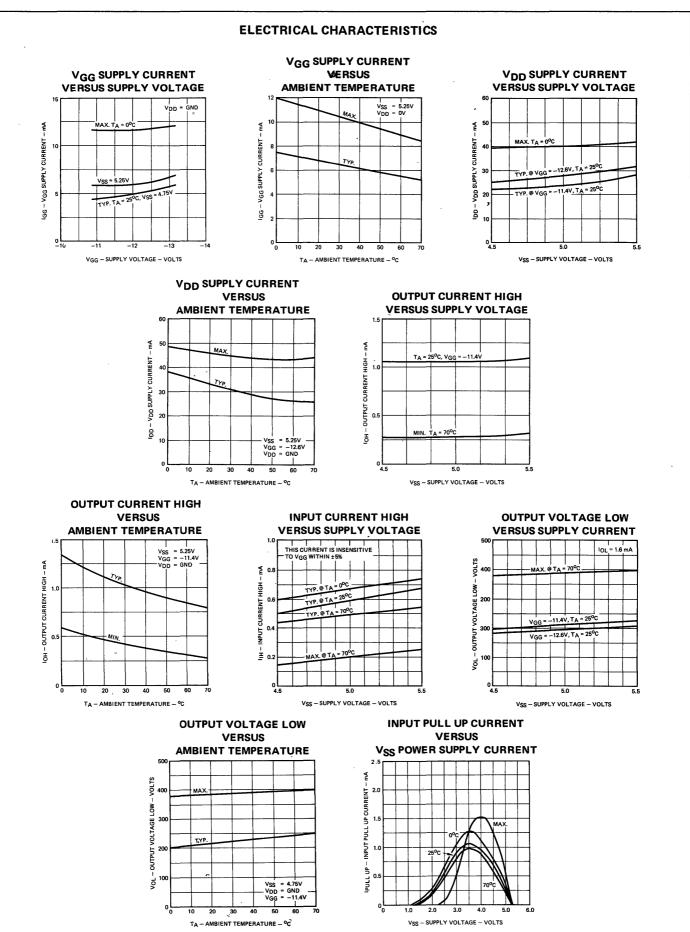

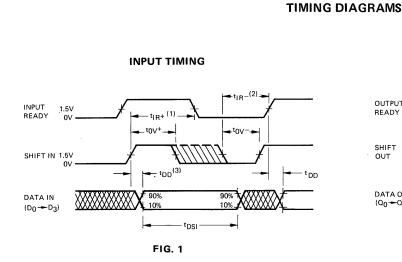

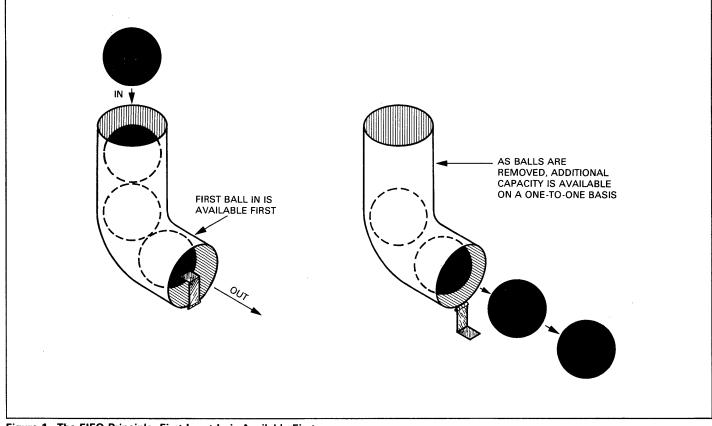

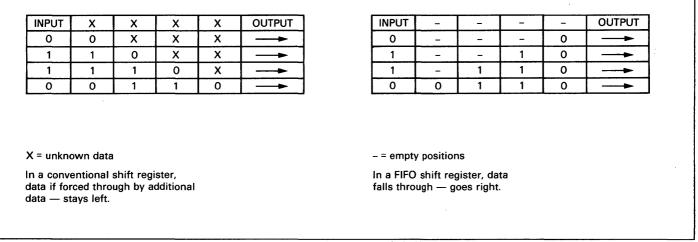

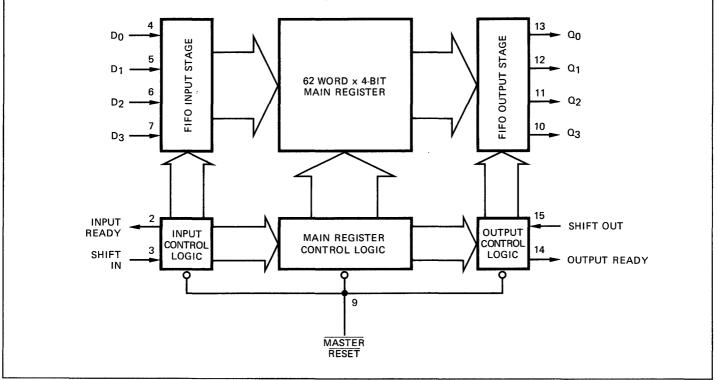

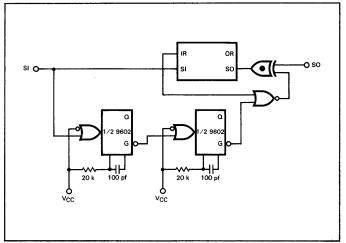

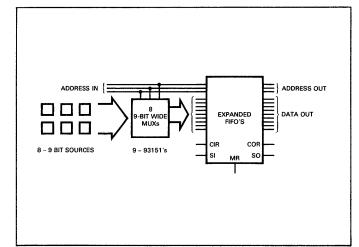

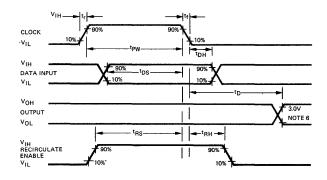

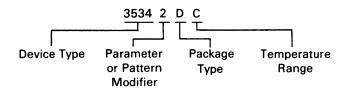

This device type and description list delineates the standard product data sheets included in this portion of the appendices. The silicon gate products proceed the metal gate devices. Application notes for the 3341 FIFO, 3532 512-Word by 1-Bit RAM, 3534/ 1103 1K ROM and 3814 DVM are also included. They are located with the corresponding data sheet. There is also a hybrid device included — the SH0013 2-Phase MOS Dual Clock Driver. It is useful in many MOS applications.

| Device | Description                                                 | Page | Device    | Description                                                                   | Page |

|--------|-------------------------------------------------------------|------|-----------|-------------------------------------------------------------------------------|------|

| 3257   | 64 x 5 x 7 Out Character Generator,                         |      | 3349      | Hex 32-Bit Static Shift Register                                              | 86   |

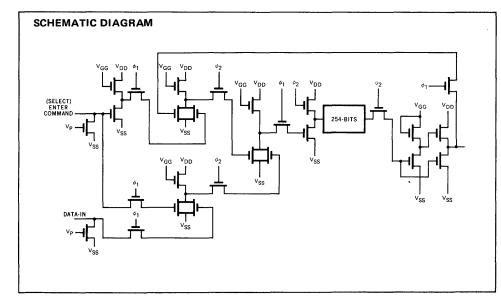

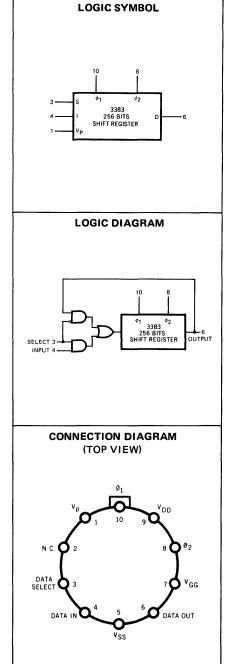

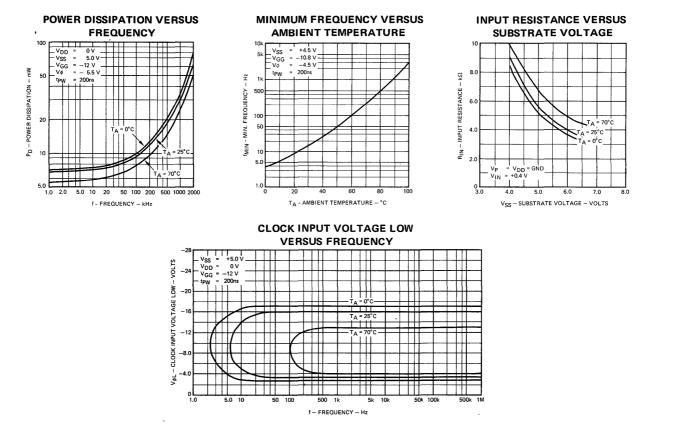

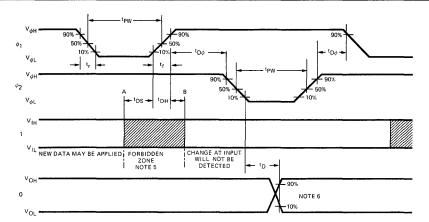

|        | Custom or ASCII Font                                        | 35   | 3383      | 256-Bit Dynamic Shift Register                                                | 88   |

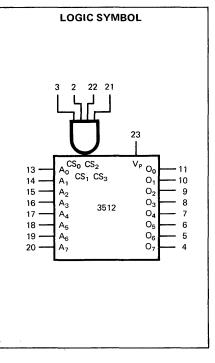

| 3258   | 64 x 7 x 5 Out Character Generator,<br>Custom or ASCII Font | 42   | 3512      | 256 x 8 (2048-Bit) Read-Only Memory,<br>Custom Pattern                        | 92   |

| 3260   | 64 x 9 x 7 Out Character Generator,<br>Custom or ASCII Font | 48   | 3512A     | 256 x 8 (2048-Bit) Read-Only Memory,<br>Selectric to ASCII/ASCII to Selectric | 96   |

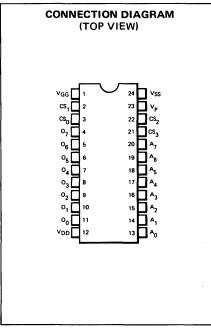

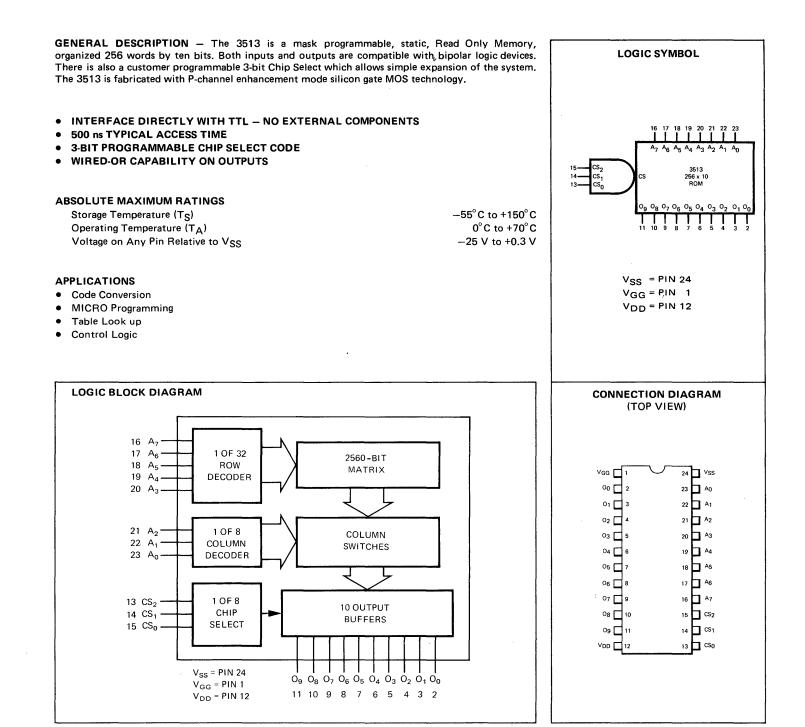

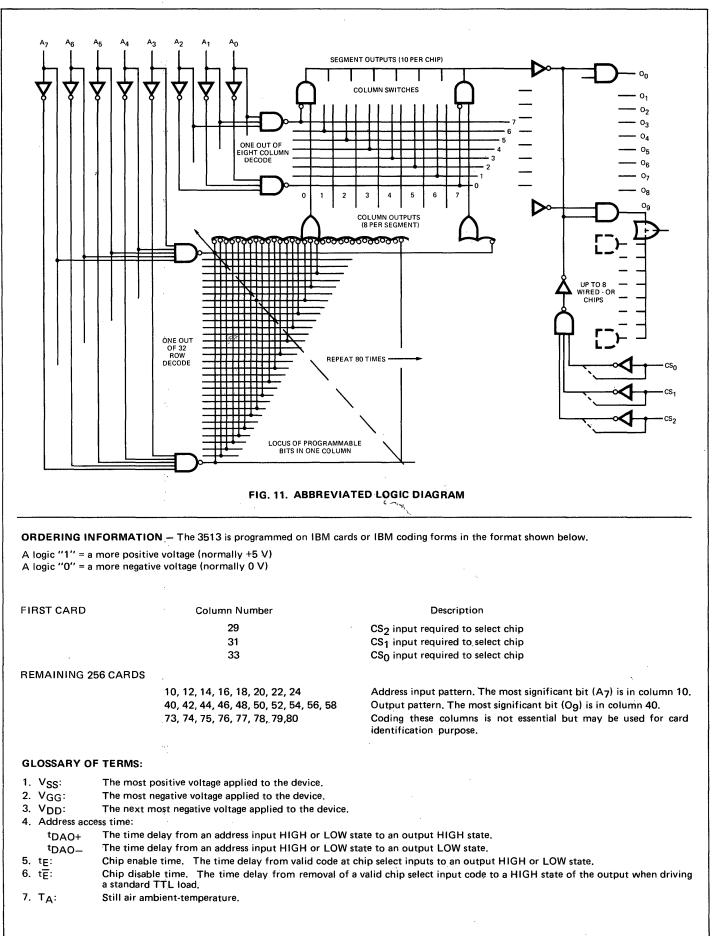

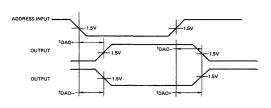

| 3261   | TV Sync Generator                                           | 56   | 3513      | 256 x 10 (2560-Bit) Read-Only Memory,                                         | 1    |

| 3325   | Quad 64-Bit Dynamic Shift Register                          | 60   |           | Custom Pattern                                                                |      |

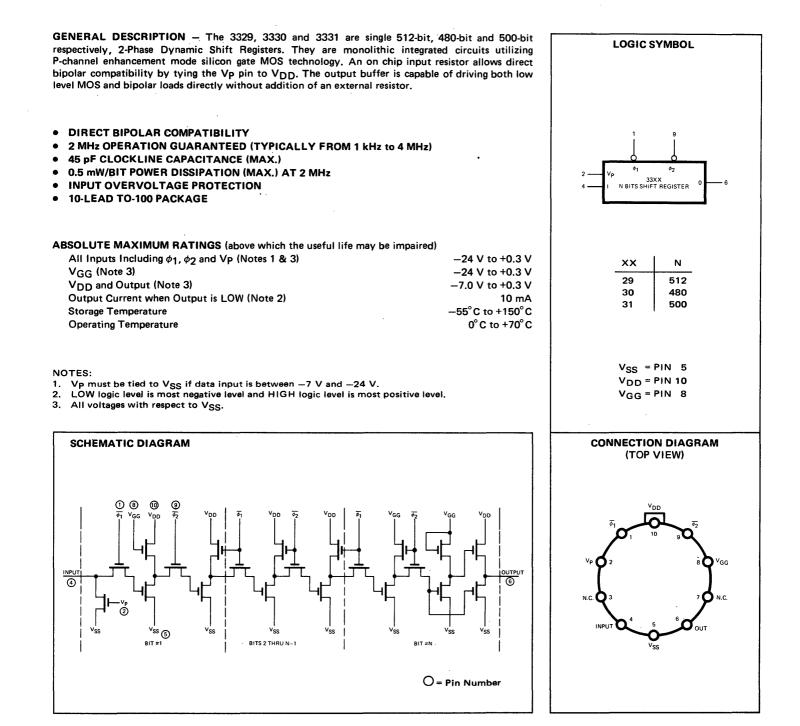

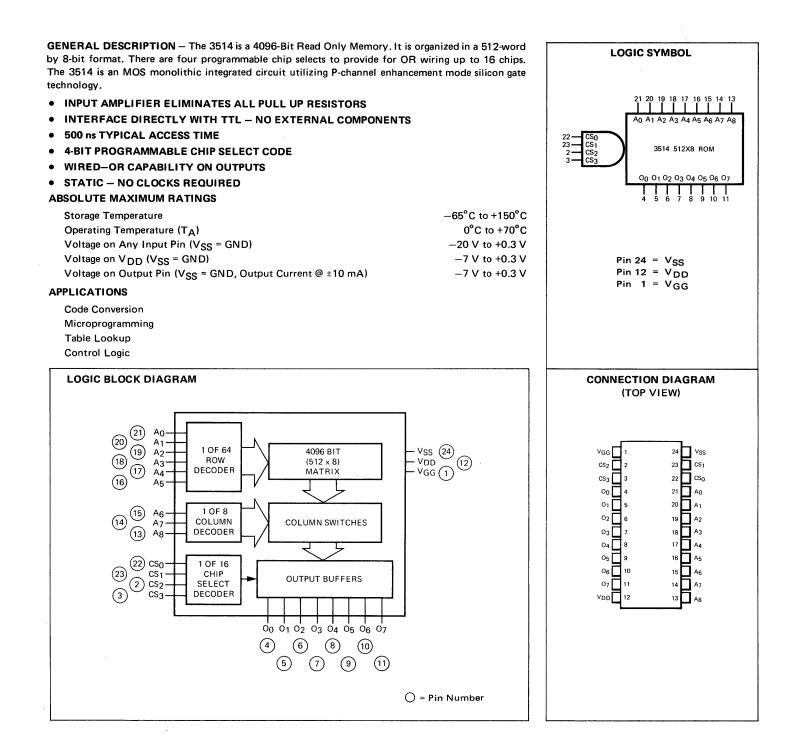

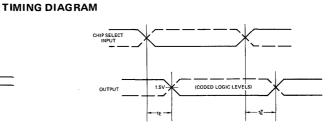

| 3329   | 512-Bit Dynamic Shift Register                              | 64   | 3514      | 512 x 8 (4096-Bit) Read-Only Memory,                                          |      |

| 3330   | 480-Bit Dynamic Shift Register                              | 64   |           | Custom Pattern                                                                | 103  |

| 3331   | 500-Bit Dynamic Shift Register                              | 64   | 3514A     | 512 x 8 (4096-Bit) Read-Only Memory,<br>ASCII-EBCDIC/EBCDIC-ASCII             | 107  |

| 3341   | 64 x 4 First-In First-Out Memory                            | 68   | 3532      | 512 x 1 Static Read/Write Memory                                              | 109  |

| 3341   | Application Note                                            | 74   | 3534/1103 | 1024 x 1 Dynamic Read/Write                                                   |      |

| 3342   | Quad 64-Bit Static Shift Register                           | 80   |           | Memory, 300 ns Access Time                                                    | 120  |

| 3343   | Dual 128-Bit Static Shift Register                          | 82   | 3534/1103 | Application Note                                                              | 127  |

| 3344   | Dual 132-Bit Static Shift Register                          | 82   | 3708      | 8-Channel Decoded Multiplexer                                                 | 150  |

| 3345   | Dual 136-Bit Static Shift Register                          | 82   | 3814      | Digital Voltmeter Logic                                                       | 154  |

| 3346   | Dual 144-Bit Static Shift Register                          | 82   | 3814      | Application Note                                                              | 158  |

| 3347   | Quad 80-Bit Static Shift Register                           | 84   | *3815     | 5-Decade Counter                                                              | 163  |

| 3348   | Hex 32-Bit Static Shift Register with Buffer Enable         | 86   | *3816     | ÷3 to 261,145 Programmable Counter                                            | 163  |

### **SILICON GATE**

### METAL GATE

| Device | Description                          | Page | Device | Description                   | Page |

|--------|--------------------------------------|------|--------|-------------------------------|------|

| 3100   | 5-Input Gate                         | 164  | 3700   | 4-Channel Multiplexer         | 180  |

| 3101   | Dual JK Flip-Flop                    | 166  | 3701   | 6-Channel Multiplexer         | 184  |

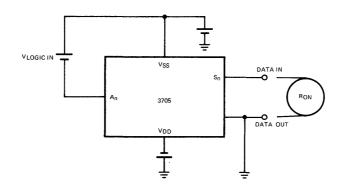

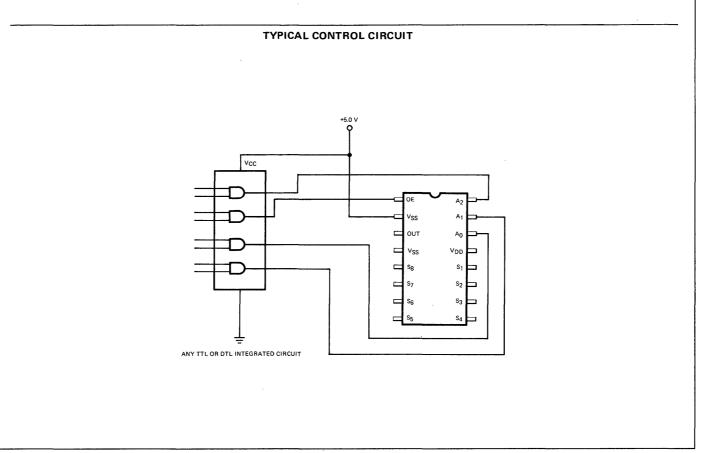

| 3102   | 3-Input Gate                         | 168  | 3705   | 8-Channel Decoded Multiplexer | 186  |

| 3300   | 25-Bit Static Shift Register         | 171  | 3750   | 10-Bit D to A Converter       | 190  |

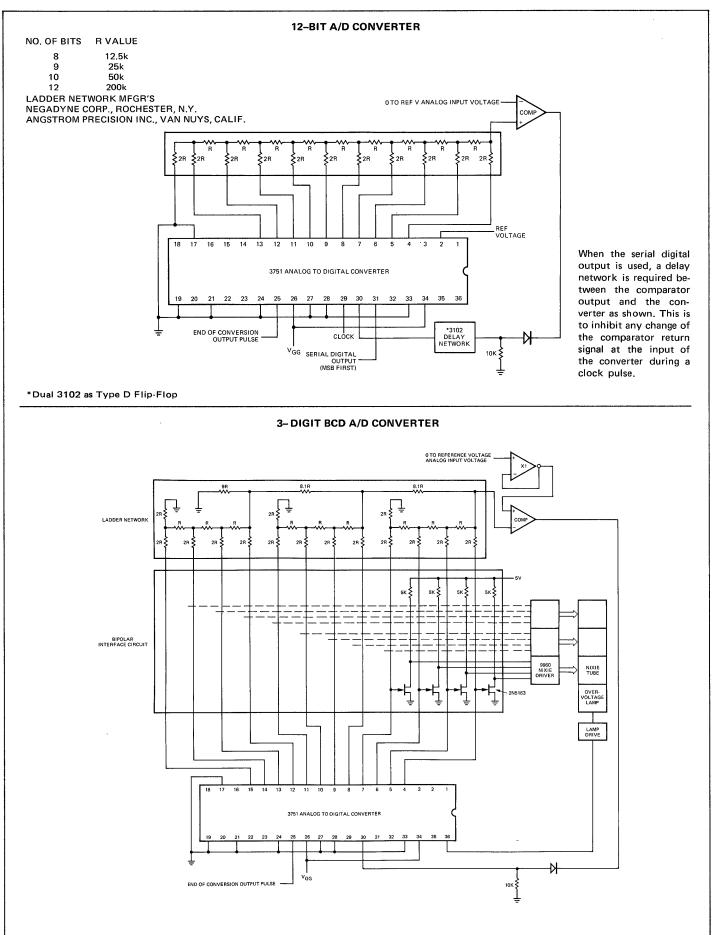

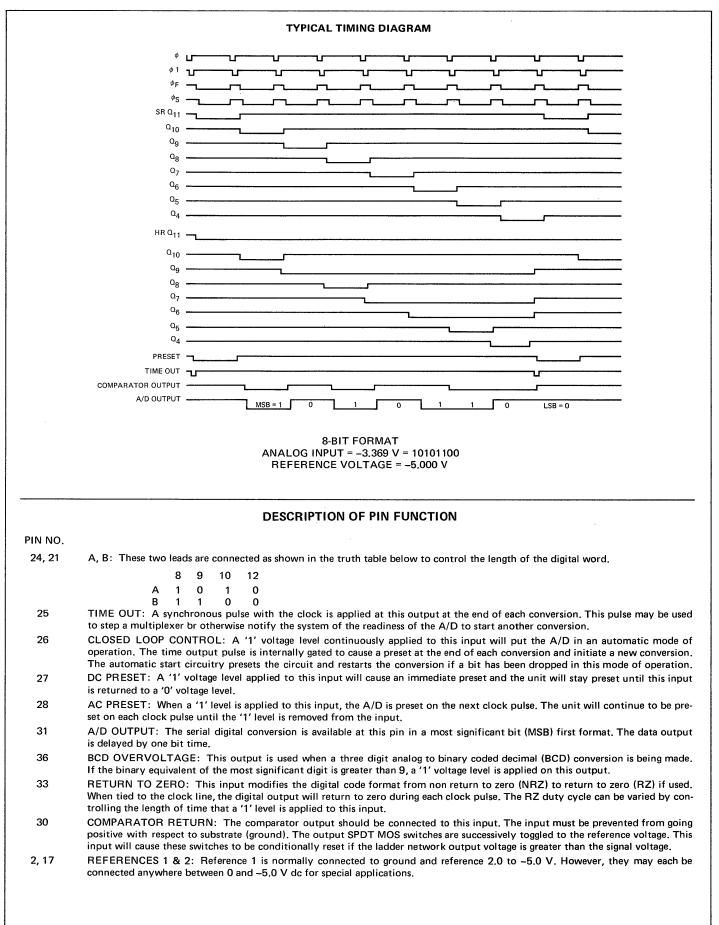

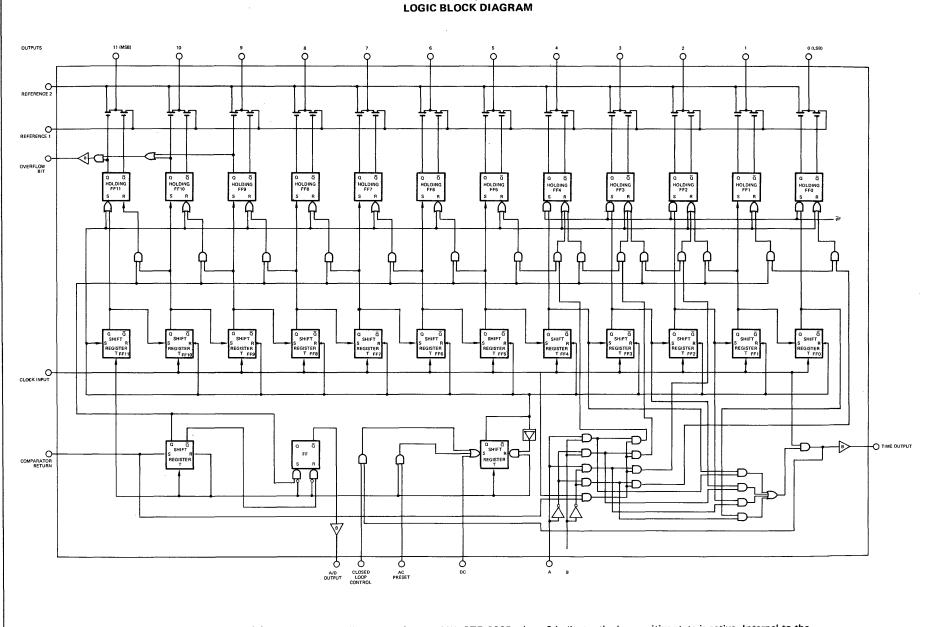

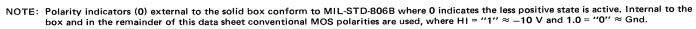

| 3326   | Triple 66-Bit Dynamic Shift Register | 173  | 3751   | 12-Bit A to D Converter       | 194  |

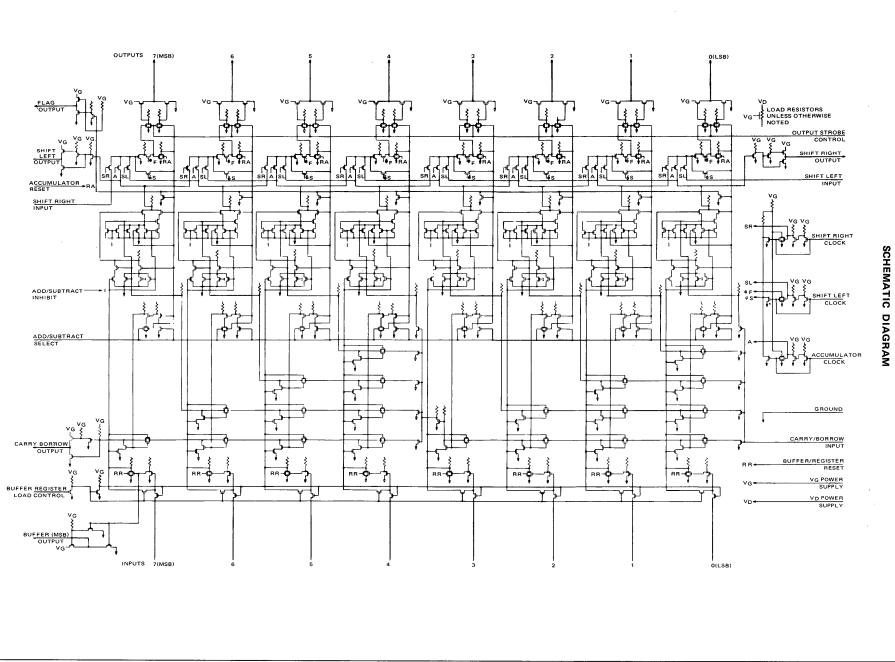

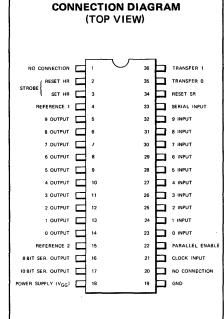

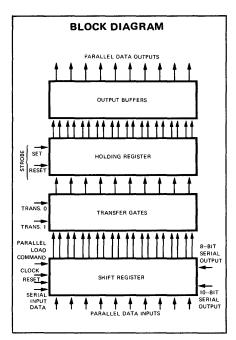

| 3501   | 128 x 8 (1024-Bit) Read-Only Memory, |      | 3800   | 8-Bit Parallel Accumulator    | 200  |

|        | Custom Pattern                       | 176  | 3801   | 16-Bit S-P,P-S Converter      | 205  |

#### HYBRID

| Device | Description                   | Page |

|--------|-------------------------------|------|

| SH0013 | 2-Phase MOS Dual Clock Driver | 208  |

Fairchild cannot assume responsibility for use of any circuitry described other than circuitry entirely embodied in a Fairchild product. No other circuit patent licenses are implied.

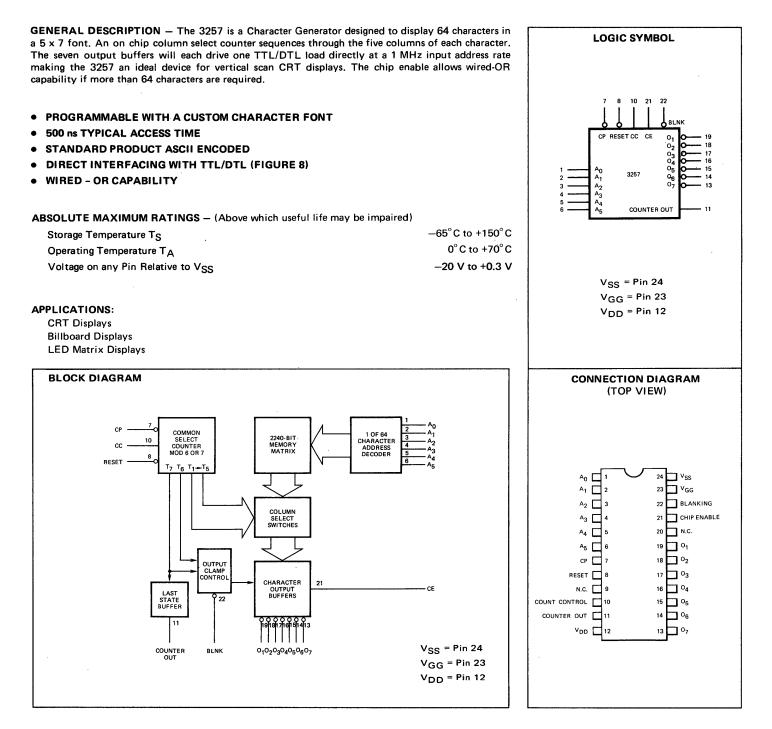

### 3257 DOT MATRIX CHARACTER GENERATOR 64 CHARACTERS 5×7 BITS FAIRCHILD SILICON GATE MOS INTEGRATED CIRCUITS

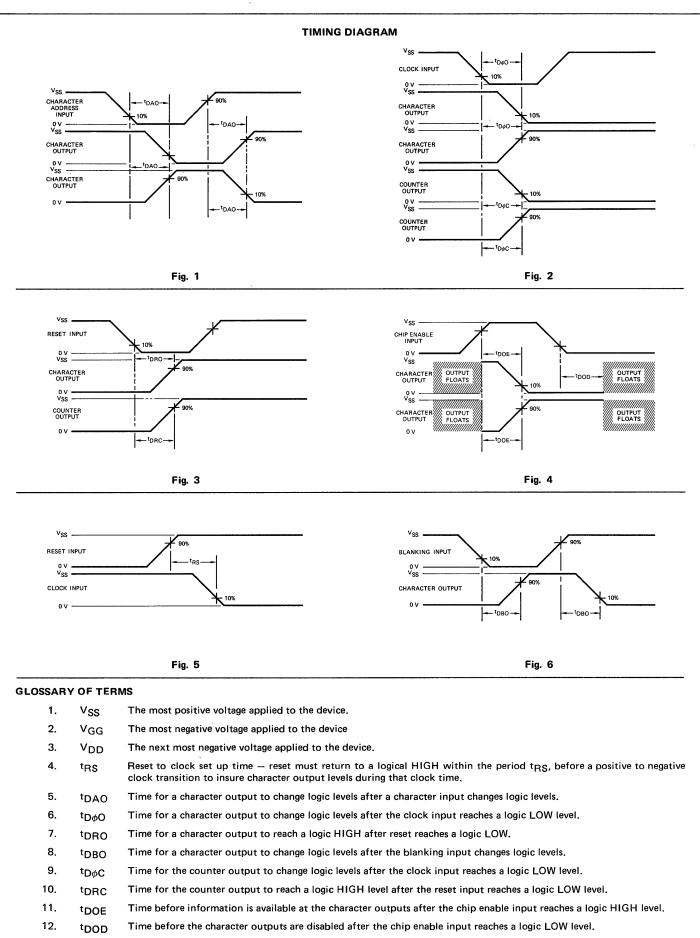

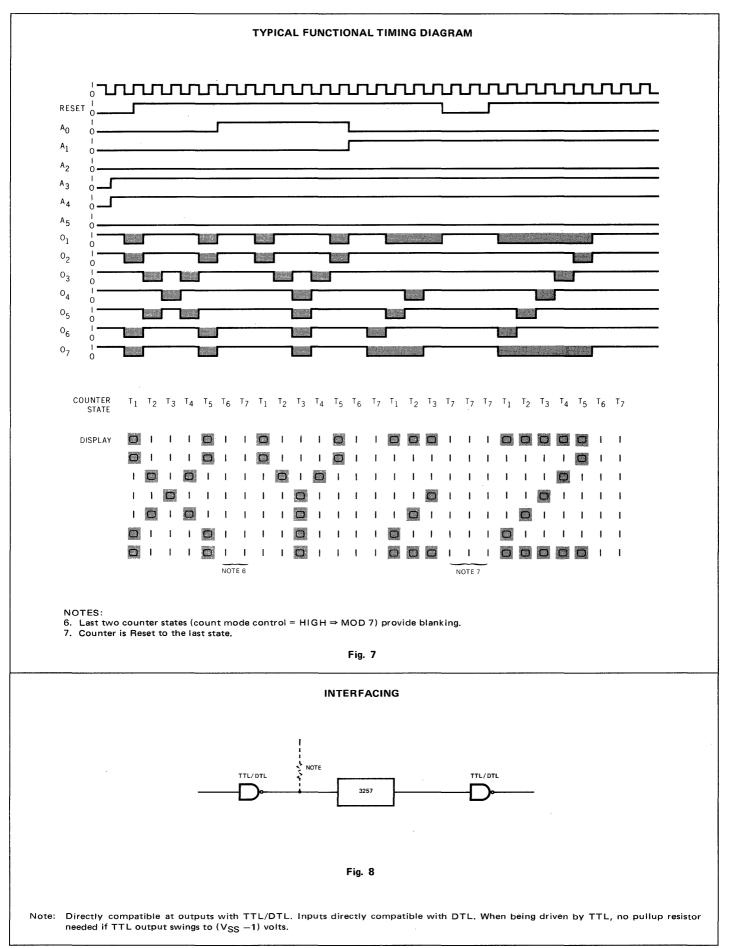

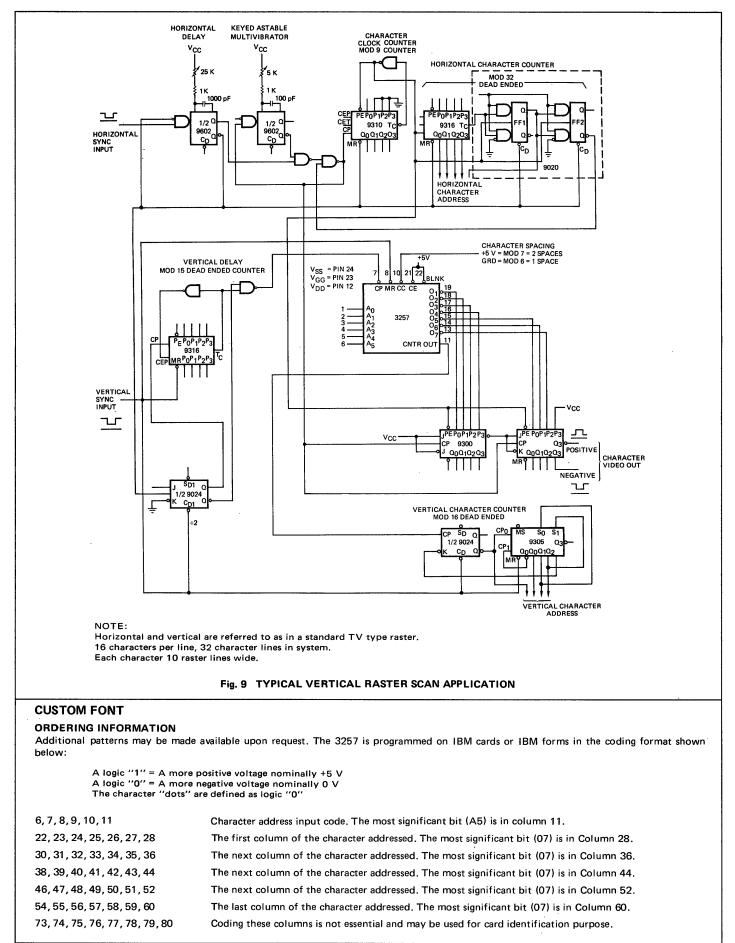

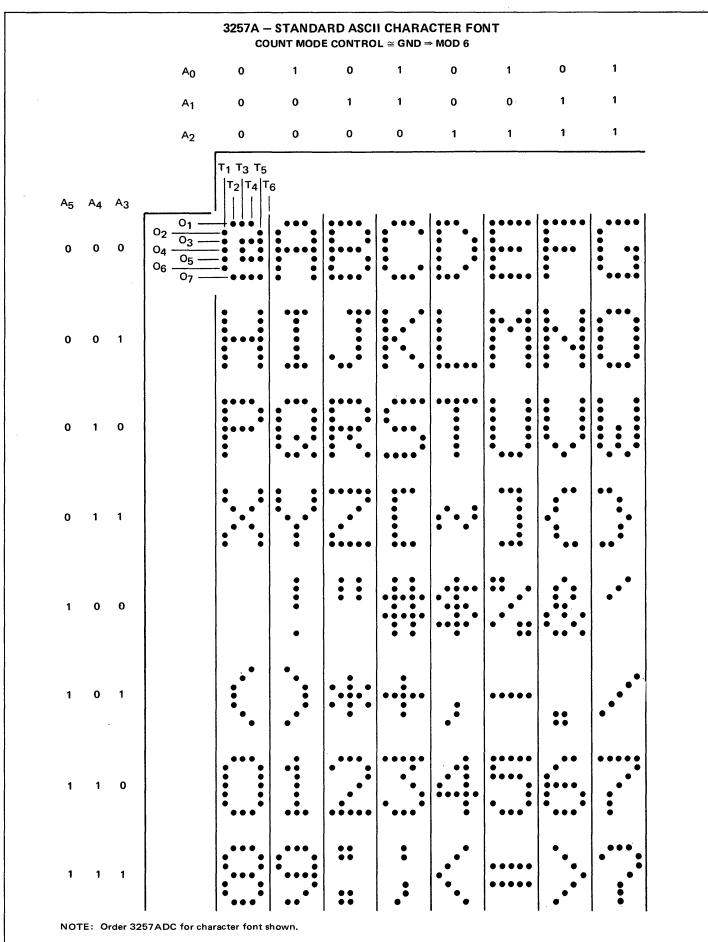

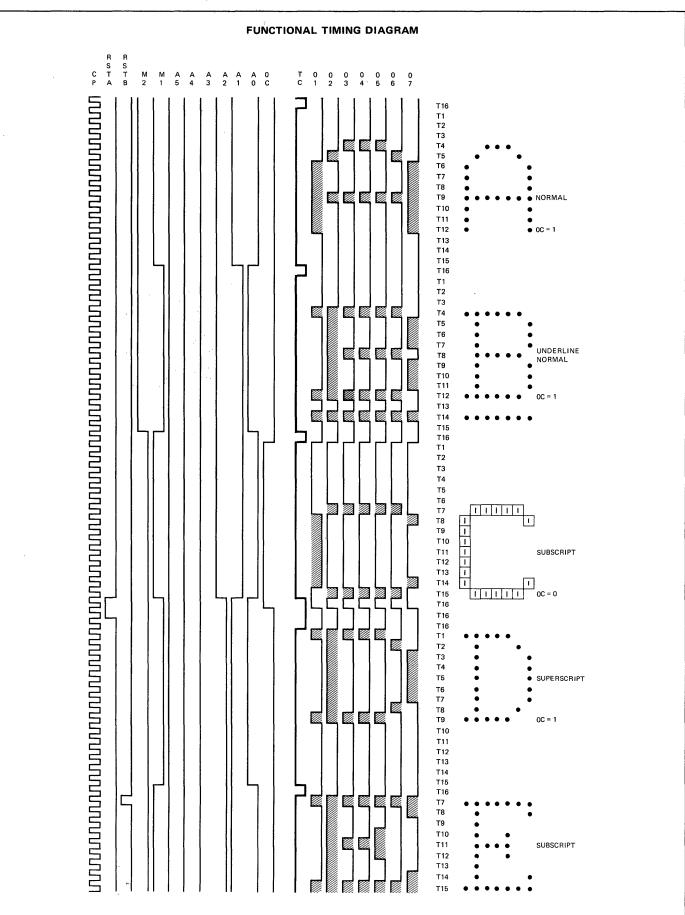

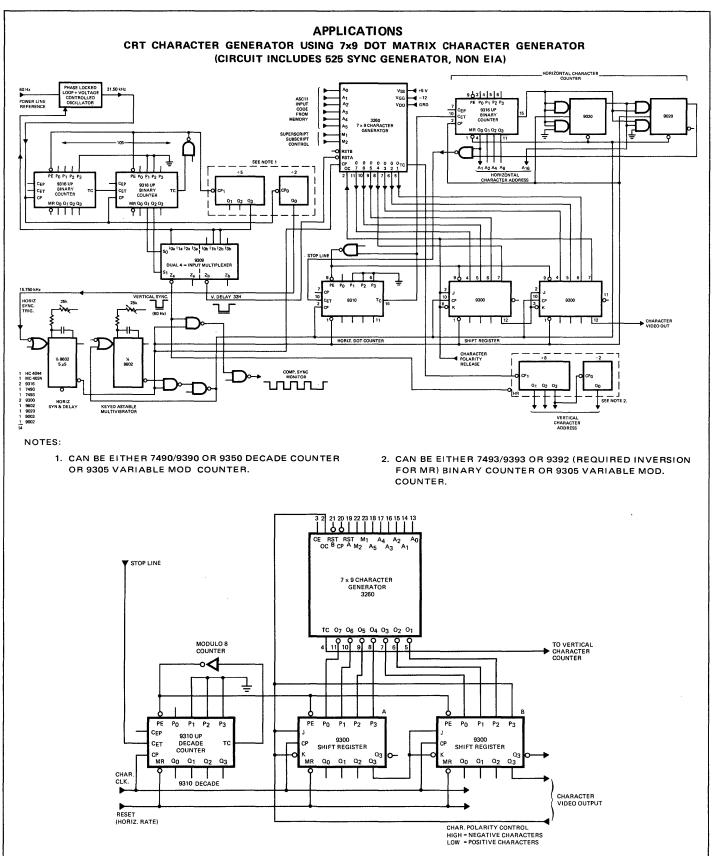

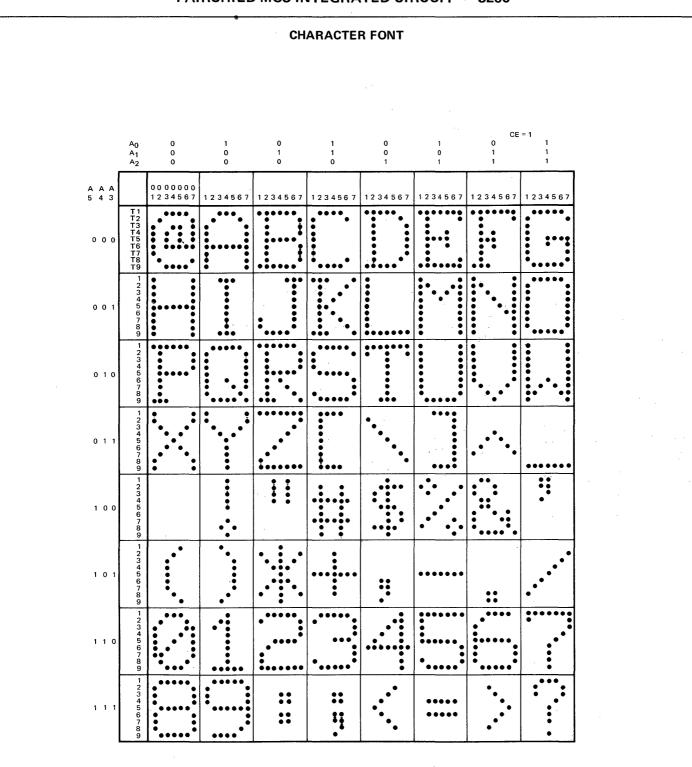

**FUNCTIONAL DESCRIPTION** – A Reset pulse (~GND) is required to set the counter to the last state. A 6-bit binary word presented to the character address inputs is decoded to select 1 of 64 characters in the memory. Information, representing the first column of the character is available the next clock time after Reset returns HIGH (~V<sub>SS</sub>). The remaining four columns are sequentially selected by the next four states of the counter. The last state of the counter clamps the outputs HIGH (~V<sub>SS</sub>) to provide 1 or 2 space blanking between characters (Count Control ~V<sub>SS</sub>  $\Rightarrow$  MOD 7, Count Control ~ GND  $\Rightarrow$  MOD 6). When the last state (6th or 7th) of the counter is reached, the Counter Output goes HIGH (~V<sub>SS</sub>). When Chip Enable goes HIGH (~V<sub>SS</sub>), the chip is activated while a LOW (~ GND) at this lead floats the outputs to allow common output bussing. A LOW (~ GND) on the Blanking input pulls the outputs HIGH (~V<sub>SS</sub>), providing blanking independent of the counter state or the character address.

#### DC CHARACTERISTICS:

$V_{SS}$  = +5 V ±5%,  $V_{GG}$  = -12 V ±5%,  $V_{DD}$  = 0 V,  $T_A$  = 0°C to +70°C (Standard operating conditions unless otherwise specified)

| SYMBOL         | CHARACTERISTIC          | MIN.                       | TYP. | MAX.                               | UNITS  | CONDITIONS                                                          |

|----------------|-------------------------|----------------------------|------|------------------------------------|--------|---------------------------------------------------------------------|

| VIH            | Input Voltage HIGH      | V <sub>SS</sub> –1         |      | V <sub>SS</sub>                    | v      | Note 1                                                              |

| VIL            | Input Voltage LOW       | V <sub>GG</sub>            | 0    | 0.8                                | V      | Note 1                                                              |

| Vон            | Output Voltage HIGH     | V <sub>SS</sub> 0.5<br>2.4 | 3.0  | V <sub>SS</sub><br>V <sub>SS</sub> | v<br>v | I <sub>OH</sub> = -10 μA<br>I <sub>OH</sub> = -0.5 mA               |

| VOL            | Output Voltage LOW      | 0                          | 0.3  | 0.4                                | V      | IOL = 1.6 mA                                                        |

| 1              | Input Leakage Current   |                            |      | -1.0                               | μA     | V <sub>SS</sub> = 0 V, V <sub>IN</sub> = -18 V, Note 1              |

| ILO            | Output Leakage Current  |                            |      | 1.0                                | μA     | V <sub>SS</sub> = 0 V, V <sub>OUT</sub> = -6 V, Note 2              |

| ISS            | V <sub>SS</sub> Current |                            | 20   | 40                                 | mA     | $V_{SS} = 5.25 \text{ V}, V_{GG} = -12.6 \text{ V}$<br>Outputs Open |

| P <sub>D</sub> | Power Dissipation       |                            | 360  | 715                                | mW     |                                                                     |

NOTES:

ST 0.30

1. Inputs include Character Address, Count Control, Clock and Reset.

2. Chip Enable = LOW.

3.  $I_{SS} = -I_{GG}$  (V<sub>GG</sub> Supply Current)

OUTPUT VOLTAGE LOW VERSUS AMBIENT TEMPERATURE

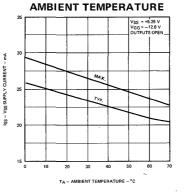

WORST CASE V<sub>SS</sub> SUPPLY CURRENT VERSUS

| SYMBOL                          | CHARACTÉRISTIC                             | MIN. | TYP. | MAX. | UNITS | CONDITIONS                      |

|---------------------------------|--------------------------------------------|------|------|------|-------|---------------------------------|

| f                               | Clock Frequency                            | dc   |      | 1.0  | MHz   |                                 |

| <sup>t</sup> PWφ                | Clock Pulse Width                          | 500  |      |      | ns    |                                 |

| t <sub>r</sub> , t <sub>f</sub> | Clock Rise & Fall Time (10%-90%)           |      |      | 2.0  | μs    | · · · · · ·                     |

| <sup>t</sup> PWR                | Reset Pulse Width                          | 500  |      |      | ns    |                                 |

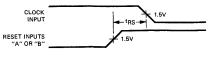

| tRS                             | Reset to Clock Set Up Time                 | 100  | 300  |      | ns    | Fig. 5                          |

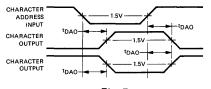

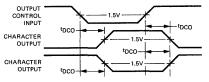

| <sup>t</sup> DAO                | Character Address to Output<br>Access Time |      | 500  | 1000 | ns    | Notes 4 & 5, Fig. 1             |

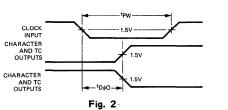

| <sup>t</sup> DøO                | Clock to Output Access Time                |      | 500  | 1000 | ns    | Notes 4 & 5, Fig. 2             |

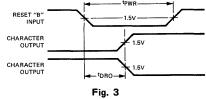

| <sup>t</sup> DRO                | Reset to Output Time Delay                 |      | 300  | 600  | ns    | Notes 4 & 5, Fig. 3             |

| <sup>t</sup> DBO                | Blanking to Output Time Delay              |      | 300  | 1000 | ns    | Notes 4 & 5, Fig. 6             |

| <sup>t</sup> DøC                | Clock to Counter Output Time Delay         |      | 300  | 500  | ns    | Notes 4 & 5, Fig. 2             |

| <sup>t</sup> DRC                | Reset to Counter Output Time Delay         |      | 300  | 500  | ns    | Notes 4 & 5, Fig. 3             |

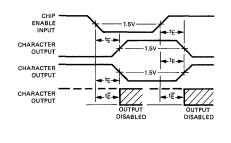

| <sup>t</sup> DOE                | Output Enable Delay Time                   |      | 300  | 600  | ns    | Notes 4 & 5, Fig. 4             |

| tDOD                            | Output Disable Delay Time                  |      | 300  | 600  | ns    | Notes 4 & 5, Fig. 4             |

| CI                              | Input Capacitance                          |      | 5.0  | 1.0  | pF    | f = 1.0 MHz, 0 V Bias<br>Note 1 |

4. AC Output LOW level is defined as 0.4 V @ 1.6 mA, current sinking (i.e., 1 TTL load).

5. AC Output HIGH level is defined as 2.4 V @ -0.6 mA, current sourcing (i.e., 1 TTL load).

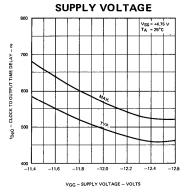

CHARACTER ADDRESS TO OUTPUT

ACCESS TIME VERSUS

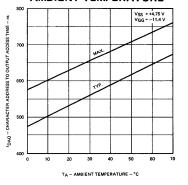

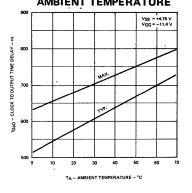

CLOCK TO OUTPUT TIME DELAY VERSUS

CLOCK TO OUTPUT TIME DELAY VERSUS AMBIENT TEMPERATURE

$\tau^{2}$

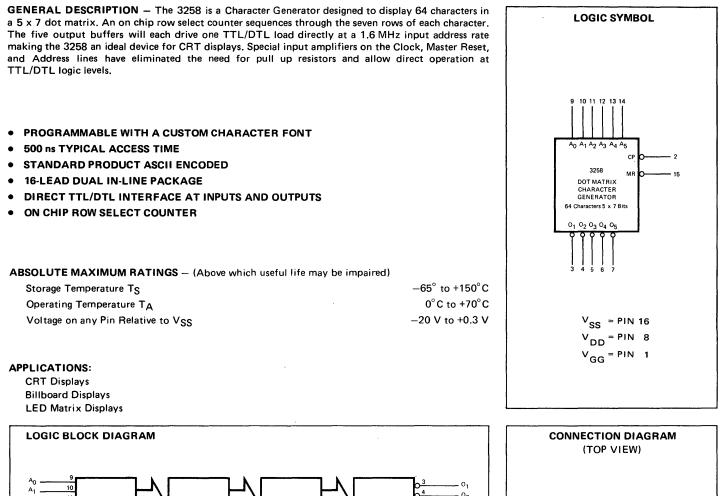

# **3258** DOT MATRIX CHARACTER GENERATOR

64 CHARACTERS 5 × 7 BITS FAIRCHILD SILICON GATE MOS INTEGRATED CIRCUIT

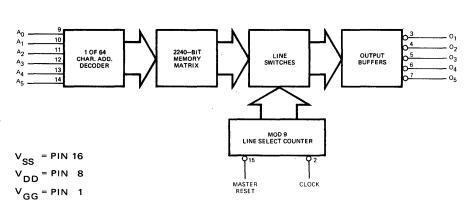

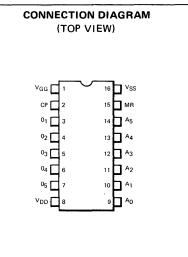

**FUNCTIONAL DESCRIPTION** – A Master Reset pulse ( $\cong$  GND) is required to set the Modulo 9 counter to the first state. A 6-bit binary word present at the address inputs is decoded to select 1 of 64 characters in the memory. Information, representing the first row of the character, will be available at the five outputs the next clock time after the Master Reset goes HIGH ( $\cong$  V<sub>SS</sub>). The next six rows of the character are sequentially selected by the counter. The last state of the counter, like the first state, clamps the outputs HIGH ( $\cong$  V<sub>SS</sub>) which provides 2-space blanking between lines. The counter dead ends at the last state and the outputs will remain HIGH ( $\cong$  V<sub>SS</sub>) providing blanking, until another Master Reset pulse is provided.

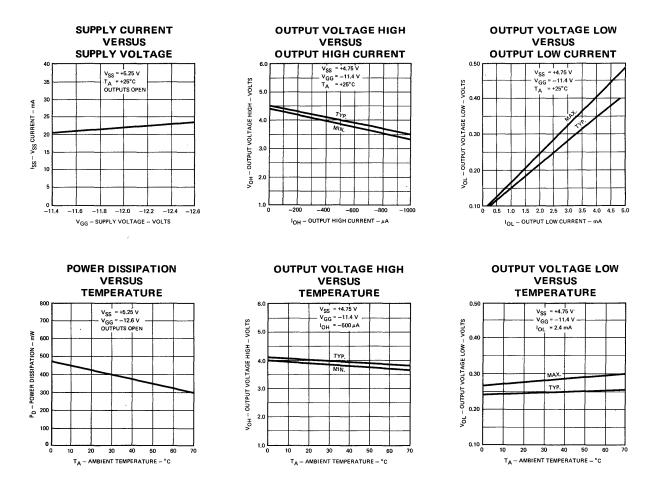

| SYMBOL                             | CHARACTERISTIC          | MIN.                  | TYP. | MAX.            | UNITS | CONDITIONS                                                           |

|------------------------------------|-------------------------|-----------------------|------|-----------------|-------|----------------------------------------------------------------------|

| VIH                                | Input Voltage HIGH      | V <sub>SS</sub> -2.75 |      | V <sub>SS</sub> | v     | Note 1                                                               |

| V <sub>IH</sub><br>V <sub>IL</sub> | Input Voltage LOW       | V <sub>GG</sub>       | 0    | 0.55            | V     | Note 1                                                               |

| VOH                                | Output Voltage HIGH     | 2.4                   | 3.5  | V <sub>SS</sub> | ۲V    | IOH =0.5 mA                                                          |

| V <sub>OH</sub><br>Vol             | Output Voltage LOW      | 0                     | 0.3  | 0.4             | V     | IOL = 2.4 mA                                                         |

| JLI                                | Input Leakage Current   |                       |      | 1.0             | μA    | V <sub>IN</sub> = -13 V (Note 1)                                     |

| ISS                                | V <sub>SS</sub> Current |                       | 23   | 28              | mA    | V <sub>SS</sub> = +5.25 V, V <sub>GG</sub> = -12.6 V<br>Outputs Open |

| I <sub>GG</sub>                    | V <sub>GG</sub> Current |                       | -23  | -28             | mA    | V <sub>SS</sub> = +5.25 V, V <sub>GG</sub> = -12.6 V<br>Outputs Open |

| PD                                 | Power Dissipation       |                       | 410  | 500             | mW    |                                                                      |

#### DC CHARACTERISTICS: $V_{SS}$ = +5 V ±5%, $V_{GG}$ = -12 V ±5%, $V_{DD}$ = 0 V, $T_A$ = 0°C to 70°C.

NOTE 1: Inputs include Character Address, Count Control, Clock, and Master Reset.

# TYPICAL ELECTRICAL CHARACTERISTICS

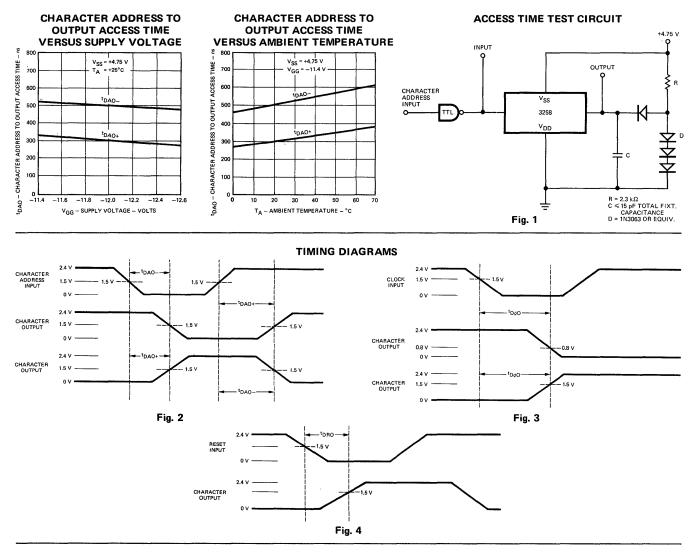

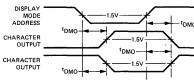

| SYMBOL                          | CHARACTERISTIC                         |       | MIN. | TYP. | MAX. | UNITS | CONDITIONS   |

|---------------------------------|----------------------------------------|-------|------|------|------|-------|--------------|

| f                               | Clock Frequency                        |       | 0    |      | 500  | kHz   | ·····        |

| t <sub>ØW</sub>                 | Clock Pulse Width                      |       | 1.0  |      |      | μs    |              |

| t <sub>r</sub> , t <sub>f</sub> | Clock Rise and Fall Time               |       |      |      | 2.0  | μs    |              |

| tRW                             | Reset Pulse Width                      | 500   |      |      | ns   |       |              |

| tCRD                            | Clock to Reset Time Delay              |       | 200  |      |      | ns    |              |

| <sup>t</sup> AO                 | Character Address to Output Time Delay | 3258A |      |      | 625  | ns    | Figure 1 & 2 |

|                                 |                                        | 3258B |      |      | 695  | ns    |              |

|                                 |                                        | 3258C |      |      | 780  | ns    |              |

|                                 |                                        | 3258D |      |      | 1    | μs    |              |

| tCO                             | Clock to Output Time Delay             |       |      |      | 2.0  | μs    | Figure 1 & 3 |

| tRO                             | Reset to Output Time Delay             |       |      |      | 2.0  | μs    | Figure 1 & 4 |

#### GLOSSARY OF TERMS

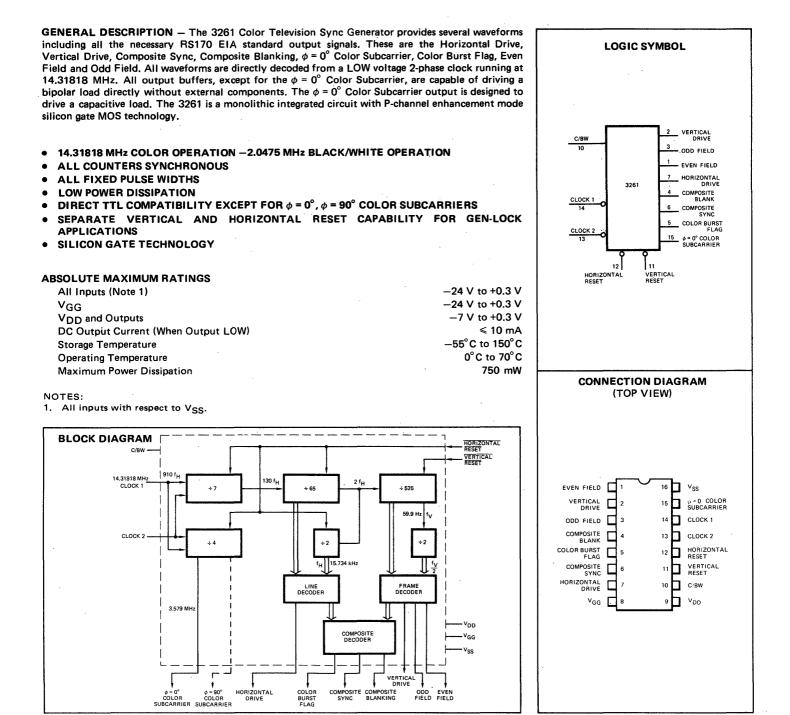

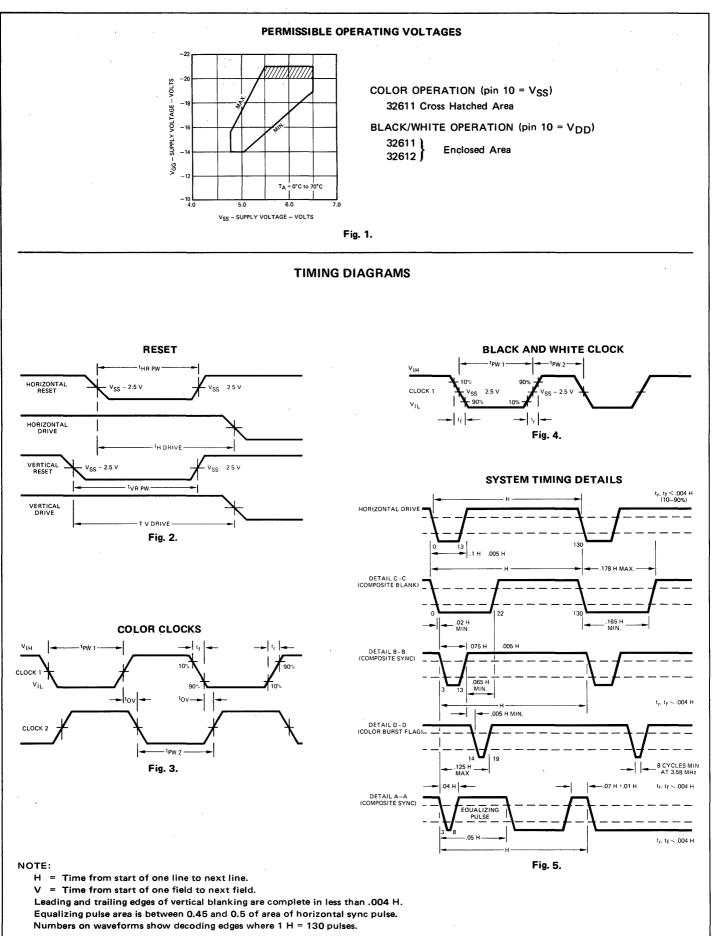

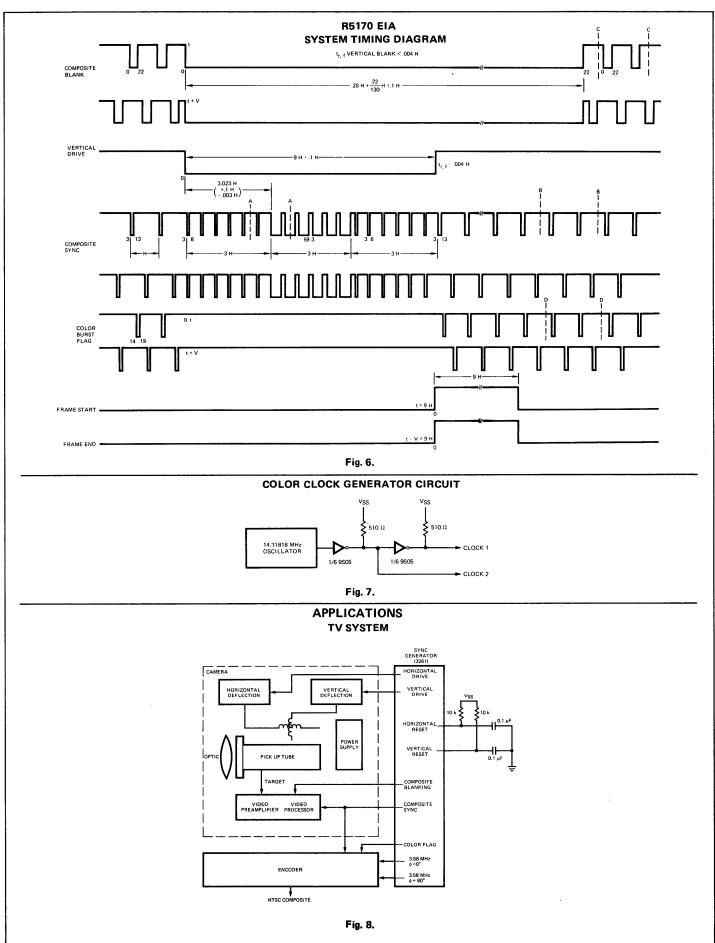

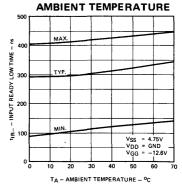

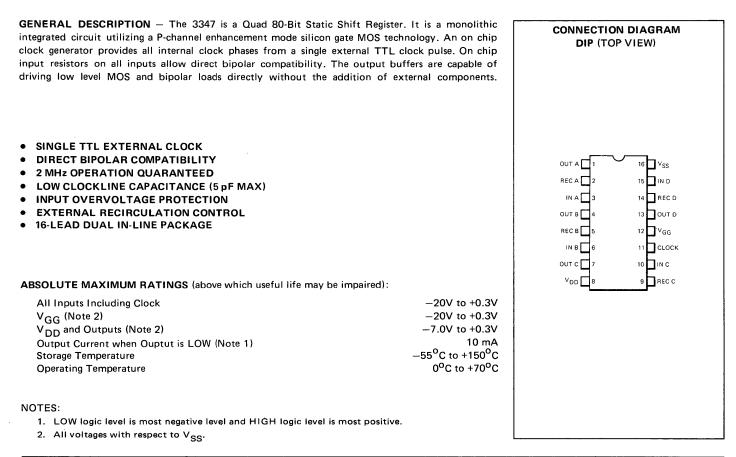

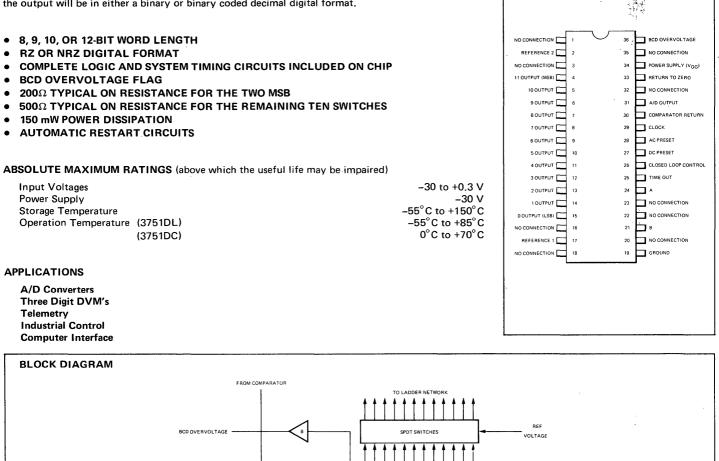

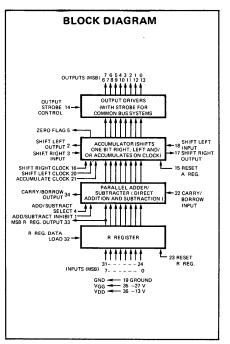

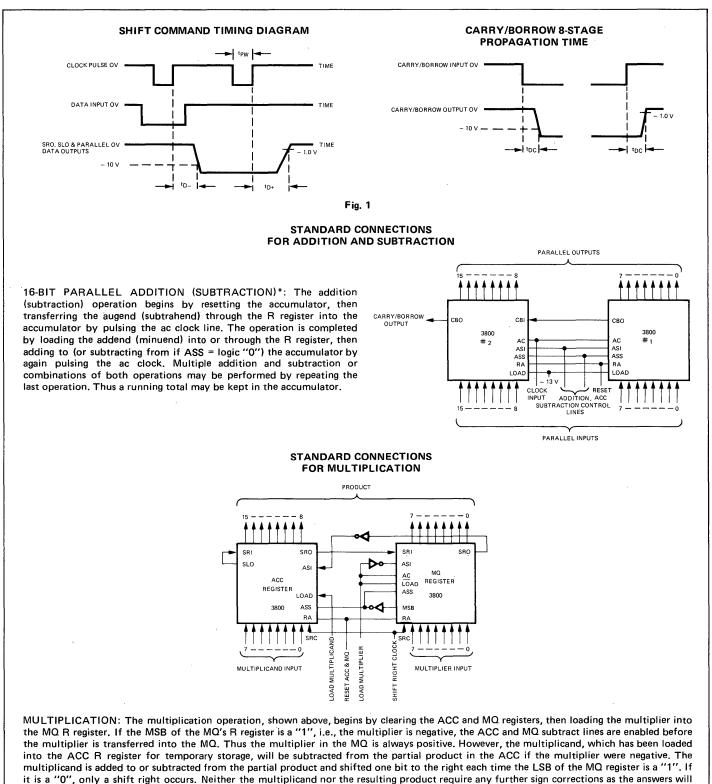

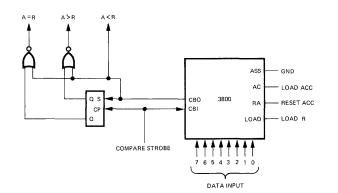

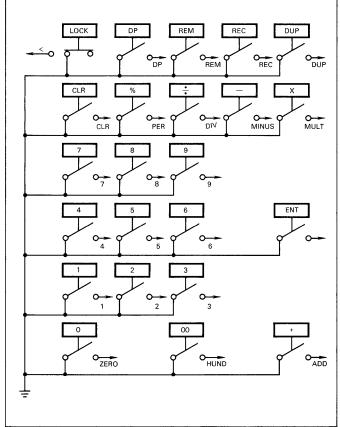

| 00/111 |                  |                                                                                                                                                                                                               |