# FEATURES

#### Microcontroller Interface

- Supports high-speed microcontroller interfaces (e.g., 16 MHz 80C188, 12 MHz 68HC11, 30 MHz HPC460X3)

- Supports comprehensive masked interrupt and polled structures for firmware flexibility

- Complements and shares address space with companion CL-SM331 SCSI Disk Controller

- Provides single-pin selection of direct compatibility with Intel®-or Motorola®-style microcontrollers

#### **Optical Format Support**

- Incorporates embedded (2,7) RLL ENDEC

- Fully supports ANSI/ISO standard re-writable, partial ROM, and WORM (Write-Once, Read-Many) optical formats using continuous/composite servoing

- Supports ANSI/ISO standard ECC/CRC codes

- Provides internal programmable voting thresholds for Sector Mark, ID Fields, Data Sync Mark, and Resync Marks

- Provides hardware PLL re-synchronization capability for automatic detection of and recovery from loss of frequency lock

#### High Performance

Supports up to 24 MHz NRZ data rates

# Optical Disk ENDEC/ECC

# **OVERVIEW**

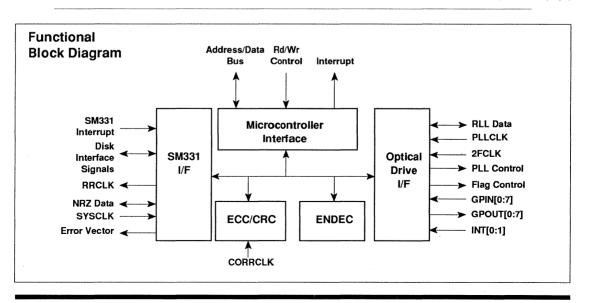

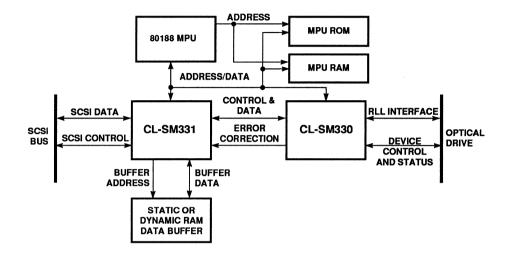

The CL-SM330 Optical Disk ENDEC/ECC is a VLSI component designed to work with the CL-SM331 SCSI Optical Disk Controller to provide the majority of hardware required to implement a Small Computer System Interface (SCSI) optical disk controller. The combination of the CL-SM330 and the CL-SM331 has been designed for embedded optical disk drive applications where minimal real estate, reduced microcontroller intervention, and maximum performance capability are required. The CL-SM330 incorporates a high-speed microcontroller interface, (2,7) RLL Encoder/ Decoder, error-correcting code and CRC code generator, full hardware error detection and correction circuitry and additional logic required to support ANSI/ISO standard re-writable and writeonce optical drives using continuous/composite servoing.

(cont. next page)

(cont. next page)

# FEATURES (cont.)

- Provides 'on-the-fly' hardware error correction without microcontroller intervention

- Allows multiple-sector transfers without microcontroller intervention

#### Comprehensive Interface

- Direct connection to companion CL-SM331 SCSI Optical Disk Controller without 'glue' logic

- Provides address-decoded, eight-bit, generalpurpose I/O ports and external interrupt sources for drive control requirements

#### Technology

- 100-pin Quad Flat Pack (QFP) package

- Pinout coordinated with CL-SM331 for optimum board layout efficiency

- Advanced, low-power, double-metal CMOS technology

# ADVANTAGES

#### Unique Features and Benefits

- Pin configurable microcontroller control interface

- Allows direct connection to Intel- or Motorolastyle microcontrollers

- 'On-the-fly' error correction is transparent to local microcontroller

- Relieves microcontroller of error-correction overhead

- Sophisticated track-format-related error retry sequences

- Highest error recovery capability

- Automatic bad-sector slipping support

- Avoids loss of disk orientation for known defective sectors

- Proprietary error-correcting code generator and corrector designs

- Image: Minimum gate count

- Diagnostic modes for testing EDAC circuitry without writing to the medium

- High testability

# OVERVIEW (cont.)

A local microcontroller sets the initial operating parameters for both the CL-SM330 and CL-SM331. Once initialized, multiple-sector operations may be executed without microcontroller intervention. Features such as auto-incrementing ID registers and fully automated error correction relieve the microcontroller of real-time interaction with disk activity. Virtually all controller functions are programmable by the microcontroller via read/write registers. This provides substantial firmware control over drive operation to allow for unique requirements, various retry methods, etc.

Full ANSI/ISO format support provides for programmable Sector Mark, ID Field, Data Sync Mark, and Resync Mark thresholds, automatic hardware PLL re-synchronization capability, compensation for Sector Mark Asymmetry, and Flag Generation and Detection. Output signals are provided to indicate the position of the Pre-Formatted Data Area, the Track Offset Flag Area and the Automatic Laser Power Control Area. Other output signals are provided for data synchronizer (PLL) control. During either normal phase lock, or if phase lock is lost while reading, these output signals can properly coordinate and control Phase/Frequency or Phase-Only Lock Mode, reference oscillator or data input multiplexing, and wide or narrow PLL loop bandwidth.

The CL-SM330 supports standard 512-byte sectors with five ECC interleaves or 1024-byte sectors with ten ECC interleaves. The absolute address of sector data in the data buffer is tracked by the CL-SM330, thereby allowing the generation of correction vectors for erroneous data. These vectors are transferred to CL-SM331, which corrects the erroneous data in the buffer, without microcontroller intervention. Vendor unique or control pointer data can also be stored in the buffer RAM and be accessible to either the local microcontroller or the SCSI host interface. All but worst-case consecutive sector errors are corrected without loss of disk orientation.

Page

# TABLE OF CONTENTS

Section

#### Section Page 1. PIN INFORMATION ......5 Pin Diagram for the 100-pin Quad Flat Pack 1.1 (QFP) Package .....5 2. PIN ASSIGNMENTS ......6 2.1 22 CL-SM331 Interface Pins ......8 Device Interface Pins ......10 23 2.4 Power, Ground and Misc. Pins ......12 Interrupt Registers ......14 3.2 Mark Detection Control Registers ......14 3.3 3.4 Window Control Registers ......14 3.5 ECC Control Registers ......15 Miscellaneous Registers ......15 3.6 3.7 Register and Bit Table ......16 4. FUNCTIONAL DESCRIPTION ......22 Read Sector Operation ......22 4.1 Write Sector Operation ......24 4.2 Read ID Operation ......24 4.3 Search ID Operation ......25 4.4 4.5 Blank Sector Operations ......25 RLL Encode/Decode Circuits ......26 4.6 47 Mark Generation ......28 4.8 Timing Strategy and Window 4.9 4.10 Data Synchronization Functions .......29 4.15 ECC Hardware Correction

#### 5.1 Reset Conditions 36 5.2 6.1

11H Configuration Register 2 ...... 39 6.2 12H Configuration Register 3 ...... 41 6.3 13H Sectors Per Track ...... 43 6.4 6.5 14H ID Target Sector ...... 43 15H ID Target Track LSB ...... 43 6.6 16H ID Target Track MSB ...... 44 6.7 6.8 17H ID Compare Sector ..... 44 18H ID Compare Track LSB ...... 44 69 6.10 19H ID Compare Track MSB ...... 44 6.11 1AH Sector Transfer Count ...... 45 6.12 1BH Sector Correction Count ...... 45 6.13 1CH. 57H Data Buffer Address 6.14 1DH. 58H Data Buffer Address Middle ...... 46 6.15 1EH. 59H Data Buffer Address High ...... 47

# 6.16 1FH Revision Number ...... 47

# 7. INTERRUPT REGISTERS ......48

- 7.1 20H Interrupt Enable Register ....... 48

- 7.2 21H Media Error Enable Register ..... 49

- 7.3 22H Interrupt Status Register ...... 51 23H Media Error Status Register ..... 54 7.4

# 8. MARK DETECTION CONTROL

| REC | REGISTERS56 |                                |  |  |  |  |

|-----|-------------|--------------------------------|--|--|--|--|

| 8.1 | 24H         | Sector Mark Control 56         |  |  |  |  |

| 8.2 | 25H         | Resync Mark Control 57         |  |  |  |  |

| 8.3 | 26H         | ID Field/Data Sync Control 58  |  |  |  |  |

|     |             | ID Error Status (Read Only) 59 |  |  |  |  |

# TABLE OF CONTENTS (cont.)

| Se | ection Pag                                                                          | e Section  | Page                     |

|----|-------------------------------------------------------------------------------------|------------|--------------------------|

| 9. | WINDOW CONTROL REGISTERS6                                                           |            | Vendor Unique Byte 370   |

|    | 9.1 28H Window Control Register                                                     |            | Vendor Unique Byte 470   |

|    | 9.2 29H TOF Window Control                                                          |            | General Purpose Input71  |

|    | 9.3 2AH Sector Mark/ALPC Length 6                                                   | 2 11.6 39H | General Purpose Output71 |

|    | 9.4 2BH LFLD Control/ALPC Delay 6                                                   | 3 11.7 2FF | I, 33H, 3AH-3DH Reserved |

|    | 9.5 2CH PLL Polarity/Lock Control 6                                                 |            | Set Sector Mark Window71 |

|    | 9.6 2DH PLL Relock Control                                                          | 4 11.9 3F⊦ | I Test Register72        |

|    | 9.7 2EH LFLD Window Control                                                         | 5          |                          |

|    |                                                                                     | 12. ELECTF | RICAL SPECIFICATION74    |

| 10 | . ECC CONTROL REGISTERS6                                                            | 6 12.1 Abs | olute Maximum Ratings74  |

|    | 10.1 30H Error Correction Status                                                    | 6 12.2 DC  | Characteristics75        |

|    | 10.2 31H Error Corrector RAM Address 6                                              | 7 12.3 AC  | Characteristics75        |

|    | 10.3 32H Error Corrector RAM Data                                                   | 8          |                          |

|    |                                                                                     |            | L APPLICATION84          |

| 11 | . MISCELLANEOUS REGISTERS                                                           | 0          |                          |

|    | 11.1 34H Vendor Unique Byte 1       7         11.2 35H Vendor Unique Byte 2       7 |            | ING INFORMATION84        |

# APPENDIX A

# Section

# Page

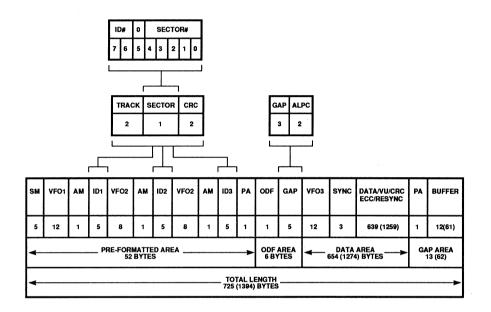

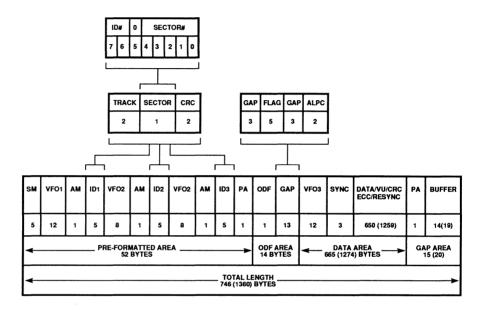

| 1. | ANS  | SI/ISO STANDARD TRACK FORMATS        | A-2  |

|----|------|--------------------------------------|------|

|    |      | 90 mm Sector Format                  |      |

|    | 1.2. | 130 mm Sector Format                 | A-5  |

|    | 1.3. | Sector Format Description            | A-8  |

|    | 1.4. | Error Correction and Detection Codes | A-10 |

# Figures

# Page

| Figure A-1. | 90 mm 512 (1024) Byte Sector Format      | A-2 |

|-------------|------------------------------------------|-----|

| Figure A-2. | 512-Byte Sector Data Field Organization  | A-3 |

| Figure A-3. | 1024-Byte Sector Data Field Organization | A-4 |

| Figure A-4. | 130mm 512 (1024)-Byte Sector Format      | A-5 |

| Figure A-5. | 512-Byte Sector Data Field Organization  | A-6 |

| Figure A-6. | 1024-Byte Sector Data Field Organization | A-7 |

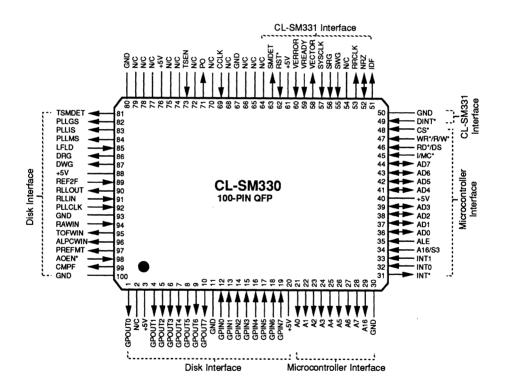

# 1. **PIN INFORMATION**

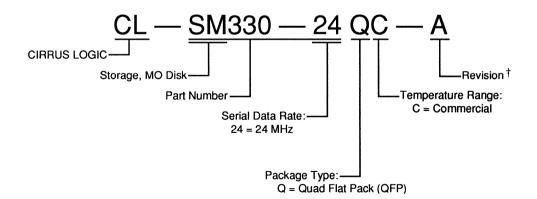

The CL-SM330 is available in a 100-pin Quad Flat Pack (QFP) package. The pin diagram below shows this package. All unused inputs must be tied to the inactive state, VDD or VSS, as appropriate.

# 1.1 Pin Diagram for the 100-Pin Quad Flat Pack (QFP) Package

# 2. PIN ASSIGNMENTS

The following conventions are used in the pin assignment tables. An asterisk (\*) denotes a negative-true (low-active) signal. An input pin is indicated by (I). An output pin is indicated by (O). An open-drain output pin is indicated by (OD). A high-impedance output is indicated by (Z). An input/output pin is indicated by (I/O). All unused inputs must be tied to the inactive state, VDD or VSS, as appropriate.

| SYMBOL   | PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT      | 31  | OD/O | <b>INTERRUPT:</b> This signal is an interrupt line to the microcon-<br>troller. Its polarity and output driver type (push-pull or open<br>drain) are programmable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CS*      | 48  | I    | CHIP SELECT: This signal must be asserted for all microcon-<br>troller accesses to the CL-SM330 registers. It is low active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

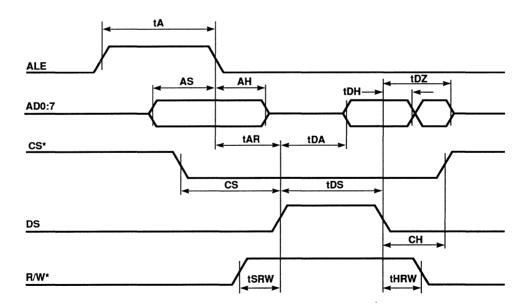

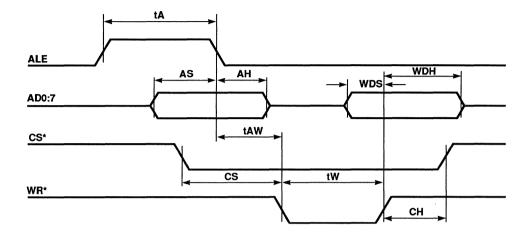

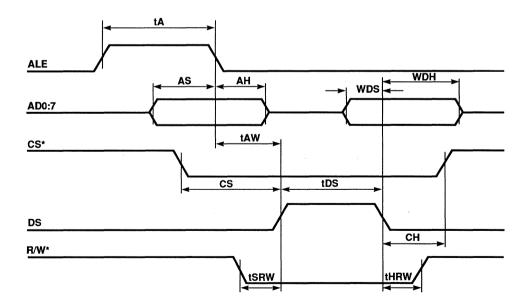

| WR*/R-W* | 47  | I    | WRITE STROBE/READ-WRITE: When the I/MC* Input is<br>high, this signal acts as the WR* Signal; when CS* and WR*<br>are asserted, the data on the AD Bus will be written to the<br>specified register. When the I/MC* Input is low, this signal<br>acts as the R-W* Signal, that determines the direction of data<br>transfer when accessing the CL-SM330 registers. When CS*<br>and DS are asserted and R-W* is high, a register read oper-<br>ation is in progress. When CS* and DS are asserted and R-<br>W* is low, a register write operation is in progress.                                                                                                                                                         |

| RD*/DS   | 46  | I    | <b>READ STROBE/DATA STROBE:</b> When the I/MC* Input is high, this signal acts as the RD* Signal; when CS* and RD* are asserted, the data from the specified register will be driven onto the AD Bus. When the I/MC* Input is low, this signal acts as the DS Signal, that determines the data timing of a register access. When CS* is asserted and R-W* is high, the rising edge of DS indicates when the CL-SM330 may start driving data onto the AD Bus. When CS* is asserted and R-W* is low, the trailing edge of DS indicates when the CL-SM330 may start driving data onto the AD Bus. When CS* is asserted and R-W* is low, the trailing edge of DS indicates when the CL-SM330 may latch data from the AD Bus. |

### 2.1 Microcontroller Interface Pins

# 2.1 Microcontroller Interface Pins (cont.)

| SYMBOL    | PIN         | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                          |

|-----------|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/MC*     | 45          | I    | <b>INTEL/MOTOROLA:</b> This signal selects the microcontroller interface to be used. When this signal is high, it selects the Intel Bus Control Interface. When this signal is low, it selects the Motorola Bus Control Interface. An internal pull up allows this signal to be legally 'floated' to select the default Intel Bus Control Interface. |

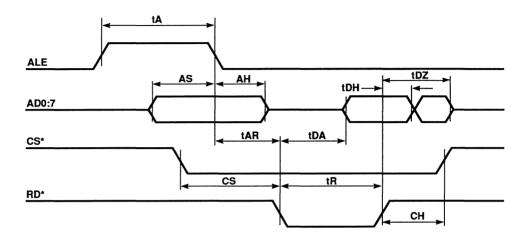

| AD[7:0]   | 44-41,39-36 | I/O  | <b>MICROCONTROLLER ADDRESS/DATA BUS:</b> These eight signals are the tristate Address/Data signals that interface with a multiplexed Microcontroller Address/Data Bus.                                                                                                                                                                               |

| A16/S3    | 34          | I    | <b>MICROCONTROLLER ADDRESS BIT 16:</b> This is the ninth address bit to allow addressing of up to 128K bytes of memory when in the Intel Mode.                                                                                                                                                                                                       |

| AOEN*     | 98          | I    | ADDRESS OUTPUT ENABLE: This signal is the tristate en-<br>able control for the A[16,7:0] Latched Address Output buffers.<br>A zero at this input will enable A[16,7:0]. This input must not<br>be allowed to float.                                                                                                                                  |

| ALE       | 35          | 1    | ADDRESS LATCH ENABLE: On the trailing edge of this signal, the CL-SM330 latches the address present on the AD Bus and the A16/S3 Input.                                                                                                                                                                                                              |

| RST*      | 62          | I    | <b>RESET:</b> Assertion of this signal halts all operations within the CL-SM330 and deasserts all output signals except A[16,7:0] and the AD Bus. With the exceptions listed above, all input/output signals and the INT Signal are set to the high-impedance state.                                                                                 |

| A[16,7:0] | 29-21       | Z    | <b>MICROCONTROLLER LATCHED ADDRESS:</b> This bus presents the nine address bits latched by ALE. These signals are provided for general system use and are always available, regardless of the state of CS*. They are controlled by the AOEN* Input.                                                                                                  |

# 2.2 CL-SM331 Interface Pins

| SYMBOL | PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

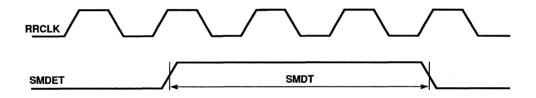

| SMDET  | 63  | 0    | SECTOR MARK DETECTED: This signal is asserted when a Sector Mark is detected or a Pseudo Sector Mark is gener-<br>ated.                                                                                                                                                                                                                                                                                                           |

| IDF    | 51  | 0    | <b>ID FOUND:</b> This signal is connected to the IDF Signal of the CL-SM331. It is asserted after the ODF (Offset Detection Flag, see Appendix A) when a Read, Write, or Blank Sector Operation is in progress. The ID Track and Sector numbers of the current sector match the ID Target registers when the ID Voting Threshold has been met.                                                                                    |

| SRG    | 56  | ł    | SEQUENCER READ GATE: This signal is connected to the Read Gate from the CL-SM331.                                                                                                                                                                                                                                                                                                                                                 |

| SWG    | 55  | I    | <b>SEQUENCER WRITE GATE:</b> This signal is connected to the Write Gate from the CL-SM331.                                                                                                                                                                                                                                                                                                                                        |

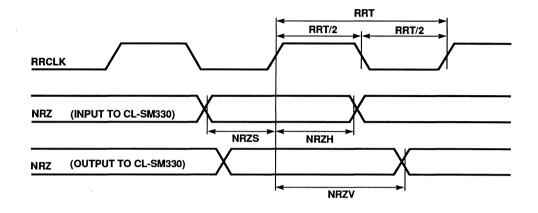

| RRCLK  | 53  | 0    | <b>READ REFERENCE CLOCK:</b> This signal clocks the NRZ Data Signal to or from the CL-SM331.                                                                                                                                                                                                                                                                                                                                      |

| NRZ    | 52  | I/O  | NON RETURN TO ZERO: This signal is the Read Data Out-<br>put to the CL-SM331 when SRG is asserted. It is the Write<br>Data Input from the CL-SM331 when SWG is asserted. In<br>both cases, it is synchronized to RRCLK. Data transferred<br>over the NRZ line is protected by an eight-bit CRC checksum.<br>The NRZ I/O Buffer has an internal pull-down resistor to pre-<br>vent the signal from floating when not being driven. |

| DINT*  | 49  |      | <b>DISK INTERRUPT INPUT:</b> This signal can be used to com-<br>bine interrupts from the CL-SM331 with interrupts generated<br>by the CL-SM330. Bits in the Interrupt Enable and Interrupt<br>Status registers are used to enable and distinguish the inter-<br>rupt sources. If not used, this input must be tied to VDD.                                                                                                        |

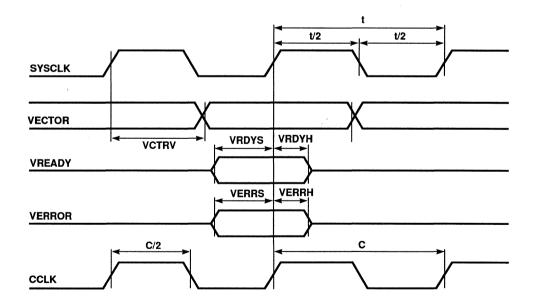

| SYSCLK | 57  | I    | SYSTEM CLOCK: This signal is used to clock the error vec-<br>tor transmission circuitry. It must be the same SYSCLK Sig-<br>nal used by the CL-SM331.                                                                                                                                                                                                                                                                             |

| CCLK   | 69  | Ι    | <b>CORRECTOR CLOCK:</b> This signal is used to clock the error corrector. For optimum performance, this signal should be connected to the fastest clock available, not exceeding 25 MHz.                                                                                                                                                                                                                                          |

# 2.2 CL-SM331 Interface Pins (cont.)

| SYMBOL | PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                  |

|--------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VECTOR | 58  | 0    | <b>ERROR CORRECTION VECTOR:</b> This signal is used to serially output error addresses and values for correction by the CL-SM331. Information transferred over the VECTOR line is protected by an eight-bit CRC code.                                                                                                        |

| VERROR | 60  | I    | <b>ERROR CORRECTION ERROR:</b> This signal is asserted by the CL-SM331 to indicate that it detected a vector transfer protocol error or that the error correction process was not successful (e.g., a buffer parity error was detected during error correction).                                                             |

| VREADY | 59  | I    | <b>ERROR CORRECTION READY:</b> This signal is deasserted<br>by the CL-SM331 after an error correction vector transfer is<br>initiated and reasserted when it is ready to accept another er-<br>ror correction vector. The CL-SM330 will not initiate an error<br>correction vector transfer while this signal is deasserted. |

### 2.3 Device Interface Pins

| SYMBOL  | PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                                 |

|---------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRG     | 86  | 0    | <b>DEVICE READ GATE:</b> This signal is the Read Gate sent to the device.                                                                                                                                                                                   |

| DWG     | 87  | 0    | <b>DEVICE WRITE GATE:</b> This signal is the Write Gate sent to the device.                                                                                                                                                                                 |

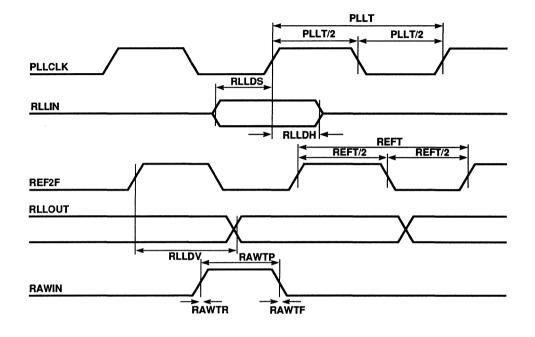

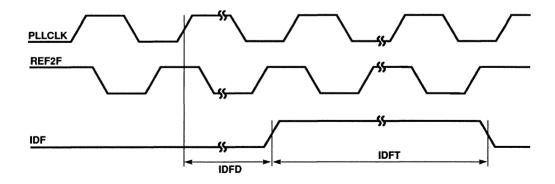

| PLLCLK  | 92  | I    | <b>PLL CLOCK:</b> This signal is the PLL clock from the data syn-<br>chronizer in the device (2F - two times NRZ frequency). It is<br>used to clock read data from the RLLIN line.                                                                          |

| REF2F   | 89  | I    | <b>2F REFERENCE CLOCK:</b> This signal is the reference clock from the device (2F - two times NRZ frequency). It is used to clock write data onto the RLLOUT line and to control windowing.                                                                 |

| RLLIN   | 91  | I    | <b>RLL DATA IN:</b> This signal is the RLL read data from the device PLL (synchronized to PLLCLK).                                                                                                                                                          |

| RLLOUT  | 90  | 0    | <b>RLL DATA OUT:</b> This is the RLL write data sent to the device (synchronized to REF2F).                                                                                                                                                                 |

| RAWIN   | 94  | I    | <b>RAW INPUT:</b> This signal is the Raw Read Data Signal used for Sector Mark Detection, and for WORM (Write-Once, Read-Many) applications, Flag Field, and Blank Sector Detection.                                                                        |

| TOFWIN  | 95  | 0    | TRACK OFFSET FLAG WINDOW: This signal is asserted<br>when the optical head is over the Offset Detection Flag. This<br>signal is not asserted unless the Sector Mark or either ID1 or<br>ID2 is error-free preceding the ODF (see Appendix A).               |

| ALPCWIN | 96  | 0    | ALPC WINDOW: This signal is asserted when the optical head is over the Automatic Laser Power Control Area after a good Sector Mark or Error-Free ID.                                                                                                        |

| PREFMT  | 97  | 0    | <b>PRE-FORMAT WINDOW:</b> This signal is always asserted when the optical head is over the Pre-Formatted Area. When the Disable Pre-Format Window Bit in Window Control Register 1 is not set, this signal is deasserted over the Gap and Data Field areas. |

# **CL-SM330** Optical Disk ENDEC/ECC

# 2.3 Device Interface Pins (cont.)

.....

| SYMBOL     | PIN     | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                        |

|------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

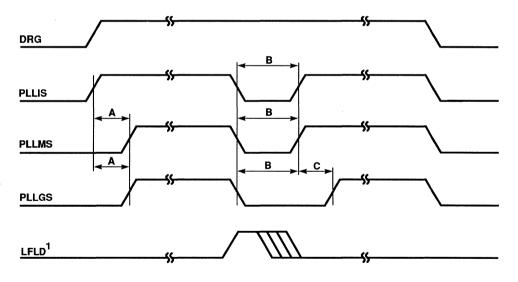

| PLLIS      | 83      | 0    | <b>PLL INPUT SELECT:</b> This signal is used to control the PLL Input Source. When this signal is deasserted, the reference input to the PLL is selected. When this signal is asserted, the Data Input to the PLL is selected. Use of this signal is optional.                                     |

| PLLMS      | 84      | 0    | <b>PLL MODE SELECT:</b> This signal is used to control the PLL Detection Mode. When this signal is deasserted, the Phase-Frequency Detection Mode is selected. When this signal is asserted, the Phase-Only Detection Mode is selected. Use of this signal is optional.                            |

| PLLGS      | 82      | 0    | <b>PLL GAIN SELECT:</b> This signal is used to control the PLL Gain Mode. When this signal is deasserted, the PLL is placed in High-Gain Mode. When this signal is asserted, the PLL is placed in Low-Gain Mode. Use of this signal is optional.                                                   |

| LFLD       | 85      | I    | LOSS OF FREQUENCY LOCK DETECTED: This signal is<br>asserted by external circuitry when it detects Loss-Of-Fre-<br>quency-Lock. Use of this signal is optional. The CL-SM330<br>has internal circuitry for detection of PLL Loss-Of-Frequency-<br>Lock. If unused, this signal must be tied to VSS. |

| TSMDET     | 81      | 0    | <b>TRUE SECTOR MARK DETECTED:</b> This signal is asserted<br>when a Sector Mark is detected. It is not asserted when a<br>pseudo sector mark is generated. This signal is provided for<br>use by the drive servo system. Use of this signal is optional.                                           |

| CMPF       | 99      | 0    | <b>COMPARE REGISTER FOUND:</b> This signal is asserted<br>when the CL-SM330 determines that it is at the beginning of<br>the sector specified in the compare register. The signal is a<br>pulse of width 32 RRCLK periods.                                                                         |

| GPIN[7:0]  | 19-12   | I    | <b>GENERAL-PURPOSE INPUTS:</b> These signals are Gener-<br>al-Purpose inputs suitable for device control. They are<br>Schmitt Trigger inputs. If unused, they must be tied to either<br>VSS or VDD.                                                                                                |

| GPOUT[7:0] | 10-4, 1 | 0    | <b>GENERAL-PURPOSE OUTPUTS:</b> These signals are General-Purpose outputs suitable for device control.                                                                                                                                                                                             |

**2.3 Device Interface Pins** (cont.)

| SYMBOL    | PIN   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                           |

|-----------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT [1:0] | 33-32 | I    | <b>INTERRUPT 1-0:</b> These signals are general-purpose edge-<br>sensitive interrupts with programmable polarity. When dis-<br>abled by writing a '0' to the appropriate Interrupt Enable Reg-<br>ister bits, these inputs may be used in the same manner as<br>the GPIN inputs. If unused, these pins must be tied to VDD or<br>VSS. |

# 2.4 Power, Ground and Miscellaneous Pins

| SYMBOL | PIN                                   | TYPE | DESCRIPTION                                                                         |

|--------|---------------------------------------|------|-------------------------------------------------------------------------------------|

| VDD    | 3,20,<br>40,61,<br>76,88              | N/A  | Power Supply (+5 VDC).                                                              |

| VSS    | 11,30,<br>50,67,<br>80,93,100         | N/A  | Ground Pins.                                                                        |

| N/C    | 2,54,64-66<br>68,70,72<br>74,75,77-79 | N/A  | No Connection.                                                                      |

| TSEN   | 73                                    | I    | <b>TRISTATE ENABLE:</b> Must be tied to VDD for proper functioning of the CL-SM330. |

| PO     | 71                                    | 0    | PARAMETRIC TEST OUTPUT: Do not load.                                                |

# 3. REGISTER TABLES

# 3.1 Configuration Registers

Convention: xxH indicates a hexadecimal number.

| ADDRESS  | ТҮРЕ | DESCRIPTION/FUNCTION                          |

|----------|------|-----------------------------------------------|

| 10H      | R/W  | Configuration Register 1                      |

| 11H      | R/W  | Configuration Register 2                      |

| 12H      | R/W  | Configuration Register 3                      |

| 13H      | R/W  | Sectors Per Track                             |

| 14H      | R/W  | ID Target Sector                              |

| 15H      | R/W  | ID Target Track LSB                           |

| 16H      | R/W  | ID Target Track MSB                           |

| 17H      | R/W  | ID Compare Sector                             |

| 18H      | R/W  | ID Compare Track LSB                          |

| 19H      | R/W  | ID Compare Track MSB                          |

| 1AH      | R/W  | Sector Transfer Count                         |

| 1BH      | R    | Sector Correction Count                       |

| 1CH, 57H | R/W  | Data Buffer Address Low                       |

| 1DH, 58H | R/W  | Data Buffer Address Middle                    |

| 1EH, 59H | R/W  | Data Buffer Address High (Bit 7 is read only) |

| 1FH      | R    | Revision Number                               |

# 3.2 Interrupt Registers

| ADDRESS | TYPE | DESCRIPTION/FUNCTION                                                            |

|---------|------|---------------------------------------------------------------------------------|

| 20H     | R/W  | Interrupt Enable Register                                                       |

| 21H     | R/W  | Media Error Interrupt Enable Register                                           |

| 22H     | R/W  | Interrupt Status Register<br>(some bits are read only under certain conditions) |

| 23H     | R/W  | Media Error Interrupt Status Register                                           |

# 3.3 Mark Detection Control Registers

| ADDRESS | TYPE | DESCRIPTION/FUNCTION       |

|---------|------|----------------------------|

| 24H     | R/W  | Sector Mark Control        |

| 25H     | R/W  | Resync Mark Control        |

| 26H     | R/W  | ID Field/Data Sync Control |

| 27H     | R    | ID Error Status            |

# 3.4 Window Control Registers

| ADDRESS | ΤΥΡΕ | DESCRIPTION/FUNCTION                                                          |

|---------|------|-------------------------------------------------------------------------------|

| 28H     | R/W  | Window Control Register                                                       |

| 29H     | R/W  | TOF Window Control                                                            |

| 2AH     | R/W  | Sector Mark/ALPC Length                                                       |

| 2BH     | R/W  | LFLD Control/ALPC Delay<br>(some bits are read only under certain conditions) |

| 2CH     | R/W  | PLL Polarity/Lock Control                                                     |

| 2DH     | R/W  | PLL Relock Control                                                            |

| 2EH     | R/W  | LFLD Window Control                                                           |

# 3.5 ECC Control Registers

| ADDRESS | TYPE | DESCRIPTION/FUNCTION        |  |

|---------|------|-----------------------------|--|

| 30H     | R    | Error Correction Status     |  |

| 31H     | R/W  | Error Corrector RAM Address |  |

| 32H     | R/W  | Error Corrector RAM Data    |  |

# 3.6 Miscellaneous Registers

| ADDRESS              | TYPE | DESCRIPTION/FUNCTION                        |

|----------------------|------|---------------------------------------------|

| 34H                  | R/W  | Vendor Unique Byte 1                        |

| 35H                  | R/W  | Vendor Unique Byte 2                        |

| 36H                  | R/W  | Vendor Unique Byte 3                        |

| 37H                  | R/W  | Vendor Unique Byte 4                        |

| 38H                  | R    | General-Purpose Input                       |

| 39H                  | R/W  | General-Purpose Output                      |

| 2FH, 33H,<br>3AH-3DH |      | Reserved<br>Reserved                        |

| 3EH                  | W    | Set Sector Mark Window (test purposes only) |

| 3FH                  | R/W  | Test Register (test purposes only)          |

# 3.7 Register and Bit Table

| ADDRESS | TYPE | DESCRIPTION/FUNCTION                                                                                                                                                                                                                                                                                    |

|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10H     | R/W  | Configuration Register 1Bit 7:Chip ResetBit 6:Operation Halt/Chip BusyBit 5:Error ResetBit 4:Start Error Corrector/Error Corrector BusyBit 3:Suppress Correction VectorsBits 2-0:Operation Mode                                                                                                         |

| 11H     | R/W  | Configuration Register 2Bit 7:ReservedBit 6:Enable Buffer SegmentationBit 5:Enable Correction/Transfer of VU/PTR BytesBit 4:VU/PTR Source ModeBit 3:0.5/1% Speed Tolerance SelectBit 2:ReservedBit 1:90/130 mm Mode SelectBit 0:512/1024-byte Sector Mode Select                                        |

| 12H     | R/W  | Configuration Register 3Bit 7:Disable INT Output DriverBit 6:Negative INT PolarityBit 5:Enable ALPC Window on Read operationsBit 4:Enable DWG and DRG during ALPCBit 3:Disable Error CorrectionBit 2:Enable Erasure Pointer GenerationBit 1:Force RLLOUT High During DWG (Erase)Bit 0:Read Continuously |

| 13H     | R/W  | Sectors Per Track<br>Bit 7-6: INT1-0 Polarity<br>Bit 5-0: Sectors Per Track                                                                                                                                                                                                                             |

| 14H     | R/W  | ID Target Sector<br>Bit 7-6: ID Field Identifier<br>Bit 5-0: ID Target Sector                                                                                                                                                                                                                           |

| 15H     | R/W  | ID Target Track LSB<br>Bit 7-0: ID Target Track LSB                                                                                                                                                                                                                                                     |

| 16H     | R/W  | ID Target Track MSB<br>Bit 7-0: ID Target Track MSB                                                                                                                                                                                                                                                     |

CL-SM330 Optical Disk ENDEC/ECC

| ADDRESS  | TYPE | DESCRIPTION/FUNCTION                                                                                                                                                                                                                                                                                                                                                |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17H      | R/W  | ID Compare Sector<br>Bit 7-6: Reserved<br>Bit 5-0: ID Compare Sector                                                                                                                                                                                                                                                                                                |

| 18H      | R/W  | ID Compare Track LSB                                                                                                                                                                                                                                                                                                                                                |

| 19H      | R/W  | ID Compare Track MSB                                                                                                                                                                                                                                                                                                                                                |

| 1AH      | R/W  | Sector Transfer Count                                                                                                                                                                                                                                                                                                                                               |

| 1BH      | R    | Sector Correction Count                                                                                                                                                                                                                                                                                                                                             |

| 1CH, 57H | R/W  | Data Buffer Address Low                                                                                                                                                                                                                                                                                                                                             |

| 1DH, 58H | R/W  | Data Buffer Address Middle                                                                                                                                                                                                                                                                                                                                          |

| 1EH, 59H | R/W  | Data Buffer Address HighBit 7:Data Transfer Active (read only)Bit 6:ReservedBit 5-0:Data Buffer Address High                                                                                                                                                                                                                                                        |

| 1FH      | R    | Revision Number                                                                                                                                                                                                                                                                                                                                                     |

| 20H      | R/W  | Interrupt Enable RegisterBit 7:Enable Media Error InterruptsBit 6:Enable ECC Error InterruptsBit 5:Enable General-Purpose Int 1Bit 4:Enable General-Purpose Int 0Bit 3:Enable DINT* Pass-ThroughBit 2:Enable ID Compare Register Found IntBit 1:Enable Sector Transfer Count=0 IntBit 0:Enable Operation Complete Int                                               |

| 21H      | R/W  | Media Error Enable RegisterBit 7:Enable R/W Attempted After PSM IntBit 6:Enable Sector Mark Selected Outside Window IntBit 5:Enable ID Error IntBit 4:Enable Recovered Data Sync Error IntBit 3:Enable Fatal Data Sync Error IntBit 2:Enable Resync Mark Threshold Error IntBit 1:Enable Operation Attempted After Flag Detected IntBit 0:Enable Operation Complete |

| ADDRESS | TYPE | DESCRIPTION/FUNCTION                                                                                                                                                                                                                                                                                          |

|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22H     | R/W  | Interrupt Status RegisterBit 7:Media Error PendingBit 6:ECC Error PendingBit 5:General-Purpose Int 1 Asserted (read only if disabled)Bit 4:General-Purpose Int 0 Asserted (read only if disabled)Bit 3:DINT* AssertedBit 2:ID Compare Register FoundBit 1:Sector Transfer Count=0Bit 0:Operation Complete     |

| 23H     | R/W  | Media Error Status RegisterBit 7:Pseudo Sector Mark GeneratedBit 6:Sector Mark Detected Outside WindowBit 5:ID ErrorBit 4:Recovered Data Sync ErrorBit 3:Fatal Data Sync ErrorBit 2:Resync Mark Error Threshold ExceededBit 1:Written Flag Field DetectedBit 0:Error Correction Complete/Blank Error Detected |

| 24H     | R/W  | Sector Mark Control<br>Bit 7-6: Sector Mark, ID Read Gate, ID AM, and<br>Data Sync Window Position<br>Bit 5-3: Sector Mark-Mark Threshold (0-5)<br>Bit 2-0: Sector Mark-Space Threshold (0-4)                                                                                                                 |

| 25H     | R/W  | Resync Mark ControlBit 7:Enable False Resync ProtectionBit 6:False Resync Protection ModeBit 5-4:Resync Mark Skip Count (0-3)Bit 3-0:Resync Mark Error Threshold (0-15)                                                                                                                                       |

| 26H     | R/W  | ID Field/Data Sync ControlBit 7:Enable Modified ID Read GateBit 6:Disable Track AutoincrementBit 5-4:ID Voting Threshold (0-3)Bit 3-0:Data Sync Mark Threshold (0-12)                                                                                                                                         |

| 27H     | R    | ID Error Status<br>Bit 7: ID Threshold Error<br>Bit 6: ID Greater Than Target<br>Bit 5-3: CRC Error Detected For ID 3-1<br>Bit 2-0: ID AM Not Detected For ID 3-1                                                                                                                                             |

CL-SM330 Optical Disk ENDEC/ECC

| ADDRESS | TYPE | DESCRIPTION/FUNCTION                                                                                                                                                                                                |

|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28H     | R/W  | Window Control RegisterBit 7:Disable Pre-Format WindowBit 6:Disable Sector Mark WindowBit 5:Disable ID AM WindowBit 4:Disable Data Sync WindowBit 3-2:Resync Mark Window ControlBit 1-0:ID Skip Control             |

| 29H     | R/W  | <b>TOF Window Control</b><br>Bit 7-4: TOF Window Delay<br>Bit 3-0: TOF Window Length                                                                                                                                |

| 2AH     | R/W  | Sector Mark/ALPC Length<br>Bit 7: Enable Relaxed Sector Mark Detection<br>Bit 6: Enable Sector Mark Asymmetry Compensation<br>Bit 5: Shorten/Lengthen Sector Marks (if Bit 6 is set)<br>Bit 4-0: ALPC Window Length |

| 2BH     | R/W  | LFLD Control/ALPC Delay<br>Bit 7: Loss-Of-Frequency-Lock Detected (read only)<br>Bit 6: LFLD Polarity Select<br>Bit 5: Internal/LFLD Input Select<br>Bit 4-0: ALPC Window Delay                                     |

| 2CH     | R/W  | PLL Polarity/Lock ControlBit 7:PLLIS Polarity SelectBit 6:PLLMS Polarity SelectBit 5:PLLGS Polarity SelectBit 4:PLLMS Lock Delay EnableBit 3-0:PLL Lock Delay Count                                                 |

| 2DH     | R/W  | PLL Relock Control<br>Bit 7-4: PLL Relock Time Count<br>Bit 3-0: PLL Relock Delay Count                                                                                                                             |

| 2EH     | R/W  | LFLD Window Control<br>Bit 7-4: Internal Loss-of-Frequency-Lock Window Count<br>Bit 3-0: Internal Loss-of-Frequency-Lock Tolerance Count                                                                            |

| ADDRESS              | TYPE | DESCRIPTION/FUNCTION                                                                                                                                                                                                                                                                                                         |

|----------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30Н                  | R    | Error Correction StatusBit 7:Uncorrectable Error Detected by ECCBit 6:Uncorrectable Error Detected by CRCBit 5:Error Exceeding Threshold DetectedBit 4:ECC Correction Time Overrun OccurredBit 3:CL-SM330 Hardware Error DetectedBit 2:VREADY/VERROR Signal ErrorBit 1:NRZ CRC Checksum ErrorBit 0:Operational Overrun Error |

| 31H                  | R/W  | Error Corrector RAM Address                                                                                                                                                                                                                                                                                                  |

| 32H<br>RAM Addr 00H  | R/W  | Error Corrector RAM Data<br>Sector Correction Threshold<br>Bit 7: Reserved<br>Bit 6-0: Maximum Errors/Sector Allowed (0-40 or 0-80)                                                                                                                                                                                          |

| RAM Addr 01H         |      | Interleave Correction Threshold<br>Bit 7-4: Reserved                                                                                                                                                                                                                                                                         |

| RAM Addr 38H         |      | Bit 3-0: Maximum Errors/Interleave Allowed (0-8)<br><b>Total Sector Error Status</b><br>Bit 7: Reserved                                                                                                                                                                                                                      |

| RAM Addr 39H         |      | Bit 6-0: Maximum Errors/Sector Detected (0-40, or 0-80)<br>Interleave Error Status<br>Bit 7-6: Bits will be set if an uncorrectable ECC error was detected.<br>Bit 5-4: Reserved<br>Bit 3-0: Maximum Errors/Interleave Detected (0-7)                                                                                        |

| 34H                  | R/W  | Vendor Unique Byte 1                                                                                                                                                                                                                                                                                                         |

| 35H                  | R/W  | Vendor Unique Byte 2                                                                                                                                                                                                                                                                                                         |

| 36H                  | R/W  | Vendor Unique Byte 3                                                                                                                                                                                                                                                                                                         |

| 37H                  | R/W  | Vendor Unique Byte 4                                                                                                                                                                                                                                                                                                         |

| 38H                  | R    | General-Purpose Input                                                                                                                                                                                                                                                                                                        |

| 39H                  | R/W  | General-Purpose Output                                                                                                                                                                                                                                                                                                       |

| 2FH, 33H,<br>3AH-3DH |      | Reserved<br>Reserved                                                                                                                                                                                                                                                                                                         |

| 3EH                  | W    | Set Sector Mark Window                                                                                                                                                                                                                                                                                                       |

| ADDRESS | ТҮРЕ | DESCRIPTION/FUNCTION                                                                                                                      |

|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 3FH     | R/W  | Test RegisterBit 7:ReservedBit 6:Disable DWGBit 5:Enable Short Sector Test ModeBit 4:Enable ECC Diagnostic ModeBit 3-0:Test Mode Bits 3-0 |

# 4. FUNCTIONAL DESCRIPTION

The operation of the CL-SM330 is divided into several major functions:

- (2,7) RLL Encoding and Decoding

- Mark Generation and Detection

- ECC Redundancy and Remainder Generation

- Error Correction

An overview of the interaction of these functions during Read Sector, Write Sector, Read ID, Search ID, and Blank Sector operations is given below, followed by more detailed description of individual functions.

#### 4.1 Read Sector Operation

At initialization, the microcontroller programs the Writable Control Store of the CL-SM331 and configures the CL-SM330, including the medium size, medium type, and sector size to be employed. The physical track and sector address of the first sector to be read is written to the ID Target registers. The address in the data buffer, where the CL-SM331 will store the first byte of the first sector, is written to the Data Buffer Address registers. When the optical head has been positioned, the microcontroller initiates the Read Sector Operation by writing the Format Sequencer Start Address Register of the CL-SM331 and writing the number of sectors to be read to the Sector Transfer Count Register of the CL-SM330.

The CL-SM331 begins waiting for the CL-SM330 to assert the SMDET Signal. When the CL-SM330 detects a Sector Mark or generates a Pseudo Sector Mark, it asserts SMDET. If a Sector Mark was detected, the CL-SM330 also asserts TSM-DET. If a Pseudo Sector Mark was generated, the CL-SM330 also sets the Pseudo Sector Mark Generated Bit. The CL-SM331 begins waiting for assertion of IDF Output of the CL-SM330, within a programmable time-out window. The CL-SM330 asserts DRG and begins reading the ID fields, verifying their contents using the ID CRC check,

and comparing them to the ID Target registers. If the value in the ID Target registers is not matched. or if the ID Voting Threshold is not met, the CL-SM330 will not assert IDF and the CL-SM331 will time out and return to wait for the next assertion of SMDET. If the values in the ID Target registers are not matched within two disk revolutions, or if the values in the ID Target registers are matched. but the ID Voting Threshold is not met, or if the values in the ID Target registers are exceeded, the CL-SM330 will halt the Read Sector Operation. set the ID Error and Operation Complete bits, and optionally generate a microcontroller interrupt. Otherwise, it will wait for the Sector Mark of the next sector and repeat the ID Field validation process. If none of the ID fields of a sector are errorfree, the sector may be recovered by executing a Read ID Operation for a preceding sector to establish orientation, then setting the ID Voting Threshold to zero, and executing a single-sector Read Sector Operation for the desired sector.

If the value in the ID Target registers is matched and the ID Voting Threshold is met, the target sector has been located. If the Sector Mark was not detected, the CL-SM330 sets the Pseudo Sector Mark Generated Bit; if the Enable R/W Attempted After PSM Int Bit is set, the CL-SM330 halts the Read Sector Operation, sets the Operation Complete Bit, and generates a microcontroller interrupt. Otherwise, the CL-SM330 asserts IDF nominally two bytes after the last ID CRC Bit. The CL-SM331 then begins searching for a 'Valid Data Sync' Byte (hex '0D') on the NRZ line.

The CL-SM330 deasserts DRG and the CL-SM331 waits until the beginning of the Data Field VFO Area before it asserts SRG and begins searching for a 'Valid Data Sync' Byte (hex '0D') on the NRZ line. The CL-SM330 asserts DRG and attempts to detect the Data Sync Mark under its window. If the Data Sync Mark Threshold is met under the Data Sync Mark Window, the CL-SM330 transfers a 'Valid Data Sync' Byte (hex '0D') over the NRZ line to synchronize the NRZ data stream to the CL-SM331. The CL-SM330 then begins decoding the RLL-encoded data and

serially transferring the decoded NRZ data to the CL-SM331, that de-serializes the NRZ data stream and writes it to the data buffer.

If the Data Sync Mark Threshold is not met under the Data Sync Mark Window, the CL-SM330 attempts to synchronize using the first Resync Mark. It transfers a 'Valid Data Sync' Byte (hex '0D') over the NRZ line to synchronize the NRZ data stream to the CL-SM331, and transfers the appropriate number of dummy data bytes. If the CL-SM330 detects the first Resync Mark under a widened window, it sets the Recovered Data Sync Error Bit, synchronizes the NRZ data stream, continues the Read Sector Operation, and optionally generates a microcontroller interrupt at the end of the sector. If the CL-SM330 cannot detect the first Resync Mark, it aborts the Read Sector Operation, sets the Fatal Data Sync Error Bit, and optionally generates a microcontroller interrupt. The microcontroller may then use the Skip Data Sync Mark Mode in attempt to recover the sector.

When the data transfer begins, the CL-SM330 decrements the Sector Transfer Count. If the Sector Transfer Count is then zero, the CL-SM330 sets the Sector Transfer Count=0 Bit, and optionally generates a microcontroller interrupt. If the microcontroller writes a non-zero value to the Sector Transfer Count Register before the end of the ECC transfer, another Read Sector Operation will begin without loss of disk orientation while correction is completed for the previous Read Sector Operation.

Resync Marks occur every 15 or 20 bytes, depending on the selected sector size. Each time the appropriate number of user data or redundancy bytes have been transferred, the CL-SM330 attempts to find a Resync Mark under its window. If a Resync Mark is detected in the proper position, the CL-SM330 removes the Resync Mark from the data stream by pausing RRCLK, then continues to decode the RLL data and transfer NRZ data to the CL-SM331.

If a Resync Mark is detected in the wrong position, the CL-SM330 reestablishes bit and byte synchronization and continues to decode and transfer data to the CL-SM331 while assuring the correct number of data bits are transferred. If a Resync Mark is not detected, the CL-SM330 continues to decode and transfer data as if a Resvnc Mark had been detected in the correct position; optionally, the window for the next Resync Mark is made wider and when a valid Resync Mark is detected, the CL-SM330 automatically switches back to the selected initial Resync Mark Window size. If the number of 'used' and 'missing' Resync Marks exceeds the programmed Resync Error Threshold, the CL-SM330 continues the Read Sector Operation and sets the Resync Error Threshold Exceeded Bit and optionally generates a microcontroller interrupt at the end of the sector.

The CL-SM330 decodes the ECC remainder bytes to generate error correction vectors, that the CL-SM331 uses to correct the bytes in error. If the CRC or ECC redundancy bytes read from the medium differ from those calculated for the data bytes read from the medium, an error has been detected. When all redundancy bytes have been read, the CL-SM330 latches the Sector Transfer Count Register into the Sector Correction Count Register; if the Sector Transfer Count Register has decremented to zero, then zero will be loaded into the Sector Correction Count Register at the appropriate time, regardless of whether or not the microcontroller has already written a new transfer count. If an error has been detected, the CL-SM330 begins calculating the locations and patterns of errors while the header and data fields of the next sector, if any, are read. Unless inhibited by setting the Suppress Correction Vectors Bit, the addresses and patterns of errors in data are transferred serially via the VECTOR line to the CL-SM331, that is responsible for correcting the data in the data buffer. When the CL-SM331 is able to accept another error correction vector, it asserts the VREADY Signal. If the CL-SM331 is not able to correct the data byte due to a buffer RAM parity error or some other unforeseen circumstance, it asserts the VERROR Signal. The

CL-SM330 stores the CRC residue bytes internally and adjusts them as necessary to account for errors detected in the data and VU/PTR bytes.

After correction is complete, or no error is detected in a sector, the CL-SM330 sets the Error Correction Complete Bit, posts the error correction status and updates the Data Buffer Address registers. If the Enable Error Correction Complete Int Bit is set, a microcontroller interrupt is generated. If any of the status bits in the ECC Error Status Register has been set and the Enable ECC Error Int Bit is set, the CL-SM330 aborts the Read Sector Operation and generates a microcontroller interrupt. If the Sector Correction Count Register went to zero, the CL-SM330 sets the Operation Complete Bit, and if the Enable Operation Complete Int Bit is set, it generates a microcontroller interrupt. Otherwise, the CL-SM330 will begin to correct the next sector, if necessary, as soon as it has been read.

#### 4.2 Write Sector Operation

The configuration, start, Sector Mark, and ID validation processes for a Write Sector Operation are performed in a manner similar to that for a Read Sector Operation.

After locating the target sector, the CL-SM330 asserts IDF at the end of the third ID Field and deasserts DRG. The CL-SM331 waits until the beginning of the Data Field VFO Area before it asserts SWG and transfers 11 bytes of all '1's data followed by one byte of all '0's data over the NRZ line, followed by the three bytes of the NRZ representation of the Data Sync Mark. The CL-SM330 asserts DWG and synthesizes and writes the 12byte VFO pattern, then encodes and writes the Data Sync Mark. The CL-SM331 then fetches user data from the data buffer and serially transfers it over the NRZ line to the CL-SM330, that encodes and writes it, following the encoded Data Sync Mark. When data transfer begins, the CL-SM330 decrements the Sector Transfer Count. If the Sector Transfer Count is zero, the CL-SM330 sets the Sector Transfer Count=0 Bit and optionally generates a microcontroller interrupt. If the microcontroller writes a non-zero value to the Sector Transfer Count Register before the end of the ECC transfer, another Write Sector Operation will begin without loss of disk orientation.

Resync Marks occur every 15 or 20 bytes, depending on the selected sector size. Each time the appropriate number of data bytes has been written, the CL-SM330 pauses RRCLK for eight periods, writes the Resync Mark pattern, and continues to transfer, encode, and write the NRZ data from the CL-SM331.

As the CL-SM330 encodes and writes user data and Vendor Unique/Pointer (VU/PTR) bytes, it generates the CRC and ECC redundancy bytes. The CL-SM330 will encode the CRC and ECC redundancy bytes and write them to the disk following the user data and VU/PTR bytes. One or more bytes of padding, as determined by the programming of the Writable Control Store of the CL-SM331, are written after the last ECC Byte. The first byte of padding is written using the Resync Mark Pattern.

#### 4.3 Read ID Operation

The Read ID Operation is provided to allow the microcontroller to determine the current position of the optical head. The microcontroller first selects the Read ID Mode, then writes any non-zero value to the Sector Transfer Count Register. The CL-SM330 reads the next error-free ID Field and stores it in the ID Target registers, sets the Operation Complete Bit, and optionally generates a microcontroller interrupt. If no error-free ID is read within two disk revolutions, the CL-SM330 will abort the Read ID Operation, set the ID Error Bit, and optionally generate a microcontroller interrupt.

### 4.4 Search ID Operation

The Search ID Operation is provided to allow the microcontroller to automatically determine when the optical head is at a specified position; typically, the microcontroller will then execute a 'jumpback' sequence for the optical drive. If desired, the microcontroller first determines the current position of the optical head and positions it ahead of the sector for that the CL-SM330 is to search. The microcontroller then writes the ID Track and sector values of the sector for that the CL-SM330 is to search to the ID Compare registers and writes any non-zero value to the Sector Transfer Count Register. The CL-SM330 reads the next error-free ID Field into the ID Target registers. As each succeeding sector mark is encountered, the CL-SM330 increments the ID Target registers until the ID Target registers match or exceed the ID Compare registers. The CL-SM330 then asserts CMPF and sets the ID Compare Register Found Bit and optionally generates a microcontroller interrupt. If Enable ID Error is set and no error-free ID is read within two disk revolutions, the CL-SM330 will abort the Search ID Operation, set the ID Error and Operation Complete bits, and optionally generate a microcontroller interrupt. If Enable ID Error is not set, the ID Search Operation will not terminate due to not finding an ID within two revolutions. ID Search is never terminated due to not meeting the ID voting threshold or because of the ID being greater than the target.

After a 'jump-back' operation has been initiated, the CL-SM330 will continue the search/compare operation until the microcontroller halts the CL-SM330 by writing a '1' to the Operation Halt Bit (Register 10H, Bit 6), or an ID Error causes abnormal termination. After asserting CMPF, the CL-SM330 waits eight sector times before attempting to read an ID. It is advised that the drive complete its 'jump-back' within that eight sector time to avoid false ID detection.

#### 4.5 Blank Sector Operations

The configuration, start, and Sector Mark and ID validation processes for a (Non) Blank Verify Operation are performed in the same manner as for a Read Sector Operation. Because no data is transferred to the buffer, the CL-SM331 is not involved in (Non) Blank Verify operations. The (Non) Blank Verify and Flag Detection features of the CL-SM330 are intended for use in WORM type application; the RAWIN Signal must be valid in the absence of DRG for these functions to work.

After locating the target sector, the CL-SM330 asserts IDF at the end of the third ID Field and deasserts DRG. Blank sectors are detected by counting transitions on the RAWIN Signal line in the Data Field Area and comparing this count to a threshold. If the threshold is not exceeded, the sector is considered to be blank. If the threshold is exceeded, the sector is considered to be nonblank. If a non-blank sector is detected during a Blank Verify Operation or if a blank sector is detected during a Non-Blank Verify Operation, the CL-SM330 will abort the operation, set the Blank Sector Error Bit, and optionally generate a microcontroller interrupt.

The transition counter is designed to support both Pulse-Position and Pulse-Width modulation. If RAWIN is asserted for less than two REF2F clock periods, the counter will be incremented once for each pulse. If RAWIN is asserted for greater than 2 1/2 REF2F periods, the counter will be incremented twice for each pulse. The window used to count for transitions on the RAWIN Signal line are the first 64 NRZ bytes of the sector data field. A count of less than 63 transitions indicates a blank sector. A count of 63 transitions or more indicates a non-blank sector.

### 4.6 RLL Encode/Decode Circuits

The (2,7) RLL encoder circuitry encodes the NRZ Data Bit stream into a run-length-limited code bit stream, in that each pair of '1's is separated by at least two '0's and by, at most, seven '0's.

The (2,7) RLL decoder is designed for minimum error propagation and to produce the most probable output data value when an invalid decode or run-length violation is detected. An optional mode is available in that run-length violations and invalid decodes, 'used' Resync Marks, and Loss-Of-Frequency-Lock are combined to generate erasure pointers for use by extended error-correction algorithms resident in the microcontroller firmware. The run-length violation detection taps are positioned for best erasure pointer accuracy.

#### 4.7 Mark Detection

#### 4.7.1 Sector Mark Detection

A Sector Mark is located at the beginning of each sector. The CL-SM330 and CL-SM331 use the Sector Mark to synchronize with the ID fields and Data fields on the medium.

The ANSI/ISO standards define a Sector Mark composed of long marks and spaces that are readily distinguishable in the RLL-encoded Bit stream. Furthermore, the Sector Mark is designed to be detectable without recourse to phase-locked circuitry. The CL-SM330 uses the reference clock to detect the Sector Mark in the RLL-encoded Bit stream.

The CL-SM330 Sector Mark Detection circuitry employs majority voting on the long marks and spaces with separate voting thresholds. When the number of long marks detected equals or exceeds the Sector Mark-Mark Threshold and the number of spaces detected equals or exceeds the Sector Mark-Space Threshold, the CL-SM330 asserts SMDET, an output to the CL-SM331. The Sector Mark Detection circuitry is designed to achieve a significant degree of tolerance to media defects and read-channel asymmetries. Both the long marks and spaces of the Sector Mark should be decoded; otherwise, overwritten sectors might trigger Sector Mark Detection.

The microcontroller can set the Sector Mark-Mark Detection Threshold to any value between zero and five inclusive, and the Sector Mark-Space Detection Threshold to any value between zero and four inclusive. Threshold values of three may provide adequate performance under normal conditions. Note that lower thresholds can increase the probability of false Sector Mark Detection. Error recovery algorithms should use the highest threshold that will permit the Sector Mark to be reliably detected. Optionally, relaxed Sector Mark Detection circuitry and/or a Dual-Mode Sector Mark asymmetry compensation circuit can be enabled.

To minimize the possibility of false detection, Sector Marks are detected under a window. The initial width of the Sector Mark Window is controlled by the selected maximum speed tolerance (0.5 or 1.0%). After a Sector Mark Reset, Sector Mark Windowing begins after the second detection of an un-windowed Sector Mark. Sector Mark Windowing can also be completely disabled by the microcontroller, that may be useful in sector size determination.

When a Sector Mark is not detected, a Pseudo Sector Mark is generated when the CL-SM330 expected to see the Sector Mark. Writing the Sector Mark Control Register causes the CL-SM330 to block the generation of Pseudo Sector Marks and inhibit Sector Mark windowing until after a Sector Mark is detected. The CL-SM330 can be programmed to abort Read Sector and Write Sector operations if the Sector Mark of a sector is not detected. This option supports the ANSI/ISO recommendation that a sector is not to be used if its Sector Mark is defective.

#### 4.7.2 ID Address Mark Detection

The detection of ID Address Marks establishes bit and byte synchronization for ID fields. ID Address Marks contain a (2,7) RLL code run-length violation, so they are detected in the RLL channel bit stream. Detection of ID Address Marks is windowed to minimize the probability of false detection.

It is possible for defects in the VFO Area to drive the PLL to a state from that it cannot recover in time to read subsequent ID fields. To aid in recovering from this situation, the CL-SM330 can be programmed to skip the first or first and second ID fields and attempt to acquire frequency and phase lock over the second or third VFO Area, or to skip all three ID fields. The CL-SM330 can be programmed to deassert DRG for one byte time after the last CRC Byte of the first and second ID fields.

#### 4.7.3 Data Sync Mark Detection

The detection of the Data Sync Mark establishes initial bit and byte synchronization for the Data Field. The Data Sync Mark is detected in the RLL channel bit stream; this prevents error propagation by the (2,7) RLL decoder and allows maximum error tolerance. Detection of the Data Sync Mark is windowed to minimize the probability of false detection.